Автор: Казённов Г.Г.

Теги: электротехника компьютерные технологии схемы интегральные схемы

ISBN: 5-94774-232-2

Год: 2005

Текст

Г. Г. Казённов

Основы

проектирования

интегральных

схем и систем

Москва

БИНОМ. Лаборатория знаний

2005

УДК 621.3.049.77

ББК 32.973.26я73

К14

Казённов Г. Г.

К14 Основы проектирования интегральных схем и систем

/Г. Г. Казённов. — М.: БИНОМ. Лаборатория знаний,

2005. — 295 с: ил.

ISBN 5-94774-232-2

В книге рассматриваются вопросы, связанные с методикой проек-

проектирования интегральных схем и систем, в том числе СБИС и систем на

кристалле (SoC). Акцентируется внимание на основных этапах процесса

проектирования (системный, микросхемный, регистровый, логический,

схемотехнический, топологический, компонентный).

Приводятся сведения о средствах автоматизированного проектиро-

проектирования, а также о применении для этих целей систем искуственного ин-

интеллекта.

Для студентов вузов, специализирующихся в области электроники

и изучающих дисциплины, связанные с проектированием интеграль-

интегральных схем и систем. Книга также может быть полезна разработчикам

микроэлектронной аппаратуры.

УДК 621.3.049.77

ББК 32.973.26я73

По вопросам приобретения обращаться:

БИНОМ. Лаборатория знаний

@95) 955-03-98, e-mail: LBZ@aha.ru

http://www.LBZ.ru

© Казённов Г. Г., 2005

ISBN 5-94774-232-2 © БИНОМ. Лаборатория знаний, 2005

Оглавление

Предисловие 6

Сведения об авторе 12

Глава 1. Методология проектирования интегральных

схем 13

Введение 13

1.1. Классификация интегральных схем 13

1.2. Классификация параметров интегральных

схем 20

1.3. Принципы проектирования 23

1.4. Методы проектирования 25

1.5. Этапы проектирования БИС 30

1.5.1. Разработка спецификации 31

1.5.2. Логическое проектирование 33

1.5.3. Схемотехническое проектирование 36

1.5.4. Топологическое проектирование 45

1.5.5. Компонентное проектирование 53

1.6. Проектные процедуры процесса

проектирования ¦ . . 56

1.7. Выводы и пути развития 58

Литература 61

Глава 2. Архитектура САПР БИС. Маршруты

проектирования 62

Введение 62

2.1. Классификация САПР 63

2.2. Методология построения САПР 69

2.3. Архитектура САПР . . 72

2.3.1. Технические средства 72

2.3.2. Программные средства проектирования. ... 73

2.4. Маршруты проектирования БИС 82

2.4.1. Автоматизация проектирования

полузаказных БИС 83

Оглавление

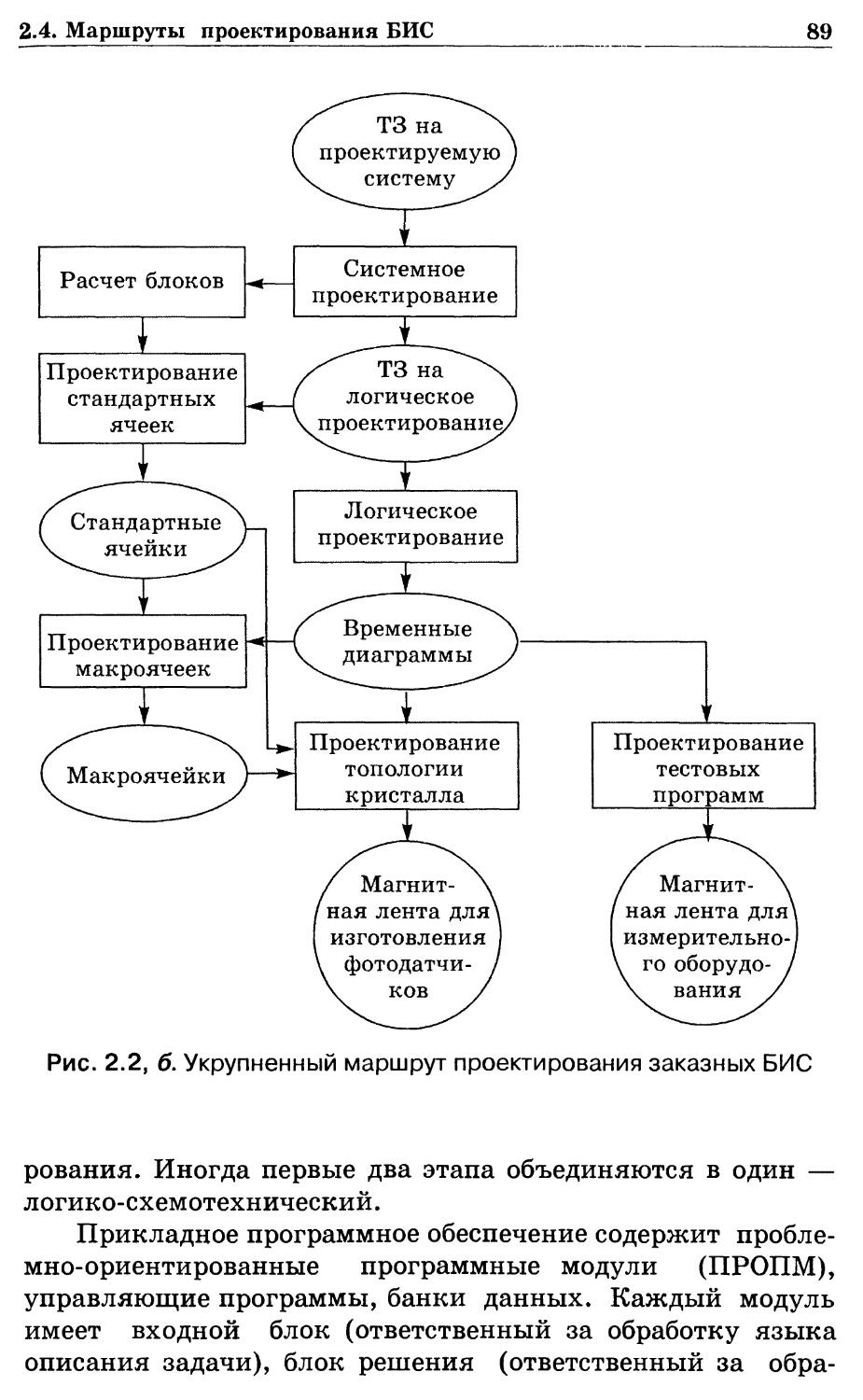

2.4.2. Автоматизация проектирования

заказных БИС 87

2.4.3. Средства проектирования компании

CADENCE 93

2.4.4. Средства проектирования компании

SYNOPSYS 101

2.4.5. Средства проектирования компании

MENTOR GRAPHICS 105

2.4.6. Выводы и проблемы 113

Литература 115

Глава 3. Проектные процедуры 116

Введение 116

3.1. Структурный синтез 116

3.1.1. Методы решения задач структурного

синтеза 117

3.1.2. Структурный синтез СБИС 120

3.2. Математические модели 131

3.2.1. Классификация математических

моделей 133

3.2.2. Компонентные и топологические

уравнения (на этапе схемотехнического

проектирования) 144

3.2.3. Различные формы математических

моделей 147

3.2.4. Математическая модель на этапе

схемотехнического проектирования 149

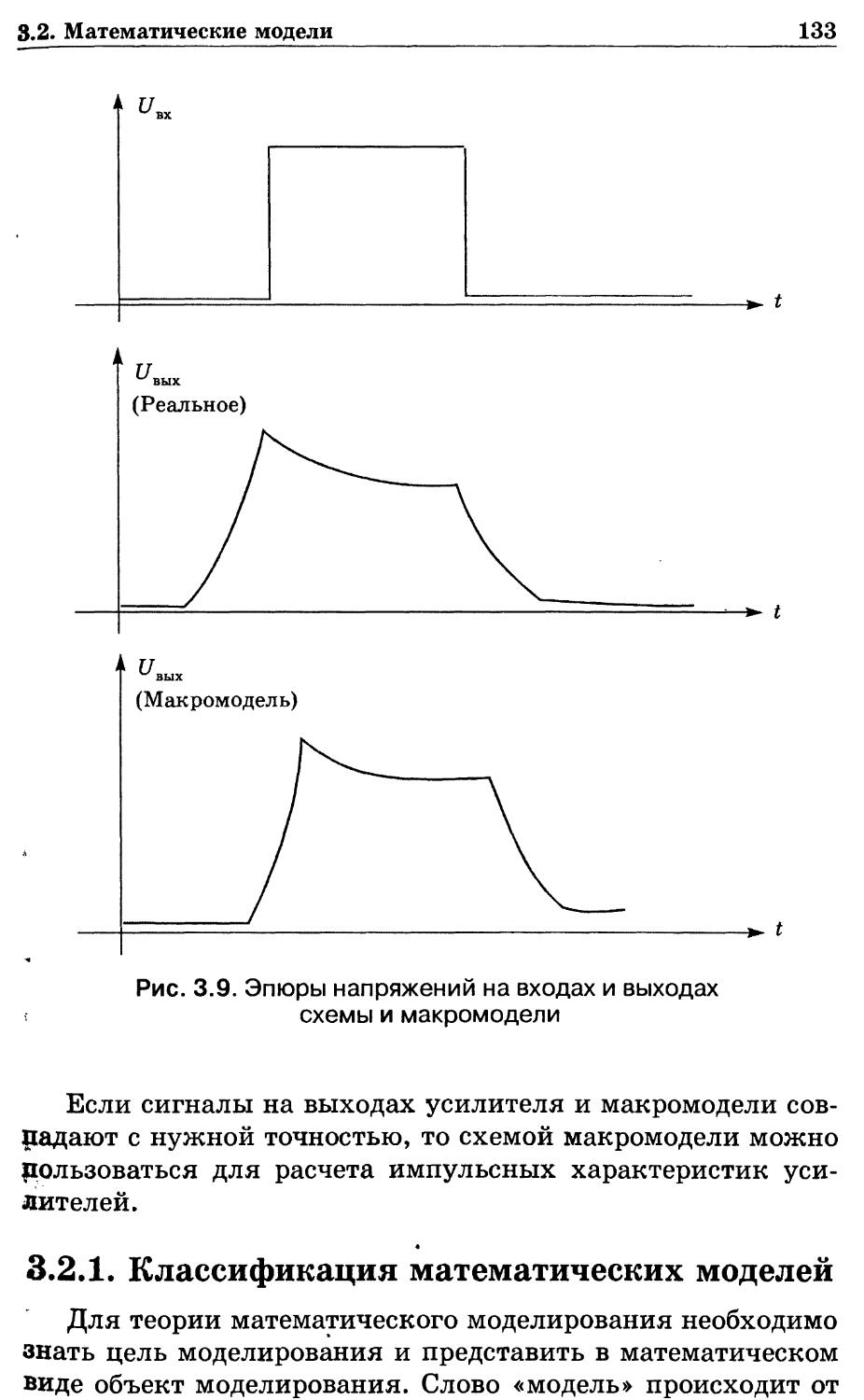

3.2.5. Макромодели 154

3.2.6. Математическая модель на этапе

логического проектирования 155

3.3. Анализ математических моделей 158

3.3.1. Особенности математических моделей .... 159

3.3.2 Схемотехническое моделирование 160

3.3.3. Логическое моделирование 173

3.4. Параметрическая оптимизация 183

3.4.1. Экстремальные задачи

в проектировании ИС 184

3.4.2. Алгоритмы решения экстремальных

задач 189

3.4.3. Обобщенный метод граничных

испытаний 193

3.5. Статистический анализ 194

3.5.1. Метод наихудшего случая 194

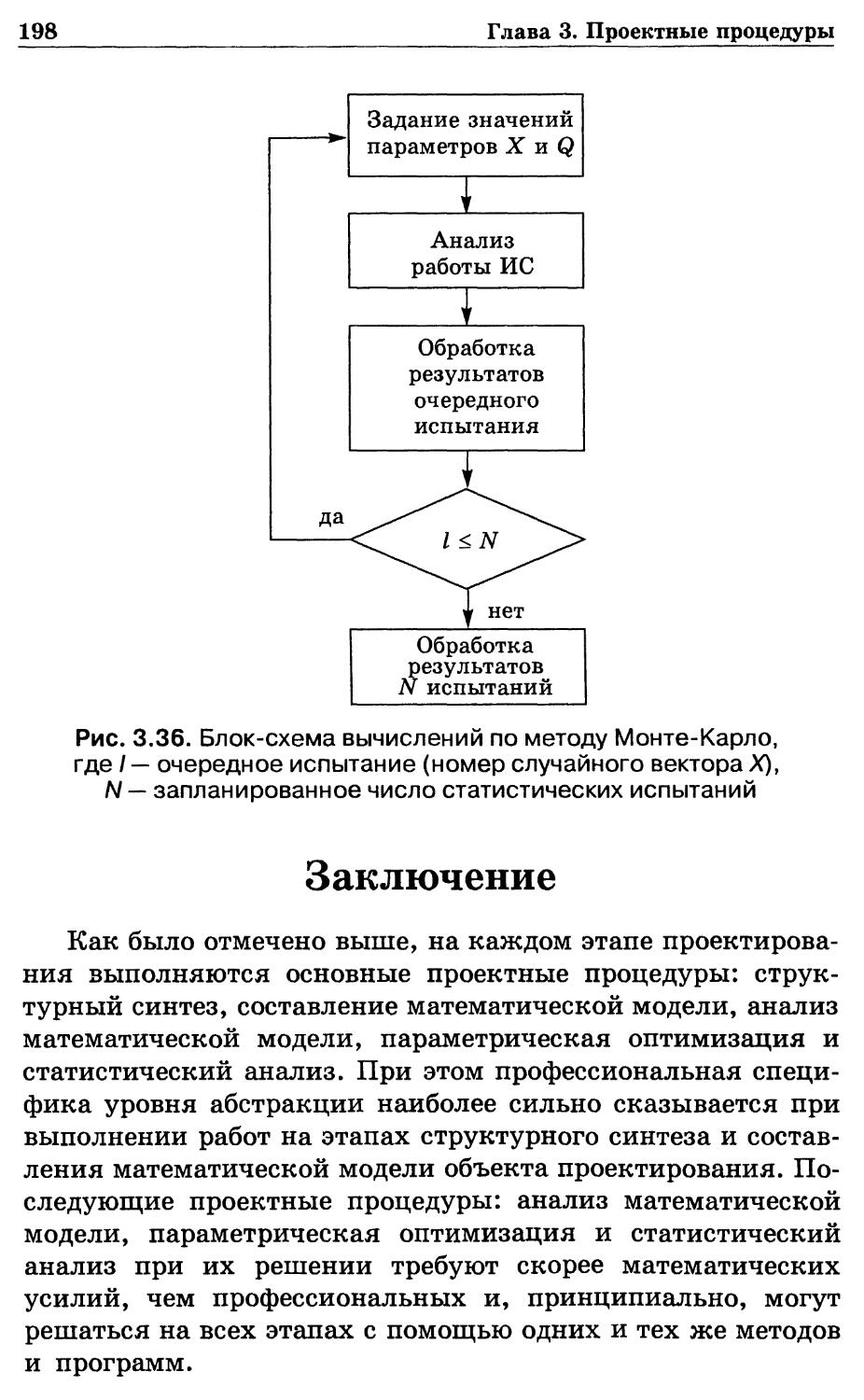

3.5.2. Метод Монте-Карло 197

Оглавление

Заключение 198

Литература 199

Глава 4. Проектирование интегральных систем 200

Введение 200

4.1 Классификация уровней проектирования 200

4.2. Высокоуровневое проектирование 207

4.3. Особенности проектирования систем

на кристалле 218

4.4. Проектирование систем на кристалле 220

4.4.1. Архитектура систем на кристалле 223

4.4.2. Автоматизация проектирования систем

на кристалле 226

4.4.3. Этапы поведенческого синтеза 237

4.5. Моделирование на уровне регистровых

передач 242

4.6. Моделирование на уровне транзакций 244

4.7. Особенности тестирования систем

на кристалле 248

Заключение 251

Литература 252

Глава 5. Автоматическое проектирование

и искусственный интеллект 253

Введение 253

5.1. Системы автоматического проектирования ... 253

5.1.1. Структура системы 258

5.1.2. Язык описания поведения 260

5.1.3. Методология проектирования ^ 265

5.2. Модель топологии для автоматического

проектирования 266

5.2.1. Топологический подход 266

5.2.2. Математическая модель топологии 270

5.2.3. Геометрическая модель топологии 274

5.3. Искусственный интеллект

в проектировании 275

5.3.1. Задачи искусственного интеллекта 277

5.3.2. Экспертные системы 280

Заключение 294

Литература 295

Предисловие

Если смотреть на процесс проектирования, исходя из кон-

концепции нисходящего проектирования, то в случае сложных

электронных систем необходимы семь уровней абстракции

представления проекта: системный, микросхемный, регистро-

регистровый, логический, схемотехнический, топологический, компо-

компонентный. Полный цикл проектирования также предполагает,

что на каждом уровне (этапе) проектирования должны быть

выполнены пять проектных процедур: структурный синтез,

составление математической модели, анализ математиче-

математической модели, параметрическая оптимизация и статистиче-

статистический анализ. В книге рассмотрены все уровни (этапы) проекти-

проектирования интегральных схем и систем и все проектные процеду-

процедуры. Это и является основной целью написания книги. Однако

уровни проектирования представлены не в перечисленном

выше порядке, а в том, в котором они реализуются на практи-

практике. Конечно, существует традиционное разделение инженеров

на разработчиков радиоэлектронной аппаратуры и разработчи-

разработчиков элементной базы аппаратуры. Однако в последние годы

тенденция интеграции процессов проектирования аппарату-

аппаратуры и ее элементной базы стала очевидной. Наиболее показате-

показательным примером в этом плане является бурный рост произ-

производства систем на кристалле (SoC) и средств автоматиза-

автоматизации их проектирования. Именно это обстоятельство

послужило побудительным мотивом для написания данной

книги. Весь материал книги распределен по пяти главам. Пер-

Первые две главы предназначены для студентов и инженеров, на-

начинающих свою профессиональную деятельность в области

проектирования интегральных схем и систем, а последующие

три главы-для продвинутых читателей.

Современные средства автоматизации проектирования изде-

изделий электронной техники позволяют создавать сложнейшие

Предисловие

электронные системы, содержащие миллионы электронных

компонентов. Соответственно растет и число уровней абстрак-

абстракции, на которых приходится проектировать эти системы. На

каждом уровне абстракции имеется свое понятие системы и

элементов системы, в базисе которых ведется проектирование.

То, что было системой на предыдущем уровне, на следующем,

более высоком уровне, становится элементом. Существуют две

концепции проектирования любого изделия: сверху вниз и сни-

снизу вверх. Практическая реализация каждой отдельной концеп-

концепции невозможна. В первом случае это обусловлено тем, что для

каждого изделия необходимо разрабатывать индивидуальный

реальный элементный базис низшего уровня абстракции, что

противоречит требованиям времени проектирования, возмож-

возможности серийного производства и разумной стоимости проекти-

проектируемого изделия. Во втором случае нереализумость концепции

определяется отсутствием обоснованных требованиий к функ-

функциональному составу и параметрам структурных компонентов

любого более высокого уровня. Поэтому на практике использу-

используется разумное сочетание этих концепций. Довольно распро-

распространенным представлением процесса проектирования являет-

является следующее: на каждом уровне представления проекта реша-

решаются две задачи — синтез и анализ, причем под синтезом

понимается получение структуры системы в виде соединенных

между собой структурных компонентов данного уровня, а под

анализом — составление и решение математической модели

этой структуры. Например, при схемотехническом проектиро-

проектировании структура системы представляется списком цепей, сое-

соединяющих транзисторы, резисторы, емкости и другие компо-

компоненты, а анализ — составлением математической модели схе-

схемы в виде системы обыкновенных дифференциальных

уравнений и ее численного решения, которое и позволяет рас-

рассчитать функциональные параметры схемы. Ошибочность дан-

данного представления состоит в следующем: при недостаточно

обоснованном выборе параметров математических моделей

структурных компонентов может быть забракована хорошая

структура системы. Чтобы избежать подобную ситуацию, необ-

необходимо в обязательном порядке выполнить процедуру парамет-

параметрической оптимизации. Но и этого недостаточно для оценки

правильности выбора структуры. Чтобы параметры выбранной

структуры системы удовлетворяли предъявляемым требовани-

требованиям при разбросе параметров структурных компонентов, необхо-

необходимо проведение статистического анализа. Учитывая, что про-

Предисловие

цедуры параметрической оптимизации и статистического ана-

анализа реализуются соответствующим образом организованным

многократным решением математических моделей, теоретиче-

теоретически идеальное проектирование требует колоссальных вычисли-

вычислительных ресурсов, даже несмотря на огромный прогресс в раз-

разработке современных средств автоматизации проектирования.

Первая глава посвящена методологии проектирования ин-

интегральных схем, в том числе больших интегральных схем

(БИС). В ней последовательно описаны общие принципы проек-

проектирования сложных технических систем и методы проектиро-

проектирования интегральных схем и систем. В соответствии с приведен-

приведенной выше классификацией, в первой главе рассмотрены следу-

следующие этапы проектирования: логический, схемотехнический,

топологический и компонентный, а также проектные опера-

операции, выполняемые на каждом этапе: структурный синтез, со-

составление математической модели, анализ, параметрическая

оптимизация и статистический анализ. Обращено внимание

читателя на важность решения экстремальных и статистиче-

статистических задач. Реализация принципа унификации нашла отраже-

отражение в создании на каждом этапе проектирования библиотек

структурных компонентов, использование которых позволяет

значительно сократить цикл проектирования

Во второй главе рассматривается архитектура САПР и ти-

типовые маршруты проектирования БИС и СБИС крупнейших за-

зарубежных компаний-разработчиков и поставщиков средств ав-

автоматизации проектирования изделий электронной техники. В

начале главы традиционно рассматривается классификация

САПР по девяти признакам. В разделе, посвященном методоло-

методологии построения САПР, приведены концептуальные аспекты их

создания, роль методов искусственного интеллекта, перечень

требований, которые предъявляются к современным САПР,

основные идеи построения САПР, удовлетворяющих предъяв-

предъявляемых требованиям. Далее приводится описание возможных

архитектур САПР и структуры прикладного программного

обеспечения САПР БИС, а также информационного и лингви-

лингвистического обеспечения. После краткого рассмотрения методов

проектирования заказных и полузаказных БИС приводится

описание средств автоматизации проектирования интеграль-

интегральных схем и систем следующих американских компаний: Caden-

Cadence, Synopsys, Mentor Graphics.

Если первые две главы предназначены, в основном, для по-

пользователей САПР, т. е. инженеров, которые проектируют ин-

Предисловие

тегральные схемы, пользуясь уже разработанными САПР и хо-

хорошо отработанной документацией по их эксплуатации, то

третья глава ориентирована на разработчиков САПР, в пер-

первую очередь прикладного программного обеспечения. В ней

имеется пять разделов, каждый из которых посвящен одной из

проектных процедур, расположенных в том порядке, в котором

они используются на каждом этапе проектирования интеграль-

интегральных схем и систем. С общих позиций рассмотрены переборные

и эвристические методы и алгоритмы решения задач структур-

структурного синтеза на любом этапе проектирования. Подробно рас-

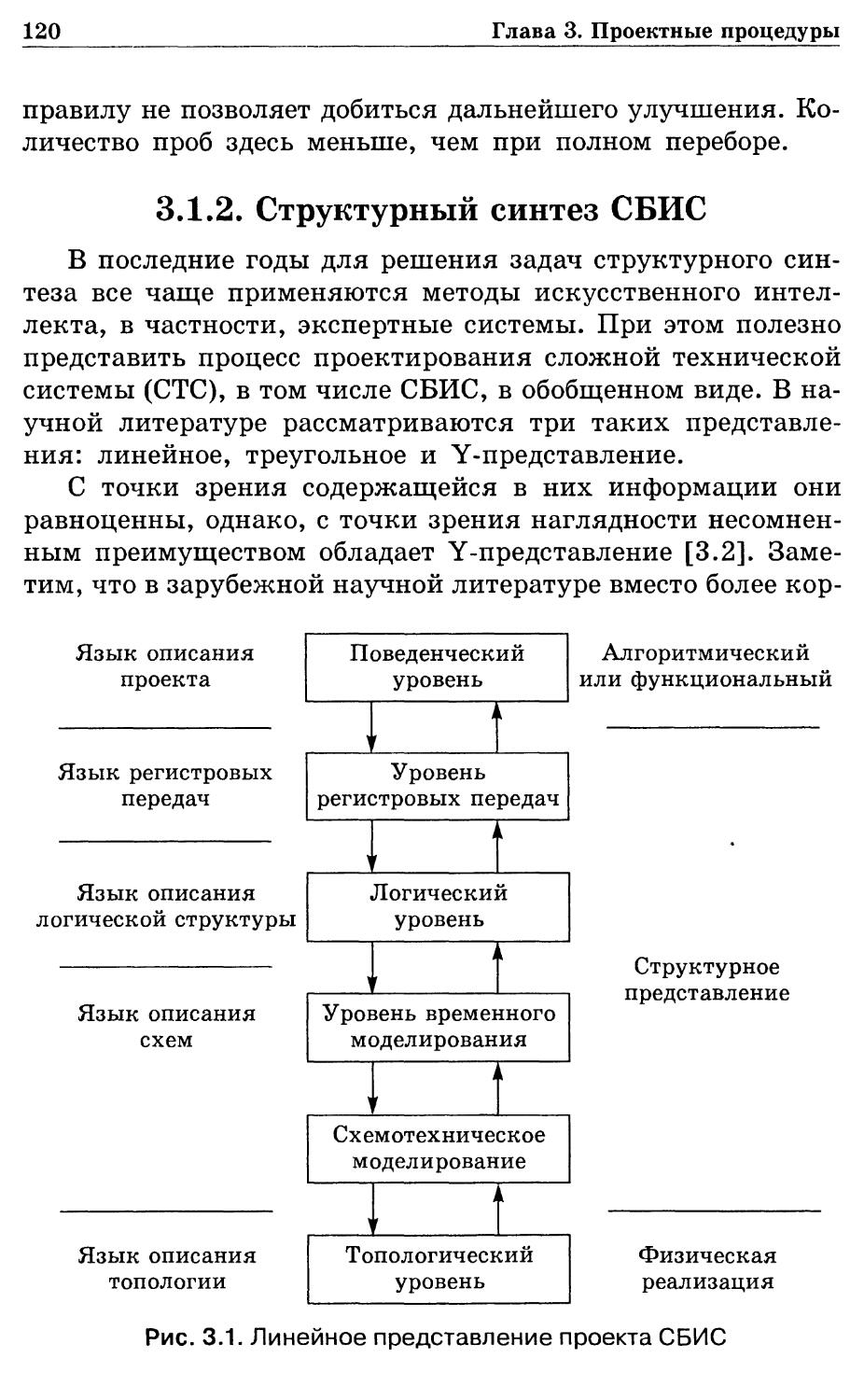

рассмотрено Y-представление проекта СБИС и его применение для

решения задач структурного синтеза. Показано, что используя

это представление и экспертные системы, можно решать задачи

синтеза как в отдельных областях представления проекта

СБИС: поведенческом, структурном и физическом, так и при

переходе из одной области в другую. Далее рассмотрены задачи

формирования математических моделей на этапах схемотехни-

схемотехнического и логического проектирования в виде систем ОДУ и бу-

булевых уравнений. Выбор этих этапов обусловлен не только их

значимостью в общем цикле проектирования, но и характером

переменных — в первом случае они непрерывные, а во вто-

втором — дискретные. В третьем разделе главы отмечены общие

характерные черты математических моделей, присущие любо-

любому этапу проектирования. Приведено описание методов анали-

анализа математических моделей, используемых на этапах схемотех-

схемотехнического и логического проектирования интегральных схем.

В следующем разделе рассматривается одна из наиболее трудо-

трудоемких проектных процедур — параметрическая оптимизация.

Задачам параметрической оптимизации транзисторов и прин-

принципиальных электрических схем дана математическая форму-

формулировка в виде общей задачи нелинейного программирования с

непрерывными переменными. Отмечено, что экстремальные

задачи других этапов проектирования БИС также могут быть

сформулированы в виде общей задачи математического про-

программирования, но с дискретными переменными. Заканчива-

Заканчивается глава рассмотрением проектной операции статистическо-

статистического анализа. В качестве примера приводится описание методов

наихудшего случая и Монте-Карло для статистического ана-

анализа на этапе схемотехнического проектирования интеграль-

интегральных схем.

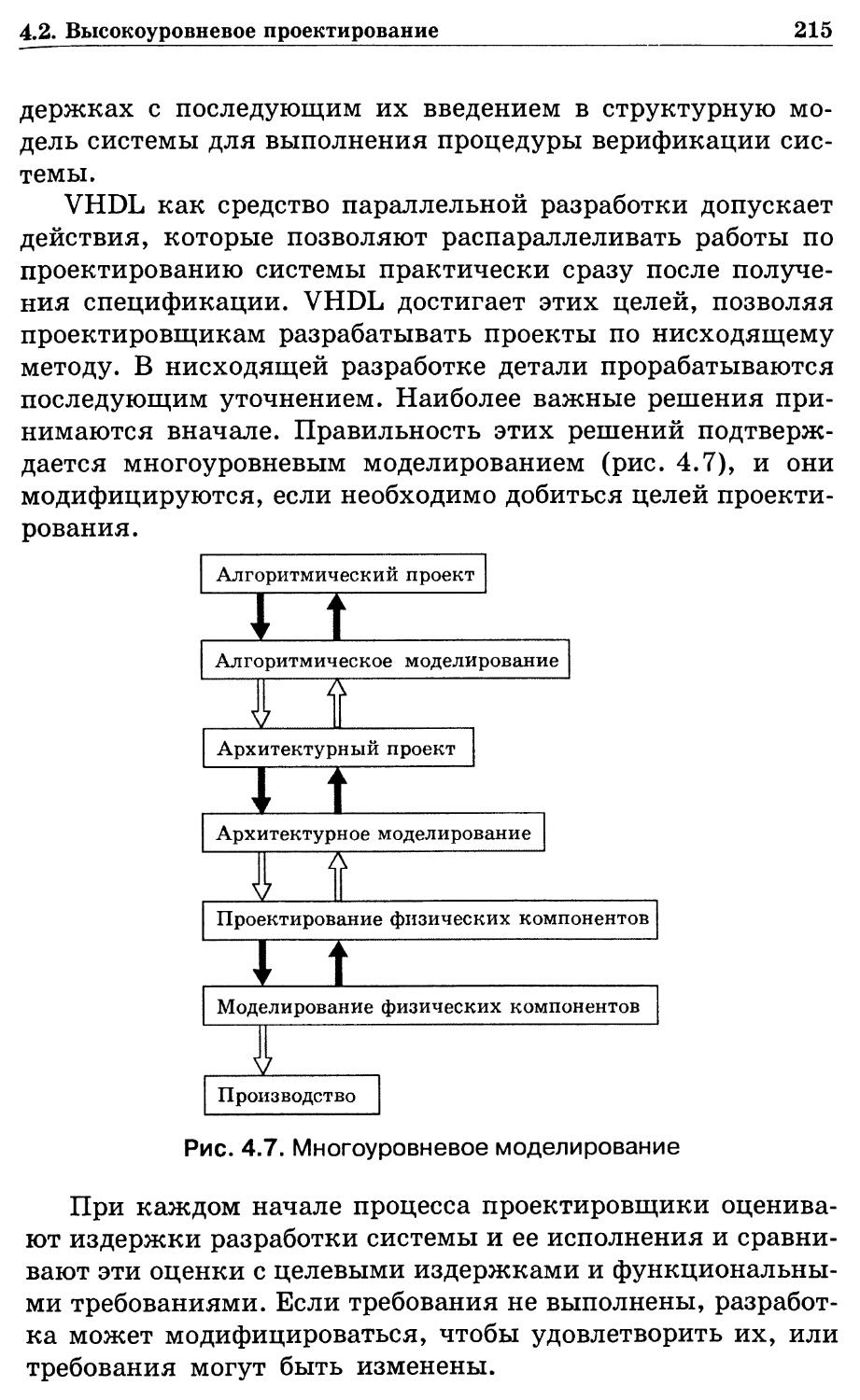

¦¦¦*¦ Четвертая глава посвящена проектированию интеграль-

интегральных систем, в основном, систем на кристалле (SoC). После

10 Предисловие

классификации уровней представления проекта обосновывает-

обосновывается целесообразность моделирования систем на микросхемном

уровне и дается его характеристика. Приводятся основные по-

понятия языка VHDL и обсуждаются его возможности при проек-

проектировании сложных технических систем. Далее в главе рас-

рассматриваются особенности проектирования систем на кристал-

кристалле с использованием IP-блоков, анализируются требования,

предъявляемые к IP-блокам, предназначенным для использова-

использования в интегральных системах. Отмечены проблемы, которые

могут возникнуть у разработчиков систем на кристалле, испо-

использующих IP-блоки от разных поставщиков. Проанализирован

перечень задач, которые приходится решать при проектирова-

проектировании систем на кристалле. Подчеркнута важность высокоуров-

высокоуровневого проекта как основного документа для всех последующих

работ по его физической реализации. После обсуждения архи-

архитектуры систем на кристалле рассматриваются проблемы раз-

разработки средств автоматизации их проектирования. В этом

плане весьма перспективной представляется реализация кон-

концепции виртуального проекта, который по существу является

структурной и функциональной инкапсуляцией реального про-

проекта, состоящего из виртуальных компонентов, виртуальных

интерфейсов и виртуальных цепей. Виртуальный проект может

быть создан, используя схемный редактор или любой аппарат-

аппаратный язык описания. Далее приведена последовательность про-

процедур для создания виртуального проекта цифровой системы

на кристалле и описан алгоритм преобразования виртуального

проекта в реальный. Так как высокоуровневое проектирование

заканчивается созданием проекта в базисе структурных компо-

компонентов регистрового уровня, в главе также кратко рассмотрено

моделирование систем на уровне регистровых передач. Факти-

Фактически описание цифровых систем на регистровом уровне —

это законченный проект системы в обобщенной форме, т. е.

без привязки к библиотекам конкретных производителей

СБИС и IP-блоков. Однако применение моделей этого уровня

для разработки и верификации программного обеспечения

проблематично, поскольку начало процесса совместной вери-

верификации программного обеспечения и аппаратной части SoC

отодвигается на поздние этапы проектирования и, кроме того,

скорость моделирования на этом уровне низкая. Эти недостат-

недостатки устраняются моделированием на уровне транзакций. Поэ-

Поэтому в четвертой главе приводится описание моделирования

на этом уровне.

Предисловие 11

В пятой главе книги рассматриваются проблемы, связан-

связанные с возможностью построения полностью автоматических си-

систем проектирования интегральных схем и систем. Привлека-

Привлекательность идеи автоматического проектирования обусловлена

не только перспективой ускорения процесса проектирования,

но и принципиальным отсутствием необходимости использова-

использования многозатратных верификационных процедур. В научной

литературе часто отождествляют понятие автоматической сис-

системы проектирования с понятием «кремниевый компилятор»,

хотя, строго говоря, это неверно. Появление термина «кремни-

«кремниевый компилятор» объясняется определенным сходством про-

процесса проектирования СБИС и разработки программного обес-

обеспечения, т. е. существует много общего между обычными про-

программными компиляторами и кремниевыми компиляторами.

Однако, так как этот термин получил широкое распростране-

распространение, в дальнейшем мы будем им пользоваться. После описания

свойств, которыми должен обладать кремниевый компилятор,

проанализирована его структура и назначение составляющих

его функциональных блоков, а также рассмотрена методология

проектирования СБИС. Далее в главе рассмотрена многоуров-

многоуровневая математическая модель топологии СБИС, алгоритмиче-

алгоритмическая и программная реализация которой позволит полностью

автоматизировать проектирование топологии СБИС теоретиче-

теоретически неограниченной степени интеграции. Практическое огра-

ограничение связано с машинными ресурсами технических средств.

В последнем разделе главы приведена классификация обла-

областей использования методов искусственного интеллекта, отме-

отмечена перспективность их применения в проектировании слож-

сложных электронных систем. Подчеркнута исключительно важная

роль экспертных систем при решении задач структурного син-

синтеза на всех уровнях абстракции представления проекта слож-

сложных технических систем.

Основным материалом для написания книги послужили

конспекты лекций по проектированию интегральных схем и те-

теоретическим основам САПР, читаемых автором в течение мно-

многих лет в Московском институте электронной техники, а также

результаты собственных исследований, опубликованные ранее

в ряде книг, статей и докладов.

Г. Г. Казённое

12

Предисловие

Сведения об авторе

КАЗЁННОЕ Геннадий Георгиевич — заведующий кафедрой

проектирования и конструирования интегра-

интегральных микросхем, профессор, д-р техн. наук,

лауреат Государственной премии СССР и

двух премий Гособразования, действитель-

действительный член Международной академии инфор-

информатизации. Окончил Ленинградский поли-

политехнический институт им. М. И. Калинина.

В период 1958-1975 гг. работал на предприя-

предприятиях электронной промышленности. Руково-

Руководил созданием первой САПР ИС в СССР. Ра-

Работает в МИЭТ с 1975 г.

Область научных интересов:

теоретические основы проектирования САПР БИС, СБИС,

УБИС, методология проектирования, структурный синтез на

этапах проектирования, параметрическая оптимизация, стати-

статистический анализ, экспертные системы, интеллектуализация

творческих процессов, функциональные подсистемы САПР

УБИС, маршруты проектирования БИС.

Подготовил 20 кандидатов и 5 докторов наук.

Опубликовано 250 научных трудов, в т. ч. учебник «Основы

построения САПР и АСТПР» в соавт. A989), монографии

«Структура, основные требования и принципы построения сис-

систем автоматизированного проектирования микроэлектронных

приборов» A978), «Принципы и методология построения

САПР БИС» A990).

С 2003 г. работает в МИЭТ на кафедре ПКИМС в должности

профессора-консультанта.

Глава 1

Методология

проектирования

интегральных схем

Введение

Современные радиотехнические устройства и системы

обеспечивают жизнедеятельность всего человеческого обще-

общества. Успехи в области ядерной физики, космонавтики,

компьютеризации и телекоммуникаций немыслимы без со-

создания средств проектирования интегральных схем и сис-

систем, т. к. основу элементной базы радиоаппаратуры состав-

составляют интегральные схемы различной степени интеграции,

включая IP-блоки. Конечно, продолжают использоваться в

радиоаппаратуре и традиционные радиокомпоненты, такие

как резисторы, конденсаторы, диоды, транзисторы и т. д.,

но их относительное содержание постоянно уменьшается.

Разнообразие конструктивно-технологических методов изго-

изготовления интегральных схем привело к необходимости со-

создания различных методологий их проектирования. Изло-

Изложенная в данной главе методология проектирования интег-

интегральных схем в значительной мере отражает личный опыт

работы автора в этой области и не претендует на исчерпыва-

исчерпывающую полноту.

1.1. Классификация

интегральных схем

Существует ряд признаков, по которым классифицируют

интегральные схемы. Рассмотрим некоторые из них. Основ-

Основной функцией, которую выполняют устройства на ИС, явля-

является обработка информации. В зависимости от того, в какой

14 Глава 1. Методология проектирования интегральных схем

форме (аналоговой или цифровой) обрабатывается информа-

информация, ИС делят на аналоговые, цифровые и аналого-цифровые

(цифроаналоговые).

По степени интеграции (числу компонентов на крис-

кристалле) условно различают ИС малой степени интеграции

(МИС) — до 103 компонентов, средней степени (СИС) — до

104 компонентов, большой степени (БИС) — до 105, сверх-

сверхбольшой степени (СБИС) — до 107 и ультрабольшой степени

интеграции (УБИС) — свыше 107.

По типу активного компонента различают интеграль-

интегральные схемы биполярные и полевые.

Интегральные схемы малой степени интеграции пред-

представляют собой логические схемы, выполняющие простей-

простейшие логические операции (И, ИЛИ, НЕ, ИЛИ-НЕ, И-НЕ),

триггерные схемы (триггеры, сумматоры, дешифраторы и

т. п.) или схемы усилителей. По мере совершенствования

технологии и соответственно повышения степени интегра-

интеграции стало возможным реализовывать функциональные бло-

блоки и узлы традиционных систем обработки и хранения ди-

дискретной информации в виде СИС. Это привело к сужению

областей црименения СИС и к увеличению числа типов СИС

при одновременном снижении объема производства и, следо-

следовательно, увеличению стоимости. По мере дальнейшего уве-

увеличения степени интеграции усиливалось противоречие

между универсальностью применения БИС и степенью их

интеграции. На ранних этапах развития микроэлектроники

казалось, что любую РЭА можно разделить на блоки,

соответствующие по сложности достигнутой в это время сте-

степени интеграции, изготовить эти части в виде ИС (СИС),

смонтировать их на платы, и это обеспечит лучшие техни-

технико-экономические показатели РЭА. Однако здесь и возник-

возникли серьезные трудности. Декомпозиция РЭА на блоки, при-

пригодные для интегрального исполнения, становилась все бо-

более затруднительной, росла номенклатура ИС (СИС) и

появились проблемы, связанные с ограничением числа вы-

выводов. Интегральные схемы стали терять универсальность.

Выходом из этой сложной ситуации явилось создание на од-

одном кристалле микропроцессора (МП), который представля-

представляет универсальную БИС, настраиваемую на решение различ-

различных задач путем программирования, подобно тому как это

1.1. Классификация интегральных схем 15

делается при решении различных задач на обычных ЭВМ.

Более того, МП позволили создать новый класс электронных

вычислительных машин — микроЭВМ, в том числе конст-

конструктивно на одном кристалле в виде БИС. Но и при таком

подходе не были решены все проблемы. Осталась необходи-

необходимость в многочисленных БИС частного применения (так на-

называемые ASIC — специализированные интегральные схе-

схемы), предназначенных для преобразования информации в

ограниченном классе РЭА. С точки зрения разработчика

РЭА ИС могут быть разделены на следующие виды: стан-

стандартные МИС, стандартные СИС, полузаказные БИС, за-

заказные БИС, СБИС и УБИС. Любой тип РЭА может быть со-

создан на перечисленных ИС. Очевидно, что на стандартных

ИС, выпускаемых массовыми сериями, РЭА будет наиболее

дешевой, а на СБИС и УБИС — будет обладать лучшими

техническими характеристиками. Конечно, реально в слож-

сложной РЭА используют почти все перечисленные ИС, что

вызвано стремлением решить компромиссно вопросы стои-

стоимости, надежности, быстродействия, массы, радиационной

стойкости РЭА и др. Наибольшим разнообразием конструк-

конструктивно-технологических решений обладают полузаказные

БИС. Полу заказные (матричные) БИС (МаБИС) в сответст-

вии с внутренней структурой делятся на четыре типа: 1) не-

скоммутированные логические матрицы (НЛМ), логические

матрицы (ЛМ); 2) матрицы стандартных ячеек (МСЯ);

3) программируемые логические матрицы (ПЛМ); 4) анало-

аналоговые матрицы (AM). Существуют матричные БИС и других

типов. Например, широко известны цифроаналоговые

(ЦАП) и аналого-цифровые (АЦП) преобразователи в интег-

интегральном исполнении. В этом случае на одном кристалле рас-

расположены цифровая и аналоговая матрицы. Нескоммутиро-

Нескоммутированная логическая матрица представляет регулярную

структуру из отдельных логических элементов или других

Компонентов, не соединенных между собой. Технологиче-

Технологический процесс изготовления таких НЛМ заканчивается перед»

Последней операцией — выполнением межсоединений. Эта

операция проводится после определения топологии послед-

последнего слоя металлизации, которая реализует определенную

системную функцию (суммирование, контроль и т. д). Преи-

Преимуществом таких матриц является большая степень интег-

16

Глава 1. Методология проектирования интегральных схем

рации. Структура ячеек зависит от используемой базовой

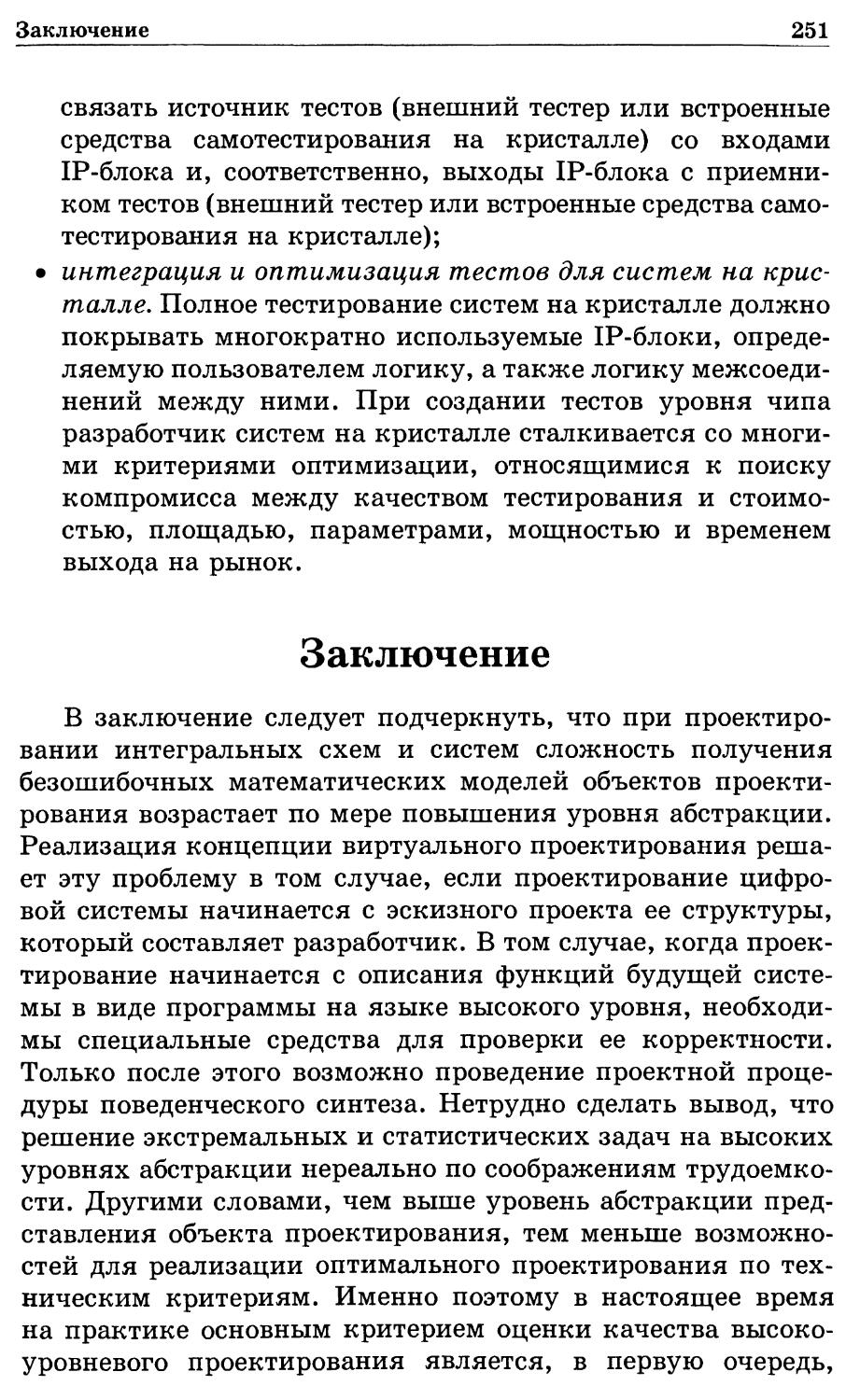

технологии. В качестве примера на рис. 1.1 представлена

последовательность получения двухвходового логического

элемента И-НЕ, реализованного на основе КМДП-техноло-

гии, что характерно для матриц рядной структуры.

р-каналы

-ЕЬ

?

?

?

?

Граница ячейки

?

?

?

?

-в-

-в-

43-

и

и

?

Шина

питания

(металл)

^ Диффузионные области

?

?

D

?

.«Земляная»

шина

Поликремний

а

D

?

?

?

—

?

I

lllllill

?

?

-а-

-S-

?

П

в

43-

¦в--

—Щ

1

I

¦

1

—I

—

—

?

?

?

?

Bxl

Вх2

Вых

Рис. 1.1. Последовательность получения двухходового логического

элемента (ЛЭ) И-НЕ: а — нанесение шин питания и земли с помощью

металлизации; б—проведение с помощью металлизации

межкомпонентных соединений; в — принципиальная схема

логического элемента И-НЕ

1.1. Классификация интегральных схем

17

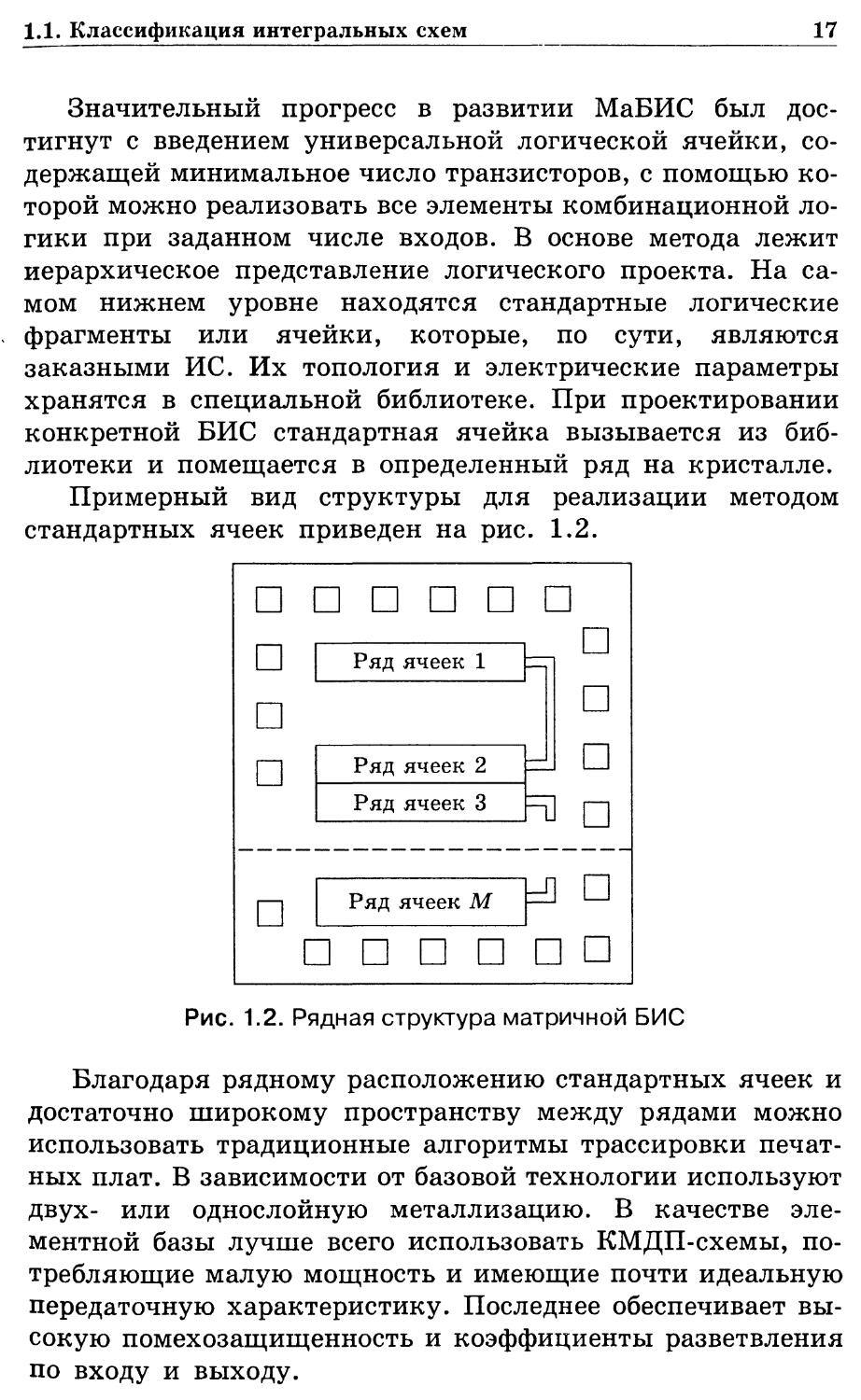

Значительный прогресс в развитии МаБИС был дос-

достигнут с введением универсальной логической ячейки, со-

содержащей минимальное число транзисторов, с помощью ко-

которой можно реализовать все элементы комбинационной ло-

логики при заданном числе входов. В основе метода лежит

иерархическое представление логического проекта. На са-

самом нижнем уровне находятся стандартные логические

фрагменты или ячейки, которые, по сути, являются

заказными ИС. Их топология и электрические параметры

хранятся в специальной библиотеке. При проектировании

конкретной БИС стандартная ячейка вызывается из биб-

библиотеки и помещается в определенный ряд на кристалле.

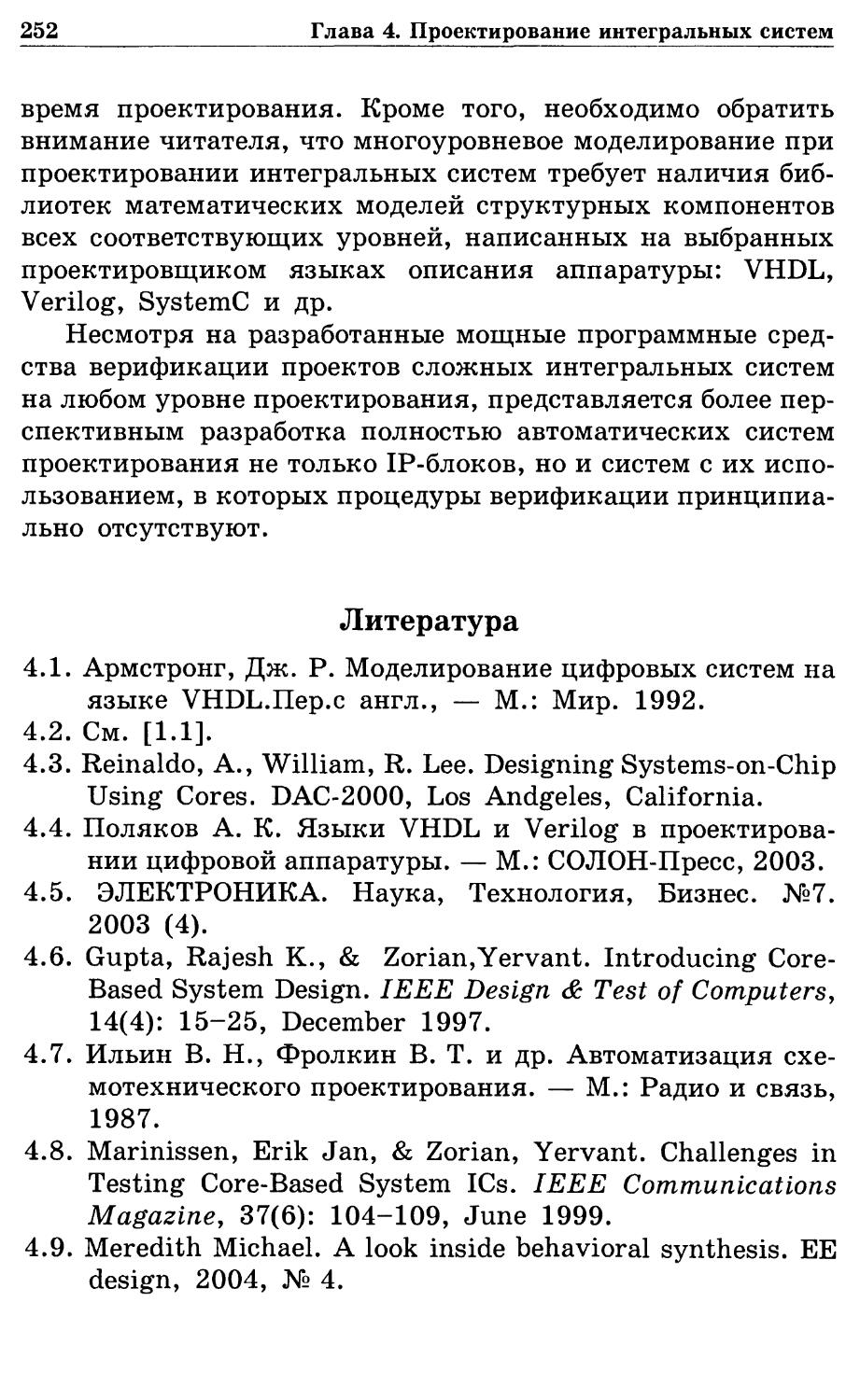

Примерный вид структуры для реализации методом

стандартных ячеек приведен на рис. 1.2.

?

?

?

?

?

Ряд ячеек 1 ~

Ряд ячеек 2

Ряд ячеек 3

Ряд ячеек М

? ? ? ?

?

?

?

?

?

Рис. 1.2. Рядная структура матричной БИС

Благодаря рядному расположению стандартных ячеек и

достаточно широкому пространству между рядами можно

использовать традиционные алгоритмы трассировки печат-

печатных плат. В зависимости от базовой технологии используют

двух- или однослойную металлизацию. В качестве эле-

элементной базы лучше всего использовать КМДП-схемы, по-

потребляющие малую мощность и имеющие почти идеальную

передаточную характеристику. Последнее обеспечивает вы-

высокую помехозащищенность и коэффициенты разветвления

по входу и выходу.

18

Глава 1. Методология проектирования интегральных схем

Библиотека стандартных ячеек может содержать сотни

видов ячеек. Процедура проектирования БИС методом стан-

стандартных ячеек напоминает использование макроопределе-

макроопределений в языках программирования высокого уровня — при

вызове макроопределения в программу вводится группа реа-

реализующих данное макроопределение инструкций. В боль-

большинстве случаев высота стандартных ячеек фиксирована, а

ширина в зависимости от сложности реализуемой логиче-

логической функции может варьироваться.

Главным преимуществом метода является высокая сте-

степень автоматизации проектирования и принципиальная воз-

возможность автоматического проектирования.

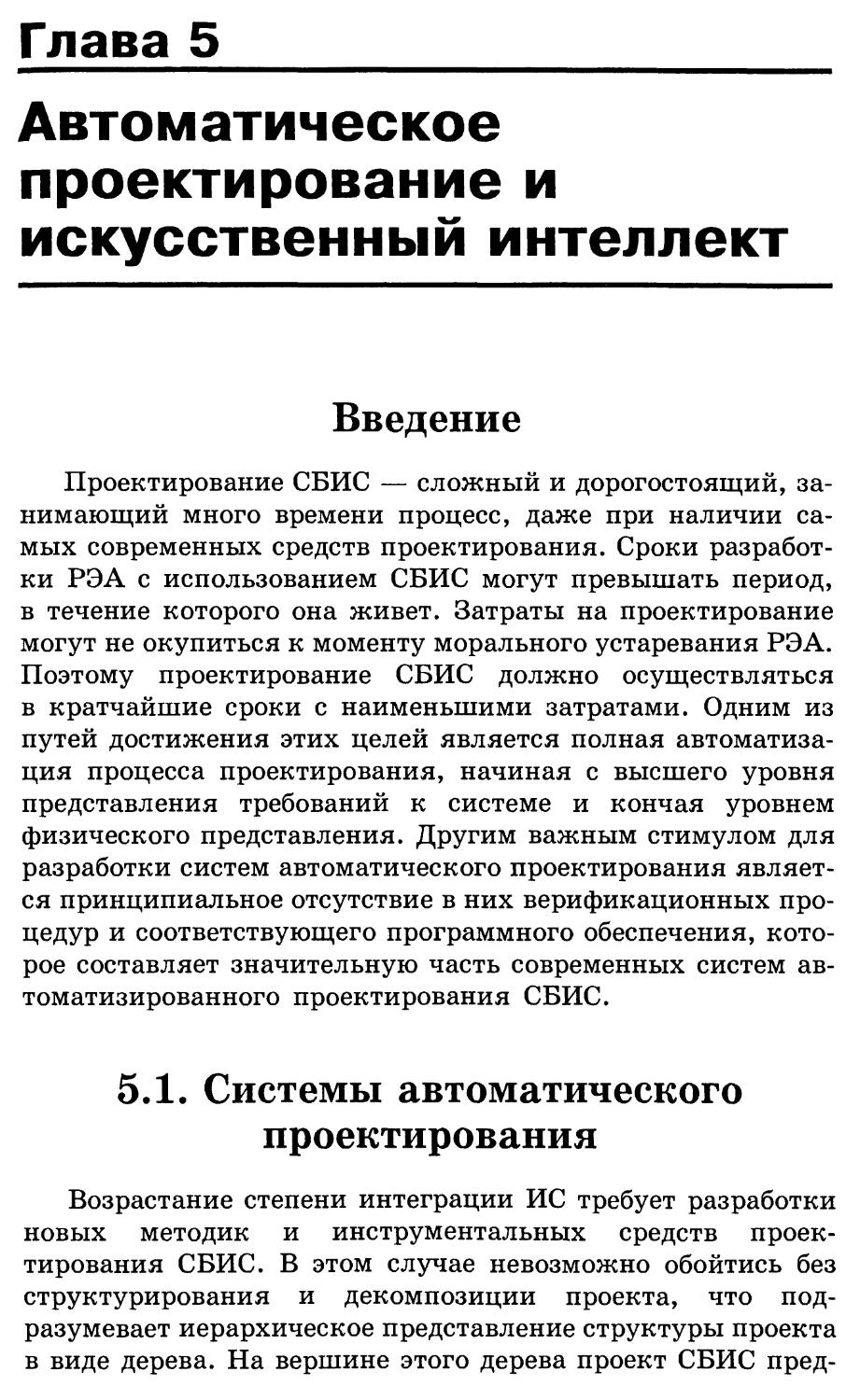

? Вх. 1 ? Вх. N

Термы

1

Матрица И

М-1

М

Матрица ИЛИ

i ••¦ i

Вых. 1 Вых. N

Рис. 1.3. Структура ПЛМ

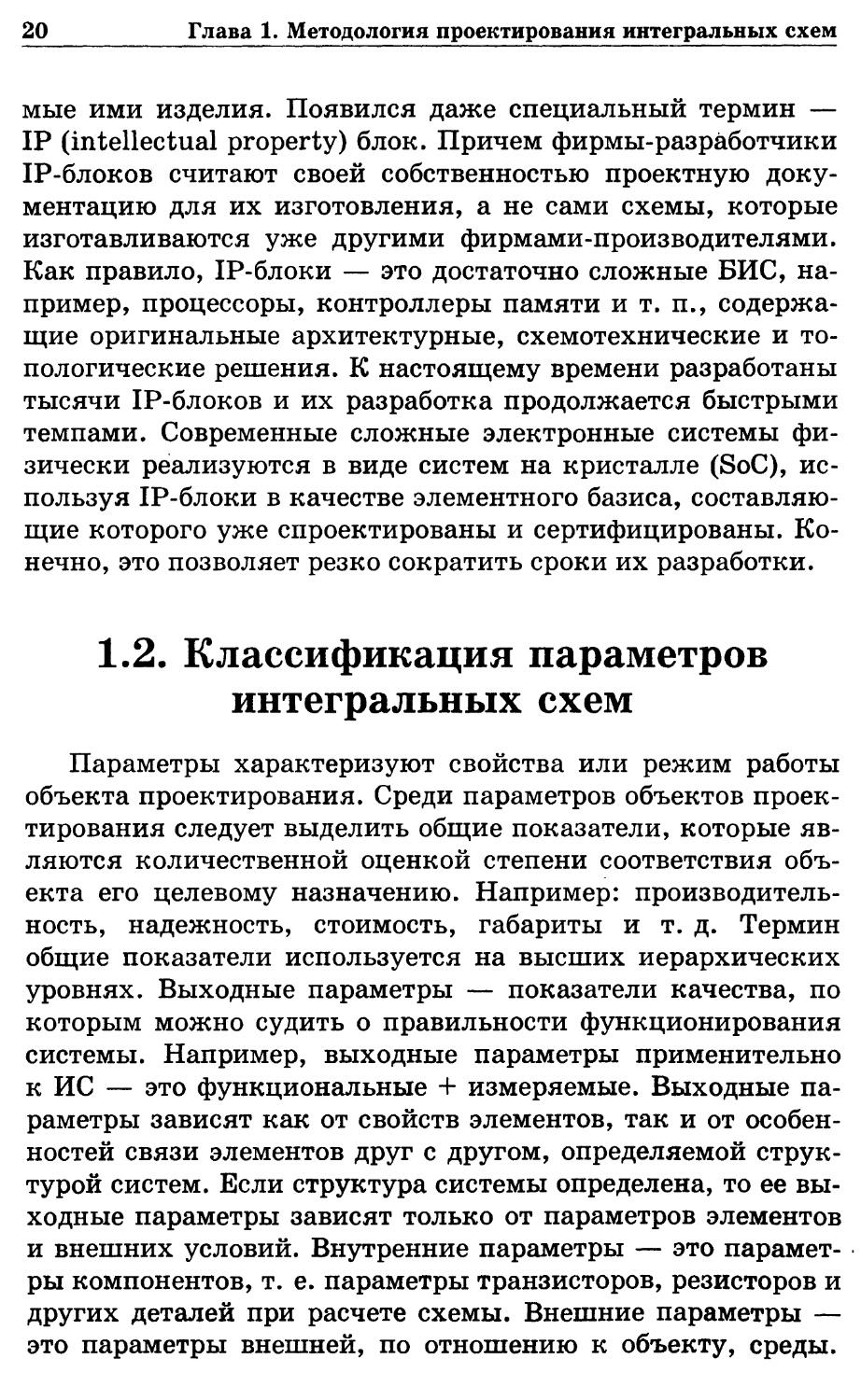

Программируемые логические матрицы (рис. 1.3) отно-

относятся к однородным регулярным структурам, реализующим

комбинационную логику в виде дизъюнктивных нормаль-

нормальных форм и последовательностную логику в виде конечных

автоматов с внешними обратными связями. Реализация

ПЛМ происходит путем нанесения металлизации в специа-

специально выделенные каналы или удаления лишних соедине-

соединений. Известно несколько модификаций ПЛМ:

• программируемое постоянное ЗУ (ППЗУ), где матрица И

программируется заранее, а матрица ИЛИ программирует-

программируется под конкретное устройство пользователем;

1.1. Классификация интегральных схем 19

• локально программируемые логические матрицы

(ЛПЛМ), где матрицы И и ИЛИ программируются под

конкретное устройство пользователем;

• программируемая матричная логика (ПМЛ), где матрица

И программируется под конкретное устройство пользова-

пользователем, а матрица ИЛИ программируется заранее;

• запоминающие логические матрицы (ЗЛМ), содержащие

в любом требуемом месте кристалла элементы памяти.

Их особенно удобно применять при структурном про-

проектировании.

Аналоговые матрицы предназначены в основном для ре-

реализации аналоговых схем, обрабатывающих непрерывные

сигналы. До недавнего времени такие матрицы строились на

основе биполярных транзисторов. В настоящее время наря-

наряду с ними используются полевые и МДП-транзисторы. В ка-

качестве стандартных элементов используют операционные

усилители, генераторы и компараторы.

Несмотря на большое разнообразие способов органи-

организации БИС, их конструируют в соответствии с обобщенной

структурной схемой (рис. 1.4).

Входные

элементы

>

>

Блок обработки

информации

>

•

>

Выходные

элементы

Рис. 1.4. Обобщенная структурная схема БИС

Любая БИС содержит три блока. Первый обеспечивает

согласование логических уровней сигналов и выполняет не-

некоторые простые логические функции. Второй содержит

комбинационные и последовательностные логические эле-

элементы для обработки информации. Третий содержит эле-

элементы, обеспечивающие работу на линии связи, и трансля-

трансляторы уровней для согласования внутренних малосигналь-

малосигнальных элементов со стандартными сериями ИС (ЭСЛ, ТТЛ,

КМДП).

В последние годы большое внимание в обществе привле-

привлечено к проблеме прав на интеллектуальную собственность.

Это коснулось и БИС. Многие производители БИС и СБИС

стали претендовать на исключительные права на выпускав-

20 Глава 1. Методология проектирования интегральных схем

мые ими изделия. Появился даже специальный термин —

IP (intellectual property) блок. Причем фирмы-разработчики

IP-блоков считают своей собственностью проектную доку-

документацию для их изготовления, а не сами схемы, которые

изготавливаются уже другими фирмами-производителями.

Как правило, IP-блоки — это достаточно сложные БИС, на-

например, процессоры, контроллеры памяти и т. п., содержа-

содержащие оригинальные архитектурные, схемотехнические и то-

топологические решения. К настоящему времени разработаны

тысячи IP-блоков и их разработка продолжается быстрыми

темпами. Современные сложные электронные системы фи-

физически реализуются в виде систем на кристалле (SoC), ис-

используя IP-блоки в качестве элементного базиса, составляю-

составляющие которого уже спроектированы и сертифицированы. Ко-

Конечно, это позволяет резко сократить сроки их разработки.

1.2. Классификация параметров

интегральных схем

Параметры характеризуют свойства или режим работы

объекта проектирования. Среди параметров объектов проек-

проектирования следует выделить общие показатели, которые яв-

являются количественной оценкой степени соответствия объ-

объекта его целевому назначению. Например: производитель-

производительность, надежность, стоимость, габариты и т. д. Термин

общие показатели используется на высших иерархических

уровнях. Выходные параметры — показатели качества, по

которым можно судить о правильности функционирования

системы. Например, выходные параметры применительно

к ИС — это функциональные + измеряемые. Выходные па-

параметры зависят как от свойств элементов, так и от особен-

особенностей связи элементов друг с другом, определяемой струк-

структурой систем. Если структура системы определена, то ее вы-

выходные параметры зависят только от параметров элементов

и внешних условий. Внутренние параметры — это парамет-

параметры компонентов, т. е. параметры транзисторов, резисторов и

других деталей при расчете схемы. Внешние параметры —

это параметры внешней, по отношению к объекту, среды.

1.2. Классификация параметров интегральных схем 21

Введем обозначения:

У — вектор выходных параметров некоторой системы,

X — вектор внутренних параметров и

Q — вектор внешних параметров. Тогда

Y = F(X),

где конкретный вид функциональной зависимости опреде-

определяется структурой системы. Часто связь между выходными,

внутренними и внешними параметрами известна не в виде

явной зависимости Y от X, а задается в алгоритмической

форме. Например, через численное решение систем уравне-

уравнений.

Проблемы контроля линейных и логических ИС сущест-

существенно отличаются. Для определенности, в дальнейшем бу-

будем рассматривать ИС, предназначенные для цифровой вы-

вычислительной техники. Цифровые ИС характеризуются

функциональными и измеряемыми параметрами. Функцио-

Функциональные параметры количественно оценивают логическую

функцию цифровой ИС и их выбор производится в процессе

синтеза логической структуры цифрового вычислительного

устройства. Поэтому сравнивать различные типы цифровых

ИС удобно именно по функциональным параметрам. Так

как процесс измерений ИС сводится к измерениям токов и

напряжений на внешних выводах схемы, функциональные

параметры должны выражаться через измеряемые. Цифро-

Цифровые ИС характеризуются следующими основными функцио-

функциональными параметрами: N — коэффициент разветвления по

выходу; Uu — помехоустойчивость, Р — мощность, потреб-

потребляемая схемой от источников питания в статическом режи-

режиме, tjcp — средняя задержка распространения сигнала. Рас-

Рассмотрим системы функциональных статических и измеряе-

измеряемых параметров, а также связывающие их соотношения.

К измеряемым параметрам цифровых ИС относятся:

• ^Овх — входной ток для состояния логического нуля на

входе;

• JlBX — входной ток для состояния логической единицы

на входе;

— выходной ток для состояния логического нуля;

22 Глава 1. Методология проектирования интегральных схем

• ^1вых — выходной ток для состояния логической едини-

единицы;

• ^Овых — выходное напряжение для состояния логическо-

логического нуля;

• ^1вых — выходное напряжение для состояния логической

единицы;

• t/0nop — пороговое напряжение для состояния логическо-

логического нуля;

• Ulnop — пороговое напряжение для состояния логической

единицы;

• ^Омакс — максимально допустимое напряжение в состоя-

состоянии логического нуля;

• ^1мин — минимально допустимое напряжение в состоя-

состоянии логической единицы;

• Jo — ток, потребляемый схемой в состоянии логического

нуля от источников питания;

• Jl — ток, потребляемый схемой в состоянии логической

единицы от источников питания.

Измеряемые и основные функциональные параметры

связаны следующими соотношениями:

а т _ ВЫХ МИН

где с/вых — измеряемый выходной ток цифровой ИС;

с/вх макс — максимально допустимый входной ток цифро-

цифровой ИС;

ТТ® — TJ —ТТ

и и ~ и Опор и Омакс >

где п — число источников питания.

При контроле измеряемых параметров на выводах ИС

устанавливаются величины токов и напряжений, соответ-

соответствующие граничным значениям измеряемых параметров.

Основная задача, которая возникает при контроле цифро-

цифровых ИС, сводится к следующему: необходимо установить

1.3. Принципы проектирования 23

нормы для измеряемых параметров и их граничных значе-

значений, обеспечивающие максимальный процент выхода год-

годных ИС по функциональным параметрам. Эти данные слу-

служат основой для составления технических условий.

Сформулированная задача может решаться в двух аспек-

аспектах: 1) когда характеристики и схемы получены теорети-

теоретически в результате статистического анализа и 2) когда ха-

характеристики и параметры схемы получены эксперимен-

экспериментально.

1.3. Принципы проектирования

Что же понимается под словом «проектирование»? Про-

Проектирование — это процесс преобразования информации,

находящейся в спецификации (техническом задании) на

разрабатываемое изделие, в информацию, необходимую

для его изготовления и контроля на технологическом и

контрольно-измерительном оборудовании.

При проектировании БИС используется прежде всего

принцип декомпозиции — разбиение сложной задачи на бо-

более простые, доступные для понимания проектировщиком.

Разбиение может быть проведено по количественным призна-

признакам (например, по числу компонентов на кристалле ИС) или

по детальности рассмотрения параметров проектируемого

объекта (например, макромоделирование ЛЭ, функциональ-

функциональных узлов, регистров и т. д.). Математически применение

принципа декомпозиции позволяет свести одну задачу боль-

большой размерности (по числу уравнений в системе, числу пере-

переменных и т. д.) к нескольким задачам меньшей размерности

(благодаря чему решить задачу можно имеющимися техниче-

техническими средствами и в разумные сроки). Разбиение по степени

детальности рассмотрения позволяет проектировщику при

разработке, например, ЛЭ оперировать десятками транзисто-

транзисторов и других элементов, при разработке блоков БИС — десят-

десятками ЛЭ, при разработке устройств — десятками блоков, при

разработке СБИС — десятками устройств и т. д.

Декомпозиция проектируемого объекта приводит к

иерархическому принципу проектирования по этапам. Чем

сложнее проектируемый объект, тем больше уровней иерар-

24 Глава 1. Методология проектирования интегральных схем

хии. Например, при проектировании транзистора (или дру-

другого компонента) имеется один уровень — компонентный,

когда выходные параметры транзистора рассчитывают по

его внутренним параметрам с учетом внешних факторов.

Проверку правильности проектных решений, их соот-

соответствие требуемым параметрам необходимо обеспечить еще

на стадии проектирования. Последовательное приближение

к выполнению заданных требований по результатам модели-

моделирования и оптимизации на каждом этапе проектирования

БИС составляет суть итерационного принципа проектирова-

проектирования. Итерации могут выполняться как внутри одного этапа

проектирования, так и между группами этапов.

Унификация задач и составляющих частей объектов про-

проектирования позволяет упростить сам процесс и представить

объекты в базе данных более компактно. Объекты должны

быть максимально унифицированы (иметь минимально воз-

возможную номенклатуру). Основная цель унификации — ми-

минимизация числа вновь разрабатываемых БИС.

Контролируемость каждого этапа проектирования —

важный принцип проектирования. Контроль может быть со-

совмещен с процессом проектирования или выделен из него.

Первый вариант имеет место, например, при размещении

элементов и трассировке внутрисхемных соединений на

кристалле ИС или печатной плате с соблюдением заданных

норм и параметров, а второй — при автоматической провер-

проверке проектных норм и параметров, полученных на любом эта-

этапе проектирования ручным, автоматизированным или авто-

автоматическим методом. Контроль правильности выполнения

проектных работ на различных этапах проектирования БИС

называют верификацией (см. гл. 3).

Результатом работы по проектированию БИС должен

быть выпуск проектной документации, включающей:

1) текстовые и текстово-графические документы — описа-

описание алгоритма функционирования на входном языке,

функционально-логическая схема, временные диаграммы,

принципиальные электрические схемы функциональных бло-

блоков БИС, электрические характеристики функциональных

блоков и компонентов, таблицы параметров компонентов;

2) графические документы — послойные и совмещенные

чертежи топологии функциональных блоков БИС;

1.4. Методы проектирования 25

3) документы на машинных носителях — контролиру-

контролирующие тесты для установок функционального контроля, ин-

информация на машинных носителях для программно-управ-

программно-управляемого технологического оборудования БИС (для изготов-

изготовления фотошаблонов или непосредственно БИС)

1.4. Методы проектирования

Разнообразие конструктивно-технологических методов

создания БИС обусловлено стремлением не только улуч-

улучшить их технико-экономические показатели, но и достичь

общих целей: минимизировать длительность процесса про-

проектирования, обеспечить проектирование БИС высокой

сложности, повысить качество проектирования БИС (глав-

(главным образом, безошибочность).

Длительность процесса проектирования значительно со-

сокращается при использовании средств вычислительной тех-

техники, библиотек компонентов, характеризующих базовый

технологический процесс, стандартизации программ и т. д.

А это, в свою очередь, сокращает сроки проектирования и

производства РЭА.

Классификация методов проектирования. Методы про-

проектирования классифицируются: 1) по способам организации

выполнения проектных процедур на экспериментальные (ма-

(макетирование, физическое моделирование) и теоретические

(расчет по аналитическим выражениям, математическое мо-

моделирование); 2) по степени автоматизации выполнения про-

проектных процедур (автоматизированные и автоматические).

Рассмотрим наиболее распространенные методы в порядке их

появления в практике проектирования.

Макетирование. Исходя из требований ТЗ на разраба-

разрабатываемую БИС выбираются два-три технологических про-

процесса, при которых предположительно могут быть удовлет-

удовлетворены требования ТЗ по функциональным параметрам ИС

(БИС). Затем для получения образцов активных компонен-

компонентов и базовых логических элементов разрабатывается специ-

специальная тестовая топологическая схема, в которую должны

входить активные компоненты и базовые аналоговые и ло-

логические элементы. Обычно такая схема включает специа-

26 Глава 1. Методология проектирования интегральных схем

льные тестовые компоненты для контроля параметров физи-

физической структуры и ошибок изготовления. С помощью тес-

тестовой схемы решаются следующие задачи: выбор

нескольких типов геометрических конфигураций активных

компонентов и ЛЭ, которые предположительно должны

удовлетворять схемотехническим требованиям; накопление

статистических данных по параметрам активных компонен-

компонентов, анализ АЭ и ЛЭ в различных режимах работы; исследо-

исследование характера и определение параметров паразитных свя-

связей между компонентами ИС; контроль процессов изготов-

изготовления фотошаблонов и фотолитографии и определение

минимально допустимых размеров топологических элемен-

элементов и запасов на совмещение, необходимых при решении то-

топологических задач; выявление систематических ошибок

процессов изготовления фотошаблонов и фотолитографии

для учета их при разработке топологических схем.

При разработке тестовой схемы необходимо учитывать

возможность выбора того или иного технологического мето-

метода изготовления БИС. Если ни по одной из имеющихся тех-

технологий невозможно спроектировать данную БИС, удовлет-

удовлетворяющую требованиям ТЗ, которые определяются на этапе

синтеза и анализа принципиальной электрической схемы,

то необходимо сформулировать требования к вновь разраба-

разрабатываемому технологическому процессу. При этом на основа-

основании справочных данных и имеющегося опыта определяются

наиболее перспективные для разрабатываемой схемы физи-

физико-топологические параметры ИС (геометрия активных и

пассивных компонентов, диффузионный профиль).

На полученных образцах активных компонентов соби-

собирается макет БИС, который затем исследуется методами,

традиционными для обычной схемотехники на дискретных

компонентах.

Основные недостатки макетирования: высокая стоимость

и значительное время проектирования. Основное достоинст-

достоинство — относительная достоверность результатов.

Физическое моделирование заключается в изучении

объектов одной физической природы с помощью объектов,

имеющих другую физическую природу, но одинаковое с

ними математическое описание. В основе метода лежит

принцип подобия (аналогий). Наиболее известным приме-

1.4. Методы проектирования 27

ром является применение электролитических ванн при мо-

моделировании поля потенциалов в транзисторной структуре.

Расчет по аналитическим выражениям. Для получе-

получения формул, связывающих выходные параметры ИС (фун-

(функциональные и измеряемые) с внутренними (параметрами

компонентов), делаются значительные упрощения (на-

(например, экспоненциальные вольт-амперные зависимости

считаются линейными).

По сложности расчеты по аналитическим выражениям

ориентированы на вычислительную мощность имеющихся.

в распоряжении каждого разработчика средств — «челове-

«человеческий мозг», логарифмическая линейка, микрокаль-

микрокалькулятор, программируемый микрокалькулятор, персональ-

персональная ЭВМ и т. д. Основные недостатки данного метода проек-

проектирования БИС — высокая трудоемкость вывода формул и,

как правило, низкая точность расчетов. Основное достоинст-

достоинство — доступность.

Математическое моделирование. Наиболее существен-

существенное отличие этого метода в том, что математические модели

БИС получают без или при минимальных упрощениях,

и они более адекватно описывают процессы, происходящие

в реальных устройствах. Кроме того, при математическом

моделировании (и только при нем) можно математически

«точно» решать экстремальные и статистические задачи,

определяющие качество проектирования.

По степени автоматизации выполнения проектных про-

процедур методы проектирования делятся на автоматизиро-

автоматизированные и автоматические. Конечно, это деление условно,

так как с развитием средств вычислительной техники,

а также в связи с успехами вычислительной математики и

программирования, роль автоматического проектирования

постоянно возрастает. В литературе понятие «авто-

«автоматическая система проектирования» часто отождествляют

с понятием «кремниевый компилятор», хотя это и неверно.

Кремниевый компилятор (см. гл. 5) действительно является

автоматической системой проектирования БИС, в которой

для описания функционирования используют ПЗУ, ПЛМ,

ОЗУ, АЛУ, ЗУ с произвольной выборкой и другие типовые

блоки. С помощью экспертных систем компилятор может

синтезировать БИС в соответствии с заложенными в него

28 Глава 1. Методология проектирования интегральных схем

правилами. Для описания схемы используют языки высоко-

высокого уровня (VHDL, Verilog и др.).

Описывать проектируемую БИС можно на различных

уровнях: поведенческом (архитектурном), структурном и др.

Создание автоматических систем проектирования требует

решения ряда сложных проблем: структурного синтеза на

всех этапах проектирования БИС, экстракции (восстановле-

(восстановления принципиальной электрической схемы по известной то-

топологии), межэтапной верификации и организации взаимо-

взаимосвязанного контроля на всех этапах проектирования, орга-

организации поддержания и совершенствования базы знаний,

обеспечение возможности моделирования разрабатываемой

БИС совместно с другими функциональными узлами в со-

составе сложной технической системы (вычислительной, ра-

радиолокационной, радионавигационной и т. д.).

Важной проблемой, которую удалось решить с помощью

автоматических систем, является относительно простой пе-

переход при проектировании БИС от одних конструктивно-

технологических ограничений к другим.

Особенности проектирования ИС. Как правило, прин-

принципиальная электрическая схема ИС содержит, помимо

функционально необходимых, большое число паразитных

компонентов, образующихся при одновременном групповом

изготовлении по планарно-эпитаксиальной технологии.

Процесс изготовления ИС приводит к необходимости учи-

учитывать в процессе проектирования следующие особенности:

параметры компонентов и допуски на них, возникающие за

счет технологических разбросов, являются взаимосвязанны-

взаимосвязанными; в схемах с изоляцией /?-д-переходами образуются пара-

паразитные четырехслойные п-р-п-р-структуры, которые могут

нарушить работу схемы; трудно изготовить большие емкости

и индуктивности; для сокращения площади, занимаемой схе-

схемой, необходимо, чтобы была минимальной сумма номиналь-

номинальных сопротивлений и емкостей схемы и т. д.

Различия в стоимости, надежности, габаритах дискрет-

дискретных компонентов наложили отпечаток и на схемотехнику.

Например, в схемах на дискретных компонентах более широ-

широко используют пассивные компоненты по сравнению с актив-

активными, что объясняется их лучшими технико-экономи-

технико-экономическими показателями. В ИС для достижения тех же показа-

1.4. Методы проектирования 29

телей чаще используют большое число активных

компонентов. В этом смысле интегральная технология от-

открывает новые потенциальные возможности в схемотехнике.

Следующая особенность создания ИС связана с оценкой

их работоспособности. Практически невозможно контроли-

контролировать характеристики ИС путем измерения параметров со-

составляющих ее элементов. Отсюда возникла так называемая

проблема тестируемости ИС. Методы обеспечения тестируе-

тестируемости в процессе проектирования ИС условно делят на кон-

конструктивные и структурно-логические. Среди конструктив-

конструктивных методов выделяют методы шинной архитектуры, сигна-

сигнатурного анализа и контрольных точек. Метод шинной

архитектуры заключается в обеспечении доступа к любому

узлу ИС путем перевода входных шин всех других узлов, за

исключением анализируемого, в высокоимпедансное состоя-

состояние. Сигнатурный анализ осуществляется с помощью сдви-

сдвигового регистра с линейной обратной связью, подключаемо-

подключаемого к выбранному контакту. В этом регистре запускается тес-

тестовая программа, в результате получается число-сигнатура,

отражающее информацию об исправности схемы. Для лока-

локализации неисправного узла следует разрывать межузловые

цепи обратной связи, соблюдая такую последовательность

тестирования: сначала основные функциональные узлы, за-

затем периферийные. Суть тестирования методом контроль-

контрольных точек очевидна. Отметим, что в качестве этих точек

можно использовать как свободные внешние контакты,

так и специальные контрольные точки на кристалле.

Структурно-логические методы (поуровневого сканиро-

сканирования и контрольных сдвиговых регистров) используют для

разработки такой логической структуры схемы, при кото-

которой можно задавать и считывать состояния всех элементов

схемы. Это принципиально позволяет свести задачу тестиро-

тестирования последовательностных схем к тестированию комбина-

комбинационных схем, которое достаточно хорошо изучено.

Метод поуровневого сканирования состоит в том, что

элементы памяти схемы в режиме тестирования соединяют-

соединяются в один сдвиговый регистр, что позволяет задавать и счи-

считывать состояние этих элементов. Объединение в единый

сдвиговый регистр элементов памяти на кристалле и созда-

создание цепей сдвиговых регистров с переходом на более высо-

30 Глава 1. Методология проектирования интегральных схем

кий системный уровень позволяют получать тесты для всех

уровней системы. Общесистемные тесты формируются пу-

путем объединения тестов подсистем. Существуют модифика-

модификации этого метода: сканирование с произвольной выборкой,

избирательное сканирование и др.

В другом методе этой группы предполагается введение

контрольных сдвиговых регистров, используемых для тес-

тестирования и занесения заданной информации в ячейки па-

памяти БИС.

Существует также комбинированный метод, реализован-

реализованный с помощью встроенных (аппаратных) средств контроля.

В нем по существу соединены методы сигнатурного анализа

и поуровневого сканирования. Основная идея заключается в

создании набора элементов памяти изменяемой конфигура-

конфигурации (в одном режиме они работают как обычные сдвиговые

регистры, в другом — как многовходовые сдвиговые регист-

регистры с обратной связью), что приводит к существенному со-

сокращению тестов. Применение структурно-логического под-

подхода для обеспечения тестируемости БИС на стадии проек-

проектирования является наиболее перспективным.

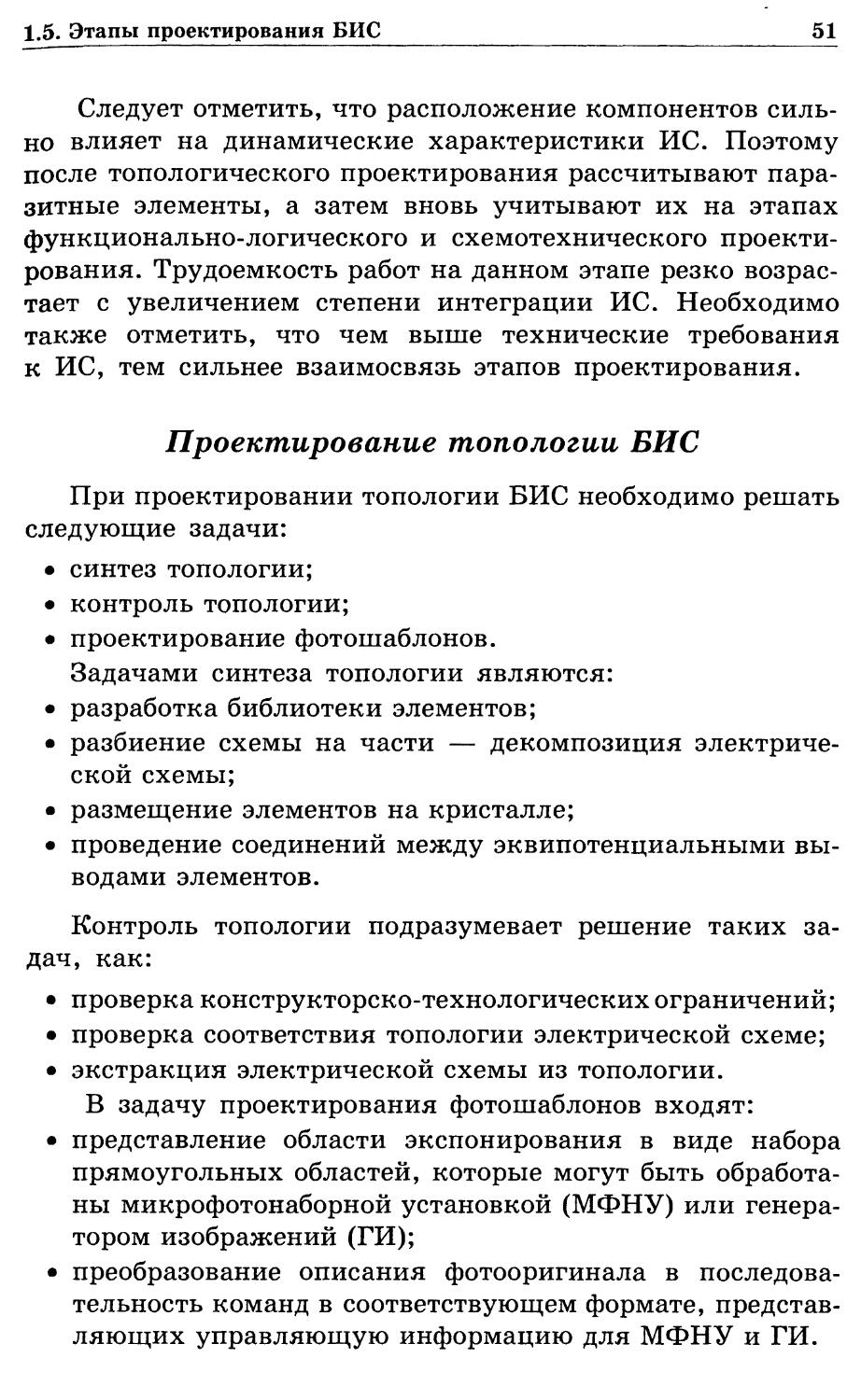

1.5. Этапы проектирования БИС

При проектировании сложных технических систем (СТС)

(в т. ч. БИС и других изделий микроэлектроники) использу-

используется блочно-иерархический подход. При блочно-иерархиче-

ском подходе процесс проектирования разделяется на уров-

уровни (этапы). На высшем уровне используется наименее дета-

детализированное представление, отражающее только самые

общие черты проектируемой системы. На каждом низшем

последовательном уровне проектирования степень подробно-

подробности рассмотрения возрастает, при этом система рассматрива-

рассматривается не в целом, а отдельными блоками, как правило, функ-

функционально законченными. Такой подход позволяет на каж-

каждом этапе формулировать и решать задачи приемлемой

сложности, поддающиеся пониманию одним человеком.

Основное достоинство блочно-иерархического подхода

состоит в том, что сложная задача большой размерности

разбивается на последовательно решаемые задачи меньшей

1.5. Этапы проектирования БИС 31

размерности. При блочно-иерархическом подходе на каж-

каждом уровне абстракции имеются свои представления о сис-

системе и элементах. То, что на одном уровне называлось эле-

элементом, становится системой на следующем уровне. При

проектировании сложных систем используются так

называемые нисходящее или восходящее проектирование

или их комбинации. Суть нисходящего — от общих требо-

требований к системе к технологическому процессу изготовле-

изготовления, а при восходящем — наоборот.

Проектирование современных СТС, в том числе и систем

на кристалле (SoC), включает следующие уровни (этапы):

• системный (процессор — память — коммутатор, ППК);

• микросхемный;

• регистровый;

• логический;

• схемотехнический;

• топологический;

• компонентный.

Целесообразно разделить их на следующие группы уров-

уровней (этапов) проектирования:

• 1 — компонентный, топологический, схемотехниче-

схемотехнический — сфера интересов только проектировщика ИС,

• 2 — микросхемный, системный — сфера интересов толь-

только разработчика аппаратуры,

• 3 — логический, регистровый, микросхемный — сфера

интересов обеих сторон.

В работе [4.1] введено понятие, связанное с указанной

иерархией, — это так называемое окно проекта. Этим тер-

термином обозначается группа уровней (этапов проекта), с ко-

которыми работает каждый конкретный проектировщик. В

данном разделе рассматриваются этапы, входящие в окно

проектировщика БИС.

1.5.1. Разработка спецификации

Разработка спецификации включает процедуры проекти-

проектирования алгоритма функционирования БИС и исходных тес-

тестовых последовательностей, моделирования алгоритма и по-

получения выходных последовательностей. Полученная спе-

32

Глава 1. Методология проектирования интегральных схем

цификация записывается в базу данных проекта и служит

основанием для проверки корректности последующих эта-

этапов проектирования. Кроме того, на этом этапе в базу дан-

данных проекта в формализованном виде вводятся требования

к конструкции БИС (размер кристалла, расположение выво-

выводов, конструкция корпуса), необходимые сведения о техно-

технологических процессах, требования на выходные электриче-

электрические параметры и т. д. Как правило, функциональный со-

состав БИС и технические требования определяются при

разработке РЭА. После этого разработчик РЭА готовит тех-

технические требования на серию, на основании которых раз-

разработчик БИС составляет техническое задание на их разра-

разработку с учетом технологических возможностей изготовления

и унификации серии БИС.

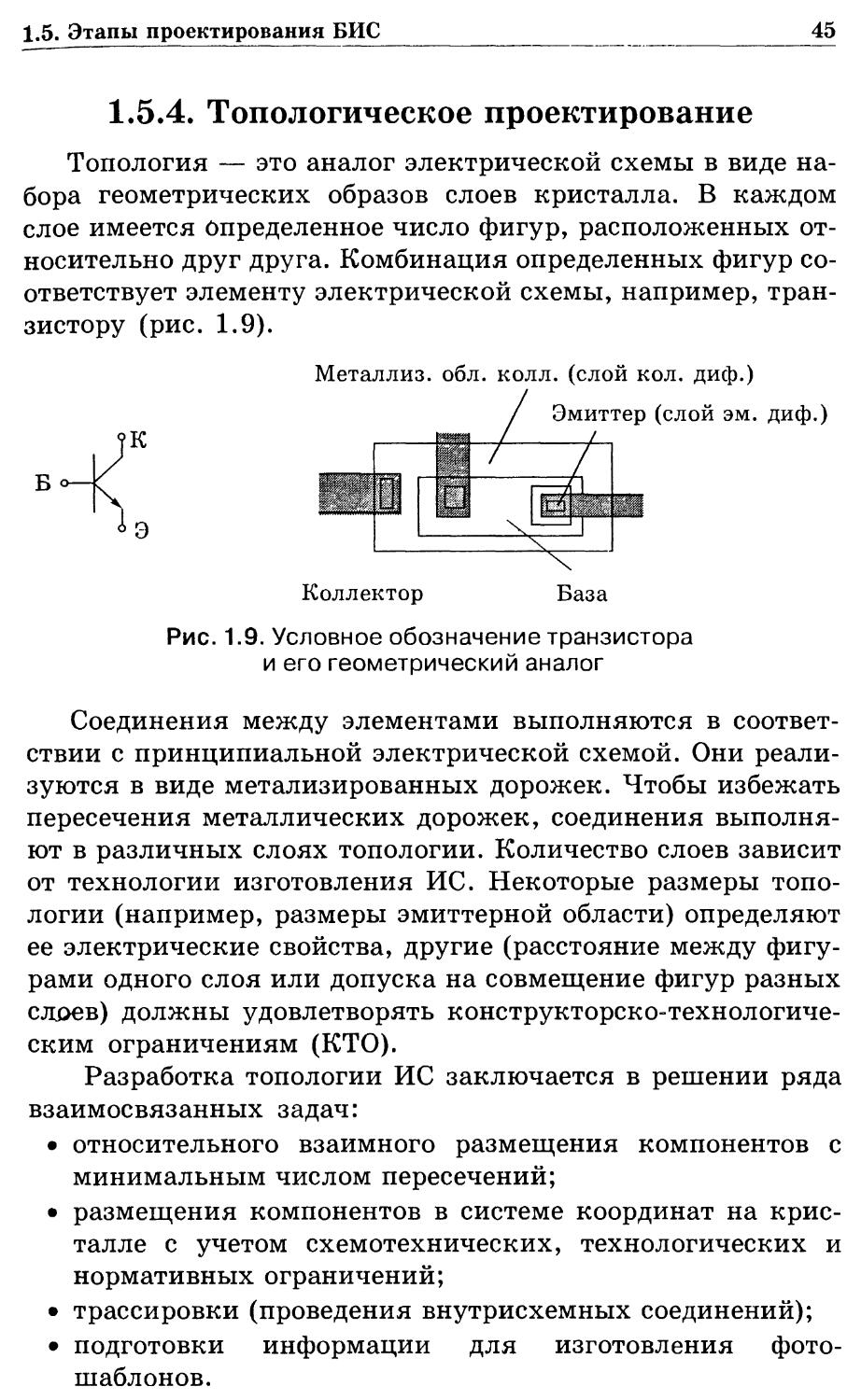

Технологические возможности изготовления БИС прак-

практически однозначно определяют сложность и предельные

технические характеристики схем, которые могут быть реа-

реализованы в виде БИС. На рис. 1.5 приведена кривая, харак-

характеризующая зависимость процента выхода годных БИС от

площади, занимаемой одной схемой. При уменьшении пло-

площади, занимаемой БИС, процент выхода годных мал из-за

ограниченной разрешающей способности технологического

оборудования, используемого для изготовления фотошабло-

фотошаблонов и процесса фотолитографии.

С другой стороны, с увеличением размеров БИС процент

выхода годных также падает из-за увеличения вероятности

появления дефектов в активных областях компонентов.

Рис. 1.5. Зависимость процента выхода годных БИС

от площади кристалла

1.5. Этапы проектирования БИС 33

1.5.2. Логическое проектирование

Процесс проектирования БИС, номенклатура которых

определяется при разработке конкретной РЭА, отличается

от проектирования МИС и СИС тем, что разработке принци-

принципиальной электрической и топологической схем предшест-

предшествует этап логического проектирования. Логическое проекти-

проектирование БИС заключается в составлении функциональных

схем БИС. Компонентами функциональной схемы являются

элементарные блоки, образующие логический базис проек-

проекта. Задачей логического синтеза, например, функционально-

функционального узла ЭВМ, является выбор базиса логических элементов

(ЛЭ) для построения различных БИС и соединение их между

собой так, чтобы осуществлялось заданное функциониро-

функционирование. На этапе логического проектирования необходимо

учитывать особенности выбранных ЛЭ и их технической ре-

реализации, т. е. учитывать схемотехнику, топологические и

технологические ограничения, а также решать следующие

взаимосвязанные задачи: логический синтез, логическое мо-

моделирование БИС на уровне ЛЭ, синтез контролирующих и

диагностических тестов. Синтез логических схем может

производиться как автоматически по структурной схеме

(или по описанию поведения схемы) в заданном логическом

базисе, так и вручную. В обоих случаях САПР поддержива-

поддерживает этот этап средствами логического моделирования. Логи-

Логическое моделирование на ЭВМ выявляет ошибки в схеме,

позволяет оценить правильность временных соотношений,

минимизировать число ЛЭ, оптимизировать перечень и со-

состав частей (блоков) системы. Проверка функционирования

логической схемы включает анализ логических функций,

реализуемых схемой, и временных соотношений (наличие

критических путей, рисков сбоя и состязаний сигналов).

Проверка реализуемых схемой логических функций выпол-

выполняется путем прогонки теста, т. е. моделирования работы

схемы при некотором наборе входных сигналов. При этом

нужно в заданные моменты времени сравнивать полученные

при моделировании значения выходных сигналов с парамет-

параметрами спецификации (ТЗ).

34 Глава 1. Методология проектирования интегральных схем

Аппарат логического моделирования работает со следую-

следующими объектами:

• с представлениями логических элементов;

• с межсоединениями этих элементов (списками цепей);

• с наборами булевых выражений и

• с описаниями временных характеристик элементов.

На уровне логического проектирования БИС и цифровой

аппаратуры с помощью аппарата моделирования решаются

следующие задачи:

1) Проверяется логическая структура БИС или цифровой

электронной аппаратуры до этапа его технологическо-

технологического воплощения.

2) Сравниваются характеристики различных вариантов

схемных решений.

3) Проверяется правильность и полнота процедур тесто-

тестового контроля БИС и цифровой аппаратуры.

4) Получается детальная информация о функционирова-

функционировании схемы с учетом временных характеристик элемен-

элементов логического базиса и межкомпонентных соедине-

соединений.

Общая схема процесса логического моделирования при-

приведена на рис. 1.6.

Процесс логического моделирования состоит из двух ша-

шагов: обработка логического описания устройства БИС и соб-

собственно моделирование. Входные данные, описывающие ло-

логику цифрового устройства, преобразуются и совмещаются

с заранее записанными данными с целью построения модели

логической схемы и при этом, как правило, происходит об-

обращение к справочному каталогу (библиотеке) заранее раз-

разработанных логических элементов. Формы входных сигна-

сигналов могут меняться в широких пределах, начиная от явно

заданных во времени значений и кончая сигнальными по-

последовательностями произвольно-сложной конфигурации.

В качестве входных данных поступают также сведения о на-

начальном логическом состоянии схемы и специальные усло-

условия (например, сведения о возможных неисправностях, не-

необходимые для описания реальных ситуаций). Описания ло-

логической схемы и условий моделирования могут быть

изменены независимо друг от друга, что позволяет исследо-

1.5. Этапы проектирования БИС

35

О

ев

?

?3

а

о

О

§

о

К

О

Входные данные:

логические элементы

и их соединения

Построение

модели

i

f Справочный Л

V каталог У

^-^-. -^

Модель

логической

схемы

Программное

моделирование

г

Выходные сигналы

Начальное состояние схемы

Специальные условия

Управление выводом

( Вывод

Рис. 1.6. Блок-схема моделирования БИС

вать различные варианты схем при одинаковых условиях

или, наоборот, одну схему при разных условиях. На печать

выводятся диаграммы, показывающие состояния выбран-

выбранных элементов в моделируемые моменты времени. Таким

образом, логическое моделирование включает:

• построение модели логической схемы;

• выполнение вычислений на модели для последовательно-

последовательности дискретно изменяющихся во времени двоичных вход-

входных сигналов.

Входной язык должен обеспечивать проектировщику

возможность полного и прямого описания логической схе-

схемы. Входные языки большинства систем логического моде-

моделирования используют описание элементов цифровой логи-

логики и их связей системой булевых уравнений. Обычно такое

описание строится на уровне логических элементов микро-

микросхем — интегральных триггеров, полусумматоров, регист-

регистров и т. д.

36 Глава 1. Методология проектирования интегральных схем

Объектами языка могут быть:

1) Основные типы логических элементов (и, или, и-не,

или-не), триггеры, инверторы, линии задержки и т. д.,

а также элементы с более сложными функциями,

представленными в виде «черного ящика».

2) Функциональное описание каждого элемента, выра-

выраженное явным или неявным образом.

3) Связи между этими элементами.

Модель цифрового устройства БИС формируется из сово-

совокупности предложений входного языка, либо компиляций

этих предложений из набора подпрограмм, каждая из кото-

которых выполняет функцию логического элемента, либо путем

трансляции входных предложений в структуру данных,

представляющих схему.

Особый интерес представляет моделирование схемы, за-

заданной в виде ЛЭ и регистровых передач. Такой подход по-

позволяет детально описывать на уровне ЛЭ некоторый фраг-

фрагмент БИС при задании большей части схемы лишь алгорит-

алгоритмом ее функционирования. Описание БИС на уровне

регистровых передач состоит из двух частей: структурного и

операционного описаний. В структурном описании выделя-

выделяются устройства типа регистр, счетчик и т. д.; в операцион-

операционном содержатся сведейия о действиях, выполняемых в

объекте проектирования.

Для моделирования цифровых устройств на уровне реги-

регистровых передач применяют специальные языки высокого

уровня. В большинстве программ данного типа используют

разновидности алгоритма асинхронного событийного моде-

моделирования (см. гл. 3).

При решении задачи логического синтеза увеличение

процента выхода годных (за счет уменьшения площади кри-

кристалла) обеспечивается методами минимизации числа ЛЭ и

связей между ними в логической схеме БИС.

1.5.3. Схемотехническое проектирование

На этапе схемотехнического проектирования решаются

задачи: 1) структурного синтеза принципиальной электри-

электрической схемы БИС; 2) анализа полученной схемы (расчет

статических состояний и переходных процессов; 3) стати-

1.5. Этапы проектирования БИС 37

стических анализа и оптимизации. Вопросы схе-

схемотехнического проектирования ИС и БИС широко осве-

освещены в литературе. Здесь же рассмотрим некоторые аспек-

аспекты решения названных задач.

Под структурным синтезом понимают получение конфи-

конфигурации принципиальной электрической схемы, оптималь-

оптимальным образом (по заданным критериям) удовлетворяющей

требованиям ТЗ. Общего научно обоснованного подхода к ре-

решению этой задачи к настоящему времени найти не удалось.

Поэтому задачи структурного синтеза пытаются решать в

рамках определенных ограничений и прежде всего в рамках

существующей классификации электронных схем. Можно

предложить следующую классификацию методов структур-

структурного синтеза:

1) классический метод, когда желаемые характеристики

аппроксимируются заданными функциями, а затем

реализуются с помощью ЛЭ и компонентов из заданно-

заданного набора;

2) метод перебора вариантов из заданного набора;

3) метод прямого неоптимального синтеза в заданном ба-

базисе ЛЭ;

4) метод локальной модификации известной схемы;

5) метод компиляции — преобразования описания функ-

функции схемы на языке высокого уровня в принципиаль-

принципиальную электрическую или логическую схему, пригодную

для разработки топологии;

6) метод экспертных оценок.

Первый метод применяют для схем, состоящих из пас-

пассивных компонентов. Второй имеет множество развет-

разветвлений, и хотя считается наиболее общим, с его помощью

йолучено минимальное число полезных решений. Локаль-

Локальная модификация известной схемы представляет пример

loro, что разделение задач проектирования на структурный

И параметрический синтез весьма условно. Суть его состоит

Й том, что после проведения процедур анализа чувствитель-

чувствительности и параметрической оптимизации определяются пары

^злов схемы, к которым с целью улучшения их характери-

характеристик целесообразно подключить новую подсхему. После это-

этого процедуры составления математической модели, анализа,

определения чувствительности и параметрической оптими-

38 Глава 1. Методология проектирования интегральных схем

зации должны быть проведены заново Доминирующим на-

направлением в решении задач структурного синтеза является

применение экспертных оценок. Инструментальным средст-

средством метода является экспертная система, содержащая ин-

информацию о проектных решениях и гипотезах. Экспертная

система получает свидетельства, подтверждающие или

отвергающие ту или иную гипотезу с определенной вероят-

вероятностью (каждое свидетельство имеет «цену»). Ее определяет

эксперт. Математической основой экспертной системы явля-

является формула Байеса, которая связывает вероятности под-

подтверждения гипотезы до и после получения свидетельства. В

качестве математического аппарата используют также аппа-

аппарат булевой алгебры, но кроме нуля и единицы разрешается

использовать любые действительные числа между ними.

Все методы решения задач структурного синтеза на-

находятся в постоянном развитии. В настоящее время пол-

полностью задача синтеза активных ИС не решена. Выбор топо-

топологии электрических схем производится исходя из опыта

предыдущих разработок с учетом возможностей предполага-

предполагаемого технологического процесса. Оптимизация схемы по

выбранному критерию проводится лишь для ограниченного

числа параметров компонентов.

Рассмотрим выбор принципиальных электрических схем

на примере разработки серии ИС для электронной вычисли-

вычислительной техники. Как правило, каждый изготовитель ИС

выпускает функционально полную и удобную для построе-

построения того или иного класса ЭВМ серию логических элемен-

элементов. В основу каждой серии положен один из типов логики.

Каждая серия логических элементов оценивается по опреде-

определенному набору параметров: задержке распространения сиг-

сигнала, потребляемой мощности, помехоустойчивости, коэф-

коэффициентам разветвления по входу и выходу, рабочему диа-

диапазону температур и т. д. В зависимости от того, какое

сочетание значений указанных параметров наиболее полно

удовлетворяет требованиям технического задания, выбира-

выбирается один из типов логических схем.

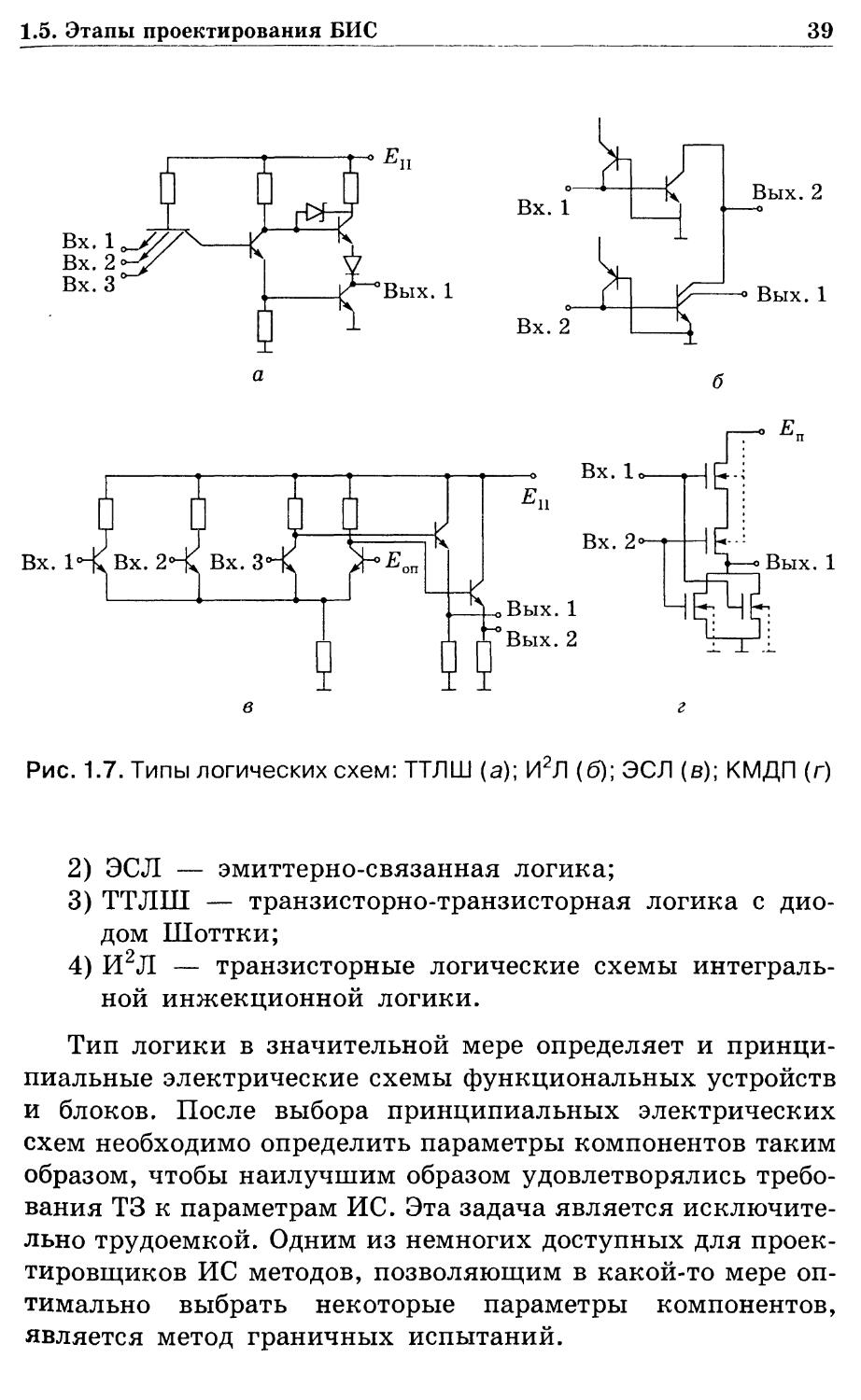

Наибольшее распространение получили следующие типы

логических схем (рис. 1.7):

1) комплементарная логика на полевых транзисторах

(КМДП);

1.5. Этапы проектирования БИС

39

Вх. 1

Вх. 2

Вых. 2

Вых. 1

Вых. 1

Рис. 1.7. Типы логических схем: ТТЛШ (а); И^Л (б); ЭСЛ (б); КМДП (г)

2) ЭСЛ — эмиттерно-связанная логика;

3) ТТЛШ — транзисторно-транзисторная логика с дио-

диодом Шоттки;

4) И2Л — транзисторные логические схемы интеграль-

интегральной инжекционной логики.

Тип логики в значительной мере определяет и принци-

принципиальные электрические схемы функциональных устройств

и блоков. После выбора принципиальных электрических

схем необходимо определить параметры компонентов таким

образом, чтобы наилучшим образом удовлетворялись требо-

требования ТЗ к параметрам ИС. Эта задача является исключите-

исключительно трудоемкой. Одним из немногих доступных для проек-

проектировщиков ИС методов, позволяющим в какой-то мере оп-

оптимально выбрать некоторые параметры компонентов,

является метод граничных испытаний.

40 Глава 1. Методология проектирования интегральных схем

Для применения метода граничных испытаний необхо-

необходимо вывести соотношения, связывающие функциональные

параметры ИС с параметрами компонентов. Функциональ-

Функциональные параметры ИС являются нелинейными функциями па-

параметров компонентов и в общем виде они могут быть запи-

записаны следующим образом:

Рп = /Х(Г, Д, С), A)

где Рп — потребляемая ИС мощность; f1 — оператор; Г, Д,

С — параметры транзисторов, сопротивлений и емкостей со-

соответственно.

Аналогичные соотношения можно записать и для других

функциональных параметров ИС:

*з.ср = /2(Г, Д, С), B)

Un0M = f3(T,R,C)f C)

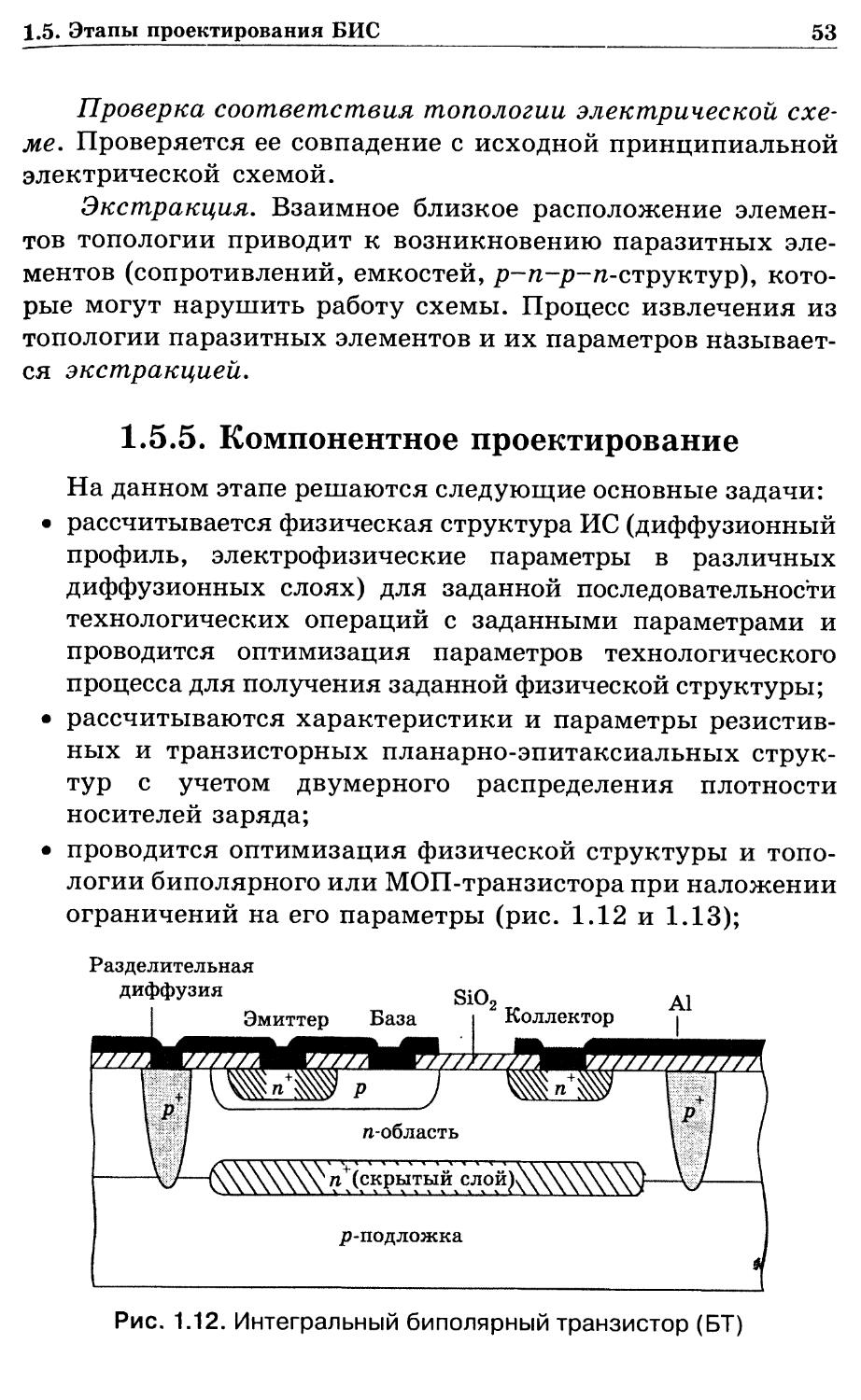

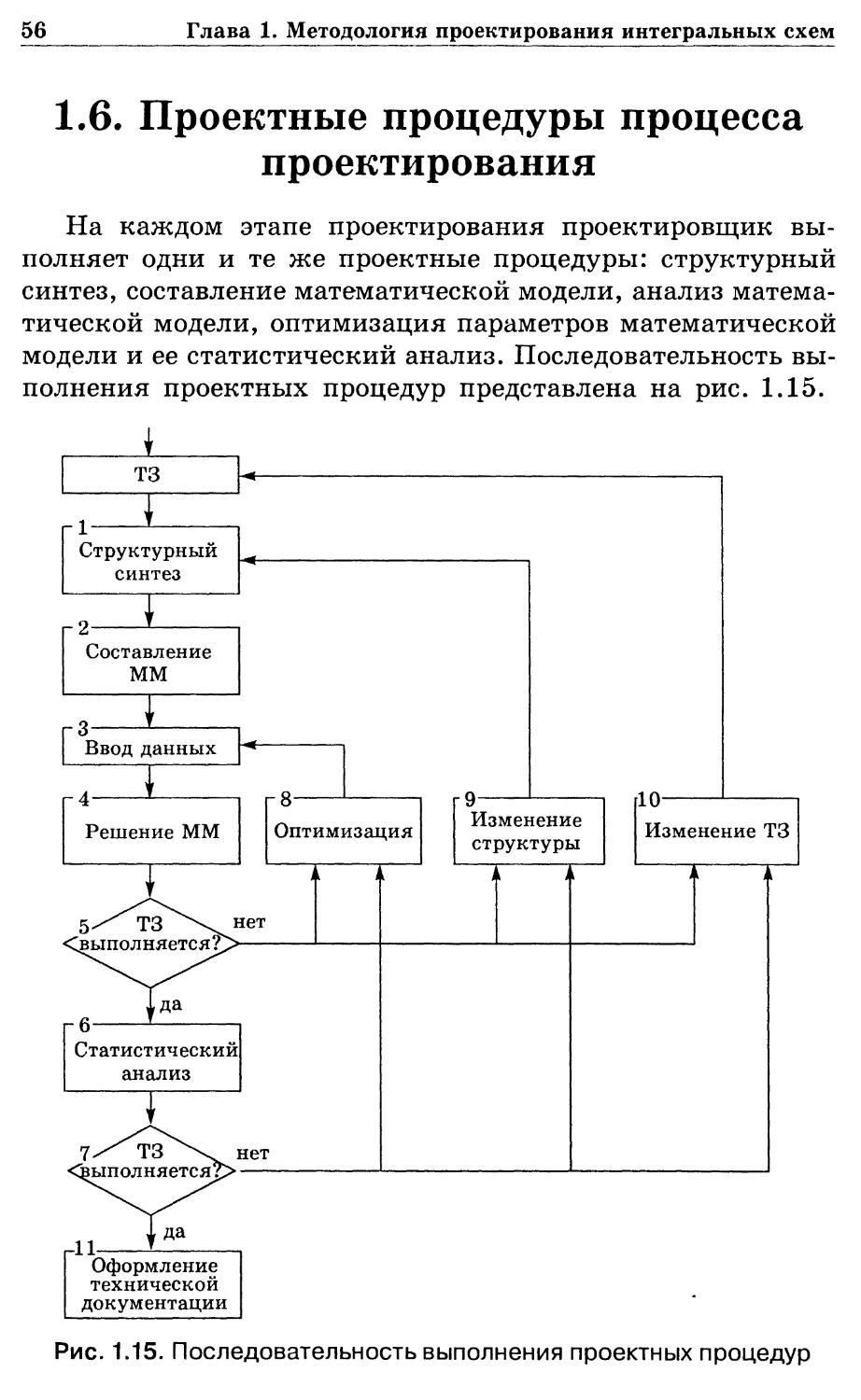

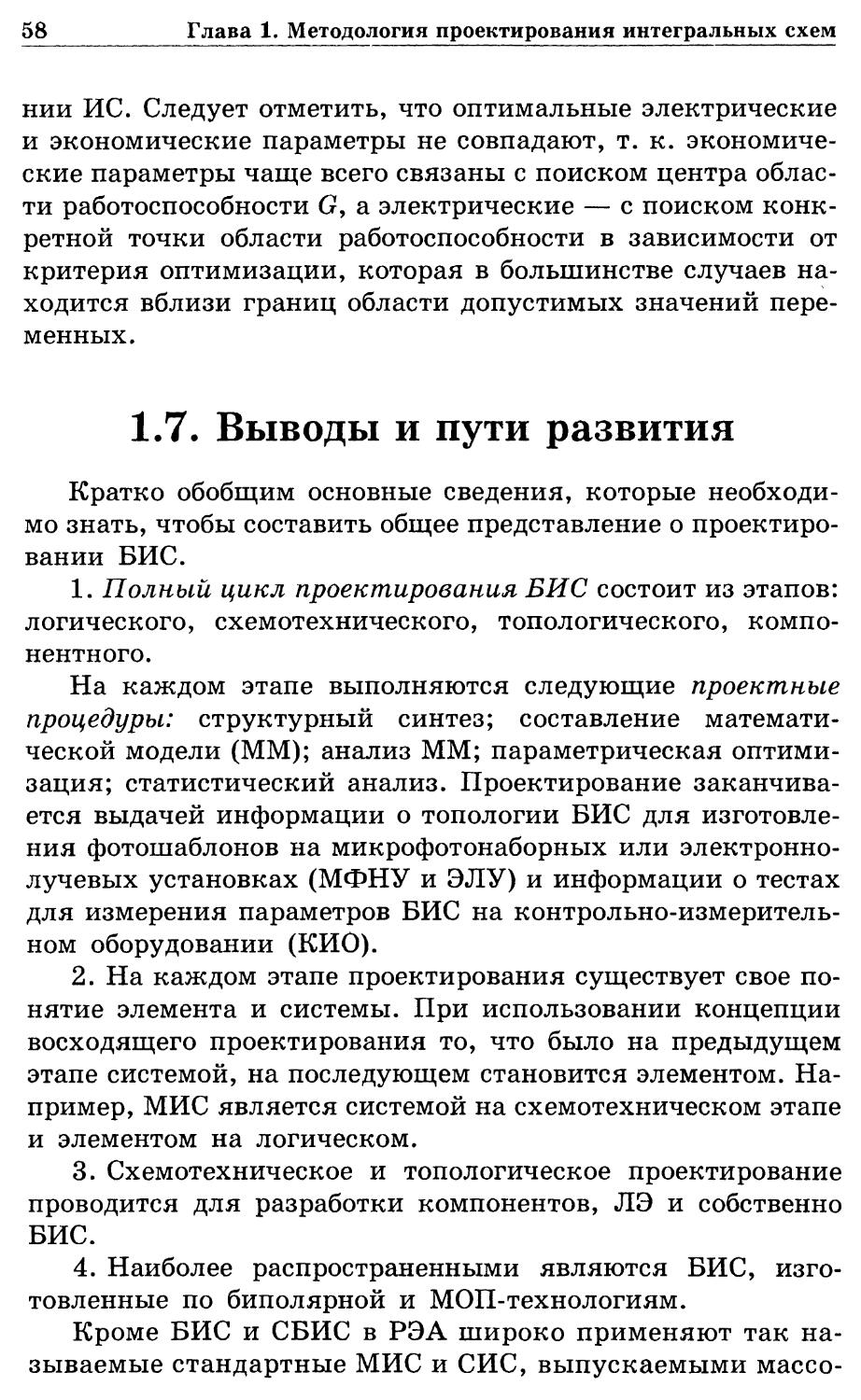

N = /4(Г, Д, С). D)