Автор: Исаков А.Б. Анисимов В.И. Азбелев П.П.

Теги: электротехника компьютерные технологии радиоаппаратура (радиоэлектронная аппаратура) микросхемы схемотехника сборник задач

ISBN: 5-283-04495-5

Год: 1991

СБОРНИК ЗАДАЧ ПО МИКРОСХЕМОТЕХНИКЕ

АВТОМАТИЗИРОВАННОЕ

ПРОЕКТИРОВАНИЕ

Под редакцией В. И. Анисимова

Допущено Государственным комитетом СССР по народному образованию в качестве учебного пособия для студентов вузов,

обучающихся по специальности "Автоматика и управление в технических системах"

Ленинград

ЭНЕРГОАТОМИЗДАТ Ленинградское отделение 1991

ББК 32.844-02 С23

УДК 621.3.032:681.3(075.8)

Рецензенты — кафедра ЭВМ МИФИ (зав. кафедрой Л. Д. Забродин), кафедра конструирования и производства электронной вычислительной аппаратуры КПИ (зав. кафедрой Ю. М. Каниболотский)

С23 Сборник задач по микросхемотехнике: Автоматизированное проектирование: Учебное пособие для вузов / В. И. Анисимов, П. П. Азбелев, А. Б. Исаков и др.; Под ред. В. И. Анисимова.—Л.: Энергоатомиздат. Ленингр.

отд-ние, 1991.—224 с.: ил.

ISBN 5-283-04495-5

Содержит около тысячи вопросов и задач, отражающих представленные в сборнике методики автоматизированного проектирования аналоговых и цифровых электронных устройств. Даны примеры решения типовых задач с применением ЭВМ. Представлены основные разделы дисциплин “Электронные элементы и устройства”, “Микросхемотехника и электронные цепи” и др.

Для студентов и преподавателей вузов, может быть полезна специалистам, занимающимся разработкой и применением микросхем.

С

2405000000-125 051(01) - 91

236-91

ББК 32.844-02

Учебное пособие

Анисимов Владимир Иванович, Азбелев Петр Павлович Исаков Александр Борисович, Капитонов Михаил Васильевич Соколов Юрий Михайлович, Хорьков Геннадий Иванович

СБОРНИК ЗАДАЧ ПО МИКРОСХЕМОТЕХНИКЕ.

АВТОМАТИЗИРОВАННОЕ ПРОЕКТИРОВАНИЕ

Редактор С. П. Левкович. Художник переплета В. Л. Черников Художественный редактор В. М. Мартынов

Технический редактор Я. А. Минеева. Корректор М. С. Мордашева ИБ № 2819

Сдано в набор 28.11.90. Подписано в печать 24.07.91 Формат 60x881/16. Бумага офсетная № 1 Гарнитура литературная. Печать офсетная. Уел. печ. л. 13,72. Уел. кр.-отг. 13,72. Уч.- изд. л. 14,35. Тираж 10 000 экз. Заказ № 1586. Цена 2 р.

Энергоатомиздат. Ленинградское отделение 191065, Ленинград, Д--65, Марсово поле, 1. .Ленинградская типография № 4 Государственного комитета СССР по печати. 191126, г. Ленинград, Социалистическая ул., 14.

ISBN, 5-283-04495-5

© В. И. Анисимов, П. П. Азбелев, А. Б. Исаков, М. В. Капитонов,

Ю. М. Соколов, Г. И. Хорьков, 1991

ПРЕДИСЛОВИЕ

В настоящее время разработка сложных микроэлектронных устройств невозможна без широкого применения систем автоматизированного проектирования (САПР). Во многих случаях использование схемотехнических САПР позволяет отказаться от экспериментальных исследований проектируемого устройства и тем самым в десятки раз ускорить процесс создания новой схемы. К настоящему моменту издано много книг, посвященных автоматизации схемотехнического проектирования и ориентированных в основном на разработчиков САПР радиоэлектронной аппаратуры; имеется обширная литература по микросхемотехнике аналоговых и цифровых устройств. Однако для большинства специалистов, работающих в области микросхемотехникй, наиболее важными являются вопросы использования отечественных и зарубежных САПР в практике схемотехнического проектирования. В учебной литературе эти вопросы отражены недостаточно.

В этой книге изложены методические аспекты использования схемотехнических САПР при проектировании различных аналоговых и цифровых микроэлектронных устройств. При этом для каждого класса электронных устройств процесс проектирования представляется в виде совокупности задач, решаемых разработчиком с помощью ЭВМ. В работе также определяется роль разработчика и ЭВМ на различных этапах автоматизированного схемотехнического проектирования микроэлектронного устройства. При этом в методическом плане авторы для каждого класса устройств старались изложить задачи в такой последовательности, чтобы результаты автоматизированных исследований способствовали углублению схемотехнического мышления разработчика.

В сборнике задач обобщен в основном оригинальный материал, накопленный авторами в процессе применения учебно-исследовательских схемотехнических САПР, разработанных в ЛЭТИ имени В. И. Ульянова (Ленина). Для большинства задач приводятся ответы. Изложение материала сопровождается примерами решения типовых задач. Большое внимание авторы

з

уделяют задачам автоматизированного параметрического синтеза микроэлектронных устройств, которые успешно решаются при использовании в схемотехнических САПР комплекса программ “Оптимизация ”.

Настоящий сборник задач может быть полезен студентам вузов, обучающихся по специальностям 2201, 2202, 2203, 2207, 1907, 2101.

Главы 1 и 2 написаны совместно В. И. Анисимовым, А. Б. Исаковым и Ю. М. Соколовым; главы 3 и 8 —А. Б. Исаковым и Ю. М. Соколовым; главы 4 и 5—М. В. Капитоновым; главы 6 и 7—Г. И. Хорьковым; главы 9, 10 и 11 —П. П. Азбе- левым.

Авторы выражают признательность разработчикам учебноисследовательских САПР ДИСП и ЭМЦ К. Б. Скобельцину, Н. К. Перкову, О. С. Белецкому, С. Н. Ежову, И. Г. Кревскому, А. И. Ларистову, А. В. Никитину, А. В. Шнайдеру, Ю. Г. Уксус- никову, Н. И. Вольской за предоставленный материал для подготовки книги, замечания и советы, которые позволили улучшить содержание сборника задач.

Авторы

ОСНОВНЫЕ ОБОЗНАЧЕНИЯ

АЛУ — арифметико-логическое устройство

АПМ — автоматная пользовательская модель

АПС — аналоговый перемножитель сигналов

ARCO активные ДС-фильтры АУ — аналоговое устройство АЧХ — амплитудно-частотная характеристика БД — база данных

БДМК — база данных моделей компонентов

БИС — большая интегральная схема БМЭ — базовая модель элемента БСР — банк схемных решений БЯ — бистабильная ячейка ВМ — пакет программ “Временное моделирование”

ГПСЧ — генератор псевдослучай¬

ных чисел

ГСА — граф-схема алгоритма ДЛС — двухъярусная логическая схема

ДН — делитель напряжения ДНФ — дизъюнктивная нормальная форма

ДПП — диалоговый пакет программ ДУ — дифференциальный усилитель ЗФ — заграждающий фильтр ИМС — интегральная микросхема ИОН — источник опорного напряжения

И ПТ — источник постоянного тока ИСН — интегральный стабилизатор напряжения ИТ—источник тока КК — карта Карно

КМОП — микросхемы на комплементарных МОП-транзисторах КФУ — комбинационный функциональный узел

КЦУ — комбинационное цифровое устройство

ЛА—линейный автомат ЛМ — логическое моделирование ЛУ — логарифмический усилитель ЛЭ — логический элемент М2 — ЛЭ “Сложение по модулю 2” МГ—модель генератора сигналов МТИ — многовыходная таблица истинности

МФЛЭ — многофункциональный логический элемент ОБС — очередь будущих событий ОДС — одноразрядный двоичный сумматор

ОЗУ — оперативное запоминающее устройство

ОУ — операционный усилитель ПЗУ — постоянное запоминающее устройство

ПЛМ — программируемая логическая матрица

ПМ — пользовательская модель ПС — принципиальная схема ПФ — пропускающий фильтр ПФУ — последовательностный функциональный узел

ПЦУ — последовательностное цифровое устройство РУ — решающий усилитель РЭ — регулирующий элемент РЭА — радиоэлектронная аппаратура САПР — система автоматизированного проектирования СБИС — сверхбольшая интегральная схема

СДНФ — совершенная дизъюнктивная нормальная форма СИС — микросхемы средней степени интеграции

СЛМ — система логического моделирования

СОЗУ — сверхоперативное запоминающее устройство

СПМ — структурная пользовательская модель

5

СтДж— счетчик Джонсона ТВ — таблица возбуждения ТВЗ — триггер с внутренней задержкой

ТЗ — техническое задание ТИ — таблица истинности ТП — таблица переходов ТТЛ — микросхемы транзисторнотранзисторной логики ТТЛШ — ТТЛ с диодами Шоттки ТФВ — таблица функций возбуждения

УВХ — устройство выборки-хранения

УГО — условное графическое обозначение

УЗСР —узел задания статического режима

УЛЭ — универсапьный логический элемент

ФВЧ — фильтр верхних частот ФНЧ — фильтр нижних частот ФП — функциональная подсхема ФС — функциональная схема ФУ — функциональный узел ФЧХ — фазо-частотная характеристика

ЦУ — цифровое устройство ЭСЛ — микросхемы эмиттерносвя- занной логики

ЯОФС — язык описания функциональных схем

РАЗДЕЛ ПЕРВЫЙ

СХЕМОТЕХНИКА АНАЛОГОВЫХ УСТРОЙСТВ

ГЛАВА ПЕРВАЯ

АВТОМАТИЗАЦИЯ СХЕМОТЕХНИЧЕСКОГО ПРОЕКТИРОВАНИЯ

1.1. Общие сведения

Под проектированием понимается процесс преобразования информации исходного описания объекта проектирования в выходное описание, необходимое и достаточное для технической реализации нового изделия, удовлетворяющего требованиям технического задания. Проектирование называют автоматизированным, если отдельные его этапы осуществляются при взаимодействии человека и ЭВМ. Проектирование называют автоматическим, если все необходимые этапы проектирования выполняются на ЭВМ без участия человека.

Проектирование радиоэлектронной аппаратуры (РЭА), как правило, выполняется автоматизированными методами. Системы автоматизированного проектирования (САПР) представляют собой сложные программно-технические комплексы средств автоматизации схемотехнического, функционально-логического и конструкторского проектирования, подготовки производства и выпуска технической документации.

Процесс структурного, функционального и схемотехнического проектирования РЭА включает в себя решение задач анализа, оптимизации и синтеза, которые называются проектными процедурами и имеют следующее содержание [1, 2]:

Одновариантный анализ (расчет) — определение характеристик устройства при постоянных значениях параметров его компонентов и неизменной структуре.

Многовариантный анализ заключается в иследовании устройства при изменении параметров компонентов и характеристик внешних информационных сигналов.

Оптимизация — процесс целенаправленного изменения параметров компонентов устройства (при параметрической оптимизации) или структуры устройства (при структурной оптимизации) для получения наилучших в том или ином смысле значений выходных параметров и характеристик проектируемого устройства. Как правило, оптимизация осуществляется по многим критериям, поскольку проектируемое устройство должно удовлетворять комплексу технико-экономических требований. Параметры компонентов устройства, в результате изменения которых

7

выполняется параметрическая оптимизация, называются варьируемыми. Закон изменения варьируемых параметров определяется конкретным алгоритмом оптимизации.

Синтезом в общем случае называется генерация исходного варианта устройства, включая его структуру (структурный синтез) и значения параметров компонентов (параметрический синтез). Полученное в результате синтеза устройство может быть не оптимальным по всем критериям, но обязательно должно быть работоспособным. Синтезированное устройство, как правило, нуждается в дополнительной оптимизации. Если же в результате синтеза удается найти вариант устройства, наилучший по нескольким критериям, то такой синтез называется оптимальным. Структурный синтез электронных устройств является творческим процессом, плохо поддающимся автоматизации. Задачи синтеза, как правило, решаются с помощью узкоспециализированных программных комплексов, ориентированных на синтез определенного класса устройств, например, созданы программы синтеза аналоговых и цифровых фильтров.

1.2. Основные виды анализа аналоговых устройств

При схемотехническом проектировании аналоговых и цифровых устройств необходимо решить такие задачи, как расчет статического режима, переходных процессов, исследовать частотные характеристики схемных функций и спектральный состав выходного сигнала. Решение этих задач позволяет определить качественные характеристики передаваемых в схеме сигналов (амплитуда и фаза, задержка и длительность импульсных сигналов и др.). Кроме этого, в некоторых случаях необходимо провести анализ нестабильности нулевого уровня и его температурного дрейфа, чувствительности схемы к изменению параметров компонентов, решить задачи анализа шумовых характеристик схемы и оптимизации ее параметров [1—3].

Анализ статического режима выполняется для построения карты режимов по постоянному току, а также для определения различных характеристик схемы в статическом режиме (анализ проходной характеристики усилительных и нелинейных устройств, расчет перегрузочной способности по входу и диапазона изменения выходных токов и напряжений и т. п.). Анализ статического режима также проводят для определения рабочей точки по постоянному току нелинейных элементов схемы перед последующим анализом переходных процессов или частотных характеристик (в последнем случае нелинейная схема автоматически линеаризуется в окрестности найденной рабочей точки).

8

Анализ схемы во временной области включает в себя решение одной или нескольких основных задач:

а) расчет переходных процессов под действием источников переменного сигнала или импульсных последовательностей;

б) отыскание периодических решений при действии периодического сигнала;

в) отыскание периодических решений автоколебательных систем при отсутствии внешних сигналов.

Анализ схемы во временной области может быть выполнен двумя методами. В первом случае, когда уровни информационных сигналов в схеме значительно меньше уровней токов и напряжений в статическом режиме, анализ переходных процессов проводится в линеаризованной схеме, где все нелинейные элементы заменены их малосигнальными аналогами. Такой анализ переходных процессов выполняется, как правило, с минимальными затратами машинного времени и ресурсов ЭВМ. Во втором случае, когда уровни информационных сигналов соизмеримы с уровнями токов и напряжений, анализ во временной области проводится в нелинейной схеме в режиме “большого” сигнала. Для проведения автоматизированного анализа нелинейной схемы требуются значительно большие затраты машинного времени.

Анализ схемы в частотной области включает в себя решение следующих задач:

а) расчет комплексных схемных функций (коэффициентов передачи, входных и выходных сопротивлений, У-пара- метров);

б) построение карты расположения нулей и полюсов, исследование устойчивости;

в) анализ шумовых характеристик и нелинейных искажений.

Анализ частотных характеристик схемных функций используется достаточно широко при проектировании усилительных и радиочастотных устройств. Для оценки устойчивости схемы целесообразно провести анализ расположения нулей и полюсов, особенно когда в схеме возможно появление резонансов. Действительно, при автоматизированном анализе частотных характеристик схемных функций достаточно узкий резонансный пик может быть пропущен в ряду дискретных частотных точек, выбранных для анализа.

Спектральный анализ используется при исследовании нелинейных радиотехнических устройств таких, как детекторы, смесители, модуляторы, амплитудные ограничители и др. Спектральный анализ позволяет определить амплитуды гармоник выходного сигнала устройства при воздействии на его вход периодического сигнала произвольной формы, а также спектральный состав периодических решений автоко¬

9

лебательных систем. Автоматизированный анализ спектрального состава выходного сигнала, как правило, выполняется на базе дискретного преобразования Фурье.

Анализ чувствительности проводят для оценки степени влияния вариации параметров компонентов на характеристики проектируемого устройства. По значениям коэффициентов чувствительности разработчик может выявить компоненты схемы,, отклонения параметров которых от номинальных значений приводят к наибольшим изменениям характеристик проектируемого устройства, а следовательно, определить требования к точности реализации тех или других элементов.

Не менее важное значение автоматизированного анализа чувствительности заключается в получении информации о том, какие именно компоненты или их параметры и в каком направлении следует изменять в процессе оптимизации, а также при настройке разработанного устройства.

Анализ нестабильности позволяет определить реакцию схемы на изменения параметров ее компонентов под воздействием совокупности внешних дестабилизирующих факторов: колебаний температуры, напряжений источников питания, старения компонентов, технологического разброса параметров компонентов. При достаточно малых изменениях параметров компонентов задача автоматизированного анализа нестабильности сводится к линейной задаче в результате замены компонентов схемы автономными многополюсниками. Автономные параметры многополюсников могут иметь различное смысловое содержание, например, отражать температурный дрейф или технологический разброс параметров компонента. Если необходимо определить нестабильность характеристик схемы в широком диапазоне изменений дестабилизирующих воздействий, целесообразно провести многовариантный анализ схемы (например, для определения температурной нестабильности статического режима нелинейной схемы в широком диапазоне температур).

Анализ шумовых характеристик позволяет оценить отношение сигнал-шум в проектируемой схеме, т. е. определить вклад источников шума и входного сигнала в выходной сигнал схемы. Наиболее важными составляющими шума в электронных цепях являются дробовой, тепловой и фликкер-шумы. Источники шума обычно моделируют в виде автономных некоррелированных источников напряжения и тока, подключенных к резисторам и полупроводниковым приборам. Вклад каждого источника шума в выходной сигнал схемы рассматривается независимо от других источников. Суммарная амплитуда шумов на выходе схемы равна квадратному корню из суммы квадратов амплитуд шумов, обусловленных отдельными источниками.

10

1.3. Оптимизация характеристик аналоговых устройств

Решение задачи проектирования обычно связано с выбором оптимального, наилучшим образом удовлетворяющего требованиям технического задания, варианта устройства из некоторого допустимого множества решений. Эффективное решение задач оптимального проектирования возможно только при разумном сочетании формальных поисковых методов оптимизации и неформальных способов принятия оптимальных проектных решений. Поэтому решение задач оптимального проектирования необходимо рассматривать не только в вычислительном аспекте, но, скорее, в творческом, учитывая опыт и знания инженера-схемотехника на всех этапах автоматизированного проектирования. Одной из наиболее сложных операций при решении задач оптимального проектирования является этап математической формулировки задачи, которая включает в себя выбор критерия оптимальности, определение варьируемых параметров и задание ограничений, накладываемых на варьируемые параметры [1, 4].

Среди задач схемотехнического проектирования, которые целесообразно решать с привлечением методов оптимизации, выделим следующие задачи параметрического синтеза и оптимизации:

определение параметров компонентов схемы, обеспечивающих ее экстремальные характеристики при заданных ограничениях;

определение параметров функциональных узлов схемы исходя из требований технического задания на характеристики устройства в целом (например, определение коэффициента усиления и полосы пропускания отдельных каскадов усилителя исходя из требований технического задания на коэффициент усиления и полосу пропускания усилителя);

определение параметров компонентов схемы, обеспечивающих специфические характеристики устройства (например, определение значений элементов цепи коррекции усилителя для обеспечения его устойчивости при заданной глубине обратной связи);

адаптация существующих схемных решений с целью подбора параметров, удовлетворяющих новым требованиям к схеме;

уточнение значений параметров компонентов схемы, полученных в результате использования методов ручного инженерного расчета.

В любой из перечисленных задач реализуемые характеристики проектируемого устройства являются функциями вектора варьируемых (настраиваемых) параметров, составляющих некоторое подмножество полного набора параметров компонентов схемы. Целью параметрического синтеза или оптимизации является определение вектора варьируемых параметров X, обес-

11

Рис. 1.1. Графическая интерпретация базового набора критериев оптимальности, используемых в задачах оптимизации

печивающего наилучшее соответствие характеристик устройства У=У(Х) требованиям технического задания. Для решения этой задачи необходимо прежде всего выбрать формальный критерий оценки качества каждого из вариантов разрабатываемого устройства, который позволил бы различать их между собой и устанавливать между ними отношения предпочтения. Если такая оценка может быть представлена функциональной зависимостью вида

F=F (У(Х)) = У(Х),

называемой обычно критерием оптимальности или целевой функцией, то задача поиска параметров компонентов схемы сводится к классической задаче оптимизации — нахождению экстремума некоторой функции качества F (X) при наличии ограничений (равенств, неравенств или двусторонних границ), накладываемых на варьируемые параметры и характеристики проектируемой схемы.

В процессе поиска оптимального решения для каждой конкретной задачи может оказаться предпочтительным определенный вид критерия оптимальности. Рассмотрим базовый набор критериев оптимальности, позволяющий удовлетворить разнообразные требования инженера-схемотехника к оптимизируемым характеристикам разрабатываемых устройств [1].

Для отыскания экстремума (минимума или максимума) показателя качества, такого, например, как потребляемая схемой 12

мощность, частота среза, используется само значение критерия оптимальности без преобразования:

М*)=уУ(Х),

где у — весовой коэффициент, задающий относительную важность этого показателя по сравнению с другими, если одновременно оптимизируется несколько показателей качества.

В задачах, требующих максимального соответствия оптимизируемой характеристики и некоторой желаемой, например, при оптимизации частотных характеристик, наиболее целесообразно использовать критерий среднего квадратического отклонения (рис. 1.1, а)

F2 (*)=у (Y(X)-Yy, (1.1)

где Y* — желаемое значение характеристики. Для характеристики, заданной дискретным набором точек, целевая функция

у,(у(х.р,)-у;)\ (12)

где ЛГ—число точек дискретизации независимой переменной р\ Y(X, р{) — значение оптимизируемой характеристики в /-й точке интервала дискретизации; у{— весовой коэффициент /-го значения оптимизируемой характеристики, отражающий важность выбранной точки по сравнению с другими.

Минимизация функций (1.1) и (1.2) обеспечивает близость характеристик по среднему квадратическому отклонению. Максимизация этих функций может быть использована при расчетах на наихудший случай.

В некоторых задачах оптимизации необходимо обеспечить превышение (рис. 1.1, б) или непревышение (рис. 1.1, в) оптимизируемой характеристикой некоторого заданного уровня. Эти критерии оптимальности реализуются следующими функциями:

для обеспечения превышения заданного уровня

F3(X) =

О при Y(X) > Ун’;

y(YH*-Y(*))2 при Y(X)< Ун\

(1.3)

для обеспечения непревышения заданного уровня

О при Y(X) < Ув*;

y{Y{X)-Ylf при Y(X)>Tt,

F4(X) =

(1.4)

где YH*, Y*— нижняя и верхняя границы допустимой области для характеристики Y (X).

Если необходимо, чтобы оптимизируемая характеристика (рис. 1.1, г) проходила в некоторой допустимой зоне (кори¬

13

доре), используют комбинацию двух предыдущих критериев оптимальности:

0

при

Гн < У(X) < у;:

>

ад-

y(Y(X)-y;)2

при

y(X)>y;-,

(1.5)

у (Гн - У(*))2

при

y(X)<y;.

В тех случаях, когда требуется реализовать лишь

форму

кривой, игнорируя при этом

постоянное

смещение по

верти-

кали (рис. 1.1, д), используется критерий сдвига:

F6(X) = i,V, (y;-Y(X, Pi)-Y\2,

/= 1 4 '

где

= (y;-y(x, р,.)).

Кроме рассмотренных выше критериев оптимальности, в задачах параметрической оптимизации и синтеза могут также использоваться критерии пропорциональности кривых и линейности характеристик при игнорировании угла наклона прямой [1, 5].

Задачи оптимального проектирования РЭА обладают специфическими особенностями, к которым относят: многоэк- стремальность функции качества, наличие ограничений на выходные параметры и характеристики проектируемого устройства, большую размерность вектора варьируемых параметров. Для решения подобных задач используют библиотеку алгоритмов поиска.

Алгоритмы глобального поиска (алгоритм случайного поиска, монотонный алгоритм глобального поиска, алгоритм сканирования на сетке кода Грея и другие), как правило, дают достаточно грубую оценку глобального экстремума при небольших затратах вычислительных ресурсов и требуют значительного увеличения числа вычислений для получения более точной оценки положения экстремума.

Алгоритмы локального поиска (алгоритм интуитивного поиска, алгоритм сопряженных направлений Пауэлла) чаще всего отыскивают ближайший локальный экстремум, а траектория их движения сильно зависит от выбора начальной точки.

Стратегия решения задач оптимального проектирования предусматривает применение глобальных процедур оптимизации на начальных этапах поиска и уточнение полученного глобального решения быстросходящимися в окрестности оптимальной точки локальными алгоритмами. Такая стратегия позволяет, во-первых, с достаточной надежностью и точностью определить значение

14

глобального экстремума и, во-вторых, существенно снизить вычислительные затраты на поиск. При этом этапы глобального поиска могут выполняться с невысокой точностью, а этапы локального уточнения проводятся в области притяжения глобального экстремума, что требует значительно меньшего числа вычислений. Так, например, хороших результатов за приемлемое время оптимизации можно достичь, применяя последовательно монотонный алгоритм глобального поиска и локальный алгоритм сопряженных направлений Пауэлла. На первом этапе требуется, как правило, 50...100 вычислений функции качества, чтобы локализовать глобальный экстремум. Несколько большее число вычислений (100...250) требуется, чтобы уточнить решение, однако оно в несколько раз ниже, чем требуется в случае применения одного локального алгоритма.

1.4. Системы

автоматизированного проектирования

Многие термины, относящиеся к САПР РЭА, имеют несколько значений. Для уменьшения неопределенности приведем термины и определения, которые используются в дальнейшем изложении.

Схему будем рассматривать как совокупность компонентов, подключенных к узлам схемы. Полюсы (выводы) компонентов, как правило, имеют свои имена, например, база, коллектор, эмиттер. Свойства каждого компонента отражает модель koai- понента, которая характеризуется набором параметров. Значения параметров определяются типоль компонента, например, параметры транзисторов КТ315 и КТ315А имеют разные числовые значения. Все компоненты, имеющие одинаковый принцип действия, относятся к одному виду. Например, к одному виду относятся все биполярные транзисторы. Отметим также, что в системах автоматизированного проектирования компоненты, относящиеся к одному виду, могут описываться несколькими моделями различной степени сложности.

В этом разделе рассматриваются основные функциональные характеристики диалоговых систем схемотехнического проектирования радиоэлектронных схем ДИСП и ЭМЦ, разработанных в ЛЭТИ имени В. И. Ульянова (Ленина). Система ДИСП ориентирована на использование персональных и мини-ЭВМ, а система ЭМЦ —на ЕС ЭВМ. Детальное описание систем ДИСП и ЭМЦ приведено в работах [1, 5].

Системы ДИСП и ЭМЦ предназначены для проведения научно-исследовательских и опытно-конструкторских работ по проектированию аналоговых и цифровых устройств РЭА. Они обеспечивают проведение непрерывного цикла проектных процедур.

15

Системы ДИСП и ЭМЦ обеспечивают многотерминальный режим работы пользователей. Программное обеспечение систем включает инвариантную обслуживающую подсистему и несколько диалоговых пакетов прикладных программ (ДПП), которые ориентированы на проведение определенного вида анализа. К настоящему времени в состав систем входят следующие пакеты прикладных программ:

1. “ Статика” — определение статических характеристик нелинейных электронных схем, построение карт режимов компонентов;

2. “Нелинейная динамика” — расчет переходных процессов и анализ прохождения сигналов различной формы в нелинейных электронных схемах;

3. “Линейная динамика” — анализ переходных процессов в линейных и линеаризованных схемах;

4. “Частота” — анализ частотных характеристик произвольных схемных функций;

5. “Оптимизация” — определение координат экстремальных точек и оптимизация частотных характеристик электронных схем;

6. “Чувствительность” — анализ функций чувствительности электронных схем в частотной области;

7. “Нестабильность” — анализ нестабильности статического режима электронных схем;

8. “Полином”—расчет численных значений схемных функций, заданных отношением полиномов, расчет корней полиномов;

9. “Спектр” — расчет спектральных характеристик сигналов;

10. “Фильтр” — автоматизированный синтез активных фильтров;

11. “Троичное моделирование” — анализ функциональных и принципиальных схем цифровых устройств без учета временных параметров;

12. “Временное моделирование” — анализ функциональных и принципиальных схем цифровых устройств во временной области и проверка их работоспособности;

13. “База данных” — управление данными в специализированной базе данных моделей компонентов и подсхем;

14. “График” — постпроцессор ббработки графической информации.

При выборе алгоритмов расчета, реализованных в ДПП, учитывались такие противоречивые требования, как универсальность, эффективность и минимизация времени проведения анализа. Так, для решения задачи анализа статического режима используется группа методов продолжения решения по параметру в сочетаний с модифицированным алгоритмом Ньютона. В качестве варьируемых параметров^ в исходной системе нелинейных уравнений выступают либо значения независимых источников напряжения и тока, либо сопро¬

16

тивления резисторов, шунтирующих все нелинейные компоненты схемы. Для анализа переходных процессов в линейных и нелинейных электронных схемах используются неявные методы интегрирования второго порядка с автоматическим выбором шага, являющиеся компромиссом между точностью расчетов и алгоритмической сложностью.

Анализ нестабильности статического режима схемы при воздействии дестабилизирующих факторов проводится на основе общей методики анализа схем с автономными многополюсниками. При анализе чувствительности схемных функций к вариации параметров компонентов используется метод дифференцирования уравнений, позволяющий при однократном решении системы уравнений определить чувствительности всех координат схемы к одному из параметров. Определение корней полиномов передаточной функции основывается на применении метода Хичхока. Анализ спектральных характеристик базируется на алгоритме дискретного преобразования Фурье.

Процедура параметрической оптимизации может быть выполнена одним из следующих алгоритмов оптимизации: глобального поиска, случайного поиска, интуитивного поиска и алгоритмом, использующим сетку кода Грея. Наличие большого числа алгоритмов оптимизации позволяет существенно повысить эффективность работы подсистемы оптймизации в зависимости от типа и сложности решаемых задач. В процессе оптимизации пользователю предоставляется возможность модифицировать информацию о векторе варьируемых параметров и критериях оптимизации. Процесс оптимизации завершается подстановкой вектора оптимальных параметров во внутреннее описание исследуемой схемы и выводом результатов оптимизации на внешнее устройство.

Практическое использование систем ДИСП и ЭМЦ предусматривает организацию активного диалога между студентом и ЭВМ, в рамках которого система сообщает пользователю перечень возможных проектных процедур, задает вопросы и подсказывает форматы ответов. Обеспечение взаимодействия с системой широкого круга пользователей достигается наличием двух форм диалога: директивной (командной) и сценарной. Основной формой для опытного пользователя является директивная, при которой инициатива принадлежит пользователю. Выполняя очередную команду, система переходит в режим ожидания следующей. При сценарной форме диалога, рассчитанной на режим обучения малоквалифицированных пользователей, на каждом шаге диалога система предлагает возможные пути продолжения работы. На любом уровне взаимодействия пользователь может обратиться к инструкции по системе. Вывод инструкции на терминал осуществляется по запросу

17

или с помощью команды, которая может быть подана на любое сообщение системы.

1.5. Подготовка описания

аналоговой схемы

для автоматизированного анализа

В состав диалоговых лингвистических средств САПР входят три языка: язык описания схем, язык управления проектированием и язык запросов к базе данных. Язык описания схемы в системах ДИСП и ЭМЦ реализован как пассивный: текст описания схем может быть передан транслятору как из файла на внешнем устройстве, так и введен в систему непосредственно с помощью клавиатуры дисплея в процессе сеанса диалогового взаимодействия пользователя с системой. Языки управления проектированием, редактирования описания схемы и запросов к базе данных являются языками диалогового типа. Диалоговые команды этих языков обрабатываются интерпретаторами и передаются соответствующим программным модулям для немедленного выполнения.

Подготовка схемы для описания ее на входном языке системы заключается в нумерации узлов и компонентов. Общий узел схемы имеет номер 0. Рекомендуется входному узлу присваивать номер 1, а выходному—2. Остальные узлы нумеруются в произвольном порядке (на рисунках показаны в кружках). Каждому компоненту схемы присваивается имя и номер (в качестве имен компонентов, как правило, используются имена моделей).

Аналоговые схемы, подлежащие анализу, могут содержать следующие компоненты: пассивные ЖС-элементы; диоды и стабилитроны; биполярные, полевые и МДП-транзисторы; операционные усилители и компараторы; взаимные индуктивности и трансформаторы; управляемые источники тока и напряжения; независимые источники напряжения и тока.

В системе ДИСП-5 пользователю предоставлена возможность самому создавать произвольные модели компонентов из перечисленных выше базовых компонентов, и записывать их в специализированную БДМК.

Язык описания схемы реализован в двух вариантах. Первый используется только в младших версиях системы ДИСП и обладает минимальной избыточностью описаний. Второй вариант является подмножеством входного языка системы ЭМЦ на ЕС ЭВМ [5]. Такая совместимость входных языков позволяет без изменения текста описания схемы переходить из системы ДИСП в более произвольную систему ЭМЦ.

При формировании текста описания схемы размерности параметров могут не указываться в явном виде. В языке системы ДИСП

18

©

Рис. 1.2. Дифференциальный усилитель (пример подготовки схемы к автоматизированному анализу)

по умолчанию приняты следующие единицы физических величин: сопротивление —

кОм; емкость —мкФ; индуктивность — Гн; напряжение —

В; ток—мА; время —мс; фаза — градус; частота — кГц.

Рассмотрим процесс подготовки описания схемы для автоматизированного анализа в системе ДИСП на примере дифференциального усилителя, представленного на рис. 1.2.

Идентификация схемы выполняется с помощью задания двух переменных NAME и N. Переменная текстового типа NAME определяет имя схемы:

NAME = flHO. УСИЛИТЕЛЬ;

Переменная N определяет число узлов в схеме и может быть явно не' задана.

Текст описания схемы состоит из предложений описания компонентов, директив и комментариев, записанных в произвольной последовательности. Обязательными элементами предложения являются: имя, знак равенства, список констант и переменных, которые отделяются друг от друга запятой, каждое предложение завершается точкой с запятой (;). Описание компонентов анализируемой схемы имеет вид:

<имя компонента>[<число компонентов>] = <номера узлов подключения компонента 1>, < список параметров компонента 1 >!...<номера узлов подключения компонента п >, <список параметров компонента п>\

Для разделения описаний компонентов, относящихся к одной модели, используется символ “!”, имеющий значение “конец описания компонента”. Имя компонента определяет символическое имя модели компонента, например, R — для резисторов, Г— для транзисторов и т. п. Параметр < число компонентов > — необязательный элемент описания, определяющий размер предложения. Номера узлов подключения и параметры компонента указываются в произвольном формате через запятую. Рекомендуемые формы описаний компонентов, модели которых имеются в базе данных системы ДИСП, приведены в Приложении 1. Комментарий может содержать произвольную последовательность символов, заключенную в апострофы (’).

19

Описание резисторов, конденсаторов и источников напряжения схемы (см. рис. 1.2) имеет вид:

R = 2,6,10! 3,6,10! 5,6,40;

С = 2,3,20Е-6; ’ЕМКОСТЬ КОРРЕКЦИИ5 Е = 0,6,10! 0,7,-10! ’ИСТОЧНИКИ ПИТАНИЯ’

0,1,0,0,1; ’ВХОДНОЙ СИГНАЛ’

При описании активных компонентов целесообразно использовать ссылки к параметрам, значения которых хранятся в базе данных системы. Описание транзисторов схемы (см. рис. 1.2) имеет вид

Т = 1,2,4,К198НТ1! 0,3,4,К198НТ1! 5,4,7,К198НТ1!

5,5,7,К198НТ1;

Если параметры компонента отсутствуют в базе данных системы, то для сокращения объема описания целесообразно использовать именованные группы параметров, называемые также описателями:

<имя описателя > = < список параметров >;

Например:

К198НТ1 = 1, 1.3Е-10, 152, 3, 0.06, 1Е4, 1Е4, 7Е-6, 12Е-6, 3.7Е-6, 1.2Е-5, 0.65, 0.7, 0.34, 0.32;

В описателе последовательно задаются параметры транзистора: тип проводимости, ток отсечки 7S, коэффициент усиления Вп и т. д. (см. приложение 1).

Для успешной работы пакетов прикладных программ необходимо предварительно определить условия выполнения анализа и указать выходные координаты схемы, значения которых будут выводиться на внешнее устройство в процессе расчета. Например, переменные STEP и NY задают начальный шаг интегрирования и выходной узел анализируемой схемы. По умолчанию в системе принято STEP=1 мкс и NY=2. Для схемы (см. рис. 1.2) необходимо переназначить выходной узел: NY=3.

Задание списка частот /i, /2, ..., /«, на которых требуется исследовать проектируемую схему в рамках пакетов программ “Частота” и “Чувствительность”, производится следующим образом:

F=/i, /2, ..., fn; или FD=FN, FK, SF; или FDL=FN, FK, NFD;

Здесь /i, /2, ..., fn — значения частот в кГц, FN и FK- начальное и конечное значения частот линейного (FD) или логарифмического (FDL) диапазонов частот в кГц, SF—шаг в кГц, с которым производится приращение частоты внутри диапазона, NFD — число частотных точек на декаду изменения частоты, в которых необходимо провести анализ. Например, для схемы (см. рис. 1.2) можно задать: FDL=0.01, ЗЕЗ, 3;

Описание схемы завершается служебным словом “КОНЕЦ” (допустимо сокращение “К”), после которого любой текст игнорируется транслятором.

Основными элементами языка описания схемы системы ЭМЦ являются структуры, массивы и директивы [5].

20

, Рассмотрим пример подготовки описания схемы (см. рис. 1.2) для ее анализа в системе ЭМЦ. Для идентификации схемы и разработчика используются директивы “СХЕМА” и “РАЗРАБОТЧИК”:

СХЕМА: ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ; РАЗРАБОТЧИК: ИВАНОВ А. А.;

Информация о компонентах схемы записывается в виде структуры с именем “ОПИСАНИЕ”. Внутри структуры рписания отдельных компонентов разделяются точкой с запятой. В последней строке после точки с запятой ставится символ имеющий значение “конец описания структуры”. Для описания каждого компонента необходимо составить отдельное предложение, включающее в себя имя модели, узлы подключения, номинал или параметры модели. Если требуемый компонент представлен в базе данных системы, достаточно указать лишь его тип. В качестве разделителей в предложениях допускается использование пробелов, запятых, звездочек, открывающих и закрывающих скобок. В любом месте текста описания схемы допускается записывать комментарий, заключенный в апострофы.

Имена видов компонентов и порядок записи узлов включения компонентов различного вида совпадают с именами и порядком записи, принятыми в системе ДИСП. Модели компонентов и порядок записи их параметров в системах ЭМЦ и ДИСП также совпадают.

Описание компонентов схемы (см. рис. 1.2) на входном языке системы ЭМЦ имеет вид:

ОПИСАНИЕ:

Rl(2,6) 15К; R2(3,6) 15К; R3(5,6) 20К;

Cl(2,3) 20Е-6;

Tl(l,2,4) 198НТ1; Т2(0,3,4) 198НТ1;

Т3(5,4,7) 198НТ1; Т4(5,5,7) 198НТ1;

Е1(0,1) OB; Е2(0,6) 10В; Е3(0,7) - 10В;*

Для облегчения описания схемы на входном языке целесообразно в описании компонентов использовать ключевые слова: ТИП = < имя типа >

МОДЕЛЬ = < имя модели >

ПАРМ = (< список параметров модели >)

РЕЖИМ = (<режим по постоянному току>) например,

Т1 (1,3,4) ТИП = 198НТ1; или Т5 (8,4,10) ПАРМ = (0,1.3Е-10,

0.025, 152, 10 ...);

Если на входном языке заданы имя типа и параметры модели, то имя типа игнорируется и обращение к базе данных не проводится.

Для вызова пакетов прикладных программ достаточно после описания схемы указать символическое имя, например: СТАТИКА; — расчет статического режима схемы

21

ЧАСТОТА 1; — расчет частотных характеристик ОПТЧХ; — оптимизация частотных характеристик

При обнаружении имени пакета прикладных программ дальнейшая трансляция текста описания схемы приостанавливается и выполняется соответствующий вид анализа. Перечень массивов и структур, необходимый для проведения каждого вида анализа, приведен в работе [5]. Например, для анализа частотных характеристик необходимо задать массив идентификаторов схемных функций, массив внешних узлов схемы и массив частот:

CO=KU, ZBX, ZBbIX; МВУ=1, 0, 2, 0; ЧАСТОТА: 3, 10, 30, 100, 300;

Имя пакета прикладных программ может быть указано в тексте описания схемы несколько раз, например, для проведения многовариантного анализа характеристик схемы.

Директива “ИЗМЕНИТЬ” (допустимо сокращение имени “ИЗМ”) позволяет изменять элементы структур описания схемы и задания на оптимизацию. Формат директивы:

ИЗМЕНИТЬ <имя структуры >: <вид и номер компонента > < ключевое слово > = < новое значение>, < ключевое слово > = < новое значением..;*

Ключевые слова: УЗЛЫ, ТИП, МОДЕЛЬ, ПАРМ, РЕЖИМ. Например, в схеме (см. рис. 1.2) необходимо изменить значение емкости конденсатора С1 и соединить базу транзистора VT2 с источником сигнала Е1:

ИЗМЕНИТЬ ОПИСАНИЕ:

С1=40Е-6; Т2 УЗЛЫ=(1, 3, 4);

По директиве “КОНЕЦ” обработка текста описания прекращается.

Описание задания на оптилшзацию в системах ДИСП и ЭМЦ включает в себя прежде всего описание варьируемых параметров компонентов и описание оптимизируемых характеристик и критериев оптимальности. Описание каждого из варьируемых параметров должно содержать имя компонента схемы, границы вариации и начальное приближение параметра. В соответствии с принятой во входном языке системы ДИСП формой представления исходных данных для описания варьируемых параметров используется массив с именем VARP:

VARP=< нижняя граница вариации >, < верхняя граница вариации>, {<начальное приближение^*}, <имя компонента >, <имя параметра модели компонента >! {< описание других варьируемых параметров > };

Здесь в фигурных скобках указаны необязательные элементы синтаксиса. В частности, если не указано начальное приближение, то за его значение будет принята середина интервала вариации. Например, запись

VARP = 5, 20, 10, Rl, R! 5Е-6, 40Е-6, Cl, С! 50, 150, 100, Tl, BN;

22

Таблица 1.1

Вид критерия оптимизации

Обозначение на входном языке

Число желаемых значений

Минимизация значений характеристики

MIN

0

Максимизация значений характеристики

МАХ

0

Среднее квадратическое отклонение от желаемой характеристики:

минимизация

MINCKO

1

максимизация

МАХСКО

1

Принадлежность зоне, заданной верхней

и нижней границами

ZONE

2

Превышение заданного уровня

EXCEED

1

Непревышение заданного уровня

UNEXCEED

1

Сдвиг по вертикали

SHIFT

1

Линейность характеристики

LIN

0

Пропорциональность по вертикали

PROP

1

означает, что варьируется сопротивление резистора R1 в пределах от 5 до 20 кОм, с начальным приближением 10 кОм, емкость конденсатора С1 в границах от 5 до 40 пФ с начальным приближением 17,5 пФ и коэффициент усиления BN биполярного транзистора 77 в границах от 50 до 150 с начальным значением 100.

Для описания критериев оптимальности и оптимизируемых характеристик используется предложение

<имя критерия> {[<число частичных сумм>, <число описателей каждой суммы > ]} = < значение частоты >, <желаемое значение 1>, {<желаемое значение 2>}, {< весовой коэффициент}, {<имя схемной функ- ции>}, {<описание других частичных сумм>};

Здесь < имя критерия > — одно из имен критериев оптимальности, приведенных в табл. 1.1. Число желаемых значений изменяется в зависимости от вида критерия оптимальности. Так, для критерия минимизации схемной функции желаемое значение отсутствует. В случае использования критерия “принадлежность зоне” необходимо указать нижнюю и верхнюю границы зоны, т. е. число желаемых значений равно двум.

Таблица 1.2

Тип схемной

Схемная функция

функции

«и

гъх

■^вых. К. 3

2ВЫХ. XX

Модуль Модуль, дБ Фаза

Вещественная часть Мнимая часть

мки

МДБКи

OKU

REKU

IMKU

MZBX

мдвгвх

Фгвх

REZBX

IMZBX

мгвыхкз

мдвгвыхкз

Фгвыхкз

REZBbIXK3

IMZBbIXK3

MZBbIXXX

MflBZBbIXXX

Фгвыххх

REZBbIXXX

IMZBbIXXX

23

Весовой коэффициент, характеризующий степень влияния данной частотной точки, является необязательным элементом предложения и имеет значение по умолчанию, равное 1. Именем схемной, функции может быть любое из имен, приведенных в табл. 1.2. Например, запись

MINCKO = (U, 60, 1, MDBKU! 1, 40, 1! 10, 220, 5! 100, 0, 10! 1000, -20, 5;

означает, что требуется оптимизировать модуль коэффициента передачи по напряжению в децибелах (MDBKU) на частотах 0,1; 1; 10; 100; 1000 кГц по критерию минимизации среднеквадратичного отклонения от желаемых значений 60, 40, 20, 0, —20 дБ с весовыми коэффициентами, соответственно равными 1, 1, 5, 10, 5. В данном примере параметры < число частичных сумм> и < число описателей каждой суммы > опущены, а описания отдельных частичных сумм отделяются восклицательными знаками. Заметим также, что имя схемной функции указано только для первой частичной суммы, а для последующих его можно опустить, при этом принимается имя схемной функции, указанное в первой строке описания.

Метод оптимизации указывается пользователем путем выбора соответствующей проектной процедуры в подсистеме оптимизации. Константы настройки метода задаются в режиме диалога после инициализации программы оптимизации, реализующей указанный пользователем метод.

ГЛАВА ВТОРАЯ

МЕТОДОЛОГИЯ АВТОМАТИЗИРОВАННОГО СХЕМОТЕХНИЧЕСКОГО ПРОЕКТИРОВАНИЯ АНАЛОГОВЫХ МИКРОЭЛЕКТРОННЫХ УСТРОЙСТВ

2.1. Общие сведения

Автоматизированное схемотехническое проектирование аналоговых электронных устройств связано с определенными трудностями, обусловленными высокой степенью неоднородности параметров их элементов. Действительно, во многих случаях аналоговая схема, содержащая сотни компонентов, может не иметь двух одинаковых по параметрам. В настоящее время не удается осуществить полную автоматизацию проектирования аналоговых микроэлектронных устройств, т. е. их проектирование без участия человека, особенно при решении задач схемотехнического синтеза. Однако при максимальном использовании квалификации разработчика и осуществлении тесного взаимодействия между разработчиком

24

и ЭВМ задачи структурного и параметрического схемотехнического синтеза могут быть успешно решены. Этому во многом способствует комплекс оптимизационных программ, имеющихся в современных САПР РЭА.

При проектировании сложных аналоговых электронных устройств используется системный подход, базирующийся на теории многоуровневых иерархических систем. При этом проектируемое электронное устройство рассматривается как система, которую можно разделить на подсистемы более низкого порядка. Подсистемами самого низкого порядка являются элементы, внутренняя структура которых не представляет интереса, однако их свойства влияют на проектируемую систему. Каждая система, в свою очередь, является подсистемой системы более высокого порядка. Однако в процессе автоматизированного проектирования сложных объектов нет необходимости строить всю иерархию систем, в нее целесообразно, как правило, включать только системы и подсистемы на два порядка выше и ниже проектируемой, существенно с ней связанные [7].

В соответствии с системным подходом осуществляется декомпозиция процесса проектирования сложных электронных устройств, т. е. разбиение общей задачи на составные части. При этом весь процесс проектирования подразделяется на несколько иерархических уровней. Каждому уровню соответствует свое определение системы и элемента. Части объекта, рассматриваемые как элементы на некотором к-м уровне, описываются как системы на соседнем более низком (к+ 1)-м уровне [6].

В качестве примера рассмотрим иерархическую структуру систем и подсистем при проектировании интегрального стабилизатора напряжения (ИСН), входящего в состав цветного телевизора:

1. Цветной телевизор;

2. Источник вторичного электропитания цветного телевизора;

3. Интегральный стабилизатор напряжения (проектируемая система);

4. Функциональные подсхемы ИСН (регулирующий элемент, источник опорного напряжения и т. д.);

5. Компоненты схемы (резисторы, транзисторы и т. д.).

Рассмотрение систем пп. 1 и 2, имеющих более высокий

порядок, чем проектируемая система, необходимо для составления грамотного технического задания (ТЗ) на проектируемый ИСН. Системы пп. 4 и 5, более низкого порядка, чем проектируемая, определяют иерархические уровни процесса проектирования. Так, при проектировании функциональной схемы электронного устройства ИСН является системой, а функциональные подсхемы — элементами (подсистемами); при

25

проектировании функциональной подсхемы стабилизатора она представляет собой систему, а в качестве элементов системы выступают компоненты схемы. При схемотехническом проектировании ИСН, как правило, не нужно подробно исследовать внутреннюю структуру компонентов схемы (транзисторов, резисторов, конденсаторов), но необходимо иметь четкое представление об ограничениях на параметры компонентов, о паразитных связях между ними, обусловленных полупроводниковой интегральной технологией.

В процессе автоматизированного проектирования аналоговой микроэлектронной аппаратуры, как правило, используются элементы как нисходящего, так и восходящего проектирования. При этом восходящее проектирование (снизу вверх) характеризуется решением задач более низких иерархических уровней перед решением задач более высоких уровней. Противоположная последовательность приводит к нисходящему проектированию [6].

2.2. Типовой маршрут процесса автоматизированного схемотехнического проектирования

Процесс автоматизированного схемотехнического проектирования электронных устройств реализуется в соответствии с определенным планом, который можно представить в виде логического графа (маршрута проектирования, логической схемы), отображающего очередность выполнения основных проектных процедур и операций [7]. При построении маршрута проектирования представляется целесообразным сформулировать рекомендации по разделению функций разработчика и ЭВМ на различных этапах схемотехнического проектирования.

Для аналоговых микроэлектронных устройств, проектируемых с использованием метода подсхем, можно предложить маршрут проектирования, представленный на рис. 2.1. Этот маршрут соответствует следующей иерархической структуре систем и подсистем проектируемого объекта: аналоговое устройство (АУ) функциональные подсхемы (ФП) компоненты (транзисторы, резисторы и т. д.). В процессе автоматизированного проектирования АУ целесообразно выделить три уровня: 1) проектирование функциональной схемы (ФС) (АУ — система, ФП — элементы системы); 2) проектирование функциональных подсхем (ФП — система, ее компоненты — элементы системы); 3) проектирование принципиальной схемы (ПС) (АУ — система, его компоненты — элементы системы).

Почему процесс автоматизированного проектирования АУ недостаточно полно охватывается первым и вторым иерархическими уровнями? Это обусловлено тем, что реальные АУ, как

26

27

правило, только в первом приближении при значительном их упрощении можно разбить на несколько слабо связанных между собой функциональных подсхем. Так, например, в интегральных операционных усилителях и стабилизаторах напряжения во многих случаях удается выделить функциональные подсхемы, только исключив из рассмотрения множество цепей, образующих дополнительные связи (цепи коррекции и защиты, общие цепи задания статического режима и т. д.). Поэтому автоматизированное проектирование АУ на третьем уровне, позволяющее учесть все многообразие реальных связей в принципиальной схеме, представляется совершенно необходимым.

Маршрут проектирования (см. рис. 2.1) отражает проектные процедуры и операции на первом и третьем уровнях проектирования. При этом предполагается, что большинство задач второго уровня (проектирование ФП) решается на стадии формирования банка схемных решений ФП.

Рассмотрим уровень проектирования функциональной схемы АУ (см. рис. 2.1, блоки 1...7). По результатам проектирования на более высоком иерархическом уровне формируется ТЗ на разработку АУ. Сначала разработчиком синтезируется первоначальный вариант ФС и рассчитываются исходные значения параметров ФП (на основании банка схемных решений, собственных оригинальных исследований и т. д.). Потом автоматизированными методами анализируются определяющие характеристики ФС (например, проводится расчет схемных функций ФС с использованием пакета программ “Частота”): Предположим, что в результате анализа ФС требования ТЗ оказываются невыполненными. В этом случае можно: 1) изменить параметры ФП и снова повторить анализ (цикл параметрического синтеза ФС —рис. 2.1, блоки 3...6); 2) перейти к другой ФС и провести анализ ее основных характеристик (цикл структурного синтеза ФС —рис. 2.1, блоки 2...5, 7); 3) осуществить корректировку ТЗ.

Следует отметить, что целесообразно переходить к другой ФС только в том случае, если несмотря на множество итераций исчерпаны все возможности получения положительного проектного решения в цикле параметрического синтеза исследуемой ФС. Очевидно, что если вся совокупность ФС, которой располагает разработчик, не обеспечивает основных характеристик проектируемого АУ, то необходимо корректировать ТЗ.

На уровне проектирования функциональных схем АУ можно широко использовать схемотехнические САПР, в частности ДИСП и ЭМЦ. Это обусловлено тем, что, во-первых, эти САПР располагают базой данных моделей компонентов (БДМК), удобной для математического описания функциональных подсхем АУ, во-вторых, например, САПР ДИСП и ЭМЦ имеют комплекс программ “Оптимизация”, позво¬

28

ляющий осуществить автоматизированный параметрический синтез ФС. Действительно, для математического описания большого числа различных функциональных подсхем АУ удобно использовать макромодель операционного усилителя, которая имеется в БДМК учебно-исследовательских САПР ДИСП и ЭМЦ.

Процесс автоматизированного схемотехнического проектирования на первом уровне продолжается до тех пор, пока не будет синтезирована приемлемая функциональная схема АУ. При этом становятся известными значения выходных параметров функциональных подсхем, которые удовлетворяют требованиям ТЗ на проектируемое АУ. На основании этих значений разработчиком из банка схемных решений выбираются ФП проектируемого АУ и синтезируется первоначальный вариант принципиальной схемы (ПС). Таким образом, использование автоматизированных проектных процедур параметрического синтеза, которыми располагают схемотехнические САПР, позволяет исключить трудоемкую задачу последовательного перебора всех схем ФП, составляющих банк схемных решений.

На уровне автоматизированного проектирования принципиальной схемы АУ (см. рис. 2.1, основные блоки 8...14) можно выделить циклы: 1) параметрического синтеза ПС (блоки

9.. .12); 2) структурного синтеза ПС (блоки 8...11, 13); 3) изменения ФС или корректировки ТЗ (блоки 5...12, 13, 6, 3, 4 или блоки 8... 11, 13, 6, 3, 4, 5, 7, 2, 3, 4 или блоки

8.. .11, 13, 6, 3, 4, 5, 7, 1, 2, 3, 4).

Очевидно, что изменять структуру ПС целесообразно, исчерпав все возможности ее параметрического синтеза для получения приемлемого проектного решения. Если все многообразие ПС проектируемого АУ, известных разработчику, не удовлетворяет требованиям ТЗ по каким-то параметрам, то может возникнуть необходимость снова ввести изменения в ФС или даже скорректировать ТЗ.

На этом уровне проектирования с максимальным использованием возможностей схемотехнических САПР не только анализируются определяющие характеристики ПС, но и решаются задачи их оптимизации, осуществляются поверочные расчеты всех параметров АУ, определяются диапазоны их изменения. Большое внимание здесь уделяется определению параметров элементов, формирующих заданные динамические свойства АУ. Как правило, именно на уровне автоматизированного проектирования ПС определяются параметры корректирующих цепей, обеспечивающих устойчивость АУ и заданное качество переходного процесса на его выходе. Следует отметить, что в маршруте проектирования (см. рис. 2.1) циклы параметрической и структурной оптимизации ПС и ФС совпадают с циклами параметрического и структурного синтеза этих схем.

29

Каково соотношение ролей разработчика и ЭВМ в процессе автоматизированного схемотехнического проектирования АУ? При решении задач структурного синтеза ФС и ПС, характеризующихся большим числом неформальных операций, основная роль принадлежит разработчику, ведущему проектирование с учетом банка схемных решений. Это обусловлено тем, что в настоящее время в схемотехнических САПР ДИСП и ЭМЦ отсутствуют программы структурного синтеза АУ. Напротив, большинство задач параметрического синтеза и параметрической оптимизации ФС и ПС, задачи анализа, поверочные расчеты решаются, как правило, автоматизированными методами. Так, например, использование программных комплексов “Статика” и “Нестабильность” систем ДИСП и ЭМЦ позволяет определить область разброса координат статического режима АУ; применение программных комплексов “Частота”, “Чувствительность” — оценить влияние разброса параметров компонентов ПС на разброс схемных функций АУ, на его устойчивость и т. д. При оценке влияния паразитных связей, вносимых полупроводниковой интегральной технологией, на основные параметры микроэлектронного АУ особенно важна способность учебно-исследовательских САПР ЭМЦ и ДИСП быстро анализировать сложные схемы в частотной области.

2.3. Методика формирования банка схемных решений

Применение в процессе автоматизированного проектирования АУ банка типовых схемных решений значительно расширяет информационные возможности разработчика, концентрирует его внимание на лучших схемных решениях, известных в мировой практике. При этом удается повысить качество проектных решений, значительно сократить сроки автоматизированного проектирования, а также снизить требования, предъявляемые к квалификации разработчика АУ в области схемотехники.

В состав банка схемных решений (БСР) могут входить наборы принципиальных схем АУ, разработанных ранее, а также наборы функциональных схем АУ и схемных решений их функциональных подсхем, известных разработчику БСР. Каждая схема в БСР характеризуется численными значениями ее основных параметров. Очевидно, что разработчик АУ, получив ТЗ на его реализацию, должен прежде всего внимательно просмотреть готовые ПС уже спроектированных АУ, имеющиеся в БСР, и только убедившись, что ни одна из них не удовлетворяет требованиям ТЗ, он может начинать самостоятельное проектирование.

30

Рассмотрим процесс формирования в БСР самого большого набора — набора схемных решений функциональных подсхем АУ. В этом процессе можно выделить следующие этапы:

1. Формирование начального набора схемных решений ФП;

2. Расчет статического режима ФП и его нестабильности;

3. Определение параметров макромоделей ФП;

4. Экспертная оценка свойств ФП по их основным параметрам;

5. Корректировка набора схемных решений ФП;

6. Выявление зависимостей параметров макромодели ФП от изменения статического режима;

7. Составление паспорта на схемные решения ФП;

8. Занесение информации в ЭВМ.

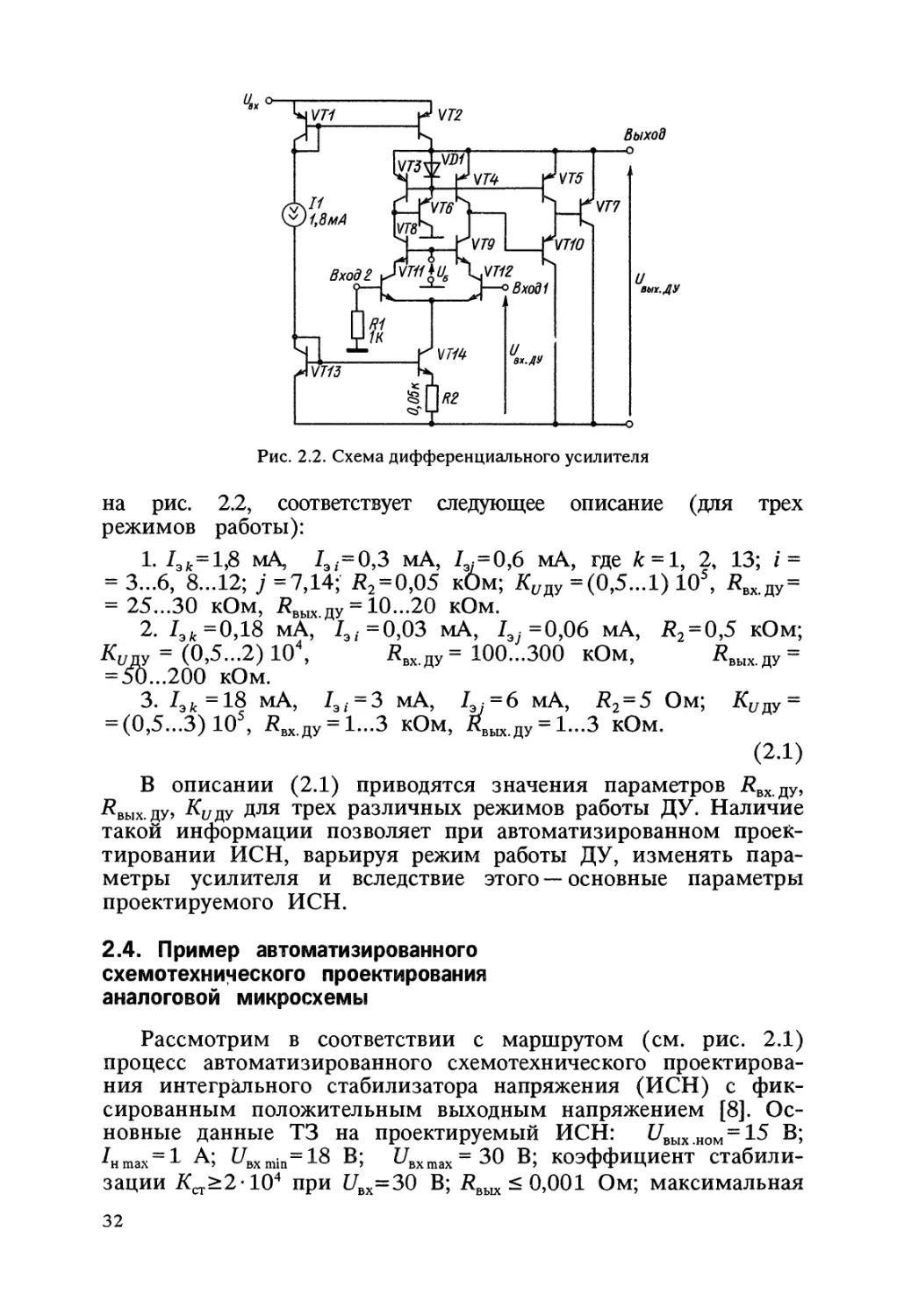

В качестве примера рассмотрим процесс формирования в БСР набора дифференциальных усилителей (ДУ) сигнала рассогласования (функциональные подсхемы интегральных стабилизаторов напряжения). Предположим, что на основании литературных источников разработчик БСР выбрал 20 схемных решений ДУ (первый этап). На втором этапе ему необходимо с использованием пакетов программ “Статика” и “Нестабильность” систем ДИСП или ЭМЦ провести расчет статического режима этих схем, определив сопротивления резисторов. При этом целесообразно для различных схем ДУ задавать одинаковые или близкие режимы по току тех транзисторов, которые определяют основные параметры усилителя. Выполнение этого условия делает правомочным проведение сравнительной характеристики ДУ по этим параметрам. На третьем этапе с использованием пакета программ “Частота” определяются параметры макромоделей всех схемных решений ДУ (входное сопротивление ЯвхДУ, выходное сопротивление i?BbIX ду, коэффициент усиления по напряжению ^ду), а на четвертом этапе разработчик БСР проводит по этим параметрам сравнительную характеристику (экспертную оценку) свойств усилителей. В результате этой экспертной оценки корректируется набор схемных решений ДУ (пятый этап), т. е. исключаются решения, в которых сложность схемной реализации не приводит к улучшению их параметров (устаревшие схемы). Таким образом, из 20 схем ДУ окончательно в БСР могут войти, например, 5...10 схем. Для схем ДУ, вошедших в банк, целесообразно с использованием ЭВМ выявить зависимость их параметров от изменений статического режима, для чего эти параметры определяются при нескольких значениях эмиттер- ных токов входных транзисторов ДУ (шестой этап).

Формирование разработчиком БСР набора схемных решений ДУ заканчивается составлением паспорта (седьмой этап), который включает в себя принципиальную схему усилителя и ее краткое описание. Например, схеме ДУ, представленной

31

Рис. 2.2. Схема дифференциального усилителя

на рис. 2.2, соответствует следующее описание (для трех режимов работы):

1. 1эк=1,8 мА, 1эг = 0,3 мА, /э/=0,6 мА, где к = 1, 2, 13; / =

= 3...6, 8...12; j =7,14; ~0,05 ким; 2С^дУ =(0,5...1) 10 , -КВх.ду =

= 25...30 кОм, RBbIX Ду = 10...20 кОм.

2. /э/с=0,18 мА, /э/=0,03 мА, /эу =0,06 мА, jR2 = 0,5 кОм;

Кипу = (0,5...2) 10 , ^вх.ду= 100...300 кОм, Двых. ду =

= 50...200 кОм.

3. Lk = 18 мА, L: = 3 мА, L • = 6 мА, i?2 = 5 Ом; iC7 пу = -(0,5..3)10s, Я„.д,-1...3 КОМ, $вых.ду = 1—3 кОм.

(2.1)

В описании (2.1) приводятся значения параметров #вх.ду, ^вых ду» Киду Для трех различных режимов работы ДУ. Наличие такой информации позволяет при автоматизированном проектировании ИСН, варьируя режим работы ДУ, изменять параметры усилителя и вследствие этого — основные параметры проектируемого ИСН.

2.4. Пример автоматизированного схемотехнического проектирования аналоговой микросхемы

Рассмотрим в соответствии с маршрутом (см. рис. 2.1) процесс автоматизированного схемотехнического проектирования интегрального стабилизатора напряжения (ИСН) с фиксированным положительным выходным напряжением [8]. Основные данные ТЗ на проектируемый ИСН: UBblX ii0M = 15 В;

4max = 1 A; C/Bxmin= 18 В; t/Bxmax = 30 В; коэффициент стабилизации Кст>2 • 104 при £/вх=30 В; Яъых < 0,001 Ом; максимальная

32

мощность рассеяния на стабилизаторе Рсттах ^ 20 Вт; ток нагрузки при срабатывании цепи защиты 1,6 А> /н к з> 1,2 А; коэффициент полезного действия стабилизатора rj =РВЬ1Х/РВХ> >0,7 при t/BX=18 В,

Процесс проектирования представим в виде совокупности задач, решаемых разработчиком в тесном взаимодействии с ЭВМ и БСР, при этом используем учебно-исследовательскую САПР ЭМЦ. Рассмотрим основные задачи на уровне автоматизированного проектирования функциональной схемы ИСЫ.

Задача 2.1. Выбрать функциональную схему ИСН (структурный синтез ФС, см. рис. 2.1, блок 2).

Проектируемый ИСН является высококачественным стабилизатором по точностным параметрам КСТ и RBblx, а также имеет сравнительно высокий КПД. Известно, что такие параметры удается обеспечить в непрерывных компенсационных стабилизаторах напряжения с последовательным включением регулирующего элемента. Поэтому выбираем типовую функциональную схему ИСН, соответствующую стабилизаторам этого подкласса (рис. 2.3). В этой ФС для повышения коэффициента стабилизации Кст подключаем ИОН к выходу стабилизатора.

Задача 2.2. Привести ФС (рис. 2.3) к виду, удобному для автоматизированного проектирования.

При автоматизированном исследовании ФС ограничимся основной проектной процедурой — определением таких значений параметров ДУ, при которых обеспечиваются заданные точностные параметры Кст и RBblx стабилизатора. В этом случае можно упростить ФС, исключив из нее УЗСР и совместив друг с другом функциональные подсхемы ИТ и ДУ. Для достаточно простых функциональных подсхем РЭ и ДН нецелесообразно вводить специальные макромодели, гораздо проще их представить на схемном уровне. При этом ФС (рис. 2.3) можно заменить эквивалентной схемой (рис. 2.4), удобной для автоматизированного проектирования. В этой схеме VT1, VT2, R1 — типовой РЭ стабилизатора, представляющий собой составной транзистор; #2, R4 — ДН, сопротивления которого легко определить по известным напряжениям £/вых ном=15 В; 1/оп« 1,2 В, задав ток ДН: IR2 = IR4=3 мА; R3=RH=UBbIx.HOM/IHmax Следует от- метить, что в схеме (см. рис. 2.4) ДУ характеризуется макромоделью ОУ с большим коэффициентом передачи по напряжению (KUDA2 > > ИОН — макромоделью ОУ с малым коэффициентом передачи (KUDAJ < < 1).

Две последующие задачи характеризуют цикл автоматизированного параметрического синтеза ФС (см. рис. 2.1, блоки 3...6).

Задача 2.3. Определить такой минимальный коэффициент усиления по напряжению ДУ KudA2, при котором обеспечи-

2-1586

33

Рис. 2.3. Функциональная схема интегрального стабилизатора напряжения

РЭ — регулирующий элемент; ДУ — дифференциальный усилитель сигнала рассогласования; ИОН — источник опорного напряжения £/оп; ДН — делитель выходного напряжения; ЯГ—источник тока; УЗСР — узел задания статического режима; /?н — сопротивление нагрузки

вается заданный коэффициент стабилизации Кст ИСН (см. рис. 2.4).

Коэффициент стабилизации ИСН Кст = (Д£/вх/Д£/вых) х x(UBblx/UBX) связан с коэффициентом передачи стабилизатора по напряжению Kv очевидным соотношением:

TS ^^ВЫХ

Л,г =

A

(2.2)

В соответствии с выражением (2.2) на основании данных ТЗ получаем желаемое значение параметра 0,25* 1СГ4.

Для данного случая при решении задачи параметрического синтеза в качестве целевой функции принимаем критерий минимального среднего квадратического отклонения (1.2), а именно:

^2 i^UDAl) = т^П \Кц O^UDAl) ^{/] > (2.3)

где Кц^Кцрм) — функция от аргумента KUDA2.

Таким образом, при автоматизированном решении этой задачи с использованием пакета программ "Оптимизация" определяется такое значение варьируемого параметра KUDA2, при котором обеспечивается желаемое значение параметра Кц стабилизатора (2.3).

Рис. 2.4. Функциональная схема стабилизатора, используемая при автоматизированном проектировании

34

При этом разработчик ИСН задает пределы, в которых варьируется параметр KUDA2 (103...106) и его начальное значение (5-103). В этом случае разработчик не имеет достаточной информации о схеме, поэтому диапазон варьирования параметра Kuda2 выбирается очень широким. При уменьшении этого диапазона, как правило, сокращается длительность оптимизационной процедуры, но при этом разработчик должен располагать предварительной информацией о том, что требуемое значение параметра находится внутри этого узкого диапазона.

Сформируем для решения поставленной задачи исходное задание на входном языке системы ЭМЦ. При этом считаем, что сопротивления резисторов схемы определены по результатам задачи 2.2, а мощные интегральные транзисторы VT1 и VT2 имеют следующие параметры: (32=100, #б2 = 0,1 кОм, R32 = 1 Ом, Rk2 = 500 кОм, рх = 50, i?61 = 0,01 кОм, Лэ1 = 0,1 Ом, i?Kl = 10 кОм. В качестве источника опорного напряжения (DA1) из БСР выбираем схему с параметрами: RbxDA1 = 7 кОм, i?BbixiMi = 0>05 кОм, Kudai = 0,01; для ДУ сигнала рассогласования (DA2), выбор которого предстоит сделать, задаем типовые значения параметров: ДвхО42 = 30 кОм; RBMX da2 = 20 кОм.

Исходное задание:

СХЕМА СТАБИЛИЗАТОР - ФС1; ОПИСАНИЕ: Rl(5,2) 05; R2(2,6) 4.6; R3(2,0)15 ОМ; R4(6,0)0.4; T2(4,l,5) ПАРМ = (100,0.1,10м,500,0,0); Т1(5,1,2) ПАРМ = (50,

0.01,0.ЮМ, 10,0,0); DA1(0,2,3) МОД=ОУЛ, ПАРМ = (7,

0.05,0.01,0,0,0); DA2(6,3,4) МОД = ОУЛ, ПАРМ = (30,20, 0,0,0,0); *NN=6; МВУ=1,0,2,0; ОПТИМИЗИРОВАТЬ: MIN CKO KU(A4X) = 0.25Е — 4; *ЧАСТОТА=0; ВАРЬИРОВАТЬ: DA2/#3/5000 (1ЕЗДЕ6); *ОПТЧХ; КОНЕЦ;

Результат автоматизированного параметрического синтеза:

ДУ min = KUDA2 = 32 200.

Задача 2.4. Определить такое максимальное выходное сопротивление ДУ Явыхслг* ПРИ котором обеспечивается заданное выходное сопротивление стабилизатора. В схеме на рис. 2.4:

йвых = 10_б кОм.

Целевая функция для данной задачи имеет вид (1.2)

^2 С^выхDA2) = m^n [ZBK3 (RBblxDA2) ~ ^вых] > (^-4)

где ZBK3 (RBblxDA2) - функция от аргумента RBblxDA2.

В этом случае стремимся получить требуемое значение выходного сопротивления ИСН в режиме короткого замыкания входа стабилизатора (ZBK3), варьируя в широких пределах (1(Г2...103 кОм) выходное сопротивление DA2 (RBblxDA2) от начального значения 50 кОм (2.4).

2*

35

Отличие исходного задания для этой задачи от предыдущего состоит в следующем (KUDA2) « 3,2-104):

ОПТИМИЗИРОВАТЬ: MIN CKO ZBK3 (АЧХ) = 1Е-6; ♦ЧАСТОТА=0; ВАРЬИРОВАТЬ: DA2/#2/50 (1Е - 2,

1ЕЗ); *ОПТЧХ; КОНЕЦ

Результат автоматизированного параметрического синтеза:

^выхДУтах ~~ ^bb\xDA2 ~ 20,7 КОМ.

Задача 2.5. Осуществить выбор схемы ДУ (см. рис. 2.3.) из банка схемных решений.

По результатам задач 2.3, 2.4 очевидно, что параметры ДУ (см. рис.2.3) должны удовлетворять условиям:

Киду — К-идутт =3,2* 10 ; ^ 5)

^выхДУ — ^выхДУтах =20,7 Юм.

В соответствии с условием (2.5) выбираем из БСР схему ДУ, приведенную на рис. 2.2 (режим 1).

Таким образом, автоматизированные исследования ФС (задачи 2.3, 2.4) позволяют исключить трудоемкий последовательный перебор всех схем ДУ из БСР на уровне проектирования принципиальной схемы ИСН

Задача 2.6. Осуществить поверочный автоматизированный расчет ФС (см. рис. 2.4) при типовых параметрах ДУ (см. рис. 2.2, Куду—6*10 , ^выхду=^ кОм).

Исходное задание:

ОПИСАНИЕ:

NN=6; СФ = Ки, ZBK3; МВУ=1,0,2,0; ЧАСТОТАМ; ЧАСТОТА 1; КОНЕЦ;

Из задания видно, что для ИСН определяются схемные функции Kv и #Bblx(ZBK3) с использованием пакета программ частотного анализа “Частота Iм.

Результаты автоматизированного расчета: Ки~0,12 -1СГ4 (Кст«4-104), Явых«0,9• 10-6 кОм удовлетворяют требованиям ТЗ.

Задача 2.7. Предположим, что ц результате автоматизированного решения задачи 2.4 все ДУ из БСР не удовлетворяют требованиям по параметру #ВЫхду (2.5). Как выйти из создавшегося затруднения?

В этом случае целесообразно изменить схему РЭ. Действительно, чем больший коэффициент усиления по току имеет РЭ, тем меньше выходное сопротивление ИСН при одном и том же выходном сопротивлении ДУ. Таким образом, используя в качестве РЭ тройной составной транзистор с большим коэффициентом усиления по току, удается выполнить требование ТЗ на ИСН по параметру ЯЪЪ1Х даже при большом выходном сопротивлении ДУ.

36

Вход

Рис; 2.5. Принципальная схема интегрального стабилизатора напряжения

VT3, VT4, R4 — регулирующий элемент; R8, R13 — делитель напряжения; VT20...VT23, R7, R10...R12, — источник опорного напряжения; ГТб...ГТ<5, VT10...VT14, VT16...VT18, VD3,R16 — дифференциальный усилитель сигнала рассогласования; VT1, VT2 — источник тока; КГ5, VD1, VD2, R1,R6, R9 — узел задания статического режима; VT9, VD4,R2,R3, Д5 — цепь защиты стабилизатора по выходному току; VT15;VT19, Дб, R17 — цепь тепловой защиты; Ci, Д/5 — цепь коррекции стабилизатора

Рассмотрим основные задачи на уровне автоматизированного проектирования принципиальной схемы ИСН.

Задача 2.8. По результатам задач 2.1...2.6 выбрать начальный вариант принципиальной схемы ИСН (структурный синтез ПС —рис. 2.1, блок 8).

Проведем синтез начального варианта ПС стабилизатора, взяв за основу ФС (см. рис. 2.3) и выбрав для каждой функциональной подсхемы соответствующую схему из БСР (в частности, ДУ—схема на рис. 2.2, РЭ — схема на составном транзисторе—рис. 2.4). Подробное обоснование выбора схемных решений ИОН, УЗСРи других дополнительных подсхем ИСН приведено в работе [8]. С учетом вышеизложенного получаем принципиальную схему стабилизатора, приведенную на рис. 2.5. Проведем автоматизированными методами анализ устойчивости этого ИСН и синтез его корректирующих цепей (задачи

2.9...2.14).

Задача 2.9. Преобразовать ПС (см. рис. 2.5) к виду, удобному для проведения автоматизированного исследования устойчивости ИСН.

Устойчивость ИСН будем оценивать на основании частотной характеристики петлевого усиления системы 7\> (/со). При построении эквивалентной схемы ИСН для определения его петлевого усиления целесообразно в схеме (см. рис. 2.5)

37

Рис. 2.6. Принципиальная схема, используемая для исследования устойчивости

стабилизатора

отключить делитель #5, R13 от выхода стабилизатора, а также исключить из схемы функциональные подсхемы и компоненты, не оказывающие существенного влияния на параметр 7^0) (УЗСР, ИОН, цепи тепловой и токовой защиты и т. д.). При этом ПС на рис 2.5 преобразуется в схему на рис 2.6, удобную для нахождения петлевого усиления автоматизированными методами,

Tv{j*>) = Um{j»)fUn (/со)

Задача 2.10. Провести автоматизированный расчет частотных характеристик (модуля и фазы) петлевого усиления нескорректированного ИСН (см. рис. 2.6, С2 = 0).

Исходное задание:

СХЕМА СТАБИЛИЗАТОР-ПС1; ОПИСАНИЕ:

NN= 14; СФ = КИ; МВУ = 1,0,2,0; ЧАСТОТА=0.01,

0.1,1,10,30,100,300,1ЕЗ,ЗЕЗ,1Е4; ЧАСТОТА1; КОНЕЦ;

Результаты автоматизированного расчета представлены в табл. 2.1.

Задача 2.11. Почему уже в диапазоне низких частот (f = = 10 Гц) фазовый сдвиг петлевого усиления ИСН (см. рис. 2.6) составляет 180° (см. табл. 2.1)?

Это объясняется тем, что при автоматизированном расчете определяется полный фазовый сдвиг схемы

<Рх = <Р и + <Рд> (2-6)

(где <ри=—180° — фазовый сдвиг, обусловленный инвертировани¬

38

ем схемой входного сигнала; (рд —дополнительный фазовый сдвиг, обусловленный реактивными компонентами схемы, а также инерционностью ее активных компонентов.

Действительно, в схеме на рис. 2.6 инвертируется фаза входного сигнала. Так, если будем рассматривать в этой схеме путь пердачи сигнала от входа до выхода: VI15 (общий эмиттер) — VT13 (общая база) — VT11—VT9—VT3—VT8 (общие коллекторы), то убедимся, что транзистор VT15 инвертирует фазу входного сигнала.

Задача 2,12. На основании результатов предыдущей задачи (см. табл. 2.1) оценить, устойчив или нет нескорректированный ИСН.

По критерию Найквиста для устойчивости электронного устройства с цепью общей отрицательной обратной связи необходимо, чтобы на частоте среза петлевого усиления системы, где его модуль равен 1(0 ДБ), абсолютное значение дополнительного фазового сдвига петлевого усиления <рд (без учета инвертирования) было меньше 180°. Из рассмотрения табл. 2.1 очевидно, что это условие не выполняется, следовательно, нескорректированный ИСН неустойчив, а значит необходимо решать задачу обеспечения его устойчивости путем введения корректирующих цепей.

Задача 2.13. Определить параметры корректирующей цеи ИСН (см. рис. 2.6), при которых обеспечивается его устойчивость (параметрический синтез ПС —рис. 2.1, блоки 9... 12).

В ИСН вводим корректирующую цепь C2,R3 и осуществляем ее автоматизированный параметрический синтез, варьируя сопротивление R3 в пределах 1,01...100 кОм, а емкость С2 в пределах 1(Г6...1(Г2 мкФ; начальные значения: R3 = l кОм, С2 = 1 нФ.

При вариации параметров R3, С2, стремимся получить желаемую частотную характеристику модуля петлевого усиления в децибелах (KU (АЧХБД)). Зададим эту характеристику четырьмя точками частотного диапазона, для каждой

Таблица 2.1

Частота, кГц

Нескорректированный ИСН

Скорректированный ИСН

Модуль, дБ

Фаза, ...°

Модуль, дБ

Фаза, ...°

0,01

86

-180

79

-244

0,1

86

-180

59

-267

1

86

-187

39

-269

10

82

-239

19

-270

30

74

-284

10

-272

100

59

-337

-0,4

-277

300

40

-27

-9

-293

1000

14

-94

-14

-347

3000

-17

-179

-19

-166

10 000

-62

-291

-55

-303

39

из которых определена приемлемая зона модуля петлевого усиления: / = 1 кГц, LT(/) = 20 lg |7/(//) I =39...41 дБ; /=

= 10 кГц Lr(f) = 19...21 дБ;/ = 100 кГц; LT(/)=-1...1 дБ;/=300 кГц, LT(f) =—11...—9 дБ. Желаемая частотная характеристика имеет наклон —20 дБ/дек около частоты среза петлевого усиления, что позволяет реализовать устойчивую систему и обеспечить сравнительно большой запас устойчивости по фазе (в несколько десятков градусов).

Следует отметить, что задание зоны для желаемой частотной характеристики во многих случаях обеспечивает более быстрое решение задачи автоматизированного параметрического синтеза по сравнению с заданием этой характеристики в однозначном виде. В исходном положении для каждой точки частотного диапазона указывается также вес, характеризующий ее значение (3; 3; 3; 1); при этом наименее важной является четвертая точка.

Исходное задание:

ОИСАНИЕ:

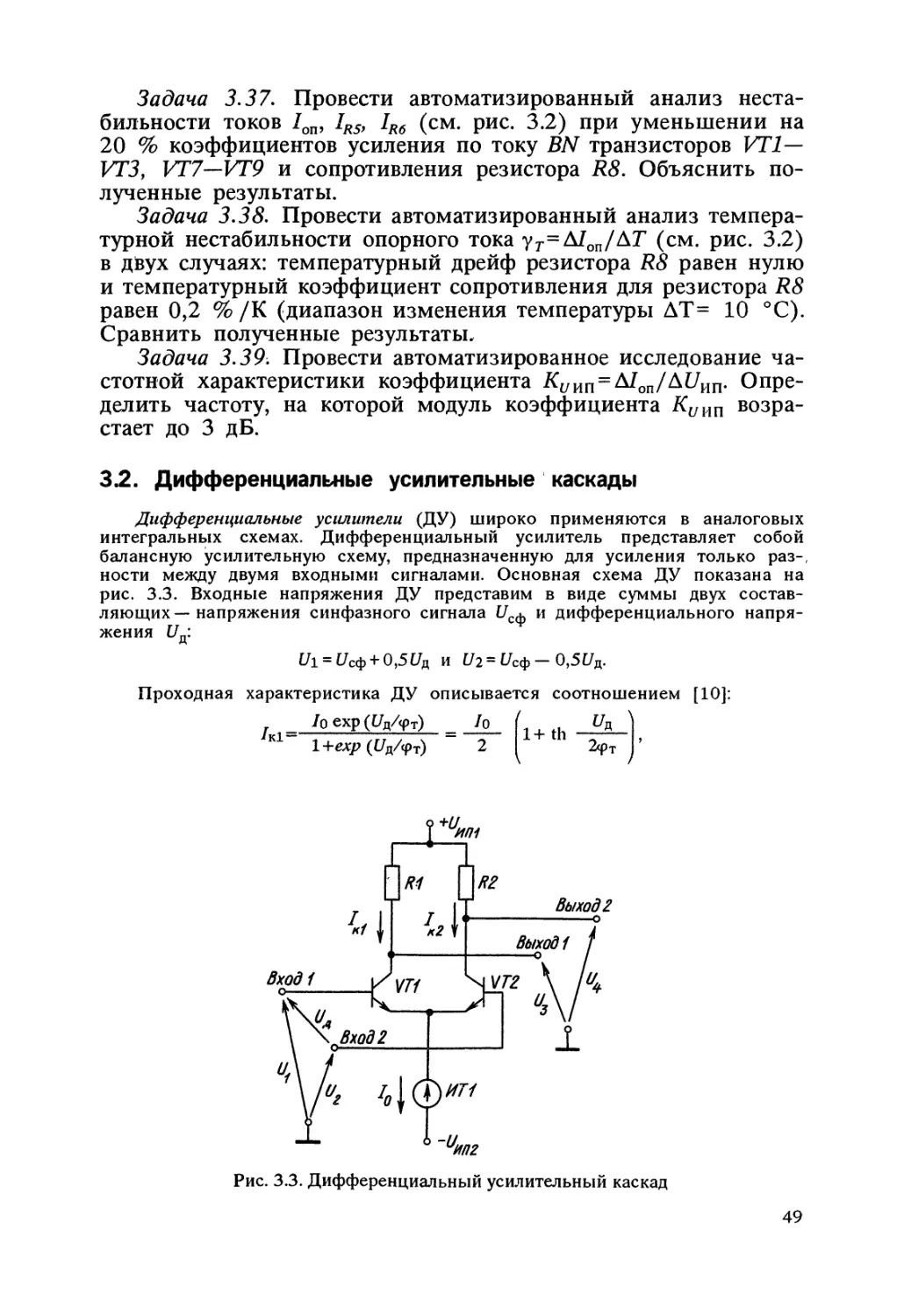

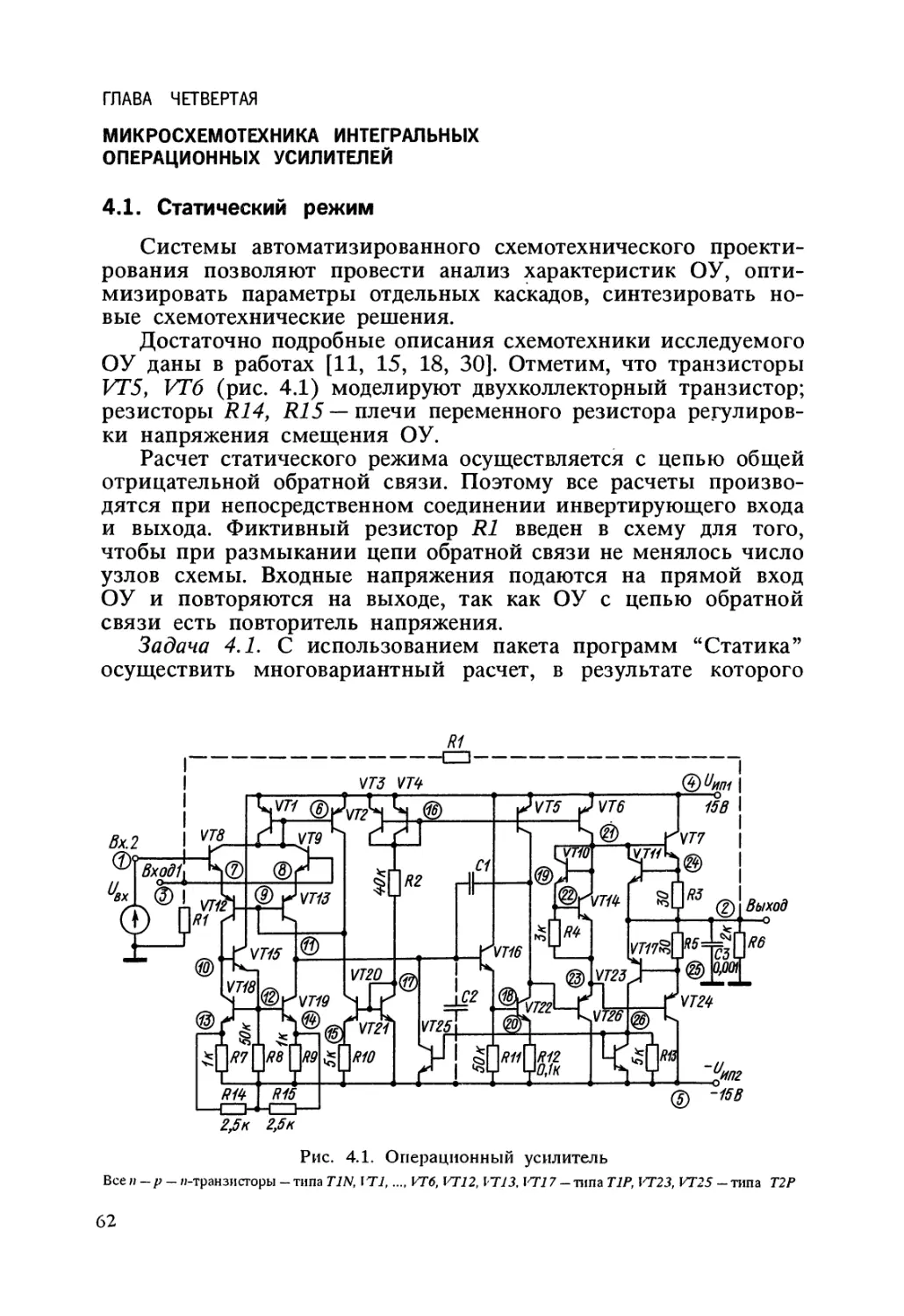

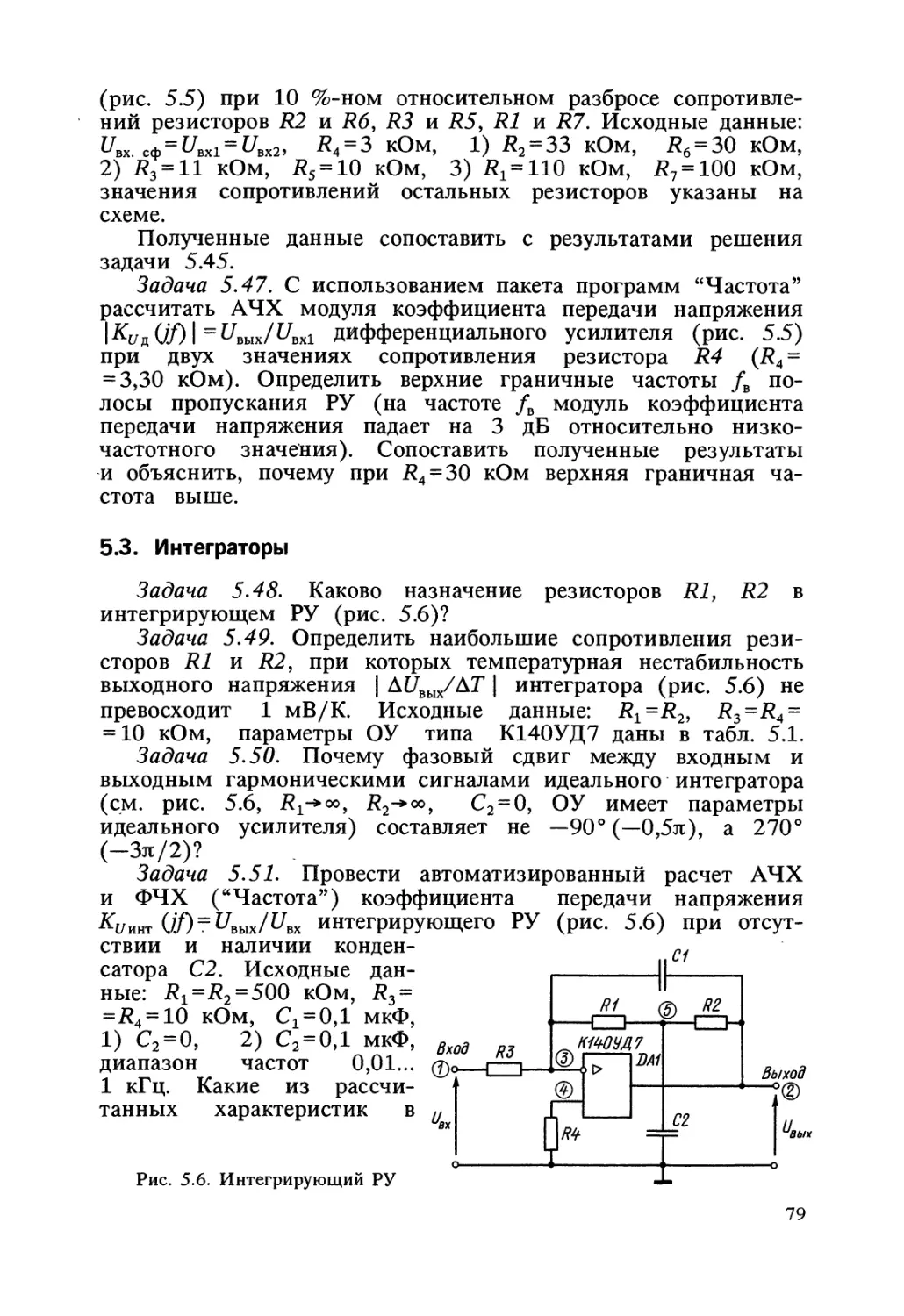

NN=14; МВУ=1,0,2,0; ОПТИМИЗИРОВАТЬ: ЗОНА KU (АЧХДБ) (39,41/19,21/-1,1/-11,-9) (3,3,3,1); *ЧАСТО- ТА= 1,10,100,300; ВАРЬИРОВАТЬ: R3(#l) 1 (0.01,100); С2(#1) 0.001(1Е-6, 1Е-2); *ОПТЧХ; КОНЕЦ;