Текст

KVPQ,

ж

s»

. „атеЛЬСТВО^Р"

Цздате

Курс цифровой электроники

Handboek digitate electronica deel 1

Bouwstenen

in TTL en CMOS

J. H. Jansen

Kluwer Technische Boeken 1982

И. Янсен

Курс цифровой

электроники

В 4-х томах

Том 1

Основы цифровой электроники

на ИС

Перевод с голландского

канд. физ.-мат. наук

В. И. ИЛЮЩЕНКО

под редакцией д-ра физ.-мат. наук

Н. Г. ВОЛКОВА

Москва «Мир» 1987

ББК 32.85

Я 65

AlVaKo 15/02/2012

УДК 621.38

Янсен И.

Я 65 Курс цифровой электроники: В 4-х т. Т. 1. Основы циф-

ровой электроники на ИС. Пер. с голланд. — М.: Мир,

1987. —334 с., ил.

Курс создан крупным голландским специалистом в области микросхемо-

техники.

В томе 1 изложены основы цифровой техники, описана элементная база

цифровых интегральных микросхем и даны практические рекомендации по мон-

тажу и наладке цифровых систем.

Для инженеров и специалистов в области электроники и вычислительной

техники, а также для аспирантов и студентов соответствующих специальностей.

л2401000000-310

”о41(О1)-87 П0АП- ИЗДф

ББК 32.85

Редакция литературы по информатике и робототехнике

© 1982 Kluwer Technische Boeken В. V. — Deventer

© перевод на русский язык, «Мир», 1987

ОТ РЕДАКЦИИ

В настоящее время во всех областях науки и техники получили широкое

распространение цифровые электронные устройства, от применения которых

зависит уровень развития народного хозяйства. Уже сейчас сотни тысяч ин-

женеров и техников работают в направлении создания элементной базы и ее

применения для разработки цифровых вычислительных машин, сетей ЭВМ,

комплексов связи, автоматизированных систем управления технологическими

и организационно-экономическими процессами, а также различного рода быто-

вой аппаратуры.

Однако в отечественной литературе отсутствуют книги, где в доступной

форме излагались бы принципы построения цифровых электронных элементов

и рекомендации по их разработке и применению-

Данный курс по цифровой электронике заполняет этот пробел. В нем

с единых технических позиций рассматривается проектирование всех типов

электронных устройств (начиная от простых и кончая самыми сложными),

что позволяет читателю, не имеющему специальной подготовки по электрони-

ке, пользоваться им в своей практической деятельности.

Курс состоит из четырех томов.

Тома 1 и 2 представляют собой общее введение в цифровую технику.

В них описаны наиболее распространенные типы логических элементов и триг-

геров, изложены методы проектирования основных цифровых узлов. В томе 3

даются сведения, необходимые для реализации перехода от сравнительно

несложных отдельных цифровых устройств к цифровым системам. В томе 4

подробно описаны микропроцессоры и рассмотрены вопросы построения и

программирования микропроцессорных систем.

Курс предназначен для специалистов, работающих в области электрони-

ки и вычислительной техники, а также для аспирантов и студентов высших

технических учебных заведений.

ПРЕДИСЛОВИЕ РЕДАКТОРА ПЕРЕВОДА

Быстрый прогресс в области технологии изготовления интегральных схем

привел к резкому росту объема их производства и снижению стоимости. В ре-

зультате использование микросхем стало возможным не только в сложных

специализированных устройствах (таких, как ЭВМ), но и в разнообразных

измерительных приборах, управляющих и контролирующих системах. Круг

потребителей микросхем непрерывно расширяется. Интенсивное производство

микропроцессоров не снижает потребности в ТТЛ- и КМОП-схемах. Сущест-

вует очень много приложений, в которых применение микропроцессора, тре-

бующего вспомогательных устройств, является неэффективным. Техническое

решение на основе интегральных схем часто обеспечивает большие быстродей-

ствие и надежность. Поэтому ознакомление с методами их использования

безусловно необходимо. Интегральные микросхемы распространены сейчас

настолько широко, что умение применять их при проектировании различных

устройств должно быть обязательным элементом профессиональной грамот-

ности современного инженера. Поэтому растет потребность в литературе,

посвященной основам проектирования различных логических устройств на

основе интегральных микросхем.

Предлагаемый вниманию советского читателя первый том четырехтомного

курса отвечает этим потребностям. В нем гораздо подробнее, чем в

большинстве существующих пособий на эту тему, излагаются основы алгебры

логики, методы временного анализа логических схем, способы условного гра-

фического изображения схем и другие вопросы. Большое место отводится

принципам работы базовых логических элементов, методам построения на их

основе сложных логических схем, а также типовым интегральным микросхе-

мам, выполненным на основе ТТЛ- и КМОП-логики, и выпускаемым серийно

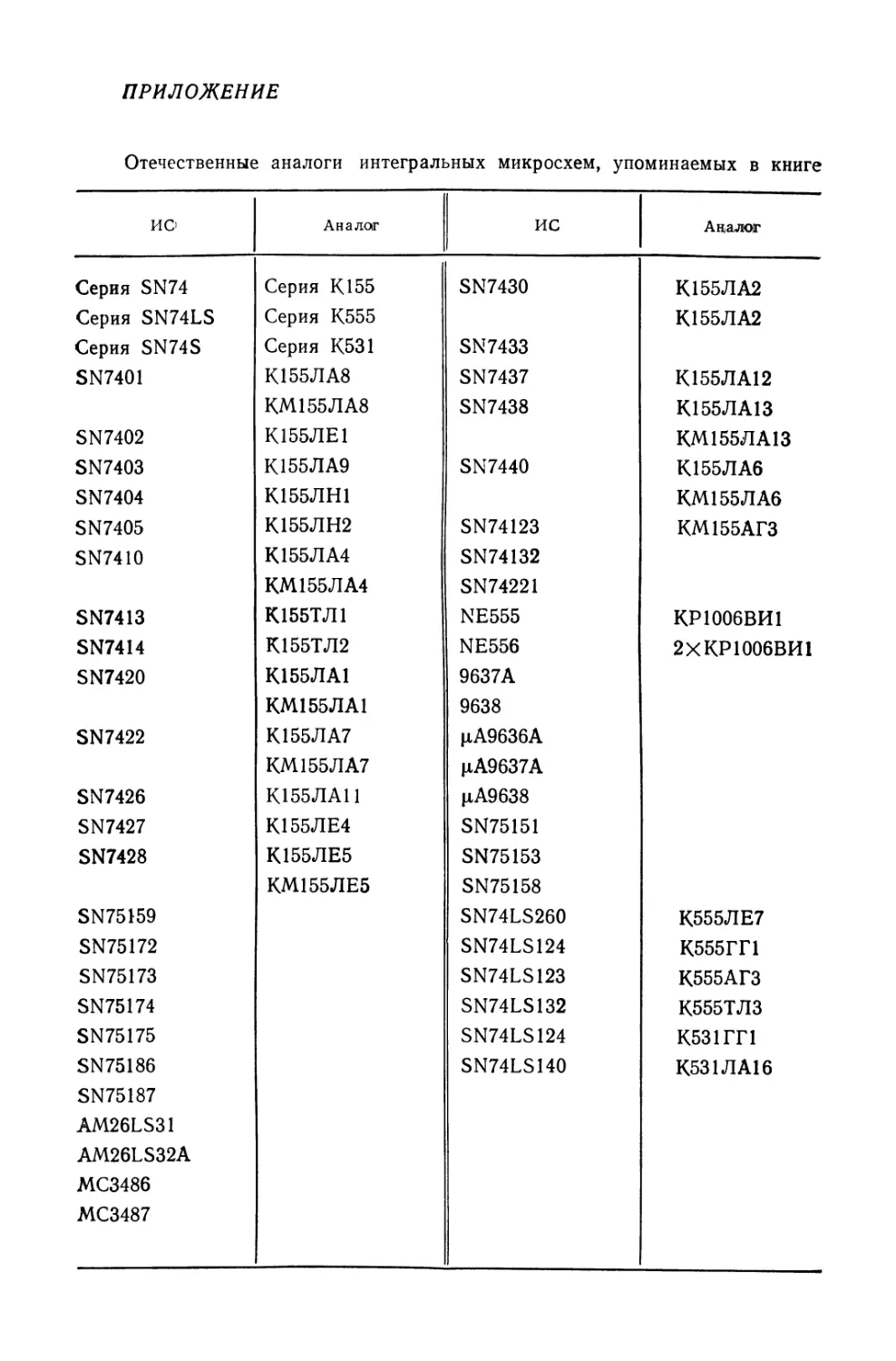

за рубежом микросхемам (серия SN74 и другие)- Чтобы эти разделы книги

не потеряли ценности для советского читателя, в приложении приводятся

отечественные аналогии зарубежных интегральных микросхем, упоминаемых

в книге (если они существуют). В большинстве случаев их эксплуатационные

параметры совпадают. Более подробно с параметрами отечественных и зару-

бежных интегральных микросхем можно ознакомиться соответственно в ра-

ботах [1, 2].

В книге используются две системы графических изображений элементов —

система, рекомендуемая Международной Электротехнической Комиссией

Предисловие редактора перевода

7

(МЭК), и американская система milspec. Что касается второй системы, то в

СССР она не употребляется, и с ней достаточно ознакомиться лишь в общих

чертах1. Система обозначений МЭК с точностью до незначительных

деталей совпадает с принятой в СССР системой регламентированной

ГОСТом 2.743-82.

Этот том предназначен для первоначального изучения предмета и рассчи-

тан на инженеров и студентов технических вузов. Для понимания его содер-

жания требуются лишь знания работы биполярных и униполярных транзисто-

ров [3] и основ теории электрических цепей.

Н. Волков

Литература

1. Интегральные микросхемы: Справочник. Под ред. Б. В. Тарабрина. — М.:

Радио и связь, 1983.

2. Ю. М. Кутыркин, А. В. Нефедов, А. М. Савченко. Зарубежные интеграль-

ные микросхемы широкого применения: Справочник— М.: Энергоатомиз-

дат, 1984.

3. И. П. Степаненко. Основы микроэлектроники. — М.: Сов. радио, 1984.

J) Правда, в большинстве переводных книг иллюстрации, как правило,

воспроизводятся без изменений, и в них можно встретить американскую си-

стему обозначений.

ПРЕДИСЛОВИЕ АВТОРА

В начале книги на простых примерах из повседневной жизни иллюстри-

руются три элементарные логические функции — И, ИЛИ и НЕ. Результаты

применения этих простых функций в жизни далеко не всегда заметны нево-

оруженным глазом — гораздо заметнее проявляется действие таких более

сложных функций, как выборка, распределение, шифрация и принятие реше-

ний.

Из анализа следует, однако, что эти сложные логические функции всегда

можно свести к элементарным, но возникает вопрос, какие комбинации эле-

ментарных функций дают данную, более сложную фунцию, т. е. как форми-

руются более сложные функции.

В цифровой электронике, к которой относятся и ЭВМ, имеются базовые

логические функции, в том числе функции И, ИЛИ и НЕ. В процессе обработ-

ки данных также возникает вопрос: как скомбинировать эти функции для

получения желаемых более сложных функций, которые, в свою очередь, мож-

но снова скомбинировать и получить функции еще более высокого порядка

сложности. Эту процедуру можно продолжать до тех пор, пока мы не полу-

чим в результате ЭВМ!

Комбинирование элементарных функций с целью получения сложных

функций осуществляется с помощью соответствующих связей между несколь-

кими указанными выше элементарными функциями.

Когда я впервые познакомился с ЭВМ, то самое сильное впечатление на

меня произвели огромное количество проводов и мощный интеллект, кото-

рым обладала эта конструкция. Вскоре, однако, я убедился, что ЭВМ состоит

из взаимозаменяемых однотипных модулей, а именно схем И-НЕ, реализую-

щих комбинацию элементарных функций НЕ и И. Блоки И-НЕ, находившиеся

в одних стойках ЭВМ, можно было заменять блоками И-НЕ из других стоек,

не нарушая работы ЭВМ. Все электронные ламповые блоки И-НЕ оказались

совершенно одинаковыми — разными были лишь межблочные связи. Другими

словами, оказалось, что функция данного узла в ЭВМ определяется способом

соединения между собой различных функциональных элементов. Монтажная

схема содержит всю информацию о том, как должен функционировать кон-

кретный автомат, ЭВМ или робот.

В настоящее время элементарные функциональные узлы, с помощью

которых формируются более сложные функции, размещаются в пластмассовом

Предисловие автора

9

или керамическом корпусе с двухрядным расположением выводов. Наиболее

сложный функциональный узел реализуется в виде микропроцессора (МП),

смонтированного в корпусе с двухрядным расположением 40 выводов и яв-

ляющегося «сердцем» микроЭВМ.

Микрокомпьютер представляет собой часть цифровой электронной «сис-

темы», которая, в свою очередь, также является частью еще более сложной

системы с определенной иерархической структурой. Это подтверждают такие

названия, как управляющая ЭВМ, устройство управления памятью, вспомога-

тельная и сателлитная ЭВМ и множество других.

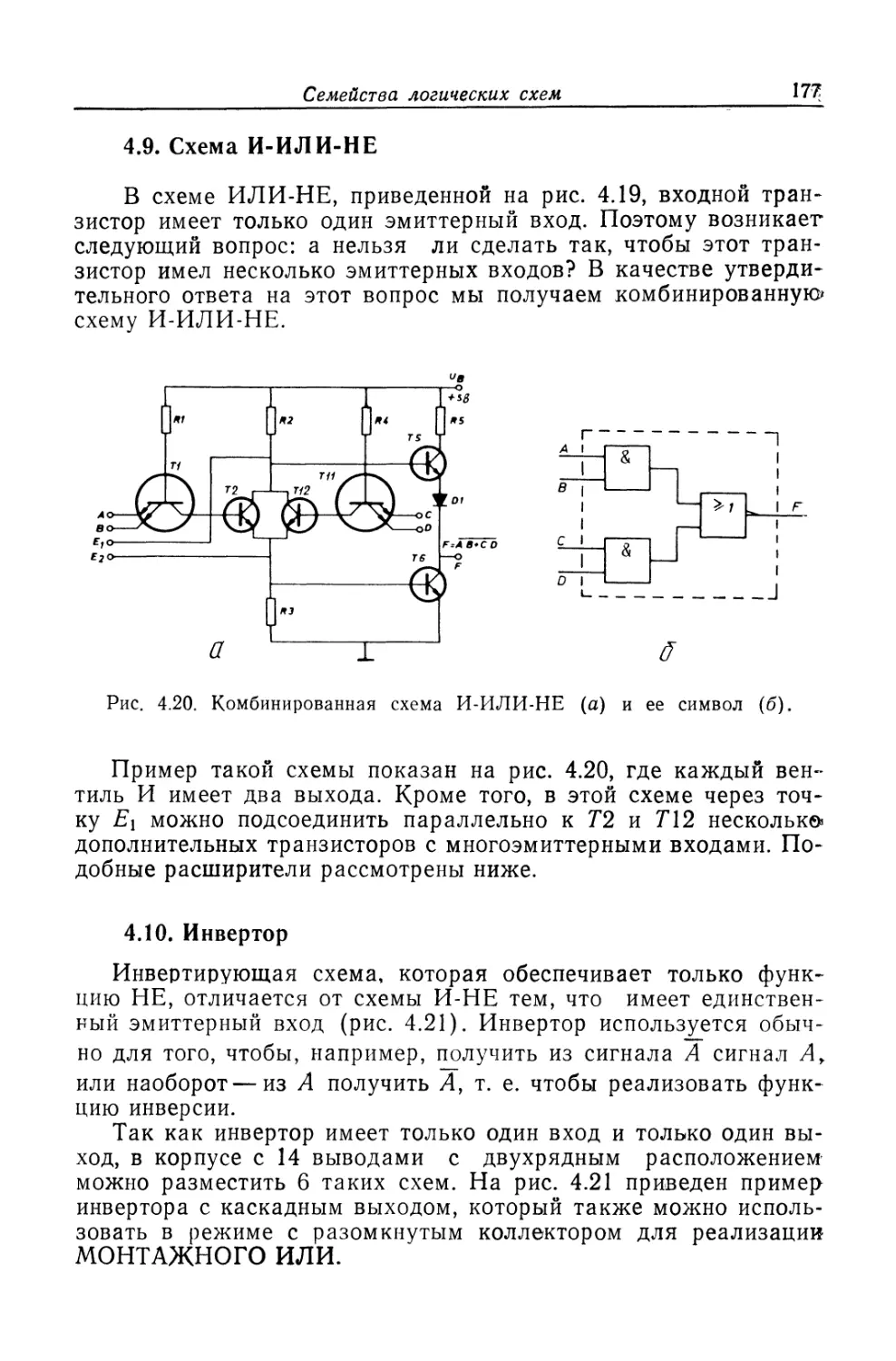

В цифровой электронике к настоящему времени осуществлен переход к

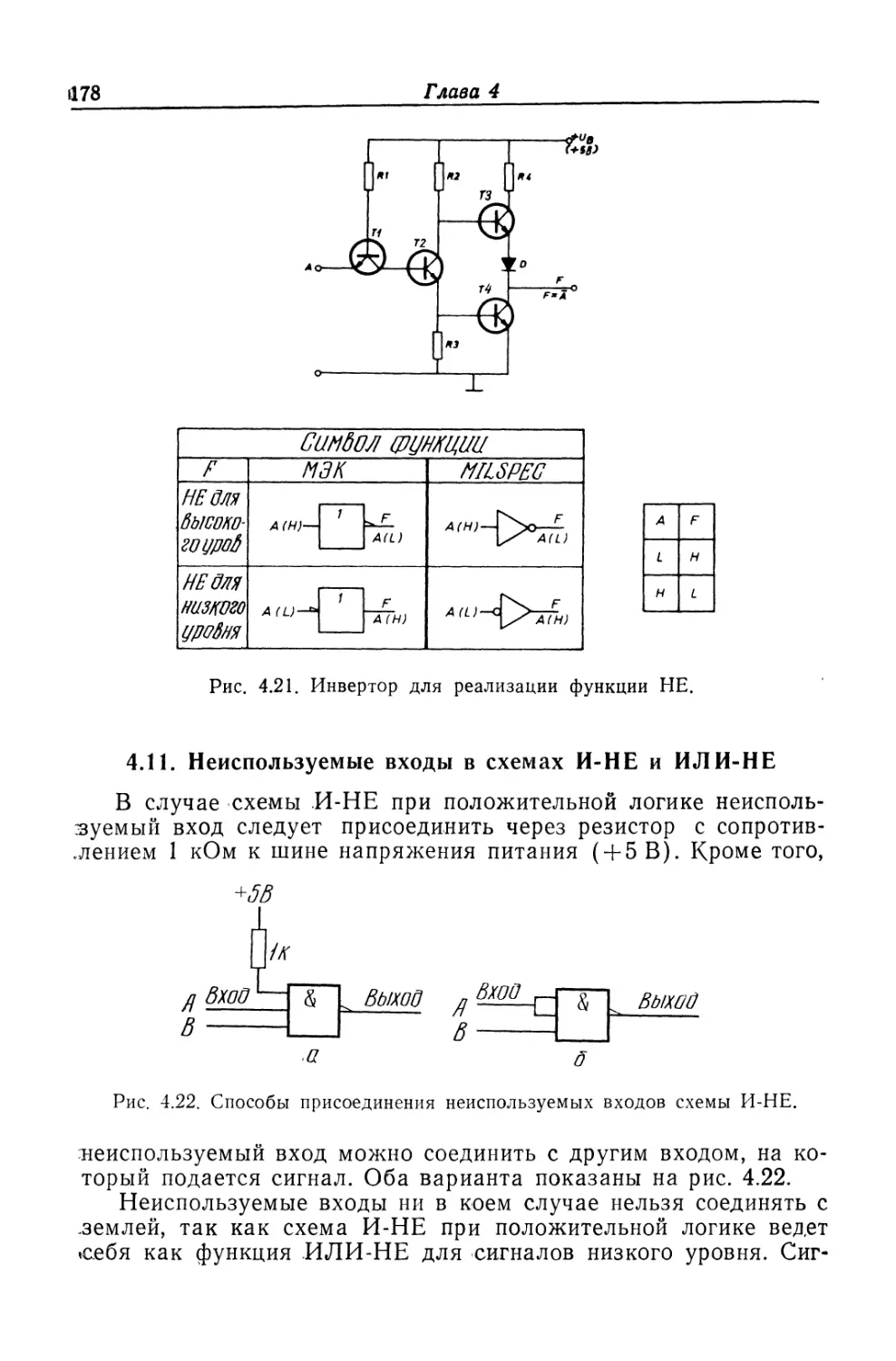

общеупотребительным символам для обозначения различных логических

функций. Например, до сих пор применяется система обозначений milspec с

ее «отличительными формами» элементов. В 1965 г. Международная Электро-

техническая Комиссия (МЭК) начала разрабатывать более удобную и более

простую символику, которая постепенно проникает и в промышленность.

В этом томе мы будем применять обе системы обозначений и поочередно

ими пользоваться- Это вызвано тем, что в настоящее время обе системы на-

ходят широкое применение.

При описании существующих КМОП-, ТТЛ- и маломощных ТТЛШ-схем

в справочниках по цифровым ИС все еще используется «старая» система

milspec, однако при составлении дополнений к этим справочникам многие из-

готовители в настоящее время предпочитают систему МЭК.

Мы много говорили здесь о постепенном переходе от системы milspec

к системе МЭК, потому что читатели этой книги, несомненно, еще встретятся

как со старой, так и с новой системами обозначений. В гл. 2 показано, что эти

системы на самом деле очень похожи друг на друга и комбинированное при-

менение тех и других символов обычно не приводит к недоразумениям.

В книге отражена небольшая часть того опыта, который автор приобрел

за 28 лет работы в области цифровой электроники, в том числе и в области

разработки ЭВМ. Я надеюсь, что читателю эта книга поможет ориентиро-

ваться в похожем на лабиринт увлекательном мире цифровой электроники.

Хазерсвуде, 1982 г.

И. Янсен

Глава 1

ВВЕДЕНИЕ В ДИСКРЕТНУЮ СХЕМОТЕХНИКУ

И ДВОИЧНОЕ ИСЧИСЛЕНИЕ

1.1. Введение

Цифровая обработка данных с помощью автоматических

устройств является результатом технического прогресса не

только последних десятилетий. Еще в средние века были со-

зданы примитивные по современным понятиям решающие

устройства, которые могли выполнять такие несложные вычис-

лительные действия, как сложение и вычитание. Эти вычисли-

тельные машины, работавшие на чисто механическом принци-

пе, были столь велики по размерам и дороги, что, конечно же,

тогда не могло быть и речи о той популярности, которой поль-

зуются, например, современные карманные калькуляторы.

Эти машины предназначались для исследовательских целей

и ими пользовались в основном их изобретатели. Впрочем, это

не означало, что подобные научные разработки были совершен-

но бесполезными. Они обогащали науку в целом и, конечно,

давали определенный вклад в развитие технологии изготовле-

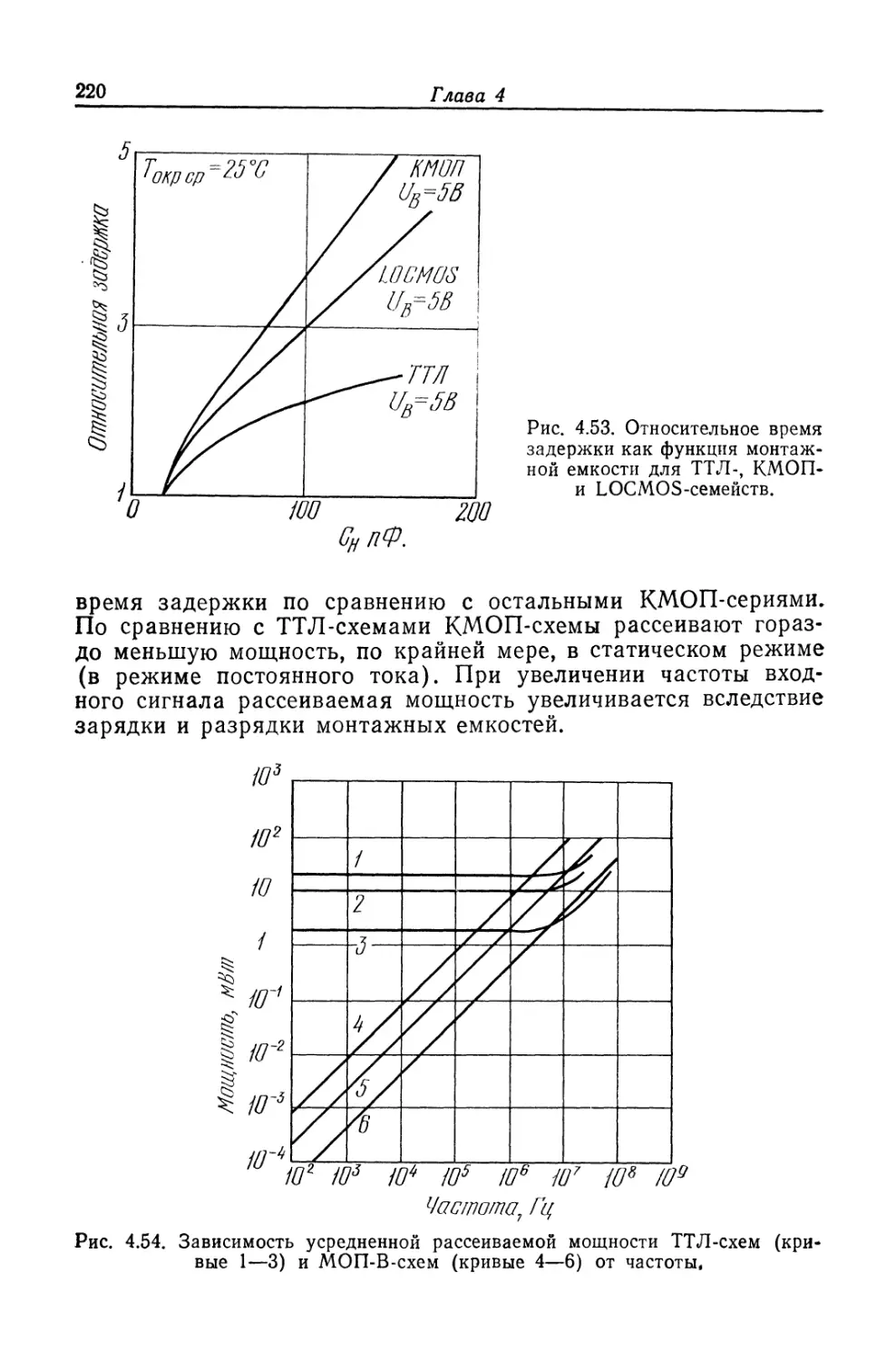

ния серийных машин и автоматов в течение последующих ве-

ков, в особенности в XIX в. Проблему создания электронных

вычислительных машин и автоматов стали широко обсуждать

впервые после изобретения радиоламп в начале XX в. В эти

годы были созданы различные схемы, которые впоследствии при-

менялись в качестве базовых элементов цифровых схем. Здесь

имеются в виду различные генераторы (типа мультивиб-

раторов), а также логические схемы, реализующие функции И,

ИЛИ и НЕ (обращения, инверсии), и усилители считывания

для магнитных запоминающих устройств (ЗУ). Перед второй

мировой войной впервые была сделана попытка создать пол-

номасштабную электронную вычислительную машину (ЭВМ),

в которой использовались радиолампы, селеновые диоды и

магнитные запоминающие элементы для регистров и ЗУ.

В Голландии развитие вычислительной техники началось

после второй мировой войны. Работы в области создания ЭВМ

были начаты почти одновременно в Математическом центре в

Амстердаме, в лаборатории РТТ!) в Лейдшендаме (д-ром Не-

п Posterijen — Telegrafie — Telefonie — Министерство связи. — Прим, пе-

рсе.

Дискретная схемотехника и двоичное исчисление п

херлабом) и в Национальной лаборатории Филипса в Эйндхо-

вене.

Как известно, первая ЭВМ, созданная в Математическом

центре, была собрана из релейных элементов. Конструкция ма-

шины была признана неудачной из-за постоянных сбоев, возни-

кающих в результате загрязнения контактов реле. Уже в на-

чале 50-х годов были разработаны электронные машины, кото-

рые имели лучшие характеристики. Первые ЭВМ назывались

ARRA (аббревиатура от словосочетания Automatische Relais

Rekenmachine Amsterdam), т. e. назывались так же, как и пре-

дыдущие машины, которые, как уже говорилось выше, были со-

браны исключительно из релейных элементов.

Для новых ЭВМ из-за интенсивного тепловыделения много-

численных радиоламп потребовалась эффективная система

охлаждения с большими вентиляторами, смонтированными

внутри корпуса ЭВМ. Вентильные схемы ARRA собирались из

селеновых диодов и радиоламп (двойных триодов), а в качест-

ве запоминающих элементов регистров применялись магнитные

кольцевые сердечники. Для хранения команд и других данных

использовались барабанные ЗУ. Ввод информации осуществ-

лялся с помощью устройства собственного изготовления для

считывания перфолент, а вывод информации — с помощью мо-

дифицированной электрической пишущей машинки.

Из-за низкого качества селеновых диодов и относительно

быстрого старения радиоламп эту ЭВМ вряд ли можно было

рассматривать как высококачественное изделие, пригодное для

крупномасштабного производства. Тем не менее ARRA в тече-

ние ряда лет использовалась для решения научно-исследова-

тельских задач.

В конце 1957 г. была создана ЭВМ XI, разработанная в

Математическом центре и выполненная полностью на транзис-

торах. Эта ЭВМ впоследствии была запущена в массовое про-

изводство существовавшей в то время фирмой N. V. Electro-

logica (г. Рейсвейк).

В ЭВМ XI, которая была значительно меньше по размерам,

чем ламповые ЭВМ, логические элементы, такие, как схемы И,

ИЛИ и обращения (инверсии), были собраны из дискретных

компонентов, смонтированных на печатной плате. Эта плата,

снабженная периферийными контактами с покрытием из тон-

кого слоя золота, собиралась в виде единого модуля. На одной

плате располагались две схемы И-НЕ с тремя входами на каж-

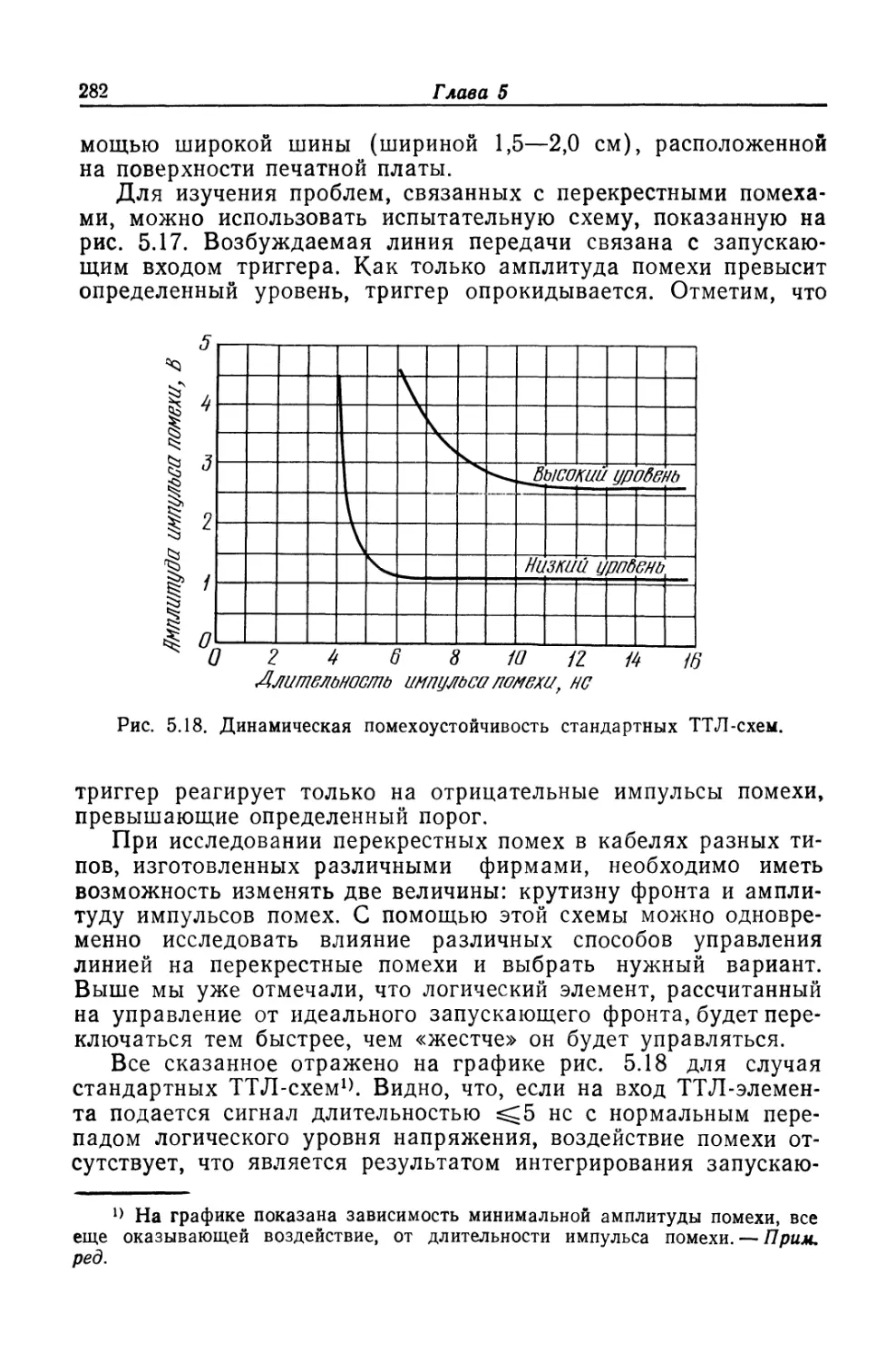

дую, которые были изготовлены из ДТЛ-элементов1). Соединения

между модулями, необходимые для реализации требуемых вы-

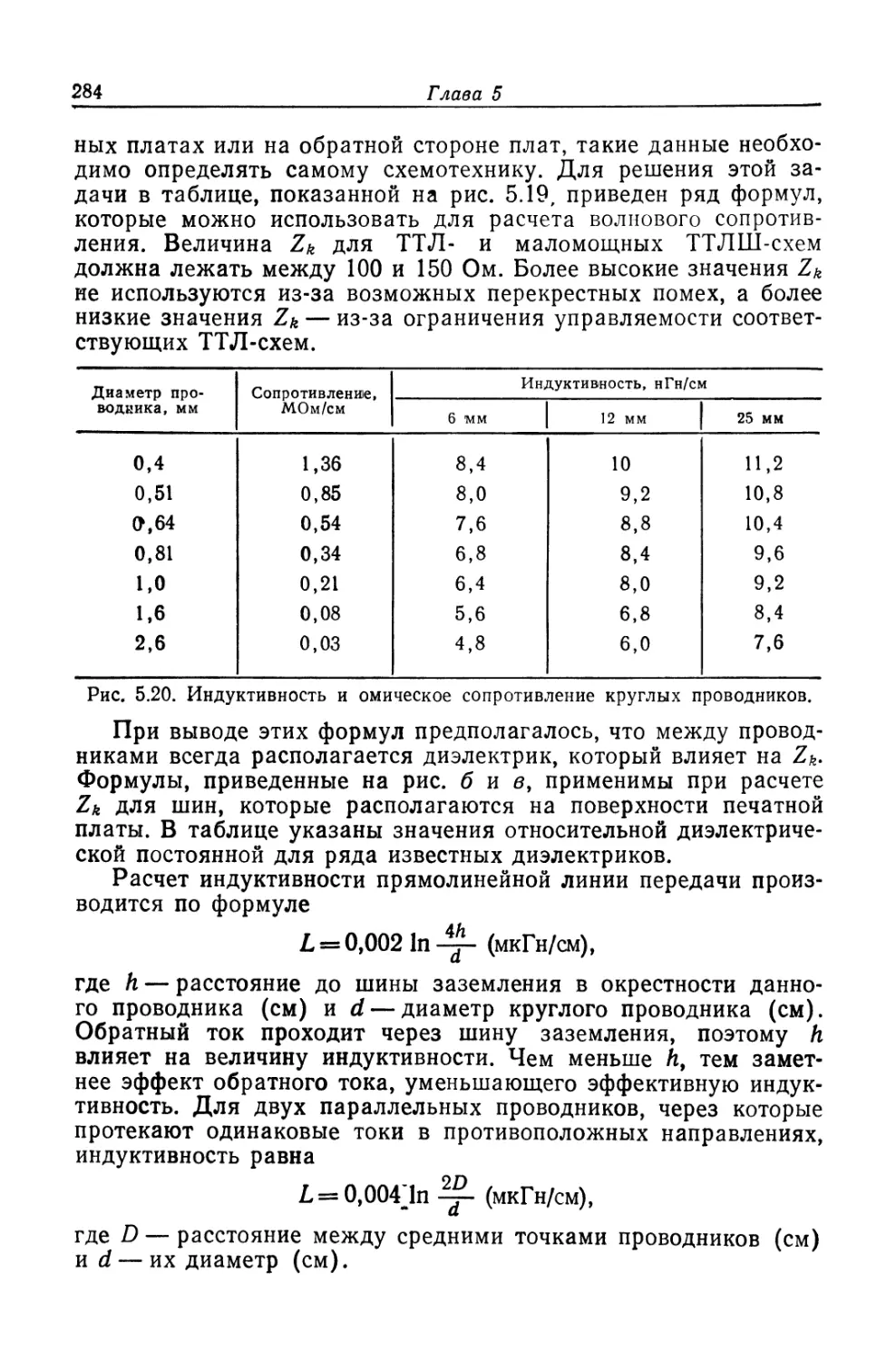

числительных функций, выполнялись с помощью проводников,

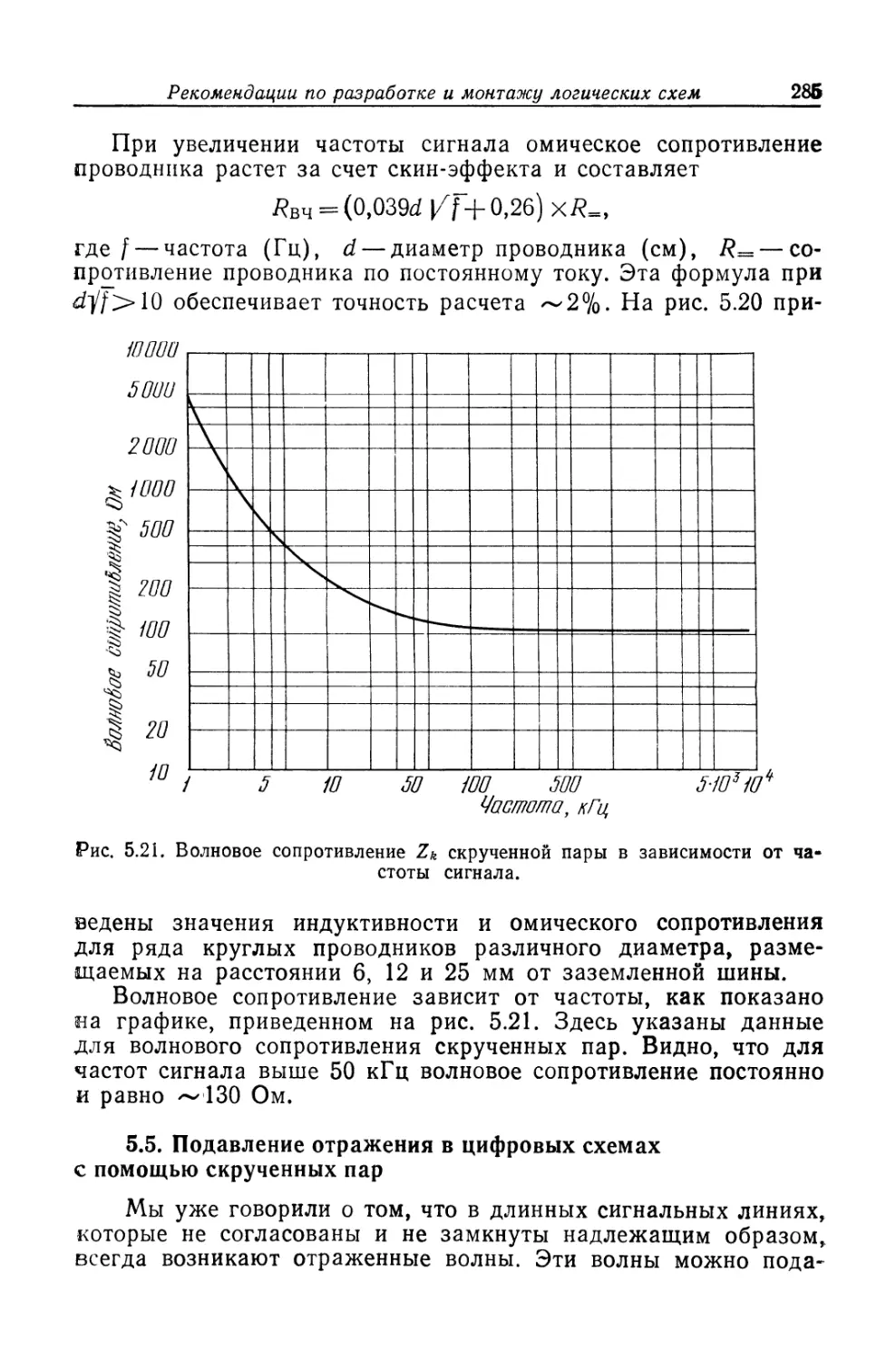

ДТЛ — диодно-транзисторная логика. — Прим, перев.

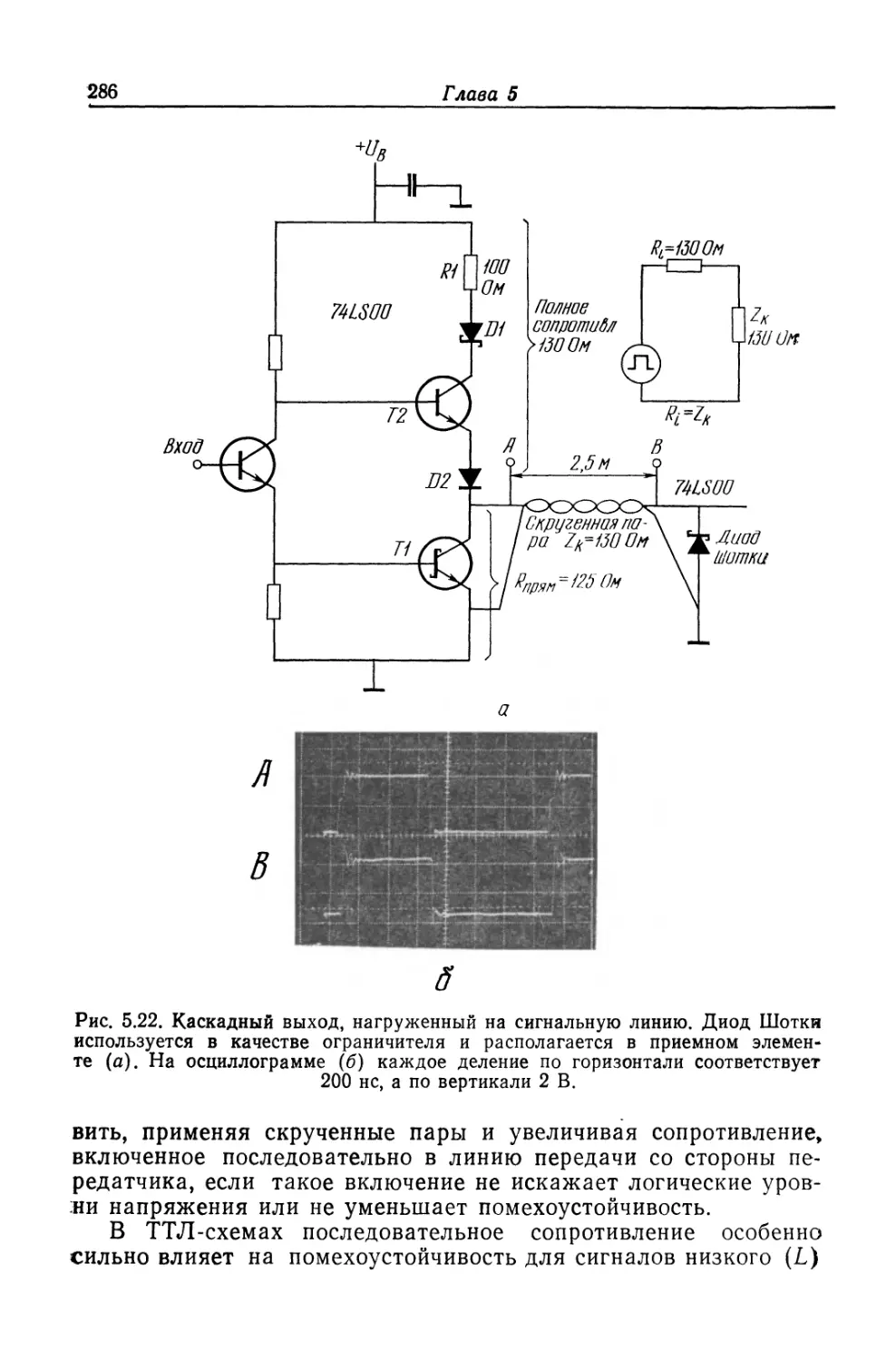

Рис. 1.1а. Внешний вид ЭВМ PTERA. На переднем плане видна панель управ-

ления с электрической пишущей машинкой и устройством для чтения перфо-

лент, которые применялись для ввода и вывода данных.

Дискретная схемотехника и двоичное исчисление

13

Рис. 1.16. Два регистра из ЭВМ

ARRA.

ко^нцы которых впаивались в разъемы, размещенные в корпусе

ЭВМ XI имела высококачественную для того времени аппа-

ратуру ввода и вывода информации, в которую входили пер-

форатор и устройство для считывания перфокарт, быстрое пе-

чатающее устройство, устройства для перфорации и чтения

перфолент, а также система для работы с магнитными лента-

ми и магнитным дисковым ЗУ.

На рис. 1.1а и 1.16 приведены фотоснимки первых ЭВМ,

иллюстрирующие достижения Голландии в области разработок

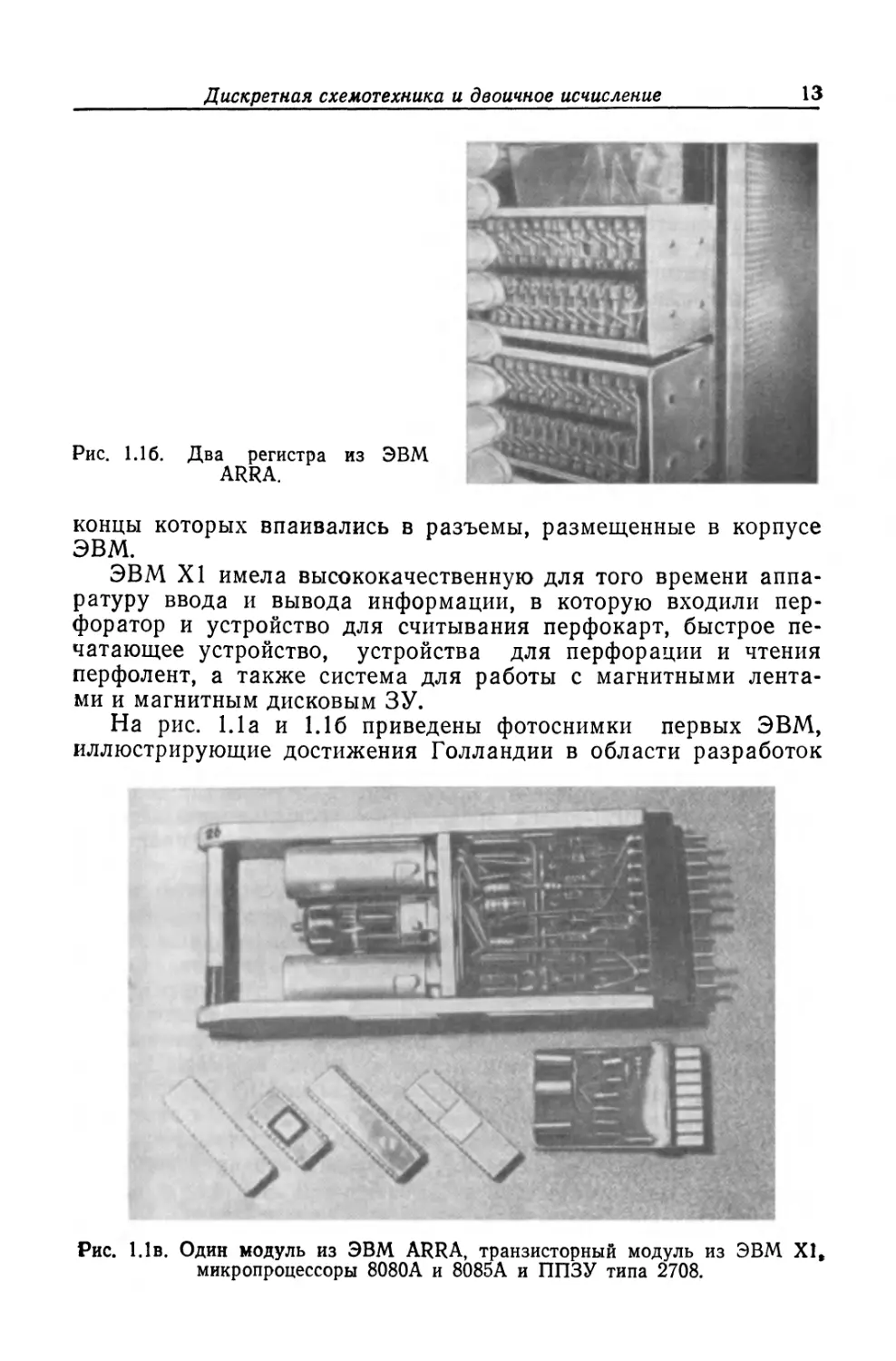

Рис. 1.1 в. Один модуль из ЭВМ ARRA, транзисторный модуль из ЭВМ XIt

микропроцессоры 8080А и 8085А и ППЗУ типа 2708.

14

Глава 1

ЭВМ. В частности, на рис. 1.1а показана ЭВМ PTERA, разра-

ботанная РТТ и содержащая около 700 радиоламп и 120 реле.

На рис. 1.16 показаны два магнитных регистра из ЭВМ ARRA,

которые вместе с АЛУ входили в состав счетно-решающего

устройства, а на рис. 1.1в — один ламповый модуль из ЭВМ

ARRA, в котором смонтированы две схемы И-НЕ. На этом ри-

сунке мы видим также двойную схему И-НЕ, которая была со-

брана на транзисторах и использовалась в ЭВМ XI, а рядом с

этой схемой — микропроцессоры 8080А и 8085А вместе с ППЗУ

типа 2708.

Монтаж ЭВМ, состоящей из дискретных компонентов и про-

волочных соединений, оказался очень трудоемким процессом,

что привело к существенному удорожанию подобных систем.

Изменение элементной базы произошло в середине 60-х годов,

когда на рынке появились интегральные схемы (ИС) первона-

чально с небольшой плотностью расположения элементов, на-

пример по четыре схемы типа И-НЕ на одном кристалле, а за-

тем и с более высокой плотностью, что позволило реализовать

более сложные функции. Под более сложными мы понимаем

функции, реализуемые в схемах селекторов, мультиплексоров,

демультиплексоров, сумматоров, декадных и шестнадцатерич-

ных счетчиков и других устройств.

Вначале устройства на интегральных схемах были выполне-

ны на ДТЛ-элементах, а затем на ТТЛ-элементах1*. Последние

применяются и в настоящее время.

Позднее семейство цифровых схем пополнилось КМОП-

структурами2*, которые в настоящее время находят все большее

применение, а ТТЛ-схемы продолжают совершенствоваться в

направлении увеличения скоростей переключения и уровня до-

пустимого тепловыделения.

Благодаря высокой степени интеграции (несколько десятков

схем И-НЕ и ИЛИ-HE на одном кристалле) стоимость цифро-

вых схем существенно снизилась. Кроме того, совершенствова-

ние технологии изготовления привело к росту производства ИС.

Указанные факторы повлияли на стоимость ЭВМ, тем более

что за счет меньших размеров модулей на одной плате стало

возможным разместить большее число ИС. Небольшие по раз-

мерам вставные модули типа использованных в ЭВМ XI были

заменены одной большой платой с десятками ИС. Такие платы

затем соединяются с другими платами.

Взаимные соединения между отдельными платами, осуще-

ствляемые с помощью разъемов, первоначально производились

> ТТЛ—транзисторно-транзисторная логика. — Прим, перев.

2> КМОП-структура — комплементарная структура металл-оксид-полупро-

водник. — Прим, перев.

Дискретная схемотехника и двоичное исчисление 15

в стойках с применением монтажа накруткой или стежковой

сваркой, однако в дальнейшем от этой технологии отказались,

чтобы освободить место для печатного монтажа на обратной

стороне платы.

В середине 60-х годов был достигнут большой прогресс в

разработке МОП-транзистора — элемента с ничтожно малым

тепловыделением и простой конструкцией. Эти факторы позво-

лили изготовить ИС с еще более высокой плотностью располо-

жения элементов, что, в свою очередь, привело к сборке целого

процессора (т. е. основы ЭВМ) на одном кристалле небольших

размеров.

В начале 70-х годов фирме Intel (США) удалось разработать

микропроцессор (цР), хотя вначале его набор команд и разряд-

ность шины данных были небольшими. За первым микропроцес-

сором типа 4004 вскоре был создан микропроцессор типа 8008

с 8-разрядной шиной передачи данных, а затем — микропроцес-

сор 8080 с более совершенной системой команд.

В настоящее время разрабатываются микропроцессоры с

16-разрядными шинами передачи данных (1 бит=1 двоичному

числу) и с еще большим набором команд. Эти микропроцессо-

ры изготавливаются теперь многими фирмами.

Одновременно с созданием микропроцессоров разрабатыва-

лись полупроводниковые ЗУ на МОП-транзисторах, поэтому в

настоящее время уже на одной плате можно разместить целый

компьютер. Цена такого компьютера составляет от сотни до

нескольких тысяч долларов, в зависимости от объема ЗУ и со-

става системы внешних устройств для ввода данных и вывода

на магнитную ленту.

С появлением микропроцессоров область применения ЭВМ

существенно расширилась. Если вначале компьютеры приме-

нялись только в научно-исследовательской работе и АСУ, то

сегодня их можно встретить и в швейных машинках, бензоко-

лонках и в кассовых аппаратах. Можно назвать также персо-

нальные компьютеры, которые используются не только люби-

телями разнообразных хобби, но и профессионалами, занимаю-

щимися разработкой проектов автоматизации систем распреде-

ления газа, электричества и воды и других систем управления

процессами.

Несмотря на интенсивную разработку микропроцессоров по-

требность в схемах на ТТЛ- и КМОП-элементах с относительно

невысокой степенью интеграции остается, как и прежде, боль-

шой. Это связано с тем, что такие элементы обеспечивают

большую гибкость при разработке логических схем, предназна-

ченных для применений, в которых важную роль играют ско-

рость переключения, небольшие размеры и небольшая стои-

мость. Микропроцессор для этих применений часто менее эф-

16

Глава 1

фективен, потому что для реализации некоторой определенной

вычислительной операции в нем используется ряд дополнитель-

ных устройств, таких, как ЗУ и система ввода-вывода, из-за

чего объем электронной аппаратуры существенно увеличива-

ется.

При последовательной обработке информации в микропро-

цессоре скорость обработки оказывается значительно меньшей,

чем в биполярных устройствах с дискретной логикой.

Что касается сборки логических устройств с применением

схем И, ИЛИ и НЕ, то здесь следует отметить, что в настоящее

время на одном кристалле удается разместить целые серии та-

ких схем и программировать желаемую операцию автономно.

Программирование осуществляется путем удаления ненужных

межсхемных соединений методом токового импульса. Линии

связи, размещенные на поверхности кристалла, имеют плавкие

соединения в форме хромоникелевых мостиков, которые при

использовании запрограммированных импульсов тока разруша-

ются, в результате чего соответствующие «лишние» соединения

разрываются.

Серийные логические элементы известны под такими назва-

ниями, как FPLA (Field Programmable Logic Array — програм-

мируемая матрица логических элементов на полевых ИС),

FPGA (Field Programmable Gate Array — программируемая

матрица вентильных элементов на полевых ИС), PMUX (Pro-

grammable Multiplexer — программируемый мультиплексор) и

PAL (Programmable Array Logic — программируемая матрич-

ная логика).

Если предусматривается массовое производство определен-

ных дискретных схем, имеется возможность создавать эти схе-

мы из полуфабрикатов, которые называются заказными ИС.

Следует также отметить, что ИС применяются в теле- и радио-

аппаратуре, причем как в цифровой, так и в аналоговой фор-

мах.

1.2. Элементы цифровых схем и логические функции

В настоящее время ИС для цифровых устройств продаются

по цене, которая не намного превышает цену одного транзисто-

ра. к ним относятся ИС, известные под названиями ТТЛ,

КМОП и ЭСЛ (транзисторная логика с эмиттерными связями).

Логическую схему можно представить в виде черного ящика с

одним или несколькими входами и выходами. Единственное,

что нам известно об этом ящике, — это функция, которая дает

связь между входными переменными и выходным сигналом.

Как реализована такая функция и сколько транзисторов, дио-

дов и резисторов содержится в нем — нам неизвестно. Имеется

Дискретная схемотехника и двоичное исчисление

\Т

несколько систем символического представления логической

функции, реализуемой данной цифровой схемой. Среди многих

систем известна американская система milspec, которая встреча-

ется преимущественно в специальной литературе. В системе,,

принятой Международной Электротехнической Комиссией

(МЭК), используется описание логической функции с помощью*

квадратной рамки, в которой находится символ данной функ-

Нспряжение питания+5В

\l4 13 12 11 10 9 8

(дорическая земля)

д

Рис. 1.2. Символы для функций И и ИЛИ.

а и в — общеупотребительные в специальной литературе; биг — символы, принятые

Международной Электротехнической Комиссией; д — ИС в корпусе с двойным располо-

жением выводов.

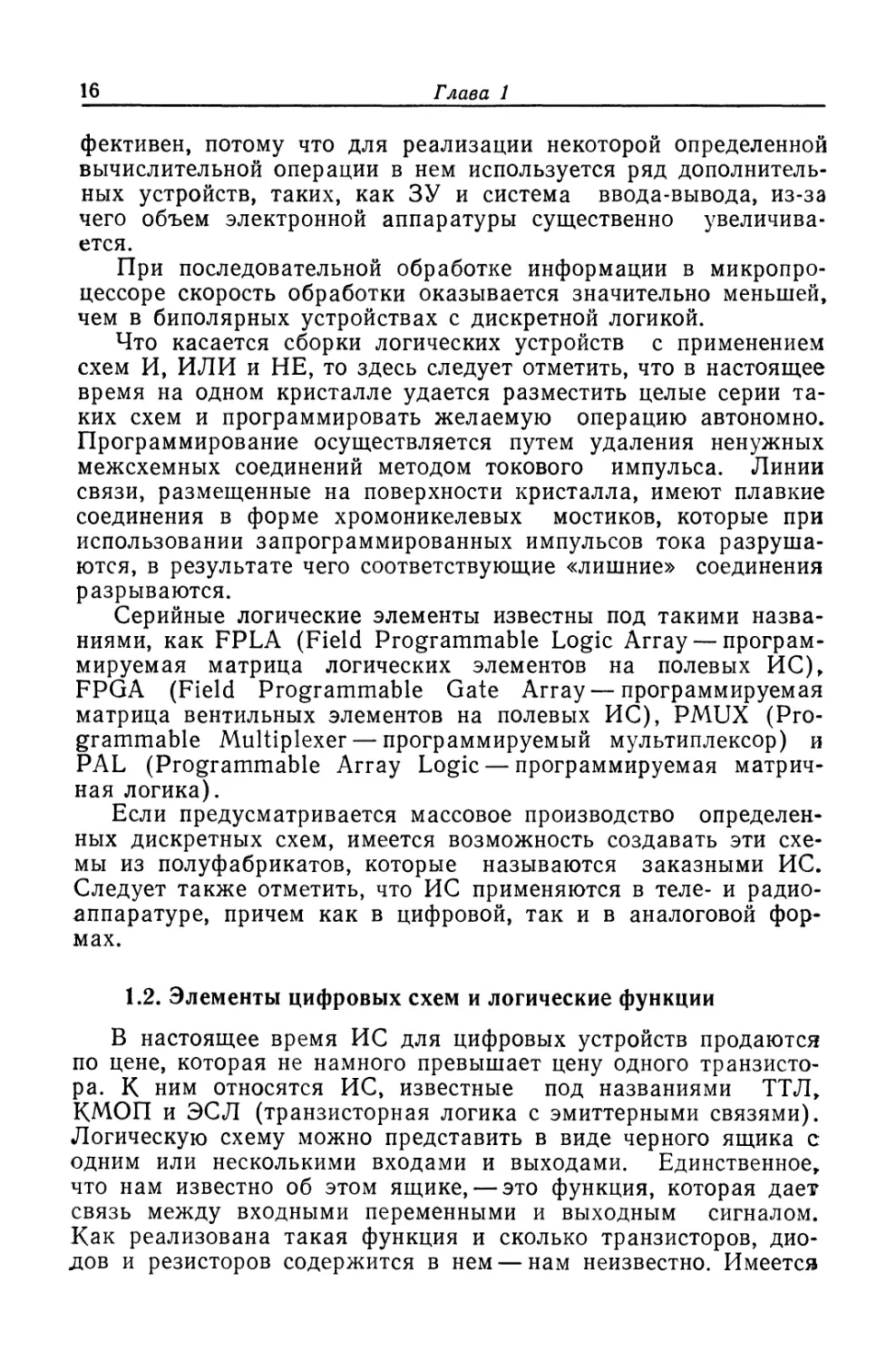

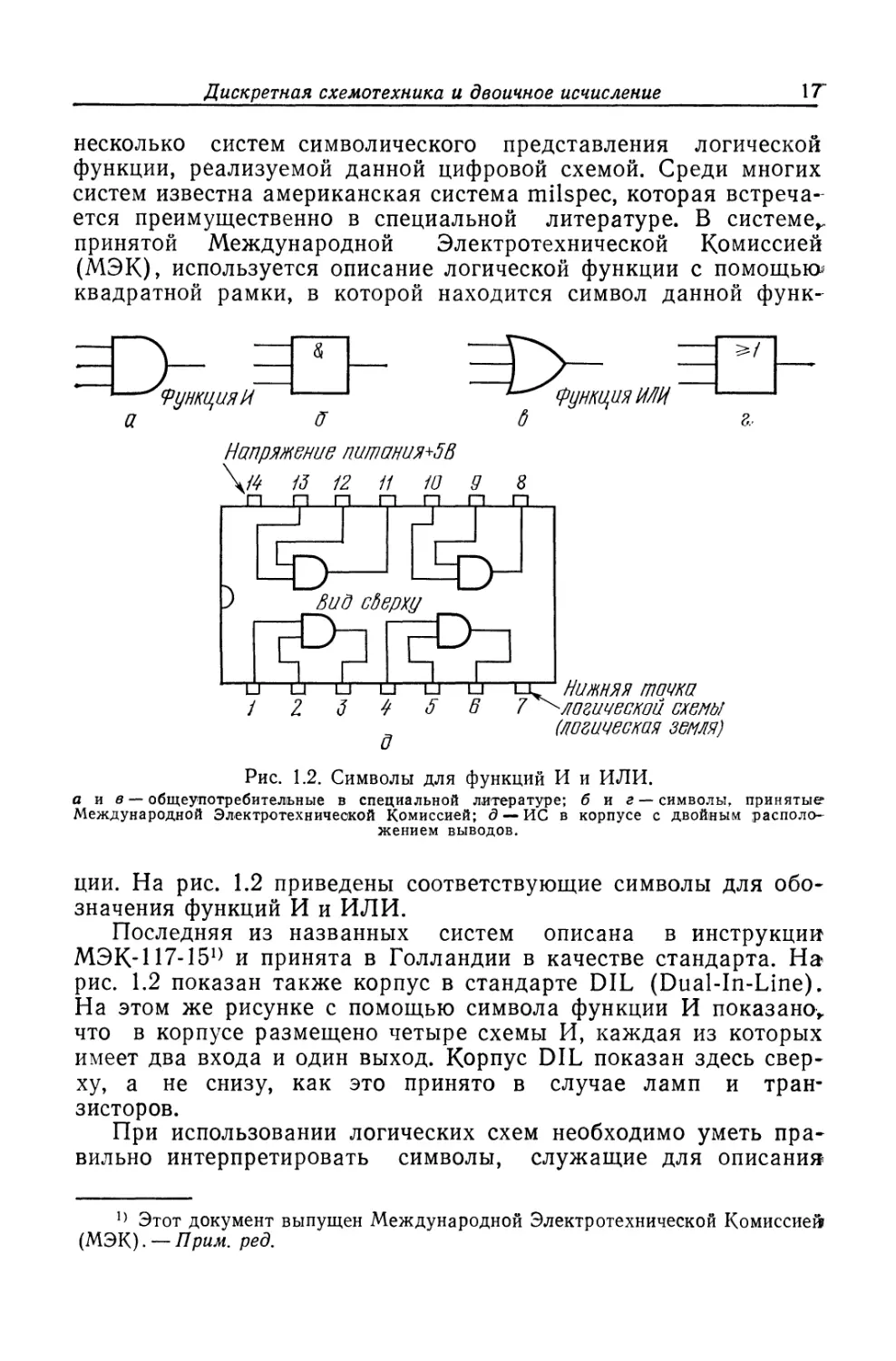

ции. На рис. 1.2 приведены соответствующие символы для обо-

значения функций И и ИЛИ.

Последняя из названных систем описана в инструкции

МЭК-И7-151) и принята в Голландии в качестве стандарта. На

рис. 1.2 показан также корпус в стандарте DIL (Dual-In-Line).

На этом же рисунке с помощью символа функции И показано,

что в корпусе размещено четыре схемы И, каждая из которых

имеет два входа и один выход. Корпус DIL показан здесь свер-

ху, а не снизу, как это принято в случае ламп и тран-

зисторов.

При использовании логических схем необходимо уметь пра-

вильно интерпретировать символы, служащие для описания

') Этот документ выпущен Международной Электротехнической Комиссией

(МЭК). — Прим. ред.

18

Глава 1

схем данного типа. Поэтому первое, что мы собираемся здесь

сделать, — это изучить более подробно основные логические

функции и их возможности.

В цифровой технике используются схемы, имеющие два со-

стояния, обозначаемые нулем и единицей или словами ДА и

НЕТ. Когда требуется обработать или запомнить какие-то чис-

ла, то они представляются в виде определенных комбинаций

единиц и нулей. Разумеется, можно задать вопрос: а почему в

цифровых схемах всегда используются только нули и единицы?

Ответ простой: это связано с тем, что вход и выход логической

схемы могут находиться только в двух состояниях. Одно состоя-

ние такой схемы характеризуется напряжением О В, а другое —

напряжением +5 В. Другая комбинация напряжений может

состоять из 0 и —5 В.

Выбор рабочего уровня напряжения зависит от параметров

транзисторных схем, которые применяются для реализации

данной функции. В ТТЛ-схемах рабочими уровнями напряже-

ния являются 0 и +5 В, при этом мы говорим, что О В соот-

ветствует нулю, а +5 В — единице. В специальной литературе

эту логику называют положительной, потому что логической

единице соответствует положительное напряжение. Это напря-

жение не обязательно должно быть равно точно +5 В (единице

может соответствовать и напряжение +3,5 В). То же самое

справедливо и для логического нуля, потому что, например,

напряжение +0,8 В наряду с напряжением 0 В можно исполь-

зовать для представления нуля.

Предельные значения напряжений для представления еди-

ницы и нуля (т. е. область допустимых значений) обычно ука-

зывает фирма — изготовитель данной схемы, потому что ей изве-

стно, как данная схема реагирует на отклонение уровня напря-

жения от номинала.

В ТТЛ-схемах на каждом из входов допускается нулевой уро-

вень не выше 0,8 В и единичный уровень не ниже 2 В. При

этом изготовитель гарантирует, что нулевой уровень всегда бу-

дет иметь значение, меньшее или равное 0,4 В, а единичный

уровень — значение, большее 2,4 В. Современные ТТЛ-схемы из

серии SN74 работают с напряжением питания +5 В, и это зна-

чение является одновременно самым высоким напряжением, ко-

торое может давать единицу.

Очевидно, что данные значения напряжения для представле-

ния единицы и нуля имеют смысл в предположении, что выход-

ная нагрузка находится в допустимых пределах. В специаль-

ной литературе для этого используется термин «коэффициент

разветвления по выходу». Под ним понимают число входов схем

определенного типа, которые могут быть связаны с одним вы-

ходом. Смысл данного термина станет более ясным, когда мы

Дискретная схемотехника и двоичное исчисление

19

рассмотрим логическую комбинацию схем, реализующих опре-

деленную логическую функцию.

Понятие функции, особенно в случае логических схем, не

всегда является тривиальным и требует пояснения. Ниже это

понятие раскрывается на ряде примеров, взятых из жизни.

Предположим, что мы хотим купить автомобиль. Исход этой

операции зависит от ряда факторов, называемых переменными.

Прежде всего мы должны располагать необходимой суммой де-

нег. Кроме того, должны иметь права на вождение автомобиля*

и потребность в приобретении автомобиля.

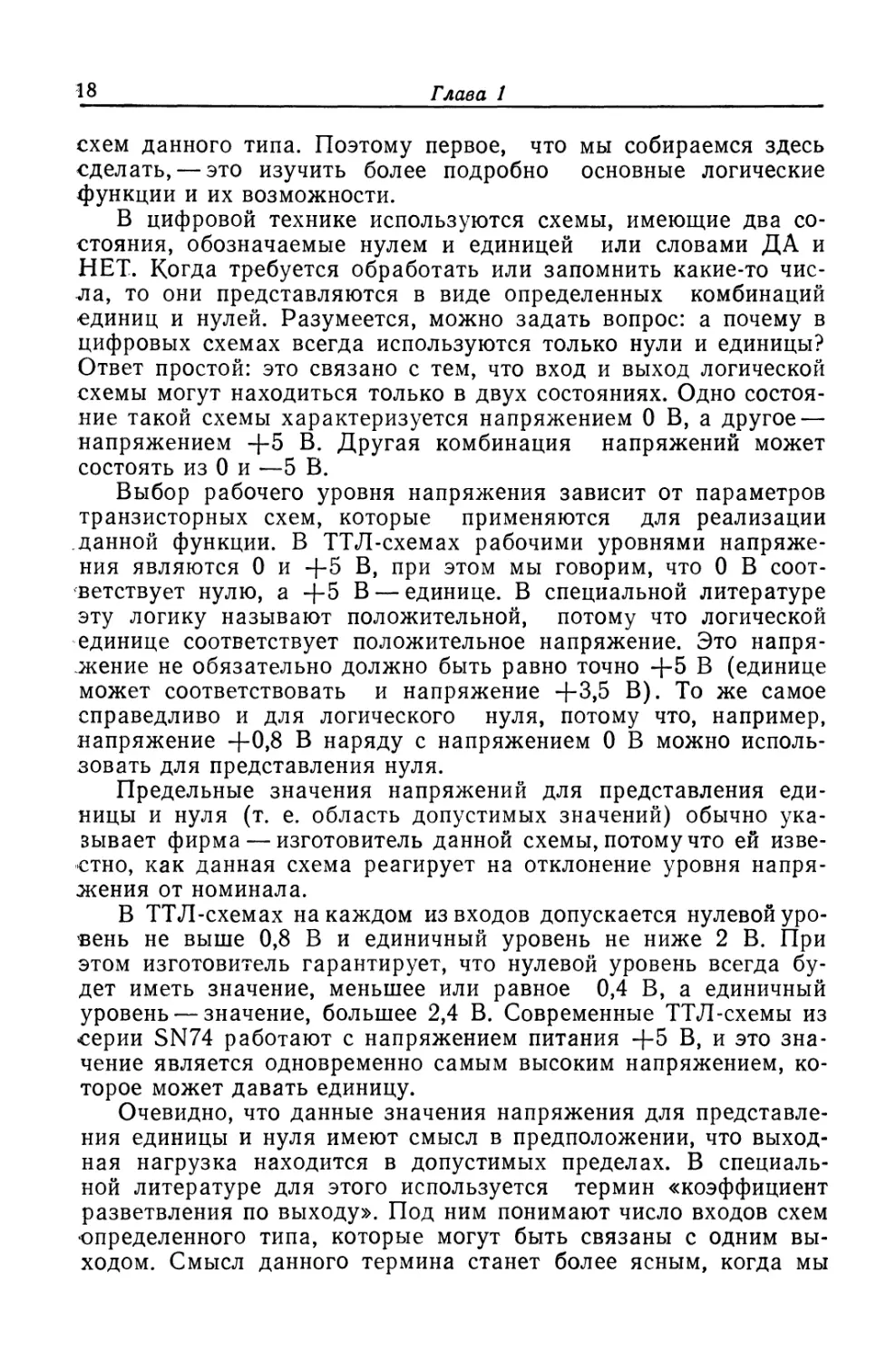

Схематически это выглядит следующим образом:

Входные переменные Логическое решение

А. Имеются ли деньги на при- Да обретение автомобиля? Б. Имеются ли права на вож- Да дение автомобиля? В. Имеется ли потребность в Да приобретении автомобиля? Приобрести автомобиль: ДА

Здесь решение зависит от трех факторов — вопросов, на

каждый из которых можно ответить словом ДА. Мы называем

такую функцию функцией И, потому что И деньги на приобре-

тение, И наличие прав на вождение должны подкрепляться

еще И потребностью в приобретении автомобиля.

Мы говорим, что все входные переменные должны иметь

значение ДА для того, чтобы результатом было также ДА.

Если же одна или большее число входных переменных име-

ет значение НЕТ, то результатом также будет НЕТ. Для этого

случая связь между логическим результатом и входными пе-

ременными выражается функцией ИЛИ.

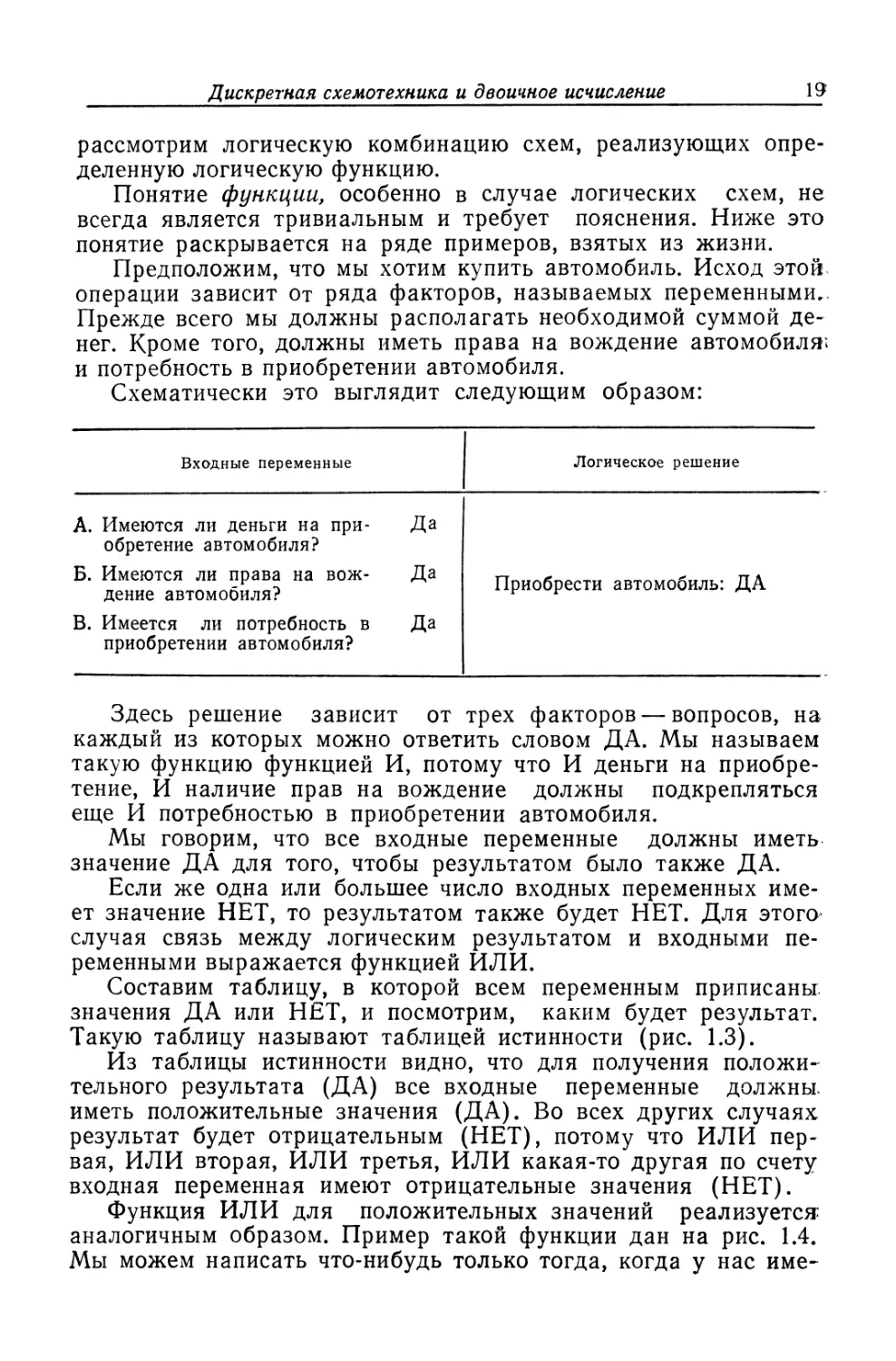

Составим таблицу, в которой всем переменным приписаны

значения ДА или НЕТ, и посмотрим, каким будет результат.

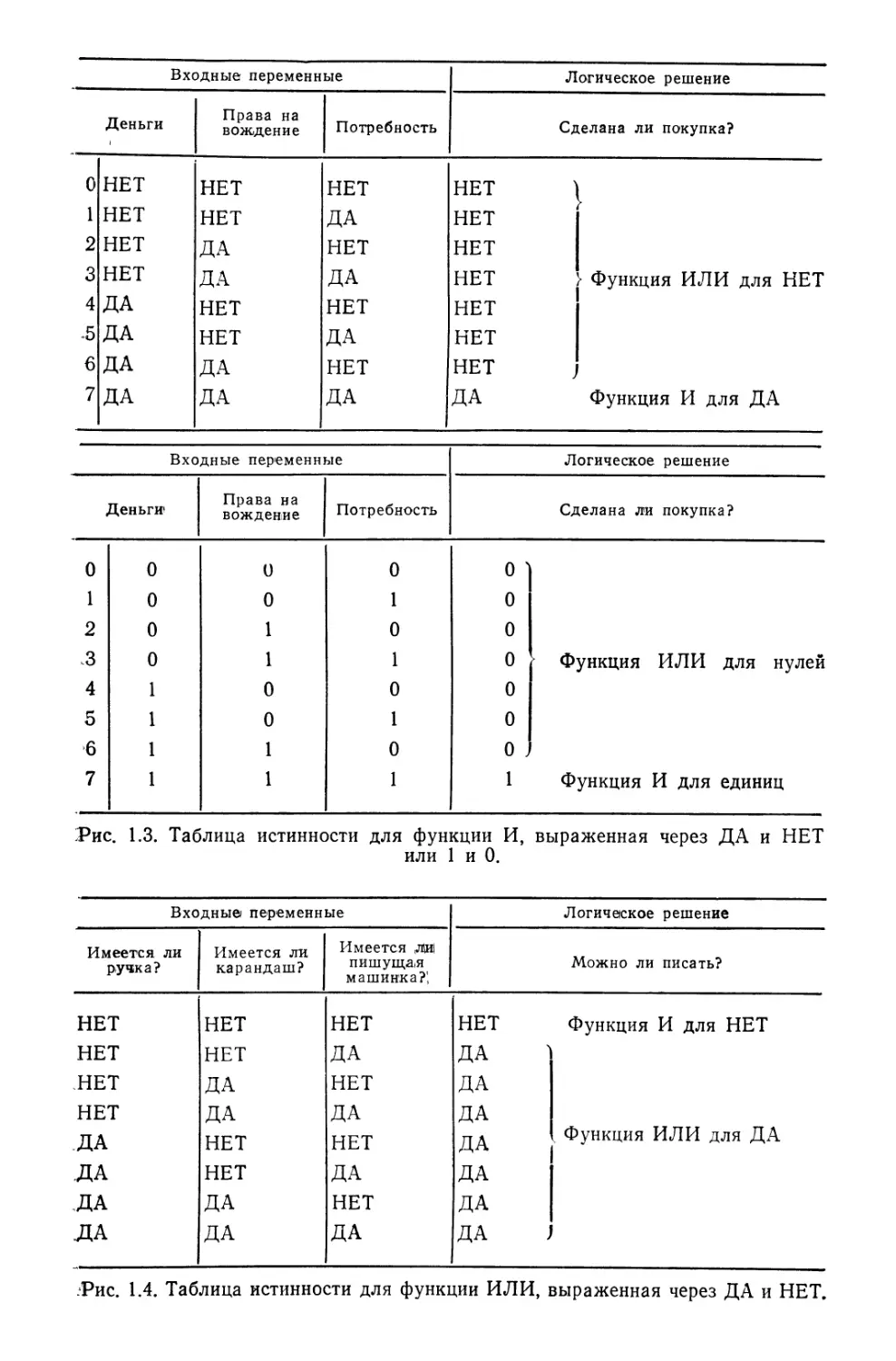

Такую таблицу называют таблицей истинности (рис. 1.3).

Из таблицы истинности видно, что для получения положи-

тельного результата (ДА) все входные переменные должны

иметь положительные значения (ДА). Во всех других случаях

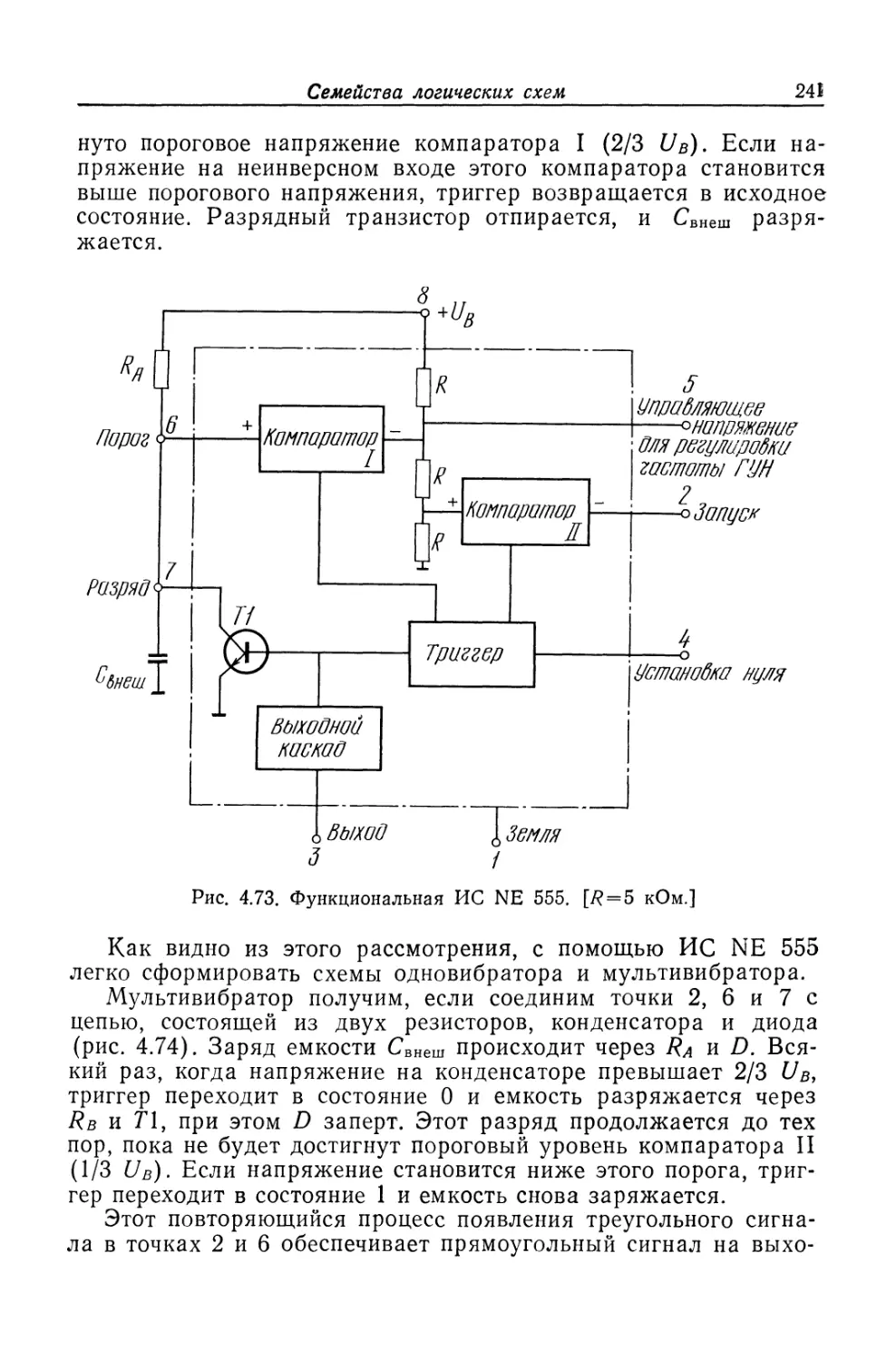

результат будет отрицательным (НЕТ), потому что ИЛИ пер-

вая, ИЛИ вторая, ИЛИ третья, ИЛИ какая-то другая по счету

входная переменная имеют отрицательные значения (НЕТ).

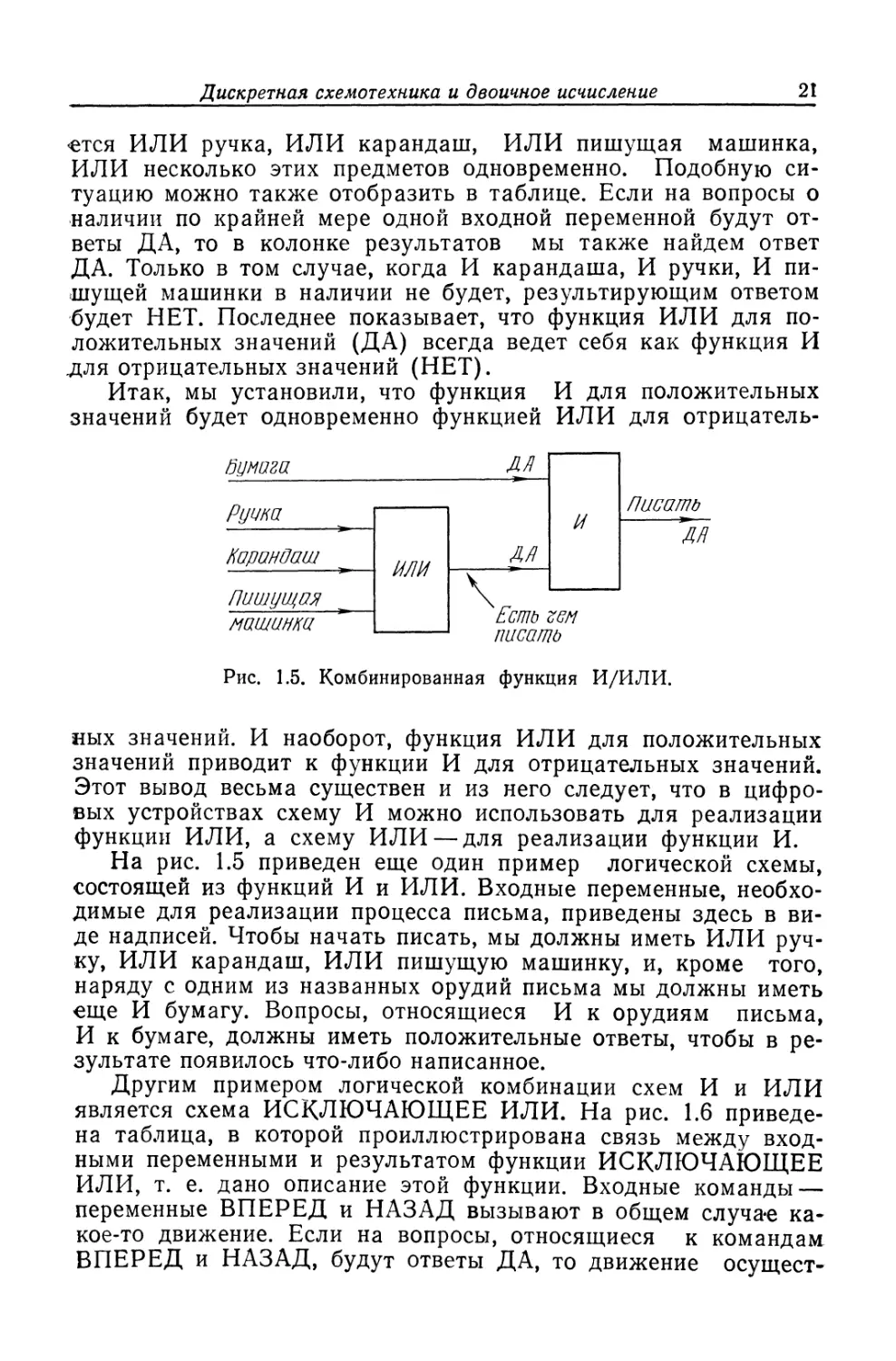

Функция ИЛИ для положительных значений реализуется

аналогичным образом. Пример такой функции дан на рис. 1.4.

Мы можем написать что-нибудь только тогда, когда у нас име-

Входные переменные Логическое решение

Деньги Права на вождение Потребность Сделана ли покупка?

0 НЕТ НЕТ НЕТ НЕТ 1 L

1 НЕТ НЕТ ДА НЕТ (

2 НЕТ ДА НЕТ НЕТ

3 НЕТ ДА ДА НЕТ • Функция ИЛИ для НЕТ

4 ДА НЕТ НЕТ НЕТ

5 ДА НЕТ ДА НЕТ

6 ДА ДА НЕТ НЕТ 1

7 ДА ДА ДА ДА Функция И для ДА

Входные переменные Логическое решение

Деньги* Права на вождение Потребность Сделана ли покупка?

0 0 0 0 0 '

1 0 0 1 0

2 0 1 0 0

.3 0 1 1 0 Функция ИЛИ для нулей

4 1 0 0 0

5 1 0 1 0

6 1 1 0 0 .

7 1 1 1 1 Функция И для единиц

Рис. 1.3. Таблица истинности для функции И, выраженная через ДА и НЕТ

или 1 и 0.

Входные; переменные Логическое решение

Имеется ли ручка? Имеется ли карандаш? Имеется ,ди( пишущая машинка?', Можно ли писать?

НЕТ НЕТ НЕТ НЕТ ДА ДА ДА ДА НЕТ НЕТ ДА ДА НЕТ НЕТ ДА ДА НЕТ ДА НЕТ ДА НЕТ ДА НЕТ ДА НЕТ Функция И для НЕТ ДА ДА ДА дд Функция ИЛИ для ДА ДА ДА ДА J

.Рис. 1.4. Таблица истинности для функции ИЛИ, выраженная через ДА и НЕТ.

Дискретная схемотехника и двоичное исчисление

21

•ется ИЛИ ручка, ИЛИ карандаш, ИЛИ пишущая машинка,

ИЛИ несколько этих предметов одновременно. Подобную си-

туацию можно также отобразить в таблице. Если на вопросы о

наличии по крайней мере одной входной переменной будут от-

веты ДА, то в колонке результатов мы также найдем ответ

ДА. Только в том случае, когда И карандаша, И ручки, И пи-

шущей машинки в наличии не будет, результирующим ответом

будет НЕТ. Последнее показывает, что функция ИЛИ для по-

ложительных значений (ДА) всегда ведет себя как функция И

для отрицательных значений (НЕТ).

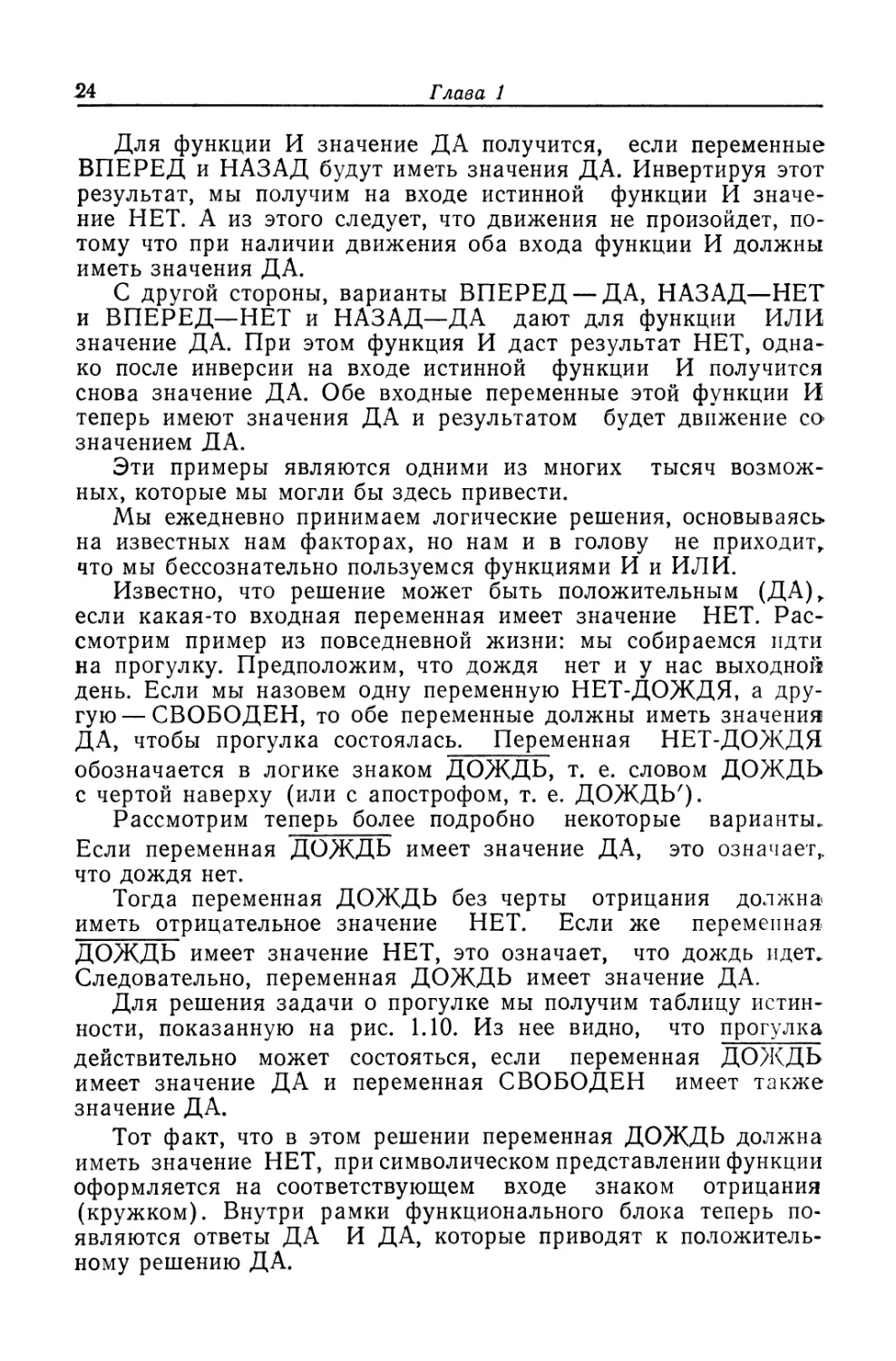

Итак, мы установили, что функция И для положительных

значений будет одновременно функцией ИЛИ для отрицатель-

Рис. 1.5. Комбинированная функция И/ИЛИ.

ных значений. И наоборот, функция ИЛИ для положительных

значений приводит к функции И для отрицательных значений.

Этот вывод весьма существен и из него следует, что в цифро-

вых устройствах схему И можно использовать для реализации

функции ИЛИ, а схему ИЛИ — для реализации функции И.

На рис. 1.5 приведен еще один пример логической схемы,

состоящей из функций И и ИЛИ. Входные переменные, необхо-

димые для реализации процесса письма, приведены здесь в ви-

де надписей. Чтобы начать писать, мы должны иметь ИЛИ руч-

ку, ИЛИ карандаш, ИЛИ пишущую машинку, и, кроме того,

наряду с одним из названных орудий письма мы должны иметь

еще И бумагу. Вопросы, относящиеся И к орудиям письма,

И к бумаге, должны иметь положительные ответы, чтобы в ре-

зультате появилось что-либо написанное.

Другим примером логической комбинации схем И и ИЛИ

является схема ИСКЛЮЧАЮЩЕЕ ИЛИ. На рис. 1.6 приведе-

на таблица, в которой проиллюстрирована связь между вход-

ными переменными и результатом функции ИСКЛЮЧАЮЩЕЕ

ИЛИ, т. е. дано описание этой функции. Входные команды —

переменные ВПЕРЕД и НАЗАД вызывают в общем случа-е ка-

кое-то движение. Если на вопросы, относящиеся к командам

ВПЕРЕД и НАЗАД, будут ответы ДА, то движение осущест-

22

Глава 1

вится. При ответах НЕТ движения не произойдет. То же самое

получится, когда переменные ВПЕРЕД и НАЗАД появятся

одновременно. Говорят, что движение происходит только тогда,

когда ВПЕРЕД имеет значение ДА или НАЗАД имеет значе-

ние ДА.

Входные переменные Результат

Вперед Назад Движение?

НЕТ НЕТ НЕТ

НЕТ ДД ДА

НЕТ ДД

~дд дГ НЕТ

Рис. 1.6. Таблица истинности

для ИСКЛЮЧАЮЩЕГО ИЛИ.

Примечательным свойством

ИЛИ является также то, что в

ременные имеют значение ДА

НЕТ.

функции ИСКЛЮЧАЮЩЕЕ

случае, когда обе входные пе-

или НЕТ, результатом будет

ДД, если вперед

ДД, если вперед Функция ДД, если вперед или

и назад одращения назад. НЕТ, если

вперед и назад

Рис. 1.7. Схема ИСКЛЮЧАЮЩЕГО ИЛИ.

Логическая схема на рис. 1.7 показывает, как можно реали-

зовать функцию ИСКЛЮЧАЮЩЕЕ ИЛИ при помощи одной

функции ИЛИ, двух функций И и одной функции НЕ. На рис.

1.8 приведена таблица истинности для функции обращения.

Здесь мы имеем весьма простую функцию, потому что значе-

ние входной переменной ДА инициирует значение выходной

переменной НЕТ для функции НЕ и, наоборот, для входных

Дискретная схемотехника и двоичное исчисление

23

Тадлица

истинности

ВХОД \ выход

ДД НЕТ

НЕТ ДЕ

ДД

Отрицание или шунк- Внешнее лега-

ция одращения ноское значение

Знак отрицания

Внутренние логические

\ значения

\нр

О.Е1—3-S _

ДЛ

Знак отрицания

Внешнее логическое

значение

Рис. 1.8. Функция обращения (инверсии) с таблицей истинности.

переменных со значениями НЕТ мы получим значение ДА для

функции НЕ.

Функция обращения (инверсии) обозначается символами,

показанными на рис. 1.9. В цифровой схемотехнике вместо тер-

мина «обращение» в большинстве случаев используется термин

«инверсия».

BmjQ

В

Знак отрицания

Рис. 1.9. Символы, применяемые для описания

функции обращения.

а и б — по американской спецификации milspec; в —

стандарт МЭК 117-15. В данном случае показан инвер-

тированный выход. Вход также может быть инвертиро-

ван и знак отрицания будет помещен у рассматриваемо-

го входа, как на рис. 1.8.

вход

д

Вход

д

Знакотрицания

о

Знакотрицания

/Выход

3----—

Если вернуться к логической схеме функции ИСКЛЮЧАЮ-

ЩЕЕ ИЛИ, можно увидеть, что для функции ИЛИ значение

ДА получится в случае, если ИЛИ переменная ВПЕРЕД, ИЛИ

переменная НАЗАД, ИЛИ обе переменные одновременно будут

иметь значение ДА.

24

Глава 1

Для функции И значение ДА получится, если переменные

ВПЕРЕД и НАЗАД будут иметь значения ДА. Инвертируя этот

результат, мы получим на входе истинной функции И значе-

ние НЕТ. А из этого следует, что движения не произойдет, по-

тому что при наличии движения оба входа функции И должны

иметь значения ДА.

С другой стороны, варианты ВПЕРЕД — ДА, НАЗАД—НЕТ

и ВПЕРЕД—НЕТ и НАЗАД—ДА дают для функции ИЛИ

значение ДА. При этом функция И даст результат НЕТ, одна-

ко после инверсии на входе истинной функции И получится

снова значение ДА. Обе входные переменные этой функции И

теперь имеют значения ДА и результатом будет движение со

значением ДА.

Эти примеры являются одними из многих тысяч возмож-

ных, которые мы могли бы здесь привести.

Мы ежедневно принимаем логические решения, основываясь

на известных нам факторах, но нам и в голову не приходит,

что мы бессознательно пользуемся функциями И и ИЛИ.

Известно, что решение может быть положительным (ДА),

если какая-то входная переменная имеет значение НЕТ. Рас-

смотрим пример из повседневной жизни: мы собираемся идти

на прогулку. Предположим, что дождя нет и у нас выходной

день. Если мы назовем одну переменную НЕТ-ДОЖДЯ, а дру-

гую— СВОБОДЕН, то обе переменные должны иметь значения

ДА, чтобы прогулка состоялась. Переменная НЕТ-ДОЖДЯ

обозначается в логике знаком ДОЖДЬ, т. е. словом ДОЖДЬ

с чертой наверху (или с апострофом, т. е. ДОЖДЬ').

Рассмотрим теперь более подробно некоторые варианты.

Если переменная ДОЖДЬ имеет значение ДА, это означает,

что дождя нет.

Тогда переменная ДОЖДЬ без черты отрицания должна

иметь отрицательное значение НЕТ. Если же переменная

ДОЖДЬ имеет значение НЕТ, это означает, что дождь идет.

Следовательно, переменная ДОЖДЬ имеет значение ДА.

Для решения задачи о прогулке мы получим таблицу истин-

ности, показанную на рис. 1.10. Из нее видно, что прогулка

действительно может состояться, если переменная ДОЖДЬ

имеет значение ДА и переменная СВОБОДЕН имеет также

значение ДА.

Тот факт, что в этом решении переменная ДОЖДЬ должна

иметь значение НЕТ, при символическом представлении функции

оформляется на соответствующем входе знаком отрицания

(кружком). Внутри рамки функционального блока теперь по-

являются ответы ДА И ДА, которые приводят к положитель-

ному решению ДА.

Дискретная схемотехника и двоичное исчисление

25

, Знак отрицания

А°ЖвЬ фП„

'И \м Решение

^~НЁТ^

1Шоден

Внешнее

логическое

значение

Внешнее

^-логическое

D значение

Внутреннее

значение

Знак отрицания

АОЖЗЬ ^ДЯ1 „

-------'И др Решение

(ДИ)

Э АЛ-------.

Свободен

ЛЯ'----

ДИ

Входные переменные Логическое решение

Отправляться ли на прогулку?

дождь СВОБОДЕН

НЕТ НЕТ НЕТ

НЕТ ДА НЕТ

ДА НЕТ НЕТ

ДА ДА ДА

Входные переменные Логическое решение

Отправляться ли на прогулку?

дождь СВОБОДЕН

0 0 0

0 1 0

1 0 0

1 1 1

Рис. 1.10. Таблица истинности для задачи «прогулка», созданная на основе

символического представления логической функции (функции И).

Если переменная ДОЖДЬ уже была в нашем распоряжении

ранее (например, получилась из предшествующего отрицания),

то знак отрицания на входе в блок функции И можно убрать,

как это показано на рис. 1.10, из которого видно, что в обоих

символических изображениях существует различие между внут-

ренними и внешними логическими значениями.

Если символическое изображение содержит один дополни-

тельный символ внутри квадратной рамки (в данном случае на

рис. 1.10 И), то это означает, что внутреннее логическое значе-

ние— как истинное, т. е. ДА, так и ложное, т. е. НЕТ — на

одном из входов-выходов совпадает с внешним логическим зна-

чением для рассматриваемого входа или выхода.

26

Глава 1

Таким образом, здесь идет речь о тождественном отображе-

нии, т. е. то, что ИСТИННО снаружи, совпадает с ИСТИННО

внутри, а то, что ЛОЖНО снаружи, совпадает с ЛОЖНО внут-

ри. Что же касается функции, то она, будучи написана допол-

нительными символами в этих примерах для И, является ИС-

ТИННОЙ, когда обе внутренние переменные, которые управля-

ют этой функцией, являются ИСТИННЫМИ.

Если некоторую внешнюю отрицательную логическую вели-

чину необходимо использовать в качестве внутренней логиче-

ской величины, то на внешнем входе ей приписывают знак от-

рицания (рис. 1.10). На второй схеме (рис. 1.10) у внешнего»

входа располагается как раз такая переменная ДОЖДЬ и, как

мы уже говорили выше, знак отрицания на входе можно опус-

тить.

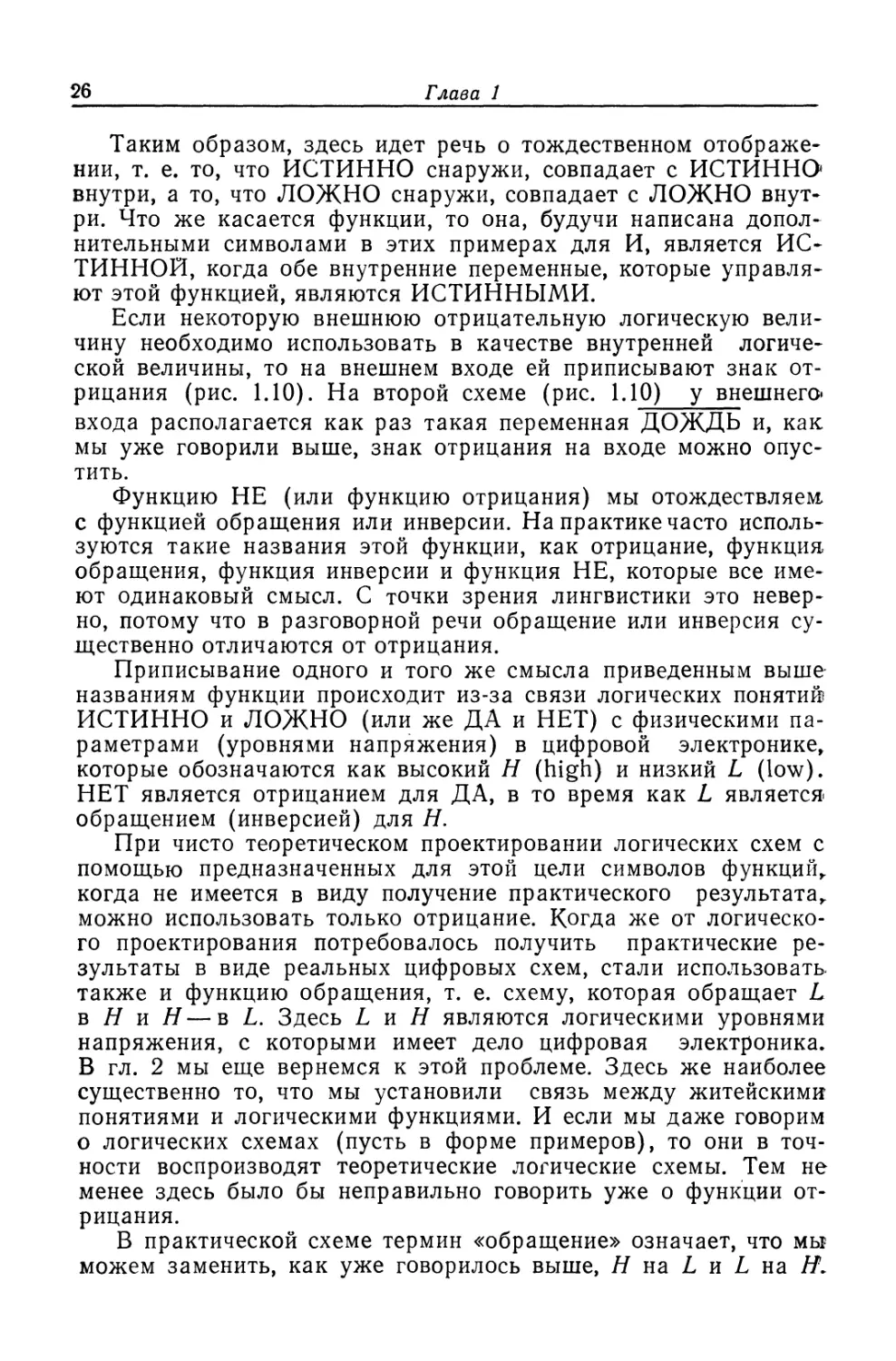

Функцию НЕ (или функцию отрицания) мы отождествляем

с функцией обращения или инверсии. На практике часто исполь-

зуются такие названия этой функции, как отрицание, функция

обращения, функция инверсии и функция НЕ, которые все име-

ют одинаковый смысл. С точки зрения лингвистики это невер-

но, потому что в разговорной речи обращение или инверсия су-

щественно отличаются от отрицания.

Приписывание одного и того же смысла приведенным выше

названиям функции происходит из-за связи логических понятий

ИСТИННО и ЛОЖНО (или же ДА и НЕТ) с физическими па-

раметрами (уровнями напряжения) в цифровой электронике,

которые обозначаются как высокий Н (high) и низкий L (low).

НЕТ является отрицанием для ДА, в то время как L является

обращением (инверсией) для Н.

При чисто теоретическом проектировании логических схем с

помощью предназначенных для этой цели символов функций,

когда не имеется в виду получение практического результата,

можно использовать только отрицание. Когда же от логическо-

го проектирования потребовалось получить практические ре-

зультаты в виде реальных цифровых схем, стали использовать

также и функцию обращения, т. е. схему, которая обращает L

в Н и Н—в L. Здесь L и Н являются логическими уровнями

напряжения, с которыми имеет дело цифровая электроника.

В гл. 2 мы еще вернемся к этой проблеме. Здесь же наиболее

существенно то, что мы установили связь между житейскими

понятиями и логическими функциями. И если мы даже говорим

о логических схемах (пусть в форме примеров), то они в точ-

ности воспроизводят теоретические логические схемы. Тем не

менее здесь было бы неправильно говорить уже о функции от-

рицания.

В практической схеме термин «обращение» означает, что мы

можем заменить, как уже говорилось выше, Н на L и L на Н.

Дискретная схемотехника и двоичное исчисление

27

С отрицанием дело обстоит сложнее. Пусть А является отрица-

нием для А, будет ли А также отрицанием для Д? Специалисты

по логике, которые ответственно подходят к разработке теоре-

тических логических схем, утверждают, что это не всегда имеет

место, однако мы склонны предполагать, что так все же можно

считать. Например, запрет «Не ставить автомобиль на стоян-

ку» сохраняет смысл и после отрицания. «Принципиальные»

разработчики, однако же, считают, что только отрицание А

приведет к А (НЕ-Л), обратное же верно не всегда1*. Если это

утверждение справедливо, то нужно учитывать и последствия,

вытекающие отсюда для логических символов, а именно что

знак отрицания можно ставить только на входе в функциональ-

ный блок, а не на выходе из него, как это следует из рис. 1.11,

где приведены две произвольные логические схемы, реализую-

щие одну и ту же функцию. На рис. 1.11, а знак отрицания по-

мещен на входах, а на рис. 1.11, б это пытались сделать на вы-

ходах функциональных блоков. К сожалению, для примера на

рис. 1.11, б попытка не удалась. На рис. 1.11, б для переменной

D осуществлен переход направо из D в D, который делает не-

избежным появление знака отрицания на входе в соответствую-

щий функциональный элемент ИЛИ. Однако отрицание D с

переходом в D противоречит правилам. Вторую схему гораздо

удобнее использовать при проектировании, чем практические

схемы, под которыми подразумеваются схемы, аналогичные

описанным в следующем разделе. Схему на рис. 1.11,6 можно

почти полностью реализовать на практике и для этого нужно

только обратить D с помощью схемы НЕ по методу, который

мы рассмотрим в гл. 2. Более подробно эти вопросы мы здесь

’не обсуждаем.

Отвечая на вопрос, какие обозначения переменных можно

использовать, мы замечаем, что в схеме на рис. 1.11, а черта

отрицания во внешних связях между символами не появляется

и подразумевается, что она имеется внутри соответствующих * В

!) Разберем более подробно пример со стоянкой автомобиля. Пусть ис-

ходным утверждением является «автомобиль можно ставить на стоянку», и вы

пользуетесь этой стоянкой. Затем вышел запрет «ставить автомобиль на сто-

янку нельзя» (отрицание исходного утверждения). Через некоторое время

вновь появляется разрешение ставить автомобиль на стоянку (отрицание от-

рицания). Узнав об этом, вы едете на стоянку и обнаруживаете, что все места

уже заняты, т. е. по-прежнему, несмотря на разрешение, вам поставить авто-

мобиль на стоянку нельзя. В этом случае вам безразлично, существует запрет

или нет.

Нечто похожее в принципе может иметь место и в логических схемах.

В результате повторного отрицания может образоваться нереализуемое при

работе схемы состояние. Такие состояния при проектировании игнорируются

и вместо них используют другие состояния, исходя из простоты проектирова-

ния. В результате может оказаться, что а=^=Л. — Прим. ред.

28

Глава 1

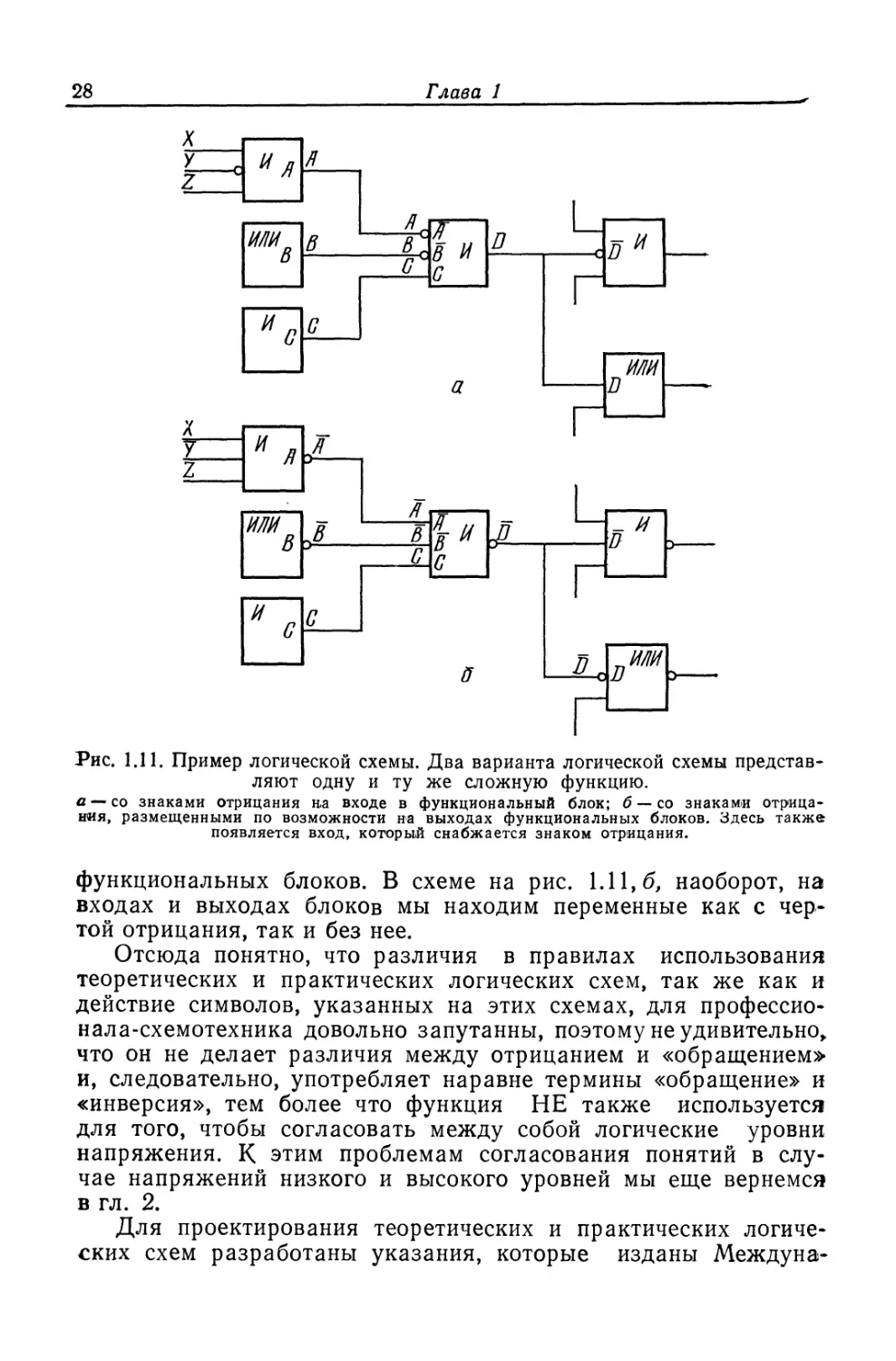

Рис. 1.11. Пример логической схемы. Два варианта логической схемы представ-

ляют одну и ту же сложную функцию.

а —со знаками отрицания н.а входе в функциональный блок; б — со знаками отрица-

ния, размещенными по возможности на выходах функциональных блоков. Здесь также

появляется вход, который снабжается знаком отрицания.

функциональных блоков. В схеме на рис. 1.11, б, наоборот, на

входах и выходах блоков мы находим переменные как с чер-

той отрицания, так и без нее.

Отсюда понятно, что различия в правилах использования

теоретических и практических логических схем, так же как и

действие символов, указанных на этих схемах, для профессио-

нала-схемотехника довольно запутанны, поэтому неудивительно,

что он не делает различия между отрицанием и «обращением»

и, следовательно, употребляет наравне термины «обращение» и

«инверсия», тем более что функция НЕ также используется

для того, чтобы согласовать между собой логические уровни

напряжения. К этим проблемам согласования понятий в слу-

чае напряжений низкого и высокого уровней мы еще вернемся

в гл. 2.

Для проектирования теоретических и практических логиче-

ских схем разработаны указания, которые изданы Междуна-

Дискретная схемотехника и двоичное исчисление_____________29*

родной Электротехнической Комиссией и были приняты после

тщательных и длительных исследований, выполненных рабочей

группой, образованной из специалистов — представителей не-

скольких стран. В соответствии с этими указаниями в теорети-

ческих и практических (электронных) схемах следует исполь-

зовать разные символы, что облегчает понимание соответству-

ющих схем. Эти символы также обсуждаются в гл. 2.

1.3. Функции И-НЕ и ИЛИ-НЕ

В предыдущем разделе было показано, что комбинатор-

ные функции, состоящие из функций И и НЕ, а также ИЛИ ш

НЕ, описываются функциями И-НЕ и ИЛИ-HE соответствен-

но. Среди логических решений, которые мы принимаем еже-

дневно, часто встречаются такие, когда для всех входных пере-

менных со значением ДА результатом оказывается решение*

НЕТ (функция И-НЕ).

Например, нам нужно принять решение о покупке велосипе-

да. Если старый велосипед еще «на ходу» и его шины хорошие^,

решение о покупке нового велосипеда может оказаться отрица-

тельным, т. е. НЕТ. Таким образом, здесь мы имеем две вход-

ные переменные со значением ДА, однако в результате прихо-

дим к отрицательному решению НЕТ.

Как уже говорилось выше, в цифровой логике нам известна^

функция инверсии (обращения, отрицания), которая обознача-

ется с помощью маленького кружка на входе или выходе соот-

ветствующего логического символа. Если этот кружок появит-

ся после символа функции И или ИЛИ, как показано на рис.

1.11, б, то такой символ с кружком будет обозначать теперь-

функцию И-НЕ или ИЛИ-HE соответственно.

1.4. Функции запоминания. Методы кодирования

(шифрации) информации

С помощью рассмотренных выше логических функций Иг

ИЛИ, НЕ образуются входные переменные, которые мы вызы-

ваем из нашего личного запоминающего устройства (ЗУ), т. е.

мозга. Глядя в окно, мы убеждаемся, что погода плохая, и от-

мечаем это в уме. При этом мы размышляем о том, распола-

гаем ли мы свободным временем. На основе этих сведений, ко-

торые мы запомнили, мы принимаем решение — следует ли вы-

ходить на улицу. Решение, которые мы примем (ДА или НЕТ),

мы также запомним.

На самом деле сейчас мы произвели обработку информации,.,

потому что значения ДА или НЕТ говорят уже нечто определен-

ное относительно входных переменных и этот факт несет те-

30

Глава 1

лерь определенную информацию, т. е. наше логическое решение

является по существу актом обработки информации. В цифро-

вой электронике для хранения информации также используют

память, которую иногда называют электронным мозгом. Его

ячейки могут запоминать 1 или 0 (ДА или НЕТ).

Запоминающее устройство, в котором можно хранить после-

довательности единиц и нулей, называется регистром. Регистр

часто используется в качестве оперативного ЗУ для временного

хранения информации. ЗУ большего объема, в котором можно

хранить несколько десятков тысяч единиц и нулей, мы будем

называть просто ЗУ, а в тех случаях, когда цифровые блоки,

вход данных

(ДР или НЕТ}

(1 или О)

Сапо-

нин а-

> ющая

ягвйка

Выход данных

(ДР или НЕТ)

(1 ил ид)

Вход для считывания

(по команде ДЕП)

передать данные)

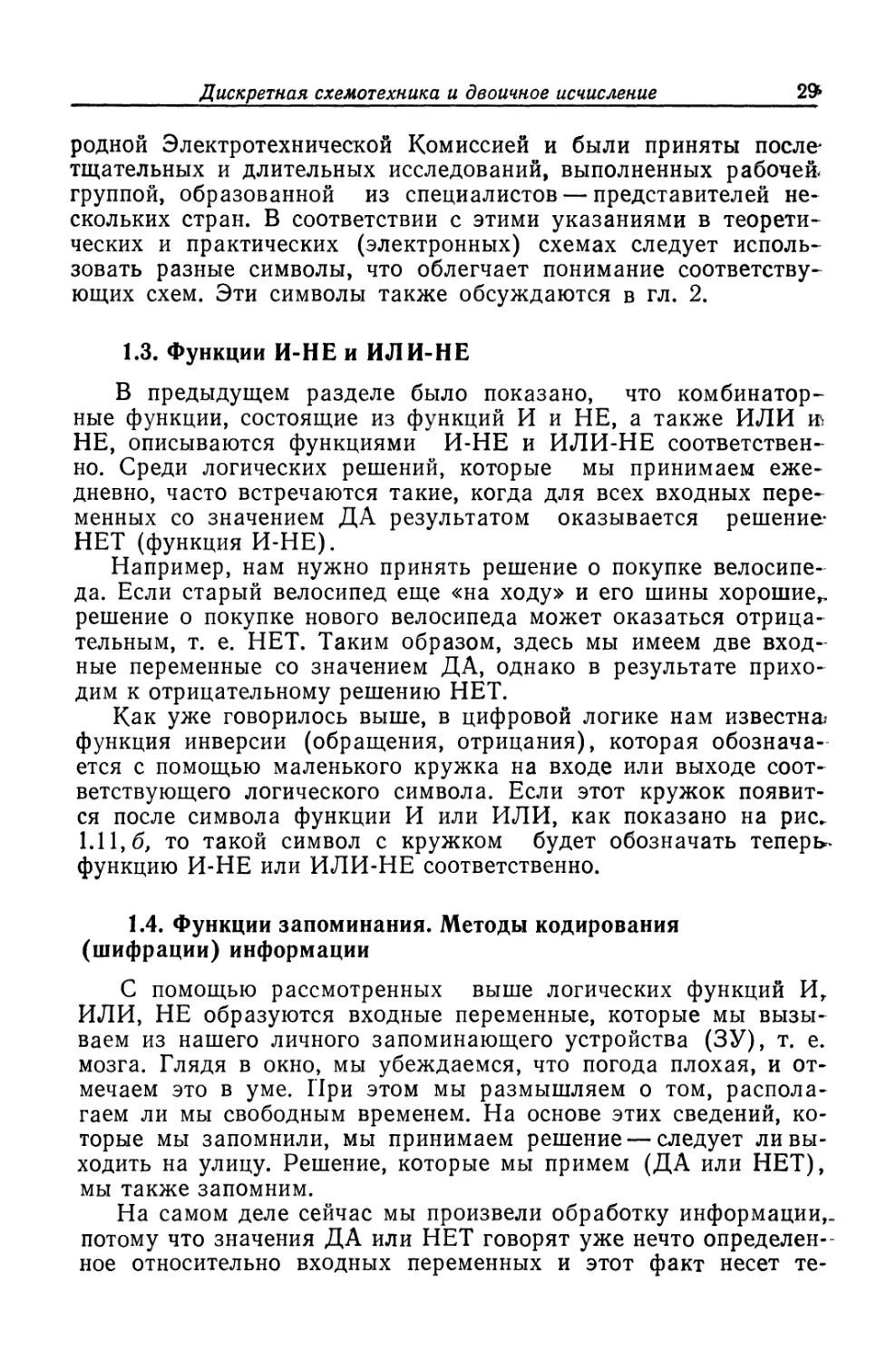

Рис. 1.12. Ячейка ЗУ.

которые обрабатывают данные, разделены с этим ЗУ в прост-

ранстве— внешним ЗУ. На рис. 1.12 приведена схема одной

ячейки ЗУ.

Вход ячейки ЗУ связан с источником информации «Данные»,

который генерирует сигналы ДА или НЕТ (1 или 0). До тех

пор пока мы не даем никакой команды о приеме информации,

в эту ячейку ничего не записывается. На выходе ячейки ин-

формация, которая была записана в нее ранее, появится в фор-

ме ДА или НЕТ (1 или 0).

Если же мы подадим команду ДА(1) на считывающий

(управляющий) вход, ячейка перейдет в новое состояние и за-

помнит входную информацию.

Если регистр состоит только из одной ячейки, как это пока-

зано на рис. 1.12, мы говорим об одноразрядном регистре. Од-

норазрядные регистры находят применение в цифровой элект-

ронике для временного хранения единиц и нулей. В электрони-

ке более широко применяются многоразрядные регистры, пото-

му что одноразрядные регистры имеют слишком малый объем

памяти.

Поговорим теперь о «шифрации информации», которая поз-

воляет представлять данную величину более подробно. Обычно

с помощью слов ДА и НЕТ мы можем описать всего лишь два

логических состояния этой величины. С другой стороны, если

Дискретная схемотехника и двоичное исчисление

3!

Десятичная цифра вз В2 В1 во

0 НЕТ НЕТ НЕТ НЕТ

1 НЕТ НЕТ НЕТ ДА

2 НЕТ НЕТ ДА НЕТ

3 НЕТ НЕТ ДА ДА

4 НЕТ ДА НЕТ НЕТ

5 НЕТ ДА НЕТ ДА

6 НЕТ ДА ДА НЕТ

7 НЕТ ДА ДА ДА

8 ДА НЕТ НЕТ НЕТ

9 ДА НЕТ НЕТ ДА

Рис. 1.13. Кодовая таблица десятичных цифр, выраженная через ДА или НЕТ.

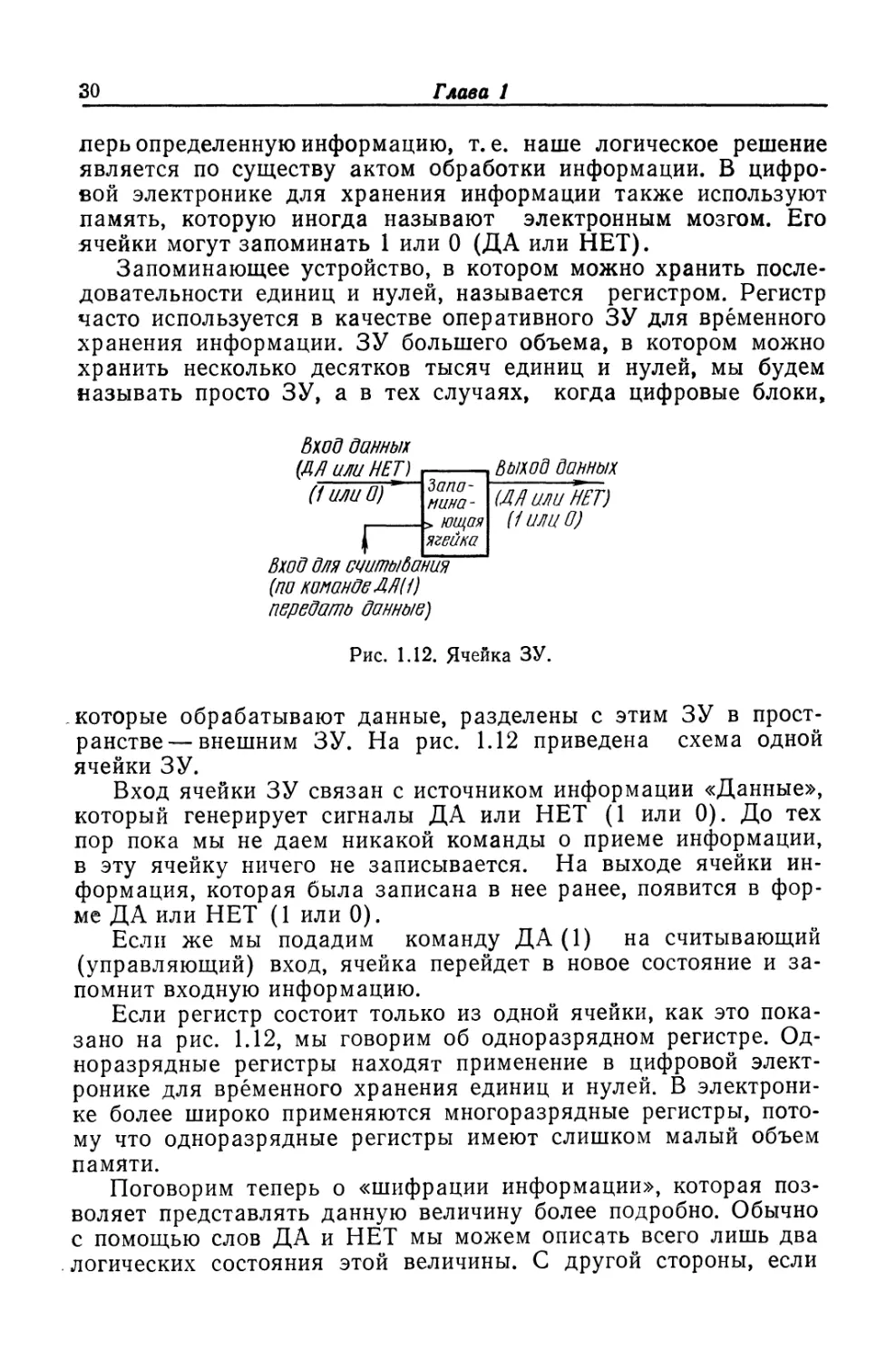

мы захотим представить один из десяти возможных символов

(слов), понадобится код, состоящий не менее чем из 4 битов0.

На рис. 1.13 приведена кодовая таблица, в которой с помо-

щью системы обозначений, использующей значения ДА и НЕТ,

показаны состояния разрядов (битов) от ВО до ВЗ включи-

тельно при реализации этих символов.

Десятичное число Кодирование 5 6 3 4

С помощью двоичных цифр С помощью слов Да (Д) и Нет (Н) 0 10 1 н д н д 0 110 н д д н 0 0 11 н н д д 0 10 0 н д н н

Рис. 1.14. Кодирование десятичного числа 5634 в виде четырех групп двоичных

цифр (1 или О, ДА или НЕТ).

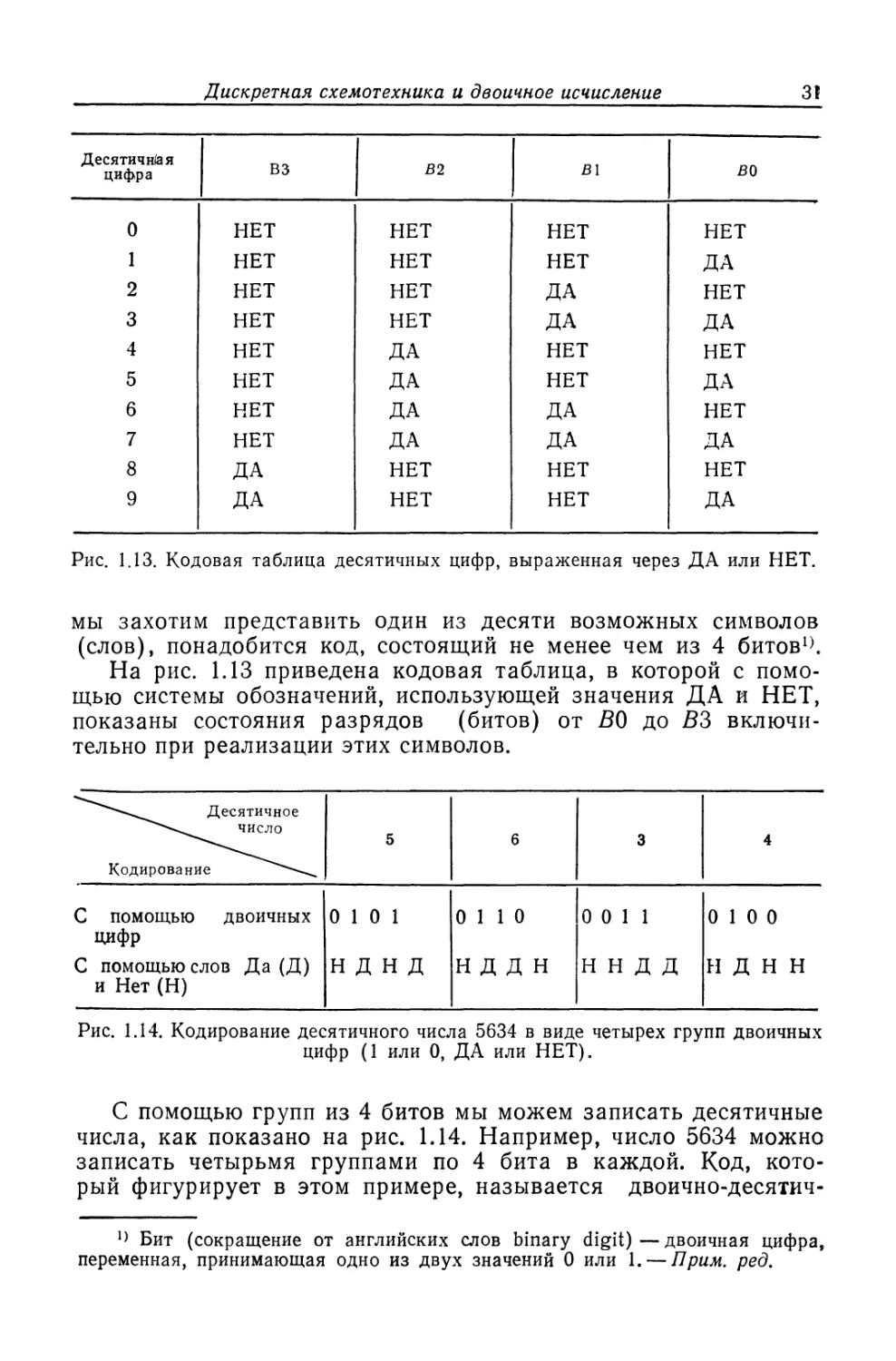

С помощью групп из 4 битов мы можем записать десятичные

числа, как показано на рис. 1.14. Например, число 5634 можно

записать четырьмя группами по 4 бита в каждой. Код, кото-

рый фигурирует в этом примере, называется двоично-десятич-

0 Бит (сокращение от английских слов binary digit)—двоичная цифра,

переменная, принимающая одно из двух значений 0 или 1. — Прим. ред.

-32

Глава 1

ным кодом (BCD-кодом0), и о нем мы еще будем говорить

ниже.

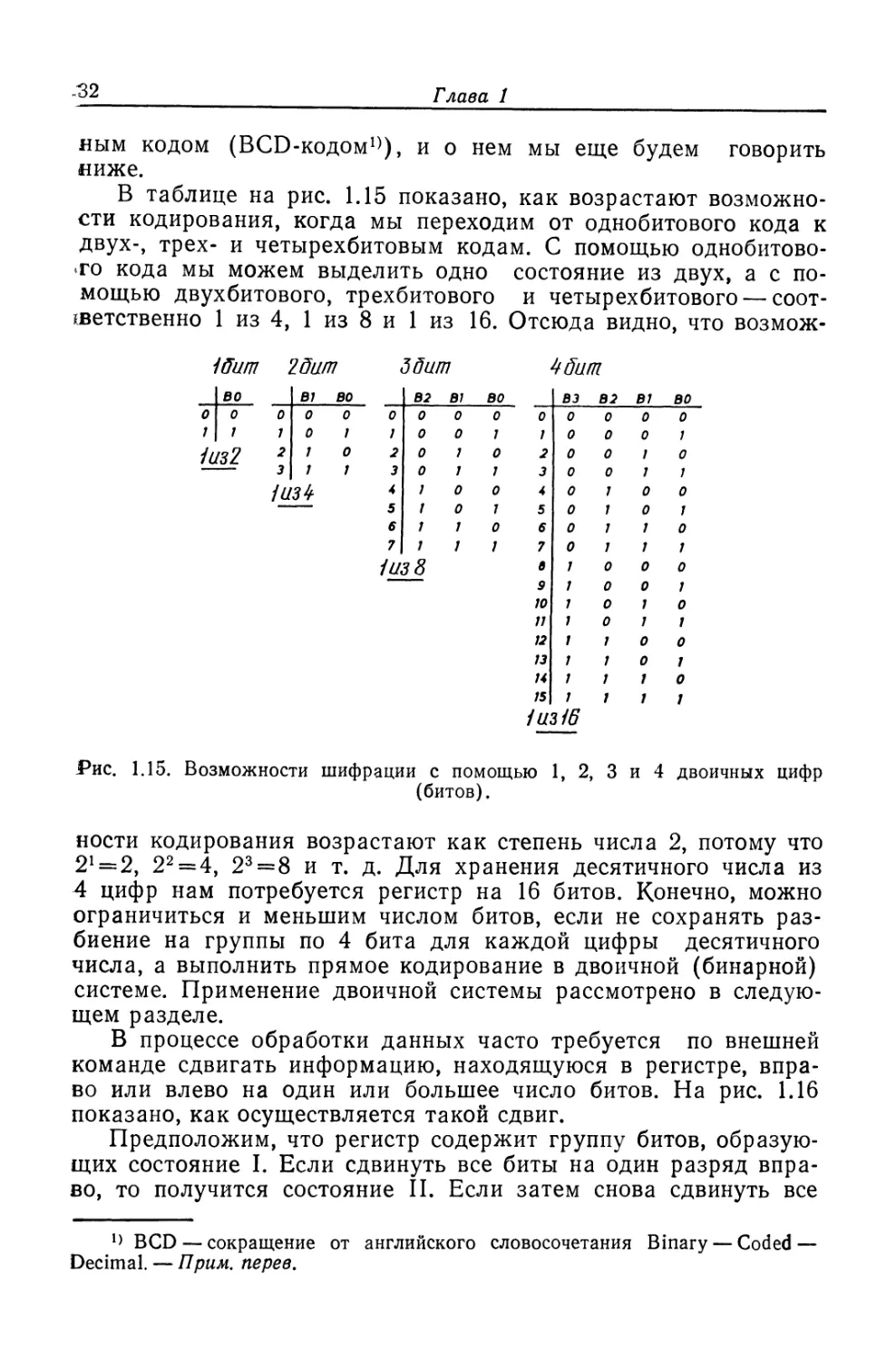

В таблице на рис. 1.15 показано, как возрастают возможно-

сти кодирования, когда мы переходим от однобитового кода к

двух-, трех- и четырехбитовым кодам. С помощью однобитово-

го кода мы можем выделить одно состояние из двух, а с по-

мощью двухбитового, трехбитового и четырехбитового — соот-

ветственно 1 из 4, 1 из 8 и 1 из 16. Отсюда видно, что возмож-

Рис. 1.15. Возможности шифрации с помощью 1, 2, 3 и 4 двоичных цифр

(битов).

ности кодирования возрастают как степень числа 2, потому что

2! = 2, 22 = 4, 23 = 8 и т. д. Для хранения десятичного числа из

4 цифр нам потребуется регистр на 16 битов. Конечно, можно

ограничиться и меньшим числом битов, если не сохранять раз-

биение на группы по 4 бита для каждой цифры десятичного

числа, а выполнить прямое кодирование в двоичной (бинарной)

системе. Применение двоичной системы рассмотрено в следую-

щем разделе.

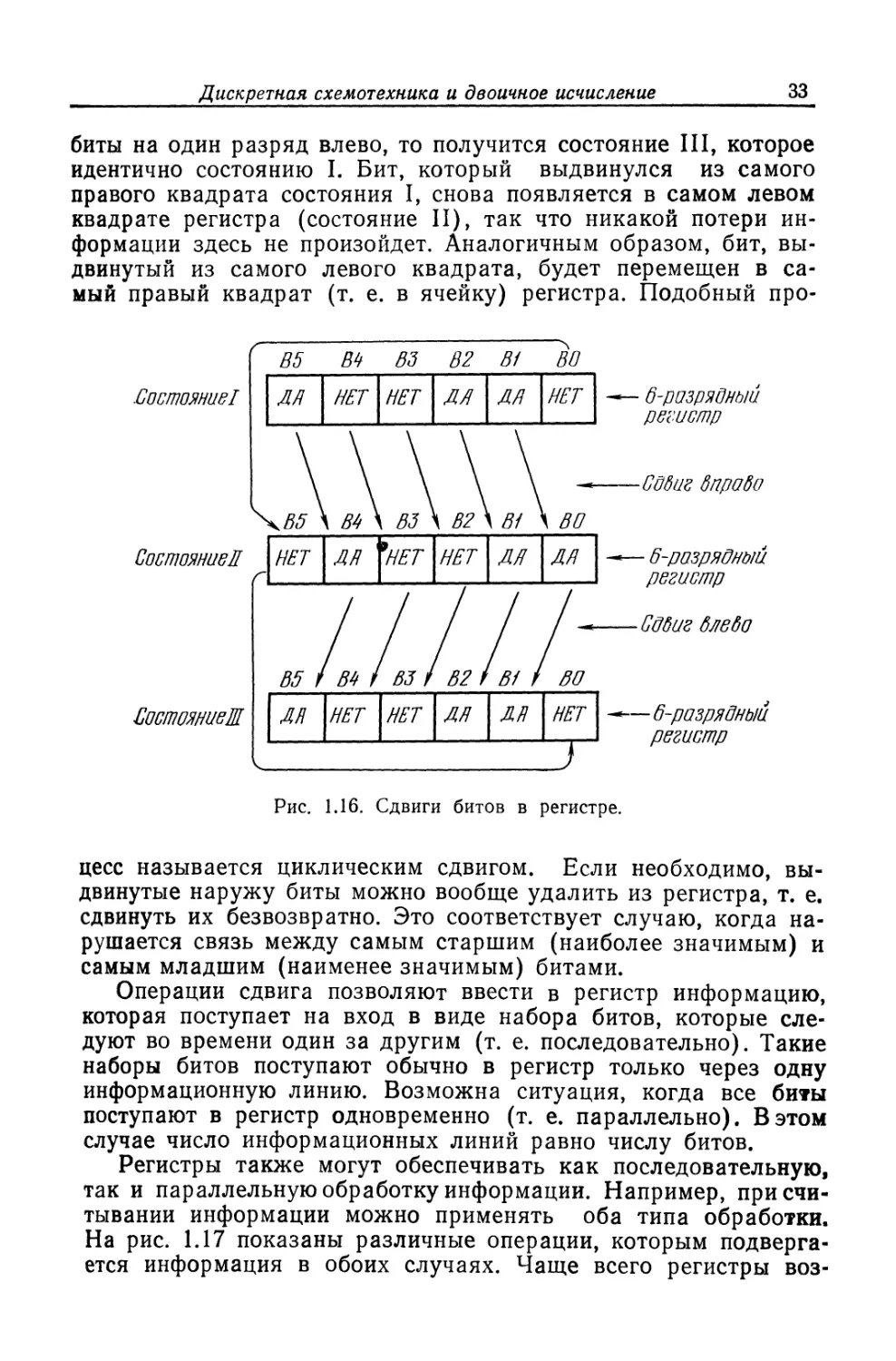

В процессе обработки данных часто требуется по внешней

команде сдвигать информацию, находящуюся в регистре, впра-

во или влево на один или большее число битов. На рис. 1.16

показано, как осуществляется такой сдвиг.

Предположим, что регистр содержит группу битов, образую-

щих состояние I. Если сдвинуть все биты на один разряд впра-

во, то получится состояние II. Если затем снова сдвинуть все

BCD — сокращение от английского словосочетания Binary — Coded —

Decimal. — Прим, перев.

Дискретная схемотехника и двоичное исчисление

33

биты на один разряд влево, то получится состояние III, которое

идентично состоянию I. Бит, который выдвинулся из самого

правого квадрата состояния I, снова появляется в самом левом

квадрате регистра (состояние II), так что никакой потери ин-

формации здесь не произойдет. Аналогичным образом, бит, вы-

двинутый из самого левого квадрата, будет перемещен в са-

мый правый квадрат (т. е. в ячейку) регистра. Подобный про-

.Состоянин!

СостояниеН

Состояние]]!

Рис. 1.16. Сдвиги битов в регистре.

цесс называется циклическим сдвигом. Если необходимо, вы-

двинутые наружу биты можно вообще удалить из регистра, т. е.

сдвинуть их безвозвратно. Это соответствует случаю, когда на-

рушается связь между самым старшим (наиболее значимым) и

самым младшим (наименее значимым) битами.

Операции сдвига позволяют ввести в регистр информацию,

которая поступает на вход в виде набора битов, которые сле-

дуют во времени один за другим (т. е. последовательно). Такие

наборы битов поступают обычно в регистр только через одну

информационную линию. Возможна ситуация, когда все биты

поступают в регистр одновременно (т. е. параллельно). В этом

случае число информационных линий равно числу битов.

Регистры также могут обеспечивать как последовательную,

так и параллельную обработку информации. Например, присчи-

тывании информации можно применять оба типа обработки.

На рис. 1.17 показаны различные операции, которым подверга-

ется информация в обоих случаях. Чаще всего регистры воз-

34

Глава 1

вращаются в исходное состояние с помощью внешней команды,

которая называется «сброс на нуль». Эта команда переводит

одновременно все биты данного регистра в состояние «О».

1.5. Сложные функции

В повседневной жизни наряду с основными (базовыми) ло-

гическими функциями типа И, ИЛИ, НЕ мы часто используем

также и более сложные функции, которые являются комбина-

циями базовых.

Две такие функции мы уже упоминали в предыдущих раз-

делах. Функция выборки (селекции) позволяет нам выбрать

Параллельный ббод

ПослеВобат. ОитВ* 5итП3 ПитО2 SumBt ВитВ0

в бод " '•

Последобат.-

быбод

-Последобат. быбод

Послвдобат.ббод

Параллельный быбод

Сдбиг блеЗо

Сдбиг бпраба

Рис. 1.17, Регистр с последовательными и параллельными вводом и выводом.

один вариант из некоторого набора возможных вариантов. На-

пример, в обувном магазине мы выбираем для себя обувь, ру-

ководствуясь определенными критериями типа времени года,

размера, цвета обуви и т. д.

Вторая функция — функция кодирования — позволяет нам

представить наши идеи, например, в виде письменного текста,

который можно затем прочитать с помощью функции дешифра-

ции. Бумага выполняет здесь роль запоминающей среды.

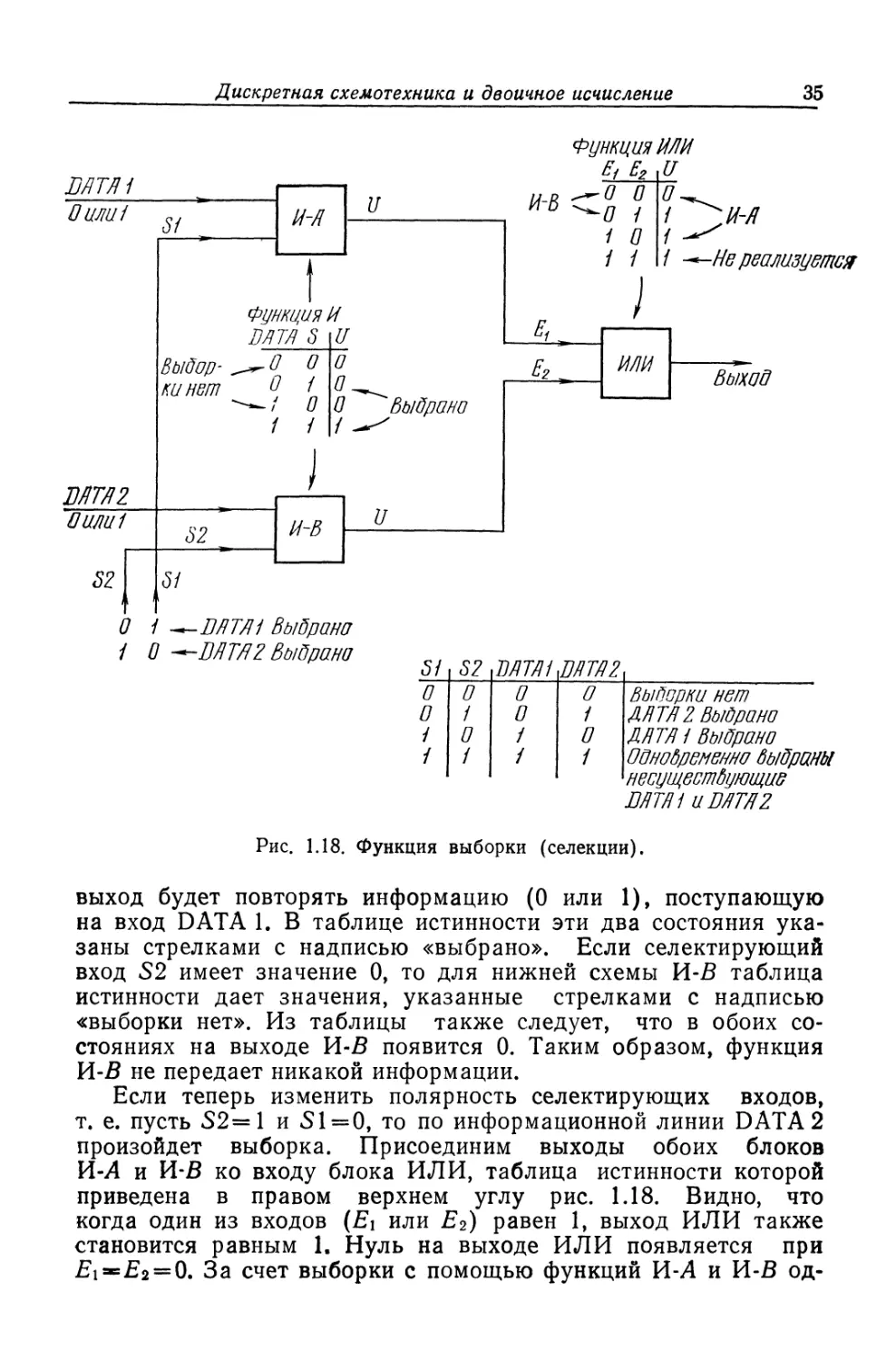

Пример функции выборки приведен на рис. 1.18. С помощью

выборочных переменных 51 и S2 мы можем производить селек-

цию данных по информационным входам DATA 1 и DATA 2.

Как происходит выборка, можно понять из следующих приме-

ров. Рассмотрим случай, когда на вход 51 поступает сигнал 1,

а на вход S2 — 0, при этом вся информация из канала DATA 1

проходит без изменений на выход. Таблица истинности функ-

ции И приведена в середине рисунка и из нее следует, что со-

ответствующий селектор И-A действительно будет выбирать

данные из канала DATA 1, если 51 равно 1. Во всех случаях,

когда DATA 1 = 0 и 51 = 1, выходное значение функции И со-

гласно таблице истинности будет равно 0. Если DATA 1 = 1 и

51 = 1, то выход И равен 1. Мы видим, что при 51 = 1 данный

Дискретная схемотехника и двоичное исчисление

35

/ 0 —-DfiTfl?Выбрано

51

О

о

1

1

82 'ШУИ JJ/ГГД2,

О О

1 О

О /

/ /

О Выборки нет

1 Д/Ш 2 Выдра но

О ДУШ / Вы Орано

1 Одновременно выдраны

несуществующие

ШТЯ1 иВШ2

Рис. 1.18. Функция выборки (селекции).

выход будет повторять информацию (0 или 1), поступающую

на вход DATA 1. В таблице истинности эти два состояния ука-

заны стрелками с надписью «выбрано». Если селектирующий

вход 52 имеет значение 0, то для нижней схемы И-В таблица

истинности дает значения, указанные стрелками с надписью

«выборки нет». Из таблицы также следует, что в обоих со-

стояниях на выходе И-В появится 0. Таким образом, функция

И-В не передает никакой информации.

Если теперь изменить полярность селектирующих входов,

т. е. пусть S2= 1 и 51 = 0, то по информационной линии DATA 2

произойдет выборка. Присоединим выходы обоих блоков

И-A и И-В ко входу блока ИЛИ, таблица истинности которой

приведена в правом верхнем углу рис. 1.18. Видно, что

когда один из входов (ft или Е2) равен 1, выход ИЛИ также

становится равным 1. Нуль на выходе ИЛИ появляется при

£i=E2 = 0. За счет выборки с помощью функций И-A и И-В од-

36

Глава 1

на из переменных (Ei или Е2) будет всегда равна 0. Другая

переменная при этом изменяется в зависимости от информации

DATA, которая поступает на соответствующие входы DATA 1 и

DATA 2. Таким образом, более сложная функция выборки дей-

ствительно является комбинацией основных (базовых) функ-

ций И и ИЛИ.

Рис. 1.19. Дешифратор двоичного кода.

а —* обращение в виде функции НЕ; б —обращение в виде знаков отрицания перед со-

ответствующими входами.

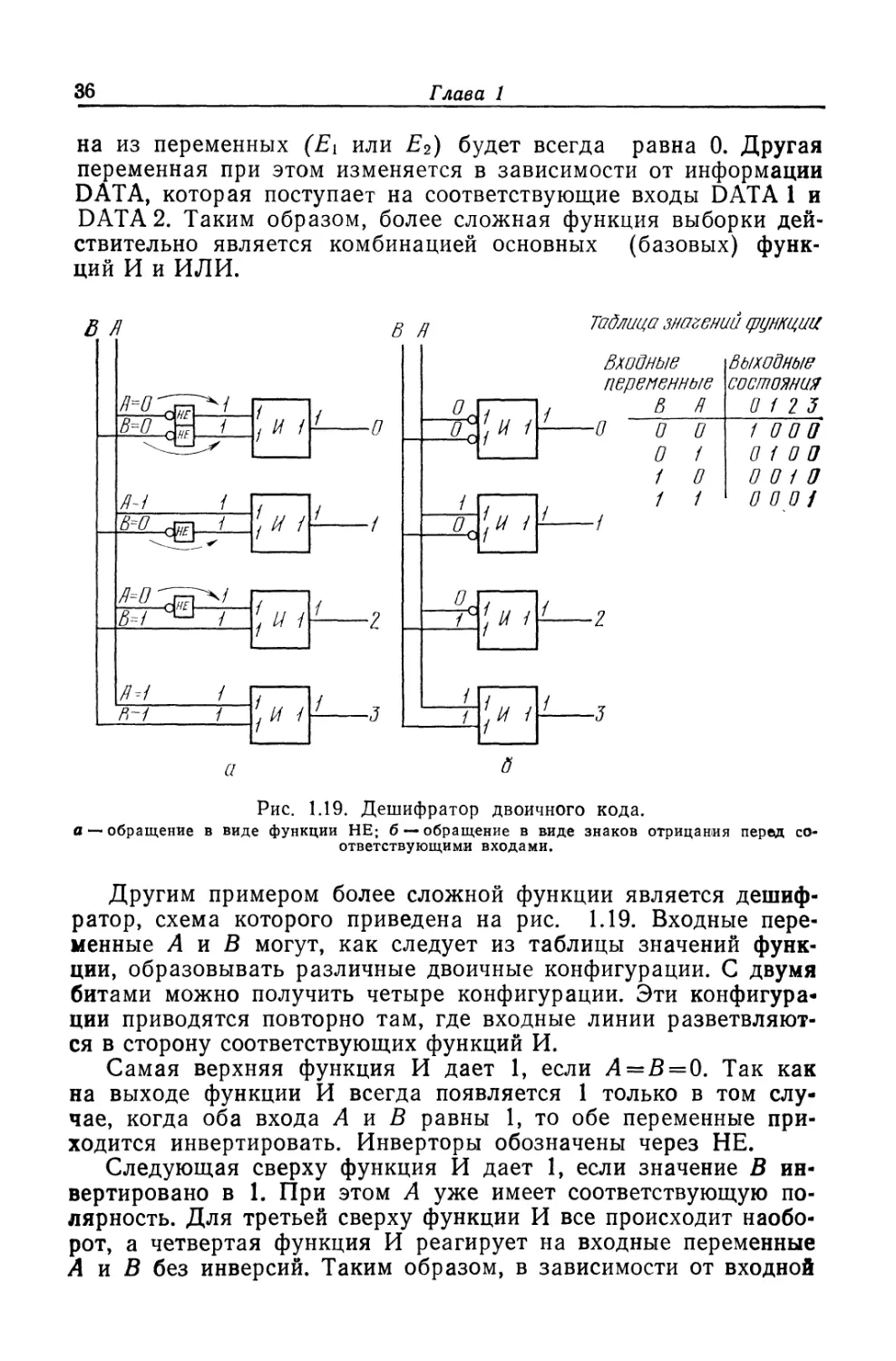

Другим примером более сложной функции является дешиф-

ратор, схема которого приведена на рис. 1.19. Входные пере-

менные А и В могут, как следует из таблицы значений функ-

ции, образовывать различные двоичные конфигурации. С двумя

битами можно получить четыре конфигурации. Эти конфигура-

ции приводятся повторно там, где входные линии разветвляют-

ся в сторону соответствующих функций И.

Самая верхняя функция И дает 1, если А = В = 0. Так как

на выходе функции И всегда появляется 1 только в том слу-

чае, когда оба входа А и В равны 1, то обе переменные при-

ходится инвертировать. Инверторы обозначены через НЕ.

Следующая сверху функция И дает 1, если значение В ин-

вертировано в 1. При этом А уже имеет соответствующую по-

лярность. Для третьей сверху функции И все происходит наобо-

рот, а четвертая функция И реагирует на входные переменные

А и В без инверсий. Таким образом, в зависимости от входной

Дискретная схемотехника и двоичное исчисление

37

двоичной конфигурации, которая будет определяться перемен-

ными А и В, только один из выходов функций И становится

равным 1, как следует из таблицы значений функции, где по-

казана связь между входными переменными и состояниями со-

ответствующих выходов.

Относительно символов, указанных на рис. 1.19, а, следует

отметить, что инверторы здесь можно не обозначать, а просто

заменить знаками отрицания, располагая их прямо на входе

соответствующих элементов схемы. В результате мы получаем

функциональную схему, показанную на рис. 1.19,6. Эта воз-

можность использования знаков отрицания была уже реализо-

вана выше на рис. 1.10 и 1.11.

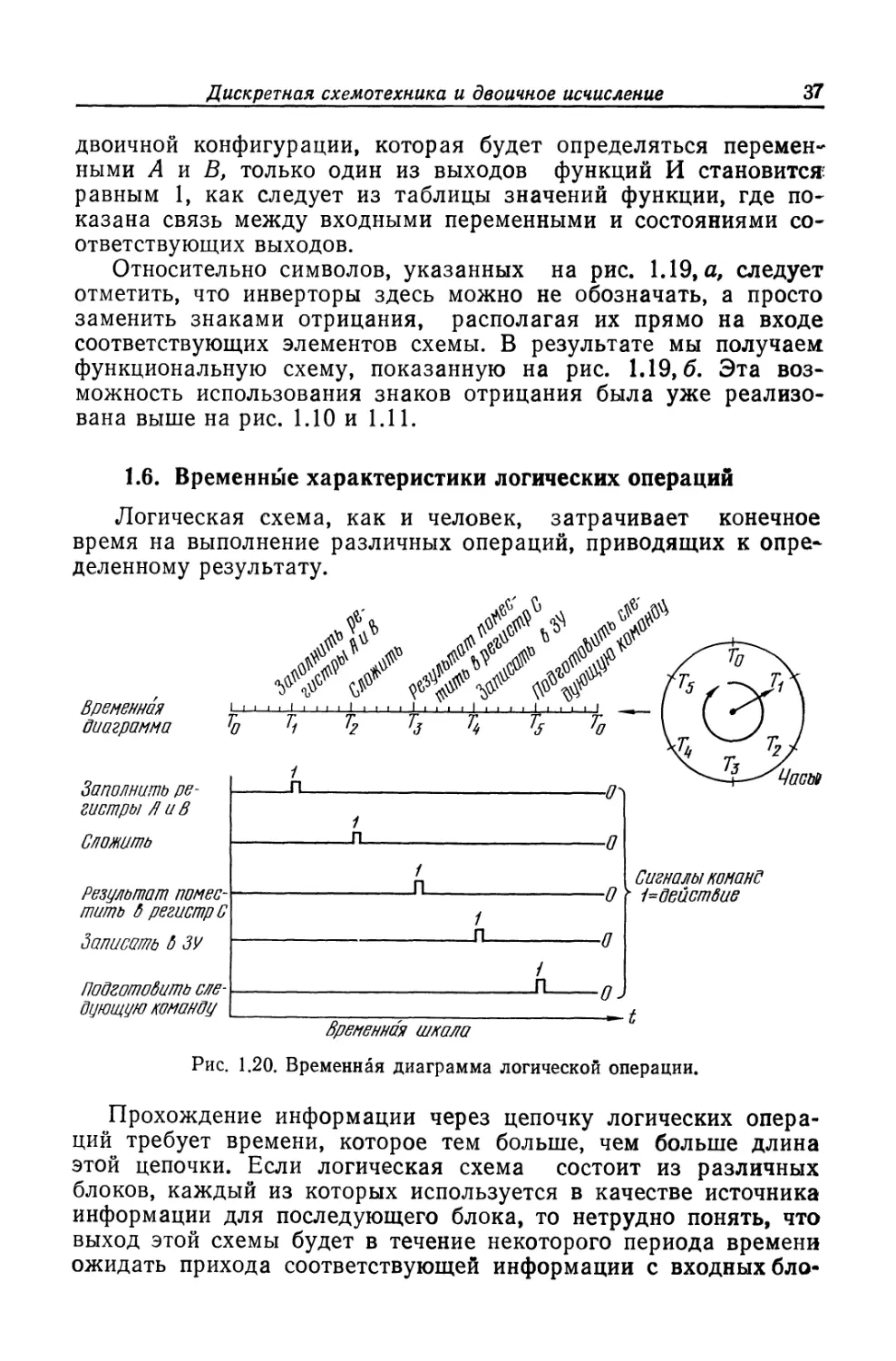

1.6. Временные характеристики логических операций

Логическая схема, как и человек, затрачивает конечное

время на выполнение различных операций, приводящих к опре-

деленному результату.

Временная

диаграмма

Заполнить ре-

гистры Вив

Сложить

А*

Цаоы

к

/7

1

л

Результат помес-

тить б регистре

Записать б ЗУ

Z7

О

Сигналы команд

" действие

Л

1

л

Подготовить сле-

дующую команду

/

л

Временная шкала

О)

Рис. 1.20. Временная диаграмма логической операции.

Прохождение информации через цепочку логических опера-

ций требует времени, которое тем больше, чем больше длина

этой цепочки. Если логическая схема состоит из различных

блоков, каждый из которых используется в качестве источника

информации для последующего блока, то нетрудно понять, что

выход этой схемы будет в течение некоторого периода времени

ожидать прихода соответствующей информации с входных бло-

38

Глава 1

ков. Поэтому при логическом проектировании для подобных

систем обычно составляется временная диаграмма, которая ото-

бражает все необходимые операции. Логическая система обыч-

но имеет внутренние часы (таймер) с временными метками, так

же, как человек, работающий по графику, сверяет график с сиг-

налами времени, измеряемыми в часах, минутах и секундах.

Так же как мы планируем свою деятельность во времени по оп-

ределенному расписанию, так и цифровая система осуществля-

ет свои операции в определенные моменты времени по коман-

дам (меткам) внутреннего таймера.

ХлеР

Масло

Лоере

Второй

зодтрок

12ч

Рис. 1.21. Понятие времени как входной переменной для логической схемы.

На рис. 1.20 приведена временная диаграмма в форме пря-

мой линии, над которой указаны моменты начала определен-

ных логических операций.

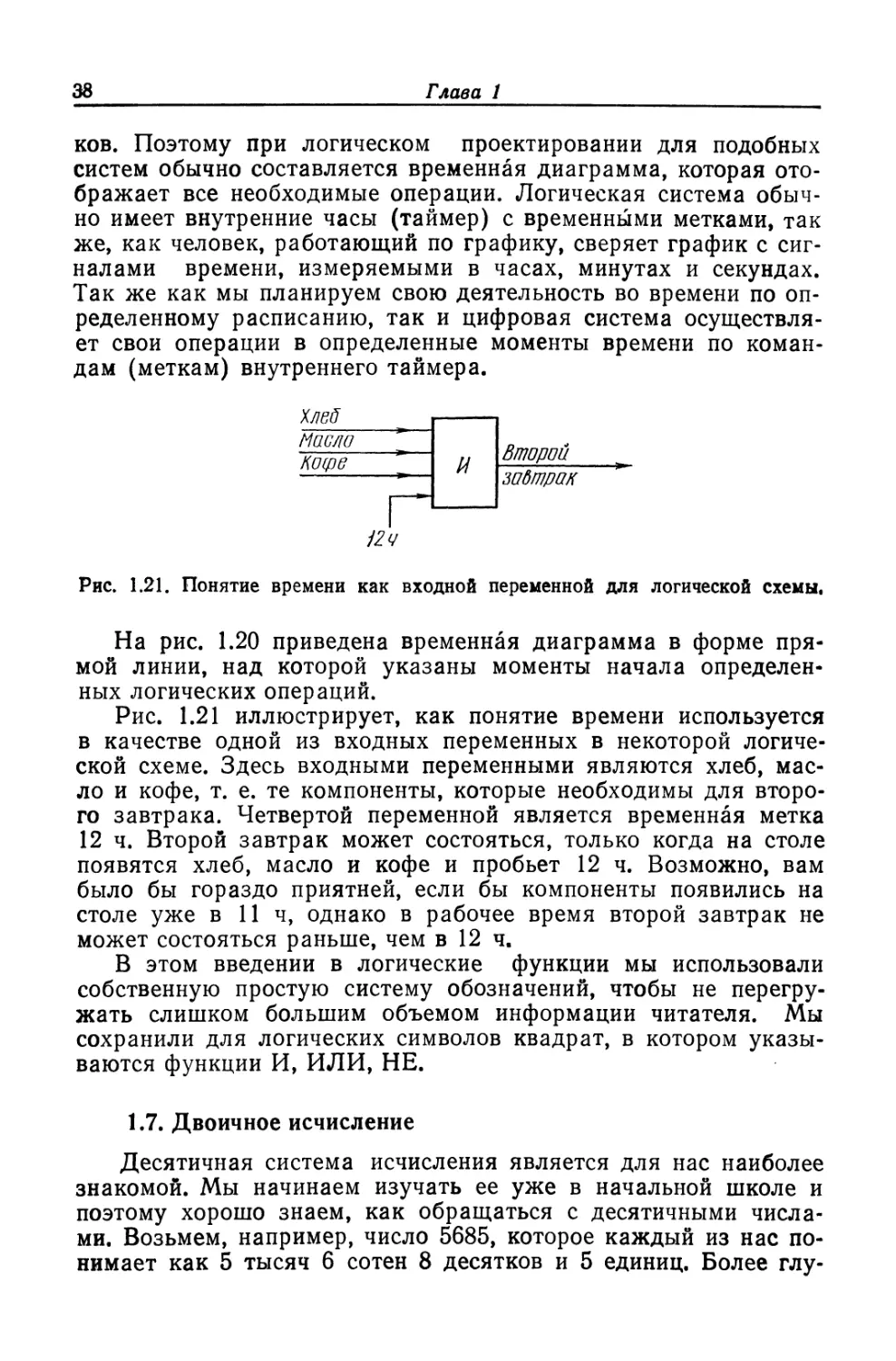

Рис. 1.21 иллюстрирует, как понятие времени используется

в качестве одной из входных переменных в некоторой логиче-

ской схеме. Здесь входными переменными являются хлеб, мас-

ло и кофе, т. е. те компоненты, которые необходимы для второ-

го завтрака. Четвертой переменной является временная метка

12 ч. Второй завтрак может состояться, только когда на столе

появятся хлеб, масло и кофе и пробьет 12 ч. Возможно, вам

было бы гораздо приятней, если бы компоненты появились на

столе уже в 11 ч, однако в рабочее время второй завтрак не

может состояться раньше, чем в 12 ч.

В этом введении в логические функции мы использовали

собственную простую систему обозначений, чтобы не перегру-

жать слишком большим объемом информации читателя. Мы

сохранили для логических символов квадрат, в котором указы-

ваются функции И, ИЛИ, НЕ.

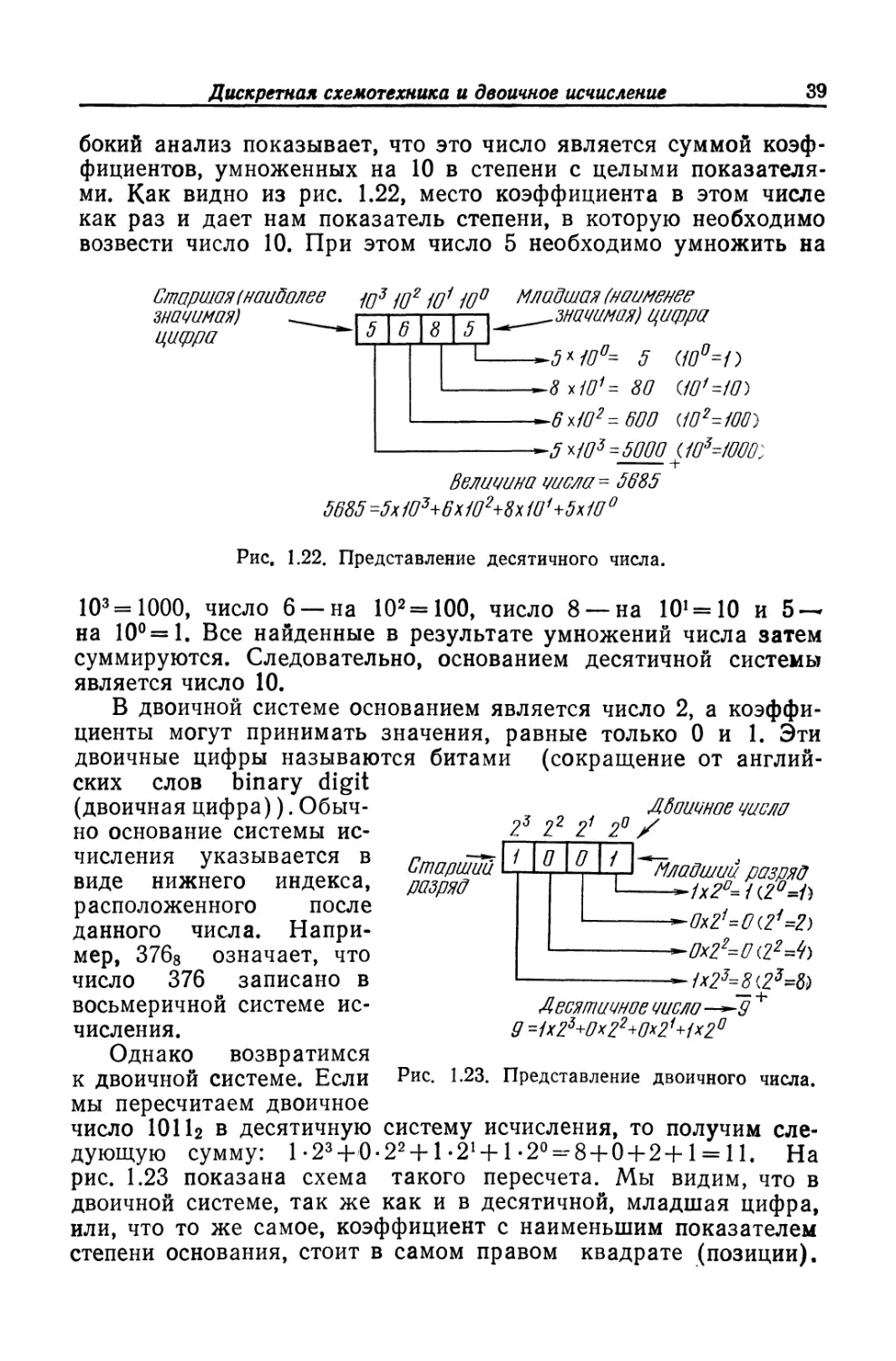

1.7. Двоичное исчисление

Десятичная система исчисления является для нас наиболее

знакомой. Мы начинаем изучать ее уже в начальной школе и

поэтому хорошо знаем, как обращаться с десятичными числа-

ми. Возьмем, например, число 5685, которое каждый из нас по-

нимает как 5 тысяч 6 сотен 8 десятков и 5 единиц. Более глу-

Дискретная схемотехника и двоичное исчисление

39

бокий анализ показывает, что это число является суммой коэф-

фициентов, умноженных на 10 в степени с целыми показателя-

ми. Как видно из рис. 1.22, место коэффициента в этом числе

как раз и дает нам показатель степени, в которую необходимо

возвести число 10. При этом число 5 необходимо умножить на

Старшая (наиболее

значимая) ______

цифра

iO3 (О21O110° Младшая (наименее

цшрра

I I I1---------—<5X//7Z7= 5 (f0°=/)

---------------~8*101=80 ЦО1=10)

---------------~6'/М2=600 <М2=100)

---------------~5*i03=5000 <Д03=Шр

-----------------------------I-

Величина числа = 5685

5685 =5х J03+6xi02+8x 10^5x10 0

Рис, 1.22. Представление десятичного числа.

103=1000, число 6 — на 102=100, число 8 — на 10‘ = 10 и 5—•

на 10°= 1. Все найденные в результате умножений числа затем

суммируются. Следовательно, основанием десятичной системы

является число 10.

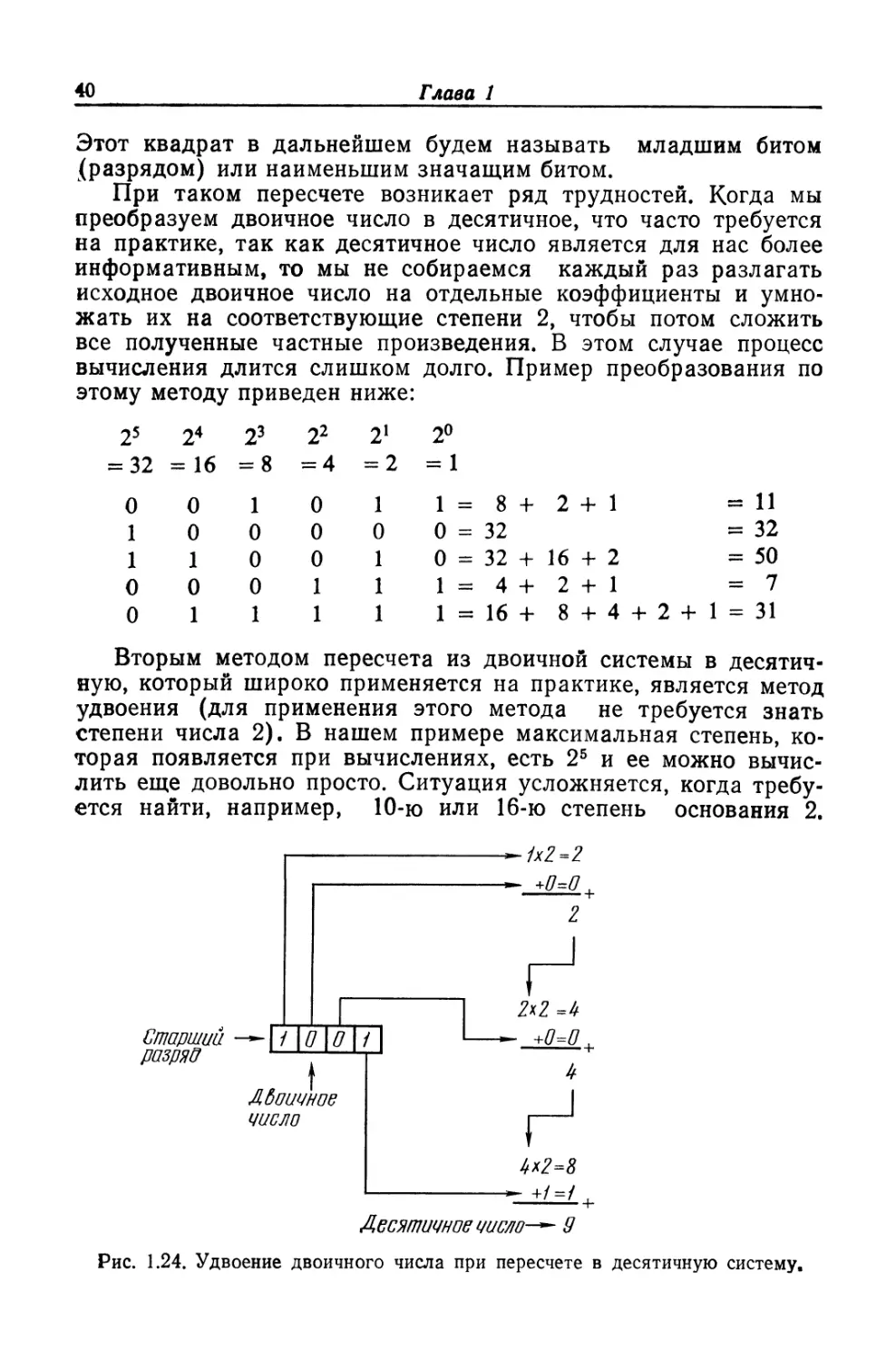

В двоичной системе основанием является число 2, а коэффи-

циенты могут принимать значения, равные только 0 и 1. Эти

двоичные цифры называются битами (сокращение от англий-

ских слов binary digit

(двоичная цифра)). Обыч- Дбоичное числа

но основание системы ис- 23 Z2 21 2° /

числения указывается в

виде нижнего индекса,

расположенного после

данного числа. Напри-

мер, 3768 означает, что

число 376 записано в

восьмеричной системе ис-

числения.

Старший

разряд

Однако возвратимся

к двоичной системе. Если

/ О О 1

Млавший разряд

—~1х2°=Ш°=1)

Ох2,=О(21=2'>

0х2г=0<22=Ь

----------------- 1х23=8_ <.23=8)

Десятичное число —9 +

9 =-/x23+Ox22+Ox21+fx2°

Рис. 1.23. Представление двоичного числа.

мы пересчитаем двоичное

число 1011г в десятичную систему исчисления, то получим сле-

дующую сумму: 1-23-|-0-22 +1-2’ +1-2° = 8 + 0 + 2+1 = 11. На

рис. 1.23 показана схема такого пересчета. Мы видим, что в

двоичной системе, так же как и в десятичной, младшая цифра,

или, что то же самое, коэффициент с наименьшим показателем

степени основания, стоит в самом правом квадрате (позиции).

40

Глава 1

Этот квадрат в дальнейшем будем называть младшим битом

(разрядом) или наименьшим значащим битом.

При таком пересчете возникает ряд трудностей. Когда мы

преобразуем двоичное число в десятичное, что часто требуется

на практике, так как десятичное число является для нас более

информативным, то мы не собираемся каждый раз разлагать

исходное двоичное число на отдельные коэффициенты и умно-

жать их на соответствующие степени 2, чтобы потом сложить

все полученные частные произведения. В этом случае процесс

вычисления длится слишком долго. Пример преобразования по

этому методу приведен ниже:

25 24 23 22 2* 2°

= 32 = 16 = 8 = 4 = 2 = 1

0 0 1 0 1 1 = 8 + 2 + 1 = 11

1 0 0 0 0 0 = 32 = 32

1 1 0 0 1 0 = 32 + 16 + 2 = 50

0 0 0 1 1 1 = 4 + 2 + 1 = 7

0 1 1 1 1 1 = 16 + 8 4- 4 + 2 + 1 = 31

Вторым методом пересчета из двоичной системы в десятич-

ную, который широко применяется на практике, является метод

удвоения (для применения этого метода не требуется знать

степени числа 2). В нашем примере максимальная степень, ко-

торая появляется при вычислениях, есть 25 и ее можно вычис-

лить еще довольно просто. Ситуация усложняется, когда требу-

ется найти, например, 10-ю или 16-ю степень основания 2.

Старший —I /1/71/71 /

разряО 1—1—1—- -

I

Двоичное

число

- +/7=/7,

2

н

2x2=4

4

н

4х2=£

Десятичное число—9

Рис. 1.24. Удвоение двоичного числа при пересчете в десятичную систему.

Дискретная схемотехника и двоичное исчисление

41

В этих случаях лучше иметь под рукой готовую таблицу степе-

ней числа 2.

Однако при использовании метода удвоения эта таблица не

нужна, и поэтому метод удвоения особенно эффективен, если

преобразования производятся с помощью карманного кальку-

лятора.

Схема метода удвое-

ния показана на рис. 1.24.

Мы начинаем с коэффи-

циента при старшем раз-

ряде (бите) и умножаем

его на 2. К полученному

произведению прибавля-

ем коэффициент следую-

щего разряда. Затем по-

лученную сумму умножа-

ем на 2 и к результату

добавляем коэффициент

следующего разряда. Та-

ким образом мы продви-

гаемся вплоть до самого

младшего разряда, т. е.

последнего разряда дан-

ного двоичного числа.

При этом, например, дво-

ичное число 1001 превра-

щается в десятичное чис-

ло 9. Теперь представим

себе, что мы сдвинули

все разряды данного чис-

ла влево на один разряд

и в освободившийся при

Десятичное число 51

I |

Старший Младший

разряд разряд

Рис. 1.25. Пересчет десятичного числа в дво-

ичную систему.

этом справа разряд по-

местили 0. Проделав такую операцию, мы обнаружили, что ре-

зультат будет равен исходному числу, умноженному на 2. При

сдвиге влево на два разряда исходное число необходимо умно-

жить уже на 4. Сдвиг на три разряда означает умножение ис-

ходного числа на 8. Чтобы быстро умножить двоичное число на

10, мы сдвигаем это число на 2 разряда (увеличение в 4 раза),

прибавляем к результату первоначальное двоичное число (уве-

личение в 5 раз) и затем снова сдвигаем полученную сумму

еще на один разряд (2X5=10).

Обратное преобразование десятичного числа в двоичное од-

нозначно выполняется путем деления каждого промежуточного

частного на 2, при этом каждый неделимый конечный остаток

дает очередную цифру для искомого двоичного числа.

42

Глава 1

На рис. 1.25 показан ход такого расчета. Число 51ю делит-

ся на 2 и дает частное 25 с остатком 1, который мы записыва-

ем в младший разряд. Затем мы делим частное 25 на 2 и по-

лучаем частное 12 и остаток 1. Эту новую единицу мы записыва-

ем слева от предыдущей. Третье деление (12:2) дает частное 6

и остаток 0. Нуль заносится в третий разряд справа и мы про-

должаем вычисление до тех пор, пока не получим в остатке

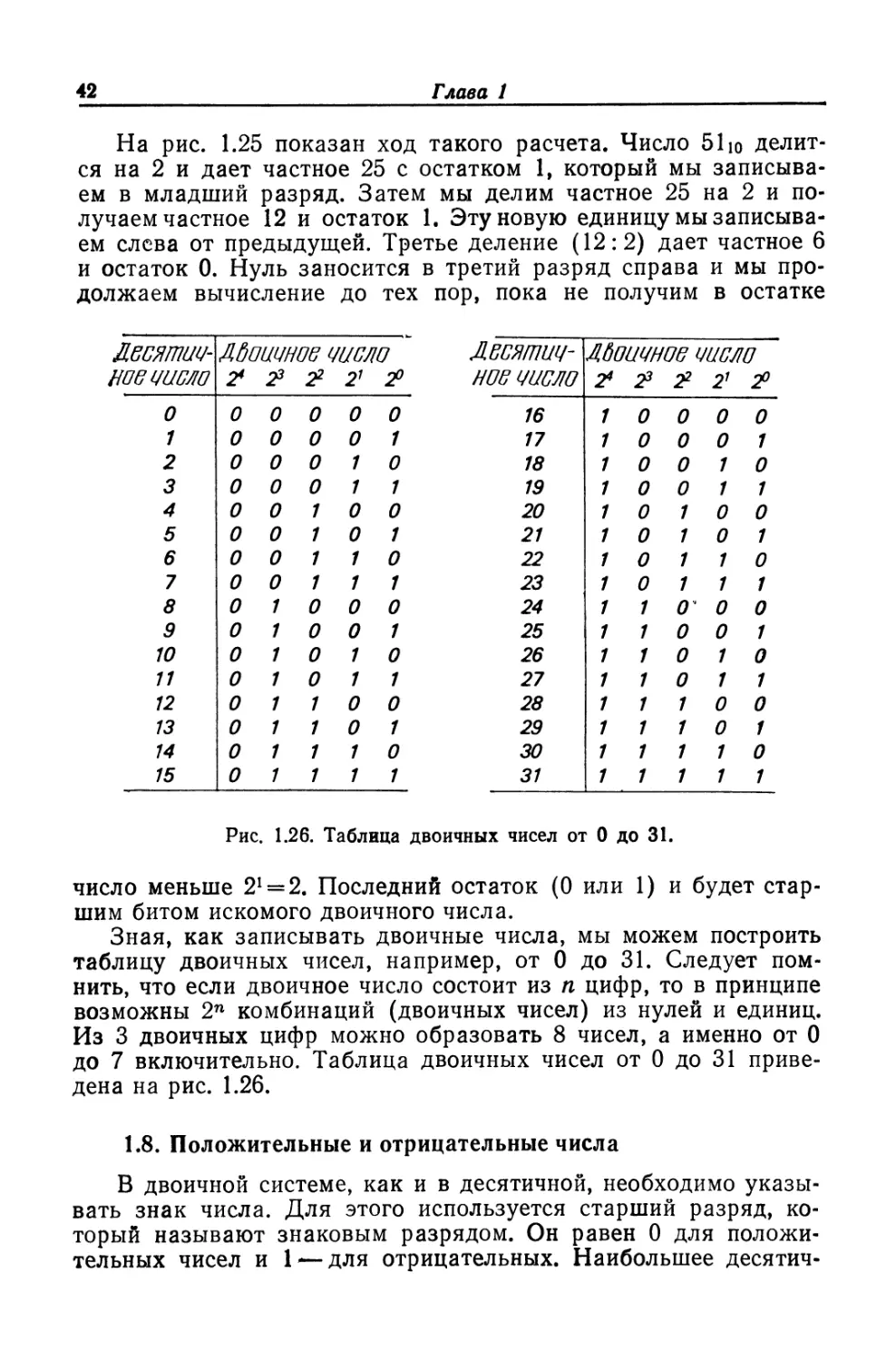

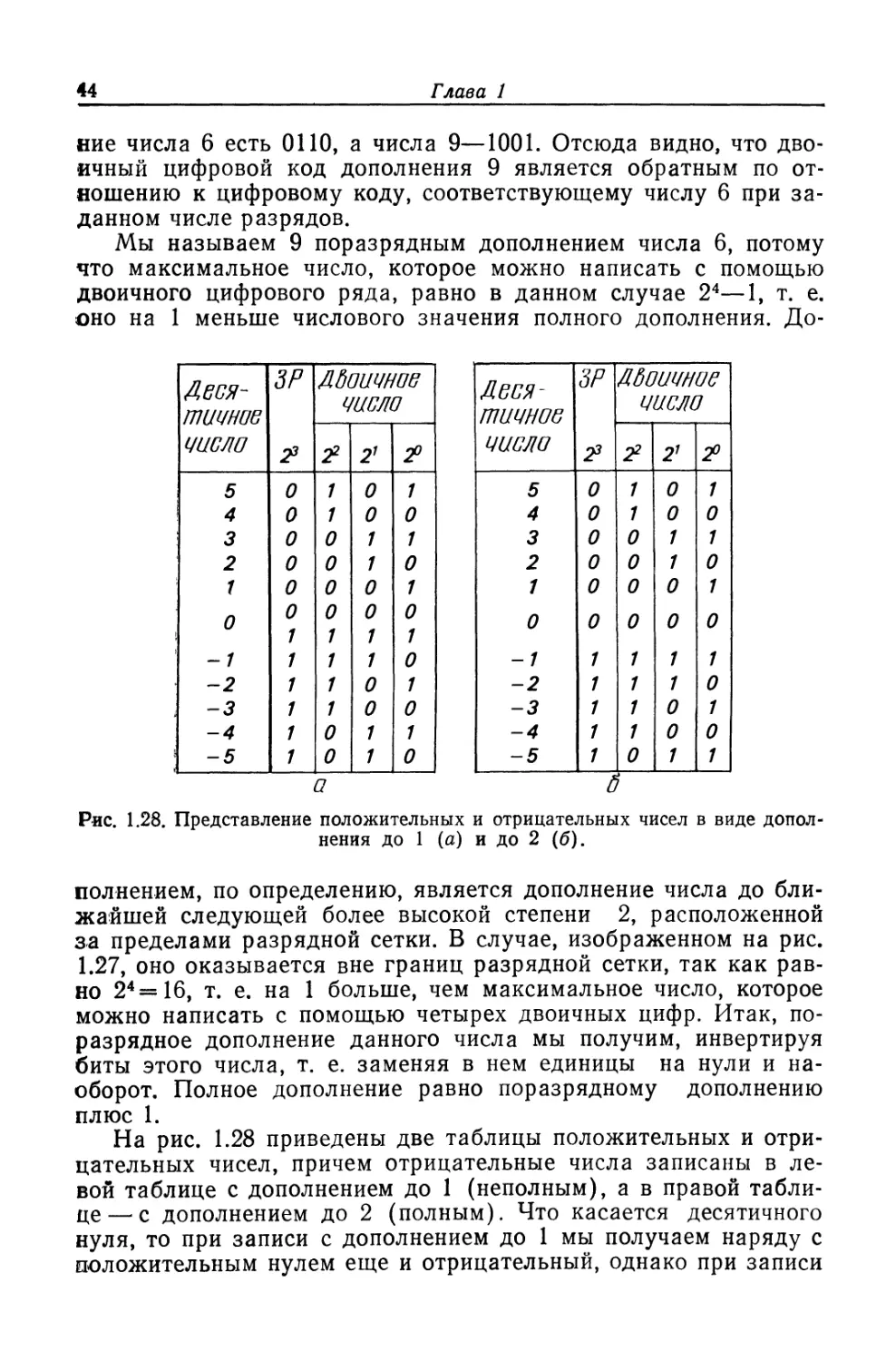

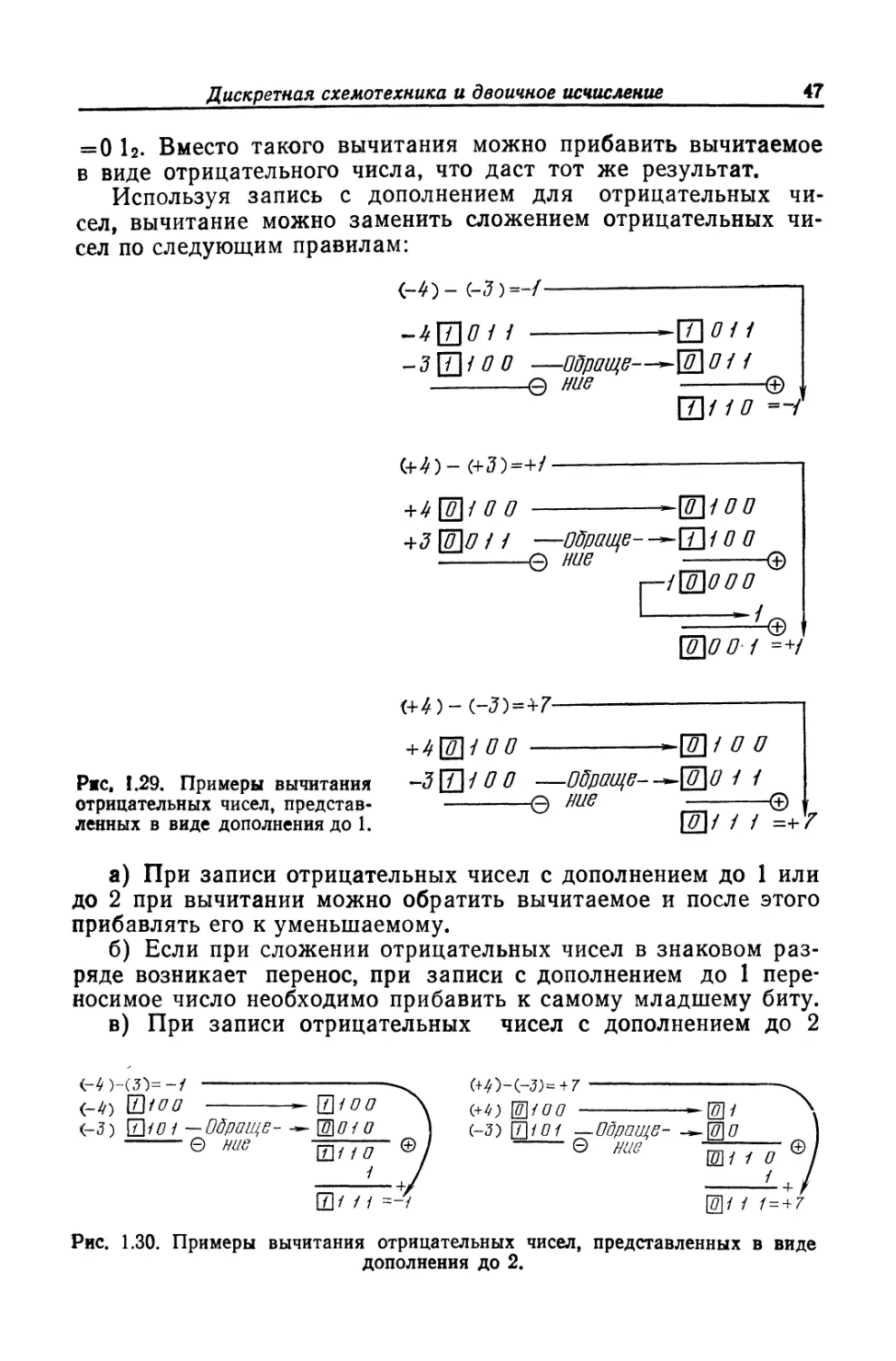

Десятич- ное число Двоичное число Десятич- ное число Двоичное число

2* 23 2? 2’ 2° 2? 23 2? 21 29

0 0 0 0 0 0 16 1 0 0 0 0

1 0 0 0 0 1 17 1 0 0 0 1

2 0 0 0 1 0 18 1 0 0 1 0

3 0 0 0 1 1 19 1 0 0 1 1

4 0 0 1 0 0 20 1 0 1 0 0

5 0 0 1 0 1 21 1 0 1 0 1

6 0 0 1 1 0 22 1 О 1 1 0

7 0 0 1 1 1 23 1 0 1 1 1

8 0 1 0 0 0 24 1 1 0й О О

9 0 1 0 0 1 25 1 1 0 0 1

10 0 1 0 1 0 26 1 1 0 1 0

11 0 1 0 1 1 27 1 1 0 1 1

12 0 1 1 0 0 28 1 1 1 0 0

13 0 1 1 0 1 29 1 1 1 0 1

14 0 1 1 1 0 30 1 1 1 1 0

15 0 1 1 1 1 31 1 1 1 1 1

Рис. 1.26. Таблица двоичных чисел от 0 до 31.

число меньше 21 = 2. Последний остаток (0 или 1) и будет стар-

шим битом искомого двоичного числа.

Зная, как записывать двоичные числа, мы можем построить

таблицу двоичных чисел, например, от 0 до 31. Следует пом-

нить, что если двоичное число состоит из п цифр, то в принципе

возможны 2П комбинаций (двоичных чисел) из нулей и единиц.

Из 3 двоичных цифр можно образовать 8 чисел, а именно от 0

до 7 включительно. Таблица двоичных чисел от 0 до 31 приве-

дена на рис. 1.26.

1.8. Положительные и отрицательные числа

В двоичной системе, как и в десятичной, необходимо указы-

вать знак числа. Для этого используется старший разряд, ко-

торый называют знаковым разрядом. Он равен 0 для положи-

тельных чисел и 1—для отрицательных. Наибольшее десятич-

Дискретная схемотехника и двоичное исчисление

43

ное число, которое в этом случае можно записать с помощью п

битов, равно 271-1—1, так как один бит всегда занят под знак

числа. Например, для числа из 5 битов максимальное значение

составляет 24—1 — 15.

Запись отрицательных чисел осуществляется методом до-

полнения, по которому 1 и 0 положительного числа при перехо-

де к соответствующему отрицательному числу заменяется на О

и 1. Эта система записи называется также записью с дополне-

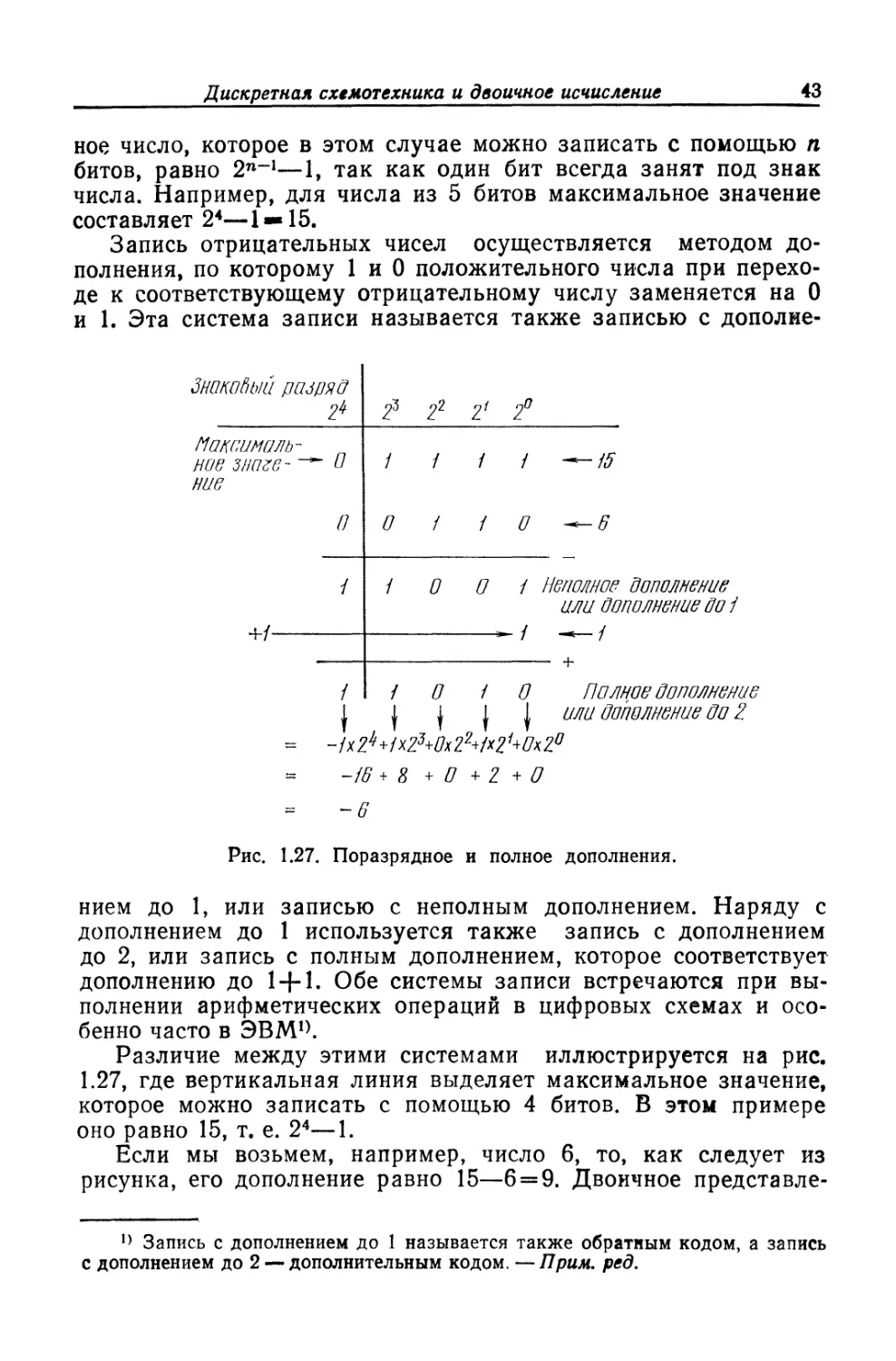

днакоёпяй разряд

2^

Максималь-

ное знаке- О

пае

О

/ 1 1 1 —15

О / / О +-В

110 0 1 Неполное дополнение

или дополнение до 1

--------------— /

110 10 Полное дополнение

| | | | | или дополнение до 2

= -1xZ^1xZ^Ox22^Z^OkZ°

= -IB + 8 + О + Z + О

= -6

Рис. 1.27. Поразрядное и полное дополнения.

нием до 1, или записью с неполным дополнением. Наряду с

дополнением до 1 используется также запись с дополнением

до 2, или запись с полным дополнением, которое соответствует

дополнению до 14-1. Обе системы записи встречаются при вы-

полнении арифметических операций в цифровых схемах и осо-

бенно часто в ЭВМ0.

Различие между этими системами иллюстрируется на рис.

1.27, где вертикальная линия выделяет максимальное значение,

которое можно записать с помощью 4 битов. В этом примере

оно равно 15, т. е. 24—1.

Если мы возьмем, например, число 6, то, как следует из

рисунка, его дополнение равно 15—6 = 9. Двоичное представле-

!) Запись с дополнением до 1 называется также обратным кодом, а запись

с дополнением до 2 — дополнительным кодом. — Прим. ред.

44

Глава 1

ние числа 6 есть ОНО, а числа 9—1001. Отсюда видно, что дво-

ичный цифровой код дополнения 9 является обратным по от-

ношению к цифровому коду, соответствующему числу 6 при за-

данном числе разрядов.

Мы называем 9 поразрядным дополнением числа 6, потому

что максимальное число, которое можно написать с помощью

двоичного цифрового ряда, равно в данном случае 24—1, т. е.

оно на 1 меньше числового значения полного дополнения. До-

полнением, по определению, является дополнение числа до бли-

жайшей следующей более высокой степени 2, расположенной

за пределами разрядной сетки. В случае, изображенном на рис.

1.27, оно оказывается вне границ разрядной сетки, так как рав-

но 24=16, т. е. на 1 больше, чем максимальное число, которое

можно написать с помощью четырех двоичных цифр. Итак, по-

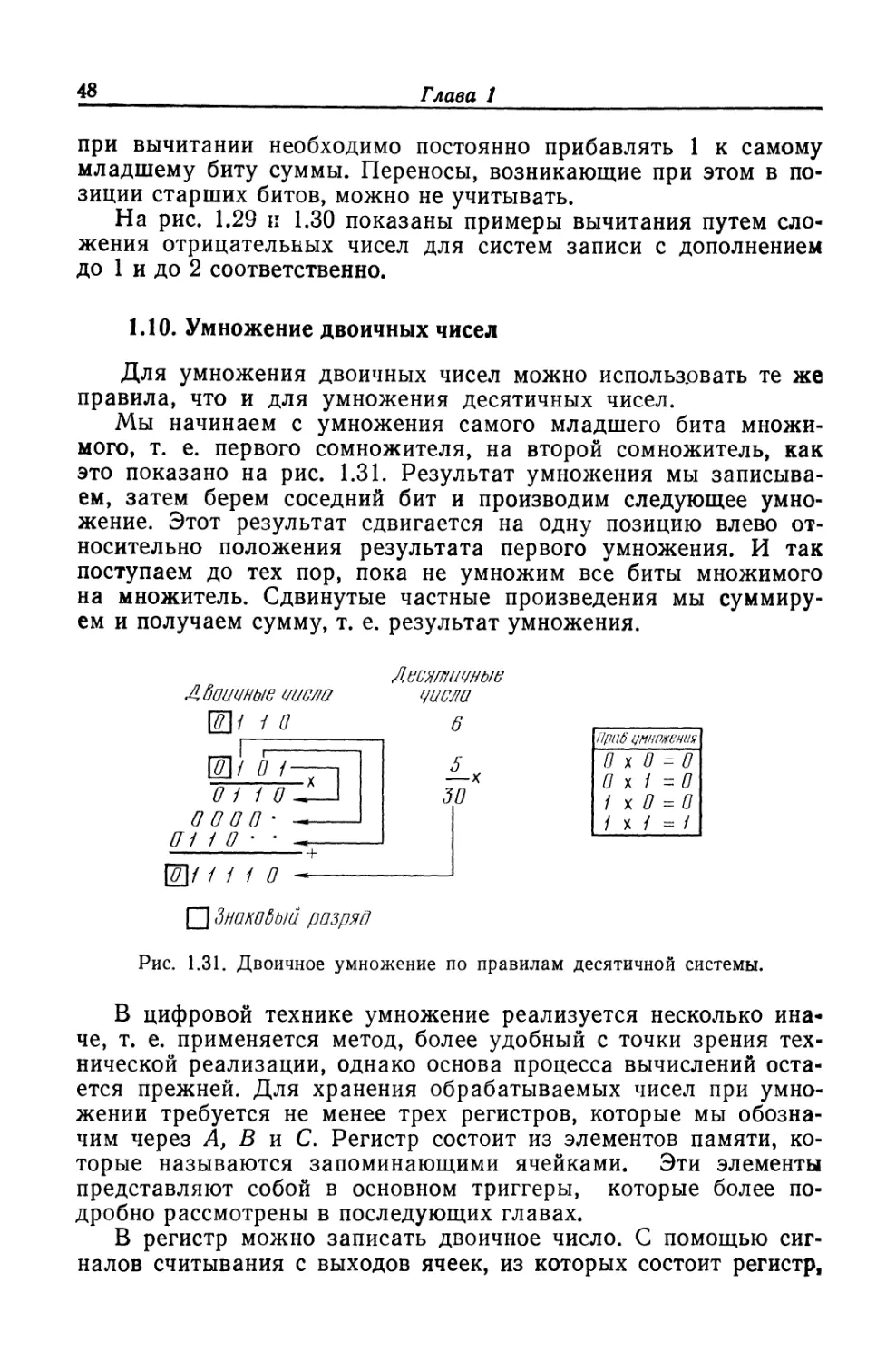

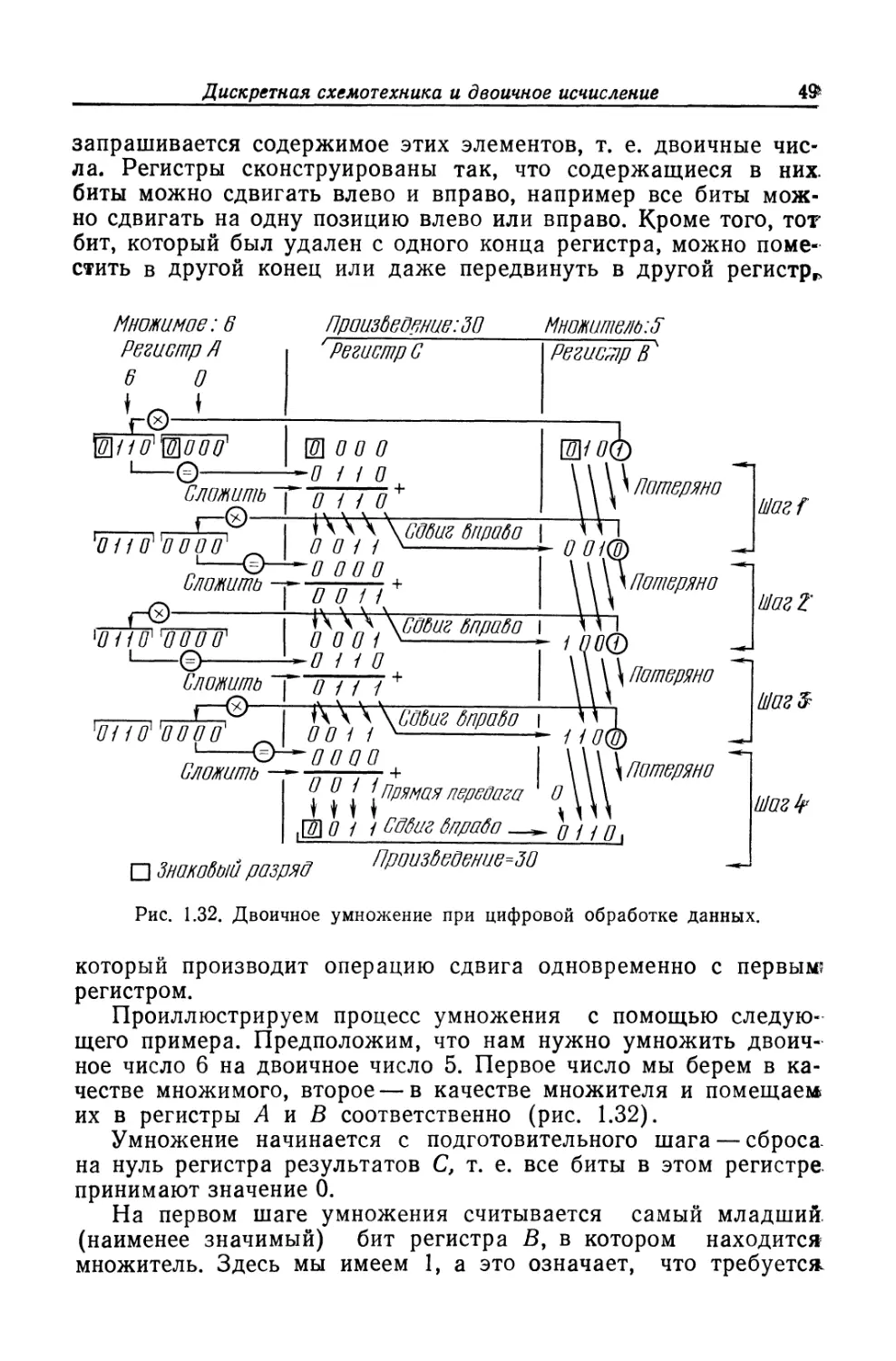

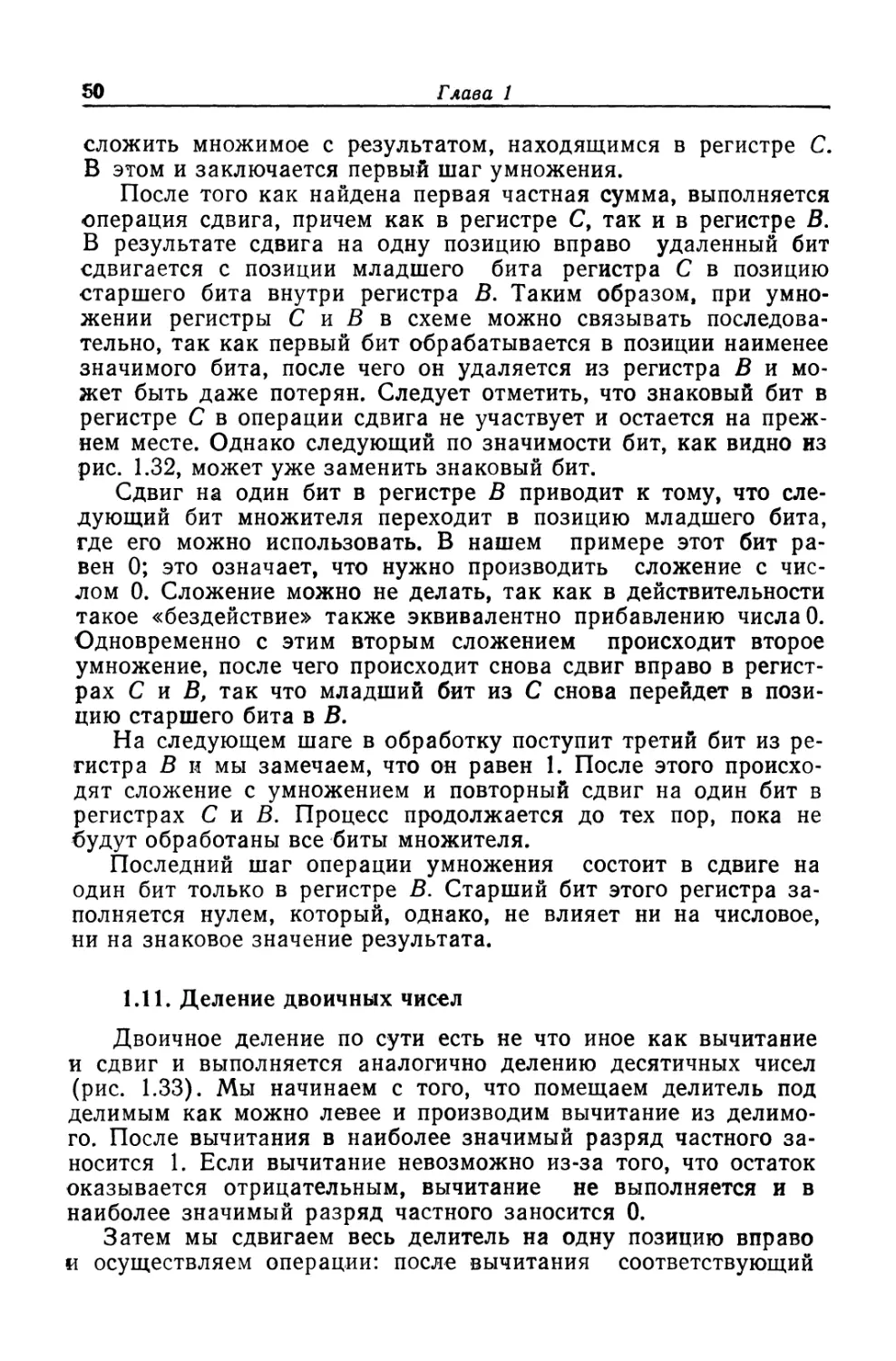

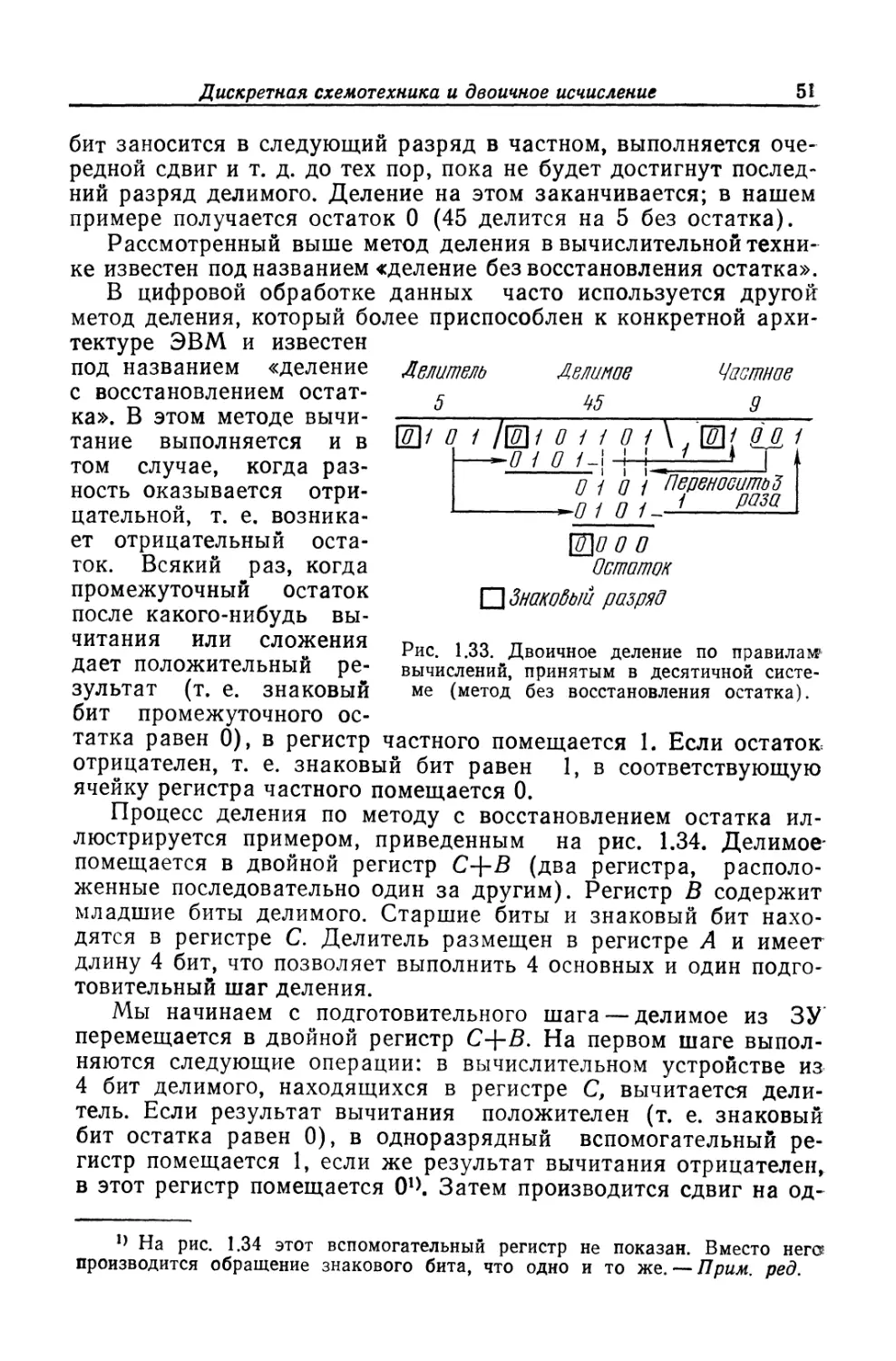

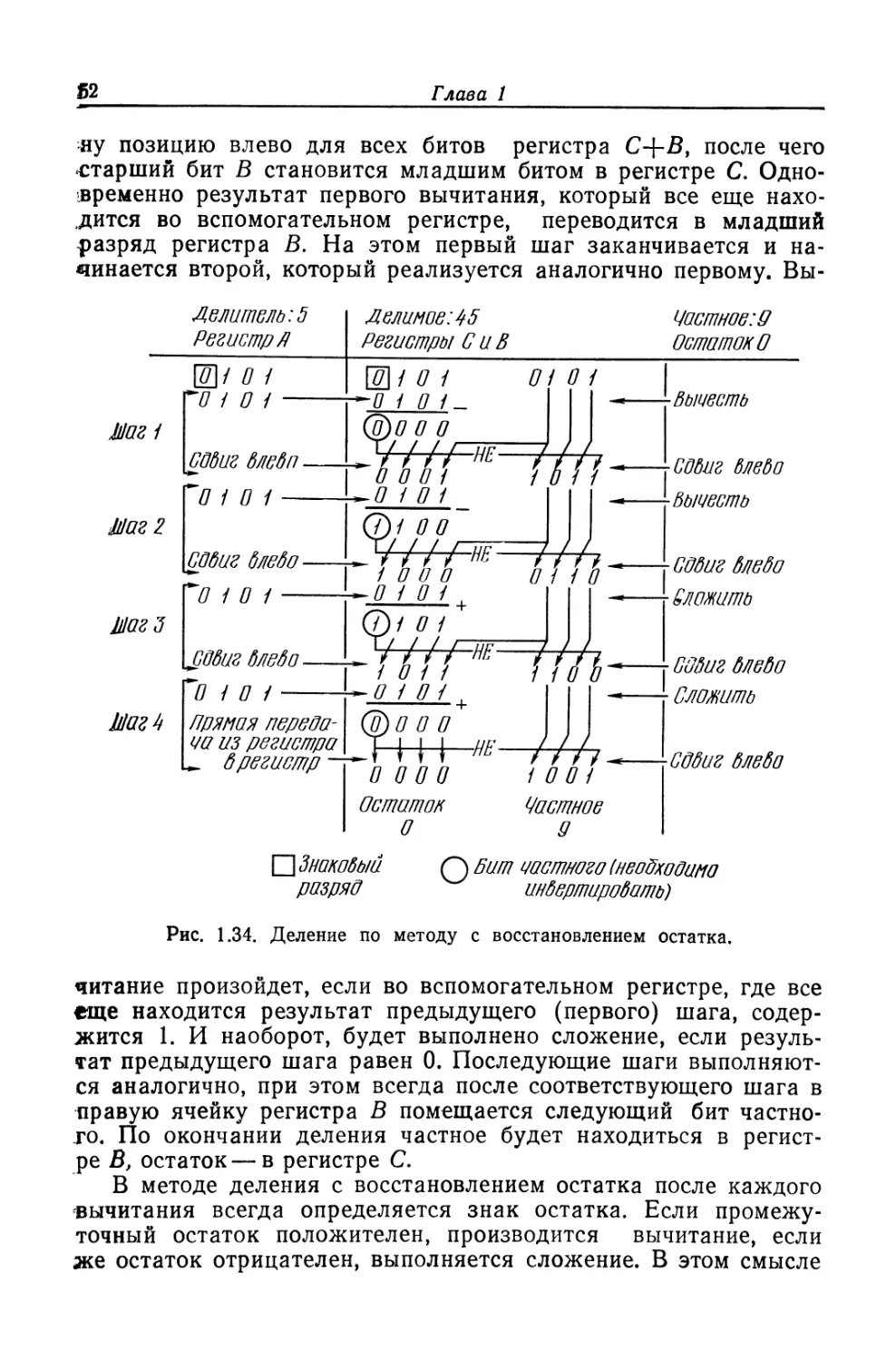

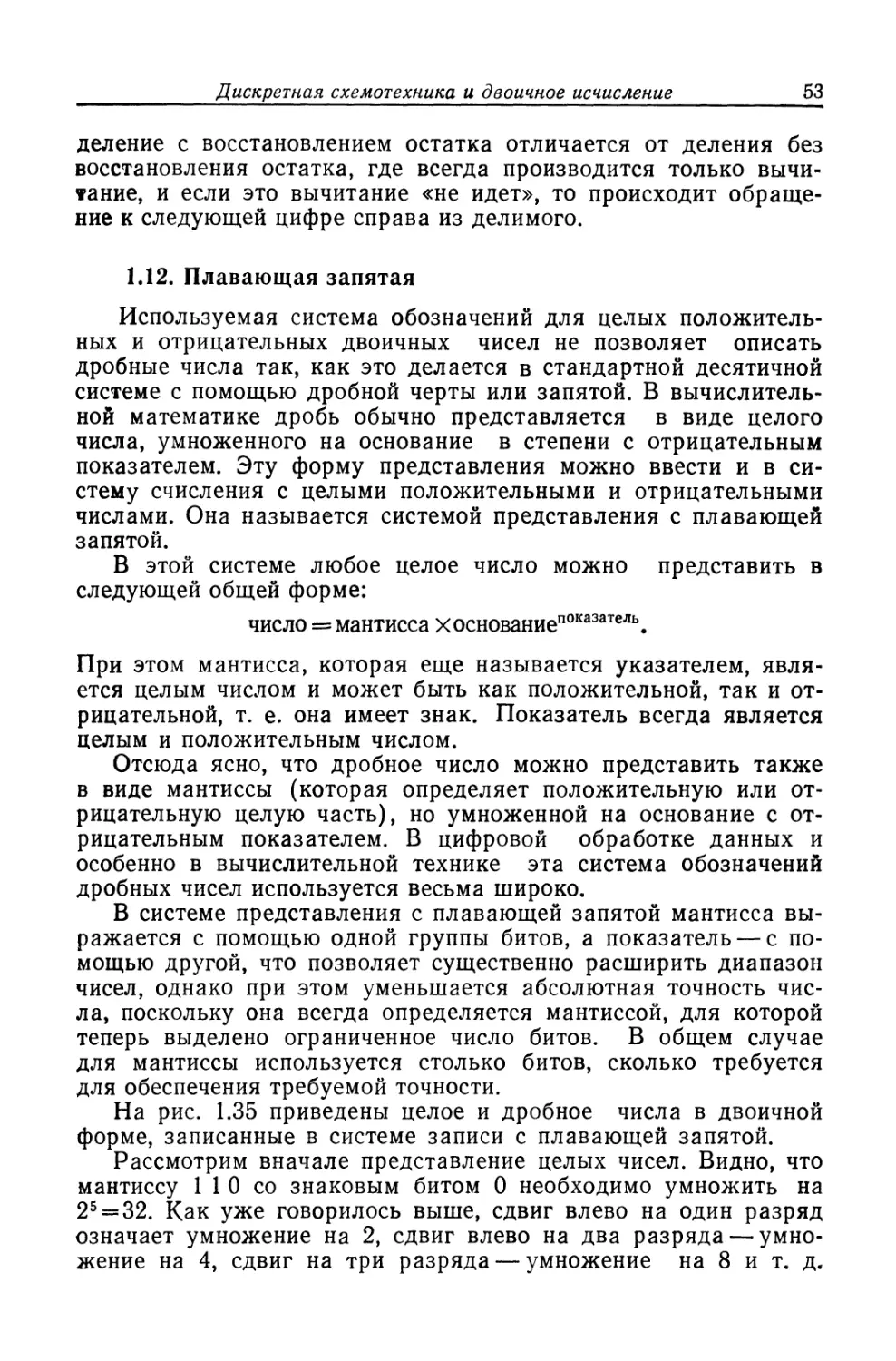

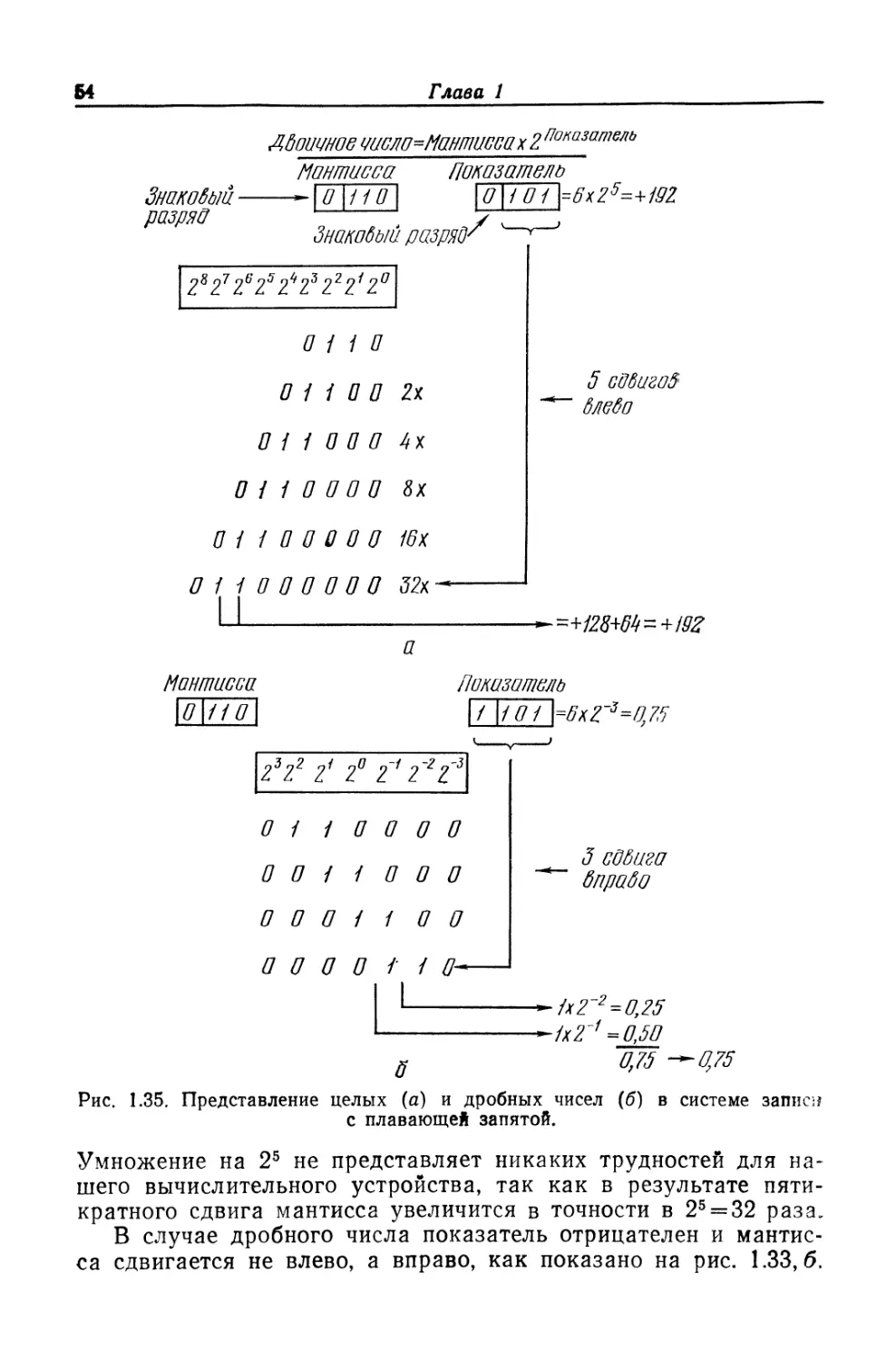

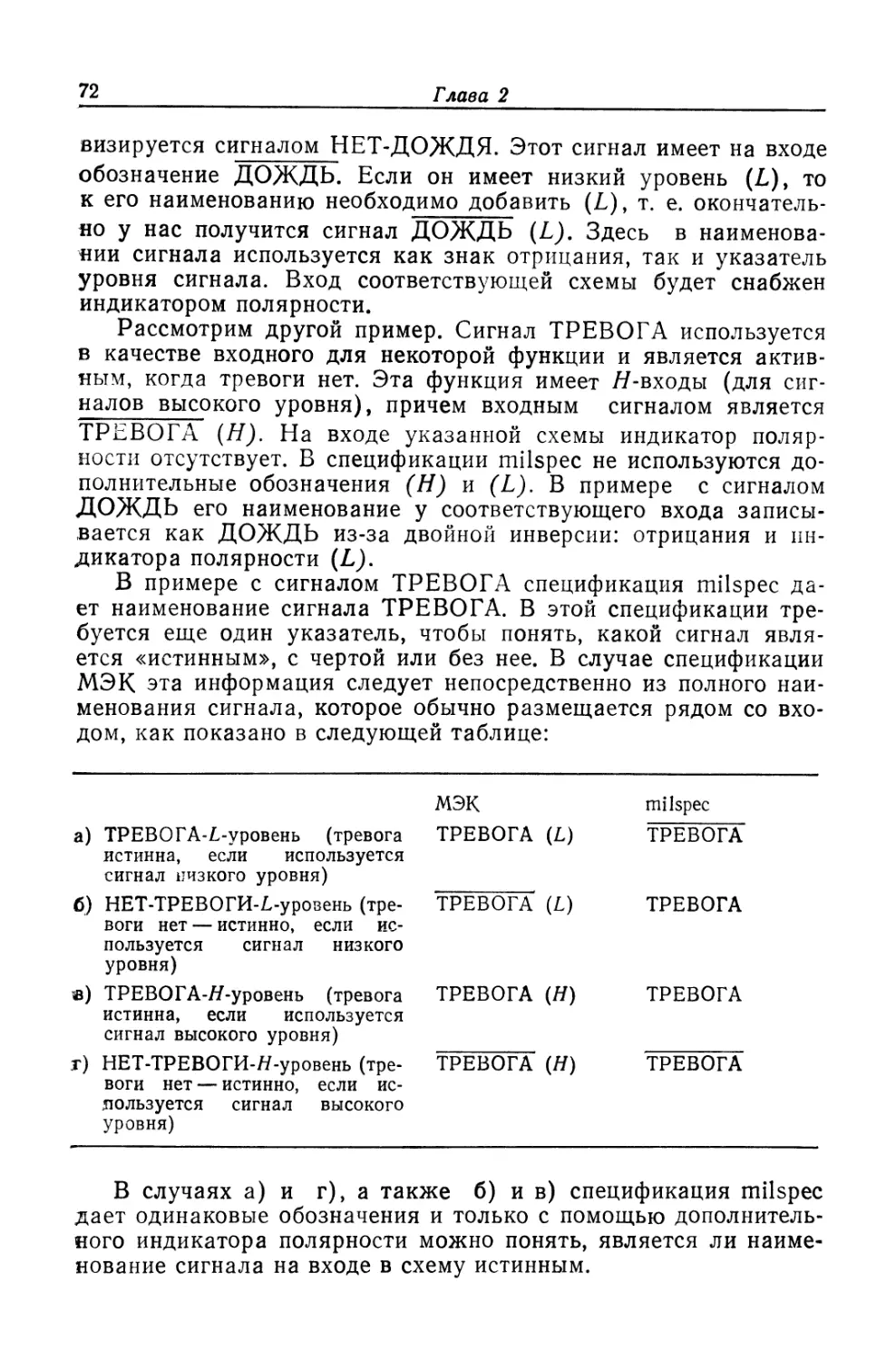

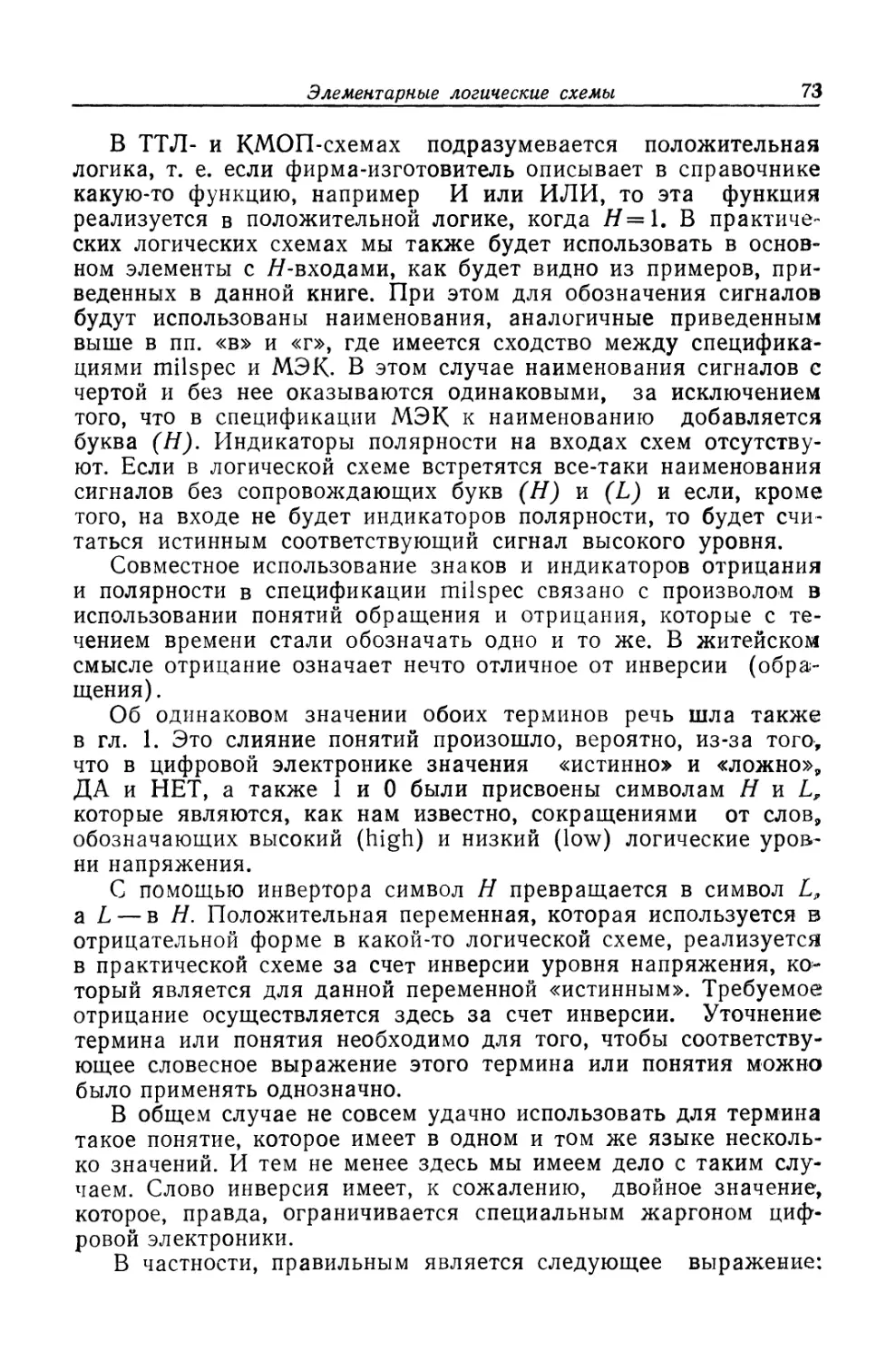

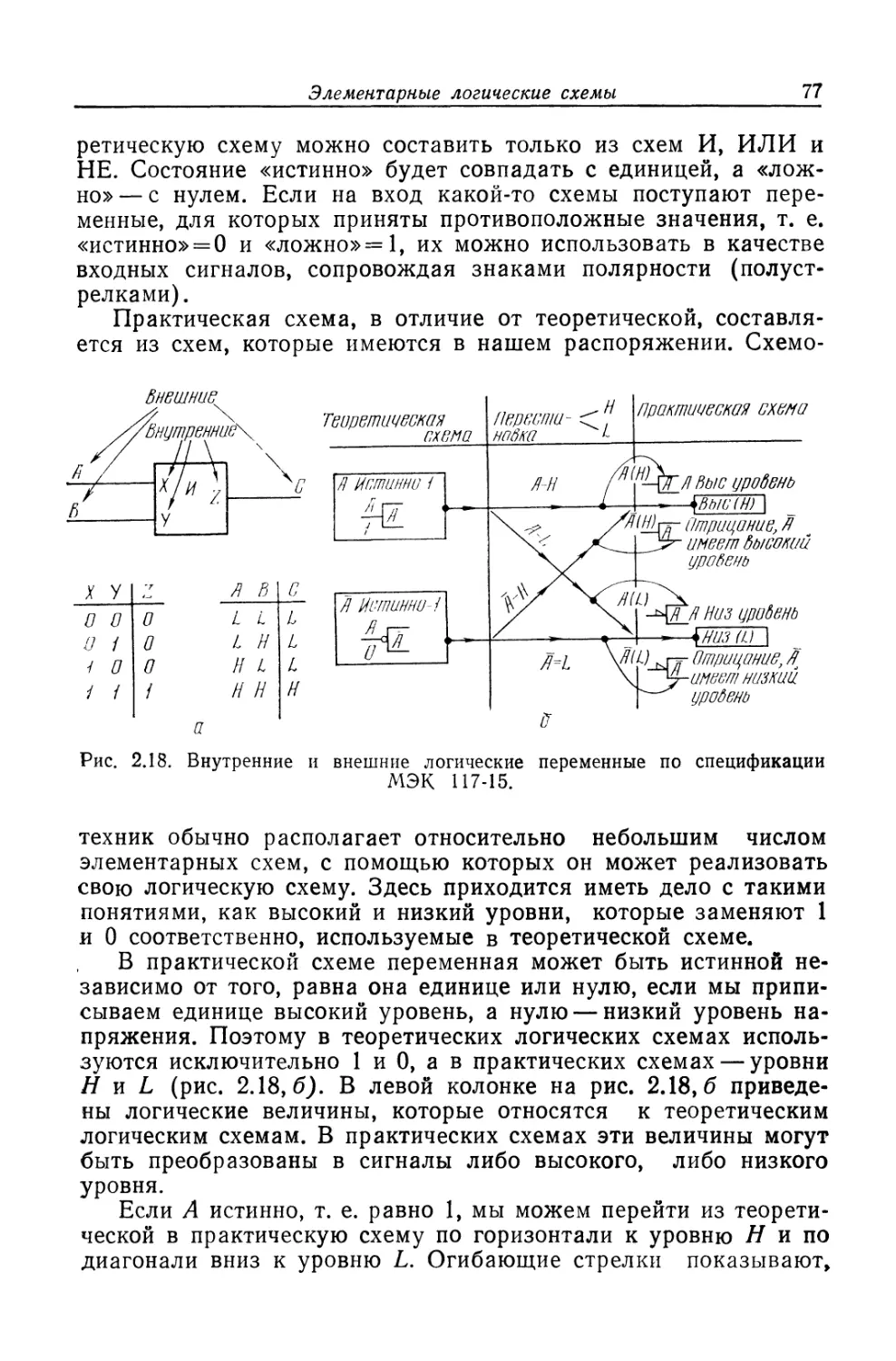

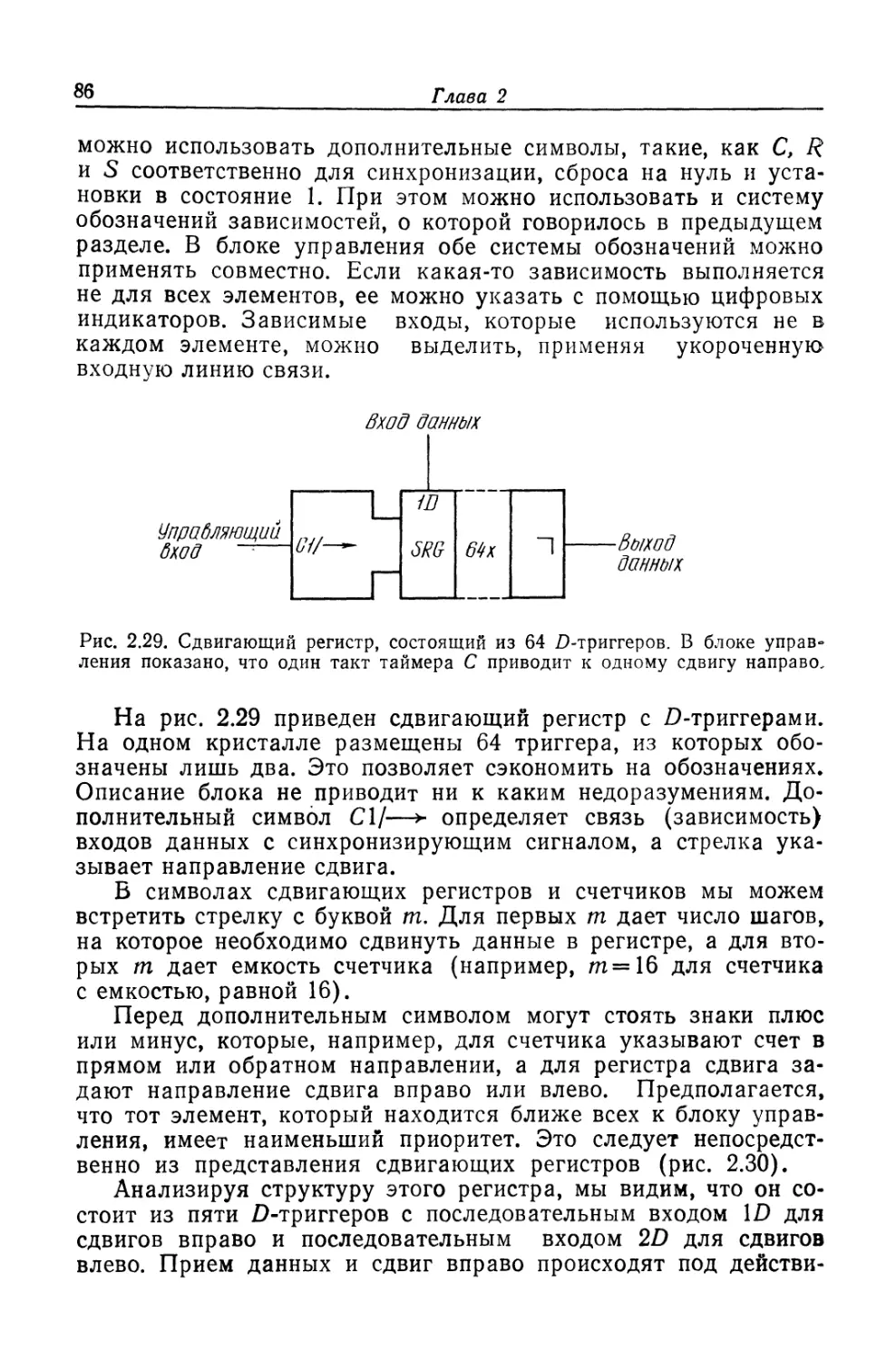

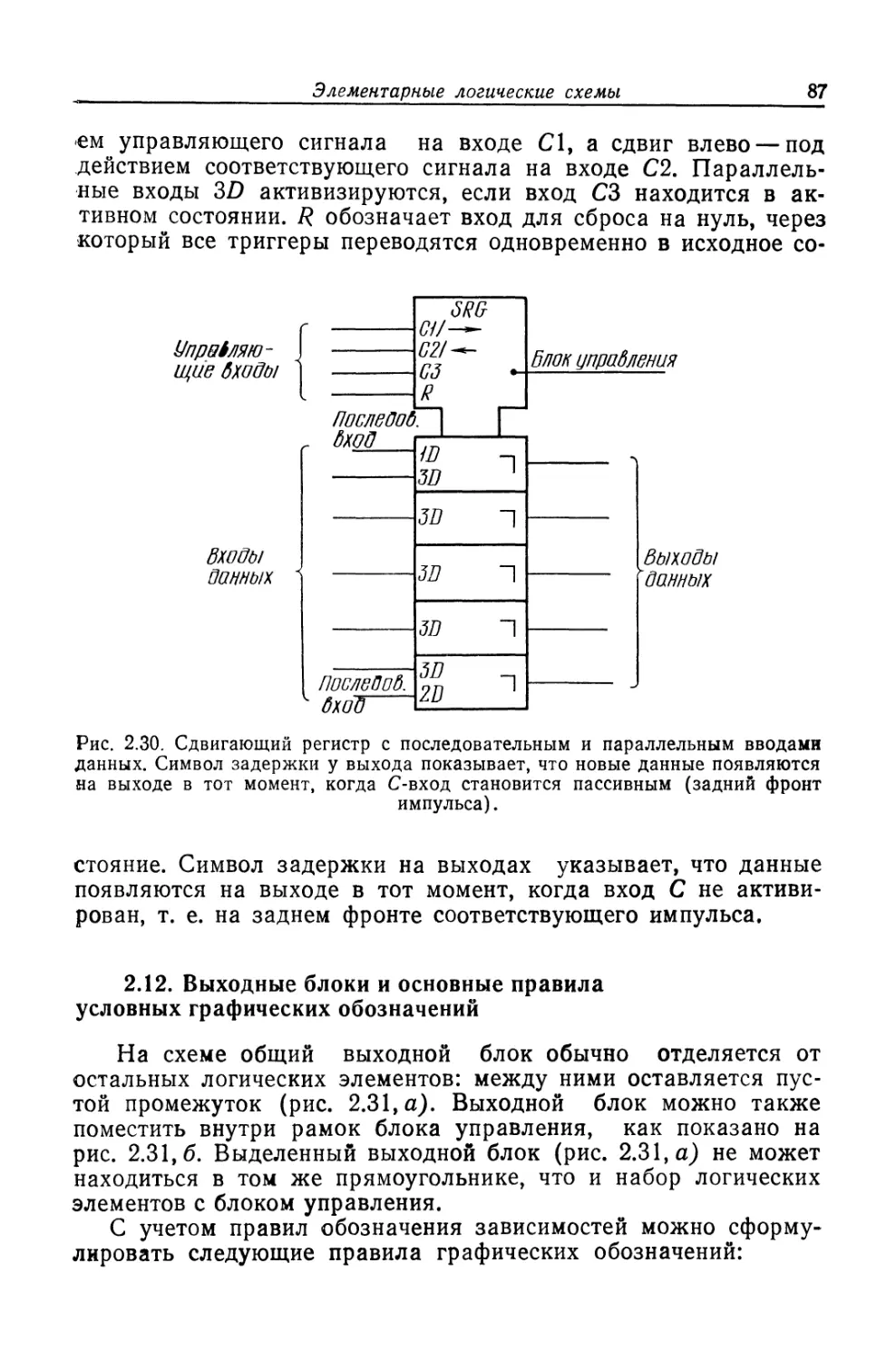

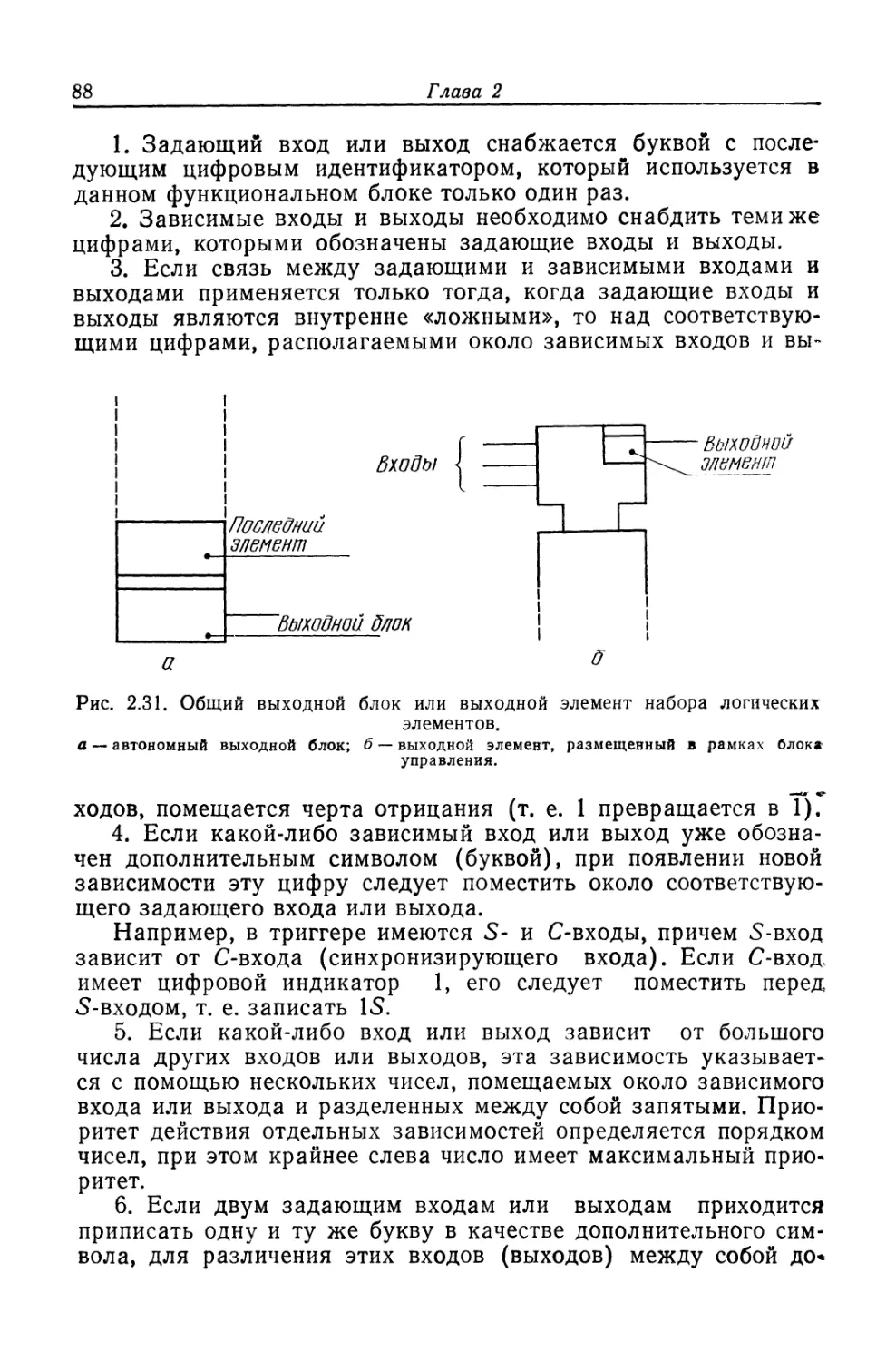

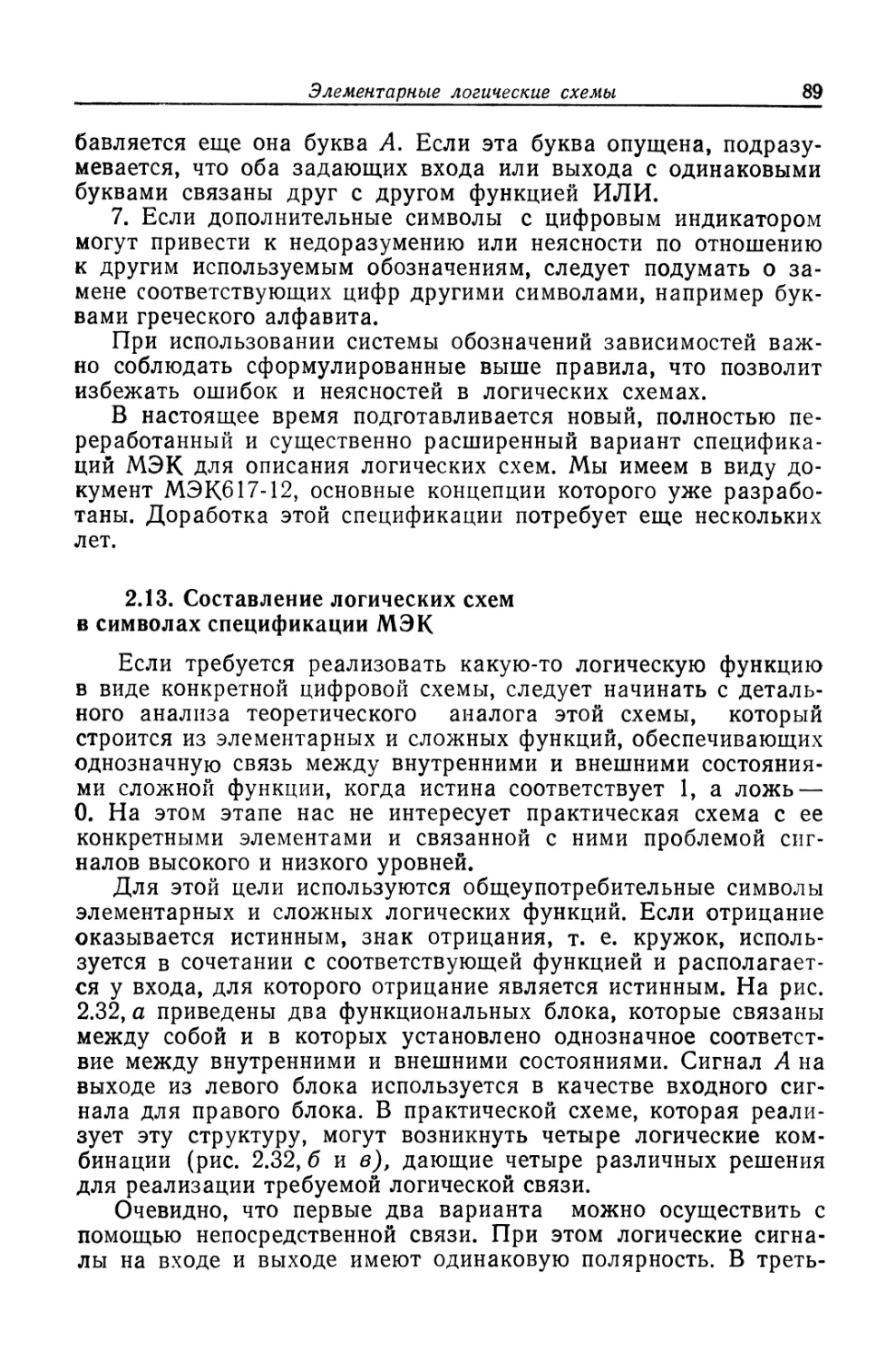

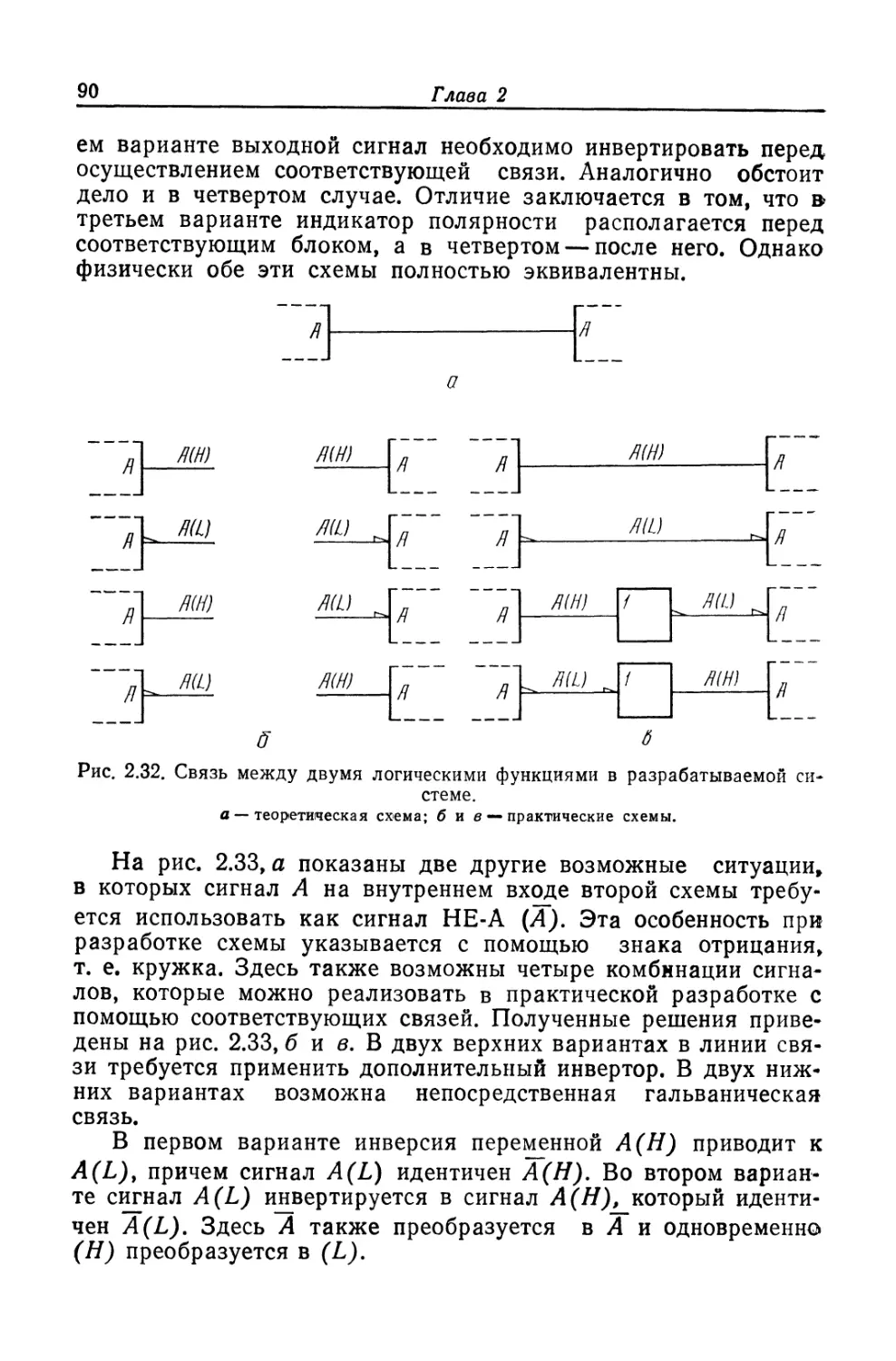

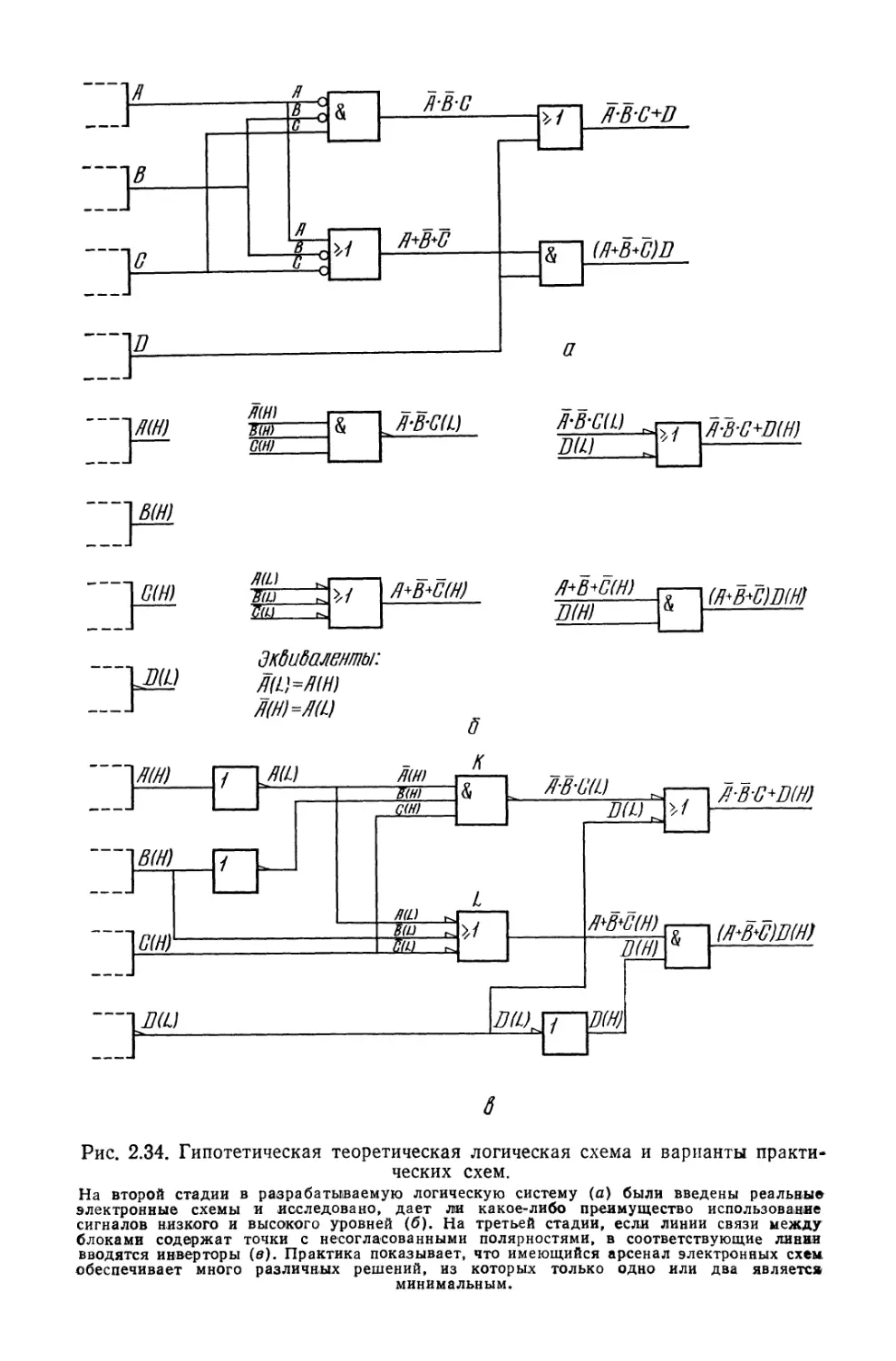

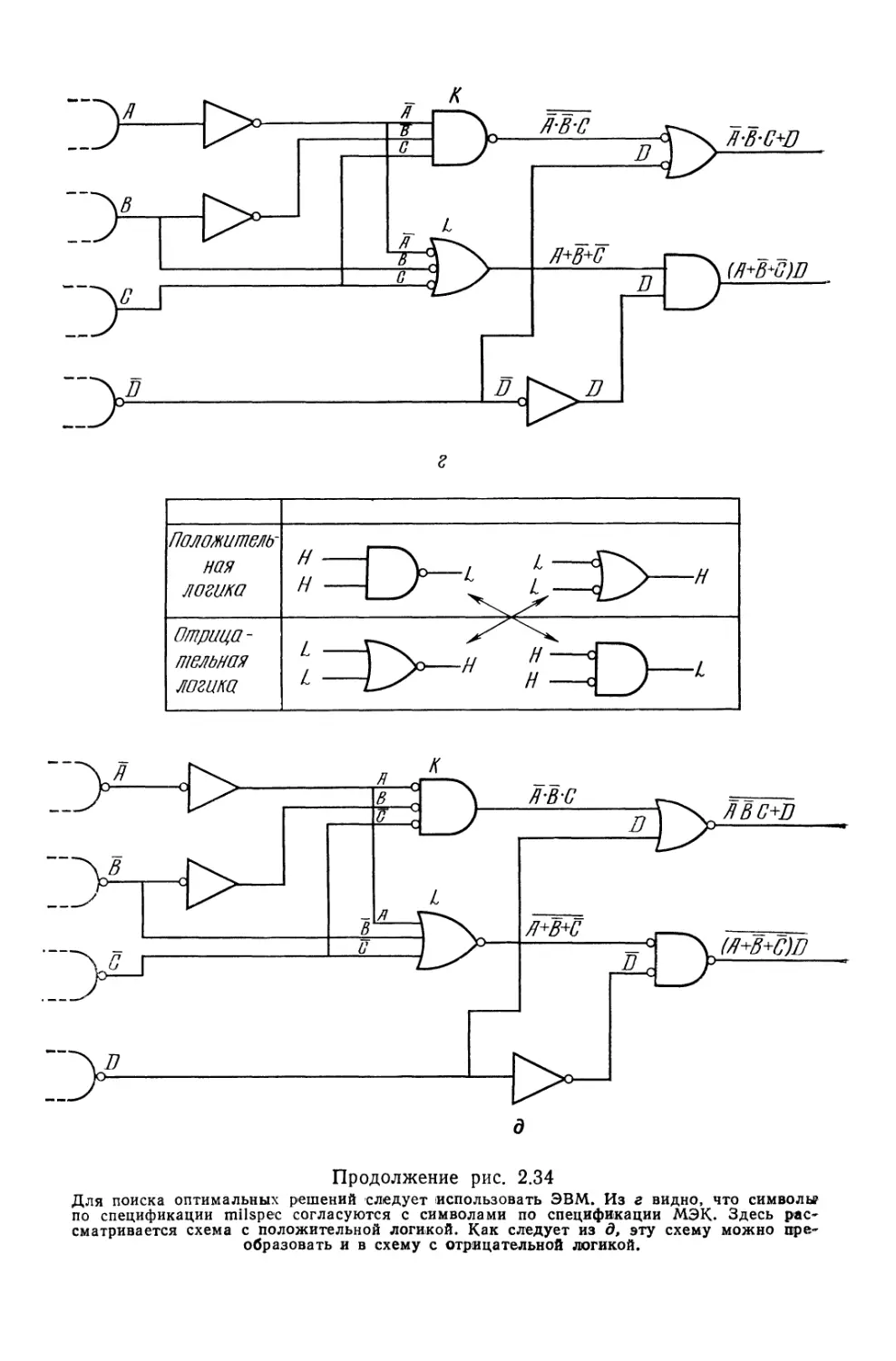

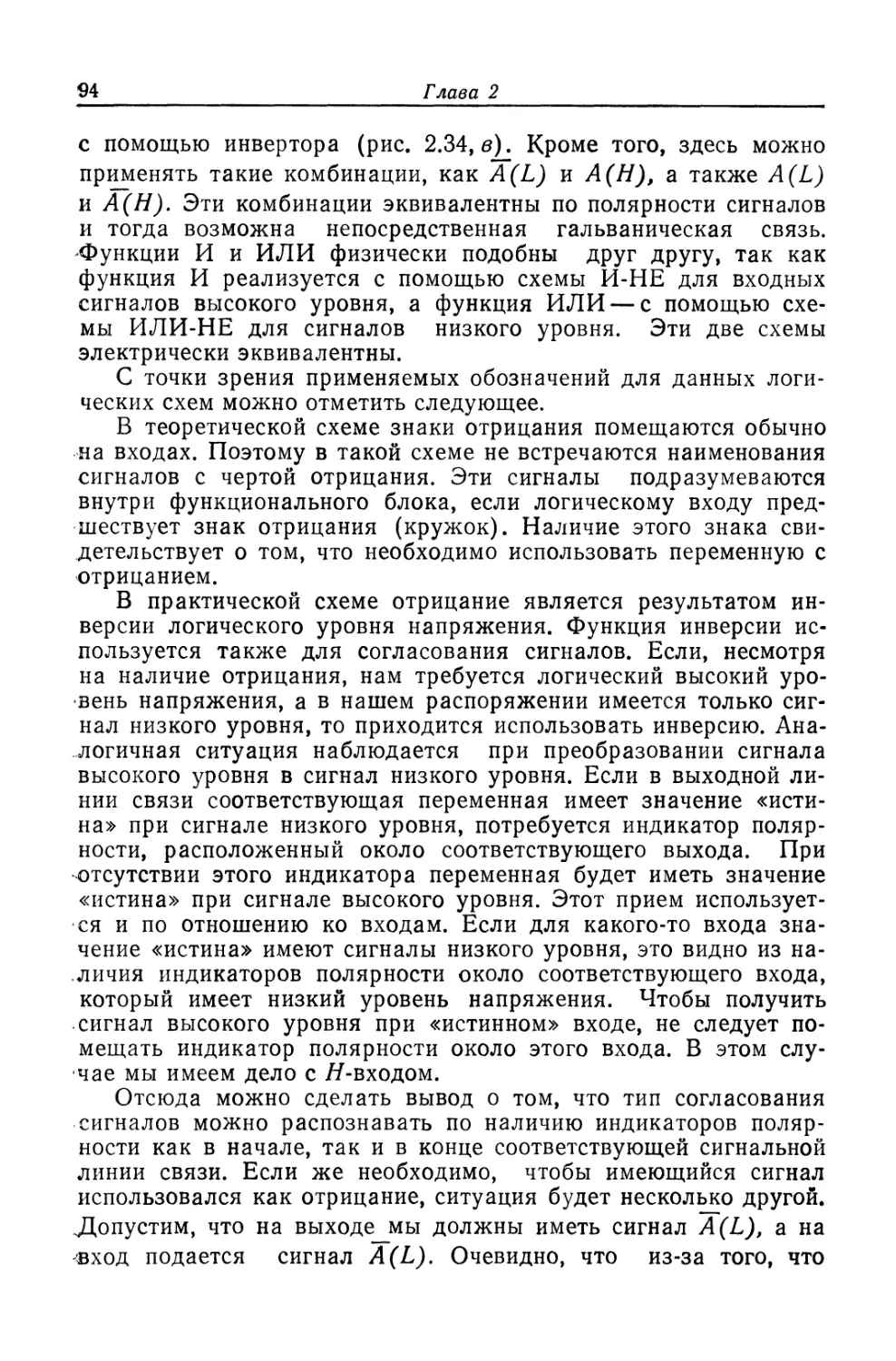

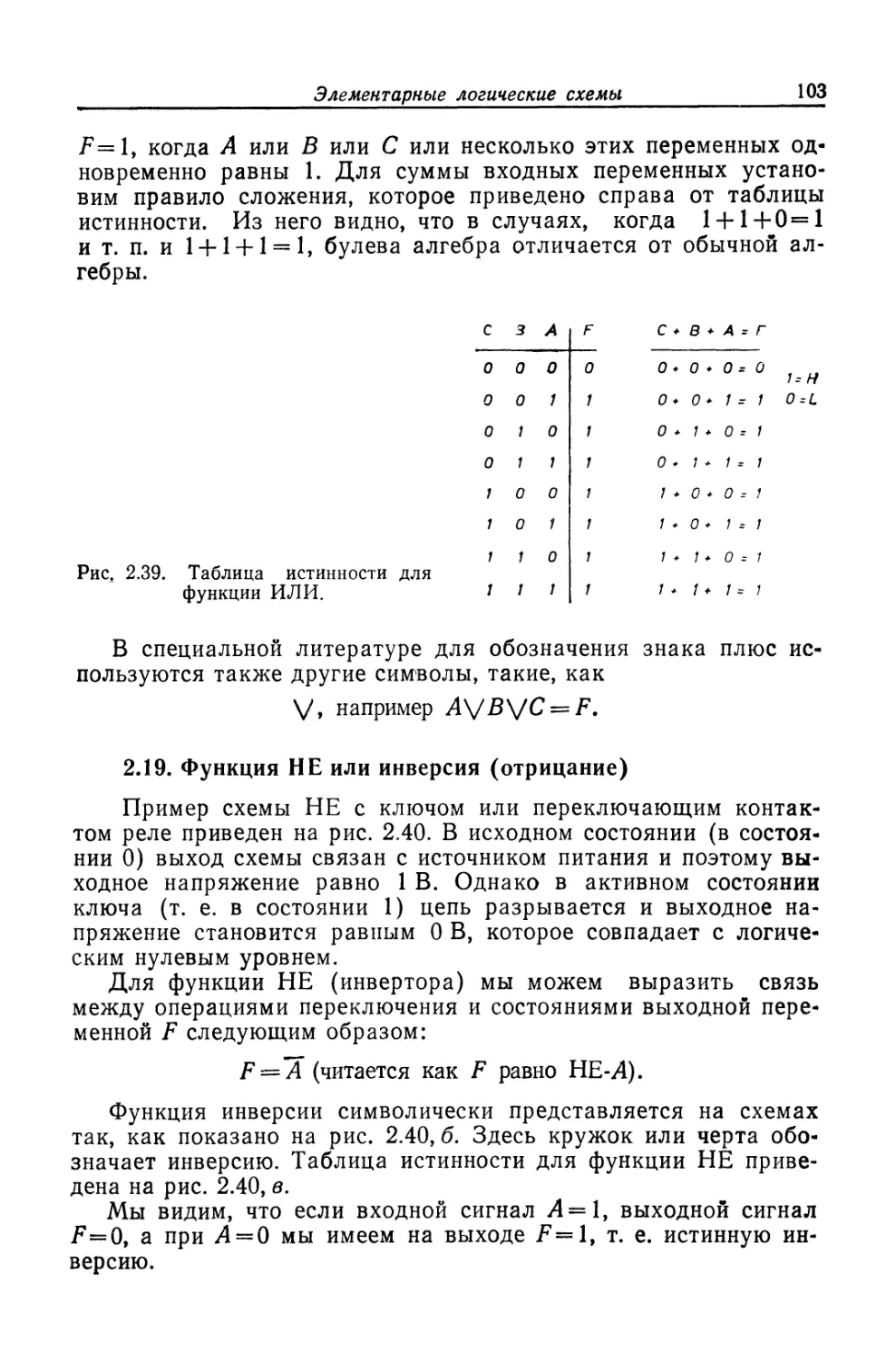

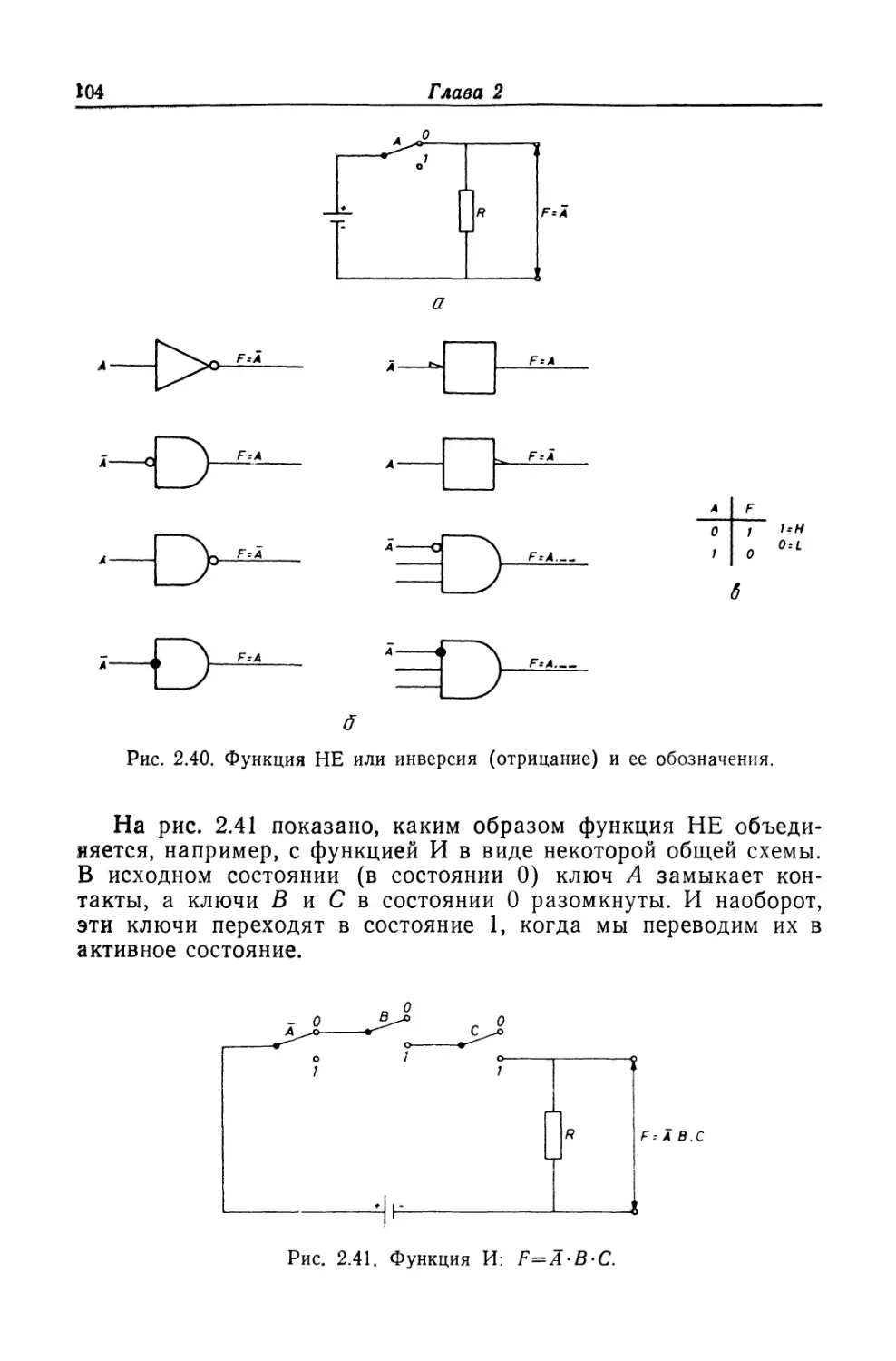

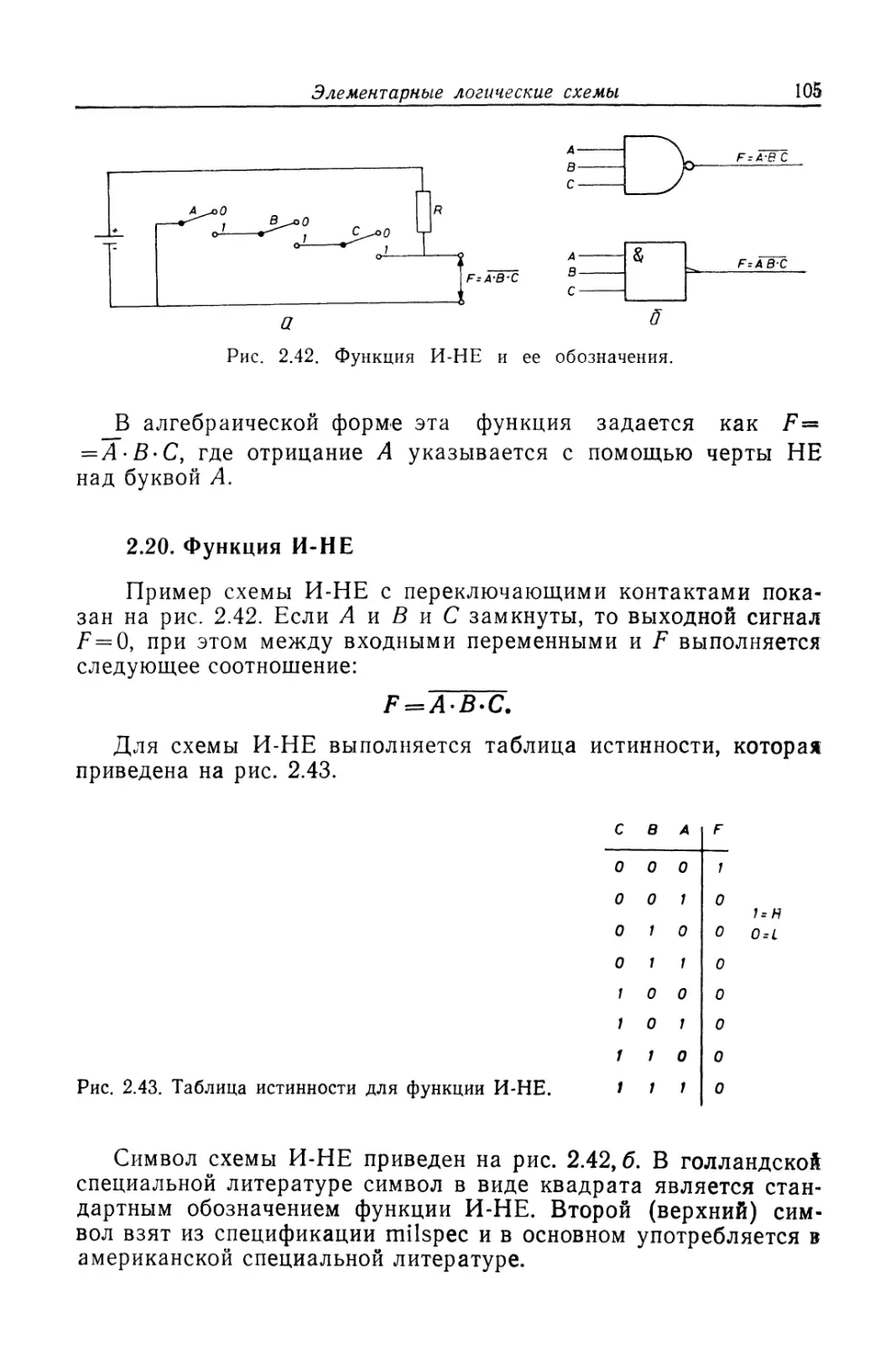

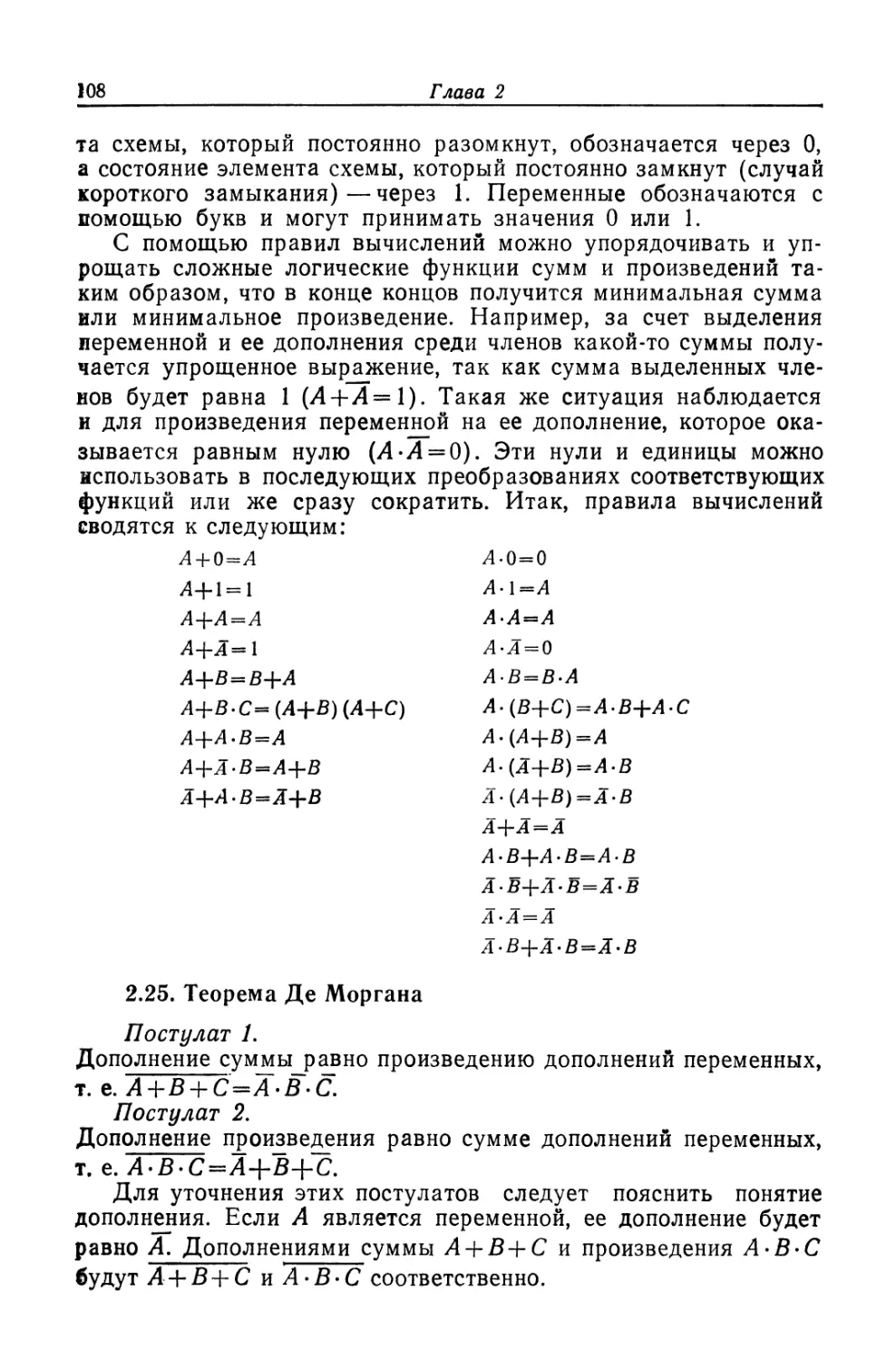

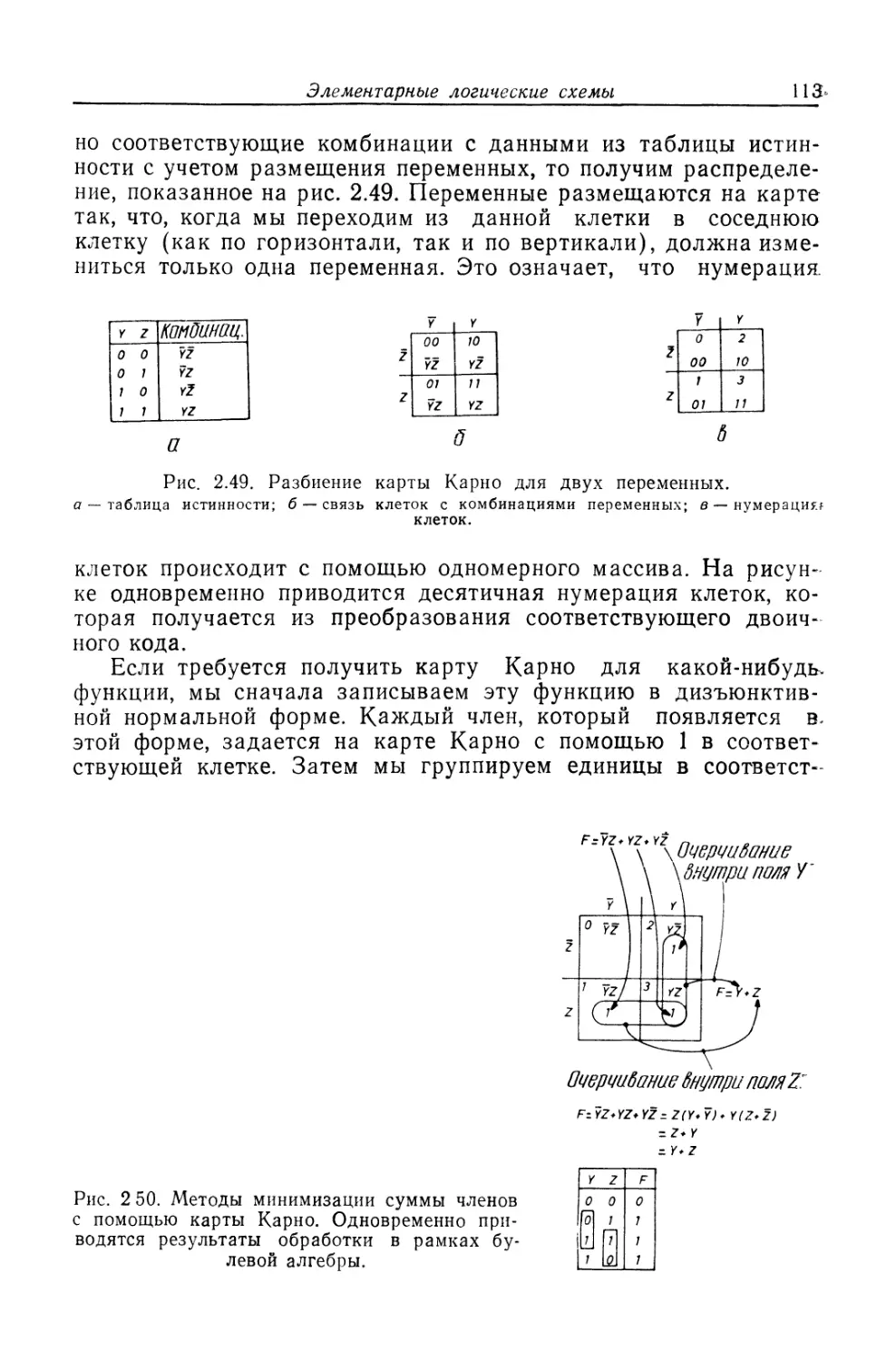

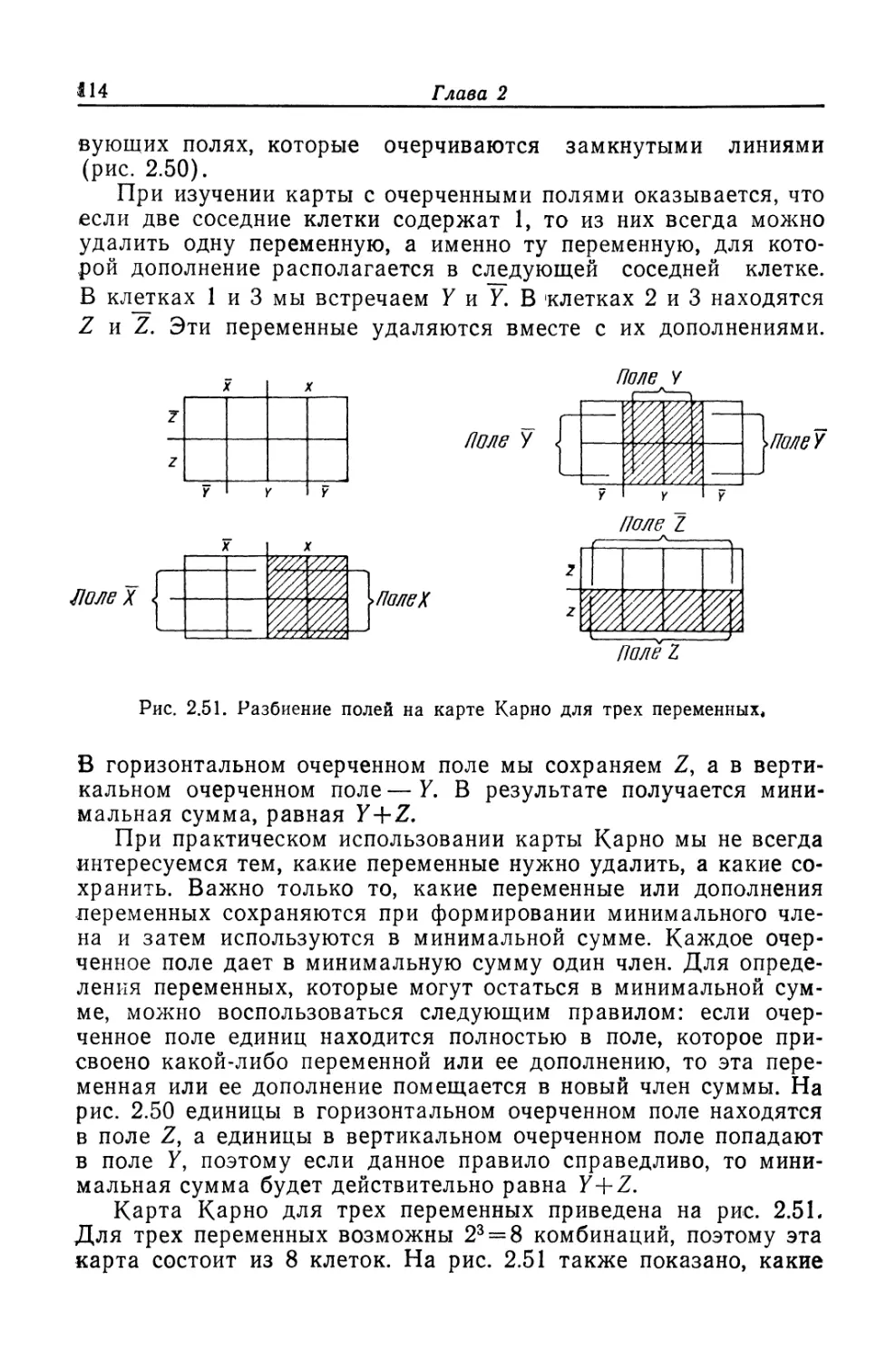

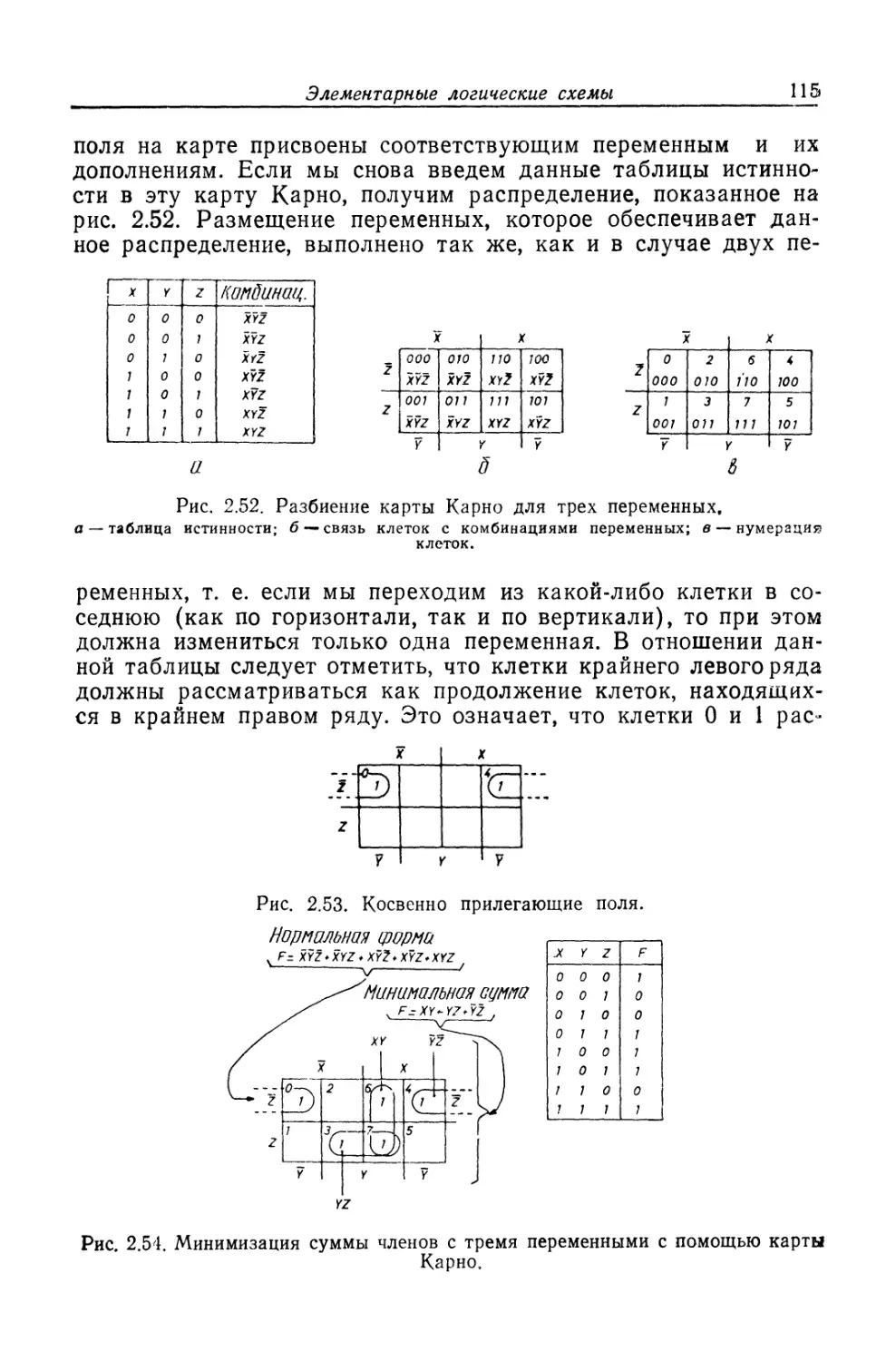

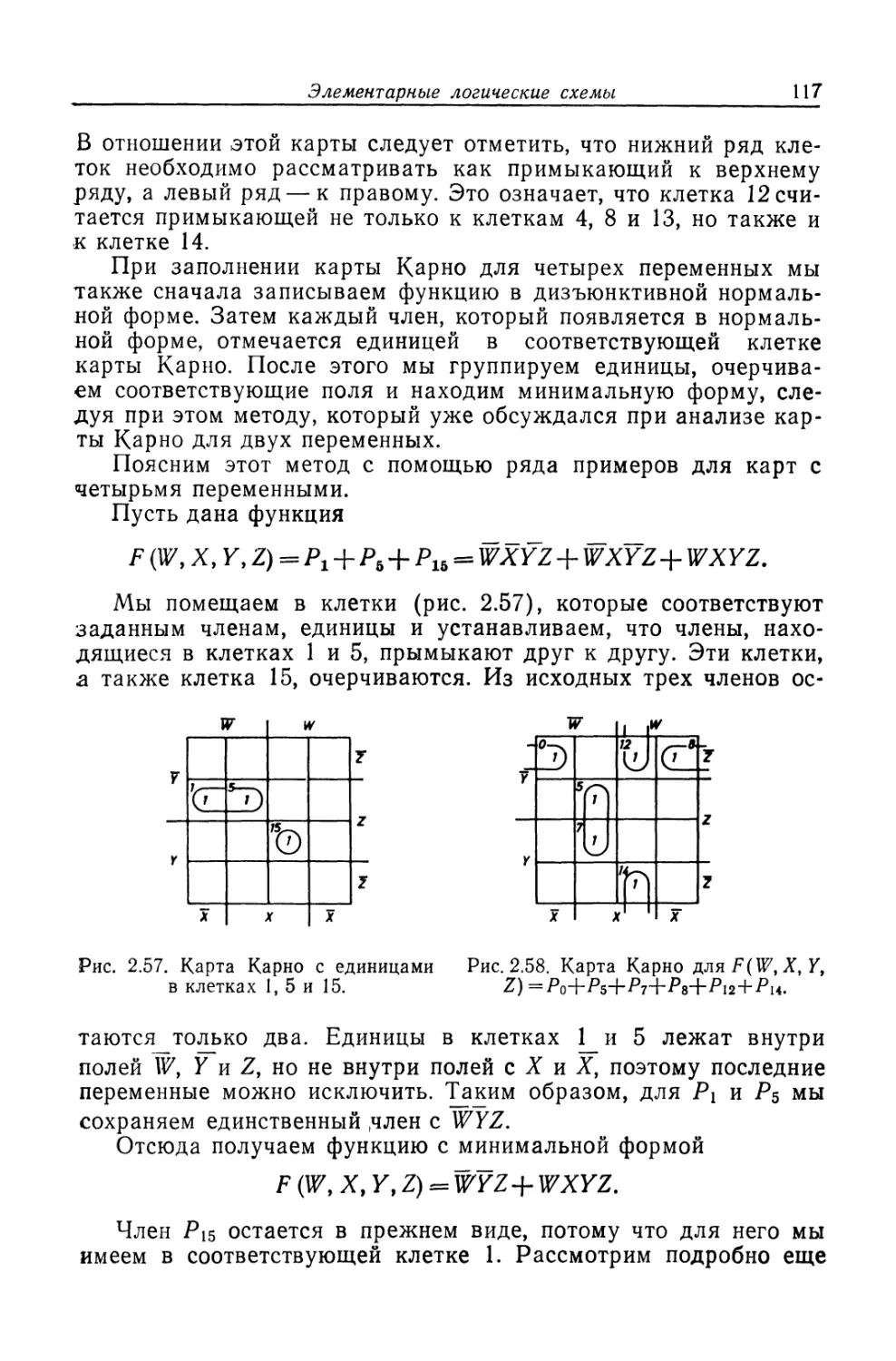

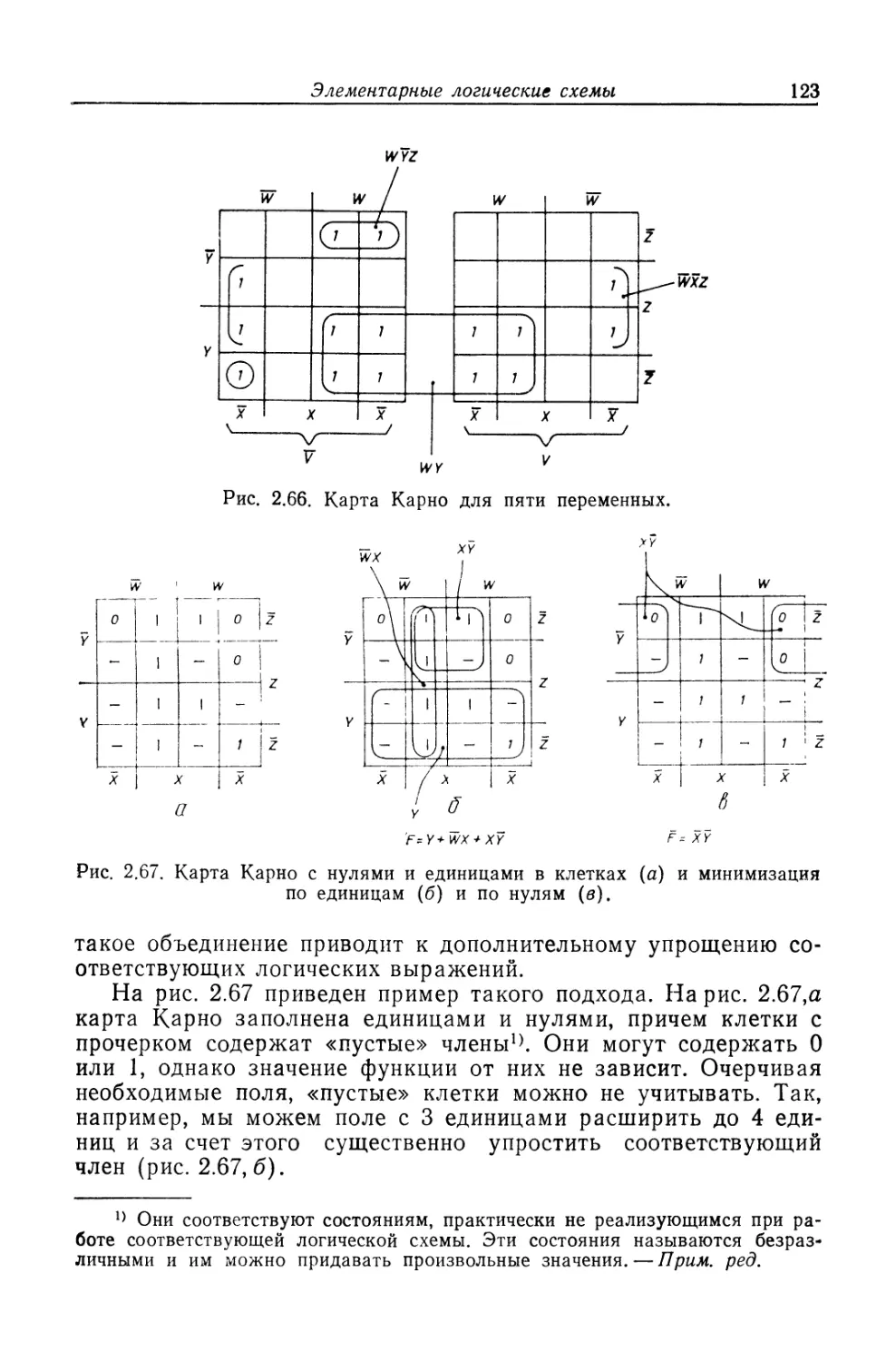

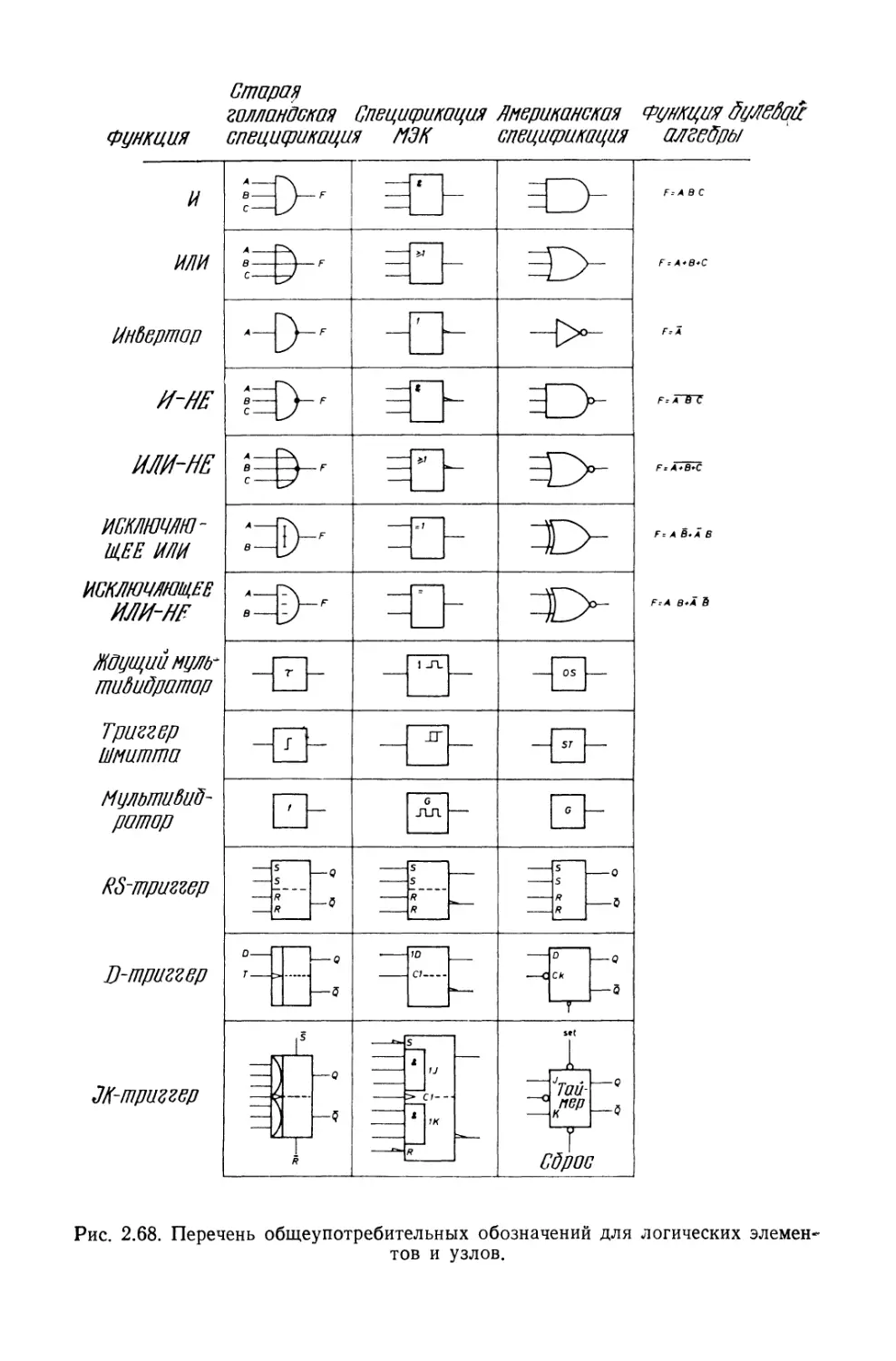

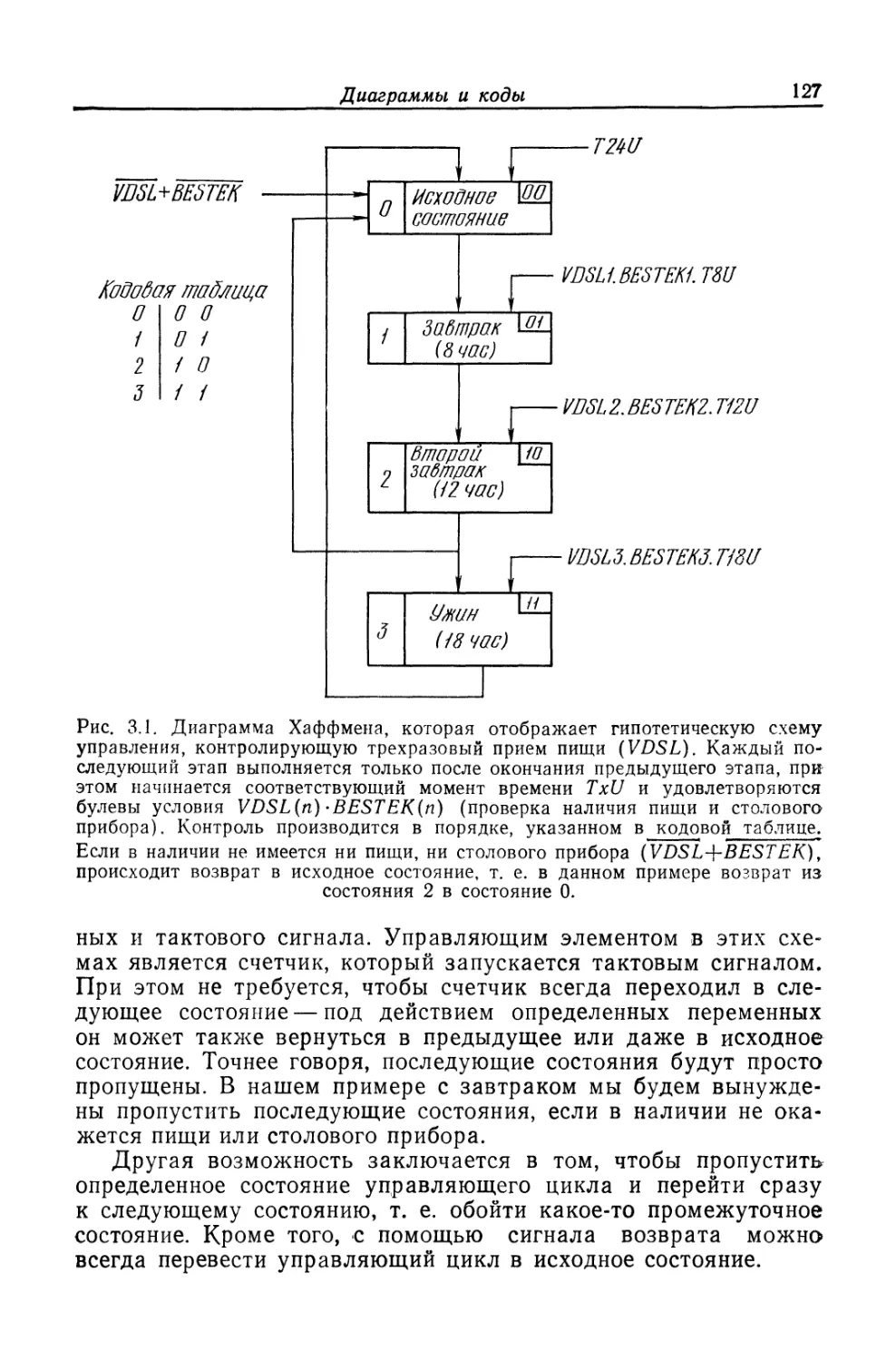

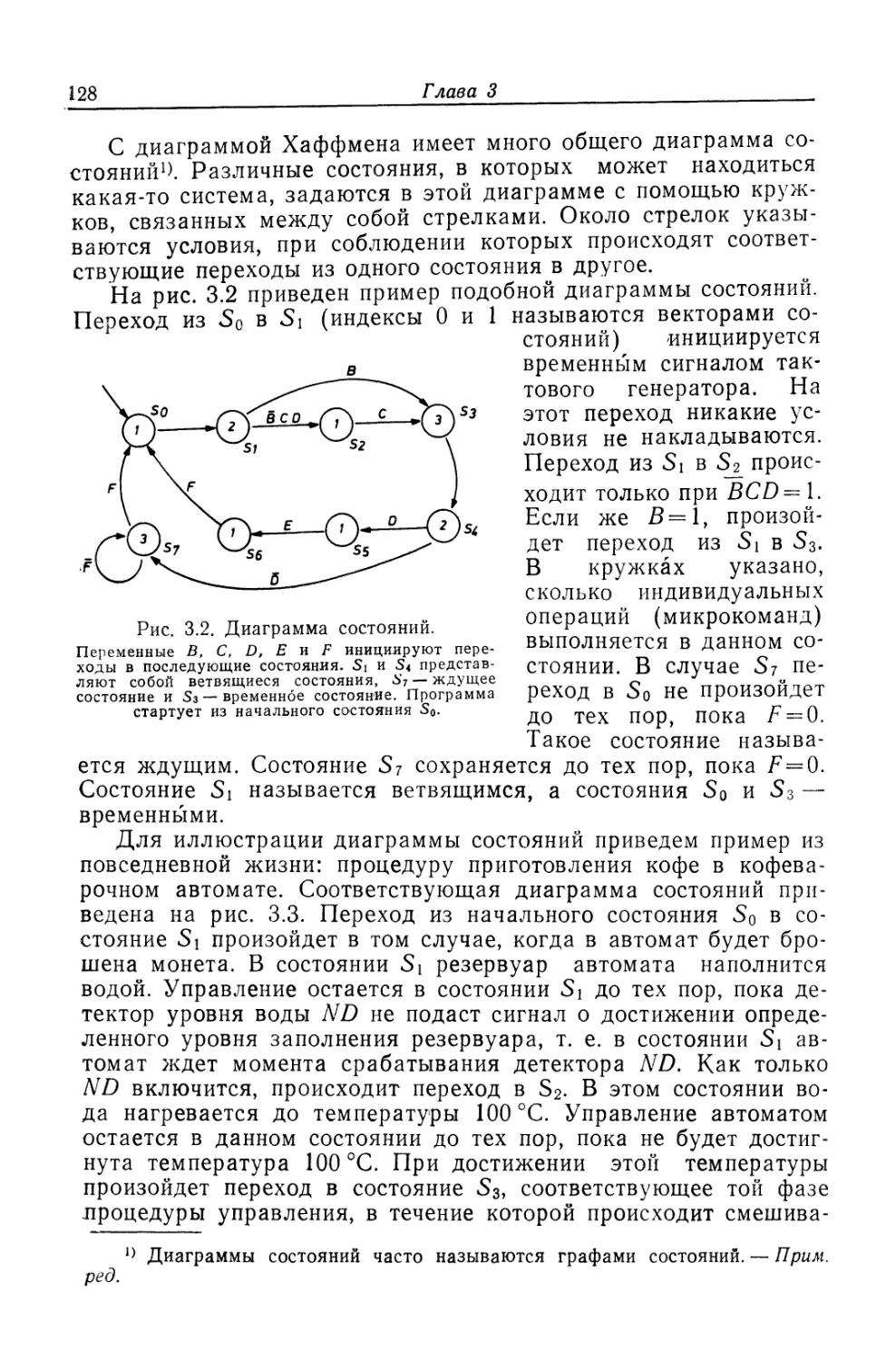

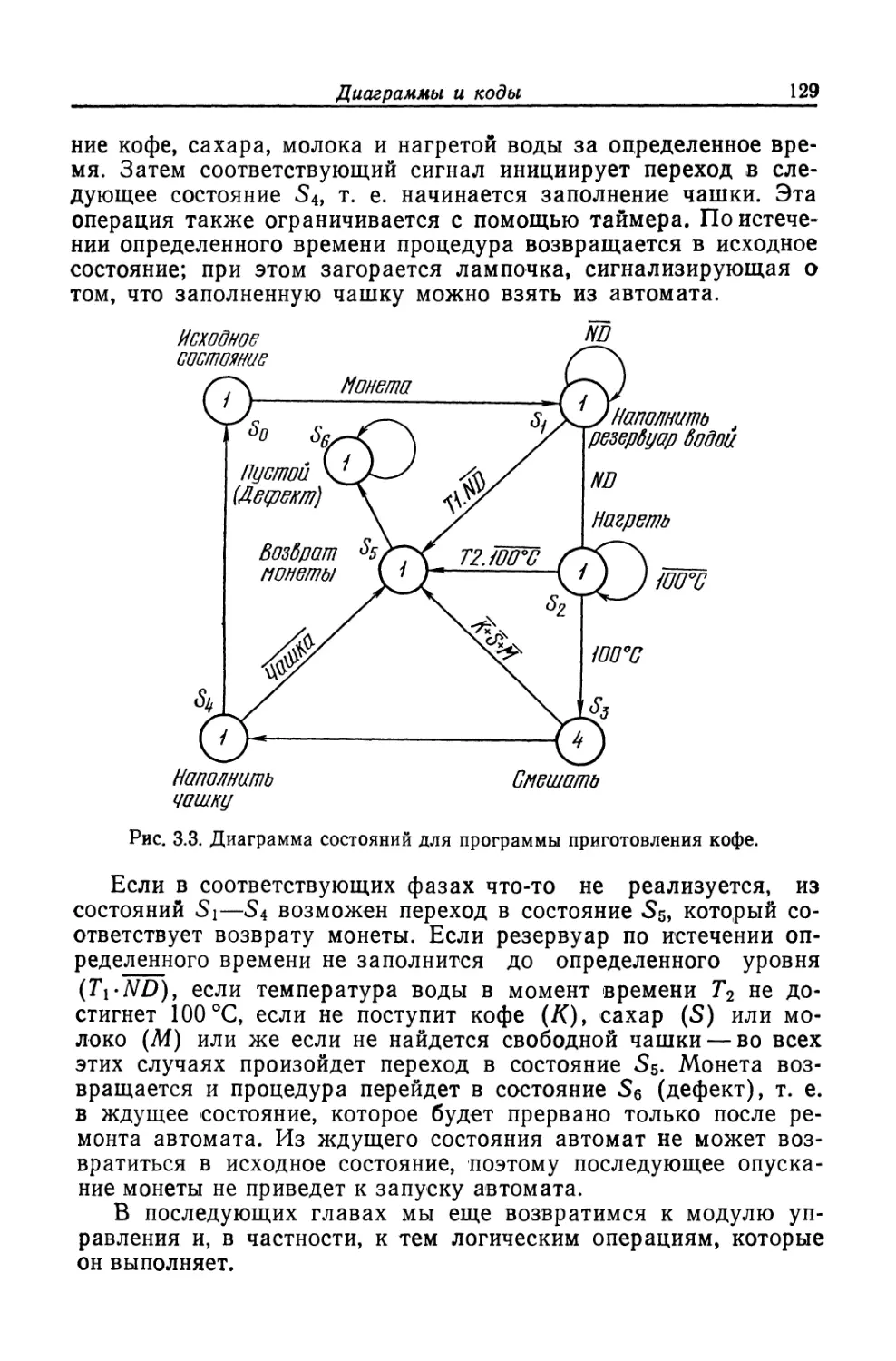

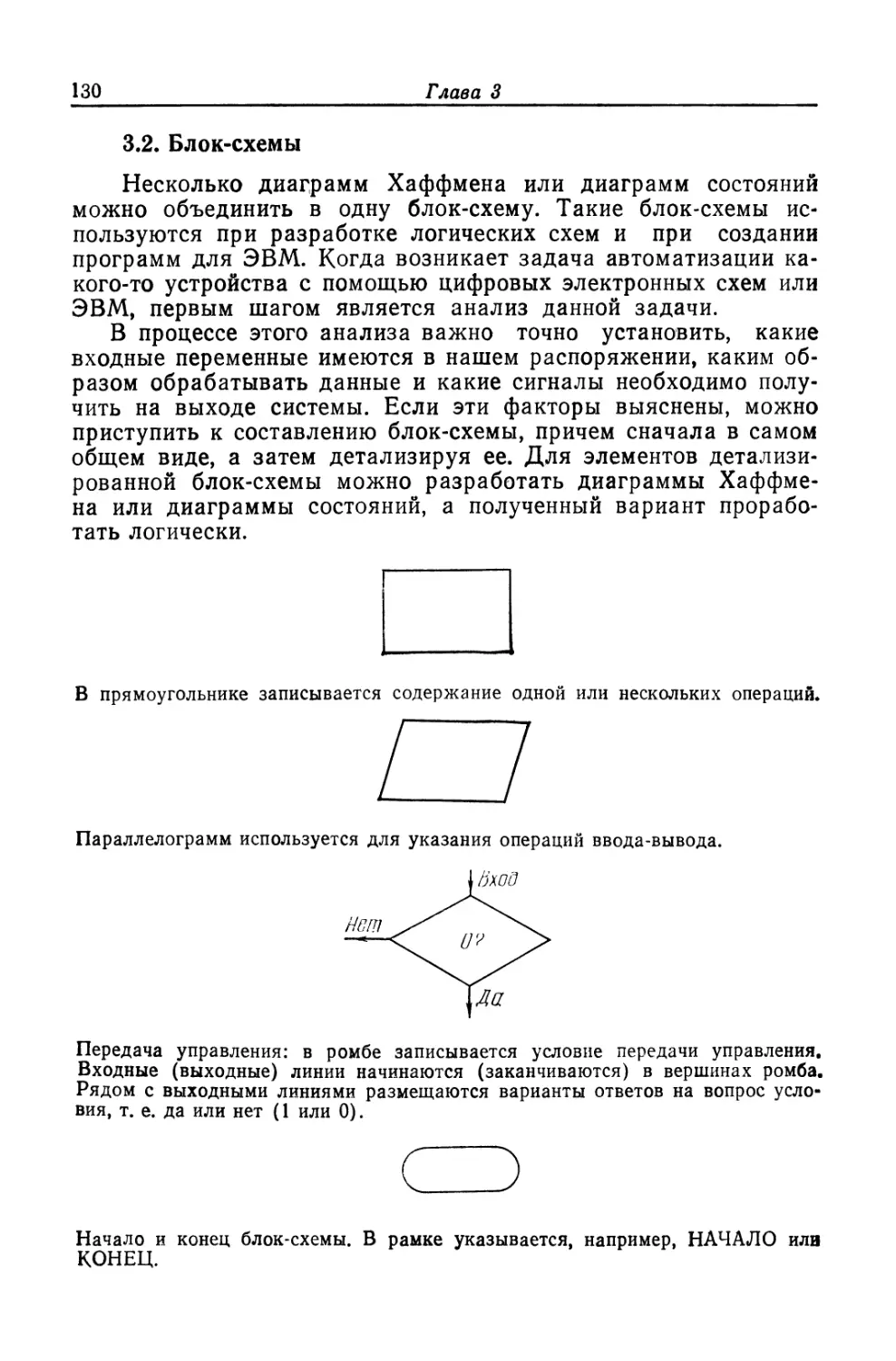

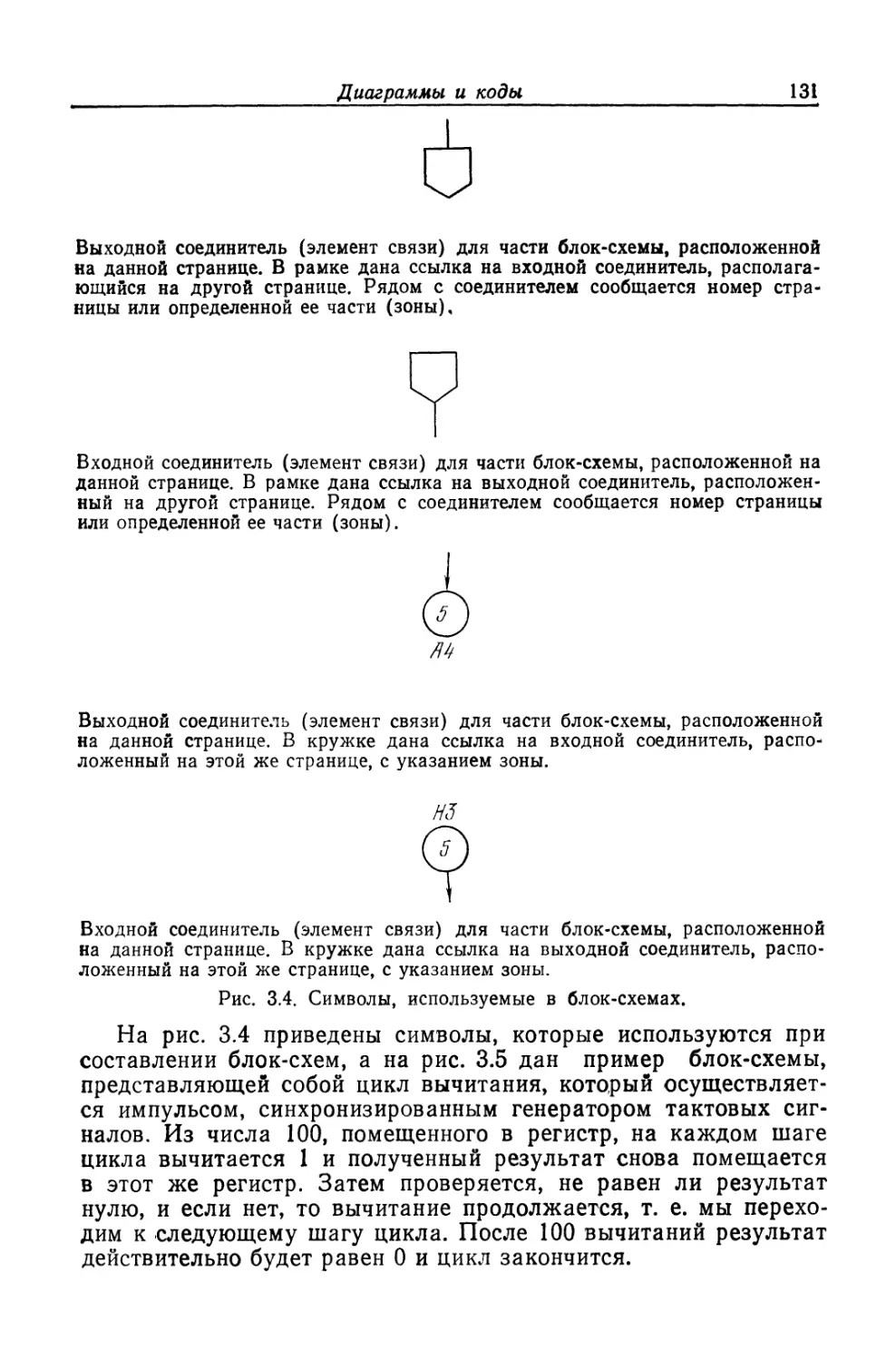

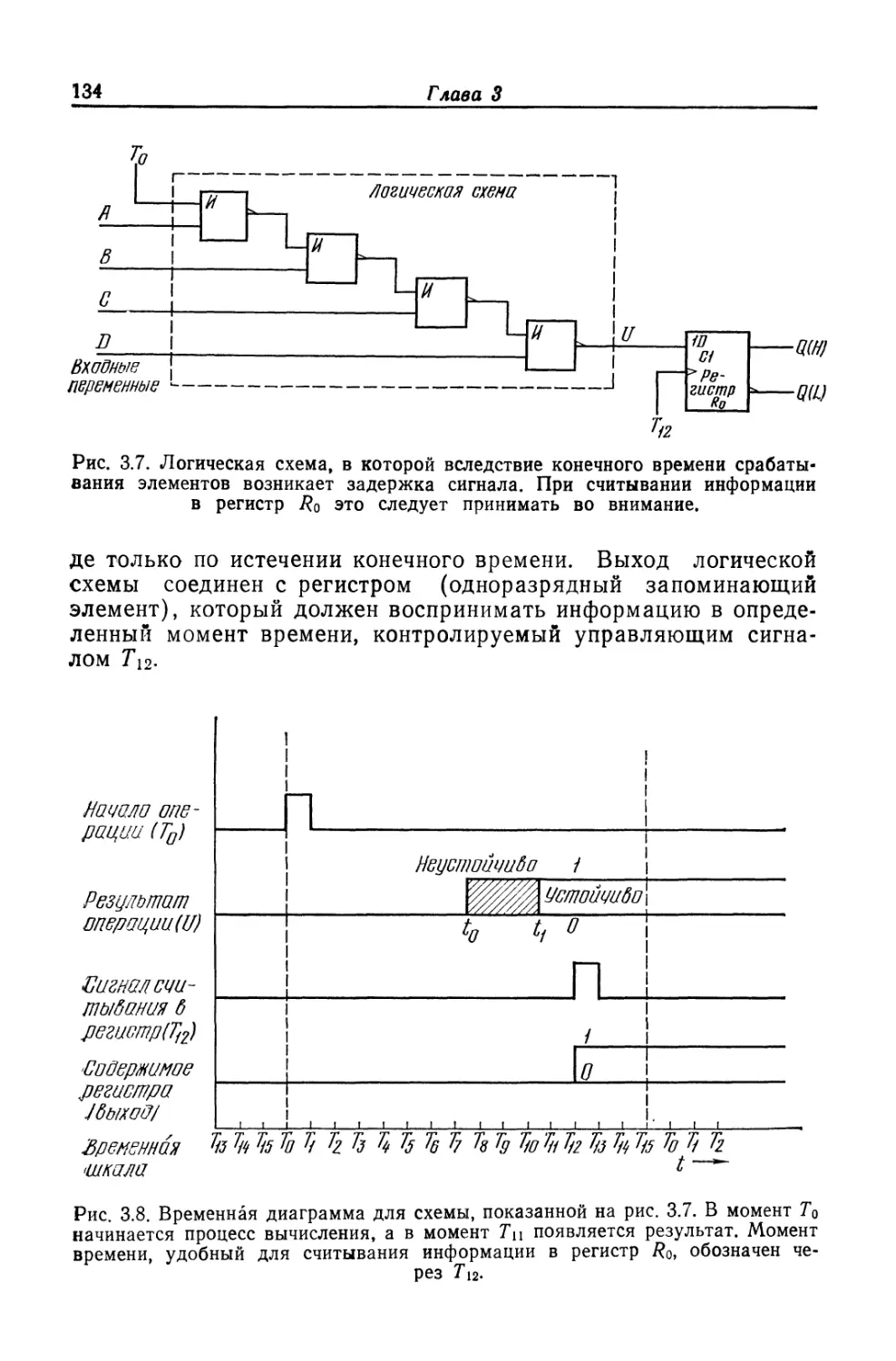

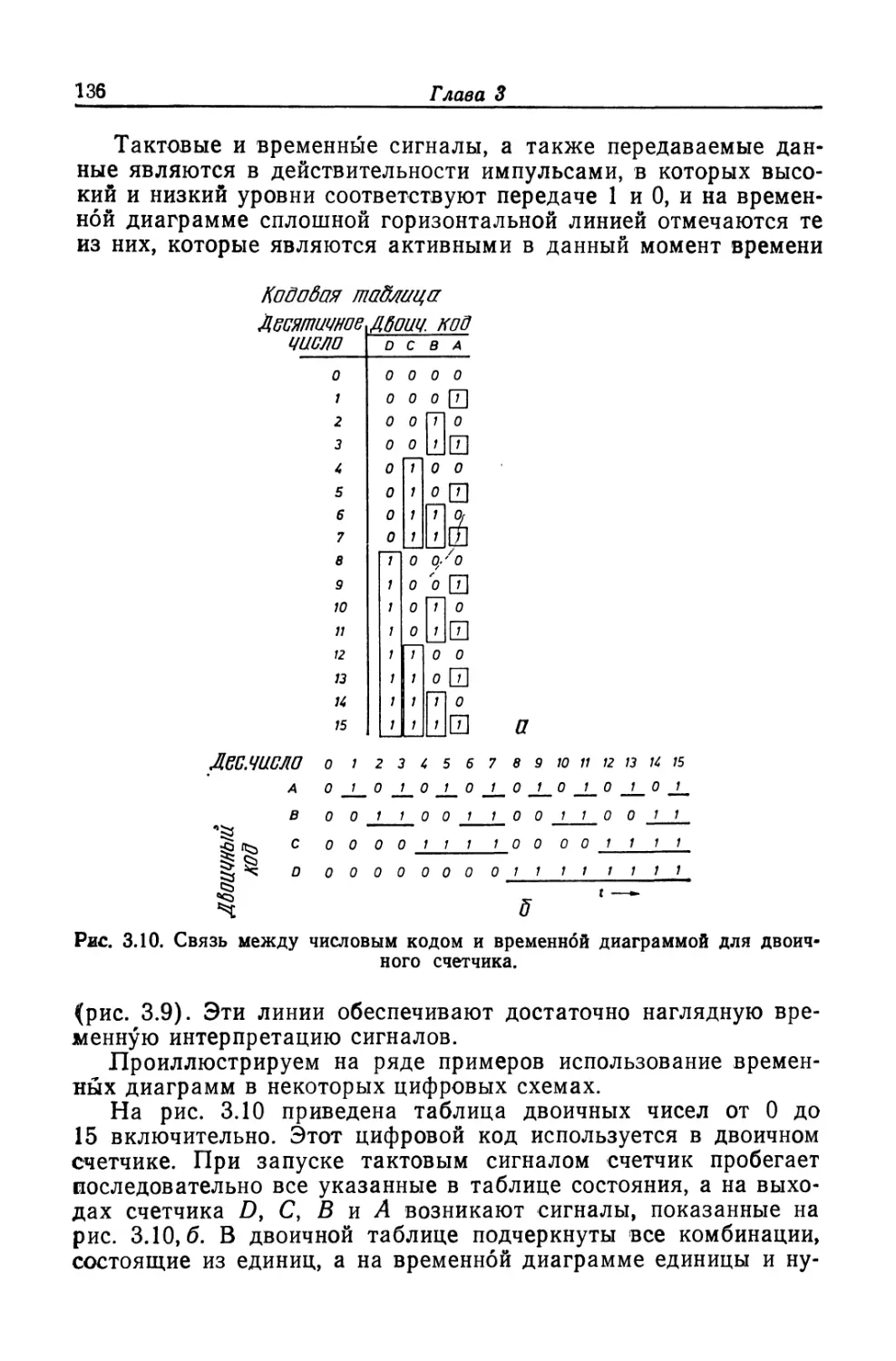

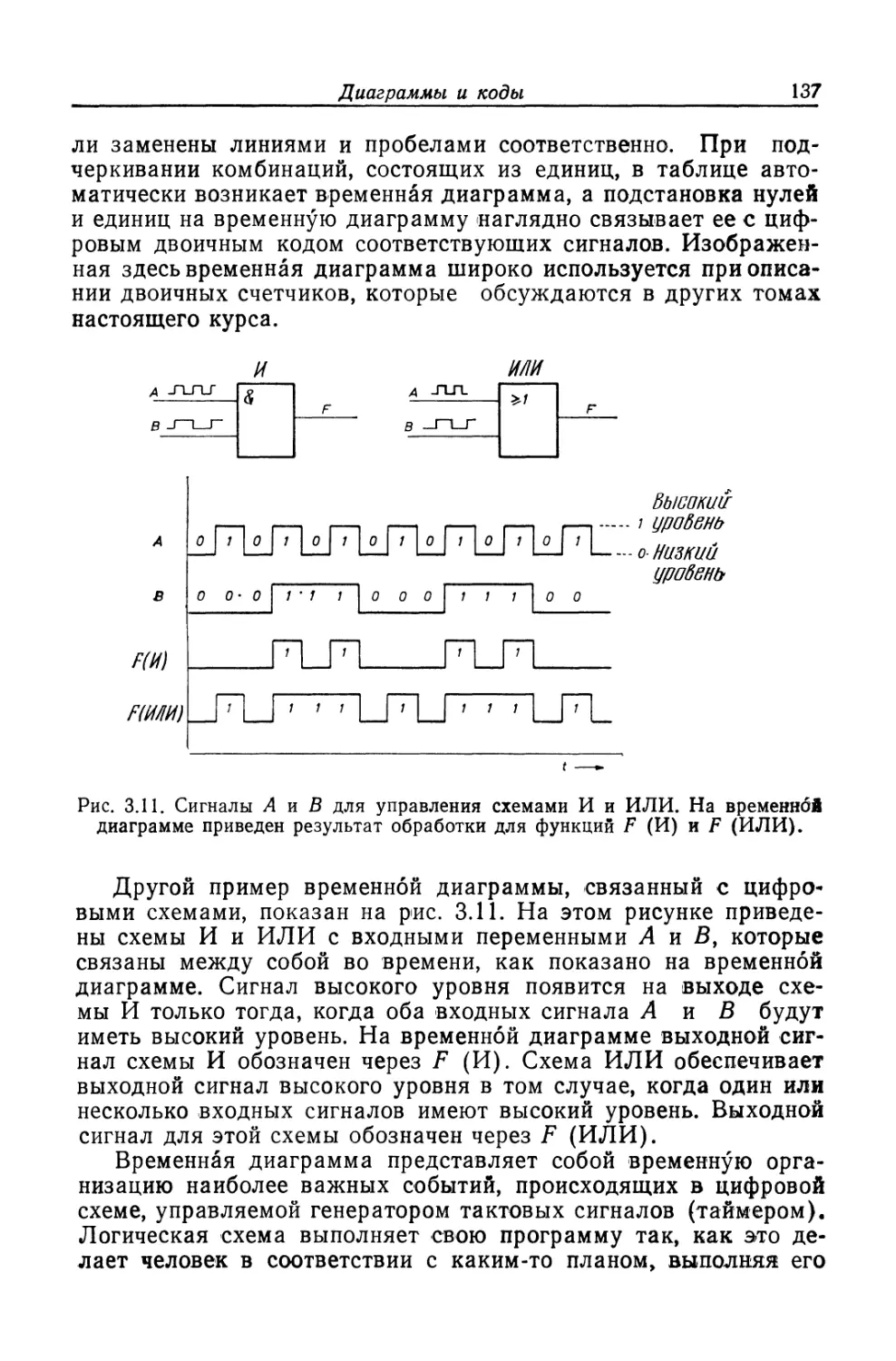

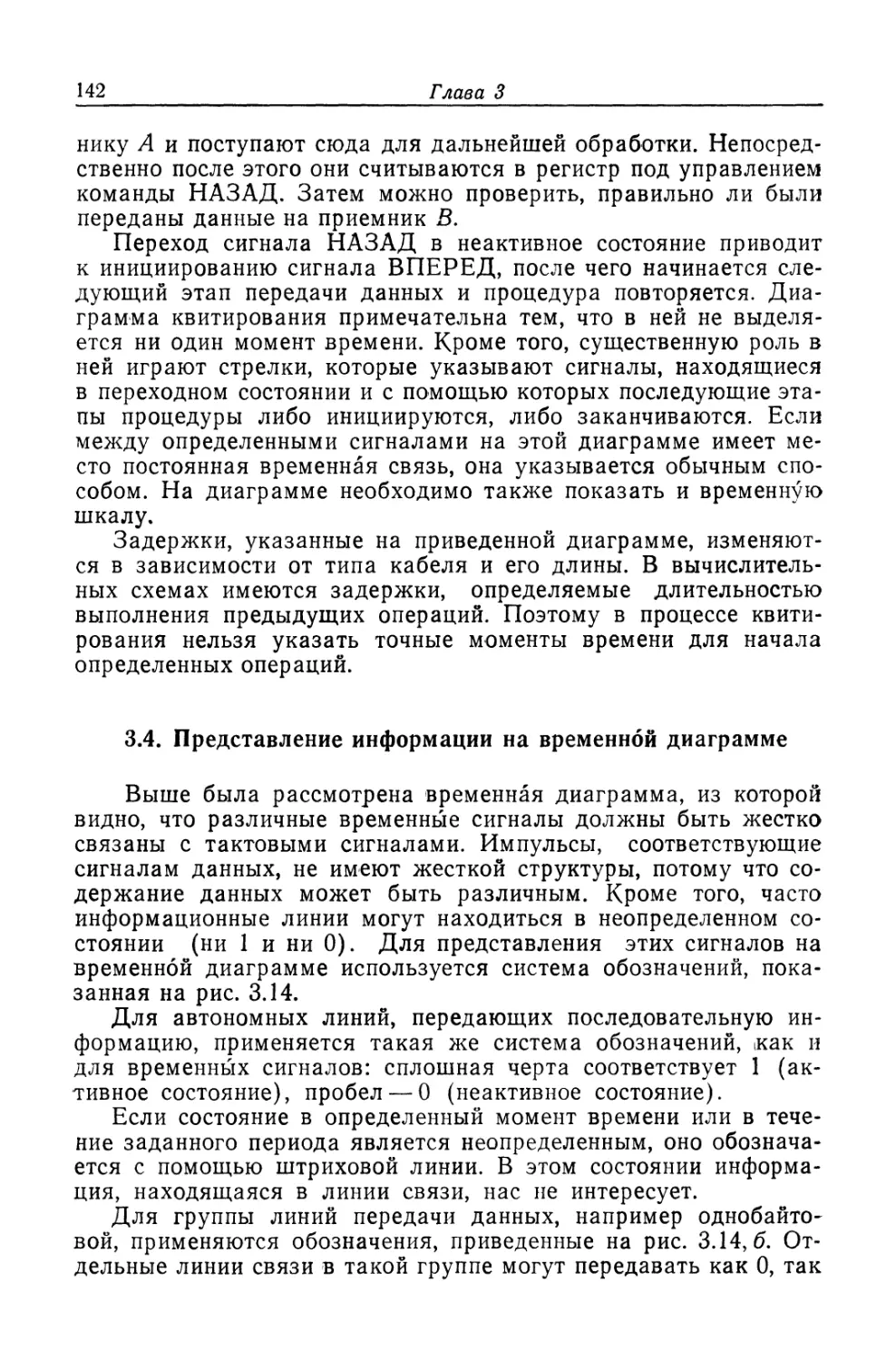

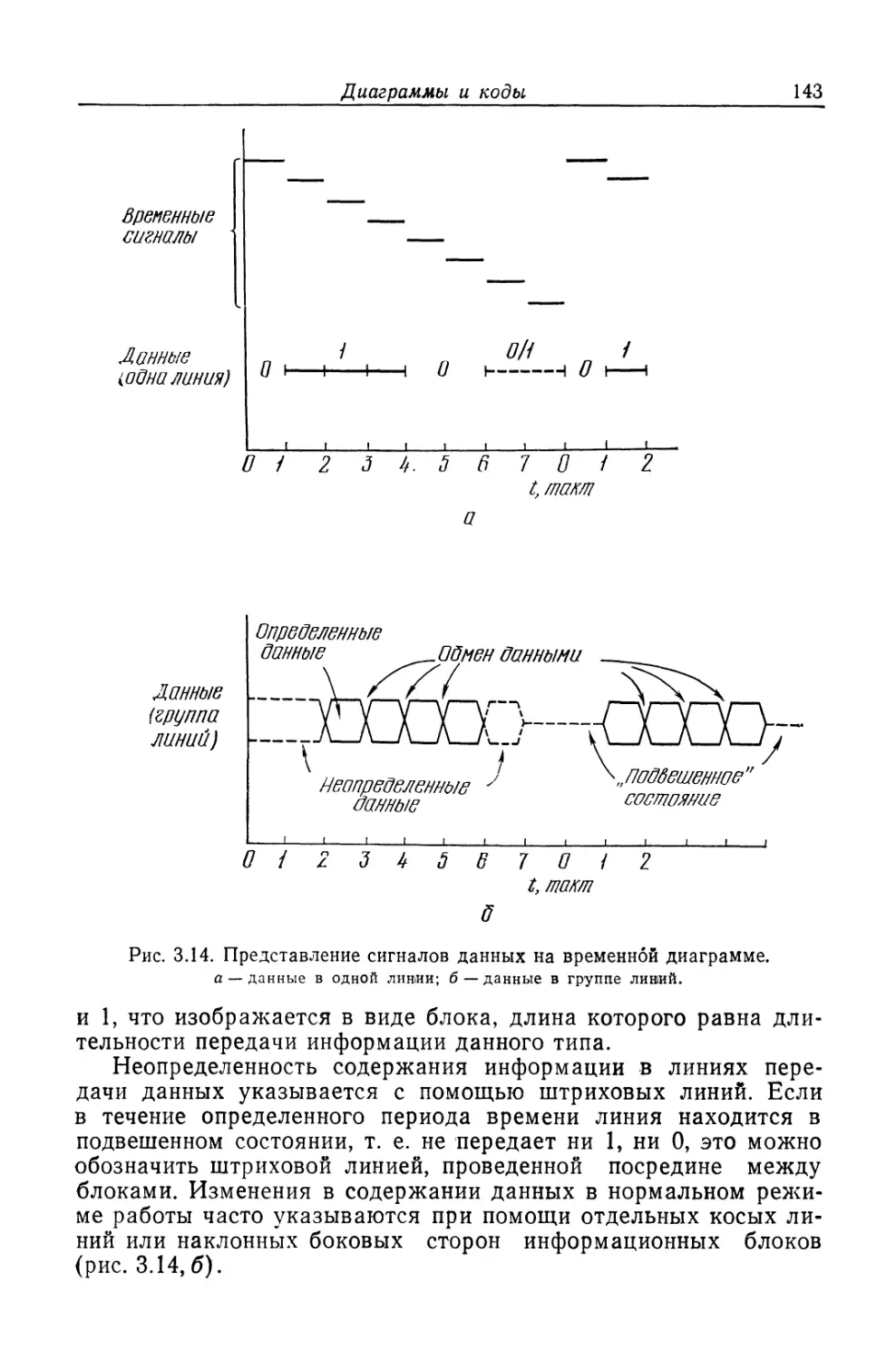

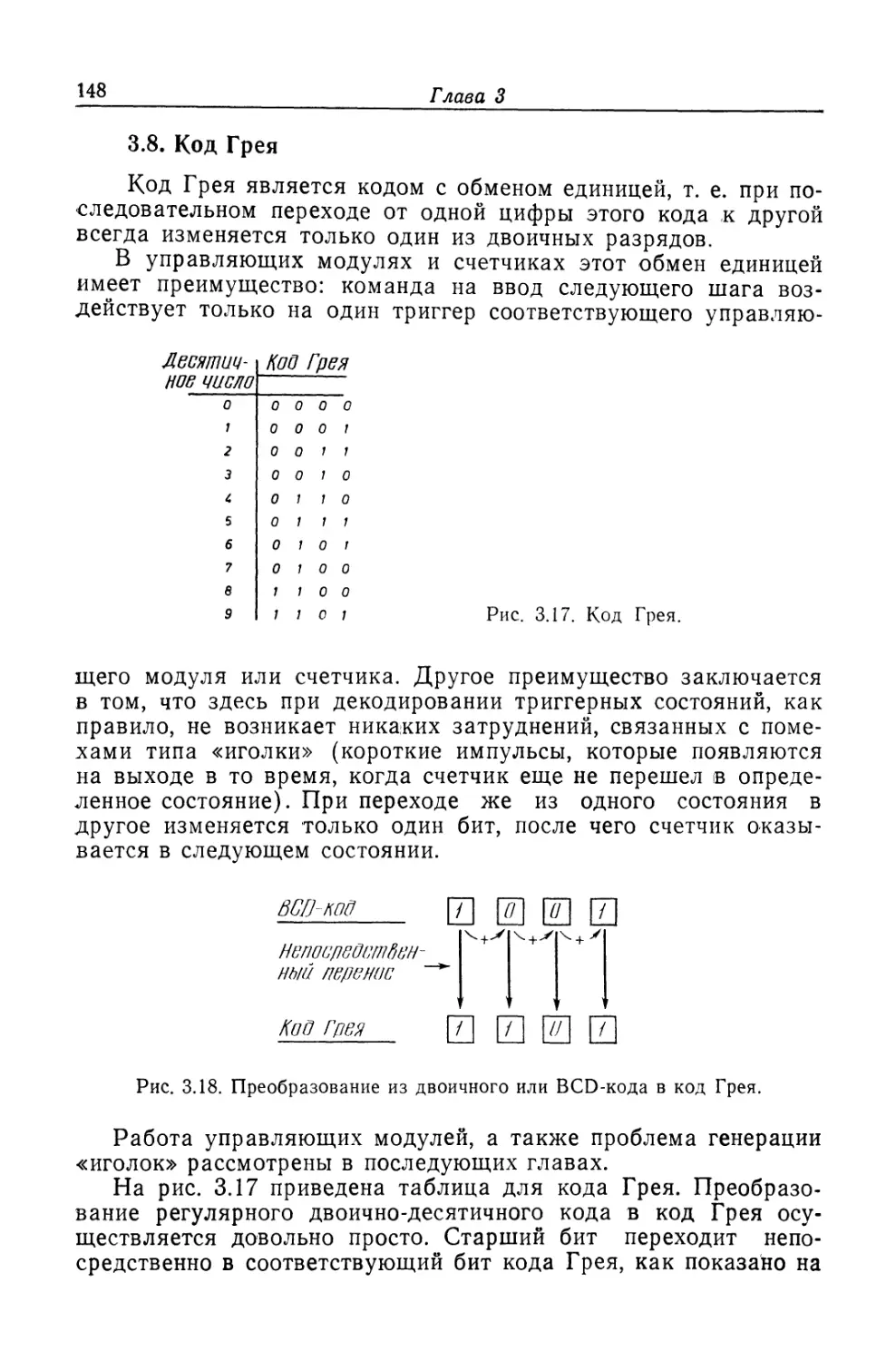

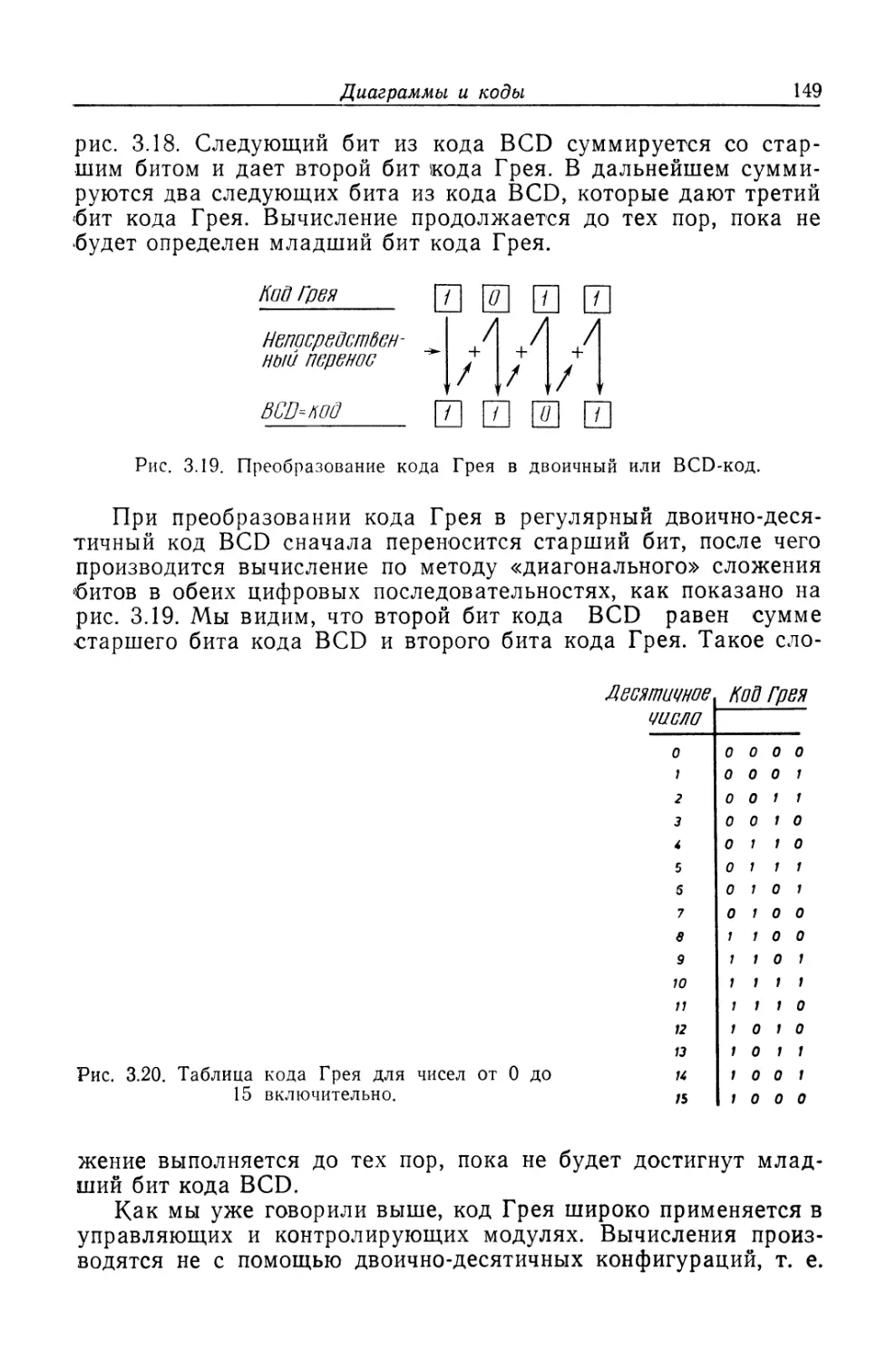

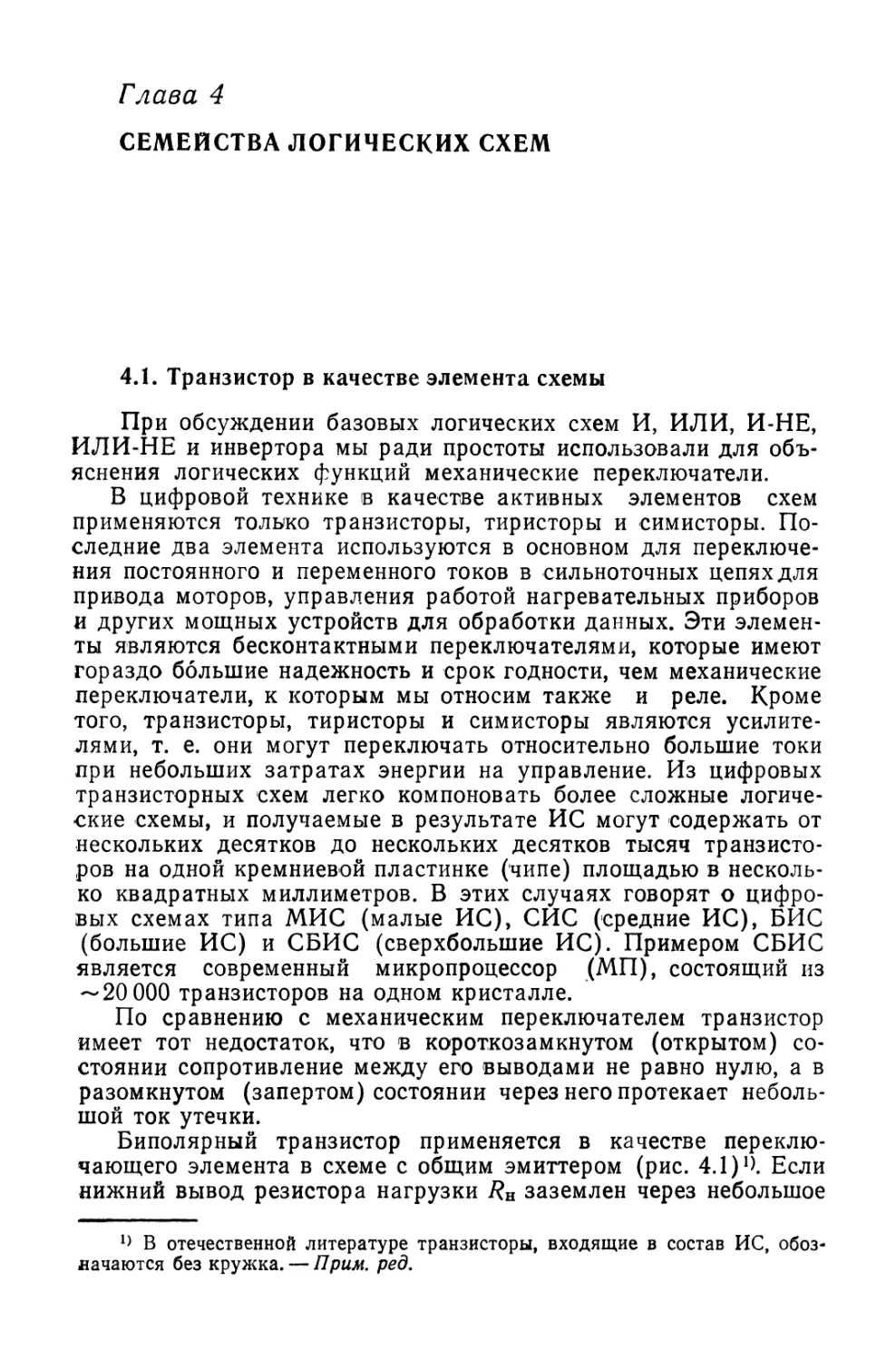

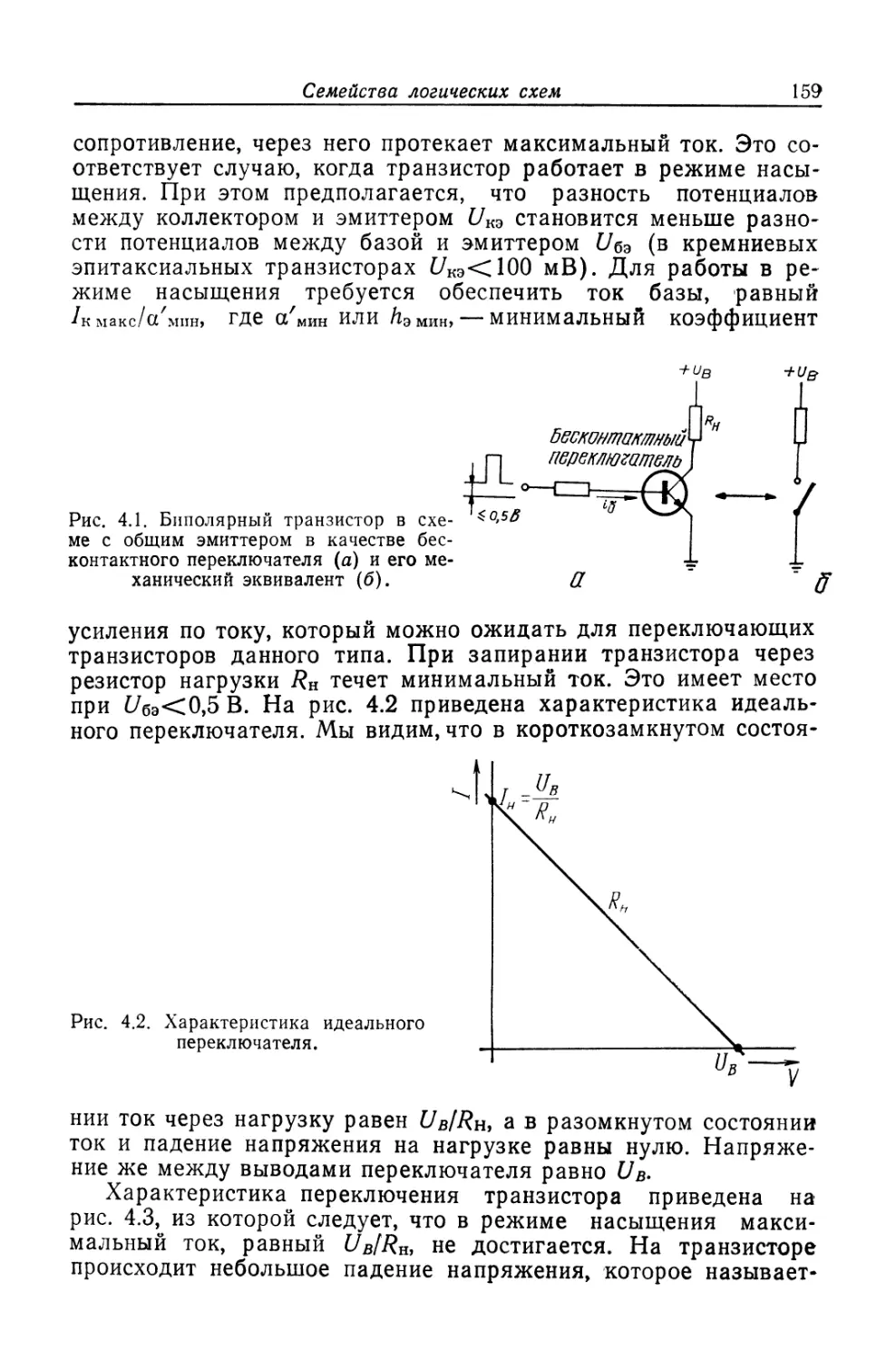

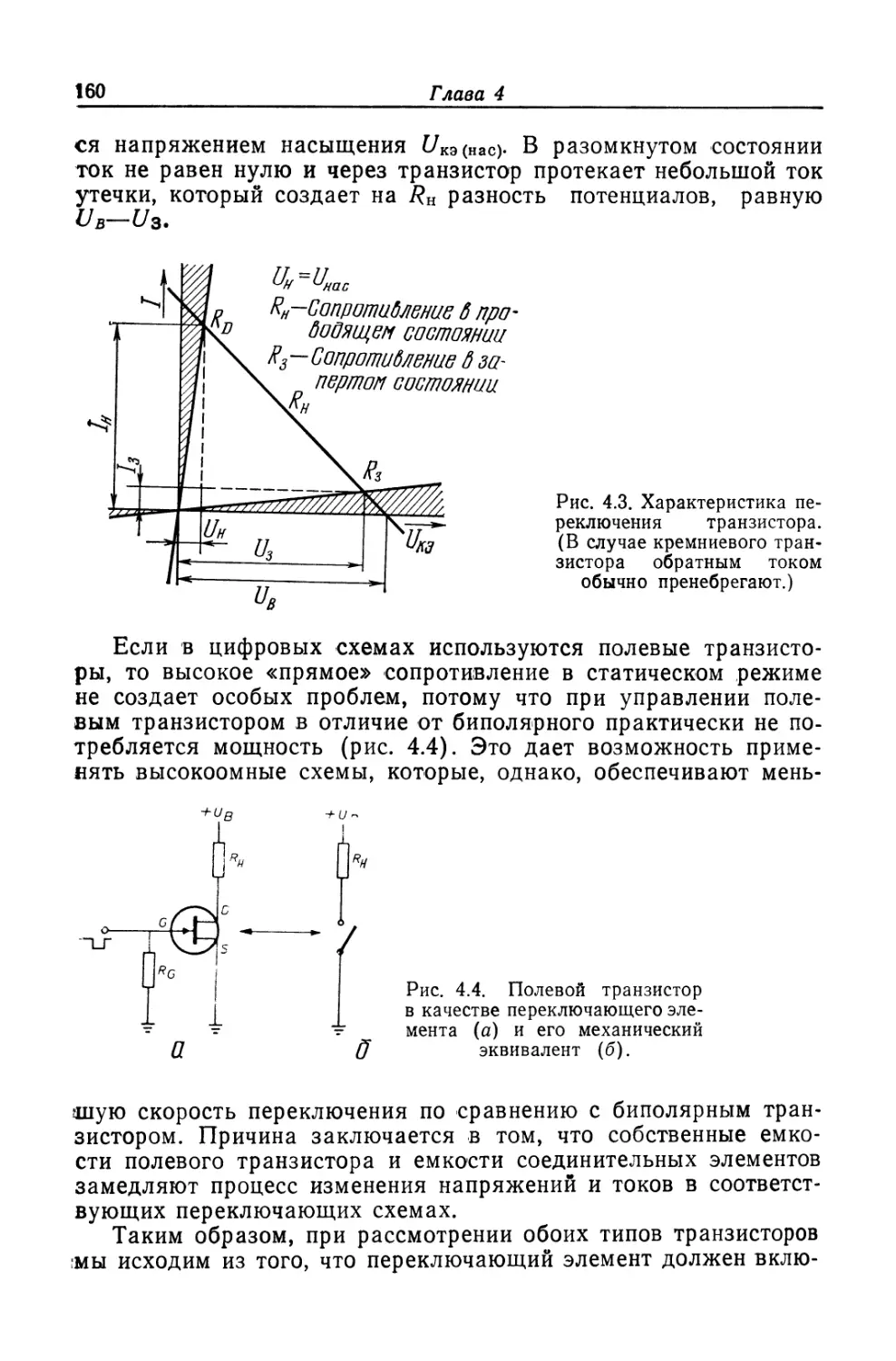

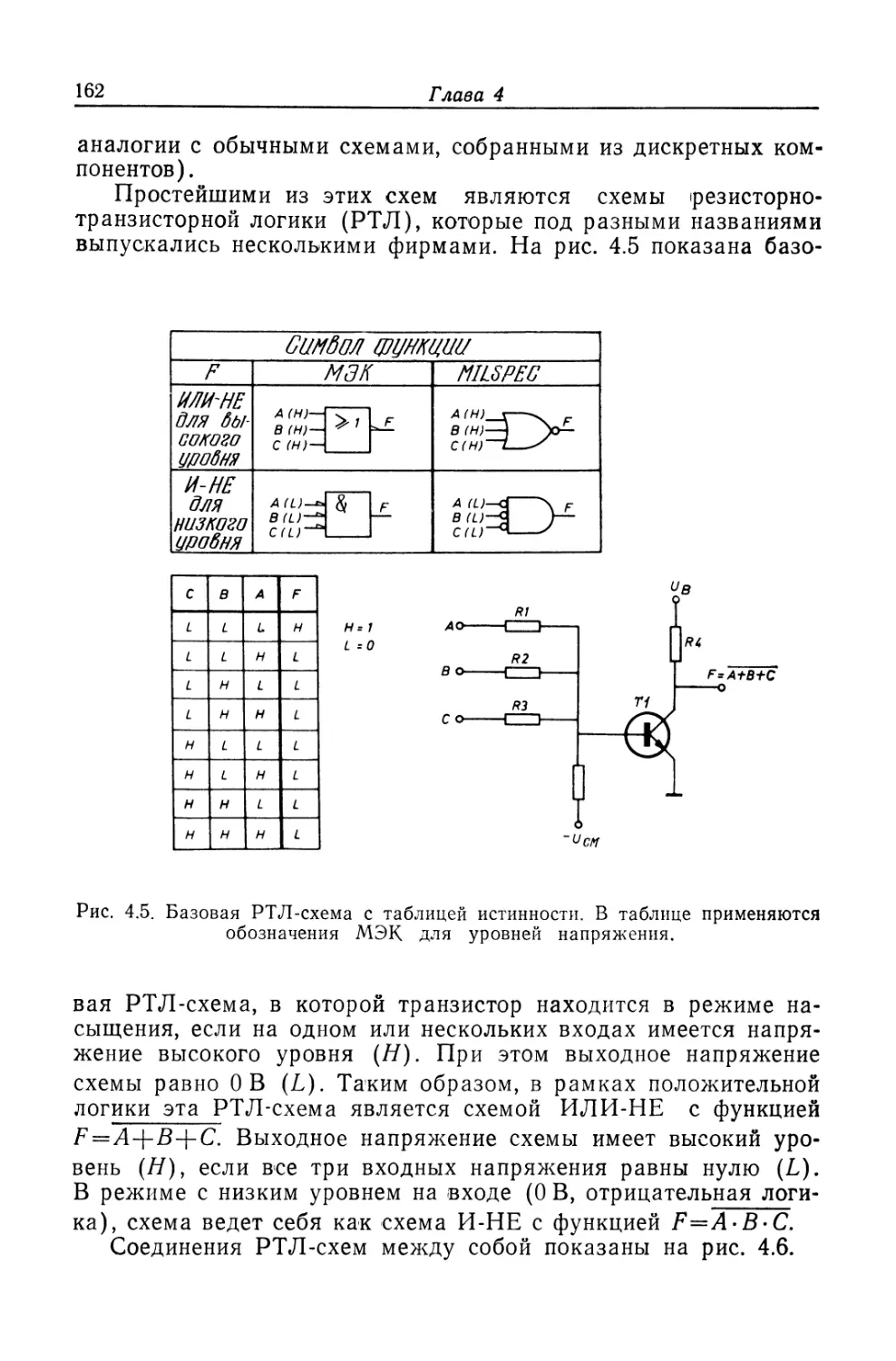

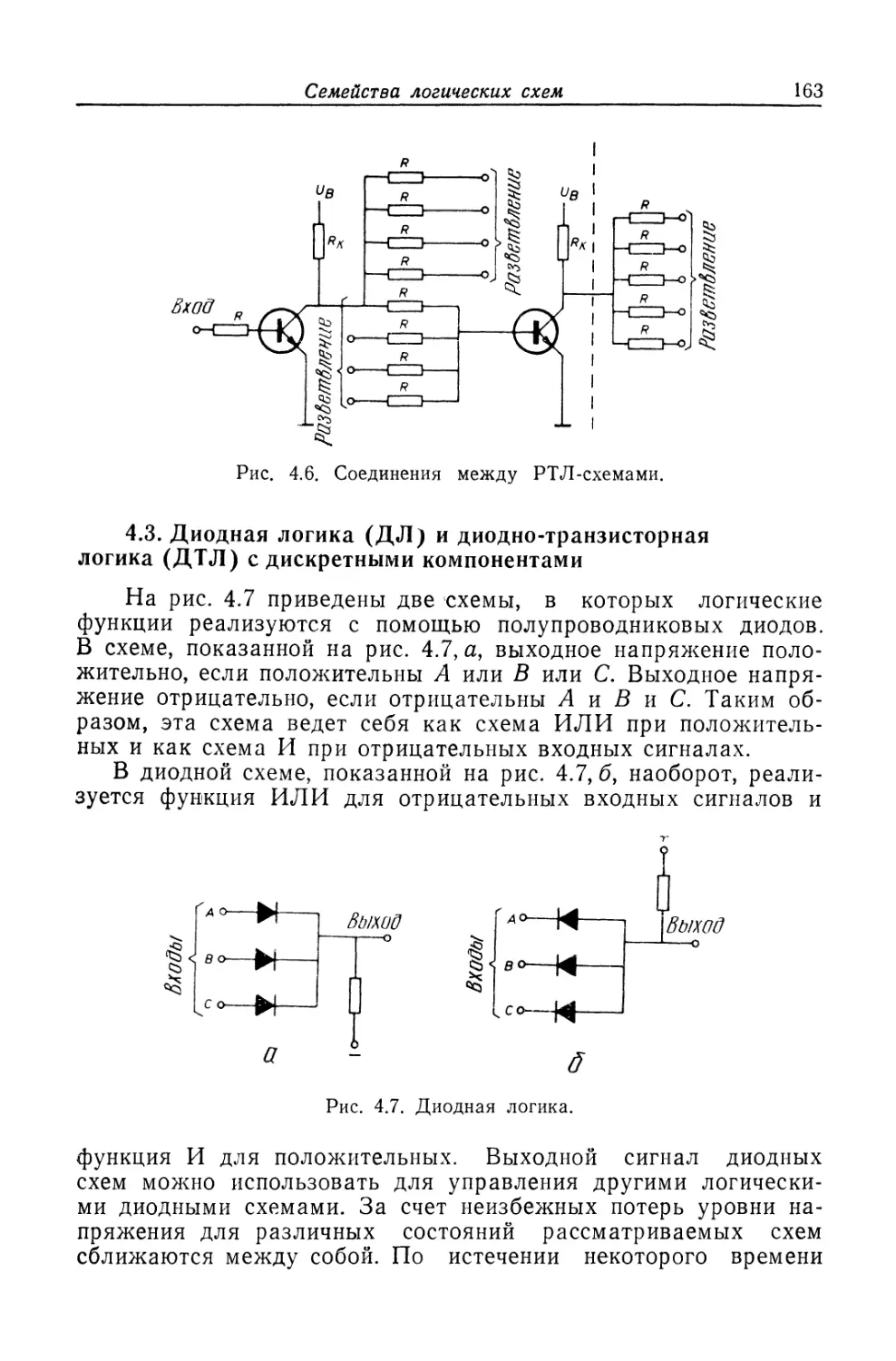

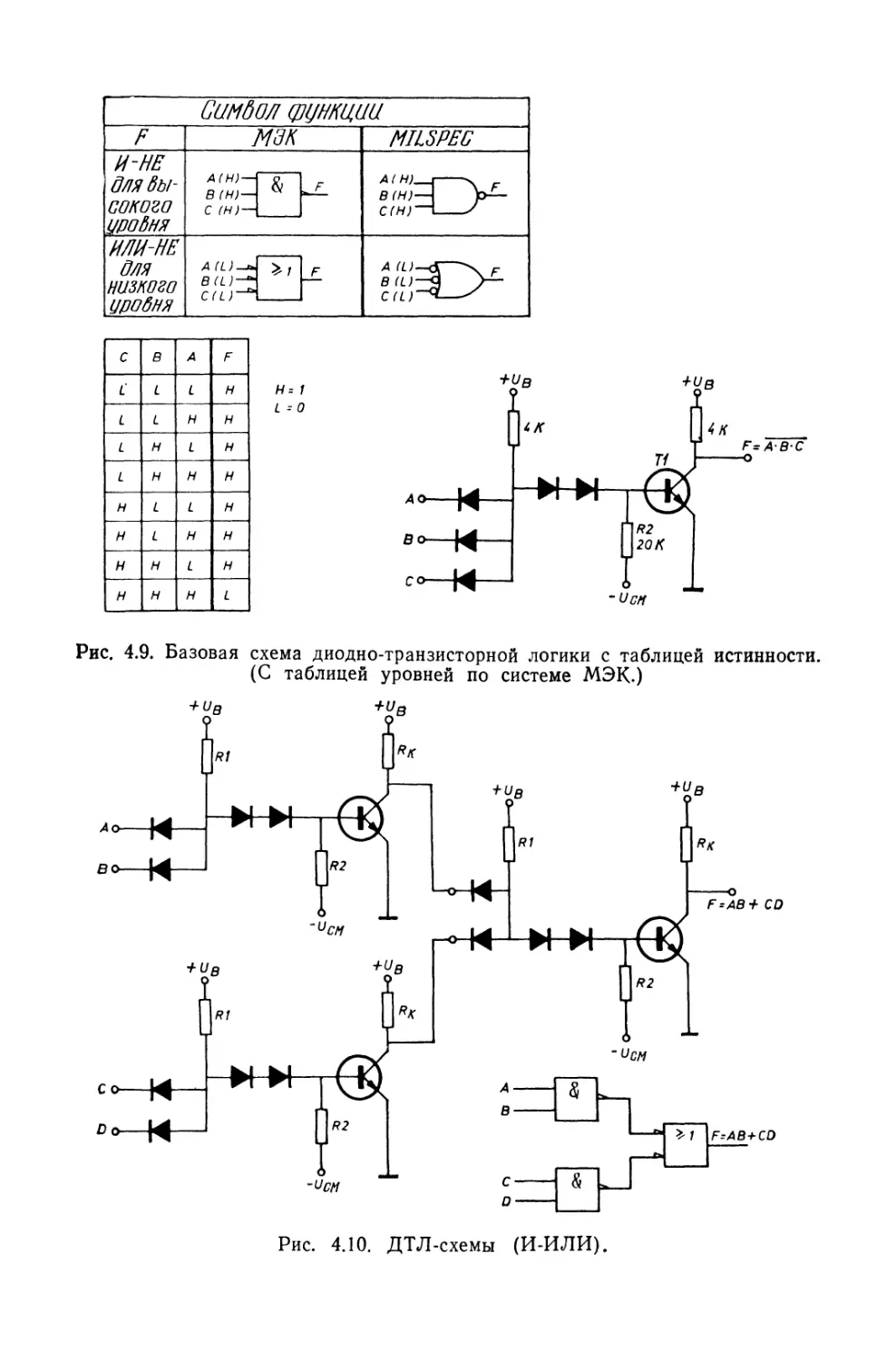

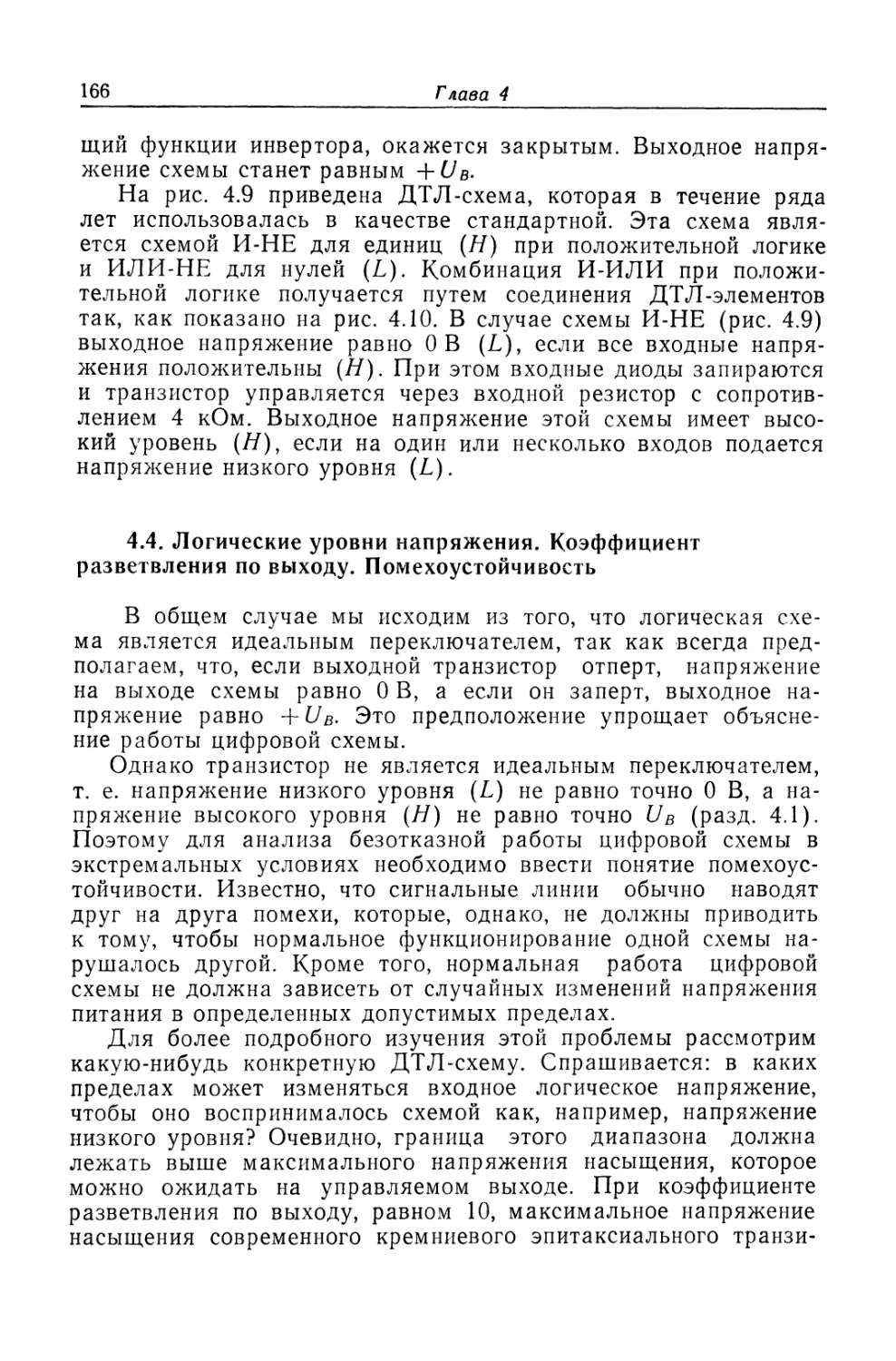

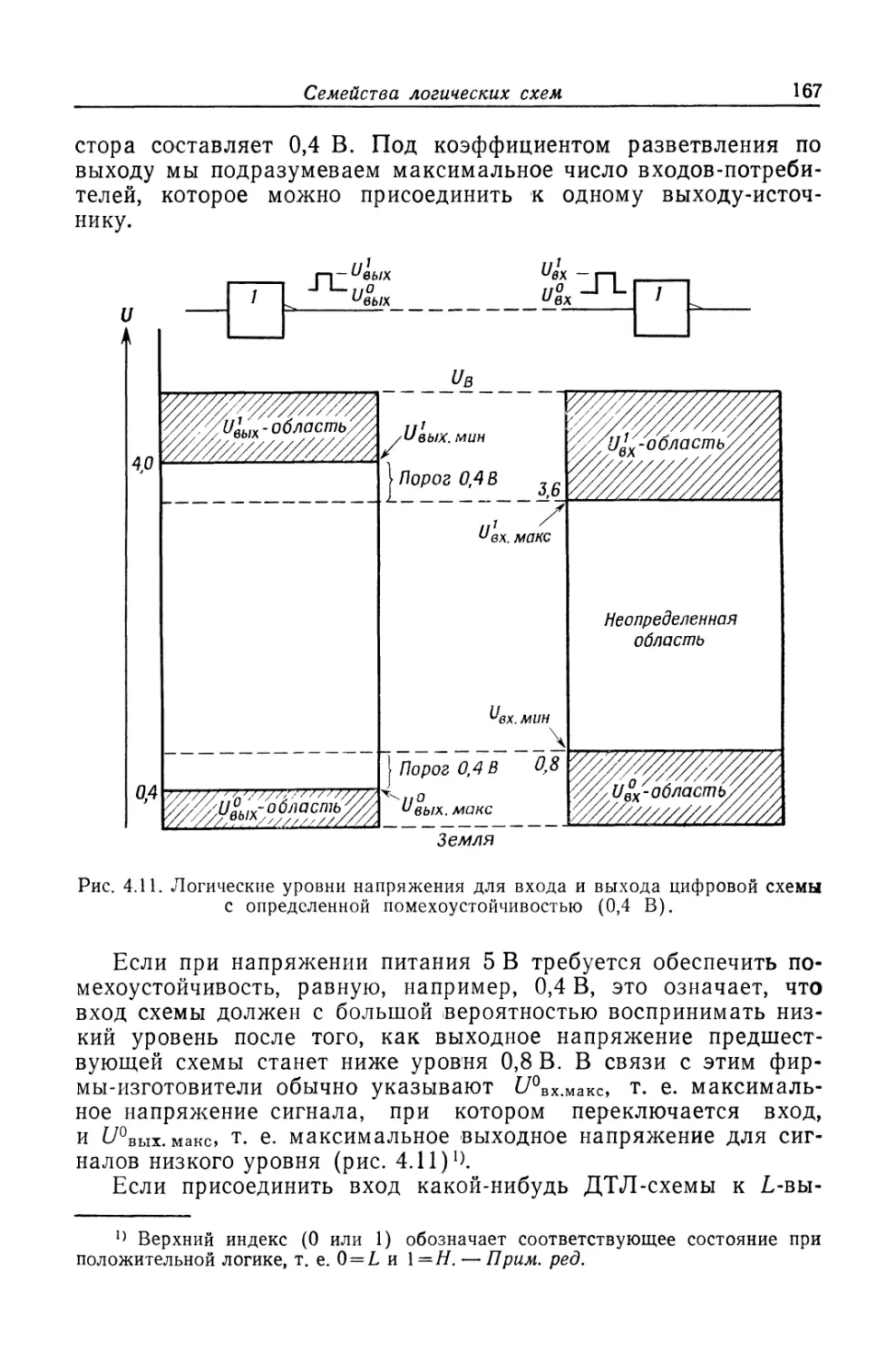

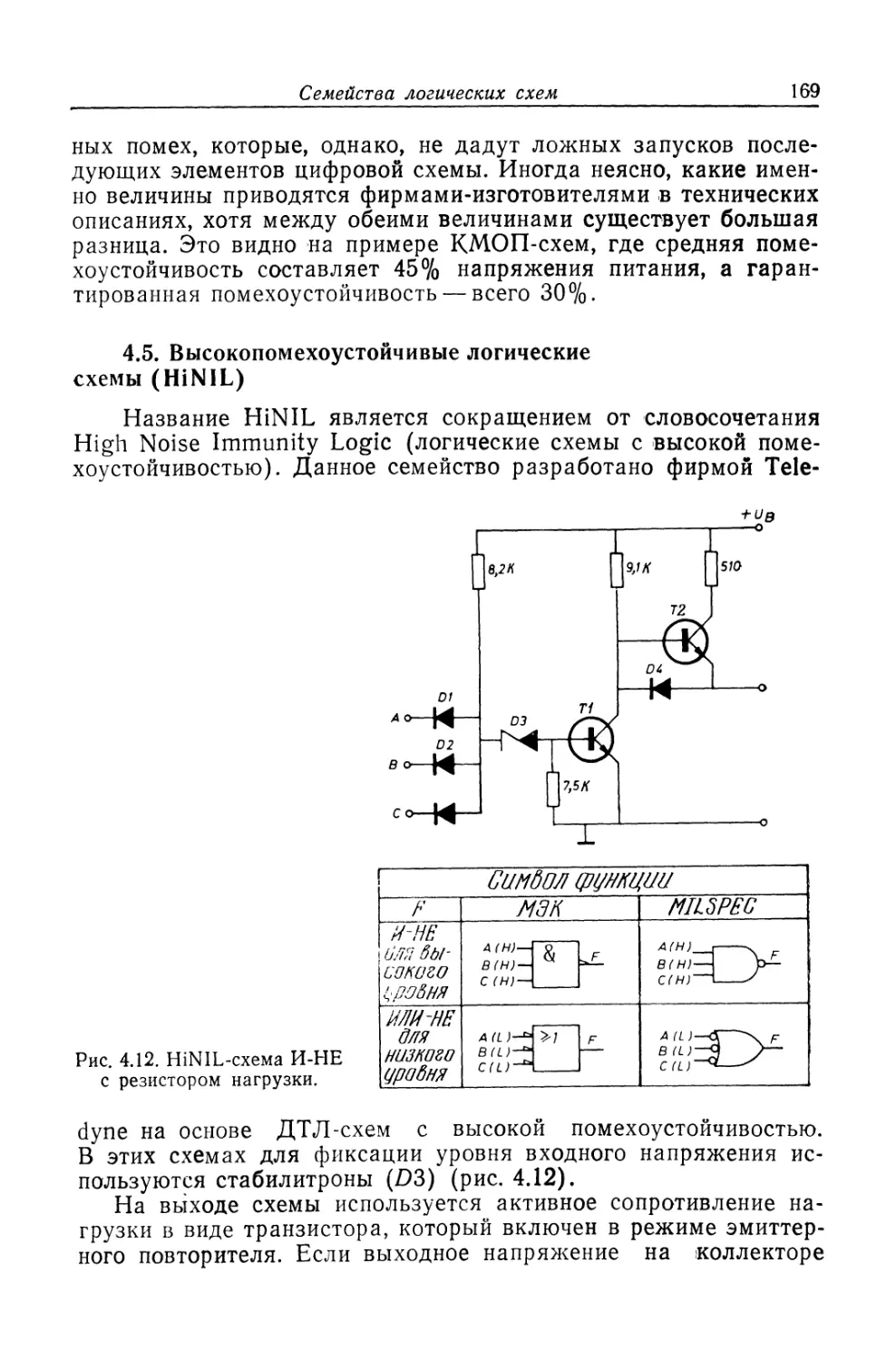

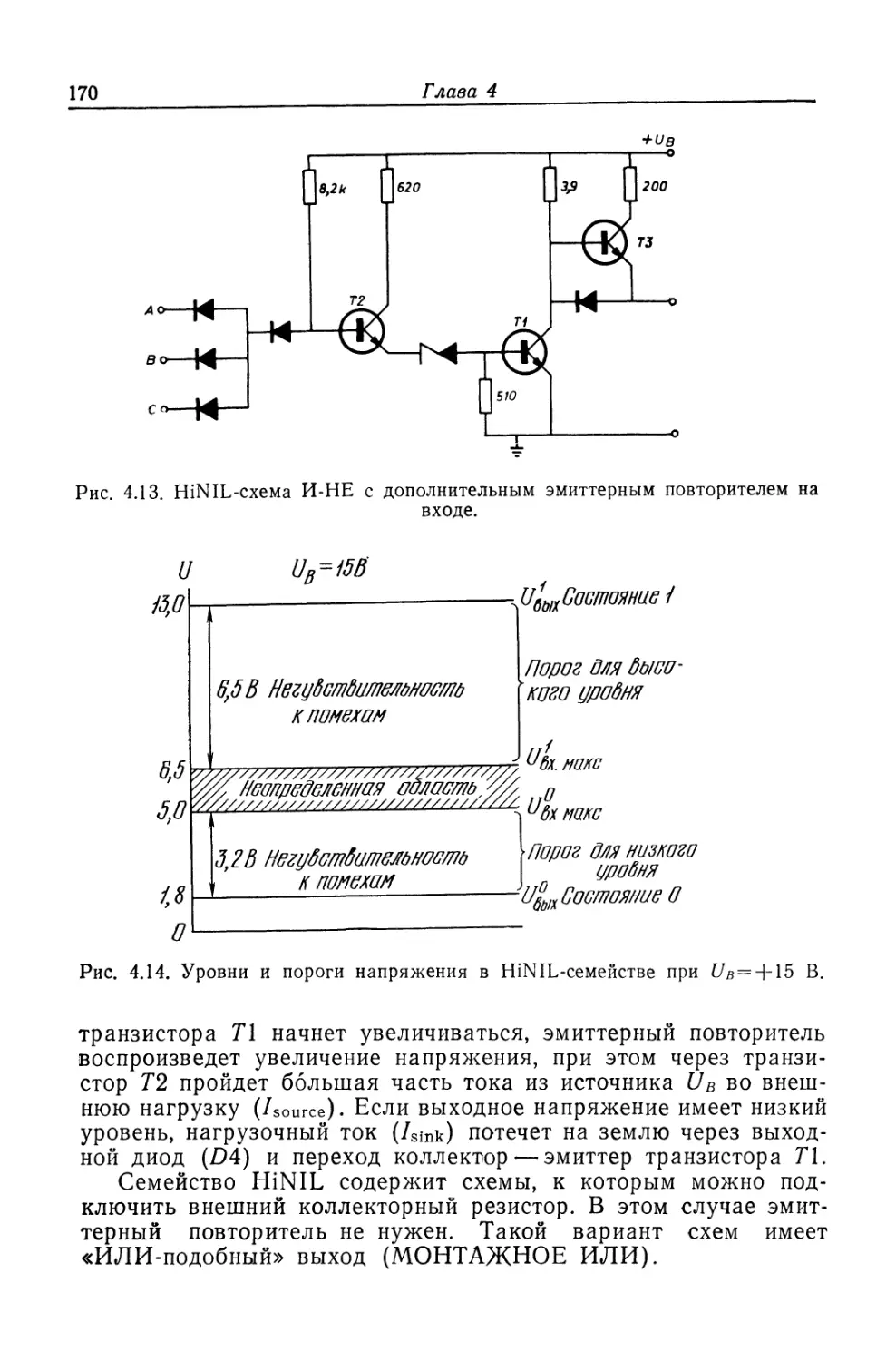

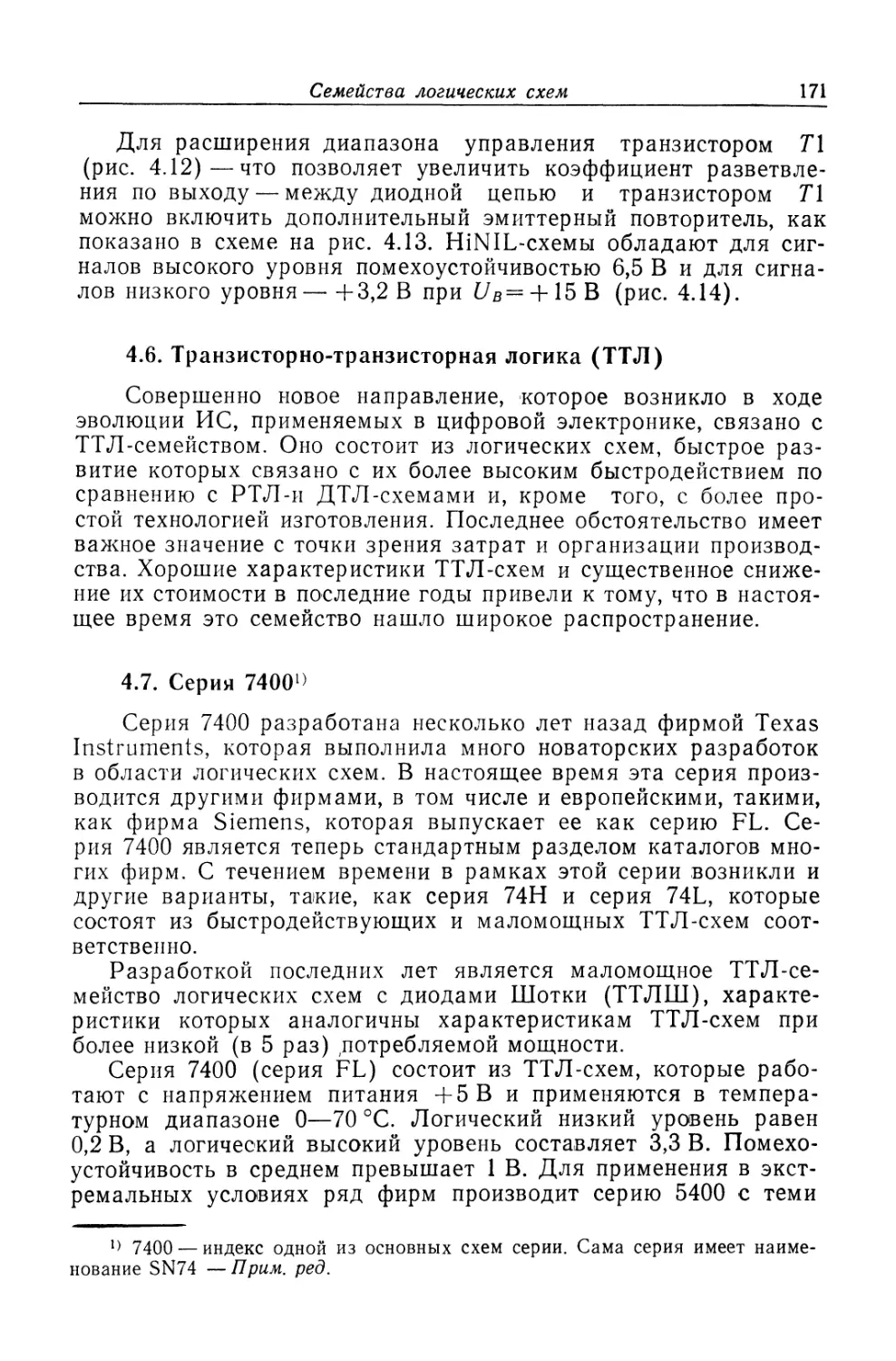

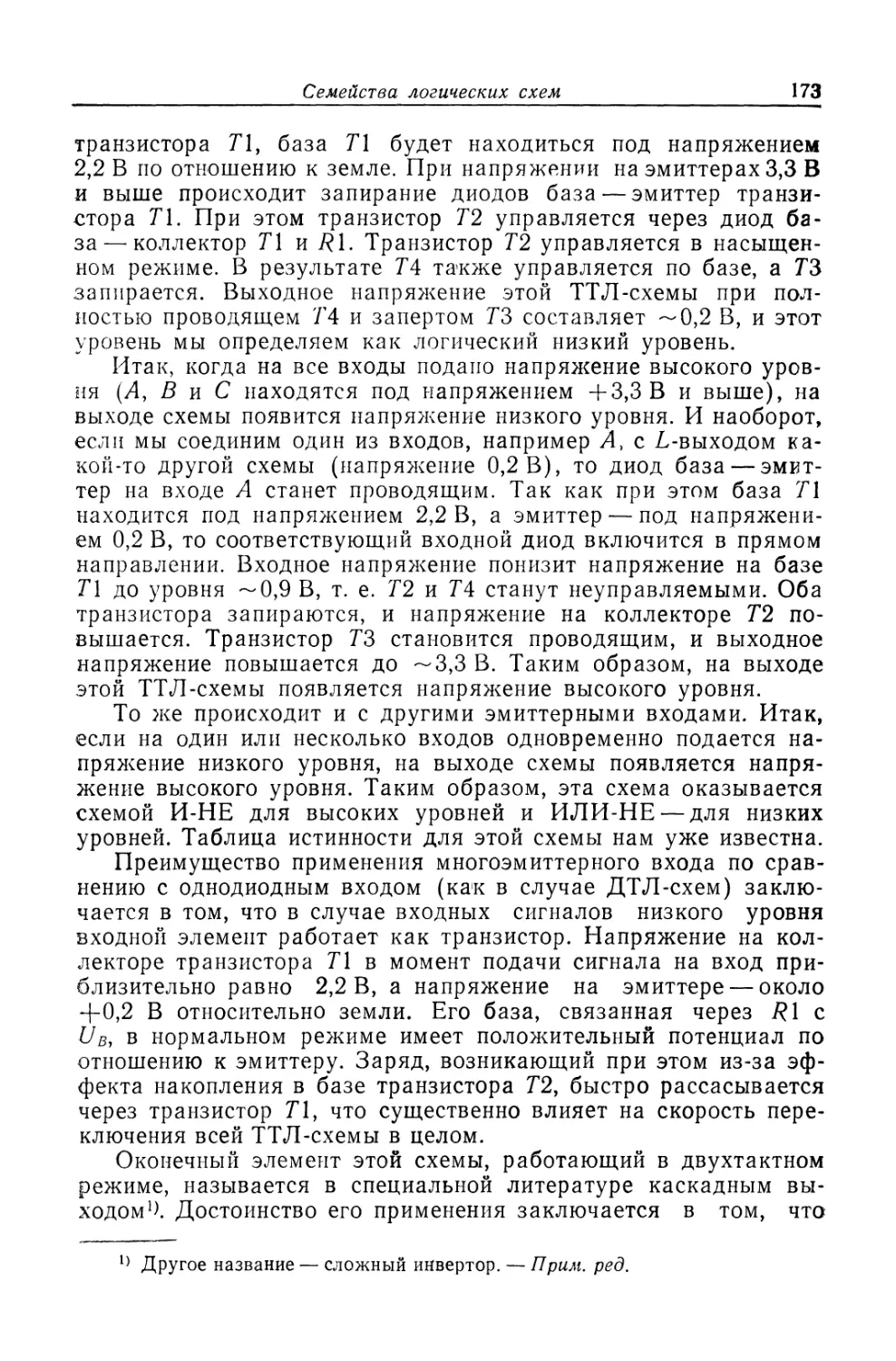

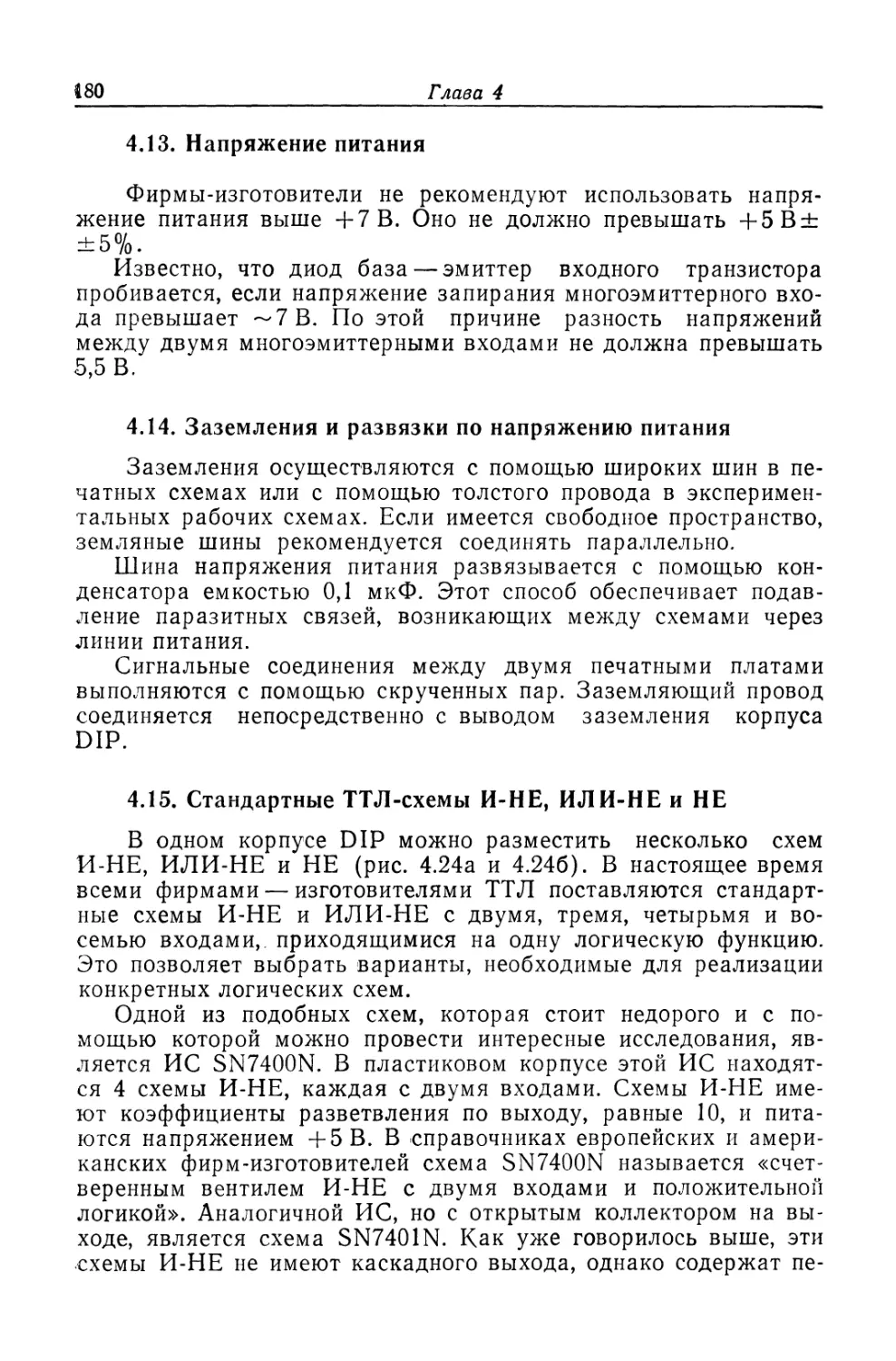

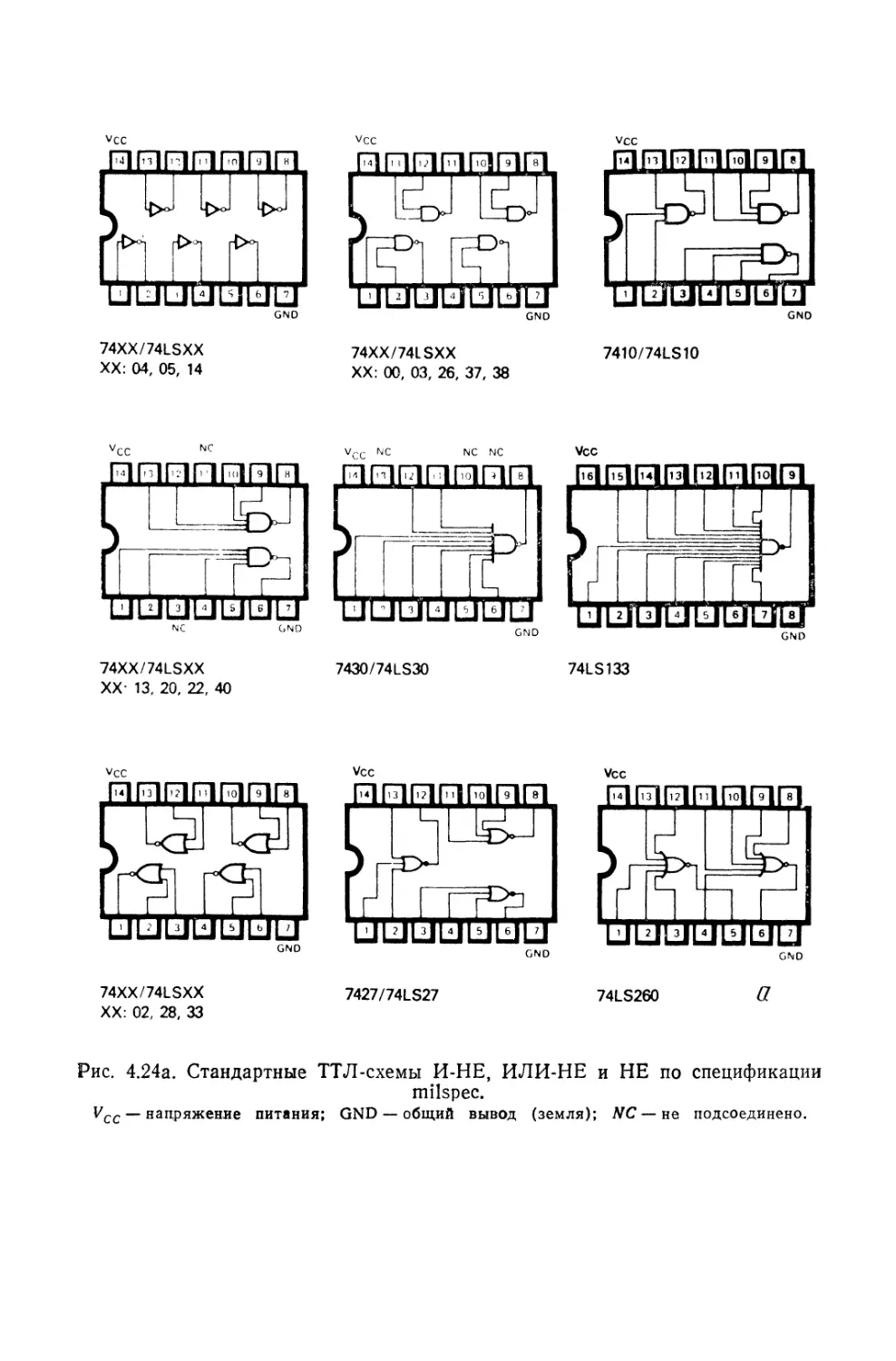

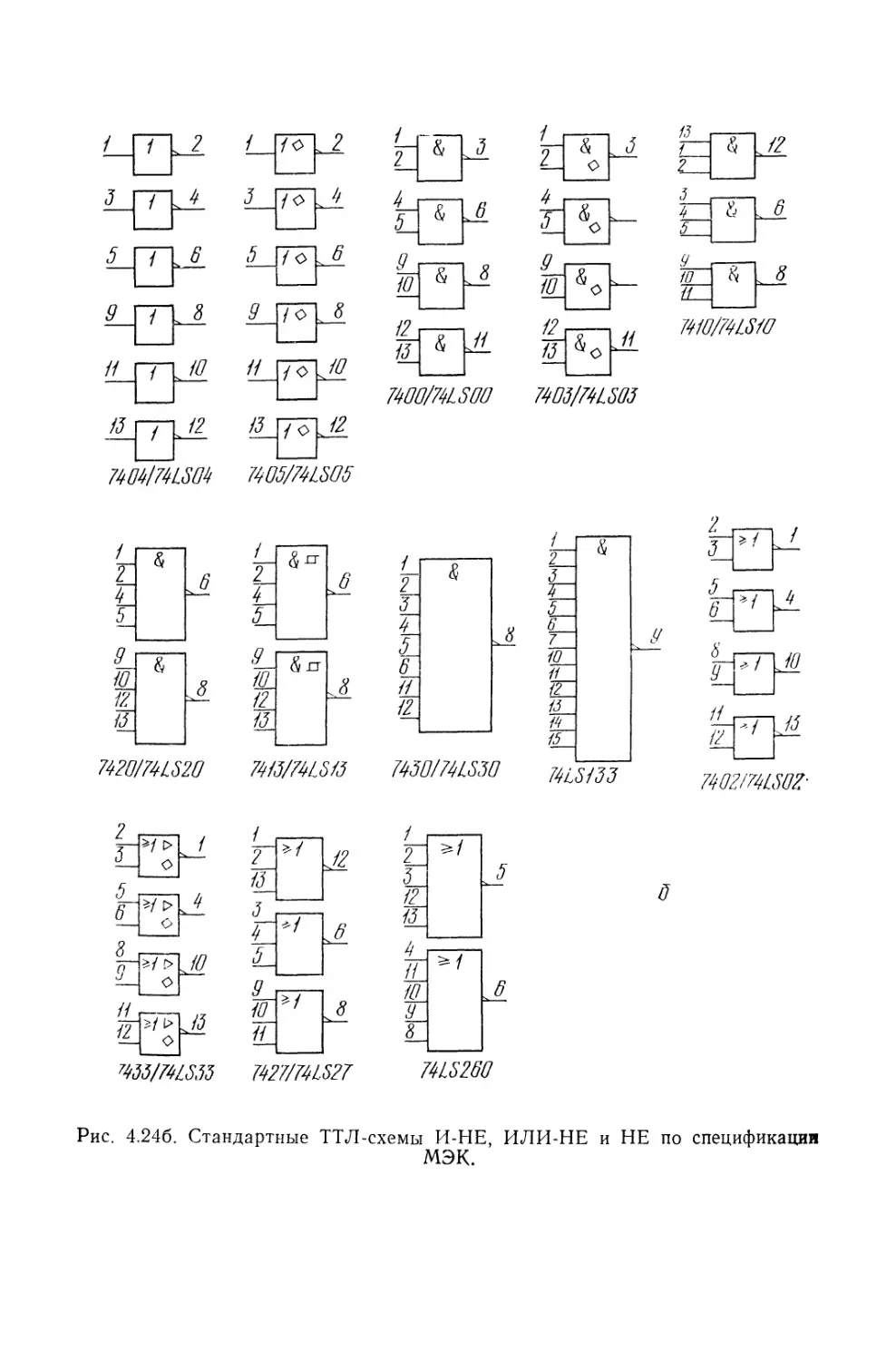

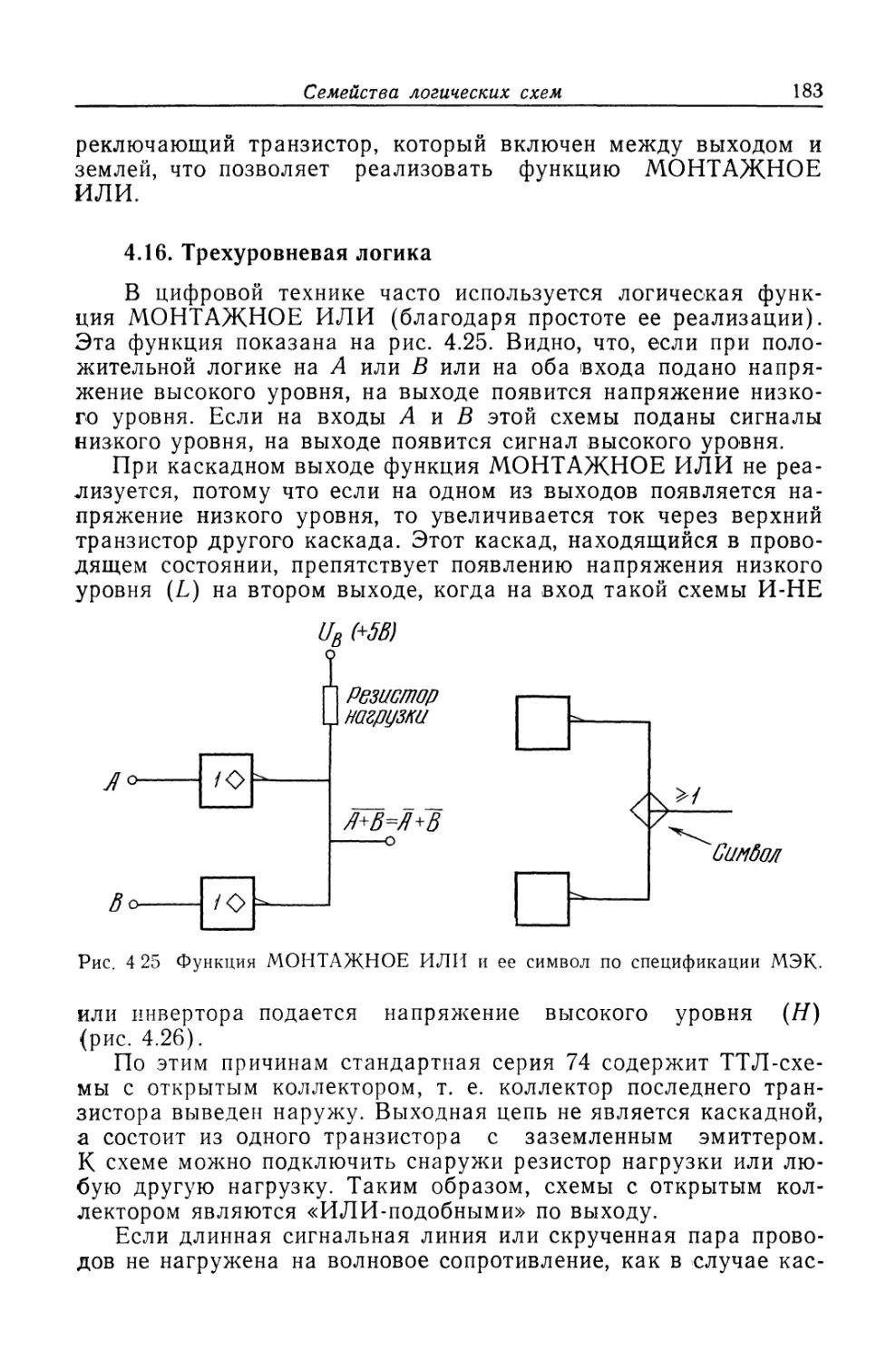

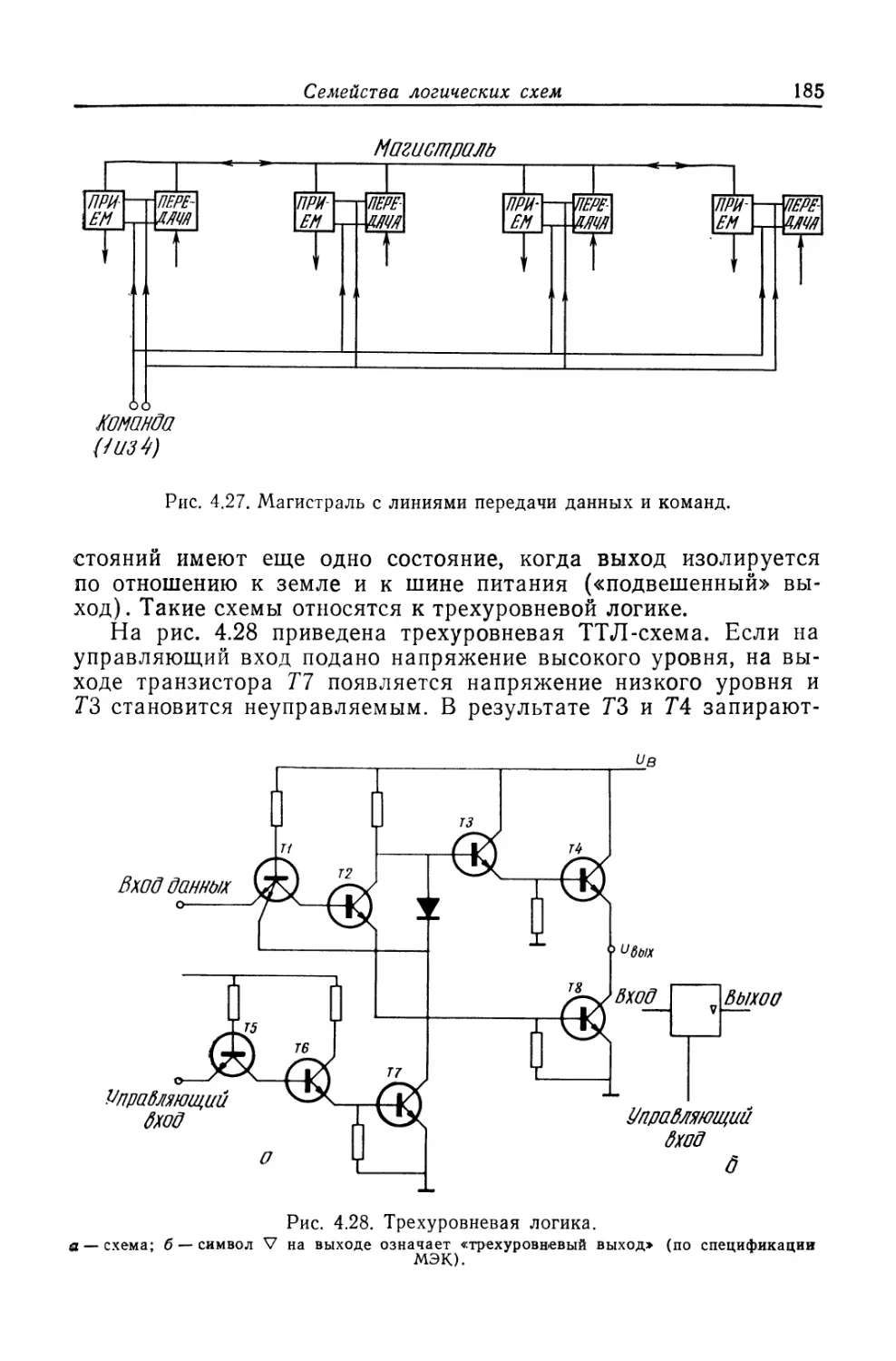

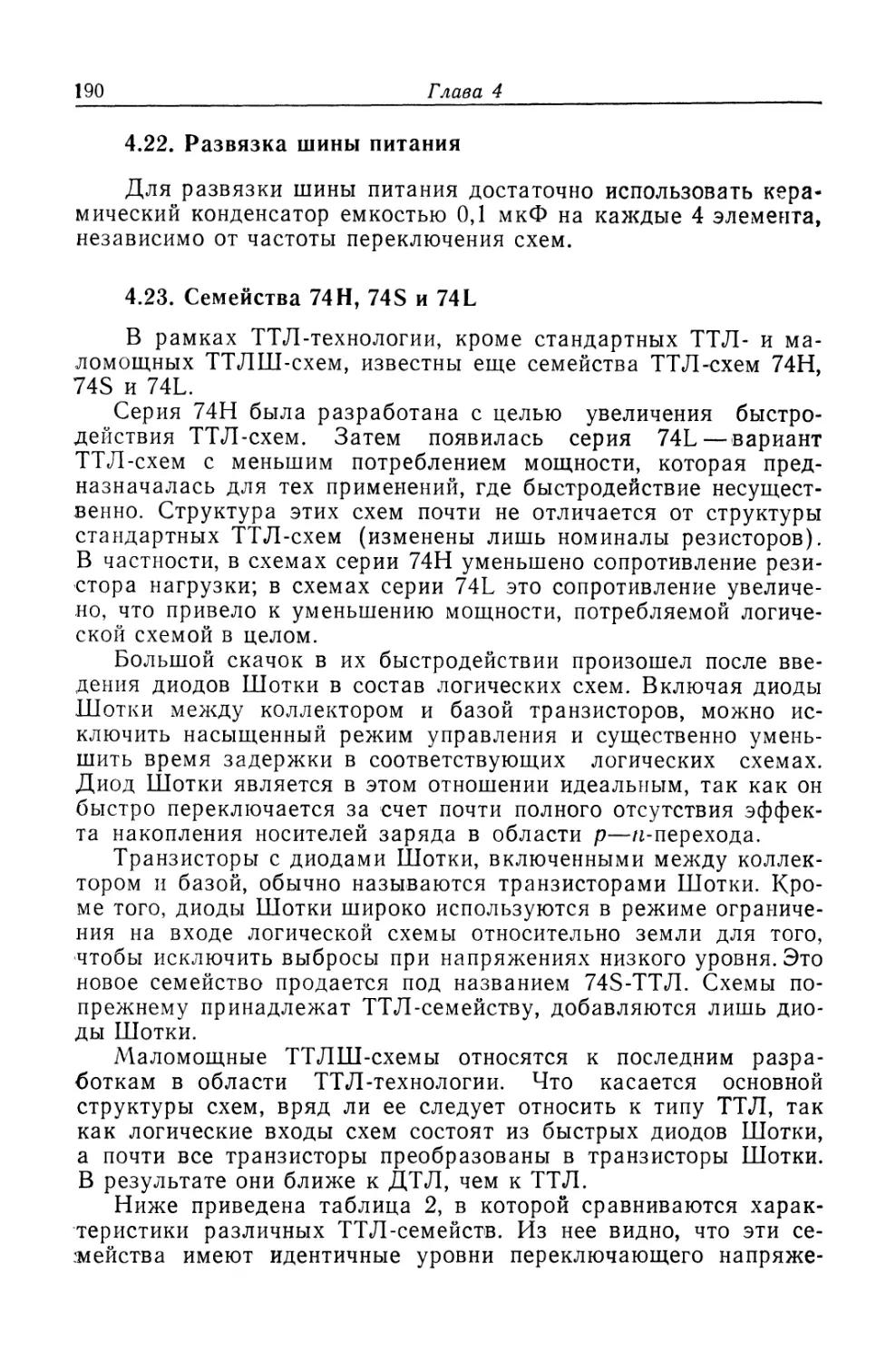

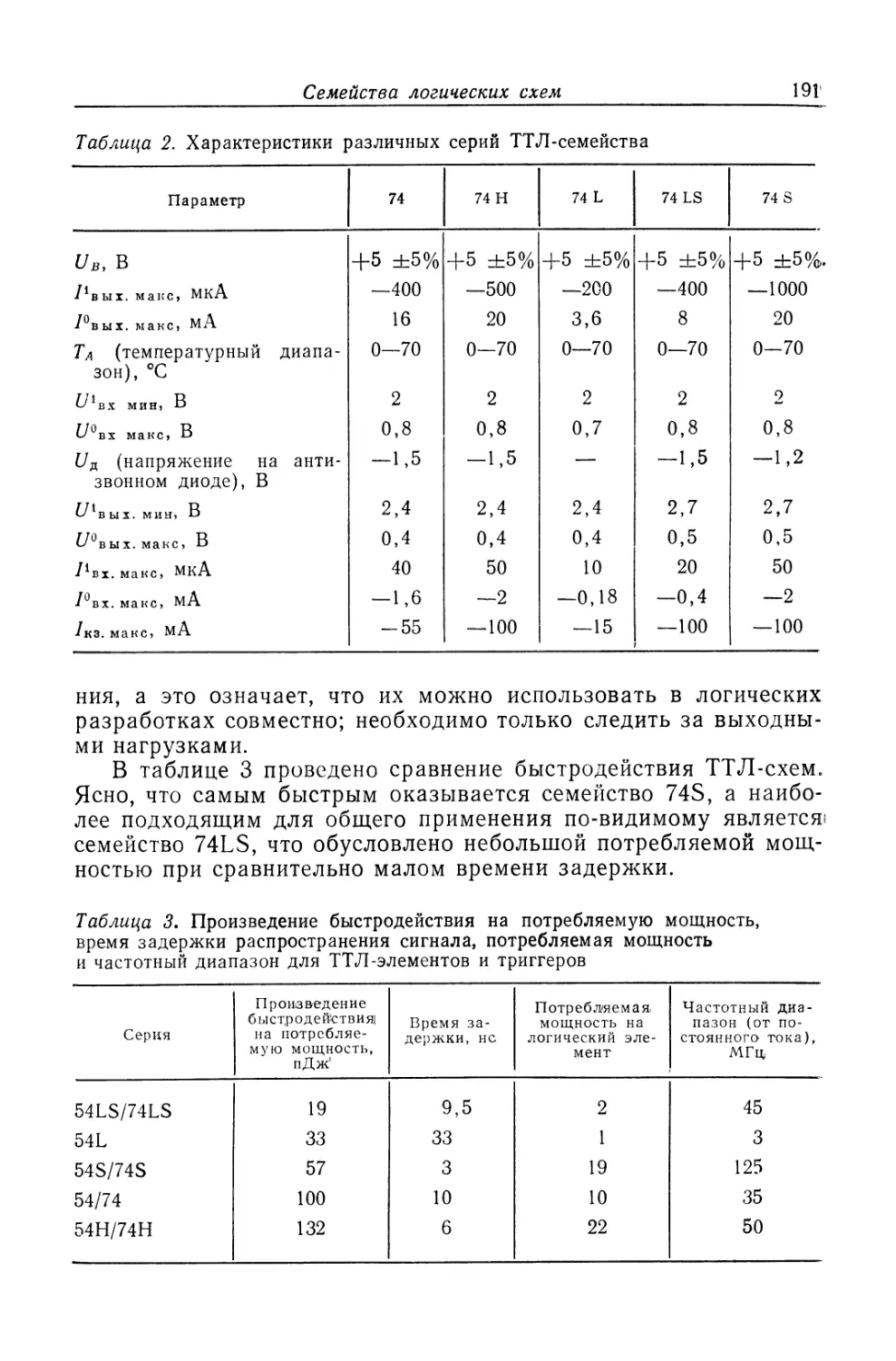

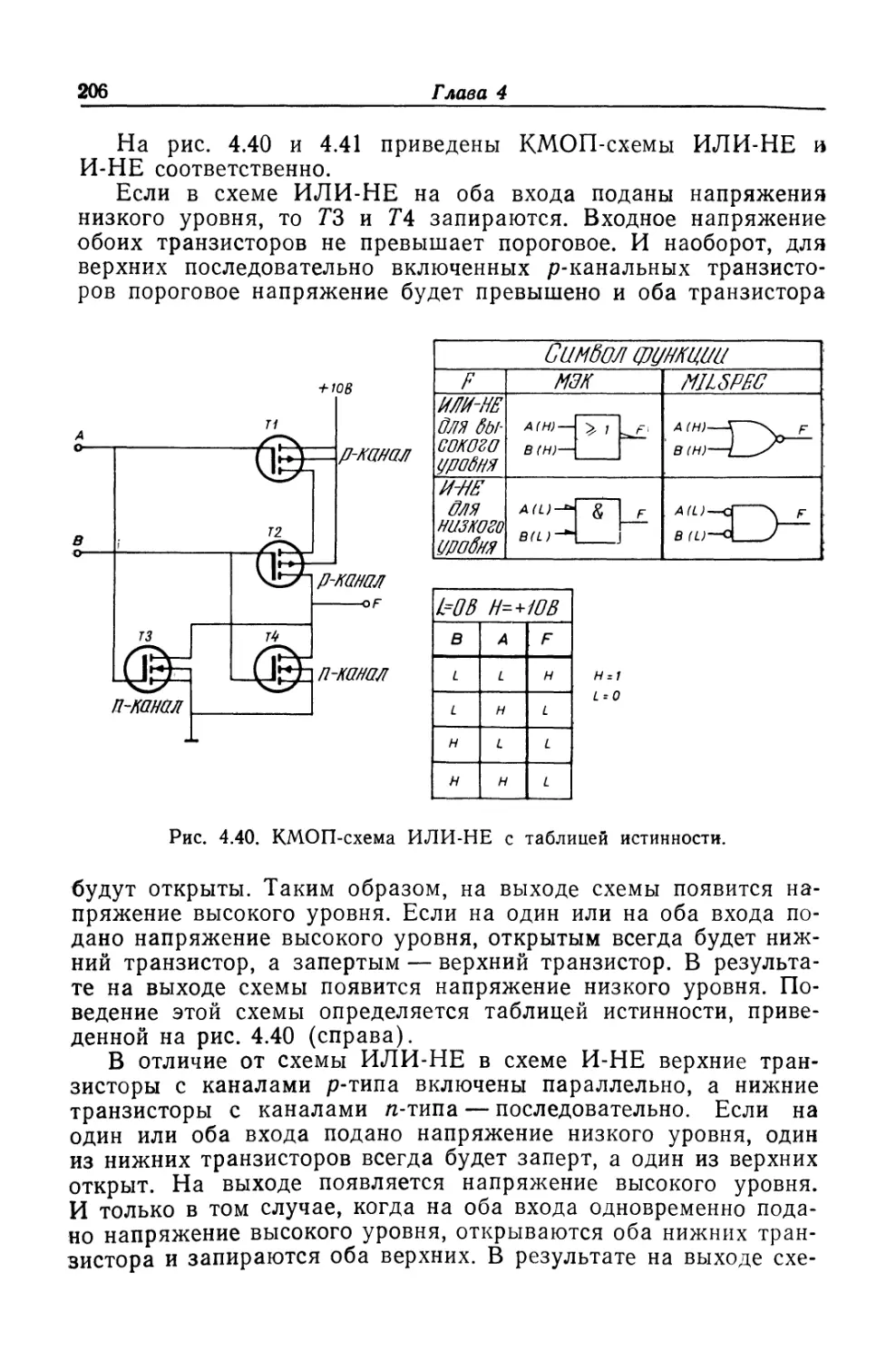

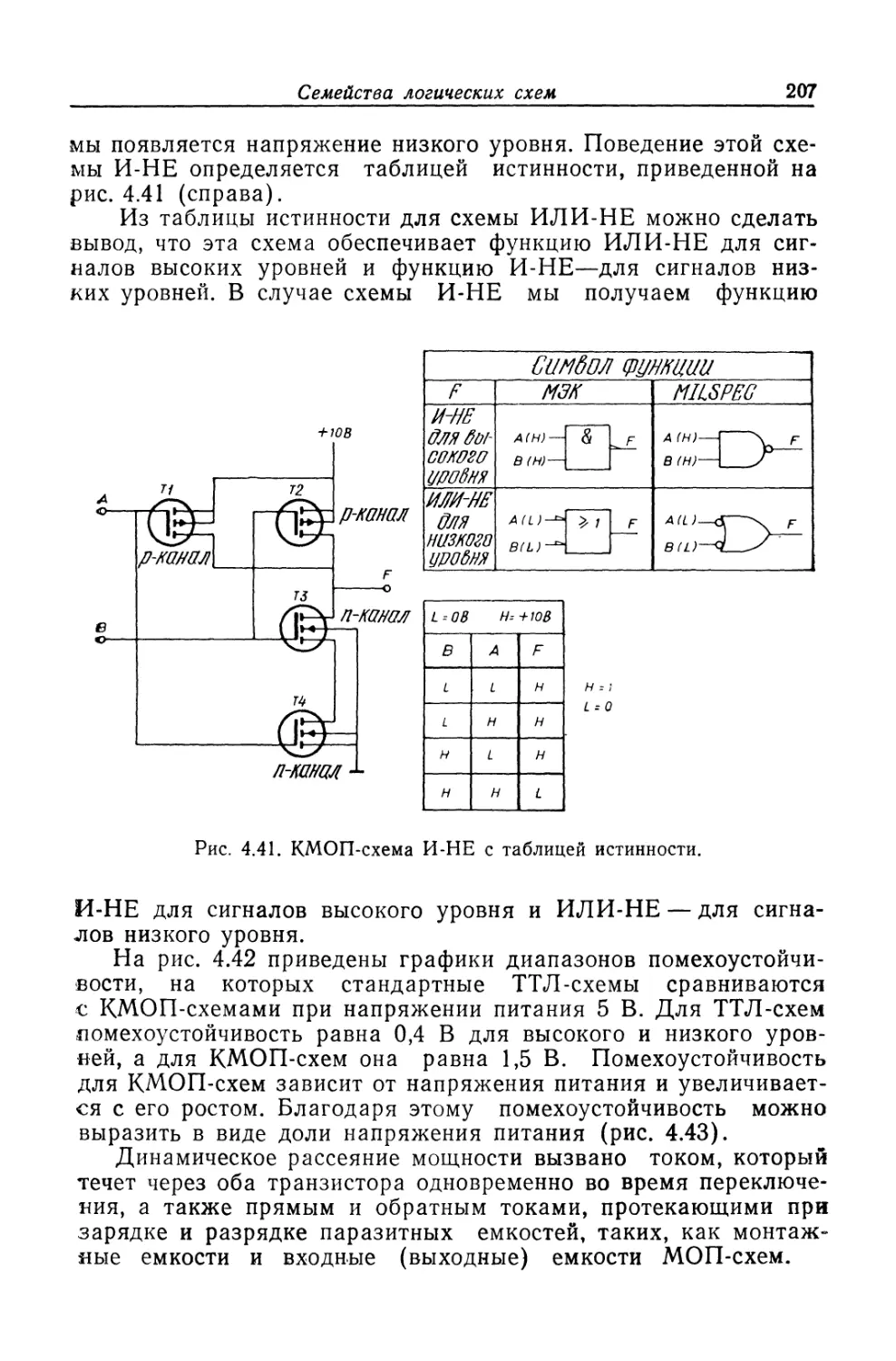

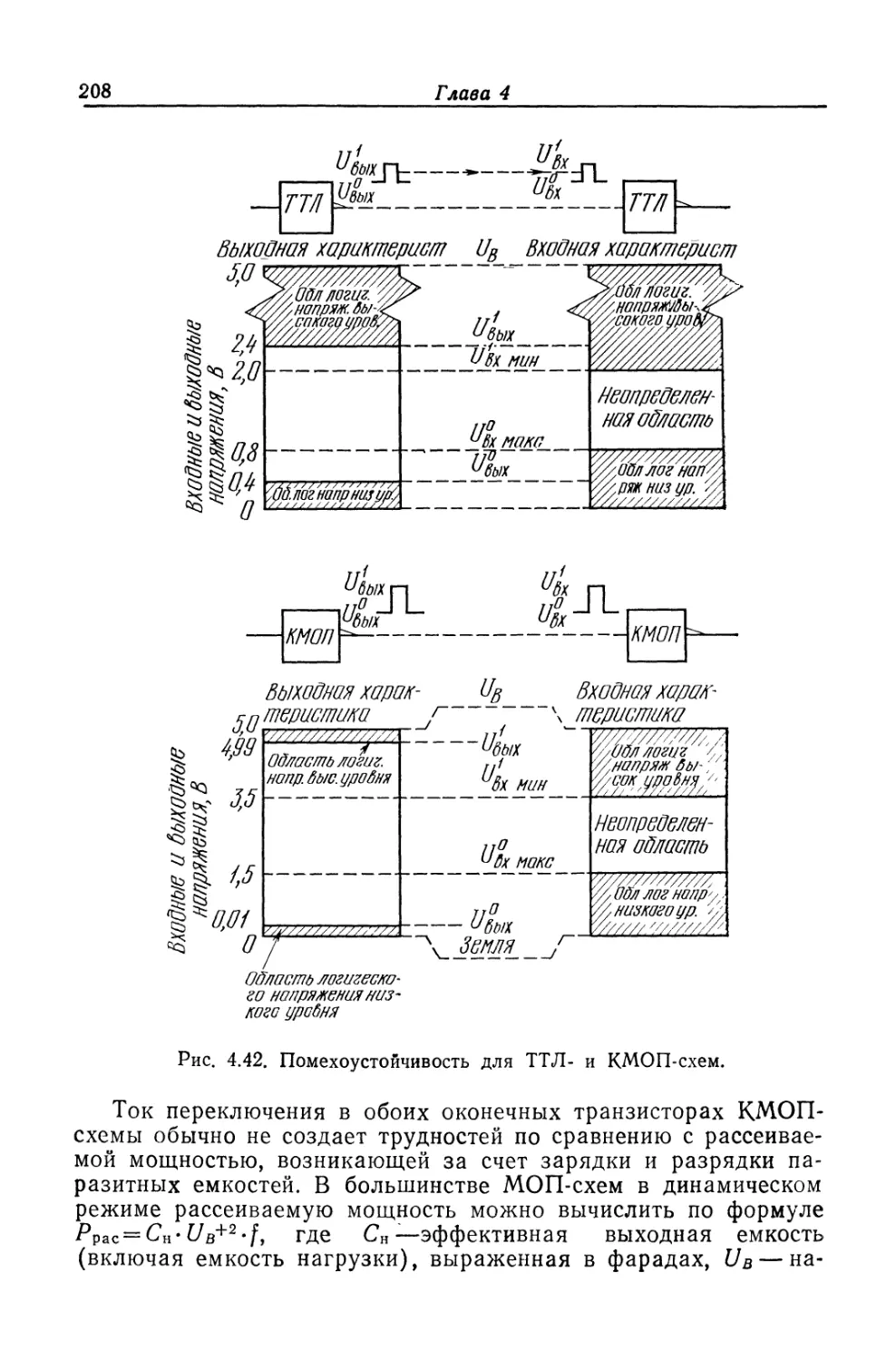

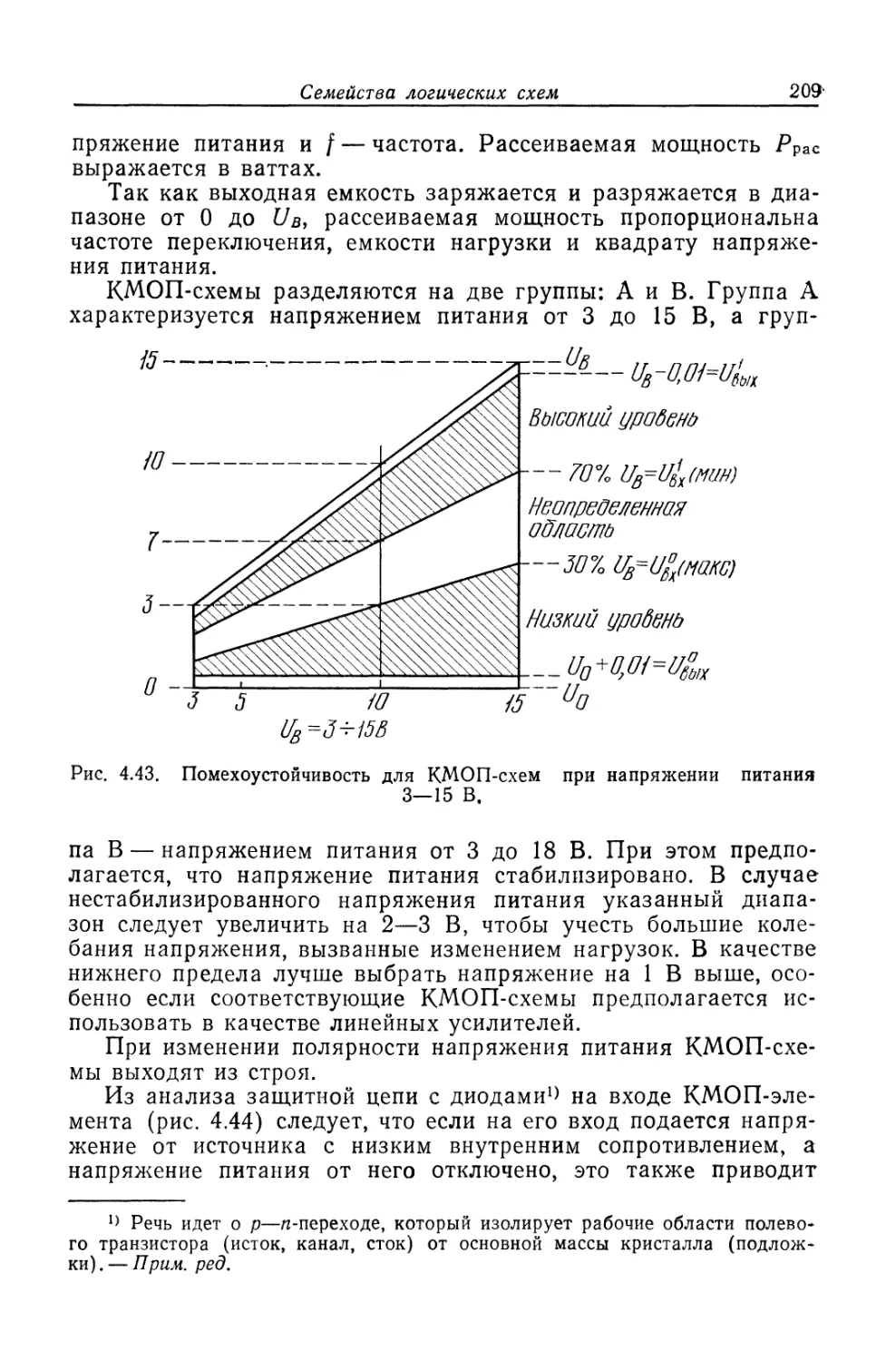

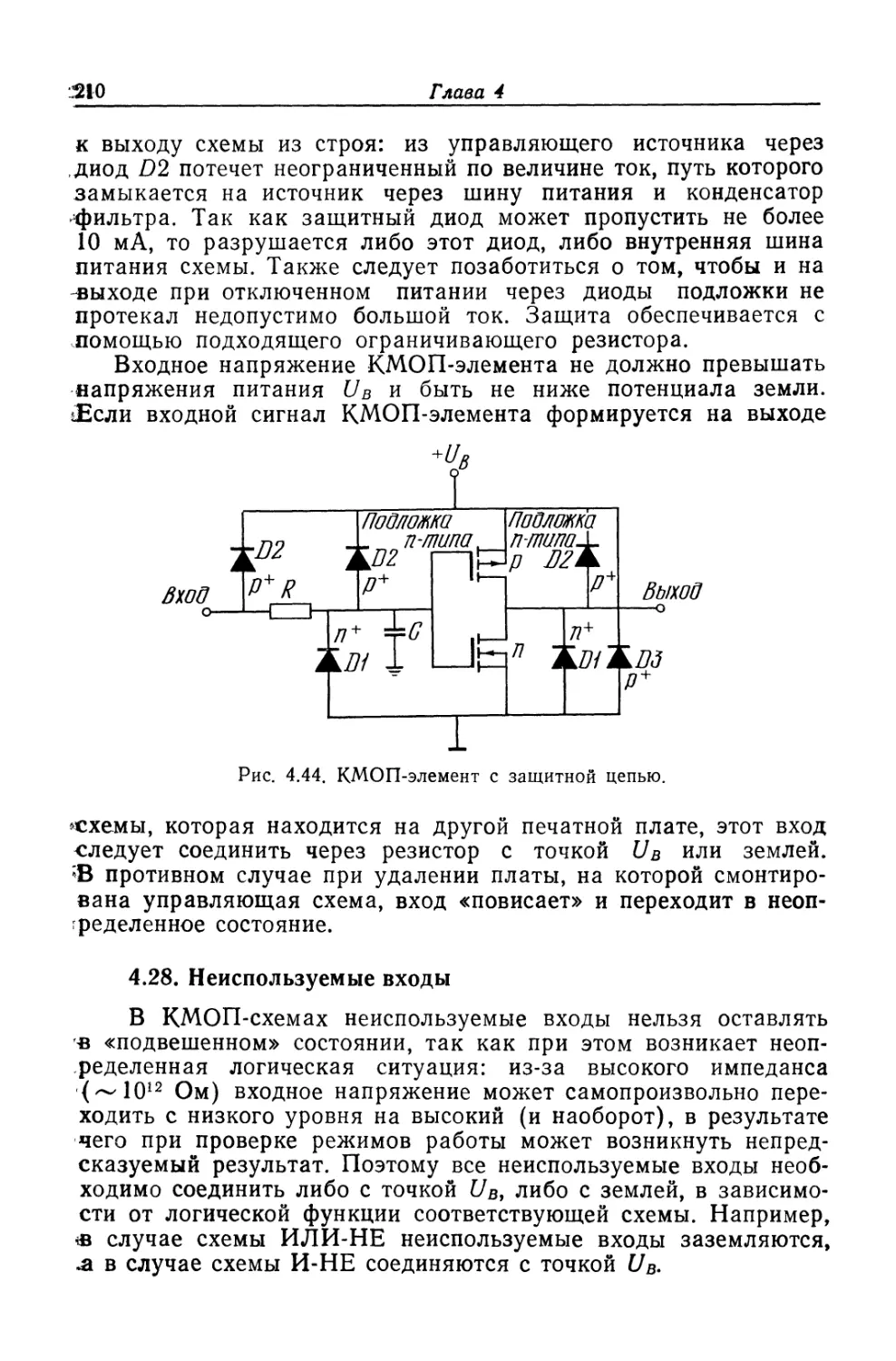

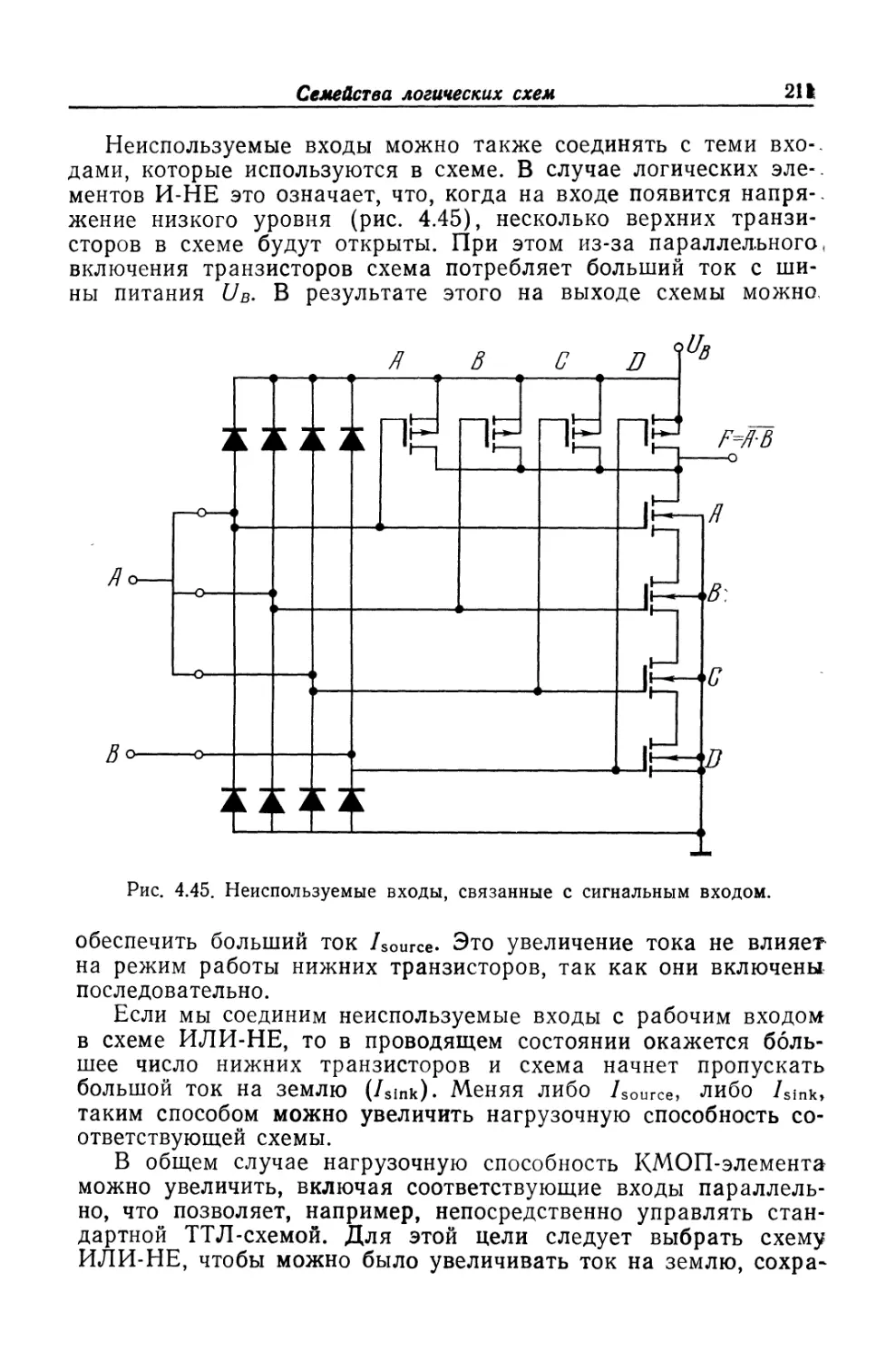

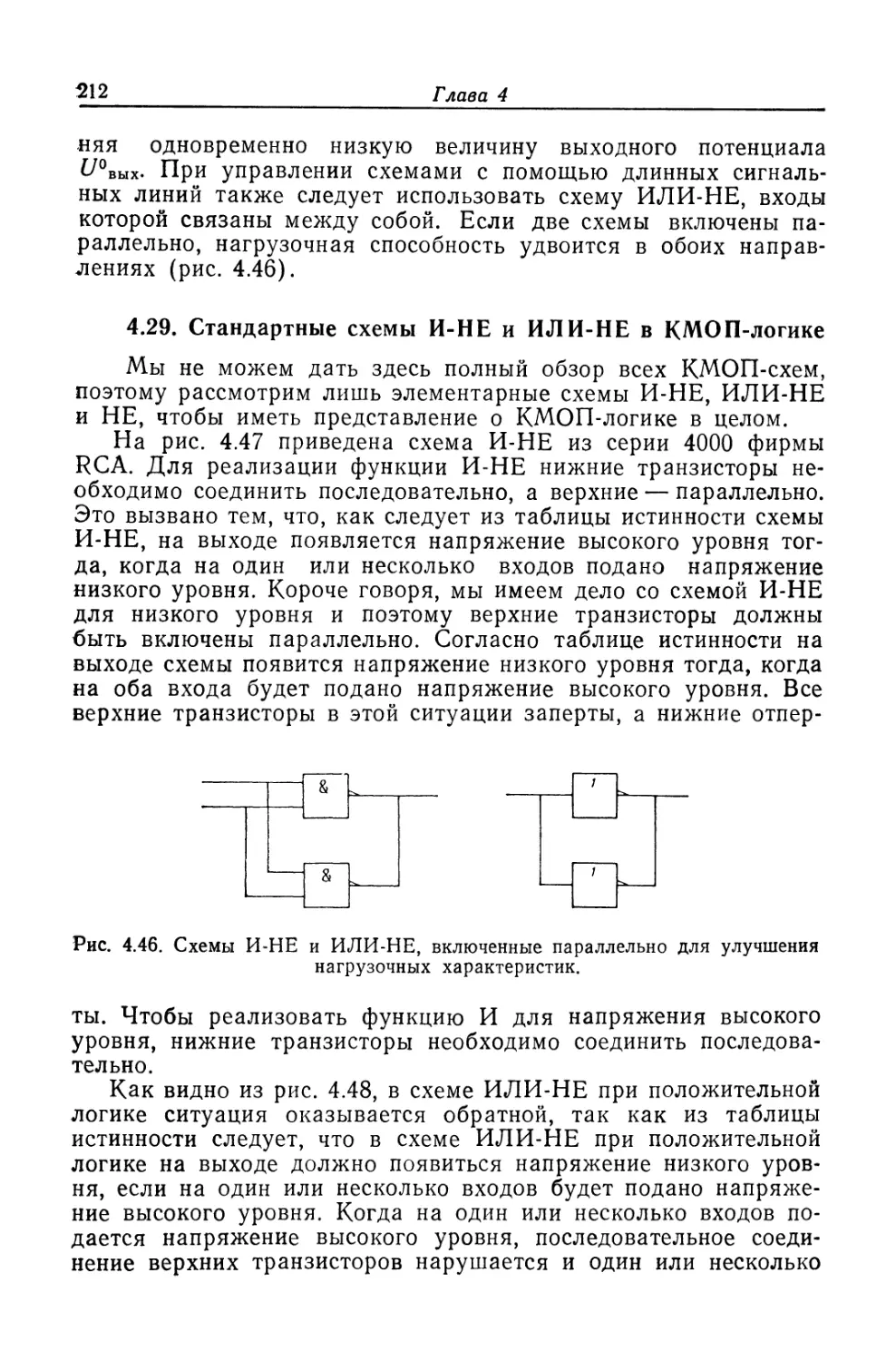

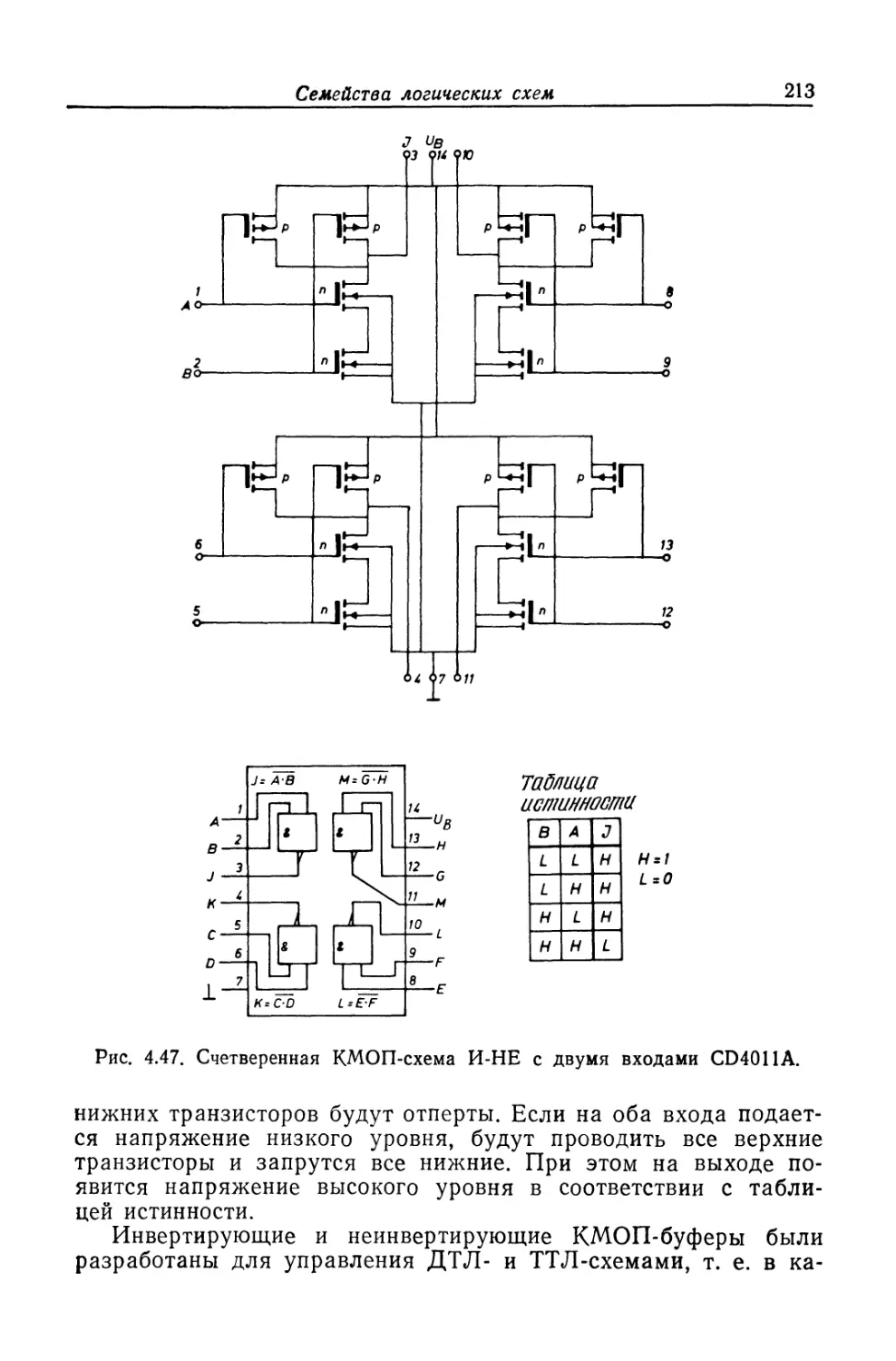

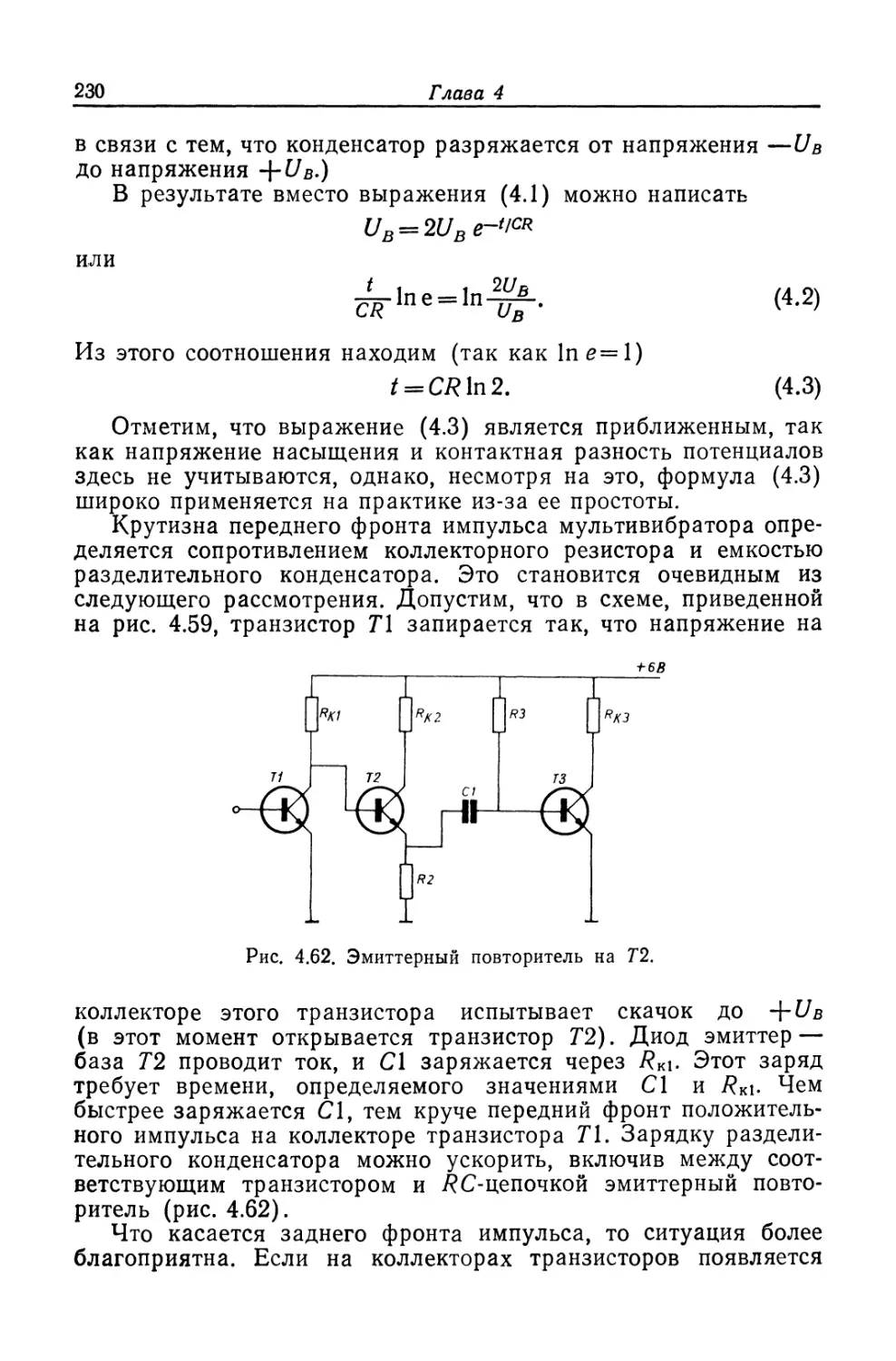

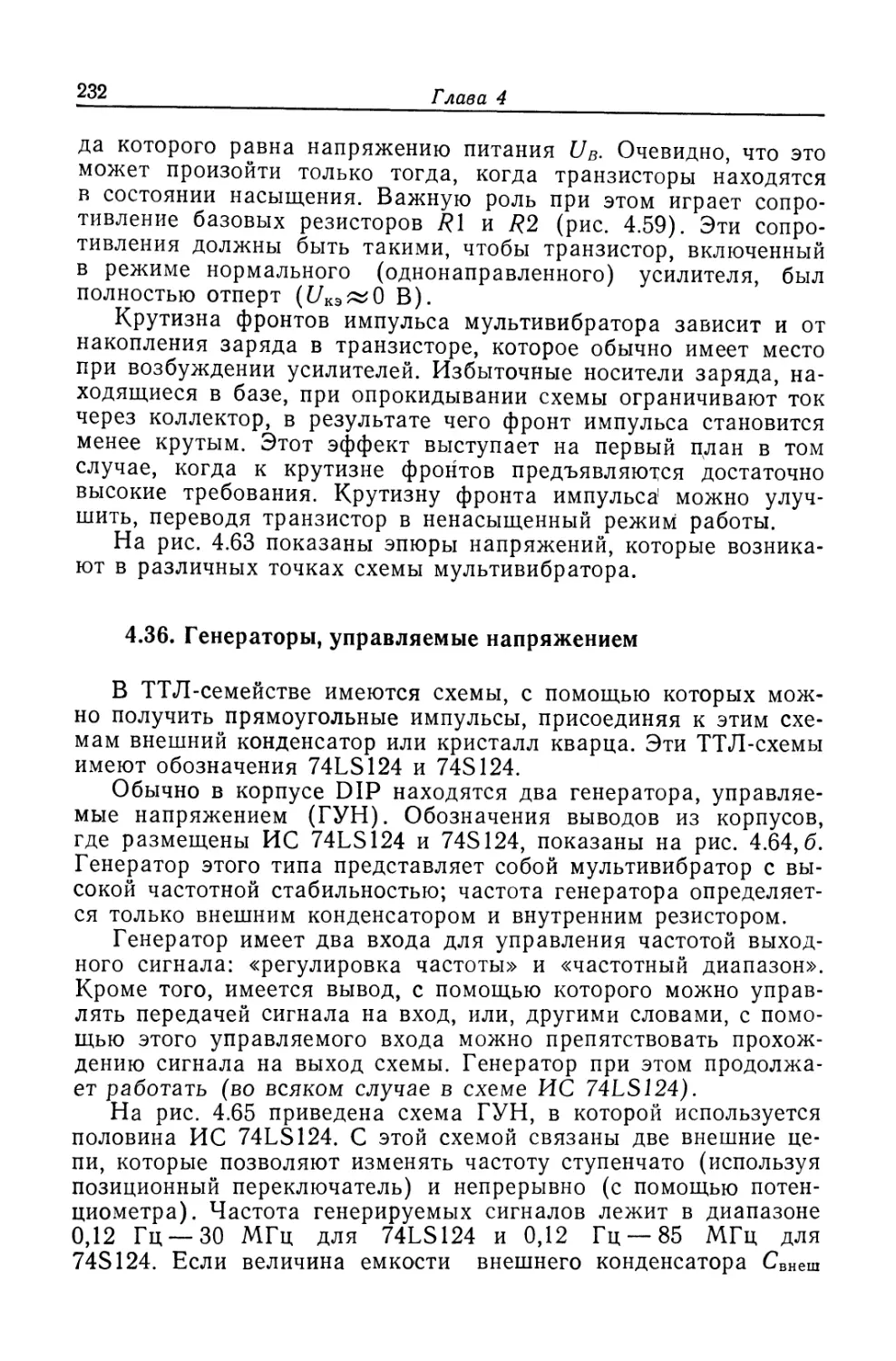

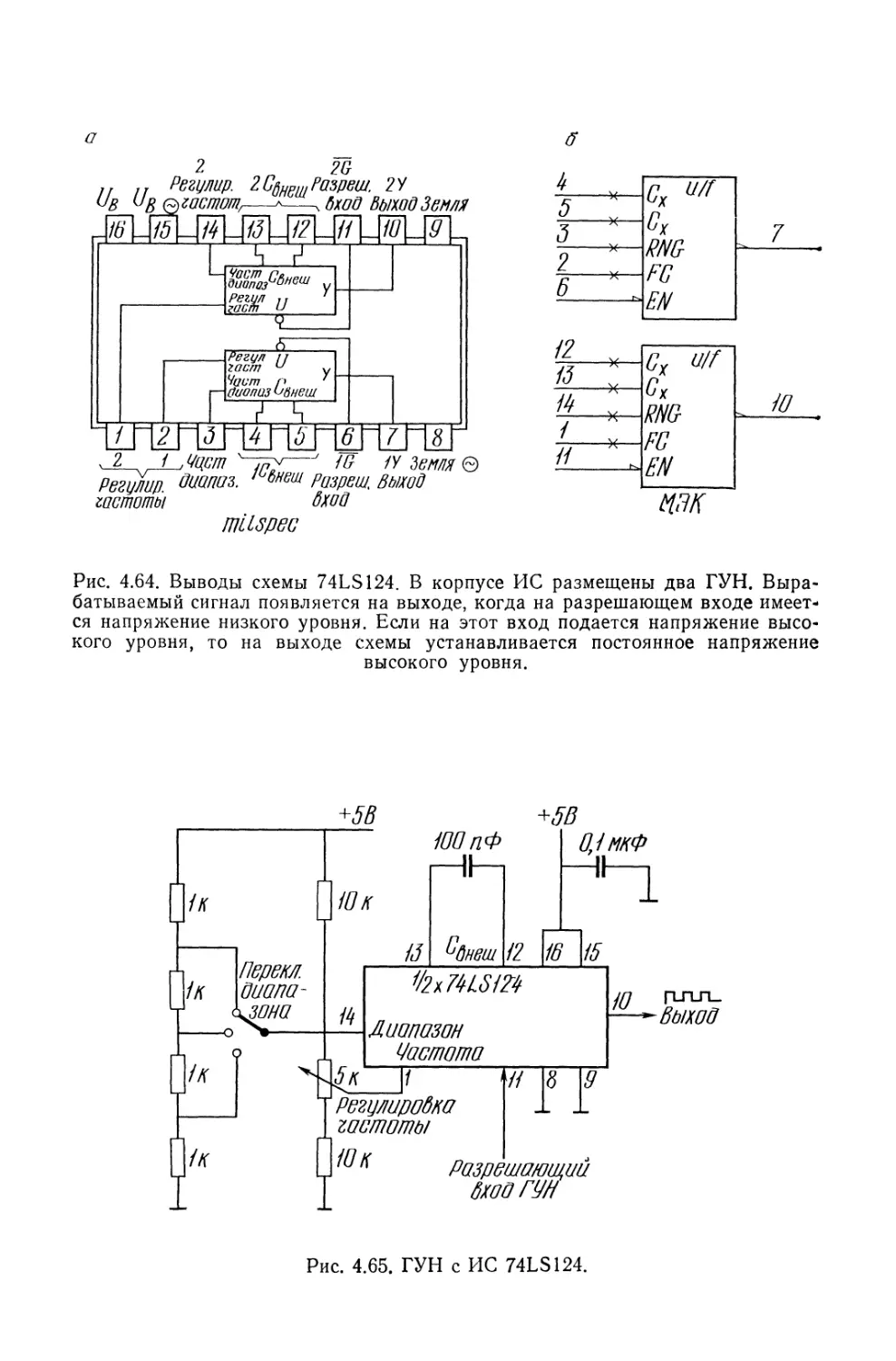

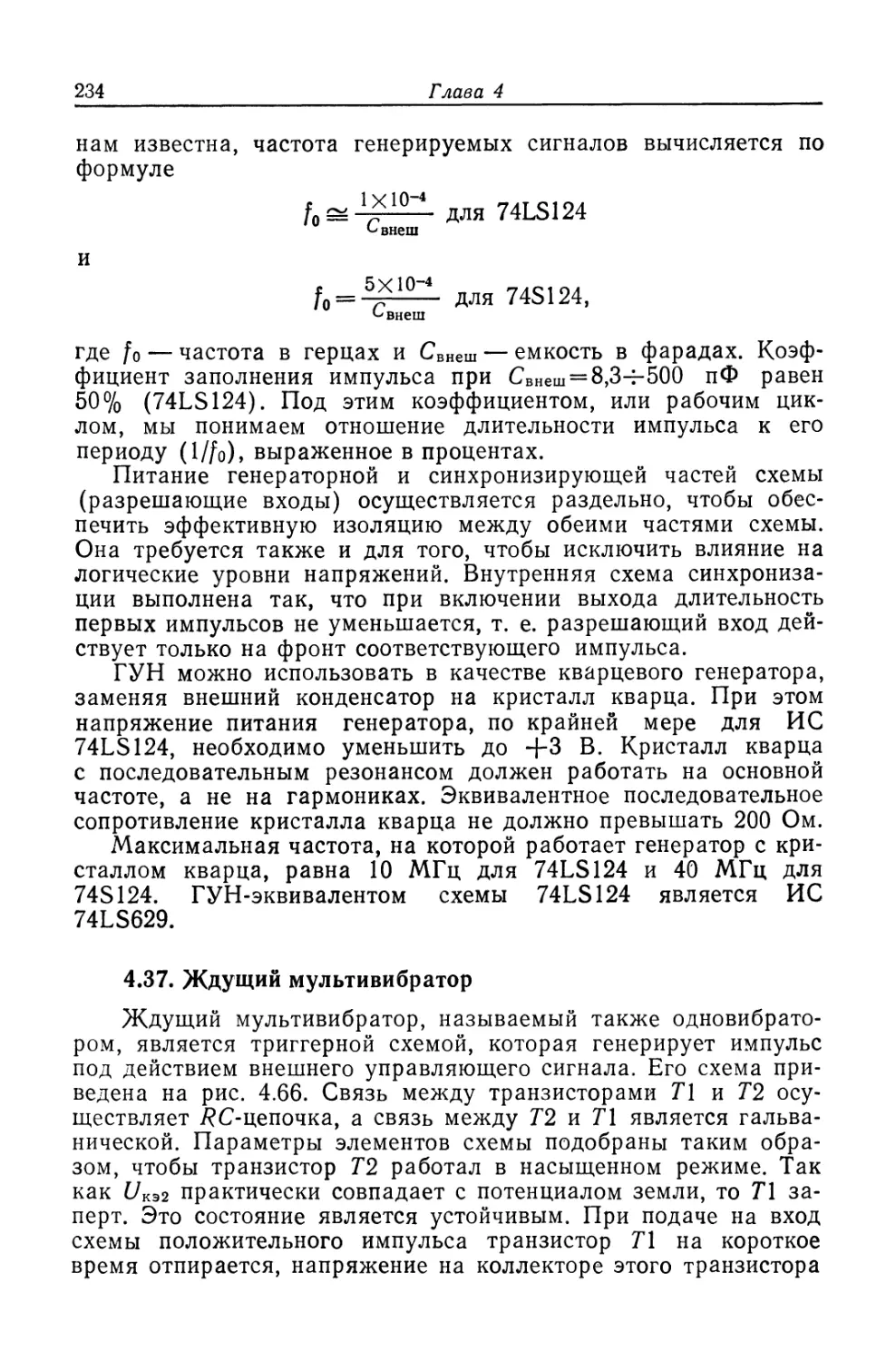

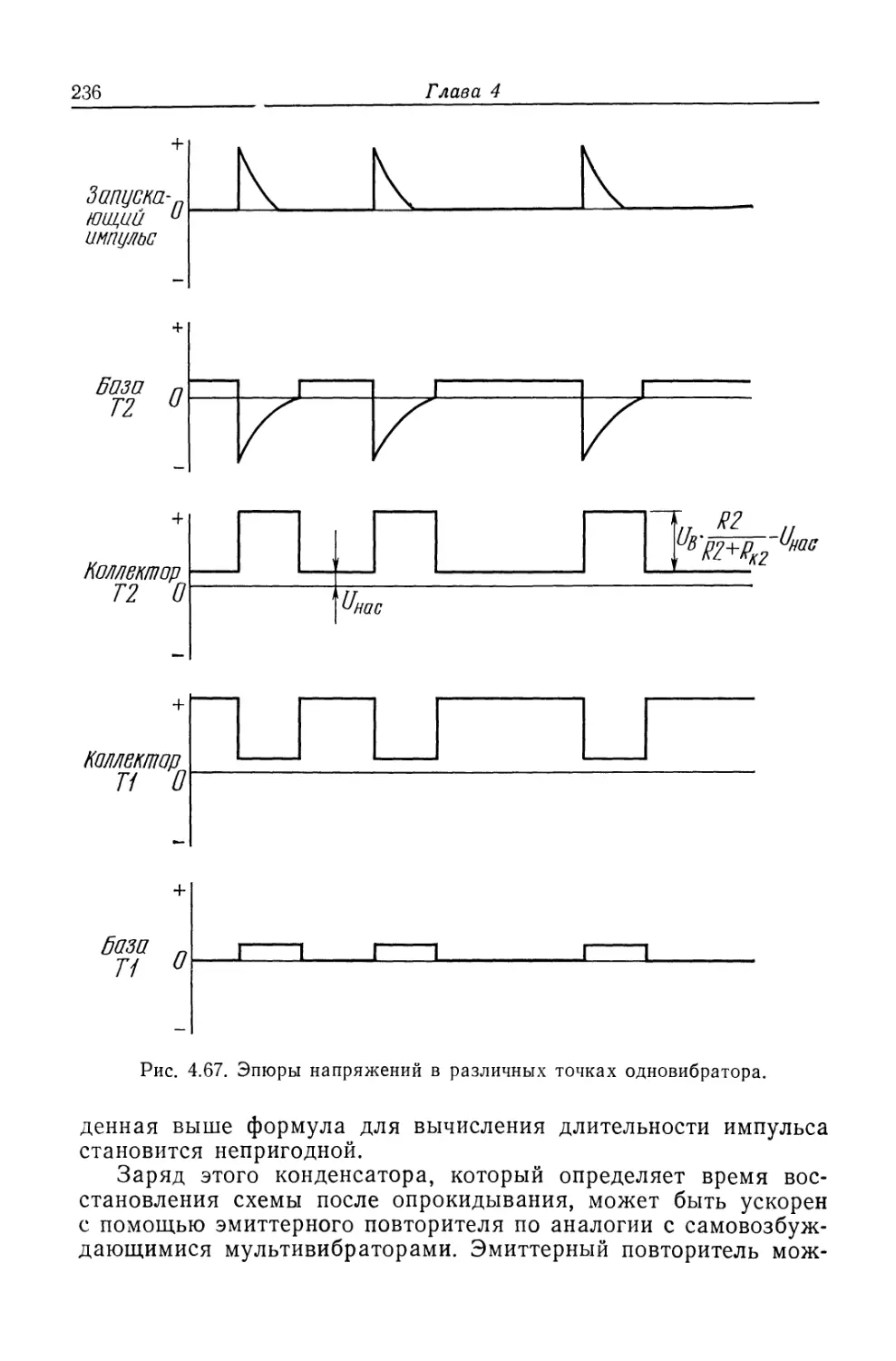

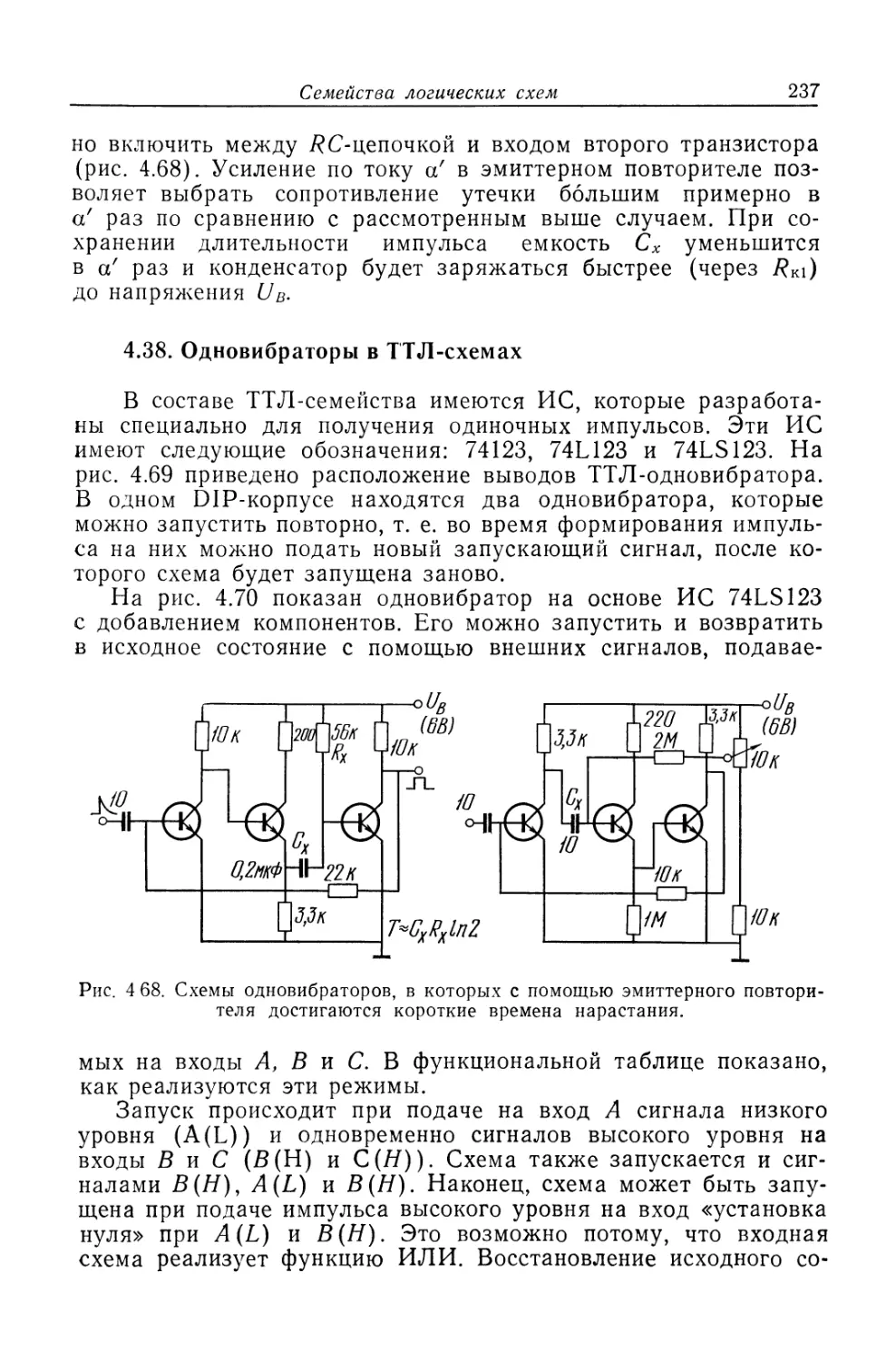

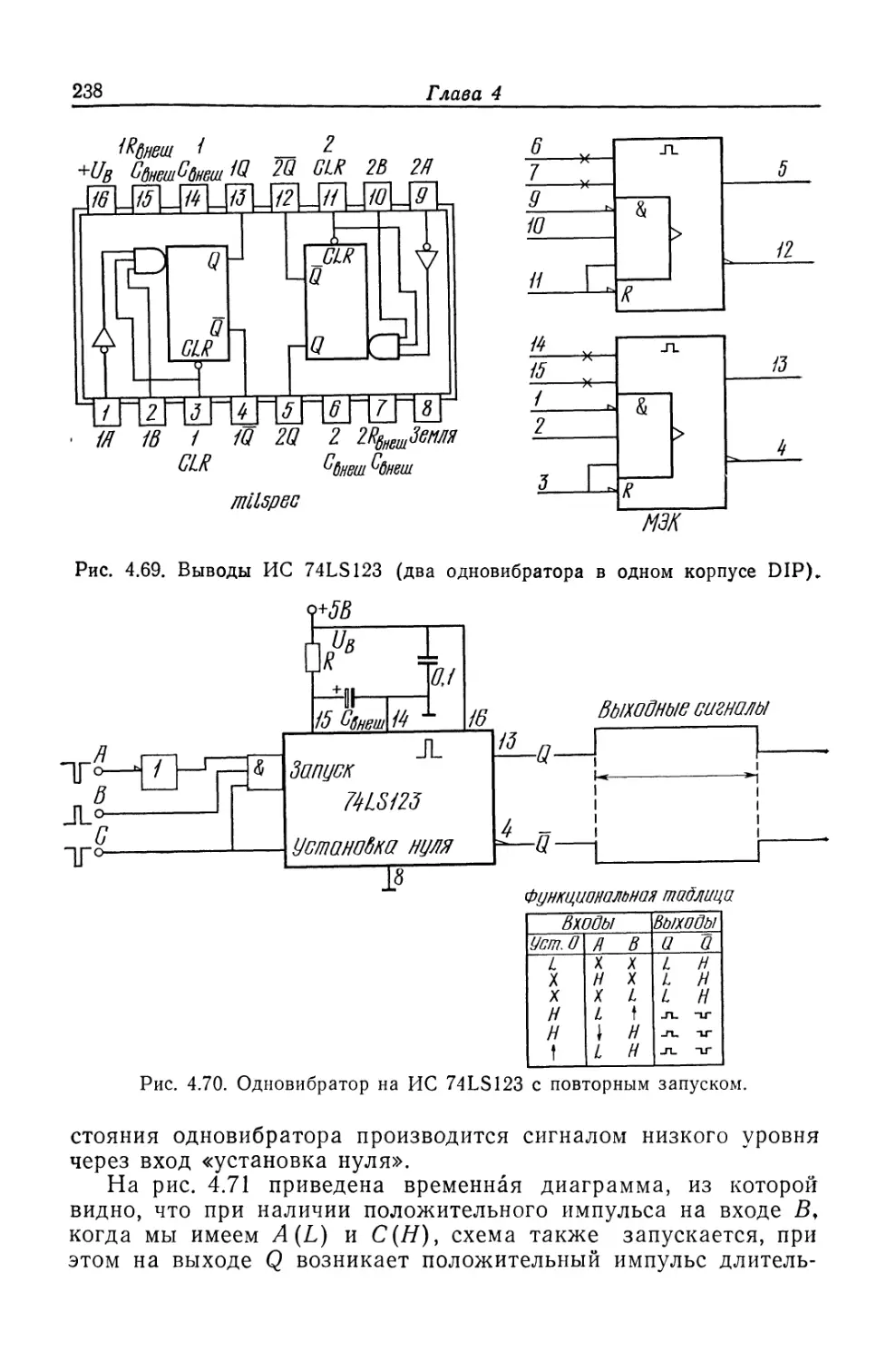

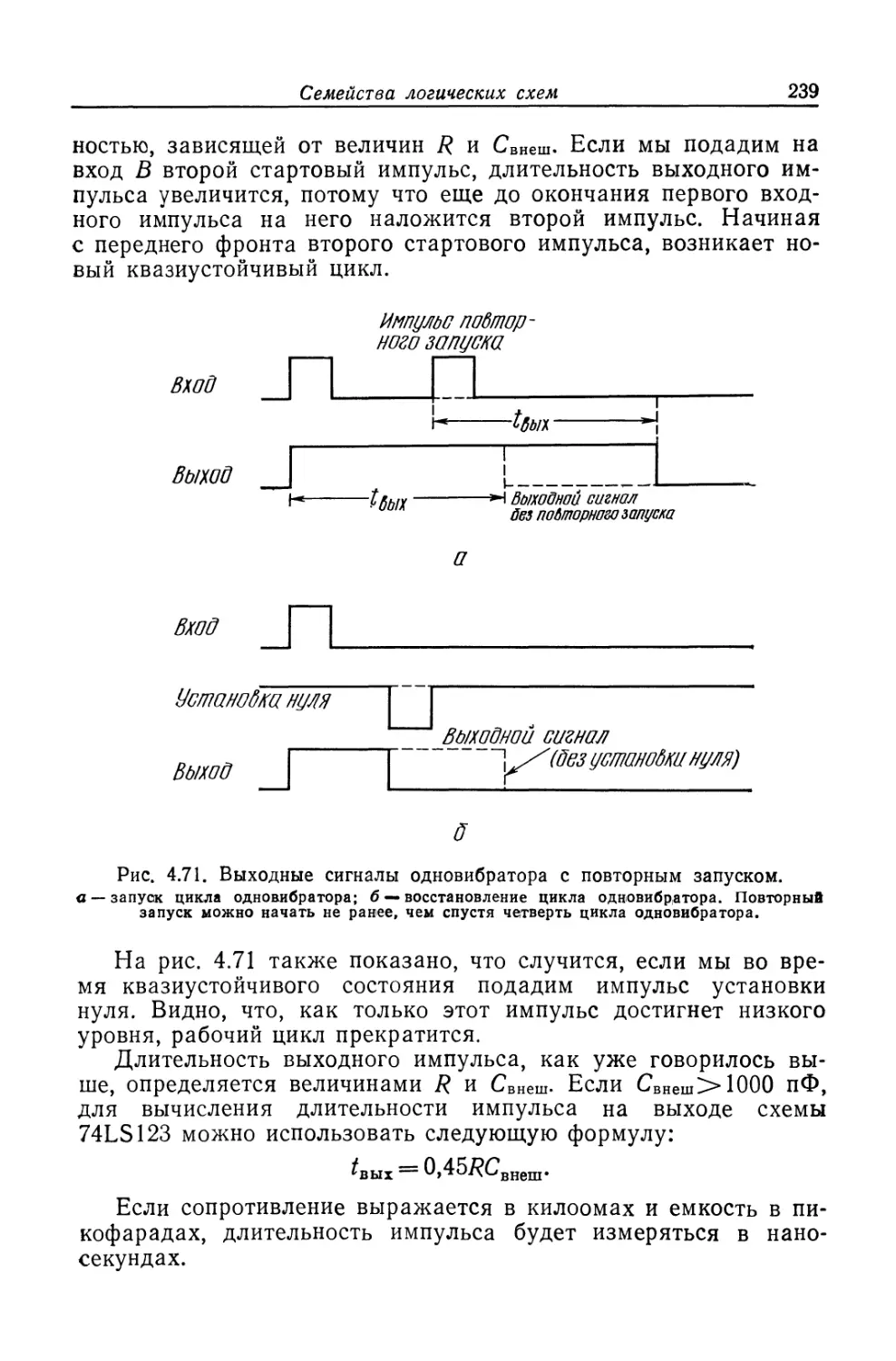

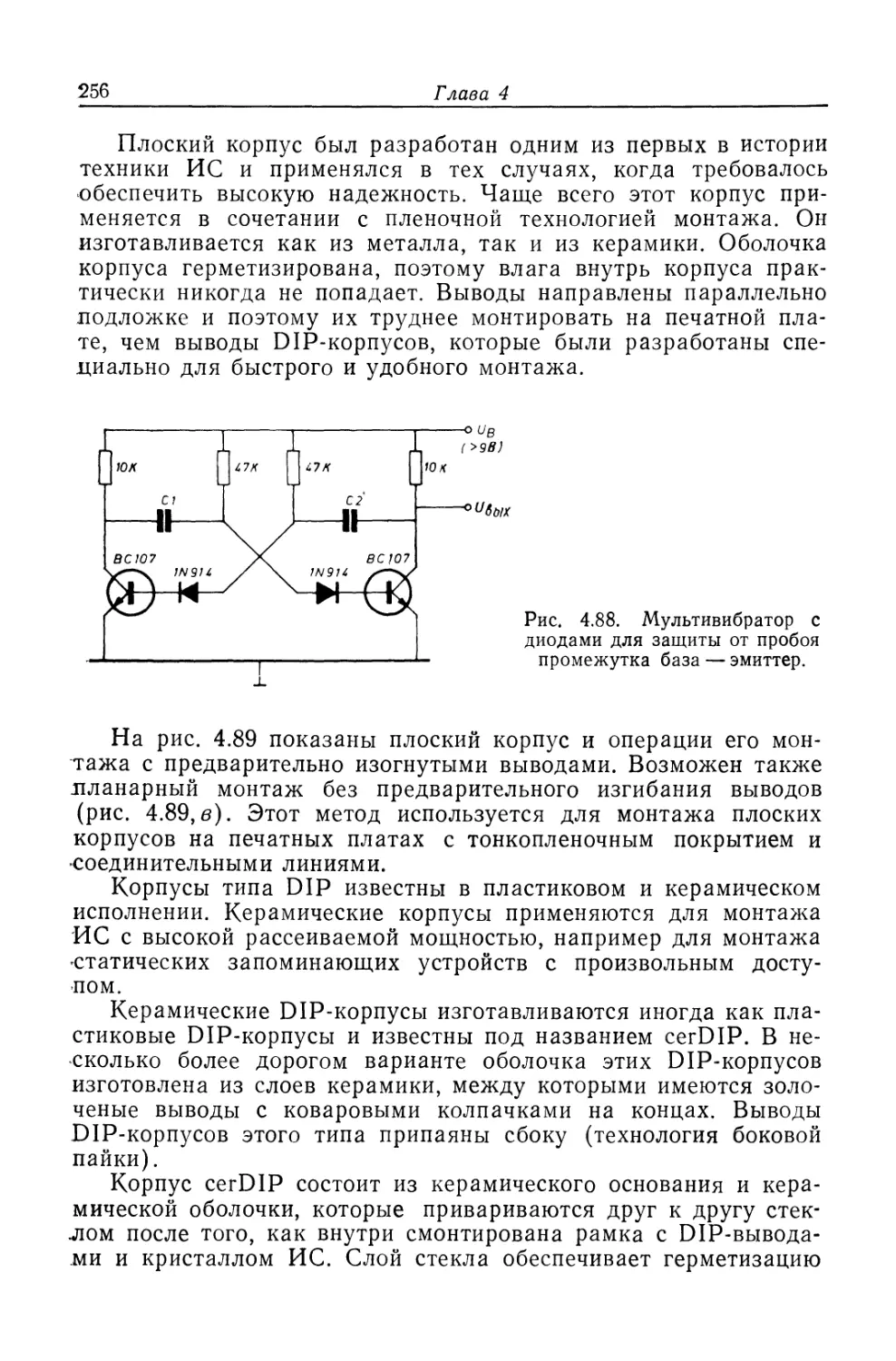

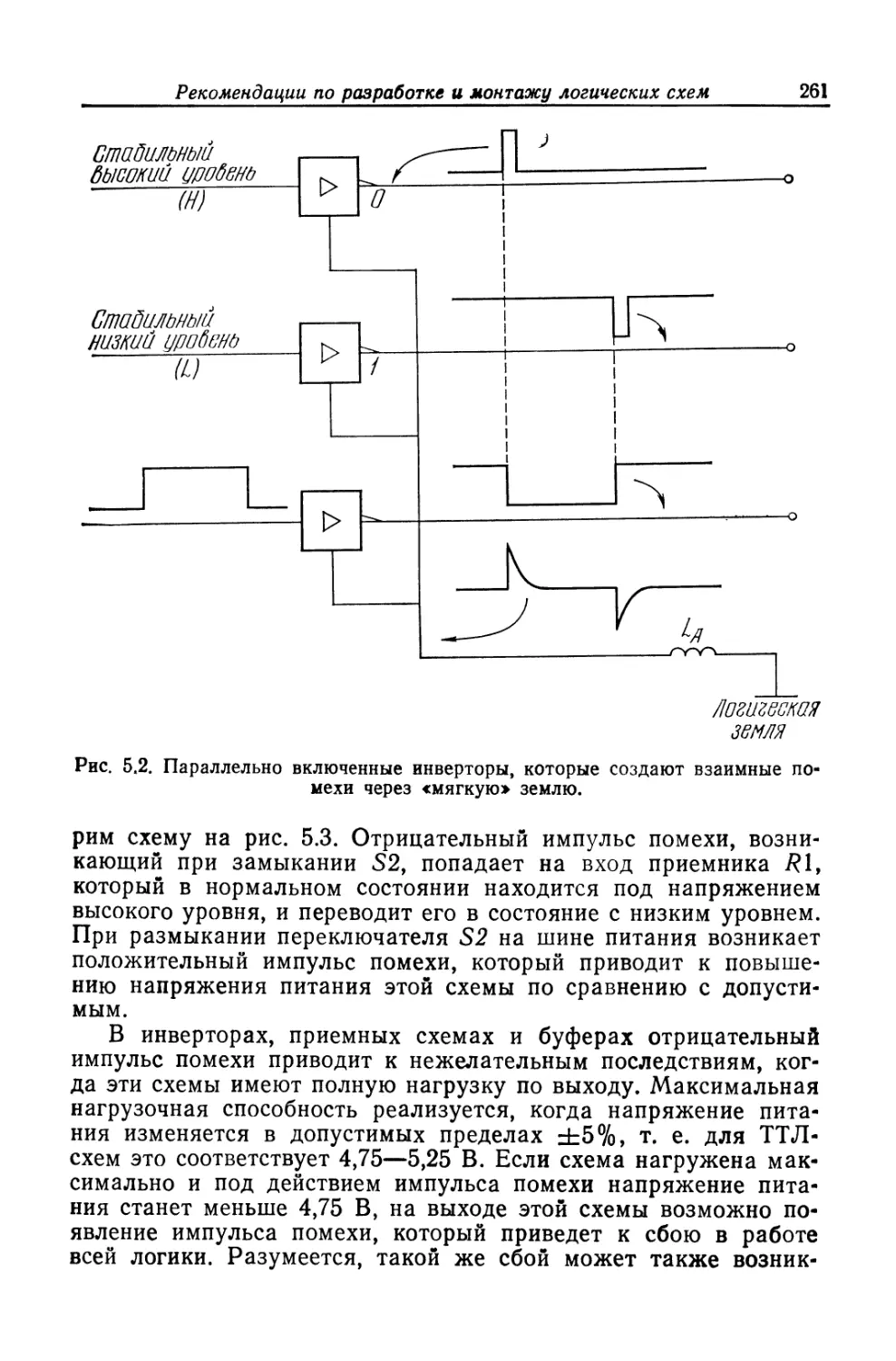

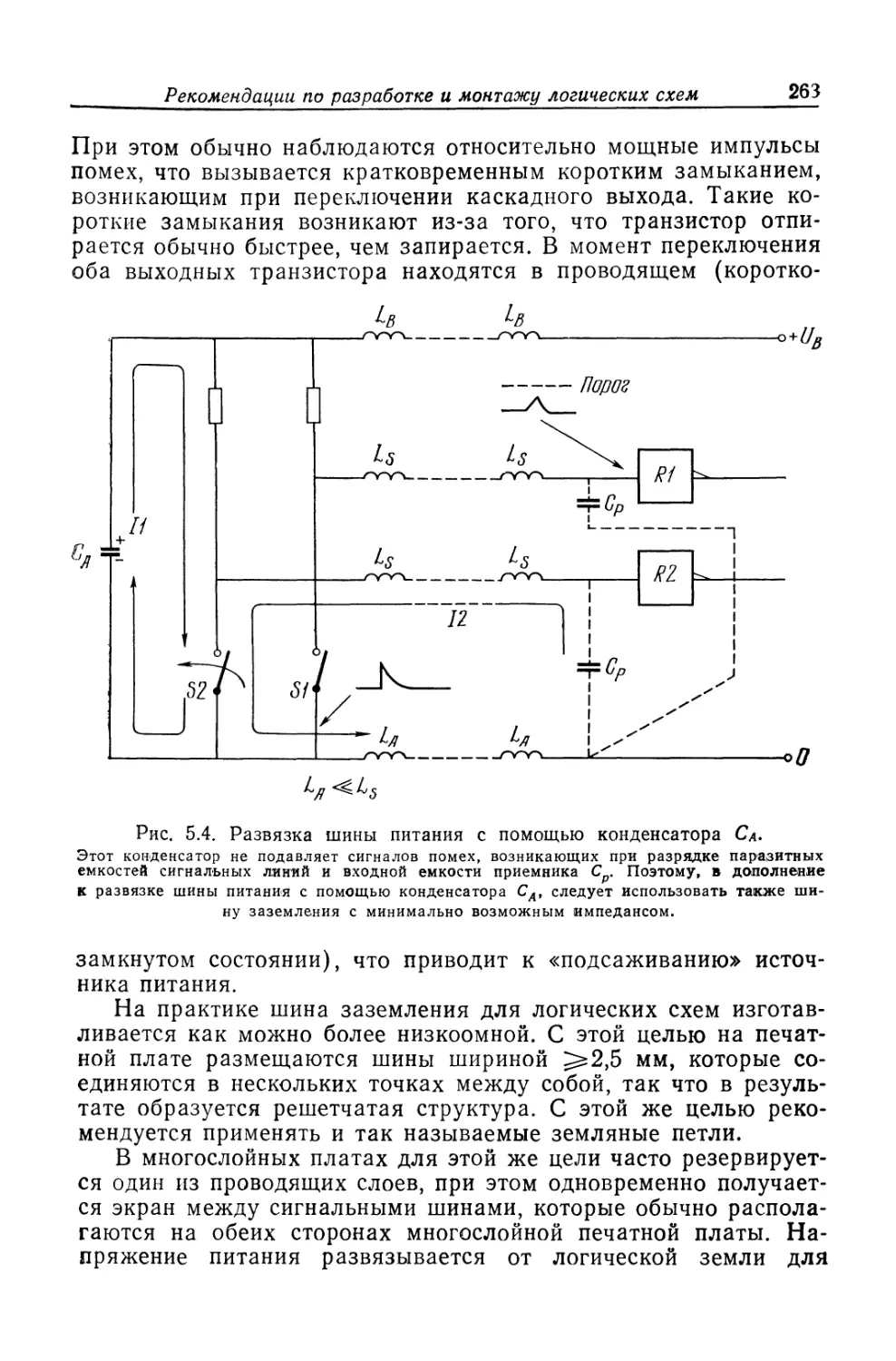

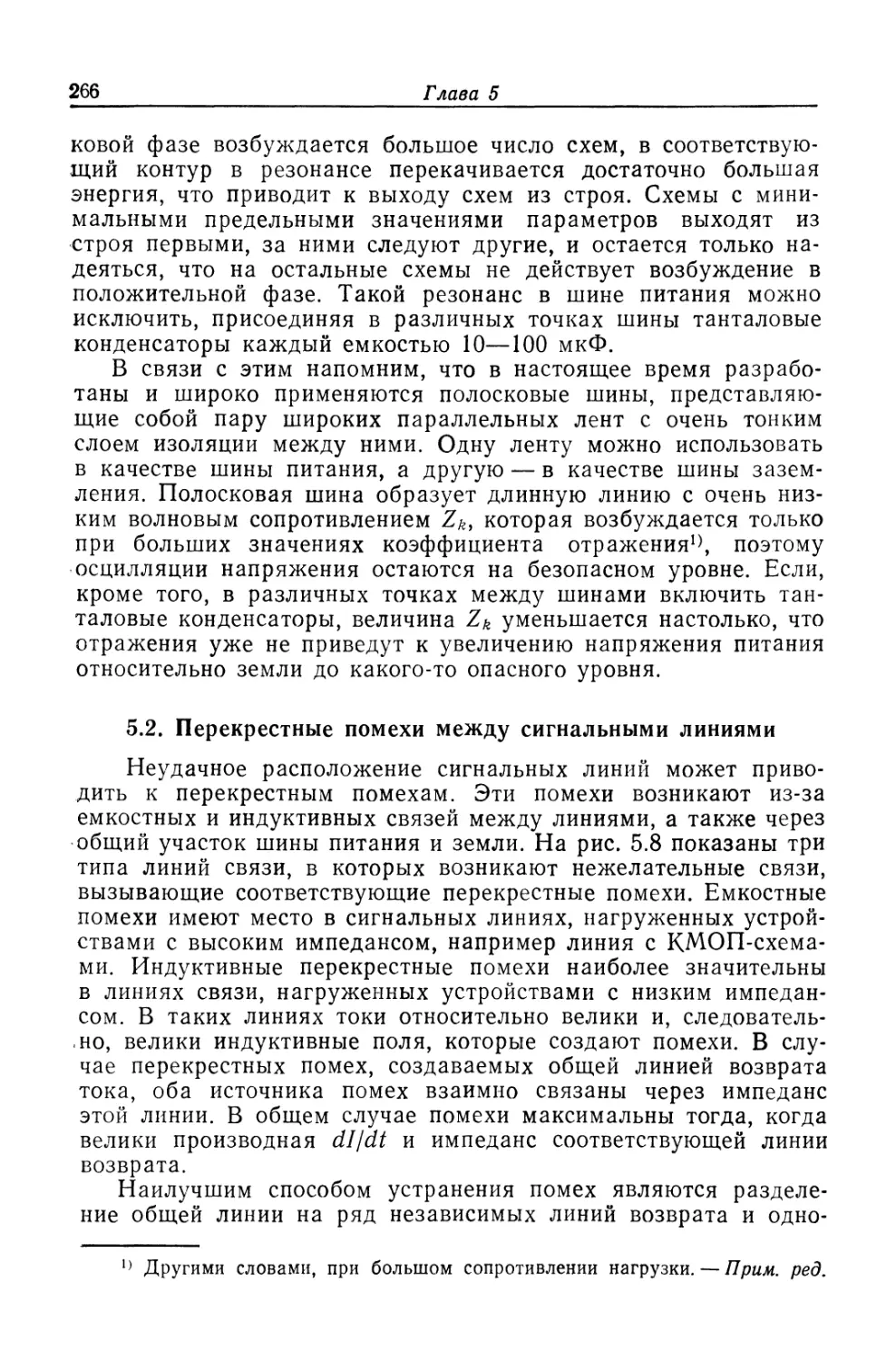

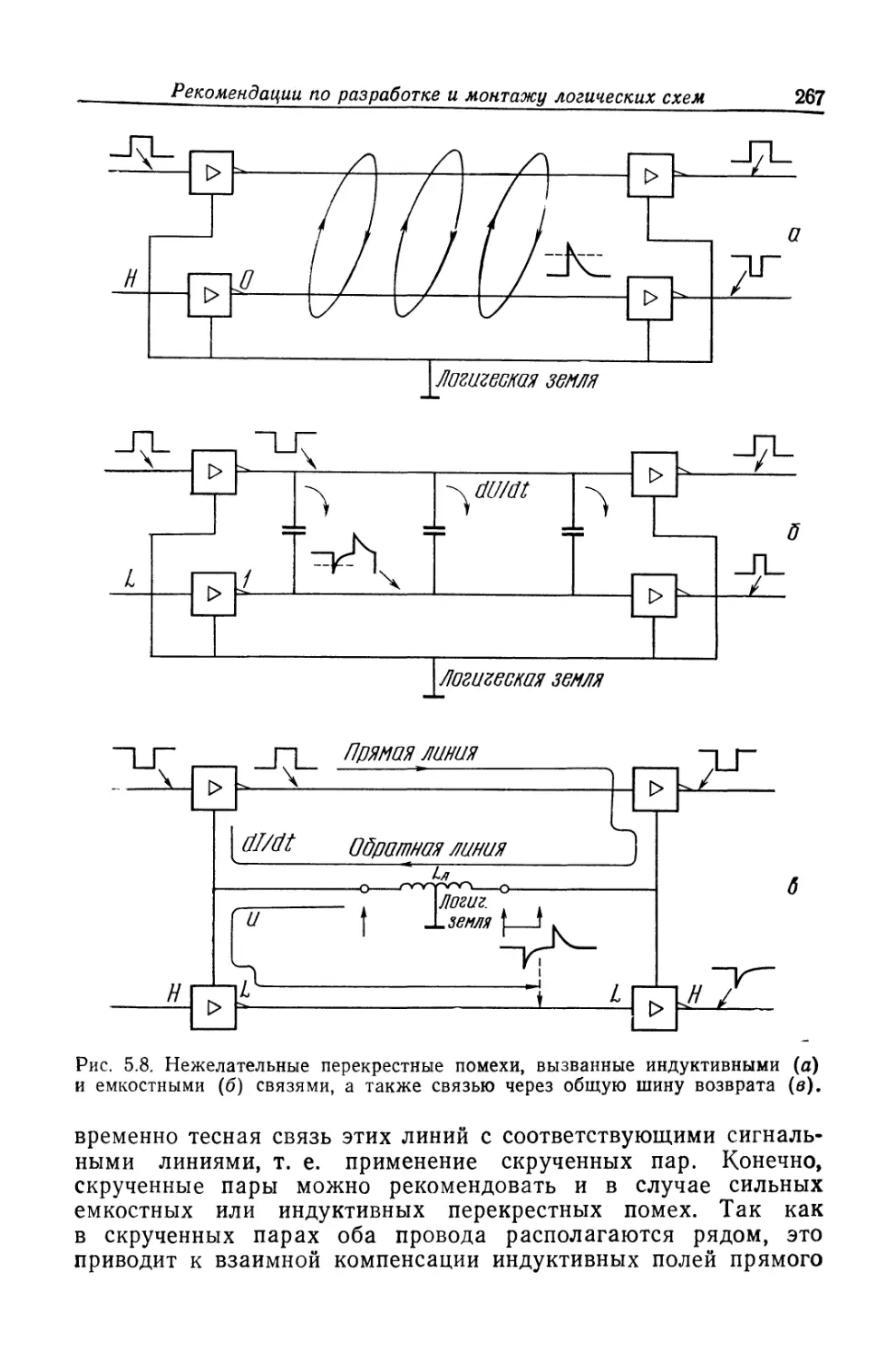

разрядное дополнение данного числа мы получим, инвертируя