Автор: Гольденберг Л.А.

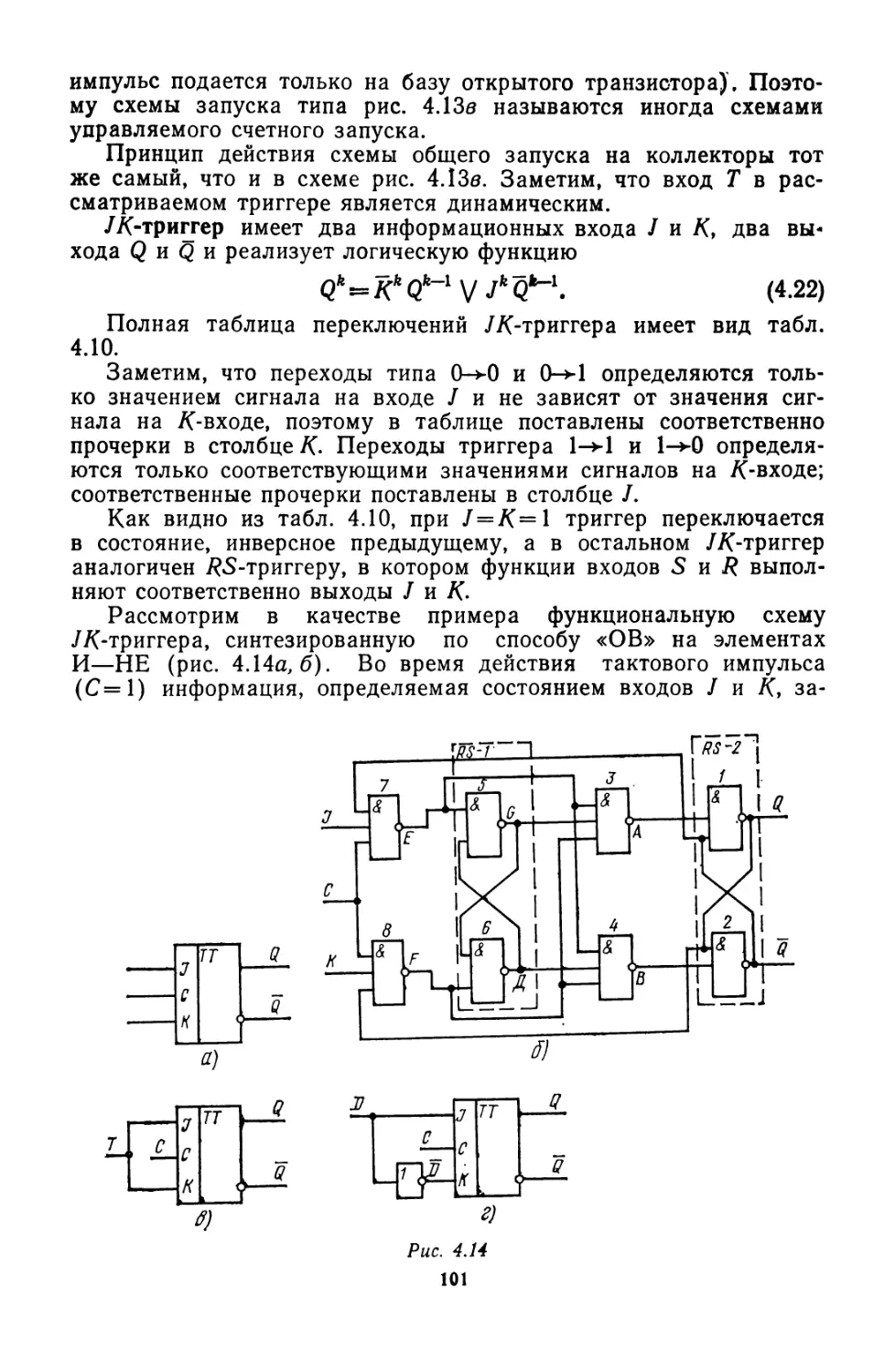

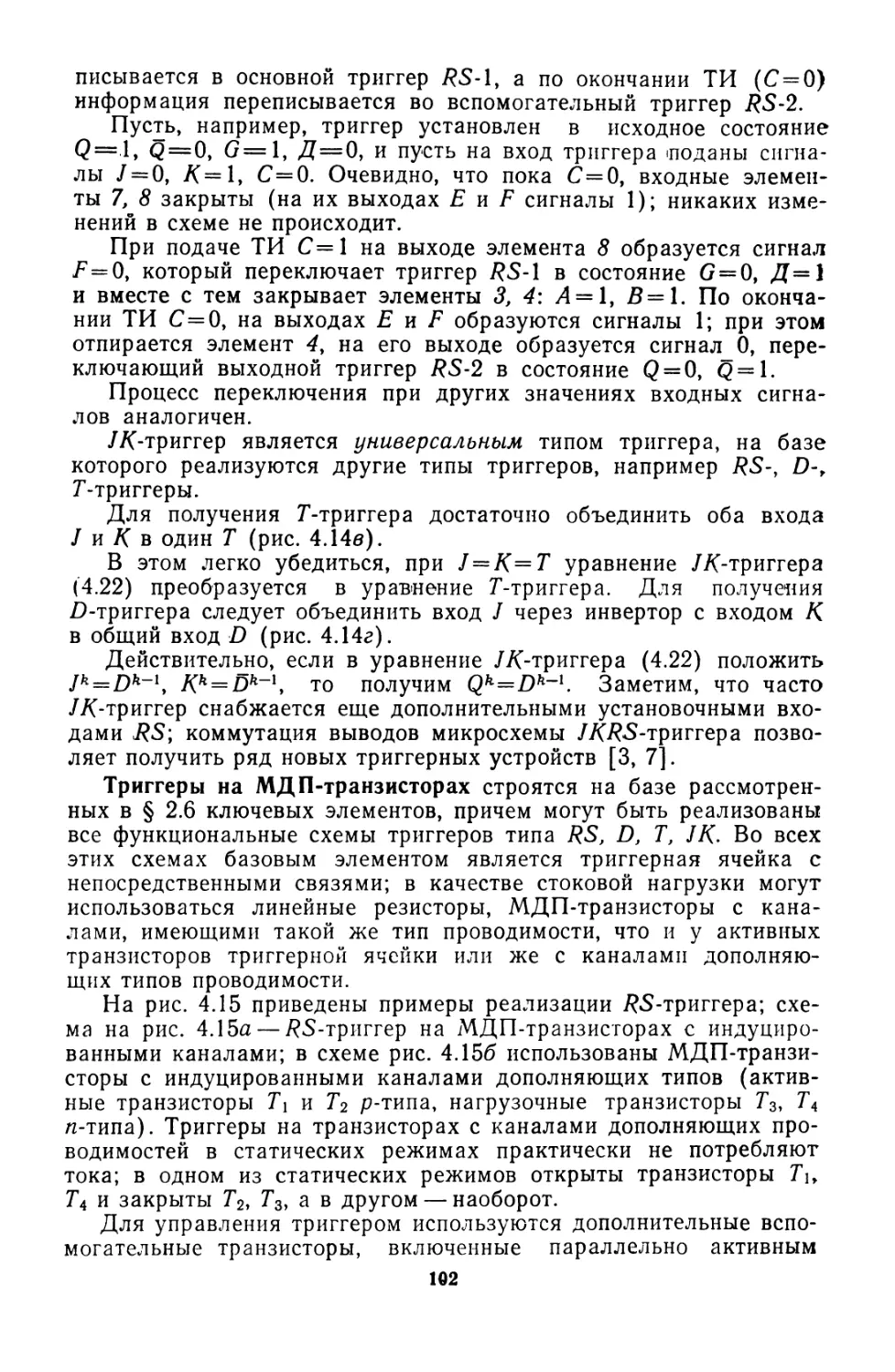

Теги: электротехника импульсные устройства электроника цифровая техника

Год: 1981

Текст

Л. М. Го льденберг

ИМПУЛЬСНЫЕ

УСТРОЙСТВА

Л.М.Гольденберг

ИМПУЛЬСНЫЕ

УСТРОЙСТВА

ДОПУЩЕНО МИНИСТЕРСТВОМ ВЫСШЕГО И СРЕДНЕГО

СПЕЦИАЛЬНОГО ОБРАЗОВАНИЯ СССР В КАЧЕСТВЕ

УЧЕБНИКА ДЛЯ СТУДЕНТОВ РАДИОТЕХНИЧЕСКИХ СПЕ-

ЦИАЛЬНОСТЕЙ ВУЗОВ

МОСКВА • РАДИО И СВЯЗЬ • 1981

ББК 32.847

Г63

УДК 621.374

Гольденберг Л. М.

Г63 Импульсные устройства: Учебник для вузов. — М.:

Радио и связь, 1981. — 224 с., ил.

85 к.

Излагаются основы теории и схемотехники импульсных устройств.

Основное внимание уделяется устройствам на интегральных схемах. Рас-

сматриваются элементная база импульсных устройств, комбинационные и

последовательностные устройства, методы и схемы формирования прямо-

угольных и непрямоугольных импульсов, функциональные устройства тех-

ники связи и управления.

Предназначен студентам вузов связи и радиотехнических факультетов,

будет полезен и специалистам, работающим в области импульсной и циф-

ровой техники.

г 30401—005

* 045(01)—81

2404000000

ББК 32.847

6Ф2

РЕЦЕНЗЕНТЫ: ДАНИИЛ ДАВЫДОВИЧ КЛОВСКИИ,

БЕНИАМИН АРШАКОВИЧ КАЛАБЕКОВ

Издательство «Радио и связь», 1981

ПРЕДИСЛОВИЕ

Современный этап развития импульсной техники связан со все

более широким применением цифровых методов и использовани-

ем интегральных цифровых и аналоговых цепей. Этим и обуслов-

лены методика построения и содержание настоящего учебника; в

отличие от предыдущих изданий (М.: Связь, 1963, 1964, 1973),

здесь основное внимание уделено теории и схемотехнике им-

пульсных устройств на интегральных схемах.

В первых двух главах рассматривается элементная база им-

пульсной техники: вначале простейшие линейные и ключевые эле-

менты, затем основные наиболее распространенные логические

элементы — транзисторно-транзисторные логические схемы

(ТТЛ) и логические схемы с соединенными эмиттерами (ЭСЛ), а

также ключевые устройства на МДП-транзисторах. Для импульс-

ных устройств характерны схемы, содержащие интегральные и

дискретные компоненты; методам их соединения посвящена гл. 3.

В гл. 4 рассматриваются методика построения комбинационных

логических устройств, теория и схемотехника триггеров, некото-

рых субсистем (регистров и счетчиков импульсов), часто исполь-

зуемых в качестве базовых устройств более сложных импульс-

ных систем. Главы 5—7 посвящены теории и схемотехнике форми1-

рователей и генераторов импульсов прямоугольной и непрямо-

угольной формы; здесь рассматриваются импульсные устройства,

построенные не только на логических, но и на аналоговых интег-

ральных элементах (операционных усилителях, интегральных тай-

мерах), а также на дискретных компонентах. В последней главе

рассмотрен ряд функциональных импульсных устройств техники»

связи и управления.

Книга предназначена служить учебником по курсу «Импульс-

ные устройства» (или «Импульсные и цифровые устройства»); ав-

тор надеется, что она будет полезна студентам при выполнении

учебно-исследовательских, курсовых и дипломных работ, а также

специалистам, работающим в области импульсной техники. Автор

благодарит сотрудников кафедры ИВТ ЛЭИС им. проф.

М. А. Бонч-Бруевича В. А. Малева, Г. Б. Малько, Л. Г. Зеличен-

ко, Ю. Т. Бутыльского, М. Н. Поляка, принимавших участие в ее

обсуждении. Автор выражает свою признательность Г. Ф. Роди-

ной за большую помощь в подготовке рукописи к печати.

Автор признателен рецензентам книги профессорах

Д. Д. Кловскому и Б. А. Калабекову за ценные замечания.

ВВЕДЕНИЕ

Импульсные устройства предназначены для формирования и

преобразования электрических сигналов, имеющих характер им-

пульсов и перепадов напряжений (потенциалов) или тока, а так-

же для управления информацией, представленной упомянутыми

сигналами.

На практике используются импульсы разнообразной формы,

прямоугольной (рис. В. 1а), трапецеидальной (рис. В. 16), пилооб-

разной (рис. B.le), остроконечной (рис. В.1г) и др. Форма им-

Рис. В.1

t

пульса (рис. В.2а) характеризуется следующими основными па-

раметрами: амплитудой (максимальным значением) Um\ на-

чальным значением £°, длительностью импульса длитель-

ностью фронта /ф1 (или /ф), длительностью среза tCi длитель-

ностью вершины /вер, снижением вершины АС/.

Понятие временных параметров импульса (/и, /ф, /с, /вер) име-

ет точный смысл только при идеализированной форме импульса

Рис. В.2

4

(см. рис. В.2а). При определении временных параметров реально-

го импульса (см. рис. В.26) пользуются условными уровнями, от-

несенными к амплитуде импульса aUm, Обычно принят уровень

отсчета а=0,1; это означает, что длительность фронта измеряет-

ся в интервале изменения напряжения 10—90% от амплитуды им-

пульса; однако в некоторых случаях принимается а=0,05 или

а=0,01.

Наряду с перечисленными параметрами используются и неко-

торые другие количественные характеристики импульсов, в част-

ности крутизна фронта (т. е. скорость изменения напряжения при

формировании фронта или среза).

Часто приходится иметь дело с последовательностью периоди-

чески повторяющихся импульсов. Такая последовательность ха-

рактеризуется скважностью g, коэффициентом заполнения т] и час-

тотой повторения f:

1 = 0/4» = Ш /=1/0=1/^и,

где 0 — период повторения импульсов.

Основными параметрами перепада напряжения (тока) (рис.

В.З) являются его амплитуда Um и длительность фронта (или

среза) /ф; при использовании в качестве потенциального сигнала

перепада напряжения он характеризуется двумя стационарными

уровнями — низким £° и высоким Е{.

Рис. В.З

Рис. В.4

Наряду с сигналами (импульсами, уровнями напряжения), па-

раметры которых являются аналоговыми величинами (т. е. могу-

щими принимать бесконечное множество значений), в книге рас-

сматриваются цифровые (дискретные) сигналы, параметры кото-

рых могут принимать лишь фиксированные значения, принадле-

жащие некоторому конечному множеству. Отдельные элементы

этого множества могут быть закодированы цифрами (отсюда и

название этих сигналов); в большинстве случаев таких элементов

только два.

Уровни напряжения (потенциалы) и импульсы могут быть за-

кодированы в двоичной системе счисления цифрами 0 и 1: низкий

потенциал или отсутствие импульса кодируется нулем, высокий

потенциал или наличие импульса кодируется единицей. Такое ко-

дирование сигналов обычно называют положительным. Естест-

венно, что допускается (и реально используется) также обратное

кодирование — отрицательное.

Б

Важно подчеркнуть, что 0 и 1 являются лишь информационны-

ми значениями сигналов и не характеризуют их реальных значе-

ний. Если обозначить информационное значение сигнала и через

х, то можно записать, что х=0 при u=EQ и х=1 при и=Е{.

С помощью цифровых сигналов можно кодировать аналого-

вые сигналы, например непрерывно изменяющееся напряжение

или временные интервалы. Идея цифрового кодирования аналого-

вой функции /(/) иллюстрируется на рис. В.4.

Непрерывная функция /(/) заменяется совокупностью ее зна-

чений— выборками — взятыми в дискретные моменты вре-

мени /г, i=0, 1, 2,... (как известно, если частотный спектр функ-

ции f(t) ограничен величиной Й, то согласно теореме Котельнико-

ва функция f(t) может быть восстановлена по выборкам

взятым через интервал дискретизации — /д = 1/2 Q).

Каждая выборка f(^) квантуется по уровню, и ей приписыва-

ется значение kh, если kh<f(ti) < Чем меньше шаг кван-

тования Л, тем точнее можно представить значения выборок. В

простейшем случае бинарного квантования число уровней равно*

двум, и они кодируются символами 0,1. Вообще же число уровней

квантования бывает много больше, например 8—12, и тогда мож-

но достаточно точно кодировать цифровыми сигналами аналого-

вые сигналы, изменяющиеся в широком диапазоне уровней.

Во многих устройствах и прежде всего в цифровых, в которых

формируются и преобразуются дискретные сигналы, их значения

могут изменяться только в результате изменения некоторых уп-

Е1

Е°

равляющих сигналов. Это значит,

— что изменения токов и напряже-

ний в устройстве могут начинать-

— i ся в дискретные моменты време-

Z 4 4 ъ ни /2> • • • ’tn'tn+b ’опреде'

1 1 ляемые моментами изменения то-

р В5 го или иного управляющего сиг-

ис’ ’ нала (см., например, рис. В.5).

Совокупность моментов времени tn, которые могут быть равноот-

стоящими или произвольными, составляет дискретное время.

В связи с этим условимся символом xni обозначать информа-

ционное значение сигнала х в f-й точке устройства на /г-м интер-

вале, т. е. в интервале tn^t<tn+li где t — текущее время.

Для построения импульсных и цифровых устройств использу-

ется элементная база, включающая как линейные элементы (ли-

нейные электрические цепи с сосредоточенными и распределенны-

ми параметрами, операционные усилители и т. д.), так и нелиней-

ные элементы — прежде всего логические, или ключевые. И те и

другие элементы могут быть реализованы как на интегральных

схемах (ИС) различного типа, так и на дискретных компонентах;

в современных импульсных устройствах широко применяются од-

новременно и ИС, и дискретные компоненты. Ниже рассматрива-

ются основные принципы функционирования и схемотехника им-

пульсных устройств на интегральных и дискретных компонентах.

6

Глава 1

ЛИНЕЙНЫЕ ЭЛЕМЕНТЫ

1.1. АНАЛИЗ ЛИНЕЙНЫХ ЭЛЕМЕНТОВ

Линейными элементами импульсных устройств являются, на-

пример, известные из курсов ТЛЭЦ и «Усилители» линейные элек-

трические цепи с сосредоточенными параметрами (состоящие из

резисторов, конденсаторов и т. п.), линейные импульсные и опера-

ционные усилители, линии задержки с распределенными и сосре-

доточенными параметрами и т. п.

Анализ линейных импульсных элементов или импульсных уст-

ройств с линеаризованными характеристиками чаще всего сво-

дится к определению функциональной зависимости напряжений

(токов) от времени после той или иной коммутации. Всякая ком-

мутация — включение или выключение пассивных и активных эле-

ментов, источников напряжения, короткие замыкания отдельных

ветвей, внезапные изменения отдельных параметров и т. д. — вы-

зывает в цепи переходный процесс. Этот процесс обусловлен тем,

что энергия электромагнитных полей, связанных с цепью, при раз-

личных установившихся режимах различна, а скачкообразное из-

менение энергии, т. е. изменение энергии на конечное значение

за бесконечно малый промежуток времени, невозможно из-за

ограниченной мощности физически существующих источников

энергии.

Исходя из этого, легко прийти к заключению, что напряжение

ис на емкости и ток iL в индуктивности не могут изменяться скач-

ками, так как этими величинами определяются соответственно

энергия электрического поля конденсатора и магнитного поля ка-

тушки. Следовательно, напряжение на емкости и ток в индуктив-

ности в момент коммутации сохраняют те же значения, какие они

имели в момент времени, непосредственно предшествующий ком-

мутации. Именно с этих значений начинают изменяться напряже-

ние на емкости и ток в индуктивности после коммутации.

Однако в ряде случаев напряжение ис на емкости и ток iL в

индуктивности изменяются (нарастают или спадают) после ком-

мутации столь быстро, что в пределах принятой точности расче-

та можно пренебречь временем нарастания (спада) напряжения

ис или тока iL и считать, что они изменяются скачкообразно. Оче-

видно, что в этих случаях следует рассматривать источники, дей-

ствующие в цепи как идеальные генераторы напряжения или то-

ка, могущие развивать в соответствующие моменты времени бес-

7

конечно большую мощность. Такая идеализация оказывается

весьма удобной для качественного и приближенного количествен-

ного исследований переходных процессов в целом ряде импульс-

ных устройств.

Для анализа и расчета переходных процессов в линейных им-

пульсных устройствах можно использовать известные методы:

классический, операторные, основанные либо на Л-преобразова-

нии (преобразовании Лапласа), либо на /-преобразовании, спект-

ральный (частотный), основанный на преобразовании Фурье, ме-

тод интеграла свертки (временной метод).

Все они тесно связаны друг с другом. В дальнейшем будем

пользоваться тем или иным методом в зависимости от того, ка-

ким из них можно наиболее быстро и наглядно получить решение

поставленной задачи. Подробное изложение этих методов, а так-

же методов расчета стационарных режимов и эквивалентных пре-

образований линейных цепей имеется в курсе теории линейных це-

пей [16]. Здесь же только отметим, что при изучении многих им-

пульсных устройств приходится иметь дело с переходным процес-

сом в цепи, описываемой дифференциальным уравнением первого

порядка xdxIdt-^-x^t) =z(t), где x(t) —искомая функция времени

(напряжение, ток); т — постоянная времени цепи; z(t)—напря-

жение (ток) внешнего источника или известная функция этого на-

пряжения (тока). Такие цепи называются цепями первого по-

рядка.

Подобными уравнениями, в частности, описываются переход-

ные процессы в цепях, содержащих наряду с активными сопротив-

лениями и внешними источниками один реактивный элемент — ем-

кость или индуктивность.

Общее решение уравнения можно представить в виде %(/) =

=х\ (0+х2(0, где *1(0—частное решение указанного уравне-

ния; х2 (/)—общее решение однородного уравнения xdx2(t)fdt+

+^2 (/) =0.

Как известно, х2(/) =A^pt, где А — произвольная постоянная;

р= — 1/т — корень характеристического уравнения тр+1 = 0.

Следовательно, x2(t) =Ae~t/x и x(t) =Xi(t)-}-Ae-t/x.

Характер частного решения x{(t) зависит от правой части

уравения z(t), т. е. от характера внешних воздействий.

Покажем важный для рассматриваемых ниже импульсных уст-

ройств случай, когда источники, действующие в цепи при /^0, яв-

ляются источниками постоянного напряжения (тока) и, следова-

тельно, z(t) =z0=const. Частное решение xJZ) тогда также бу-

дет постоянным, так как при Xi = z0 приведенное выше уравнение

превратится в тождество. Если положить в выражении для x(t)

/=оо, получим х(оо)=х1, т. е. Xi равно, как и следовало ожи-

дать, значению искомой функции (напряжения, тока) в устано-

вившемся режиме. Последнее всегда можно определить известны-

ми методами теории линейных цепей (методами законов Кирхго-

фа, контурных токов, эквивалентного генератора и т. п.).

8

Таким образом, x(t) =х(оо)-(-Ае_(/т. Положив здесь /=0, най-

дем А=х(0)—х(оо) и

X (t) = X (со) + [X (0) - X (оо)] е-//т. (1.1)

Таким образом, если в цепи пер-

вого порядка действуют лишь ис-

точники постоянного напряжения

(тока), то можно записать выраже-

ние x(t) для любого напряжения

(тока) в переходном процессе в це-

пи согласно (1.1), предварительно

определив начальное х(0) и устано-

вившееся значение х(оо) и постоян-

ную времени цепи т, что, как пра-

вило, не вызывает никаких затруд-

нений.

Рис. 1.1

Определим теперь интервал вре-

мени \t=t"—t', в течение ко-

торого экспоненциально изменяющаяся функция х(1) (напряже-

ние, ток) возрастает (или убывает) от уровня x(t') до x(t")

(рис. 1.1).

Согласно (1.1) x(t') =х(оо) + [х(0)—x(oo)]e-r/t, откуда

, . X (оо) — X (0) 1 X (оо) — X (0)

t =т1п——--------; аналогично Г = т1п ——------------.

X (оо) — X ((') X (оо) — X (Г)

Следовательно,

Д/ = Г—f = т1п

X (оо) — х (Г)

Х(оо)-Х(0

(1.2)

Этой формулой будем широко пользоваться при определении

длительностей импульсов, фронтов и различных временных интер-

валов.

В качестве примера найдем длительность установления /ф на-

пряжения (тока), изменяющегося по экспоненциальному закону от

начального х(0) до установившегося х(оо) уровня. Если выбрать

10%-ные уровни отсчета, то х(Г) =х(оо) +0,1[х(0)—х(оо)]; x(f) =

=х(оо)+0,9[х(0)—х(оо)], и согласно (1.2)

/ф = т In (0,9/0,1) 2,2 т. (1 .За)

Если приняты 5%-ные уровни отсчета, то

/ф = т1п (0,95/0,05) Зт, (1.36)

а для 1%-ных уровней

^4,6т. (1.3в)

1.2. ЯС-ЭЛЕМЕНТЫ

Свойства /?С-элементов. В импульсных устройствах широко

применяются линейные электрические цепи первого порядка, со-

стоящие из резисторов и конденсаторов. Рассмотрим некоторые

свойства этих цепей. Простейшая 7?С-цепь представлена на рис.

9

1.2а. Пусть на ее вход при /=0 подается

uBx(0 =е 1 (0, где

(1 при t > 0.

перепад напряжения

Согласно (1.1) при нулевых начальных условиях напряжения

uR(t) на резисторе и uc(i) на конденсаторе изменяются при /^0

по экспоненциальным законам: uR(t) = Ee~tlx Uc(t) =Е(1—е_(/т),

где x=RC — постоянная времени цепи.

Рис. 1.2

Временные диаграммы напряжений представлены на рис. 1.26.

Длительность установления напряжения зависит от величины т

и согласно (1.3) /ф=3т (при отсчете на 5%-ных уровнях) или

/ф=2,2т — при отсчете на 10%-ных уровнях.

Рассмотрим теперь реакции /?С-цепи при воздействии на ее

вход прямоугольных импульсов иВх(0 (рис. 1.3а). С этой целью

представим аВх(0 с помощью двух перепадов напряжений (рис.

1.36) и методом наложения определим форму напряжений uc(t)

и uR(t).

На рис. 1 .Зе, г приведены построенные указанным методом

временные диаграммы напряжений uc(t) и uR(t) при различных

соотношеЕиях между постоянной времени цепи т и длительностью

входного импульса ta. Из рис. 1.3в следует, что при малом по

сравнению с t„ значении т форма напряжения на емкости uc(t)

оказывается близкой к форме входных импульсов При

т//и<?0,03 длительность фронта напряжения ыс(^)> равная

Зт, оказывается меньшей /И/Ю, и форма входного импуль-

са может считаться практически прямоугольной. При увеличении

т//и длительность фронта uc{t) растет и при т//и>0,3 напряжение

ис(/) не успевает за время /и возрасти до стационарного значе-

ния. Форма uc(t) оказывается при этом близкой к пилообразной.

При дальнейшем увеличении x/ta амплитуда напряжения ис(/)

уменьшается.

Из рис. 1.3г следует, что при больших значениях x/tK форма

напряжения uR(t) на резисторе оказывается близкой к форме

10

uBX(t). При этом наблюда-

ется завал вершины импуль-

са uR(t) и отрицательный

выброс после его окончания.

Уровни завала и отрицатель-

ного выброса уменьшаются

при увеличении отношения

т//и- При малых значениях

отношения т//и напряжение

uR(t) представляет собой

два импульса остроконечной

формы, начала которых сов-

падают по времени с пере-

падами входного напряже-

ния и имеют полярность этих

перепадов. Амплитуда им-

пульсов оказывается равной

амплитуде Е входного нап-

ряжения, а длительность Зт

(или 2,2 т).

Дифференци р у ю щ а я

цепь. Из проведенного рас-

смотрения видно, что при ма-

лой постоянной времени цепи

т^/и на резисторе 7?С-цепи

получаются два импульса

остроконечной формы и че-

редующейся полярности, на-

чала которых совпадают во

времени с перепадами вход-

ного напряжения; амплиту-

да выходных импульсов рав-

на перепаду входного напря-

жения £, а их длительность

41.вых^ Зт=ЗТ?С. При малых

т /и.вых*С^и.вх (рис. 1.4). Таким образом, такая ЛС-цепь выполняет

задачу укорочения импульсов.

Следует отметить, что форма импульсов на выходе укорачива-

ющей цепи, показанная на рис. 1.46, имеет место лишь при иде-

альных условиях: бесконечно малой длительности фронтов перепа-

дов входного напряжения, нулевом сопротивлении генератора

входного напряжения и отсутствии паразитных емкостей. В неи-

деальных условиях [9, 10] имеет место большее или меньшее ис-

кажение формы выходных импульсов (растяжка фронта и среза,

уменьшение амплитуды, увеличение длительности).

Заметим, что укорачивающую /?С-цепь называют также диффе-

ренцирующей. Это объясняется тем, что при /</и.вх, когда вход-

ное напряжение ивх(/) постоянно, выходное напряжение цВых(0 в

большей части интервала /и.вх равно нулю.

11

Вообще говоря, дифференцирующей цепью (дифференциато-

ром) называют цепь (или устройство), предназначенную для полу-

чения выходного напряжения мВых(0> пропорционального произ-

водной ВХОДНОГО «вх(0:

«вых (0 = т duBI (f)/dt (1.4)

или в операторной форме

^вЫх(Р) = РТ^Вх(Р). (1.5)

где t/вых(р) и t/BX(p)—изображения (по Лапласу) функций

Для /?С-цепи (см. рис. 1.2а) можно записать изображение на-

пряжения на резисторе R в виде UBbiK(p) =pxUBX(p)/l +рт, причем

здесь x=RC. Если, однако, выполняется условие |рт| 1, то мож-

но приблизительно считать справедливыми (1.4) и (1.5). Для сиг-

налов с ограниченным спектром этому условию соответствует тсо<С

<С 1 для всех частот спектра. Для сигналов с неограниченным

спектром это условие не может быть выполнено для всех частот

спектра, что приводит к дополнительным погрешностям при диф-

ференцировании таких сигналов. Чем меньше т, тем точнее RC-

цепь выполняет функции дифференцирующей.

Применение обычного усилителя после дифференцирующей це-

пи позволяет увеличить амплитуду выходного напряжения, но не-

линейность характеристик транзисторов, нестабильность коэффи-

циентов усиления и инерционность транзисторов приводят к сни-

жению точности дифференцирования. Более точные результаты по-

лучаются при использовании в качестве дифференциаторов так на-

зываемых операционных усилителей.

Интегрирующая цепь. Из приведенного выше рассмотрения (см.

рис. 1.3) ясно, что чем больше постоянная времени ^С-цепи (т^>.

^>/и.вх), тем большую длительность /и.вых имеет импульс, форми-

12

руемый на конденсаторе С (рис. 1.5). Другими словами, при т^>

^^и.вх длительность выходного импульса — импульса на конден-

саторе С будет /и.вых^^и.вх- Поэтому говорят, ЧТО RC-ЦвПЬ с боль-

шой постоянной времени является расширяющей цепью.

Расширяющую цепь часто называют также интегрирующей] это

обусловлено тем, что при /^7и.вх выходное напряжение (напряже-

ние на конденсаторе С 7?С-цепи) нарастает почти по линейному

закону (так как т^>/и.вх), если входное напряжение постоянно;

при />/и.вх выходное напряжение спадает медленно и в течение

относительно длительного времени остается постоянным и прибли-

зительно равным тому значению, которое было достигнуто за вре-

мя /и.ВХ*

Вообще говоря, интегрирующей цепью (интегратором) называ-

ют цепь (или устройство), предназначенную для выполнения опе-

рации интегрирования, т. е. для получения выходного напряжения

г/вых (О, пропорционального интегралу от входного нВх(0:

t

^вых (0= f ^вх (0 (1*6)

Т J

о

или в операторной форме

^вых(Р) = -^ ^вх(р), (1.7)

рт

где 1/т—коэффициент пропорциональности.

Для /?С-цепи (см. рис. 1.2) можно записать изображение вы-

ходного напряжения (напряжения на конденсаторе) £/Вых(р) =

^вх(р)/(рт+1), причем x=iRC. Если, однако, выполняется условие

|рт|^>1, то можно приблизительно считать справедливым (1.6),

(1.7). Этому условию соответствует сот^>1, которому должны

удовлетворять частотные составляющие спектра входного сигнала,

чтобы ошибки интегрирования были невелики. Чем больше по-

стоянная времени цепи т, тем точнее /?С-цепь выполняет функции

интегрирования. Однако с увеличением т уменьшается амплитуда

выходных импульсов. Для обеспечения высокой точности интегри-

рования при больших амплитудах выходного сигнала применяют-

ся операционные усилители (см. § 1.3).

Другие применения 7?С-элементов. RC-цепи применяются также

в качестве основных компонентов элементов задержки (см. § 3.6),

в качестве разделительных цепей (не пропускающих постоянной

составляющей напряжения от одного каскада к другому), в ка-

честве цепей связи между каскадами (например, для ускорения

переходных процессов, см. § 2.3) и т. д.

1.3. ОПЕРАЦИОННЫЕ УСИЛИТЕЛИ

Как известно из курса усилителей, операционный усилитель

(ОУ) — это высококачественный усилитель постоянного тока с

большим коэффициентом усиления и обычно с дифференциальны-

ми входами (рис. 1.6а, б, в). На оба входа ОУ — инвертирующий

13

и неинвертирующий — могут подаваться сигналы различного уров-

ня и полярности; в частном случае один из входов может быть за-

землен. Основными свойствами ОУ являются: большое входное со-

противление (десятки или сотни килоом), обеспечиваемое входным

дифференциальным каскадом ОУ; малое выходное сопротивление

(сотни ом); высокий коэффициент усиления по напряжению (де-

сятки или сотни тысяч); выходное напряжение ОУ равно нулю при

нулевых входных сигналах (отклонение мВЫх от нуля при упомя-

нутых условиях невелико — десятки микровольт — и является

сшибкой ОУ; принимаются меры к уменьшению или устранению

этого отклонения).

Напряжение мВых на выходе ОУ зависит от разности входных

напряжений — дифференциального входного напряжения цд=

= ^+вх—Эта зависимость wBMx=f(w+BX—и~ът) =f (ид) имеет

форму, близкую к кусочно-ломаной. На рис. 1.66 приведены пере-

даточные характеристики ОУ; изменение напряжения на одном из

входов приводит к сдвигу передаточной характеристики по друго-

му входу.

Инвертирующий

Рис. 1.6

Линейный режим ОУ имеет место при малых входных сигна-

лах; диапазон |ид| в линейной области исчисляется долями или

единицами милливольт, а коэффициент усиления Ко в этой облас-

ти весьма велик (например, Ко=Ю5).

При достаточно больших значениях входного дифференциально-

го напряжения имеет место режим ограничения выходного напря-

жения:

14

^ВЫХ —

Е+~Е sign и+ при и+ > и~

Е-^Е sign и- при «+ < и-

где Е — имеет значение, близкое к величине напряжения источни-

ка питания ОУ. Во многих случаях при анализе устройств на ОУ

удобно пользоваться идеализированной моделью ОУ для линейно-

го режима работы; в этой модели принимается коэффициент уси-

ления /Со=°°, дифференциальное входное напряжение нд~0, вход-

ное сопротивление (т. е. отношение приращения входного напря-

жения к полученному в результате приращению входного тока)

/?вх=°°> выходное сопротивление /?Вых~0. Передаточная характе-

ристика идеализированной модели ОУ приведена на рис. 1.6в.

В различных применениях используются включение цепей об-

ратной связи (ОС) в ОУ. Пример схемы с отрицательной обратной

связью (ООС) приведен на рис. 1.7а. Здесь при любом авх уста-

Рис. 1.7

навливается такое значение мВЫх, чтобы iz_BI~u+BX~0; если ыВх>

>0, то получается иВых<0 и наоборот. Полагая входное сопро-

тивление ОУ по инвертирующему входу бесконечно большим, по-

лучаем й=12, «вых=—= и, следовательно, коэффи-

циент передачи напряжения в рассматриваемой схеме А~=

== ^вых/авх =—R2/Rl-

Аналогичные рассуждения приводят к выводу, что схема на

рис. 1.76 выполняет роль дифференцирующей цепи «Вых=

=—RCdu^ldt. Если в этой схеме поменять местами резистор и кон-

денсатор, то она будет выполнять роль интегрирующей цепи:

^вых = У

В импульсных устройствах широко применяются ОУ, охвачен-

ные положительной обратной связью; пример такой схемы пока-

зан на рис. 1.7в. Используя идеализированную модель ОУ, нахо-

дим и+вх=Ывых^4/(Яз+^4). Наличие положительной обратной свя-

зи и релейный характер зависимости мВых=/(ив1) (рис. 1.6в) дает

15

возможность применения ОУ для построения таких рассматривае-

мых в последующих разделах импульсных устройств, как триггеры

и мультивибраторы.

В заключение для примера приведем порядок значений элект-

рических параметров усилителя 140УД2: Двх=300 кОм, /?Вых=

= 100 Ом, коэффициент усиления напряжения Ло^35-1О3, выход-

ное напряжение Е-^10 В, £7Ист= 12,6 В.

В настоящее время выпускаются ОУ со значительно лучшими

электрическими параметрами, в частности, ОУ с большими вход-

ным сопротивлением, коэффициентом усиления, быстродействием и

меньшими потреблением мощности и дрейфом нуля.

Глава 2

ТРАНЗИСТОРНЫЕ КЛЮЧИ

И ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

2.1. ОСНОВНЫЕ ПОНЯТИЯ

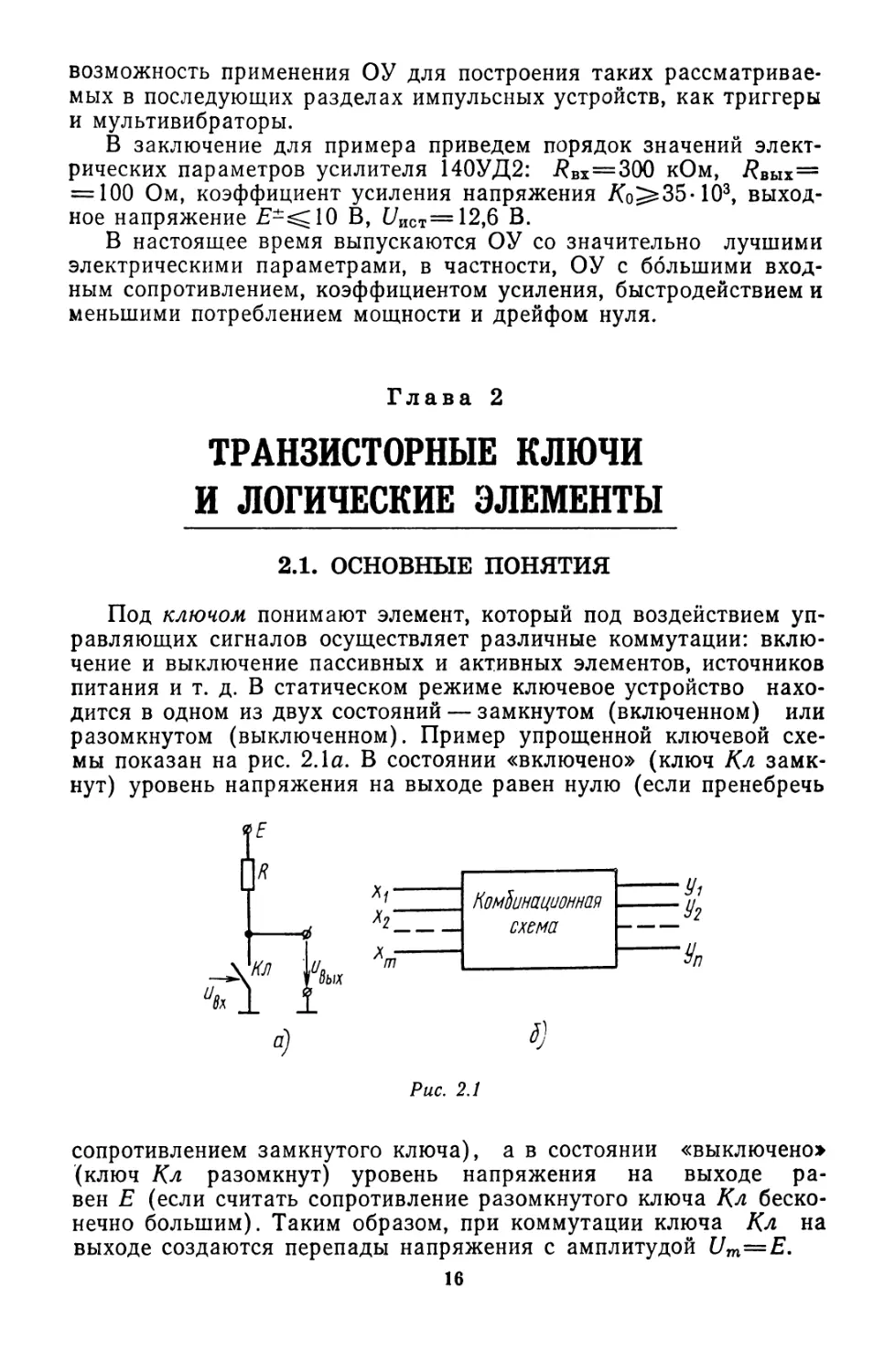

Под ключом понимают элемент, который под воздействием уп-

равляющих сигналов осуществляет различные коммутации: вклю-

чение и выключение пассивных и активных элементов, источников

питания и т. д. В статическом режиме ключевое устройство нахо-

дится в одном из двух состояний — замкнутом (включенном) или

разомкнутом (выключенном). Пример упрощенной ключевой схе-

мы показан на рис. 2.1а. В состоянии «включено» (ключ Кл замк-

нут) уровень напряжения на выходе равен нулю (если пренебречь

Рис. 2.1

сопротивлением замкнутого ключа), а в состоянии «выключено»

(ключ Кл разомкнут) уровень напряжения на выходе ра-

вен Е (если считать сопротивление разомкнутого ключа Кл беско-

нечно большим). Таким образом, при коммутации ключа Кл на

выходе создаются перепады напряжения с амплитудой Um=E.

16

Если управляющий ивх и выходной иВыХ сигналы являются циф-

ровыми двоичными сигналами, информационные значения которых

обозначены соответственно через х и у, то можно сказать, что у

есть некоторая функция х — так называемая логическая или пере-

ключательная функция: у=/(х), причем у=1 при определенном

значении х (0 или 1) и у=0 при другом значении х. Иногда эту

функцию называют также булевой.

В общем случае переключательные функции реализуются логи-

ческими (комбинационными) элементами (ЛЭ), имеющими rn^l

входов I! выходов (рис. 2.16). В комбинационных элементах,

в отличие от другого класса цифровых устройств — конечных авто-

матов (последовательностных схем) (см. гл. 4), информационные

значения у} (/=1, 2,..., п) выходных сигналов в статическом ре-

жиме зависят только от информационных значений хг- (i=l, 2,...,

..., m) входных сигналов, т. е. логический элемент реализует на

каждом выходе некоторую функцию

yj = fj(xlt х2...хт), /=1, 2......п, (2.1)

причем уi=l при некоторых определенных значениях аргументов

Xi и У] = 0 при других значениях хг-, где Xi могут в свою очередь

принимать лишь значения 1 или 0. Напомним, что мы условились

цифрой 1 кодировать высокий уровень напряжения Е1 или наличие

импульса, а цифрой б — низкий уровень напряжения Е° или отсут-

ствие импульса.

Функцию типа (2.1) задают в виде таблицы информационных

значений Хг и r/j, называемой переключательной таблицей, или

таблицей истинности.

Одновходовый ключ может реализовать переключательную

функцию одной переменной х:у=Цх). Очевидно, что здесь воз-

можны два варианта. Первый вариант (табл. 2.1) реализуется

ключом-повторителем у=х\ информационные значения выходного

сигнала равны информационным значениям управляющего сигна-

ла; второй вариант (табл. 2.2) реализуется ключом-инвертором

Таблица 2.2

Таблица 2.1

X У

0 1 0 1

Таблица 2.3

X. 1 У

0 0 1 1 0 1 0 1 0 0 0 1

(логическим элементом НЕ) у—х (читается «не х>): информаци-

онные значения выходного сигнала обратны значениям управляю-

щего^сигнала. Говорят, что инвертор реализует логическую функ-

цию НЕ или инверсию — отрицание входного сигнала (рис. 2.2а).

Теперь рассмотрим основные переключательные (логические)

функции для многовходовых элементов. Элемент с пг>\ входами

и одним выходом (рис. 2.26) называется конъюнктором, иначе —

17

логическим элементом И, если он реализует следующую логиче-

скую функцию (операцию): сигнал 1 на выходе у имеет место тог-

да и только тогда, когда поданы сигналы 1 на все входы Xi, х2,...,

..., xm одновременно; если хотя бы на один из входов подан сигнал

О, то на выходе также будет 0. Работа элемента И на два входа

Рис. 2.2

Xi, х2 описывается переключательной табл. 2.3, которая определяет

функцию у=^(%1, х2). Как видно из таблицы, у=\ только в слу-

чае, когда xi=l и х2=1. Функция y=/(xi, х2) называется логиче-

ской функцией И или конъюнкцией (логическим умножением) и

записывается в виде у=х\х2 или у=х\/\х2\ аналогично функция

И для m переменных xi, х2,..., хт: у=х\Х2... хт.

Заметим, что элемент И на два входа часто называют вентилем

(клапаном); этот элемент работает как ключ, который пропускает

или не пропускает сигнал, поступающий на один из входов (на-

пример, на вход Xi, называемый в этом случае сигнальным) в за-

висимости от того, подан или нет разрешающий сигнал на другой,

управляющий вход (например, на х2).

Схема с m входами хь х2,..., хт и одним выходом у (рис. 2.2в)

называется дизъюнктором, иначе логическим элементом ИЛИ, ес-

ли она реализует следующую логическую функцию (операцию):

сигнал 1 на выходе имеет место, если хотя бы на одном из входов

действует сигнал 1; сигнал на выходе 0 только в том случае, если

на все входы поданы сигналы 0.

Работа элемента ИЛИ на два входа xi, х2 описывается пере-

ключательной табл. 2.4. Эта таблица определяет функцию у=

=/(xi, х2), которая называется логической функцией ИЛИ, иначе

дизъюнкцией (логическим сложением), и записывается в форме

y=Xi+x2 или y=X\\JХ2. Аналогично можно записать функцию

ИЛИ для m переменных у=Х\ V х2 V • • • V хт-

Заметим, что логические элементы И и ИЛИ обладают свойст-

вом двойственнрсти, которое заключается в том, что один и тот же

элемент в зависимости от способа кодирования уровней сигналов

через 0 и 1 может выполнять функции либо элемента И, либо

ИЛИ; для доказательства этого положения достаточно сравнить

переключательные табл. 2.3 и 2.4. Следовательно, если данный эле-

18

мент выполняет функцию И для высоких уровней, то он одновре-

менно может выполнять функцию ИЛИ для низких уровней. Нао-

борот, элемент ИЛИ, выполняющий функцию для высоких уров-

ней, может выполнять роль элемента И для низких уровней.

Таблица 2.4 Таблица 2.5 Таблица 2.6

х2 1 х, 1 У *2 xi У X, 1 1 1 У

0 0 0 0 0 1 0 0 1

0 1 1 0 1 1 0 1 0

1 0 1 1 0 1 1 0 0

1 1 1 1 1 0 1 1 0

Элементы, реализующие функции И, ИЛИ, НЕ, являются ос-

новными в том смысле, что с помощью их можно создать ключевое

устройство, реализующее сколь угодно сложную логическую функ-

цию типа (2.1). Более того, можно показать, что для построения

сколь угодно сложных логических цепей достаточно использовать

только два элемента из трех основных, а именно: И и НЕ или

ИЛИ и НЕ. Каждую пару указанных элементов можно объеди-

нить и получить универсальный логический элемент, с помощью

которого можно построить любую переключательную схему. Эле-

мент И — НЕ на два входа работает в соответствии с переключа-

тельной табл. 2.5; как видно, здесь информационное значение вы-

ходного сигнала является отрицанием (инверсией) логического

произведения входных сигналов: y=xix2. Второй универсальный

элемент ИЛИ—НЕ на два входа работает в соответствии с табл.

2.6; здесь у=х{\/ х2. Естественно, что элементы И—НЕ и ИЛИ —

НЕ могут иметь не два, а т^2 входов (рис. 2.2г, д).

Широко применяется и универсальный логический элемент И—

ИЛИ — НЕ; этот элемент реализует, например, для четырех пере-

менных Xi, х2, х3, х4 функцию вида (рис. 2.2е) y=XiX2 V *3X4.

Теперь уточним понятие функции, определяемой равенством

(2.1): под /j понимается некоторое логическое выражение, содер-

жащее логические переменные (т. е. переменные, принимающие

лишь два возможных значения: 0 или 1), соединенные знаком ло-

гического сложения, умножения и отрицания. При этом можно рас-

сматривать равенство (2.1) как структурную формулу, определяю-

щую структуру логического элемента, реализующего заданную ло-

гическую функцию. Эта цепь состоит из элементов И, ИЛИ, НЕ,

соединенных в соответствии со структурной формулой. Обычно ло-

гическая функция задается таблицей истинности. При этом струк-

турная формула записывается либо в так называемой совершенной

дизъюнктивной нормальной форме (СДНФ), либо совершенной

конъюнктивной нормальной форме (СКНФ). Первая (СДНФ)

представляет собой логическую сумму (т. е. дизъюнкцию) несколь-

ких логических произведений (конъюнкций), каждое из которых

содержит все переменные (или их отрицания), например, у=

19

=Х1%2 V *1*2; СКНФ представляет собой конъюнкцию нескольких

дизъюнкций, каждая из которых содержит все переменные (или их

отрицания), например у= (xi V *2) (*1 Vxs). С помощью таблицы

истинности СДНФ логической функции записывается следующим

образом: составляется дизъюнкция конъюнкций всех независимых

переменных; число конъюнкций равно числу единичных наборов

таблицы, т. е. числу строк таблицы, где функция равна 1, знак ин-

версии ставится над теми переменными, которые в соответствую-

щих наборах равны нулю.

Например, для табл. 2.7 (в первом столбце таблицы записаны

номера наборов) СДНФ логической функции содержит три конъ-

юнкции: (/ = *3*2*1 V *3*2*1 V *3*2*Ь

Таблица 2.7

Номер набора 1 X, ха *1 У 1 1 Номер набора 1 X, 1 X. У

0 0 0 0 1 4 1 0 0 0

1 0 0 1 0 5 1 0 1 0

2 0 1 0 0 6 1 1 0 0

3 0 1 1 1 7 1 1 1 1

Структурная формула в СКНФ записывается в виде конъюнк-

ции дизъюнкций всех независимых переменных; число дизъюнкций

равно числу нулевых наборов (т. е. числу строк, где функция рав-

на 0); над теми переменными, которые в соответствующих набо-

рах равны 1, ставится знак инверсии.

Например, для табл. 2.7 СКНФ логической функции будет у=а\

= (*3 V *2 V*l) (-^3 V *2V^1) (*3 V*2V *1) (*3 V Х2 V *1) (*3 V *2 V *1)-

Как видно, любая сколь угодно сложная логическая функция мо-

жет быть выражена с помощью логических операций И, ИЛИ, НЕ

и, следовательно, может быть реализована с помощью комбинации

соответствующих логических элементов. Поэтому совокупность ло-

гических элементов И, ИЛИ, НЕ представляет собой функцио-

нально полную систему элементов или базис.

Структурные формулы могут быть подвергнуты различного ро-

да преобразованиям с тем, чтобы упростить (или минимизировать)

их запись с точки зрения, например, числа используемых логиче-

ских операций; при этом логическая функция будет реализована с

помощью меньшего числа логических элементов. Такие преобразо-

вания осуществляются на основе законов алгебры логики: пере-

местительного х\/ у=у\/ х, ху=ух\ сочетательного (*V//)VZ=:

=*VG/V 2)‘> (**/)z=*((/z); распределительного z(x\/у) =хг V yz,

(?V*) (z\Jy)—z\Jxy\ закона отрицания х\/y=xy, xy=x\/y, Для>

одной переменной справедливы соотношения: х\/0=*, * V 1= 1

х\/ х=х, х-0=0, х-1=х, х-х=х, х=х; удобны также тождест-

ва— правила поглощения: х\/ху=х, *(*Vf/)=x> правила склеи-

вания xy\J ху=х, (х\/у) (х\/у) =х и др.

Справедливость упомянутых законов может быть легко уста-

новлена непосредственной проверкой (придавая переменным х, у,

20

z произвольные значения 0 или 1); справедливость тождеств выте-

кает из основных законов и также может быть установлена непо-

средственной проверкой.

Заметим, что на основе теорем алгебры логики разработаны

специальные методы, формализующие процесс упрощения струк-

турных формул (метод карт Карно, метод Квайна — Мак-Класки

и др. [3, 14]). Рассмотрим теперь запись структурных формул в ба-

зисах И—НЕ, ИЛИ—НЕ, И—ИЛИ—НЕ.

Запись структурной формулы в базисе И—НЕ

по таблице истинности производят в следующем порядке: состав-

ляют СДНФ функции или упрощенную (минимизированную) дизъ-

юнктивную нормальную форму (ДНФ), над полученным выраже-

нием ставятся два знака отрицания и, применяя закон отрицания

и другие теоремы и тождества, переходят к базису И—НЕ. При

этом часто полезны соотношения: х=х, х=х-1, xy\J ху = ххууху9

ху=х ху.

Например, пусть ДНФ функции имеет вид: у=х2Х\ \JХъХ\. Ста-

вим два знака инверсии: y=xzX\\Jх$х\ — и используем закон отри-

цания: у = Х2Х\Х$Х\=Х2- 1 Х1- 1 -Хз*1 • 1.

Запись структурной формулы в базисе ИЛИ—

НЕ производят в следующем порядке: составляют конъюнктивную

нормальную форму (КНФ) логической функции, над полученным

выражением ставятся два знака отрицания, переходят к базису

ИЛИ—НЕ; при этом часто полезны соотношения х\/у—х\/ х\/у;

х=х\/0\ x=x\Jх, (x\Jy) (х\/у) = x\Jx\Jy\Jx\Jy\Jу. Для записи

структурной формулы в базисе И—ИЛИ—НЕ целесообразно пред-

ставить в виде ДНФ структурную формулу для инверсной логиче-

ской функции у и затем осуществить инверсию полученного выра-

жения.

Например, пусть у=х3Х2 тогда y=x3x2\J xzX\ =

= х3-х2-1 V 0»О V Х1-Хз-1\/00, где использовано соотношение ху=

=ху V 0- г; z — произвольная функция.

Заметим, что все упомянутые выше ключевые устройства реа-

лизуют логические функции (2.1) и их называют логическими или

комбинационными элементами (см. гл. 4); в этих элементах вы-

ходной сигнал в фиксированный момент времени (без учета пере-

ходных процессов) зависит только от комбинации информацион-

ных значений входных сигналов в этот же момент времени.

Другой класс переключательных схем составляют конечные ав-

томаты (последовательностные устройства) (см. гл. 4), которые

содержат элементы памяти (линии задержки, триггеры и т. п.);

информационное значение выходных сигналов автомата в момент

времени t определяется информационными значениями сигналов,,

поступивших на его вход в этот момент времени, и внутренним со-

стоянием автомата, т. е. его состоянием в предшествующий момент

21

времени. Примерами конечных автоматов являются рассматривае-

мые ниже различного типа триггеры.

Для построения комбинационных логических элементов и ко-

нечных автоматов используются в настоящее время преимущест-

венно различного рода полупроводниковые компоненты (транзис-

торы, диоды) как дискретные, так и интегральные.

2.2. НАСЫЩЕННЫЙ ТРАНЗИСТОРНЫЙ

КЛЮЧ-ИНВЕРТОР

Схема. В ключевых устройствах используются как биполярные

транзисторы с плоскостными переходами типов п-р-п и р-п-р, так

и униполярные транзисторы преимущественно типа МДП (или

МОП) — транзисторы (МДП — металл — диэлектрик — полупро-

водник; МОП — металл — окисел — полупроводник). В транзис-

торных ключах на дискретных компонентах применяются транзис-

торы типа р-п-р и реже типа п-р-п; в ключах же на интегральных

компонентах используются, как правило, кремниевые транзисторы

типа п-р-п и МДП-транзисторы.

В импульсных и цифровых устройствах находят применение все

основные схемы включения транзистора — ОЭ (с общим эмитте-

ром), ОБ (с общей базой), ОК (с общим коллектором) —эмиттер-

ный повторитель, «звезда» (ни один из электродов транзистора не

заземлен), инверсная схема включения.

Однако наибольшее распространение получили схемы с общим

эмиттером, которые и рассматриваются ниже. Для этих схем ха-

рактерно, что коэффициенты усиления тока и напряжения больше

единицы (усилитель мощности) и, кроме того, они инвертируют

уровни сигналов: высокому уровню Д1 входного сигнала соответ-

ствует низкий уровень Д° выходного и наоборот, т. е. схема ОЭ вы-

полняет логическую функцию инвертора, элемента НЕ.

Особенности ключей других типов (ОБ, ОК) будут отмечены да-

лее лишь в той мере, в какой это необходимо для понимания

принципов работы некоторых импульсных устройств.

В связи со все более широким внедрением ИС будем далее рас-

сматривать схемы на базе биполярных транзисторов типа п-р-п;

переход к схемам на транзисторах типа р-п-р сводится к измене-

ниям полярностей включения источников питания на обратные и

полярности сигналов; когда такой переход связан с какими-либо

другими схемными и расчетными изменениями, они особо оговари-

ваются.

В ключевых устройствах транзистор в статическом режиме ра-

ботает в одном из двух граничных состояний, соответствующих

уровням сигнала Е° и Е1. В одном граничном состоянии транзис-

тор открыт и на выходе формируется низкий уровень сигнала Е°;

при этом транзистор может работать как в активном режиме, так

и в режиме насыщения — соответственно говорят о ненасыщенных

и насыщенных транзисторных ключах. В другом граничном состоя-

нии транзистор работает вблизи или в самом режиме отсечки (за-

22

пирания) и на выходе формируется высокий уровень сигнала

Вначале рассмотрим насыщенные транзисторные ключи на дис-

кретных и интегральных компонентах. Схемы ключа на дискретных

компонентах приведены на рис. 2.3 (рис. 2.3а — схема на транзис-

торе типа п-р-п, рис. 2.36 — на транзисторе типа р-п-р); там же

Рис. 2.3

указаны выбранные положительные направления отсчета токов iKT

i&9 и напряжений аб.э, Иб.ю ик.э; напряжения на коллекторе и ба-

зе относительно эмиттера будем обозначать соответственно через

ик и U6-

Модели транзисторов. Для исследования и расчетов транзисторных ключей

используются известные из курса электронных приборов модели транзистора —

эквивалентные схемы, уравнения Эберса—Молла, в которых токи ia, iK, ie выра-

жены как явные функции напряжений на переходах транзистора. Упомянутые

эквивалентные схемы содержат нелинейные элементы (диоды), представляющие

коллекторные и эмиттерные переходы, а взаимодействие между переходами от-

ражено включением генераторов тока (например, генератора тока 01б — парал-

лельно диоду, представляющему коллекторный переход в схеме ОЭ).

Для графоаналитического расчета транзисторных схем используются различ-

ные семейства статических характеристик транзисторов; семейство типичных вы-

ходных и входных статических характеристик транзистора приведено на рис. 2.4.

При этом обычно нелинейные характеристики транзисторов аппроксимируются

кусочно-линейными, и в расчетах учитываются усредненные сопротивления. Так,

например, входная характеристика транзистора в схеме ОЭ имеет вид (рис. 2.5а)

7бо при иб < t/nop,

(2 2У

(“б.э~ + при иб э > t/nop.

23

»б =

где /бо — базовый ток запертого транзистора; в кремниевых ИС часто прини-

мают /бо=О (рис. 2.56); Явх.э — усредненное входное сопротивление; t/пор —

порог входного (Ыб.э) напряжения, при котором отпирается транзистор; для ди-

скретных германиевых транзисторов (и диодов) t/nop«0,l В, но часто прини-

мается в расчетах t/nop = 0; в интегральных биполярных кремниевых транзисто-

рах t/пор» 0,6 В. Аналогичную кусочно-линейную характеристику имеют полу-

проводниковые диоды. Обычно диоды ИС получают путем диодного включения

транзисторов; примеры таких включений для транзисторов с диэлектрической

изоляцией приведены на рис. 2.6.

1 2 3 4

05 05 05 05 05

Рис. 2.6

В первой и четвертой схемах используется только эмиттерный переход; на-

пряжение пробоя t/проб мало, малы также и обратные токи /обр.макс, определяе-

мые при максимальных обратных напряжениях (так как у эмиттерного перехо-

да малые площадь и ширина). В схемах второй и пятой используется коллек-

торный переход и для них характерны относительно большие значения t/проб и

/обр.макс.

В третьей схеме включены параллельно эмиттерный и коллекторные перехо-

ды, вследствие чего t/обр мало, а обратный ток равен сумме обратных токов

обоих переходов.

Упомянутые выше модели (эквивалентные схемы, уравнения Эберса—Молла)

отражают физические процессы и описывают соотношения между токами и на-

пряжениями не только в дискретных, но и в интегральных транзисторах с ди-

электрической изоляцией. Интегральный же транзистор, изолированный л-р-пе-

реходом, имеет уже не трехслойную п-р-п, а четырехслойную структуру типа

п-р-п-р (рис. 2.7а). Этой структуре можно поставить в соответствие структуру

составного транзистора (рис. 2.76), состоящего из основного типа п-р-п и пара-

зитного типа р-п-р, в котором роль коллекторного перехода выполняет изоли-

рующий л-р-переход. На практике подложка (р—область) транзистора с по-

мощью специального вывода подключается к точке с самым низким потенциа-

лом. Поэтому л-р-переход коллектор—подложка во всех режимах работы тран-

зистора оказывается смещенным в обратном направлении и этим достигается

изоляция транзистора. Однако этот закрытый переход оказывает определенное

влияние на характеристики основного транзистора, что и будет отмечено ниже

при рассмотрении статических и переходных режимов.

24

Указанными моделями можно воспользоваться и для анализа динамических

режимов в транзисторе, если только учесть, что коэффициенты передачи транзи-

стора р, а частотнозависимые. Однако более удобной для этой цели оказывает-

ся модель, отражающая процессы изменения заряда в базе транзистора {21].

—г

Б

пТ—фЗмшптвр (3)

V —$5аза (Б)

77 —^Коллектор (к)

~р -фПодложка (п)

а)

Рис. 2.7

ib(t). Однако постоянная времени накопления заряда

Обозначим через Q заряд неосновных носителей в базе (например, электро-

нов в базе типа р). В первом приближении можно считать, что изменение заря-

да во времени dQjdt обусловлено током базы ie(t) и рекомбинацией неравновес-

ных электронов в базе —Q/т, т. е. dQldt=ib(t)—Q/x или

dQ , Q

-^ + — = *6 (0, (2.3>

dt x

где x — среднее время жизни носителей в базе.

В активной области можно полагать — постоянная времени транзи-

стора, включенного по схеме ОЭ в активном режиме, и (2.3) принимает вид

dQ Q

-^- + ^ = «6(0. [(2.4>

dt

В области насыщения изменение заряда также описывается уравнением, ана-

логичным (2.4):— + — =

dt Th

тв, вообще говоря, отличается от (эффективное время жизни в режиме на-

сыщения отличается от времени жизни в активном режиме, так как в режиме

насыщения распределение неосновных носителей в базе существенно отличается

от распределения в активном режиме). Практически для различных бездрейфо-

вых транзисторов тн= (0,54-1 )т^ а для дрейфовых тн>т^ но часто для про-

стоты принимают тн«Тр. Наряду с (2.4) в основе метода заряда лежит соот-

ношение между зарядом в базе и током коллектора в активном режиме

Q(/)«Ta£K(0. (2.5>

где Ta~l/2rtfa, fа — граничная частота транзистора,

В установившемся режиме при t6=/6=const, как следует из (2.4), С=т^7б.

Различным значениям /б соответствуют различные заряды в базе. В области от-

сечки заряд неосновных носителей в базе незначителен и им обычно пренебре-

гают. С ростом тока базы заряд растет и на границе насыщения при некотором

токе базы /б.н достигает значения фгр=т&/б.н. При дальнейшем увеличении то-

ка базы, т. е. в области насыщения, в базе создается избыточный заряд физб^

= Q—Qrp=Tg (7б—/б.н), степень насыщения характеризуется величиной S=>

-Q/Qrp.

В общем случае при скачкообразном изменении тока базы (рис. 2.8) i6(t/

на значение Д/б в соответствии с (2.4) заряд изменяется по экспоненциальному

25

закону

Q (О = <2 (оо) - [Q (оо) - Q (0)] е '/Т₽ , (2.6)

где Q(0)=Tpie(0); Q(oo) =t^ie(oo) и Q(°o)— Q(0) =тр[1б(<»)— й(0)]=ТрД/в.

По такому же закону согласно (2.5) будет изменяться в активной области

и коллекторный ток. Необходимо указать, что часто при использовании высоко-

частотных транзисторов инерционность ключей, обусловленная процессами накоп-

ления и рассасывания зарядов в базе, относительно невелика и решающую роль

при переключении играют процессы перезаряда паразитных емкостей, в том чис-

ле — коллекторного Ск и эмиттерного переходов Сэ и монтажных емкостей.

Статические режимы. В статических режимах ключа транзис-

тор либо закрыт либо открыт (и, возможно, насыщен).

Транзистор закрыт. Пусть на входе ключа действует

низкий уровень напряжения £° и ключ заперт.

Рассмотрим вначале случай, когда транзистор заперт, т. е. оба

его перехода смещены в обратном направлении. Этот случай,

обычно реализуемый в ключах на дискретных компонентах, имеет

место, если для транзистора типа п-р-п ^б.э^О, Нб.к^О (для тран-

зистора типа р-п-р эти условия запишутся в виде «б.э^О, Нб.к^О).

В режиме отсечки токи базы и эмиттера отрицательны, т. е. текут

в направлениях, обратных выбранным (см. рис. 2.3); при этом по

абсолютному значению токи закрытого транзистора р’б.з|=^к.з+

+14э.з|• Если транзистор несимметричный (т. е. р^> 0/, где pj — ин-

версный коэффициент передачи), то *б.з~—/ко, *к.з~/ко, *э.з~

~0г/ко<С/ко, т. е. практически следует считаться только с обрат-

ным током перехода коллектор — база, приблизительно равным

тепловому коллекторному току при обрыве эмиттера (т. е. при

Ь.з=0); в симметричном транзисторе 4.з~ | *э.з| ~/кю/2; |/б.з| =/ко

(заметим, что в справочниках через /ко обозначают коллекторный

ток, измеренный при определенных значениях коллекторного на-

пряжения).

Ток /ко зависит от температуры. Практически считают, что он

удваивается при увеличении температуры на 10° С.

26

Однако и при высоких температурах тепловой ток кремниевых

транзисторов невелик, и поэтому в ИС им практически пренебре-

гают, т. е. считают, что в режиме отсечки ,3=t6.3=1Э.□=0. Напря-

жение на коллекторе запертого транзистора ик>3=£к—

Заметим, что входное </?Вх.з и выходное /?Вых.з сопротивления

запертого транзистора определяются в основном обратными со-

противлениями эмиттерного и коллекторного переходов и в некото-

рых случаях необходимо их учитывать.

В ИС запирающий уровень £° оказывается положительным

(входное напряжение не может менять знак) и имеет место только

«условное» запирание транзистора (ибэ==Е0<;[/ПОр), когда его

эмиттерный переход смещен в прямом направлении; однако уро-

вень Е° меньше порогового уровня £7ПОр=0,6 В и коллекторный

ток транзистора относительно мал, т. е. составляет лишь единицы

процентов от тока открытого транзистора (при воздействии вход-

ного сигнала Ех). Можно себе представить входную характерис-

тику транзистора ИС с большой «пяткой», как показано на рис.

2.56: при 0<wBx<f/nop эмиттерный переход смещен в прямом на-

правлении, но входной ток весьма мал и соответственно весьма

мал коллекторный ток.

Транзистор открыт. Пусть на входе ключа действует вы-

сокий уровень Е1. При этом ключ включен, транзистор открыт;

возможны две области работы открытого транзистора — активная

область и область насыщения.

В активной области эмиттерный переход смещен в прямом на-

правлении, а коллекторный — в обратном, т. е. ^б.эХ), Иб.к<0

(для транзистора типа р-п-р\ 1/б.э<0, ^б.к>0); заметим, что в

кремниевых транзисторах ИС в активном режиме напряжение на

эмиттерном переходе иб.э~£/акт, причем (7Пор< ^акт< t/нас (рис.

2.9) и t/акт^0,7 В. Напомним, что в активной области коллектор-

ный ток приблизительно линейно зависит от тока базы:

*к = Р1б+(Р+1)Ло = Р*б» ’

*к = «is + /ко ~ «is, Р = а/(1 —а). (2.8)

Токи и напряжения на электродах транзистора можно найти гра-

фоаналитически. Для этого достаточно построить нагрузочную ли-

нию АВ (см. рис. 2.4), соответствующую уравнению EK=iKRK+

+ wK, и найти координаты точки пересечения ее с характеристи-

кой транзистора 4к=/(цк.э, и), соответствующей заданному зна-

чению /б-

В области насыщения оба перехода транзистора смещены в

прямом направлении, т. е. «б.э>0, г/б.к>0 (для транзистора типа

р-п-р\ Цб.э<0, цб.к<0). В области насыщения рост тока базы не

приводит к изменению коллекторного тока и

iK<Pi6* (2.9)

В кремниевых транзисторах ИС напряжение на смещенном в

прямом направлении р-п-переходе равно t/Hac (см. рис. 2.9) и со-

ставляет примерно 0,8 В; у германиевых транзисторов напряжение

на открытом переходе около 0,2—0,4 В.

27

Насыщение транзистора в схеме ключа (см. рис. 2.3) можно по-

лучить увеличением тока базы 1§. При некотором значении /б =

= /б.н рабочая точка достигает положения А (см. рис. 2.4) и даль-

нейший рост тока базы практически уже не приводит к росту кол-

лекторного тока. Поэтому условие насыщения может быть запи-

сано в виде

(2.10)

Коллекторный ток достигает значения /к.н= (Ек—икя)/Кк и, сле-

довательно, /б.н=/к.н/р= (Ек—uK,B)/pRK. Напряжение «к.н пример-

но несколько десятков или сотен милливольт. В ИС обычно икл^

— 0,14-0,2 В. Если Ек^>икл, то

Л<н Ek/Rk, /бнЛ2 EK/fi RK. (2.11)

Степень насыщения транзистора характеризует коэффициент

5 = »б//б.н = ₽»б//к.н. (2.12)

На границе насыщения 1’б=/б.н, S=l. С увеличением коэффи-

циента насыщения ключа увеличивается его нагрузочная способ-

ность (условие насыщения удовлетворяется при большом значении

тока /к.н), уменьшается влияние различных дестабилизирующих

факторов на выходные параметры ключа, но, как показано ниже,

ухудшается быстродействие ключа. Поэтому коэффициент насыще-

ния S во всех случаях следует выбирать из компромиссных сооб-

ражений, исходя из условий конкретной задачи.

Во многих практических расчетах, когда можно пренебречь

межэлектродными напряжениями насыщенного транзистора по

сравнению с питающими; последний рассматривают как «стяну-

тый» в эквипотенциальную точку (точку с единым потенциалом

всех электродов), что естественно упрощает расчеты.

В связи со значительным разбросом параметра 0 у различных

транзисторов, а также зависимостью р от температуры условия

насыщения транзистора должны быть выполнены уже при мини-

мальном значении рМИн-

Амплитуды перепадов напряжения и тока

При переключении транзистора из закрытого состояния в со-

стояние насыщения образуется перепад коллекторного напряжения

U кт= ^к.э ^к.н= Ек 7к0Т?к ^к.н’ (2.13)

Так как «кн и IkoRk обычно малы, UKm достигает значения (0,90—

0,39) Ек, т. е. транзисторный ключ коммутирует почти все напря-

,жч₽ие Ек и в этом смысле приближается к идеальному ключу. Пе-

репад тока при переключении 7Кт=/к.н—/ко~7к.н.

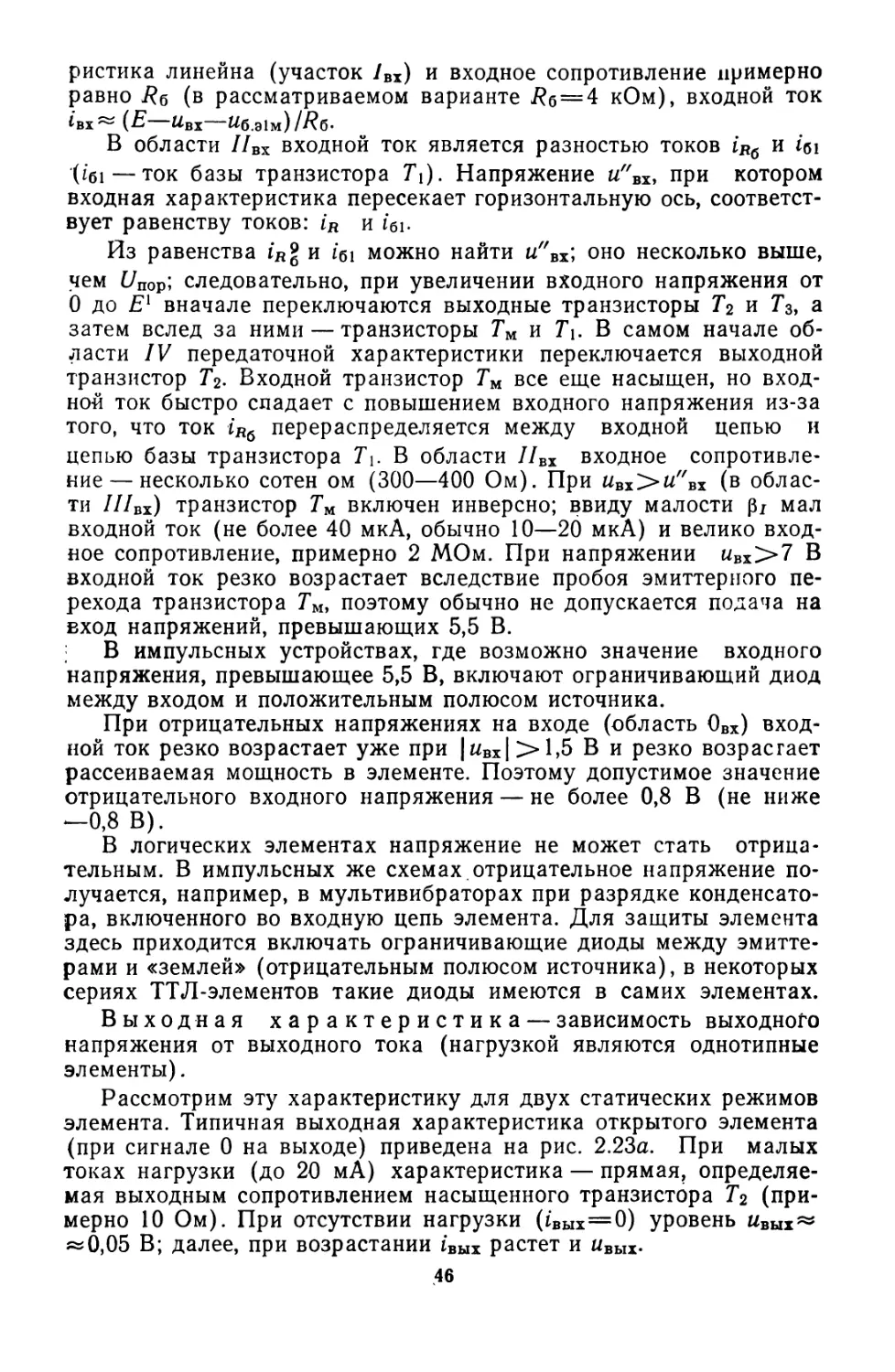

Передаточная характеристика. Наряду с входными

и выходными характеристиками транзисторного ключа часто пред-

ставляет интерес передаточная характеристика — зависимость

уровня выходного напряжения ивых=>ик от уровня входного ивх в

стационарном режиме работы ключа. Пример такой характеристи-

ки для ключа на кремниевом транзисторе типа п-р-п (см. рис. 2.3)

28

приведен на рис. 2.10. Участок характеристики MN соответствует

активному режиму работы ключа при его переходе из состояния 1

(напряжение на выходе t/’вых высокое) в состояние 0 (напряже-

ние 1/°Вых низкое).

В переключательных цепях обычно обеспечивается совмести-

мость входных и выходных сигналов, т. е. совпадение по уровням

U°BX и /7°вых, t/'вх и Ь'^ых. Передаточная характеристика позволя-

«А1

^Л/х -Г---

z Рабочая точка „ 1”

иВых / на выходе

А / м

rrO-L

идых

пом

и

ипом

I |Д-

ТО С 1 .7/1

Рабочая и

точка„Она

выходе

и%Г\О,2 & 0,6 Е* 0,86^

। Амплитуда

'сигнала на дходе^

Рис. 2.10

ет наглядно оценить помехо-

устойчивость устройств, т. е.

найти максимально допусти-

мое напряжение помехи, дей-

ствующей на входе ключа

наряду с регулярными сиг-

налами, при которой еще не

происходит изменение логи-

ческих (информационных)

состояний ключа.

Помехи в ключах могут

быть как статическими, на-

пример, изменения входных

напряжений, связанные с па-

дением напряжения на об-

щих шинах цепей питания

(«земля»), так и импульс-

ными (кратковременными).

Импульсные помехи "Обу-

словлены как внешними

электромагнитными полями,

так и индуктивной и емкост-

ной связью между сигналь-

ными линиями цепей, а так-

же переходными процесса-

ми в последних (из-за не-

согласованности линий и на-,

грузок).

29

Так, если на выходе имеется сигнал 1 (точка А рис. 2.10), то

запас помехоустойчивости МА равен разности входных напряже-

ний |£°м—{7°вх|, а если сигнал 0 (точка В), то запас помехоустой-

чивости NB равен разности входных напряжений |£^—(7^x1 •

Динамические режимы. Рассмотрим переходные процессы пере-

ключения — процессы включения и выключения.

Включение ключа. Пусть в исходном состоянии ключ

(см. рис. 2.3а) закрыт, транзистор заперт некоторым обратным

напряжением аб.э.з<0. Рассмотрим процесс включения при подаче

на вход транзистора в момент времени t' отпирающего перепада

тока /16 = const (рис. 2.11).

Задержка включения. Прямое смещение эмиттерного перехода

не может возникнуть мгновенно; задержка отпирания транзистора

после подачи отпирающего тока обусловлена изменением заряда

входной емкости Свх. Напряжение на емкости Свх в исходном со-

стоянии равно аб.э.з- Под действием входного тока это напряжение

возрастает до нуля и затем достигает установившегося значения.

Считая, что перезаряд усредненной (по интервалу изменения на-

пряжений) емкости Свх происходит постоянным током 7!б, устано-

вим, что напряжение Иб.э на входе транзистора возрастает по ли-

нейному закону.

Время задержки включения транзистора

^з.вкл = ^3° С*вх | ^б.э.з |/^б* (2. 14а)

Если, например, Свх = 50 пФ, /1б=1 мА, иб.э.з = —2 В, то /103 =

= 0,1 мкс. В (2.14а) предполагается, что отпирание транзистора

начинается при аб.э—0. Однако, как отмечалось, кремниевые

транзисторы, входная характеристика которых обладает значи-

тельной «пяткой» (см. рис. 2.9), включаются при некотором поро-

говом напряжении С7Пор>0 (t/пор~0,6 В). Тогда задержка вклю-

чения определится временем

*з.вкл = /I0 = Свх [| аб.э.з I + f/nop]//i. (2.146)

Фронт включения. С момента t=tf\ т. е. с момента отпирания

эмиттерного перехода транзистора, в его базу поступает положи-

тельный перепад тока — (см. рис. 2.11); пусть /1б=5/б.н?

S 1, /б.н = /к.н/р, 7к.н~£к//?К’

Заряд в базе Q и коллекторный ток гк будут возрастать в соот-

ветствии с (2.5) и (2.6).

В момент времени t"' заряд достигает уровня Qrp, ток /к —’

уровня /к.н- Так как процессы здесь происходят по экспоненциаль-

ному закону, можно по (1.2) определить непосредственно

/10 _т ]П <2(°°)-<2(П

Ф ₽ Q(oo)-<?(/"')

Так как Q(oo)=t3Zi6, <2(Г')=0; <2(Г) ^Сгр=т₽/б.н, то

Л° = тй1п----------= Telnf 1 +----

Ф 3 /I / Р /1 — /

Уб—/б.н \ 7б.н

(2.15)

30

За время /10ф напряжение ик достигнет уровня t/K.n~0.

В случае отпирания транзистора так называемым «сильным»

сигналом при /*б^>/б.н можно, используя соотношение 1п(1+х)~

~х при x<gl, получить из (2.15):

(2-16)

Очевидно, что сокращение длительности включения можно по-

лучить прежде всего при увеличении отпирающего тока и при-

менении более высокочастотных транзисторов.

На практике часто отпирающий перепад тока Pq оказывается

примерно равным /к.н, и, следовательно, при этом /10ф~та =1/2л/а.

Необходимо подчеркнуть, что здесь не учтено время перезаря-

да паразитных емкостей, шунтирующих коллекторную цепь тран-

зистора Свых- Как отмечалось, при использовании высокочастот-

ных транзисторов именно время перезаряда СВЫх является опреде-

ляющим в общей длительности фронта /10ф. В запертом ключе на-

пряжение на СВых=£к; с отпиранием транзистора емкость Свых

разряжается через транзистор примерно постоянным током /с=

= рЛб и время разряда оказывается приблизительно

= ^вых^к/^с* (2-17)

Общая длительность включения

/вкл = /1°4Л0- (2.18)

Длительность накопления заряда

По истечении времени /Вкл транзистор находится в режиме на-

сыщения, токи транзистора практически не меняются, а заряд в

базе продолжает нарастать до уровня ТнДб с постоянной времени

тн; за время /н= (2-?3) тн завершается процесс накопления зарядов

и транзистор переходит в стационарный режим.

Выключение ключа. Пусть в исходном состоянии ключ

открыт, транзистор насыщен.

Задержка выключения. Пусть в некоторый момент времени Р

на вход насыщенного транзистора подается запирающий перепад

тока (рис. 2.12): ток базы скачком изменяется от положительного

уровня Рь до отрицательного /°б. Отрицательный ток приводит к

уменьшению заряда, накопленного в базе (к так называемому

рассасыванию заряда), в соответствии с переходной характеристи-

кой транзистора (2.6). Очевидно, что пока заряд в базе Q>

>Qiv(Qh36=Q—Qrp>0), коллекторные ток и напряжение не ме-

няются. Длительность рассасывания /р=/013 определяется време-

нем, в течение которого заряд Q уменьшается от исходного уровня

Q(f)=Tp/16 до граничного (здесь предполагается, как было уже

отмечено, тн~Тр) Qrp — Q^')—т^б.н. Согласно (1.2)

yoi _/ ~т in т 1п /Об-!б т 1n I ;б| + 4

7б | + Z6.H

(2.19)

так как Q(oo) ==тр/°б. Следовательно, задержка выключения /013,

обусловленная рассасыванием избыточного заряда в базе /013=/р,

31

» р ₽ Q(oo)-Q(/") ₽ /0_/бн ₽

тем меньше, чем меньше степень насыщения транзистора и боль-

ше запирающий ток.

При сильном запирающем сигнале, когда

(2.20)

можно непосредственно из (2.19) получить приближенные выраже-

ния для длительности задержки выключения

I I'Sh <2-21>

Фронт выключения. В момент завершения рассасывания избы-

точного заряда режим транзистора соответствует границе активной

области. С этого момента начинается спад коллекторного тока по

экспоненциальному закону с постоянной времени -гр от начального

значения 1К.Н.

32

Согласно (1.2) длительность спада импульса тока

/01=т in Q(°°)-Q(O..=T ]п , = t lnf 1+-M, (2.22)

ф ₽ Q(oo)-Q(f") ₽ /0 ₽ |/0| J’

так как Q(oo) =тэ/°б; Q(/") =тр7б.н, Q(t"')=O. Вместе co спадом

коллекторного тока растет коллекторное напряжение: ик=Ек—

—iKRK (см. рис. 2.12). При запирании транзистора «сильным» сиг-

налом, т. е. при |/°б|^>/1б, получаем из (2.22)

I |/о|. (2.23)

ф р б.н / I о I v

Общая длительность выключения /Выкл = ^01з+^01ф, и при «силь-

ном» запирающем сигнале /выкл — трГб/рОб! • Заметим, что при ис-

пользовании высокочастотных транзисторов длительность фронта

перепада коллекторного напряжения при запирании транзистора

определяется в основном длительностью заряда выходной емко-

сти СВых, шунтирующей транзистор, т. е. /01ф~ЗСВых#вых.

По мере запирания транзистора возрастает его входное сопро-

тивление, и поэтому со временем начинает уменьшаться и ток ба-

зы транзистора, так как практически цепь базы управляется источ-

ником с конечным выходным сопротивлением (в идеализированной

модели входное сопротивление запертого транзистора бесконечно

велико и входной ток содержит только тепловую составляющую).

Быстродействие ключевого элемента определя-

ется максимально допустимой частотой следования входных сигна-

лов, представляющих кодовые символы 0 и 1, каждый из которых

приводит к переключению элемента. Очевидно, что быстродействие

зависит от разрешающего времени элемента, т. е. от общей дли-

тельности переходного процесса, возникающего при воздействии

переключающего сигнала и обусловленного инерционностью тран-

зистора и влиянием паразитных параметров (например, перезаря-

дом паразитных емкостей в процессе переключения). Для оценки

разрешающего времени используются временные параметры —

длительности задержки включения /103 и фронта выключения /10ф>

длительности задержки /013 и фронта /01ф включения. Часто для

характеристики быстродействия ключевого (логического) элемента

используется среднее время задержки сигнала при его передаче че-

рез элемент:

и = °>5(^ + ^0)- (2-24)

Заметим, что при конечной длительности фронта входного си-

гнала, что обычно и имеет место, задержки включения и выклю-

чения отсчитываются либо на 10%, либо, чаще, на 50%-ных уров-

нях входного и выходного сигналов.

2.3. ЦЕПИ СВЯЗИ МЕЖДУ КЛЮЧАМИ

Общие сведения. Управляющие сигналы, действующие на вход

ключа, формируются обычно другими ключами. Связь между клю-

чами осуществляется посредством некоторой цепи связи. Основные

2—137 зз

функции этой цепи заключаются в том, чтобы обеспечить нормаль-

ную работоспособность ключей. Это, в частности, означает, что ес-

ли уровень напряжения на выходе первого ключа высокий, то на

входе другого ключа должен действовать уровень, при котором

второй ключ открывается и работает в заданном режиме; наобо-

рот, если первый ключ открыт, то на входе второго ключа должен

действовать достаточно низкий уровень, при котором второй ключ

закрыт (или «условно» закрыт). При этом в обоих режимах обес-

печиваются необходимая надежность (помехоустойчивость) и вы-

полнение других возможных условий работоспособности. Цепь свя-

зи может оказывать существенное влияние на переходные процес-

сы, возникающие при переключении, и, следовательно, на быстро-

действие ключей.

Рассмотрим вначале некоторые цепи связи, используемые в

ключевых устройствах, на дискретных компонентах.

Ключи с резисторной связью. На рис. 2.13 приведена типовая

схема соединения транзисторных ключей с помощью резисторной

цепи связи.

Рис. 2.13

Пусть транзистор Л насыщен цВых1 = Ик.н, при этом транзистор

Т2 должен быть закрыт, т. е. Цб.э2^^пор. Определяя «б.э2 согласно

эквивалентной схеме (рис. 2.14), запишем

ик.н^2 ^6^14“ ^коа^х^а гт /п qc\

«6.32 - [Ri R* < Цюр- (2 25)

Если транзистор 1\ закрыт, то Т2 должен быть открыт и насы-

щен, т. е. ток базы Т2 должен быть

1*62 1б.н2 = ^к.нг/Рг или *62 = ^2^6.112 =

где S2 — требуемый коэффициент насыщения Т2, IK.n2f /б.н2— соот-

ветственно коллекторный ток Т2 в режиме насыщения и насыщаю-

щий ток базы Т2. Определяя ток i&2 согласно эквивалентной схеме

(рис. 2.15), запишем

“ Atoi^Ki — а Еб + ^б.н ^К.Н2 /q од\

162=----------------------------ъ (Д2Ь)

34

Заметим, что если транзисторный ключ в закрытом состоянии

работает не в режиме отсечки, а в активном режиме при малом

коллекторном токе, то последние неравенства должны удовлетво-

ряться, если вместо 7Koi и /ког писать 1К,3 [например, /к.з = (0,05.

0,1)7к.н] и 1б.3, а под UПОр понимать условный уровень запирания

транзистора.

Рис. 2.14

5

иЬ.Э2

Рис. 2.15:

Из (2.25) и (2.26) можно определить параметры цепи связи,

при которой обеспечивается выполнение условий работоспособно-

сти. При упрощающих предположениях «к.н=0, Ыб.н=0, /koi^ki'C;

<СЕК, (7пор=0 найдем из (2.25) и (2.26)

( — Е'6/?1 +/?2) < 0

ИЛИ /?2^Еб//кО2 и

Ек 1К.П2

«К1 + Rt R2 ₽»

Пренебрегая значением EdR2, найдем

7?i -С Рг^к/^к.на RvX'

(2.27)

(2.28)

(2.29)

Очевидно, что эти условия должны выполняться в худшем слу-

чае при /ко2=7ко2макс и ₽2=02мин- В частном случае, когда нагруз-

кой ключа служит только резистор Rk2, ток /к.н2=Ек//?К2 и ус-

ловие (2.29) принимает вид /?1^₽2/?к2—7?кь При нагрузке /?К1 =

=Rk2=Rk это условие будет R{^. (р2— 1)Як~02Як-

Сокращение длительности переключения. Длительность пере-

ключения можно сократить, в частности, применением ускоряющих

емкостей и отрицательной обратной связи.

Применение ускоряющей емкости. Для ускорения

переходных процессов, возникающих при переключении, исполь-

зуют так называемую ускоряющую емкость С, шунтирующую ре-

зистор Ri (см. рис. 2.13).

Благодаря емкости С при запирании через цепь базы Т2 про-

текает значительный ток, в результате чего длительность включе-

ния Т2 сокращается. Начальное значение этого тока примерно рав-

но Ек/ (7?к1+7?вх2) , где Евхг— входное сопротивление открывающе-

гося транзистора Т2. По мере заряда емкости С ток базы падает по

2* 35

экспоненциальному закону с постоянной времени тс~CCftill (/?Ki+

+#вх2)) И стремится к уровню, примерно равному £k/(^ki+#i +

“Н-^вхг)- Наоборот, при отпирании 7\ ток разряда емкости С, про-

текая через базу 7г, приводит к ускорению процессов рассасыва-

ния заряда в базе и сокращению длительности выключения тран-

зистора Т2 (емкость обычно составляет примерно сотни или тыся-

чи пикофарад).

Применение отрицательной обратной связи.

Сокращение длительности переключения может быть достигнуто,

если предотвратить сколько-нибудь существенное насыщение от-

крытого транзистора, т. е. существенное превышение базовым то-

ком открытого транзистора значения Z6>H=£K//?kp. Эта задача ре-

шается введением в схему ключа нелинейной отрицательной обрат-

ной связи (ООС).

Пример ненасыщенного ключа с ООС показан на рис. 2.16а.

Пока напряжение база — коллектор иб.к больше падения напряже-

ния Ir0Rq на сопротивлении Ro, диод Д заперт, отрицательная об-

ратная связь не действует. При увеличении входного сигнала

(входного тока) увеличивается ток базы io и соответственно ток

коллектора iK=pi6. Однако при достаточно большом входном сиг-

нале ток г’вх достигает такого значения, при котором напряжение

^б.к станет равным падению напряжения in0Ro на сопротивлении

Ro, диод Д отпирается и начинает действовать ООС. Теперь рост

тока г'вх мало влияет на режим транзистора, так как значительная

часть входного тока идет теперь непосредственно через диод, и

транзистор не переходит в режим насыщения. Другими словами, с

началом действия ООС коэффициент усиления Кг=Д/к/А/вх резко

падает действительно при запертом диоде Кг~Р, а при открытом

Лт~₽/(р+1)<1, так как /?д+'#о+#вх<С (₽+1)7?к. Заме-

тим, что на начальном этапе процесса включения рассматриваемо-

го ключа при большом входном сигнале отрицательная обратная

связь не действует (диод остается закрытым), и поэтому длитель-

ность фронта включения оказывается малой.

36

В настоящее время для устранения или уменьшения насыщения

открытого транзистора используются диоды Шоттки, включаемые

параллельно переходу база — коллектор транзистора (рис. 2.166).

Диод Шоттки ДШ представляет собой переход металл — (обычно

алюминий) — полупроводник. Диод Шоттки включается парал-

лельно коллекторному переходу транзистора, но в интегральных

схемах он вместе с транзистором составляют единую структуру —

транзистор Шоттки. Когда транзистор открыт или работает в ак-

тивном режиме, напряжение ив,к транзистора отрицательно и во

всяком случае меньше порогового уровня отпирания ДШ'. Uq,k<Z

<£Люрдш> Диод Шоттки закрыт и не влияет на работу ключа. При

росте тока базы и переходе транзистора в режим насыщения

растет г/б.к>0 и при Иб.к= f/пордщ отпирается диод

Шоттки; при этом ток базы транзистора уменьшается (t6=/BX—

—^*дш)> ток в коллекторной цепи равен сумме токов — коллектор-

ного и диода Шоттки: /кш=1к+*дш- Так как £Люрдш~0,5 В (а для

кремниевого транзистора £7ПОр~0,6 В), можно практически счи-

тать, что в транзисторе Шоттки избыточный заряд в базе не на-

капливается и отсутствует задержка на рассасывание избыточного

заряда при выключении транзистора.

Резисторно-транзисторные логические элементы. На базе рассмотренных

ключей с резисторной связью могут быть построены логические элементы, со-

ставляющие так называемую резисторно-транзисторную логику (рис. 2.17а). Эле-

мент управляется входными сигналами (перепадами напряжения), являющимися

выходными сигналами других аналогичных элементов.

Транзистор Т находится в одном из двух стационарных режимов: либо за-

перт, либо открыт (и насыщен). Транзистор заперт только в том случае, когда

на все входы поданы низкие уровни напряжения Е° (т. е. напряжения пк.н, сни-