Текст

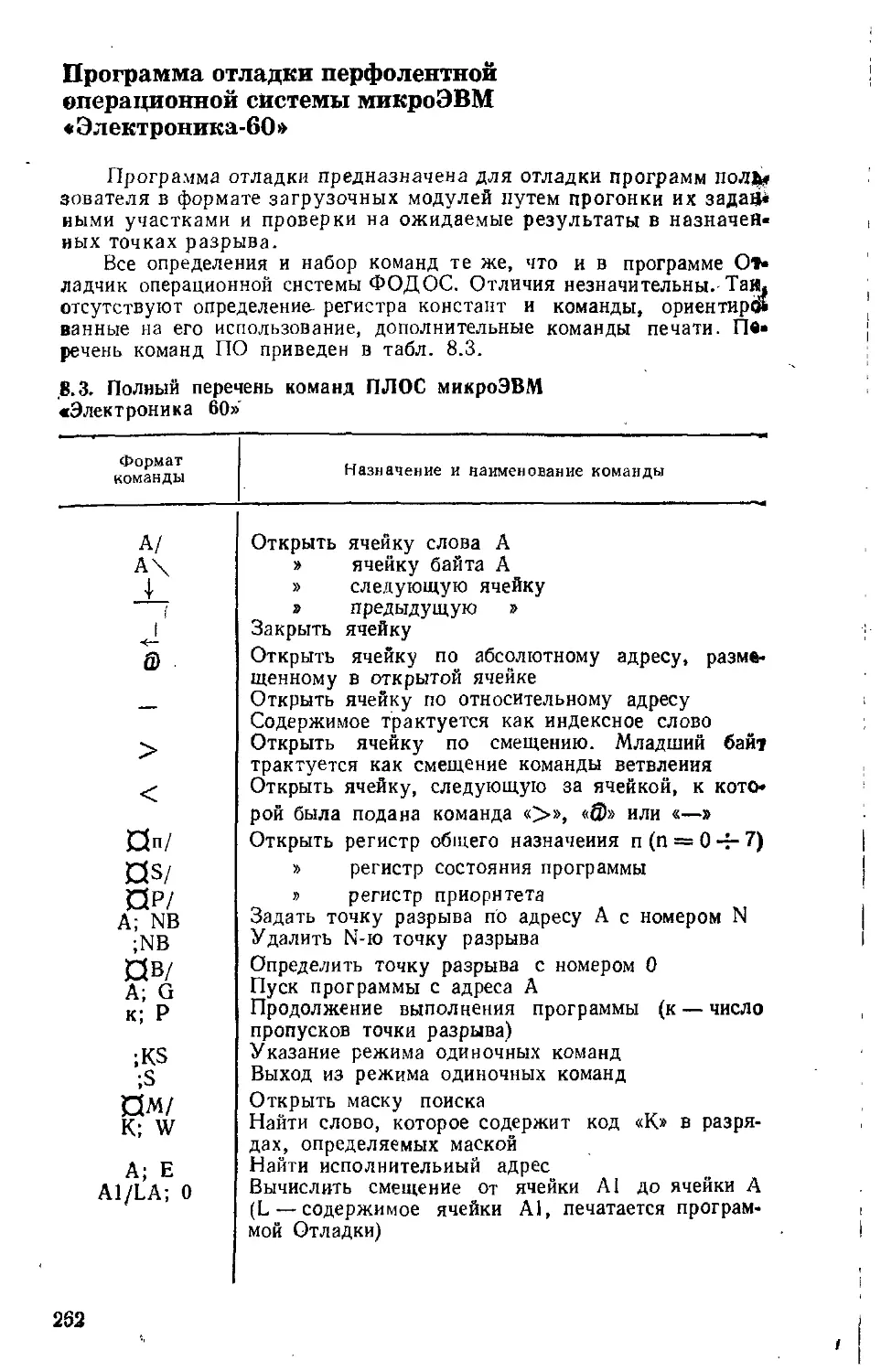

СПРАВОЧНИК

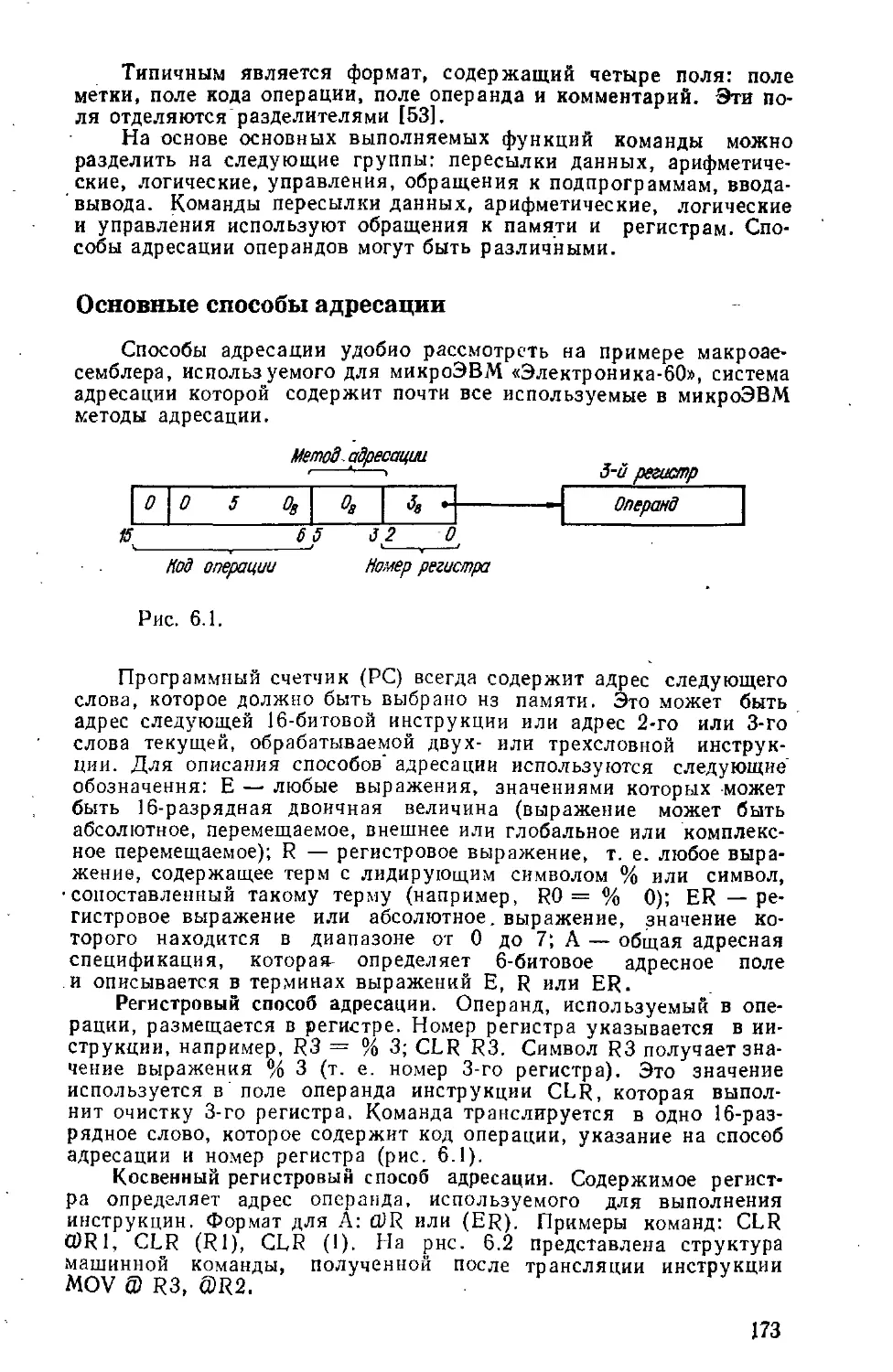

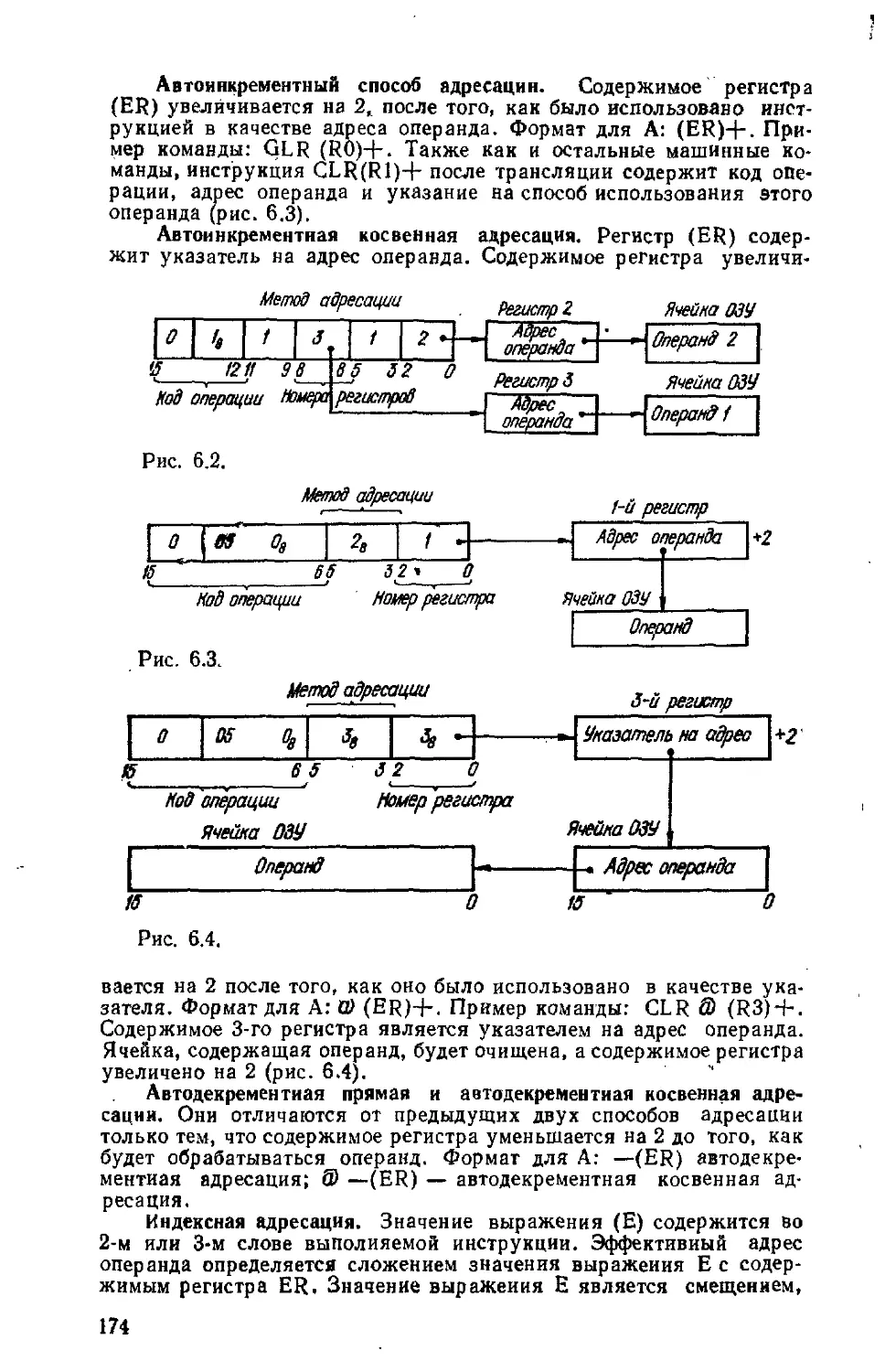

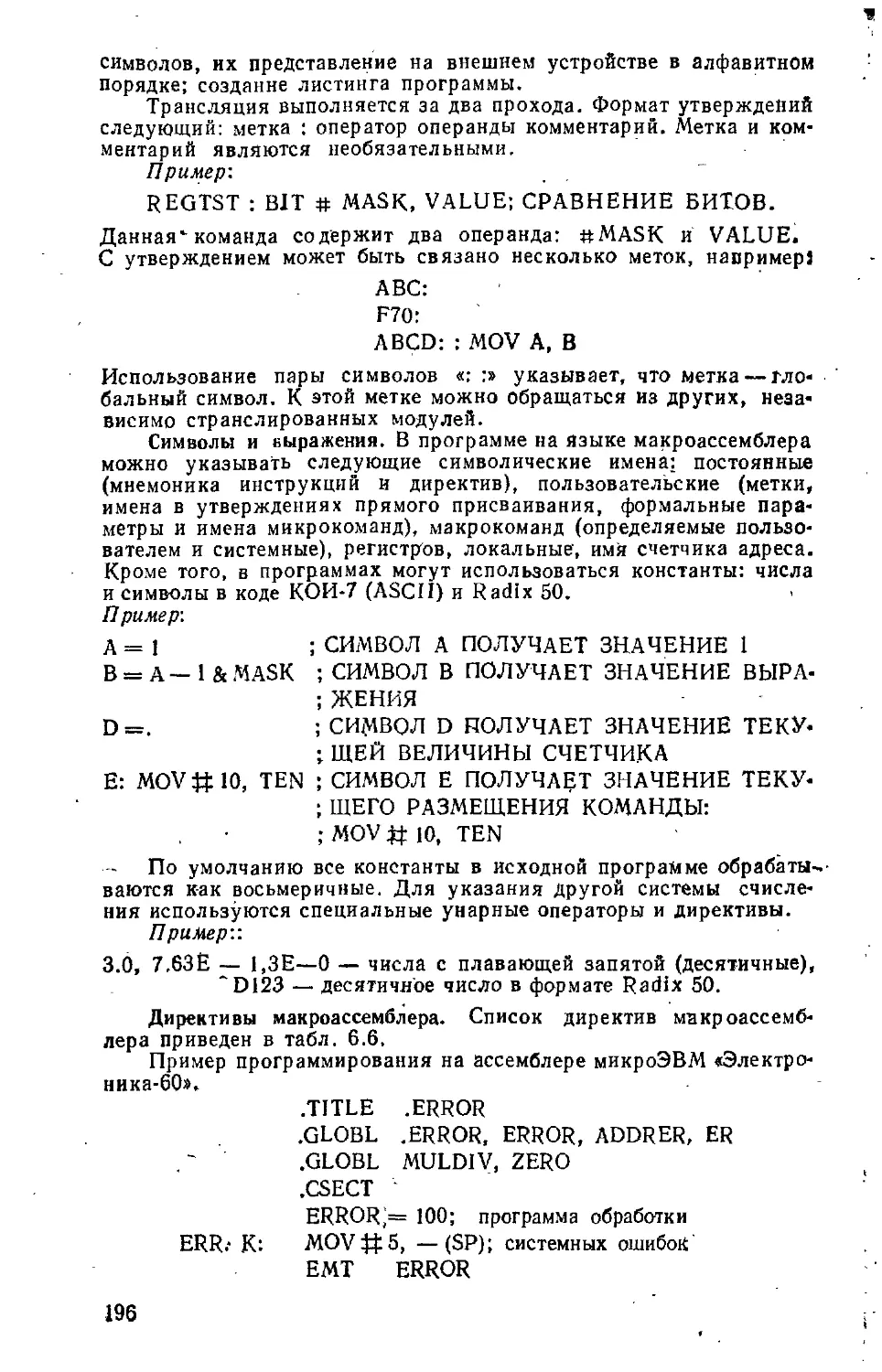

ПО МИКРО-

ПРОЦЕССОРНЫМ

УСТРОЙСТВАМ

Scan Pirat

2003 г.

Киев

лТехшка»

1987

32.973.2я2

С74

УДК 681.3

Справочник по микропроцессорным устройствам

С74 /А. А. Молчанов, В. И. Корнейчук, В. П. Тарасенко,

Д. А. Россошинский.— К.! Техн1ка, 1987.— 288 с.,

ил.—'Библиогр.: с. 279—282.

В пер. 1 р. 20 к. 80 000 экз.

В справочнике приведены схемы микропроцессоров и микропроцес-

сорных устройств, серийно выпускаемых промышленностью, а также

сведения, необходимые для проектирования микропроцессорных систем

обработки данных. Даны типовые примеры-- построения микроЭВМ

и автономных устройств обработки информации на основе микропро-

цессоров .

Предназначен для инженерно-технических работников, занимаю-

щихся проектированием и эксплуатацией вычислительной техники,

з также может быть полезай етудентам вузов.

2405000000-078

С"М202(04)-87 62,87 32.973.2Я2

Авторы: А. ГА. Молчанов, В, И. Корнейчук, В, П. Тарасенко,

Д. А. Россошинский

Рецензенты канд. техн, наук В, П. Волкогон, д-р техн, наук

А. В. Палагин

Редакция литературы по энергетике, Электронике, кибернетике

и связи

Зав. редакцией 3. В. Божко

q) Издательство «Техн1ка», 1987

ПРЕДИСЛОВИЕ

ускоренное развитие всех отраслей народного хозяйства страны

. на базе научно-технического прогресса требует значительного рас-

ширения сферы применения достижений электроники и вычислитель-

ной техники.

Основные направления экономического и социального развития

СССР на 1986—1990 годы и на период до 2000 года предусматривают

рост объема производства средств вычислительной техники в 2—

2,3 раза. При этом будет ускоренно развиваться выпуск'средств авто-

матизации управленческого и инженерного труда, малых электронно-

вычислительных машин высокой производительности, персональных

электронно-вычислительных машин, систем числового программно-

го управления для многофункциональных станков и гибких производ-

ственных модулей, программируемых командоаппаратов для различ-

ных видов оборудования. Технической основой микроЭВМ и микро-

процессорных систем служат наборы больших интегральных схем

(БИС), серийный выпуск которых освоен электронной промышлен-

ностью.

Структура настоящего справочника по микропроцессорным уст-

ройствам соответствует концепции микропроцессора как про-

граммно-управляемого средства обработки информации. Это отра-

жено в разделении материала на части, посвященные аппаратным

средствам и программному обеспечению микропроцессорных систем.

В первой части вначале подробно рассмотрены наиболее распростри-

именные серии микропроцессорных наборов, а затем, более кратко,

описаны менее распространенные и перспективные серии. Так как

микропроцессорные БИС являются весьма сложными цифровыми

устройствами, то значительное внимание уделено раскрытию внут-

ренней функциональной структуры БИС, что необходимо для пра-

вильного представления о работе микропроцессорных устройств, оп-

тимизированных по некоторым технико-экономическим показа-

телям.

Микропроцессоры и микроЭВМ становятся составной частью

самых разнообразных систем, приборов и устройств. Возможности

их использования для управления, обработки и передачи информации

во многом зависят от их оснащенности ередствами программирова-

ния. К настоящему времени общее программное обеспечение

микроЭВМ и микропроцессоров организационно и технически объеди-

няется с системами автоматизированного проектирования БИС, так

как основным носителем целевых программ в большинстве информа-

ционно-управляющих систем являются БИС постоянной памяти.

3

Широкое использование ^микропроцессоров определило развитие кроссо-

вых и резидентных систем автоматизации разработки программ

(САРП), ориентированных на различные классы пользователей. Во

второй части справочника рассматривается современное состояние

программного и математического обеспечения микропроцессоров

и микроЭВМ. Описаны операционные системы микроЭВМ, а также

ассемблерный уровень, языки программирования высокого уровня,

средства проектирования и отладки программного обеспечения, реа-

лизуемые как в кроссовых, так и в резидентных САРП микропроцес-

соров и микроЭВМ.

Первая часть справочника написана В. И. Корнейчукам

и В. П. Тарасенко, вторая часть — А. А. Молчановым и

Д. А. Россошанским.

Отзывы и пожелания просим направлять по адресу: 252601,

Киев, I, Крещатик, 5, издательство «Техника».

Часть I

АППАРАТНЫЕ СРЕДСТВА

МИКРОПРОЦЕССОРНЫХ СИСТЕМ

В номенклатуре изделий электронной промышленности, выпуска-

емых в настоящее время и предназначенных для построения

цифровых систем сбора, хранения и обработки информации наряду

с БИС полупроводниковой памяти, важнейшее место занимают ми-

кропроцессоры (МП).

Микропроцессор представляет собой автономное функциональ-

но законченное устройство, состоящее из одной или нескольких Про-

граммно-управляемых БИС, включающее все средства, необходи-

мые для обработки информации и управления данными, и рассчи-

танное на.совместную работу с устройствами памяти н ввода-вывода

информации. Создание МП привело к широкому внедрению универ-

сальных вычислительных средств в те отрасли техники, где другие

вычислительные средства, созданные ранее, не моули быть исполь-

вованы. По своей структурной и функциональной организации МП

аналогичны процессорам, реализующим программную обработку

информации. Главными же отличительными признаками МП явля-

ются выполнение всех их структурных единиц в виде БИС, неболь-

шая длина операндов, относительно небольшая емкость памяти,

храпение микропрограмм в постоянной памяти и пр.

Различают универсальные и специализированные МП. По-

следние оптимизированы по различным параметрам на конкрет-

йыс применения. Специализированные МП целесообразны при

больших сериях производства. Применяют МП совместно с микро-

процессорными наборами (МН), которые представляют собой со-

вокупности совместимых БИС, разработанных для построения раз-

личных микропроцессорных средств обработки информации. Обыч-

ио в МН входят МП; оперативное запоминающее устройство (ОЗУ);

постоянное запоминающее устройство (ПЗУ); полуПостоянное за-

поминающее устройство (ППЗУ), допускающее смену записанной

в нем информации в специальном нерабочем режиме; БИС микро-

программного управления; БИС ввода-вывода или интерфейса внеш-

них устройств.

Структура МП должна удовлетворять трем основным требова-

ниям: быть функционально гибкой, обеспечивать достаточно высо-

кое быстродействие и допускать недорогую технологическую реали-

зацию. Высокая функциональная гибкость МП, необходимая для

Создания эффективного программного обеспечения, достигается мик-

ропрограммным управлением, за счет побайтовой обработки и адре-

сации данных, развитой системы прерываний и большего числа

внутренних регистров.

Различают однокристальные и многокристальные (модульные)

МП. Структура однокристального МП показана на рис. 1.1, а. Та-

кой МП содержит арифметико-логическое устройство АЛУ, устрой-

ство управления УУ, блок внутренних регистров БР и блок интер-

фейса БИ. АЛУ, как правило, состоит из двоичного сумматора и не-

скольких регистров и аппаратным способом выполняет простейшие

операции (сложение, вычитание, пересылку, основные логические

бперацин и сдвиг). Сложные операции выполняются по микропро-

граммам, блок внутренних регистров БР образует внутреннюю

5

память МП и содержит специальные регистры и регистры общего на-

значения РОН. Регистры БР связаны с другими блоками МП общи-

ми шинами и во многом определяют вычислительные возможности

МП. Все РОН доступны выполняемой программе и часто, кроме

основных функций (хранение операндов), выполняют функции спе-

циальных регистров, например, регистров стека РСТ и индексных

регистров ИР. Существует тенденция увеличения числа РОН, об ус-

Рис. 1.1.

е

ловленная тем, что увеличение объема внутренней памяти позволяет

повысить производительность МП за счет сокращения числа обра-

щений к ОЗУ. Специальные регистры выполняют функции счетчика

команд СК и регистров команд РК, результата РР АЛУ, указателя

стека РУС, прямого доступа в память РПД и состояния PC. Послед-

ний фиксирует информацию о результатах выполнения последней

обработанной команды: например, нулевой результат, положитель-

ный или отрицательный знак, переполнение или запрос иа преры-

вание. Эта информация используется для реализации условных

переходов по программе. Стек выполняется на внутренних регист-

рах или на некоторой выделенной области ОЗУ. В последнем случае

обращение и адресация к стеку проводится через РУС. Стек на ре-

гистрах более быстродействующий, но из-за малого числа регист-

ров в МП он имеет небольшую емкость. В РУС хранится адрес

1-й свободной ячейки в стеке. При записи слова в стек значение

адреса в РУС увеличивается иа единицу, а при чтении уменьшается

на единицу. Кроме этого, в МП имеется возможность прочитать

без разрушения содержимое любой ячейки стека без изменения

слова в РУС.

Устройство управления вырабатывает серии внутренних управ-

ляющих сигналов ВУС: В2, ..., Вт с помощью дешифратора кода

операции ДСК. Блок интерфейса обеспечивает сопряжение между

МП, ЗУ и периферийными устройствами (ПУ) (внешний интер-

фейс), а также между частями МП (внутренний интерфейс). Внут-

ренняя шина данных МП представляет собой многопроводную ма-

гистраль, связывающую все узлы внутри МП. Обычно разрядность

внутренней шииы данных совпадает с разридностью внешней^шииы

данных ШД, по которой передаются операнды и команды, и опреде-

ляет разрядность слов, с которыми оперирует МП. Из-за ограничен-

ного числа внешних выводов (особенно у однокристальных МП)

шина данных часто работает через специальную буферную схему

мультиплексора в режиме двунаправленной передачи. При этом

противоположные направления обмена данными между МП и дру-

гими устройствами разделены во времени.

Многокристальный МП (рис. 1.1, б) выполняют, как правило, на

основе БИС двух типов: управляющей (БИСУ) и операционной

(БИСО). Операционные БИС содержат АЛУ и РОИ с разрядностью

в 2 или 4 бита и снабжены схемами и выводами, позволяющими

объединить их в операционную часть МП произвольной разрядно-

сти. Управляющая БИС содержит общие для МП регистры и ЗУ

микропрограмм ЗУМ, из которого считываются параллельно на

все БИСО сигналы микрокоманд МК. Наличие нескольких БИС

является недостатком многокристальных МП, но наращиваемая

разрядность и меньшая степень интеграции отдельных БИС позво-

ляют повысить точность и скорость обработки информации и приме-

нять технологию, обеспечивающую более высокое быстродействие

БИС. Кроме того, набор микрокоманд можно изменять путем за-

мены только одной БИСУ или содержимого ЗУМ (при использо-

вании ППЗУ). Однако менее жесткие требования к количеству внеш-

них выводов позволяют использовать независимые шину адреса ША,

шину управления ШУ и ШД, что также повышает быстродействие

МП, позволяет исключить мультиплексор и упростить струк-

туру МП.

Наиболее типичная система команд МП содержит набор из

70—100 команд (трех-, двух-, одно- и безадресных). Однако ограни-

чения на число выводов и сложность УУ не позволяют в полной

мере использовать преимущества трех- и двухадресных команд.

7

Вследствие этого в МП наибольшее распространение получили ко-

манды, содержащие один адрес операнда или несколько коротких

адресов операндов, хранящихся в РОН. Все команды любого микро-

процессора можно условно разбить на арифметические, логическйе

и вспомогательные. В свою очередь вспомогательные команды со-

стоят из команд пересылки, ветвления, обращения к подпрограм-

мам и управления вводом-выводом.

Арифметические команды МП состоят чаще всего из операций

сложения, вычитания, добавления или вычитания 1 н сдвига (в МП

новых серий, кроме того, еще умножение и деление). Логические

команды выполняют поразрядные операции дизъюнкции, конъюнк-

ции, неравнозначности и сравнения. Команды пересылки обеспечи-

вают двусторонний обмен информацией между внутренними регист-

рами МП или регистрами и ОЗУ. Команды ветвления реализуют

условные и безусловные переходы в программе. Команды обраще-

ния к подпрограммам реализуют вход в подпрограмму и последую-

щий возврат к основной программе. Команды управления вводом-

Выводом реализуют операции ввода-вывода информации из внешней

памяти и периферийных устройств.

В МП применяют прямую, непрямую, непосредственную и не-

явную адресации. Первые два способа адресации соответствуют

прямой и непрямой (присоединенной, относительной, косвенной)

адресации в больших универсальных ЭВМ [4,52]. При непосред-

ственной адресации содержимое адресной части команды является

операндом. Команды в этом случае не обращаются в ОЗУ за опе-

рандами, что обеспечивает экономию памяти и увеличивает скорость

обработки информации. При неявной адресации адрес в команде

Явно не указывается, но код операции автоматически задает обра-

щение к местам хранения данных, требуемых для выполнения опе-

рации. Например, для выполнения арифметических операций

с неявной адресацией данные берутся из РР.

Обмен данными в микроЭВМ происходит между МП, ОЗУ

и устройствами ввода-вывода (УВВ)^ Обмен информацией между

МП и ОЗУ часто осуществляется через интерфейс, находящийся

в МП. Обмен между МП и УВВ осуществляется или через специа-

лизированную БИС сопряжения, ориентированную на некоторый

класс УВВ, или через универсальный программируемый интерфейс

(программируемый контроллер УВВ), обеспечивающий подключение

к МП практически любого УВВ. Программируемые контроллеры

В общем случае выполняют следующие функции: управляют про-

цессом передачи данных между МП и УВВ; преобразуют фор-

маты данных; дешифрируют адреса УВВ, посылаемые МП; пере-

дают сигналы готовности УВВ к обмену данными с МП; дешиф-

рируют коды операций, посылаемые МП, и обеспечивают их выпол-

нение.

Следует отметить, что обмен данными между ОЗУ и УВВ может

осуществляться через МП, однако это снижает быстродействие

микроЭВМ. Поэтому в ряде МН имеются БИС, реализующие канал

прямого доступа УВВ к памяти, с помощью которого обмен данными

осуществляется без участия МП.

.Устройства управления первых однокристальных МП строи-

лись исключительно по схемному способу. Однако повышение

степени интеграции и требования гибкости структуры МП привели

к широкому применению микропрограммного управления не только

в многокристальных, но и в однокристальных МП. Различают три

способа размещения ЗУМ по отношению к МП: внутреннее, внеш-

нее и комбинированное.

8

При внутреннем размещении ЗУМ находится на одном кристал-

ле с МП и с точки зрения пользователя такое управление ничем не

отличается от схемного. В этом случае МП реализует фиксирован-

ное множество микропрограмм, соответствующих заданной системе

команд. Достигнутая степень интеграции ^лимитирует количество

аппаратуры в МП и позволяет реализовать только небольшое коли-

чество команд. Быстродействие МП с таким размещением ЗУМ наи-

большее, однако замена микропрограмм,а следовательно, и системы

команд невозможна. Исключение составляет случай, когда в каче-

стве ЗУМ . применяют двустороннюю (активную) память. Однако

е.мкость"такой памяти, как правило, недостаточна для хранения раз-

витой системы микропрограмм, а трудности создания полупровод-

никовой памяти, сохраняющей информацию при отключении пита-

ния, существенно сужают область применения МП с двусторонним

ЗУМ.

При внешнем размещении ЗУМ находится вне МП и может

быть выполнено в виде ПЗУ, ППЗУ или совместно с ОЗУ. Микро-

команды из ЗУМ в этом случае поступают ио ШД в регистр микро-

команд. Поэтому разрядность микрокоманд определяется разряд-

ностью ШД. Быстродействие МП ограничено длительностью цикла

внешнего ЗУМ и меньше, чем прн внутреннем размещении ЗУМ.

Однако внешнее размещение ЗУМ позволяет ие только разработ-

чику, но и пользователю изменять и расширять систему команд,

приспосабливая ее к специфике конкретного применения.

При комбинированном размещении ЗУМ имеется как внутрен-

няя, так и внешняя микропрограммная память, благодаря чему та-

кой вариант объединяет в себе преимущества обоих способов: от

внутреннего ЗУМ — быстродействие, от внешнего ЗУМ —гиб-

кость. Однако при таком размещении ЗУМ возникают трудности

вследствие малого количества шин, связывающих ЗУМ и МП. Для

преодоления этих трудностей используют двухуровневое микро-

программирование, прн котором во внешнем ЗУМ хранятся только

адреса микрокоманд, записанных во внутреннем ЗУМ. При этом

адресоваться могут не только отдельные микрокоманды, но и микро-

Подпрограммы илн микропрограммы базовой системы команд.Одним

Из эффективных способов реализации такого микропрограммирова-

ния является применение механизма блокировки, позволяющее

значительно расширить набор исходных микрокоманд. При этом

внешняя микрокоманда (хранящаяся во внешнем ЗУМ) имеет струк-

туру вида А, М, где А — адрес внутренней микрокоманды (храня-

щейся во внутреннем ЗУМ); М — маска, указывающая группу

микроопераций, которую надо блокировать при выполнении данной

микрокоманды. Упрощенная схема, реализующая двухуровневый

Принцип микропрограммирования, показана иа рис. 1.1, в. В этой

схеме внешняя микрокоманда разбивается на две части А и М.

Часть А поступает на регистр адреса внутренней микрокоманды

РАМ, вследствие чего из внутреннего ЗУМ выбирается внутренняя

микрокоманда, часть управляющих сигналов которой блокируется

узлом блокировки УБ, управляемым маской М. Для уменьшения

длины адреса А можно использовать один из методов непрямой

адресации, например, присоединенную или относительную. Однако

в этом случае необходимо иметь внешнюю микрокоманду записи

слова в регистр базового адреса микрокоманды.

Другой особенностью управления МП является широкое приме-

нение программируемых логических матриц (ПЛМ) вместо ПЗУ.

ПЛМ, как и ПЗУ, строят по схеме дешифратор — шифратор, однако

в отличие от ПЗУ программирование структуры ПЛМ (электриче-

9

ским или масочным способами) возможно не только на уровне шиф-

ратора, но и на уровне дешифратора. ПЛМ в устройствах управле-

ния МП применяют для преобразования микрокоманд или адресов,

в качестве ЗУМ, или для выполнения всех указанных функций одно-

временно. В последнем случае микропрограммное ЗУ предельно

простое и состоит из одной или нескольких параллельно работаю-

щих ПЛМ (рис. 1.1, г). Регистр РК выбирает требуемую совокуп-

ность микрокоманд, отдельные микрокоманды из которой выбира-

ются содержимым регистра адреса микрокоманд РАМ и логически-

ми условиями ЛУ. Адрес микрокоманды может задавать внешняя

МК или же он может быть сформирован с помощью ПЛМ за счет

обратной связи (которая на рис. 1.1, г показана штриховой линией).

Применение вместо ПЛМ ПЗУ, все адреса которого дешифрируют-

ся, потребовало бы технически недостижимой емкости иа одном

кристалле.

В микропроцессорной схемотехнике установлены следующие ос-

новные понятия и термины [51].

Интегральной микросхемой (ИМС) называют микроэлектрон-

ное изделие, выполняющее определенную функцию преобразова-

ния, обработка сигнала и (или) накапливания информации и имею-

щее высокую плотность упаковки электрически соединенных эле-

ментов (или элементов и компонентов) и (или) кристаллов, которое

с точки зрения требований к испытаниям, приемке, поставке и экс-

плуатации рассматривается как единое целое.

Элемент ИМС — часть ИМС, выполняющая функцию какого-

либо электрорадиоэлемеита, которая изготовлена нераздельно от

кристалла или подложки и не может быть выделена как самостоя-

тельное изделие с точки зрения требований к испытаниям, приемке,

поставке и эксплуатации (под электрорадиоэлементом понимают

транзистор, диод, резистор, конденсатор и др.). .

Компонент ИМС — часть ИМС, выполняющая функции какого-

либо электрорадиоэлемеита, которую можно рассматривать как

самостоятельное изделие с точки зрения требований к испытаниям,

приемке, поставке и эксплуатации.

Корпус ИМС — часть конструкции ИМС, предназначенная для

защиты ИМС от внешних воздействий и для соединения с внешними

электрическими цепями посредством выводов.

Степень интеграции ИМС — показатель степени сложности

ИМС, характеризуемый числом содержащихся в ней элементов

и компонентов. Степень интеграции определяется по формуле

К = 1g N, где N — число компонентов и элементов ИМС (в том

числе содержащихся в составе компонентов), входящих в ИМС,

а значение К округляется до ближайшего большего целого числа.

ИМС первой степени интеграции содержит до 10 элементов и компо-

нентов включительно, ИМС второй степени интеграции —от 11 до

100 и т. д.

Серия ИМС — совокупность типов ИМС, которые могут выпол-

нять различные функции, имеют единое конструктивно-технологи-

ческое исполнение и предназначены для совместного применения.

Используемые в микропроцессорных устройствах ИМС харак-

теризуются большим количеством показателей, которые опреде-

ляют их функциональные возможности, быстродействие, эконо-

мичность, надежность, условия эксплуатации, стоимость и парамет-

ры входных н выходных сигналов [25].

По схемно-технологической реализации МН делят на следую-

щие виды: змиттерносвяааиные транзисторные схемы (ЭСЛ), тран-

зисторно-транзисторные схемы (ТТЛ), интегральные инжекцион»

10

ные схемы (ИИЛ или И2Л), ТТЛ- и ИИЛ-схемы с диодами Шот-

ки (соответственно ТТЛШ и ИИЛШ), схемы на р- и п-канальных

транзисторах со структурой металл — окисел — полупроводник

(соответственно рМОП и пМОП), схемы на дополняющих (компле-

ментарных) МОП-транзисторах (КМОП).

Потребляемая мощность и быстродействие ИМС зависят от ре-

жима работы (статический 0 или 1 иа выходе, переключение из 1

в 0 или из 0 в 1), параметров нагрузки и других факторов. Если спе-

циально не оговорено, то под потребляемой мощностью понимают

ее среднее значение. Аналогично для оценки скоростных свойств

ИМС используют среднее время задержки распространения сигна-

ла, равное полусумме времени задержки распространения сигнала

при включении и выключении ИМС.

Функциональные возможности ИМС характеризуются коэф-

фициентами объединения по входу и выходу и коэффициентом раз-

ветвления. Коэффициент объединения по входу — это число входов

ИМС, по которым реализуется логическая функция. Коэффициент

объединения по выходу — это число соединяемых между собой вы-

ходов ИМС для получения монтажных схем И, ИЛИ. Коэффициент

разветвления по выходу — это число единичных нагрузок, которое

можно одновременно подключать к выходу ИМС (единичной нагруз-

кой является один вход основного логического элемента данной

серии ИМС).

По выполняемым функциям ИМС делят иа комбинационные*

запоминающие и содержащие нак комбинационные, так и запоми"

иающие схемы. Комбинационной схемой (КС) называют цифровое

устройство, сигналы иа выходе которого не зависят от инутреннего

состояния и определяются только сигналами на входах схемы, дей-

ствующими в данный момент времени. Правила функционирования

КС можно задать, указав соответствующую систему переключатель-

ных функций (ПФ). Реализуемая ИМС переключательная функция

зависит не только от конструктивных особенностей ИМС, но и от

способа кодирования 0 н 1. Таких способа два, так как логической

1 может соответствовать высокий (В) уровень сигнала (напряжения,

тока) или низкий (Н). Первый способ называют положительной ло-

гикой, а второй — отрицательной. Если ИМС в одной системе ко-

дирования реализует ПФ у f (*!, xt, ..., хп), то в другой системе

оиа будет реализовать ПФ вида у — f (хп х2, ..., хп).

Запоминающие схемы осуществляют фиксацию и хранение по-

ступающей на их входы информации.

Схемы, содержащие как комбинационные, так и запоминаю-

щие части, получили название схем с памятью. Таи как в реальных

схемах число элементов памяти конечное, то нх также называют

цифровыми автоматами с конечной памятью или просто конечными

или цифровыми автоматами. К этому классу относится большин-

ство ИМС в микропроцессорных сериях. По конструктивно-техно-

логическому исполнению ИМС подразделяют на три группы: полу-

проводниковые (обозначаются цифрами 1, 5, 6 или 7), гибридные

(2, 4 и 8) и прочие .(пленочные, вакуумные, керамические и Другие

обозначаются цифрой 3). Цифра 7 присвоена бескорпусным полу-

проводниковым ИМС. Указанные цифры являются первым элемен-

том (Эх) в условном обозначении ИМС, состоящем всего нз четырех

алементов. Второй элемент (Э2) состоит из двух-трех цифр и явля-

ется порядковым номером серии (от 00 до 999). Элементы и Э,

в совокупности образуют полный иомер серии ИМС. Третий эле-

мент (Э8) — две буквы, обозначающие функциональное назначение

И

1.1. Условные обозначения функциональных типов ИМС

Функциональное назначение Эз И-ИЛИ-НЕ И-ИЛИ-НЕ/И-ИЛИ ЛР лк

Схемы вычислительных ИЛИ-НЕ/ИЛИ ЛМ

средств Расширители лд

МикроЭВМ Микропроцессоры Микропроцессорные секции BE ВМ ВС Прочие дп

ИМС микропрограммного управления ВУ Накопители ЗУ

Функциональные, расшири- ВР Оперативные РМ

тели ВБ Постоянные РВ

Синхронизации ПЗУ со схемами управле-

Управления прерыванием ВН ния:

Управления вводом-выводом вв масочные РЕ

Управления памятью ВТ с однократным програм- РТ

Функциональные преобразо- мированнем

вателн информации ВФ с многократным програм- РР

Сопряжения с магистралями ВА мированнем

Времязадающие ИМС ВИ с ультрафиолетовым сти- РФ

Ми крокалькуляторы вх раннем и электрической

Контроллеры вг записью информации

Комбинированные ИМС вк ЗУ со схемами управления:

Специализированные ИМС вж оперативные РУ

Прочие вп ассоциативные РА

на цилиндрических маг- РЦ

Схемы цифровых устройств Арифметико-логические ИА нитных доменах Прочие РП

Регистры ИР

Сумматоры им Т риегеры

Полусумматоры ил

Счетчики ИЕ JK-типа ТВ

Шифраторы ИВ RS-типа ТР

Дешифраторы ИД D-типа тм

Комбинированные ик Т-типа ТТ

Прочие ип Динамические тд

Шмитта тл

Коммутаторы и ключи Комбинированные (DT, RST и др.) тк

Тока Напряжения Прочие кт КН кп Прочие ТП

Логические элементы Многофункциональные ИМС

И-НЕ ИЛИ-НЕ и ЛА ЛЕ ЛИ Аналоговые Цифровые ХА хл

или лл Комбинированные хк

НЕ лн Матрицы: хн XT ХП

И-ИЛИ И-НЕ, ИЛИ-НЕ лс ЛБ аналоговые комбинированные Прочие

12

1.2. Основные характеристики микропроцессорных серий БИС

Серия Тип t*. НС п, бит т р*, мВт Р/м*. мВт Р/пт\ мВт Е. В АГ, тыс. шт. в Примечание

-

536 МОП 101 >8 2 70 8,75 4,4 —24; 12 2 48 Средства вычислительной техники

низкой стоимости для устройств цифровой автоматики

145 КМОП 10е 4 12 3,3 750 0,22 0,018 1,5 16 48 Микрокалькуляторы и микропроцес- сорные устройства бытовой техники

< 580 МОП 500 8 19 94 4,9 —5; 5; 12 5 48 Средства вычислительной техники

581 МОП 400 8 28 1000 112 4,0 —5; 5; 12 7 48 среднего быстродействия с побайт-

586 МОП 500 16 22 900 56 2,5 —5; 5; 12 8 48 ной обработкой информации

1801 МОП 125 16 150 1020 64 0,4 5 300 42

1810 МОП 200 16 28 1750 110 4,0 5 29 40

582 пил 1000 . >4 15 200 50 3,3 1,2 .6,5 48 Средства вычислительной техники

583 пил 1000 >8 22 360 45 2,0 1,2 11 48 среднего быстродействия с произ-

584 пил 1000 >4 15 140 35 3,0 1,2 3 48 вольной (аппаратно-наращиваемой)

1883 МОП 1400 >8 21 1000 125 6,0 5 48 разрядностью обрабатываемых слов

587 кмоп 2000 >4 13 10/200 2,5/50 0,2/3.8 9 4,8 48 Средства вычислительной техники

588 КМОП 1000 >16 21 1/35 0,06/2,2 0,03/0,1 5 9 42 с малой потребляемой мощностью

589 ттлш 98 >2 12 725 362 30,2 5 1,4 28 Быстродействующие средства вы-

1802 ттлш 105 >8 3 1200 150 50 5 3,5 42 числительной техники

1804 ттлш ПО >4 18 1200 300 16,7 5 4,2 40

1800 эсл 28 >4 1250 312 —2; —5; 2 48 Цифровые ЭВМ высокой произво-

• дительностн

। Примечания: 1. Приняты следующие обозначения: t — период синхронизирующих сигналов для основной ИМС серин (напри-

мер, для арифметико-логического устройства): п —- разрядность (>п означает возможность наращивания разрядности путем каскадного

включения ИМС): т — число внутренних регистров (РОН, РК, РМК, РА и др.) как программно-доступных, так и вспомогательных;

Р — потребляемая мощность; р/п — потребляемая мощность, приведенная к одному разряду; Pfnm — потребляемая мощность, приведен-

ная к одному разряду внутренних регистров: Е •— напряжение питания; W — число компонент в ИМС; В — число выводов в корпусе ИМС.

2. Звездочкой (*) отмечены характеристики, которые могут изменяться от многих факторов (напряжения питания, температуры

окружающей среды, монтажных емкостей и др.).

. t 3. Потребляемая мощность ИМС серий 587 и 588 зависит от режима работы, поэтому для этих серий указаны два значения Р\

со в числителе для статического режима, а в знаменателе для динамического режима.

ИМС (табл. 1.1). Четвертый элемент (Э4) — порядковый номер разработ-

ки ИМС в данной серии, в которой могут быть несколько одинаковых

по функциональному назначению ИМС. Элемент Э4 может состоять

из одной или нескольких цифр. Таким образом, условное обозначе-

ние типа ИМС имеет структуру Э^Э^.

В некоторых сериях ИМС в конце условного обозначения до-

бавляется буква, определяющая технологический разброс пара-

метров ИМС. Ряд букв может предшествовать номеру серии

ИМС. Например, буква «К» означает, что данная серия ИМС пред-

назначена для использования в устройствах широкого применения.

Сочетание букв «КМ» означает, что данная серия в керамическом

корпусе, буквы «ЭК» обозначают выпуск серин на экспорт, а буквы

«КБ» означают выпуск серии в беекорпусиом варианте.

Основные характеристики микропроцессорных серий БИС при-

ведены в табл. 1.2.

Глава 1

МИКРОПРОЦЕССОРНЫЙ НАБОР СЕРИИ 580

1.1. СОСТАВ МИКРОСХЕМ СЕРИИ 580

Серия выпускается в виде модификаций К580 и КР580 и состоит

из восьми ИМС (табл. 1.3) [4, 8, 7, 38f. Микросхема ИК51

(рис. Г.1, б) осуществляет преобразование параллельного 8-раз-

рядного кода и последовательный и наоборот. Необходимость в та-

ком преобразовании возникает при передаче данных на большие

расстояния, например по телефонной линии. Внутренняя 8-раз-

рядиая шина ВШ ИМС связана с 8-разрядиой шиной данных ШД

микропроцессорной системы буфером данных БД, состоящим из

1.3. Состав и функциональное назначение ИМС 580 серин

ИМС 580 серии Функциональное назначение (номер поясняющего рисунка) Зарубеж- ный ана- лог Тип корпуса

ИК51 Программируемый интерфейс связи 2121.28-5

ВВ51 (1.1, д) 8251 244.48-8

ИК53 Программируемый таймер (1.1, е) 2120.24-3

ВМ53 8253 2106.24-1

ИК55 Программируемый интерфейс периферий- 8255 2123.40-2

ВВ55 ных устройств (1.1, ж) 244.48-8

ИК57 Программируемый контроллер прямого 8257 2123.40-2

ВТ57 доступа к памяти

ИК59 Программируемый контроллер прерыва- 2121.28-5

ВН59 НИЙ 8259 2123.40-2

ИК80 Центральный процессорный элемент 8080 2123.40-2

ВМ80 (1.1,з)

ИР82 Буферные 8-разрядиые регистры 8282

ИР83 8283 2140.20-1

ВА86 Шинные 8-разрядЯые формирователи 8286. 2140.20-1

ВА87 8287

14

входного и выходного регистров данных, входного регистра состоя-

ний, а также схем, обеспечивающих переключение выводов ИМС

в высокоомное состояние. Блок управления БУ обеспечивает ра-

боту ИМС в соответствии с поступающими на ее входы сигналами

(табл. 1.4) и управляющей информацией, хранящейся в регистрах

режима и команды в блоке регистров управления БРУ. Блок

передачи БПЧ предназначен для преобразования параллельного

кода в последовательный. Для этого к 8-разрядиому коду данных

или сиихросимволу, поступающему по ВШ, добавляется пять слу-

жебных разрядов (два разряда для записи стоп-бита, бит контроля,

старт-бит и разряд признака синхронизации выхода передатчика),

формируемых в БПЧ. Указанные 13 разрядов фиксируются на ре-

гистре н разряд за разрядом выдаются иа выход БПЧ. Блок при-

ема- БПМ осуществляет прием последовательного кода и передачу

иа ВШ сформированного из принятой информации 8-разрядного

кода.

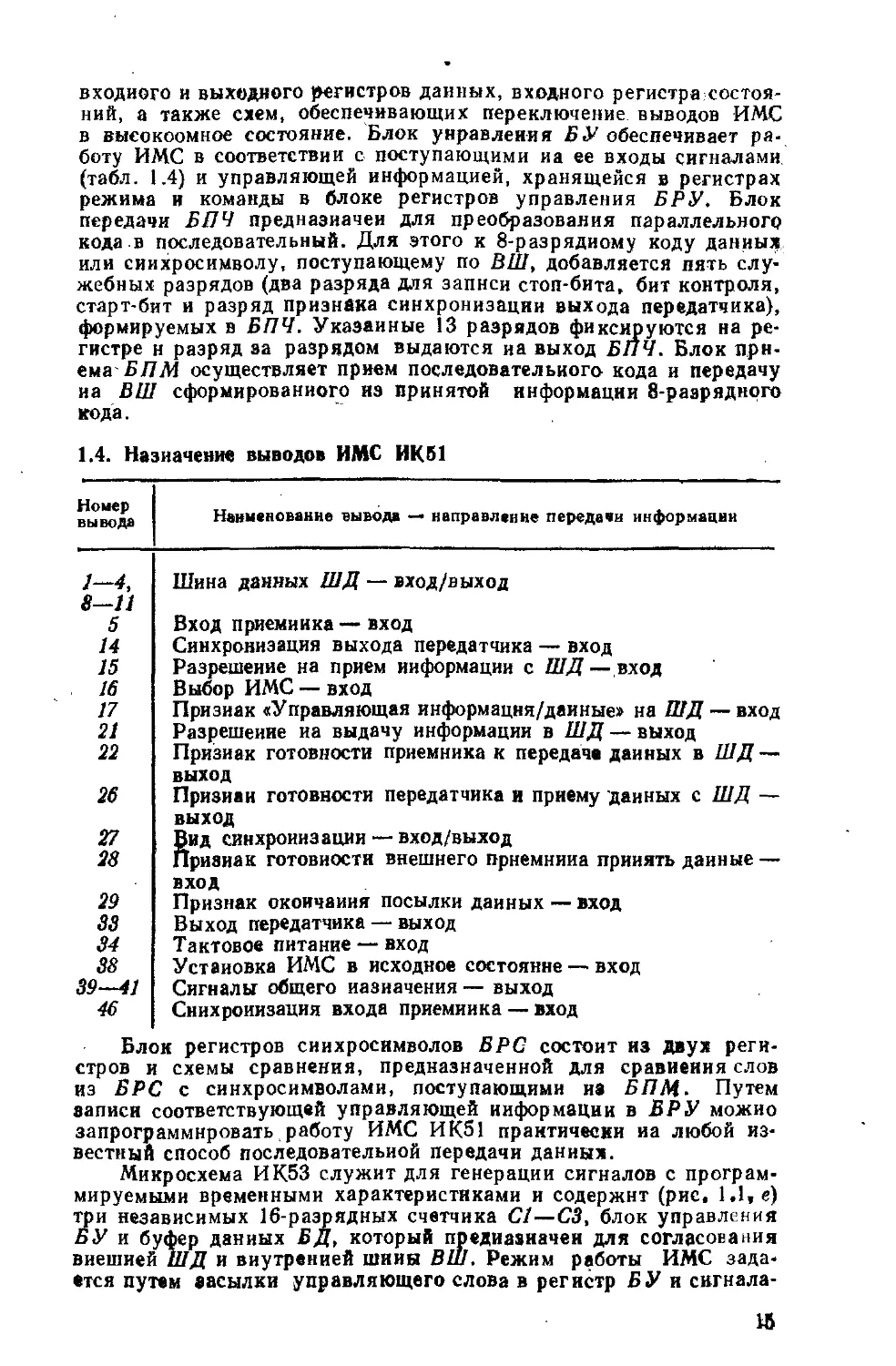

1.4. Назначение выводов ИМС ИК61

Номер

вывода

Наименование вывода —* направление передачи информации

1—4, 8—11 5 14 15 16 17 21 22 Шина данных ШД — вход/выход Вход приемника — вход Синхронизация выхода передатчика — вход Разрешение на прием информации с ШД — вход Выбор ИМС — вход Признак «Управляющая информацня/даиные» на ШД — вход Разрешение иа выдачу информации в ШД — выход Признак готовности приемника к передаче данных в ШД — выход

26 Признан готовности передатчика и приему данных с ШД —

27 28 выход Вид синхронизации — вход/выход Признак готовности внешнего прнемнииа принять данные —

29 33 34 38 39—41 46 вход Признак окончания посылки данных — вход Выход передатчика — выход Тактовое питание — вход Установка ИМС в исходное состояние — вход Сигналы общего назначения — выход Снихроиизация входа приемника — вход

Блок регистров сиихросимволов БРС состоит из двух реги-

стров и схемы сравнения, предназначенной для сравнения слов

из БРС с синхросимволами, поступающими из БПМ. Путем

записи соответствующей управляющей ииЗюрмации в БРУ можно

запрограммировать работу ИМС ИК51 практически иа любой из-

вестный способ последовательной передачи данных.

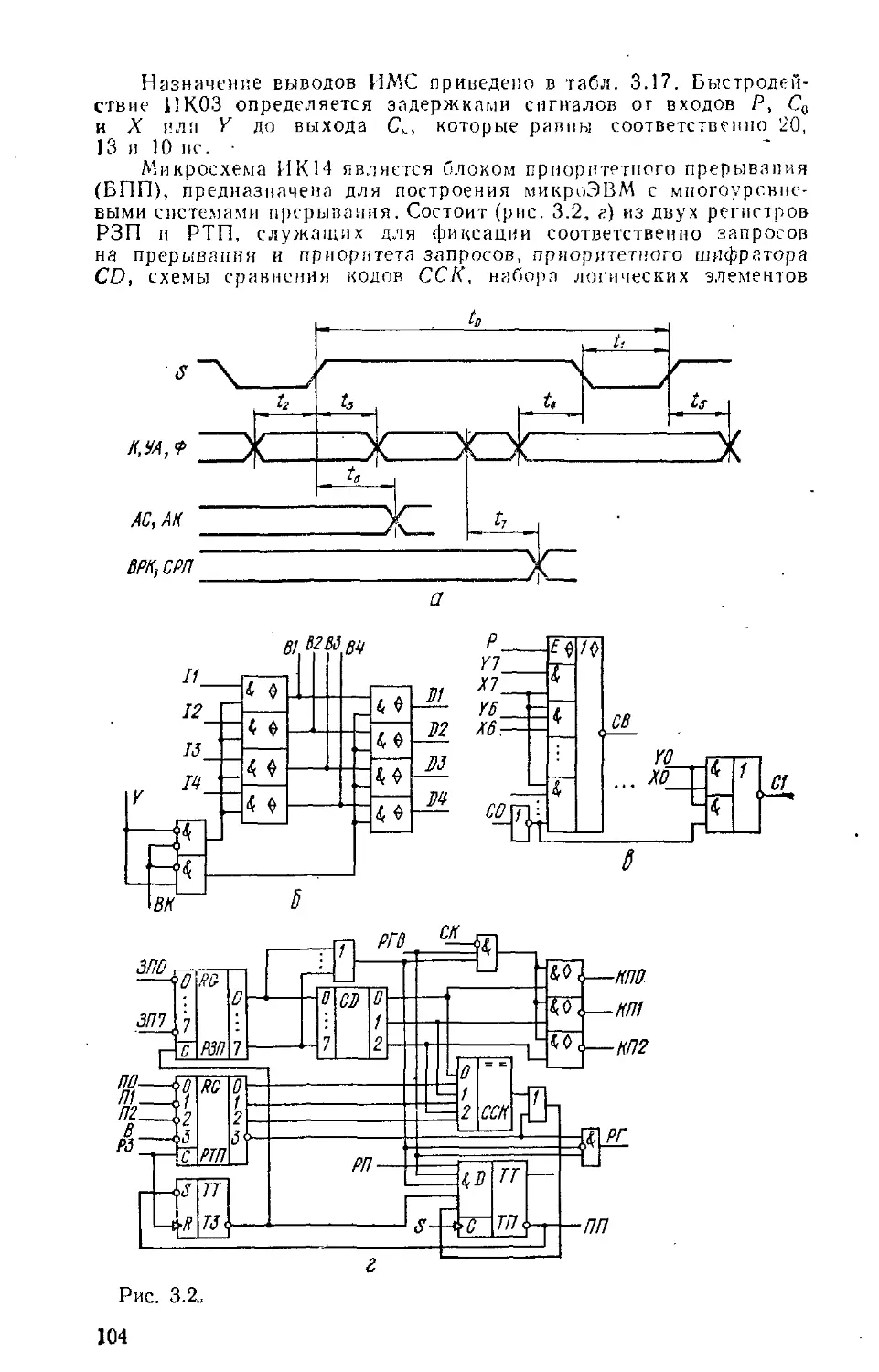

Микросхема ИК53 служит для генерации сигналов с програм-

мируемыми временными характеристиками и содержит (рис, 1.1, е)

три независимых 16-раэрядных счетчика Ct—СЗ, блок управления

БУ и буфер данных БД, который предиазиачеи для согласования

внешней ШД и внутренней шииы ВШ. Режим работы ИМС зада-

ется путем засылки управляющего слова в регистр БУ и сигнала-

16

1.5. Назначение выводов

ИМС ИК53

Л Я

р. Kt

£ о

9 й

£ з

1—8

9

10

11

13

14

15

16

17

18

19,

20

21

22

23

Наименование вывода

Шина данных ШД

Вход счетчика 1 (С1)

Выход Cl (В1)

Разрешение счета в С!

Вход счетчика 2 (С2)

Разрешение счета в С2

Выход С2 (В2)

Разрешение счета в счет-

чике 3 (СЗ)

Выход СЗ (ВЗ)

Вход СЗ

Адрес счетчика

Выбор ИМС

Чтение

Запись

|.6. Назначение выводов

ИМС ИК55

0.3 Наименование выводам

82 направление передачи

информации

U-i я

1—6, 46, 47 Шины канала 3 ШКЗ — вход/выход

9—16 Шины канала 2 ШК2 — вход/выход

20—27 Шины канала 1 ШК1 — вход/выход

29 Установка ИМС в исход- ное состояние — вход

31 Разрешение приема инфор- мации с ШДЗ — вход

92—39 Шина данных ШД — вход/выход

41 Разрешение выдачи ин- формации в ШД4 — вход

42 Выбор ИМС — вход

44, 45 Адрес канала АО, А1 — вход

вом.

Микросхема ИК57 предназначена для ускорения параллель-

ного обмена данными между памятью и периферийными устрой-

ствами путем прямого доступа к памяти по четырем каналам. Управ-

ляющее слово программы задает режим работы ИМС, приоритет-

ми, поступающими на входы

ИМС (табл. 1.5). Коэффициент

пересчета счетчиков задается

путем записи двух 8-разряд-

ных слов в соответствующий

счетчик. Последнее состояние

счетчика, означающее заверше-

ние запрограммированного вре-

менного интервала, передается

в микропроцессорное устройст-

во и вызывает прерывание, по

которому включается подпро-

грамма, связанная с заверше-

нием временной выдержки.

Если одного счетчика недоста-

точно для задания данного

временного интервала, имеется

возможность увеличения его

разрядности путем подключе-

ния двух других счетчиков.

Кроме того, ИК53 можно .ис-

пользовать в качестве счетчи-

ка тактовых сигналов, двоич-

ного умножителя и генератора

импульсов реального времени

(часы, минуты, секунды).

Микросхема ИК55 (рис.

1.1, ж) применяется для сопря-

жения периферийных устройств

(дисплей, телетайп, ЗУ) с

ШД микропроцессорных уст-

ройств и состоит из трех ка-

налов К1 — КЗ, блока выбора

канала БВК и регистра управ-

ления РУ, содержимое кото-

рого совместно с сигналами на

выводах ИМС (табл. 1.6) опре-

деляет режим работы каналов

и всей ИМС. Режимы работы

каналов К1 и К2 устаиавли-'

ваются независимо, а режим

КЗ зависит от режимов работы

К! и К2. Направление переда-

чи информации между шинами

UIKt (I = 1, 2, 3) и ШД зада-

ется сигналами чтения Ч и за-

писи 3 и адресом канала АО,

А1 и разрешается либо запре-

щается сигналом выбора ИМС.

Комбинирование регистров

обеспечивает работу ИМСс лю-

бым периферийным устройст-

16

ность каналов, начальный адрес и длину передаваемого массива

данных. Микросхема принимает и определяет приоритет сигнала

запроса от ПУ; приостанавливает выполнение программы в микро-

процессоре и отключает его от ШД, освобождая последнюю для об-

мена данными между ПУ н памятью; формирует адреса записывае-

мых в память или считываемых из памяти слов; подсчитывает коли-

чество выполненных циклов записн-считываиия; вырабатывает

сигнал завершения обмена после достижения запрограммирован-

ного числа циклов, по которому происходит переход к- прерванной

программе. Счетчики количества циклов каналов имеют 14, и ре-

гистры начальных адресов — 16 разрядов.

Микросхема ИК59 предназначена для управления многоуров-

невым прерыванием с обслуживанием восьми запросов. Количе-

ство обслуживаемых запросов на прерывание работы микропро-

цессора можно увеличить до 64 путем каскадирования. Приоритет

отдельных запросов устанавливается путем записи соответствую-

щего кода в регистр маски ИМС. Поступающие в ИМС запросы

фиксируются в регистре запросов, ИМС определяет на основании

приоритетов очерёдность их обслуживания и выдает иа управляю-

щую тину в микропроцессор общий сигнал на прерывание. Приме-

нение ИК59 для обслуживания запросов от периферийных устройств

значительно увеличивает быстродействие микроЭВМ.

Микросхема ИК80 представляет собой 8-разрядный функцио-

нально законченный процессорный элемент без возможности аппа-

ратного наращивания разрядности обрабатываемых данных. Со-

стоит (рис. 1.1, з) из устройства управления МУ, арифметико-логи-

ческого устройства АЛУ и блока регистров БР. Все эти устройства

связаны между собой внутренней шиной ВШ, которая через буфер

данных БД подключается к двунаправленной внешней шине данных

ШД. Устройство управления включает в себя регистр команд РК,

Дешифратор ДК команд и схемы синхронизации и управления-

ЙМС. Ввод, и вывод управляющих сигналов осуществляется по

шине управления ШУ. Побайтная обработка информации реали-

вуется в АЛУ, которое состоит из сумматора и комбинационных

схем, объединенных в арифметико-логической блок АЛБ, и четы-

рех регистров Pl, Р2, РА и РП, служащих соответственно для

приема операндов, запоминания результата и его признаков. Каж-

дый триггер 5-разрядного РП предназначен для запоминания со-

ответствующего ему признака или сигнала, а именно: нулевой ре-

вультат Z, отрицательный результат S (бит знака), перенос или

ваем Q, полуперенос (из младшей тетрады в старшую) q и чет-

ность результата р.

Блок регистров БР содержит шесть 8-разрядных регистров

общего назначения РВ, PC, РД, РЕ, PH, PL, два 8-разрядных

регистра младших разрядов команды РВ2 и РВЗ, предназначенных

Для хранения 2-го и 3-го байтов команд соответствующей длины;

два 16-разрядных регистра адреса Ра и указателя стека РУ, предна-

вначенных соответственно для хранения н выдачи через буфер

адреса БА на шину адреса ША адресов команды илн операнда,

Для обращения по нему к памяти или устройству ввода-ввода ин-

формации и хранения адреса ячейки стека, к которой было послед-

нее обращение, и 16-разрядного счетчика команд СК, предназна-

ченного для формирования адреса следующей команды.

Наименование и назначение выводов ИК80 приведена

в табл. 1.7. В ИК80 используются команды длиной в один, два или

три байта. Первый байт команды указывает ее длину, код опера-

ции, вид адресации и номера регистров, если они участвуют в

17

1.7. Назначение вы годов ИМС ИК80

Номер вывода Наименование вывода

/— выход Подтверждение захвата ПЗ. Единица на выходе ПЗ указывает, что выводы МП, которые подключаются к ШД и ША микропроцессорной системы, находятся в высокоомном состоянии и внешние устройства могут управлять ШД и ША системы

2 и 40~— входы Тактовое питание Ф1 и Ф2. Сигналы Ф1 и Ф2 являются неперекрывающимися сериями импульсов с амплитудой 12 В и частотой не более 2 МГц (2,5 МГц для ИК80А)

3 — вход Готовность ГТ. Нуль на входе ГТ означает, что уст- ройство, с которым МП обменивается информацией, не готово к передаче данных. Если после выдачи МП адреса действует сигнал ГТ — 0, то МП переходит в состояние ожидания и остается в нем до прихода сигнала ГТ — 1. Сигнал ГТ можно использовать для организации режима работы МП с остановом после выполнения одного ма- шинного цикла, одной команды или выдачи на ША заданного адреса команды или операнда, а также для согласования работы МП с памятью или УВВ любого быстродействия

4—выход Ожидание ОЖ. Сигнал ОЖ — I означает, что МП нахо- дится в состоянии ожидания или останова

6, 24 и 48 Питание 12 В, —5 В и 5 В

7—9 и 11—23 — Шина адреса ША. Выходы МП, которые подключаются к ША микропроцессорной системы

выходы

25 Общий вывод

26—28 и 81—35 — входы- выходы Шина данных ШД. Двунаправленные выводы МП, кото- рые подключаются к ШД микропроцессорной системы

18

П родолжение табл. 1.7

Номер вывода Наименование вывода

37 — вход Сброс СБ. При СБ = 1 выполнение операций в МП пре- рывается; счетчик команд, регистр команд, внутренние триггеры разрешения прерывания и подтверждения за- хвата сбрасываются в нулевые состояния, а МП выводится из состояния останова или захвата. Во время действия сигнала СБ = 1 ША и ШД МП переходят в высокоом- ное состояние, а все выходные сигналы управления МП— в неактивное состояние. Сигнал СБ = 1 должен длиться не менее трех периодов Ф1 и Ф2. По началу сигнала СБ = 0 МП начинает работать с такта Т1 цикла Ml

38 — вход Захват ЗХ. Сигнал ЗХ = 1 переводит МП в состояние захвата, при котором ША и ШД находятся в высоко- омном состоянии, что позволяет, например, ИМС ИК57, использовать ША и ШД для прямого доступа к памяти минуя МП

39 — вход Запрос прерывания ЗП. Сигнал ЗП анализируется в конце выполнения очередной команды или в состоянии останова. Если МП находится в состоянии захвата или триггер разрешения прерывания установлен в 0, то сиг- нал 317 не анализируется

42 — вы- ход Разрешение прерывания Р/7. Сигнал РП отображает состояние триггера разрешения прерывания и при РП == 1 указывает на то, что прерывание разрешено

43 — вы- ход Прием ПМ. Сигнал ПМ — 1 указывает, что ШД нахо- дится в режиме приема, ПМ можно использовать как строб разрешения приема информации с ШД в МП

44— вы- ход Выдача БД. Сигнал БД = 0 указывает, что МП выдал информацию на ШД. ВД используется и для управления записью информации во внешние устройства

45 — вы- ход Синхронизация G. Сигнал G = 1 выдается в первом такте каждого цикла выполнения команды. При С= 1 иа ШД выдается информация о состоянии МП

19

выполнении операции. При этом три младших разряда первого

байта команды указывают номер регистра-источника, а следую-

щие три разряда — номер регистра-приемиика информации. Адре-

са регистров РВ, PC, РД, РЕ, PH, PL кодируются двоичными

числами от ООО до 101 соответственно. Код ПО является косвенным

адресом ячейки ЗУ, 16-разрядный адрес которой указан в двух

8-разрядных регистрах РН'н PL, а код 111 является номером РА

(аккумулятора). Если же один или два из указанных регистров не

участвуют в выполнении данной команды, то соответствующие им

разряды совместно с двумя старшими разрядами первого байта

команды используются для представления кода операции. Второй

и третий байты команд соответствующей длины используются для

непосредственной адресации ячеек ЗУ или устройств ввода-вывода.

1.2. СИСТЕМА КОМАНД МИКРОСХЕМЫ ЙК80

Список команд ИМС ИК80 приведен в табл. 1.8, где первый байт

команды и ее длина заданы с помощью пяти символов. Первые три

символа являются цифрами, замена которых двоичными эквива-

лентами длиной в два (для первой) и три бита (для второй и третьей)

дает восемь бит первого байта команды. Код команды длиной

в два и три байта дополнен символами соответствующих байт В2

и В3, например, команда АС/ является двухбайтовой, так как код

команды состоит из трех цифр (3; 1 и 6) и символа второго байта

Ва. При этом первый байт команды будет иметь вид 11001110.

Принцип кодирования команд поясняет табл. 1.9,- в которой

приведены все 256 возможных кодовых комбинаций из восьми сим-

волов (D^sDjDjDjDjDjDo) и соответствующие им команды. Из

табл. 1.9 видно, что например, цифры 01 и 10 в двух старших раз-

рядах являются признаками соответственно команды MOV (НЕТ)

или арифметической (логической) операции. При этом вид арифме-

тической или логической операции задают символы О8О463. Из

256 кодовых комбинаций 13 не использованы для кодирования

команд (например,‘001ХХООО).

1.8. ВЫПОЛНЕНИЕ КОМАНД

В МИКРОПРОЦЕССОРЕ СЕРИИ 580

Команды в ИК80 выполняются по машинным циклам (МЦ),

продолжительность которых составляет 3—5 периодов тактового

питания (тактов), отсчитываемых по нарастающим перепадам сиг-

нала Ф1 (рис. 1.2, а). Число МЦ и общее количество тактов, необ-

ходимое для выполнения команды, определяются типом выпол-

няемой команды (табл. 1.8). При этом число МЦ равно суммарному

числу обращений к ЗУ и УВВ, необходимых для выборки и выпол-

нения данной команды. Например, самые короткие команды RAL

выполняются за одни МЦ в течение 4 тактов (2 мкс), так как тре-

буют только одного обращения к ЗУ для выборки байта команды,

а самая длинная команда XTHL выполняется за пять МЦ в течение

18 тактов (9 мкс), так как необходимо выбрать из ЗУ три байта

н записать в ЗУ два байта. Исключения составляют команды

DAD и НЕТ, которые выполняются соответственно за три и два

машинных цикла, но обращение к ЗУ происходит только один раз

в первом цикле. Первый МЦ (сокращенно Ml) является всегда

циклом выборки первого байта команды и состоит из 4 или 5

20

1.8. Список команд ИМС ИК80__________________________________,

Обозначе- ние Код Содержание Число тактов для выполнения команды. Вектор изменения приз^ наков (Z, S, Q, р). Пояснения

Арифметические операции

АС1 AD1 SBI SU1 316 B2 306 B2 336 B, 326 B2 a+b2-+pa A—B%—Q-+-PA A—B^PA 7. (+++++). К содержимому РА прибавляется (вычитается) второй байт команды с учетом или без учета переноса (зае- ма), образовавшегося при выпол- нении предыдущей команды, а результат записывается в РА- Признаки (Z, S, Q, q, р) уста- навливаются в соответствии с результатом операции

ADC ADD SB В SUB 21 X 20 X 23X 22 X A^R+Q.-+PA A-\-R-+PA A—R—Q-+-PA A-R-+PA 4 (7). (+++++)• К содержи- мому РА прибавляется (вычита- ется) с учетом или без учета переноса (заема) содержимое R регистра, номер X которого указан на третьей позиции кода команды (при X = 6 R — содер- жимое ячейки памяти, адрес которой указан в регистрах PH и PL, а время выполнения команды увеличивается до 7 тактов)

’ DAA 047 (Десятичная коррекция Л) -* -+PA 4. (+++++)• Команда DAA позволяет организовать обра- ботку двоично-десятичных чисел за счет коррекции суммы этих чисел, полученной на двоичном сумматоре, путем добавления кода 6 к старшей и младшей тетрадам в зависимости от их величин и наличия сигналов Q и <?

DAD В DADD DAD И DAD SP Oil 031 051 071 BC-\-HL-+PHL DE-\-HL-+PHL HL+HL-^PHL Y+HL-+PHL 10. ( 1 ). Два 8-разряд- иых числа Н и L, рассматри- ваемые как одно 16-разрядное число HL, находящееся в реги- страх PH и PL (PHL), склады- ваются с аналогично образо- ванным 16-разрядным числом ВС (DE, или HL, или К), распо- ложенным в регистрах РВС (PDE, или PHL, mhPY), а ре- зультат заносится в регистр PHL. В соответствии с результатом операции устанавливается толь- ко признак Q, остальные приз- наки остаются без изменений

21

Продолжение табл. 1.8

Обозначе- ние Код Содержание Число тактов для выполнения команды. Вектор изменения признаков (Z, S, Q, Q, р). Пояснения

DCR INR 0X5 0X4 R-X-+PR R+X-+PR 5 (10). (+-| Н-)- Содержимое регистра, номер X которого указан на второй позиции кода команды, уменьшить (увеличить) на 1 (при X = 6 R является содержимым ячейки памяти, адрес которой указан в регист- рах PH и PL, а время выпол- нения команды увеличивается до 10 тактов). В соответствии с результатом операции уста- навливаются все признаки кроме переноса

DCX В DCXD DCXH DCXSP INX В INXD 1NXH 1NXSP 013 033 053 073 003 023 043 063 ВС—Х^-РВС DE-X-*-PDE HL—X-+PHL Y-X-+PV ВС-\-Х->-РВС DE+X^-PDE HL+X-+PHL ¥-\-\-*РУ 5. ( —). Два 8-разряд- ных числа В и С (D и Е, или Н и L, или У), рассматриваемые как одно 16-разрядное число BC'(DE, HL или У), находя- щееся в регистре РВС (РОЕ, или PHL, или РУ), уменьша- ются (увеличиваются) на 1, а результат заносится в регистр РВС (PDE, ялв PHL, или РУ), образованный парой регистров РВ и PC (PD и РЕ, или PH и PL, или РУ)

RAL RAR 027 037 2A+Q-+PA l/24+128Q->7M 4. ( ) Триггер пере- носа и РА объединяются в 9- разрядный кольцевой регистр, на котором производится цикли- ческий сдвиг на один разряд влево (вправо). В триггер пе- реноса при сдвиге записывается старший (младший) разряд А

RLC RRC 007 017 Левый цикли- ческий сдвиг на РА Правый цикли- ческий сдвиг на РА 4. ( 1 ). На основе РА образуется 8-разрядный коль- цевой регистр, на котором про- изводится циклический сдвиг на один разряд влево (вправо). В триггер переноса и младший (старший) разряд РА записыва- ется старший (младший) раз- ряд Л

22

Продолжение табл. 1.8

Обозначе- ние Код Содержание Число тактов для выполнения команды. Вектор изменения приз- наков (Z, 3, Q, q, р). Пояснения

Логические операции

ANA ORA XRA 24 X 26 X 25 JV A/\R-+PA A\/P-+PA avp-^pA 4 (7). (++00+). Над кодами А и R, где R— содержимое ре- гистра, иомер X которого ука- зан на третьей позиции команды, выполняется поразрядная опе- рация И (Д), HJlH(V) или сумма по модулю 2 (V) (при Л = 6 R — содержимое ячейки памяти, адрес которой указан в регистрах PH и PL, а время выполнения команды увеличи- вается до 7 тактов). Признаки Q и q устанавливаются в 0, а остальные — в соответствии с результатом операции

ANI QRI XRI 346 Bt 366 Bt 356 Bt . A/\Bt-+PA A\/B2-+PA АуВ^+РА 7. (++00+). Команды отли- чаются от команд ДАМ, OR А и XRA тем, что в качестве второго операнда берется вто- рой байт В8 команды

CMA 057 A-+PA 4. ( ). Поразрядная инверсия всех разрядов РА

CMC 077 Q-+-TQ 4. ( j ). Инверсия содер- жимого триггера переноса (за- ем а)

CMP 27 X A—R 4 (7). (+++++)• Сравне- ние (путем вычитация) А с со- держимым регистра, номер X которого указан иа третьей по- зиции кода команды (при Х=6 R — содержимое ячейки памяти, адрес которой указан в реги- страх PH и PL, а время вы- полнения команды увеличива- ется до 7 тактов). Результатом операции являются значения признаков, а коды в регистрах, хранящих А и R, не изменя- ются

23

Продолжение табл. 1.8

06q зна- чение Код Содержание Число тактов для выполнения команды. Вектор изменения при- знаков (Z, S, Q, q, р). Пояснения

CPI 376 В2 А—Вг 7. (+++++). Команда СР1 отличается от команды СМР только тем, что в качестве вто- рого операнда берется второй байт В2 команды

STC 067 1-»TQ 4. (——] ). Триггер TQ пе- реноса устанавливается в состоя- ние 1

Команды перехода к подпрограммам (ПП) и возврата из ПП

CALL 334 В2В3 Вызов ПП 17. ( •—). Выполняется пер- вая часть действий команды СС

Вызов ПП: 11(17). ( ). Если

сс 334 по Q = 1 условие вызова ПП выполняется

см 374 по S = 1 (например, Q = 1 для коман-

cwc 324 52В3 по Q = 0 ды СС), то содержимое счетчика

CNZ 304 2^2^з по Z = 0 команд (СК) увеличивается иа 3

СР 364 В2В3 по S — 0 и записывается в стек по адре-

СРЕ 354 В2Ва по Р = 1 сам У—Г и У —2. Содержи-

СРО 344 BtBs по Р = 0 мое РУ уменьшается на 2.

CZ 314В2Ва по Z = 1 В СК передается адрес ВаВ2 первой команды ПП. Если усло- вие вызова ПП не выполняется (например, Q = 0 для команды СС), то управление передается следующей команде программы, для чего содержимое СК уве- личивается на 3. В первом слу- чае команда выполняется за 17, а во втором—за 11 тактов

Возврат: 5 (11). ( ). Если уело"

КС 330 no Q = 1 вие возврата из ПП выполни"

RM 370 по S = 1 ется (например, Q = 1 для коман-

RNC 320 по Q = 0 ды RC), то управление пере-

RNZ 300 по Z = 0 дается команде, адрес которой

RP 360 по S — 0 записан в верхней паре ячеек

RPE 350 по Р— 1 стека, для чего в СК записыва-

RPO 340 по Р = 0 ются два байта, извлеченные по

RZ 310 по Р = 1 адресам У и У + 1, а содержимое РУ увеличивается на 2. Если

условие возврата из ПП не вы- полняется (например, Q = 0 для команды RC), то управление передается следующей команде, для чего содержимое СК увели- чивается иа 1. В первом случав команда выполняется за 11, а во втором — за 5 тактов

24

Продолжение табл. 1.8

Обозначе- ние Код Содержание Число тактов ’для выполнения команды. Вектор изменения приз- наков (Z, S, Q, q, р). Пояснения

RET DI El 311 команды г 363 373 Возврат из ПП /правления и вво Запрет преры- вания Разрешение прерывания 10. ( ). Выполняется первая часть действий команды RC да-вывода информации 4. ( :—). Триггер разре- шения прерывания устанавли- вается в состояние запрета (разрешения) прерывания. Во время выполнения команд сигнал запроса прерывания не воспри- нимается

НЕТ 166 Останов 7. ( ). В СК формиру- ется адрес следующей команды, состояния регистров',, и памяти ие изменяются н МП переходит в состояние останова с воз- можностью последующего за- пуска при возникновении запро- сов на 'Прерывание

IN 333 В, Ввод в РА 10. (— -—). С устройства ввода информации, иомер В2 которого указан во втором байте команды, осуществляется прием слова на РА

NOP ООО Нет операции 4. ( ). Операция ие выполняется. На СК формиру- ется адрес следующей команды

OUT 323 В, Вывод А 10. ( ). Содержимое РА передается в устройство вывода информации, номер Вг которого указан во втором байте команды

RST 3X7 Начальный за- пуск прерыва- ющей подпро- граммы 11. ( ). Команда RST поступает в МП от источника запроса на прерывание. Содер- жимое СК записывается в стек по адресам Y — 1 и У — 2 для последующего возврата из пре- рывающей подпрограммы. Со- держимое РУ уменьшается на 2, а в СК записывается адрес 0000000000X000 (X— двоичная запись кода, указанного на вто- рой позиции команды RST) пер- вой команды прерывающей под- программы

•25

Н рооолжение табл, i.8

Обоанжче- W’ Код Содержание । Число тактов для выполнения команды. Вектор изменения приз- । каков (Z, S, Q, q, р). Пояснения

й JNC INZ JP JPE JPO 12 Команда 332 5,5, 372 5,5, 322 5,5, 302 5,5, 362 5,5, 352 5,5, 342 5,5, 312 5,5, и условного и бе. Переход: по Q « 1 по S =« 1 по Q = 0 по Z == 0 по S =» 0 по Р •= 1 по Р » 0 по 2 « 1 ^условного переходов 10. ( ). Если условие перехода выполняется (напри- мер, Q=1 для команды I С), то в СК записывается адрес 5,5,. Если условие перехода не выполнено (например, Q = 0 для команды УС), то управление передается следующей команде, для чего содержимое СК уве- личивается иа 3

IMP 303 5,5, Переход без- условный 10. ( ). Выполняется первая часть действий коман- ды JC

LDA ST А I 0725,5, 062 5,5, команды пересыл ЗУ-*-РА РА-*-ЗУ хи информации 13. ( ). По адресу 5,5,. образованному из третьего и второго байтов команды, выбрать из ЗУ слово и запи- сать его в РА. По команде ST А осуществляется обратная пересылка по тем же адресам

LDAXB LDAXD STAX В STAX D 012 032 002 022 а, а, ело-; f t t t co co о. о. 7. ( ). По адресу ВС (DE), образованному из со- держимого регистров РВ и PC (PD и РЕ), выбрать из ЗУ слово и записать его в РА. В коман- дах 57’ЛЛ' В и D осуществля- ется обратная пересылка по тем же адресам

LHLD SHLD 052 5,5, 042 5,5, ЗУ -> PHL PHL-*-ЗУ 16. ( ). По адресам 5,5, + 1 н 5а5, выбрать из ЗУ два слова и записать их соот- ветственно в PH и PL. В ко- манде SHLD осуществляется обратная пересылка по тем же адресам

LX1 В LXI D LXIH LXI SP 001 5,5, 021 5,5, 041 5,5, 061 5,5, CXjtOtoCo ! ее co co w to to tu to 1 to to te № Illi 4 &!(□$» 10. ( ). Третий и вто- рой байты команды заносятся в регистровую пару РВС (PDE или PHL или РУ), образованную из регистров РВ и PC (PD к РЕ, или PH и PL, или РУ)

Продолжение табл. 1.8

Обозна- чение K04 Содержание Число тактов для выполнения1 команды. Вектор изменения приз- наков (Z, 5, Q, 4, р). Пояснения

MOV 1 x2x. Ri -* PRt 5 (7). ( ). Содержимое R регистра, номер Xj которого указан иа третьей позиции кода команды, пересылается в ре- гистр PR2, номер Х2 которого указан на второй позиции кода команды. При Х[ или Х2 = = 6 в качестве источника или приемника информации служит ячейка памяти, адрес которой указан в регистровой паре PHL, а время выполнения команды увеличивается в этом случае до 7 тактов. При Xj — Х2 = 6 выполняется команда HLT

MV1 OX e Bi Bi-*-PR 7(10). ( ). Второй байт команды записывается в регистр, номер X которого указан на второй позиции кода команды (при X = 6 запись производится в ячейку памяти, адрес которой указан в регистровой паре PHL). Время выполнения команды в этом случае увеличивается до 10 тактов

PCHL SPHL 361 371 HL-*-CK HL-*-PV 5. ( ). Содержимое HL регистровой пары PHL, образ'л- ванной из регистров PH и Pl, пересылается в СК (для ко- манды SPHL — в РУ)

POP В POP D POP H POP PSW 301 321 341 361 [Y]-+PC, [Y+ij-*.PB Y]-*-PE, У + 1]->PD YI-+PL, y_|_ i]_>Ptf У]-+РП, У+U — PA 10. ( -). Выбрать из стека по адресам У и У + 1 два байта и записать нх в регистры PC и РВ (РЕ и PD, нли PL и PH, или РП и РЛ). Содер- жимое РУ увеличить на 2

Z1

Продолжение табл. 1.8

Обозна- чение .Код Содержание Число тактов для выполнения команды. Вектор изменения при- знаков (Z, S, Q, q. р}. Пояснения

PUSH в PUSH D PUSH н PUSH PSW 305 325 345 365 ВС Стек DE Стек HL -> Стек ПА ->- Стек 11., ( -). Содержимое ВС (DE, или HL, или ПА) ре- гистровой пары, образованной регистрами РВ и PC (PD и РЕ, нли PH и PL, или РП и РД), записать в стек по адресам Y — 2 и Y = 1. Содержимое РУ уменьшить на 2

XCHG 353 PH <+PD, PE^PL 4. ( ——). Регистры PH н PD н регистры РЕ и PL об- мениваются своим содержимым

XTHL 343 PHL <-> Стек 18. ( ). Верхушка стека с адресами Y + 1 и Y обменивается своим содержи- мым с регистровой парой PHL, образованной из регистров PH и PL

тактов. Три последующих МЦ (М2, М3 и М4) выполняются всегда за

три такта, а пятый МЦ — за три или пять тактов. Каждый МЦ со-

провождается- выдачей сигнала «Синхронизация» (С) в такте Т1

(рис. 1.2, а). При этом на ШД выдается байт состояния, определя-

ющий действия, которые будут выполняться в данном МЦ. По

совпадению сигналов Ф1 = 1 и С = 1 байт состояний должен быть

зафиксирован во внешнем 8-разрядном регистре и использован

в микропроцессорной системе для управления. Назначение отдель-

ных разрядов Di (i = 0,7) байта состояния приведено в табл. 1.10.

Организация вычислительного процесса в простых микроЭВМ

возможна и без учета байта состояний. Из 256 возможных кодов

байта состояний в МП использованы только 10, задающих 10 раз-

личных машинных циклов, из которых формируются все команды

(табл. 1.11). Схема алгоритма работы МП показана на рис. 1.3.

Из такта Т1 МП всегда переходит в такт Т2, в котором анали-

зируются входные сигналы «Готовность» (ГТ) и «Захват» (ЭХ)

и сигнал «Подтверждение останова» (ПО) из байта состояний. Если

ПО = 1, то МП переходит в состояние останова СО, выход из кото-

рого возможен при поступлении сигналов СБ = 1 (сброс), ЗП = 1

(запрос прерывания) или ЗХ = Г (захват). Переход в СО проис-

ходит во втором цикле команды HLT (рис. 1.2, б). Если (ПО) (ГТ) =*

= 1, то МП переходит в состояние ожидания СОЖ, нз которого

МП выходит по сигналу ГТ = 1.

Если (ПО) (ГТ)=1, МП анализирует сигнал ЗХ. Если ЗХ = 0,

выполняется такт ТЗ, в течение которого происходит ввод в МП

или вывод из МП информации. После завершения такта" ТЗ анали-

зируется внутренний сигнал конец цикла (КЦ), по которому осу-

ществляются дальнейшие переходы МП. Такты Т4 и Т5, если

они в данном цикле присутствуют, используются для завершений

28

выполнения команды за счет внутренних (без обращения к другим

ИМС) операций МП.

Если ЗХ = 1, по фазе Ф2 такта Т2 этот сигнал фиксируется

на внутреннем триггере захвата шин ЗШ, что обеспечивает перевод

ШД и III А в высокоомное состояние и, после завершения текущего

машинного цикла команды, переход МП в состояние захвата СЗХ..

\ Tt \ Т2 \ ТЗ \ 74 \ ТЗ \

С I--------1_____________________

а

Mi I М2

1Г/ I Z? I 73 I W I Г/ t 7? I \ П I

»/П п п п п п п п п

ФЭ п п_ п____________п____п п п п

ША----\ Счетчик команд

ШД —У^бС^Команд^-----------X У

С 1 1--------1 1_____

ПМ _____I I------------

СО,СОШ______________I

5

I Ml I М2 I мз I

КВК \Т1 \ Т2 \ ТЗ \ П \Т5 \ Т1 \Т2 \ТЗ \ Т1 \Т2 \ ТЗ \ Т1 \

Ф1 пппппппппппп

02 JT__n n n—л п_п п п п п п л

—X С/Г %--------X Y-1 Х~ Г-2

шд —УдсУястУг----------ХбсХсмз-вМдс'х ска-о/

Рис. 1.2.

Перевод ШД и ША в высокоомное состояние всегда происходит

по фазе Ф2 соответственно в такте ТЗ и в следующем за ним такте.

Если данный цикл не является циклом записи ' и, следовательно,

на ШД не надо удерживать подлежащее записи в ЗУ слово, то ШД

переходит в высокоомное состояние на такт раньше, т. е. по фазе

Ф2 такта ТЗ. Этот перевод индицируется с упреждением сигналом

1 на выходе подтверждения захвата ПЗ, который появляется по на-

растанию Ф1 того такта, в котором ШД переходит в высокоомное

состояние.

29

g 1.9. Кодирование команд ИМС ИК80

D?D gD ‘D4D3

йоо 001 «to Oil

00 ООО 1ЮР LXIB STAX В I NX В

001 МО (Ml ТОО ММ ио 1Ы DAD В LDAXB DCX В

LXI D STAXD INXD

DAD D LDAXD DCX D

LXI И SHLD INXH

DAD Я LHLD DCX H

LXI ЭР STA 1NX SP

DADSP LDA DCX SP

ООО 001 @10

D^D.D,

100 101 no in

INR DCR MV1 RLC

RRC

RAL

RAR

DAA

CMA

STC

CMC

01 on 100 101 по 111 MOV 1 HLT 1

10 ООО add

001 ADC

010 SUB

он sbb

100 ANA f

101 XRA

но ORA

111 CMP

11 ООО RNZ POP В JNZ JMP CNZ PUSH в ADI RST

001 RZ RET JZ CZ CALL ACI

010 RNC [POP D JNC OUT CNC PUSH D SUI

Oil RC JC IN CC SBI

100 RPO POPH JPO XTHL CPO PUSH H ANI

101 RPE PCHL JLE XCHG CPE XRI

но RP POPPSw JP DI CP PUSH PSW ORI

111 RM SPHL JM El CM CPI

г

Выход МП из состояния захвата осуществляется по сигналу

ЗХ = 0, который сбрасывает в 0 внутренний триггер захвата шин,

и МП начинает выполнять следующий цикл с такта Т1, так как не-

смотря на то, что ША и ШД переходят в состояние захвата, МП

завершает текущий цикл. Для надежного приема сигнала ЗХ его

нарастание должно быть стробировано нарастанием Ф2 или спадом

Ф1, а спад ЗХ — спадом Ф2,

Рис, 1,3.

32

J.10. Назначение разрядов байта состояния

Di Наименование сигнала ИМС ИК 80

DO Подтверждение прерывания ПП. По сигналу 2777=1 начи- нается прерывание, для чего МП принимает от прерывающего устройства команду RST, которая обеспечивает передачу уп- равления одной из восьми прерывающих подпрограмм

DI Запись — вывод ЗВ. Сигнал 327=0 означает, что в данном машинном цикле происходит выдача информации из МП в ЗУ или УВВ _

D2 Стек СТ. Сигнал СТ = 1 является признаком того, что иа ША установлено содержимое указателя стека

D3 Подтверждение останова ПО. Сигнал ПО=\ свидетельствует о том, что МП перешел в состояние останова по команде HLT

D4 Вывод В. Сигнал 27=1 указывает на то, что на ША уста- новлен номер У ВВ, а на ШД — выводимая информация

D5 ЛИ. Сигнал Л7/=1 является признаком того, что в данном МЦ вы'ирается первый байт очередной команды по адресу, который в данном такте выведен со счетчика команд на ША

D6 . Ввод ВВ. Сигнал ВВ—\ указывает на то, что на ША ус- тановлен номер УВВ, - и МП принимает слово с ШД в ре- гистр результата

D7 Чтение Ч. Сигнал Ч—\ указывает на то, что в МЦ считы- вается информация из ЗУ

После завершения цикла как по ветви с захватом, так н по

ветви без него происходит анализ внутреннего сигнала КВК. (конец

выполнения команды). Если выполнение команды не окончено, осу-

ществляется переход к такту Т1 следующего цикла данной ко-

манды. Если же выполнение команды завершено,.то анализируются

внешний сигнал запроса прерывания (ЗГГ) и внутренний сигнал

разрешения прерывания РП. Эти же сигналы анализируются и при

состоянии СС, если ЗХ = 0. Если (ЗП) (РП) = 0, МП переходит на

начало цикла Ml очередной команды или в состояние СО (рнс. 1.3).

Если же (ЗП) (РП) = 1, то внутренний триггер запроса прерывания

1ТП) устанавливается в 1 (УТП), и МП переходит к выполнению

машинного цикла подтверждения прерывания, который является

1-м циклом выполнения, команды RST. Временная диаграмма ра-

боты МП при выполнении команды RST показана на рис. 1.2, в.

Для надежной фиксации сигнала ЗП на ТП он должен быть

подай на вход ЗП не менее, чем за 120 нс до спада Ф2 (Ф1 при СО)

последнего такта последнего цикла команды. По Ф2 в Т1 сигнат

РП и триггер ТП сбрасываются в 0, запрещая новые прерывания.

2 в-451

33

1.11. Коды машинных циклов в ИМС ИК80

Байт состояния Название цикла

DO D1 D2 D3 D4 D5 D6 D7

пп ЗВ ст по В Ml вв ч

0 1 0 0 0 1 0 1 Выборка команды

0 1 0 0 0 0 0 1 Чтение слова из ЗУ

0 0 0 0 0 0 0 0 Запись слова в ЗУ

0 1 1 0 0 0 0 1 Чтение слова из стека

0 0 1 0 0 0 0 0 Запись слова в стек

0 1 0 0. 0 0 1 0 Чтение слова из УВВ

0 0 0 0 1 0 0 0 Запись слова в УВВ

1 1 0 0 0 1 0 0 Подтверждение прерывания

0 1 0 1 0 0 0 1 » останова

. 1 1 0 1 0 1 0 0 » прерывания

при останове

Снятие запрета на прерывания в дальнейшем осуществляется вклю-

чением в программу команды EI (разрешения прерывания). Сигнал

ЗП можно сбросить в 0 устройством, вызвавшим прерывание в лю-

бой момент после начала цикла подтверждения прерывания, но

обязательно до появления команды EI для предотвращения повтор-

ного прерывания по одному и тому же запросу. Этот сброс можно

осуществить сигналом [DO из байта состояний Б С. На IIIЛ выво-

дится содержимое счетчика команд СТС, однако оно не изменяется

на +1, какобычпо.м не используется для обращения к внешним уст-

ройствам или ЗУ, так как в режиме прерывания команда выбирает-

ся не по адресу из памяти, а поступает во время действия сигнала

ПМ .(прием) из устройства, вызвавшего прерывание. Принятая

команда RST обеспечивает запись в верхушку стека по адресам

¥ — 1 и У — 2 в М2 и М3 содержимого СК по сигналам ВД (выда-

ча) и переход к одной из восьми Подпрограмм анализа запроса пре-

рывания.. Возврат к основной программе после завершения обслу-

живания подпрограммы прерывания осуществляется командой

RET.

Прерывающее устройство может подать на МП вместо команды

RST любую однобайтную команду. В этом случае содержимое СК

в стек не записывается и не вырабатывается адрес перехода на

подпрограмму обслуживания, но так же, как и при выполнении

команды RST, содержимое СК в Т2 не изменяется. Такой режим

можно использовать, например, для организации в ячейке памяти

или в одном из регистров МП счетчика количества сигналов ЗП от

какого-либо устройства без прерывания '(только с приостановкой)

основной программы. При этом следует учитывать, что после выпол-

нения такой операции следует путем периодического включения

в программу команды. EI снимать запрет на новые прерывания.

После включения напряжения питания и подачи тактовых

сигналов Ф1 и Ф2 МП запускается подачей 1 на вход «Сброс» в те-

чение не менее трех периодов Ф1, вследствие чего счетчик и ре-

гистр команд и внутренние триггеры разрешения прерывания,

подтверждения захвата и ожидания сбрасываются в нулевое состоя-

34

ние. Содержимое регистров общего назначения, результата и при-

знаков изменяется только в процессе выполнения команд. После

окончания действия сигнала «Сброс» МП начинает выполнять

цикл ,М/ и выдает на ША нулевой адрес.

При обработке данных на МП ИК80 необходимо учитывать

особенность реализации операций сложения и вычитания, которая

состоит в том, что операция вычитания выполняется как операция

сложения первого операнда с дополнительным кодом второго опе-

ранда. При этом бит переноса Q в регистре признаков устанавли-

ваетвя в 1, если выполнялась операция вычитания и переноса из

старшего разряда сумматора не было' или_ если выполнялась опе-

рация сложения и перенос -из старшего разряда сумматора был,

а бит знака 5 повторяет значение старшего разряда байта резуль-

тата. В дальнейших операциях Q учитывается по-разному: при

сложении (ACI или ADC) Q = 1 увеличивает, а при вычитании

(SBl, SBB) уменьшает результат на единицу младшего разряда.

Такая организация обработки признака Q облегчает выполнение

многобайтовых операций.. Например, операция 270—529 выполня-

ется по следующей схеме:

старший и младший байты чисел

270 = 256+ 14 00000001 00001110

529 = 512 + 17 00000010 00010001

14 00001110

—17 11101'110

_______1

11111101

переноса из сумматора нет, следовательно, Q = 1

256 = 00000001

—512=4 11111101

1

— 1

11111110-

11111110 11111101

дополнительный код числа

—259 = —(256 + 3) = —00000001 00000011.

Указанная особенность выполнения операций приводит к то-

му, что байт можно интерпретировать тремя способами.

1. Двоичное число со знаком, представленное в дополйитель-

ном коде. Нуль в старшем разряде байта означает знак плюс,

а единица — минус. Остальные семь бит определяют величину

числа. '

2. Двоичное число без знака. В этом случае все 8 бит опреде-

ляют величину числа.

3. Двухразрядвое десятичное число, две десятичные цифры

которого представлены соответственно четырьмя старшими и млад-

шими разрядами байта. В этом случае результаты операций долж-

ны корректироваться путем -применения DAA.

Возможны и другие способы интерпретации байта, которые

Должны учитывать указанные особенности ’реализации арифмети-

ческих операций. Рассмотрим примеры.

Процессы выполнения в МП однобайтовых жомалд сложения

И вычитания при 1-м способе интерпретации байта на примере

2* 35

1.12. Сложение чисел 14 и —17

Представление чисел Действия в АЛУ МП | Команда

деся- тичное двоичное

14 -17 000011Ю 11101111 0 00001110 11101111 11111101 ADD

14 17 00001110 00010001 1 00001110 11101110 1 11111101 SUB

чисел 14 и’—17 приведены в

табл. 1.12. Следует заметить,

что в МП отсутствует аппарат-

ное генерирование сигнала пе-

реполнения разрядной сетки,

возникающего при данной ин-

терпретации байта, например,

при сложении чисел одинако-

вого знака, сумма которых по

модулю больше 128.

Второй способ интерпре-

тации байта удобен при опе-

рациях с числами одного знака

и при многобайтовых опера-

циях. Переполнение разрядной

сетки в этом случае фиксирует-

ся признаком Q = 1.

1.13. Примеры действий нал

двоично-десятичными числами

Действия над числами Команда

десятичными ДВОИЧНЫМИ

Qv Сумматор АЛУ

.. 23 +15 38 0010 ООП 0001 0101 ADD

00 ООН 1000 0000 0000 DAA

Коррекция +00

ООН 1000

.23 + 18 0010 ООН 0001 1000 ADD

41 00 ООН 1011

0000 ОНО DAA

Коррекция +06 01 0100 0001

,28 +79 107 0010 1000. 0111 1001 ADD

01 1010 0001 ОНО оно DAA

Коррекция +66 10 0000 0111

Третий способ интерпретации байта совместно с командой

десятичной коррекции позволяет организовать в МП обработку

десятичных чисел, представленных в двоично-десятичном, коде

с весами 8, 4. 2 и 1. Необходимость в коррекции, обусловлена тем,

что двоично-десятичные цифры суммируются на двоичном сумма-

торе. Вследствие этого возникающий из тетрады перенос .уменьшает

ее значение на 16 (вес переноса в единицах младшего разряда дан-

ной тетрады), а не на 10, как это должно быть при десятичном сло-

жении. С другой стороны, перенос из тетрады сумматора возникает

при условии, что сумма больше 15, а не 9, как это должно.быть при

десятичном сложении. Вызвать перенос и откорректировать двоич-

но-десятичную цифру как в первом, так и во втором случае можно

за счет прибавления к данной тетраде цифры 6. Указанное прибав-

ление надо делать, если был перенос из данной тетрады или содер-

жимое данной тетрады больше 9, или цифра в старшей тетраде рав-

на 9, а в младшей — больше 9. Для фиксации переноса из младшей

тетрады байта служит признак q, а из старшей — Q. Действия над

двоично-десятичными числами приведены в табл. 1.13.

Десятичной коррекции для команд вычитания в МП нет. По-

этому десятичное вычитание в МП следует реализовать путем при*

бавления дополнительного ко-

да вычитаемого, формируе-

мого по правилу 10* — Y, где

k — число десятичных разря-

дов, отведенных для представ-

ления Y. При этом 10* — Y

получают в два этапа. На пер-

вом этапе формируют обратный

код по правилу 10* — 1 — Y,

а иа втором — к обратному

коду добавляется Г. Прибав-

ление 1 совмещают с опера-

цией суммирования путем ис-

пользования команды сложе-

ния с учетом переноса, уста-

новленного предварительно в 1.

Примеры вычитания по описан-

ному правилу десятичных чи-

сел 63 и 79 приведены в табл.

1.14. Признак Q = 1, появля-

ющийся после коррекции ре-

зультата операции 79—63, со-

ответствует числу 10* =s= 100,

возникающему в виде переноса

,из старшего разряда сумма-

тора, который . при операциях

в дополнительных, кодах, как

известно, игнорируется. Ука-

занный признак можно исполь-

зовать для определения знака

числа, а именно: при отрица-

тельном результате Q = 0, а

результат представлен в допол-

нительном коде.

Во многих применениях

МП 8 бит недостаточно для до-

стижения заданной точности

представления чисел. В этом

случае числа представляются

двумя -или более байтами,

основные арифметические one-

рации над которыми реализуются программным путем. В табл.

1.15 приведена программа многобайтового сложения двоичных

1-14. Действия над десятичными

числами 63 и 79

Действия над числами

двоичными

десятичными

Сумматор

АЛУ

99

“63

,36

+

116

Коррекция

+66

1001 1001

1001 1100

01 ООП ОНО

11 ।

0111 1001

01 1011 0000

оно оно

10 0001 оно

99

—79

,20

+ 1

63

84

Коррекция

00

Дополни-

тельный

код—16

SUB

STC

ADG

DAA

SUB

STC

ADC

DAA

01

11

1001 1001

юоо оно

1

0010 0000

1

ОНО ООН

00 1000 0100

0000 0000

00 1000 0100

чисел, расположенных в п ячейках, начиная соответственно с адре-

сов а и р (старшие байты чисел расположены в ячейках с боль-

шими адресами), с занесением результата на место первого числа.

Регистр PD служит в качестве счетчика циклов. При подготовке

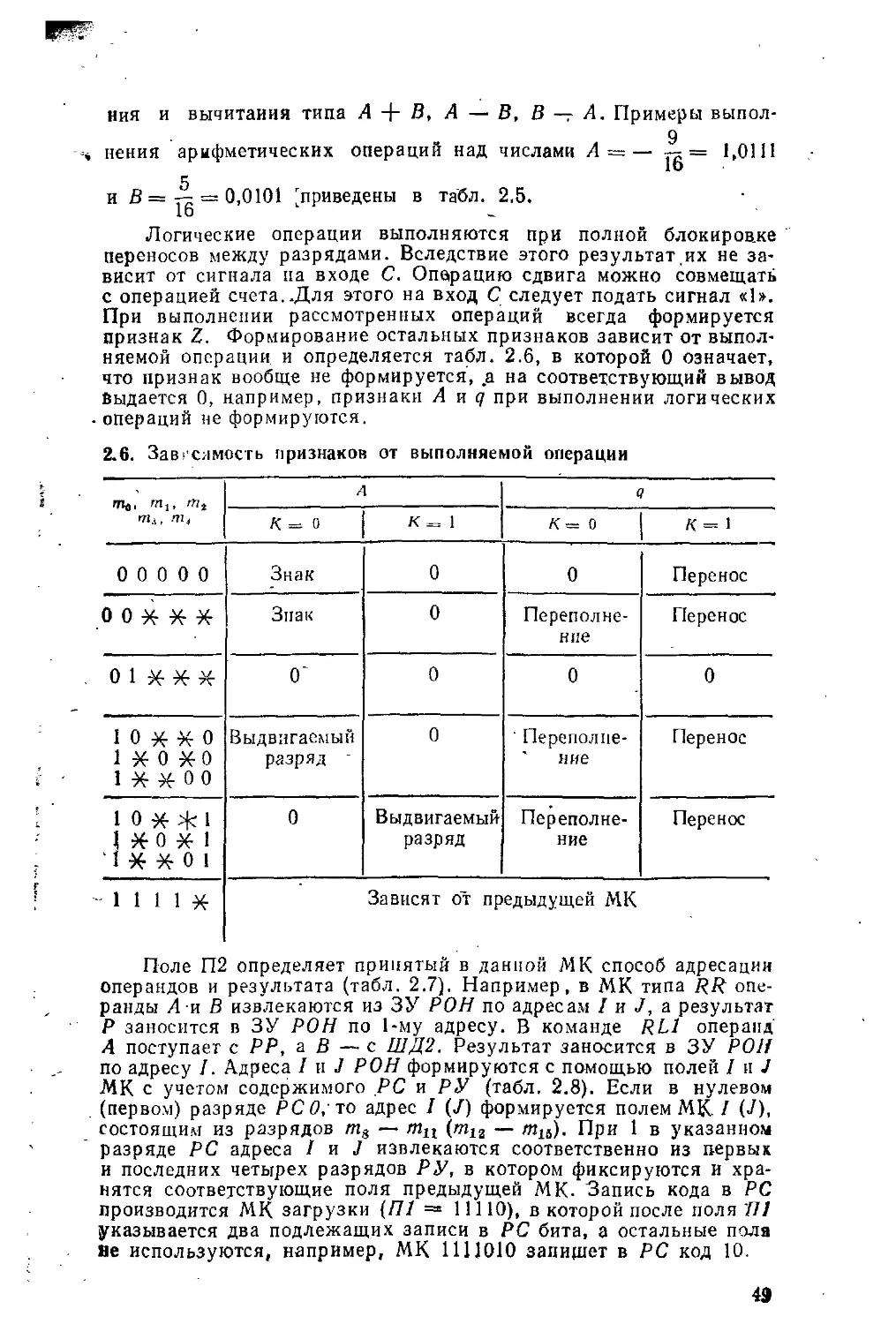

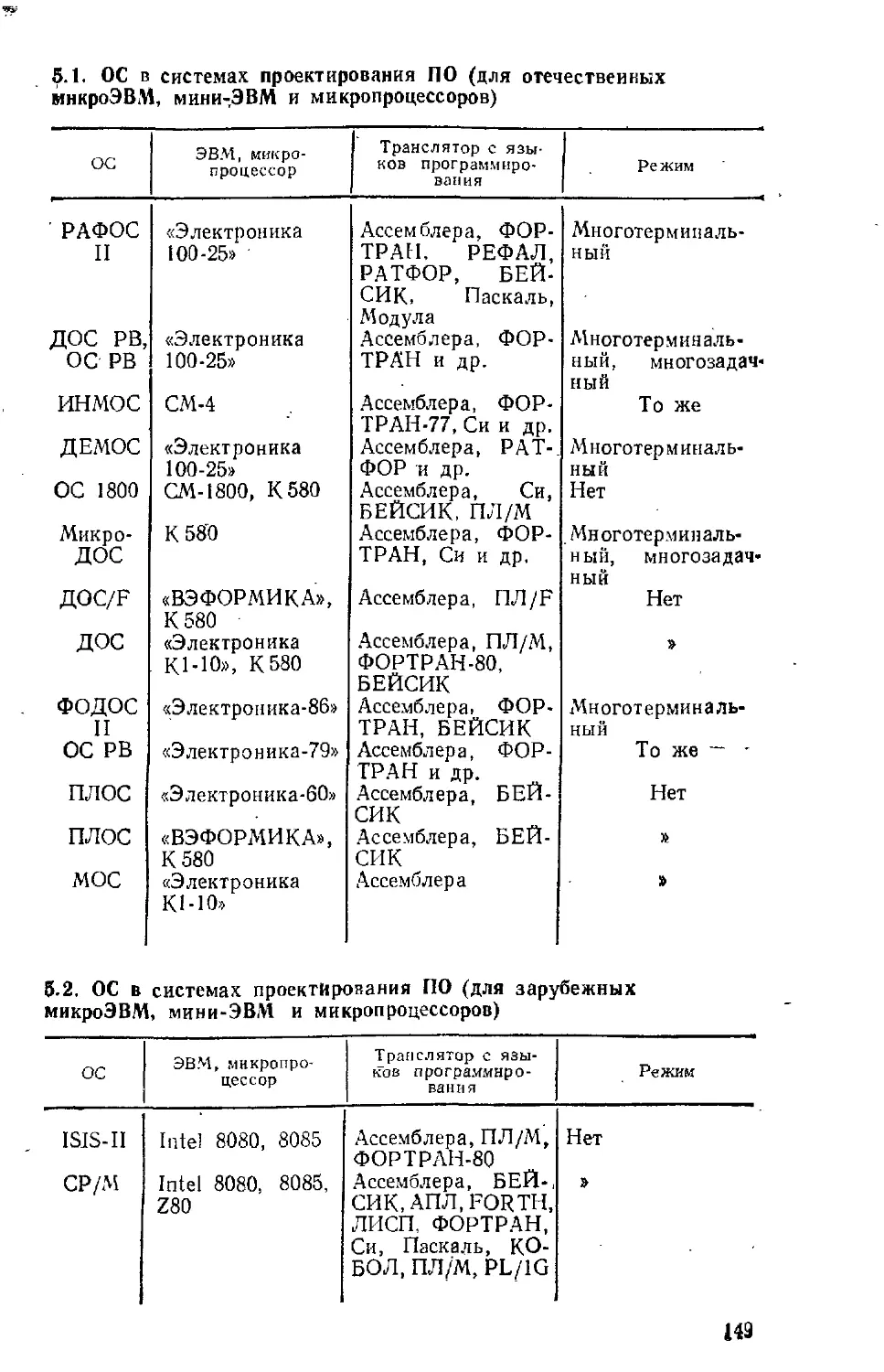

цикла в него командой МVI, в адресной части которой и втором