Автор: Григорьев В.Л.

Теги: компьютерные технологии математика программирование электроника электротехника микропроцессоры

ISBN: 5-900676-02-1

Год: 1993

Текст

В.Л. Григорьев

Микропроцессор i486

Архитектура

и программирование

(в 4-х книгах)

КНИГА 2

КНИГА 3

КНИГА 4

Москва 1993

Совместное издание

В.Л. Григорьев

Микропроцессор i486. Архитектура и npoiраммирование. (в 4-х

книгах). Кинга 2. Аппаратная архиickiура. Книга 3. Устройство с

плавающей гонкой Книга 4. Справочник ио cncicxtc команд.— М.,

ГРАНАЛ, 1993.- с. 382, ил. 54

ISBN 5-900676-02-1

В новых кишах извссиною авюра описаны впущенная архи iскiура

процессора i4<So. внешняя намян». шипа процессора, циклы шины,

с 1111 i.l 11>н ыс Шинн процессора, opiaim зацня памяш н ввода-вы вода на шине,

передача данных, управление шиной, управление клн-памянио. управление

ошибками с нлаваюшеп ючкои. приведены синииы и временные дшп раммы

ею paooibi. подрооно рассмощена впущенная ор|апизапня. про1раммпая

модель (ины oopauai ывасмых данных н снсчема команд ycipoiiciBa с

нлаваюшеп ючкои. ocooeiniocin спсчемы команд п справочные сведения по

командам процессора t4<Sn

Kiihih рассчн ।апы па снсцналнсчов

В.Л. Григорьев

Микропроцессор i486. Архитектура и программирование

(в 4-х книгах). Книга 2. Аппаратная архитектура. Книга 3.

Устройство с плавающей точкой. Книга 4. Справочник по

системе команд.

Главный редактор Андрей Артамошкин

Издание подготовлено совместно с ТОО «БИНОМ»

ISBN 5-900676-02-1

© IOO «I РЛНАЛ» 1993 I

Оглавление

млЗйллй. Si Al —... JJX .rj_. a.»- . а» j-S^. Х/л ij

* f, ~ t *.• - • t i -X •» •** I > ** — • * * * * £ -J " »«’•«“ *> *\ * *• <|

Глава!. Внутренняя архитектура........................... 9

1.1. Обзор новых средств и применений

процессора i486.................................. 9

1.2. Внутренняя архитектура.................... 17

1.3. Производительность........................ 33

1.3.1. Влияние внутренней кэш-памяти....... 35

1.3.2. Внутренние буферы записи............ 37

1.4. Внешняя память............................ 38

1.4.1. Особенности проектирования

динамических ЗУПВ........................... 41

1.5. Производительность операций с плавающей

точкой........................................ 42

Глава 2. Сигналы и временные диаграммы

работы процессора i486................................ 43

2.1. Шина процессора........................... 43

2.2. Циклы шины................................ 44

2.3. Сигнальные линии процессора............... 46

2.4. Временная диаграмма и формирование

синхронизации................................... 56

2.5. Организация памяти и ввода-вывода на шине.. 59

2.6. Передачи данных......................... 65

2.6.1. Непакетные циклы.................... 67

2.6.2. Пакетные циклы...................... 73

2.6.3. Размер шины......................... 83

Оглавлений

2.7. Управление шиной........................ 88

2.7.1. Сброс............................. 88

2.7.2. Прерывания.......................... 89

2.7.3. Специальные циклы шины.............. 93

2.7.4. Захват шины......................... 94

2.7.5. Блокировка шины..................... 96

2.7.6. Псевдоблокировка шины............... 99

2.7.7. Отступление шины....................101

2.8. Управление кэш-памятью.....................103

2.8.1. Управление кэш-памятью на уровне

страниц......................................104

2.8.2. Недостоверность внутренней кэш-

памяти......................................105

2.8.3. Очистка внутренней кэш-памяти.......107

2.8.4. Цикл очистки кэш-памяти.............107

2.8.5. Цикл обратной записи и очистки кэш-

памяти ....................................107

2.9. Управление ошибками с плавающей точкой....108

Литература ..............................................110

Предисловие..............................................113

Глава 1. Архитектура устройства с плавающей точкой.......121

1.1. Сопроцессорные конфигурации..............121

1.2. Внутренняя организация устройства FPU....123

1.3. Программная модель устройства FPU........125

1.4. Форматы численных данных.................132

1.5. Режимы работы и состояние................141

1.6. Система команд...........................148

1.6.1. Особенности задания команд.........149

1.6.2. Машинные форматы команд............150

1.6.3. Особенности программирования на

языке ассемблера..........................151

1.6.4. Команды передач данных.............153

1.6.5. Арифметические команды.............157

1.6.6. Команды сравнения..................163

1.6.7. Команды трансцендентных функций.....167

1.6.8. Команды управления.................170

1.7. Внешний интерфейс устройства FPU.........176

Микропроцессор i486. Архитектура и программирование

Глава 2. Специальные вычислительные ситуации...........179

2.1. Специальные численные значения............180

2.1.1. Денормализованные

вещественные числа.........................180

2.1.2. Нули................................184

2.1.3. Бесконечность..................... 186

2.1.4. Нечисла........................... 188

2.1.5. Неопределенность....................190

2.1.6. Кодирование типов данных............191

2.1.7. Неподдерживаемые форматы............193

2.2. Численные особые случаи...................195

2.2.1. Обработка численных особых случаев...195

2.2.2. Недействительная операция...........197

2.2.3. Деление на нуль.....................199

2.2.4. Денормализованный операнд...........199

2.2.5. Численные переполнение

и антипереполнение.........................200

2.2.6. Неточный результат (точность).......203

2.2.7. Приоритет особых случаев............204

Глава 3. Вопросы системной организации и совместимости..205

3.1. Особенности архитектуры...................205

3.2. Инициализация.............................206

3.3. Эмуляция..................................208

3.4. Обработка численных особых случаев........208

3.5. Совместимость

с сопроцессорами 8087, 80287 и 80387...........210

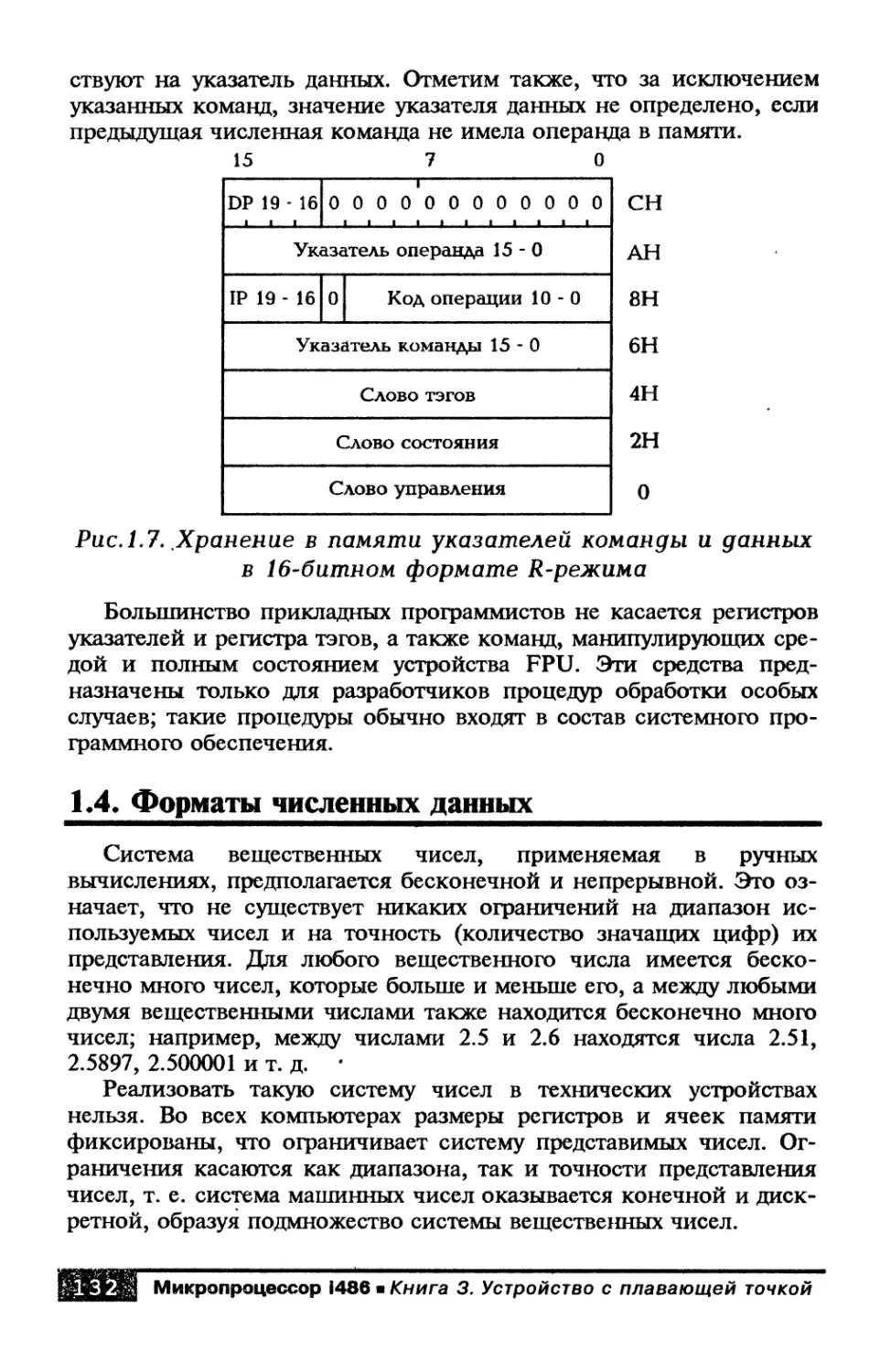

3.5.1. Отличия от систем 80386/80387.......211

3.5.2. Отличия от систем 80286/80287...... 213

3.5.3. Отличия от систем 8086/8087.........219

Глава 4. Особенности программирования устройства FPU...221

4.1. Инструментальные

средства программирования......................221

4.1.1. Языки высокого уровня...............221

4.1.2. Ассемблер ASM386/486................224

4.1.3. Сравнительный

пример программирования....................227

4.2. Параллельная работа..................:....231

4.2.1. Управление параллельностью..........231

4.3. Примеры численного программирования........234

4.3.1. Пример условного перехода...........234

4.3.2. Примеры обработки особых случаев.....237

4.3.3. Примеры численных программ..........239

Литература........................................244

Оглавление

Глава 1. Особенности описания системы команд.............247

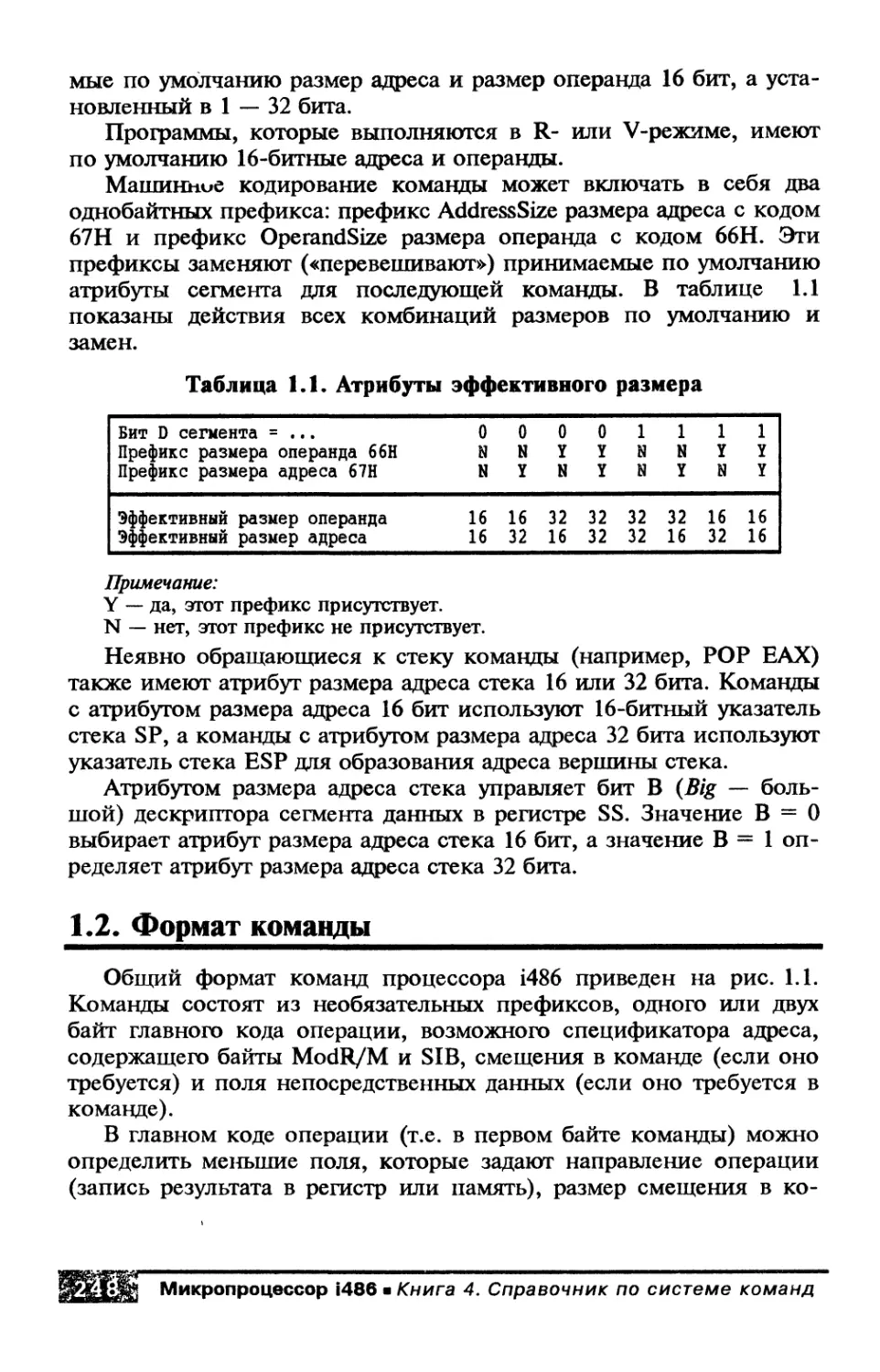

1.1. Атрибуты размера операнда и размера адреса..247

1.2. Формат команды..............................248

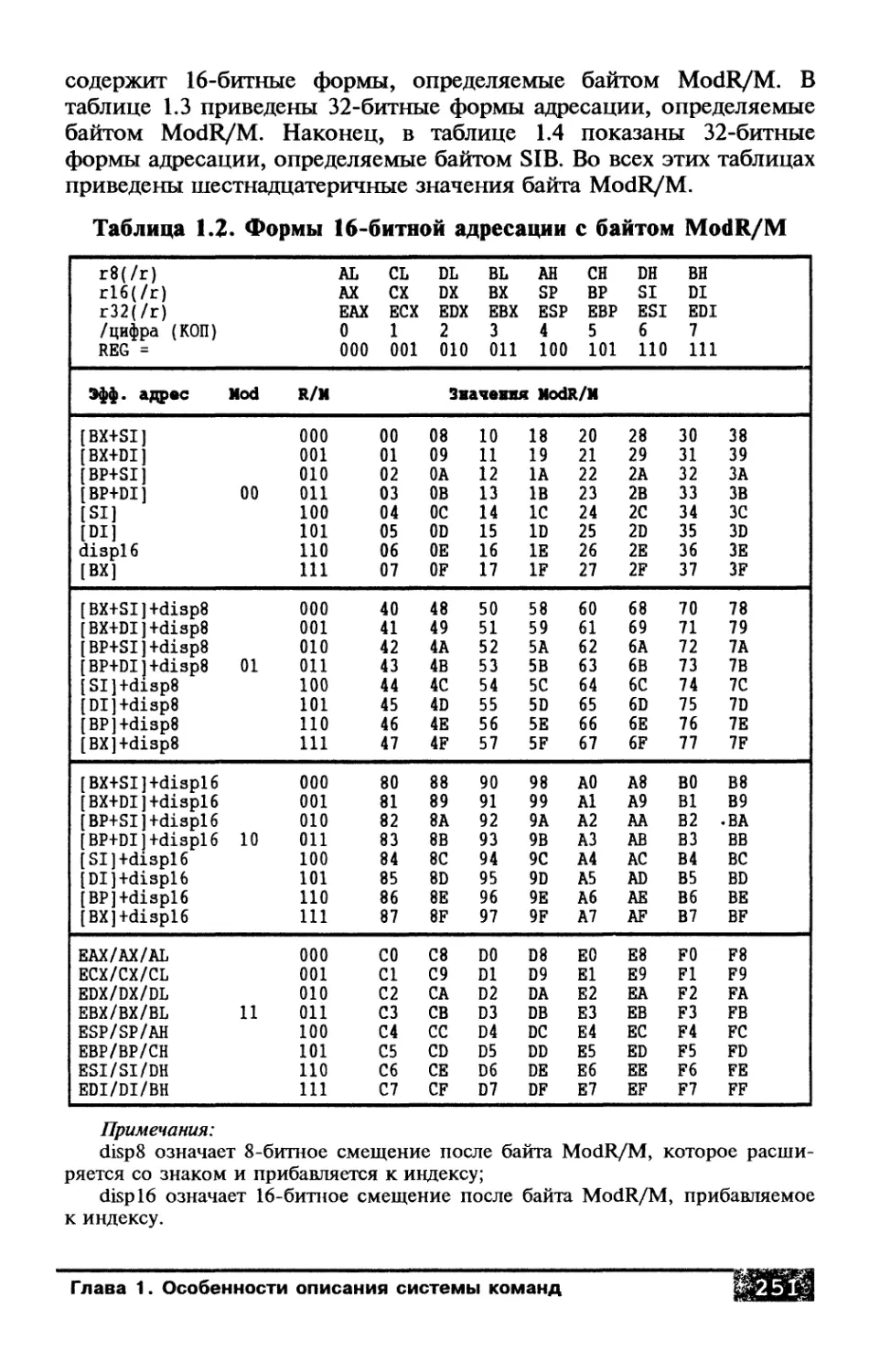

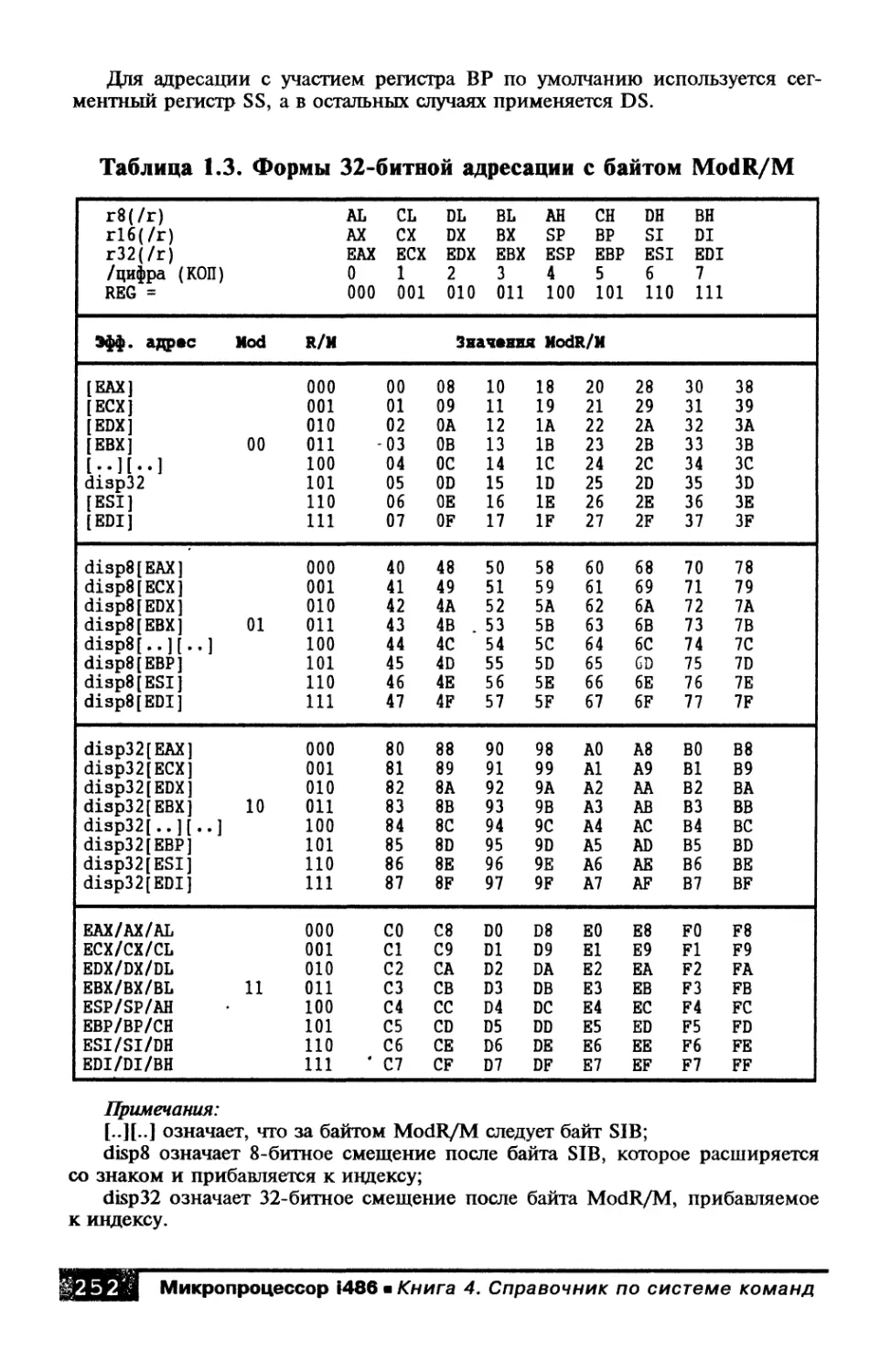

1.3. Байты ModR/M и SIB..........................250

1.4. Как знакомиться с системой команд...........254

Глава 2. Справочные сведения по командам процессора i486.264

Литература...............................................382

Zt _

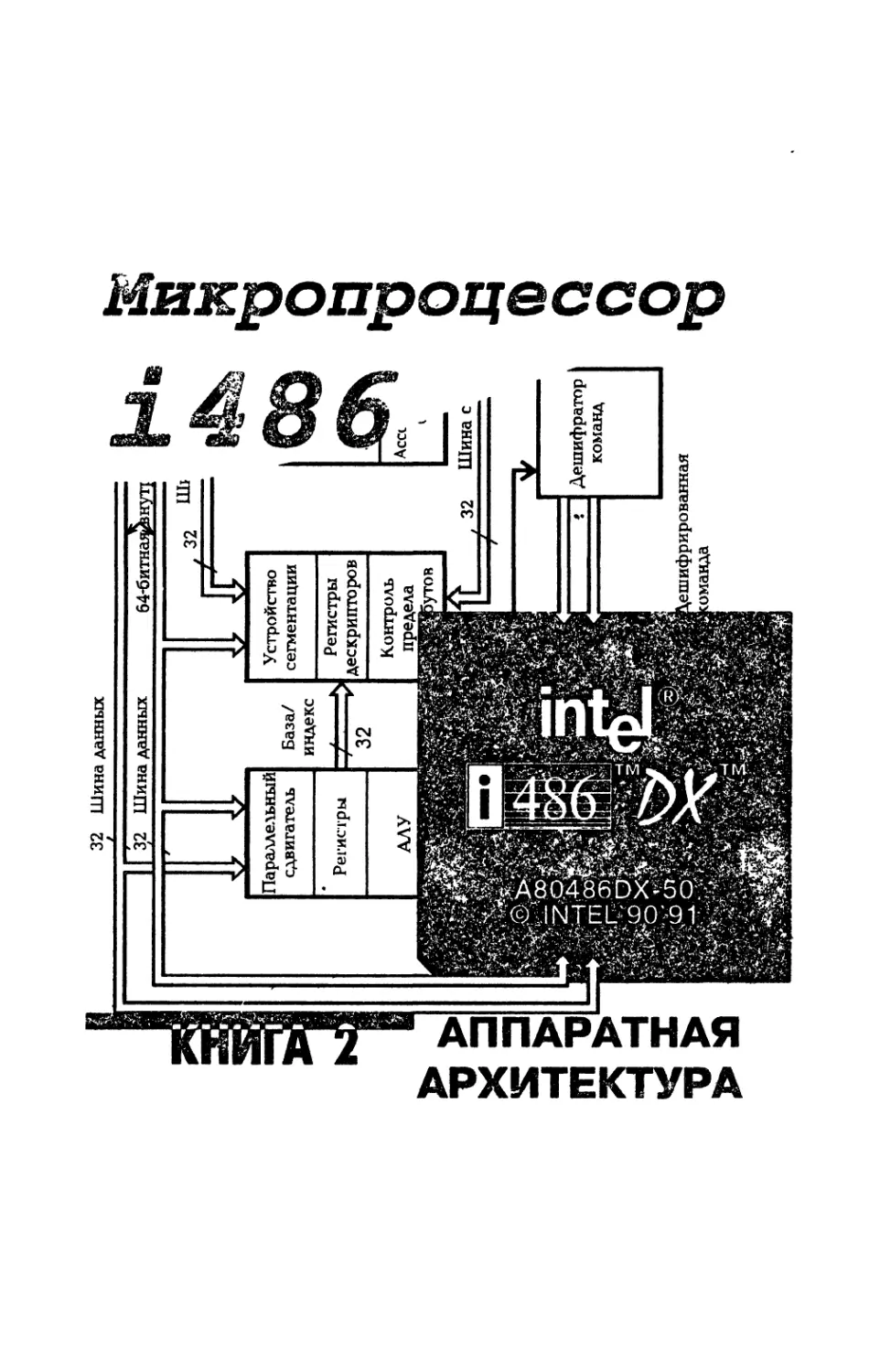

I43G. Архитектура

АППАРАТНАЯ

АРХИТЕКТУРА

Микропроцессор

Внутренняя архитектура

1.1. Обзор новых средств и применений

процессора i486

Процессор i486 фирмы Intel представляет собой наиболее произ-

водительный процессор семейства 80x86. Он совместим вверх по

двоичному коду с предыдущими процессорами 8086/8088, 80186,

80286, 80386 (модели 386DX и 386SX) и привносит в персональные

компьютеры средства процессоров больших машин.

Среди наиболее важных внутренних устройств процессора i486

отметим наличие целочисленного операционного устройства, уст-

ройства с плавающей точкой, заменяющего собой отдельную мик-

росхему математического сопроцессора, устройства управления па-

мятью и кэш-памяти. Благодаря размещению устройств на одном

кристалле многие связывающие их сигналы стали внутренними, что

обеспечивает большую производительность процессора. Повыше-

ние уровня интеграции позволяет сократить размеры печатной пла-

ты, а это снижает стоимость и упрощает проектирование систем.

В зависимости от частоты синхронизации и особенностей конк-

ретного применения производительность процессора i486 в

2—4 раза выше производительности процессора 80386. В

процессоре i486 (как и в процессоре 80386) реализована сегментная

и страничная защита памяти.

Внутренняя конвейеризация команд сокращает время их выпол-

нения. Реализуя внутренние управление памятью и кэширование,

процессор i486 снижает требования к быстродействию памяти.

Шина процессора i486 значительно быстрее шины процессора

80386.

В ней применяется одночастотная синхронизация (1х) и под-

держиваются контроль по паритету (четности), пакетные циклы,

Глава 1. Внутренняя архитектура

кэшируемые циклы, циклы недостоверности кэш-памяти и 8/16-

битные шины данных. Применение синхронизации 1х упрощает

проектирование системы, сокращая в два раза частоту синхрониза-

ции для внешних устройств, уменьшает высокочастотное излучение

и упрощает генерирование сигналов синхронизации.

В процессоре i486 предусмотрены быстрые пакетные циклы для

таких операций считывания, которые требуют несколько циклов

шины. В пакетных циклах процессор передает 32-битное двойное

слово за один такт синхронизации (в процессоре 80386 на одну пе-

редачу требуются минимум два такта). Чтобы в пакете память рабо-

тала без состояний ожидания, можно использовать внешнюю кэш-

память, банки памяти с расслоением или микросхемы дина-

мических ЗУПВ с адресацией статического столбца.

По сравнению с процессором 80386 команды выполняются за

меньшее число тактов, а многие команды выполняются всего за

один такт. Внутренняя кэш-память обеспечивает непрерывную ско-

рость в один запрос процессора на каждый такт. Для эффективного

переключения задач в многопользовательских и мультизадачных

системах реального времени процессор i486 (как и процессор 80386)

одной командой или прерыванием осуществляет полное пере-

ключение задачи.

Тестирование процессора поддерживается встроенным самокон-

тролем, причем результаты встроенного самоконтроля доступны во

внутреннем регистре. Предусмотрена проверка кэш-памяти и ассо-

циативного буфера преобразования на уровне языка ассемблера.

ВОЗМОЖНОСТИ ПРОЦЕССОРА. Среди наиболее важных от-

метим следующие возможности процессора i486:

Совместимость по двоичному коду с процессорами 8086/8088,

80186, 80286, 80386.

Выполнение полного набора арифметических и логических

операций над 8/16/32-битными данными с использованием полно-

разрядного арифметико-логического устройства и восьми регистров

общего назначения.

Прямая адресация физической памяти 4 Гбайт при наличии

внешних 32-битных шин адреса и данных.

Поддержка внутренним устройством с плавающей точкой

32/64/80-битных форматов чисел, удовлетворяющих стандарту

IEEE-754 на операции с*плавающей точкой. Это устройство совме-

стимо по двоичному коду с сопроцессорами 8087, 80287, 80387.

Целостность памяти поддерживают механизмы сегментного и

страничного управления адресами и защиты в составе внутреннего

устройства управления памятью. Это требуется в мультизадачной

среде и при организации виртуальной памяти.

Микропроцессор i486 и Книга 2. Аппаратная архитектура

Внутренняя кэш-память со сквозной записью может хранить

8 Кбайт данных и команд. При попадании кэш-память действует с

такой же скоростью, как и регистры процессора.

В процессоре предусмотрено управление обратной записью и

очисткой внешней кэш-памяти, поэтому он может обеспечить со-

гласованность содержимого кэш-памяти в мультипроцессорной

среде.

Совмещение выборки, декодирования, выполнения команды и

преобразование адреса, т.е. конвейеризация команд, обеспечивает

выполнение многих команд за один такт.

Пакетные циклы позволяют считывать из памяти двойное слово

на каждый такт. Благодаря этому можно очень быстро заполнять

внутреннюю кэш-память и буфер опережающей выборки

(предвыборки) команд.

С помощью внутренних буферов записи процессор после записи

продолжает внутренние операции, не ожидая окончания операции

записи на шине.

Средство отступления (bus backoff) шины позволяет процессору

i486 передать управление шиной другому ведущему шины, а когда

шина становится доступной, осуществить рестарт своего цикла

шины.

Возможность рестарта команды допускает продолжение Про-

граммы после особого случая, вызванного безуспешной попыткой

обращения к памяти. Такая возможность имеет важное значение

для организации виртуальной памяти с заменой страниц по требо-

ванию.

Внешние контроллеры могут динамически изменять эффек-

тивную ширину шины данных (8, 16 или 32 бита).

РЕЖИМЫ РАБОТЫ И СОВМЕСТИМОСТЬ. Процессор i486

может выполнять программы в нескольких режимах, которые обес-

печивают совместимость по объектному коду с программами, разра-

ботанными для процессоров 8086, 80286 и 80386. Программно уста-

навливаются такие режимы работы:

Реальный режим (R-режим). После сброса или включения

питания процессор работает в R-режиме. Этот режим опирается на

базовую архитектуру процессора 8086, но допускает обращение к

32-битным регистрам. Механизм образования адреса, максималь-

ный размер памяти 1 Мбайт и обработка прерываний идентичны

И~режиму4 процессора 80286. Доступны почти все команды

процессора i486, но принимаемый по умолчанию размер операндов

составляет 16 бит; чтобы использовать 32-битные регистры и

режимы адресации, перед командами требуются префиксы замены.

Гжша 1. Внутренняя архитектура

Основное назначение R-режима состоит в том, чтобы подготовить

процессор к работе в защищенном режиме.

Защищенный режим (P-режим). Когда программы выполняются

в P-режиме, становятся доступными все возможности процессора

i486. В дополнение к сегментной защите допускается страничная

организация памяти. Линейное адресное пространство составляет

4 Гбайт и можно выполнять программы, рассчитанные на

виртуальную память 64 Тбайт. Программы для процессоров 8086,

80286 и 80386 можно выполнять с привлечением средств аппарат-

ной защиты процессора i486. В P-режиме применяется более слож-

ный механизм адресации, чем в R-режиме.

Режим виртуального 8086 (VM86- или V-режим). Этот режим,

являющийся подрежимом P-режима, допускает выполнение

программ процессора 8086 с привлечением механизмов сегментной

и страничной защиты Р-режима. V-режим предоставляет большую

гибкость для выполнения программ процессора 8086 по сравнению

с R-режимом. Работая в V-режиме, процессор i486 может выпол-

нять операционные системы и прикладные программы процессора

8086 одновременно с операционной системой и прикладными про-

граммами процессоров 80286 и 80386.

УПРАВЛЕНИЕ ПАМЯТЬЮ. Устройство управления памятью

поддерживает сегментную и страничную организацию памяти. Сег-

ментация обеспечивает несколько независимых защищенных ад-

ресных пространств. Такое средство защиты ограничивает те по-

вреждения, которые может вызвать ошибка в программе. Устрой-

ство сегментации отображает видимые программистам отдельные

адресные пространства на единое ^сегментированное адресное

пространство.

Страничная организация обеспечивает доступ к структурам дан-

ных, которые больше пространства физической памяти, путем хра-

нения данных частично в памяти и частично на диске. При этом

линейное адресное пространство разбивается на блоки по 4 Кбайт,

называемые страницами. Обычно программы одновременно ис-

пользуют небольшое число страниц, поэтому процессор со стра-

ничной памятью может моделировать большое адресное простран-

ство, используя относительно небольшое ЗУПВ и дисковую память.

ВНУТРЕННЯЯ КЭШ-ПАМЯТЬ. Прозрачная для программ

кэш-память 8 Кбайт хранит внутри процессора те команды и дан-

ные, к которым производились последние обращения. Если про-

цессору требуется считать данные, имеющиеся в кэш-памяти, она

предоставляет их и сравнительно медленного обращения к внешней

памяти производить не нужно. При этом повышается скорость пе-

редач и сокращается загрузка шины процессора. Кэш-память реа-

Микропроцессор i486 * Книга 2. Аппаратная архитектура

лизована по принципу сквозной записи: все записи в кэш-память

немедленно передаются и в основную память, которую представ-

ляет кэш-память (в кэш-памяти с обратной записью обновление

основной памяти производится отдельной операцией). Запись во

внутреннюю кэш-память производится только при попадании. Для

уменьшения влияния операций записи на производительность про-

цессор буферирует циклы записи; операция, которая записывает

данные в память, может закончиться до фактического производства

цикла записи на шине.

Для помещения новой информации во внутреннюю кэш-память

процессор осуществляет заполнение строки кэш-памяти. В этой

операции в строку кэш-памяти считываются четыре двойных слова,

т.е. 16 байт; это наименьшая единица хранения, которую можно

распределить в кэш-памяти. Большинство циклов считывания на

шине процессора возникают из-за промахов в кэш-памяти, которые

вызывают заполнения строк кэш-памяти.

Для систем с несколькими ведущими шины предусмотрены ме-

ханизмы обеспечения согласованности содержимого памяти и кэ-

шированных данных. Они защищают процессор i486 от считывания

неверных данных из внутренней или внешней кэш-памяти. Когда,

например, процессор i486 пытается считать из памяти операнд, ко-

торый хранится в кэш-памяти другого ведущего шины, этот другой

ведущий шины должен форсировать запись своих кэшированных

данных в память прежде, чем процессор может завершить свое

считывание из памяти. Такая операция требуется потому, что кэ-

шированные данные могут быть обновлены и, следовательно, от-

личаются от данных, хранимых в памяти.

Большинство систем памяти оптимизируют скорость обращения

для цикла считывания, так как в типичной системе большинство

обращений к памяти являются считываниями. Внутренняя кэш-па-

мять процессора i486 изменяет эту пропорцию. Большинство зап-

росов считывания возникает из-за промахов в кэш-памяти, поэтому

на внешней шине преобладают циклы записи.

УСТРОЙСТВО С ПЛАВАЮЩЕЙ ТОЧКОЙ. Внутреннее уст-

ройство с плавающей точкой осуществляет операции с плавающей

точкой над 32/64/80-битными числами, форматы которых опреде-

лены в стандарте IEEE-754. Архитектура этого устройства совмес-

тима по двоичному коду с сопроцессорами 808? и 80287 и полнос-

тью совместима с сопроцессором 80387.

Команды с плавающей точкой выполняются наиболее быстро,

когда они целиком находятся в процессоре, т.е. все операнды ока-

зываются во внутренних регистрах или кэш-памяти. Если же дан-

ные приходится считывать из внешних ячеек или записывать в них,

требуемое для этого время минимизируют пакетные передачи, а ме-

--'.v

н!3‘

Глава 1. Внутренняя архитектура

ханизм блокировки шины обеспечивает монополизацию шины на

все время передачи. Предусмотрены сигналы шины для контроля

ошибок в операциях с плавающей точкой и управления реакцией

процессора на такие ошибки.

КОхМПОНЕНТЫ СИСТЕМЫ. Фирма Intel предлагает не-

сколько микросхем, которые полностью совместимы с процессором

i486 и используются для проектирования высокопроизводительных

систем с минимальными усилиями и расходами. Для компонент,

которые не допускают прямого подключения к шине процессора

i486, применяются стандартные промышленные интерфейсы, на-

пример системная шина MULTIBUS II.

Среди компонент, которые обеспечивают прямой интерфейс С

шиной процессора i486, следует отметить однокристальный 32-бит-

ный сетевой сопроцессор 82596, предназначенный для управления

сетевыми данными и функциями физического слоя сети. Систем-

ные 32-битные периферийные микросхемы семейства 82320 обес-

печивают эффективный и дешевый интерфейс с шинами расшире-

ния Микроканала для систем PS/2, а микросхемы семейства 82350

предназначены для интерфейса с шинами расширения EISA. Для

построения внешней кэш-памяти емкостью 64К или 128К (с нара-

щиванием до 512 Кбайт), полностью совместимой с процессором

i486, выпускается модуль 485Turbocache Module. Наконец, в систе-

мах с процессором i486 можно применять разнообразные програм-

мируемые логические устройства.

СФЕРЫ ПРИМЕНЕНИЯ. Процессор i486 рассчитан на широ-

кий спектр однопроцессорных и мультипроцессорных систем.

Примером однопроцессорной системы может служить персональ-

ный компьютер, который обеспечивает высокую производитель-

ность благодаря встроенным операциям с плавающей точкой, уп-

равлению памятью и кэшированию. В более сложных системах

можно ввести несколько процессоров, которые обеспечивают на

уровне микросхем эквивалентные функции уровня плат. Такие раз-

работки обычно применяются в многопользовательских машинах,

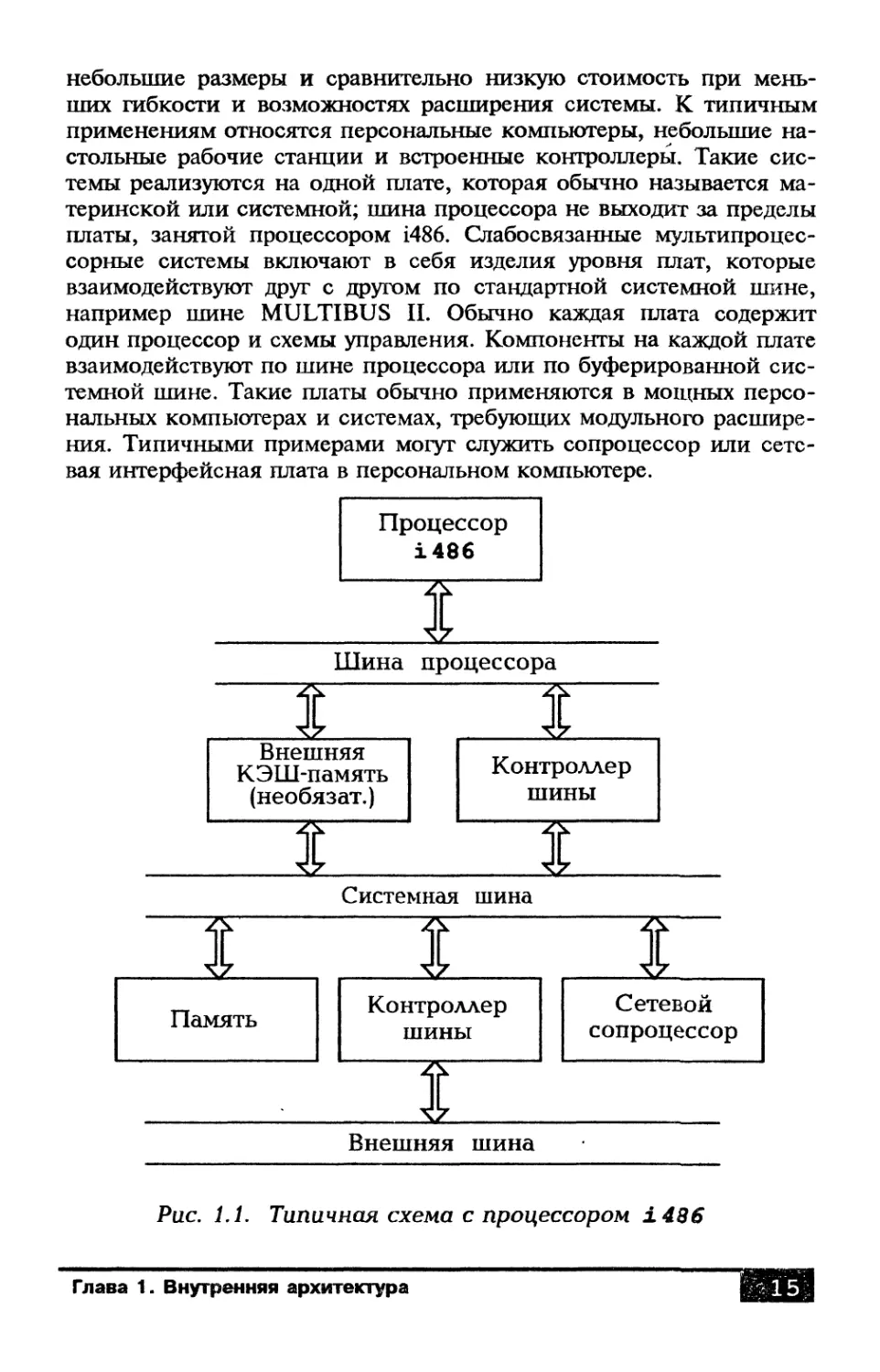

научных и инженерных рабочих станциях. Типичная система, пред-

ставляющая собой нечто среднее между однопроцессорной систе-

мой и более сложной мультипроцессорной системой, представлена

на рис. 1.1. В этой системе применяется один процессор i486 с

внешней кэш-памятью и сетевым сопроцессором 82596.

В однопроцессорных системах процессор управляет всеми пе-

риферийными ресурсами и интеллектуальными устройствами, а

также выполняет все программы. Процессор i486 реализует эти

функции более эффективно и для более широкого круга задач, чем

прежние процессоры. Однопроцессорные системы обеспечивают

Микропроцессор i486 и Книга 2. Аппаратная архитектура

i-'.e tC

небольшие размеры и сравнительно низкую стоимость при мень-

ших гибкости и возможностях расширения системы. К типичным

применениям относятся персональные компьютеры, небольшие на-

стольные рабочие станции и встроенные контроллеры. Такие сис-

темы реализуются на одной плате, которая обычно называется ма-

теринской или системной; шина процессора не выходит за пределы

платы, занятой процессором i486. Слабосвязанные мультипроцес-

сорные системы включают в себя изделия уровня плат, которые

взаимодействуют друг с другом по стандартной системной шине,

например шине MULTIBUS IL Обычно каждая плата содержит

один процессор и схемы управления. Компоненты на каждой плате

взаимодействуют по шине процессора или по буферированной сис-

темной шине. Такие платы обычно применяются в мощных персо-

нальных компьютерах и системах, требующих модульного расшире-

ния. Типичными примерами могут служить сопроцессор или сете-

вая интерфейсная плата в персональном компьютере.

Внешняя шина

Рис. 1.1. Типичная схема с процессором i486

Глава 1. Внутренняя архитектура

115

Внешняя кэш-память позволяет достичь максимально высокой

производительности системы. Особенно важную роль внешняя

кэш-память играет в сильносвязанных мультипроцессорных систе-

мах. В состав внешней кэш-памяти входят собственно микросхемы

памяти (обычно микросхемы быстрых статических ЗУПВ) и кон-

троллер. Подавляющее большинство систем с процессором i486 от-

носятся к следующим типам: персональные компьютеры, мини-

компьютеры и рабочие станции, а также встроенные контроллеры.

В обычной архитектуре персонального компьютера большинство

периферийных устройств размещается на отдельных съемных пла-

тах. Расширение обычно ограничено платами памяти и платами

ввода-вывода. Применяется стандартная архитектура ввода-вывода,

например архитектура Микроканала или EISA. Очень важную роль

играют стоимость и размеры системы. В такой среде применять

внешнюю кэш-память не обязательно, особенно если производи-

тельность системы не является критическим параметром.

Миникомпьютеры и рабочие станции можно реализовать по

слабосвязанной архитектуре. Обычно здесь допускается расширение

числа центральных процессоров, модулей памяти и устройств

ввода-вывода. Применяются стандартные системные шины, напри-

мер MULTIBUS II. По сравнению с персональными компьютерами

миникомпьютеры и рабочие станции больше ориентируются на

производительность и меньше на стоимость. Для высокопроизводи-

тельных систем может потребоваться сильносвязанная архитектура.

Высокая производительность процессора i486 размывает совре-

менные различия между персональными компьютерами, миником-

пьютерами и рабочими станциями. Персональные компьютеры

можно рассматривать как дешевые миникомпьютеры, разделяющие

программы и данные с настольными рабочими станциями. В

отличие от персональных компьютеров в миникомпьютерах приме-

няется память с исправлением ошибок и внешняя кэш-память. К

шине процессора подключаются быстрые коммуникационные кон-

троллеры, например сетевой сопроцессор 82596.

Большинство встроенных контроллеров выполняют задачи ре-

ального времени. Производительность процессора i486 и его совме-

стимость с огромной базой программного обеспечения для процес-

сора 80386 оказываются при выборе процессора важнейшими фак-

торами. Обычно встроенные контроллеры реализуются как авто-

номные системы с меньшими возможностями, чем другие приклад-

ные системы, так как они специально приспосабливаются к одной

среде.

Если код (программа) должен храниться в энергонезависимом

ПЗУ или стираемом ППЗУ, но критическим параметром оказывает-

ся и производительность, то код можно скопировать в специально

предусмотренное для этого ЗУПВ («теневое» ЗУПВ). Часто исполь-

Микропроцессор i486 Книга 2. Аппаратная архитектура

зуемые процедуры и переменные, например обработчики прерыва-

ний и стеки прерываний, можно заблокировать во внутренней кэш-

памяти процессора и к ним всегда обеспечивается быстрый доступ.

Обычно во встроенных контроллерах требуется меньше памяти,

чем в других прикладных системах, а управляющие программы

представляют собой тщательно отработанные процедуры машин-

ного уровня, которые обеспечивают оптимальную производитель-

ность дая ограниченного круга задач. Процессор непосредственно

взаимодействует с устройствами ввода-вывода и динамическим

ЗУПВ, а другие периферийные устройства подключаются к систем-

ной шине.

1.2. Внутренняя архитектура

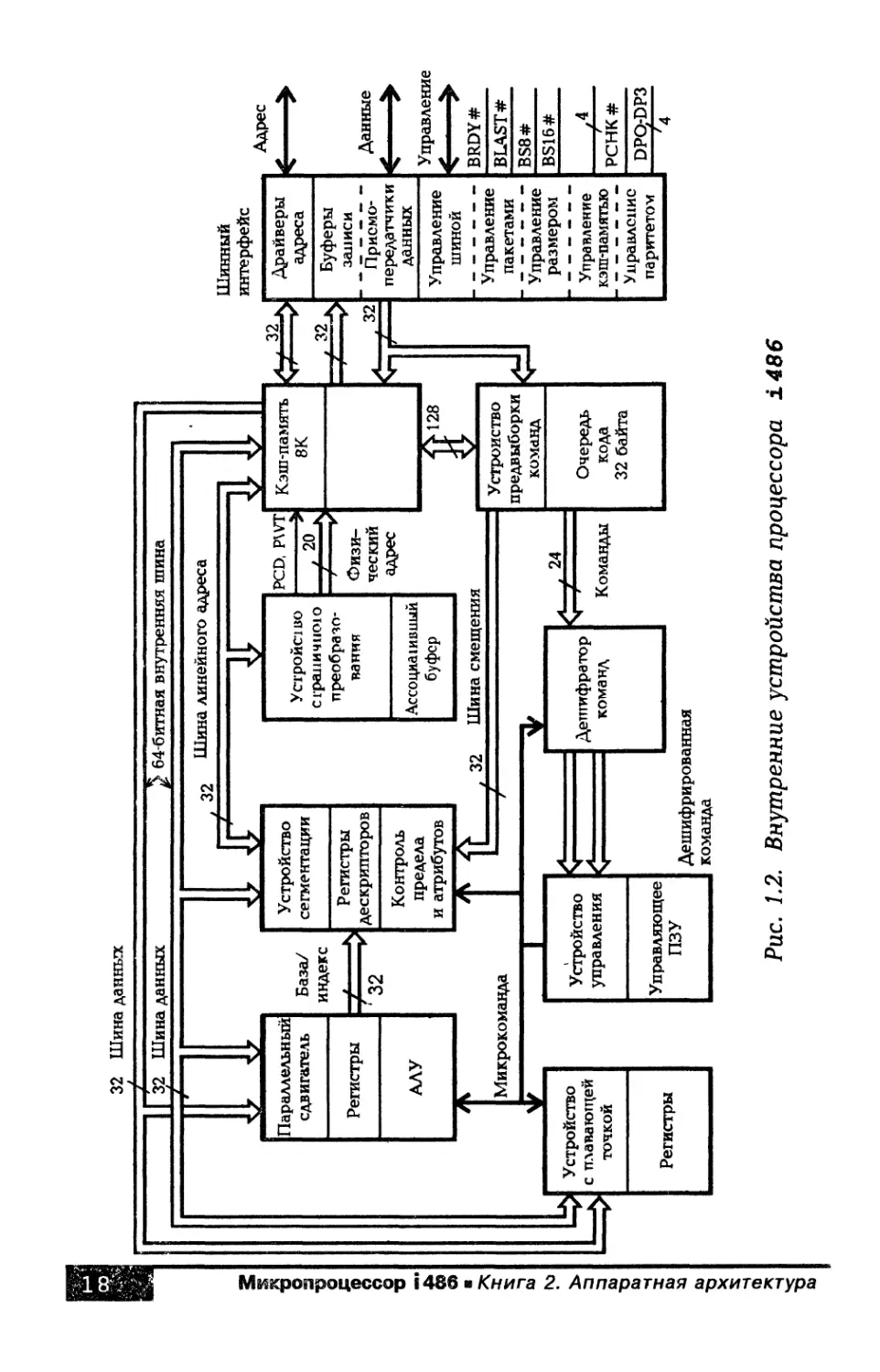

В состав процессора i486 входят девять внутренних функцио-

нальных устройств, которые работают параллельно. Подробная

внутренняя архитектура процессора приведена на рис. 1.2, а менее

подробная, но достаточная для ознакомления, на рис. 1.3. Сравни-

тельно автономными внутренними устройствами процессора i486

являются:

— устройство шинного интерфейса или просто шинный

интерфейс;

— внутренняя кэш-память;

— устройство опережающей выборки (предай борки) команд;

— двухступенчатый дешифратор команд;

— устройство управления;

— целочисленное устройство;

— устройство с плавающей точкой;

— устройство сегментации;

— устройство страничного преобразования адреса.

Отметим, что внутренняя архитектура процессора i486 очень по-

хожа на архитектуру процессора 80386, разумеется, с добавлением

внутренней кэш-памяти и устройства с плавающей точкой.

Сигналы внешней 32-битной шины процессора подаются во

внутренние устройства через шинный интерфейс. На внутренней

стороне шинный интерфейс и кэш-память передают адреса по 32-

битной двунаправленной шине. Данные передаются из кэш-памяти

в шинный интерфейс по 32-битной шине данных. Тесно связанные

кэш-память и устройство предвыборки одновременно восприни-

мают выбранные с опережением команды из шинного интерфейса

по разделенной 32-битной шине данных, которую кэш-память ис-

пользует также дая получения операндов. Находящиеся в кэш-па-

мяти команды доступны устройству предвыборки, которое имеет

32-байтную очередь команд, ожидающих выполнения.

Глава 1. Внутренняя архитектура

Макропроцессор i486 и Книга 2. Аппаратная архитектура

32 Шина данных

32

Рис. 1.2. Внутренние устройства процессора i486

Шинный

интерфейс

Драйверы

адреса

Буферы

записи

Приемо-

передатчики

данных

Управление

шиной

Управление

пакетами

Управление

размером

Управление

кэш-памятью

Управление

паритетом

Адрес

Данные

«—>

Управление

<----->

BRDY#

BLAST#

BS8#

BS16#

,4

PCHK#

DPO/DP3

*4

Шина процессора

Рис. 1.3. Упрощенная внутренняя архитектура

процессора i486

Когда внутренние запросы данных или команд можно удовлет-

ворить из кэш-памяти, сравнительно медленные циклы внешней

ншны процессора не выполняются. Шинный интерфейс привлека-

» юн, если операция требует обращения к шине процессора. Таким

образом, многие внутренние операции оказываются «прозрачными»

/|дя внешней системы.

Гл.?<;а 1. Внутренняя архмтозпура

Дешифратор команд преобразует команды в управляющие сиг-

налы низкого уровня и точки входа в микрокод (микропрограммы).

Устройство управления выполняет микрокод и управляет це-

лочисленным устройством, устройством с плавающей точкой и уст-

ройством сегментации. Результаты вычислений помещаются во

внутренние регистры целочисленного устройства и устройства с

плавающей точкой или в кэш-память. Кэш-память разделяет две

32-битные шины данных с устройством сегментации, целочислен-

ным устройством и устройством с плавающей точкой. Эти две

шины можно использовать совместно как 64-битную шину для

передач между устройствами. Когда 64-битные дескрипторы

сегментов передаются из кэш-памяти в устройство сегментации, 32

бита прямо передаются по одной шине данных, а другие 32 бита

передаются через целочисленное устройство, поэтому все 64 бита

достигают устройства сегментации одновременно.

Формирование адреса производят устройства сегментациии

страничного преобразования. Логические адреса преобразуются ус-

тройством сегментации в линейные адреса, которые передаются в

устройство страничного преобразования и кэш-память по 32-бит-

ной шине линейного адреса. Устройство страничного преобразова-

ния превращает линейные адреса в физические, которые направля-

ются в кэш-память по 20-битной шине.

КОНВЕЙЕРИЗАЦИЯ КОМАНД. Не все команды требуют при

своем выполнении участия всех внутренних устройств. Когда же

команда требует участия нескольких устройств, каждое устройство

обрабатывает параллельно другие команды на различных этапах

выполнения. Несмотря на то, что каждая команда обрабатывается

последовательно, в процессоре в различной стадии выполнения

всегда находятся несколько команд. Такой прием называется кон-

вейеризацией команд (см. рис. 1.4). Одновременно выполняются

операции, связанные с предвыборкой команд, дешифрированием

команд, выполнением микрокода, а также целочисленные опера-

ции, операции с плавающей точкой, сегментации, страничного

преобразования, управления кэш-памятью и шинного интерфейса.

На рис. 1.4 показан эффект параллелизма для одной команды:

предвыборка команды, двухступенчатое дешифрирование, выпол-

нение и запись в регистр результата выполнения команды. Каждый

элемент в этом конвейере реализует свою функцию за один такт

синхронизации. Внутренняя конвейеризация в процессоре i486

обеспечивает выигрыш в производительности по сравнению со

многими однотактными RISC-процессорами: в процессоре i486

данные можно загрузить из кэш-памяти одной командой и исполь-

зовать следующей командой уже в очередном такте синхронизации.

Такой выигрыш объясняется наличием первой ступени дешифри-

е20

Микропроцессор i486 Книга 2. Аппаратная архитектура

рования, которая инициирует обращение к памяти до собственно

выполнения. Так как в большинстве компиляторов и прикладных

программ после команды загрузки находятся команды, оперирую-

щие загруженными данными, подобный прием оптимизирует вы-

полнение имеющихся программ.

CLK

Синхро-

низация

Выборка

команды

Первая сту-

пень деши-

фрирования

Вторая сту-

пень деши-

фрирования

Выполнение

Запись

в регистр

Рис. 1.4. Конвейеризация команд

Однако в этом методе пришлось пойти на компромисс: последо-

вательность команд, которая изменяет содержимое регистра, а за-

гс м использует этот регистр для обращения к памяти, длится три

такта вместо двух. Но этот компромисс оказывается не-

значительным недостатком, так как большинство команд с обраще-

нием к памяти используют «устойчивое» содержимое указателя сте-

ка или указателя кадра, поэтому дополнительный такт требуется

редко. Компиляторы часто вводят «буферную» команду между ко-

мандой, которая изменяет регистр адреса, и командой, которая ис-

пользует этот регистр. Такой код совместим с процессором 80386, а

в процессоре i486 введены специальная схема инкремен-

ia/декремента стека и дополнительный регистровый порт для вы-

полнения соседних команд включения в стек и извлечения из стека

за один такт каждая.

ШИННЫЙ ИНТЕРФЕЙС. Это устройство учитывает приорите-

ты обращений к шине и координирует передачи данных, осуществ-

ляет предвыборку команд и выполняет функции согласования дей-

ствий между внутренними устройствами процессора и внешней си-

стемой. На внутренней стороне это устройство взаимодействует с

кэш-памятью и устройством предвыборки по трем 32-битным ши-

Глава 1. Внутренняя архитектура №

нам, как показано на рис. 1.2. На внешней стороне шинный интер-

фейс формирует сигналы шины процессора. За исключением сиг-

налов определения цикла все циклы внешней шины (считывание

из памяти, предвыборки команд, заполнения строк кэш-памяти и

др.) выглядят для внешних схем обычными циклами процессора,

причем все циклы имеют одинаковую временную диаграмму. В со-

ставе шинного интерфейса имеются следующие компоненты:

Драйверы адреса для формирования сигналов адреса А2—А31 и

сигналов разрешения байт ВЕ#0—ВЕЗ#. Старшие 28 сигналов ад-

реса являются двунаправленными, позволяя внешней схеме пере-

дать в процессор адрес строки кэш-памяти, содержимое которой

объявляется недостоверным.

Приемопередатчики шины данных, предназначенные для

управления двунаправленными сигналами данных DO—D31 шины

процессора.

Схемы для управления (по тактам синхронизации) размером

шины данных с помощью двух входных сигналов BS8# и BS16#.

Можно задать три размера внешней шины данных — 32, 16 и 8 бит.

Буферы записи, обеспечивающие буферирование до четырех

запросов записи, что позволяет продолжать многие внутренние

операции, не ожидая окончания циклов записи на шине процессо-

ра.

Схемы формирования циклов шины и управления шиной, которые

реализуют большой набор циклов шины и управляющих функций,

включая пакетные передачи, непакетные передачи (одно- и

многотактные), арбитраж шины (запрос шины, захват шины, под-

тверждение захвата шины, блокировка шины, псевдоблокировка

шины и отступление шины). Два программно-управляемых выхода

обеспечивают кэширование страниц по тактам. Предусмотрены

один вход и один выход для управления пакетными считываниями.

Схемы формирования и контроля паритета (четности), с по-

мощью которых четный паритет формируется при записи и контро-

лируется при считывании. Сигнал ошибки PCHK# фиксирует

ошибку паритета при считывании.

Схемы управления кэш-памятью поддерживают операции

управления и согласования кэш-памяти. Три входа позволяют

внешней системе управлять согласованностью данных, хранимых во

внутренней кэш-памяти. Два специальных цикла шины предостав-

ляют процессору возможность управлять согласованностью внеш-

ней кэш-памяти.

Для поддержки кэш-памяти шинный интерфейс считывает 16-

байтные кэшируемые операнды, команды и другие данные на шине

процессора и передает их во внутреннюю кэш-память. Когда со-

держимое кэш-памяти обновляется от внутреннего источника, на-

пример из регистра, шинный интерфейс записывает обновленную

1436 а Книга 2. Аппаратная архитектура

информацию во внешнюю память. Некэшируемые передачи

считывания передаются в целочисленное устройство или устрой-

ство с плавающей точкой без помещения в кэш-память.

В ходе предвыборки команд шинный интерфейс считывает ко-

манды с шины процессора и передает их в устройство предвыборки

команд и кэш-память. Устройство предвыборки команд после этого

может получать команды непосредственно из кэш-памяти.

Шинный интерфейс имеет временные регистры для буфериро-

вания до четырех 32-битных передач записи в память. Можно бу-

ферировать адреса, данные или управляющую информацию. Нельзя

буферировать одиночные записи с отображением на ввод-вывод, но

многократные записи ввода-вывода допускается буферировать. Бу-

феры могут воспринимать записи в память со скоростью одной

операции за такт синхронизации. После буферирования запроса за-

писи внутреннее устройство, сформировавшее запрос, освобожда-

ется для продолжения обработки. Если не ожидается запрос с более

высоким приоритетом и шина свободна, на шине процессора сразу

же инициируется цикл записи. Когда заполнены все четыре буфера

записи, все последующие передачи записи ожидают в процессоре

освобождения буфера записи.

Шинный интерфейс может пропускать ожидающие запросы

считывания вперед буферированных записей. Объясняется это тем,

что ожидающие считывания могут задержать работу внутреннего ус-

тройства, а ожидающие записи не оказывают заметного воздей-

ствия на скорость обработки. Записи передаются на шину процес-

сора в том же порядке, в котором они были получены от внутрен-

них устройств («первый пришел — первый ушел»). Однако сформи-

рованный впоследствии запрос считывания (данных или команды)

может быть пропущен раньше буферированных записей. Для защи-

। ы от считывания неверных данных такое пропускание считываний

раньше буферированных записей разрешается, если только все бу-

ферированные записи привели к попаданию в кэш-памяти. Так как

внешнее считывание формируется только при промахе в кэш-памя-

П1 и пропускается вперед буферированных записей, если все эти

шписи вызвали попадание в кэш-памяти, любое считывание на

внешней шине с рассмотренным средством защиты никогда не

приведет к считыванию из той ячейки, в которую будет произво-

питься буферированная запись. Для конкретного набора буфериро-

ванных записей такое «пропускание вне очереди» можно произвес-

ти только один раз, так как возвращаемые при считывании данные

могут заменить данные, готовые к записи из буферов записи. Чтобы

идя конкретного набора буферированных записей «пропускание вне

очереди» происходило не более одного раза» все буферированные

шписи при пропускании вперед запроса считывания отмечаются

как промахи в кэш-памяти. Отмеченные таким образом буфериро-

Глава 1. Внутренняя архитектура

<’23:

ванные записи передаются на шину процессора ранее следующего

запроса считывания. При объявлении данных во внутренней кэш-

памяти недостоверными все ожидающие запросы также отмечаются

как промахи в кэш-памяти. Запрещение кэш-памяти запрещает и

буферы записи, что устраняет возможность изменения порядка

циклов шины.

Процессор может сформировать сигналы дая блокирования пос-

ледовательной серии циклов шины. После этого такие циклы мож-

но выполнить без вмешательства других ведущих шины, если вне-

шняя схема учитывает сигналы блокирования. Одним из примеров

блокированной операции является считывание-модификация-за-

пись семафора, когда обновляется ячейка управления ресурсом.

Никакие другие операции на шине не разрешаются до завершения

заблокированного обновления семафора.

Когда формируется блокированный цикл считывания, попытка

считывания из внутренней кэш-памяти не производится. Первыми

заканчиваются все ожидающие записи из буферов. Только после

этого выполняется часть считывания блокированной операции,

данные обновляются, результат помещается в буфер записи и на

шине процессора производится цикл записи. Такая последователь-

ность действий гарантирует, что все записи выполняются в том по-

рядке, в каком они были запрошены.

Для поддержания целостности данных накладываются некото-

рые ограничения на передачи в ячейки ввода-вывода и из них:

Считывания ввода-вывода никогда не кэшируются;

Считывания ввода-вывода никогда не производятся раньше

буферированных записей в память. Благодаря этому процессор за-

кончит модификацию всех ячеек памяти до считывания состояния

из устройства;

Одиночные записи ввода-вывода никогда не буферируются.

Следовательно, при выполнении команды OUT внутренние

операции прекращаются до завершения на шине процессора всех

буферированных записей и записи ввода-вывода. При этом

внешней схеме отводится время сформировать цикл

недостоверности кэш-памяти или замаскировать прерывания до

выполнения процессором следующей команды. Процессор

закончит модификацию всех ячеек памяти перед записью в ячейку

ввода-вывода. Однако повторяющиеся команды OUT можно

буферировать.

ВНУТРЕННЯЯ КЭШ-ПАМЯТЬ. Кэш-память хранит копии

последних считанных команд, операндов и других данных. Когда

процессор запрашивает информацию, уже находящуюся в кэш-па-

мяти (попадание), цикл шины не нужен. Когда же процессор зап-

рашивает информацию, отсутствующую в кэш-памяти (промах),

Микропроцессор i486 • Книга 2. Аппаратная архитектура

информация считывается в кэш-память за одну или несколько

16-байтных кэшируемых передач данных, называемых заполнением

строки кэш-памяти. Если формируется запрос записи в область,

находящуюся в кэш-памяти, выполняются два действия: обновляет-

ся кэш-память и записываемые данные передаются в основную па-

мять. Эти действия называются сквозной записью. Кэш-память пе-

редает данные в другие устройства по двум 32-битным шинам. Она

воспринимает линейные адреса по 32-битной шине и соответству-

ющие физические адреса по 20-битной шине. Кэш-память и уст-

ройство предвыборки команд тесно связаны. 16-байтные блоки ко-

манд из кэш-памяти можно быстро передать в устройство предвы-

борки. Оба устройства считывают информацию 16-байтными бло-

ками. К кэш-памяти можно обращаться в каждом такте синхрони-

зации. Она работает с физическими адресами, что минимизирует

число раз очистки кэш-памяти. Когда запрещена сама кэш-память

и функции сквозной записи, кэш-память можно использовать как

быстродействующее ЗУПВ. Кэш-память имеет четырехнаправ-

ленную (или четырехканальную) ассоциативную по множеству

организацию. Для хранения данных из конкретной области памяти

в кэш-памяти есть четыре места.

Блок

Направление

Физический адрес

Рис. 1.5. Организация внутренней кэш-памяти

Четырехнаправленная ассоциативность является компромиссом

между быстродействием кэш-памяти с прямым отображением при

попаданиях и большим коэффициентом попаданий полностью ас-

Глава 1. Внутренняя архитектура

социативной кэш-памяти. Как показано на рис. 1.5, блок данных

8 Кбайт разделен по четырем направлениям, каждое из которых

имеет 128 16-байтных множеств или строк кэш-памяти. Строка

кэш-памяти содержит данные из 16 соседних байтных адресов в

памяти, начиная с адреса, кратного 16. Адресация кэш-памяти осу-

ществляется путем разделения старших 28 бит физического адреса

на три части (см. рис. 1.5). Семь бит поля индекса определяют но-

мер множества из 128 множеств, имеющихся в кэш-памяти. Стар-

шие 21 бит являются полем тэга (признака); эти биты сравниваются

с тэгами каждой строки в индексированном множестве и показы-

вают, хранится ли 16-байтная строка кэш-памяти по данному фи-

зическому адресу. Младшие четыре бита физического адреса выби-

рают байт внутри строки кэш-памяти.

Находящееся в блоке достоверности/LRU 4-битное поле досто-

верности показывает, являются ли в данный момент кэшированные

данные по имеющемуся физическому адресу достоверными. Когда

при считывании возникает промах, в кэш-память записывается

16-байтный блок, содержащий запрошенную информацию.

Соседние с запрошенными данные также считываются в кэш-

память, но точная позиция данных в строке кэш-памяти зависит от

ее расположения в памяти, относительно адресов, кратных 16.

Допускается кэширование произвольной области памяти, но

любую страницу в памяти можно объявить некэшируемой, устанав-

ливая бит в ее элементе таблицы страниц. Когда на шине иниции-

руется считывание из памяти, внешняя схема может сообщить,

можно ли поместить данные в кэш-память. Если считывание кэши-

руется, процессор пытается считать всю 16-байтную строку кэш-

памяти.

В кэш-памяти реализован принцип сквозной записи. Заполне-

ние строки выполняется только при промахе в операции

считывания и никогда при промахе в операции записи. Когда в

процессоре разрешены обычное кэширование и сквозная запись,

каждая внутренняя запись в кэш-память (попадание) не только об-

новляет кэш-память, но передается в устройство шинного интер-

фейса и по шине процессора записывается в память. Единственная

ситуация, в которой данные в кэш-памяти отличаются от соответ-

ствующих данных в памяти, возникает, когда цикл записи процес-

сора в память задерживается из-за буферирования в устройстве

шинного интерфейса или когда внешний ведущий шины изменяет

область памяти, отображенную на внутреннюю кэш-память.

Замещение в кэш-памяти реализуется по алгоритму псевдо-LRU

(наиболее давно используемый). Здесь для каждого множества в

блоке достоверности/LRU отведено три бита (см. рис. 1.5). Биты

LRU обновляются при каждом попадании в кэш-памяти или за-

полнении строки. Каждая строка кэш-памяти имеет свой бит

ж®

Микропроцессор i486 Книга 2. Аппаратная архитектура

достоверности, показывающий, содержит ли строка достоверные

данные.

При очистке кэш-памяти или сбросе процессора все биты дос-

товерности сбрасываются в 0. Когда производится заполнение

строки кэш-памяти, место дня заполнения выбирается просто на-

хождением любой недостоверной строки. Если недостоверных

строк нет, то заменяемую («перезаписываемую») строку кэш-памя-

ти выбирают биты LRU. Биты достоверности не устанавливаются

для строк, являющихся частично достоверными.

Алгоритм псевдо-LRU действует следующим образом. Когда в

цикле считывания происходит промах и в кэш-память необходимо

передать из памяти новую строку, приходится выбирать для запол-

нения одну из четырех строк множества. Если в множестве есть не-

достоверная строка (ее бит достоверности содержит 0), то для за-

полнения выбирается именно эта строка. Когда же все строки в

множестве достоверны (все 4 бита достоверности содержат 1), за-

меняемая строка выбирается с привлечением бит из блока LRU.

Обозначим строки в множестве через L0, LI, L2 и L3. Каждому

множеству в блоке LRU соответствуют три бита ВО, В1 и ВЗ, кото-

рые модифицируются при каждом попадании и заполнении следу-

ющим образом:

—- если последнее обращение в множестве было к строке L0 или

LI, то бит ВО устанавливается в состояние 1, а при обращении к

строке L2 или L3 бит ВО сбрасывается в 0;

— если последнее обращение в парс L0—L1 было к строке L0, то

бит В1 устанавливается в состояние 1, а при обращении к строке L1

бит В1 сбрасывается в 0;

— если последнее обращение в паре L2—L3 было к строке L2, то

бит В2 устанавливается в состояние 1, а при обращении к строке L3

бит В2 сбрасывается в 0.

Выбор заменяемой строки (когда все строки в множестве досто-

верны) определяет содержимое бит ВО, В1 и В2:

ВО Bl В2

0 0 х заменяется строка L0;

0 1 х заменяется строка L1;

1x0 заменяется строка L2;

1.x 1 заменяется строка L3.

Строки кэш-памяти можно по отдельности объявить недосто-

верными, задавая операцию недостоверности кэш-памяти на шине

процессора. При инициировании такой операции кэш-память

сравнивает объявляемый недостоверным адрес с тэгами строк, на-

ходящихся в кэш-памяти, и сбрасывает бит достоверности при об-

наружении соответствия (равенства). Предусмогрена также опера-

- 1

Глава 1. Внутренние архитэхтур^

ция очистки кэш-памяти, которая превращает в недостоверное все

содержимое кэш-памяти.

Конфигурацией кэш-памяти управляют два бита в регистре со-

стояния машины (CR0). Один из этих бит разрешает кэширование

(заполнение строк кэш-памяти), а второй — сквозную запись в па-

мять. Четыре возможные конфигурации приведены в таблице 1.1.

Таблица 1.1. Виды конфигурации кэш-памяти

Разревевве кэв-памятв Разревевве сквозной записв Режвм работы

нет нет Заполнения строк, сквозная запись и объявление кэш-памяти недостоверной запрещены. Такая конфигурация позволяет использовать внутреннюю кэш- память как быстродействующее ЗУПВ.

нет да Заполнения строк запрещены, а сквозная запись и объявлеиие кэш-памяти недостоверной разрешены. Эта конфигурация позволяет программе запрещать кэш-память на короткое время, а затем разрешать без очистки содержимого.

да нет Недопустимая конфигурация.

да Да Заполнения строк, сквозная запись и объявление кэш-памяти недостоверной разрешены. Это обычная рабочая конфигурация кэш-памяти.

Когда кэширование разрешено, кэшируются считывания из па-

мяти и предвыборки команд. Такие передачи кэшируются, если

внешняя схема подает входной сигнал разрешения кэш-памяти в

данном цикле шины и если текущий элемент таблицы страниц раз-

решает кэширование. В тех циклах, где кэширование запрещено

при промахе, заполнение строки кэш-памяти не производится. Од-

нако кэш-память продолжает действовать, несмотря на то, что она

запрещена для заполнения. Уже находящиеся в кэш-памяти данные

используются, если, конечно, они являются достоверными. Только

когда все данные в кэш-памяти отмечены как недостоверные, что

происходит при очистке кэш-памяти, все внутренние запросы

считывания приводят к формированию внешних циклов шины.

Микропроцессор i486 • Книга 2. Аппаратная архитектура

Когда разрешена сквозная запись, все записи, включая и вызвав-

шие попадания, инициируют запись в память. Операции недосто-

верности удаляют строку из кэш-памяти, если адрес недостоверных

данных отображается на строку кэш-памяти. Когда сквозная запись

запрещена, внутренний запрос записи, вызвавший попадание в

кэш-памяти, не приводит к производству записи в память, а опера-

ции недостоверности запрещены. Когда запрещены кэширование и

сквозная запись, кэш-память можно использовать как быстродей-

ствующее статическое ЗУПВ. В такой конфигурации на шину про-

цессора передаются только записи, вызвавшие промах, а операции

недостоверности игнорируются.

УСТРОЙСТВО ПРЕДВЫБОРКИ КОМАНД. Когда шинный

интерфейс не выполняет циклов шины выполнения команды, уст-

ройство предвыборки команд привлекает его для опережающей вы-

борки (предвыборки) команд. Считывая команды заранее, процес-

сор редко должен ожидать в цикле предвыборки команды на шине

процессора.

Циклы предвыборки команд считывают 16-байтные блоки ко-

манд, начиная по адресам, численно больших адреса последней

выбранной команды. Начальный адрес формирует устройство пред-

выборки, которое напрямую соединено с устройством страничного

преобразования (это соединение на рис. 1.3 не показано). 16-байт-

ные блоки предварительной выборки одновременно подаются в ус-

тройство предвыборки и кэш-память. В устройстве предвыборки

имеется очередь предвыборки, которая хранит 32 байта команд.

Когда каждая команда считывается из очереди, ее код операции

подается в устройство дешифрирования команд, а смещение, т.е.

константа в команде, подается в устройство сегментации, где

участвует в вычислении адреса. Если в выполняемой протрамме

встречаются циклы, устройство предвыборки получает копии ранее

выполненных команд из кэш-памяти, т.е. считываний из основной

памяти не производится.

Запрос шины от устройства предвыборки имеет низший приори-

тет. Если предположить обращение к памяти без состояний ожида-

ния, то действия предвыборки никогда не задерживают выполне-

ние. Однако при отсутствии ожидающей передачи опережающая

выборка использует те циклы шины, которые иначе оказывались

бы холостыми. Устройство предвыборки очищается, когда наруша-

ется естественный порядок выполнения команд, например при пе-

реходах, переключениях задач, особых случаях и прерываниях.

Устройство предвыборки никогда не обращается за конец сег-

мента кода и к странице, которая не присутствует в памяти. Однако

в некоторых аппаратных механизмах предвыборка может вызвать

проблемы. Например, предвыборка может вызвать прерывание,

Глава 1. Внутренняя архитектура

когда выполнение программы приближается к концу памяти.

Чтобы предотвратить опережающее считывание за конкретный ад-

рес, команды не должны быть ближе к этому адресу на один байт

плюс один выравненный 16-байтный блок.

УСТРОЙСТВО ДЕШИФРИРОВАНИЯ КОМАНД. Устройство

дешифрирования команд получает команды от устройства предвы-

борки и в двухступенчатом процессе преобразует их в управляющие

сигналы низкого уровня и точки входа микрокода, т.е. микропрог-

рамм (см. рис. 1.3). Первая ступень дешифрирования, показанная

на рис. 1.4, инициирует обращение к памяти. Эго позволяет вы-

полнить двухкомандную последовательность, которая загружает и

обрабатывает данные, всего за два такта.

Устройство дешифрирования команд одновременно обрабаты-

вает байты префиксов команд, коды операций, байты адресации

modR/M и смещения. На его выходах формируются аппаратные

микрокоманды для устройства сегментации, целочисленного уст-

ройства и устройства с плавающей точкой. Рассматриваемое уст-

ройство очищается при каждой очистке устройства предвыборки

команд.

УСТРОЙСТВО УПРАВЛЕНИЯ. Устройство управления интер-

претирует слово команды и точки входа микрокода, полученные от

устройства дешифрирования команд. Оно имеет выходы дня управ-

ления целочисленным устройством и устройством с плавающей

точкой, а также управляет сегментацией, так как команды могут

определять выбор конкретного сегмента.

Устройство управления содержит микрокод (управляющие мик-

ропрограммы) процессора. Многие команды имеют всего одну

строку микрокода, поэтому в среднем они выполняются за один

такт синхронизации. На рис. 1.4 показано, как механизм конвейе-

ризации расчленяет выполнение команд.

ЦЕЛОЧИСЛЕННОЕ УСТРОЙСТВО. Целочисленное опсраци-

онное устройство (называемое также трактом данных — datapath)

идентифицирует, где хранятся данные, и выполняет все арифме-

тические и логические команды из системы команд процессора

80386 и несколько новых команд. Оно имеет восемь программно-

доступных 32-битных регистров общего назначения, несколько спе-

циализированных регистров, арифметико-логическое устройство

АЛУ и параллельный сдвигатель, обеспечивающий сдвиг в любом

направлении и на любое число разрядов. Команды загрузки, сохра-

нения, сложения, вычитания, логических операций и сдвигов вы-

полняются за один такт.

^z J Микропроцессор i486 а Книга 2. Аппаратная архитектура

Целочисленное устройство и устройство с плавающей точкой

соединены двумя 32-битными двунаправленными шинами, которые

применяются совместно для передач 64-битных операндов. Эти же

шины связывают операционные устройства с кэш-памятью. Содер-

жимое регистров общего назначения подается по отдельной

32-битной шине в устройство сегментации для формирования

эффективных адресов.

УСТРОЙСТВО С ПЛАВАЮЩЕЙ ТОЧКОЙ. Устройство с пла-

вающей точкой имеет такие же систему команд и набор регистров,

как и математический сопроцессор 80387. Оно содержит регистро-

вый стек из восьми 80-битных регистров и специализированные

схемы для интерпретации 32/64/80-битных форматов чисел, опре-

деленных в Стандарте IEEE 754. Выходной сигнал на шине процес-

сора сообщает внешней подсистеме об ошибках с плавающей

точкой, а она может подать в процессор входной сигнал, показы-

вающий, что процессор должен игнорировать ошибки и продолжать

обычные операции.

УСТРОЙСТВО СЕГМЕНТАЦИИ. Под сегментом понимается

защищенное независимое адресное пространство. Сегментация

применяется для изолирования прикладных программ, вызова про-

цедур восстановления и локализации влияния ошибок программи-

рования.

47 32 31 0

Селектор сегмента Смещение в сегменте

После сегментации Логический адрес 31 22 21 12 11 0

Смещение в каталоге Смещение в таблице Смещение в странице

После Линейный адрес 31 12 11 0

страничного преобразования Базовый адрес страницы Смещение в странице

Физический адрес

Рис. 1.6. Форматы адресов в процессоре i486

Устройство сегментации преобразует сформированный програм-

мой сегментированный адресу называемый логическим или вирту-

альным адресом, в несегментированный линейный адрес. Местона-

хождения и атрибуты сегментов в линейном адресном пространстве

Глава 1. Внутренняя архитектура

хранятся в структурах данных, называемых дескрипторами сегмен-

тов. Устройство сегментации производит вычисление адреса, при-

влекая дескрипторы сегментов и смещения, выделенные из команд.

После этого линейные адреса посылаются в устройство стра-

ничного преобразования и кэш-память. Параллельно с вычисле-

нием линейного адреса производится контроль атрибутов сегмента.

При обращении к сегменту первый раз его дескриптор копиру-

ется во внутренний регистр процессора и в дальнейшем при необ-

ходимости берется из этого регистра. Программа может иметь до

16383 сегментов. В любой момент времени во внутренних регистрах

процессора могут находиться до шести дескрипторов сегментов. На

рис. 1.6 показаны взаимосвязи между логическим, линейным и фи-

зическим адресами памяти.

УСТРОЙСТВО СТРАНИЧНОГО ПРЕОБРАЗОВАНИЯ. Устрой-

ство страничного преобразования обеспечивает доступ к структурам

данных, которые больше имеющегося пространства памяти, храня

их частично в памяти и частично на диске. При страничном преоб-

разовании линейное адресное пространство разделяется на блоки

по 4 Кбайт, называемые страницами, а дня отображения линейного

адреса в физический применяются структуры данных в памяти, на-

зываемые таблицами страниц. Элементами таблиц страниц являют-

ся своеобразные дескрипторы страниц, которые проще дескрипто-

ров сегментов. Физические адреса используются кэш-памятью

и/или выдаются на шину процессора. Устройство страничного пре-

образования фиксирует такие ситуации, как обращение к странице,

отсутствующей в памяти, и формирует особые случаи, называемые

страничными нарушениями. При страничном нарушении операци-

онная система должна передать нужную страницу с диска в память.

При необходимости она может освободить пространство в памяти,

отсылая некоторую другую страницу на диск (такая замена одной

страницы на другую называется свопингом). Если страничное пре-

образование программно запрещено, физический адрес совпадает с

линейным адресом. В устройство страничного преобразования вхо-

дит ассоциативный буфер преобразования {Translation Lookaside

Buffer или TLB), который хранит 32 наименее давно используемых

элемента таблицы страниц. Структуры данных буфера TLB показа-

ны на рис. 1.7. Устройство страничного преобразования просматри-

вает линейные адреса в TLB. Если оно не находит линейного адре-

са в TLB, устройство формирует запрос на загрузку в TLB правиль-

ного физического адреса из таблицы страниц в памяти. Только ког-

да правильный элемент таблицы страниц находится в TLB, иници-

ируется цикл шины. Когда устройство страничного преобразования

отображает страницу из линейного адресного пространства на стра-

ницу в физической памяти, оно изменяет только 20 старших бит

Микропроцессор i486*Книга 2. Аппаратная архитектура

линейного адреса. Младшие 12 бит физического адреса берутся не-

изменными из линейного адреса.

Рис. 1.7. Организация буфера TLB

В течение достаточно короткого временного интервала боль-

шинство программ обращаются только к небольшому числу стра-

ниц. В такой ситуации страницы обычно находятся в памяти, а ин-

формация о преобразовании адреса содержится в буфере TLB. В

типичных системах TLB удовлетворяет до 99% запросов на доступ к

шблицам страниц. В качестве стратегии замещения в буфере TLB

применяется такой же алгоритм псевдо-LRU, как и во внутренней

кэш-памяти. Буфер TLB очищается при загрузке базового регистра

каталога страниц (регистр CR3). При считывании из каталога стра-

ниц или таблицы страниц могут возникать страничные нарушения.

Для передач новых данных в буфер TLB можно использовать кэш-

память, но это нежелательно, когда обновлением буфера TLB уп-

равляет внешняя схема. В отличие от сегментации страничное пре-

образование невидимо для прикладных программ и не защищает от

изменения программами данных вне ограниченной части памяти.

Страничное преобразование видимо операционной системе, кото-

рая использует его для удовлетворения требований памяти при-

кладных программ.

1.3. Производительность

Производительность является важнейшим параметром любой

вычислительной системы. Общепринятым показателем производи-

н льности является скорость выполнения программы, которая зави-

Глава 1. Внутренняя архитектура

: Заказ 4317

сит от множества факторов: быстродействия процессора, частоты1

синхронизации, запаздывания памяти, скорости передачи данных,

памяти, размера памяти, времени обращения к диску, скорости

дисковых передач, времени обращения к дисплею, эффективности

компилятора, эффективности операционной системы, особеннос-

тей реализованных в программе алгоритмов и т.д. В этом разделе

показано влияние на производительность параметров памяти.

Проектирование системы памяти имеет важное значение. Про-

цессор i486 быстрее любой практической системы памяти. Однако

его внутренние устройства (например, кэш-память, буферы записи,

устройство предвыборки команд) позволяют работать даже с мед-

ленной внешней памятью.

Идеальная подсистема памяти должна работать без состояний

ожидания. Все циклы шины в процессоре i486 завершаются всего за

два такта при одиночном обращении и за пять тактов при заполне-

нии строки кэш-памяти. Следовательно, для работы на частоту

33 МГц потребуется много микросхем памяти с временем

обращения 15 нс. В реальных системах применяются микросхемы

динамических ЗУПВ с временем обращения 60—100 нс.

Максимальную производительность определяет частота синхро-

низации процессора. Чем выше частота, тем быстрее работает про-

цессор, но для повышения производительности всей системы тре-

буется все более быстрая память. Процессор i486 спроектирован та-

ким образом, что рост общей производительности обеспечивается

при повышении частоты и постоянстве быстродействия памяти.

Главной характеристикой памяти является число состояний

ожидания при считывании элемента данных. На частоте 33 МГц

операция считывания требует память с временем обращения 15 нс

Для медленной памяти с состояниями ожидания к времени обра-

щения на частоте 33 МГц добавляются 30 нс. Состояния ожидания

вводятся во всех практических разработках системы памяти.

В процессоре i486 появился новый показатель системы

памяти — скорость передач при считывании, который играет

важную роль при заполнении внутренней кэш-памяти. В

большинстве считываний процессор может передавать данные из

памяти каждый такт, что вдвое скорее отдельных циклов памяти

Системы памяти, поддерживающие столь высокую скорость

передач, повышают производительность на 10—20%.

Еще одним важйым показателем является время цикла записи

Внутренняя кэш-память со сквозной записью формирует записей

примерно вдвое больше, чем считываний. Скорость записи особен-

но важна для 16-битных программ, которые формируют больше за-

писей, чем 32-битные программы. Время цикла записи огра-

ничивает производительность системы, когда загрузка шины при-

ближается к допустимому максимуму. Общий метод повышения

Микропроцессор i486 Книга 2. Аппаратная архитектура

производительности системы памяти заключается в применении

к > ш-памяти. Процессор i486 имеет внутреннюю кэш-память, кото-

рая удовлетворяет большинство запросов считывания. Выигрыш

производительности при введении внешней кэш-памяти у процес-

< ора i486 меньше, чем у процессора 80386 и он сильно зависит от

особенностей применения. В некоторых применениях внешняя

к нп-память обеспечивает рост производительности менее 5%, в

большинстве применений он составляет 10—15%, а в небольшом

числе применений даже до 40%. Для многих применений процес-

i ора i486 внешняя кэш-память не нужна.

Процессор i486 выполняет команды за меньшее число тактов,

чем предыдущие процессоры фирмы Intel. В нем реализовано не-

»колько приемов, обеспечивающих выполнение многих часто

встречающихся команд за один такт. Процессор имеет внутреннюю

к и и-память для кода и данных, а также конвейерное операционное

устройство; он дешифрирует многие простые команды непосред-

। гвенно в аппаратные действия и использует буферы записи для со-

। пасования скорости выполнения с быстродействием шины памяти.

Один из приемов анализа влияния этих способов на производи-

нльность заключается в сравнении среднего времени выполнения

идной команды. Для этого фирма Intel измерила по множеству про-

|рамм частоты использования команд. После умножения частот на

число тактов и суммирования произведений получается среднее

число тактов на команду. Результаты расчетов показали, что в про-

цессоре i486 среднее время выполнения команды составляет

I 95 тактов, а в процессоре 80386 — 4.919 тактов, т. е. для це-

иочисленных программ производительность повышена в 2.5 раза.

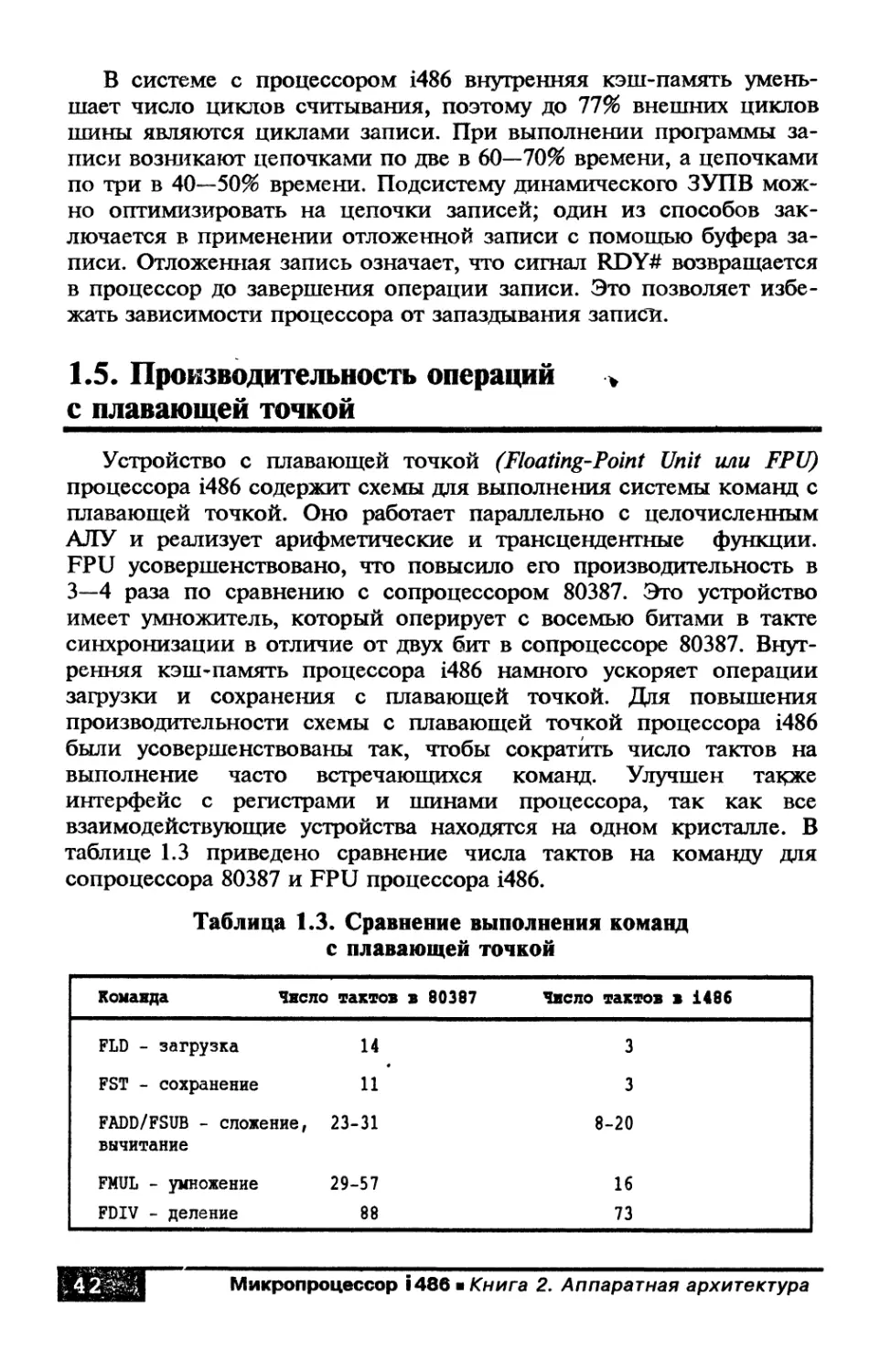

Для команд с плавающей точкой повышение производительности

। щс больше.

Важно отметить, что процессор i486 не может обеспечить высо-

кую скорость при запрещенной кэш-памяти. Его внутренняя кэш-

память удовлетворяет большинство (90—95%) запросов считывания,

л нее записи требуют производства циклов внешней шины.

1.3.1. Влияние внутренней кэш-памяти

Процессор i486 имеет очень высокую скорость выполнения опе-

раций, составляющую для наиболее распространенных команд

нее in один такт. Так как внешняя память не может обеспечивать

на иные в каждом такте, для повышения общей производительности

фсбуется внутренняя кэш-память, допускающая очень быстрое об-

ращение и скрывающая различия в скорости внешней шины и про-

цессора. Размер, организация, принцип записи, замещение при

промахе и шинная организация внутренней кэш-памяти процессора

i486 были выбраны для поддержки широкого круга применений.

I лава 1. Внутренняя архитектура

Размер внутренней кэш-памяти составляет 8 Кбайт. Она содер-

жит код и данные и организована как четырехнаправленная ассо-

циативная по множеству кэш-память с дайной строки 16 байт.

Строки могут быть достоверными или недостоверными, а частично

достоверных строк нет. Запросы считывания формирует либо про-

грамма (запрос данных), либо устройство предвыборки команд

(запрос кода). Обычно эти запросы удовлетворяет внутренняя кэш-

память, но в случае промаха формируется запрос внешней шины.

Считывание из некэшируемых областей памяти представляет собой

обычное считывание. Если же запрос считывания обращается к

кэшируемой области памяти, процессор инициирует заполнение

строки, которое требует производства дополнительных циклов

шины.

На производительность системы влияет размер строки кэш-па-

мяти. Если он слишком велик, то сокращается число блоков, кото-

рые могут разместиться в кэш-памяти. Кроме того, при увеличении

дайны строки растет запаздывание внешней памяти при заполне-

нии строки. Сокращение размера строки приводит к уменьшению

коэффициента попаданий. Шина процессора i486 оптимизирована

на размер строки 16 байт. Так как процессор может обращаться к

четырем байтам памяти в каждом цикле шины и дайна строки со-

ставляет 16 байт, дая заполнения строки требуются четыре цикла

шины. Для уменьшения запаздывания при считывании строк кэш-

памяти процессор допускает пакетные циклы, в которых четыре

байта данных можно считывать в процессор каждый такт. Благо-

даря пакетным циклам 16-байтная строка считывается в процессор

за пять тактов.

Для обновления содержимого основной памяти применяется

принцип сквозной записи, т.е. все операции записи от процессора

инициируют цикл внешней шины. Кроме того, при попадании об-

новляется и внутренняя кэш-память. Принцип сквозной записи

обеспечивает автоматическую согласованность между внутренней

кэш-памятью и внешней памятью. Если все операции программы

используют внутренние ресурсы, достигается ее самое быстрое вы-

полнение, так как все запросы удовлетворяют внутренние регистры

и кэш-память. Однако при промахах в операциях считывания и во

всех операциях записи приходится обращаться к внешней шине,

что снижает производительность системы. В зависимости от при-

менения коэффициент попаданий внутренней кэш-памяти достига-

ет примерно 95%. Такой высокий коэффициент попаданий имеет

три основных следствия:

1. Повышается производительность. Процессор i486 может

считывать данные из внутренней кэш-памяти каждый такт, что по-

зволяет операционному устройству выполнять многие команды за

один такт.

Микропроцессор i486 л Книга 2. Аппаратная архитектура

2. Сокращается использование шины. Так как подавляющее

большинство считываний удовлетворяет внутренняя кэш-память,

процессор i486 значительную часть времени не обращается к шине.

В систему можно вводить дополнительные ведущие шины, не на-

сыщая шину и, как следствие, не ухудшая производительность.

3. На внешней шине увеличивается отношение числа записей к

числу считываний. Число считываний сокращается, но число запи-

сей остается неизменным. Следовательно, основная память должна

иметь малое запаздывание в операциях записи.

Внутри процессора к кэш-памяти подключены два отдельных

128-битных буфера предвыборки. Их можно заполнить данными из

внутренней кэш-памяти или внешней памяти всего за один такт.

Поскольку широкие буферы удовлетворяют несколько операций

предвыборки, удается избежать ухудшения производительности,

связанного с объединением кэш-памяти данных и кэш-памяти ко-

манд. Для оптимизации производительности при заполнении стро-

ки применяется так называемый обход. Считанные в первом цикле

данные посылаются прямо запрашивающему устройству. Благодаря

этому до использования запрошенных данных не нужно ожидать

заполнения всей строки.

В процессорах без внутренней кэш-памяти значительная часть

времени выполнения приходится на обращения к внешней шине.

Предвыборки кода и считывания данных должны производиться из

внешней памяти; следовательно, большинством обращений к шине

являются считывания и обычно системы памяти оптимизируются

на считывание (см. табл. 1.2).

Таблица 1.2. Операции на, шине процессора

Операция Вез кэв-памяти С кзш-памятыо

Считывание 42% 8%

Опережающая выборка 22% 15%

Запись 36% 77%

Высокий коэффициент попаданий во внутренней кэш-памяти

сокращает число внешних считываний. Из-за применения в кэш-

памяти принципа сквозной записи число записей на шине не

уменьшается, но теперь циклы считывания составляют не-

значительную часть всех циклов шины (см. табл. 1.2). Для повыше-

ния производительности систем с процессором i486 внешнюю па-

мять следует оптимизировать по циклам записи.

1.3.2. Внутренние буферы записи

Выше показано, что в системах с процессором i486 малое запаз-

дывание записи важнее, чем в предыдущих процессорах. Процессор

i486 имеет четыре буфера записи, позволяющие ему работать без

Глава 1. Внутренняя архитектура

запаздывания в операциях записи. Буферы можно заполнять каж-

дый такт. Когда все четыре буфера пустые и шина холостая, запрос

записи проходит на внешнюю шину, обходя буферы. Если же при

формировании внутреннего запроса записи шина недоступна, то

запись буферируется и передается на шину, как только она осво-

бождается. Когда при записи возникает попадание в кэш-памяти,

она сразу же обновляется.

Обычно записи выполняются на внешней шине в том порядке, в

каком они поступили в буферы записи. Однако иногда считывание

из памяти можно пропустить раньше всех записей. Если все записи

в буферы вызвали попадание в кэш-памяти, а считывание вызвало

промах, то считывание наверняка не будет конфликтовать с ожи-

дающими записями.

Следовательно, циклы шины можно переупорядочить, чтобы

операция считывания была произведена раньше освобождения бу-

феров записи. Буферы записи как бы изолируют внутреннее опера-

ционное устройство от шины. Выполнение программы продолжа-

ется без задержек на запаздывание записи. Кроме того, переупоря-

дочивание иногда позволяет продолжить выполнение программы,

даже если некоторые буферы записи заполнены.

1.4. Внешняя память

Достижение высокой производительности систем с процессором

i486 требует тщательно спроектированной внешней памяти. Для

повышения экономичности память реализуется на микросхемах

статических и динамических ЗУПВ. Микросхемы статических

ЗУПВ имеют меньшее время обращения и не требуют циклов реге-

нерации. Микросхемы динамических ЗУПВ характеризуются боль-

шей плотностью и меньшей стоимостью, но требуют Схем регенера-

ции и введения состояний ожидания из-за большего времени об-

ращения.

Общая производительность системы прямо связана с быстродей-

ствием памяти. Подавляющее большинство циклов шины использу-

ется для обращения к памяти за командами и данными. По мере

повышения быстродействия процессора требуется все более быст-

рая память.

Применение в системке только быстрой статической памяти ока-

зывается слишком дорогим. При введении менее дорогих медлен-

ных микросхем увеличивается число состояний ожидания и снижа-

ется производительность. На частотах выше 25 МГц оптимальной

производительности памяти можно достичь, применяя очень быст-

рые микросхемы памяти, но применять только такие микросхемы

неэкономично. Реализация памяти на медленных микросхемах

I3

Микропроцессор i486 Книга 2. Аппаратная архитектура

снижает стоимость, но при этом снижается производительность си-

стемы.

Компромисса между стоимостью и производительностью можно

достичь, разделяя функции и применяя комбинацию медленной и

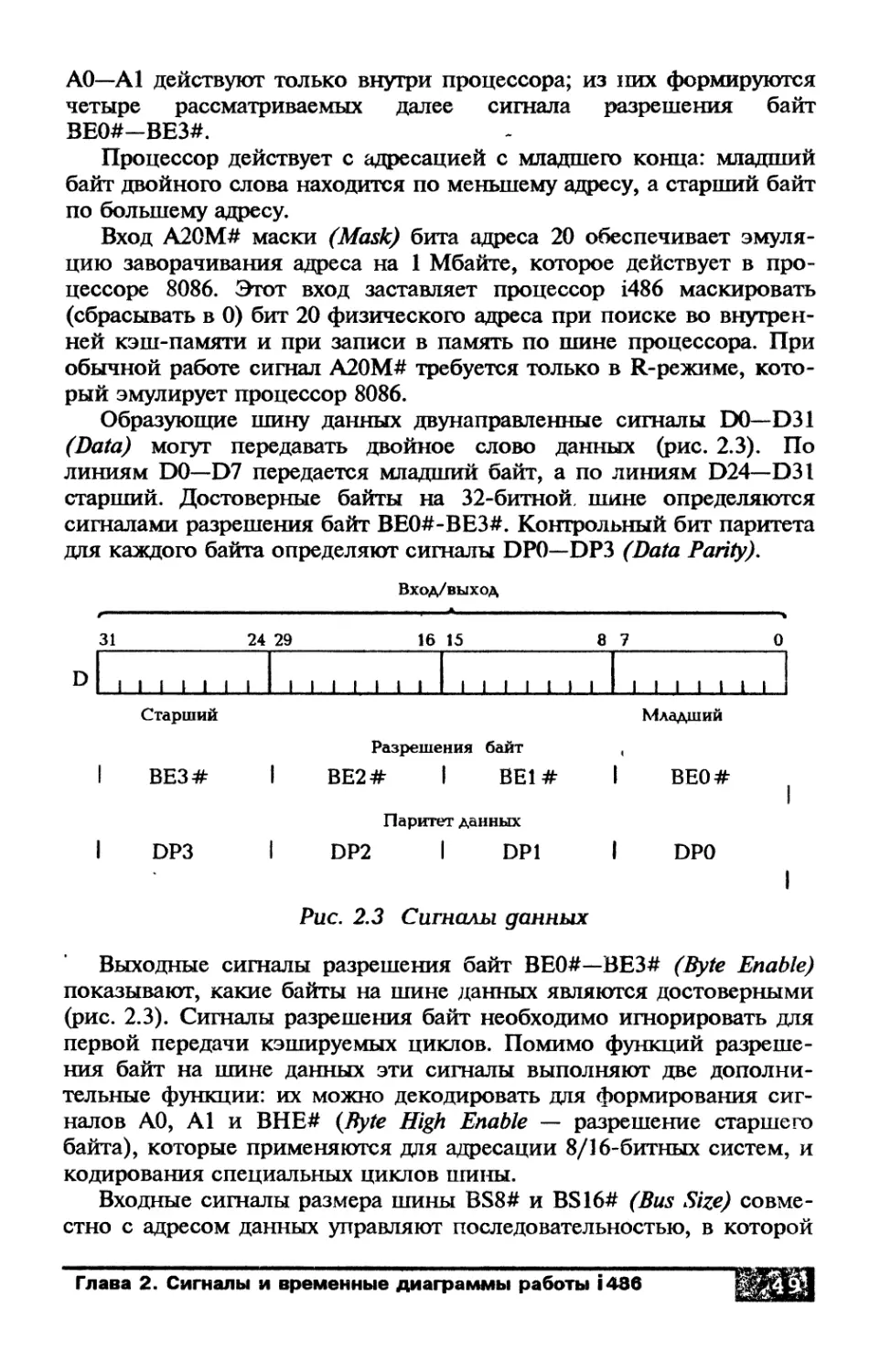

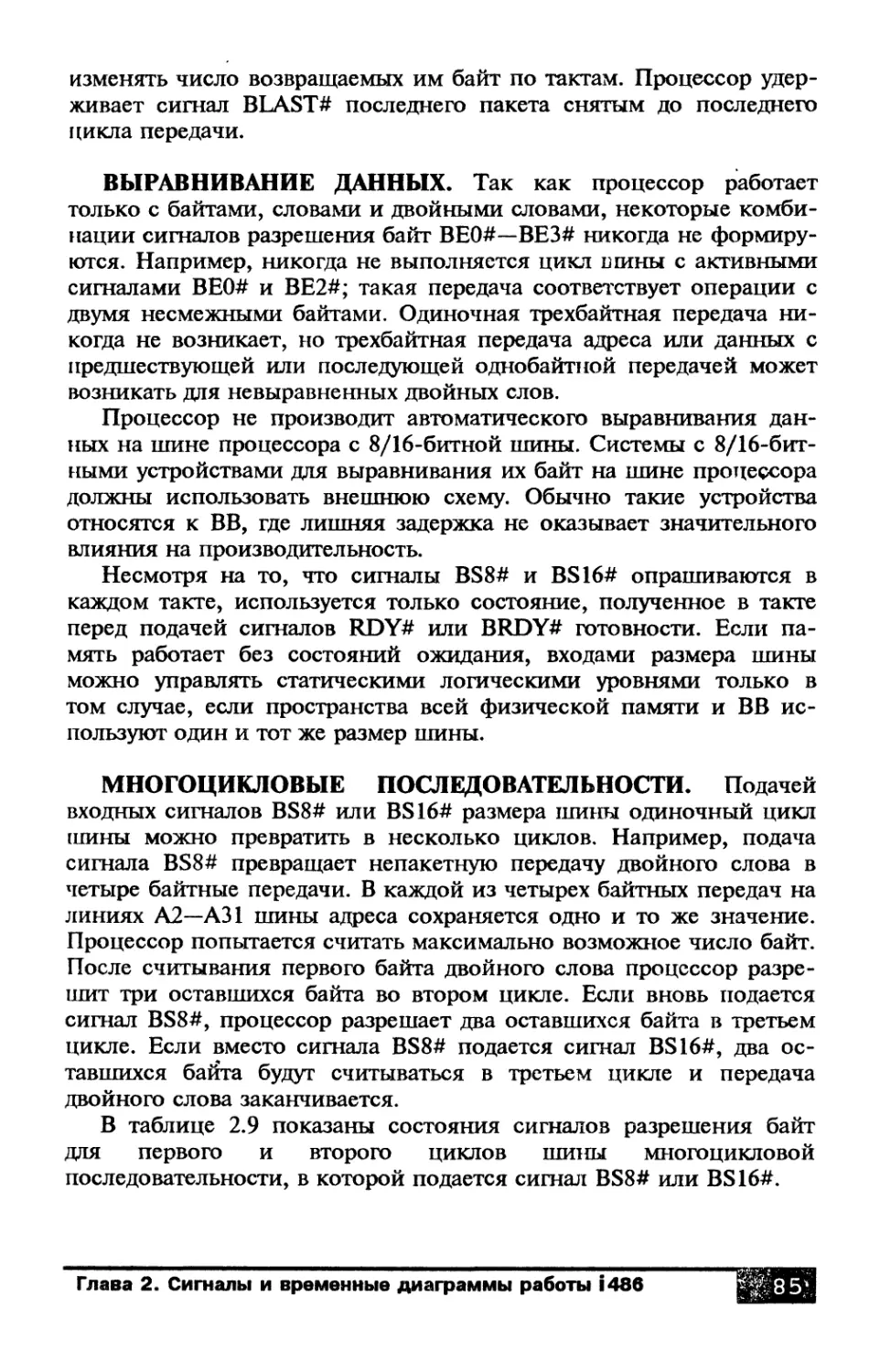

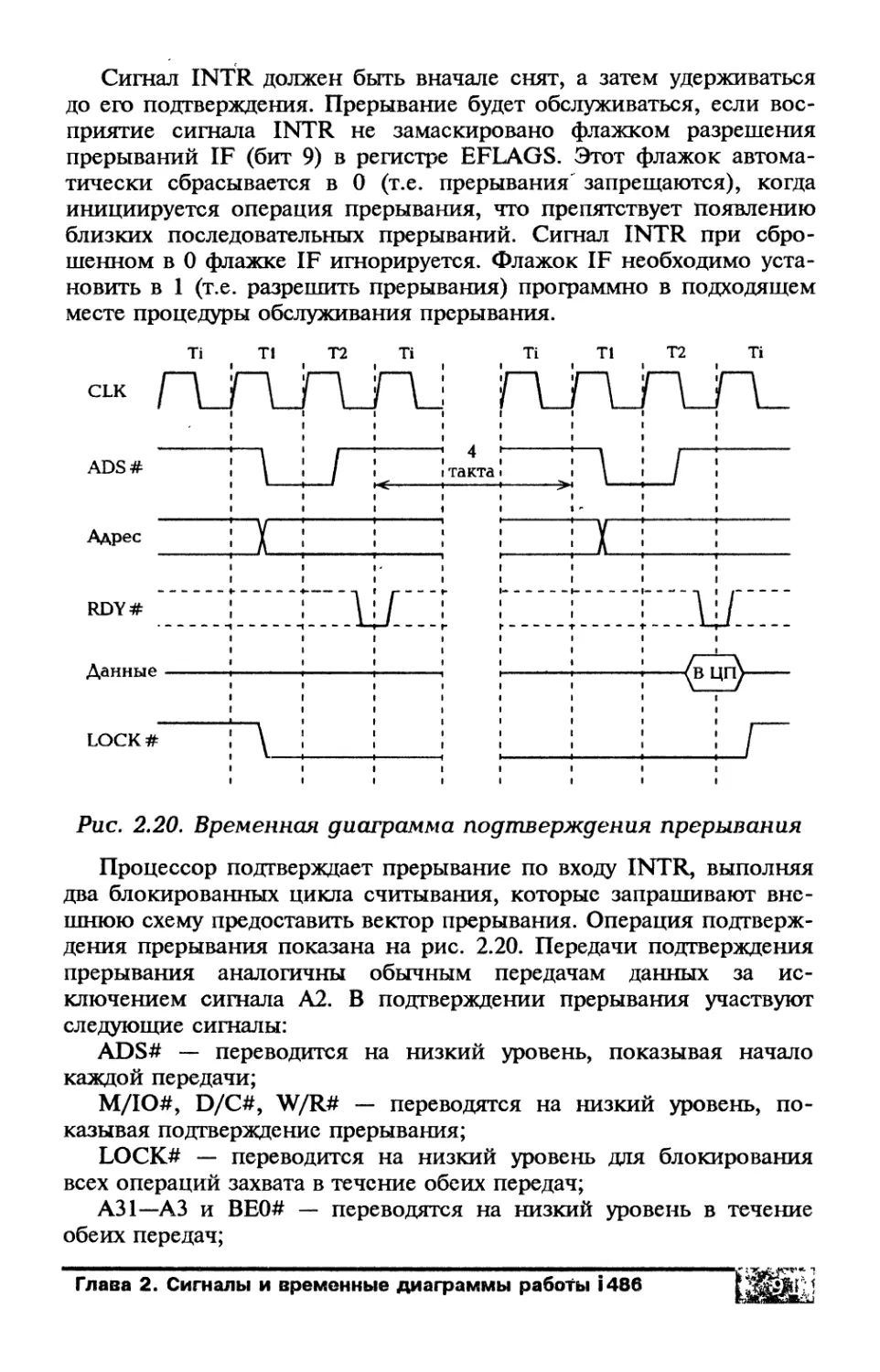

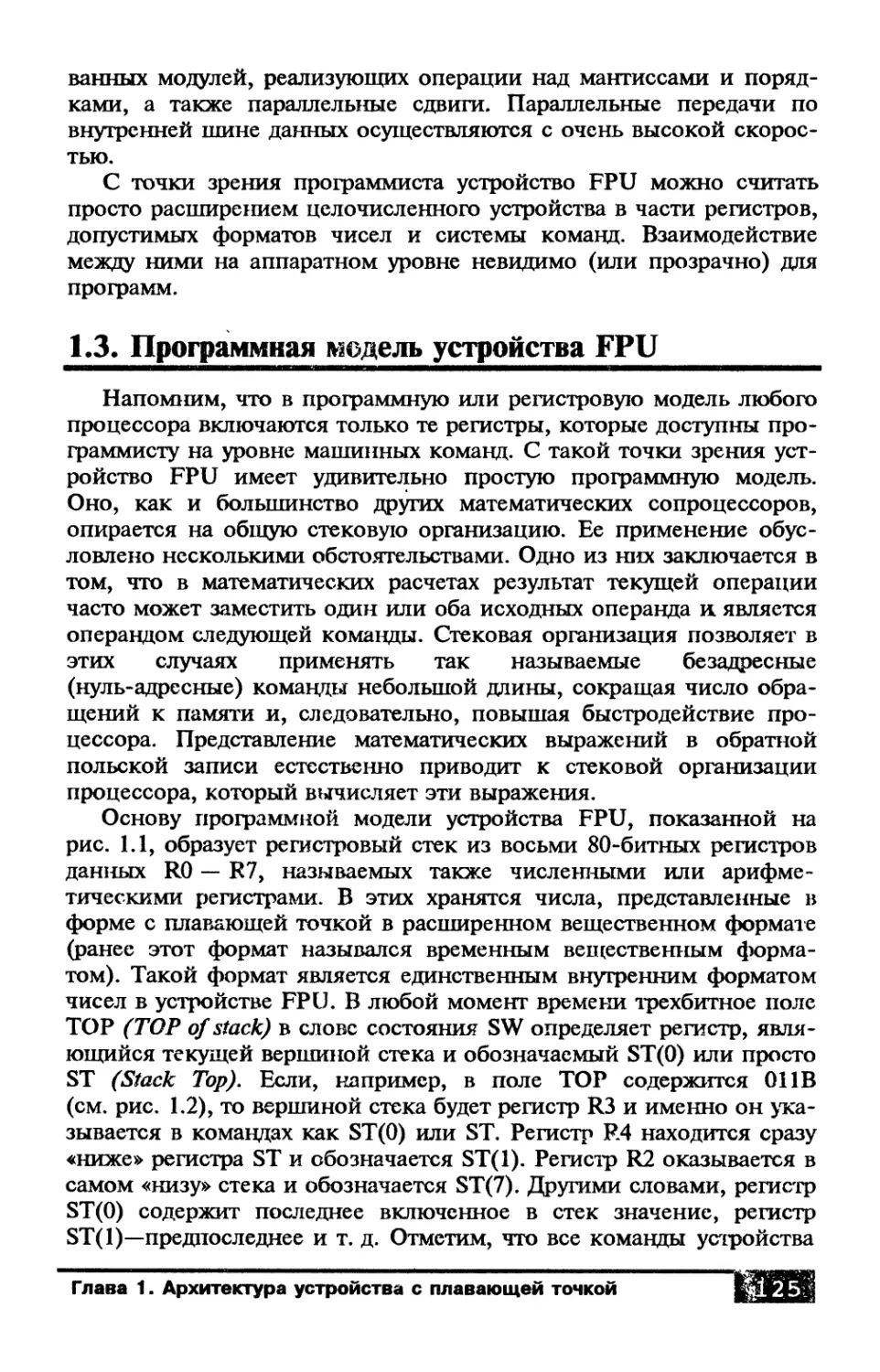

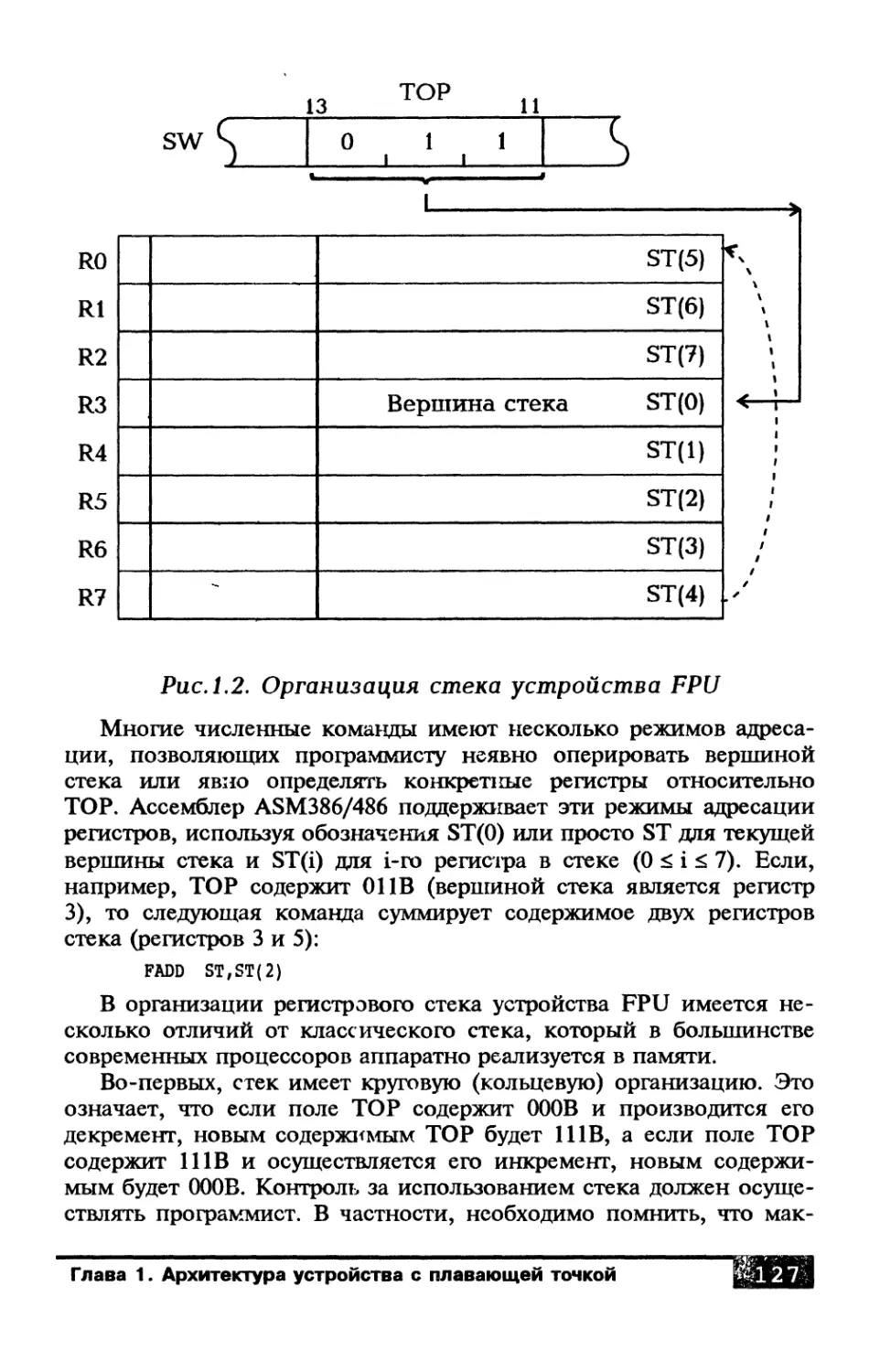

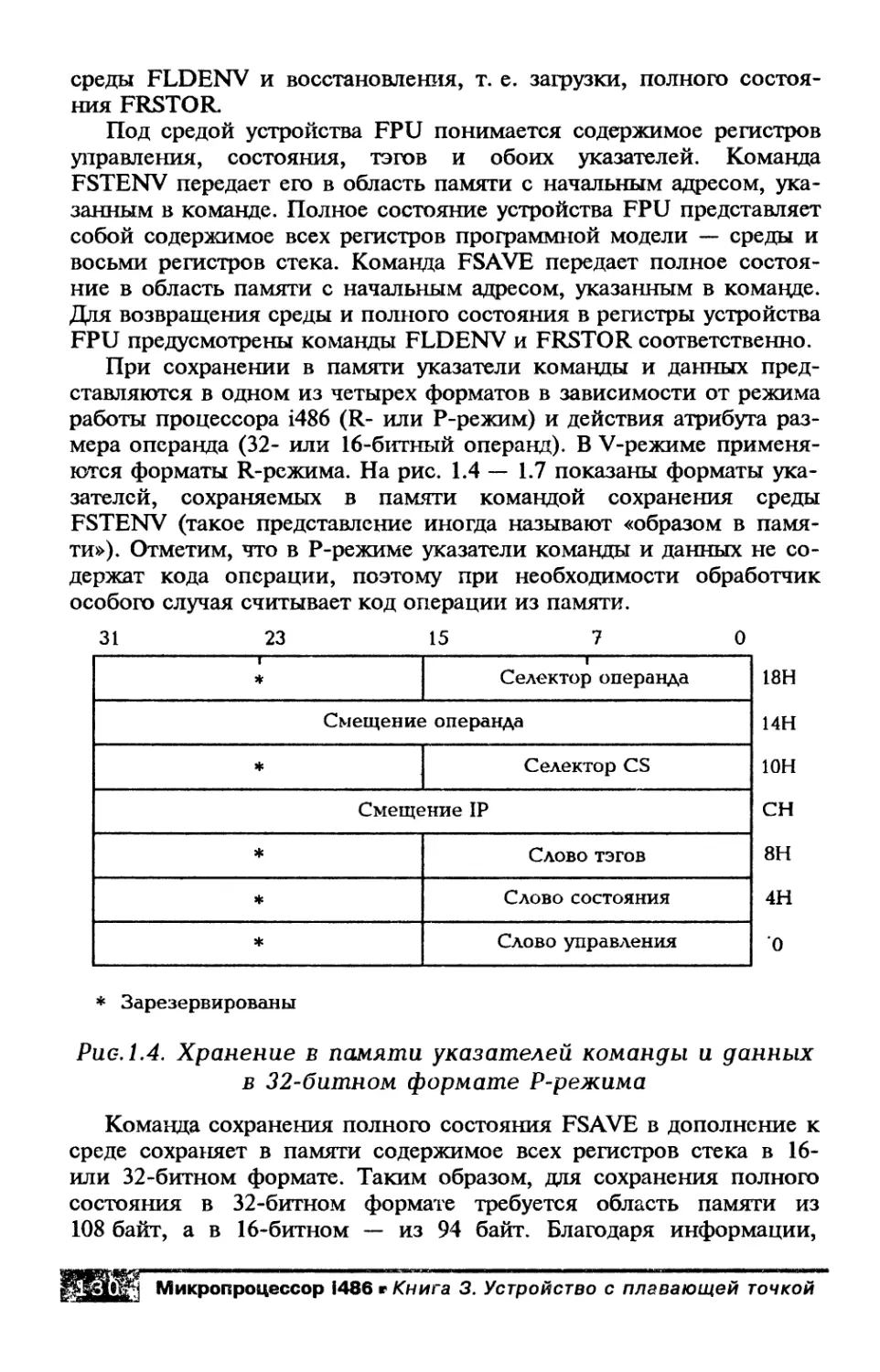

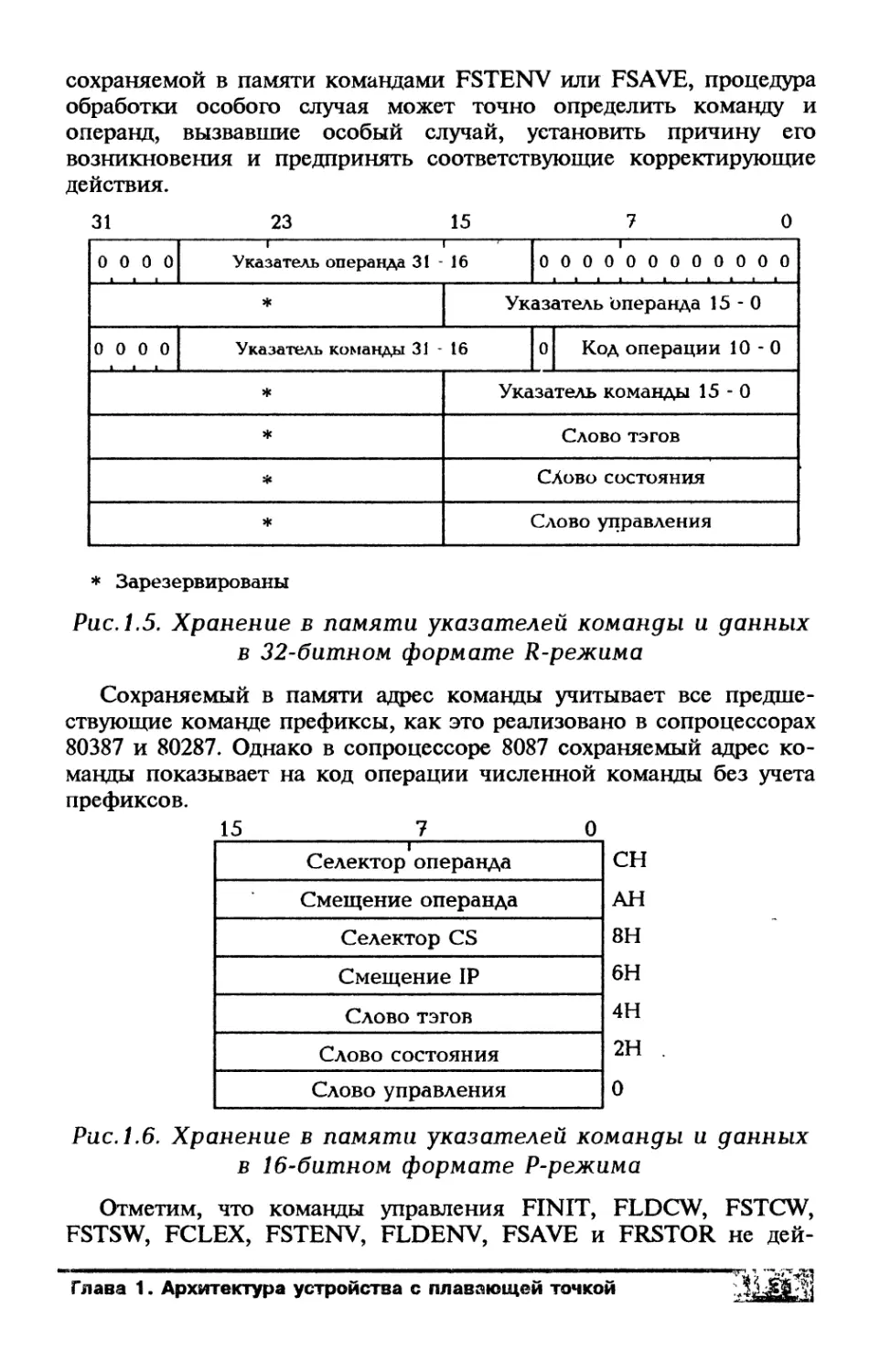

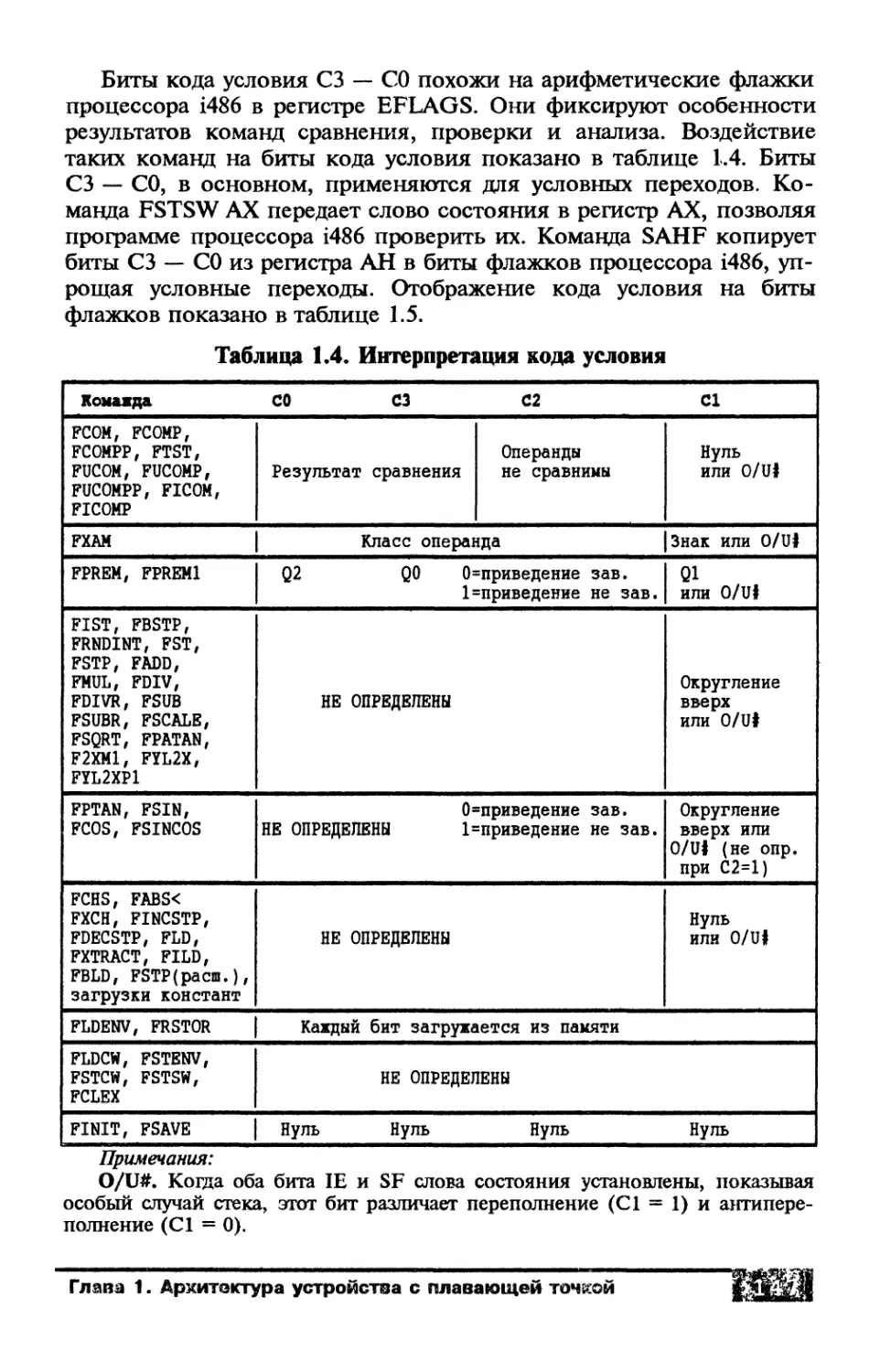

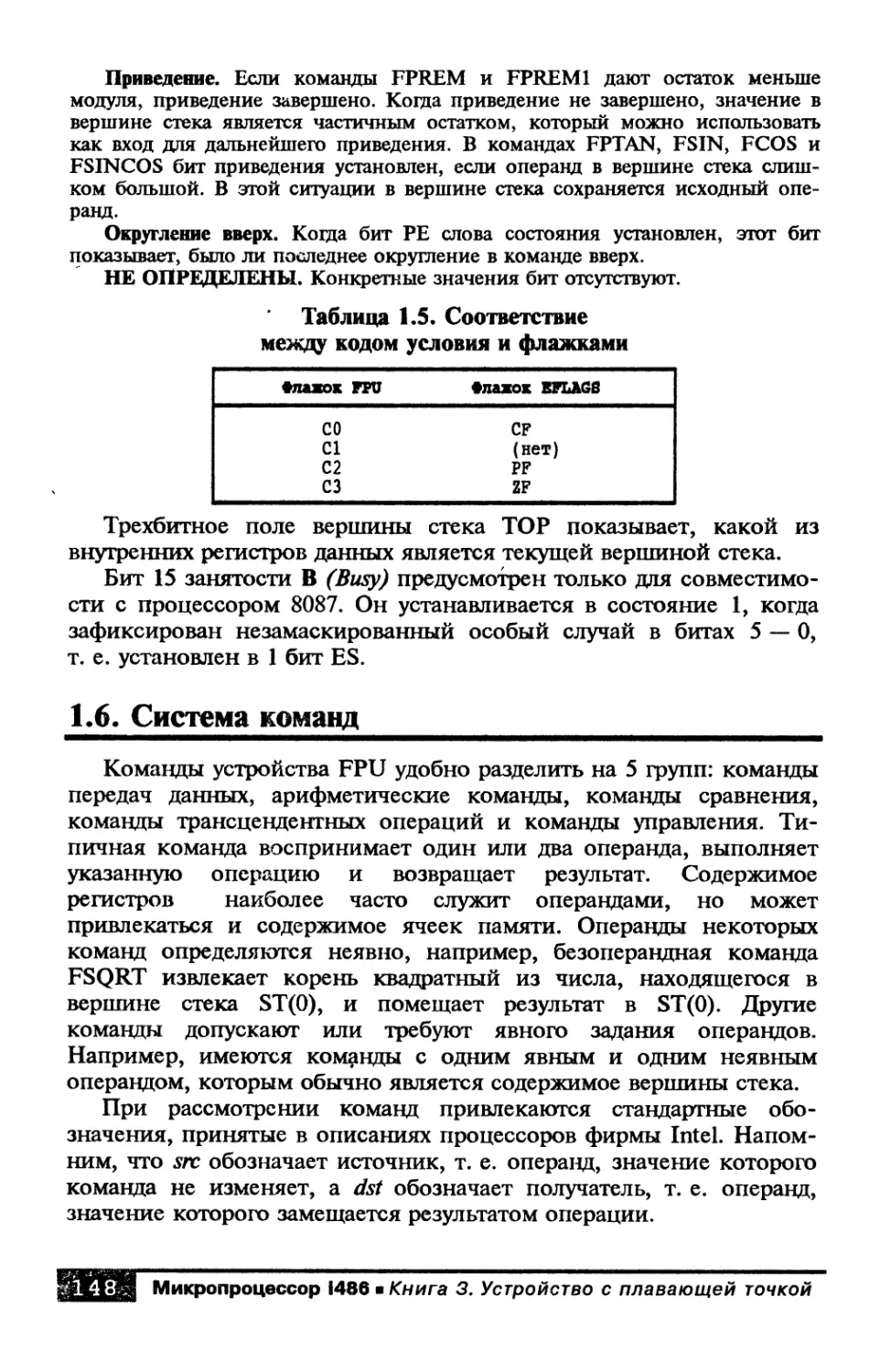

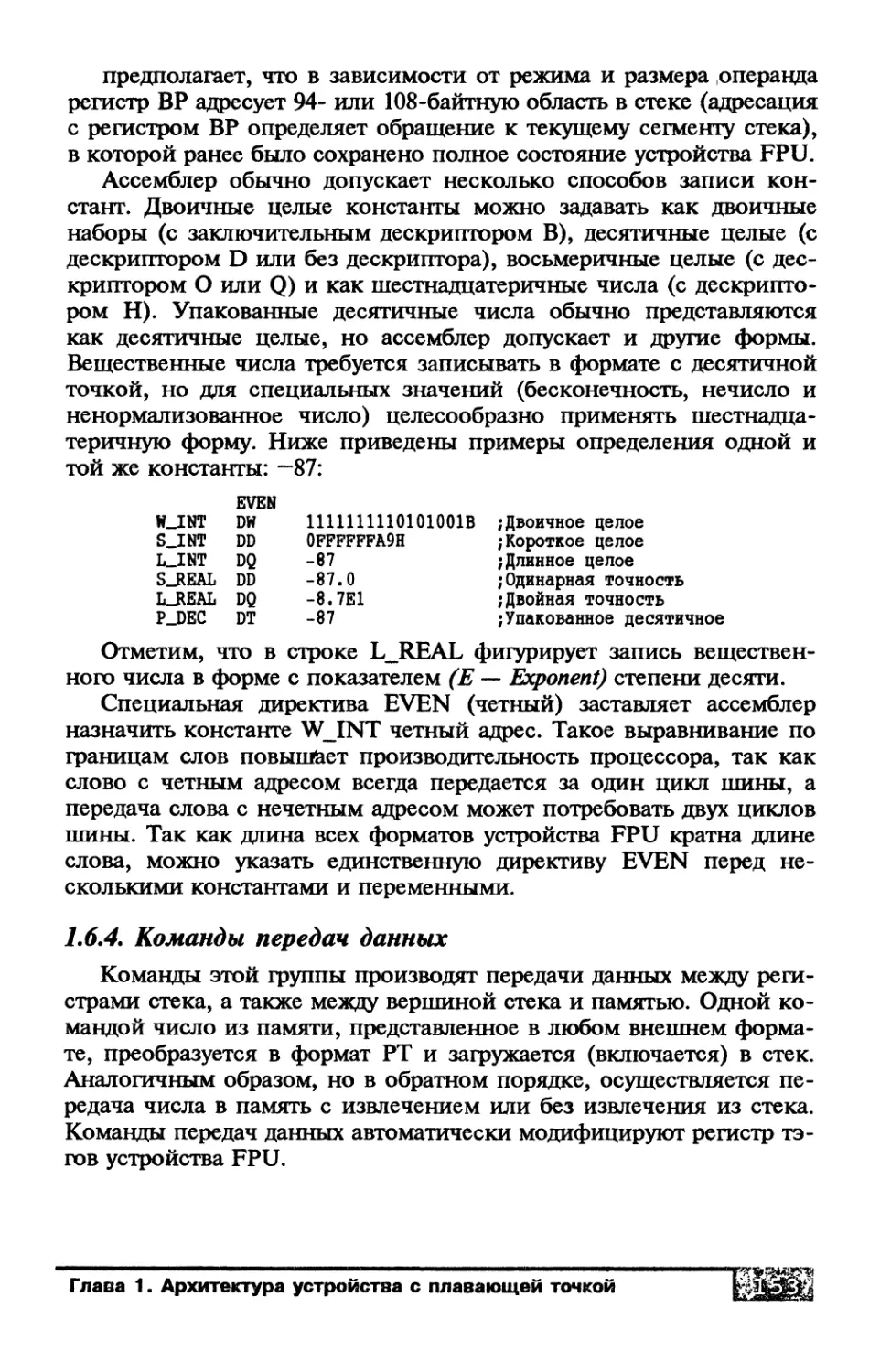

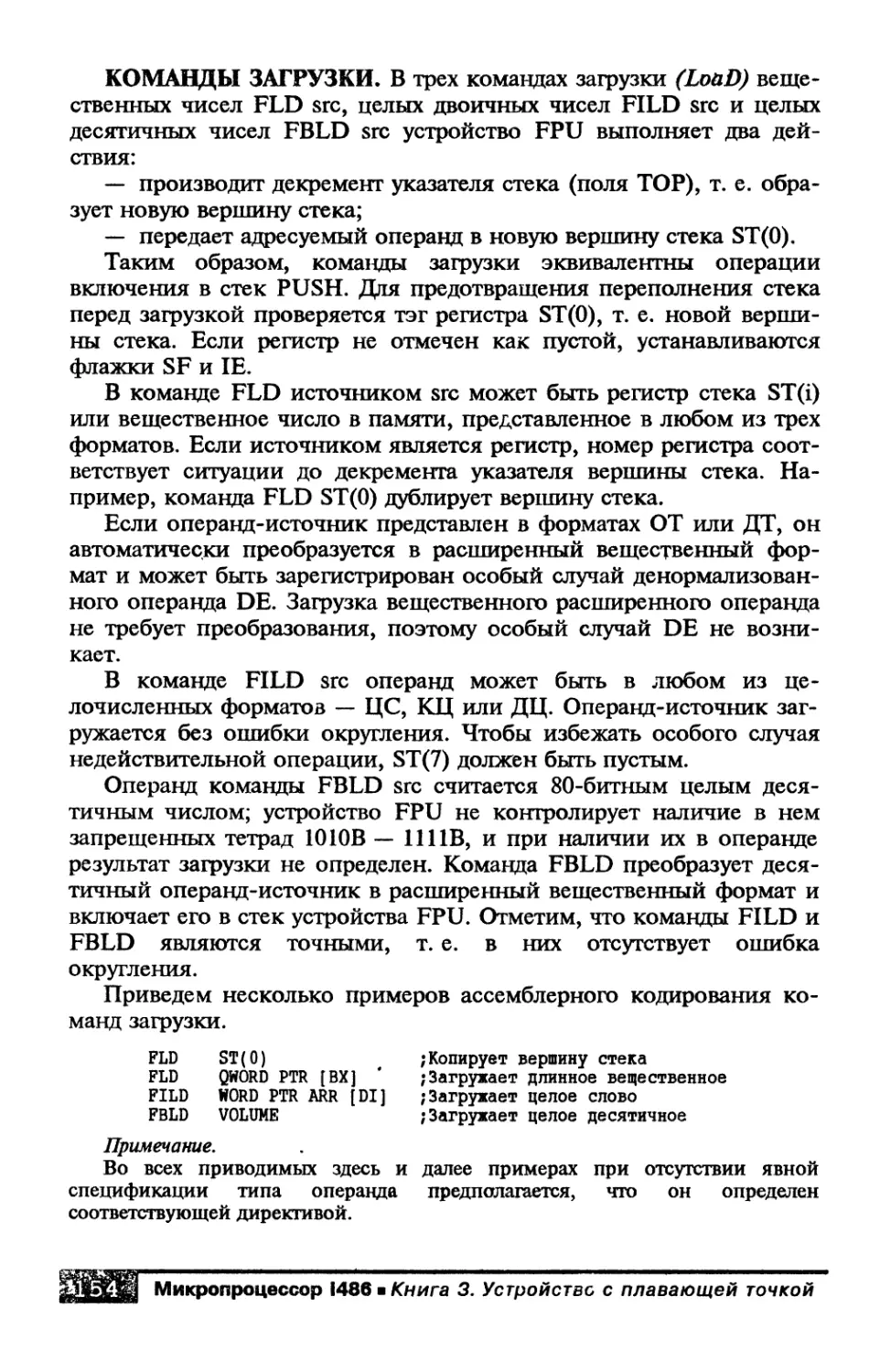

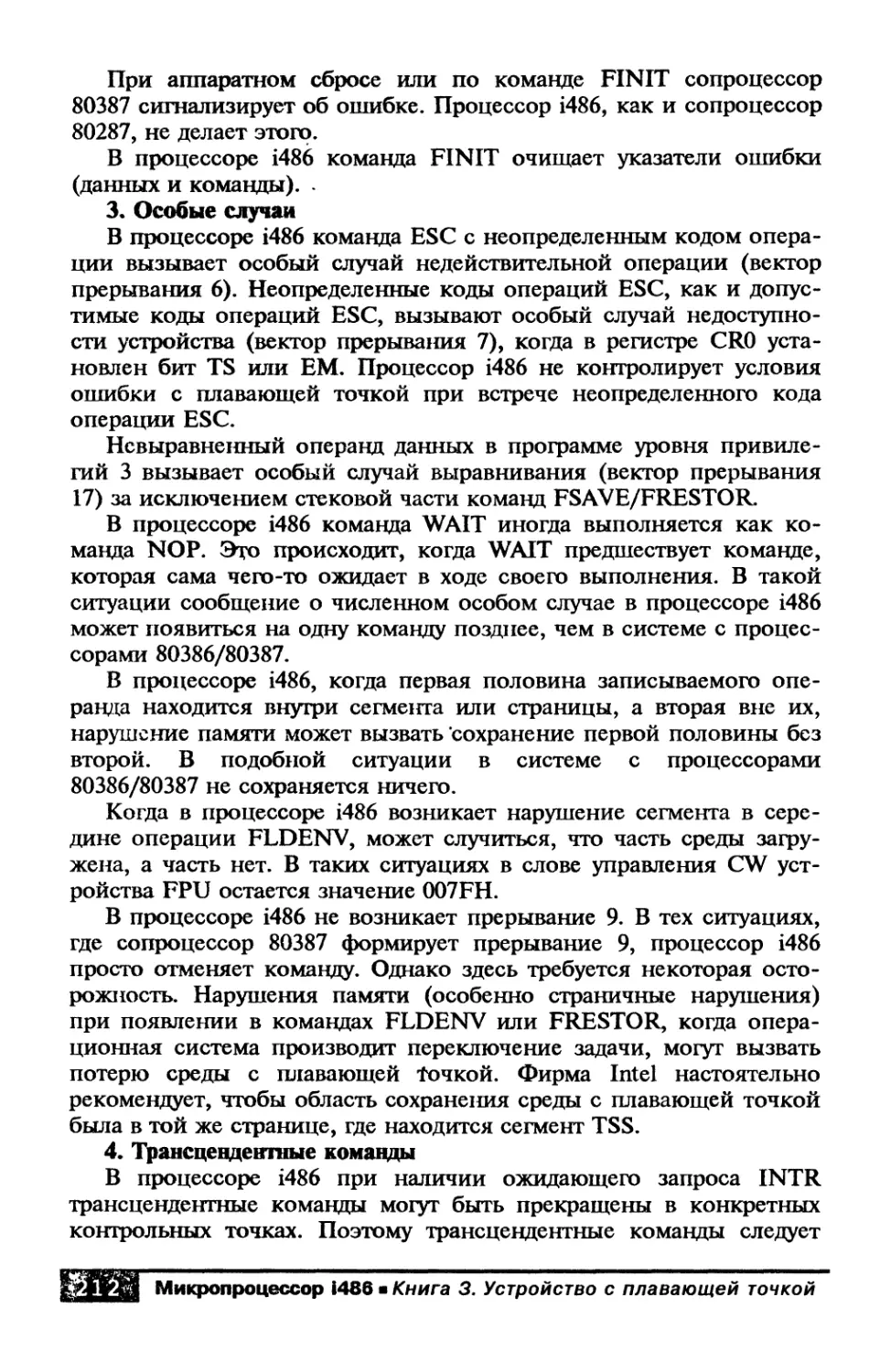

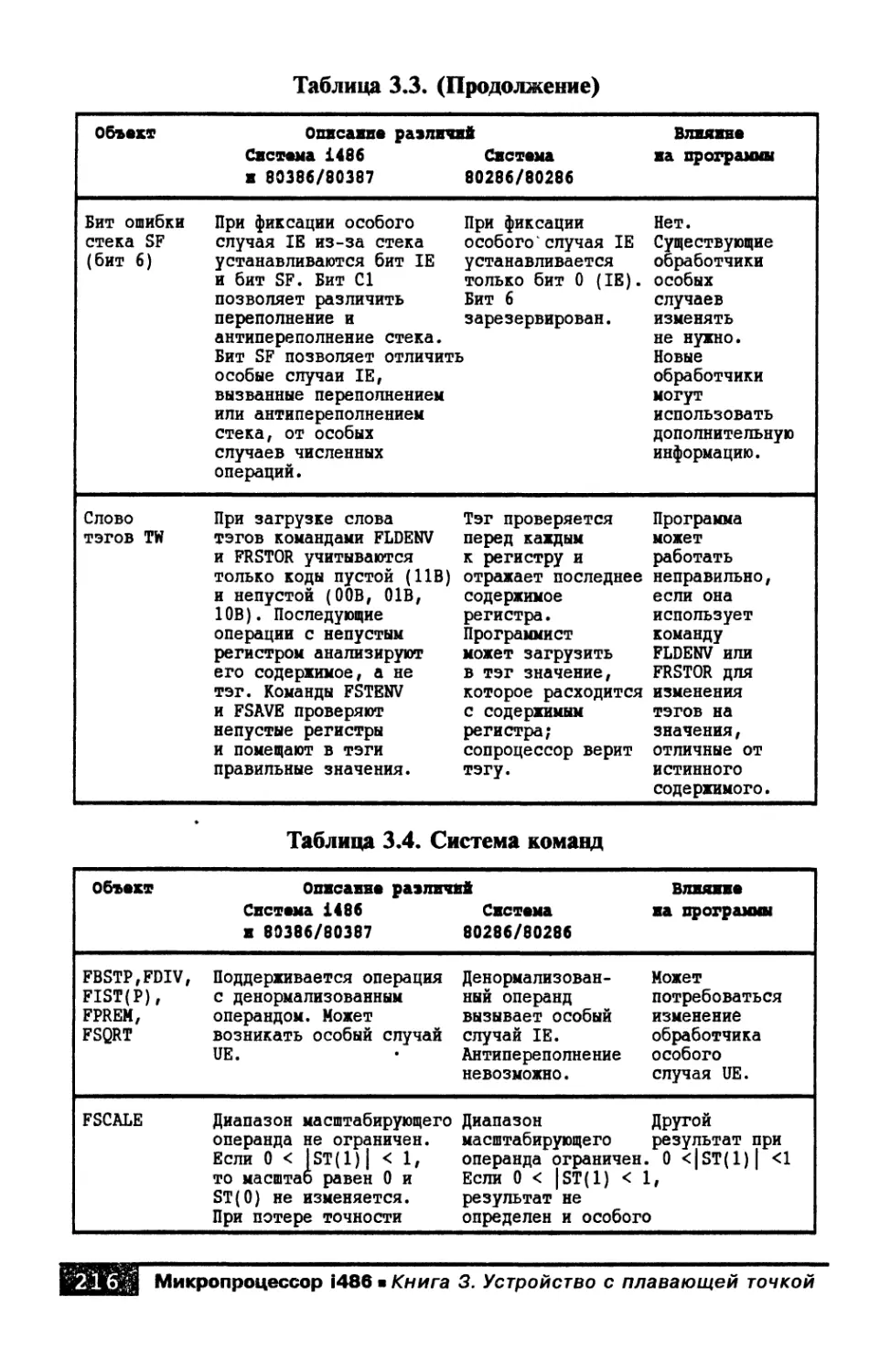

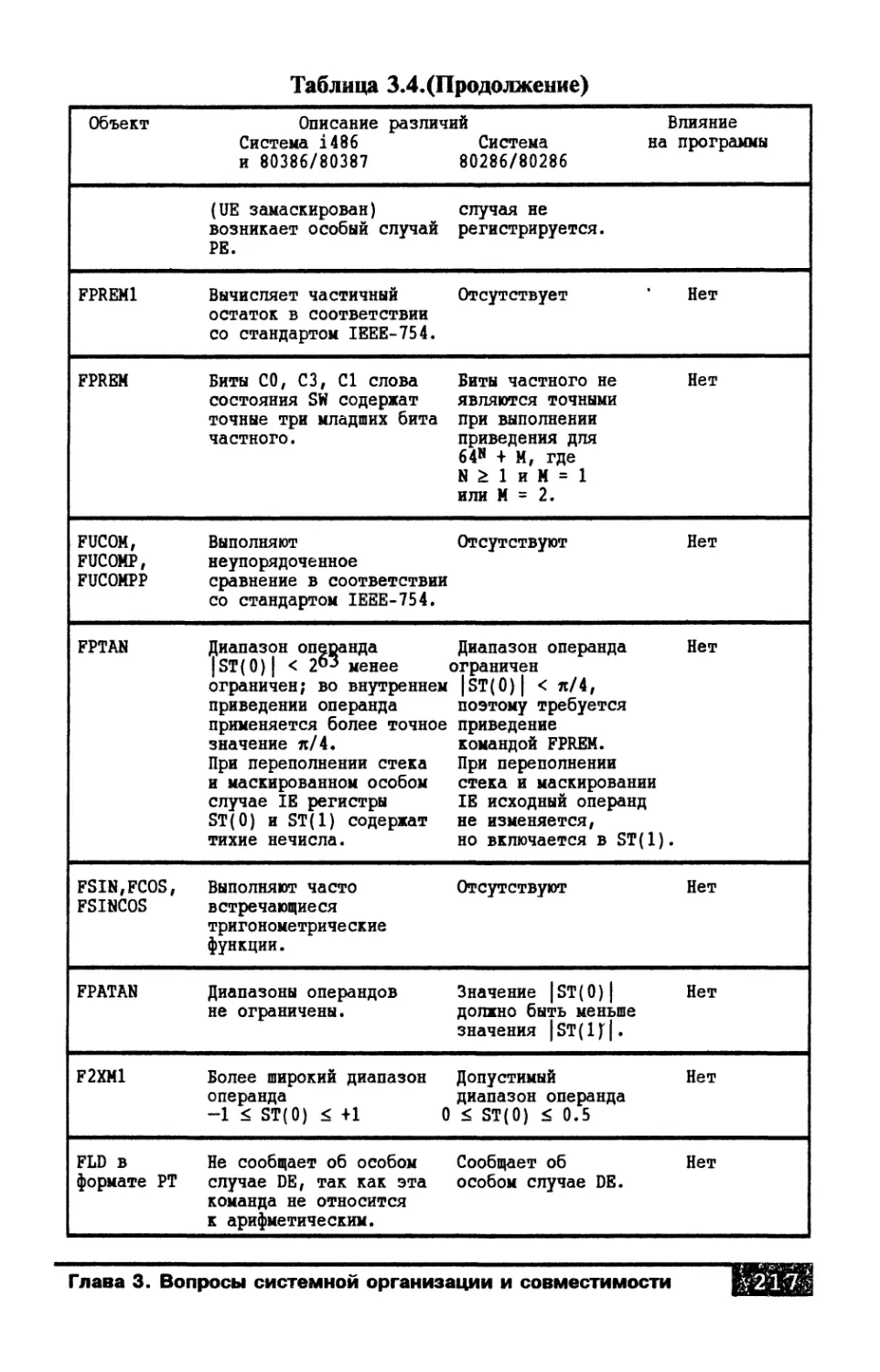

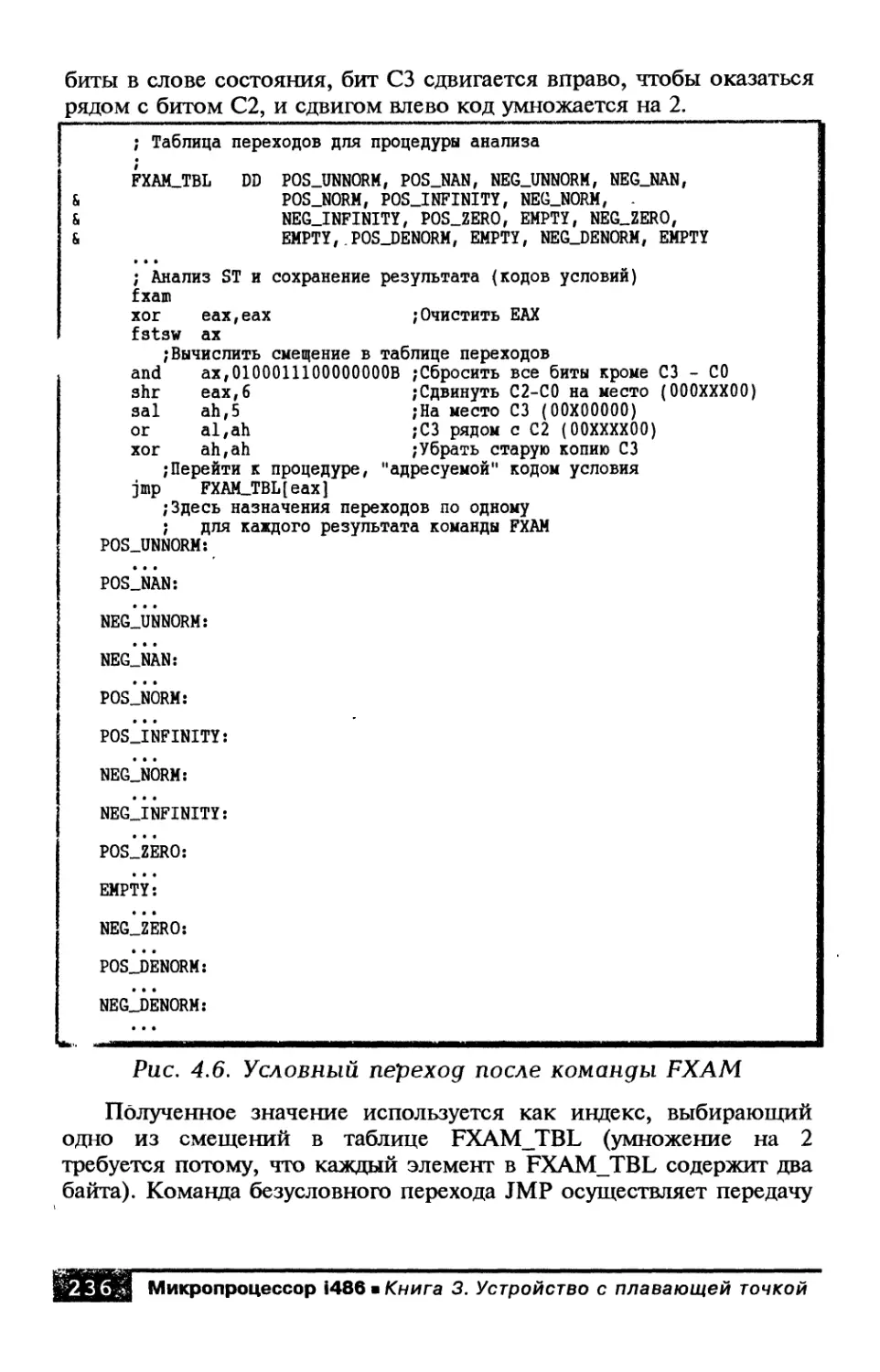

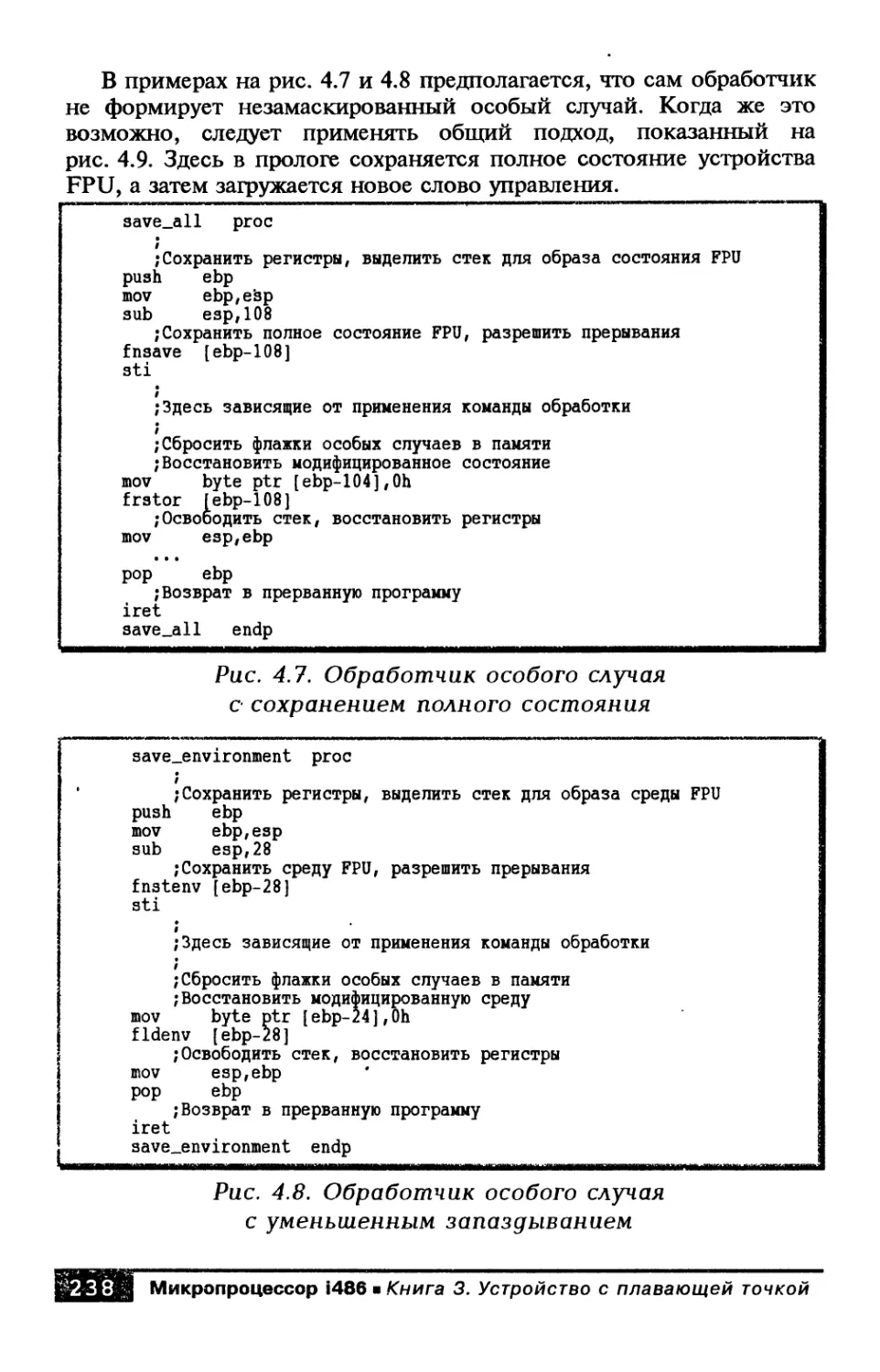

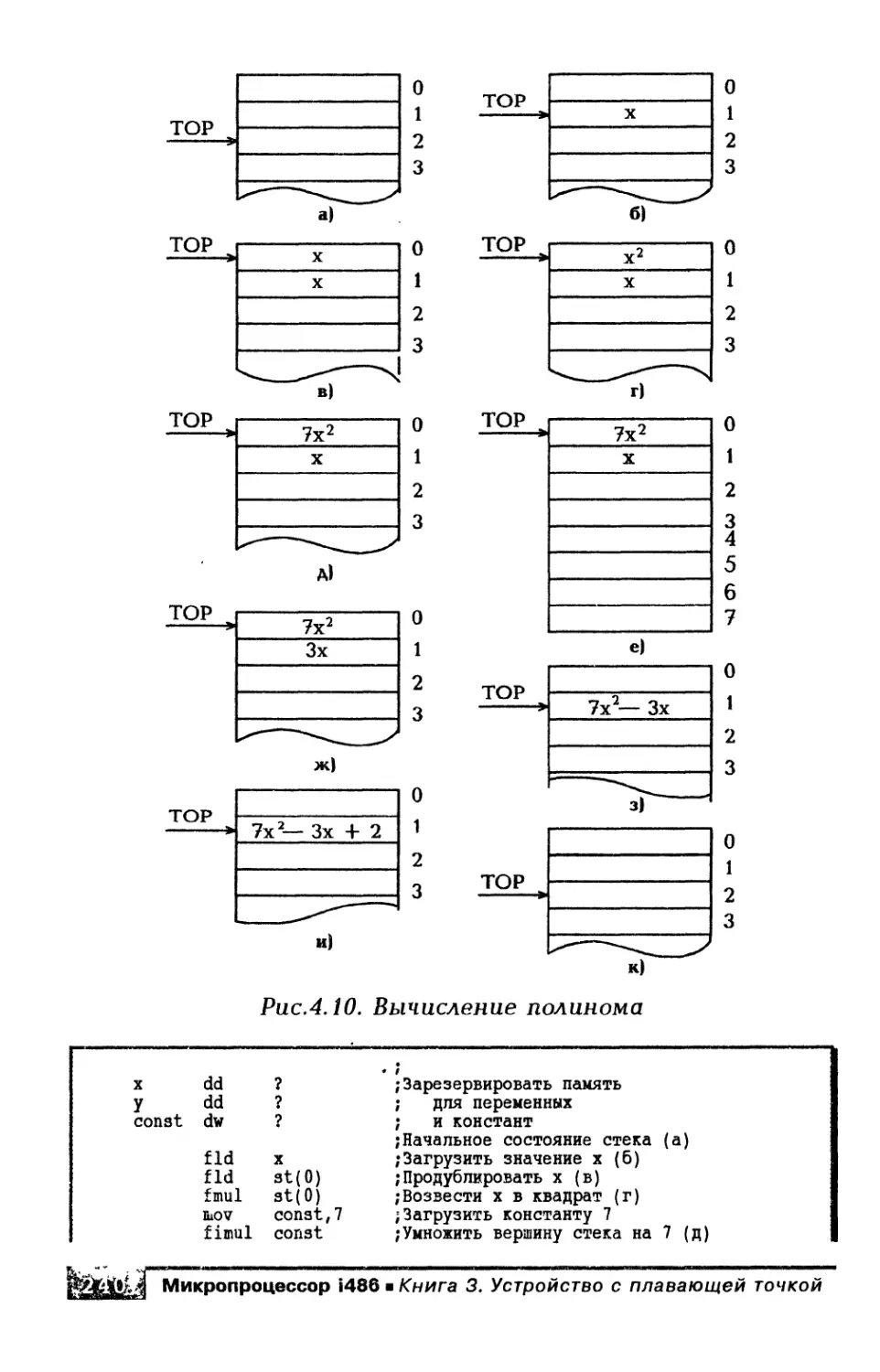

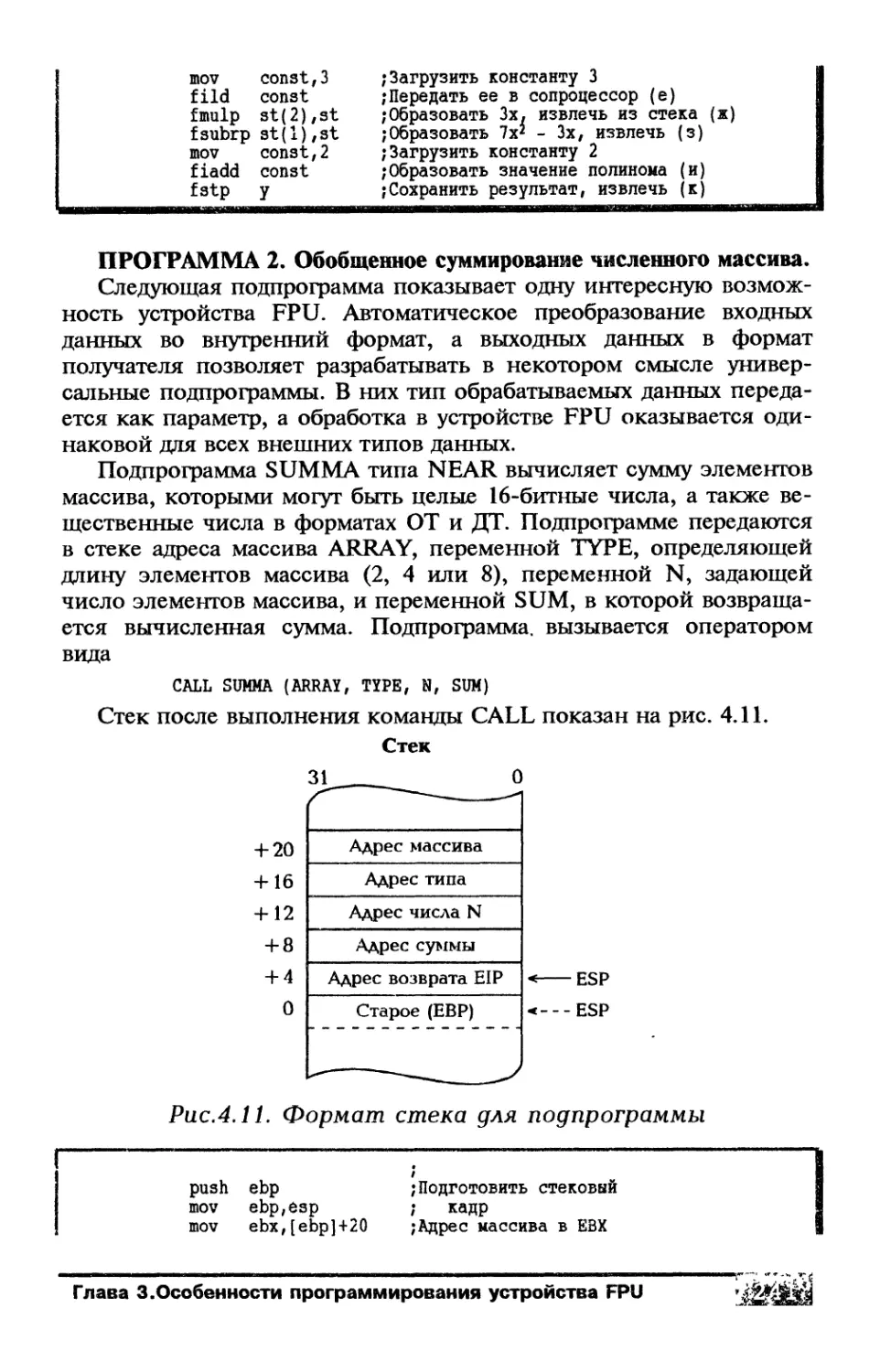

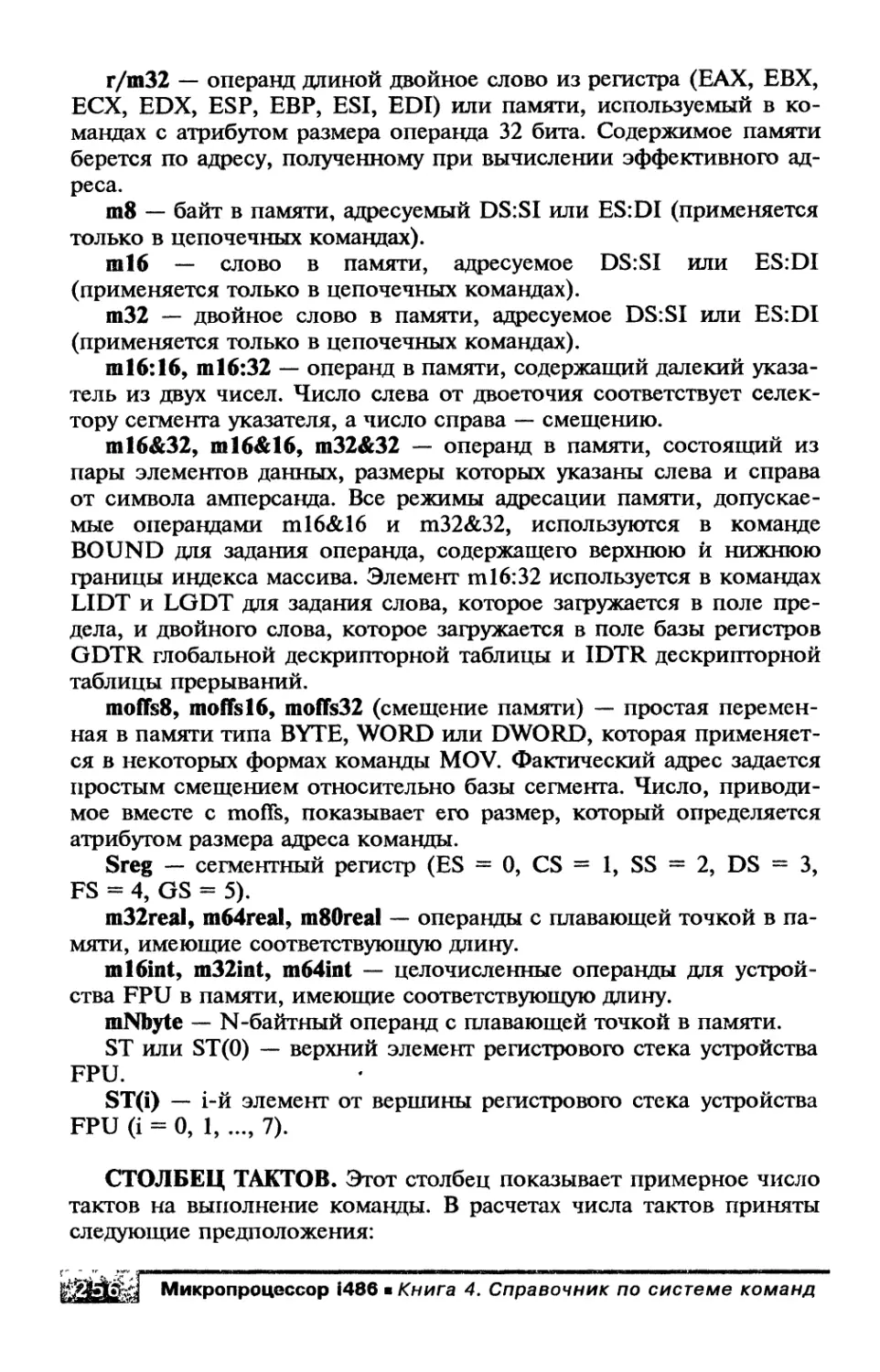

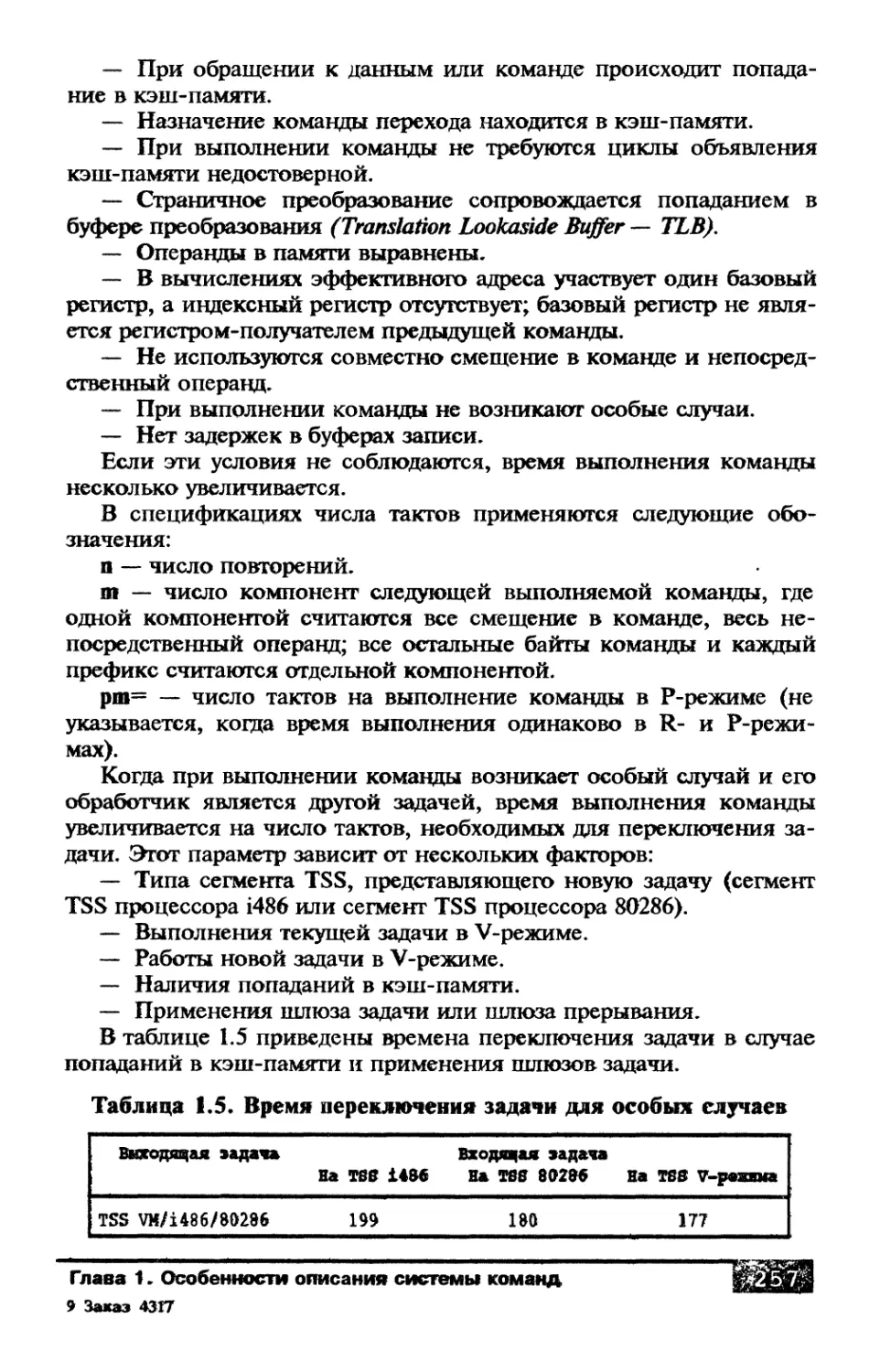

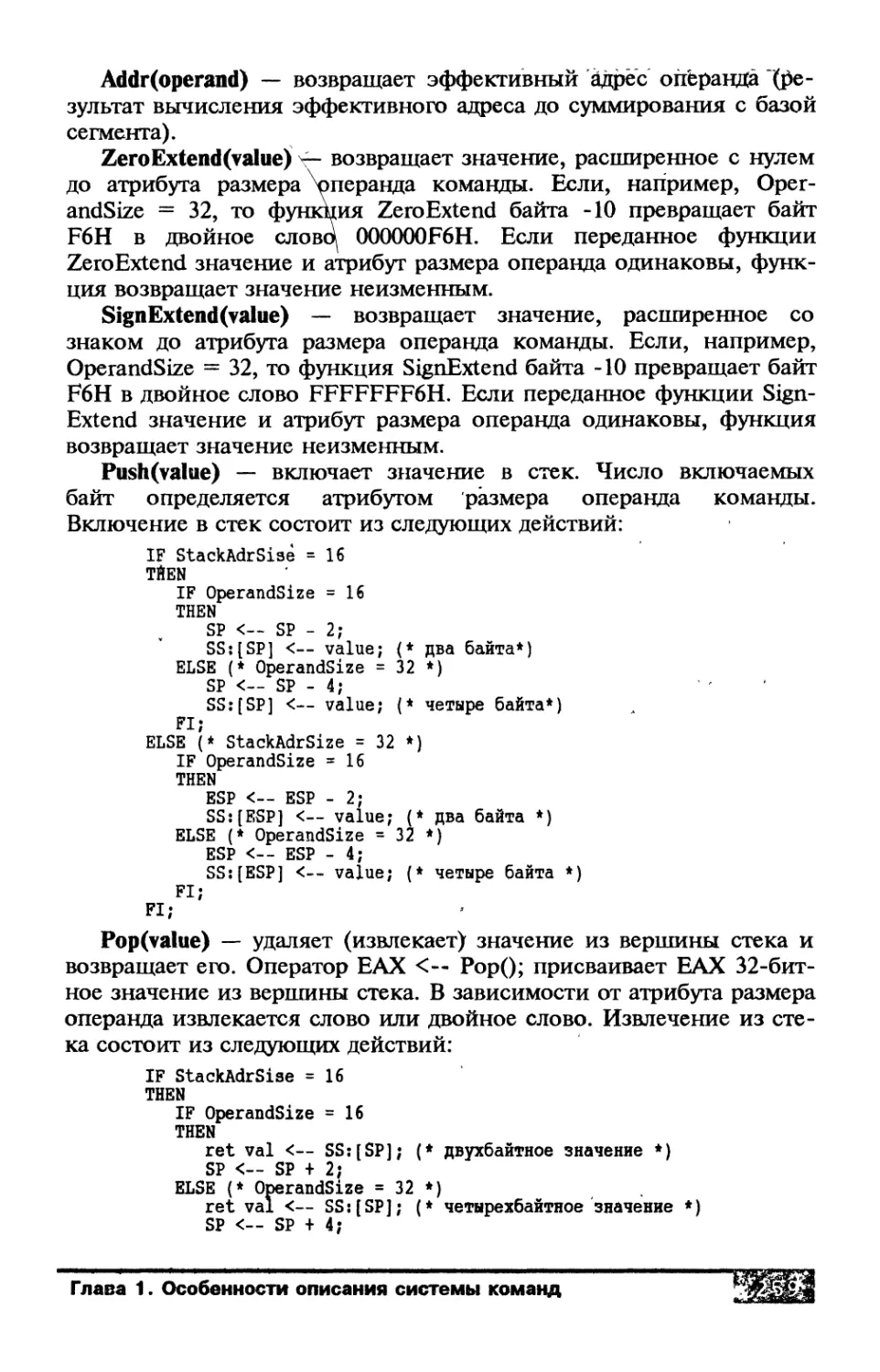

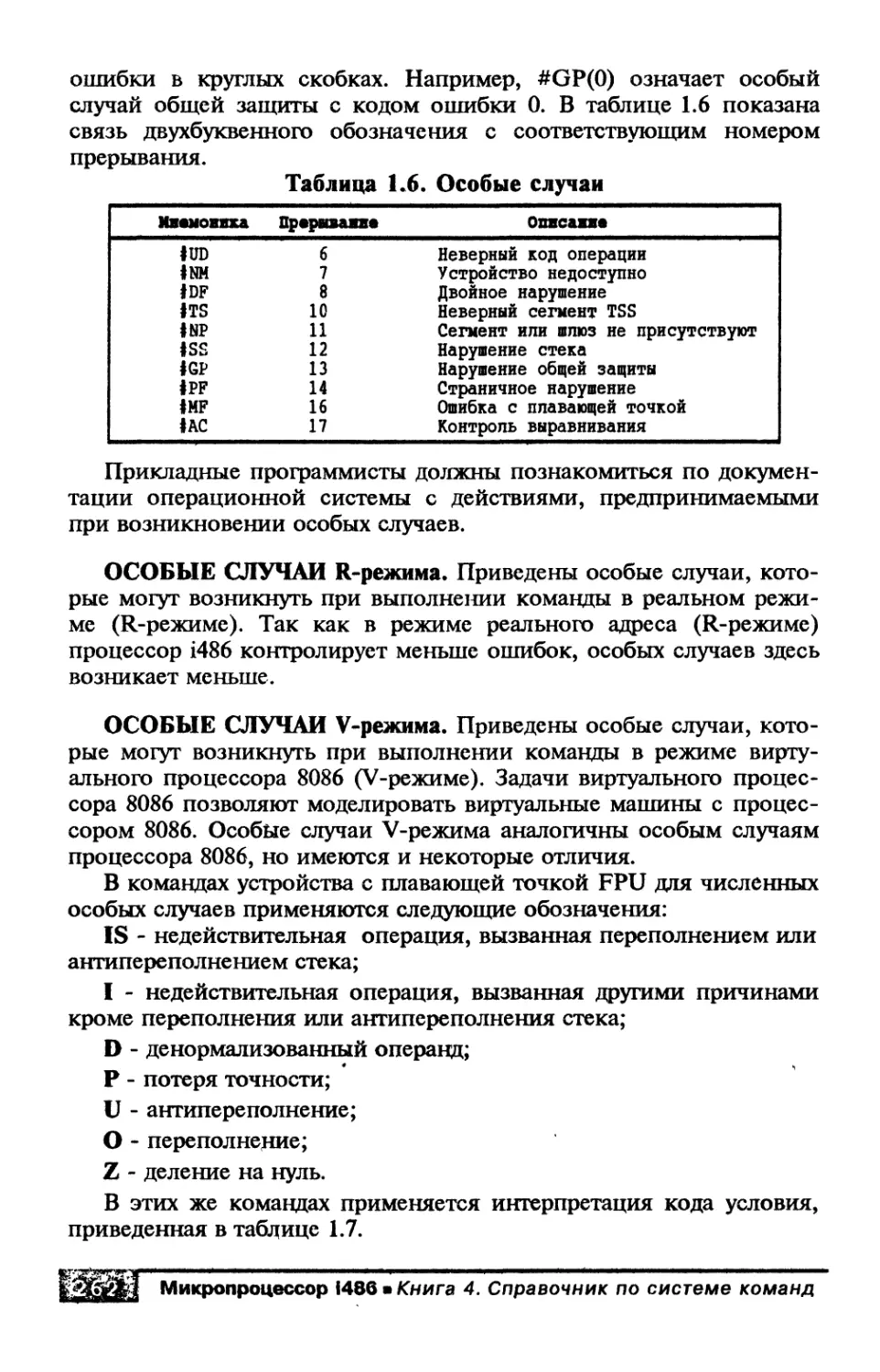

быстрой памяти. Наиболее часто используемые функции возлага-