Теги: компьютерные технологии специализированные и управляющие электронные вычислительные машины дискретного действия программирование комп

ISBN: 5-318-00559-4

Год: 2001

Текст

анатомия^

ПК ♦

Процессоры

Pentium 4

Athlon и Duron

СЕРИЯ

анатомия

пк<

^ППТЕР’

анатомия ч

пке

Пр©це«©ры

РегоШот 4

ЖЫ©и ю ®йрэй

Михаил Гук

Виктор Юров

Санкт-Петербург • Москва • Харьков • Минск

ПИТЕР*

2001

Михаил Гук, Виктор Юров

Процессоры Pentium 4, Athlon и Duron

Главный редактор

Заведующий редакцией

Литературный редактор

Художник

Иллюстрации

Корректор

Верстка

Е. Строганова

И. Корнеев

А. Жданов

Н. Биржаков

М. Жданова

В. Листова

Р. Гришанов

ББК 32.973.23

УДК 681.325.5

Гук М., Юров В.

Г93 Процессоры Pentium 4, Athlon и Duron. — СПб.: Питер, 2001. — 512 с.: ил.

ISBN 5-318-00559-4

Книга посвящена архитектуре, системе команд, интерфейсам и функционированию современных

процессоров семейства х86 как фирмы Intel, так и совместимых с ними изделий конкурирующих фирм.

Подробно рассмотрена архитектура 32-разрядных процессоров, со всеми ее расширениями. В книге име-

ется объяснение многих системных функций реального и защищенного режимов, которые не рассмат-

риваются в большинстве распространенных литературных источников. Приводится описание всех команд

микропроцессоров Pentium 4 и Athlon (и всех младших моделей). Уделено внимание применению процес-

соров в персональных компьютерах, совместимости с программным обеспечением, особенностям много-

процессорных систем. Материал иллюстрирован временными диаграммами, блок-схемами и справочными

таблицами, необходимыми разработчикам как программных, так и аппаратных средств. Книга предназ-

начена для широкого круга читателей, ее можно рассматривать и как учебное пособие для студентов,

углубленно изучающих вычислительную технику, и как справочник прикладного и системного програм-

миста.

© М. Гук, В. Юров, 2001

© Издательский дом «Питер», 2001

Все права защищены. Никакая часть данной книги не может быть воспроизведена в какой бы то ни было

форме без письменного разрешения владельцев авторских прав.

Информация, содержащаяся в данной книге, получена из источников, рассматриваемых издательством как

надежные. Тем не менее, имея в виду возможные человеческие или технические ошибки, издательство не

может гарантировать абсолютную точность и полноту приводимых сведений и не несет ответственность за

возможные ошибки, связанные с использованием книги.

ISBN 5-318-00559-4

ЗАО «Питер Бук», 196105, Санкт-Петербург, Благодатная ул., д. 67.

Лицензия ИД № 01940 от 05.06.00.

Налоговая льгота — общероссийский классификатор продукции ОК 005-93, том 2; 95 3000 — книги и брошюры.

Подписано к печати 26.09.01. Формат 70x100/16. Усл. п. л. 41,28. Тираж 5000. Заказ

Отпечатано с готовых диапозитивов в ФГУП ордена Трудового Красного Знамени «Техническая книга»

Министерства РФ по делам печати, телерадиовещания и средств массовых коммуникаций

198005, Санкт-Петербург, Измайловский пр., 29

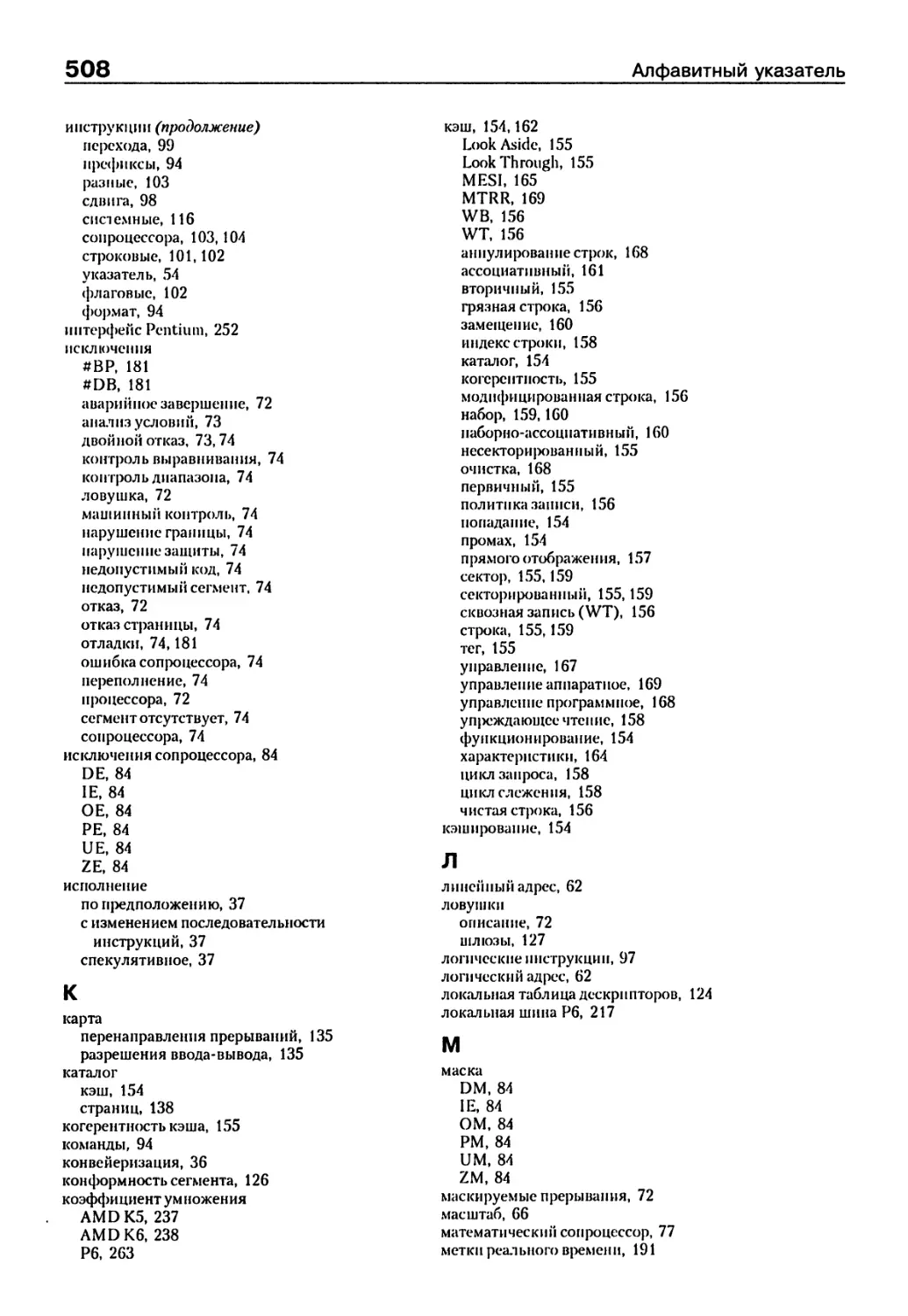

Краткое содержание

Предисловие...........................................18

1. Введение..........................................21

2. Программная модель 32-разрядных процессоров.......47

3. Математический сопроцессор, блоки ММХ и ХММ.......76

4. Система команд....................................94

5. Защищенный режим...............•.................119

6. Кэширование памяти...............................154

7. Особые режимы работы процессоров.................174

8. Совместимость, различия и идентификация процессоров.196

9. Процессоры фирмы Intel...........................216

10. Процессоры AMD и других фирм.....................236

11. Применение процессоров в PC......................250

Приложение 1. Команды процессоров х86................280

Приложение 2. Список сокращений, включая имена регистров,

структур данных и флагов.............................491

Алфавитный указатель.................................500

Содержание

Предисловие.....................................................18

Интернет................................................................19

От издательства.................................................20

1. Введение....................................................21

1.1. Что делает процессор в компьютере?.........................21

1.2. Краткий исторический экскурс...............................32

1.3. Архитектура, микроархитектура и поколения процессоров......35

1.4. NetBurst — микроархитектура процессора Pentium 4...........42

2. Программная модель 32-разрядных процессоров .... 47

2.1. Типы данных................................................48

2.2. Регистры процессора........................................52

2.3. Организация памяти.........................................61

2.3.1. Модель памяти в реальном режиме......................63

2.3.2. Режимы адресации.....................................65

2.3.3. Стек.................................................67

2.3.4. Плоская и многосегментная модели памяти и «нереальный» режим.69

2.4. Ввод-вывод.................................................70

2.5. Прерывания и исключения....................................71

3. Математический сопроцессор, блоки ММХ и ХММ ... 76

3.1. Математический сопроцессор х87.............................77

3.1.1. Форматы данных FPU...................................77

3.1.2. Программная модель FPU...............................79

3.1.3. Исключения сопроцессора..............................84

3.1.4. Интерфейс сопроцессора...............................85

3.2. Технология ММХ.............................................86

3.3. Расширение SSE и SSE2 — блок ХММ...........................89

3.4. Расширение 3DNow!..........................................92

4. Система команд..............................................94

5. Защищенный режим ......................................... 119

5.1. Основные понятия защищенного режима.......................119

5.2. Дескрипторы и таблицы.....................................123

Содержание

7

5.3. Привилегии................................................128

5.4. Защита....................................................130

5.5. Переключение задач........................................132

5.6. Страничное управление памятью.............................136

5.7. Виртуализация прерываний..................................145

5.8. Режим виртуального процессора 8086 (V86 и EV86)...........147

5.9. Переключение между реальным и защищенным режимами.........151

6. Кэширование памяти........................................ 154

6.1. Принципы кэширования......................................154

6.1.1. Кэш прямого отображения.............................157

6.1.2. Наборно-ассоциативный кэш...........................160

6.1.3. Ассоциативный кэш...................................161

6.1.4. Пакетный режим передачи данных......................161

6.2. Кэширование в современных процессорах.....................162

6.3. Управление кэшированием...................................167

7. Особые режимы работы процессоров.......................... 174

7.1. Начальный сброс и тестирование............................174

7.2. Обновление микрокода......................................178

7.3. Программные средства отладки..............................180

7.4. Режим зондовой отладки....................................184

7.5. Режим системного управления SMM...........................185

7.6. Метки реального времени и мониторинг производительности...191

7.7. Синхронизация и управление энергопотреблением.............193

8. Совместимость, различия и идентификация

процессоров................................................... 196

8.1. Совместимость процессоров.................................196

8.2. Идентификация процессоров.................................200

8.2.1. Инструкция CPUID....................................205

8.3. Основные характеристики процессоров.......................212

9. Процессоры фирмы Intel.................................... 216

9.1. Процессоры Р6.............................................216

9.1.1. Конструктивы процессоров шестого поколения..........224

9.2. Процессор Pentium 4.......................................226

10. Процессоры AMD и других фирм............................ 236

10.1. Процессоры фирмы AMD для сокетов 5 и 7...................236

10.2. Процессоры Athlon и Duron фирмы AMD......................239

10.3. Процессоры фирм Cyrix, VIA, IBM и другие.................247

11. Применение процессоров в PC............................. 250

11.1. Установка и замена процессоров — сокеты и слоты..........250

11.1.1. Выбор частоты и напряжения питания.................261

8

Содержание

11.2. Синхронизация и разгон......................................269

11.3. Охлаждение процессоров......................................273

11.4. Мультипроцессорные и избыточные системы.....................276

11.4.1. Симметричные мультипроцессорные системы...............276

11.4.2. Системы с избыточным контролем функциональности.......279

Приложение 1. Команды процессоров х86 ............... 280

П1.1. Целочисленные команды.......................................281

ААА...........................................................281

AAD...........................................................282

ААМ...........................................................282

AAS...........................................................282

ADC приемник, источник........................................282

ADD приемник, источник........................................283

AND приемник, источник........................................283

ARPL приемник, источник.......................................284

BOUND индекс, границы массива.................................284

BSF результат, источник.......................................285

BSR результат, источник.......................................285

BSWAP источник................................................286

ВТ источник, индекс...........................................286

ВТС источник, индекс..........................................286

BTR источник, индекс..........................................287

BTS источник, индекс..........................................287

CALL цель.....................................................287

CBW...........................................................289

CDQ...........................................................289

CLC......................................................... 289

CLD...........................................................289

CLI...........................................................289

CLTS..........................................................289

СМС...........................................................290

CMOVcc приемник, источник.....................................290

СМР операнд!, операнд2........................................291

CMPS приемник, источник.......................................292

CMPXCHG приемник, источник....................................292

CMPXCHG8B приемник............................................293

CPUID.........................................................293

CWD...........................................................300

CWDE..........................................................300

DAA...........................................................300

DAS...........................................................300

DEC операнд...................................................300

DIV делитель..................................................301

ENTER размер_кадра, лексический_уровень.......................301

HLT...........................................................302

IDIV делитель.................................................302

Содержание

9

IMUL множитель-1............................................302

IN аккумулятор, ном_порта...................................303

INC операнд.................................................304

INS приемник, порт..........................................304

INT номер_прерывания, INTO..................................305

INVD........................................................306

INVLPG адрес................................................306

IRET........................................................306

Jcc метка...................................................307

JCXZ........................................................309

}МРцель.....................................................309

LAHF........................................................310

LAR приемник, источник......................................310

LDS приемник, источник, LES приемник, источник, LFS приемник,

источник, LGS приемник, источник, LSS приемник, источник....311

LEA приемник, источник......................................312

LEAVE.......................................................312

LGDT источник...............................................312

LIDT источник...............................................313

LLDT источник...............................................313

LMSW источник...............................................313

LOCK........................................................313

LODS источник...............................................314

LOOP метка..................................................314

LOOPE..................................................... 315

LSL приемник, источник......................................315

LTR источник................................................316

MOV приемник, источник......................................316

MOVS приемник, источник.....................................317

MOVSX приемник, источник....................................318

MOVZX приемник, источник....................................318

MUL множитель_1.............................................319

NEG приемник................................................319

NOP.........................................................319

NOT приемник................................................320

OR приемник, маска..........................................320

OUT ном_порта, аккумулятор..................................320

OUTS порт, источник.........................................321

POP приемник................................................321

POPA/POPAD..................................................322

POPF........................................................322

PREFETCHT0 источник.........................................323

PUSH источник...............................................323

PUSH А......................................................324

10

Содержание

PUSHF.........................................................324

RCL операнд, количсство_сдвигов...............................324

RCR операнд, количество_сдвигов...............................325

RDMSR.........................................................325

RDPMC.........................................................326

RDTSC.........................................................326

REP...........................................................326

RET...........................................................327

ROL операнд, количество_сдвигов...............................328

ROR операнд, количество_сдвигов...............................329

RSM...........................................................329

SAHF..........................................................330

SAL операнд, кол ичество_сд вигов.............................330

SAR операнд, количество_сдвигов...............................330

SBB операнд_1, операпд_2......................................331

SCAS приемник.................................................331

SETcc операнд.................................................332

SFENCE........................................................333

SGDT источник.................................................333

SIDT источник.................................................333

SHL операнд, количество_сдвигов...............................334

SHLD приемник, источник, количество_сдвигов...................334

SHR операнд, кол-во_сдвигов...................................335

SHRD приемник, источник, количество сдвигов...................335

SLDT приемник.................................................336

SMSW приемник.................................................336

STC...........................................................336

STD...........................................................336

STI...........................................................336

STOS приемник.................................................337

STR приемник..................................................337

SUB операнд_1, операнд_2......................................337

SYSENTER......................................................338

SYSEXIT приемник, источник....................................339

TEST приемник, источник.......................................340

UD2..........................:................................340

VERR селектор.................................................340

VERW селектор.................................................341

WAIT..........................................................341

WBINVD........................................................341

WRMSR.........................................................341

XADD приемник, источник.......................................342

XCHG операнд_1, операнд_2.....................................342

XLAT адрес_таблицы_байт.......................................343

XOR приемник, источник...................................... 343

П1.2. Команды сопроцессора.........................................344

F2XM1.........................................................344

Содержание 11

FABS......................................................344

FADD......................................................344

FADDP.....................................................345

FBLD источник.............................................345

FBSTP приемник............................................346

FCHS......................................................346

FCLEX.....................................................346

FCMOVcc приемник, источник................................346

FCOM......................................................347

FCOMI операнд_1, операнд_2................................348

FCOMIP операнд_1, операпд_2...............................349

FCOMP.....................................................349

FCOMPP....................................................349

FCOS......................................................349

FDECSTP...................................................350

FDIV......................................................350

FDIVP.....................................................351

FDIVR.....................................................351

FDIVRP....................................................352

FFREE регистр_сопроцессора................................352

FIADD слагаемое_1.........................................352

FICOM операнд_2...........................................353

FICOMP операнд............................................353

FIDIV источник............................................353

FIDIVR делимое............................................354

FILD источник.............................................354

FINCSTP...................................................354

FIMUL сомпожитель_2.......................................354

FINIT.....................................................355

FIST приемник.............................................355

FISTP приемник............................................356

FISUB вычитаемое..........................................356

FISUBR уменьшаемое........................................356

FLD источник..............................................357

FLDCW источник............................................357

FLDENV источник...........................................357

FLD1......................................................358

FLDL2T....................................................359

FLDL2E....................................................359

FLDLG2....................................................359

FLDLN2....................................................359

FLDPI.....................................................360

FLDZ......................................................360

FMUL......................................................360

FMULP.....................................................361

FNCLEX....................................................361

FNINIT....................................................361

12

Содержание

FNOP...................................................361

FNSAVE приемник........................................362

FNSTCW приемник........................................363

FNSTENV источник.......................................363

FNSTSW приемник........................................364

FPATAN.................................................364

FPREM..................................................365

FPREM1.................................................365

FPTAN..................................................366

FRNDINT................................................366

FRSTOR источник........................................367

FSAVE приемник.........................................367

FSCALE.................................................368

FSIN...................................................368

FSINCOS................................................368

FSQRT..................................................368

FST приемник...........................................368

FSTCW приемник.........................................369

FSTENV приемник........................................369

FSTP приемник..........................................370

FSTSW приемник.........................................370

FSUB...................................................370

FSUBP..................................................371

FSUBR..................................................371

FSUBRP.................................................372

FTST...................................................372

FUCOM..................................................373

FUCOMI значение_1, значепие_2..........................373

FUCOMIP значение!, зпачепие_2..........................374

FUCOMP.................................................374

FUCOMPP................................................375

FWAIT..................................................375

FXAM...................................................375

FXCH...................................................375

FXTRACT................................................376

FYL2X..................................................376

FYL2XP1................................................376

П1.3. Команды блока MMX............’.......................377

EMMS...................................................377

MASKMOVQ источник, маска...............................377

MOVD приемник, источник................................377

MOVNTQ. приемник, источник.............................378

MOVQ приемник, источник................................378

PACKSSWB приемник, источник............................379

PACKUSWB приемник, источник............................379

PADDB приемник, источник...............................380

Содержание

13

PADDSB приемник, источник.......................................380

PADDUSB приемник, источник......................................381

PAND приемник, источник.........................................382

PANDN приемник, источник........................................382

PAVGB приемник, источник........................................382

PCMPEQB приемник, источник......................................382

PCMPGTB приемник, источник......................................383

PEXTRW приемник, источник, маска................................384

PINSRW приемник, источник, маска................................384

PMADDWD приемник, источник......................................384

PMAXSW приемник, источник.......................................385

PMAXUB приемник, источник.......................................385

PMINSW приемник, источник.......................................386

PMINUB приемник, источник.......................................386

PMOVMSKB приемник, источник.....................................386

PMULHUW приемник, источник......................................387

PMULHW приемник, источник.........................:.............387

PMULLW приемник, источник.......................................388

POR приемник, источник..........................................389

PSADBW приемник, источник.......................................389

PSHUFW приемник, источник, маска................................389

PSLLW приемник, источник........................................390

PSRAW приемник, источник........................................391

PSRLW приемник, источник........................................392

PSUBB приемник, источник........................................392

PSUBSB приемник, источник.......................................393

PSUBUSB приемник, источник......................................393

PUNPCKHBW приемник, источник....................................394

PUNPCKLBW приемник, источник....................................395

PXOR приемник, источник.........................................396

П1.4. Команды блока ХММ............................................396

ADDPS приемник, источник........................................396

ADDSS приемник, источник........................................396

ANDNPS приемник, источник.......................................397

ANDPS приемник, источник........................................397

CMPPS приемник, источник, условие...............................397

CMPSS приемник, источник, условие...............................399

COMISS приемник, источник.......................................399

CVTPI2PS приемник, источник.....................................400

CVTPS2PI приемник, источник.....................................400

CVTSI2SS приемник, источник.....................................401

CVTSS2SI приемник, источник.....................................401

CVTTPS2PI приемник, источник....................................402

CVTTSS2SI приемник, источник....................................403

DIVPS приемник, источник........................................403

DIVSS приемник, источник........................................404

FXRSTOR источник................................................404

14

Содержание

FXSAVE приемник...................................................405

LDMXCSR источник..................................................405

MAXPS приемник, источник..........................................405

MAXSS приемник, источник..........................................406

MINPS приемник, источник..........................................406

MINSS приемник, источник..........................................406

MOVAPS приемник, источник.........................................407

MOVHLPS приемник, источник........................................407

MOVHPS приемник, источник.........................................407

MOVLHPS приемник, источник........................................408

MOVLPS приемник, источник.........................................408

MOVMSKPS приемник, источник.......................................409

MOVNTPS приемник, источник........................................409

MOVSS приемник, источник..........................................409

MOVUPS приемник, источник.........................................410

MULPS приемник, источник..........................................410

MULSS приемник, источник..........................................411

ORPS приемник, источник...........................................411

RCPPS приемник, источник..........................................412

RCPSS приемник, источник..........................................412

RSQRTPS приемник, источник........................................412

RSQRTSS приемник, источник........................................413

SHUFPS приемник, источник, маска..................................413

SQRTPS приемник, источник.........................................414

SQRTSS приемник, источник.........................................415

STMXCSR приемник..................................................415

SUBPS приемник, источник..........................................415

SUBSS приемник, источник..........................................415

UCOMISS приемник, источник........................................416

UNPCKHPS приемник, источник.......................................416

UNPCKLPS приемник, источник.......................................417

XORPS приемник, источник..........................................417

П1.5. Команды блока ХММ (SSE2)........................................417

ADDPD приемник, источник..........................................417

ADDSD приемник, источник..........................................418

ANDPD приемник, источник..........................................418

ANDNPD приемник, источник.........................................418

CLFLUSH адрес_байта...............................................419

CMPPD приемник, источник, условие.................................419

CMPSD приемник, источник, условие.................................420

COMISD приемник, источник, условие................................420

CVTDQ2PD приемник, источник.......................................421

CVTDQ2PS приемник, источник.......................................421

CVTPD2DQ приемник, источник.......................................422

CVTPD2PI приемник, источник.......................................423

CVTPD2PS приемник, источник.......................................423

CVTPI2PD приемник, источник.......................................424

Содержание 15

CVTPS2DQ приемник, источник................................425

CVTPS2PD приемник, источник................................425

CVTSD2SI приемник, источник................................426

CVTSD2SS приемник, источник................................427

CVTSI2SD приемник, источник................................427

CVTSS2SD приемник, источник...j............................428

CVTTPD2PI приемник, источник............................. 429

CVTTPD2DQ приемник, источник...............................429

CVTTPS2DQ приемник, источник...............................430

CVTTSD2SI приемник, источник...............................431

DIVPD приемник, источник...................................431

DIVSD приемник, источник...................................432

LFENCE адрес_байта.........................................432

MASKMOVDQU источник, маска.................................432

MAXPD приемник, источник...................................433

MAXSD приемник, источник...................................433

MFENCE.....................................................434

MINPD приемник, источник...................................434

MINSD приемник, источник...................................434

MOVAPD приемник, источник..................................435

MOVD приемник, источник....................................435

MOVDQA приемник, источник..................................436

MOVDQU приемник, источник..................................436

MOVDQ2Q приемник, источник.................................436

MOVHPD приемник, источник..................................436

MOVLPD приемник, источник..................................437

MOVMSKPD приемник, источник................................437

MOVNTDQ приемник, источник.................................438

MOVNTI приемник, источник..................................438

MOVNTPD приемник, источник.................................438

MOVQ приемник, источник....................................438

MOVQ2DQ приемник, источник.................................439

MOVSD приемник, источник...................................439

MOVUPD приемник, источник..................................439

MULPD приемник, источник...................................440

MULSD приемник, источник...................................440

ORPD приемник, источник....................................440

PACKSSWB/PACKSSDW приемник, источник.......................441

PACKUSWB приемник, источник................................442

PADDB/PADDW/PADDD приемник, источник.......................443

PADDQ приемник, источник...................................443

PADDSB/PADDSW приемник, источник...........................444

PADDUSB/PADDUSW приемник, источник.........................444

PAND приемник, источник....................................445

PANDN приемник, источник...................................445

PAUSE......................................................445

PAVGB/PAVGW приемник, источник.............................446

16

Содержание

PCMPEQB/PCMPEQW/PCMPEQD приемник, источник................446

PCMPGTB/PCMPGTW/PCMPGTD приемник, источник................447

PEXTRW приемник, источник, маска..........................447

PINSRW приемник, источник, маска..........................448

PMADDWD приемник, источник................................448

PMAXSW приемник, источник.................................448

PMAXUB приемник, источник.................................449

PMINSW приемник, источник.................................449

PMINUB приемник, источник.................................449

PMOVMSKB приемник, источник...............................450

PMULHUW приемник, источник................................450

PMULHW приемник, источник.................................451

PMULLW приемник, источник.................................451

PMULUDQ приемник, источник................................452

POR приемник, источник....................................452

PSADBW приемник, источник.................................453

PSHUFD приемник, источник, маска..........................454

PSHUFHW приемник, источник, маска.........................455

PSHUFLW приемник, источник, маска.........................456

PSLLDQ приемник, количество_сдвигов.......................458

PSLLW/PSLLD/PSLLQ приемник, количество_сдвигов............458

PSRAW/PSRAD приемник, количество_сдвигов..................459

PSRLDQ приемник, количество сдвигов.......................459

PSRLW/PSRLD/PSRLQ приемник, количество_сдвигов............460

PSUBB/PSUBW/PSUBD приемник, источник......................460

PSUBQ приемник, источник..................................461

PSUBSB/PSUBSW приемник, источник..........................461

PSUBUSB/PSUBUSW приемник, источник........................462

PUNPCKHBW/PUNPCKHWD/PUNPCKHDQ/PUNPCKHQDQ

приемник, источник........................................462

PUNPCKLBW/PUNPCKLWD/PUNPCKLDQ/PUNPCKLQDQ

приемник, источник........................................463

PXOR приемник, источник...................................464

SHUFPD приемник, источник, маска..........................465

SQRTPD приемник, источник.................................465

SQRTSD приемник, источник.................................465

SUBPD приемник, источник..................................466

SUBSD приемник, источник..................................466

UCOMISD приемник, источник, условие.......................466

UNPCKHPD приемник, источник...............................467

UNPCKLPD приемник, источник...............................467

XORPD приемник, источник..................................467

П1.6. Команды 3DNow!™........................................468

FEMMS.....................................................469

PAVGUSB приемник, источник................................469

PF2ID приемник, источник..................................470

PFACC приемник, источник..................................470

Содержание

17

PFADD приемник, источник...........................................470

PFCMPEQ приемник, источник.........................................470

PFCMPGE приемник, источник.........................................471

PFCMPGT приемник, источник.........................................471

PFMAX приемник, источник...........................................471

PFMIN приемник, источник...........................................471

PFMUL приемник, источник...........................................472

PFRCP приемник, источник...........................................472

PFRCPIT1 приемник, источник........................................472

PFRCPIT2 приемник, источник........................................473

PFRSQIT1 приемник, источник........................................473

PFRSQRT приемник, источник.........................................473

PFSUB приемник, источник...........................................474

PFSUBR приемник, источник..........................................474

PI2FD приемник, источник...........................................474

PMULHRW приемник, источник.........................................475

PREFETCH источник..................................................475

П1.7. Расширение набора команд 3DNow!™ и ММХ™

для микропроцессора AMD Athlon™...................................475

PF2IW приемник, источник...........................................476

PFNACC приемник, источник..........................................477

PFPNACC приемник, источник.........................................477

PI2FW приемник, источник...........................................477

PSWAPD приемник, источник..........................................478

П1.8. Исключения.......................................................478

П1.8.1. Общие исключения (для всех режимов) — вектор прерывания 13.478

П1.8.2. Исключения защищенного режима (РМ).........................479

П 1.8.3. Исключения реального режима (RM)..........................485

П1.8.4. Исключения режима виртуального 8086 (VM)...................487

П1.8.5. Исключения с плавающей точкой (NE) — вектор прерывания 16..490

Приложение 2. Список сокращений, включая имена

регистров, структур данных и флагов................................... 491

Алфавитный указатель.................................................. 500

Предисловие

Эта книга стала очередной в серии книг о процессорах: «Процессоры Intel: от 8086

до Pentium II» (1997 г.), «Процессоры Pentium II, Pentium Pro и просто Pentium»

(1999 г.), «Процессоры Pentium III, Athlon и другие» (2000 г.). За «отчетный» год

для персональных компьютеров получили массовое распространение процессоры

Pentium III, Athlon и Duron и вышел очередной процессор Pentium 4. Принципи-

альных архитектурных расширений он не внес — появились только новые инст-

рукции, в основном для блоков регистров ХММ и ММХ. Однако в микроархитекту-

ре фирма Intel оторвалась от своей «рабочей лошадки» Р6, прослужившей с 1995 г.,

выдержавшей почти 10-кратное повышение тактовой частоты и обросшей всячес-

кими расширениями. Все эти новшества нашли отражение в новой книге. Книга

начинается с вводной «экскурсии» по компьютеру с объяснением задач и возмож-

ностей процессора, а завершается полным описанием всех команд, написанным

Виктором Юровым (см. приложение 1). Процессоры пятого поколения и ниже из

книги исключены (остались лишь упоминания о том, чем они не располагали),

описание шестого поколения сокращено в пользу «бенефициантов». При необхо-

димости сведения о них можно почерпнуть в [10,11]. Информация о процессорах

дана по состоянию на лето 2001 года — сюда попали процессоры Pentium 4, Athlon,

Duron, Pentium III для сокета 370 и описывается отличие этого сокета от сокета

для Celeron. Новшества архитектурных расширений — SSE2, ХММ, «приключе-

ния» серийного номера, управление кэшируемостью через РАТ и кое-что еще —

также можно найти в этой книге. Дополнено описание идентификации процессо-

ров, особенно для процессоров AMD. Как всегда, исправлены некоторые неточно-

сти, обнаруженные при пересмотре ранее написанного текста. Некоторые ошиб-

ки были обнаружены читателями предыдущих книг, за что им большое спасибо.

Процессоры в книге рассматриваются больше с точки зрения программиста,

и прикладного, и системного. Книга ориентирована на подготовленных читателей,

которые прекрасно знают, что такое биты и байты, низкие и высокие логические

уровни и не путают вольты, ватты и амперы. Книга поможет разобраться в режи-

мах работы современных процессоров — реальном, защищенном, виртуальном и

режиме системного управления. Эти знания полезны не только разработчикам

аппаратуры и программного обеспечения, но и любознательным пользователям

PC. Вы узнаете, что делается «за кулисами» операционной системы, откуда берет-

ся сообщение «Нарушение общей защиты» и какие «недопустимые операции»

пыталось выполнить приложение, снятое операционной системой защищенного

режима. Конечно, все технические подробности и нюансы в одной книге изложить

Интернет

19

невозможно — это займет много места (книга станет толстой и дорогой), времени

(книга устареет до своего появления) и утомит тех многочисленных читателей,

которым эти сведения вряд ли понадобятся. Для читателей, более углубленно

интересующихся работой компьютера, можно посоветовать книгу М. Гука «Аппа-

ратные средства IBM PC. Энциклопедия», 2-е издание. В энциклопедии, конеч-

но же, информации по процессорам меньше, чем в данной книге, зато там есть

масса сведений о смежных предметах — системных платах, подсистеме памяти,

шинах и т. д.

Предыдущими книгами для изучения микропроцессоров пользуются студен-

ты ряда вузов, в том числе и «Политеха» (СПбГТУ), часть из которых проходят

подготовку в «базовом лагере» Михаила Гука — ЦНИИ робототехники и техни-

ческой кибернетики (http://www.rtc.neva.ru). Надеюсь, эта книга будет не менее

полезной.

Для удобства восприятия материала в книге принята система текстовых выделе-

ний. Курсивом выделены ключевые слова (например, первый раз встречающиеся

определения), а также названия состояний, в которых могут пребывать некоторые

объекты. В названиях электрических сигналов, например НИМ#, символ «#» ука-

зывает на инверсность (низкий уровень сигнала отвечает активному состоянию).

Названия инструкций (команд), регистров и бит имеют иной вид — например HALT

(инструкция), CRO.PE (бит РЕ регистра CR0). Исключения (особые случаи) обозна-

чаются, например, как #GP (общая защита). Список сокращенных названий регис-

тров, флагов и т. п. специфических категорий приведен в приложении 2.

Книга не могла бы появиться без мощной информационной поддержки, обеспе-

ченной коллективом создателей сети RUSNet (http://www.neva.ru) в ЦНИИ РТК.

Благодаря возможности работы по высокоскоростному каналу связи с Интерне-

том авторы не испытывали затруднений с получением PDF-документов мегабайт-

ных размеров.

Оперативную web-поддержку книги (дополнения, исправления и статьи по смеж-

ным темам) можно найти на сайте Михаила Гука по адресу http://www.neva.ru/

mgook. Свои замечания и пожелания присылайте по электронной почте на адрес

Mgook@stu.neva.ru.

Интернет

♦ Фирма Intel: http://www.intel.com, http://www.intel.ru (на русском языке).

♦ Фирма AMD: http://www.amd.com.

♦ Аппаратные средства компьютеров iXBT Hardware: http://ixbt.stack.net (на рус-

ском языке).

♦ Недокументированные свойства и ошибки процессоров х86: http://www.x86.org.

♦ Разгон процессоров: http://www.overclock.com.

♦ Применение процессоров, аппаратные средства PC: http://www.sysdoc.pair.com.

♦ Поддержка книг Михаила Гука, статьи: http://www.neva.ru/mgook.

20

Предисловие

От издательства

Ваши замечания, предложения, вопросы отправляйте по адресу электронной по-

чты comp@piter.com (издательство «Питер», компьютерная редакция).

Мы будем рады узнать ваше мнение!

Подробную информацию о наших книгах вы найдете на web-сайте издательства

http://www.piter.com.

1. Введение

1.1. Что делает процессор в компьютере?

Как известно, процессор является основным вычислительным блоком компьюте-

ра, в наибольшей степени определяющим его мощь (или немощь, нужное подчерк-

нуть). Процессор является устройством, исполняющим программу — последова-

тельность команд (инструкций), задуманную программистом и оформленную в

виде модуля программного кода: Чтобы понять, что делает процессор, рассмотрим

его в окружении системных компонентов IBM PC-совместимого компьютера.

Этой компьютерной архитектурой, естественно, не ограничивается сфера приме-

нения процессоров семейства х86, которым посвящена данная книга.

Всем известный IBM PC-совместимый компьютер представляет собой реализа-

цию так называемой фон-неймановской архитектуры вычислительных машин.

Эта архитектура была предложена Джорджем фон Нейманом еще в 1945 году и

имеет следующие основные признаки. Машина состоит из блокауправления, ариф-

метико-логического устройства (АЛУ), памяти и устройств ввода-вывода. В ней

реализуется концепция хранимой программы', программы и данные хранятся в од-

ной и той же памяти. Выполняемые действия определяются блоком управления

и АЛУ, которые вместе являются основой центрального процессора. Центральный

процессор выбирает и исполняет команды из памяти последовательно, адрес оче-

редной команды задается «счетчиком адреса» в блоке управления. Этот принцип

исполнения называется последовательной передачей управления. Данные, с ко-

торыми работает программа, могут включать переменные — именованные облас-

ти памяти, в которых сохраняются значения с целью дальнейшего использования

в программе. Фон-неймановская архитектура — не единственный вариант по-

строения ЭВМ, есть и другие, которые не соответствуют указанным принципам

(например, потоковые машины). Однако подавляющее большинство современных

компьютеров основано именно на этих принципах, включая и сложные многопро-

цессорные комплексы, которые можно рассматривать как объединение фон-ней-

мановских машин. Конечно же, за более чем полувековую историю ЭВМ класси-

ческая архитектура прошла длинный путь развития. Тем не менее ПК можно

разложить «по полочкам» следующим образом.

Центральный процессор (АЛУ с блоком управления) реализуется микропроцес-

сором семейства х86 — от 8086/88 до Pentium 4 и Athlon (и это не конец исто-

рии). При всей своей внутренней суперскалярности, суперконвейеризированнос-

ти и спекулятивности (см. п. 1.3), внешне процессор соблюдает вышеупомянутый

принцип последовательной передачи управления. Набор арифметических, логи-

22

1. Введение

ческих и прочих инструкций (см. главу 4) насчитывает несколько сотен, а для

потоковой обработки придуман принцип SIMD — множество комплектов данных,

обрабатываемых одной инструкцией (расширения MMX, 3DNow!, SSE). Процес-

сор имеет набор регистров (см. п. 2.2), часть которых доступна для хранения опе-

рандов, выполнения действий над ними и формирования адреса инструкций и

операндов в памяти. Другая часть регистров используется процессором для слу-

жебных (системных) целей, доступ к ним может быть ограничен (есть даже про-

граммно-невидимые регистры).

Память «расползлась» по многим компонентам. Оперативная память (ОЗУ) —

самый большой массив ячеек памяти со смежными адресами — реализуется, как

правило, на модулях (микросхемах) динамической памяти. Для повышения про-

изводительности обмена данными (включая и считывание команд) оперативная

память кэшируется сверхоперативной памятью (см. п. 6.1). Первый, а зачастую и

второй уровень кэширования территориально располагается в микропроцессоре.

Оперативная память вместе с кэшем всех уровней (теперь даже до трех) представ-

ляет собой единый массив памяти, непосредственно доступный процессору для

записи и чтения данных, а также считывания программного кода. Кроме опера-

тивной память включает также и постоянную (ПЗУ), из которой можно только

считывать команды и данные, и некоторые виды специальной памяти (например,

видеопамять графического адаптера). Вся эта память вместе с оперативной рас-

полагается в едином пространстве с линейной адресацией. В любом компьютере

обязательно есть постоянная память, в которой хранится программа начального

запуска компьютера и минимально необходимый набор сервисов (ROM BIOS).

Память дополняется устройствами хранения данных, например дисковыми. Эти

устройства предназначены для записи данных с целью последующего считывания

(возможно, и на другом компьютере). От рассмотренной выше памяти, называе-

мой также внутренней, устройства хранения отличаются тем, что процессор не

имеет непосредственного доступа к данным по линейному адресу. Доступ к дан-

ным на устройствах хранения выполняется с помощью специальных программ,

обращающихся к контроллерам этих устройств.

Устройства ввода-вывода (УВВ) служат для преобразования информации из

внутреннего представления в компьютере (биты и байты) в форму, доступную

окружающим, и обратно. Под окружающими понимаем как людей, так и другие

машины (например, технологическое оборудование, которым управляет компью-

тер). К устройствам ввода относятся клавиатура, мышь, джойстик, микрофон, ска-

нер, видеокамера, различные датчики; к устройствам вывода — дисплей, принтер,

плоттер, акустические системы (наушники), исполнительные механизмы. Список

устройств ввода-вывода безграничен — благодаря фантазии и техническому про-

грессу в него входят все новые и новые устройства; так, например, шлем виртуаль-

ной реальности из области фантастики вышел в производственно-коммерческую.

Устройства хранения к УВВ относить некорректно, поскольку здесь преобразования

информации ради доступности внешнему миру не происходит — что сохранил

(неважно, на каком носителе), то и прочитал (если удалось). Устройства хране-

ния вместе с УВВ можно объединить общим понятием периферийные устройства.

1.1. Что делает процессор в компьютере?

23

Существует еще большой класс коммуникационных устройств, предназначенных

для передачи информации между компьютерами и(или) их частями. Эти устрой-

ства обеспечивают, например, соединение компьютеров в локальные сети или под-

ключение терминала (это УВВ) к компьютеру через пару модемов.

Периферийные и коммуникационные устройства (и даже память) снабжаются

контроллерами или адаптерами, которые доступны процессору. Все компоненты

компьютера представляются для процессора в виде наборов ячеек памяти или(и)

портов ввода-вывода. Процессор может адресоваться к ним с точностью до одного

байта — набора смежных восьми бит. Каждый байт (ячейка памяти, порт) имеет

собственный уникальный физический адрес. Этот адрес устанавливается на сис-

темной шине процессором, когда он инициирует обращение к данной ячейке или

порту. В семействе х86 и PC-совместимых компьютерах пространства адресов

ячеек памяти и портов ввода-вывода разделены. Это предусмотрено с обеих

сторон: процессоры позволяют, а компьютеры используют данное разделение.

В принципе это разделение не обязательно, существуют процессоры, для которых

все внешние ячейки рассматриваются только как память. Контроллеры и адапте-

ры периферийных устройств могут и не использовать порты в пространстве вво-

да-вывода, если их регистры отображены на пространство памяти. Отображение

на память неудобно тем, что для регистров ,периферийных контроллеров трудно

выбрать постоянное место приписки. Оперативную память всегда стремятся пред-

ставлять в виде единого непрерывного массива ячеек со смежными физическими

адресами, следовательно, для регистров можно выделить зону адресов либо до

начального адреса ОЗУ, либо после конечного. То и другое плохо: либо из адресов

ОЗУ уйдет область, начинающаяся с нулевого адреса (процессоры х86 использу-

ют ее для векторов прерываний), либо начало зоны регистров придется отодви-

нуть очень далеко в область старших адресов, чтобы ее не «достала» оперативная

память. Напомним, что за историю PC типовой объем ОЗУ вырос уже на три по-

рядка и подбирается к гигабайту. Семейство х86 стартовало с разрядности шины

адреса памяти 20 бит (8086/88), что позволяло адресовать 210 e 1 048 576 ячеек

(1 Мбайт). Нынешние процессоры имеют разрядность физического адреса памя-

ти 32 и даже 36 бит, что позволяет адресовать до 4 и 64 Гбайт соответственно.

Пространство ввода-вывода использует только младшие 16 бит адреса, что позво-

ляет адресовать до 65 384 однобайтных регистров. Адреса «исторических» систем-

ных устройств PC не изменились с самого рождения — это дань совместимости,

которая без разделения пространств вряд ли бы просуществовала столько лет.

Пространства памяти и ввода-вывода неравнозначны не только по объему, но и по

способам обращения. Способов адресации к ячейке памяти в х86 великое множе-

ство (см. п. 2.3), в то время как для адресации ввода-вывода их существует только

два. К памяти возможна (и широко используется) виртуальная адресация, при

которой для программиста, программы и даже пользователя создается иллюзия

оперативной памяти гигантского размера. В этом случае реальный физический

адрес процессор формирует из логического адреса (указанного программистом) под

управлением операционной системы, поддерживающей виртуальную память.

Иллюзия большого объема создается операционной системой с помощью уст-

ройств хранения и специальных аппаратных средств процессора (см. п. 5.6). Воз-

24

1. Введение

можна и реальная адресация к памяти — в этом случае физический адрес совпада-

ет с логическим. К портам ввода-вывода обращаются только по реальным адресам,

правда, и здесь возможна виртуализация, но уже чисто программными средства-

ми операционной системы. И, наконец, самое существенное различие пространств

памяти и ввода-вывода: процессор может считывать инструкции для исполнения

только из пространства памяти. Конечно, через порт ввода можно считать фраг-

мент программного кода (что и происходит, например, при считывании данных с

диска), но для того, чтобы этот код исполнить, его необходимо записать в память.

Процессор исполняет программный код, находящийся к моменту исполнения в

пространстве памяти. Программный код — это последовательность команд, или

инструкций, каждая из которых определенным образом закодирована и располо-

жена в целом числе смежных байт памяти. Каждая инструкция обязательно имеет

операционную часть, несущую процессору информацию о требуемых действиях.

Операндная часть, указывающая процессору, где находится его «предмет труда» —

операнды, может присутствовать в явном или неявном виде и даже отсутствовать.

Операндная часть может описывать от нуля до двух операндов, участвующих в

данной инструкции (есть инструкции, в которые кроме двух операндов задается

еще и параметр инструкции). Здесь могут быть сами значения операндов (непо-

средственные операнды); явные или неявные указания на регистры процессора,

в которых находятся операнды; адрес ячейки памяти (или его составная часть);

регистры процессора, участвующие в формировании адреса, и разные комбина-

ции этих компонентов. Длина инструкции в семействе х86 может быть от одного

до 12 байт и определяется типом инструкции. Исторически сложившийся формат

инструкций х86 довольно сложен, и «понять», сколько байт занимает конкретная

инструкция, процессор может, лишь декодировав ее первые 1-3 байт. Инструк-

ции могут предшествовать префиксы (к счастью, всегда однобайтные), указываю-

щие на изменение способа адресации, размера операнда или(и) необходимость

многократного (по счетчику и условию) повторения данной инструкции (см. гла-

ву 4). Адрес (логический) текущей исполняемой инструкции хранится в специ-

альном регистре — указателе инструкций (Instruction Pointer, IP), который соот-

ветствует счетчику команд фон-неймановской машины. После исполнения так

называемой линейной инструкции этот указатель увеличивает свое значение на ее

длину, то есть указывает на начало следующей инструкции. Линейная инструк-

ция не нарушает порядок выполнения, определяемый последовательностью рас-

положения инструкций в памяти (по нарастанию адреса). Кроме линейных инст-

рукций существуют инструкции передачи управления, среди которых различают

инструкции переходов и вызовов процедур. Эти инструкции в явном или неявном

виде содержат информацию об адресе следующей выполняемой инструкции, ко-

торый может указывать на относительно произвольную ячейку памяти. Инструк-

ции переходов и вызовов могут быть безусловными (ни от чего не зависящими) и

условными. Произойдет условный переход (вызов) или нет, зависит от состояния

флагов (признаков) на момент исполнения данной инструкции. Если переход (вы-

зов) не состоится, то исполняется инструкция, расположенная в памяти следом за

текущей. Вызов процедуры характерен тем, что перед ним процессор сохраняет в

стеке (стек — это область ОЗУ) адрес следующей инструкции, и на этот адрес пе-

1.1. Что делает процессор в компьютере?

25

редается управление после завершения исполнения процедуры (этот адрес извле-

кается из стека при выполнении инструкции возврата). При переходе в стеке ни-

чего не сохраняется, то есть переход выполняется безвозвратно.

Последовательность исполнения инструкций, предписанная программным кодом,

может быть нарушена под воздействием внутренних или внешних (относительно

процессора) причин. К внутренним причинам относятся исключения (exceptions) —

особые ситуации, возникающие при выполнении инструкций (см. п. 2.5). Нагляд-

ным примером исключения является попытка деления на ноль. При возникнове-

нии условия исключения процессор автоматически выполняет вызов процедуры

обработки исключения, после которой он может вернуться к повторному испол-

нению инструкции, породившей исключение, или следующей за ней. Вариант

поведения зависит от типа произошедшего исключения. Исключения широко

используются современными операционными системами, на основе обработки

исключений строится система виртуальной памяти и реализуются многие функ-

ции многозадачных операционных систем. Внешними причинами изменения нор-

мальной последовательности инструкций являются аппаратные прерывания —

вызовы процедур под воздействием электрических сигналов, поступающих на

специальные выводы процессора (см. п. 2.5). Эти сигналы могут подаваться со-

вершенно неожиданно для исполняемой программы, правда, у программиста есть

возможность заставить процессор (компьютер) игнорировать все прерывания или

их часть. Злоупотреблять этой возможностью нельзя (да и не всегда она есть),

поскольку на аппаратных прерываниях строится, например, отсчет времени и дру-

гие системные и прикладные функции компьютера. Источниками аппаратных

прерываний являются контроллеры и адаптеры периферийных устройств, гене-

раторы меток времени, системы управления питанием и другие подсистемы. Есть

еще так называемые программные прерывания, но они отнюдь не нарушают после-

довательность инструкций, предписанную программистом. Поэтому прерывани-

ями они, по сути, не являются — это всего лишь особый способ вызова процедур,

широко используемый для вызова системных сервисов BIOS и операционной

системы. И наконец, последовательность инструкций может изменяться по сиг-

налу аппаратного сброса или инициализации процессора. С этого, собственно,

и начинается функционирование компьютера: процессор переводится в исходное

состояние и запускается. При этом указатель инструкций совместно с другими

регистрами, участвующими в формировании адреса инструкции, генерирует адрес,

на 15 байт меньший максимального физического адреса (у процессоров Р6 возмо-

жен выбор между значением FFFFFFFFOh и FFFFOh). По этому адресу должна

располагаться инструкция, с которой начинается инициализация компьютера.

Итак, начнем с аппаратного сброса. Во время действия этого сигнала процессор

пассивен — он не управляет системной шиной. Процессор подготавливается к ра-

боте, воспринимая со своих выводов сигналы, задающие его конфигурацию (ко-

эффициент умножения, роль в многопроцессорных системах и некоторые другие

параметры). Внутренний кэш очищается, регистры (не все) приводятся в опреде-

ленное состояние. После окончания сигнала процессор по определенному адресу

(см. выше) выбирает из памяти и исполняет первую инструкцию — управление

передается на точку входа в программу инициализации компьютера. Программа

26

1. Введение

инициализации, называемая POST (PowerOn Self Test — самотестирование по вклю-

чению), хранится в постоянной памяти ROM BIOS (ПЗУ базовой системы вво-

да-вывода). Первым делом необходимо выполнить инициализацию процессора —

установить желаемый режим и значения некоторых регистров. Далее выполняет-

ся проверка работоспособности и инициализация подсистем компьютера. Эта

«раскрутка» выполняется в несколько этапов, постепенно вовлекая в работу про-

тестированные подсистемы. Поначалу программа может смело пользоваться толь-

ко регистрами процессора и постоянной памятью, предварительно ее проверив

(например, путем подсчета контрольной суммы). Если ПЗУ исправно, можно дви-

гаться дальше, в противном случае лучше остановиться. Пока неизвестна работо-

способность ОЗУ, оперативной памятью пользоваться нельзя и, следовательно,

недоступны вызовы процедур и обработка прерываний (вызвать-то процедуру

можно, а вот возврат не гарантируется, поскольку адрес возврата берется из стека,

то есть из ОЗУ). Далее инициализируется ОЗУ (программируются регистры чип-

сета, управляющие параметрами контроллера памяти и регенерацией) и выпол-

няется тестирование небольшого блока в его начале. Если тест прошел успешно,

то для дальнейшей работы можно уже пользоваться вызовами и прерываниями

(не забыв проинициализировать таблицу прерываний), а также памятью для хра-

нения переменных — в таком окружении работать гораздо удобнее. Теперь можно

проинициализировать и протестировать дисплейный адаптер, — дальнейшая рас-

крутка пойдет уже с «ожившим» экраном. Далее тестируется ОЗУ в полном объе-

ме, определяется наличие контроллеров и адаптеров, они инициализируются и

тестируются. Теперь система BIOS «знает» реальную конфигурацию компьюте-

ра и готова к загрузке операционной системы. Векторы прерываний, за которые

отвечает BIOS, проинициализированы — ими можно пользоваться. В этот момент

можно войти в меню встроенной утилиты конфигурирования — BIOS Setup, ко-

торая позволяет изменять настройки различных подсистем компьютера. После

окончания работы этой утилиты программу инициализации (POST) приходится

выполнять снова — конфигурация может стать уже иной. Программа POST завер-

шается вызовом процедуры начальной загрузки.

Для процессоров, начиная с шестого поколения, у POST есть дополнительная забо-

та — загрузить «заплатки» микропрограмм самого процессора (update microcode,

см. п. 7.2). Эти заплатки позволяют исправить некоторые ошибки, выявленные в

процессорах определенных моделей и партий выпуска. Без них основные функ-

ции процессор, конечно, выполнять будет, но в современных сложных операцион-

ных системах и приложениях, как говорится, возможны варианты. Информация

о том, какие заплатки требуются конкретному процессору, и сами заплатки хранят-

ся в ROM BIOS. Если BIOS про установленный процессор (какой именно про-

цессор установлен, POST может определить программно, см. п. 8.2) ничего не «зна-

ет», то и заплатки не загрузит. По этой причине может потребоваться обновление

версии BIOS, которое на современных системных платах выполняется довольно

просто (если производитель своевременно «выкладывает» образ BIOS на своем

web-сайте).

Процедура начальной загрузки (bootstrap loader) вызывается как программное пре-

рывание (BIOS Int 19h). Эта процедура определяет первое готовое устройство из

1.1. Что делает процессор в компьютере?

27

списка разрешенных и доступных (гибкий или жесткий диск, компакт-диск, сетевой

адаптер) и пытается загрузить с него в ОЗУ короткую программу загрузки. Эта

программа может выполняться в два этапа: сначала с жесткого диска загружается

главный загрузчик MBR (Master Boot Record) и ему передается управление. Глав-

ный загрузчик определяет на диске активный раздел, загружает загрузчик этого

раздела и передает управление ему. В свою очередь загрузчик активного раздела

загружает необходимые файлы операционной системы и передает ей управление.

Напомним, что «передать управление» означает выполнить инструкцию перехо-

да на адрес точки входа в программу, загруженную в оперативную память. Опера-

ционная система выполняет инициализацию подведомственных ей программных

и аппаратных средств. Она добавляет новые сервисы, вызываемые, как правило,

тоже через программные прерывания, и расширяет некоторые сервисы BIOS. Под

управлением операционной системы загружаются и исполняются пользователь-

ские приложения и разные вспомогательные процессы и утилиты. Операционная

система ведает распределением всех ресурсов компьютера — памяти (как опера-

тивной, так и пространства на устройствах хранения данных), процессорного

времени (в многозадачных системах), периферийных и коммуникационных уст-

ройств. Она же предоставляет интерфейс пользователя, с помощью которого за-

пускаются приложения, настраиваются параметры ОС и выполняются иные дей-

ствия пользователя. По окончании работы современные ОС требуют корректного

закрытия (shutdown) — завершения работы приложений и сохранения информа-

ции, необходимой пользователю и операционной системе, на энергонезависимых

носителях (на диске). Только после этого компьютер можно выключать или вы-

полнять аппаратный сброс кнопкой Reset. Если выключить или сбросить компью-

тер (в смысле нажать кнопку Reset) до выполнения операций завершения, могут

появиться проблемы при последующей загрузке: потеря несохраненных данных

(пользовательских или системных настроек), потеря фрагментов дисковой памя-

ти (кластеров) и даже разрушение ОС, требующее ее переустановки. Компьюте-

ры в конструктиве АТХ «умеют» сами выключать питание по завершении рабо-

ты ОС, что упрощает правила поведения пользователя.

После этого беглого описания цикла работы компьютера (от включения до вы-

ключения) чуть подробнее остановимся на таких моментах, как прерывания, за-

щищенный режим, многозадачность, виртуальная память.

Процессор фон-неймановской машины фактически может выполнять только один

процесс, передавая управление от инструкции к инструкции согласно исполняе-

мой программе. При этом могут исполняться переходы, ветвления и вызовы про-

цедур, но вся эта цепочка запрограммирована разработчиком программы. Теперь

рассмотрим случай, когда во время этого процесса случается асинхронное по от-

ношению к процессу событие, требующее реакции компьютера. Для примера рас-

смотрим нажатие клавиши на клавиатуре. Клавиатура (это устройство ввода) по

нажатию (как и отпусканию) любой клавиши по своему интерфейсу генерирует

специальное сообщение, содержащее код этого события (скан-код клавиши). Кон-

троллер клавиатуры, находящийся на системной плате, принимает этот код в свой

внутренний регистр и сигнализирует об этом двумя способами: устанавливает

флаг готовности (бит в регистре состояния, который может быть прочитан про-

28

1. Введение

цессором по адресу известного порта ввода) и генерирует сигнал запроса прерыва-

ния (сигнал IRQ1). Этот сигнал поступает на вход контроллера прерывания — сис-

темного устройства, обслуживающего запросы от множества линий (о дисципли-

не обслуживания здесь говорить не будем). Контроллер прерываний формирует

сигнал запроса, поступающий на вход маскируемого прерывания процессора (сиг-

нал INTR). Если у процессора маскируемые прерывания разрешены, то он запро-

сит у контроллера номер вектора прерывания, соответствующего данному источ-

нику прерывания. В нашем случае (сигнал от клавиатуры) это будет вектор 9.

Получив значение вектора, процессор сохранит в стеке адрес следующей инструк-

ции исполняемого процесса и выполнит вызов процедуры обработки прерывания,

адрес которой задан в 9-м элементе таблицы прерываний. В нашем компьютере эта

процедура считает скан-код из контроллера клавиатуры (в ответ он сбросит бит

готовности в своем регистре состояния), выполнит минимально необходимые дей-

ствия, связанные с получением этого кода, и некоторые манипуляции с контрол-

лером прерываний, позволяющие ему правильно реагировать на последующие

запросы прерываний. Процедура обработки прерывания завершается специаль-

ной инструкцией возврата (IRET), по которой управление вернется прерванному

процессу. Кроме маскируемых прерываний есть и немаскируемое прерывание с

фиксированным вектором 2, для которого у процессора имеется отдельный вход

NMI, а также системное прерывание SMI. Нюансы обработки прерываний процес-

сором рассмотрены в п. 2.5. Альтернативой прерываниям для реакции на асинх-

ронное событие может быть программный опрос готовности УВВ — полинг. Чтобы

обеспечить реакцию на асинхронное событие, исполняемый процесс в нашем слу-

чае должен периодически опрашивать (читать из порта ввода) регистр состояния

контроллера клавиатуры и, если будет замечен установленный флаг готовности,

исполнять процедуру обработки данного события. Непригодность такого подхо-

да в данном случае вполне очевидна — любой процесс, во время которого требует-

ся реакция на асинхронное событие (а самому процессу это событие может быть и

безразлично), должен быть загроможден периодическими вставками программно-

го кода опроса готовности. Кроме «лохматого» вида самой программы, на опрос

тратится процессорное время, и в основном бесполезно (клавиши нажимают не

так уж часто). Если опрос производить редко, то время реакции на событие может

недопустимо возрасти. Прерывания могут использоваться и в сочетании с Полин-

гом: процесс опроса готовности (возможно, нескольких устройств) периодически

запускается по прерываниям от системного таймера.

Прерывания используют и для переключения задач в многозадачных системах (см.

п. 5.5). Пусть, например, имеются два процесса (грубо говоря, две прикладные

программы), которые должны выполняться как бы одновременно (по-настоящему

одновременно один фон-неймановский процессор их выполнить не может). Можно

запустить один процесс, а через некоторое время его работы по аппаратному преры-

ванию (от таймера) сохранить в памяти контекст задачи — образ ее текущего состо-

яния (все регистры, программно-доступные этому процессу) и запустить другой

процесс. Через некоторое время по следующему прерыванию выполнить обратное

переключение контекста: сохранить состояние второго процесса (в другом месте

памяти), загрузить в регистры процессора образ состояния первого процесса и про-

1.1. Что делает процессор в компьютере?

29

должить его выполнение. Эти переключения задач следует выполнять с частотой,

создающей у пользователя иллюзию непрерывности и одновременности исполне-

ния обеих программ. Понятно, что ресурсы процессора (производительность) в

этом случае делятся между задачами пропорционально выделяемым им квантам

времени. Чтобы пользователя такая производительность процессов удовлетворя-

ла (а еще учтем накладные расходы на сохранение и восстановление образов при

переключениях), у процессора должна быть достаточная мощность. Процессоры

семейства х86, начиная со второго и, особенно, с третьего (386) поколения, имеют

встроенные средства многозадачности (число задач почти не ограничено), работа-

ющие в защищенном режиме. Переключение задач производится по сигналу преры-

вания от таймера совершенно «прозрачно» для процессов, работающих псевдопарал-

лельно. Благодаря этой прозрачности программисту, разрабатывающему прикладную

программу, в большинстве случаев не надо заботиться о реализации многозадачной

работы. В распоряжение его программы предоставляется виртуальная машина

(тоже фон-неймановская), в которой управление передается последовательно этой

программой, как будто она — единственный процесс. Конечно, поддержка виртуаль-

ных машин требует определенных усилий со стороны многозадачной операцион-

ной системы, которой приходится распределять не только процессорное время, но

и память, устройства хранения, ввода-вывода и коммуникационные устройства —

то есть все ресурсы реального компьютера. В этом ей помогают специальные сред-

ства, введенные в процессоры х86 2-3-го поколений и постоянно развиваемые в

следующих поколениях.

Чтобы процессы не мешали друг другу (по недосмотру или умышленно), требу-

ются меры принудительной защиты критически важных ресурсов. Современные

операционные системы используют защищенный режим процессора, в котором эти

меры реализуются на аппаратном уровне. Поскольку программа может взаимо-

действовать с подсистемами компьютера только через пространства памяти и пор-

тов ввода-вывода, а также аппаратные прерывания, то защищать нужно эти три

типа ресурсов. Самую сложную защиту имеет память. Операционная система

выделяет каждому процессу области памяти — сегменты — различного назначе-

ния и с разными правами доступа. Из одних сегментов можно только читать дан-

ные, в другие возможна и запись. Для программного кода выделяются специаль-

ные сегменты, инструкции могут выбираться и исполняться только из них. По

отношению’к принципу хранимое™ программы это является искусственным ог-

раничением для фон-неймановской машины, но его целесообразность очевидна.

Процессору «безразлично» содержимое ячейки памяти, на которую передано уп-

равление, — он всегда пытается трактовать ее как код инструкции (или префикс).

Если ошибочно управление передано на область данных, то дальнейшее поведе-

ние процессора непредсказуемо — это так называемый «вылет». Защита не позво-

ляет передать управление на сегмент данных — сработает исключение защиты,

которое обрабатывается операционной системой, и ошибочный процесс будет

принудительно завершен. Таким образом, вероятность вылета уменьшается. Что-

бы выдержать принцип хранимое™ программы, на время ее загрузки в память или

на время программной модификации ту же область объявляют и сегментом данных,

в который разрешена запись. Система защиты может полностью контролировать

30

1. Введение

распределение памяти, генерируя исключения в случаях различных нарушений.

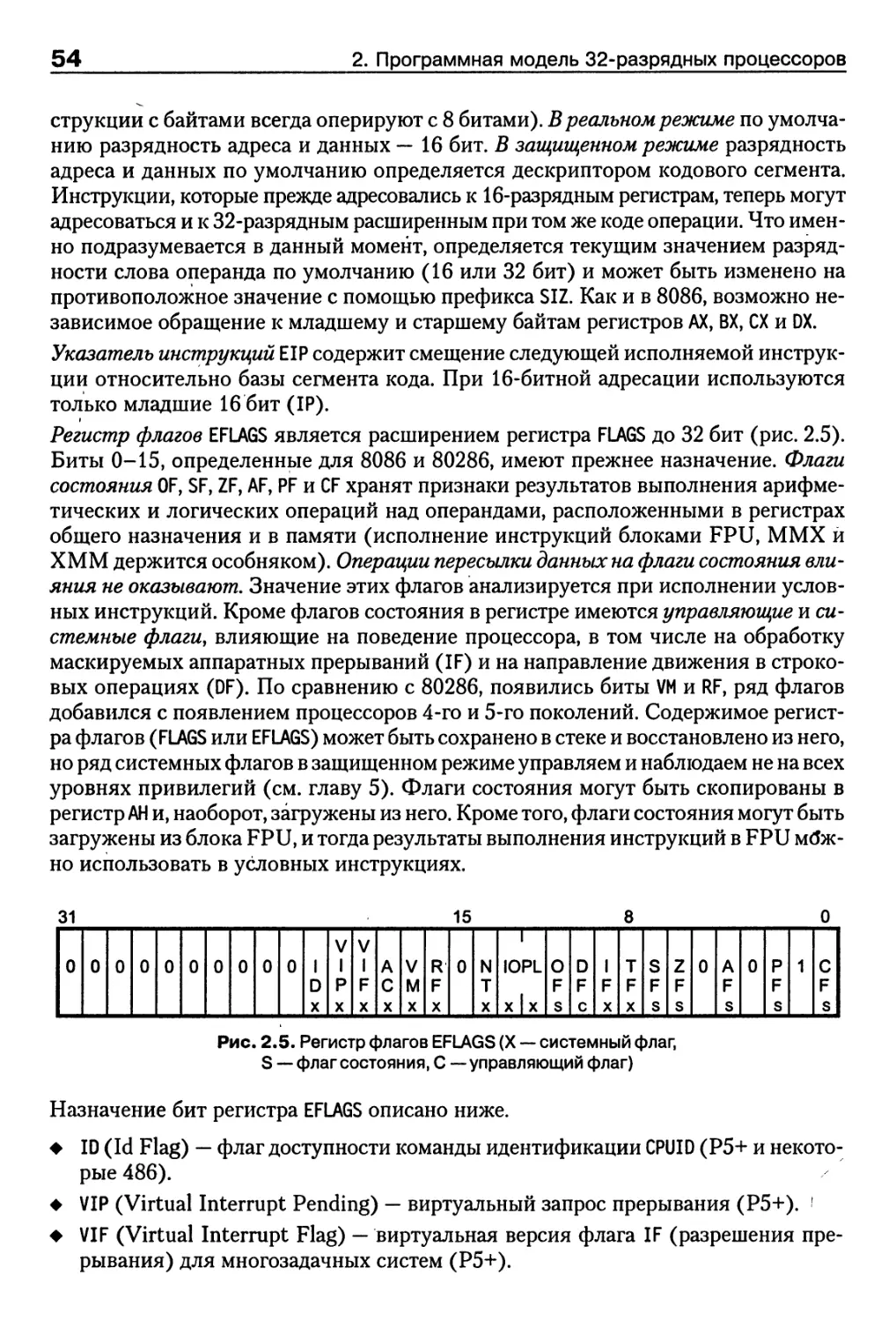

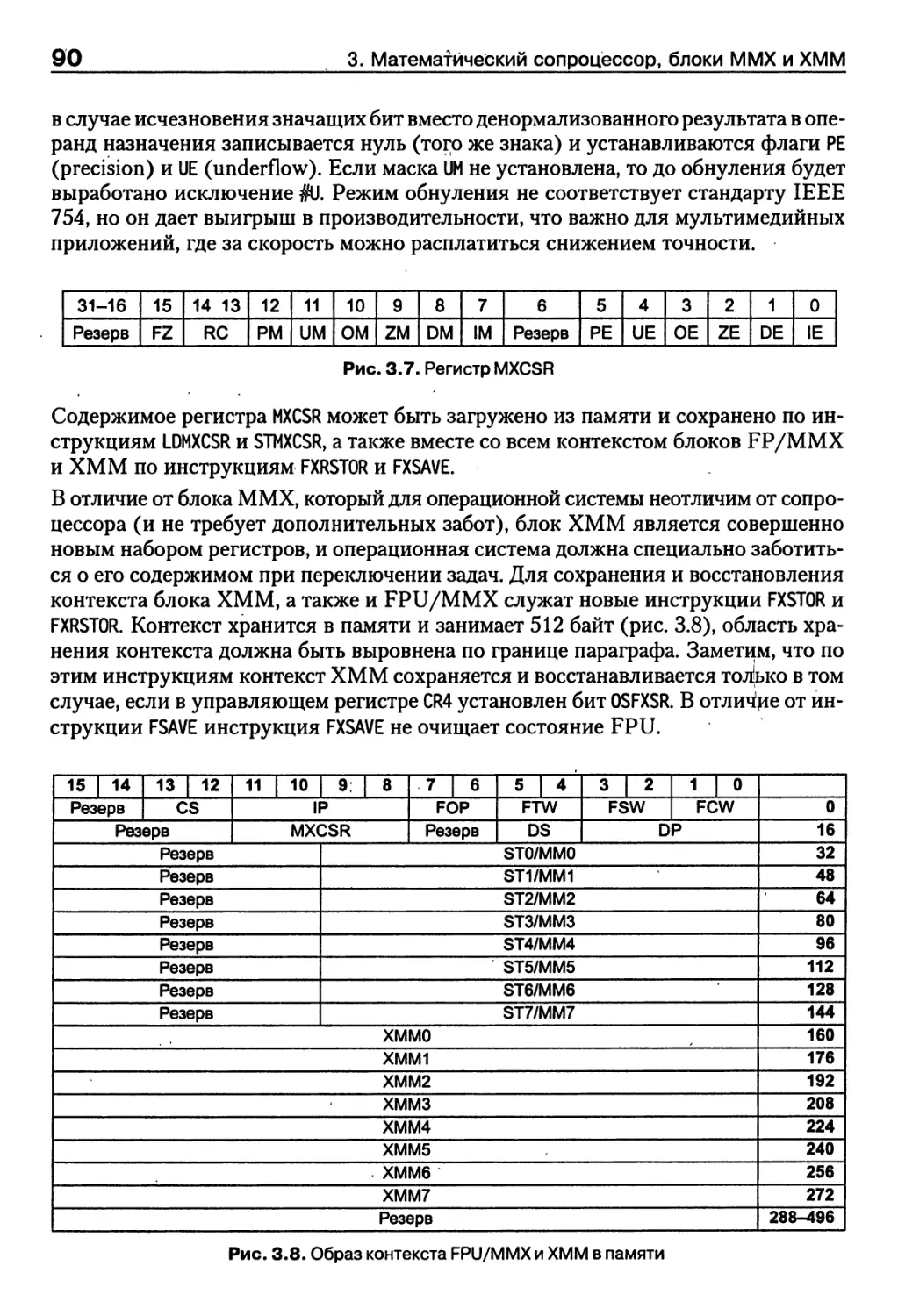

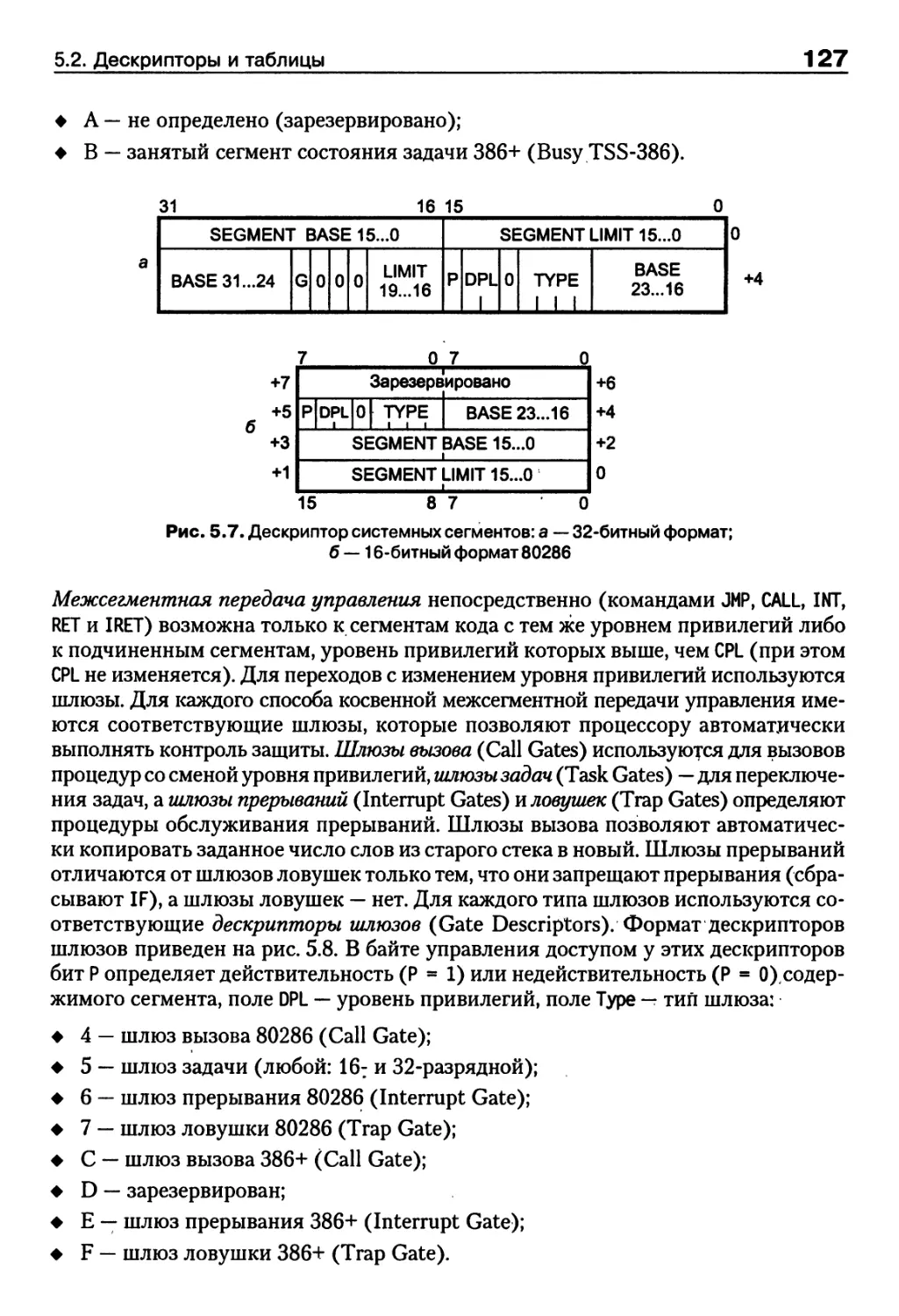

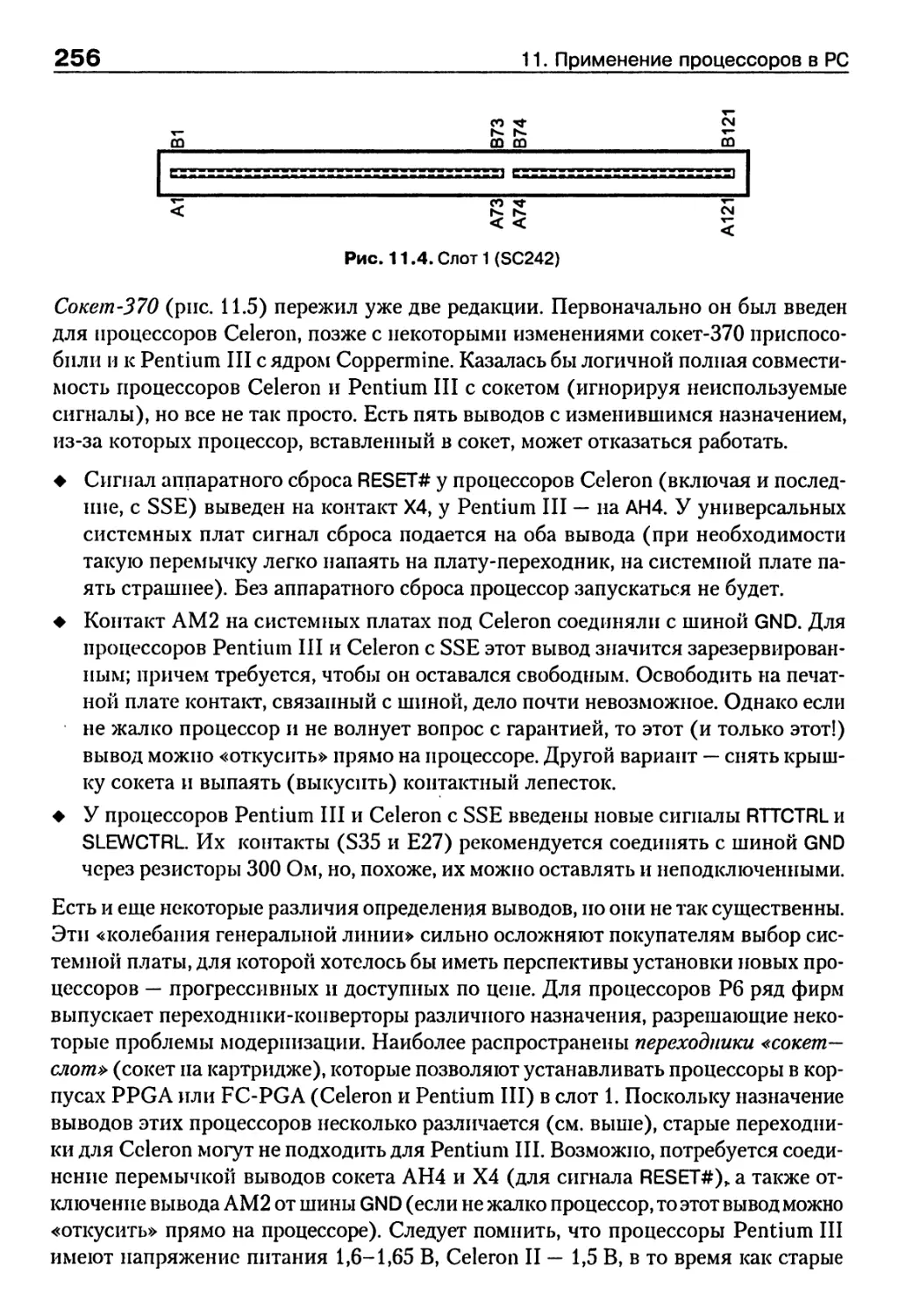

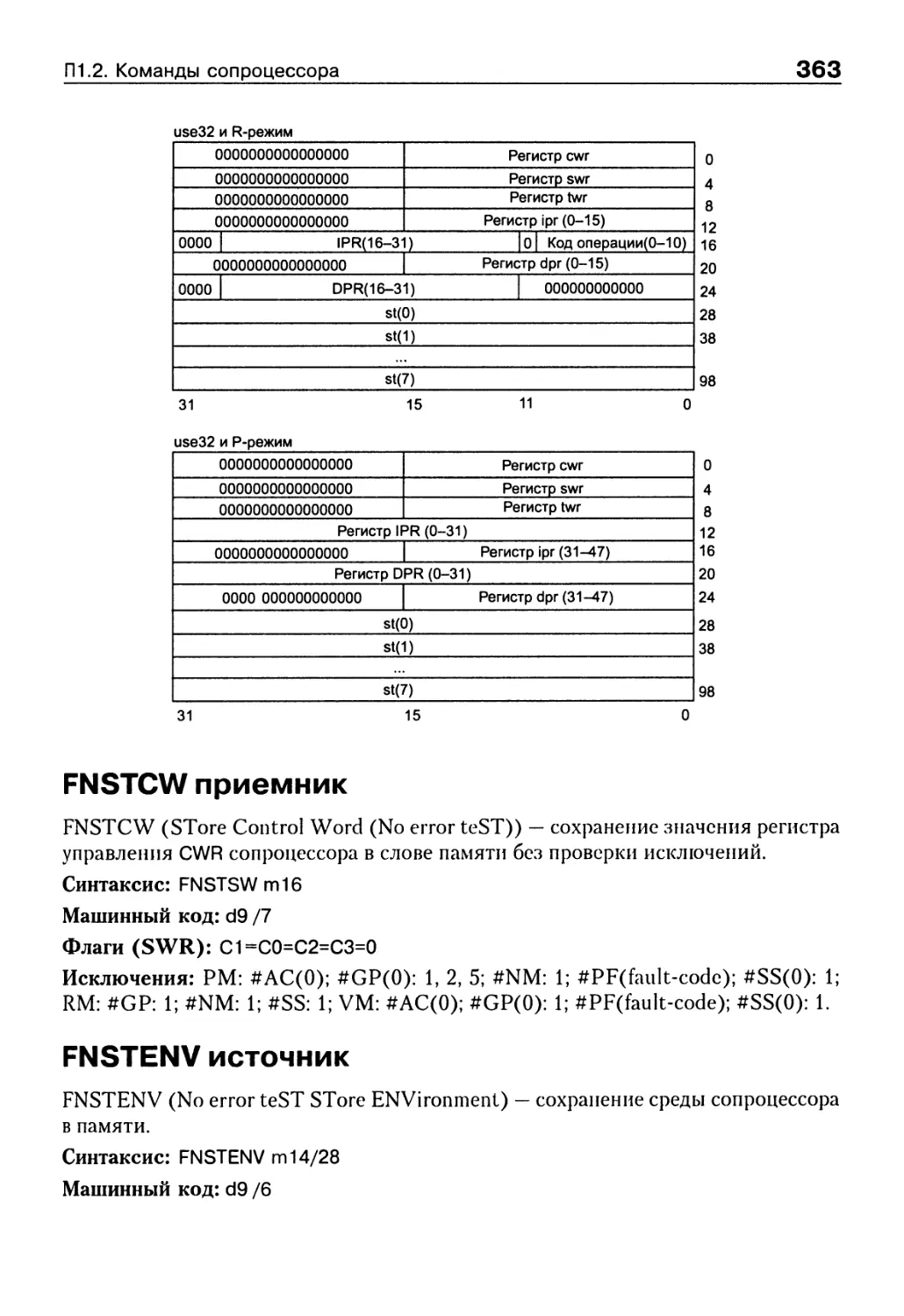

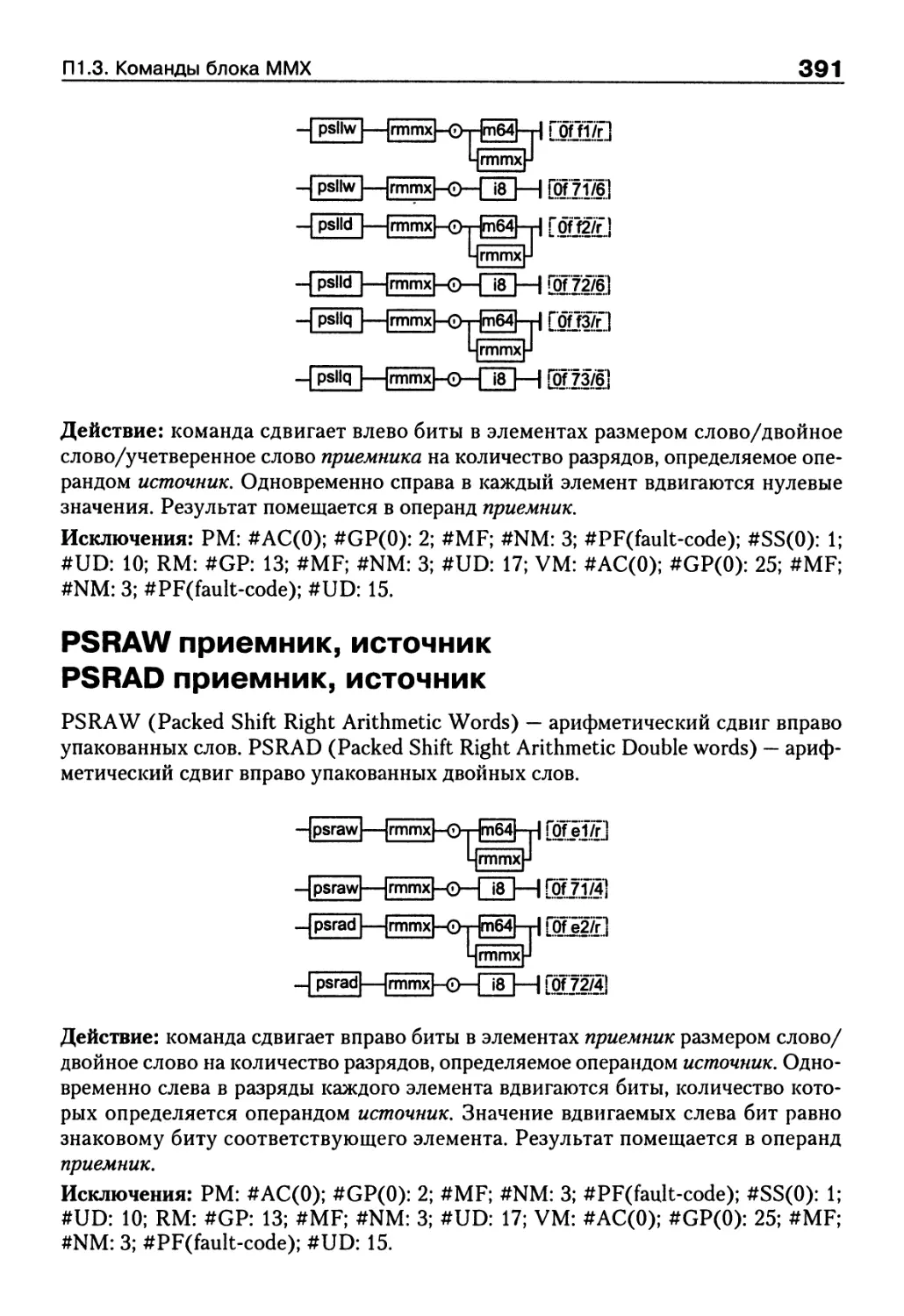

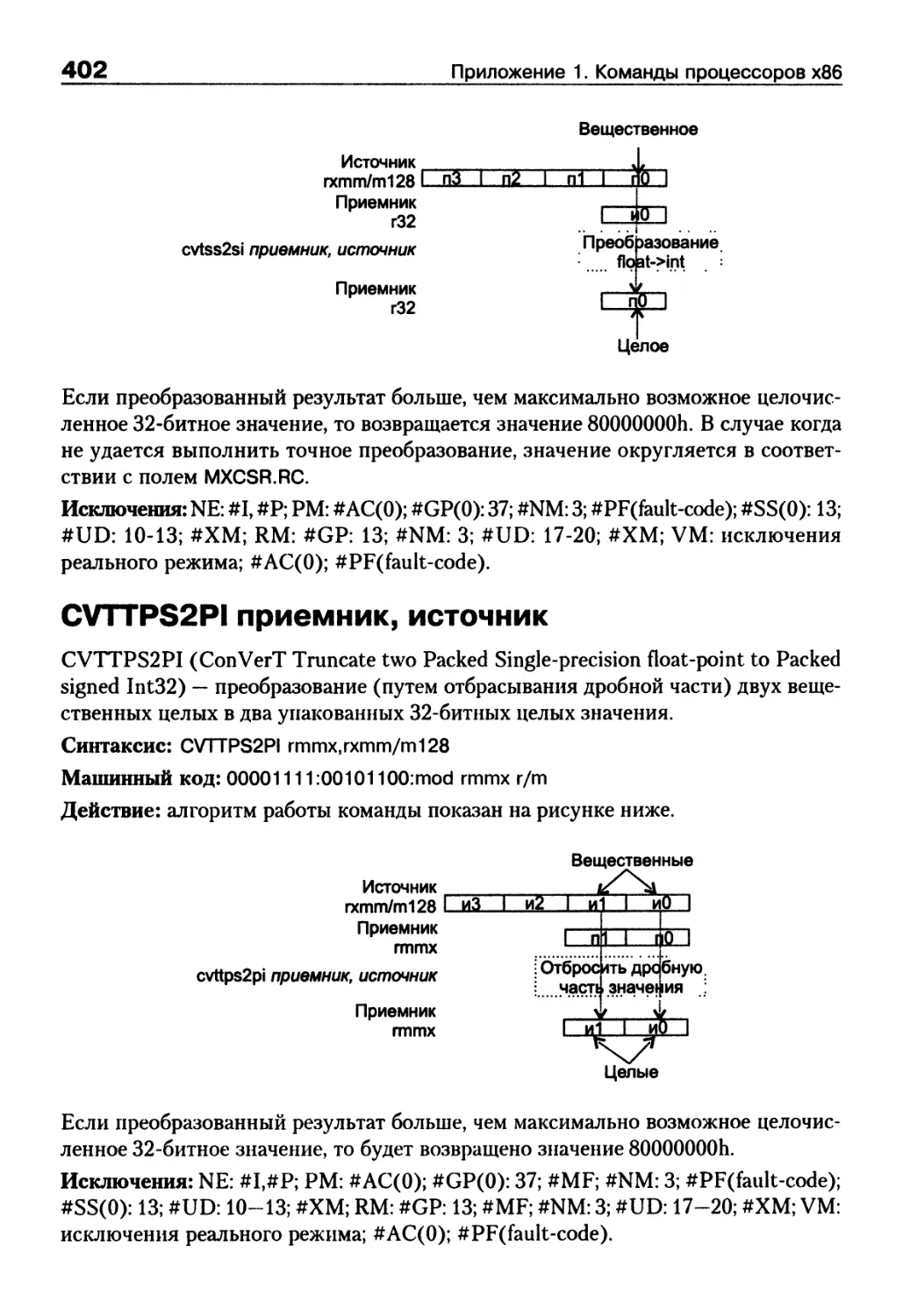

Конечно же, эффективность защиты (устойчивость компьютера к ошибкам) в зна-