Автор: Кестер У.

Теги: мир электроники переводная литература издательство техносфера вспомогательные схемы преобразователи

ISBN: 978-5-94836-146-8

Год: 2007

Текст

Аналого-цифровое

преобразование

Аналого-цифровое

преобразование

□ ANALOG

DEVICES

www.analog.com

□ ANALOG

DEVICES

□ ANALOG

DEVICES

Представительство

Analog Devices Inc. в России

http://www.analog.com/ru

♦7 812 327-45-90, +7 812 336-25-00

Факс.: +7 812 327-45-91

I й

ар

Официальные Дистрибьюторы Analog Devices Inc. в России и Украине

analog is everywhere:

Аналого-

цифровое

преобразование

Редактор

оригинального

издания

Уолт Кестер

Перевод с английского

под редакцией Е. Б. Володина

ТЕХНОСФЕРА

Москва

2007

Под ред. Уолта Кестера

Аналого-цифровое преобразование

Москва:

Техносфера, 2007. - 1016 с. ISBN 978-5-94836-146-8

Книга написана для инженеров - конструкторов, которые используют

преобразователи данных и связанные с ними вспомогательные схемы.

Поэтому в тексте встречаются много практических советов. Большая часть

материала была взята — с необходимыми обновлениями — из предыдущих

популярных выпусков книг для семинаров Analog Devices. Много разделов

подверглись переработке для того, чтобы материал был изложен более

точно и ясно. Различные технические специалисты Analog Devices внесли

свой вклад в книгу и их имена упоминаются в начале каждой большой

секции.

Analog-Digital Conversion

© 2004, Analog Devices, Inc.

© 2007, ЗАО «РИЦ «Техносфера» перевод на русский язык,

оригинал-макет, оформление

ISBN 978-5-94836-146-8

ISBN 0-916550-27-3 (англ.)

СОДЕРЖАНИЕ

Глава 1. ИСТОРИЯ ПРЕОБРАЗОВАТЕЛЕЙ (Уолт Кестер)..........................11

Предисловие к главе................................................. 11

1.1. Ранняя история.................................................. 11

Ранние годы: от телеграфа до телефона............................ 13

Изобретение импульсно-кодовой модуляции (РСМ).................... 15

Математическое обоснование ИКМ .................................. 16

Патент Алекса Харли Ривза на ИКМ................................. 18

ИКМ и Bell System: Вторая мировая война, и до 1948 года...........20

ОУ и регенеративные импульсные ретрансляторы: от электронно-вакуумных

до полупроводниковых устройств....................................23

Список литературы к 1.1. Ранняя история..............................25

1.2. Преобразователи 1950-х и 1960-х годов (Уолт Кестер).............27

Коммерческие преобразователи: 1950-е годы.........................27

История развития преобразователей: 1960-е годы....................29

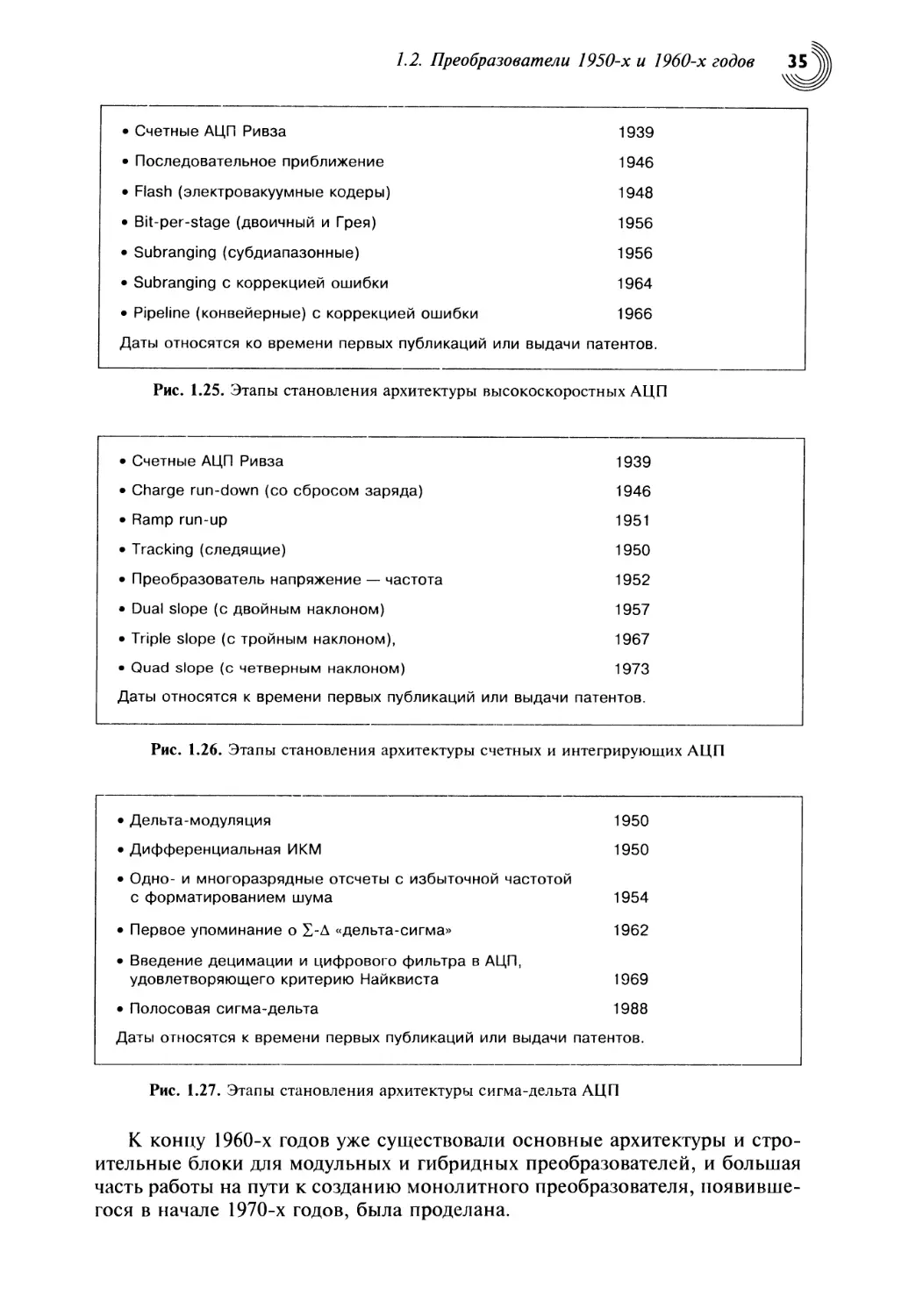

Архитектуры преобразователей......................................33

Список литературы к 1.2. Преобразователи 1950-х и 1960-х годов.......36

1.3. Развитие преобразователей в 1970-е годы.........................37

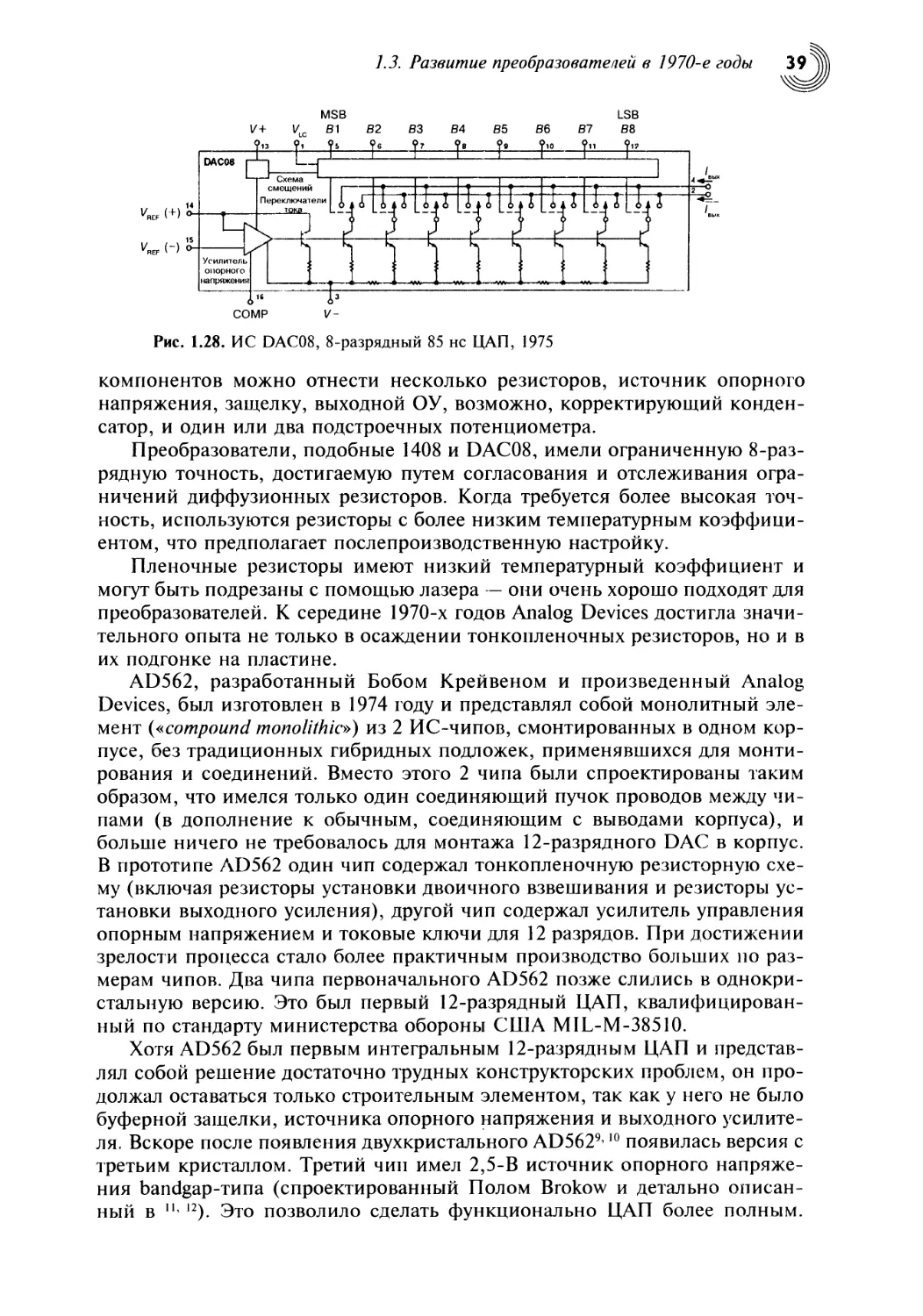

Монолитные преобразователи 1970-х годов...........................38

Модульные преобразователи 1970-х годов............................48

Список литературы к 1.3. Развитие преобразователей в 1970-е годы.....50

1.4. Преобразователи данных в 1980-е годы (Уолт Кестер)..............51

Введение..........................................................51

Монолитные ЦАП в 1980-е годы......................................52

Монолитные АЦП 1980-х годов.......................................53

Монолитные параллельные АЦП в 1980-е годы.........................54

Гибридные и модульные ЦАП и АЦП в 1980-е годы.................... 55

1.5. Преобразователи в 1990-е годы (Уолт Кестер) ....................56

Введение..........................................................56

Монолитные ЦАП в 1990-х годах.....................................58

Монолитные АЦП в 1990-е годы......................................60

Гибридные и модульные ЦАП и АЦП в 1990-е годы.....................65

1.6. Преобразователи в 2000-х годах (Уолт Кестер)....................66

Глава 2. ОСНОВЫ СЧИТЫВАНИЯ ДАННЫХ

В АНАЛОГОВО-ЦИФРОВЫХ СИСТЕМАХ............................................68

2.1. Кодирование и квантование (Уолт Кестер, Дэн Шайнголд,

Джеймс Брайант)......................................................68

Однополярные коды.................................................71

Код Грея..........................................................73

Биполярные коды...................................................75

Комплементарные коды..............................................80

Статические передаточные характеристики ЦАП и АЦП и погрешности

постоянного тока..................................................80

Список литературы к 2.1. Кодирование и квантование...................88

2.2. Теория отсчетов (Уолт Кестер)...................................89

Содержание

Необходимость в наличии функции выборки-хранения .....................90

Критерий Найквиста....................................................93

Фильтры для устранения эффекта наложения спектров (антиалайзинговые

фильтры)..............................................................95

Субдискретизация (Undersampling) (гармоническая дискретизация (Harmonic

Sampling), дискретизация модулированных сигналов (Bandpass Sampling),

дискретизация на промежуточной частоте (ПЧ) (IF Sampling), прямое

преобразование ПЧ в цифровую форму (Direct IF-to-Digital)) ...........97

Фильтры для устранения эффектов смещения и наложения спектров

в приложениях с субдискретизацией.....................................99

Список литературы к 2.2. Теория отсчетов............................... 100

2.3. Погрешности переменного тока преобразователей (Уолт Кестер,

Джеймс Брайант)....................................................... 101

Теория шума квантования идеального TV-разрядного преобразователя ... 101

Шум в реальных АЦП.................................................. 107

Динамические характеристики преобразователей........................ 110

Динамические характеристики ЦАП..................................... 143

Список литературы к 2.3. Погрешности переменного тока

преобразователей....................................................... 152

2.4. Общие технические характеристики преобразователей

(Джеймс Брайант)...................................................... 153

Общие положения..................................................... 153

Логический интерфейс................................................ 155

Логическая часть преобразователей: тактирование и другие показатели. 156

2.5. Определение технических характеристик (Дэн Шайнголд,

Уолт Кестер)........................................................ 157

Общая библиография по преоборазованию данных и сопутствующим вопросам.. 180

Глава 3. АРХИТЕКТУРЫ ПРЕОБРАЗОВАТЕЛЕЙ ДАННЫХ............................... 182

3.1. Архитектуры ЦАП (Джеймс Брайант, Уолт Кестер)..................... 182

Введение............................................................ 182

Обсуждение выходов ЦАП.............................................. 184

Базовые структуры ЦАП............................................... 185

Другие архитектуры с малыми искажениями..............................211

Обсуждение логики ЦАП............................................... 213

Список литературы к 3.1. Архитектуры ЦАП................................215

3.2. Архитектуры АЦП (Уолт Кестер, Джеймс Брайант)......................216

Введение............................................................ 216

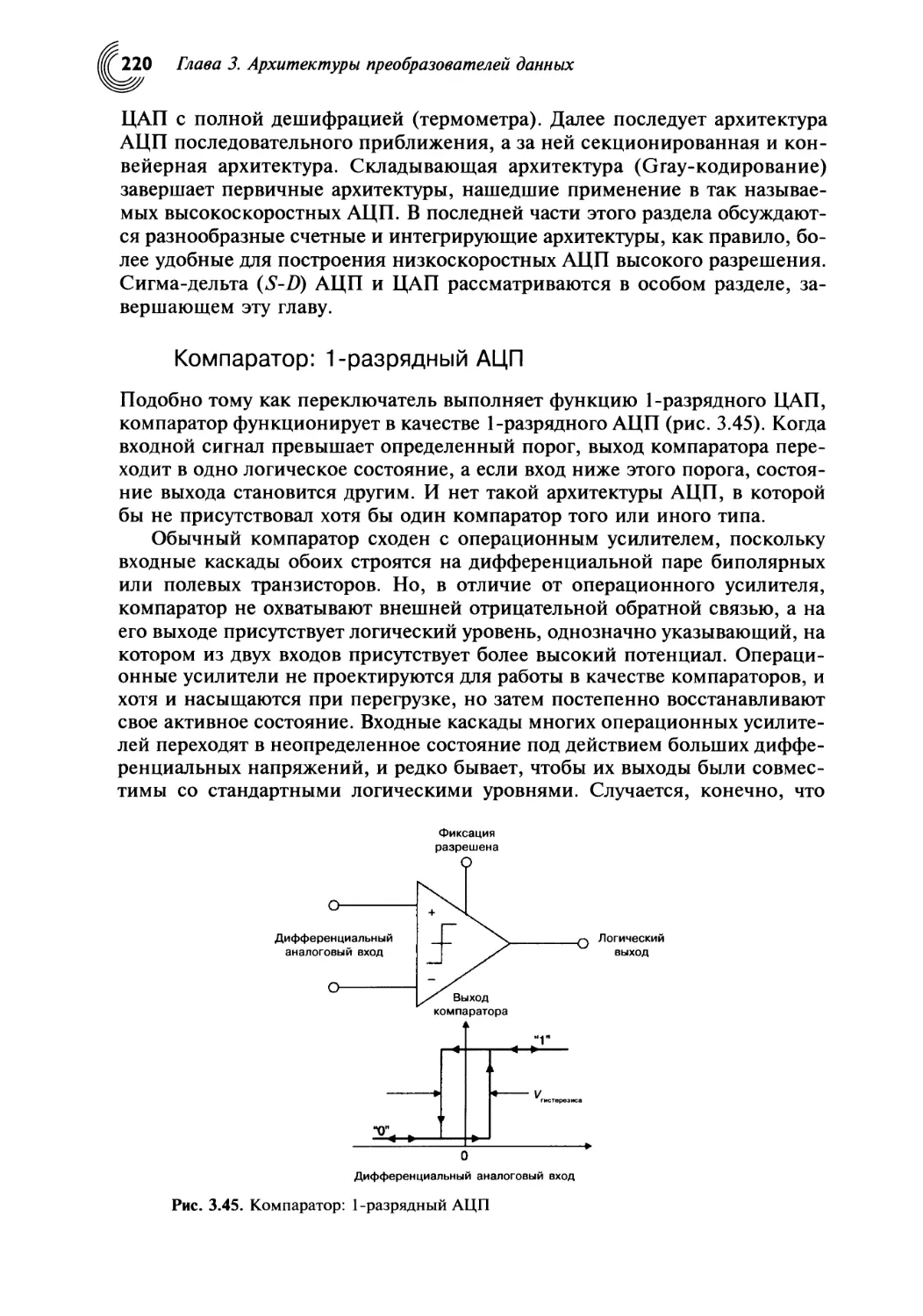

Компаратор: 1-разрядный АЦП..........................................220

Архитектуры высокоскоростных АЦП.....................................223

Архитектуры счетных и интегрирующих АЦП..............................262

Список литературы к 3.2. Архитектуры АЦП................................277

3.3. Сигма-дельта преобразователи (Уолт Кестер, Джеймс Брайант).........282

Историческая перспектива.............................................282

Основы сигма-дельта АЦП............................................. 286

Обсуждение систем более высокого порядка.............................294

Измерительные сигма-дельта АЦП высокого разрешения...................298

Полосовые сигма-дельта преобразователи ..............................303

Сигма-дельта ЦАП.................................................... 304

Выводы...............................................................305

Список литературы к 3.3. Сигма-дельта преобразователи...................306

Содержание 5

Глава 4. ТЕХНОЛОГИЯ ПРЕОБРАЗОВАТЕЛЕЙ...................................310

4.1. Ранние процессы (Уолт Кестер)..................................310

Электронно-вакуумные преобразователи........................... 310

Полупроводниковые модульные и гибридные преобразователи........ 312

Процесс калибровки............................................. 317

Список литературы к 4.1. Ранние процессы............................317

4.2. Современные процессы (Уолт Кестер. Джеймс Брайант).............318

Биполярные процессы............................................ 318

Технология тонкопленочных резисторов........................... 319

Комплементарные биполярные технологии ......................... 320

Технологии КМОП (CMOS)......................................... 321

Технологии и архитектура преобразователей...................... 323

Список литературы к 4.2. Современные процессы.......................327

4.3. Разумное разделение (Дэйв Робертсон, Мартин Кесслер)...........327

Когда полная интеграция не является оптимальным решением....... 327

Для чего необходимо разумное разделение?....................... 332

Что меняется? ................................................. 333

Глава 5. ТЕСТИРОВАНИЕ ПРЕОБРАЗОВАТЕЛЕЙ ДАННЫХ..........................337

5.1. Тестирование ЦАП (Уолт Кестер, Дэн Шейнголд)...................337

Тестирование статических характеристик ЦАП..................... 337

Тестирование динамических показателей ЦАП...................... 349

Список литературы к 5.1. Тестирование ЦАП...........................361

5.2. Тестирование АЦП (Уолт Кестер).................................362

Краткий исторический обзор спецификаций и методов тестирования

преобразователей данных.........................................362

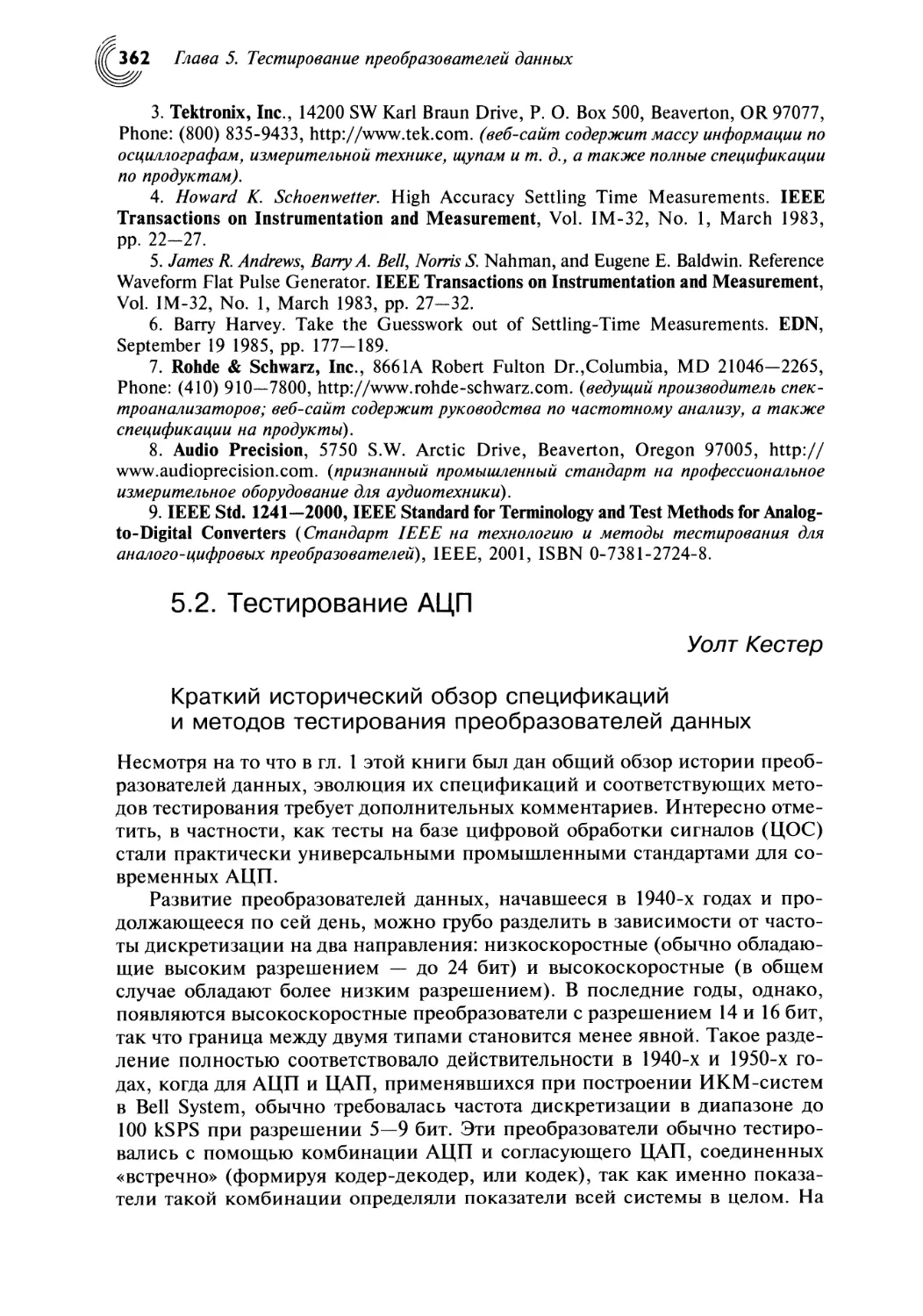

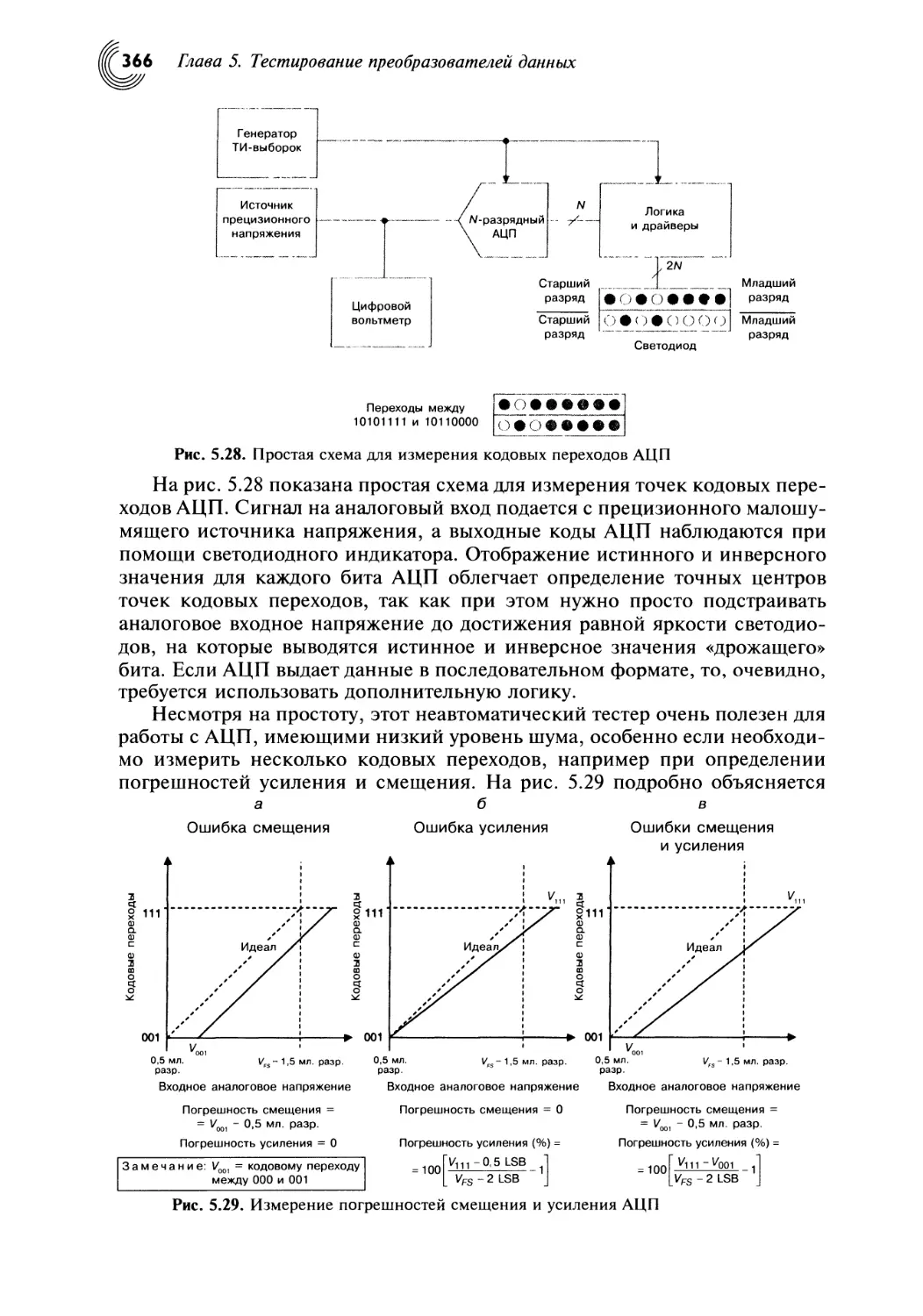

Тестирование статических характеристик АЦП..................... 364

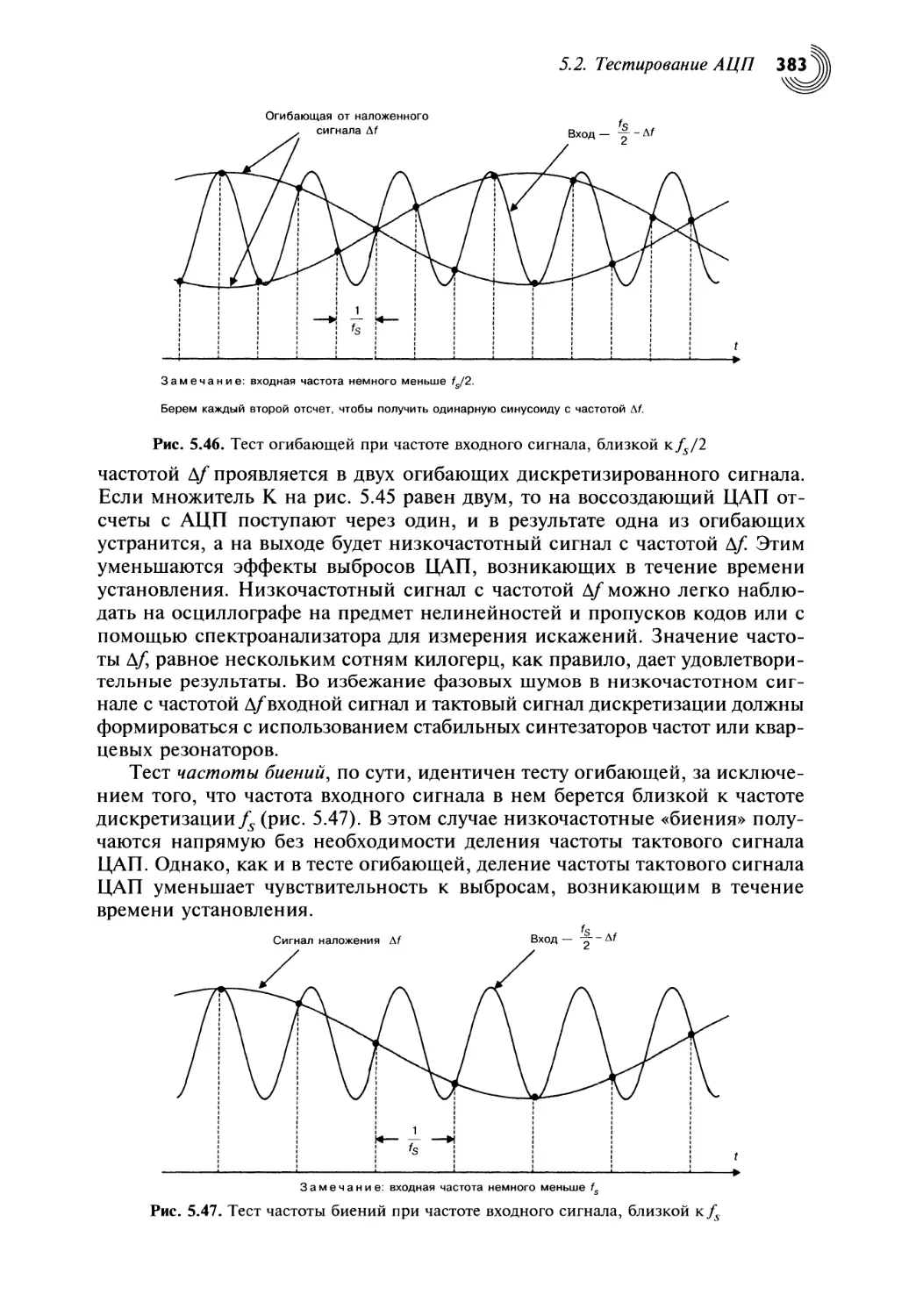

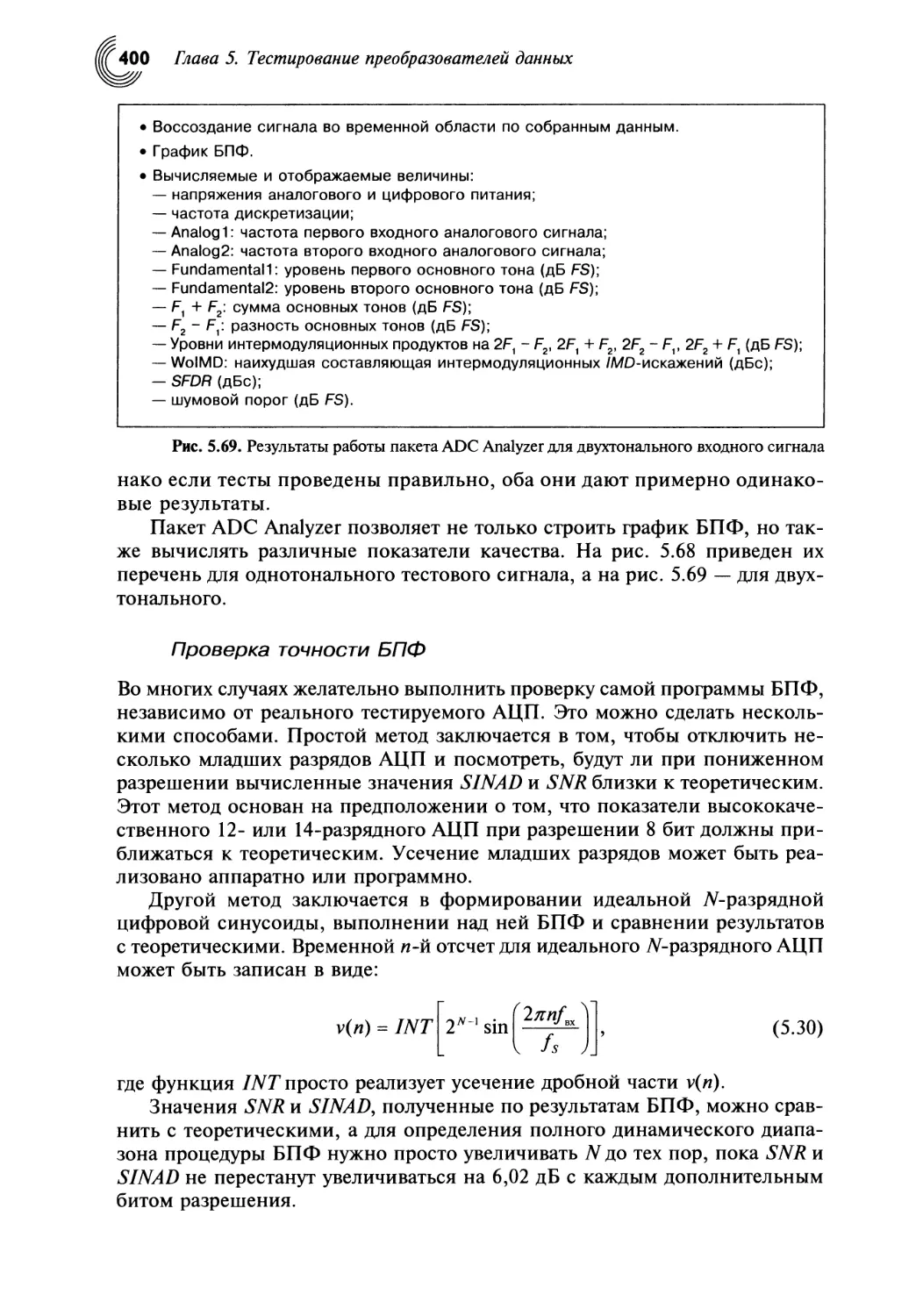

Тестирование динамических характеристик........................ 380

Список литературы к 5.2 .Тестирование АЦП...........................421

Дополнительная литература по БПФ и ЦОС .........................423

Программные пакеты для вычисления БПФ и анализа технических данных.423

Общая литература по преобразованию данных и смежным вопросам........423

Глава 6. ИНТЕРФЕЙСЫ ПРЕОБРАЗОВАТЕЛЕЙ ДАННЫХ............................425

6.1. Сопряжение аналоговых входов АЦП (Уолт Кестер).................425

Введение........................................................425

Анализ работы усилителя на постоянном и переменном токе ........427

Сопряжение измерительных £-Д АЦП высокого разрешения ...........439

Сопряжение АЦП последовательного приближения с одним входом

и однополярным питанием 1,6—3,6 В...............................440

Сопряжение АЦП с однополярным питанием с масштабируемыми входами...442

Сопряжение CMOS АЦП с коммутируемыми конденсаторами

и дифференциальным входом.......................................443

Схемы подключения по одному входу CMOS АЦП с дифференциальным

входом ....................................................... 444

Драйверы АЦП с дифференциальным входом..........................447

Сопряжение АЦП с дифференциальными усилителями..................452

Список литературы к 6.1. Сопряжение аналоговых входов АЦП..........466

6.2. Цифровые интерфейсы АЦП И ЦАП (и связанные темы)

(Уолт Кестер)......................................................467

Введение........................................................467

Содержание

Инициализация преобразователей данных при включении..............467

Инициализация внутренних регистров управления преобразователя данных.468

Экономичный режим, спящий режим и режим готовности...............469

Ждущий режим, толчковый режим и режим дискретизации на минимальной

частоте..........................................................469

Цифровые выходные интерфейсы АЦП.................................471

Цифровые входные интерфейсы ЦАП .................................481

Список литературы к 6.2. Цифровые интерфейсы АЦП и ЦАП

(и связанные системы)...............................................485

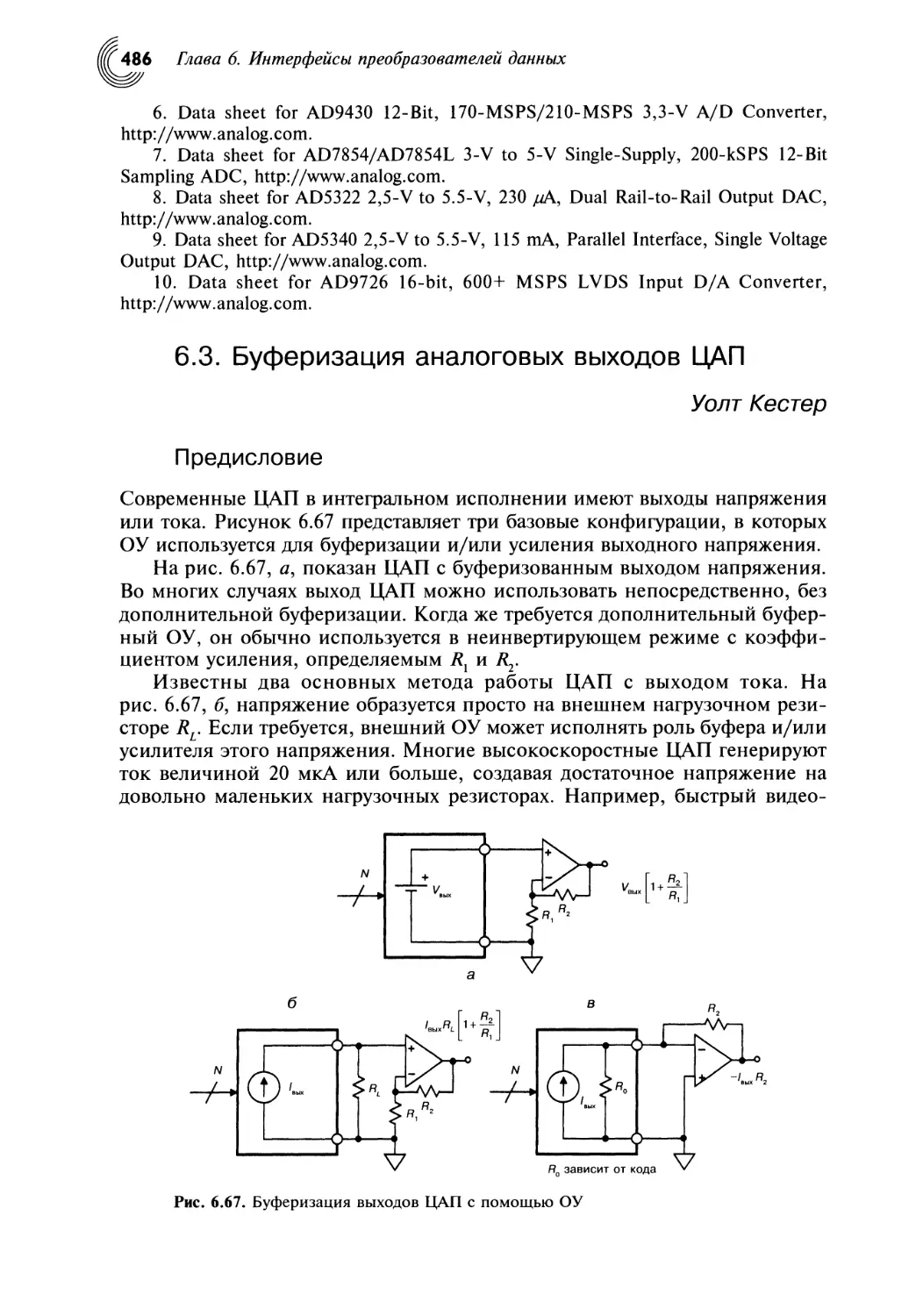

6.3. Буферизация аналоговых выходов ЦАП (Уолт Кестер)...............486

Предисловие .....................................................486

Техника преобразования дифференциального сигнала к одному выходу.....487

Преобразование ток-напряжение с одним выходом....................490

Преобразование дифференциального тока в дифференциальное напряжение..491

Активные фильтры НЧ для аудио ЦАП ...............................492

Список литературы к 6.3. Буферизация аналоговых выходов ЦАП.........493

6.4. Опорные напряжения преобразователей данных (Уолт Кестер)........493

Введение.........................................................493

6.5. Формирование синхроимпульсов дискретизации (Уолт Кестер)........496

Введение.........................................................496

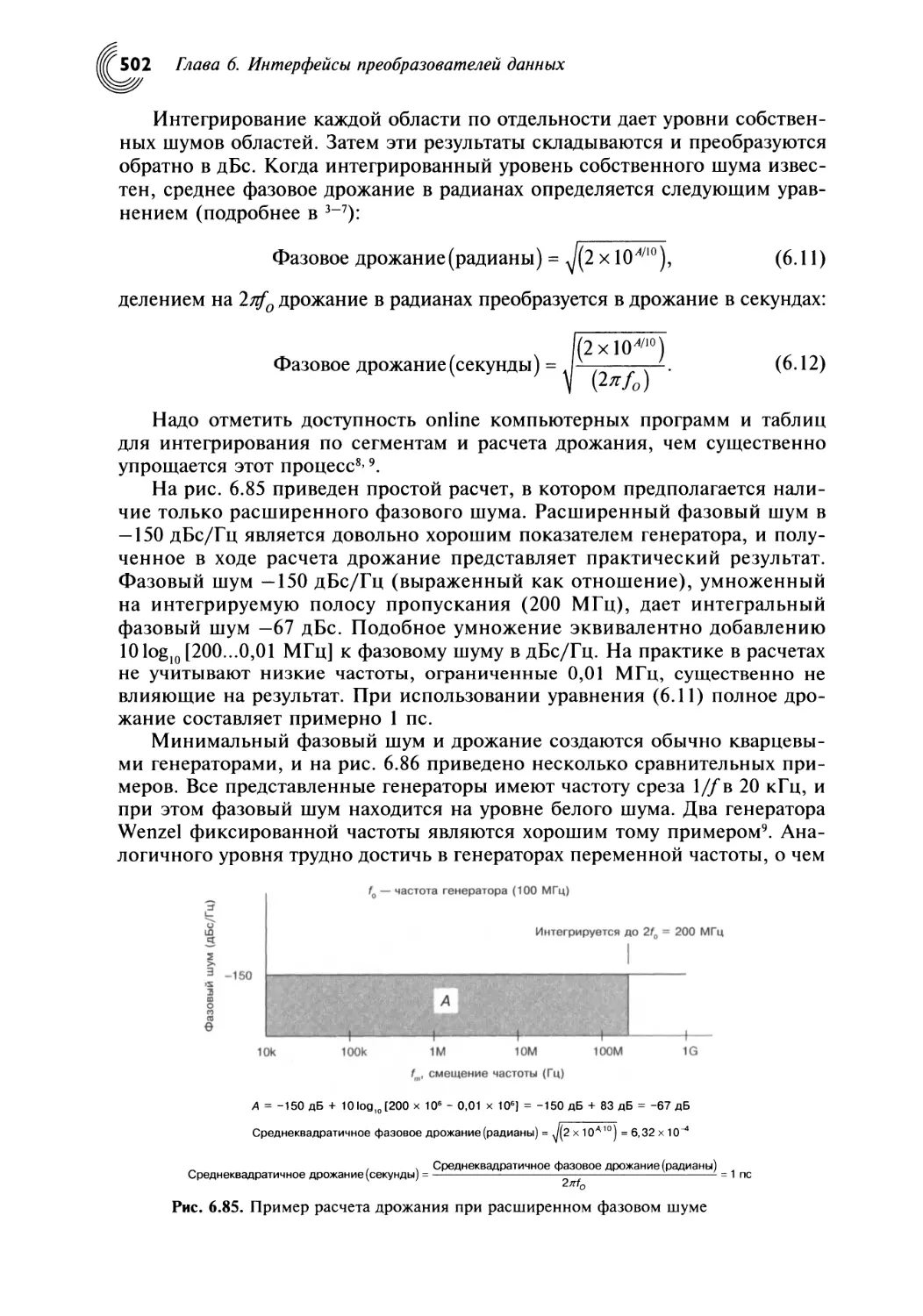

Фазовый шум и дрожание генератора................................499

«Гибридные» генераторы частоты.................................. 506

Подключение дифференциальных входов синхронизации............... 507

Выводы по тактированию выборок.................................. 509

Список литературы к 6.5. Формирование синхроимпульсов

дискретизации.......................................................509

Глава 7. СХЕМЫ ПОДДЕРЖКИ ПРЕОБРАЗОВАТЕЛЕЙ ДАННЫХ........................511

7.1. Источники опорного напряжения (Уолт Джанг, Уолт Кестер,

Джеймс Брайант).....................................................511

Прецизионные источники опорного напряжения...................... 511

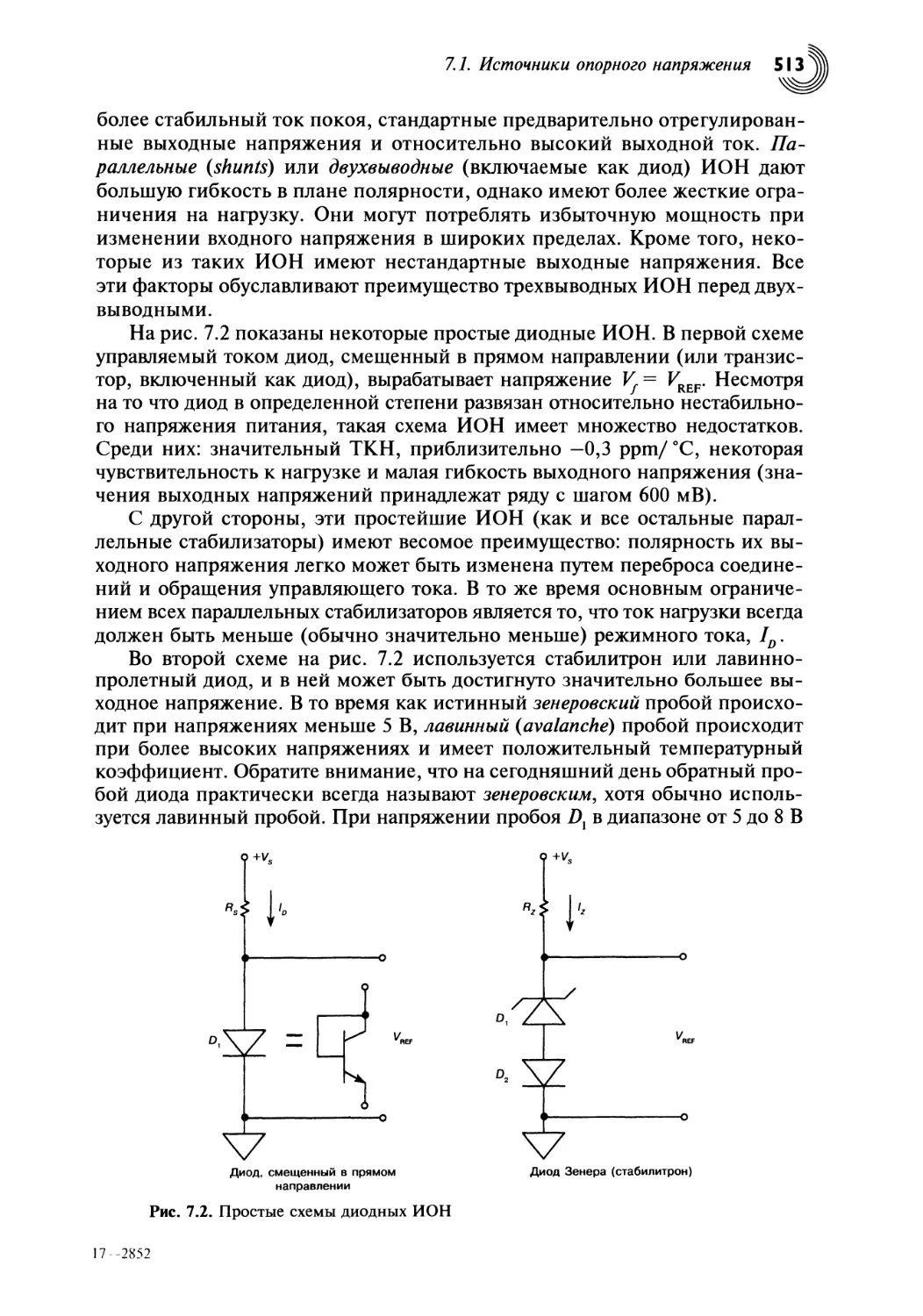

Типы источников опорного напряжения............................. 512

ИОН с напряжением запрещенной зоны.............................. 514

ИОН на заглубленных стабилитронах............................... 520

ИОН XFET® ...................................................... 521

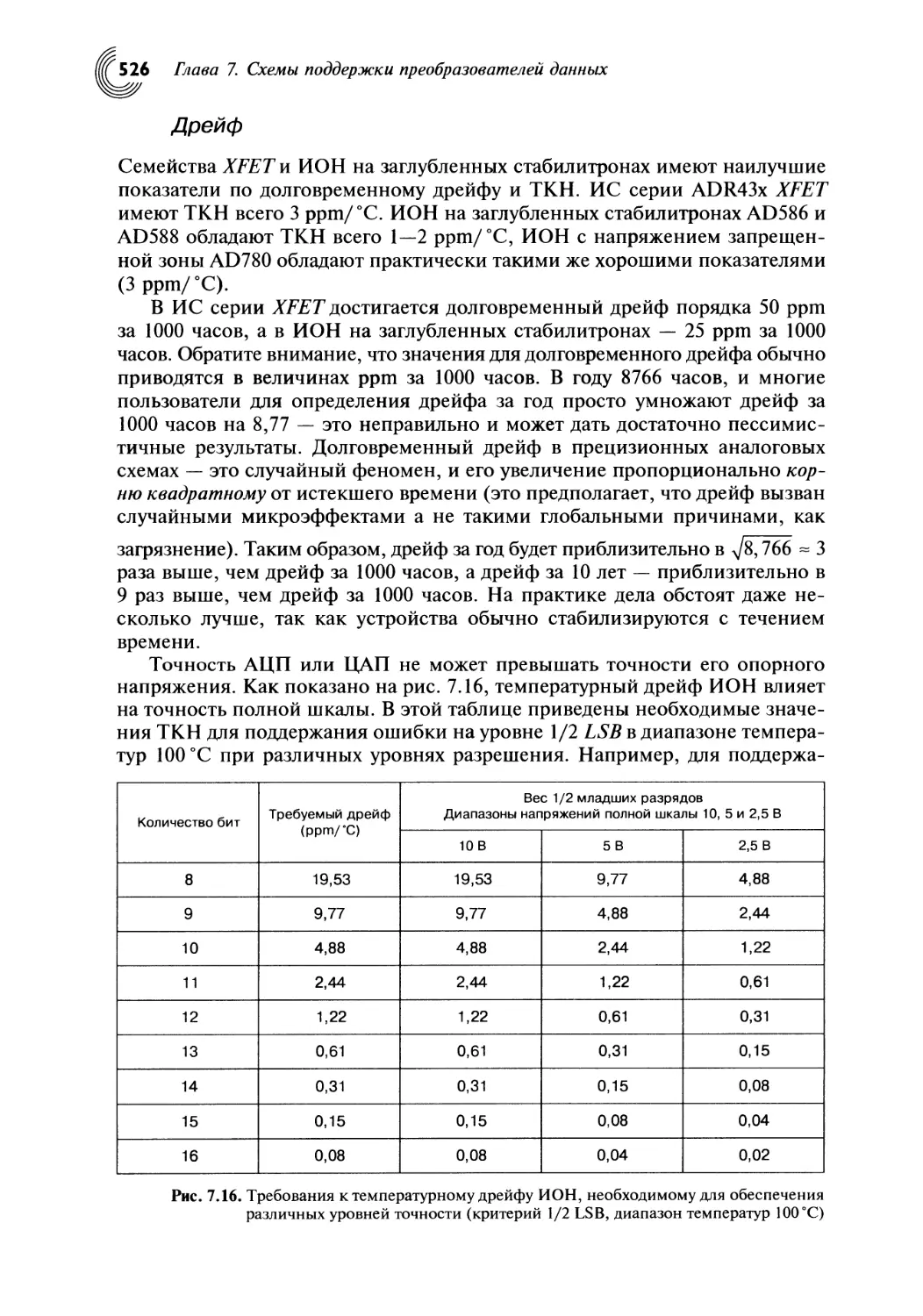

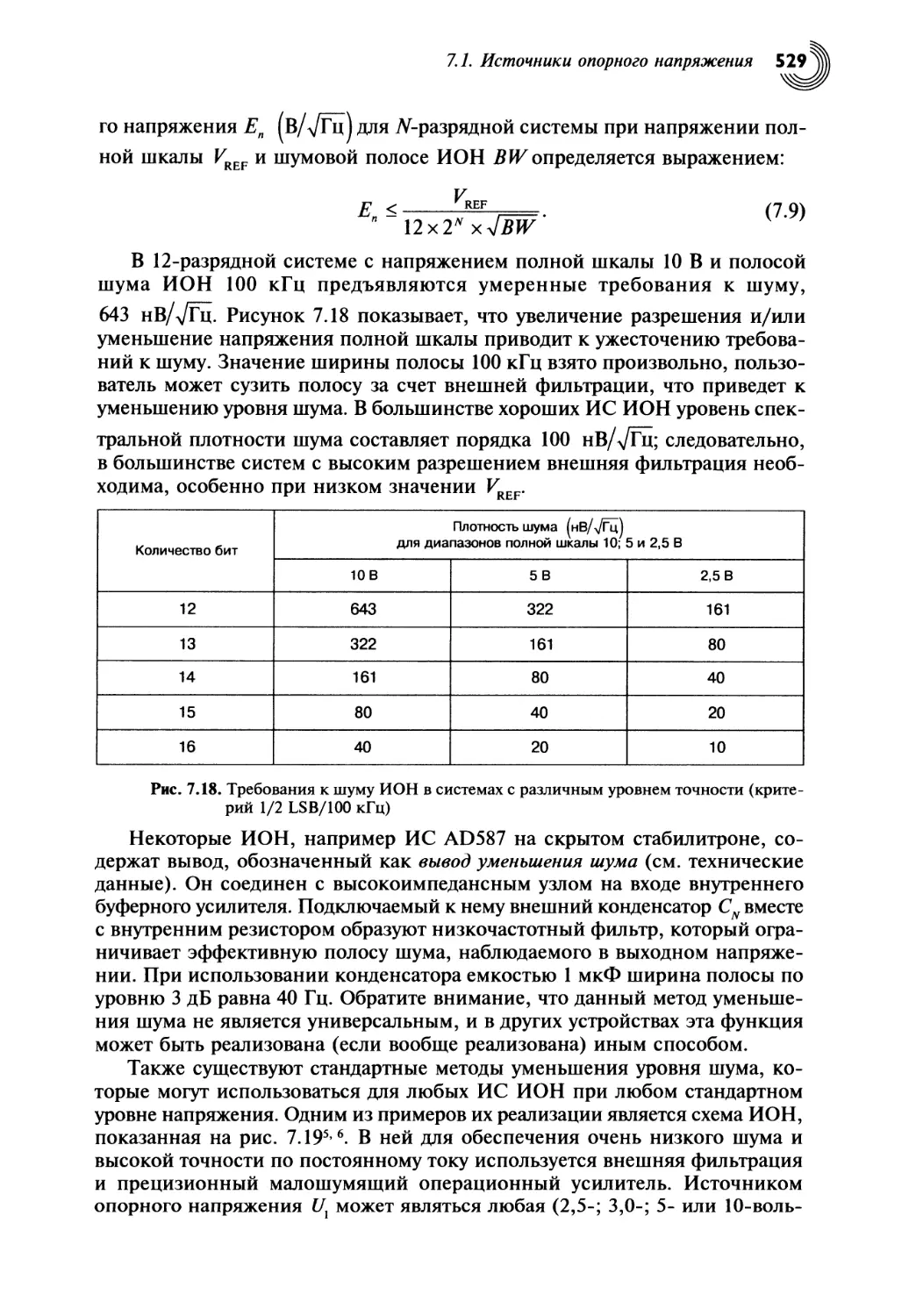

Характеристики ИОН...............................................525

Список литературы к 7.1. Источники опорного напряжения..............536

7.2. Линейные стабилизаторы с малым падением напряжения

(Уолт Джанг)........................................................537

Введение........................................................ 537

Основы линейных стабилизаторов напряжения....................... 538

Проходные элементы, их преимущества и недостатки................ 540

Архитектуры стабилизаторов с малым падением напряжения.......... 545

Семейство стабилизаторов с малым падением напряжения апуСАР®.....549

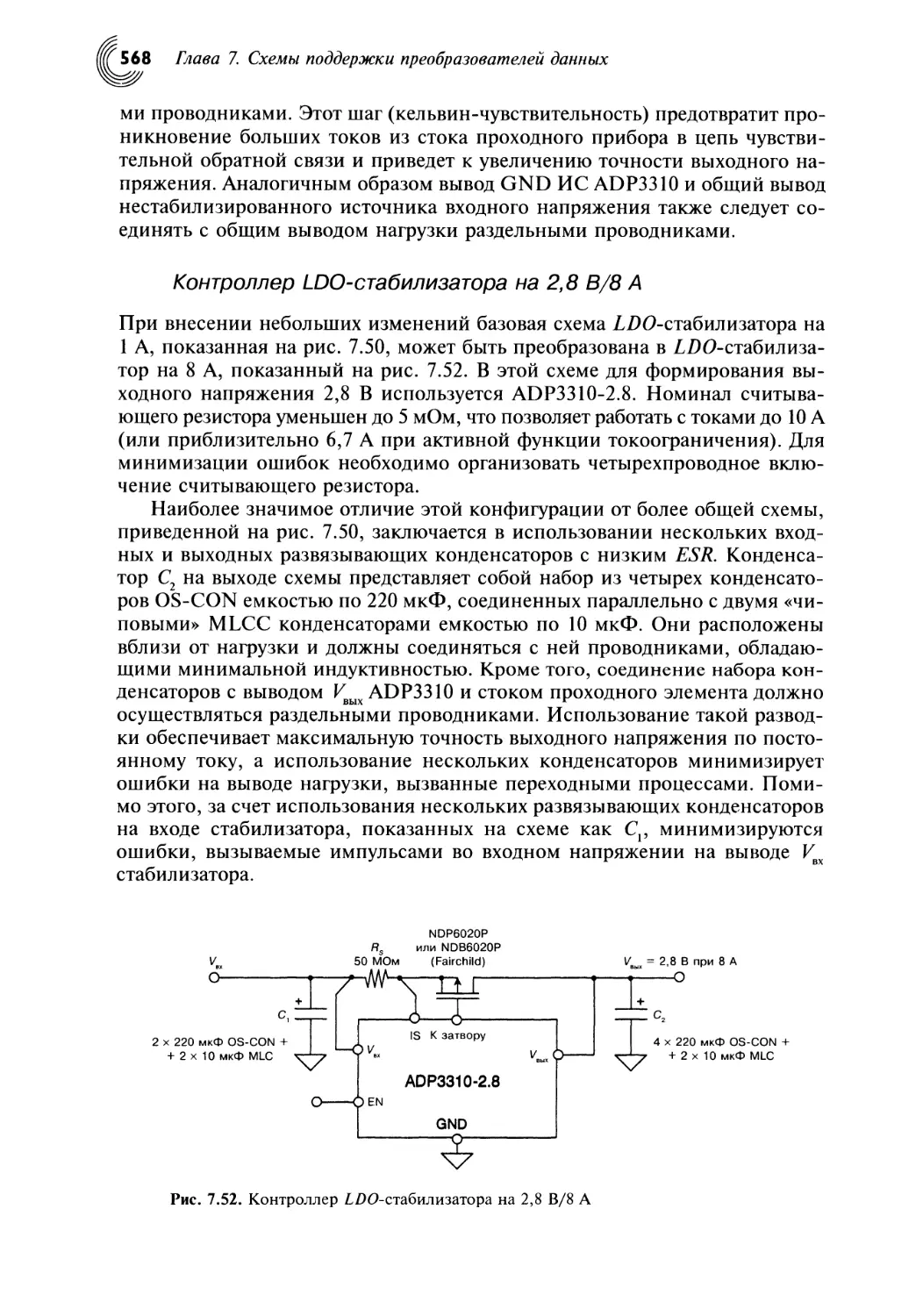

Контроллеры LDO-стабилизаторов.................................. 560

Список литературы к 7.2. Линейные стабилизаторы с малым падением

напряжения..........................................................569

7.3. Аналоговые ключи и мультиплексоры (Уолт Кестер)................569

Введение........................................................ 569

Основы КМОП-ключей.............................................. 571

Источники ошибок в КМОП-ключах.................................. 573

Применение аналоговых ключей.................................... 580

КМОП-ключи с полосой 1 ГГц...................................... 584

Содержание 7

Видеоключи и мультиплексоры.......................................585

Видео кросс-коммутаторы.......................................... 588

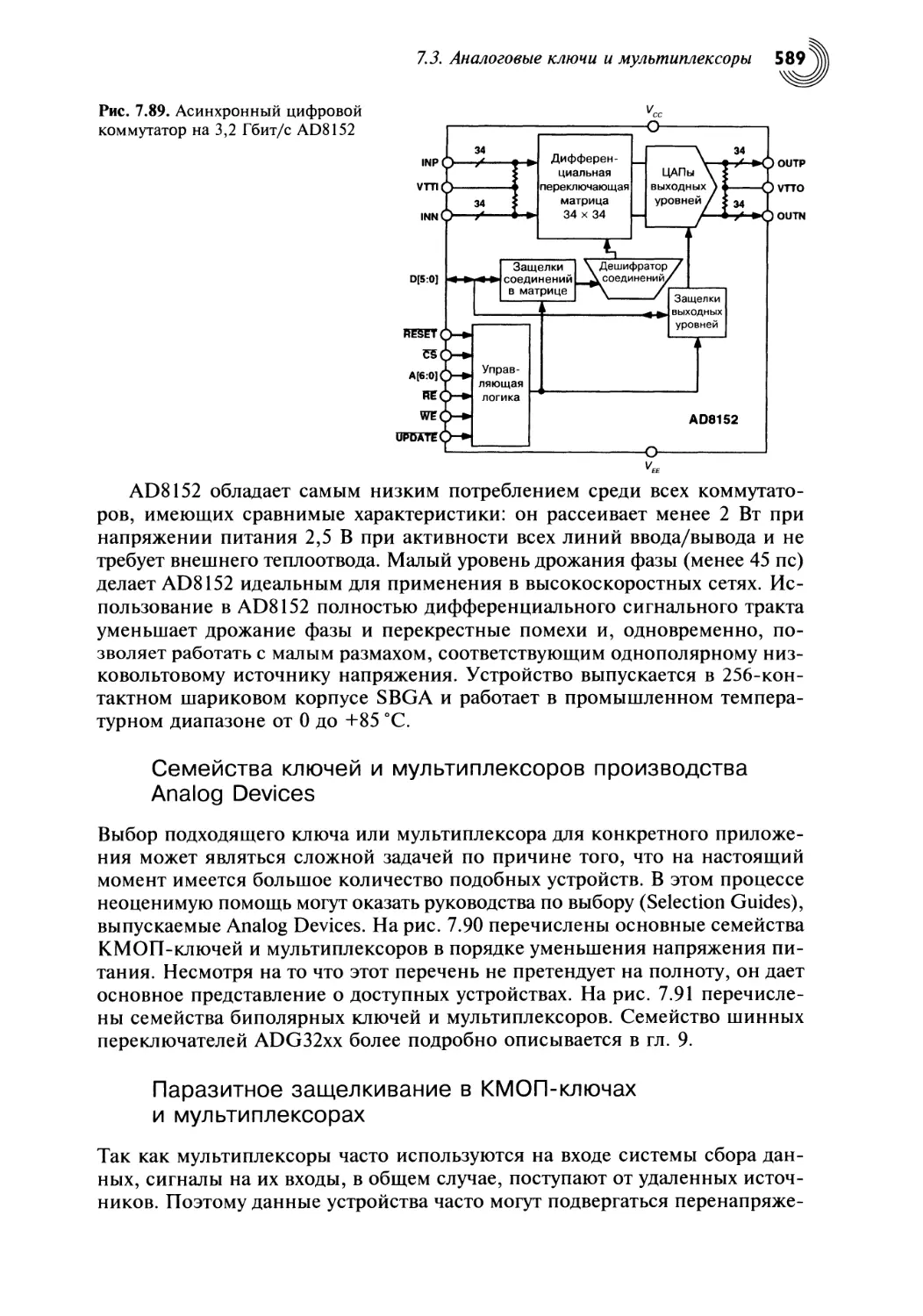

Цифровые коммутаторы............................................. 588

Семейства ключей и мультиплексоров производства Analog Devices....589

Паразитное защелкивание в КМОП-ключах и мультиплексорах.......... 590

7.4. Схемы выборки и хранения (Уолт Кестер)...........................594

Введ ение и исторический обзор...................................594

Основные принципы работы УВХ................................... 596

Характеристики режима слежения................................... 597

Характеристики режима перехода от выборки к хранению............. 598

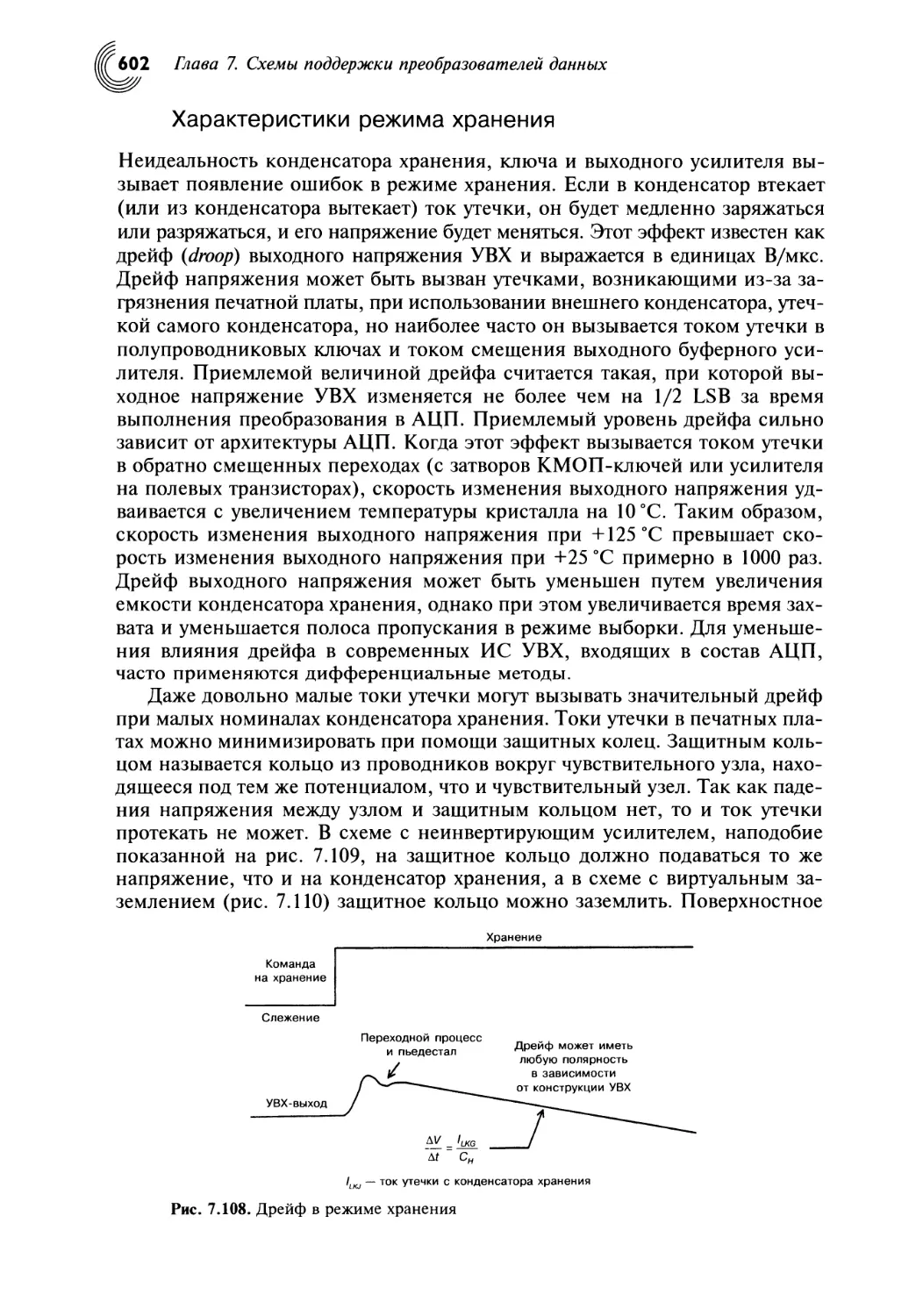

Характеристики режима хранения ...................................602

Характеристики в режиме перехода от хранения к выборке............605

Архитектуры УВХ...................................................605

Внутренние УВХ ИС АЦП ........................................... 608

Применение УВХ....................................................611

Список литературы к 7.4. Схемы выборки и хранения.....................613

Глава 8. ПРИМЕНЕНИЕ ПРЕОБРАЗОВАТЕЛЕЙ ДАННЫХ..............................615

8.1. Прецизионные измерения и преобразование сигналов датчиков........615

Введение..........................................................615

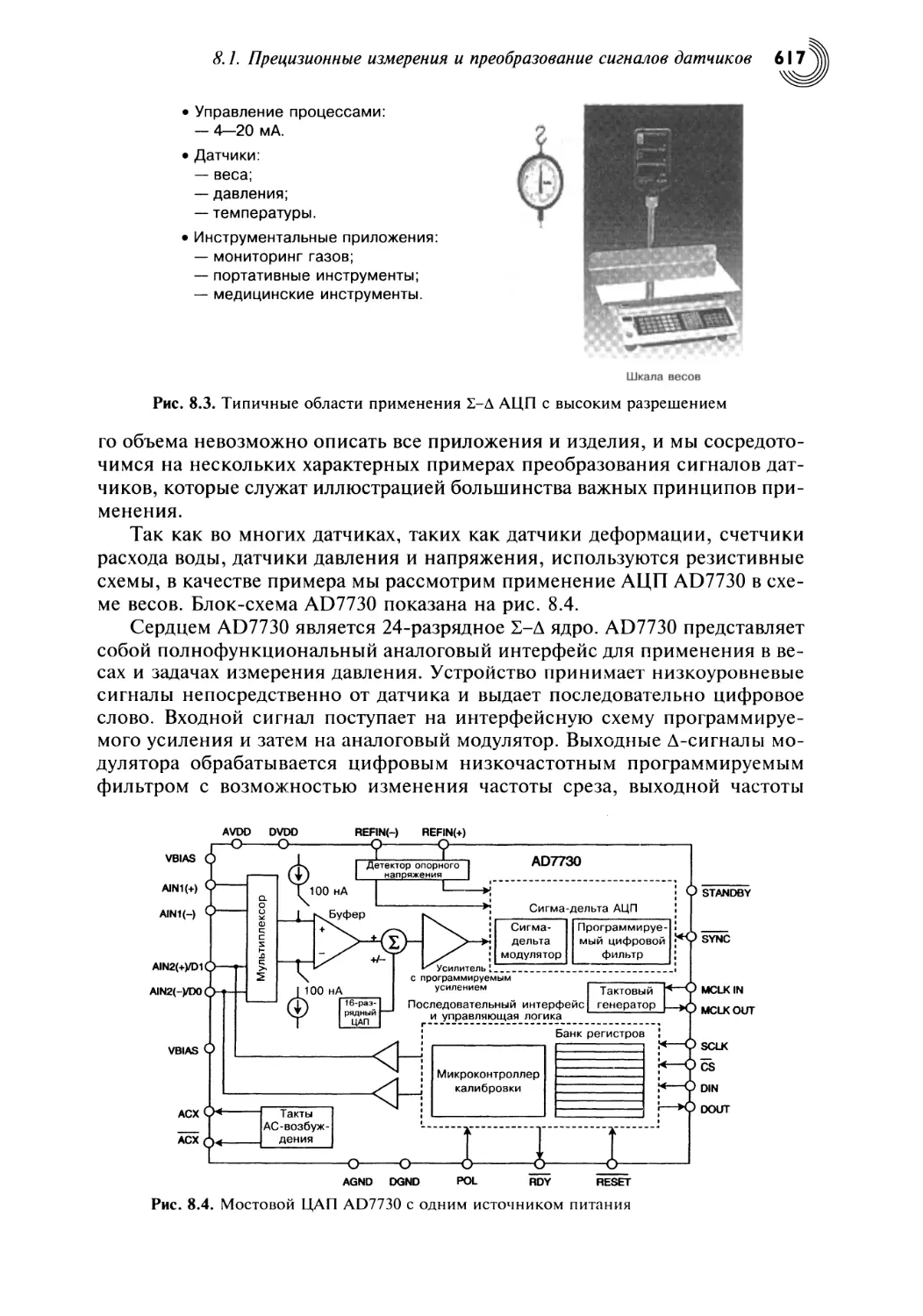

Применение прецизионных измерительных Е-Д АЦП.....................616

Анализ проекта весов на базе AD7730.............................. 620

Термопара с AD7793 .............................................. 626

Прямые цифровые измерения температуры.............................628

Датчики температуры микропроцессорных подложек....................633

Применение АЦП в ваттметрах.......................................636

Список литературы к 8.1. Прецизионные измерения и преобразование

сигналов датчиков.....................................................639

8.2. Многоканальные системы сбора данных (Уолт Кестер)................639

Конфигурации систем сбора данных................................. 639

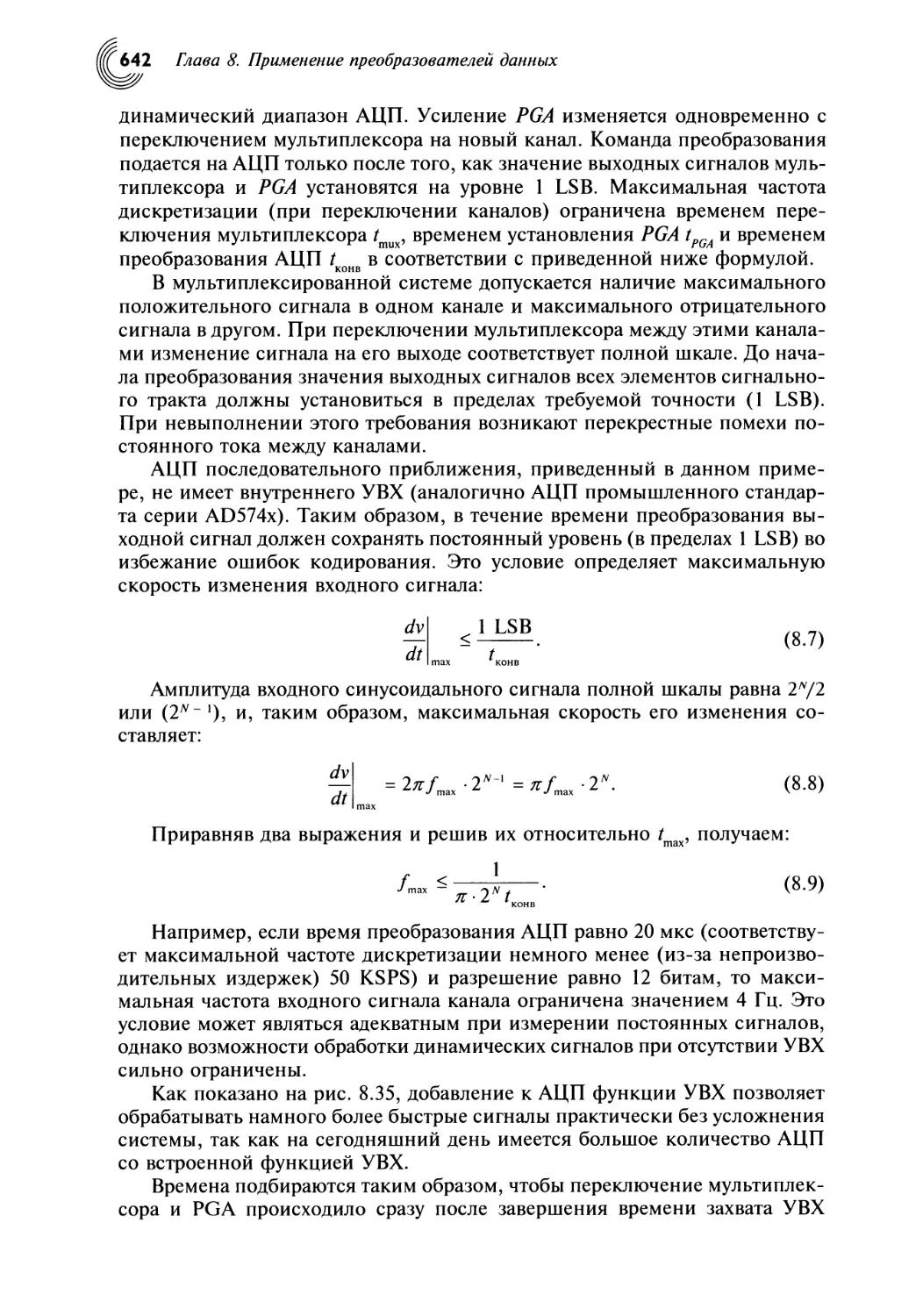

Мультиплексирование.............................................. 640

Фильтрация в системах сбора данных................................643

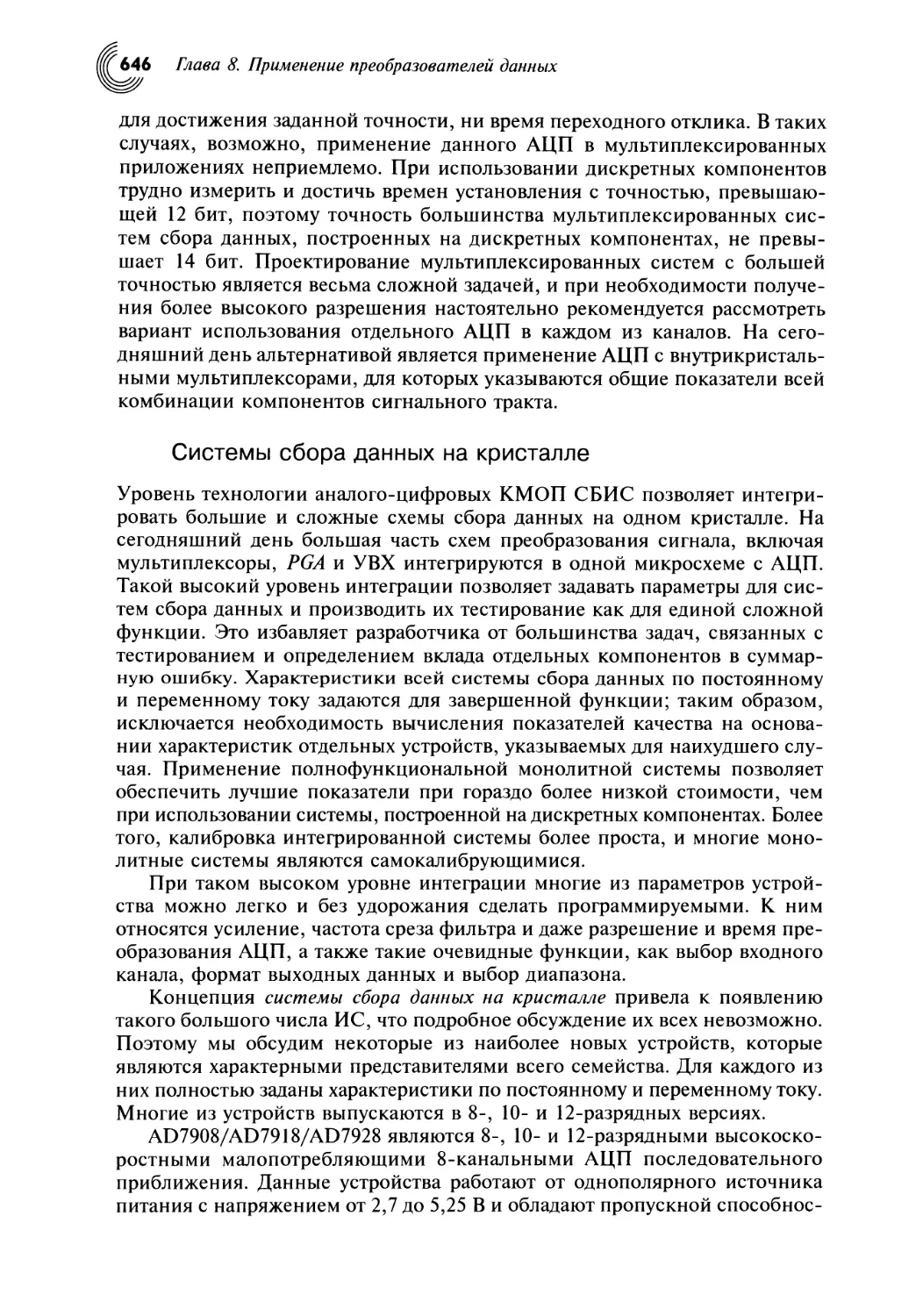

Системы сбора данных на кристалле ............................... 646

Мультиплексирование входов Е-Д АЦП................................648

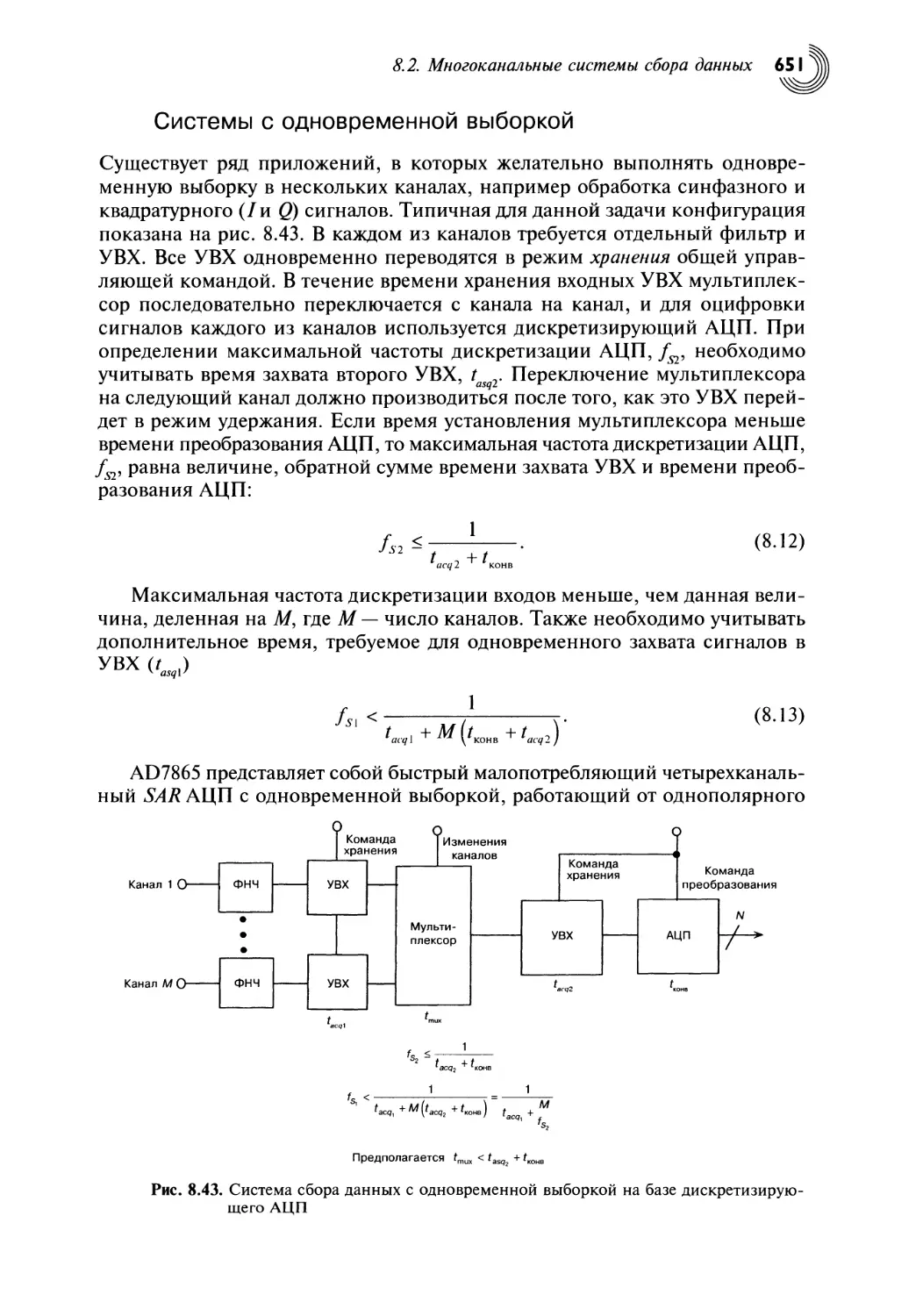

Системы с одновременной выборкой................................. 651

Системы распределения данных..................................... 653

Распределение данных при помощи схем с выборкой и бесконечным

хранением.........................................................658

Список литературы к 8.2. Многоканальные системы сбора данных......... 661

8.3. Цифровые потенциометры (Уолт Кестер, Уолт Хайнцер)...............661

Введение..........................................................661

Современные цифровые потенциометры в миниатюрных корпусах.........663

Цифровые потенциометры с энергонезависимой памятью................664

Однократно программируемые (ОТР) цифровые потенциометры.......... 665

Характеристики цифровых потенциометров по переменному току........667

Примеры применения .............................................. 668

Резюме............................................................669

Список литературы к 8.3. Цифровые потенциометры.......................670

8.4. Цифровой звук (Уолт Кестер)......................................671

Введение..........................................................671

Требования к частоте дискретизации и THD + N для цифрового звука..673

Общие тенденции в аудио АЦП и ЦАП.................................676

Речевые кодеки....................................................678

Высококачественные аудио АЦП и ЦАП в раздельных корпусах .........679

Содержание

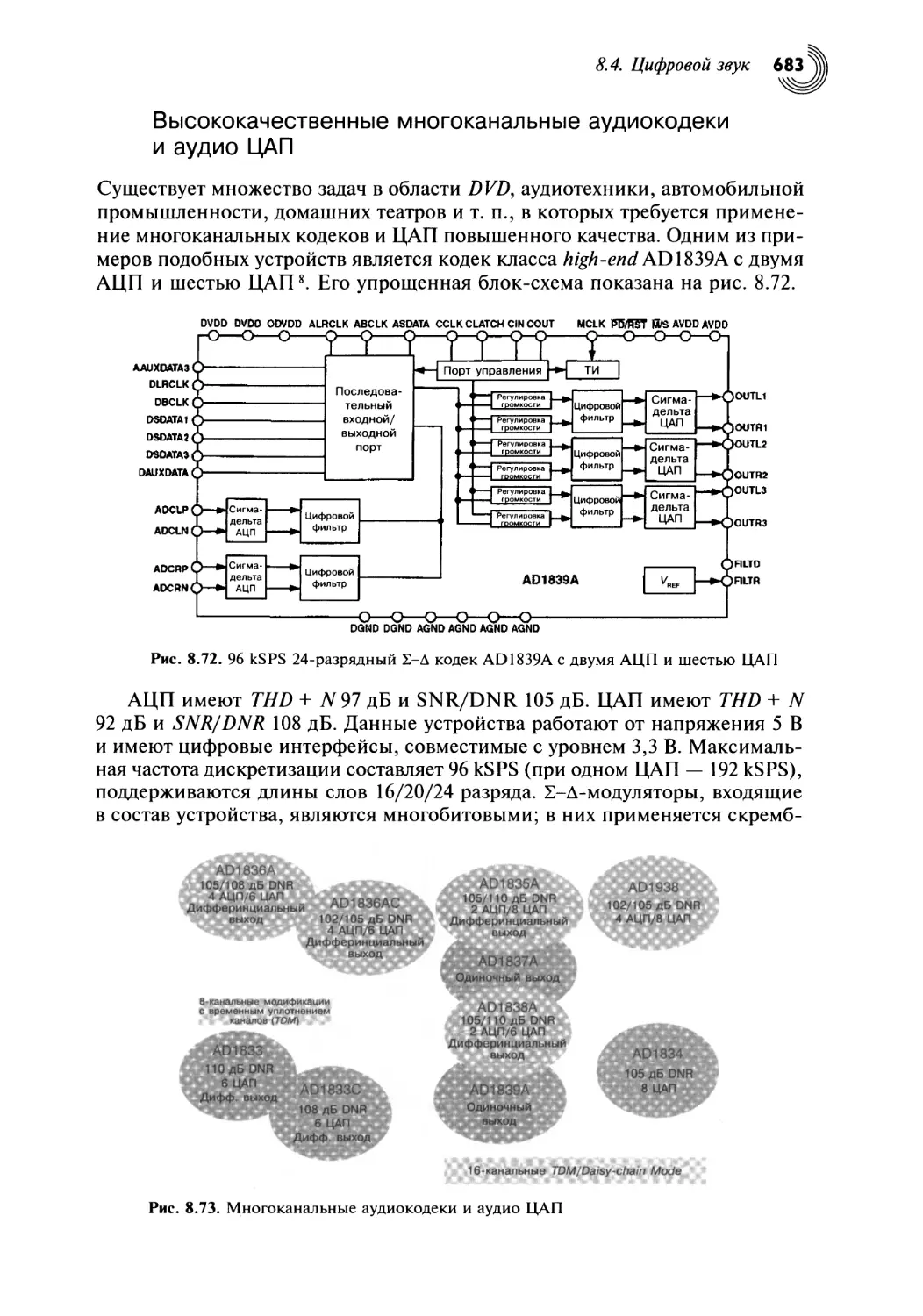

Высококачественные многоканальные аудиокодеки и аудио ЦАП.........683

Преобразователи частоты дискретизации.............................684

Список литературы к 8.4, Цифровой звук...............................687

8.5. Цифровое видео и цифровая электроника дисплеев (Уолт Кестер)....687

Цифровое видео....................................................687

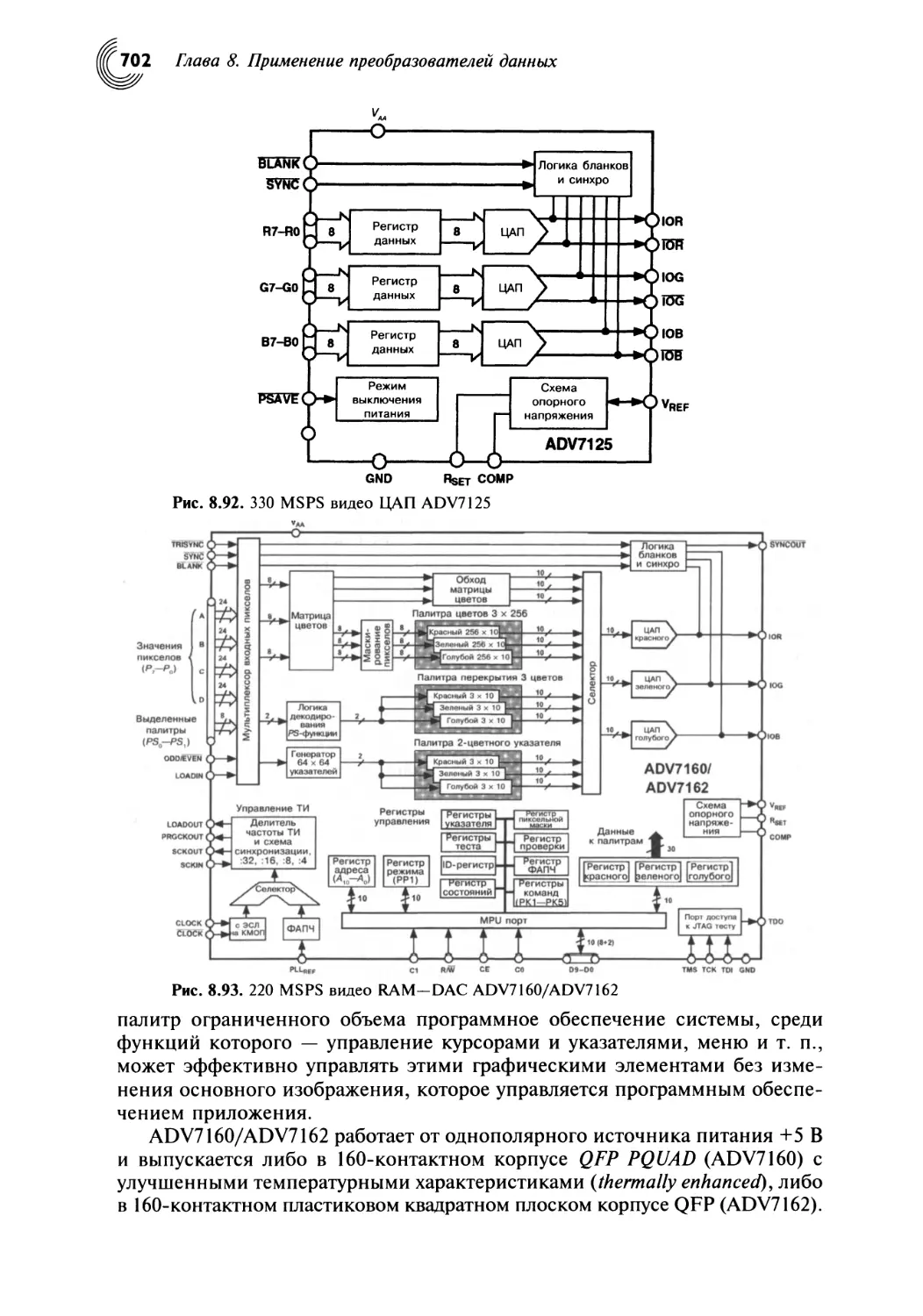

Электронные компоненты дисплеев ..................................697

Электроника плоских дисплеев..................................... 703

Электроника ПЗС...................................................706

Устройства оцифровки сенсорных экранов........................... 712

Список литературы к 8.5. Цифровое видео и цифровая электроника

дисплея..............................................................716

8.6. Программное радио и дискретизация на промежуточной частоте

(Уолт Кестер)........................................................717

Введение..........................................................717

Развитие беспроводного радио......................................718

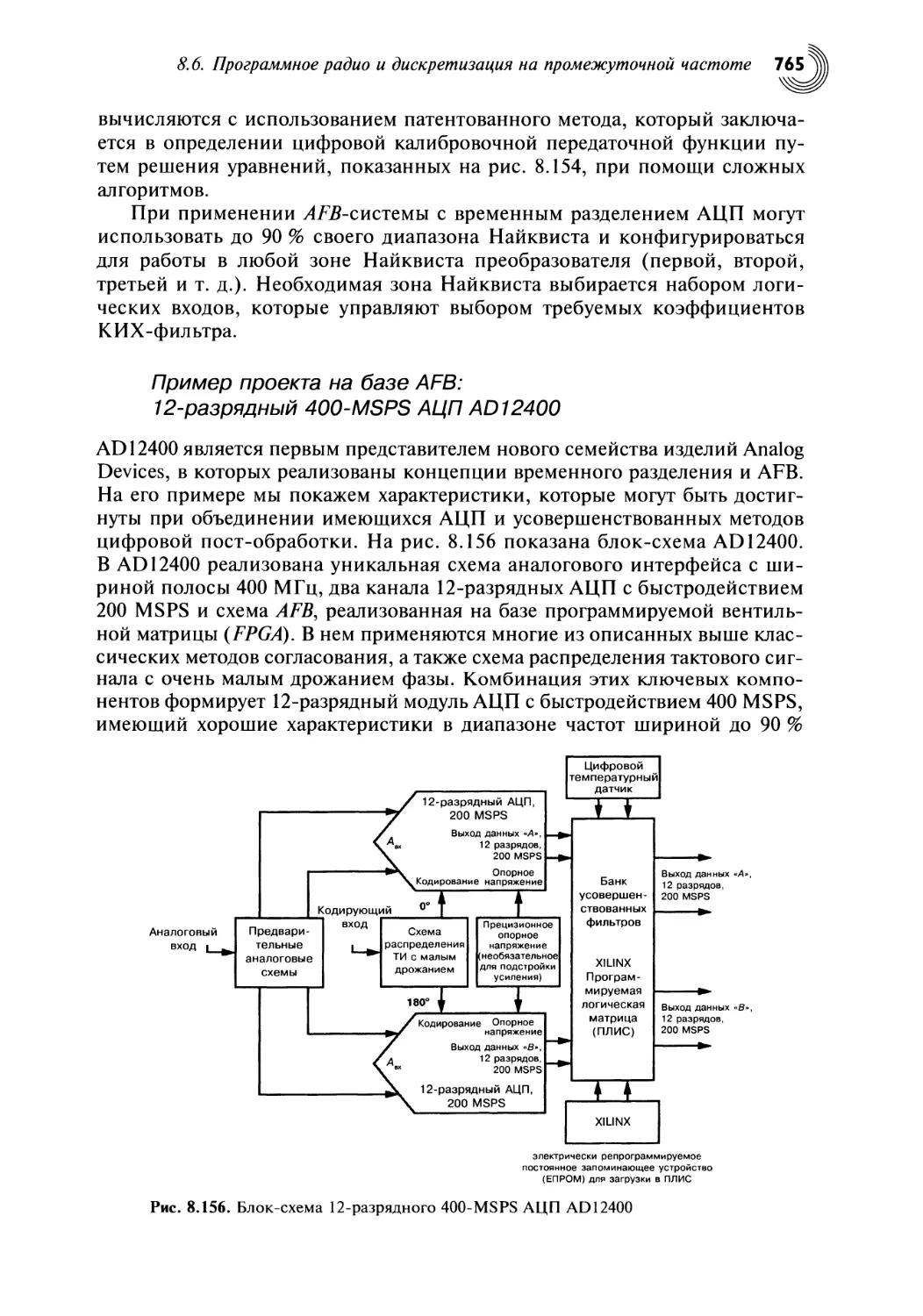

АЦП с дискретизацией на ПЧ в режиме разделения во времени с цифровыми

пост-процессорами (Марк Луни).....................................758

Список литературы к 8.6. Программное радио и дискретизация

на промежуточной частоте.............................................767

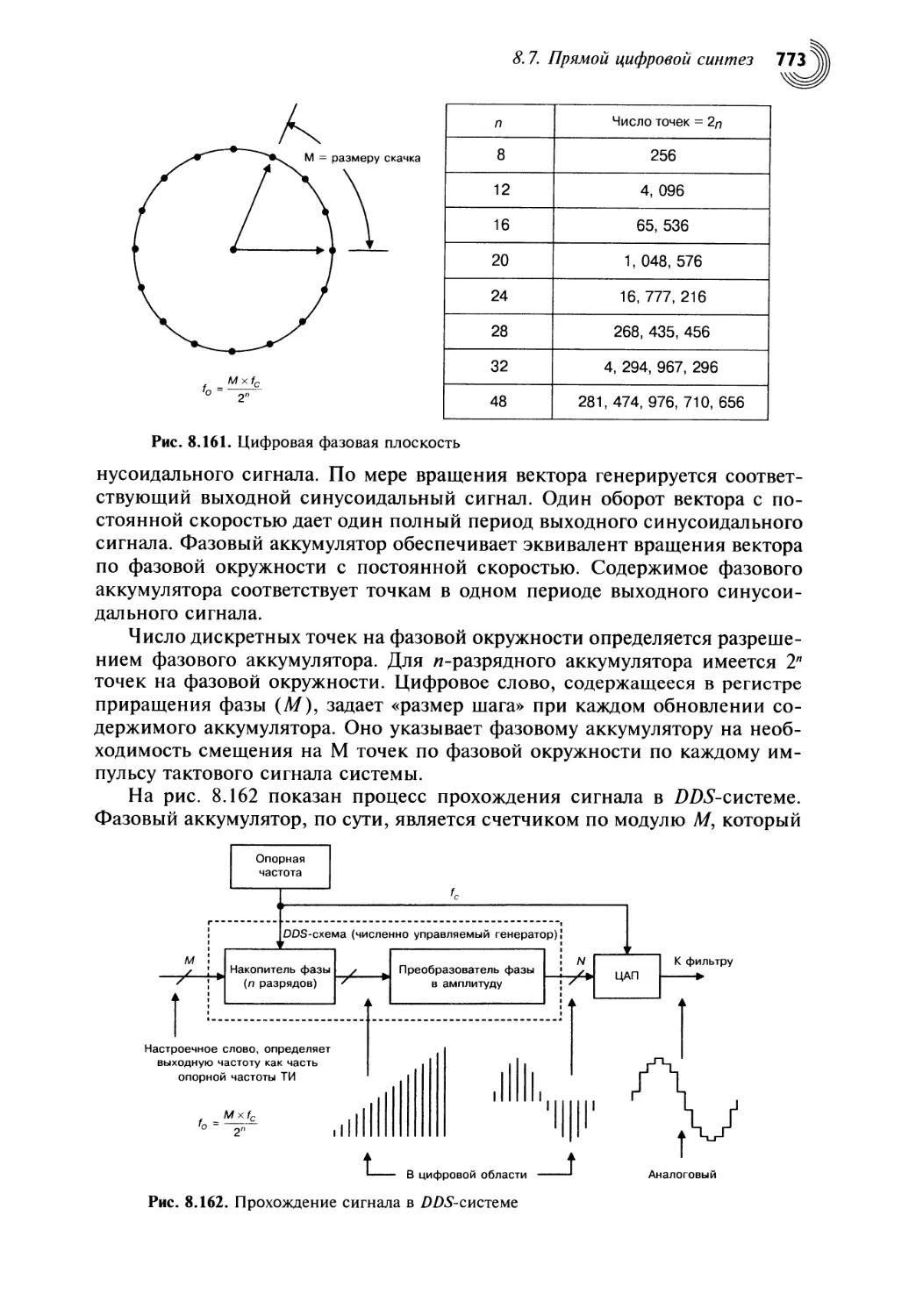

8.7. Прямой цифровой синтез (Уолт Кестер)............................769

Введение в технологию DDS........................................ 769

Наложение в /)£)5-системах........................................774

Частотное планирование в /)7)5-системах...........................775

Современные интегрированные Ш)5-системы...........................777

Список литературы к 8.7. Прямой цифровой синтез......................785

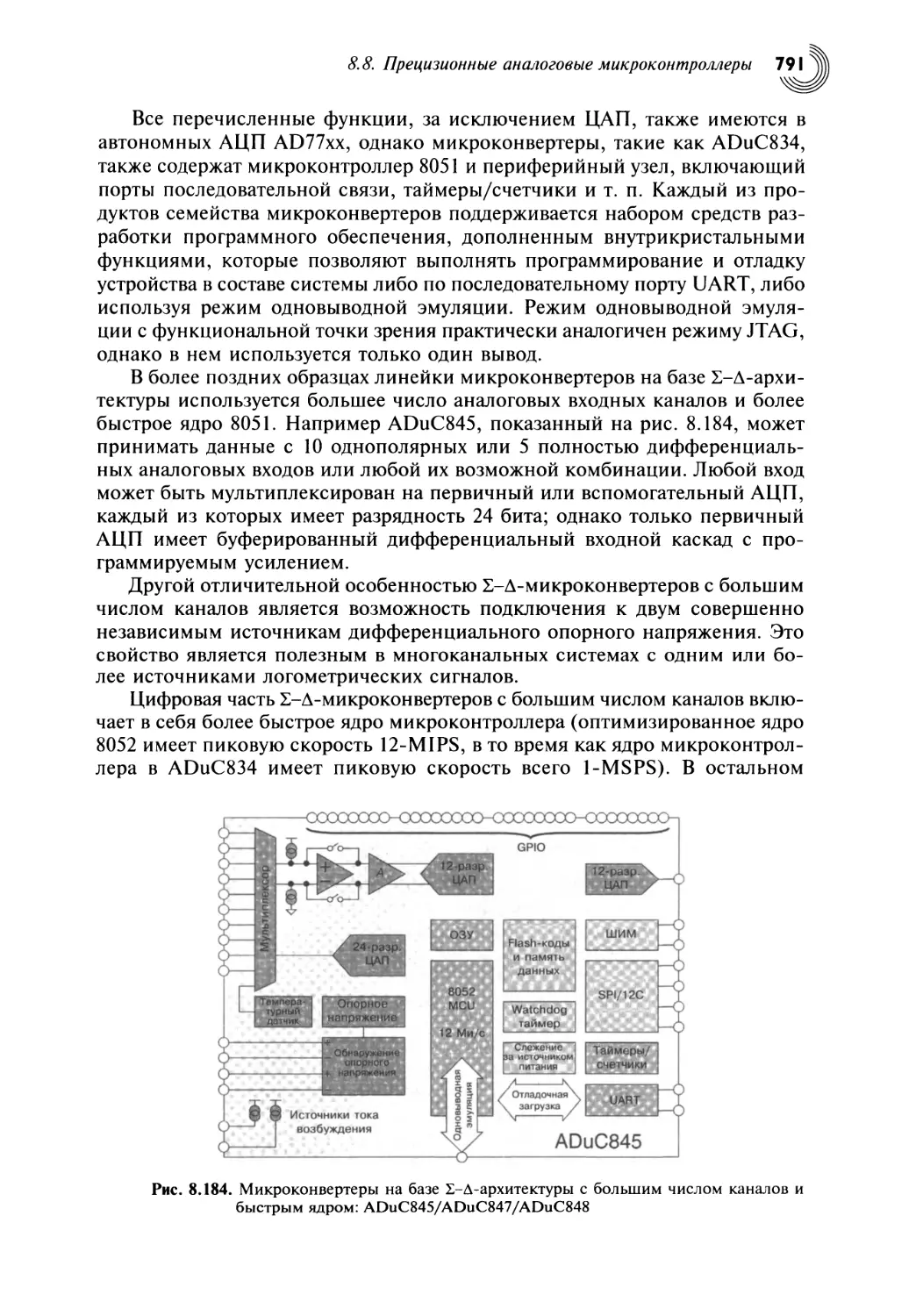

8.8. Прецизионные аналоговые микроконтроллеры (Грэйсон Кинг).........786

Введение......................................................... 786

Характеристики семейства микроконвертеров.........................787

Некоторые примеры применения Z-Д-микроконвертеров.................793

Микроконвертеры ADuC7xxx на базе ядра процессора ARM7T............797

Список литературы к 8.8. Прецизионные аналоговые микроконтроллеры....800

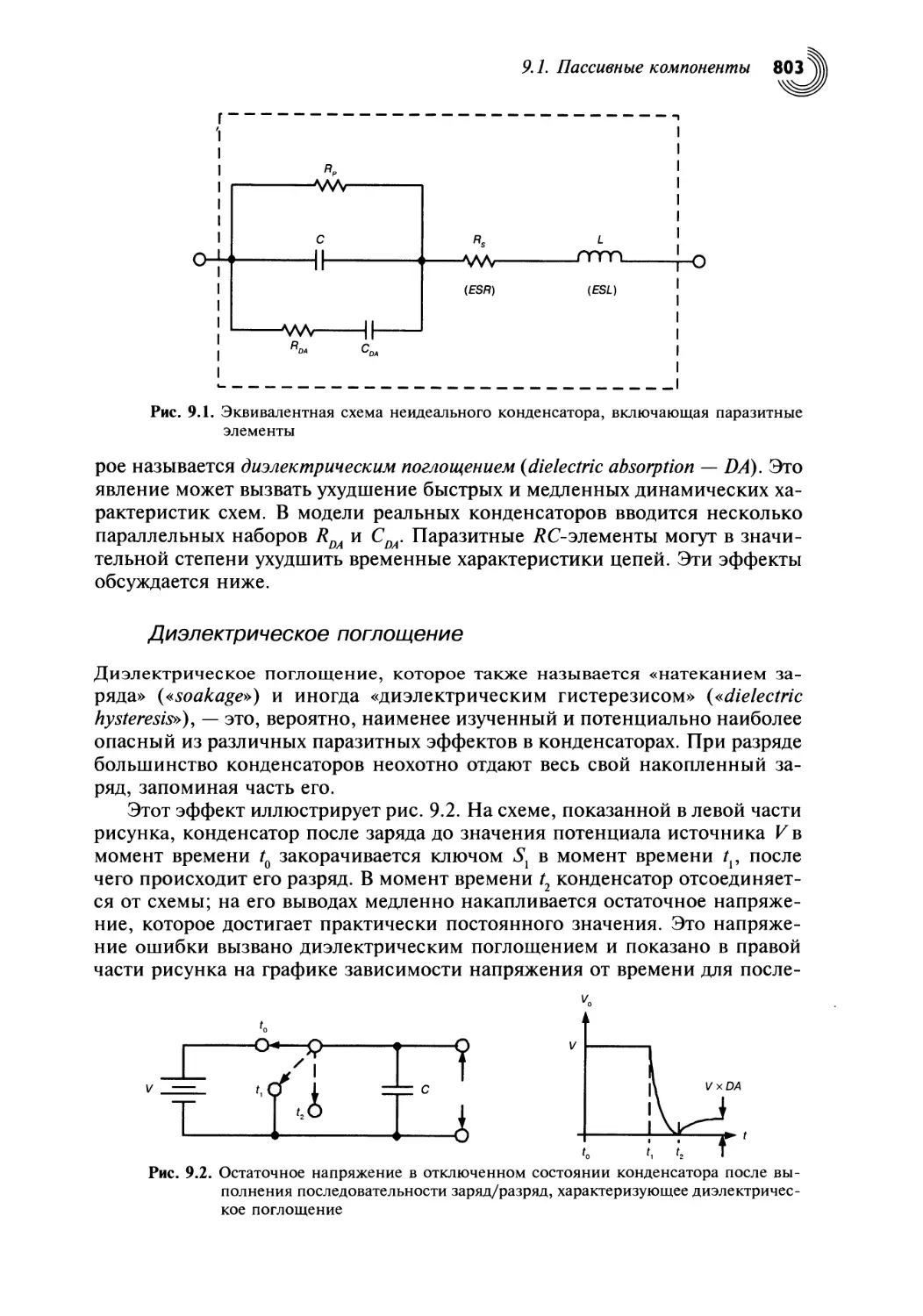

Глава 9. МЕТОДЫ ПРОЕКТИРОВАНИЯ АППАРАТУРЫ................................801

9.1. Пассивные компоненты

(Джеймс Брайант, Уолт Джанг, Уолт Кестер) ...........................801

Введение......................................................... 801

Конденсаторы......................................................802

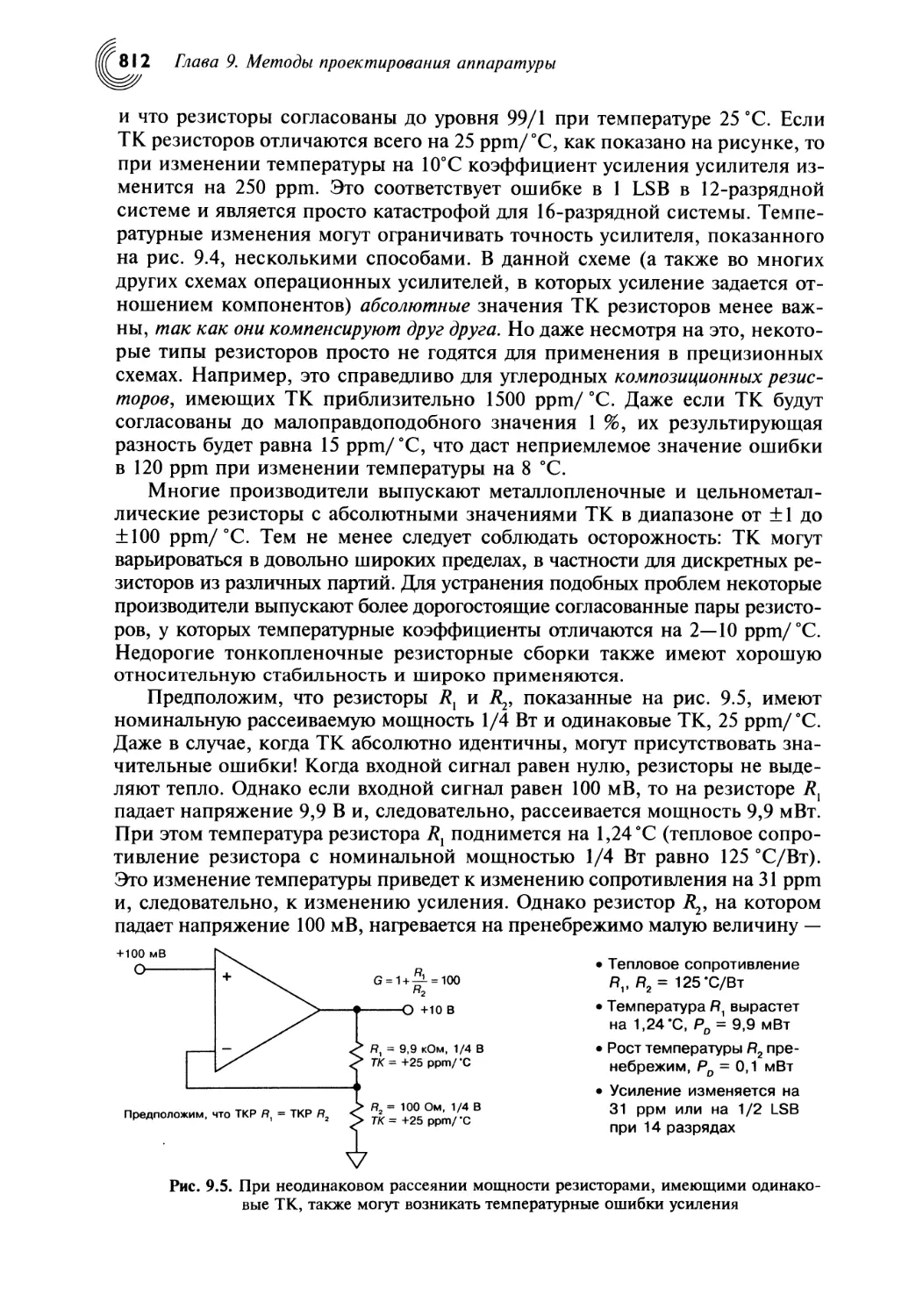

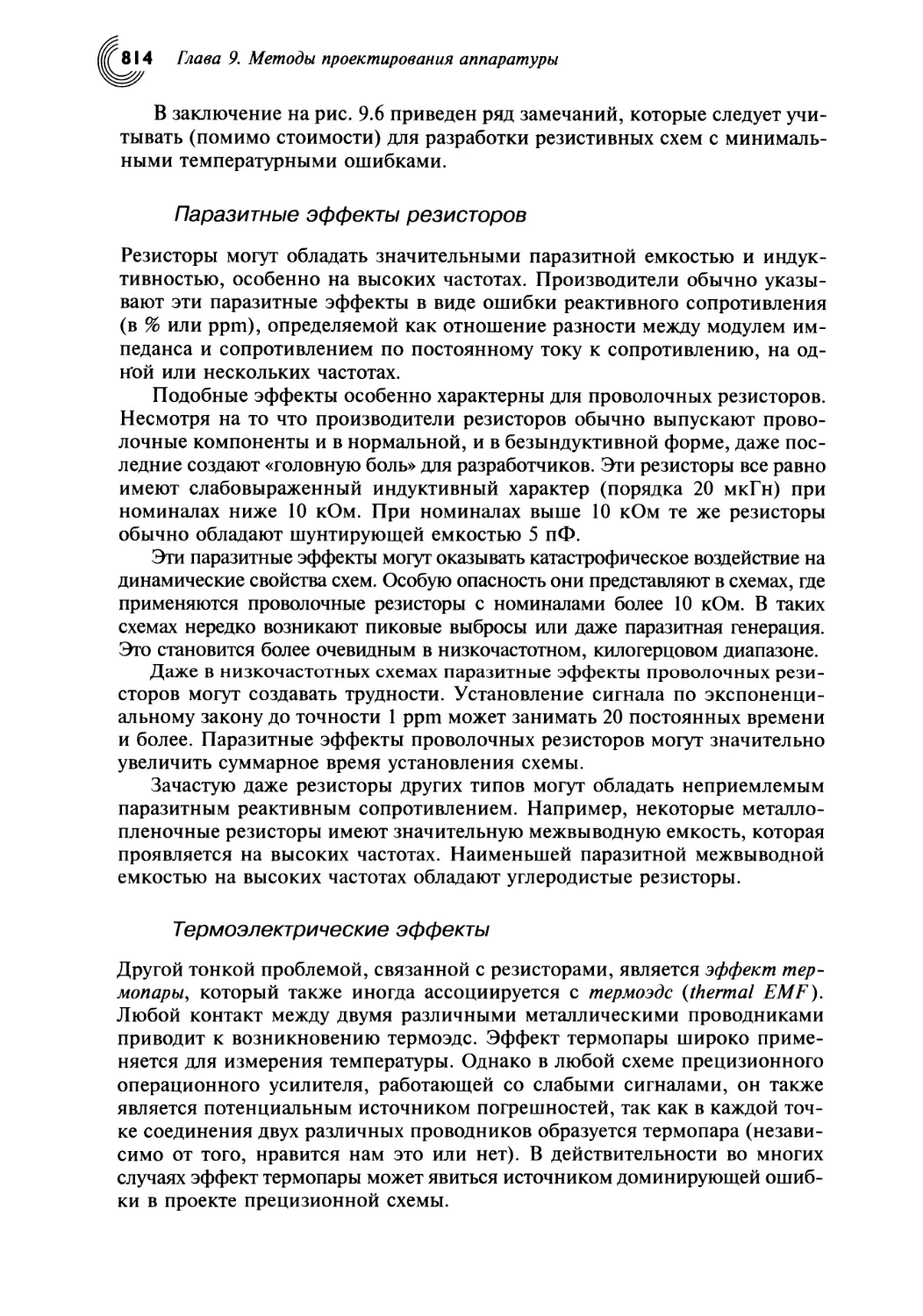

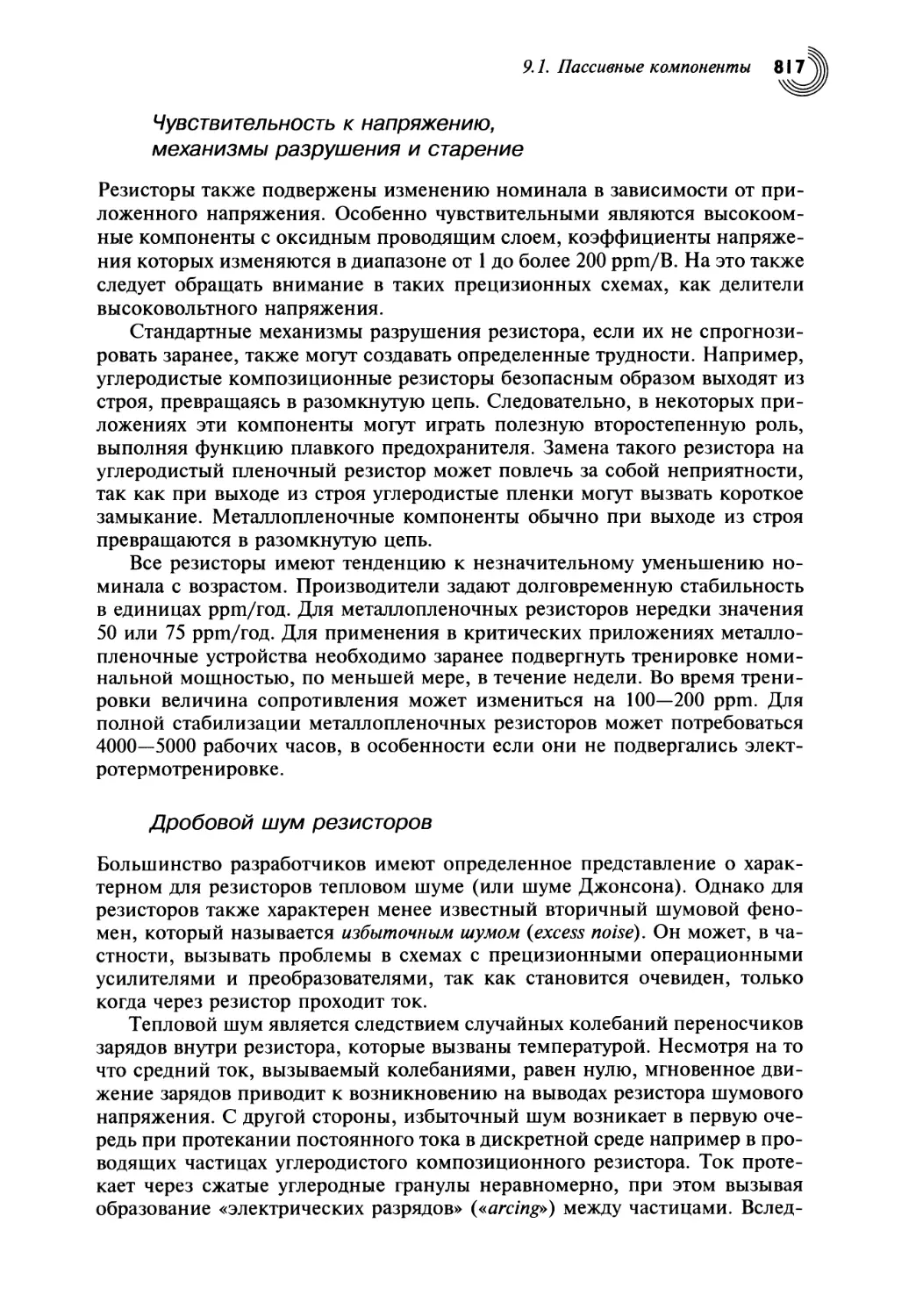

Резисторы и потенциометры........................................ 811

Индуктивность.................................................... 821

Список литературы к 9.1. Пассивные компоненты........................827

9.2. Вопросы конструирования печатных плат

(Джеймс Брайант, Уолт Кестер, Уолт Джанг) ...........................828

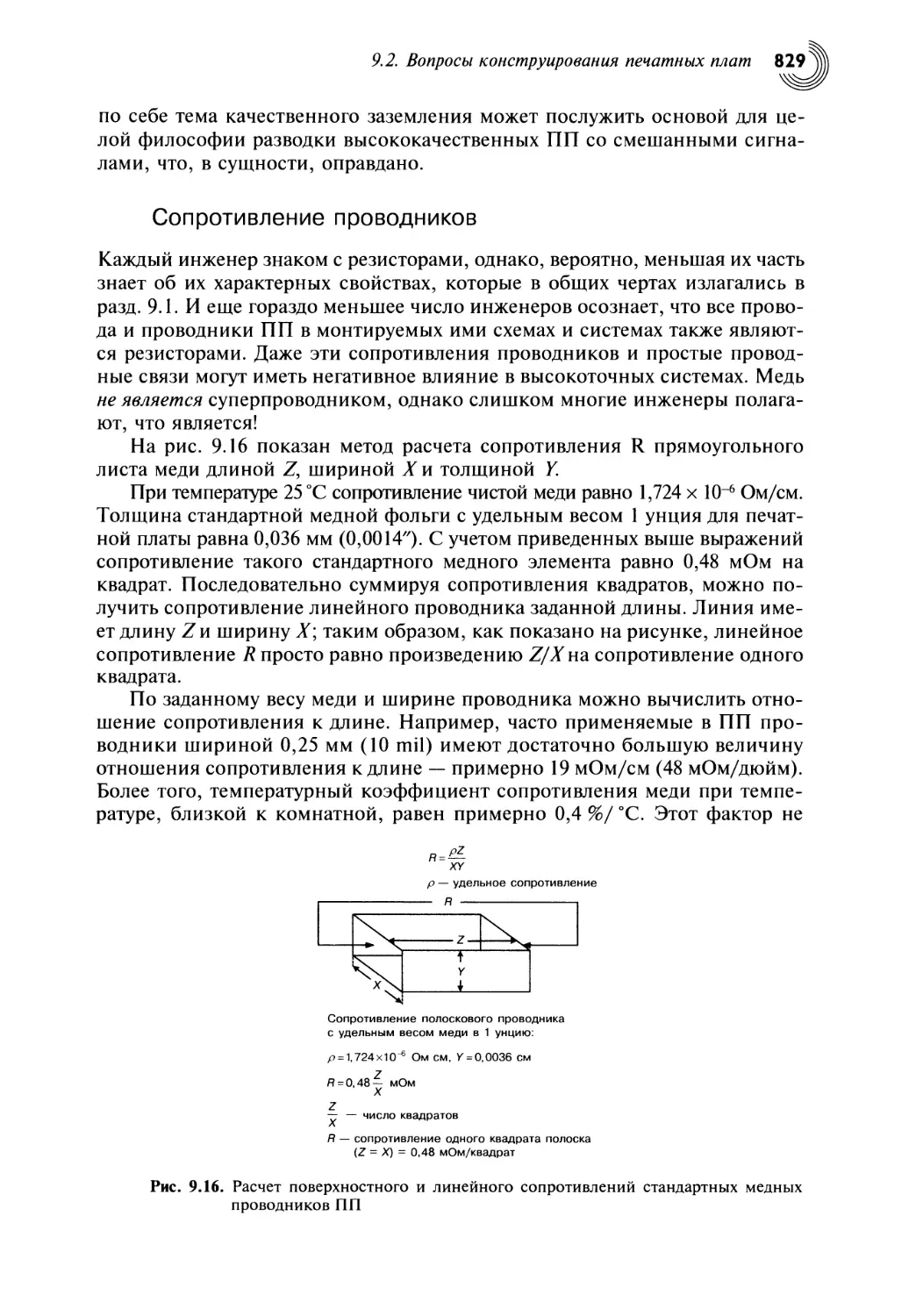

Сопротивление проводников........................................ 829

Падение напряжения на сигнальных проводниках — обратная связь

Кельвина......................................................... 830

Обратные сигнальные токи......................................... 831

Заземление в системах со смешанными аналого-цифровыми сигналами

(Уолт Кестер, Джеймс Брайант, Майк Бирн) ........................ 833

Некоторые общие правила разводки ПП для систем

со смешанными сигналами.......................................... 849

Скин-эффект...................................................... 851

Линии передачи (длинные линии)....................................852

Будьте внимательны к разрывам в заземляющих поверхностях......... 853

Методы изоляции заземления....................................... 854

Содержание 9

Статические эффекты ПП............................................ 857

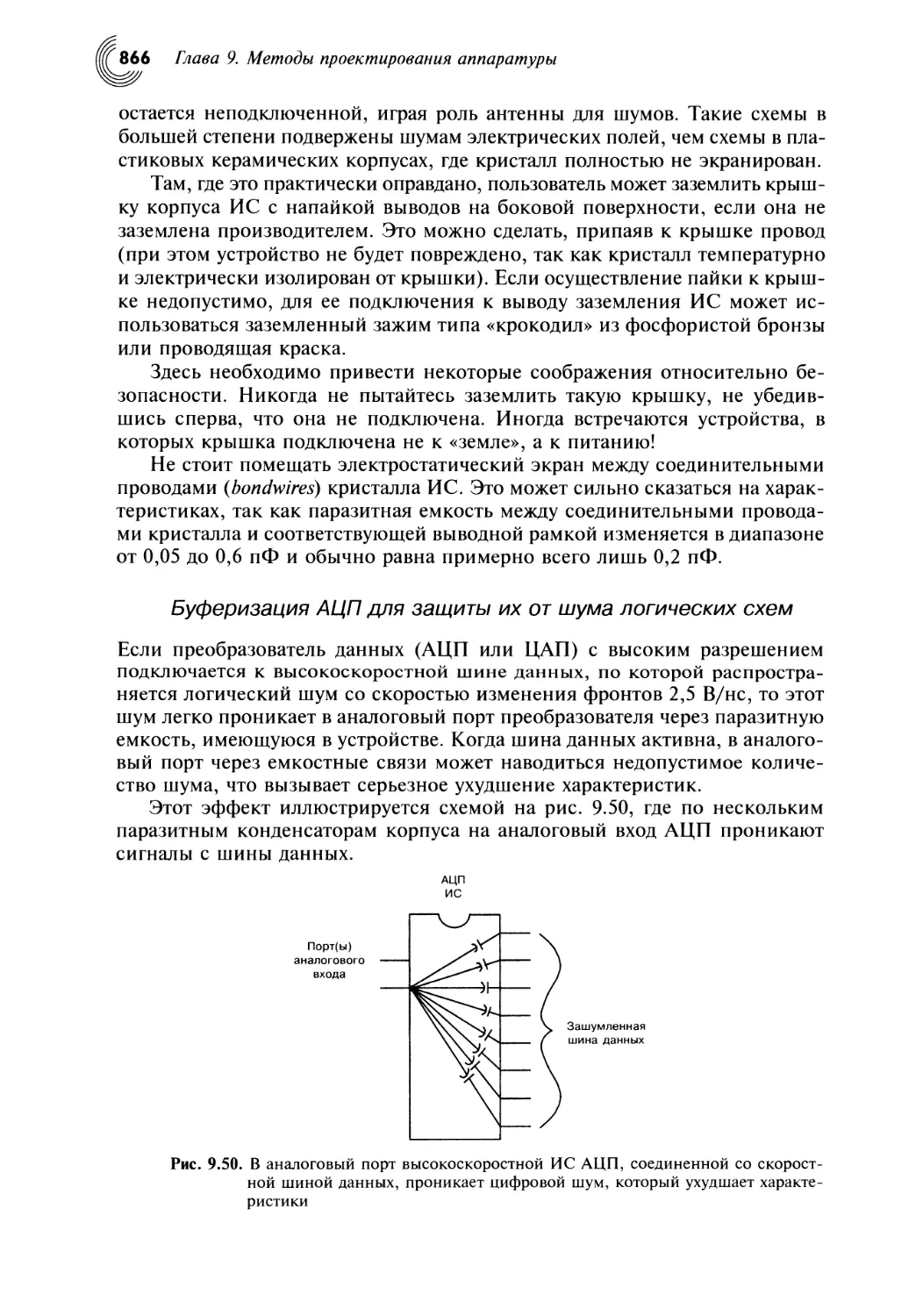

Динамические эффекты ПП........................................... 862

Список литературы к 9.2. Вопросы контруирования печатных плат..........867

9.3. Системы «аналогового» питания (Уолт Джанг, Уолт Кестер)...........868

ИС линейных стабилизаторов........................................ 869

Некоторые основы линейных стабилизаторов напряжения .............. 870

Проходные элементы................................................ 872

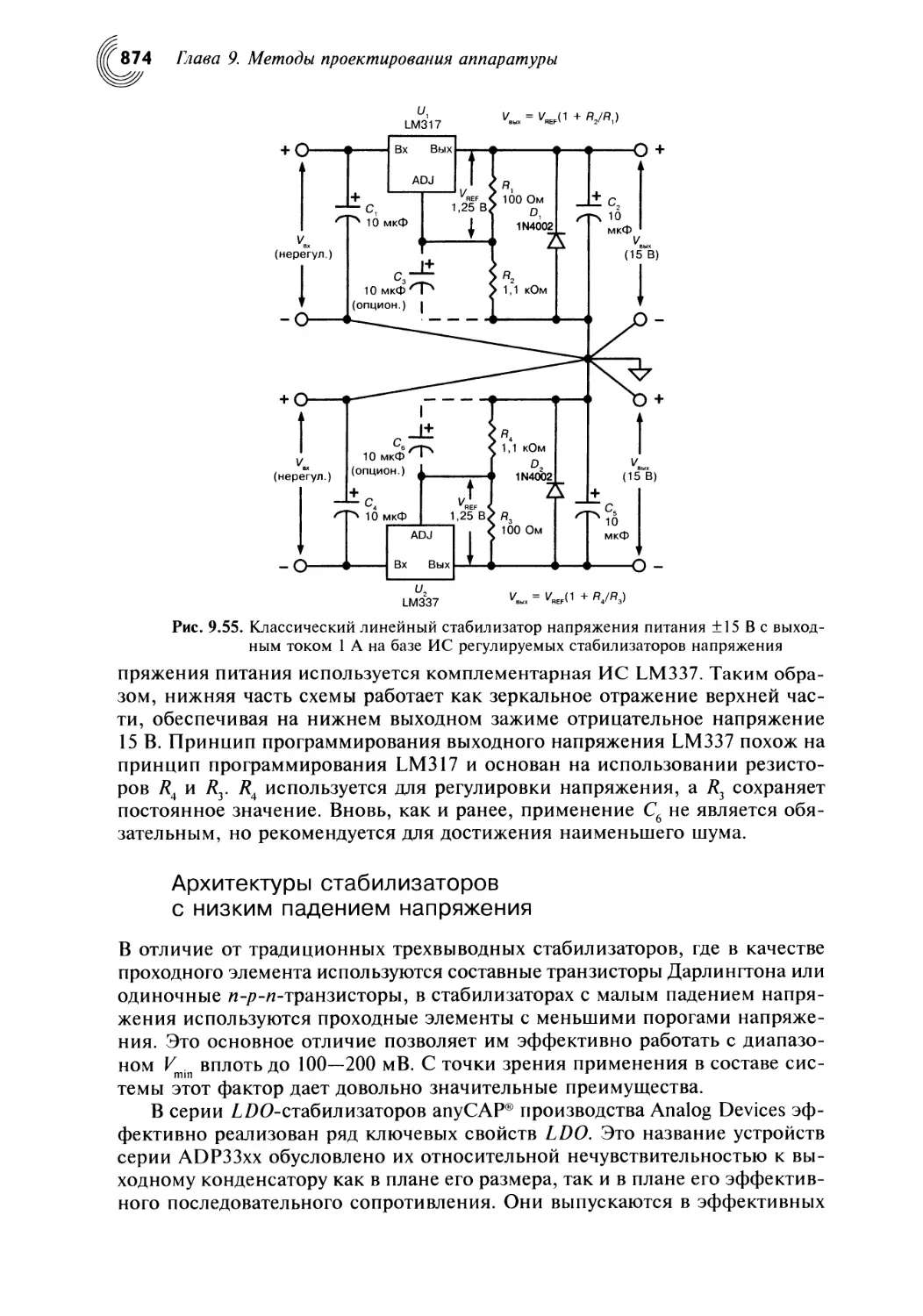

±15 В стабилизатор на базе ИС с регулируемым напряжением.......... 873

Архитектуры стабилизаторов с низким падением напряжения............874

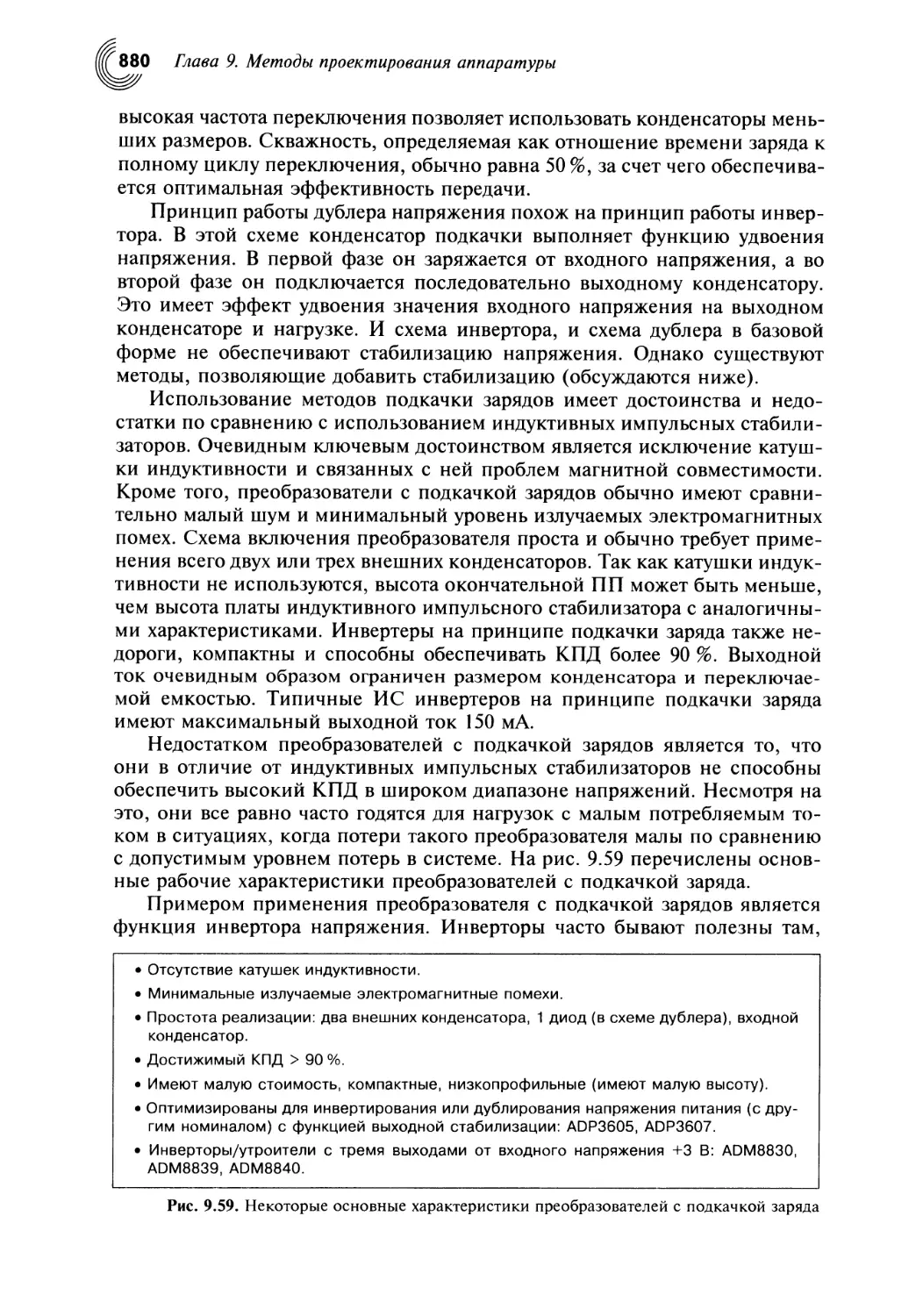

Преобразователи напряжения с подкачкой заряда..................... 879

Преобразователи напряжения на принципе подкачки зарядов

со стабилизированным выходом...................................... 881

Линейные постстабилизаторы для импульсных источников питания...... 882

Заземление линейных и импульсных стабилизаторов................... 884

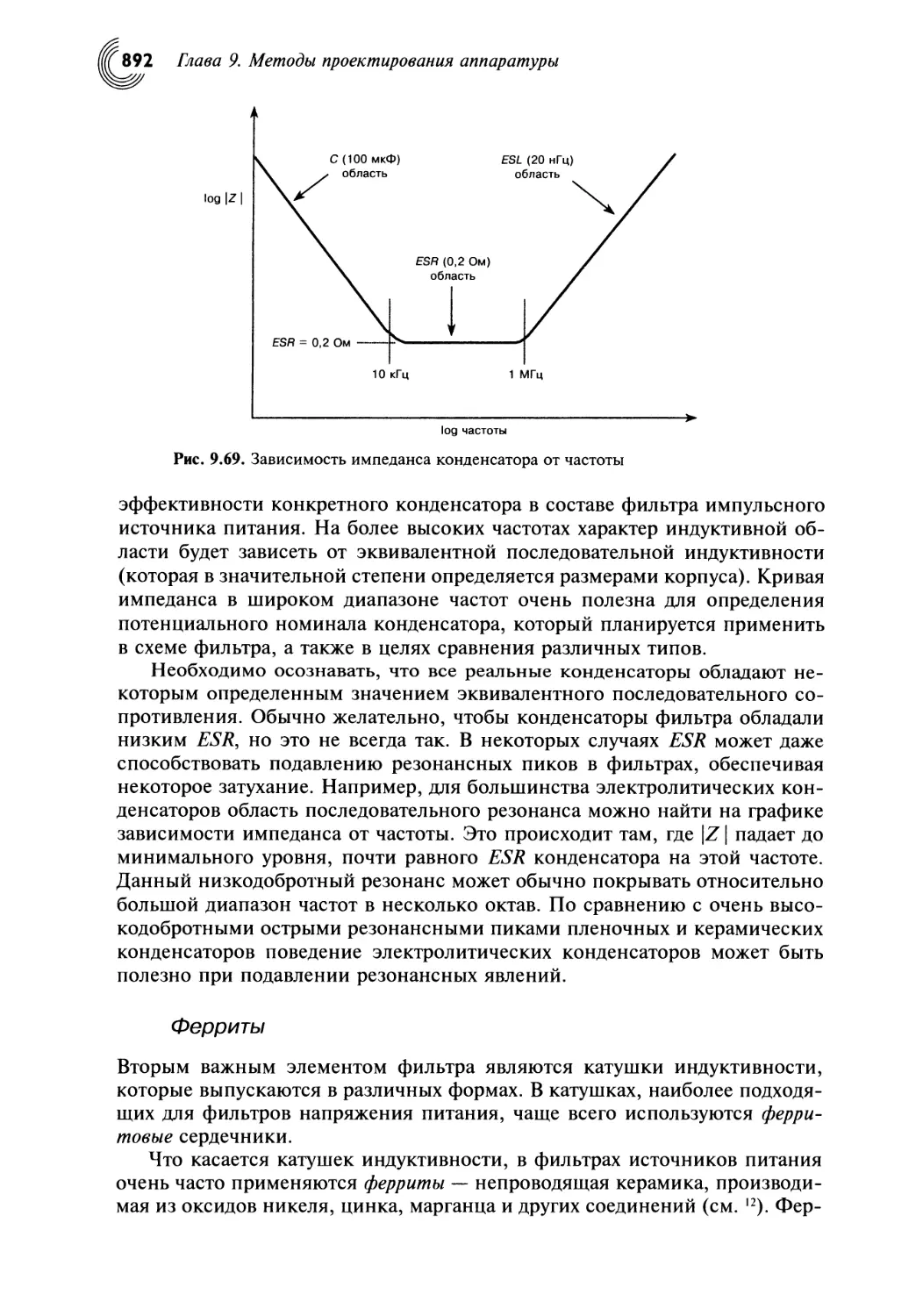

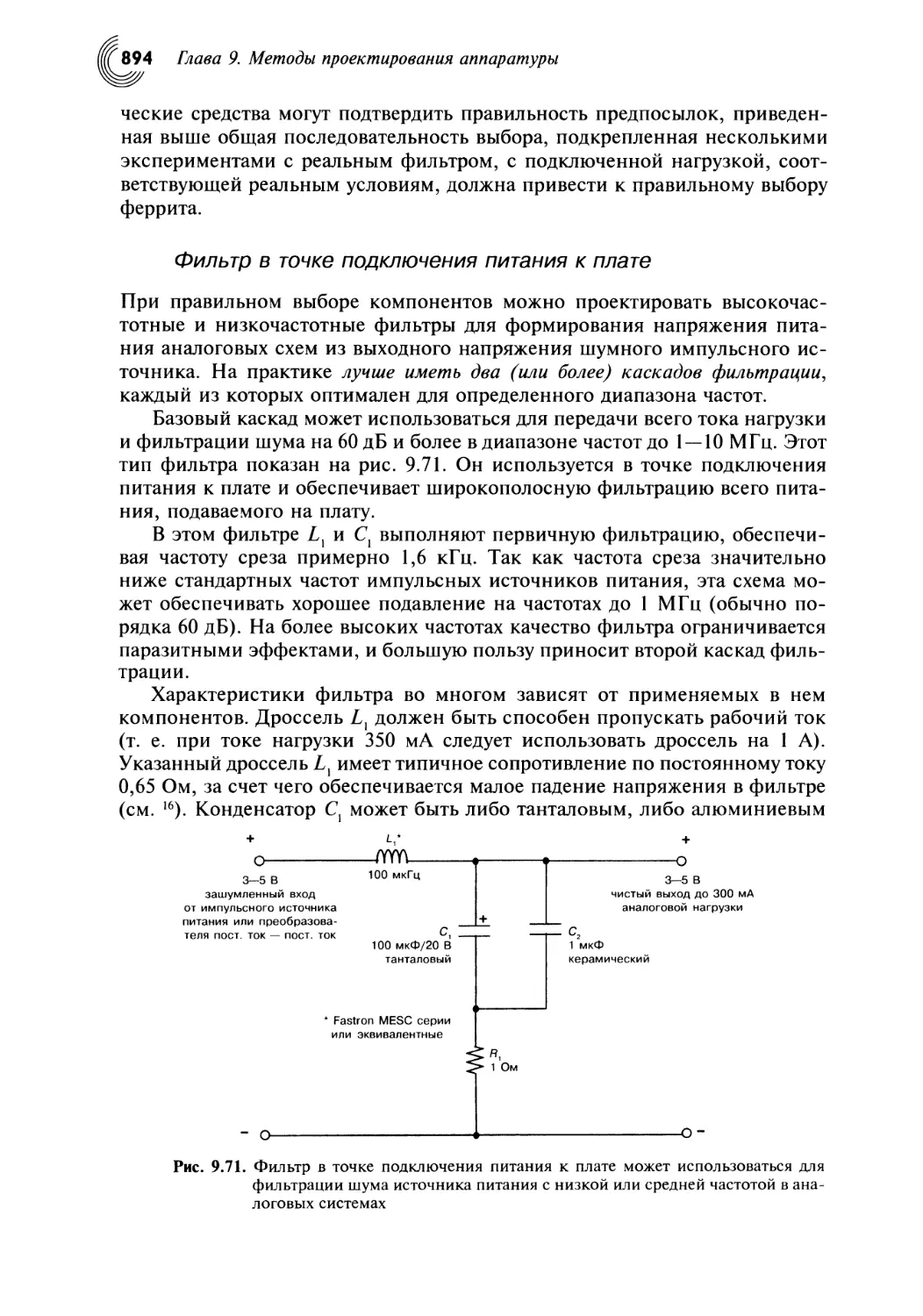

Снижение шумов и фильтрация напряжения источника питания.......... 887

Список литературы к 9.3. Системы «аналогового» питания.................898

9.4. Защита от перенапряжения (Уолт Джанг, Уолт Кестер,

Джеймс Брайант, Джо Бакстон, Вес Фримэн)...........................899

Защита от внутрисхемного перенапряжения .......................... 899

Защита от внесхемного перенапряжения...............................924

Список литературы к 9.4. Защита от перенапряжения......................931

9.5. Управление тепловым режимом (Уолт Джанг)..........................932

Основные тепловые характеристики...................................933

Отвод тепла........................................................934

Список литературы к 9.5. Управление тепловым режимом...................943

9.6. Вопросы электромагнитных/радиочастотных помех (Джеймс Брайант,

Уолт Джанг, Уолт Кестер)...........................................944

Механизмы электромагнитных/радиочастотных помех................... 945

Список литературы к 9.6. Вопросы электромагнитных/радиочастотных

помех..................................................................982

9.7. Интерфейс с низковольтной логикой (Уолт Кестер, Этан Бордо,

Йоханнес Хорват, Кэтрин Редмонд, Ева Мерфи)...........................984

Устойчивость к повышенному напряжению и совместимость по напряжению ... 988

Соединение 5-вольтовых и 3,3-вольтовых систем с помощью «шинных

переключателей» на л-МОП полевых транзисторах..................... 989

Интерфейс между логиками с питанием 3,3 и 2,5 В....................992

Интерфейсы 3,3 В/2,5 В; 3,3 В/1,8 В; 2,5 В/1,8 В...................994

Применение шинных переключателей для горячей замены и горячего

подключения........................................................997

Устойчивость и совместимость по напряжению, обеспечиваемая внутренними

средствами схемы...................................................998

Список литературы к 9.7. Интерфейс с низковольтной логикой............ 1 000

9.8. Макетирование и создание прототипов (Уолт Кестер,

Джеймс Брайант, Уолт Джанг)......................................... 1000

Создание прототипов — «мертвых жуков»............................ 1001

Макетирование на Solder-Mount.................................... 1004

Создание прототипов на фрезерованных ПП.......................... 1005

Остерегайтесь панелек!............................................ 1007

Некоторые дополнительные вопросы, касающиеся создания прототипов.. 1008

Оценочные платы.................................................. 1008

Оценочные платы общего назначения для операционных усилителей

в середине 1990-х годов.......................................... 1009

Резюме........................................................... 1014

Список литературы к 9.8. Макетирование и создание прототипов......... 1015

БЛАГОДАРНОСТИ

Огромное спасибо техническому персоналу Analog Devices из отделов

разработки, маркетинга и внедрения готовых устройств, который обеспе-

чил поддержку данного проекта. Особая благодарность отдельным авторам,

чьи имена появляются в книге в начале соответствующих глав.

Дэн Шеинголд предоставил свой классический труд 1986 года — спра-

вочник «Аналого-цифровое преобразование». С того времени книга Дэна

стала стандартом в технической литературе не только для журнала Analog

Dialogue, но и для многих книг, выпускаемых Analog Devices.

Я должен поблагодарить также Бреда Браннона, Уэз Фриман, Уолта

Джанга, Боба Марвина, Ханка Замбахлена и Скота Уэйна, который испра-

вил много неточностей в материале.

Джудит Доувилл подготовила алфавитный указатель, а также сделала

много полезных замечаний в рукописи.

Я должен поблагодарить ADI management, особенно Дейв Кресс, кото-

рая вдохновляла и поддерживала проект.

Уолт Кестер,

май 2004 года

Главный отдел внедрения

Analog Devices

Вопросы, замечания и комментарии можно направлять по адресу:

Linear.Apps@analog.com, указав в теме письма «Data Conversion Handbook».

ГЛАВА 1

ИСТОРИЯ

ПРЕОБРАЗОВАТЕЛЕЙ

УОЛТ КЕСТЕР

Предисловие к главе

На написание этой главы автора вдохновило исследование истории созда-

ния операционных усилителей Уолтом Юнгом в гл. 1 своей книги «Приме-

нение операционных усилителей»1. При раскрытии темы автор ссылается на

сотни интересных статей, патентов и т. п. Если рассматривать их все как

единое целое, они рисуют картину развития операционных усилителей —

начиная с очерка Гарольда Блэка о ранних усилителях с обратной связью и

заканчивая современными высокопроизводительными ОУ на ИС.

Мы старались достичь подобного при раскрытии истории создания пре-

образователей. Рассматривая масштабы этого намерения, мы столкнулись с

проблемой организации материала. Вместо того чтобы охватывать весь исто-

рический материал в одной главе, мы часть исторических сведений, относя-

щихся к архитектуре преобразователей, включили в гл. 3 (Архитектуры пре-

образователей данных) наряду с описанием отдельных архитектур. Подобно

этому, гл. 4 (Технология преобразователей) включает большинство значимых

событий, относящихся к технологическому процессу создания преобразо-

вателей. Глава 5 (Тестирование преобразователей данных) затрагивает основ-

ные исторические этапы, касающиеся их тестирования.

При раскрытии сущности каждой главы нам придется упоминать одни

и те же исторические данные несколько раз по ходу повествования, следо-

вательно, читатель должен осознавать, что эти повторы сделаны намеренно

и не являются результатом небрежного редактирования.

1.1. Ранняя история

Сейчас трудно определить, когда точно был создан первый преобразователь

и какую форму он имел. Самым первым бинарным ЦАП, известным авто-

рам этой книги и официально отраженным в документах, является гидрав-

лический ЦАП, а не электронный. В Турции, во времена господства Отто-

манской империи, существовала проблема в сфере общественного водо-

снабжения. Для измерения при раздаче воды использовались сложные

системы. Одна из этих систем показана на рис. 1.1 и датирована XVIII веком.

Примером реальной водораздачи, использующей эту измеряющую систему,

была дамба Махмуда II, построенная в начале XIX века вблизи Стамбула2.

Измерительная система использовала резервуар (на схеме помечен как вер-

Глава 1. История преобразователей

Уровень

Патрубок

Слив

Головная

цистерна

воды

Части отмеряющей системы

б

Главная система:

заметьте - слив и патрубок

на разных уровнях

а

Adapted from:

Kazim Qegen, «Sinan's Water

Supply System in Istanbul,»

Istanbul Technical University/

Istanbul Water and Sewage

Administration, Istanbul Turkey,

1992-1993, pp. 165-167.

Вид сверху на детали отмеряющей

системы, содержащие двоично

взвешенные патрубки

Рис. 1.1. Двоично-взвешенная система измерения воды, относящаяся к началу

XVIII века

хняя, головная, цистерна), в котором поддерживался постоянный уровень

(соответствующий опорному потенциалу) при помощи водослива. По этому

водосливу вода сочилась тонкой струйкой (критерием являлся поток, спо-

собный сдвинуть соломинку). Этот пример проиллюстрирован на рис. 1.1, а.

Выход воды из головной цистерны контролировался затворами двоично взве-

шенных отверстий патрубков, погруженных в воду на 96 мм ниже поверхно-

сти воды. Слив из отверстий поступал на выход, как показано на рис. 1.1, б.

Размеры отверстий патрубков соответствовали потоку двоично кратному

основной единице 1 liile (равной 36 л/мин или 52 м3/день). Патрубок, соот-

ветствующий 8 liile, назывался «sekizli liile», 4 liile — «dortlii liile», l/4 liile —

«kamus», l/8 liile называлась «masura», a 732 liile — «uvaldiz». Более детально

измеряющая система на основе двоично-взвешенных патрубков показана

на рис. 1.1, в. Функционально эта система представляет собой 8-разрядный

ЦАП, с ручным (без сомнения, не цифровым) вводом и «мокрым» выходом

и, вероятно, является самым древним ЦАП в мировой истории.

Возможно, существуют и другие примеры ранних преобразователей, но

сейчас мы обратим наше внимание на те, что базируются на электронных

технологиях.

Вероятно, единственной самой значительной движущей силой развития

электронных преобразователей на протяжении многих лет была система

коммуникаций. Телеграф привел к созданию телефона и формированию

Bell System. Распространение телеграфа и телефона и возросшее требова-

ние к емкости каналов связи привели к необходимости уплотнения более

чем одного канала в одну пару медных проводов. К этому времени времен-

ное уплотнение каналов (TDM) достигло определенной популярности, а

частотное уплотнение каналов (FDM), основанное на использовании раз-

личных несущих частот, получило уже широкое применение.

/. 1. Ранняя история

Импульсно-кодовая модуляция

ИКМ (РСМ) стала причиной пере-

ключения всеобщего внимания на преобразователи, и с этого момента на-

чалось их эволюционное развитие.

Материал для последующих разделов был взят из многих источников, но

наиболее известным и значимым является классическая работа К.В. Каттер-

моула «Принципы импульсно-кодовой модуляции» 1969 года3. В ней отражен

не только исторический материал по ИКМ, но и материал по истории со-

здания преобразователей. Кроме того, помимо исторического материала,

книга содержит прекрасный обучающий материал по теории дискретиза-

ции, по типам архитектур преобразователей и многим другим темам, отно-

сящимся к тематике повествования. Приведена обширная библиография,

содержащая важные публикации и патенты, определившие основные дос-

тижения. Кроме книги Каттермоула, внимание автора привлекла серия книг,

опубликованных Белл Системз под одним заголовком «А History of Engineering

and Science in the Bell System»4-8. Эти книги от Белл Системз являются

замечательным источником для получения дополнительного материала, от-

носящегося к сфере коммуникаций.

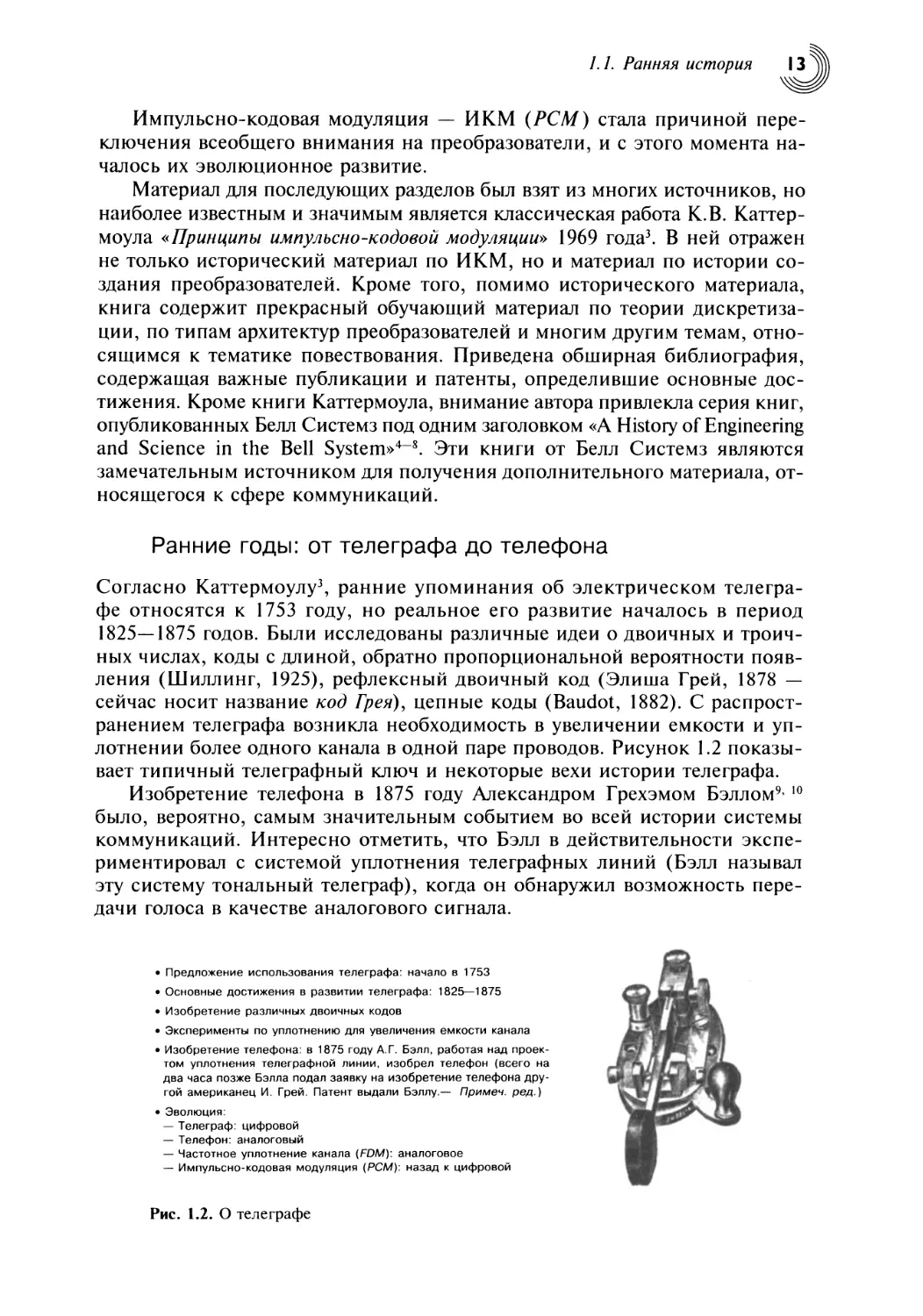

Ранние годы: от телеграфа до телефона

Согласно Каттермоулу3, ранние упоминания об электрическом телегра-

фе относятся к 1753 году, но реальное его развитие началось в период

1825—1875 годов. Были исследованы различные идеи о двоичных и троич-

ных числах, коды с длиной, обратно пропорциональной вероятности появ-

ления (Шиллинг, 1925), рефлексный двоичный код (Элиша Грей, 1878 —

сейчас носит название код Грея), цепные коды (Baudot, 1882). С распрост-

ранением телеграфа возникла необходимость в увеличении емкости и уп-

лотнении более одного канала в одной паре проводов. Рисунок 1.2 показы-

вает типичный телеграфный ключ и некоторые вехи истории телеграфа.

Изобретение телефона в 1875 году Александром Грехэмом Бэллом9’ 10

было, вероятно, самым значительным событием во всей истории системы

коммуникаций. Интересно отметить, что Бэлл в действительности экспе-

риментировал с системой уплотнения телеграфных линий (Бэлл называл

эту систему тональный телеграф), когда он обнаружил возможность пере-

дачи голоса в качестве аналогового сигнала.

• Предложение использования телеграфа: начало в 1753

• Основные достижения в развитии телеграфа: 1825—1875

• Изобретение различных двоичных кодов

• Эксперименты по уплотнению для увеличения емкости канала

• Изобретение телефона: в 1875 году А. Г. Бэлл, работая над проек-

том уплотнения телеграфной линии, изобрел телефон (всего на

два часа позже Бэлла подал заявку на изобретение телефона дру-

гой американец И. Грей. Патент выдали Бэллу.— Примеч. ред.)

• Эволюция:

— Телеграф: цифровой

— Телефон: аналоговый

— Частотное уплотнение канала (FDM): аналоговое

— Импульсно-кодовая модуляция (РСМ): назад к цифровой

Рис. 1.2. О телеграфе

Глава 1. История преобразователей

United States Patent Office.

Рис. 1.3. Телефон

Фрагмент патента США 174,465,

заявленного 14 февраля 1876 г.,

выданного 7 марта 1876 г.

На рис. 1.3 представлена схема из оригинала патента Бэлла, в которой

отражены его основные предложения относительно телефона. Вибрации

звука, воздействующие на передатчик А. заставляют вибрировать мембрану

а. Вибрация а вызывает вибрацию якоря с, которая создает ток в проводе е

при помощи электромагнита Ь. Ток в е создает соответствующие колебания

магнитного поля в электромагните/ таким образом заставляя вибрировать

мембрану приемного устройства /.

Распространение телефона вызвало острую необходимость в увеличе-

нии емкости канала путем его уплотнения. Необходимо отметить, что ис-

следования по возможности уплотнения в телеграфных линиях привели к

зарождению информационной теории. Теория временного уплотнения (TDM )

была предложена в начале 1853 года малоизвестным американским изобре-

тателем М.Б. Фармером, а реализована в 1875 году J.M.E. Baudot при помо-

щи вращающихся механических коммутаторов, использованных в качестве

мультиплексоров.

В 1903 году в патенте Уиларда М. Майнера11 были описаны эксперимен-

ты, использующие электромеханические вращающиеся коммутаторы этого

типа для уплотнения нескольких аналоговых телефонных разговоров в од-

ной паре проводов, как представлено на рис. 1.4. Процитируем его патент,

в котором он говорит, что каждый канал должен иметь отсчеты:

Фрагмент патента США 745,734

У.М. Майнера «Телефонная сис-

тема с уплотнением», заявлен-

ного 26 февраля 1903 г., выдан-

ного 1 декабря 1903 г.

Рис. 1.4. Мультиплексор и демультиплексор телефонных каналов. Одно из ранних

исследований критерия, определяющего темп отсчетов

1.1. Ранняя история

«...на частоте или периодичности, как приближения к частоте или на сред-

ней частоте чистых или более сложных вибраций, которые являются характе-

ристиками голоса или артикуляции речи... при таких высоких прерываниях,

как 4320 в секунду, я обнаружил, что при этом темпе весь действительный

тембр и индивидуальность могут быть успешно воспроизведены в приемном

инструменте. ...я также получил положительные результаты, которые можно

рассматривать как коммерческие, при использовании темпа прерываний, схо-

жего с говорением и составляющего 3500 в секунду, практически это темп

самой высокой ноты, которая характеризует гласные звуки».

При использовании более высокой частоты отсчетов Майнер не обна-

ружил значительного улучшения в качестве передаваемой речи, возможно,

это было вызвано ошибками в его достаточно несовершенной системе. После

Майнера никто не занимался дальнейшими исследованиями в сфере диск-

ретизации и временного уплотнения. Возможной причиной этого можно

назвать отсутствие адекватных электрических компонентов, позволяющих

провести практические эксперименты. Сфера частотного уплотнения была

достаточно изучена и имела необходимые компоненты.

Изобретение импульсно-кодовой модуляции (РСМ)

Импульсно-кодовая модуляция впервые была раскрыта в относительно не-

вразумительном патенте, опубликованном Полом М. Рейни (Paul М. Rainey)

из Western Electric в 1921 году12. В патенте описывается метод передачи

факсимильной информации в закодированной форме по телеграфной ли-

нии с применением 5-разрядной ИКМ. На рис. 1.5 представлена иллюс-

трация из патента (для большей ясности автором добавлены пояснения

к оригиналу).

Рейни предложил просвечивать сфокусированным лучом света прозрач-

ность материала, который необходимо передать. На другой стороне транспа-

Рис. 1.5. Открытие ИКМ: Пол Рейни. Факсимильная телеграфная система. Патент

США 1 608 527 от 20 июля 1921, опубликован 30 ноября 1926

Глава 1. История преобразователей

ранта нужно установить фотоэлемент для сбора света, который создаст ток,

пропорциональный интенсивности света. Ток в свою очередь отклоняет

гальванометр, что приводит в движение другой луч света, активирующий

один из 32 отдельных фотоэлементов, в зависимости от отклонения гальва-

нометра. Выход с каждого отдельного фотоэлемента замыкает соответству-

ющее реле. Выходы от 5 реле объединены таким образом, что вырабатыва-

ют определенный код, присущий местоположению фотоэлемента. Таким

образом, цифровой код генерируется как «М-hot out of 32», что напоминает

современный параллельный /Zas/z-преобразователь. Выходной сигнал с это-

го простого электро-оптико-механичесого параллельного преобразователя

передается последовательно с использованием вращающегося электромеха-

нического коммутатора, называемого распределителем.

Данные передаются последовательно, получаются и преобразуются в

параллельный формат при помощи второго распределителя и ряда реле.

Полученный код определяет комбинацию из реле, которые должны приво-

диться в действие. Выходы реле подсоединяются к соответствующим кон-

тактам резистора, который подключен последовательно с принимающей

лампой. Значение тока в принимающей лампе находится в зависимости от

полученного кода. Как мы видим, интенсивность тока прямо пропорцио-

нальна полученному коду, что является примером цифро-аналогового пре-

образования. Свет с принимающей лампы фокусируется на фоточувстви-

тельной пластине, таким образом исходное изображение воспроизводится,

пройдя квантованную форму.

Патент Рейни иллюстрирует несколько важных понятий: квантование с

использованием параллельного АЦП, передача последовательных данных,

восстановление квантованных данных при помощи ЦАП. Эти идеи явля-

ются основополагающими для ИКМ. Однако его изобретение не вызвало

особого интереса в то время и фактически было забыто инженерами ком-

пании Бэлл Систем. Его патент был обнаружен спустя много лет, когда

появились и другие патенты на изобретение ИКМ.

Математическое обоснование ИКМ

В середине 20-х годов XX века Гарри Найквист изучал телеграфные сигна-

лы. Его целью было определить максимальную частоту сигнала, которая

может проходить по каналу с определенной полосой пропускания. Резуль-

таты его исследований были обобщены в двух классических трудах, выпу-

щенных в 192413 и 1928 годах14 соответственно.

В своей модели телеграфной системы он определил свой сигнал как:

к

В уравнении f(t) — базисная форма импульса, ак — амплитуда &-го импуль-

са, Т — время между импульсами. Телеграф постоянного тока подходит под

эту модель при условии, что f(t) — это прямоугольный импульс с продол-

жительностью Г, а ак равняется 0 или 1.

Простая модель изображена на рис. 1.6. Частота сигнала ограничена

полосой частот (IT) передающего канала.

• До 2И/ импульсов в секунду

можно передать по каналу,

который имеет полосу И/.

• Если из сигнала непрерыв-

но через регулярные интер-

валы в темпе, по крайней

мере вдвое превышающем

максимальную частоту в

спектре сигнала, делаются

отсчеты, то они содержат

всю информацию о сигнале.

Ключ выборок

Рис. 1.6. Классическая теорема Гарри Найквиста

Его вывод заключался в следующем: частота импульсов 1/Т не может

быть увеличена за пределы 2 Wимпульсов в секунду. Другими словами, его

заключение звучит так: если сигнал дискретизирован мгновенными отсчета-

ми с постоянными интервалами, частота которых по крайней мере в 2 раза

превышает самое высокое значение частоты сигнала, то в результате вы-

борка содержит всю информацию об исходном сигнале. Это понятно из

рис. 1.6, где каждый из отфильтрованных прямоугольных сигналов пред-

ставлен в виде sin х/х характеристики. Временной отклик на импульс типа

sinx/x идеального ФНЧ с полосой пропускания РГимеет нули в интервалах,

равных 72И< Следовательно, не будут наблюдаться помехи от соседних

импульсов, если выходная волна дискретизирована в точках, указанных на

схеме, при условии Т> (или более привычно^ > 2PF), и амплитуда

индивидуальных импульсов может быть однозначно восстановлена.

За исключением обобщающей статьи, написанной Хартли в 1928 году15,

до 1948 года не было дополнительных значимых публикаций на тему диск-

ретизации. В 1948 году вышли в свет классические работы, написанные

Шенноном, Беннеттом, Оливером1619, в которых авторы окончательно обо-

сновали теорию ИКМ.

Библиография этих трудов приведена в ссылке рис. 1.7.

• Multiplexing experiments such as Williard Miner. Multiplex Telephony. U.S. Patent 745,

734, filed February 26, 1903, issued December 1, 1903.

• H. Nyquist. Certain Factors Affecting Telegraph Speed. Bell System Technical Journal, Vol. 3,

April 1924, pp. 324—346.

• H. Nyquist. Certain Topics in Telegraph Transmission Theory. A.I.E.E. Transactions, Vol. 47,

April 1928, pp. 617—644.

• P.V.L. Hartley. Transmission of Information. Bell System Technical Journal, Vol. 7, July

1928, pp. 535-563.

• Note: Shannon's classic paper was written in 1948, well after the invention of PCM:

• C.E. Shannon. A Mathematical Theory of Communication. Bell System Technical Journal,

Vol. 27, July 1948, pp. 379—423, and October 1948, pp. 623—656.

• W.R. Bennett. Spectra of Quantized Signals. Bell System Technical Journal, Vol. 27, July

1948, pp. 446—471.

• B.M. Oliver, J.R. Pierce, C.E. Shannon. The Philosophy of PCM. IRE Proceedings. Vol. 36,

November 1948, pp. 1324—1331.

• W.R. Bennett. Noise in PCM Systems. Bell Labs Record, Vol. 26, December. 1948,

pp. 495—499.

Рис. 1.7. Библиография трудов по математическому базису ИКМ

Глава 1. История преобразователей

Патенты Алекса Харли Ривза на ИКМ

До 1937 года частотное уплотнение (FDM), основанное на электронно-ва-

куумной технологии, широко использовалось в телефонной индустрии при

передаче на дальние расстояния. Однако шум и искажения были ограничи-

вающими факторами, влияющими на дальнейшее расширение возможнос-

тей этих систем. Несмотря на то что в микроволновых радиолиниях полосы

пропускания были шире, дополнительный шум и искажения затрудняли их

использование для передачи частотно-уплотненных сигналов.

В начале своей карьеры, в 1920-х годах, Алекс Харли Ривз изучал техно-

логию аналого-временного преобразования, основанного на использова-

нии время-импульсной модуляции (РТМ). Фактически он был первым, кто

начал использовать счетчики для точного определения временной разверт-

ки, используя бистабильные мультивибраторы, изобретенные за несколько

лет до этого Экклесом и Джорданом. Во время импульсной модуляции ам-

плитудой импульса является постоянная величина, а аналоговая информа-

ция содержится в определенном положении импульсов во времени. Эта

технология имела более высокую помехоустойчивость, чем строго аналого-

вая передача.

Ривз был близок к изобретению системы, которая произвела бы рево-

люционные изменения в системе коммуникации, но тогда он не пошел

дальше достигнутого им в этой области.

Существовала необходимость в системе, имеющей шумоустойчивую

характеристику подобно той, что существовала в телеграфе. Поэтому в

1937 году Ривз, работая в Парижской лаборатории Международной теле-

фонно-телеграфной корпорации, переосмыслил ИКМ. Самый первый па-

тент по ИКМ был получен Ривзом в Париже. Но сразу же после этого

последовали подобные патенты в Англии и США, в которых упоминался

Ривз как изобретатель20. Эти патенты всесторонне раскрывали следующие

темы:

1) основные принципы квантования и кодировки;

2) выбор разрешения, соответствующего шуму и полосе пропускания

передающего канала;

3) передача сигналов в цифровой форме последовательно, параллельно

и как модуляция несущих;

4) базовая конструкция на основе счетчиков, необходимых для 5-раз-

рядных ЦАП и АЦП.

Отличие этого патента Ривза от его предыдущего патента (1926) состоит

в том, что он использовал в своих разработках все преимущества существу-

ющей электронно-вакуумной технологии ЦАП и АЦП. Эти изобретения Ривза

заслуживают более детального рассмотрения, так как они являются первыми

документально зафиксированными электронными преобразователями. Его

техника АЦП (рис. 1.8) использует дискретные импульсы для выборки от-

счетов из аналогового сигнала, установку 7?/5-триггера и одновременный

старт контролируемого пилообразного напряжения. Пилообразное напря-

жение сравнивается с входным сигналом, и в момент их совпадения выра-

батывается сигнал, который сбрасывает 7?/5-тригер. Выходной сигнал с триг-

гера является импульсом, ширина которого прямо пропорциональна ана-

1.1. Ранняя история

А.Х. Ривса «Электрическая система сиг-

налов», заявленного 22 ноября 1939 г.,

Импульсы разрешения выдачи

данных, 6 тысяч отсчетов в с

Выход

данных

выданного 3 февраля 1942 г.

Рис. 1.8. 5-разрядный АЦП Ривза с последовательным счетом

логовому сигналу в момент отсчета. Этот импульс с ШИМ управляет стро-

бируемым генератором. Число выходных импульсов со стробируемого ге-

нератора представляет собой квантованное значение аналогового сигнала.

Эту последовательность импульсов можно легко преобразовать в бинарное

слово путем активации счетчика. В системе Ривза использовался задающий

генератор с частотой 600 кГц и 100 : 1 делитель, вырабатывающий 6-кГц

импульсы отсчетов. Система использует 5-разрядный счетчик на 31 отсчет

(из 100 импульсов, приходящихся на каждый импульс отсчетов), таким об-

разом представляя сигнал полной шкалы.

ЦАП использует подобный счетчик и источник тактовых импульсов,

как представлено на рис. 1.9. Полученный бинарный код сначала загружа-

ется в счетчик, и 7?/5-триггер устанавливается в «1». Затем счетчик начина-

ет считать от низшего к высшему, используя тактовые импульсы. Когда

счетчик переполняется и достигает 00000, источник тактовых импульсов

отсоединяется, поскольку Я/5-триггер обнуляется. Число импульсов, по-

считанных кодирующим счетчиком, представляет собой дополнение входя-

щего слова. Выходным сигналом с триггера является ШИМ-сигнал, чье

аналоговое значение представляет собой дополнение входного бинарного

Приводится из патента США 2,272,070

Входные

данные

Рис. 1.9. 5-разрядный ЦАП Ривза с последовательным счетом

(TlO Глава 1. История преобразователей

слова. Ривз использовал простой ФНЧ для получения аналогового сигнала

от ШИМ-выхода. Фазовая инверсия в ЦАП с легкостью корректируется

или в логике, или в усилителе, расположенных далее.

Патенты Ривза раскрывают все основные составляющие ИКМ: отсчеты,

квантование, кодирование дискретных отсчетов для последовательной, па-

раллельной, фазо-модулированной и других методов передачи. Для восста-

новления исходного аналогового сигнала Ривз предложил декодер на при-

нимающем конце. Интересно отметить, что, несмотря на значимость своей

работы, после опубликования патентов Ривз направил свое внимание на

передачу речи в коротковолновом диапазоне с использованием импульсно-

амплитудной, широтно-импульсной, импульсно-позиционной модуляций,

вместо того чтобы более глубоко изучить возможности ИКМ.

ИКМ и Bell System: Вторая мировая война и до 1948 года

По договору о взаимном лицензировании с Международной телефонно-те-

леграфной корпорацией инженеры телефонной лаборатории Бэлла пересмот-

рели исследования Ривза в отношении описания цепей и начали свои разра-

ботки в сфере ИКМ-технологии. Начав свои исследования в 1940 году и

продолжая их в течение Второй мировой войны, главным образом посвяща-

ли их секретной передаче речи, что сделало изучение ИКМ обязательным.

В 1940 году разработчики лаборатории Бэлла начали работу по исследо-

ванию системы секретности речи, получившей название «Project-Х», более

детальное описание указано в 6 (с. 296—317). В этих исследованиях использу-

ется сложная техника, основанная на электронно-вакуумной технологии. При

этом использовался разработанный ранее вокодер, технология ИКМ и уни-

кальная техника скремблирования данных (защита от несанкционированно-

го доступа. — Примеч. ред.\ использующая грамзапись с содержанием элек-

тронного кодового «ключа» к кодам. Система была спроектирована в Бэлл

и запущена в производство компанией Вестерн Электрик в конце 1942 года.

К апрелю 1943 года несколько терминалов было закончено и установлено в

Вашингтоне, Лондоне и Северной Африке. Вскоре после этого дополни-

тельные терминалы были установлены в Париже, на Гавайях, в Австралии

и на Филиппинах.

К концу войны несколько групп инженеров в Бэлл занимались изуче-

нием ИКМ; однако большинство из разработок военного времени не было

опубликовано и долгое время в период послевоенного времени, так как они

имели гриф секретности. Труды Х.С. Блэка, Д.О. Эдсона и В.М. Гуддалла

были изданы в 1947—1948 годах.21”23. Они акцентировали свое внимание на

системе шифровки речи, основанной на технике ИКМ. В результате их

исследований родилось большое количество важных открытий, например

система ИКМ, которая оцифровывает полную ширину голосового спектра

в 5-разрядной системе, со скоростью дискретизации 8 kSPS (8 тысяч отсче-

тов в секунду), используя при этом АЦП последовательного приближения

(которые были описаны Эдсоном и Блэком2122).

Опытная система ИКМ В.М. Гудалла основана на схожей технике и

описана в его классическом груде. Среди наиболее важных разработок, явив-

шихся результатом этой работы, стали: ЦАП последовательного приближе-

• Секретная система шифровки голоса с использованием HKM-«Project-X», 1940—1943.

• 5-разрядный АЦП последовательного приближения с частотой дискретизации 8 kSPS.

• Логарифмическое квантование речи (компандирование).

• Кодирующая электронная трубка, 7-разрядная, с частотой дисктретизации 100 kSPS.

• Декодер «Шеннона—Рэка» (ЦАП).

• Удачная демонстрация опытных терминалов ИКМ.

• Теоретические положения ИКМ, расширенные и опубликованные Шенноном.

• Изобретение германиевого транзистора в 1947 году.

Рис. 1.10. Исследования лаборатории Белл в сфере ИКМ, проведенные в период Вто-

рой мировой войны (и до 1948 года)

ния, кодирующая электронная трубка, декодер Шэннона—Рэка, логариф-

мический отсчет уровней квантования (компандинг) и практическое дока-

зательство возможности использования ИКМ. Результаты исследований были

обобщены в 1948 году в статье, написанной Л.А. Мичамом и Е. Петерсо-

ном, где описывалась опытная система использования 24-канальной ИКМ24.

В ссылке рис. 1.10 обобщены результаты исследований ИКМ, проведенные

лабораторией Белл в 1948 году.

Важным достижением в области АЦП-технологии в этот период стало

изобретение кодирующей электронной трубки. Трубка, описанная Р.В. Сир-

зом в его работе25, дискретизировала со скоростью 96 kSPS, с разрешением

в 7-бит. Концепции электронно-лучевого кодера для 4-разрядного устрой-

ства отражены на рис. 1.11. Предшествующие аналоги использовали после-

довательный режим (рис. 1.11, а). Аналоговый сигнал сначала проходил

через устройство выборки—хранения и во время интервала «хранения» луч

разворачивался в трубке горизонтально. При этом Y-отклонение соответ-

ствует значению аналогового сигнала от устройства выборки—хранения.

Теневая маска закодирована для получения соответствующего бинарного

кода, зависящего от вертикального отклонения. Код регистрируется кол-

лектором, и биты вырабатываются в последовательном формате. Позже в

Последовательного типа

а

Параллельного типа

б

пушка

Рис. 1.11. Кодирующая электронная трубка

Глава 1. История преобразователей

трубках начали использовать ленточный луч (см. рис. 1.11, 0, создав пер-

вый электронный //^-преобразователь, выдающий параллельно выходное

слово.

Ранние электронно-вакуумные кодеры использовали бинарно-кодиру-

ющую теневую маску. Существовали большие погрешности, если луч рас-

пространялся на 2 соседних кода и освещал оба из них. Иллюстрация этого

явления приведена на рис. 1.12, а. Горизонтальная линия представляет раз-

вертку луча в точке перехода (перехода между кодом 0111 и кодом 1000).

Например, ошибка в самом старшем значащем разряде (MSB) составит 1/2

шкалы. Подобные ошибки были минимизированы путем установки гори-

зонтальных чувствительных проволочек по ширине границ каждого уровня

квантования. Если луч первоначально падает на одну из проволок, неболь-

шое напряжение добавляется к напряжению вертикального отклонения,

которое сдвигает луч от переходной зоны.

Ошибки бинарных теневых масок были устранены путем использова-

ния теневой маски с кодом Грея, пример которой приведен на рис. 1.12, б.

Настоящее его название звучит как «рефлексный бинарный код»; он был

изобретен в 1878 году Элишем Греем и впоследствии пересмотрен Фрэн-

ком Греем в 1949 году26. Достоинство кода Грея состоит в том, что соседние

уровни отличаются друг от друга на одну цифру в соответствующем слове,

кодируемом с помощью кода Грея. Следовательно, если есть ошибка в оп-

ределении разряда для определенного уровня, то соответствующая ошибка

после преобразования в бинарный код будет всегда соответствовать млад-

шему значащему биту (LSB). В случае попадания луча в середину шкалы

меняется старший значимый бит, но ошибка только 1 LSB. Интересно от-

метить, что подобный феномен может происходить в современных flash-

преобразователях, использующих компараторы, вследствие метастабильно-

сти компаратора. При небольшом перевозбуждении существует определен-

ная вероятность того, что компаратор будет вырабатывать неверное решение

а б

4-разрядный двоичный код 4-разрядный рефлексно-

двоичный код (код Грея)

1111

1110

110 1

110 0

10 11

10 10

10 0 1

Теневая маска 1 0 0 0

0 111

0 110

0 10 1

0 10 0

0 0 11

0 0 10

0 0 0 1

0 0 0 0

MSB LSB

Теневая маска

10 0 0

10 0 1

10 11

10 10

1110

1111

110 1

110 0

0 10 0

0 10 1

0 111

0 110

0 0 10

0 0 11

0 0 0 1

0 0 0 0

MSB LSB

Рис. 1.12. Теневая маска кодирующей электронной трубки для двоичного кода и кода

Грея

1.1. Ранняя история

на своем выходе с защелкой, создавая тот же самый эффект при использо-

вании техники прямого бинарного кодирования. Во многих случаях код

Грея или коды «псевдоГрея» используются для декодировки выходных дан-

ных компаратора перед окончательным преобразованием в бинарно-кодо-

вый выходной сигнал (см. гл. 3 с более детальным описанием архитектур-

ных конструкций).

Несмотря на множество механических и электрических проблем, отно-

сящихся к центрированию луча, технология кодирования на электронной

трубке достигла своего пика в середине 1960-х годов с использованием эк-

спериментального 9-разрядного кодера со скоростью дискретизации, рав-

ной 12 MSPS27. Только открытие в области технологий полупроводниковых

АЦП сделало существование преобразователей, основанных на технологии

электронной трубки, ненужным.

ОУ и регенеративные импульсные ретрансляторы:

от электронно-вакуумных до полупроводниковых устройств

За исключением ранних относительно малоэффективных электромехани-

ческих усилителей5, развитие электронных усилителей началось с изобре-

тения электронно-вакуумной технологии Ли де Форестом в 1906 году28 29.

Иллюстрация из патента де Фореста приведена на рис. 1.13.

К 1914 году электронно-вакуумные усилители были внедрены на теле-

фонном заводе. Развитие усилителей всегда было особенно важным для

разработки преобразователей данных, начиная с ранних электронно-ваку-

умных схем. Ключевым этапом развития этой технологии было изобрете-

ние усилителя с обратной связью Гарольдом С. Блэком в 1927 году30-32. На

протяжении Второй мировой войны продолжалась работа по исследова-

нию цепей усилителей; много важных разработок было сделано инжене-

рами лаборатории Бэлл (более полная история исследований ОУ дана в 1).

На рис. 1.14 дается схема усилителя с обратной связью, взятая из поздней

статьи Блэка.

Изобретение германиевого транзистора в 1947 году33-35 явилось толчком

для развития как ИКМ, так и других электронных систем. Для практичес-

Е'

Фрагмент патента США 841,387

Л.Д. Фореста «Прибор для усиле-

ния слабых электрических токов»,

заявленного 25 октября 1906 г.,

выданного 15 января 1907 г.

Рис. 1.13. Изобретение электронно-вакуумной лампы

Глава 1. История преобразователей

Harold S. Black. Stabilized Feedback

Amplifiers. Bell System Technical

Journal, Vol. 13, No. 1, January 1934

Выход = Д |вход - (3 x выход]

Выход _ 1

Вход (3

Рис. 1.14. Усилитель с обратной связью Гарольда Блэка, 1927

кого использования ИКМ необходимо было установить восстанавливаю-

щие ретрансляторы периодично на линиях передачи. До изобретения тран-

зистора удачно спроектированные вакуумные ретрансляторы несколько лет

применялись в телеграфе и телефонной связи, но возникали серьезные про-

блемы, касающиеся их надежности. Однако полупроводниковые восстанав-

ливающие ретрансляторы, разработанные Л.Р. Рэтхоллом в 1956 году, при-

вели фазу исследования ИКМ к впечатляющим результатам36. Этот ретран-

слятор демонстрировался на опытной кабельной системе с использованием

ретрансляционного интервала в 2,3 мили с кабелем 19 калибра, а также на

0,56 мили с кабелем 32 калибра. Схематический чертеж ретранслятора пред-

ставлен на рис. 1.15.

В ретрансляторе Рэтхолла использовался германиевый транзистор, раз-

работанный в Бэлл и внедренный Вестерн Электрик. Кремниевый транзи-

стор был изобретен в 1954 году Гордоном Тилом из Техас Инструменте. Он

получил широкое коммерческое применение, вызванное увеличенным тем-

пературным диапазоном эксплуатации и надежностью. В конечном счете

Из L.R.Wrathall, «Транзисторный

двоично-импульсный регенера-

тор», Bell System Technical

Journal, Vol. 35, September 1956.

pp.1059-1084

Вход

Рис. 1.15. Твердотельный И KM-ретранслятор Л.Р. Рэтхолла, 1956

• Изобретение в 1947 году германиевого транзистора инженерами лаборатории Белл:

Джон Бардин, Уолтер Браттейн, Вильям Шокли.

• Кремниевый транзистор: Гордон Тил, Тексэс Инструменте, 1954.

• Рождение интегральной схемы:

— Джек Килби, Тексэс Инструменте, 1958 (использовал соединяющие провода для

связи компонентов в ИС);

— Роберт Нойс, Фэйрчайлд Семикондактор, 1959 (использовал металлизацию для

межсоединений).

• The Planar Process: Jean Hoerni, Fairchild Semiconductor, 1959.

Рис. 1.16. Ключевые достижения в развитии твердотельной технологии

изобретение интегральных схем в 1958 году37 38 и последующий планарный

процесс в 1959 году39 установили новую эпоху дальнейшего развития ИКМ.

Эти базовые полупроводниковые исследования обобщены в ссылке рис. 1.16

и описаны более детально в гл. 4 данной книги.

С изобретением ретранслятора Рэтхолла в 1956 году стало очевидным,

что ИКМ может эффективно использоваться для увеличения количества

голосовых каналов на существующих медных кабельных парах. Это было

особенно заманчиво для крупных городов, где многие передающие каналы

были полностью заполнены. Многие из этих пар были оборудованы согла-

сующими катушками на расстоянии 1,8 км друг от друга для улучшения

чувствительности в голосовой полосе. Возникало естественное желание за-

менить согласующие катушки полупроводниковыми ретрансляторами и

увеличить таким образом емкость с 1 до 24 каналов, используя ИКМ.

По этой причине в лаборатории Белл было принято решение разра-

ботать высокочастотную систему связи, основанную на ИКМ. Прототип

24-канальной системы был спроектирован и проверен в 1958 и 1959 годах

на линии между Саммитом и Нью-Джерси и Саут-Ориндж и Нью-Джерси.

Эта система, названная высокочастотной системой связи Т-1, передавала

24 голосовых канала и использовала 1,544-МГц последовательность им-

пульсов в биполярном коде. Система использовала 7-разрядное логариф-

мическое кодирование с 26-дБ компандированием и позже начала использо-

вать 8-разрядное кодирование. Полупроводниковые ретрансляторы были рас-

положены на интервалах 1,8 км в соответствии с расположением существующих

согласующих катушек. Первая линия Т-1 была пущена в работу в 1962 году, а к

1984 году в США существовало более 200 млн км линий связи Т-1.

Список литературы

1.1. Ранняя история

1. Walter G. Jung. Op Amp Applications Handbook. Newnes (an imprint of Elsevier

Science and Technology Books), ISBN 0-7506-7844-5, 2005.

2. Kazim Cecen. Sinanys Water Supply System in Istanbul. Istanbul Technical University/

Istanbul Water and Sewage Administration, Istanbul Turkey, 1992—1993, pp. 165—167.

3. K. W. Cattermole. Principles of Pulse Code Modulation. American Elsevier Publishing

Company, Inc., 1969, New York NY, ISBN 444-19747-8. (Блестящий взгляд на истори-

ческие аспекты теории и практики не только Puise Code Modulation (кодово-импульс-

ной модуляции), но и вообще преобразования данных. Предназначена для всех, кто серь-

езно интересуется данной областью знаний.)

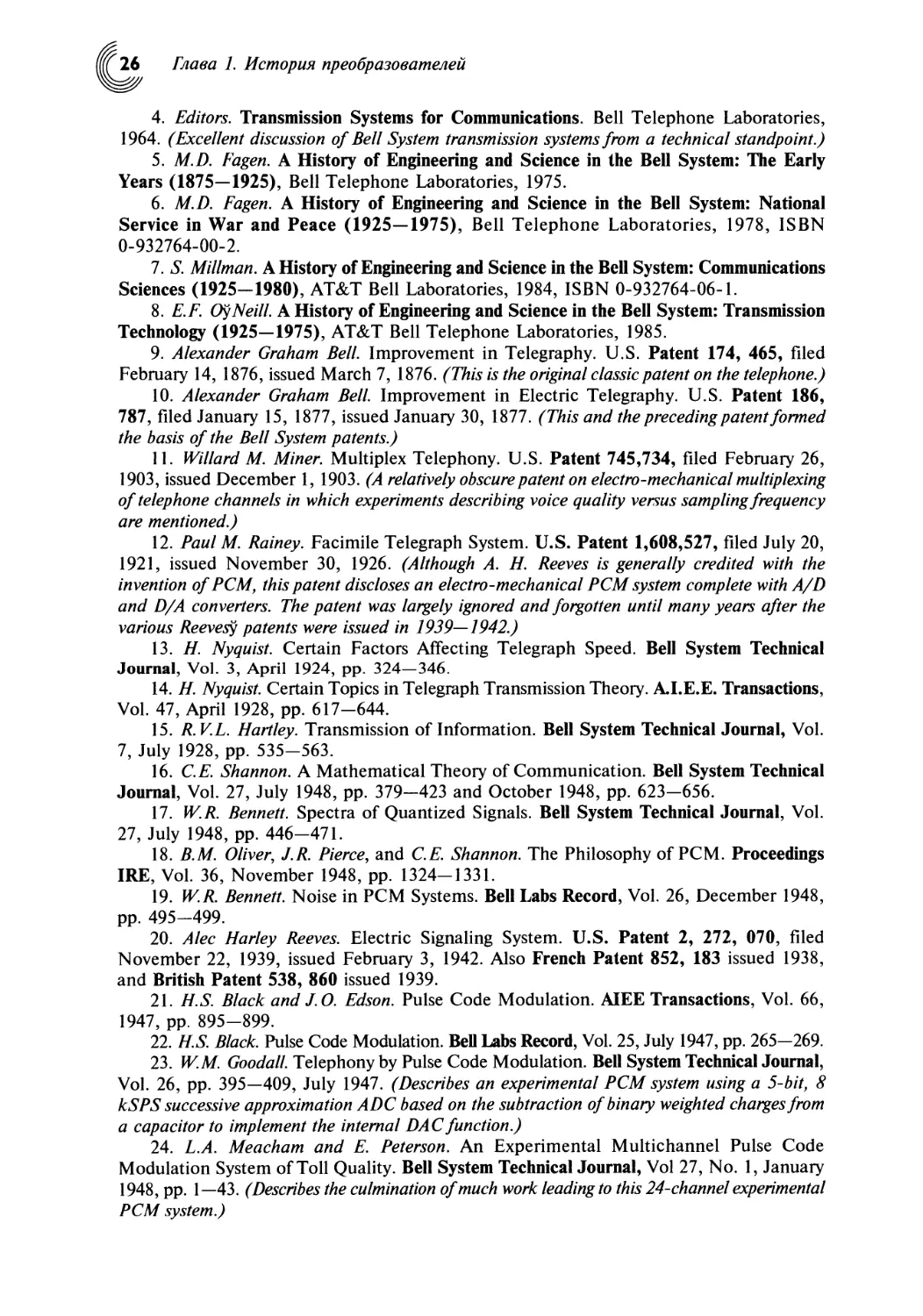

Глава 1. История преобразователей

4. Editors. Transmission Systems for Communications. Bell Telephone Laboratories,

1964. (Excellent discussion of Bell System transmission systems from a technical standpoint.)

5. M.D. Fagen. A History of Engineering and Science in the Bell System: The Early

Years (1875—1925), Bell Telephone Laboratories, 1975.

6. M.D. Fagen. A History of Engineering and Science in the Bell System: National

Service in War and Peace (1925—1975), Bell Telephone Laboratories, 1978, ISBN

0-932764-00-2.

7. S. Millman. A History of Engineering and Science in the Bell System: Communications

Sciences (1925-1980), AT&T Bell Laboratories, 1984, ISBN 0-932764-06-1.

8. E.F. OyNeill. A History of Engineering and Science in the Bell System: Transmission

Technology (1925—1975), AT&T Bell Telephone Laboratories, 1985.

9. Alexander Graham Bell. Improvement in Telegraphy. U.S. Patent 174, 465, filed

February 14, 1876, issued March 7, 1876. (This is the original classic patent on the telephone.)

10. Alexander Graham Bell. Improvement in Electric Telegraphy. U.S. Patent 186,

787, filed January 15, 1877, issued January 30, 1877. (This and the preceding patent formed

the basis of the Bell System patents.)

11. Willard M. Miner. Multiplex Telephony. U.S. Patent 745,734, filed February 26,

1903, issued December 1, 1903. (A relatively obscure patent on electro-mechanical multiplexing

of telephone channels in which experiments describing voice quality versus sampling frequency

are mentioned.)

12. Paul M. Rainey. Facimile Telegraph System. U.S. Patent 1,608,527, filed July 20,

1921, issued November 30, 1926. (Although A. H. Reeves is generally credited with the

invention of PCM, this patent discloses an electro-mechanical PCM system complete with A/D

and D/А converters. The patent was largely ignored and forgotten until many years after the

various Reevesy patents were issued in 1939—1942.)

13. H. Nyquist. Certain Factors Affecting Telegraph Speed. Bell System Technical

Journal, Vol. 3, April 1924, pp. 324—346.

14. H. Nyquist. Certain Topics in Telegraph Transmission Theory. A.I.E.E. Transactions,

Vol. 47, April 1928, pp. 617-644.

15. R. V.L. Hartley. Transmission of Information. Bell System Technical Journal, Vol.

7, July 1928, pp. 535-563.

16. C.E. Shannon. A Mathematical Theory of Communication. Bell System Technical

Journal, Vol. 27, July 1948, pp. 379-423 and October 1948, pp. 623-656.

17. W.R. Bennett. Spectra of Quantized Signals. Bell System Technical Journal, Vol.

27, July 1948, pp. 446-471.

18. B.M. Oliver, J.R. Pierce, and C.E. Shannon. The Philosophy of PCM. Proceedings

IRE, Vol. 36, November 1948, pp. 1324-1331.

19. W.R. Bennett. Noise in PCM Systems. Bell Labs Record, Vol. 26, December 1948,

pp. 495—499.

20. Alec Harley Reeves. Electric Signaling System. U.S. Patent 2, 272, 070, filed

November 22, 1939, issued February 3, 1942. Also French Patent 852, 183 issued 1938,

and British Patent 538, 860 issued 1939.

21. H.S. Black and J.O. Edson. Pulse Code Modulation. AIEE Transactions, Vol. 66,

1947, pp. 895-899.

22. H.S. Black. Pulse Code Modulation. Bell Labs Record, Vol. 25, July 1947, pp. 265—269.

23. W.M. Goodall. Telephony by Pulse Code Modulation. Bell System Technical Journal,

Vol. 26, pp. 395—409, July 1947. (Describes an experimental PCM system using a 5-bit, 8

kSPS successive approximation ADC based on the subtraction of binary weighted charges from

a capacitor to implement the internal DACfunction.)

24. L.A. Meacham and E. Peterson. An Experimental Multichannel Pulse Code

Modulation System of Toll Quality. Bell System Technical Journal, Vol 27, No. 1, January

1948, pp. 1—43. (Describes the culmination of much work leading to this 24-channel experimental

PCM system.)

1.2. Преобразователи 1950-х и 1960-х годов

25. R.W. Sears. Electron Beam Deflection Tube for Pulse Code Modulation. Bell

System Technical Journal, Vol. 27, pp. 44—57, Jan. 1948. (Describes an electon-beam

deflection tube 7-bit, 100 kSPS flash converter for early experimental PCM work.)

26. Frank Gray. Pulse Code Communication. U.S. Patent 2, 632, 058, filed November

13, 1947, issued March 17, 1953. (Detailedpatent on the Gray code and its application to

electron beam coders.)

27. J.O. Edson and H.H. Henning. Broadband Codecs for an Experimental 224Mb/s

PCM Terminal. Bell System Technical Journal, Vol. 44, pp. 1887—1940, Nov. 1965.

(Summarizes experiments on ADCs based on the electron tube coder as well as a bit-per-stage

Gray code 9-bit solid state ADC. The electron beam coder was 9-bits at 12 MS PS, and

represented the fastest of its type.)

28. Lee de Forest. Device for Amplifying Feeble Electrical Currents. U.S. Patent 841,

387, filed October 25, 1906, issued January 15, 1907.

29. Lee de Forest, Space Telegraphy. U.S. Patent 879, 532, filed January 29, 1907,

issued February 18, 1908.

30. H.S. Black. 'N&nq Translation System. U.S. Patent 2, 102, 671, filed August 8,

1928, issued December 21, 1937. (The basis of feedback amplifier systems.)

31. H.S. Black. Stabilized Feedback Amplifiers. Bell System Technical Journal, Vol.

13, No. 1, January 1934, pp. 1—18. (A practical summary of feedback amplifier systems.)

32. Harold S. Black. Inventing the Negative Feedback Amplifier. IEEE Spectrum,

December, 1977. (Inventory s 50th anniversary story on the invention of the feedback amplifier.)

33. C. Mark Melliar-Smith et al. Key Steps to the Integrated Circuit. Bell Labs Technical

Journal, Vol. 2, #4, Autumn 1997.

34. J. Bardeen, W.H. Brattain. The Transistor, a Semi-Conductor Triode. Physical

Review, Vol. 74, No. 2, July 15, 1947 pp. 230—231. (The invention of the germanium

transistor.)

35. W. Shockley. The Theory of p-n Junctions in Semiconductors and p-n Junction

Transistors. Bell System Technical Journal, Vol. 28, No. 4, July 1949, pp. 435—489. (Theory

behind the germanium transistor.)

36. L.R. Wrathall. Transistorized Binary Pulse Regenerator. Bell System Technical

Journal, Vol. 35, September 1956, pp. 1059—1084.

37. J. S. Kilby. Invention of the Integrated Circuit. IRE Transactions on Electron Devices,

Vol. ED-23, No. 7, July 1976, pp. 648-654. (Kilbyys IC invention at 11.)

38. Robert N. Noyce. Semiconductor Device-and-Lead Structure. U.S. Patent 2, 981,

877, filed July 30, 1959, issued April 25, 1961. (Noyceys IC invention at Fairchild.)

39. Jean Hoemi. Planar Silicon Diodes and Transistors. IRE Transactions on Electron

Devices, Vol. 8, March 1961, p. 168.

40. Jean A. Hoemi. Method of Manufacturing Semiconductor Devices. U.S. Patent 3,

025, 589, filed May 1, 1959, issued March 20, 1962. (The planar process— a manufacturing

means of protecting and stabilizing semiconductors.)

1.2. Преобразователи 1950-х и 1960-х годов

Уолт Кестер

Коммерческие преобразователи: 1950-е годы

До середины 1950-х годов преобразователи были уже основательно развиты

и использовались в специализированных сферах применения, например

таких, как ИКМ-лаборатории Белл и система шифрования сообщений, ис-

пользовавшаяся в период Второй мировой войны. Из-за применения тех-

Глава 1. История преобразователей

нологии вакуумных трубок преобразователи были очень дорогими, громоз-

дкими и имели высокое энергопотребление. Практически они не могли

иметь коммерческого использования.

Цифровой компьютер был важной движущей силой коммерческого раз-

вития АЦП. Проект по созданию компьютера ENIAC начался в 1942 году и

был представлен широкой публике в феврале 1946 года. Проект ENIAC

привел к созданию первого коммерческого цифрового компьютера UNIVAC,

разработанного Eckert и Mauchly. Первый UNIVAC был доставлен в United

States Census Burea в июне 1951 года.

Применение в военной сфере, например вычисление баллистической

траектории, стимулировало создание цифрового компьютера. Но время шло,

и интерес к цифровым вычислениям возрастал, так как их можно было

применить и в других областях — при анализе данных, в промышленных

процессах управления, а отсюда возросла необходимость в использовании

преобразователей. В 1953 году Бернард М. Гордон, пионер в области преоб-

разования данных, основал компанию под названием Эпско Инжениринг в

Конкорде, МА, где он сам проживал. Гордон раньше работал над создани-

ем компьютера UNIVAC и осознал необходимость создания коммерческих

преобразователей. В 1954 году Эпско представил 11-разрядный АЦП на

основе вакуумной трубки со скоростью дискретизации 50-kSPS. Этот пре-

образователь считается первым коммерческим устройством данного типа.

Преобразователь «Datrac», выпущенный Эпско, потреблял 500 Вт,

был спроектирован для стоечного монтажа (19" х 15" х 26") и продан за

8000—9000 долларов1. Фотография этого устройства приведена на рис. 1.17.

Datrac был первым коммерчески доступным АЦП, использовавшим сдви-

гово-программируемую архитектуру последовательного приближения. Гор-

дон получил патент на логику, необходимую для выполнения алгоритма

преобразования2. Из-за того, что в нем имелась функция выборки—хране-

ния, Datrac от Эпско был первым коммерческим АЦП, подходящим для

оцифровки сигналов переменного тока, таких как речь.

• 19" х 15" х 26"

• 500W

• 150 lbs

• $8 500 00

Courtesy,

Analogic Corporation

8 Centennial Drive Peabody,

MA 01960

www.analogic.com

Рис. 1.17. 11-разрядный 50-kSPS АЦП на электронной вакуумной трубке DATRAC,

1954

1.2. Преобразователи 1950-х и 1960-х годов

В этот же период несколько других компаний производили низкоско-

ростные АЦП, подходящие для применения при цифровых замерах вольт-

метром. Также существовали оптические преобразователи, основанные на

кодирующих дисках, для измерения дуговой координаты вала в авиацион-

ных приложениях1. С середины до конца 1950-х годов в преобразователях

использовались комбинации вакуумных трубок, полупроводниковых дио-

дов и транзисторов для осуществления процесса преобразования. Компа-

нии Эпско, Нон-Линеар Системз, J.B. Rea, Adage занимались разработкой