Автор: Гун С. Уайтхаус Х. Кайлат Т.

Теги: электротехника компьютерные технологии кибернетика радиотехника математика цифровая обработка сигналов компьютерные науки схемы радиосхемы радиосвязь

ISBN: 5-256-00179-5 (рус. )

Год: 1989

Сверхбольшие

I интегральные схемы

и современная

обработка сигналов

VLSI and Modern

Signal Processing

11 I

II

/

I

/

I

VLSI and Modern

Signal Processing

S.Y. KUNG, H.J. WHITEHOUSE andT. KAILATH

Editors

PRENTICE-HALL, INC., Englewood Cliffs, New Jersey 07632

Сверхбольшие

интегральные схемы

и современная

обработка сигналов

ПОД РЕДАКЦИЕЙ

С. ГУНА, X. УАЙТХАУСА, Т. КАЙЛАТА

ПЕРЕВОД С АНГЛИЙСКОГО

ПОД РЕДАКЦИЕЙ

В. А. ЛЕКСАЧЕНКО

Ер Москва «Радио и связь» 1989

ББК 32.811.3

С 24

УДК 621.3.049.771.14:681.3

Переводчик и: Ю. С. Малофеев, К, Т. Михайлуца, В, В. Никонов,

В. Г. Челпанов

Редакция переводной литературы

I

I

।

Сверхбольшие интегральные схемы и современная обработка

С 24 сигналов: Пер. с англ ./Под ред. С. Гука, X. Уайтхауса, Т. Кайла»

та. — М.: Радио и связь, 1989. — 472 с.: ил.

ISBN 5-256-00179-5.

Книга специалистов из многих стран является введением в круг разно-

образных проблем, возникающих при создании высокопроизводительных

систем обработки информации. Рассмотрены типичные задачи обработки

сигналов, иллюстрирующие возможности организации параллельных вычис-

лений. Проведен обзор перспективных разработок специализированных

процессоров на основе применения сверхбольших интегральных микро-

схем: в виде систолической матрицы и со связью через систему програм-

мируемых коммутаторов. Приведены примеры различного применения па-

раллельных вычислительных систем и их конкретной реализации.

Для инженерно-технических работников.

с 1402030000-183

046(01)-89

68—89

ББК 32.811.3

ISBN 5-256-00179-5 (рус.)

ISBN 0-13-942699-Х (англ.)

© 1985 by Prentice-Hall, Inc., Englewood Cliffs,

New Jersey 07632

© Перевод на русский язык, примечания.

Малофеев Ю. С., Михайлуца К. Т., Нико-

нов В. В., Челпанов В. Г., 1989

© Предисловие, примечания. Лексаченко В. А.

1989

ПРЕДИСЛОВИЕ РЕДАКТОРА ПЕРЕВОДА

После нескольких десятилетий развития теории и техники радиосистем

в среде радиоинженеров созрело понимание того, что эти системы состоят

в основном из двух частей: датчика сигналов и вычислительного устрой-

ства, осуществляющего обработку сигналов. Все остальное по сути предназ-

начено для сопряжения этих частей и вывода информации. Первые радиосис-

темы выполняли скромные задачи. Поэтому их вычислительная часть была

проста и обработка сигналов осуществлялась аналоговыми устройствами.

Разрабатываемые в настоящее время радиосистемы будут выполнять слож-

ные задачи, решение которых под силу только современным цифровым вы-

числительным машинам.

В связи с этим радиоинженеры — разработчики современных радиосис-

тем оказались в ситуации, когда им необходимо быть и специалистами по

вычислительной технике, и программистами, и математиками-прикладника-

ми. К сожалению, эта ситуация осложняется острым дефицитом научно-тех-

нической литературы по вопросам применения средств вычислительной тех-

ники в современных радиосистемах.

Предлагаемая книга, являющаяся одной из первых в указанной области,

представляет собой сборник статей известных зарубежных (в основном -

американских) специалистов, написанных в форме научно-технических от-

четов. Она является по существу введением в круг разнородных проблем,

возникающих перед создателями современных высокопроизводительных

систем обработки информации. Технической основой решения этих проблем

являются новые возможности, предоставляемые технологией сверхбольших

интегральных схем. Но не технологии, а математическим и алгоритмичес-

ким аспектам создания вычислительных систем обработки сигналов посвя-

щена эта книга.

Здесь нет необходимости характеризовать ее содержание, которое кратко •

изложено в предисловии редакторов к книге и во введениях к отдельным ее

частям. Необходимо только отметить, что широкий круг рассмотренных

вопросов и ’’отчетный” стиль отдельных глав не способствуют легкому чте-

нию. Однако этот недостаток является обратной стороной главных досто-

инств — актуальности рассматриваемых проблем и новизны предлагаемых

решений. Активный исследователь может найти в книге много новых идей,

которые окажут стимулирующее влияние на его деятельность. Книга полез-

на также студентам старших курсов радиотехнических специальностей и

инженерам, желающим повысить свою квалификацию в области обработ-

ки сигналов.

Переводчики приложили немало усилий по согласованию английских и

русских терминов. Предисловие к книге, введение к части I и гл. 1, 2, 3, 6 пе-

ревел К. Т. Михайлуца; гл. 4, 5, 19 - В. Г. Челпанов; введение к части И,

главы 7—16, 20, 26 — В. В. Никонов; введение к части III, гл. 17, 18, 21 — 25 -

Ю. С. Малофеев.

5

ЧАСТЬ I

ОБРАБОТКА СИГНАЛОВ: ТЕОРИЯ И АЛГОРИТМЫ

Современная обработка сигналов характеризуется усилением взаимодей-

ствия нескольких областей науки и техники: анализа сигналов, теории сис-

тем, статистических методов и численного анализа. Революция в технологии

СБИС способствует слиянию областей разработки интегральных схем и вы-

числительной техники. Объединение СБИС и современной обработки сигна-

лов приводит к еще более поразительному взаимопроникновению этих об-

ластей знаний. В каждой из них нам приходится пересматривать заново тра-

диционные решения, которые когда-то были ’’оптимальными” в своей об-

ласти.

Это основная тема гл. 1, в которой приводится несколько примеров

плодотворного взаимодействия между математическими решениями и су-

ществующими многообещающими технологическими возможностями. В ка-

честве примера рассмотрен известный алгоритм Левинсона, используемый в

технике кодирования с линейным предсказанием (КЛП) для анализа и син-

теза речи. В алгоритме Левинсона используется свойство стационарности

процесса для уменьшения количества вычислительных операций с О(п3) до

О(п2) при построении его модели /г-го порядка. В том случае, когда исполь-

зуется один процессор, время вычисления пропорционально количеству вы-

числительных операций. Естественно возникает вопрос о том. нельзя ли с

появлением СБИС использовать параллельную обработку для увеличения

скорости вычислений. Оказывается, что поскольку алгоритм Левинсона тре-

бует формирования скалярных произведений и-мерных векторов, то даже

при параллельной работе п процессоров время вычислений можно умень-

шить только с О(п2) до О(п log п). Однако, используя другой, менее извест-

ный (но более старый) алгоритм, можно избежать формирования скалярных

произведений и уменьшить время вычисления при применении п процессо-

ров до О (и). Более того, эта структура вполне удовлетворяет требованиям

ее реализации в виде СБИС и в действительности образец такой СБИС уже

создан (см. гл. 17).

Этот другой алгоритм — алгоритм Шура обладает многими интересными

свойствами, включая тесную связь с теорией длинных линий. В эпоху СБИС,

когда стоимость запоминающих устройств резко снижается, модели линей-

ных систем в виде длинных линий оказываются полезными альтернативами

современным, более популярным, по крайней мере в теории систем и управ-

ления, моделям, основанным на понятиях пространства состояний. Некото-

рые из этих положений рассмотрены в гл. 1 и работах, указанных в списке

литературы к ней.

8

Удивительной особенностью современной обработки сигналов является

широкий диапазон математических идей, которые возникают при решении

кажущихся ясными проблем. Однако основу составляют линейная алгебра и

теория линейных операторов. К специфическим задачам, которые необхо-

димо решать в реальном масштабе времени в современных системах обработ-

ки сигналов, относятся матричные умножения для оценки ковариации, реше-

ние линейных уравнений для адаптивной обработки, вычисление собствен-

ных значений и векторов для определения направления с высокой разрешаю-

щей способностью и адаптивного формирования лучей. Для каждого TV-мер-

ного вектора входных данных эти задачи обычно требуют от 7V3 до 7V4 эле-

ментарных операций (умножений и сложений). Выполнение этих вычислений

с достаточной скоростью, для того чтобы справиться с потоком входных дан-

ных, трудно даже в случае очень узкополосных сигналов. Глава 2 начинается

с формулировки этих проблем, а затем в ней обсуждается архитектура парал-

лельных матричных процессоров, позволяющая надеяться на решение этих

проблем.

Однако, прежде чем ринуться изобретать новые изящные структуры па-

раллельных вычислителей для решения множества линейных алгебраичес-

ких задач, следует учесть болезненный урок, полученный в теории цифро-

вой фильтрации за последние два десятилетия: необходимо обращать самое

пристальное внимание на такие вопросы, как накопление погрешностей

округления даже в простых численных расчетах, появление осцилляций,

вызванных переполнением, а также на предельные циклы в цифровых фильт-

рах. Было установлено, что ряд предложенных систолических матричных

процессоров, предназначенных для умножения матрицы на вектор и матри-

цы на матрицу, рекуррентного оценивания, нахождения наибольшего общего

делителя и т. д., по существу, представляют собой вариант прямой реализа-

ции цифровых фильтров. Основное отличие этих процессоров от указанных

цифровых фильтров состоит в ’’конвейеризации” вычислений, обеспечиваю-

щей более высокую скорость обработки данных. Однако из теории цифро-

вых фильтров хорошо известно, что прямые способы реализации всегда бы-

ли уязвимы с точки зрения ошибок вычислений, в связи с чем от них отка-

зывались в пользу каскадных способов реализации. Каскады ортогональ-

ных секций особенно предпочтительны в связи с отсутствием проблем, свя-

занных с предельным циклом и осцилляциями, вызванными переполнением.

Можно получить конвейерные структуры каскадных ортогональных фильт-

ров, и они могут оказаться достаточно эффективными на практике. В гл. 15

и работе [1-46] описан расчет и анализ таких структур.

Численные задачи другого рода входят составной частью в проблему вы-

числения собственных значений и собственных векторов, в особенности боль-

ших матриц. В гл. 3 — 5 рассматриваются развитие и современное состояние

спектрального оценивания с высокой разрешающей способностью и методов

измерения угловых координат. Эти новые методы оценивания угловых ко-

ординат и тесно связанные с ними методы адаптивного формирования луча

оказались очень эффективными. Удивительно, что они основаны главным

9

образом на вычислении минимальных собственных значений и соответствую-

щих им собственных векторов. г.

Проблема собственных значений интенсивно изучалась многими теорети-

ками начиная с 1947 г., когда собственные значения стали рассчитывать с

помощью настольных калькуляторов. В гл. 6, которой завершается часть I,

делается несколько убедительных замечаний по многим аспектам этой проб-

лемы, включая вопрос о том, как эффективные параллельные вычисления

будут использованы для получения полезной информации о собственных и

сингулярных значениях.

Т. Кайлат

I I

1

ОБРАБОТКА СИГНАЛОВ В ЭПОХУ СБИС

Т. Кайлат1

1.1. ВВЕДЕНИЕ

Предложенное Кули и Тьюки почти два десятилетия назад быстрое преоб-

разование Фурье (БПФ) в сочетании с накопленным к тому времени опытом

в технологии цифровых систем привело к революции в обработке сигналов.

Наряду с прочим эта революция характеризуется развитием нового направ-

ления, которое получило название цифровой фильтрации или цифровой об-

работки сигналов (см., например, хорошо известную книгу Оппенгейма и

Шафера2).

Около десяти лет назад пионерской работой Атала и его сотрудников из

фирмы Bell Laboratory, а также Итакурой и Сайто в Японии идеи времен-

ной обработки были вновь применены к анализу и синтезу речи (см., напри-

мер, [45]). В сочетании с развитием'технологии интегральных схем это на-

правление возвещает об еще одной революции в обработке сигналов, о чем

свидетельствует, например, появление кристалла Speak-and-Spell фирмы 1

Texas Instruments и возрастающий интерес к параллельным алгоритмам и

| архитектурам (см., например, специальный выпуск журнала IEEE Computer

Magazine за январь 1982 г., посвященный быстрым параллельным вычисле-

ниям).

Основной особенностью нового направления является акцент на форму-

I лировку оптимизационных критериев в задачах обработки сигналов. Цель

состоит в том, чтобы, не связываясь преждевременно с конкретным спосо-

I бом реализации, создать математическую модель с определенным критери-

ем эффективности, удовлетворение которому будет определять последова-

тельность операций обработки сигналов. Конечно, всегда имеются ограниче-

1 Стэнфордский университет, Станфорд, Калифорния.

2 Оппенгейм Л. В., Шафер Р. В. Цифровая обработка сигналов: Пер. с англ. - М.:

Радио и связь, 1979.

НО

ния при создании реалистичных, но не очень сложных математических моде-

лей и подходящих критериев оптимизации. Однако подобные проблемы уже

встречались и были удачно преодолены в статистической теории связи, уп-

равления и идентификации.

Специфические особенности задач обработки сигналов часто дела.ют же-

лательным применение процедуры линеаризации, поэтому значительная часть

теории и практики современной обработки сигналов в конечном счете свя-

зана с решением систем линейных уравнений. На первый взгляд зто разоча-

ровывает, поскольку подобные вопросы изучаются в течение настолько

длительного времени, что сказать что-то новое о них, кажется, уже нельзя.

Но дело в том, что для наиболее интересных физических задач непосредст-

венное численное решение уравнений не представляет большой ценности;

весь интерес заключается в специальной структуре уравнений и методах

согласования с ней современных аппаратурных средств, позволяющих сок-

ращать время нахождения решений и уменьшать сложность реализации.

Так БПФ и структуры матричных процессоров оказали решающее влия-

ние на традиционные представления о том, как находить эмпирические спект-

ральные оценки. Аналогично этому модели с пространством состояний в

теории управления привели в 60-х гг. к революции в возможностях обра-

ботки больших массивов данных вследствие осознания того факта, что для

обработки достаточно отслеживать изменения фиксированного конечно-

мерного марковского вектора состояний. В настоящее время относительная

доступность устройств памяти делает менее необходимым концентрацию

предыдущей информации в фиксированном конечномерном векторе состоя-

ний; теперь часто проще наращивать память, приводя в соответствие ее ем-

кость с объемом данных. Проиллюстрируем это в данной главе. Появление

однокристальных арифметических устройств с плавающей запятой может

вскоре изменить некоторые из наших представлений о том, что является

хорошим алгоритмом в той или иной конкретной задаче. Многие ухищрения,

используемые для того, чтобы преодолеть эффекты ограниченной точности,

становятся ненужными, когда появляется возможность проведения вычис-

лений с удвоенной точностью.

В этой главе попытаемся показать некоторую взаимосвязь между алгорит-

мами обработки сигналов и технологией интегральных схем. В разд. 1.2

рассмотрим некоторые задачи обработки сигналов, связанные со стационар-

ными стохастическими моделями, или, что то же самое, задачи, приводящие

к линейным уравнениям с теплицевыми матрицами. Эта специальная форма

уравнений, одна из первых в статистической обработке сигналов, была рас-

смотрена в работах Винера и Левинсона в 40-50-х гг. Однако технологичес-

кие ограничения на емкость элементов памяти, как об этом уже упомина-

лось, привели к тому, что в 50- 60-х гг. основное развитие получили устрой-

ства обработки типа калмановского фильтра с фиксированной памятью

(см., например, [26]). Алгоритм Левинсона продолжали применять в зада-

чах обработки сигналов в геофизике (сейсмологии), где было возможным

использование больших вычислительных ресурсов; в конце 60-х гг. он опять

нашел свое применение в задачах синтеза речи (Атал, Шредер, Итакура, Сайто

11

и др.) - Мы разовьем их выводы в разд. 1.2, показав, как теплицева форма

при современной технологии СБИС и возможно оптической и волновой

технологии приводит к очень изящным результатам.

Хотя предположение о стационарности во многих случаях упрощает ана-

лиз, часто встречаются ситуации, когда это предположение несправедливо.

Мы рассматриваем такие ситуации в разд. 1.3 и показываем, как некоторые

относительно новые теоретические исследования позволяют сохранить пре-

имущества стационарного приближения для некоторых нестационарных

задач обработки сигналов за счет использования дополнительной памяти.

По различным причинам изложение будет кратким и не будет содержать

доказательств, которые можно найти в работах, упомянутых в списке лите-

ратуры. Цель состоит в том, чтобы проиллюстрировать некоторые аспекты

развивающейся взаимосвязи теории и техники обработки сигналов. Книга

содержит много других примеров на эту тему.

1.2. НЕКОТОРЫЕ АЛГОРИТМЫ ДЛЯ ТЕПЛИЦЕВЫХ МАТРИЦ

Хорошо известные в настоящее время методы кодирования с линейным

предсказанием (КЛП) для анализа речевых сигналов основаны на гипотезе

о том, что речевые сигналы могут быть смоделированы как результат про

хождения белого шума через линейный инвариантный во времени фильтр.

Данная гипотеза основывается на том, что процессы переноса информации,

по существу, случайны (на это впервые обратил внимание Норберт Винер).

Применительно к анализу речевых сигналов воздух, выходящий из легких,

можно представить как белый шум, который модулируется колебаниями

голосового тракта (голосовых связок, нбеа, губ) и создает звуковые волны.

Линейный инвариантный во времени фильтр может быть смоделирован

различными способами,, однако по разным причинам первоначально внима-

ние было сосредоточено на использовании моделей, в которых речь представ-

ляется в виде стационарного дискретизированного по времени случайного

процесса авторегрессии:

У, + Лл j)', 1 -I- ' ’ • + Ах. ivEi-х ~

где {eJV (} — белый шум с нулевым математическим ожиданием.

Проблемы, возникающие при моделировании, состоят в выборе порядка

N, значений коэффициентов {Аи дисперсии’шума для наилучшего

описания исследуемого речевого сигнала , t > 0}.

Обычная процедура состоит в получении выборочной ковариационной

функции

нахождении коэффициентов! Л N,} из

стационарного процесса !yt, г >0J и

уравнения Юла—Уокера

ГАх, X • ЛХ.1Л 1 . . >3 >3 о К. ?•

12 *Х

*х

«г

= [() 0 /].

0-1)

Допущения, лежащие в основе этой формулировки, более подробно ис-

следуем в разд. 1.3 и найдем некоторые основания, чтобы не согласиться с

ней. Однако одна из причин широкого распространения формулировки (1.1)

состоит в том, что специальная с постоянными элементами вдоль диагона-

лей (теплипева) форма матрицы в уравнении (1.2) приводит к удобному

быстрому рекурсивному алгоритму решения уравнения — алгоритму Левин

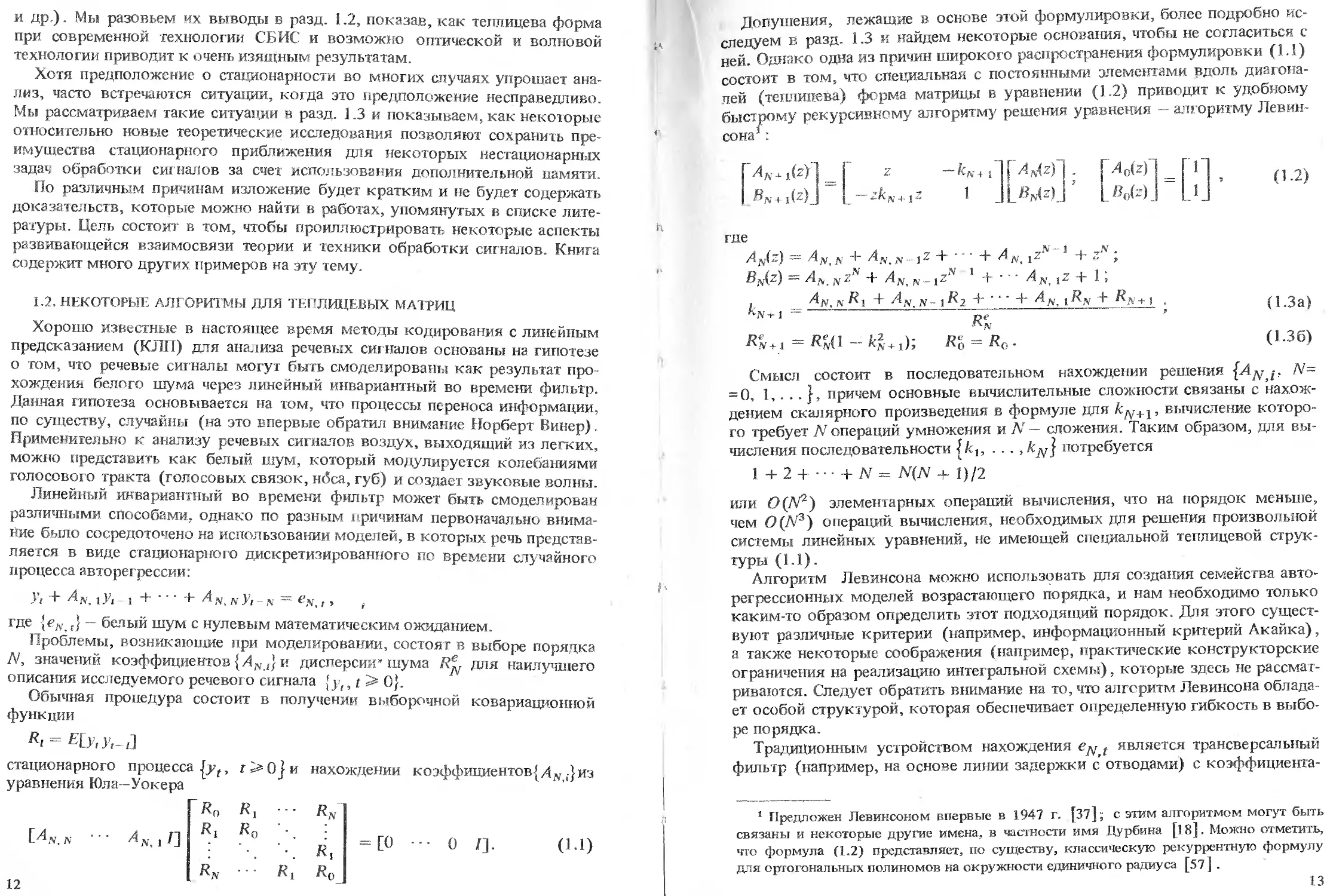

сона1 :

Лдг х i (z)

z -kNil

1 JJW.

.40(zH = 1

ЗД. 1

(1-2)

где

Лдг) — Ддг,л + Av,n iz + + an 1 + ;

= Aft. NZ^ + Aft, ft- -\ZN 1 + AN lz + 1;

k An, л + AN jv- 1^2 + ' " + An, i^n + Av-n . (13a)

ReN " " ’

^+l = ^(l-^+1); К£ = *о- (1-36)

Смысл состоит в последовательном нахождении решения [Av/- А=

= 0, 1,... }, причем основные вычислительные сложности связаны с нахож-

дением скалярного произведения в формуле для к^+^, вычисление которо-

го требует N операций умножения и Л' — сложения. Таким образом, для вы-

числения последовательности fkt, . .. ,kN] потребуется

1 + 2 + + N = N(N + 1) /2

или О(№) элементарных операций вычисления, что на порядок меньше,

чем O(N3) операций вычисления, необходимых для решения произвольной

системы линейных уравнений, не имеющей специальной теплицевой струк-

туры (1.1).

Алгоритм Левинсона можно использовать для создания семейства авто-

регрессионных моделей возрастающего порядка, и нам необходимо только

каким-то образом определить этот пояходящий порядок. Для этого сущест-

вуют различные критерии (например, информационный критерий Акайка),

а также некоторые соображения (например, практические конструкторские

ограничения на реализацию интегральной схемы), которые здесь не рассмат-

риваются. Следует обратить внимание на то, что алгоритм Левинсона облада-

ет особой структурой, которая обеспечивает определенную гибкость в выбо-

ре порядка.

Традиционным устройством нахождения eN t является трансверсальный

фильтр (например, на основе линии задержки с отводами) с коэффициента-

’ Предложен Левинсоном впервые в 1947 г. [37]; с этим алгоритмом могут быть

связаны и некоторые другие имена, в частности имя Дурбина [1 8]. Можно отметить,

что формула (1.2) представляет, по существу, классическую рекуррентную формулу

для ортогональных полиномов на окружности единичного радиуса [57 ] .

13

Рис. 1.1. Реализация фильтра в виде линии задержки с отводами:

а — выбеливающий фильтр; б ~ моделирующий фильтр

mh^AN q, ... (рис. 1.1); необходимо только заметить, что во избежа-

ние недоразумений передаточной характеристикой фильтра для расчета eN t

должна быть не A^(z), а

Лдг. ;v + AN n_ tz 1 + • • + z N = z N/4n(z) .

Однако если нет уверенности в выборе порядка, а необходимо подсчи-

тать, скажем, е^+2 t, то уже нельзя только повысить порядок трансверсаль-

ного фильтра, а следует заменить все коэффициенты [ANq, ... ,AN Л4 на

{^jV+2,0’ >-^7V+2 7V+2 } • Существует много примеров, когда, прежде чем

остановиться на выборе определенного порядка N, желательно оценить отк-

лик фильтра в некотором диапазоне изменения величины N, а это неудобно

делать при трансверсальной реализации фильтра. Из выражения (1.2) сле-

дует, что коэффициенты {к^ i = ,n} вместе с условием Ао (z) -Во (z) =

= 1 дают другую параметризацию фильтра: знание этих величин позволяет

определить AN(z) и, следовательно, коэффициенты {Ajyj } из (1.2). Если

есть желание выбрать другой порядок, скажем 7V+2, то в этой параметриза-

ции придется добавить еще только два коэффициента {к}у+1, fcy+jJ без из-

менения ранее найденных величин. Это свойство инвариантности параметри-

зации {кг-| можно использовать, осуществляя реализацию фильтров в терми-

нах ] <г <Л'} , а не [а^ / }. Из выражения (1.2) следует, что фильтр

можно создать в виде каскадного соединения решетчатых секций, как на

рис. 1.2,а, или в некотором нормализованном виде (см. далее формулу

(1.5)), как на рис. 1.2,6?.

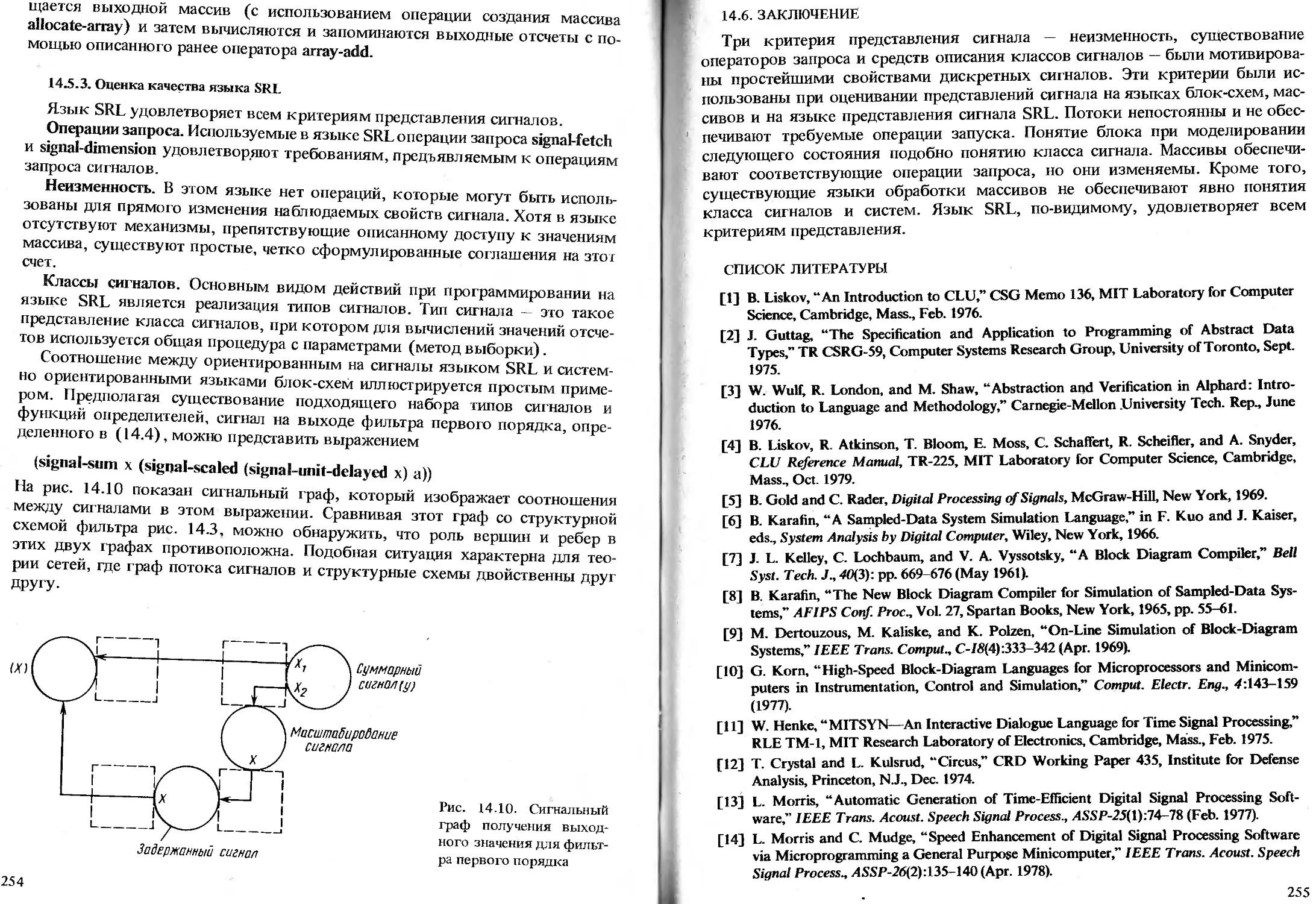

С помощью методов теории сигнальных графов легко осуществить обра-

щение решетчатых фильтров. Результат такого преобразования — моделирую-

щий фильтр — показан на рис. 1.3. Он имеет вид дискретной длинной линии

и помогает объяснить, почему J часто называют коэффициентами отобра-

ЖСНИЯ.

При гакой физической интерпретации предполагается, что должно выпол-

няться условие

1^-1 <1- (1.4)

14

a)

Рис. 1.2. Реализация выбеливающих фильтров в виде решетчатого фильтра:

а — ненормализованный вид; б — нормализованный вид

Рис. 1.3. Моделирующие фильтры:

а — решетчатый фильтр с обратной связью — нормализованный вид; б — фильтр в виде

длинной надписи

которое следует также из (1.36) (так как значения дисперсии должны быть

неотрицательными) . UaAN(z) должны быть наложены определенные ограни-

чения: корни полинома z^A (z) должны лежать в круге единичного радиуса,

однако это условие не так просто перевести на интервал изменения коэффи-

циентов {ах j j. По этой и другим причинам характеристики (нормализован-

ного) решетчатого фильтра лучше аналогичных характеристик трансверсаль-

15

Гюго фильтра. Поэтому не удивительно, что фирма Texas Instruments выбра-

ла для использования именно эту структуру при создании своих кристаллов

синтезатора речи, имеющих большой успех [60]: модульная структура, ло-

кальные соединения, ритмичный поток данных — все это сделало удобным

реализацию данного фильтра в виде СБИС [27 — 30, 39].

1.2.1. Методы реализации алгоритма CORDIC

Для реализации каждого блока на рис. 1.2,а необходимы две операции ум-

ножения и две — сложения. Поскольку операции умножения являются более

дорогостоящими, были осуществлены дополнительные преобразования,

чтобы ограничиться одной операцией умножения (см., например, [1.38,

разд. 5.5]). По причинам вычислительного характера часто приходят к блоку

с четырьмя умножителями, как это изображено на рис. 1.2,5. Однако оказы-

вается, что этот блок в действительности может быть реализован вовсе без

операций умножения.

Чтобы показать это, вначале заметим, что при условии |/с| < 1 типичный

блок решетчатого фильтра в нормализованном виде (см. рис. 1.2,6) можно

характеризовать матрицей

1 -к

1

(1.5 а)

Причиной для такого названия является свойство

ej0* = j, j =

1 0

0 -1

(1.56)

где * — знак комплексного сопряжения.

Это свойство означает, что матрица 0 сохраняет ’’длину” любого вектора

w* = [wM], на который она воздействует, при условии, что длина измеряет-

ся в метрике J, т. е.

||0u||2= Hull2, II и II2 = II Uj II2 - I U2 I2 .

Матрицу 0 часто называют J-ортогональной, а результат ее умножения на

вектор — J-вращением или гиперболическим вращением в противополож-

ность обычному круговому вращению.

Как указывается в [31], Д. Волдер еще в 1969 г. [58] предложил простые

схемы для осуществления вращений с помощью так называемых ’’коорди-

натных цифровых вычислителей”, или CORDIC1. В этих схемах используют-

ся только регистры, элементы сдвигов и сумматоры для итеративного расче-

та таких функций, как arctg(y/x), х/с2 — у2, arctb(y/x), х cos а —

— у sin а и т. д.; подобные схемы были использованы для этих целей во мно-

гих микрокалькуляторах, например в НР-35 [11,54, 59].

1 CORDIC — Coordinate Rotation Digital Computer. - Прим, перев.

В последние годы по алгоритму CORDIC строились различные одно- и дву-

мерные вычислительные структуры систолического и волнового матричного

типов на СБИС Сем., например, [2, 46, 47], а также гл. 15, 16 этой книги).

Автор работ [14, 15] был одним из первых, кто привлек внимание к принци-

пу CORDIC для обработки сигналов по алгоритмам типа БПФ, а недавно в ра-

боте [20] было приведено описание СБИС, реализующей алгоритм CORDIC

для арифметических вычислений. Следует отметить, что до того, как присту-

пить к действительной реализации этого принципа (а также других схем вы-

числений, как, например, схем матричных умножителей), следует рассмот-

реть ряд факторов, таких как быстродействие, точность и др.

Хочется подчеркнуть, что рассмотрение специальной математической

структуры решетчатого блока позволяет построить новый макроблок для

обработки сигналов.

1.2.2. Параллельные вычисления и алгоритм Шура

Естественный вопрос, который возникает при использовании технологии

СБИС, насколько можно ускорить процесс вычисления коэффициентов

применяя параллельные вычисления, скажем, с помощью N процес-

соров, работающих совместно. Надежда на успех состоит в том, что если

одному процессору требуется некоторый отрезок времени на каждую эле-

ментарную операцию вычисления, то, применяя TV процессоров, можно рас-

считывать на получение ответа через период времени O(N), а не 0(1^), как

в случае одного процессора.

Однако нетрудно заметить, что длительность параллельной реализации

алгоритма Левинсона составит О (TV log TV) из-за наличия операций вычисле-

ния скалярного произведени/i, необходимых для формирования последова-

тельности N процессоров могут выполнять А7 операций умножения, не-

обходимых для формирования Ajy+1 последовательностей параллельно в еди-

ницу времени, но необходимые при этом операции сложения потребуют по

меньшей мере log TV шагов.

Это кажется обескураживающим, но вселяет надежду на успех. Оказыва-

ется, что существует математически эквивалентный алгоритм, предложенный

Щуром [55], который позволяет избежать вычислений скалярных произве-

дений при формировании {&г-} и тем самым обеспечить с помощью TV процес-

соров вычисления за период времени <9 (TV).

Алгоритм Шура был впервые предложен в 1917 г. в качестве теста для

определения, того, является ли степенной ряд аналитическим и ограниченным

в круге единичного радиуса. В нашем случае он приводит к простой трехша-

говой процедуре [17, 35] расчета последовательности связанной с кова-

риационной последовательностью ,, .. ,R0 = i.

1. Начнем с порождающей матрицы (символ * означает операцию транспо-

нирования)

17

и сдвинем первую строку Gg вправо для того, чтобы получить

Р* = Г° «<> K/V-.

'* Г° -К. -KN

2. Вычислим k-i по формуле кг = { Gj} 2.2/ Г } 2.1

3. Сформируем матрицу

0(/С1) =

—

1

и получим новую порождающую матрицу

~ [ 0 х х • ’ ’ х

ct-e№,)cr= 0 0 х ... ,]>

где х — элементы, точное значение которых в данный момент несуществен-

но; Q известна как матрица J-вращения, поскольку

0(k)J0*(A) = J, J= ’ ° •

Ее роль состоит во вращении в ./-метрике (т. е. в гиперболической метри-

ке) второй строки матрицы G для того, чтобы она расположилась вдоль пер-

вого координатного направления.

Затем шаги 1, 2 и 3 могут быть повторены для получения значения к2 и

новой порождающей матрицы G2 и т. д.

Можно показать, что рассчитанные по алгоритму Illypa, имеют точно

такие же значения, что и при расчете по алгоритму Левинсона. Заметим, од-

нако, что алгоритм Шура требует выполнения последовательности умноже-

ний век тора-строк и размера 2X1 на матрицу размера 2X2, которые могут

быть выполнены параллельно на каждом этапе. Поэтому для реализации ал-

горитма Шура с помощью N процессоров требуется период времени О (Д'), а

не О (Д'log TV), как при выполнении алгоритма Левинсона. В действительнос-

ти параллельная поточная вычислительная структура на СБИС, основанная на

алгоритме Шура, уже разработана и создана (см. [29] и гл. 17 этой книги).

1.2.3. Разложение Холсцкого

Алгоритм Шура тесно связан с разложением Холецкого ковариационной

матрицы R в (1.1). Такое разложение применимо во многих вычислениях,

связанных со стохастическими процессами. Множителем Холецкого С мат-

рицы R называется единственная нижняя треугольная матрица с положитель-

ными диагональными элементами, удовлетворяющая соотношению

R=CC*.

Матрица С непосредственно определяется алгоритмом Шура:

г-й столбец С = первому столбцу Gz-, (1.6)

где {С.;-| — приведенные порождающие матрицы, полученные с помощью

алгоритма Шура.

18

Таким образом, в случае разложения Холецкого для теилицевых матриц

имеется быстрый алгоритм, согласно которому выполняется <?(№) опера-

ций вместо О (/V3) в общем случае.

Следует упомянуть, что процедура Шура для быстрого разложения Холец-

кого теилицевых матриц много раз переоткрывалась в различных контекс-

тах. Так, в [3,40, 50, 5 J ] был, по существу, вновь найден алгоритм Шура при

решении обратной задачи теории рассеяния в слоистой модели Земли. В тех-

нике алгоритм Шура был, по-видимому, впервые использован Девильдом

(Dewilde) в начале 70-х гг. при решении задачи синтеза функции полных

сопротивлений пассивных систем. Его приложение к задачам статистическо-

го оценивания было впервые описано в [17] ив дальнейшем использовано

в [16, 33—35]; применение в теории цифровых фильтров опубликовано

в [13] (см. гл. J 5 этой книги, а также [46,47]). Новые структуры, получен-

ные в этих работах, по-видимому, являются лучшими претендентами для

реализации в виде СБИС.

1.2.4. Интерпретация в виде длинной линии и обратные задачи теории рассеяния

Хорошей иллюстрацией естественной связи между алгоритмом Шура и

его реализацией в виде СБИС (или другими методами) служит графичес-

кое представление этого алгоритма, изображенное на рис. 1.4. В этом слу-

чае полученная ранее связь между матрицами С и {Gy} означает, что элементы

г-го столбца представляют собой множитель Холецкого С. Следовательно,

можно сказать, что данные на входах элементов задержки в любой момент

времени I суть элементы Z-й строки множителя С. Между прочим, такая ин-

терпретация в значительной мере снимает налет таинственности, которая

иногда связана с быстрыми алгоритмами Холецкого для строк и столбцов.

Интерпретацией в виде длинной линии предполагается, что расчеты могут

быть выполнены путем возбуждения структур, подобных приведенным на

Рис. 1.4. Формы представления алгоритма Шура:

а — прямая форма; б — модель в виде длинной линий

19

рис. 1.4, с помощью световых или других электромагнитных волн в зави-

симости от среды, выбранной для реализации.

Отметим, что, используя графические представления рис. 1.4 и фундамен-

тальные законы распространения волн и сохранения энергии, можно полу-

чить простые доказательства всех предыдущих результатов и постепенно

выяснить тонкие и полезные связи между теорией длинных линий, разложе-

нием Холецкого (прямым и обратным), обратными задачами теории рас-

сеяния и алгоритмами Шура [6]. Подобное представление в виде длинной

линии оказалось также полезным при получении некоторых ортогональных

каскадных схем реализации БИХ-фильтров1 с прекрасными характеристика-

ми [46,47].

С другой стороны, к тем же результатам можно прийти, используя совер-

шенно иной подход, если заметить, что разложение Холецкого есть не что

иное, как метод проверки матрицы на положительную определенность; ес-

ли теперь спросить, какие матричные структуры легко поддаются такой

проверке, то придем к классу матриц, в котором семейство теплицевых мат-

риц представляет только один частный случай [35]. При таком подходе все

ранее упомянутые результаты по параллельным вычислениям и интерпрета-

ции в виде длинных линий, а также их реализации можно распространить на

значительно более широкий круг задач, что и рассмотрим кратко в разд. 1.3.

1.2.5. Алгоритмы удвоения

Последний интересный результат, о котором здесь стоит упомянуть, сос-

тоит в том, что алгоритм Шура может лежать в основе получения самой

простой формы алгоритма ’’удвоения” (или алгоритма ’’разделяй и власт-

вуй”) для расчета последовательности \ki | и для решения уравнений Юла—

Уокера. Применяя алгоритмы быстрой свертки для объединения импульс-

ных откликов пар соседних 0-секций на рис. 1.4, количество вычислитель-

ных операций можно свести к 12ATog2A' [42,43] (точка пересечения данной

зависимости с аналогичной зависимостью для прямого алгоритма Шура при

решении теплицевых уравнений соответствует значению А'=128). Результа-

ты, подобные O(ATog2Ar), были впервые получены в работах [4, 5, 41], од-

нако в действительности алгоритмы были довольно сложными и, например,

в работе [56] было подсчитано, что для метода Битмида (Bitmead) и Андер-

сона коэффициент при членах A1og2Ar равен 7000! Алгоритм, основанный

на процедуре Шура, не только дает меньший коэффициент, но также более

пригоден для потенциальной реализации в виде СБИС.

1.3. РАСПРОСТРАНЕНИЕ РЕЗУЛЬТАТОВ РАЗД. 1.2 НА МАТРИЦЫ.

БЛИЗКИЕ К ТЕПЛИЦЕВЫМ

В начале разд. 1.2 отмечалось, чти обычным методом подгонки авторег-

рессионных моделей к временным рядам является решение линейных урав-

нений Юла—Уокера с теплицевой матрицей коэффициентов. Было упомяну-

1 БИХ-фильтр — фильтр с импульсной характеристикой бесконечной длительности. —

Прим, перев.

20

то, что это не обязательно единственный или наилучший путь решения проб-

лемы; сейчас поясним почему.

Кратко проблема состоит в следующем: дана последовательность резуль-

татов наблюдений [у0,... ,уг] ; необходимо выбрать набор коэффициен-

тов {fli } так, чтобы

£ е2, = minimum , (1.7)

т

где еп t — ошибка (остаток при попытке предсказать yt по п предыдущим

значениям):

e„.t = У, + «1У<1 + • + а„у,_„ . (1.8)

Трудности возникают при 0<Т <и, так как в этом случае нет всех п преды-

дущих значений. Один из выходов состоит в расчете остатков только для

но по ряду причин (некоторые из которых сейчас станут понятными)

мы часто рассматриваем случай Т<п, полагая, что отсутствующие значения

{у_„, Т-и+1’ • • • ’ Т-1} Равны нулю. Одна из причин - предположение о

том, что при 7’>и произвольность такого начального допущения не скажется

сильно на результатах решения в целом. Это вполне разумно, но иногда мож-

но сделать более кардинальное допущение: расчеты вести только для T<t <

СТ’+и. полагая, что последующие значения {yj’+j, • • • ,Ут+n} также равны

нулю. Далее покажем, какие для этого есть основания, но вначале запишем

последовательность остатков в матричной форме:

е = Ya,

где

ег = К. о <?„, ।

а=[1 о, •••

(1-9)

Уо

У1 Уг

Уо

Уt—п

Ут п

Ут

Наименьшее среднее квадратическое решение а, которое минимизирует

||е||2, может быть теперь вычислено как решение ’’нормальных” уравнений:

[Y7’Y]a=[R: 0 ОГ, (1.10)

где Rf, = min||e||2. Теперь можно провести один из доводов для продолжения

функции п0 °бе стороны данной выборки Го,... ,Уу} • Только в

этом случае матрица коэффициентов Y^Y будет теплицевой и, в частности,

21

ковариационной матрицей выборок, использованной в уравнениях Юла—

Уолкера в разд. 1.2.

Можно, однако, возразить, что вообще нет необходимости принимать

какие-либо допущения относительно несуществующих данных, и поэтому ис-

пользовать лишь остатки { е ,..., у-} или, быть может, основываясь

на допущениях только относительно прошлых данных, использовать {еп 0,...

..., еп т } . В любом случае матрица Y'Y уже не будет теплицевой, и поэтому

окажется, что ’’изящные” результаты разд. 1.2 по уменьшению сложности вы-

числений до О(№) или О (A'log 2 А') при наличии нескольких процессоров, а

также при реализации решетчатых фильтров и интерпретации в виде длин-

ных линий больше непригодны.

Это было бы весьма грустно, если бы более детальное рассмотрение не

показало, что дело можно в значительной степени исправить, введя понятие

’’смещения” матрицы [23 — 25], которое, как будет показано, определит

естественное семейство структур ковариационных матриц, обеспечивающих

быстрое разложение Холецкого [35].

Не будем излагать здесь изящную и всеобъемлющую теорию, которая бы-

ла разработана. Ее детальное рассмотрение можно найти в уже упомянутой

работе [35] и в работах [8,12, 31, 33, 36,42,44].

Тем не менее будет полезным привести некоторые основные положения.

Определим ’’нижнюю матрицу сдвига” как

Z-матрицу с единицами на первой поддиагонали и нулями в остальной части.

С помощью Z определим смещение R формулой

смещение R- R - ZRZr. (1-11)

Причина такого названия состоит в том, что, за исключением границ, элемент

(г,/) матрицы R —ZRZ2 есть [Аг- .• — ] - Когда R — теплицева мат-

рица, только первые строка и столбец матрицы R — ZR7 ? будут ненулевыми.

Определим ранг смещения R как

ранг {R-ZRZ^} =а (1.12а)

и инерцию смещения R как

инерция {R-ZRZ7} = {1,-jj, (1.126)

где J — диагональная матрица с членами +1 или —1. Для теплицевой матрицы

« = 2 и J = 1. Матрицы Y'Y, которые появились в уравнениях в начале это-

го раздела, имели {а = 1, J =0} при остатках [еп0,..., еп •?-} и {а = 3, J =

= диаг {1,1}} при остатках . . . ,епТ] .

1.3.1. Обобщенные стационарные решетчатые секции

Для матриц с рангом смещения а и инерцией смещения }l,-j} можно

осуществить каскадную реализацию в виде общих решетчатых секций, но

каждая секция будет определяться (а—1)-мерным вектором-строкой К

(а не скалярной величиной, см. рис. 1.5) , удовлетворяющим условию

1-КЖ*>0. (1.13)

22

Рис. 1.5. Обобщенная

решетчатая секция

Величины {Д'- } могут быть найдены с помощью обобщенного алгоритма Шу-

ра. Видно, что основная стоимость аппаратурной реализации связана с нали-

чием а—1 элементов задержки вместо одного элемента, как в теплицевом

случае; однако это не очень высокая цена при современном уровне техно-

логии, особенно если мы сохраним достоинства регулярных структур с ло-

кальными связями.

1.3.2. Нестационарные решетчатые секции

По-другому реализовать решетчатую структуру можно с помощью обыч-

ной двухлинейной решетки, но с изменяемыми во времени коэффициентами

отражения. Действительно, можно показать [23], что такая решетчатая

структура может быть использована для любого нестационарного процесса.

Однако, применяя структуру со смещением, можно получить простые кор-

ректирующие формулы для определения коэффициентов отражения с по-

мощью только О (а) элементарных вычислительных операций на каждом ша-

ге. Для 7V операций и 7Vкоэффициентов отражения это потребует О(№а) опе-

раций вычисления, а не (?(7V3) , как в общем случае.

Кратко остановимся на этих формулах. Коэффициент отражения н-й сек-

ции удовлетворяет соотношению

S(1 - »/n,r>?L)1/2/c«+l.r lO-A'n.r 1РиЛ i)'/2 + ’/„.«Pnu i, (114)

где д ] -a-мерные векторы-строки, подчиняющиеся рекуррентным соот-

ношениям

Чп+i.i ~~ 1 Н/п. г ? кп f-1, г > В„, t -1} > (1.14 а)

Мп+1.» = ПМил-о J , (1.146)

а функция F ( •) определяется как

Д{Л, В, С} = (1 - ВВтУ1'2(А - ВСТ)(1 - СС') 7/2 •

Эти рекуррентные соотношения могут быть представлены так, как изобра-

жено на рис. 1.6.

23

Рис. 1.6. Представление временной корректировки

В частных случаях эти общие результаты могут быть существенно упро-

щены [36]. Например1, значения t и ди f с точностью до масштабного

коэффициента выбираются равными ’’начальному” остатку ent с нормиро-

ванной дисперсией или имеющему соответствующую задержку ^’конечному”

остатку 7И?_Г На рис. 1.6 величины t]nt и pnt — сигналы, передаваемые по

линиям, соединяющим элементы решетки.

В этом случае сам решетчатый фильтр может быть использован для адап-

тации коэффициентов отражения. Расчеты дают следующий результат:

где Фп f_j — величина, лежащая между 0 и 1. Эта величина имеет некоторую

полезную статистическую интерпретацию (например, как логарифм отно-

шения правдоподобия), которая была использована при решении специаль-

ных прикладных задач [32]. Мы упомянули об этом, так как формула

(1.14) для кп+1 с Фи?_] = 1 была первоначально получена многими автора-

ми для так называемого приближенного адаптивного решетчатого фильтра,

известного также как фильтр Итакуры—Сайто, или градиентного решетчато-

го фильтра. Удивительно, приятно и важно, что имеется такая ’’изящная”

форма (1.15) для точного решения, точного в том смысле, что минимизи-

руется сумма квадратов остатков для каждого значения t; ее важность

следует из того, что при точных решениях оценки по методу наименьших

квадратов обладают свойствами состоятельности, несмещенности, быстрой

сходимости и т.п. Поэтому данные и аналогичные им алгоритмы, такие как

алгоритмы трансверсальной фильтрации фиксированного порядка, были ис-

пользованы в задачах сопровождения сигнала, компенсации искажений в ка-

налах, подавления отраженных сигналов и др. [8, 9, 10, 21, 48, 49, 53]. Спе-

циализированные СБИС, по крайней мере для одной из этих прикладных

1 В оригинале ’’prewindowed least-squares”. — Прим. ред.

24

задач [19], уже разработаны, а другие, без сомнения, — в процессе проекти-

рования.

В качестве примера другого приложения можно упомянуть архитектуру

систолической процессорной матрицы для адаптивных вычислений в калма-

новском фильтре [22]; зта архитектура основана на специальном методе

квадратного корня для оценки состояния.

Другой областью, в которой используются идеи, подобные рассмотрен-

ным в данной главе, является вычислительная томография [7]. Системы

обработки речевых, связных сигналов, изображений также являются воз-

можными областями применения: система моделирования и распознавания

голоса, ко деры-декодеры, вокодеры, системы кодирования в остаточных

классах и многие другие. Приложения к радио- и звуколокации рассматри-

ваются более подробно в последующих главах.

1.4. ЗАКЛЮЧЕНИЕ

Мы попытались рассмотреть некоторые из многих направлений, в которых

могут успешно взаимодействовать, оказывая влияние друг на друга, матема-

тические достижения в алгоритмах обработки сигналов и новые возмож-

ности технологии СБИС. Такое взаимодействие приводит как к появлению

новых способов физической реализации, так и к стимулированию новых тео-

ретических достижений. Однако в этой главе был затронут только поверх-

ностный слой, и поэтому есть много возможностей для стимулирования ис-

следований в области обработки сигналов и методов теории систем и их при-

менения в эпоху СБИС. Недавний отчет [47] показывает, кроме всего проче-

го, тесную взаимосвязь между систолическими процессорными матрицами

[39] и прямыми формами цифровой фильтрации и теорией систем.

СПИСОК ЛИТЕРАТУРЫ

[1] Н. М. Ahmed, “Signal Processing Algorithms and Architectures,” Ph.D. dissertation,

Department of Electrical Engineering, Stanford University, Stanford, Calif., 1982.

[2- ] H. M. Ahmed, J. M. Delosme, and M. Morf, “Highly Concurrent Computing Structures

for Digital Signa) Processing and Matrix Arithmetic,” IEEE Comput. Mag., (Feb. 1982).

[3] E. H. Bareiss, “Numerical Solution of Linear Equations with Toeplitz and Vector

Toeplitz Matrices, Numer. Math., 13:404—424 (1969).

[4] R. R. Bitmead, and B. D. O. Andersen, “Asymptotically Fast Solution of Toeplitz and

Related Systems of Linear Equations,” J. Linear Algebra Appl., 34:103-116 (Dec. 1980).

[5] R. P. Brent, F. G. Gustavson, and D. Y. Y. Yun, “Fast Solution of Toeplitz Systems of

Equations and Computation of Pade Approximants,” J. Algorithms, 7(3):259-295

(1980).

[6] T. Kaiiath, A. Bruckstein and D. Morgan, “Fast Matrix Factorizations via Discrete

Transmission Lines,” submitted for publication, 1984.

[7] M. Buonocore, “Fast Minimum Variance Estimators for Limited Angle Computed

Tomography Image Reconstruction,” Ph.D. dissertation, Department of Electrical En-

gineering, Stanford University, Stanford, Calif., 1981.

[8] J. Cioffi, “Fast Transversal Filters for Communications Applications,” Ph.D. disserta-

tion, Department of Electrical Engineering, Stanford University, Stanford, Calif., 1984.

[9] J. Cioffi, and T. Kailath, “An Efficient, Exact Least-Squares Fractionally Spaced Equal-

izer Using Intersymbol Interpolation,” IEEE Journal on Selected Areas in Communi-

cations, Special Issue on Voiceband Data Transmission, (May 1984).

[10] J. Cioffi, and T. Kailath, “Fast Recursive Least Squares Transversal Filter Algorithms

for Adaptive Filtering," IEEE Trans. Acoust. Speech Signal Process., ASSP-32 (1984).

[11] D. Cochran, “Algorithms and Accuracy in the HP-35,” Hewlett-Packard J., 1972, pp.

10-11.

[12] J. M. Delosme, “Algorithms and Architectures for Finite Shift-Rank Processes,” Ph.D.

dissertation, Department of Electrical Engineering, Stanford University, Stanford, Calif.,

Sept. 1982.

[13] E. Deprettere and P. Dewilde, “Orthogonal Cascade Realization of Real Multiport

Digital Filters,” Circuit Theory Appl., 8:245-212 (1980).

[14] A. M. Despain, “Fourier Transform Computers Using CORDIC Iterations,” IEEE

Trans. Comput., C-23:993-1001 (1974).

[15] A. M. Despain, “Very Fast Fourier Transform Algorithms for Hardware Implemen-

tation,” IEEE Trans. Comput., C-2£(5):333-341 (1979).

[16] P. Dewilde and H. Dym, “Schur Recursions, Error Formulas, and Convergence of

Rational Estimators for Stationary Stochastic Processes,” IEEE Trans. Inf. Theory,

I T-27(4)-.446-461 (1981).

[17] P. Dewilde, A. C. Vieira, and T. Kailath, “On a Generalized Szego Levinson Realiza-

tion Algorithm for Optimal Linear Predictors Based on a Network Synthesis Ap-

proach,” IEEE Trans. Circuits Syst., CAS-25(9):663-675 (1978).

[18] J. Durbin, “The Fitting of Time -Series Models,” Rev. Int. Inst. Stat., 28:233-244 (1960).

[19] D. L. Duttweiler, “A Twelve-Channel Digital Echo Canceler,” IEEE Trans. Commun.,

COM-28-.641- 653 (1978).

[20] G. L. Haviland and A. Tuszynski, “A CORDIC Arithmetic Processor Chip,” IEEE

Trans. Comput., C-29( 2) :68-79 (1980).

[21] W. S. Hodgkiss and J. A. Presley, “Adaptive Tracking of Multiple Sinusoids Whose

Power Levels Are Widely Separated,” IEEE Trans. Acoust. Speech Signal Process.,

ASSP-29(3):710-721 (1981).

[22] J. M. Jover and T. Kailath, “A Parallel Architecture for Kalman Filter Measurement

Update,” Proc. IF AC Congress, Budapest, Hungary, July 1984.

[23] T. Kailath, “Time-Variant and Time-Invariant Lattice Filters for Nonstationary Pro-

cesses,” Proc. Fast Algorithms for Linear Dynamical Systems, Aussois, France, Sept.

21-25, 1981, pp. 417-464. Reprinted as Oulils et modeles mathematiques pour I'Automa-

tique, I'Analyse de Systemes et le Traitement du Signal, Vol. 2,1. D. Landau, ed., CNRS,

France, 1982, pp. 417-464.

[24] T. Kailath, S. Y. Kung, and M. Morf, “Displacement Ranks of Matrices and Linear

Equations,” J. Math. Anal. Appl., 6S(2):395-407 (1979).

[25] T. Kailath, S. Y. Kung, and M. Morf, “Displacement Ranks of a Matrix,” Bull. Am.

Math. Soc., I(5):769-773 (1979).

[26] T. Kailath, Lectures on Wiener and Kalman Filtering, Springer-Verlag, New York, 1981.

[27] H. T. Kung, “Let’s Design Algorithms for VLSI Systems,” Proc. First Caltech VLSI

Symp., 1979, pp. 65-90.

[28] H. T. Kung, “Why Systolic Arrays?” IEEE Computer, /5(1):37-Л6 (1982).

[29] S. Y. Kung and H. Hu, “A Highly Concurrent Algorithm and Pipelined Architecture for

Solving Toeplitz Systems,” IEEE Trans. Acoust. Speech Signal Process., ASSP-3I(1):66-

75 (1983).

26

[30] S. Y. Kung, K. S. Arun, R. J. Gal-Ezer, and D. V. Bhaskar Rao, “Wavefront Array

Processor: Language, Architecture and Applications,” IEEE Trans. Comput.,

C-3/:1054-1066 (1982).

[31] D. T. Lee, “Canonical Ladder Form Realizations and Fast Algorithms,” Ph.D. disserta-

tion, Department of Electrical Engineering, Stanford University, Stanford, Calif., 1980.

[32] D. T. Lee and M. Morf, “A Novel Innovations Based Approach to Pitch Detection,”

Proc. 1980 IEEE Int. Conf. Acoust. Speech Signal Process., Denver, Colo., Apr. 9-11,

1980, pp. 40-44.

[33] H. Lev-Ari, “Parameterization and Modeling of Nonstationary Processes,” Ph.D. dis-

sertation, Stanford University, Stanford, Calif., 1983.

[34] H. Lev-Ari, "Modular Architectures for Adaptive Multichannel Lattice Algorithms,”

IEEE Int. Corf. Acoust. Speech Signal Process., Boston, Apr. 1983, pp. 455-458.

[35] H. Lev-Ari and T. Kailath, “Lattice Filter Parametrization and Modeling of Non-

stationary Processes,” IEEE Trans. Inf. Theory, IT-30, (Jan. 1984).

[36] H. Lev-Ari, T. Kailath, and J. Cioffi, “Least-Squares Adaptive Lattice and Transversal

Filter for Nonstationary Processes,” IEEE Trans. Inform. Theory, IT-30, (Mar. 1984).

[37] N. Levinson, “The Wiener RMS (Root-Mean-Square) Error Criterion in Filter Design

and Prediction,” J. Math. Phys., 25(41:261 278 (1947).

[38] J. Markel and A. H. Gray, Jr., Linear Prediction of Speech, Springer-Verlag, New York,

1976.

[39] C. Mead and L. Conway, Introduction to VLSI Systems, Addison-Wesley, Reading,

Mass., 1980.

[40] M. Morf, “Fast Algorithms for Multivariable Systems,” Ph.D. dissertation, Department

of Electrical Engineering, Stanford University, Stanford, Calif., 1974.

[41] M. Morf, “Doubling Algorithms for Toeplitz and Related Equations,” Proc. IEEE Int.

Conf. Acoust. Speech Signal Processing, Denver, Colo., Apr. 9-11,1980, pp. 954-959.

[42] D. R. Morgan, “Orthogonal Triangularization Methods for Fast Estimation Algo-

rithms,” Ph.D. dissertation, Department of Electrical Engineering, Stanford University,

Stanford, Calif., Dec. 1984.

[43] B. Musicus, “Levinson and Fast Cholesky Algorithms for Toeplitz and Almost Toeplitz

Matrices,” MIT Internal Report, submitted for publication, 1981.

[44] B. Porat, “Contributions to the Theory and Applications of Lattice Filters,” Ph.D.

dissertation, Dept, of Electrical Engineering, Stanford University, Stanford, Calif., 1982.

[45] L. R. Rabiner and R. W. Schafer, Digital Processing of Speech Signals, Prentice-Hall,

Englewood Cliffs, N. J., 1978.

[46] S. K. Rao and T. Kailath, “Orthogonal Digital Filters for VLSI Implementation,” IEEE

Trans. Circuits Systems, CAS-3I, (1984).

[47] S. K. Rao and T. Kailath, “Digital Filtering in VLSI,” Technical Report ISL, Stanford

Univ., Stanford, Calif., Jan. 1984.

[48] V. U. Reddy, B. Egardt, and T. Kailath,” Optimized Lattice-Form Adaptive Line En-

hancer for a Sinusoidal Signal in Broadband Noise,” IEEE Trans. Circuits Syst., CAS-

25:542-550 (June 1981).

[49] V. U. Reddy, T. J. Shan, and T. Kailath, “Application of Modified Least-Squares

Algorithms to Adaptive Echo Cancellation,” Proc. 1983 Int. Conf. Acoust. Speech Signal

Process., Boston, 1983, pp. 53-56.

[50] J. Rissanen, “Algorithms for Triangular Decomposition of Block Hankel and Toeplitz

Matrices,” Math. Comp., 27:147-154 (1973).

27

[51] E. A. Robinson, “Dynamic Predictive Deconvolution,” Geophys. Prospect., 23319-191

(1975).

[52] E. A. Robinson, “Spectral Approach to Geophysical inversion by Lorentz, Courier and

Radon Transforms,” Proc. IEEE, 70:1039-1054 (1982).

[53] E. Satorius and J. Pack, “Application of Least-Squares Lattice Algorithms to Adaptive

Equalization,” IEEE Trans. Common., COM-29:! 36-142 (1981).

[54] C. W. Schelin, “Calculator Function Approximation,” Am. Math. Monthly, 90:311-32-5

(1983).

[55] I. Schur, “Ober Potenzreihen, die im Innern des Einheitskreises beschrankt sind,” J.

Reine Angew. Math., 147:205-232 (1917).

[56] H. Sexton, M. Shensa, and J. Speiser, “Remarks on a Displacement-Rank Inversion

Method for Toeplitz Systems,” Linear Algebra Appl., 45:127-130 (1982).

[57] G. Szego, Orthogonal Polynomials, 4th cd., Colloquium Publications, 23, American

Mathematical Society, Providence, R. I„ 1975. Originally published in 1939.

[58] J. E. Voider, “The CORDIC Trigonometric Computing Technique,” IRE Trans. Elec-

tron. Compute EC-8(3):33O-334 (1959).

[59] J. S. Walther, “A Unified Algorithm for Elementary Functions,” Proc. 1971 Spring Joint

Comput. Conf., 1971, pp. 379- 385.

[60] R. Wiggins and L. Brantingham, “Three Chip System Synthesizes Human Speech,”

Electronics, 5/(18):109-116 r.1978).

2

ПРИМЕНЕНИЕ ПАРАЛЛЕЛЬНЫХ МАТРИЧНЫХ ПРОЦЕССОРОВ

ДЛЯ ОБРАБОТКИ СИГНАЛОВ

X. Уайтхаус, Дж. Спейзер, К. Бромли1

2.1. ВВЕДЕНИЕ

Как было показано ранее, основные вычислительные процедуры при реше-

нии большинства задач обработки сигналов в реальном масштабе времени

могут быть сведены к набору операций над матрицами [1 — 3], Он включает

умножение матрицы на вектор, умножение матрицы на матрицу и сложение,

обращение матриц, решение линейных систем уравнений, приближенное

решение линейных систем по методу наименьших квадратов, вычисление соб-

ственных значений, нахождение сингулярного разложения матриц. Широкие

исследования в области вычислительных методов линейной алгебры привели

к созданию двух устойчивых, хорошо документированных пакетов стандарт-

ных программ для выполнения этих операций с помощью однопроцессорных

компьютеров последовательного действия. Один из этих пакетов, называе-

мый UNPACK |4], предназначен для решения линейных систем уравнений

и вычислительных задач, основанных на применении метода наименьших

квадратов. Другой, называемый EISPACK [5], охватывает задачи вычисле-

1 Центр океанических систем ВМС, Сан-Диего, Калифорния.

28

ния собственных значений. Эти алгоритмы по вычислительным затратам

достаточно сложны и требуют примерно N3 или А'4 операций умножения для

каждого набора из N входных отсчетов. Дли сравнения современный алго-

ритм обработки сигналов — БПФ — требует только Mog2 TV операций умно-

жения и тем не менее его реализация в реальном масштабе времени на совре-

менных однокристальных арифметических процессорных модулях ограничи-

вается полосой звуковых частот. Очевидно, что потребуется на порядок уве-

личить скорость вычислений, для того чтобы обеспечить выполнение в реаль-

ном масштабе времени этих перспективных алгоритмов.

Несмотря на гигантские достижения за последнее десятилетие в техноло-

гии цифровых ИС, нельзя просто рассчитывать на дальнейшие успехи в произ-

водстве быстродействующих элементов вычислительных устройств. В настоя-

щее время уровень технического развития кристаллов СБИС обеспечивает

реализацию технологических размеров от 1 до 2 мкм. Целью фазы П про-

граммы ССИС (сверхскоростные ИС) Министерства обороны США служит

уменьшение этих размеров до 0,5 мкм к 1987 г., что позволит увеличить

функциональную скорость передачи данных (т.е. тактовую частоту, отне-

сенную к плотности компоновки) на кристалл от 5 1011 Гц до 1013 Гц вен-

тиль/см2 . По-видимому, потребуется по крайней мере еще три года усилий

для такого повышения производительности, когда эта технология будет эко-

номически выгодна. Так что можно ожидать немногим более 20-кратного

улучшения функциональной скорости передачи данных кристаллов СБИС к

1990 г. Более того, в большинстве современных проектов показывается,

что дальнейшее уменьшение размеров до 0,5 мкм и менее будет возможно

только ценой значительных усилий. Авторы утверждают, что если исключить

из рассмотрения непредвиденные в настоящее время успехи в технической

реализации процессора сигналов, то увеличение на несколько порядков про-

изводительности процессора для обработки в реальном масштабе времени

алгоритмов UNPACK и EISPACK должно осуществляться эффективным

использованием параллелизма при вычислениях.

Самым непосредственным способом реализации параллельной обработки

сигналов является простое присоединение ряда процессоров к общей шине.

Действительно, большинство современных серийных микропроцессорных

комплектов отличается такой ’’мультипроцессорностью”.

Однако производительность повышается линейно с увеличением числа

процессоров только до тех пор, пока не наступают ограничения, связанные с

проблемами соединения с общей шиной. Согласно хорошо известному пред-

положению Минского для широкого класса алгоритмов конфликт между Л

процессорами с коллективным распределением ресурсов, соединенными с

общей шиной, ограничивает повышение производительности величиной

iog2A'. Современные конструкторы ’’суперкомпьютеров” использовали

ряд параллельных структур и достигли повышения производительности

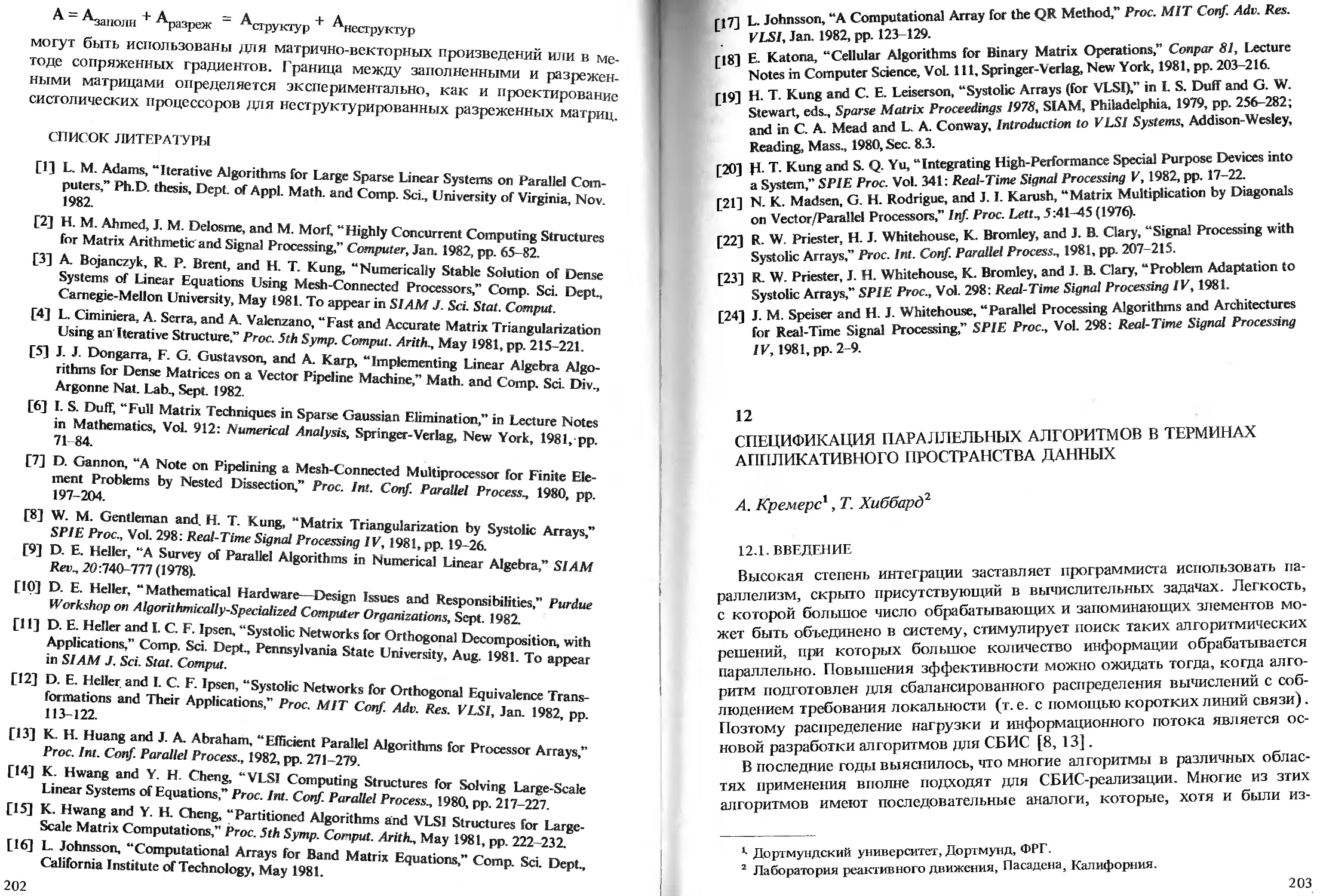

в соответствии с законом Амдала (Amdahl)’. A'/log^A'. В 1978 г. С. Т. Кунг

(Н. Т. Kung) представил свою пионерскую работу по архитектурам систоли-

ческих процессорных матриц, в которой был достигнут исключительно

высокий коэффициент повышения производительности, равный N [6].

2S

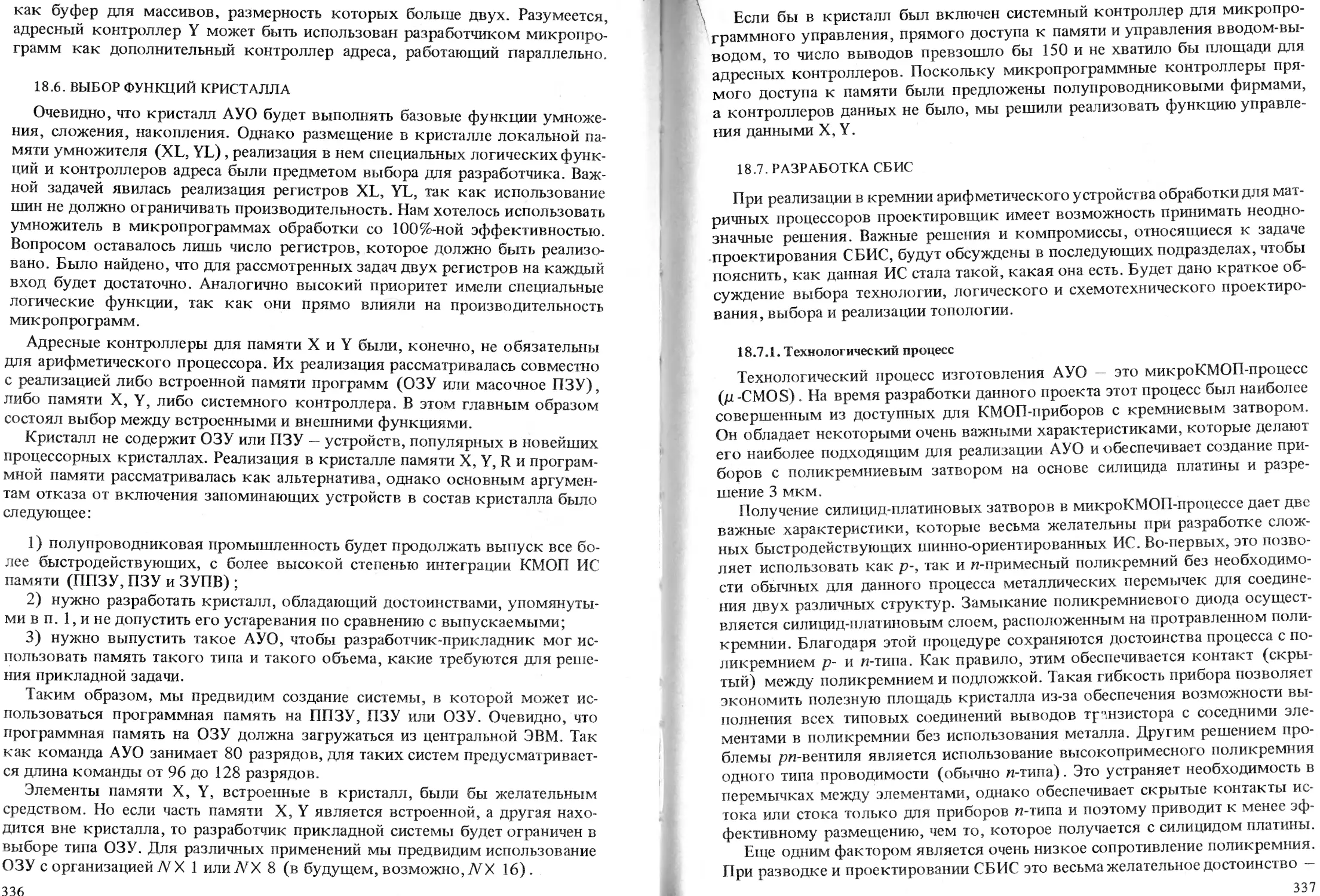

Рис. 2.1. Графическое представление уве-

личения быстродействия, обеспечиваемо-

го перспективной архитектурой работаю-

щих одновременно N процессоров:

1 — 100%-ная производительность (сис-

толические решетки); 2 — закон Амда-

ла (суперкомпьютеры); 3 — предложе-

ния Минского (ограничения, связанные

с конфликтами на шине в многопроцес-

сорных системах)

На рис. 2.1 графически представлено увеличение быстродействия при па-

раллелизме для трех случаев.

В работах [1 — 3] рассмотрены параллельные архитектуры и сделан вы-

вод, что систолические и волновые матричные архитектуры [6, 7] обеспе-

чивают наиболее перспективную совокупность характеристик при исполь-

зовании технологии СБИС и ССИС для обработки сигналов в реальном масш-

табе времени: параллелизм на уровне модулей с пропускной способностью,

прямо пропорциональной числу вычислительных ячеек, простое управление,

синхронный поток данных, локальные связи, достаточную гибкость для вы-

полнения матричных операций, необходимых при обработке сигналов.

Систолические и волновые процессоры имеют линейную структуру для

умножения матрицы на вектор и решения линейных уравнений с треуголь-

ными матрицами коэффициентов, а также гексагональную структуру для

матричных операций умножения-сложения и /.//-разложения матриц. Эти

архитектуры особенно привлекательны в случае разреженных ленточных

матриц.

В этой главе обсуждаются процессоры новой архитектуры для умножения

заполненных матриц, для операций над блочными матрицами, а также при-

кладные задачи вычисления функций неопределенности. Читателя, интере-

сующегося аппаратурной реализацией систолической и волновой архитектур,

отсылаем к работе [8], где описана одномерная процессорная матрица,

содержащая 200 МО11-кристаллов, к работе [9], где описан макет двумерной

процессорной матрицы, к гл. 8 этой книги, посвященной заказной систоли-

ческой БИС, к гл. 22, в которой содержится описание двух заказных систо-

лических СБИС, и к гл. 17, где имеется описание кристалла СБИС для реше-

ния теплицевой системы уравнений [10]. Читателя, интересующегося систо-

лическими матричными структурами для реализации более сложных алго-

ритмов, чем те, которые описаны здесь, отсылаем к работам: [11] — по воп-

30

росам приведения матрицы к треугольному виду, [12] — о сингулярном раз-

ложении, [13, 14] — о проблеме собственных значений и [10] - о решении

теплицевых систем уравнений,

2.2. ЗАДАЧИ МЕТОДА НАИМЕНЬШИХ КВАДРАТОВ

Рассмотрим метод наименьших квадратов применительно к задачам трех

типов: детерминированной, стохастической с известными вторыми момента-

ми и стохастической с неизвестными вторыми моментами, которые надо оце-

нить. Покажем, что стохастическая задача с оцениваемыми вторыми момен-

тами в вычислительном отношении идентична детерминированной задаче

и поэтому основной метод решения для многих случаев обработки сигналов

в реальном масштабе времени может быть основан на формировании и ре-

шении нормальных уравнений путем систолических матричных умножений,

умножения матрицы на вектор и обращения матриц. Известны другие мето-

ды решения задач наименьших квадратов [19], а в работе [11] рассматри-

вается систолическая реализация.

Детерминированная задача состоит в выборе вектора х таким образом,

чтобы минимизировалось значение в2 в уравнении

е2 = || Ах — у||2 = хгАгАх—2угАх+ ||у||2, (2.1)

где А — известная матрица, а у — известный вектор, индекс Т обозначает

транспонирование матрицы или вектора.

Стохастическая задача наименьших квадратов состоит в выборе детер-

минированного весового вектора w для минимизации средней квадратичес-

кой ошибки Е2:

е| = E(w'z - d}1 = v? Rzw- 2R£ w + E(d2), (2.2)

где z — случайный вектор; d — случайная величина. Скалярная случайная

величина wyz представляет собой линейную комбинацию компонентов слу-

чайного вектора z и используется как линейная оценка случайной величины

d. Математическое ожидание обозначается символом Д, через Rz обозначе-

на матрица вторых моментов случайного вектора z: Rz = Еггт. Аналогично

вектор R(/z определяется как R^z =E(dz).

Для того чтобы сравнить две задачи, предположим, что А имеет размер

(Л'ХА), х—(5X1), y-(A'Xl), z-(AXl), w-(5Xl). Для стохастической

задачи наименьших квадратов с оценкой вторых моментов предположим,

что наблюдаются N отсчетов случайного вектора z и случайной величины d,

например z (и, s) nd (и) при и = 1,. .., Ен s = 1,. .., 5.

Стандартные несмещенные оценки вторых моментов даются выражениями

(KJws2=i Ez(n, Si)z(H, s2), (2.3)

/V я “ 1

Л 1 j (V

(RazL. = Т7 Е d(n)7.(n, Sl) = - £ zr(s„ n)d(n), (2.4)

2 ’ n — 1 2 ’ n = 1

31

Таблица 2.1. Таблица соответствия величии в эквивалентных детерминированной и

стохастической задачах

Детерминирован- ный случай Стохастический слу- чай с оценкой вторых моментов Детерминирован- ный случай Стохастический слу- чай с оценкой вторых моментов

2V~0,5z (п, s) АГА R2

У («) A^-O’SJ(«) у7 А

X(s) w(s) ПУН2

1 Л

(Ed2) = — £</2(н). (2.5)

Соответствующая ошибка для оценки d через w7’z определяется формулой

е| = w7 Rz w-2R^z w+ (Ed2). (2.6)

Соотношения, приведенные в табл. 2.1, иллюстрируют вычислительную эк-

вивалентность стохастической задачи наименьших квадратов с оценкой вто-

рых моментов и соответствующей детерминированной задачи. Поэтому до-

статочно рассмотреть вычислительные методы только для детерминирован-

ной задачи наименьших квадратов.

2.2.1. Применение метода наименьших квадратов к задачам гидролокации

Метод наименьших квадратов применяется при решении трех проблем

улучшения характеристик гидролокатора: подавления шума, подавления по-

мех и спектрального анализа по методу максимума энтропии. При решении

проблемы подавления шума полагают, что выходной сигнал гидрофона

представляет собой линейную комбинацию напряженности окружающего

акустического поля с составляющими локальных источников шума, такими,

как, например, шум двигателей собственного корабля. Чтобы выделить

только сигналы шума, вблизи от двигателей можно установить вспомога-

тельные датчики. Для дальнейшего улучшения этого метода на входы устрой-

ства подавления могут быть поданы задержанные копии сигналов каждого

эталонного источника шума. Тогда линейные комбинации этих задержан-

ных копий будут аппроксимировать отфильтрованный сигнал шума, при-

нятый гидрофоном от источника после его распространения по корпусу

корабля.

Задача подавления помех аналогична задаче подавления шума, за исклю-

чением того, что входными сигналами адаптивного устройства компенса-

ции являются выходные сигналы лучеобразующих устройств. Для форми-

рования одного луча без помех в заданное положение направляется обычный

луч и формируется S ’’нулевых лучей”. Чувствительность нулевых лучей рав-

на нулю при приеме сигнала с заданного направления, и они используются

I для приема помех. В общем случае требуется столько линейно независимых

32

нулевых лучей, сколько помех необходимо подавить. Если выходы каждой

из этих лучеобразующих схем объединить через весовой сумматор с выхо-

дом лучеобразующей схемы, принимающей сигнал с заданного направления,

то минимизация общей мощности уменьшит помехи в выходном сигнале.

Если составляющие помехи не коррелированы с сигналом, принимаемым с

заданного направления, то вклад полезного сигнала в выходную мощность

остается постоянным. Однако при определенных условиях это допущение

может нарушаться. При многолучевом распространении полезный сигнал

может быть принят нулевым лучом так же, как и лучом, ориентированным

в заданном направлении. В этом случае подстройка весовых коэффициентов,

направленная на уменьшение общей мощности выходного сигнала, может

привести к уменьшению как помех, так и полезного сигнала.

Подавление шума и помех, как правило, осуществляется адаптивными

трансверсальными фильтрами, реализующими метод градиентного спуска —

алгоритм минимизации средней квадратической ошибки (МСКО) Уидроу

[15]. Цель таких способов реализации — обеспечить адаптацию при неболь-

шом числе операций умножения, т.е. при относительно простой аппаратур-

ной реализации. Скорость адаптации уменьшается при большом разбросе

собственных значений ковариационной матрицы данных [16], что, к сожале-

нию, имеет место при сильных источниках помех. Это может привести к вре-

мени сходимости, значительно превышающему период, в течение которого

процессы, воздействующие на систему подавления, можно считать стационар-

ными. В этом случае более быстрая сходимость может быть получена непос-

редственным обращением ковариационной матрицы выборок и решением

нормальных уравнений, что приведет к более эффективному (в статисти-

ческом смысле) использованию имеющихся данных [17].

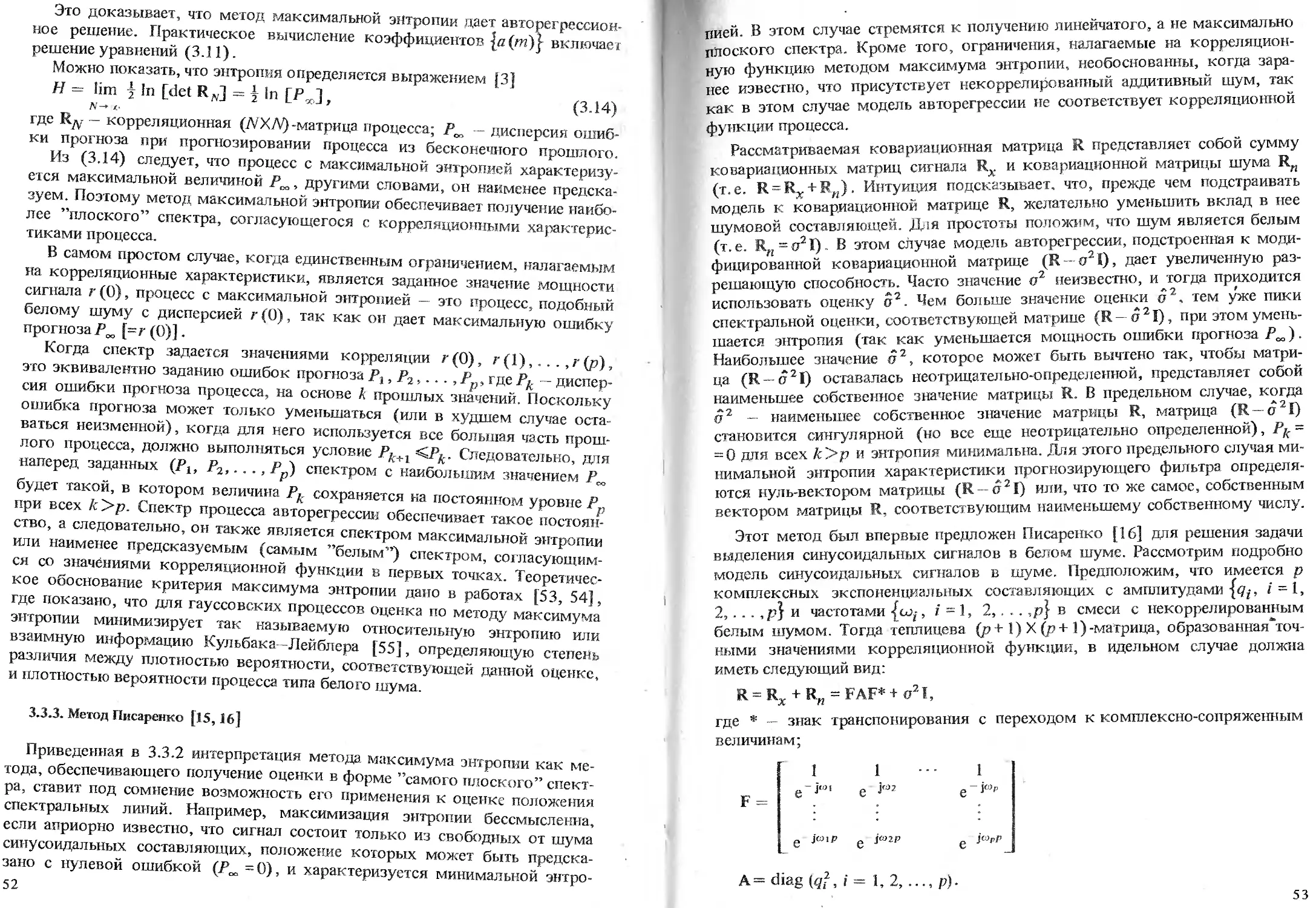

Современные методы спектрального анализа обеспечивают повышенную

разрешающую способность при использовании параметрической модели

сигнала. В методе максимума энтропии сигнал моделируется как выходной

сигнал фильтра, имеющего только полюсы, на вход которого подан белый

шум [18]. Обратным такому фильтру служит трансверсальный фильтр,

преобразующий сигнал в белый шум, весовые коэффициенты которого

рассчитываются путем решения задачи линейного прогноза сигнала на один

шаг вперед. Известно, что для стационарного процесса ошибка прогноза

по методу наименьших квадратов представляет собой белый шум. Тогда оце-

ниваемая функция спектральной плотности пропорциональна величине,

обратной квадрату передаточной функции прогнозирующего фильтра. Этот

метод спектральной оценки, обеспечивающий повышенную разрешающую

способность в том случае, когда модель применима и отношение сигнал-

шум достаточно велико, может быть также использован для формирова-

ния луча [18].

Задачи, решаемые с помощью метода наименьших квадратов примени-

тельно к подавлению шума, подавлению помех и спектральному анализу

методом максимальной энтропии, сведены в табл. 2.2.

33

Таблица 2.2. Таблица соответствия величин в методе наименьших квадратов примени-

тельно к гидролокации

Задача z d

Подавление шума zx,...,zf (эталонные ис- Сигнал + шум

точники шума)

Подавление помех (адаптив- bt,...,by (выходные сиг- Ьо (выходной сигнал луча,

нал обработка с фиксирован- налы ’’нулевых лучей”) ориентированного в заданном

ными лучами) направлении)

Спектральный анализ мето- х,,...,х4 (временные от- ху+1

дом максимума энтропии счеты сигнала)

2.3. ВСТРЕЧНО-ПОТОЧНЫЙ ПРОЦЕССОР

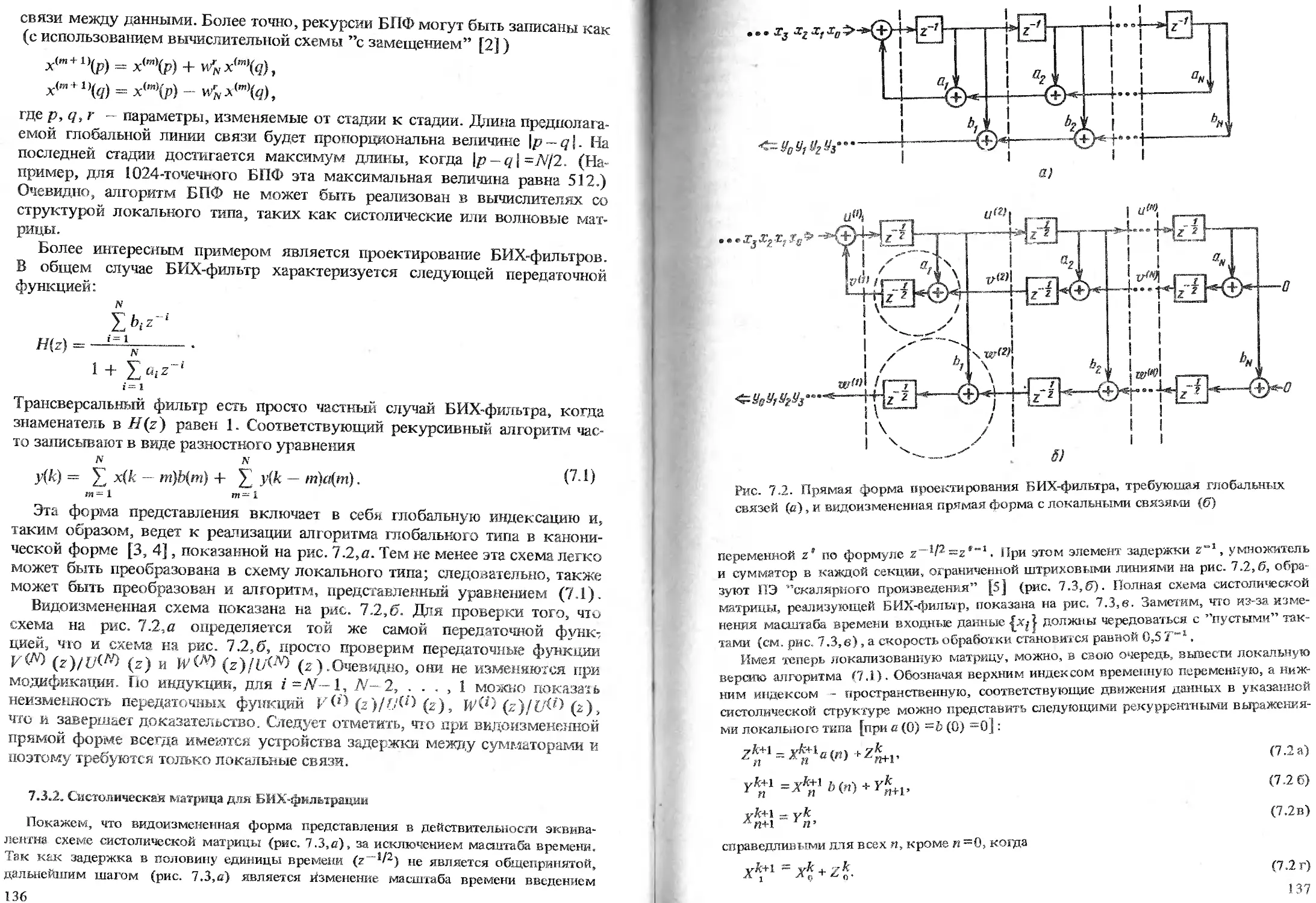

Систолическую архитектуру можно рассматривать как результат реали-

зации последовательности рекурсивных алгоритмов с помощью сети иден-

тичных (или большей частью идентичных) вычислительных ячеек. При вычис-

лении произведения матриц С = АВ каждый элемент cp(j матрицы С являет-

ся скалярным произведением строки А и столбца В:

N

ем= Y.apshsq (2-7)

5= 1

Матричное умножение можно также рассматривать как рекуррентную

процедуру:

4ч = 0, (2.8 а)

= 1) + «psbs4 при s= t ...» А, (2.86)

где — искомый результат.

Такие операции сложения могут быть представлены в виде рекурсивных

выражений, содержащих промежуточные члены, перемещающиеся вдоль

структуры, или в виде накопления частичных сумм ”с замещением” [4,5].

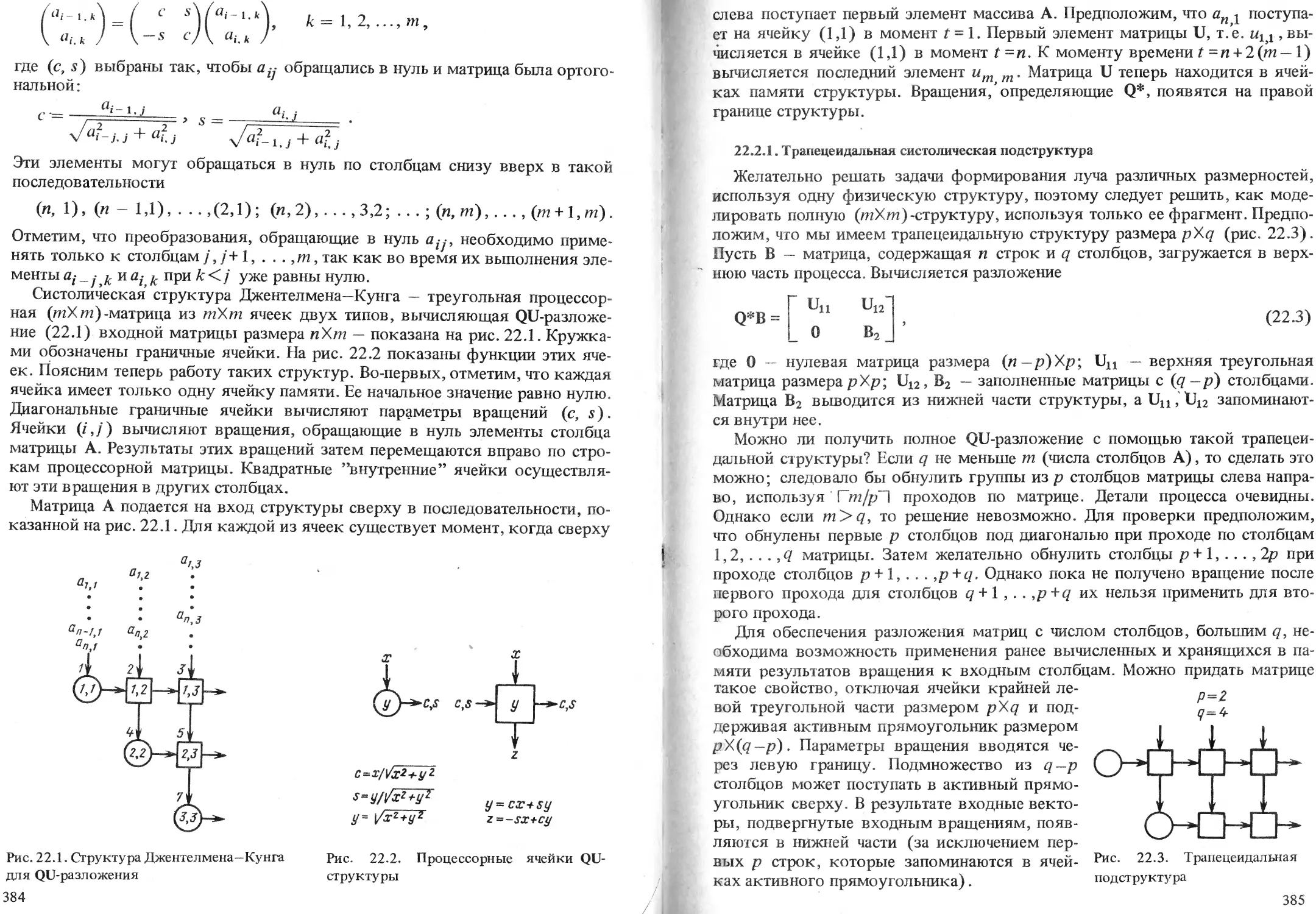

Главной систолической ячейкой для операций линейной алгебры является

процессор скалярного произведения [6], изображенный на рис. 2.2 в виде

прямоугольной и гексагональной структур [6]. В оставшейся части этой

главы будет использоваться гексагональное представление систолической

ячейки. При соединении порта С’в через цепь обратной связи с Свх конфи-

гурация ячейки будет особенно хорошо приспособлена для вычисления

скалярного произведения по формулам (2.8). Если предположить, что Свх =

= 0 в момент времени п-0, то при и =N значение Свых будет искомым ска-

лярным произведением. Необходимо обратить внимание на то, что значение

суммы в выражении (2.7) остается неизменным при перестановке индек-

сов слагаемых. В этой главе в дальнейшем будут использованы две специаль-

ные перестановки: обратная и циклическая.

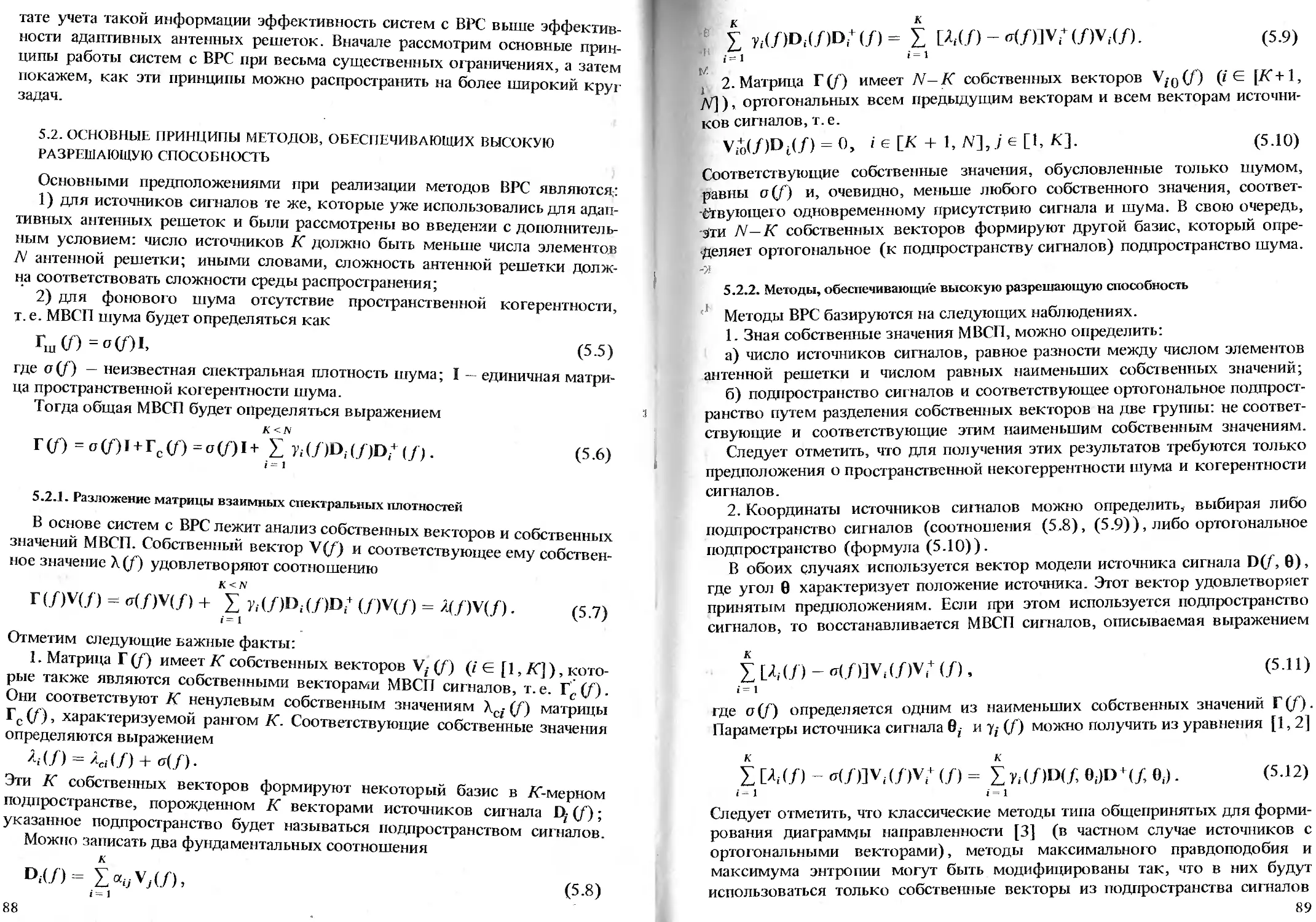

Встречно-поточный процессор (рис. 2.3) производит перемножение матри-

цы на матрицу или умножение-сложение с помощью процессора, состоящего

34

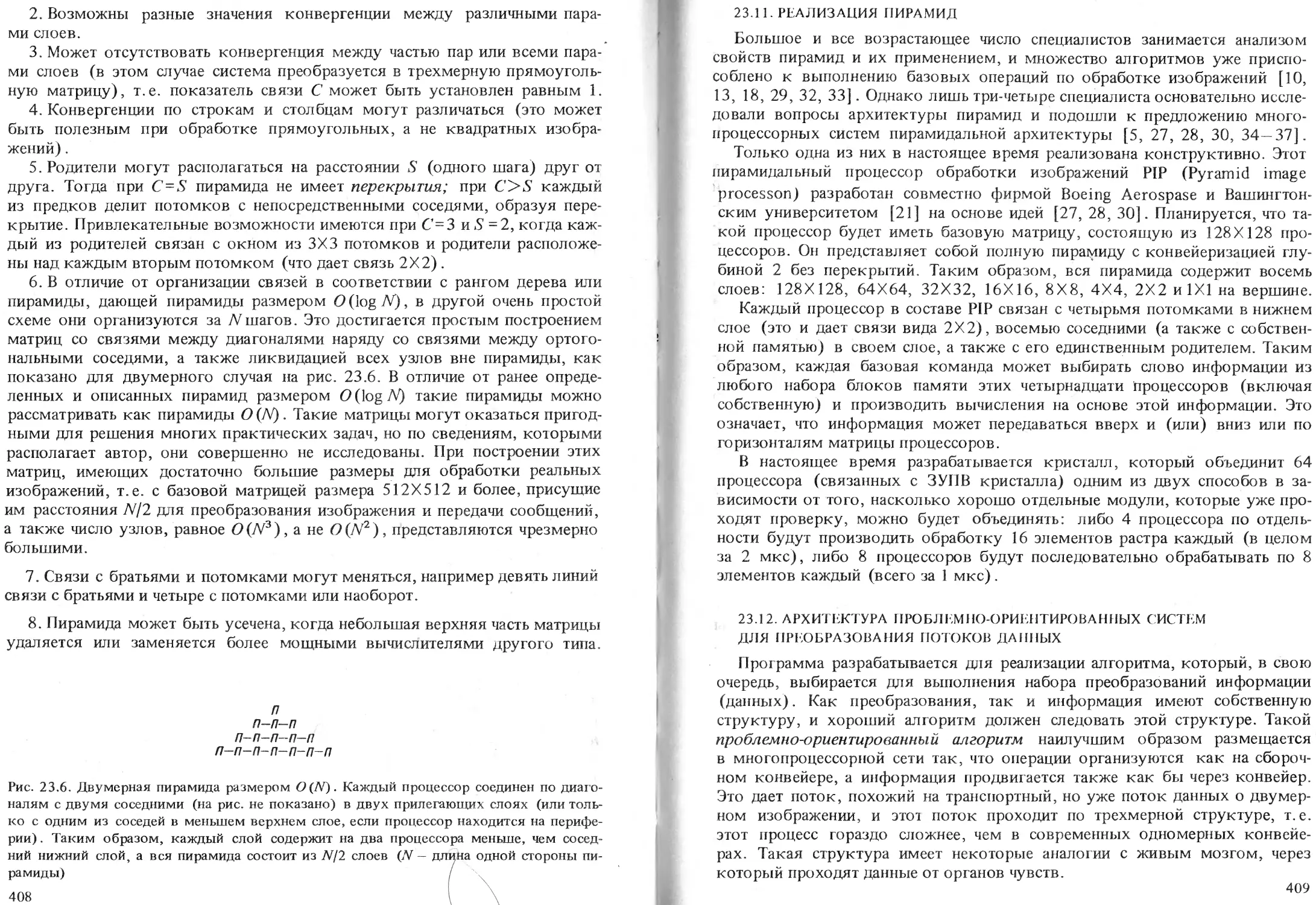

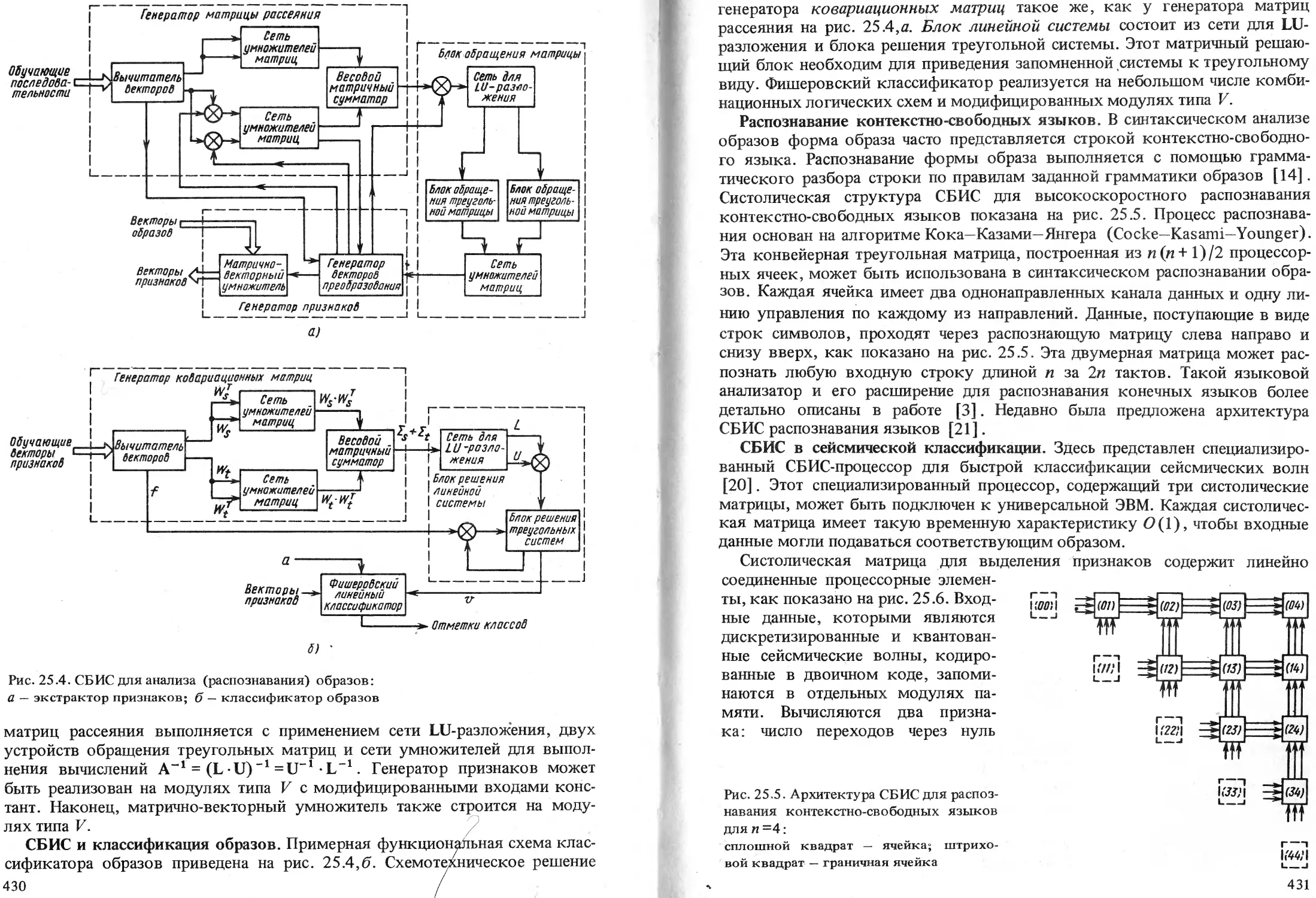

Рис. 2.2. Геометрическое представление

процессора для вычисления скалярного

произведения

ьгз

b>z ьгз

Рис. 2.3. Перемножение полных матриц

встречно-поточным процессором

из ячеек, подобных той, которая показана на рис. 2.2, осуществляя вычис-

ление частичных сумм с замещением. Элементы строк матрицы А и элементы

столбцов матрицы В вводятся в процессор через память интерфейсных уст-

ройств. Последовательные строки и столбцы вводятся с единичной задерж-

кой так, что в памяти имитируется набор линий задержки, создавая сдвиг на

один временной такт между вводом последовательных строк и столбцов.

Каждая ячейка процессора имеет конфигурацию, показанную на рис. 2.2, и

вычисляет сумму скалярного произведения и начального значения Свых.

Для вычисления произведения матриц значение принимается равным

нулю в начальный момент времени, с2] и <?i2 принимаются равными нулю

в момент времени 1, с13, с22 и с31 принимаются равными нулю в момент

времени 2 и т. д., элементы Л'-й побочной диагонали принимаются равными

нулю в момент времени к — 1. В момент времени k+N скалярные произве-

дения всех элементов, соответствующих /с-й побочной диагонали, будут

записаны в памяти. Если элементы изначально не равны нулю, то произво-

дится матричное умножение-сложение: Сконеч =СТ1ач *В. Запись послед-

него члена завершается за время Г = (N— 1) + (A— 1) +N=3N— 2. Это означа-

ет, что встроечно-поточный процессор производит матричное умножение или

умножение-сложение заполненных АХ А матриц за время ЗА—2 при исполь-

зовании А2 ячеек, обеспечивая выигрыш в эффективности приблизительно в

четыре раза по сравнению с обычной гексагональной систолической структу-

рой матричного умножителя. Поскольку при обработке сигналов часто тре-

буется перемножение заполненных матриц, этот выигрыш является значи-

тельным.

Встроечно-поточный процессор вычисляет матричное произведение (2.1)

согласно рекуррентным соотношениям

,.Кт-1)+(*- DI = о

.М ’

Cj"k ° = n) + (J-l) + (* „) + (> 1) + (* D.*>

где обозначает содержимое ячейки (/, к) в момент времени п.

(2.9)

(2.10)

35

В момент времени n=(j — 1) + (А,— 1) + Nячейка (/,к) содержит (j.k)-n

элемент матричного произведения.

Если эффективность определить как

число выполняемых умножений-сложений

Эффективность =---------------------------------------, (2.11)

число ячеек X суммарное время

то можно увидеть, что при неконвейерном режиме эффективность встречно-

поточного процессора составляет N(3N— 2), т. е. больше 1/3.

Встречно-поточный процессор можно также использовать для умножения

прямоугольных матриц. Если А имеет размер (./ХА), а В — размер (ЛЛХ/<*),

то необходимый размер процессорной структуры равен J УК и последнее вы-

числение заканчивается в момент времени N+ (.7 1) + (К— 1) =N+J +К— 2.

В этом случае эффективность равна (NJK)/JK(N+J+K— 2) =Ni(N+J +К--2)

и велика, когда ЛЛ велико по сравнению с J+K. В дальнейшем в этой главе

будет показано, что часто имеется возможность конвейеризовать матричные

умножения с помощью встречно-поточного процессора с достижением эф-

фективности, близкой к 100%. Далее рассмотрим некоторые специальные

случаи матричных умножений с использованием процессоров рассмотренно-

го типа.

2.3.1. Вычисление внешнего произведения векторов с использованием

встречно-поточного процессора

Вычисление внешнего произведения двух векторов представляет собой

важный вырожденный случай умножения матрицы на матрицу. В векторной

и покомпонентной записи оно определяется выражениями

С = аЬг, (2.12а)

(2.126)

«1 «ib* atbl

«2 ГЬ* Л* ь*] = а2 bl а2 bl а2 bl (2.13)

_«3_ «з bl а3 bl а3 bf_

Внешнее произведение двух векторов используется, например, при вычисле-