Похожие

Текст

МИКРОПРОЦЕССОРНЫЙ

КОМПЛЕКТ

БИС серии КР588

Инструкция по применению

(Справочный материал)

- 1-

i

I

СОДЕРЖАНИЕ •

i

। Стр.

Назначение и состав серии КР586 .................2

Микросхема КР588ВУ2........................ . ц

Микросхема КР586ВС2............................Уб*

Микросхема КгбввВП..............................55

Микросхема KF568BP2.............................

Микросхема KP588BAI .......................... 55"

Микросхема КР566ИР1.............................SO

Микросхема КР586ВГ2............................53~

Микросхема KF568BTI.............................72

Электрические параметры микросхем серии KP58S .

Габаритные чертежи корпусов .................. ££

Рекомендации по применяемости МП комплекта . , . 90

МИКРОПРОЦЕССОРНЫЙ КОМПЛЕКТ БИС СЕРИИ KF588

Серия КР588 предназначена для построения встраиваемых микро-

процессорыIX систем автоматического управления и регулирования,про-

граммно совместимых с микро-ЭВМ типа "Электроника-60"

Выбор пороговых напряжений транзисторов в пределах от 0,8 до

1,6 В обеспечивает хорошую помехоустойчивость микросхем. Нагрузоч-

ные свойства микросхем серии KF588 обеспечивают согласование их с

двумя маломощными ТТЛШ входами микросхем без усиления.

ОСНОВНЫЕ ХАРАКТЕРИСТИКИ :

Напряжение источника питания . ....................5 В - 51'

Температурный диапазон...............от минус 10 до *70°C

Технология...........................................КЩП

Разрядность..........................................16

Длительность цикла ..... ....................... 0,8 мкс

Прямое согласование с ТТЛШ микросхемами

Мощная универсальная система команд

Универсальность применения

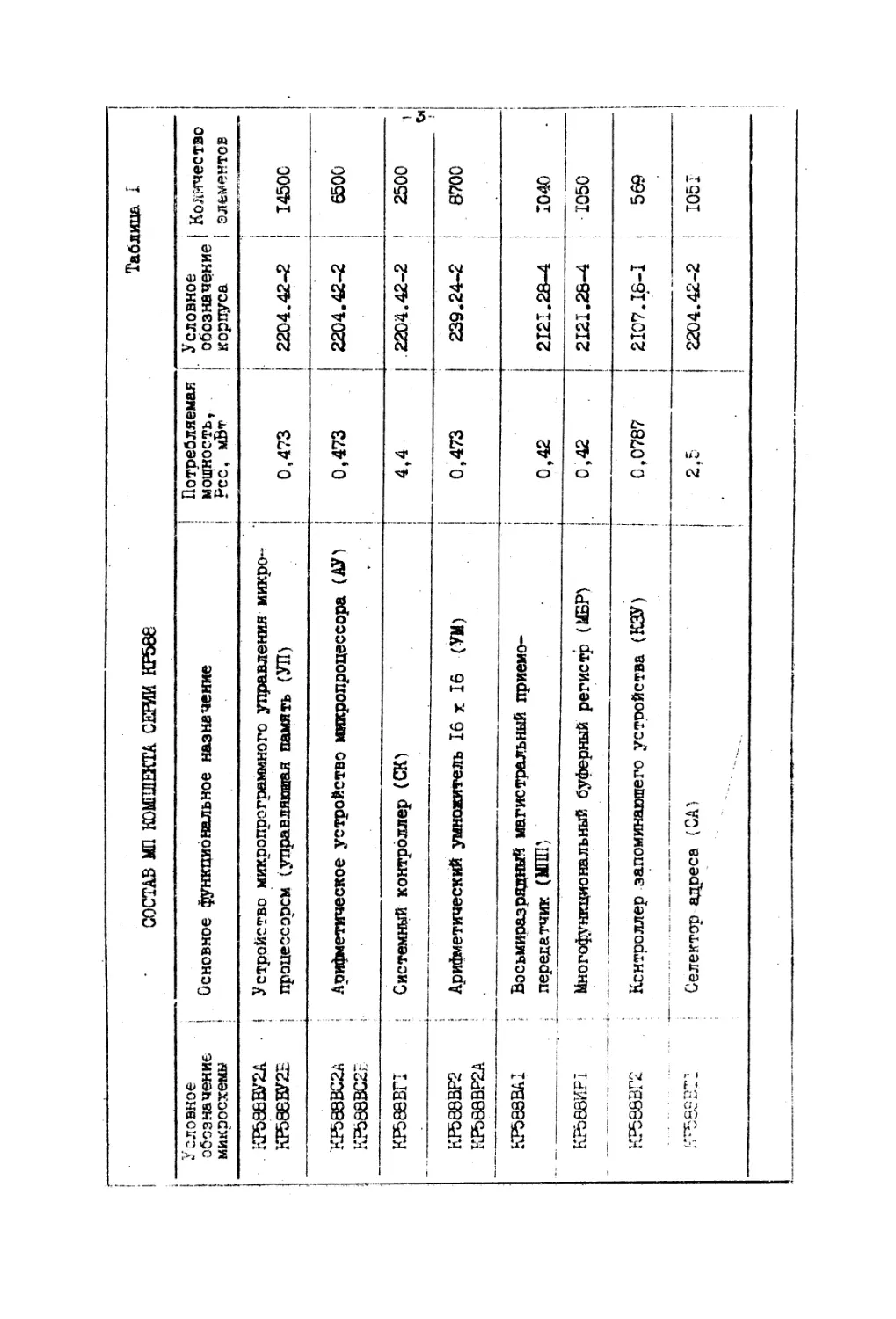

Типы Микросхем, основное функциональное назначение,условные

обозначения корпусов, количество элементов и потребляемая мощность

микросхем серии KF588 приведены в табл. I

ПЬоийВодительность процессора на базе серии КР588:

- сложение типа ADD % - 250 тыс. сл/сек

« умножение типа Ml/L R/,Ry - 10 тыс. сл/сек

( для процессора с аппаратной реализацией функций

умножения - 50 тыс. сл/сек)

В качестве элемента ОЗУ рекомендуется применение КМЦП БИС

0Э КР53?#Ю (2048 х 8)бит, КР537РУ13 (1024 х 4)бит, КР537РУ14

СОСТАВ МП КОМПЛЕКТА СЕРИИ KF588

Таблица I

Условное обозначение микросхемы 1 Основное функциональное назначение I Потребляемая [ Условное i

мощность, I Рсс, мВт i обозначение ।

j корпуса j 1 элементов

. КР588ВУ2А • КР588БУ2Б 1 Устройство микропрограммного управления микро- ’ процессорсм (управляющая память (УП) 1 0,473 I' ! [ 2204.42-2 1 14500

КР588ВС2А КР588ВС2Е Арифметическое устройство микропроцессора (АУ) 0,473 2204.42-2 6500 i

КР588ВП Системный контроллер (СК) 4,4 I .2204.42-2 I j । 2500 ,

КР588ВР2 КР588ВР2А i Арифметический умножитель 16 х 16 (УМ) 0,473 | 239.24-2 I 1 [ ! 6700

KP588BAI Восьмиразрядный магистральный приемо- । передатчик (МПП) 0,42 2121.28-4 1040 • |

КР588ИР1 Многофункциональный буферный регистр (МБР) 1 L 0,42 2121.28-4 • 1050

КР588ВГ2 Контроллер запоминающего устоойства (КЗУ) i 0,0787 2107.I8-I 569

Селектор адреса (СА) j 2,5 2204.42-2 1051

Микросхема КР588ВУ2 - устройство микропрограммного управле-

ния микропроцессором (управляющая память УП). Автономный асинхрон-

ный формирователь последовательностей 12-раэрядных параллельных

кодов. Предназначена для построения блоков микропрограммного управ-

ления различной информационной емкости и служит в качестве генера-

тора микрокоманд. В автономном режиме служит для построения прос-

тейших схем цифрового управления.

Кодировки микросхемы КР588ВУ2 (0001 - 0007) реализуют систему

команд ряда микро-ЭВЛ ”Электроника-60”, за исключением операций с

плавающей запятой.

Микросхема обеспечивает управление двумя ТТЛШ нагрузками.Со-

гласование по входам можно обеспечить ТТЛ схемами с открыть»! коллек-

тором.

Микросхемы поставляют двух типономиналов: КР588ВУ2А,КР588ВУ2Б

Назначение выводов

IMS [о - 15] - магистраль команд

- вход синхросигнала для

приема команд

В [О - 4] - магистраль состояний

S RI - вход сигнала обнуления

регистра следующего ад-

реса и регистра состоя-

ний

3F2 - вход сигнала обнуления

регистра состояний и

перевода регистра сле-

дующего адреса в состоя-

ние ”0000001”

PZ А К 2 - вход синхросигнала кви-

тирования приема микро-

команды

- 12] - магистраль микро- 1

команд '

RC.W - выход синхросигнала к я? j

тирования приема команду]

- пыхоц сигнала "Коч»'» кс- I

цы

УСТРОЙСТВО И ПРИНЦИП РАБОТУ

Микросхема КР588ВУ2 (УП) представляет собой программируемую ло-

гическую матрицу (Р/.М) с памятью, предназначена для формирования по-

следовательности микрокоманд (МК) по заданной команде.

Структурная схема микросхемы приведена на рис.2.

Регистры RGINS и PGSA предназначены для приема и хранения по-

ступающей извне информации.

Блок ЗУ# предназначен для формирования внутренних сигналов,фор-

мирующих временную диаграмму работы микросхемной внешнего сигнала,

задаваемого на вывод ЕА/Ь . функционирование блока 6У# зависит от

сигнала на входе ?СШ и происходит в соответствии с временной

диаграммой, приведенной на рис.3

Связи PLMI,h Р1М2 и подключение блока IN программируются фото-

шаблоном в процессе изготовления микросхем.

Блок IN предназначен для расширения логических возможностей УП.

Регистр ГОА предназначен для организации запоминания следующего

адреса, считанного из PtM2.

Регистр RGMINS предназначен для записи считанной микрокоманды.

Блок TOMINS предназначен для организации вадачи микрокоманды

43 RGMINS на внешние выводы.Регистры RGINS и PGSA предназначены для

приема и хранения поступающей извне информации.

Для обеспечения правильной работы микросхемы после включения

питания следует провести начальную установку. Для этого на любой

из входов IRI или подается шцульс длительностью не ме.чее 0,5мкс

в соответствии с временной диаграммой. Этот импульс вызывает обну-

ление RGSA и установку блока<$У# в исходное состояние. Кроме этого

происходит обнуление шести триггеров ГОА, седьмой триггер обнуляет

SRI, а 3£2 переводит седьмой Триггер ГОА в состояние логической

единицы.

Подача импульса по входу S RI обеспечивает начальную установку

микросхемы и считывание первой микрокоманды с адреса 0000000.

Подача импульса по входу SR2 обеспечивает начальную установку

микросхемы с адреса 0000001. Одновременная подача синфазных импуль-

сов по входам SRI и не допускается.

По положительному фронту сигнала на выводе SRI или 5R2 микросхе-

ма переходит к формированию микрокоманды. Сформированная микрокоман-

да записывается в RGMINS и микросхема переходит к формированию сле-

дующей МК.

По отрицательному фронту сигнала на входе RCм2 прекращается вада-

ча МК и устанавливается высокий уровень на выводах MIN50 - М1АШ2.

Если к этому моменту сформирована следующая МК, то происходит ее

запись в RGMINS с последующей вадачей.

Структурная схема микросхемы КР588ЕУ2

Рис 2

Команда

Ни (sm SUZ-KtMn]* 2000 нс; W^^J-aX) нсу t^H (млк?.} = 500 нс; = 100 нс

,^0^с pj,c<<3.

......" ........... ........- ...........................

Если в МК сформирован признак ЕМ, то после её записи в FGMINS

на выводе £NZ) сформируется высокий уровень. _____

Для дальнейшей работы необходимо подать сигнал на вход 3 УАЙС. При

наличии сигнала на выводе происходит прием информации с маги-

страли INS в регистр RGINS и по магистрали В в регистр RGSA.

Для правильного приема информации необходимо устанавливать и снимать

информацию одновременно с отрицательным и положительным фронтом сиг-

нала S УМКС соответственно.

Приняв информацию в RGINS, RGSA микросхема отвечает по выходуRCA/q

и устанавливает активный низкий уровень на выходе END. По снятию

сигнала на выводе «ХУМЙС снимается сигнал RCAK4/

Приняв информацию в RGINS микросхема приступает к формированию

новой микрокоманды.

С целью расширения объема управляющей памяти несколько микросхем

КР588ВУ2 могут быть объединены в блок управляющей памяти.(рис.Ч ).

Расширение управляющей памяти по разрядности невозможно.

Перечень кодировок микросхемы КР588ВУ2

КР588ВУ2 - 0001

КР588ВУ2 - 0002

КР588ВУ2 - 0003

КР588ВУ2 - 0004

КР588ВУ2 - 0005

КР588ВУ2 - 0006

КР588ВУ2 - 0007

Кодировки микросхемы КР588ВУ2 - 0001, - 0002,

- 0003, -0004, - 0005 предназначены для сов-

местной работы с микросхемами КР588ВС2(АУ) и

КР568ВГ1 (СК) в составе процессора с системой

команд микро-ЭВМ "Электроника-60”, за исклю-

чением операций с плавающей запятой. !

В кодировке КР588ВУ2 - 0003 записаны команды !

умножения (MUL), деления (DIV ) и сложных I

сдвигов с фиксированной запятой (ASH, ASH3).

Кодировки микросхемы КР588ВУ2 - 0001, - 0002.

- 0004, - 0006, -0007 предназначены для исполь-

зования в составе процессора микро-ЭВМ с аппя- р

ратным выполнением команд умножения совместно !

с микросхемами КР588ВС2, КР588ВГ1, К.Р588ВР2,

KP588BTI.

Структурная схема процессора на базе микросхем серии

приведена на рис.5*.

Структурная схема включения микросхем

КР568ВУ2 в блоке управления памяти

Рис.

Структурная схема процессора на базе микросхем серии KF588

Рис. 5"

-01

I

Процессор реализует систему кимацц» приведенную в табл*2 . Система

комацд, приведенная в табл.2, содержит все команды, указанные в

ОСТ П 305.909-82, за исключением команд плавающей запятой АЛ/W ,

FSU3 'PrtUL t PblV , Подробное описание каждой команды приведено а

OCT II 305.909-82,

Кодировки микросхем КР588ВУ2-0001 + КН588ВУ2-0004 предназначены

для вццачи последовательности управляющих кодов (микропрограмм) для

микросхемы КР588ВС2 (АУ). Мнемокоды микрокоманд соответствуют систе-

ме микрокоманд АУ,приведенной в табл.З,

Кодировка микросхемы КР588ВУ2-0005 предназначена для выдачи ник-

ропрограммы для микросхемы КР588ВГ1 (СК). Мнемокоды микрокоманд соот-

ветствуют системе микрокоманд СК, приведенной в табд.ХГ

Мнемонические обозначения прерываний и соответствующие им коды

приведены в табл.#

Таблица 2

Система команд центрального процессора на базе

микросхем серии KI588 и распределение микропро -

грамм по кодировкам микросхемы КР588ВУ2

Код команды Признаки ; Команда : Номер :коци~ :ровки

мнемоника :восьмирична i i ГЮ : Г-С

1.Одноадресные команды:

СГ₽(В) нО&ООО 0 I 0 0 Очистка OQ01

СОМ(В) и()!51 OD 4 4 0 г Инвертирование 0001

INC(B) *052*» 1 4 4 - Прибавление единицы рос 1

ОЙС(В) xOE>3ZU> ♦ 4 4 Вычитание единицы 0001

V 133(B) ie0fc4№ 1 4 4 4 Изменение знака 0001

TST(B) «0571Ф t 4 0 0 Проверка (ЯД,Ч

A5k(В) *обгш, i 4 4 4 Арифметический спьяг ьнр«ви 0601

AU(B) 1Й1(53ВГ> 4 4 4 4 Арифметический сдвиг влево 6001 I

ЮК(В) «O6W» ♦ 4 t 4 Циклический сдвиг вправо 1)66! 1

ROZ, (В) *061710 4 4 4 4 Циклический сдвиг влево ЫИ)1 hi

АПС(В) ♦ i 4 4 Прибавление переноса

SBC(B) i l 4 4 Вычитание переноса (ЯЮ1

5 XT ♦ 0 - Расширение знака 0062 i

S HzkB 0003 Ы) t 4 0 0 Пе 1) ос т.; 1 и о в к в б6 Й т о в

MIT'S 1067М> 1 0 - Чтение СС!1 I Н/,.7

MTl s 106-1 по -I i t ♦ Зап иг, ь С(",П ((;>

я Пятнадцатый («азряд ко?. idriiiU f ipllftHOdOT .jib iEH.ie НУна a.iii ;-.:i 1 : ii.iiii-i -1

В ЭВВИСИЛОСТИ ОТ длины операндоь (сЛ;;ВО Г.-Ш О; h i ) i

Продолжение табл.2

Код команды : Признаки :N: 7: V: С : Команде : :Номер :коди- ровки

мнемоника • :восьмиричн.

2.Двухадресные команды

МОИ В) mISSW 4 4 0 - Пересылка ООО!

СМР(В) M2SSBD 4 4 4 4 Сравнение ООО!

АТО 06SSDD 4 4 4 4 Сложение ООО!

SUB I6SSDD 4 4 4 4 Вычитание ООО!

ВГГ(В) K3SSDD 4 4 0 - Проверка разрядов ООО!

В1С(В) M4SSDJ) 4 4 0 - Очистка разрядов ООО!

BIS (В) «5SSDI» 4 4 0 - Логическое сложение ООО!

XOR 074SSDD 4 4 0 - Исключающее ИЛИ 0002

3.Команды управления программ ЛОЙ

BR 000400+ХХХ Ветвление безусловное 0002

ВМЕ ооюоо+ххх 2 - 0 Ветвление,если не равно(нулю' 0002

: beql 001400*ХХХ И « I Ветвление,если равно(нулю) 0002

ВРЬ I000004-XXX N = 0 Ветвление, если плюс 0002

BMI I00400+XXX Н » I Ветвление, если минус 0002

BVC I02000+XXX V «= 0 Ветвление, если нет ариф- метического переполнения 0002

1 BVS I02400+XXX / = I Ветвление,если арифмети- ческое переполнение 0002

все юзооо+ш с = 0 Ветвление,если нет переноса 0002

' BCS I03400+XXX С Ж 1 Ветвление, если перенос 0002

BGE 002000+ХХХ N(±)K •- : 0 Ветвление,если больше или равно (нулю) 0002

BLT 002400шХХХ N@v« : 1 Ветвление,если меньше(нуля) 0002

; BGT 003000+Ш • -0 Ветвление,если больгае(нуля) 0002

1 BLE 003400+ХХХ Ветвление,если меньше или

равно (нулю) 0002

ВНХ ЮЮ00-+Ш г * ; 0 Ветвление, если больше 00:02'

ВЦ* I0I400-+XX.X N - I Ветвление,если меньше или равно 0002

BHIS IC3000+XXX C •- . c Ветвление,если больше или равно 0002

) BLO Ю3400*ХХХ r* 1. Ветвление, если меньше 0002

Ь мр OOOIM) Безусловный переход, 0004

004 R М) Обращение к поп,про грамме 0004

ETS 00020F Возврат из поппротряммы 0004

Щ.Ж {'(V?4 У Ч Восстановление УС роге

$'4 i 1 оу; рм 7 Вычитание ►тчичи’П’ ” НИР г t .

Продолжение табл„2

- 15 -

Код команды ^Признаки ; .‘Номер

____________________ *____________♦ Ч г\ к □ и п й *иппм_

мнемоника восьмиричн. iv и м а п Д cl U 1• v c • ЛЦЦ11- :ровки

4.Комаццы прерывания пр о г рам. 1 мы

ЕМТ 104000 - 104377 Командное прерывание для системных программ 0004

TRAJ-" 104400 - 104777 Командное прерывание 0004

ЮТ 000004 Командное прерывание для ввода-вывода 0004

ВЕГ 000003 Командное прерывание для отладки 0004

RTI 000002 Возврат из прерывания 0004

ш 000006 Возврат из прерывания 5„Команды управления машиной 0004

HALT 000000 Останов 0004

Ml IT uOOOOI Ожидание 0004

RESbT 000005 Сброс внешних устройств 0004

6.Команды изменения признано! •з

СМ/ 000250 0 - - - Очистка Jl " 0002

CLZ 000244 - 0 - - Очистка Л" 0002

CLV 000242 - - 0 - Очистка У’ 0002

CLC 000241 - - - 0 Очистка С" 0002

CCC 000257 0 0 0 0 Очистка всех признаков(А/ ZJ'H 0002

SEA/ 000270 I - - - Установка „ А/ 0002

SEZ 000264 - I - - Установка „1" 0002

SEV 000262 _ - I Уюыъъкь У” 0002

sac 000261 - - - I Установка „С ” 0002

see 000277 I I I I Установка всех признаков ^ЛУУ-У 0002

WOP 000240 Нет операции 0002

7.Команды расширенной арифметики

MOL 070RSS t f 0 t Умножение 0003

DIV 071RSS 4 4 4 4 Деление 0003

ASH 072RSS 4 4 4 + Арифметический сдвиг 0003

ash: 073RSS 4 4 4 4 Арифметический сдвиг двой- ного слова 001'3

Схема входного каскада выводов IWS[O-I5], $УЙРС, ВО-ЕИ,

SKI, Ж Л Ж? микросхем КР588ВУ2

----nuranrie

в схему

микросхемы

ой'щии

Рис. 6

Схема выходного каскада вывода END

Гис.?

С.хчмя "'«одного каскада выводов MM5[0-I2] , RCAK1

пигоииг

выход

-

Микросхема KP5B8BC2 - арифметическое устройство микропроцессора

(АУ) .Автономный 16-разрядный управляемый микропрограммно асинхрон-

ный модуль обработки цифровой информации.

Микросхема предназначена для приема, оперативного хранения,об ра-

ботки и выдачи информации. Служит onePa4MOHHUX бло-

ков цифровых вычислительных системТИ?6-разрядной шиной адресов и

данных.

Микросхема обеспечивает управление двумя ТТЛШ нагрузками.

Согласование по входам может быть обеспечено с помощью ТТЛ схем

с открытым коллектором.

Микросхемы поставляют двух типономи-

34 35 31— л 25 «о Qi ог , оъ '* О ►— ми I a ч» /*. *» «*^5: . На : налов КР5860С2А, КР568ВС2Б. Назначение выводов ~~~ MWfb-Il) - магистраль микрокоманд i °® 5УЙ1 - вход синхросигнала для приема 10 микрокоманды 1 у - ... . 1 Т/Ш1 - вход/выход синхросигнала кви- .<* _ тиоования выдачи

13 ₽ t

14 ЯСАК1 - вход/выход синхросигнала кви-

оч 41 д-. тирования приема it _ D [0-1б1 - двунаправленная магистраль

2? данных

)ЗУАН 11

ЯСАК2 - выход синхросигнала квитировав — ния приема микрокоманды

R ; 1 2. ‘ 3 2* 20 В0-ВЗ- магистраль состояний Выводы RI-P4 рекомендуется под- - — ключать к источнику питания че- рез отдельные резисторы номина- --- лом 4,7 - 10 кОм. Допускается объединять выводы R3t R4 и под- ключать их к источнику питания через обший оезистоо 4.7-10 кОм.

Т 0 i 3

21 выводы RI, R2 оставлять при этом ~J~ свободными.

Рис. 9

, УСТРОЙСТВО И ПШНЦИП РАБОТЫ

Микросхема состоит из следующих основных блоков:

I)блока управления (СО),предназначенного для дешифрации

кодов микрокоманд и выработки управляющих сигналов к блокам схемы:

2)блока регистров общего назначения ( RG^ ) Тб х 16;

3)арифметическо-логического устройств^ ALU ),предназначен

ного для выполнения арифметических и логических операций;

4)регистра микрокоманд ),предназначенного для хране-

ния двенадцатиразрядного уг.равляющего слова во время цгпсла выполне-

ния микрокоманды;

5)регистра состояний (RGSA ) шестнадцатиразрядного регмст

ра хранения информации. Старший полубайт состоит из триггера знака»

триггера сравнения о нулем,триггера переполнения,триггера расширения

В ряде микрокоманд регистр состояний используют как регистр общего

назначения;

6) блока квитирования приема команды ( RCAK ^предназначен-

ного для формирования цикла работы микросхемы;

7)блока формирования признаков состояний ( FSA ),предназ-

наченного для формирования признаков результата выполнения операции;

8)буфера магистрали признаков состояний (ВЛ?А),предназна-

ченного для временного хранения и выдачи в однонаправленную магист-

раль состояний старшего полубайта регистра состояний;

9)буфера входа-выхода ( В Г )предназначенного для осуществ

ления асинхронного приема, и выдачи информации по шестнадцатиразряд-

ной магистрали данных;

10)аккумулятора на регистрах ( RG5 ) предназначенного для

временного хранения шестнадцатиразрядного слова;

И)блока синхронизации - определяющего асинхронный

обмен по магистрали данных; j

12)регистра управляющего олова - служащего для хра '

нения дешифрированного набора управляющих сигналов.

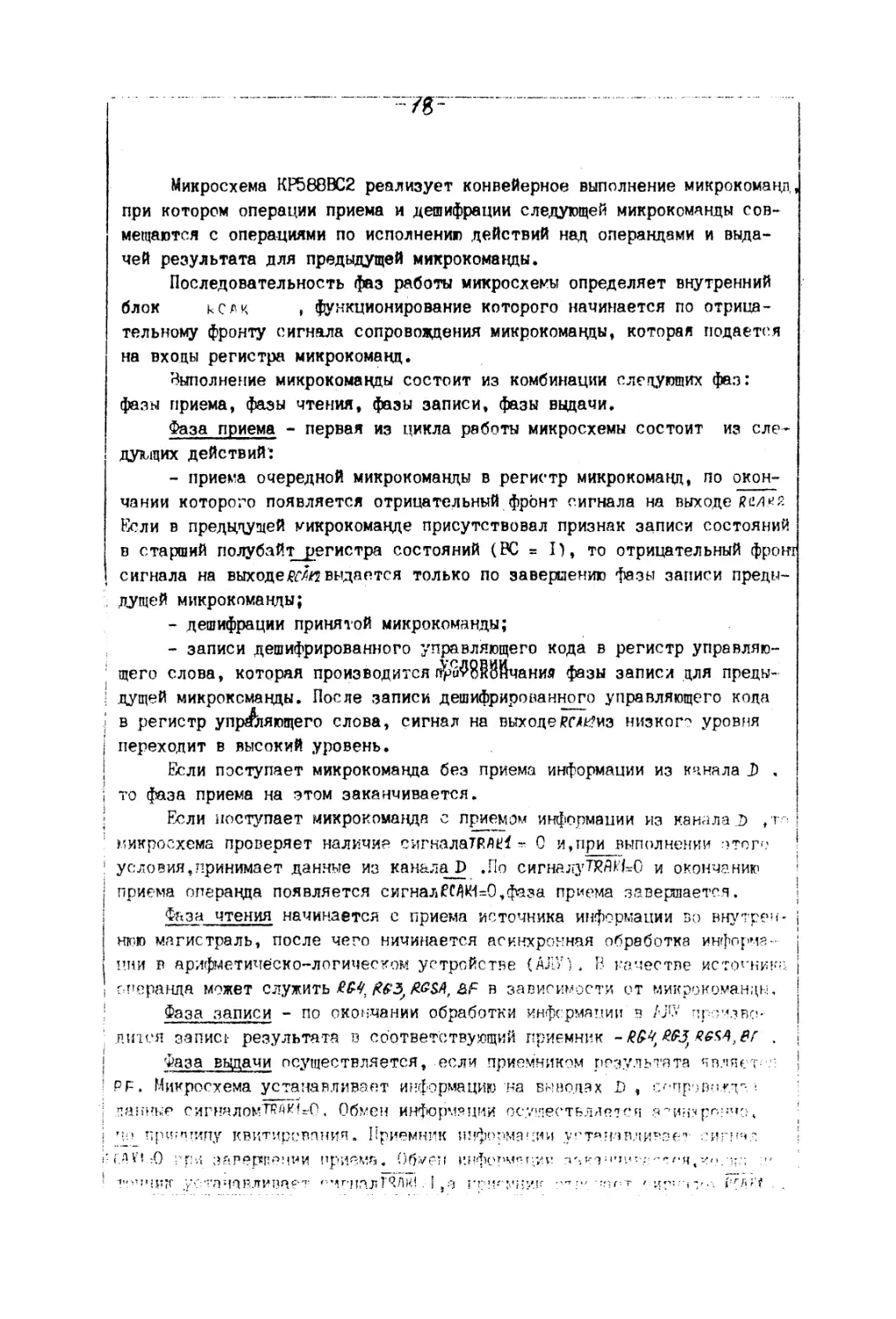

Микросхема КР588ВС2 реализует конвейерное выполнение микрокоманд,

при котором операции приема и дешифрации следующей микрокоманды сов-

мещаются с операциями по исполнению действий над операндами и выда-

чей результата для предыдущей микрокоманды.

Последовательность фаз работы микросхемы определяет внутренний

блок ьсак , функционирование которого начинается по отрица-

тельному фронту сигнала сопровождения микрокоманды, которая подается

на входы регистра микрокоманд.

Выполнение микрокоманды состоит из комбинации следующих фаз:

фазы приема, фазы чтения, фазы записи, фазы выдачи.

Фаза приема - первая из цикла работы микросхемы состоит из сле-

дующих действий’:

- приема очередной микрокоманды в регистр микрокоманд, по окон-

чании которого появляется отрицательный фронт сигнала на выходея

Если в предыдущей микрокоманде присутствовал признак записи состояний

в старший полубайт регистра состояний (PC = I), то отрицательный фрож

сигнала на выходевыдается только по завершению фазы записи преды-

, дущей микрокоманды;

- дешифрации принятой микрокоманды;

- записи дешифрированного управляющего кода в регистр управляю-

: щего слова, которая производитсяг^и#813Йчани$ фазы записи для преды-

! дущей микрокоманды. После записи дешифрированного управляющего кода

в регистр управляющего слова, сигнал на выходе £(7Е?из низкого уровня

переходит в высокий уровень.

Если поступает микрокоманда без приема информации из канала J) ,

j то фаза приема на этом заканчивается.

! Если поступает микрокоманда с приемом информации из канала D ,т-

; микросхема проверяет наличие сигналаТР.Ак!1 - 0 и,при выполнении этого

j уеловия,принимает данные из канала D .По сигналу ЯШМ} и окончанию

приема операнда появляется сигналфаза приема завершается. I

Фаза чтения начинается с приема источника информации во внутрен- i

нюю магистраль, после чего начинается асинхронная обработка инфпрме- |

пни в арифметичёско-логическом устройстве (АЛУ). В качестве источника j

; операнда может служить £££ ^£3, в зависимости от микрокоманды.

; Фаза записи - по окончании обработки информации в МУ про’.-'.? во-

лгпея запись результата в соответствующий приемник - &Г .

I Фаза выдачи осуществляется, если приемником результата являетI

' PF. Микросхема устанавливает информацию на выводах D , ч

1 панны? сигналомТСАЙх-О. Обмен информации осуществляется

i пршщипу квитирования. Приемник информации устанавливает сигнал ;

lU.AVbQ завершении приема. Обмен информации

' устанавливает . I ,а грун-мник т < цр:.

.. '..... - 79 -------------------------------

Микрокоманды микросхем КИ)88ВС2 по наличию фаз можно условно раз-

делить на следующие виды:

- микрокоманда без обмена данной с магистралью данных ЦЦ;

~ микрокоманда с приемом операнда по ЦЦ;

- микрокоманда с веда чей результату операции в ЦД;

- микрокоманда с приемом операнда и выдачей результата операции

в ад.

Микрокоманда без обмена данными с магистралью данных

Устройство микропрограммного управления ведает микрокоманду (если

она сформирована) на входы МШ 10:11] микросхемы. Ив вход сопровож-

дения микрокоманды УМ? должен подаваться низкий логический уровень.

Если по отрицательному фронту сигналаГУЛ? принята микрокоманда без об

мена данными с ЦД, то по окснчании^приема микрокоманды микросхема ус-

танавливает сигнал низкого уровня на выходе ШК2начиная исполнение

микрокоманды. В то время, как микросхема выполняет текущую микро-

команду» устройство микропрограммного управления формирует следующую

микрокоманду* Закончив выполнение микрокоманды микросхема устанавли-

вает сигнал высокого уровня на выходейса^и начинается новый цикл при

ема и исполнения микрокоманды.

Микрокоманда с приемом операнда по магистрали данных о

Приняв микрокоманду в регистр микрокоманд микросхема, после её

дешифрации, переходит в режим ожидания приема информации из ЦД. Прием

информации из ЦД начинается при появлении сигнала низкого уровня на

выводеTRAM. Закончив прием операнда микросхема устанавливает сигнал

низкого уровня на выводах ИВысокий уровень сигнала на выводе

Йш устанавливается микросхемой после установки сигнала высокого уров-

ня на выводе TRAM.

Микрокоманда с выдачей результата операций в магистраль данных

Начало цикла выполнения такой микрокоманды аналогично случаю при-

ема микрокоманды без обмена данными до того момента, когда микросхема

переходит к выдаче результата в ЦД, сопровождая её установкой сигнала

низкого уровня на вынонеТШ1. Одновременно с выдачей микросхема может

принять новую микрокоманду и приступить к её выполнению. Микросхема

осуществляет вида чу информации в ЦД де. получения ответного сигнала

об окончание приема информации - сигнала низкого уровня на выводе? ДАМ.

При пое^плении этого сигнала микросхема прекращает выдачу информ г» пни

и устанавливает сигнал высокого уровня на вывоце*Ш1. Во время и

информации микросхема может принимать следующую микрокоманду об-

мена данными по Ц!Е Торца она выпол^ется неэльисимс от того,закон-

чился ли цикл обмена предыдущей МН чин нет. ! ли донная .ч-.икрокома1Цй1

с ьыдачей, п ещё не закончилась ведама информации в предыдущей ММ/го

S

временная диаграмма работы микрбс.-:емы КгЪ68££2 (операция с псиемом

В

i

Временная диаграмма работы микросхемы KF588BC2 ; операций с выдаче? по

12 ,

] коЗ HltfS j

MINS

(CVO«,5^

КОЭ f~NS~>~

! : tvfwiMS-STHi)

itsv(SYNi-MlNS) tsufSW-MlNS}

tpfswwmf

-t £ у (TR AKA-ЯСАКА)

.tHTRMA-RCAK/ '

•4CVK‘

3)

tpfswv в!

X 3 J ( SVNA - MINS '; £50 HC

* . , [т P &KA - BCAW)* M OO HC S

третье

состояние

третье

состояние

[ *у(ТР**И-ЙСММ) tS0frKMfr*K^4'

tv(M!WS-S4HA> & 50Ие. , tv'Tk AM-RCAM’i^ 10нс

РИС . /£

Временная диаграмма работы микросхемы КРЬ88ВС2

-С а ; . опеоапия без обмена по Ъ )

1^2500кс, tsu(SVNl-MINS)^5OHC ;

100 rtC tv(MINS-S'fNl) 4-. 50нс )

DMC. Z3

Временная диаграмма работы микросхемы КР588ВС2

при выполнении микрокоманды "начальная установка”

±4^400 КС , *twu C&’nt4)> 4000 НС ,

£ SV (ъ'Ж! - MIMS) k 5ОИС i

-t V ( MXHS - SVH4 ) 50 НС ?

Рис.

------------- ----------- Ж-----------------------------.........-..

микросхема, окончив фазе чтения и записи и установив сигнал высокого

уровня на выходе RUK2останавливается до появления сигнала на выводе

ЯСАМ. После этого микросхема устанавливает сигнал высокого уровня на

выводеТкдк-/ и, при наличии сигнала высокого уровня на выводеРСЛК],ры-

дает новую информацию.

Микрокоманда с приемом операнда и выдачей результата операции в МД

Выполнение этой микрокоманды аналогично микрокоманде с приемом

операнда из магистрали плюс фаза выдачи результата операции в МД.

Таким образом, в процессе выполнения фазы выдачи одной микроко-

манды могут выполняться все фазы - до фазы записи другой микрокоман-

ды и фазы приема третьей микрокоманды.

Структурная схема соединения микросхем КР588ВС2 и КР588ВУ2

Аус /У

~2G~

Система микрокоманд микросхемы КР588ВС2 Таблица 5

Номер разряда микрокоманды Фор- мат Операция Номер табл.

0 I 2 3 4 5 6 7 8 9 10 II

о а 0 КОП I Р/ ВС БРА < Р/> (х) £ А > -* Ъ1 .Д'

g 0 D 1 11 I I КОП I ВС БРСА < РС>®<А>—

35 CQ 0 0 I I I КОП I ВС БКА 4 <А >—*2)7 6

I Ъц КОП 2 Р/ ВС УР <л <4> 7

0> 3 X I S X сб 11 I I КОП 2 ВС урс d. /РС>—-м $

i I SS I I 0 I КОП 2 ВС УА Л С А? —*М

>1 I cSc 0 I I I КОП 2 ВС УК_ у 4 К ? —*2)2 10

Байтовые операции проводятся только над старшим байтом.

Врпшшия гпппя 9 ’ операция над полным словом

‘«личина слова j _ старв111М байтом

Рг - адрес 4-го регистра; © - операция по К0П1;

< >* содержимое источника информации; <К_ - операция по К0П2;

Di- адрес приемника результата операции КОПТ;

Л- адрес приемника результата операции К0П2;

ВС = I - запись состояний в старший полубайт PC.

Di - БИНАРНЫЕ ОПЕРАЦИИ Ьг - УНАРНЫЕ ОПЕРАЦИИ

00 - < й/ > = Р; УР 0 -2^2>= Р/

БРА 01 - < 2>: > = А I • 4 Dj? > = P< 4. К

10 - < DO = PC УРС 0 “42)2 > « PC

II - < bi > = Кл.А I - 2 D2> = РСдК

БКА 01 - < I>i> = А УА 0 - / D?_ > - Л

10 - < А> = PC I - / Р2; - А Л К

II - < J)f > = КлА

БРСА 01 -z!)o = А УК 0 - / Z>2 Т . A

10 - < b-t> = PC I " 4 D о z " A.®

II - < D< > = КлА

К - канал (буферной регистр магистрали д-знных)

А ~ аккумулятор

БИНАРНЫЕ ОПЕРАЦИИ НАД РОЮЫ И АККУМУЛЯТОРОМ

Таблица 4

Операция С 1 I 2 i 3 4 5 6 7 8 9 10 II Описание Загрузка PC(BC=I)

КОП1 ВС TP T3H ТПП TPH

Конъюнкция Л | 0 0 0 0 0 4 р(> Л - X 0 X

Конъюнкция байт А/б ; о ! _ । 10 0 0 4 Pi 6>y[<A6> -if - X 0 X

Вычитание - о С 0 0 I 1 <Pt> -<A> X X X X

| Вычитание байт - б | о 10 0 1 zPf 6> - zA6>— X X X X

1 1 j Не эквивалент ® ! -с 0 0 10 <P/> ©zA> -Д — X 0 X

: Не эквивалент байт @ 6 0 >10 10 ZPzrf> ®<A6>— — X 0 X

Сложение + 0 | 0 0 I I t P/> + 4 A> X X X X

Сдвиг байт 0 I 0 I I C Pz> &-=-* *2), — X 0 X

Пересылка 2 Пе2 О ! 0 10 0 4 A > —-2) у — X 0 X

Пересылка 2 байт Пе2б 0 I I С 0 <A6> — X 0 X

Пересылка I Пе1 0 0 10 1 <Pz> - X 0 X

Пересылка I байт Пе1б с I I 0 I <рг'б>— — X 0 X

| Дизъюнкция V О 0 110 4Pi>V4A> -J), - - X 0 X

1 Дизъюнкция байт V б 1 О I I I 0 L <Pi6>VzA6>— — X 0 X

и! см. табл.

БИНАРНЫЕ ОПЕРАЦИИ НАД КАНАЛОМ И АККУМУЛЯТОРОМ

Таблица 5

Операция * о I 2 3 4 5 6 < ‘ 7 8 9 IO II Описание Загрузка PC(ВС»I)

Z)/ КОП I 0C TP - T3H ТПП ТРИ

Конъюнкция Л О О I I I oooo. 4 K> jUA> -Э/ - X . 0 X

Конъюнкция байт Л б О О I I I | 1 I 0 0 0 4 Кб>Л.<Аб> -Z>z — X 0 X

Вычитание 0 0 I I I j |0_C 0 I <K> - ZA> ^2)f X X X х

? Вычитание байт -б 0 -° I I_I_ 10 0 1 ZK6> -<A6> >Z)/ X X X х i

• Не эквивалент © О i О I I I 0 0 10 i z К > © z A > *7)/ — X 0 X

• Не эквивалент байт © б 1 i ! o i i i : 10 10 z K6> ®ZA6> — X 0 X

\ Сложение + ! 0 0 I I I io о i i <K>+ ZA> X X X X

! >двиг байт 8 2 *2 И. 0 I I I_ fi_o_V _ <K6> - X 0 х' |

• Пересылка 2 Пе2 О 0 I I I_ QIC 0 < A > - X 0 х i

Пересылка 2 байт Пе2б 1 0 ; _O I I I 110 0 < A6 / ~bf - X с X

. Пересылка I Пе! i О_ •_0 I I I_ ! 0 I X I i_ _< K> — - X 0 X

• Пересылка I байт Пе1б ! О । °_l L1 II _I_X 1 K6> ►?>/ — i X 0 X

. Дизъюнкция V i и 1 O I I I jo I I 0 j I 4E>r/A> -D1 ,, — j с X

Дизъюнкция байт Тб * О i 0 I I I j I I I 0 i । 4 Кб > rz A6 > — i с _Х I

*2 ем.табл. 12.

БИНАРНЫЕ ОПЕРАЦИИ НАД РЕГИСТРОМ СОСТОЯЛ® И АККУМУЛЯТОРОМ

Таблица 6

Операция С I 2 3 4 5 6 | i 7 8 9 I0| II I i Описание i L i Загрузка PC(BC=I) :

КОП I BC TP ’ T3H | ТПП| TPH

i Конъюнкция Л 0 I I I I i G C 0 0 i 4PC>_A < A> -if - X 1 Г X

Конъюнкция байт Аб .0 11 i i 10 0 0 4PC6> A<<A6> ^2)i — X 0 X

' Вычитание 0 i i i i 0 0 0 1 4PC> 4A> if X X X X

? Вычитание байт - б 0 11 i i I C 0 I <PC6> zA6> ►ix X X X i x

: Не эквивалент © с 11 i i 0 0 10 <PC> © <A> - X 0 X

; Не эквивалент байт @ б Q i i i i 10 10 <PC6>SzA6>—-Ы - X 0 X

! Сложение * 0 i i i i 0 0 11 ZPC> + ik>—~Ы X X X X

: ^пвиг байт 8ь^ * *j 0 i i i i I 0 I I ZPC> 2ZET -if • X 0 X

• Пересылка 2 Пе2 0 i i i i 0 I 0 c (!l> — X c X

| Пересылка 2 байт Яе2б у> I i i i I I 0 0 <A6> ~ц — X 0 X

i Пересылка I Пе! г i i i i 0 I X I < PC> - X Г; X

i Пересылка 1 байт Пе1б 0 1 i i i i i i i x i 4PC6> -if_ - X 0 X

I Дизъюнк.. .ия V Till 0 110 1 1 1 <PC> V <A>—-if - X 0 ! X

I Дизъюнкция байт V6 ! 0 । i i i i i i I I I 0 1 1__<ГСб> V<A6>—♦J)/ - X j 0 :

1 лзчалъная установка 1 С 0 ix i i : i X X X X

см.табл- <5

об ?_

УНАРНЫЕ ОПЕРАЦИИ НАД РОКАМИ

1 0 I 2 3 4 5 6 7 8 9 10

КОП 2

Сдвиг логич.влево Л -*— I 0 0 0 0

|Сдвиг циклич,влево Ц—— I i 10 0 0

^Вычитание единицы -I I 1 0 0 0 1

«Дополнение Д I 10 0 1

{Сложение с ТР -ТР \ I 0 0 10

вычитание ТР -ТР I у ! 10 10 i

Сложение с I +1 I ! i • о о i i

Сдвиг с ТР влево _ <*— i т [ J ! I 0 I I

Диверсия _ 3 > i 0 100

Сдвиг с ТР вправо —* 1 i [ - - 110 0

Солем константы liL. i 0 I 0 I [kohctJ

Сдвиг логич.вправо Л —I 1 I ! 0 I I 0

=С д з а г цикл. вг ра в о Ц ~ 1 I I I 0

Дрием константы *4 I i 0 ! 0 I 0 I 1

Таблица F

. II Описание Загрузка PC(BC=I)

TP T3H ТПП TPH

( 4 Pz> Л*-) ►д? X X X X

( z Ц—)— X X X X

(<Рг>-1 ) - X X X

( д<Рг> ) — "-Й X X X X

( ZPi> +ТР) *Z>2 X X X X

( 4 Pt > -ТР) *$2. X X X X

( Z Pz)> +1 ) — - X X X

( г Pi>c ТР*-)— X X X X

(7 zPt-> ) —bi I X 0 X

( z Р£ >с ТР-»)—-it X X X X

- - - - 1

(Z Рг> Л-Ч *2)2 X X X X i

(< PzMW— —“bi X X X

<К>~*’Рс 1 X 0 X ! i 1

См:

о;

УНАРНЫЕ ОПЕРАЦИИ НАД РЕГИСТРОМ СОСТОЯНИЙ

Таблица S

Операции 0 I h 3 4 5 6 7 8 9 10 i II Описание ! Загрузка PC(BC=I>

| КОП 2 BC | TP t j ТЗН1ТПП i tph

Сдвиг логич.влево Л I I I I I ; 0.0 0 0 ( 4. PC > Л i - i — i - |

Сдвиг цикл.влево Ц I I I I I 10 0 0 1 —1 ( 4РС>Ц-) i — ’ - 1 - i i

Вычитание единицы -I I I I I I j 0 0 0 d ( <PC> -I) ! - — у-' — i i 1 • 1

| Дополнение Д I • I I I I 10 0 1 ( Д 4 PC > ) *$2\ -

; Сложение с ТР *ТР I ! I I I 1 0 C_I 0_ ( 4 PC> +TP) ——4?! — — L ;

| Вычитание TP -ТР I XIII I 0 I 0 ! i ( < PC > -TP) — — I

?Сложение с I +1 I ! I I I I 00 I I - 1 i 1 j ( 4pc>+i у— *** - — '! —

! Сдвиг с ТР влево I ! XIII I 0 I I j ! [ ( 4 PC> С TP^)-^,; • - — — i

! Инверсия 7 I i I I I I 0 10 0 i (*7 4 PC _> ) — i — - Г- —

: Сдвиг с ТР вправо — ; Т I I I I 110 0 ( 4PC5 с TP-Й— •- — - .

Очистка I = i I I I I 0 I 0 I 1 0 ->2>2 — -* - - i

| Пересылка I Пе! | I 1 ! ! । I I I I I I IO I <rc> - - - —

! Сдвиг логич.вправо ! I XIII 0 I 10 ( 4PC> Л-») *.2>2 — • -

1 Сдвиг цикл.вправо Ц~Н I 1 Till i —1 I I I 0 ( 4PC> Ц—) — i

I Пересылка I Не! J ! Illi XIII j 4PC> “ i — — I “

УНАРШЕ ОПЕРАЦИИ НАД АККУ^’ЛЯТОРОМ

3 4 5 6 7 8 9 10

10 I 1: i 2

! ^2 \ 23<?Л 1 ел- I КОП 2

Сдвиг логич,влево Л I I I 0 I j 0 0 0 0

Сдвиг цикл.влево Ц ~ г I I 0 I | I 0 0 G

; Вычитание единицы -I I I I о I i ,0 0 0 1

Дополнение Д I I I 0 I I i 10 0 1

: Сложение с ТР +ТР I ! I I 0 I s S 0 0 I 0

j Вычитание ТР -ТР I I I 0 I Г I 0 I 0

; Сложение с I +1 I I I 0 I 0 0 I I 1

; Сдвиг с ТР влево * I I 10 I i о и ;

; Инверсия 7 т I I 0 I 0 10 0 !

i Сдвиг с ТР вправо — 1 I 10 г i 110 0 ’

1 Очистка * ! 1 I 1 I I 0 I Г 0 10 1 ; L 1

Г I ?Сдвиг логич.вправо Л—Ч I ! I I 0 I i 0 I I 0

* Сдвиг цикл. вправо Ц ~Ч I I I 0 I | I I I 0

Таблица 9

тТ I I Загрузка РС(0С«1)1

—i Описание *---------,--------j

Г~ — ВС 1 ТР 1тзн тли |трн '

( 4А> Л *2>2 X X, X х S

(<А>Ц—1 X X X X !

-I ) гд2 - X X х :

( Д<А> ) X X X х i

( 4 А>+ТР ) X X X X i

(4 А> -ТР ) X X X I 1 X j

(< А> +1 ) - X 1 х ! X !

( 4 А> ТР<-) —2>г| X 1 1 X X : X ’

7 4 А > ) ^2 1 * х ' 0 ' X i

( 4 А>с ТР— X ! X X ! X !

: 0 ’ " * 0 1 ° °

i ( 4 А > Л —) *2>г X i . J X X -- 1 х i

| ( 4А>Ц—*) ^-i2 X I X X I • Х !

УНАРНЫЕ ОПЕРАЦИИ НАД КАНАЛОМ

1 Операция : ... , , --I 0 ! I j 2 I 3 4 5 6 j I 7 e 9 10!

iej>. ; 1 КОП 2 I

1 Сдвиг логич.влево J?-*— 1 i i » 0 I I I c co c

; Сдвиг циклич. влево ц**- x i i C I I I I о о о i

j Вычитание единицы -I ; I t ; ‘Gill 0 0 0 I !

| Дополнение Д ; I j 1 0 I I I I CO I ;

1 Сложение с ТР +ТР : ’ i o i i i 00 I 0 i

! Вычитание ТР -ТР : ; T i .1 ' j О I I I 10 10!

Сложение с I *1 . i ‘ I ! * i о i i i ... j 00 I I i

; Сдвиг с ТР влево ; -r t ’ 7 1 1 1 1 1 .0111 ! I 0 I I | j - -. . 1

; Инверсия 7 : ! X J : ' 0 I I I I 1 — 1 i G I 0 0 I 1 - -

; Сдвиг с ТР вправо — 1 ! ? i i 0 I I I ' 1 110 0 j

j Очистка ; -l ! i i о i I i I 0 I 0 I i

i Пересылка I Пе! : 1 • •' i 0 I I I i - - ! I I 0 I i

i Сдвиг логич.вгравоЛ —* x i : ! c i i i ! о i 1 c

; Сдвиг цикл.вправо V—* ; i c 1 i I [ I I I o .

; Пересылка 1 Пе! X ; C 1 I ! | X I I 1 i

Таблица to

ВС Описание Загрузка PC(BC=I) !

TP T3H ТПП I TPHj

( <K> Ji-*—A X X X x i

(<К>Ц —) ^2 X X X x

(<K>-I — X ; X X

(Д <K> ) X X X X

I 1 I ( 4K> -rTP ) X X X I X !

i ( < K> -TP ) *Z>2 X X X 1 1 X

(<K>-rI > *J>2 — X X X

i ( <K> с TP-H—-J>2 X X X X

; ( 7 4Ki A I X 0 X i

i (ZK> C TP—A— X X X X ; i . •

1 о -— >2) 2 0 0 0 1 * 1

< K> *2», — X 0 1 L2J

( 4 K> JI — X X X ! i x!

( 4K> Ц —) X X X 1 xi

j 4 К > - X u i ! ~Xl

££

Таблица М

i‘H ! 1 2 3 4 5 6 7 8 9 10 II Описание

операция ' К0П1 ВС

Сдвиг байт |0 10 0 10 I I I i ! I До операции

8 . 1 i I ' ; 1 ! 1 P; I Ст.б I Мл.б ' j | После операции Pi |Мл.б. 1 Мл.б I

1 I 0 I I i i 1 Мл.б PC Ст.б PC PC |Мл.б PC |Мл.б Pz ! j ?i. 1Мл.б Рг 1 Ст.б Pz 1

: ; 0 • С* I } 10 11 i i Мл.б А Ст.б А А |Ст.б Ст.б А | ! 1 Pfc 1 Ст.б Р1 |

О • 1 л. : .011 ; i { Мл.б К Ст.б К ; Г__=;Г . i ; ! • МЛ.б А СТ.6 А ! i i : А |Ст.б i 1 J • ; I Pz । Мл.б PZ I Ст.б ?- I ;

Операция О 1.2 3 45 6 7 8 9 IO II

Di КОП BC

Сдвиг байт 8-^ 1 ' ! j 0 I С С 1 I I I 0 I I

0 i О I ! о I I I i I । I 0 I I

0 1 1 * 1 ' 1 i о 111 i ! .10 11

Таблица

Описание 1

Мл.б PC СТ.б PC

PC 1 Мл.б ГС] Мл.б к 1

KI !мл.б .....К.1 Ст.б к |

Мл.б А Ст.б А

А | Ст. б К 1 I

Мл.б к\ ч^Ст.б к

KI i 1 .1. ... .... |

До операции

А |Мл.б А | Ст.б

KI 1мл.б К1 Ст.б kJ

После операции

Мл.б А Ст.б А

А |Ст.б _ Ki Ст.б А 1

Мл.б к Ст.б К

KI I Ст.б к ! Ст.б к ]

I Операция j 0 i : 2 3 4 5 6

i bi i

Сдвиг байт | \ I olio ! i ! I I I I I

i

I

j 0 j О I j I I I I

I

’а блица /3

7 8 9 10 II

----------------Описание

КОП

I 0 I I i До операции pc | Мл.б j Ст.б | После операции PC IМл.б. | Мл.б 1

I I 0 I I ’ Мл.б А СТ.б А А | Ст.б РС| | PC | Мл.б РС| Ст.б PC |

!=:1 ' 1 Мл.б KI | Ст.б Мл.б К pci Ст.б Ст.б К ] А

! А I Ст.б PC j Мл.б ?с| PCj Ст.б 1 ; PC j

Таблице '/4

Описание

; Триек коне-

I *регистр POHa

L__Нанах KI

j

i

I ю' е 1 6 i 7 i

j m/x /?/> <ч1к'\н1к !

.. ...------------ —----— _______Д______£___*----j,

I Ст.п/б j 3 n/6 i 2 п/б I Мл.п/б i

|l0 9 8 !7 j

\»/k I

----------(-------—4—i—i ц______________,

l Ст.п/б j 3 п/б | 2 n/6 j Мл.п/б I

z^£

10 9 j 8 j 7 j

___________; i I ‘ i ‘i J

L Ст.п/б ! 3 п/б j 2 n7f

[10 I 9 je i 7 i

H/р j/У/АС;

Д____i___!____i______________________________,______

! Ст.п/б : 3 п/б j 2 п/б j Мл.п/б

Условные обозначения к табл,

X - содержимым разряда может быть либо 0 либо I.

— разряд, не принимающий участия в описываемой операции,

п/б - полубайт

ст.б - старший байт

мл.б - младший байт

мл,п/б - младший полубайт

ст.п/б - старший полубайт

м/к - разряд микрокоманды

Триггеры*четвертого полубайта PC:

ТР - триггер расширения

ТЗН - триггер знака

ТПП - триггер переполнения

ТРИ - триггер равенства нулю

Пересылка I - для формата БРА пересылка РОНа

- для формата БКА пересылка канала

- для формата БРСА пересылка PC

Пересылка 2 - пересылка аккумулятора

39 -

Схема входного каскада выводов IMS [О -II] SWVf микросхемы КРЬ88ВС<

Ьход >

RI

г vol

Г~7

Питание

в схему

микросхемы

SVD2

1_-------------Обилий

ГУС- ---ь

Схема выходного каскада выводов В [р - 3/,ясяк2

микросхемы КР&88ВС2

1Я

Схема входного-выходного каскада выводов

микросхемы КР&88ВС2

£[0 - ЯСЯМ

Питание

Общин

В схем у

микросхемы

4V

Микросхема КР588ВГТ - системный контроллер(СК).Микропрограммно

интерфейс

интерфейсом

управляемый асинхронный модель, обеспечивающий внутренний

процессора, а также его взаимосвязь с внешним стандартным

Микросхема предназначена для применения совместно с

КР588ВУ2,КР588ВС2, согласования работы этих микросхем и сопряжения

процессора на базе микросхем серии КР588 с каналом типа”0-шинэ”слу-

жит для построение процессора с системой команд по ОСТ ТТ 305.909-82

и интерфейсом по ГОСТ 26765.5Т-86(соответствует в части алгоритма ра-

боты4 .

Микросхема обеспечивает управление двумя ТТЛ111 нагрузками.

Согласование по входам может быть обеспечено ТТЛ схемами с открытым

oflhi

микросхемами

коллектором.

/7 , _<lJ /з , мм J ► / >2 >3 4

56 , > HLT

30 , PS 8

35 t a NOT

5/ , >INRO

3fy t INR1

33 , WR2

U . HNR3

21 ( , AN

2i . •rq

39 ,

3J , >8 O'5 У

2.0 y ^_OS7_

n t * W

03 Cher

OS

09 j

' ГЖ •

/2 ,

Q1 rso

O2__ PSA

СО

Назначение

8 0 7 2 3

•" da иды разрядов маги- А*/ с трали микрокоманд

HLT - вход сигнала прерывания

07 "Останов”

PSB - вход сигнала прерывания /л ’’Авария источника питания' } *

RCA№

INRT- вход сигнала прерывания от таймера

ТШ2<

// INRO - INR3 - входы сигналов пре

1 рывания с фиксированными адресами/векторами ду - вход сигнала Ответ 2^ — устройства" н— PQ - вход сигнала "Запрос преры- } вания с вводимым адресом/

ЗУЛ1А , XZ> i W - НМ/0У<

г 23 вектором" DMA - вход сигнала "Запрос пря- 1 мого доступа к памяти" 57 ь BUSY- вход сигнала "Канал занят" от устройства,запросившего

EOQ <

EDM 1

CO1 CO2

прямой доступ к памяти

MOST- вход режима начального 2?. пуска процессора ? 1 5УМ1» вход синхросигнала для при ) ема микрокоманды

SR2 '

f>oc. 2C

... ... ............ ” 47...... ..... .

CHER - вход/выход "Контроль ошибки"

SRI - вход/выход "Установка в исходное состояние"

ГА?АК1 - вход/выход синхросигнала квитирования вцдачи

RCARl - вход/выход синхросигнала квитирования приема

TSA - вход для установки Т-бита слова состояния

PSA - вход для установки P-бита слова состояния

ВО-ВЗ - выходы разрядов магистрали кода прерывания

AR2___~ ВХ°А синхросигнала квитирования приема микрокоманд

7ТАК2,Т/Ш3- выходы синхросигнала квитирования выдачи

Sy/VA - выход сигнала "Синхронизация обмена"

- выход сигнала "Чтение данных"

___ 2^ - выход сигнала "Запись данных"

И'Р/НУ - выход сигнала "Запись/Байт"

ЕЮ - выход сигнала * Разрешение прерывания"

EDMA - выход сигнала "Разрешение на прямой доступ к памяти"

СО1,СО2 - выходы сигналов управления магистральными приемо-

___ передатчиками

SR2 - выход сигнала "Сброс"

УСТРОЙСТВО И ПРИНЦИП PABOIH МИКРОСХЕМ КР588ВН

Микросхема КР688ВГ1 обеспечивает взаимосвязь всех микросхем

процессора (КР588ВС2 (АУ), КР588ВУ2 (УН), КР588ВП СК),КИ>88ВА1(МПП)

и позволяет процессору выполнять следующие фуггкцим:

- ввод/вывод шестнадцатиразрядного слова или байта

- обслуживание внешних и внутренних прерываний

- управление прямым доступом к памяти

-управление двунаправленЛи приемо-передатчиками.

Структурная схема микросхемы КР588ВП, включающая в сеон

пять блоков, приведена на рис. 21

Блок IA/R предназначен для приема запросов на обслуживание

прерывания и выдачи кода прерываний.

Блок 10 предназначен для формирования на шинах ввода^вывэда

стандартной временной последовательности.

Блок C0I предназначен для формирования в микросхеме внутрен-

них. синхросигналов.

БлокРМА предназначен для приема запросов на захват канала

при прямом доступе к памяти.

Блок С02 предназначен для включения и выключения канильмих

приеме-передатчиков.

Вывод 03 предназначен для подключения емкости,определяющей

время ожидания микросхемой сигнала AR. Величина емкости зависит от

быстродействия модуля памяти и внтних устройство

' ' ' - ' 41.............- ' ...... ' j

Микросхема KF588HH предназначена для согласования внутреннего ин

терфейса процессора с внешним стандартным интерфейсом Q - шины.

Структурная схема соединения микросхем KF588RTI ,КВ588ВУ2,КРо88’оС;.’

KF588BAI в составе процессора приведена на рис.5.

Внутренний интерфейс процессора содержит линии квитирования АУ и

блока УП/Т 6-раз рядной информационной магистрали, 4-раз рядной магист-

рали кода прерываний, линии управления МПП.

Блок микросхем УП обеспечивает управление микросхемами АУ и СК.

Кодировки микросхем блока УП КР588ВУ2-000Т,-0002, -0003,-0006 прини-

мают по магистрали ВОСТ) - ВЗСТ) признаки результатов Выполнения опа

раций от арифметического устройства. Кодировки микросхем блока УП

(КР588ВУ2-0004, -0005, -0007) принимают по магистрали ВО(2) - ВЗС2)

код прерывания от системного контроллера.

Выводы КАК/ _микросхем блока УП и микросхемы АУ объединены и

соединены выводом^ А’СА/С? микросхемы СК. _ _...

Выводы микросхем блока УП разбиты на две группы (I)

и SYKRC. (2), причем выводы каждой из групп соединены между собой.Труп

па выводов SWRC (I) предназначена для приема данных по магистрали

LVSO-IMS/5 в те микросхемы блока УП, магистраль ВО* ИЗ которых

соединена с магистралью ВО(2) - В3(2). Группа выводов S/aZ?? (2) пред

назначена для приема данных по магистрали IMS0 - M'S в те мик-

росхемы блока УП, магистраль ВО-ВЗ которых соединена с магистралью

ВОСТ) - Б3(1), ______ _____ ______ ______

Сигналы квитирования IRAKI, 1RAK2t 1RAK3, RCA KI обеспечивают

передачу по 16-разрядной двунаправленной магистрали AtXMMh'5 команд,

адресов, данных и векторов прерывания.

4-разрядная магистраль кода прерывания ВО-ВЗ служит для сообще-

ния в УП какое из прерываний в данный момент обслуживается.

| Сигналы СОТ,С02 служат для управления МПП.Сигнал СОТ синхронизм

руст передачу информации из магистрали процессора. Сигнал С02 синхрони-

зирует передачу информации в магистраль процессора.

Внешний интерфейс процессора содержит линии,обеспечивающие рабо

ту всех устройств канала. Это информационные шины,шины управления

вводом выводом,шины прерываний и шины^фямиго доступа к памяти.

Сигналы на шинах ввода-вывода ЗУКА, Kl)t WR, WK/Ъу t Лк/

обеспечиваюг передачу по 16-разрядной двунаправленной шине ADc> 5

команд.адресов,данных и векторов. Шины прерываний //ZT?

PSftt RQ,£RQ,1KRT служат для приема запросов на пре^шании и сброса

прерываний от внешних устройств,

Шинл прямого доступа к памяти ЬМА, tbMAf служат для при

им» запросов ня прямой доступ к памяти и сброса запросов на внешни/

устройствах,

I Шины инициализации SRZ для привидения системы а исход

i состояние.

i Система микрокоманд приведена я тяблЛЬ

-.......... ....... ....м........ ....—...... ...'

В соответствии с сигналами внешних и внутренних прерываний микро-

схема в составе процессора, обеспечивает выдачу на входы УП кодов

прерываний, представленных в табл./8.

Временные диаграммы выполнения микрокоманд DATI, вдпк ,Dato

приведены на рис. 22-^

Микрокоманда DATI Код 10 ( цикл ввода данных)

I) На СК подается сигналТ^Ш = 0 из АУ, свидетельствующий о том,

что адрес данных находится на шинах магистрали данных. По этому сигна-

лу СК устанавливает сигналы ЗУМА «= 0 и, с некоторой задержкой относи- :

тельно сигнала 5УМА, RCAK1« 0, тем самым разрешая АУ снять адрес с

шин магистрали данных. ___

2) Сняв адрес данных, АУ вырабатываетТРД/П ~ I. По этому сигналу

СК устанавливает RCAK1 = I и ДО в 0.

3) На СК подается сигнал А А -0 (данные находятся на шинах ма-

гистрали данных). По этому сигналу СК устанавливаетТЫ/</ разрешая АУ

принять данные.

4) Приняв данные АУ вырабатывает сигнал RCAK1= 0. По этому сиг-

налу СК снимает сигналыТШ/,. RD (так/= I, RD = I). ____

5) Получив сигнал Л// = I, СК вырабатывает сигналы 5УА/А = I.

Микрокоманда D/ПТ К КОД II (цикл ввода команды)

I) На вывод га Ж микросхемы СК подается сигнал из АУ (лог.0),сооб-

щающий о том, что адрес команды находится на шинах магистрали данных.

По этому сигналу СК устанавливает сигналы разрешения обмена (ЗУЛ/А = 0)

а также разрешает АУ снять с магистрали данных адрес комары, выдав

на вывод RCAK1 лог.О.

2) Сняв адрес команды, АУ подает на выводТРАК1 лог.1, на что СК

отвечает RCAK « I и RD = 0.

3) На вывод ЛА подается лог.О, сигнализирующий о том, что счи-

танная команда находится на шинах магистрали данных. По этому сигналу

СК разрешает УП принять команду, выработав сигналыТРАК? = 0 и7к/Ш = О,

если прерываний нет; либо только тан*3 = 0, если к данному моменту пре-

рывание установлено.

4) Приняв команду, УП отвечает сигналом RCAK1- 0. По этому сигна-

лу СК снимает сигналы(Т₽АК2-«1,Т^КЗ» I, RD = I). _________

5) По снятию сигнала М (ЛА/ « I) СК снимает сигнал $УА/А($УМА^1)

Микрокоманда DAT0 < Код 12 (цикл вывода данных)

I) На СК подается сигналТММ- 0 из АУ, свидетельствующий о том,

что адрес данных находится на шинах магистрали данных. По этому сиг-

налу СК устанавливает сигналы й/к/ВУ = ОДУА/А с 0 и, с некоторой за-

держкой относительно сигнала 5УАА, сигнал RCAK1= 0, тем самым раз-

решая АУ снять адрес данных. __

2) Сняв адрес данных АУ вырабатываетI. По этому сигналу

СК отвечает сигналами О/ЙУ = I, ЙСАК1» I.

3) АУ выставляет на шины магистрали данных данные и сигнализиру-

ет об этом СК установкой сигналам Axle 0. По этому сигналу СК уста-

навливает сигнал » 0.

4) После того, как данные запишутся в ОЗУ (ВУ), на СК подается

сигнал АН *0 .

5) Получив сигнал ЯСАК!» О, АУ снимает с шин магистрали данные

и устанавливаетШ-d = I. По этому сигналу СК устанавливает RCAK1-1.

По сигналу /17 в I СК устанавливает ЗУ^А « I.

...

СИСТЕМА МИКРОКОМАНД

Расшифровка кодов микрокоманд,поступающих из УП

(КР588ВУ2. кодировка 0005) ня входы NIW$ [Oi4J СК

Таблица

ричный 'микроко-1 Наименование микрокоманда

код ’манды I

00 • INIT ’Инициализация внешних устройств

01 ! ’Загрузка слова состояния процессора (ССП)

02 ! мпг {Ввод вектора прерывания

03 i H'AIT 1Ожидание прерывания

04 1 1 Разрешение прерывания

05 ! 10 !3япрет прерывания

10 ! О ATI ’Ввод слова

ТТ ’ DATIH 1Ввод команды

12 ! РАТО ’Вывод слова

13 1 РАТОВ I Вывод байта

14 ! WTje ! Ввод'вывод с лова

15 I ТЛИ 08 ’Ввод7вывод байта

20 ! RTO ’Сброс прерывания /МО

21 1 NH 1 Запрет прерывания HU

22 ! КП I Сброс прерывания 7WA7

23 ! KT2 ! Сброс прерывания

24 ! Rrs 1 Сброс прерывания ТА'Л’З

25 ! RH ’Сброс прерывания HLT

26 ! RTM !Сброс триггера маски

27 ! res ’Начальная установка

30 ! RTE ’Сброс триггера

31 ! RTP ’Сброс триггера PSB

32 I его !Очистка триггера то

33 ’ NIT !Запрет прерывания TI

34 ! rev IСброс триггера TNPT

37 ! A/OP ’Нет операции

Расшифровка кодов прерывания, вырабатываемых СК

на выходах ВО - ВЗ

Таблица /6

Код на вы- -’Мнемокод ! Наименование прерывания

водах ВО -г ВЗ ’прерываний I i

ТОЮ ! W (ЪВЕ) ’Режим начального пуска(двойнэя ошибка канала)

ШО ! Т(ТЕЙКО) ’Прерывание по Т биту ССП(ошибка канала)

ШТ \ PSB (TERRI) ’Прерывание по пропаданию питания(ошибка

’канала)

ОШ ! PLT (ТЕМ2) ’Прерывание по входу ОСТАНЗВ( ошибка канала)

ОТО! ! INRO ’Требование прерывания от ВУ

0Т00 ’ TNRt | н

ОНО ! INRZ !

0010 ! IN RS ’

ООП ! I NET !Прерывание пс внешнем7 событию

ОСОТ ! RQ. ’Запрос прерывания от ЙУ

0000 ' • — ’Нет прерывания

Примечание: Прерывания расположены в порядке убывания приоритетов

и

Впеменнял пиягпяммя выполнений микопкоманлы 2>ЛП

Рис,2Я

Временная диаграмма выполнения микрокоманды DATO

Pwc.2z/

- .........~

Схема входного каскада микросхемы КРЬ88ВГ1

ь сх.емо

микросхемы

питание

обилии

Схема выходного каскада выводов во вз,^л2/^4л;'/*ш со2

в схему

микросхемы

р---------------— Питание

t™

------------------------Ььио'д

_____4wa_______________________

Рае. 26 o5lu,uu

Схема вход кого-выходного каскада выводов

и выходного каскада выводов ЗУЛА, RD , И4?, И^/ВУ,EkQ,EDMAt 5 R2

У

£ схему у

микросхемы \

>

Для вывица

Ch'Ek схема

на с кап, а бе;

сопротивле-

ния к .

R - резистор 10 - 30 кОм

Рис 2? ___

Схема ^одного-выходного каскада вывода SRi

вход

Вы tod

К - резистор К) - 3^ иСм

/’от*- 2£

49

Микросхема КРЬ88ВР2 - арифметический умножитель 16 х 16 (УМУ

Управляемый внешними синхросигналами модуль, выполняющий аппарат-

ное умножение двух 16-разрядных чисел с получением 32-разрядного

результата и последовательной вццачей его в вцце младшей и стар-

шей части.

Микросхема предназначена для применения совместно с про-

цессором или другим устройством синхронизации для ускоренного вы-

полнения команды умножения. Служит для построения блоков аппарат-

ного умножения.

Микросхема обеспечивает управление одной ТТЛШ нагрузкой.

Согласование по входам может быть обеспечено с помощью ТТЛ

схем с открытым^ коллектором.

* Микросхемы поставляют двух типоно-

миналов: КР508ВР2, КР588ВР2А.

Назначение выводов

D [о - 1б] - двунаправленная

магистраль данных

5EAI - 5ЕАЗ - входы выбора адреса

ТКГ> - вход "вццача резуль-

тата в магистраль

данных”

RCT) - вход ’’прием операн-

да в регистр”

RA - выход сигнала ’’го-

товность микросхемы

к выполнению следую-

щего цикла"

...-.......... ......... ’• <0 '' •• ................................

УСТРОЙСТВО И ШЖЖ'РАБОТи

Структурная схема микросхемы КР588ВР2 приведена на рис.З^

Буфер входной-выходной( &FIO ) предназначен для приема и выдачи

информации.

Регистр множимого(RG2) предназначен ддя приема и хранения опе-

ранда множимого. '

Регистр множителя(РЯ) предназначен для приема и хранения опе-

ранда множителя.

Буфер выдачи младшей части произведения (В? 2 ) предназначен для

выдачи младшей части произведения на магистраль данных.

Буфер выдачи старшей части произведения (&Р1) предназначен для

выдачи старшей части произведения на магистраль данных.

Блок формирования признаков (FF1*) предназначен для формирования

признаков( М - знака, £ - равенства, V- переполнения,С-расшире-

ния) результата операции умножения.

Д/ « Г, если старший разряд тридцатидвухразрядного произведения

равен единице.

~ D

'Z s= 0, всегда.

В шестнадцатиразрядном коде, выдаваемом микросхемой в магистраль

данных, признаки занимают следующие разряды:

V- 15 и 3

Z - 14 и 2

V - 13 и I

С- 12 и О

В остальных разрядах этого кода выдаются уровни логической

единицы.

Блок умножения матричного типа( MPL ) предназначен для выпол-

нения операции умножения двух шестнадцятиразрядошх чисел.

Блок синхрониэацииС ) предназначен для организации цикла

Z » I, если тридцатидвухразрядное произведение равно нулю.

С = 0, если результат лежит в пределах от минус 2^ до(2^

выполнения команды умножения.

Прием операндов, выполнение умножения и выдача результата выпол-

няются микросхемой под управлением внешних сигналив синхронизации.

временная диаграмма работы микросхемы приведена на рис.ЗЛ

В исходномСне-рабочем) состоянии на управляющие входы микросхемы

тяъ,SPA3 подают напряжение высокого уровня.

Полный цикл работы микросхемы состоит из двух циклов приема и

трех циклов выдачи. В зависимости от комбинации адресных сигналовМЛI

Ш5 ’ в совокупности с сигналами приема Fra и выдачи W

микросхема выполняет циклы работ, приведенные в таЖ //

Последовательность и количество циклов приема и выдачи можно

произвольно изменять по необходимости.

Окончание каждого цикла работы и гоч юности микросхемы к шлюп-

СХЕМА ЭЯШРИЧЕСКАЯ СТРУКТУРНАЯ МИКРОСХЕМЫ КР588ВР2

DO-Ы5

Рис. 30

""..... .......... 5L ........................... .....

нению следующего цикла определяется появлением на выходе /М сигнала

низкого уровня. При приеме это свидетельствует о завершении записи one

ранда в регистр, а при выдаче - об окончании формирования на внешних

выводах магистрали данных!)О -DI5 шестнадцатиразрядного результата.

Таким образом, минимальная длительность сигналов Rci, (S'E/ft SEM)

в цикле приема определяется временем задержки распространения сигнала

tpt. Максимальное быстродействие микросхема достигается при использо

вании ее в асинхронном режиме.

Умножение начинается одновременно с записью операнда в один из

регистров, так как выхода регистров непосредственно подключены к

входам блока умножения MPL.

возведения в квадрат запись операнда производится одновре-

менно в регистр множителя и регистр множимого.

Таблица /7

Информация на входах

SEA1 Sf А 2 гяь Цикл работы

0 Т I 0 I Прием шестнадцатиразрядного операнда из магистрали данных в регистр множимого

I 0 т 0 I Прием шестнадцатиразрядного опе- ранда из магистрали данных в ре- чистр множителя ;

0 I I Т 0 Выдача младшей части произведения (0-15 разряда) в магистраль данных

1 0 I I 6 Выдача старшей части произведения (16-31 разряда) в магистраль данных

I I 0 I 0 Выдача шестнадцатиразрядного резуль тата из блока формирования призна- ков в магистраль данных

0 0 I 0 I Прием шестнадцатиразрядного опе- ранда из магистрали данных в оба регистра одновременно:(для возведе- ния в квадрат)

Рис. 5/

* При изменении времени выполнения операции trip; ч положение входных сигналов

показано штриховой линией

Авремя выполнения операции умножения, - время задержки приема множителя,

tpz - время задержки сброса сигнала^ после окончания приема.

” .’ S4 - ~

Структурная схема применения микросхемы КР588ВР2

в составе внешнего устройства

Магистраль передачи информации

flue. 32.

55

Вход

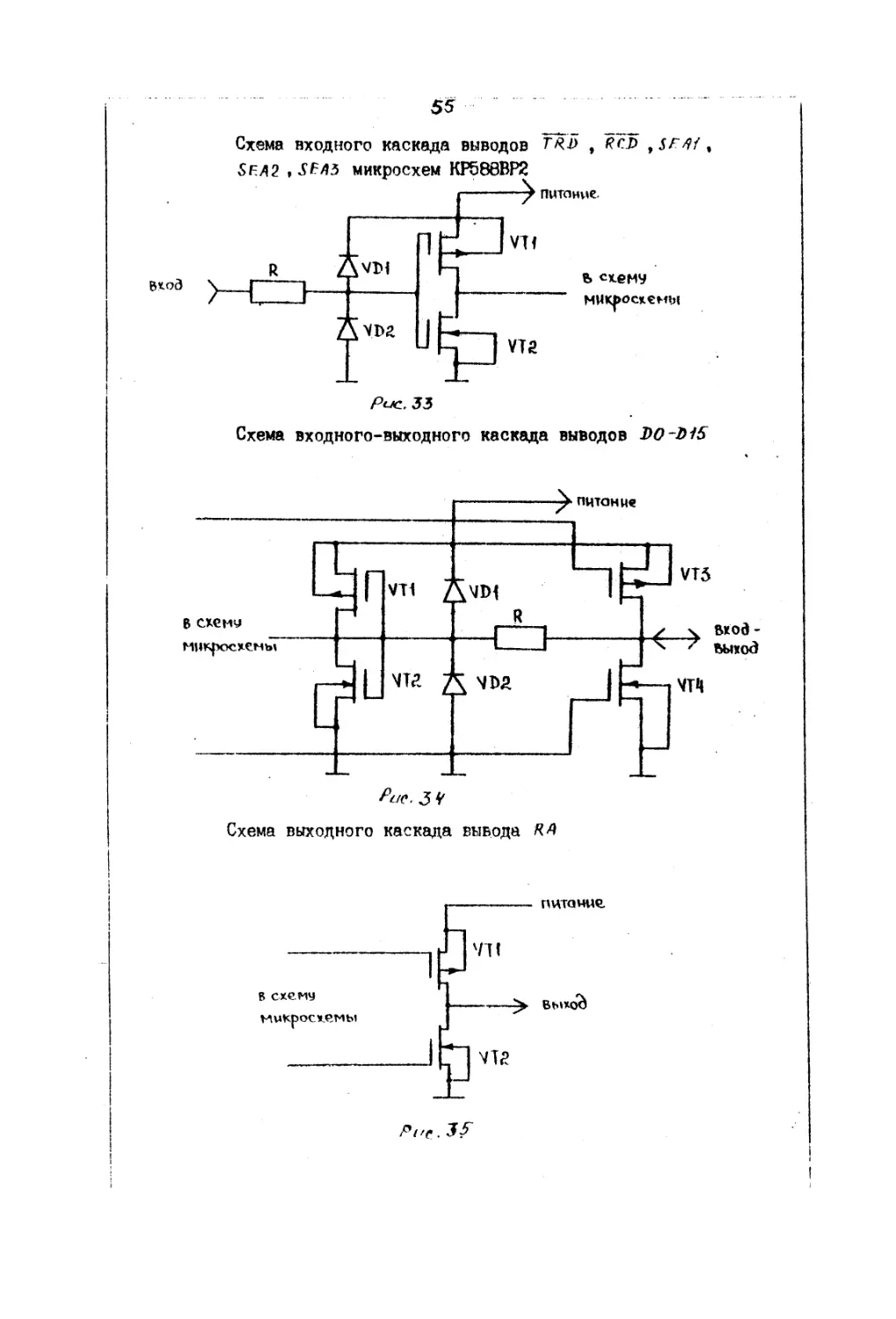

Схема входного каскада выводов TR1> , RCD

Рис. 33

Схема входного-выходного каскада выводов D0-D15

Схема выходного каскада вывода RA

В схему

микросхемы

Pl'C .

......~............... .. ....................... ’. .... • ...........

Микросхема KP588BAI ~ 8-разрядный магистральный приемо-передат-

чик (МПП), Лод управлением внешних синхронизирующих сигналов произво -

дит двунаправленную передачу байтов с инверсией или без инверсии, а

также контроль четности.

Микросхема предназначена для улучшения нагрузочных свойств мик-

росхем серии КР588, обеспечения работы на линию связи. Служит для

построения интерфейсных блоков процессоров, контроллеров внешних

устройств.

Согласование по входам может быть обеспечено ЧТЛ схемами с открытым

коллектором. Значение выводов

/6 _ лз ги D / 2 3 4 S' 6 7 aw JS» ест? Mi 0 1 2 J f J 6 9 airi X>l [0~7l - двунаправленные информа- Г) 2 [o-7] ционные магистрали BITI,fiIT2 -входы/выходы битов чет- 57 ности магистралей -Ы, D2 FCHIJ’CFE - входы сигналов у прав де- Pi ния контролем/формирова- нием битов четности для магистралей DI f D2 р/ - вход управления режимом прямой/инверсной передачи информации Of,’ C0I - вход управления передачей из магистрали В2 в магистраль М ~ С02 - вход управления передачей из магистрали D1 в ма- гистраль D2 Ей - выход сигнала “Ошибка” Efc'D - выход сигнала “Передача выполнена

27 26 FCH2. ГУ со/ с 02 cs EK ENS)

..h CS вход сигнала выбора мик- росхемы

Ал-.35

54

Схема электрическая структурная микросхемы КР5В6ВМ

СОТ БЛОК

-Sfig УПРАВЛЕНИЯ УСИЛИТЕ- ЛЯМИ СО £Оп

CS

Гос. 3?

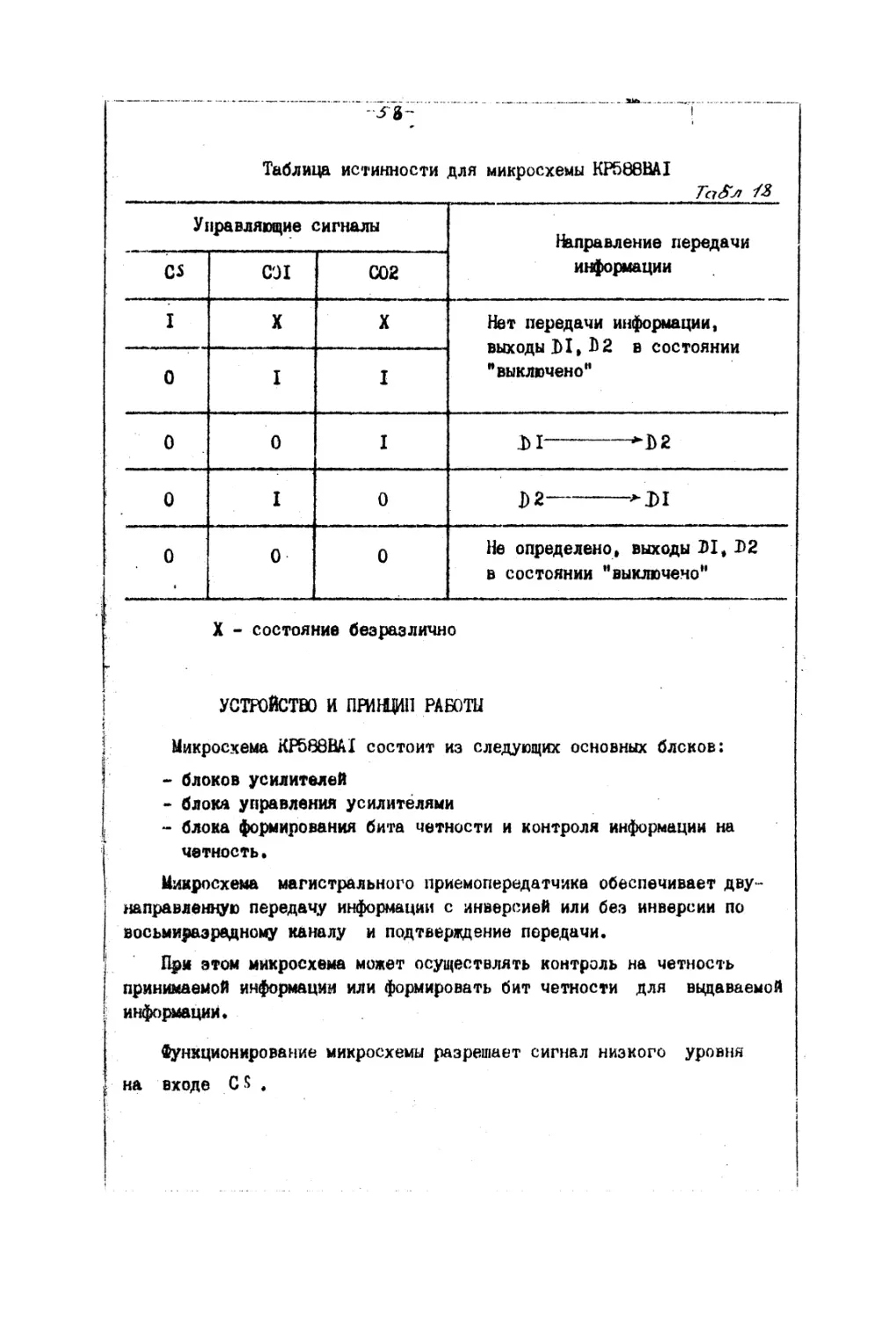

Таблица истинности для микросхемы KP588UAI

____________ 12

Управляющие сигналы Направление передачи информации

С5 СЭ1 СОй

I X X Нет передачи информации, выходы Ы, В 2 в состоянии "выключено"

0 I I

0 0 I DI *Ь2

0 I 0 D2

0 0 0 Не определено, выходы DI, D2 в состоянии "выключено"

X - состояние безразлично

УСТРОЙСТВО И ПРИНЦИП РАБОТЫ

Микросхема KP588BAI состоит из следующих основных блоков:

- блоков усилителей

- блока управления усилителями

- блока формирования бита четности и контроля информации на

четность.

Микросхема магистрального приемопередатчика обеспечивает дву-

направленную передачу информации с инверсией или без инверсии по

восьмиразрядному каналу и подтверждение передачи.

При этом микросхема может осуществлять контроль на четность

принимаемой информации или формировать бит четности для вццаваемой

информаций.

Функционирование микросхемы разрешает сигнал низкого уровня

на входе C S .

^ 59..............................’

С помощью двух входов FGHI и FCH2 задаются следующие ре-

жимы работы микросхемы:

Р FCHI « FCH2 « О

Информация, пришедшая с любого канала, контролируется на чет-

ность. В случае возникновения ошибки формируется сигнал низкого

уровня на выходе ER. Этот сигнал сохраняется до тех пор, пока сох-

раняется информация, вызвавшая его. Вит четности при этом переда-

ется без изменения.

$ fchi « о, гонг = 1.

Информация, прошедшая по каналу И, контролируется на чет-

ность и формируется сигнал бита четности BIT2.

FCHI = I, FCH2 «= 0.

Информация, поступающая по каналу В 2 контролируется на чет-

ность и формируется сигнал бита четности BITI.

FCHI « FCH2 « I.

Для информации, поступающей по любому каналу, формируется со-

ответствующий бит четности. Передача информации из канала DI в ка-

нал ])2 и из канала D2 в канал DI управляется сигналами COI, 002.

Если на входе C0I формируется низкий уровень, а на входе С02 -вы-

сокий уровень, то информация передается из канала DI в каналВИ.

Если на входе 001 формируется высокий уровень, а на входе 002-

низкий уровень, то информация передается из канала D2 в канал DI.

При одновременной установке C0I и 002 в состояние низкого уров

ня не гарантируется однонаправленной передачи информации. При фор-

мировании бита четности обеспечивается нечетное количество "высо-

ких уровней” на девяти выходах ( восемь-канала и одного бита чет-

ности). По такому же принципу проводится контроль информации на

четность.

Состояние низкого уровня на выходе END сигнализирует о завер-

шении подачи информации.

Е!сли на входе установлен высокий уровень, информация при

передаче не изменяется. В случае, если на входе IN установлен

низкий уровень, информация при передаче инвертируется.

Если на входах C0I и С02 установлен высокий уровень, то выходы

ТН.О - 1)1.7 и®2.0 -D2.7 переводятся в состояние "выключено".

Последовательность подачи сигналов CS ,001,002 в каналы JDI,D2 не

рег памеятируется.

Все функции микросхемы выполняются под управлением внешних

: синхронизации.

60

Схема входного каскада выводов СЯ^С.О/ ^COZwi КР588ВА1

(Для выводов EtHl'FCHl!. 9lrt эта же схема без инвертора)

----------------------------------------------------пи Га НОС

Рис И

Вход

Ь схему

микросхемы

Схема выходного каскада выводов ER,

В схему

микросхемы

Схема входного-выходного каскада выводов Вф-7.| »

1ф~7] ЛГ^.вИ?

пиюиие

из схемы

микросхемы

V01

R

fz:±

VD2

VII

BULK?

выход

via

HHKf-ocxei

. к&ци

1

М’лкр'-'схемз КГЪбнПГ, - 8 разряд?^ ммптч>4ункционэлъный буферный

регистр ГМБГУПол управлением внешних синхронизирующих сигналов промз

во,пит запись или выдачу байта с инверсией или без инверсии, а также

контроль четности и формирования бита четности.

Микросхема предназначена для фиксации цифровой информации.Слу-

жит для построения интерфейсных блоков процессоров запоминающих

устройств, контроллеров внешних устройств.

Микросхема, обеспечивает управление одной ТЕПЛ! нагрузкой.

Согласование по входим может быть обеспечено с помощью ТТЛ схем

с открытым коллектором.

Назначение выводов

М[0-7] - входная информацион-

ная магистраль

R - вход установки в состояние

"логический О"

FCH - управление контролем/

формированием четности

BIT - вход/выход бита четности

__ сигнала

CS - вход'*' ^выбора микросхемы”

- вход сигнала "Запись"

- вход сигнала "Чтение"

IW - вход сигнала "Инверсия"

D 210-7.1 - выходная информацион-

ная магистраль

J® ~ гыхсд сигнала "Ошибка"

WPQ - выход сигнала "Запись вы-

полнена

РЭО - выход сигнала "Чтение вы-

полнено

СХЕМА ЭПВОТИЧЕСКАЯ СТРУКТУРНАЯ

cs пи къ

I I I !

,—lilt—t

I БЛОК УПРАВЛЕНИЯj

j ЗАШСЫЗ/СЧИТНВАНИ05 f

ИНФОРМАЦИИ 1

~ Л1.0»М.Т

62

Рис

....... .~ 63 :

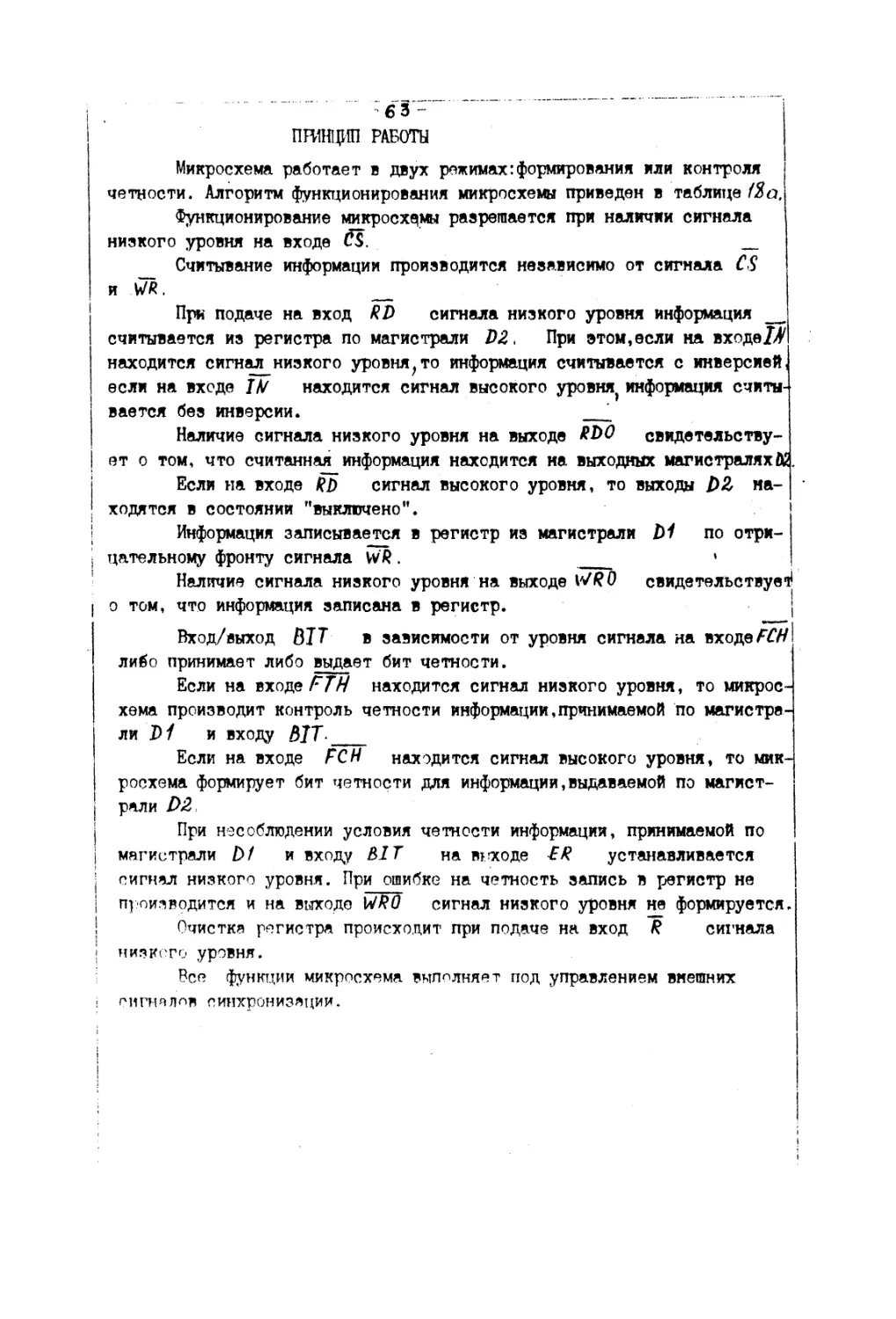

ПРИНЦИП РАБОТЫ

Микросхема работает в двух режимах формирования или контроля

четности. Алгоритм функционирования микросхемы приведен в таблице fia.

Функционирование микросхемы разрешается при наличии сигнала

низкого уровня на входе CS. _

Считывание информации производится независимо от сигнала CS

иЯ _

При подаче на вход RD сигнала низкого уровня информация _______

считывается из регистра по магистрали D2 > При этом, если на входе/Л

находится сигнал низкого уровня,то информация считывается с инверсией,

если на входе TV находится сигнал высокого уровня^ информация считы-

вается без инверсии. ___

Наличие сигнала низкого уровня на выходе RDO свидетельству-

ет о том, что считанная информация находится на выходных магистралях ДО.

Если на входе RD сигнал высокого уровня, то выходы DZ на-

ходятся в состоянии ’’выключено”.

Информация записывается в регистр из магистрали D1 по отри-

цательному фронту сигнала Vv₽. ___ *

Наличие сигнала низкого уровня на выходе WR0 свидетельствует!

о том, что информация записана в регистр. |

Вход/выход BIT в зависимости от уровня сигнала на входе FCH

либо принимает либо выдает бит четности.

Если на входе FTH находится сигнал низкого уровня, то микрос-

хема производит контроль четности информации,принимаемой по магистра-

ли D1 и входу RJT-_______

Если на входе FCH находится сигнал высокого уровня, то мик-

росхема формирует бит четности для информации, выдаваемой по магист-

рали D2

При несоблюдении условия четности информации, принимаемой по

магистрали D1 и входу BIT на втгходе FR устанавливается

сигнал низкого уровня. При ошибке на четность запись в регистр не

производится и на выходе IV/?О сигнал низкого уровня не формируется.

Очистка регистра происходит при подаче на вход R сигнала

низкого уровня.

Все функции микросхема выполняет под управлением внешних

। сигналив синхронизации.

Таблица

Входы управления RD vr I Содержание операции I

R !1? ’«w*

I I X 1 X ! X 1 X ! X 1 ! нет выбора микросхемы

0 I 0 I X ! X 1 X ! X 1 1 0 RG

0 I I । I » I I 0 1 I ! 1 RG~*~D2, выдача - BIT

0 ! I 1 0 ! I 1 0 ! T 1 1 RG —* bZ выдача - Sir

0 I I t X ! 0 ! I ! 0 ! I контроль четностийцяг

6 I I t I ! I I 0 ! 0 ! I M—-RGt R& выдача-дгг

0 I ! I 1 0 ! 1 0 ! ! 1 0 ! 0 ! ! ! ! D/~^RG, Конт- ! роль четности 8ГМ

1 ! X ! I I X ! 0 ! X I 1 RG DZ

I I X ! 0 I X ! 0 ! X ! 1 RG —- DZ

X - состояние безразлично

выдача - BIT - формирование и выдача бита четности

для информации,выдаваемой по магистрали D2

контроль четности ( BIT ) - контроль на четность информа-

ции, принимаемой по магистрали и входу

BIT (если условие четности не выполняется,

то - 0),

- -S9

66 _ _____

Схема входного каскада выводов РСН ,

, Щ) , CJ , 7 микросхем КР568ИР1

-------------------- питдниЕ

вход

VDI

VD2

в схему

микросхемы

R

I----------------- o£u±UU

Рис. ЧЧ

Схема входного-выходного каскада вывода BIT

Схема выходного каскада выводов Ь2[0-?] t ЬЯ

>—

В скемм

микросхемы

>

питание

Выход

обиден?

Микросхема КГ588ВГ2 - контроллер запоминающего устройства(КЗУ)

Под управлением процессора формирует синхронизирующие сигналы для

записи и чтения в ОЗУ.

Микросхема предназначена- для создания модулей ОЗУ произволь-

ной емкости и организации, совместима с каналом микро-ЭВМ по

ГОСТ 26765.51-86. служит для согласования интерфейса ОЗУ с интер-

фейсом магистрали передачи информации.

Микросхема обеспечивает управление двумя ТТЛШ нагрузками.

Согласование по входам может быть обеспечено ТТЛ схемами с откры-

тым коллектором.

Назначение выводов

- вход ’’Синхронизация об-

мена”

RD - вход "Чтение данных"

h/R - вход "Запись данных"

ДТ^А/ИЗ, ADI4, ADIS-входы 0,13,14,15*

разрядов магистрали адреса данных

А13,А14,А15 - входы сигналов,

сравниваемых с ADI3,ADI4,

ADI5

CSI - выход выборки кристалла

для старшего байта

CSO - выход выборки кристалла

для младшего байта

DLM^R - вход/выход "Задержка при

записи”

HERD - вход/выход "Задержка при

чтении”

АН ” выход "Ответ устройства”

^R/ЕУ - вход "Признак запись/байт

68

Схема электрическая структурная микросхем КР608ВГ2

Рае 4g

69-...........

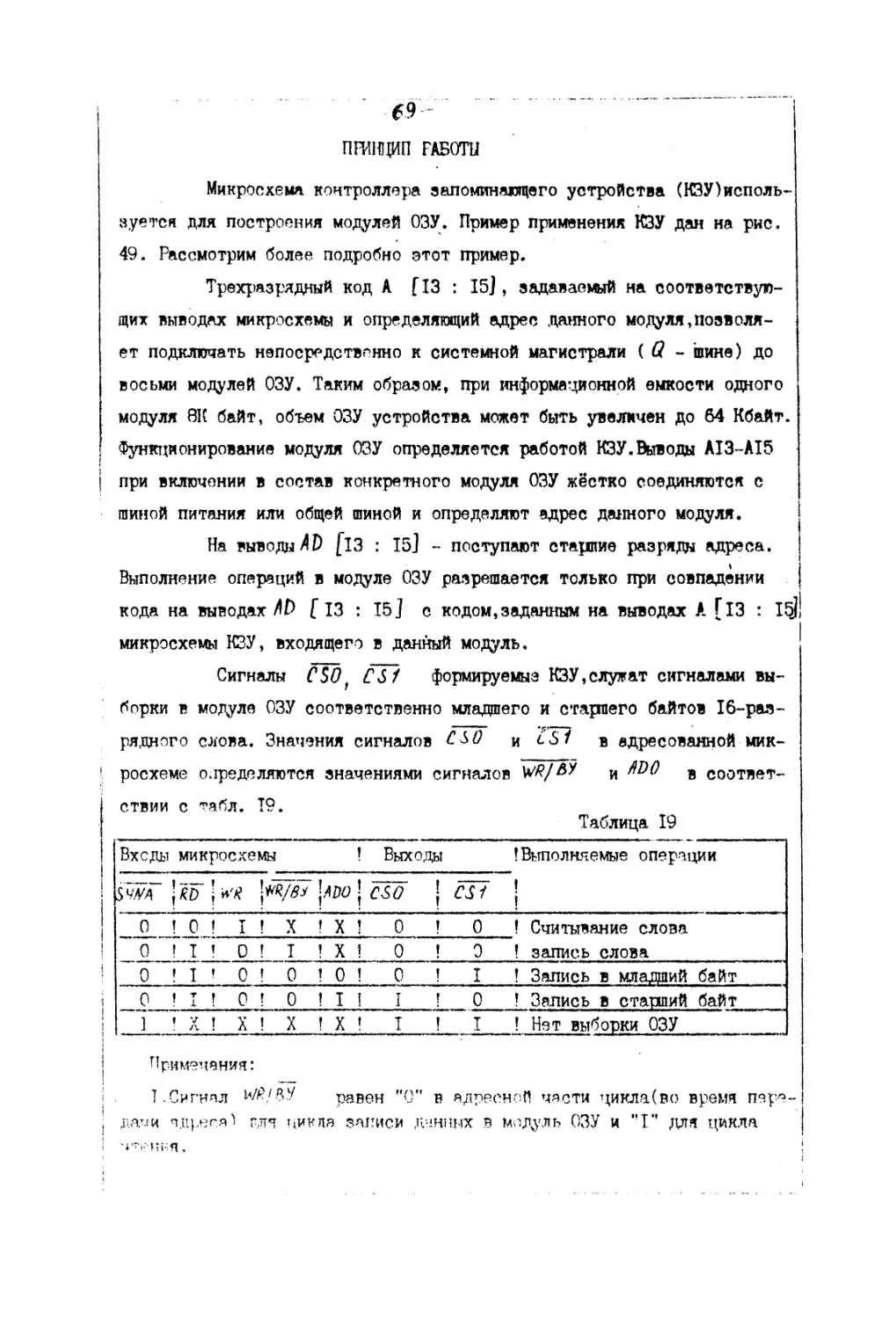

ПРИНЦИП РАБОТЫ

Микросхема контроллера запоминающего устройства (КЗУ)исполь-

зуется для построения модулей ОЗУ. Пример применения КЗУ дан на рис.

49. Рассмотрим более подробно этот пример.

Трехразрядный код А [13 : 15], задаваемый на соответствую-

щих выводах микросхемы и определяющий адрес данного модуля,позволя-

ет подключать непосредственно к системной магистрали ( Q - шине) до

восьми модулей ОЗУ. Таким образом, при информационной емкости одного

модуля 8К байт, объем ОЗУ устройства может быть увеличен до 64 Кбайт.

Функционирование модуля ОЗУ определяется работой КЗУ.Выводы AI3-AI5

j при включении в состав конкретного модуля ОЗУ жёстко соединяются с

шиной питания или общей шиной и определяют адрес данного модуля.

На вывода AD [13 : 15] - поступают старшие разряды адреса.

Выполнение операций в модуле ОЗУ разрешается только при совпадении

кода на выводах [ 13 : 15] с кодом, заданным на выводах А [13 : 15

микросхемы КЗУ, входящего в данный модуль.

Сигналы CSOf ЛИ формируемые КЗУ,служат сигналами вы-

борки в модуле ОЗУ соответственно младшего и старшего байтов I6-раз-

ря,иного слова. Значения сигналов £^0 ц LS1 в адресованной мик-

росхеме о.тределяются значениями сигналов U^/^У и ^0 в соответ-

ствии с табл. T9.

Таблица 19

Входы микросхемы ! Выхода !Выполняемые операции I i

S4.VA рг> \*’Ц j-Wj cso" 1 CS1

0 ! 0 ! I ! X ! X ! ' 0 ! 0 Считывание слова

0 1 I ! 0 ! I ! X ! 0 ! 0 ! запись слова

0 ! I ’0’0 ! 0 ! 6 ! I ! Запись в младший байт

! I ’0’0 1 I I I ! 0 ! Запись в старший байт

1 ! X ! X ! X ! X ! ' т ! I ! Нет выборки ОЗУ

Примечания:

i I.Сигнал равен ”0” в адресной части цикла (во время пере-

дачи адреса^ для цикля записи донных в модуль ОЗУ и ”Г’ для цикла

i -ГП'-НЕЯ,

— —........“-------:-------~vo ....... 27 ; ...

2. В таблице приведено значение сигнала 1^/^У во время

передачи данных.

3. Микросхема функционирует в соответствии с таблицей, если

во время прохождения фронта из логической ”1” в логический

“О" сигнала код на входах А [13-15] совпал с ко-

дом на входах AD f 13 - 15)

К выводам DLWR и DttfD подключаются. резисторы(на ши-

ну питания) и емкости (на общую шину),которые определяют задержку вы-

дачи сигнала Л У относительно сигналов С 30 и С Si при считыва-

нии или записи данных в модуле ОЗУ.Параметры ЕС-цепей должны подбира-

ться в зависимости от быстродействия используемых в модуле микросхем

ОЗУ таким обрезом, чтобы при наличии сигнала Ео сигнал ЛУ

не опережал выдачу информации из модуля ОЗУ на шину данных МП системы,

а при наличии сигнала WR гарантировалась запись информации в мо-

дуле ОЗУ.

Микросхема обеспечивает управление выполнением циклов "Ввод”,

"Вывод","Ввсд-Модификация-Вывод". Временная диаграмма выполнения цикла

”Ввод-Модификация-Вывод” приведена на рисЛР,

ЧТЕНИЕ ДАННЫХ ИЗ МОДУЛЯ ОЗУ (ЦИКЛ "ВВОД”)

Сигнал iWA =0 закрывает входные ключи в регистре адреса КЗ^ |

записывая адрес AD[I3:I5] сравнивая его с кодом А[13:15] - адресом [

данного модуля ОЗУ. При совпадении обоих кодов устанавливается на вы-

воде DLRD низкий уровень напряжения(разряжается емкость ЕС-цепи).

По сигналу /?/) формируются сигналы выборки кристалла С SO, С Si ОЗУ

в соответствии с табл.19. Напряжение на выводе начинает расти

с постоянной времени, подключенной к нему ЕС-цепи. После того, как это

напряжение достигает определенного уровня, микросхема с некоторой задер-

жкой формирует сигнал ЛУ. По положительному фронту сигнала ED мик-

росхема прекращает выборку ОЗУ.Цикл завершается сигналом ЗУУА =1,пс

которому регистр адреса КЗУ открывается для приема следующего кода

AD [13:15] и КЗУ устанавливается в исходное состояние.

ЗАПИСЬ ДАННЫХ В МОДУЛЬ ОЗУ (ЦИКЛ "ВЫВОД”)

При совпадении кодов А1)[13:15] и А (13:15] КЗУ ожидает прихода

сигнала W* =0 и по его приходу устанавливает на выводе !Ни/£ низкий

уровень напряжения(разряжает емкость ЕС-цепи)формирует сигналы вы-

борки 4'30, С $/ в соответствии с табл. 19. Напряжение на выводе 04^

начинает расти с постоянной времени,подключенной к этому выводу КС-

цепи, что с определенной задержкой,вызывает формирование КЗУ сигнала

kN =0. По положительному фронту сигнала т3 микросхема инициирует за-

вершение обмена. Завершение цикла ’’^вод/* происходит по установлению

высокого уровня напряжения на выводе ЗУ к'А

Временная диаграмма работы микросхемы КРЬ68ВГ2

при выполнении цикла "Ввод-модификация-вывод"

системы

Структурная схема модуля ОЗУ (4К х 16)

pifO Jf)

73

Схема входного каскада выводов

Л»Г13-4б], Л W, £W4 микросхем КР588ВГ2

ВхоЭ

питание

Б схему

микросхемы

одщии

Схема выходного каскада вывода Я/V

----------питание

?, СУ..РНЧ

MUhpCCjiCMbl

Схема выходного каскада выводов Гл?

питание.

____Вы у од

VT2

---------общий

. .. -V4-

Микросхема KP588BTI - селектор адреса (СА). Асинхронный програм

мируемый модуль,предназначенный для дешифрации адресов на Q - шине и

организации обмена данными.

и,

Микросхема предназначена для дешифрации адресов^формировании си

налов выбора регистров внешних устройств,организации обмена данными

между активным устройством и регистрами количеством до восьми.

Микросхема обеспечивает управление* одной ТТЛШ нагрузкой.Согласи

вание по входам может быть обеспечено с помощью ТТЛ схем с открытым

коллектором. съ

г2

11- ЗЯ 0 SL 0 0 32

i /1 -IL

н 2 3 2 4

10 т т J -JS.

11

OS 5 • j , 17

0? 6 0 i , 26

? 3

05 i

0

03 ю

01 и п

33 А ч ММ (

li— 5

35 6 —

i£— 7 KPI) (

&

31- •21- 9 10 м <

4о 11

41 П

15

14

It А их?

11- о °

20

Г?1

^ис 5

Назначение выводов

DА[0-12] - входы данных адреса

А4 - AI2 - входы адреса

5УА/А - вход синхронизации обмена

- вход выбора внешнего уст

ройства

МНУ - вход признака записи байта

Й4? - вход"запись данных4*

RD - вход "Чтение данных”

RA - вхоХ’Готовность устройства’’

SF (0-7] - выходы ’’Выбор внешнего

устройства

ЙФВУО - выход "Запись младшего

байта"

И’ЙВУ! - выход "Запись старшего

байта"

A N - выход отвела устройства для

процессора

P.W чтение для oHcnmf го у сpos5

ст на

СШ ЭЛШтаЧЕСКАЯ СТРУКТУРНАЯ

"Об-

устройство И ПРИНЦИП РАБОТЫ

Микросхема входит в состав процессора,реализованного на базе МП -

комплекта серии КР588 и выполняет следующие функции:

I)выбор регистров внешних устройств;

2)управление чтением регистров внешних устройств

3)управление записью в регистра внешних устройств слова

4)управление записью в регистры внешних устройств старшего байта.

5Управление записью в регистры внешних устройств младшего байта.

Структурная схема приведена на рис.<5^

Функционирование микросхемы

Функционирование микросхем производится во взаимодействии с

центральным процессором микро-ЭВМ. Регистры внешних устройств участву-

ют в обмене информацией с центральным процессором при помощи микрос-

хевы-селектора адреса.

Микросхема выполняет следующие циклы:

I) ввод

2) вывод

3) вывод байт

4) ввод-модификация-вывод

5) ввод-модификация-вывод-байт

Управлению чтением регистра внешних устройств соответствует

цикл "ВВОД". Управлению записью в регистр внешнего устройства соответ-

ствуют циклы "ВЫВОД”, "ВВ0Д-М0ДОЙ1КАЦИЯ-ШВ0Д".Управлению записью в

регистр внешнего устройства старшего и младшего байта соответствуют

циклы "ВЫВОД БАЙТ”, "ВВОД-МОДИ^КАЦИЯ-ВЫВОД-БАЙТ".

Цикл обмена "ВВОД" выполняется следующим образом:

Центральный процессор устанавливает адрес на входа микросхемы

и выдает сигналы 5Б^ и svw.

Микросхема сравнивает разряда DAI2 -£А4 с разрядами AI2-A4

адреса, набранного на перемочках, разряда -РАЗ - PAI дешифрируются и

в соответствии с этим выбирается одно из внешних устройств посредством

соответствующего сигнала SE » что соответствует выбору регистра

внешнего устройства. Соответствие разрядов .РАЗ—-DAT номеру вывода &Е

приведено в табл. ТаЛ'ли 20

Разряд — выхода SE ! Вход DA3 ! Вход ялг ! Вход 7)Af ! Вход DAO

0 ! 0 ! 0 ! 0 Состояние

1 ! 0 I 0 ! Т безразлично

2 ! 0 ! I I 0 f

_3 ! 0 ! I ! I 1

* ! I ! 0 ! 0 I

! I ! 0 ! Т I

Продолжение таблицы W

Разряд _ ! выхода 5Е ! Вход ЪАЬ | Вход ! * 1 Вход 1 Вход ' /ио

6 ! I ! Т ! 0 {Состояние —!безразлично

1 ! I ! I ! I