Текст

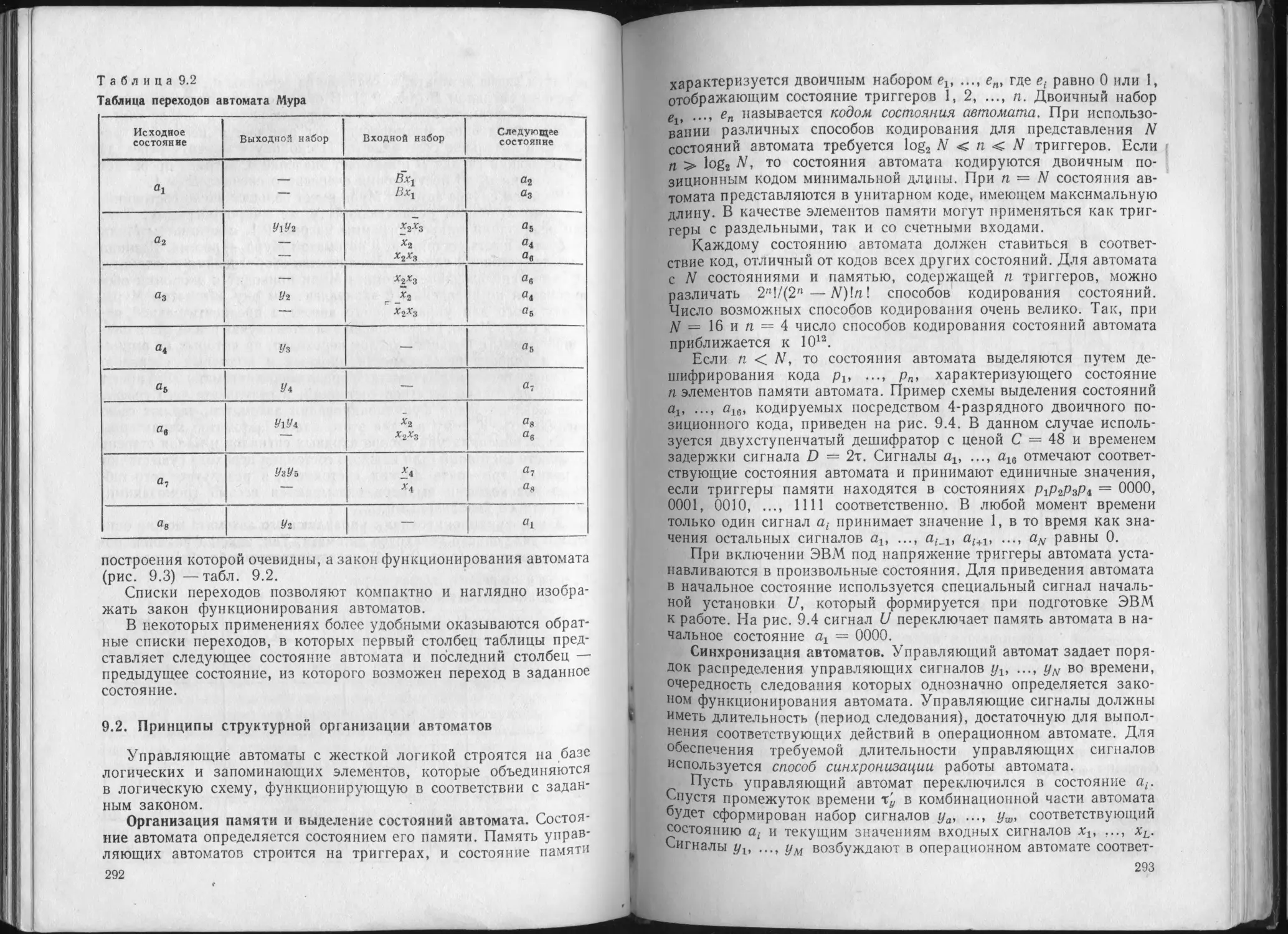

-А. МАЙОРОВ • Г. И. НОВИКОВ

z i*

СТРУКТУРА

ЭЛЕКТРОННЫХ

ВЫЧИСЛИТЕЛЬНЫХ

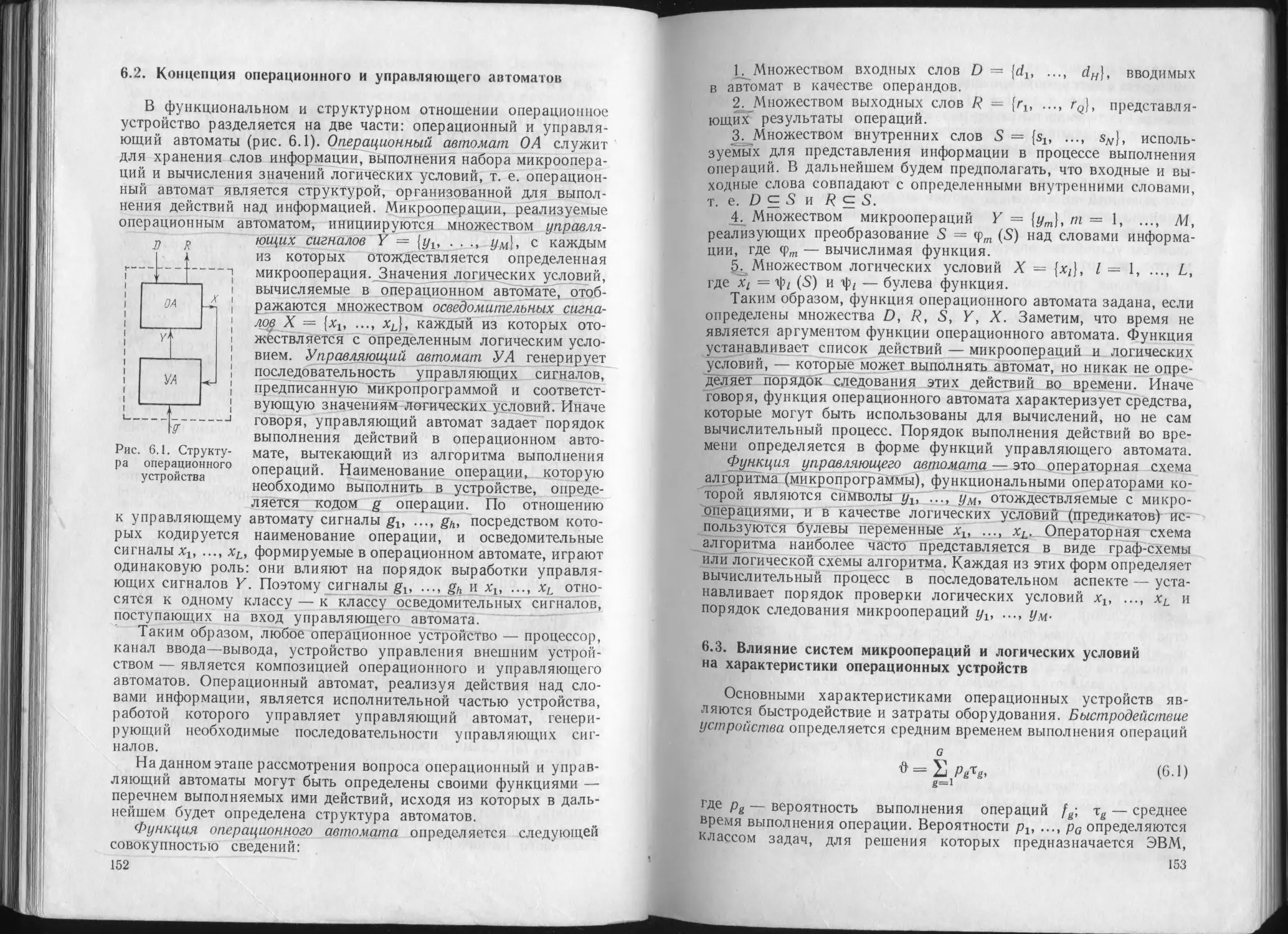

МАШИН

С. А. МАЙОРОВ, Г. И. НОВИКОВ

СТРУКТУРА

ЭЛЕКТРОННЫХ

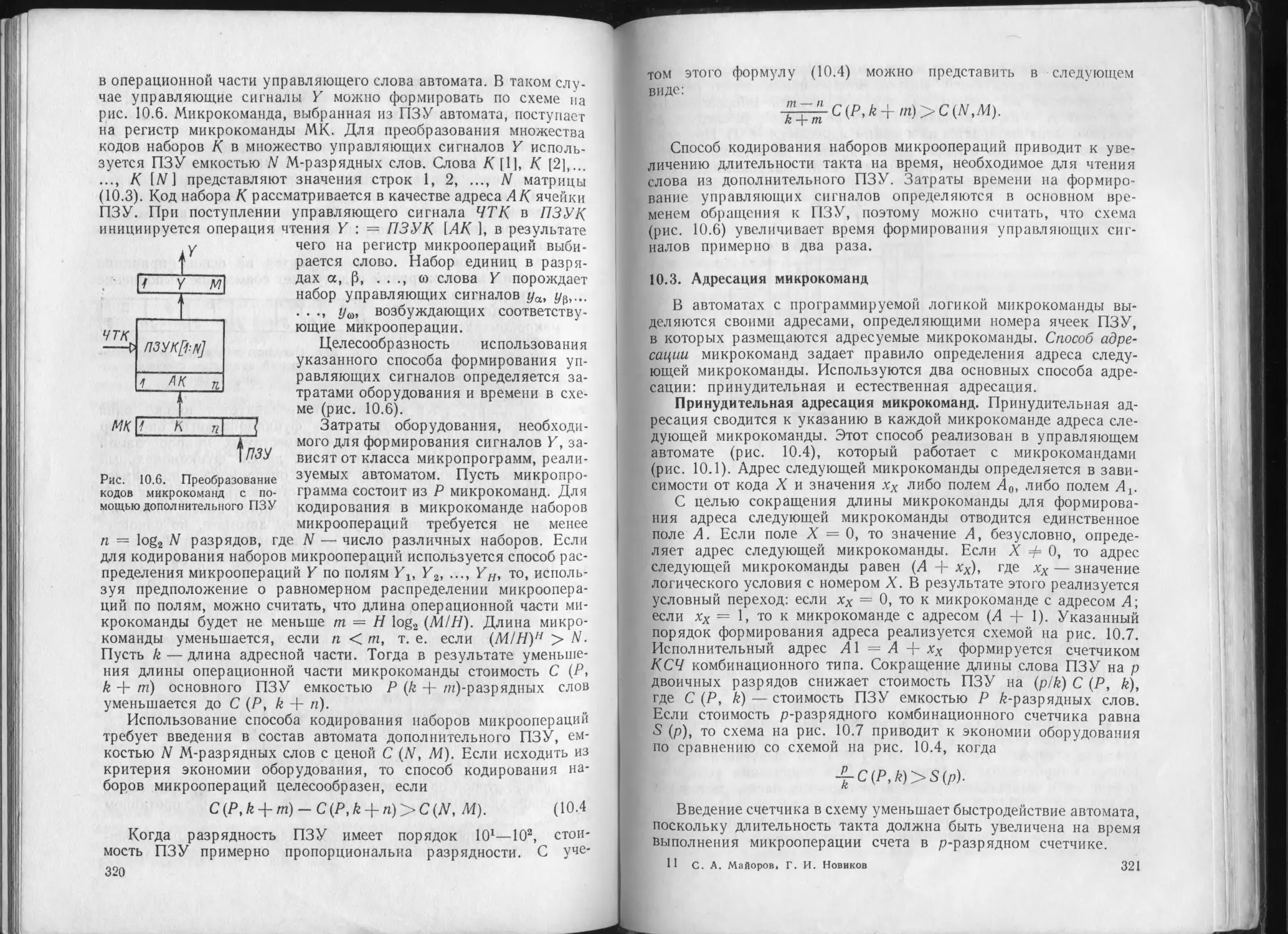

ВЫЧИСЛИТЕЛЬНЫХ

МАШИН

Второе издание

переработанное и дополненное

ЛЕНИНГРАД «МАШИНОСТРОЕНИЕ»

ЛЕНИНГРАДСКОЕ ОТДЕЛЕНИЕ

1979

ББК 32.973

М14^

УДЙ4б81.32

Майоров С. А., Новиков Г. И.

М14 Структура электронных вычислительных машин. —Л.:

Машиностроение. Ленингр. отд-ние, 1979. — 384с., ил.

1 р. 60 к.

В книге изложены принципы построения и методы схемотехнического проек-

тирования ЭВМ и устройств цифровой вычислительной техники. В ней описаны

структуры ЭВМ общего назначения, мини- и микро-ЭВМ; рассмотрены методы

проектирования структурных и функциональных схем процессоров, каналов

ввода — вывода и средств управления внешними устройствами, методы синтеза

операционных и управляющих автоматов.

Во втором издании (1-е изд. вышло в 1970 г. под названием «Структура циф-

ровых вычислительных машин») изложен функциональный подход к проектиро-

ванию структур ЭВМ, а также описаны новые принципы построения схем управ-

ления и обработки информации.

Книга предназначена для инженерно-технических работников, занимаю-

щихся проектированием и эксплуатацией ЭВМ и систем на их основе.

„ 30502—50 2405000000

М 038(01 )-=79~5° ~79

ББК 32.973

6Ф7.3

© Издательство «Машиностроение», 1979 г.

Памяти

Ф. Г. Староса посвящается

ПРЕДИСЛОВИЕ

Вычислительная техника играет значительную роль в научно-

техническом прогрессе нашей страны, способствуя повышению

эффективности общественного производства, улучшению качества

продукции, росту производительности труда. С каждым годом

увеличиваются масштабы применения электронных вычислитель-

ных машин (ЭВМ) во всех отраслях народного хозяйства, в связи

с чем возрастают требования к характеристикам ЭВМ и, следова-

тельно, к принципам их построения и проектирования.

Цель этой книги, как и ее первого издания, — изложить основ-

ные принципы построения и проектирования схем ЭВМ. Однако

это издание значительно отличается от предыдущего в следующих

аспектах.

В основу методики изложения положен принцип первичности

функций в отношении структур, из которого следует, что струк-

тура ЭВМ, т. е. конфигурация схем, предопределяется функцией

(назначением) ЭВМ. Этот принцип предопределил порядок изло-

жения материала в книге. В отличие от традиционного подхода,

когда принципы построения и проектирования ЭВМ начинают

рассматриваться от элементов и заканчиваются описанием ЭВМ

как целого, материал излагается в обратном порядке: сначала

выявляются функции ЭВМ, которые затем детализируются до

отдельных устройств, узлов и, наконец, до элементов. Такой

порядок изложения представляется наиболее результативным,

поскольку, во-первых, совпадает с порядком проектирования

ЭВМ и, во-вторых, упрощает изучение основ вычислительной

техники, так как в этом случае каждое схемотехническое решение

воспринимается как необходимое, предопределенное предыдущими

решениями.

Для унификации многочисленных структурных решений, при-

меняемых в инженерной практике, используются понятия опе-

рационного устройства и интерфейса. Эти понятия вводятся на

функциональном уровне и соответствуют преобразователю ди-

скретной информации с произвольной функцией и алгоритму

обмена информаций между устройствами. Столь широкое толко-

вание указанных понятий создает основу для построения мето-

дики проектирования разнообразных операционных устройств,

в частности процессоров, каналов ввода—вывода и контроллеров

внешних устройств ЭВМ.

В основу проектирования операционных устройств различного

назначения положен принцип функционального микропрограм

1* 3

мирования и представления устройства как композиции опера-

ционного и управляющего автоматов. При этом содержание тер-

мина микропрограммирование расширено по сравнению с тради-

ционным. В этой книге микропрограммирование понимается как

способ описания функций операционных устройств безотноси-

тельно к техническим средствам, используемым для их реализации.

Такое толкование микропрограммирования позволяет формали-

зовать синтез структур любых операционных устройств независимо

от способа управления работой устройства. Наиболее детально

описываются принципы структурной организации операционных

автоматов, формализованные методы синтеза которых только

начинают разрабатываться. Следует отметить, что ^принципы

построения и методы проектирования операционных и управля-

ющих автоматов являются той основой, на которой базируется

теория и практика проектирования большей части устройств ЭВМ.

В инженерной практике используется широкая номенклатура

устройств, каждое из которых может быть реализовано большим

числом способов. Естественно, что в рамках книги, затрагивающей

обширный круг вопросов вычислительной техники, невозможно

даже перечислить все многообразие способов построения ЭВМ

и устройств. По этой причине основное внимание уделялось изло-

жению общих принципов и основополагающих вариантов схем,

а частные случаи использовались только для их иллюстрации.

Авторы стремились излагать материал в наиболее доступной

форме и поэтому намеренно опускали из рассмотрения отдельные

детали, которые могут оказаться в какой-то степени существен-

ными при практическом применении описываемых схем и методов.

Предполагается, что читатель знаком с двоичной арифметикой,

булевой алгеброй, основами теории автоматов (переключательных

схем) и программирования.

Авторы глубоко благодарны всем, кто прислал свои замечания

по первому изданию книги, и с признательностью примут новые

отзывы и замечания, которые просим направлять в адрес Ленин-

градского отделения издательства «Машиностроение».

ВВЕДЕНИЕ

Методы описания и проектирования столь сложных объектов,

какими являются ЭВМ, базируются па основополагающих прин-

ципах, сформулированных в общей теории систем [47]. Поэтому,

прежде чем приступить к изложению способов построения и ме-

тодов проектирования ЭВМ, раскроем смысл основных понятий

и принципов, которые относятся к общей теории систем и широко

используются для ЭВМ.

Функция, структура и организация систем. Система — это

совокупность элементов, объединенных в одно целое для дости-

жения определенной цели. При этом под целью понимается мно-

жество результатов, определяемых назначением системы. ЭВМ

в смысле указанного определения является системой, предназна-

ченной для автоматизации вычислений на основе алгоритмов.

Дополнительно отметим, что понятие система приложимо как

к ЭВМ в целом, так и к отдельным частям ЭВМ, например к устрой-

ствам ЭВМ. И в дальнейшем будем пользоваться термином система

в качестве эквивалента фразы «ЭВМ или отдельное устройство»,

считая, что все утверждения о системах в равной степени отно-

сятся и к ЭВМ, и устройствам ЭВМ.

Чтобы описать систему, необходимо определить функцию

системы и структуру системы.

Функция системы. — правило получения результатов, опре-

деляемых назначением системы. Иначе говоря, функция системы —

это описание процессов, которые имеют место в системе. Функции

систем стремятся описывать в математической форме ввиду ее

компактности и четкости. Наряду с этим, для описания функций

широко используется и словесная форма, которая, впрочем,

является далеко не худшим способом выражения существа

вещей. Функции ЭВМ чаще всего описываются в форме алго-

ритмов.

Структура системы—фиксированная совокупность элемен-

тов и связей между ними. Структура наглядно изображает, как

устроена система — из каких частей она состоит и как эти части

связаны друг с другом. Математической, а в этом смысле наиболее

абстрактной и универсальной, формой изображения структуры

является граф. Граф есть совокупность вершин и дуг (ребер),

представляющих однонаправленные (соответственно двунаправ-

ленные) связи между вершинами. Вершины графа отождеств-

ляются с элементами (минимальными частями) системы, а дуги

и ребра графа — со связями между соответствующими элементами.

5

Инженерная форма отображения структуры —схема. Схема и

граф тождественны по своему содержанию и различаются лишь

по форме. В схемах для обозначения элементов используются

различные геометрические фигуры, разнообразие форм которых

облегчает чтение схем.

Система описана, если заданы ее функция и структура. Функ-

ция определяет порядок процессов в системе, а структура — состав

и взаимосвязь частей (элементов), из которых состоит система.

Системам присуще следующее качество. Свойства совокуп-

ности элементов, объединенных в одну систему, не являются про-

стой суммой свойств элементов, а имеют новое качество, отсут-

ствующее в элементах. Например, в совокупности электронных

элементов (транзисторов, резисторов и т. п.), определенным об-

разом соединенных между собой, появляется эффект, который

отождествляется с операциями математической логики, т. е. сово-

купность электрических элементов превращается в систему, функ-

ции которой описываются не законами электротехники, а зако-

нами математической логики. Такого рода система из электронных

элементов приобретает новое свойство и становится логическим

элементом. В свою очередь, объединение логических элементов,

каждый из которых реализует логическую операцию, приводит

к схеме, которая обладает свойством складывать числа. Принцип

(способ), по которому объединение элементов приводит к появле-

нию новых свойств, отличных от свойств элементов, называется

принципом организации. Другими словами, организация—это

способ аранжировки с целью осуществления определенных функ-

ций в системах, состоящих из большого числа элементов.

Организация — понятие более высокого ранга, чем функция

и структура. Конкретный принцип организации—это способ

построения различных систем, обладающих одинаковыми свой-

ствами, т. е. один принцип организации, применяемый к различ-

ным случаям, приводит к системам с различными функциями и

структурами. Так что функция и структура — это конкретизация

принципа организации, всего лишь один вариант организации.

В свою очередь, различные принципы организации приводят

к системам, различающимся своими функциями и структурами, но

тождественным по своим свойствам, своему назначению.

Когда речь идет о принципе порождения функций, необходи-

мых и достаточных для обеспечения определенных свойств систем,

пользуются термином функциональная организация. Функцио-

нальная организация — это принципы построения абстрактных

систем, заданных своими функциями. Об абстрактной системе

известно только ее назначение и не известно, как она устроена,

из каких элементов состоит, т. е. абстрактная система—это

лишь описание, существующее на бумаге. Когда речь идет о прин-

ципе порождения структур, необходимых и достаточных для реа-

лизации заданных функций, используется термин структурная

организация. Структурная организация — это принципы перевода

6

абстрактных систем, заданных в виде функций, в материальные

системы, состоящие из физически существующих элементов.

Проектирование систем — ЭВМ и составляющих их устройств —

базируется на определенных принципах организации систем

с требуемыми свойствами: автоматически выполнять вычисления,

хранить информацию, выполнять арифметические операции и т. д.

Эти принципы изобретаются людьми и используются всякий раз,

когда необходимо создать систему с заданными свойствами.

Принцип иерархии в сложных системах. Существенной особен-

ностью ЭВМ является сложность. Сложность —это свойство си-

стем, состоящих из большого числа элементов. Для сложных

систем характерно, что функция, реализуемая системой, не может

быть представлена как композиция функций, реализуемых наи-

меньшими элементами системы. Так, порядок функционирования

ЭВМ невозможно рассмотреть с точки зрения лишь электрических

процессов, происходящих в цепях ЭВМ. Функции ЭВМ выяв-

ляются только в том случае, если процессы в ЭВМ рассматриваются

в информационном и алгоритмическом аспекте. Это объясняется

эффектом организации, порождающим в совокупностях элементов

новые свойства: в совокупности электронных элементов ЭВМ —

свойство выполнять логические операции над значениями «ложь»

и «истина»; в совокупности логических элементов — свойство

складывать или сравнивать числа; в совокупности устройств —

свойство реализовать вычисления на основе алгоритма. Сказанное

свидетельствует об органической потребности в использовании

нескольких форм описания функции и структуры системы —

иерархии функций и структур.

Иерархический подход к описанию сложных систем предпо-

лагает, что на высшем уровне иерархии система рассматривается

как один элемент, имеющий входы и выходы для связи с внешними

объектами. В этом случае функция системы не может быть задана

подробно и представляется как отображение состояний входов на

состояния выходов системы. Чтобы раскрыть устройство и по-

рядок функционирования системы, глобальная функция и сама

система разделяются на части — функции и структурные элементы

следующего, более низкого уровня иерархии. В свою очередь,

эти части опять детализируются, и так до тех пор, пока функция

и структура системы не будут раскрыты полностью, с необходимой

степенью подробности.

Становится очевидным, что элемент — это прежде всего удоб-

ное понятие, а не физическое свойство. То, что элементарно на

одном уровне рассмотрения процессов и структуры системы, ока-

зывается разложимым на совокупность объектов — элементов

низшего уровня, взаимосвязь которых порождает определенные

свойства в элементах высшего уровня иерархии.

Таким образом, любая сложная система содержит в себе иерар-

хию процессов и элементов, наличие которой приводит к необ-

ходимости использовать иерархию функций и структур для

7

описания того, как устроена и работает система. Нижележащий

уровень иерархии раскрывает сущность процессов и устройство

элементов, относящихся к более высокому уровню.

Стратегия проектирования сложных систем. Устройство и по-

рядок функционирования систем, в том числе и ЭВМ, предопре-

деляются, с одной стороны, назначением системы, а с другой сто-

роны, — элементной базой, «материалом», из которого строится

система. Отсюда следует, что система должна проектироваться

исходя из ее назначения с учетом свойств материальной базы,

существующей на момент проектирования или потенциально воз-

можной.

Наиболее естественным представляется следующий подход

к проектированию систем. Пусть назначение системы задается

в виде функции F. Исходя из содержания и свойств функции F,

можно определить номенклатуру элементов, пригодную для

создания системы. Когда номенклатура элементов определена,

становится известной номенклатура функций фх, ..., фд,, реали-

зуемых элементами. Заметим, что функция системы F относится

к верхнему уровню иерархии, и, следовательно, она описана

в базисе операций, отличных от операций, которые используются

в функциях q?!, ..., фЛ, относящихся к более низкому уровню опи-

сания системы. Функции элементов фъ ..., фд, более просты, чем

функция системы F. По этой причине, чтобы выявить структуру S,

реализующую функцию F, необходимо путем формальных пре-

образований построить эквивалентную F функцию Ф, представ-

ленную в виде композиции функций ф1( ..., фЛ>. Этим самым функ-

ция F будет детализирована до элементарных функций фъ ..., фЛ.,

для реализации каждой из которых имеется определенный струк-

турный элемент. Местоположение функций фх, ..., фд, в записи

функции Ф предопределяет места соответствующих элементов

в структуре. Поэтому функцию Ф можно использовать в качестве

формы для построения структуры S, состоящей из элементов типа

Фх, ..., фд, и реализующей заданную функцию Ф = F, т. е. функ-

цию системы. Если система сложная, указанная процедура повто-

ряется по отношению к каждой из функций фх, ..., фд,, реализуе-

мых элементами структуры S. В результате этого будет выявлена

структура элементов верхнего уровня иерархии и т. д.

Описанный подход к проектированию систем базируется на

предположении о доминирующей роли функций в отношении

структур. Это означает, что функции первичны, а структуры,

их реализующие, вторичны, т. е. функция предопределяет струк-

туру. Как следствие доминирующей роли функций, структуры

системы, определенные для верхних уровней иерархии, играют

преобладающую роль в отношении структур низших уровней,

т. е. состав элементов и связей в структурах верхних уровней пре-

допределяет состав элементов и связей в структурах низших

уровней. Из сказанного следует, что системы должны проекти-

роваться по принципу «сверху—вниз» — от верхнего уровня

8

представления функций и структур к нижнему. Подход к проек-

тированию систем, основанный на признании доминирующей

роли функций в отношении структур, можно назвать функцио-

нальным подходом.

Способы преобразования функций, присущих верхнему уровню

иерархии, в функции, соответствующие нижнему уровню, а также

способы порождения структур по заданным функциям являются

следствием определенных принципов функциональной и струк-

турной организации систем. Эти способы порой удается формали-

зовать и тем самым упростить процесс проектирования, а когда

формальные методы отсутствуют, приходится прибегать к нефор-

мальным методам синтеза систем, которые в таких случаях носят

характер инженерной импровизации.

Глава 1

ПРИНЦИПЫ ПОСТРОЕНИЯ

И ФУНКЦИОНИРОВАНИЯ ЭВМ

1.1. Основные факторы,

влияющие на принципы построения ЭВМ

ЭВМ —это искусственная (инженерная) система, предназна-

ченная для выполнения вычислений на основе алгоритмов. Прин-

ципы построения ЭВМ определяются, с одной стороны, назначе-

нием ЭВМ и, с другой стороны, элементной базой — набором

элементов, который может быть использован для создания ЭВМ.

Назначение ЭВМ — выполнение вычислений на основе алгорит-

мов, и поэтому свойства алгоритмов предопределяют принципы

построения ЭВМ — организацию ЭВМ.

К числу важнейших свойств алгоритмов, наиболее существенно

влияющих на организацию ЭВМ, относятся: 1) дискретность

информации, с которой оперируют алгоритмы; 2) конечность и

элементарность набора операций, выполняемых при реализации

алгоритмов; 3) детерминированность вычислительных процессов,

порождаемых алгоритмами. Перечисленные свойства алгоритмов

обусловливают необходимость представления информации в ди-

скретной (числовой, символьной) форме, реализации в ЭВМ огра-

ниченного числа достаточно простых операций и использова-

ния алгоритмов как источника управления процессом вычис-

лений.

Характеризуя назначение ЭВМ, указывают не только класс

алгоритмов (задач), выполнение которых является функцией

ЭВМ, но и требования к производительности и надежности ЭВМ.

Производительность определяется числом задач, решаемых ЭВМ

в единицу времени, и для достижения требуемой производитель-

ности ЭВМ приходится наделять специальными функциями, обес-

печивающими, например, параллельную обработку нескольких

задач. Таким образом, существенное влияние на организацию

ЭВМ оказывают не только свойства алгоритмов, но и требования

к производительности — времени выполнения алгоритмов. То же

самое можно сказать и о влиянии надежности на функциональную

организацию ЭВМ.

Влияние элементной базы на принципы построения ЭВМ сво-

дится, в основном, к следующему. Оказывается, что конструкция

ЭВМ предельно упрощается и ЭВМ работает наиболее надежно

(устойчиво), если сигналы, циркулирующие в электронных схе-

мах ЭВМ, используются для представления только двух значе-

ний — 0 и 1. Таким образом, свойства электронных элементов

заставляют представлять информацию, с которой оперирует ЭВМ,

исключительно в двоично-кодированной форме — в виде последо-

вательностей из нулей и единиц. Столь же существенное влияние

10

па принципы построения ЭВМ оказывает специфика средств,

используемых для организации машинной памяти, а также для

ввода в ЭВМ и вывода информации.

1.2. Принцип программного управления

Современные ЭВМ строятся на одном принципе — принципе

программного управления. В основе этого принципа лежит пред-

ставление алгоритма в форме операторной схемы, которая задает

правило вычислений как композицию операторов (операций над

информацией) двух типов: операторов, обеспечивающих преобра-

зование информации, и операторов, анализирующих информацию

с целью определения порядка выполнения операторов. Принцип

программного управления может быть реализован в ЭВМ многими

способами. Один из способов реализации программного управле-

ния был предложен в 1945 г. Дж. фон Нейманом [12], и с тех

пор неймановский принцип программного управления исполь-

зуется в качестве основного принципа построения всех современ-

ных ЭВМ.

Неймановский принцип программного управления. Этот прин-

цип состоит в следующем.

1. Информация кодируется в двоичной форме и разделяется

на единицы (элементы) информации, называемые словами.

2. Разнотипные слова информации различаются по способу

использования, но не способами кодирования.

3. Слова информации размещаются в ячейках памяти машины

и идентифицируются номерами ячеек, называемыми адресами

слов.

4. Алгоритм представляется в форме последовательности упра-

вляющих слов, которые определяют наименование операции и

слова информации, участвующие в операции, и называются ко-

мандами. Алгоритм, представленный в терминах машинных

команд, называется программой.

5. Выполнение вычислений, предписанных алгоритмом, сво-

дится к последовательному выполнению команд в порядке, одно-

значно определяемом программой.

Прокомментируем происхождение и содержание перечислен-

ных пунктов принципа программного управления.

Использование в ЭВМ двоичных кодов продиктовано, как уже

отмечалось, спецификой электронных схем, применяемых для

передачи, хранения и преобразования информации. Совокупности

нулей и единиц (битов информации), используемые для представ-

ления отдельных чисел, команд и т. п., рассматриваются как

самостоятельные информационные объекты и называются словами.

Слово обрабатывается в ЭВМ как одно целое — как машинный

элемент информации.

Во втором пункте утверждается, что нет необходимости в сред-

ств ах, позволяющих различать разнотипные слова информации.

11

Поэтому все слова, представляющие числа, команды и прочие

объекты, выглядят в ЭВМ совершенно одинаково и сами по себе

неразличимы. Только порядок использования слов в программе

вносит различия в слова. Благодаря такому «однообразию» слов

оказывается возможным использовать одни и те же операции для

обработки слов различной природы, например для обработки

и чисел, и команд. Так что команды программы становятся в та-

кой же степени доступными для отработки, как и числа, а это

приводит к интересным возможностям.

Третий пункт принципа программного управления фиксирует

специфику хранения и идентификации (обозначения) информации,

порождаемую свойствами машинной памяти. Дело в том, что ныне

машинная память не имеет ничего общего с памятью, существу-

ющей в живой природе. Машинная память — совокупность ячеек,

каждая из которых служит местом для хранения слова информа-

ции, и наиболее подходящий синоним термина «машинная па-

мять»— «склад информации». Ячейка памяти выделяется для

хранения значения величины, в частности константы или команды.

Чтобы записать слово в память, необходимо указать адрес ячейки,

отведенной для хранения соответствующей величины. Чтобы

выбрать слово из памяти (прочитать его), следует опять же ука-

зать адрес ячейки памяти. Таким образом, адрес ячейки, в кото-

рой хранится величина или команда, становится машинным иден-

тификатором (именем) величины и команды. Для обозначения

величин и команд в ЭВМ нет никаких средств, кроме адресов,

присваиваемых величинам и командам в процессе составления

программы вычислений. Дополнительно отметим, что выборка

(чтение) слова из памяти не разрушает информацию, хранимую

в ячейке. Это позволяет любое слово, записанное однажды, чи-

тать какое угодно число раз, т. е. из памяти выбираются не слова,

а копии слов.

Принцип программного управления работой ЭВМ предпола-

гает, что алгоритм представляется в ЭВМ в виде упорядоченной

последовательности команд следующего вида:

bb ... b bb ... b bb ... b ... bb ... b

КО AL А2 Ak

Здесь b —двоичная переменная, принимающая значение 0 или 1,

так что команда — это последовательность нулей и единиц.

Определенное число первых разрядов команды характеризует

код операции (КО). Код —это любое обозначение, отличное от

общепринятого. Так, операция сложения может представляться

в команде кодом 001010. Последующие наборы двоичных пере-

менных bb ... b определяют адреса Alt .... Ak операндов (аргумен-

тов и результатов), участвующих в операции, заданной кодом КО.

12

Чтобы изобразить, из каких частей состоит команда, обычно поль-

зуются следующей формой:

1 /1 т 1 т

1 tn

ко А А, . . . Ak

(1-1)

Здесь прямоугольник обозначает слово информации, части кото-

рого, имеющие определенный смысл, принято называть полями.

Так КО, Av А2, ..., Ак — поля команды, представляющие соот-

ветственно код операции и адреса операндов, участвующих в опе-

рации. Сверху указаны номера разрядов полей: поле КО состоит

из I двоичных разрядов, каждое поле Alt А2, .... Ak содержит т

двоичных разрядов. Известно, что с помощью К двоичных разря-

дов можно закодировать различных значений или объектов.

С учетом этого команда (1.1) позволяет инициировать одну из 2*

операций и каждый адрес может принимать до 2т различных

значений, обеспечивая ссылку на любую из 2т величин или команд.

Форма (1.1) характеризует структуру, или иначе формат команды.

Требуемый порядок вычислений предопределяется алгоритмом и

описывается последовательностью команд, образующих программу

вычислений.

Процесс вычислений, выполняемых ЭВМ по заданной про-

грамме, состоит в последовательном выполнении команд. Первой

выполняется команда, заданная пусковым адресом программы.

Обычно это адрес первой команды программы. Адрес следующей

команды однозначно определяется в процессе выполнения текущей

команды и может быть либо адресом следующей по порядку

команды, либо адресом любой другой команды. Процесс вычисле-

ний продолжается до тех пор, пока не будет выполнена команда,

предписывающая прекращение вычислений.

Важно видеть, что вычисления, производимые машиной, опре-

деляются программой. Именно программа «настраивает» ЭВМ

на получение требуемых результатов. Замена программы приводит

к изменению функций, реализуемых ЭВМ. Следовательно, много-

образие программ, которые могут быть выполнены ЭВМ, опре-

деляет класс функций, который способна реализовать ЭВМ.

Другие принципы программного управления. Неймановский

принцип не является единственно возможнйхлтринципом функ-

циональной организации ЭВМ. Так, Дж. Айлиф в [1 ] предлагает

принципы построения машины, отличной от традиционных ней-

мановских машин. Отличия сводятся в основном к следующему.

Во-первых, неймановский принцип программного управления

предполагает, что коды слов информации не зависят от типа

информации. Это приводит к тому, что программист сам обязан

следить за тем, чтобы для обработки информации определенного

типа, например целых или действительных чисел, использовались

соответствующие операции, чтобы был запрограммирован перевод

13

чисел из одной формы представления в другую и т. д. Если эти

правила не соблюдаются, то в программе появляются ошибки,

приводящие к получению курьезных результатов. Дж. Айлиф

предлагает тип информации отображать в кодах данных. В ре-

зультате этого числа, адреса, команды оказываются различными

и операция, указываемая в команде, производится машиной

в форме, соответствующей типам операндов. Это приводит к сокра-

щению списка машинных операций и уменьшению числа ошибок

в программе. Во-вторых, память неймановской машины сугубо

линейна —это последовательность адресов от 0 до L. И какой бы

не была структура данных, т. е. из каких бы элементов (скаляров,

векторов, матриц) не состояли данные, и как бы они не были

взаимосвязаны, программист должен эти данные спроецировать

на линейную цепочку адресов 0, 1, ..., L. Затем при составлении

программы приходится находить способ выделения адресов, соот-

ветствующих отдельным структурным элементам данных. Про-

цедуры размещения информации в памяти и выделения элементов

информации весьма сложны. Дж. Айлиф предлагает вносить опи-

сание структуры информации непосредственно в память машины,

за счет чего обеспечивается возможность автоматического выявле-

ния адресов отдельных элементов в процессе работы машины.

Благодаря этому значительно упрощается как процесс программи-

рования, так и сами программы, что уменьшает число содержа-

щихся в программах ошибок.

Ясно, что дополнительные возможности ЭВМ обеспечиваются

за счет введения в машину дополнительной аппаратуры, что

приводит к увеличению стоимости ЭВМ. К настоящему времени

попытки определить наиболее рациональные принципы построе-

ния ЭВМ обычно заканчиваются созданием машин, построенных па

неймановском принципе. Это объясняется тем, что возможности

неймановских машин, хотя они и доведены до предела, пока

обеспечивают потребности в вычислениях. Однако к настоящему

времени сложность задач, для решения которых применяются

ЭВМ, достигла такого уровня, что затраты на программирование

и решение задач близки к экономическим возможностям общества,

а порой, по-видимому, превышают их. В связи с этим уже сейчас

ощущается потребность в пересмотре классического неймановского

принципа построения ЭВМ с тем, чтобы приблизить машинные

формы представления данных и алгоритмов к естественным,

повседневно используемым способам представления и обработки

информации.

В настоящее время наращивание возможностей машин произ-

водится в основном за счет программных средств. Наряду с этим

делаются попытки изменить принципы построения самих машин.

Так, широкое распространение получил принцип построения

ЭВМ с развитыми системами интерпретации [17], разработанный

коллективом, возглавляемым академиком В. М. Глушковым.

ЭВМ этого класса обеспечивают восприятие алгоритмов, записан-

14

пых на языках высокого уровня — в виде знаков операций, наи-

менований величии и данных, представляемых в естественной

форме, причем указанные возможности реализуются за счет

введения в ЭВМ нетрадиционных средств адресации и операций

над информацией.

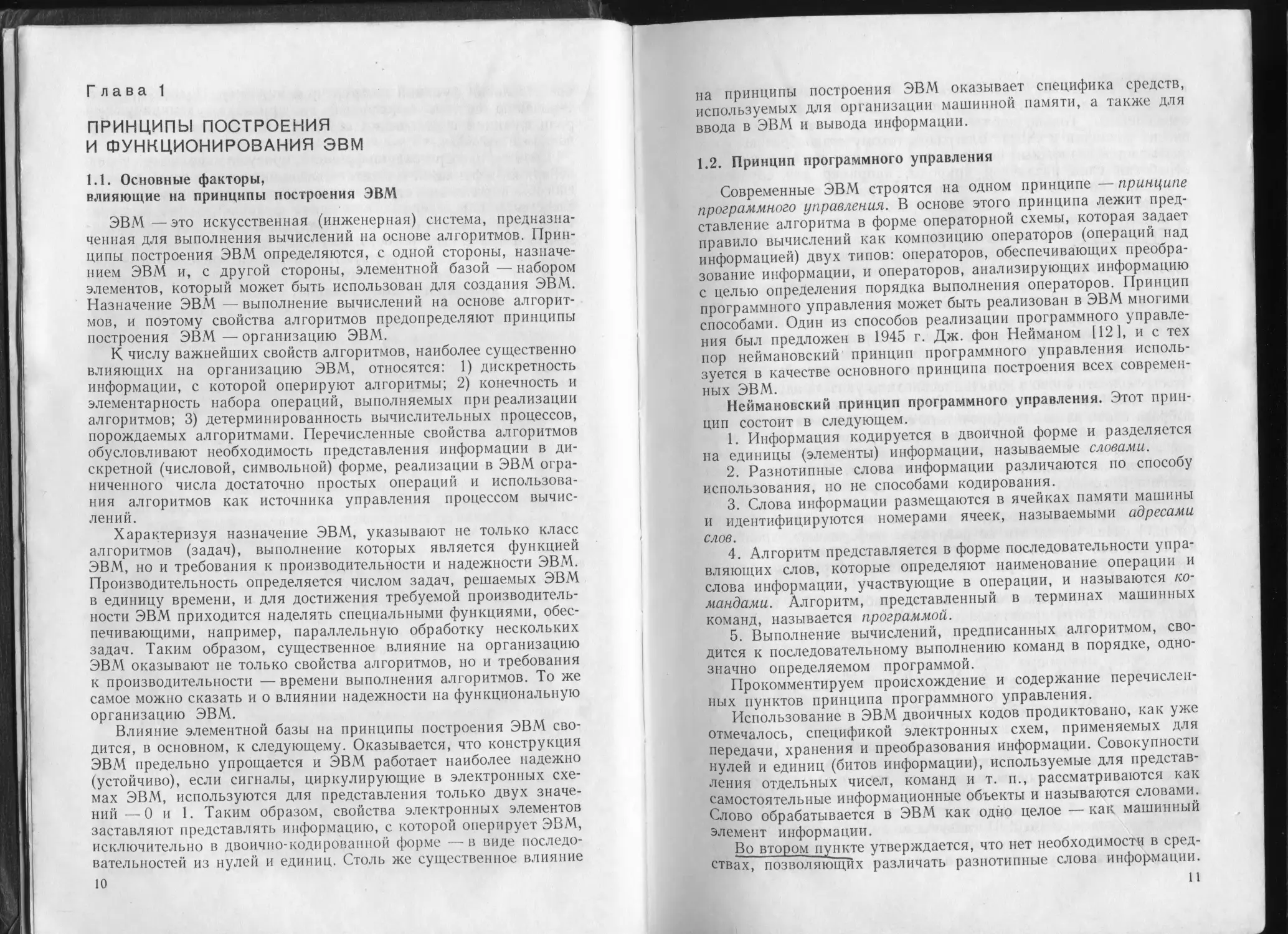

1.3. Состав и порядок функционирования ЭВМ

Теперь определим номенклатуру устройств, из которых должна

состоять ЭВМ. Номенклатура устройств органически проистекает

из неймановского принципа программного управления и свойств

технических средств, обеспечивающих хранение, обработку, ввод

и вывод информации.

Основные устройства ЭВМ. Принцип программного управления

предполагает, что ЭВМ строится по рис. 1.1. Для хранения инфор-

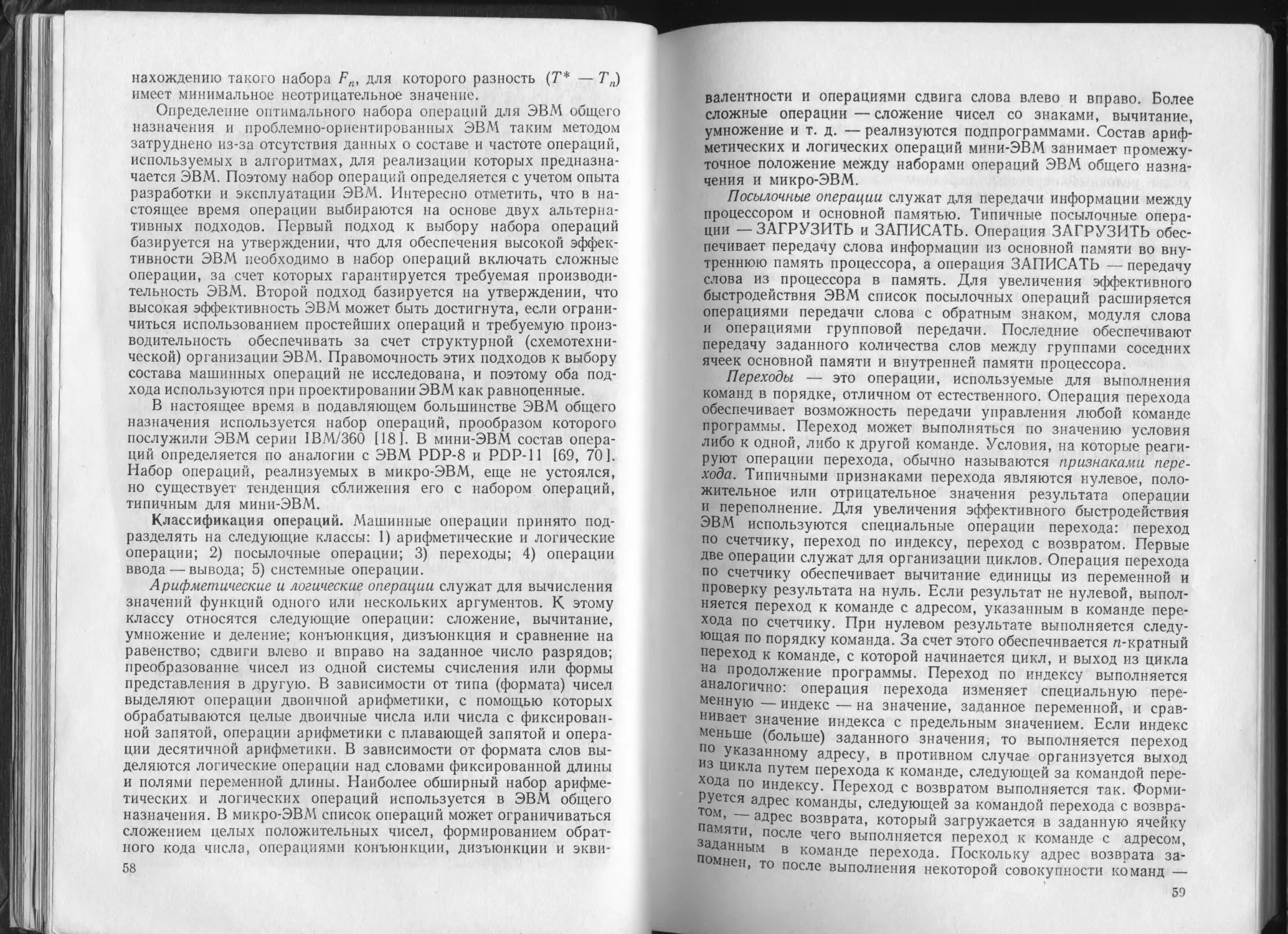

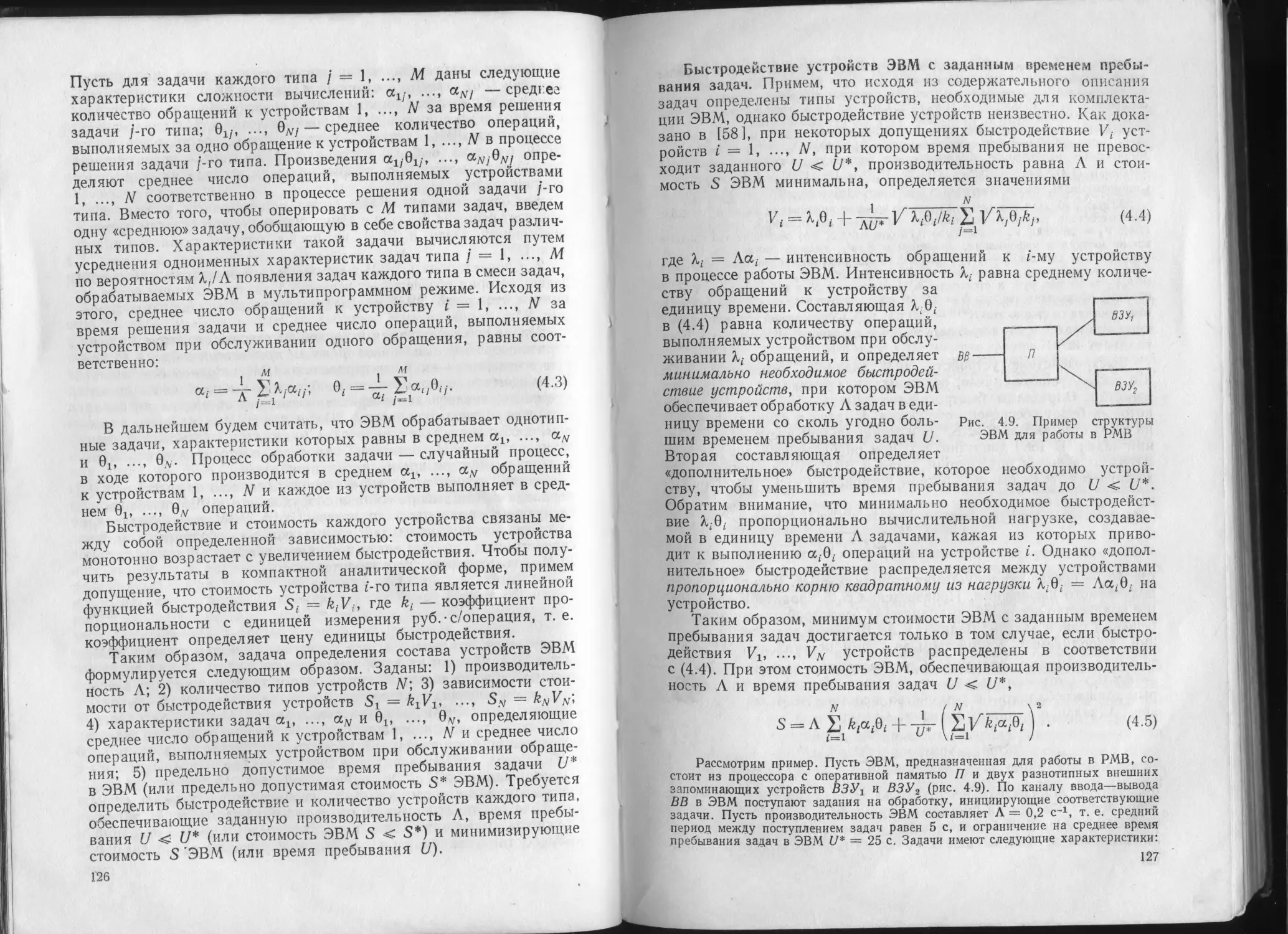

Рис. 1.1. Состав ЭВМ

мации, необходимой для производства вычислений, служит па-

мять. В памяти размещаются программы, задающие порядок

вычислений, и данные, представляющие исходные значения,

промежуточные и конечные результаты вычислений. Для ввода

информации — программ и данных — в память ЭВМ исполь-

зуются устройства ввода, которые обеспечивают считывание инфор-

мации с определенных носителей (перфокарт, перфолент, кла-

виатур и т. и.) и представление считанной информации в форме

электрических сигналов, воспринимаемых памятью. Вывод инфор-

мации из памяти для ее последующего использования обеспечи-

вается устройствами вывода, которые преобразуют электрические

сигналы, поступающие из памяти и несущие в себе информацию

о результатах вычислений, в форму печатного текста, пробивок

на перфолентах и перфокартах и т. п. Одним словом, устройства

ввода и вывода обеспечивают обмен информацией со средой,

внешней по отношению к ЭВМ. В отдельных случаях ввод

и вывод реализуются одним физическим устройством, например

15

электрической пишущей машинкой, с клавиатуры которой

вводится информация, а иа лист бумаги выводится информация.

Устройства, обеспечивающие как ввод, так и вывод информации,

называются устройствами ввода—вывода. Этим же термином поль-

зуются для обозначения любого устройства, относящегося к классу

устройств ввода и вывода информации.

Вычисления, заданные программой, реализуются процессором.

Функцией процессора является выборка команд из памяти и

выполнение действий, предписанных командами. Команды выби-

раются последовательно одна за другой из ячеек памяти, адреса

которых определяются во время выполнения предшествующей

команды. Процессор выполняет все операции за исключением

операций ввода—вывода информации. Команды ввода—вывода,

как и любые другие команды, поступают в процессор, но функции

процессора в отношении этих команд ограничиваются иницииро-

ванием операций ввода—вывода, а сами операции реализуются

устройствами ввода—вывода.

Процессор — это центральное устройство ЭВМ. Процессор

«воспринимает» программу и на ее основе управляет работой всех

устройств ЭВМ, инициируя выполнение действий в памяти и

устройствах ввода—вывода.

Порядок функционирования ЭВМ. Работа ЭВМ протекает

следующим образом. Программа и исходные данные, представлен-

ные на машинном носителе информации, например на перфокартах,

считываются устройством ввода и загружаются в память ЭВМ.

Затем в процессор посылается пусковой адрес программы, и про-

цессор начинает выполнять программу от команды с заданным

адресом, что сводится к последовательной выборке команд из

памяти и их выполнению средствами процессора и устройств

ввода—вывода. Этот процесс заканчивается в момент выборки

команды, отмечающей конец вычислений.

Для загрузки и запуска программы необходимо выполнить

определенную последовательность действий: указать адрес об-

ласти памяти, в которую должна быть загружена программа;

инициировать операцию ввода в определенном устройстве; пере-

дать в процессор пусковой адрес программы и т. д. Для таких

действий служит инженерный пульт управления, который снаб-

жается органами управления и средствами индикации состояний

процессора. Чтобы упростить процесс загрузки и запуска про-

грамм, используется специальная программа — программа на-

чальной загрузки. После включения ЭВМ под напряжение про-

грамма начальной загрузки вводится в память под управлением

с инженерного пульта. Загрузка и запуск всех последующих

программ производятся уже в автоматическом режиме под управ-

лением программы начальной загрузки, которая задает необходи-

мую последовательность действий, обеспечивающих ввод про-

граммы в память и запуск программы. Для инициирования про-

граммы начальной загрузки и других вспомогательных программ

16

выделяется устройство ввода—вывода (обычно электрическая

пишущая машинка), которое используется как пульт оператора

ЭВМ. С (пульта посылаются директивы на загрузку и запуск

программ, прекращение вычислений и т. п. На пульт оператора

выводятся сообщения о завершении вычислений и особых ситуа-

циях, возникающих при выполнении программ. Таким образом,

включение ЭВА'! в работу производится с инженерного пульта,

а в дальнейшем управление ходом решения задач осуществляется

с пульта оператора.

1.4. Организация машинной памяти

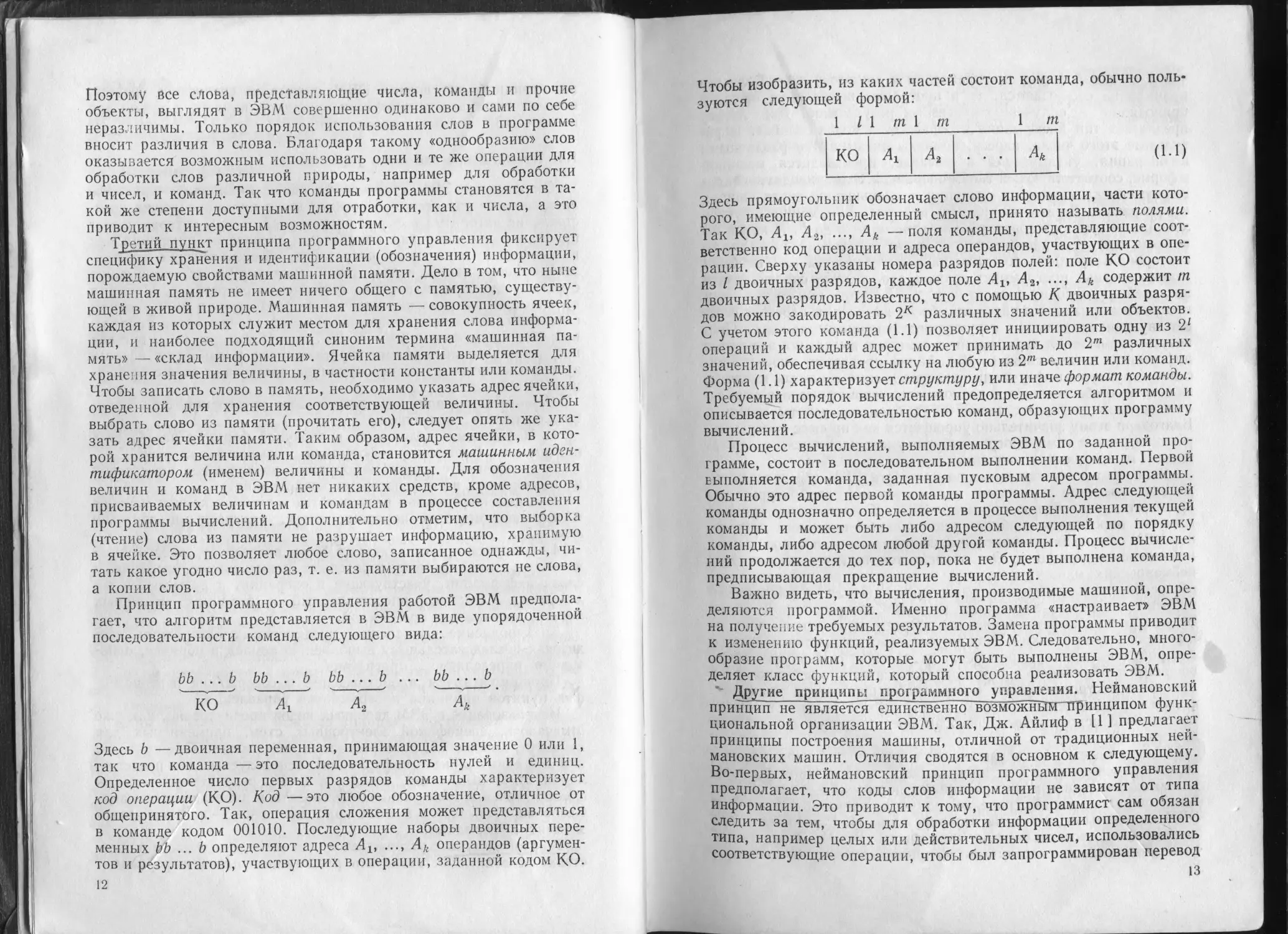

Номенклатура запоминающих устройств. Для хранения инфор-

мации могут использоваться средства различной физической

природы: полупроводниковые приборы, ферритовые сердечники

и магнитные пленки, наносимые на поверхность барабанов, дисков

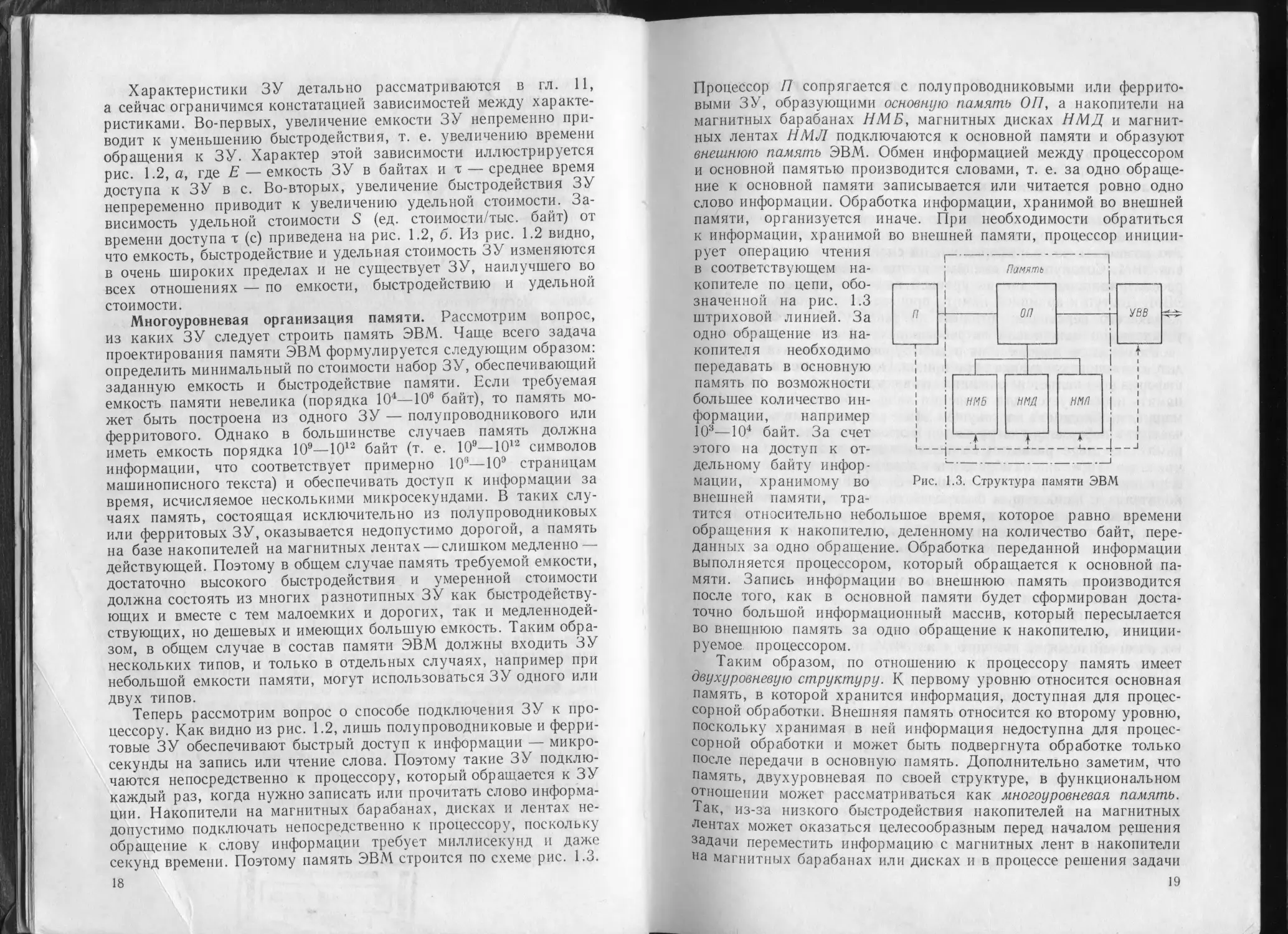

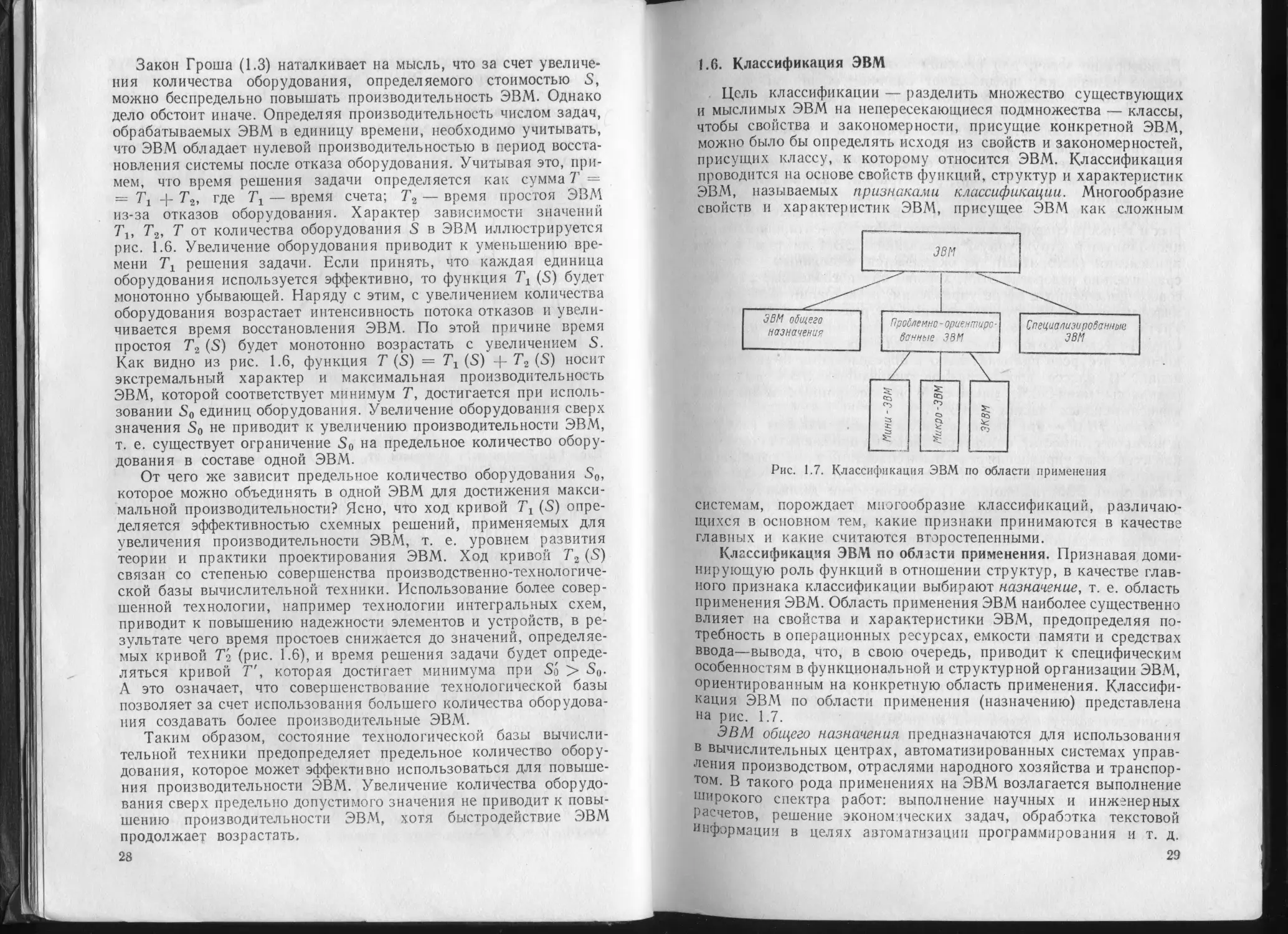

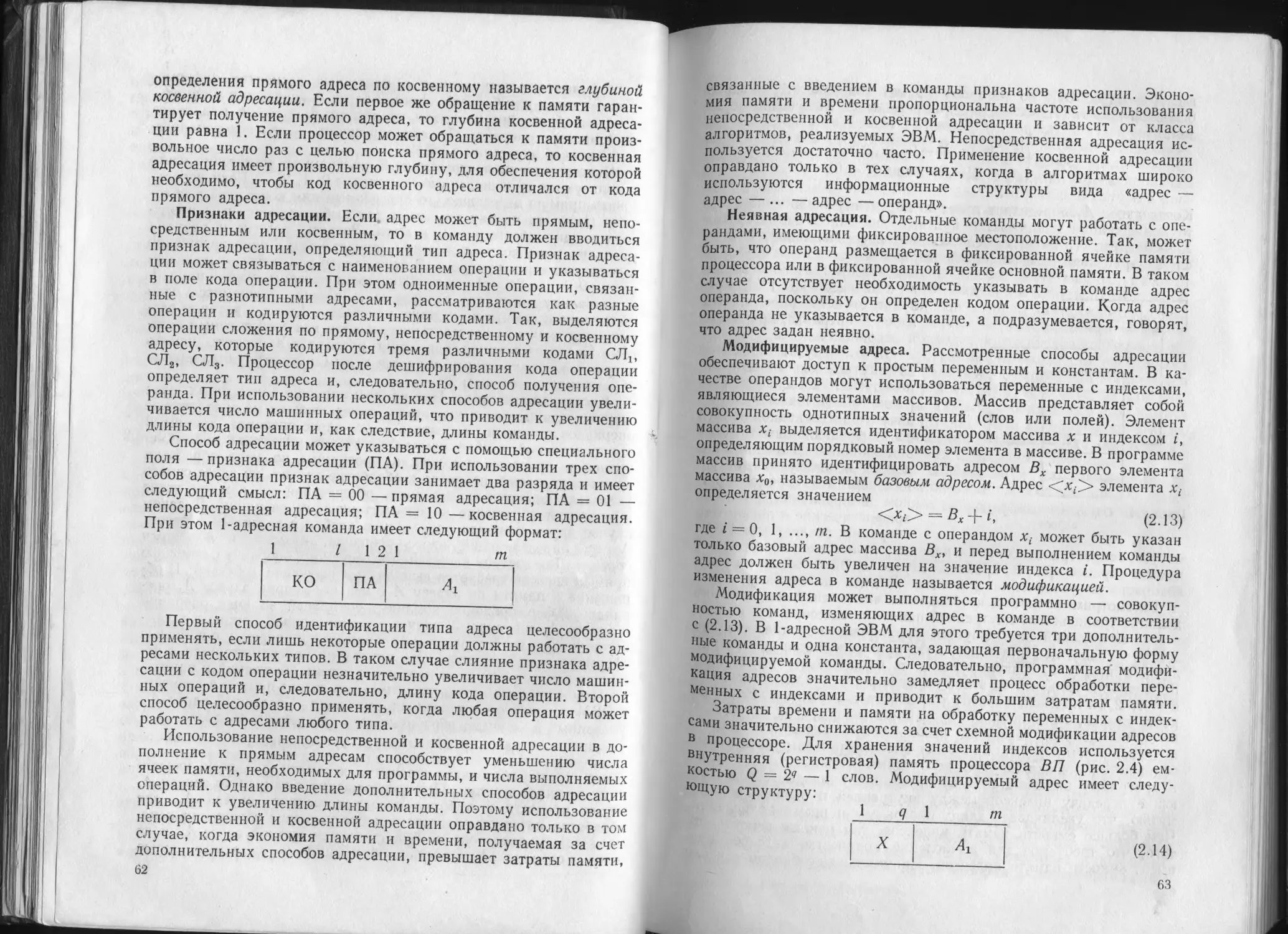

Рис. 1.2. Характеристики запоминающих устройств ЭВМ (П— полу-

проводниковые ЗУ; Ф—ферритовые ЗУ; МБ—накопители на ма-

гнитных барабанах; МД — накопители па магнитных дисках; МЛ —

накопители на магнитной ленте)

и лент. На их основе создана широкая номенклатура запомина-

ющих устройств (накопителей информации)', полупроводниковые

и ферритовые запоминающие устройства, накопители на магнит-

ных барабанах, дисках и лентах. Основные характеристики за-

поминающего устройства (ЗУ) — емкость, быстродействие и удель-

ная стоимость. Емкость ЗУ определяется предельным количеством

информации, размещаемым в ЗУ. Емкость исчисляется в битах,

байтах 1 и иногда в словах. Быстродействие ЗУ определяется

затратами времени на обращение к ЗУ с целью чтения или записи

информации. Удельная стоимость — это затраты средств (в руб-

лях) на хранение единицы информации (бита или байта).

1 Байт — единица информации, состоящая из восьми бит. Байт исполь-

зуется для кодирования одного символа (буквы, цифры, знака) или двух деся-

тичных цифр. • t-jir । ' ~ -t 1

полг-.те»

Я

1

17

Характеристики ЗУ детально рассматриваются в гл. И,

а сейчас ограничимся констатацией зависимостей между характе-

ристиками. Во-первых, увеличение емкости ЗУ непременно при-

водит к уменьшению быстродействия, т. е. увеличению времени

обращения к ЗУ. Характер этой зависимости иллюстрируется

рис. 1.2, а, где Е — емкость ЗУ в байтах и т — среднее время

доступа к ЗУ в с. Во-вторых, увеличение быстродействия ЗУ

непреременно приводит к увеличению удельной стоимости. За-

висимость удельной стоимости S (ед. стоимости/тыс. байт) от

времени доступа т (с) приведена на рис. 1.2, б. Из рис. 1.2 видно,

что емкость, быстродействие и удельная стоимость ЗУ изменяются

в очень широких пределах и не существует ЗУ, наилучшего во

всех отношениях — по емкости, быстродействию и удельной

стоимости.

Многоуровневая организация памяти. Рассмотрим вопрос,

из каких ЗУ следует строить память ЭВМ. Чаще всего задача

проектирования памяти ЭВМ формулируется следующим образом:

определить минимальный по стоимости набор ЗУ, обеспечивающий

заданную емкость и быстродействие памяти. Если требуемая

емкость памяти невелика (порядка 104—10е байт), то память мо-

жет быть построена из одного ЗУ — полупроводникового или

ферритового. Однако в большинстве случаев память должна

иметь емкость порядка 109—1012 байт (т. е. 109—101а символов

информации, что соответствует примерно 10я—109 страницам

машинописного текста) и обеспечивать доступ к информации за

время, исчисляемое несколькими микросекундами. В таких слу-

чаях память, состоящая исключительно из полупроводниковых

или ферритовых ЗУ, оказывается недопустимо дорогой, а память

на базе накопителей на магнитных лентах — слишком медленно —

действующей. Поэтому в общем случае память требуемой емкости,

достаточно высокого быстродействия и умеренной стоимости

должна состоять из многих разнотипных ЗУ как быстродейству-

ющих и вместе с тем малоемких и дорогих, так и медленнодей-

ствующих, но дешевых и имеющих большую емкость. Таким обра-

зом, в общем случае в состав памяти ЭВМ должны входить ЗУ

нескольких типов, и только в отдельных случаях, например при

небольшой емкости памяти, могут использоваться ЗУ одного или

двух типов.

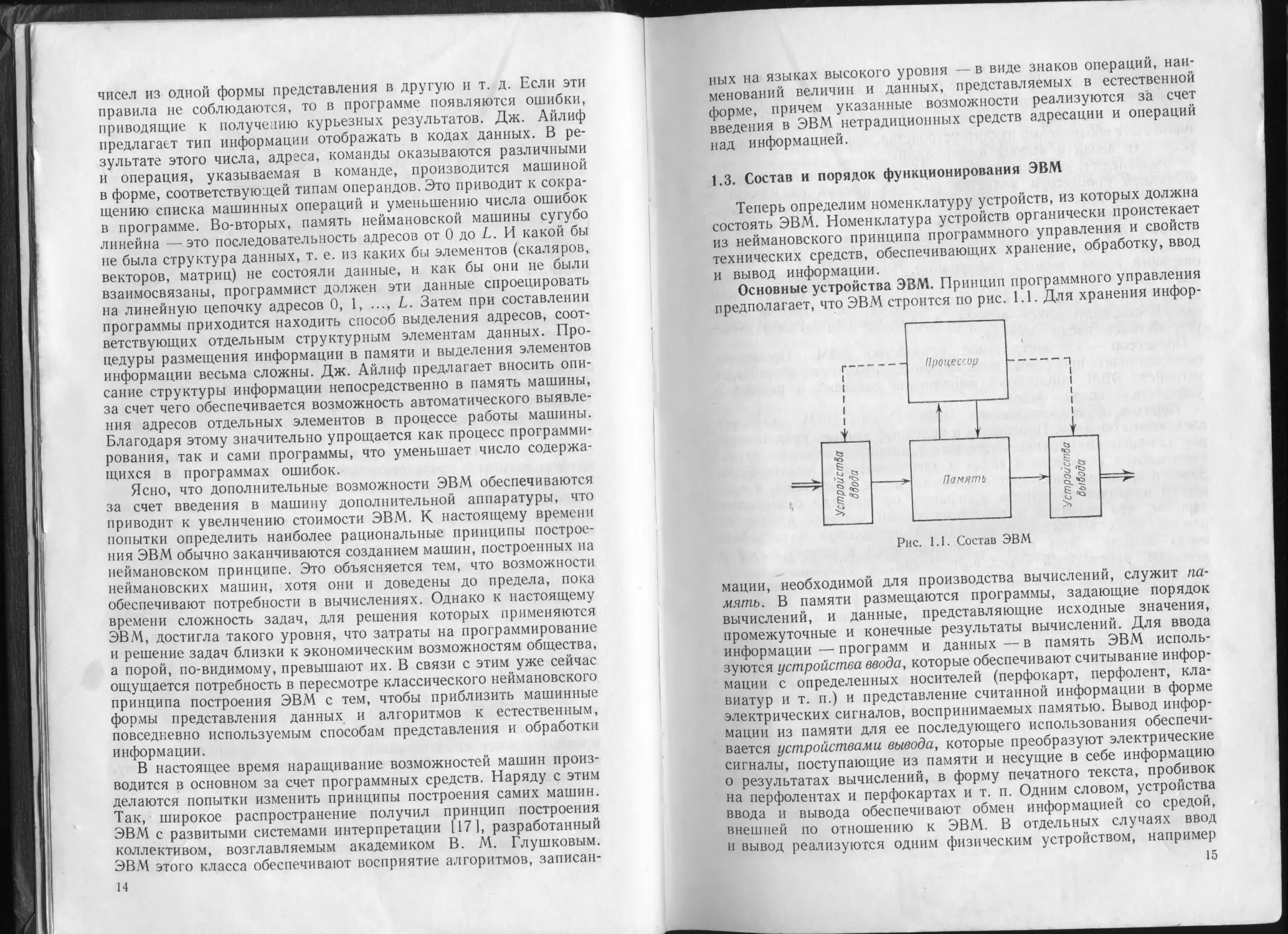

Теперь рассмотрим вопрос о способе подключения ЗУ к про-

цессору. Как видно из рис. 1.2, лишь полупроводниковые и ферри-

товые ЗУ обеспечивают быстрый доступ к информации — микро-

секунды на запись или чтение слова. Поэтому такие ЗУ подклю-

чаются непосредственно к процессору, который обращается к ЗУ

каждый раз, когда нужно записать или прочитать слово информа-

ции. Накопители на магнитных барабанах, дисках и лентах не-

допустимо подключать непосредственно к процессору, поскольку

обращение к слову информации требует миллисекунд и даже

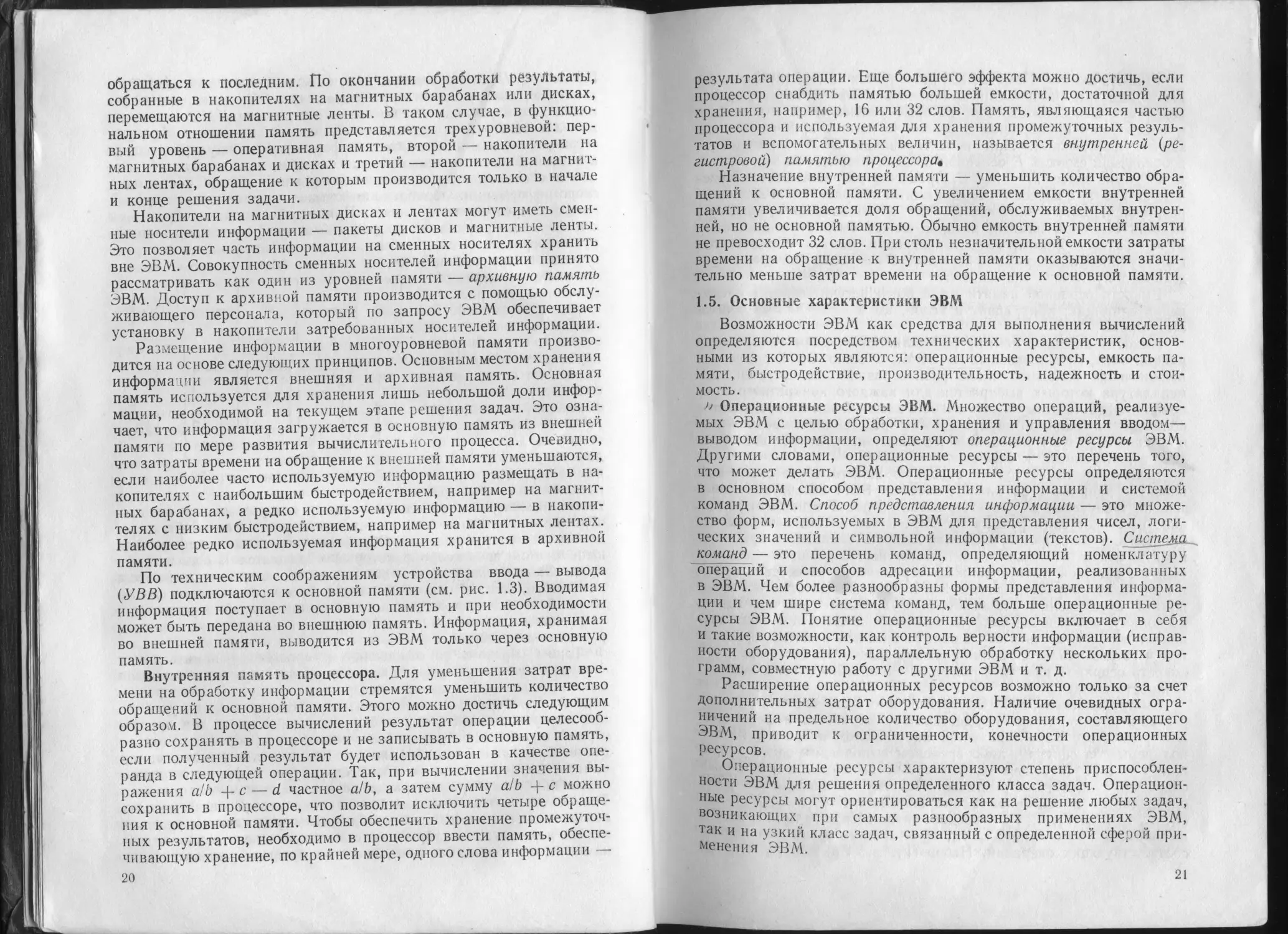

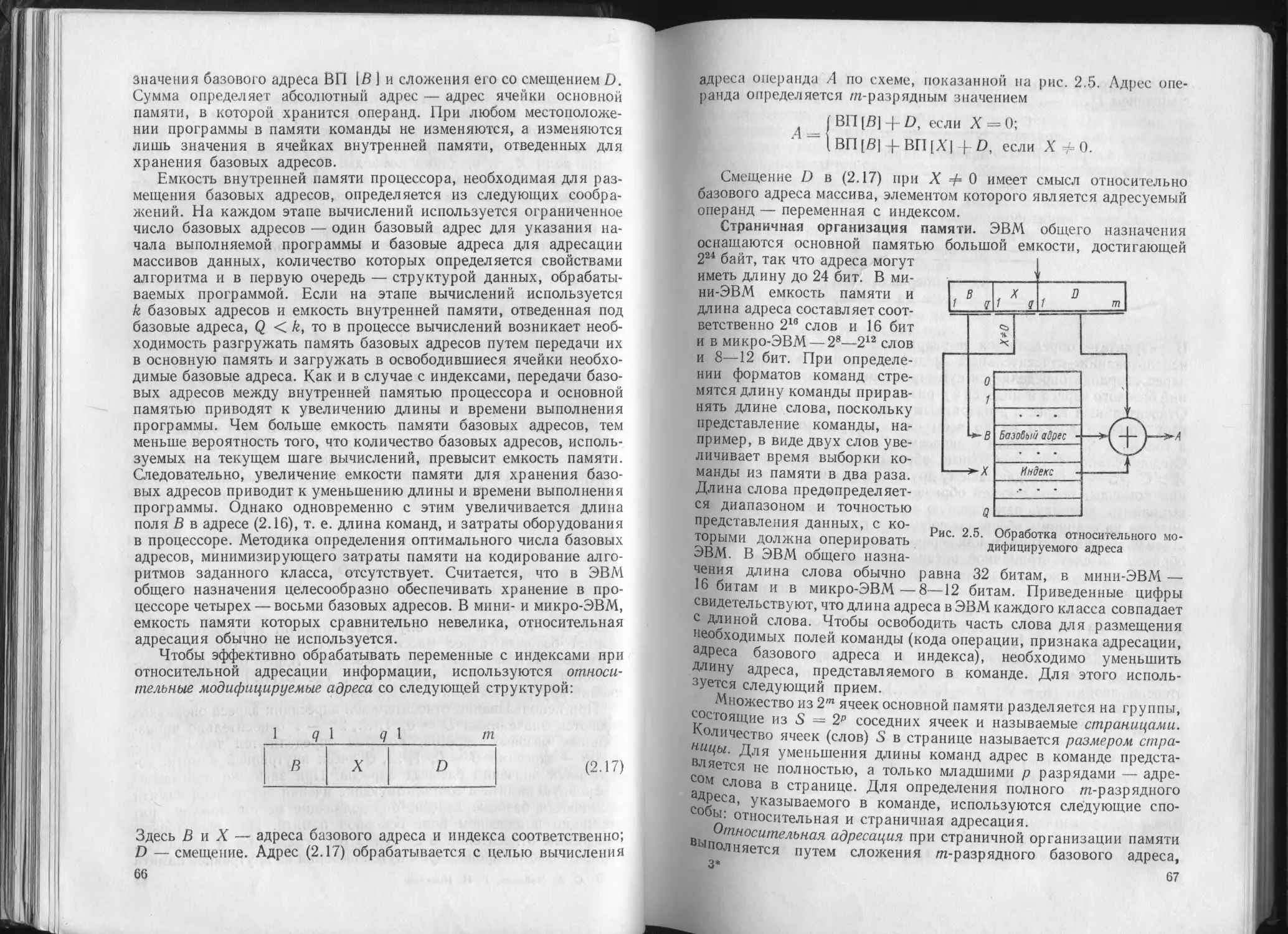

секунд времени. Поэтому память ЭВМ строится по схеме рис. 1.3.

18

Процессор П сопрягается с полупроводниковыми или феррито-

выми ЗУ, образующими основную память ОП, а накопители на

магнитных барабанах НМ.Б, магнитных дисках НМД и магнит-

ных лентах НМЛ подключаются к основной памяти и образуют

внешнюю память ЭВМ. Обмен информацией между процессором

и основной памятью производится словами, т. е. за одно обраще-

ние к основной памяти записывается или читается ровно одно

слово информации. Обработка информации, хранимой во внешней

памяти, организуется иначе. При необходимости обратиться

к информации, хранимой во внешней памяти, процессор иниции-

рует операцию чтения

в соответствующем на-

копителе по цепи, обо-

значенной на рис. 1.3

штриховой линией. За

одно обращение из на-

копителя необходимо

передавать в основную

память по возможности

большее количество ин-

формации, например

103—104 байт. За счет

этого на доступ к от-

дельному байту инфор-

мации, хранимому во

внешней памяти, тра-

Рис. 1.3. Структура памяти ЭВМ

тится относительно небольшое время, которое равно времени

обращения к накопителю, деленному на количество байт, пере-

данных за одно обращение. Обработка переданной информации

выполняется процессором, который обращается к основной па-

мяти. Запись информации во внешнюю память производится

после того, как в основной памяти будет сформирован доста-

точно большой информационный массив, который пересылается

во внешнюю память за одно обращение к накопителю, иниции-

руемое процессором.

Таким образом, по отношению к процессору память имеет

двухуровневую структуру. К первому уровню относится основная

память, в которой хранится информация, доступная для процес-

сорной обработки. Внешняя память относится ко второму уровню,

поскольку хранимая в ней информация недоступна для процес-

сорной обработки и может быть подвергнута обработке только

после передачи в основную память. Дополнительно заметим, что

память, двухуровневая по своей структуре, в функциональном

отношении может рассматриваться как многоуровневая память.

Так, из-за низкого быстродействия накопителей на магнитных

лентах может оказаться целесообразным перед началом решения

задачи переместить информацию с магнитных лент в накопители

на магнитных барабанах или дисках и в процессе решения задачи

19

обращаться к последним. По окончании обработки результаты,

собранные в накопителях на магнитных барабанах или дисках,

перемещаются на магнитные ленты. В таком случае, в функцио-

нальном отношении память представляется трехуровневой: пер-

вый уровень — оперативная память, второй — накопители на

магнитных барабанах и дисках и третий — накопители на магнит-

ных лентах, обращение к которым производится только в начале

и конце решения задачи.

Накопители на магнитных дисках и лентах могут иметь смен-

ные носители информации — пакеты дисков и магнитные ленты.

Это позволяет часть информации на сменных носителях хранить

вне ЭВМ. Совокупность сменных носителей информации принято

рассматривать как один из уровней памяти — архивную память

ЭВМ. Доступ к архивной памяти производится с помощью обслу-

живающего персонала, который по запросу ЭВМ обеспечивает

установку в накопители затребованных носителей информации.

Размещение информации в многоуровневой памяти произво-

дится на основе следующих принципов. Основным местом хранения

информации является внешняя и архивная память. Основная

память используется для хранения лишь небольшой доли инфор-

мации, необходимой на текущем этапе решения задач. Это озна-

чает, что информация загружается в основную память из внешней

памяти по мере развития вычислительного процесса. Очевидно,

что затраты времени на обращение к внешней памяти уменьшаются,

если наиболее часто используемую информацию размещать в на-

копителях с наибольшим быстродействием, например на магнит-

ных барабанах, а редко используемую информацию — в накопи-

телях с низким быстродействием, например на магнитных лентах.

Наиболее редко используемая информация хранится в архивной

памяти.

По техническим соображениям устройства ввода — вывода

(УВВ) подключаются к основной памяти (см. рис. 1.3). Вводимая

информация поступает в основную память и при необходимости

может быть передана во внешнюю память. Информация, хранимая

во внешней памяти, выводится из ЭВМ только через основную

память.

Внутренняя память процессора. Для уменьшения затрат вре-

мени на обработку информации стремятся уменьшить количество

обращений к основной памяти. Этого можно достичь следующим

образом. В процессе вычислений результат операции целесооб-

разно сохранять в процессоре и не записывать в основную память,

если полученный результат будет использован в качестве опе-

ранда в следующей операции. Так, при вычислении значения вы-

ражения alb с — d частное alb, а затем сумму alb 4- с можно

сохранить в процессоре, что позволит исключить четыре обраще-

ния к основной памяти. Чтобы обеспечить хранение промежуточ-

ных результатов, необходимо в процессор ввести память, обеспе-

чивающую хранение, по крайней мере, одного слова информации —

20

результата операции. Еще большего эффекта можно достичь, если

процессор снабдить памятью большей емкости, достаточной для

хранения, например, 16 или 32 слов. Память, являющаяся частью

процессора и используемая для хранения промежуточных резуль-

татов и вспомогательных величин, называется внутренней (ре-

гистровой) памятью процессора»

Назначение внутренней памяти — уменьшить количество обра-

щений к основной памяти. С увеличением емкости внутренней

памяти увеличивается доля обращений, обслуживаемых внутрен-

ней, но не основной памятью. Обычно емкость внутренней памяти

не превосходит 32 слов. При столь незначительной емкости затраты

времени на обращение к внутренней памяти оказываются значи-

тельно меньше затрат времени на обращение к основной памяти.

1.5. Основные характеристики ЭВМ

Возможности ЭВМ как средства для выполнения вычислений

определяются посредством технических характеристик, основ-

ными из которых являются: операционные ресурсы, емкость па-

мяти, быстродействие, производительность, надежность и стои-

мость.

» Операционные ресурсы ЭВМ. Множество операций, реализуе-

мых ЭВМ с целью обработки, хранения и управления вводом—

выводом информации, определяют операционные ресурсы ЭВМ.

Другими словами, операционные ресурсы — это перечень того,

что может делать ЭВМ. Операционные ресурсы определяются

в основном способом представления информации и системой

команд ЭВМ. Способ представления информации — это множе-

ство форм, используемых в ЭВМ для представления чисел, логи-

ческих значений и символьной информации (текстов). Сис/пелцу

команд — это перечень команд, определяющий номенклатуру

операций и способов адресации информации, реализованных

в ЭВМ. Чем более разнообразны формы представления информа-

ции и чем шире система команд, тем больше операционные ре-

сурсы ЭВМ. Понятие операционные ресурсы включает в себя

и такие возможности, как контроль верности информации (исправ-

ности оборудования), параллельную обработку нескольких про-

грамм, совместную работу с другими ЭВМ и т. д.

Расширение операционных ресурсов возможно только за счет

дополнительных затрат оборудования. Наличие очевидных огра-

ничений на предельное количество оборудования, составляющего

ЭВМ, приводит к ограниченности, конечности операционных

ресурсов.

Операционные ресурсы характеризуют степень приспособлен-

ности ЭВМ для решения определенного класса задач. Операцион-

ные ресурсы могут ориентироваться как на решение любых задач,

возникающих при самых разнообразных применениях ЭВМ,

так и на узкий класс задач, связанный с определенной сферой при-

менения ЭВМ.

21

Емкость памяти. Память ЭВМ разделяется на основную и внеш-

нюю. Доступ к информации, хранимой в основной памяти, произ-

водится с помощью адресов, которые указываются в командах

и посылаются процессором в основную память при чтении или

записи информации. При проектировании ЭВМ определяется

необходимая емкость Е основной памяти и исходя из этого нахо-

дится длина адреса т = log2 Е. Процессор разрабатывается в рас-

чете на работу с адресами, содержащими не более чем т двоичных

разрядов. Поэтому значение Е = 2т обусловливает предельную

емкость основной памяти, которой может быть укомплектована

ЭВМ. Таким образом, емкость основной памяти определяется

конструкцией процессора и не может быть увеличена сверх пре-

дельно допустимого значения Е.

Емкость основной памяти чаще всего рассчитывают в следу-

ющих единицах: кбит, кбайт и кслов, где к = 210 = 1024 и чита-

ется «кило».

Емкость внешней памяти определяется суммарной емкостью

накопителей, подключаемых к ЭВМ. Обычно ЭВМ допускает

подключение большого числа разнообразных накопителей, но-

менклатура которых выбирается для каждого конкретного при-

менения ЭВМ. Поэтому задать емкость внешней памяти предельным

количеством хранимой информации не представляется возможным

и ее характеризуют косвенно — максимальным числом накопите-

лей, подключаемых к ЭВМ.

Если ЭВМ имеет только основную память, то ее емкость Е

вносит ограничение на класс решаемых ЭВМ задач, поскольку

задача, требующая для своего решения более Е единиц информа-

ции, не может быть решена на ЭВМ в автоматическом режиме,

без помощи со стороны человека. Емкость внешней и архивной

памяти может считаться практически неограниченной, поэтому

наличие внешней памяти снижает ограничение на степень слож-

ности задач, обрабатываемых ЭВМ. Однако емкость основной

памяти существенно сказывается на времени решения задач,

поскольку чем меньше емкость основной памяти, тем чаще воз-

никает необходимость в обращениях к внешней памяти, в резуль-

тате чего увеличивается время решения задачи. Из этого ясно, что

емкость основной памяти в конечном счете влияет на производи-

тельность ЭВМ.

Быстродействие ЭВМ. Быстродействие ЭВМ определяет ско-

рость, с которой может осуществляться обработка информации.

Быстродействие характеризуется либо числом операций V, вы-

полняемых за секунду, либо временем выполнения одной опера-

ции т = 1/V. В общем случае время выполнения различных

операций существенно различно. Поэтому быстродействие ЭВМ

определяется в векторной форме значениями (У1( ..., или

(тх...хм), где Е1( ..., VM — среднее число операций типа 1, ..., М,

выполняемых за секунду; тх, ..., хм — среднее время выполнения

соответствующих операций. Набор (Ех, ..., ЕЛ)) или (tx, ..., тм)

22

характеризует номинальное быстродействие ЭВМ, т. е. потен-

циальные возможности ЭВМ без учета частоты использования

различных операций и простоев из-за недогрузки ЭВМ и отказов

оборудования.

Номинальное быстродействие (1^..... ЕД1) определяет скорость

выполнения всех без исключения операций — процессорных опе-

раций и операций ввода—вывода. Имея в виду, что ЭВМ может

комплектоваться различными наборами внешних устройств, но-

минальное быстродействие чаще всего характеризуют скоростью

(Vi, ..., ЕЛ1) или временем (тх, ..., тм) выполнения только процессор-

ных операций.

Размерность М наборов (Ръ ..., УЛ1) и (ту, ..., тЛ) весьма вели-

ка— порядка 102, что затрудняет сравнение быстродействий различ-

ных ЭВМ. Процедура сравнения становится простой, если быстро-

действие оценивать скалярной величиной — средним быстродейст-

вием. Среднее быстродействие (операция/с) определяется как вели-

чина, обратная математическому ожиданию длительности операции,

^Z = -yL—> (1-2)

У, Р/Т/

i = i

где Pi — вероятности выполнения операций i = 1, .... Л-1 и,

следовательно, рг + ... -j- рм = 1; тг— среднее время выпол-

нения операции. Вероятности р1, ..., рм характеризуют долю

операций каждого наименования, выполняемых при решении

одной задачи или класса задач. Таким образом, среднее быстро-

действие зависит от номинального быстродействия, т. е. от техни-

ческих характеристик ЭВМ, а также от класса задач, по отноше-

нию к которому определяется среднее быстродействие. Если два

класса задач различаются составом выполняемых операций, то

среднее быстродействие, определенное для одного класса задач,

отличается от среднего быстродействия для другого класса задач.

Чтобы использовать среднее быстродействие для сравнения

характеристик различных ЭВМ, необходимо принять соглашение

о классе задач, по отношению к которому оценивается среднее

быстродействие, т. е. установить значения вероятностей pY, ..., рм.

Производительность ЭВМ. Производительность Л опреде-

ляется средним количеством задач, обрабатываемых ЭВМ за еди-

ницу времени. Если в любой момент времени ЭВМ занята обра-

боткой только одной задачи, то величина U = 1/Лопределяет

среднее время решения задачи в ЭВМ, иначе называемое средним

временем ответа. Если ЭВМ работает в режиме параллельной

обработки М задач, то среднее время решения задачи U = М/А.

Среднее время решения задачи U можно определить, если из-

вестны: среднее число операций 9, выполняемых за один прогон

программы; вероятности ри .... рм операций; номинальное бы-

стродействие ЭВМ, характеризуемое средними значениями вре-

мени выполнения операций (тх, ..., ти). В этом случае на основе

23

(1.2) определяется среднее быстродействие V и среднее время

решения задачи U — Q/V. Следовательно, производительность

ЭВМ Л = MU. Указанный способ определения производитель-

ности ЭВМ применим только в том случае, если все операции

в ЭВМ выполняются сугубо последовательно, без какого-то ни

было параллелизма в работе устройств ЭВМ. Однако в совре-

менных ЭВМ для повышения производительности широко исполь-

зуется принцип параллельной обработки информации, основан-

ный на совмещении во времени процесса выполнения нескольких

операций. Например, совмещается во времени процессорная

обработка и ввод—вывод информации. В таком случае определение

производительности ЭВМ оказывается далеко не тривиальной

задачей, для решения которой используется аппарат теории вы-

числительных систем [58].

Производительность ЭВМ — это характеристика, зависящая

от большого числа факторов: 1) номинального быстродействия

ЭВМ; 2) параметров класса задач, которые определяют число

операций, выполняемых в процессе решения задачи, включая

операции обращения к устройствам ввода—вывода и внешней

памяти; 3) порядка прохождения задач через ЭВМ, определяе-

мого количеством одновременно обрабатываемых задач и способом

распределения ресурсов ЭВМ (устройств и памяти) между парал-

лельно обрабатываемыми задачами. Производительность ЭВМ,

определяемая с учетом быстродействия устройств ЭВМ, параметров

задач и порядка прохождения задач через ЭВМ, называется си-

стемной производительностью.

Надежность ЭВМ. Надежность — это свойство ЭВМ выпол-

нять возложенные на нее функции в течение заданного проме-

жутка времени. Работоспособность ЭВМ нарушается в резуль-

тате отказов оборудования, возникающих из-за неисправности

элементов и соединений. Отказы — случайные события, частоту

которых принято характеризовать величиной, называемой интен-

сивностью отказов. Интенсивность отказов — это среднее число

отказов за единицу времени. Обычно интенсивность отказов за-

дается в расчете на 1 ч, т. е. имеет размерность ч-1. Интенсивность

отказов зависит от сложности объекта, характеризуемой числом

составляющих его элементов и соединений, и технологии произ-

водства, с определенной вероятностью гарантирующей соответ-

ствующие свойства объектов.

При расчете надежности принимается, что интенсивность

отказов — постоянная во времени величина. Если предположить,

что отказы различных элементов взаимонезависимы и любой отказ

носит катастрофический характер, полностью нарушая работу

устройства, то интенсивность отказов устройства равна сумме

интенсивностей отказов элементов, входящих в состав устрой-

N

ства, т. е. X = У Х(п(-, где — интенсивность отказов элементов

i=i

24

типа i — 1, .... N‘, nL — количество элементов типа i в уст-

ройстве.

Интенсивность отказов — основная характеристика надеж-

ности, на основе которой определяется ряд других характеристик.

Величина Т = 1/Л равна среднему промежутку времени между

двумя отказами и называется наработкой на отказ. Вероятность

исправной работы в течение произвольного интервала времени t

равна р (/) = e-w.

После возникновения отказа устройство ремонтируют для

восстановления работоспособности. Затраты времени на восста-

новление складываются из времени поиска неисправности и вре-

мени замены вышедшего из строя элемента. Это время называется

временем восстановления. Оно является случайной величиной,

которая характеризуется средним значением Тв, называемым сред-

ним временем восстановления. Значение Тв зависит от количества

оборудования, составляющего устройство, и от техники поиска

и устранения отказов.

С позиций надежности эксплуатационные свойства ЭВМ при-

нято характеризовать коэффициентом готовности Кг = Т/(Т 4-

4- Тв), где Т — наработка на отказ; Тв — среднее время восста-

новления. Коэффициент готовности имеет двоякий смысл. Во-

первых, он характеризует долю времени, в течение которого ЭВМ

работоспособна, т. е. может решать задачи. С учетом этого значе-

ние Кп = 1 — Лг определяет долю времени, в течение которого

ЭВМ простаивает из-за отказов оборудования. Во-вторых, коэф-

фициент готовности Кг характеризует вероятность того, что в лю-

бой произвольный момент времени t ЭВМ работоспособна. С уче-

том этого значение (1 — Кг) определяет вероятность того, что

в момент времени t ЭВМ не работает из-за отказа оборудования.

Для увеличения надежности ЭВМ применяется способ резер-

вирования. Резервирование основывается на введении в состав

системы избыточного оборудования — параллельного включения

нескольких элементов, устройств или машин. При возникновении

отказа в одном из элементов система сохраняет работоспособность

за счет наличия резервного элемента, выполняющего функции

вышедшего из строя элемента. Способ резервирования позволяет

строить системы со сколь угодно высокими показателями надеж-

ности. Увеличение надежности достигается за счет двух-, трех-,

четырехкратного резервирования элементов различных уровней

иерархии. Если надежность характеризуется вероятностью р

безотказной работы в течение промежутка времени t и р0 — надеж-

ность одного элемента (блока, устройства, ЭВМ), то для полу-

чения требуемой надежности р необходимо параллельное соеди-

нение k элементов, при котором (1 —р) = (1 —р0)*. Отсюда

следует, что количество элементов, обеспечивающее требуемую

надежность р, равно k = lg (1 — p)/lg (1 — р0). График,

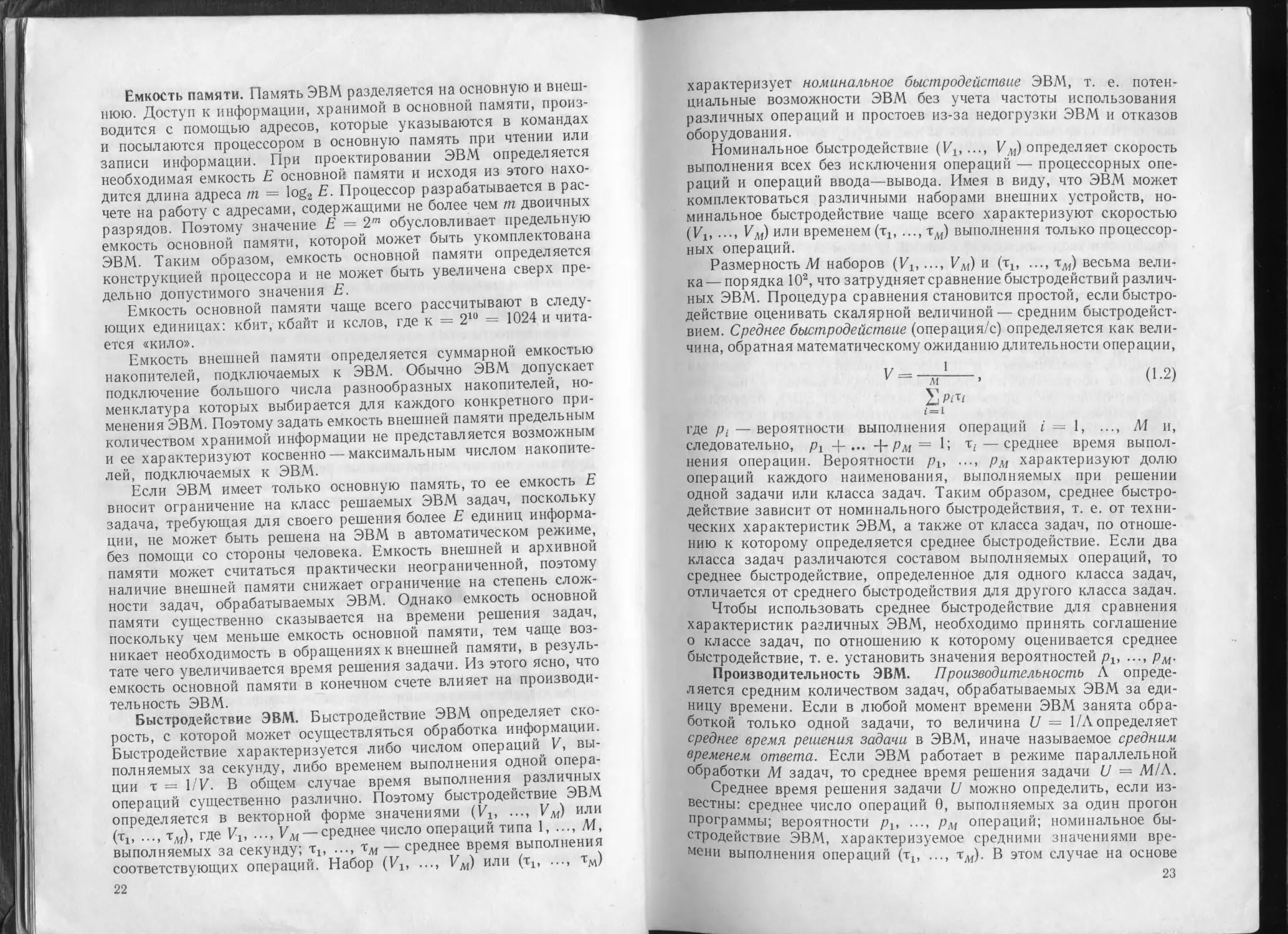

иллюстрирующий зависимость кратности 1г резервирования от

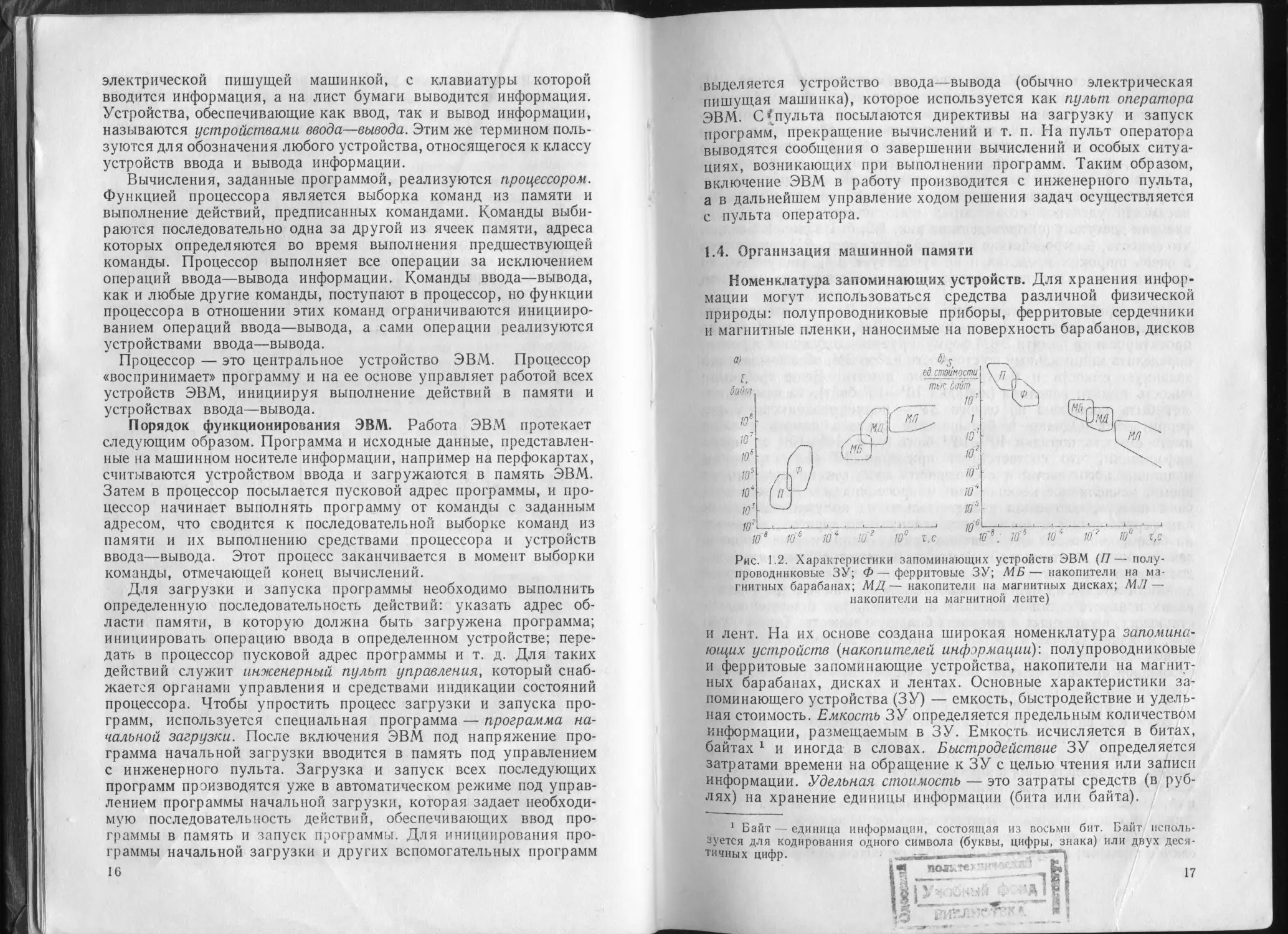

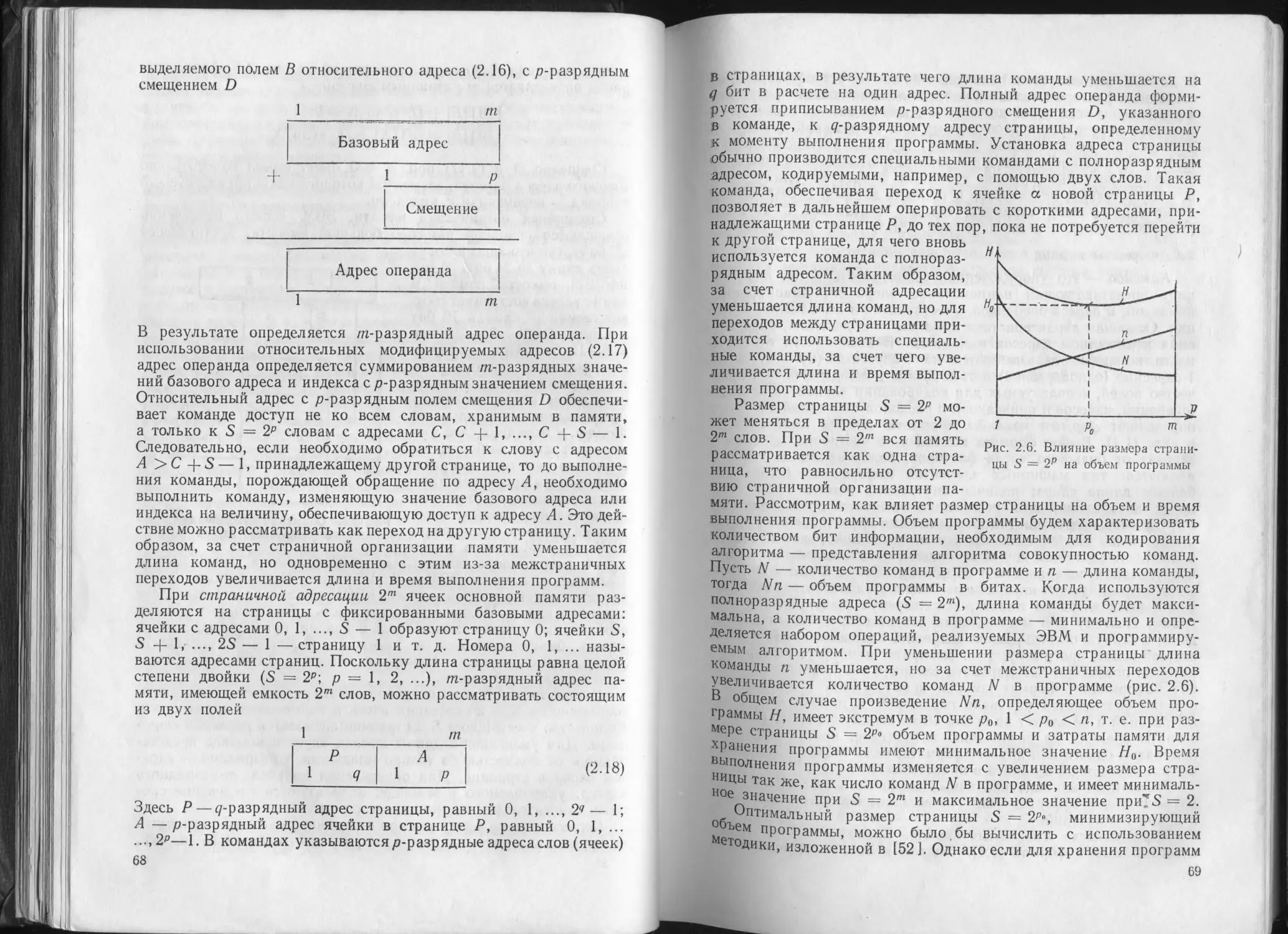

надежности элементов р0 и системы р, приведен на рис. 1.4.

25

Резервирование приводит к увеличению стоимости системы в k

раз, т. е. увеличение надежности достигается за счет увеличения

стоимости системы.

Стоимость ЭВМ. Стоимость ЭВМ равна суммарной стоимости

оборудования, входящего в состав ЭВМ. Чем больше оборудования

(элементов, устройств) используется в ЭВМ, тем выше стоимость

ЭВМ.

Возникает вопрос, что заставляет увеличивать количество

оборудования и, как следствие, стоимость ЭВМ. Необходимость

в этом порождается требованиями к надежности и производитель-

к

5

0,9 0,95 0,99 0,995- 0,999 р0

Рис. 1.4. Кратность резерви-

рования, обеспечивающая на-

дежность системы р при на-

дежности элементов р0

ности ЭВМ, которые зависят от назна-

чения, т. е. области применения ЭВМ.

Как только что отмечалось, для повы-

шения надежности необходимо вводить

в ЭВМ избыточное оборудование, при

наличии которого ЭВМ становится бо-

лее устойчивой к отказам отдельных

элементов и устройств. Для обеспече-

ния требуемой производительности

ЭВМ могут использоваться следующие

способы.

-Д. Расширение операционных ресур-

сов, что сводится к введению в систему

команд ЭВМ дополнительных операций,

способов адресации информации, ко-

манд и т. д., без использования которых

соответствующие действия пришлось бы

программировать последовательностями команд. За счет расши-

рения операционных ресурсов уменьшается количество команд,

выполняемых в процессе решения задачи, и, как следствие,

уменьшается время решения задачи, т. е. увеличивается произ-

водительность ЭВМ.

2. Увеличение быстродействия ЭВМ за счет использования

более быстродействующих и, следовательно, более дорогих эле-

ментов, а также за счет использования дополнительного оборудо-

вания, наличие которого позволяет распараллеливать во времени

выполнение операций, т. е. уменьшать время их выполнения.

3. Обеспечение параллельной обработки нескольких задач пу-

тем совмещения этапов процессорной обработки одних задач с вво-

дом— выводом информации для других задач (мультипрограммиро-

вание), а также путем использования нескольких процессоров

(мультипроцессирование).

Ясно, что каждый из этих способов, повышая производитель-

ность, приводит к увеличению затрат оборудования и стои-

мости ЭВМ.

Во сколько же раз увеличится производительность ЭВМ,

если затраты оборудования, т. е. стоимость ЭВМ, увеличить, ска-

жем, в два раза? Дать точный ответ на этот вопрос можно только

26

в конкретном случае, когда четко определен каждый из двух

вариантов построения ЭВМ. Такого рода задачи решаются ме-

тодами теории вычислительных систем [58]. В общем случае ответ

на этот вопрос может быть дан только в статистической форме —

в виде статистической зависимости между производительностью и

стоимостью ЭВМ, справедливой лишь в среднем, в отношении боль-

шого количества ЭВМ. Такого рода статистическая зависимость

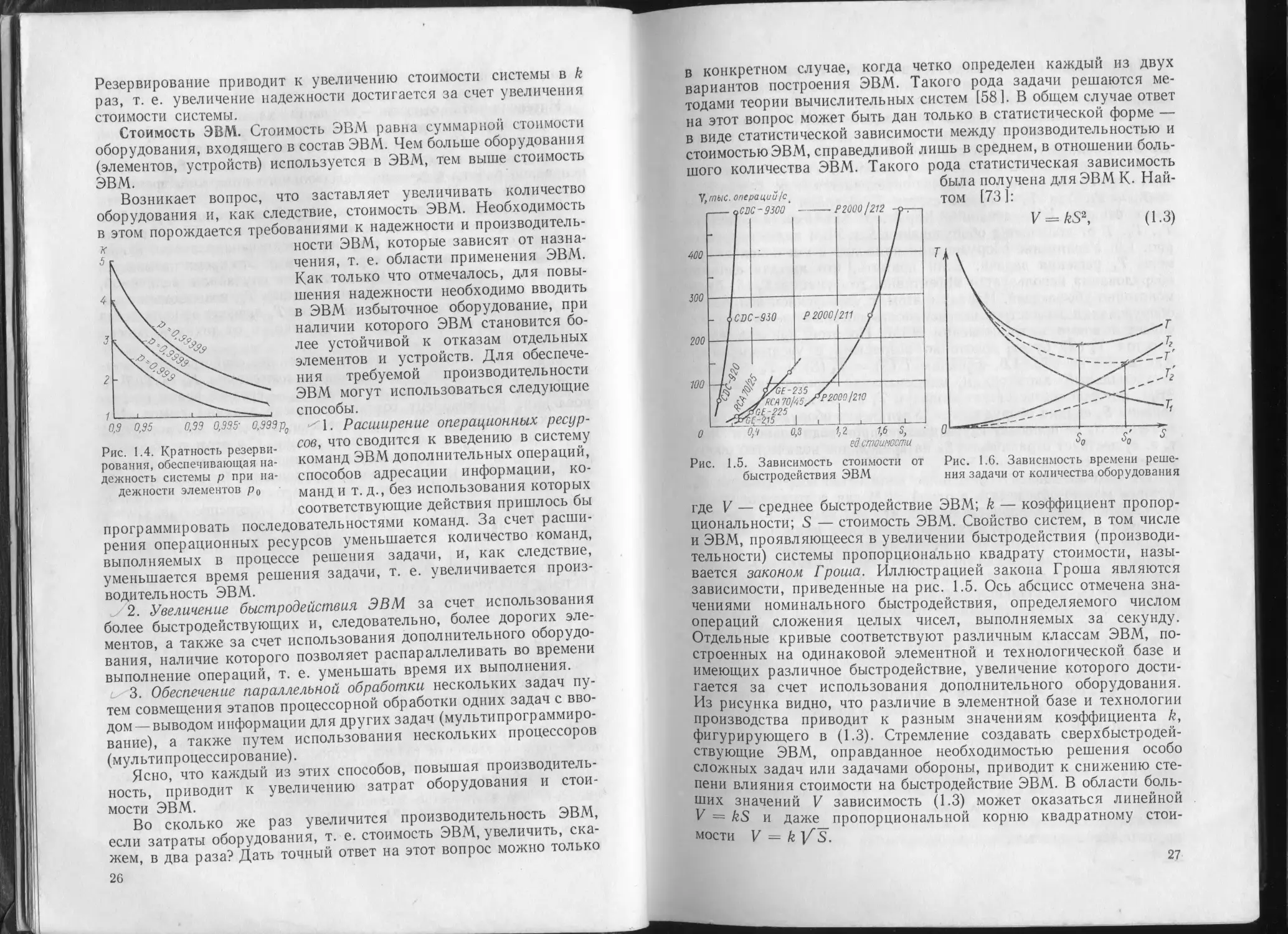

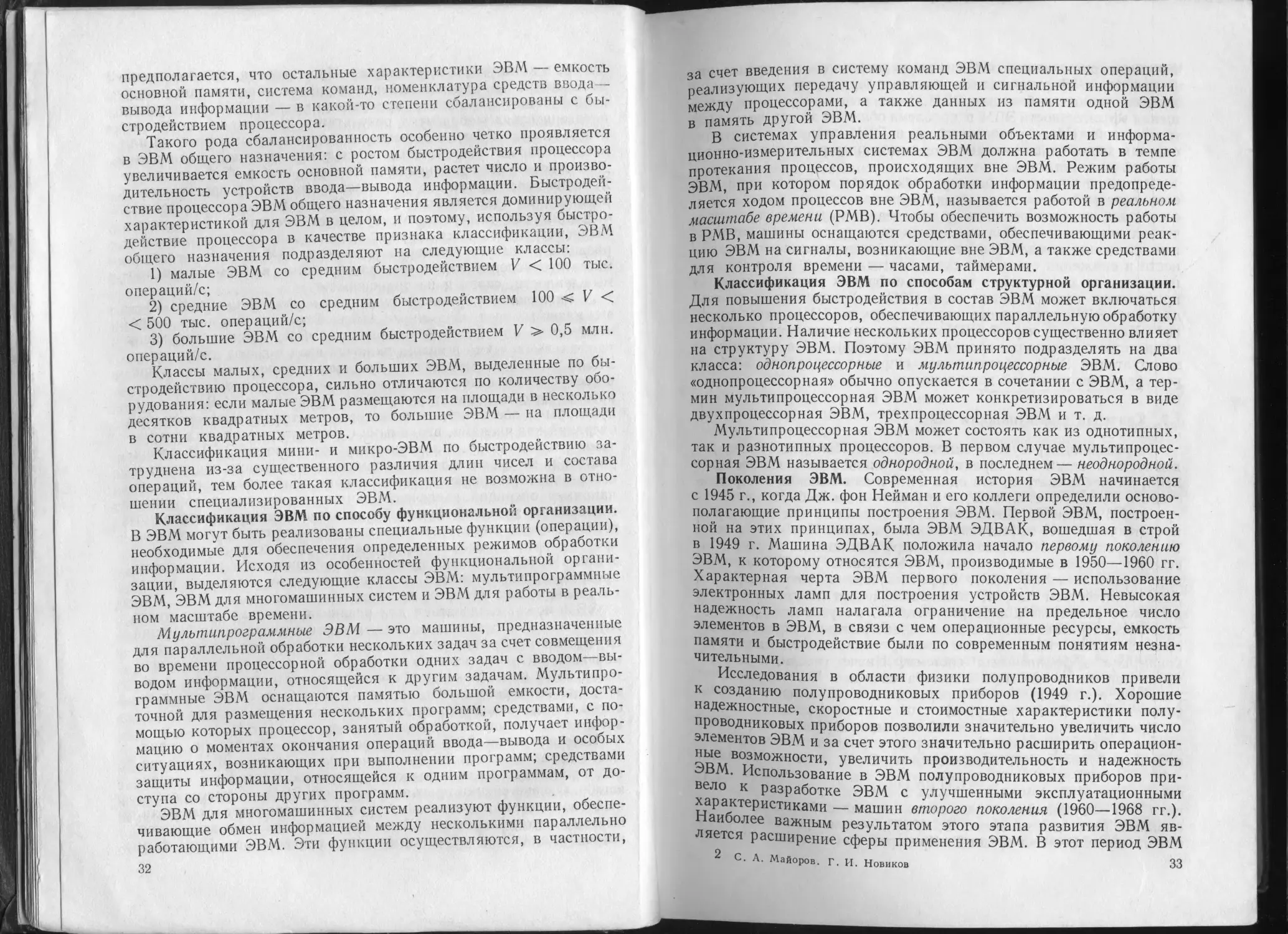

была получена для ЭВМ К. Най-

Рис. 1.5. Зависимость стоимости от

быстродействия ЭВМ

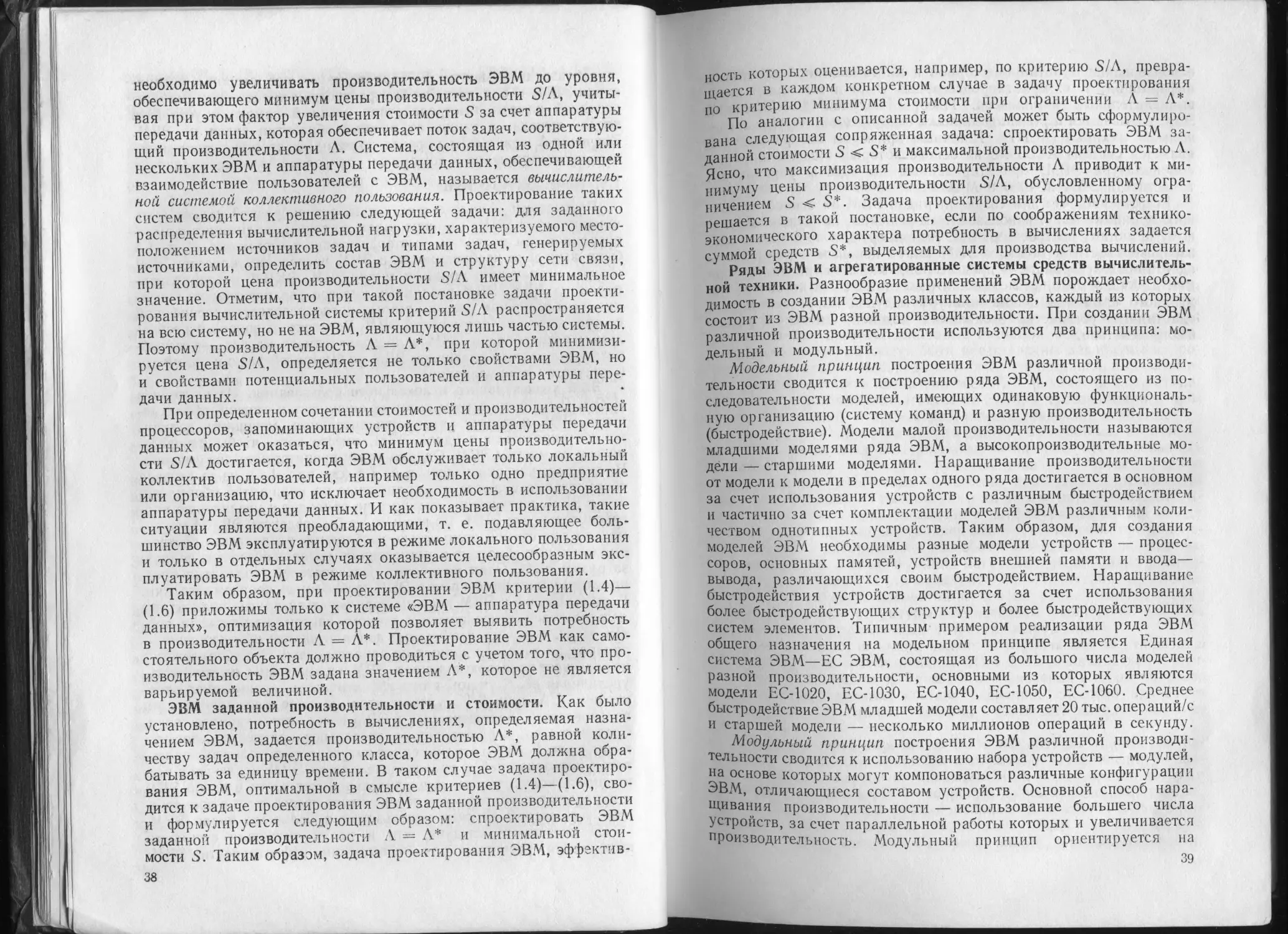

Рис. 1.6. Зависимость времени реше-

ния задачи от количества оборудования

где V — среднее быстродействие ЭВМ; k — коэффициент пропор-

циональности; S — стоимость ЭВМ. Свойство систем, в том числе

и ЭВМ, проявляющееся в увеличении быстродействия (производи-

тельности) системы пропорционально квадрату стоимости, назы-

вается законом Гроша. Иллюстрацией закона Гроша являются

зависимости, приведенные на рис. 1.5. Ось абсцисс отмечена зна-

чениями номинального быстродействия, определяемого числом

операций сложения целых чисел, выполняемых за секунду.

Отдельные кривые соответствуют различным классам ЭВМ, по-

строенных на одинаковой элементной и технологической базе и

имеющих различное быстродействие, увеличение которого дости-

гается за счет использования дополнительного оборудования.

Из рисунка видно, что различие в элементной базе и технологии

производства приводит к разным значениям коэффициента k,

фигурирующего в (1.3). Стремление создавать сверхбыстродей-

ствующие ЭВМ, оправданное необходимостью решения особо

сложных задач или задачами обороны, приводит к снижению сте-

пени влияния стоимости на быстродействие ЭВМ. В области боль-

ших значений V зависимость (1.3) может оказаться линейной

V = kS и даже пропорциональной корню квадратному стои-

мости v = k уз.

27

Закон Гроша (1.3) наталкивает на мысль, что за счет увеличе-

ния количества оборудования, определяемого стоимостью S,

можно беспредельно повышать производительность ЭВМ. Однако

дело обстоит иначе. Определяя производительность числом задач,

обрабатываемых ЭВМ в единицу времени, необходимо учитывать,

что ЭВМ обладает нулевой производительностью в период восста-

новления системы после отказа оборудования. Учитывая это, при-

мем, что время решения задачи определяется как сумма Т =

= А + ^2, где Ту — время счета; Т2 — время простоя ЭВМ

из-за отказов оборудования. Характер зависимости значений

Ту, Т2, Т от количества оборудования S в ЭВМ иллюстрируется

рис. 1.6. Увеличение оборудования приводит к уменьшению вре-

мени Ту решения задачи. Если принять, что каждая единица

оборудования используется эффективно, то функция 7\ (S) будет

монотонно убывающей. Наряду с этим, с увеличением количества

оборудования возрастает интенсивность потока отказов и увели-

чивается время восстановления ЭВМ. По этой причине время

простоя Т2 (S) будет монотонно возрастать с увеличением S.

Как видно из рис. 1.6, функция Т (S) = Ту (S) + Т2 (S) носит

экстремальный характер и максимальная производительность

ЭВМ, которой соответствует минимум Т, достигается при исполь-

зовании So единиц оборудования. Увеличение оборудования сверх

значения So не приводит к увеличению производительности ЭВМ,

т. е. существует ограничение 30 на предельное количество обору-

дования в составе одной ЭВМ.

От чего же зависит предельное количество оборудования So,

которое можно объединять в одной ЭВМ для достижения макси-

мальной производительности? Ясно, что ход кривой Ту (S) опре-

деляется эффективностью схемных решений, применяемых для

увеличения производительности ЭВМ, т. е. уровнем развития

теории и практики проектирования ЭВМ. Ход кривой Т2 (S)

связан со степенью совершенства производственно-технологиче-

ской базы вычислительной техники. Использование более совер-

шенной технологии, например технологии интегральных схем,

приводит к повышению надежности элементов и устройств, в ре-

зультате чего время простоев снижается до значений, определяе-

мых кривой T'i (рис. 1.6), и время решения задачи будет опреде-

ляться кривой Т', которая достигает минимума при So > So.

А это означает, что совершенствование технологической базы

позволяет за счет использования большего количества оборудова-

ния создавать более производительные ЭВМ.

Таким образом, состояние технологической базы вычисли-

тельной техники предопределяет предельное количество обору-

дования, которое может эффективно использоваться для повыше-

ния производительности ЭВМ. Увеличение количества оборудо-

вания сверх предельно допустимого значения не приводит к повы-

шению производительности ЭВМ, хотя быстродействие ЭВМ

продолжает возрастать.

28

1.6. Классификация ЭВМ

Цель классификации — разделить множество существующих

и мыслимых ЭВМ на непересекающиеся подмножества — классы,

чтобы свойства и закономерности, присущие конкретной ЭВМ,

можно было бы определять исходя из свойств и закономерностей,

присущих классу, к которому относится ЭВМ. Классификация

проводится на основе свойств функций, структур и характеристик

ЭВМ, называемых признаками классификации. Многообразие

свойств и характеристик ЭВМ, присущее ЭВМ как сложным

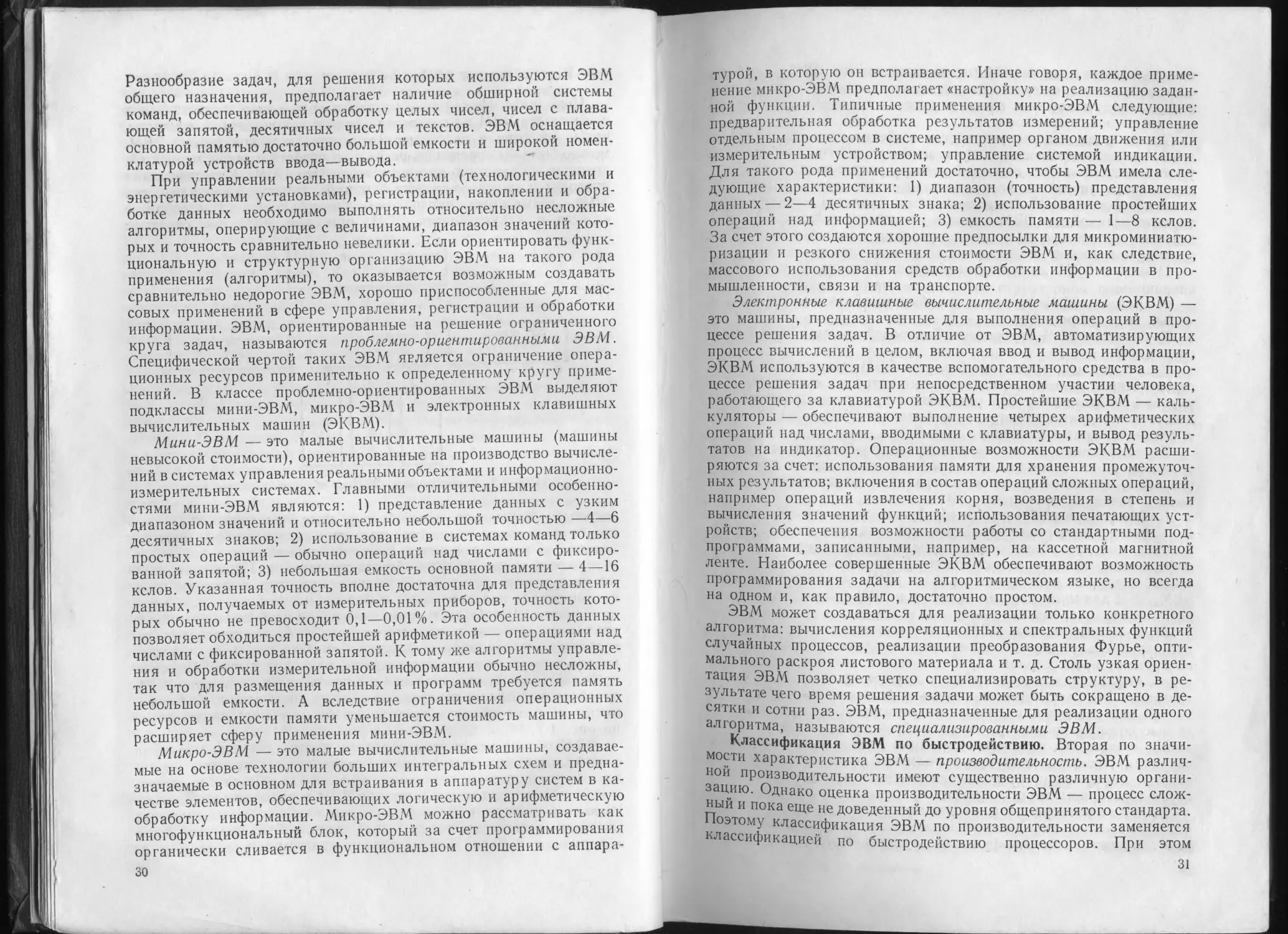

Рис. 1.7. Классификация ЭВМ по области применения

системам, порождает многообразие классификаций, различаю-

щихся в основном тем, какие признаки принимаются в качестве

главных и какие считаются второстепенными.

Классификация ЭВМ по области применения. Признавая доми-

нирующую роль функций в отношении структур, в качестве глав-

ного признака классификации выбирают назначение, т. е. область

применения ЭВМ. Область применения ЭВМ наиболее существенно

влияет на свойства и характеристики ЭВМ, предопределяя по-

требность в операционных ресурсах, емкости памяти и средствах

ввода—вывода, что, в свою очередь, приводит к специфическим

особенностям в функциональной и структурной организации ЭВМ,

ориентированным на конкретную область применения. Классифи-

кация ЭВМ по области применения (назначению) представлена

на рис. 1.7.

ЭВМ. общего назначения предназначаются для использования

в вычислительных центрах, автоматизированных системах управ-

ления производством, отраслями народного хозяйства и транспор-

том. В такого рода применениях на ЭВМ возлагается выполнение

широкого спектра работ: выполнение научных и инженерных

расчетов, решение экономических задач, обработка текстовой

информации в целях автоматизации программирования и т. д.

29

Разнообразие задач, для решения которых используются ЭВМ

общего назначения, предполагает наличие обширной системы

команд, обеспечивающей обработку целых чисел, чисел с плава-

ющей запятой, десятичных чисел и текстов. ЭВМ оснащается

основной памятью достаточно большой емкости и широкой номен-

клатурой устройств ввода—вывода.

При управлении реальными объектами (технологическими и

энергетическими установками), регистрации, накоплении и обра-

ботке данных необходимо выполнять относительно несложные

алгоритмы, оперирующие с величинами, диапазон значений кото-

рых и точность сравнительно невелики. Если ориентировать функ-

циональную и структурную организацию ЭВМ на такого рода

применения (алгоритмы), то оказывается возможным создавать

сравнительно недорогие ЭВМ, хорошо приспособленные для мас-

совых применений в сфере управления, регистрации и обработки

информации. ЭВМ, ориентированные на решение ограниченного

круга задач, называются проблемно-ориентированными ЭВМ.

Специфической чертой таких ЭВМ является ограничение опера-

ционных ресурсов применительно к определенному кругу приме-

нений. В классе проблемно-ориентированных ЭВМ выделяют

подклассы мини-ЭВМ, микро-ЭВМ и электронных клавишных

вычислительных машин (ЭКВМ).

Мини-ЭВМ — это малые вычислительные машины (машины

невысокой стоимости), ориентированные на производство вычисле-

ний в системах управления реальными объектами и информационно-

измерительных системах. Главными отличительными особенно-

стями мини-ЭВМ являются: 1) представление данных с узким

диапазоном значений и относительно небольшой точностью —4—6

десятичных знаков; 2) использование в системах команд только

простых операций — обычно операций над числами с фиксиро-

ванной запятой; 3) небольшая емкость основной памяти — 4—16

кслов. Указанная точность вполне достаточна для представления

данных, получаемых от измерительных приборов, точность кото-

рых обычно не превосходит 0,1—0,01%. Эта особенность данных

позволяет обходиться простейшей арифметикой — операциями над

числами с фиксированной запятой. К тому же алгоритмы управле-

ния и обработки измерительной информации обычно несложны,

так что для размещения данных и программ требуется память

небольшой емкости. А вследствие ограничения операционных

ресурсов и емкости памяти уменьшается стоимость машины, что

расширяет сферу применения мини-ЭВМ.

Микро-ЭВМ — это малые вычислительные машины, создавае-

мые на основе технологии больших интегральных схем и предна-

значаемые в основном для встраивания в аппаратуру систем в ка-

честве элементов, обеспечивающих логическую и арифметическую

обработку информации. Микро-ЭВМ можно рассматривать как

многофункциональный блок, который за счет программирования

органически сливается в функциональном отношении с аппара-

30

турой, в которую он встраивается. Иначе говоря, каждое приме-

нение микро-ЭВМ предполагает «настройку» на реализацию задан-

ной функции. Типичные применения микро-ЭВМ следующие:

предварительная обработка результатов измерений; управление

отдельным процессом в системе, например органом движения или

измерительным устройством; управление системой индикации.

Для такого рода применений достаточно, чтобы ЭВМ имела сле-

дующие характеристики: 1) диапазон (точность) представления

данных — 2—4 десятичных знака; 2) использование простейших

операций над информацией; 3) емкость памяти — 1—8 кслов.

За счет этого создаются хорошие предпосылки для микроминиатю-

ризации и резкого снижения стоимости ЭВМ и, как следствие,

массового использования средств обработки информации в про-

мышленности, связи и на транспорте.

Электронные клавишные вычислительные машины (ЭКВМ) —

это машины, предназначенные для выполнения операций в про-

цессе решения задач. В отличие от ЭВМ, автоматизирующих

процесс вычислений в целом, включая ввод и вывод информации,

ЭКВМ используются в качестве вспомогательного средства в про-

цессе решения задач при непосредственном участии человека,

работающего за клавиатурой ЭКВМ. Простейшие ЭКВМ — каль-

куляторы — обеспечивают выполнение четырех арифметических

операций над числами, вводимыми с клавиатуры, и вывод резуль-

татов на индикатор. Операционные возможности ЭКВМ расши-

ряются за счет: использования памяти для хранения промежуточ-

ных результатов; включения в состав операций сложных операций,

например операций извлечения корня, возведения в степень и

вычисления значений функций; использования печатающих уст-

ройств; обеспечения возможности работы со стандартными под-

программами, записанными, например, на кассетной магнитной

ленте. Наиболее совершенные ЭКВМ обеспечивают возможность

программирования задачи на алгоритмическом языке, но всегда

на одном и, как правило, достаточно простом.

ЭВМ может создаваться для реализации только конкретного

алгоритма: вычисления корреляционных и спектральных функций

случайных процессов, реализации преобразования Фурье, опти-

мального раскроя листового материала и т. д. Столь узкая ориен-

тация ЭВМ позволяет четко специализировать структуру, в ре-

зультате чего время решения задачи может быть сокращено в де-

сятки и сотни раз. ЭВМ, предназначенные для реализации одного

алгоритма, называются специализированными ЭВМ.

Классификация ЭВМ по быстродействию. Вторая по значи-

мости характеристика ЭВМ — производительность. ЭВМ различ-

ной производительности имеют существенно различную органи-

зацию. Однако оценка производительности ЭВМ — процесс слож-

ный и пока еще не доведенный до уровня общепринятого стандарта,

оэтому классификация ЭВМ по производительности заменяется

классификацией по быстродействию процессоров. При этом

31

предполагается, что остальные характеристики ЭВМ — емкость

основной памяти, система команд, номенклатура средств ввода—

вывода информации — в какой-то степени сбалансированы с бы-

стродействием процессора.

Такого рода сбалансированность особенно четко проявляется

в ЭВМ общего назначения: с ростом быстродействия процессора

увеличивается емкость основной памяти, растет число и произво-

дительность устройств ввода—вывода информации. Быстродей-

ствие процессора ЭВМ общего назначения является доминирующей

характеристикой для ЭВМ в целом, и поэтому, используя быстро-

действие процессора в качестве признака классификации, ЭВМ

общего назначения подразделяют на следующие классы:

1) малые ЭВМ со средним быстродействием V < 100 тыс.

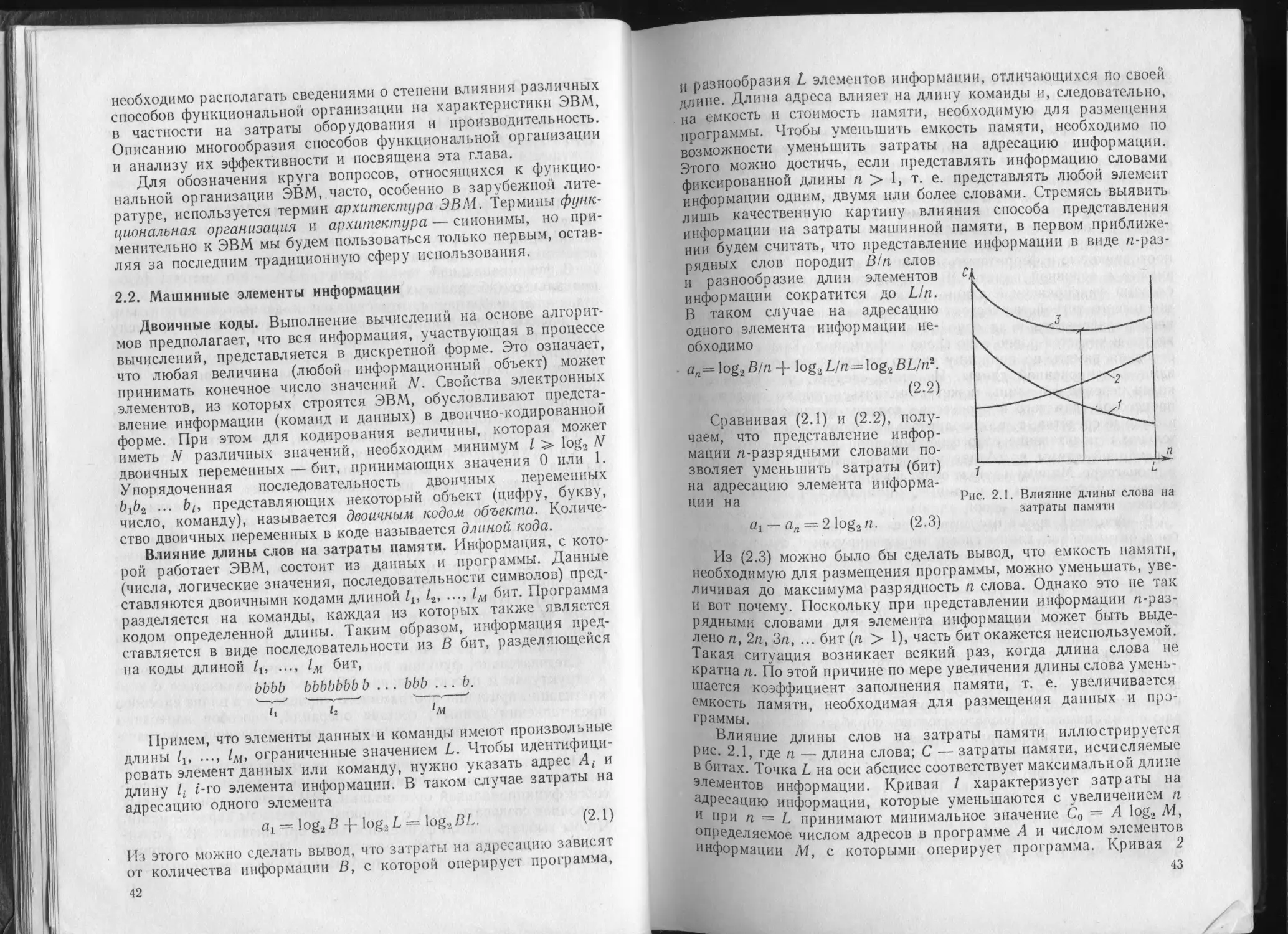

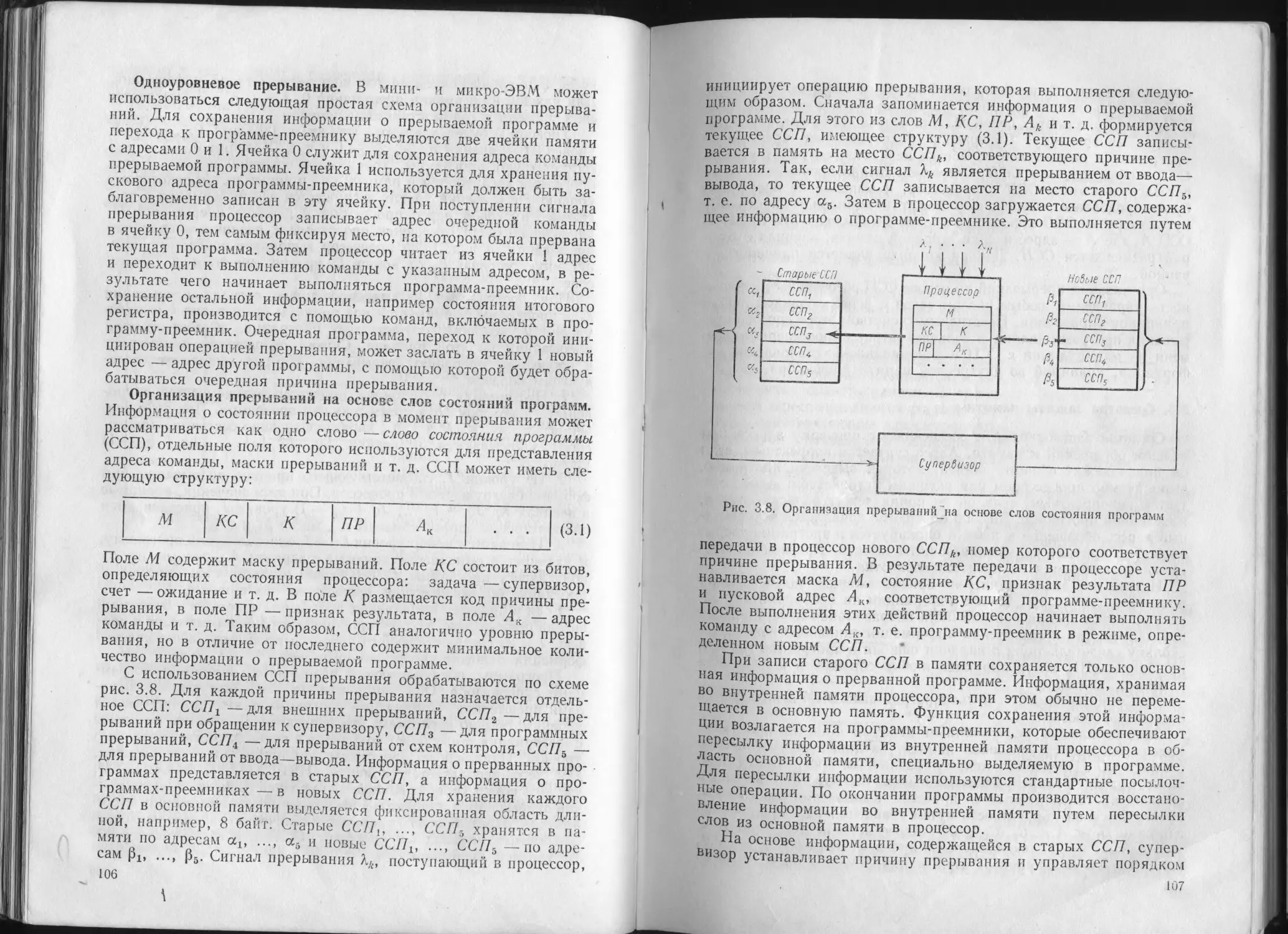

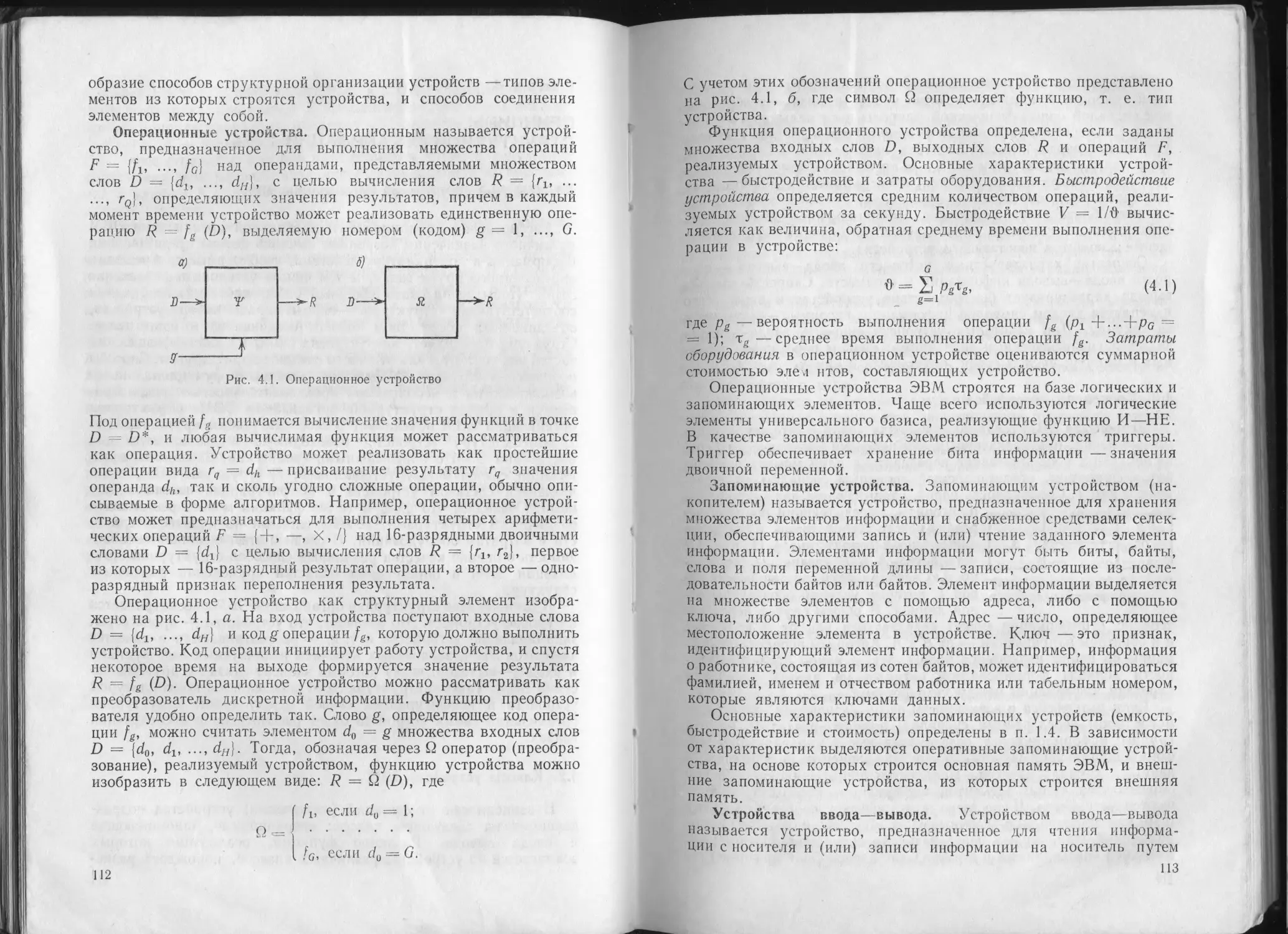

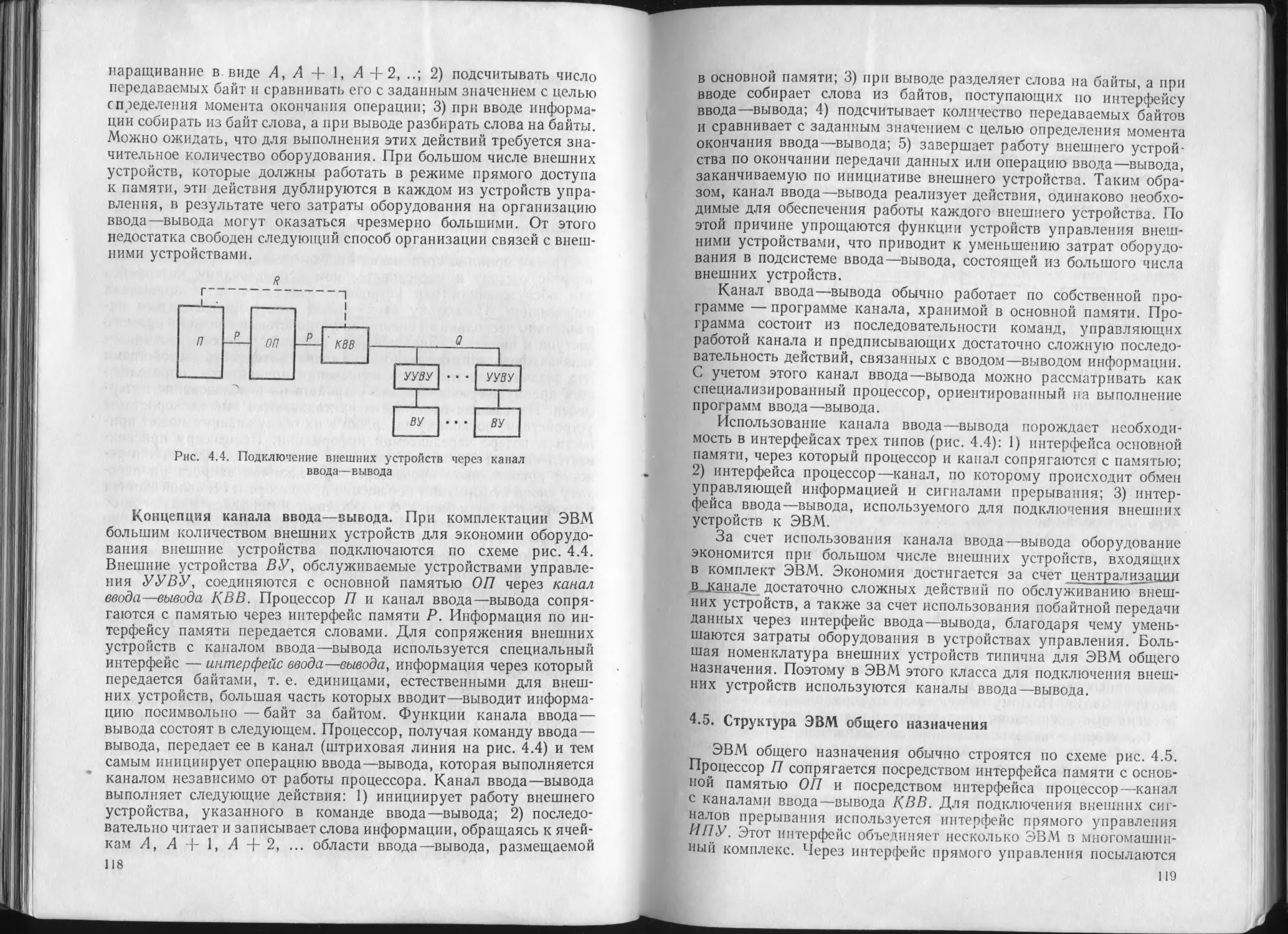

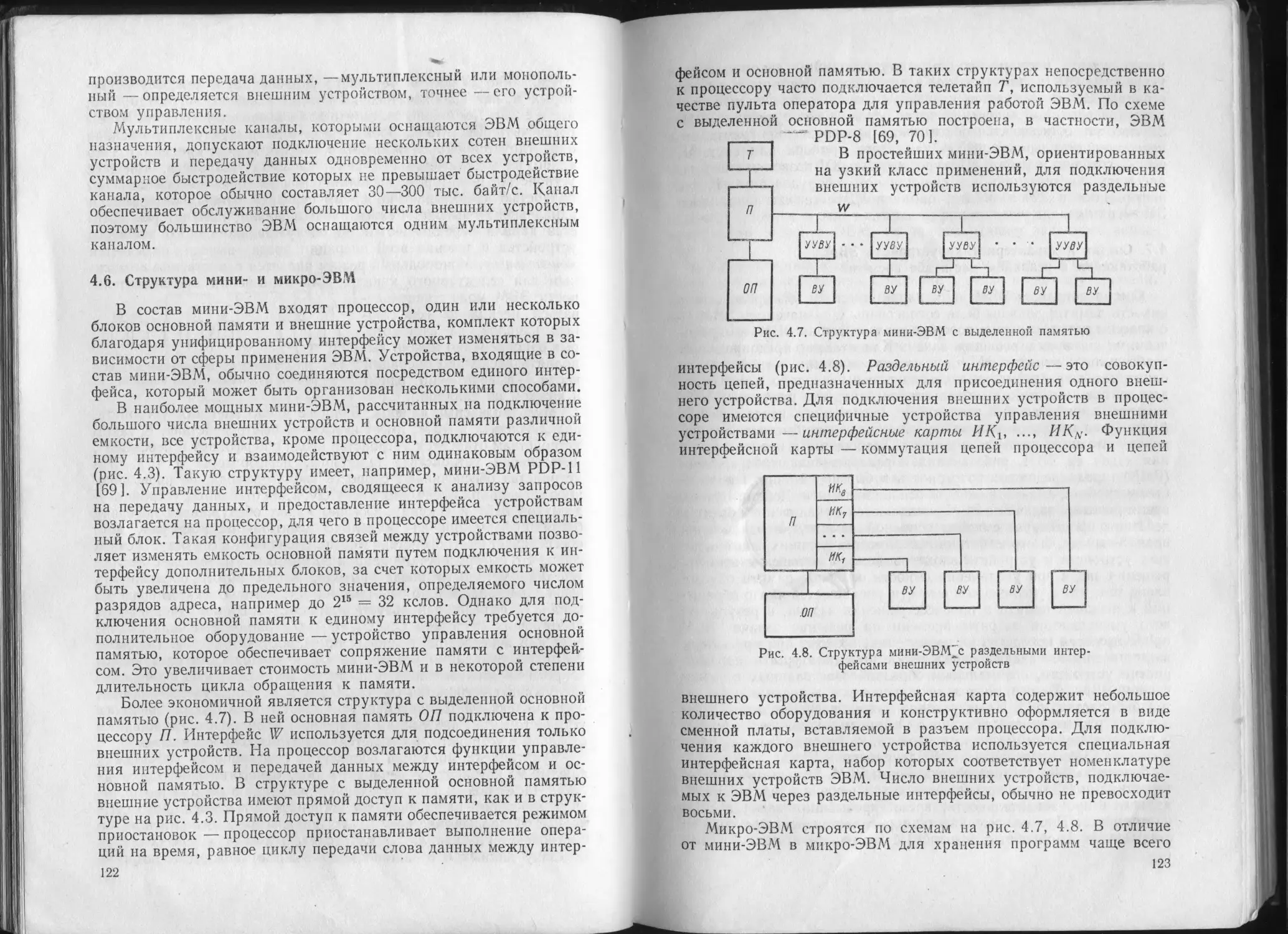

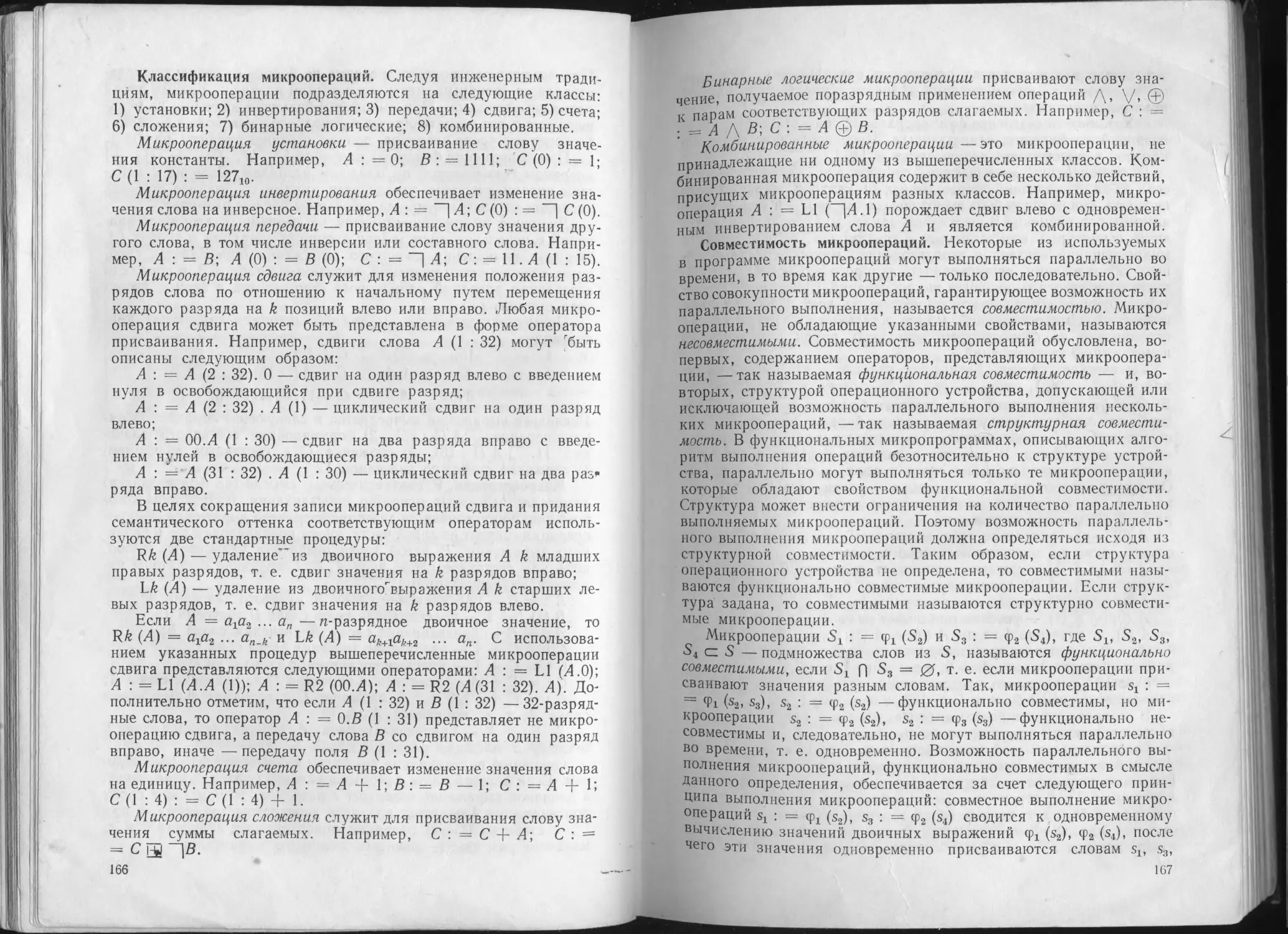

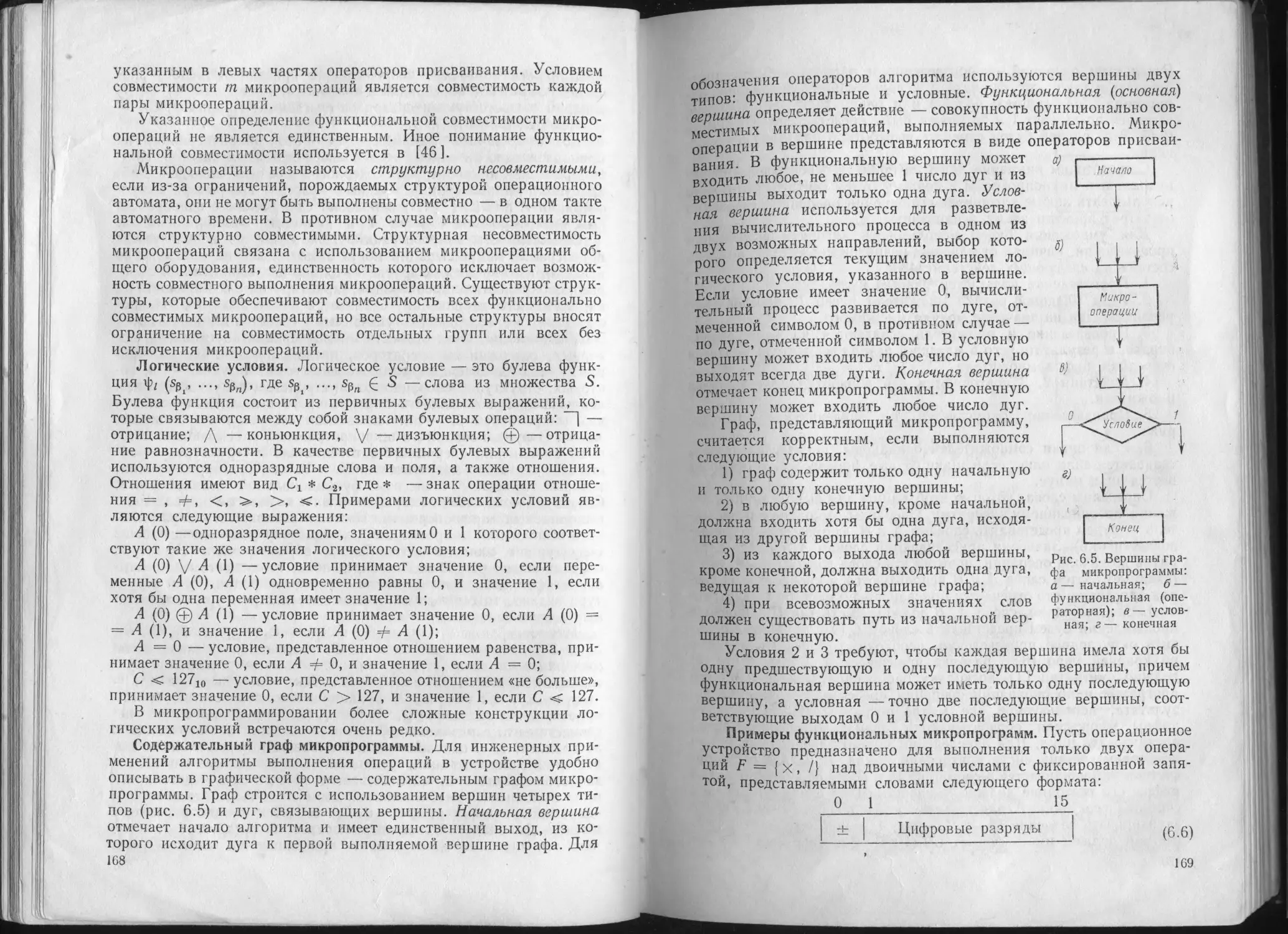

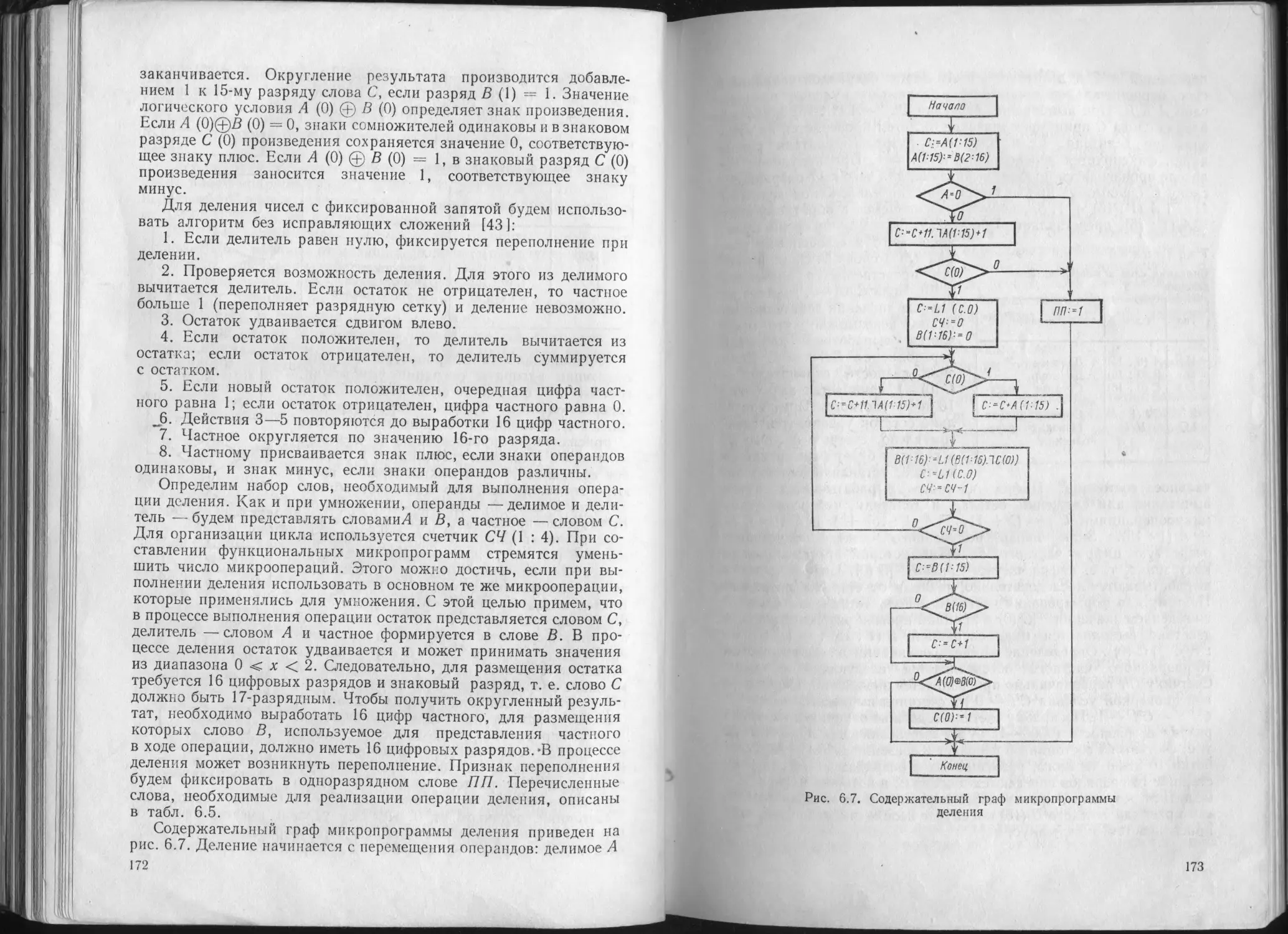

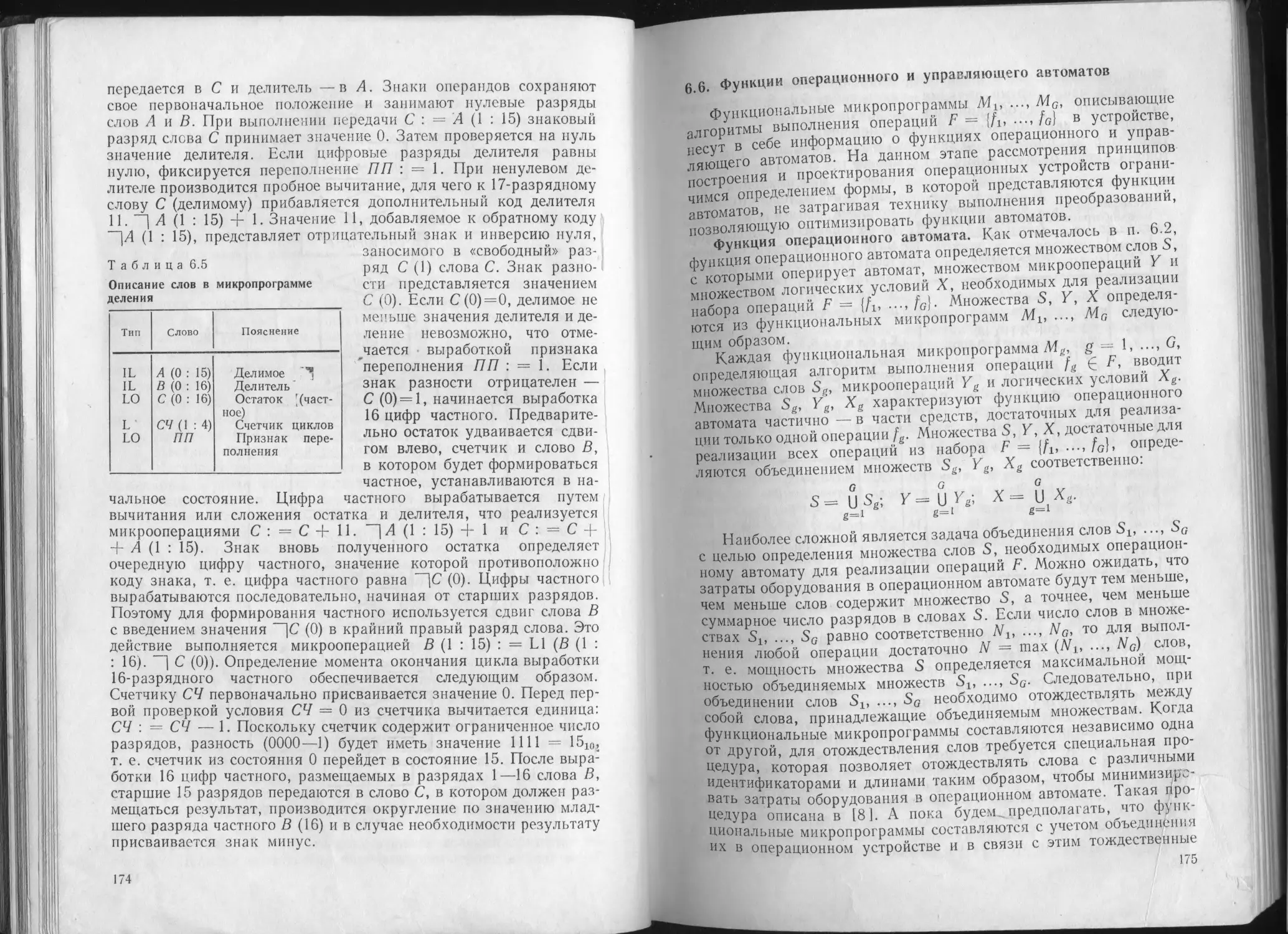

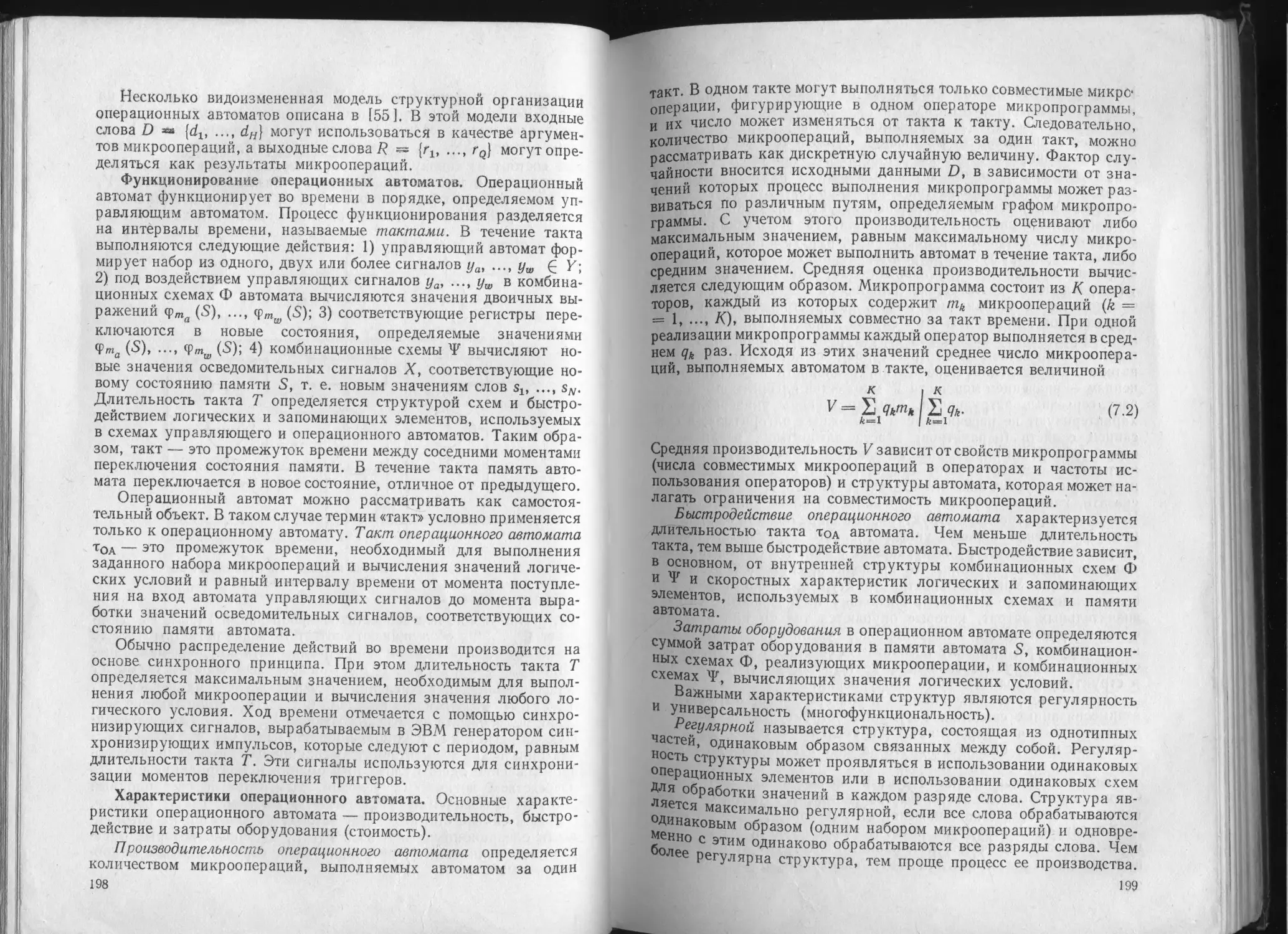

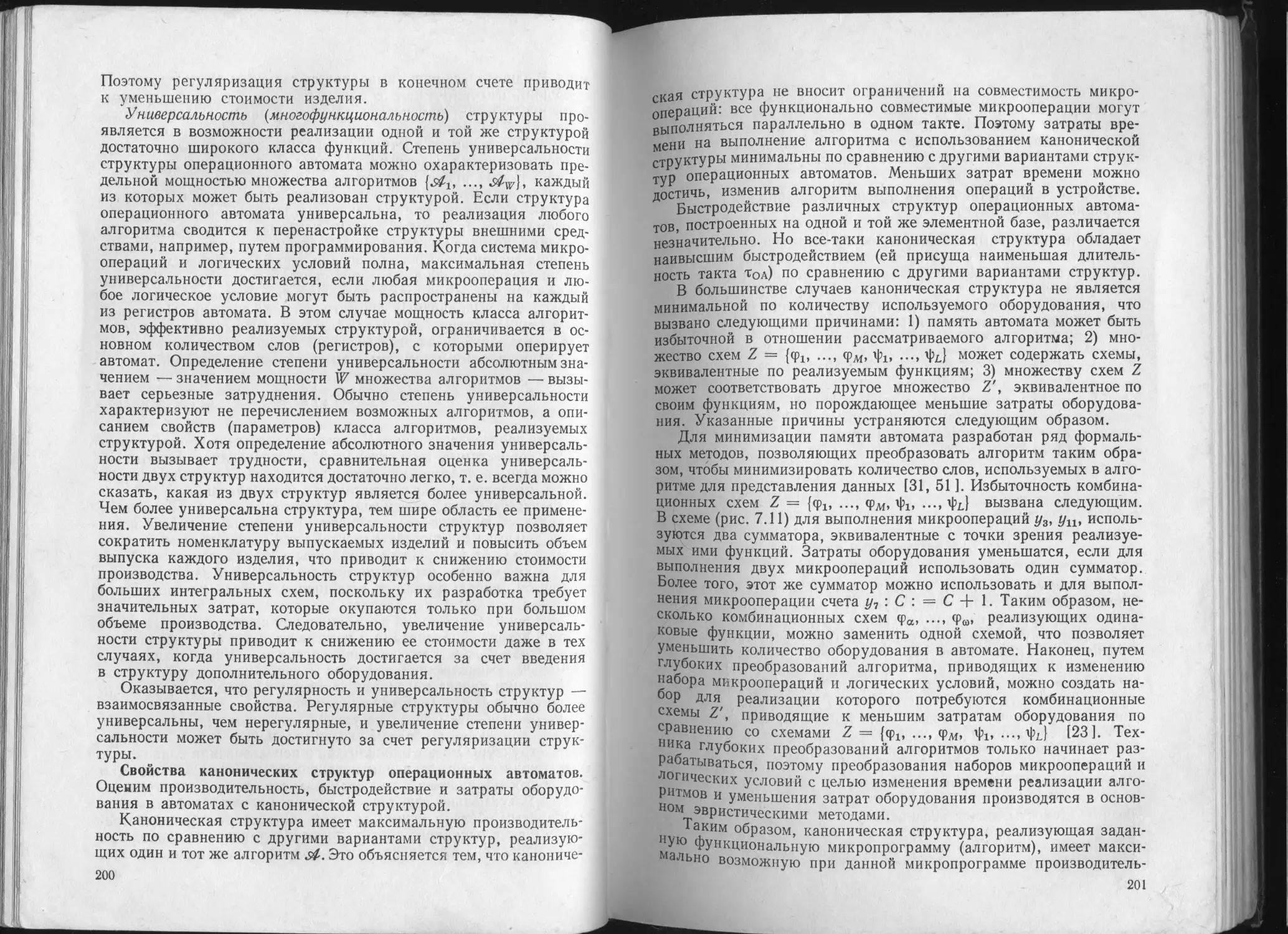

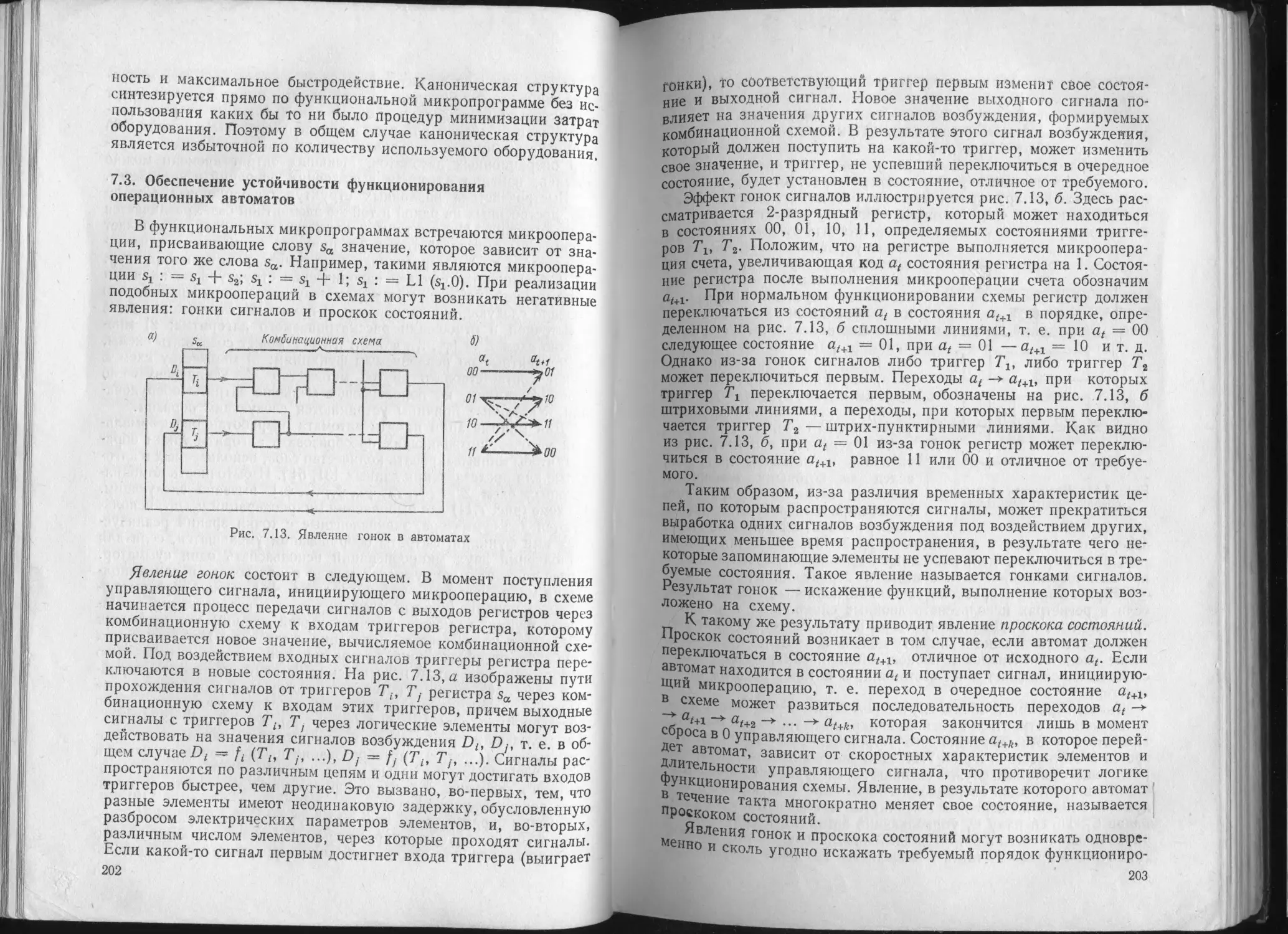

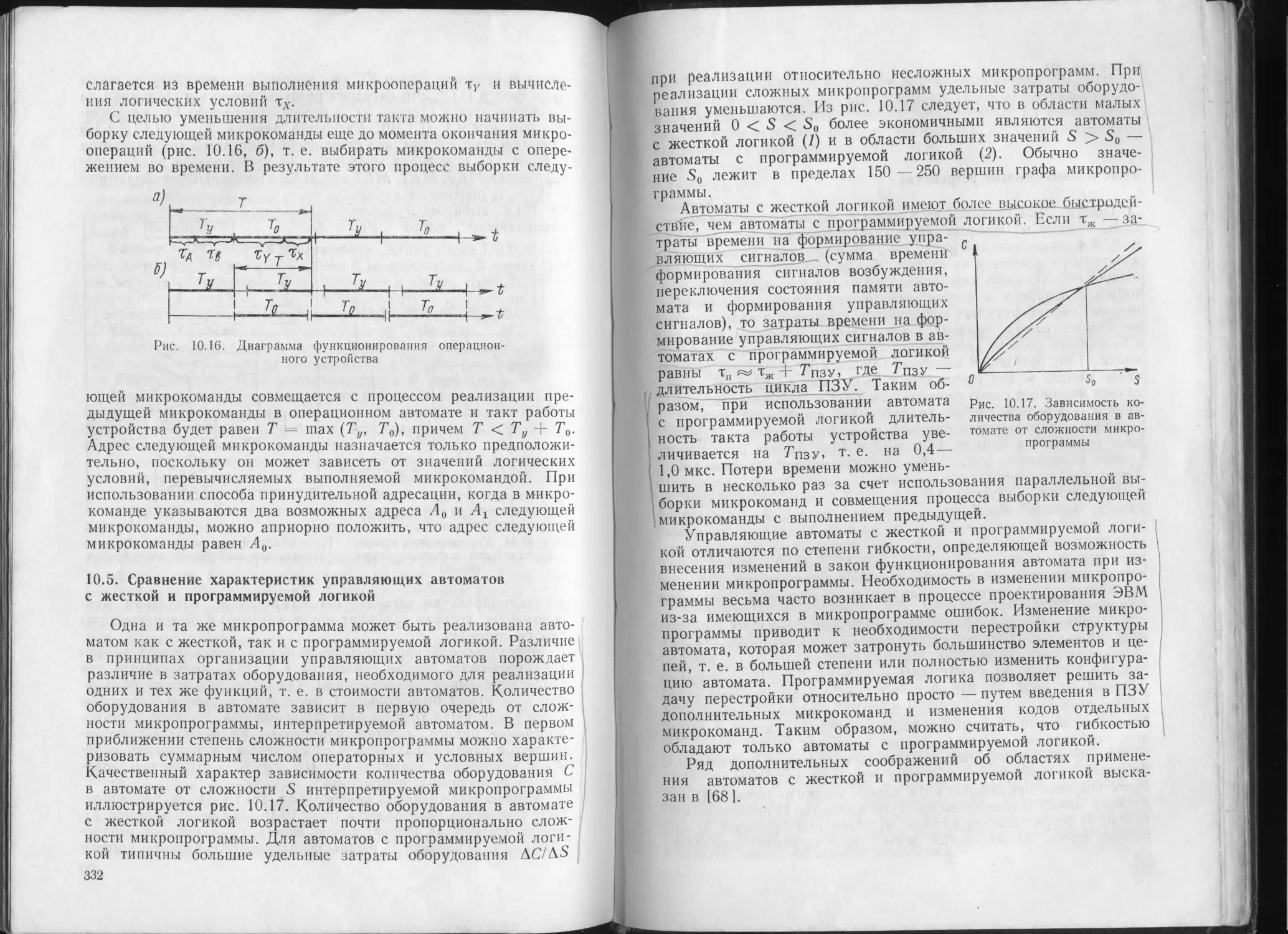

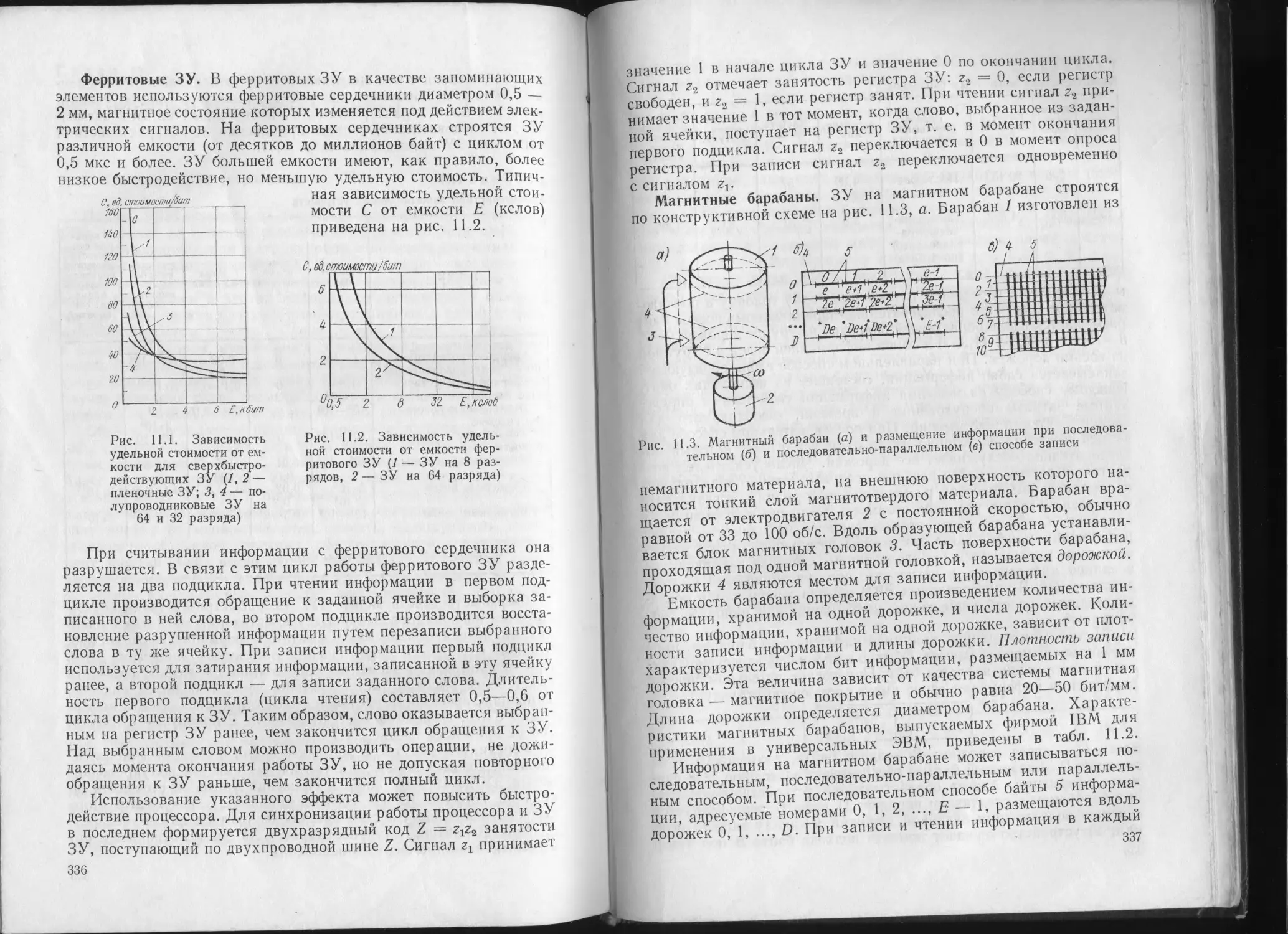

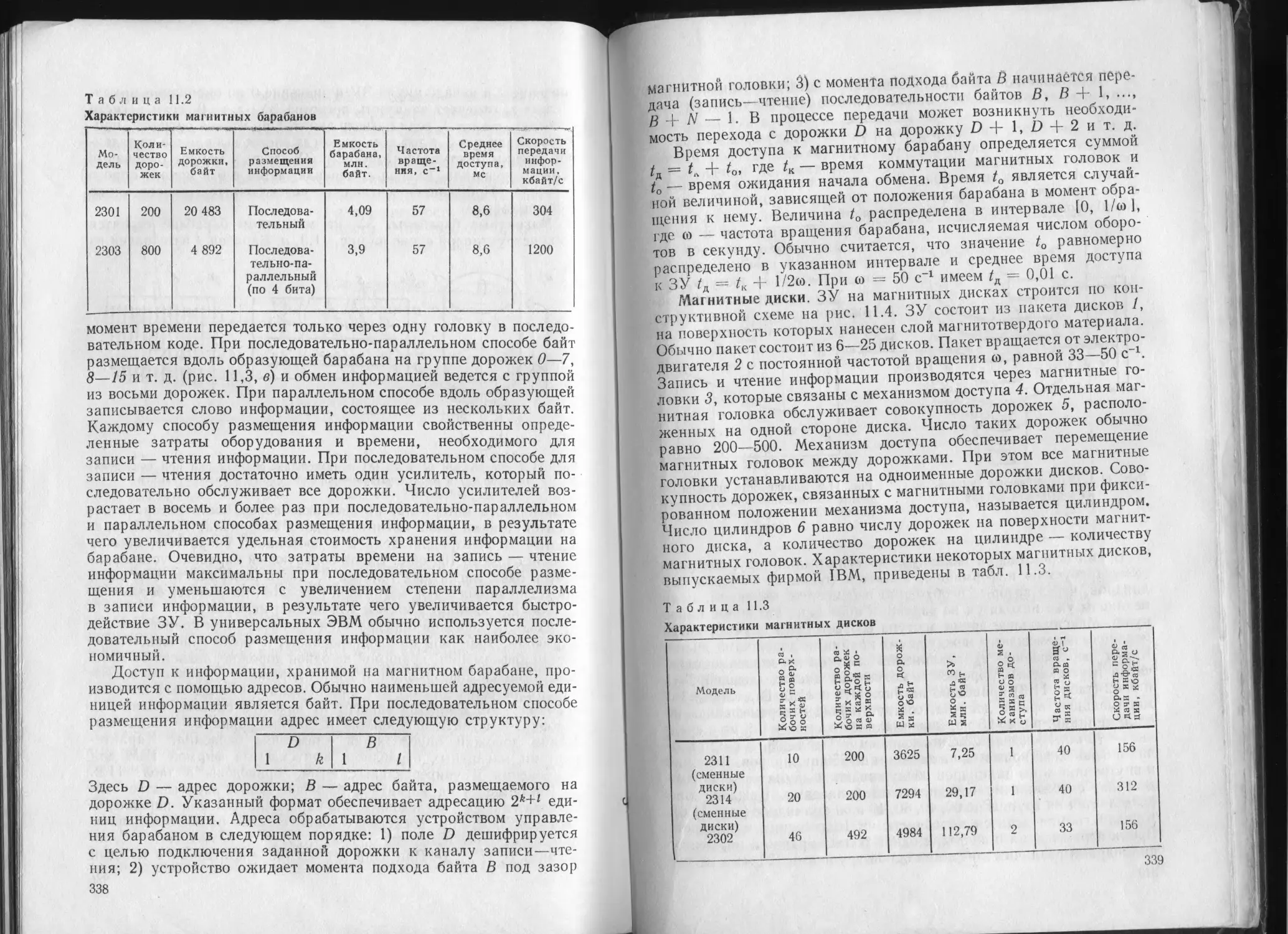

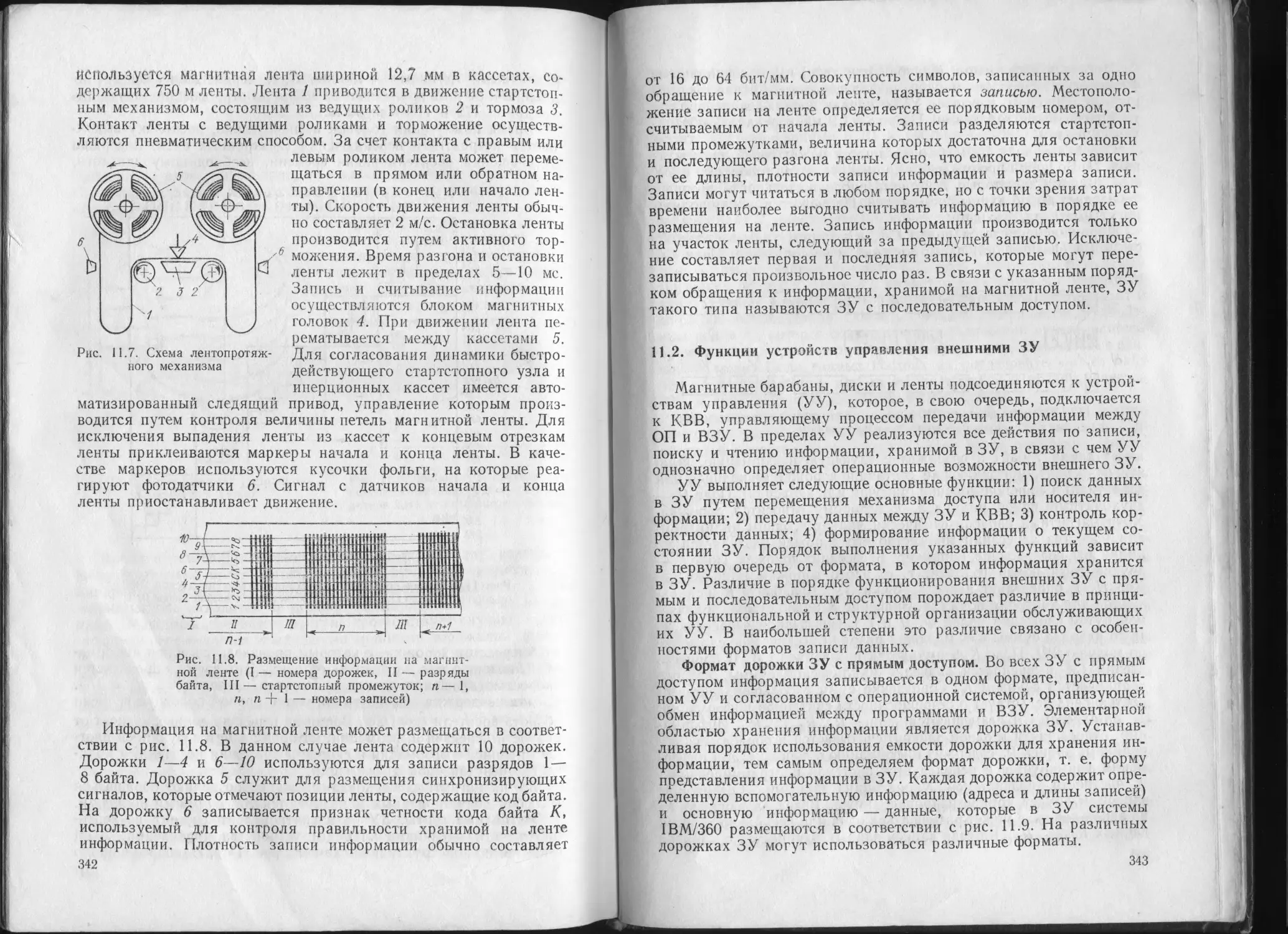

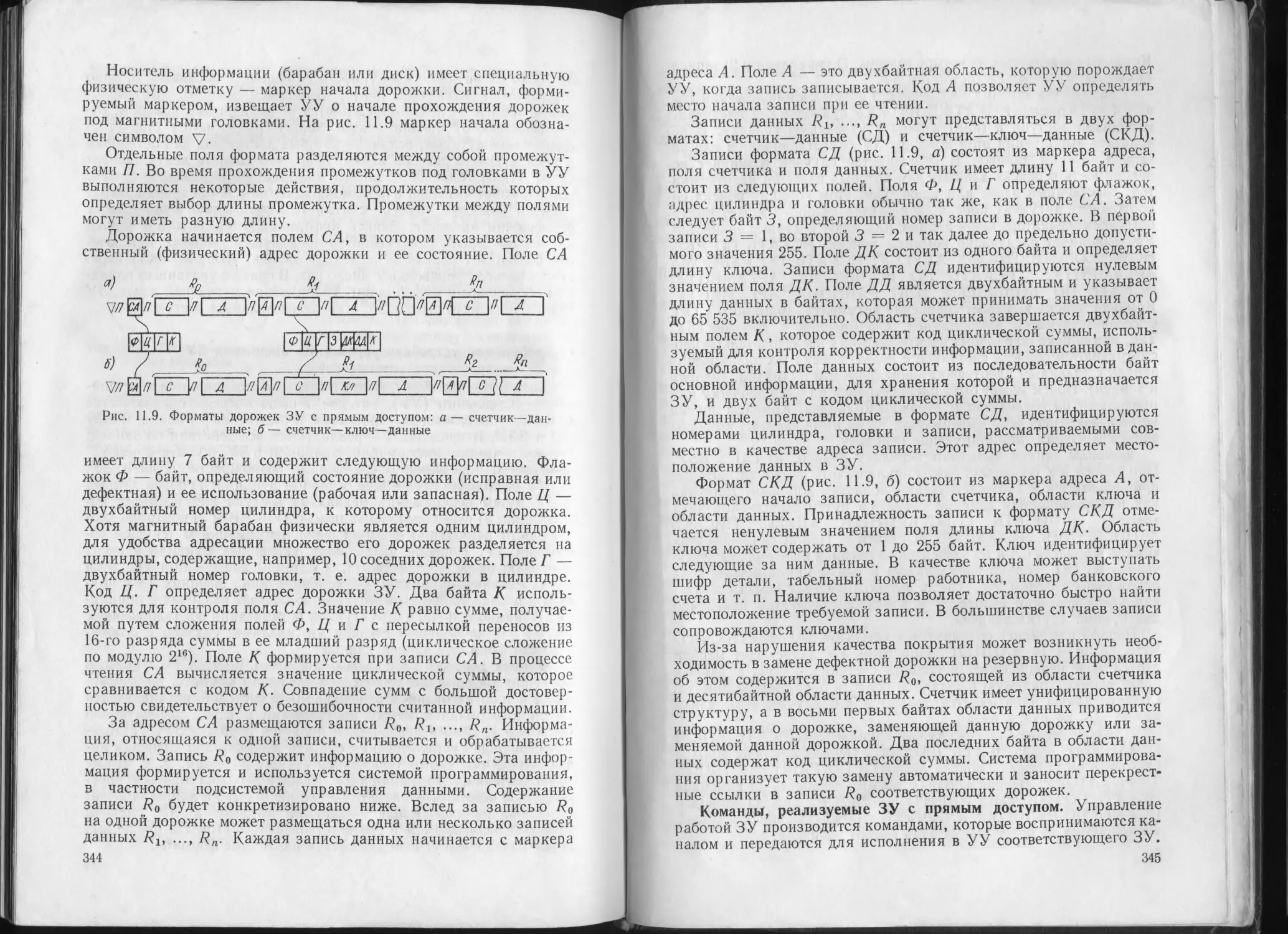

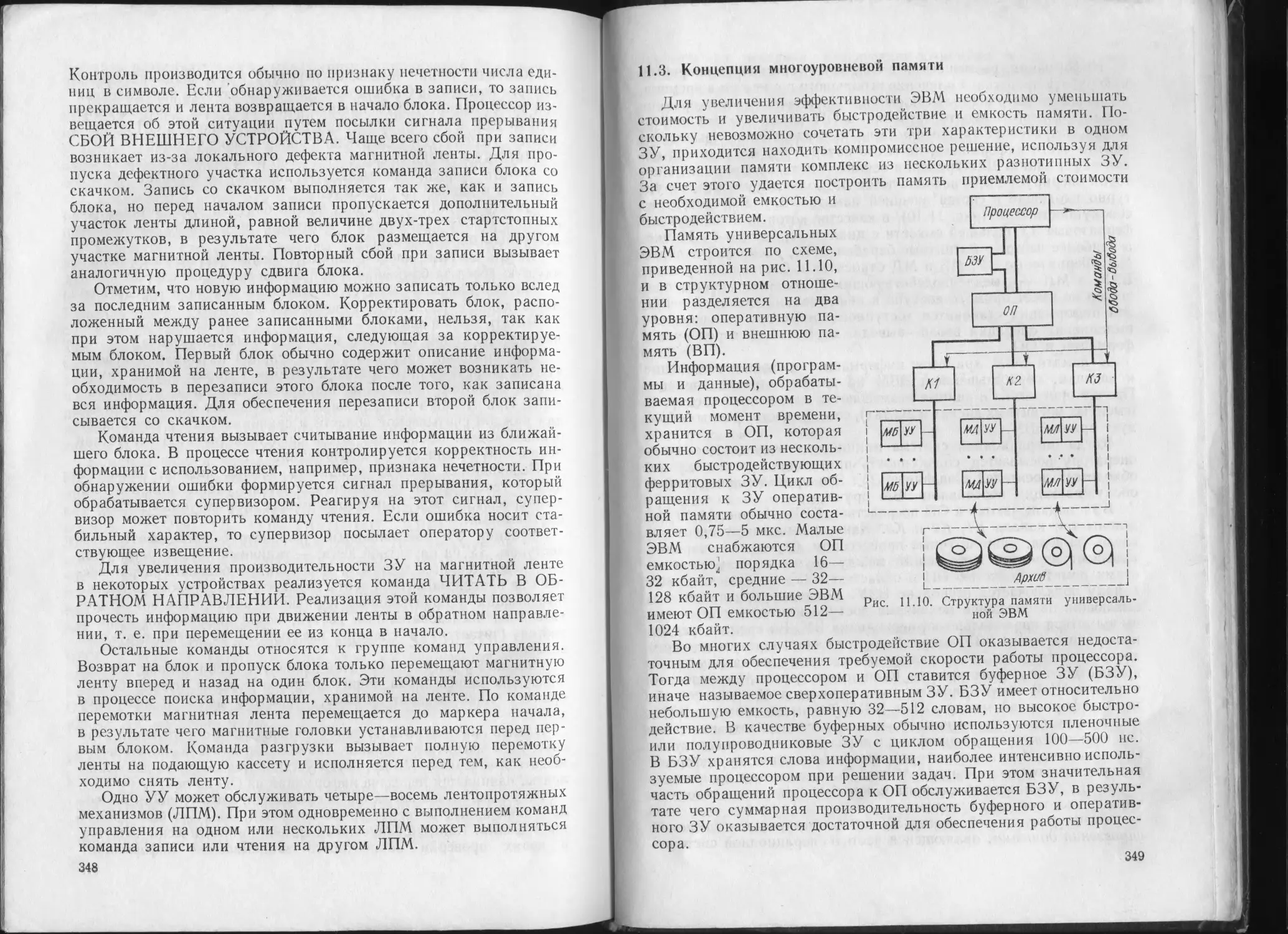

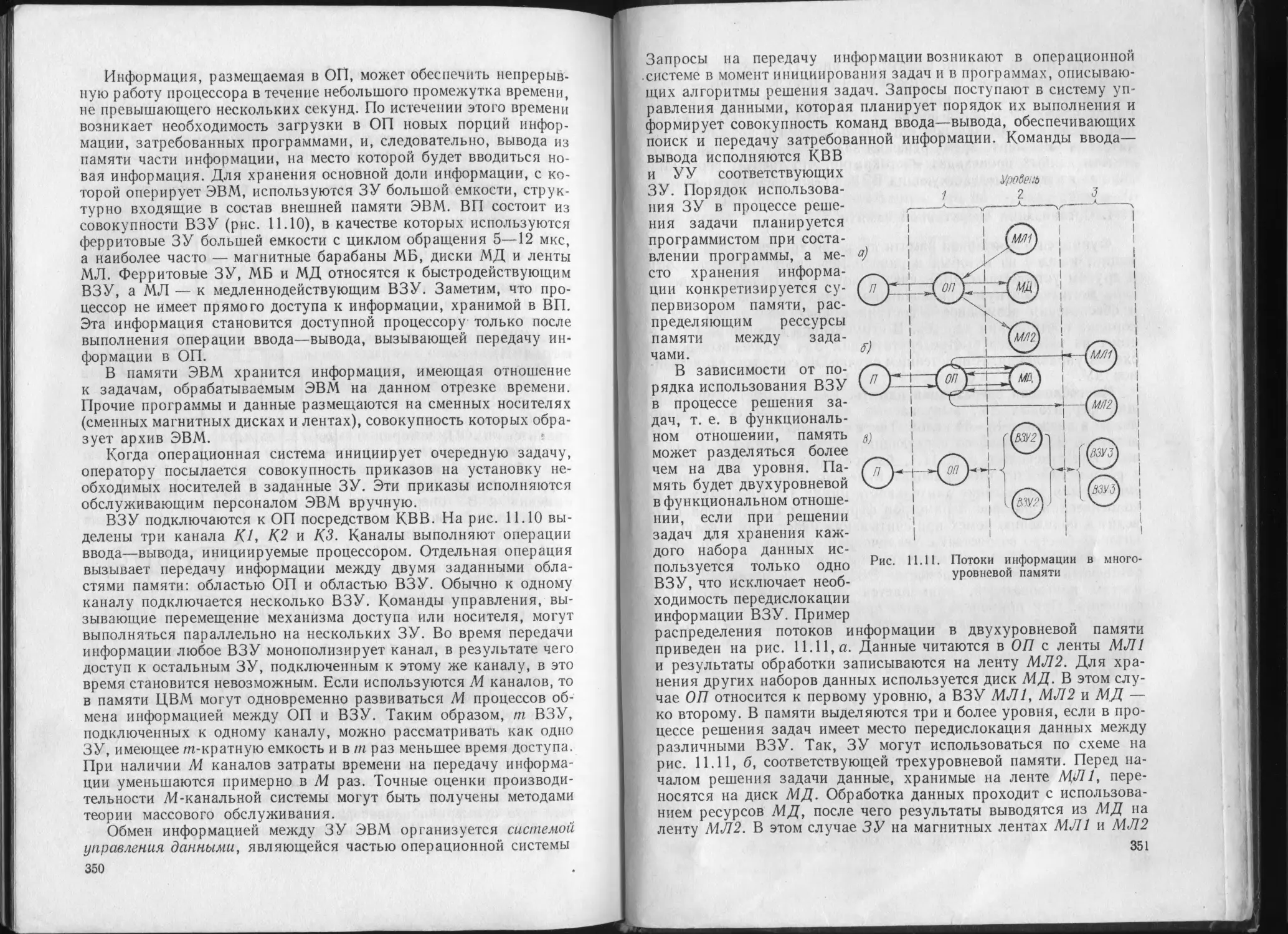

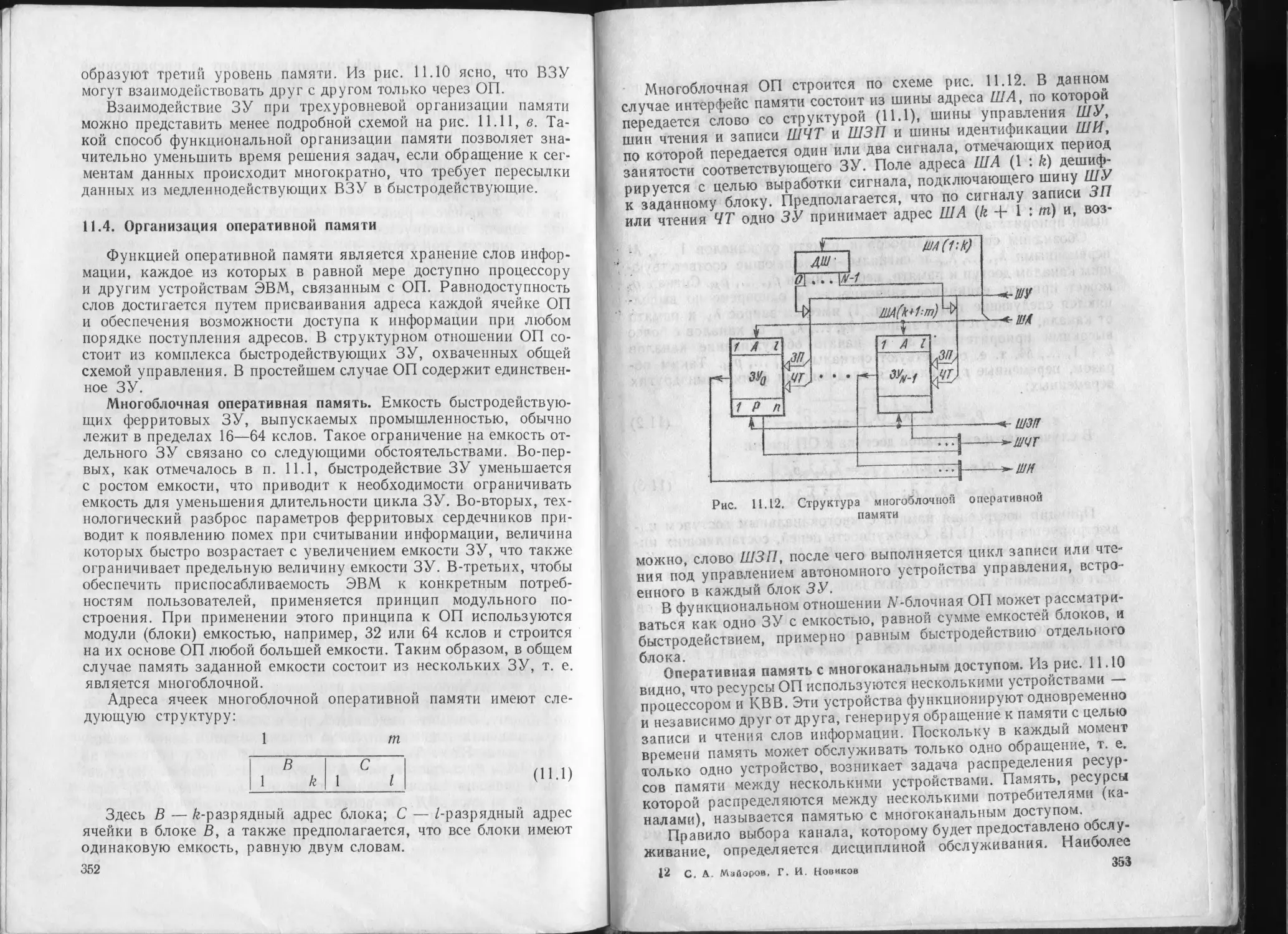

операций/с;