Автор: Богатырев Е.А Ларин В.Ю. Лякин А.Е.

Теги: электротехника электроника справочник энциклопедия

ISBN: 5-9900833-1-9

Год: 2006

Текст

ЭНЦИКЛОПЕДИЯ

ЭЛЕКТРОННЫХ

КОМПОНЕНТОВ

Синтезаторы

• ф1:'iфfфЦil'1

ПJIИС

Память

·- ··

-

....:"

.::::

эн.. ц··и

.."

..

кn::"........ ';.::: .. ··

"",."

ЭЛЕКТРС?81f1Ь111

КОМПОМЕ;нтов

·· :: :;:.: ·:.

.. "._,.,_,~ :-.' :,.".

. ... ······"='~ ..

. : ·· = "'~"" '='"· '"'"' "'·" '"·"'

Том.:·1....

.·

:::.....

··1пьн~1е

схе~~'~!.

. . ... . :..~:::;._:+'

··--:····:....."".....::.:;·

····:·:.,",,:!:::::;.;::~:;;;~,;;,~ ~~;:,:~'''i":;;: .....

~'\ ''!•'\

'

..

"

"

МаКрD·:·~". . •

.. :у·J·м

Москва, 2006

2

ПРЕДИСЛОВИЕ

Появление этой книги - мера вынужденная, обусловленная отсутствием

небольших по объему изданий, содержащих основные сведения о современ

ной элементной базе в объеме, достаточном для понимания принципов, за

ложенных в основу функционирования изделий современной микроэлект

роники и необходимом для грамотного их применения. Однако это не краткий

конспект учебника и не справочник инженера, а энциклопедия, содержащая

короткие статьи о физике процессов, основных принципах построения и то

пологии БИС, справочную информацию о типовых схемах подключения, на

значении выводов БИС и перечень ведущих фирм-производителей.

Развитие микроэлектроники происходит настолько стремительно, что из

дание справочной литературы по данной тематике идет с некоторым опоз

данием. Информация, представленная в настоящем издании базируется на

данных, доступных в 2006 году, однако мы понимаем, что некоторые недостат

ки могут быть обнаружены в ходе ее практического использования.

Будем признательны за информацию обо всех замеченных неточностях,

которые мы обязательно устраним в последующих изданиях энциклопедии.

Генеральный директор ООО «МАКРО ТИМ»

Л.IО. Биленко

ISBN 5-9900833 -1-9 (978-5-9900833- 1-8)

© Богатырев Е. А., Ларин В. IO" Лякин А. Е.

©ООО «МАКРО ТИМ», 2006

МИКРОСХЕМЫ ЦИФРО-АНАЛОГОВЫХ

ПРЕОБРАЗОВАТЕЛЕЙ (ЦАП}

МИКРОСХЕМЫ АНАЛОГО-ЦИФРОВЫХ

ПРЕОБРАЗОВАТЕЛЕЙ (АЦП}

БОЛЬШИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

ЦИФРОВЫХ СИНТЕЗАТОРОВ ЧАСТОТ

ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ ПАМЯТИ

БОЛЬШИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

УНИВЕРСАЛЬНЫХ МИКРОПРОЦЕССОРОВ

БОЛЬШИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

МИКРОКОНТРОЛЛЕРОВ

ЦИФРОВЫЕ СИГНАЛЬНЫЕ ПРОЦЕССОРЫ (DSP}

ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ

ИНТЕГРАЛЬНЫЕ СХЕМЫ (ПЛИС}

БОЛЬШИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ ЦИФРОВЫХ

КВАДРАТУРНЫХ ПРЕОБРАЗОВАТЕЛЕЙ СИГНАЛА

ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ КОДЕКОВ

3

СОДЕРЖАНИЕ

4

ЧАСТЬ 1. АНАЛОГО-ЦИФРОВЫЕ &ИС

1.1. МИКРОСХЕМЫ ЦАП •....•.••....•..••.....•........•....••"........................ 1О

1.1 .1 . Характеристики и классификация ЦАП """"""""""""""""""""""""".. """ 1О

1. 1. 1. 1. Статические характеристики ЦАП"""""" .. """.""""."""""" ......". 1О

1.1.1 .2 . Динамические характеристики ЦАП""""""""".""""".".""" .. " " .. 12

1.1.1.З. Классификация ЦАП""".""" ... """" "."""" """"." """"." . . . " " " " " ." " ." 13

1.1 .2 . Структурные схемы и принципы работы ЦАП""""""""""""""""""" .. ". "" 14

1.1.2 .1 . ЦАП с широтно-импульсной модуляцией

(Pulse-Width Modulatioп, PWM) """"""""". " """" """ """" """" """ .. " "" ." ... ... . " 14

1.1.2 .2 . Последовательный ЦАП на переключаемых

конденсаторах".. "." .. ".. "." .. "."." .. ".""."." .. "...... ".. "."."." .. ".. ""."." ... "...... "... ".. 15

1.1.2.З. Параллельный ЦАП с суммированием весовых токов"" ..... " " 1 6

1.1.2 .4 . ЦАП с резисторной матрицей R-2R"""""""""""""""."""" .. " . . . " ]6

1.1.2.S. ЦАП на источниках тока """"" "." ". """"""" """"""" "." """"" . .. " ." 1 8

1./.2.6 . Параллельный ЦАП на переключаемых конденсаторах" .. .... " 1 8

1.1.2.1. ЦАП с суммированием напряжений"""" ......"""""".".""."".""". 19

1.1 .2.8 . Умножающие ЦАП"""".""""""""".""""""""""."""""".""""" . . . " . . . . 20

1.1 .3 . Перечень ведущих фирм

-

производителей ИМС ЦАП""""."."""."" .. 21

1.1 .4 . Обозначения контактов ИМС ЦАП, применяемые

производителями при составлении документации "". "" " "" "" ". " ." "" " ..... 2 1

1.1 .5 . Типовые схемы включения ИМС ЦАП""""."""".".""""".""""""."."""" . . ". 42

1.2. МИКРОСХЕМЫ АЦП .••••.•..••......••••...•.••.•••.•....••••••.•.•.••••••.•.••••". 26

1.2 .1 . Хапактеристики и классификация АЦП

.""""""""".. "" """ "". .. "" .. " "" "... ". 2 6

1.2. /.1 . Характеристики АЦП."""""""""".".""."""""."""""""""""."." . . " ." . 26

1.2.1 .2 . Классификация АЦП"".".".""""""."""""""""."""""""".""""" .. ... ... 31

1.2 .2 . Основные принципы построения и структурные схемы ИМС АЦП.""."". 31

1.2.2. /. Параллельные АЦП""""""""""""" .. "" """" """ .. " .. " " "" " . ". " " . .. ... .. .. 32

1.2.2.2. Интегрирующие АЦП".""" ..." .... ""."."""""" .."""""""."."" ........""" 32

1.2.2.З. АЦП последовательного приближения

(Successive approxima tioп, SAR-ADQ.""""""""""""""."."""""."".""" .......... 36

1.2.2.4. Многокаскадные АЦП (sub-raпgiпg) ..""""."."" ..""." ..........." .......... 37

1.2 .2.S. АЦП с «плавающей запятой» (Floating poiпt)""""""""" ... ". " . . " " . 3 9

1.2 .2.6 . Сигма-дельта АЦП"""""""""""""""""""""" .. " " ." " " " "" " ." ." " ..... " . . 40

1.2 .2.7 . Преобразователи напряжение-частота".""" .... " " " " .. " " " " " . .. .. .. .. 4 2

1.2 .2 .8 . Особенности схемотехники АЦП

на переключаемых конденсаторах ".... " .. " ... " ..... ".""." .... "." .. """"."." ... " ..... 42

1.2 .3 . Перечень ведущих фирм

-

производителей ИМС АЦП """". ". 49

1.2 .4 . Обозначения контактов ИМС АЦП, применяемые

производителями при составлении документации ". " ". ". "" """ "" "" . .. " " .. 5 1

1.2.5. Типовые схемы включения ИМС АЦП." ...""............""""........""".".............. 53

СОДЕРЖАНИЕ

1.3 . &ИС ЦИФРОВЫХ СИНТЕЗАТОРОВ ЧАСТОТ ••.•...•••••••...••••...•••••• 55

1.3 .1 . Характеристики и классификация синтезаторов частот

......... " ................ 55

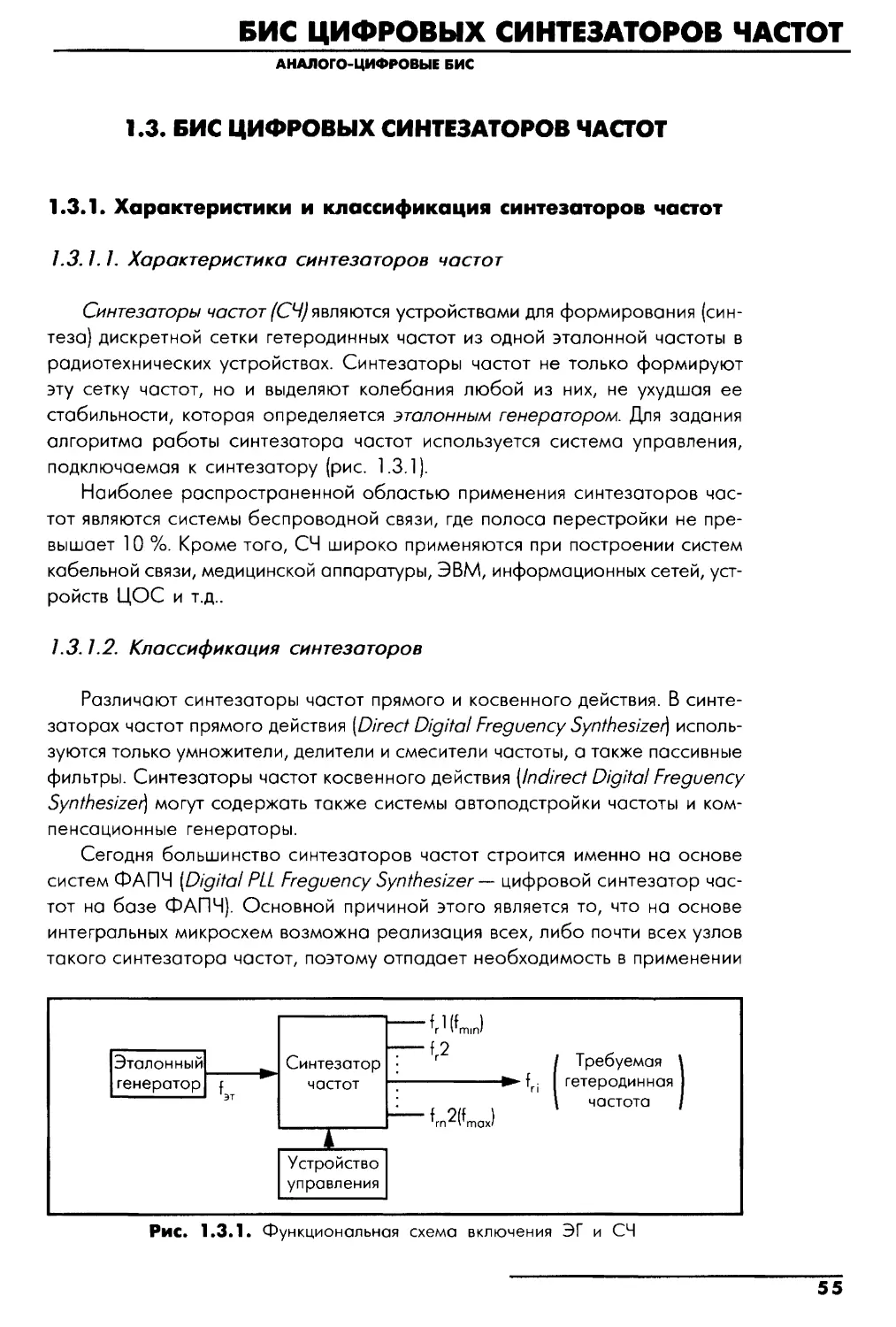

1.3.1 .1 . Характеристика синтезаторов частот""""""""""""""""""""."". 55

1.3.1 .2 . Классификация синтезаторов"""""""""""""""""."""".""""".".". 55

1.3 .1.3. Компоненты синтезаторов частот"""""""."."."""""""""""""""." 56

1.3.1 .4 . Параметры синтезаторов".""""""""""."."""""""""""".""""".""" 57

1.3.2. Основные принципы построения и структурные схемы

.""""""...."."."." 58

1.3.3.

1.3.4.

1.3.5.

1.3.6.

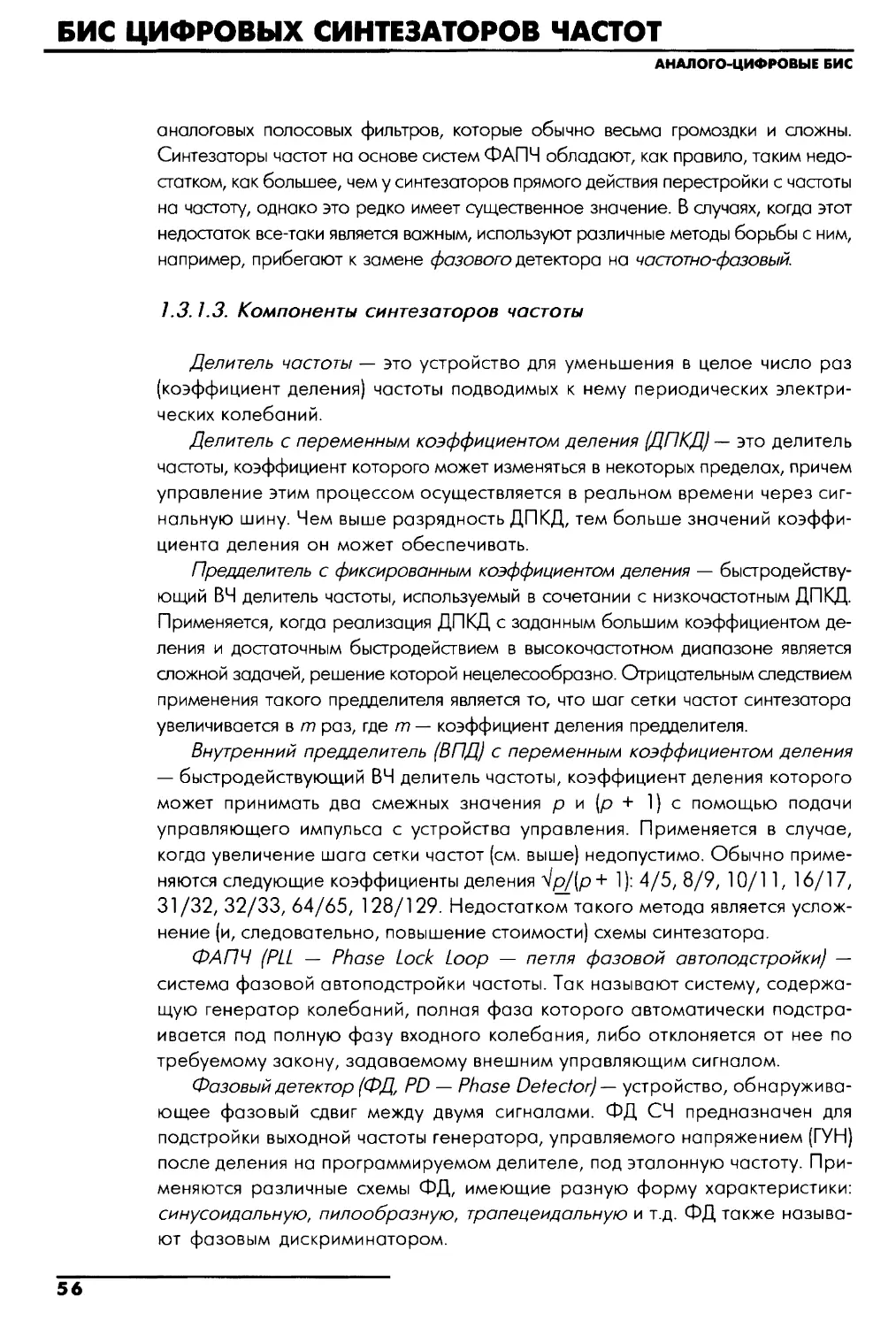

1.3.2 .1 . СЧ прямого синтеза """ """ """" """ """" """ "". "" """" """ """" ". "" 5 8

1.3.2 .2 . Синтезаторы частот косвенного синтеза"""""""""""""."""""" 59

1.3.2.3. Частотно-фазовые детекторы"""""""""""""".""."""""""""""".". 60

1.3.2 .4 . Импульсно-фазовые детекторы""""""""""""""""""""""""""""". 61

1.3.2.5. Синтезатор частот с внутренним предделителем """"". """""" 6 4

Примеры СЧ на основе ФАПЧ ведущих фирм-производителей ."" ." " 6 5

Перечень фирм - производителей СЧ косвенного действия " ."." " "." 6 5

Обозначения контактов ИМС СЧ косвенного действия,

применяемые производителями при составлении документации .. ". " ". 6 6

Пример цокопевки и типовой схемы включения СЧ с ФАПЧ .. " ." "" . ". 6 6

ЧАСТЬ 2. ЦИФРОВЫЕ &ИС И С&ИС

2.1. МИКРОСХЕМЫ ПАМЯТИ ...................•..•..•...•....•...•.••............•..• 75

2.1 .1 . Классификация ИМС памяти"""""""""""""""."""""""""""""""""" . . " ."" ." 7 5

2.1 .1.1. Микросхемы ОЗУ""" .. """."""" """."".""""". "".""""""""."". """"." 75

2.1.1.2. Микросхемы ПЗУ.""""""."""".""""""""""".""""""""".""""""""". 78

2.1.2. Параметры ИМС памяти ..." .."""""".".".."""""".." .."."..""""".."."..... """""" 78

2.1.3. Основные принципы построения и структурные схемы

.. """"""".""""". 80

2. 1.3. 1. Динамическое ОЗУ."""."""""."".""""".""".".""""""."."."."""""". 80

2.1 .3.2. Статическое ОЗУ"""""""""""""""""""""""""""".".".""""""""." .. 86

2.1.3.3. ПЗУ.. "... "..... "." .. """." ... ".".""...."." .. ".. ""."".. "."."." ... "."".".. "".""""". 89

2.1.4. Перечень основных фирм

-

производителей ИМС памяти" .. " ". " " " "" 9 4

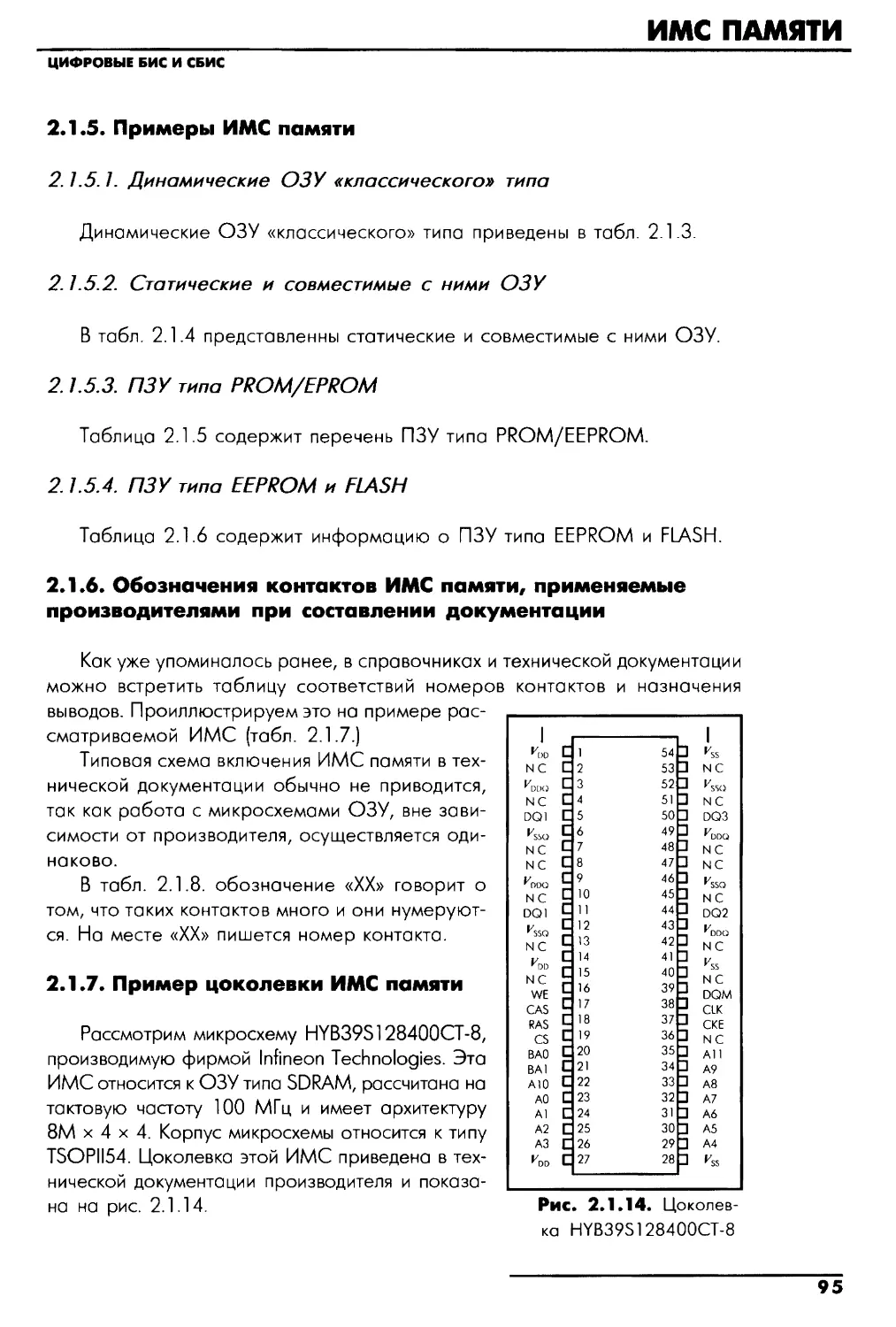

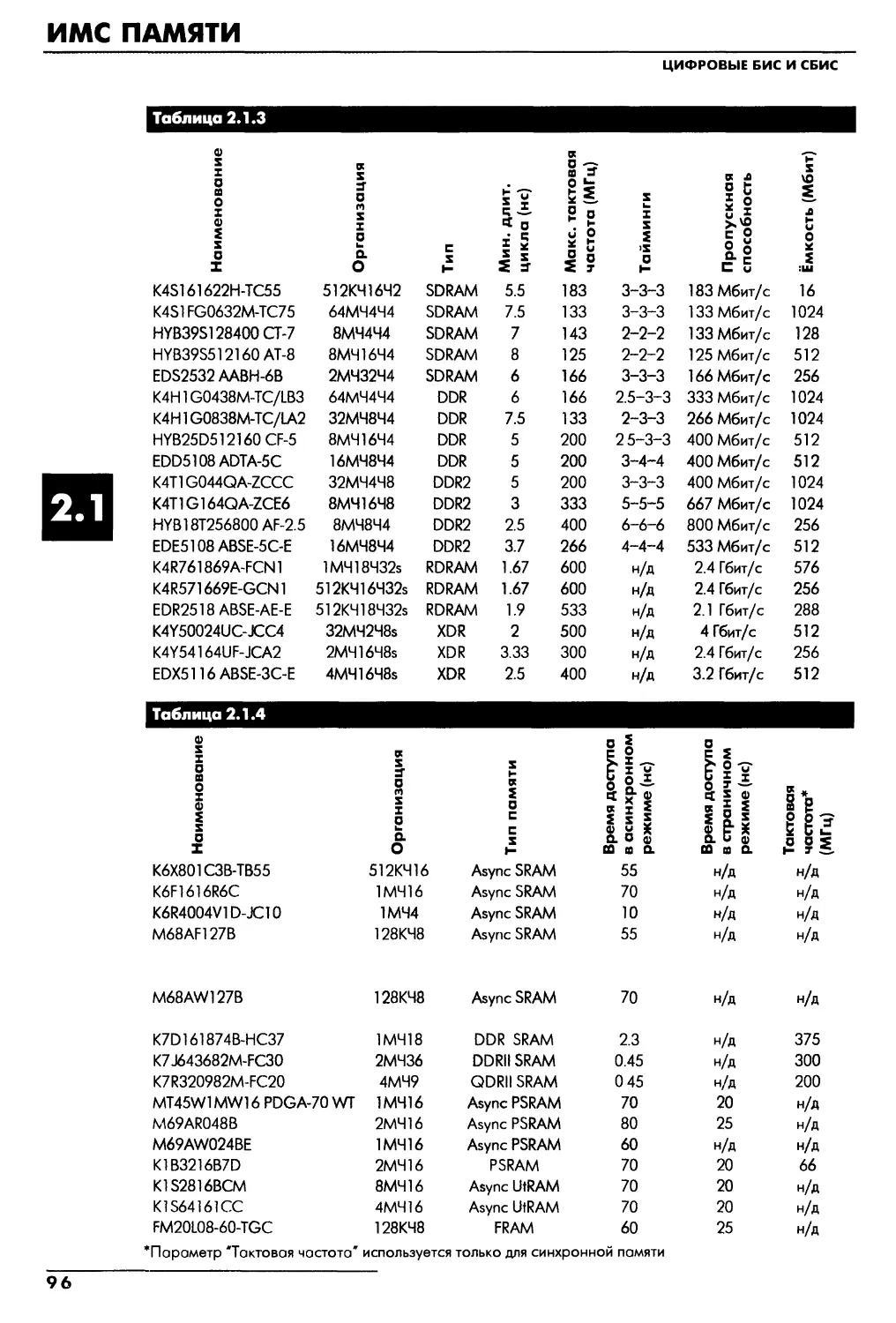

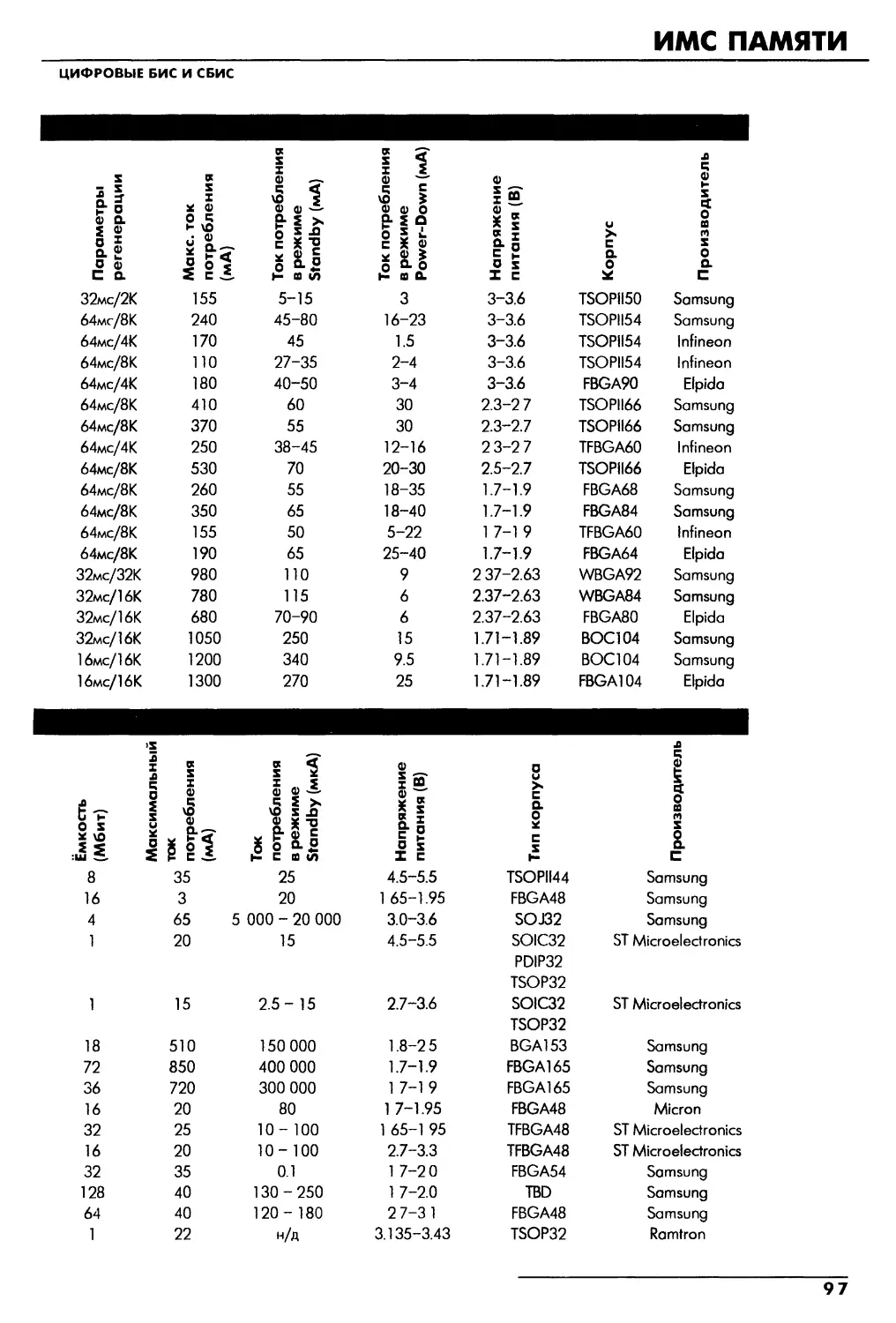

2.1.5. Примеры ИМС памяти"""""." . . "." .""."."" . . ".""" . . " . . " . . " ."""""""""" ."""""" 95

2.1 .5.1. Динамические ОЗУ «классического» типа""."""""""""."" . . "" " 9 5

2.1.5.2. Статические и совместимые с ними ОЗУ."."""".""""."""""" ... 95

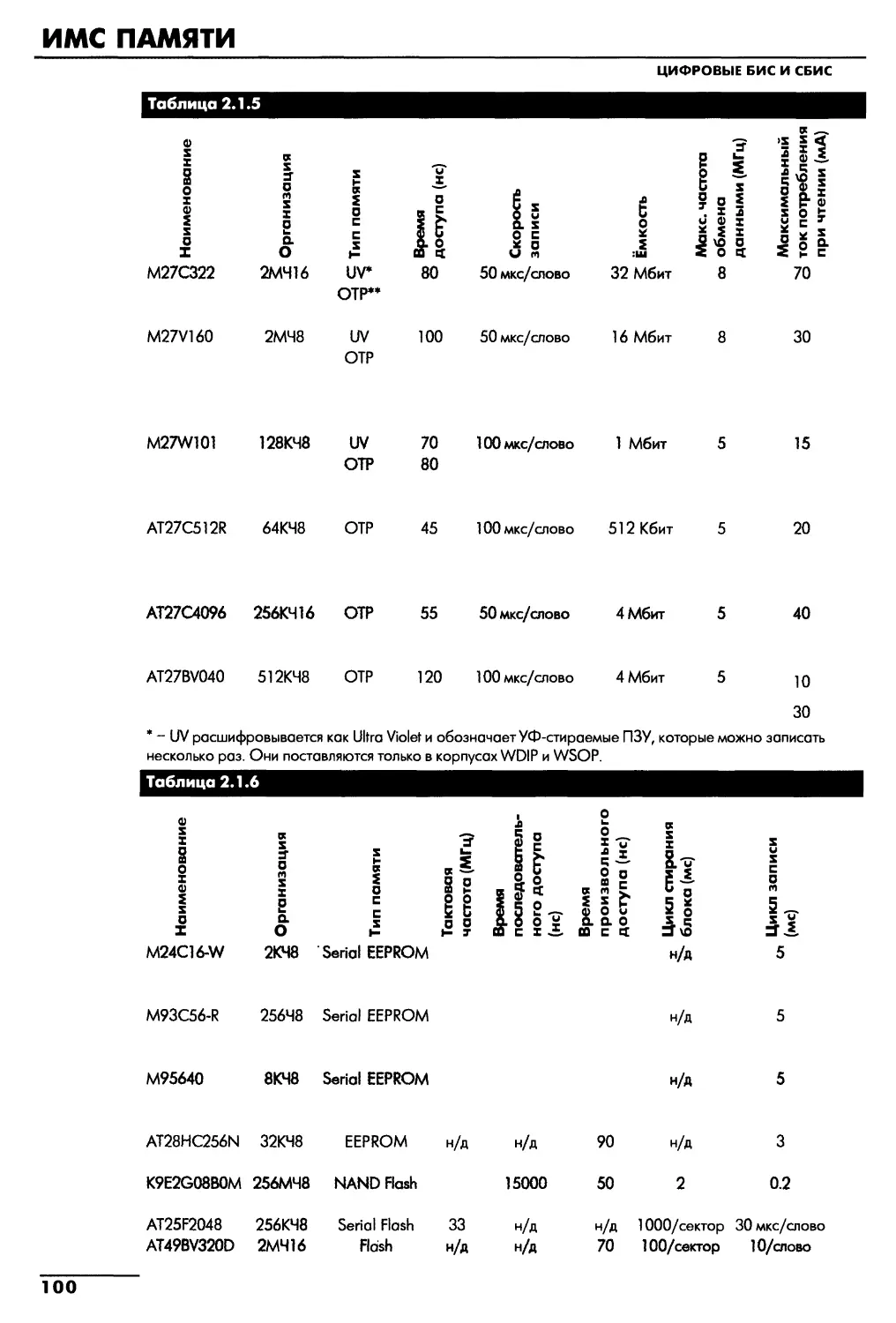

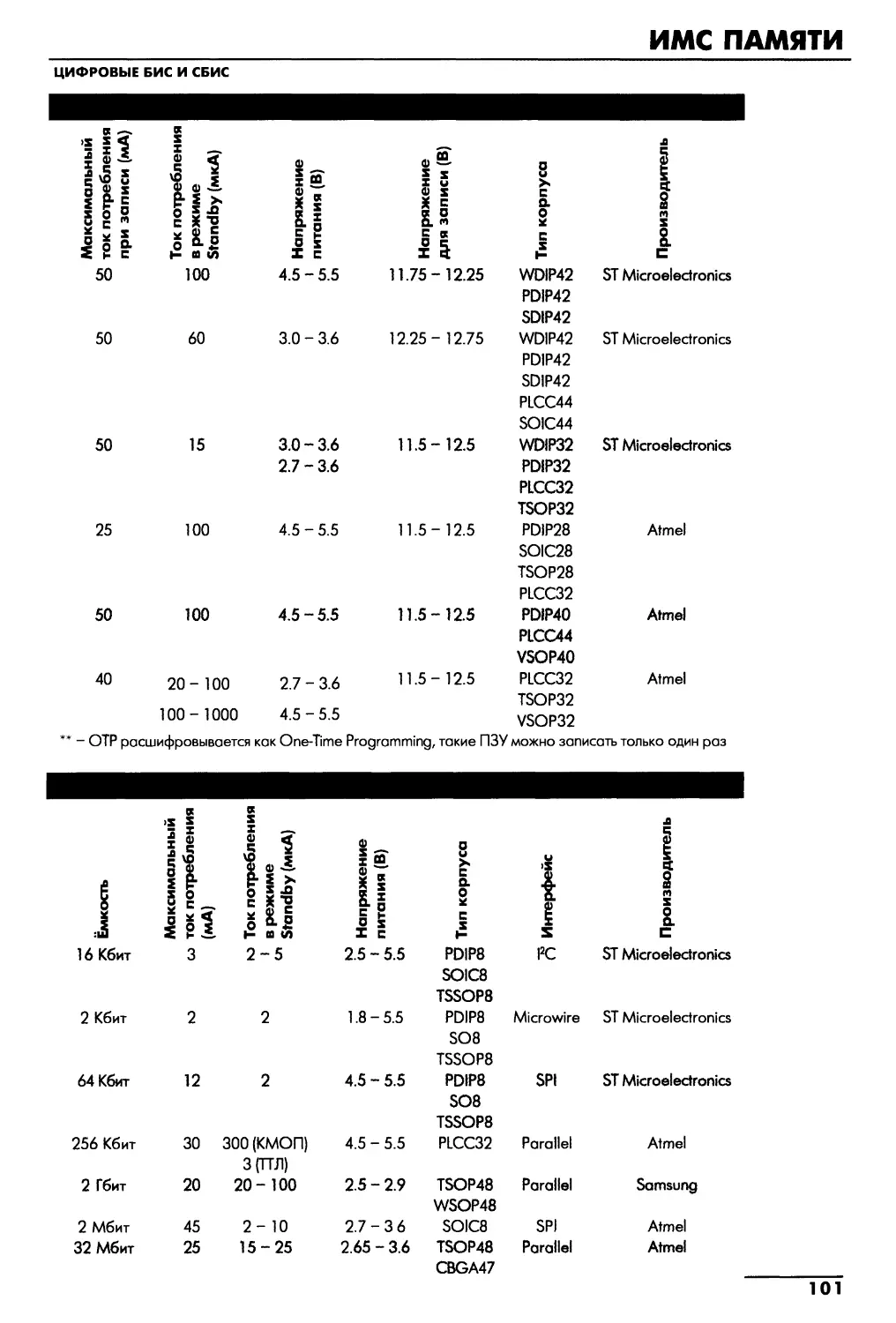

2.1.5.3. ПЗУ типа PROM/EPROM """""."".".""."."."""".""""""""".""." .. " 95

2.1.5.4. ПЗУ типа EEPROM и FLASH"."."""""."""""."."".""."""."".""""". 95

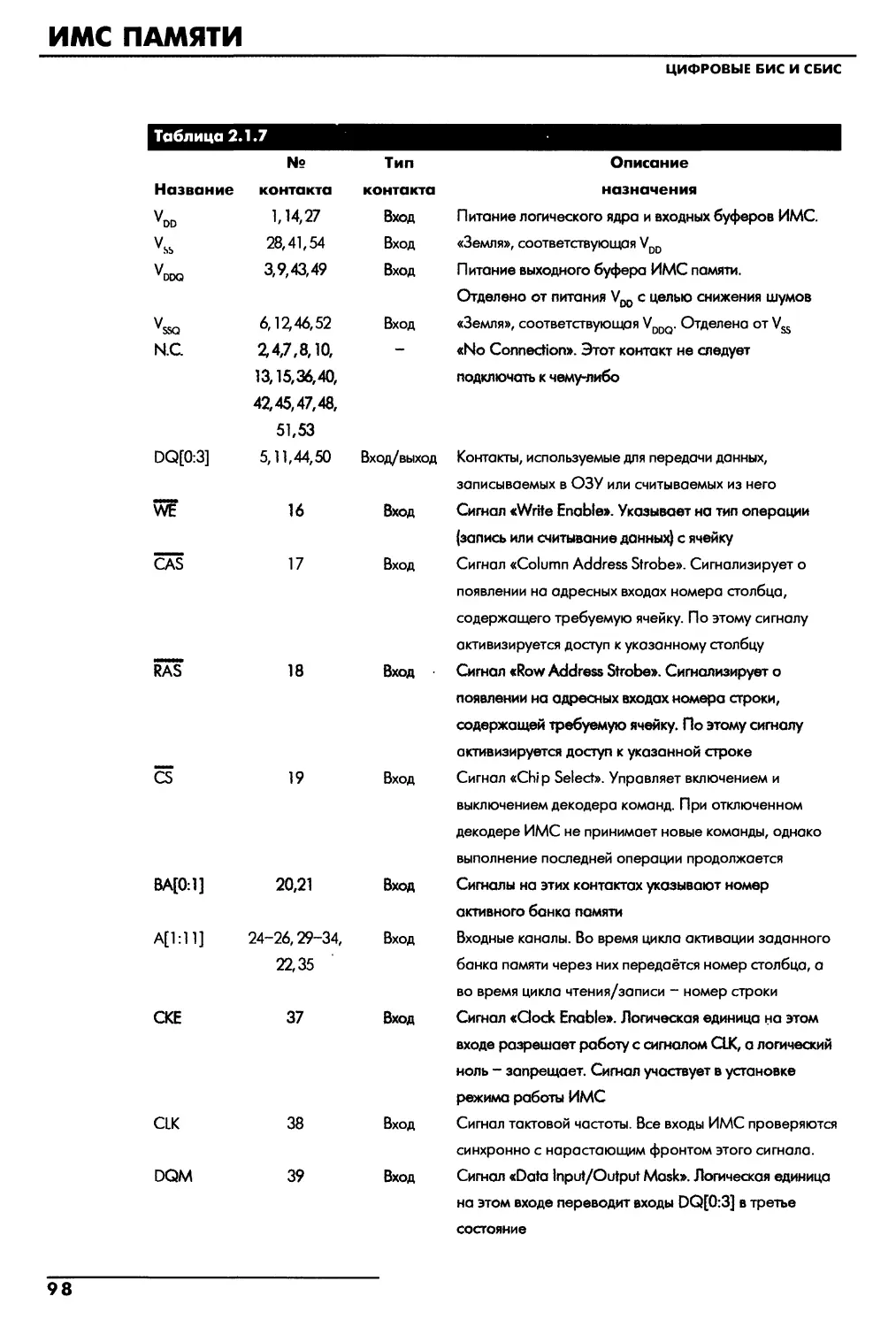

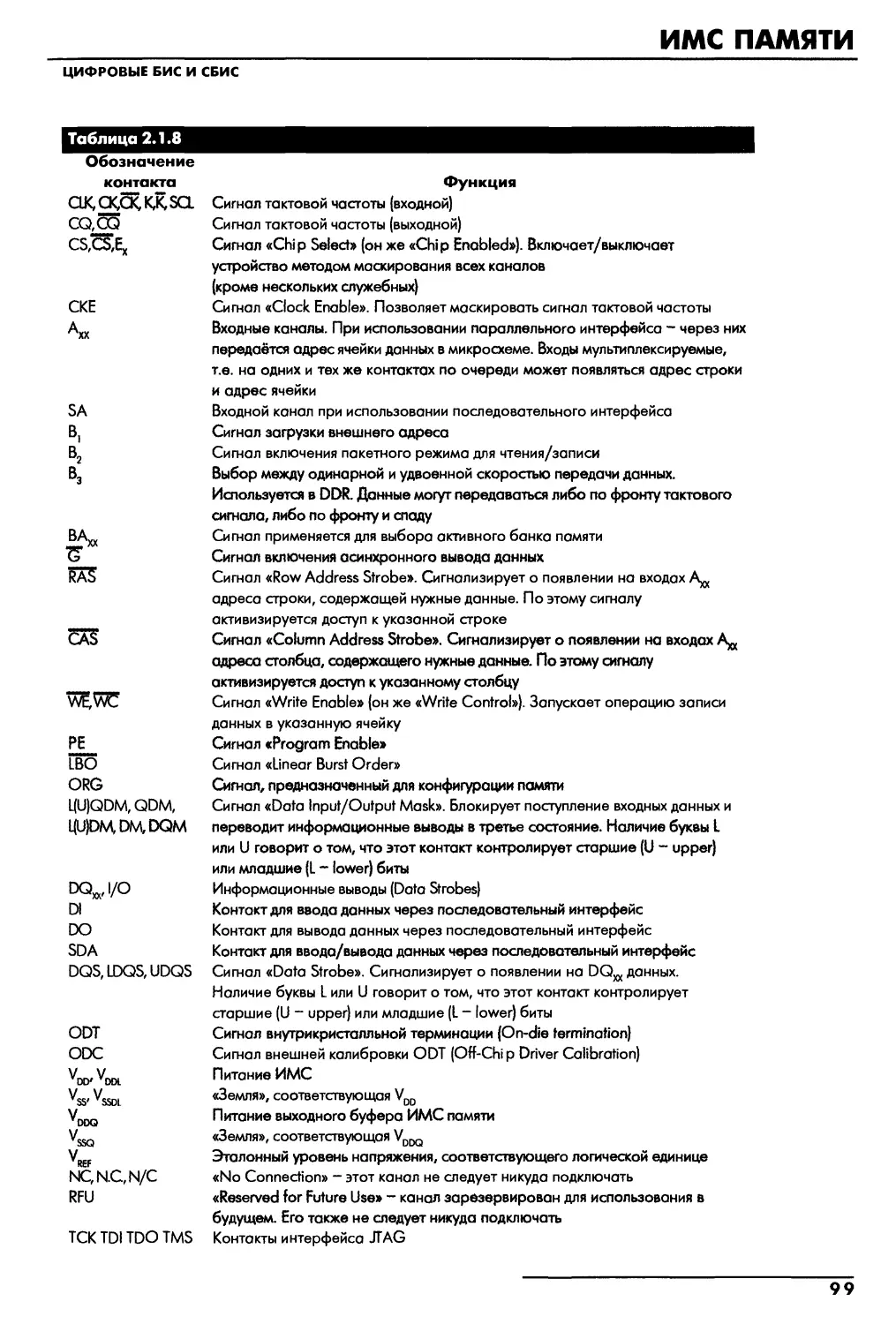

2.1 .6 . Обозначения контактов ИМС памяти, применяемые""""".""""."""""" 95

производителями при составлении документации """". "" "" . "" "" "" ." "" . 9 5

2.1 .7 . Пример цоколевки ИМС памяти

. . " . . """""""" . . """"""""""""" ." ."""""""" . 95

5

СОДЕРЖАНИЕ

6

2.2. УНИВЕРСАЛЬНЫЕ МИКРОПРОЦЕССОРЫ •..••••••• .••• .•....•• .......•• 102

2.2.1.

2.2.2.

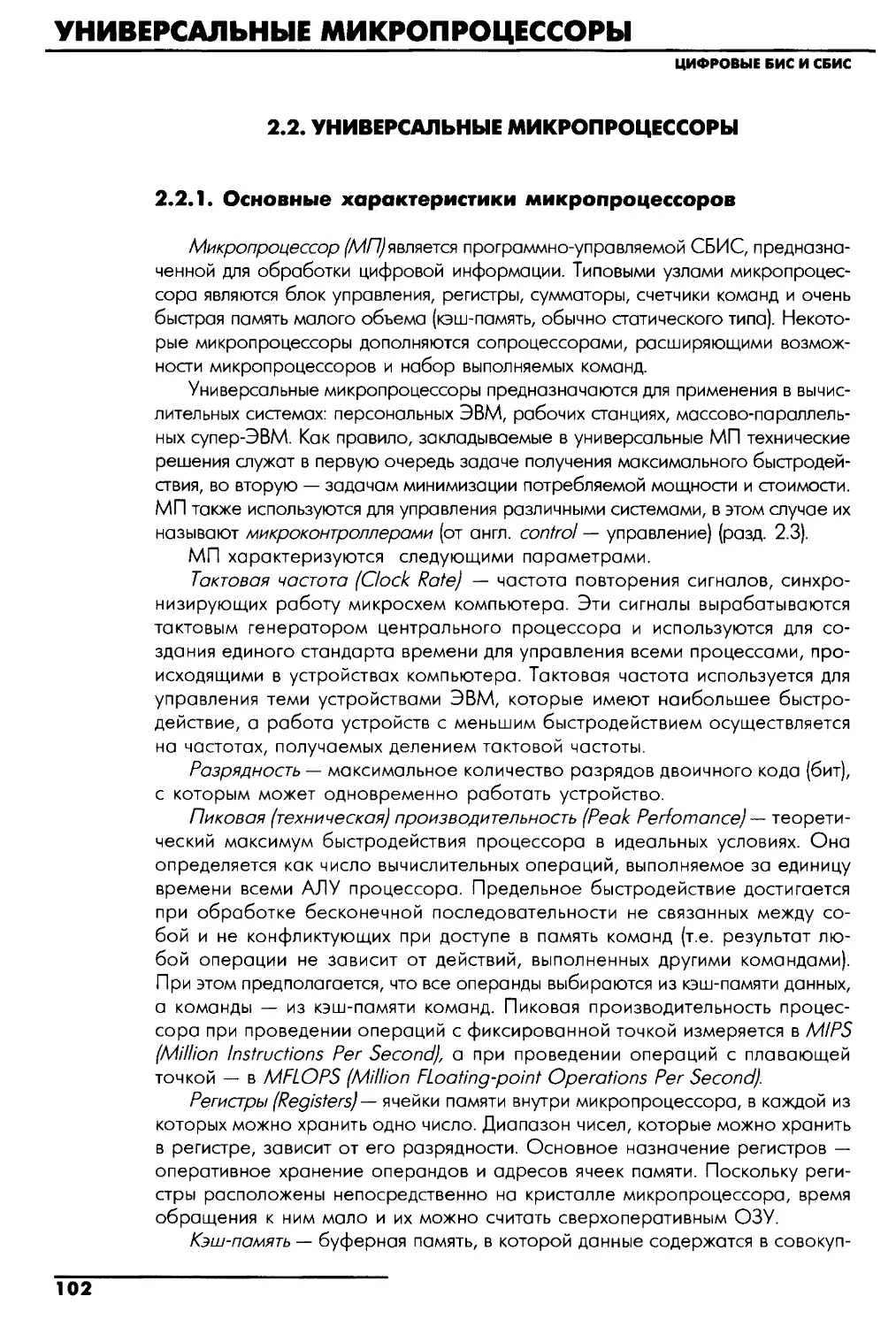

Основные характеристики микропроцессоров .......................................... 102

Классификация микропроцессоров ................................................................. 102

2.2.2.1. Используемый нобор комонд ........................................................... 103

2.2 .2.2 Методы работы с памятью ................................................................... 103

2.2.2.3. История развития МП ......................................................................... 105

2.2.3. Основные принципы построения и структурные схемы

..........................

108

2.2.3. /. Арифметико-логическое устройство (АЛУ) ................................... 108

2.2.3.2. Программный счетчик ......................................................................... 109

2.2.3.3. Регистры общего назначения (РОН} .............................................. 109

2.2.3.4. Управляющее устройство (УУ) ........................................................... 112

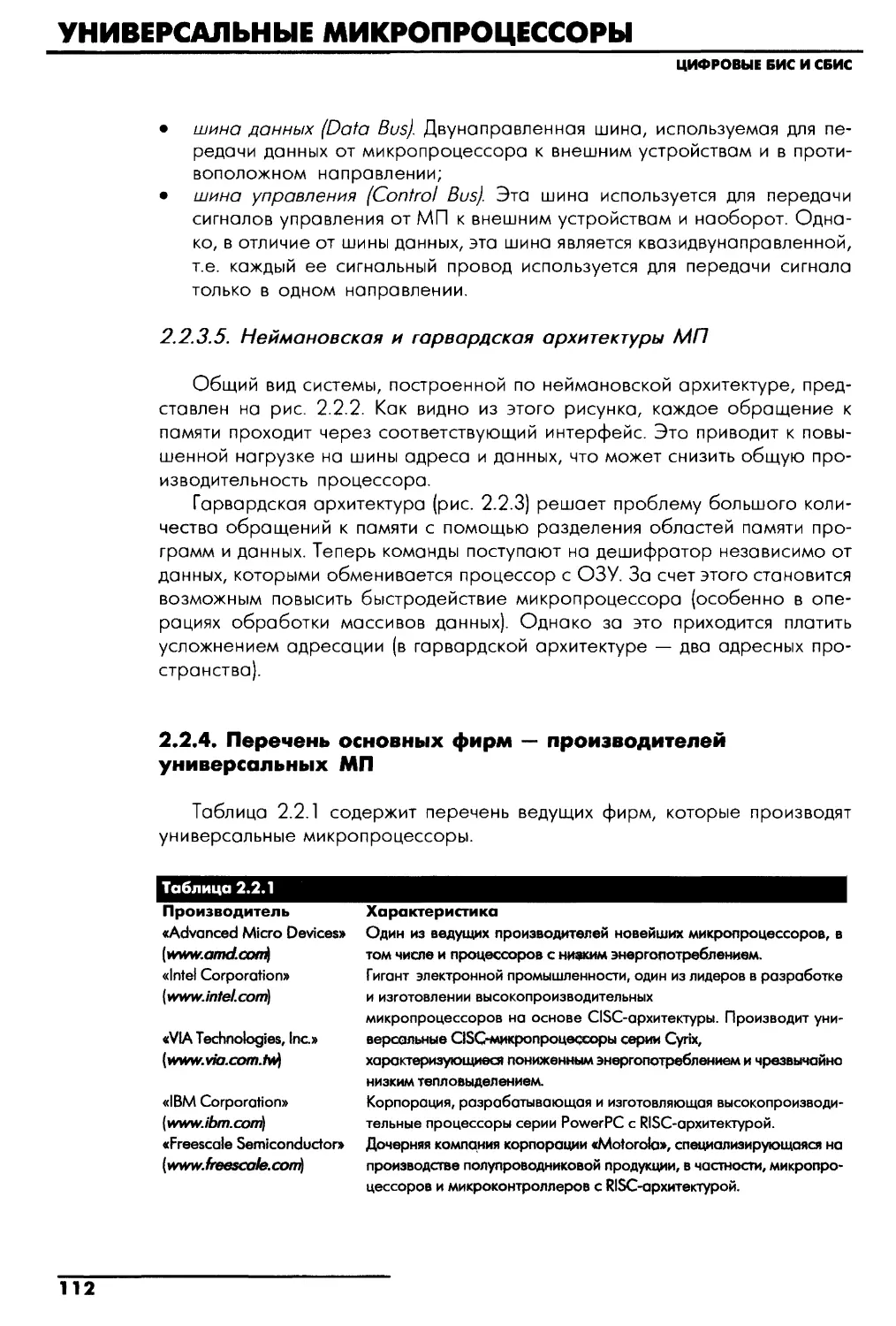

2.2.3.5. Неймановская и гарвардская архитектуры МП .. . .. .. . .. .. . .. .. . .. .. . . 112

2.2.4 . Перечень основных фирм

-

производителей универсальных МП ........ 113

2.2.5 . Типовая цоколевка универсального МП

...........................................................

113

2.2 .6 . Примеры современных универсальных МП

....................................................

113

2.2.7. Обозначения контактов универсальных МП в документации .. .. . .. .. .. . .. .. .. 113

2.3 . МИКРОКОНТРОЛЛЕРЫ ..•• .••••••••• ....••.• ..•. .•.• .•• ....•••. ....•. ..•..••.••. 123

2.3 .1 . Назначение микроконтролперов

....................................................................

123

2.3.2. Терминология микроконтроллеров ..............................................................." 124

2.3.3. Классификация микроконтроллеров

...............................................................

125

2.3.3.1. Семейство lпtel MCS-51 .....................................................................126

2.3.3.2. Семейство lпtel MCS-151/251 ......................................................... 126

2.3.3.3. Семейство lпtel MCS-96/196/296 .................................................. 127

2.3 .3 .4 . Семейство Motorola HC05/HCl05 ................................................. 128

2.3 .3 .5 . Семейство Motoгola HCLOS .............................................................. 131

2.3.3.6. Семейство Moforola НСО8 ................................................................ 131

2.3.3.7. Семейство Moforola НС/ 1 ................................................................ 132

2.3.3.8. Семейство Motarola НС/2 ................................................................ 133

2.3.3.9. Семейство Moforola НС/6 ................................................................ 134

2.3 .3 . /О. Семейство Moforola 68300 ............................................................. 134

2.3.3.11. Семейство ZilOG Z8 ......................................................................... 135

2.3 .3 .12. Сеt,-1ейство Microchip PIC/O ........................................................... 135

2.3 .3 .13. Семейство Microchip PIC/2 ........................................................... 136

2.3 .3 .14. Семейство Microchip PIC/4 ........................................................... 136

2.3.З. /5. Семейство Micrachip PIC/6 ........................................................... 137

2.3.3.16. Семейство Atmel AVR .................................................................. " .. . 13 7

2.3.4. Основные принципы построения и структурные схемы МК .. .. .. .. . .. .. .. .. .. 138

2.3.4./. Семейство lntel MCS-51 ..................................................................." 138

2.3.4.2. Семейство lпtel MCS-251 .................................................................. 140

2.3.4.3. Семейство lntel MCS-96/196/296 .................................................. 142

2.3.4.4. Семейство Motorola HC05/HCL05 ................................................. 144

2.3 .4 .5 . Семейство Moforola НСО8 ................................................................ 145

2.3.4.6. Семейство Motorola НС/ 1................................................................ 148

СОДЕРЖАНИЕ

2.3.5.

2.3 .6.

2.3 .7.

2.3.8 . .

2.3.4.1. Семейство Motorolo НС12 ....................................................... " " . .. .. 1 49

2.3.4.8. Семейство Motorolo НС16 ................................................................ 150

2.3 .4 . 9 . Семейство Motorolo 68300 ............................................................... 151

2.3.4.10. Семейство ZilOG Z8......................................................................... 152

2.3 .4 .11. Семейство Microchip PIClO ........................................................... 153

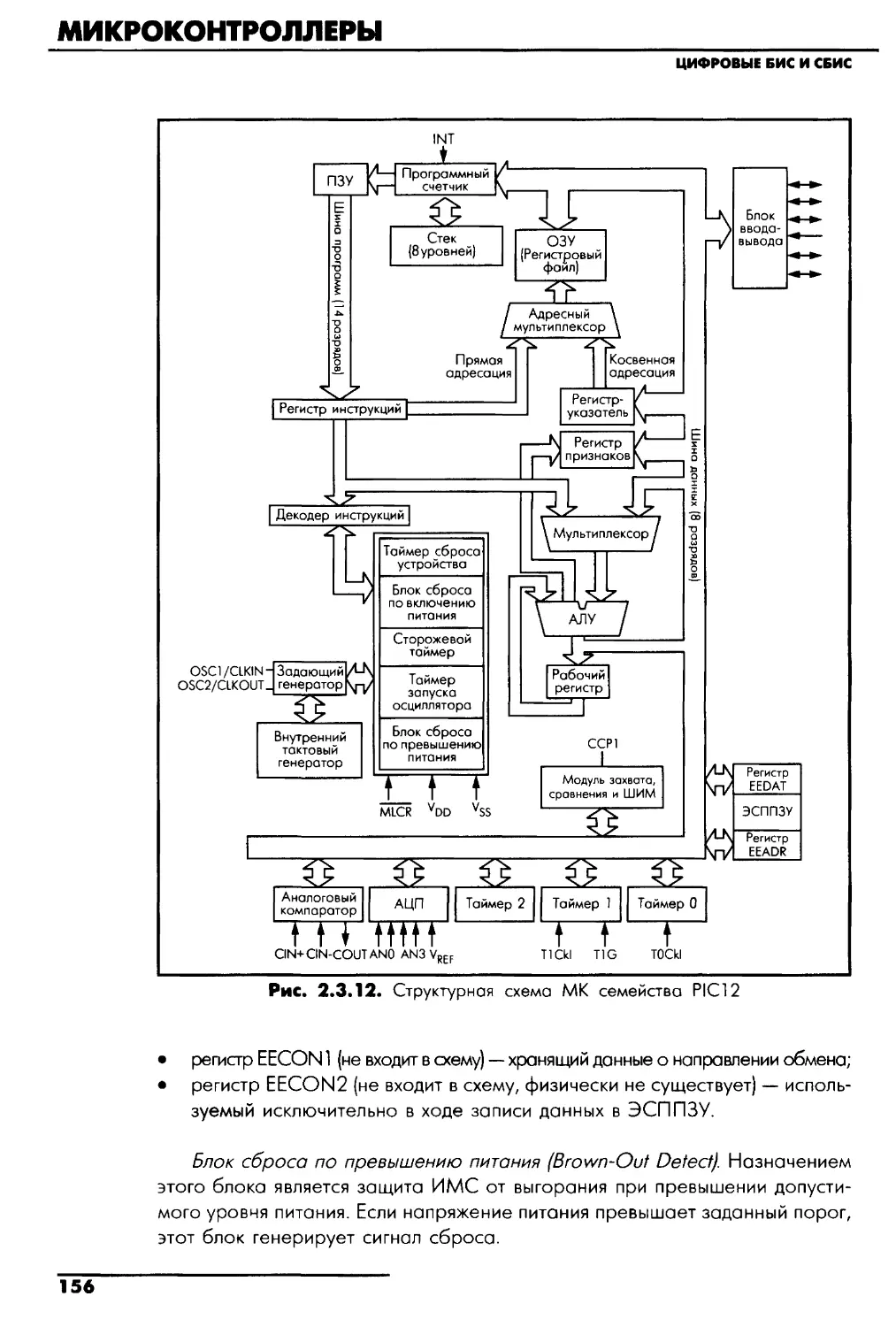

2.3 .4 .12. Семейство Microchip PIC12 ........................................................... 155

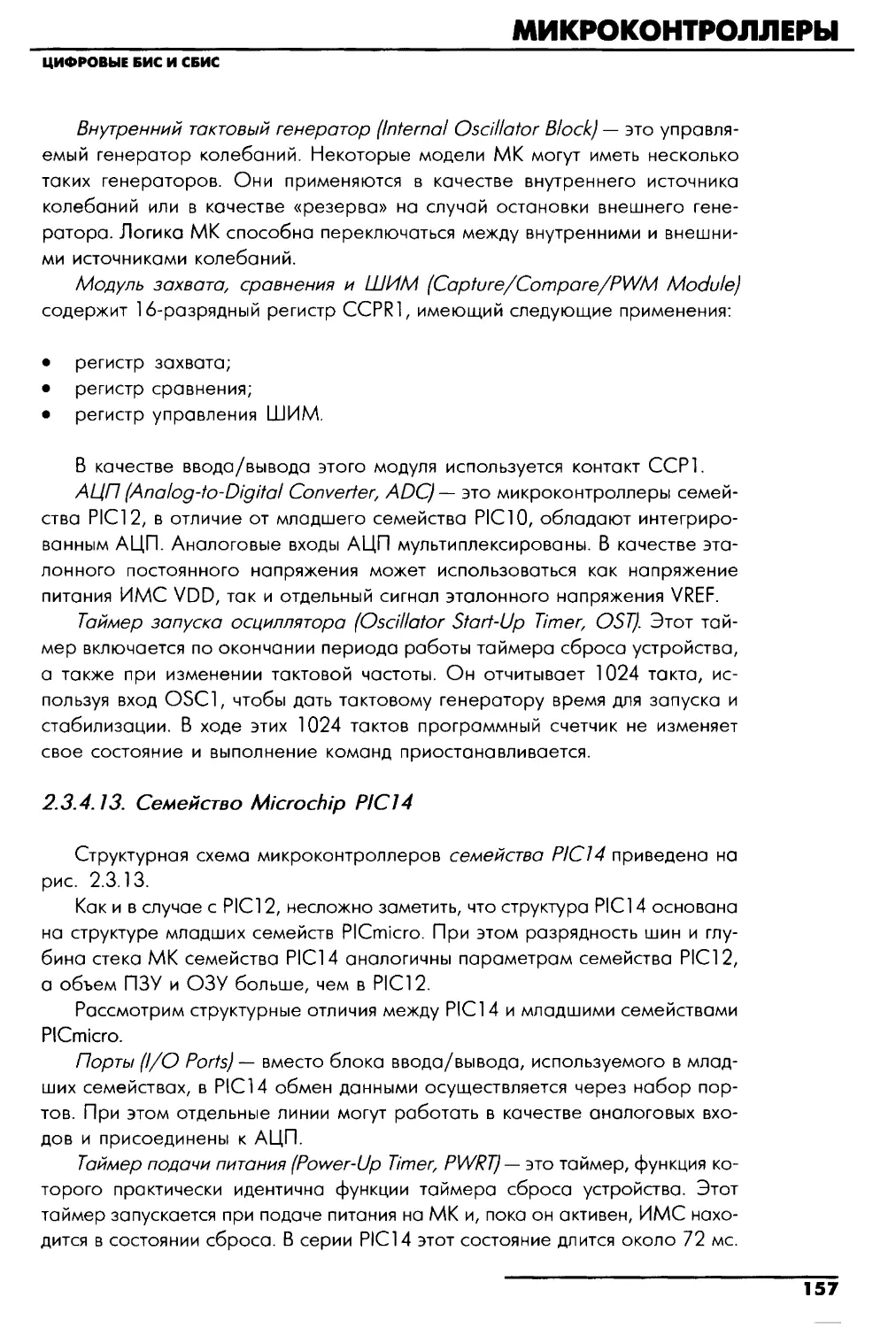

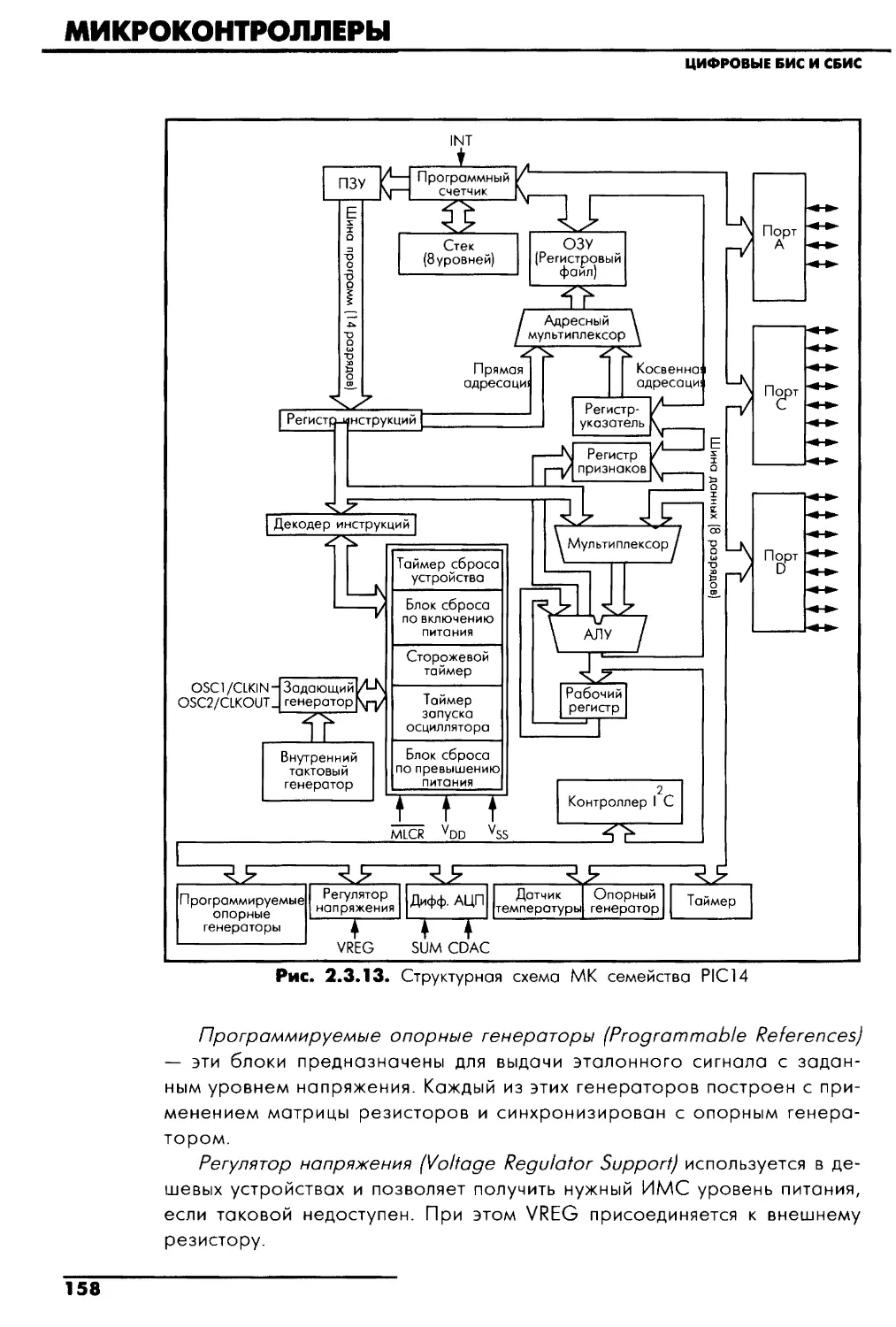

2.3 .4 .13. Семейство Microchip Р/С/4 ................................... " .. . .. .. . .. . .. .. . .. .. . . 1 5 7

2.3.4. 14. Семейство Microchi р PIC 16 ........................................................... 159

2.3.4. 15 . Семейство Atmel ТinyAVR ................................................................ 160

2.3 .4 .16. Семейство Atmel MegoAVR............................................................. 162

Перечень основных фирм - производителей МК .................................... 163

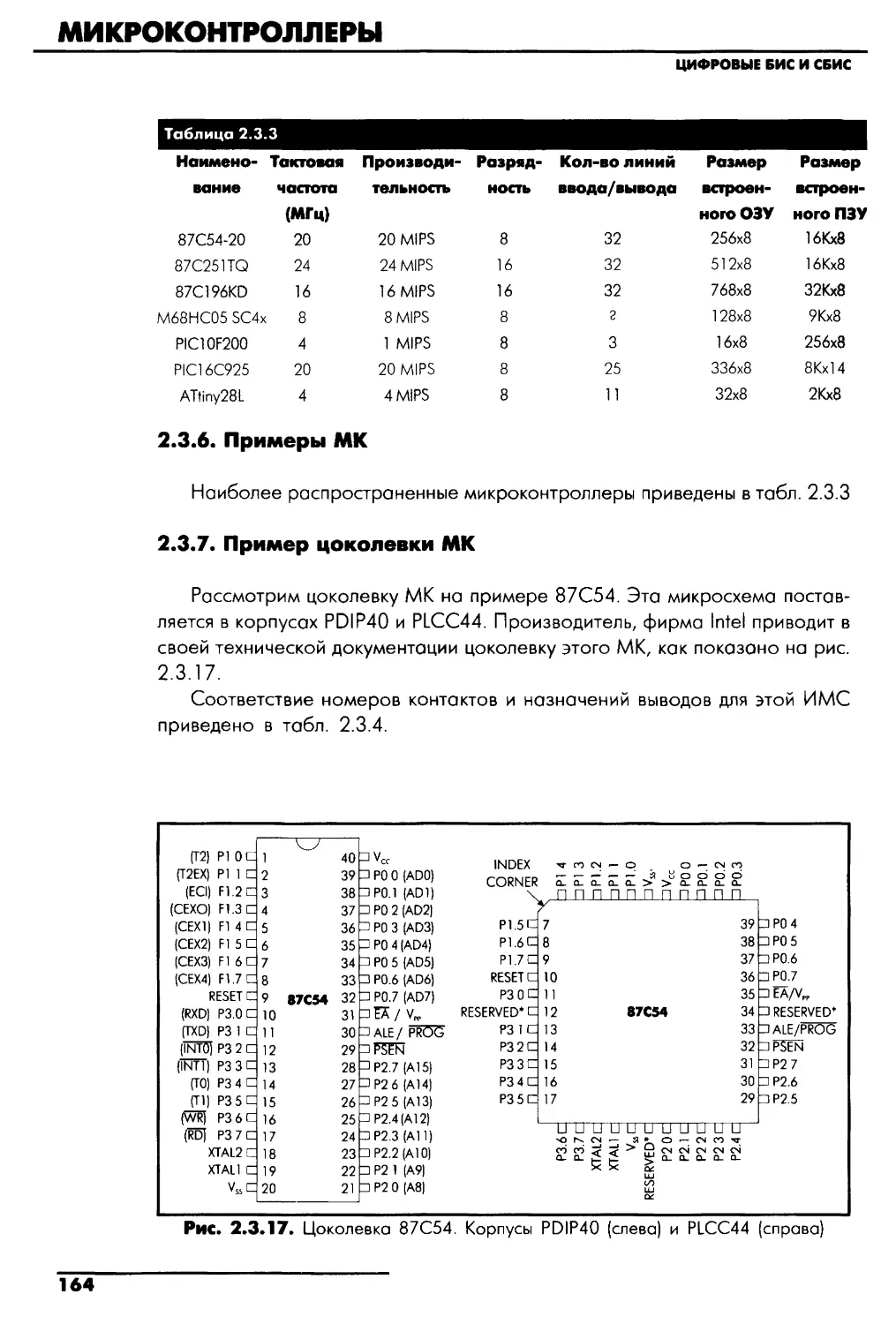

Примеры МК ........................................................................................................... 164

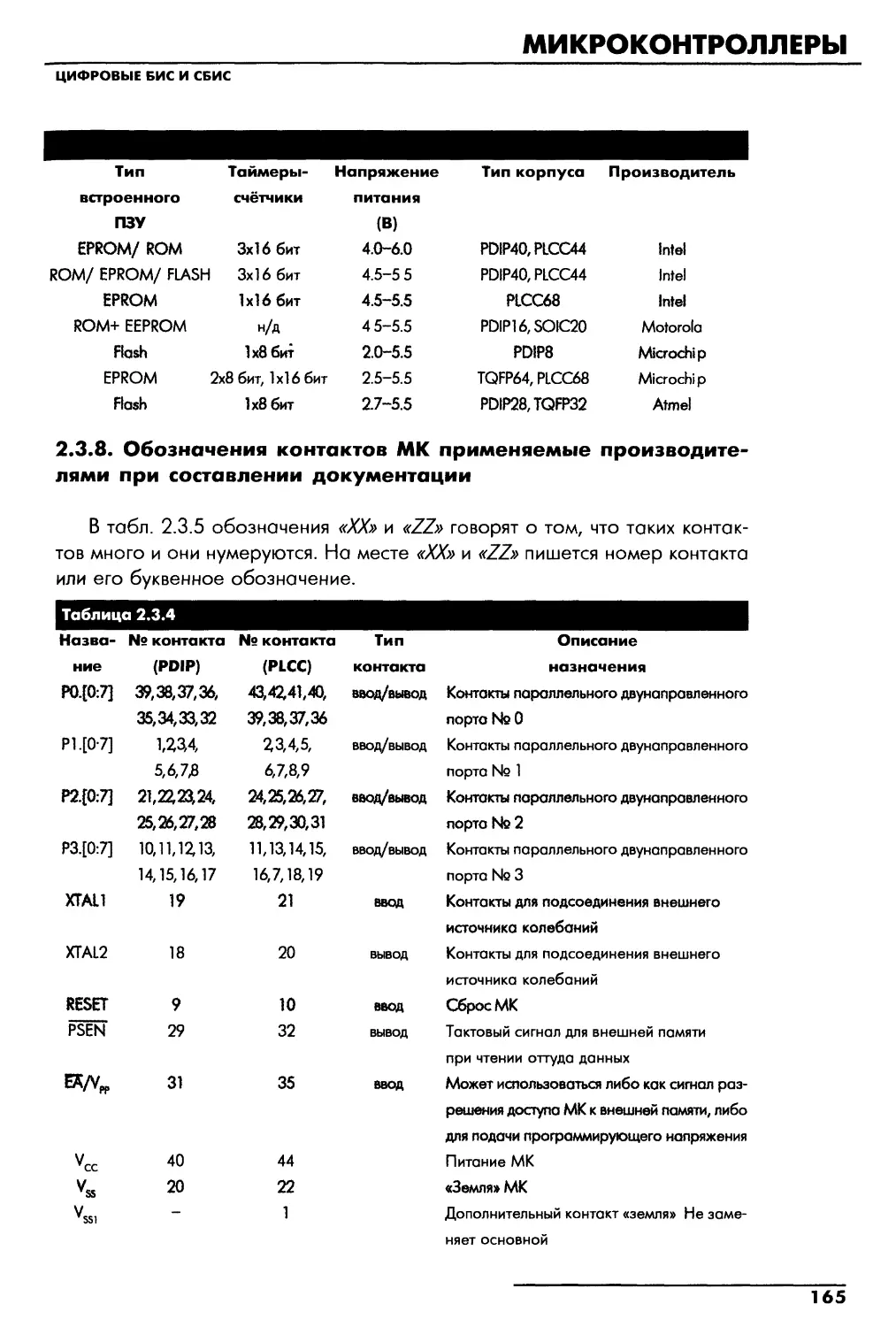

Пример цокопевки МК ........................................................................................ 164

Обозначения контактов МК, применяемые

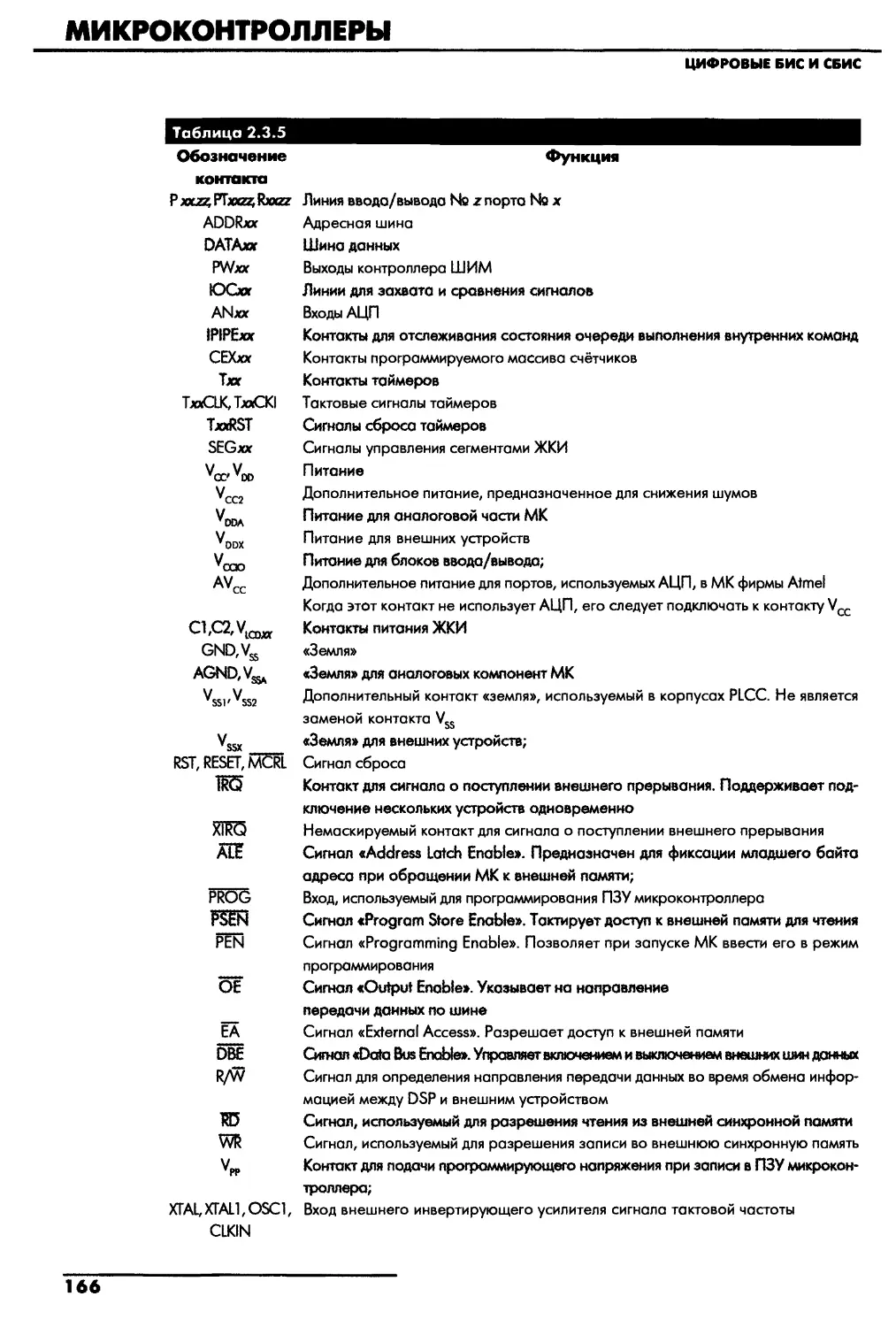

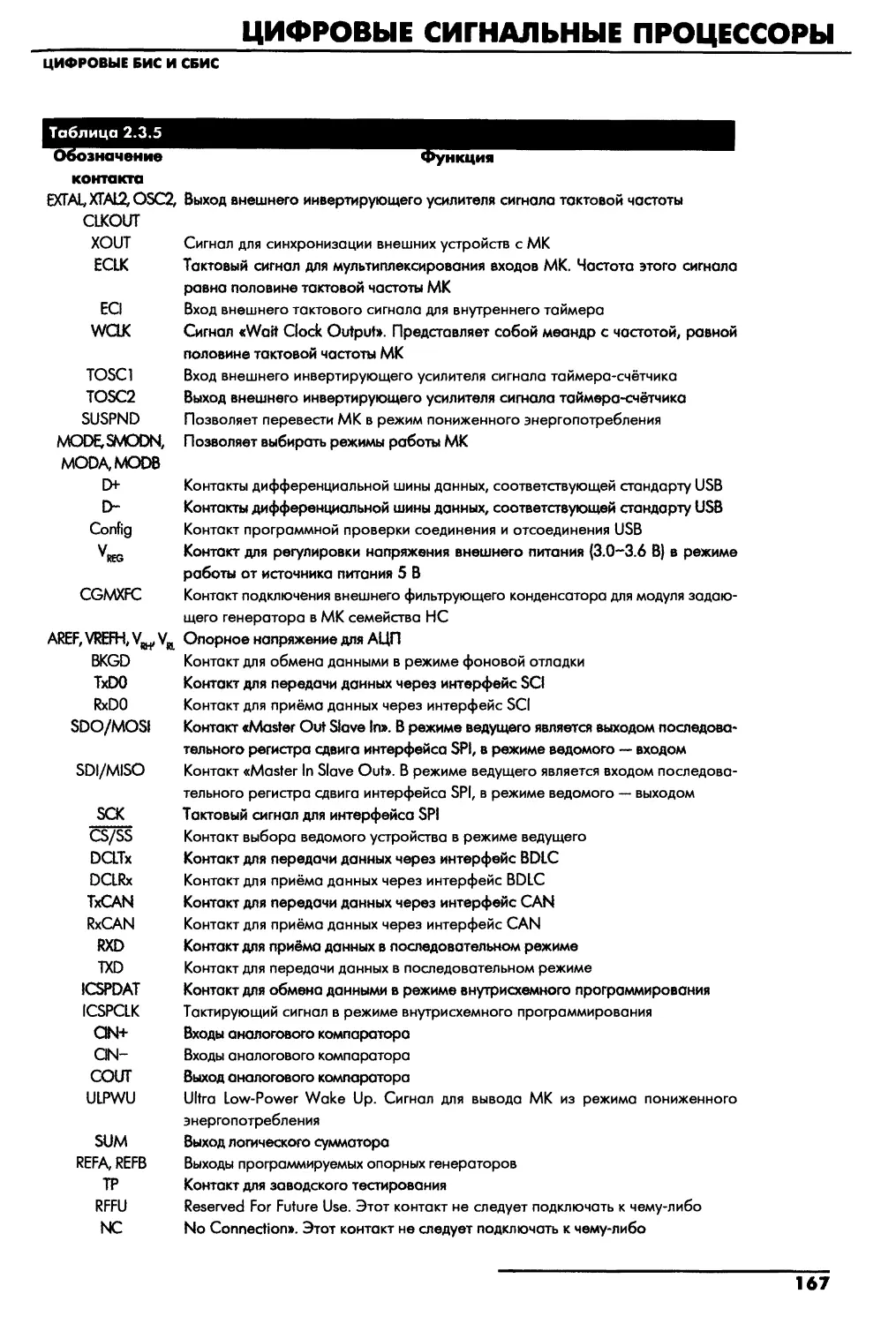

производителями при составлении документации .................................... 165

2.4. ЦИФРОВЫЕ cиrHAJlbHЫE ПРОЦЕССОРЫ (DSP) ••••••...••••• .. .•••• 168

2.4 .1. Назначение и классификация DSP ................................................................ 168

2.4.2. Классификация DSP .............................................................................................. 169

2.4.2.1. Texos lnstruments С2000 ..................................................................... 169

2.4.2.2. Texos lnstruments С5000 ..................................................................... 170

2.4.2.З. Texos lnstruments С6000 ..................................................................... 171

2.4.2.4. Anolog Devices ADSP-21хх ................................................................. 172

2.4 .2 .5 . Anolog Devices Blockfin ....................................................................... 173

2.4.2.6. Anolog Devices SHARC ....................................................................... 174

2.4.2.7. Anolog Devices ТigerSHARC .............................................................. 175

2.4 .2 .8 . lucent Technologies DSP/6000 .......................................................... 175

2.4.2. 9 . Freescole Semicondutor DSP56000/DSP563xx ............................ 176

2.4.2. 1О. Freescole Semicondutor DSP56xxx ................................................ 176

2.4.2. 11. Stor*Core ............................................................................................... 177

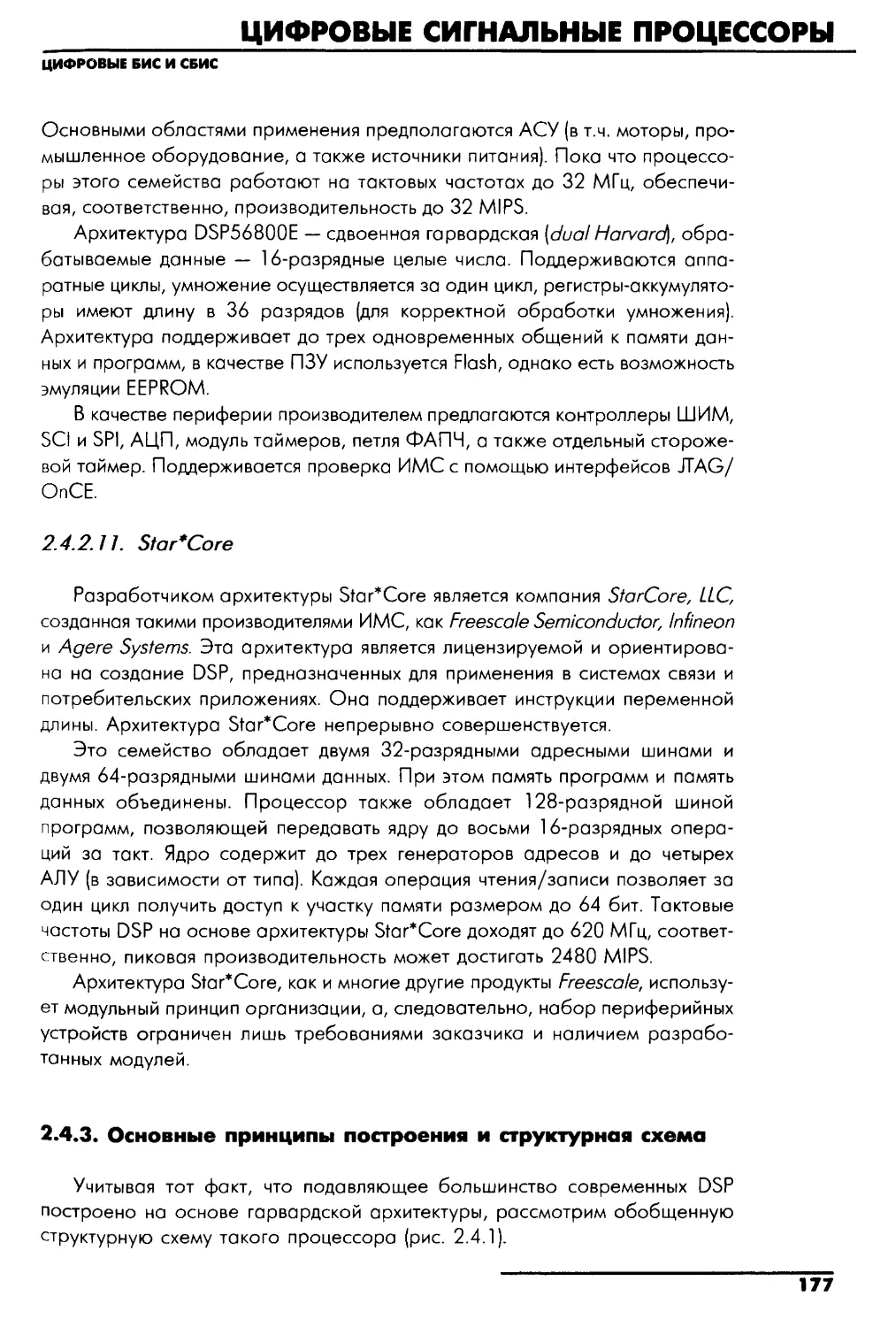

2.4.3. Основные принципы построения и структурная схема ...........................177

2.4.4. Перечень основных фирм

-

производитепей DSP .................................. 182

2.4.5. Примеры DSP ......................................................................................................... 182

2.4.6. Обозначения контактов DSP в документации ........................................... 183

2.5 . ПРОrРАММИРУЕМЫЕ лоrичЕСКИЕ

ИHTErPAJlbHЫE СХЕМЫ .••••.•• ..••.••••••• .•••••.••.•• .•.••. .•••. ..•••••. . .• .. . ..••••• 188

2.5.1. Характеристика и классификация ПЛИС .....................................................188

2.5.1./. Терминология ПЛИС ........................................................................... 189

2.5.1.2. Клоссификоция ПЛИС ......................................................................... 191

2.5.2. Основные принципы построения и структура ПЛИС ............................... 192

2.5.2.1. ПЛИС типо CPLD...................".........".................................................. 192

2.5 .2 .2 . ПЛИС типо FPGA .................................................................................. 195

7

СОДЕРЖАНИЕ

8

2.5.3.

2.5.4.

Перечень основных фирм, выпускающих ПЛИС ........................................ 198

Справочные данные по конкретным примером современных ПЛИС ......... 199

2.5.4. 1. ПЛИС типа CPLD """" ." .. """"" . .. " .. """. """ """"" .. "" """ """ """ ..... 19 9

2.5.5.2. ПЛИС типа FPGA """".""""""".""""" .. """"""."."""""."."""""""" 199

2.5 .5 . Примеры цоколевки и типовой схемы включения ПЛИС .. . " .. . .. .. . .. .. "" . 19 9

2.5.6. Обозначения контактов ПЛИС в документации .... " ............. " ........... """. 200

2.6. БИС ЦИФРОВЫХ КВАдРАТУРНЫХ

ПРЕОБРАЗОВАТЕЛЕЙ СИГНАЛА .................................................... 205

2.6.1.

2.6.2.

2.6.3.

2.6.4.

2.6.5.

2.6.6.

Характеристики и классификация .. """" .. ... .. " .. .. ... .. .. "."" .... ... " .. "" .. ... .. .. " .. " 206

2.6 . 1. 1 . Характеристика""".""""""" . .. """ """. """""" ""." """"" ".""" """"" . 2 05

2.6. 1.2. Кпассификация ........... "........ "" ............... "......................... """........""" 206

Основные принципы построения и струк~урные схемы " ." " ." "" " "" ".. " 2 07

2.6 .2. 1 . Квадратурные преабразаватепи на основе выделения

квадратурных составляющих из аналагавага сигнала ." " "" .. " ." ." " "" " . 2 07

2.6.2.2. Квадратурные преобразователи с выделением

квадратурных составляющих из оцифрованного сигнала ." "." . .. "" .... ," 208

Перечень основных фирм - производителей квадратурных

преобразователей частоты.""............ "." .. .. .. . .. .. .. " .. .. ... .. .. "." ... ... .. ""." .. .. .. " •. " 210

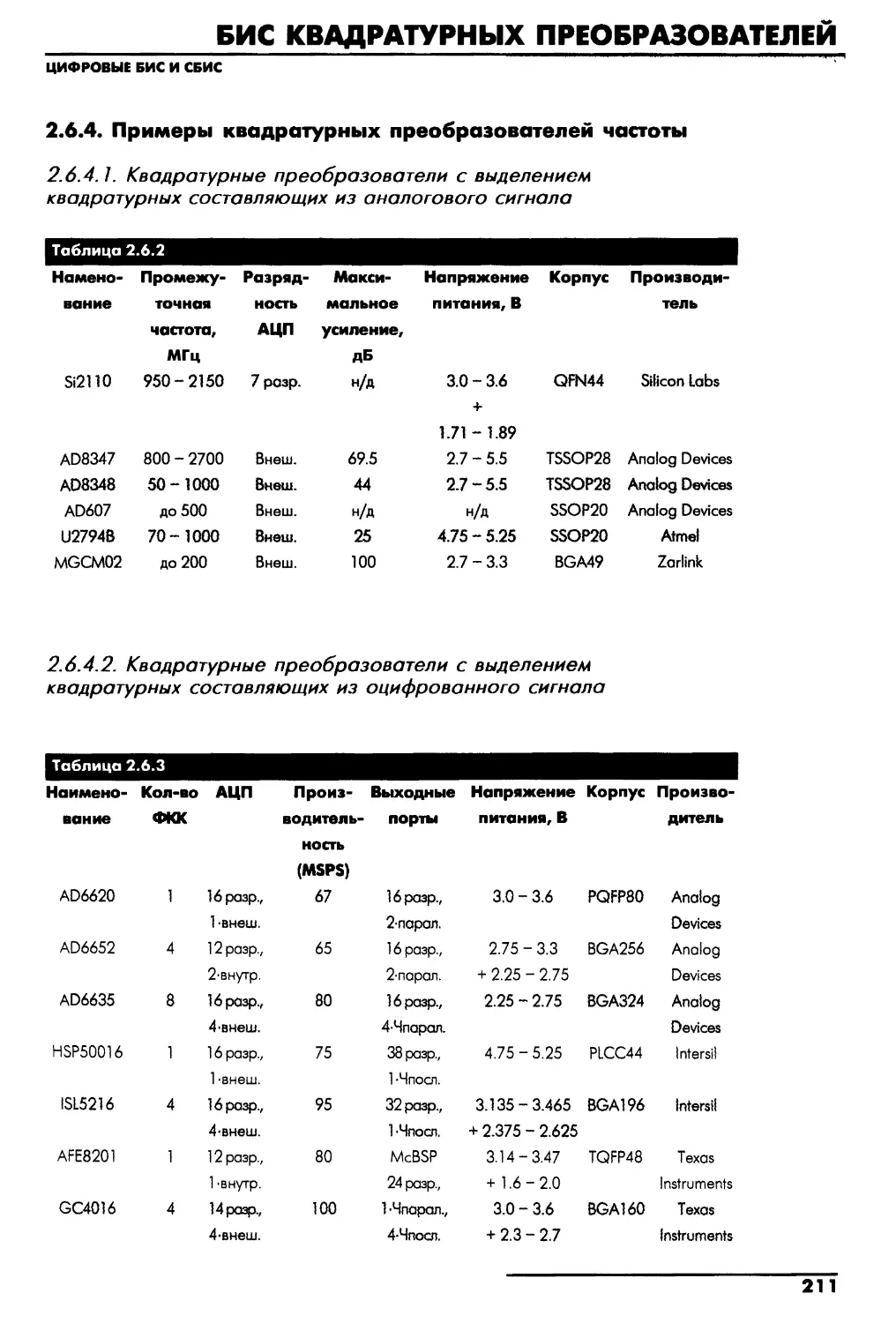

Примеры квадра~урных преобразователей частоты ..... " ...... "" .. . " ... ... "" . 2 11

2.6.4. 1. Квадратурные преобразователи с выделением

квадратурных составляющих из аналогового сигнала "" .. " "" . "" " .. " ." .. 21 1

2.6.4.2. Квадратурные преобразователи с выделением

квадратурных составляющих из оцифрованного сигнала"".. " . "" " . ... " . 2 11

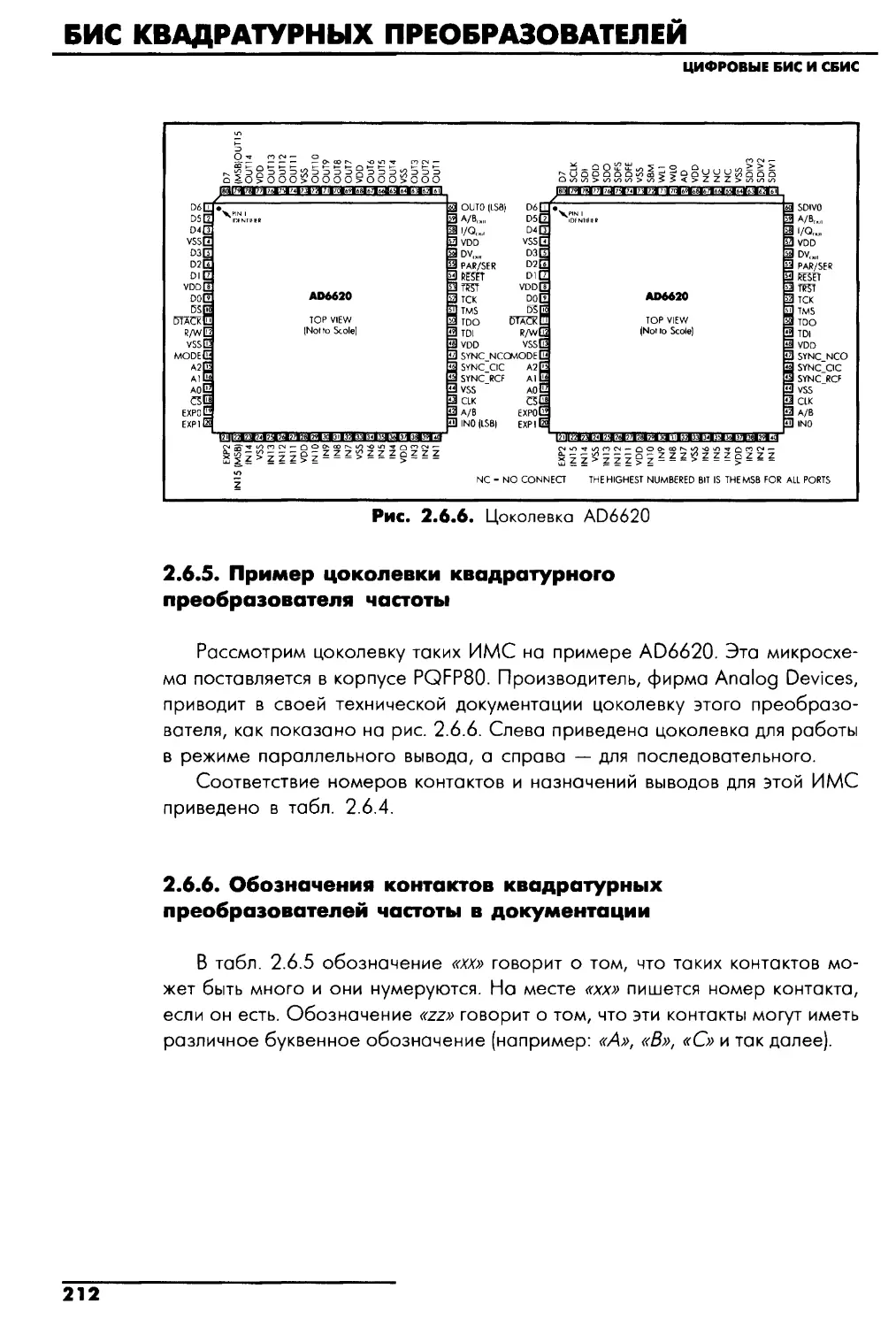

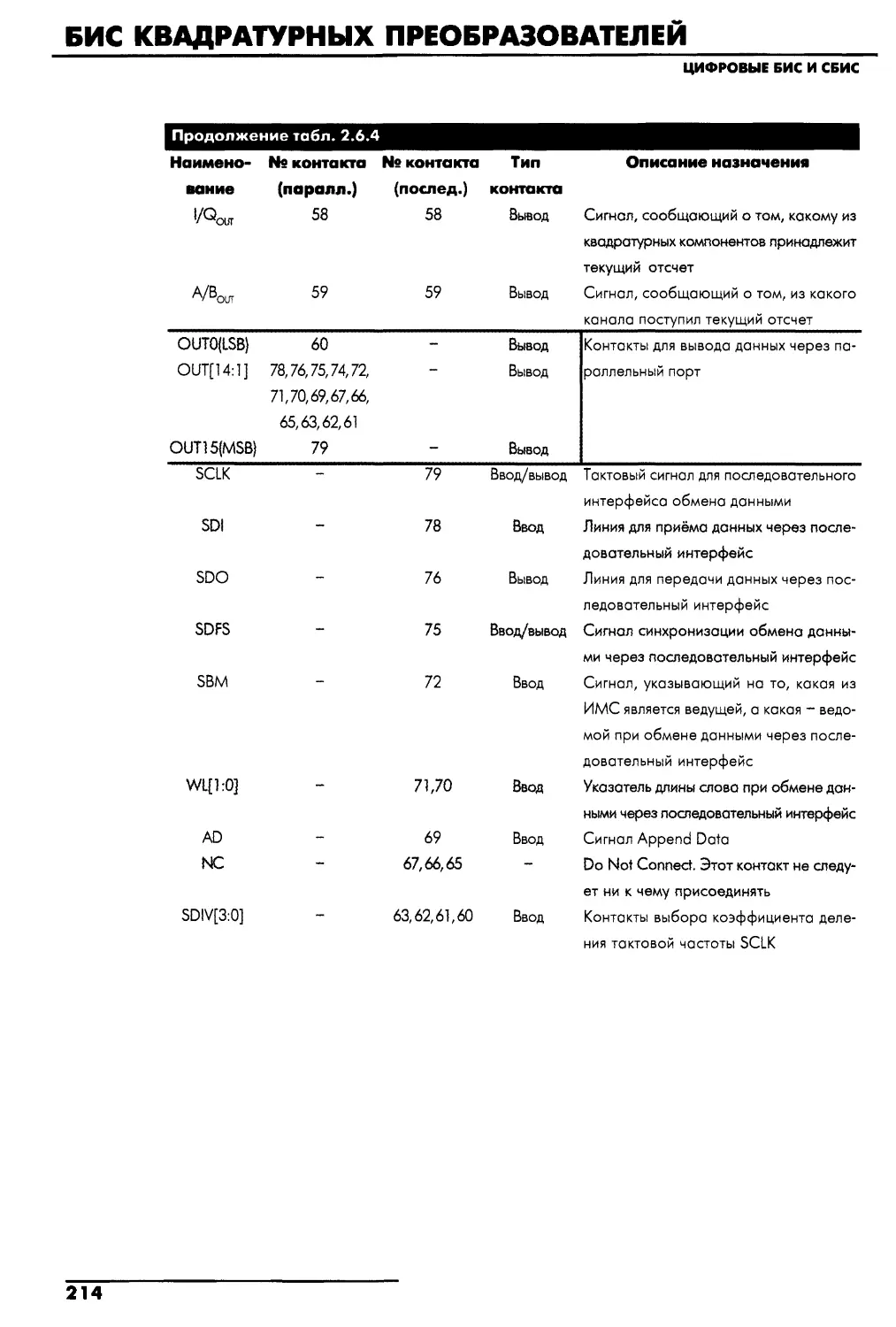

Пример цоколевки квадратурного преобразователя частоты""" ........ 212

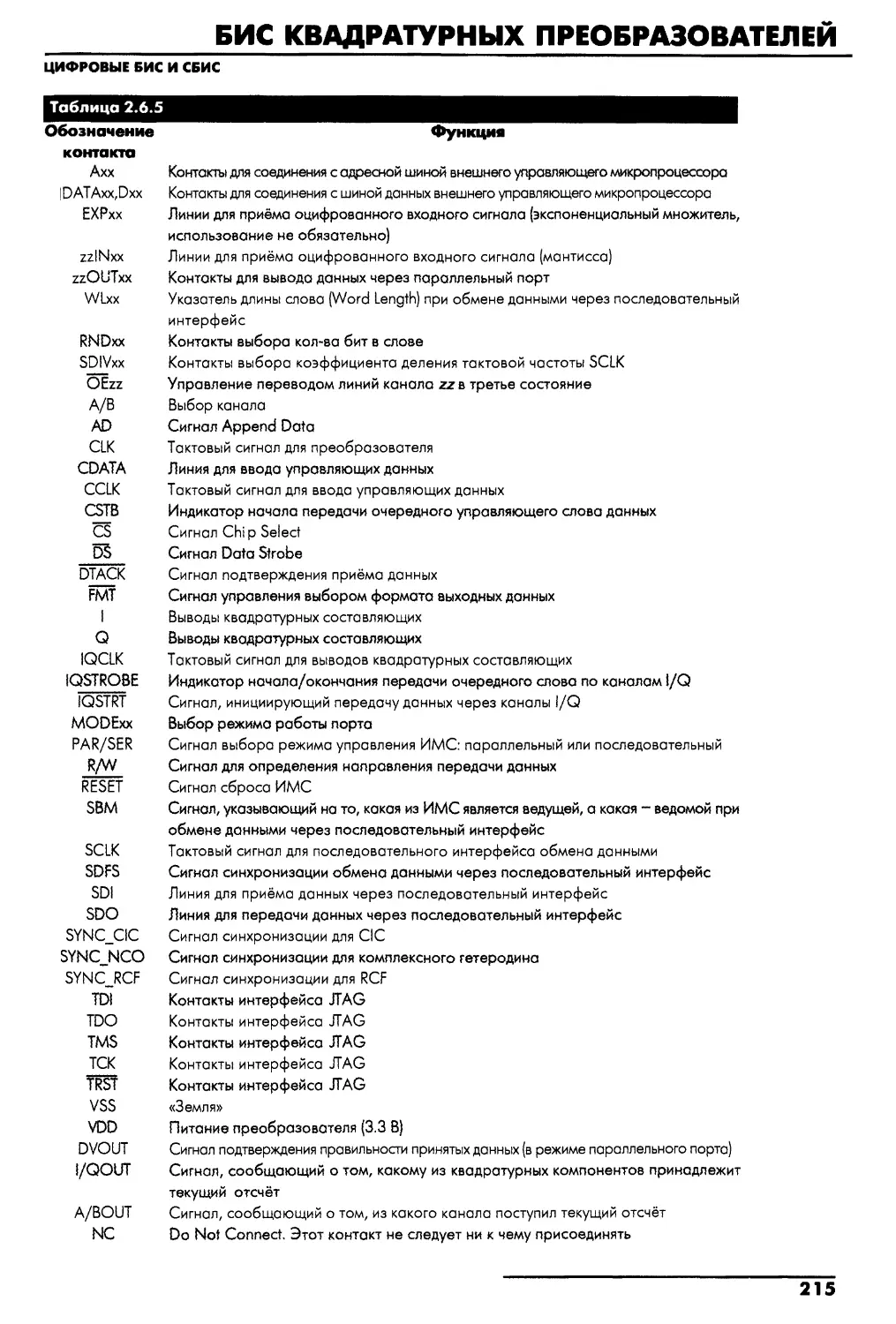

Обозначения контактов квадратурных

преобразователей частоты в документации"".".. " "" ". .. " .. """ "".. . .. . . .. . .. " 2 12

2.7. МИКРОСХЕМЫ КОДЕКОВ .... ..... .... .... .... .... ..... .... .... .... ..... .... ."

216

2.7.1. Терминология и характеристики кодеков ..... ". "" "... ... """ "" . . .. ". " . . "" " . .. "216

2.71.1. Параметры кадеков ....""."""."." ....".."." ........"................".."" ....".". 217

2.7. 1.2. Основные узлы кадеков ."""" .... ".""""".. "".""""" .. "".""""" ......... 218

2.7.2. Классификация помехоустойчивых кодов""." .. " "..... " .. " " ." .... ... """. ".. .. . .. .. 2 1 9

2.7.3.

2.7.4.

2.7.5.

2.7.6.

2.7.7.

2.7.2. 1. Линейные коды"." .."...""." ...."." ..""." ..."" ..........."." .........."." .....".". 220

2.7.2.2. Нелинейные коды"." .."." ..""."." ........"." .."............".........."" ............. 222

Принципы построения и структурные схемы кодеков "". ".. ... .. " " " .. .. .. .. .. 2 24

Перечень основных фирм, выпускающих кодеки ..... " .. """. " . . .. """" . .. " .". 2 26

Примеры современных кодеров, декодеров и кодеков """ ." ." "" . "" " ." . 22 6

2.7.5. 1. ИКМ кодеки ......."" ..........." ............"" .........."""." ....." ........."" ....""""" 226

2.7 .5 .2 . Кодеры и декодеры корректирующих кодов ." " "" ...... "" .. .. .. . .. .. . 2 26

Пример цоколевки ИКМ кодека......." .." .." .......""".".".....".".""...""""".." .. 227

Обозначения контактов ИКМ кодеков в документации." ...... " ." " .. ... .. .. 2 27

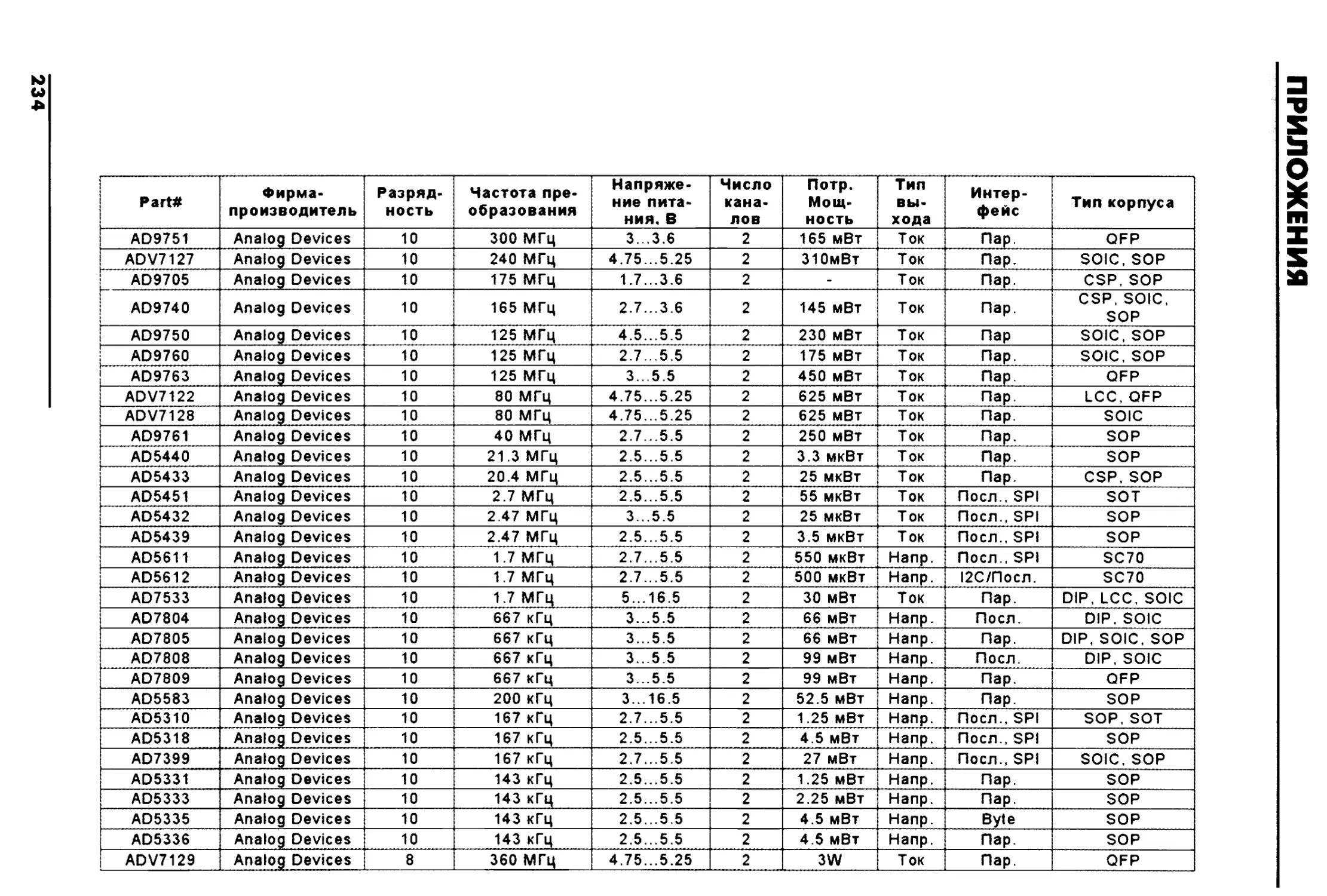

ПРИЛОЖЕНИЯ ............................................................................... 233

ЧАСТЬ 1

АНАЛОГО-ЦИФРОВЫЕ БИС

МИКРОСХЕМЫ ЦАП

10

АНАJIОrО-ЦИФРОВЫЕ &ИС

1.1 МИКРОСХЕМЫ ЦАП

1. 1.1. Характеристики и кпассификаци111 ЦАП

Цифро-аналоговый преобразо

ватель (ЦАП) предназначен для пре

образования цифрового сигнала, за

данного

в

виде двоичного

N-разрядного кода, в соответствую

щее напряжение или ток. Зависимость

выходного напряжения (тока) Ивых И

от входного цифрового сигнала О(~,

изменяющегося от О до 2N- 1

, называ

ют характеристикой преобразования

ЦАП. Эта характеристика может быть

представлена в виде ступенчатой кри

вой. Величина ступеньки соответствует

единице младшего значащего разря-

да (МЗР).

В отсутствие аппаратных погреш

ностей средние точки ступенек распо

ложены на прямой 1, которой соот

ветствует идеальная характеристика

преобразования (рис. 1.1.1 ). Реаль

Ивых

Unw 1-------------.,..,.--т

Рис. 1.1.1. Характеристика

преобразования ЦАП

Есм

Еnш

ная характеристика преобразования может отличаться от идеальной рас

положением, размерами и формой ступенек. Для количественного описания

этих различий используются характеристики, называемые статическими. Из

менения выходного сигнала во времени при скачкообразном изменении

входного кода от минимума («все нули») до максимума («все единицы») опи

сываются динамическими характеристиками ЦАП.

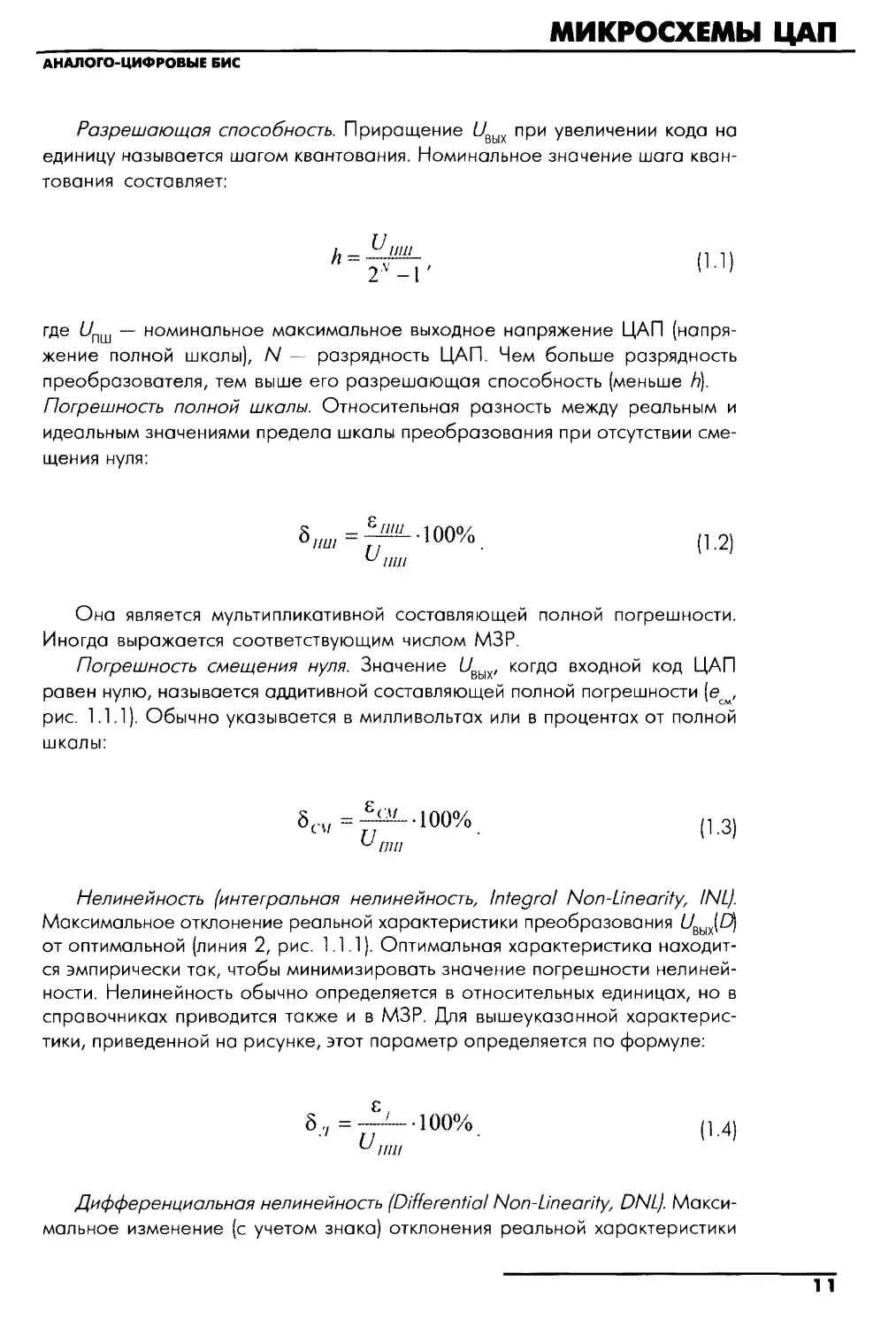

1.1.1. 1. Статические характеристики ЦАП

Разрядность. Число разрядов (двоичных символов) N, передающих коди

рованный входной сигнал. Ему соответствует число уровней квантования 2N_

Число каналов. Число аналоговых выходов ЦАП, на которых формиру

ется выходное напряжение. В зависимости от схемы построения цифровой

код для каждого из каналов подается либо на различные цифровые вхо

ды ЦАП, либо на один и тот же с разделением по времени. Как правило,

частота преобразования и напряжение полной шкалы для всех каналов

ЦАП равны. Однако в некоторых моделях ИМС ЦАП напряжение полной

шкалы для каждого канала задается отдельно и зависит от опорного

напряжения.

МИКРОСХЕМЫ ЦАП

АНАЛОrО-ЦИФРОВЫЕ &ИС

Разрешающая способность. Приращение Ивых при увеличении кода на

единицу называется шагом квантования. Номинальное значение шага кван

тования составляет:

и

J1 = .........JJ!jj_

2\ -1'

(l.l)

где Ипш - номинальное максимальное выходное напряжение ЦАП (напря

жение полной шкалы), N - разрядность ЦАП. Чем больше разрядность

преобразователя, тем выше его разрешающая способность (меньше h).

Погрешность полной шкалы. Относительная разность между реальным и

идеальным значениями предела шкалы преобразования при отсутствии сме

щения нуля:

о =еnш ·100%

lf/11

и

.

11111

(1.2)

Она является мультипликативной составляющей полной погрешности.

Иногда выражается соответствующим числом МЗР.

Погрешность смещения нуля. Значение Ивых' когда входной код ЦАП

равен нулю, называется аддитивной составляющей полной погрешности (е,м,

рис. l. l. l ). Обычно указывается в милливольтах или в процентах от полной

шкалы:

Oc11=f;o1 ·100%

и(]/[/

.

(1.3)

Нелинейность (интегральная нелинейность, /пtegrol Noп-Liпeaгify, INL).

Максимальное отклонение реальной характеристики преобразования Ивых(О)

от оптимальной (линия 2, рис. l. l. l ). Оптимальная характеристика находит

ся эмпирически так, чтобы минимизировать значение погрешности нелиней

ности. Нелинейность обычно определяется в относительных единицах, но в

справочниках приводится также и в МЗР. Для вышеуказанной характерис

тики, приведенной на рисунке, этот параметр определяется по формуле:

е

о. =-1

-·100%

·'

и,1111

·

(1.4)

Дифференциальная нелинейность (Oiffeгeпfial Noп-Liпearity, ONL). Макси

мальное изменение (с учетом знака) отклонения реальной характеристики

11

МИКРОСХЕМЫ ЦАП

12

АНАJIОГО·ЦИФРОВЫЕ &ИС

преобразования Ивых(Оj от оптимальной при переходе от одного значения

входного кода к другому смежному значению. Определяется в относитель

ных единицах или в МЗР:

Е+Е

8=1

J•I ·100%

.Ll

и

/1111

(1.5)

Монотонность характеристики преобразования. Этот параметр харак

теризует увеличение (уменьшение) выходного напряжения ЦАП Ивых при уве

личении {уменьшении) входного кода О. Если дифференциальная нелиней

ность больше относительного шага квантования h/ И , то характеристика

преобразователя немонотонна. В этом случае «опти~~льная прямая» выхо

дит за пределы «ступенек».

Температурная нестабильность. Температурная нестабильность ЦАП

характеризуется температурными коэффициентами погрешности полной

шкалы, погрешности смещения нуля и погрешности нелинейности.

Погрешности полной шкалы и смещения нуля могут быть устранены ка

либровкой (подстройкой). Погрешности нелинейности простыми средства

ми устранить нельзя.

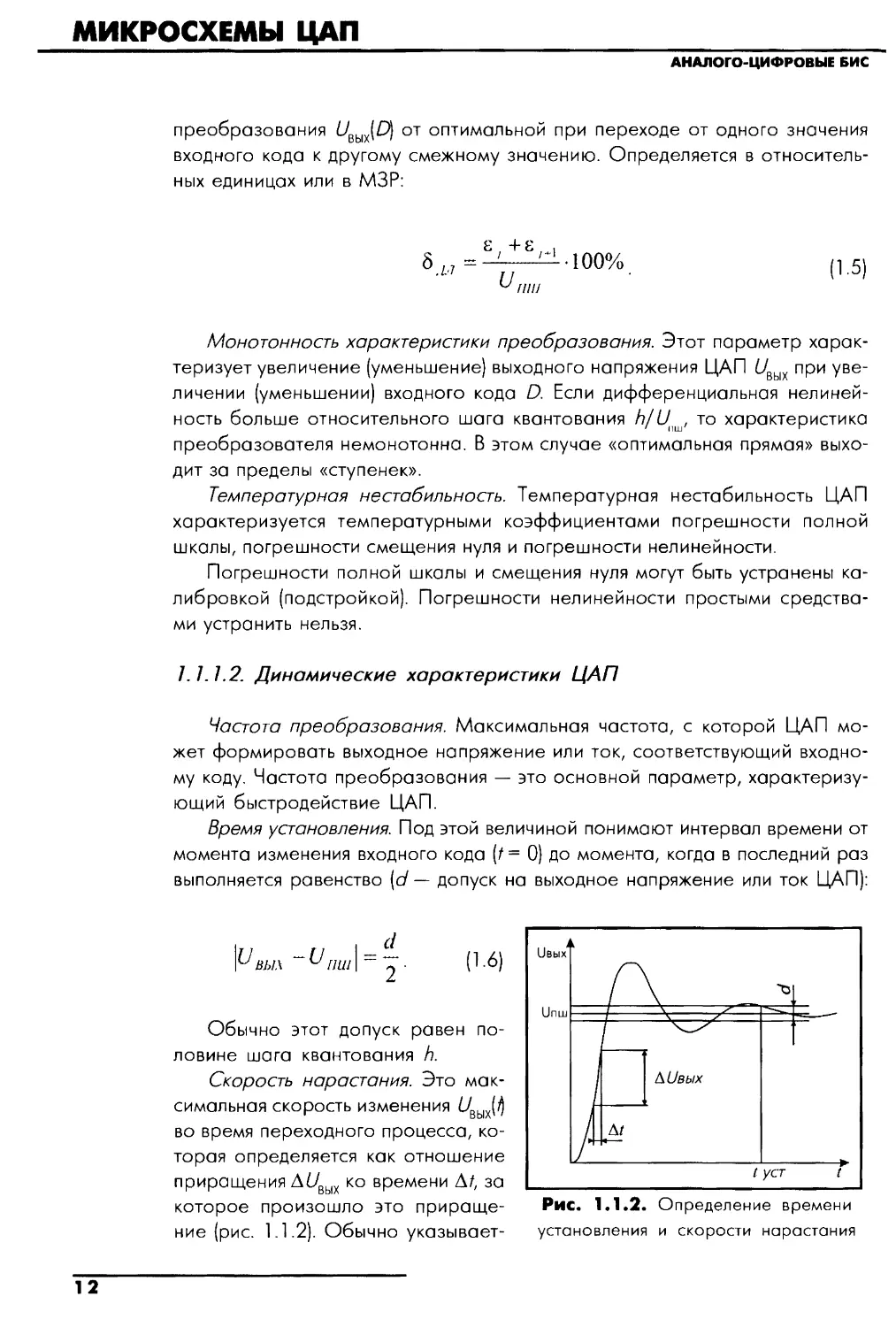

1.1 .1.2. Динамические характеристики ЦАП

Частота преобразования. Максимальная частота, с которой ЦАП мо

жет формировать выходное напряжение или ток, соответствующий входно

му коду. Частота преобразования - это основной параметр, характеризу

ющий быстродействие ЦАП.

Время установления. Под этой величиной понимают интервал времени от

момента изменения входного кода (t = О) до момента, когда в последний раз

выполняется равенство (d - допуск на выходное напряжение или ток ЦАП):

,,

IVвы.1 - Ипш1= 2. (1.6)

Обычно этот допуск равен по

ловине шага квантования h.

Скорость нарастания. Это мак

симальная скорость изменения Ивых(~

во время переходного процесса, ко

торая определяется как отношение

приращения ЛИвых ко времени Лt, за

которое произошло это прираще

ние (рис. 1.1 .2). Обычно указывает-

Uвых

ЛИвых

1 уст

Рис. 1. 1 .2 . Определение времени

установления и скорости нарастания

МИКРОСХЕМЫ ЦАП

АНАЛОГО-ЦИФРОВЫЕ &ИС

ся в технических характеристиках ЦАП с выходным сигналом в виде напряже

ния. У ЦАП с токовым выходом этот параметр в большой степени зависит от

типа выходного ОУ. Для перемножающих ЦАП с выходом в виде напряжения

часто указываются частота единичного усиления и мощностная полоса пропус

кания, которые в основном определяются свойствами выходного усилителя.

Шумы ЦАП Шум на выходе ЦАП может появляться по различным при

чинам, вызываемым физическими процессами, происходящими в полупровод

никовых устройствах. Для оценки качества ЦАП с высокой разрешающей

способностью принято использовать понятие среднеквадратического зна

чения шума. Спектральную плотность шума измеряют обычно в нВ/"\/'(ГЦ) в

заданной полосе частот.

Выбросы (импупьсные помехи). Выбросы представляют собой крутые

короткие всплески или провалы в выходном напряжении, возникающие во

время смены значений выходного кода за счет несинхронности размыкания

и замыкания аналоговых ключей в разных разрядах ЦАП. Например, если

при переходе от значения кода О 11 ... 111 к значению 100... 000 ключ само

го старшего разряда ЦАП с суммированием весовых токов откроется поз

же, чем закроются ключи младших разрядов, то на выходе ЦАП некоторое

время будет существовать сигнал, соответствующий коду 000... 000.

Выбросы характерны для быстродействующих ЦАП, где сведены к мини

муму емкости, которые могли бы их сгладить. Радикальным способом подав

ления выбросов является использование устройств выборки-хранения. Выб

росы оцениваются по их площади в единицах пВ·с.

1.1.1.З. Классификация ЦАП

Классификация ЦАП по схемотехническим признакам представлена на

рис. 1.1 .3 . По принципу работы имеются две основные группы ЦАП: после

довательные и параллельные. Достоинством последовательных ЦАП явля-

Цифро-анапоrовые преобразоватепи

Последовательные

шим

Но переключаемых

конденсаторах

Многоканальные

Параллельные

Суммирование

напряжений

Суммирование

токов

На источниках

тока

Дифференци

альные каскады

Рис. 1.1.3 . Классификация ЦАП по схемотехническим признакам

13

МИКРОСХЕМЫ ЦАП

14

АНАЛОГО-ЦИФРОВЫЕ &.ИС

ется простота схемотехнической реализации, недостатком - невысокое бы

стродействие. Параллельные ЦАП обеспечивают максимально возможное

быстродействие, но это достигается за счет значительного усложнения схемы

по сравнению с последовательными ЦАП.

•

•

•

•

•

•

ЦАП могут также классифицироваться по:

виду выходного сигнала: с токовым выходом; с выходом в виде напря

жения;

полярности выходного сигнала: однополярные; биполярные;

характеру опорного сигнала: с постоянным опорным сигналом; с изме

няющимся опорным сигналом; умножающие;

быстродействию: умеренного быстродействия; высокого быстродействия;

типу цифрового интерфейса (ввод исходного кода): с последовательным

вводом; с параллельным вводом;

числу ЦАП на кристалле: одноканальные; многоканальные .

1. 1 .2 . Структурные схемы и принципы работы ЦАП

1.1.2.1 . ЦАП с широтно-импульсной модуляцией

(Pulse-Width Modulation, PWM)

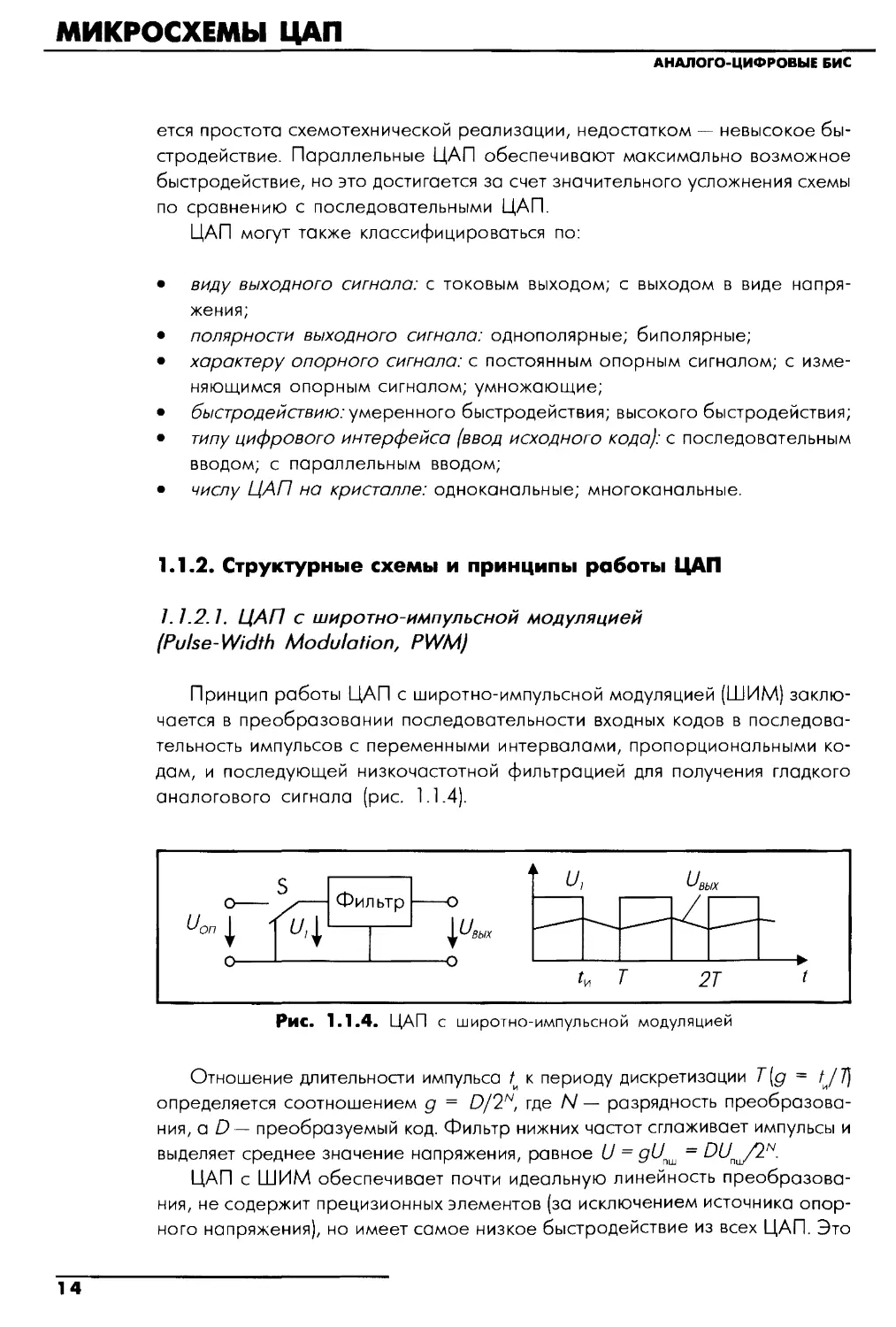

Принцип работы ЦАП с широтно-импульсной модуляцией (ШИМ) заклю

чается в преобразовании последовательности входных кодов в последова

тельность импульсов с переменными интервалами, пропорциональными ко

дам, и последующей низкочастотной фильтрацией для получения гладкого

аналогового сигнала (рис. 1.1.4).

tиТ

2Т

Рис. 1.1.4 . ЦАП с широтно-импульсной модуляцией

"t

Отношение длительности импульса 1, к периоду дискретизации Т (g = tj ry

определяется соотношением g = D/2N, где N - разрядность преобразова

ния, а О - преобразуемый код. Фильтр нижних частот сглаживает импульсы и

выделяет среднее значение напряжения, равное И= gИ,ш = DU,fiN.

ЦАП с ШИМ обеспечивает почти идеальную линейность преобразова

ния, не содержит прецизионных элементов (за исключением источника опор

ного напряжения), но имеет самое низкое быстродействие из всех ЦАП. Это

МИКРОСХЕМЫ ЦАП

АНАЛОГО-ЦИФРОВЫЕ &ИС

связано с тем, что в его схеме N-разрядный цифровой код преобразуется во

временной интервал, длина которого равна сумме всех единиц (тактов) в

числе, т.е. 2N (это осуществляется с помощью двоичного счетчика). Поэтому

для получения N-разрядного преобразования необходимо большое число

(2NJ временных тактов.

ЦАП с ШИМ часто входит в состав микропроцессорных систем с невы

соким быстродействием, микроконтроллер которых имеет встроенную функ

цию ШИМ (например, AT90S85 l 5 фирмы Atmel или 87С51 GB фирмы lпtel).

Для реализации ЦАП достаточно к выходу ШИМ подключить ключ и фильтр

нижних частот (в простейшем случае это конденсатор).

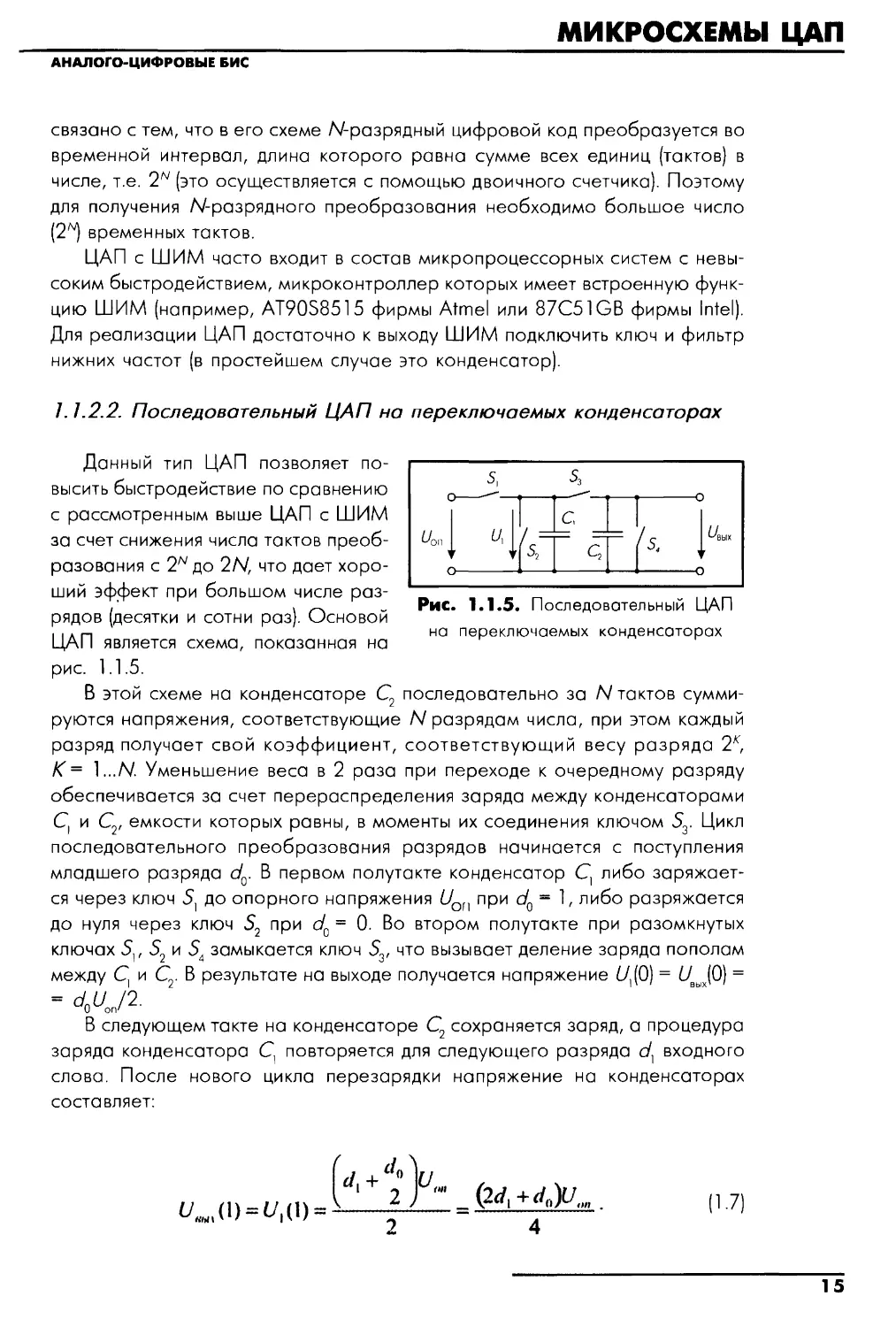

1.1 .2.2 . Последовательный ЦАП на переключаемых конденсаторах

Данный тип ЦАП позволяет по

высить быстродействие по сравнению

с рассмотренным выше ЦАП с ШИМ

за счет снижения числа тактов преоб

разования с 2N до 2N, что дает хоро

ший эффект при большом числе раз-

рядов (десятки и сотни раз). Основой

ЦАП является схема, показанная на

рис. 1.1 .5.

5,

s,

Рис. 1.1.5 . Последовательный ЦАП

на переключаемых конденсаторах

В этой схеме на конденсаторе С2 последовательно за N тактов сумми

руются напряжения, соответствующие N разрядам числа, при этом каждый

разряд получает свой коэффициент, соответствующий весу разряда 2к,

К= l ... N. Уменьшение веса в 2 раза при переходе к очередному разряду

обеспечивается за счет перераспределения заряда между конденсаторами

С1 и С2 , емкости которых равны, в моменты их соединения ключом 53 . Цикл

последовательного преобразования разрядов начинается с поступления

младшего разряда d0 . В первом полутакте конденсатор С1 либо заряжает

ся через ключ 51 до опорного напряжения И0г 1 при d0 = 1, либо разряжается

до нуля через ключ 52 при d0 = О. Во втором полутакте при разомкнутых

ключах 51, 52 и 54 замыкается ключ 53 , что вызывает деление заряда пополам

между С1 и С2 • В результате на выходе получается напряжение И1 (0) = И",,(О) =

= d0U0/2

В следующем такте на конденсаторе С2 сохраняется заряд, а процедура

заряда конденсатора С1 повторяется для следующего разряда d1 входного

слова. После нового цикла перезарядки напряжение на конденсаторах

составляет:

И(1)=И(1)=(d, + t~ )и"" =(2d, +tl,JU"".

""''

1

2

4

(1.7)

15

МИКРОСХЕМЫ ЦАП

16

АНАЛОrО-ЦИФРОВЫЕ &ИС

В результате N-кратного повторения циклов заряда выходное напря

жение N-разрядного ЦАП стонет равным:

N-1

где D = L:dk2k - цифровой код (или входное слово).

k=O

(1.8)

Если требуется сохранять результат преобразования в течение некоторого

времени, то к выходу схемы подключается устройство выборки-хранения (УВХ).

Дополнительным достоинством данного ЦАП является то, что конфигурация

аналоговой части схемы не зависит от разрядности преобразуемого кода.

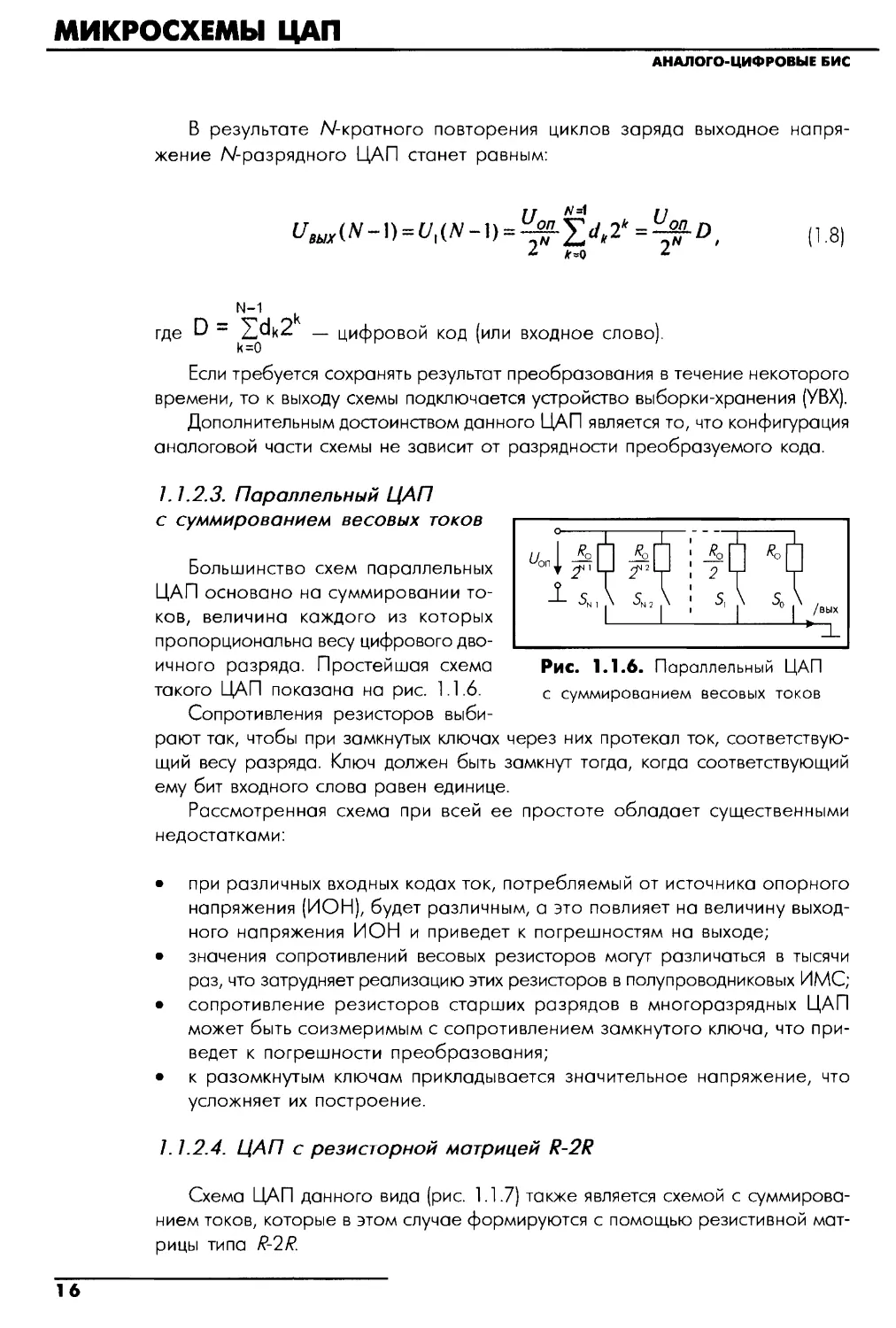

1.1.2 .3 . Параллельный ЦАП

с суммированием весовых токов

Большинство схем параллельных

ЦАП основано на суммировании то

ков, величина каждого из которых

пропорционально весу цифрового дво

ичного разряда. Простейшая схема

такого ЦАП показана но рис. l. l .6 .

Сопротивления резисторов выби

Рис. 1.1.6. Параллельный ЦАП

с суммированием весовых токов

рают так, чтобы при замкнутых ключах через них протекал ток, соответствую

щий весу разряда. Ключ должен быть замкнут тогда, когда соответствующий

ему бит входного слова ровен единице.

Рассмотренная схема при всей ее простоте обладает существенными

недостатками:

•

при различных входных кодах ток, потребляемый от источника опорного

напряжения (ИОН), будет различным, о это повлияет но величину выход

ного напряжения ИОН и приведет к погрешностям но выходе;

•

значения сопротивлений весовых резисторов могут различаться в тысячи

роз, что затрудняет реализацию этих резисторов в полупроводниковых ИМС;

•

сопротивление резисторов старших разрядов в многорозрядных ЦАП

может быть соизмеримым с сопротивлением замкнутого ключа, что при

ведет к погрешности преобразования;

•

к разомкнутым ключам прикладывается значительное напряжение, что

усложняет их построение.

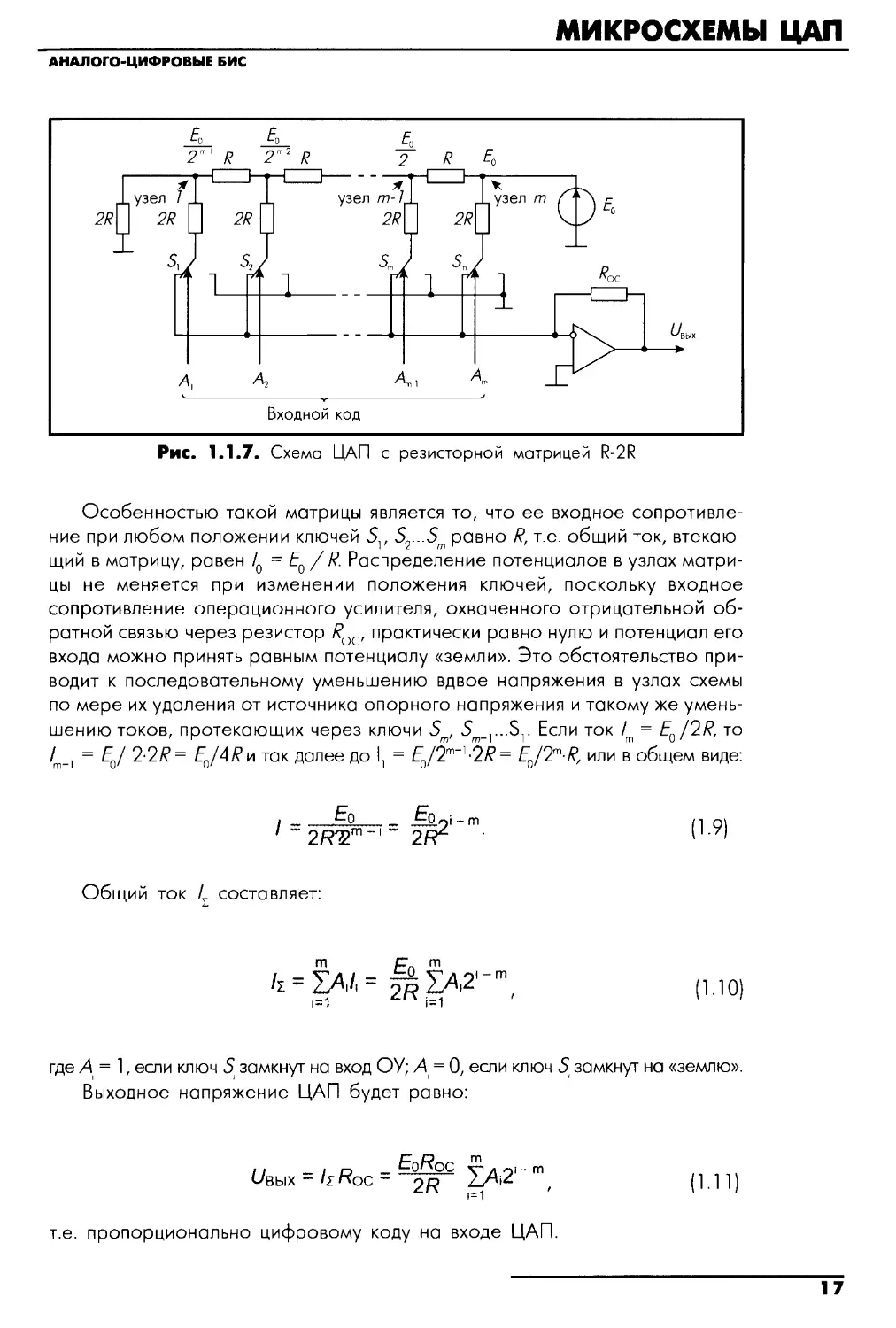

1.1.2 .4 . ЦАП с резисторной матрицей R-2R

Схема ЦАП донного вида (рис. l. l .7) также является схемой с суммирова

нием токов, которые в этом случае формируются с помощью резистивной мат

рицы типа R-2R .

МИКРОСХЕМЫ ЦАП

АНАЛОГО-ЦИФРОВЫЕ БИС

RЕо

узел

2R

2R

А1

А,

А,,

Входной код

Рис. 1.1.7. Схема ЦАП с резисторной матрицей R-2R

Особенностью такой матрицы является то, что ее входное сопротивле

ние при любом положении ключей 5 1, 52 ... Sm равно R, т.е. общий ток, втекаю

щий в матрицу, равен /0 = Е0 / R. Распределение потенциалов в узлах матри

цы не меняется при изменении положения ключей, поскольку входное

сопротивление операционного усилителя, охваченного отрицательной об

ратной связью через резистор R0 u практически равно нулю и потенциал его

входа можно принять равным потенциалу «земли». Это обстоятельство при

водит к последовательному уменьшению вдвое напряжения в узлах схемы

по мере их удаления от источника опорного напряжения и такому же умень

шению токов, протекающих через ключи 5m, 5m_гS 1 • Если ток /m = Е0 /2R, то

/m-I = ~/ 2·2R = Eof 4R и так далее до 11 = ~;2m- 1 .2R= ~/2m·R, или в общем виде:

(1.9)

Общий ток /: составляет:

l'i. =fAJi=Еоfд21-m

1=1

2Ri=1 1

'

(1.10)

где А,= 1, если ключ 5, замкнут на вход ОУ; А,= О, если ключ 5, замкнут на «землю».

Выходное напряжение ЦАП будет равно:

и 1R EoRoc ~л,2,_m

вых = г. ос =-2R L/'1

1=1

'

(1.11)

т.е. пропорционально цифровому коду на входе ЦАП.

17

МИКРОСХЕМЫ ЦАП

18

АНАЛОГО-ЦИФРОВЫЕ &ИС

/вых

R

R

Рис. 1.1 .8. Схема ЦАП на источниках тока

Схемы ЦАП на основе резистивных матриц R-2R практичны, надежны,

обладают высокой скоростью преобразования и легко реализуются в ин

тегральном исполнении. В отличие от ЦАП с взвешивающими резисторами

здесь не требуется широкого диапазона номиналов и прецизионной точно

сти при их подгонке.

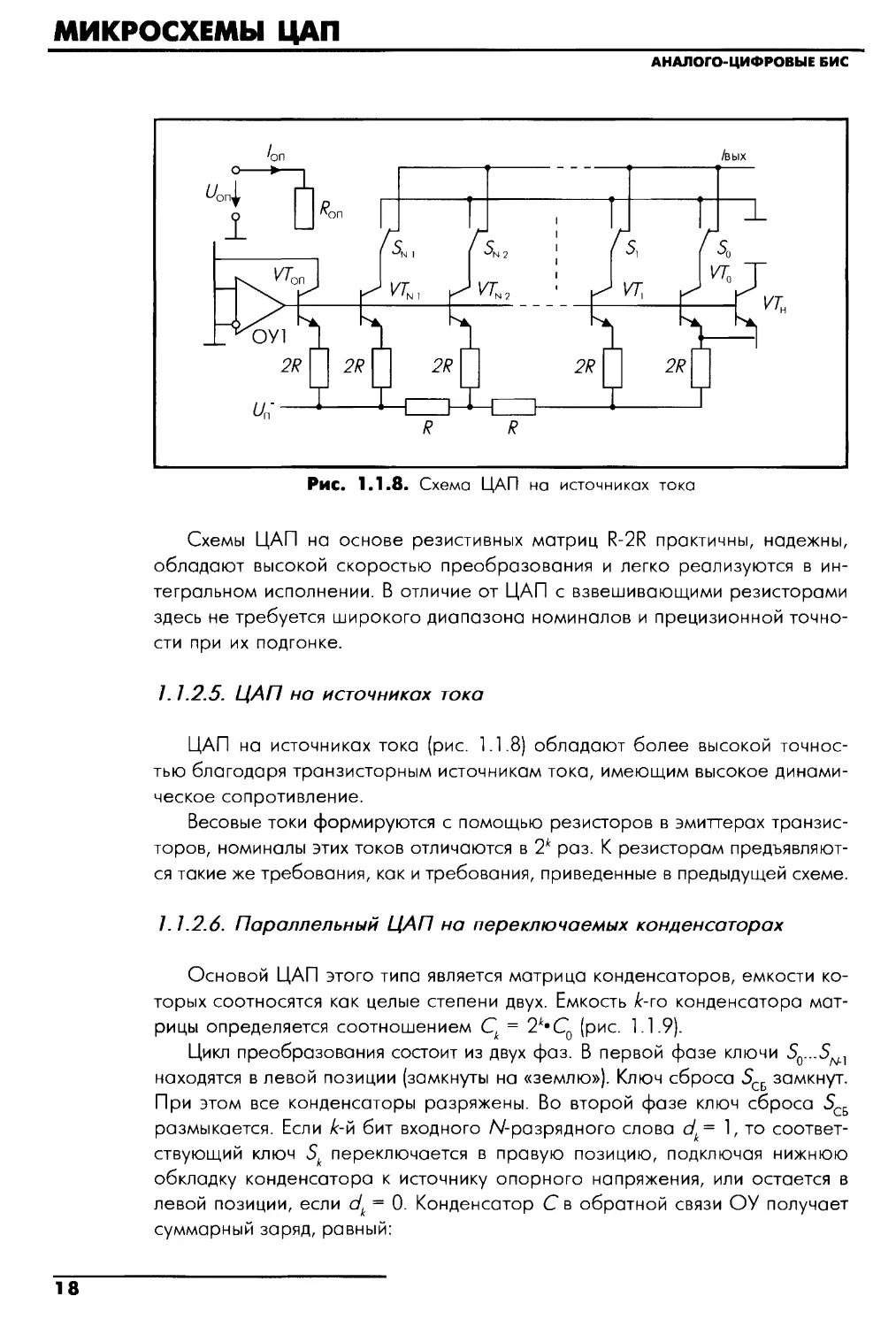

1.1.2 .5 . ЦАП но источниках тока

ЦАП на источниках тока (рис. 1.1 .8) обладают более высокой точнос

тью благодаря транзисторным источникам тока, имеющим высокое динами

ческое сопротивление.

Весовые токи формируются с помощью резисторов в эмиттерах транзис

торов, номиналы этих токов отличаются в 2k раз. К резисторам предъявляют

ся такие же требования, как и требования, приведенные в предыдущей схеме.

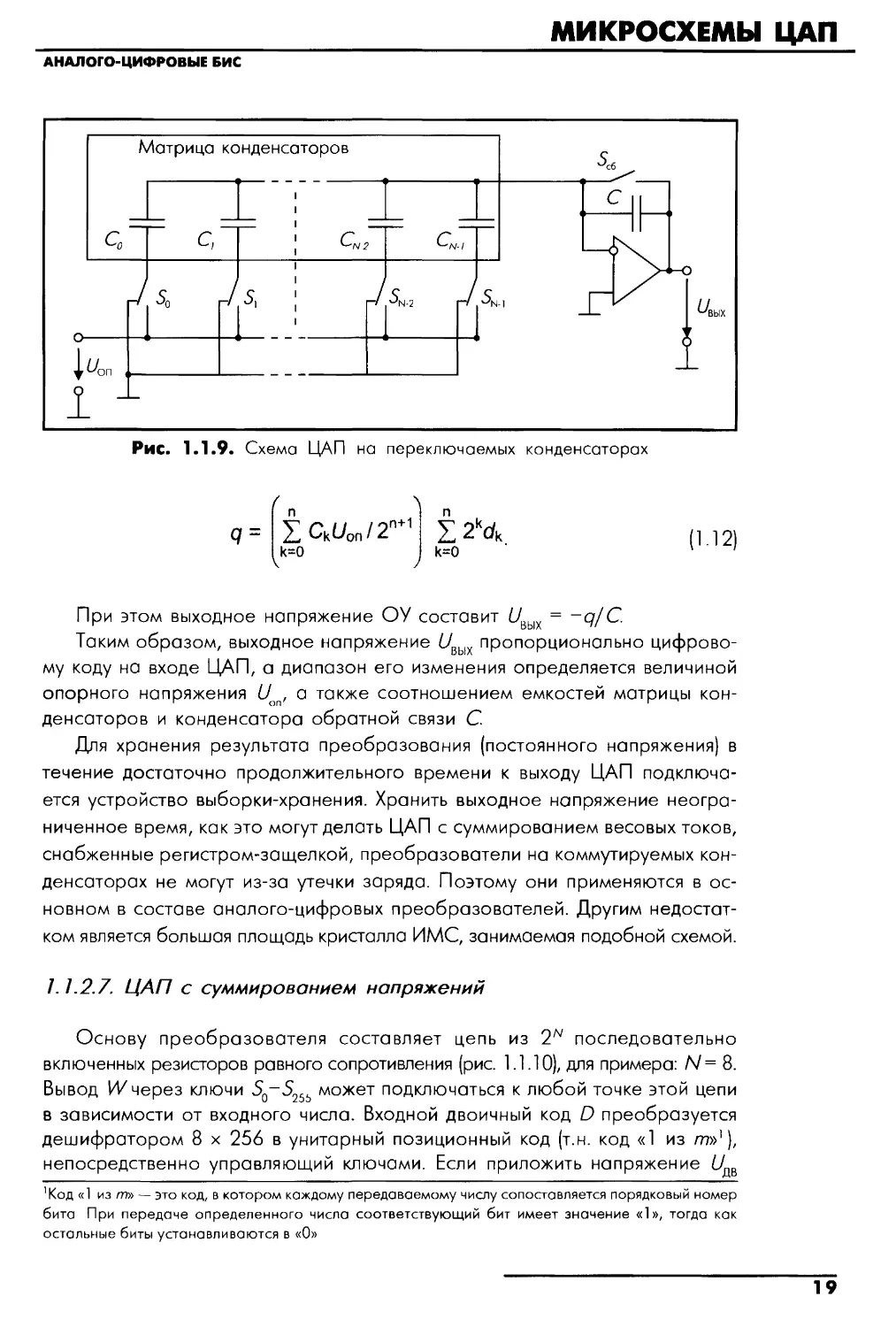

1.1.2 .6 . Параллельный ЦАП но переключаемых конденсаторах

Основой ЦАП этого типа является матрица конденсаторов, емкости ко

торых соотносятся как целые степени двух. Емкость k-го конденсатора мат

рицы определяется соотношением Ck = 2'•С0 (рис. 1.1 .9).

Цикл преобразования состоит из двух фаз. В первой фазе ключи 50 ."5N 1

находятся в левой позиции (замкнуты на «землю»). Ключ сброса 5СБ замкнут.

При этом все конденсаторы разряжены. Во второй фазе ключ сброса 5с 6

размыкается. Если k-й бит входного N-разрядного слова d1 = 1, то соответ

ствующий ключ sk переключается в правую позицию, подключая нижнюю

обкладку конденсатора к источнику опорного напряжения, или остается в

левой позиции, если d1 = О. Конденсатор С в обратной связи ОУ получает

суммарный заряд, равный:

МИКРОСХЕМЫ ЦАП

АНАJIОrО-ЦИФРОВЫЕ &ИС

Матрица конденсаторов

L IС,

s.

Рис. 1.1.9 . Схема ЦАП на переключаемых конденсаторах

(l.12)

При этом выходное напряжение ОУ составит Ивых = -q/C

Таким образом, выходное напряжение Ивых пропорционально цифрово

му коду на входе ЦАП, а диапазон его изменения определяется величиной

опорного напряжения И , а также соотношением емкостей матрицы кон

денсаторов и конденсат;;'ра обратной связи С

Для хранения результата преобразования (постоянного напряжения) в

течение достаточно продолжительного времени к выходу ЦАП подключа

ется устройство выборки-хранения. Хранить выходное напряжение неогра

ниченное время, как это могут делать ЦАП с суммированием весовых токов,

снабженные регистром-защелкой, преобразователи на коммутируемых кон

денсаторах не могут из-за утечки заряда. Поэтому они применяются в ос

новном в составе аналого-цифровых преобразователей. Другим недостат

ком является большая площадь кристалла ИМС, занимаемая подобной схемой.

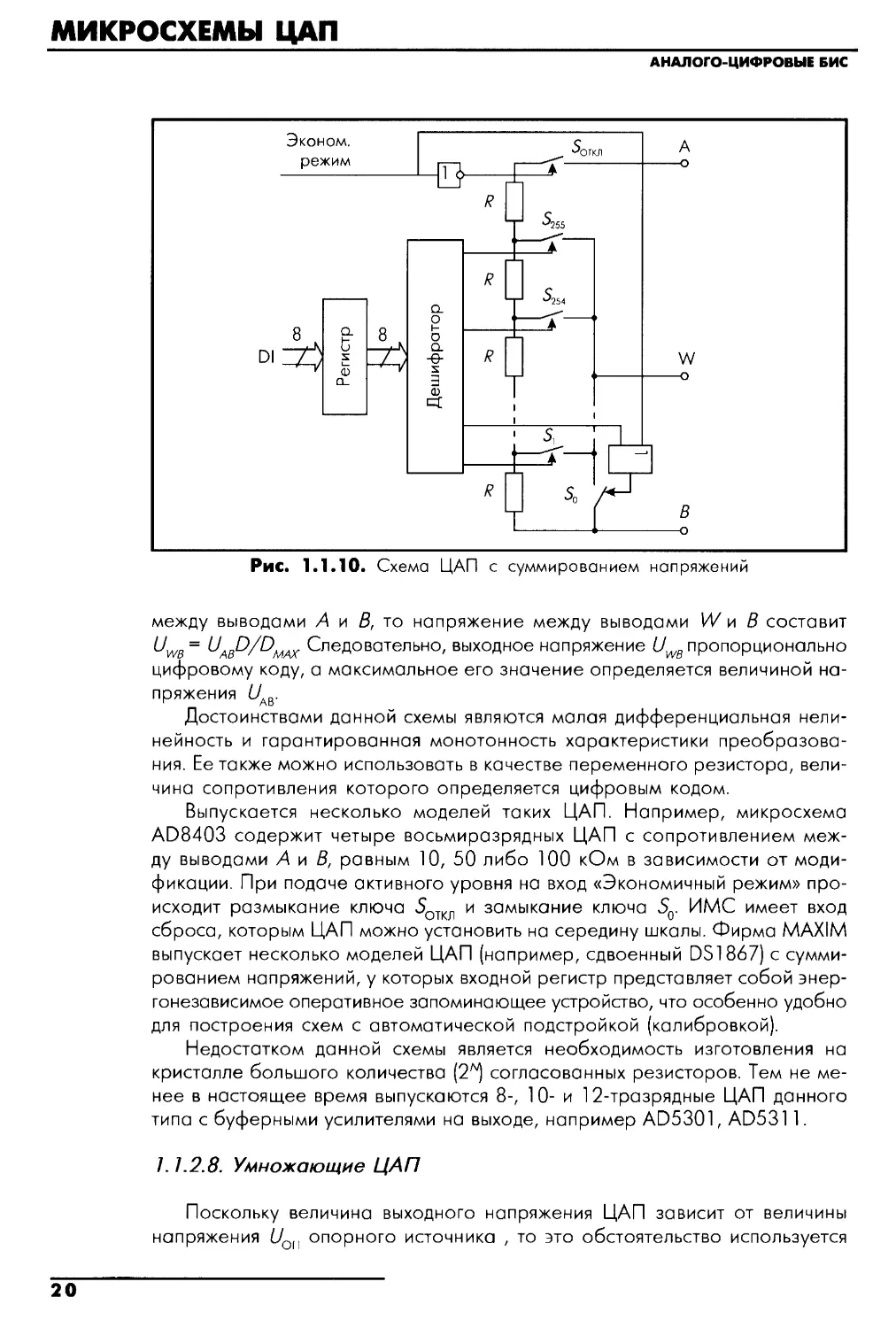

1.1 .2 .7 . ЦАП с суммировонием напряжений

Основу преобразователя составляет цепь из 2N последовательно

включенных резисторов равного сопротивления (рис. l. l. l О), дnя примера: N = 8.

Вывод W через ключи 50 - 5щ может подключаться к любой точке этой цепи

в зависимости от входного числа. Входной двоичный код О преобразуется

дешифратором 8 х 256 в унитарный позиционный код (т.н. код « l из m» 1 ),

непосредственно управляющий ключами. Если приложить напряжение Идв

1Код « 1 из m» - это код, в котором каждому передаваемому числу сопоставляется порядковый номер

бита При передаче определенного числа соответствующий бит имеет значение «1», тогда как

остальные биты устанавливаются в «0»

19

МИКРОСХЕМЫ ЦАП

20

DI

Эконом.

режим

в

в

Q_

о

f-

о

Q_

-е-

"3

ф

q:

АНАЛОГО-ЦИФРОВЫЕ &.ИС

5откл

А

w

R

в

Рис. 1.1.10. Схема ЦАП с суммированием напряжений

между выводами А и В, то напряжение между выводами W и В составит

Иwв = UA8D/DмAX Следовательно, выходное напряжение Иwв пропорционально

цифровому коду, о максимальное его значение определяется величиной на

пряжения илв·

Достоинствами донной схемы являются малая дифференциальная нели

нейность и гарантированная монотонность характеристики преобразова

ния. Ее также можно использовать в качестве переменного резистора, вели

чина сопротивления которого определяется цифровым кодом.

Выпускается несколько моделей таких ЦАП. Например, микросхема

AD8403 содержит четыре восьмиразрядных ЦАП с сопротивлением меж

ду выводами А и В, ровным 1О, 50 либо 100 кОм в зависимости от моди

фикации. При подаче активного уровня но вход «Экономичный режим» про

исходит размыкание ключа Sоткл и замыкание ключа 50 . ИМС имеет вход

сброса, которым ЦАП можно установить но середину школы. Фирма MAXIM

выпускает несколько моделей ЦАП (например, сдвоенный DS 1867) с сумми

рованием напряжений, у которых входной регистр представляет собой энер

гонезависимое оперативное запоминающее устройство, что особенно удобно

для построения схем с автоматической подстройкой (калибровкой).

Недостатком донной схемы является необходимость изготовления но

кристалле большого количество (2") согласованных резисторов. Тем не ме

нее в настоящее время выпускаются 8-, l О- и 12-трозрядные ЦАП донного

типа с буферными усилителями но выходе, например AD5301, AD5311 .

1.1 .2.8. Умножающие ЦАП

Поскольку величина выходного напряжения ЦАП зависит от величины

напряжения U011 опорного источника , то это обстоятельство используется

МИКРОСХЕМЫ ЦАП

АНАЛОrО-ЦИФРОВЫЕ &ИС

для построения так называемых умножающих ЦАП. В таких ЦАП в каче

стве опорного применяют источник изменяющегося напряжения, тогда пре

образователь будет формировать выходной сигнал, пропорциональный

произведению управляющего кода на изменяющееся напряжение (2]. Сле

дует отметить, что в этом случае опорное напряжение f 0 может принимать

как положительные, так и отрицательные значения. Поэтому для правильной

работы схемы необходимо, чтобы ключи Sm, Sт- 1 •. 5 1 (рис. l. l О) имели ампли

тудную характеристику, симметричную относительно нулевого напряжения.

Таким свойством обладают ключи, изготовленные на базе полевого тран

зистора, в частности по МОП-технологии.

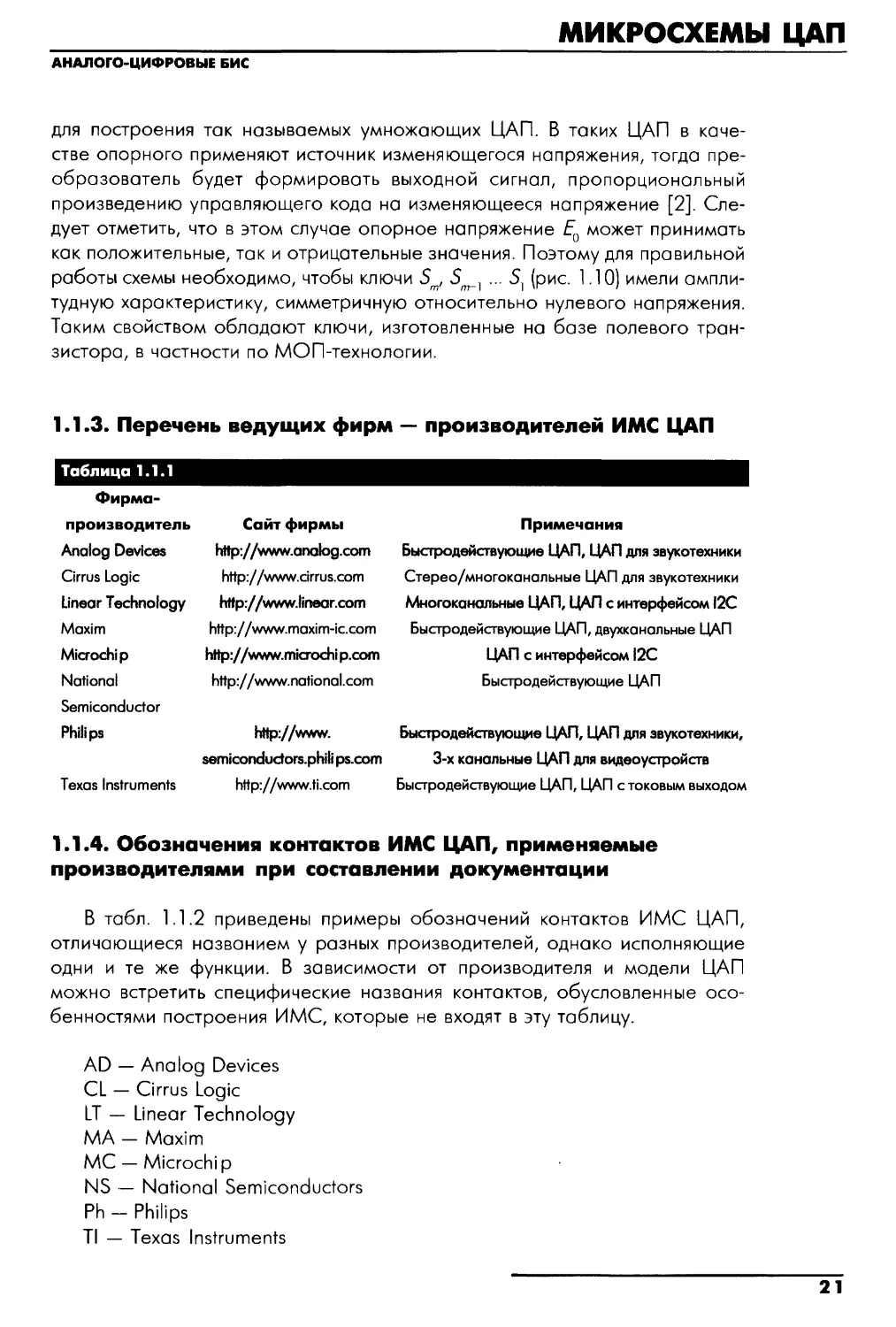

1. 1 .3 . Перечень ведущих фирм - производитеяей ИМС ЦАП

Табяица 1.1 .1

Фирма

производитеяь

Analog Devicвs

Ciггus Logic

Linвoг Тechnology

Maxim

Microchip

National

Semiconductoг

Philips

Тexas lnstгuments

Сайт фирмы

hffp://www.analog.com

http://www.ciггus.com

hffp://www.lineaг.com

http://www.maxim-ic.com

hffp://www.microchip.com

http://www.national.com

hffp://www.

зemiconductors.phili ps.com

http://www.ti.com

Примечани11

Быстродействующие ЦАП, ЦАП дnя звукотехники

Стерео/многоканальные ЦАП для звукотехники

Многоканальные ЦАП, ЦАП с интерфейсом 12С

Быстродействующие ЦАП, двухканальные ЦАП

ЦАП с интерфейсом 12С

Быстродействующие ЦАП

Быстродействующие ЦАП, ЦАП дnя звукотехники,

3-х канальные ЦАП дnя видеоустройств

Быстродействующие ЦАП, ЦАП с токовым выходом

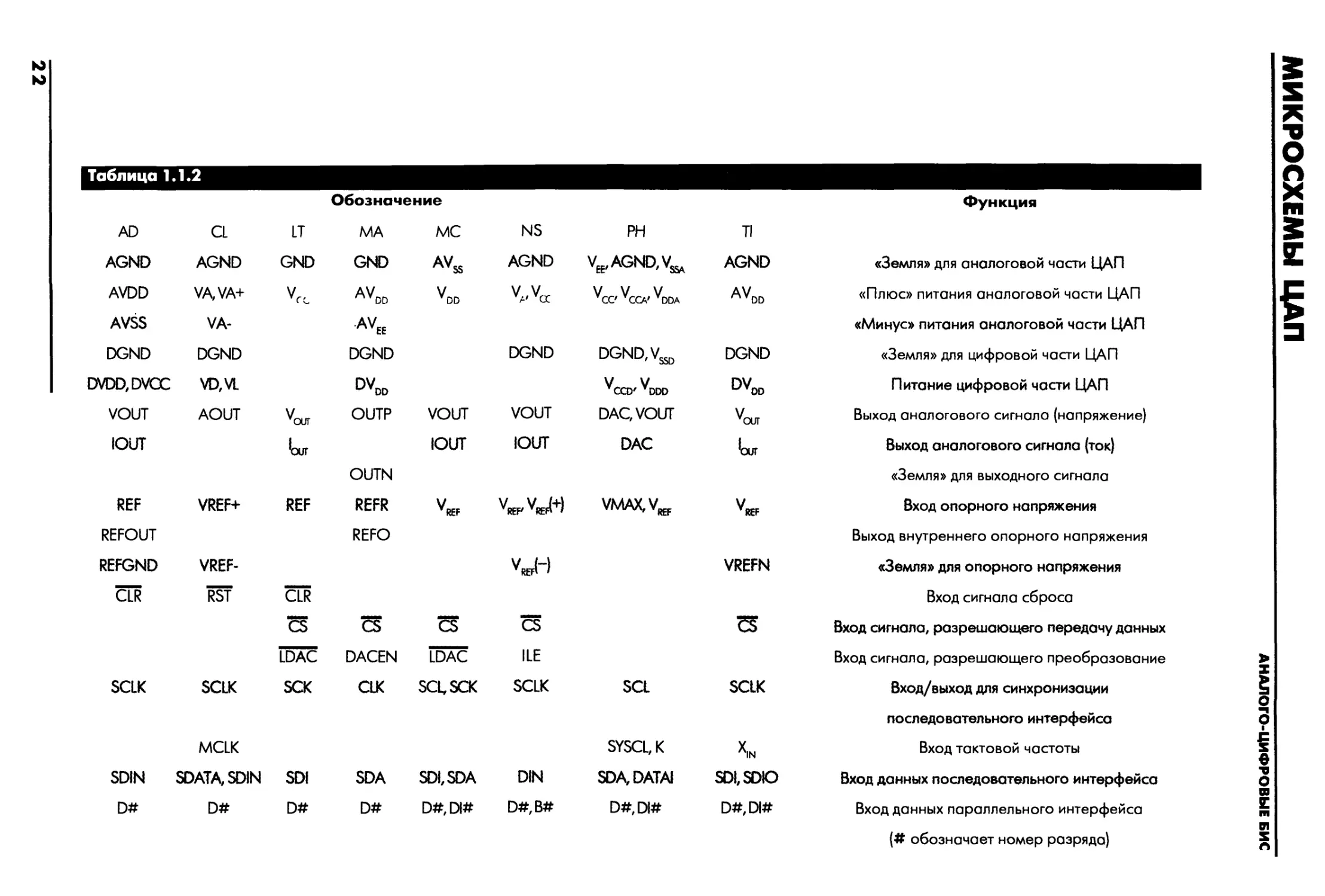

1. 1 .4 . Обозначени11 контактов ИМС ЦАП, примен11емые

производитея11ми при составяении документации

В табл. l. l .2 приведены примеры обозначений контактов ИМС ЦАП,

отличающиеся названием у разных производителей, однако исполняющие

одни и те же функции. В зависимости от производителя и модели ЦАП

можно встретить специфические названия контактов, обусловленные осо

бенностями построения ИМС, которые не входят в эту таблицу.

AD - Aпalog Devices

CL - Cirrus Logic

LT - Liпear Techпology

МА- Maxim

МС - Microchip

NS - Natioпal Semiconductors

Ph - Philips

Т1 - Тexas lnstruments

21

t.)

t.)

Табпица 1.1.2

AD

CL

AGND

AGND

AVDD

VA, VA+

AVSS

VA-

DGND

DGND

DVDD,DVCC VD ,Vl

VOUT

AOUT

IOUТ

REF

VREF+

REFOUT

REFGND

VREF-

ш

RST

SCLK

SCLK

MCLK

SDIN SDATA,SDIN

D#

D#

Обозначение

LT

МА

мс

GND

GND

AVSS

vrc

AVDD

VDD

-AVEE

DGND

DVDD

voor

OUTP

VOUT

'=

IOUТ

OUTN

REF

REFR

v",

REFO

ш

ёS

ёS

ёS

LDAC DACEN I5Ac'

sск

СLК SCL,SCK

SDI

SDA SDl,SDA

D#

D#

D#,DI#

NS

РН

TI

AGND V",AGND , Vsso.

AGND

v,, vc<

VCC' VCO/ VDDA

AVDD

DGND

DGND, VSSD

DGND

Va:D,VDDD

DVDD

VOUT

DAC,VOLЛ

voor

IOUТ

DAC

'=

v.,,,v"~+! VМIV<, V.. ,

v..,

v"~-!

VREFN

ёS

ёS

ILE

SCLK

SCl

SCLK

SYSCL,K

XIN

DIN

SDA,DATAI

SDJ,SDIO

D#,В#

D#,DI#

D#,DI#

ФункциА

«Земля» для аналоговой части ЦАП

«Плюс» питания аналоговой части ЦАП

«Минус» питания аналоговой части ЦАП

«Земля» для цифровой части ЦАП

Питание цифровой части ЦАП

Выход аналогового сигнала {напряжение)

Выход оноnогового сигнала (ток!

«Земля» для выходного сигнала

Вход опорного напряжения

Выход внутреннего опорного напряжения

.Земля» для опорного напряжения

Вход сигнала сброса

Вход сигнала, розрешоющеrо передачу донных

Вход сигнала, разрешающего преобразование

Вход/ выход для синхронизации

последовательного интерфейса

Вход тактовой частоты

Вход донных последовательного интерфейса

Вход данных параллельного интерфейса

(# обозначает номер разряда!

1О

:i:

~о

"

9.r:

s

е.,,

о

111

11:

m

111

s

...

з:

:s:

jllll;

.,,

о

Q...

з:

!2:

s:::1

МИКРОСХЕМЫ ЦАП

АНАЛОrО-ЦИФРОВЫЕ БИС

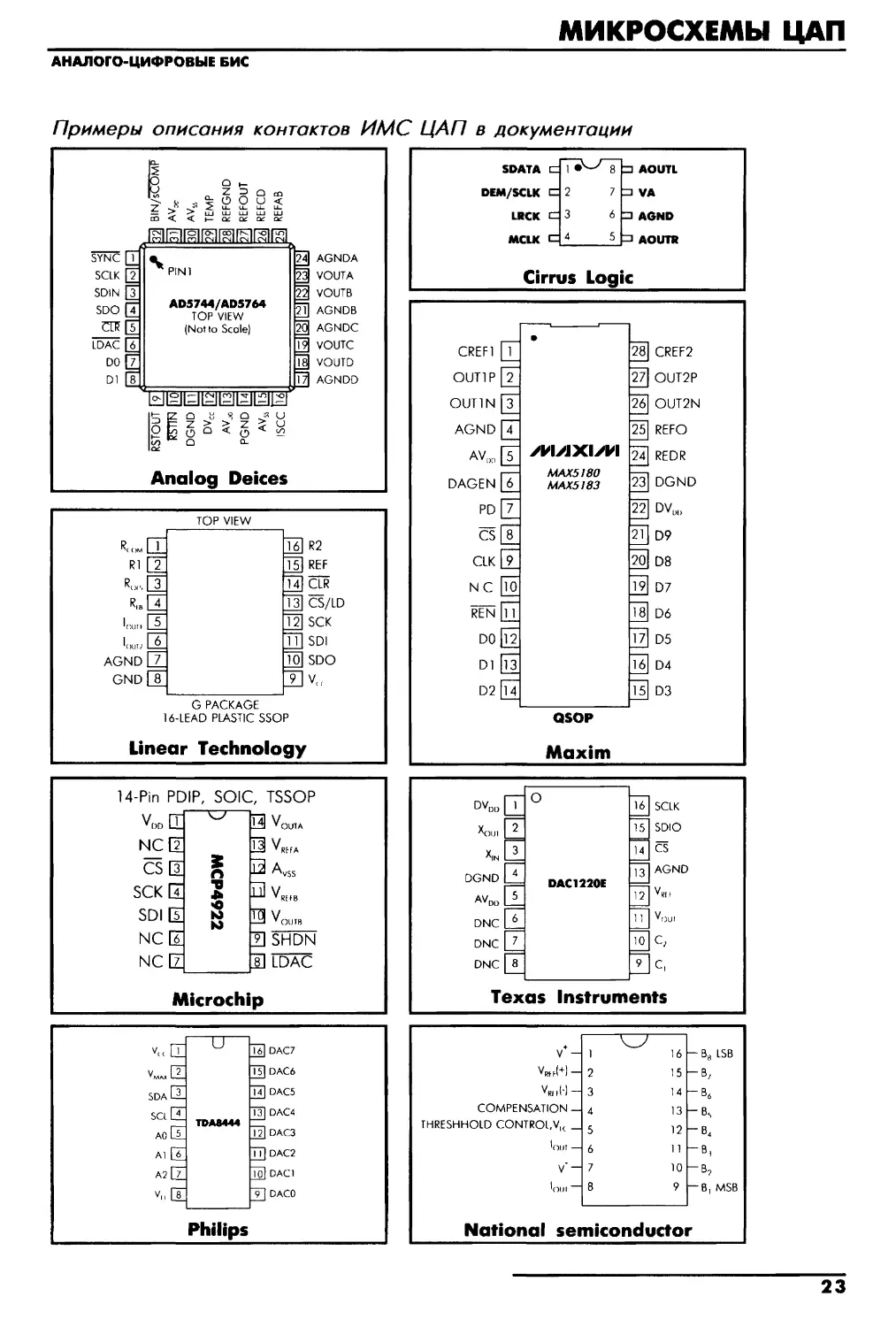

Примеры описания контактов ИМС ЦАП в документации

5YNC

SClK

SD\N 3

SDO

т

VOUTA

vоuтв

1 AGNDB

2 AGNDC

vouтc

1 VOUTD

Щ.1;==;;;======;/Р AGNDD

Analog Deices

ТОР VIEW

R2

REF

14 CLR

CS/LD

1"""

1"""

AGNO

GND

G PACKAGE

16-lEAD PLASТIC SSOP

Linear Technology

14-Pin PDIP, SOIC, TSSOP

VOD

NC

cs

sск

SDI

NC

SDA

Philips

SDATA

DEМ/SCLK

AOUTL

УА

LRCK

AGND

МСLК ~----~ AOUТR

Cirrus Logic

CREFI

OUTIP

OUTIN

AGND

AVI)[)

. ;11'1 .;JXl.;ll'I

МАХ5180

DAGEN

МАХ5183

PD

cs

CLK

NC

Dl

D2

QSOP

Maxim

о

Хо1н

X,N

DAC1220E

v·-

\___)

1

V~н(+) - 2

VR11H- 3

COMPENSATION - 4

THRESHHOLD CONTROL, V1( _

5

lо1н- 6

v·-

7

10111- 8

CREF2

OUT2P

REFO

REDR

DGNO

DVLJ()

09

08

07

06

05

04

03

SCLK

SDIO

в

AGND

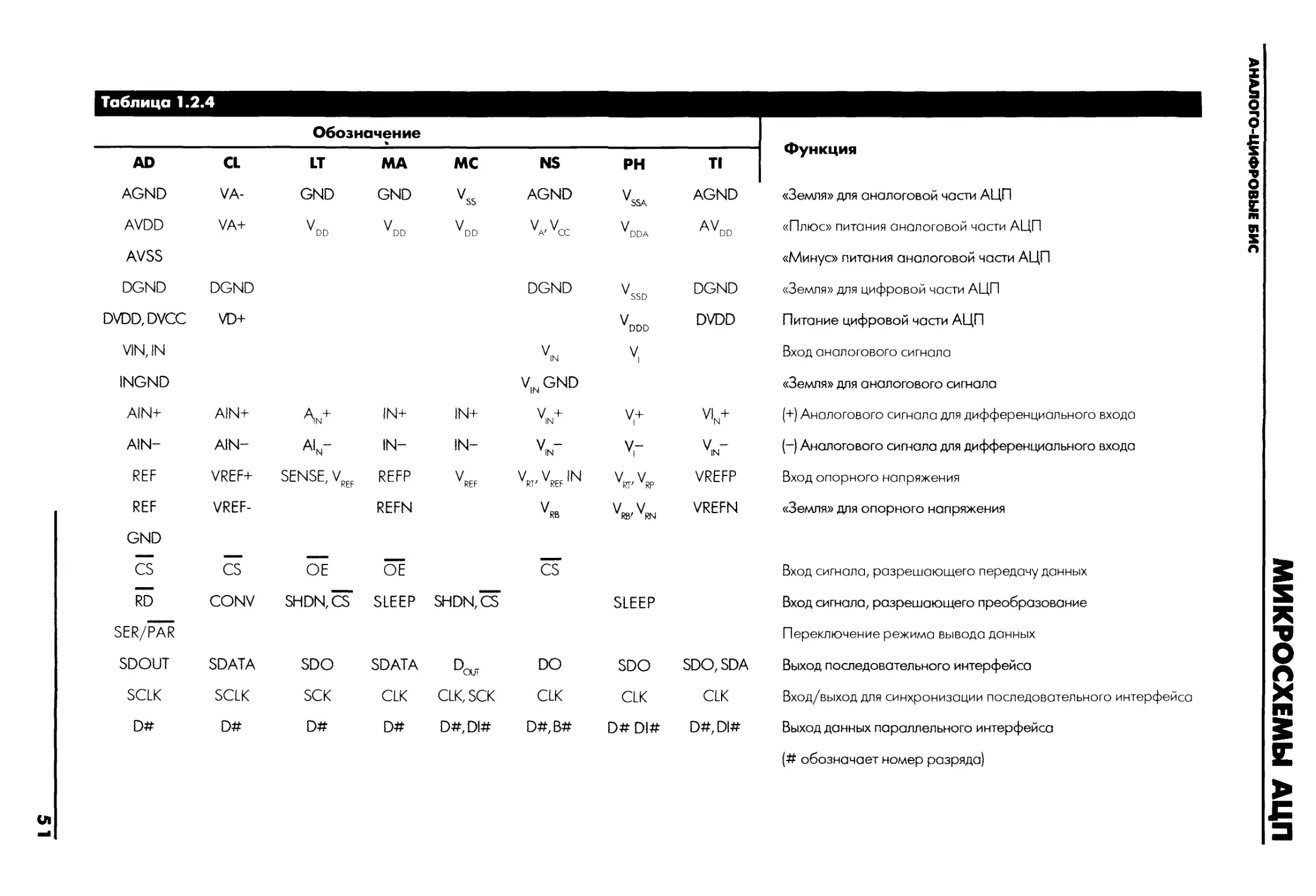

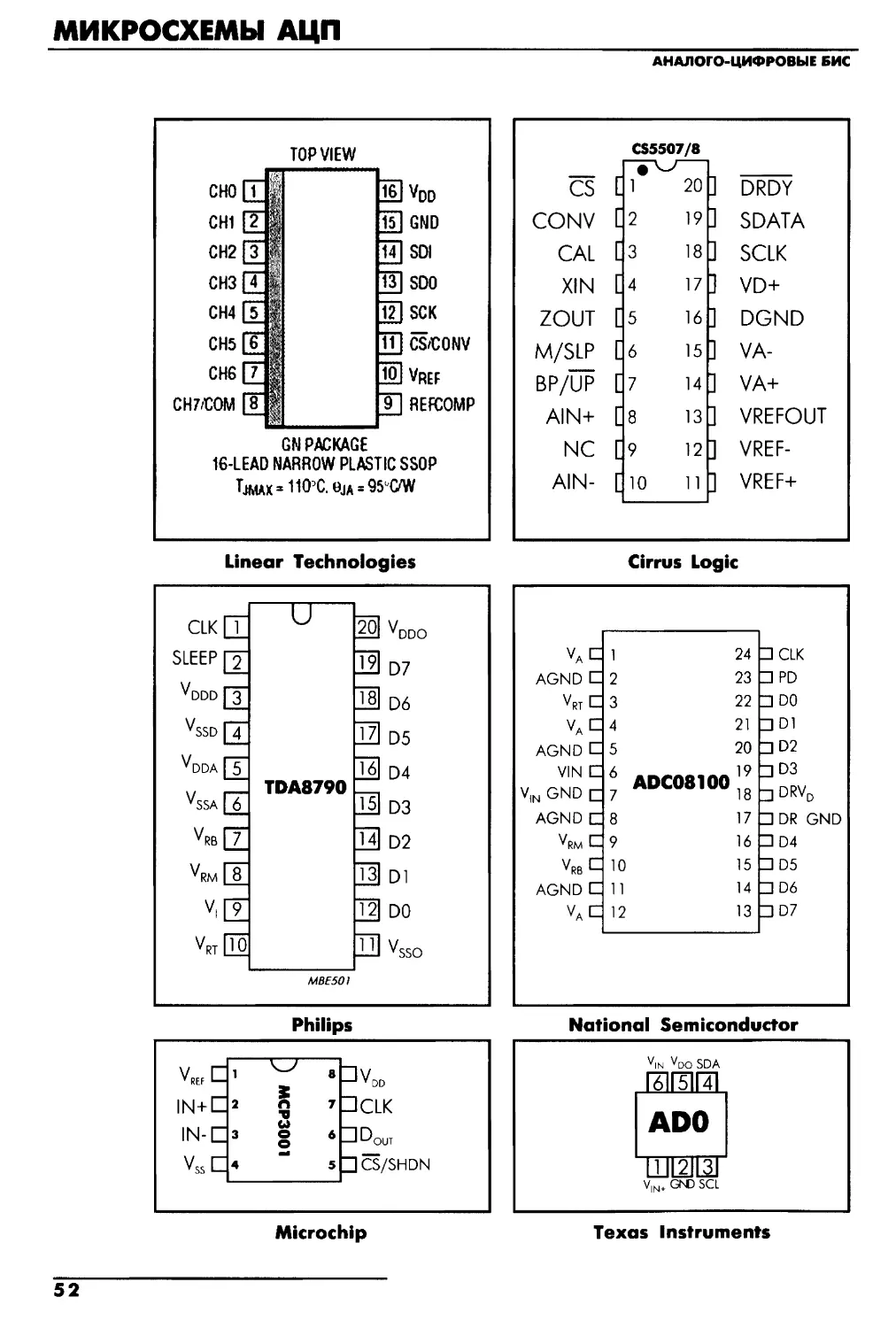

16 '-- В8 LSB

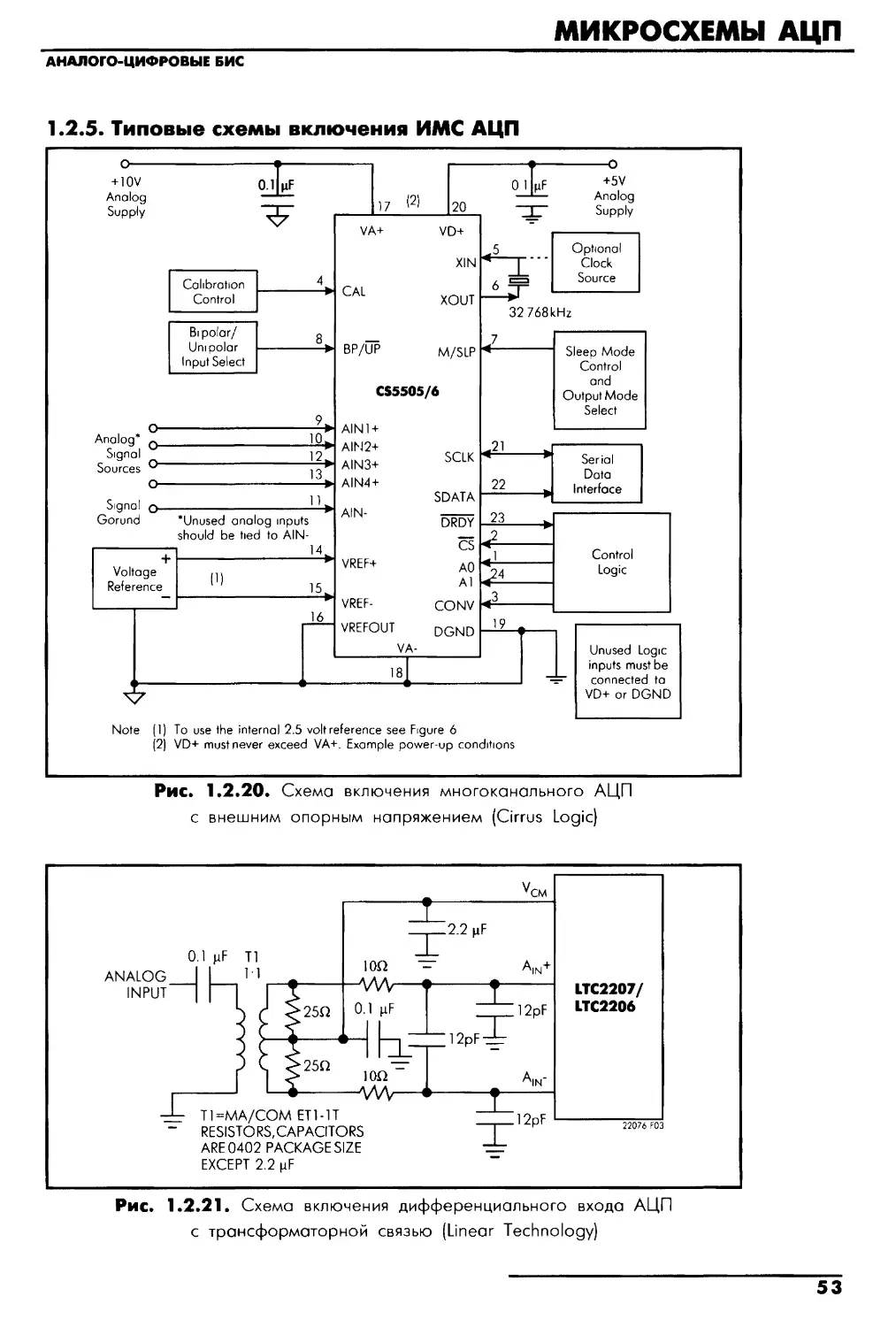

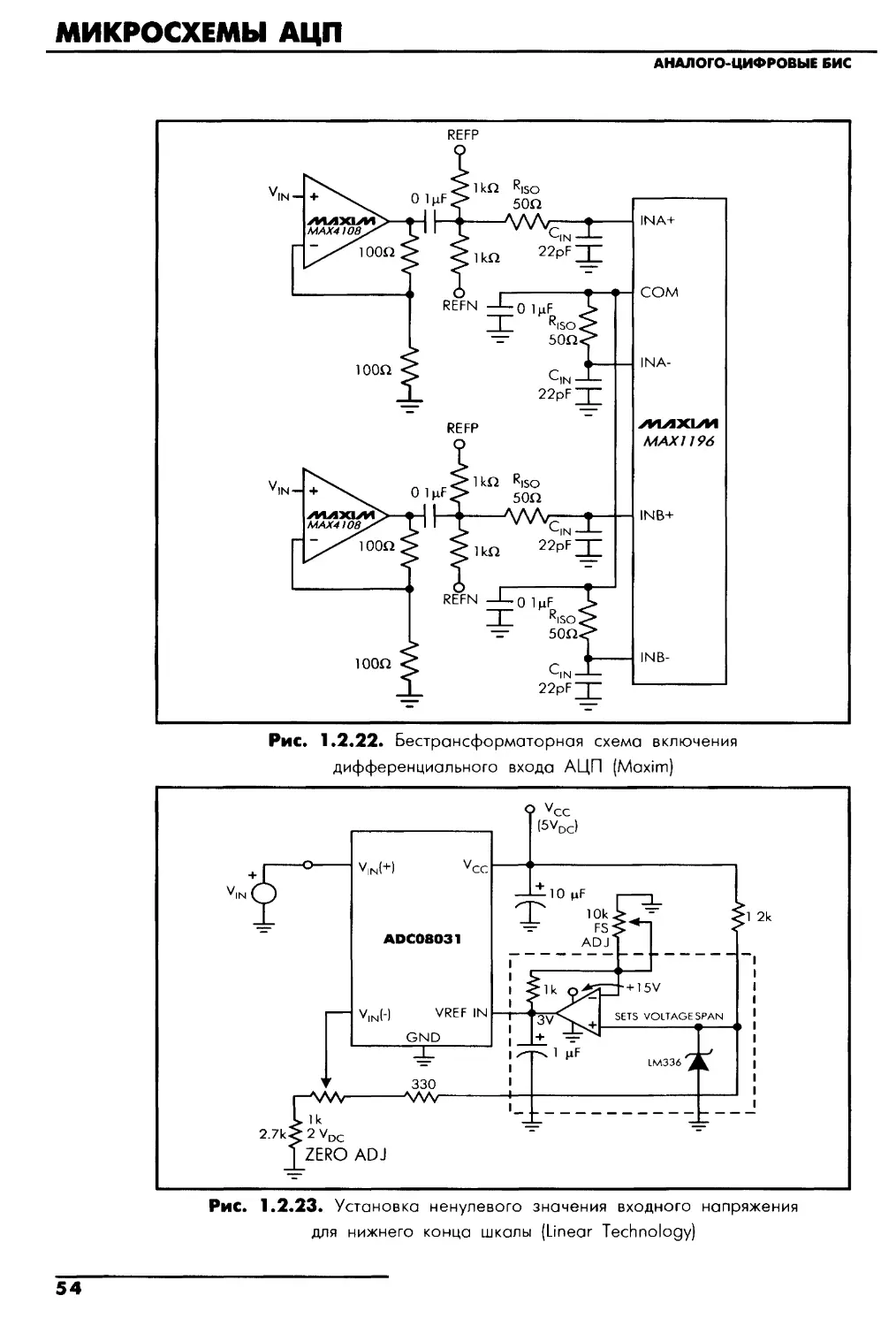

1s 1-в1

1<11- В6

~з1- в~

12.__

В4

11 в'

io -в.1

9 -в1 мsв

National semiconductor

23

МИКРОСХЕМЫ ЦАП

24

АНАЛОГО-ЦИФРОВЫЕ БИС

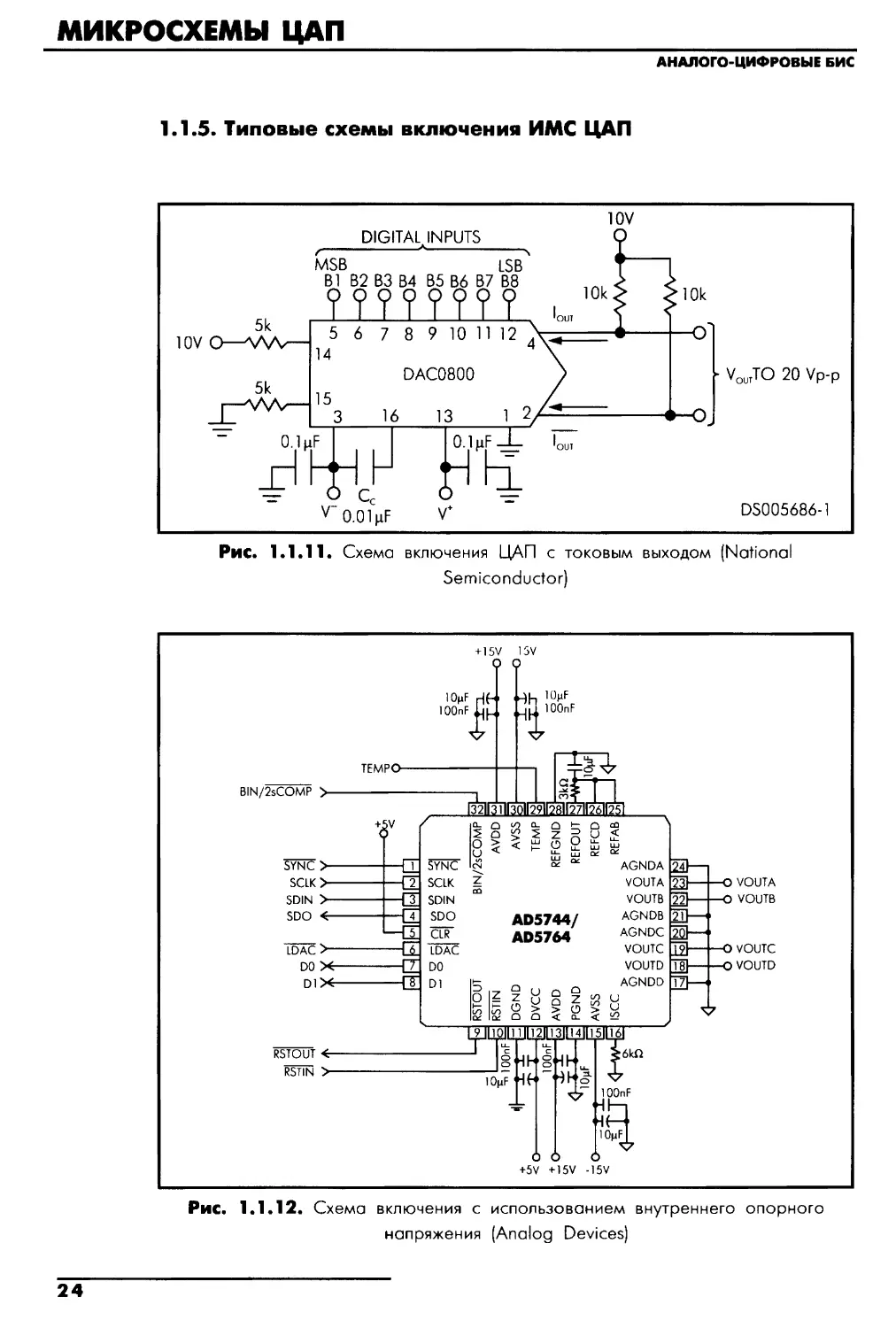

1. 1.5. Типовые схемы вкnючени11 ИМС ЦАП

lOV

lOV

DIGIТAL INPUTS

MS8

LS8

8182838485868788

lOk

lOk

5k

lour

5 6 7 891011124

-

14

DACOBOO

16

13

12

-

0. lμF

Q

с

v·

DS005686-l

Рис. 1. 1 . 11 . Схема включения ЦАП с токовым выходом (National

Semiconductor)

+ISV 1.JV

lOOnF

IOμF..f

ТЕМР

BIN/2sCOMP

+v

,~с<Л~с,_

с

"'

::;;с~~

z:о

~~

о'<

~~

SYNC

SYNC ~

AGNDA

SCLK

SCLK z

VOUTA

VOUTA

о;

SDIN

SDIN

VOUTB

SDO

SDO

AD5744/

CLR

AD5764

LDAC

LDAC

vouтc

DO

DO

VOUTD

VOUTD

DI

DI

AGNDD

u

:;;

RSТOUT

RSTIN

+SV +15V -15V

Рис. 1.1.12. Схема включения с использованием внутреннего опорного

напряжения (Analog Devices)

МИКРОСХЕМЫ ЦАП

АНАnОrО-ЦИФРОВЫЕ &ИС

+5V

о1μf

1μf

г-----1--.!...1 SDATA

Audю

v,

Doto

5rЦ7SCLK

Processor

L--~--r--~ LRCK

Externol Clock

MCLK

С54334

С54335

С54338

С54339

AGND

AOUТL

AOUT R

267Ш

267Ш

33μF

560il

rn lehAudю

+

Output

10

R,

33μf

560il

rnRoghtAudю

+

Outpul

10

R,

с~~

4•fs(R,560j

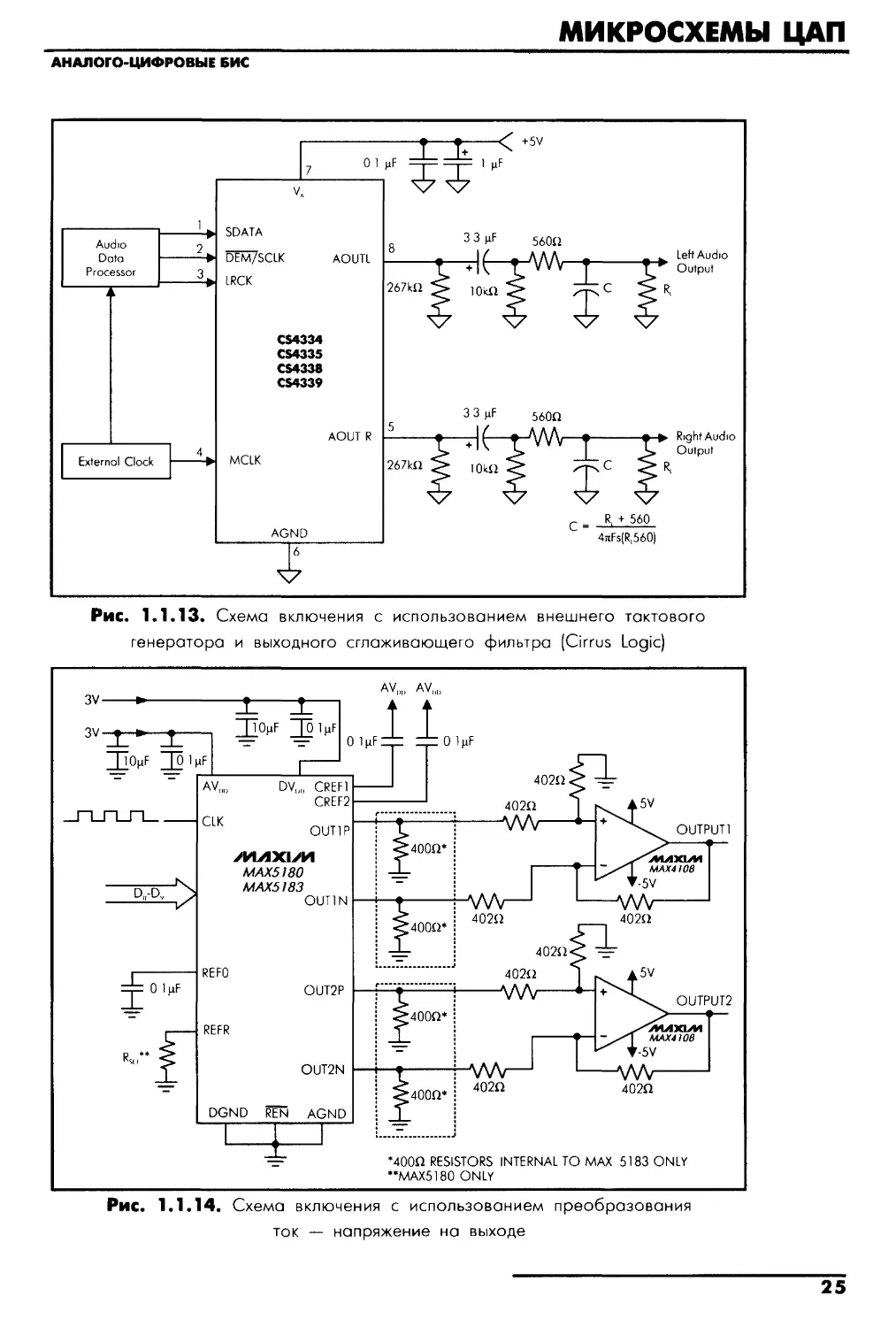

Рис. 1.1.13. Схема включения с использованием внешнего тактового

генератора и выходного сглаживающего фильтра (Cirrus Logic)

D"- D,

Ro;11"'"'

-::-

CLK

REFO

REFR

OUТlP

.. .. илх1 .. ..111

MAXS/80

MAXS/83

OUTINt--+-....----+-~r,/\,~~

OUT2P

OUT2N

OUTPUТl

OUTPUT2

DGND REN AGND

-::-

---=-----------J

'4 00 il RESISTORS INTERNAL ТО МАХ 5183 ONLY

"МАХ5180 ONLY

Рис. 1.1.14. Схема включения с использованием преобразования

ток - напряжение на выходе

25

МИКРОСХЕМЫ АЦП

26

АНАllОfО-ЦИФРОВЫЕ &ИС

1.2. МИКРОСХЕМЫ АЦП

1.2. 1. Характеристики и кпассификаци11 АЦП

1.2.1 .1. Характеристики АЦП

Аналого-цифровой преобразователь (АЦП) представляет собой устрой

ство для преобразования непрерывно меняющихся во времени аналоговых

сигналов {обычно электрических напряжений) в эквивалентные значения чис

ловых кодов. АЦП характеризуется набором параметров, используемых при

выборе типа прибора.

В разных источниках информации под одним и тем же термином может

скрываться различное понимание того или иного явления. Различия, суще

ствующие в определении основных метрологических характеристик АЦП и

способов их нормирования, могут привести к значительным ошибкам в оценке

точности аналого-цифрового преобразования и к неправильному выбору

конкретного преобразователя. Например, при расчете предельно допусти

мого значения абсолютной статической погрешности аналого-цифрового

преобразования следует учитывать, каким образом определяется и норми

руется напряжение смещения нуля и включена ли эта величина в погреш

ность в конечной точке шкалы; как производится линеаризация характери

стики АЦП; включена ли погрешность квантования в погрешность

дифференциальной линейности. Ответы на эти вопросы позволят потреби

телю не только правильно рассчитать погрешность преобразования по

приведенным в паспорте параметрам, но и грамотно выбрать преобразо

ватель.

Характеристика преобразования АЦП - это зависимость между напря

жением на его аналоговом входе и множеством возможных значений вы

ходного кода, заданная в виде таблицы, графика или формулы.

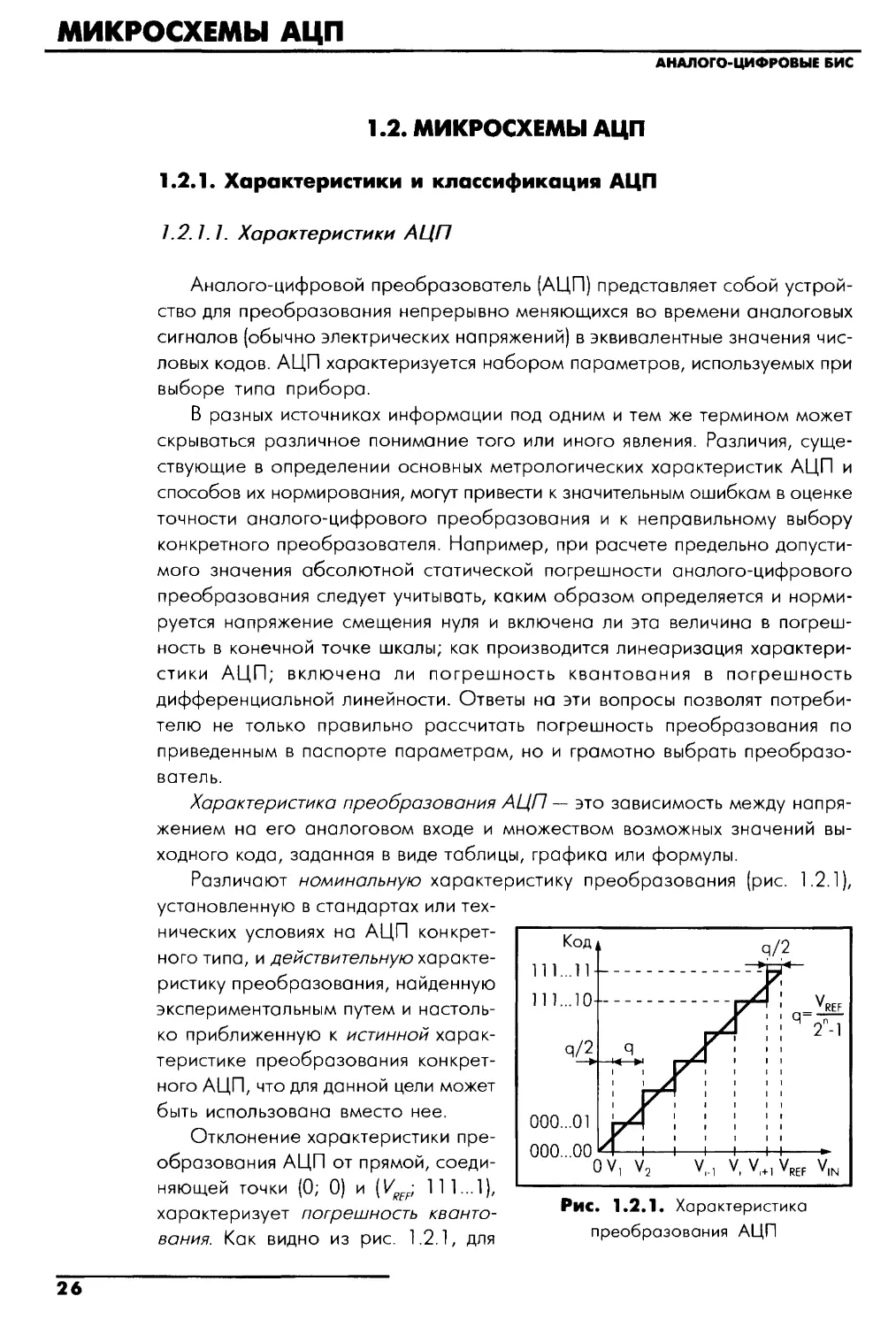

Различают номинапьную характеристику преобразования (рис. 1.2 .1 ),

установленную в стандартах или тех-

нических условиях на АЦП конкрет

ного типа, и действительную характе

ристику преобразования, найденную

экспериментальным путем и настоль

ко приближенную к истинной харак

теристике преобразования конкрет

ного АЦП, что для данной цели может

быть использована вместо нее.

Отклонение характеристики пре

образования АЦП от прямой, соеди

няющей точки (О; О) и ( VREF; 111 ... 1),

характеризует погрешность кванто

вания. Как видно из рис. 1.2.1, для

Код

g/2

111". 11

111". 10

000".0 1

000" . 00 L+--+ --lf--+--+ --+---

0V1 V2

v,.1 v, v,+1 ReF v,N

Рис. 1.2.1. Характеристика

преобразования АЦП

МИКРОСХЕМЫ АЦП

АНАЛОrО-ЦИФРОВЫЕ БИС

идеального АЦП, имеющего номинальную характеристику преобразования,

максимальная величина этого отклонения составляет q/2 и зависит только

от количества разрядов АЦП.

Разрядность. Это основной параметр АЦП, он определяет максималь

ное двоичное число на выходе. Применительно к АЦП, вырабатывающим

недвоичные числовые коды, под разрядностью понимают число эквивалент

ных двоичных разрядов, равных двоичному логарифму максимального числа

возможных значений выходного кода.

Разрешающая способность (resolution)- это величина, обратная макси

мальному числу кодовых комбинаций на выходе АЦП. Разрешающая спо

собность выражается в процентах, разрядах или децибелах и характеризу

ет потенциальные возможности АЦП с точки зрения достижимой точности.

Например, 12-разрядный АЦП имеет разрешающую способность 1/4096,

или 0.0245 % от полной шкалы, или -72.2 дБ. В табл. 1.2.1 приведен ряд

числовых соотношений между количеством разрядов, разрешающей спо

собностью, а также зависимость значения МЗР от диапазона входного

напряжения и т.п.

Главный переход. Под этим понимают смену кода с О 11 ... 111 на 100... 000

или наоборот.

Частота Найквиста. Это частота, равная 1/2 частоты дискретизации.

Отношение «сигнал/шум» (Signal to Noise Ratio, SNR) - это отношение

эффективного значения входного сигнала к среднеквадратическому значе

нию «шума». «Шум» состоит из всех остальных спектральных компонент, вклю

чая гармоники, но исключая постоянную составляющую. Уровень входного

сигнала берется равным (-1 дБ) от полной шкалы. Для идеального АЦП

определяется по формуле: SNR = (6.02 п + 1.76) дБ, где п - количество

двоичных разрядов. Таким образом, для идеального 12-разрядного АЦП

получаем SNR = 7 4 дБ.

Отношение «сигнал/(шум+искажения)» (SINAD или S/(N+D)) - это отно

шение суммарной мощности выходного сигнала (полезный сигнал + шум +

искажения) к суммарной мощности всех компонент, вплоть до 1/2 частоты

дискретизации, за исключением полезного сигнала (шум+ искажения). Те

оретическое отношение 5 / (N + О) для п-разрядного идеального АЦП,

на вход которого подано синусоидальное колебание, можно оценить по

формуле, аналогичной SNR. В ряде случаев возможно добавление ела-

Табпица 1.2. 1

Раз-

Значение младшего значащего

р!IДЬI

Разре- dB

1/n

о/о ppm

разряда (МЗР)

(n)

шение

1208110815812.58118

2

2·2 1/4 -12

0.25

25 250000 5В 2.5 в 1.25 в 625мВ 250мВ

4

2·•

1/16 -24.1 0 .0625 62 62500 1.25 в 625мВ 312мВ 156мВ 62.5мВ

6

2·•

1/64 -36.1 0.015625 1.6 15625 312мВ 156мВ 78.1 мВ 39.lмВ 15.6мВ

8

2' 1/256 -48.2 0.003906 0 .4 3906 78.1 мВ 39.1 мВ 19.SмВ 9.77 мВ 3.91 мВ

10 2·•0

1/1024 -60.2 0 .0009766 0 .1 977 19.5мВ 9.77 мВ 4.86мВ 244мВ 977 мкВ

27

МИКРОСХЕМЫ АЦП

28

АНАJIОrО-ЦИФРОВЫЕ &ИС

гаемых, учитывающих частоту дискретизации и полосу частот входного сиг

нала.

Количество эффективных разрядов (ENOB). Если основным источником

погрешности являются собственные шумы АЦП (тепловой и пр.), то количе

ство эффективных разрядов N определяется из выражения: N = (SINAD -

1.16) / 6.02, где SINAD- это реальное значение отношения «сигнал/(шум +

искажения)» для конкретного АЦП. Вместо SINAD можно подставлять SNR.

Необходимо заметить, что большое влияние на этот параметр оказывают

динамические характеристики АЦП (скорость нарастания, время выборки УВХ

и т.п.), которые делают N сильно зависимым от частоты входного сигнала.

Интермодуляционные искажения (/MD). Когда на вход подаются два гар

монических колебания с разными частотами (f0 и fj, то на выходе любого

устройства с нелинейностями будут присутствовать искажения порядка (m +

п) на суммарных и разностных частотах mf0 ± пf6, где m, п =О, 1, 2 , 3 . .. Интер

модуляционными искажениями называются те, для которых ни m, ни п не

равны нулю. Например, искажения второго порядка - это частоты (f0 + fj и

(f0 - fJ, а искажения третьего порядка - частоты (2f0 + fJ, (2f0 - fj, (f0 + 2fJ и

(f0 - 2fJ.

В случае, когда АЦП тестируется по стандарту CCIF, на вход подаются

два гармонических колебания с частотами вблизи верхнего края входной

полосы частот. В этом случае члены 2 и 3 порядков имеют различное зна

чение. Члены 2 порядка обычно значительно отстоят по частоте от входных

колебаний, тогда как частоты членов 3 порядка обычно близки к входным

частотам. Вследствие этого члены 2 и 3 порядков в спецификациях указаны

отдельно. IMD равно отношению суммы среднеквадратических значений

отдельных интермодуляционных искажений к эффективному значению ос

новной составляющей, выраженному в дБ.

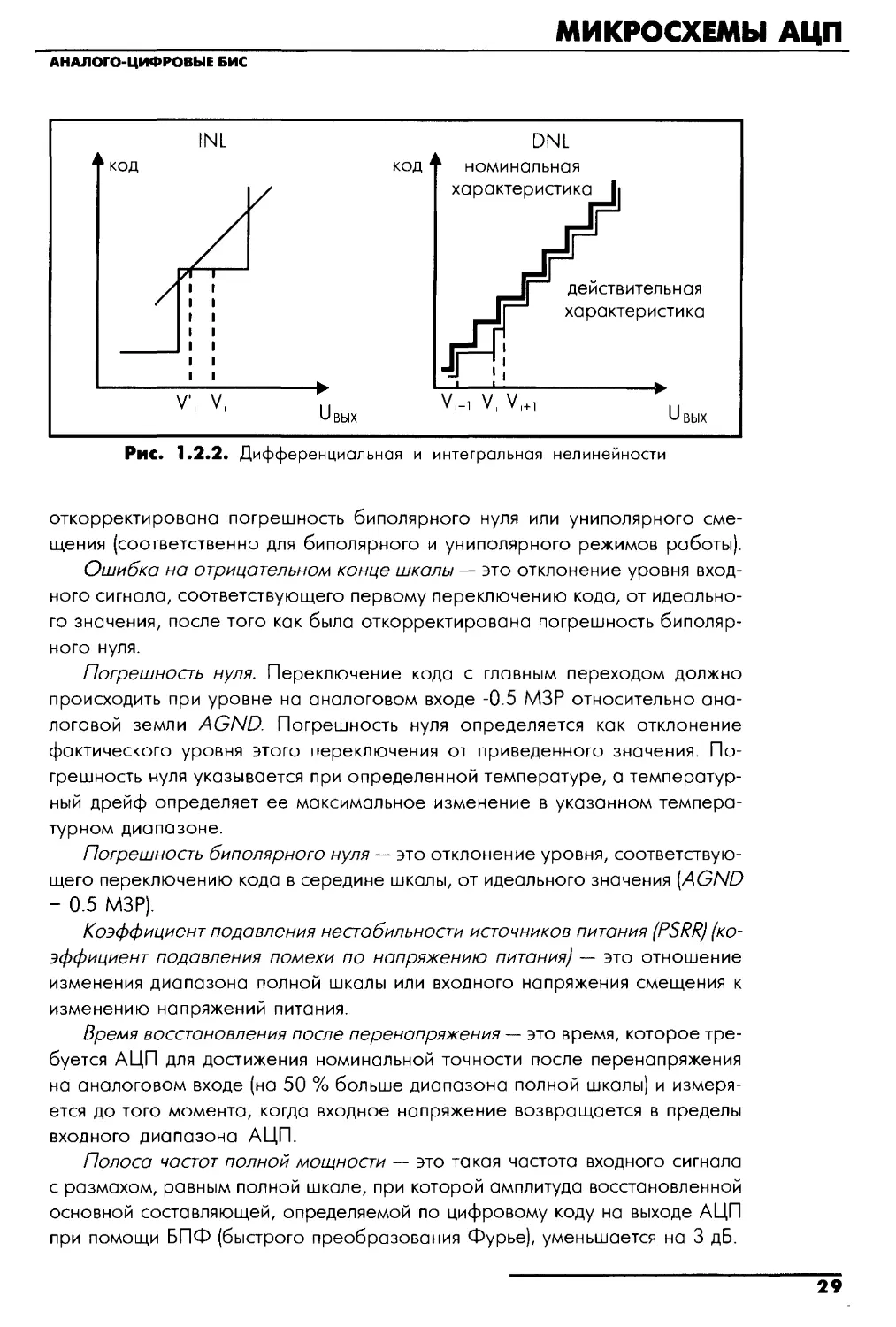

Интегральная нелинейность (/ntegгal Non-Lineaгify, INL) (погрешность не

линейности) - это разность между расчетным значением входного напряже

ния v· определенным по линеаризованной характеристике преобразования

АЦП," и действительным значением входного напряжения V, соответствую

щим заданной точке характеристики преобразования (рис. 1.2 .2):

INL = v:- V:.

(2.1)

Дифференциальная нелинейность (Diffeгenfia/ Non-Linearify, DNL) - это

разность между значением кванта преобразования (q) и средним действи

тельным значением кванта преобразования (q):

DNL=q, - q =V:-V:-i

-

q.

(2.2)

Погрешность полной шкалы или ошибка на положительном конце шка

лы - это отклонение уровня входного сигнала, соответствующего после

днему переключению кода, от идеального значения, после того как была

МИКРОСХЕМЫ АЦП

АНАЛОrО-ЦИФРОВЫЕ &ИС

INL

код

КОД

V', V,

Uвых

DNL

номинальная

V,-1 V, V,+1

действительная

характеристика

uвых

Рис. 1.2.2. Дифференциальная и интегральная нелинейности

откорректирована погрешность биполярного нуля или униполярного сме

щения (соответственно для биполярного и униполярного режимов работы).

Ошибка но отрицательном конце школы - это отклонение уровня вход

ного сигнала, соответствующего первому переключению кода, от идеально

го значения, после того как была откорректирована погрешность биполяр

ного нуля.

Погрешность нуля. Переключение кода с главным переходом должно

происходить при уровне на аналоговом входе -0.5 МЗР относительно ана

логовой земли AGND. Погрешность нуля определяется как отклонение

фактического уровня этого переключения от приведенного значения. По

грешность нуля указывается при определенной температуре, а температур

ный дрейф определяет ее максимальное изменение в указанном темпера

турном диапазоне.

Погрешность биполярного нуля - это отклонение уровня, соответствую

щего переключению кода в середине шкалы, от идеального значения (AGND

-

05 МЗР).

Коэффициент подавления нестабильности источников питания (PSRR) (ко

эффициент подавления помехи по напряжению питания} - это отношение

изменения диапазона полной шкалы или входного напряжения смещения к

изменению напряжений питания.

Время восстановления после перенапряжения - это время, которое тре

буется АЦП для достижения номинальной точности после перенапряжения

на аналоговом входе (на 50 % больше диапазона полной шкалы) и измеря

ется до того момента, когда входное напряжение возвращается в пределы

входного диапазона АЦП.

Полоса частот полной мощности - это такая частота входного сигнала

с размахом, равным полной шкале, при которой амплитуда восстановленной

основной составляющей, определяемой по цифровому коду на выходе АЦП

при помощи БПФ (быстрого преобразования Фурье), уменьшается на 3 дБ.

29

МИКРОСХЕМЫ АЦП

30

АНАЛОГО-ЦИФРОВЫЕ &ИС

Рабочая полоса частот - это номинальный диапазон частот входного

сигнала, заданный разработчиком прибора, в котором при заданной часто

те дискретизации нормируются метрологические характеристики Она уже,

чем полоса пропускания частот полной мощности.

Время выборки УВХ - это время, которое требуется после окончания

преобразования (именно в этот момент УВХ возвращается в режим выбор

ки), чтобы напряжение на выходе УВХ достигло своего окончательного зна

чения с точностью ± 1/2 МЗР. Этот временной параметр применим также к

тем случаям, когда входное напряжение на аналоговом входе имеет ступен

чатый характер. Это означает, что нужно выждать в течение этого времени

после окончания преобразования или после ступенчатого изменения вход

ного напряжения, прежде чем начинать очередное преобразование, чтобы

гарантировать работу ИМС в соответствии со спецификациями.

Апертурная задержка характеризует работу входного УВХ и измеряет

ся от переднего фронта тактового сигнала или сигнала управления до

фактического момента начала выборки входного сигнала.

Время установления - это время, необходимое АЦП для достижения но

минальной точности после того, как на его вход (или вход встроенного УВХ)

был подан ступенчатый сигнал, равный полному диапазону входного сигнала.

Конвейерная задержка (латентность} ·-

это число тактовых периодов

между началом преобразования и появлением на выходных линиях соот

ветствующего результата. После этого на каждом тактовом периоде выво

дится новый результат преобразования.

Входной диапазон. Эта спецификация определяет минимальные и мак

симальные входные напряжения от нуля до полной шкалы, которые АЦП

может воспринимать и при этом точно калибровать усиление.

Запас по выходу за положительный или отрицательный конец шкалы.

Выход входного напряжения за пределы входного диапазона может приве

сти к появлению ошибок, обусловленных перегрузкой аналогового модуля

тора или переполнением цифрового фильтра. Чтобы избежать подобных

ошибок, вводится понятие запаса по выходу входного напряжения за пре

делы шкалы.

Запас по выходу за положительный конец шкалы - это интервал на

пряжения, на который входное напряжение на AIN(+) может превышать уро

вень AIN(-) + VREF/GAIN, не приводя при этом к перегрузке аналогового

модулятора или к переполнению цифрового фильтра. Здесь GAIN - коэф

фициент усиления встроенного программируемого усилителя, VREF- значе

ние опорного напряжения. AIN(+) - вывод, на который подается преобра

зуемый сигнал. AIN(-} - вывод, на который подается потенциал «аналоговой

земли», т.е. при UA!Nf+! = UAIN(-! значение кода на выходе равно О.

Запас по выходу за отрицательный конец шкалы - это интервал напря

жения, на который входное напряжение на AIN(+} может быть ниже уровня

AIN(-) - VREF/GAIN, не приводя при этом к перегрузке аналогового модуля

тора или к переполнению цифрового фильтра.

МИКРОСХЕМЫ АЦП

АНАJIОrо-ЦИФРОВЫЕ &ИС

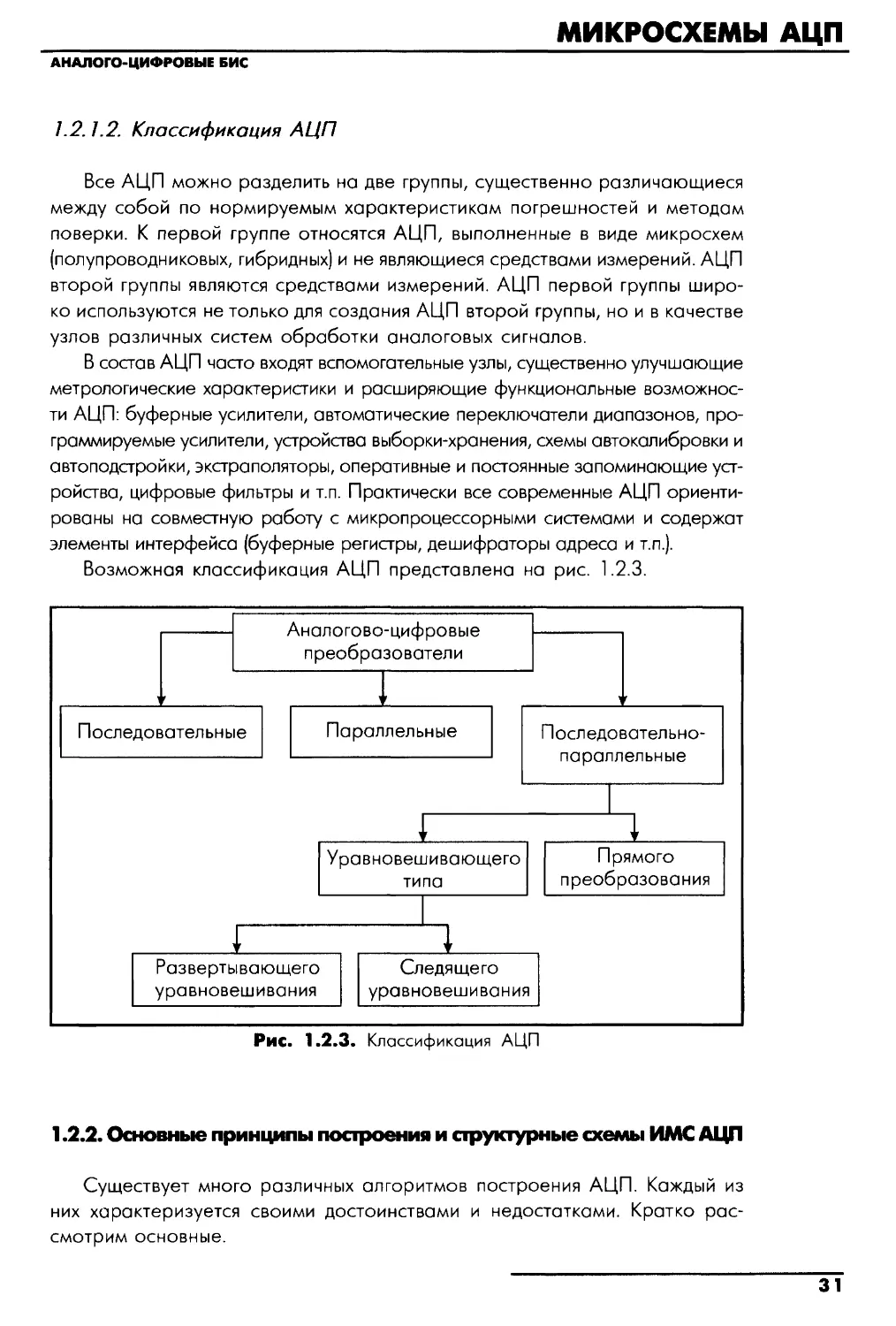

1.2 .1 .2 . Классификация АЦП

Все АЦП можно разделить на две группы, существенно различающиеся

между собой по нормируемым характеристикам погрешностей и методам

поверки. К первой группе относятся АЦП, выполненные в виде микросхем

(полупроводниковых, гибридных) и не являющиеся средствами измерений. АЦП

второй группы являются средствами измерений. АЦП первой группы широ

ко используются не только для создания АЦП второй группы, но и в качестве

узлов различных систем обработки аналоговых сигналов.

В состав АЦП часто входят вспомогательные узлы, существенно улучшающие

метрологические характеристики и расширяющие функциональные возможнос

ти АЦП: буферные усилители, автоматические переключатели диапазонов, про

граммируемые усилители, устройства выборки-хранения, схемы автокалибровки и

автоподстройки, экстраполяторы, оперативные и постоянные запоминающие уст

ройства, цифровые фильтры и т.п. Практически все современные АЦП ориенти

рованы на совместную работу с микропроцессорными системами и содержат

элементы интерфейса (буферные регистры, дешифраторы адреса и т.п.).

Возможная классификация АЦП представлена на рис. 1.2 .3 .

Последовательные

Аналогово-цифровые

преобразователи

Параллельные

Уравновешивающего

типа

Развертывающего

уравновешивания

Следящего

уравновешивания

Рис. 1.2.3 . Классификация АЦП

Последовательно

параллельные

Прямого

преобразования

1.2.2 . Основt...е принципы nocrpoeнИll и сrруктурные схемы ИМС АЦП

Существует много различных алгоритмов построения АЦП. Каждый из

них характеризуется своими достоинствами и недостатками. Кратко рас

смотрим основные.

31

МИКРОСХЕМЫ АЦП

32

АНАJIОrО-ЦИФРОВЫЕ &ИС

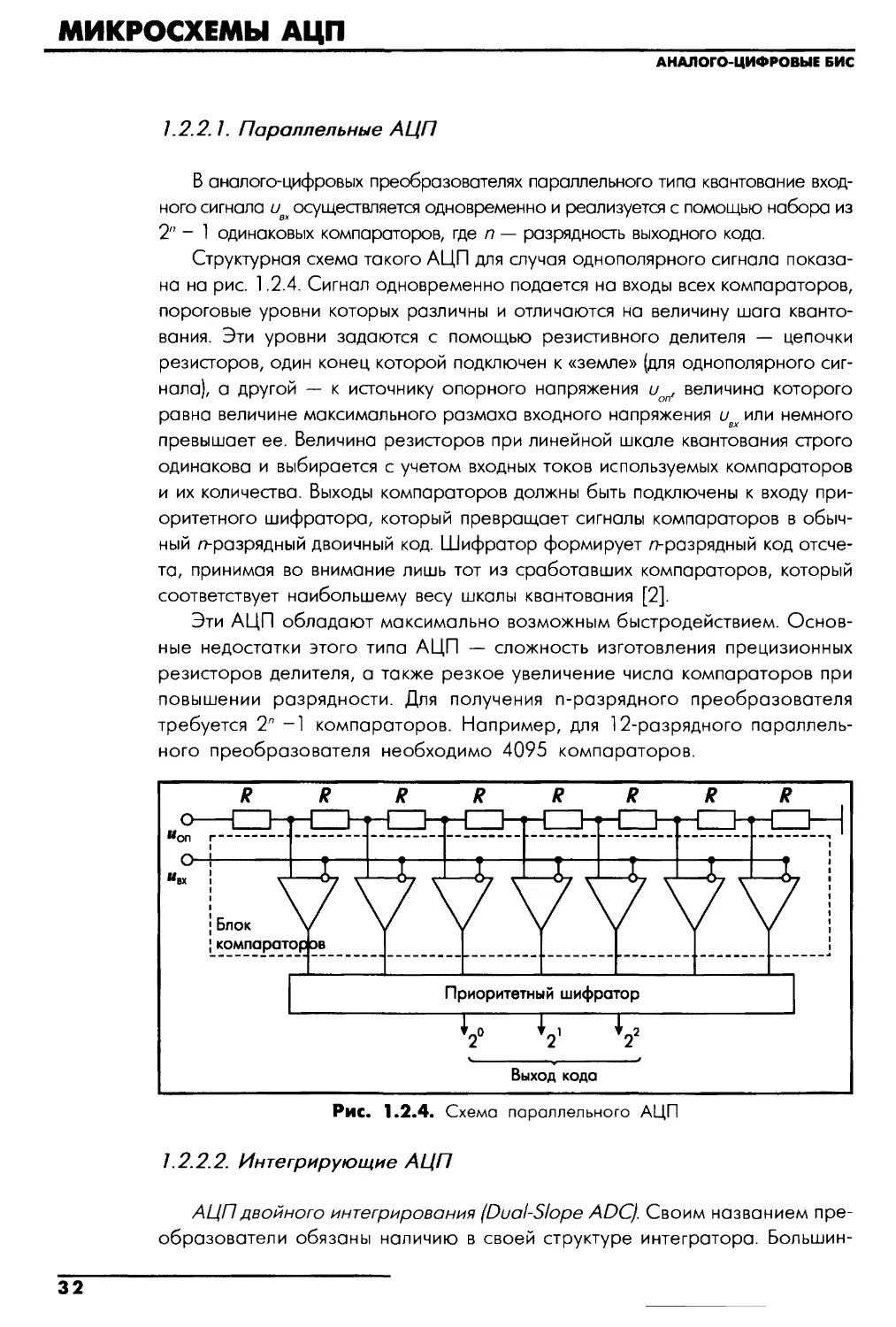

1.2 .2 .1. Параллельные АЦП

В аналого-цифровых преобразователях параллельного типа квантование вход

ного сигнала и" осуществляется одновременно и реализуется с помощью набора из

2"-

1 одинаковых компараторов, где п - разрядность выходного кода.

Структурная схема такого АЦП для случая однополярного сигнала показа

на на рис. 1.2.4. Сигнал одновременно подается на входы всех компараторов,

пороговые уровни которых различны и отличаются на величину шага кванто

вания. Эти уровни задаются с помощью резистивного делителя - цепочки

резисторов, один конец которой подключен к «земле» (для однополярного сиг

нала), а другой - к источнику опорного напряжения и0,., величина которого

равна величине максимального размаха входного напряжения и" или немного

превышает ее. Величина резисторов при линейной шкале квантования строго

одинакова и выбирается с учетом входных токов используемых компараторов

и их количества. Выходы компараторов должны быть подключены к входу при

оритетного шифратора, который превращает сигналы компараторов в обыч

ный п-разрядный двоичный код. Шифратор формирует п-разрядный код отсче

та, принимая во внимание лишь тот из сработавших компараторов, который

соответствует наибольшему весу шкалы квантования [2].

Эти АЦП обладают максимально возможным быстродействием. Основ

ные недостатки этого типа АЦП - сложность изготовления прецизионных

резисторов делителя, а также резкое увеличение числа компараторов при

повышении разрядности. Для получения п-разрядного преобразователя

требуется 2" -1 компараторов. Например, для 12-разрядного параллель

ного преобразователя необходимо 4095 компараторов.

R

R

R

R

R

R

R

R

Выход кодо

Рис. 1.2 .4. Схема параллельного АЦП

1.2 .2 .2. Интегрирующие АЦП

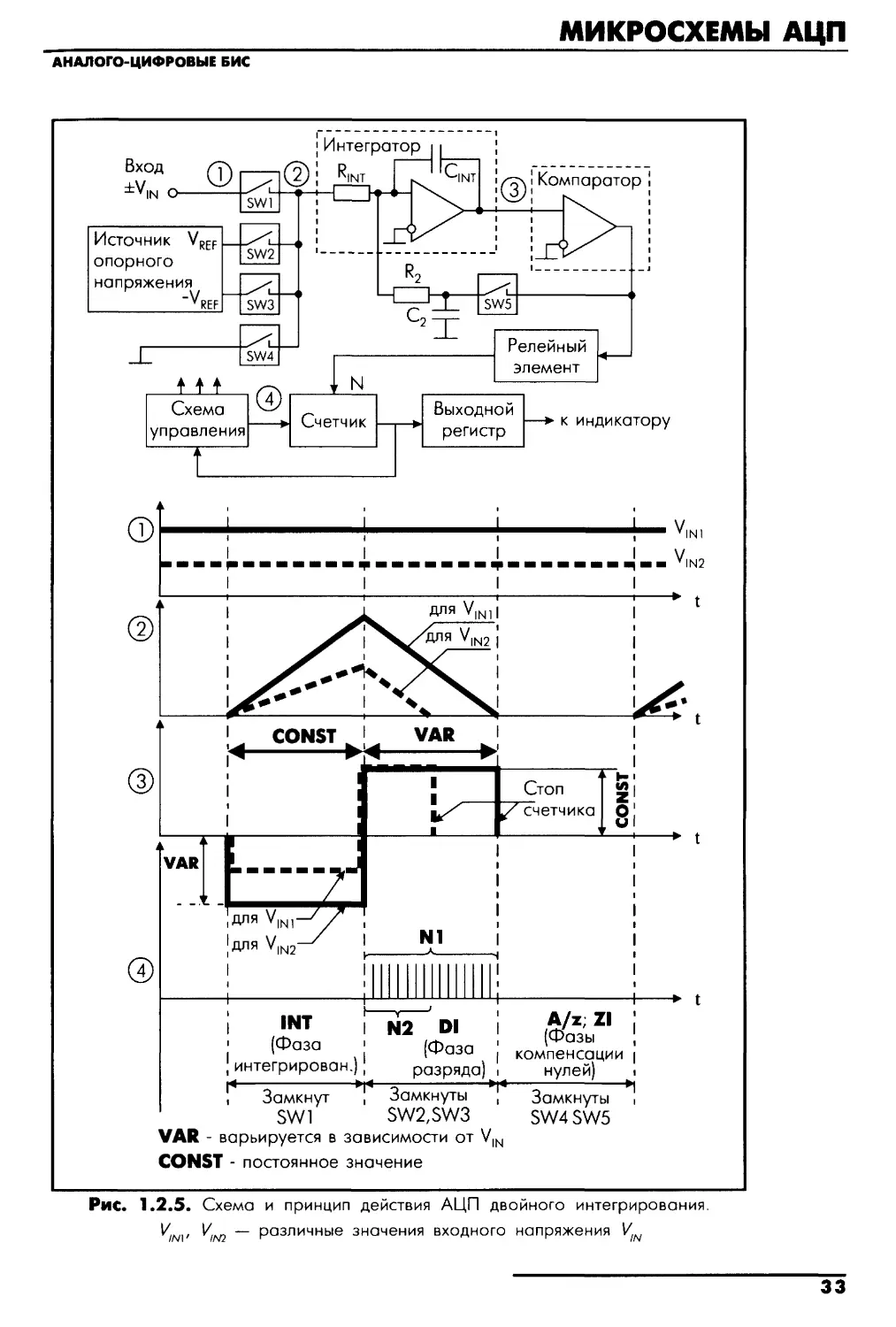

АЦП двойного интегрирования (Dual-5/ope ADC). Своим названием пре

образователи обязаны наличию в своей структуре интегратора. Большин-

МИКРОСХЕМЫ АЦП

АНАЛОrО-ЦИФРОВЫЕ &ИС

Вход

±VIN о---=-+~

Источник

опорного

к и нди катару

CD ~---.-------.-------.-------.-- VINI

---~-------~-------~-------~--~~

VAR

1

1

1

CONST

,дпя VINI

~дпя V1N2

1

VAR

.....

f------.---- '

1

INT

1N2DI

1

(Фаза '

(Фаза

1

)1

, интегрирован. ,

разряда) ,

Замкнут

Замкнуты

SWl

SW2,SW3

VAR - варьируется в зависимости от V1N

CONST - постоянное значение

A/z; ZI

(Фазы

компенсации

нулей)

Замкнуты

SW4SW5

".

Рис. 1.2.5 . Схема и принцип действия АЦП двойного интегрирования.

v;м, v;N2 - различные значения входного напряжения v;N

33

МИКРОСХЕМЫ АЦП

34

АНАЛоrо-ЦИФРОВЫЕ &ИС

ство современных микросхем работает в два такта интегрирования, что

позволяет называть их как АЦП двойного интегрирования.

Преобразователь (рис. 1.2 .5) состоит из аналоговой (ключи SWl .. .4, ис

точники опорных напряжений +VREF и -VREF, интегратора, компаратора и

схемы компенсации нуля SW5, R2, С2) и цифровой частей. Цикл аналого

цифрового преобразования состоит из четырех фаз:

•

автоматической коррекции погрешности (А/2);

•

интегрирования входного напряжения в течение фиксированного вре

мени ~ (IN~;

•

интегрирования опорного напряжения, т.е. разряд интегрирующего кон

денсатора за время Т2 (О~;

•

коррекции нуля интегратора (Z~.

Цифровой код на выходе АЦП получается как отношение времени Т2

разряда емкости интегратора к фиксированному периоду времени Т1 .

АЦП двойного интегрирования может работать как с однополярным,

так и с двухполярным напряжением. Диапазон входного сигнала определя

ется значением внешнего опорного напряжения. Для увеличения коэффици

ента подавления помехи нормального вида рекомендуется время преобра

зования выбирать равным или кратным периоду помехи, чаще всего это

период питающей сети, т.е. 50 или 60 Гц [1 ].

Малое число компонент обеспечивает низкое потребление и делает

такие приборы незаменимыми при построении переносных приборов с ав

тономным питанием. Эти АЦП используются в основном для измерения на

пряжения, тока, сопротивления, температуры, веса и др. с выводом информа

ции в специальном коде для управления семисегментными жидко

кристаллическими (ЖКИ) или светодиодными индикаторами (СДИ).

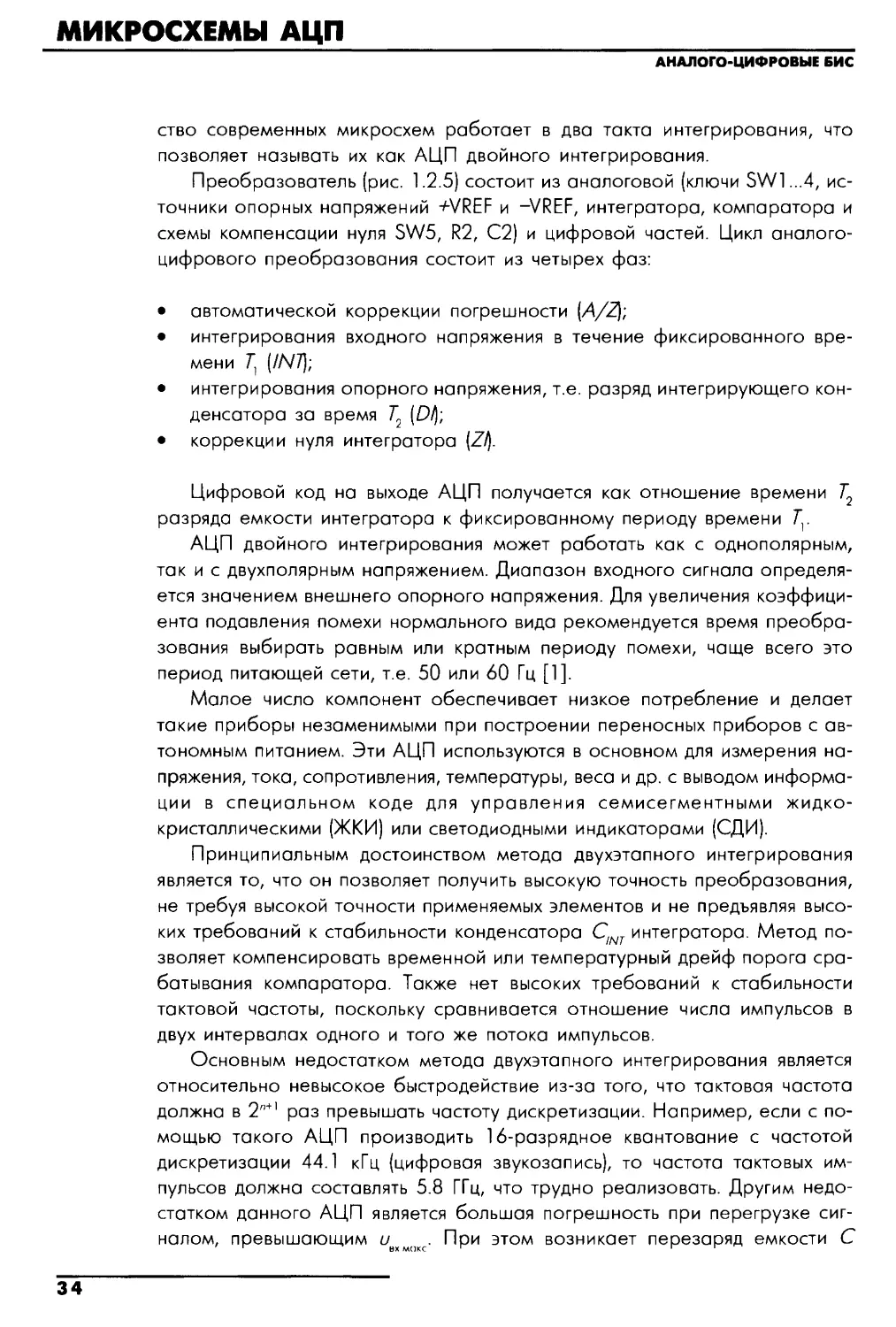

Принципиальным достоинством метода двухэтапного интегрирования

является то, что он позволяет получить высокую точность преобразования,

не требуя высокой точности применяемых элементов и не предъявляя высо

ких требований к стабильности конденсатора ~NТ интегратора. Метод по

зволяет компенсировать временной или температурный дрейф порога сра

батывания компаратора. Также нет высоких требований к стабильности

тактовой частоты, поскольку сравнивается отношение числа импульсов в

двух интервалах одного и того же потока импульсов.

Основным недостатком метода двухэтапного интегрирования является

относительно невысокое быстродействие из-за того, что тактовая частота

должна в 2п+~ раз превышать частоту дискретизации. Например, если с по

мощью такого АЦП производить 16-разрядное квантование с частотой

дискретизации 44.1 кГц (цифровая звукозапись), то частота тактовых им

пульсов должна составлять 5.8 ГГц, что трудно реализовать. Другим недо

статком данного АЦП является большая погрешность при перегрузке сиг

налом, превышающим и"м'"'. При этом возникает перезаряд емкости С

МИКРОСХЕМЫ АЦП

АНАЛОrО-ЦИФРОВЫЕ &ИС

R2

Sl

52~

"'

12l

l13

"

оI

::;: ф

с::

ф

"'

хо

uQ_

с:

>-

Управление

ключами

а)

Ynp. Sl

to

tl

Выход OYl

Упр. S2

t2

Упр. SЗ

6)

tз

Рис. 1.2 .6. Схема и принцип действия АЦП

интегратора и преобразователь, даже после снятия перегрузки, в течение

нескольких циклов работает с большой погрешностью.

АЦП «быстрого интегрирования» в основном применяются для звуковой

техники. Основным метрологическим параметром является коэффициент

нелинейных искажений. В литературе этот метод называется «двухтактным

интегрированием»; условно его можно назвать «быстрым интегрировани

ем». Упрощенная схема этих преобразователей и временные диаграммы

работы приведены на рис. 1.2.6 (а, б). В этой схеме вначале конденсатор С

заряжается до значения входного напряжения (Rl = R2), а затем разряжает

ся в два этапа источниками токов /2 и /З' величины которых отличаются 2п

раз (например, 256). Значение кода определяется как отношение соответ

ствующих временных интервалов.

35

МИКРОСХЕМЫ АЦП

36

АНАllОrQ-ЦИФРОВЫЕ &ИС

Характеристики этих преобразователей в большой степени зависят от

качества и размещения внешних элементов и от топологии «земли». В

настоящее время выпускаются АЦП с тремя источниками разряжающих

токов.

Основным преимуществом данной структуры по сравнению с интегриру

ющими АЦП является значительно большее быстродействие, что позволяет

использовать данную структуру не только в измерительной аппаратуре, но

и для обработки звукового сигнала.

1.2.2 .3 . АЦП последовательного приближения

(Successive appгoximalioп, SAR-ADC)

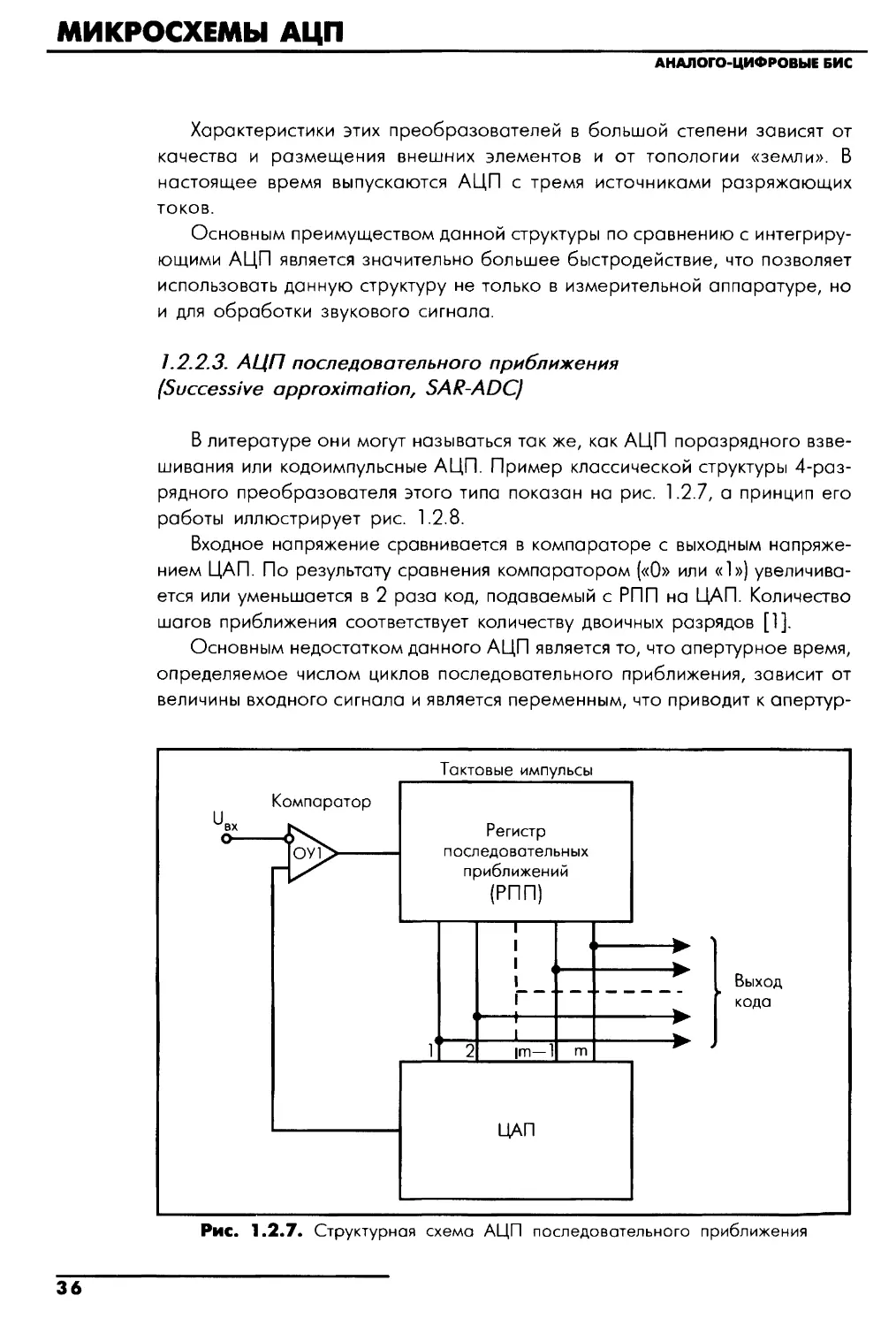

В литературе они могут называться так же, как АЦП поразрядного взве

шивания или кодоимпульсные АЦП. Пример классической структуры 4-раз

рядного преобразователя этого типа показан на рис. 1.2.7, а принцип его

работы иллюстрирует рис. 1.2 .8.

Входное напряжение сравнивается в компараторе с выходным напряже

нием ЦАП. По результату сравнения компаратором («0» или « 1») увеличива

ется или уменьшается в 2 раза код, подаваемый с РПП на ЦАП. Количество

шагов приближения соответствует количеству двоичных разрядов [ 1].

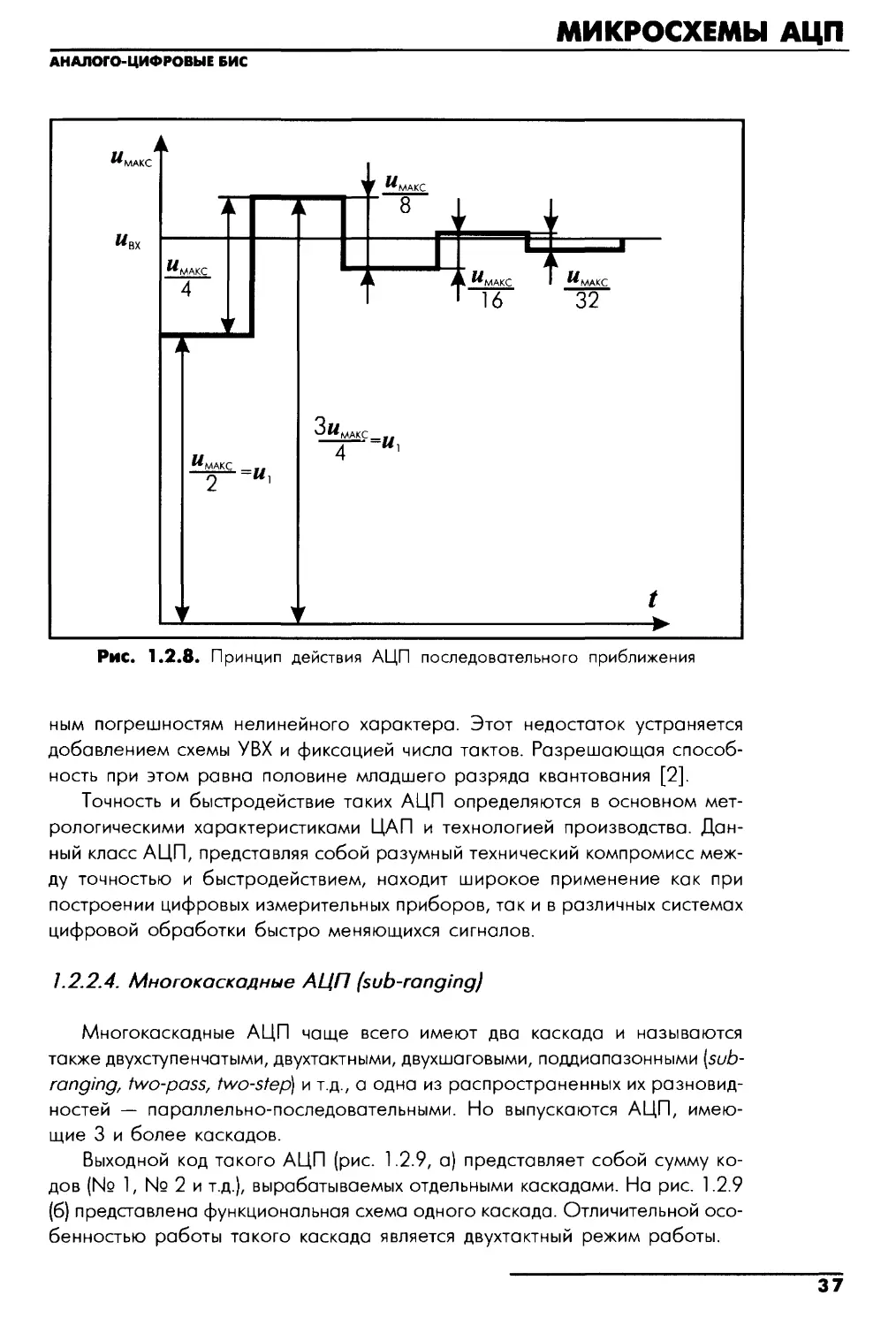

Основным недостатком данного АЦП является то, что апертурное время,

определяемое числом циклов последовательного приближения, зависит от

величины входного сигнала и является переменным, что приводит к апертур-

Тактовые импульсы

u..ох

Компаратор

Регистр

OYl

последовательных

приближений

(РПП}

1

1

....

....

1

-

1

~

г- - -----

-

1

~

-

12

1m-l m

~

}

Выходкода

ЦАП

Рис. 1.2.7. Структурная схема АЦП паследавательнага приближения

МИКРОСХЕМЫ АЦП

АНАЛОrО-ЦИФРОВЫЕ &ИС

UмдксJ'

1 f UMAKC

А•

8

•

Uвх

1

.

.

Uмдкс

J•

-4-

н

'~ Uмдкс

Uмлкс

16

32

.

j

ЗимАКс

Uмдкс =и

-4-·=и,

21

,,

н

t~~

Рис. 1.2 .8 . Принцип действия АЦП последовательного приближения

ным погрешностям нелинейного характера. Этот недостаток устраняется

добавлением схемы УВХ и фиксацией числа тактов. Разрешающая способ

ность при этом равна половине младшего разряда квантования [2].

Точность и быстродействие таких АЦП определяются в основном мет

рологическими характеристиками ЦАП и технологией производства. Дан

ный класс АЦП, представляя собой разумный технический компромисс меж

ду точностью и быстродействием, находит широкое применение как при

построении цифровых измерительных приборов, так и в различных системах

цифровой обработки быстро меняющихся сигналов.

1.2.2 .4 . Многокаскадные АЦП {sub-гanging}

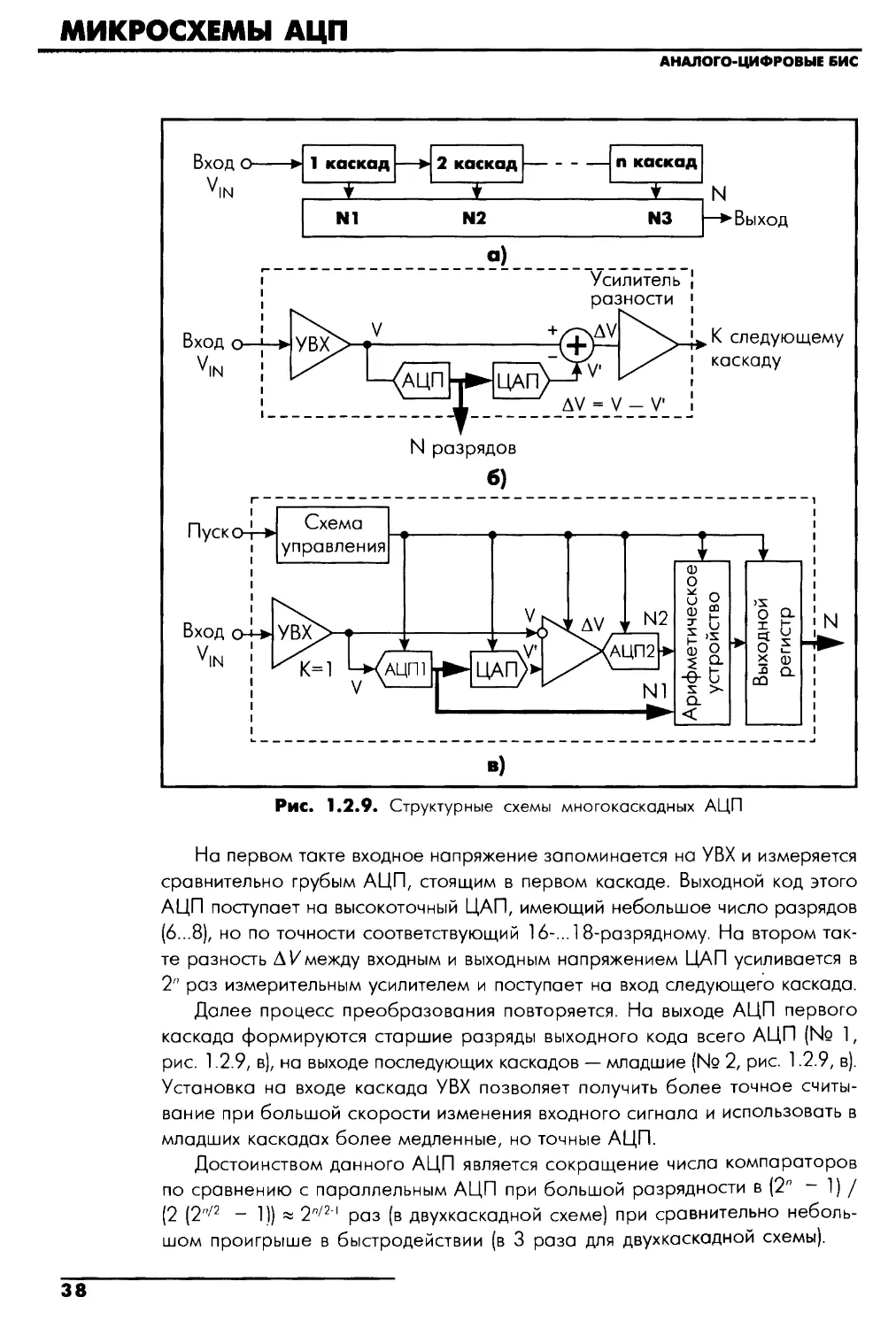

Многокаскадные АЦП чаще всего имеют два каскада и называются

также двухступенчатыми, двухтактными, двухшаговыми, помиапазонными (sub-

гanging, two-pass, two-step) и т.д., а одна из распространенных их разновид

ностей - параллельно-последовательными. Но выпускаются АЦП, имею

щие 3 и более каскадов.

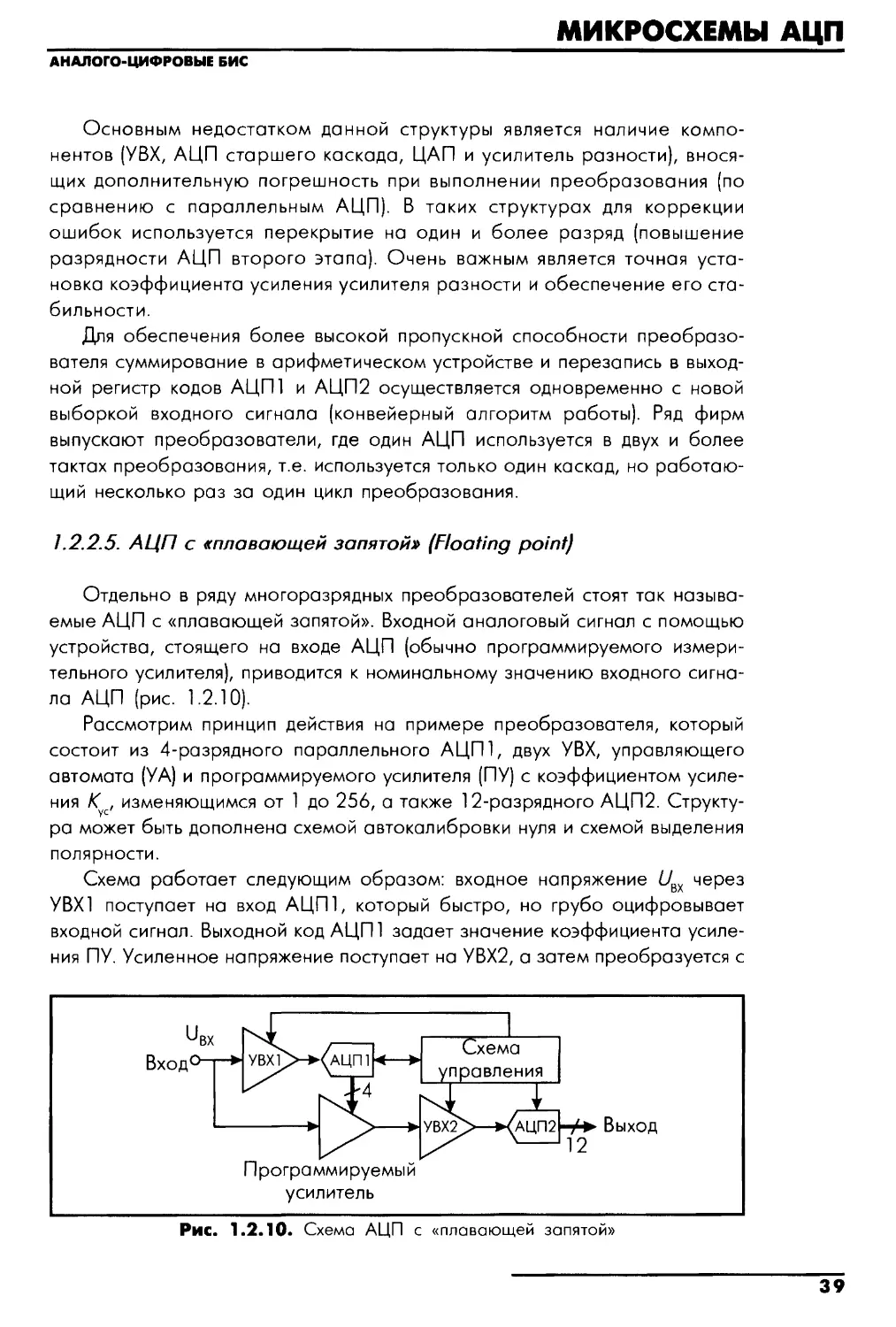

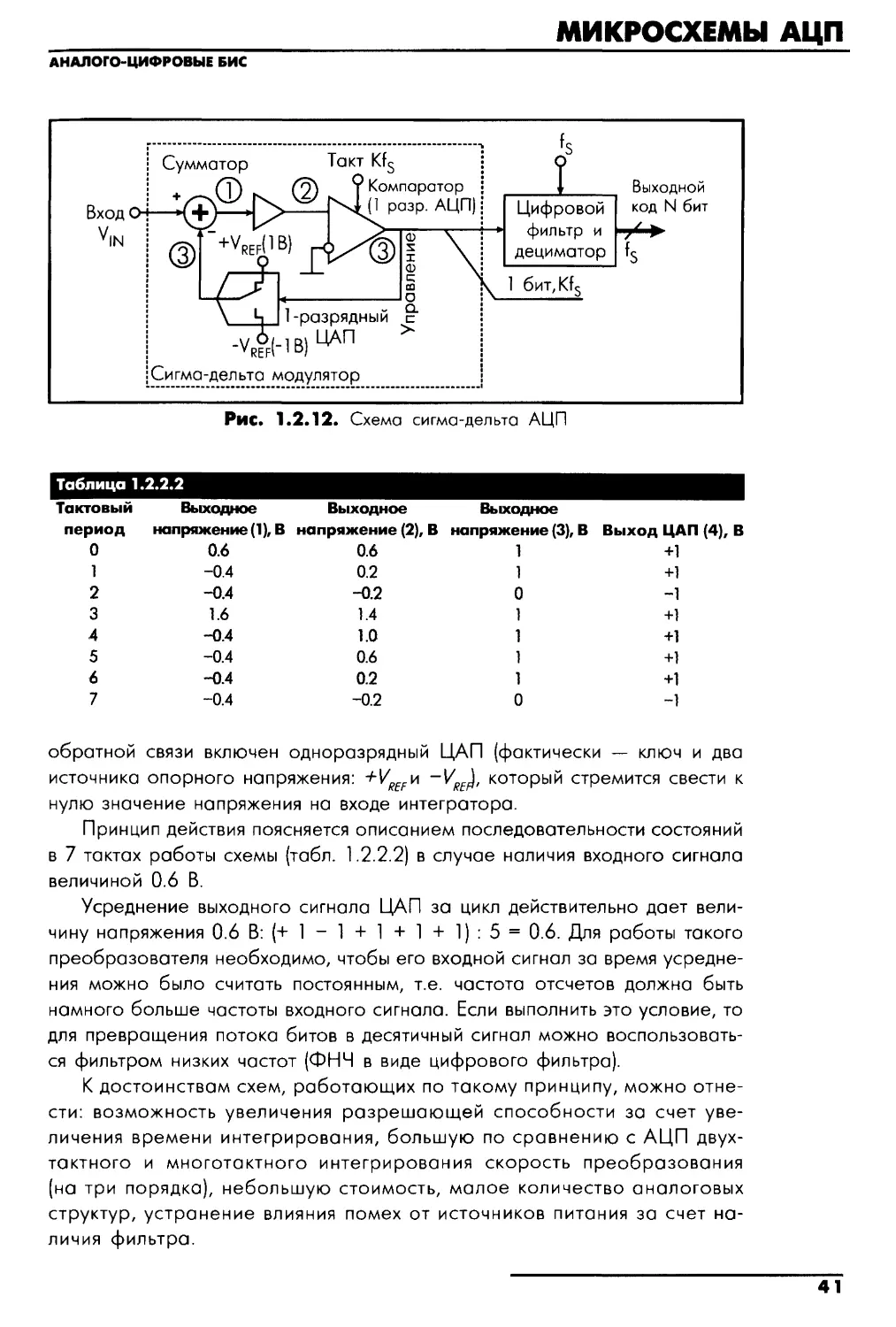

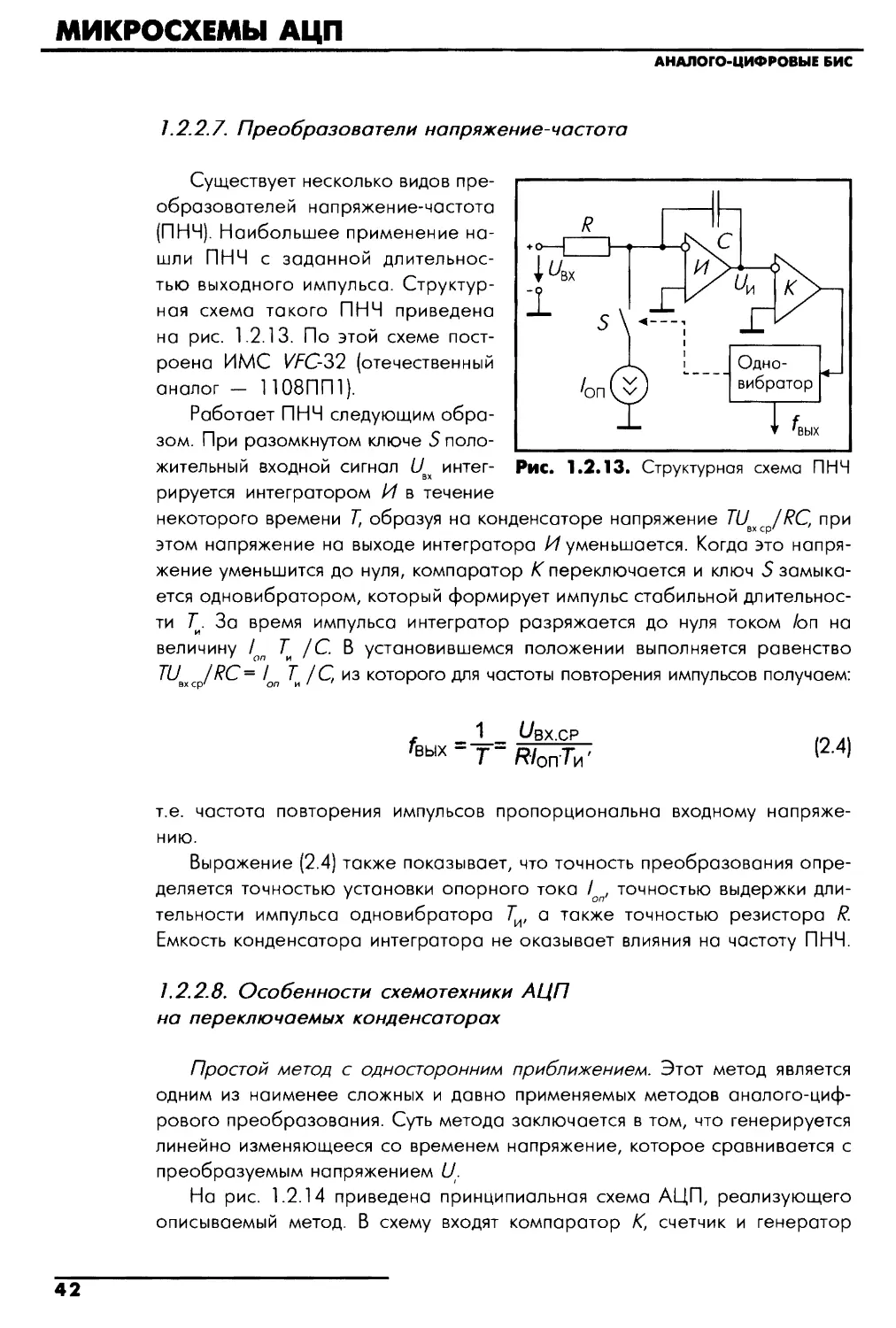

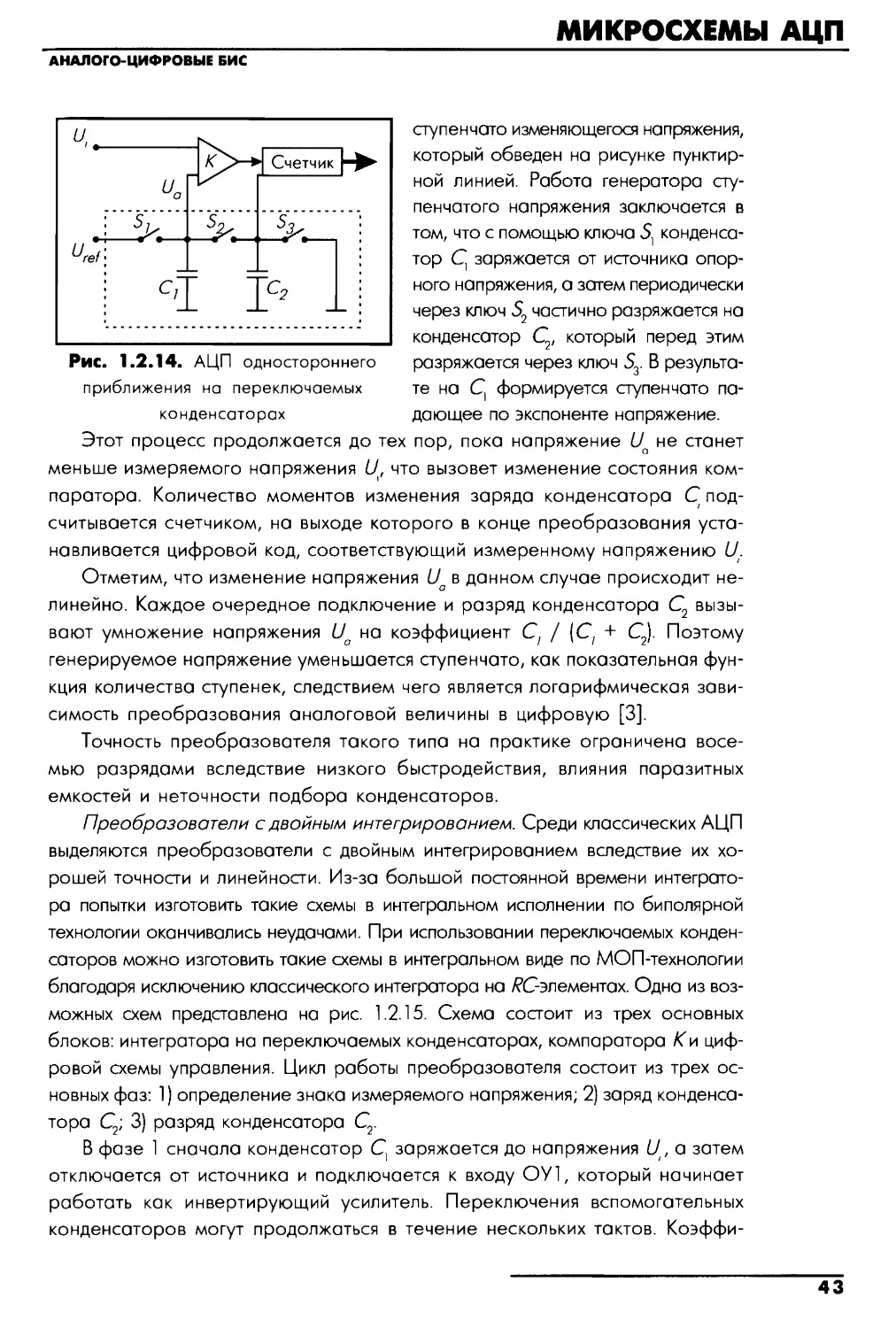

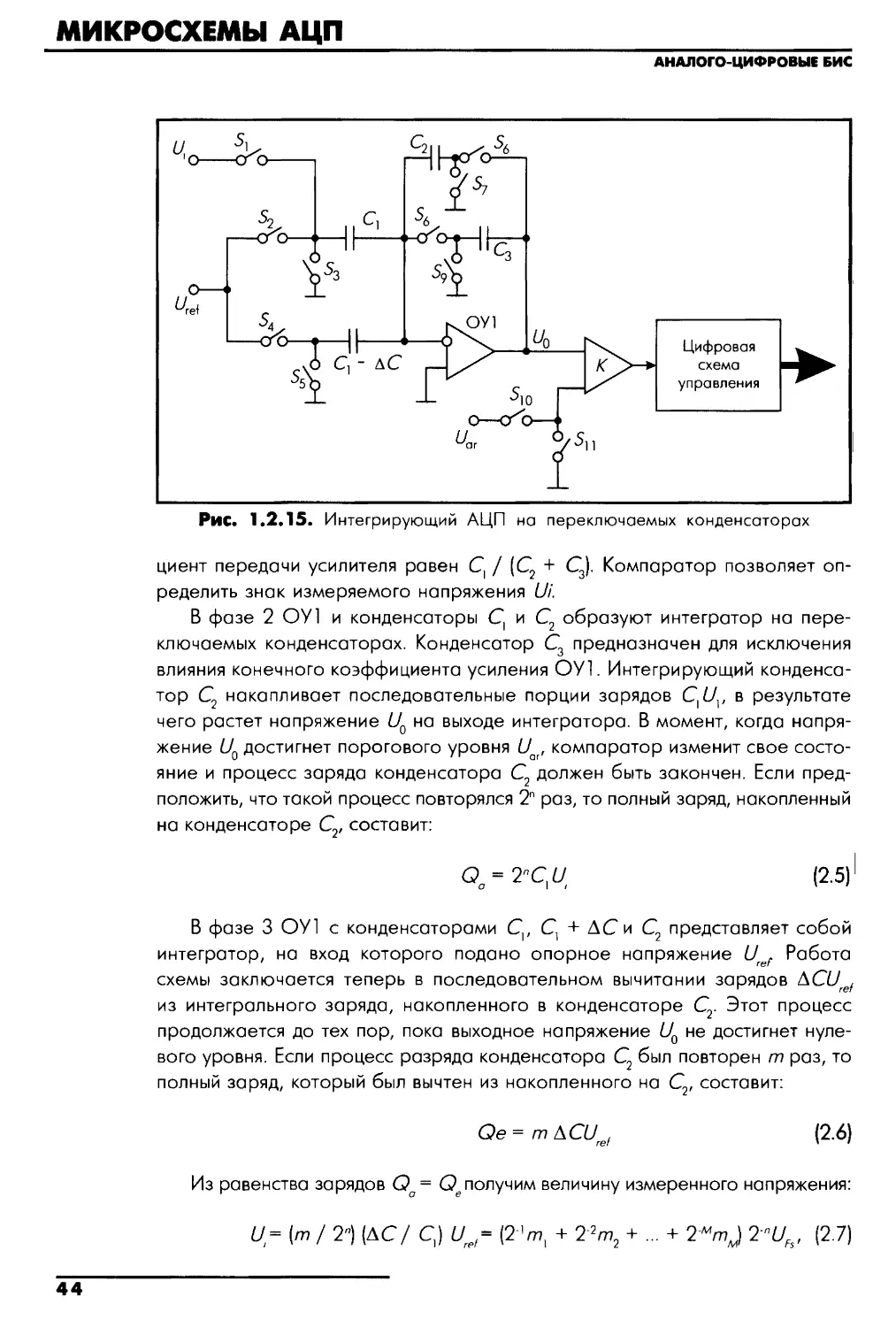

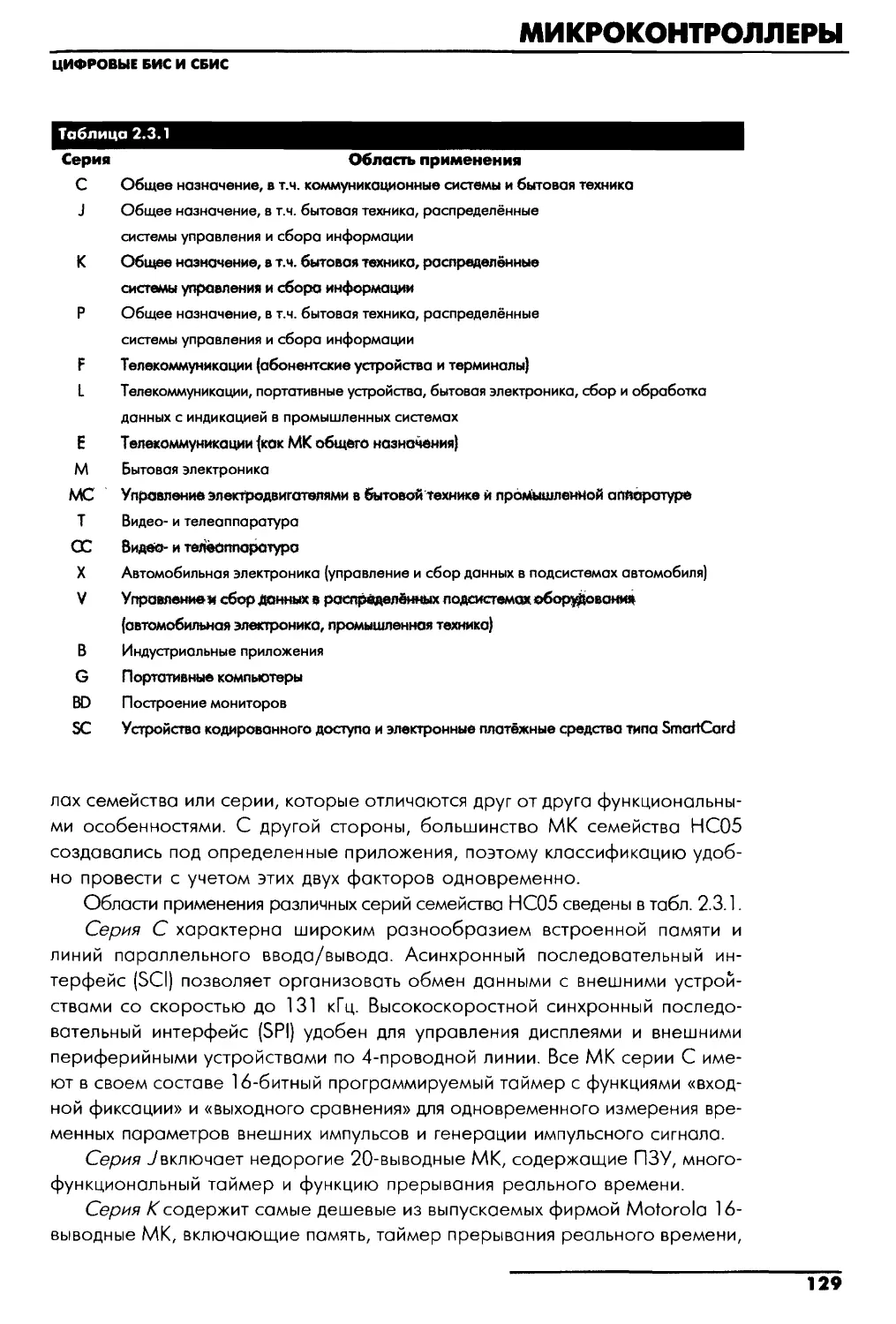

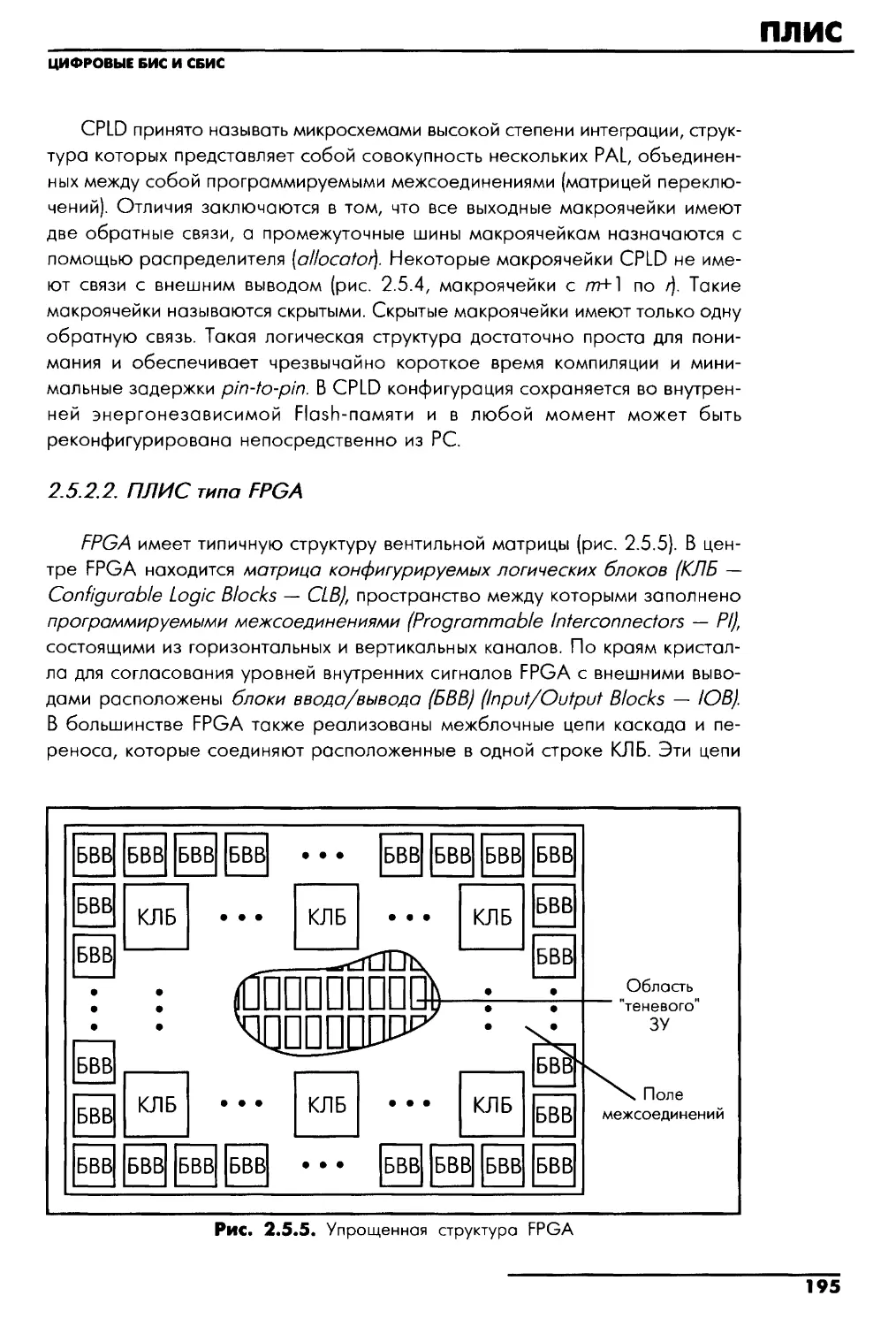

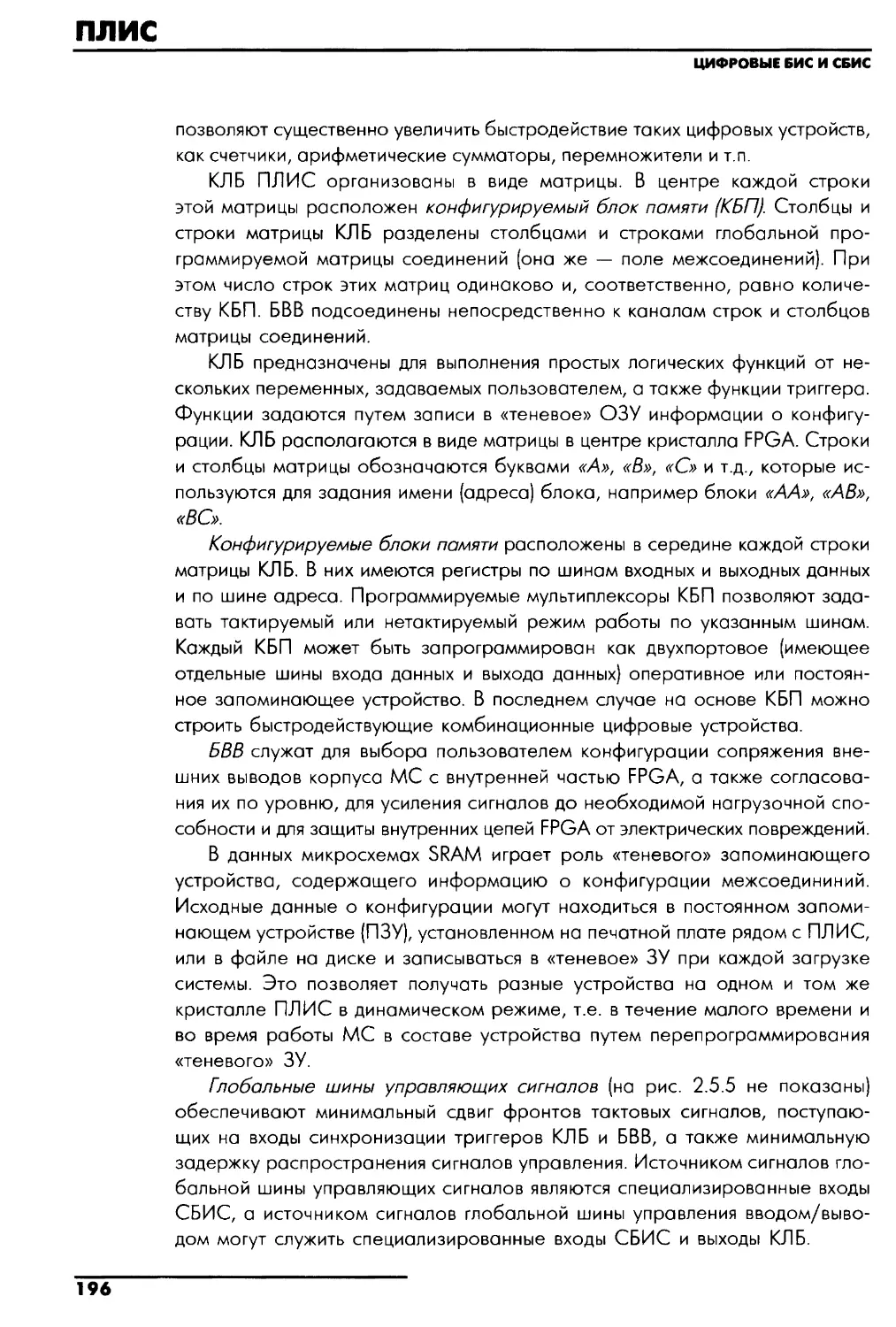

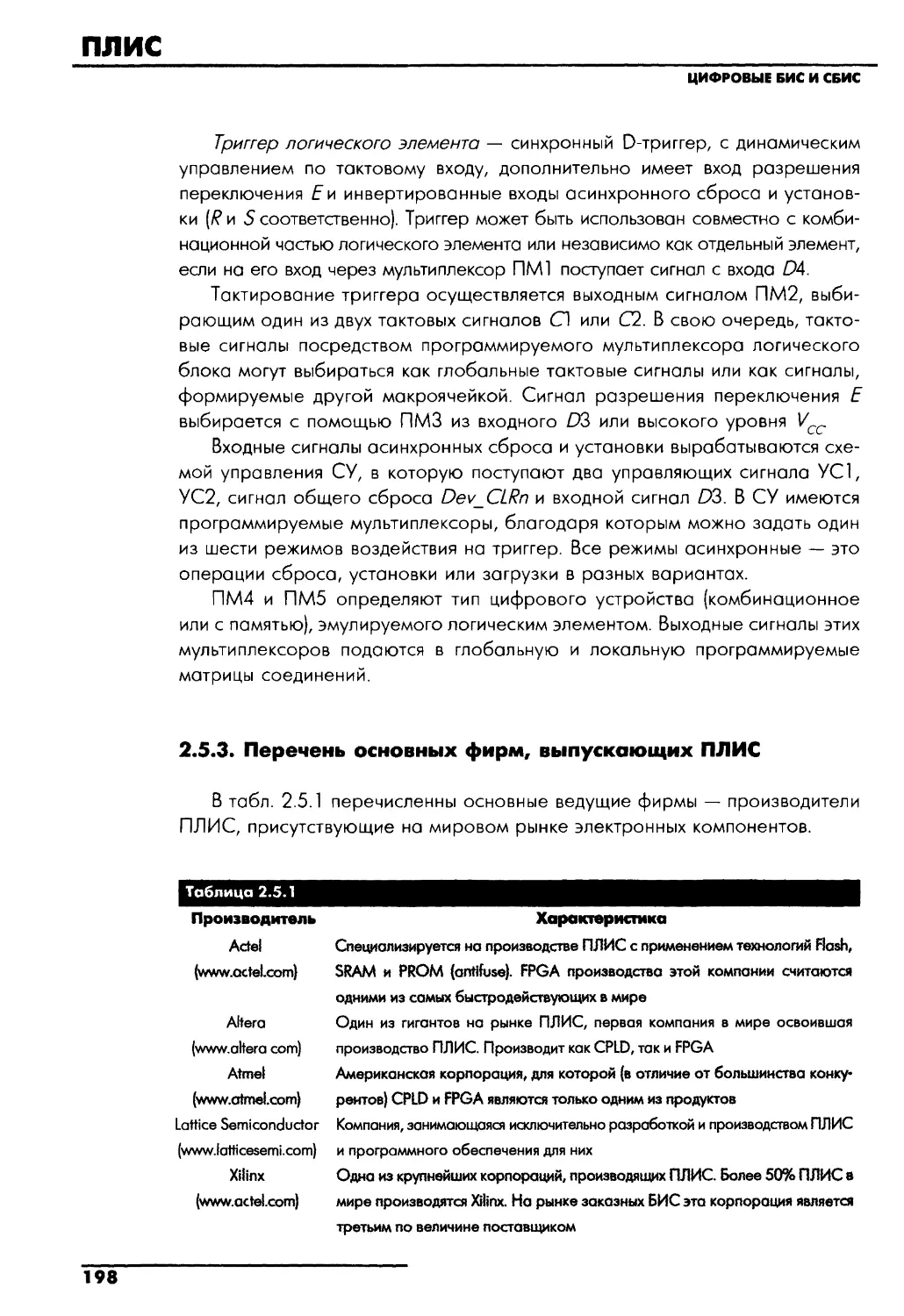

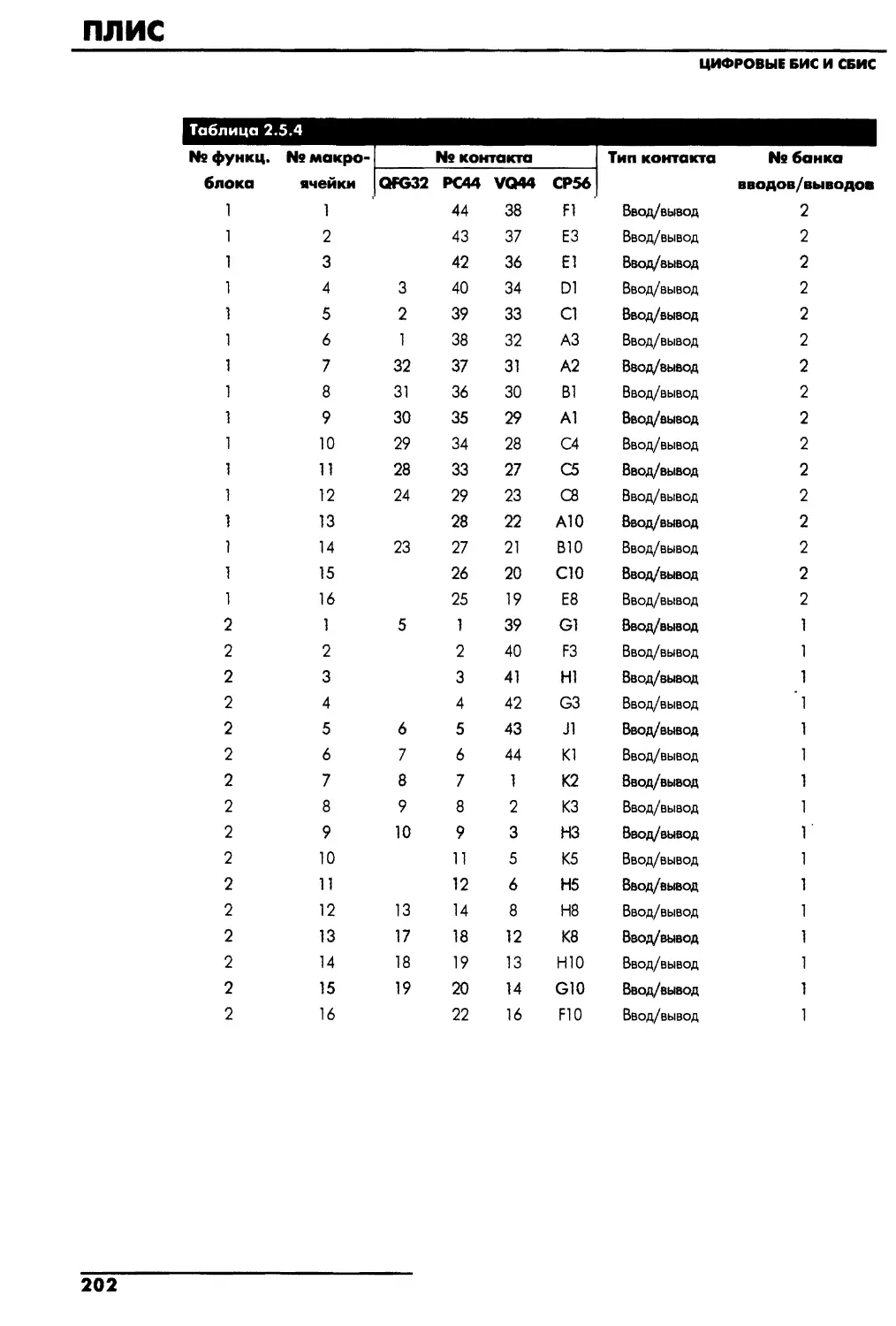

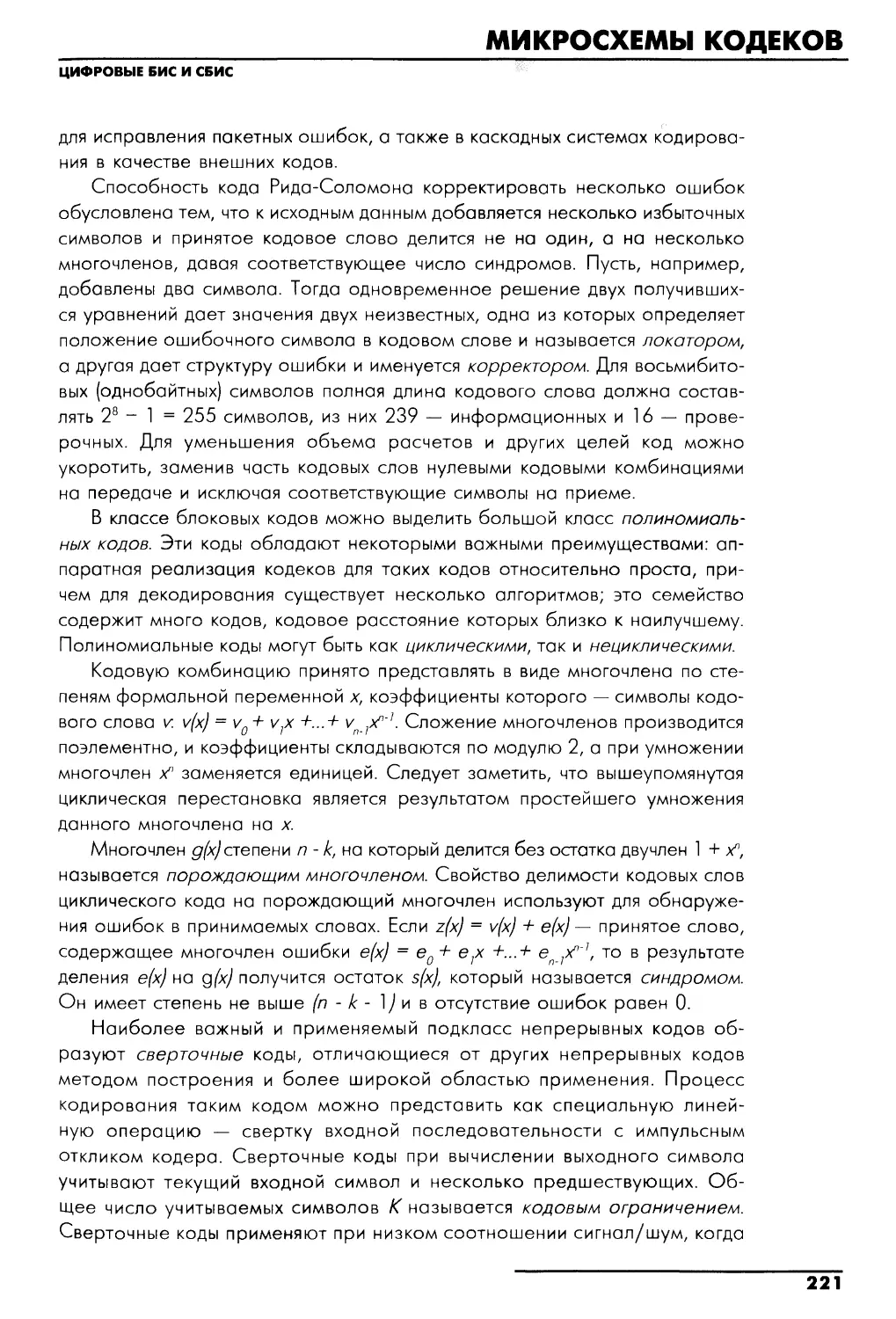

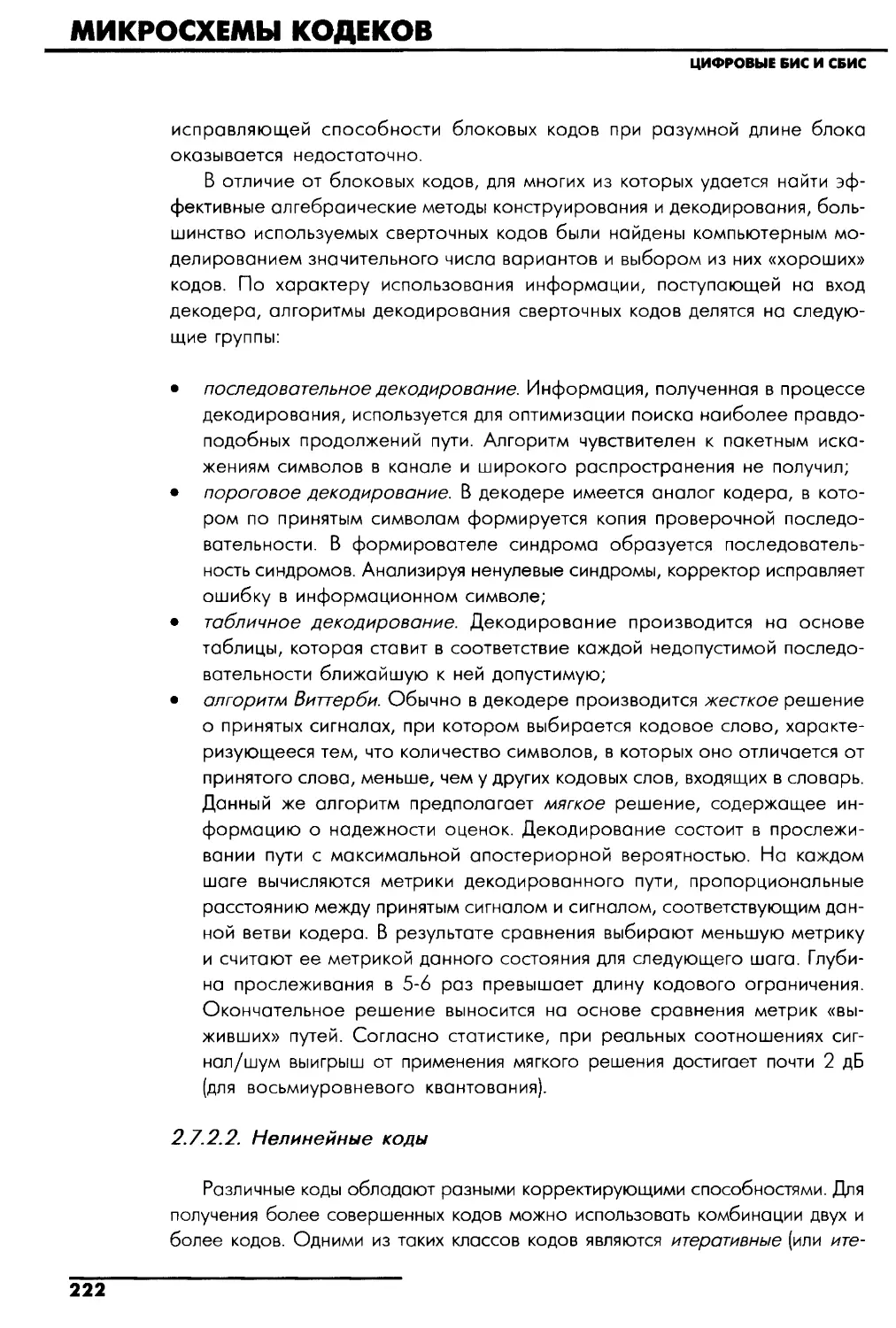

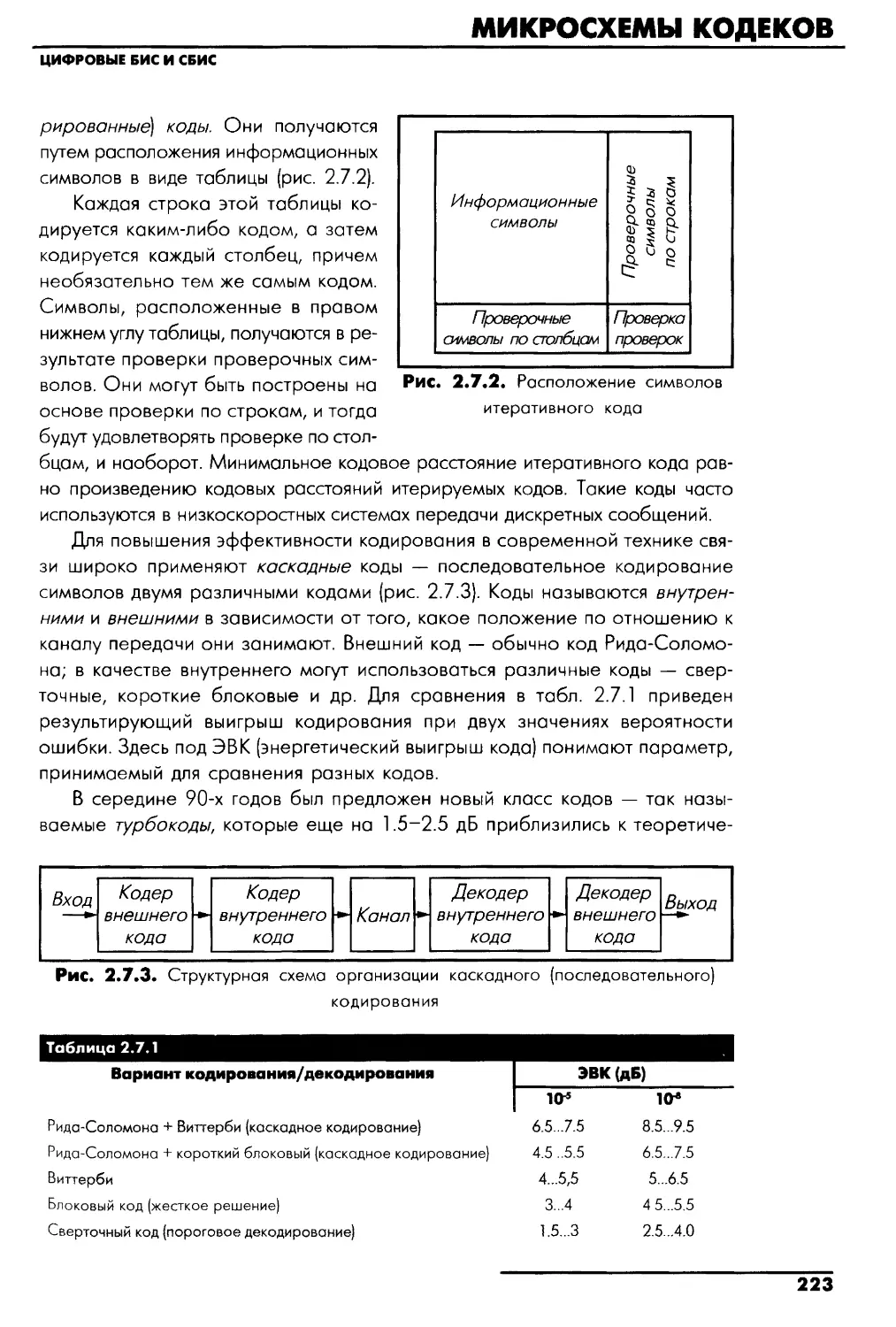

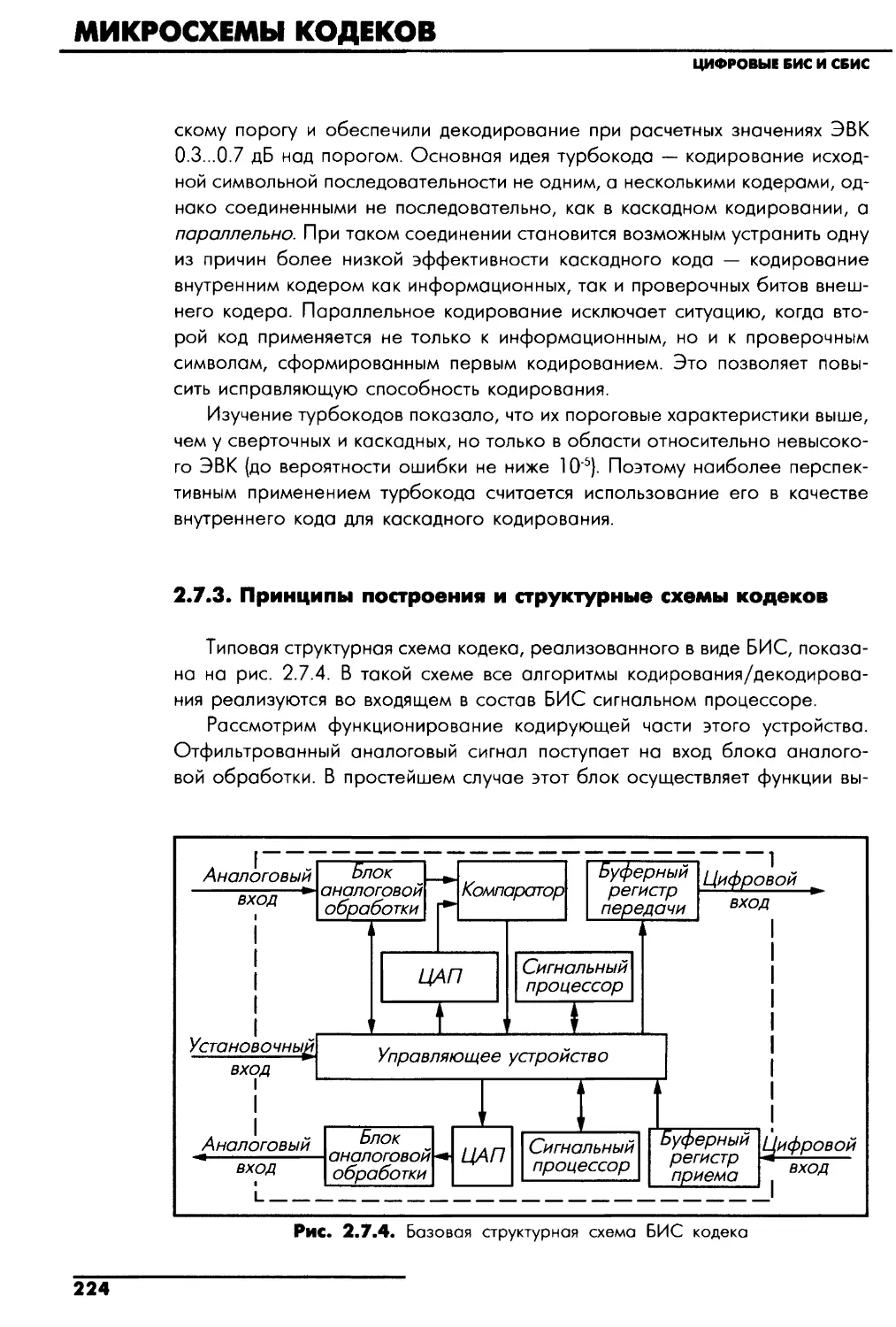

Выходной код такого АЦП (рис. 1.2 .9 , а) представляет собой сумму ко