Автор: Мальцев П.П. Долидзе Н.С. Критенко М.И.

Теги: электротехника электроника радиотехника цифровая техника вычислительная техника

ISBN: 5-256-00845-5

Год: 1994

Текст

СПРАВОЧНИК

ЦИФРОВЫЕ

ИНТЕГРАЛЬНЫЕ

МИКРОСХЕМЫ

©

МОСКВА „РАДИО И СВЯЗЬ”

1994

Scan AAW

ББК 32.85

Ц75

УДК 621.3.049.77

Федеральная целевая программа книгоиздания России

Авторы: П. П. Мальцев, Н. С. Долидзе, М. И. Критенко,

|С. Н. Пономарев~|, В. В. Портянко, Т. Т. Посысаева, Л. 3. Ми-

халева

Рецензент В. И. Старосельский

Редакция литературы по электронике

Цифровые интегральные микросхемы: Справочник /

Ц75 П. П. Мальцев, Н. С. Долидзе, М. И. Критенко и др.—

М.: Радио и связь, 1994.— 240 с.: ил.

ISBN 5-256-00845-5.

Приводятся функциональный состав серий цифровых универсальных

микросхем, базовых матричных кристаллов, программируемых логически^

интегральных микросхем и их структурные электрические схемы. Рассмат-

риваются особенности работы и параметры. Даются практические рекомен-

дации по применению цифровых микросхем, изготавливаемых по, различ-

ным технологиям.

Для инженерно-технических работников, занятых в области цифровой

вычислительной техники и автоматики, а также радиолюбителей.

.. 2302030700-011 kkv qo як

Ц ~046(0» Й4 КБ-52-135-92 ББК 32.85

Справочное издание

Мальцев Петр Павлович, Долидзе Надежда Сергеевна,

Критенко Михаил Иванович, Пономарев Сергей Николаевич,

Портянко Вячеслав Васильевич, Посысаева Татьяна Терентьевна,

Михалева Людмила Захаровна.

ЦИФРОВЫЕ ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ

Справочник

Заведующий редакцией Ю. Н Рысев

Редакторы Е Н Гарденина, М М Лисина

Обложка художника Н А Пашуро

Художественный редактор В И Мусиенко

Технический редактор Л А Горшкова

Корректор Н В Козлова

ИБ № 2384

ЛР № 010164 от 04 01 92

Сдано в набор 15 04 93 Подписано в печать 19 1193 Формат 84X108/16 Бумага писчая Гарнитура

литературная Печать офсетная Усл печ л 25,2 Усл кр-отт 25,62 Уч-изд л 34,76 Тираж 50 000 экз

Изд № 23360 Зак № 1328 С-011

Издательство «Радио и связь» 101000 Москва, Почтамт, а/я 693

Ордена Трудового Красного Знамени Чеховский полиграфический комбинат 142300, г Чехов Московской обл

ISBN 5-256-00845-5

© Мальцев П. П., Долидзе Н. С.,

Критенко М. И. и др., 1994

Оглавление

Предисловие........................................ 4

РАЗДЕЛ 1 ЦИФРОВЫЕ МИКРОСХЕМЫ....................... 5

Глава 1. Обшие сведения о цифровых микросхемах

средней степени интеграции ........................ 5

1.1. Классификация.............................. 5

1.2. Основные характеристики и параметры ЛЭ ... 6

1.3. Сравнение обобщенных параметров цифровых

микросхем ......................................... 9

1.4. Типовые корпуса микросхем..................... 10

Глава 2. Микросхемы на основе ТТЛШ................. 15

2.1. Маломощные ТТЛШ ИС............................ 15

2.2. Базовый логический элемент ИС 533 (К533,

КМ533, К555, КМ555).......................... 28

2.3. Базовый логический элемент ИС 1533 (КР1533) 29

2.4. Быстродействующие ТТЛШ ИС.................... 29

2.5. Базовый логический элемент ИС 530 (К530,

КМ530, КМ531, КР531)......................... 29

2.6. Базовый логический элемент ИС 1531 (КР1531) 30

2.7. Логические элементы.......................... 30

2.8. Магистральные элементы ...................... 32

2.9. Мультиплексоры............................... 32

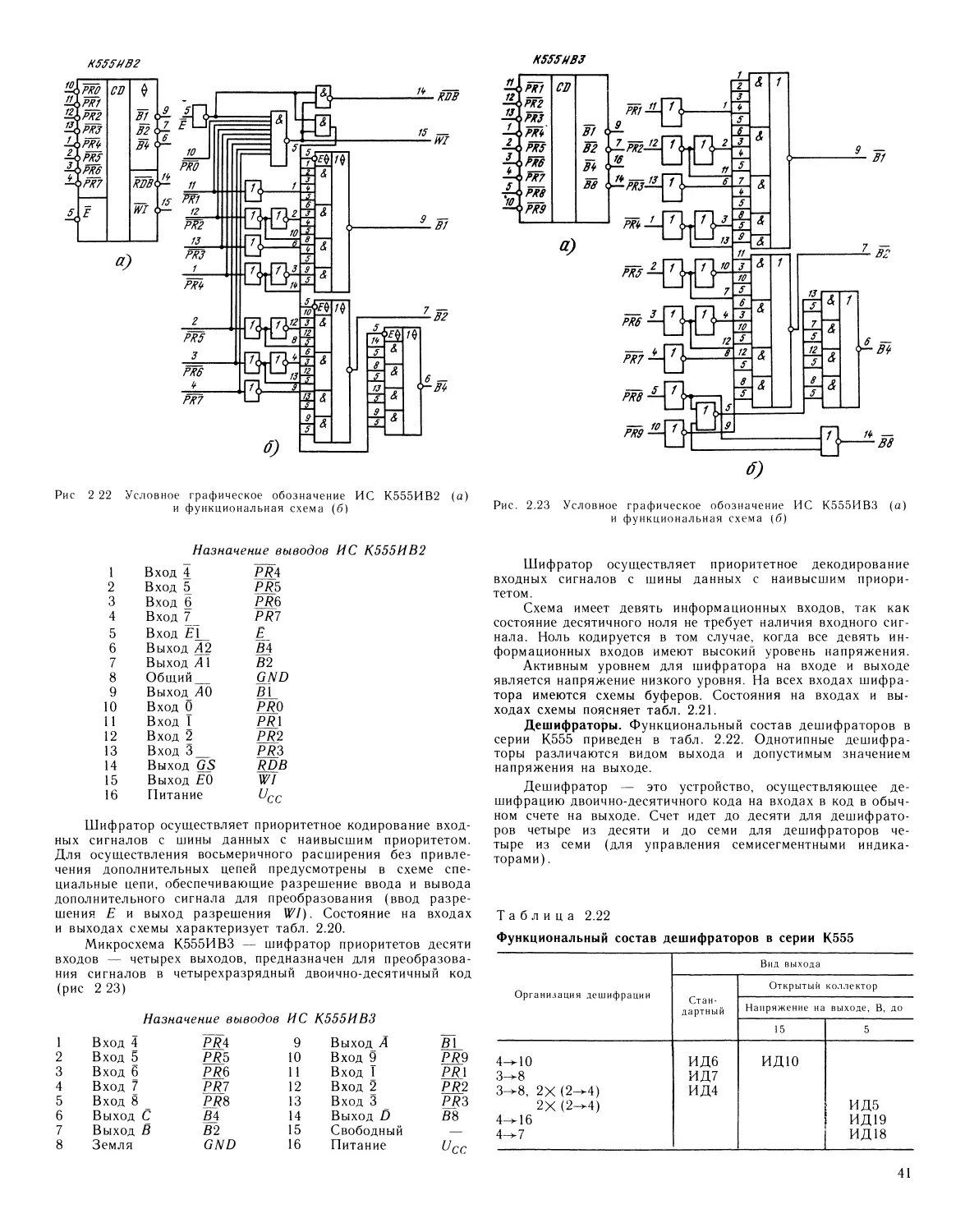

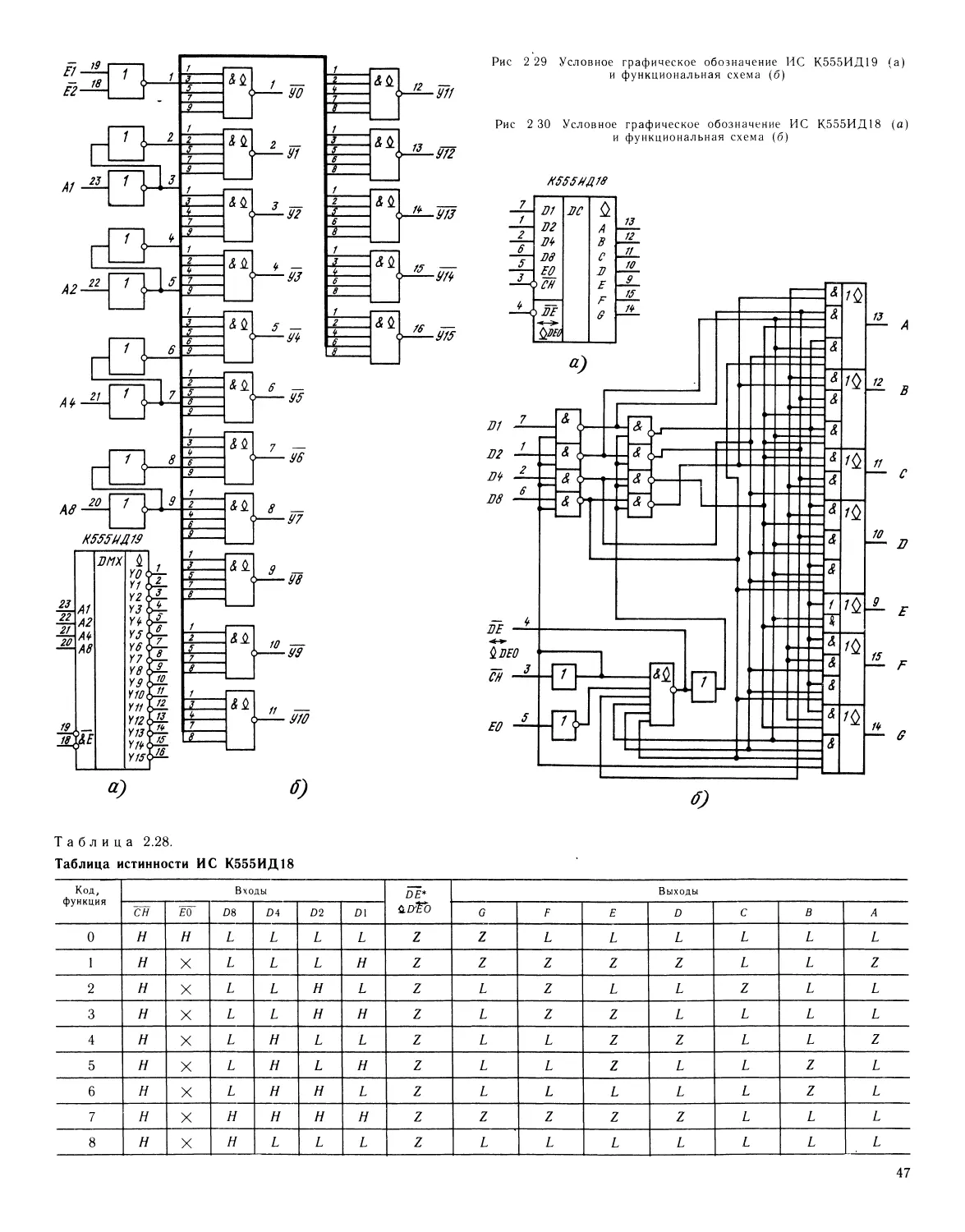

2.10. Шифраторы и дешифраторы..................... 40

2.11. Триггеры.................................... 48

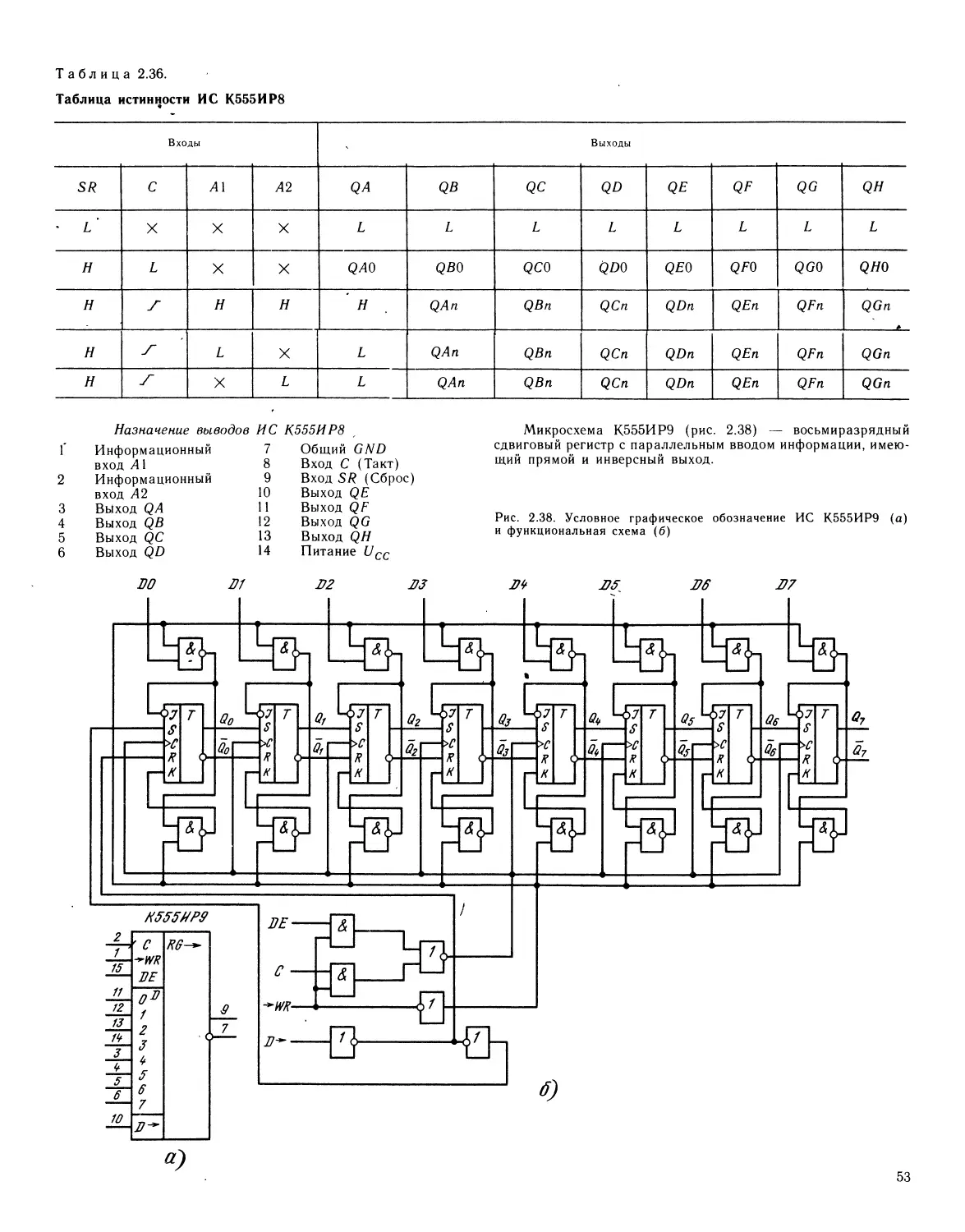

2.12. Регистры.................................... 52

2.13. Счетчики.................................. 62

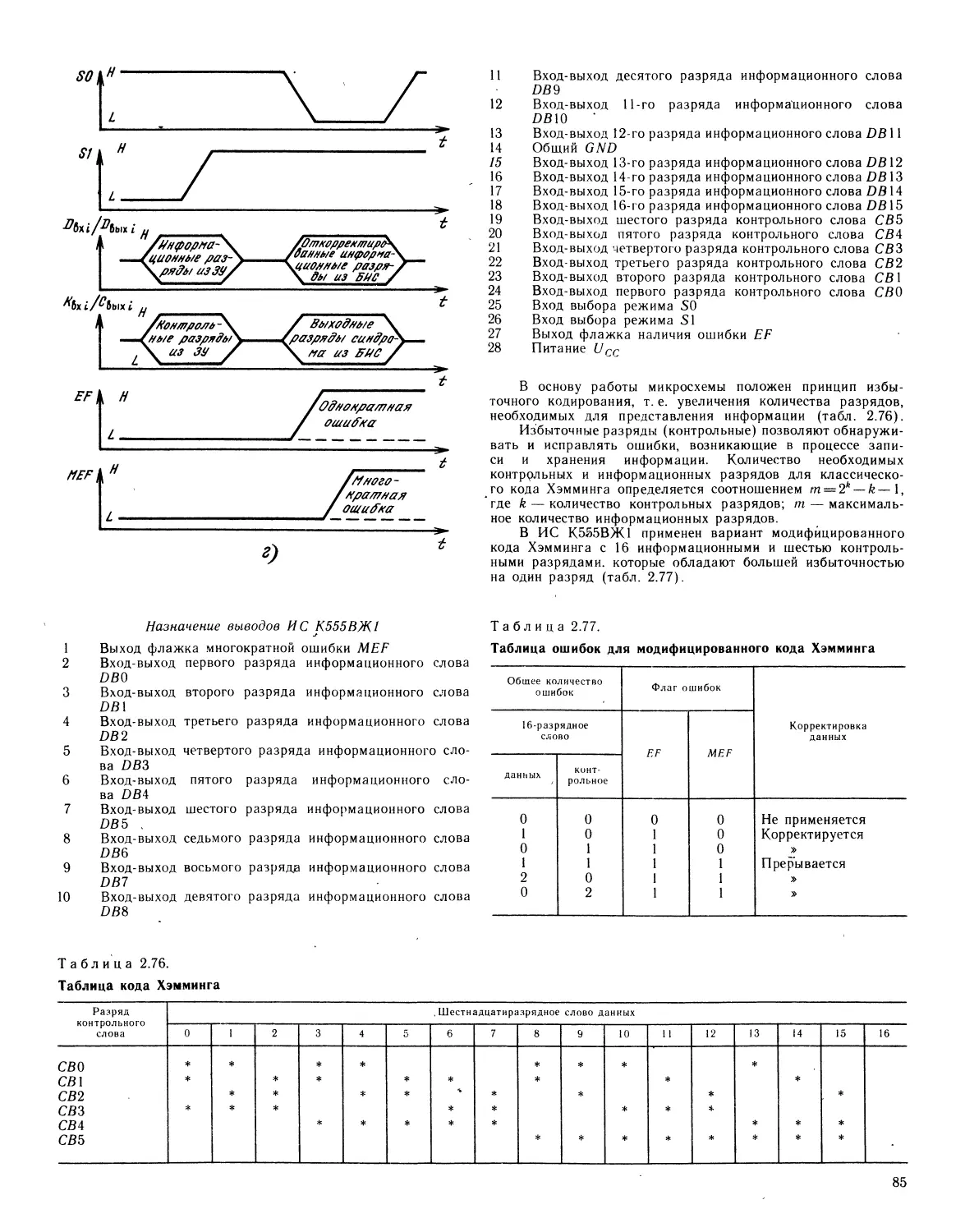

2.14 Арифметическо-логические устройства.......... 74

2.15. Приемопередатчики........................... 86

2.16. Формирователи............................... 87

2.17. Мультивибраторы............................. 89

2.18. Зависимость параметров микросхем от режимов

работы и условий эксплуатации..................... 91

Глава 3. Микросхемы на основе КМОП-технологии 94

3.1. Основные характеристики ИС К564 ............. 94

3.2. Сопряжение ИС К564 с другими сериями ... 101

3.3. Базовые логические элементы................. 103

3.4. Комбинационные устройства.................. 104

3.5. Последовательностные устройства..............127

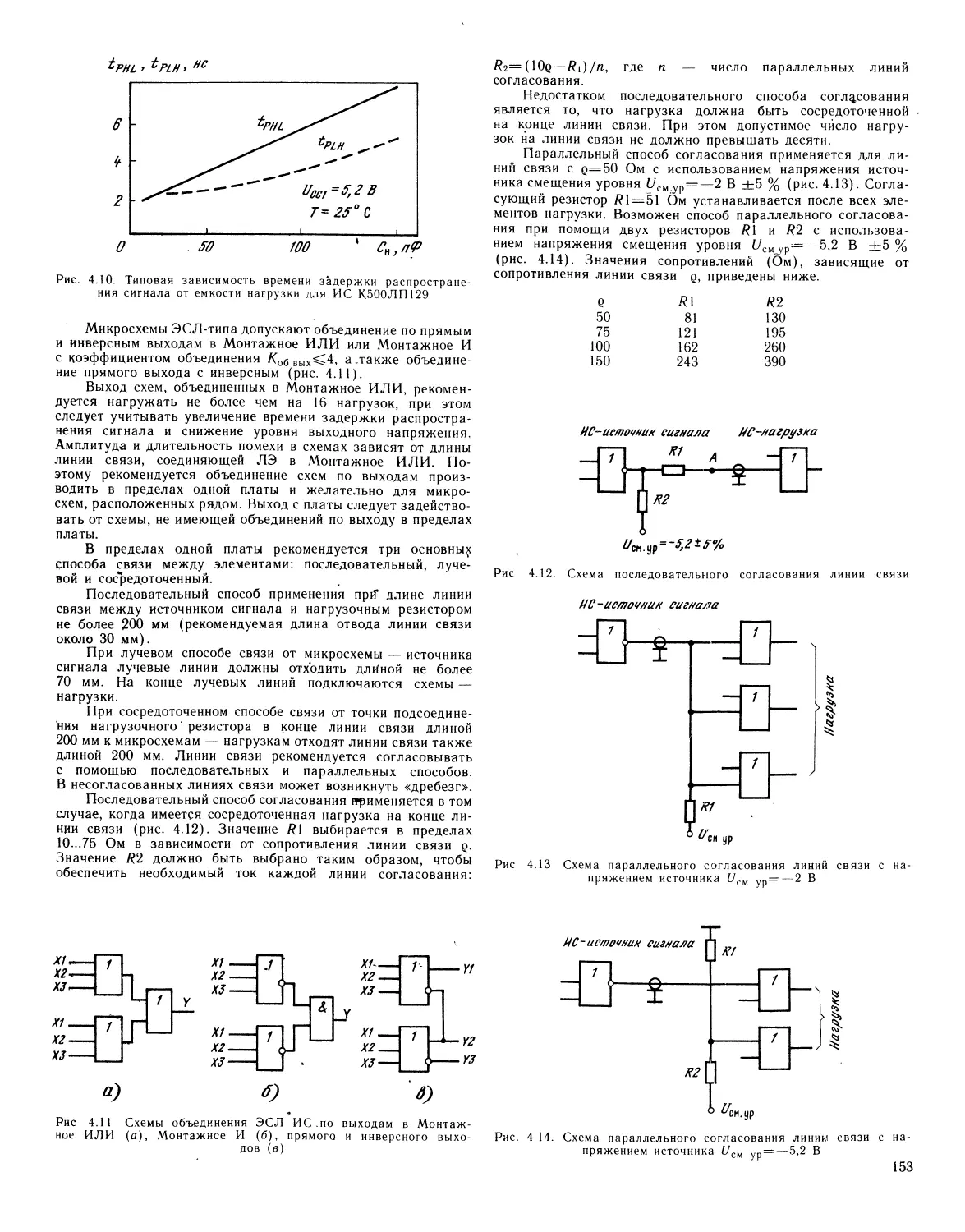

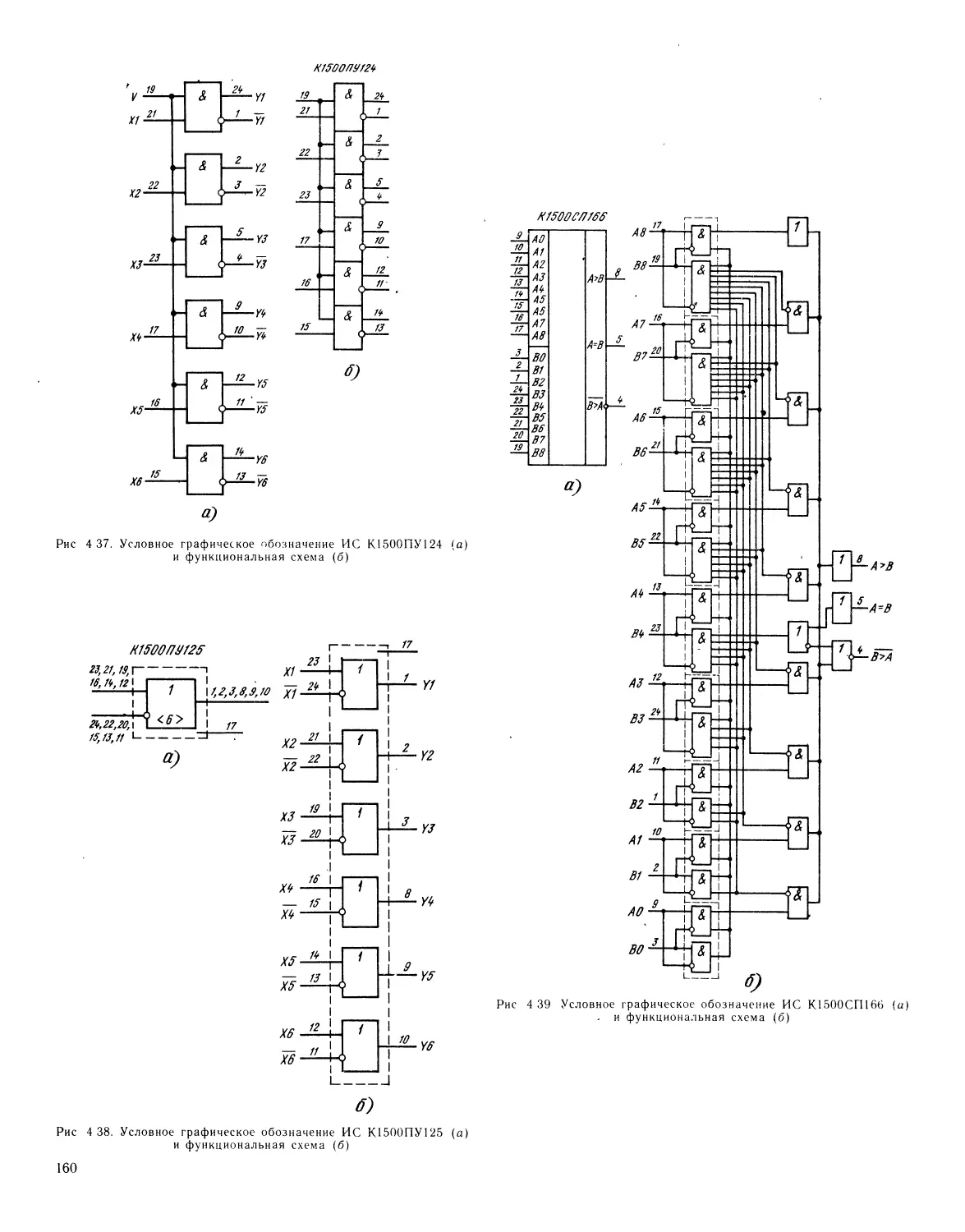

Глава 4. Микросхемы на основе ЭСЛ.................147

4.1. Быстродействующие микросхемы.................147

4.2. Базовый логический элемент ИС К500 (100, КЮ0,

500)............................................ 149

4.3. Базовый логический элемент ИС К1500 (1500) 150

4.4. Особенности применения ЭСЛ ИС................152

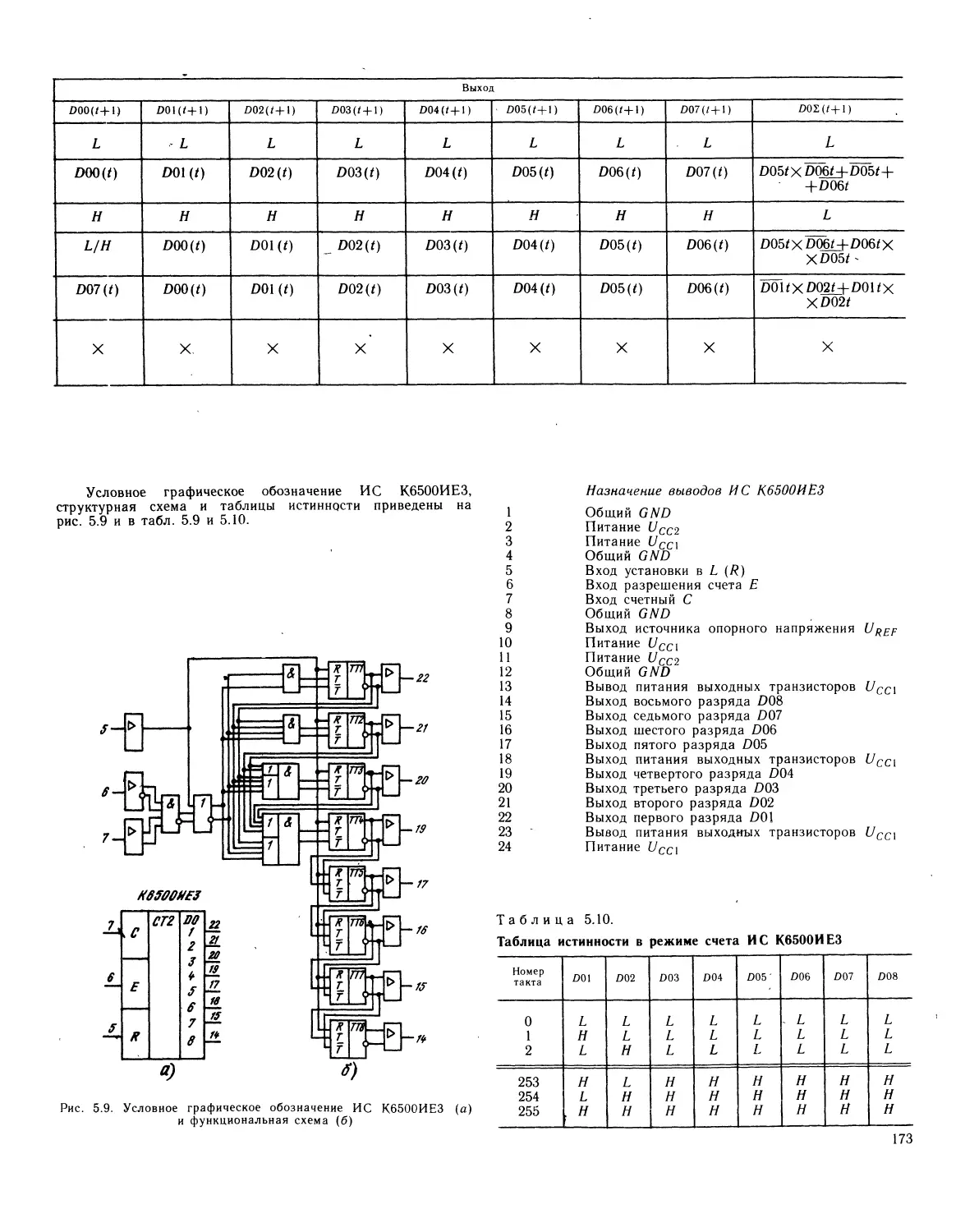

Глава 5. Микросхемы на основе арсенида галлия . . 168

5.1. Базовый логический элемент сверхбыстродей-

ствующих ИС К6500 ........................... 168

5.2. Логические элементы, триггер, счетчики, регистры 168

РАЗДЕЛ II. ЦИФРОВЫЕ БАЗОВЫЕ МАТРИЧНЫЕ КРИСТАЛЛЫ 174

Глава 6. Проектирование полузаказных БИС на

основе базовых матричных кристаллов . . 174

6.1. Классификация методов проектирования спе-

циализированных БИС............................. 174

6.2. Особенности конструкции БК.................. 174

6.3. Терминология, основные параметры и характе-

ристики БК...................................... 175

6.4. Основные направления развития БМК .... 176

6.5. Организация разработки БИСМ................177

6.6. Применение матричных БИС в унифицирован-

ных узлах РЭА................................... 178

Глава 7. Цифровые базовые матричные кристаллы

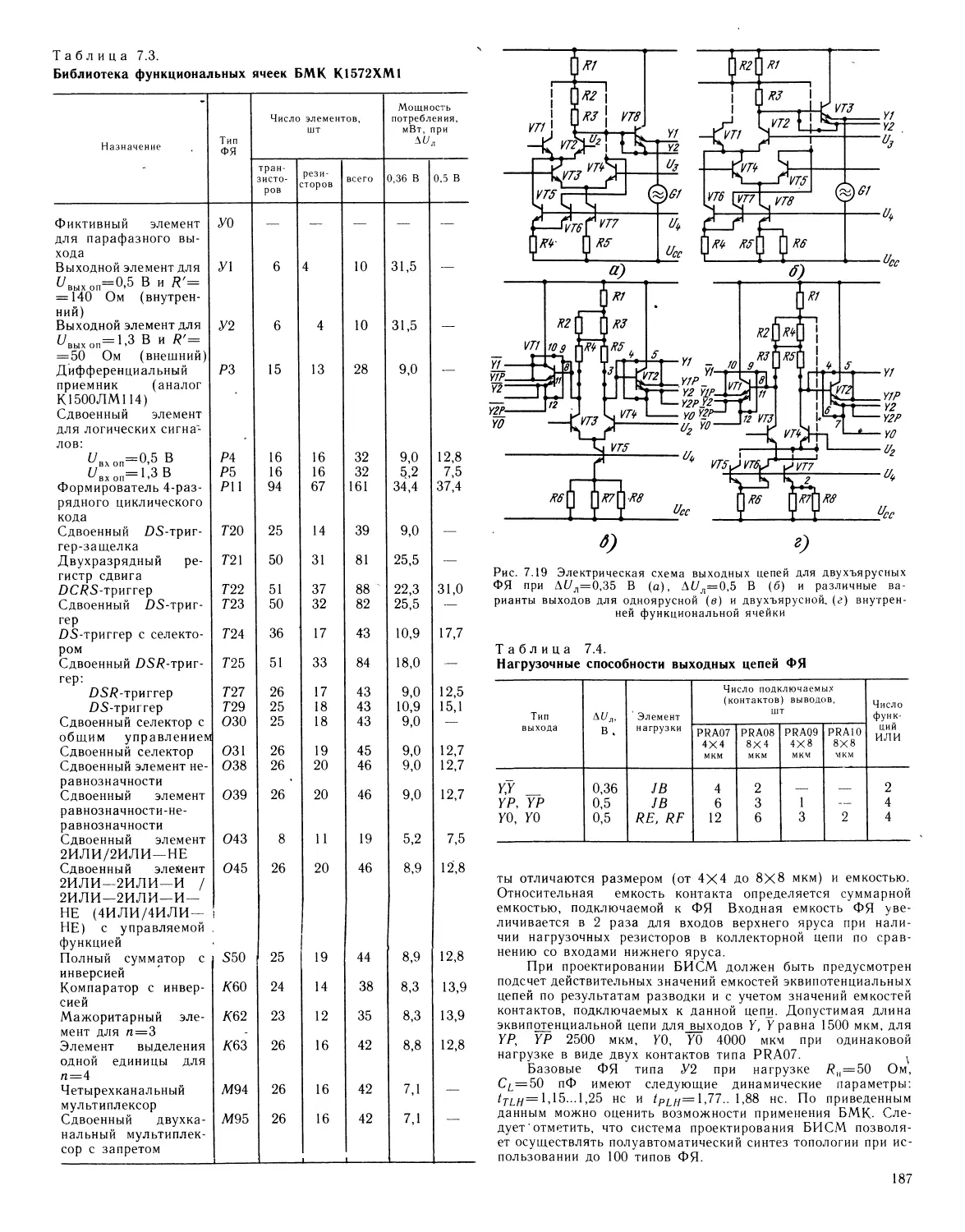

на основе эмиттерно-связанной логики . . 179

7.1. Базовые матричные кристаллы типа К1520ХМ1,

К1521ХМ1..................................... . 179

7.2. Базовый матричный кристалл типа К1520ХМ2 183

7.3. Базовый матричный кристалл типа К1572ХМ1 184

Глава 8. Цифровые базовые матричные кристаллы

на основе транзисторно-транзисторной ло-

гики с диодами Шодки............................ 188

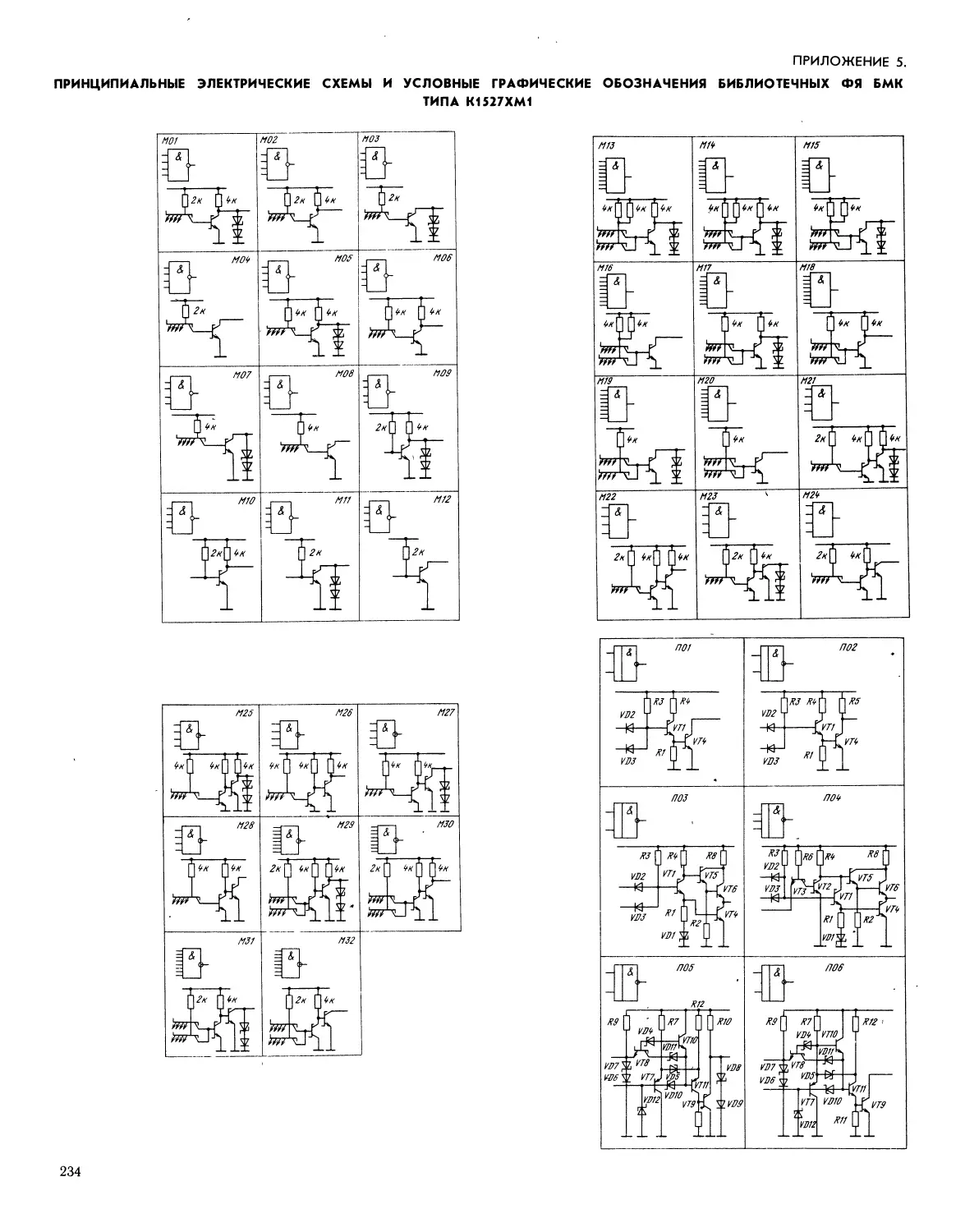

8.1. Базовый матричный кристалл типа К1527ХМ1 188

8.2. Базовый матричный кристалл типа К1548ХМ1 189

Глава 9. Цифровые базовые матричные кристаллы

на основе л-МОП-структур типа К1801ВП1 191

Глава 10. Цифровые базовые матричные кристаллы

на основе КМОП-структур . . . . 192

10.1. Базовые матричные «кристаллы типа К1806ВП1,

КР1806ВП1.................................. 192

10.2. Базовый матричный кристалл типа К1515ХМ1 193

Глава 11. Цифровые базовые матричные кристаллы

на новых материалах типа К6501ХМ1 . .194

РАЗДЕЛ III. ПРОГРАММИРУЕМЫЕ ПОТРЕБИТЕЛЕМ ЛОГИ-

ЧЕСКИЕ МИКРОСХЕМЫ . . .196

Глава 12. Ресурс программируемых логических мик-

росхем ........................................ 196

Глава 13. Программируемые логические микросхемы 198

13.1. Микросхемы К556РТ1, К556РТ2 ... 198

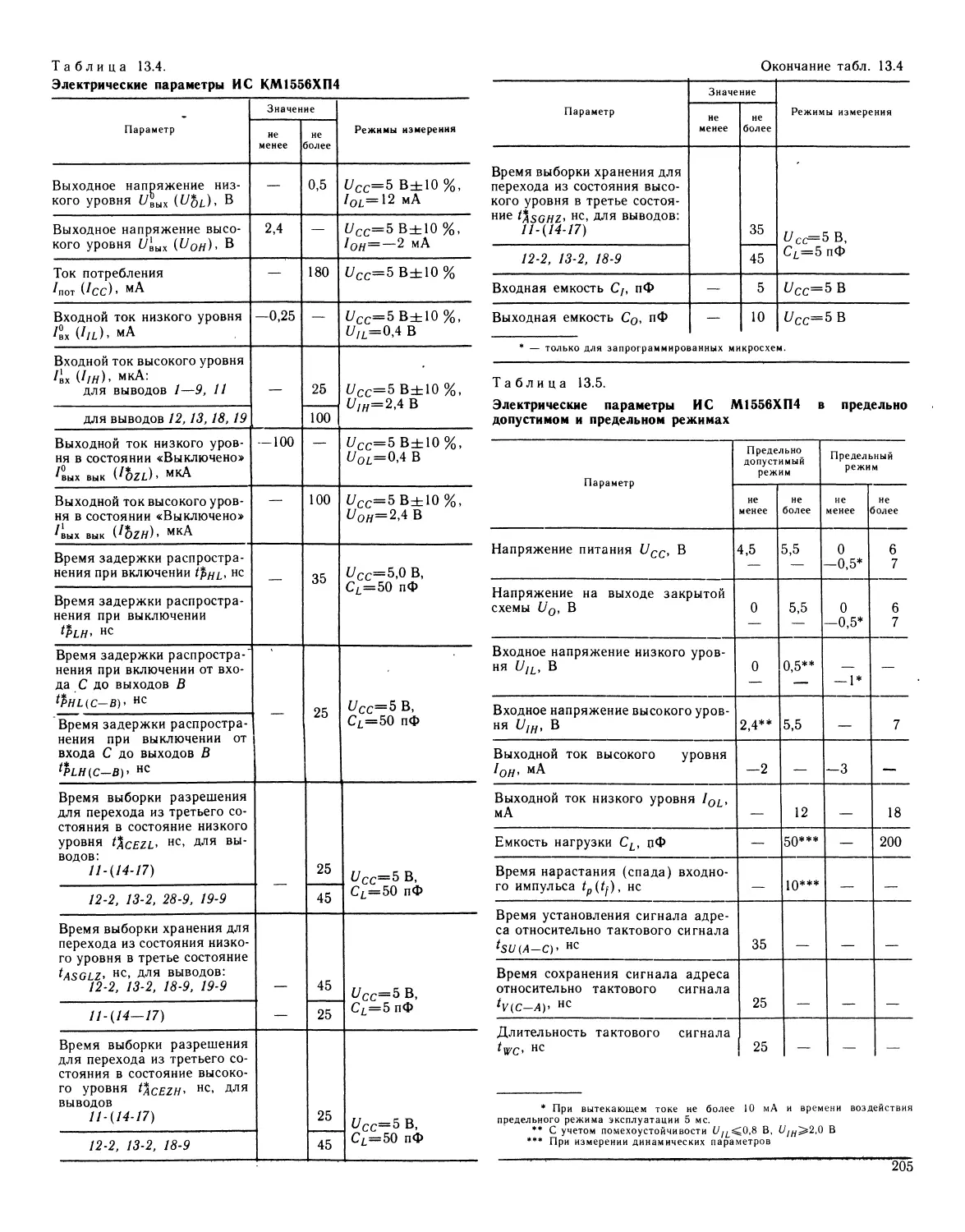

13.2. Микросхема КМ1556ХП4......................202

13.3. Микросхема КМ1556ХП6......................209

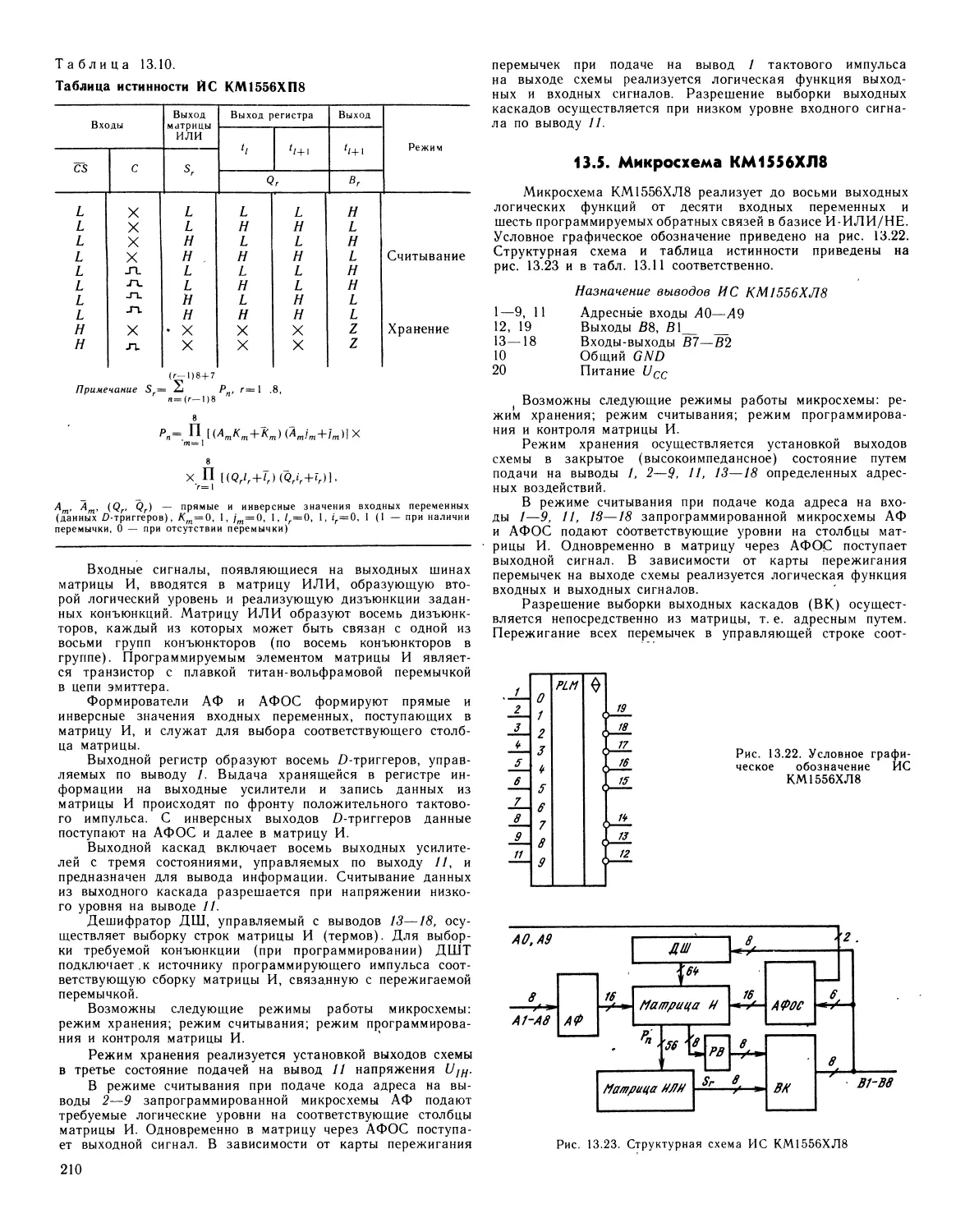

13.4. Микросхема КМ1556ХП8..................... 209

13.5. Микросхема КМ1556ХЛ8......................210

13.6. Программируемая логическая интегральная

микросхема с ультрафиолетовым стиранием ин-

формации ........................................211

13.7. Расширение логических возможностей ПЛМ . . 213

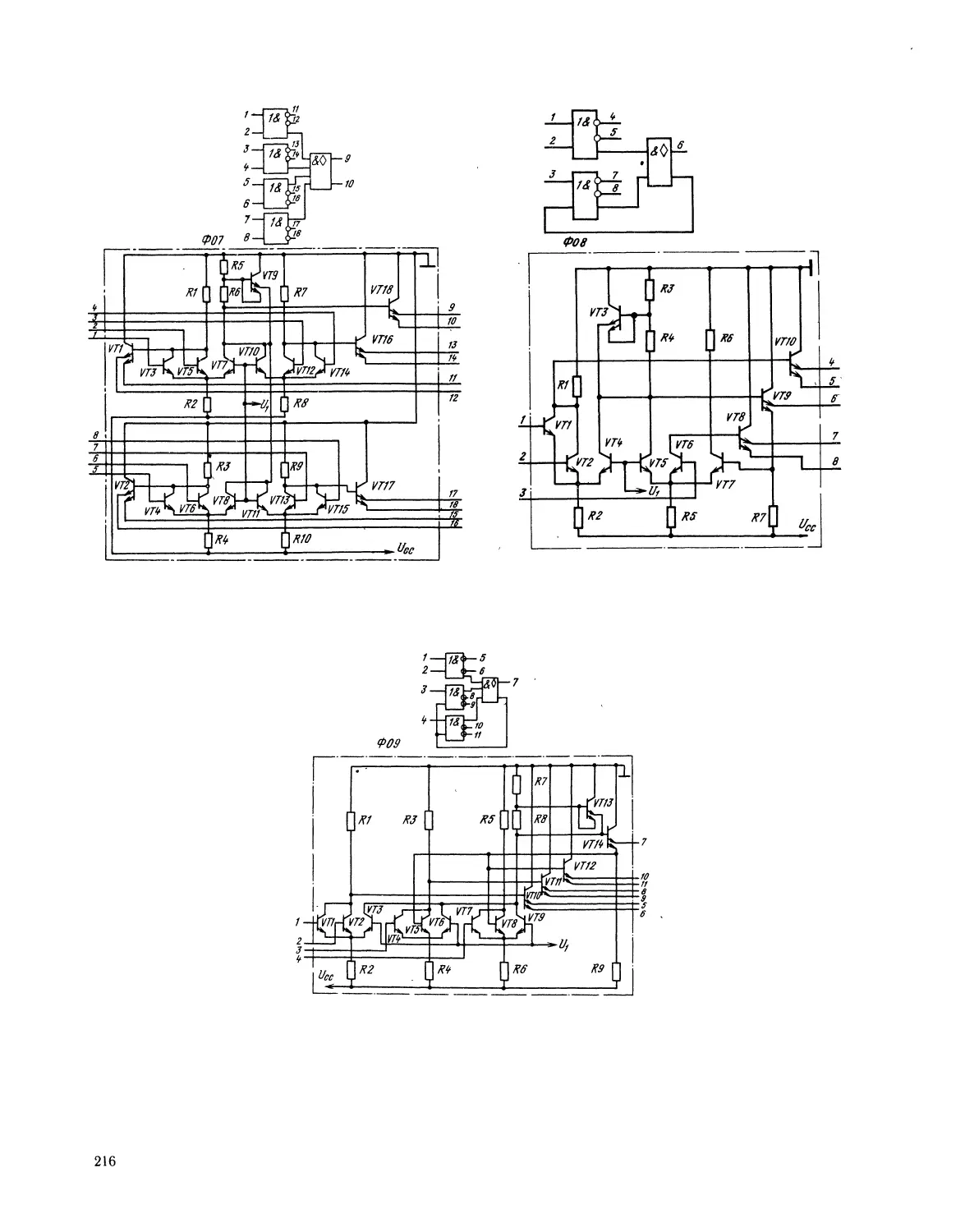

Приложение 1. Принципиальные электрические схемы

и условные графические обозначения

библиотечных ФЯ БМК типа К1521ХМ1 215

Приложение 2. Принципиальные электрические схемы

и условные графические обозначения

библиотечных ФЯ БМК типа К1520ХМ1 217

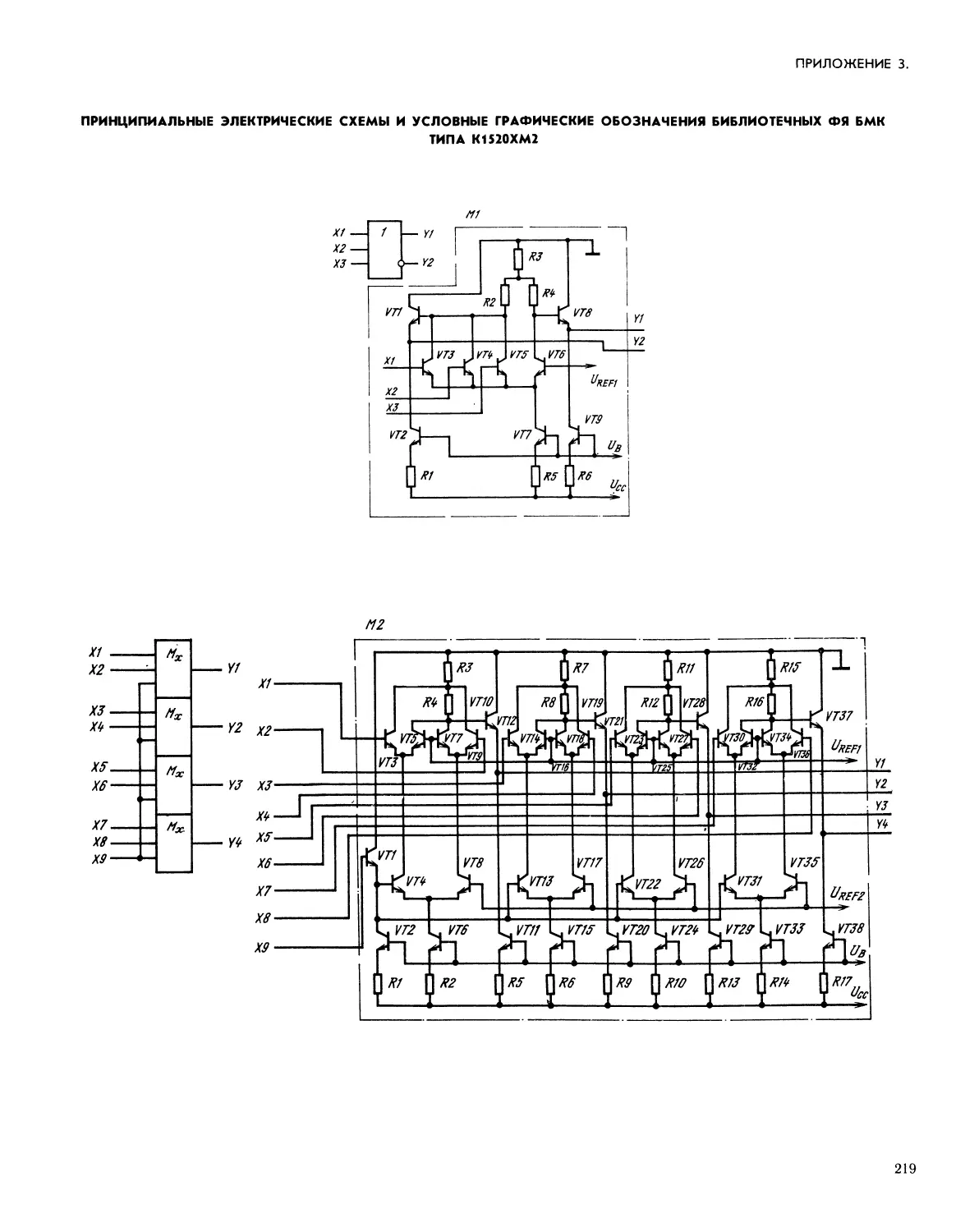

Приложение 3. Принципиальные электрические схемы

и условные графические обозначения

библиотечных ФЯ БМК типа К1520ХМ2 219

Приложение 4. Принципиальные электрические схемы

и условные графические обозначения

библиотечных ФЯ БМК типа К1572ХМ1 224

Приложение 5. Принципиальные электрические схемы

и условные графические обозначения

библиотечных ФЯ БМК типа К1527ХМ1 234

Приложение 6. Принципиальные электрические схемы

и условные графические обозначения

библиотечных ФЯ БМК типа К1548ХМ1 235

Приложение 7. Условные графические обозначения

библиотечных ФЯ БМК типа К1801ВП1 236

Приложение 8. Принципиальные электрические схемы

и условные графические обозначения

/ библиотечных ФЯ БМК типа К1515ХМ1 237

Приложение 9. Условные графические обозначения

библиотечных ФЯ БМК типа К6501ХМ1 238

Список литературы .............................. 239

1*

3

Предисловие

Стремительный переход к широкому использованию ми-

кропроцессорной техники в радиоэлектронной аппаратуре

(РЭА) повлиял на развитие цифровых интегральных ми-

кросхем средней (СИС) и большой (БИС) степени интегра-

ции. Цифровые микросхемы используют для обрамления или

интерфейса с микропроцессорами или запоминающими устрой-

ствами (ЗУ) и выполняют в виде универсальных микросхем

или полузаказных БИС на основе базовых матричных кристал-

лов (БМК) и программируемых логических интегральных

схем (ПЛИС).

В данном справочнике приведены расширенные сведения

по цифровым микросхемам по сравнению с изложенными в

справочнике «Цифровые и аналоговые интегральные микро-

схемы» под ред С. В. Якубовского («Радио и связь», 1990 г.),

которые являются естественным дополнением к специализи-

рованным справочникам «Микропроцессоры и микропроцессор-

ные комплекты интегральных микросхем» («Радио и связь»,

1988 г.), «Большие интегральные схемы запоминающих уст-

ройств» («Радио и связь», 1990 г.)/ «Микросхемы ЦАП и

АЦП» («Энергоатомиздат», 1990 г.).

Справочник содержит три раздела. В первом рассматри-

ваются универсальные цифровые микросхемы, разработанные,

по заказам для создания функционально полных серий ми-*

кросхем с целью ускоренного изготовления РЭА на их основе,

а также общие сведения по условным обозначениям, пара-

метрам и конструктивному оформлению. Приводятся функцио-

нальные аналоги различных серий микросхем для основных

базовых технологий: ТТЛ и ТТЛШ ИС-133; К155, КМ155,

533, К555, КМ555, 530, К530, К531, КР531, 1531, КР1531,

1533, КР1533; КМОП ИС-561, К561, 564, 564В, К564, Н564,

КР1-561, 1564; ЭСЛ ИС-100, КЮО, 500, К500, 1500, К1500. Для

наиболее функционально полных серий (К555, К564, К1500)

приводятся условное графическое обозначение микросхемы,

структурная или функциональная схема, таблицы назначений

выводов и истинности. Аналогичные сведения приведены и для

арсенид-галлиевых ИС К6500. Изложены особенности построе-

ния микросхем по базовым технологиям ТТЛШ, КМОП, ЭСЛ,

ПТШ на основе арсенида галлия.

Во втором' разделе описываются цифровые БМК, выпол-

ненное по различным технологиям: ЭСЛ, ТТЛШ, п-МОП,

КМОП, арсенид-галлиевые ПТШ. Приводятся описание рас-

положения базовых4 элементов на кристалле и их электри-

ческие схемы. Составы библиотек функциональных ячеек с

электрическими схемами для каждого кристалла приведены

в приложениях (К1520ХМ1, К1520ХМ2, К1521ХМ1, К1573ХМ1,

К1527ХМ1, К1548ХМ1, К1801ВП1, К1515ХМ1, К6501ХМ1).

Следует отметить, что создание в короткие сроки совре-

менной номенклатуры специализированных схем высокой сте-

пени интеграции с использованием автоматизированных ме-

тодов проектирования (САПР) обеспечивается применением

БМК.

Разрабатываемые матричные большие интегральные схемы

(БИСМ) на основе БМК позволяют заменить десятки ми-

кросхем малой и средней степени интеграции. Это обеспе-

чивает разработчику РЭА уменьшение массогабаритных харак-

теристик аппаратуры в 4...6 раз, экономию затрат на комплек-

тующие изделия и материалы, в 5...8 раз снижение трудоем-

кости сборки и регулировки аппаратуры, снижение энерго-

емкости производства и эксплуатации РЭА, в 2...3 раза уве-

личение, надежности РЭА.

Однако до настоящего времени практически отсутство-

вала литература по вопросу конкретного применения БМК

отечественного производства. Предлагаемый справочник вос-

полняет этот пробел и является логическим дополнением к

книгам «Автоматизированное проектирование СБИС на базо-

вых кристаллах» («Радио и связь», 1988 г.) и «Быстродейст-

вующие матричные БИС и СБИС. Теория и проектирование»

(«Радио и связь», 1989 г.), освещающим прежде всего

теоретические основы проектирования БМК и БИСМ.

Третий раздел посвящен ПЛИС. Следует отметить, что

одним из возможных способов сокращения сроков разра-

ботки РЭА является применение пользователем ПЛИС на

этапе проектирования и отладки устройств и узлов аппаратуры.

Их использование в РЭА позволяет резко сократить сроки

ее разработки и промышленного освоения, поднять на новый

уровень технические характеристики микропроцессорных уст-

ройств и систем для всех областей народного хозяйства,

таких как гибкие системы управления различными техно-

логическими процессами, персональные ЭВМ, связь, бытовая

аппаратура.

Зависимости основных электрических параметров схем от

режимов и условий их эксплуатации приводятся в технических

условиях (ТУ) и руководстве по применению микросхем.

Описание принципов работы схем, их функциональные и

условно-графические обозначения, а также таблицы истинности

и назначения выводов представлены на примере наиболее

распространенной серии К555.

В справочнике рассматривается специфика программируе-

мых микросхем, связанная с необходимостью их функцио-

нальной настройки потребителем перед , непосредственным

включением в аппаратуру. В ней систематизированы сведения

о методиках проектирования устройств на основе ПЛИС,

освещены вопросы автоматизации различных работ по их

применению и описаны наиболее типичные программируемые

микросхемы. Это отечественные ПЛИС типа программируемые

логические матрицы (ПЛМ) и программируемая матричная

логика (ПМЛ). К первой группе относятся К556РТ1,

КМ556РТ2, К556РТЗ с программируемыми матрицами И и

ИЛИ; ко второй — КМ 1556ХП4, КМ1556ХП6, КМ1556ХП8,

КМ1556ХЛ8 с программируемой матрицей И.

Для обеспечения проектирования дискретных устройств

в базисе ПЛИС экономически целесообразно использовать

персональные ЭВМ, позволяющие реализовать сквозную САПР

и оптимизировать устройства авггоматики и РЭА.

РАЗДЕЛ I.

ЦИФРОВЫЕ МИКРОСХЕМЫ

Глава 1.

Общие сведения о цифровых микросхемах средней степени интеграции

1.1. Классификация

Большое разнообразие современных цифровых логических

схем можно разделить: в зависимости от схемотехники ло-

гического элемента (ЛЭ) — типа логики — на схемы тран-

зисторно-транзисторной логики (ТТЛ), транзисторно-транзи-

сторной логики с диодами Шотки (ТТЛШ), эмиттерно-свя-

занной логики (ЭСЛ), с комплементарными МОП-транзисто-

рами (КМОП); по принципу построения активного элемента —

на биполярные и полевые; способу передачи информации —

на синхронные и асинхронное; типу информационных сигна-

лов — на потенциальные, импульсные, импульсно-потенциаль-

ные. В последние годы получило развитие новое направ-

ление — схемы на основе арсенида галлия.

Для удобства разработчиков аппаратуры по технологи-

ческим, схемотехническим и конструктивным признакам цифро-

вые интегральные микросхемы (ИС) выпускаются сериями.

Серия — это совокупность ИС различного функционального

назначения, имеющих общие электрические и эксплуатацион-

ные характеристики, выполненных по единой технологии и

объединенных одним конструктивным решением (видом кор-

пуса) .

Функционально полная серия обычно содержит в своем

составе несколько десятков типов ИС, выполняющих раз-

личные логические и арифметические операции и представ-

ляющих собой как простые логические элементы И, ИЛИ —

НЕ, И — НЕ, И — ИЛИ — НЕ, так и целые узлы и блоки

аппаратуры (регистры, счетчики, сумматоры, дешифраторы,

арифметическо-логические устройства (АЛУ), схемы сравнения

и др.).

Степень интеграции цифровых схем — число элементов на

кристалле, в зависимости от которого микросхемы делятся на

простые интегральные схемы, средней степени интеграции

(СИС), большие ИС (БИС) и- сверхбольшие ИС (СБИС).

Число

элементов

на кристалле

ИС До 100

СИС 101...1000

БИС 1001...10 000

СБИС Более 10 000

По функциональному назначению цифровые микросхемы

разделяются на подгруппы (ЛЭ, триггеры, сумматоры и т. д.)

и виды внутри подгрупп (триггеры: счетные, универсальные,

Шмитта и т. д.). Условные обозначения подгрупп и видов

цифровых микросхем приведены ниже.

Формирователи

АА Адресных токов (формирователи напряжения или

токов)

АГ Импульсов прямоугольной формы

АП Прочие

АР Разрядных токов (формирователи напряжения или

токов)

АФ Импульсов специальной формы

Схемы вычислительных средств

ВА Схемы сопряжения с магистралью

ВГ Контроллеры

ВЖ Специализированные схемы

Генераторы

ГГ Прямоугольных импульсов

ГФ Сигналов специальной формы

Схемы цифровых устройств

ИА АЛУ

ИВ , Шифраторы

ИД Дешифраторы

ИЕ Счетчики

ИК ' Комбинированные схемы

ИЛ Полусумматоры

ИМ Сумматоры

ИП Прочие

ИР Регистры

Коммутаторы и ключи

КН Напряжения

КП Прочие

КТ Тока

Логические элементы

ЛА Н—НЕ

ЛБ И—НЕ — ИЛИ—НЕ

ЛД Расширители

ЛЕ ИЛИ—НЕ

ЛИ И

ЛК И—ИЛИ—НЕ — И—ИЛИ

ЛЛ ИЛИ

ЛМ ИЛИ—НЕ — ИЛИ

ЛН НЕ

ЛП Прочие

ЛР И—ИЛИ—НЕ

ЛС И—ИЛИ

Преобразователи сигналов

ПП Прочие

ПР Код-код

ПУ Уровня (согласователи)

ПЦ Делители частоты цифровые

Схемы запоминающих устройств

РЕ Постоянные запоминающие устройства (ПЗУ, масоч-

ные)

РМ Матрицы оперативных запоминающих устройств

(ОЗУ)

РП Прочие

РР ПЗУ с возможностью многократного программирова-

ния

РТ ПЗУ с возможностью однократного программиро-

вания

РУ ОЗУ

РФ ПЗУ с ультрафиолетовым стиранием и электрической

записью информации

5

Схемы сравнения

СК Амплитудные (уровня сигналов)

СВ По времени

СП Прочие

Триггеры

ТВ Универсальные (/-А)

ТД Динамические

ТК Комбинированные (D-T, R-S-T и др.)

ТЛ Шмитта

ТМ С задержкой (/))

ТП Прочие

TP С раздельным запуском 1A-S)

ТТ Счетные (Г)

Многофункциональные схемы

ХК Комбинированные

ХЛ Цифровые

ХП Прочие

Отечественной промышленностью выпускается достаточно

большое число серий цифровых микросхем, предназначенных

для построения ЭВМ, контрольно-измерительной, связной ап-

паратуры и других видов радиоэлектронных устройств [3—5].

Общие сведения о микросхеме указаны в ее условном

обозначении. Для характеристики материала и типа корпуса

перед цифровым обозначением серии добавляются буквы: Б — х

бескорпусные; И, С — стеклокерамический корпус; М — метал-

локерамический корпус; Н — микрокорпус; Р — пластмассовый

корпус. Для микросхем широкого применения в начале обо-

значения серии добавляется буква К.

Итак, ИС КР1533ЛА8 означает, что микросхема пред-

назначена для широкого использования (К), выполнена в

пластмассовом корпусе (Р), имеет номер серии 1533, от-

носится к логической подгруппе (Л), по функциональному

назначению является элементом И — НЕ (А) и имеет порядко-

вый номер разработки микросхемы в данной серии 8.

Развитие цифровых микросхем идет по следующим на-

правлениям:

микромощные на основе КМОП-структур (561, К561, 564,

К564, 564В, Н564, КР1554, КР1561, К1564);

среднего быстродействия ТТЛ-логики (133, КМ133, К155,

КМ155);

маломощные на основе ТТЛ-, ТТЛШ-логики (134, КР134,

533, КМ533, К555, КМ555, КР1533);

быстродействующие на основе ТТЛ-, ТТЛШ-логики (К130,

К131, КМ131, Н530, 530, М530, КР531, КР1531);

высокого быстродействия на основе ЭСЛ-логики (100,

КЮО, 500, К500, 1500, К1500);

сверхвысокого быстродействия на основе арсенида гал-

лия (К6500).

В зависимости от требований, предъявляемых к аппарату-

ре, можно использовать различные серии микросхем. В радио-

электронной аппаратуре с повышенными требованиями по

быстродействию находят применение ИС 100, К500, К1500, с

жесткими требованиями по потребляемой мощности при от-

носительно невысоком быстродействии — ИС К561, К564,

а быстродействующую аппаратуру с малой потребляемой

мощностью позволяют создавать ИС 533, КМ533, К555.

КР1533, КР1531.

1.2. Основные характеристики и параметры ЛЭ

Важнейшей характеристикой ЛЭ является передаточная

характеристика: зависимость выходного напряжения от вход-

ного U0=f . Вид характеристики зависит от типа ЛЭ

(ЭСЛ, ТТЛ, К.МОП) и может изменяться при воздействии

дестабилизирующих факторов (температуры, напряжения пи-

тания, числа нагрузок и др.).

С целью нормального функционирования цифровых уст-

ройств логические схемы потенциального типа должны иметь

три точки пересечения с обращенной передаточной характе-

ристикой (рис. 1.1). Разность между пороговыми значениями

Рис. 1.1. Передаточная характеристика ЛЭ

верхнего и нижнего выходных уровней Сонт—U0LT=\U

является логическим перепадом схемы. Выходные пороговые

напряжения находят с помощью пороговых точек а и Ь, в

которых дифференциальный коэффициент усиления по напря-

жению Ku=—i-

Логические схемы в устройствах соединяются последо-

вательно, поэтому их входные напряжения определяются вы-

ходными напряжениями предыдущих схем.

Помехоустойчивость микросхемы по верхнему CNIH и

нижнему UNJL уровням входного сигнала (рис. 1.1) опреде-

ляется выражениями

Unih =Uoht — Uiht', 00

Unil=>Uilt — Uolt , (1.2)

где Uонт и U0LT — выходные пороговые напряжения высо-

кого и низкого уровней; U1HT и UILT — входные пороговые

напряжения высокого и нижнего уровней.

Идеальная передаточная характеристика, для которой по-

мехоустойчивость максимальна, должна соответствовать усло-

виям ^о£7’==6; U/2,\ тогда

UNih=Unil=W/2. (1.3)

Выражение (1.3) определяет предельные» значения по-

мехоустойчивости для ЛЭ потенциального типа.

Для повышения статической помехоустойчивости ЛЭ ис-

ходя из передаточной характеристики необходимо увеличи-

вать логический перепад и значения входных пороговых

напряжений. Однако увеличение логического перепада свя-

зано с ростом напряжения питания схемы Ucc и увеличением

потребляемой мощности Р, так как для большинства логи-

ческих схем P~U2CC. В свою очередь, увеличение пороговых

напряжений приводит к увеличению средней задержки ми-

кросхемы [1].

Для создания помехоустойчивого ЛЭ необходимо иметь

передаточную характеристику, близкую к симметричной отно-

сительно середины области переключения (заштрихованная

область ла рис. 1.1) для сближения значений помехоустой-

чивости по верхнему и нижнему уровням входного сигнала,

а также уменьшить зависимости пороговых напряжений от

режима работы схемы.

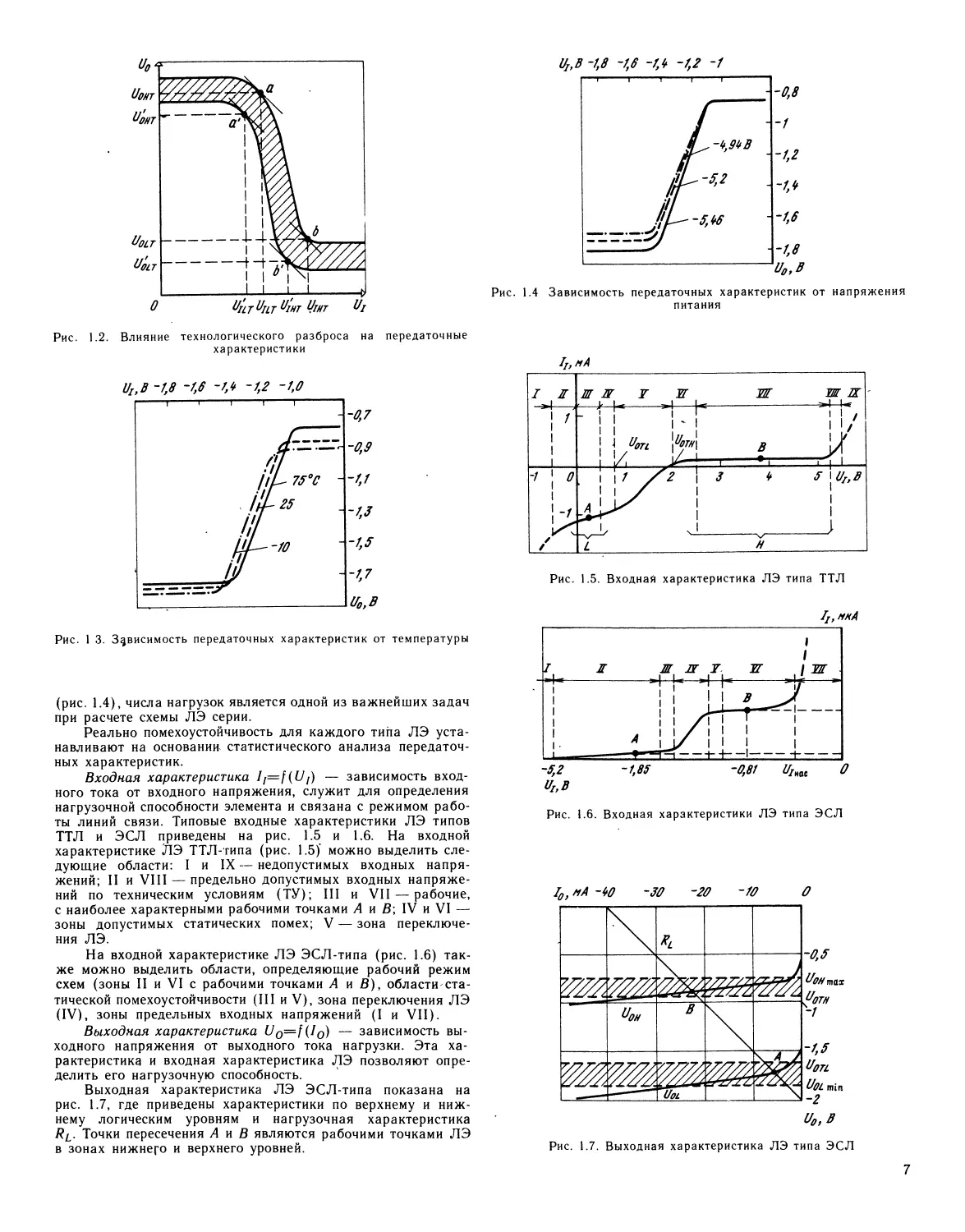

На помехоустойчивость ЛЭ в значительной степени влияет

технологический разброс пороговых напряжений (рис. 1.2), по-

этому выбор пороговых напряжений ЛЭ с учетом их уходов

(изменений) от температуры (рис. 1.3), напряжения питания

6

Рис. 1.2. Влияние технологического разброса на передаточные

UJfB -1,8 -1,6 -1,Ь -1,2 -/

питания

характеристики

Рис. 1 3. Зависимость передаточных характеристик от температуры

Рис. 1.4 Зависимость передаточных характеристик от напряжения

(рис. 1.4), числа нагрузок является одной из важнейших задач

при расчете схемы ЛЭ серии.

Реально помехоустойчивость для каждого типа ЛЭ уста-

навливают на основании статистического анализа передаточ-

ных характеристик.

Входная характеристика /z=f(t/z) — зависимость вход-

ного тока от входного напряжения, служит для определения

нагрузочной способности элемента и связана с режимом рабо-

ты линий связи. Типовые входные характеристики ЛЭ типов

ТТЛ и ЭСЛ приведены на рис. 1.5 и 1.6. На входной

характеристике ЛЭ ТТЛ-типа (рис. 1.5)' можно выделить сле-

дующие области: I и IX—недопустимых входных напря-

жений; II и VIII — предельно допустимых входных напряже-

ний по техническим условиям (ТУ); III и VII — рабочие,

с наиболее характерными рабочими точками А и В; IV и VI —

зоны допустимых статических помех; V — зона переключе-

ния ЛЭ.

На входной характеристике ЛЭ ЭСЛ-типа (рис. 1.6) так-

же можно выделить области, определяющие рабочий режим

схем (зоны II и VI с рабочими точками А и В), области ста-

тической помехоустойчивости (III и V), зона переключения ЛЭ

(IV), зоны предельных входных напряжений (I и VII).

Выходная характеристика Uo—fUo) — зависимость вы-

ходного напряжения от выходного тока нагрузки. Эта ха-

рактеристика и входная характеристика ЛЭ позволяют опре-

делить его нагрузочную способность.

Выходная характеристика ЛЭ ЭСЛ-типа показана на

рис. 1.7, где приведены характеристики по верхнему и ниж-

нему логическим уровням и нагрузочная характеристика

Rl. Точки пересечения А и В являются рабочими точками ЛЭ

в зонах нижнего и верхнего уровней.

Рис. 1.6. Входная характеристики ЛЭ типа ЭСЛ

Рис. 1.7. Выходная характеристика ЛЭ типа ЭСЛ

7

Входные и выходные характеристики ЛЭ ТТЛ-типа могут

быть использованы для оценки уровня помех, возникающих

в линиях связи во время переключения ЛЭ [3, 6].

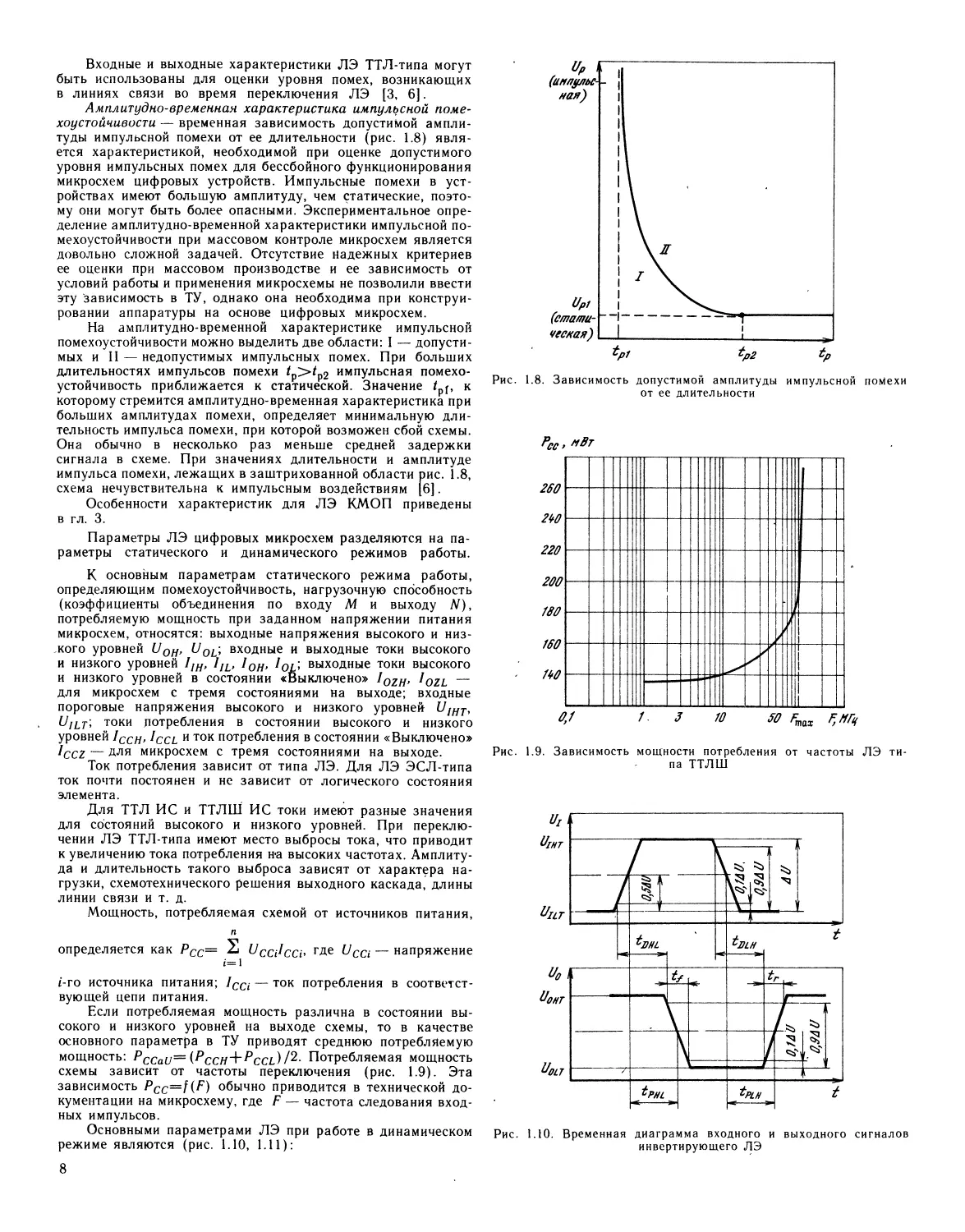

Амплитудно-временная характеристика импульсной поме-

хоустойчивости — временная зависимость допустимой ампли-

туды импульсной помехи от ее длительности (рис. 1.8) явля-

ется характеристикой, необходимой при оценке допустимого

уровня импульсных помех для бессбойного функционирования

микросхем цифровых устройств. Импульсные помехи в уст-

ройствах имеют большую амплитуду, чем статические, поэто-

му они могут быть более опасными. Экспериментальное опре-

деление амплитудно-временной характеристики импульсной по-

мехоустойчивости при массовом контроле микросхем является

довольно сложной задачей. Отсутствие Надежных критериев

ее оценки при массовом производстве и ее зависимость от

условий работы и применения микросхемы не позволили ввести

эту зависимость в ТУ, однако она необходима при конструи-

ровании аппаратуры на основе цифровых микросхем.

На амплитудно-временной характеристике импульсной

помехоустойчивости можно выделить две области: I — допусти-

мых и II — недопустимых импульсных помех. При больших

длительностях импульсов помехи /р>^р2 импульсная помехо-

устойчивость приближается к статической. Значение /рр к

которому стремится амплитудно-временная характеристика при

больших амплитудах помехи, определяет минимальную дли-

тельность импульса помехи, при которой возможен сбой схемы.

Она обычно в несколько раз меньше средней задержки

сигнала в схеме. При значениях длительности и амплитуде

импульса помехи, лежащих в заштрихованной области рис. 1.8,

схема нечувствительна к импульсным воздействиям [6].

Особенности характеристик для ЛЭ КМОП приведены

в гл. 3.

Параметры ЛЭ цифровых микросхем разделяются на па-

раметры статического и динамического режимов работы.

К основным параметрам статического режима работы,

определяющим помехоустойчивость, нагрузочную способность

(коэффициенты объединения по входу М и выходу А),

потребляемую мощность при заданном напряжении питания

микросхем, относятся: выходные напряжения высокого и низ-

кого уровней Uон> UOL* входные и выходные токи высокого

и низкого уровней IIH, IIL, 10Н, 10, ; выходные токи высокого

и низкого уровней в состоянии «Выключено» Iozh> ^ozl —

для микросхем с тремя состояниями на выходе; входные

пороговые напряжения высокого и низкого уровней U1НТ,

UjLT'y токи потребления в состоянии высокого и низкого

уровней ICCHt ICCL и ток потребления в состоянии «Выключено»

Iccz — Для микросхем с тремя состояниями на выходе.

Ток потребления зависит от типа ЛЭ. Для ЛЭ ЭСЛ-типа

ток почти постоянен и не зависит от логического состояния

элемента.

Для ТТЛ ИС и ТТЛШ ИС токи имеют разные значения

для состояний высокого и низкого уровней. При переклю-

чении ЛЭ ТТЛ-типа имеют место выбросы тока, что приводит

к увеличению тока потребления н*а высоких частотах. Амплиту-

да и длительность такого выброса зависят от характера на-

грузки, схемотехнического решения выходного каскада, длины

линии связи и т. д.

Мощность, потребляемая схемой от источников питания,

п

определяется как Рсс— 2 UccJccb где Уса — напряжение

Z-го источника питания; ICCi — ток потребления в соответст-

вующей цепи питания.

Если потребляемая мощность различна в состоянии вы-

сокого и низкого уровней на выходе схемы, то в качестве

основного параметра в ТУ приводят среднюю потребляемую

мощность: PccaU— (^cch~^^ccl)Потребляемая мощность

схемы зависит от частоты переключения (рис. 1.9). Эта

зависимость Pcc=f(F) обычно приводится в технической до-

кументации на микросхему, где F — частота следования вход-

ных импульсов.

Основными параметрами ЛЭ при работе в динамическом

режиме являются (рис. 1.10, 1.11):

8

Рис. 1.8. Зависимость допустимой амплитуды импульсной помехи

от ее длительности

Рис. 1.9. Зависимость мощности потребления от частоты ЛЭ ти-

па ТТЛШ

Рис. 1.10. Временная диаграмма входного и выходного сигналов

инвертирующего ЛЭ

Рис. 1.11 Временная диаграмма входного и выходных сигналов

для ЛЭ с тремя состояниями на выходе

время задержки распространения сигнала при включении

и выключении tPLfj, tPnL> представляющее собой интервал

времени между входным и выходным импульсом при пере-

ходе напряжения на выходе схемы от напряжения низкого

уровня к напряжению высокого уровня и наоборот, изме-

ренное на уровне 0,5 от амплитуды сигнала или при заданном

напряжении;

среднее время задержки распространения сигнала

tpav= (tpHL + tpUi) /2;

время спада tf и нарастания tr выходного импульса —

интервал времени, в течение которого выходное напряжение

изменяется от уровня 0,9 до 0,1 и соответственно нарастает

от уровня 0,1 до 0,9 от установившегося значения (ампли-

туды сигнала);

время задержки включения tDHL и выключения tDLH —

интервал времени между входным и выходным импульсами,

измеренные на уровне 0,1 входного и 0,9 выходного сигналов

и соответственно 0,9 входного и 0,1 выходного сигналов или

на заданных значениях напряжения;

время задержки распространения при переходе из состоя-

ния «Выключено» в состояние низкого уровня tPZL и обратно

tpLz> а также из состояния «Выключено» в состояние высо-

кого уровня tPZfj и обратно tPHZ — для схем с тремя со-

стояниями на выходе (рис. 1.10);

максимальная рабочая частота схемы Fmax — частота, при

которой сохраняется работоспособность схемы.

Быстродействие ЛЭ микросхемы определяется его схемо-

техникой, технологией и зависит от емкости нагрузки, темпе-

ратуры окружающей среды, напряжения источника питания.

1.3. Сравнение обобщенных параметров

цифровых микросхем

Основными параметрами, позволяющими производить

сравнение базовых ЛЭ различных серий, являются время

задержки распространения сигнала /р, потребляемая ЛЭ мощ-

ность Рсс и работа переключения — произведение потребляе-

мой мощности на время задержки A = Pcctp (рис. 1.12).

Работа переключения обычно выражается в пикоджоулях,

если мощность потребления — в милливаттах, а задержка

распространения сигнала — в наносекундах. При сравнении

базовых ЛЭ чаще, всего используют типовые значения па-

раметров. По величине работы переключения и числу ЛЭ

на кристалле можно судить об уровне развития технологии и

схемотехники цифровых микросхем.

Сравнение различных серий, выпускаемых отечественной

промышленностью (табл. 1.1), показывает, что наименьшая

работа переключения для биполярной технологии достигнута

на ИС КР1533, а для КМОП-технологии — на КР1554. Еще

более впечатляющие результаты получены с использованием

арсенида галлия — ИС К6500.

Использование диодов Шотки и усовершенствованного

технологического процесса, в том числе применение изопланар-

ной технологии, позволило уменьшить потребляемую мощ-

ность и времена задержек и создать маломощные (533, К555,

КР1533) и быстродействующие (530, КР531, КР1531)

ТТЛШ* ИС.

Дальнейшее усовершенствование КМОП-технологии, со-

здание транзисторов с длиной канала 1,2 мкм позволило

разработать новую микромощную серию ИС КР1554 с быстро-

действием до 125 МГц, аналогичным для быстродействую-

щих биполярных ТТЛШ ИС. Однако малая потребляемая

мощность таких схем характерна на частотах до 10...30 МГц.

С увеличением рабочей частоты переключения КМОП ИС

растет динамическая потребляемая мощность. На частотах

Рис. 1.12. Зависимость времени задержки распространения сигна-

ла от мощности потребления для различных технологий

Рис. 1.13. Зависимость динамической потребляемой мощности от

частоты для ТТЛШ и КМОП ИС

9

Таблица 1.1.

Сравнение различных серий микросхем, выпускаемых отечественной промышленностью

Технология Схемотехни- ческое исполнение ИС Электрические параметры Зарубежный функциональ- ный аналог, фирма

СС’ мВт/ЛЭ /р, тип нс/ЛЭ (Сн=15 пФ) Работа переключения (Рсс/р), пДж Частота пере- ключения триг- геров, МГц

ТТЛ (Si) К155, КМ155, К133, КМ 133 10 10 100 До 35 SN74, Texas Instruments

Биполярная ттлш (Si) 530, КР531, КМ531 КР1531 533, К555, КМ555 1533; КР1533 19 4 2 1 3 2 9,5 4 57 8 19 4 До 125 До 130 До 45 До 100 SN54S/74S, Texas Instruments 74F (FAST), Fairchild SN54LS/74LS Texas Instruments SN54ALS/74ALS Texas Instruments

ЭСЛ (Si) 100, К500 К1500 25 40 2 0,75 50 30 До 125 До 300 MC 10000, Motorola F100K, Motorola

Униполярная КМОП (Si) 564, К561 1564 КР1554 0,0025 на 1 МГц 0,0025 на 1 МГц 0,0025 на 1 МГц 45 10 3,5 0,1 0,025 0,008 До 10 До 30 До 125 СД4000А, RCA 54HC, National Semiconductor 74AC (FACT), Fairchild

НОПТШ (GaAs) К6500 3...6 0,1 L 0,3...0,6 1000 10G000, Gigabit Logic

свыше 10 МГц мощность потребления возрастает и становится

соизмеримой с мощностью потребления ТТЛШ ИС (рис. 1.13).

Наибольшее быстродействие в биполярных схемах на

кремнии достигнуто на ЛЭ ЭСЛ-типа, однако работа пере-

ключения таких микросхем довольно велика иЗ-за большой

мощности потребления. Минимальное время задержки, полу-

ченное в ЭСЛ ИС (К1500), составляет 0,7 нс/ЛЭ при мощ-

ности потребления 40 мВт (рис. 1.12).

Сверхвысокое быстродействие при малой мощности по-

требления удалось достичь в микросхемах на арсениде гал-

лия. Работа переключения ЛЭ таких схем составляет деся-

тые доли пикоджоуля при быстродействии 100... 150 пс.

Снижение работы переключения цифровых микросхем раз-

личных схемотехнических решений за последнее десятилетие

составило несколько порядков. Дальнейшее ее уменьшение

связано с технологическими ограничениями (минимальными

размерами элементов, глубинами залегания переходов и т. д.).

Минимальные топологические размеры, реализованные в

микросхемах, близки к предельно достижимым значениям,

поэтому дальнейший прогресс в микроэлектронике возможен в

результате использования новых полупроводниковых материа-

лов со значительно большей подвижностью носителей заряда.

Такими перспективными материалами являются арсенид гал-

лия GaAs, фосфид индия InP и др. Реально ограничения

работы переключения обусловлены физическими процессами

в транзисторах и основными свойствам^ полупроводникового

материала [7].

1.4. Типовые корпуса микросхем

Условия применения микросхем,иих функциональные и

энергетические характеристики, а также размеры кристаллов,

методы их монтажа и защиты от внешних воздействующих

факторов и используемые при этом материалы способство-

вали развитию широкой номенклатуры корпусов микросхем.

Существует 4песть типов корпусов, конструктивные особен-

ности которых приведены в табл. 1.2, а внешний вид широко

применяемых корпусов изображен на рис. 1.14.

- Каждый тип в зависимости от конструктивных особен-

ностей подразделялся на несколько (от двух до пяти) подти-

пов, их отличие в размерах, количестве и расположении вы-

водов формирует целую гамму типоразмеров корпусов. Так,

корпуса второго типа (DIP) имеют более полусотни типо-

размеров. Основные характеристики корпусов различных типов

приведены в табл. 1.3.

Условное обозначение корпусов микросхем состоит из

шифра типоразмера, включающего подтип корпуса и двухзнач-

ного числа, обозначающего порядковый номер типоразмера,

а также цифрового индекса количества выводов или выводных

площадок и порядкового регистрационного номера корпуса:

21 20 2Ь 20

Порядковый регис/т/раииояяый кокер

Ноличее/т/до дл/додод

Порядковый кокер /т/илоразкера

Подл/ил

Шифр

л/илоразнера

корлрса

10

Ключ

Рис. 1.14. Типовые корпуса микросхем: а — планарный с двусторонним расположением выводов; б — типа DIP, в — планарный с четырех-

сторонним расположением выводов

Таблица 1.2.

Основные конструктивные особенности корпусов

Тип Под- тип Форма проекции тела корпуса на основание Располо- жение вы- водов отно- сительно плоскости основания Число рядов выводов Число типо- разме- ров корпу- сов

1 11 Прямо- угольная Перпен- дику- лярное В один ряд 8

12 В два ряда 17

13 В три и более рядов 2

14 По контуру прямо- угольника 5

15 В один или два ряда 5

2 21 В два ряда 44

22 В четыре ряда в шах- матном порядке 10

3 31 Круглая Овальная

Последовательное по окружности 9

32 То же 4

4 41 Прямо- угольная Парал- лельное По двум противопо- ложным сторонам 78

42 По четырем сторонам 25

43 По двум противопо- ложным сторонам 25

44 По четырем сторонам 2

45 То же 20

5 51 Перпен- дику- лярное » 36

52' По двум сторонам 2

61 Квадрат- ная В четыре и более ря- дов 15

62 В два и более рядов 28

Иногда в условных обозначениях корпусов отражаются

и другие особенности корпусов, например, размер монтажной

площадки, наличие или отсутствие металлизации на монтажной

площадке или плоскости основания корпуса, длина выводов,

завод-изготовитель, что также учитывается в условном обозна-

чении корпуса 4204.24-2 и 4204.24-2.01. Система условных обо-

значений корпусов, ранее выпускаемых промышленностью, от-

личалась от приведенной. Соответствие габаритно-присоеди-

нительных размеров микросхем в корпусах по старой и новой

системам условных обозначений* приведено ниже.

Старое условное обозначение Шифр типоразмера по ГОСТ 17467—88 Старое условное обозначение Шифр типоразмера по ГОСТ 17467—88

109.7 1101 2102.14 2102

111.12 1216 2103.16 2103

111.14 1215 2104.12 2103

115.9 1109 2104.18 2104

118.16 1222 2107.18 2107

124.18 1222 2108.22 2108

151.14 1203 2109.16 2109

151.15 1203 2115.14 2115

151.20 1402 2118.60 2118

153.14 1206 2120.24 2120

152.15 1206 2121:28 2121

157.29 1210 . 2121.29 2121

153.40 1304 2123.40 2123

155.15 1207 2124.42 2124

160.40 1212 2126.48 2126

1101.7 1101 2127.14 2127

1102.8 1106 1502.11 1502

1102.9 1102 1503.17 1503

1103.5 1103 201.8 2103

1105.3 1105 201.9 2102

1220.36 1220 201.12 2103

1221.18 1221 201.14 2102

1501.5 1501 201.16 2103

210Б.24 2120 201А.16 2106

212.32 2114 206.14 2127

218.30 2138 209.18 2129

238.12 2202 209.24 2130

238.16 2103 210А.22 2108

238.18 2104 210Б.16 2106

239.24 2120 302.4 3104

* Нумерация выводов микросхем в корпусах, выпущенных

до 01.01.89 г , не регламентируются.

11

Старое условное обозначение Шифр типоразмера по ГОСТ 17467—88 Старое условное обозначение Шифр типоразмера по ГОСТ 17467—88 Старое условное обозначение Шифр типоразмера по ГОСТ 17467—88 Старое условное обозначение Шифр типоразмера по ГОСТ 17467—88

302.8 3104 244.48 2205 402.16 4108 4117.22 4160

311.8 3203 2203.40 2203 Н02.8 5114 4118.24 4118

311.10 3204 2204.42 2204 Н02.14 5116 4119.28 4119

3101.8 3101 2205.48 2205 Н02.16 5116 Н04.16 5117

3103.12 3103 2206.42 2206 427.6 4115 Н06.24 5122

401.14 4105 2207.48 2207 427.8 4115 Н08.24 5124

402.16 4112 301.8 3101 427.18 4161 Н08.24 5123

405.24 4110 301.12 3103 461.5 4180 Н09.18 5120

405.28 4119 4122.40 4122 4101.6 4101 Н09.28 5126

411.34 4137 4131.24 4176 4103.8 4103 Н 13.40 5129

413.48 4181 4134.40 4167 4105.14 4105 Н14.12 5130

421.48 4142 4134.48 4134 4106.16 4106 Й15.42 5132

425.64 4146 4135.64 4135 4109.20 4109 Н16.48 5133

2130.24 2130 4137.34 4137 4112.16 4108 Н 18.64 5134

2137.64 2136 4138.42 4138 4112.16 4112 Н 18,64 5135

2138.18 2138 4151.42 4151 4114.24 4114 Н23.16 5118

2140.20 2140 4151.42 4180 4116.8 4116 Н21.24 5201

2142.24 2142 4153.20 4153 4117.22 4117 Н22.50 5202

Таблица 1.3.

Основные характеристики корпусов

Условное обозначение Габаритные размеры, мм (номинальное значение), Е—D—А Размеры монтажной площадки в корпусе, мм Расстояние между рядами выводов, мм Метод герметизации Наличие металлизации

на монтажной площадке на плос- кости основания

Стеклокерамические

1104.11-1 27,5X4,0X3,2 2,8X2,4 — Пайка стеклом

2102.14-2 19,5X6,7X4,0 3,5X2,5 7,5 то же —

2102.14-3 19,5X6,7X4,0 3,5X2,5 7,5 » +

201.14-8 19,5X6,5X5,0 3,2X2,5 7,5 »

201.14-9 19,5X6,5X5,0 3,5X2,5 7,5 » +

2103.16-3 19,5X6,7X4,0 3,5X2,5 7,5 » —

2103.16-4 19,5X6,7X4,0 3,5X2,5 7,5 ». +

201.16-6 19,5X6,5X5,0 3,5X2,5 7,5 » ' +

201.16-5 19,5X6,5X5,0 3,5X2,5 7,5 » —

2103.16-14 19,5X7,4X5,8 7,5X3,1 7,5 » +

2104.18-8 21,9X7,4X5,8 8,2X3,8 7,5 » +

2104.18-8.01 21,9X7,4X5,8 5,2X3,2 7,5 » + —

2107.18-5.01 21,9X9,2X5,5 6,0Х 4,0 10 »

2107.18-5.02 21,9X9,2X5,5 6,0X4,0 10 » + —

2140.20-6 25,5X7,4X5,8 5,5X3,5 7,5 » +

2140.20-10 24,6X7,4X5,0 9,0Х 3,7 7,5 » +

2142.24-4 30,5X7,4X5,0 9,0X3,7 7,5 » +

2120.24-12.01 30,6X14,9X6,3 7,5X6,5 15 » + —

2120.24-14 30,5Х 13,5X5,8 5,4X4,4 15 Пайка стеклом +

2120.24-21 30,5X14,9X6,0 7,5X6,5 15 то же +

2121.28-13 36,5X14,9X6,3 7,5X6,5 15 » + —

2121.28-14 36,5X13,5X5,8 5,4X4,4 15 » + —

2123.40-8 50,0X14,9X6,3 9,5X7,0 15 » +

2207.48-3 30,7Х 13,5X5,5 5,4X4,4 15 » +

4105.14-1 9,8X6,5X2,2 2,9X1,9 — »

4105.14-2 9,8X6,5X2,2 3,2X2,2 — » +

4105.14-9 9,8X6,5X2,3 3,2X2,2 — »

4105.14-10 9,8X6,5X2,3 3,2X2,2 — » +

406.16-2 9,8X6,5X2,2 2,9X1,9 — » —

4106.16-3 9,8X6,5X2,2 3,2X2,2 — » +

4108.16-1 9,8X6,5X2,3 3,2X2,2 — »

4108.16-2 9,8X6,5X2,3 3,2X2,2 — » ' + —

4106.16-4 9,8X9,8X2,5 4,1X4,1 — » + —

4112.16-19 9,8X9,8X2,5 4,7X4,7 — »

4112.16-19.01 9,8X9,8X2,5 4,7X4,7 — » +

4116.18-2 9,8X9,8X2,5 4,1X4,1 — »

4116.18-3 9,8X9,8X2,5 4,1X4,1 — »

4116.18-6 12 9,8X9,8X2,5 4,7X4,7 — » —

Продолжение табл. 1.3

Условное обозначение Габаритные размеры, мм (номинальное значение), E—D—А Размеры монтажной площадки в корпусе, мм Расстояние между рядами выводов, мм Метод герметизации Наличие металлизации

на монтажной площадке на плос- кости основания

4116.18-6.01 9,8X9,8X2,5 4,7X4,7 — » + —

4153.20-4 12,5X12,0X3,0 4,6X6,6 — » + —

4114.24-1 14,8X9,8X3,0 4,1X4,1 — » + —

4114.24-2 14,8X9,8X3,0 4,1X4,1 — » — —

4114.24-3 14,8X9,8X3,0 4,1X4,1 — » + —

4177.-24-1 18,3X18,3X4,1 10,6X10,6 — + —

4204.24-2 9,8X9,8X2,5 4,1X4,1 — » — —

4204.24-2.01 9,8X9,8X2,5 4,1X4,1 — » + —

4119.28-9 18,0Х 12X3 5,4X5,4 — Пайка стеклом 4- —

4178.28-1 18,3X18,3X4,1 10,6X10,6 — » —

Металлостеклянные

1203.15-1 19,5Х 14,5X5 14,0X6,2 10 Сварка — —

1203.15-2 19,5Х 14,5X4 14,0X6,2 10 — —

1203.15-3 19,5Х 14,5X3,2 14,0X6,2 10 » — —

153.15-2 22Х 19,5X5 15,7X16,8 17,5 » — —

155.15-2 29,5X19,5X5 16,8X23,2 25 » — —

157.29-1 39X29X5 34,0X20 22 » — —

302.4-7 9,5X6,6 3,6x3,6 5 » ’ + —

3101.8-1 9,4X4,6 3,0 5 » + —

3101.8-2.01 9,4X4,7 4,0X4 5,8 » + —

3101.8-2.02 9,4X4,7 4,0X4 5,8 » + —

311.8-1 39X25,0X7 8 12,5 » Основание металлическое

311.8-2 39X25,0X7,5 8 12,5 » То же

301.8-2 9,5X4,6X20 3 5 » + —

301.8-2-02 9,5X4,6X13,5 3 5 » + —

301.12-1 9,5X4,6X20,5 3 5 » + —

301.12-1.02 9,5X4,6X13,5 3 5 » + —

302.8-1 9,5X6,5X20 3 5 » + —

302.8-1.02 9,5Х6,5±13,5 3 5 » + —

401.14-5 10X6,7X1,9 4,9X2 — » + +

311.10-1 39X25X7,5 8 12 Сварка Основание металлическое

460.24-1 15X4,3 8 — Пайка То же

460.24-3 15X4,3 8 — »

460.24-4 15X4,3 8 — Заливка »

компаундом

413.48-1 15X4,3 8 — Пайка Основание металлическое

413.48-3 15X4,3 8 — » То же

413.48-4 15X4,3 8 — Заливка >:

компаундом

4134.40-1 28,8Х 15X3,8 26X10 — Сварка — —

421.48-34 36,0X24X3,9 34X47 — » — —

Металлокерамические

201.8-1 19,2X7,3X5 5X3 7,5 » + +

201.14-10 19,2X7,3X5' 5X3 7,5 » +

201.16-15 19X7,2X5 4,4X2,2 7,5 » —

201А.16-1 19X9,7X4,7 6X5 10 + —

201.16-8 19,2X7,3X5 5X3 7,5 » + —

201.16-13 19X7,2X5 4,4X2,2 ' 7,5 » 4- —

201.16-17 19,2X7,3X5 7X3,5 7,5 » + —

238.18-1 21,9X7,3X5 5,5X3,7 7,5 » 4- —

2104.18-1 21,9X7,3X5 7X3,5 7,5 » 4- —

1104.18-2 21,9X7,3X5 7X3,5 7,5 » 4- —

2140.20-4 24X7,2X4,6 5,6X3,8 7,5 » + —

210А.22-1 27,9X9,8X5 5X4 10 » 4- —

2108.22-1 27,6X9,7X4,7 7,5X7,5 10 + —

2108.22-9.01 27,9X9,8X4,9 8X6 10 4- —

2108.22-9.02 27,9X9,8X4,9 8X6 10 » —

2108.22-10 27,5X9,7X4,6 7,5X5,5 10 » 4- —

2108.22-12.01 27,5X9,7X4,6 7,5X5,5 10 » 4- —

2105.24-1 29,5Х 14,7X4,6 7,5X7,5 15 » 4- —

2106.24-3 29,5Х 14,7X4,6 7,5X1,5 15 » 4- —

2120.24-1 29,1X14,7X4,6 4,5X4,5 15 Сварка + —

2120.244.02 29,2X14,7X4,6 7,5X7,5 15 » 4- —

2120.24-19 29,5Х 14,7X4,8 7,5X7,5 15 Сварка + —

2120.24-19.01 29,5Х 14,7X4,8 7,5X7,5 15 » 4- —

2120.24-20 29,5X14,7X4,8 7,5X7,5 15 » — —

13

w w ND to Ю СЛСЛСЛСЛСЛСЛСЛСЛ

CO -q 00

X СП

coX

сл Си Си СП Си СП 00

о

го

5а

Ф

X

О

<т>

X ф

Окончание табл. 1.3

Условное обозначение Габаритные размеры, мм (номинальное значение), E—D—A Размеры монтажной площадки в корпусе, мм Расстояние между рядами выводов, мм Метод герметизации Наличие металлизации

на монтажной площадке на плос- кости основания

4119.28-6 18,25X12,7X3,26 6,8X6,8 » + 4-

4119.28-10 18,3X12,7X3,46 9,5X7 — » + —

4119.29-10.01 18,25X12,7X3 5X5 — » + 4-

4119.28-11 18,25X12,7X3 5X5 — » + +

4119.28-8 18,25X12,7X3,26 6,8X6,8 — Сварка — 4-

4120.32-1 18,3X12,7X3,46 9,5X7 — » — —

4122.40-1 20,4X16,2X3,2 12X6 — » + 4-

4122.40-1.01 25,75X 12,7X2,9 6X5 — » + 4-

4122.40-1.01 25,75X 12,7X2,9 5X4 — » + 4-

4122.40-2 25,75X12,7X2,93 6X5 — » — 4-

4122.40-2.01 25,75X 12,7X2,93 5X4 — » — —

4122.40-3.01 25,75X 12,7X3,25 6,8X6,8 — » 4- 4-

4122.40-3.02 25,75X 12,75X3,25 6,8X6,8 — » — 4-

429.42-1 26,62X 16,74X3,13 6,2X6,2 — » 4- —

429.42-3 26,62X16,74X3,13 6,2X6,2 — » — —

429.42-5 26,62X 16,74X3,17 7,2X7 — » 4- —

429.42-6 26,62X 16,74X3,17 7,2X7 — » — —

4138.42-1 26,52X 19,5X2,97 10,7X8,3 — » + —

4138.42-2 26,52X 19,5X2,97 10,7X8,3 — » — —

4138.42-3 26,62X16,74X3,13 6,2X6,2 — » .4- —

4138.42-4 26,62Х 16,74X3,13 6,2X6,2 — » — —

4138.42-5 26,5X19,5X3,1 11X10 — » + —

4138.42-10.01 26,5Х 19,5X3,1 нхю — » — —

4123.48-1.01 30, IX 12,6X3,2 7X5,5 — » + —

4134.48-2 30,1X16,2X3,2 7,5X7 — » + —

4134.48-4 30,1X16,2X3,2 8X8 — » + —

4136.54-1 36,2X15,6X3,3 7X7 — » 4- 4-

4135.54-2 36,2Х 15,6X3,3 7X7 — » 4- —

4135.64-1 40,2X19,7X3,2 7,5X7,5 — » 4- —

4135.64-2 40,2Х 19,7X3,2 7,5X7,5 — » — —

4209.68-1- 28,0X28,0X3,15 8,2X8,2 — » 4- —

Глава 2.

Микросхемы на основе ТТЛШ

2.1. Маломощные ТТЛШ ИС

Микросхемы 533, КМ533, К555, КМ555, 1533, КР1533

представляют собой цифровые маломощные схемы, выпол-

ненные по биполярной технологии на основе транзисторно-

транзисторной логики с диодами Шотки (ТТЛШ). В состав

этих серий входит функционально полный набор устройств

цифровой обработки информации, включая ЛЭ, арифмети-

ческие и логические устройства, триггеры, счетчики, регистры

хранения и сдвига, шифраторы, дешифраторы, мультиплек-

соры, магистральные элементы и др. (табл. 2.1 и 2.2).

Микросхемы полностью совместимы с ИС К133, К155, КМ 155 по

логическим уровням, напряжению питания, помехоустойчи-

вости и при одинаковом быстродействии потребляют в 5 раз

меньшую мощность от источника питания на один базо-

вый ЛЭ.

Логические уровни напряжения составляют не более 0,4 В

при нагрузке 4 мА и 0,5 В при нагрузке 8 мА для низкого

уровня и не менее 2,4 В — для высокого уровня (для ряда

микросхем высокий уровень напряжения 2,5 В). Помехо-

устойчивость схем — не менее 0,3 В, нагрузочная способность

при нагрузке схем друг на друга — не менее 10.

Конструктивно-технологически ИС 533, КМ533, К555,

КМ555 выполнены по планарно-эпитаксиальной технологии с

изоляцией р-п переходами, имеют унифицированные корпуса

(табл. 2.3), число выводов которых составляет 14...28.

Микросхемы 533, КМ533, 1533 выполнены в плоских пла-

нарных корпусах, а К555, КР1533 и КМ555 — в пластмас-

совых и стеклокерамических корпусах соответственно, с двух-

рядным расположением выводов (типа DIP).

15

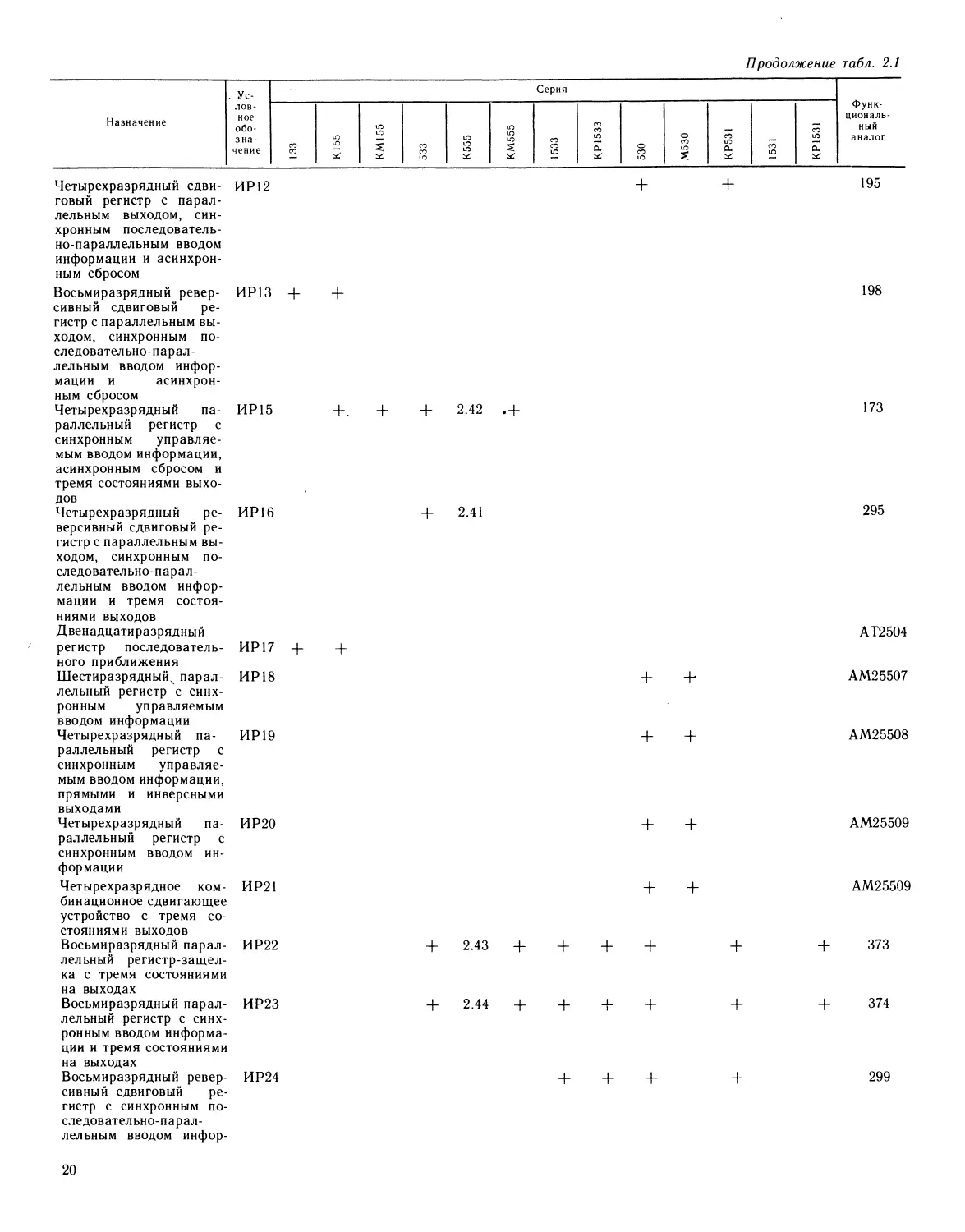

Таблица 2.1.

Функциональный состав ТТЛ ИС и ТТЛШ ИС

Назначение Ус- лов- ное обо- зна- чение Серия Функ- циональ- ный аналог

К155 КМ155 2 К555 КМ555 1533 КР1533 о со М530 КР531 1531 КР1531

Одновибратор АП + +

Два одновибратора с по- вторным запуском и сбро- АГЗ + + + + 2.79*

сом

Два одновибратора со сбросом АГ4 + 2.80

Формирователь разряд- АП1 +

ной записи, усилитель воспроизведения и схема установки нуля Двунаправленный неин- вертирующий формиро- ватель с открытым кол- лектором АП2

Два четырехканальных АПЗ + 2.75

инвертирующих форми-

рователя с тремя состоя- ниями на выходах * Два четырехканальных инвертирующих форми- рователя с тремя состоя- ниями на выходах АП4 + 2.76

Два четырехканальных неинвертирующих фор- мирователя с тремя со- АП5 + 2.77

стояниями на выходах

Восьмиканальный двуна- правленный формирова- АП6 + 2.78

тель с тремя состояниями на выходах Схема сопряжения с ма- гистралью ВА1

Схема контроллера ВГ1

Шестнадцатиразрядная схема контроля по коду ВЖ1 + 2.72

Хемминга Два управляемых напря- жением генератора ГГ1

Приоритетный шифратор 8->3 ИВ1 + + + 2.21

Приоритетный шифратор 8-^3 с тремя состояниями ИВ2 + 2.22

на выходах

Приоритетный шифратор ИВЗ + 2.23

10->4 Двоично-десятичный де- шифратор с высоковольт- ными выходами ИД1 + + +

Дешифратор-демультип- лексор на 16 выходов идз + + +

Сдвоенный дешифратор- ИД4 + + + + 2.24

мультиплексор 2->4 Сдвоенный дешифратор- ИД5 + 2.27

демультиплексор на че- тыре выхода с открытым

коллектором Двоично-десятичный де- ИД6 + 2.25

шифратор 4Х Ю Двоичный дешифратор ИД7 + 2.26

на восемь выходов

* Указан номер рисунка с данной микросхемой

121

+ + 123

+ 221

+ +

+ + + + + 240

+ + + + + 241

+ + 244

+ 245

+

+ 482

630

+ + 124

+ 148

348

147

141

+ + 154

+ +’ + 155

156

+ 42

+ + + + + + V38

16

Продолжение табл. 2.1

Назначение Ус- лов ное обо- зна- чение Серия Функ- циональ- ный аналог

СО £2 К155 КМ 155 со со ю К555 КМ555 1533 KPI533 530 М530 КР531 1531 КР1531

ИД8

Дешифратор на 18 выхо-

дов для управления не-

полной матрицей 7X5 на

дискретных светоизлу-

чающих диодах

Дешифратор на 13 выхо-

дов для управления не-

полной матрицей 7X4 то-

чек на светодиодах

ИД9

Двоично-десятичный де- идю + +

шифратор с открытым коллектором на выходах 1

Дешифратор на восемь выходов для управления шкалой с запоминанием иди + +

Дешифратор на восемь выходов для управления шкалой со сдвигом од- ной точки ИД12 + +

Дешифратор на восемь выходов для управления шкалой со сдвигом на ИД 13 + +

ИД14

2.28

145

две точки

Два дешифратора-де-

мультиплексора на четы-

ре' выхода

Дешифратор на семь вы-

ходов для управления ли-

нейной светоизлучающей

шкалой красного цвета

Дешифратор на семь вы-

ходов для управления ли-

нейной светоизлучающей

шкалой зеленого или

желтого цвета

Дешифратор состояний

Дешифратор двоично-де-

сятичного кода в семи-

сегментный с мощными

выходами

Дешифратор-демульти-

плексор на 16 выходов

с открытым коллектором

Дешифратор для управ-

ления светоизлучающей

шкалой, составленной из

набора полупроводнико-

вых шкальных знакосин-

тезирующих индикаторов

или светоизлучающих

диодов

ИД15

ИД16

ИД17 ИД18 + 2.30 + -I- -I-

ИД19 + 2.29

ИД20

Дешифратор для управ- ИД21 +

ления’ набором шкальных полупроводниковых зна- косинтезирующих инди- каторов Декадный счетчик с фа- зоимпульсным представ- лением информации Четырехразрядный дво- ИЕ1 ИЕ2 + + + + 2.50 +

ично-десятичный счетчик Четырехразрядный счет- чик-делитель на 12 Четырехразрядный дво- ИЕ4 ИЕ5 + + + + + + + 2.51 -|-

ичный счетчик

139

247

159

90

92

93

17

Продолжение табл. 2.1

Назначение Ус- лов- кое обо- зна- чение Серия Функ- циональ- ный аналог

со со К155 КМ 155 со со ш К555 КМ555 1533 КР1533 о ю М530 КР531 со ю КР1531

Четырехразрядный дво- ично-десятичный ревер- сивный счетчик ИЕ6 + \ + + + 2.52 + + 192

Четырехразрядный дво- ичный реверсивный счет- ИЕ7 + + + + 2.53 + + 193

чик

Шестиразрядный дели- тель частоты с перемен- ным коэффициентом де- ИЕ8 + + + 97

ления

Четырехразрядный дво- ично-десятичный счетчик ИЕ9 + + 2.54 + + + 160 А

с асинхронным сбросом Четырехразрядный дво- ИЕ10 + 2.55 + + + 161А

ичный счетчик с асин- хронным сбросом Четырехразрядный дво- ично-десятичный счетчик ИЕ11 + + + 162А

с синхронным сбросом Четырехразрядный синх- ИЕ13 + 2.56 191

ронный реверсивный дво- ичный счетчик Двоично-десятичный счетчик-делитель с про- ИЕ14 + + + 2.57 + + 196

граммированным коэф- фициентом деления Четырехразрядный дво- ичный счетчик с пред- ИЕ15 + 2.58 + + 197

варительной установкой Четырехразрядный синх- ИЕ16 + + 168

ронный реверсивный дво- ично-десятичный счетчик Четырехразрядный синх- ронный реверсивный двоичный счетчик ИЕ17 + 2.59 + + + 169 163 А

Четырехразрядный дво- ичный счетчик с син- хронным сбросом ИЕ18 2.60 2.61 + + +

393

Два ( четырехразрядных двоичных счетчика с ин- ИЕ19 + +

дивидуальной синхрони- зацией и сбросом Два четырехразрядных ИЕ20 + 2.62

двоично-десятичных счет-

чика с индивидуальной синхронизацией и сбро-

сом АМ25505

Схема быстрого умноже- ния 2X4 разряда ИК1 + + +

381

Четырехразрядное АЛУ ИК2 +

(восемь функций) Одноразрядный полный ИМ1 + + + 80

сумматор И М2 QO

Двухразрядный двоич- + + + OZ

ный сумматор Четырехразрядный дво- ичный сумматор ИМЗ + + + 2.63 83 183

Два одноразрядные пол- ИМ5 +

ных сумматора Четырехразрядный дво- ИМ6 + 2.64 + + 283

ичный сумматор с уско- ренным переносом Четыре одноразрядных ИМ7 + 2.65 385

последовательных сумма- тора-вычитателя с об- щими цепями сброса и синхронизации

18

Продолжение табл. 2.1

Назначение Ус- лов- кое обо- зна- чение Серия Функ- циональ- ный аналог

со со К155 КМ 155 со К555 КМ555 i 1533 КР1533 о ю М530 КР531 со ю K.PI53I

Восьмиразрядная схема ИП2 + + + 180

контроля четности и не-

четности

Четырехразрядное АЛУ ИПЗ + + + 2.66 + + + + + 181

(32 функции)

Схема ускоренного пере- ИП4 + + + + 2.67 + + + + + + 182

носа

Девятиразрядная схема ИП5 + 2.68 + + + + -г 280

контроля четности и не-

четности

Четырехканальный дву- ИП6 + 2.73 + + + 242

направленный инверти-

рующий формирователь с

тремя состояниями на вы-

ходах

Четырехканальный дву- ИП7 + 2.74 + + + 243

направленный неинвер-

тирующий формирова-

тель с тремя состояниями

на выходах

Параллельный двоичный ИП8 + 2.69 261

умножитель 4X2 разря-

да с £)-триггерами-за-

щелками на выходах

Восьмиразрядный после- ИП9 + 2.70 384

довательно-параллель-

ный двоичный умножи-

тель

Двенадцатиразрядная ИП10 + АМ93648

схема контроля четности

и нечетности

Четырехразрядный неин- ИП12 ' +

вертирующий приемопе-

редатчик

Четырехразрядный ин- ИП13 +

вертирующий приемопе-

редатчик

Четырехразрядный уни- ИР1 + + + 95

версальный сдвиговый

регистр с параллельным

выходом и раздельной

синхронизацией после-

довательного и парал-

лельного ввода информа-

ции

Восьмиразрядный после- ИР8 + 2.37 + 164

довательный сдвиговый

регистр с параллельным

выходом информации и

асинхронным сбросом

Восьмиразрядный сдви- ИР9 + 2.38 + 165

говый регистр с парал-

лельным вводом инфор-

мации

Восьмиразрядный сдви- ИР10 + 2.39 + + 166

говый регистр с последо-

вательно-параллельным

вводом информации и

асинхронным сбросом

Четырехразрядный ре- ИР11А + 2.40 + + + + 194

версивный сдвиговый ре-

гистр с параллельным

выходом, синхронным по-

следовательно-парал-

лельным вводом инфор-

мации и асинхронным

сбросом

19

Продолжение табл. 2.1

Назначение . Ус- лов- кое обо- зна- чение Серия Функ- циональ- ный аналог

СО К155 КМ 155 со ю К555 КМ555 СО КР1533 о СО М530 КР531 СО КР1531

Четырехразрядный сдви- ИР 12 4~ + 195 говый регистр с парал- лельным выходом, син- хронным последователь- но-параллельным вводом информации и асинхрон- ным сбросом Восьмиразрядный ревер- ИР 13 4- 4~ 198 сивный сдвиговый ре- гистр с параллельным вы- ходом, синхронным по- следовательно-парал- лельным вводом инфор- мации и асинхрон- ным сбросом Четырехразрядный па- ИР15 +. + + 2.42 .4- 173 раллельный регистр с синхронным управляе- мым вводом информации, асинхронным сбросом и тремя состояниями выхо- дов Четырехразрядный ре- ИР 16 4~ 2.41 295 версивный сдвиговый ре- гистр с параллельным вы- ходом, синхронным по- следовательно-парал- лельным вводом инфор- мации и тремя состоя- ниями выходов Двенадцатиразрядный АТ2504 регистр последователь- ИР 17 4~ 4~ ного приближения Шестиразрядныйч парал- ИР 18 4~ + АМ25507 лельный регистр с синх- ронным управляемым вводом информации Четырехразрядный па- ИР 19 4- 4~ АМ25508 раллельный регистр с синхронным управляе- мым вводом информации, прямыми и инверсными выходами Четырехразрядный па- ИР20 4~ + АМ25509 раллельный регистр с синхронным вводом ин- формации Четырехразрядное ком- ИР21 4~ 4~ АМ25509 бинационное сдвигающее устройство с тремя со- стояниями выходов Восьмиразрядный парал- ИР22 4- 2.43 4~ + 4~ + + + 373 лельный регистр-защел- ка с тремя состояниями на выходах Восьмиразрядный парал- ИР23 4- 2.44 4~ 4~ 4~ 4~ 4~ 4~ 374 лельный регистр с синх- ронным вводом информа- ции и тремя состояниями на выходах Восьмиразрядный ревер- ИР24 4~ 4~ + 4~ 299 сивный сдвиговый ре- гистр с синхронным по- следовательно-парал- лельным вводом инфор-

20

Продолжение табл. 2.1

Назначение Ус- лов- кое обо- зна- чение Серия Функ- циональ- ный аналог

с? К155 КМ155 533 К555 КМ555 1533 КР1533 530 М530 КР531 1531 КР1531

мации, асинхронным сбросом и двунаправлен- ной шиной данных Четырехразрядный сдви- ИР25 +

говый регистр с парал- лельным выходом, синх- ронным параллельно-по- следовательным вводом

информации, асинхрон- ным сбросом и тремя

состояниями выходов 4X4 регистровый файл с тремя состояниями выхо- дов ИР26 + 2.46 + +

Восьмиразрядный парал- лельный регистр с синх- ИР27 + 2.45 +

ронным управляемым вводом информации Восьмиразрядный сдви- говый регистр с синхрон- ИР28 +

ным последовательно-

параллельным вводом информации, асинхрон- ным сбросом и двуна- правленной шиной дан-

ных

Восьмиразрядный ревер- сивный регистр с син- хронным последователь- ИР29 +

но-параллельным вводом информации, синхронным сбросом и двунаправлен- ной шиной данных Восьмиразрядный - ре- ИРЗО + 2.48

гистр-защелка с парал- лельным выходом, после-

довательным поразряд- ным вводом информации и асинхронным сбросом > 24-разрядный сдвиговый регистр с синхронным по- ИР31 + +

следовательным вводом информации и парал- лельным выходом 4X4 регистровый файл с ИР32 + + 2.47 + +

открытым коллектором на выходах z Восьмиразрядный парал- лельный регистр-защел- ИРЗЗ -р +

ка с тремя состояниями на выходах Два несвязанных четы- ИР34 + +

рехразрядных регистра- защелки со сбросом и

тремя состояниями на вы- ходах Восьмиразрядный парал- лельный регистр с син- хронным вводом инфор- ИР35 + 2.49

мации и асинхронным сбросом Пятиразрядный регистр с полным дешифратором, синхронным вводом ин- формации и открытыми коллекторами на выхо- дах ИР36 4-

395

670

377

322

323

259

170

573

873

273

21

Продолжение табл. 2.1

Назначение Ус- лов- ное обо- зна- чение Серия Функ- циональ- ный аналог

й К155 КМ 155 533 К555 КМ555 1533 КР1533 530 М530 КР53! й КР1531

+ +

+ +

+ +

Восьмиразрядный парал- лельный регистр с син- хронным вводом инфор- мации и тремя состоя- ниями на выходах ИР37

Два несвязанных четы- рехразрядных парал- лельных регистра с син- хронным вводом инфор- мации и тремя сбстояния- м.и на выходах ИР38

Регистры общего назна- чения с многоканальным доступом ИР39

Восьмиразрядный парал- лельный неинвертирую- щий приемопередающий регистр с тремя состоя- ниями на выходах ИР40

Восьмиразрядный парал- лельный инвертирующий приемопередающий ре- гистр с тремя состоя- ниями на выходах ИР41

Четырехразрядное ком- бинационное устройство сдвига ИР42

Селектор-мультиплексор 16 каналов с инверсным выходом и стробирова- нием КП1 +

Сдвоенный селектор- мультиплексор четырех каналов с прямыми вы- ходами, общими адрес- ными входами и раз- дельным стробированием выходов КП2 +

Селектор-мультиплексор КП5 +

восьми каналов с инверс- ным выходом

Селектор-мультиплексор восьми каналов с пря- мым и инверсным выхо- дом и стробированием КП7 +

Счетверенный селектор- мультиплексор двух ка- налов с прямыми выхо- дами, общим адресным входом и тремя состоя- ниями на выходах КПП

Сдвоенный селектор- мультиплексор четырех каналов с прямыми вы- ходами, общими адрес- ными входами и раз- дельным управлением выходами и тремя со- стояниями КП 12

Счетверенный селектор- мультиплексор двух ка- налов с общим адресным входом и прямыми выхо- дами с запоминанием на синхронных D-триггерах КП13

Счетверенный селектор- мультиплексор двух ка- 22 КП14

+

+ + + 2.12 + + +

+ +

+ + + 2.13 + +

+ 2.16 + +

+ 2.19 + +

+ 2.15 + +

+ 2.17 + +

574 874

4-

4-

4-

150

4~ 4- 153

152

+ 4- 4- 151

+ + + 257

4- 253

298

4- 4- 4- 258

Продолжение табл. 2.1

Назначение Ус- ** лов- кое обо- зна- чение Серия Функ- циональ- ный аналог

со К155 КМ 155 СО со К555 КМ555 1533 КР1533 ' 530 М530 КР531 1531 КР1531

налов с инверсными вы-

ходами, общим адресным

входом на выходах

Селектор-мультиплексор КП15 +

восьми каналов с прямым и инверсным выходами и тремя состояниями на выходах Счетверенный селектор- мультиплексор двух кана- лов с прямыми выхода- ми, общим адресным вхо- дом и стробированием Сдвоенный селектор- мультиплексор четырех каналов с инверсными выходами, общими ад- ресными входами и раз- дельным управлением выходами с тремя со- стояниями Счетверенный селектор- мультиплексор двух ка- налов с инверсными вы- ходами, общим входом и стробированием Сдвоенный селектор- мультиплексор четырех каналов с инверсными выходами, общими ад- ресными входами и раз- дельным стробированием выходов КП16 КП17 КП18 КП19 + +

Два ЛЭ 4И—НЕ (один расширяемый по ИЛИ в К155, КМ 155) ЛА1 + + + +

ЛЭ 8И—НЕ ЛА2 т + + +

Четыре ЛЭ 2И—НЕ ЛАЗ + + + +

Три ЛЭ ЗИ—НЕ ЛА4 + + + +

Два ЛЭ 4И—НЕ с боль- шим коэффициентом раз- ветвления по выходу ЛА6 + + + +

Два четырехвходовых ЛЭ И—НЕ с открытым коллектором и повышен- ной нагрузочной способ- ностью ЛА7 + + + +

Четыре ЛЭ 2И—НЕ с открытым коллектором (элементы контроля) Четыре ЛЭ 2И—НЕ с открытым коллектором ЛА8 ЛА9 + + + +

Три ЛЭ ЗИ—НЕ с открытым коллектором ЛАЮ + + + +

Четыре ЛЭ 2И—НЕ с открытым коллектором и повышенным выходным напряжением ЛАИ + + + +

Четыре буферных ЛЭ 2И—НЕ с высокой нагру- зочной способностью ЛАЮ + + + +

Четыре буферных ЛЭ 2И—НЕ с открытым кол- лектором и высокой на- грузочной способностью Четыре ЛЭ 2И—НЕ ЛАЮ ЛАЮ + + + + +

2.14 + + + + + 251

2.18 + + + + 157

2.20 + + + 353

+ + + + + + 158

+ 352

2.5 + + + + + + + 20

2.5 + + + + + + 30

2.5 + + + + + + + + 00

2.5 + + + + + + + + 10

2.5 + 40

2.5 + + + 22

+ + 01

2.5 + + + + + 03

2.5 + 12

2.5 + 26

2.5 + + + + 37

2.5 + + + + 38

23

Продолжение табл. 2.1

Назначение Ус- лов- ное обо- зна- чение Серия Функ- циональ- ный аналог

СО К155 КМ 155 533 К555 КМ555 1533 КР1533 530 М530 КР531 1531 КР1531

Два ЛЭ 4И—НЕ (ма- ЛА16

гастральный усилитель)

Два ЛЭ 4И—НЕ (ма- ЛА17

гистральный усилитель)

с тремя состояниями на

выходе

Два ЛЭ 2И—НЕ с мощ- ЛА18

ным открытым коллек- торным выходом ЛЭ 12И—НЕ с тремя ЛА19

состояниями на выходе Два четырехвходовых ло- ЛД1

гических расширителя по ИЛИ Восьмивходовый расши- лдз

ритель по ИЛИ Четыре ЛЭ 2ИЛИ—НЕ ЛЕ1

Два стробируемых ЛЭ ЛЕ2

4ИЛИ—НЕ, один расши- ряемый по ИЛИ Два стробируемых ЛЭ ЛЕЗ

4ИЛИ—НЕ Три ЛЭ ЗИЛИ—НЕ ЛЕ4

Четыре буферных ЛЭ ЛЕ5

2ИЛИ—НЕ Четыре ЛЭ 2ИЛИ—НЕ ЛЕ6

(магистральный усили- тель) Два ЛЭ 5ИЛИ—НЕ ЛЕ7

Четыре ЛЭ 2И ЛИ1

Четыре ЛЭ 2И с от- ЛИ2

крытым коллектором Три ЛЭ ЗИ ЛИЗ

Три ЛЭ ЗИ с открытым ЛИ4

коллектором Два мощных ЛЭ 2И с ЛИ5

открытым коллектором и повыщенным напряже- нием Два ЛЭ 4И ЛИ6

Четыре ЛЭ 2ИЛИ ЛЛ1

Два мощных ЛЭ 2ИЛИ ЛЛ2

с открытым коллектором Шесть ЛЭ НЕ ЛН1

Шесть ЛЭ НЕ с от- ЛН2

крытым коллектором Шесть ЛЭ НЕ с от- ЛНЗ

крытым коллектором и повышенном выходным напряжением Шесть буферных инвер- ЛН5

торов с открытым кол- лектором Шесть буферных инвер- ЛН6

торов с тремя состоя- ниями на выходе Три мажоритарно-муль- ЛПЗ

типлексорных элемента Шесть буферных форми- ЛП4

рователей с открытым коллектором Четыре двухвходовых ЛЭ ЛП5

Исключающее ИЛИ Два ЛЭ 2И—НЕ с об- ЛП7'

щим входом и двумя

мощными транзисторами

+

+ + +

+ + +

+ + + + + 2.6

+ + +

+ + + + 2.6

+ +

+ + + + + 2.6 2.6

+ 2.6 2.6

+ +

+ + + + + + 2.6 2.6

+ + + + + + + 2.7 2.7

+ +

+ +

+ + 2.8

+ +

+ + + + 2.9

+ +

+ + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + + +

+ 140

+

75 452

+ 134

60

+ + + 02

23

25

66

28

128

+ 260

+ + 08

09

+ + + И

18

21

+ + + 32

75 453

+ + + 04

+ 05

06

16

366

17.

+ + + 86

75 450

24

Продолжение табл. 2.1

Назначение Ус- лов- ное обо- зна- чение Серия Функ- циональ- ный аналог

Л К155 KMI55 и? К555 КМ555 1533 КР1533 530 М530 КР531 1531 КР1531

Четыре буферных ЛЭ с тремя состояниями на вы- ЛП8 + + + +

ходе

Шесть буферных форми- рователей с открытым ЛП9 + + +

коллектором и повышен- ным выходным напряже- нием

Шесть буферных повто- рителей с тремя состоя- ЛП10 +

ниями на выходе

Шесть буферных повто- рителей с тремя состоя- ниями на выходе (две раздельно управляемые ЛП11 +

группы по два и четыре повторителя) Четыре двухвходовых ЛЭ Исключающее ИЛИ с от- ЛП12

крытым коллектором Два ЛЭ 2—2И—2ИЛИ— ЛР1 + + +

НЕ, один расширяемый по ИЛИ ЛЭ 2—2—2—ЗИ — ЛРЗ + + +

4ИЛИ—НЕ, расширяе- мый по ИЛИ

ЛЭ 4—4И-2ИЛИ— НЕ, ЛР4 + + +

расширяемый по ИЛИ ЛЭ 4—2—3—2И— ЛР9

4ИЛИ—НЕ ЛЭ 4—2—3—2И— 4ИЛИ—НЕ с открытым ЛР10

коллектором Два ЛЭ 2—2И—2ИЛИ— ЛР11 +

НЕ и 2—ЗИ—2ИЛИ—НЕ ЛЭ 2—3—3—2И— 4ИЛИ—НЕ ЛР13 +

Преобразователь двоич- но-десятичного кода в се- ПП4 +

мисегментный с откры- тым коллектором Преобразователь двоич- ПР6 + +

но-десятичного кода в двоичный Преобразователь двоич- ного кода в двоично- десятичный ПЗУ на 1024 бит с ис- ПР7 + +

пользованием в качестве преобразователя . двоич- ного кода в код:

русского алфавита РЕ21 +

знаков латинского ал- РЕ22 +

фавита арифметических знаков и цифр РЕ23 +

дополнительных знаков РЕ24 +

и цифр Однократно программи- руемое ПЗУ на 256 бит РЕЗ +

ПЗУ на 16 Кбит с от- крытым коллектором На выходах РЕ4

, Шестнадцатиразрядное 8X2 регистровое ЗУ с РПЗ + +

двумя каналами доступа

и тремя состояниями на

2.11 + 125 07

365

367

2.10 + + 136

50

53

2.7 + +- 55

+ + + + + 64

+ + 65

2.7 + + + + + 51

2.7 + + + 54

49

184

185

187

+

+ 172

выходах

Окончание табл. 2.1

Назначение Ус- лон- ное обо- зна- чение Серия Функ- циональ- ный аналог

со К155 КМ 155 со СО ш К555 КМ555 СО СО ш КР1533 о 4 СО М530 KP53I СО ю КР1531

Программируемое ПЗУ на 1024 бит РТ1 + МС9001

ОЗУ на 16 бит (16X1) со схемами управления РУ1 + + + 81

ОЗУ на 64 бит с про- РУ2 + + + 89

извольной выборкой (16X4) ОЗУ на 256 бит (256X1) со схемами разрядного и РУ5 + +

адресного управления ОЗУ на 1024 бит (1024Х РУ7 + + 93 425

XI) со схемами управ- ления ОЗУ на 64 бит (16X4) с открытым коллектором на выходах РУ9 + 289

ОЗУ на 64 бит (16X4) с синхронной записью ин- формации и с тремя со- РУН + —

стояниями на выходах Схема сравнения двух четырехразрядных чисел СП1 + 2,71 + + + + 85

/-К-триггер с логикой на ЗИ на входах /, К ТВ1 + + + 72

со сбросом и установкой Два /-К-триггера со ТВ6 + 2.32 + 107

сбросом Два J-K-триГгера со сбросом и установкой ТВ9 + 2.33 + + + + 112

Два J-K-триггера с уста- ТВ10 + + + 113

новкой

Два J-K-триггера со сбросом и установкой, ТВ11 + + + 114

входы синхронизации и установки сдвоены Два J-K-триггера со сбросом и установкой, ТВ15 + + + + + 109

вход К проинвертирован Цва D-триггера со сбро- < ом и установкой ТМ2 + + + + 2.34 + + + + + + + 74

Четыре D-триггера-за- щелки (две группы по ТМ5 + + + 77

два триггера) Четыре D-триггера-за- ТМ7 + + + +. 2.35 + 75

щелки с прямыми и ин- версными выходами (две группы по два триггера) Четыре D-триггера с пря- ТМ8 + + + + 2.36 + + + + + + 175

мыми и инверсными вы-

ходами и входом сброса , Шесть синхронных D- ТМ9 + 2.36 + + + + + + 174

триггеров со входом сбро-

са

Два триггера Шмитта с ЛЭ 4И—НЕ на входе ТЛ1 + + + 13

.Шесть триггеров Шмит- та-инверторов ТЛ2 + + + 2.7 + + 14

Четыре двухвходовых триггера Шмитта ТЛЗ + + + + 132

Четыре /?-5-триггера ТР2 + 2.31 + + + 279

Многофункциональный элемент для ЭВМ ХЛ1 + + ' +

Примечания: I. Полное условное обозначение микросхемы образуется из номера серни и обозначения, например 133АГ1 или КР1533ИДЗ. 2. Обозначение

.функционального аналога для приведенных микросхем следует читать: I33/KI55, КМ 155 — SN54/SN74; 530, М530/КР531 — SN54S/SN74S; 533/К555;

КМ555 — SN54LS/SN74LS; I533/KP1533 — SIM54ALS/SN 74ALS; 1531/KP153I — 54F/74F. 3. Полное условное обозначение функционального аналога обра-

зуется из обозначения соответствующей серин и номера, например для 133АГ1 — SN5412I; КР1533 — SN74ALSI54.

26

Таблица 2.2.

Основные параметры и характеристики ТТЛ и ТТЛШ ИС

Параметр, характеристика Серии микросхем

Стандартные (133, К155, КМ155) Маломощные с дио- дами, Шотки (533, КМ533, К555, КМ555) Быстродействую- щие с диодами Шатки (530, К530, КМ530, К531, КР531) Маломощные усо- вершенствованные с диодами , Шотки (1533, КР1533) Быстродействую- щие усовершен- ствованные с дио- дами, Шотки <1531, КР1531) Примечание

Входной ток, мА, не более: низкого уровня — 1,6 —0,4 —2 —0,1 —0,6

высокого уровня 0,04 0,04 0,05 —0,2 0,02 0,02

Выходное напряжение, В: низкого уровня, не более 0,4 0,4 0,5 0,4 0,5

высокого уровня, не менее - 2,4 2,5 2,5 2,5 2,5

Выходной ток, мА: низкого уровня, не более 16 4 20 4 20

высокого уровня, не менее —0,4 —0,4 — 1 —0,4 — 1

Нагрузочная способность 10 10 10 . 10 30.

Время задержки распростране- ния сигнала, нс, при: включении 18,5 20 5 14 5,16 Для ЛЭ

(Сн=15 пФ) (Сн=15 пФ). (Сн=15 пФ) (Сн=50 пФ) (Сн—50 пФ) ЛАЗ

выключении 18,5 20 4,5 14 6 То же

(С„=15 пФ) Средний ток потребления, мА, не более 15 (С„=15 пФ) 3 (Сн=15 пФ) 26 (Сн=50 пФ) 1,91 (Сн=50 пФ) 6,5

Помехоустойчивость, В, не более 0,4 0,3 0,3 0,4 0,3 Наименьшее

Частота переключения, МГц, не более 15 25 75 30 100 значение Частота пе-

Максимальное напряжение пита- ния, В 6 5,5 6 6 6 реключения триггеров

Максимальное напряжение на входе, В 5,5 5,5 5,5 5,5 5,5

Минимальное напряжение на входе, В —0,4 —0,4 —0,4 —0,4 —0,5

Напряжение питания, В Максимальная емкость нагруз ки, пФ Диапазон рабочих температур, °( 200 5+10 % 5+5% 150 (133, 533, 530, М530, 1533, 1531) (К155, К555, КР531, КР1533, КР1531) 150 200 200

2 —60...+ 125 — 10...+ 70 (133, 533, 530, М530, 1533, 1531) (К155, К555, КП531, КР1533, КР1531)

Таблица 2.3.

Типы корпусов для ТТ и ТТЛШ ИС

Серия Тип корпуса Расположение выводов Материал корпуса Диапазон температур, °C

Число выводов

14 .1 16 1 20 1 24 | 28 42

533 401.14-4 401.14-5 Планарное Металлокера- мический Металлостек- лянный —60...+ 125

402.16-18 402.16-32 402.16-33 405.24-2 4118.24-1 4119.28-1 Металлокера- мический —60.. . + 125

КМ533 201.14-8 201.14-9 201.14-10 2102.14-3 201.16-5 201.16-6 201.16-13 2103.16-4 2140Ю.20-2 Двухрядное, перпенди- кулярное Стеклокерами- ческий. —60.. .4-125

К555 201.14-1 201.14-2 2103.16-2 238.16-2 238.16-1 2140Ю.20-1 239.24-1 2121.28-1 Двухрядное, перпенди- кулярное Пластмассовый (полимерный) — 10...+70

27

Окончание табл. 2.3

Серия Тип корпуса Расположение выводов Материал корпуса Диапазон температур, °C

Число выводов

14 16 . 20 | 24 1 28 1 1 42

КМ555 201.14-8 201.14-9 201.14-10 2102.14-3 201.16-5 201.16-6 201.16-13 2103.16-4 То же Стеклокерами- ческий

1533 401.14-5 402.16-32 4153.20-1.01 4118.24-1 4119.28-1 429.42-1 Планарное Металлостек- лянный Металлокера- мический —60...+ 125

КР1533 201.14-1 2103.16-2 2140Ю.20-1 239.24-1 2121.28-1 Двухрядное, перпенди- кулярное Пластмассовый —1О...-|-7О (полимерный)

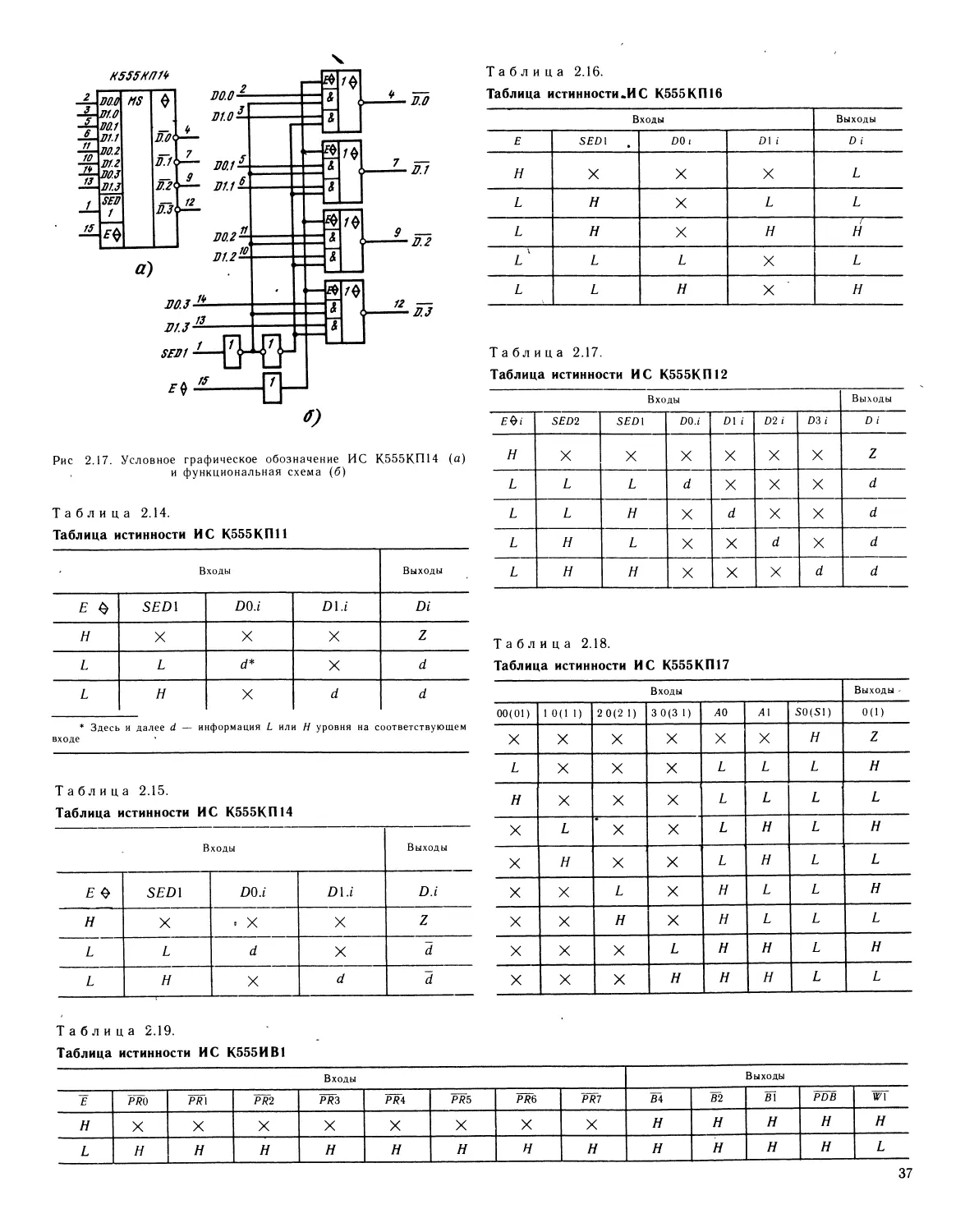

2.2. Базовый логический элемент ИС 533 (К533,

КМ533, К555, КМ555)

В качестве базового ЛЭ микросхем 533 (К533, КМ533,

К555, КМ555) использован ЛЭ типа И — НЕ.

Схема базового ЛЭ приведена на рис. 2.1 и содержит

три основных каскада: входной, реализующий функцию И,

выполненный на диодах VD3, VD4 и резисторе /?1; фазо-

вращательный, включающий транзисторы VT1, VT2, диод ED5

и резисторы R2—/?4; выходной усилитель, состоящий из тран-

зисторов VT3 — VT5 и резисторов /?5, R6.

Отличительной особенностью ТТЛШ ИС является наличие

в активных элементах схемы кроме транзистора VT5 диодов

Шотки, которые шунтируют коллекторные переходы тран-

зисторов. Диод Шотки имеет более низкое прямбе падение

напряжения, чем кремниевый р-п переход, и предохраняет

транзистор от насыщения. Введение диодов Шотки исключает

накопление зарядов, увеличивающих время выключения тран-

зистора, и способствует стабильности временных параметров

транзистора в рабочем диапазоне температур, поэтому ско-