Автор: Якуюовский С.В.

Теги: электротехника компьютерные технологии электроника микросхемы связь интегральные микросхемы

Год: 1985

Текст

ПРОЕКТИРОВАНИЕ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ.

НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ

АНАЛОГОВЫЕ

И ЦИФРОВЫЕ

ИНТЕГРАЛЬНЫЕ

МИКРОСХЕМЫ

Справочное пособие

ИЗДАНИЕ ВТОРОЕ,

ПЕРЕРАБОТАННОЕ И ДОПОЛНЕННОЕ

Под редакцией

С. В. ЯКУБОВСКОГО

Scan Pirat

ИЮСКВА «РАДИО И СВЯЗЬ» 1985

ББК 32.85

А64

УДК 621.3:681.3

„ „Р®ДЛДМИОНН АЯ КОЛЛЕГИЯ: А. Г. АЛЕКСЕНКО,

С. С. БАДУЛИН, И. Н. БУКРЕЕВ, А. А. ВАСЕНКОВ, Б. Ф. ВЫСОЦКИЙ

(отв. редактор), В. И. КОТИКОВ (зам. отв. редактора), Ю И. КОНЕВ,

С. В. ЯКУБОВСКИЙ .

С. В. Якубовский, Н. А. Барканов, Л. И. Ниссель-

сон, М. Н. Топешкин, В. А. Ушибышсв

Аналоговые и цифровые интегральные микросхемы.

А64 Справочное пособие/С. В. Якубовский, Н. А. Бар-

канов, Л. И. Ниссельсон и др.; Под ред.

С. В. Якубовского. — 2-е изд., перераб. и доп.—М.:

Радио и связь, 1985. — 432 с., ил. — (Проектирование

РЭА на интегральных микросхемах).

В пер.: 1 р. 80 к.

Дан обзор номенклатуры основных серий отечественных аналоговых

и цифровых интегральных микросхем. Приведены их наиболее важные

параметры н характеристики и показаны тенденции развития. Изложены

основные сведения по микропроцессорам и особенностям их применения

и даны рекомендации по предупреждению отказов микросхем при различ-

ных внешних воздействиях. Описаны особенности применения микросхем

в радиоэлектронной аппаратуре. По сравнению с первым изданием

(1979 г.) значительно обновлена номенклатура приводимых микросхем и

расширен раздел по микропроцессорам.

Для широкого круга инженерно-технических работников.

. 2403000000-021 . ББК 32.85

А—---------------161-84

046(01 )-85 6Ф0.3

РЕЦЕНЗЕНТ В. Л. ШИЛО

Редакция литературы по электронной технике

Сергей Викторович Якубовский

Николай Арсеньевич Барканов

Лев Ионович Ниссельсон

Михаил Никифорович Топешкин

Виктор Алексеевич Ушибышев

АНАЛОГОВЫЕ И ЦИФРОВЫЕ

ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ

Редакторы Е. В. Вязова, В. М. Ларионова

Научный редактор В. Л. Шило

Художественный редактор Н. С. Шеин

Технический редактор Г. И. Колосова

Корректор Т. В. Покатова

ИБ № 472

Сдано в набор 15.05.84 Подписано в печать 21.08.84

Т-15148 Формат 60X90/i6 Бумага кн-журн. Гарнитура литературная

Печать высокая Усл. печ. л. 27,0 Усл. кр.-отт. 27,0 Уч.-изд. л. 29,94

Доп. тираж 60 000 экз Изд. № 20312 Зак. № 50

Цена 1 р. 80 к.

Издательство «Радио и связь». 101000 Москва, Почтамт, а/я 693

Московская типография № 5 ВГО «Союзучетиздат»

101000 Москва, ул. Кирова, д. 40

© Издательство «Радио и связь», 19

Предисловие

В Основных направлениях экономического и социального раз-

вития СССР на 1981—1985 годы и на период до 1990 года, при-

нятых XXVI съездом КПСС, указано на необходимость развивать

производство и обеспечить широкое применение автоматических

манипуляторов (промышленных роботов), встроенных систем ав-

томатического управления с использованием микропроцессоров и

микро-ЭВМ, создавать автоматизированные цехи и заводы и со-

средоточить усилия на повышении качества, надежности, эконо-

мичности и производительности машин и оборудования, совершен-

ствовании вычислительной техники и ее элементной базы.

Выполнить эти задачи невозможно без дальнейшего развития

электроники, которое обеспечит не только создание сложных ав-

томатизированных систем управления производственными процес-

сами в самых различных отраслях народного хозяйства, но и раз-

работку принципиально новых изделий, как, например, адаптив-

ных систем управления для промышленных роботов или персо-

нальных ЭВМ.

Развитие электроники с начала 60-х годов связано с совершен-

ствованием интегральных микросхем (ИС). Спустя 10 лет практи-

чески все серийные ЭВМ строились не на транзисторах (ЭВМ

второго поколения), а на цифровых ИС (ЭВМ третьего поколе-

ния). Тогда же появились первые разработки ЭВМ четвертого по-

коления, отличающиеся широким внедрением больших интег-

ральных микросхем (БИС). Именно свойства и характеристики

БИС определяют технические характеристики перспективных

ЭВМ. Среди современных БИС особое место занимают микропро-

цессоры (МП). Освоение в производстве МП, представляющих

собой ИС с повышенной функциональной гибкостью (программу

работы МП нетрудно изменить), позволяет по-новому организо-

вать обработку цифровых сигналов и поэтому надеяться на широ-

кое внедрение цифровых методов обработки информации даже

там, где применение электроники ранее не давало существенного

эффекта. На базе микропроцессорных комплектов создаются до-

статочно емкие как универсальные, так и специализированные вы-

числительные устройства четвертого поколения.

В двадцатилетней истории развития технологии и схемотехни-

ки цифровых ИС (ЦИС) можно условно выделить четыре этапа.

з

Первый (60-е годы)—разработка базовых серий ЦИС малой

степени интеграции, выполняющих простые логические функции.

Такие ЦИС принципиально повысили надежность ЭВМ. Их при-

менение стандартизовало многие процессы проектирования вычис-

лительных средств. Были внедрены новые приемы конструирова-

ния РЭА (например, машинное проектирование многослойных пе-

чатных плат).

Второй этап (70-е годы) — разработка ИС средней степени

интеграции, таких как счетчики, регистры, дешифраторы, матрицы

ЗУ с числом эквивалентных элементов не более 1000. Функцио-

нальный состав разработанных на предыдущем этапе серий посто-

янно расширяется именно за счет таких ИС.

Массовое производство ЦИС малой и средней степени интег-

рации стало отправным пунктом для выпуска первых БИС с чис-

лом элементов до 10 тыс. Этот (условно — третий) этап развития

относится к концу 70-х годов. Как пример можно вспомнить о

широком распространении в то время карманных калькуляторов

(простейших — школьных, программируемых — инженерных).

На четвертом, современном, этапе имеются технологические

Возможности изготавливать серийно БИС с числом элементов, на

порядок большим (и даже свыше 100 тыс!). Отметим, что таким

количеством элементов весьма трудно распорядиться разработ-

чику, даже оснащенному мощной системой машинного проектиро-

вания. Поэтому сейчас характерны различные БИС с повторяю-

щейся, т. е. регулярной (например, матричной), структурой. Обыч-

но это запоминающие устройства (ЗУ): постоянные (ПЗУ) и опе-

ративные (ОЗУ). Применяется и другой прием: на большом по

размеру кристалле объединяется несколько ранее оправдавших се-

бя БИС. Получается так называемая «сверхбольшая» БИС

(СБИС). Эти СБИС могут быть однокристальными микро-ЭВМ.

Весьма перспективны программируемые логические матрицы.

Отметим также, что на протяжении этих четырех этапов до-

стигли максимального совершенства ИС трех типов логики: тран-

зисторно-транзисторной (ТТЛ)—универсальной, эмиттерно-свя-

занной (ЭСЛ)—сверхскоростной и КМОП — экономичной. По-

явились также БИС на перспективной биполярной логике, на-

зываемой интегральной инжекционной логикой (И2Л). Поэтому

во втором, дополненном и расширенном, издании книги акценти-

ровано внимание на сложных ИС. Приводится больше информа-

ции по схемам ЗУ на биполярных и полевых структурах. Рассмат-

риваются ближайшие перспективы развития ЦИС. В этом аспек-

те уделено внимание БИС И2Л. Даются характеристики микропро-

цессорных комплектов (МПК), в частности серии КР580. В книге

приведены также характеристики микро-ЭВМ, их типовая струк-

тура. Приведен новый материал и по традиционным сериям ИС,

таким как К155, К176, К531, К555.

К концу 70-х годов разработчики РЭА получили также анало-

говую элементную базу: большой ассортимент универсальных опе-

рационных усилителей, компараторов, АЦП и ЦАП, стабилизато-

4

ров напряжения, коммутаторов, а также набор усилителей низ-

кой, промежуточной и высокой частоты. Применение АИС позво-

лило увеличить надежность и точность устройств, упростить их

наладку, а во многих случаях и исключить обслуживание во вре-

мя эксплуатации.

Совместное применение АИС и ЦИС позволяет включить циф-

ровую ЭВМ в непрерывный (аналоговый) контур. Такая схема

широко применяется, например, в робототехнике или медицинской

электронике. Номенклатура АИС и ЦИС сейчас очень велика.

Разработчики могут применять (или делать выбор) как БИС, так

и ИС традиционной структуры.

Во втором издании сведения по устаревшим аналоговым ИС

(АИС) не приводятся. Здесь описаны новые операционные уси-

лители (ОУ), цифро-аналоговые (ЦАП) и аналого-цифровые

(АЦП) преобразователи. Дана информация по телевизионным и

радиосхемам.

Залогом высокой надежности РЭА являются правильное при-

менение микросхем и соблюдение режимов их эксплуатации, на-

рушение же этих условий из-за недостаточного знания технических

свойств, электрических параметров и режимов эксплуатации мо-

жет приводить к отказам изделий.

Одна из задач настоящего справочного пособия — дать не

только основные характеристики ЦИС и АИС и описать методы их

изготовления, но также обратить внимание разработчиков аппа-

ратуры на особенности применения ИС в РЭА (на этапах разра-

ботки, монтажа и эксплуатации), т. е. дать рекомендации по обес-

печению надежности работы ИС в аппаратуре.

Материал, изложенный в книге, базируется на результатах

обобщения опыта разработки и применения ИС.

Отзывы и замечания по книге просим направлять по адресу:

101000 Москва, Почтамт, а/я 693.

Авторы.

ГЛАВА 1

ТЕРМИНОЛОГИЯ В МИКРОЭЛЕКТРОНИКЕ

И КЛАССИФИКАЦИЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

1.1. История вопроса

Микроэлектроника — ведущее направление электроники, кото-

рое изучает проблемы исследования, конструирования и приме-

нения электронных устройств с высокой степенью миниатюриза-

ции. Ход развития электроники был предопределен резким увели-

чением функций, выполняемых РЭА, и повышением требований к

надежности особо сложной аппаратуры.

Прогресс технологических процессов, давших разработчикам

аппаратуры новую элементную базу, был в 60—70-х годах столь

быстрым, что он не только сместил акценты во многих устояв-

шихся терминах радиоэлектроники, но и значительно пополнил со-

ответствующий словарный запас. Известная стихийность данного

процесса развития привела ко многим разночтениям понятий и

терминов. Следует учесть, что процесс начального развития тер-

минологии шел одновременно на нескольких языках при интенсив-

ном обмене информацией между странами.

Первые попытки упорядочить вопросы терминологии в микро-

электронике были сделаны еще в 1969 г., когда Международной

электротехнической комиссией (МЭК) было издано второе допол-

нение (1966 г.), которое включало в себя определение нескольких

самых общих терминов, таких как микроэлектроника, интеграль-

ная микросхема.

Первые попытки упорядочить отечественные термины и опре-

деления были предприняты в 1967 г. В связи со значительным

расширением в последующие годы применения ИС возникла необ-

ходимость в Государственном стандарте по терминологическим во-

просам в области микроэлектроники, который был разработан и

утвержден в 1971 г. (ГОСТ 17021—71). Он включал 16 терми-

нов, причем наряду с общими, такими как интегральная микро-

схема, полупроводниковая интегральная микросхема, были даны

однозначные определения и для частей интегральных схем (на-

пример, подложка, корпус).

Термины, определение которых было дано в указанном ГОСТе,

нашли самое широкое применение в технической документации.

В 1975 г. терминологический стандарт был расширен (ГОСТ

17021—75), поскольку к этому времени словарный базис микро-

электроники сформировался.

В 1979 г. был утвержден стандарт СЭВ по терминам и опреде-

лениям в области микроэлектроники (СТ СЭВ 1623—79). В свою

очередь, в ГОСТ 17021—75 были введены изменения (1981 г.),

соответствующие этому стандарту СЭВ. Тогда же в ГОСТ были

введены термины и определения, касающиеся БИС и микропро-

цессоров.

6

1.2. Терминология в микроэлектронике согласно

ГОСТ 17021—75

1.2.1. ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ, ЭЛЕМЕНТЫ, КОМПОНЕНТЫ

Интегральная микросхема — микроэлектронное изделие, вы-

полняющее определенную функцию преобразования и обработки

сигналов и имеющее высокую плотность упаковки электрически

соединенных элементов (или элементов и компонентов) и (или)

кристаллов. Это изделие с точки зрения требований к испытаниям,

приемке, поставке и эксплуатации рассматривается как единое це-

лое. Термин «интегральная микросхема» имеет два подчиненных

понятия: элемент ИС (или просто элемент) и компонент ИС (или

просто компонент).

Элемент — это часть ИС, реализующая функцию какого-либо

простого электрорадиоэлемента (например, транзистора, диода,

резистора, конденсатора). Элемент нельзя отделить от кристалла

ИС (или ее подложки) как самостоятельное изделие, следователь-

но, его нельзя испытать, упаковать и эксплуатировать. Примеры

интегральных элементов: пленочный резистор в гибридной ИС,

транзистор в полупроводниковой ИС.

Компонент — это часть ИС, также реализующая функцию ка-

кого-либо электрорадиоэлемента, однако компонент перед сборкой

ИС был самостоятельным изделием в специальной упаковке (ком-

плектующее изделие). Компонент в принципе может быть отде-

лен от изготовленной ИС (например, для замены при ремонте).

Примеры интегральных компонентов: бескорпусный транзистор,

керамический конденсатор в гибридной ИС.

1.2.2. ЭЛЕМЕНТЫ КОНСТРУКЦИИ ИС

При разработке технической документации йли при составле-

нии описаний конструкций ИС ГОСТ обязывает пользоваться об-

щими терминами: корпус, подложка, плата, пластина, кристалл,

а также некоторыми специальными, которыми определяются осо-

бенности внутреннего строения ИС.

Корпус — это часть конструкции ИС, которая защищает кри-

сталл от внешних воздействий и соединяет его с внешними элек-

трическими цепями. Типы и размеры корпусов ИС, а также рас-

положение и число их выводов стандартизованы (см. ГОСТ

17467—79).

Подложка ИС—заготовка, предназначенная для изготовле-

ния на ней элементов гибридных и пленочных ИС, межэлемент-

ных и (или) межкомпонентных соединений, а также контактных

площадок.

Плата ИС — часть подложки (или вся подложка) гибридной

(или часто пленочной) интегральной микросхемы, на поверхности

которой сделаны пленочные элементы ИС, межэлементные и меж-

компонентные соединения и контактные площадки.

Полупроводниковая пластина — заготовка из полупроводнико-

вого материала (обычно это круглый тонкий диск), используемая

7

для создания полупроводниковых ИС. Следует отметить, что при

производстве ИС этим термином называется не только первона-

чальная заготовка, но и пластина со сформированными элемента-

ми полупроводниковых микросхем (следовательно, этот термин ис-

пользуется в течение всего технологического процесса от его на-

чала до разделения группового изделия на отдельные кристаллы).

Кристаллы ИС — это части пластины, получающиеся после ее-

резки (обычно они образуют сетку в виде одинаковых прямоуголь-

ников), в объеме и на поверхности которых сформированы эле-

менты полупроводниковой микросхемы, межэлементные соедине-

ния и контактные площадки.

Контактные площадки, имеющиеся в любой ИС — это металли-

зированные участки на плате или на кристалле, предназначенные

для присоединения к выводам корпуса ИС, а также для контроля

ее электрических параметров и режимов.

Бескорпусная микросхема. Этот термин в последнее время при-

обрел большое значение в связи с тем, что такие ИС широко при-

меняются при создании микросборок и микроблоков. Если для

обычной ИС корпус служит для защиты от внешних воздействий^

то бескорпусная ИС такой собственной защиты (по крайней мере.,,

от механических воздействий) не имеет. Для соединения с внеш-

ними электрическими цепями бескорпусная ИС имеет собствен-

ные выводы, а ее полная защита обеспечивается корпусом устрой-

ства, в которое эта ИС установлена.

Вывод бескорпусной ИС — это проводник, соединенный элек-

трически с контактной площадкой кристалла и механически с его

поверхностью. Главным назначением вывода является обеспече-

ние электрического контакта одной из цепей бескорпусной ИС

при ее соединении с внешними электрическими цепями. По выво-

дам от бескорпусной ИС отводится значительная часть тепла. Вы-

воды бескорпусной ИС могут быть жесткими (шариковые, стол-

биковые, балочные) или гибкими (лепестковые и наиболее прос-

тые— проволочные). Жесткие выводы могут использоваться для

механического крепления бескорпусной ИС без ее приклеивания.

1 2 3 ПРОСТЫЕ И СЛОЖНЫЕ ИС

В настоящее время стандартизованы количественные и качест-

венные меры определения сложности ИС. Количественный фактор

соответствует порядку числа элементов на кристалле ИС или в,

ее корпусе.

В ГОСТ 17021—75 определен термин степень интеграции ин-

тегральной схемы как показатель степени сложности ИС, харак-

теризуемый числом содержащихся в ней элементов и компонен-

тов, причем степень интеграции определяется формулой К —

= lgN, где К — коэффициент, округляемый до ближайшего боль-

шего целого числа, а W — число элементов и компонентов, входя-

щих в ИС. В соответствии с этой формулой ИС первой степенй

8

интеграции называется микросхема, содержащая до 10 элементов

и компонентов включительно, ИС второй степени интеграции со-

держит от 11 до 100 элементов и компонентов. Соответственно ИС,

имеющую в своем составе от 101 до 1000 элементов и компонен-

тов, следует называть ИС третьей степени интеграции. Аналогич-

но ИС, имеющие число элементов и компонентов от 1001 до 10 000

или от 10 001 до 100 000, — это ИС четвертой и пятой степеней

интеграции. Практически сейчас реальны даже ИС шестой степе-

ни интеграции. Кроме того, имеют место количественные оценки

понятий сложности ИС: малая, средняя, большая, сверхбольшая.

Эти определения зависят от числа элементов и компонентов, тех-

нологии изготовления и функционального назначения ИС и могут

изменяться. Взаимное соответствие качественных наименований и

количества элементов ИС на сегодняшний день дано в табл. 1.1.

Таблица 1.1

Взаимное соответствие количественных и качественных мер сложности ИС

Наименование ИС Вид ИС Технология изготовления ИС Количество элементов и/нли компо- нентов на кристалле

Малая интегральная микросхема (МИС) Цифровая Аналоговая Биполярная, униполярная Биполярная I ...100 1...30

Средняя интегральная микросхема (СИС) Цифровая » Аналоговая Униполярная Биполярная Биполярная, униполярная 101...1000 101.. 500 31...Ю0

Большая интегральная микросхема (БИС) Цифровая » Аналоговая Униполярная Биполярная Биполярная, униполярная 1001... 10 000 501...2000 101...300

Сверхбольшая интег ральная микросхема {СБИС) Цифровая » Аналоговая Униполярная Биполярная Биполярная, униполярная Более 10 000 Более 2 000 Более 300

Нетрудно отметить, что аналоговые БИС насыщены элемента-

ми во много раз меньше, чем цифровые БИС (особенно униполяр-

ные).

Особо следует сказать о том, что сверхскоростной интеграль-

ной микросхемой (ССИС) названа микросхема, имеющая время

установления для цифровых сигналов 2,5 нс/ЛЭ (ЛЭ — логический

элемент) или нижнюю границу рабочего диапазона частот не ме-

нее 300 МГц. Кроме того, как при построении РЭА, так и при

выборе ее элементной базы большое значение имеет так называе-

мая плотность упаковки элементов. Под плотностью упаковки по-

нимается отношение числа элементов и компонентов ИС к ее объ-

ему (без учета объема выводов).

9

1.2.4. МИКРОСБОРКИ И МИКРОВЛОКИ

В ГОСТ 17021—75 кроме терминов, имеющих прямое отноше-

ние к ИС дается в виде справочного материала целый ряд терми-

нов, связанных с областью применения ИС. Особо следует ука-

зать на термины: микросборки и микроблоки.

Термин микросборка имел в литературе ряд синонимов. В

ГОСТ 17021—75 введено определение микросборки как микроэлек-

тронного изделия, выполняющего определенную функцию и состо-

ящего из элементов, компонентов и ИС (корпусных и бескорпус-

ных), а также других электрорадиоэлементов, находящихся в раз-

личных сочетаниях. Это изделие разрабатывается и изготавлива-

ется конструкторами РЭА с целью ее миниатюризации.

ГОСТ не определяет микросборку как корпусное или бескор-

пусное изделие, т. е. микросборка может иметь или не иметь соб-

ственный корпус. Таким образом, микросборка не классифициру-

ется в ГОСТе по своей сложности.

Микроблок — это микроэлектронное изделие, которое, кроме

микросборок, может содержать ИС и компоненты.

Термин уровень миниатюризации микроэлектронного изделия

характеризует выгоды, получаемые от снижения объема, массы

и потребляемой аппаратурой энергии. Показателями уровня ми-

ниатюризации РЭА являются: соответствие ее современному тех-

ническому уровню микроэлектронных изделий; соответствие дру-

гих применяемых в РЭА изделий современному уровню миниатю-

ризации; эффективность комплексной миниатюризации аппарату-

ры; техническая совместимость «неинтегральных» изделий элект-

ронной техники и электротехники с ИС.

1.3. Классификация ИС

В зависимости от технологии изготовления ИС могут быть по-

лупроводниковыми, пленочными или гибридными. В ГОСТ

17021—75 даются следующие определения этим трем разновидно-

стям ИС.

В полупроводниковой 1 ИС все элементы и межэлементные со-

единения выполнены в объеме и на поверхности полупроводника.

В пленочной ИС все элементы и межэлементные соединения

выполнены только в виде пленок проводящих и диэлектрических

материалов. Вариантами пленочных являются тонкопленочные и

толстопленочные ИС.

Различие между тонкопленочными и тол'стопленочными ИС

может быть количественным и качественным. К тонкопленочным

1 Иногда полупроводниковую ИС называют «твердой» (или «твердотель-

ной») схемой, что является буквальным переводом с английского. В ГОСТ

17021—75 такое определение признано недопустимым (solid state — твердое

состояние, твердое тело в физике).

10

условно относят ИС с толщиной пленок до 1 мкм, а к толстопле-

ночным — ИС с толщиной пленок свыше 1 мкм. Качественные раз-

личия определяются технологией изготовления пленок. Элементы

тонкопленочной ИС наносятся на подложку, как правило, с помо-

щью термовакуумного осаждения и катодного распыления, а эле-

менты толстопленочной ИС изготавливаются преимущественно

методом шелкографии с последующим вжиганием.

Наконец, к гибридным микросхемам относят ИС, содержащие,

кроме элементов, простые и сложные компоненты (например, кри-

сталлы полупроводниковых ИС). Частным случаем гибридной ИС

является многокристальная ИС (совокупность нескольких бескор-

пусных ИС на одной подложке).

В зависимости от функционального назначения ИС делятся на

две основные категории — аналоговые и цифровые. Аналоговые

ИС (АИС) предназначены для преобразования и обработки сигна-

лов, изменяющихся по закону непрерывной функции. Частным

случаем АИС является ИС с линейной характеристикой (линейная

микросхема, ЛИС). К цифровым относятся ИС, с помощью кото-

рых преобразуются и обрабатываются сигналы, выраженные в

двоичном или другом коде. Вариантом определения ЦИС явля-

ется термин логическая микросхема (операции с двоичным кодом

описываются логической алгеброй).

Одновременно с понятием БИС в ГОСТ 17021—75 присутству-

ют два термина: БИС и базовый комплект БИС. Это обстоятельст-

во вызвано необходимостью совместной комплексной разработки

и применения БИС, представляющих собой в этом случае по сути

узлы и блоки микроэлектронной аппаратуры.

БИС, составляющие комплект, хотя и выполняют различные

функции, но совместимы по конструктивному исполнению и элек-

трическим параметрам. Они обеспечивают возможность приме-

нять при построении микроэлектронной аппаратуры общие «ар-

хитектурные» приемы. Минимальный состав комплекта БИС, не-

обходимый для решения определенного круга аппаратурных за-

дач, называется базовым.

Как отклик на появление микропроцессорной техники в 1981 г.

в ГОСТ 17021—75 были добавлены четыре термина. Микропро-

цессор определен как устройство, управляемое программным спо-

собом, осуществляющее процесс обработки цифровой информации

и управления. Это устройство изготовлено на основе одной или

нескольких БИС.

В свою очередь, микропроцессорной названа ИС, выполняющая

функцию МП или его части. Совокупность этих и других ИС,

совместимых по архитектуре, конструктивному исполнению и элек-

трическим параметрам, названа микропроцессорным комплектом

(МПК). По аналогии с базовым комплектом БИС базовым МПК

называется минимальный состав такого комплекта, т. е. набор

ИС, необходимый для построения основных узлов МП или конт-

роллера.

11

1.4. Система условных обозначений ИС

Аналоговые и цифровые ИС разрабатываются и выпускаются

предприятиями-изготовителями в виде серий. Каждая серия от-

личается степенью комплектности и содержит несколько ИС, ко-

торые, в свою очередь, подразделяются на типономиналы.

К серии интегральных микросхем согласно ГОСТ 17021—75 от-

носят совокупность ИС, которые могут выполнять различные

функции, но имеют единое конструктивно-технологическое испол-

нение и предназначены для совместного применения. Как прави-

ло, с течением времени состав перспективных серий расширяется.

Под типономиналом ИС понимается ИС, имеющая конкретное

функциональное назначение и свое условное обозначение. Под

типом ИС понимается совокупность типономиналов ИС, имеющих

конкретное функциональное назначение и свое условное обозна-

чение.

Все многообразие выпускаемых серий ИС согласно принятой

системе условных обозначений по конструктивно-технологическо-

му исполнению делится на три группы: полупроводниковые, гиб-

ридные, прочие. К последней группе относят часто пленочные ИС,

которые в настоящее время выпускаются в ограниченном количе-

стве, а также вакуумные и керамические ИС. Указанным груп-

пам в системе условных обозначений присвоены следующие циф-

ры: 1, 5, 6, 7 — полупроводниковые ИС (обозначение 7 присвоено

бескорпусным полупроводниковым ИС); 2, 4, 8 — гибридные ИС;

3 — прочие ИС.

По характеру выполняемых функций в радиоэлектронной аппа-

ратуре ИС подразделяются на подгруппы (например, генера-

торы, модуляторы, триггеры, усилители) и виды (например, пре-

образователи частоты, фазы, длительности, напряжения). Клас-

сификация ИС по функциональному назначению приведена в

табл. 1.2. Здесь буквенные обозначения расставлены по алфавиту.

По принятой системе обозначение ИС должно состоять из че-

тырех элементов. Первый элемент—-это цифра, соответствующая

конструктивно-технологической группе. Второй элемент — две-три

цифры, присвоенные данной серии ИС как порядковый номер раз-

работки. Таким образом, первые два элемента составляют три-че-

тыре цифры, определяющие полный номер серии ИС. Третий эле-

мент — две буквы, соответствующие подгруппе и виду ИС (см.

табл. 1.2). Четвертый элемент — порядковый номер разработки

ИС в данной серии, в которой может быть несколько одинаковых

по функциональному признаку ИС. Он может состоять как из од-

ной цифры, так и из нескольких.

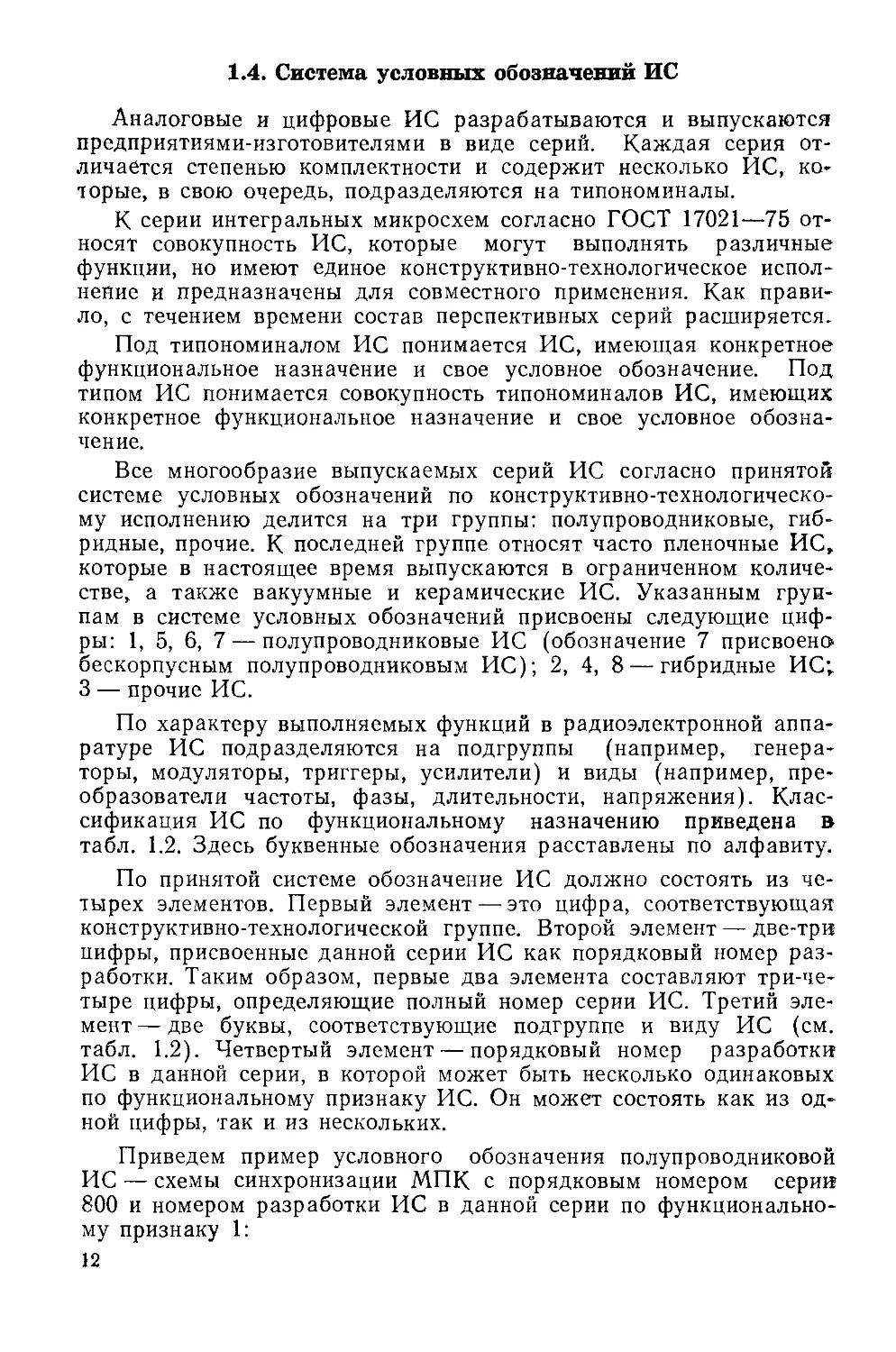

Приведем пример условного обозначения полупроводниковой

ИС — схемы синхронизации МПК с порядковым номером серии

800 и номером разработки ИС в данной серии по функционально-

му признаку 1:

12

Серия

1 ~"~800 В Б 1

— — — — —1~Условиый номер разработки ИС в данной

I серии по функциональному признаку

Вид (по функциональному назначению)

Подгруппа

Порядковый номер данной серии

Группа (по конструктивно-технологическому исполнению)

Полное обозначение ИС: 1800ВБ1.

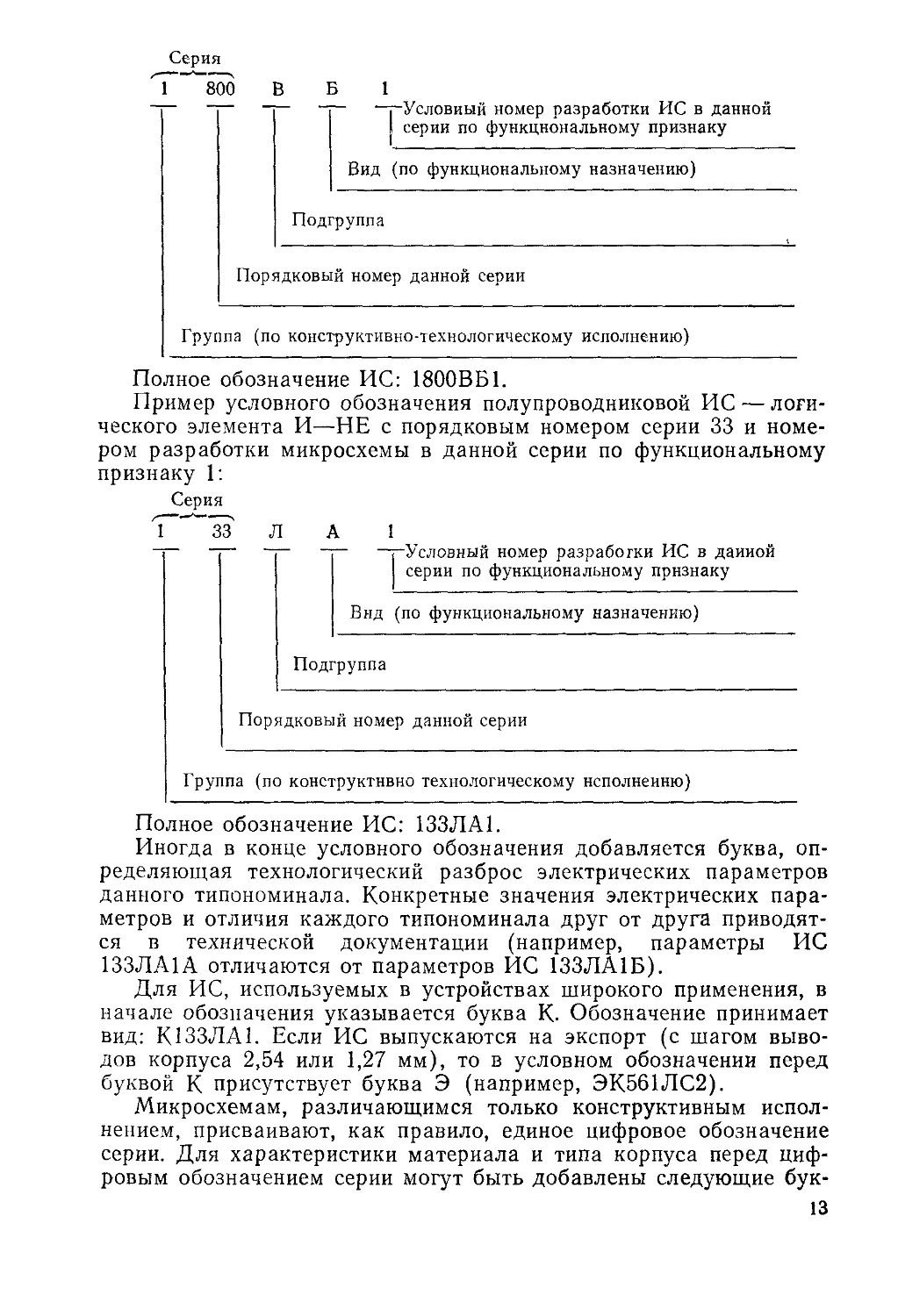

Пример условного обозначения полупроводниковой ИС — логи-

ческого элемента И—НЕ с порядковым номером серии 33 и номе-

ром разработки микросхемы в данной серии по функциональному

признаку 1:

Серия

5 ”зз Л А 1

— — — — —«-Условный номер разработки ИС в данной

серии по функциональному признаку

Внд (по функциональному назначению)

Подгруппа

Порядковый номер данной серии

Группа (по конструктивно технологическому исполнению)

Полное обозначение ИС: 133ЛА1.

Иногда в конце условного обозначения добавляется буква, оп-

ределяющая технологический разброс электрических параметров

данного типономинала. Конкретные значения электрических пара-

метров и отличия каждого типономинала друг от друга приводят-

ся в технической документации (например, параметры ИС

133ЛА1А отличаются от параметров ИС 133ЛА1Б).

Для ИС, используемых в устройствах широкого применения, в

начале обозначения указывается буква К. Обозначение принимает

вид: К133ЛА1. Если ИС выпускаются на экспорт (с шагом выво-

дов корпуса 2,54 или 1,27 мм), то в условном обозначении перед

буквой К присутствует буква Э (например, ЭК561ЛС2).

Микросхемам, различающимся только конструктивным испол-

нением, присваивают, как правило, единое цифровое обозначение

серии. Для характеристики материала и типа корпуса перед циф-

ровым обозначением серии могут быть добавлены следующие бук-

13

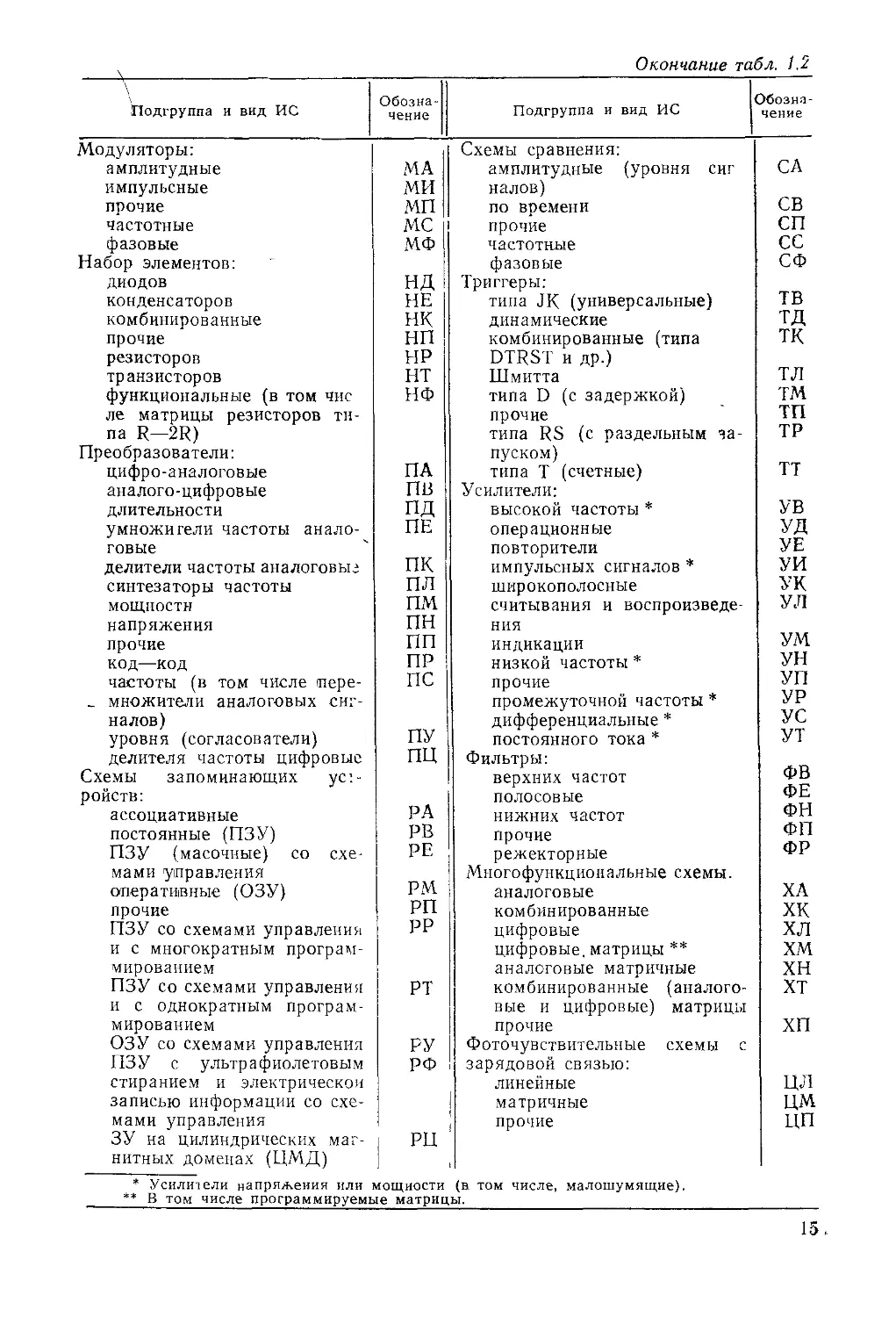

Таблица 1.2

Классификация ИС по функциональному назначению________

Подгруппа и вид ИС Обозна- чение Подгруппа и вид ИС Обозна- чение

Формирователи; шума гм

адресных токов (формирова- АА прочие гп

тели напряжения или токов) гармонических сигналов ГС

импульсов прямоугольной формы (ждущие мультивиб- АГ сигналов специальной формы Детекторы: ГФ

раторы, блокинг-генераторы амплитудные ДА

и др.) импульсные ДИ

разрядных токов (формиро- АР прочие ДП

ватели напряжения нлн то- частотные дс

ков) фазовые ДФ

прочие АП Схемы вторичных источников

импульсов специальной фор- АФ питания:

МЫ выпрямители ЕВ

Схемы задержки: стабилизаторы напряжения ЕК

пассивные БМ импульсные

активные БР преобр азователи ЕМ

прочие Схемы вычислительных средств: БП стабилизаторы напряжения непрерывные ЕН

схемы сопряжения с маги- ВА прочие ЕП

стралью схемы источников вторично- ЕС

схемы синхронизации ВБ го питания

схемы управления вводом- ВВ стабилизаторы тока ЕТ

выводом (схемы интерфей- са) схемы управления импульс- ными стабилизаторами ЕУ

контроллеры ВГ напряжения

микро-ЭВМ BE Схемы арифметических и диск-

специализированные схемы вж ретных устройств:

времязадающие схемы ВИ арифметическо - логические ИА

комбинированные схемы вк устройства

микропроцессоры вм шифраторы ИВ

схемы управления прерыва вн дешифраторы ИД

нием счетчики ИЕ

прочие вп комбинированные ик

функциональные расширите ВР полусумматоры ИЛ

ли (в том числе расширите сумматоры ИМ

ли разрядности данных) прочие ИП

микропроцессорные секции ВС регистры ИР

схемы управления памятью ВТ Коммутаторы и ключи:

схемы микропрограммного ВУ напряжения КН

управления прочие КП

функциональные преобразо- ватели информации (ариф- ВФ тока Логические элементы: кт

метические, тригонометриче- ские, логарифмические, бы строго преобразования Фу- элемент И—НЕ ЛА

элемент И—НЕ/ИЛИ—НЕ ЛБ

расширители лд

рье н др.) элемент ИЛИ—НЕ ЛЕ

микрокалькуляторы вх элемент И ЛИ

Генераторы: элемент И—ИЛИ—НЕ/И— лк

прямоугольных сигналов (в гг ИЛИ

том числе автоколебательные элемент ИЛИ ЛЛ

мультивибраторы, блокинг- элементы ИЛИ—НЕ/ИЛИ ЛМ

генераторы и др.) элемент НЕ ЛН

линейно изменяющихся сиг- гл прочие ЛП

налов элемент И—ИЛИ—НЕ элемент И—ИЛИ ЛР лс

- 14

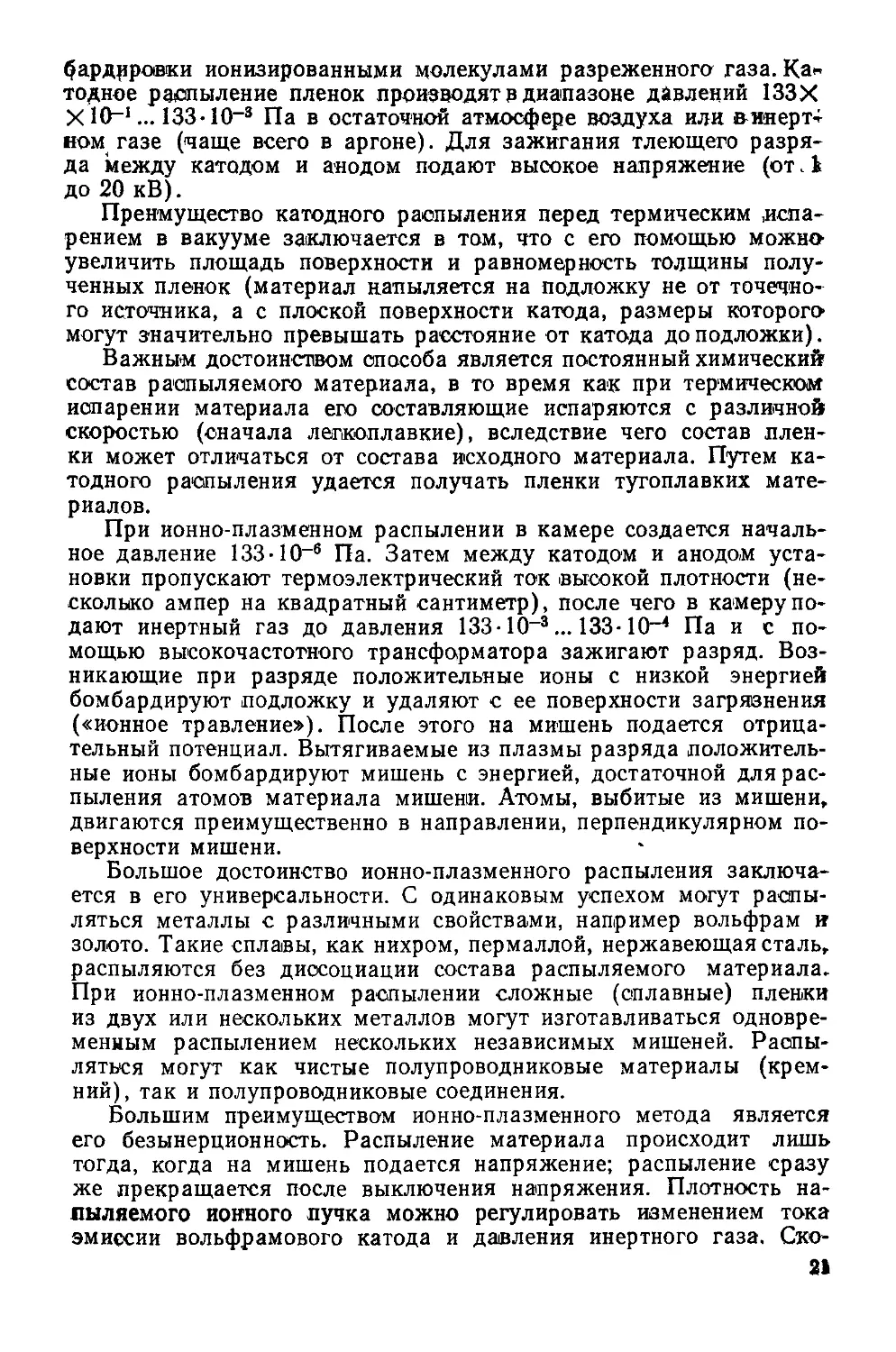

Окончание табл. 1.2

Подгруппа и вид ИС Обозна- чение Подгруппа и вид ИС Обозна- чение

Модуляторы: Схемы сравнения:

амплитудные МА амплитудные (уровня сиг СА

импульсные МИ налов)

прочие МП по времени СВ

частотные мс прочие СП

фазовые МФ частотные сс

Набор элементов: фазовые СФ

диодов ид Триггеры:

конденсаторов НЕ типа JK (универсальные) ТВ

комбинированные НК динамические тд

прочие НП комбинированные (типа тк

резисторов HP DTRST и др.)

транзисторов нт Шмитта тл

функциональные (в том чис НФ типа D (с задержкой) тм

ле матрицы резисторов тн- прочие ТП

па R—2R) типа RS (с раздельным за- ТР

Преобразователи: пуском)

цифро-аналоговые ПА типа Т (счетные) тт

аналого-цифровые ПВ Усилители:

длительности пд высокой частоты * УВ

умножители частоты анало- ПЕ операционные УД

говые повторители УЕ

делители частоты аналоговые ПК импульсных сигналов * УИ

синтезаторы частоты ПЛ широкополосные к

мощности пм считывания и воспроизведе- УЛ

напряжения ПН НИЯ

прочие пп индикации УМ

код—код ПР низкой частоты * УН

частоты (в том числе пере- ПС прочие УП

_ множители аналоговых сиг- промежуточной частоты * УР

налов) дифференциальные * УС

уровня (согласователи) ПУ постоянного тока * УТ

делителя частоты цифровые ПЦ Фильтры:

Схемы запоминающих ус:- верхних частот ФВ

ройств: полосовые ФЬ

ассоциативные РА нижних частот ФИ

постоянные (ПЗУ) РВ прочие ФП

ПЗУ (масочные) со схе- РЕ режекторные ФР

мами управления Многофункциональные схемы.

оперативные (ОЗУ) РМ аналоговые ХА

прочие РП комбинированные хк

ПЗУ со схемами управления рр цифровые ХЛ

и с многократным програм- цифровые, матрицы ** ХМ

мированием аналоговые матричные хн

ПЗУ со схемами управления РТ комбинированные (аналоге- XT

и с однократным програм- вые и цифровые) матрицы

мированием прочие хп

ОЗУ со схемами управления РУ Фоточувствительные схемы с

ПЗУ с ультрафиолетовым РФ зарядовой связью:

стиранием и электрической линейные цл

записью информации со схе- матричные цм

мами управления прочие ЦП

ЗУ на цилиндрических маг- РП

нитных доменах (ЦМД)

* Усилители напряжения или мощности (в том числе, малошумящие).

** В том числе программируемые матрицы.

15.

вы: Р — для пластмассового корпуса второго типа, М — для кера-

мического, металлокерамического и стеклокерамического корпу-

са второго типа, Е — для металлополимерного корпуса второго

типа, А — для пластмассового планарного корпуса и И — для

стеклокерамического планарного корпуса.

В условных обозначениях ИС, выпускаемых в бескорпусном

варианте, перед номером серии добавляют букву Б. Таким обра-

зом, бескорпусные аналоги обычной серии 155 обозначаются

Б155. Для бескорпусных ИС в состав условного обозначения через

дефис вводится цифра, характеризующая соответствующую моди-

фикацию конструктивного исполнения: с гибкими выводами— 1, с

ленточными (паучковыми) выводами, в том числе на полиимидной

пленке, — 2, с жесткими выводами — 3, на общей пластине (не-

разделенные) — 4, разделенные без потери ориентировки (напри-

мер; наклеенные на пленку) — 5, с контактными площадками без

выводов (кристалл) —6 (например, Б533ЛА1-1, Б533ЛА1-2,

Б533ЛА1-6).

Самая большая по составу — серия К155. Она содержит более

100 типономиналов.

ГЛАВА 2

МЕТОДЫ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

2.1. Пленочная и гибридная технология

В Настоящее время с помощью пленочной технологии можно де-

лать пассивные элементы (резисторы, конденсаторы, катушки ин-

дуктивности), а также изготавливать соединительные проводники,

контактные площадки и элементы СВЧ схем (такие, как полоско-

вые волноводы, аттенюаторы, разветвители). Активные пленочные

элементы (транзисторы и диоды) изготавливаются пока только в

лабораторных условиях для исследовательских целей. Таким обра-

зом, выпускаемые в СССР и за рубежом чисто пленочные ИС яв-

ляются пассивными (обычно — это резистивные делители напряже-

ния, наборы резисторов и конденсаторов, резистивно-емкостные це-

пи). Пленочные интегральные элементы гораздо чаще используют-

ся совместно с миниатюрными дискретными ЭРЭ — компонентами

гибридных ИС. Гибридные ИС, уступая полупроводниковым ИС по

надежности, плотности упаковки и себестоимости, имеют в ряде

случаев особые схемотехнические преимущества за счет примене-

ния широкой номенклатуры навесных компонентов (транзисторов,

индуктивностей, конденсаторов).

Гибридная технология весьма гибкая. Она позволяет относи-

тельно быстро создавать электронные устройства, выполняющие

достаточно сложные функции. Комплект оборудования для изготов-

ления гибридных ИС, а также микросборок и микроблоков (см.

п. 1.2.4), дешевле, чем для изготовления полупроводниковых ИС.

В настоящее время освоение гибридной технологии доступно прак-

тически любому предприятию [1].

16

Элементы пленочных и гибридных ИС и микросборок (резисто-

ры, конденсаторы, индуктивности) Выполняются на поверхности

подложки в виде пленок резистивных, проводящих и диэлектри-

ческих материалов.

Преимуществом гибридной технологии является и более высо-

кий процент выхода годных ИС (60... 80% по сравнению с 5...30%

для полупроводниковых ИС). Брак, возникший при изготовлении-

гибридной ИС, часто можно исправить. Методы расчета и проек-

тирования гибридных ИС практически не отличаются от методов

расчета обычных электронных схем. Однако подложка гибридной

ИС мала и изготовлена из высококачественного диэлектрика. По-

этому из-за малых паразитных емкостей и хорошей взаимной изо-

ляции элементов и компонентов гибридная ИС имеет лучшие вы-

сокочастотные и импульсные электрические свойства, чем схема,

собранная из дискретных «больших» ЭРЭ. Гибридные ИС наибо-

лее часто применяются в прецизионной аппаратуре.

При изготовлении гибридных ИС используются как тонкие, так

и толстые пленки. Толстопленочные ИС [2] дешевле. Для органи-

зации их производства требуются меньшие капитальные затраты

(проще оборудование, менее жесткие требования к производствен-

ным помещениям). Кроме того, толстопленочные ИС обладают

большей механической прочностью, имеют лучшую коррозионную

и теплоустойчивость, повышенную перегрузочную способность эле-

ментов, а также меньшие паразитные емкости межсоединений и

слабое взаимовлияние (наводки и паразитные связи) элементов.

Тонкопленочные ИС отличаются тем, что без подгонки можно

получать более узкие допуски на номиналы элементов (резисторов

и конденсаторов), достигается более высокая плотность размеще-

ния элементов на подложке. Они обладают меньшими высокоча-

стотными потерями и имеют более высокую радиационную стой-

кость (за счет использования меньшей номенклатуры химических

элементов с большой атомной массой).

В аналоговых системах повышенной сложности, где требуется

высокая стабильность резисторов, предпочтительнее использовать

тонкопленочные гибридные ИС и микросборки. Масштабы пред-

полагаемого производства также определяют выбор типа пленок.

Если требуется небольшое количество изделий, то нецелесообразно

создавать производство тонкопленочных ИС, которое требует зна-

чительно больших капитальных затрат, и предпочтение следует от-

дать толстопленочной технологии.

Отметим, что в обоих случаях более 50% затрат приходится на

фотолитографическое оборудование.

2.1.1. МАТЕРИАЛЫ ДЛЯ ГИБРИДНЫХ ИС И МИКРОСБОРОК

Подложки для гибридных структур изготавливаются из ситал-

ла, стекла, керамики. Основные требования к подложкам: хоро-

шие механические и диэлектрические свойства, согласование по

температурному коэффициенту расширения с другими материала-

17

ми, а также высокая чистота поверхности (12—14-й класс по ГОСТ

278а—73). Наиболее распространены прямоугольные подложки с

размерами: 6X15, 8X12, 11X11, 10X16, 12X12, 12X16, 12x20,

16x20, 24x30, 48x60 мм (при этом отклонения от номинального

размера составляют не более 0,3 мм и непараллельность сторон не

превышает 0,5 мм). Используются подложки толщиной 0,6; 1,0 и

1,6 мм (с отклонением не более 0,1 мм) [3].

Подложка для толстопленочных ИС должна быть теплостой-

кой, чтобы выдерживать обжиг при температурах в сотни граду-

сов, когда происходит оплавление и закрепление материалов, из

которых изготавливаются элементы ИС. Чтобы уменьшить пара-

зитную емкость между элементами, выбираются материалы с не-

большой диэлектрической проницаемостью (если этот эффект не

используется как полезный). При изготовлении мощных ИС ис-

пользуют подложки с высокой теплопроводностью, например из бе-

риллиевой керамики, теплопроводность которой только в 5 раз

хуже теплопроводности меди.

Резистивные пленки независимо от материала характеризуют-

ся удельным сопротивлением квадрата поверхности рп. Эта вели-

чина является объективной характеристикой пленок и зависит от

удельного сопротивления материалов и толщины пленки (но не

зависит от размеров квадрата по поскости).

Для изготовления резисторов используют хром, нихром, тантал,

сплав МЛТ, металлокерамику, проводящие краски и пасты. Эти

материалы позволяют получить диапазон значений рп от 20Ом до

20 кОм. Для лучшей адгезии к подложке резистивные металличе-

ские слои располагаются на вспомогательных подслоях металлов.

Параметры некоторых резистивных материалов приведены в табл.

2.1 [3].

Наиболее подходящей для тонких резистивных пленок считает-

ся толщина от 0,01 до 0,2 мкм. Задавшись толщиной пленки в этих

пределах, подбирают материал, обеспечивающий необходимое

удельное сопротивление рц . При этом следует учитывать, что вы-

Таблица 21

Параметры резистивных материалов

Материал р|—। Ом ткс 10 тс Допустимая мощность, Вт/см2 Допуск на но ми ->а п, %

Хром (на Си с подслоем Сг) Нихром (на Си с подслоем Сг) Тантал (на Аи с подслоем Сг) Окись олова Сплав МЛТ 34 (на Си с подслоем С ) Металлокерамика на основе окисла палладия Проводящая краска на основе угле рода 20 . 800 100 300 50 500 500 300 500 До 20 000 10 000 4-180 4-250 —400 ±300 ±200 ±200 500 . 1000 2,0 2,0 3,0 2 3 4,0 1,0 До 1 0 0,15 0,35 ±5 ±5 ±5 ±2 ±5 ± ю ±10

18

бирать материалы с высоким сопротивлением не всегда выгодно,

так как при извлечении из вакуумной камеры в результате окис-

ления на воздухе тонкие пленки иногда изменяют свое сопротив-

ление до 50%. Для тонкопленочных резисторов лучше всего выби-

рать материалы с рп = 100 ...500 Ом, для толстопленочных —

10 Ом... 20 кОм.

В качестве материалов для тонкопленочных проводников ис-

пользуют медь и золото с подслоем нихрома, алюминий, никель.

Если при изготовлении пленочных конденсаторов диэлектриком

служит моноокись кремния как материал обкладок, лучше всего

применять алюминий, поскольку его электрофизические свойства

хорошо согласуются со свойствами кремния. Толщина проводни-

ков выбирается в пределах 0,3... 1 мкм (толщина адгезионного

подслоя 0,01 ...0,03 мкм). Для изготовления контактных площадок

часто используется золото. Толщина контактных площадок обычно

выбирается большей 0,5 мкм.

Толстопленочные проводники должны иметь удельное сопротив-

ление не более 0,1 Ом/D и допускать пайку в зоне контактных

площадок. Применяют два вида толстопленочных проводниковых

материалов: пасты на основе золота и платины, допускающие об-

жиг при температуре до 900° С, и на основе серебра, обжигаемые

при температуре до 700° С.

В качестве диэлектриков при изготовлении пленочных конден-

саторов применяются моноокись кремния, сульфид цинка, аноди-

рованный тантал, халькогенидные стекла (ХГ-44, ИКС-24). Свой-

ства пленок из моноокиси кремния в сильной степени зависят от

скорости испарения и состава остаточных газов в вакуумной каме-

ре. Пленки из сульфида цинка менее критичны к условиям напы-

ления. При выборе материала диэлектрика следует по возможности

лучше согласовывать его структуру со структурой остальных мате-

риалов пленочной схемы. Максимальная толщина диэлектрических

пленок ограничивается результирующим внутренним механическим

напряжением и составляет около 1,5 мкм. Минимальная толщина

пленки диэлектрика ограничивается пористостью структуры и за-

данными рабочими напряжениями (около 0,06 мкм). Чтобы полу-

чить минимальное количество «проколов» диэлектрика, напыление

делают в несколько приемов (часто—'различными материалами).

В «слоёном» диэлектрике вероятность совпадения дефектов очень

невелика.

Удельные емкости, получаемые при использовании моноокиси

кремния (е = 6), лежат в пределах 5000.. 10 000 пФ/см2 Для по-

лучения больших емкостей можно использовать анодированный

тантал (е = 25), окислы титана (е = 80) и титанат бария (е=1000).

Электрическая прочность диэлектрических пленок в значительной

степени зависит от металла обкладок конденсатора. Металлы с до-

вольно высокой температурой испарения (например, никель и

хром) дают большое число коротких замыканий, так как атомы

этих металлов, обладая высокой кинетической энергией, проходят

сквозь тонкую пленку диэлектрика при нанесении на нее верхней

19

обкладки. Золото и серебро также могут быть причиной замыка-

ния обкладок, которое происходит из-за интенсивной диффузии

(миграции) атомов этих металлов из обкладок вдоль границ зерен

пленки спустя некоторое время после нанесения.

Для обкладок тонкопленочных конденсаторов чаще применяют

алюминий, который имеет невысокую температуру испарения и

малую миграционную подвижность из-за окислительной самопас-

сивации его поверхности. Электрическая прочность зависит и от

наличия пор в диэлектрической пленке, так как воздух в порах

ионизируется при меньшем напряжении, чем напряжение пробоя

сплошной пленки. Наличие микроскопических пор может быть свя-

зано с присутствием в испаряемом материале примесей в виде га-

зовых включений. Для межслойной изоляции применяются моно-

окись кремния и халькогенидное стекло ИКС-24 (s = 6, tg 6^0,03,

пробивное напряжение ие менее 0,8-106 В/см, ТКЕ=5-10~4 1/°С в

диапазоне температур —60... +'125°С).

2 1.2. ИЗГОТОВЛЕНИЕ ЭЛЕМЕНТОВ ГИБРИДНЫХ ИС И МИКРОСБОРОК

Основными способами получения тонкопленочных элементов яв-

ляются термическое испарение в вакууме, катодное и ионно-плаз-

менное распыление, осаждение пленок из паровой и газовой фазы.

Толстопленочные элементы создаются на подложке методом шел-

кографии. Выбор конкретного метода получения пленок зависит от

многих факторов, особенно от состава наносимого вещества, состо-

яния поверхности, температуры подложки, требуемой толщины и

используемого метода ее контроля. В промышленности широкое

применение получил метод напыления тонких пленок путем терми-

ческого испарения в вакууме. Основные достоинства этого мето-

да— простота и универсальность. На термовакуумных установках

одного типа можно быстро получать однородные слои металлов,

сплавов, полупроводников и диэлектриков различной толщины, а

также изготавливать тонкие пленки из разнородных веществ при

различной толщине подслоя.

Для испарения вещество нагревают. При этом используется

джоулево' тепло, выделяющееся в проводниках при прохождении

через них электрического тока. Можно применять также нагрев

электронным пучком, высокочастотным полем, электрической дугой.

При нагреве в вакууме вещество плавится, а затем переходит в па-

рообразное состояние. В обычных промышленных вакуумных уста-

новках используют давление в пределах 133-10~5... 133-10-6 Па.

Однако часто для улучшения структуры пленок требуется более

глубокий вакуум (до 133-10~8... 133-10-9)..

Процесс получения пленок путем термического испарения в ва-

кууме имеет стадии испарения вещества и свободной конденсации

его паров на подложке. Подложка располагается над тиглем с ве-

ществом (рабочей поверхностью вниз).

Для нанесения тонких пленок методом катодного распыления

используется явление разрушения катода в результате его бом-

20

бардировки ионизированными молекулами разреженного газа. Ка*

годное распыление пленок производят в диапазоне давлений 133Х

X10-1... 133-10-3 Па в остаточной атмосфере воздуха или винерт-^

ном газе (чаще всего в аргоне). Для зажигания тлеющего разря-

да между катодом и анодом подают высокое напряжение (от. к

до 20 кВ).

Преимущество катодного распыления перед термическим испа-

рением в вакууме заключается в том, что с его помощью можно

увеличить площадь поверхности и равномерность толщины полу-

ченных пленок (материал напыляется на подложку не от точечно-

го источника, а с плоской поверхности катода, размеры которого1

могут значительно превышать расстояние от катода до подложки).

Важным достоинством способа является постоянный химический

состав распыляемого материала, в то время как при термическом

испарении материала его составляющие испаряются с различной

скоростью (сначала легкоплавкие), вследствие чего состав плен-

ки может отличаться от состава исходного материала. Путем ка-

тодного распыления удается получать пленки тугоплавких мате-

риалов.

При ионно-плазменном распылении в камере создается началь-

ное давление 133-10-6 Па. Затем между катодом и анодом уста-

новки пропускают термоэлектрический ток высокой плотности (не-

сколько ампер на квадратный сантиметр), после чего в камеру по-

дают инертный газ до давления 133-10-3... 133-10-4 Па и с по-

мощью высокочастотного трансформатора зажигают разряд. Воз-

никающие при разряде положительные ионы с низкой энергией

бомбардируют подложку и удаляют с ее поверхности загрязнения

(«ионное травление»). После этого на мишень подается отрица-

тельный потенциал. Вытягиваемые из плазмы разряда положитель-

ные ионы бомбардируют мишень с энергией, достаточной для рас-

пыления атомов материала мишени. Атомы, выбитые из мишени,

двигаются преимущественно в направлении, перпендикулярном по-

верхности мишени.

Большое достоинство ионно-плазменного распыления заключа-

ется в его универсальности. С одинаковым успехом могут распы-

ляться металлы с различными свойствами, например вольфрам и

золото. Такие сплавы, как нихром, пермаллой, нержавеющая сталь,

распыляются без диссоциации состава распыляемого материала.

При ионно-плазменном распылении сложные (сплавные) пленки

из двух или нескольких металлов могут изготавливаться одновре-

менным распылением нескольких независимых мишеней. Распы-

ляться могут как чистые полупроводниковые материалы (крем-

ний), так и полупроводниковые соединения.

Большим преимуществом ионно-плазменного метода является

его безынерционность. Распыление материала происходит лишь

тогда, когда на мишень подается напряжение; распыление сразу

же прекращается после выключения напряжения. Плотность на-

пыляемого ионного пучка можно регулировать изменением тока

эмиссии вольфрамового катода и давления инертного газа. Ско-

21

рость осаждения может изменяться в очень широких пределах: от

десятых долей нанометра до десятых долей микрона в минуту.

Равномерность толщины пленки при ионно-плазменном распылении

достигает 1...2%, что значительно выше, чем при катодном рас-

пылении, где вносятся искажения непроводящей подложкой, рас-

положенной между катодом и анодом. Благодаря высокой энергии

попадающих па подложку атомов прочность сцепления с подлож-

кой пленки, полученной при ионно-плазменном методе, получается

очень высокой.

Для напыления диэлектрических материалов плазма зажигает-

ся с помощью радиочастотного излучения.

Недостатком ионно-плазменного распыления считается меньшая

скорость наращивания пленки, однако в ионно-плазменные установ-

ки можно одновременно загружать десятки подложек. Такие уста-

новки часто имеют автоматическое управление.

Главное преимущество метода осаждения из газовой фазы со-

стоит в легкости управления процессом и его отдельными стадия-

ми. При этом можно сравнительно легко вводить в растущую плен-

ку примеси и получать слои с заранее заданными свойствами. Ме-

тод применяется при изготовлении металлических, резистивных и

диэлектрических пленок. При этом в результате разложения слож-

ного химического соединения или химической реакции двух или бо-

лее веществ продукт реакции осаждается в виде пленки на под-

ложку. Реакция может происходить под воздействием тепла (пи-

ролитическое разложение), света (фотохимическое разложение), в

результате гидролиза, воздействия электрического поля и других

факторов.

После нанесения на подложку пленочных,пассивных элементов

на ней монтируются компоненты транзисторы, диоды, конденсато-

ры, трансформаторы, кристаллы полупроводниковых ИС [4]. Ком-

поненты с жесткими выводами крепятся' к пЛате путем пайки или

приварки их выводов к контактным площадкам платы. Компонен-

ты с гибкими выводами крепятся к плате с Помощью эпоксидных

клеев или припаиваются. В первом случае компонент электрически

изолирован от платы, во втором — он может иметь электрический

контакт. Способ крепления компонентов к плате должен обеспечи-

вать хорошую механическую прочность крепления, отсутствие на-

пряжений в месте крепления, химическую стойкость и нейтраль-

ность материалов, применяемых для креплейия, их высокую теп-

лопроводность, низкую температуру образования и высокую рабо-

чую температуру получающих соединений.

Эпоксидные клеи имеют небольшую усадку при отвердении, хо-

рошую адгезию к различным материалам, не выделяют побочных

продуктов, химически стабильны. Температура их полимеризации

подбором отвердителей может быть выбрана в широком диапазоне

значений, включая нормальную. Очень удобны в применении клее-

вые пленки.

Крепление с помощью спая кристаллов бескорпусных полупро-

водниковых ИС, транзисторов, диодов осуществляется образованн-

ой

ем эвтектических сплавов между поверхностью полупроводника и

слоем золота на плате. Плату подогревают до температуры при-

мерно 370° С, кристалл помещают на золотую контактную площад-

ку и прижимают с определенным усилием. В результате происходит

взаимное растворение кремния и золота с образованием эвтекти-

ческого оплара на границе раздела.

2 1 3 МОНТАЖ ЭЛЕКТРИЧЕСКИХ СОЕДИНЕНИИ В ГИБРИДНЫХ ИС

И МИКРОСБОРКАХ

Выводы компонентов, прикрепленных к плате, присоединяют к

контактным площадкам, а выходные контактные площадки соеди-

няют с выводами корпуса. В большинстве случаев такие соедине-

ния осуществляются с помощью золотых или алюминиевых прово-

лочек диаметром 25... 50 мкм термокомпрессионной, контактной

или ультразвуковой сваркой.

Наиболее широко применяется термокомпрессионная сварка,

при которой совмещается давление с подогревом. Плату и золотую

проволочку в месте контакта нагревают до температуры 200 ...

... 400° С, проволочку прижимают к контактной площадке платы с

усилием от 0,05 до 0,5 Н в течение нескольких секунд. Метод тер-

мокомпрессии требует тщательного подбора и контроля основных

параметров процесса: давления, температуры и времени сварки.

Контактная сварка осуществляется расщепленным электродом.

Качество контакта зависит от его площадки, удельного сопротив-

ления поверхности раздела, сопротивления свариваемых деталей.

В связи с этим режим сварки следует тщательно подбирать для

конкретных условий.

Ультразвуковая сварка, основанная на одновременном воздей-

ствии колебаний ультразвуковой частоты, возбужденных в свари-

ваемых деталях, и давления в области сварки, обеспечивает луч-

шее качество сварного соединения, меньшую температуру сварки,

более широкий набор свариваемых металлов, чем термокомпрессия.

Она позволяет также осуществлять сварку групповым способом.

2.2. Полупроводниковая технология

Особенности полупроводниковых ИС следующие [5] Стоимость элементов

микросхемы в значительной степени определяется площадью, занимаемой ими

иа полупроводниковой пластине Таким образом, стоимость транзистора оказы-

вается приблизительно равной стоимости диода, которая, в свою очередь, при-

мерно соответствует стоимости резистора с номиналом 4 кОм при допуске ±30%

или с номиналом 1 кОм при допуске ±20%. Номиналы элементов, имеющих

дискретные прототипы, ограничены. Практически нецелесообразно использовать

для массовых ИС «чистые» резисторы с номиналами свыше 50 кОм Конденса-

торы с емкостью, превышающей несколько сотен пикофарад, приходится при-

менять в виде отдельных навесных элементов Желаемые номиналы резисторов

не могут иметь малые допуски, хотя отношение сопротивлений одинаковых по

форме резисторов иа одной пластине можно выдерживать довольно точно

23

(1...2%), причем их температурная зависимость будет одинакова. Все элементы

полупроводниковой структуры связаны между собой паразитными емкостями

и проводимостями, что обусловлено плотной упаковкой н несовершенством ме-

тодов изоляции элементов.

Преимущества полупроводниковых ИС перед гибридными таковы:

более высокая надежность вследствие меньшего числа контактных соедине-

ний, ограниченного количества используемых материалов, а также из-за того,

что полупроводниковую ИС можно изготовить только из монокристаллической,

сверхчистой, полупроводниковой структуры;

большая механическая прочность благодаря меньшим (примерно на поря-

док) размерам элементов;

меньшая себестоимость изготовления полупроводниковых ИС вследствие бо-

лее эффективного использования преимуществ групповой технологии.

В полупроводниковых ИС в качестве активных элементов могут использо-

ваться биполярные и униполярные (полевые) интегральные структуры. Полу-

проводниковые ИС (особенно цифровые) с биполярными транзисторами отли-

чаются более высоким импульсным быстродействием (или рабочей частотой).

Полупроводниковые цифровые ИС с униполярными транзисторами со структу-

рой МОП отличаются наиболее высокой плотностью упаковки элементов и наи-

меньшей стоимостью изготовления.

Цифровые ИС со структурой КМОП очень экономичны по потребляемой

мощности. Аналоговые ИС с полевыми приборами имеют большое входное со-

противление (более 109 Ом). Технология униполярных транзисторов позволяет

добиваться лучших шумовых характеристик. Биполярные транзисторы увели-

чивают стабильность работы схем в широком диапазоне температур, позволяют

реализовать наибольшее быстродействие н создать схемы с лучшей нагрузочной

способностью. Биполярные структуры более устойчивы к электрическим нагруз-

кам Перспективны биполярные цифровые структуры И2Л, конкурентоспособ-

ные с КМОП по экономичности и плотности упаковки элементов

Следует заметить, что возможности униполярных структур пока раскрыты

далеко не полностью (особенно онн хороши для перспективных радиочастотных

приборов и операционных усилителей).

Ввиду сложности оборудования и жестких требований к условиям произ-

водства полупроводниковых ИС изготовление их становится экономически целе-

сообразным только при массовом производстве (миллионы штук в год на одном

комплекте оборудования). Поэтому по полупроводниковой технологии целесо-

образно изготавливать: цифровые ИС н ИС для реализации стандартных ана-

логовых функций, а также высоконадежные микросхемы для построения аппа-

ратуры с наивысшей плотностью упаковки.

2 2 1. МАТЕРИАЛЫ ДЛЯ ЭЛЕМЕНТОВ ПОЛУПРОВОДНИКОВЫХ ИС

И ИХ ИЗГОТОВЛЕНИЕ

Для изготовления полупроводниковых ИС используют в большинстве слу-

чаев пластины монокристаллического кремния р- или n-типа проводимости,

снабженные эпитаксиальными н так называемыми «скрытыми» слоями. В ка-

честве легирующих примесей, с помощью которых изменяют проводимость

исходного материала пластины, применяют соединения бора, сурьмы, фосфора,

алюминия, галия, индия, мышьяка, золота. Для создания межсоединений и кои-

24

тактных площадок используют алюминий и золото. Весьма перспективен как

материал проводников кристаллический поликремний, который ие обладает по-

лупроводниковыми свойствами, как материал диэлектрических покрытий н изо-

ляции элементов двуокись кремния н нитрид кремния. Применяемые материалы

должны обладать очень высокой чистотой: содержание примесей в большинстве

материалов, используемых при изготовлении полупроводниковых микросхем, не

должно превышать 10-5 ... 10~9 частей основного материала.

Изменяя определенным образом концентрацию примесей в различных частях

монокристаллической полупроводниковой пластины, можно получить многослой-

ную структуру, воспроизводящую заданную электрическую функцию и до из-

вестной степени эквивалентную обычному дискретному резистору, конденсатору,

диоду или транзистору [5].

Процесс изготовления современных полупроводниковых ИС весьма сложен.

Он проводится только в специальных помещениях с микроклиматом на преци-

зионном оборудовании. Основные технологические операции изготовления полу-

проводниковых микросхем можно разделить на шесть этапов.

1. Механическая обработка кремния. От цилиндрического слитка монокри-

сталлического кремния отделяются круглые пластины толщиной 250...600 мкм

(прн этой операции толщина нарушенного приповерхностного слоя монокристал-

ла может превышать 80 мкм). Для снятия нарушенного слоя пластины шлифуют-

ся и нумеруются, в результате толщина этого слоя уменьшается до 1...2 мкм.

Для окончательной доводки поверхности пластин применяется химическое трав-

ление. В настоящее время диаметр пластин доходит до 150 мм.

2. Эпитаксиальное наращивание. Термин «эпитаксия» обозначает процесс

ориентированного наращивания монокристаллической решетки кремния пластины

за счет осаждения слоев. Прн введении дополнительных примесей получают

эпитаксиальные слои (пленки с заданным типом проводимости). Например, иа

пластине кремния с проводимостью л-тила можно получить эпитаксиальную

пленку с проводимостью p-типа. Эпитаксиальный слой, представляющий собой

монокристаллическое продолжение основного материала, ие имеет механических

дефектов и напряжений. Эпитаксиальное наращивание производят в специаль-

ных печах прн температуре около 1200°С. Скорость увеличения толщины плеи-

кн — несколько микрометров в час.

Наиболее широко используются эпитаксиальные пленки толщиной 1... 10 мкм,

однако для получения современных полупроводниковых цифровых ИС с высо-

ким быстродействием толщину пленки приходится уменьшать до единиц микро-

метров

3. Окисление поверхности пластины. Для защиты и маскирования поверх-

ности кремния при операциях диффузии применяется окисление пластин в

атмосфере кислорода или паров воды при температуре 1000...1300°С. Толщина

наращиваемого окисла — около 1 мкм.

4. Фотолитография. Комплекс фотолитографических процессов повторяется

в технологическом процессе изготовления полупроводниковых микросхем не-

однократно (от 3 до 14 раз). Каждый раз на окисленную пластину кремния

наносится тонкий слой (толщиной около 1 мкм) светочувствительной эмуль-

син— органического фоторезиста, который засвечивается через фотошаблон от

источника ультрафиолетового излучения. После проявления фоторезиста слабым

раствором щелочи можно «вскрыть» необходимые «окна» иа поверхности окисла

кремния. В этих окнах смесью фтористого аммония и плавиковой кислоты

25

двуокись кремния SiOj стравливается н тем самым селективно (выборочно)

открывается поверхность кремния.

5. Диффузия примеси в кремнии. Этот процесс проводят в диффузионных

печах при температуре примерно 1200°С с применением специальных примесей.

Для получения проводимости л-типа применяют диффузанты: фосфор, сурьму,

мышьяк; для получения проводимости р-типа— бор, галлий, индий.

6. Создание межсоединений. Для создания «монтажа» между элементами

подложки полупроводниковой ИС пластина кремния со сформированными эле-

ментами (транзисторами, диодами и резисторами) покрывается слоем осаж-

денного алюминия толщиной 0.5...2 мкм, который затем в ненужных местах

стравливается через соответствующие окна фоторезиста (после заключительной

операции фотолитографии). При этом на поверхности полупроводника остается

рисунок соединительных алюминиевых проводников, имеющих ширину около

10 мкм, а также контактных площадок.

В настоящее время для создания полупроводниковых ИС на биполярных

транзисторах используется несколько разновидностей технологических процессов,

отличающихся главным образом способами создания изоляции между отдель-

ными элементами.

Наиболее широко применяется традиционная плаиарио-эпитаксиальная тех-

нология с изоляцией элементов при помощи обратносмещенных р-п переходов.

Недостатками такого метода изоляции структур считаются увеличенные пара-

зитные емкости и токи утечки между отдельными элементами, большая площадь

элементов (с учетом площади изолирующих областей), относительно невысокие

пробивные напряжения, низкая радиационная стойкость. Однако структуры с

р-п изоляцией наиболее просты в изготовлении.

В изопланарной технологии изоляция элементов осуществляется травлением

канавок между элементами с последующим термическим окислением поверхности

этих канавок. При этом удается примерно вдвое повысить плотность разме-

щения элементов, повысить радиационную стойкость и надежность ИС, увели-

чить процент выхода годных ИС.

Полипланарная технология предусматривает заполнение зазоров между эле-

ментами поликристаллическим кремнием, что позволяет еще больше увеличить

плотность размещения элементов (в три раза больше, чем в планарном про-

цессе), уменьшить паразитные емкости между элементами, увеличить надеж-

ность ИС.

Еще большую плотность размещения элементов позволяет получить техно-

логия с использованием анизотропного травления каиавок (травление вдоль

кристаллографических осей).

Большое многообразие технологических процессов (как более простых, так

и более сложных, чем биполярные) используется и при изготовлении полупро-

водниковых ИС иа МОП структурах [6]. Эти структуры образованы тремя

слоями: металл (затвор), окисел (изоляция затвора), полупроводник (области

истока, канала и стока). Стандартная технология (металлический затвор с

однослойной диэлектрической изоляцией толщиной около 1 мкм) позволяет

изготавливать МОП транзисторы как с p-каналом, так и с л-каналом (в пер-

вом случае носителями заряда являются дырки, во втором — электроны, по-

этому n-канальные МОИ ИС обладают более высоким быстродействием, чем

р-канальные). Рабочая частота цифровых МОП ИС, выполненных по стандарт-

26

ной технологии, не превышает 1...2 МГц, аналоговых — 300...500 МГц (за счет

большого тока питания).

В МНОП ИС используется двухслойный диэлектрик между металлическим

затвором н полупроводником: слой двуокиси кремния толщиной около 50 мкм

и слой нитрида кремния (Н) толщиной 10...20 мкм. МНОП структуры имеют

пониженное пороговое напряжение по сравнению со стандартными МОП струк-

турами.

С целью повышения быстродействия МОП ИС применяется также прогрес-

сивная технология с использованием кремниевых затворов. Вместо слоя металла

используются области сильнолегироваиного кремния толщиной около 1 мкм.

Этим приемом удается повысить быстродействие цифровых ИС в 3...5 раз, сни-

зить пороговое напряжение открывания ключа н увеличить в 1,5 раза плот-

ность размещения элементов. Изготовление МОП ИС на изолирующих подлож-

ках (сапфир или шпинель с эпитаксиально выращенным слоем кремния тол-

щиной около 1 мкм) позволяет в настоящее время повысить быстродействие

таких ИС до 100 МГц (до 250 МГц в перспективе).

Применение в составе МОП ИС транзисторов с разным типом проводимости

(р-канальных и п-канальных) позволяет создавать цифровые ИС с относительно

высоким быстродействием (до 20 МГц) при очень малой статической потреб-

ляемой мощности (произведение потребляемой мощности на быстродействие

составляет около 1 пДж). Эти структуры называются КМОП (буква К — от

слова комплементарный, дополнительный).

Изготовление МОП ИС с применением двойной диффузии (сначала созда-

ется p-канал, а затем в нем л-слой) позволяет уменьшить длину канала до

1...2 мкм (прн стандартной технологии не удается сделать канал длиной менее

5 мкм), в результате пропорционально увеличивается быстродействие каскада.

На основе арсенида галлия удается изготовить МОП транзисторы с часто-

той генерации до 10 ГГц. В цифровой технике на таких транзисторах можно

получить ключи с временем задержки сигнала менее 1 не.

2.2.2. ТИПОВЫЕ ИНТЕГРАЛЬНЫЕ СТРУКТУРЫ

При создании полупроводниковых ИС наиболее широко применяется пла-

нарно-эпитаксиальная технология (она же используется для изготовления со-

временных дискретных транзисторов). Различие в характеристиках транзисторов

полупроводниковых ИС и «обычных» транзисторов может быть обусловлено

свойствами изолирующей области, в которой находится транзистор на кристалле

полупроводниковой ИС, а также расположением коллекторного вывода (в ин-

тегральных структурах он почти всегда «верхний»).

Интегральные диоды обычно создаются нз транзисторных структур. В ка-

честве диодов могут быть использованы переходы эмиттер — база и коллектор—

база. В некоторых случаях переход эмиттер—база используется как стабилитрон

(диод Зенера).

После формирования р-п перехода необходимо сделать в нужных местах

контактные площадки и соединить между собой отдельные элементы полупро-

водниковой ИС. Если р-п переход был образован методом диффузии, то для

получения хорошего контакта необходимо нанести на поверхность полупровод-

никовой пластины слой металла. Это можно сделать, например, вакуумным

напылением. После вплавления металла в полупроводник образуются низко-

27

омные структуры тина р-р+ или л-л+. К металлическим контактам методом тер-

мокомпрессии прикрепляются внешние выводы. В процессе эпитаксиального на-

ращивания можно избежать напыления металлических контактов, вводя там, где

•то необходимо, сильнолепированные слои типа р+ или п+. Тогда внешние вы-

воды можно присоединять непосредственно к этям слоим тем же методом

термокомпрессии.

Отдельные элементы соединяются друг с другом или с контактными пло-

щадками — дорожками, изготовленными напылением в вакууме алюминия на

предварительно окисленную поверхность полупроводниковой пластины, в кото-

рой протравлены окна для осуществления контакта с полупроводниковой струк-

турой. Область между любой парой омических контактов на полупроводниковой

пластине можно использовать как резистор. Сопротивление такого резистора

будет зависеть от длины и поперечного сечения участка, удельного сопротив-

ления кремния.

Ток в таком объемном полупроводниковом резисторе будет течь по телу

полупроводника, поэтому он меньше подвержен влиянию внешних условий, чем

пленочный резистор. Температурный коэффициент сопротивления в зависимости

от концентрации примесей может быть различным, однако он, как правило,

велик и имеет положительный знак. Сопротивление объемных полупроводни-

ковых резисторов ограничивается только размерами полупроводниковой под-

ложки и практически может доходить до 40 кОм. Резисторы, выполненные в

объеме полупроводниковой пластины, применяются нередко в качестве термо-

компенсирующих (по названию области, где они располагаются, их называют

коллекторными).

Более известны так называемые «базовые» резисторы (их изготавливают

одновременно с базовыми областями п-р-п транзисторов). Это основной тип

диффузионных резисторов, у которых проводящий канал имеет проводимость

/j-типа. Такой канал «ограждается» л-областыо. После подачи иа кристалл

питающих напряжений изолирующие р-п переходы запираются и ток из рези-

стивного канала ие может перетекать в соседние области. Кроме того, в ИС

широко используются нелинейные, «сжатые» сверху запертым р-п переходом

пинч-резисторы. Они высокоомны и не имеют «обычного» эквивалента (это

полевой транзистор с малой крутизной).

Для изготовления прецизионных резистивных матриц полупроводниковых

•цифро-аналоговых преобразователей используются напыленные на поверхност-

ный слой окисла тонкопленочные резисторы. Их номинал легче юстировать

с помощью импульсов лазерного излучения.

Для создания в полупроводниковых структурах конденсаторов небольшой

емкости можно использовать трехслойную структуру типа p+-i-n+. Два слоя

такой структуры очень сильно легируют соответствующими примесями, средний

слой — беспримесный. Емкость структур р+-1-п+ определяется толщиной бес-

примесного слоя и мало зависит от значения обратного напряжения.

В качестве конденсатора малого номинала чаще используют смещенный в

обратном направлении р-п переход. Диэлектриком в таком конденсаторе служит

обедненная носителями область перехода. Для любого полупроводника ем-

кость является функцией ширины обедненной зоны и площади перехода. При

использовании кремния можно получить удельную емкость р-п перехода до

200 000 пФ/см2 при пробивном напряжении в несколько сотен вольт. Так как

28

ширина обедненной зоны зависит от приложенного напряжения, то и емкость

р-п перехода имеет нелинейную зависимость от напряжения.

Конденсаторы иа основе р-п перехода полярные, поэтому они не пригодны

для работы в цепях с переменной составляющей напряжения. Последний не-

достаток можно устранить, если использовать два последовательно соединен-

ных р-п перехода. Емкость такой структуры становится не зависимой от по-

лярности рабочего напряжения и меньше зависит от его амплитуды.

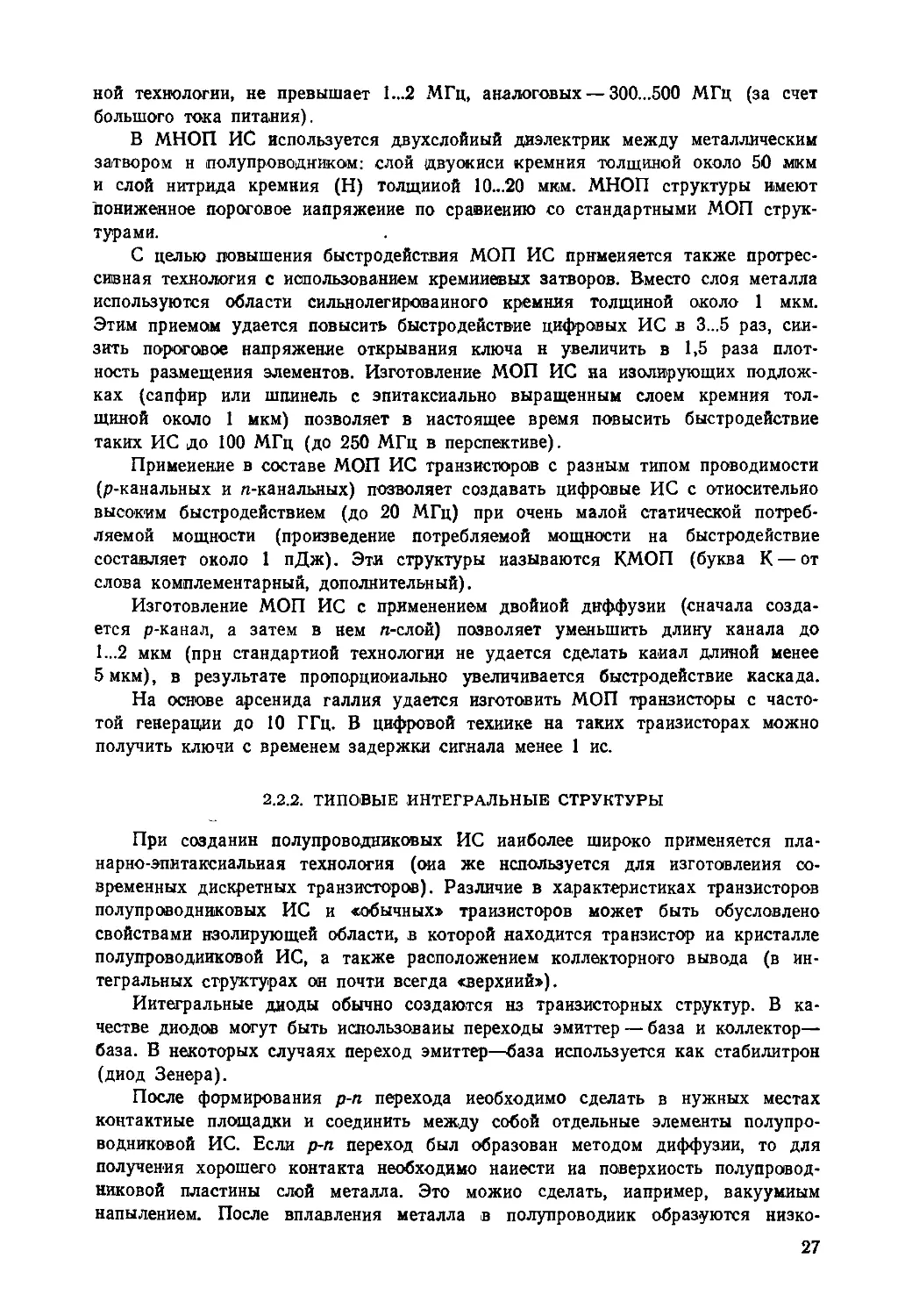

Рассмотрим подробнее некоторые особенности типовых интегральных струк-

тур. Структура эпитаксиально-диффузионного транзистора полупроводниковой

ИС показана на рис. 2.1. На вертикальном разрезе структуры обозначены пять

диффузионных областей: эмиттер, база, эпитаксиальный коллектор, скрытый

диффузионный слой Л+-типа и пластина (подложка). Удельное сопротивление

p-типа равно 10 Ом-см. Эпитаксиальный слой n-типа толщиной 25 мкм, выра-

щенный иа поверхности пластины, имеет удельное сопротивление 0,5 Ом-см.

Под ним расположены диффузионный слой л+-типа (обычно мышьяк) с высо-

кой концентрацией примесей (более Ю19 атом/см3).

Рис. 2.1. Структура транзистора с изоляцией р-п переходом (планарная техно-

логия)

Электрическая изоляция коллекторной области от соседних транзисторов

(когда на схему будет подано положительное относительно подложки питание)

обеспечивается наличием области глубокой разделительной диффузии примеси

p-типа через эпитаксиальный слой в пластину. Эта диффузия проводится пер-

вой. База образуется в процессе второй диффузии примеси p-типа вглубь

эпитаксиальной области коллектора (в это же время делаются базовые и пиич-

резисторы). Типичное сопротивление слоя, образованного во время второй

диффузии (например, диффузант бор, глубина области 2,7 мкм), составляет

200 Ом/О. Эмиттер представляет область n-типа, которая образована во время

третьей диффузии (например, фосфора в область базы иа глубину около

2 мкм). Сопротивление слоя эмиттера составляет приблизительно 2 Ом/П.

Глубина залегания переходов; эмиттер — база 2 мкм, коллектор — база 3 мкм,

коллектор — подложка 25 мкм.

Топология транзистора дает представление о размещении такой структуры

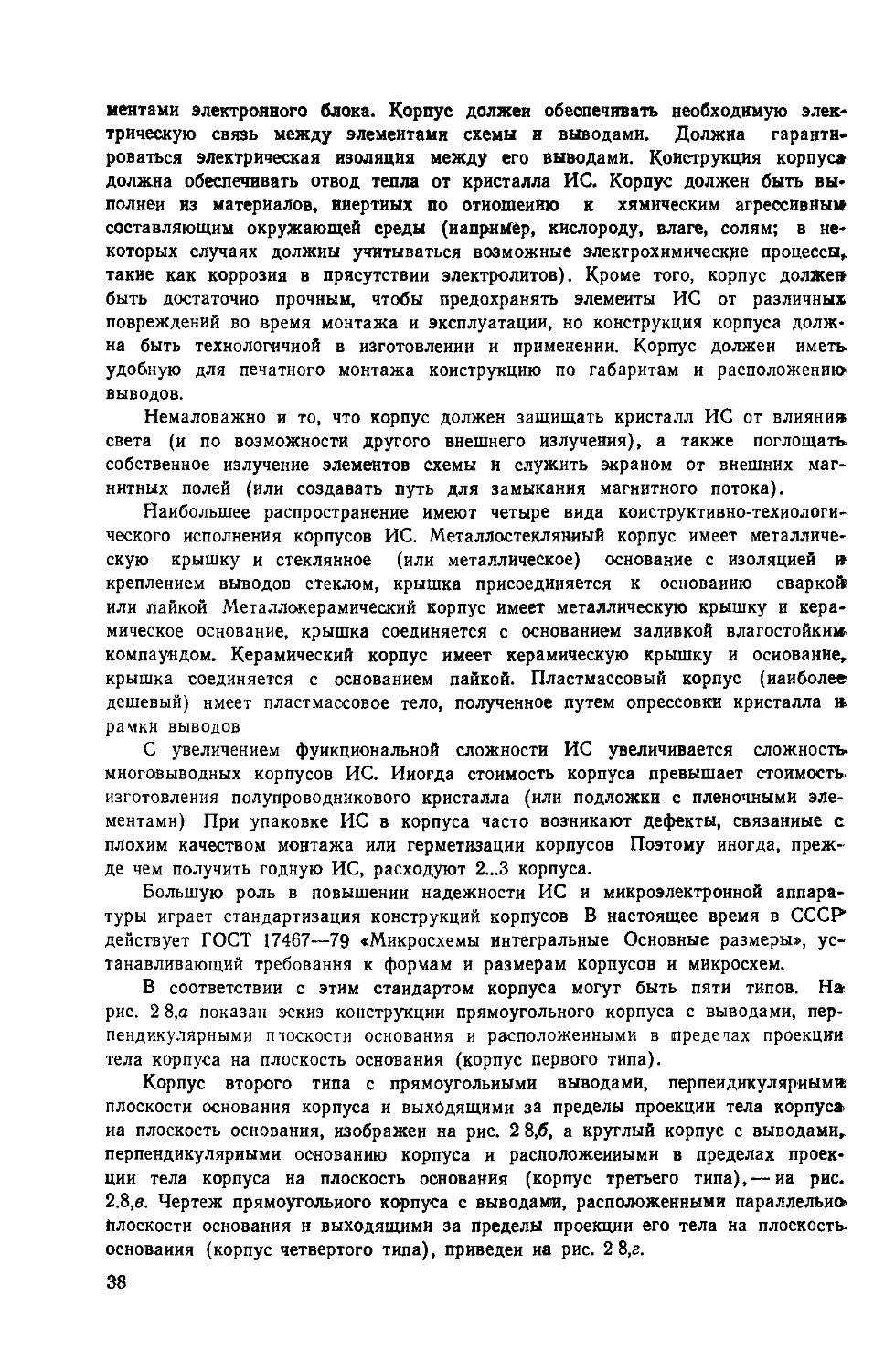

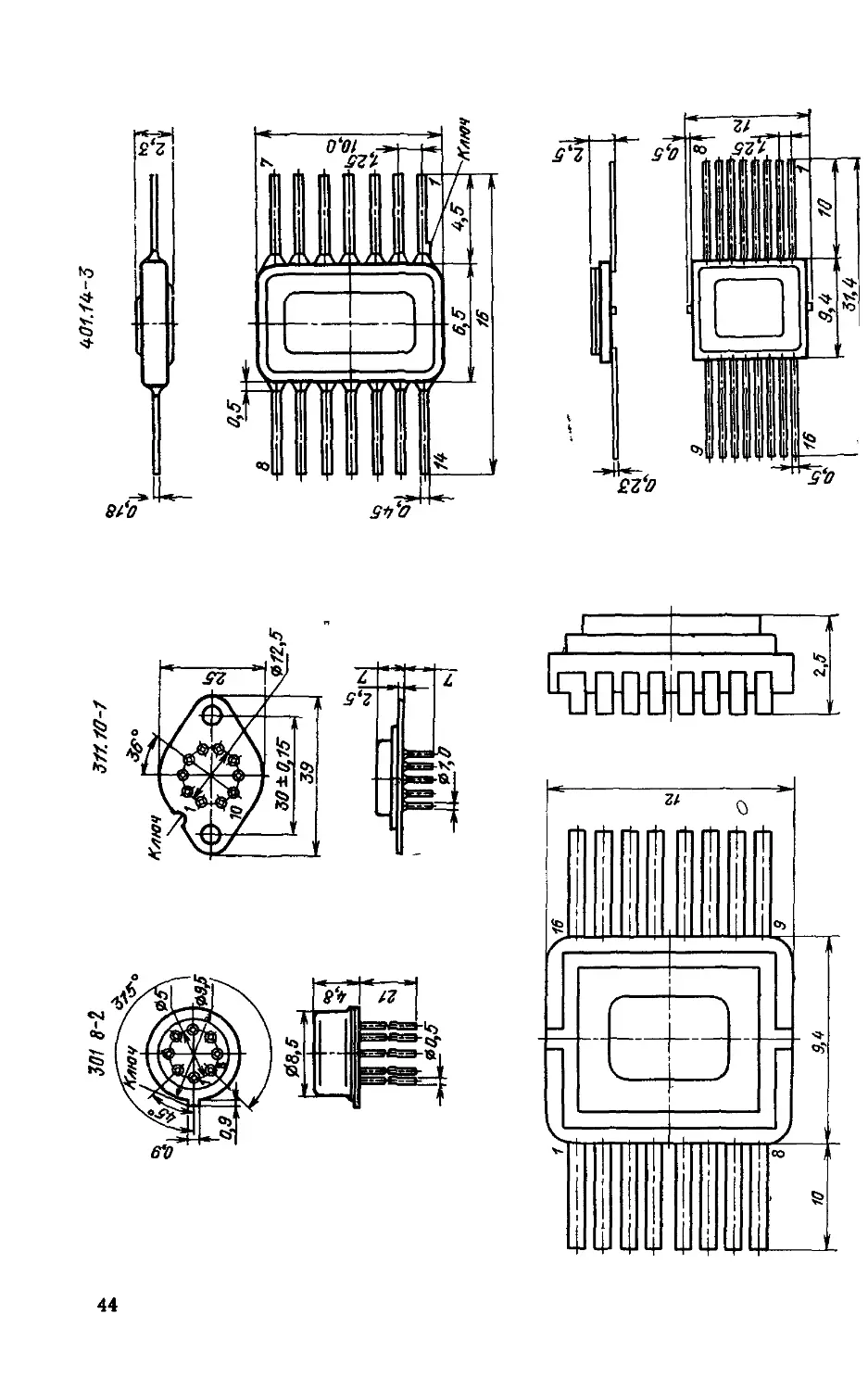

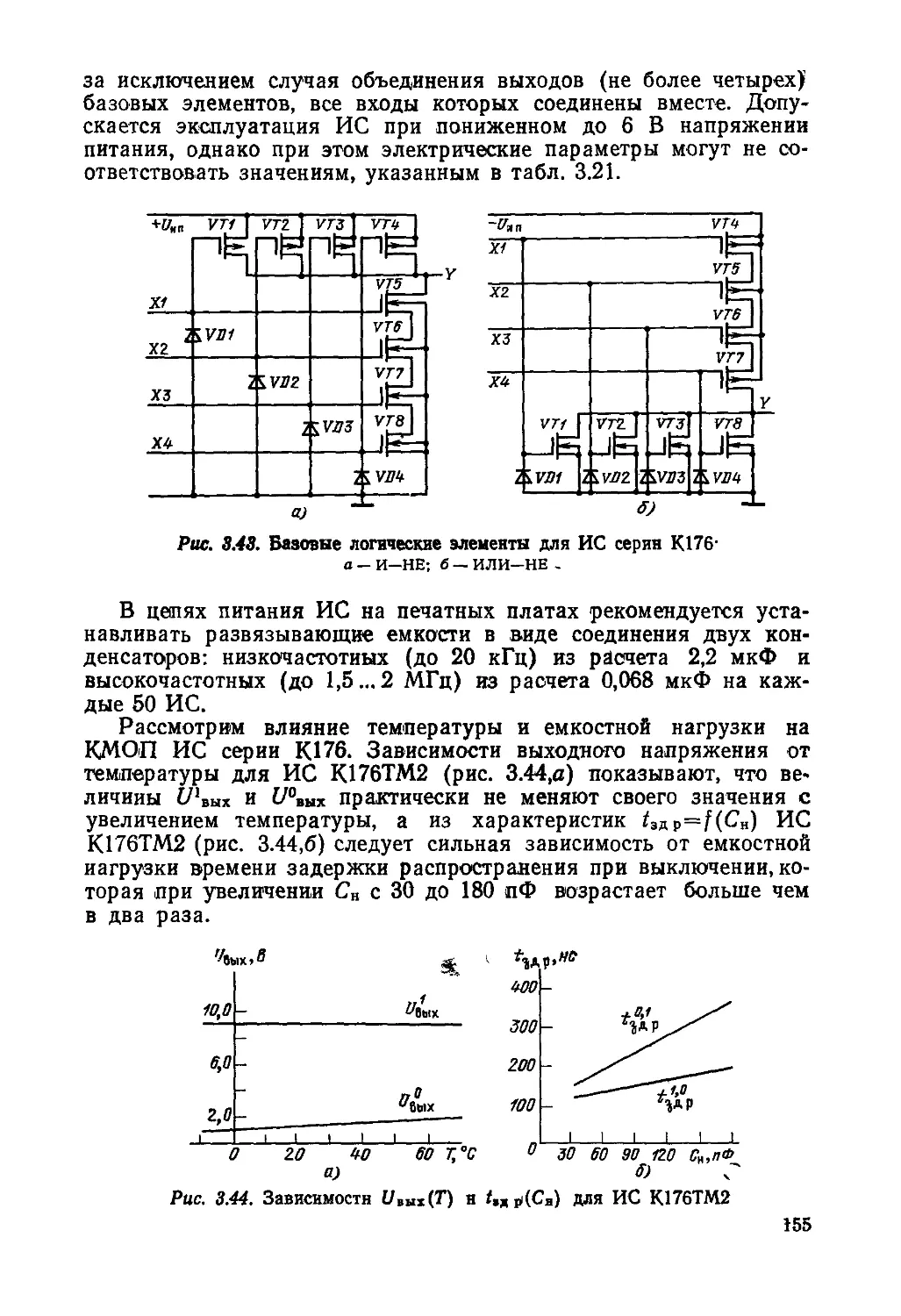

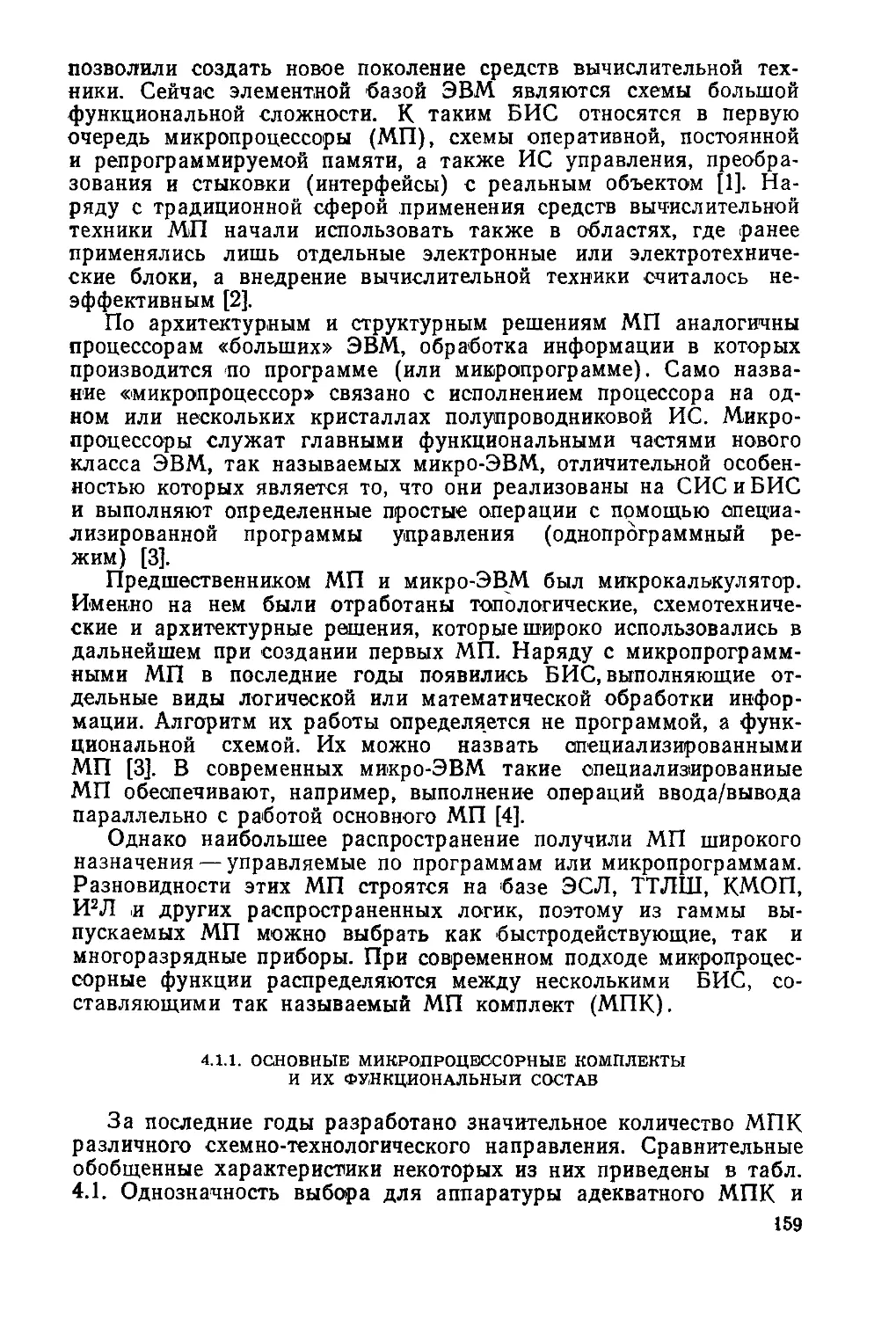

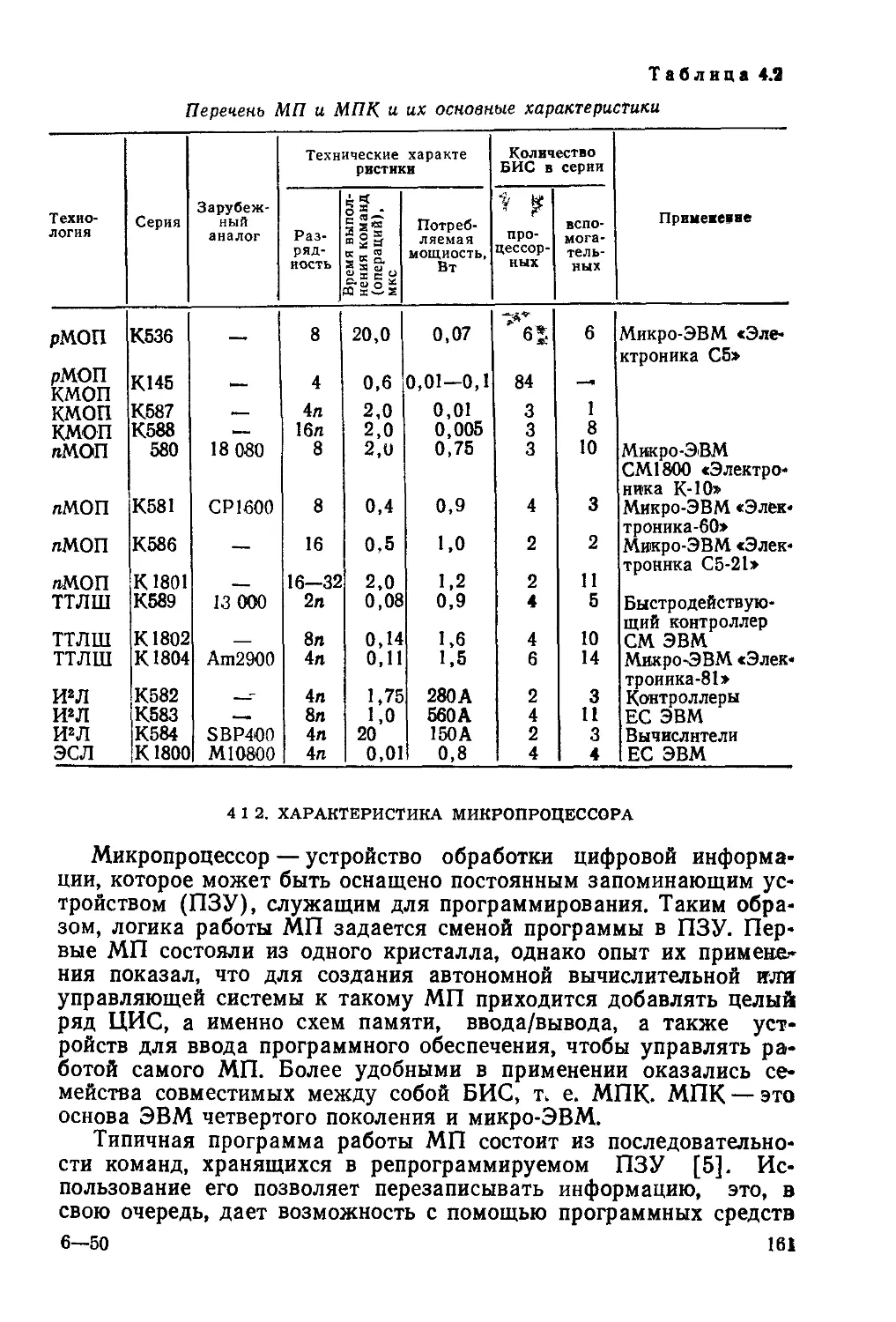

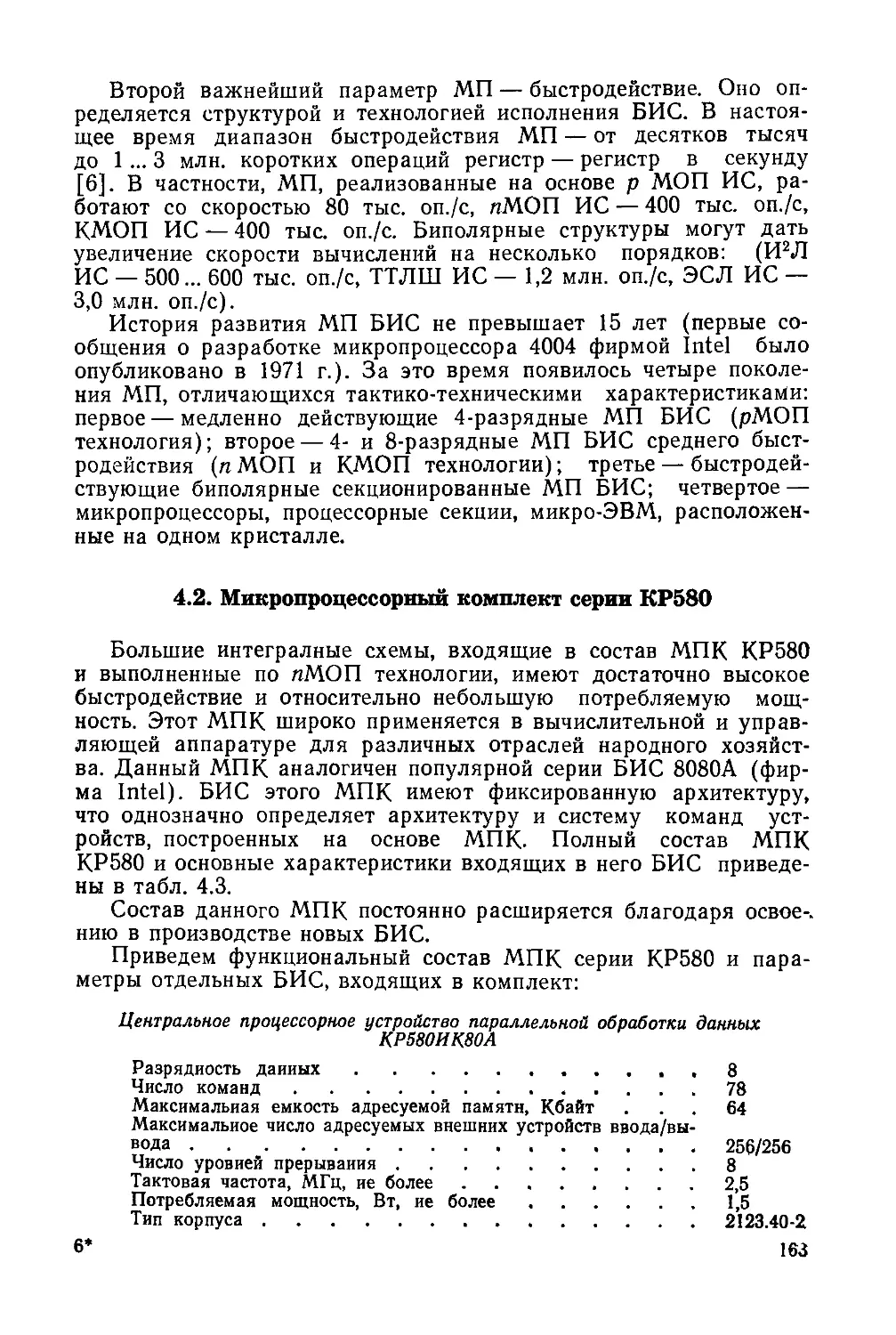

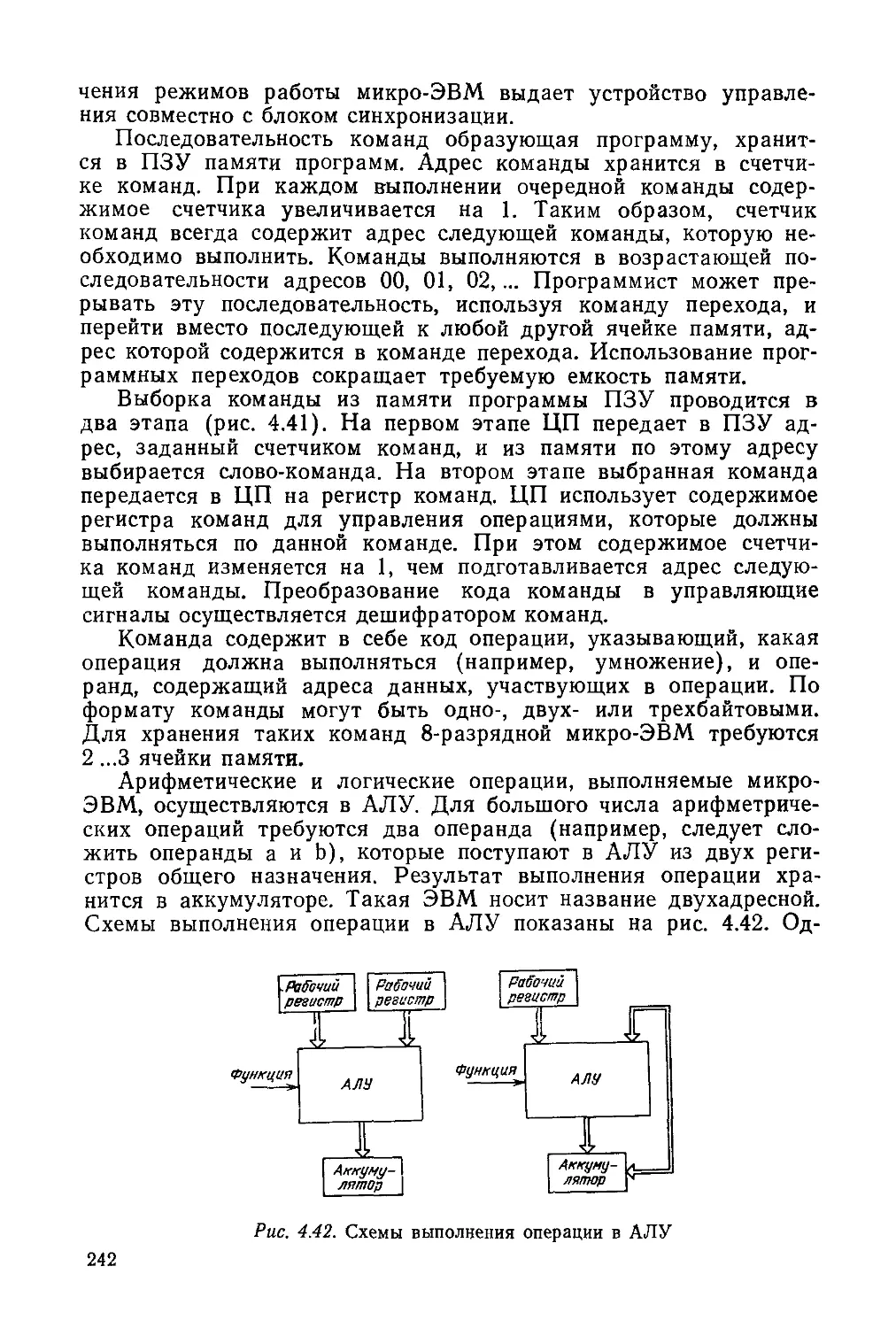

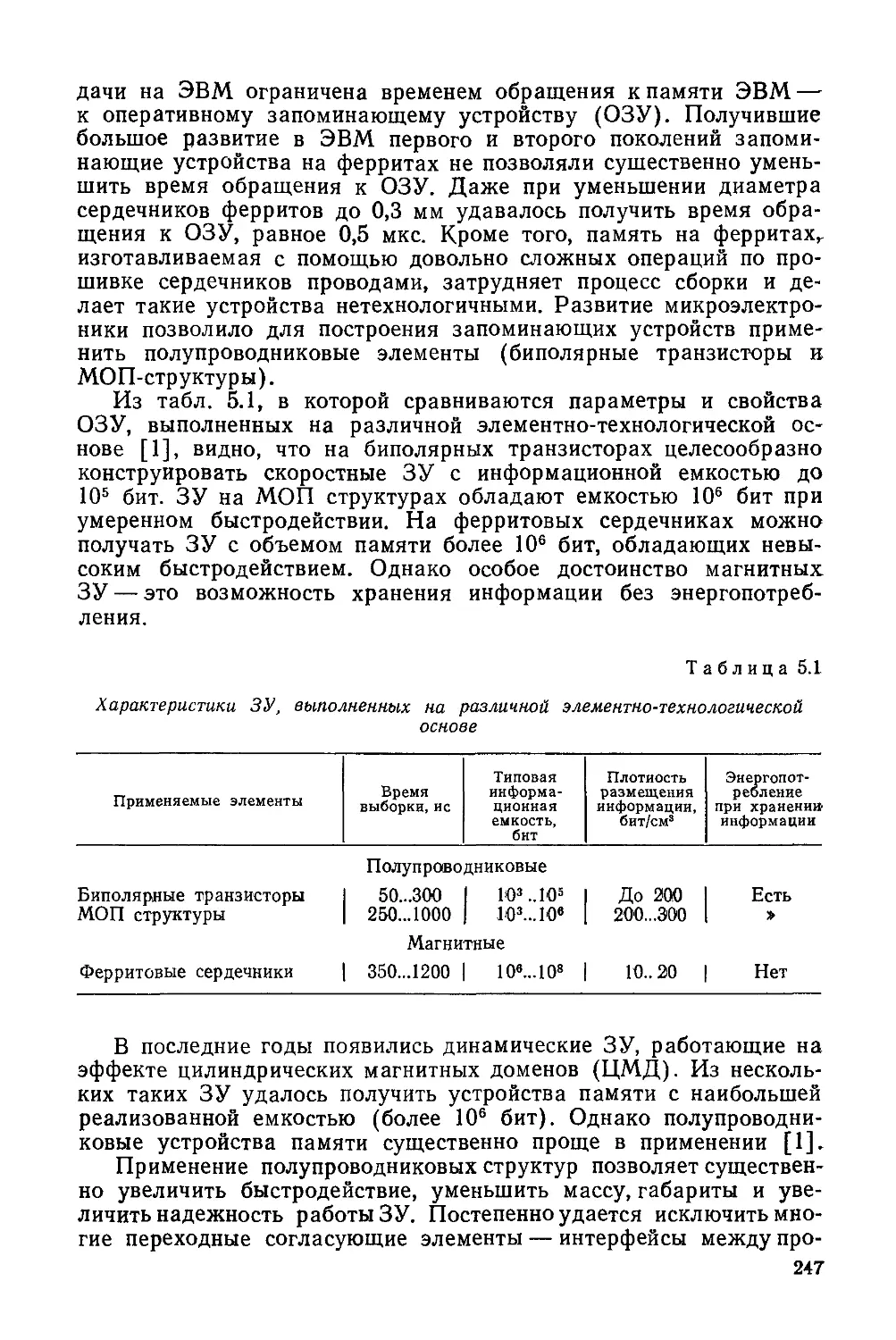

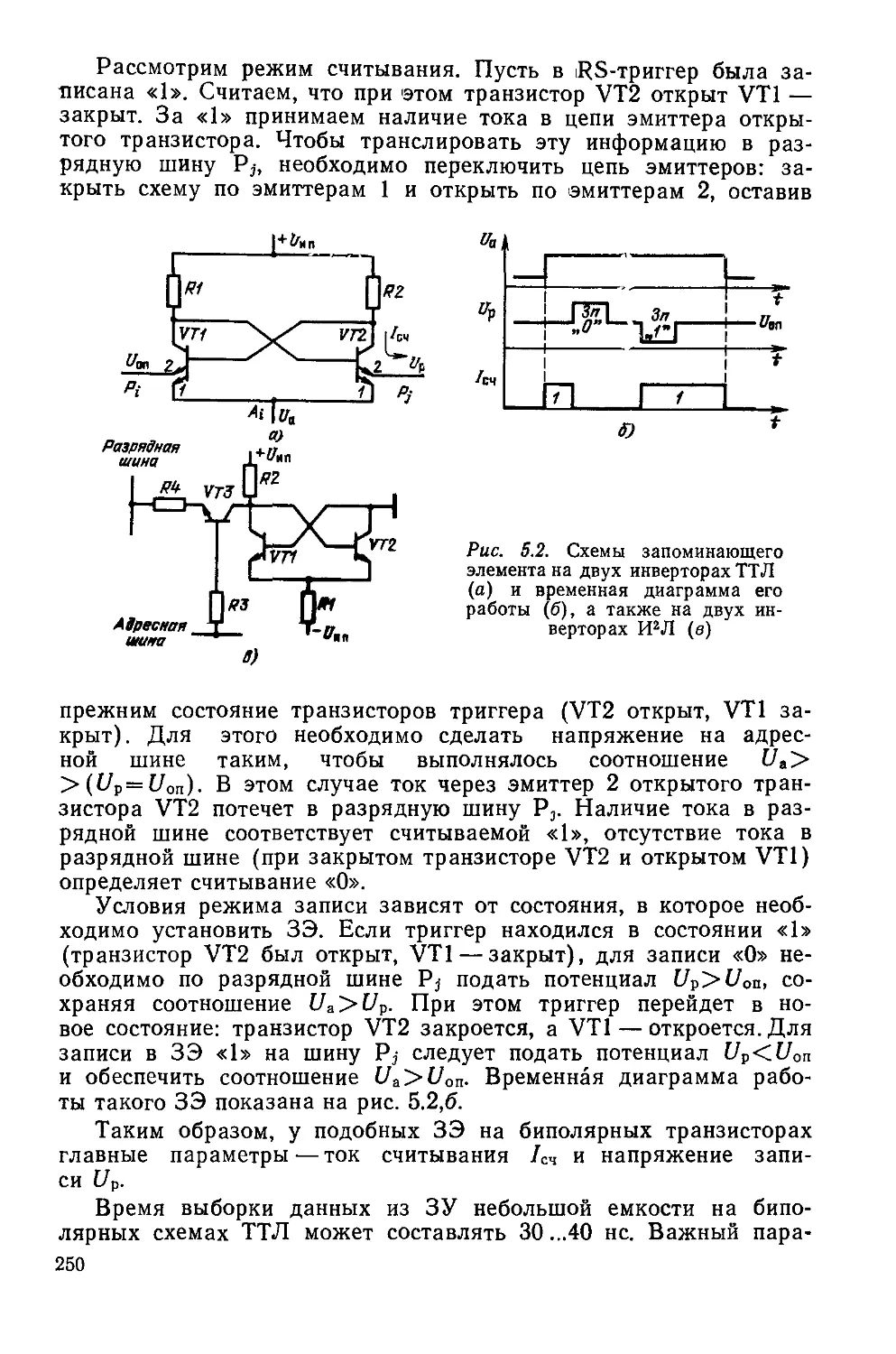

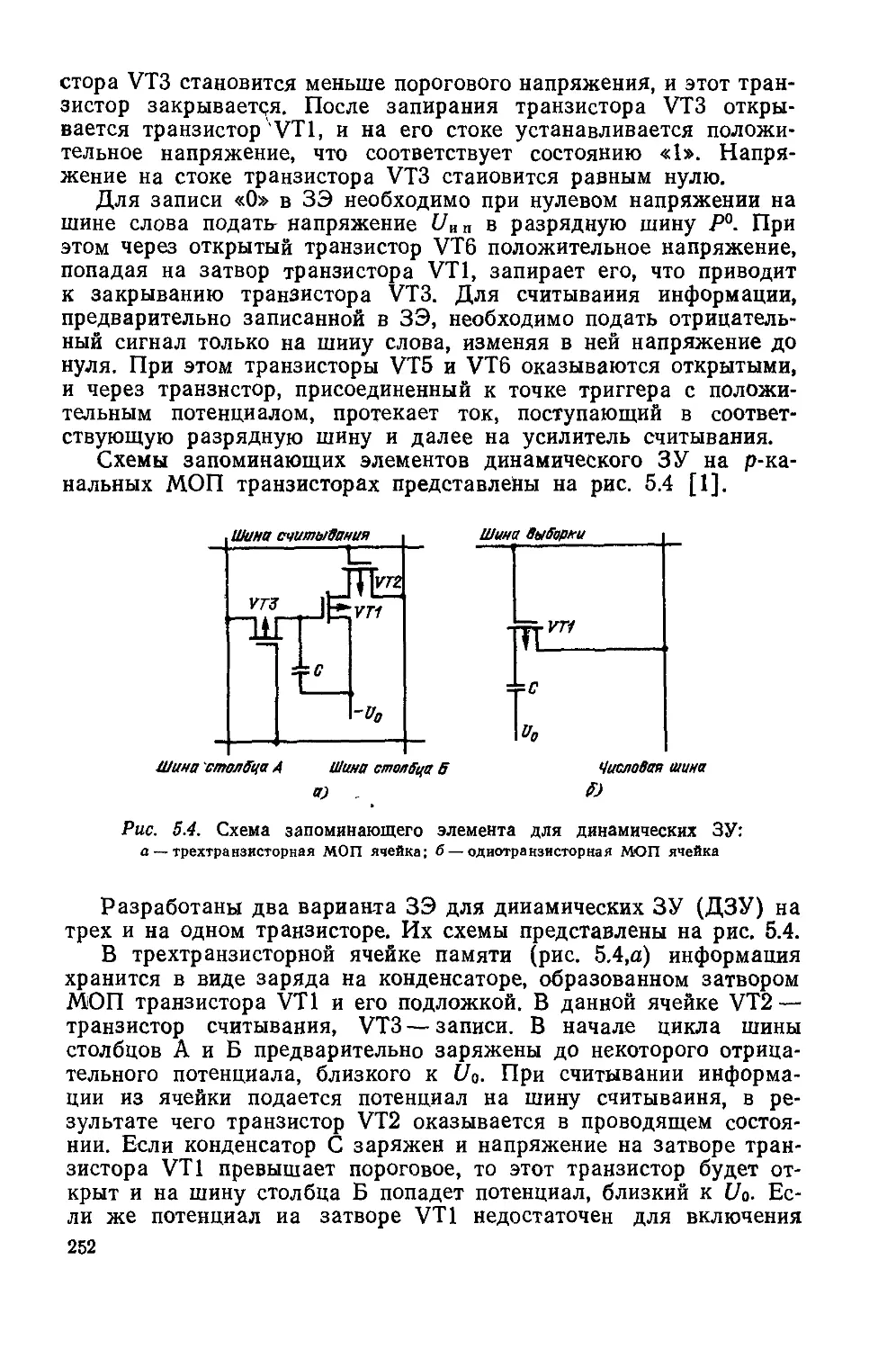

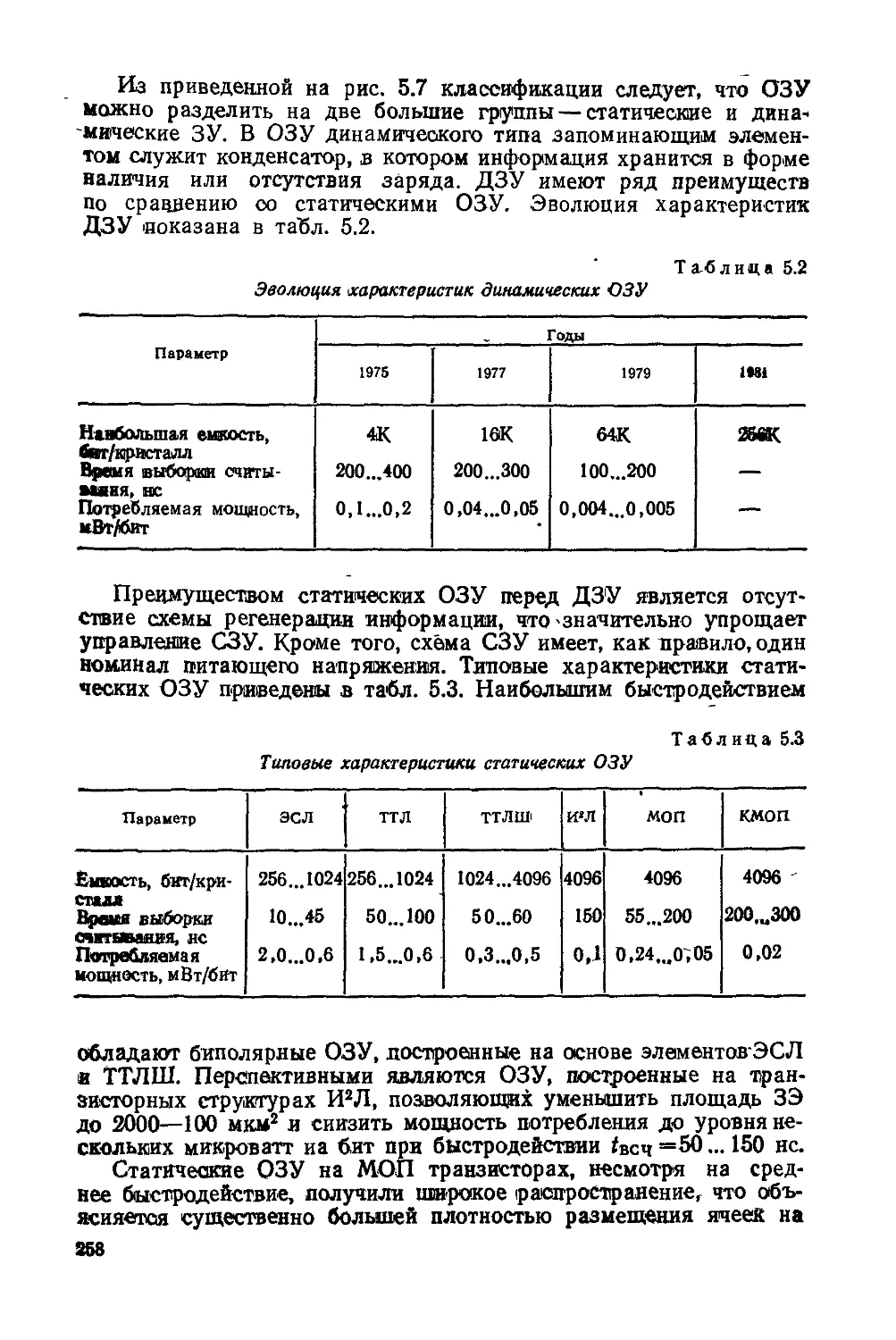

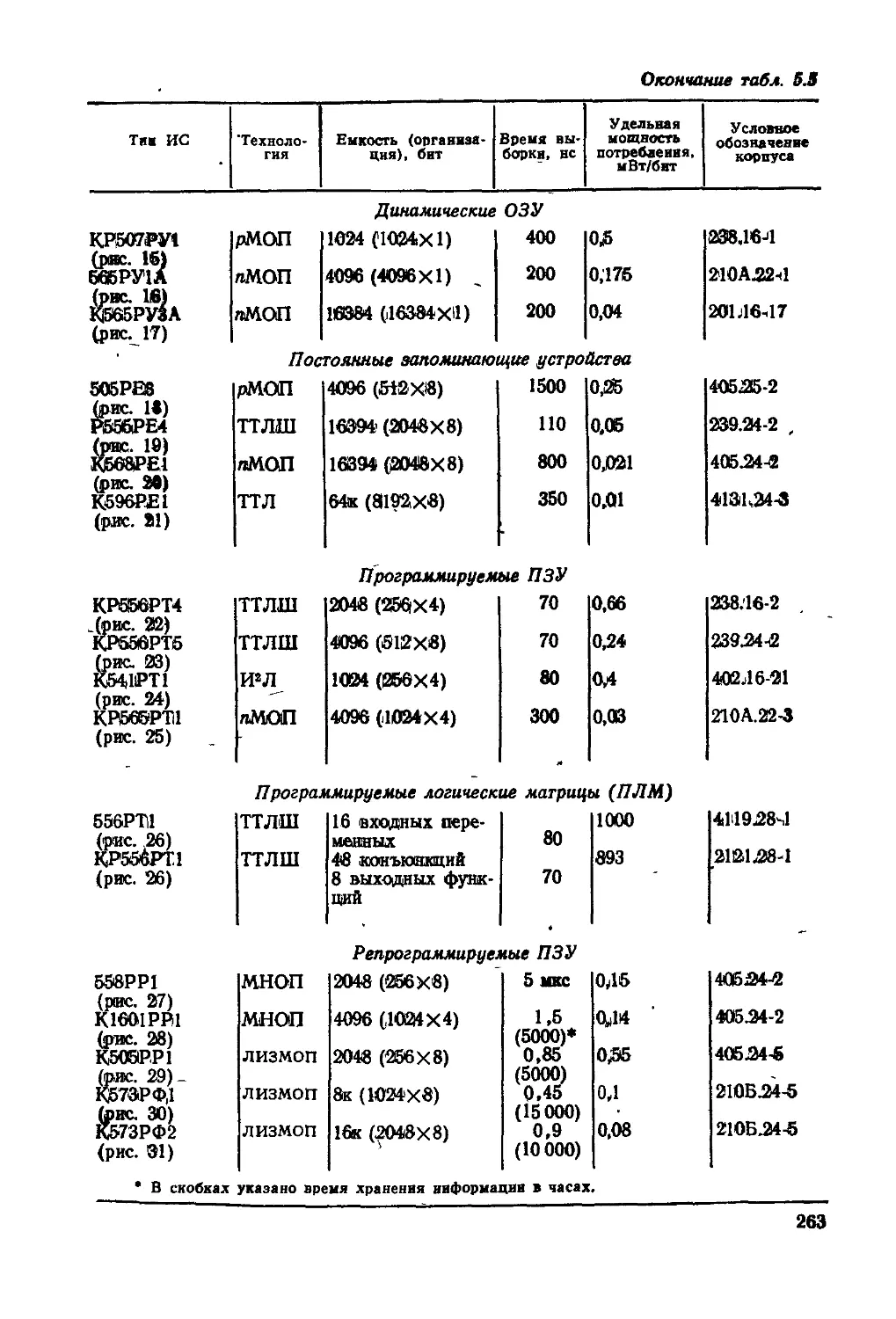

Иа поверхности пластины. Эмиттер — это диффузионная область прямоуголь-