Author: Пухальский Г.И. Новосельцева Т.Я.

Tags: электротехника радиоэлектроника радиотехника справочник полупроводники интегральные схемы издательство радио и связь

ISBN: 5-256-00701-7

Year: 1990

СПРАВОЧНИК

• РАДИО И СВЯЗЬ •

СПРАВОЧНИК

ГИ.ПУХАЛЬСКИЙ

ТЯ. НОВОСЕЛЬЦЕВА

ПРОЕКТИРОВАНИЕ

ДИСКРЕТНЫХ

УСТРОЙСТВ

НА ИНТЕГРАЛЬНЫХ

МИКРОСХЕМАХ

СПРАВОЧНИК

Г И ПУХАЛЬСКИЙ

Т Я. НОВОСЕЛЬЦЕВА

ПРОЕКТИРОВАНИЕ

ДИСКРЕТНЫХ

УСТРОЙСТВ

НА ИНТЕГРАЛЬНЫХ

МИКРОСХЕМАХ

МОСКВА „РАДИО И СВЯЗЬ

1990

ББК 32 844 1

П 90

УДК 621.3.049.77.037.372.001.63 (035)

Рецензенты: А. В. Соловьев,

каид техн наук А. Е. Жестерова

Редакция литературы по электронике

Пухальский Г. И., Новосельцева Т. Я.

П 90 Проектирование дискретных устройств па инте-

гральных микросхемах: Справочник. — М.: Радио

и связь, 1990. — 301 с.: пл.

ISBN 5-256-00701-7.

Рассх отрсны вопросы проектирования дискретных

устройств на микросхемах средней и большой степени интег-

рации. Приведено полное аналитическое описание законов

функционирования микросхем серий 133, 164, 176, 530, 533,

555, 561, 564, 1533 и их применение в электронной аппаратуре.

Для нпженсрпо-техпи lecKnx работников, занимающихся

проектированием РЭА, и для студентов радиотехнических спе-

циальностей.

П

2304030000—102

046(01)—90

130—90

ББК 32.844.1

Справочное издание

Пухальский Геннадий Иванович, Новосельцева Татьяна Яковлевна

ПРОЕКТИРОВАНИЕ ДИСКРЕТНЫХ УСТРОЙСТВ

НЛ ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ

Справочник

Заведующий редакцией Ю И Рысев

Редактор Е. II. Гарде нива

Переплет художника II Л Лашуро

Художественный редактор А С. Широков

Технический редактор Т. Г. Родина

Корректор Л. А Будаицсва

ИС № 1811

Сдано набор I 08 89. Подписано в печать 25.04.90. Т 08927. Формат

84Х108'/з2. Бумага тип. № 2. Гарнитура литературная. Печать высокая. Усе.

печ л 15,96 Усл. кр ОТТ. 15.9G. Уч-изд. л. 19 83 Тираж 100 000 экз.

Изд. № 22304. Зак. № 376 Цепа I р 30 к

Издательство «Радио и связьэ. ЮЮ00 Москва Почтамт, а/я 693

Владимирская типография Госкомпечати СССР

600000. г. Владимир, Октябрьский проспект^ л. 7

ISBN 5-256-00701-7

'С Пухальский Г. И.,

Новосельцева Т. Я., 1990

Содержание

Предисловие .... .........

I. Основы теории переключательных функций

1.1. Аксиомы, основные теоремы и тождества алгебры

логики . . ........................ 5

1 2 Переключательные функции............................ 8

1.3. Минимизация переключательных функций ... 20

1 4. Комбинационные схемы.......................

2. Интегральные микросхемы ................................33

2.1. Сравнительная характеристика стандартных инте-

гральных схем ....................................... 33

2.2. Логические элементы с открытым коллекторам и тре-

мя состояниями выхода ... ... 44

2.3. Приемопередатчики .......................

2.4. Преобразователи уровней напряжений и токов . . 60

• 2.5 Триггеры .................................. .... 61

2 6. Триггеры Шмитта и мультивибраторы .... 91

3. Типовые комбинационные схемы ....

3.1. Дешифраторы, демультиплексоры, .мультиплексоры

и мультиплексоры демультиплексоры

3.2. Синтез комбинационных схем па мультиплексорах ИЗ

3.3. Шифраторы ........................................115

3.4. Схемы контроля четности, равнозначности кодов

и сравнения двоичных чисел...........................129

3.5. Сумматоры и арифметическо-логическис устройства 131

3.6. Пороговые схемы и мажоритарные элементы . . 145

3 7. Умножители двоичных чисел ...... 147

3.8 Постоянные запоминающие устройства и программи-

руемые логические матрицы .... . . 157

3.9 Преобразователи кодов ... . . 170

3.10. Знакогенераторы и индикаторные устройства . . 178

3.11. Конвейерные устройства...........................191

3.12 Линейные комбинационные схемы....................193

4 Типовые последовательностные схемы .....................2)3

41 Сдвигающие регистры . 206

4.2, Оперативные запоминающие устройства . . . . 214

4.3. Регистровые файлы...........................230

4 4 Счетчики ........................................233

4.5. Цифровые фазовращатели......................261

4.6. Синтезаторы частот ... 266

4 7 Примеры проектирования последовательностных схем 278

4.8. Часовые интегральные схемы..................281

4.9. Линейные автоматы...........................2.11

Приложение.................................................294

Список литературы . .......................................302

Г

3

Предисловие

Труд, затрачиваемый инженером па разработку цифровых

устройств, во многом зависит от имеющейся у него информации о се-

рийно выпускаемых интегральных схемах (ИС). Цифровое устрой-

ство может быть спроектировано правильно только при наличии точ-

ных описаний ИС. Болес того, спроектированное устройство долж-

но содержать наименьшее число ИС для снижения его стоимости.

Этого можно требовать от разработ шка только при предоставлении

ему полного их описания. Задание ИС с помощью таблиц истинно-

сти не только громоздко, но и, являясь первой ступенью синтеза

любого цифрового устройства, ие содержит описания его работы

в минимальной форме, необходимой для облегчения анализа воз-

можностей ИС для конкретных приложений.

Изложение материала выполнено не по сериям ИС, а по их

функциональному назначению, поскольку ИС, описываемые одним

и тем же аналитическим выражением, выпускаются в различных се-

риях. Целью же настоящего справочника является рассмотрение

основного этапа разработки цифровых устройств — их логического

проектирования на базе современных ИС.

При описании функционирования ИС указывается принадлеж-

ность ее к каю п-либо одной серин, хотя такие же ИС могут выпу-

скаться и в других сериях. Для удобства пользования справочни-

ком ИС, выпускаемые в преемственных ТТЛ-сериях, сведены в табл П1

приложения (они отмене (ы знаком «+»). Так, табл П1 указывает,

что ИС 133ИДЗ, 155ИДЗ 533ИДЗ и 1533ИДЗ имеют одинаковые

функциональное описание и нумерацию выводов. Следует отметить,

что могут быть отличия в разных сериях ИС с одинаковым назва-

нием в нумерации выводов (папри.мер, ИС 555ИР22 и 533ИР22)

и даже функциональном назначении (например, ИС 533ЛПЗ и

1533ЛПЗ, 155ХЛ1 и 531ХЛ1). Известные авторам подобные несоот-

ветствия отражены при описании соответствующих ИС.

Изготовляемые по КМОП технологии и имеющие одинаковые

функциональное назначение и расположение выводов ИС для удоб-

ства пользователя сведены в табл П2. В тексте так же, как и для

преемственных ИС ТТЛ серий, указывается ИС только одной серин.

Табл. ПЗ поможет ориентироваться пользователю в отыскании ин-

формации о прив денных в ней ИС, изготовляемых по ТТЛ-, КМОП-

и п МОП-технологпям и не имеющих аналогов среди ИС, помещен-

ных в табл II н табл. П2.

Параграфы 2.1, 2.2, 2.4, 2.6, 3.1, 3.3, 3.4, 4.1, 4.4 и 45 написа-

ны Т. Я Новосельцевой, остальные— Г. И. Пухальским.

4

1. Основы теории переключательных функций

1.1. Аксиомы, основные теоремы и тождества алгебры логики

В алгебре логики рассматриваются переменные, которые могут

принимать только два значения: 0 и I. В дальнейшем переменные

будем обозначать латинскими буквами х у, г,... В алгебре логики

определено отношение эквивалентности ( = ) и три операции [1]:

дизъюнкция (операция ИЛИ), обозначаемая знаком V; конъюнкция

(операция И), обозначаемая точкой, которую можно опускать (на-

пример, х-у=ху); отрицание (инверсия, операция НЕ), обозначаемое

чертой над переменными или элементами 0 и 1 (например, х, 0, 1).

Отношение эквивалентности удовлетворяет следующим свойствам:

х=х — рефлексивность-, если х=у, то у—х—симметричность; если

х=у н y=z, то x=z— транзитивность. Из отношения эквивалент-

ности следует принцип подстановки: если х=у, то в любой формуле,

содержащей х, вместо х можно подставить у, и будет получена эк-

вивалентная формула.

Алгебра логики определяется следующей системой аксиом:

х = 0, если х =/= 1,1 х = 1, если х + 0;) (1 1)

1 V I = 1, 1 0-0 = 0; J (1.2)

оуо = о, 1 1-1 = 1; ) (13)

0 V 1 = 1 vo = 1,1 1-0 = 0-1—0; J (1.4)

6=1, 1 (1-5)

Аксиома (1.1) утверждает, что в алгебре логики рассматрива-

ются только двоичные, переменные, аксиомы (1.2) —(14) определя-

ют операции дизъюнкции н конъюнкции, а аксиома (15)—опера-

цию отрицания. Если в аксиомах (1.2) — (1.5), заданных парами, про-

извести взаимную замену операций дизъюнкции и конъюнкции,

9 также элементов Он 1, то из одной аксиомы пары получится дру-

гая. Это свойство называется принципом двойственности.

5

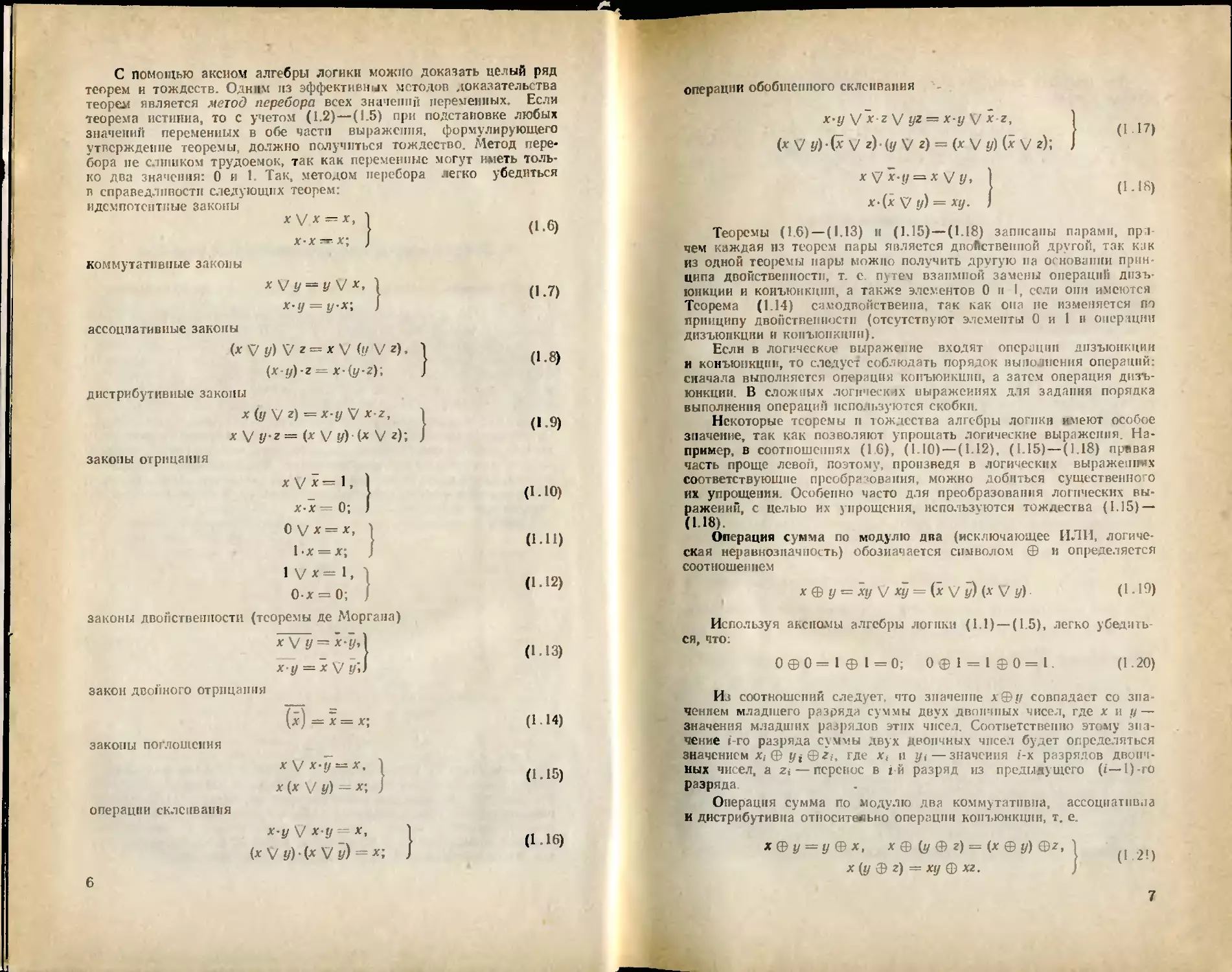

С помощью аксиом алгебры логики можно доказать целый ряд

теорем и тождеств. Одним из эффективных методов доказательства

теорем является метод перебора всех значений переменных. Если

теорема истинна, то с учетом (1.2)—(1.5) при подстановке любых

значений переменных в обе части выражения, формулирующего

утверждение теоремы должно получиться тождество. Метод пере-

бора не слишком трудоемок, так как переменные могут иметь толь-

ко два значения: 0 и 1 Так, методом перебора легко убедиться

в справедливости следующих теорем:

идемпотентные законы

х '*="*> 1 (1.6)

x-х — х; )

коммутативные законы

xV y — yV х, 1

х-у = ух\ J

ассоциативные законы

(х V у) V z = х V <У V г),

(ху)-г = х-{у-г);

дистрибутивные законы

х (у V г) = х-у V х г,

х V у-г = (х V у) (х V г)-.

законы отрицания

xV х^ 1, 1

х-~х = 0; J

О V х= х, 1

Ьх = х; )

1 V х— 1,

0-х = 0;

законы двойственности (теоремы де Моргана)

х V {/ = хг/,|

х-t/ = х V y'J

закон двойного отрицания

(х) — х = х;

законы поглощения

х V х-у — х, 1

X (X V у) - х; J

операции склеивания

х-у V х у = х,

(х V У) • (х V у) = х;

(1.7)

(1.10)

(1.Н)

(1.12)

(1.13)

(1 И)

(1.15)

(1-16)

6

операции обобщенного склеивания

х-у у х г у уг — х-у ух г,

(х V !/)(*- V г) (уУг) = (ху у) (х V г);

(1 17)

х У х-у = х у у,

х-(х у у) = ху.

(I.IS)

Теоремы (16) — (1.13) и (1.15)—(1.18) записаны парами, пр i

чем каждая из теорем пары является двойственной другой, так как

из одной теоремы пары можно получить другую на основании прин-

ципа двойственности, т. с путем взаимной замены операций дизъ-

юнкции и конъюнкции, а также элементов 0 и I, если они имеются

Теорема (1.14) самодвойственна, так как она не изменяется по

принципу двойственности (отсутствуют элементы 0 и 1 н операции

дизъюнкции и конъюнкции).

Если в логическое выражение входят операции дизъюнкции

и конъюнкции, то следует соблюдать порядок выполнения операций:

скачала выполняется операция конъюнкции, а затем операция дизъ-

юнкции. В сложных логических выражениях для задания порядка

выполнения операций используются скобки.

Некоторые теоремы и тождества алгебры логики имеют особое

значение, так как позволяют упрощать логические выражения. На-

пример, в соотношениях (16), (1 10) — (1.12), (1.15) — (1.18) правая

часть проще левой поэтому, произведя в логических выражениях

соответствующие преобразования, можно добиться существенного

их упрощения Особенно часто для преобразования логических вы

ражеиий, с целью их упрощения, используются тождества (1.15) —

(1 18)-

Операция сумма по модулю два (исключающее ИЛИ, логиче-

ская неравнозначность) обозначается символом ф н определяется

соотношением

х Ф у = ху У ху — (х у у) (х V у) (119)

Используя аксиомы алгебры логики (1.1) — (15), легко убедить

ся, что:

0ф0=1ф1=0; 0®1 = 1®0=1.

(1-20)

Из соотношений следует, что значение хфу совпадает со зпа

чением младшего разряда суммы двух двоичных чисел, где х и у —

значения младших разрядов этих чисел. Соответственно этому зна-

чение i-го разряда суммы двух двоичных чисел будет определяться

значением х, ф у, фг,-. где х, и г/,—значения i-x разрядов двоич-

ных чисел, a Zi— перенос в i-й разряд из предыдущего (1—1)-го

разряда

Операция сумма по модулю два коммутативна, ассоциативна

и дистрибутивна относительно операции конъюнкции, т. е.

хфу = уфх, х ф (у ф г) = (х ф у) фх,

х (у ф г) = ху ф хг.

(1 2!)

7

Дчя операции сумма по модулю два справедливы также еле

дующие тождества:

хфО = х; = х; х©х=0; хфх=1;

X ® tj — X у XJ Ху = (х XJ у)(х XJ у) — х® у - X® у.

(1-22)

1 2. Переключательные функции

Любое логическое выражение, составленное из п переменных

х„,.... xt с помощью конечного числа операций алгебры логики, мож-

но рассматривать как некоторую функцию п переменных. В соответ-

ствии с аксиомами (1.1)—(1.5) функция может принимать в зави-

симости от значений переменных только два значения: 0 и 1. Такие

функции являются весьма удобным инструментом для описания,

анализа я синтеза переключательных схем, выходные сигналы кото-

рых характеризуются лишь двумя уровнями напряжения; высоким

(1) и низким (б). В связи с этим такие функции называются пере-

ключательными (термин «перекчючательиая» часто будем опускать,

так как никакие другие функции не рассматриваются).

Позиционные системы счисления. Совокупность правил записи

чисел называется системой счисления. Наиболее часто используются

позиционные системы счисления, в которых целое положительное

число записывается в виде последовательности символов

- ер. e2et, а вес каждого символа ер определяется его позицией в за-

писи числа. В дальнейшем будут использоваться только позицион-

ные системы счисления, в которых вес символа ер равен qp~', где у —

основание системы счисления, а е₽=0 1, ...,q—1. Тогда любое целое

положительное число Е в системе счисления с основанием q можно

записать в виде Е= (еп...ер...е])11=епУп~,+

п

-- Л epqp~1. При вычислении суммы полагаем, что все значения

р=1

ер и qv~l представлены в привычной десятичной системе счисления.

Максимальное «-разрядное число получается при ep=q—1 для

всех р: £пм>х= Zj (<7—1)<70-|=<7"—1. Из этого следует, что существу-

р—I

ет qn различных «-разрядных чисел (с учетом нуля). В табл. 1.1

показан перевод 16 чисел из одной системы в другую при наиболее

часто используемых основаниях систем счисления q=2, 10, 8, 16.

Перевод чисел из системы счисления с произвольным основани-

ем q в десятичную систему счисления (<?=10) выполняется по при-

веденным формулам, для чего требуется перевести в десятичную

систему счисления только числа е„ и q. Несколько сложнее произ-

вести перевод чисел из десятичной системы счисления в систему

счисления с основанием <7=#10 Наиболее просто такой перевод вы-

полняется для q=2, 8, 16. Пусть требуется перевести число (1987)10

в указанные системы счисления. Перевод осуществляется последова-

тельным делением числа, заданного в десятичной системе счисления,

на q—8:

8

Таблица 1.1

«=2 0= ю в = 8 q =16

0 0 0 0 о 0 0

0 0 0 1 1 1 I

0 0 10 2 2

0 0 11 3 3 3

0 10 0 4 4 4

0 10 1 5 5 5

0 110 6 6 6

0 111 7 7 7

10 0 0 8 10 «

10 0 1 9 И 9

10 10 10 12 А

10 11 11 13 В

110 0 12 14 С

110 1 13 15 D

1110 14 16 Е

1111 15 17 F

Таким образом, (1987) |0= (3703)8- Для перевода полученною

числа в двоичную систему счисления достаточно каждую цифру

представить В двоичном коде: (3703)а—(11-111.000.011)2- Перевод

полученного двоичного числа в 16-ричную систему счисления вы-

полняется его разбиением на тетрады (тетрада — четыре разряда)

н переводом каждой тетрады в 16-ричную систему счисления:

(111.1100 0011)2= (7СЗ) |в Итак, получили (1987) |0= (3703).,=

= (11111000011)2= (7СЗ),в-

Для обозначения произвольных десятичных чисел используются

символы I, / и тому подобное, а’ двоичные числа записываются в ви-

де еп...ер...е\, где ер=0 или 1. Равенства для десятичных и двоичных

чисел записываются, опуская индекс, указывающий основание систе-

мы счисления i=en -er.. et.

Свойства переключательных функций. Для функций п перемен

9

пых xn, х, используется общее обозначение f(v)=f(xn.....х ), где

v= (t)i,.., Л)), т. е. совокупность переменных х„, ... х, можно р -

сматривать как n-мерный вектор. Каждая переменная хр(р=1, 2..п)

может принимать только два значения: б и 1, поэтому число всех

возможных комбинации значений хп,- ,х, конечно. В общем виде

конкретное значение переменной хр (0 или 1) обозначается ер.

Областью определения функции п переменных хп, х, является

совокупность точек «-мерного пространства, причем каждая из то-

чек задается определенной комбинацией значений этих переменных

х„=еп....хр=ер,.... x,=ei, где ер=0 или 1 (р= 1, 2,.... п). Точки, за-

дающие область определения функции f(v), — это v, = (en....е„...

.../?/), где i=en. .Ср. .С\, т.с. все точки области определения функции/»

переменных можно пронумеровать с помощью двоичных //-разряд-

ных чисел* en-..eP...et пли с помощью десятичных чисел I. Так как

имеется всего 2П различных «-разрядных двоичных чисел, то область

определения функции п переменных состоит нз 2" точек, т е.

ve{v, v( .... v

Для задания функции (v) следует указать се значения во всех

точках области определения, т. е. задать значения f(v.)=O или I,

где /=0, 1,..., 2"—1 Каждой конкретной функции п переменных мож

но поставить в соответствие 2"-разрядное число, составленное нз

значений f(v,) = O или I (/=0, !,..., 2”—1), которые она принимает

в 2" точках области определения. Так как имеется всего (22)" раз-

личных 2"-разрядных двоичных чисел, то и число различных фупк-

ций п переменных равно 22 .

Функции п переменных могут зависеть не от всех переменных

хп,.., х,. Такне функции называются вырожденными. В частности,

функция f(v), равная нулю во всех точках vf, и функция f(v), рав-

ная единице во всех точках V/ (i=0, I, ...,2"—1), не зависят пи от

одной переменной. Эти функции называются константой нуль и кон-

стантой единица соответственно.

Значительный интерес представляют невырожденные функции

двух переменных х2 и X/ названия которым даны по используемым

для их образования операциям алгебры логики:

i (х2, Xj) = х2 V Xj — дизъюнкция (ИЛИ);

I (х2, х,) = х2-х1 — конъюнкция (И);

f (х2, X!) = x2-xt— функция И—НЕ;

/ (х2. *1) = х-2 V *1 —функция ИЛИ—НЕ!

f (*2- *1) = х2 Ф Ai — сумма по мо. улю два.

Область определения этих функций состоит из четырех точек.

*о= (0,0), vi=(0,l), v2=(l,0), v3=(l,l), так как 2" = 22=4.

* Значения еР — 0и1 являются элементами алгебры логики (бу-

левой а /гебры), если они используются в качестве значений пере-

менных хв. Для этих элементов не существует соотношений больше

н меньше В записи же двоичного числа en...ei значения ер=0 и 1

считаются элементами кольца целых чисел (1>0 и 0<1). Какими

элементами являются символы 0 и 1, всегда ясно из контекста или

используемых в выражениях операций. На основании этого, напри-

мер, можно записать, что е,,— 1—еР.

10

Таблица 1.2

t А> x,Vx, ЛГ8 X, Xt Х| x,V X, Л'вФ*! f (V)

0 0 0 0 0 1 1 0 с0

1 0 1 1 0 1 0 1 Ф

2 1 0 1 0 1 0 1 аг

3 1 1 1 1 0 0 0 «3

Так как об iac-гь определения любой функции п переменных ко-

нечна (2Л точек), то она может быть задана таблицей значений

f(vj)=fli=O или 1, которые она принимает в точках V,, где 1=0,

1,2"—1. Такне таблицы называются таблицами истинности.

Табл. 1.2, которая составлена в соответствии с аксиомами (1.1)—

(1.5) для указанных функций двух переменных, представляет собой

таблицу истинности, задающую эти функции.

В кранном правом столбце помещена функция, заданная в об-

щем виде коэффициентами а,=Цх\), где i—О, 1, 2, 3. Подставляя

различные значения а,=0 или 1, можно задать все 16 функций двух

переменных (22) =24 = 16. В частности, можно получйть вырожден-

ные функции: константа нуль (а,-=0, i=0...3) и константа единица

(fli=l, i=0._.3), а также функции /(х2, X|)=x2(ao=«t= 1, «2=Яз=0)

nf(x2, *i)=*i(«o=<h=l, Oi=fls=0), называемые инверсиями пере-

менных.

Используя только функции двух переменных, можно построить

функции от большого числа переменных с помощью операций ком-

позиции, под которыми понимается подстановка <них функций

вместо переменных в другие функции. Такая подстановка возмож-

на в силу того, что области значений функции и переменных сов-

падают (0 и 1).

Функция п переменных f(v) называется полностью определен-

ной, если ее значения f(v,)=ai = 0 пли 1 заданы во всех 2" точках

V,- области определения. Если же значение функции не задано хо-

тя бы в одной точке vj, то она называется не полностью определен-

ной. Пе определенное в точке v, значение функции будем задавать

произвольным коэффициентом щ=Ф (Ф— совмещенные символы 0

и 1, что указывает па неопределенность значения с,), т е если

в точке у,- значение функции нс задано, то f(v,•)—£<. Не полностью

определенные функции можно доопределять произвольным спосо-

бом, полагая с,=0 или I Если значения функции не заданы в m

точках, то функцию можно доопределить 2’’ способами, так как

имеется 2,п различных m разрядных двоичны чисел, соответствую-

щих различным способам доопределения функции в m точках. Та-

ким образом ие определенной в m точках функции соответствует

совокупность 2™ полностью определенных функций Если значения

функции at не заданы ни в одной точке у,, то опа называется пол-

ностью неопределенной и обозначается через ti (у) [2].

Принцип и закон двойственности. Алгебра логики обладает

замечательным свойством, которое называется принципом двойст-

венности, если имеет место тождество f(v, 0, 1/V. &) =g(v, О, 1/V,

&), где v= (хп,..., Xj), то справедливо также тождество /(у, 1, 0/&,

И

\Z)=g(v, 1, 0/&, V). т e. если в каком-либо тождестве произвести

взаимную замену символов 0 и 1 (если они имеются) и операций

дизъюнкции и конъюнкции, то будет получено также тождество.

Два тождества, связанные между собой таким образом, являются

двойственными. Истинность самого принципа двойственности не до-

казывается, так как данный принцип является внутренним свойст-

вом алгебры логики (заключен в ее аксиомах).

Законы двойственности {теоремы де Моргана) (1.13) устанав-

ливают способ отыскания инверсных функций, представляющих

собой дизъюнкцию и конъюнкцию двух переменных. Клод Шеннон

предложил обобщение этих теорем, позволяющее отыскивать инвер-

сию любой функции f(v), где v=(xn...........Xi). Закон двойственности,

установленный К. Шенноном, имеет вид

f (v/V.&) = f (v/&, V), (• -23)

где v= (х1ь .... Xi), v=(xn,.... xj, т. е. инверсию любой функции f(v)

можно получить взаимной заменой переменных хр и их инверсий

хр(р=1...и) и операций дизъюнкции и конъюнкции.

Рассмотрим несколько примеров на примепепие_закона двойст-

венности Пусть f(v)— x2xiVx?Xi, тогда f(v) = (x2Vxi)(x2\/xt).__

Пусть f(v)=j(X2X£V^a)^tVX3Xl]JX2XlVX3)\/X4. тогда f(v) =

={[ U2VX1) • {хзХ/х2) X/xA/xJ (x3V*i) V (x2\/xi) -х3)х4.

п

В дальнейшем часто будут использоваться обозначения: \/Хр=

р=1

•=*.>V-Vxi; П хр=хп---*|

p=i

На основании закона двойственности легко показать, что

А г-г "

V Xp = njfc; П Хг= Хр.

Р=1 п—1 р=1 р=1

Теоремы разложения и связанные с ними тождества. В теории

переключательных функций особо важное значение имеет теорема

разложения: любую функцию f(v) можно разложить по переменной

хр в форме

f {хп,..., хр,..., Xi) = хр- f (хп,... О,..., х,) V

V Хр /(хп,...Л.......xj. (1.24)

Эта теорема легко доказывается методом перебора:

a) x„=O=>f(xn,...,O,..„ xt)=O-f(xn....0,...,xi)VO-f(x„,..., 1,..., х,)=>

•=f(xn,..., О.xi), т e. при xP=0 теорема справедлива независимо от

значений других переменных,

б) xP=l=>f(x„,..., l,...,x1) = l.f(xn.О.X|)Vl-f(*n.-. 1,-.X|)“

=f(xn,..., !,..., Х|), т. e. при xp=l теорема справедлива независимо

от значений других переменных, а значит теорема истинна при лю-

бых значениях всех переменных, что и требовалось доказать.

По принципу двойственности получается двойственная теорема

разложения

1{хп,...,хр,...,х1) = (хр v f (xn,..., 1......X1)I (Хр vf (хП1...

0.....XJ)]. (1.25)

12

Теорема разложения (1.24) является удобным инструментом

для преобразования логических выражений, содержащих операцию

сумма по модулю два, так как в ряде практических случаев позво-

ляет свести данную операцию над функциями к простейшим one-

ршиям (1 20) и (1 22), например

xz х, ф (х3 V xi) ® х,х, ф (х2 \J = х, (х2-0 ф (x3 V 0) ®

©Хз-0 ® (*2 V 6)1 V х, (х2-1 ф (х3 V Г) ф х3-1 Ф (х2 V Т)1 =

= xi (0 ф 1 ф 0 © 1) V г, (х2 ф ха ф х3 ф х2) = х,-1 V х,-1 =

= X, V X, = I.

Приведем доказательство дистрибутивного закона (1.21) для

операции сумма по модулю два относительно операции конъюнкции

ху ф хг = х (0-р ф 0-z) V х (I-у ф 1-г) = х (у ф г).

С теоремой разложения (1.24) связаны тождества

хр-( (хп,..., хр>..., х,) = Хр-1 (хп.0.....х,). 1 ц 26)

Хр-1 (Хп Хр,.. ,Х,)=Хр-/(Хп...........I,. , х,) '

По принципу двойственности этим тождествам соответствуют

двойственные тождества

~хр\/ ) (xni...,xp,...ixl)^xp V/(xn......1, - .*i). | (i,27)

Хр V f(xn,...,Xp,...,x,) = xp V f(xn,...,O,. ..Xi). J

Тождества (1.26) легко доказать методом перебора или с помо-

щью теоремы разложения (1.24). Тождества (1.26) н (1.27) явля-

ются мошным средством для упрощения логических выражений.

Легко доказать закон поглощения (1 15) и (1 18), используя второе

тождество (1.27): х V ху = х у 0-у = х; х \/ ху — х V 0 у = х V !/•

Пусть требуется упростить функцию

) (V) = Х2 X, ф х3 х-г ф X, V Ха х; -х2.

Используя первое из тождеств (1.26) относительно х2, полу-

чаем

/ (v) = О х, ф ха-0 ф х, V *3-0-х2 = х, ф х, V хя~х2.

Для упрощения выражения х3®х(ух3 можно использовать вто-

рое из тождеств (1.27), тогда /(v)=0©XiVx3-X2=x,Vx3jXj=xiX2X3.

Первичные термы. Переменные хр и их инверсии хр называ-

ются первичными термами, для которых используется символическое

обозначение

= ёйе V Ср х„ = eD ф хр, (1.28)

где ег-=0 или 1. Данное символическое обозначение объединяет

в одном символе хрр оба первичных терма хр и хР. Действительно,

при подстановке в (1.28) значений ео=0 и 1 получается, что

x«j,=J*p> СЛ" еР~°1

° |хр, если ер = 1.

13

Только 6.'iai одари введению данного символического обозначе-

ния удается формализовать вывод общих соотношений для переклю-

е е

чательных функций. Очевидно, что два первичных терма х рг и хрр

равны только в том случае, если е£>=ер(еслп ер=£ер, то ер=ер.).

Для первичных термов справедливы соотношения:

# = (1.29)

xeJ>-xp=Q, x>v$=i; (1-30)

Х?=[0’ еСЛ" Х!> = еР' (1.31)

р II, если хр ер.

Истинность этих соотношений элементарно проверяется на ос-

новании определения первичных термов (1.28).

Минтермы и макстермы. Мпнтермом (конституентой единицы)

называется функция п переменных

*?= П х'р, (1.32)

p=i

где v= (Хп,..., Xt), еР = 0 или 1, i=e„...ei Из данного определения

следует, что имеется 2" различных минтермов п переменных, так как

имеется 2" различных п разрядных двоичных чисел t = 0, 1,...,2П—1

Минтермы обладают следующими свойствами:

{I. если v = V,-,

0, если v = V; =/= V,-;

Ki (V) К j (V) S= О, если i =# /

2"-1

V К, (V) == I.

i=o

(1.33)

(1-34)

(1.35)

Свойство минтермов (133), заключающееся в том, что любой

минтерм Ki(v) равен 1 только в одной точке vt области определе-

ния, состоящей из 2" точек, легко доказать, испотьзуя свойство

первичных термов (131). Свойства (1 14) и (1.35) доказываются на

основании свойства (I 33)

Запишем все минтермы двух переменных х2 и xt: Ao(v) =

=Х;Х( ="x2xi; Ki(v)=X2x{=x2xi; K2(v)=x^=x2x,; K2(v)=x>x{ =

х2хь где v (x2, xi). Таким же способом можно записать любой

минтерм Ki(v) большего числа переменных. Пусть, например, п—4

II 1=13, ТОГДа Kl3(v)=X4XiX2XII =XtX3X2Xt.

Макстсрмом (конституентой пуля) называется функция п пере-

II п —

мепных (v) = К, (v) — Г1 х р = V х р.

ры1 ₽=’

14

Согласно свойству первичных термов (1.29) можно записать

A1,(v)=V (1-3б)

₽=1

где v=(xn,..., Xi), i=en...es. Макстермы обладают следующими свой-

ствами:

ГО, если v = vs,

Alf(v)= ’

(1, если v = vj vf;

Alj (v) V Aly (v) =s 1, если i =/= /;

2n-l

П Alf(v)-0

i=0

Свойства макстермов могут быть получены из свойств мпитср-

мов (1.33)—(1.35) па основании определения макстермов (1.36).

Макстермы — это функции, равные нулю только в одной точке v(

области определения, состоящей из 2" точек.

Запишем все макстермы двух переменных х2 и хр M0(v)-=

=x^Vx^=x2\/xr, A1|(v)=x^Vx} =x2V*i; A12(v)=x|\/x^=xsV*:

A/3(v)=x'\/x}=x2\/xi, где v=(x2, x,). Запишем макстерм All3(v)

для n=4: Ali3(v) xiVxaV^zV-J =**Vx3V*2V*i-

Для большей наглядности в табл. 1.3 (таблица истинности) при-

ведены все минтермы и макстермы двух переменных х2 и xj.

Таблица 1.3

L Л, Кс к, К, к. Л». и, м, м,

0 0 0 1 0 0 0 0 1 1 1

1 0 1 0 1 0 0 1 0 1 1

2 1 0 0 0 1 0 1 1 0 1

3 1 1 0 0 0 1 1 1 1 0

Минтермы (макстермы) представляют собой функции, прини-

мающие минимальное (максимальное) значение из зна |енпй своих

еи

первичных термов xf', т. е если хотя бы один из первичных термов

е

хрг равен 0(1), то и минтерм (макстерм) равен 0(1).

Совершенная дизъюнктивная нормальная форма (СДНФ) Тео-

рему разложения (1.24) для функций и переменных можно исполь-

зовать п раз, т е функцию можно разложить по всем п перемен-

ным хр, где р= 1 .... и В качестве примера рассмотрим разложение

функции f(v)=f(x2, Х|) двух переменных х2 п х( По теореме раз-

ложения (124) получим Цхг, xI) = x2-f(0, Xi)Vx2-f(l х,).

Далее каждую из функций f(0, xj и f(l, х,) можно разложить

15

по переменной Г|

I (Ч, *1) = Хг lxt-f (0,0) v *1-/ (0,1)1 V *2 [xvf (1,0) V *i-f (1.1)1 =

= xzxvf (0,0) \Zx2xt f (0 1) V *2*17(1,0) V *2*17(1,1) =

= *2 *?• I (0, 0) V *?*}7 (0,1) V *J *?7 (1,0) V *' *} 7 (1,1) =

л з

= Vo x'4 (e2t ej = у f (Vi) Ki (V),

где v = (xa, *i) v.= (e8, <?i) I = e2ei, K((v) = x.^xp —- мнптермы

двух переменных x2 в х, Так как f(v1)=n,=0 или 1 (значение

J

функции В точке V,-), ТО f(v) = V С;Л;(х).

1=0

Такая форма представления функции двух переменных называ-

ется СДНФ. Разложение функции п переменных будет представ-

лять собой дизъюнкцию2" членов вида х,1п...хрр...Х|1/(еп, et) =

=f(vi)Ki(v)=« Ki (v):

2п-1

f(v) = V atKi (V). (1ST)

i=()

Выражение (137) представлист собой СДПФ функции п пере-

менных

Так как значения функции а,=0 или 1, то а*-К,(х-)=0. если

а, =0. и а;-К,(т)=К< (v), если п(=1. Поэтому СДНФ функции

можно представить в виде

f(v)= V Kis(v), (1.38)

Ч

где is — номера тех точек, в которых функция f(v) равна 1, т. е.

f(v1(.)=aie =1.

В качестве примера рассмотрим функцию f(v) трех перемен

них: х3, х2 н Х| заданную табчицей истинности (табл. 1.4), Из

Таблица 1.4

i хя х, лг, /(V)

0 0 0 0 0

1 0 0 1 1

2 0 1 0 1

3 0 1 1 0

4 1 0 0 0

5 1 0 1 1

6 1 1 0 0

7 1 1 1 1

16

табл. 1.4 следует, что ап=а1=а1=аб=О, а, =a2=as=c?= 1, по-

этому на основании^ (1.38) Kvl^KtMVKHvJVKsMVKHv) =

= x3x2XiVm?xIV*3*2*i\/X3X2-Xi Это и есть СДНФ функции f(v).

Совершенная дизъюнктивная нормальная форма полностью неопре-

2П—1

деленной функции имеет вид ft (v) = \/ c(K. (v) где Ci — неопреде-

t=0

ленные значения функции

Совершенная конъюнктивная нормальная форма (СКНФ) Та-

кую форму функции п переменных f(v) можно получить па основа-

нии двойственной теоремы разложения (1.25). Одиако СКНФ мож-

но получить и более простым способом, записав СДНФ инверсии

функции f(v) Инверсия функции в каждой точке vt должна иметь

инверсные значения а,- по отношению к значениям at самой функ-

ции, т. е J(vi) ==а<, если f(v,) —at.

На основании (1.37) запишем СДНФ инверсной функции

2°-1

Ч')= V azKifv).

=о

И данного соотношения на основании закона двойственное ги сле-

дует

2П_! 2"—I_________ 2П-.

f(v) = V ^»Xi(v) = П ^K, (v)= П |Of v KHvjl.

i=0 1=0 i=0

Из определения макстермов следует, что

2П—I

f(v) = П f«i VAliMl- (1.39)

Г=П

Данная форма представления функции и переменных называ-

ется СКНФ.

Так как значение функции a =0 или 1, то a,V И,==Л(, (v), ес-

ли <ii = 0, и a1Vi'l<(v) = l если a, = l. Поэтому СКНФ можно

представить в виде

f(v) = IlAl/s{v), (1.40)

*s

где i,— номера тех точек, в которых функция f(v)=O, т. е. f(v/ .) =

—а (,=0.

В качестве примера рассмотрим функцию трех переменных, за-

данную табл. 1.4. Так как только значения функции а0-- а3 — а1 =

—а6=0, то на основании Ц.40)_ /(v) =Л1„-Л1з-^1-Л1в= (л'зХ/^гХ/

Vxi) (x«V*2V*i) (X3VX2VX1) (*з\/*г\/Х|). Это и есть СКНФ фун-

кции

Совершенные нормальные формы в базисах И—НЕ и ИЛИ—НЕ

Совокупность элементарных функций, с помощью которых можно

записать любую функцию f(v), называется функционально полной

системой функций или базисом. Из выражений (1.38) и (1.40) сле-

дует, что для представления любой функции f(v) в СДНФ и СКНФ

достаточно использовать только функции (операции) И, ИЛИ и НЕ

2—376 17

(операция НЕ необходима для получения первичных термов х₽,

входящих в минтермы и макстермы), т е. совокупность этих фун-

кций является базисом

Преобразуем СДНФ функции 1.37) с помощью закона двой-

ного отрицания и закона двойственности

2п_, ' 2п—1

f(v) = V aiKt{v}= п а. Ki (V). (1.41)

f=0 1=0

Данная форма представления функций называется совершенной

нормальной формой (СНФ) в базисе И — НЕ так как она требу-

ет использования только функций (операций) И — НЕ.

Преобразуем теперь СКНФ функции (1.39) с помощью закона

двойного отрицания и закона двойственности

/(*) = П [flfVAlf(v)]= V «fVAhN- (Г-42)

i =0 =0

Данная форма представления функций называется СНФ в ба-

зисе ИЛИ — НЕ, так как она требует использования только фун-

кций (операций) ИЛИ—НЕ

На основании (1.41) и (1.42) из СДНФ н СКНФ функции, за-

данной табл. 1.4, можно получить СНФ этой функции в базисах

И —НЕ н ИЛЛ —НЕ /(у)=л'з<2Х|Л3лгх|-ХзХгХ|Л'зХ;Х1; f(v) —

=x3Vx2VxW*3Vx2V-4V*W*W*W*‘sV*2V*i-

Решение систем логических уравнений Пусть задана система

логических уравнении с одним неизвестным у

fj(v. У) = gj (v, у), (1-43)

где v=(x,„ ..., *(), /=1..Л. Необходимо решить ее относительно

у, т е. найти такие значения у=у(у), которые обращают в тожде-

ства все уравнения системы (I 43)

Из равносильных соотношений U =W <==>(/$ 117=0 следует, что

fi(v, у) ф gy(v у) 0 Тогда на основании равносильных соотно-

шений U 0,117 0<==> Uv W7 = 0 получим

k

V [fj('’.y)®gj(v,g)l = O- (1.44)

/= i

Решение системы логических уравнений (143) свелось к реше-

нию одного логического уравнения (1.44) Разложив левую часть

k

этого уравнения по у, получим (/ф|\/(/ф2=0, где ф| = V [fy(v, 0) ф

;=1

ft

®gj (v.O)J, ф2 = V 1/7 (v, 1) ® gj (v, 1)].

r=i

Тогда: ф2=0, ф1=0=Ф-у=Й(у)—произвольная (полностью неопре-

деленная) функция; фг=О. 4i = 1=>V= 1; фг=1, ф|=О=>у = О; ф!=1,

ф| = 1=>1=0 решение не существует, а значит, можно положить

т/=с=Ф (0 или 1). Из этого следует, что y=h (у)&ф2ф|\/1 •'M’lX/OX

Хф2ф|\/Сф2ф|.

18

Если взять с=1, то

V = ij>i V Л (v) ф2- (1 45)

Решение (1 45) существует лишь при

Ф2-ф!=0, (1.46)

Несмотря на кажущуюся сложность выражения (1.45), его до-

статочно просто применять при решении многих практических за-

дач. Докажем, например, тождество xy\/xz\/yz=xy\/xz. Решим

уравнение относительно х : х= (0-ууО-гуу?) ®(0-«/уО-г)уй(1&

&уУ 1 -z\/yz} ф (1 -г/Vl-г) =гфгуй.(/ф{/=й(т/, г). Решение сущест-

вует, так как 4z?-'F1=0-0=0. Уравнение имеет решение x=h, т. е

оно справедливо для произвольных значений х независимо от зна-

чений остальных переменных, а значит, является тождеством.

Решение систем логических уравнений с двумя неизвестными

Ь(У,У. 2)^gj(v,y,z}, (1.47)

где у и z — неизвестные, /=1...й, v=(xn, ... Xi) сводится к их по-

следовательному решению относительно неизвестных у и г. Решив

систему (147) относительно у, в соответствии с (1.45) и (1.46)

получим

У = ЧТ (V. г) у ft, Ч~2 (V, г), 1 „ 4

Ч'г (V, г) Чч (V, г) = у|(V, г),

где

А'

4*1 (V, г) = V Uj (V, о, г) ф Sj (V, 0, г)];

/-1

k

4’2(v,z)= V ff;(v l,2)©g;(v, 1,г)]. Й,-ft,(v).

/=i

Если функция У(с, г)— 0, то это означает что решение систе-

мы (1.47) относительно у существует независимо or значений г.

Поэтому можно взять z~ ftj(v).

Рассмотрим случаи, когда функция Vlv, z) =#0. Так как усло-

вием существования решения системы логических уравнений (1 47)

относительно у звляется уравнение ’Ir(v, z)=0, то, возможно, оно

будет удовлетворено соответствующим выбором неизвестного z

Следовательно, нужно найти решение данного уравнения относи-

тельно z z=4f(v, 0)уй2Чг(х, I) которое существует только в том

случае, если выполняется условие 44v, l)-‘lf(v, 0)=0 (It, и й2—

независимые произвольные функции) Если данное условие выпол-

няется, то решение системы логических уравнений (147) относи-

тельно у находится подстановкой в (1.48) найденною значения г,

В результате будут получены функции f/=<fi(v) и z=<p2(v), не за-

висящие от неизвестных у и г.

Пусть требуется найти решение уравнения Q+ = Qjy(2/( отно-

сительно неизвестных 1 и К. Тогда

Q+ = QJ V Q К => J = <2+ Ф QK V й, <2+ ф (Q V К),

Ч’гЧ’г - (Q+ ф QK) [<2+ ф (QV К)]

Приравняв последнее уравнение нулю, находим

2* 19

к - (Q+ е (?) (Q+ ф I) v я2 <2+ (<?+ е <?) = <?+<? v Q

Подставив найденное значение К в функцию для 1, получим

J = Q+ ф Q Q i-Q V»is(? V /Ц Q+ ® (Q V Q+ Q V h2Q) =

= Q+ ф (?(?+ v й1 <2+ О (<2 V <2+) = <2+ Q V <2-

1 3. Минимизация переключательных функций

Одной из основных задач, возникающих при синтезе комбина-

ционных схем (КС), является минимизация переключательных фун-

кций, которые эти КС реализуют. Чем проще логическое выраже-

ние, описывающее функцию, гем проще и дешевле реализующая ее

КС. Аналитический метод минимизации в общем случае весьма тру-

доемок, поэтому наибольшее распространение получил графический

метод минимизации с помощью диаграмм Вейча, несомненным до-

стоинством которого является наглядность и простота использова-

ния при неболтшом числе переменных (лк 6).

В качестве критерия сложности логического выражения, описы-

вающего функцию, целесообразно принять число первичных термов

херр, в него входящих Очевидно, что любой метод минимизации

может основываться только на тождественном преобразовании ло-

гических выражений.

Конъюнктивные и ди1ыонктивные термы Конъюнктивным тер-

мом (коптермом, элементарной конъюнкцией) называется конъюнк-

ция любого числа первичных термов хрр если каждый перви1 пый

терм с индексом р входит в нее не более одного раза Любой кон-

терм представляет собой функцию п переменных Ki.j(v), которую

можно записать в виде

К. , (v) = П V хСр]• (1-49)

р—1

где v==(xB.... Xi); es=0 или 1; ер=0 или 1; еР<е0; i=eB...ei,

j—en е [.

Действительно, в соответствии с выражением (1.30)

v

Хрр , если ер = ср,

1, если ер ¥=ер (<?’ = ₽₽)»

поэтому функция Kr.j(v), будет представлять собой конъюнкцию

первичных термов хрр Запишем, например, в явном виде кон-

терм A', ?(v) трех переменных Для этого воспользуемся символи-

ческой схемой

J) 0

ял я *1

V

1 „I г1~/~7

*3 *2 *1

1 • 1 -х{ = Xj — Kj 7 (v).

20

Если е„—ер для всех р, то l—j и Vx//’=XpP Для пссх

р=1...л, поэтому, как следует из (1 49). (v) = — П хрр =

р=1

— (v)> т е- контерм Kt.tiy) является мннгермом /G(v).

Если же ер^ер для всех p(epce’, т.е. ег = 0, ер = 1) то 1=>

=0, /=2П—1 и XpPV*pP — 1 Для всех Р. поэтому К 2'i_1(v) = l.

Из определения (1.49) и рассмотренных частных примеров следует,

что все контермы, за исключением X<,<(v) = K<(v), являются вырож-

денными функциями п переменных.

Всего имеется 3" различных контермов и переменных. Деветви

тельно т.тк как х рр\/хГ1р=Хр,Хр или 1 (дизъюнкция первичных тер-

мов может принимать любое из этих трех значений), то каждой

функции Kij(v) можно поставить в соответствие одно из л-разряд-

ных чисел с основанием системы счисления q=3, а поскольку име-

ется 3" различных n-разрядных чисел при q=3, то и число различ-

ных контермов равно Зп.

Дизъюнктивным термом (дизтермом) называется функция п

переменных

MM(v)=X(i/(v)= П Хр1' V V == \/ xpP-xet>. (|.5О)

r=i p=i

Дизтермы представляют собой дизъюнкцию любого числа г<,п

первичных термов хр' , причем каждый первичный терм с индексом

р входит в нее только один раз Всего имеется Зп различных диз-

термов, так как имеется 3" различных контермов.

Правила минимизации переключательных функций Общие пра-

вила минимизации можно установить только для случаев, когда

В результате минимизации получаются так называемые минималь-

ные нормальные формы (МНФ) функций (термин «нормальные

формы» означает, что в логическом выражении, определяющем

функцию f(v), последовательно выполняются не более чем две опе-

рации из совокупности операций И, ИЛИ, И — НЕ и ИЛИ — НЕ).

Два минтерма /G(v) и Kj(v) будем называть соседними, если

оии различаются только одним первичным термом хрр , т. е. если

для одного из минтермов ер=0, а для другого еР = 1 (все же ос-

тальные первичные термы одинаковые). Так, например, если л=3,

то минтермы K3(v)=x3x2X] и K?(v) =ХзХ2Х| являются соседними,

так как они различаются только одним первичным термом х®’. Для

минтерма X3(v) соседними являются также минтермы Ki(v) =

=х3х2х1 и Ka(v) =х3хгхь Понятно, что каждый минтерм п пере-

менных Ki(v) имеет по п соседних минтермов из общею числа 2п

Минтермов

Рассмотрим контерм п переменных Ki,j(v), ие зависящий от

одной переменной хР, т.е. случай, когда контерм является конъюнк-

цией (п—1)-го первичного терма Данный контерм можно предста-

21

вить в виде Ki.jiv) = (хр\/Хр)Хр-К, j(v)\/Xf-Ki,i(v)

= Ki(v)\/Kj(v) Очевидно, что полученные минтермы Ki(v) и K,(v)

являются соседними, так как они различаются только одним пер-

вичным термом херр(хг и х,,). Отсюда следует правило минимиза-

ции: дизъюнкцию двух соседних мннтермов можно заменить одним

коитермом, не зависящим от одной переменной.

Пусть контерм п переменных Ki j(v) не зависит от двух пере-

менных Хр и хч (п>2). Тогда можно записать, что К/л (v) = (хр V

V*7) Kij(v) = Xpxq К i(v)\/XpXq-Ki.i(v) У ХрХч К}.,(к)\/

W,A'ij(v)=^(v)VKr(v)VKs(v)VKJ(v). Из этих соотношений

видно что каждый из четырех полученных мннтермов имеет среди

остальных по два соседних. Отсюда следует правило минимизации:

дизъюнкцию четырех мннтермов, каждый из которых имеет среди

остальных по два соседних, можно заменить одним коитермом, не

зависящим от двух переменных, причем исключаются те перемен-

ные, которые входят в мнптермы как с инверсией, так и без ин-

версии.

Пример. Было показано, что контерм Ki,t=Xi (п=3), т. е. кон-

терм не зависит от двух переменных ха и xt. Тогда легко показать,

что К, 7 (v) = ( х3 V хл ) ( х.2 У х2) -Л'117 (v) = х3 L> х, V *3 х.2 х, V

V*3*2*i У х3 x2*'i = Ki (v) V К, (v) V К-г (v) V К7 (v) , где каждый

мннтерм имеет по два соседних.

Продолжив рассуждения дальше, можно установить общее

правило минимизации одним конгермом п переменных K;,j(v), ,1е

зависящим от т переменных (wen), можно заменить дизъюнкцию

2т мннтермов если каждый нз них имеет по т соседних минтер-

мов среди остальных 2т—1 мннтермов.

Если контерм не зависит от т переменных, то принято

говорить, что он покрывает 2т мннтермов На этом свойстве кои-

термов и основывается минимизация функций f(v), заданных в

СДНФ, которая в соответщвпи с выражением (1 38) представляет

собой дизъюнкцию некоторого числа мннтермов К; • f(v)= V^i (v) •

Ч

Заменяя дизъюнкцию 2т (т—0. 1, ... п) мннтермов (2°= 1 в еду

чаях, когда какие-либо минщрмы не имеют ни одного соседнего

мпптерма) соответствующими контермамн JGj(v), функцию можно

представить в виде дизъюнкции некоторого числа контермов, по-

крывающих вес минтермы At-g, входящие в СДНФ функции:

Hv)=V О-51)

(J./)

Такая форма представления функций называется дизъюнктивной

нормальной формой (ДПФ). Если ДПФ содержит минимально воз-

можное число первичных термов х р' , то она называется минималь-

ной ДНФ (МДНФ). Следует отметить, что любые правила мини-

мизации сводяшя к сформулированному общему правилу, в то

время как алгоритмы (методы) минимизации могут сильно разли-

чаться .между собой

На основании идемпотентных законов один и тот же минтерм

X; (v), входящий в СДНФ, может использоваться несколько раз

22

для образования различных контермов K.-.j(v), так как Kis = Kis\7

УК; у VK^.

В общем случае для минимизации функций п переменных воз-

никает необходимость использовать любой мннтерм не более п раз,

так как он может быть соседним не более чем с п другими мин гер-

мами

Пример Пусть задана СДНФ функиии_трех переменных f(v) =

=K3(v)VA'j(v) VKt(v) VK?(v) =х3х2х( V x3x2xj V x3x2X| VWi-

Здесь для получения МДНФ мннтерм Ki(v)=X3X2Xi необходимо ис-

пользовать три раза: f(v) = (х3х2х,\/£зХ2Х1)\/(А'зХгХ1ух3х2х )V

V (x3x2xi У*'зх2Х1) == хгх (х3 у х3) Vx3Xi(x2Vx2) V x3x2(XiVxi) —

«=X2XiVx3Xi VXjX2.

Уже из этого элементарного примера видно, сколь сложно ис-

пользовать аналитический метод минимизации из-за трудоемкости

работы по отысканию соседних мннтермов (задача сше более ус-

ложняется при наличии в СДНФ группы, состоящей из 2т минтер-

мов при т>1, которые можно заменять одним коитермом).

Рассмотрим теперь методику получения МНФ в других базисах.

Для этой цели наиболее удобно использовать закон двойственности,

который обладает замечательным свойством- при преобразовании

любого логического выражения на основании закона двойствеиио-

е

сти ни число первичных термов хрр, ни общее число операции дизъ-

юнкции и конъюнкции, входящих в исходное логическое выраже-

ние, нс изменяется.

Пусть получена МДНФ некоторой функции f(v). Используя за-

кон двойного отрицания и закон двойственности, получаем

г <v> = VKuM = п ^77F’)- (1 • 52>

<*./> (/.л

Это соотношение и дает МИФ функции f(v) в базисе II — НЕ,

так как для ее реализации требуются только операции И — НЕ.

Запишем МНФ в базисе И НЕ функции трех переменных, МДНФ

которой была найдена: f(v) =хгХ|\/ХзХ1\/хзх2=х2Х|-х3Х|-ХзХе.

Получение минимальной конъюнктивной нормальной формы

(МКНФ) функции [(у) легко сводится к получению МДНФ ин-

версной функции f(v) и преобразованию ее с помощью закона двой-

ственности:

f(v)= У Ки<уу, (153)

«,/)

f (V) = П KZ7I4 = П Л1< j (г), (1.54)

(*./) (i-/>

где Mt.) — дизъюнктивные термы (1 50)

Пример. Пусть требуется найти МКНФ функции трех перемен-

ных f(v), значения которой равны 0 только в точках v0, Vi и v«

Совершенная ДН_Ф инверсной функции f(v)=Ko(v)V Ki(v)V

yKt(v) =х3х2х1\/х3х2х1\/х3х2Х1. Используя мннтерм Kc(v) =х3х2х1

дважды, легко показать, что МДНФ (1 53) инверсной функции

f(у) — х2Х|\/ХзХ2 Тогда МКНФ функции /(у) получается с помо-

щью закона двойственности f(v) =x»XiV*s**= (x2V*i) • (xsV*z).

23

Z,|| Z? I Z7 I g I ff

T.J

*2

Ю

0 0 10

X?

e)

W

ci о ГГ

Рис. 1 1

В базисе ИЛИ — НЕ МИФ функции /(v) может быть получе-

на непосредственно из МКНФ (1 54) с помощью закона двойного

отрицания и закона двойственности

/ (V) = П.Иг;(т) = V Al/J (v)- (1.55)

(i./)

Найдем МИФ в базисе ИЛИ — НЕ для функции /(v), рассмот-

ренной в предыдущем примере:

f (v) = (*! VM) (Хз\/Хг) =Х2У-Ч\/*'з'А2-

Таким образом, получение МКНФ и МНФ в базисах И—НЕ

п ИЛИ —НЕ функции j‘(v) все1да можно свести к получению

МДНФ либо функции f(v), либо ее инверсии f(v).

Диаграммы Вейча. Опп представляют собой один из табличных

способов задания функций и состоят из клеток, каждая из которых

соответствует определенной точке v, области определения функций.

Диаграммы Вепча для функции н переменных состоят из 2’1 клеток,

которые можно пронумеровать с помощью чисел i=0, 1........ 2"—1.

Чтобы с помощью диаграммы Вейча задать функцию f(v), необхо-

димо в каждую клетку с номером i занести значение функции /(v,) =

=а, = 0 или 1, которое оно принимает в точке v,

Рассмотрим диаграммы Вепча для функций трех переменных

(п = 3). Так как 2’!=23=8 то диаграмма Вейча состоит из восьми

клеток (рис. 1.1). Каждой стороне диаграммы Вейча соответствует

своя переменная хр (р=1, 2, 3), причем одной половине стороны

соответствует первичный терм хрр=хр — хр, а другой — первичный

терм херр=Хр—хр. Поэтому каждой клетке будет соответствовать

совокупность первичных термов xj, Xе,, х,1, а номер дайной клетки

будет определяться числом i=e3e2ei (рис. 1.1, а).

Любой миптерм A'i(v) представляет собой функцию, равную 1

только в одной точке v, области определения, поэтому иа диаграм-

ме Вейча он представляется единицей, стоящей только в одной клет-

ке с номером I. Например, на рис. 1.1,6 показана диаграмма Вей-

ча для минтерма K2(v) =*зх»*? = *зх2*1 • На Р|,с- 1 в- г ис-

пользованы упрощенные обозначения сторон диаграммы Вейча,

полностью соответствующие обозначениям иа рнс. 1.1, а (одна поло-

вина сторон соответствует хр, а другая — хР). Клетке с номером

(=2 соответствует на основании принятых обозначений совокуп-

ность первичных термов Хз, Ха и Xi, конъюнкция которых и пред-

ставляет собой миитерм K2(v). Таким образом, можно сказать, что

каждой клетке с номером i соответствует минтерм К,(\) Две клет-

24

ки диаграммы Вейча называются соседними, если им соответствуют

‘Лоседиие минтермы.

Основной особенностью диаграмм Вейча является то, что обо-

Значения их сторон с помощью первичных термов производятся

так, чтобы как можно больше соседних клеток имели общую грань.

Этому требованию могут удовлетворять многие варианты обозначе-

ний сторон диаграммы Вейча. Указанное требование к диаграммам

Вейча предъявляется для удобства отыскания контермов, покрыва-

ющих 2т минтермов (т<п, где п — число переменных). Изображе-

ние диаграмм Вейча на плоскости приводит к тому, что не все

клетки, которым соответствуют соседние минтермы, имеют общую

{рань Легко убедиться (рис, 1.1,а), что клеткам с номерами 0 и 4,

1 и 5 соответствуют соседние минтермы Поэтому диаграмму Вейча

/Ля трех переменных следует представлять себе свернутой в цилиндр

путем совмещения боковых сторон Тогда клетки с номерами 0 и 4,

а также с номерами 1 н 5 будут иметь общую грань.

Пример. Требуется составить диаграмму Вейча для функции

f(v), заданной табл 1.4. Для этого в клетки с номерами i диаграм-

мы Вейча следует занести значения функции f(v,)=O или 1, кото-

рые она принимает в точках vf (рис. 1 1, в) В § 1 2 было показа-

но. что СДНФ данной функции имеет вид f(v) = K1(v)V^2(v)\/

VKs(v) VK?(V) т е в диаграмме Вепча единицами заполняются

клетки, соответствующие этим минтерма.м. Таким образом, сущест-

вует однозначная связь между таблицей истинности (табл. 1.4),

аналитическим выражением для функции и диаграммой Вепча (рис,

1.1, в).

Некоторые особенности взаимосвязи таблицы истинности н диа-

граммы Вейча требуют пояснений. В табл 1 4 значения аргументов

указаны в явном виде в трех столбцах, обозначенных х.-„ х2,

а в диаграмме Вейча эти значения в явном виде отсутствуют Од-

нако поскольку каждой клетке с номером i соответствует точка vj

области определения функции, то данной клетке соответствует впол-

не определенная совокупность значений переменных х3, х2 и ху

(это соответствие указано в табл. 1.4). Легко заметить, что поло-

вине клеток диаграммы Вейча, обозначенной хр( р=1 2, 3), соот-

ветствуют значения л'₽=1, а другой половине клеток — х =0 Дру-

гая особенность взаимосвязи заключается в том, что минтермы,

равные 1 в точке с номером I, в диаграмме Вейча указаны в явном

виде, а в таблице истинности — в неявном виде (с помощью значе-

ний аргументов хг). Например, строке с номером 1=2 соответству-

ют значения л'з=0, *2=1 и *1 = 0. Поэтому K;(v)=K2(v) =

=ХзХ2х?=:Хзл:2х1 • а в Диаграмме Вейча клетка с номером 1=2 не-

посредственно обозначена через x3XjX| (рис 1.1,6).

Указание в явном виде одних величин вместо других в табли-

цах истинности и диаграммах Вейча связано с различием их назна-

чения: таблицы истинности наиболее удобны д-тя первоначального

описания переключательных функций, а диаграммы Вейча — для их

минимизации. Клетки, содержащие в диаграмме Вейча единицы, бу-

дем называть 1-клеткамп а клетки, содержащие нули—О-клетка-

ми. Было показано, что любой контерм K.„j(v). не зависящий от т

переменных (т<л, где п — число переменных), представляет собой

дизъюнкцию 2т минтермов, каждый из которых имеет средн осталь-

25

пых по т соседних. Поэтому диаграмма Вейча для таких контор

мов содержит 2m 1-клеток.

Основное свойство диаграмм Вейча заключается в том, что

1-клетки любого контерма K.j(v) образуют на ней область, япля-

ющуюся прямоугольником и только прямоугольником (для трех

переменных эта область представляет собой прямоугольник на ци-

линдре), причем переменные хР. от которых контерм K,j(v) не за-

висит, имеют в этой области различные значения^ (хр н хр), а ос-

тальные переменные — только одно значение (хр пли хг). Такне

области называются m-кубами («1=0, 1, .... п; 0-кубу соответству-

ет минтерм, а и-кубу — константа единица) Так как m-куб пред-

ставляет собой область, состоящую из 2"* 1-клеток, то говорят, что

от-куб покрывает 2"‘ 1-клеток Чтобы записать контерм Ki.j(v), со-

ответствующий некоторой прямоугольной области (некоторому

m-кубу) в явном виде, необходимо просто составить конъюнкцию

из первичных термов х^р, которые в этой области на диаграмме

Вейча имеют постоянные значения (только хр или только х,,).

В cooiBCTCiBHH с общим правилом минимизации получение

МДНФ с помощью диаграмм Вейча сводится к отысканию мини-

мального числа «i-кубов максимального размера, состоящих из

1-клеток, т. е. к отысканию минимального покрытия /п-кубами

I-клеток и составлению дизъюнкции контермов (v), соответст-

вующих этим /н-кубам (любая 1-клетка должна войти хотя бы

в один щ-куб) Согласно идемпотентным законам любая 1-клетка

может входить в несколько различных т кубов.

На рис. 1.1 в штриховыми линиями обозначены два 1-куба,

образованные 1-клетками с номерами 5 и 7, 1 п 5, которым соот-

ветствуют коптермы х8Х| и x2Xi, а 1-клетка с номеро- 2 не имеет

ни одной соседней 1 клетки, поэтому ей соответствует 0-куб, пред-

ставляемый миптерыо.м хлЛ'г*|._МДНФ данной функции записыва-

ется в виде /(v) =.VxXiV*'?xiVa’x2*i- МИФ в базисе И — НЕ этой

функции получается из МДНФ в соот-ветствии с (1.52) /(v) =

= Х’зХ1 V*2*l \Аз-ЧЛ| =Xs*l • Л'гХ1 -ХзЛ/Л1.

Для получения МКНФ функции f(v) следует найти МДНФ ин-

версной функции f(v), т. е. следует иайгп минимальное покрытие

всех 0-клеток функции f(v) f(v)—XsXiV-^a'iУхзХг* а МКНФ

получается на основании закона двойственности f(v) =x3XiV-*:,v1\/

\/х3х2Х|= (х3ух ) • (х2у.Т1) (*'з\/*'/\Л1) МИФ в базисе ИЛИ НЕ

данной функции получается из МКНФ в соответствии с (1.55)

f(y) =Хз\Лч V*'2V*'i V*sV*i.

Из рне. 1.1, г следует, что минимальное покрытие 1-клеток

функции f(v) состоит из двух 2-кубов, которым ^соответствуют кон-

термы Хг И Xi, поэтому МФНФ функции f(v)=X2V*'l. МКНФ фун-

кции в данном случае совпадает с МДНФ, a )(v)=x2xl— МНФ

в базисе И—НЕ и f(v) x2V*'i—МНФ в базисе ИЛИ — НЕ.

Диаграммы Вейча для четырех переменных показаны на рис.

12. Так как v— (лц, х3, х2, xj) п тч=(е4, е3, е2, еО, еде /=£463^2^1,

то номера клеток i диа<раммы Вейча вычисляются па основании пер-

26

б)

Рис 1 2

внчных термов хр', используемых для обозначения ее сторон (рис.

I 2, а) Легко убедиться, что к теткам с номерами 0 и 2; 0 и 8; 2 и

10 8 и 10 соответствуют соседние минтермы. Чтобы эти клетки

имели общую грань, следует диаграмму Вейча для четырех пере-

менных представлять себе свернутой в тор путем соединения боко-

вых сторон (получается цилиндр) и совмещения оснований цилинд-

ра Тогда, например, область, состоящая из I-клеток с номерами

0, 2, 8 и 10, буде! представлять собой прямоугольник на торе, т. е.

2-куб, который соответствует контерму х3х>.

Диаграмма Вейча, показанная на рис. 1.2,6, задает некоторую

функцию /(v). Минимальное покрытие 1-клеток состоит из одного

3-куба и двух 2-кубов, которым соответствуют контермы х2. x3xt

и Хзлт, поэтому МДНФ данной функции f(v) —хг\/ХзХ1\/ХзХ1 Ми-

нимальное же покрытие 0-клеток состоит из двух 1-кубов, которым

соответствуют контермы ХзХ2х'| н х3х2Х|, поэтому МКНФ этой функ-

ции f(v) — (хзVх-* V-*i)/ (л*з\/л'2VA'i) Из МДНФ и МКНФ ие со-

ставляет труда получение МИФ в базисах И — НЕ н ИЛИ — НЕ.

Выбор »п-кубов, покрывающих 1-клетки диаграммы Вейча, не

всегда столь очевиден, как это было в предыдущих примерах. На

рис. 1.2,6 часть 1-клеток можно было бы покрыть 2-кубом (ему

соответствует контерм Xt-vJ. Однако при покрытии остальных четы-

рех 1 клеток 1-кубами становится понятным, что необходимость ис-

пользования 2-куба отпадает МДНФ этой функции f(v) = x<x'3x2V

Vx3x2xtV-V3X2X1VXjXjX? Таким образом, ие всегда следует начинать

покрытие 1-клеток с отыскания m-кубов максимального размера.

Сформулируем общие правила минимизации функций с помо-

щью диаграмм Вейча, справедливые для любого числа перемен-

ных п-

для получения МДНФ необходимо найти минимальное покры-

тие 1 клеток, которое состоит из минимального числа m-кубов мак-

симального размера;

m-кубу, покрывающему 2т 1-клеток, соответствует контерм, не

зависящий от л> переменных, причем исключаются те т перемен-

ных которые в прямоугольной области на дпаграмме_ Вейча, со-

стоящей из 1 клеток, имеют различное значение jq, и хр\

прямоугольные области на диаграммах Вейча, используемые

при минимизации, могут состоять только из 2т клеток, где т=0,

1, .... п, т. е из 1, 2, 4; 8; 16 и т. д 1-клеток;

27

покрытие 1-клеток следует начинать с выбора тех 1-клеток, ко-

торые могут войти в один и только один m-куб, а затем выбранные

таким образом 1-клетки покрываются от-кубами максимального раз-

мера (это правило позволяет исключить возможность появления

лишних /n-кубов, как это могло иметь место в примере, приведен-

ном на рнс. 1" 2, я);

если 1-клеток, входящих только в одни /n-куб, нет, то следует

рассмотреть несколько вариантов минимизации.

Диаграммы Вейча для числа переменных и >4 составляются нз

идентичных (в смысле обозначения сторон первичными термами

диаграмм Вейча для четырех переменных. Па рис. 1 3 пред-

ставлены диаграммы Вейча для п — 5 и 6. Две диаграммы Вейча

для четырех переменных будем называть соседними, если они име-

ют общую грань. Клетки, расположенные в одинаковых местах со-

седних диаграмм Вейча для четырех переменных, являются сосед-

ними, так как им соответствуют соседние ыиптермы. Так, например,

клетки с номерами 0 и 16; 5 и 21 и т п. (рис. 1.3. а), 0 и 16; 0 к 32;

5 и 21; 5 п 37 и т.п. (рнс. 1 3, в) являются соседними, но клетки О

и 48; 5 и 53; 16 и 32 и т.п (см. рис. 1.3, е) не являются соседними,

так как они расположены не в соседних диаграммах Вейча для че-

тырех переменных.

Легко убедиться в том, что т кубы, расположенные в одинако-

вых местах двух соседних диаграмм Вейча для четырех перемен-

ных, образуют (т+1)-куб С учетом этого МДНФ функцни_Нм),

представленной на рнс. 13,6, имеет вид /(v) V*2*i

В диаграммах Вейча для шести переменных /n-кубы располо-

28

Рис 1 4

женныс в одинаковых местах всех четырех диаграмм Вейча для

четырех переменных, образуют ('н+2)-куб. Поэтому МДНФ функ-

ции, представленной на рнс, 1.3 г, имеет вид f(у) =x^cj\/X5*4XiV

V*e*'4vlV*'6*5*4

Минимизация неполностью определенных функций Основная

задача минимизации неполностью определенных функции заключа-

ется в отыскании оптимального варианта се доопределения, позво-

ляющего получить минимальную из всех возможных ДПФ пли КНФ.

Если значения функции не заданы в т точках, то ее можно доопре-

делить 2т способами. Поэтому .минимизация неполностью опреде-

ленной функции состоит в выборе одной из 2"1 полностью опреде-

ленных функций, которая имеет минимальную ДНФ пли КНФ.

СДНФ неполностью определенной функции / (v) можно представить

в виде

Z(v) = VKi.(v) V®VK;r(v),

fs ‘

где v=(x,. Xi); i«—номера тех точек области определения, в ко-

торых функция f(v/s) = l, a t, — номера тех точек области определе-

ния, в которых функция f(v) имеет неопределенное значение, т. е.

f(v/r)=<D.

Пусть задана СДНФ неполностью определенной функции четы-

рех переменных; х,, х3, х2, хи /(v)=KoVK:V^V/<sVa>(/(iV/<-1V

VKeVKcVKis), где Ki—Ki(v). Составим для этой функции диаграм-

му Вейча (рис. 1.4). Для этого в клетки с номерами 1 = 0, 4, 7 i 8

следует занести значения функции, равные I, а в клетки с номерами

1=1, 5, 6, 9 и 12 — неопределенные значения Ф. С помощью диаг-

раммы Вейча легко найти все минимальные покрытия, полагая ли-

бо Ф=0, либо Ф-1. На рнс. 1.4 представлены два варианта доопре-

деления^ функции f(y), которые дают минимальные ДНФ, f(v) —

=x4x3\/X2Xi, f(v) — x-iXsX/xiXi (Ф = 0, если символ Ф нс вошел пи

в одни m-куб, и Ф=1, если он вошел хотя бы в один т-куб)

Аналогично этому можно найти п МКНФ данной неполностью

определенной функции, произведя оптимальным способом доопре-

деление инверсной функции. f(v) =xix3\z'^3x2, f(у) = (Х4\Дз) (x<V

V-^г). Для данной функции имеется только один способ доопределе-

ния, дающий минимальную КНФ.

1.4. Комбинационные схемы

Логическая схема, выходные сигналы zq которой описываются

системой переключательных функций

гч fq (*п > • • > *1) .

(1.56)

29

Рис 1.5

Рис. 1 6

Рис 1.7

где хр — входные сигналы логической схем л р -1...Л, q=\...k, на-

зывается КС. Из системы (1.5b) следует, что КС реализует однознач-

ное соответствие между значениями входных и выходных сигналов.

При синтезе КС, имеющих несколько выходов zq, независимая ми-

нимизация каждой функции ..., Xi), как правило, не дает оп-

тимального результата в смысле суммарного числа первичных тер-

мов, требуемых для представления функций.

Совместная минимизация функций. МДНФ функций fi(v)

и fa(v), заданных диаграммами Вейча иа рис. 1 5,

/1 ('’) = Х-1 Хд V *4 X2; f2 (v) = Л'д Х3 \/ Х3 Х2- (1 • 57)

На рис. 1.6,а показана КС, реализующая эти функции. Из рис.

1.5 следует, что функции fi(v) и J2(v) можно представить также

в форме (не МДНФ):

/1 (v) = х3 V х3 х2; /2 (V) = х4 хя V *4 *'s *2 (1.58)

Контерм X4*‘3x2 входит в обе функции, а для его реализации тре-

буется только одни логический элемент (ЛЭ) И. Для реализации

функций в форме (1.58) требуется семь первичных термов, а в фор-

ме (1.57)—восемь первичных термов. На рис. 1.6,6 показана КС,

реализованная в соответствии с (1.58). Сложность реализации КС

можно оценивать также по суммарному числу входов используемых

ЛЭ.

При совместной минимизации нескольких функций следует отыс-

кивать конъюнктивные термы, входящие более чем в одну функ-

цию, что, как правило, дает лучший результат, чем независимая ми-

нимизация каждой функции в отдельности. Или, более строго, сле-

дует отыскивать совместное покрытие всех функций минимальным

числом m-кубов (контермов) максимального размера.

Порядок КС. Максимальное число последовательно выполняемых

логических операций для реализации функции [(хп Xi) называ-

ется порядком переключательной функции. Функции, представлен-

1

ные в любой нормальной форме, имеют порядок нс выше второго.

Порядком КС называется максимальное число последовательно

Ьключепных ЛЭ. Порядки КС и соответствующих iui функций сов-

падают. Па рис. 1.6 КС реализованы в соответствии с МДНФ и ДНФ,

которые имеют второй порядок, и максимальное число последова-

тельно включенных ЛЭ равно двум.

При вынесении в ДНФ обшпх членов за скобки порядок функ-

ции увеличивается. Функция

f(y) = -'1 *3 *2 V *4 *'з V *4 х2 Xi (1.59)

представлена в МДНФ. Этой функции соответствует КС второго по-

рядка, показанная па рнс. 1.7, а. Иначе эта КС называется двухъ-

ярусной. На основании дистрибутивных законов функцию (1.59)

можно представить в форме

f (*) = х41 (х.2 \J лу) V х, xj, (1.60)

которой соответ :твует схема на рис. 1.7,6. В этой КС максимальное

число последовательно включенных ЛЭ равно четырем, т. е. КС

имеет четвертый порядок (четырехъярусная КС).

Каждый ЛЭ имеет конечное быстродействие, которое можно ха-

рактеризовать задержкой распространения сигналов t3 от входов

к выходу. Чем выше порядок КС, тем меньше ее быстродействие.

Скобочные формы представления функций типа (1.60) используются

для уменьшения стоимости КС. Так, суммарное число входов ЛЭ на

.рис. 1.7, а равно 12, а на рис. 1.7,6—10. В обшем случае стоимость

КС и ее быстродействие жестко связаны. Реализация КС с большим

числом входов на основании функций, представленных в ДНФ

(МДНФ), практически неприемлема нз за большого числа требую-

щихся ЛЭ. Па практике очень часто используются КС, имеющие по-

рядок выше десяти. В таких КС уменьшение быстродействия оправ-

дывается существенным снижением стоимости их реализации.

Переходные процессы в КС. При изменении входных сигналов

КС из-за инерционности ЛЭ в пей начинает протекать переходный

процесс. Максимальная длительность переходною процесса опреде-

ляется максимальным числом последовательно включенных ЛЭ (по-

рядком КС). Входные сигналы хр изменяются не мгновенно, т. е. сиг-

налы имеют фронты конечной длительности (рис. 1.8). В момент

изменения входных сигналов хр они имеют неопределенное значе-

ние Ф. По этой причине, а также из-за задержек сигналов в ЛЭ

выходные сигналы КС при переходном процессе могут принимать

значения, не соответствующие описывающим их функциям (1.56).

Из этого следует, что функции (1.56) описывают КС только в ус-

тойчивом состоянии (после окончания переходных процессов). По-

явление кратковременных ложных значений выходных сигналов КС

может привести к неправильному срабатыванию других схем, в ко-

торых выходные сигналы КС используются в качестве входных.

Из рис. 1.9, а следует, что МДНФ функции f(v) — jr3x2V-*3^i«

Этой функции соответствует схема па рис. 19,6. Временные диа-

граммы иа рис. 1.10 поясняют повеление КС при х2 х, 1 и нзме-

31

Рис 1.9

Рис 1 10

пенни входного сигнала х3 при различных соотношениях задержек

1з| И 1J2 сигналов вЛЭИ«|ниг Из МДНФ функции следует, что

при х2- Х1=1 функция f(v)=x3Vx3=I. При переходном же процес-

се, как видно из рис. 1.10, на выходе КС появляется кратковремен-

ное ложное значение f(v)=O. Явление неодновременности изменения

выходных сигналов ЛЭ при одновременном изменении их входных

сигналов называется состязание.» ЛЭ. Они называются критическими,

если приводят к появлению на выходе КС кратковременного ложно-

го значения функции f(v)

Синтез КС, свободных от состязаний Если в каждый момент

времени допускается изменение только одного входного сигнала КС,

то ее синтез можно выполнить так, что при изменении любого вход-

ного сигнала выходные сигналы при переходном процессе не будут

иметь ложных значений [1, 2]. Такие КС называются свободными от

состязаний. Методика синтеза КС, свободных от состязаний, с по-

мощью диаграмм Вейча изложена в [2] и заключается в следующем

все соседние 1-клетки должны быть покрыты хотя бы одним m ку-

бом Если иа рис. 1.9,а добавить 1-куб, которому соответствует

контерм х2хь то все соседние 1-клетки будут покрыты »г-кубами,

а функция f(v) будет иметь вид

f (V) = Х2 X/ Х3 V х2 Xi (1.61)

Такая форма представления функции называется МДНФ, сво-

бодной от состязаний. Из (1.61) следует что при Jt»=Xi=l функция

f(v) = l независимо от значения сигнала л'з, т. е изменения сигнала

х3 не оказывают воздействия на выходной сигнал КС.

Закон двойственности для комбинационных схем. Пусть КС вы-

полняет функцию f(v)=x3X2V*'s*i (рис 19,6). Тогда f(v)=x3x2&

&x3xt—МНФ функции в базисе И—НЕ (рис. 1.11, а) и f(v) —

Vx’sV^i — МНФ инверсной функции в базисе ИЛИ—НЕ

(рис. 1 11,5) Из рис. 1 11 следует, что при замене ЛЭ И—НЕ на

32

Рис. 1.11

ЛЭ ИЛИ—НЕ необходимо все входные и выходные сигналы заме-

нить иа инверсные. Рассмотренный пример иллюстрирует закон двой-

ственности для двухъярусных КС. Данный закон справедлив и для

более сложных логических схем (многоярусных КС в схем с обрат-

ными связями, которые в большинстве случаев не являются КС).

Действительно, ЛЭ И—НЕ, имеющий т входов, выполняет функцию

ft(xm...., х,)=Лт-а ЛЭ ИЛ И—НЕ — Функцию fs(x„..............Х|) =

==XmV-. V*2Vxi=*m’ >*) Следовательно, для пре-

образования любой логической схемы, выполненной на ЛЭ И—НЕ,

в схему, выполненную на ЛЭ ИЛИ—НЕ, достаточно все ЛЭ И—НЕ

заменить на ЛЭ ИЛИ—НЕ, а все входные н выходные сигналы ис-

ходной схемы заменить их инверсиями

Хорошей иллюстрацией закона двойственности являются схемы

асинхронных потенциальных R-S-трпггеров (см. § 2.5).

2. Интегральные микросхемы

2.1. Сравнительная характеристика стандартных интегральных схем

В зависимости от технологии изготовления ИС подразделяются

на серии (семейства), различающиеся физическими параметрами ба-

зовых элементов, а также числом и функциональным назначением

входящих в их состав микросхем В настоящее время разработано

несколько десятков технологий изготовлении ИС. Наиболее широ-

кое применение находят ИС, изготовляемые по ТТЛ-, КМОП-

и п МОП технологиям Каждая технология непрерывно совершенст-

вуется с целью увеличения быстродействия ИС, уменьшения по-

Таблица 2.1

Серия ИС эн d3V Р, мВт/вент. I , мкА вх X о ® VTJW J : * S 3 * СО < а к 3 о х -- С 5 е с. о

SN74 10 10 40 —1,6 35 -400 16 10 100

SN74L 33 1 10 —0,18 3 —200 3,6 10 33

SN74H 6 22 50 —2 50 —500 20 10 132

SN74I S 9,5 2 20 —0,36 45 —400 8 20 19

SN74S 3 19 50 —2 125 —1000 20 10 57

SN74ALS 4 1 10 —0,2 50 -400 8 40 4

SN74AS 1.5 22 — 200 —. 20 100 33

SN74F 2 4 20 —0,6 130 —1000 20 33 8

3-376

33

Таблица 22

Серия ИС Серия НС

отечественная зарубежная отечественная зарубежная

155 SN74 133 SN54

158 SN74L 136 SN54L

131 SN74H 130 SN54H

555 SN74LS 533 SN54L.S

531 SN74S 530 SN54S

КР1533 SN74AI.S 1533 SN54ALS

KP153I SN74F 1531 SN54F

требляемой мощности и увеличения степени интеграции — числа эле-

ментов, разметаемых на кристалле заданной площади.

ТТЛ ИС. В табл. 2.1 [3] приведены основные параметры базо-

вых алемеитов различных серий зарубежных ИС, изготавливаемых

по ТТЛ-технологиям, а в табл. 2.2 - соответствие зарубежных ИС

отечественным.

Кроме серий SN74, зарубежными фирмами выпускаются серии

SN54 и SX84, различающиеся только температурным диапазоном

н допустимым отклонением напряжения источника питания от но-

минала (табл. 2.3) [3, 4].

Таблица 23

Серия НС Диапазон рабочих температур. еС Напряжение питания» В

SN54 —55. .4-125 4,5. ..5,5

SN74 0. 70 4,7о. 5,25

SN84 —25. . |-85 4,75. 5,25

Наиболее важным параметром, характеризующим качество се-

рий НС, является работа переключения — произведение среднего

времени задержки сигналов в пентиле /3 ср иа мощность потребления

вентиля Р (табл. 2.1). Остальные параметры в табл. 2.1 означают:

— входной ток при подаче на вход уровня логического нуля;

/вЧ—входной ток при подаче па вход уровня логической единицы;

Ртах — максимальная частота переключения; /'Ь1Х—выходной ток

при уровне логической единицы на выходе,/дЫХ—выходной ток при

уровне логического нуля на выходе, и-пагрузочная способность (от-

ношение

Серия SN74F/SN54F [5, 6] разработана фирмой Fairchild

в 1979 г, остальные серин — фирмой Texas Instruments за 1963—

1982 гг. Семейство SN54 выпускается для военных применений,

а семейство SN74 — коммерческих (табл. 2 3) Первой была выпу-

34

•цена серия SN74/SN54 (стандартная). В 1967 г. в дополнение к ука-

занной серии были разработаны серии SN74H/SN54H (High speed—

быстродействующая) н SN74L/54L (Low power — маломощная), что

позволило разрабатывать более высокочастотные цифровые устрой-

ства при обшем снижении потребляемо!! мощности (высокочастотные

узлы выполняются па ИС серии S \I74H, среднечастотпые — SN74.

а ппзк (частотные — S\ 4L)

В 1969 г была разработана серия SN74S/SN54S, 1971 г, —се-

Ьрия SN74LS/SN54LS. 1980 г. — SX74ALS/SN54ALS, 1982 г. —се-

рия S\'74AS/SN54AS (S — Schottky, LS—Low power Schottky;

ALS — Advanced Low power Schottky, AS — Advanced Schottky;

(Advanced — усовершенствованная) [3]. Все эти серии, как и серия

SN74F/SX54F (FAST — Fairchild’s Advanced Shottky TTL), осно-

ваны на использовании диодов Шотки, предотвращающих режим

глубокого насыщения транзисторов, что значительно увеличивает

скорость переключения вентилей Наиболее перспективными явля-

ются ИС с диодами Шоткп. В настоящее время широкое применение

при проектировании цифровой аппаратуры находит серия

SN74LS/SX54LS (серия 555 533).

Все серин, указанные в табл. 2.1 н 2.2, совместимы по входам

и выходам: выходное напряжение логического нуля 67„ых<0,4 В;

входное напряжение логического нуля U^x СО,4 В; выходное на-

пряжение логической единицы £7*ых.>2,4 В; входное напряжение

логической единицы £/^^2,4 В. При использовании ИС различных

серий в одном устройстве следует учитывать взаимную нагрузочную

способность (табл. 2.4). Все серин ИС содержат кроме элементов со

Таблица 2.4

Вход ИС серий

Выход 1-1 С серий SN74 SN74LS SN74S SN74ALS SN74AS

155 SN74 10/30 40'120 8/24 80 /240 30/240 26/80

555 SN74LS 5/15 20/60 4/12 40/120 40/120 13 40

531 SN74S 12/30 50/120 10(24 100/240 100/240 30 100

КР1533 SN74ALS 5/15 20/60 4/12 40/120 40/120 13'40

— SN74AS 12/35 50/150 10/30 100 300 100/300 30/80

КР1531 SN74F 12/40 50/150 10/25 100 250 100 250 30'100

стандартным выходом (параметры приведены в табл. 2.1) элементы

с повышенной нагрузочной способностью (буферы) В табл. 2.4 пер-

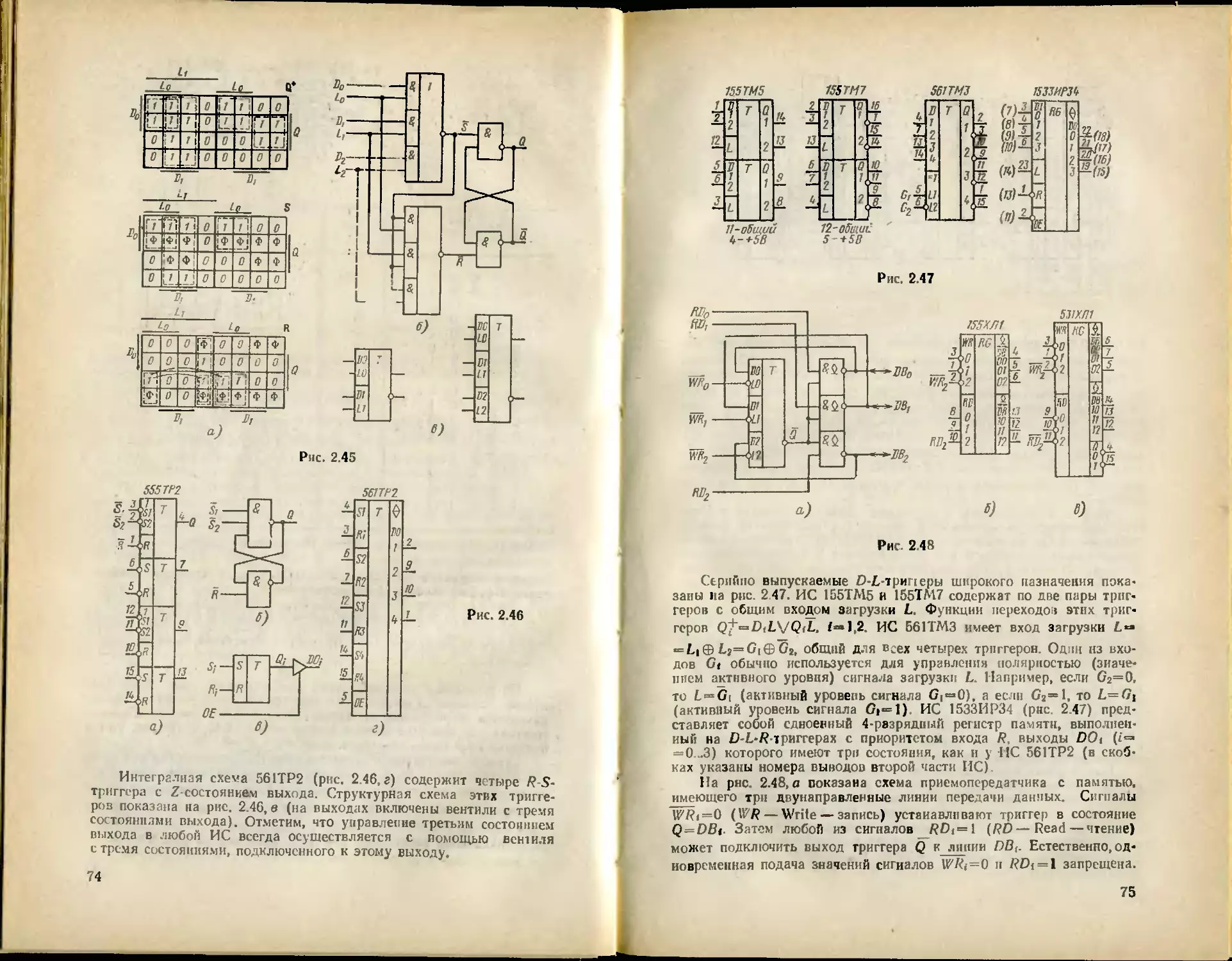

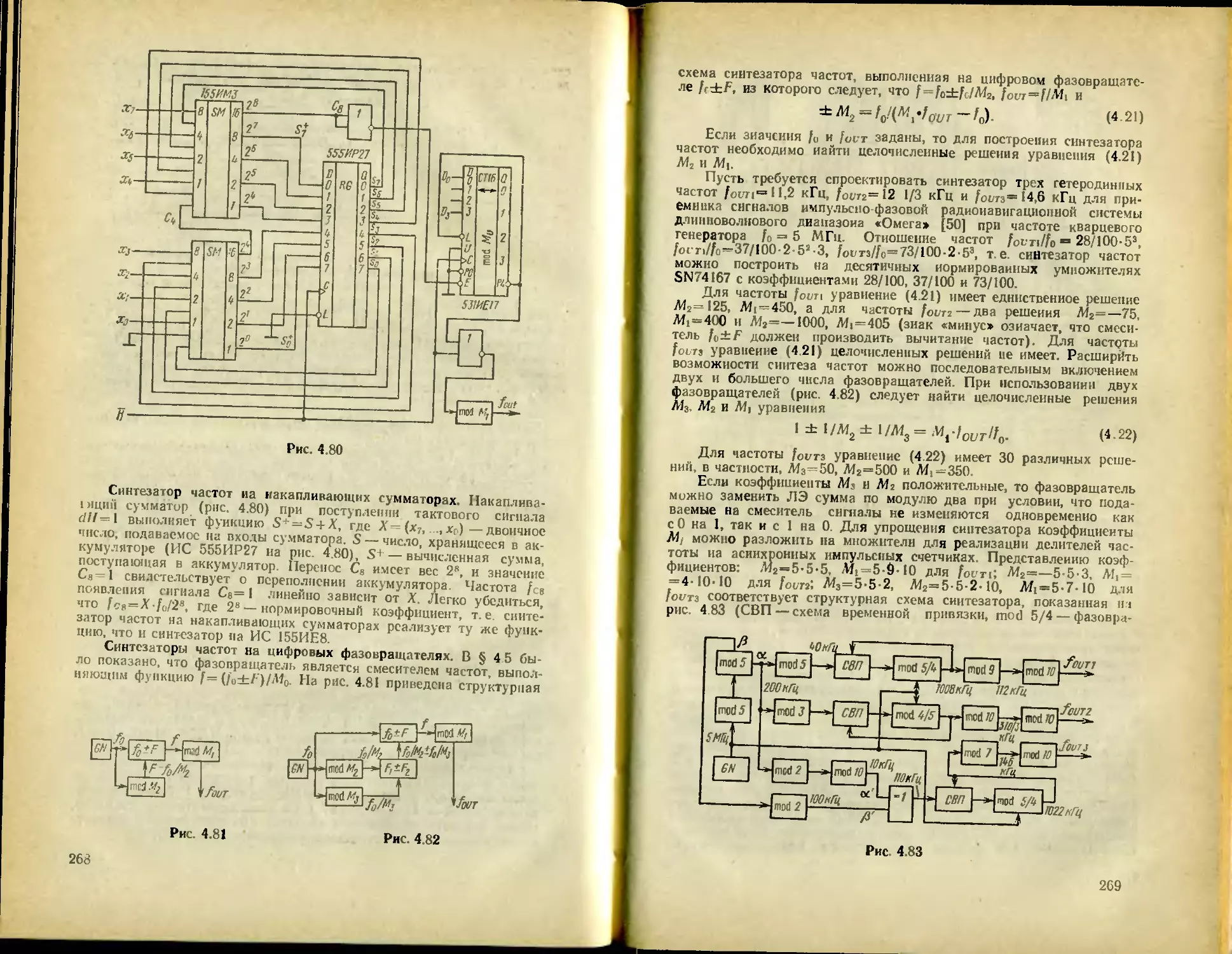

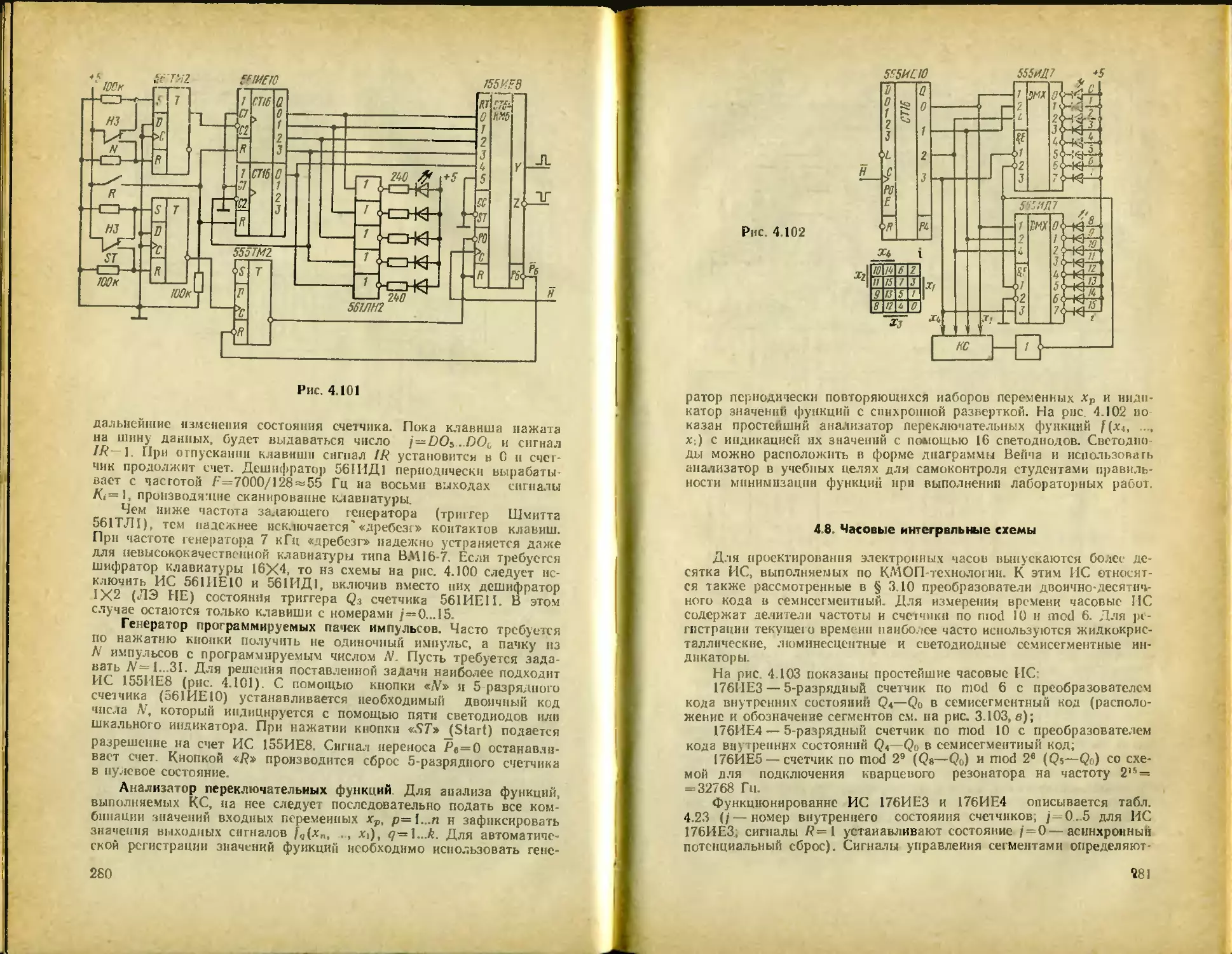

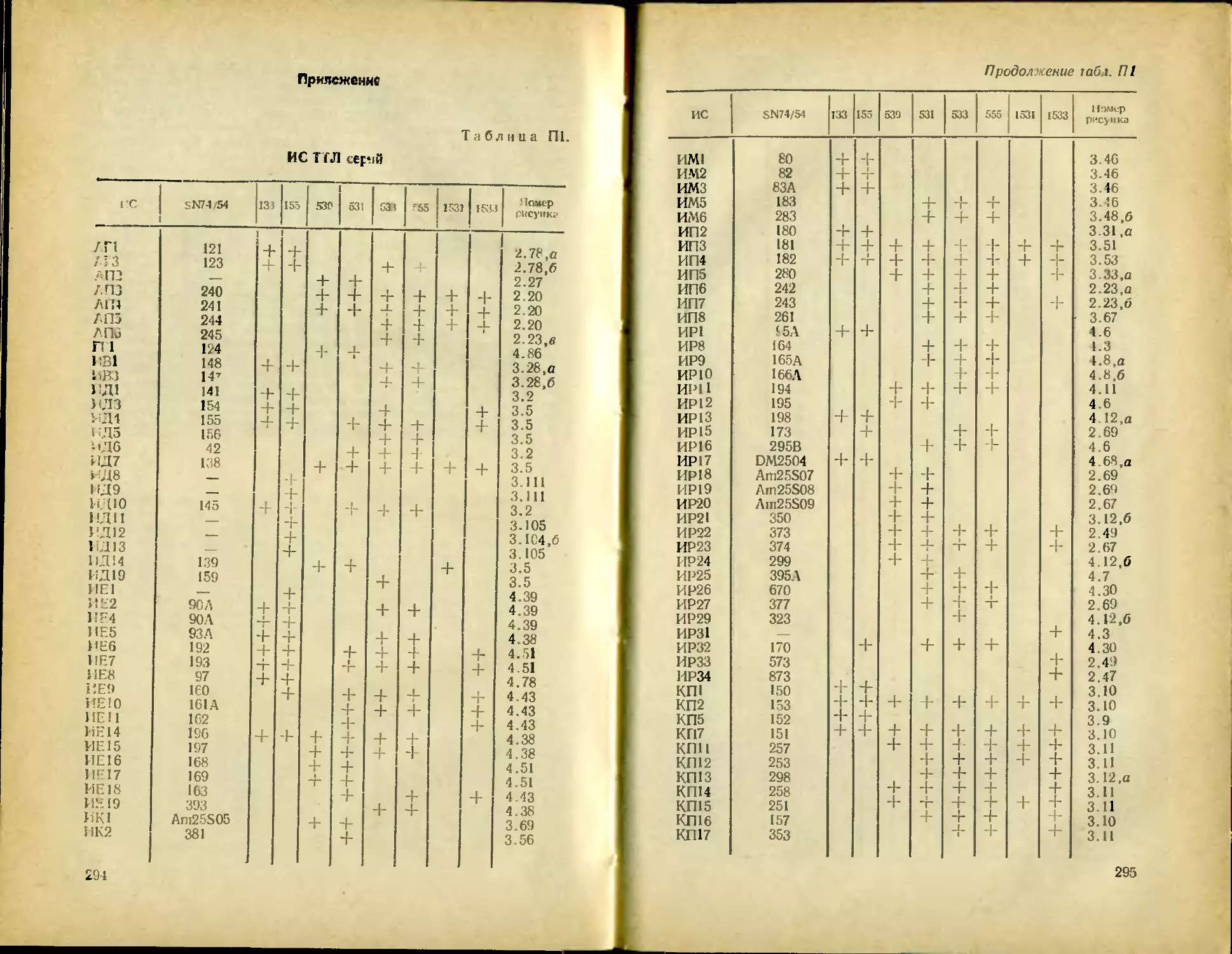

вое число указывает нагрузочную способность для элемента со