Текст

nr Б.Ю.Семенов

В ШИНА |2С |> в РАДИОТЕХНИЧЕСКИХ

[Ц.

КОНСТРУКЦИЯХ

" УСТРОЙСТВО ш

МИКР С ИНТЕ

к МИКРОСХЕМЫ ДЛЯ АУДИОАППАРАТУРЫ 5\ ВСПОМОГАТЕЛЬНЫЕ МИКРОСХЕМЫ

ЭЛЕКТРОННЫЕ КОМПОНЕНТЫ

ВАШЕГО УСПЕХА

Всегда На складе 8 Промышленных количествах широчайший ассортимент компонентов заводов России и ближнего зарубежья ;<

EPCOS

IOR

АМР

MITSUBISHI

ELECTRIC

xntersil

inuRtdu

Melleman

Продукция ведущих мировых производителей: • активные компоненты

Bet- товары н розницу а магазинах

• разъемы и соединители

* пассивные компоненты с

ферриты, трансформаторы, керамические фильтры, термисторы, варисторы, разрядники, конденсаторы.

потенциометры, самовосстанавлиеающиеся предохранители

• широкий выбор датчиков

• TVS. диоды, диодные мосты

• жидкокристаллические индикаторы

• оптоэлектронные приборы

• электролитические конденсаторы

• электромагнитные и твердотельные реле

• программаторы, эмуляторы, тестеры -

* паяльное оборудование, радиомонтажный инструмент, газовые паяльники <'

• мультиметры, осциллографы

* вентиляторы для охлаждения аппаратуры

• плоский, коаксиальный, телефонный, акустический кабель

• акустические компоненты

• корпуса для электронной аппаратуры

• радиоконструкторы

Пассивные компоненты гарантированного качества производства Тайвань. Гонконг: реле, полипропиленовые и танталовые конденсаторы, индуктивности, резисторы, чип-компоненты. разъемы

бесплатный каталог И CD С ТЕХНИЧЕСКОМ документацией высылается по ЗАЯВКАМ ПРЕДПРИЯТИЙ.

121351,Москва,

ул. Ивана Франко, д. 40, стр. 2

Тел/факс: (095) 73-75-999

Почта: 121351. Москва, а. я 100

E-matl. platanCwaha ru

факсг 13832) 16-33-66 . tert Ф<иг«. (3432) 13-02 57 ten, факс,- (8462)35 26 09 тег» факс; (8352)64-05 61 teft-фам 13822) 41-55 .'О факе, <3472) 32 33-42

Моемы ул Бегония. 2 Тел: <095* 384-S8-78

Миомга. ул. Гил«р«>вск<ио, 33

Тол фат. <095)284-56 78

Е mail 0»р гм

М«с»ва, ул Низка Франко, д 40, сф. 2

Тел {095)417 33 55

E-mail dipi*ot pus "> plat an to

С -Петер&ур» Кроииергипни проси., 73

Тел, 18П) 232 83 06, 232-59-87

E-mail ptataniimM wplu&.net

Ярославль, tip Ленина, 8а

Тел. (0852) 30-15-68

E-mail: chip сИрйуа»tele-pott,«u

Б. Ю. Семенов

ШИНА 12С В РАДИОТЕХНИЧЕСКИХ КОНСТРУКЦИЯХ

Москва СОЛОН-Р 2002

Семенов Б. Ю.

Шина 12С в радиотехнических конструкциях / Б. Ю. Семенов. — М.: СОЛОН-Р, 2002. 192 с. — (Серия «Просто и доступно»)

ISBN 5-93455-168-Х

В книге рассказывается о принципах построения и логике работы последовательной шины обмена данными Inter-Integrated Circuit Bus (l2C), разработанной фирмой Philips. Приводятся сведения о микросхемах, имеющих интерфейс )2С, а также несложные конструкции на их основе, доступные для повторения радиолюбителями. Книга может быть полезна радиолюбителям, инженерам, студентам радиотехнических специальностей вузов, специалистам-ремонтникам бытовой аппаратуры.

Описанные в книге программы можно загрузить с сайта http://www.remserv.ru (раздел «Программы»).

Эту книгу можно заказать по почте (наложенным платежом — стоимость 110 руб.) двумя способами:

1) выслать почтовую открытку или письмо по адресу: 123242, Москва, а/я 20;

2) передать заказ по электронной почте (e-mail) по адресу: magazin@solon-r.ru.

Необходимо написать полный адрес, по которому выслать книги.

Обязательно указывать индекс н Ф. И. О. получателя!

При наличии — указать телефон, по которому с вами можно связаться, и адрес электронной почты (E-mail).

Цены действительны до 1 сентября 2002 г.

Вы можете в любое время получить свежий каталог издательства «СОЛОН-Р» по Интернету, послав пустое письмо на робот-автоответчик по адресу katalog@solon-r.ru, а также подписаться на рассылку новостей о новых книгах издательства, послав письмо по адресу news@solon-r.ru с текстом «SUBSCRIBE» (без кавычек) в теле письма.

ISBN 5-93455-168-Х

© Макет и обложка «СОЛОН-Р», 2002

© Б. Ю. Семенов, 2002

От автора

Однокристальные микроконтроллеры стремительно занимают ведущее место в электронной аппаратуре. И если каких-нибудь десять лет назад они могли быть использованы при проектировании только профессионалами — слишком много требовалось дорогостоящих средств для их программирования, — то сегодня «однокристалки» используют даже радиолюбители. Просмотрите подшивку журнала «Радио» за последние несколько лет, и вы убедитесь в справедливости сказанного.

Именно микроконтроллер сегодня формирует облик бытовой аудиотехники, видеотехники, средств связи. С передних панелей радиоприемников, магнитол, телевизоров исчезли шкальные индикаторы, ручки настройки, ползунковые регуляторы, переключатели. Их заменили жидкокристаллические табло и кнопки. Значительно усложнилась «начинка» аппаратуры. Очевидно, что десятки разнообразных микросхем, составляющих электронное «нутро» аппаратуры, должны согласованно функционировать, обеспечивая наилучшие технические характеристики и удобство эксплуатации. Решая задачу сопряжения цифровых устройств, разработчики компьютерной техники связали их между собой посредством шин, а способы передачи информации назвали протоколами и стандартизировали их основные принципы. Каждое устройство было снабжено интерфейсом; посредством которого стало возможным подключать его к шине.

Если говорить об аналоговой технике, то специализированные аналоговые микросхемы испокон веков имели уникальные собственные выводы для подключения элементов, с помощью которых устанавливались их рабочие режимы или осуществлялись регулировки в процессе эксплуатации. Например, регулировалась громкость звука, контрастность изображения и т. д. Объединять эти выводы с целью выполнения универсальной регулировки не представлялось возможным. Современные микросхемы, предназначенные для использования в новой аппаратуре, решено было снабдить цифровым интерфейсом, «спрятать» настроечные выводы внутрь микросборок, а управлять их режимами программно.

4

Осуществлять управление одной микросхемой очень просто, для этого даже не всегда нужен внешний цифровой интерфейс. А если микросхем несколько, если они должны взаимодействовать друг с Другом, обмениваться информацией? Решая эти вопросы, разработчики перспективных микросхем пришли к мысли о необходимости введения общей шины и протокола обмена информацией по ней. Известные по компьютерной технике шины оказались здесь совершенно негодными в силу своей сложности. Только представьте, что для реализации обмена по шине ISA или РС1 в состав аппаратуры нужно ввести полноценный компьютер...

Для этих целей фирмой Philips была разработана шина Inter-Integrated Circuit Bus (сокращенно 12С, ай-ту-си). Принадлежа к классу шин с последовательным способом передачи данных, отличаясь чрезвычайной простотой реализации, Шина стала быстро развиваться. Конечно, в основном свое детище продвигала фирма-разработчик, но сегодня и другие фирмы, оценившие по достоинству возможности шины, поддерживают ее своей продукцией.

К сожалению, на сегодняшний день отсутствует русскоязычная литература, позволяющая быстро освоить приемы работы с шиной 12С и в какой-то мере обобщить разрозненные, неполные сведения. В Интернете, на конференциях, посвященных вопросам программирования, то и дело возникают вопросы об основах работы с 12С, но далеко не всегда появляются дельные ответы. Весьма заманчивы перспективы использования микросхем 12С в несложных радиолюбительских конструкциях, обладающих тем не менее высокими потребительскими характеристиками. Все конструкции, в которых задействуется шина 12С, обязательно должны включать в себя простейшие однокристальные микроконтроллеры, что также свидетельствует в пользу их доступности радиолюбителям.

В этой книге рассказывается об основных принципах устройства шины 12С, о микросхемах, поддерживающих этот протокол обмена, о программных способах его реализации. Приведены практические схемы, позволяющие не только закрепить полученные знания, но и изготовить полезную в быту вещь. Автор надеется, что чтение этой книги будет занимательным и легким.

Б. Ю. Семенов.

Декабрь 2001 г.

1. Как устроена шина 12С

Классический вариант обмена данными между любыми устройствами заключается в том, что одно устройство передает информацию, а другое ее принимает. Устройства могут при необходимости поменяться ролями, то есть передатчик может стать приемником и, наоборот, приемник — передатчиком. Но в любом случае важно четко определить, какое из устройств является главным, задающим правила и последовательность обмена, а какое — подчиненным.

Устройства, подключаемые к шине 12С, также подчиняются этому принципу. Договорились, что одно из устройств будет ведущим (master), а остальные — ведомыми (slave). Такая организация шины называется master-организацией и является наиболее типичным случаем (рис. 1.1).

Master-устройством обычно назначается микроконтроллер. Именно он задает основной поток данных на шине, формирует необходимые временные интервалы и т. д.

Гораздо реже используется в аппаратуре режим multi-master (рис. 1.2), когда к одной шине подключено несколько master-устройств.

Рис. 1.1. Master-организация шины 12С

Рис. 1.2. Multi-master организация шины 12С

6

Как устроена шина 12С

Сложность такой организации шины состоит главным образом в том, что master-устройства должны решать, кто из них будет работать в данный момент со slave-устройствами. Одновременно на шине может совершать операции только одно master-устройство, остальные обязаны отключаться. В противном случае возникает ситуация, называемая шинным конфликтом. Информация может попросту не дойти до адресата, нарушится работа устройства.

Для того чтобы исключить шинные конфликты, в режиме multi-master должны содержаться процедуры арбитража и синхронизации, устанавливающие порядок работы master-устройств. В книге мы не будем рассматривать этот режим подробно с точки зрения аппаратной реализации, разберемся лишь, как осуществляется арбитраж устройств и их синхронизация. Основное внимание сосредоточим на классическом режиме с одним master-устройством.

История шины 12С в том виде, в котором она представлена сейчас, началась в 1992 году, когда фирмой Philips была выпущена ее первая спецификация версии 1.0. Эта спецификация исключала возможность задания адреса slave-устройства программным способом как наиболее сложную процедуру. Наряду со стандартным режимом скорости передачи данных 100 кбит/с (low-speed) был введен режим быстрой передачи (fast-speed) со скоростью до 400 кбит/с. Появился также режим 10-разрядной адресации.

Версия 2.0, выпущенная в 1998 году, ввела в спецификацию шины быстродействующий режим (Hs-mode) со скоростью передачи до 3,4 Мбит/с. Причем требования предписали вводить обязательную возможность совместимости с режимами low-speed и fast-speed. К моменту появления версии 2.0 шина 12С распространилась по всему миру, став международным стандартом. Было разработано более 1000 интегральных схем, лицензия на официальное использование спецификации приобретена более чем 50 фирмами.

Версия 2.1, датируемая 2000 годом, включает в себя незначительные модификации, не нашедшие отражения в версии 2.0. На момент написания этой книги версия 2.1 является последней действующей версией, выпущенной Philips. Не исключено, что в процессе подготовки книги в печать выйдет очередная модификация. Спешу успокоить читателя — едва ли новая версия будет содержать кардинальные отличия, да и в любом случае совместимость сохранится.

Как устроена шина 12С

7

Мы не будем вдаваться во все тонкости и хитросплетения названных версий, разберем лишь самые необходимые для практики положения. Желающие подробнее ознакомиться с официальной документацией [4] без труда смогут получить ее с Интернет-сервера фирмы Philips (http://www.semiconductors.philips.com).

Интересно отметить, что фирма Philips особо выделяет в своей документации микросхемы, оснащеннь/ё интерфейсом 12С. Обложка или первый лист фирменных datasheet обязательно сопровождается значком, показанным на рис. 1.3.

Рис. 1.3. Фирменный знак интерфейса 12С

Полная гамма микросхем с интерфейсом 12С, выпускаемых фирмой, насчитывает в настоящее время более 150 наименований, выполненных с применением как перспективной КМОП-технологии, так и с уже ставшей. традиционной — биполярной. Номенклатура продолжает расти, так что следите за новинками!

Определившись с главными положениями шины, перейдем к рассмотрению ее аппаратной реализации. Взгляните на рис. 1.4, отражающий устройство современной автомобильной магнитолы.

Шина

12С

Рис. 1.4. Пример взаимодействия устройств на шине 12С

8

Как устроена шина 12С

В составе магнитолы обязательно имеется микроконтроллер, выполняющий роль master-устройства, формирующий необходимые сигнальные последовательности, «рассылающий» информацию по slave-устройствам и принимающий от них какие-либо сведения. Остальные устройства, подключенные к шине, как мы уже договорились, будут подчинены микроконтроллеру. По определенному правилу, называемому протоколом, микроконтроллер может «отправить» на индикаторную панель (slave-устройство 1) данные, отражающие, к примеру, уровень громкости, принимаемую частоту радиостанции или хронометраж аудиокассеты. Синтезатор частоты (slave-устройство 2) по команде микроконтроллера перестроит частоту приема, регулятор громкости и тембра (slave-устройство 3) изменит громкость звука и его «окраску». И так далее...

Каким образом slave-устройства разбираются, что текущая порция информации предназначается кому-то одному и кому именно, об этом мы поговорим, но позже. А сейчас настала пора задать себе важный вопрос: «В чем заключается уникальность такого вида управления устройствами?» Действительно, в чем? Оказывается, управлять всеми подчиненными slave-абонентами можно всего по двум линиям (если не считать третью линию — общий провод схемы). Slave-абонент должен иметь два вывода, которые объединяются с такими же выводами другого slave-устройства, а также с mas-ter-абоненТом. Собственно, внешне так и выглядит шина 12С.

Концепция шины настолько проста, что позволяет быстро разрабатывать принципиальную схему устройства, опробовать ее и в случае необходимости «нарастить» конструкцию новыми элементами или удалить ненужные безболезненно для других узлов. Также может быть упрощен метод разработки программного обеспечения, использованы стандартные библиотеки-подпрограммы. Практически все микросхемы с интерфейсом 12С имеют такие характеристики, которые позволяют использовать их в низковольтной портативной аппаратуре с питанием от гальванических элементов. Например, они обладают высокой помехоустойчивостью, низким потреблением тока, широким диапазоном питающего напряжения и слабой зависимостью параметров от температуры окружающей среды.

Обратим внимание на рис. 1.5.

Как устроена шина 12С

9

Рис. 1.5. Аппаратная реализация шины 12С в режимах low-speed и fast-speed

Интерфейс любого устройства, подключенного к шине 12С, как видно из рисунка, отличается предельной простотой. Он состоит из двух транзисторов с открытым стоком (коллектором) и двух буферных элементов с высоким входным сопротивлением. Один из выводов назван SDA (Serial Data Line), предназначается для связи с линией последовательных данных. Второй вывод имеет сокращенное название SCL (Serial Clock Line), предусмотрен для связи с линией синхронизации.

Как известно, по любым цифровым шинам передаются сигналы, характеризуемые только двумя электрическими состояниями — «О» и «1» («низкий уровень» и «высокий уровень»). Состояние, когда обе линии (SDA и SCL) установлены в состояние «1», считается свободным шинным состоянием. Шина в этот момент не занята и готова к трансляции данных (иначе говорят, что шина находится в состоянии ожидания). Но каким образом обеспечить это состояйие, если интерфейсные элементы не имеют активных выходов, если наружу выведены открытые выводы элементов? Для обеспечения логических состояний к шине подключаются два внешних резистора R^, (pull-up resistors), «подтягивающие» линии к напряжению питания UnHT. Типичная величина этих резисторов колеблется в пределах 1...10 кОм. На рис. 1.5 эти резисторы показаны внешними, и такая ситуация прослеживается часто. Но иногда они имеются в составе master-абонента. Вообще интерфейс master-абонента желательно изучить досконально, поскольку его выходы могут быть активными (иметь вместо

10

Как устроена шина Рс

pull-up резисторов транзисторные ключи) и тогда на шине возникнет конфликт.

Здесь мы можем четко сказать, в чем главное отличие master-абонента от slave-абонента. Это очень просто: только master-абонент может генерировать сигнал SCL.

Важнейшим критерием, определяющим возможность использования той или иной шины, является ее спектр технических характеристик. Шина 12С относится к классу двунаправленных асинхронных шин с последовательной передачей данных и, как следствие, обладает достаточно низкой пропускной способностью. Поэтому ее почти не используют в составе персональных компьютеров, разве что как вспомогательную для идентификации установленных устройств [1]. А вот для согласования работы устройств, наполняющих изделия бытовой техники, она вполне годится.

Основные технические характеристики шины 12С по спецификации 1.0 приведены в табл. 1.1.

Таблица 1.1. Основные технические характеристики шины 12С

(спецификация 1.0)

Наименование параметра Значение параметра

Скорость обмена low-speed не более 100 кбит/с

Скорость обмена fast-speed не более 400 кбит/с

Число адресуемых устройств (7 бит) до 128

Суммарная длина линий SCL и SDA не более 4 м

Суммарная паразитная емкость относительно общего провода не более 400 пФ

Входная емкость на каадый вывод абонента не более 10 пФ

Изучая данные табл. 1.1, можно сделать заключение, что шина 12С совершенно не подходит для связи между удаленными абонентами, а значит, может быть использована только в составе одного прибора. Главным образом этот вывод исходит из малой протяженности линий SDA и SCL. Собственно говоря, в интернете автором была найдена страница, на которой ее создатель сообщил о том, что его конструкции без проблем работают при суммарной длине шины около 100 метров (естественно, с понижением скорости обмена данны

Как устроена шина Рс

11

ми). Но этот режим уже не нормируется оригинальной спецификацией, а значит, и надежная работа устройств не гарантируется.

Пропускная способность шины определяется как параметрами интерфейсов, так и паразитными параметрами линий SDA и SCL. На рис. 1.6 показаны эти паразитные параметры:

• GiP — распределенная емкость линии относительно общего провода;

• Свх — входная емкость интерфейса;

• £пР — индуктивность проводника линии.

Рис. 1.6. Паразитные параметры, влияющие на пропускную способность шины 12С

В протоколе обмена по шине используются не только статические состояния линий («О» и «1»), но и перепады уровней («О» -> «1» и «1» —> «О») и наличие паразитных параметров выражается в «затягивании» фронтов, а также спадов импульсов, как показано на рис. 1.7, что может нарушить нормальный обмен данными.

Рис. 1.7. «Затяжка» импульса при передаче по шине — результат влияния паразитных параметров

12

Как устроена шина 12С

Еще одна опасность, скрытая в слишком длинных проводниках, связана с перенапряжениями, которые могут возникнуть на интерфейсных элементах при значительных величинах паразитной индуктивности проводов (Lnp). Эта ситуация отражена на рис. 1.8.

Рис. 1.8. Перенапряжения, связанные с наличием паразитной индуктивности линии связи

Как показано в [3], резкое закрытие транзистора VT характеризуется индуктивным выбросом на его стоке. Это явление используется в так называемых бустерных схемах источников питания, но здесь оно крайне вредно. И хотя в подавляющем большинстве случаев внутри микросхем предусматривается защита входных цепей, например, по варианту рис. 1.9, а, позволяющая «сбросить» энергию импульса в источник питания, все же лучше дополнительно ввести защиту по варианту рис. 1.9, б. Когда может потребоваться такая защита?

Рис. 1.9. Варианты защиты: а) внутренняя, б) внешняя

Как устроена шина 12С

13

л------------------!----------------------------------------------

Ц процессе экспериментов и отладки схемы, когда обычно микроконтроллер и slave-устройства устанавливаются на отдельных платах и связи между ними не удается сделать короткими. Напряжение пробоя стабилитрона VD следует выбирать на 0,5... 1 В больше уровня «1» на линиях SDA и SCL. И хотя в документации [4] такой способ защиты не встречается по вполне понятной причине — профессиональные разработчики обладают гораздо «более солидными возможностями по выполнению макетных работ, — радиолюбителю лучше обезопасить себя от возможных путей выхода микросхем из строя. Поиск причины пробоя — долгое и мучительное занятие, связанное к тому же с дополнительными финансовыми расходами, так что осторожность не помешает! Стабилитрон можно не устанавливать на печатной плате в законченной и отлаженной конструкции.

Рассмотрим теперь способ защиты от высоковольтных наводок, приведенный в фирменной документации [4] и отраженный на рис. 1.10. Важно отметить, что данный способ предпочтительнее использовать в режиме Hs-mode. Согласно рекомендациям, в схему вводятся защитные резисторы Rs. Чтобы сократить время нарастания сигнала синхронизации, в интерфейс master-устройства вводится источник тока MCS. Сами же сигналы SDA и SCL здесь именуются SDAH и SCLH соответственно (индекс «Н» — это сокращение от слова high — высокий).

Рис. 1.10. Структура шины 12С врежиме Hs-mode

14 Как устроена шина 12С у

Каким способом можно определить величину резисторов и Rs? В фирменной документации [4] есть ответ на этот вопрос. Там приводятся графики, оптимизирующие способ выбора резисторов. Графики отнормированы относительно разных напряжений питания, но поскольку наиболее вероятным видится вариант использования микросхем при VDD = 5 В, то сведения ограничены только этим напряжением.

Вначале производится выбор резистора RpU по рис. 1.11. Рассматривая этот рисунок, можно сделать попутный вывод о том, что паразитная емкость практически не оказывает влияния на методику выбора резистора Rs. Читатель также вправе задать следующий вопрос: Как определить величину паразитной емкости? Действительно, сделать это не так-то просто. Современные пакеты компьютерного схемотехнического моделирования при «разводке» печатных плат позволяют отмоделировать паразитные элементы, определить их величину. Однако такие программы доступны далеко не всем и далеко не все умеют ими правильно пользоваться, поэтому при разработке радиолюбительских конструкций можно придерживаться «золотой середины», приняв значение паразитной емкости не более 100...200 пФ.

Итак, после определения R^ по рис. 1.13 определяем номинал резистора Rs (если, конечно, его предполагается ввести в схему). В заключение проверяем по рис. 1.12 номинал резистора Rpu. К примеру,

максимальной величины резистора Rpu от емкости шины

величины резистора Rpu от

напряжения питания

Как устроена шина 12С

15

Рис. 1.13. Зависимость максимальной величины резистора Rs от величины резистора Rpu

для напряжения питания 5 В оно должно быть не менее 1,5...2 кОм. Выполнение требований графиков позволит получить в режиме Hs-mode максимальную скорость передачи.

Не следует также забывать и о топологии печатной платы. Линии подвержены не только внешним помехам, но также и перекрестной связи, когда сигнал SDA наводится в линию SCL, и наоборот. Если суммарная длина линии превышает 10 см, рекомендуется располагать токоведущие дорожки в такой последовательности:

SDA

V

v DD

Общий

SCL

Хорошо использовать печатные платы с отдельными слоями, специально выделенными под общий провод и провод VDD, что, конечно, в радиолюбительских условиях едва ли осуществимо. Удачным также является использование экранированных кабелей, экранная жила которых соединена с общим проводом схемы. Возможно также применить скрученные попарно проводники.

Как уже было сказано ранее, скорость передачи по шине 12С ограничена не только внешними факторами, но и внутренними параметрами интерфейсов, их схемотехникой. Едва ли разработчик принципиальных схем сможет исправить интерфейс, заставить его работать быстрее — эта задача под силу только разработчику интегральной

16 Как устроена шина 12С

схемы. Но узнать, почему это ограничение наложено, полезно буде; даже радиолюбителю. Итак, взглянем на рис. 1.14 и рис. 1.15. /

Рис. 1.14. Упрощенная схема интерфейса 12С, выполненного по КМОП-технологии.

Рис. 1.15. Упрощенная схема интерфейса 12С, выполненного по биполярной технологии

В обоих схемах очень важно сделать так, чтобы транзистор VT открывался и закрывался как можно быстрее. Казалось бы, нет никаких препятствий, чтобы его открывание происходило мгновенно. Однако (и это показано в [3]) из-за наличия так называемой емкости Миллера СтЯ образуется местная отрицательная обратная связь, которая не дает транзистору быстро войти в состояние насыщения. Читатель может возразить, обратив внимание на величину резистора R, и предложить уменьшить его номинал. Но тогда мы столкнемся со значительным увеличением тока потребления микросхем, что, конечно, тоже нехорошо.

Ограничения, накладываемые на минимальную величину резистора RpU, связаны с тем, что через него в состоянии линии «О» должен протекать ток не более 3 мА. Легко заметить, что для напряжения питания VDD = 5 В величина ограничена номиналом 1,7 кОм. Соответственно емкость линии не должна превышать 200 пФ. Но если линия имеет большее значение паразитной емкости? Тогда можно использовать схему, изображенную на рис. 1.16. В течение времени нарастания или спада сигнала линии микросхема НСТ4066 подключает в промежутке между 0,8 и 2,0 В форсирующий резистор R^.

Как устроена шина 12С

17

Рис. 1.16. Использование способа динамического подключения резистора Rpu для выполнения требований спецификации шины 12С

Еще одной важной технической характеристикой шины является ее совместимость. Ранее разработанные элементы, обладающие только возможностями низкоскоростного обмена, должны без проблем связываться с высокоскоростными, и наоборот. Давайте сейчас рассмотрим поподробнее вопрос совместимости устройств, подключаемых к шине, тем более что мы не вернемся к нему в рамках этой книги.

Итак, к шине 12С могут быть подключены интерфейсы трех типов: low-speed, fast-speed, Hs-mode. Понятно, что обмен данными может быть осуществлен со скоростью, доступной самому медленному интерфейсу. В табл. 1.2 приведены возможные предельные скорости обмена по совмещенной шине.

Таблица 1.2. Скорость обмена данными в совмещенных шинах

Направление передачи Конфигурация шины PC

Hs + fast + low Hs + fast Hs + low fast + low

Hs-Hs 0—3,4 Мбит/с 0—3,4 Мбит/с 0—3,4 Мбит/с -

Hs - fast 0...100 кбит/с 0—400 кбит/с - -

Hs-low 0—100 кбит/с - 0—100 кбит/с -

fast - low 0...100 кбит/с - — 0—100 кбит/с

fast - fast 0—100 кбит/с 0—400 кбит/с - 0—100 кбит/с

low-low 0—100 кбит/с - 0—100 кбит/с 0—100 кбит/с

18

Как устроена шина 12С

Если соединить устройства разных типов по классической схеме, то разные скорости обмена могут быть и не реализованы. Поэтому приходится группировать эти устройства, как показано на рис. 1.17, и вводить между группами мосты (bridge). Назначение моста —отсоединить более медленные элементы в моменты обмена между более быстрыми.

Дополнительное удобство, обеспечиваемое мостом, — возможность использования для питания шины двух напряжений (VDD1 и VDD2). Мост включается как master/slave-устройство Hs-режима и управляется сигналами SDAH, SCLH, SDA, SCL. Он может также присутствовать в составе отдельных микросхем (например, микроконтроллеров) как самостоятельное устройство.

Отметим также, что шина 12С позволяет совмещать устройства с разными напряжениями питания. Pull-up резисторы желательно подключать к питающему напряжению 5 В, как показано на рис. 1.18.

Прежде чем перейти к описанию протокола обмена по шине, отметим, что собственно ее устоявшееся название (ай-ту-си), равно как и наименования линий (SDA и SCL), является зарегистрированным наименованием. Авторские права на эти названия принадлежат фирме Philips. Соответственно другие фирмы, производящие микросхемы с интерфейсом 12С и указывающие его наличие, как такового, в технической документации, делают это по лицензии разработчика [2]. К примеру, фирма Microchip, специализирующаяся на выпуске

Как устроена шина 12С

19

Рис. 1.18. Соединение элементов с разными напряжениями питания

микроконтроллеров, имеет такую лицензию. Однако и фирмы, не имеющие лицензии, производят микросхемы с интерфейсом, очень похожим на 12С, но как 12С его не обозначают, а значит, протокол обмена может немного отличаться от стандартизованного. Делается это для обеспечения чистоты правовых отношений, которые за рубежом соблюдаются несколько более жестко, нежели у нас в стране. В любом случае, используя в своих разработках аналоги фирменных микросборок, рекомендуется внимательно ознакомиться с технической документацией.

Самой простой конфигурацией шины 12С, как уже было сказано, является master-организация. С нее мы и начнем рассмотрение протокола обмена данными.

Передача любого бита по шине происходит при условии стробирования данных SDA по линии SCL. Предположим, что master-устройство выставило бит данных «О» или «1» на линию SDA. Slave-устройство получит этот бит только тогда, когда на линии SCL произойдет перепад сигнала из низкого уровня в высокий (так называемый положительный перепад). Отсюда следует первое правило организации протокола шины: смена информации на линии SDA может быть произведена только при нулевом состоянии линии SCL.

Рис. 1.19. Передача бита по шине 12С

20

Как устроена шина /2С

Мы уже знаем, что шина в неактивном состоянии имеет на линиях SDA и SCL высокие уровни. Но каким образом slave-устройства могут узнать, что началась передача и что она окончилась? Для распознавания начала и конца передачи в спецификацию шины были введены условия Start и Stop. На рис. 1.20 представлено условие Start, на рис. 1.21 — условие Stop. В фирменной документации условие Start имеет условное сокращение «S», условие Stop — «Р».

г-1

SCL ------1---

SDA

Рис. 1.20. Условие START

U---!---Н

I

scl--------- :

SDA-----------------

Рис. 1.21. Условие STOP

Условие Start образуется при отрицательном перепаде сигнала на линии SDA при единичном состоянии линии SCL. И наоборот, условие Stop возникает при положительном перепаде линии SDA при единичном состоянии линии SCL. Эти состояния всегда должны генерироваться master-устройствами. Таким образом, укрупненно информационный пакет, передаваемый по шине 12С, выглядит так, как показано на рис. 1.22.

Для определения состояний Start и Stop в составе slave-устройства обычно предусматривается специальная аппаратная схема, так как реализовать программно интерфейс slave-абонента довольно трудно: появляется необходимость постоянной проверки линии SDA на предмет опознавания данных.

Рис. 1.22. Информационный пакет данных на шине 12С '

Как устроена шина 12С

21

Существует также состояние «повторный Start», которое может возникнуть в середине информационного пакета. Чуть позже мы рассмотрим ситуации, когда появляется условие «повторный Start».

Передача данных по шине производится по 8 битов, после чего следует сигнал подтверждения (acknowledge). Сигнал подтверждения свидетельствует о том, что данные нормально приняты и обработаны... Но обо всем по порядку! Взгляните на рис. 1.23, отражающий

После отработки состояния Start передатчик последовательно выставляет на линии SDA данные, начиная со старшего бита (MSB) и заканчивая младшим (LSB). Данные стробируются по линии SCL импульсами 1...8.

Обратите внимание: линия SDA приемника (slave-абонента) в момент приема информационных битов (MSB-LSB) должна быть выставлена в единичное состояние. Физически это означает, что транзистор, подключенный к линии SDA, должен быть закрыт. В момент отрицательного перепада импульса 8 на линии SCL slave-абонент должен выставить на линию SDA нулевой уровень -— открыть транзистор. Тем самым приемник подтверждает нормальный прием байта. Передатчик (master-абонент) должен выставлять на линию SDA единичное состояние. Благодаря тому что линия организована по способу «монтажное И», ее состояние будет определяться только slave-абонентом. Передатчик должен проверить состояние линии SDA, затем выдать девятый стробирующий импульс, с которым slave-абонент выставит на линию SDA высокий уровень, проверить выполнение этой операции и лишь после продолжить передачу (рис. 1.24). В случае неподтверждения нормального приема (сигнал АСК имеет высокий уровень) передатчику желательно выполнить условие Stop и повторить передачу.

22

Как устроена шина 12С

Третья ситуация, которая может возникнуть при получении сигнала АСК, связана с задержкой обработки данных в slave-абоненте, как показано на рис. 1.25.

Рис. 1.25. Задержка состояния acknowledge

Задержка освобождения линии SDA не свидетельствует о неправильном обмене информацией, поэтому master-абоненту достаточно дождаться окончания АСК и продолжить передачу. Добавим также, что в фирменной документации состояние acknowledge условно именуется буквой «А». Если байт, переданный по шине, является последним в пакете, master-устройство вместо проверки сигнала АСК может выставить состояние Stop, и slave-абонент должен освободить линию SDA.

Описанные состояния являются вполне достаточными для функционирования шины 12С с одиночным master-устройством. Как правило, master-абонента очень легко организовать программным способом, что и используется многими разработчиками. Для реализации режима multi-master, как уже было сказано, должны быть реализованы дополнительные состояния синхронизации и арбитража. Вначале рассмотрим синхронизацию.

Как устроена шина 12С

23

Действительно, если на шине присутствует несколько master-абонентов, все они наделены возможностью генерации сигнала SCL. Синхронизация между этими сигналами достигается благодаря функции «монтажное И» на линии SCL. Таким образом, состояние «О» продлится до тех пор, пока все master-устройства не выставят на линии SCL высокий уровень, и линия SCL будет задержана в состоянии «О» абонентом с самым длинным циклом нулевого уровня. Остальные абоненты, уже освободившие линию, должны войти в состояние ожидания (рис. 1.26).

Теперь поговорим об арбитраже. Согласно спецификации режима multi-master, передатчик может начинать передачу данных только после того, как убедится, что шина свободна (линии SDA и SCL имеют высокий уровень). Но несколько передатчиков могут сгенерировать состояние Start практически одновременно, поэтому нужно определить, какое устройство первым выставило Start-условие. Как это возможно выполнить с помощью достаточно скудных (с точки зрения возможностей серьезных шин, конечно!) средств 12С? Дело в том, что линия SDA выполнена также по способу «монтажное И». В течение процедуры передачи все master-абоненты проверяют состояние линии SDA. Если обнаружено несоответствие (выставляется высокий уровень, а при проверке читается низкий), передатчик, выставляющий высокий уровень, отключается. Естественно, что в процессе передачи бита осуществляется синхронизация.

24

Как устроена шина 12С

Как показывает практика, процедура арбитража наиболее трудна для понимания. Поэтому, чтобы досконально разобраться, приведем наглядную аналогию. Представьте себе шеренгу людей, синхронно поднимающих руки по команде ведущего. Если рука поднята, это свидетельствует о передаче единицы, если опущена — нуля. Допустим, в первом такте все подняли руки, а во втором — двое руки не подняли. Согласно принципу арбитража, из шеренги выбывают все, кроме этих двоих. Далее они, подчиняясь командам ведущего, будут поднимать или опускать руки, пока в каком-либо такте не окажется, что один руку поднял, а другой — опустил. Так вот, «поднявший руку от руки и погибнет» — перефразируем известное выражение. Он выбывает, а передачу до окончания продолжит оставшийся — в единственном числе. Рис. 1.27 отражает процедуру арбитража для двух master-абонентов.

Разобравшись с условиями передачи данных по шине 12С, обратим внимание на форматы передачи (протоколы). Что такое формат? И не проще ли использовать передачу по 8 битов, как это предписывается, наполняя их содержимым по своему усмотрению? Оказывается, нет. Каждое устройство должно иметь на шине свой уникальный адрес, по которому к нему можно обратиться. Адрес устройства всегда располагается в определенном месте (специалисты говорят: в определенных ячейках внутренней памяти). Адрес может быть назначен, а может быть жестко определен. В случае шины 12С адреса устройств, называемые slave-адресами, жестко определяются.

Как устроена шина 1гС

25

Они «закладываются» при изготовлении микросхем и не подлежат переназначению, то есть модификации. В принципе часто все же переназначить адрес можно (и,это делается с помощью 2—3 битов), но, за редким исключением, эти биты нужно предварительно определить аппаратно, то есть установить перемычки на соответствующие выводы. Этот принцип был заложен еще на заре возникновения шины для того, чтобы предельно упростить протокол обмена и аппаратную реализацию интерфейсов. Отметим, что значение slave-адреса можно узнать из документации на соответствующую микросхему.

Поскольку все абоненты шины не имеют иных способов общения, кроме обмена данными по линиям SDA и SCL, в момент начала передачи все slave-абоненты «слушают» линию на предмет опознавания своего slave-адреса. Опознавший свой адрес абонент продолжает прием данных и выдачу сигналов АСК, остальные только следят за моментом выдачи состояния Stop. В связи с этим возможны три формата передачи, определяемые как 7-битные (традиционные):

• master транслирует данные на slave;

• master читает данные со slave;

• комбинированный формат трансляции/чтения.

Исторически сложилось, что вначале возник формат 7-битной адресации, при котором осуществляется передача slave-адреса 7 битами, а восьмой бит должен содержать признак операции «чтение/запись» (R/W). Легко посчитать—при 7-битной адресации на шине может присутствовать только 128 устройств с уникальными адресами. Реально устройств и того меньше, так как некоторые адреса зарезервированы под некоторые служебные функции, о которых мы расскажем ниже.

На рис. 1.28 приведен формат передачи данных от master-устройства к slave-абоненту. Заметим, что, прямоугольники, отображенные на этом и последующих рисунках серым тоном, относятся к направлению передачи от master к slave, а белым цветом — от slave к master.

1юредача информационных опт

Рис. 1.28. Master транслирует данные на slave

26

Как устроена шина 17С

Необходимо сразу оговориться, что первый бит, передающий slave-адрес устройства, содержит признак операции R/W. Когда этот бит установлен в «О», будет осуществляться запись в slave-устройство, когда в «1» — чтение из него.

На рис. 1.29 приведен формат передачи данных от slave-абонента к master-устройству.

Обратите внимание: после чтения информационного байта DATA master-абонент обязан подтвердить получение байта сигналом АСК.

Рис. 1.29. Master читает данные со slave

На рис. 1.30 показан так называемый комбинированный формат, применяющийся в случаях, когда осуществляется запись и чтение в одном цикле.

data ы

о.

Повторное условие

Рис. 1.30. Комбинированный формат

Обычно комбинированные форматы используются для работы с последовательной памятью (для сокращения времени доступа к данным). Изучая рис. 1.30, мы можем заметить, что здесь повторяются знакомые нам по рис. 1.28 и рис. 1.29 форматы. Единственное новшество, введенное в комбинированный формат, — повторное условие Start (repeated Start condition), обозначаемое на рисунке сокращением «Sr». Чуть позже, в соответствующей главе, мы рассмотрим типы последовательной памяти и способы работы с ней.

Как уже было сказано ранее, некоторые slave-адреса используются не для прямой адресации устройств на шине 12С, а для служебных сообщений. Рассмотрим эти сообщения с учетом рис. 1.31, на котором укрупненно показана структура байта адресации.

Как устроена шина 12С

27

MSB LSB

Slave-адрес

Рис. 1.31. Структура байта адресации

Таблица 1.3. Служебные адреса

Slave-адрес R/W L Описание служебного адреса

0000 000 0 Общий вызов

0000 000 1 Программный Start

0000 001 X Адрес шины CBUS

0000 010 X Зарезервирован для других форматов шины

0000 011 X Зарезервирован на будущее

0000 1хх X Код режима Hs-mode

1111 1 хх X Зарезервирован на будущее

1111 Охх X 10-битная адресация slave-абонентов

Разберемся подробнее в функциональном назначении служебных адресов.

Общий вызов может адресовать все устройства, подключенные к шине 12С, в этом случае при получении общего вызова устройства должны подтверждать прием выдачей сигнала АСК. Устройства, которые не нуждаются в сведениях, передаваемых при общем вызове, могут игнорировать этот адрес, не выставляя сигнал АСК. Если же устройство выполнено так, что обязательно требует данных общего вызова, оно ведет себя точно так же, как обыкновенный slave-абонент. Второй байт, следующий за общим вызовом, обычно содержит информационную часть. На рис. 1.32 представлен формат общего вызова.

0 0 0 0 0 0 0 0 А X X X X X X X в А

Общий вызов | Информационная часть |

АСК АСК

Рис. 1.32. Общий вызов

28

Как устроена шина 12С

Обратите внимание — информационная часть содержит бит В, который в сочетании с битами 7...1 (обозначенными на рис. 1.32 символом «X») регламентирует назначение информации, передаваемой в данном случае. Регламентируются следующие комбинации:

• 0000 0110 (06h) — аппаратный сброс. При получении этой комбинации все абоненты, реагирующие на общий вызов, производят внутренний сброс (рестарт). Естественно, аппаратный сброс этих абонентов не должен блокировать шину;

• 0000 0100 (04h) — запись программируемой части адреса slave-абонента с помощью аппаратных средств. Все абоненты, ответившие на этот адрес, будут блокированы и не смогут быть сброшены;

• 0000 0000 (00h) — этот код запрещается использовать;

• хххх ххх 1 — используется, когда на шине присутствует много совмещенных master/slave-абонентов. В таких случаях часто необходимо генерировать запрос об адресе устройства, которому должна быть передана информация. К примеру, устройство «А», получив от устройства «Б» данные, обработав их, передает информацию устройству «В» вместе с собственным адресом (обычно адреса «master/slave» в совмещенных абонентах совпадают). 11

На рис. 1.33 представлен формат передачи hardware general call.

LS0

I_____________I

Общий вызов В

Рис. 1.33. Формат hardware general call

Программный Start удобно использовать тогда, когда устройство, соединенное с шиной 12С, не имеет аппаратного интерфейса. Собственно, если встроенный интерфейс 12С есть, скажем, в микроконтроллере, его очень просто использовать. Достаточно запрограммировать микроконтроллер на прерывание от шины, и при наличии передачи будет выполняться программа обработки данных, поступающих с шины. Если встроенного интерфейса 12С нет, микроконтроллер обязан постоянно опрашивать шину на предмет получения данных.

Как устроена Шина PC

29

Процедура опознавания в таком случае выглядит следующим образом, отраженным на рис. 1.34.

Рис. 1.34. Программный START

Из рисунка видно, что микроконтроллеру достаточно опрашивать линию SDA с низкой частотой, определяя один из нулей в стартовом бите. После обнаружения этого нуля на линии SDA микроконтроллеру необходимо переключиться на более высокую частоту опроса, чтобы зафиксировать состояние «повторный Start» (Sr). Обычный аппаратный приемник игнорирует состояние S и дождется Sr.

Адрес шины CBUS возможно использовать при работе с элементами, оснащенными этой шиной. В задачи этой книги не входит рассказ о шине CBUS, но тем не менее она по своей реализации достаточно близка к шине 12С, поэтому имеется возможность их совмещения.

В спецификации CBUS имеется третья линия, обозначаемая как DLEN. Диаграммы сигналов, отражающие способ работы с этой шиной в условиях совмещения с 12С, приведены на рис. 1.35.

Следующие служебные адреса относятся к расширениям шины I С. Мы уже знаем, что первоначально шина имела 7-разрядную адре-

записи

Рис. 1.35. Совместимость с шииой CBUS

30

Как устроена шина 12С

сацию и скорость передачи до 100 кбит/с. Но даже несмотря на эти скромные возможности, шина быстро завоевала популярность. Очень быстро были заняты все доступные адреса, да и скорость передачи данных быстро росла, улучшалась технология производства микросхем. И шину модернизировали, наделив ее новыми возможностями:

• режим fast-speed с возможностью передачи до 400 кбит/с;

• режим Hs-mode — до 3,4 Мбит/с;

• адресация с помощью 10 разрядов, расширенные возможности адресации до 1024 абонентов.

Все новые абоненты, доступные для использования в шинах с расширениями, естественно, совместимы и со старыми форматами передачи (приема). «Соль» скоростных режимов заключается в единственном обстоятельстве — в укорочении стробирующего импульса на линии SCL. Поэтому для совместимости со старыми интерфейсами стробирующий импульс может быть продлен до необходимой величины.

Работа шины в режиме fast-speed характеризуется следующими важными свойствами:

• отсутствие совместимости с шиной CBUS, так как эта шина не имеет возможности работать на таких скоростях; ,-т>

• наличие входных формирователей (триггеров Шмитта) SDA и SCL линий.

Если элементы, обладающие возможностью работы в режиме fast-speed, обесточены, они не должны влиять на работу шины.

В документации [4] подробнейшим образом разобраны форматы передачи в режиме Hs-mode, принципы совместимости его с другими режимами. Мы не будем останавливаться на описании этих режимов, поскольку они пока мало распространены. Значительно более существенный практический интерес для нас представляет 10-разрядная адресация шины 12С.

Поскольку форматом шины предусмотрена передача только «порции» из 8 байтов, 10-разрядные адреса приходится транслировать 2 байтами. Первый байт имеет структуру 11110xx(R/W), в котором биты, обозначенные символом «х», являются старшими разрядами 10-разрядного адреса slave-устройства. Естественно, в составе первого байта должен быть передан бит R/W.

Как устроена шина 12С

31

Адресация с помощью 10 разрядов аналогична 7-разрядной адресации, то есть основана на тех же принципах. Устройство, получив служебный код в первом байте и опознав возможность приема 10-разрядного адреса, подтверждает это и принимает второй байт. При совпадении принятого адреса с содержащимся внутри устройства собственным адресом выдается подтверждение АСК и ведется прием данных в обычном режиме до появления состояния Stop.

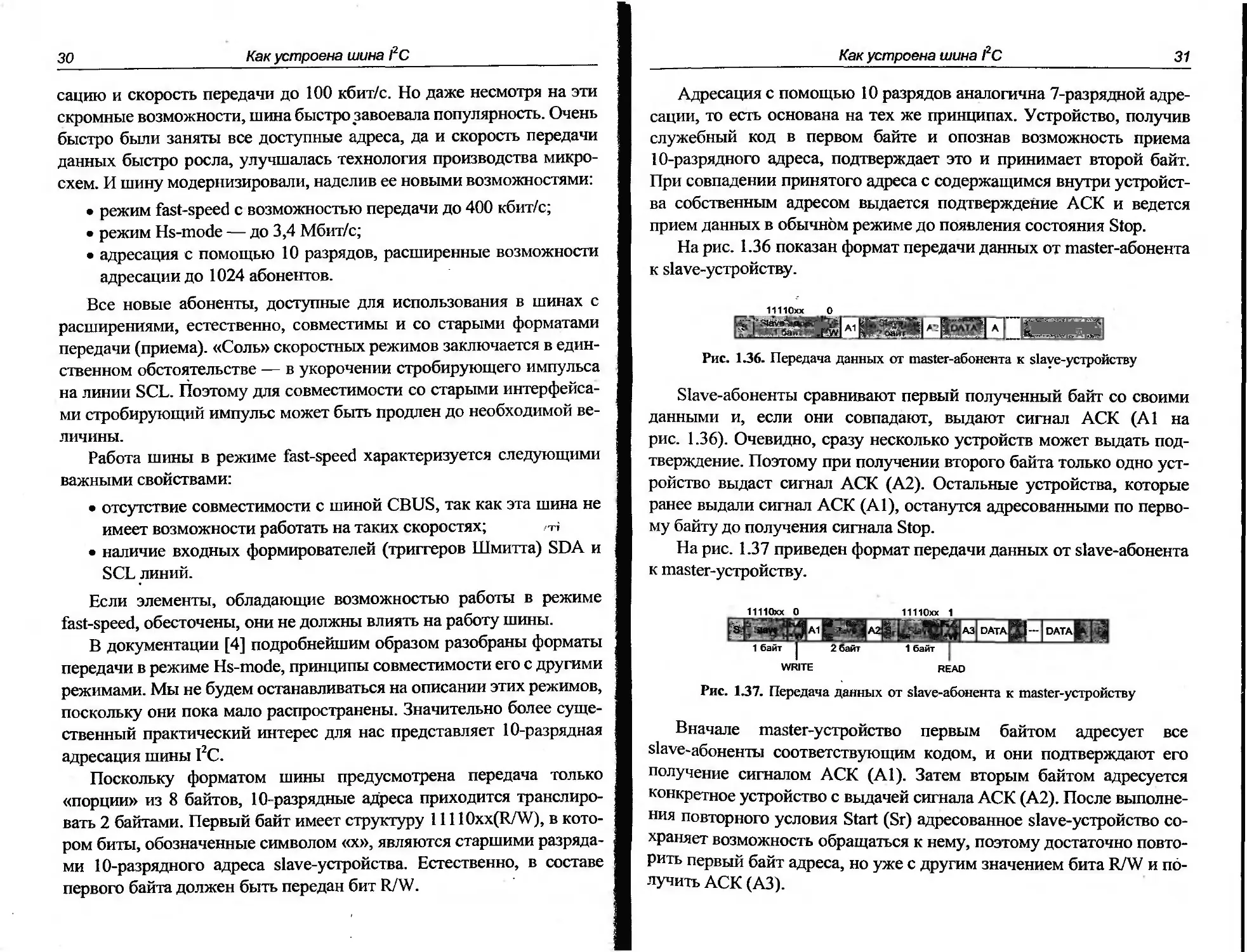

На рис. 1.36 показан формат передачи данных от master-абонента к slave-устройству.

11110» О

Рис. 1.36. Передача данных от master-абонента к slave-устройству

Slave-абоненты сравнивают первый полученный байт со своими данными и, если они совпадают, выдают сигнал АСК (А1 на рис. 1.36). Очевидно, сразу несколько устройств может выдать подтверждение. Поэтому при получении второго байта только одно устройство выдаст сигнал АСК (А2). Остальные устройства, которые ранее выдали сигнал АСК (А1), останутся адресованными по первому байту до получения сигнала Stop.

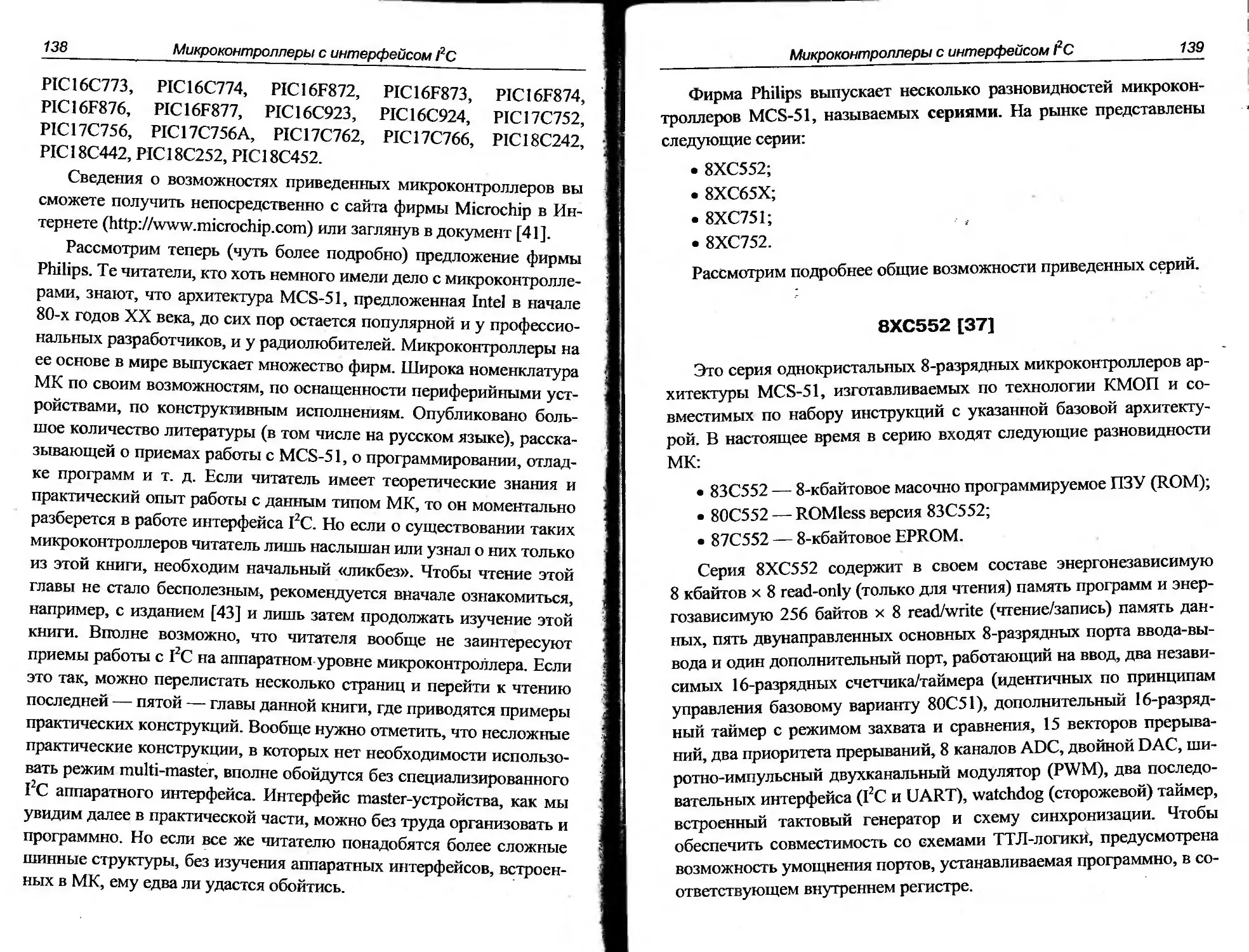

На рис. 1.37 приведен формат передачи данных от slave-абонента к master-устройству.

1111ОХХ О

11110хх 1

1 байт

1 байт

2 байт

WRITE

READ

Рис. 1.37. Передача данных от slave-абонента к master-устройству

Вначале master-устройство первым байтом адресует все slave-абонента соответствующим кодом, и они подтверждают его получение сигналом АСК (А1). Затем вторым байтом адресуется конкретное устройство с выдачей сигнала АСК (А2). После выполнения повторного условия Start (Sr) адресованное slave-устройство сохраняет возможность обращаться к нему, поэтому достаточно повторить первый байт адреса, но уже с другим значением бита R/W и получить АСК (АЗ).

32

Как устроена шина 12С

На рис. 1.38—1.40 приведены комбинированные форматы передачи данных. Они могут использоваться, например, при управлении микросхемами последовательной памяти.

11110хх О

адрес адрес

1 байт 2 байт

WRITE

11110ХХ 1

адрес |

1 байт ।

READ

data";,?' |

Рис. 1.38. Комбинированный формат. Master-абонент адресует slave-устройство с 10-разрядным адресом, затем передает данные и читает данные

11110хх О 1111ОХХ о

адрес адрес

1 байт J 2 байт •

адрес I адрес 1 байт | 2 байт

WRITE

WRITE

Рис. 1.39. Комбинированный формат. Master-устройство передает данные двум slave-абонентам с 10-разрядным адресом

разр | WRITE

Рис. 1.40. Комбинированный формат. Master-абонент передает данные двум slave-устройствам: одному с 7-разрядным адресом, а другому с 10-разрядным адресом

В заключение этой главы приведем основные электрические характеристики шины 12С для всех упомянутых режимов.

Таблица 1.4. Параметры режимов low-speed, fast-speed

Параметр Символ Режим low-speed Режим fast-speed Ед. изм.

МИН. макс. МИН. макс.

Низкий уровень (LOW) входного напряжения v1L 0,5 1.5 - - в

Высокий уровень (HIGH) входного напряжения Чн 3,0 Чх) + - - в

Входная емкость, приходящаяся на один вывод С, - 10 - 10 пФ

Частота на линии SCL *sci 0 100 0 400 кГц

Время удержания условия Start Ihd.sta 4,0 - 0,6 - МКС

Как устроена шина 12С

33

Окончание таблицы 1.4

Параметр Символ Режим low-speed Режим fast-speed Ед-изм.

МИН. макс. МИН. макс.

Период низкого уровня (LOW) сигнала SCL kow 4,7 - 1.3 - мкс

Период высокого уровня (HIGH) сигнала SCL *НЮН 4,0 - 0,6 - мкс

Время установки повторного условия Start tsu,STA ,4,7 - 0,6 - мкс

Время удержания данных klO.OAT 0 3,45 0 0,9 мкс

Время установки данных ku.DAT 250 - 100 - НС

Время нарастания сигналов SDA и SCL V - 1000 20+O.tCb 300 НС

Время спада сигналов SDA и SCL k - 300 20 + 0,1Сь 300 нс

Время установки условия Stop ku.sro 4,0 - 0,6 - мкс

Время паузы между условиями Stop и Start w 4,7 — 1.3 - мкс

| Паразитная емкость линии Ct, - 400 - 400 пФ

Рис. 1.41. Временные соотношения между сигналами в режиме Hs-mode

Рис. 1.42. Временные соотношения между сигналами в режимах low-speed и fast-speed

34

Как устроена шина 12С

Таблица 1.5. Параметры режима Hs-mode

Параметр Символ Режим Hs-mode q ИЗМ.

МИН. макс.

Низкий уровень (LOW) входного напряжения V|L 0,5 0,3^ В

Высокий уровень (HIGH) входного напряжения V.H O.TVdq Vdo+0,5 В

Входная емкость, приходящаяся на один вывод Q - 10 пФ

Частота на линии SCIH 'sClH 0 3,4(0,= 100) 1,7(0 = 400) МГц

Время задержки условия Start 'hO.STA 160 - НС

Период низкого уровня (LOW) сигнала SCLH *ww 160(0,= 100) 320 (Сь = 400) - НС

Период высокого уровня (HIGH) сигнала SCLH 'high 60(0=100) 120(Сь = 400) - НС

Время установки д анных 'su.tw 10 - НС

Время удержания данных *HO,OAT 0 70(0=100) 150(0 = 400) НС

Время нарастания сигнала SCLH kl 10(0=100) 20(0 = 400) 40(0='00) 80(0 = 400) НС

Время нарастания сигнала SCLH при повторе условия Start ku 10(0='00) 80 (Сь = 400) 20(Q,= 100) 160(O>=400) НС

Время спада сигнала SCLH kL 10(Cb= 100) 20(0 = 400) 40(0=100) 80(0 = 400) НС

Время нарастания сигнала SDAH kA 10(0=100) 20(0 = 400) 80(O)= 100) 160(0 = 400) НС

Время спада сигнала SDAH kA 10(0 ='00) 20(0 = 400) 80(0=100) 160(0 = 400) НС

Время установки условия Stop tsu,sro 160(0='00) 160(0 = 400) - НС

Паразитная емкость линии Cb - . 400 пФ

2. Адреса некоторых микросхем 12С

В документе [8], разработанном Philips, содержатся сведения о slave-адресах микросхем с интерфейсом 12С. Биты А7...А4 определяют группы принадлежности микросхем. Внутри группы идентифи-. цировать конкретное устройство можно по битам АЗ...А1. Впрочем, деление на группы весьма условно. Бит АО — признак чтения/записи (R/W). Перевод специальных терминов приводится по [9].

Таблица 2.1. Группы микросхем с интерфейсом 12С

Группа (А7...А4) Обозначение Функциональное назначение

«0»(0000)

0 0 0 - Общий вызов

X X X - Зарезервировано

«1»(0001)

1 А1 АО SAA2530 ADR/DMX цифровой приемник

1 А1 АО TDA8045 QAM-64 демодулятор

«2»(0010)

0 0 АО SAA4700A Процессор цифровой линии VPS

0 0 АО SAA5233 Двухстандартный PDC-декодер

0 0 1 SAA5243 Контроллер потока телетекста

0 0 1 SAA5244 Интегрированный VIP и телетекст

0 0 1 SAA5245 Декодер/контроллер 525-строчного телетекста

0 0 1 SAA5246A Интегрированный VIP и телетекст

0 0 1 SAA5249 Интегрированный VIP и телетекст

0 А1 АО CCR921 Декодер RDS/RBDS

0 А1 АО SAF1135 Цифровая линейка 16 декодеров VPS

1 0 0 SAA5252 Декодер 21 линии

1 1 АО SAB9075H PIP-процессор системы NTSC

36

Адреса некоторых микросхем /2С

Группа (А7...А4) Обозначение Функциональное назначение

«3»(0011)

0 0 АО SAA7370 CD-декодер и цифровой сервопроцессор

0 А1 АО PCD5096 Универсальный кодек

0 1 АО SAA2510 Видео CD-MPEG-декодер

0 1 1 PDIVSB11 Универсальная последовательная шина

1 0 1 SAA2502 MPEG аудиодекодер

1 1 АО SAA1770 D2MAC декодер для спутникового TV

«4» (0100)

0 0 0 SAA6750 MPEG2 энкодер для Desk Top Video

0 0 0 TDA9177 YUV transient improvement processor

0 0 0 TDA9178 YUV transient improvement processor

0 0 АО РСА1070 Programmable speech transmission IC

0 А1 АО SAA1300 Tuner swith circuit

А2 А1 АО TDA8444 6-битный ЦАП

А2 А1 АО PCF8574 8-битный I/O порт l2C

1 0 АО PCD3311C DTMF тональный генератор

1 0 АО PCD3312C DTMF тональный генератор

1 1 1 PCD5002 Декодер страниц

«6»(0110)

0 0 0 SAA5301 MOJI-процессор для Японии/Китая

0 1 1 РСЕ84С46718 8-битный КМОП автосинхр. контроллер-монитор

0 1 1 РСЕ84С882 8-битный микроконтроллер

0 1 1 РСЕ84С886 8-битный микроконтроллер

«7» (0111)

0 0 АО SAA7140B High performance video scaler

0 0 АО PCF8576C 16-сегментный LCD-драйвер

Адреса некоторых микросхем 12С

37

Группа (А7...А4) Обозначение Функциональное назначение

0 А1 АО SAA1064 4-цифровой LED-драйвер

А2 А1 АО PCF8574A 8-битный I/O порт 12С

0 1 0 PCF8577C 32/64-сегментный LCD-драйвер дисплея

0 1 АО SAA2116 LCD контроллер/драйвер

1 0 АО PCF8578/9 Матричный LCD-драйвер

1 0 АО PCF8568 LCD-драйвер столбцов матричного дисплея

1 0 АО PCF8569 LCD-драйвер колонок матричного дисплея

1 1 АО PCF8566 96-сегментный драйвер с мультиплексированием

«8» (1000)

0 0 0 ТЕА6300 Регулятор громкости звука для предусилителей

0 0 0 ТЕА6320/1/2/3 Регулятор громкости звука

0 0 0 ТЕА6330 Регулятор громкости и тембра

0 0 АО NE5751 Аудиопроцессор

0 0 АО TDAB421 Аудиопроцессор

0 0 АО TDA9860 Hi-R аудиопроцессор

0 0 1 TDA8424/5/6 Аудиопроцессор

0 1 0 TDA8415 TV/VCR стереозвуковой процессор

0 1 0 TDA8417 TV/VCR стереозвуковой процессор

0 1 0 TDA9840 IV стереозвуковой процессор

о 1 АО TDA8480T Корректор RGB для IV

1 0 0 TDA4670/1/2 Picture signal improvement (PSI) circuit

1 0 0 TDA4680/5/7/8 Видеопроцессор

1 0 0 TDA4780 Контроллер цветопередачи

1 0 0 TDA4885 150-МГц видеоконтроллер

1 0 0 TDA8442 Интерфейс декодера цветности

1 0 1 TDA8366 Мультистацдартный видеопроцессор

38

Адреса некоторых микросхем 12С

Группа (А7..Л4) Обозначение Функциональное назначение

1 0 1 TDA8373 NTSC видеопроцессор

1 0 1 TDA8374 Мультистацдартный видеопроцессор

1 0 1 ТОА8375/А Мультистацдартный видеопроцессор

1 0 1 TDA8376/A Мультистацдартный видеопроцессор

1 0 1 TDA9161A Контроллер шины процессора синхронизации

1 А1 1 SAA7151B 8-битный мультистацдартный декодер для TV

1 А1 1 SAA7191B Цифровой мультистацдартный TV декодер

1 А1 1 SAA9056 Цифровой SCAM декодер цвета

1 А1 1 TDA9141/3/4 Мультистацдартный декодер

1 А1 1 TDA9160 Мультистацдартный декодер-процессор

1 А1 1 TDA9162 Мультистацдартный декодер-процессор

1 1 0 ТОА4853/4 Автосинхронизирующийся дефлектор

1 1 0 TDA9150B Процессор-дефлектор

1 1 0 TDA9151B Программируемый процессор-дефлектор

1 1 АО ТЕА6360 5-полосный эквалайзер

1 1 АО TDA8433 Процессор-дефлектор

«9»(1001)

1 А1 АО PCF8591 4-кан. 8-битный АЦП и 1-кан. ЦДЛ

1 А2 А1 АО TDA8440 Переключатель аудио/видео

А2 А1 АО TDA8540 4x4 переключаемая видеоматрица

1 А1 АО TDA8752 Быстрый АЦП для LCD

1 1 АО SAA7110A Цифровой мультистацдартный декодер

«А» (1010)

0 0 0 РСВ2421 1к последовательная EEPROM

0 0 АО PCF8583 256 х 8-битный RAM/часы/калецдарь

0 0 1 PCF8593 Часы-календарь с низковольтным питанием

Адреса некоторых микросхем ?С

39

Группа (А7..Л4) Обозначение Функциональное назначение

А2 А1 АО PCF8570 256 х 8-битный статическая RAM

А2 А1 АО PCF8522/4 512 х 8-битный КМОП EEPROM

А2 А1 АО РСА8581/С 128 х 8-битный EEPROM

А2 А1 АО PCF8582/A 256 х 8-битный EEPROM

А2 А1 РО РСХ8594 512 х 8-битный КМОП EEPROM

А2 А1 РО РСХ8598 1024 х 8-битный КМОП EEPROM

«В-(1011)

0 0 АО SAA7199B Цифровой мультистандартный декодер

0 1 0 TDA8416 TV/VCR стереолроцессор

0 1 АО TDA9850 BTSC стерео/SAP декодер

0 1 АО TDA9855 BTSC стерео/SAP декодер

0 1 1 TDA9852 BTSC стерео/SAP декодер

1 0 0 TDA9610 Аудио FM процессор для VCR

1 0 0 TDA9614H Аудиопроцессор для VHS

1 А1 0 SAA7186 Цифровой регулятор линейности строк

1 0 1 РСА8516 Stand-alone OSD IC

1 1 1 SAA7165 Видео D/А процессор

1 1 1 SAA9065 Видео D/А процессор

«С» (1100)

1 0 0 1 ТЕА6100 FM/1F для р/приемников с микроконтроллерами

0 1 0 ТЕА6821/2 Автомобильный AM приемник

0 1 0 ТЕА6824/Т IF IC для автомобильных приемников

0 А1 АО TSA5511/2/4 1,3-ГГц PLL синтезатор частоты для TV

0 А1 АО TSA5522/3M 1,4-ГГц PU. синтезатор частоты для IV

0 1 АО ТОА8735 150-МГц PU. синтезатор частоты

0 1 АО TSA6057 Синтезатор частоты для радиоприемников

40 Адреса некоторых микросхем ?С

Группа (А7..Л4) Обозначение Функциональное назначение

0 1 АО TSA6O6O Синтезатор частоты для радиоприемников

0 1 АО UMA1014 Синтезатор частоты для мобильных телефонов

1 0 0 TDA8722 Negative video modulator with FM sound

«D» (1101)

0 0 АО TDA8O43 QPSK демодулятор и декодер

0 0 АО ТОА9170 YUV processor with picture improvement

0 А1 АО PCF8573 Часы/календарь

А2 А1 АО TDA8443A YUV/RGB переключаемая матрица

0 1 АО TDA8745 Декодер звука для спутникового TV

1 0 0 TDA1551Q 2 х 22 Вт автомобильный стерео УНЧ

1 А1 АО TDA4845 Векторный процессор для кинескопов

1 А1 АО UMA1000T Цифровой процессор для мобильн. телефонов

1 1 АО PCD4440 Звуковой скрамблер/дескр. для мобильн. телеф.

«Е» (1110)

0 0 0 TDA9177 2nd адрес для LT1 (Is* is ‘40’)

0 0 0 TDA9178 2nd адрес для ЕЛ (Is* is ‘40’)

0 0 АО SAA7192 Цифровой конвертор цвета

«F» (1111)

X X X - Зарезервированные адреса

«0...F» (0000...1111)

X X X PCF8584 |2С контроллер шины

Примечания:

х — не определено;

А — программируемый бит;

Р — бит переключения страницы;

QAM-64 — квадратурная амплитудная модуляция с 64 значащими позициями амплитуды и фазы является спектрально-эффективным методом модуляции;

Адреса некоторых микросхем 12С

41

VPS — система программирования работы видеомагнитофона с помощью закодированных в телепрограмме сигналов, система распознавания видеопрограмм, специальная служба на TV-станциях; каждая программа передается со специальным кодом, воспринимаемым декодером VPS, который управляет записью по таймеру; если кодовые сигналы телепрограммы и внутренних установок совпадают, производится запись (управляющая информация передается в 16-й строке);

RDS/RBDS — система передачи данных в диапазоне FM; используется для передачи информации в цифровом виде и отображения ее на дисплее радиоприемника;

VIP — входной видеопроцессор;

PIP — эффект «кадр в кадре», специальное устройство, позволяющее «врезать» в текущее изображение одно или несколько дополнительных изображений меньшего формата;

D2MAC — система цветного телевидения — аналоговый сигнал, частичная цифровая обработка, цифровой сигнал звукового сопровождения; распространена в основном в кабельных и спутниковых системах;

LCD — жидкокристаллический индикатор;

LED — светодиодный индикатор;

EEPROM — электрически программирумая/репрограммируемая память;

OSD — отображение на экране телевизора дополнительной информации;

QPSK — квадратурная фазовая модуляция (манипуляция); применяется в системах спутникового TV.

Представители микросхем с интерфейсом ?С

43

3. Представители микросхем с интерфейсом 12С

В этой главе приводятся сведения, необходимые для проектирования несложных конструкций на основе микросхем с интерфейсом I С. Как показывает практика, далеко не все микросхемы возможно использовать в радиолюбительском творчестве. Например, достаточно трудно применять такие варианты, как микросхемы для телевизионных приемников, формирователи сигналов разверток, корректоры цветовых переходов, декодеры цветности, синтезаторы частоты для мобильных телефонов и т. д. Поэтому в рамках данной книги рассматриваются микросхемы, которые могут быть использованы преимущественно в домашней аудиоаппаратуре, такой, как, например, усилители низкой частоты, усилители мощности, радиоприемники. Что-то подойдет для создания несложных и полезных устройств на основе микроконтроллера — охранные системы, системы сбора информации, электронные частотомеры, фазометры, генераторы. При необходимости получить информацию по другим типам микросхем можно непосредственно с сайта фирмы Philips (http.//www.senuconductors.philips.com). Следует отметить, что оригинальная документация требует перевода с английского языка, а значит, необходимо приложить некоторые усилия тем, кто английский знает плохо или вообще не знает. Но при определенном навыке глубоких знаний не требуется и смысл большинства слов становится ясным без перевода.

Итак, перейдем к рассмотрению микросхем.

3.1. ЭСППЗУ с последовательным доступом

Микросхемы ЭСППЗУ (электрически стираемые постоянно программируемые запоминающие устройства) с последовательным доступом появились на рынке сравнительно недавно, но тем не менее они прочно вошли в арсенал разработчика. Международная аббревиатура микросхем — EEPROM (electrically erasable PROM). Истори

чески первыми появились, впрочем, микросхемы с параллельным доступом, когда каждый бит байта мог быть считан или записан по отдельной линии, а значит, одновременно с другими битами. Адрес хранения байта задавался также параллельным способом. То есть, к примеру, память 8-разрядных данных на 256 ячеек должна содержать 8 линий данных и 8 линий адреса данных. Достоинством памяти с параллельным доступом является достаточно малое время доступа — данные транслируются одновременно по всем линиям. Управлять такой памятью тоже очень просто, достаточно выставить адрес, и данные будут считаны (записаны).

Гораздо сложнее работать с последовательной памятью. Во-первых, необходимо последовательно, бит за битом, передать адрес ячейки памяти, затем точно так же передать (или считать) данные. Очевидно, скорость обмена с такой памятью в десятки раз меньше, чем с памятью параллельной. Что и сдерживало появление такого вида памяти. Массовый выпуск последовательных EEPROM начался после того, как в составе малогабаритной техники появились несложные микроконтроллеры. В основном такая техника не критична к высокой производительности вычислительных устройств, к ней относится бытовая и управляющая аппаратура. Еще одно важное обстоятельство, расширяющее возможности применения последовательных микросхем ЭСППЗУ, — их достаточно низкая стоимость.

Следует отметить, что для доступа к данным последовательной памяти используются разные интерфейсы: I2C, Microwire, SPI, CBUS. Некоторые сведения относительно номенклатуры микросхем можно почерпнуть в литературе [2]. Мы коснемся только тех, которые имеют интерфейс 12С. Обратите внимание: ЭСППЗУ с интерфейсом 12С, выпускаемые разными фирмами (SGS-Thomson microelectronics, Philips, Microchip) и имеющими одно наименование (например, 24С01), могут немного отличаться по расположению выводов, способу задания slave-адреса, особенности внутренней организации, принципам защиты от записи и др. При проектировании конкретных устройств рекомендуется ориентироваться не только на наименование ЭСППЗУ, но также и поинтересоваться фирмой-производителем, получить оригинальную техническую документацию.

Примеры применения EEPROM с последовательным доступом рассмотрим по документации [10, 11], относящейся к микросхемам

44

Представители микросхем с интерфейсом 12С

РСА8581 (128 х 8 битов) и PCF85xx (256... 1024 х 8 битов), производимых Philips, а также по мануалам [12, 13], описывающим микросхемы 24LC16B (2048 х 8 битов) и 24LC32A (4096 х 8 битов) производства фирмы Microchip.

РСА8581

Микросхема имеет два исполнения (без буквы «С» в окончании названия и с буквой), отличающихся по некоторым основным эксплуатационным характеристикам. Основные параметры микросхемы:

• питающее напряжение от 4,5 до 5,5 В (РСА8581) и от 2,5 до 6,0 В (РСА8581С);

• встроенный импульсный умножитель напряжения «зарядовый насос» для обеспечения режима записи (для программирования памяти нужно напряжение 12 В, в то время как микросхемы питаются пониженным напряжением);

• автоматическое стирание ранее записанной информации перед записью новой (режим automatic erase/write);

• ток потребления в дежурном режиме 10 мкА;

• задание slave-адреса с помощью трех внешних выводов (АО, А1,А2);

• автоматический инкремент адреса при обращении;

• минимально гарантированное число циклов записи — 10 000;

• минимально гарантируемое время сохранения записанной информации—10 лет;

• бесконечно возможное число циклов чтения;

• рабочая температура окружающей среды от -25 до +85 °C;

• возможность использования на одной шине до 8 однотипных микросхем без дополнительных аппаратных средств переключения и расширения;

• максимальная частота SCL сигнала — 100 кГц (режим low-speed).

Микросхема выпускается в 8-выводном корпусе типа DIP8 или SO8 (с планарными выводами). Расположение выводов приведено на рис. 3.1, а их назначение — в табл. 3.1.

Представители микросхем с интерфейсом Рс

45

Таблица 3.1. Назначение выводов РСА8581

Символ Вывод Описание

АО 1 slave-адрес 0

А1 2 slave-адрес 1

А2 3 slave-адрес 2

Vss 4 Общий вывод

SDA 5 Линия SDA вход/выход

SCL 6 Линия SCL вход

TEST 7 Тестовый вывод

Voo 8 Питание«+»

АО [7 ~8~| Vdd

А1 [г 7] TEST

А2[3 б] SCL

Vss |~4 s] SDA

Рис. 3.1. Расположение выводов микросхемы РСА8581

Внутреннее устройство микросхемы показано на рис. 3.2.

Чтобы предохранить микросхему от перегрузок, например при воздействии статического электричества, разработаны и используются разные методы защиты. Наиболее эффективны, дешевы и носят массовый характер методы встраивания защитных диодов. Один из таких способов, примененный в данной микросхеме, показан на рис. 3.3.

Выводы конфигурации slave-адреса А0...А2 снабжены двумя последовательно включенными диодами. При превышении напряжения на выводах А0...А2 порога, заданного напряжением VDD, открывается верхний диод и «притягивает» вывод к потенциалу питания VDD. Если напряжение становится ниже Vss (потенциал общего провода), открывается нижний диод и «притягивает» вывод к потенциалу «земли» Vss. Обратите внимание: в данном случае выводы SDA и SCL имеют только защиту от отрицательного напряжения и не имеют за-

46

Представители микросхем с интерфейсом 12С

Рис. 3.2. Внутреннее устройство микросхемы РСА8581

Рис. 3.3. Защита от перегрузок

щиты от положительного (верхний диод отсутствует), поскольку микросхема может быть использована при напряжениях на шине, отличных от напряжения питания микросхемы.

Мы уже знаем, что обращение к микросхеме происходит посредством передачи по шине 12С slave-адреса, как показано на рис. 3.4. Адрес в данном случае состоиг из 7 битов. Старшие 4 бита (1010) оп

Представители микросхем с интерфейсом PC

47

ределяют принадлежность микросхемы к группе EEPROM, младшие 3 бита — АО, Al, А2 — задают уникальный идентификационный номер в группе однотипных микросхем. Если на шине присутствует несколько микросхем с одинаковыми старшими 4 битами slave-адреса, необходимо с помощью перемычек, подключаемых к напряжению питания или к общему проводу, задать на выводах А0...А2 потенциалы, назначить микросхемам уникальные идентификационные номера, например, как показано на рис. 3.5. Обращение к соответствующему элементу будет производиться программно, заданием битов А0...А2.

1 1 0 | 1 | 0 А2 | А1 | АО

Группа! Группа 2

Рис. 3.4. Построение slave-адреса

Vdd

SDA SCL

Рис. 3.5. Соединение однотипных микросхем на шине 12С

48

Представители микросхем с интерфейсом ?С

Рис. 3.6. Матрица памяти

|s| |о|а|< |а| , 1аЦП

R/W задается ||

пользователем автоинкремент

адреса

Рис. 3.7. Master передает данные к slave

Разберемся теперь, как устроена матрица памяти микросхемы и каким образом осуществить запись (считывание) данных.

Рассмотрим сначала ситуацию, когда устройство master передает данные к slave-абоненту (режим записи WRITE). Формат сообщения представлен на рис. 3.7.

Вначале осуществляется передача slave-адреса и признака R/W (в данном случае этот бит установлен в «О»), Второй байт — адрес ячейки матрицы памяти, изображенной на рис. 3.6. Обратите внимание: старший бит этого байта, помеченный на рис. 3.7 знаком «х», не определяется или, другими словами, может быть установлен в «О» или в «1». Почему? Это станет понятным, когда мы представим, что с помощью 8 битов возможно задание 256 адресов, но в данной микросхеме присутствует только 128 ячеек (а значит, столько же и адресов). Старшие. 128 адресов здесь просто не определены.

После передачи адреса ячейки осуществляется передача байта данных (DATA). Биты 7...0 последовательно занимают ячейки памяти. После приема бита «О» данных осуществляется автоинкремент (увеличение на единицу) адреса памяти. Естественно, завершение передачи должно сопровождаться появлением условия Stop.

Чтение из памяти осуществляется по протоколу, показанному на рис. 3.8.

АСК АСК АСК

slave slave slave

|s| ;о|а|»; «ус-н-i |a|s|: Z

В этот момент FVW master начинает--------

принимать данные, a slave - передачу

АСК отсутствие АСК

master master

автоинкремент автоинкремент адреса адреса

Рис. 3.8. Чтение из памяти

Представители микросхем с интерфейсом 12С

49

Вначале необходимо передать slave-адрес с признаком R/W — «О», затем адрес ячейки. После получения master-абонентом сигнала АСК, свидетельствующего о нормальном приеме адреса ячейки памяти, master-абонент должен выставить повторное условие Start и передать slave-устройству slave-адрес с признаком R/W — «1», получить АСК от slave-устройства и начать считывание данных, выставляя после каждого полученного байта ^сигнал АСК. После получения последнего байта master-абонент не выставляет сигнала АСК, а выполняет условие Stop. Заметим, что в данном случае также справедлив автоинкремент адреса ячейки.

Master-абонент может начать непосредственное чтение со slave-устройства, но в этом случае он должен учитывать, что чтение будет производиться не с нулевого адреса, а с увеличенного на единицу адреса, операция с которым была последней в предыдущем цикле (рис. 3.9).

АСК slave

АСК slave

АСК slave

автоинкремент автоинкремент адреса адреса

Рис. 3.9. Чтение без предварительной установки адреса байта

PCF85XX

Эта серия микросхем EEPROM имеет увеличенный объем памяти по сравнению с предыдущей микросборкой. Емкость микросхем серии указана в табл. 3.2.

Таблица 3.2

Микросхема Емкость Организация

PCF8582 2 кбита 256 х 8 битов

PCF8594 4 кбита 512 х 8 битов

PCF8598 вкбитов 1024 х 8 битов

Микросхемы обеспечивают 1 000 000 гарантированных циклов стирания/записи (E/W) и 10 лет хранения записанной информации,

50

Представители микросхем с интерфейсом 12С

Рис. ЗЛО. Внутреннее устройство микросхем PCF8582, PCF8594, PCF8598

Представители микросхем с интерфейсом ?С 51

совместимы с чипами PCF8570, PCF8571, PCF8572 и PCF8581 по расположению выводов. Внутренее устройство микросхем PCF8582, PCF8594 и PCF8598 приведено на рис. 3.10.

Расположение выводов указанных микросхем приведено на рис. 3.11, назначение выводов — в табл. 3.3—3.5.

АО [7 8~| Vod wp [7 8~] Vdd wp [7 ~8~| Vod

АТ [7 7] ртс Al U 7] ptc -n 7] ptc

А2 [з e]scL A2 [7 e] SCL A2 [з б] SCL

Vss[~4 5] SDA Vss [T J]sda Vss fT 5] SDA

PCF8582 PCF8594 PCF8598

Рис. 3.11. Расположение выводов

Таблица 3.3. Назначение выводов PCF8582

Символ Вывод Описание

AO 1 Slave-адрес 0

Al 2 Slave-адрес 1

A2 3 Slave-адрес 2

vss 4 Общий вывод

SDA 5 Линия SDA вход/выход

SCL 6 Линия SCL вход

PTC 7 Контроль времени программирования

Vdd 8 Вывод питания«+»

Таблица 3.4. Назначение выводов PCF8594

Символ Вывод Описание

WP 1 Защита записи

А1 2 Slave-адрес 1

А2 3 Slave-адрес 2

Vss 4 Общий вывод

SDA 5 Линия SDA вход/выход

52

Представители микросхем с интерфейсом ?С

Окончание таблицы 3.4

Символ Вывод Описание

SCL 6 Линия SCL вход

РТС 7 Контроль времени программирования

Уро 8 Вывод питания «+»

Таблица 3.5. Назначение выводов PCF859B

Символ Вывод Описание i

WP 1 Защита записи

- 2 Не используется

А2 3 Slave-адрес 2

Vss 4 Общий вывод

SDA 5 Линия SDA вход/выход

SCL 6 Линия SCL вход

PTC 7 Контроль времени программирования

Уро 8 Вывод питания«+»

Протокол программирования памяти микросхем аналогичен приведенному ранее, но имеет некоторые особенности. Одна из особенностей связана с тем, что адрес ячейки памяти не может содержать число, превышающее 255. Но приведенные типы микросхем содержат 512 и 1024 ячейки. Что это означает? Все очень просто: в slave-адресе биты А0...А2 уже не все программируются внешними перемычками. Часть из них выбирается программно, при задании slave-адреса. Мы словно объединяем в одном корпусе несколько микросхем PCF8582. Структура памяти, состоящая из блоков по 256 байтов, называется страничной организацией. К слову, максимальное число страниц в одной микросхеме 8.

Интересной возможностью, реализованной в описываемых микросхемах, является возможность защиты от повторной записи. Если вывод WP имеет низкий уровень, работа с EEPROM не имеет ограничений. Если WP устанавливается в состояние «1», верхняя половина памяти EEPROM защищается от записи. В таком случае сигнал АСК не будет генерироваться при адресации к верхней половине (256 байтов) PCF9594 и PCF8598 (512 байтов).

Представители микросхем с интерфейсом 12С

53

При записи данных в память EEPROM должны быть выдержаны определенные временные соотношения (циклы erase/write). Длительность этих циклов формируется внутри микросхемы и в большинстве случаев не требует коррекции. Если коррекции не требуется, вывод РТС может быть подключен к VDD или оставлен не подключенным. Типичное значение времени tF/w = 7 мс, оно может быть задано внешне в пределах 4... 10 мс.

Как уже ранее было сказано, микросхемы EEPROM с последовательным доступом по шине 12С выпускает не только фирма Philips, но и другие не менее известные фирмы. Для сравнения приведем описания микросхем 24LC16B и 24LC32A, производимых Microchip.

24LC16B

Емкость микросхемы — 16 кбитов, организованных в 8 блоков по 256 битов. Основные характеристики:

• возможность питания пониженным напряжением (до 2,5 В);

• наличие входных формирователей (триггеров Шмитта) для обеспечения помехоустойчивости;

• ток потребления в активном режиме 1 мА;

• потребление в режиме ожидания — 10 мкА при питании 5,5 В и 5 мкА при питании 3,0 В;

• организация 8 х 256 х 8 битов;

• защита входов от потенциального пробоя 4 кВ;

• возможность работы в режиме fast-speed;

• автоматическое выполнение цикла E/W;

• внутренний буфер данных размером 16 байтов;

• типичный цикл записи страницы данных — 2 мс;

• аппаратная защита от перезаписи;

• гарантированное число циклов E/W — 1 000 000;

• сохранность записанных данных — не менее 200 (!) лет;

• коммерческое (0...+70 °C) и индустриальное (-40...+85 °C) исполнения;

• корпуса DIP и SOIC.

Расположение выводов показано на рис. 3.12.

54

Представители микросхем с интерфейсом PC

8JVOO

7] WP 6]scl я] SDA

Рис. 3.12. Расположение выводов 24LC16B

Запись в память и считывание из нее осуществляется по принципам, описанным выше, поэтому мы не будем повторяться.

Очень важный момент, на который обращают внимание разработчики микросхемы, связан с повторным обращением к памяти вслед за завершением предыдущего цикла. Другими словами, после установки условия Stop внутри микросхемы начинается процесс записи в матрицу памяти и, пока он не закончится, совершать повторные операции не представляется возможным.

Особенно это будет заметно в режиме fast-speed, поскольку в нем используются ускоренные шинные циклы. Сообщить об окончании внутренних операций микросхема может только при помощи установки сигнала АСК в состояние «О». Для сокращения времени опознавания разработчики рекомендуют производить эту процедуру с помощью так называемого поллинга (acknowledge polling flow), то есть постоянного опроса состояния готовности. Процедура поллинга приведена на рис. 3.13.

Как следует из рис. 3.13, master-абонент вслед за передачей условия Stop выставляет условие Start, передает slave-адрес и проверяет сигнал АСК. Если АСК = 1 (занято), передается повторно условие Start, slave-адрес, осуществляется проверка АСК. Если АСК = 0 (свободно), master-абонент переходит к следующей операции.