Текст

Учебно-методическое пособие

по курсу «Компьютерная электроника»

для студентов специальности 6.091501. - компьютерные сети и системы

образовательно-квалификационного уровня «бакалавр»

Составители: Григорьев Евгений Владимирович, доцент кафедры

радиофизики и электроники;

Зуев Сергей Александрович, старший преподаватель кафедры

радиофизики и электроники;

Старостенко Владимир Викторович, доцент, зав. кафедрой

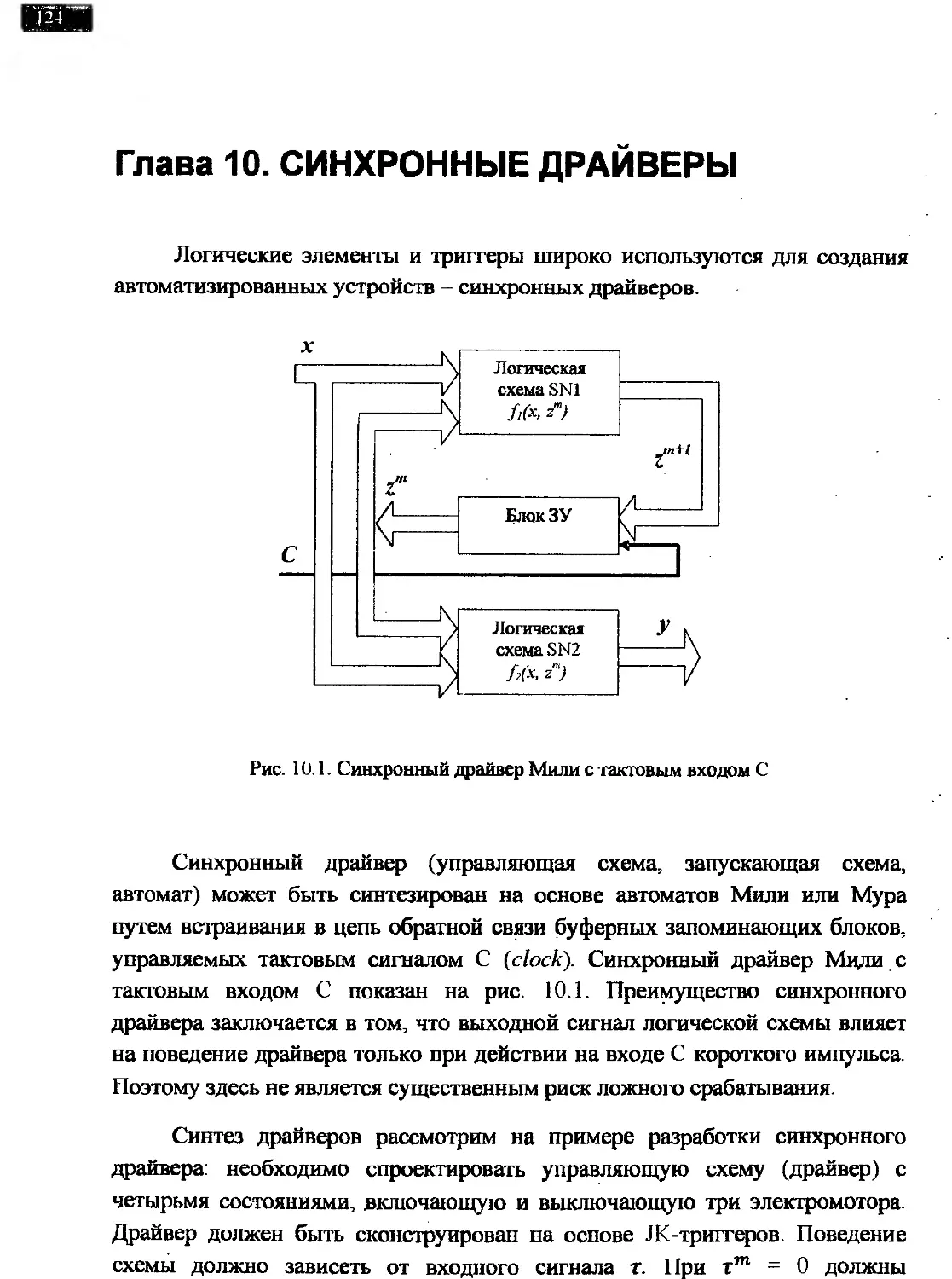

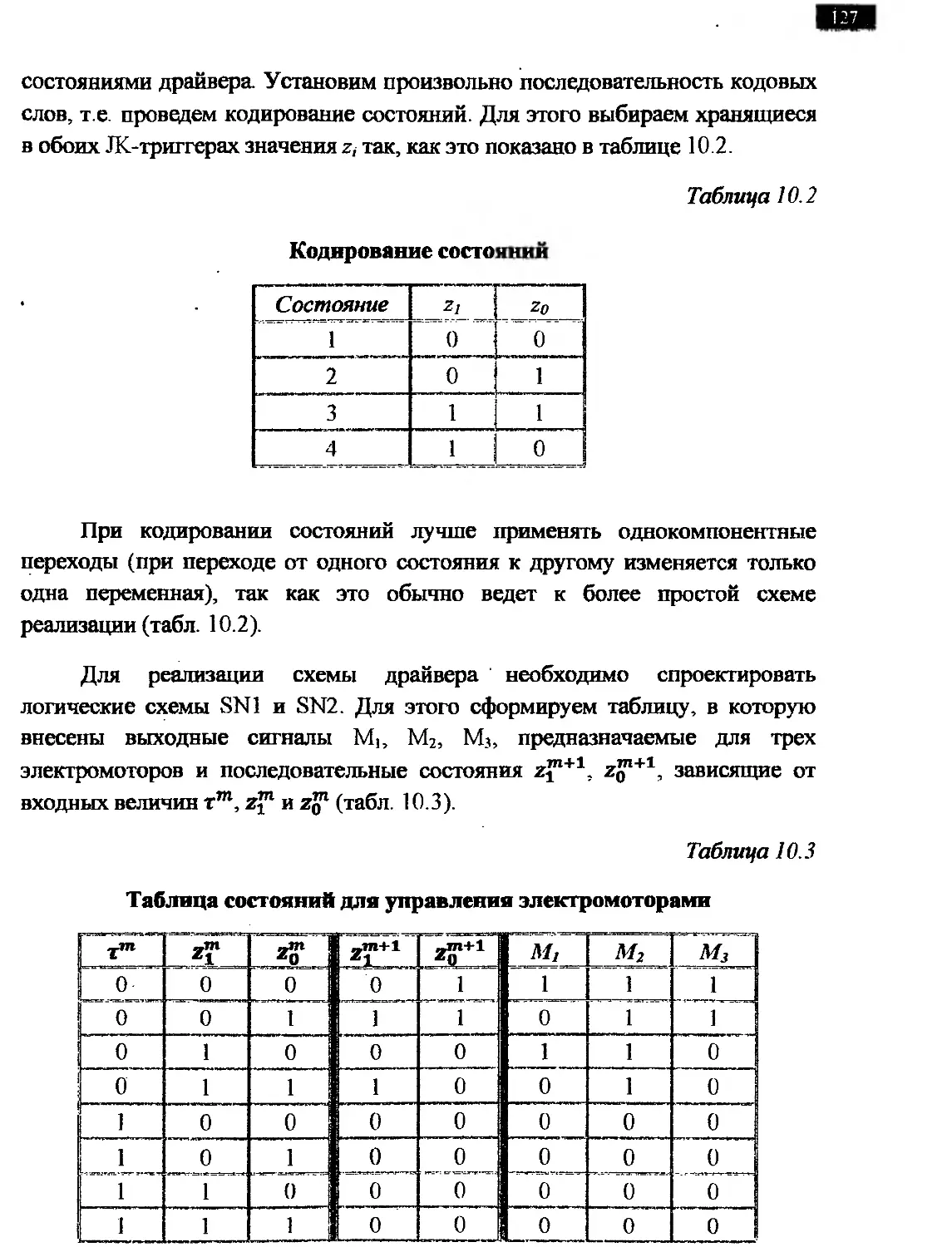

радиофизики и электроники.

Редактор Н. А. Василенко

Подписано к печати Формат 60x84 */|6 Бумага тип. ОП

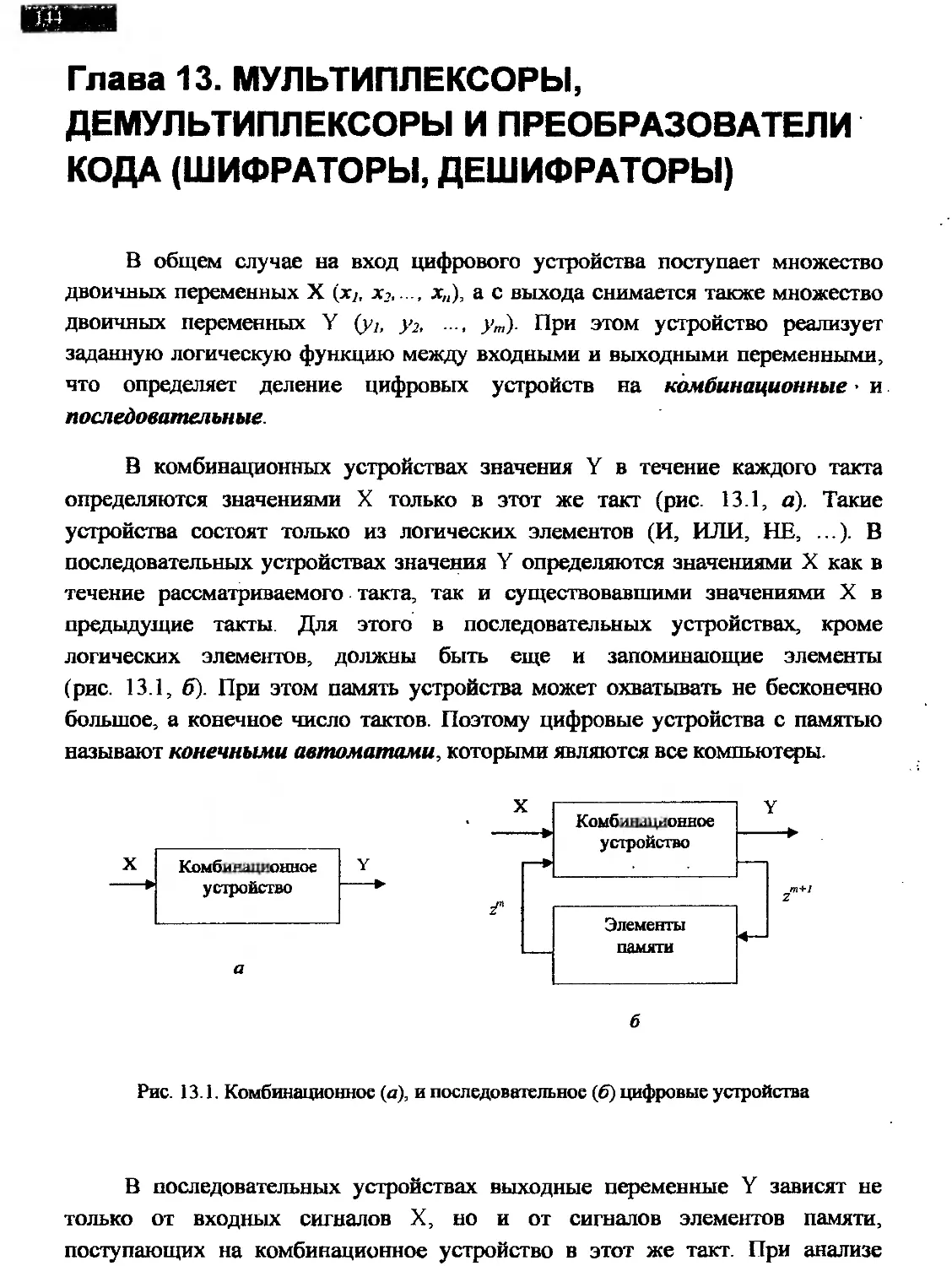

Объем Тираж - 100 заказ. Бесплатно

95007, г. Симферополь, пр. Вернадского, 4

Таврический национальный университет им. В. И Вернадского

глава 1. импульсный способ

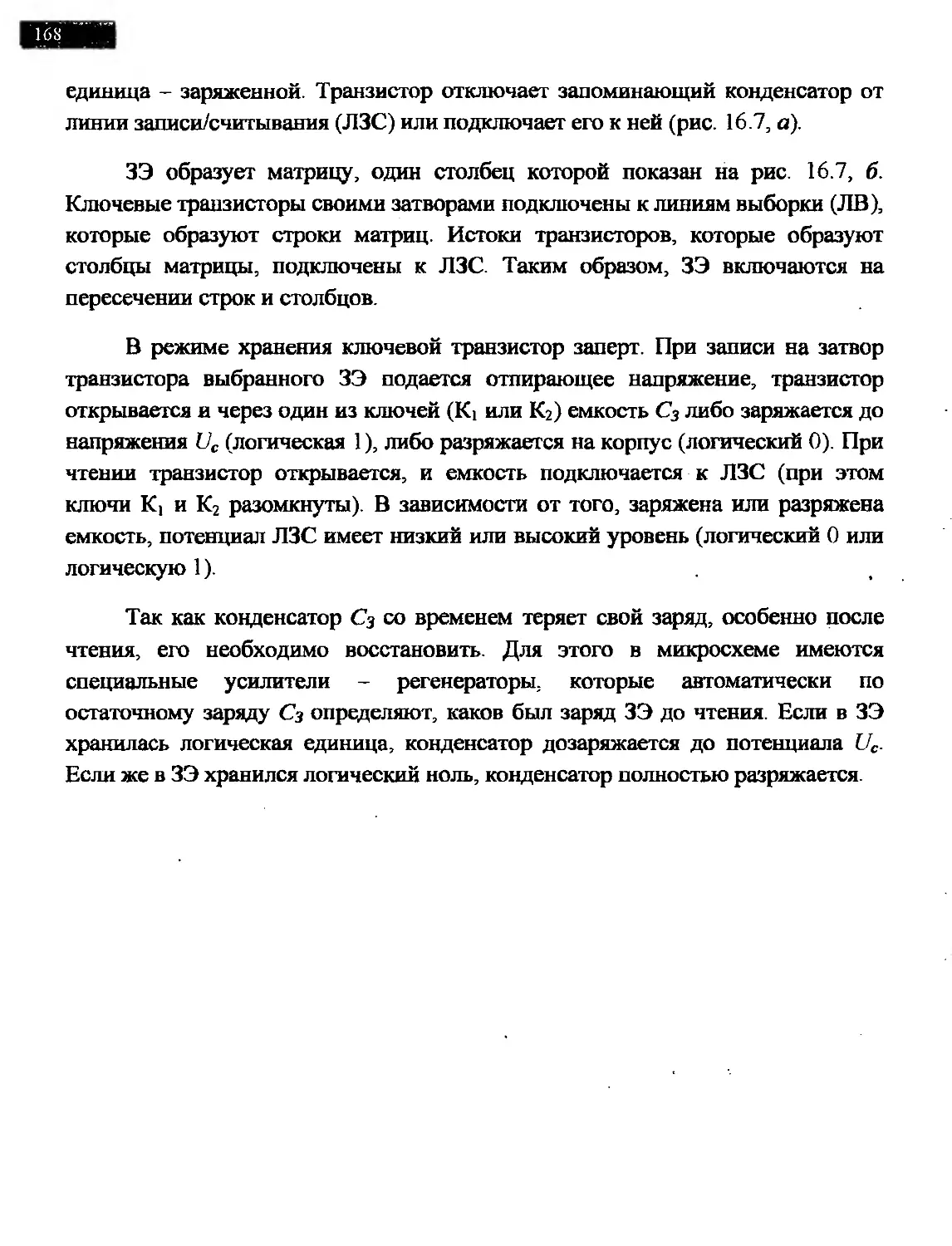

ПРЕДСТАВЛЕНИЯ СИГНАЛОВ ИНФОРМАЦИИ

В повседневной жизни термин «сигнал» мы отождествляем с полученным

сообщением, передаваемой информацией. Приступая к изучению

компьютерной электроники, следует уточнить смысл понятия «сигнал».

Сигналом называют процесс изменения во времени физического состояния

какого-либо объекта, служащий для отображения, регистрации и передачи

сообщений. В практике человеческой деятельности сообщения неразрывно

связаны с заключенной в них информацией. Часто физический процесс,

порождающий сигнал, развивается во времени таким образом, что значения

сигнала можно измерять в любые моменты времени. Сигналы этого класса

принято называть аналоговыми (рис. 1.1, а). Термин «аналоговый сигнал»

подчеркивает, что такой сигнал «аналогичен», полностью подобен

порождающему его физическому процессу. Аналоговый сигнал может наглядно

представляться своим графиком (осциллограммой). Первоначально в

радиоэлектронике использовались исключительно аналоговые сигналы,

которые было просто генерировать, принимать и обрабатывать. Однако из-за

нелинейности волыамперных характеристик полупроводниковых приборов

(транзисторов, диодов и др.) форма сигнала искажается, что приводит к

информационным ошибкам. В процессе обработки аналоговых сигналов

происходит накопление их искажений.

1110

1101

1011

1010

в

Рис. J. 1. Примеры сигналов: а - аналоговый; б - дискретный; в - цифровой

Возросшие требования к радиоэлектронным системам потребовали

искать новые принципы их построения. На смену аналоговым пришли в

основном импульсные системы, работа которых основана на использовании

дискретных сигналов. Простейшая математическая модель дискретного

сигнала Sd (t) - это счетное множество точек на оси времени, в каждой из

которых определено отсчетное значение сигнала Si (где i - целое число). Как

правило, шаг дискретизации А = ti+1 - tj для дискретных сигналов постоянен.

Разновидностью дискретных сигналов являются цифровые сигналы, которые

могут обрабатываться цифровыми системами с сильно нелинейными

передаточными характеристиками без сбоев, накопления и дальнейшего

распространения искажений сигналов.

Рис. 1.2. Пример «оцифровывания» сигналов: а - зависимость сигнала S от времени г,

б - квантованная зависимость от времени сигнала при четырех амплитудных ступенях,

в - приведение амплитуд в соответствие с записью величин в виде двоичного кода

Если сигналы с непрерывной величиной должны обрабатываться

цифровыми системами, то с помощью процесса дискретизации их необходимо

перевести в цифровую форму. Процесс дискретизации состоит из двух этапов:

дискретизации по времени и дискретизации (квантования) по уровню

(рис. 1.2).

Глава 2. КОДИРОВАНИЕ И СИСТЕМЫ

СЧИСЛЕНИЯ

2.1. Коды

Коды используются для оптимального представления сигнала в случае

его обработки цифровыми системами. Код отображает символы одного

множества через символы другого множества. Известным примером кода

является международный код Морзе (таблица 2.1).

Таблица 2.1

Примеры символов кода Морзе

Алфавит Код Морзе

\ • —

В — . .

С

D — . .

Е •

Т —

Определение кода производится с помощью таблицы соответствия.

Комбинацию нескольких символов кода называют словом (word). Для каждого

применения имеется более или менее подходящий код. Те., например, для

проведения операций над числами в компьютере рационально применять иной

код, чем для передачи чисел по линии связи. В связи с этим необходимо

рассмотреть различия между отдельными кодами и специфику их применения.

2,2. Двоичный код

Двоичный код является универсальным в цифровых системах. В нем

применяются только символы 1 и 0, что делает возможным обработку сигналов

с помощью схемных элементов, работающих как переключатели. Кроме того,

двоичный код позволяет использовать арифметику, аналогичную арифметике

десятичных систем. Двоичную систему счисления можно рассматривать как

кодирование десятичной, где двоичное число состоит из слова, образованного

символами Q G{0,l} Символы С; одного слова в цифровой технике называют

битами. Слово Z2 (двоичное) формируется путем последовательного

присоединения отдельных битов:

= Сп •]Сп_2 ...CiC0,C^iC-г ••• С_т (2-1)

Двоичное число Z2 имеет п разрядов перед запятой и т разрядов после

запятой. Каждому биту, в соответствии с его позицией i в слове, присвоен

весовой коэффициент 2* - показывающий, на какую величину изменяется бит

при перестановке с нулевого разряда на данный. На основе этого можно

рассчитать эквивалентное десятичное число Z ю aM1«wuuJc):

Zlo Сп_! • 2П“Г + Сп_2 • 2"2 + + Сх • 21 + Со • 2° + С_i • 21 + - + Cm • 2т (2.2)

Рассмотрим в качестве примера двоичное число 10110.01Ь , которое

интерпретируется как:

Z10 = 1 • 24 + 0 • 23 + 1 • 2Z + 1 • 21 + 0 • 2° + 0 • 21 + 1 • 2 Z + 1 • 2 3 = 22,37510

Двоичный код обозначается как взвешенный, поскольку стоящие далее

влево биты обладают более высокими весовыми коэффициентами. Уравнение

(2.2) можно рассматривать как правило, в соответствии с которым

производится преобразование двоичных чисел в десятичные.

2.3. Основные арифметические операции в

двоичной системе

Перед анализом операций над двоичными числами, рассмотрим

изображение двоичных чисел, соответствующих десятичным от 0 до 15:

Десятичные Двоичные 0000

0

1 0001

2 0010

3 ООН

4 0100

5 0101

6 оно

7 0111

Десятичные Двоичные

8 1000

9 1001

10 1010

11 1011

12 1100

13 1101

14 1110

15 1111

Целочисленное сложение двух чисел А и В производится в двоичной

системе точно также как и в десятичной - по разрядам. В каждом разряде

должны быть просуммированы двоичные числа а„ и Ь„, и перенос из

предыдущего разряда Сп.ь При сложении возникает новая сумма Su и новый

перенос Сп.

Сложим теперь, для примера, числа 00012 (110) и 01012 (510), проводя

поразрядное сложение с учетом переносов:

_|_ 0101 В крайнем справа столбце (младший разряд)

------- 0001 1+1=0 и перенос 1 в следующий разряд.

(сумма) 0

(перенос) 1

0101 По втором справа столбце 0+0+1 = 1 (учтем

+ 0001 перенос 1), переноса в третий разряд нет.

____1

10

+0101

0001 В третьем столбце справа 1 +0= 1 (переноса нет).

110

+0101

0001 В крайнем левом столбце - 0+0=0.

ОНО

Возможность сложения в одном разряде отображена в таблице 2.2, где

а„ и Ь„ - слагаемые, Сп 4 - перенос из предыдущего разряда; Sn - сумма; Сп -

новый перенос.

Таблица 2.2

Сложение в двоичной системе

Ь;, Sn Cn

0 0 0 0 0

0 0 1 1 о j i ! i i

о 1 0 1* : 0

Г о 1 1 ° Ii 1 i u

Г 1 0 0 1 0

1 0 1 0 1

[ 1 1 1 "" 1 г ‘ я г 11 ! ii So 0 1 1 ... I-...

В случае, когда суммируются два числа с фиксированной запятой,

важно, чтобы обе запятые стояли друг под другом. Например:

Таблица 2.3

Представление положительных и отрицательных двоичных чисел

Десятичное число Двоичное число Десятичное число Двоичное число

+15 bodoiii i -1 11111111

+14 _ Г ~ ' J 00001110 -2 11111110 111 11101

00001161 -3

+ 12 00001100 -4 11111100

+11 00001011 -5 11111011

+10 " +9 ’ ’ " 00001010 -6 11111010

00001661 ...... 11111001

+8 00001000 -8 11111000

+7 00000111 -9 11110111

+6 00000110 -10 11110110

+5 00000101 -11 11110101

_ _+4 ... -J 00000100 -12 inioioo

+3 00000011 -13 11110011

+2 00000010 -14 11110010

+i 00000001 15 11110001

0 00000000

При переходе к дополнительному коду представление положительных

чисел не меняется, а представление отрицательных чисел можно получить

путем инвертирования кода с последующим прибавлением единицы в

младшем разряде. Технически задачу представления в дополнительном коде

можно осуществить с помощью инверторов, а сложение с единицей - с

помощью суммирующей схемы.

Пусть, например, требуется получить двоичное представление

десятичного отрицательного числа -110 в дополнительном коде.

Положительное десятичное число 110 = 000000012 двоичному

Инвертиров й (обратный) код для него есть 111111102

+

Складываем с единицей 1г

Получаем дополнительный код отрицательного 111111112

десятичного числа -110.

Проведем несколько вычитаний в двоичной системе по формуле Л -- В

= А + (- В) с использованием дополнительного кода.

Вычислим 5)0 - 2ю или 510 +(- 210) = Зю.

510 составляет 000001012 (уменьшаемое)

- 2ю в дои.1льителыюм коде 111111102 (вычитаемое)

В результате их сложения получим 000000112 (разность)

и единицу переноса из старшего разряда-

Если оставить пока перенос без внимания, то полученный результат

составляет при переводе в десятичную систему 310, те. получился

правильный ответ.

Вычислим Зю - 5ю или Зю +(- 5ю) = -2ю-

310есть 000000112 (уменьшаемое)

- 5|о в дополнительном коде 111110112 (вычитаемое)

В результате их сложения получим 111111102 (разность)

без переноса из старшего разряда.

По таблице убеждаемся, что полученный нами результат соответствует

отрицательному десятичному числу -210, те. ответ правильный.

Однако как быть с возникающими в процессе вычислений переносами

из крайнего левого разряда? Если проинвертировать сигнал переноса, то

получится С. Данный сигнал С теперь представляется в качестве сигнала

заема. Вычитание выполняется путем сложения уменьшаемого с вычитаемым

в дополнительном коде, так что перенос при сложении в дополнительном

коде служит той же цели, что и заем в обычном вычитании.

Перед тем, как рассмотреть операции, которые проводит компьютер

при умножении и делении двоичного чисел, умножим числа 1012 = 510 и

1102=610.

х101

110

ООО

101

101

11110= 301О

Как видно из примера, операцию умножения можно свести к сложению

двоичных чисел, полученных из множимого путем его сдвига влево в

соответствии с распределением значащих разрядов в множителе. Сдвиг

двоичных слагаемых выполняется в последовательных регистрах, откуда они

поступают в сумматор для поразрядного сложения. На выходе сумматора

появляется число, представляющее собой произведение двух двоичных

чисел. Необходимо учесть, что сдвиг двоичного числа на один разряд влево

(в сторону старших разрядов) соответствует его умножению на 2, а вправо -

его делению на 2.

2.4, Шестнадцатеричный и восьмеричный

КОДЬ»

На практике наряду с двоичным кодом внедрился шестнадцатеричный

код, так как он обеспечивает лучшее обозрение длинных двоичных чисел.

Шестнадцатеричные цифры определены в табл. 2.4. Как видно, цифры

больше девяти представлены буквами А - F.

Таблица 2.4

Шестнадцатеричные числа

Г~~ ’ Десятичные Двоичные Шестнад- цатеричные Десятичные Двоичные Шестнад- цатеричные

0 0000 0 8 1000 8

1 0001 1 9 1001 9

ii ч L. „2 0010 2 10 1016 А

„3 ООН 3 И 1011 В

L...4 0100 4 12 1100 С

1 5 0101 5 13 1101 D

! б оно 6 14 1110 Е

( 7 6111 7 15 1111 F

Для преобразования двоичных чисел в шестнадцатеричные

объединяют по четыре цифры двоичного числа, которые интерпретируются,

как шестнадцатеричный код. Например:

ОНО 1100 1111

6 с F

Итак, справедливо выражение 0110110011112 = 6CF16.

Для восьмеричного кода применяются цифры десятичного кода от 0 до

7. Восьмеричный код применяется аналогично шестнадцатеричному, только

объединяются лишь по три разряда двоичного числа. Например:

НО 101 100 ОН

6 5 4 3

Следовательно, справедливо 1101011000112 - 65438.

2.5. Код Грэя

Часто в цифровой технике для числового кода требуегся схема

кодирования, в соответствии с которой при переходе от одного числа к

следующему изменялась бы только одна цифра. Это необходимо, когда из-за

технических неточностей момент переключения в двух разрядах может не

совпасть. Из-за этого при переключении двух цифр могут возникнуть

неправильные коммутационные операции. В качестве примера подобной

ошибки рассмотрим переключение от 110 к 210 в двоичном коде:

При данном переключении изменяются биты 0 и 1. При

одновременном переключении в двух разрядах возникает новое

(необходимое) число. Если моменты переключений в разрядах не совпадают,

то при первоначальном изменении бита 0 появляется число 0000 и только

когда изменяется бит 1, получаем правильное число 0010. Если же сначала

изменяется бит 1 и потом изменяется бит 0, то в промежутке возникает число

ООН.

Коды Грэя позволяют избежать этой очень серьезной ошибки за счет

того, что при переходе от одного слова к следующему изменяется только

один разряд. В таблице 2.5 представлен 4-разрядный код Грэя.

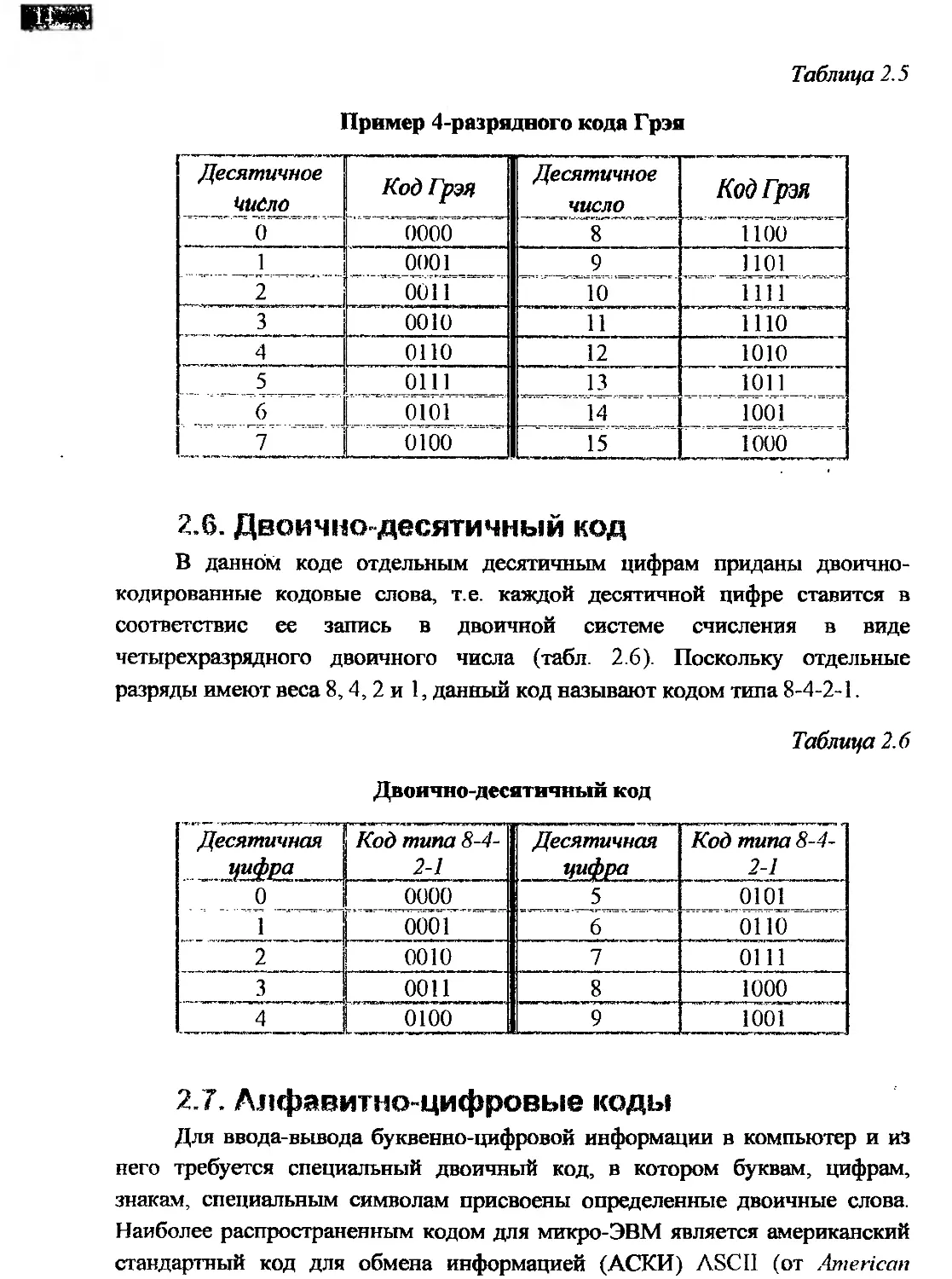

Таблица 2.5

Пример 4-разрядного кода Грэя

Десятичное Число Код Грэя Десятичное число Код Грэя

б бобо 8 ибо

_ 1 _ 0001 9 1101

ООН 10 11! 1

3 0010 11 ' ню'

4 оно 12 1010

5 0111 13 1011

6 7 0101 0100 14 1001 1000

2.6. Двоично-десятичный код

В данном коде отдельным десятичным цифрам приданы двоично-

кодированные кодовые слова, т.е. каждой десятичной цифре ставится в

соответствие ее запись в двоичной системе счисления в виде

четырехразрядного двоичного числа (табл. 2.6). Поскольку отдельные

разряды имеют веса 8,4,2 и 1, данный код называют кодом типа 8-4-2-1.

Таблица 2.6

Двоично-десятичный код

Десятичная цифра Код типа 8-4- 2-1 Десятичная ... Цифра Код типа 8-4- 2-1

0 0000 5 0101

1 0001 6 ОНО

2 0010 7 0111

3 ООП 8 1000

4 0100 9 1661

2.7. Алфавитно-цифровые коды

Для ввода-вывода буквенно-цифровой информации в компьютер и из

него требуется специальный двоичный код, в котором буквам, цифрам,

знакам, специальным символам присвоены определенные двоичные слова.

Наиболее распространенным кодом для микро-ЭВМ является американский

стандартный код для обмена информацией (АСКИ) ASCH (от American

Standard Code for Information Interchange) - семиразрядный код для

представления текстовой информации в компьютере; используется с

отдельными модификациями в большинстве вычислительных систем

В таблице 2.7 приведены некоторые примеры представления буквенно-

цифровой информации и некоторых знаков посредством кода ASCII

Табл ица 2.7

Пример кода ASCH

Символ Код ASCII

А 1000001

а 1100001

4 0110100

9 0111001

+ 0101011

— 0111101

Глава 3. ПЕРЕКЛЮЧАТЕЛЬНАЯ АЛГЕБРА

При обработке аналоговых сигналов, в которых информация заложена

в изменении их формы (амплитуда, частота, фаза), применяются методы

усиления, амплитудного и частотного детектирования, фильтрации и т.д.

Данные методы обработки из-за нелинейности характеристик элементов схем

обязательно искажают сигнал, что приводит к недостоверности полученной

информации.

Цифровая техника имеет то преимущество перед аналоговой, что

форма сигналов (наиболее подверженная искажениям) в обработке

информации не участвует Информация в цифровой технике определяется

наличием или отсутствием сигнала (при этом важен уровень сигнала, а не

его форма), а также положением сигнала в кодовой посылке (рис. 3.1).

Рис. 3.1. Цифровые сигналы: а - несмотря на изменение формы, цифровые сигналы несут

одинаковую информацию; б - изменение положения сигнала в кодовой посылке -

источник информации

Поэтому методы, применяемые для обработки аналоговых сигналов,

неприемлемы. В цифровой технике в первую очередь необходимо

определить есть сигнал или нет, т е. замкнут переключатель или разомкнут. В

связи с этим цифровую технику можно базировать на мощной теории

булевой алгебры, называемой также переключательной алгеброй,

позволяющей решать почти все проблемы, возникающие при разработке

цифровых схем.

3.1. Переключательная переменная и

переключательная функция

В цифровой технике под булевой переменной понимают переменную,

которая может принимать только значения 0 и 1. С булевыми переменными

могут быть образованы функции:

у = /(%!, х2, х3 ... х„) при хи у G {0,1}

Данную функцию называют n-разрядной переключательной или

двоичной функцией. Такие функции могут быть определены таблицами,

которые называются таблицами истинности.

Простейшая функция, связывающая входную переменную х с

выходной переменной у, представлена в табл. 3.1.

Таблица 3.1

Таблица истинности инвертора

Данную переключательную функцию именуют как «отрицание»,

«дополнение» или НЕ (NOT). Она читается: «у равен не х».

у = х.

Отрицание является одноразрядной переключательной функцией,

поскольку обладает только одной входной переменной. На рис. 3.1

представлено схемное обозначение инвертора:

Рис. 3.2. Схемное обозначение инвертора

Можно образовывать двоичные функции многих входных переменных,

но удобнее рассматривать функции с одной или двумя входными

переменными, а функции с большим количеством переменных сводить к

ним. Основные двоичные функции с входными переменными х0 и х1

представлены в табл. 3.2.

Таблица 3.2

Основные двухразрядные двоичные функции

’ Таблица ’ истинности Функции Схемное обозначение Наименование

i •Го •Г/ 1 1 0 1 1 0 0 0

V 1 1 1 0 у = xovXl Xc Xf 1 у OR, ИЛИ, дизъюнкция

—

i 1' i ...... "'Я .1 k 1 1 у = (Xo Vx}) Xo Xi 1 ( ’— У NOR, НЕ-ИЛИ, отрицание дизъюнкции

ч 9 у = Х0ЛХ] & Л’ AND, И, конъюнкция

Y 0 0 0 XO Xi

—

у - (Xof\X1) & < ) Л’ NAND, НЕ-И, отрицание конъюнкции

1 !z_ _2_ _L 1 1 Xo X,

i

5 II II i Ki Ki о II II J J £ £ NOT, НЕ, дополнение, отрицание, инверсия

iHv j 1 — 1 v F 0 0 ЗЕ 1 0 T 0 1 ±i 1 1 Xo. X) 1 < 5 У

0 у = (x<v>xt) Xo Xl = 1 — У EXOR, исключающее ИЛИ

y= (Xo^X!) = '—~ У эквивалентность

1V ) 1 .0. ° 1 Xo X)

3.2. Вычислительные правила

Важными для упрощения сложных функций являются вычислительные

правила булевой алгебры.

Переместительный (коммутативный) закон:

x0Axi - Х]Лх0,

Xo^Xj = X^Xq.

Сочетательный (ассоциативный) закон:

fx0AxjAx2 = XohfohXi),

(x<yxi)^x2= Xo^fx^Xi).

Распределительный закон (закон дистрибутивности):

= (XohXi)V (x0Kx2),

Xo^(XihX2) = (Xo^X^^Xo^Xi).

Закон поглощения (закон абсорбции):

Хо^(Хо^Х1) = Хо,

Хо^(Хо^Х1) = Хо.

Существование нейтральных элементов:

х0А7 = х0,

Хо^О = х0.

Существование дополнительных элементов:

х0ь~х0= О,

XoV-Xo^ 1.

Теорема Де-Моргана:

Х0ЛХ1= --'(-^Xo'V^Xi),

X0VX!= ^(^Xo^Xj).

На основе симметрии законов можно сделать вывод: если справедлив

один закон, то справедлив и закон, полученный путем взаимной замены AND

и OR и постоянных 0 и 1. Полученный таким образом закон называют

дуальным законом.

3.3. Каноническая дизъюнктивная нормальная

форма (KDNF)

Любую логическую функцию можно представить с использованием

только логических элементов AND, OR, NOT, НО ДЛЯ ЭТОГО функцию С

большим количеством входных переменных необходимо привести к виду,

позволяющему применять эти логические элементы. Это можно сделать,

применив для решения задачи каноническую дизъюнктивную нормальную

форму (KDNF).

Рассмотрим решение функции, указанной в таблице 3.3 методом KDNF.

Таблица 3.3

Таблица истинности для примера с KDNF

х2 Х1 х0 Десятичный эквивалент у

0 0 0 0 1

0 0 1 1 0

0 1 0 2 1

0 1 1 з 1

1 0 0 4 0

1 0 1 , 5 1

1 1 0 6 i

1 1 1 7 0

Сначала рассмотрим значения х0, xh х2 для которых функция у = f(x)

принимает значение 1. В нашем случае это справедливо для строк 0,2, 3, 5, 6.

Для этих строк проведем операцию конъюнкции (логическое умножение, И):

-'Х2Л~'Х1Л-'Хо,

т2 ~ ~,х2Лх1Л~'х0,

П13 = ^X^i^Xq,

ГП 5 = X^-'XjKXq,

т6 = х2КХ1^х0.

ffloxw _ называют «минтермами». Минтермы содержат всегда все

входные переменные, поэтому их называют полной конъюнкцией. В случае

минтерма входные переменные могут быть инвертированными либо

неинвертированными, в зависимости от того, что представляет собой

переменная 1 или 0 (если х, - 1 она не инвертируется; если х( = 0 она

инвертируется и в полную конъюнкцию входит как 1).

Следовательно, при определенном варианте входных переменных

минтерм имеет значение 1.

Теперь вся функция может быть представлена на основе дизъюнкции

(логическое сложение) минтермов. Функция получает значение 1, когда, по

крайней мере, один из минтермов равен 1.

у = ^X2A^X7A^X0J V^X2AX/A^X0> V^X2AX/AX0J V(x2A^X7AX0J VfoAX/A^XtJ

Этот способ представления функции называется канонической

дизъюнктивной нормальной формой (KDNF).

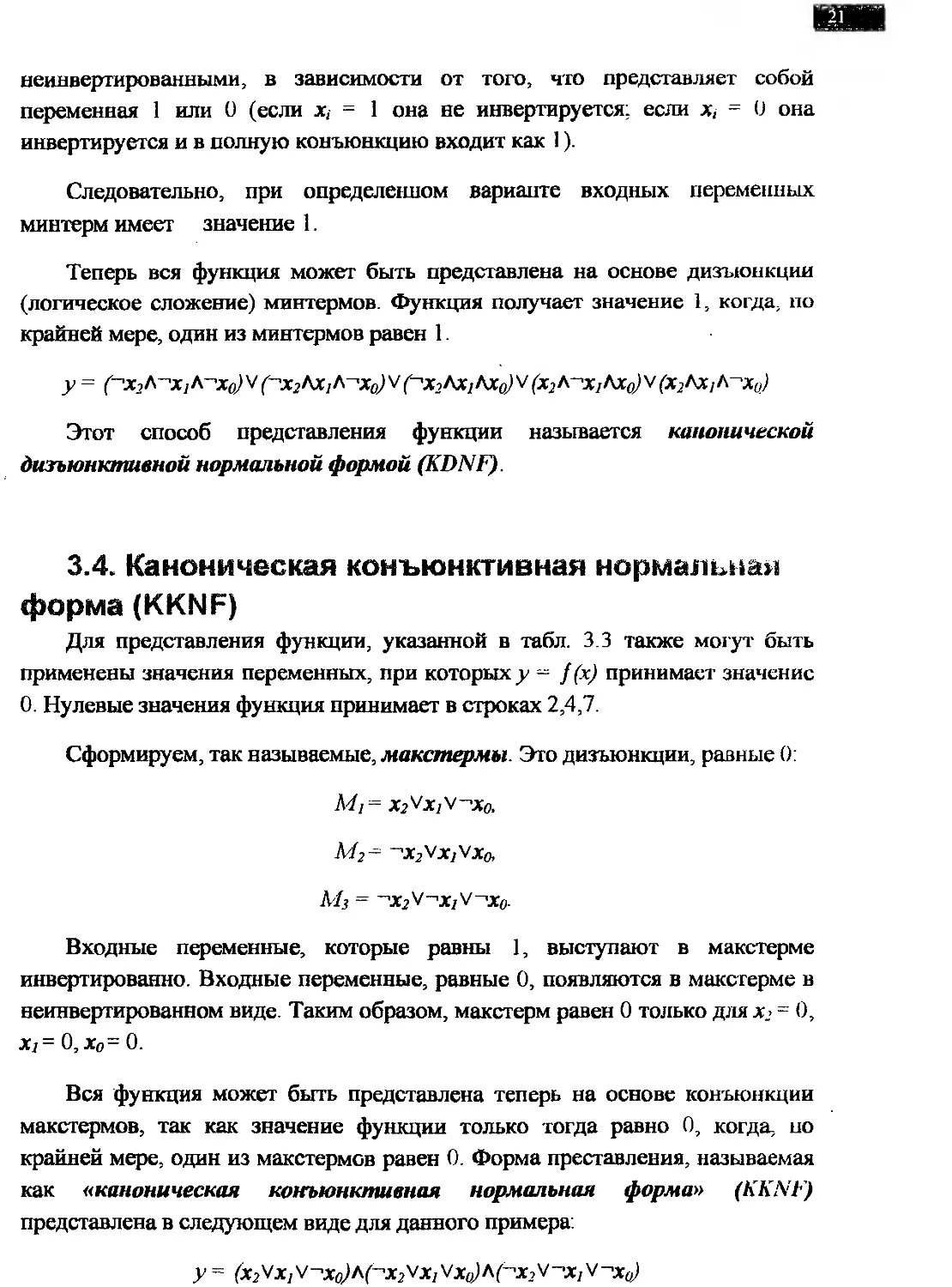

3.4. Каноническая конъюнктивная нормальная

форма (KKNF)

Для представления функции, указанной в табл. 3.3 также могут быть

применены значения переменных, при которых у = f(x) принимает значение

0. Нулевые значения функция принимает в строках 2,4,7.

Сформируем, так называемые, макстермы. Это дизъюнкции, равные 0:

-’x2Vx/Vx0,

М3 = ~'Х2У~1Х1У~,Хо-

Входные переменные, которые равны 1, выступают в макстерме

инвертированно. Входные переменные, равные 0, появляются в макстерме в

неинвертированном виде. Таким образом, макстерм равен 0 только для х2 = 0,

xi= 0,хо= 0.

Вся функция может быть представлена теперь на основе конъюнкции

макстермов, так как значение функции только тогда равно 0, когда, но

крайней мере, один из макстермов равен 0. Форма преставления, называемая

как «каноническая конъюнктивная нормальная форма» (KKNF)

представлена в следующем виде для данного примера.

У = fx2Vx/V-X0)A(-’X2Vx/Vxe)A(-’X,V--X/V--Xe)

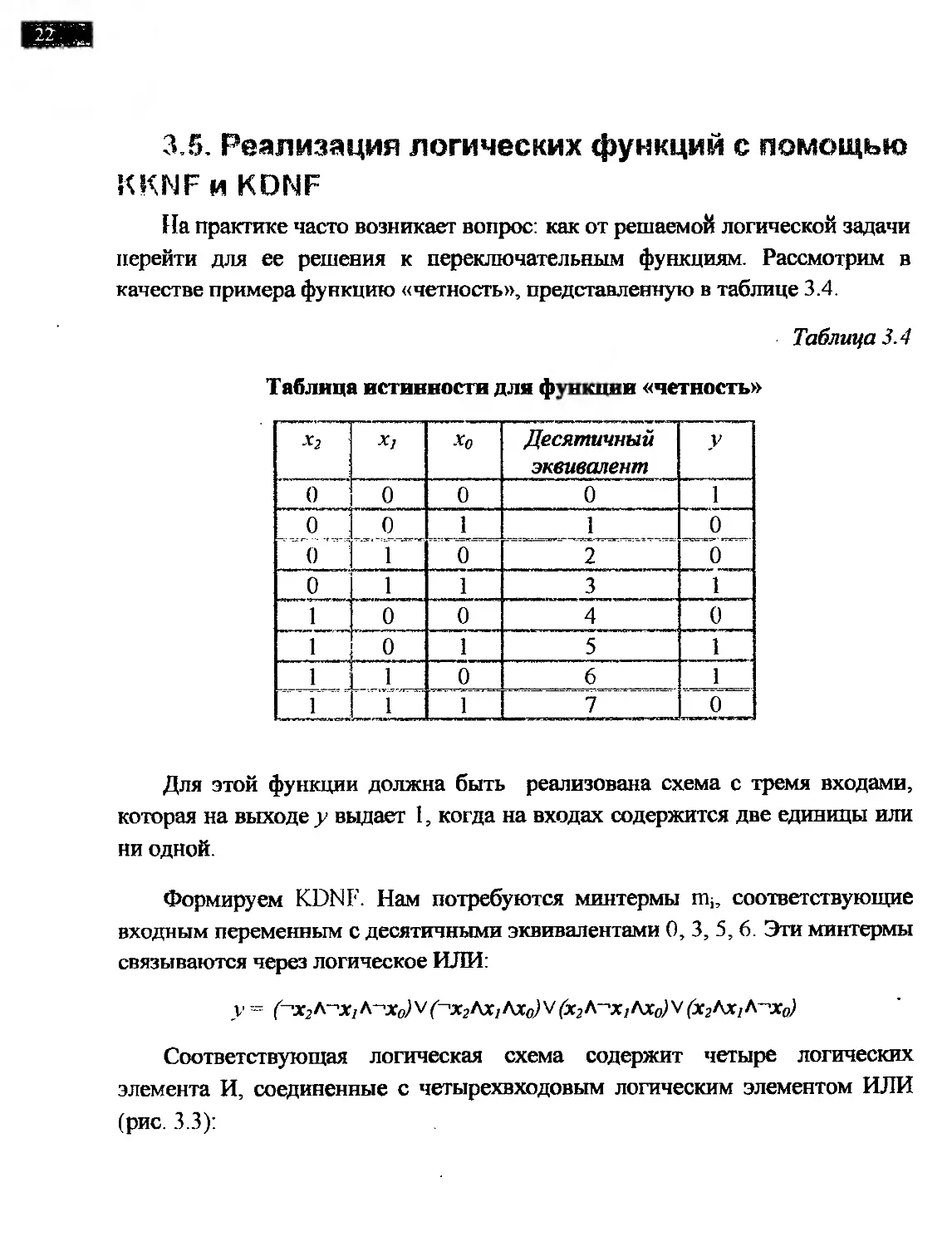

3,5. Реализация логических функций с помощью

KKNFmKDNF

На практике часто возникает вопрос: как от решаемой логической задачи

перейти для ее решения к переключательным функциям. Рассмотрим в

качестве примера функцию «четность», представленную в таблице 3.4.

Таблица 3.4

Таблица истинности для функции «четность»

х2 X] Хо Десятичный эквивалент у

0 0 0 0 1

0 0 1 1 0

'О Г б 2 ' 0

0 1 1 3 1

1 0 0 4 0

1 0 1 5 1

1 1 0 6 1

1 1'" 1 7 0

Для этой функции должна быть реализована схема с тремя входами,

которая на выходе у выдает 1, когда на входах содержится две единицы или

ни одной.

Формируем KDNF. Нам потребуются минтермы т„ соответствующие

входным переменным с десятичными эквивалентами 0, 3, 5, 6. Эти минтермы

связываются через логическое ИЛИ:

У С-1Х2Л-'Х/Л-'Хо)v(-‘Х2Лх}Лх0)V (х2Л-'Х1Лх0)v (XhAXiA-'Xq)

Соответствующая логическая схема содержит четыре логических

элемента И, соединенные с четырехвходовым логическим элементом ИЛИ

(рис. 3.3):

Рис. 3.3. Логическая схема реализации KDNF, соответствующая функции «четность»

KKNF образует макстермы с десятичными эквивалентами 1, 2, 4, 7. Их

связывают логические элементы И (рис 3 .4):

у = (Х2^Х1^-'Х^^(Х2^~'Х1 УХО)Н~'Х2^Х1УХ^^(-'Х2^Х1 V-'Xft)

Рис. 3.4. Логическая схема реализации KKNF, соответствующая функции «четность»

Для работы с KKNF и KDNF важным является обобщение законов Де-

Моргана, так называемое «правило Шеннона», которое гласит:

Для любой булевой функции

У = f(x0, хь ... хп, К, V, <-», 1, 0)

существует инвертированная функция

“V " К~Ыхг, ... ~,х„, V, А, <->, 0, !).

Это означает, что все переменные должны быть проинвертированны, а

все операции должны быть заменены на дуальные им. Например, пусть дана

функция:

у= (Х2^Х1^Х0)^(Х2^-'Х1^Х0)

Тогда имеем инвертированную функцию следующего вида:

(-'Х2К-'Х1^Х0)У (~'Х2^]К-'Х0)

3.6. Минимизация с помощью

переключательной алгебры

Формы KKNF и KDNF хорошо подходят для составления булевых

функций. Но, с точки зрения затрат по количеству логических элементов, они

не идеальны. Поэтому целесообразно проанализировать полученные

уравнения на предмет их упрощения, для чего хорошо подходит тождество:

(Х0ЬХ1)У(Xo^-Xi) = Xohfav-'Xi) = х0Л/ = Хо

Следовательно, справедливо в соответствии с правилами дуализма:

(х0^х1)Г\(х0^-'х1) = Хо

Например, необходимо минимизировать функцию:

у - v fo, Ах 1 Лх2Лхj) v (Х0^Х/ ^х2 Лх3) V (-Х0Лх! *Х2ЛХз) V f-’XoAX/ Л-^Лх3)

Для упрощения функции могут быть объединены термы 1 и 2, 2 и 3, 4 и

5. Сначала объединяем два первых терма, сохранив второй, так как он еще

понадобится для объединения с третьим термом.

V т (Х0Лх2ЛХз) V (Хо^1^2^з) V V f-’X0Ax;hX2/\X3) V (~‘Х0(<Х1^~'Х2^Хз),

у = (3c0Ax2Axj7 v(x0Ax/Ax3J V f_’x0Ax/AxJ.

Объединяем два последних терма.

у= (х0^х2Лх3)\/(Х]ЛХз)

Для реализации этой функции требуются два логических элемента И и

один ИЛИ.

Глава 4. ЛОГИЧЕСКИЕ ВЕНТИЛИ

В цифровой технике работают с переключателями, выдающими только

два различных уровня напряжения. Высокий уровень напряжения

выражается через Н {High), низкий — через L {Low), соответствующими

символами булевой алгебры 1 и 0. В электрической цифровой схеме высокое

напряжение может соответствовать логической 1, а низкое напряжение - 0

(табл. 4.1).

Таблица 4.1

Соответствие уровней напряжения логическим состояниям

Напряжение Уровень Логическое состояние j

Положительная логика Отрицательная ' логика

^5В Н 1 0

=ЮВ L 0 1 1

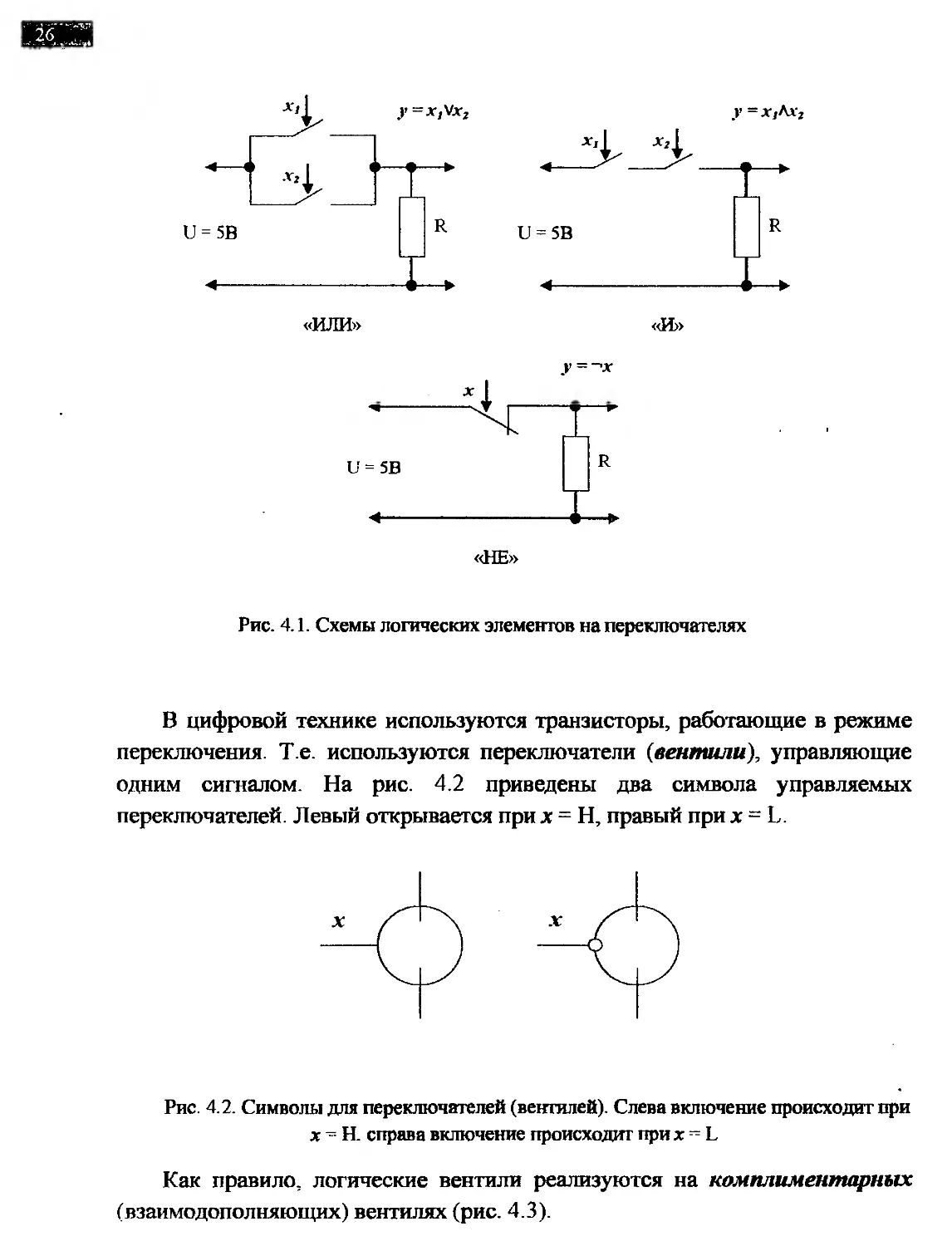

Посредством переключателей могут быть реализованы основные

элементы ИЛИ, И, НЕ (рис 4.1).

«или»

«и»

«НЕ»

Рис. 4.1. Схемы логических элементов на переключателях

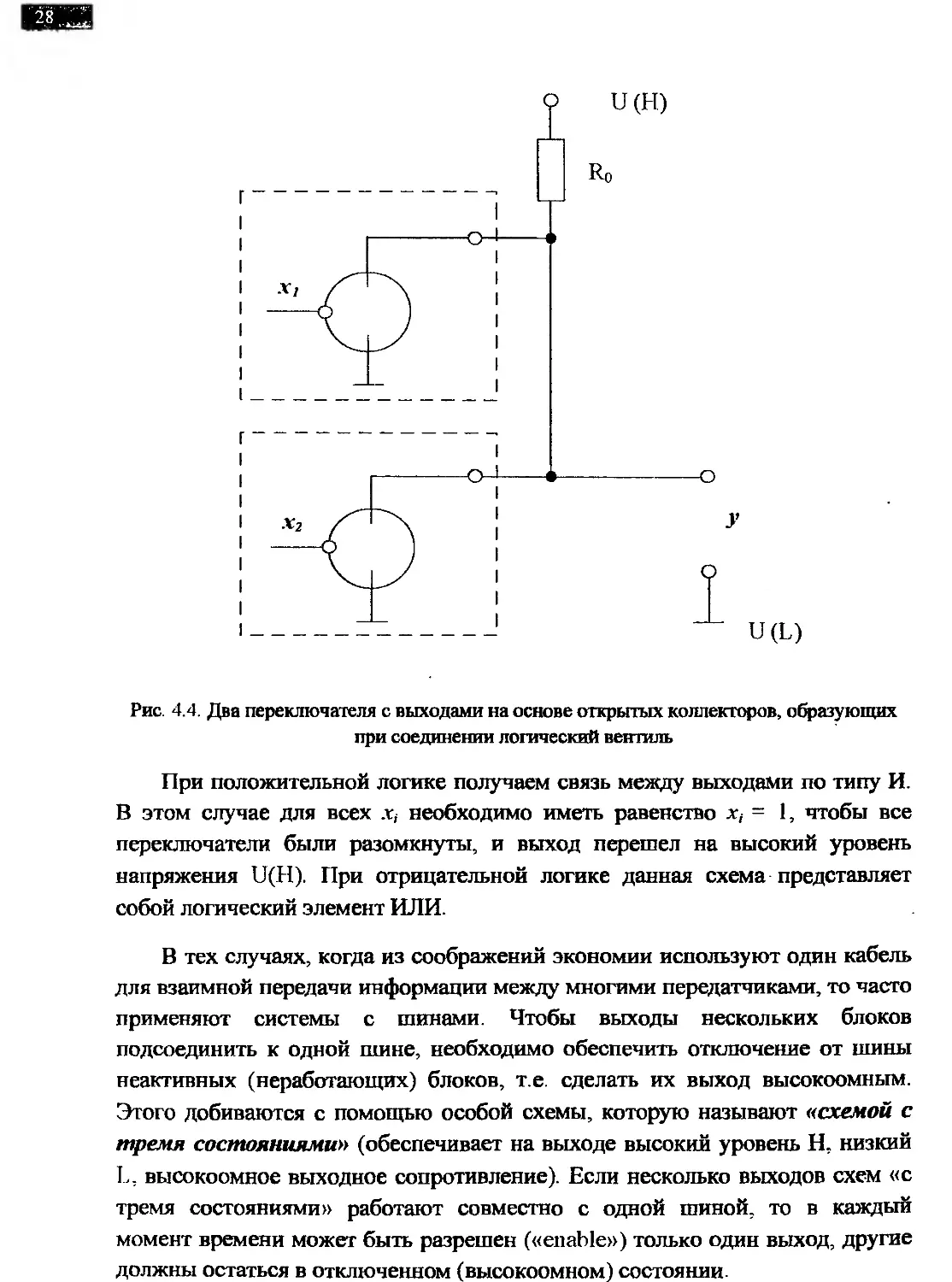

В цифровой технике используются транзисторы, работающие в режиме

переключения. Т е. используются переключатели (вентили), управляющие

одним сигналом. На рис. 4.2 приведены два символа управляемых

переключателей. Левый открывается при л = Н, правый при х = L.

Рис. 4.2. Символы для переключателей (вентилей). Слева включение происходит при

х "= Н. справа включение происходит при х = L

Как правило, логические вентили реализуются на комплиментарных

(взаимодополняющих) вентилях (рис. 4.3).

щн)

Рис. 4.3. Комплиментарный инвертор

Такое включение вентилей позволяет значительно снизить токи в схеме

и обеспечить малую мощность рассеяния, так как когда один из

переключателей открыт, другой закрыт и наоборот.

Если х - Н, то нижний переключатель открыт, и выход Н подсоединен к

О, т.е. лежит на L. Если х - L, то выход у замкнут с напряжением высокого

уровня U(H), т.е. лежит на Н.

Одним из вариантов схем являются вентили с открытым коллектором.

В этом варианте схемы вентиль состоит только из одного переключателя,

выделенного пунктирным прямоугольником (рис. 4.4). Один вывод

переключателя через резистор Ro присоединяется к положительному

напряжению питания U(H). К общему резистору Ro может быть подключено

большое число выходов переключателей.

Рис. 4.4. Два переключателя с выходами на основе открытых коллекторов, образующих

при соединении логический вентиль

При положительной логике получаем связь между выходами по типу И.

В этом случае для всех х, необходимо иметь равенство х, = 1, чтобы все

переключатели были разомкнуты, и выход перешел на высокий уровень

напряжения U(H). При отрицательной логике данная схема представляет

собой логический элемент ИЛИ.

В тех случаях, когда из соображений экономии используют один кабель

для взаимной передачи информации между многими передатчиками, то часто

применяют системы с шинами. Чтобы выходы нескольких блоков

подсоединить к одной шине, необходимо обеспечить отключение от шины

неактивных (неработающих) блоков, т.е. сделать их выход высокоомным.

Этого добиваются с помощью особой схемы, которую называют «схемой с

тремя состояниями» (обеспечивает на выходе высокий уровень Н, низкий

L, высокоомное выходное сопротивление). Если несколько выходов схем «с

тремя состояниями» работают совместно с одной шиной, то в каждый

момент времени может быть разрешен («enable») только один выход, другие

должны остаться в отключенном (высокоомном) состоянии.

На рис. 4.5 показана схема, в которой оба выходных переключателя

мотут быть одновременно переведены в высокоомное состояние с помощью

enable-сигнала («разрешающего» сигнала) Е.

щн)

Рис. 4.5. Схема с тремя состояниями

В цифровых логических схемах в качестве переключателей (вентилей)

в основном используются такие полупроводниковые приборы как

транзисторы.

Глава 5. ФИЗИЧЕСКИЕ ОСНОВЫ

ПОЛУПРОВОДНИКОВОЙ ЭЛЕКТРОНИКИ

Электронными называют приборы, в которых ток создается движением

электронов в вакууме, газе или полупроводнике. Для решения таких задач,

как преобразование вида энергии, усиление сигналов, генерирование

мощных излучений, управление сигналами, обработка цифровой

информации, ее отображения и т.д., используются все виды электронных

приборов, но явное преимущество сохраняется за полупроводниковыми

приборами и интегральными микросхемами

5.1. Электрофизические свойства

полупроводников

Все вещества образованы атомами, состоящими из положительно

заряженных ядер и вращающихся вокруг них отрицательно заряженных

электронов. Электроны вращаются вокруг ядра по орбитам,

сгруппированным в слои. Каждому слою соответствует строго определенная

энергия электрона W (так называемый разрешенный энергетический

уровень). Количество электронов в слоях строго определено: в первом,

ближайшем к ядру слое может находиться не более двух электронов, во

втором - не более восьми и т.д. Электроны целиком заполненных слоев

устойчивы к внешним воздействиям. «Неуместившиеся» во внутренних

слоях электроны определяют валентность элемента при химических

реакциях. Чем дальше от ядра расположена орбита электрона, тем большей

энергией он обладает. Под воздействием энергии теплоты, света, радиации

или других внешних факторов электрон из валентной зоны может перейти на

новую, более удаленную от ядра орбиту. Такой электрон называется

возбужденным и при дальнейшем увеличении энергии, называемой работой

выхода, электрон может покинуть поверхность вещества.

В твердом теле (кристалле) соседние атомы расположены настолько

близко друг к другу, что между ними происходит взаимодействие. При этом

на электроны влияет не только ядро собственного атома, они так же

подвергаются влиянию ядер соседних атомов, вследствие чего характер их

движения изменяется. Взаимодействие многих атомов вызывает смещение и

расщепление энергетических уровней - по числу соседних атомов в

кристаллической решетке. Эти уровни создают энергетические зоны.

Совокупность энергетических уровней, соответствующих внешнему слою

электронов образует валентную зону. Разрешенные уровни энергии, которые

остаются незанятыми, составляют зону проводимости, так как ее уровни

могут занимать возбужденные электроны, обеспечивающие

электропроводность вещества. Между валентной зоной и зоной

проводимости располагается запрещенная зона. Запрещенные зоны

соответствуют таким значениям энергии, которыми электрон обладать не

может.

Зонная структура лежит в основе разделения веществ на проводники,

полупроводники и диэлектрики. На рис. 5.1 показано расположение

энергетических зон для этих групп веществ.

Рис. 5.1. Электрические зоны проводника (а), диэлектрика (б), полупроводника (в):

1 - валентная зона, 2 - зона проводимости; 3 - запрещенная зона

У проводников (металлов) зона проводимости и зона валентных

электронов перекрывают друг друга, т е. запрещенная зона отсутствует, и

валентные электроны легко переходят в зону проводимости, обеспечивая

хорошую электропроводность. У диэлектриков ширина запрещенной зоны

велика (более 6 эВ (электрон-вольт)) и для перехода валентных электронов в

зону проводимости надо сообщить им значительную энергию (такой процесс

происходит при пробое изоляции). У полупроводников запрещенная зона

относительно мала и колеблется от 0,1 до 3,0 эВ.

К полупроводникам относится большое количество веществ и

элементов, которые по своим электрическим свойствам занимают

промежуточное положение между проводниками и диэлектриками. Наиболее

широкое применение в полупроводниковой технике получили кремний,

германий, арсенид галлия, карбид кремния и др. Для полупроводников

характерно кристаллическое строение, т е. закономерное и упорядоченное

расположение их атомов в пространстве. В кристаллах связанные между

собой атомы располагаются строго определенным образом и на одинаковых

расстояниях друг от друга, в результате чего образуется своеобразная

решетка из атомов, которую назвали кристаллической решеткой твердого

тела. В кристаллической решетке четырехвалентного полупроводника

(например, кремния) каждый атом связан с четырьмя соседними атомами с

помощью двух валентных электронов - по одному от каждого атома. Такая

связь называется ковалентной (рис. 5.2).

Рис. 5.2. Ковалентная связь атомов кремния

5.2. Собственная проводимость

полупроводников

Под действием внешних факторов некоторые валентные электроны

атомов кристаллической решетки приобретают энергию, достаточную для

освобождения от ковалентных связей. При освобождении электрона из

ковалентной связи, в последней возникает как бы свободное место (дырка),

обладающее положительным зарядом, равным по абсолютной величине

заряду электрона. Дырка обладает положительным зарядом, поэтому она

может присоединить к себе электрон соседней заполненной ковалентной

связи. В результате этого восстанавливается одна связь (этот процесс

называют рекомбинацией) и разрушается соседняя, т.е. возникает новая

дырка. Такой процесс непрерывно повторяется и дырка, переходя от одной

связи к другой, будет перемещаться по кристаллу, что равносильно

перемещению положительного заряда. При отсутствии внешнего

электрического поля электроны и дырки перемещаются в кристалле

хаотически, вследствие теплового движения. Если же на кристалл действует

электрическое поле, движение дырок и электронов становится

упорядоченным и в кристалле возникает электрический ток. Чтобы понять,

как перемещаются дырки, рассмотрим рис. 5.3, на котором изображено

несколько одних и тех же атомов, расположенных вдоль полупроводника, в

различные моменты времени.

33

>----(направление вектора электрического ноля)

Рис. 5.3. Принцип дырочной проводимости

Пусть в начальный момент времени в крайнем атоме (рис. 5.3, а)

появилась дырка вследствие «ухода» из этого атома электрона. В этом случае

атом становится заряженным положительно и может притянуть к себе

электрон соседнего атома. При наличии электрического поля электрон атома

2, двигаясь против силовых линий поля, заполнит дырку в первом атоме, но

зато образуется новая дырка в атоме 2 (рис. 5.3, б). Последовательно

переходя от одного атома к другому, дырка через некоторое время образуется

в крайнем правом атоме 4 (рис. 5.3, г).

Таким образом, проводимость полупроводника обусловлена

перемещением, как свободных электронов, так и дырок. Соответственно

различают два вида проводимости полупроводников - электронную, или

проводимость п-типа (от слова negative - отрицательный); и дырочную,

или проводимость p-типа (от слова positive - положительный).

5.3. Примесная проводимость полупроводников

Для создания полупроводниковых элементов широко применяют

примесные полупроводники, которые получают путем введения в кристалл

четырехвалентного кремния или германия пятивалентных веществ (мышьяк,

сурьма, фосфор) или трехвалентных веществ (бор, алюминий, индий,

галлий).

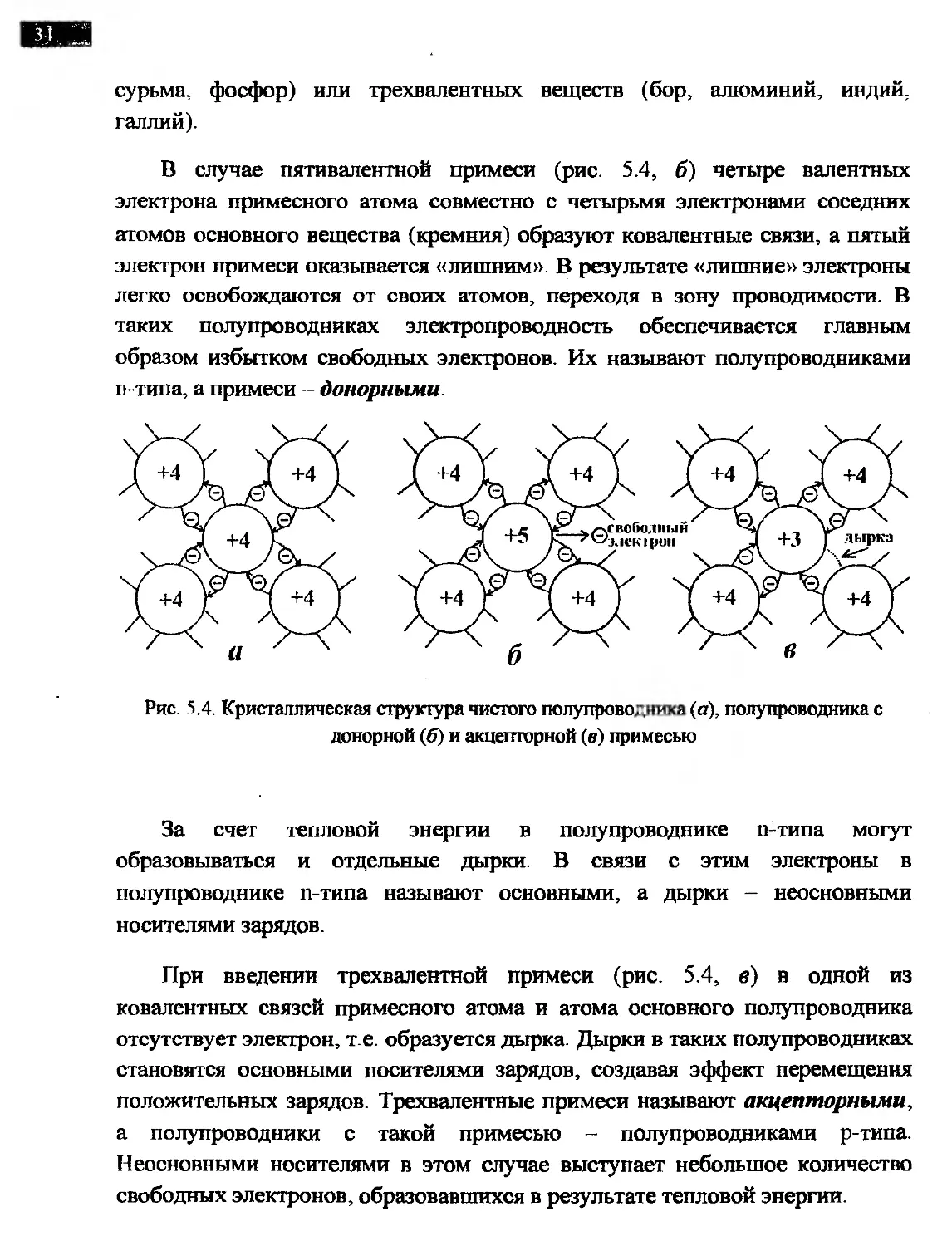

В случае пятивалентной примеси (рис. 5.4, б) четыре валентных

электрона примесного атома совместно с четырьмя электронами соседних

атомов основного вещества (кремния) образуют ковалентные связи, а пятый

электрон примеси оказывается «липшим». В результате «лишние» электроны

легко освобождаются от своих атомов, переходя в зону проводимости. В

таких полупроводниках электропроводность обеспечивается главным

образом избытком свободных электронов. Их называют полупроводниками

n-типа, а примеси - донорными.

Рис. 5.4. Кристаллическая структура чистого полупроводника (а), полупроводника с

донорной (б) и акцепторной (в) примесью

За счет тепловой энергии в полупроводнике n-типа могут

образовываться и отдельные дырки. В связи с этим электроны в

полупроводнике n-типа называют основными, а дырки - неосновными

носителями зарядов.

При введении трехвалентной примеси (рис. 5.4, в) в одной из

ковалентных связей примесного атома и атома основного полупроводника

отсутствует электрон, т.е. образуется дырка. Дырки в таких полупроводниках

становятся основными носителями зарядов, создавая эффект перемещения

положительных зарядов. Трехвалентные примеси называют акцепторными,

а полупроводники с такой примесью - полупроводниками р-типа.

Неосновными носителями в этом случае выступает небольшое количество

свободных электронов, образовавшихся в результате тепловой энергии.

5.4. Р-п-переход и его свойства

Электрический переход между двумя областями полупроводника, одна

из которых имеет электропроводность n-типа, а другая p-типа, называют

электронно-дырочным, или р-п-переходом (рис 5.5).

р-п переход

11 полупроводник | > | 1 | полупроводник

п-тта 1 1 !_ 1 р-типа 1 1

Рис. 5.5. Электронно-дырочный переход

Рассмотрим явление, возникающее при электрическом контакте между

полупроводниками п- и p-типа с одинаковой концентрацией донорных и

акцепторных примесей в них.

Вследствие того, что концентрация электронов в n-области выше, чем в

p-области, а концентрация дырок в p-области выше, чем в n-области, на

границе этих областей существует градиент концентраций носителей,

вызывающий диффузионный ток дырок из p-области в п-область. За счет

диффузии дырки из p-области и электроны из n-области стремятся

равномерно распределиться по всему объему. Если бы электроны и дырки

были нейтральными, то диффузия в конечном итоге привела бы к полному

выравниванию их концентраций по всему объему кристалла. Однако этого не

происходит. Из рис. 5.6, а видно, что уход электронов из приконтактной п-

области приводит к тому, что здесь возникает нескомпенсированный

положительный заряд ионов донорной примеси. Точно также в р-области

вследствие ухода дырок возникает нескомпенсированный отрицательный

заряд ионов акцепторной примеси. Таким образом, на границе областей п- и

p-типа образуется два слоя противоположных по знаку зарядов. Область

образовавшихся пространственных зарядов, представляет собой р-п-переход.

Его ширина не превышает десятых долей микрометра.

Пространственные заряды в переходе образуют электрическое поле,

направленное от положительно заряженных ионов доноров к отрицательно

заряженным ионам акцепторов (рис. 5.6, б). Это поле является тормозящим

для основных носителей заряда Теперь любой электрон, проходящий из п-

области в p-область, попадает в электрическое поле, стремящееся возвратить

его обратно в электронную область. Точно так же и дырки, попадая из р-

области в электрическое поле р-п-перехода, будут возвращены этим полем

обратно в р-область.

Рис. 5.6. Образование р-п-перехода: а - распределение электрических зарядов; б -

направление электрического поля; в - распределение напряженности Е; г - потенциальная

диаграмма

На рис 5.6, в показано распределение напряженности электрического

поля Е в р-п-переходе. Наибольшая величина напряженности Е наблюдается

в сечении х0, так как через это сечение проходят все силовые линии,

начинающиеся на положительных зарядах, расположенных левее Хо- По мере

удаления от Хо влево, количество нескомпенсированных положительных

зарядов будет уменьшаться, следовательно, и напряженность поля будет

уменьшаться. Аналогичная картина будет наблюдаться и при удалении

вправо от сечения х0.

Потенциальная диаграмма р-п-перехода показана на рис 5.6, г. За

нулевой потенциал условно принят потенциал слоя Хо. При перемещении от

х0 к хп потенциал повышается, а при перемещении от х0 к хр - снижается.

Перепад потенциала в переходе равен контактной разности потенциалов Uk.

Этот перепад называют потенциальным барьером, так как он препятствует

перемещению основных носителей заряда.

5.5. Свойства р-п-перехода при наличии

внешнего напряжения

Свойства р-п-структуры изменяются, если к ней приложить внешнее

напряжение. Вначале рассмотрим случай, когда внешнее напряжение

противоположно по знаку контактной разности потенциалов (рис. 5 .7).

Рис. 5.7. Прямое включение р-п-перехода

При этом включении электрическое поле, создаваемое внешним

напряжением, направлено навстречу полю р-п-перехода, ослабляя его Это

приводит к снижению высоты потенциального барьера, через него начинают

проникать дырки из p-области и электроны из n-области. Через р-п-переход

начинает течь ток. Такое включение называют прямым.

Рассмотрим свойства р-п-перехода, к которому подведено обратное

внешнее напряжение (рис. 5.8).

Рис. 5.8. Обратное включение р-п-перехода

При таком включении электрическое поле, создаваемое внешним

источником, совпадает с полем р-п-перехода. Потенциальный барьер между

р- и n-областями возрастает и количество основных носителей, способных

преодолеть действие результирующего поля, уменьшается. Электрическое

сопротивление р-п-перехода при этом возрастает. Такая полярность внешнего

напряжения называется обратной, запирающей. При подаче такого

напряжения р-п-переход закрыт. Под действием электрического поля,

создаваемого внешним источником, основные носители будут оттягиваться

от приконтактных слоев вглубь полупроводника. В результате ширина р-п-

перехода увеличивается.

При таком (обратном) включении р-п-переход уподобляется

конденсатору, пластинами которого являются р- и n-области, разделенные

диэлектриком, роль которого выполняет область почти свободная от

носителей заряда. Эту емкость р-п-перехода называют барьерной.

5,6. Полупроводниковые диоды

Полупроводниковым диодом называется прибор с двумя выводами и

одним р-п-переходом.

По функциональному назначению, принципу образования р-п-перехода

и использованию тех или иных его свойств диоды делятся на

выпрямительные, импульсные, варикапы, стабилитроны, фотодиоды,

светодиоды и т.д. Один из вариантов конструкции и условное обозначение

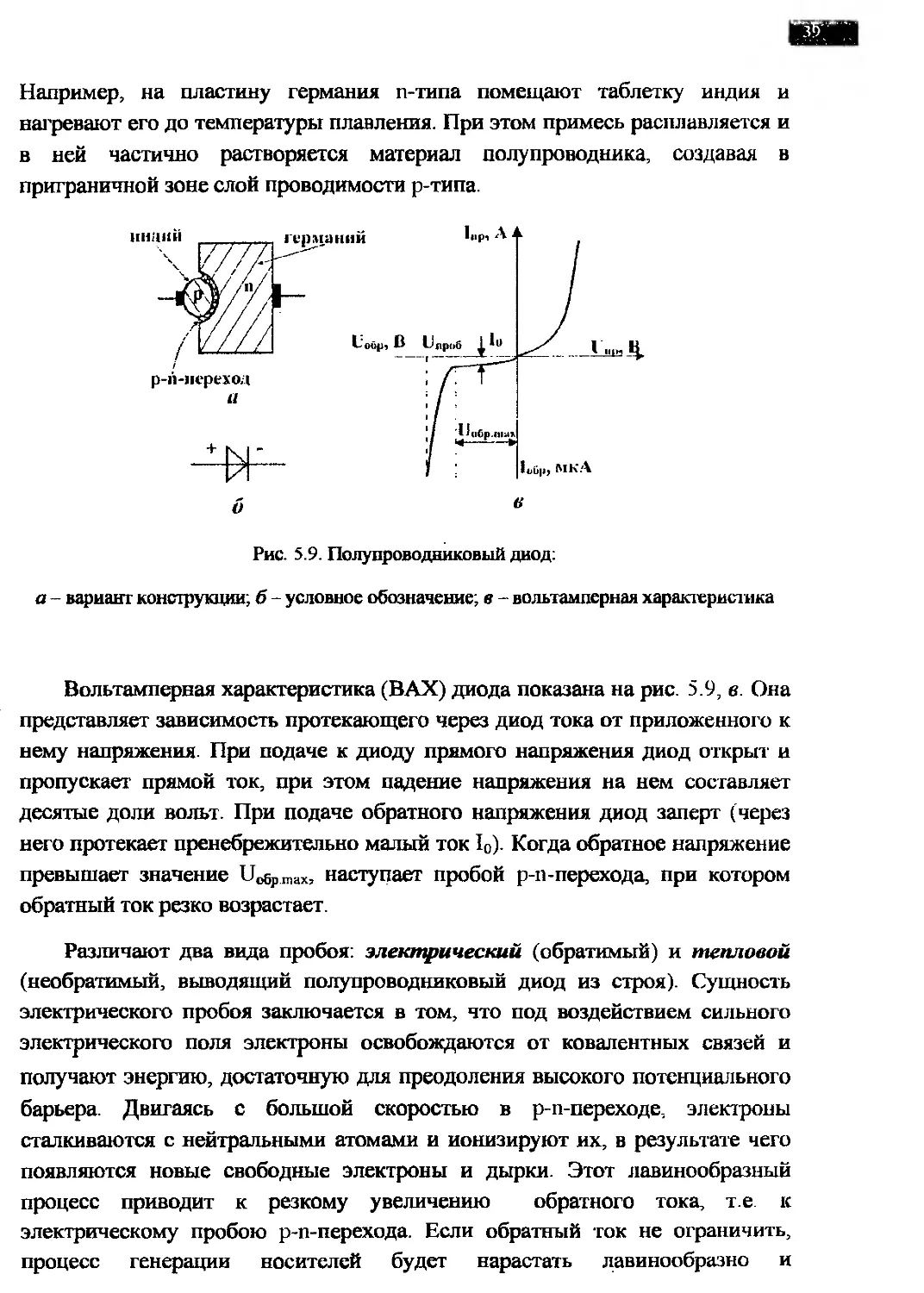

диода приведены на рис. 5.9, а, б. Данный диод изготовлен методом

сплавления. Технологический процесс этого метода заключается в том, что в

пластину полупроводника одного типа проводимости вплавляют примесь,

необходимую для образования полупроводника другого типа проводимости.

Например, на пластину германия n-типа помещают таблетку индия и

нагревают его до температуры плавления. При этом примесь расплавляется и

в ней частично растворяется материал полупроводника, создавая в

приграничной зоне слой проводимости р-типа.

Рис. 5.9. Полупроводниковый диод:

а - вариант конструкции; б - условное обозначение; в - вольтамперная характеристика

Вольтамперная характеристика (ВАХ) диода показана на рис. 5.9, в. Она

представляет зависимость протекающего через диод тока от приложенного к

нему напряжения. При подаче к диоду прямого напряжения диод открыт и

пропускает прямой ток, при этом падение напряжения на нем составляет

десятые доли вольт. При подаче обратного напряжения диод заперт (через

него протекает пренебрежительно малый ток 10). Когда обратное напряжение

превышает значение Uogpmax, наступает пробой р-п-перехода, при котором

обратный ток резко возрастает.

Различают два вида пробоя: электрический (обратимый) и тепловой

(необратимый, выводящий полупроводниковый диод из строя). Сущность

электрического пробоя заключается в том, что под воздействием сильного

электрического поля электроны освобождаются от ковалентных связей и

получают энергию, достаточную для преодоления высокого потенциального

барьера. Двигаясь с большой скоростью в р-п-переходе, электроны

сталкиваются с нейтральными атомами и ионизируют их, в результате чего

появляются новые свободные электроны и дырки. Этот лавинообразный

процесс приводит к резкому увеличению обратного тока, т е к

электрическому пробою р-п-перехода. Если обратный ток не ограничить,

процесс генерации носителей будет нарастать лавинообразно и

электрический пробой перейдет в тепловой, при котором резко

увеличивается температура р-п-перехода и диод выходит из строя (сгорает)

Выпрямительные диоды

Эти диоды предназначены для преобразования (выпрямления)

переменного тока в постоянный. Выпрямительные диоды характеризуются

малым сопротивлением в прямом направлении и позволяют пропускать

большие токи (до десятков и сотен ампер) при допустимых обратных

напряжениях 1 000 и более вольт.

Стабилитроны

Явление электрического пробоя, опасное для обычных диодов, находит

полезное применение в кремниевых стабилитронах Нормальным режимом

работы стабилитронов является работа при обратном напряжении,

соответствующем обратимому электрическому пробою р-п-перехода. Важной

характеристикой стабилитрона является его вольтамперная характеристика

(рис 5.10, в). В прямом направлении ВАХ стабилитрона практически не

отличается от прямой ветви кремниевого диода. Обратная ветвь ее имеет вид

прямой вертикальной линии, проходящей почти параллельно оси токов.

Поэтому при изменении в широких пределах тока падение напряжения на

стабилитроне практически не изменяется, что позволяет использовать его в

качестве стабилизатора напряжения. Одним из основных параметров

кремниевых стабилитронов является напряжение стабилизации Ue„ -

падение напряжения на стабилитроне в области стабилизации при

номинальном значении тока.

-и

Рис. 5.10. Стабилитрон:

а - условное обозначение; б - схема включения; в - вольтамперная характеристика

Во избежание теплового пробоя последовательно со стабилитроном

включают резистор Ro (рис. 5.10, б), ограничивающий ток 1ст.

Варикапы

Варикапами называют полупроводниковые диоды, у которых

используется барьерная емкость запертого р-п-перехода, зависящая от

величины приложенного к диоду обратного напряжения.

Внешнее обратное напряжение, втягивая электроны вглубь n-области, а

дырки - вглубь p-области, расширяет р-п-переход и изменяет* барьерную

емкость. Для использования свойств варикапа к нему необходимо подвести

обратное напряжение (рис. 5.11, б).

Рис. 5.11. Варикап;

а

а условное обозначение; б - схема включения в качестве конденсатора переменной

емкости

Основной характеристикой варикапа является зависимость его емкости

от значения обратного напряжения - вольтфарадная характеристика (рис.

5 12). Варикапы в основном применяются для электрической перестройки

колебательных контуров в радиоаппаратуре.

Рис. 5.12. Вольтфарадная характеристика варикапа

Светодиоды

Светодиодом называют излучающий полупроводниковый прибор с

одним электронно-дырочным переходом, предназначенный для

непосредственного преобразования электрической энергии в энергию

некогерентного светового излучения при подаче в р-п-переход прямого

напряжения. При этом происходит интенсивная инжекция (процесс

введения носителей заряда через р-п-переход при понижении высоты

потенциального барьера в область полупроводника, где эти носители заряда

являются неосновными), т.е. переход электронов из n-области в р-’область,

дырок из p-области в п-область.

Инжектированные неосновные носители рекомбинируют с основными

носителями (дырка присоединяет к себе электрон и восстанавливается одна

связь) При встрече электрона и дырки их заряды компенсируются, и данные

носители заряда исчезают. Поэтому при рекомбинации выделяется энергия.

У многих полупроводников рекомбинация носит безызлучательный характер

- энергия, выделяющаяся при рекомбинации, отдается кристаллической

решетке, те. превращается в тепло. Однако у полупроводников,

выполненных на основе карбида кремния SiC (желтое свечение), фосфида

галлия GaP (зеленое свечение) и некоторых других материалов,

рекомбинация является излучательной - энергия рекомбинации выделяется в

виде квантов излучения - фотонов. Структура и условное обозначение

светодиода показаны на рис. 5.13

Рис. 5.13. Светодиод: а - структурное представление; б - условное обозначение

Фотодиоды

Фотодиоды представляют собой полупроводниковые приборы,

предназначенные для преобразования светового излучения в электрический

сигнал. Фотодиод выполнен так, что его р-п-переход одной стороной

обращен к окну, через которое поступает свет.

В рабочем режиме фотодиода на его р-п-переход подается обратное

напряжение. Если фотодиод не освещен, в цепи проходит обратный ток

небольшой величины 1-10 мкА (рис. 5.14). При освещении фотодиода

появляется дополнительное число электронов и дырок, вследствие чего

увеличивается ток в цепи.

Рис. 5.14. Фотодиод: а - схема включения; б - условное обозначение

Оптроны

Светодиоды и фотодиоды часто используют в паре. При этом они

помещаются в один корпус таким образом, чтобы светочувствительная

площадка фотодиода располагалась напротив излучающей площадки

светодиода. Полупроводниковые приборы, использующие такие пары

«светодиод-фотодиод» называются оптронами (рис. 5.15).

Рис. 5.15. Оптрон:

1 - светодиод; 2 - фотодиод

Передача информации с помощью оптронов позволяет развязать

электрические цепи питания источника и приемника информации, так как

носителями информации является электрически нейтральное оптическое

излучение. Передача сигнала в оптроне возможна, даже если цепи светодиода

и фотодиода находятся под разными (до 500 В) напряжениями.

5.7. Биполярные транзисторы

Биполярный транзистор - это полупроводниковый прибор, состоящий

из трех чередующихся областей полупроводника с различным типом

проводимости (р-п-р или п-р-п) с выводом от каждой области, пригодный для

усиления мощности.

Схематическое устройство биполярных транзисторов с двумя р-п-

переходами показано на рис. 5.16.

Рис. 5.16. Схематическое изображение транзисторов:

а - транзистор п-р-п типа; б - транзистор р-п-р типа;

в - условное обозначение транзистора п-р-п типа; г - условное обозначение транзистора р-п-р

типа

Две крайние области всегда обладают проводимостью одинакового типа,

противоположной проводимости средней области. На рис. 5.16, а изображен

биполярный транзистор, у которого крайние области обладают электронной

проводимостью, а средняя - дырочной. Такие приборы называются

транзисторами п-р-п типа. У транзистора, показанного на рис. 5.16, б,

крайние области обладают дырочной проводимостью, а средняя -

электронной. Такие приборы называются транзисторами р-п-р типа.

Физические процессы, протекающие в транзисторах обоих типов,

аналогичны.

Средняя область транзистора называется базой Б, одна крайняя область

называется эмиттером Э (от англ, emit - испускать), другая - коллектором

К (от англ, collect - собирать). Из рис. 5.16 видно, что в транзисторе имеется

два р-п-перехода: эмиттерный (между эмиттером и базой) и коллекторный

(между базой и коллектором). Расстояние между ними очень мало - от 0,1 до

нескольких микрометров. Следовательно, область базы представляет очень

тонкий слой, у которого концентрация атомов примеси во много раз меньше,

чем в эмиттере. Это является важнейшим условием работы транзистора.

Для изучения принципа работы биполярного транзистора воспользуемся

схемой, приведенной на рис 5.17. Из рисунка видно, что транзистор

представляет собой по существу два полупроводниковых диода, имеющих

одну общую область - базу, причем к эмиттерному р-п-переходу приложено

напряжение Е] в прямом направлении, а к коллекторному переходу - Е2 в

обратном направлении. Обычно |Е2|»|Е]|.

Рис. 5.17. Схема изучения принципа работы биполярного транзистора

При замыкании выключателей SA] и SA2 через эмиттерный переход

осуществляется инжекция дырок из эмиттера в область базы. Одновременно

электроны базы будут проходить в область эмиттера и через эмиттерный

переход потечет значительный ток. Если SAi разомкнуть, а выключатели SA2

и SAj замкнуть, то в коллекторной цепи пойдет крайне незначительный ток,

обусловленный направленным движением неосновных носителей заряда -

дырок базы и электронов коллектора, для которых поле р-п-перехода

является ускоряющим.

Рассмотрим процессы в транзисторе при замыкании всех трех ключей.

Потенциальный барьер эмиттерного перехода понижается, а коллекторного

увеличивается. В транзисторах, как было сказано выше, концентрация

носителей заряда в базе значительно меньше, чем в эмиттере. Это приводит к

тому, что число дырок, инжектированных из эмиттера в базу, во много раз

превышает число электронов, движущихся в противоположном направлении.

Следовательно, почти весь ток через эмиттерный р-п-переход обусловлен

дырками, которые, попав в базу, начинают рекомбинировать с электронами.

Но рекомбинация - процесс не мгновенный, да и количество дырок в базе

значительно превышает количество электронов. Поэтому почти все дырки

успевают пройти через очень тонкий слой базы и достигнуть коллекторного

р-п-перехода прежде, чем произойдет рекомбинация. Подойдя к коллектору,

дырки начинают испытывать действие электрического поля коллекторного

перехода. Это поле для дырок является ускоряющим, и они быстро

втягиваются из базы в коллектор, участвуя в создании тока коллектора.

Учитывая малую степень рекомбинации дырок с электронами в области

базы, можно считать:

1К~1Э

То незначительное количество дырок, которые все же рекомбинируют в

базе, участвует в создании тока базы.

Необходимо обратить внимание на то, что, хотя электроны и дырки

движутся в противоположных направлениях, токи в цепях транзистора

проходят в одном направлении, совпадающем с направлением движения

носителей заряда положительной полярности - дырок. Это можно понять,

если учесть, что противоположное направление движения электронов и

дырок компенсируется их противоположным знаком. Следовательно, ток в

цепях транзистора определяется суммой электронной и дырочной

составляющих.

Одним из основных параметров транзистора является коэффициент

передачи тока эмиттера при неизменном напряжении на коллекторном

переходе:

Д1К

а = — , откуда 1К = а • 1Э,

Д1Э

где а = 0,95-0,99 - коэффициент передачи тока эмиттера.

Как видно, транзистор представляет собой управляемый прибор, так как

величина его коллекторного тока зависит от величины тока эмиттера.

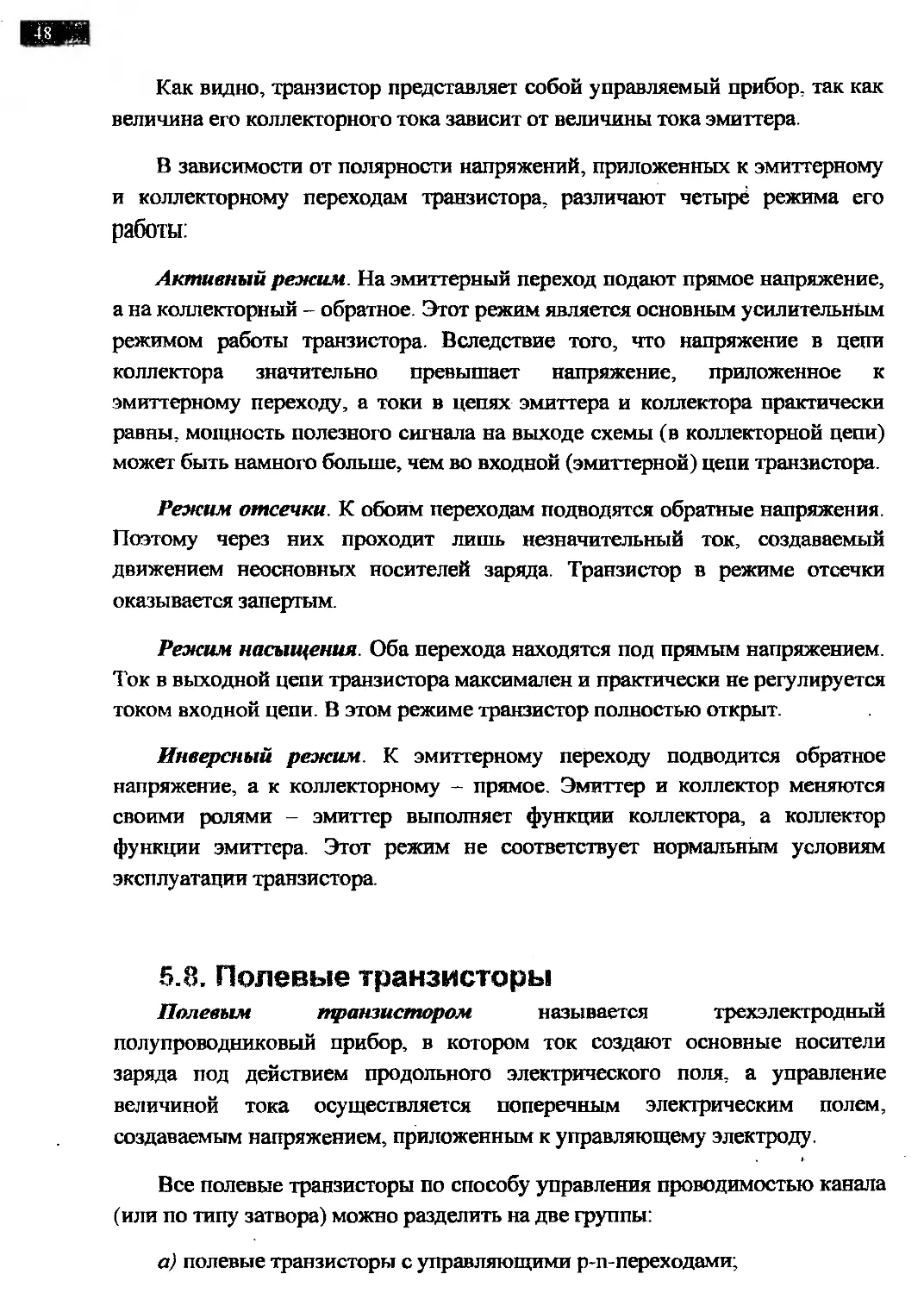

В зависимости от полярности напряжений, приложенных к эмиттерному

и коллекторному переходам транзистора, различают четыре режима его

работы:

Активный режим. На эмиттерный переход подают прямое напряжение,

а на коллекторный - обратное. Этот режим является основным усилительным

режимом работы транзистора. Вследствие того, что напряжение в цепи

коллектора значительно превышает напряжение, приложенное к

эмиттерному переходу, а токи в цепях эмиттера и коллектора практически

равны, мощность полезного сигнала на выходе схемы (в коллекторной цепи)

может быть намного больше, чем во входной (эмиттерной) цепи транзистора.

Резким отсечки. К обоим переходам подводятся обратные напряжения.

Поэтому через них проходит лишь незначительный ток, создаваемый

движением неосновных носителей заряда. Транзистор в режиме отсечки

оказывается запертым.

Режим насыщения. Оба перехода находятся под прямым напряжением.

Ток в выходной цепи транзистора максимален и практически не регулируется

током входной цепи. В этом режиме транзистор полностью открыт.

Инверсный режим. К эмиттерному переходу подводится обратное

напряжение, а к коллекторному - прямое. Эмиттер и коллектор меняются

своими ролями - эмиттер выполняет функции коллектора, а коллектор

функции эмиттера. Этот режим не соответствует нормальным условиям

эксплуатации транзистора.

5.8. Полевые транзисторы

Полевым транзистором называется трехэлектродный

полупроводниковый прибор, в котором ток создают основные носители

заряда под действием продольного электрического поля, а управление

величиной тока осуществляется поперечным электрическим полем,

создаваемым напряжением, приложенным к управляющему электроду.

. »

Все полевые транзисторы по способу управления проводимостью канала

(или по типу затвора) можно разделить на две группы:

а) полевые транзисторы с управляющими р-п-переходами;

нш

6) полевые транзисторы с изолированным затвором (МДП- или МОП-

транзисторы), которые, в свою очередь, делятся на МДП-транзисторы с

индуцированным каналом и МДП-транзисторы со встроенным каналом

На рис. 5.18 показано схематическое изображение конструкции и схема

включения полевого транзистора с управляющими р-п-переходами. Тонкий

слой полупроводника р- или n-типа, ограниченный с двух сторон электронно-

дырочными переходами, называется каналом Включение канала в

электрическую цепь обеспечивается с помощью двух электродов, один из

которых (И) называется истоком, а второй (С) - стоком. Вывод,

подсоединенный к областям полупроводника противоположной примеси,

является управляющим электродом и называется затвором (3).

Рис. 5.18. Полевой транзистор с управляющими р-п-переходами:

а схематическое изображение конструкции и схема включения; б - условное

обозначение транзистора с каналом p-типа; в - условное обозначение транзистора с

каналом п-типа

Величина тока в канале зависит от напряжения между стоком и истоком

Uc, нагрузочного сопротивления RH и сопротивления полупроводниковой

пластины между стоком и истоком. Если Uc и RH величины постоянные, то

ток в канале зависит только от эффективной площади поперечного сечения

канала.

Источник изи создает отрицательное напряжение на затворе, что

приводит к увеличению толщины р-п-перехода и уменьшению

токопроводящего сечения канала. С уменьшением сечения канала

увеличивается сопротивление между стоком и истоком и снижается величина

тока 1С. Уменьшение напряжения на затворе вызывает уменьшение

50

сопротивления канала и возрастание тока 1с. Подключив последовательно с

изи источник усиливаемого переменного напряжения U, можно изменять ток

через канал rib закону изменения входного напряжения. Ток стока, проходя

через сопротивление нагрузки RH, создает на нем падение напряжения,

изменяющееся по закону U (входного). При соответствующем подборе

величин RH можно добиться увеличения уровня выходного напряжения по

сравнению с входным, т.е. усилить сигнал.

Полевые транзисторы с изолированным затвором имеют структуру

металл - диэлектрик (оксид) - полупроводник. Поэтому их называют МДП

или МОП-транзисторами.

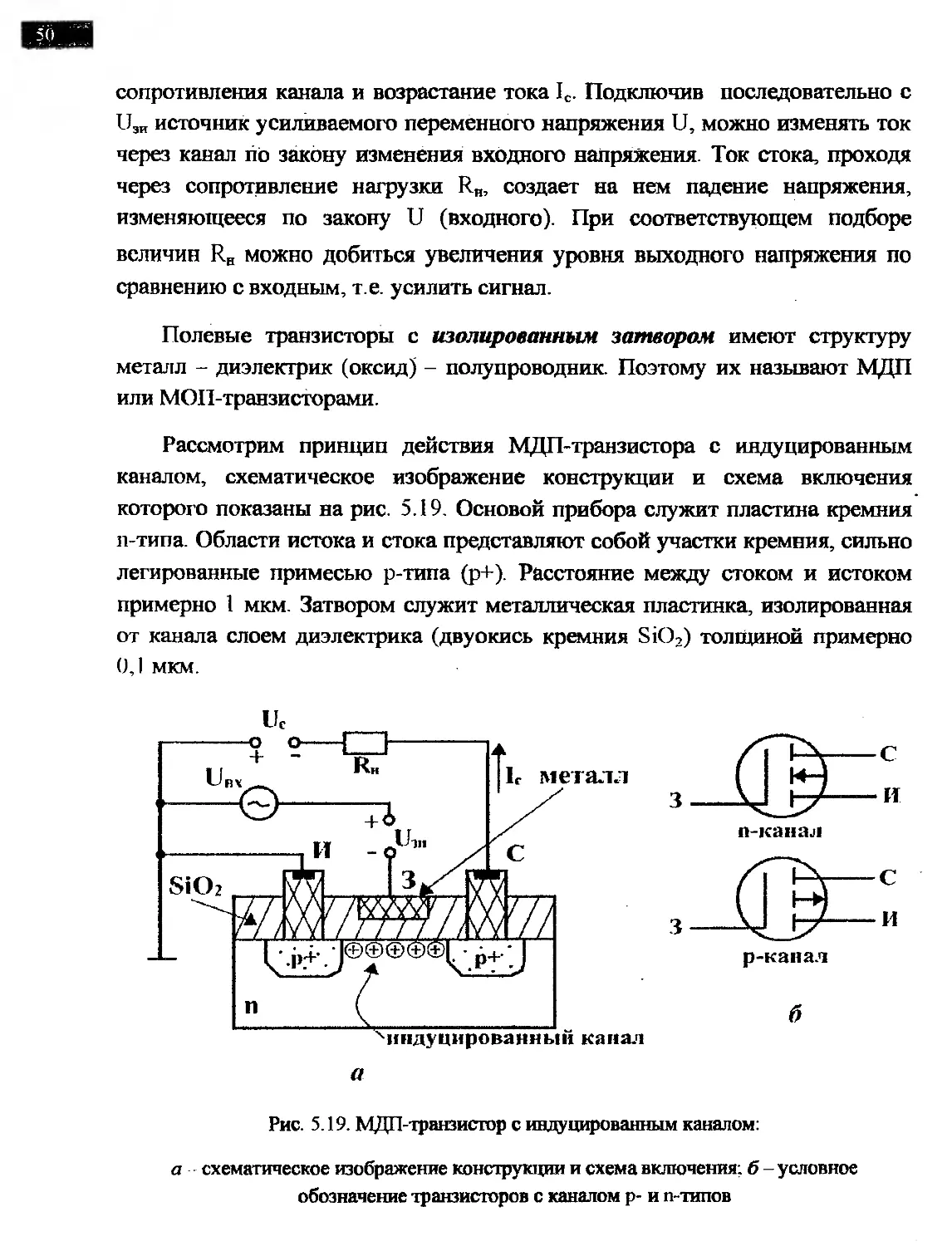

Рассмотрим принцип действия МДП-транзистора с индуцированным

каналом, схематическое изображение конструкции и схема включения

которого показаны на рис. 5.19. Основой прибора служит пластина кремния

n-типа. Области истока и стока представляют собой участки кремния, сильно

легированные примесью p-типа (р+). Расстояние между стоком и истоком

примерно I мкм. Затвором служит металлическая пластинка, изолированная

от канала слоем диэлектрика (двуокись кремния SiO2) толщиной примерно

0,1 мкм.

а

Рис. 5.19. МДП-транзисгор с индуцированным каналом:

а схематическое изображение конструкции и схема включения; б-условное

обозначение транзисторов с каналом р- и п-типов

Работа МДП-транзисторов основана на изменении удельного

сопротивления канала. При создании разности потенциалов между объемом

полупроводника и затвором, у поверхности полупроводника образуется слой

с концентрацией носителей зарядов, отличной от концентрации в остальном

объеме полупроводника, - канал, сопротивлением которого можно

управлять, изменяя напряжение на затворе.

В МДП-транзисторе с индуцированным каналом (рис. 5.19) при U3H= О

канал отсутствует, так как между стоком и истоком оказываются встречно

включенными два р-п-перехода и 1с в этом случае будет практически равен

нулю. Если подать на затвор отрицательное напряжение иаи < 0, то

возникающее электрическое поле будет отталкивать электроны вглубь

п-полупроводника, и между стоком и истоком образуется проводящий канал

из дырок. Толщина этого канала 1 - 2 нм. Сопротивление канала зависит

только от концентрации дырок в нем, поэтому, изменяя напряжение между

затвором и истоком, можно менять ток такого МДП-транзиетора.

Необходимо отметить, что МДП-транзисторы с индуцированным

каналом работают либо при положительных, либо при отрицательных

напряжениях на затворе в зависимости от типа канала. Это приводит к

усложнению электрической схемы при использовании таких транзисторов в

качестве усилителей двуполярных сигналов за счет дополнительных

радиодеталей.

В МДП-транзисторах со встроенным каналом (рис. 5.20) при I.J3H= 0

между стоком и истоком будет протекать некоторый средний ток Tvo Такие

транзисторы работают как при положительных, так и при отрицательных

напряжениях на затворе. При положительном напряжении наблюдается

режим обеднения, когда электрическое поле, создаваемое напряжением U3U,

выталкивает дырки из канала, уменьшая его удельную проводимость. При

отрицательном напряжении IJ3H наблюдается режим обогащения, когда

электрическое поле втягивает дырки в канал из п-области, что увеличивает

удельную проводимость канала.

Рис. 5.20. МДП-траязистор со встроенным каналом:

а - схематическое изображение концентрации и схема включения; б - условное

обозначение транзисторов с каналами р- и п-типов

Глава 6. АНАЛОГОВАЯ СХЕМОТЕХНИКА

6/1. Усилители

Информацию о различных физических величинах и контролируемых

процессах получают с помощью датчиков, которые осуществляют

преобразование измеряемой величины в пропорциональный ей

электрический сигнал. Очень часто эти сигналы измеряются тысячными

долями вольт, а после передачи по каналам связи сильно ослабляются, и для

нормальной работы приемников информации с этими сигналами требуется

их усиление. Также невелик уровень электрических сигналов, считываемых с

носителей информации во всевозможных магнитных и оптических

запоминающих устройствах. Поэтому усилители являются одними из

основных узлов различной аппаратуры в устройствах автоматики,

вычислительной и информационно-измерительной техники.

Усилитель - это устройство, увеличивающее интенсивность входного

сигнала, используя энергию источника питания. В зависимости от

назначения, различают усилители напряжения, тока и мощности, усилители

сигнала переменного и постоянного тока, усилители, предназначенные для

усиления сигналов в разных диапазонах частот.

Получить увеличение мощности выходного сигнала по сравнению с

входным за счет использования энергии стороннего источника (батарея,

аккумулятор и т.д.) позволяет такой активный элемент как транзистор. При

использовании транзистора в электронных устройствах нужны два вывода

для входного сигнала и два - для выходного, а у транзистора имеется три

вывода. В связи с этим различают три возможные схемы включения

транзисторов: с общей базой (ОБ), с общим эмиттером (ОЭ) и общим

коллектором (ОК).

Такая терминология указывает, какой из электродов транзистора

является общим для его входной и выходной цепей.

Схема с общей базой

Схема включения транзистора с общей базой (ОБ) показана на рис. 6.1.

Рис. 6.1. Схема включения транзистора с общей базой

Входным напряжением для схемы с ОБ является напряжение, поданное

между эмиттером и базой: UBA = иЭБ, выходным - напряжение, выделяемое на

нагрузке - IKRH (т е. напряжение между коллектором и базой); входным

током - ток эмиттера 1„ = 1э, выходным - ток коллектора 1вых = 1К. Входное

напряжение Use является управляющим для транзистора и его небольшое

изменение (на доли вольт) приводит к изменению 1э в очень широких

пределах.

Для оценки работы транзистора и его усилительных свойств в

различных схемах включения рассматривают приращения входных и

вызванных ими выходных величин. Рассматривая транзистор как

усилительный элемент, можно характеризовать его свойства

коэффициентами усиления и значением входного сопротивления.

Различают три вида коэффициентов усиления:

- коэффициент усиления по току К/ = ;

- коэффициент усиления по напряжению Ку =

- коэффициент усиления по мощности КР - КгКц.

Величина входного сопротивления определяется как отношение

изменения входного напряжения к изменению входного тока:

Любой реальный источник сигнала, который необходимо усилить, обладает

некоторым внутренним сопротивлением. Поэтому чем выше усилителя,

тем большая часть сигнала будет выделяться на этом сопротивлении и

усиливаться, и тем меньшая часть этого сигнала будет теряться на

внутреннем сопротивлении этого источника.

Так как^^^^ициепт т^к^^итте^а определяется кака= —,

а для схемы с ОБ ток эмиттера является входным током, а ток коллектора -

выходным, коэффициент усиления по токуёудет равен: '

Д/к

—^ = а = 0,95 ...0,99

Д/э

(индекс «Б» в обозначении КЛ показывает, что этот коэффициент

характеризует работу схемы с ОБ).

Так как входным напряжением UBX является Пэб, подключенное в

прямом направлении, а входным током - ток эмиттера, то входное

сопротивление равно:

Д^вх Д^ЭБ

и составляет обычно единицы - десятки ом.

Коэффициент усиления по напряжению в схеме с ОБ составляет:

Д^вых _ Д^вых ~ /?Н _ ~ ^Н

Д^вх Д^вх ’ ^вхБ Д^Э " Квх Б

Учитывая, что 1э ~ 1к, имеем А\,ъ ~ -— - т е. Kl!S определяется

соотношением сопротивлении нагрузки и входного. Если Rh - килоомы, А?®

может достигать g 100 ... 1 000.

Коэффициент усиления по мощности определяется как произведение

коэффициентов по току и напряжению:

/?Н «н

КрБ “ К!Ъ ’ КиБ ~ а ‘ г> г>

**вх Б *»вх Б

- таким образом, он тоже определяется соотношением сопротивлений

Схема включения транзистора с общей базой применяется в основном

тогда, когда необходимо усиливать высокочастотные сигналы.

Схема с общим эмиттером

В схеме с общим эмиттером (рис. 6.2) входной сигнал прикладывается

к выводам эмиттера и базы, а выходной сигнал снимается с нагрузки,

включенной ме5аду ^мйттером и коллектором. Следовательно? эмиттер

является общим электродом для входабиивыходной цепей.

Рис. 6.2. Схема включения транзистора с общим эмиттером

Основной особенностью схемы с общим эмиттером (ОЭ) является то,

что входным током в ней является не ток эмиттера, а малый по величине ток

базы. Выходным током в этой схеме является ток коллектора. Исходя из

этого, коэффициент прямой передачи тока для схемы с ОЭ:

К1Э =

^вых

Д/Вх

Д/б

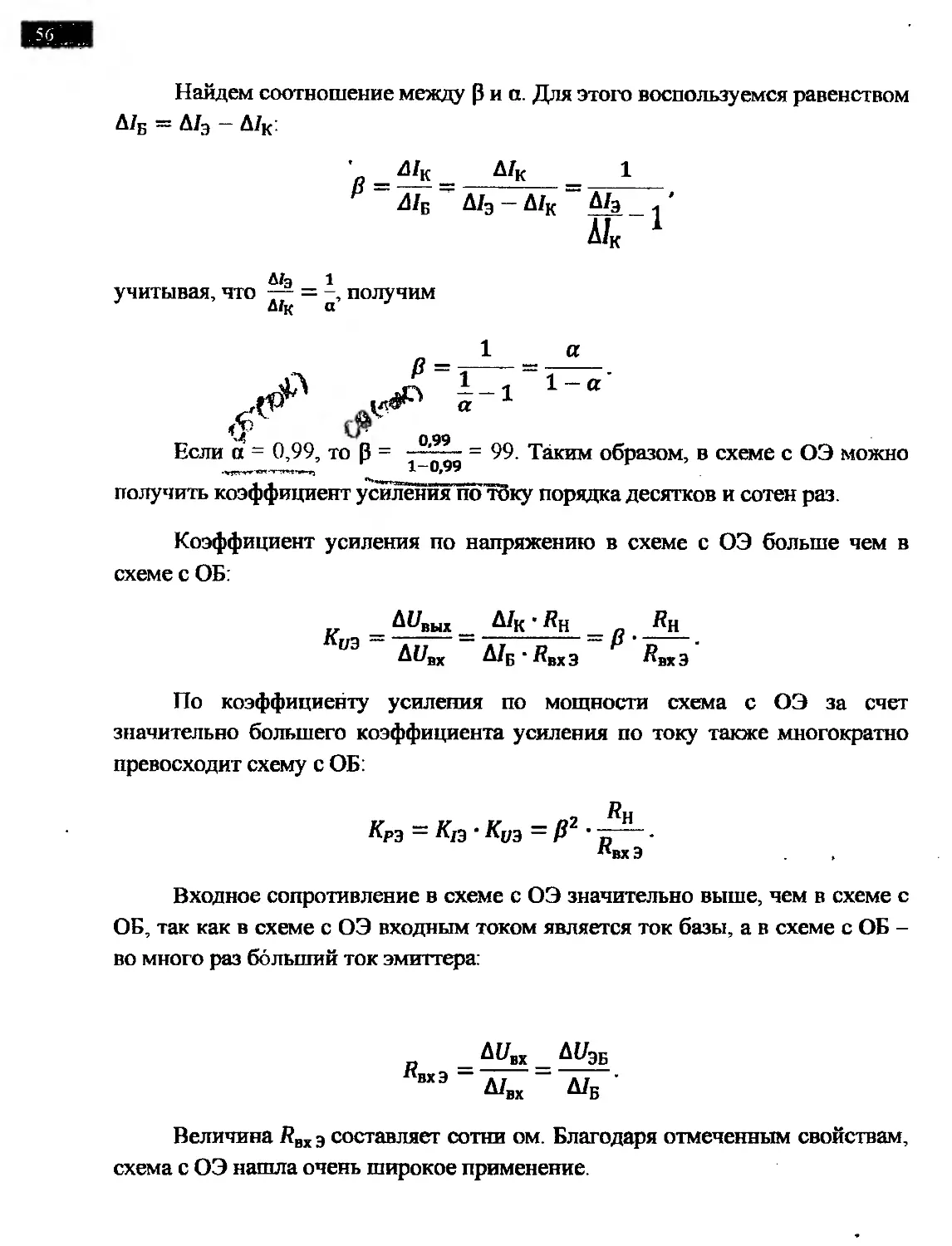

Найдем соотношение между Р и а. Для этого воспользуемся равенством

Д7б ~ Д^э ~ ДЛс

R = _ 1

Д^э — Д*к Д^э _ 1

А/к 1

Д/э 1

учитывая, что — = -, получим

а

1 - а

1

irtCF*’ а

г

•-> О 99

Если а = 0,99, то Р = —= 99. Таким образом, в схеме с ОЭ можно

Wvr'H'i ни rj 0,99

получить коэффициент усиления по току порядка десятков и сотен раз.

Коэффициент усиления по напряжению в схеме с ОЭ больше чем в

схеме с ОБ:

„ _ Д^вых _ Д^к ’ R

U3 Д^Б'ЯвхЭ ^вхЭ

По коэффициенту усиления по мощности схема с ОЭ за счет

значительно большего коэффициента усиления по току также многократно

превосходит схему с ОБ:

, Ян

Крэ — Ъэ • Киэ = Р • -- .

ЛвхЭ

Входное сопротивление в схеме с ОЭ значительно выше, чем в схеме с

ОБ, так как в схеме с ОЭ входным током является ток базы, а в схеме с ОБ -

во много раз больший ток эмиттера:

Д[/вх ДПэб

вхэ Д/Вх Д/Б •

Величина Явх э составляет сотни ом. Благодаря отмеченным свойствам,

схема с ОЭ нашла очень широкое применение.

57

Схема с общим коллектором

В схеме с общим коллектором (рис. 6.3) входной сигнал подается на

участок база-коллектор. Входным является ток базы, а выходным - ток

—— ---------—— .-------------------------------- _

эмиттера. Поэтому коэффициент усиления по току с учетом того, что р = —,

равен~

К1К —

Л1Э Д/к + Д/Б _ _

Л1Ъ Д/Б Л1Б р

т е. примерно такой же, как в схеме с ОЭ.

Рис. 6.3. Схема включения транзистора с общим коллектором

Особенностью схемы с ОК является отсутствие усиления по

напряжению? 1Сак видно из схемы, Цныт отличается от на величину иБЭ

(Ubx = П^П-”иБэ), которое при открытом транзисторе составляет доли вольт.

Если входное напряжение увеличится на небольшую величину AUBX, то в

первый момент произойдет увеличение Оьэ> что приведет к увеличению

коллекторного тока. Но с ростом тока увеличится и напряжение на RH, а это

приведет к уменьшению управляющего напряжения иБэ = UBX - UBbDt.

Изменение входного напряжения AU^ будет скомпенсировано аналогичным

изменением выходного напряжения, т.е. выходное напряжение отслеживает

(повторяет) все изменения входного. Поэтому схема с ОК получила название

«эмиттерный повторитель». Схема с ОК имеет Кик — 1 (0,98 - 0,99).

Оценим величину входного сопротивления схемы с ОК. Входное

напряжение для этой схемы складывается из небольшого падения

напряжения на эмиттерном переходе (UB3) и падения напряжения на RHs л

входным током является ток базы. Поэтому:

D _ Mhx _ Д^БЭ + Д/э •

Й”к“^й" лй

Поскольку иБЭ « b R-H, а 1э ~ 0 Ь, получим:

_ /? • А/б • RH

RbxK " Д/Б

= P-Rh-

Таким образом, входное сопротивление схемы с ОК в несколько раз

превосходит входное сопротивление схем с ОЭ и ОБ и составляет десяТКИ,

сотни килом при небольшой величине RH.

JJ .. JIM.IMIUJ

Несмотря на малый коэффициент усиления напряжения, схема с ОК

(эмиттерный повторитель) находит широкое применение в электронных

схемах, когда требуется согласовать большое сопротивление одного каскада

с малым сопротивлением другого. При этом эмиттерный повторитель

Позволяет усйлигьток и мощностьсигнала.

Каскад усиления напряжения на биполярном транзисторе

В рассматриваемом усилительном каскаде (рис. 6.4) п-р-п-транзистор

включен по схеме с общим эмиттером.

Режим каскада подбирают таким образом, чтобы транзистор находился

в активном режиме, т е. на эмиттерный переход подают прямое напряжение,

а на коллекторный - обратной Напряжение источника! Ев подбйрайугтаким

образом (выбирают рабочую точку), чтобы каскад усиливал как

положительные, так и отрицательные сигналы. Если бы источник Ев

отсутствовал, то транзистор открывался бы только во время действия

положительных полуволн, а при отрицательных был бы закрыт. Включение

источника Ев определенного напряжения при отсутствии Ura создает в схеме

начальные токи 1Б 1к (токи покоя). С появлением входного сигнала токи

будут изменяться: положительная полуволна будет их увеличивать, а

отрицательная - уменьшать, что приведет к появлению : переменных

составляющих во всех токах транзистора (Д1Б, Д1к) Во входной и выходной

цепях каскада будут происходить изменения тока и напряжения около

постоянного значения, которое определяется режимом покоя (рис. 6.4, б).

Для работы усилительного каскада важно, что изменения выходного

(коллекторного) тока происходят в такт с изменениями входного (базового)

тока. А так как транзистор является усилительным прибором, в котором ток

коллектора в 0 раз превышает ток базы, в рассматриваемом~каскаде

происходит усиление тока и напряжения. Последнее наблюдается в том

случае, если выходное напряжение, которое равно падению напряжения на

резисторе RK, при правильном подборе коллекторного резистора оказывается

больше Пвх. При этом выходное напряжение UBMx~ 1к противоположно

по фазе входному (рис. 6.4, б).

Рис. 6.4. Усилительный каскад на биполярном транзисторе:

а - схема каскада, б - временные диаграммы его работы

В схеме усилительного каскада на рис. 6.4, а используются два

источника постоянного напряжения ЕБ и Ек, что неудобно с конструктивной

точки зрения. Более удобны схемы с одним источником постоянного

напряжения. В простейшей схеме с фиксированным током_базы (рис. 6.5) в

отсутствие сигнала ток базы определяется напряжениям!

сопротивлением RB. лр

Uro, а также

О +EK

ЦгЭ

Рис. 6.5. Усилительный каскад на биполярном транзисторе с фиксированным током базы

Все величины связаны соотношением:

^к = • /б + ^бэ »

откуда получаем, что ток базы в режиме покоя (ток в рабочей точке):

. _ Ек — Убэ

*Бнач п

«Б

При проведении инженерных расчетов можно принять, что для

германиевых транзисторов иБЭ~ 0,2 В, а для кремниевых - иБЭ~ 0,5 В. Тогда

при расчете тока базы транзистора в режиме покоя можно пользоваться

такими соотношениями:

fEK - 0,2

—-------для германиевого транзистора;

Кб

Ек - 0,5

—-—- для кремниевого транзистора.

Если Ек >10 В, то можно пренебречь напряжением между базой и

эмиттером и использовать еще более простое соотношение:

>нач D •

«Б

Конденсатор СР, который называют разделительным, служит для

предотвращения попадания постоянного напряжения'ю внешней цепи на

баз)ГтранЗистора"“^^ ‘

Однако этот способ смещения пригоден лишь тогда когда каскад

работает при малых колебаниях температуры транзистора. Кроме того,

большой разброс и нестабильность параметра р даже у однотипных

транзисторов делают режим работы каскада весьма неустойчивым при смене

- ,1«1Г , , ,-|| ТГ»1^ •'•г-.ПППГГ'" I J --— — -Ullin. IL . I ищи - , г __...... ... •

транзисторов.

' *•—? - -----—- _ t .

Более эффективной является схема с фиксированным напряжением

смещения на базе (рис. 6.6).

Рис. 6.6. Усилительный каскад на биполярном транзисторе с фиксированным

напряжением смещения на базе

Сопротивления делителя определяются из соотношений.

_ЕК~ ^БЭ

Б="^’

R" - 1

«Б -“jp-

Ток делителя 1д обычно выбирают в пределах 1Д ~ (2-J-5) 1Б.

В этой схеме повышается стабильность работы, так как изменения

токов транзистора незначительно влияют на величину напряжения смещения.

Усилительные каскады на полевых транзисторах

В усилительном каскаде на полевом транзисторе с управляющим р-п-

переходом (рис. 6.7) необходимо создать нужный режим по постоянному

току. Наиболее распространенной является схема автоматического смещения

(рис. 6.7), в которой через резистор R3 постоянный ток не проходит, поэтому

потенциал затвора оказывается равным нулю (потенциалу «земли»).

Потенциал истока равен UH ~ Rh'Ih, следовательно, напряжение между

затвором и истоком оказывается отрицательным и равным

^зи ~ — ~(ЯИ ‘ 4i) -

Постоянное напряжение между стоком и истоком:

^си ~ - «с • /с -

Рис. 6.7. Схема усилительного каскада на полевом транзисторе с управляющим р-п-

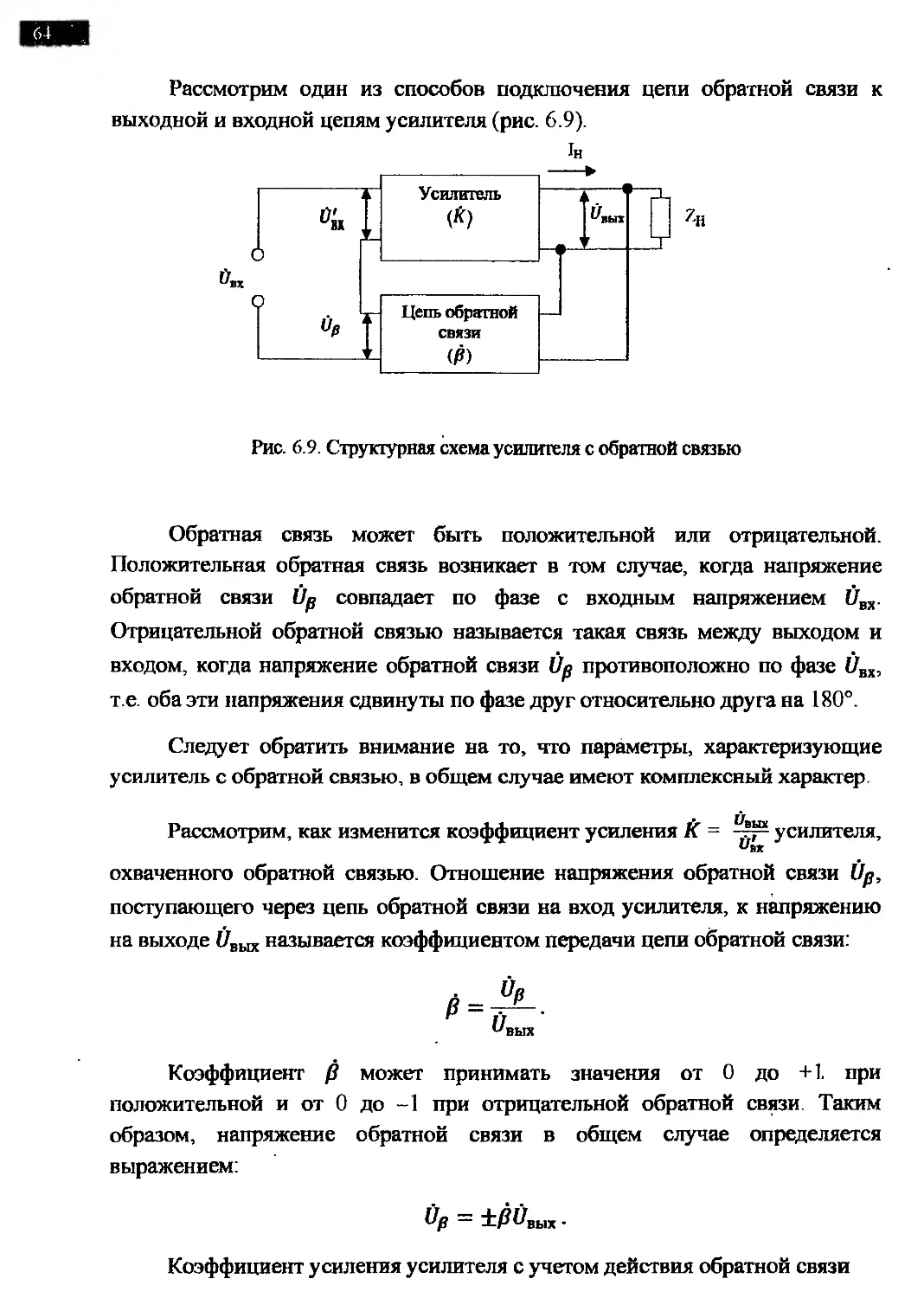

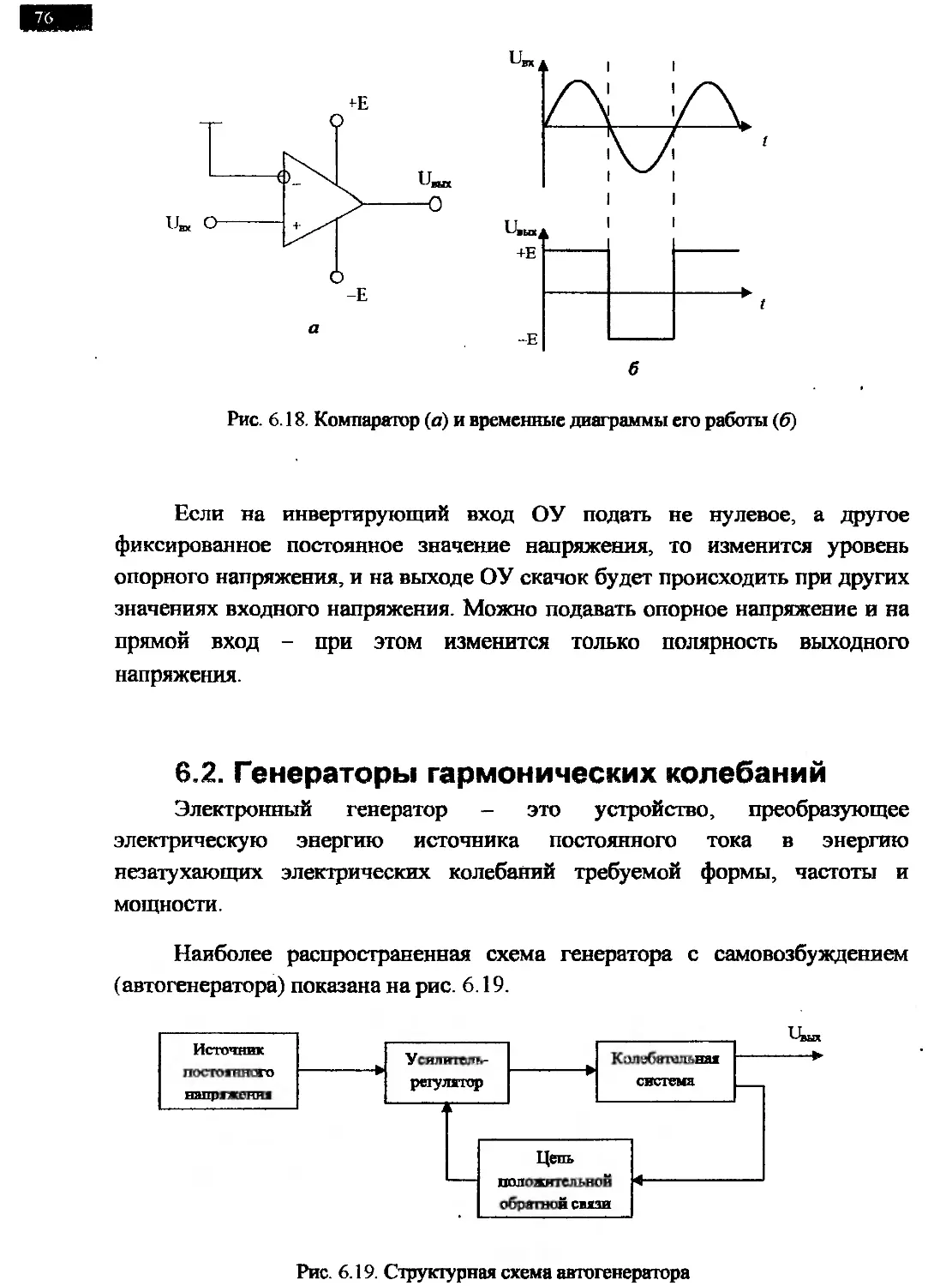

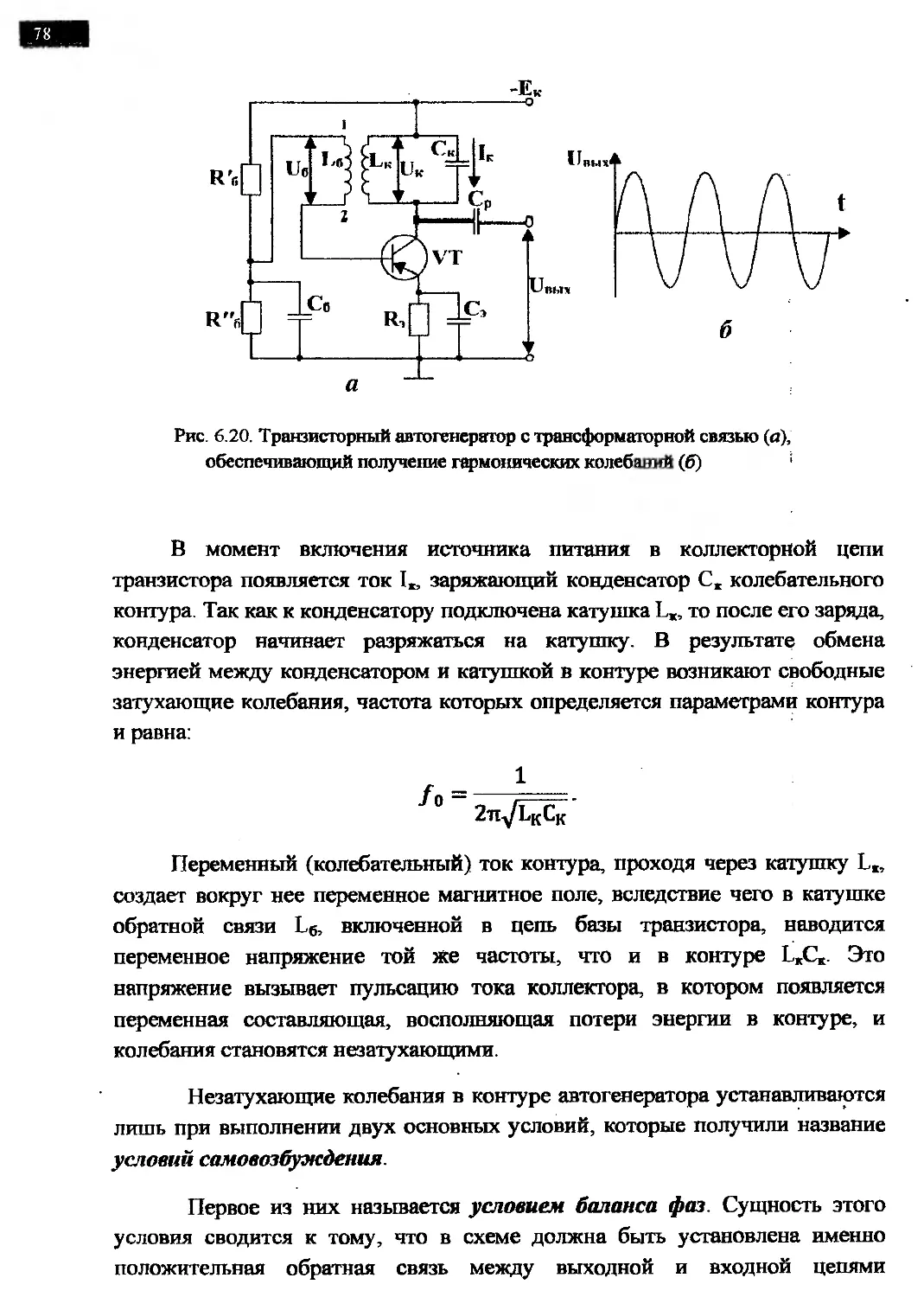

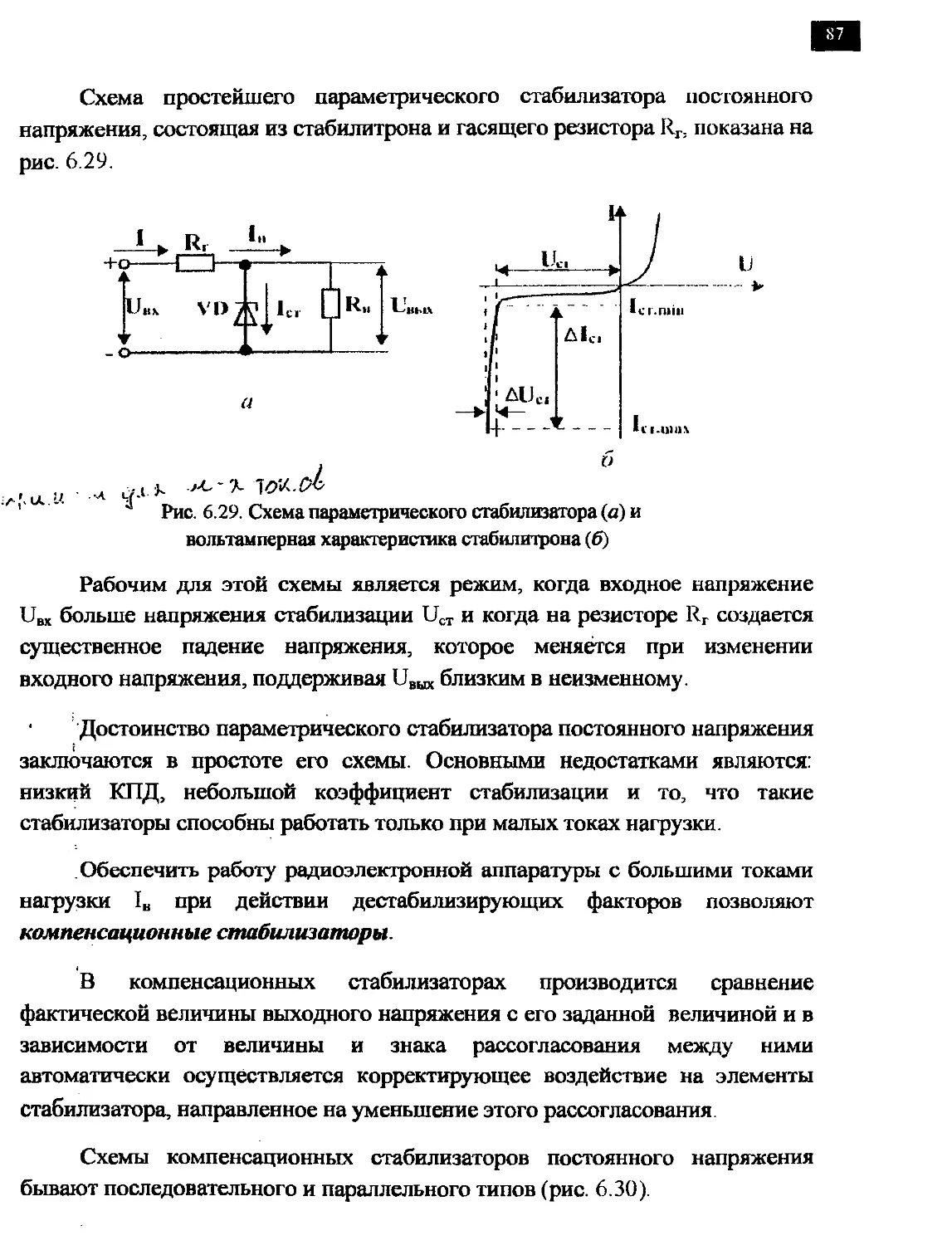

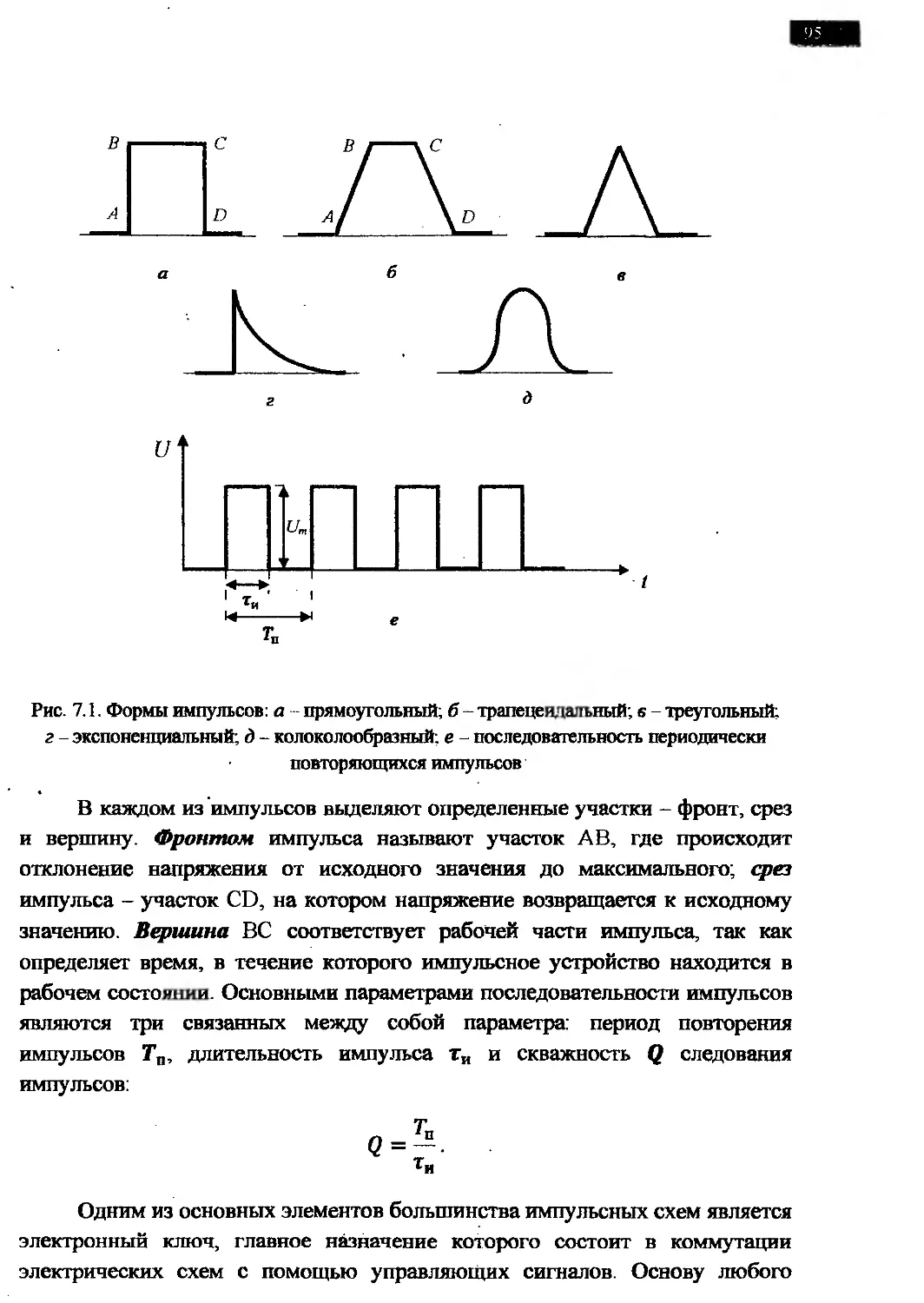

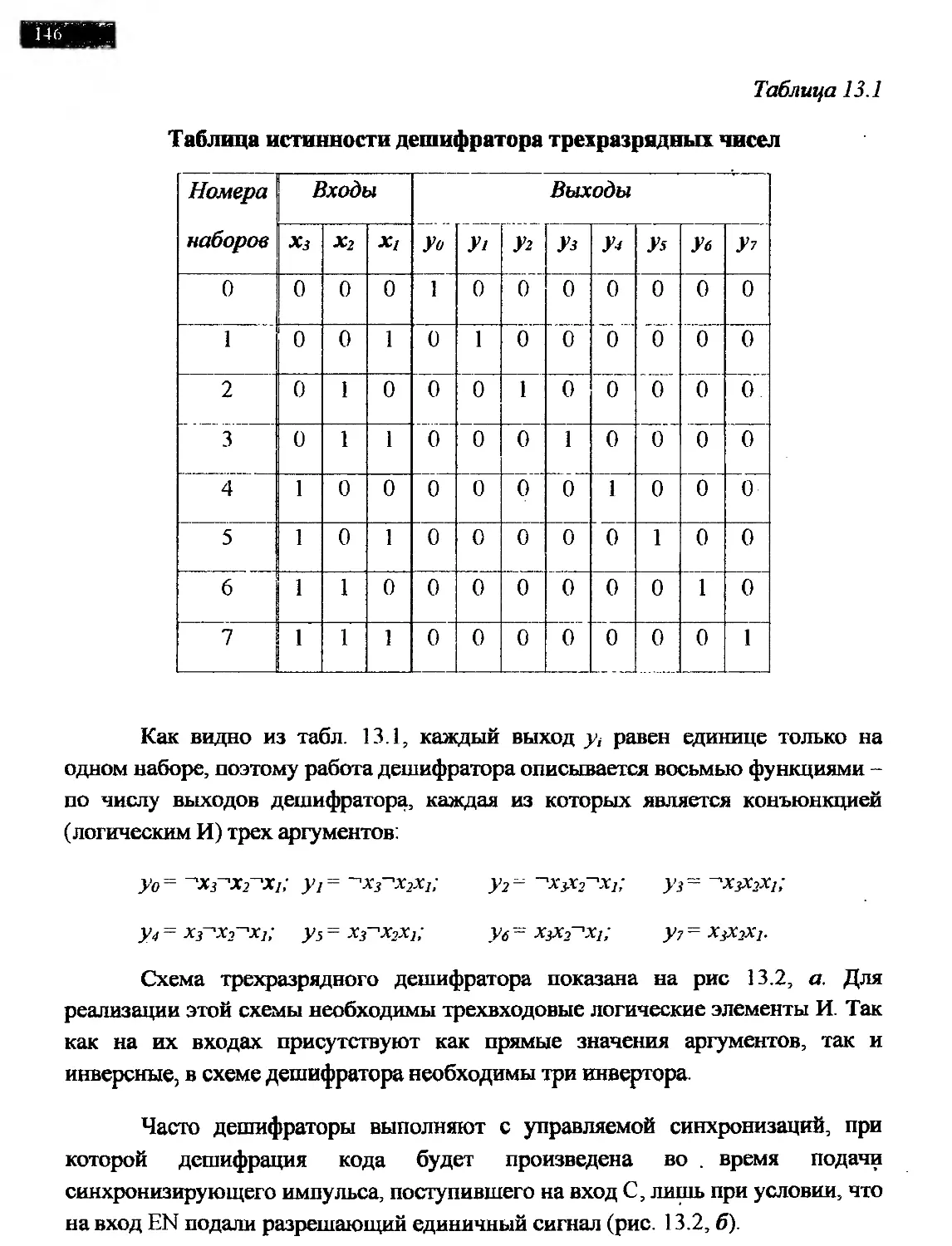

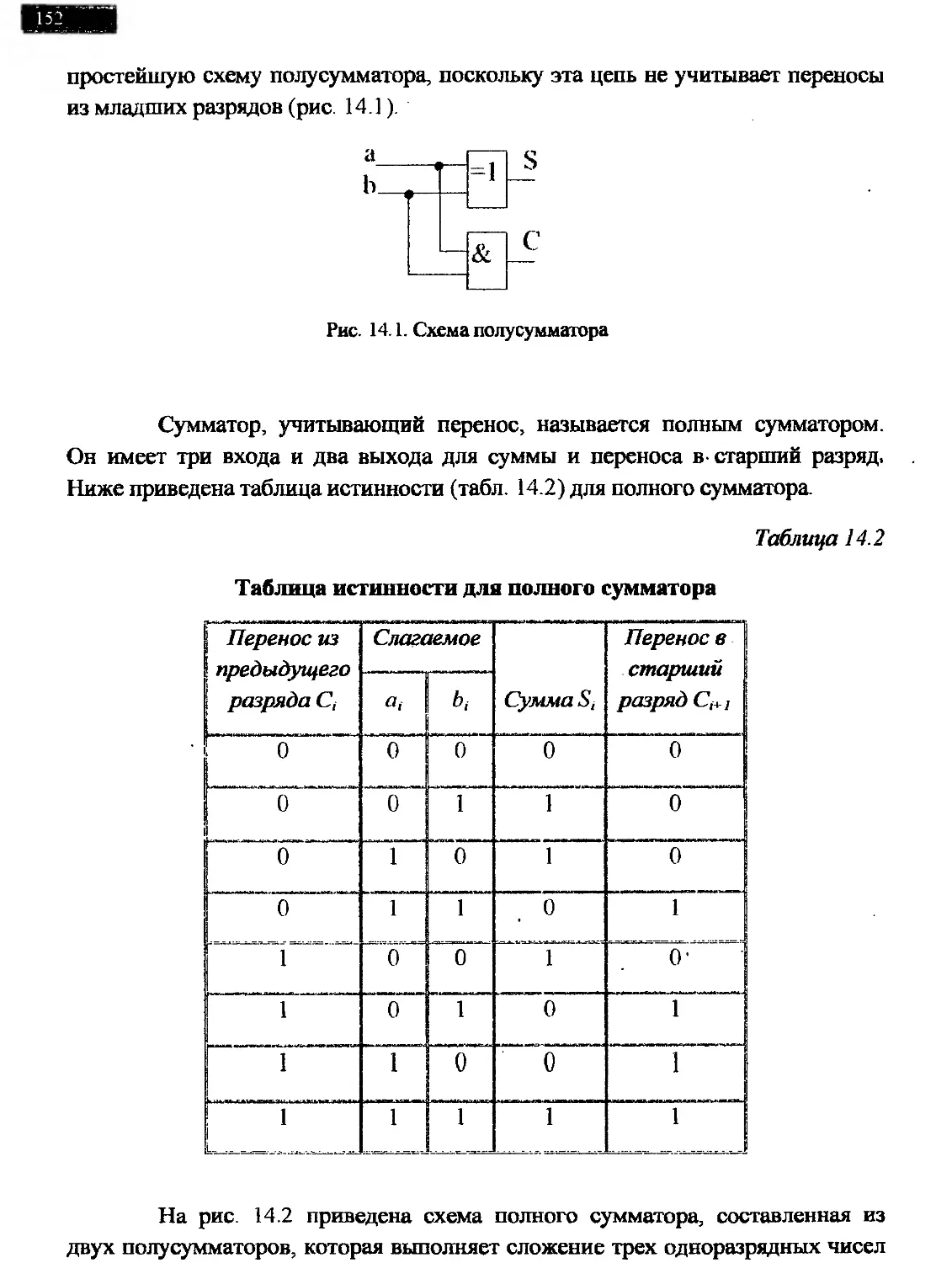

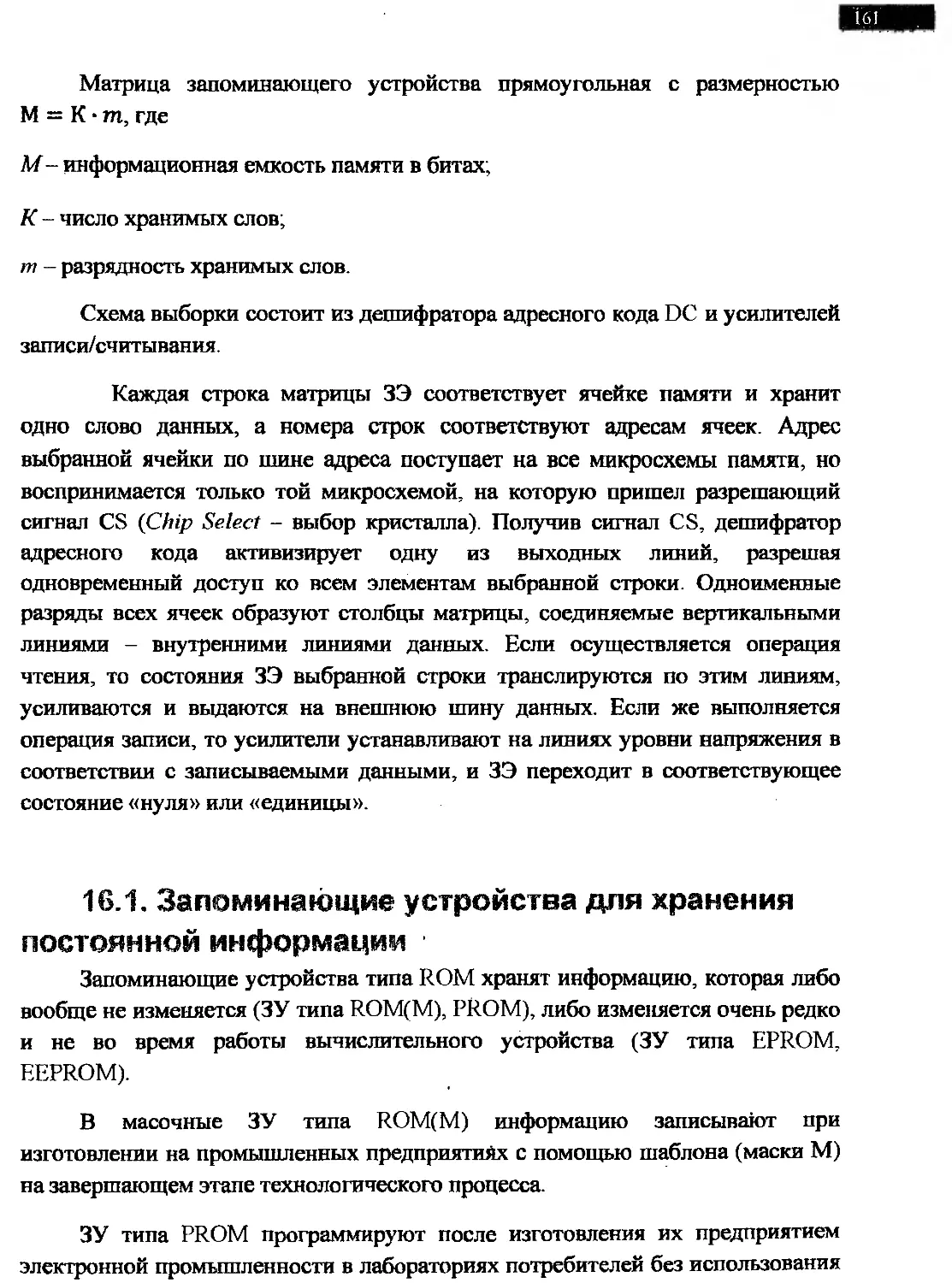

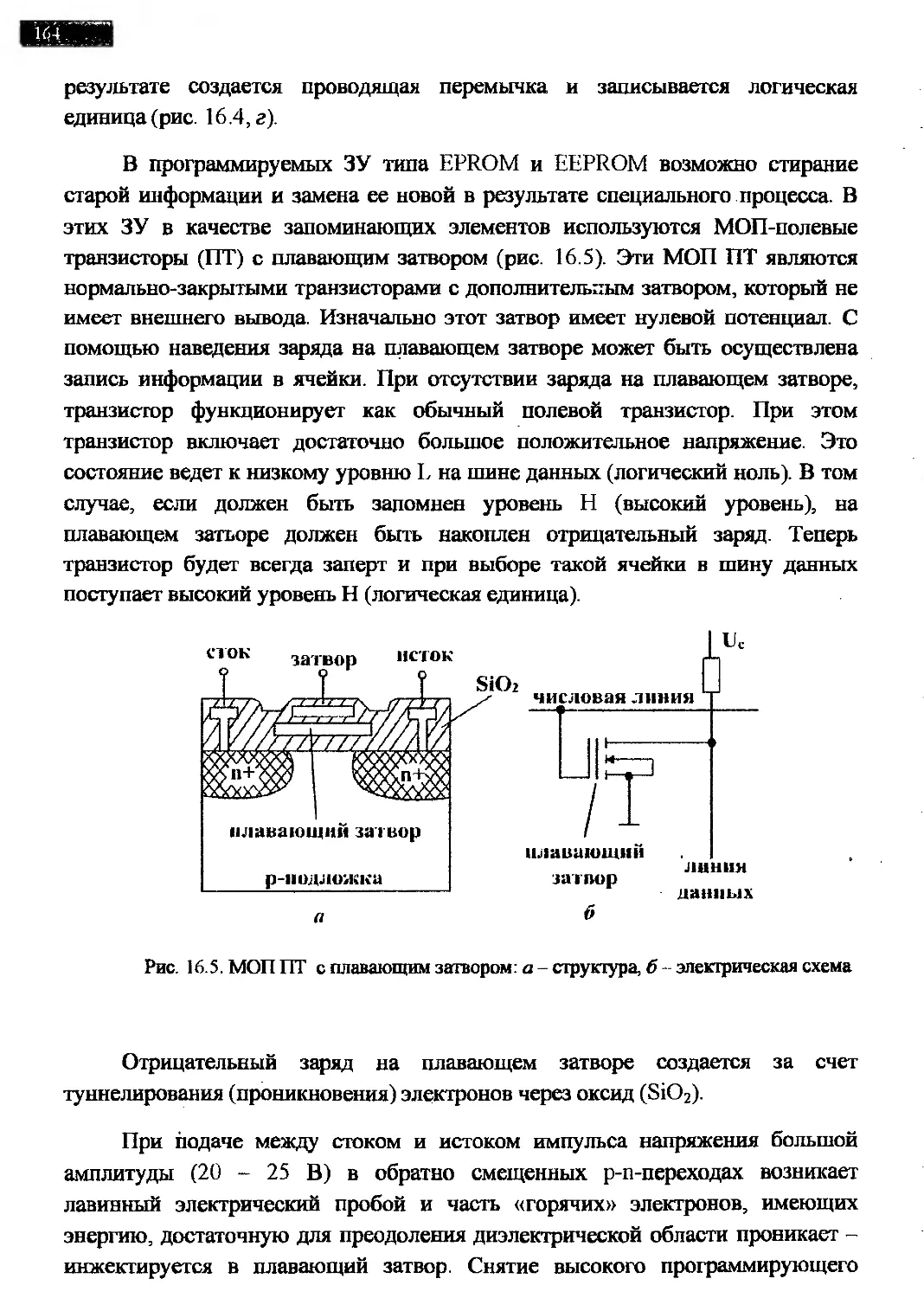

переходом