Текст

Основы проектирования

цифровых схем

Барри Уилкинсон

Университет штата Северная Каролина, США

Издательский дом “Вильямс”

Москва ♦ Санкт-Петербург * Киев

2004

Издательский дом “Вильямс”

Зав. редакцией С. И. Тригуб

Перевод с английского М.В. Бойко

Под редакцией А.А. Голубченко

Уилкинсон, Барри.

У36 Основы проектирования цифровых схем. : Пер. с англ. — М. :

Издательский дом “Вильямс”, 2004. — 320 с.: ил. — Парал. тит. англ.

ISBN 5-8459-0685-7 (рус.)

Эта книга посвящена вопросам проектирования цифровых ло-

гических схем. В краткой, но строгой форме в ней излагаются ме-

тоды проектирования основных классов логических схем — от вен-

тилей до схем на программируемых логических матрицах. Данная

книга будет особенно полезной для студентов, изучающих электро-

нику и вычислительную технику. Великолепная методика изложе-

ния, наличие большого количества примеров и заданий для само-

проверки с ответами делает ее незаменимой для тех, кто совершает

первые шаги в области проектирования сложных цифровых систем.

ISBN 5-8459-0685-7 (рус.)

ISBN 0-13-570110-4 (англ.)

© Издательский дом “Вильямс”, 2004

© Prentice Hall Europe, 1998

Оглавление

Предисловие 14

Глава 1. Цифровые системы и представление

информации 19

Глава 2. Логические вентили 51

Глава 3. Проектирование комбинационных схем 99

Глава 4. Триггеры и счетчики 153

Глава 5. Проектирование последовательных схем 195

Глава 6. Проектирование устройств

на программируемых логических

интегральных схемах (ПЛИС) 233

Глава 7. Тестирование логических схем 275

Ответы на задания для самопроверки 303

Предметный указатель 315

Содержание

Предисловие м

Глава 1. Цифровые системы и представление

информации 19

1.1. Цифровые системы 19

1.1.1. Управляющие системы 20

Логические сигналы и функции 21

Положительная и отрицательная логика 22

Логические функции 22

Вычисления 24

Цифровой компьютер 24

1.2. Представление чисел в цифровых системах 26

1.2.1. Двоичные числа 26

1.2.2. Преобразование чисел 30

1.2.3. Шестнадцатеричные и восьмеричные числа 31

1.3. Арифметические операции над двоичными числами 34

1.3.1. Сложение 34

1.3.2. Отрицательные числа и вычитание 36

Вычитание 38

Обратный код 42

1.3.3. Двоично-десятичное представление

десятичных чисел 42

1.4. Представление алфавитно-цифровых символов 44

1.5. Пример цифровой логической схемы 45

1.6. Резюме 47

1.7. Упражнения 48

1.8. Список дополнительной литературы 50

Глава 2. Логические вентили 51

2.1. Логические сигналы 51

Алгебраические операции над двузначными

переменными 52

2.2. Базовые логические функции 53

2.2.1. Вентиль НЕ 53

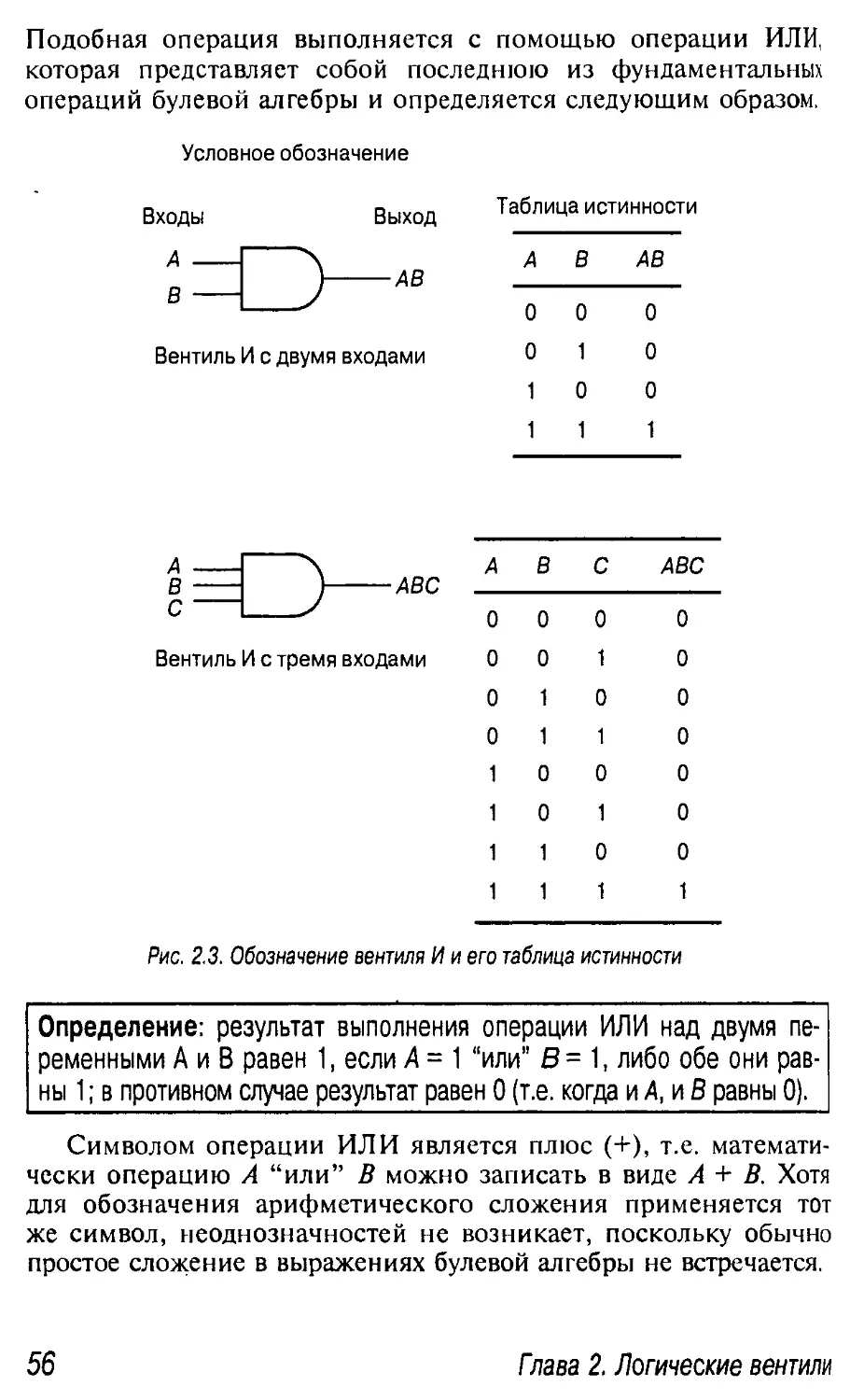

2.2.2. Вентиль И 54

2.2.2. Вентиль ИЛИ 55

2.3. Основные соотношения булевой алгебры 58

2.3.1. Тождества и их применение 58

Применение соотношений 59

2.3.2. Основные алгебраические правила 62

Применение основных законов булевой

алгебры в логическом проектировании 65

2.3.3. Принцип дуализма 67

Дуальные функции 67

Дуальные равенства. Принцип дуализма 69

2.3.4. Теорема де Моргана 70

2.4. Универсальные вентили 73

2.4.1. Вентиль И-НЕ 73

2.4.2. Вентиль ИЛИ-НЕ 75

2.5. Другие вентили 77

2.5.1. Вентиль исключающее ИЛИ 77

2.5.2. Вентиль исключающее ИЛИ-НЕ 79

2.5.3. Коммутативные функции 80

2.6. Проектирование вентилей 81

2.6.1. Комбинационные логические ТТЛ-схемы 81

2.6.2. Мсталл-оксид-полупроводниковые (МОП) вентили 85

Ключи на МОП-транзисторах 85

Базовые КМОП-ветили 91

Комбинационные функции 91

Произвольные функции 94

2.7. Резюме 94

2.8. Упражнения 95

2.9. Список дополнительной литературы 97

Содержание

7

Глава 3. Проектирование комбинационных схем 99

3.1. Комбинационные схемы 99

3.2. Реализация булевых выражений 102

3.2.1. Дизъюнктивная форма логических выражений 102

Выражения в канонической форме 103

Описание с помощью таблиц истинности 104

Преобразование выражений в каноническую форму 104

3.2.2. Выражения в конъюнктивной форме 105

Преобразование в каноническую форму 107

3.3. Альтернативные реализации 108

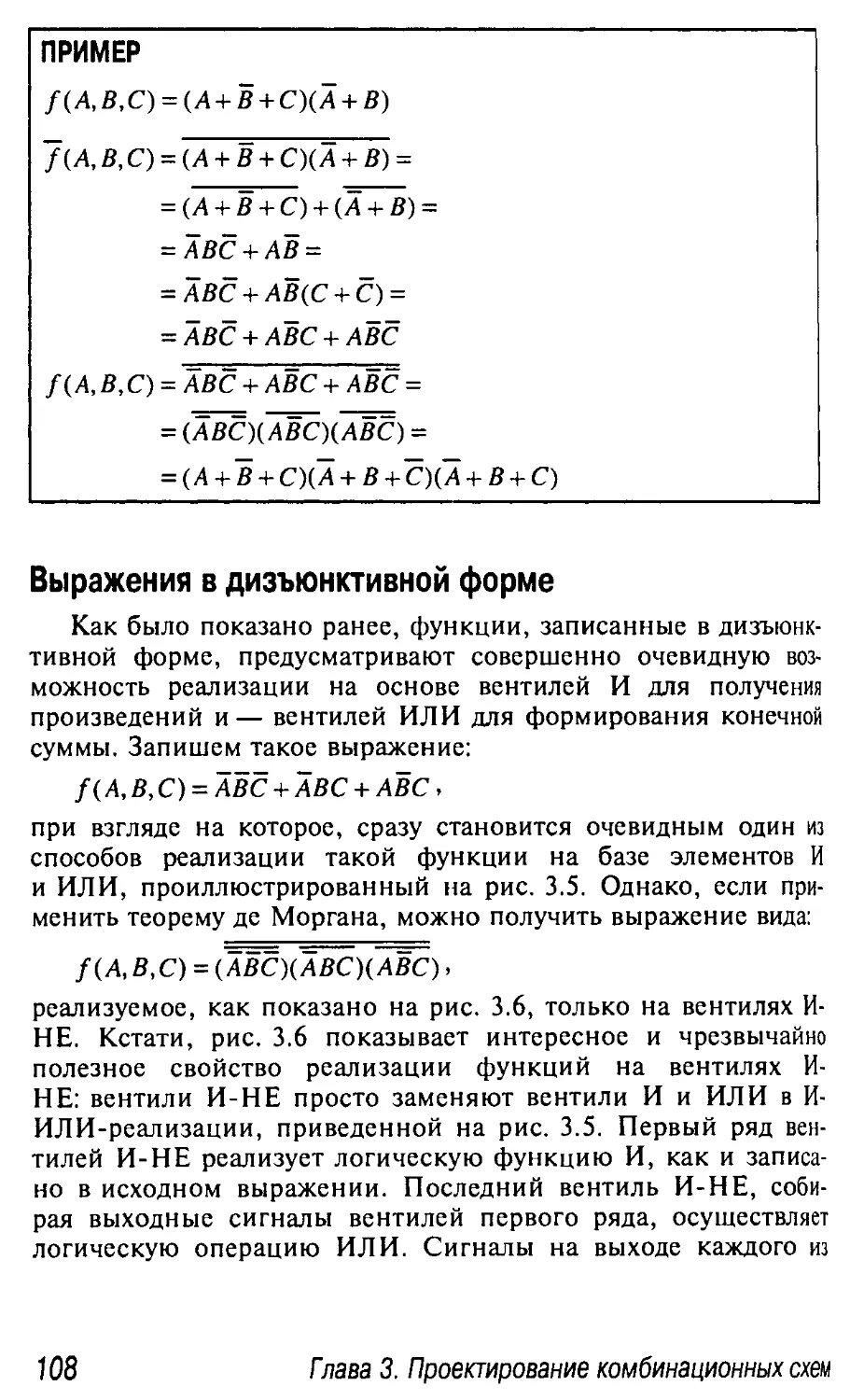

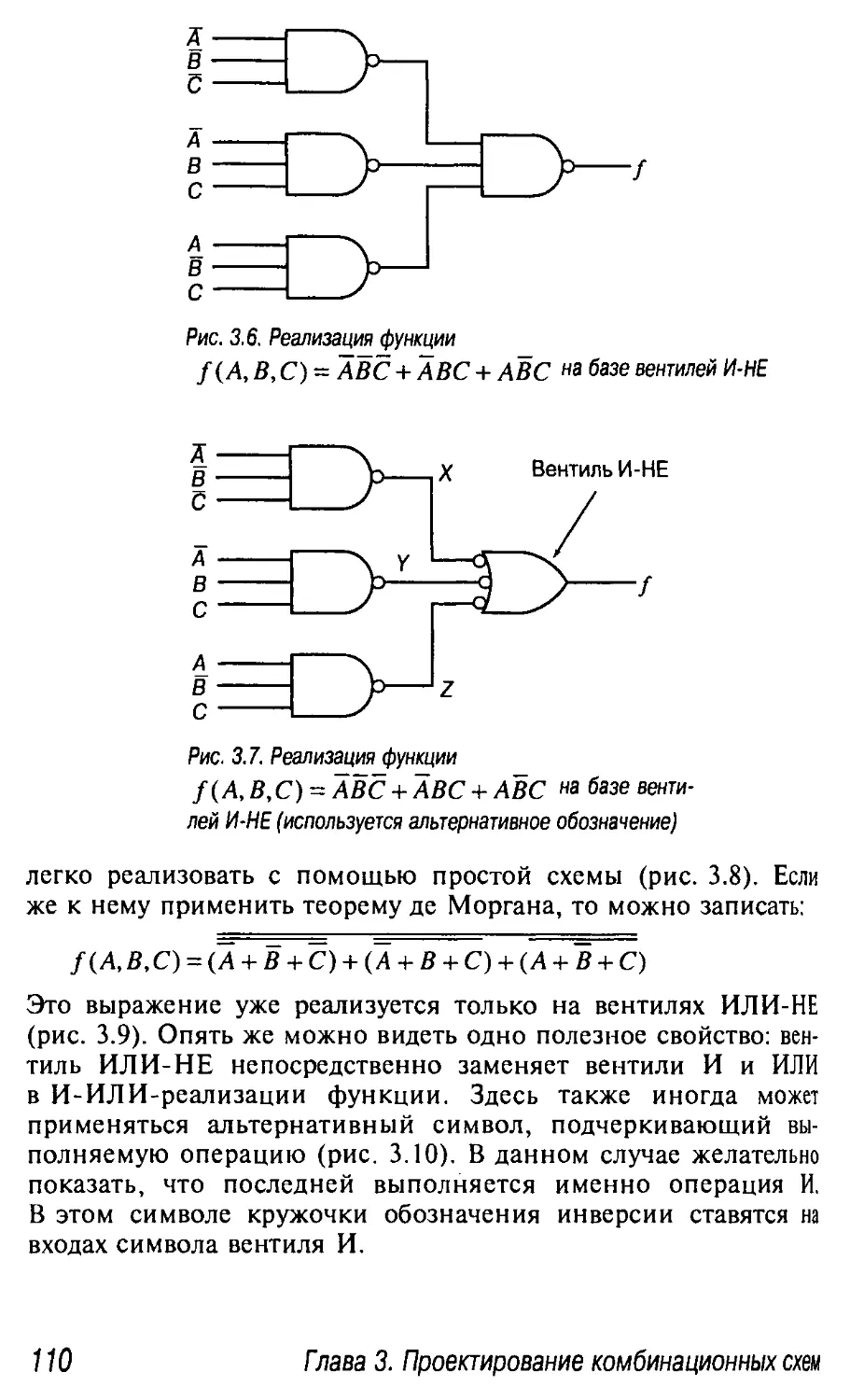

Выражения в дизъюнктивной форме 108

Выражения в конъюнктивной форме 109

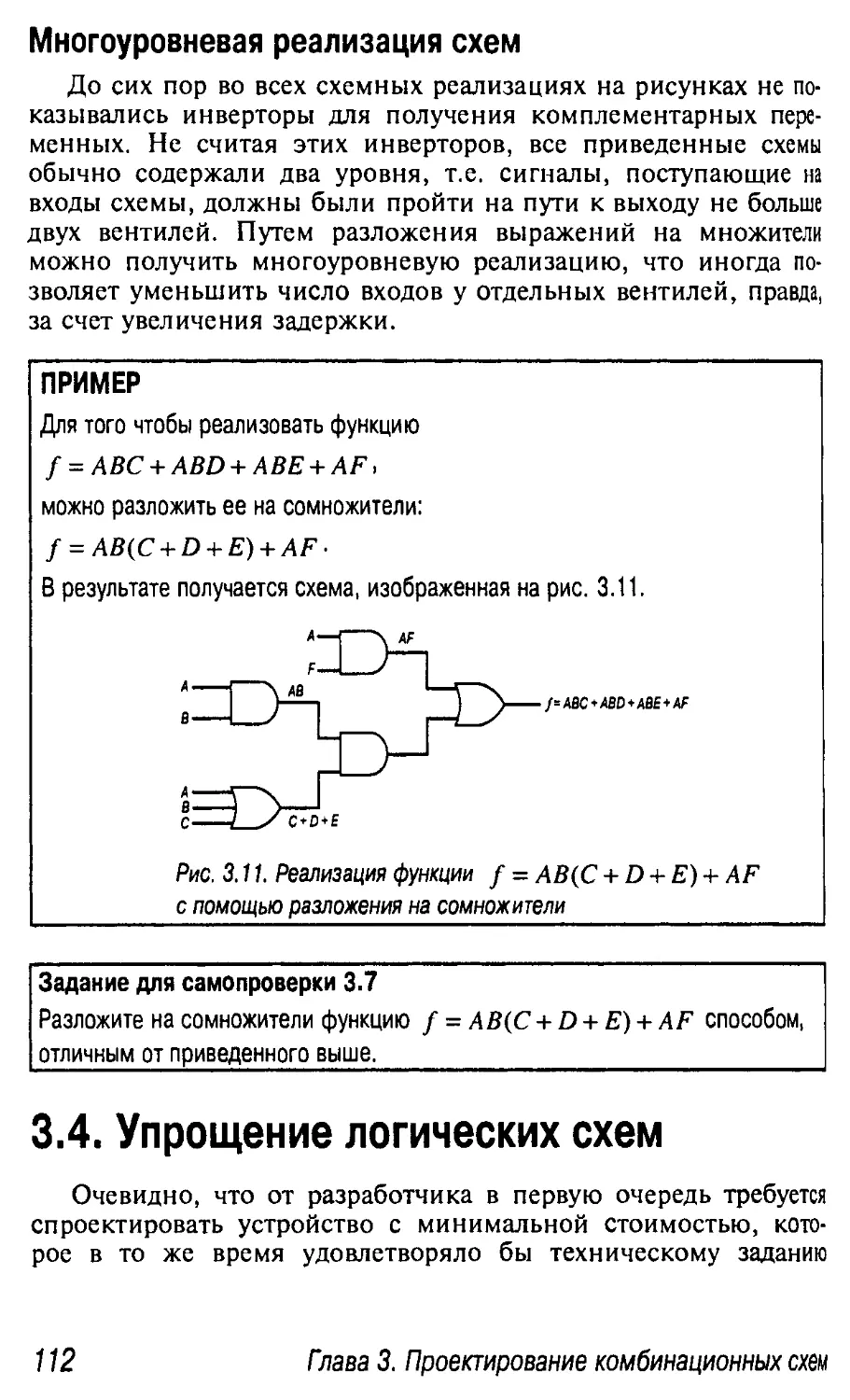

Многоуровневая реализация схем 112

3.4. Упрощение логических схем 112

3.4.1. Алгебраическое упрощение булевых выражений 113

1. Группировка членов с последующим

применением тождеств ИЗ

2. Приведение выражения в каноническую

форму с последующим упрощением 115

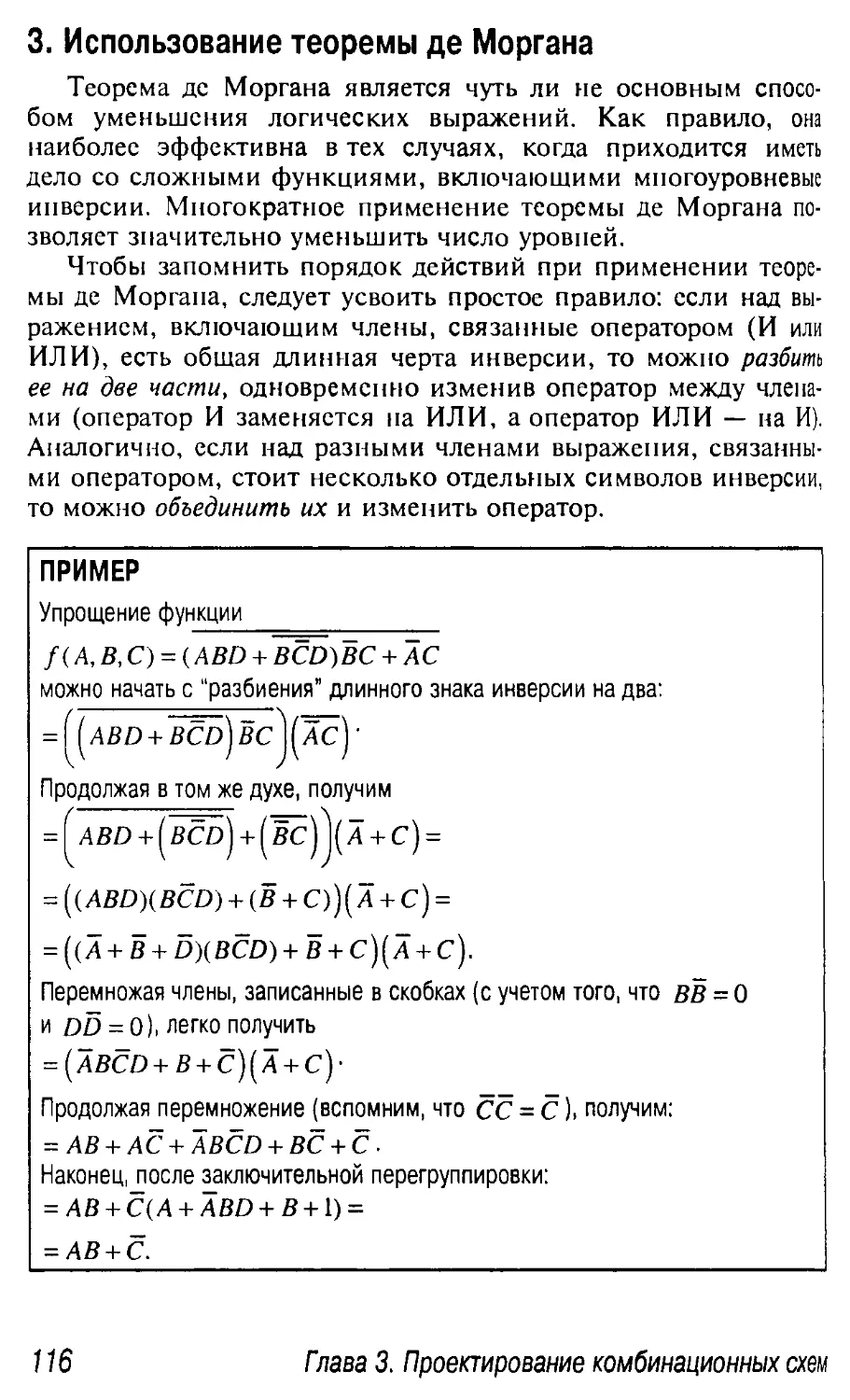

3. Использование теоремы де Моргана 116

3.4.2. Метод минимизации с помощью карт Карно 117

Алгоритм минимизации 120

Группирование ячеек по краям карты Карно 121

Большие группы 122

Карты Карно для четырех переменных 123

Выбор оптимальных групп 124

Карты Карно и таблицы истинности 126

Нумерация минтермов в карте Карно 127

Функции в неканонической виде 127

Неполно заданные функции 128

Примеры входных комбинаций, которые

никогда не случаются 130

Минимизация с использованием нулей на

карте Карно 132

Минимизация систем со многими выходами 133

Карты Карно большего размера 135

8

Содержание

3.5. Комбинационные логические микросхемы средней

степени интеграции 135

3.5.1. Дешифраторы/демультиплексоры 136

Области применения

дешифратора/демультиплексора 139

3.5.2. Мультиплексоры 141

Области применения селекторов

данных/мультиплексоров 144

3.5.3. Арифметические схемы 145

Сложение 146

Вычитание 148

3.6. Резюме 149

3.7. Упражнения 149

Глава 4. Триггеры и счетчики 153

4.1. Последовательные схемы 153

4.2. Проектирование элементов с памятью на основе вентилей 155

4.3. Триггеры 157

4.3.1. RS-триггер 158

Таблица истинности 158

Характеристическое уравнение триггера 159

Переключение по уровню 159

4.3.2 D-триггер 161

Переключение по фронту 162

Асинхронные входы установки и сброса 165

Диаграмма состояния триггера 165

4.3.3. JK-триггер 167

4.4. Регистры 169

4.4.1. Регистры сдвига 170

Области применения регистров сдвига 172

4.5. Счетчики 176

4.5.1. Счетчики на JK-триггерах 177

Нахождение функций на входах триггеров 177

Таблица возбуждения 179

Таблица (переходов) состояний 179

4.5.2. Счетчики на D-триггерах 184

Содержание

9

4.5.3. Начальные условия 186

4.5.4. Двоичные счетчики с обратным счетом 186

4.5.5. Двоичный счетчик со сквозным переносом 188

4.6. Резюме 190

4.7. Упражнения 190

Глава 5. Проектирование последовательных схем 195

5.1. Модель синхронной последовательной схемы 195

5.2. Проектирование синхронных последовательных схем 198

5.2.1. Задача 1: счетчик с двумя произвольными

счетными последовательностями 199

Диаграмма состояний 199

Таблица (переходов) состояний 199

Назначение состояниям значений переменных 200

Входные функции триггеров 200

5.2.2. Задача 2: детектор последовательности 202

Алгоритм проектирования 203

Диаграмма состояний 203

Таблица (переходов) состояний 204

Назначение состояниям значений переменных 205

Входные функции триггеров 208

Выходная функция 209

Логическая схема 209

5.2.3. Использование JK-триггеров 210

5.2.4. Проектирование на основе модели Мили 210

Диаграмма состояний модели Мили 211

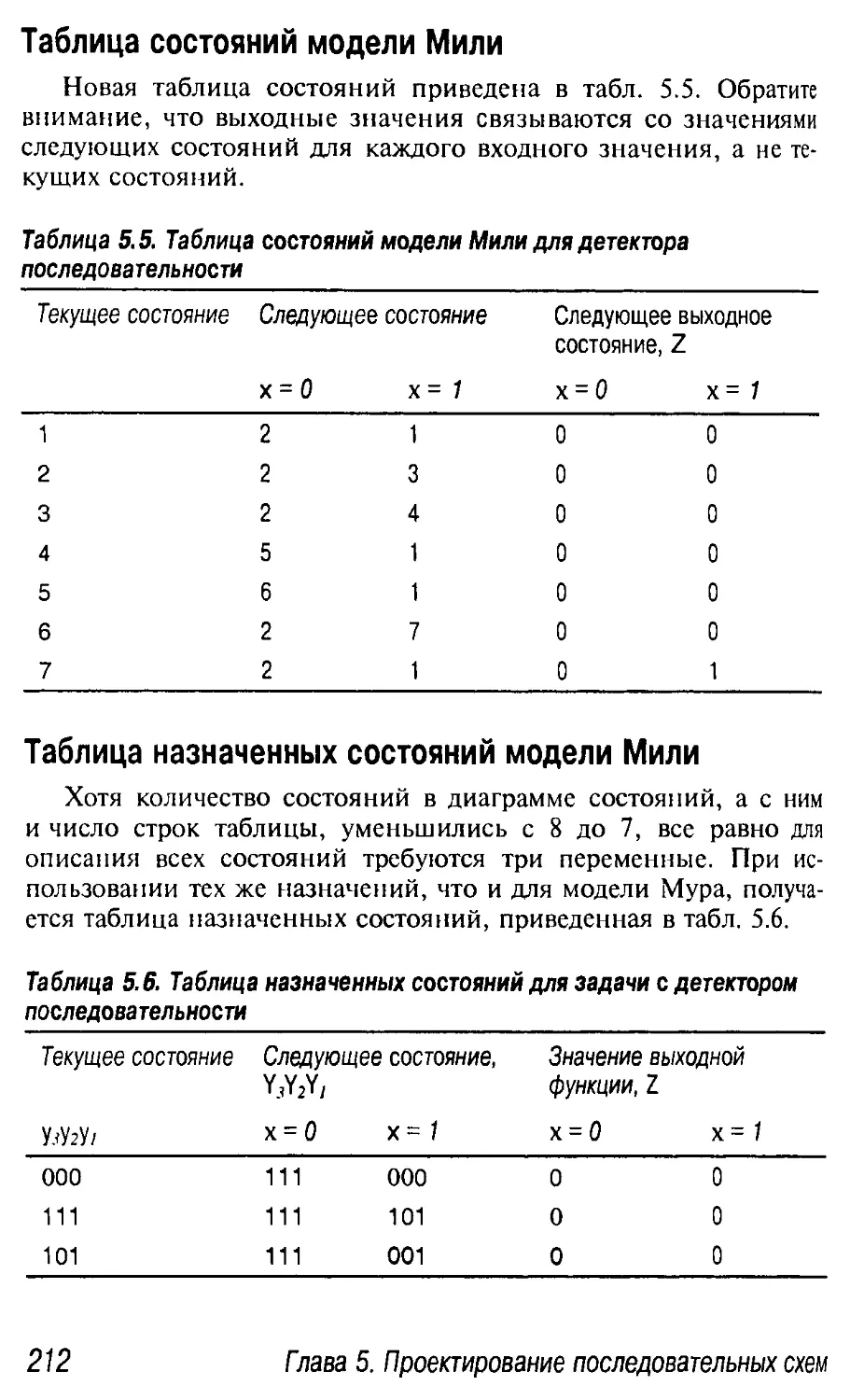

Таблица состояний модели Мили 212

Таблица назначенных состояний модели Мили 212

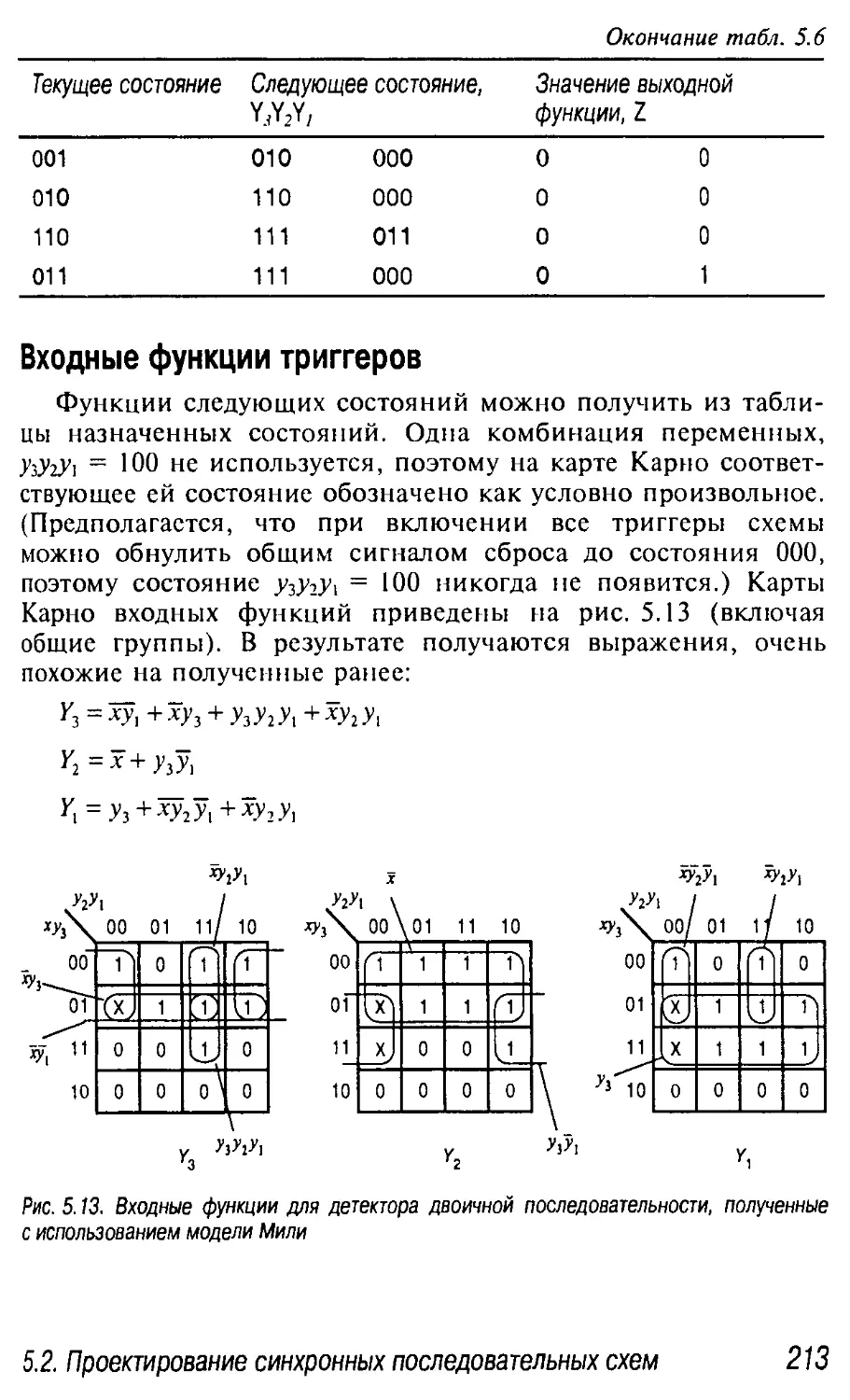

Входные функции триггеров 213

Выходная функция 214

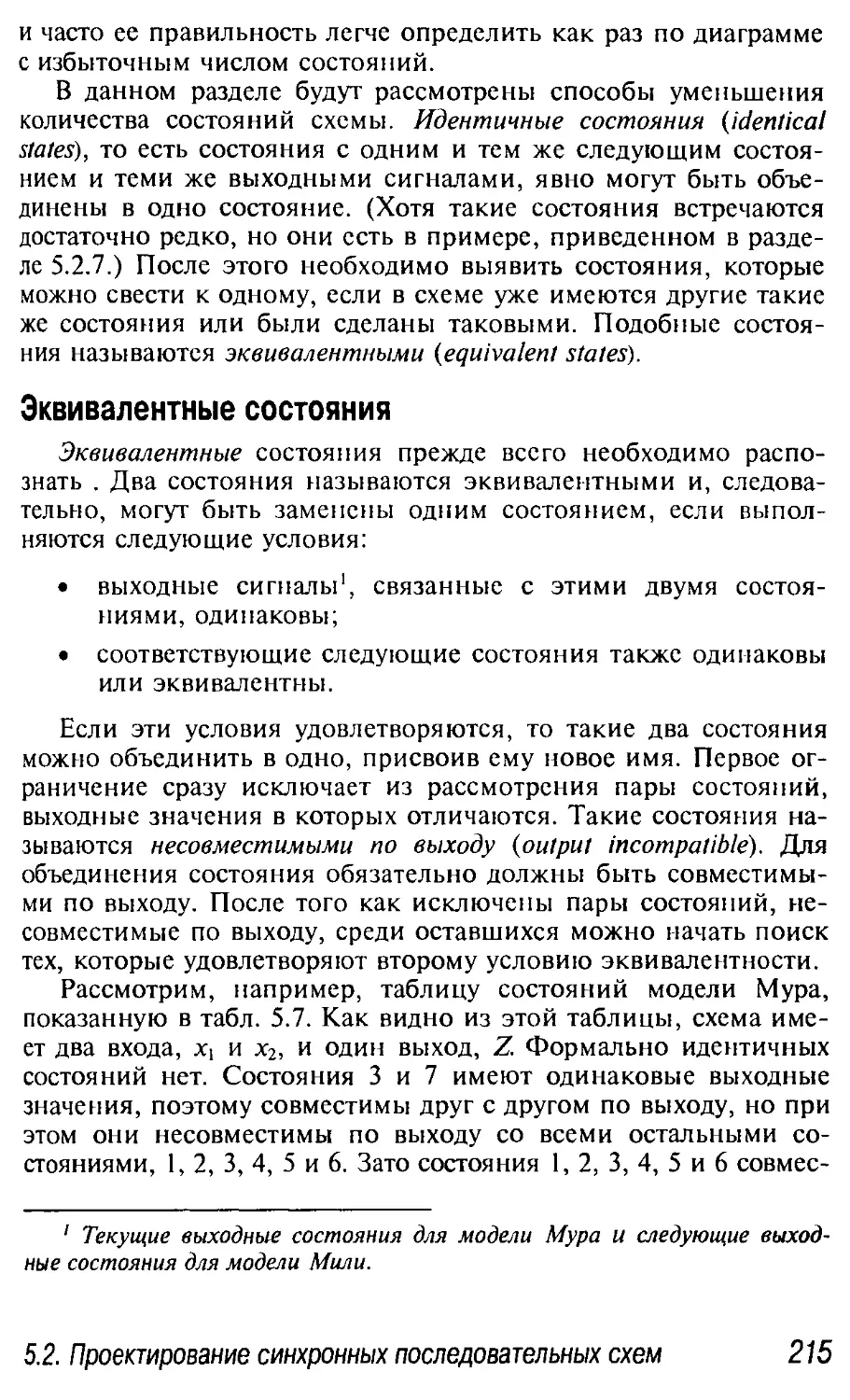

5.2.5. Минимизация количества состояний 214

Эквивалентные состояния 215

Минимизация таблиц состояний модели Мили 218

5.2.6. Диаграммы состояний с использованием

выражений перехода 218

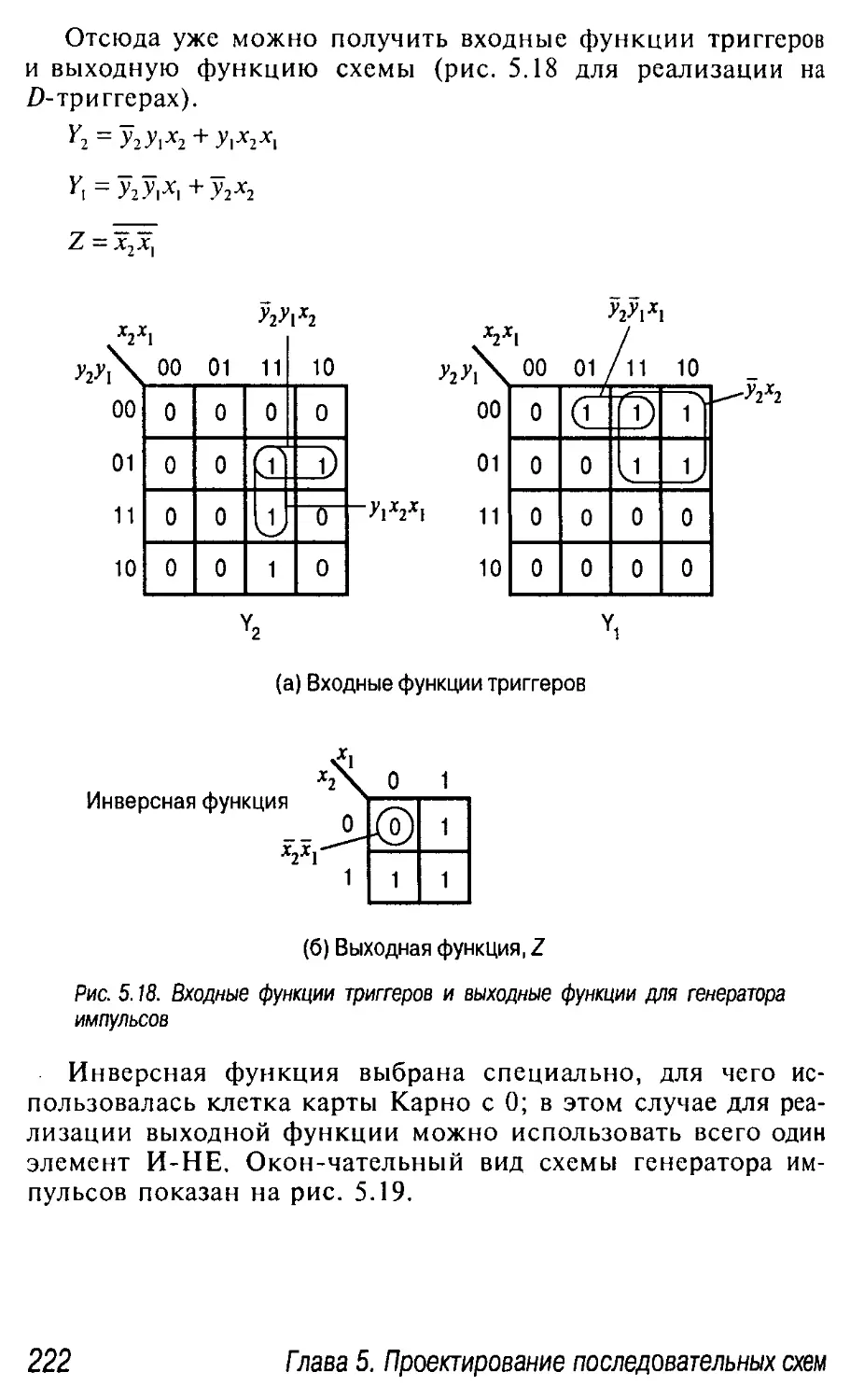

Пример: проектирование генератора импульсов

переменной длительности 219

10

Содержание

Таблица состояний с использованием

выражений переходов 223

5.2.7. Неполно заданные системы 224

Задача: проектирование интерфейсной логики 225

5.2.8. Прямое назначение переменных 229

5.3. Резюме 230

5.4. Упражнения 230

Глава 6. Проектирование устройств

на программируемых логических

интегральных схемах (ПЛИС) 2зз

6.1. Программируемые логические интегральные схемы 233

6.2. Комбинационные ПЛИС 235

6.2.1. Программируемые логические матрицы (ПЛМ) 235

6.2.2. Программируемая матричная логика (ПМЛ) 240

6.3. ПЛИС для реализации последовательных логических схем 246

6.3.1. Регистровые ПЛИС 247

6.3.2. Макроячейки 251

6.4. Инструментальные средства программирования ПЛИС 252

6.4.1. Структура файла с исходным кодом языка ABEL 253

Независимое от архитектуры проектирование 255

6.4.2. Комбинационные функции 255

Операторы множеств и отношений 259

Метод таблиц истинности 262

Тестовые векторы 262

6.4.3. Последовательные функции 263

Метод уравнений 263

Метод диаграмм состояний 264

Метод таблиц истинности 266

Тестовые векторы 266

Архитектурно независимое проектирование 266

6.5. Использование постоянных запоминающих устройств (ПЗУ) 268

6.6. Резюме 273

6.7. Упражнения 273

Содержание / /

Глава 7. Тестирование логических схем 275

7.1. Необходимость тестирования электронных схем 275

7.2. Неисправности 276

Константные неисправности 277

Другие неисправности 277

Одиночная константная неисправность 278

7.3. Формирование тестовых векторов для

комбинационных схем 280

7.3.1. Табличный и алгебраический методы 281

7.3.2. Метод активизации пути 281

Установка сигнала на выходе базовых вентилей

с заданным логическим уровнем 283

Активизация пути 285

Активизация пути благодаря проходу в прямом

и обратном направлении 286

Эквивалентные неисправности в элементах 288

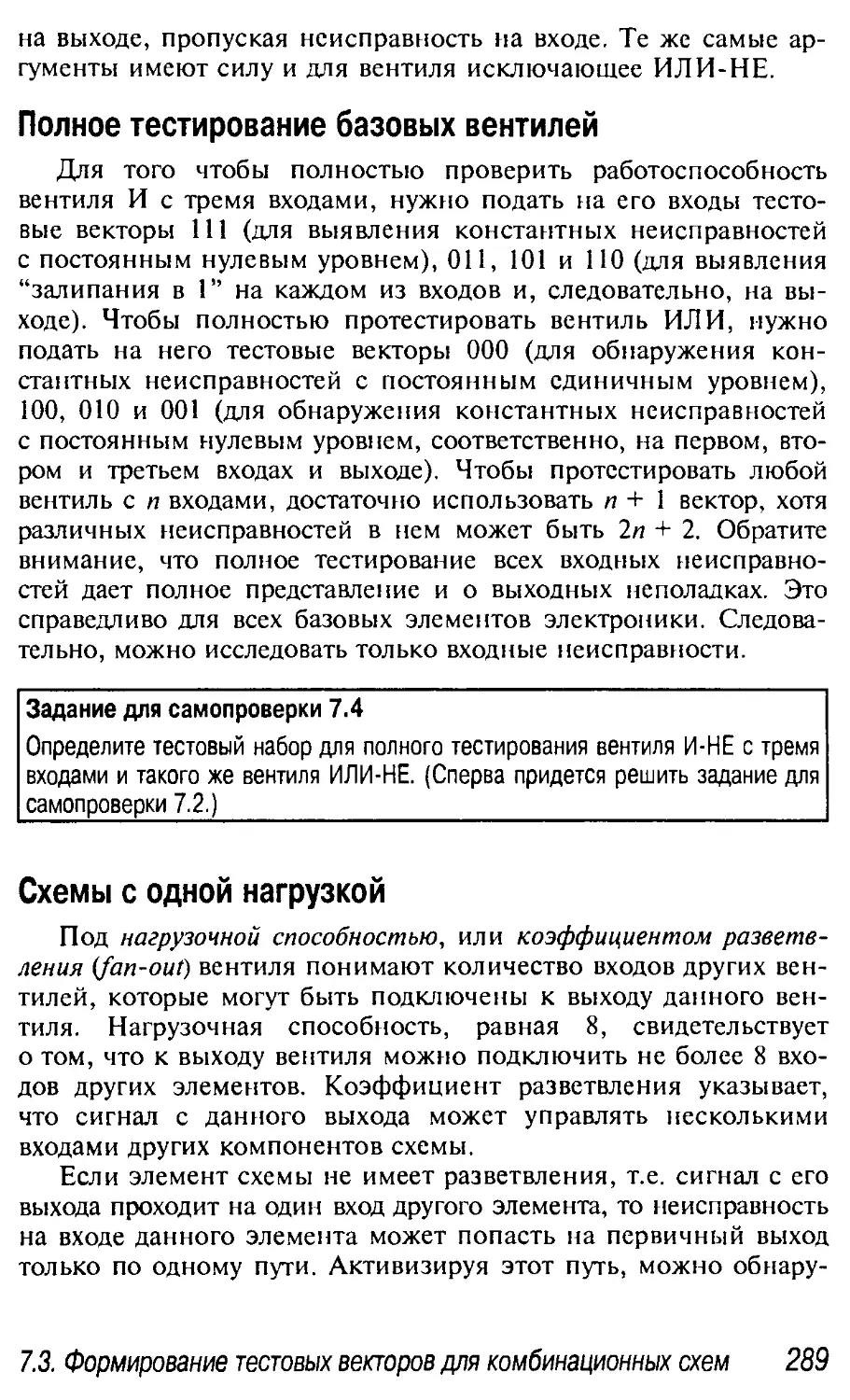

Полное тестирование базовых вентилей 289

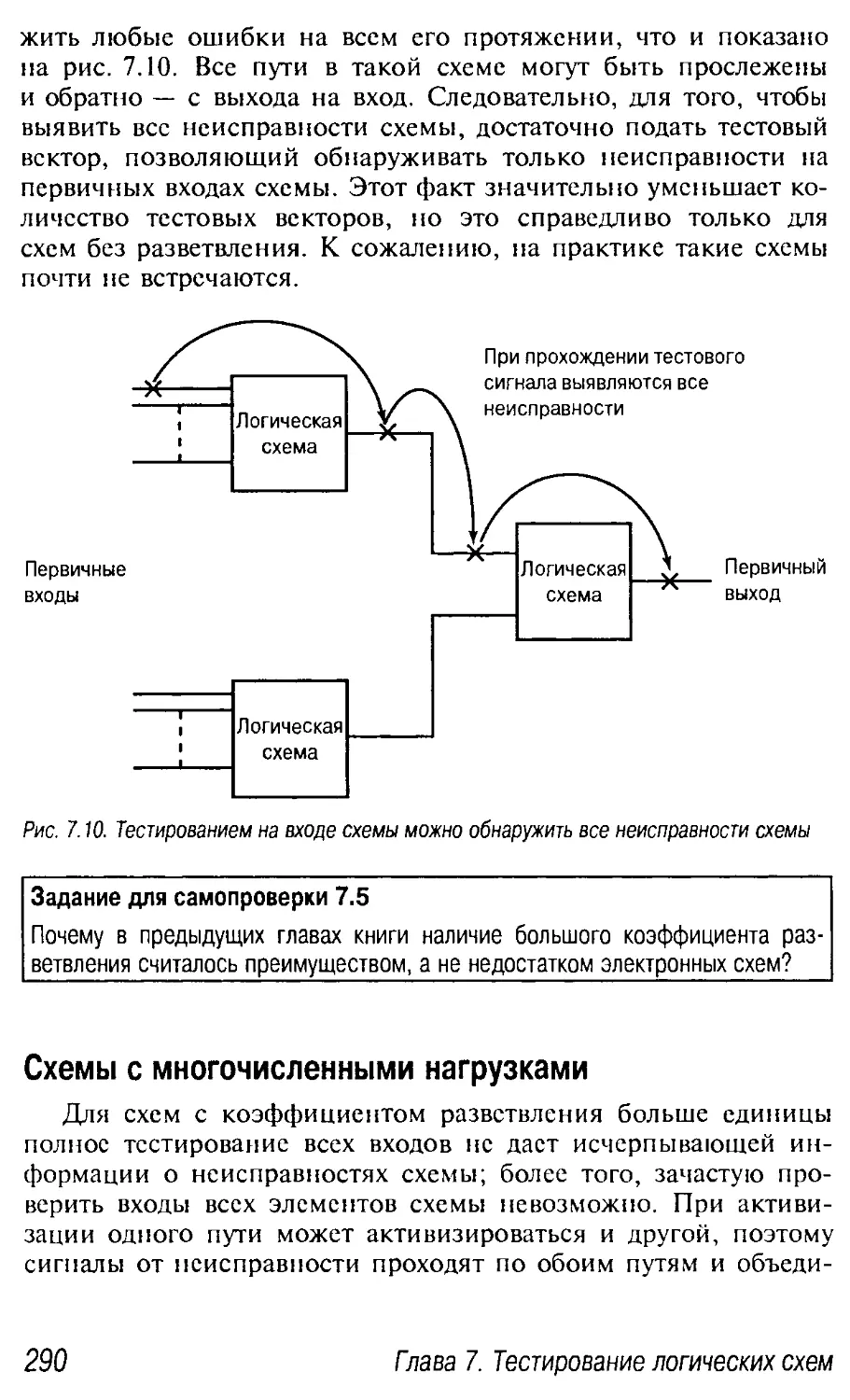

Схемы с одной нагрузкой 289

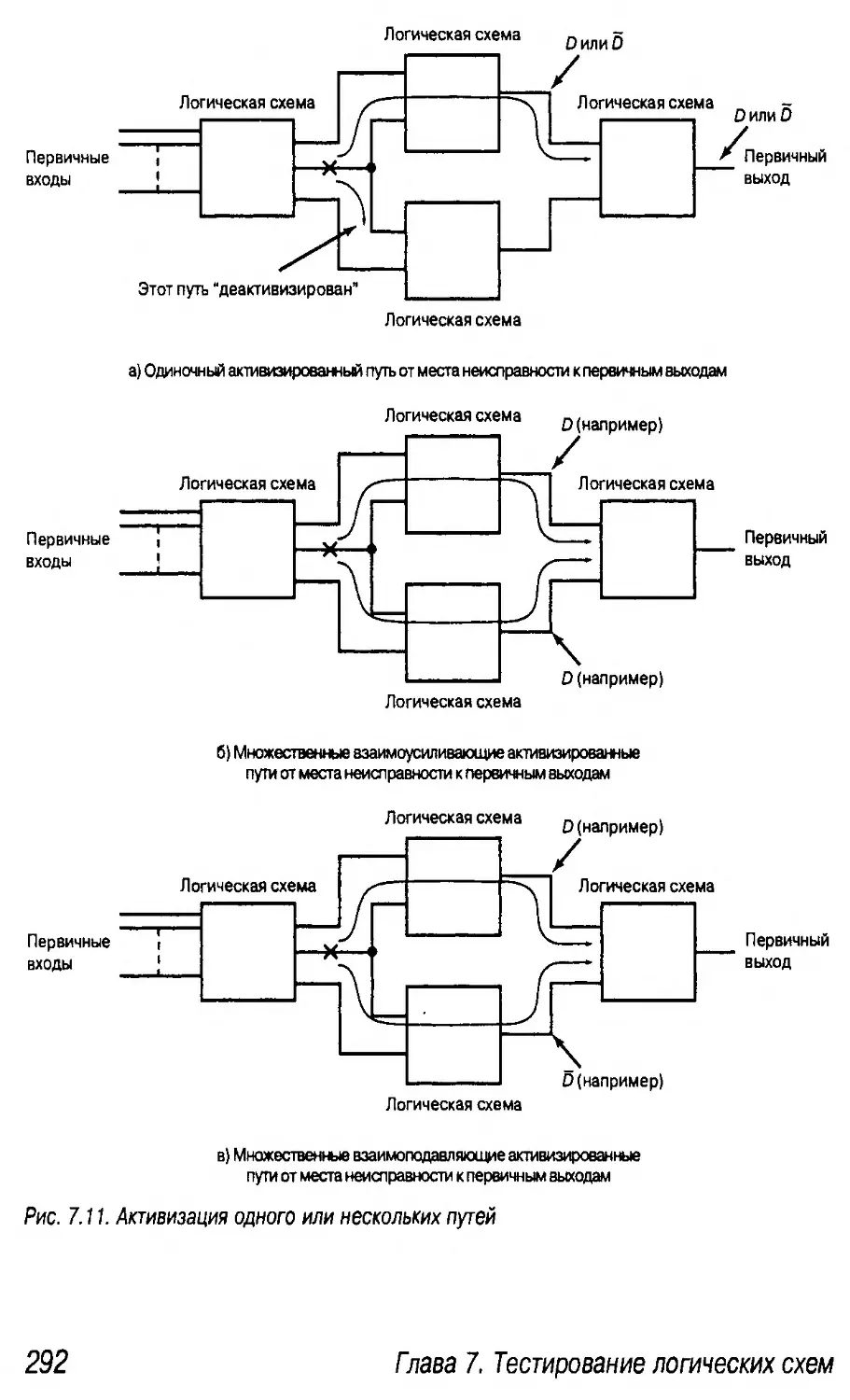

Схемы с многочисленными нагрузками 290

Необнаруживаемые неисправности 293

7.4. Тестирование последовательных схем и сложных

электронных систем 296

7.4.1. Метод сканирования пути 296

7.4.2. Встроенное самотестирование 298

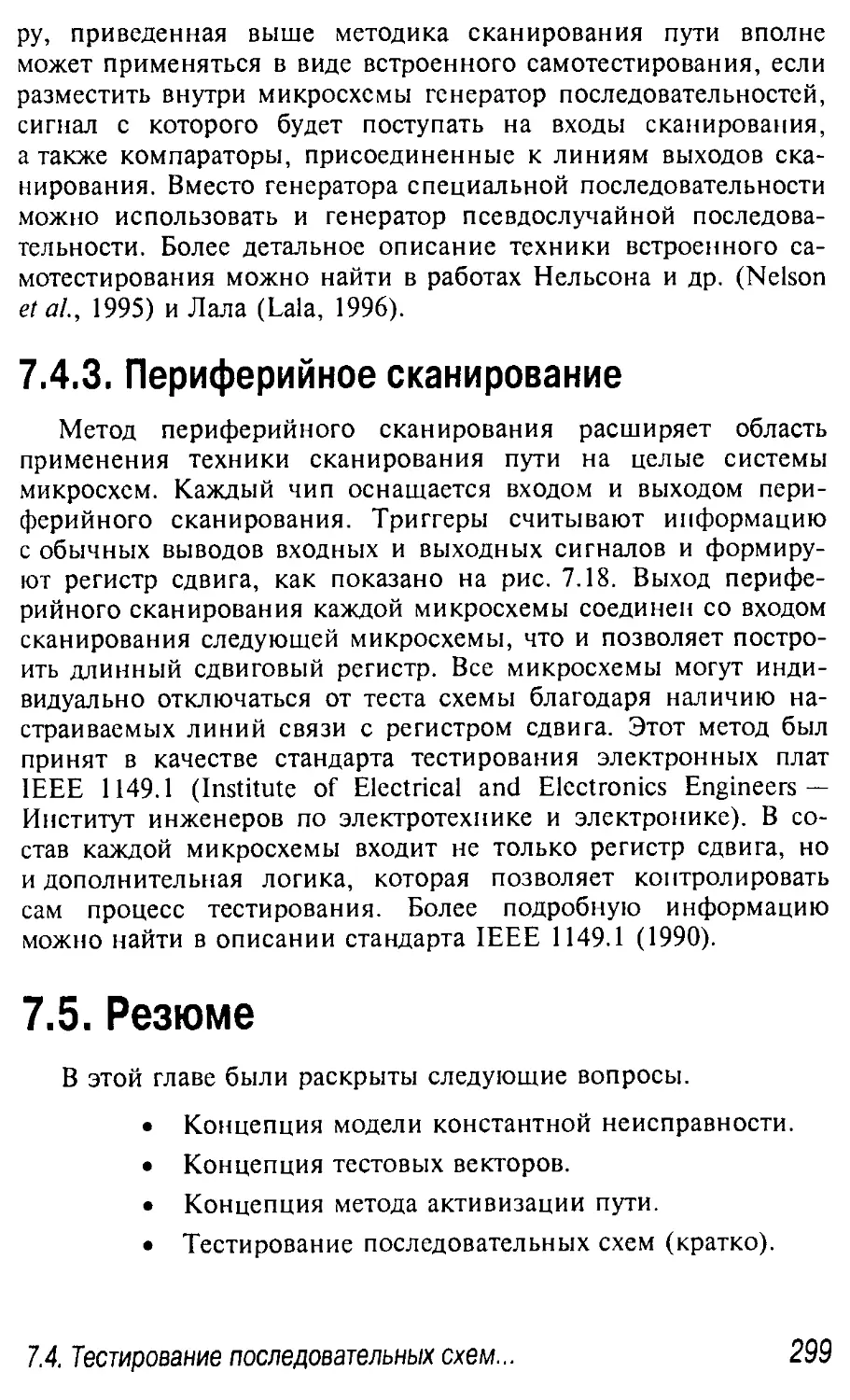

7.4.3. Периферийное сканирование 299

7.5. Резюме 299

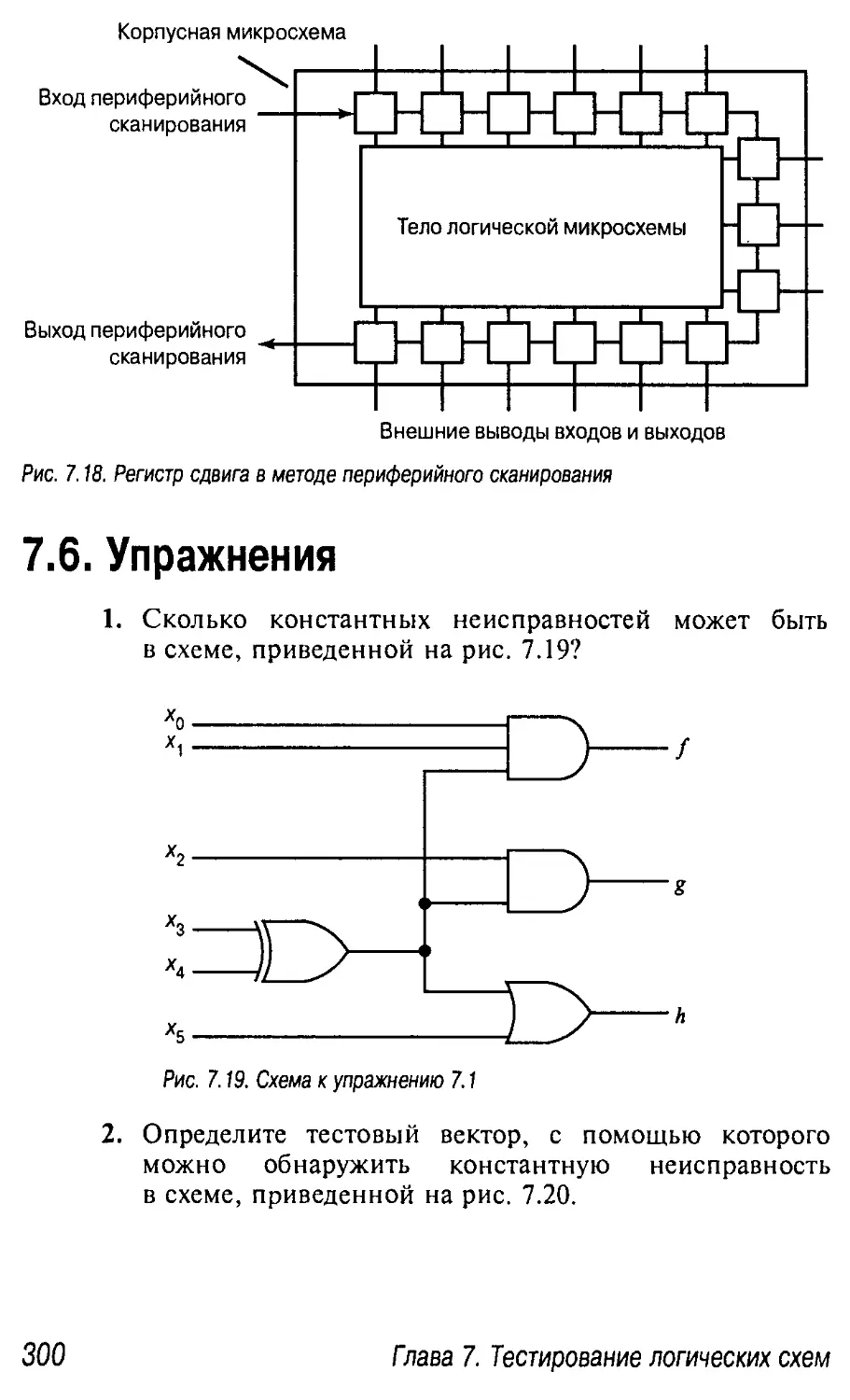

7.6. Упражнения 300

Ответы на задания для самопроверки зоз

Предметный указатель 315

12

Содержание

Предисловие

Эта книга написана для того, чтобы дать представление

о ключевых аспектах проектирования логических схем студен-

там электротехнических и компьютерных специальностей.

Структура материала была специально разработана таким обра-

зом, чтобы изложить курс за один семестр.

В главе 1 вы ознакомитесь с общими концепциями построе-

ния цифровых систем и основными областями их применения.

Здесь вводится понятие логического сигнала, имеющего два

возможных состояния. Такие сигналы используются во всех

цифровых системах; они могут принимать одно из двух значе-

ний — 0 или 1 — и применяться либо для управления, либо для

представления чисел (в двоичной форме). В этой же главе

в общих чертах в рамках вопросов проектирования цифровых

схем поясняются двоичная система счисления и двоичная

арифметика. Поскольку книга посвящена только основам, то

преобразование чисел из одной системы счисления в другую

описано весьма поверхностно. Однако в книге приводятся

ссылки на литературу, в которой можно найти более подробное

описание затрагиваемых в ней тем.

Математическим базисом цифровых систем является булева

алгебра, которая в данном контексте определяет выполнение

операций над бинарными переменными. Именно эти операции

реализуются в логических вентилях, делая такие вентили фун-

даментом любой цифровой системы. Различные типы логиче-

ских вентилей вместе с соответствующими функциями булевой

алгебры описываются в главе 2. В конце главы кратко рассмат-

риваются простейшие схемотехнические решения логических

вентилей. Данный материал будет интересен прежде всего ин-

женерам-электрикам; студенты компьютерных специальностей

могут опустить этот раздел без ущерба для целостности изложения.

Логические вентили часто называют комбинационными ло-

гическими схемами, поскольку состояния на их выходах зависят от

комбинаций значений входных сигналов. В главе 3 описывается

методика проектирования более сложных комбинационных

цифровых систем на основе вентилей. Одним из ключевых ас-

пектов при проектировании цифровых систем является количе-

ство и типы используемых вентилей. Часто желательно, чтобы

количество вентилей в системе было минимальным. В этой

же главе описываются методики уменьшения количества вен-

тилей, в частности метод минимизации с использованием

карт Карно. Минимизация очень сложных логических схем

часто выполняется с помощью специализированных компью-

терных программ. Описание методов, более пригодных для

программной реализации, можно найти в литературе, список

которой приведен в конце главы.

Большинство цифровых систем имеет память, в которой

хранится информация о прошлых событиях. От этих событий

может зависеть реакция таких систем. Базовыми логическими

компонентами, обладающими свойством памяти, являются

триггеры, которым посвящена глава 4. Триггеры составляют ос-

нову более сложных схем “последовательной логики”, на выходе

которых могут формироваться последовательности различных со-

стояний. Еще одной широко распространенной последователь-

ной логической схемой является счетчик, состояния па выходе

которого воспроизводят числовые последовательности, например

возрастающую двоичную последовательность. Принципы по-

строения счетчиков описываются в этой же главе. Сведения

о внутренней структуре триггеров можно найти в дополнитель-

ной литературе, хотя зачастую это и необязательно, так как в по-

давляющем большинстве случаев используются уже готовые

триггеры или стандартные схемотехнические решения.

В главе 5 продолжается описание проектирования последо-

вательных схем. Значительное внимание уделено методу диа-

грамм состояний, который поясняется с помощью практиче-

ских примеров. Все рассматриваемые устройства относятся

к так называемым синхронным последовательным схемам, ко-

торые управляются с помощью внешнего тактового сигнала.

Благодаря простоте организации временных диаграмм выпол-

нения операций при наличии тактового сигнала подобные схе-

мы составляют подавляющее большинство цифровых устройств.

Описание проектирования асинхронных последовательных

схем, в которых такой сигнал отсутствует, можно найти в лите-

ратуре, список которой дан в конце главы.

Глава 6 целиком посвящена программируемым логическим

интегральным схемам (ПЛИС). ПЛИС представляют собой

логические компоненты с изменяемой внутренней структурой

Предисловие

15

связей, которые позволяют создавать различные устройства на

базе одной микросхемы. ПЛИС широко используются для

уменьшения количества компонентов и общей стоимости ко-

нечного изделия. Для получения необходимой внутренней

структуры связей такие ИС должны “программироваться”.

Процедура программирования описывается с использованием

языка программирования ПЛИС, синтаксис которого представ-

лен в главе 6. Здесь же приведены все детали, необходимые для

практического программирования. Более подробные сведения

о языках программирования ПЛИС можно найти в предложен-

ном списке литературы.

В главе 7 представлены методики тестирования логических

схем для выявления ошибок, которые могли появиться в про-

цессе производства или эксплуатации устройства. Тестирование

является крайне важным моментом, но почему-то до сих пор

в имеющейся литературе по проектированию логических схем

эта тема опускалась. К изготовлению работоспособной систе-

мы, как и к проектированию, следует относиться со всей серь-

езностью, и в этом контексте тестирование устройств является

неотъемлемой частью процесса проектирования.

Как видно из краткого описания материала, есть несколько

ключевых моментов, на которых строится изложение. Для препо-

давателей имеется специальный раздел с ответами к упражнениям.

Автор хотел бы выразить глубокую признательность Кристо-

феру Гленни (Crostopher Glennie) из издательства Prentice Hall за

постоянную помощь в ходе подготовки этой книги и конструк-

тивную критику рукописи. Также автор считает своим долгом

поблагодарить Жаклин Харбор (Jackueline Harbor) за работу над

рукописью, а весь коллектив Prentice Hall — за профессионализм.

Наконец, отдельное спасибо анонимным рецензентам за прило-

женные ими усилия и ценные комментарии. Автор оценит лю-

бые пожелания или предложения по исправлению материала, ко-

торые можно присылать по электронному адресу abw@uncc.edu;

они будут учтены в последующих изданиях книги.

Барри Уилкинсон

16

Предисловие

От издательства

Вы, читатель этой книги, и есть главный ее критик и ком-

ментатор. Мы ценим ваше мнение и хотим знать, что сделано

правильно, что можно было сделать лучше и что еще вы хотели

бы увидеть изданным. Нам интересны любые ваши замечания

по поводу книги.

Мы ждем ваших комментариев. Вы можете прислать нам

обычное или электронное письмо либо просто посетить наш

Web-сервер и оставить свои замечания там. Одним словом, лю-

бым удобным для вас способом дайте нам знать, нравится или

нет вам эта книга, а также выскажите свое мнение о том, как

сделать наши книги более интересными для вас.

Посылая письмо или сообщение, не забудьте указать назва-

ние книги и ее авторов, а также ваш обратный адрес. Мы вни-

мательно ознакомимся с вашим мнением и обязательно учтем

его при отборе и подготовке к изданию последующих книг.

Наши координаты:

E-mail: inf oSwilliamspublishing . com

WWW: http:/ /www.williamspublishing.com

Информация для писем из:

России: 115419, Москва, а/я 783

Украины: 03150, Киев, а/я 152

Глава 1

Цифровые системы

и представление

информации

Цели и задачи

В этой главе описаны основные элементы цифровых систем

и области их применения. Большая часть материала по-

священа представлению информации в таких системах.

Здесь вводится понятие логического сигнала, имеющего

всего два возможных значения, и показывается, как подоб-

ные сигналы могут использоваться для представления

управляющих сигналов и числовых данных.

1.1. Цифровые системы

Как правило, цифровые системы разрабатываются для ре-

шения двух тесно взаимосвязанных задач:

• управления устройствами;

• выполнения вычислений.

Цифровая система может сначала выполнять вычисления и

на основе полученных результатов предпринимать определен-

ные действия по управлению. В качестве примеров таких сис-

тем можно назвать: а) системы управления промышленным

оборудованием и б) автомобильные системы.

1.1.1. Управляющие системы

Давайте рассмотрим простой пример управления количест-

вом материала в бункере (рис. 1.1). Целью является поддер-

жание количества материала в бункере между уровнями L1

и L2, причем известно, что материал отбирается с определен-

ными интервалами. Цифровая система управляет клапаном

подачи материала в бункер. В системе имеются два датчика,

один из которых определяет момент достижения материалом

уровня L1, а второй — момент достижения уровня L2. Каж-

дый датчик при прохождении материалом заданного уровня

формирует сигнал. Как правило, такой сигнал представляет

собой некоторый уровень напряжения, скажем, 5 вольт, когда

уровень материала пересекает линию датчика, и 0 вольт, когда

этого не происходит. Таким образом, входной сигнал имеет

два состояния: одно индицирует прохождение материалом оп-

ределенного уровня, а второе — отсутствие данного события.

Клапан подачи материала также управляется сигналом, имею-

щим всего два состояния, в нашем случае это состояния ВКЛ

и ВЫКЛ. Например, сигнал напряжением 50 вольт может

открывать клапан, а сигнал напряжением 0 вольт — закрывать

Выходной

сигнал

Сигнал об

ошибке

Рис. 1.1. Контроль расхода материала в бункере

20

Глава 1. Цифровые системы и представление информации

его. Клапан должен открываться, когда уровень материала

в бункере опускается ниже отметки L1, и оставаться откры-

тым до тех пор, пока уровень материала не поднимется выше

отметки L2, после чего он должен закрыться. Кроме того,

клапан остается закрытым, пока уровень материала не падает

ниже отметки L1. Наша цифровая система должна вырабаты-

вать сигнал, реализующий такой “алгоритм”, при этом сигнал

имеет два состояния: для включения и для выключения кла-

пана подачи материала.

В системе индицируются два уровня, поэтому подача материала

в бункер осуществляется через определенные интервалы времени.

Если бы система решала задачу поддержания объема материала

на одном фиксированном уровне, закрывая клапан при превы-

шении этого уровня и открывая его, когда уровень опустится

ниже отметки, то клапан постоянно закрывался бы и открывался.

Логические сигналы и функции

В последующих главах будут рассмотрены законы проекти-

рования цифровых систем, в том числе и таких, как показанная

на рис. 1.1, а пока отметим, что входные и выходные сигналы

таких систем имеют лишь два значения, обычно передаваемых

в виде двух уровней напряжения. Внутри самой цифровой сис-

темы могут использоваться, скажем, 5 вольт для передачи од-

ного значения и 0 вольт — для передачи второго. Чтобы не

привязываться к конкретным величинам напряжений, далее

такие сигналы с двумя возможными значениями будут назы-

ваться логическими. Любая проектируемая цифровая система

разрабатывается на основе компонентов, которые восприни-

мают и формируют на выходе двузначные логические сигна-

лы. В приведенном выше примере значения сигнала соответ-

ствовали состояниям “включено” (ВКЛ) и “выключено”

(ВЫКЛ). Иногда могут использоваться термины ИСТИННЫЙ

(TRUE) и ЛОЖНЫЙ (FALSE): скажем, сигнал с первого

датчика считается ИСТИННЫМ, когда уровень материала

выше отметки 1, и ЛОЖНЫМ, если уровень материала ниже

ее. Значение ИСТИНННЫЙ здесь соответствует состоянию

ВКЛ, а ЛОЖНЫЙ — состоянию ВЫКЛ. Обычно при проекти-

ровании логических схем вместо терминов используют число-

вые значения 1 (ИСТИНННЫЙ) и О (ЛОЖНЫЙ). Ниже при-

ведена таблица для рассматриваемой ситуации с указанием со-

ответствующих “логических” сигналов.

1.1. Цифровые системы

21

Таблица 1.1. Логические сигналы

Ситуация Логическое напряжение Состояние ключа Логическое значение

Ниже уровня ОВ ВЫКЛ ЛОЖНЫЙ (0)

Выше уровня 5В ВКЛ ИСТИННЫЙ (1)

Положительная и отрицательная логика

В реальных системах, как правило, используются напряже-

ния 0 и 5 вольт, хотя для внутренних вентилей таких сложных

устройств, как микропроцессоры, эти уровни могут быть суще-

ственно ниже. Имея два напряжения, скажем, эти же 0 и 5 вольт,

необходимо решить, какое из них приписать каждому логиче-

скому значению. К примеру, можно использовать напряжение О

вольт для представления логической 1 и 5 вольт — для представ-

ления логического 0, но какое бы напряжение ни было выбрано,

оно должно быть одинаковой величины во всей системе. Обычно

для представления логической 1 выбирается более высокое на-

пряжение, а для представления логического нуля — более низкое

(т.е. 5 вольт = 1 и 0 вольт — 0). Такая логика получила название

положительной (positive logic representation). Можно использовать

и обратное представление, когда высокое напряжение соответству-

ет логическому 0, а низкое — логической 1. Такая логика назы-

вается отрицательной. Возможно также и одновременное исполь-

зование в одной системе обеих логик (при этом по-прежнему

должны использоваться только два напряжения). Использование

двух представлений в одной логической системе получило назва-

ние смешанной логики. В этом случае для именования логических

сигналов требуются специальные условные обозначения (см. ра-

боты Флетчера (Fletcher), 1980 или Тиндера (Tinder), 1991).

Логические функции

Для того чтобы разработать “алгоритм” или выходную логиче-

скую функцию цифровой системы, логическим сигналам необхо-

димо присвоить имена, как переменным в алгебре. Например,

входные сигналы от изображенных на рис. 1.1 датчиков можно

назвать 5, и S2 (от первого и от второго, соответственно). Выход-

ной управляющий сигнал пусть называется Z. На рисунке также

показан второй выходной сигнал, который указывает на наличие

в работе системы ошибки. Такая ошибка может возникнуть,

22

Глава 1. Цифровые системы и представление информации

например, в том случае, если первый датчик показывает, что ко-

личество материала ниже отметки L1, в то время как второй, —

что уровень материала превышает отметку L2, что, понятно, при

правильной работе всех компонентов системы невозможно. Обо-

значим этот выходной сигнал ошибки Е. Алгоритм генерации

сигнала ошибки можно записать в следующем виде:

Е — 1, если 5, = 0 и 5, = 1

Данная логическая функция может быть записана в виде

выражения булевой алгебры:

e = s[s2

В данной записи переменная будет равна нулю, если

5, = 1, и единице, если 5, = 0. Символ точки (•) обозначает

логическую операцию И.

В общем случае в системе может быть более одного сигнала

ошибки, например Е,, Е2, Е3 и т.д., каждый из которых указы-

вает на возникновение того или иного сбоя в работе системы.

Если необходимо, чтобы при выполнении условия Е, = 1 или

Ег = 1, или Е3 = 1 звучал сигнал тревоги, то алгоритм генера-

ции такого сигнала будет выглядеть так:

Тревога = 1, если Е, = I, или Е2 = I, или Е3 = 1

Логическая функция данного условия в булевой алгебре за-

писывается следующим образом:

Тревога = Е, + Е2 + Е3

Здесь символ (+) соответствует операции булевой алгебры

ИЛИ. Итак, рассмотренный пример познакомил с тремя ос-

новными операциями булевой алгебры: И (), ИЛИ (+) и НЕ

(—). Пользуясь ими, можно создать любую логическую функ-

цию. Полнее возможности булевой алгебры будут описаны

в главе 2. Таким образом, для решении задачи управления не-

обходимо иметь логическую схему с двумя входными сигнала-

ми, 5, и S2, и одним выходным сигналом, Е, который будет

принимать значение 1, если 5, = 0 и 52 = 1, в противном случае

Е = 0. Выполнение данного условия требует применения ком-

бинационных логических схем, поскольку значение на выходе

системы зависит от комбинации сигналов на входе. Функция

генерации сигнала тревоги также реализуется с использованием

схем комбинационной логики.

Выходная функция Z носит более сложный характер, по-

скольку требует наличия в схеме памяти для запоминания

1.1. Цифровые системы

23

логических значений. Z будет равна 1 при 5, = 0, но не перей-

дет обратно в 0, когда 5, станет равным 1, а сделает это только

при S2= 1. Схемы, на основе которых можно реализовать по-

добную функцию, носят название последовательных логических

схем, поскольку в общем случае сигналы на их выходах следуют

некоторым последовательностям. Проектирование таких логи-

ческих схем рассматривается в главе 4.

Вычисления

Более сложные задачи управления часто связаны с приме-

нением измерительных датчиков. Например, это могут быть

датчики измерения температуры. Скажем, необходимо, чтобы

с помощью нагревательных элементов температура материала

в бункере поддерживалась на определенном уровне. К примеру,

нагреватель должен включаться, если температура материала

опускается ниже 40°С, и работать до тех пор, пока температура

не поднимется до 45°С, после чего он должен отключиться до

того момента, пока температура вновь не опустится до 40°С.

Этот алгоритм очень похож на используемый для контроля ко-

личества материала в бункере, за исключением того, что теперь

необходимо работать с числовыми данными, а не с простыми

сигналами типа ВКЛ и ВЫКЛ. В этой и других задачах могут

иметь место многочисленные измерения и сложные расчеты,

основанные на полученных данных. Например, современный

автомобильный двигатель управляется с помощью цифровой

системы. В этом случае управленческие воздействия для полу-

чения оптимального режима работы зависят от значений не-

скольких переменных, включая текущую скорость, нагрузку,

температуру и т.д. Совершенно ясно, что в этом случае придет-

ся иметь дело не только с логическими двузначными перемен-

ными, но и с числовыми данными.

Цифровой компьютер

Полуавтоматическое выполнение вычислений для облегче-

ния тяжелых ручных расчетов долго оставалось мечтой. Но

в 1850-х годах Ч. Бэббиджем была изобретена механическая

счетная машинка, электронные версии которой начали разра-

батываться во время второй мировой войны и использовались

для расчетов траектории реактивных снарядов. Бэббидж пер-

вым сформулировал идею универсального программируемого

24

Глава 1. Цифровые системы и представление информации

калькулятора, электронная версия которого сейчас называется

“цифровым компьютером”. Такие компьютеры находятся на

вершине цифровых систем и представляют собой сложные

устройства, которые оперируют числами и с помощью про-

грамм, хранящихся в памяти, вычисляют необходимые вы-

ходные значения. Наиболее сложные задачи управления, на-

пример управление автомобилем, в настоящее время решают-

ся уже не специализированными контроллерами, а с помо-

щью именно цифровых компьютеров.

На рис. 1.2 показана обобщенная структурная схема циф-

рового компьютера. Процессор способен выполнять различ-

ные арифметические операции над числами, после чего при-

нимать основанные на результатах расчетов решения. Выпол-

няемые компьютером действия кодируются в числовой форме

и записываются в память в виде команд. Для этой цели чаще

всего используется двоичная числовая форма, которая будет

описана ниже. Закодированные команды последовательно по-

даются в процессор для выполнения. Конечно, последова-

тельность этих команд (программа) создается человеком

(программистом). Процессору необходимо абсолютно точно

указывать, какие вычисления он должен выполнить и какие

решения принять в зависимости от полученного результата,

что и делается в процессе разработки программы.

Рис. 1.2. Структура программируемого компьютера

1.1. Цифровые системы

25

1.2. Представление чисел в цифровых

системах

1.2.1. Двоичные числа

Имеем ли мы дело с полностью программируемым компью-

тером или с узкоспециализированной управляющей системой,

в любом случае приходится оперировать числами, а значит,

представлять их в виде напряжений. Предположим, использу-

ются десятичные числа, при этом каждому разряду соответству-

ет один сигнал. В этом случае каждый сигнал должен представ-

ляться десятью различными уровнями напряжения — по одно-

му для каждого возможного значения цифры в каждом разряде.

Например, цифра 0 могла бы представляться напряжением О

вольт, цифра 1 — напряжением 1 вольт и т.д. Тогда электрон-

ные схемы должны проектироваться таким образом, чтобы они

могли воспринимать и генерировать десять различных уровней

напряжения, по одному для каждого разряда числа.

Десятичная система счисления является позиционной. В ней

используются цифры, умноженные на степень числа 10, при

этом величина показателя степени зависит от положения

цифры в числе. Например, возьмем десятичное число

235 = 2 х 102 + 3 х 10' + 5 х 10°. Здесь 10 является основанием

системы счисления и показывает, что для представления любой

числовой величины требуется 10 различных цифр: 0, 1, 2, 3, 4,

5, 6, 7, 8 и 9. Само число десять было выбрано, вероятно, бла-

годаря тому, что у человека на руках десять пальцев, однако

в качестве основания можно выбрать любое число. В общем

случае «-разрядное число в системе счисления с основанием b

может быть представлено в виде:

дп.1дп_2...ц...д2д|ц) = a^lF' + У*2 +- + а$+... + а-fi + аф' + д#,

где а, — z-тый разряд числа.

Если бы люди использовали в качестве основания число 9,

то применялось бы только девять цифр: 0, 1, 2, 3, 4, 5, 6, 7

и 8, и любое число выражалось бы исключительно с их по-

мощью. Число 235 в этой системе счисления представляло

бы величину 2 х 92 + 3 х 9' + 5 х 9° = 194. Если бы исполь-

зовалась восьмеричная система (с основанием 8), то цифр

было бы, соответственно, 8: 0, 1, 2, 3, 4, 5, 6 и 7, а число 235

равнялось бы 2 х 82 + 3 х 8' + 5 х 8° = 157. Для однозначно-

сти определения основания системы счисления его можно

26

Глава 1. Цифровые системы и представление информации

показывать справа от числа в виде нижнего индекса. Таким об-

разом, запись 235|О указывает на использование десятичной сис-

темы, 2359 — системы с основанием 9, 2358 — восьмеричной.

С уменьшением величины основания системы уменьшается

и количество цифр. При уменьшении основания до трех (так на-

зываемая троичная система счисления) придется оперировать

цифрами 0, 1 и 2, а при уменьшении основания до 2 (двоичная

система) остаются только цифры 0 и 1. Эти цифры двоичной

системы называются битами (от англ. nary digits — двоичные

разряды). Бит может принимать только одно из двух значений:

О или 1. В качестве примера двоичного числа можно, например,

назвать число 1100012, которое в десятичной системе счисления

равно 1 х 25 + 1 х 24 + 0 х 23 + 0 х 22 + 0 х 2' + 1 х 2° = 49.

Задание для самопроверки 1.1

Чему равно двоичное число 11012 в десятичной системе счисления?

Числа могут быть не только целыми, но и дробными. Разряды

дробной части представляют собой основание, показатели степе-

ни которого не положительны, а отрицательны. Например, за-

пись в десятичной системе выглядит так: 0,12,0 = 1 х КГ1 + 2 х 1(Г2,

а в двоичной системе: 0,1012 = 1 х 2~' + 0 х 2-2 + 1 х 2-3.

Задание для самопроверки 1.2

Чему будет равно двоичное число 1101,1012 в десятичной системе счисления?

Двоичная система счисления идеально подходит для систем,

оперирующих двузначными управляющими сигналами типа

ВКЛ/ВЫКЛ, однако еще более важным ее преимуществом пе-

ред другими системами счисления является то, что с ее помо-

щью любые числа можно выразить с помощью всего двух цифр:

0 и 1. Для выражения любого разряда необходимы лишь два

уровня напряжения. Например, значение 0 вольт может пред-

ставлять двоичный ноль, а 5 вольт — двоичную единицу. Все

это существенно упрощает проектирование цифровых систем,

в частности проектирование электронных схем. Использование

всего двух напряжений также облегчает борьбу с колебанием их

уровней, которые могут возникать вследствие изменения харак-

теристик компонентов схемы, внешних электромагнитных по-

мех и электрических шумов.

1.2. Представление чисел в цифровых системах

27

Часто в цифровой системе необходимо запомнить числовые

значения. В таком случае для хранения каждого разряда пона-

добится одна “ячейка” памяти. В этом смысле двоичное пред-

ставление информации также обладает преимуществом, по-

скольку большинство современных запоминающих устройств

естественным образом позволяют хранить два значения. На-

пример, в памяти на магнитных носителях (дискеты и жесткие

магнитные диски) двузначная информация может храниться

в виде двух направлений вектора намагниченности — вдоль или

поперек материала с магнитными свойствами. Каждому биту

выделяется участок носителя, вектор намагниченности которого

может находиться в одном из двух состояний, соответствующих

двум направлениям намагниченности1. Существует еще один

широко используемый тип запоминающих устройств, основан-

ный на полупроводниковых технологиях, когда для представле-

ния информации используется заряд конденсатора. Присутствие

заряда соответствует наличию единицы, а его отсутствие — нулю.

В оптических системах для представления информации может

использоваться присутствие или отсутствие светового пучка, при

этом присутствие пучка света будет соответствовать 1, а отсутст-

вие — 0. Даже простейшие механические переключатели или ре-

ле могут находиться в двух состояниях, то есть быть включенны-

ми или выключенными. Преимущество использования только

двух состояний было взято за основу и в одном из старейших ме-

тодов храпения информации — на перфорированных лентах

и картах. Отверстие в определенном месте перфокарты означало

1, а отсутствие — ноль. Можно сказать, что присутствие или от-

сутствие “чего-либо” является достаточно универсальным прин-

ципом для представления значений двоичной логики.

По описанным выше причинам двоичная система полу-

чила всеобщее распространение и нашла самое широкое

применение в цифровых системах2.

1 Не только направления вектора магнитного поля представляют со-

бой логические значения; к примеру, логическую единицу может представ-

лять и изменение направления этого вектора, а ноль — отсутствие из-

менений. Более полное описание различных методов хранения информации

на магнитных носителях можно найти в книге Уилкинсона (Wilkinson)

и Хоррокса (Horroks), 1987.

2 Вообще говоря, для наиболее экономичного представления информа-

ции величина основания системы счисления должна стремиться к числу е

(основанию натурального логарифма), равному 2,71828. — Прим, перев.

28

Глава 1. Цифровые системы и представление информации

Задание для самопроверки 1.3

Какие еще методы вы можете предложить для хранения информации в двоим-

ной форме?

Однако преимущества двоичной системы не даются даром.

Поскольку размер основания уменьшается, при этом уменьша-

ется и количество используемых цифр, но это же увеличивает

количество разрядов, требующихся для представления чисел.

В табл. 1.2 показано, что происходит при изменении основа-

ния от 10 до 2 (2 — это наименьшее возможное основание).

Видно, что с уменьшением основания количество разрядов

увеличивается. Например, представление числа 15 в десятич-

ной системе требует лишь двух разрядов, в то время как

в троичной оно записывается тремя, а в двоичной — четырь-

мя цифрами. Количество разрядов зависит от величины числа.

При использовании системы счисления с основанием b для

представления любого числа имеется b различных цифр, и для

записи числа х понадобится [log^x] разрядов. Представление

чисел в двоичной системе счисления обычно требует в три

раза больше разрядов, чем в десятичной, и, таким образом,

использование двоичной логики дается ценой тройного уве-

личения количества проводов и схемных элементов, так как

для каждого разряда обычно требуется свой провод/элемент.

Однако сами схемы при этом оказываются значительно проше.

В цифровой системе или компьютере двоичные числа, как

правило, состоят из фиксированного числа битов. Группа из

восьми битов называется байтом (byte) и является удобной

единицей для представления буквенно-цифровой информа-

ции; подробно см. в разделе 1.5. Числа довольно часто пред-

ставляются с использованием больших групп битов. В компь-

ютерах, например, для представления чисел часто выделяются

тридцать два бита; при необходимости представления не столь

больших положительных чисел в старшие разряды просто до-

бавляются нули (способ представления отрицательных чисел

будет рассмотрен ниже).

Задание для самопроверки 1.4

Какое наибольшее положительное двоичное число может быть представ-

лено байтом?

1.2. Представление чисел в цифровых системах

29

Таблица 1.2. Представление чисел в различных системах счисления

Основание

2 3 4 5 6 7 8 9 10

0 0 0 0 0 0 0 0 0

1 1 1 1 1 1 1 1 1

10 2 2 2 2 2 2 2 2

11 10 3 3 3 3 3 3 3

100 11 10 4 4 4 4 4 4

101 12 11 10 5 5 5 5 5

110 20 12 11 10 6 6 6 6

111 21 13 12 11 10 7 7 7

1000 22 20 13 12 11 10 8 8

1001 100 21 14 13 12 11 10 9

1010 101 22 20 14 13 12 11 10

1011 102 23 21 15 14 13 12 11

1100 110 30 22 20 15 14 13 12

1101 111 31 23 21 16 15 14 13

1110 112 32 24 22 20 16 15 14

1111 113 33 30 23 21 17 16 15

1.2.2. Преобразование чисел

Итак, почему двоичная система счисления заняла доми-

нирующее положение в электронике, понятно. Однако на

практике намного удобнее пользоваться привычной десятич-

ной системой (даже если не пользоваться для счета пальца-

ми). Поэтому чаще всего числовые данные вводятся

в электронные системы в десятичном виде. Результаты вычис-

ления также предпочтительно иметь в десятичной форме. По-

этому необходим способ преобразования двоичных чисел

в десятичные, и наоборот, но только такой, чтобы его мог

использовать компьютер.

Небольшие десятичные числа довольно легко преобразовать

в двоичный вид, зная значения степеней двойки:

30

Глава 1. Цифровые системы и представление информации

Десятичное 64 32 16 8 4 2 1

число

26 25 24 23 22 21 2°

Двоичное 1000000 0100000 0010000 0001000 0000100 0000010 0000001

число

Если необходимо преобразовать десятичное число 25 в дво-

ичную систему, то следует просто разложить его на числа, являю-

щиеся степенями двойки, начиная со степени, наиболее близкой

по значению, но меньшей 25:

25 = 16 + 8 + 1 = 10000 + 01000 + 00001 = 11001

Более формальный метод преобразования можно вывести на

основе определения “позиционной” системы счисления (см.

работу Уилкинсона (Wilkinson), 1992).

Задание для самопроверки 1.5

Как выглядит число 23410 в двоичной системе счисления?

Неформальный способ преобразования двоичных чисел

в десятичные заключается в суммировании степеней двойки,

начиная с наибольшей степени, меньшей десятичного числа,

и заканчивая наименьшей (нулевой), например:

11001 = 16 + 8 + 1

Более формальный алгоритм можно найти, взяв за основу оп-

ределение позиционных систем счисления (см. работу Уилкин-

сона (Wilkinson), 1992).

1.2.3. Шестнадцатеричные и восьмеричные

числа

Позиционная система счисления, основание которой равно

16, называется шестнадцатеричной. Эта система имеет шестна-

дцать различных цифр, и для обозначения значений первых де-

сяти значений от 0 до 9 используются цифры 0, 1,2, 3, 4, 5, 6,

7, 8 и 9. Остальные значения, а именно: 10, 11, 12, 13, 14

и 15, записываются в виде больших букв латинского алфавита:

А= 10, В = 11, С = 12, D = 13, Е = 14 и F = 15. На англий-

ском часто слово “шестнадцатеричный” (hexadecimal) сокра-

щают до “hex”. Цифры шестнадцатеричной системы счисления

и их двоичные эквиваленты приведены в табл. 1.3.

1.2. Представление чисел в цифровых системах

31

Таблица 1.3. Двоичные, десятичные и шестнадцатеричные числа

Десятичная система Двоичная система Шестнадцатеричная система

0 0000 0

1 0001 1

2 0010 2

3 0011 3

4 0100 4

5 0101 5

6 0110 6

7 0111 7

8 1000 8

9 1001 9

10 1010 А

11 1011 В

12 1100 С

13 1101 D

14 1110 Е

15 1111 F

Шестнадцатеричная система счисления играет важную роль

в электронике, поскольку позволяет очень просто преобразовы-

вать числа в двоичную систему и обратно. Благодаря тому что

основание шестнадцатеричной системы (16 = 24) равно двум

(основанию двоичной системы) в четвертой степени, одному

шестнадцатеричному разряду соответствует четыре двоичных.

Для того чтобы преобразовать двоичное число в шестнадцате-

ричное, нужно просто разбить двоичное число на группы по

четыре цифры и преобразовать каждую такую группу в шестна-

дцатеричный разряд. Переведем, к примеру, двоичное число

101001112 в шестнадцатеричную систему счисления:

101001112 = А716

(10102 = 10 в десятичной системе или А в шестнадцатерич-

ной). Количество разрядов полученного шестнадцатеричного

эквивалента вчетверо меньше, чем у исходного двоичного числа

при условии, что количество двоичных битов было кратно

32

Глава 1. Цифровые системы и представление информации

четырем. Следовательно, двоичные числа легко записать в ше-

стнадцатеричном виде с меньшим количеством разрядов, при-

чем картина распределения “1” и “0” исходного двоичного

числа остается прозрачной. Именно по этой причине шестна-

дцатеричное написание используется в технической документа-

ции значительно чаще, чем двоичное.

Метод преобразования чисел из шестнадцатеричной систе-

мы в двоичную можно получить все из того же определения по-

зиционной системы счисления. В качестве примера рассмотрим

преобразование шестнадцатеричного числа IАС16:

1АС16 = (00012) х 162 + (10102) х 161 + (11002) х 16",

что равняется

(О х 23 + 0 х 22 + 0 х 2' + 1 х 2") х 162 + (1 х 23 + 0 х 22 + 1 х

х2' + 0 х 2°) х 16' + (1 х 23 + 1 х 22 + 0 х 21 + 0 х 2") х 16".

Пользуясь тем, что 162 = 28, 161 = 24, 16° = 2", можно записать:

(О х 2" + 0 х 2'° + 0 х 29 + 1 х 28) + (1 х 27 + 0 х 26 + 1 х 25 +

+ 0 х 24) + (1 х 23 + 1 х 22 + 0 х 21 + 0 х 2°), что эквивалентно за-

писи 0001 101011002.

Задание для самопроверки 1.6

Преобразуйте шестнадцатеричное число ЗР|6 в двоичное.

Задание для самопроверки 1.7

Преобразуйте двоичное число 1000010101000102 в шестнадцатеричное.

Метод преобразования из восьмеричной системы счисления

в двоичную также достаточно прост. Следует принять во вни-

мание, что основание 8 представляет собой 2 в третьей степени,

поэтому три двоичных бита соответствуют одному восьмерич-

ному разряду. Например, восьмеричное число 345м преобразует-

ся в двоичный эквивалент следующим образом:

3458 = (011 100 101)2.

Однако восьмеричная система по столь удобна как шестнадца-

теричная, поскольку в большинстве систем используются двоич-

ные слова, количество битов в которых кратно байту, а один байт

записывается в виде двух шестнадцатеричных разрядов. Восьме-

ричная система была удобна в старых компьютерных системах,

где использовались 24-битовые слова, и в этом случае восемь

восьмеричных разрядов как раз и составляли одно такое слово.

1.2. Представление чисел в цифровых системах

33

1.3. Арифметические операции над

двоичными числами

1.3.1. Сложение

Понятно, что, поскольку внутри цифровой системы исполь-

зуются двоичные числа, над ними необходимо выполнять ариф-

метические операции. К счастью, двоичная математика предель-

но проста. В школе мы сталкиваемся с таблицами десятичного

сложения, вычитания и умножения, в которых приведены различ-

ные комбинации чисел, включающие все десять используемых

цифр. Точно такие же таблицы можно построить и для двоичной

системы счисления, но в данном случае существует всего четыре

возможных комбинации из двух цифр: 0 и 0, 0 и 1, 1 и 0, 1 и 1.

Возьмем, например, сложение: 0 + 0 = 0, 0+1 = 1, 1+0=1,

1 + 1 = 10. Если сравнить с десятичной арифметикой (0 + 0 = 0,

0+1 = 1, 0 + 2 = 2... 9 + 9= 18), то налицо явное упрощение.

Правила двоичного сложения представлены в табл. 1.4.

Таблица 1.4. Сложение двоичных цифр

А В Сумма Десятичная система

0 0 0 0 0

0 1 0 1 1

1 1 0 1 0 1 1 0 1 2

Предположим, необходимо просуммировать два двоичных

числа, каждое из которых состоит из нескольких битов. Снача-

ла, как и в десятичной системе счисления, складываются млад-

шие значащие биты чисел. В десятичной системе, если резуль-

тат сложения превышает цифру 9, то появляется перенос, при-

бавляющийся к следующему по величине разряду (например,

7 + 8 = 5 и перенос в разряд десятков). Для двоичной системы

справедливо то же самое, только перенос формируется при по-

явлении числа, большего 1 (например, 1 + 1 = 0 и перенос 1

в следующий по величине разряд). В следующем же разряде,

как для десятичной системы, складываются уже три числа: со-

ответствующие биты слагаемых плюс бит переноса. Всего, та-

ким образом, как показано в табл. 1.5, возможны восемь ком-

бинаций сложения трех двоичных цифр.

34

Глава 1. Цифровые системы и представление информации

Таблица 1.5. Сложение трех двоичных цифр

А В Сах ^вых Сумма Десятичная система

0 0 0 0 0 0

0 0 1 0 1 1

0 1 0 0 1 1

0 1 1 1 0 2

1 0 0 0 1 1

1 0 1 1 0 2

1 1 0 1 0 2

1 1 1 1 1 3

Для того чтобы сравнить операции сложения в десятичной

и двоичной системах, давайте сложим десятичные числа 22](1 и 2810:

Десятичная система Двоичная система

2 2 10 110

2,8 ,1,1,1 0 0

5 0 110010

Итак, основные правила, по существу, не меняются и не за-

висят от того, какая система используется (это справедливо для

любого основания). Кратко их можно сформулировать так:

слагаемые суммируются поразрядно, начиная с младшего зна-

чащего разряда. Если результат сложения разряда равен или

превышает число b (величину основания), то формируется пе-

ренос, который складывается с цифрами в следующем по стар-

шинству разряде. Единственное отличие в том, что для деся-

тичной системы счисления перенос возникает в случае превы-

шения числа 9, а для двоичной — единицы.

Задание для самопроверки 1.8

Сложите в двоичной системе числа 81 w и 63,0. Проверьте правильность отве-

та, преобразовав полученный результат в десятичную систему.

Для того чтобы реализовать сложение с помощью электрон-

ных компонентов, необходимо использовать схему, на первый

каскад которой поступают биты двоичных слагаемых, а па выходе

1.3. Арифметические операции над двоичными числами

35

формируются бит суммы и бит переноса, поступающий в следую-

щий каскад. Каждый же последующий каскад такой схемы дол-

жен складывать уже три бита: два бита соответствующих разрядов

двоичных чисел и бит переноса предыдущего каскада. Пример

проектирования подобной схемы будет рассмотрен в главе 3.

1.3.2. Отрицательные числа и вычитание

Двоичное вычитание может выполняться по таким же прави-

лам, как и в десятичной системе, т.е. с “заимствованием” в случае

необходимости из предыдущего разряда. В десятичной системе та-

кое заимствование происходит в том случае, когда вычитаемое

(число, которое вычитается) больше уменьшаемого (числа, из кото-

рого вычитают). К примеру, чтобы отнять 7 от 6, нужно взять 10

из предыдущего разряда и вычесть 7 уже из 16. Однако из сооб-

ражений простоты реализации схемы вычитание обычно выпол-

няется как “сложение с дополняющим числом”. Такой метод

применим в любой системе счисления и основан на замене от-

рицательного числа его дополнением. В десятичной системе чис-

ло, дополнительное данному, вычисляется следующим образом:

10" - А,

где п — количество разрядов десятичного числа. Предположим,

есть число с тремя разрядами, и пусть это будет 235. Тогда до-

полнительное ему число находим как 1000 — 235 = 765.

Аналогичным образом можно найти и дополнительное чис-

ло в двоичной системе счисления:

2" - А,

где п — количество разрядов двоичного числа. Предположим,

есть трехразрядное число 011 (3|0). Найдем число, дополнитель-

ное ему: 1000 - 011 = 101.

В двоичной системе счисления дополнительное число или

дополнительный код (2’s complement) служит для представле-

ния отрицательных чисел. Например, представление числа —3

в двоичном виде будет выглядеть как 101. Положительные же

числа, как, скажем, +3, представляются обычным образом:

011. Для того чтобы можно было выражать как положитель-

ные, так и отрицательные числа, необходимо иметь достаточ-

ное количество разрядов, так как перед положительными числа-

ми будет стоять как минимум один ноль. Отрицательные же чис-

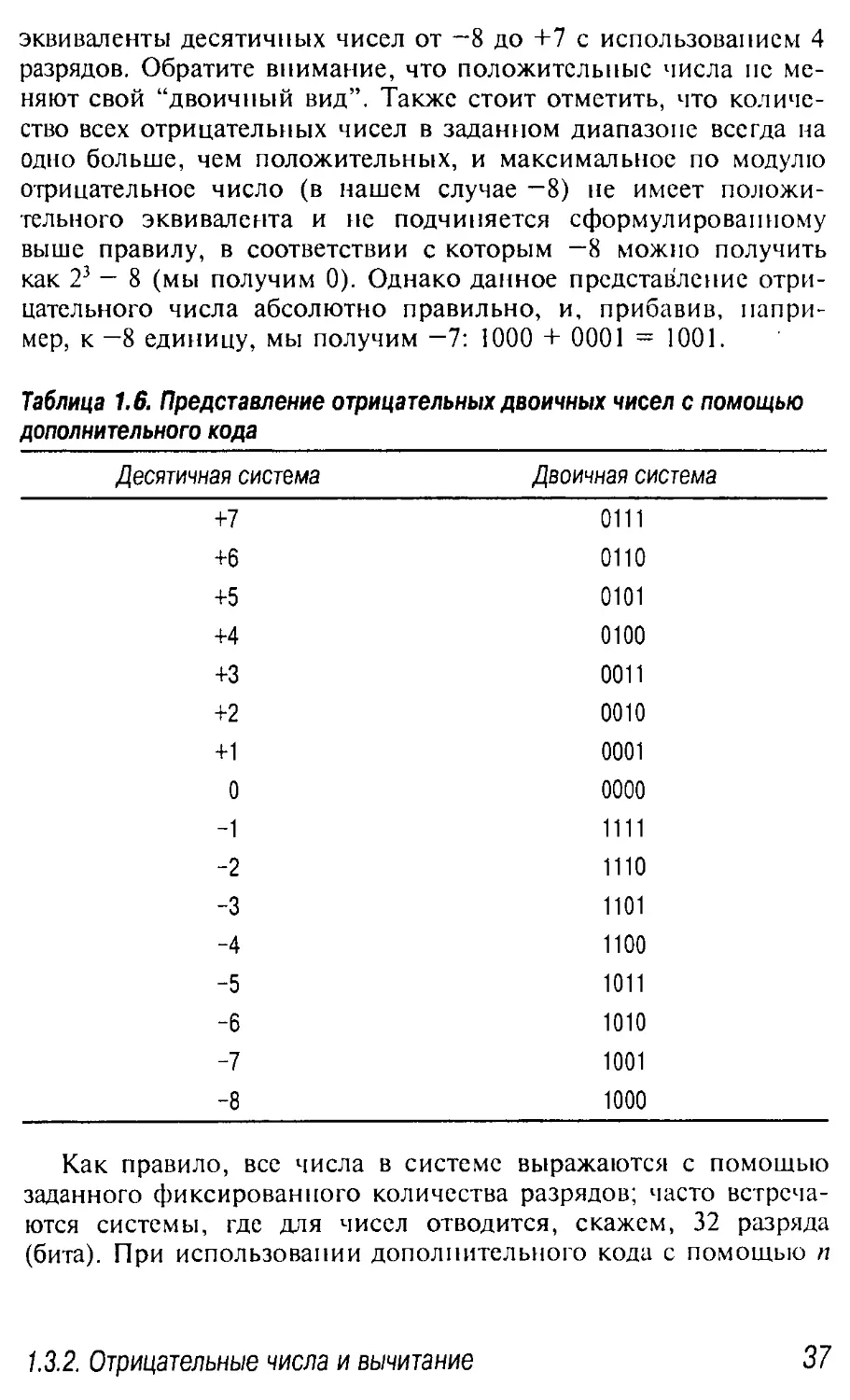

ла всегда будут начинаться с I. В табл. 1.6 приведены двоичные

36

Гпава 1. Цифровые системы и представление информации

эквиваленты десятичных чисел от —8 до +7 с использованием 4

разрядов. Обратите внимание, что положительные числа не ме-

няют свой “двоичный вид”. Также стоит отметить, что количе-

ство всех отрицательных чисел в заданном диапазоне всегда на

одно больше, чем положительных, и максимальное по модулю

отрицательное число (в нашем случае —8) не имеет положи-

тельного эквивалента и не подчиняется сформулированному

выше правилу, в соответствии с которым —8 можно получить

как 23 — 8 (мы получим 0). Однако данное представление отри-

цательного числа абсолютно правильно, и, прибавив, напри-

мер, к —8 единицу, мы получим —7: 1000 + 0001 = 1001.

Таблица 1.6. Представление отрицательных двоичных чисел с помощью

дополнительного кода

Десятичная система Двоичная система

+7 0111

+6 0110

+5 0101

+4 0100

+3 0011

+2 0010

+1 0001

0 0000

-1 1111

-2 1110

-3 1101

-4 1100

-5 1011

-6 1010

-7 1001

-8 1000

Как правило, все числа в системе выражаются с помощью

заданного фиксированного количества разрядов; часто встреча-

ются системы, где для чисел отводится, скажем, 32 разряда

(бита). При использовании дополнительного кода с помощью п

1.3.2. Отрицательные числа и вычитание

37

разрядов можно задать любые числа, значения которых лежат

в диапазоне от -2" до +2" — 1, включая ноль. Чтобы добрать ко-

личество разрядов до заданного, в случае положительных чисел

к ним впереди при необходимости дописываются нули. Для от-

рицательных чисел впереди дописываются единицы. Например,

число —6 в случае использования четырех разрядов имеет вид

1010, а при использовании восьми разрядов — 11111010.

В большинстве цифровых систем и компьютеров отрицатель-

ные величины представляются именно в виде дополнительного

кода, так как такое представление значительно упрощает сложе-

ние и вычитание. Давайте на примерах рассмотрим, в чем же

преимущества дополнительного кода для двоичной арифметики.

Следует отметить, что все описанные ниже ситуации одинаково

справедливы и для десятичных чисел, в чем легко убедиться.

Вычитание

Для того чтобы вычесть из числа X число У, нужно найти

дополнительный код числа У, т.е. получить —У Затем X и ~¥

складываются:

X- У= Х+ (-Y) = X + (2" - У) = X- Y+ 2".

Если X больше, чем У, то их разность, X — У, окажется поло-

жительной. Член 2” представляет собой число, которое выражает-

ся 1 и л нулями (1000...000). Если оставить в результате только п

битов, то этот член можно игнорировать, и тогда получим кор-

ректный положительный результат. Если же разность X— У от-

рицательная, то корректное отрицательное число в форме допол-

нительного кода формируется естественным образом: 2П — (У— X).

Чтобы убедиться, что представление чисел в дополнитель-

ном коде всегда адекватно, нужно доказать, что при любой

комбинации положительных и отрицательных чисел результат

будет верным. Если число У уже отрицательно, то отрицание

отрицательной величины даст положительное число:

-(-У) = 2" - (2П - У) = 2" - 2" + У= У

Таким образом, видно, что пользоваться дополнительным

кодом можно всегда.

ПРИМЕРЫ

(а) X и У — положительные числа, Х> У Результат положи-

тельный.

38

Гпава 1. Цифровые системы и представление информации

Пусть Х = 0110(6), a Y = ООН (3). Тогда ~Y= 1101 (-3),

и 6 — 3 можно вычислить следующим образом:

Десятичная система Двоичная система

6 0 110

-3 .1.1 0 1

3 0 0 11

Обратите внимание, что соответствующий члену 2П бит пе-

реноса в последнем разряде формируется, но игнорируется.

б) X и Y— положительные числа, Х<. Y. Результат отрица-

тельный.

Пусть Х = 0011(3), a Y= ОНО (6). Тогда-Y = 1010 (-6),

и разность 3 — 6 определяется так:

Десятичная система Двоичная система

3 0 0 11

-6 1,0 1 0

-3 110 1

В данном случае перенос в последнем разряде не появ-

ляется, и ответ представляет собой отрицательный ре-

зультат — число —3.

в) X — положительное, а У — отрицательное числа. Резуль-

тат всегда положительный.

Пусть Х= ООН (3), а У= 1101 (-3). Тогда -У = 0011

(+3), и 3 — (—3) вычисляется таким образом:

Десятичная система Двоичная система

3 0 0 11

-(-3) 0 0,1,1

6 0 110

1.3.2. Отрицательные числа и вычитание

39

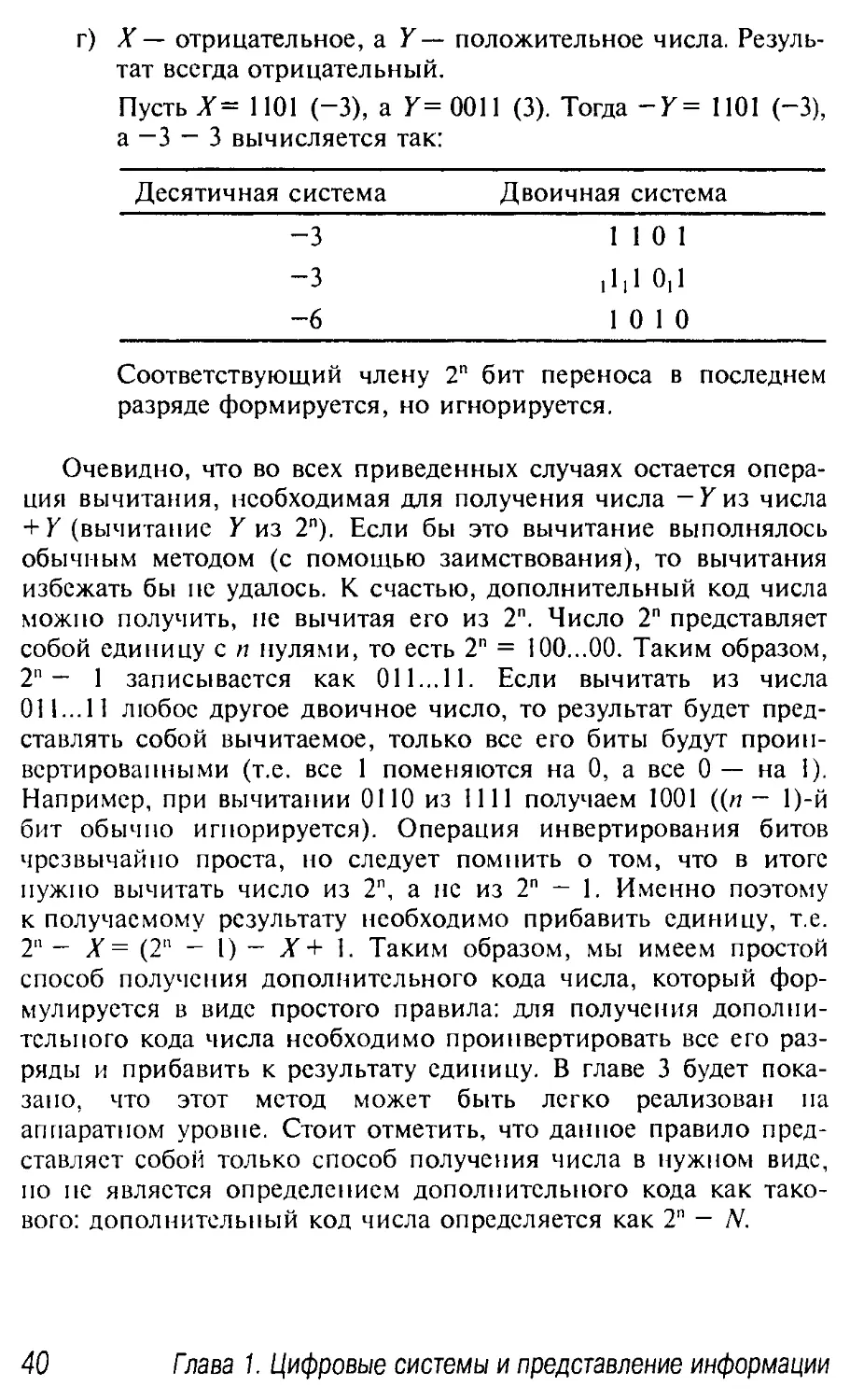

г) X — отрицательное, a Y — положительное числа. Резуль-

тат всегда отрицательный.

Пусть Х = 1101 (-3), a Y= 0011 (3). Тогда-Г = 1101 (-3),

а —3 — 3 вычисляется так:

Десятичная система Двоичная система

-3 110 1

-3 ,1,1 0,1

-6 10 10

Соответствующий члену 2П бит переноса в последнем

разряде формируется, но игнорируется.

Очевидно, что во всех приведенных случаях остается опера-

ция вычитания, необходимая для получения числа — У из числа

+ Y (вычитание Y из 2"). Если бы это вычитание выполнялось

обычным методом (с помощью заимствования), то вычитания

избежать бы не удалось. К счастью, дополнительный код числа

можно получить, не вычитая его из 2П. Число 2" представляет

собой единицу с п нулями, то есть 2П = 100...00. Таким образом,

2"— 1 записывается как 011...11. Если вычитать из числа

011...11 любое другое двоичное число, то результат будет пред-

ставлять собой вычитаемое, только все его биты будут проин-

вертировапными (т.е. все 1 поменяются на 0, а все 0 — на 1).

Например, при вычитании ОНО из 1111 получаем 1001 ((« — 1)-й

бит обычно игнорируется). Операция инвертирования битов

чрезвычайно проста, но следует помнить о том, что в итоге

нужно вычитать число из 2", а не из 2" — 1. Именно поэтому

к получаемому результату необходимо прибавить единицу, т.е.

2" — Х= (2П — 1) — X + 1. Таким образом, мы имеем простой

способ получения дополнительного кода числа, который фор-

мулируется в виде простого правила: для получения дополни-

тельного кода числа необходимо проипвертировать все его раз-

ряды и прибавить к результату единицу. В главе 3 будет пока-

зано, что этот метод может быть легко реализован па

аппаратном уровне. Стоит отметить, что данное правило пред-

ставляет собой только способ получения числа в нужном виде,

по не является определением дополнительного кода как тако-

вого: дополнительный код числа определяется как 2" — N.

40

Гпава 1. Цифровые системы и представление информации

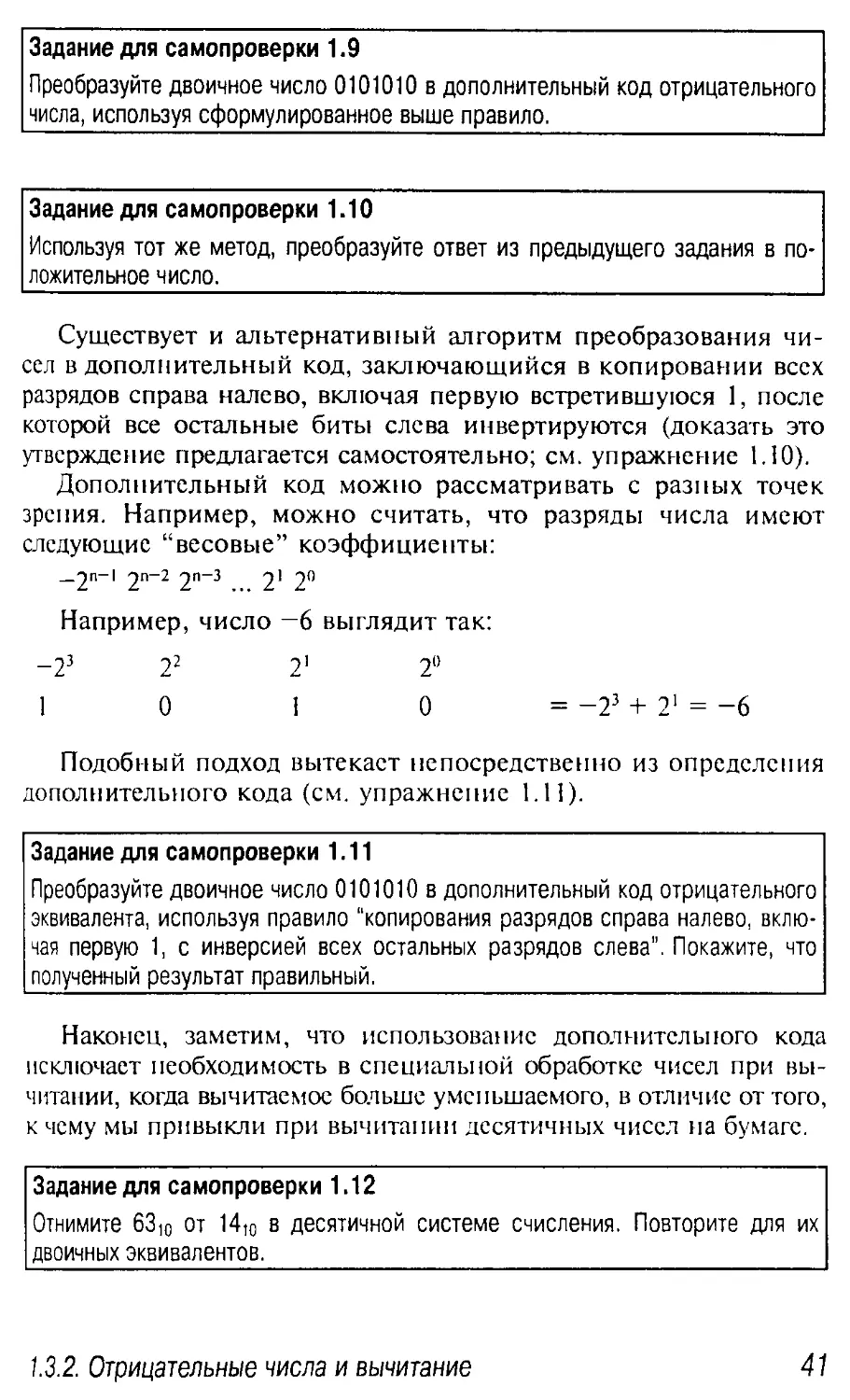

Задание для самопроверки 1.9

Преобразуйте двоичное число 0101010 в дополнительный код отрицательного

числа, используя сформулированное выше правило.

Задание для самопроверки 1.10

Используя тот же метод, преобразуйте ответ из предыдущего задания в по-

ложительное число.

Существует и альтернативный алгоритм преобразования чи-

сел в дополнительный код, заключающийся в копировании всех

разрядов справа налево, включая первую встретившуюся 1, после

которой все остальные биты слева инвертируются (доказать это

утверждение предлагается самостоятельно; см. упражнение 1.10).

Дополнительный код можно рассматривать с разных точек

зрения. Например, можно считать, что разряды числа имеют

следующие “весовые” коэффициенты:

_2п-| 2П-2 2П-3 21 2°

Например, число —6 выглядит так:

_23 22 21 2°

1 0 1 0 = —23 + 21 = -6

Подобный подход вытекает непосредственно из определения

дополнительного кода (см. упражнение 1.11).

Задание для самопроверки 1.11

Преобразуйте двоичное число 0101010 в дополнительный код отрицательного

эквивалента, используя правило “копирования разрядов справа налево, вклю-

чая первую 1, с инверсией всех остальных разрядов слева". Покажите, что

полученный результат правильный.

Наконец, заметим, что использование дополнительного кода

исключает необходимость в специальной обработке чисел при вы-

читании, когда вычитаемое больше уменьшаемого, в отличие оттого,

к чему мы привыкли при вычитании десятичных чисел на бумаге.

Задание для самопроверки 1.12

Отнимите 6310 от 14)0 в десятичной системе счисления. Повторите для их

двоичных эквивалентов.

1.3.2. Отрицательные числа и вычитание

41

Обратный код

Результат инверсии всех разрядов двоичного числа называ-

ется обратным кодом (l’s complement) и определяется как

—Х = (2" - 1) - Y.

Оказывается, что арифметические операции можно выпол-

нять непосредственно и над обратным кодом, не используя до-

полнительный, хотя в этом случае появление переноса в по-

следнем разряде показывает, что к полученному результату сле-

дует добавить 1. Это следует из определения обратного кода

(упражнение 1.12). Однако в большинстве компьютеров для

представления отрицательных чисел используется именно до-

полнительный код. Десятичный вариант двоичного обратного

кода (на английском носит название 9’s complement) определя-

ется следующим образом:

-Х = (10" - 1) - Y.

1.3.3. Двоично-десятичное представление

десятичных чисел

В некоторых практических задачах применения арифметики,

например в калькуляторах и кассовых аппаратах, необходимо

осуществлять простые операции над десятичными числами

и выводить результат на экран или индикатор в десятичном ви-

де. В этом случае десятичные числа вводятся с клавиатуры,

и полученные результаты в десятичном же виде выводятся на

экран устройства отображения. Понятно, что десятичные числа

можно преобразовать в двоичные, а полученный двоичный ре-

зультат можно снова преобразовать в десятичный и вывести на

экран. В качестве альтернативы можно сохранить информацию

внутри системы в десятичном виде, воспользовавшись двоично-

десятичным представлением (binary-coded decimal — BCD). В дво-

ично-десятичном представлении каждый десятичный разряд

представляется в виде 4-разрядного двоичного кода. Далее эти

4-разрядные группы просто ставятся друг за другом, образуя еди-

ную цепочку. Например, десятичное число 234510 можно пред-

ставить в двоично-десятичном коде как 0010 0011 0100 0101.

Числа в таком представлении можно суммировать как двоич-

ные, соблюдая, правда, при этом определенные правила. Пусть

необходимо сложить два десятичных числа: 243110 и 5425,п:

42

Глава 1. Цифровые системы и представление информации

2431

5425

7856

0010 0100 ООН 0001

0101 0100 0010 0101

0111 1000 0101 ОНО

Можно видеть, что сложение двоично-десятичных кодов чи-

сел по методике сложения обычных двоичных чисел дает пра-

вильный двоично-десятичный результат. Однако данный при-

мер был тщательно подобран, чтобы ни в одном десятичном

разряде сумма не превысила 10. Если же такое превышение все-

таки произойдет, то для получения верного результата необходи-

мо произвести так называемую коррекцию. Поправочный коэф-

фициент, который обязательно нужно учесть, равен 6, и его надо

прибавить к полученному числу. Такой прыжок позволяет

“перескочить” шесть неиспользуемых кодовых комбинаций дво-

ично-десятичного кода, которые представляют числа 10, 11, 12,

13, 14 и 15 (а именно: 1010, 1011, 1100, 1101, 1110 и 1111).

Если получаемый в результате сложения двух разрядов чисел

разряд суммы будет находиться между 10 и 15, то достаточно

просто работать с четырьмя битами двоично-десятичного разряда:

36

2 5

5 11

6 — поправочный коэффициент

6 1

ООН оно

0010 0101

0101 1011

оно

ОНО 0001

Если же результирующий разряд суммы оказывается равным

16, 17 или 18, то четыре бита двоично-десятичного разряда

принимают вид 0000, 0001 и 0010, соответственно. Возникнет

перенос, который прибавится к следующему по старшинству

двоично-десятичному разряду. Здесь уже недостаточно работы

только с четырьмя битами двоично-десятичного разряда, и не-

обходимо распознавать возникновение бита переноса:

3 8

2 9

6 1

6 — поправочный коэффициент

67

ООН 1000

0010J001

ОНО 0001

ОНО

ОНО 0111

Компьютеры, спроектированные для выполнения операций над

двоично-десятичными числами, имеют специальные команды для

1.3.2. Отрицательные числа и вычитание

43

автоматической коррекции результатов. При вычитании поправоч-

ный коэффициент в случае необходимости просто отнимается.

В прошлом, когда использовались однокристальные 4-разрядные

микропроцессоры, двоично-десятичный код был очень удобен,

но в наши дни спектр его применения уже не столь широк.

1.4. Представление алфавитно-цифровых

символов

Кроме чисел компьютеры должны представлять буквы алфа-

вита и другие символы, которые могут вводиться с клавиатуры

или выводиться на монитор либо принтер. Для описания таких

символов часто используется термин буквенно-цифровые символы,

поскольку они включают в себя и десятичные цифры от 0 до 9.

Для их кодирования специалистами был разработан стандартный

код, получивший название ASCII-код (от англ. American Standard

Code for Information Interchange — Американский стандартный

код для обмена информацией); этот код показан в табл. 1.7.

В соответствии с этой таблицей, 7-разрядный код получается пу-

тем взятия трех битов b7,bb,b5 из верхней строчки, к которым под-

ставляются справа четыре бита Ь^,Ь3,Ьг,Ьу, стоящие в правом

крайнем столбце. Например, ASCII-код буквы В будет 1000010.

Таблица 1.7. 7-разрядный ASCII-код

bzbebs ООО 001 010 011 100 101 110 111

Ь^ЬзЬгЬ^ 0 1 2 3 4 5 6 7

0000 0 NUL DLE SP 0 @ Р Р

0001 1 SOH DC1 ! 1 А Q а q

0010 2 STX DC2 U 2 В R b Г

0011 3 ЕТХ DC3 # 3 С S С s

0100 4 EOT DC4 $ 4 D т d t

0101 5 ENQ NAK % 5 Е и е u

0110 6 АСК SYN & 6 F V f V

0111 7 BEL ЕТВ 7 G W 9 w

1000 8 BS CAN ( 8 Н X h X

1001 9 НТ ЕМ ) 9 I Y I У

44

Гпава 1. Цифровые системы и представление информации

Окончание табл. 1.7

bzbsbs ООО 001 010 011 100 101 110 111

Ь^зЬгЬ 0 1 2 3 4 5 6 7

1010 10 LF SUB t J Z j z

1011 11 VT ESC + < К [ k {

1100 12 FF FS 1 < L \ I I

1101 13 CR GS - = M ] m }

1110 14 SO RS > N n -

1111 15 SI US / ? 0 0 DEL

Задание для самопроверки 1.13

Как выглядит ASCII-код буквы w?

Задание для самопроверки 1.14

Как заменить коды строчных букв на коды прописных букв независимо от са-

мой буквы?

1.5. Пример цифровой логической схемы

В этом разделе мы рассмотрим простой пример применения

цифровой логики, который послужит своеобразным введением

к более детальному изучению материала последующих глав.

Этот пример раскроет особенности двух базовых типов логиче-

ских схем: комбинационных и последовательных. Каждому из

них в книге посвящены отдельные главы.

Клавиатура компьютера организована таким же образом, как

у печатной машинки, и вмещает все символы алфавита, цифры, зна-

ки препинания и специальные символы1. Обычно клавиши кла-

виатуры электрически объединяются в двумерную матрицу, имею-

щую, скажем, п столбцов и т строк (см. рис. 1.3). Сигнал с уров-

1 Расположение клавиш печатной машинки было придумано много лет

назад с целью замедлить работу машинистки, поскольку старые механи-

ческие машинки не могли печатать со столь высокой скоростью, которая

была бы доступна оператору, если бы клавиши располагались удобным для

набора образом! Подобное выдуманное расположение клавиш продолжает

использоваться и сегодня, хотя современные клавиатуры выдерживают

любую скорость набора.

1.5. Пример цифровой логической схемы

45

нем логической единицы поступает поочередно на каждую строку

матрицы и при нажатии клавиши передается на столбец, в пересе-

чении которого со строкой находится эта клавиша. Затем определя-

ется номер столбца, т.е. идентифицируется нажатая клавиша. (Для

того чтобы избежать возникновения ошибочных путей прохожде-

ния сигнала при одновременном нажатии сразу нескольких кла-

виш, необходимо использование дополнительных компонентов.)

Клавиша

Ключ

Строка

Столбец

Выбор

столбца

Идентификатор нажатой клавиши

Рис. 1.3. Дешифратор клавиатуры

Предположим, что в описанной выше матрице имеется четыре

строки. Тогда для определения номера строки будет достаточно

двух битов. Это двухразрядное число должно быть преобразовано

в 4-разрядную кодовую группу, положение единицы в которой по-

кажет номер строки с нажатой клавишей (табл. 1.8). Электронная

схема, которая преобразует 2-битовые кодовые комбинации в 4-

битовые, называется дешифратором “из 2 направлений в 4” (2-line-

46

Глава 1. Цифровые системы и представление информации

to-4-line decoder). Его название говорит о том, что комбинация

сигналов на двух входах определяет выбор одного из четырех вы-

ходов. Проектирование дешифраторов будет описано в главе 3.

Таблица 1.8. Кодовые комбинации определения номера строки

Строка Яз я2 Ri Ro

0 0 0 0 0 1

0 1 0 0 1 0

1 0 0 1 0 0

1 1 1 0 0 0

Для того чтобы последовательно проходить все эти кодовые

комбинации, можно воспользоваться 2-разрядным счетчиком:

логической схемой, сигналы на выходе которой последователь-

но принимают значения: 00, 01, 10 и 11. Тема проектирования

счетчиков будет рассмотрена в главе 4.

Наконец, необходима логическая схема, которая бы принима-

ла сигналы от столбцов и формировала двоичное число, опреде-

ляющее номер столбца с активным логическим сигналом. Пред-

положим, у нас есть шестнадцать столбцов. Тогда понадобится 4-би-

товое число и шифратор из 16 направлений в 4. Такая схема

осуществляет операцию, обратную той, которую выполняет де-

шифратор из 4 направлений в 16. Шифратор реализует функцию,

таблица истинности которой имеет вид, показанный в табл. 1.9.

Это еще один пример логической схемы, проектирование кото-

рой будет рассмотрено позже. Из рис. 1.3 видно, что результа-

том работы системы является адрес строки и столбца, на пере-

сечении которых находится нажатая клавиша. В действительно-

сти каждому символу клавиатуры присваивается уникальный

ASCII-код, и необходимо дополнительное преобразование.

1.6. Резюме

Бесспорно, нет человека, который бы не сталкивался с ком-

пьютером. Наиболее важным моментом в данной главе являет-

ся вывод о том, что для представления числовых и логических

значений в компьютерах и других цифровых системах должны

использоваться сигналы, имеющие всего два состояния.

Из прочитанной главы необходимо усвоить следующее.

Сигналы с двумя состояниями являются наиболее удобными

и универсальными для использования в цифровых системах.

1.5. Пример цифровой логической схемы

47

Таблица 1.9. Таблица истинности шифратора “из 16 направлений в 4”

С15 Cl4 Ci3 С,2 C11 Сю c9 c8 c7 Ce c5 c4 Сз c2 Ci Co Состояние на выходе

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 oooo

0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0001

0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 00 1 0

0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 00 1 1

0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 00

0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 101

0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 1 0

0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 111

0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 000

0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 001

0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 1 0

0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 10 11

0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1100

0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1101

0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1110

1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1111

Двузначные сигналы используются для решения двух основ-

ных задач: для управления (включение/выключенис самых раз-

нообразных приводов) и для представления чисел в двоичной

системе счисления.

Шестнадцатеричные числа очень удобны для промежуточ-

ного представления информации.

Сложение двоичных чисел подобно сложению десятичных.

Вычитание двоичных чисел удобнее всего выполнять, пред-

ставляя отрицательные числа с помощью дополнительного кода.

1.7. Упражнения

1. Напишите первые тридцать чисел в системах счисле-

ния с основаниями 11 и 12.

2. В 1951 году Тьюринг (изд. Hodges, 1983) в одной из

первых работ по проектированию компьютеров ис-

48

Глава 1. Цифровые системы и представление информации

пользовал систему счисления с основанием 32. На-

пишите первые тридцать два числа этой системы. Как

вы думаете, почему автор выбрал именно эту систему?

3. Преобразуйте в двоичную форму следующие десятич-

ные числа:

. 56

. 102

4. Преобразуйте в десятичную форму следующие целые

двоичные числа:

. 1011

• 11111

5. Преобразуйте в двоичную форму следующие шестна-

дцатеричные числа:

. 77

• АА

6. Преобразуйте в шестнадцатеричную форму следую-

щие двоичные числа:

• 1010101010

• 1111111111

7. Преобразуйте в дополнительный двоичный код сле-

дующие отрицательные десятичные числа:

• -12

. -345

8. Преобразуйте в десятичную форму следующие 8-раз-

рядные отрицательные двоичные числа:

• 111111111

. 10010000

9. Преобразуйте следующие десятичные числа в двоичную

форму и выполните указанные арифметические операции,

используя там, где необходимо, дополнительный код:

. 32 + 32

. 67 + 132

. 67-32

. -24 + 43

. -88 - 99

1.7. Упражнения

49

10. Докажите, что число действительно может быть пре-

образовано в дополнительный код по следующему

алгоритму: “копирование всех разрядов справа нале-

во, включая первую встретившуюся 1, после которой

вес остальные биты слева инвертируются”.

11. Покажите, что дополнительный код можно получить с по-

мощью следующих “весовых” коэффициентов разрядов:

______2п-1 2П~2 2П~3 21 2°

12. Пользуясь определением обратного кода, докажите, что

формат может быть использован при вычитании, если

прибавлять к результату 1 в случае появления переноса в

последнем разряде (так называемый циклический перенос).

13. Определите, какие действия с клавиатурой (ее функ-

циональная схема описана в разделе 1.6) приведут

к возникновению ошибочных путей прохождения

сигнала и ошибкам в работе (предполагается, что до-

полнительных элементов нет).

1.8. Список дополнительной литературы

1. Fletcher, W.I., An Engineering Approach to Digital Design,

Prentice Hall: Englewood Cliffs, New Jersey, 1980.

2. Hodges, A., Alan Turing: The Enigma, Simon and Schuster:

New York, 1983. (В этой книге приводится замечатель-

ная биография Алана Тьюринга (советуем прочесть пе-

ред выполнением упражнения 1.2), которую просто

обязаны знать студенты факультетов, связанных с вы-

числительной техникой!)

3. Karam, G.M. and Bryant, J.C., Principles of Computer

Systems, Prentice Hall: Englewood Cliffs, New Jersey, 1992.

4. Page, E.S. and Wilson, L.B., Information Representation and

Manipulation in a Computer, Cambridge University Press:

Cambridge, England, 1973. (Немного старая (но никак не

устаревшая) книга, посвященная исключительно вопро-

сам представления информации.)

5. Tinder, R.F., Digital Engineering Design, A Modem Ap-

proach, Prentice Hall: Englewood Cliffs, New Jersey, 1991.

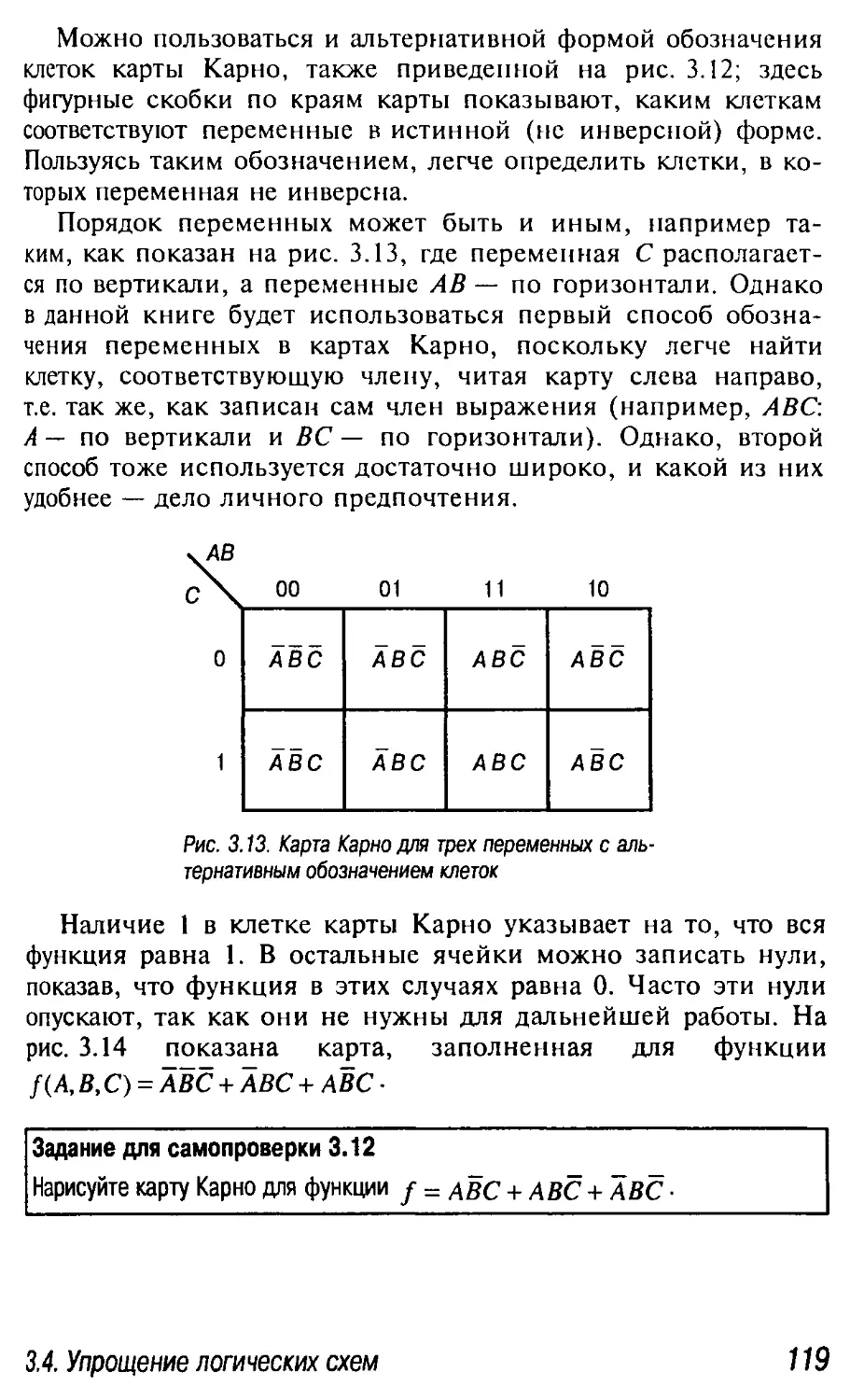

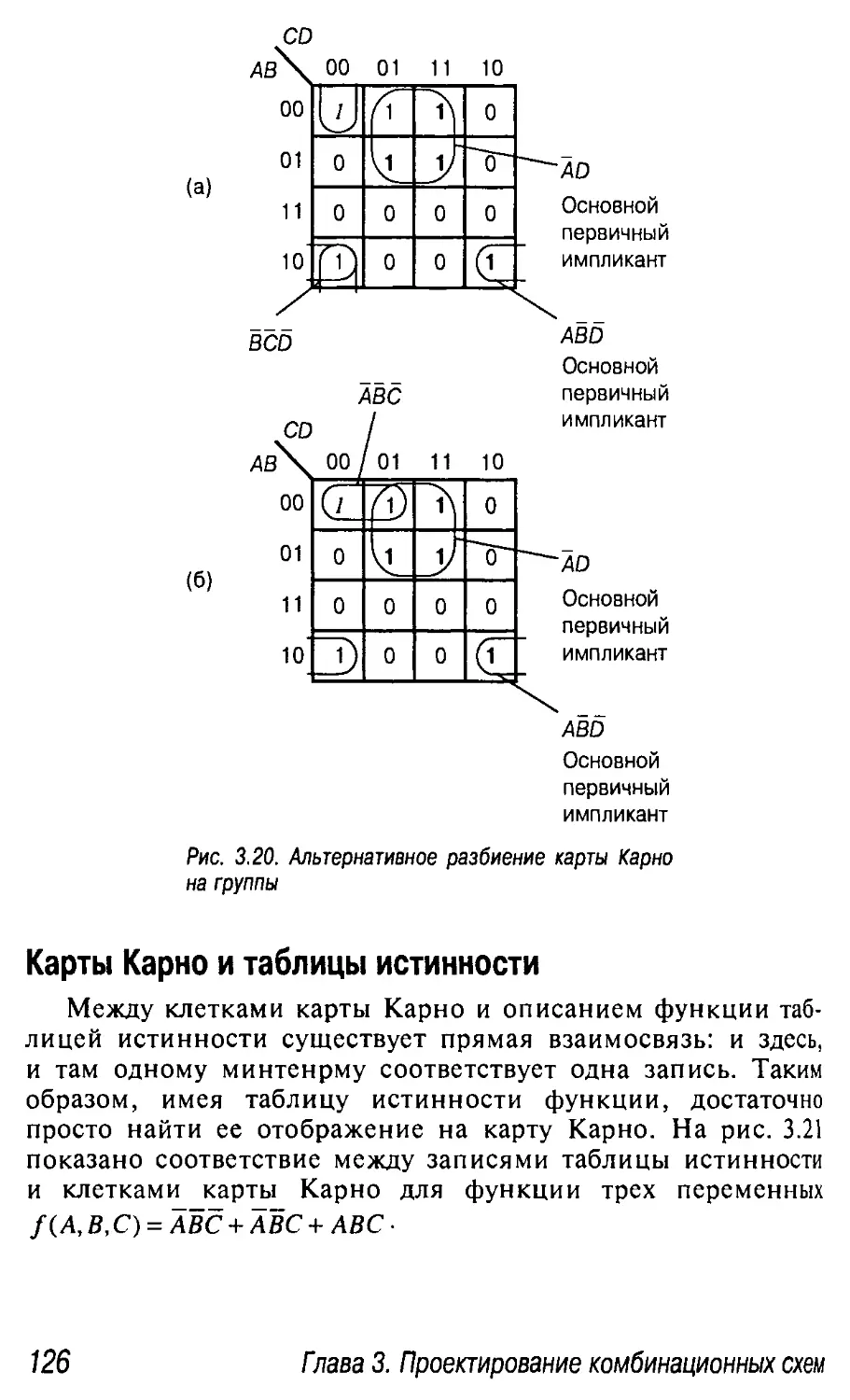

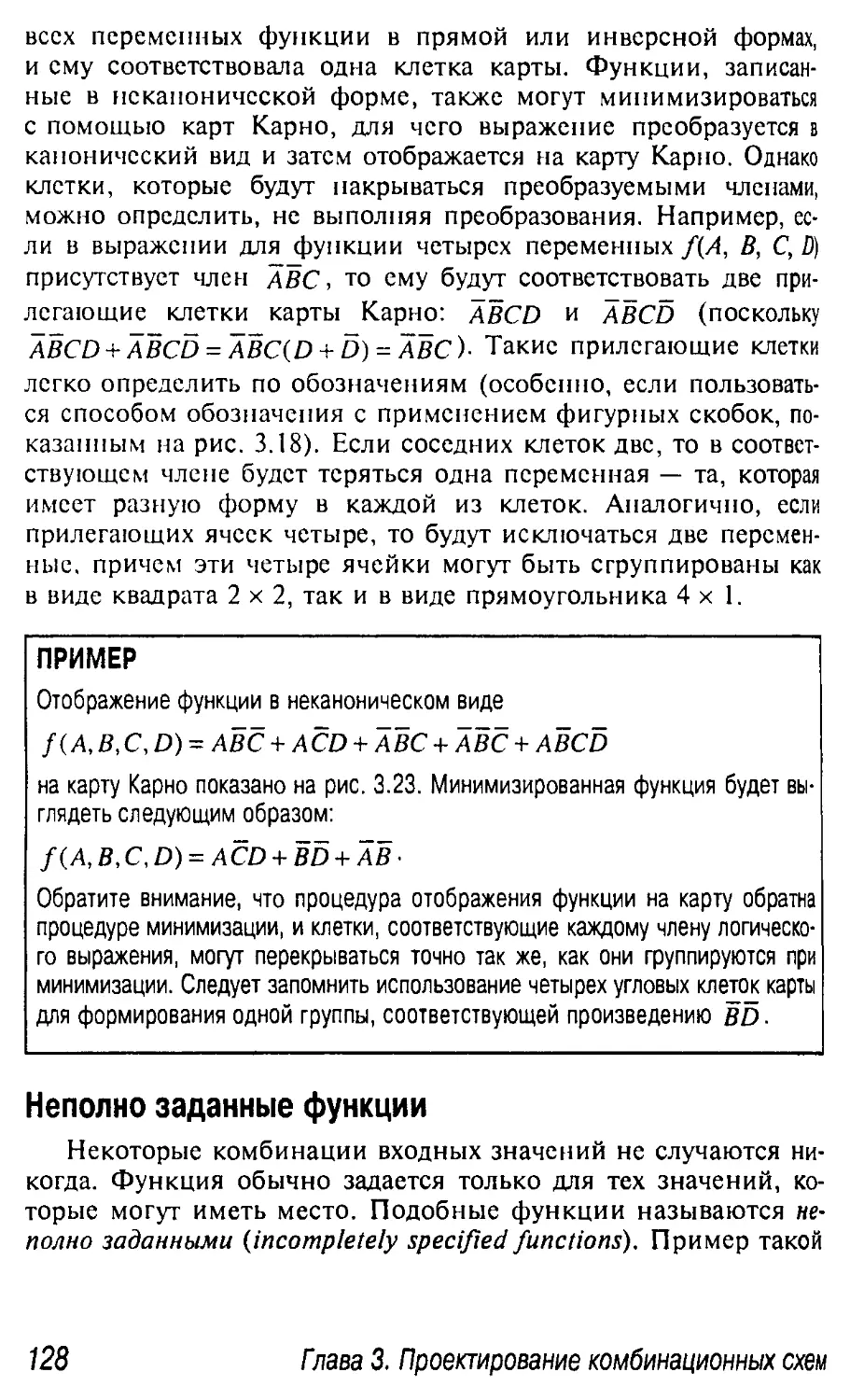

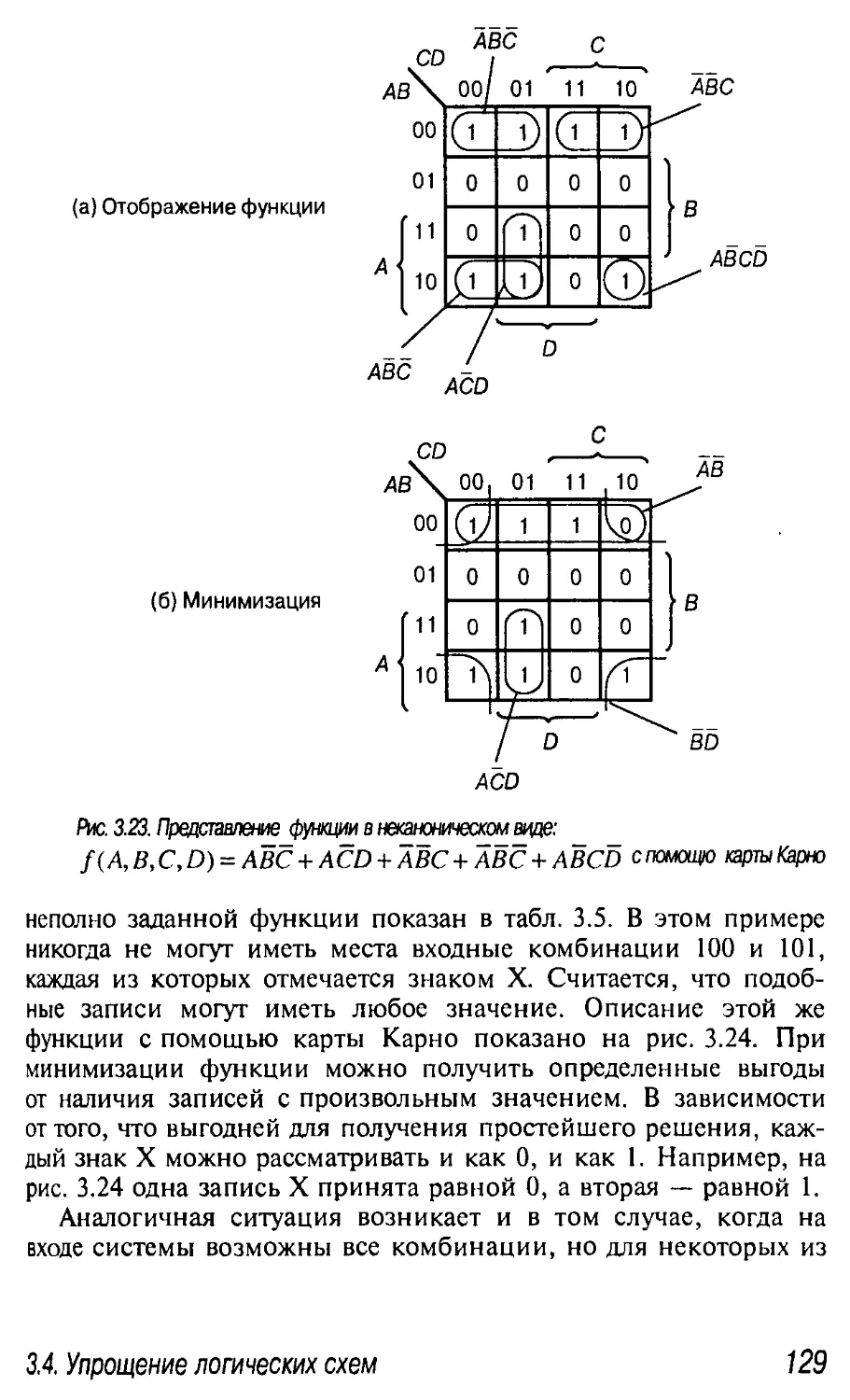

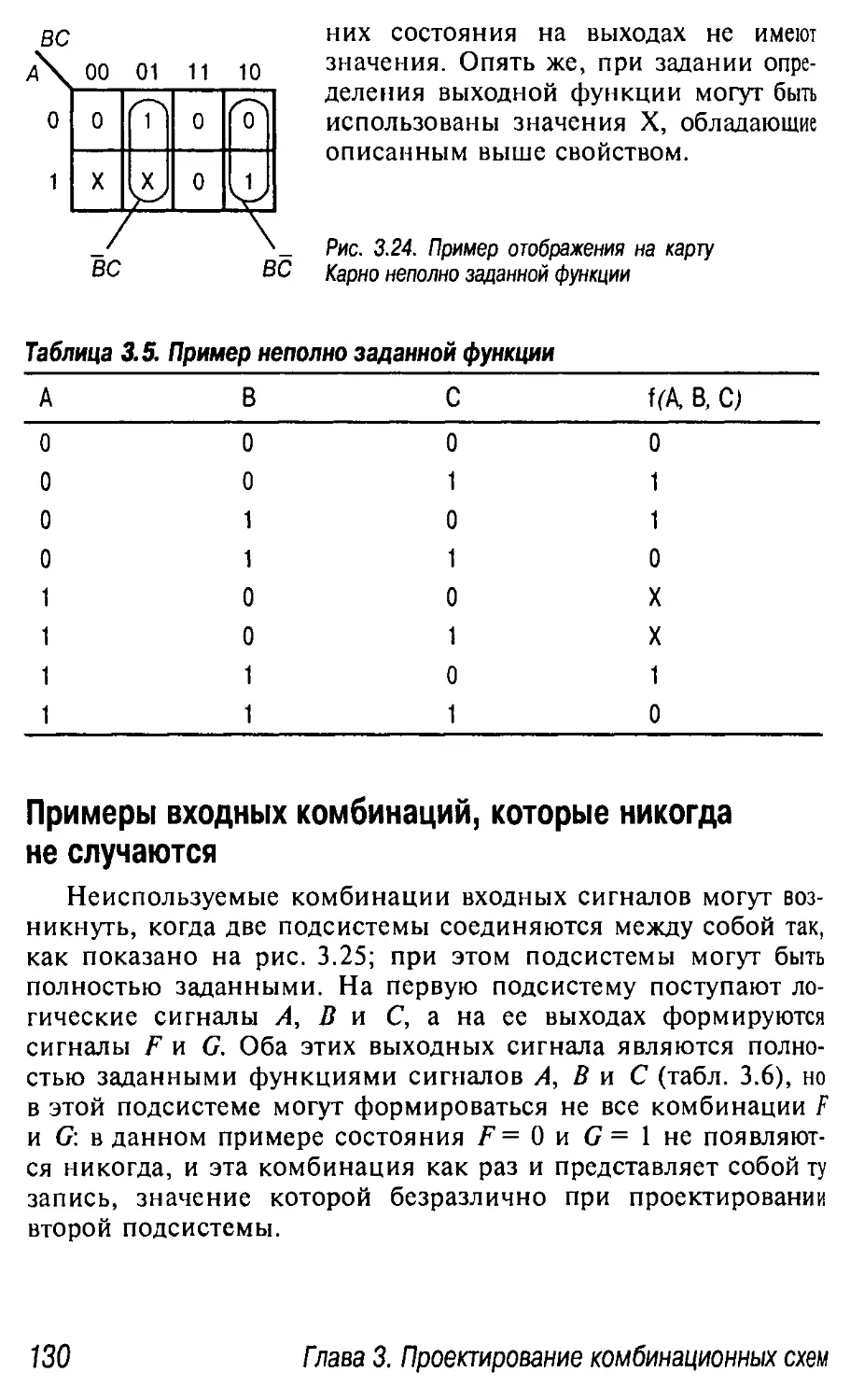

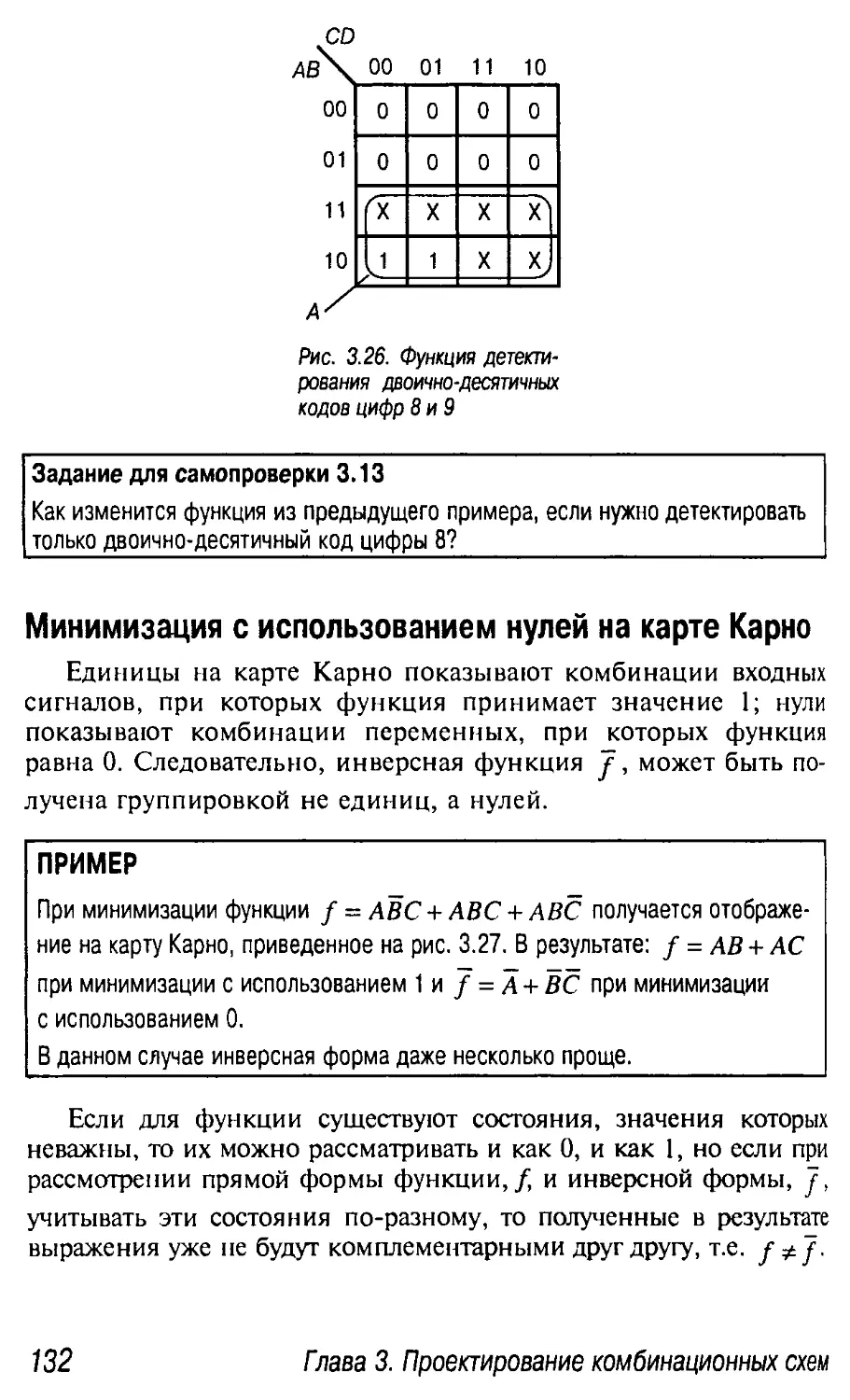

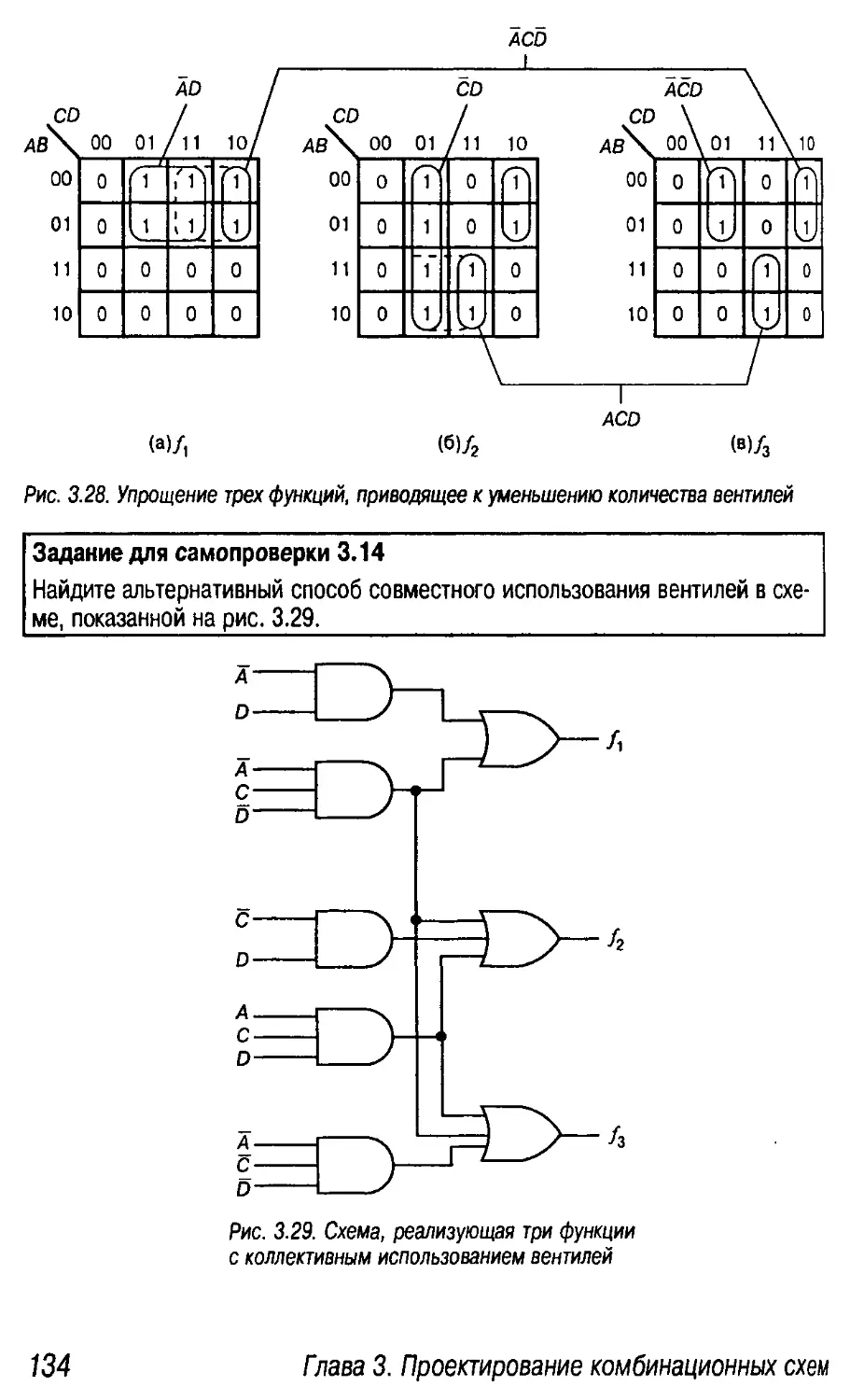

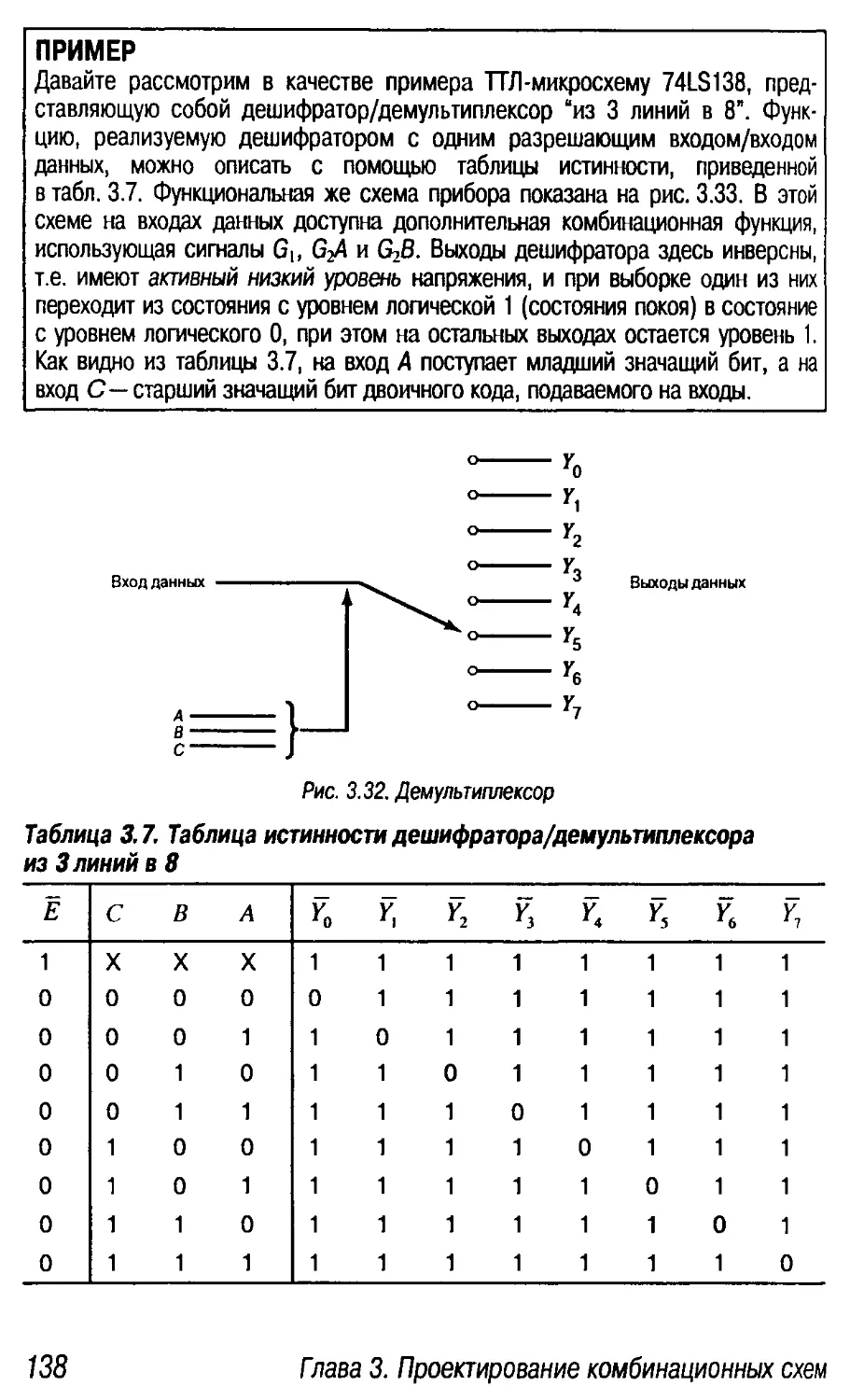

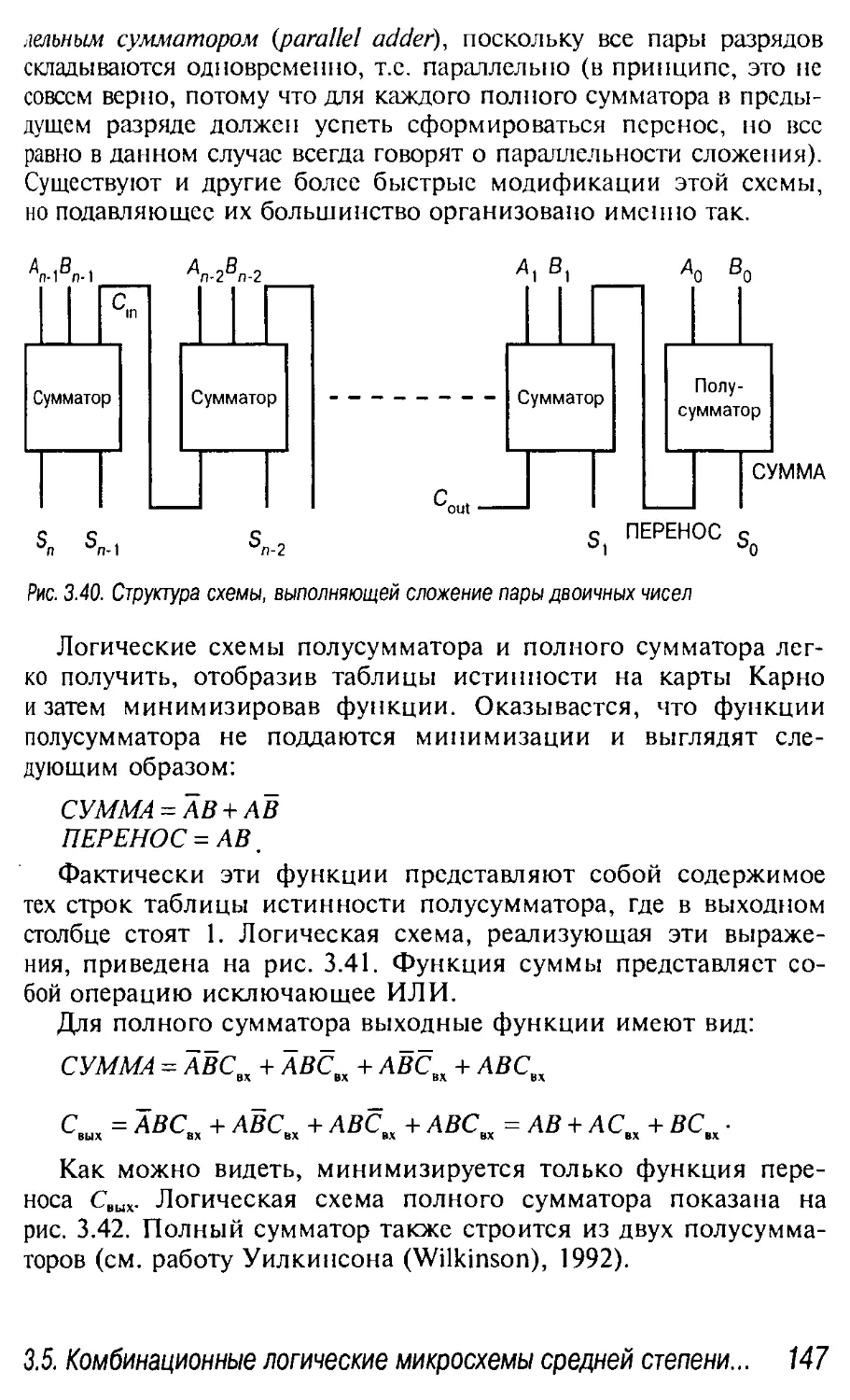

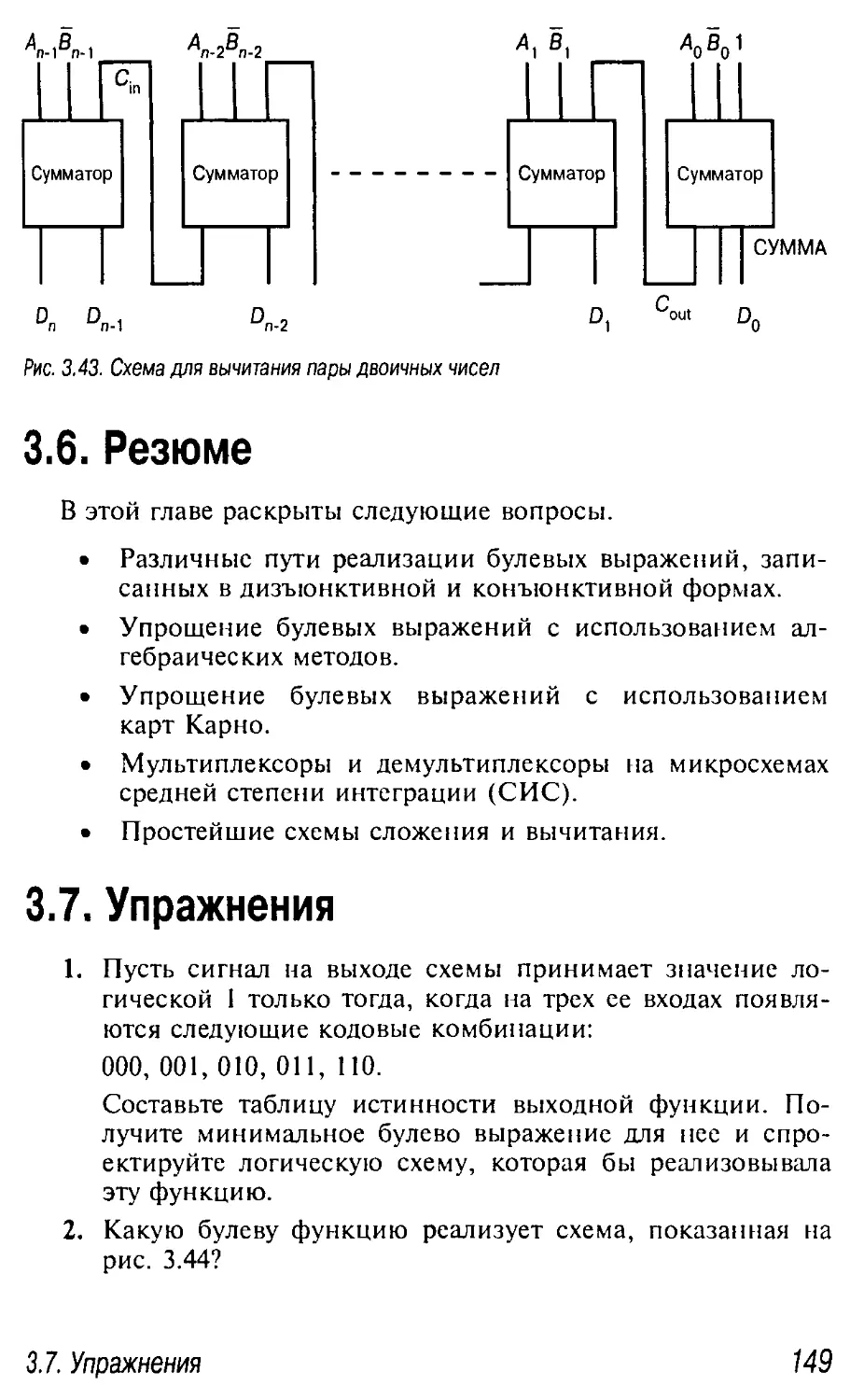

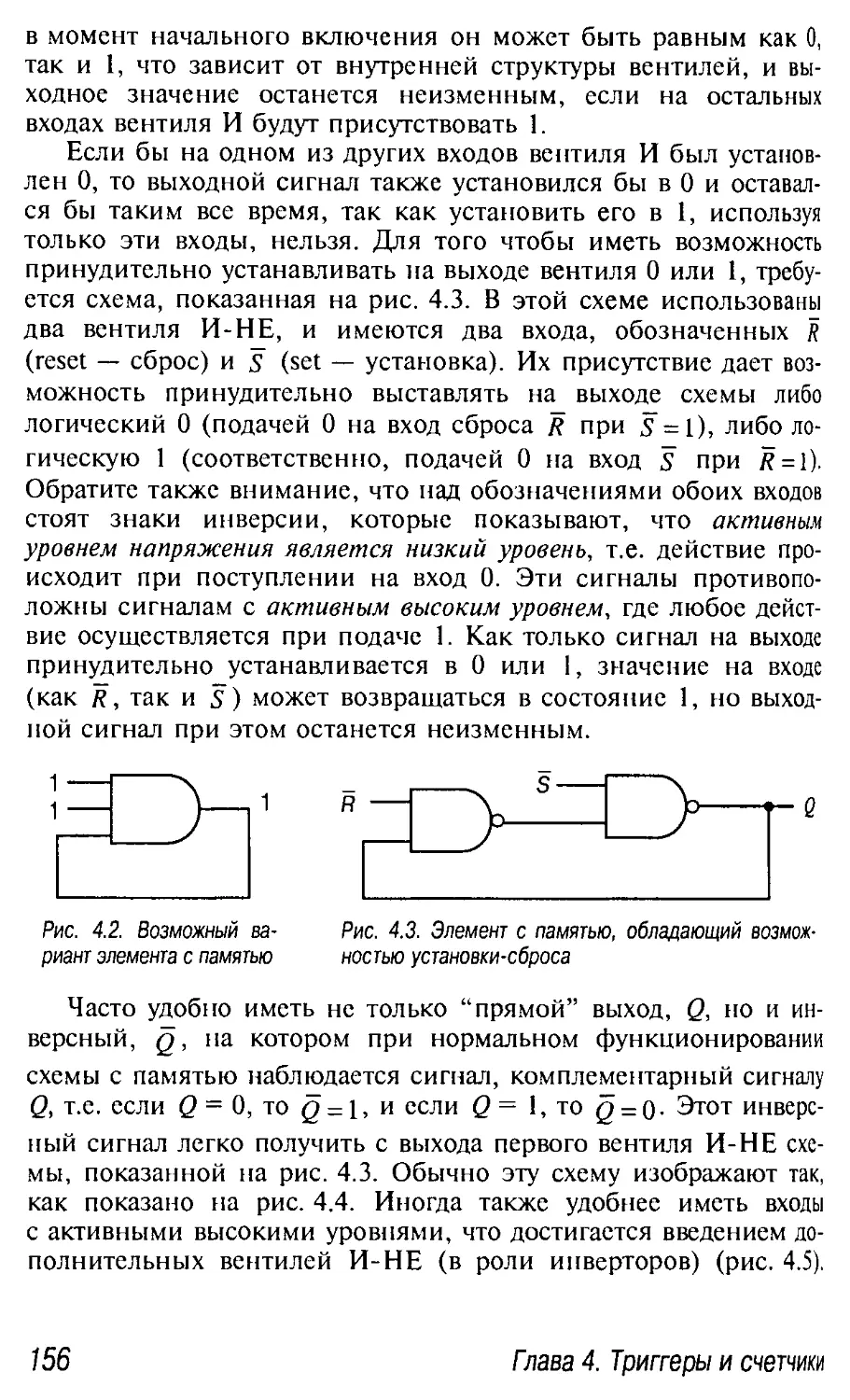

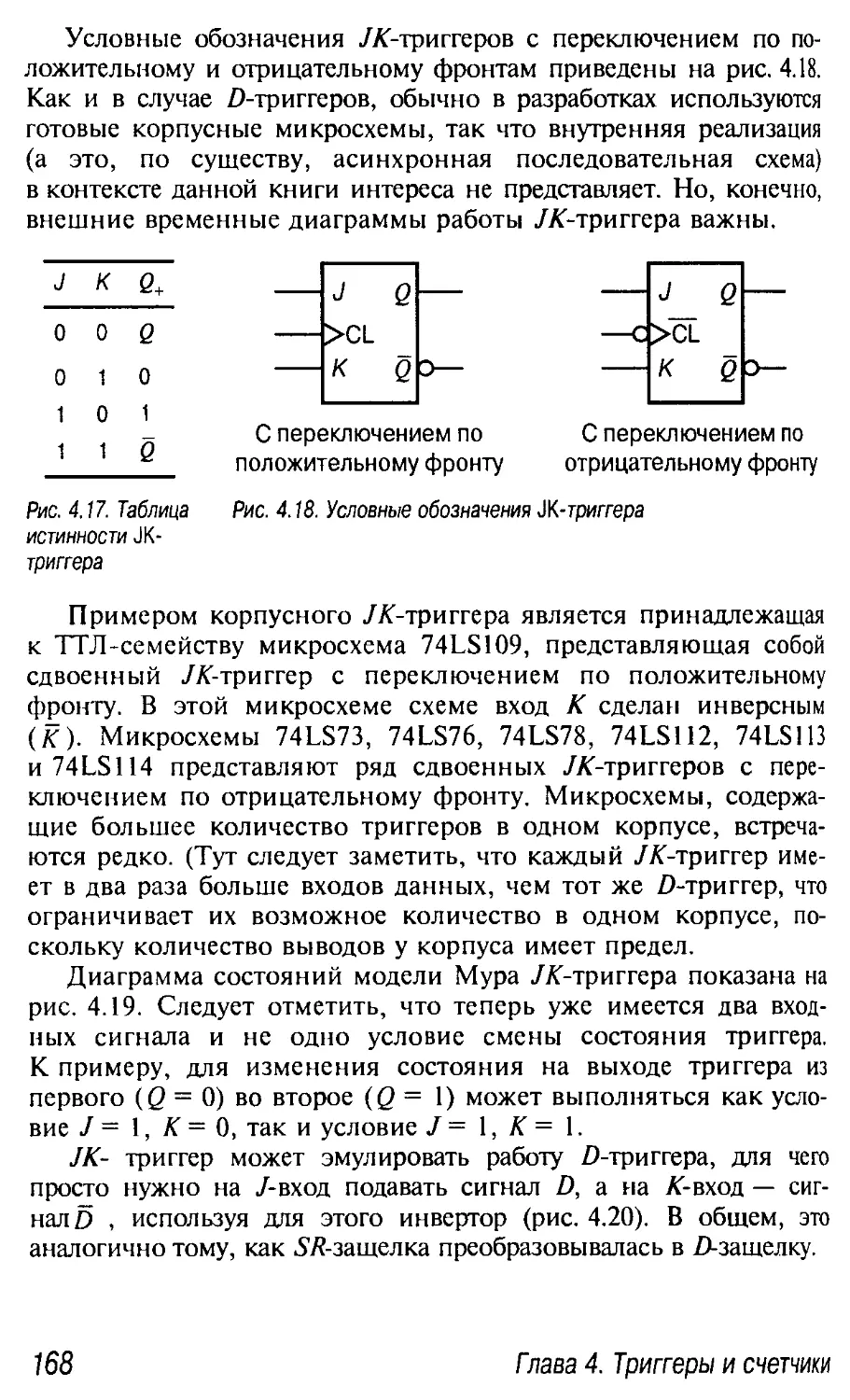

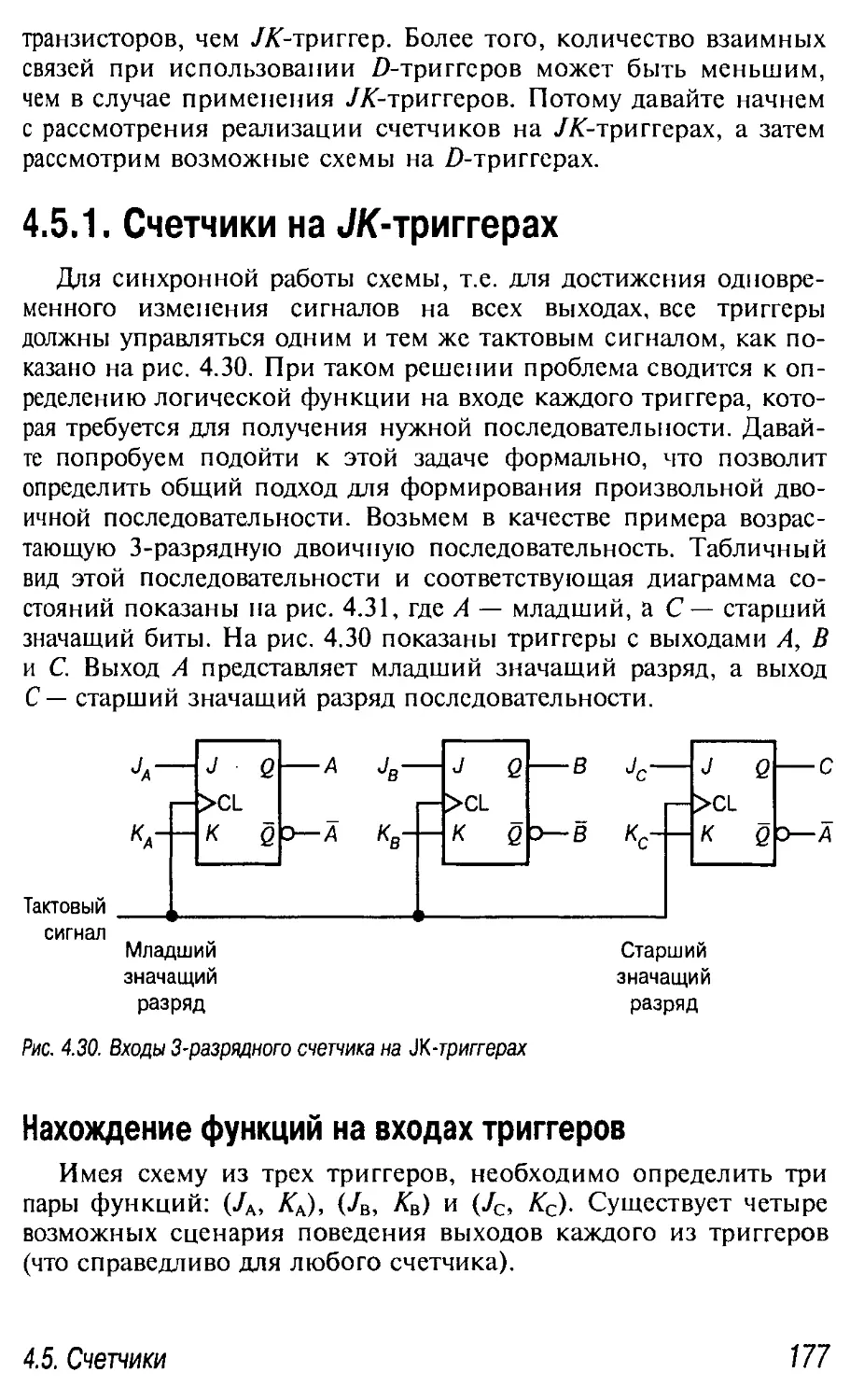

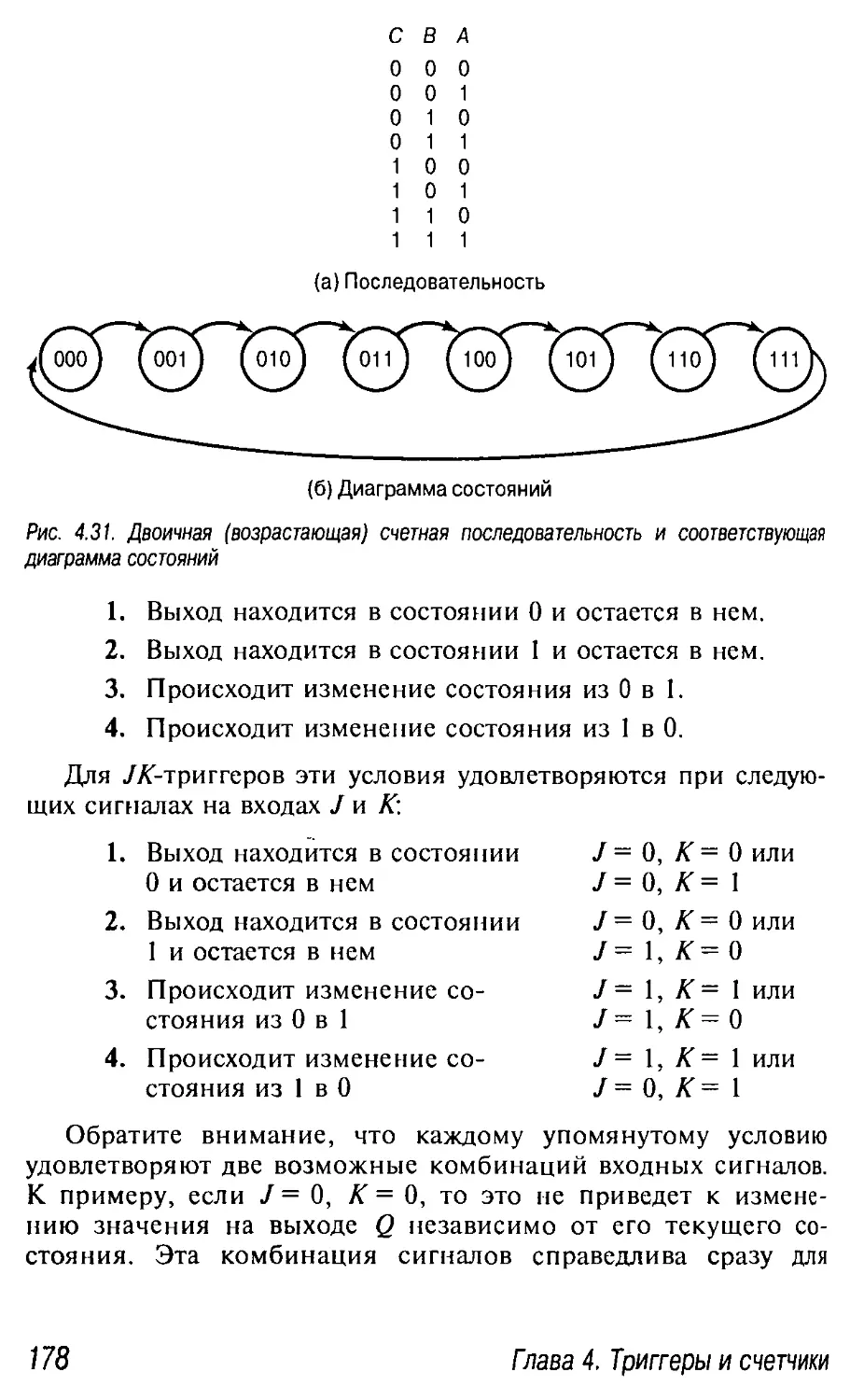

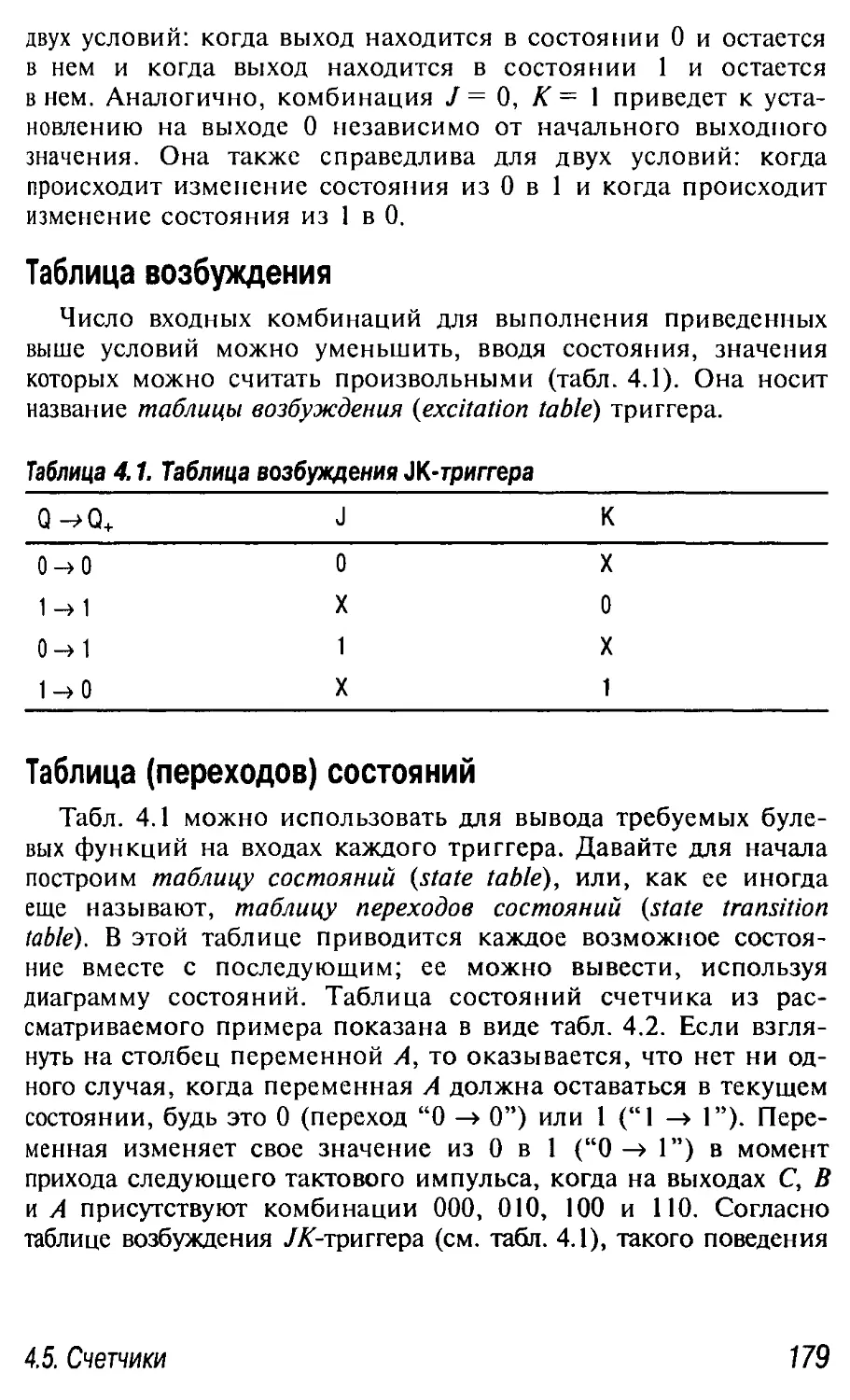

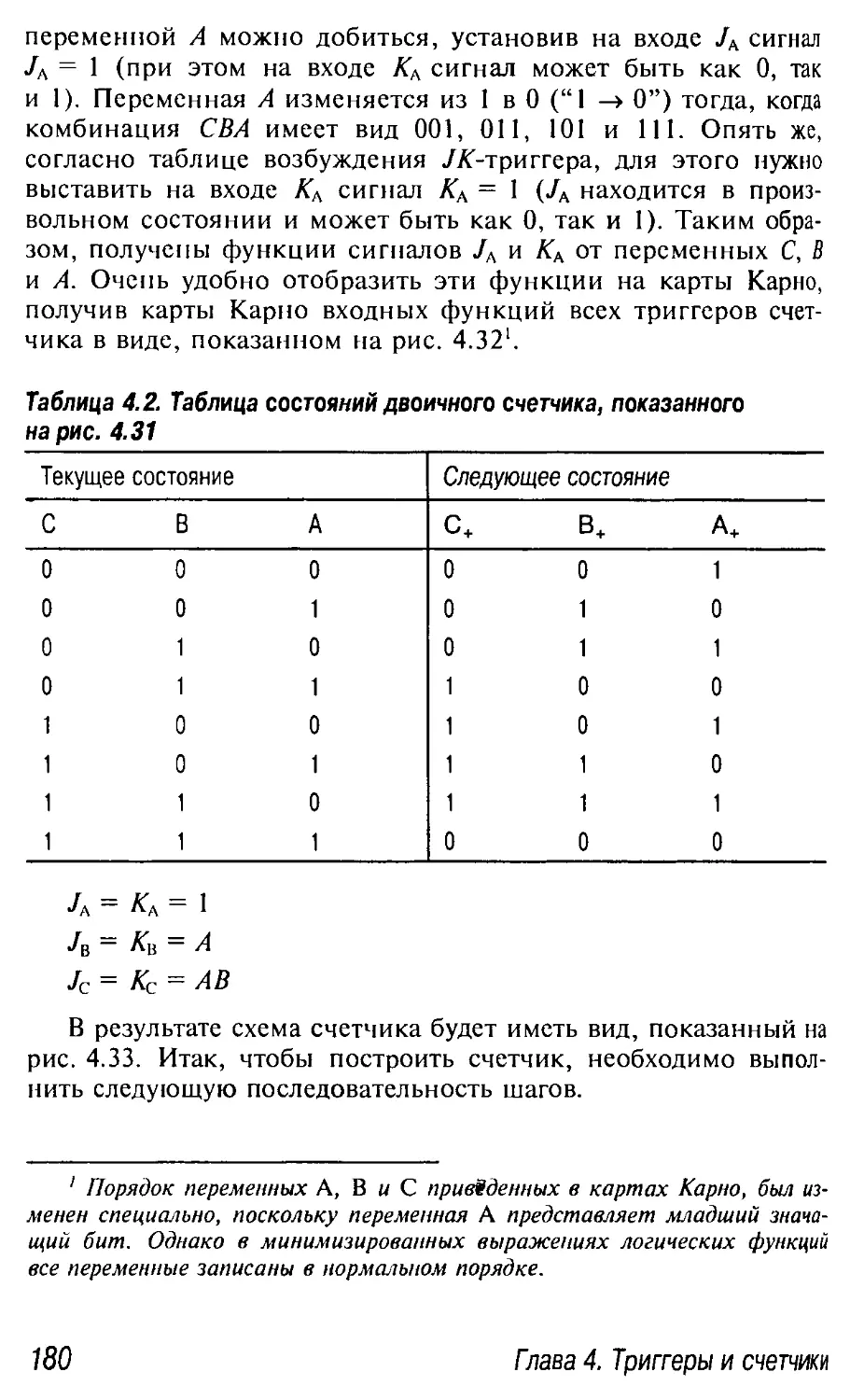

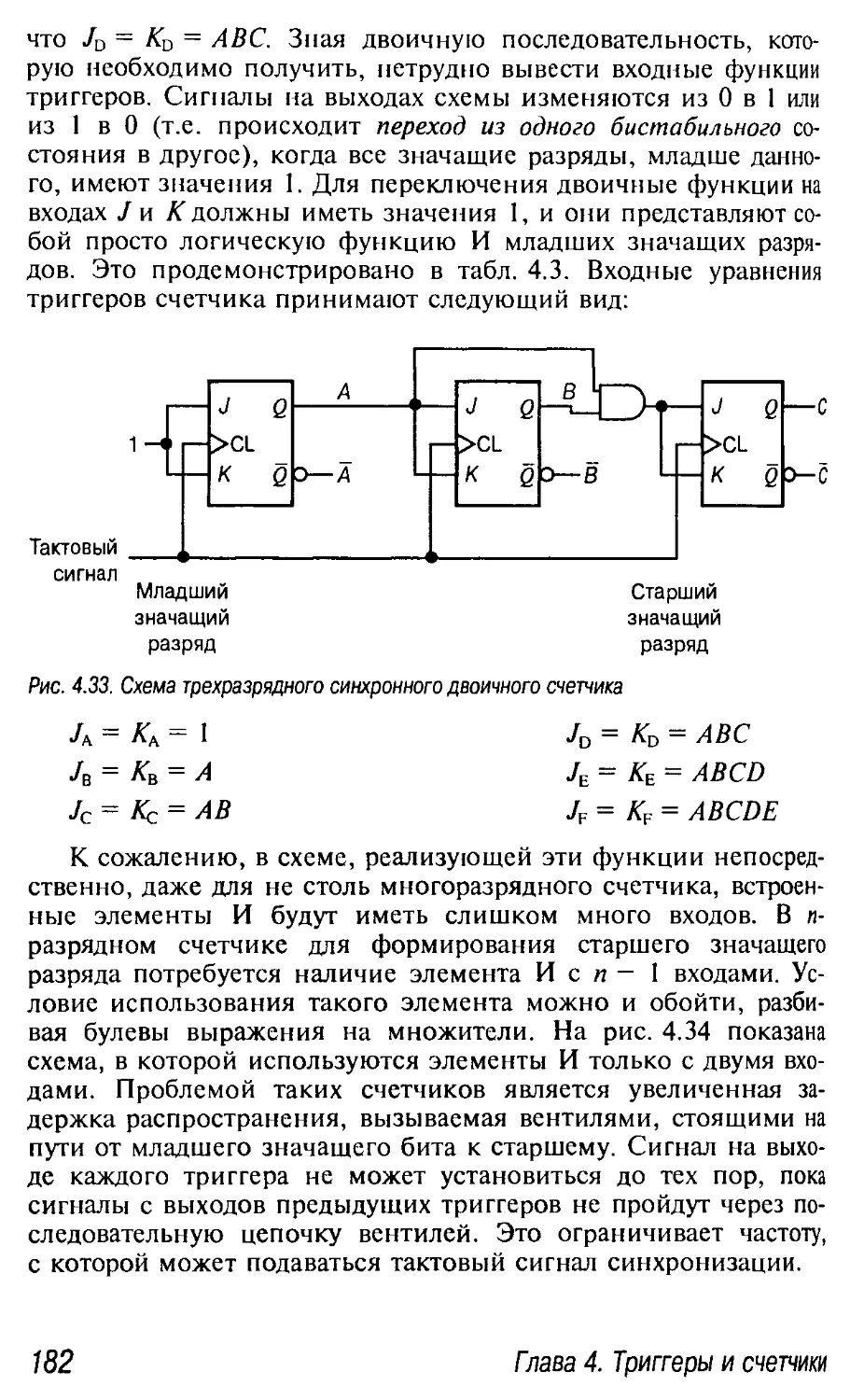

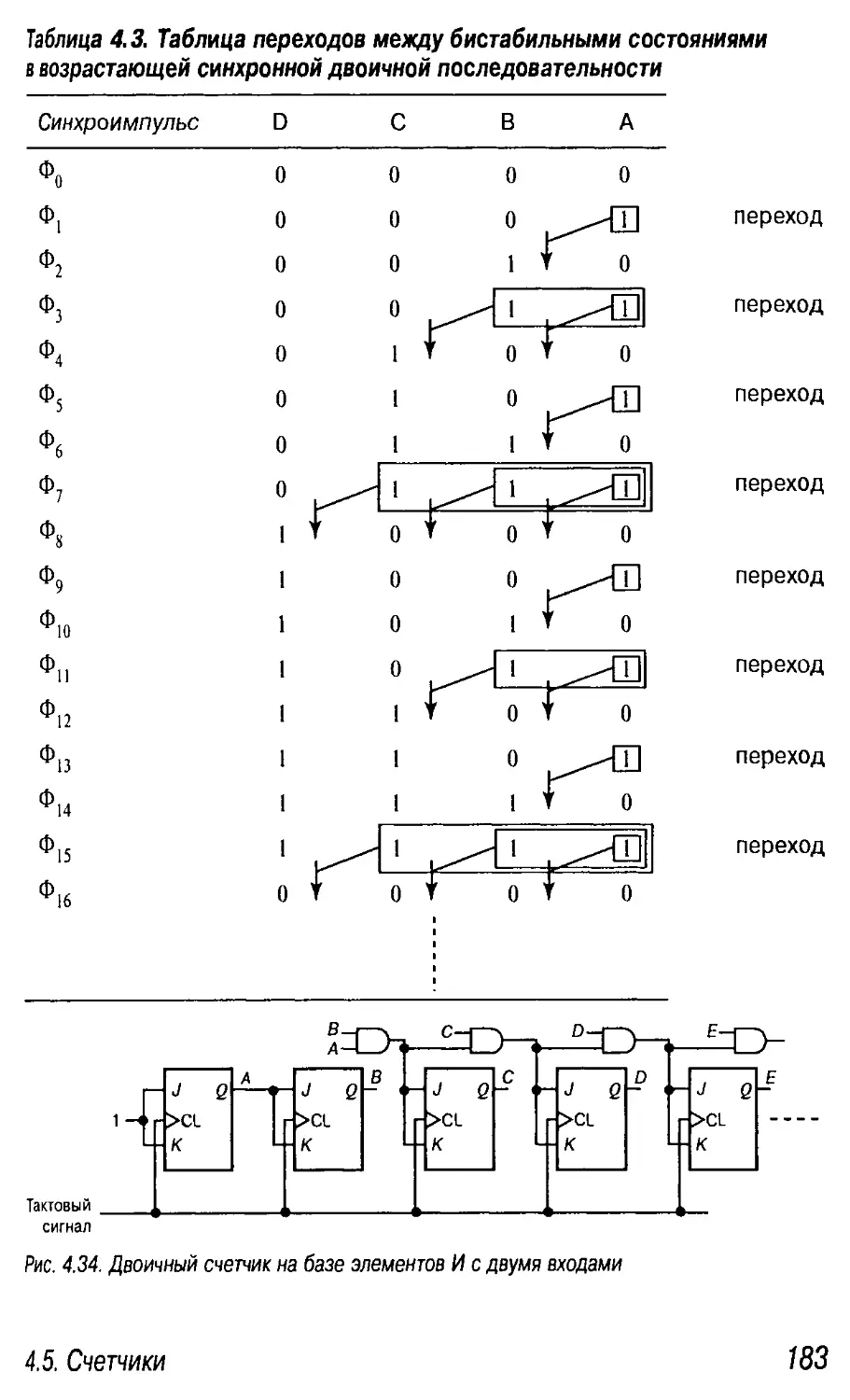

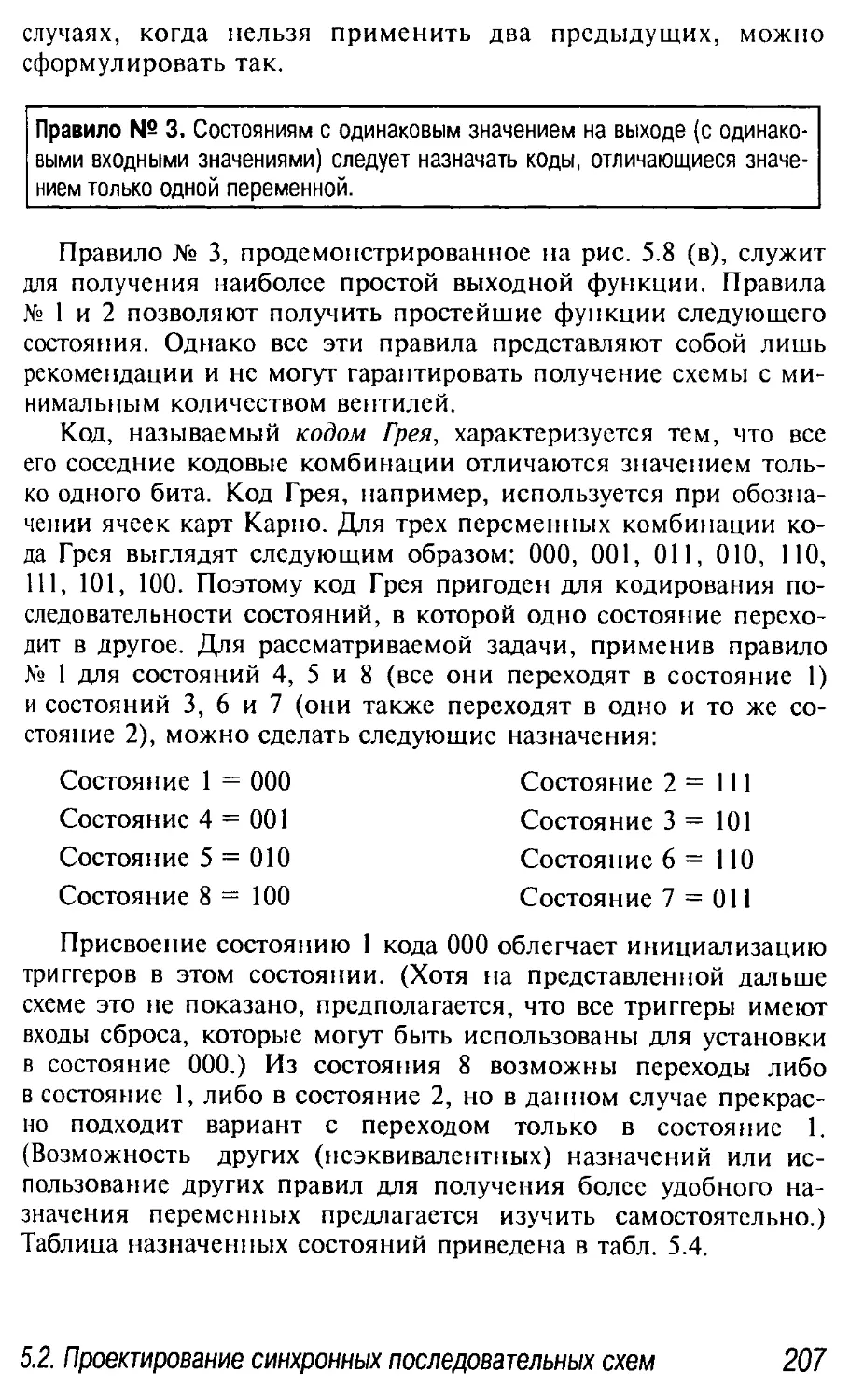

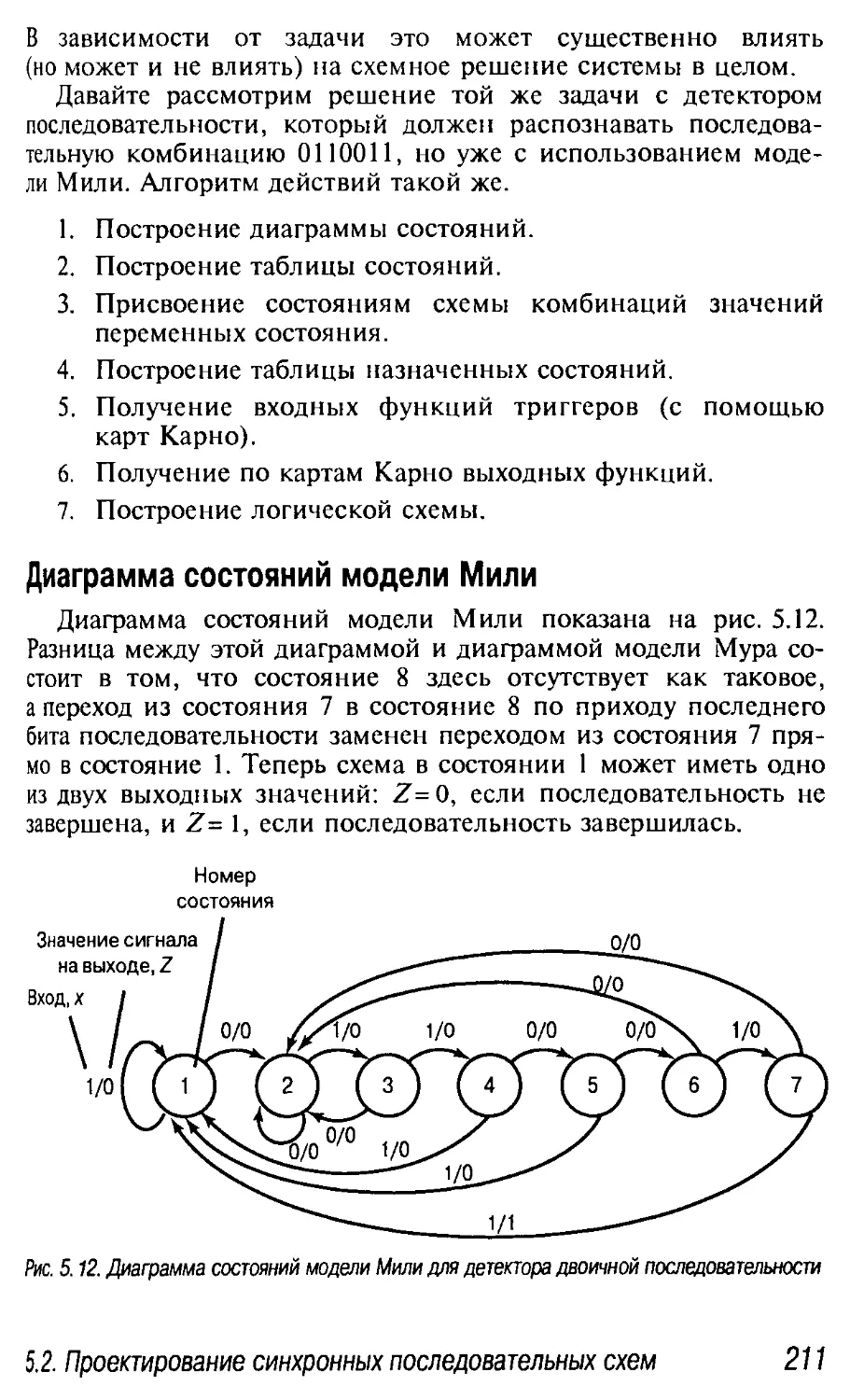

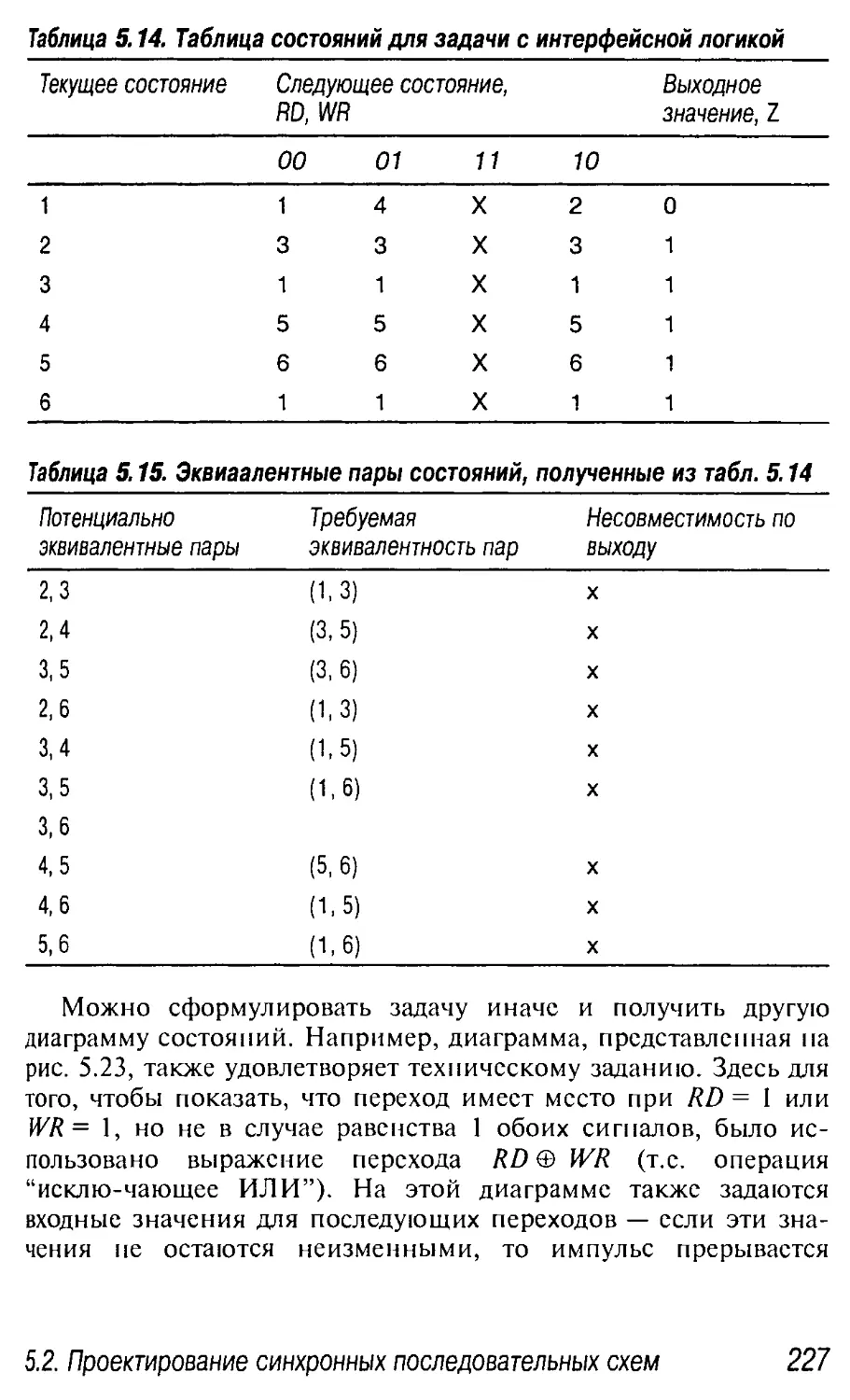

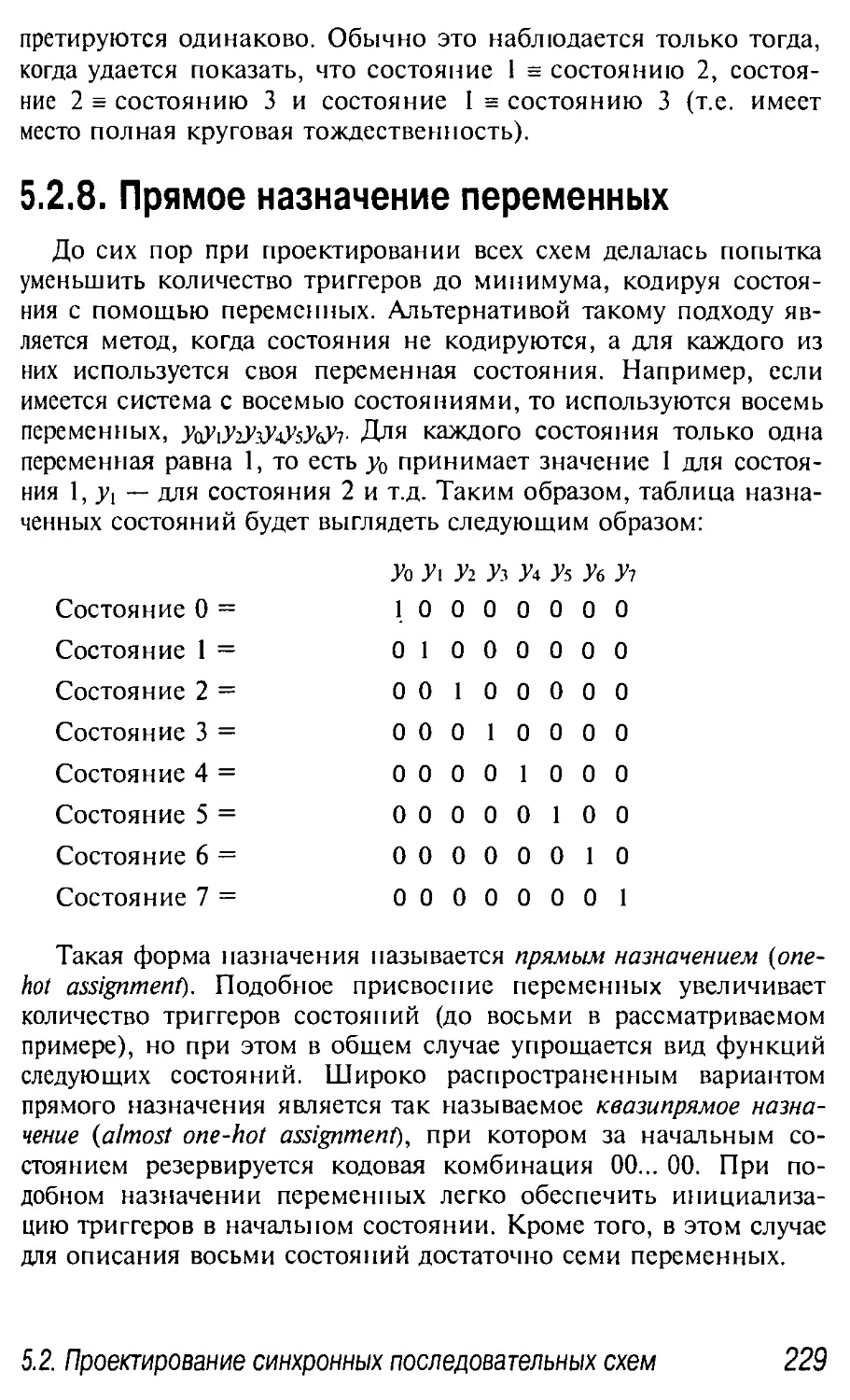

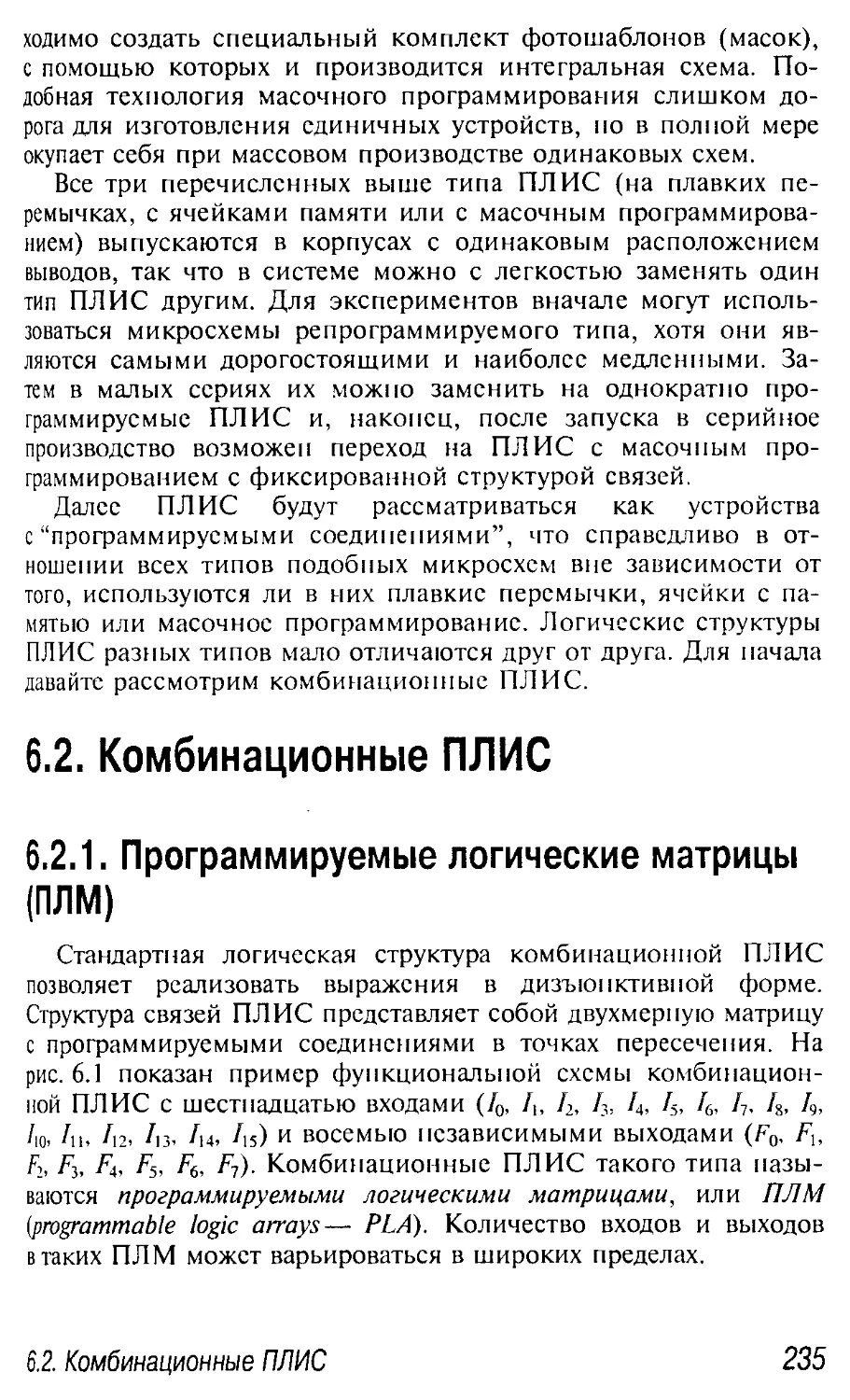

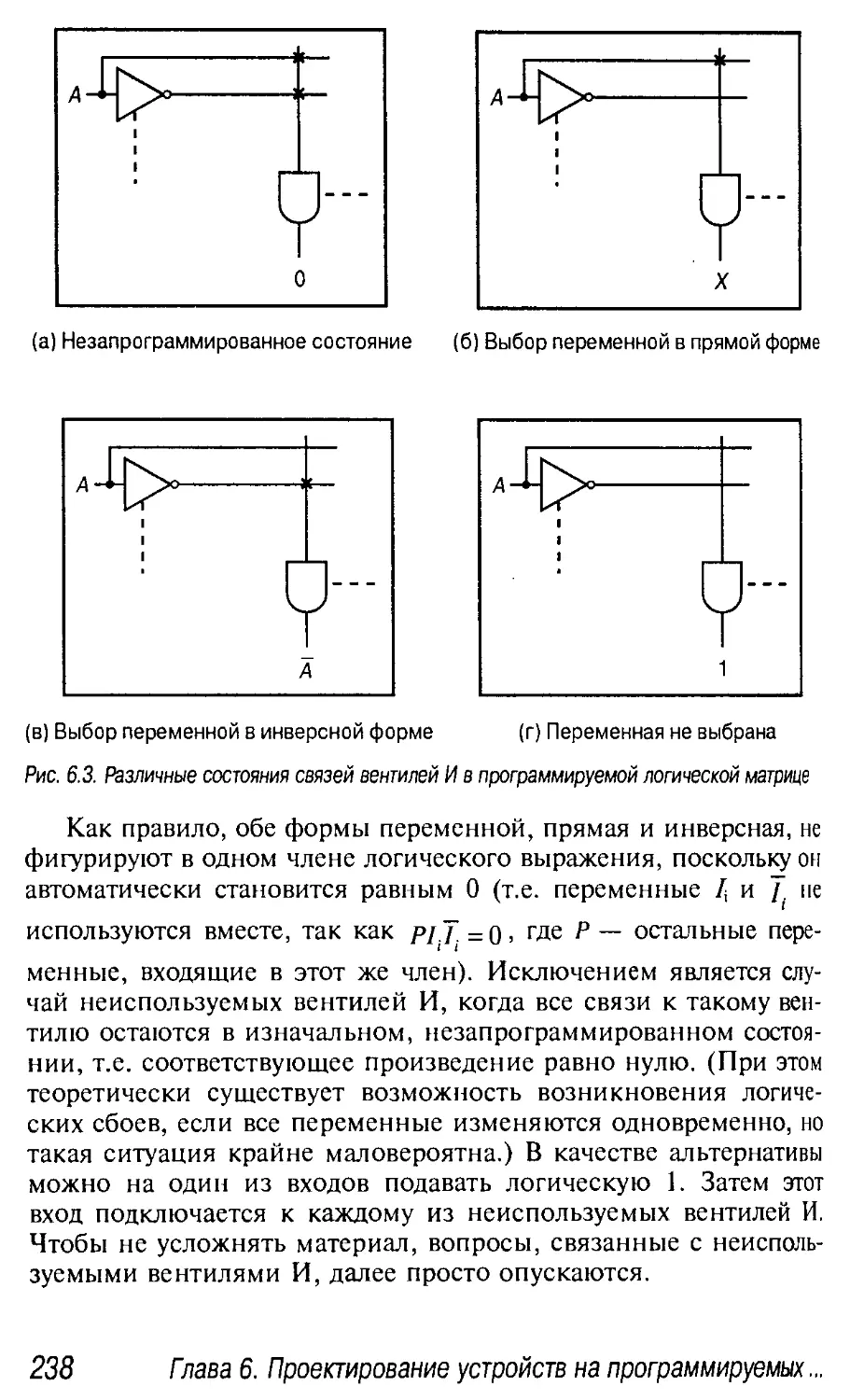

6. Wilkinson, B. and Horrocks, D., Computer Peripherals, 2nd