Автор: Лехин С.Н.

Теги: компьютерные технологии компьютерные науки схемотехника издательство бхв-петербург

ISBN: 978-5-9775-0353-2

Год: 2010

Текст

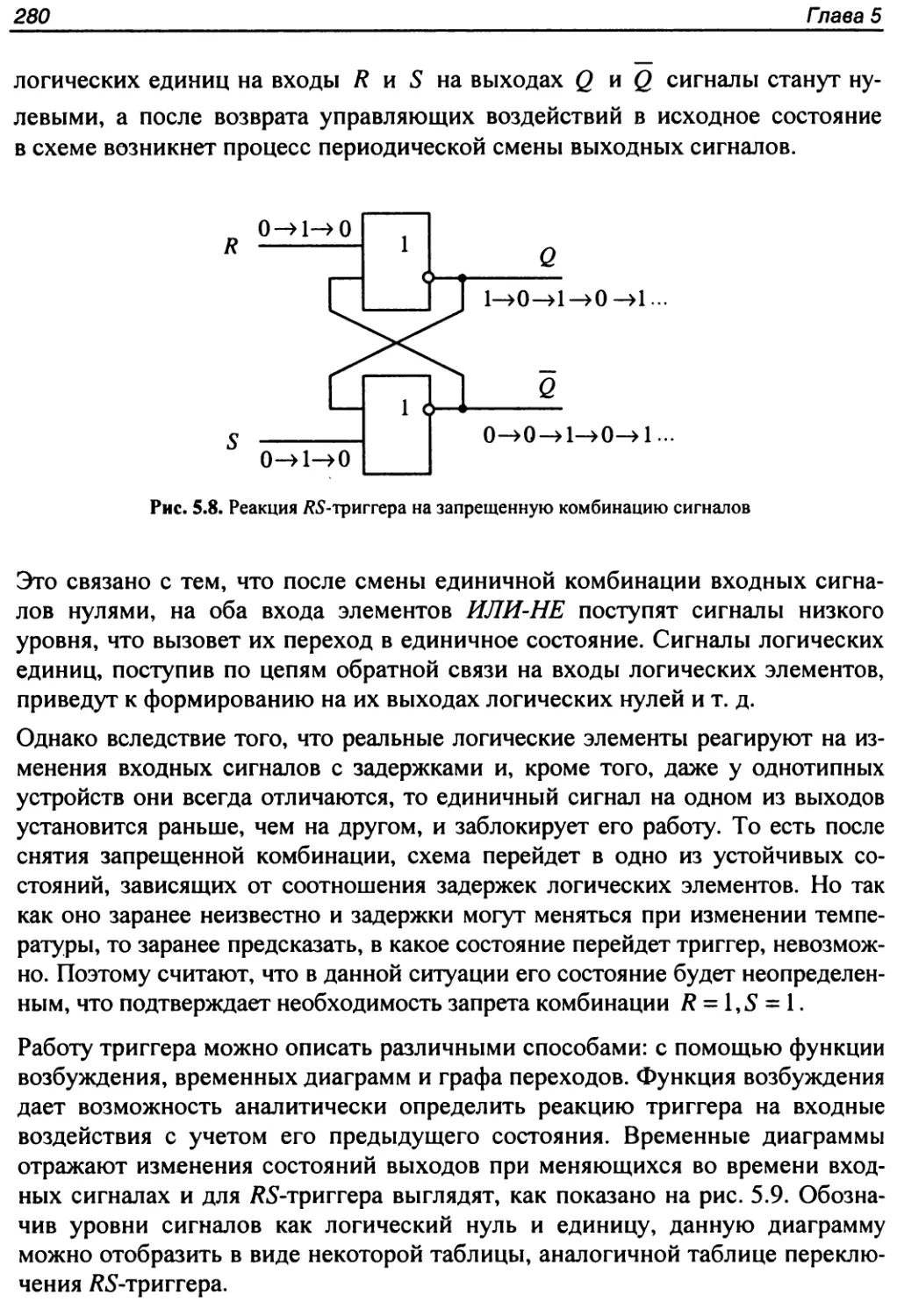

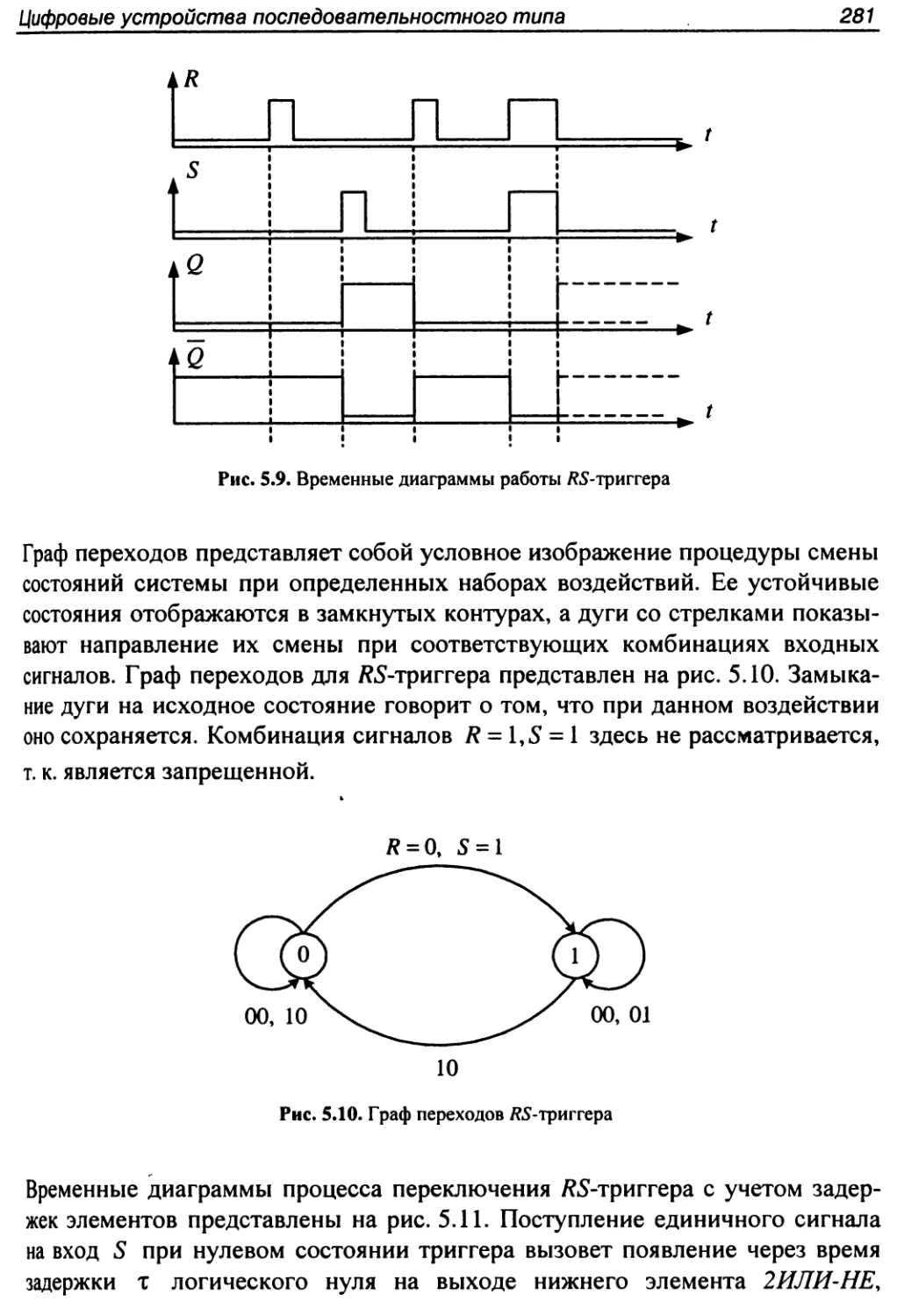

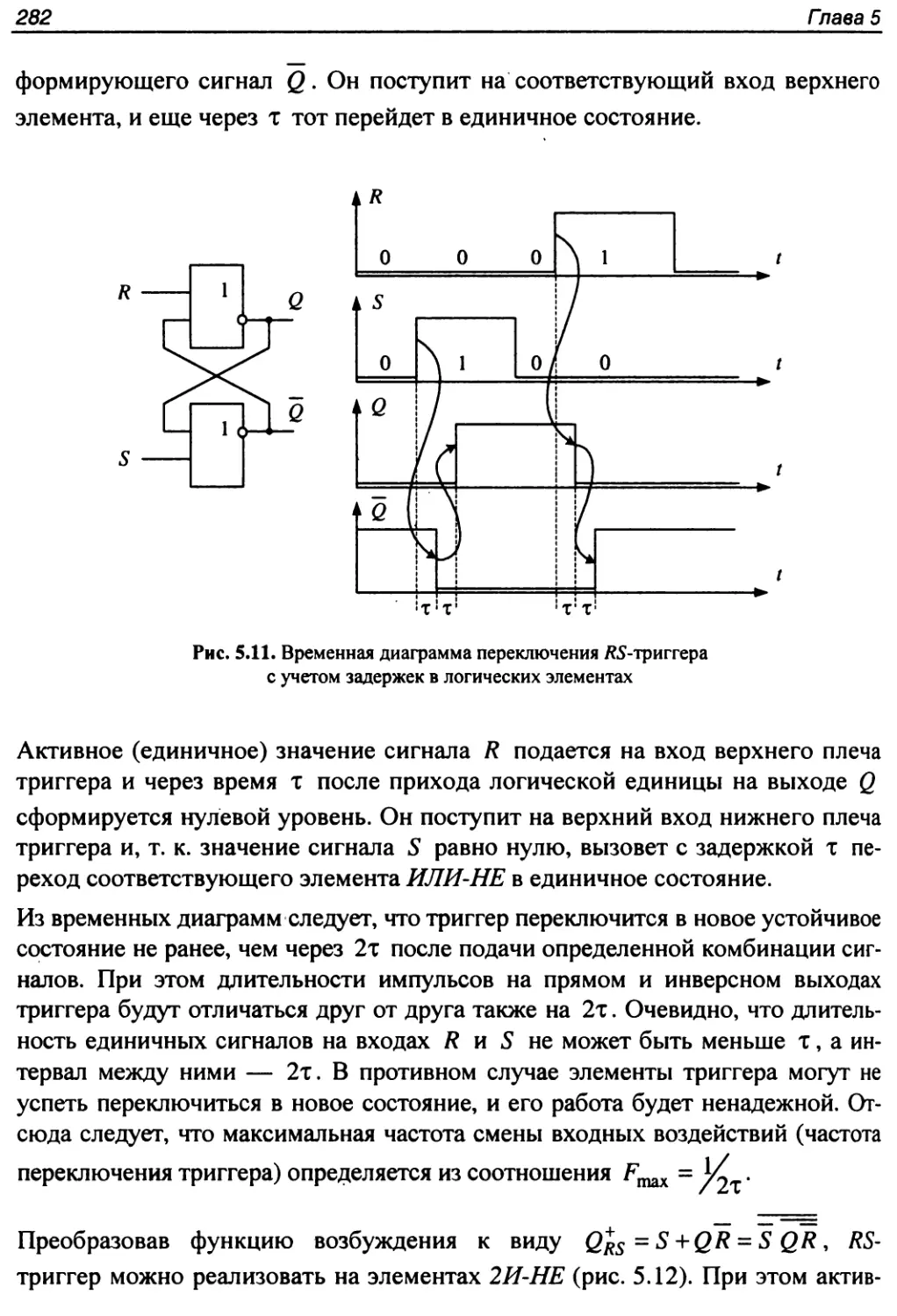

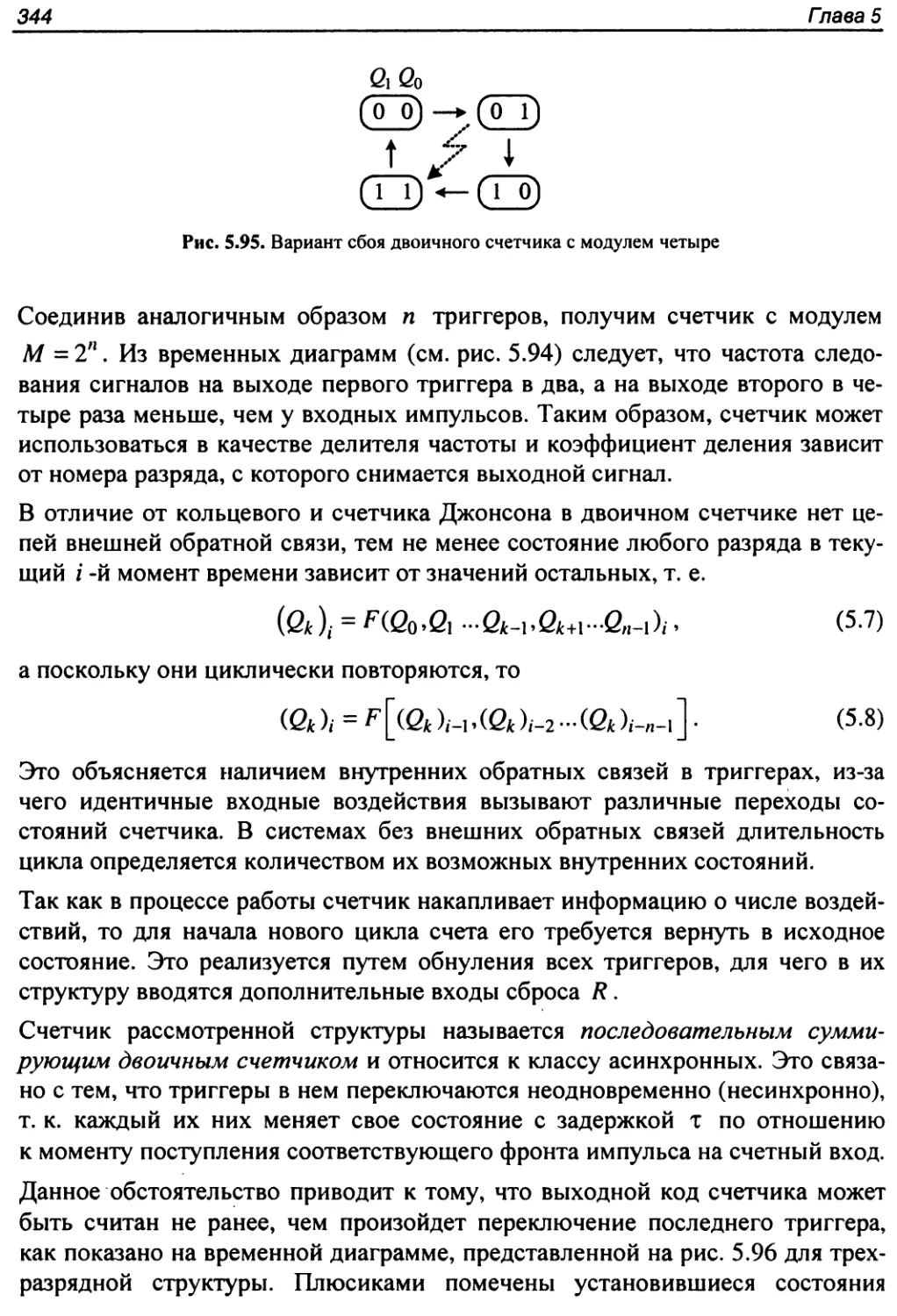

СХЕМОТЕХНИКА

ЭВМ

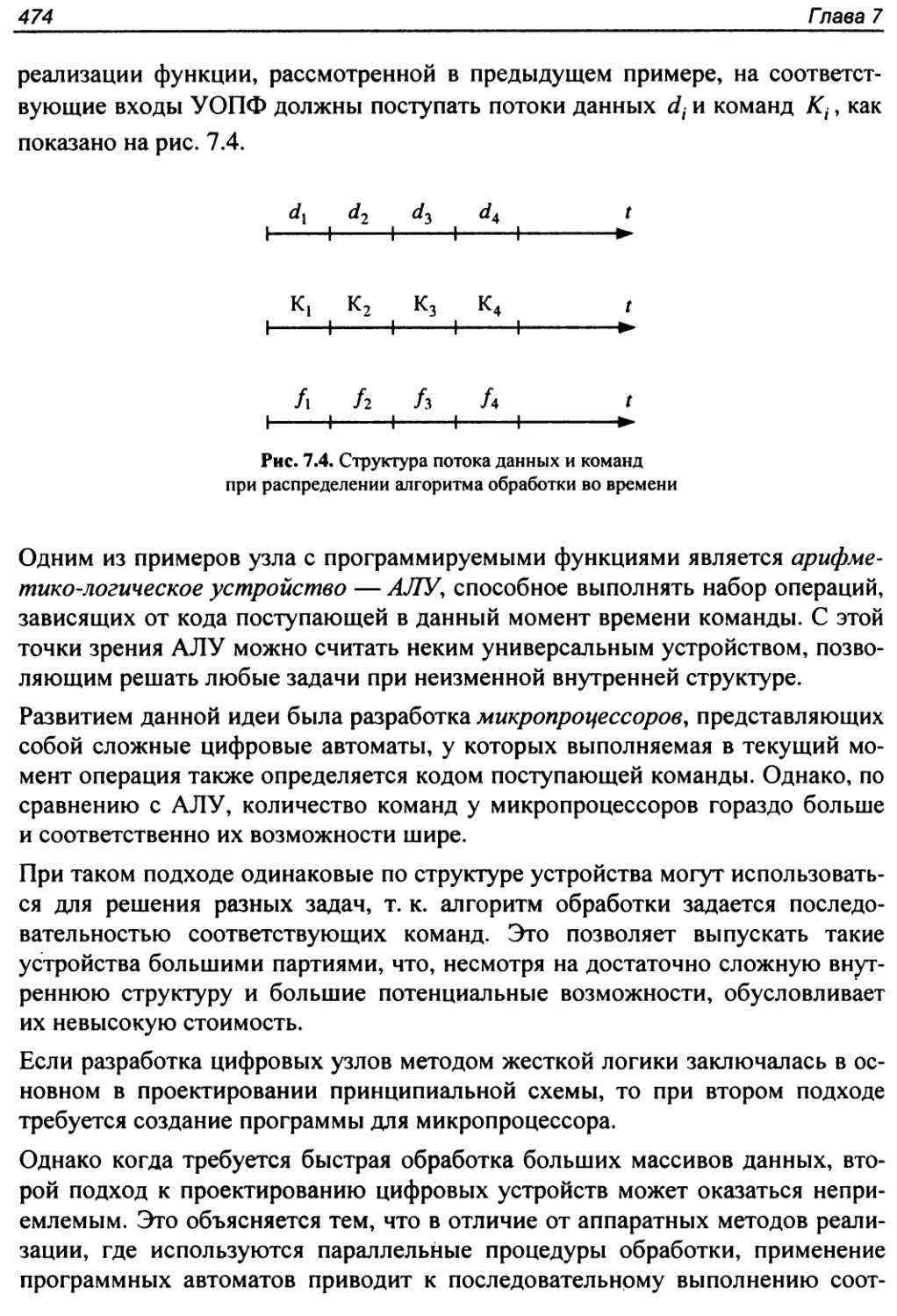

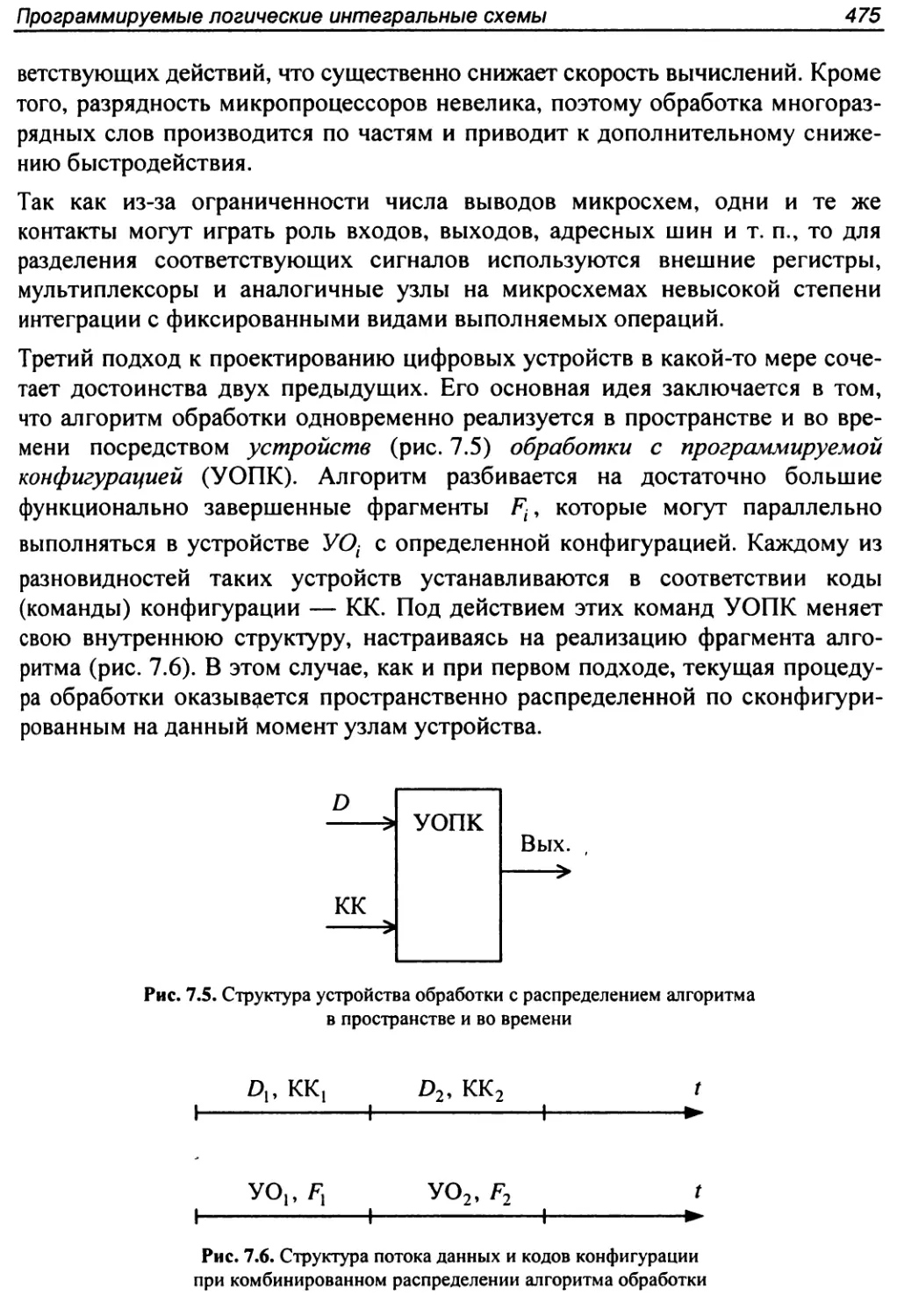

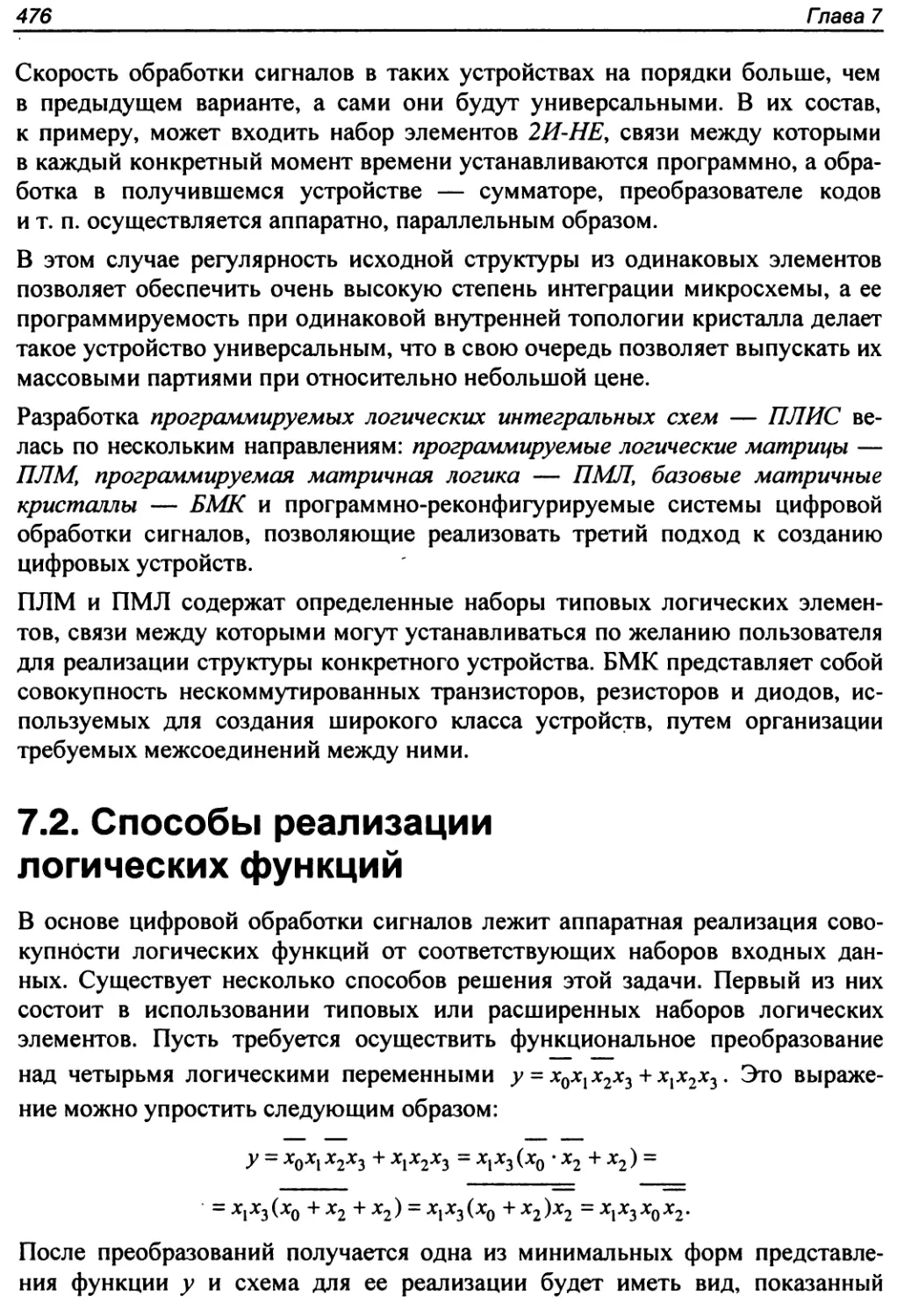

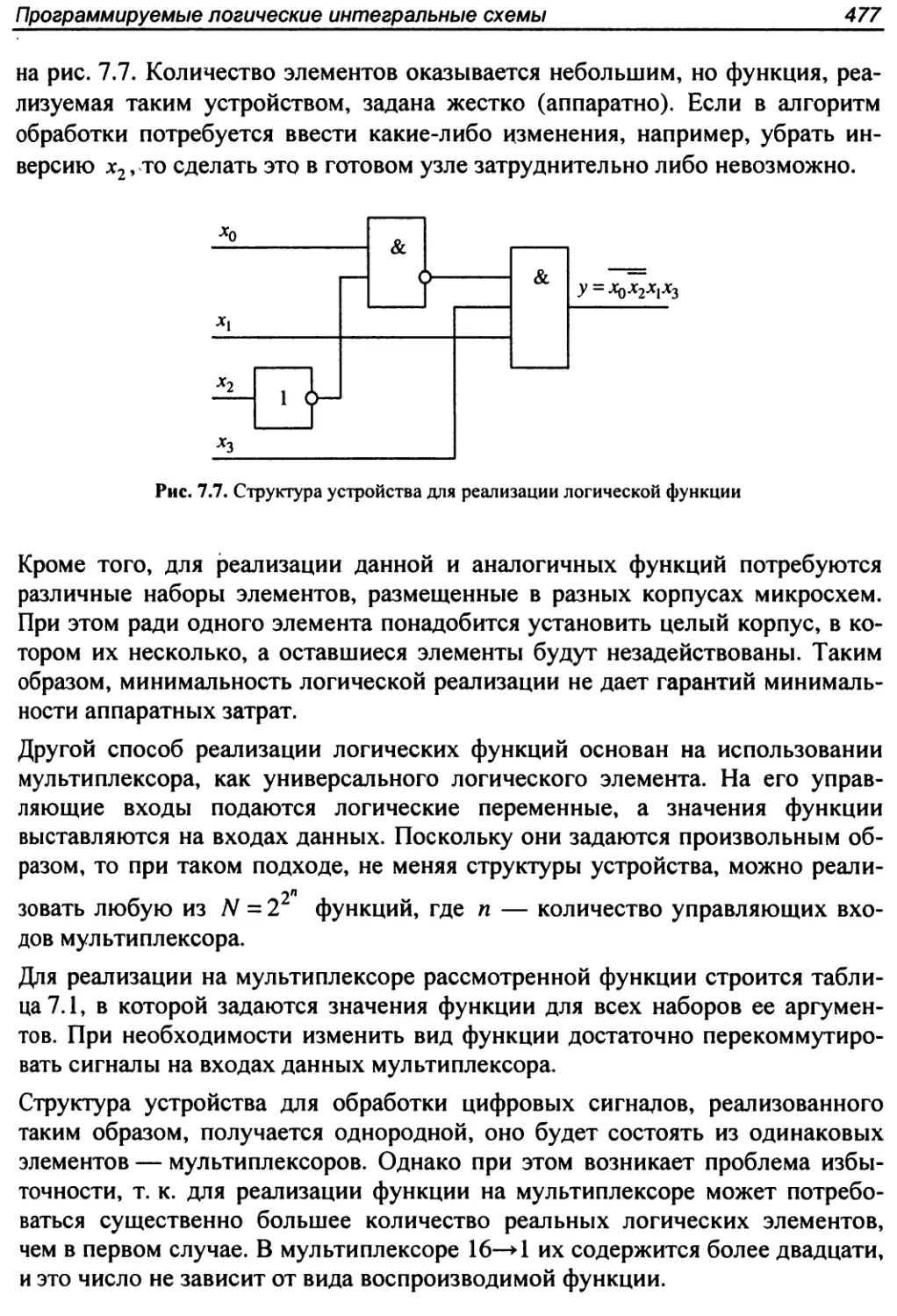

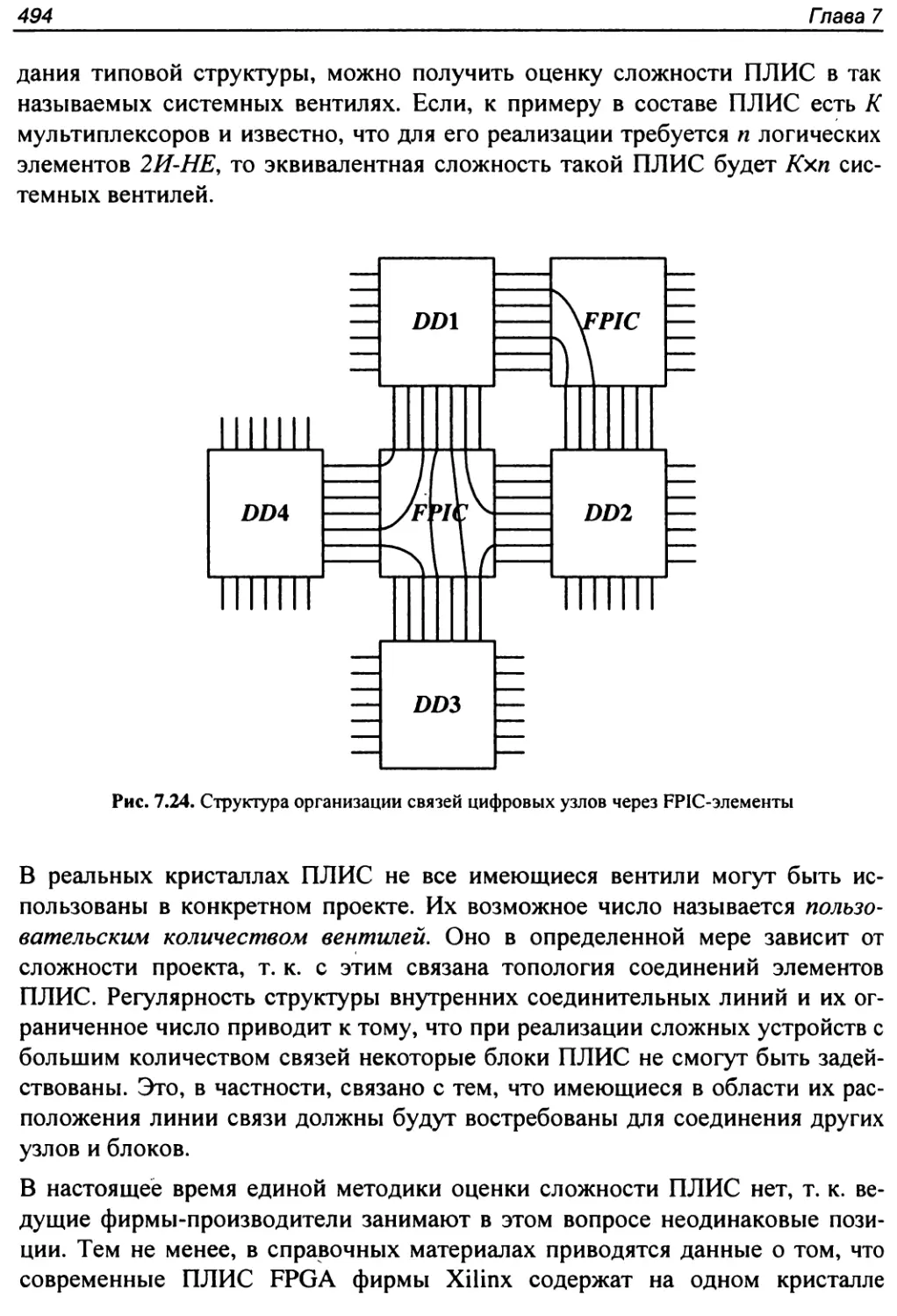

Арифметические и логические основы цифровой техники

Схемотехника цифровых логических элементов

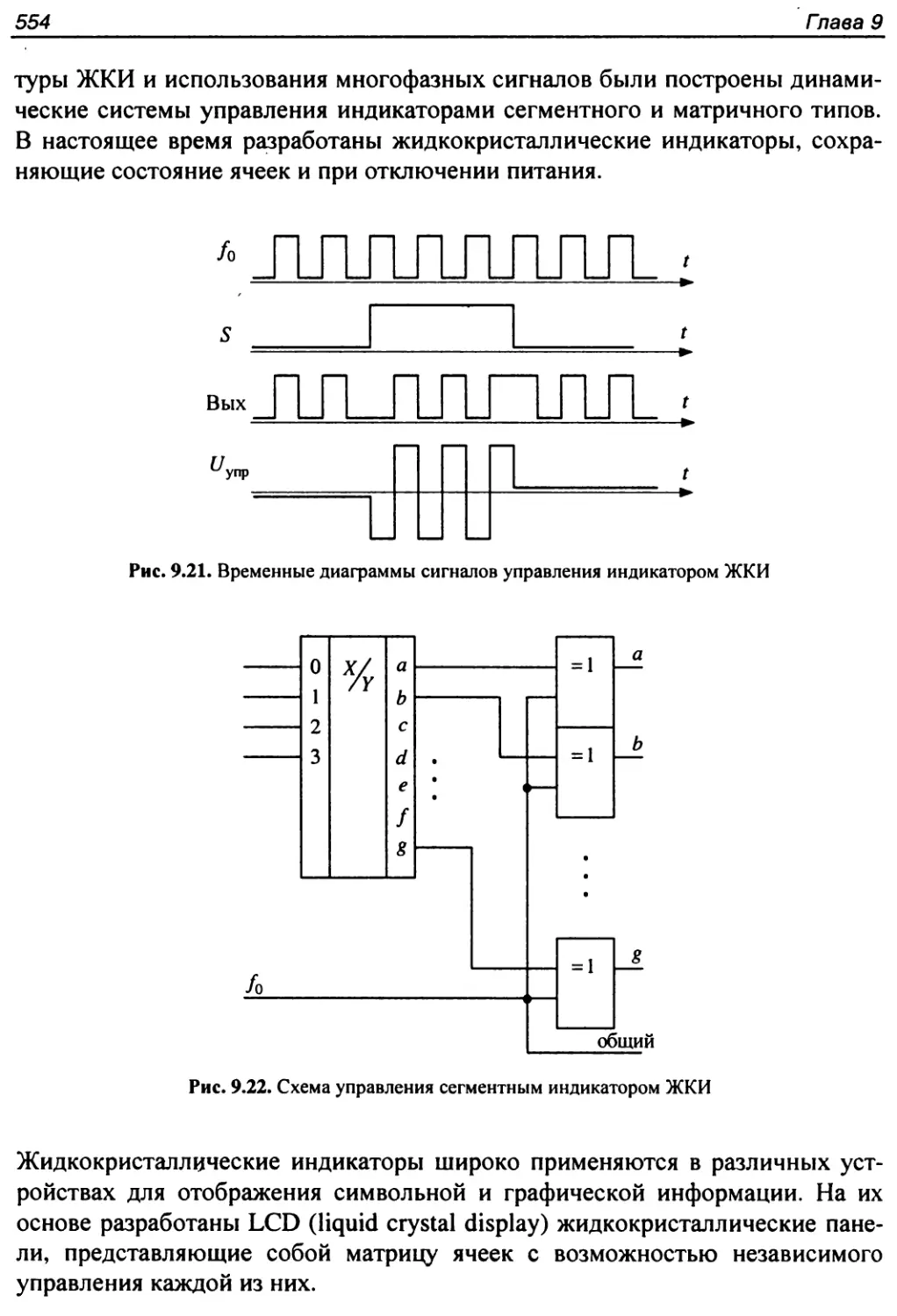

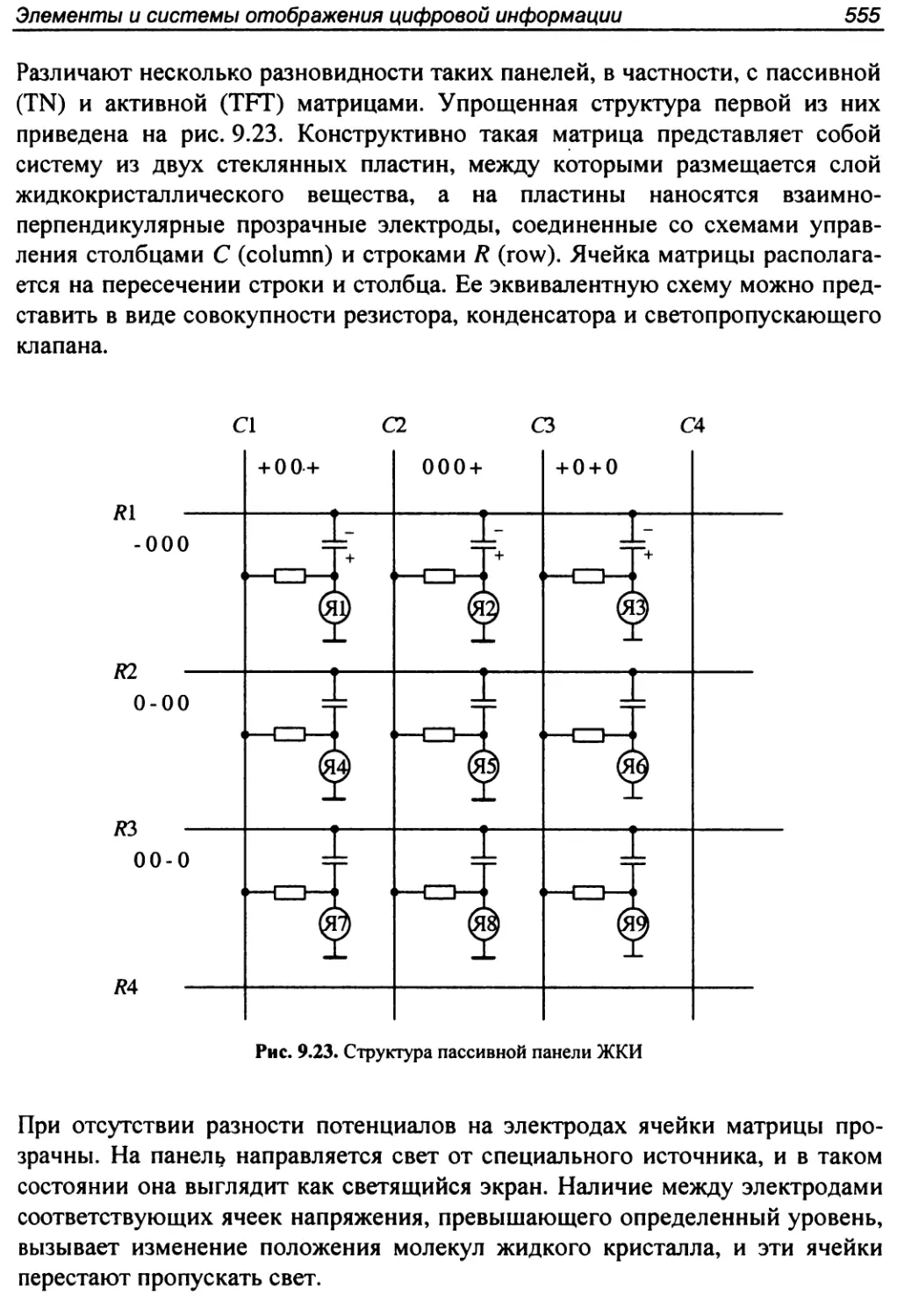

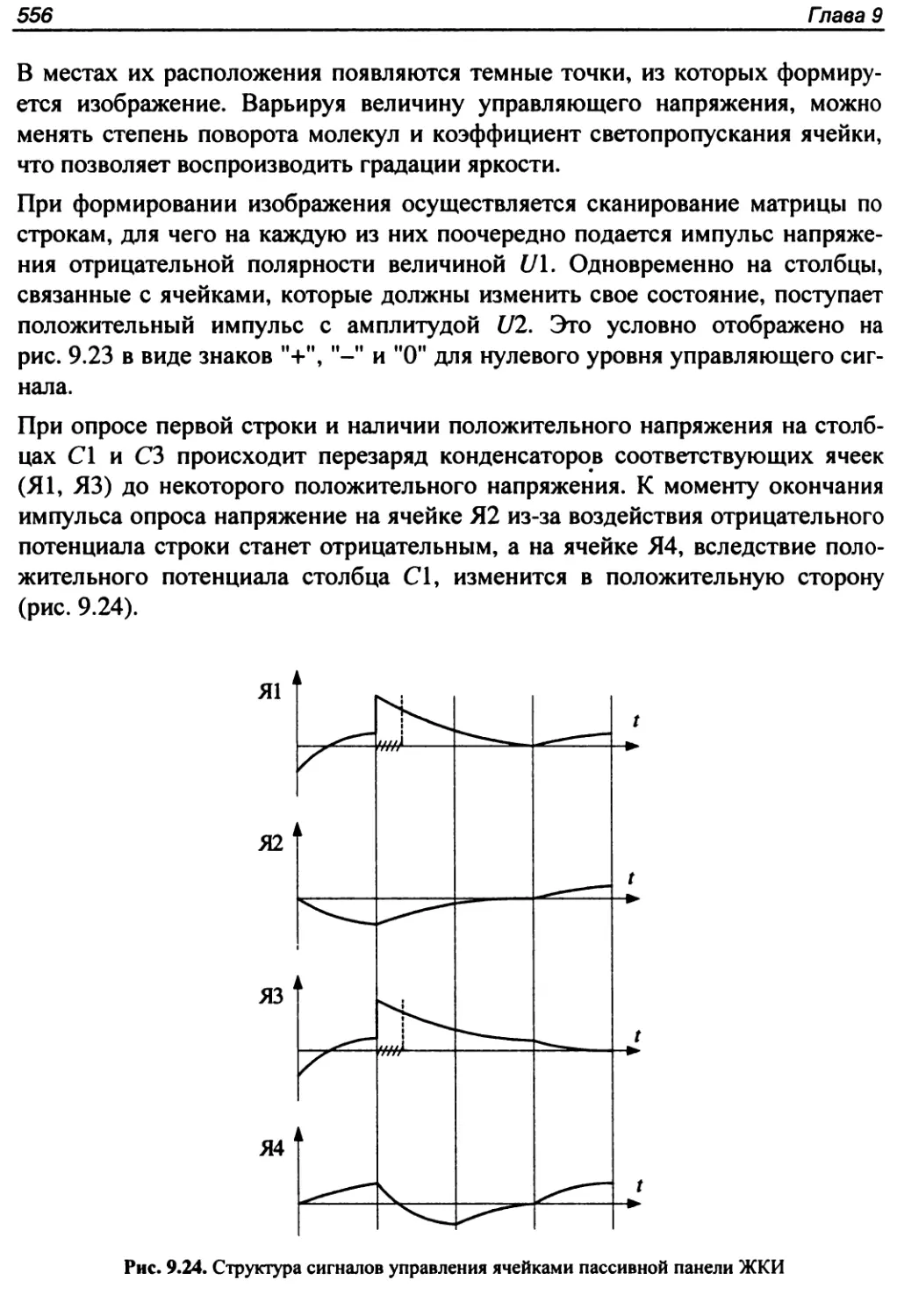

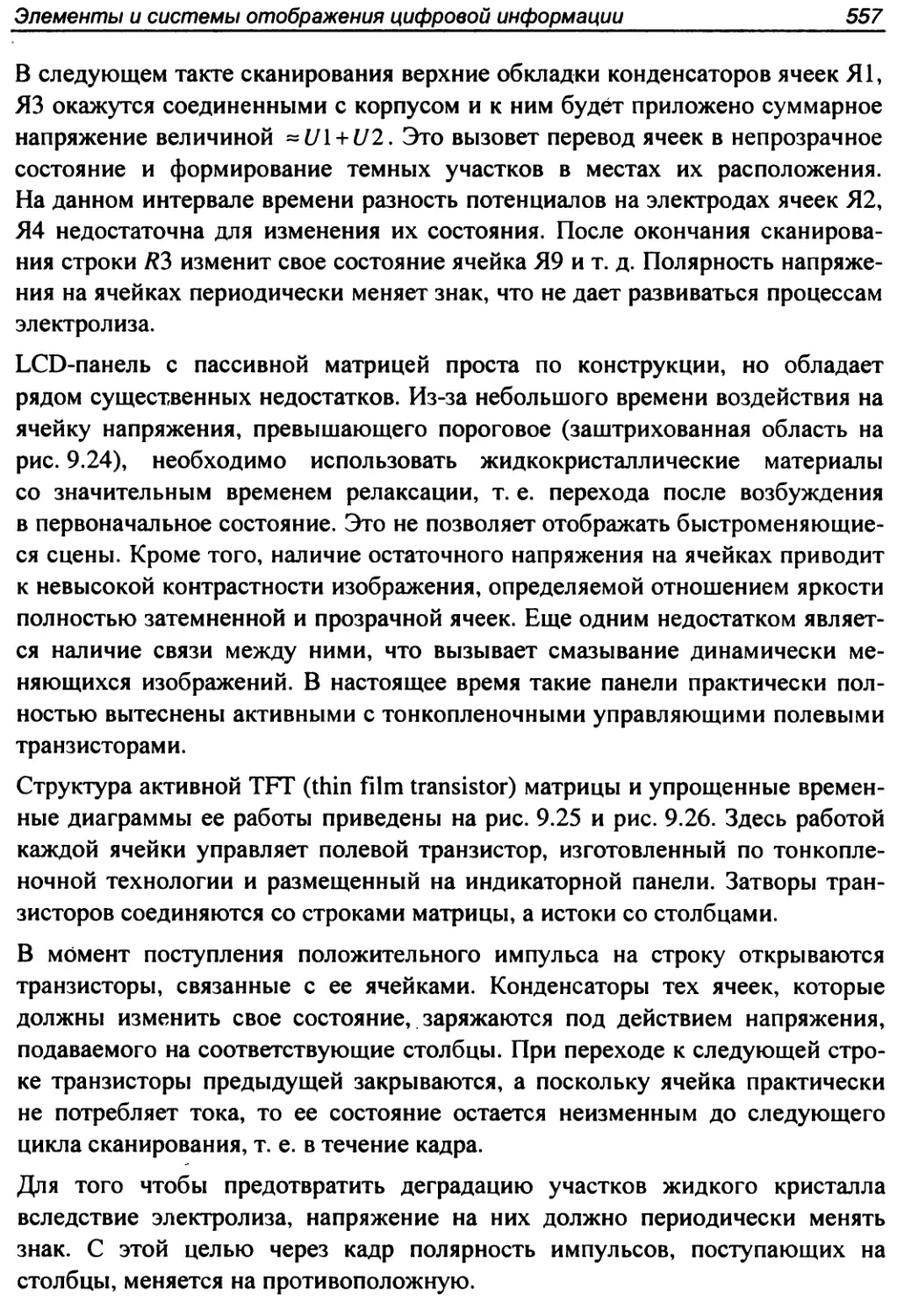

Комбинационные и последовательностные схемы

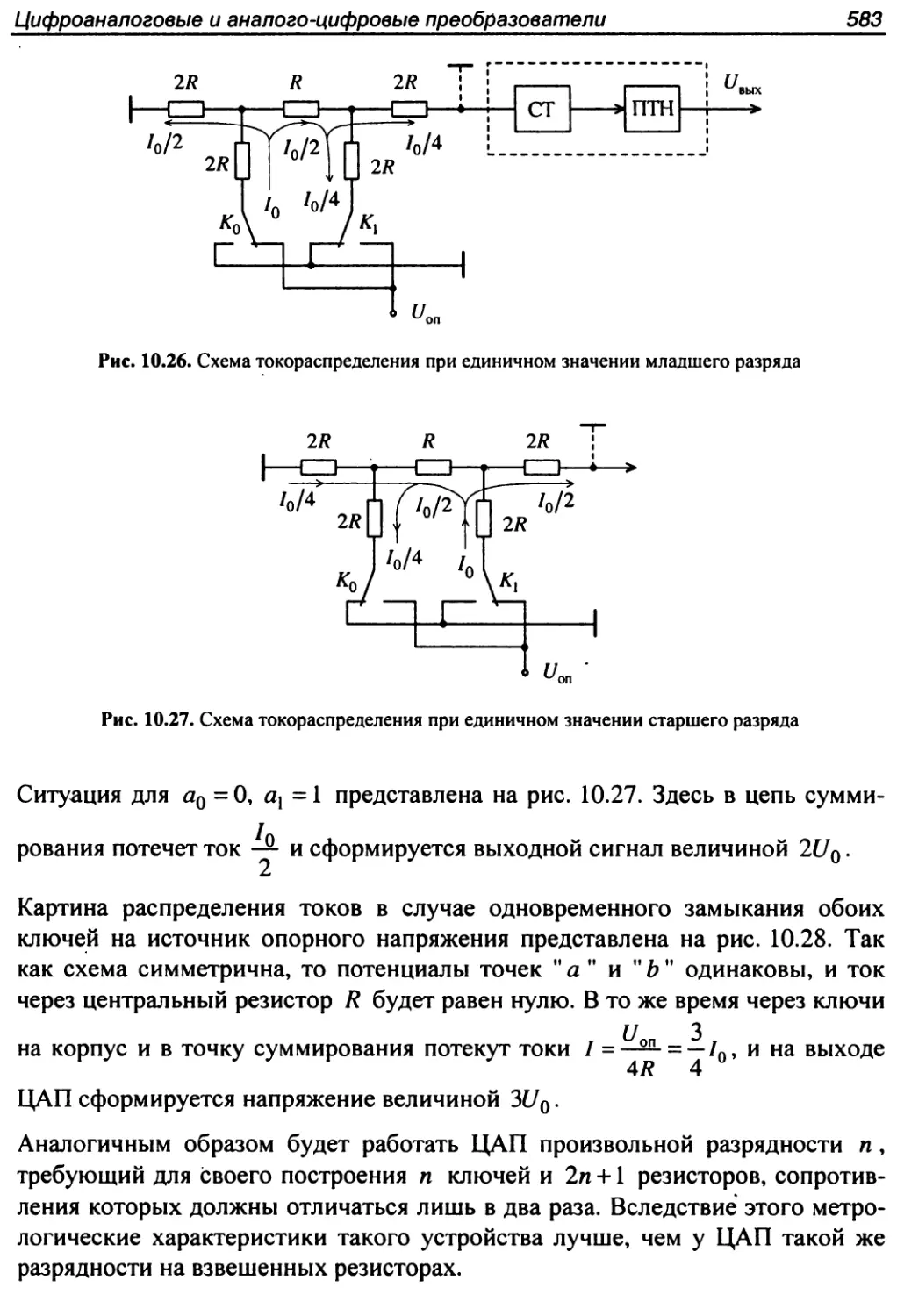

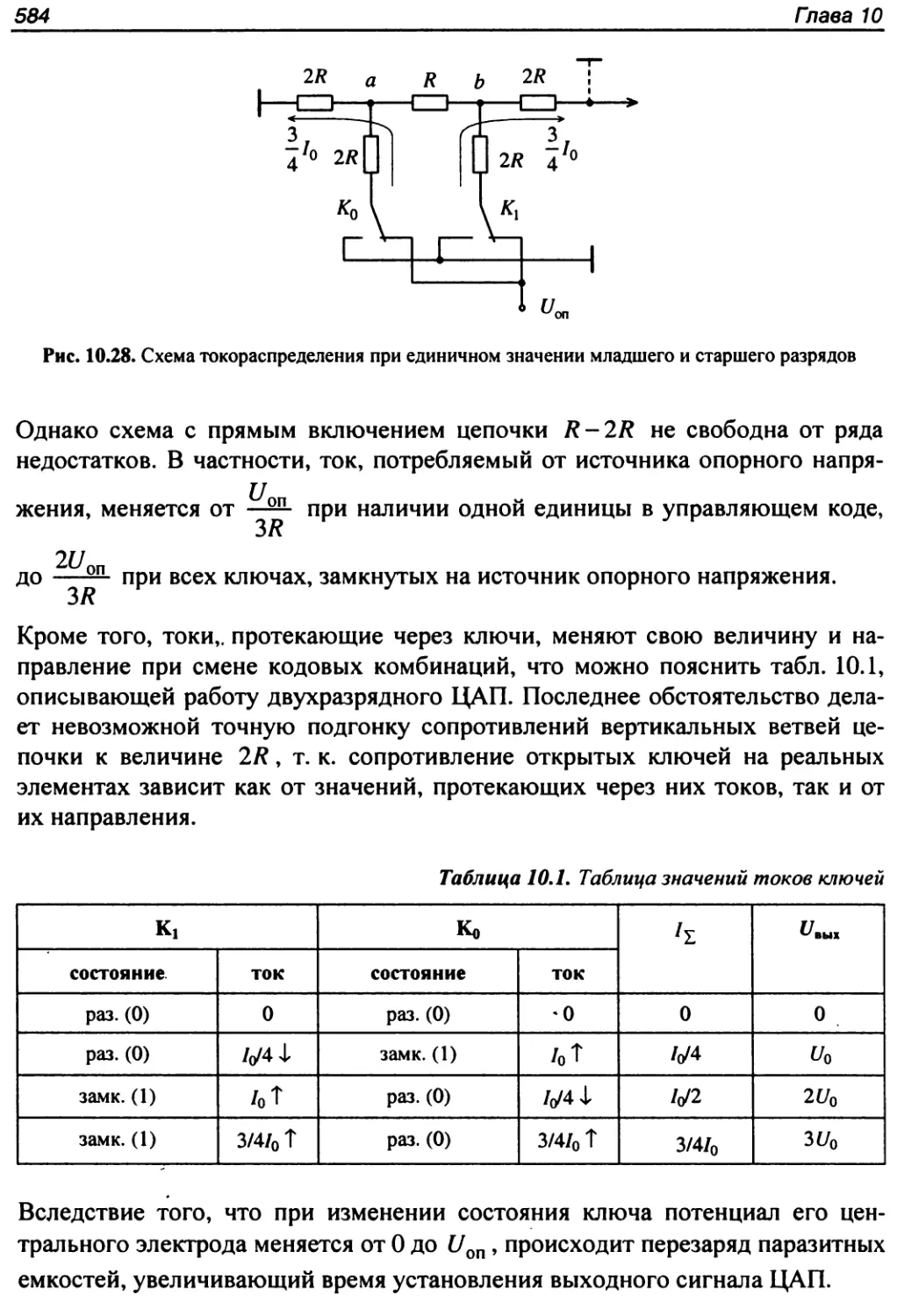

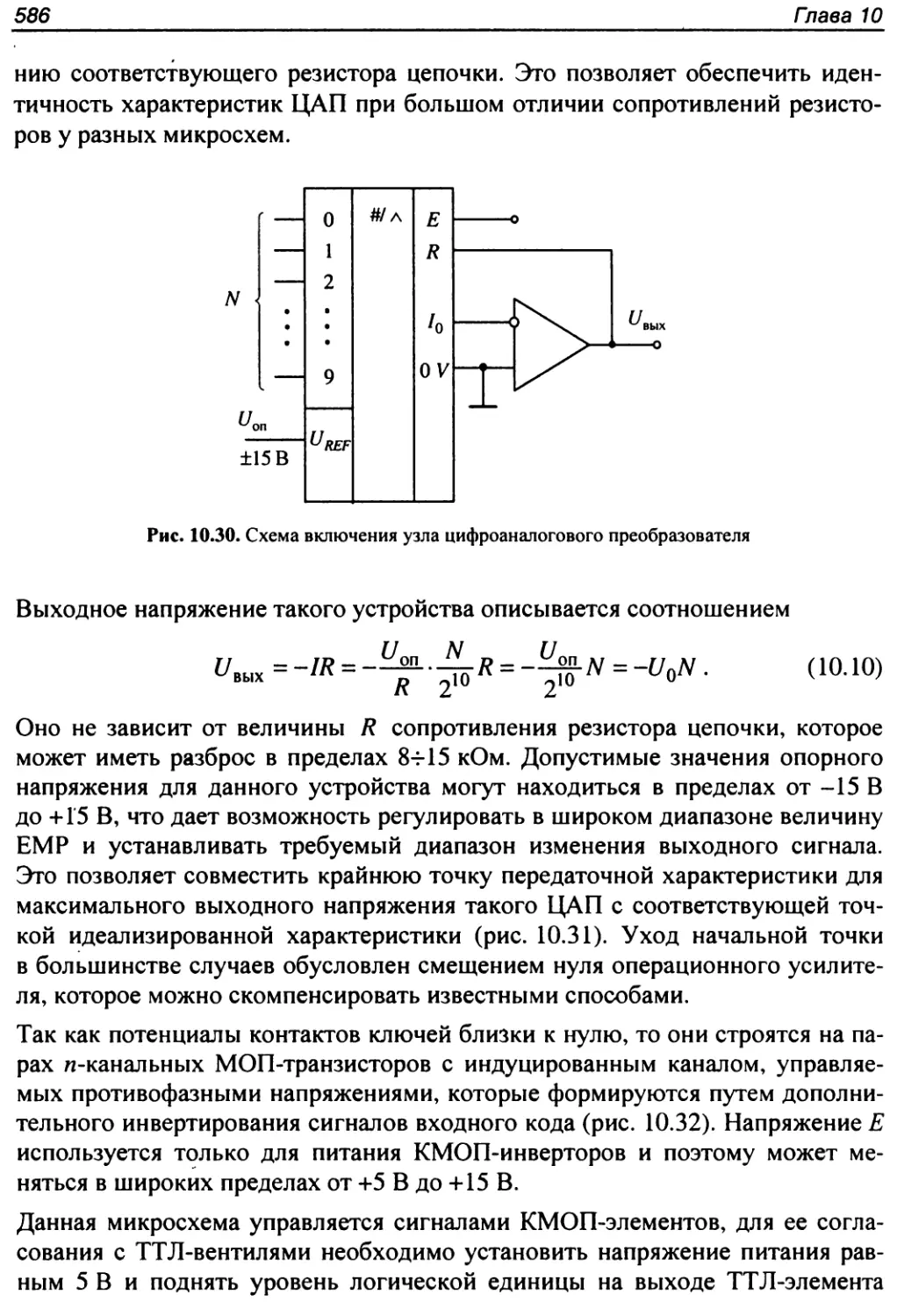

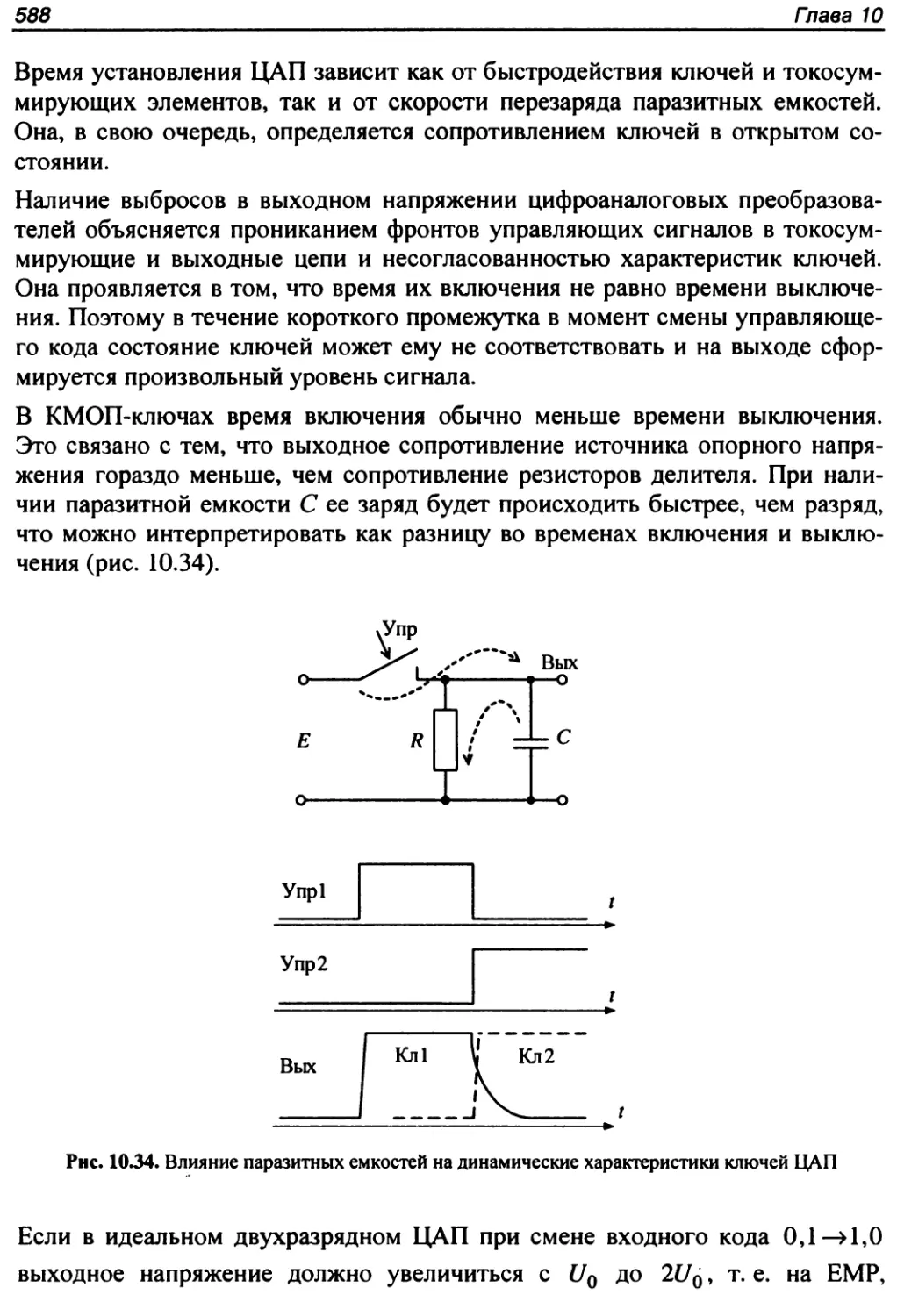

Полупроводниковые запоминающие устройства

Программируемая логика

Цифроаналоговые и аналого-цифровые преобразователи

С. Н. Лехин

СХЕМОТЕХНИКА

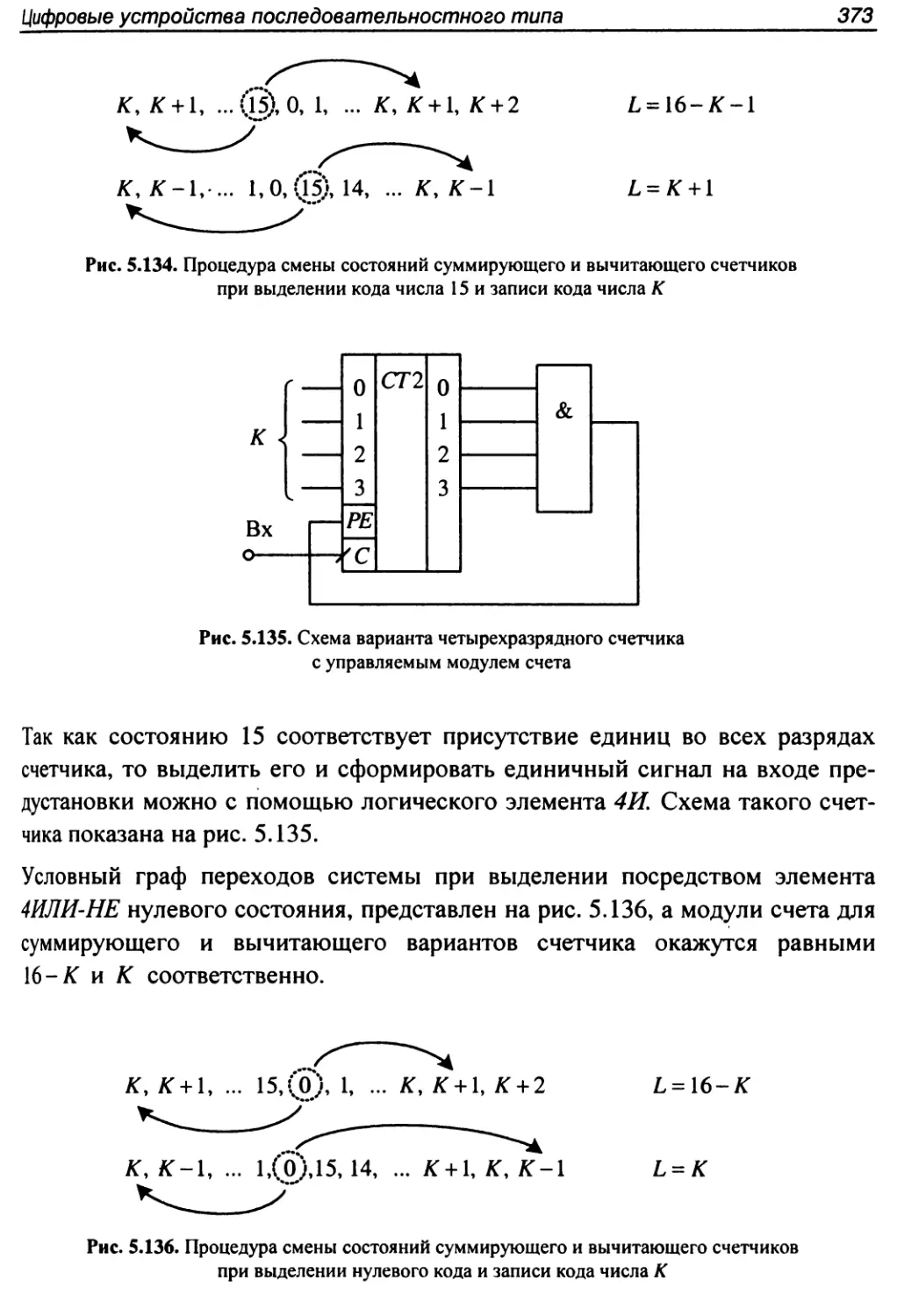

ЭВМ

Рекомендовано учебно-методическим объединением вузов

по университетскому политехническому образованию в качестве

учебного пособия для студентов высших учебных заведений,

обучающихся по специальности 230101

«Вычислительные машины, комплексы, системы и сети»

Санкт-Петербург

«БХВ-Петербург»

2010

УДК 681.3.06

ББК 32.973.26-018.2

Л52

Лехин С. Н.

Л52 Схемотехника ЭВМ. — СПб.: БХВ-Петербург, 2010. — 672 с.: ил. —

(Учебная литература для вузов)

ISBN 978-5-9775-0353-2

Рассматриваются схемотехнические решения, используемые при построении цифро-

вых логических элементов, вопросы синтеза комбинационных и последовательностных

цифровых устройств по заданному алгоритму работы, а также процедуры анализа их

функционирования. Освещены методы анализа помех в линиях передачи цифровых сиг-

налов и цепях питания. Приведены структуры и схемотехника полупроводниковых запо-

минающих устройств, схем программируемой логики и вспомогательных узлов цифровой

техники. Рассмотрены вопросы схемотехники цифроаналоговых и аналого-цифровых

преобразователей информации.

Для студентов технических вузов, инженеров и специалистов,

работающих в области разработки цифровой аппаратуры

УДК 681.3.06

ББК 32.973.26-018.2

Рецензенты:

Ю. М. Смирнов, д. т. н., профессор, член-корреспондент РАН, завкафедрой “Интегрированные

системы управления" Санкт-Петербургского государственного политехнического университета;

Г. М. Емельянов, д. т. н., профессор, завкафедрой программного обеспечения вычислительной

техники института электронных и информационных систем Новгородского государственного

университета им. Я. Мудрого.

Группа подготовки издания:

Главный редактор

Зам. главного редактора

Зав. редакцией

Редактор

Компьютерная верстка

Корректор

Дизайн серии

Оформление обложки

Фото

Зав. производством

Екатерина Кондукова

Евгений Рыбаков

Григорий Добин

Юрий Рожко

Натальи Караваевой

Виктория Пиотровская

Инны Тачиной

Елены Беляевой

Кирилла Сергеева

Николай Тверских

Лицензия ИД № 02429 от 24.07.00. Подписано в печать 01.10.09.

Формат УОхЮО’Дв. Печать офсетная. Усл. печ. л. 32,25.

Тираж 1500 экз. Заказ № 3985

"БХВ-Петербург", 190005, Санкт-Петербург, Измайловский пр., 29.

Санитарно-эпидемиологическое заключение на продукцию

Ne 77.99.60.953.Д.005770.05.09 от 26.05.2009 г. выдано Федеральной службой

по надзору в сфере защиты прав потребителей и благополучия человека.

Отпечатано с готовых диапозитивов

в ГУП "Типография "Наука"

199034, Санкт-Петербург, 9 линия, 12

ISBN 978-5-9775-0353-2

О Лехин С. Н., 2009

О Оформление, издательство "БХВ-Петербург". 2009

Оглавление

Введение........................................................1

Глава 1. Арифметические и логические основы цифровой техники.....3

1.1. Системы счисления, кодированное представление чисел

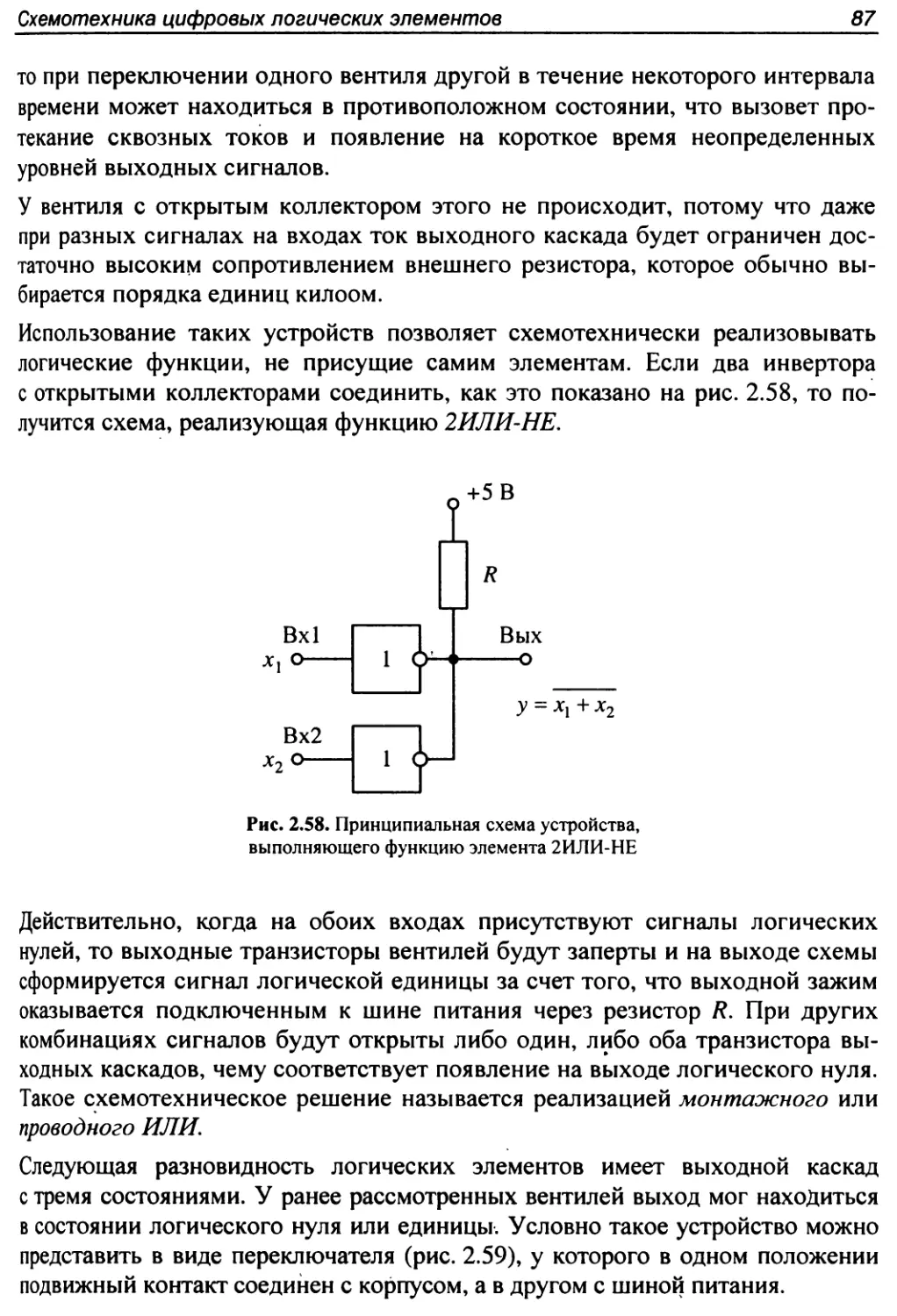

для обработки в ЦВМ..........................................3

1.2. Логические переменные и функции...........................10

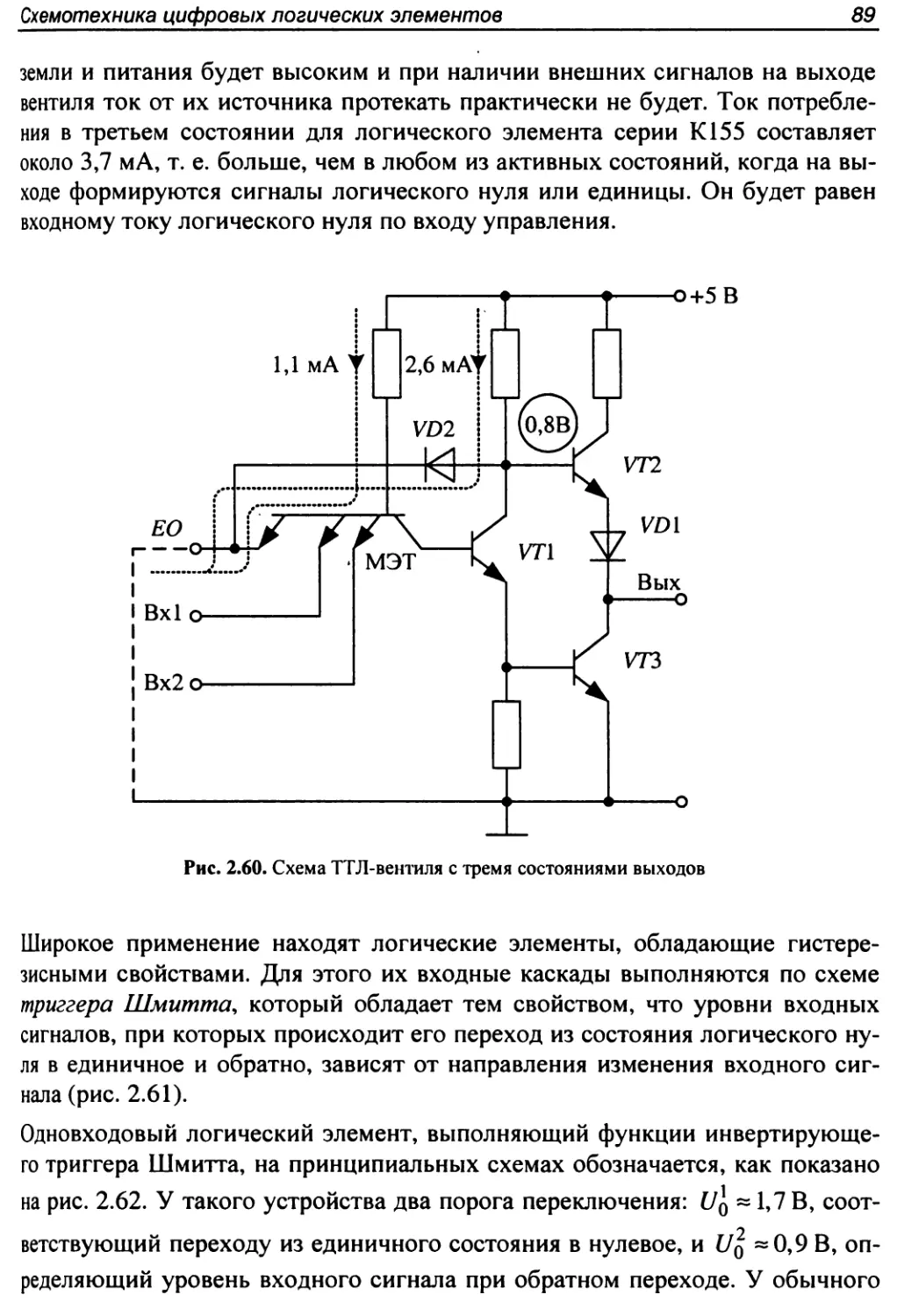

Контрольные вопросы............................................30

Глава 2. Схемотехника цифровых логических элементов............31

2.1. Принципы построения логических элементов..................31

2.2. Основные параметры и характеристики логических элементов..41

2.3. Транзисторный ключ........................................48

2.4. Схемотехника ТТЛ-вентилей.................................55

2.5. Разновидности ТТЛ и ТТЛШ логических элементов.............84

2.6. ЭСЛ логические элементы...................................94

2.7. Логические элементы на КМОП-структурах...................104

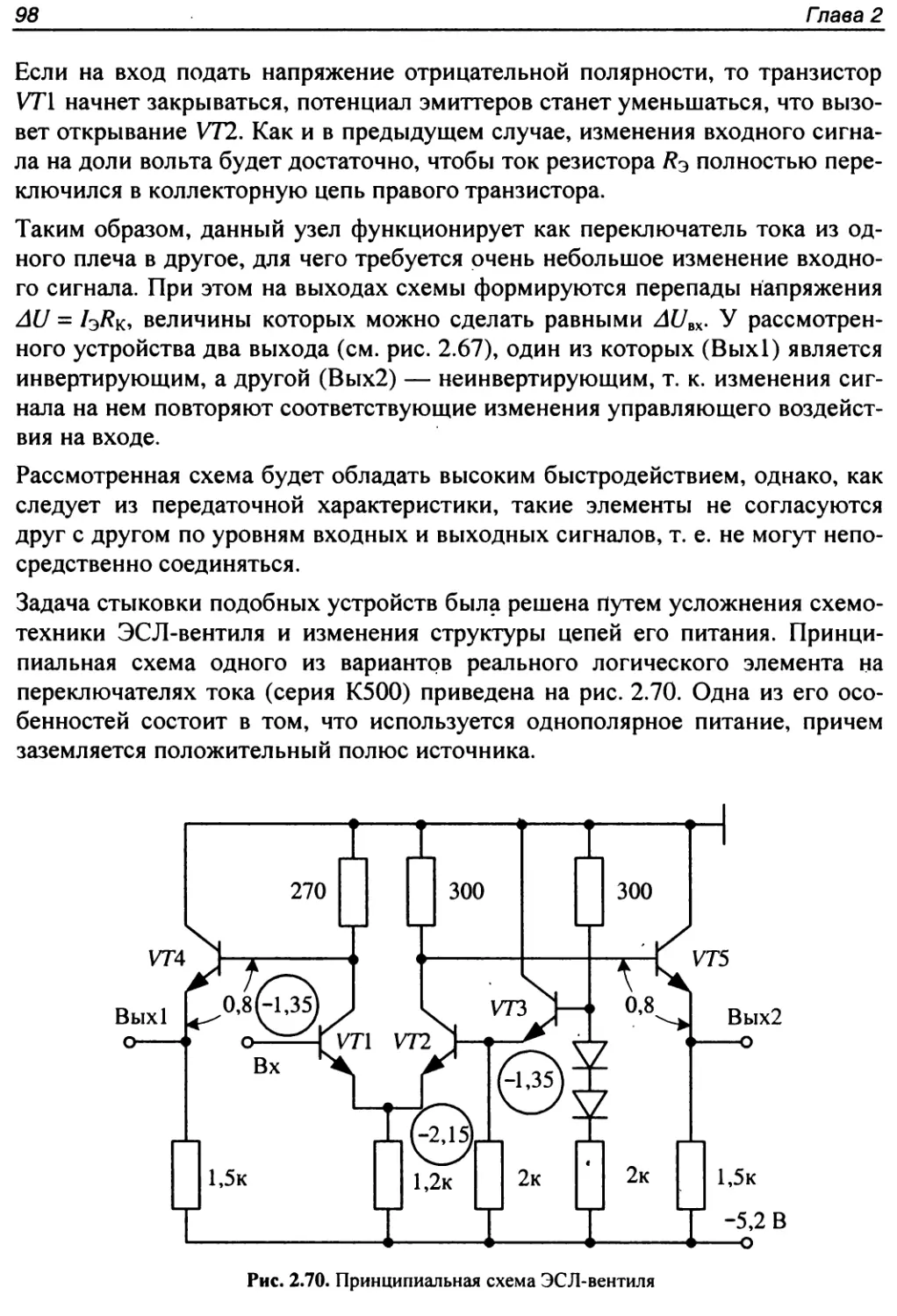

2.8. Способы согласования логических элементов................119

Контрольные вопросы...........................................125

Глава 3. Помехи в цепях питания цифровых узлов

и линиях передачи управляющих сигналов........................127

3.1. Причины возникновения помех по цепям питания и методы

борьбы с ними.................................................. 127

3.2. Влияние параметров линий связи на процессы передачи

цифровых сигналов.............................................137

3.3. Методы согласования линий связи..........................165

3.4. Способы уменьшения помех при передаче цифровых сигналов..173

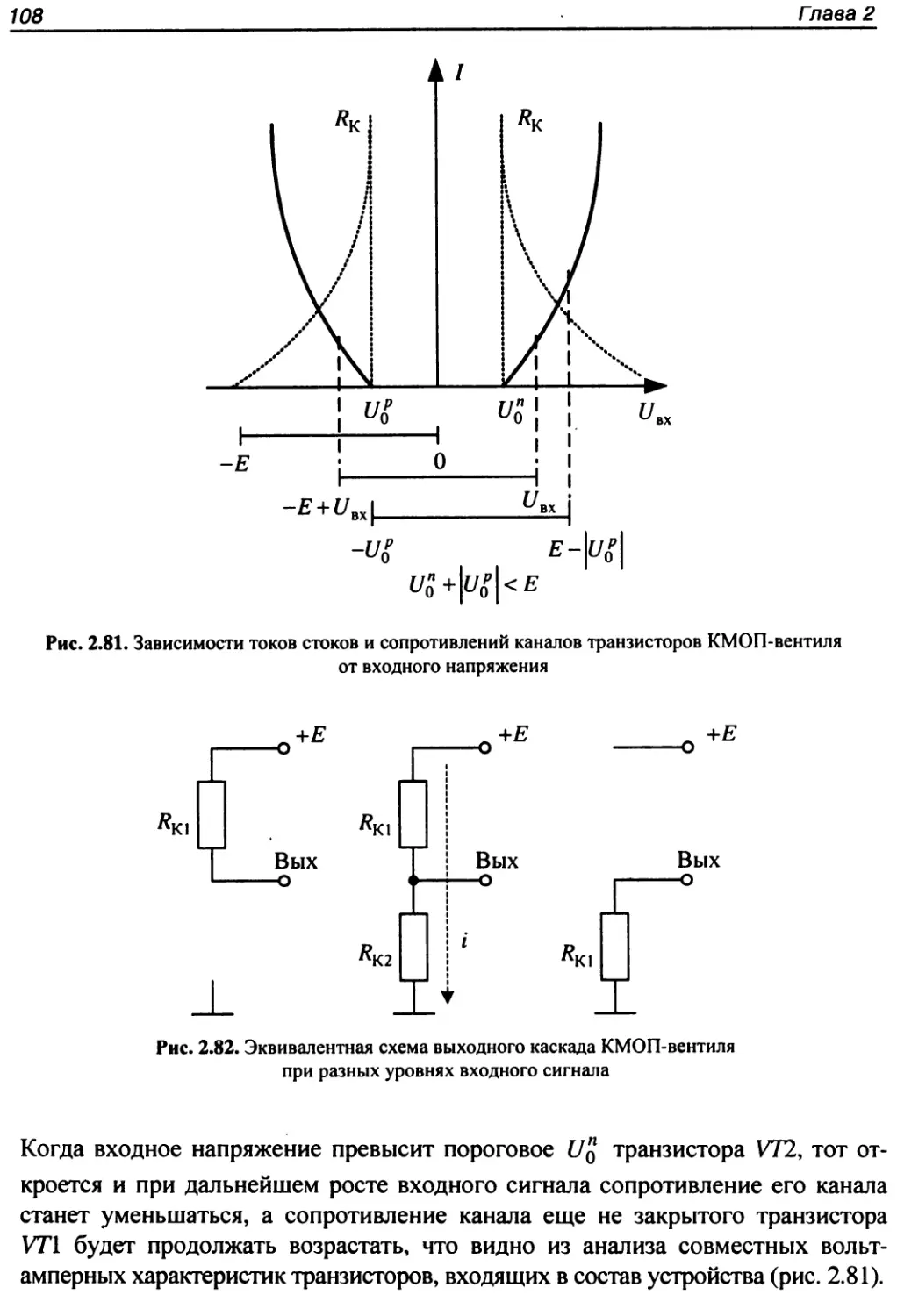

Контрольные вопросы...........................................176

IV

Оглавление

Глава 4. Цифровые узлы и устройства комбинационного типа......177

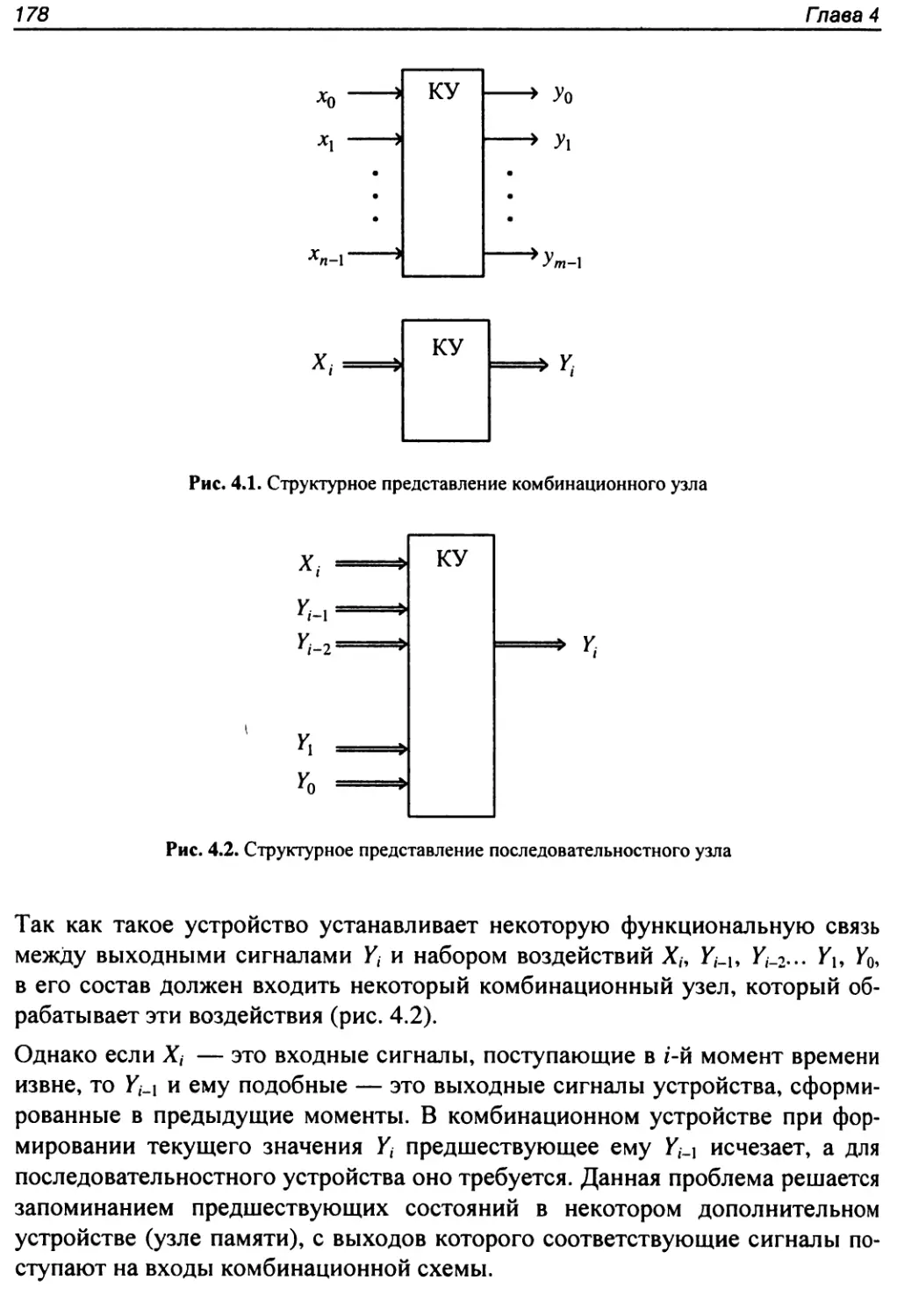

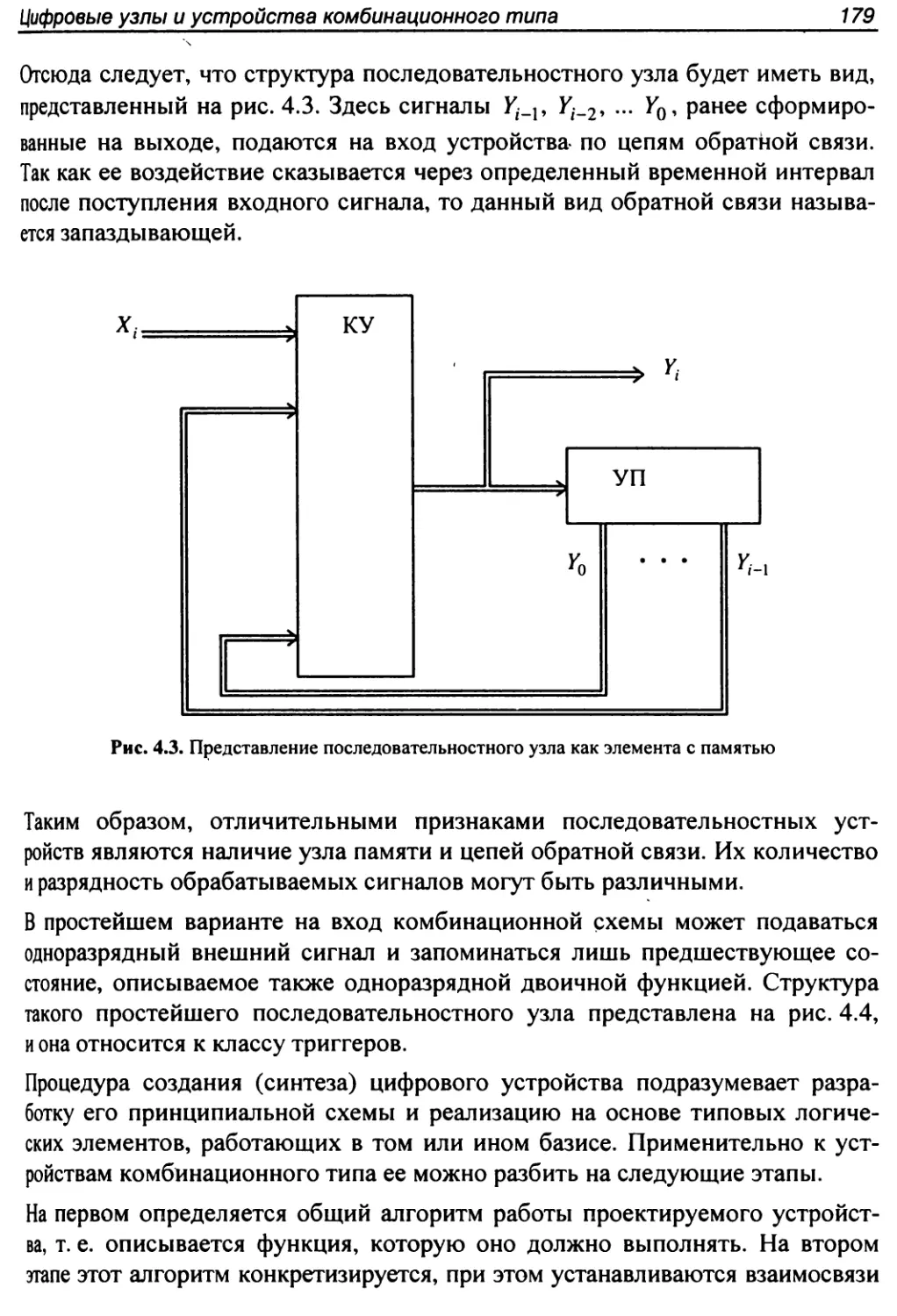

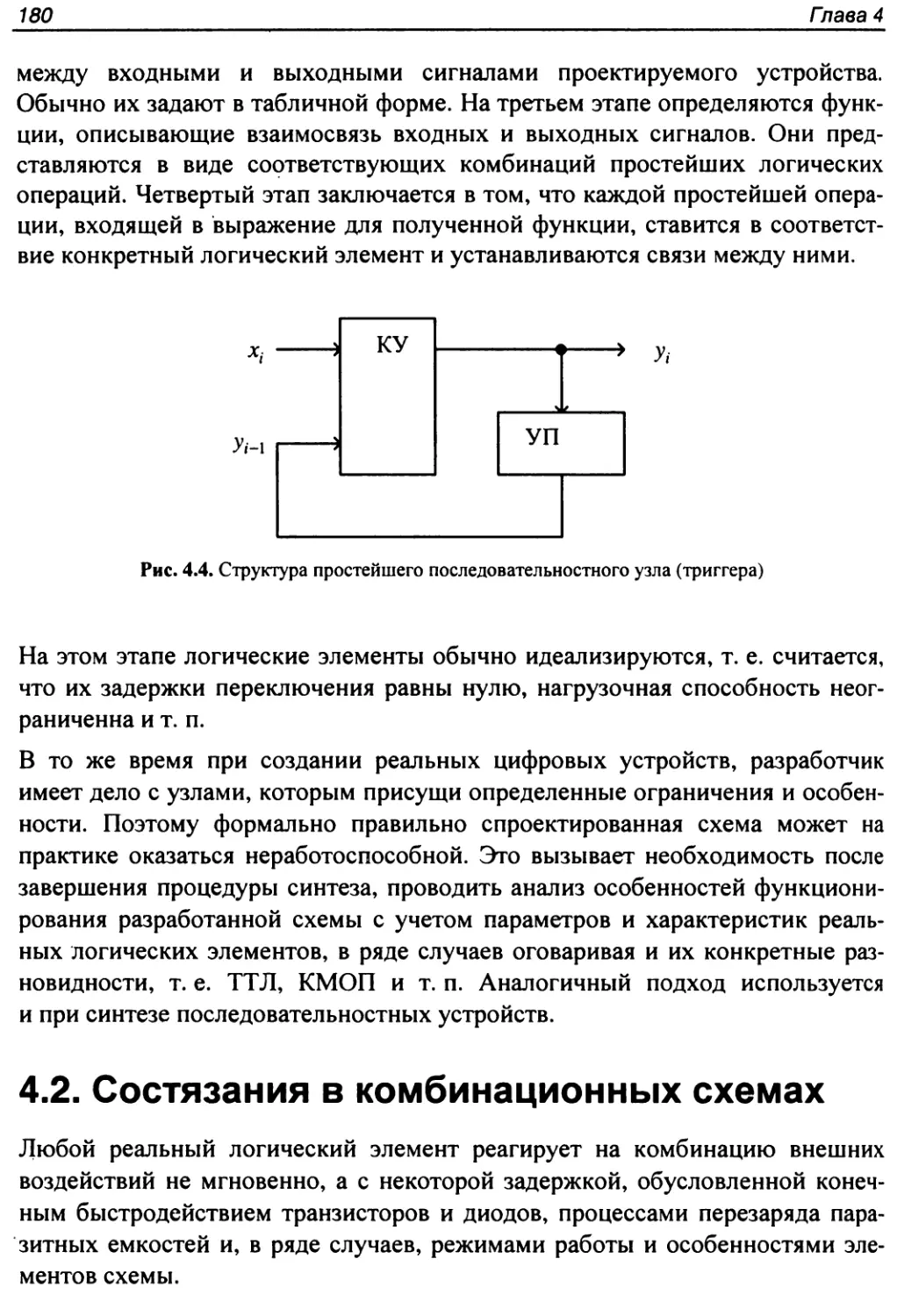

4.1. Классификация цифровых устройств........................177

4.2. Состязания в комбинационных схемах......................180

4.3. Преобразователи кода....................................194

4.4. Дешифраторы.............................................197

4.5. Шифратор приоритетов....................................213

4.6. Мультиплексоры..........................................220

4.7. Схемы контроля четности.................................230

4.8. Мажоритарные элементы...................................235

4.9. Цифровые компараторы....................................238

4.10. Сумматоры двоичных кодов чисел..........................243

4.11. Устройства вычитания двоичных кодов чисел..............258

4.12. Сумматоры двоично-десятичных кодов.....................262

4.13. Арифметико-логические устройства.......................267

4.14. Умножители двоичных кодов чисел........................270

Контрольные вопросы........................................ 274

Глава 5. Цифровые устройства последовательностного типа......275

5.1. Триггеры................................................275

5.2. Регистры................................................301

5.3. Накапливающий сумматор..................................318

5.4. Кольцевой счетчик.......................................321

5.5. Счетчик Джонсона........................................332

5.6. Двоичные счетчики.......................................340

5.7. Счетчики с произвольным и управляемым модулем счета.....360

5.8. Делители и синтезаторы частоты..........................382

Контрольные вопросы..........................................393

Глава 6. Полупроводниковые запоминающие устройства...........395

6.1. Классификация и структурная организация полупроводниковых

запоминающих устройств.......................................395

6.2. Схемотехника ячеек накопителей статических запоминающих

устройств....................................................422

6.3. Динамические запоминающие устройства....................430

6.4. Постоянные и перепрограммируемые запоминающие устройства.456

Контрольные вопросы..........................................469

Глава 7. Программируемые логические интегральные схемы.......471

7.1. Принципы обработки цифровых данных......................471

7.2. Способы реализации логических функций...................476

Оглавление

V

7.3. Принципы построения и элементы программируемых логических

интегральных схем.............................................483

7.4. Периферийное сканирование цифровых устройств.............496

Контрольные вопросы...........................................500

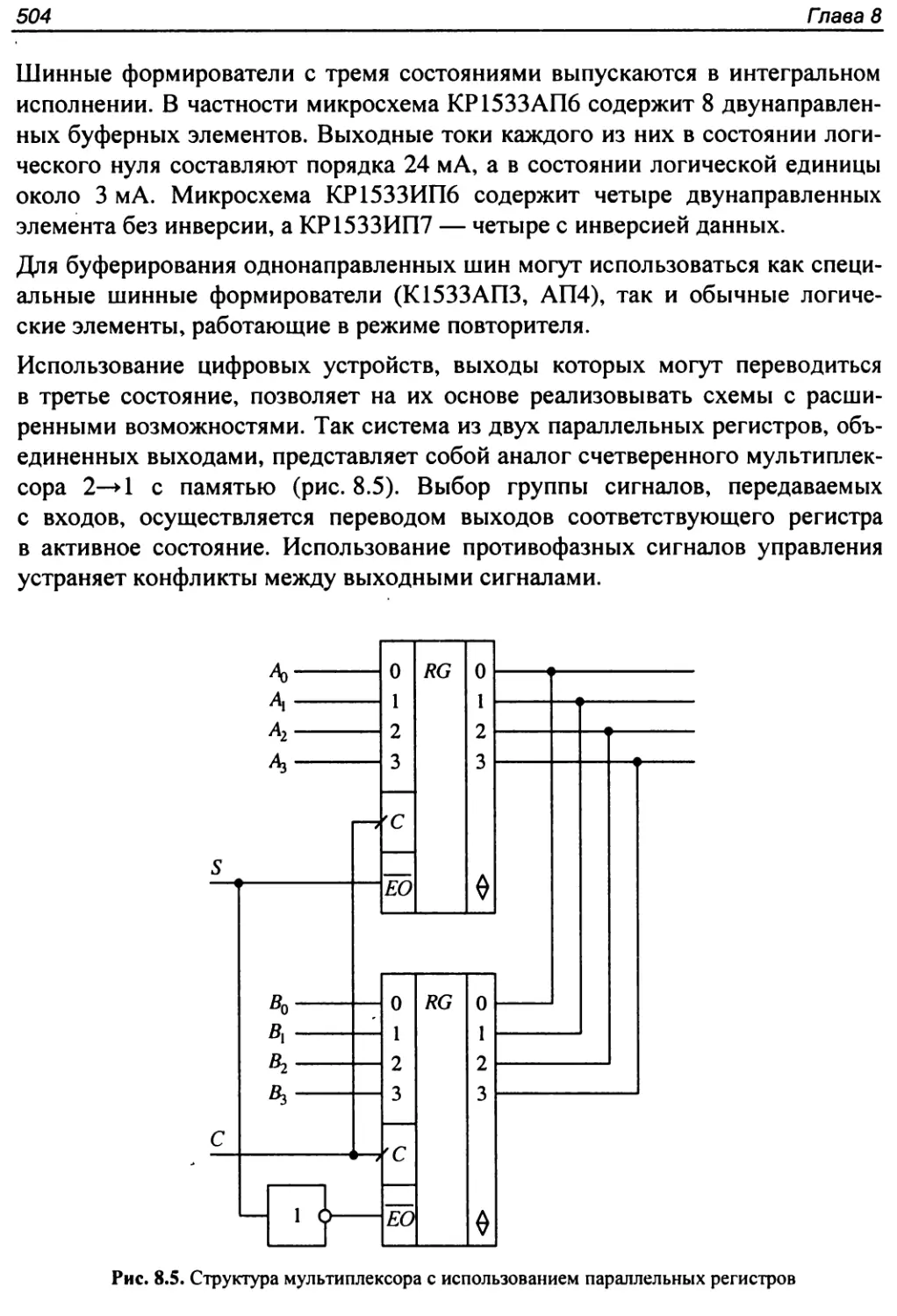

Глава 8. Интерфейсные и вспомогательные цифровые узлы.........501

8.1. Периферийные узлы цифровых устройств.....................501

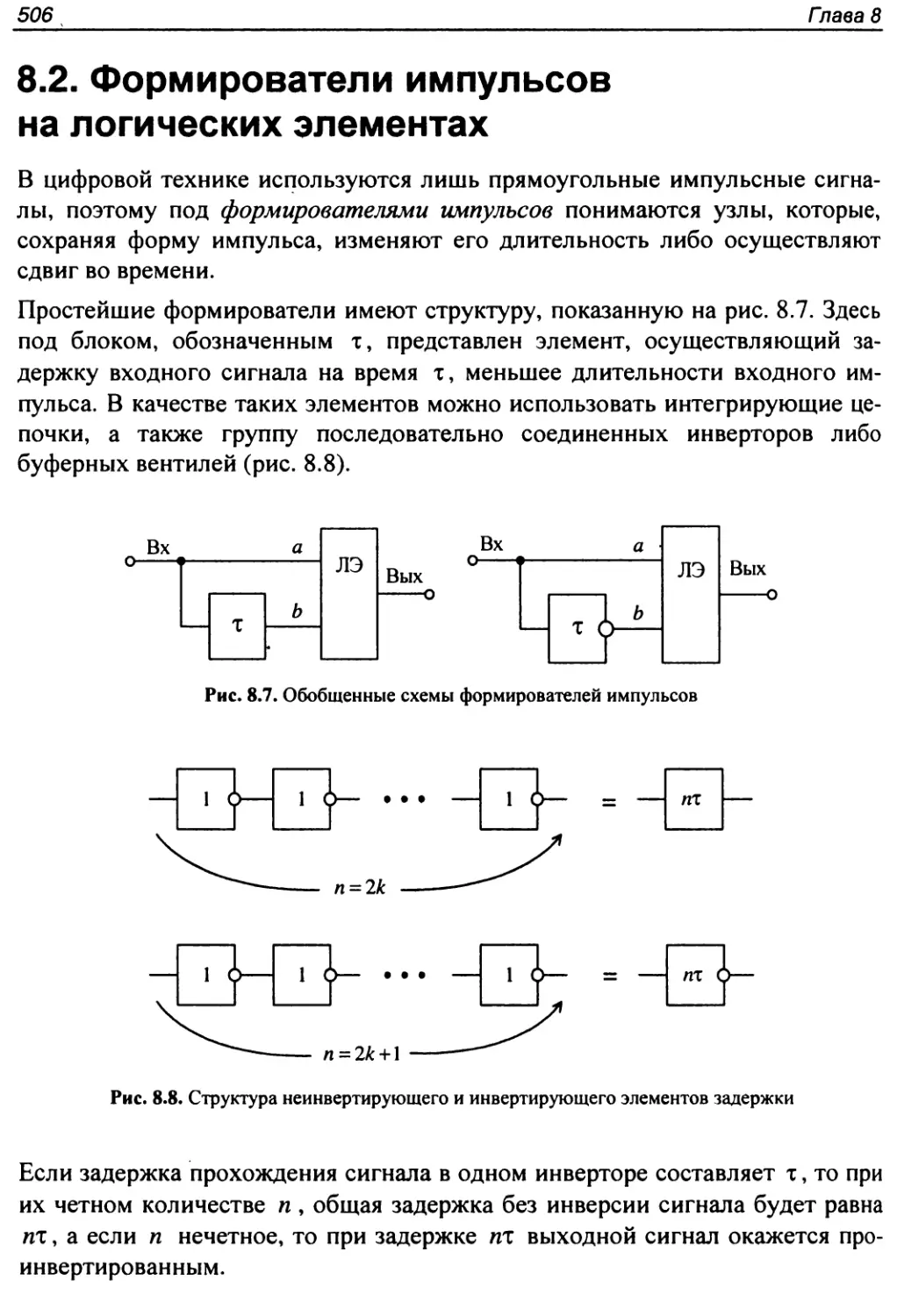

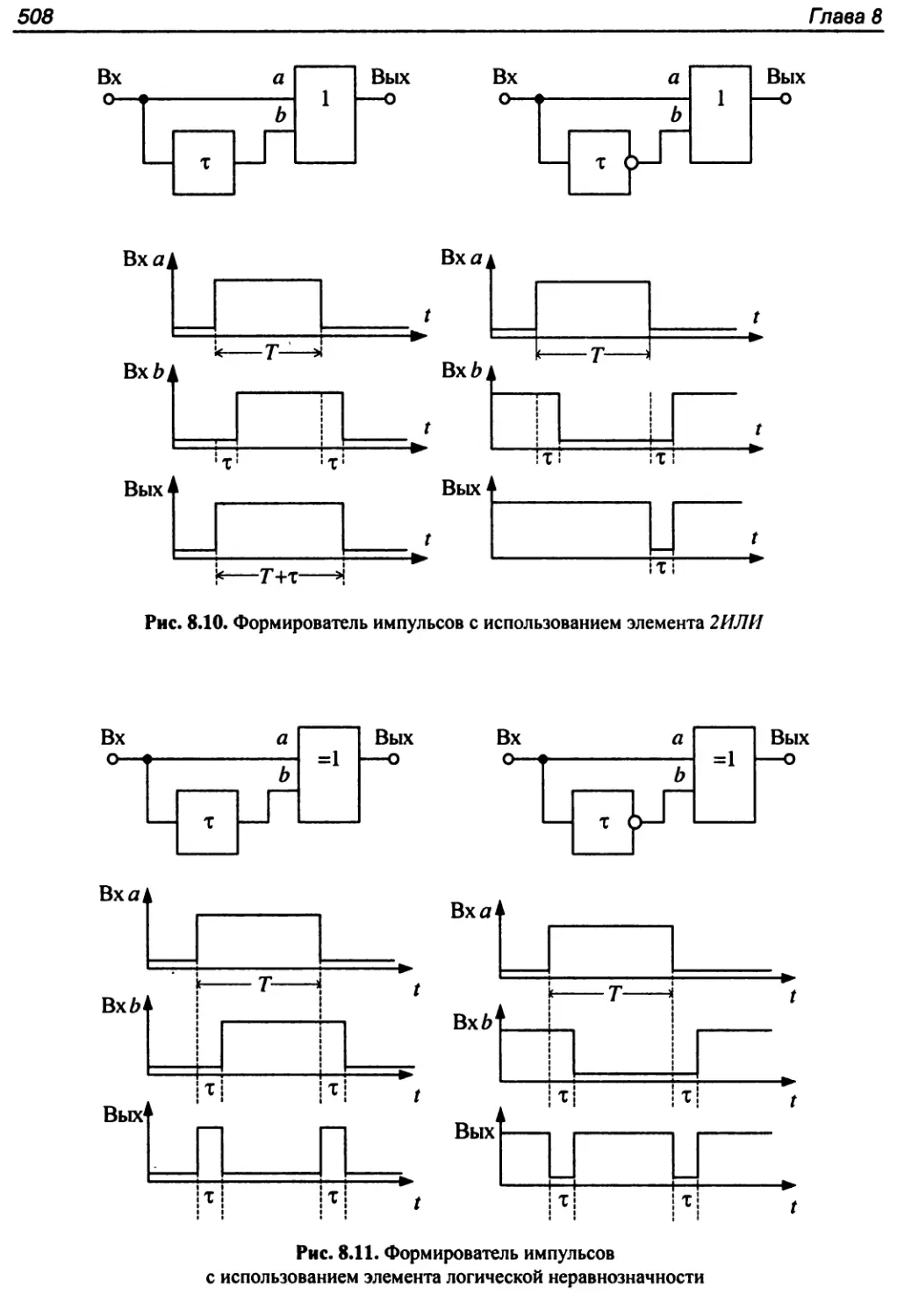

8.2. Формирователи импульсов на логических элементах..........506

8.3. Генераторы цифровых сигналов на логических элементах.....514

8.4. Генераторы с кварцевой стабилизацией частоты.............531

Контрольные вопросы...........................................538

Глава 9. Элементы и системы отображения цифровой информации...539

9.1. Способы управления одиночными светодиодными индикаторами.539

9.2. Системы отображения многоразрядных цифровых данных.......543

9.3. Жидкокристаллические индикаторы и способы управления ими.550

Контрольные вопросы...........................................560

Глава 10. Цифроаналоговые и аналого-цифровые преобразователи..561

10.1. Основные параметры и характеристики ЦАП.................568

10.2. Принципы построения ЦАП прямого преобразования..........571

10.3. Умножающие ЦАП..........................................594

10.4. ЦАП с косвенным преобразованием.........................598

10.5. Области применения ЦАП..................................602

10.6. Основные параметры и характеристики аналого-цифровых

преобразователей..............................................604

10.7. Аналого-цифровые преобразователи с непосредственным

преобразованием...............................................609

10.8. АЦП с косвенным преобразованием.........................629

10.9. Области применения АЦП..................................647

Контрольные вопросы...........................................648

Литература....................................................651

Предметный указатель..........................................655

Введение

Современные средства цифровой вычислительной техники строятся на раз-

личной элементной базе, в состав которой входят как узлы, выполняющие

конкретные операции обработки цифровых сигналов, так и сложные про-

граммируемые устройства. Они реализуются на различной элементной базе,

включающей диоды, биполярные и полевые транзисторы.

Основой любого цифрового устройства являются простейшие элементы, вы-

полняющие основные логические операции. Они изготавливаются с исполь-

зованием различных схемотехнических и технологических решений (транзи-

сторно-транзисторная логика, вентили на комплементарных полевых

транзисторах, эмиттерно-связанная логика и т. п.). На первых этапах развития

цифровой схемотехники эти элементьГбыли основными "кирпичиками", из

которых собирались сложные цифровые устройства.

С развитием полупроводниковой микроэлектроники появилась возможность

создавать на одном кристалле функционально законченные цифровые узлы

(сумматоры, мультиплексоры, счетчики и т. п.), выполняющие конкретные

операции. При этом требовалась достаточно широкая номенклатура микро-

схем. Несмотря на возможности изготовления сложных функционально за-

конченных узлов цифровой обработки на одном кристалле, практическая

реализация микросхем конкретных устройств экономически не оправдана.

Это связано с высокими затратами на их проектирование, что при небольшом

объеме выпуска приводит к очень высокой стоимости.

В дальнейшем были разработаны большие и сверхбольшие интегральные

схемы с программируемыми свойствами — микропроцессоры и программи-

руемые логические интегральные схемы (ПЛИС). Особенностью микропро-

цессоров является возможность при неизменной внутренней структуре на-

страиваться на выполнение той или иной операции. Задавая последовательно

во времени определенный набор таких операций, можно решить задачу обра-

ботки сигналов по любому требуемому алгоритму.

Введение

В ПЛИС, представляющей собой набор логических блоков, пользователь

имеет возможность организовать межсоединения между ними в соответствии

с требуемой конфигурацией устройства обработки. Здесь в отличие от после-

довательной процедуры, характерной для микропроцессоров, реализуются

распределенные параллельные структуры, что позволяет существенно повы-

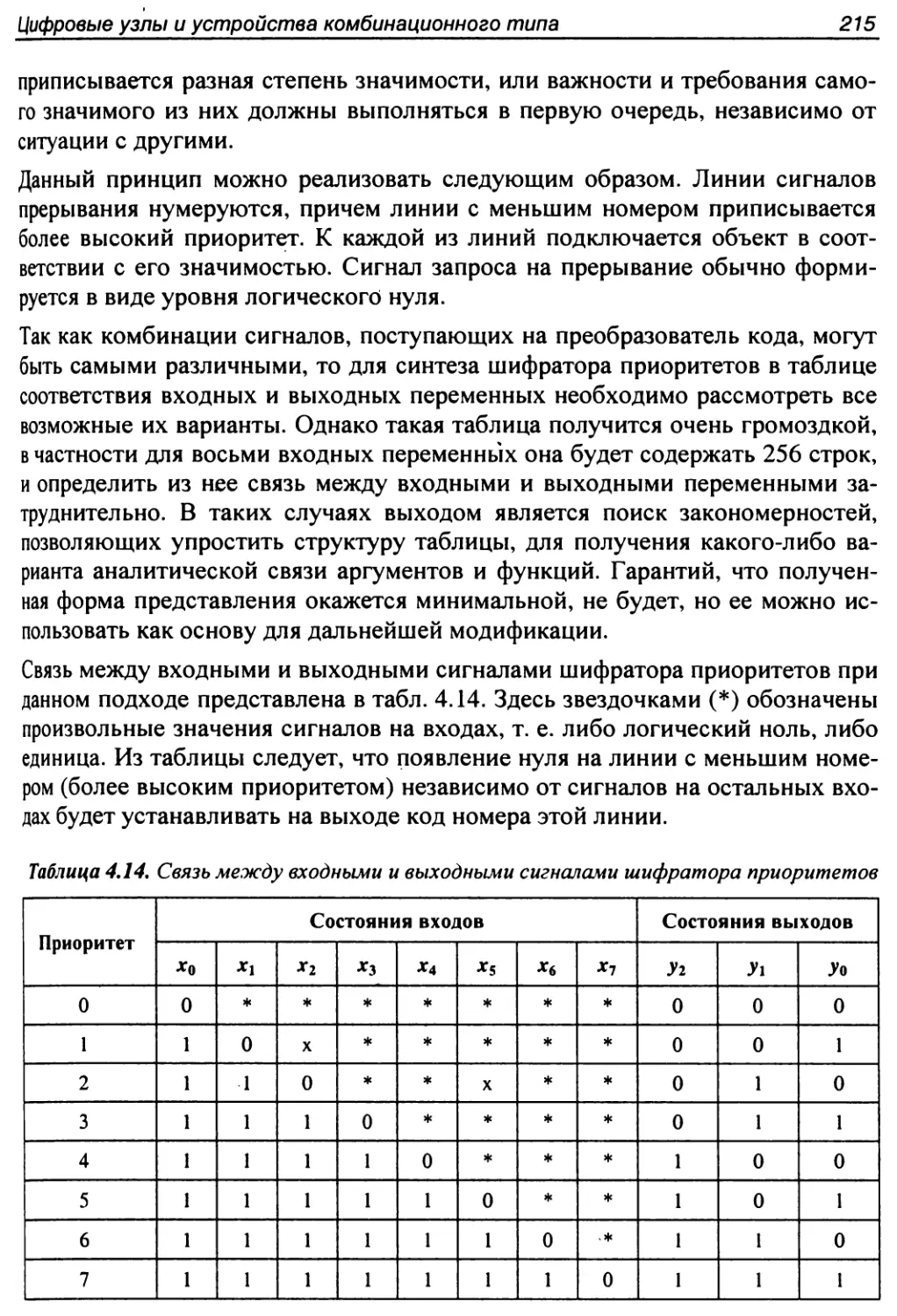

сить скорость обработки.

При таком подходе возможно массовое изготовление идентичных кристал-

лов, так как их программируемость позволяет решать различные задачи циф-

ровой обработки сигналов.

Глава 1

Арифметические и логические

основы цифровой техники

1.1. Системы счисления, кодированное

представление чисел для обработки в ЦВМ

Для записей результатов количественных (числовых) измерений используют-

ся наборы символов. Способ представления чисел, при котором они отобра-

жаются определенными комбинациями символов, называется системой счис-

ления. Одно и то же число допускает различные варианты его представления.

Числовые данные отличаются от остальных тем, что с ними могут произво-

диться арифметические операции (сложение, умножение и т. п.). От выбран-

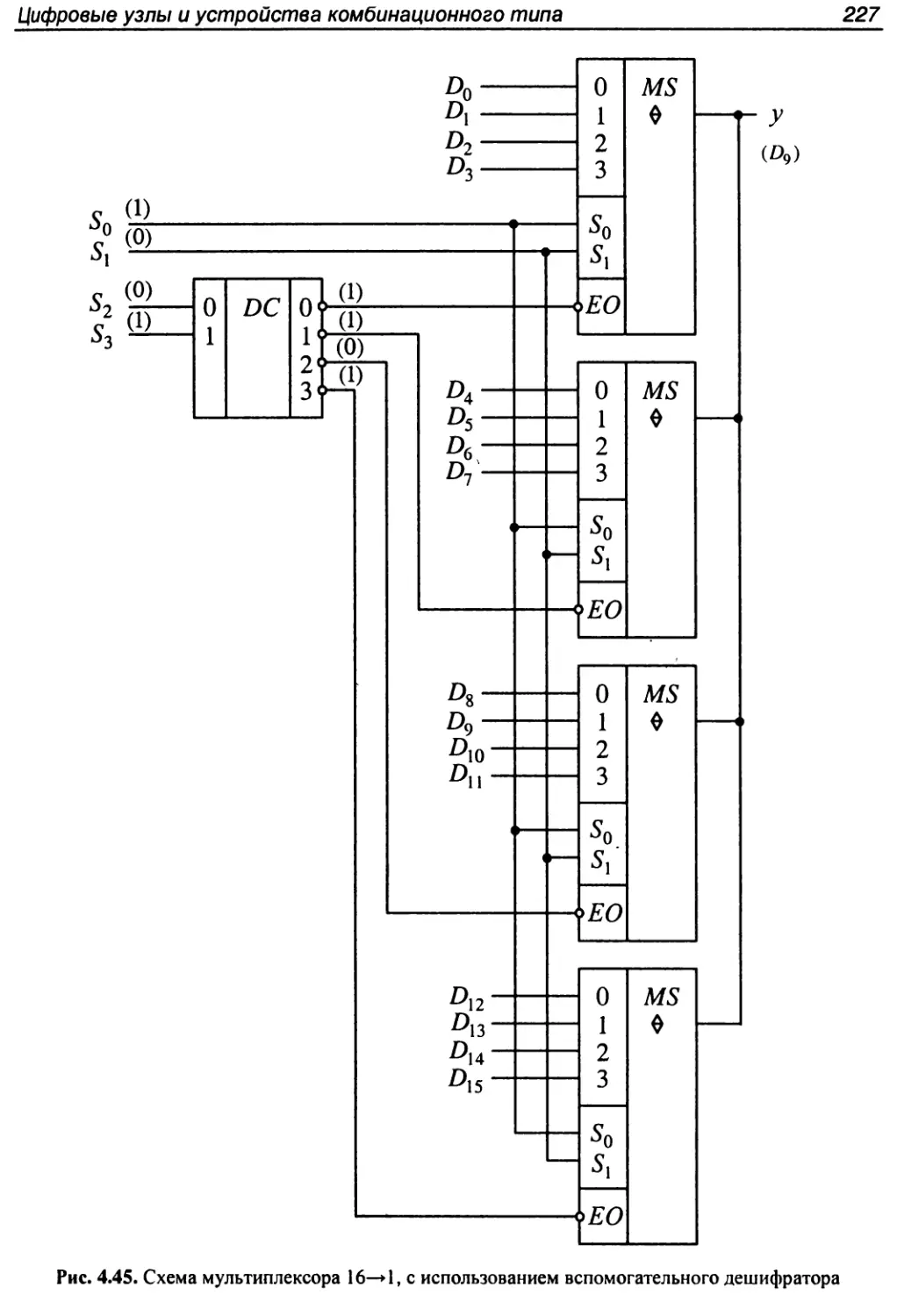

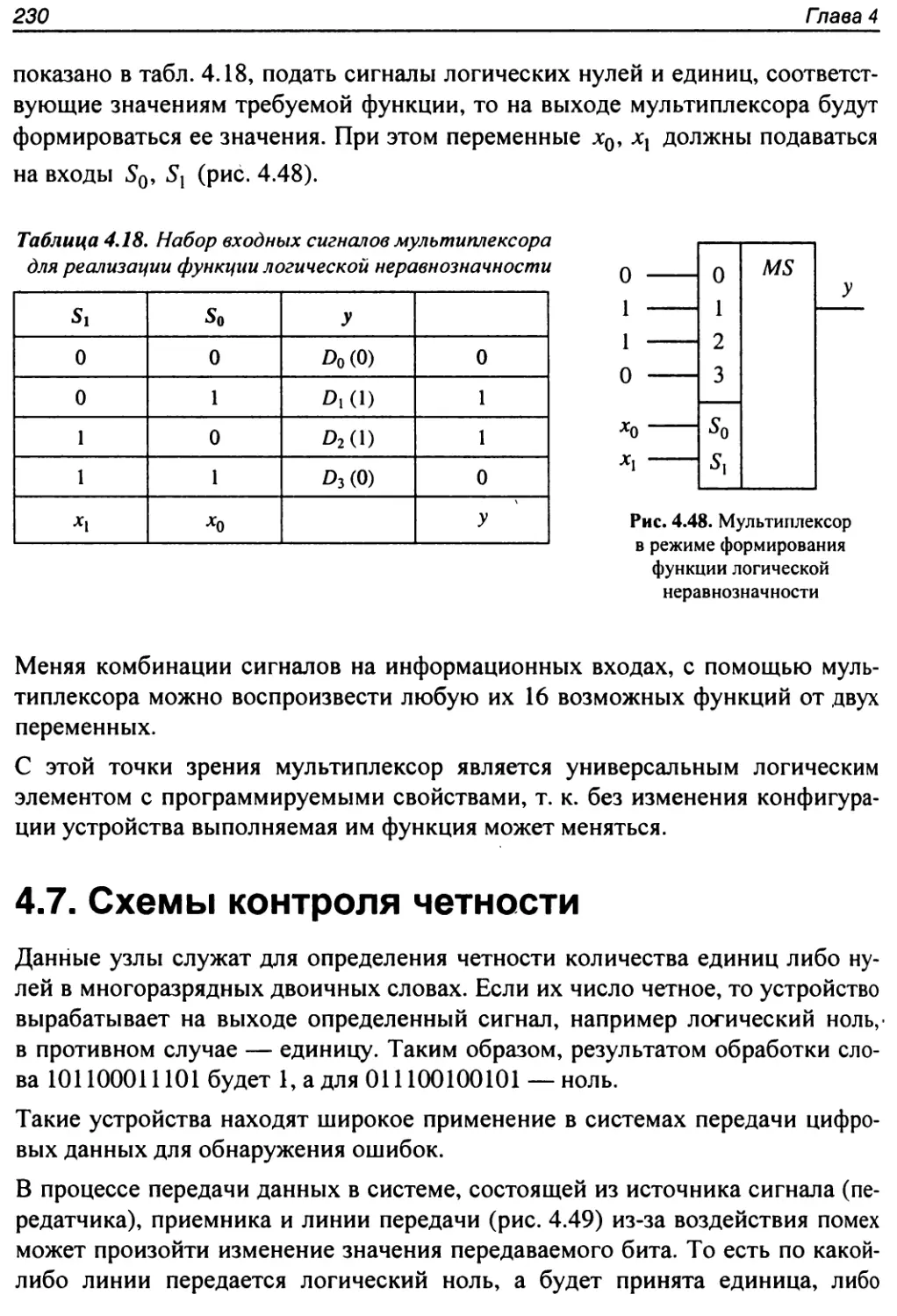

ного способа записи чисел, т. е. от системы счисления, зависит как нагляд-

ность их представления, так и сложность выполнения процедур обработки.

Обычно количество символов (цифр) для записи чисел ограничено, поэтому

для больших чисел цифры в его записи будут повторяться. Если значение

цифры не зависит от ее местоположения в записи числа, то такая система

счисления называется непозиционной. Примером является римская, с помо-

щью которой, например, размечаются циферблаты некоторых часов.

Здесь используются так называемые римские цифры I, V, X, L и другие. Пер-

вая соответствует единице, вторая пятерке, третья десятке, а четвертая —

сотне. Запись XXVII означает 10 +10+ 5 + 1 + 1= 27, запись XI соответству-

ет числу 10+1 (одиннадцать) и т. д. В римской и аналогичных непозицион-

ных системах счисления можно записать любое число, однако для этого по-

требуется достаточно большое количество символов и, кроме того, имеются

определенные проблемы с выполнением арифметических операций.

Поэтому в цифровой технике используются позиционные системы счисления.

Их особенность в том, что значение одной и той же цифры зависит от ее ме-

стоположения в записи числа, т. е. от позиции, в которой она располагается.

Например, запись 222 в десятичной системе счисления, где используются

4

Глава 1

десять цифр от 0 до 9, означает, что данное число содержит две сотни,

два десятка и две единицы. Позиция, которую занимает цифра, называется

разрядом. Таким образом, в рассматриваемой записи имеются разряды сотен,

десятков и единиц. Числовое значение разряда соответствует его весу.

То же число 222 можно представить как 2-100 + 2-10 + 2-1, откуда следует,

что веса разрядов отличаются в десять раз. Если отношение соседних весов

одинаково и равно Р, это число называется основанием системы счисления.

Обычно в позиционных системах значения весов определяются степенями ее

основания, и число 222 представляется как 2102 + 2101 + 2-10°.

Номер разряда, отсчитываемый справа налево, начиная с нуля, соответствует

показателю степени, в которую требуется возвести основание системы счис-

ления, чтобы получить величину веса разряда. Количество символов (цифр)

для отображения чисел в позиционных системах счисления не может превы-

шать величины основания, в противном случае возникает неоднозначность

записи числа.

Веса разрядов в позиционных системах счисления могут и не находиться

в одинаковых отношениях, к примеру 40, 20, 10, 8, 4, 2, 1. В этом случае по-

нятие основания не вводится, и запись произвольного n-разрядного числа

хп_2...%] Xq может быть представлена следующим образом:

л-1

хл-1 ?п-\ + хп-2?п-2 + + Х1 Л + Х0Р0 = S Xi * (1-0

i=0

Здесь Xi — цифра /-того разряда, а Р, — его вес.

Если веса находятся в отношениях, пропорциональных основанию Р, то пре-

дыдущее соотношение можно преобразовать к виду:

+ хй_2Р""2 +... + х1Р1 +ХОР° =51х,Р'. (1.2)

1=0

Аналогичным образом представляются и числа меньшие единицы, для чего

используются отрицательные степени основания. К примеру, число 12,34 за-

писывается как 1 • 101 + 2 • 10° + 3 • 10"1 + 3 • 10"2.

Основание системы счисления может быть произвольным, но обычно оно

выбирается из требований удобства выполнения действий над числовыми

данными в конкретной ситуации. В частности, когда требуется обрабатывать

данные в цифровых вычислительных машинах, целесообразным является ис-

пользование двоичной системы счисления.

Это связано с тем, что в цифровой технике применяются элементы, обла-

дающие двумя устойчивыми состояниями, одному из которых можно припи-

Арифметические и логические основы цифровой техники

5

сать нулевое значение, а другому — единичное. В двоичной системе счисле-

ния основание равно двум и для отображения чисел имеется лишь две цифры

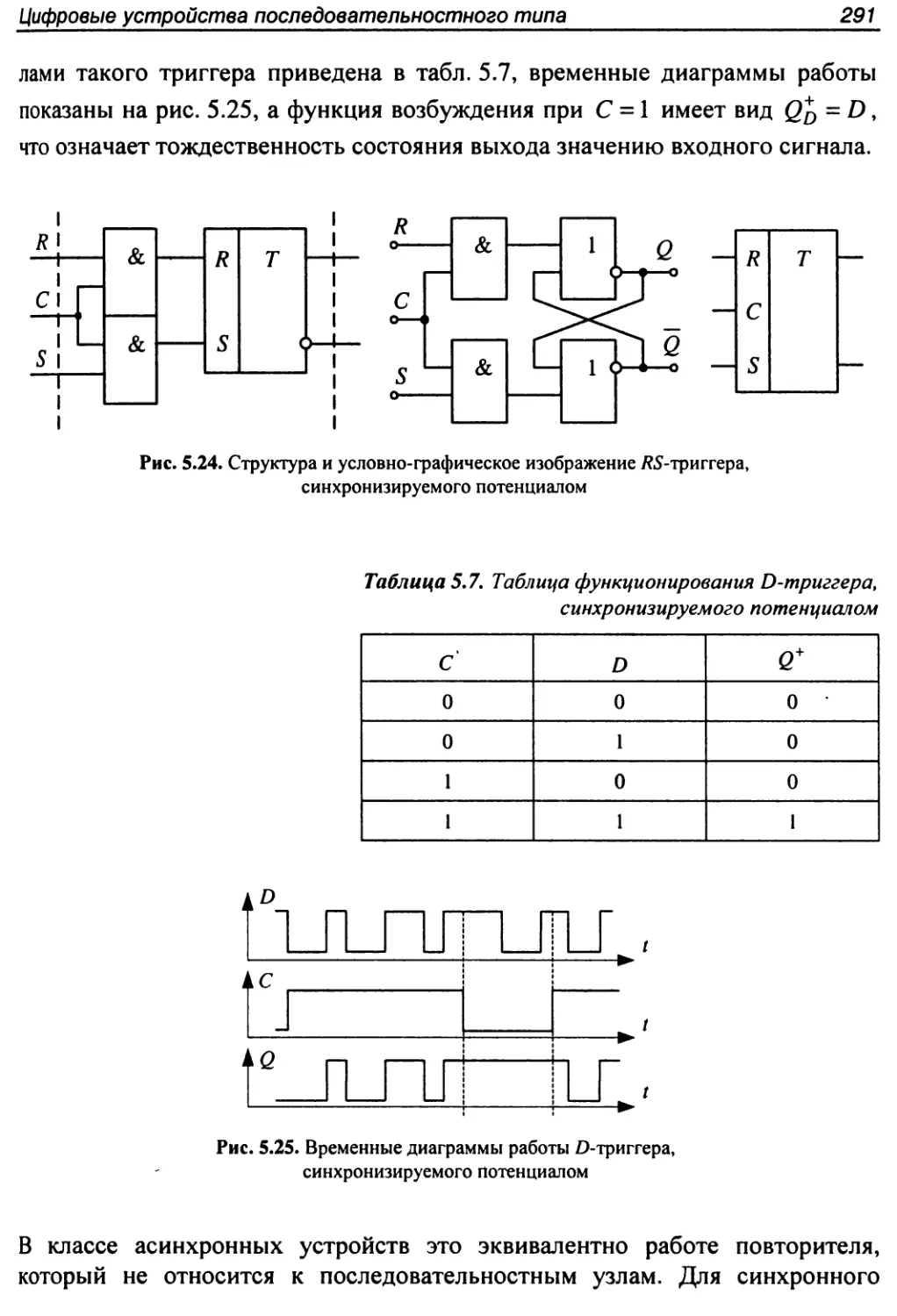

Ои 1.

Любое целое число в такой системе может быть представлено в виде

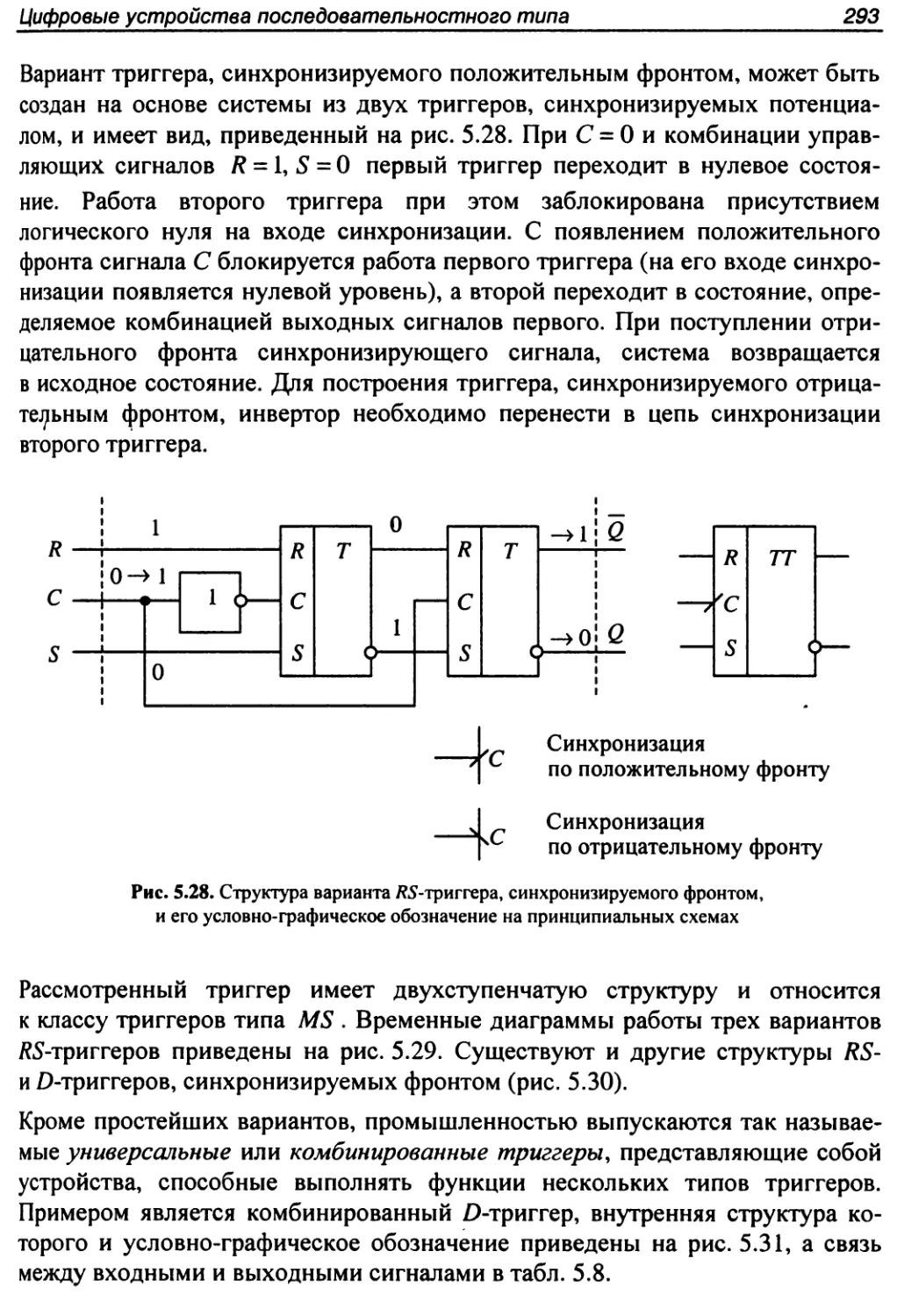

W = an_{ 2”-1 + ап_2 2”~2 +... + Я] 2* + а0 2°. (1.3)

Здесь веса разрядов равны соответствующим степеням двойки, т. е. 1, 2, 4, 8,

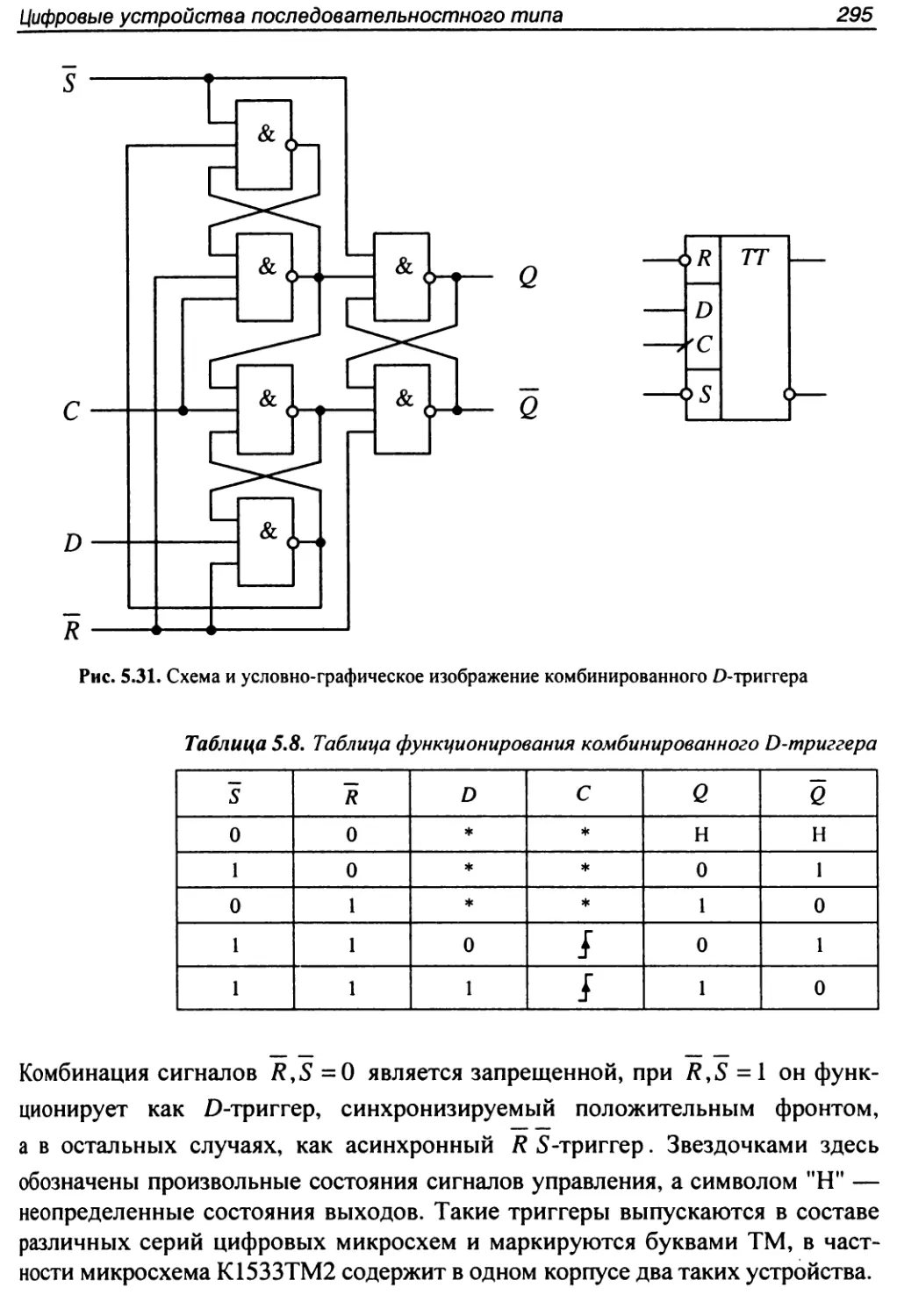

16 и т. д.

При необходимости перевода числа из десятичной системы счисления в дво-

ичную его требуется представить в виде суммы степеней основания, т. е.

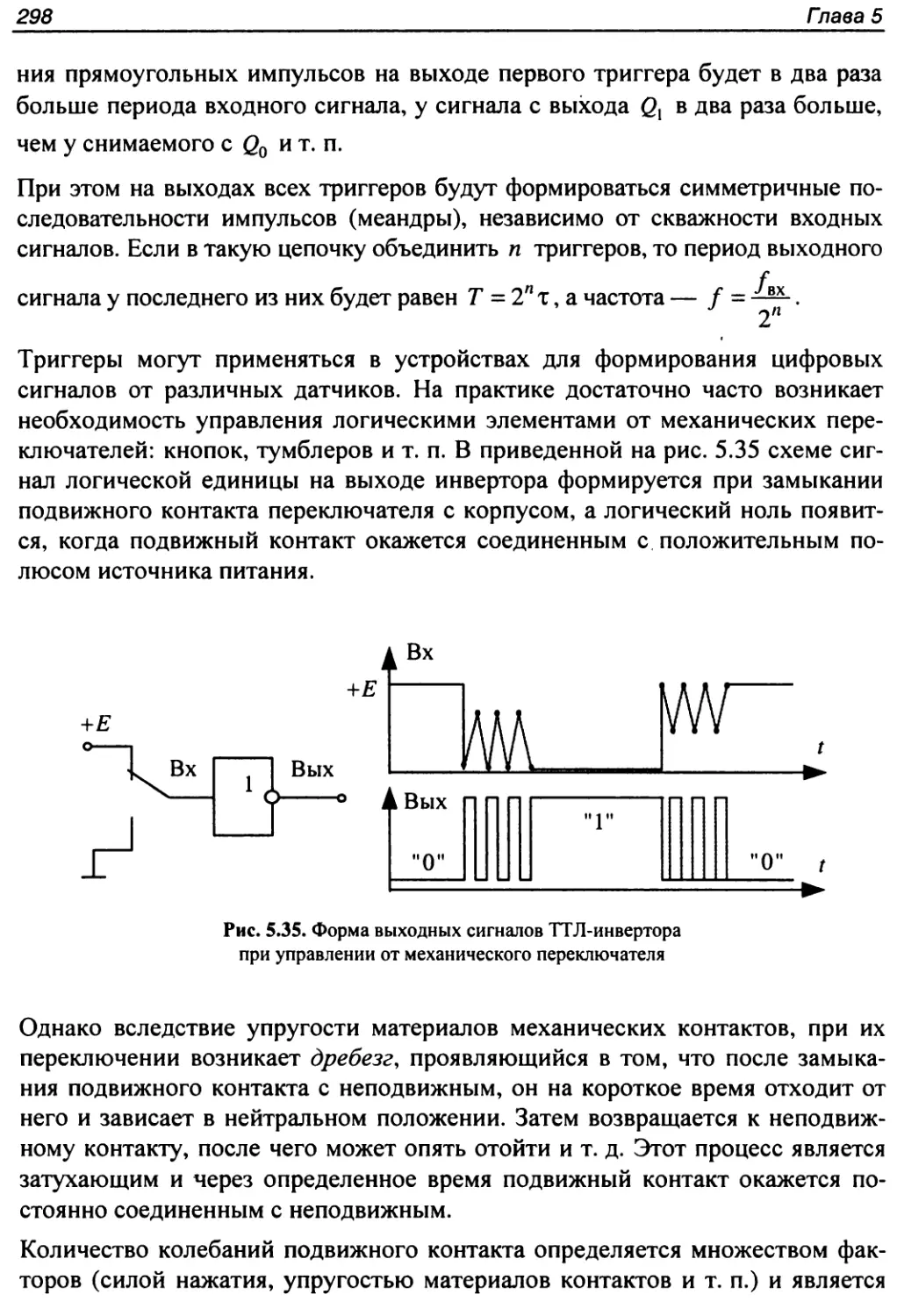

двойки. Например: 21 = 16 + 4+1 = 24 + 22 +2°. Однако, с учетом того, что

в записи числа должны присутствовать все разряды, полученное соотношение

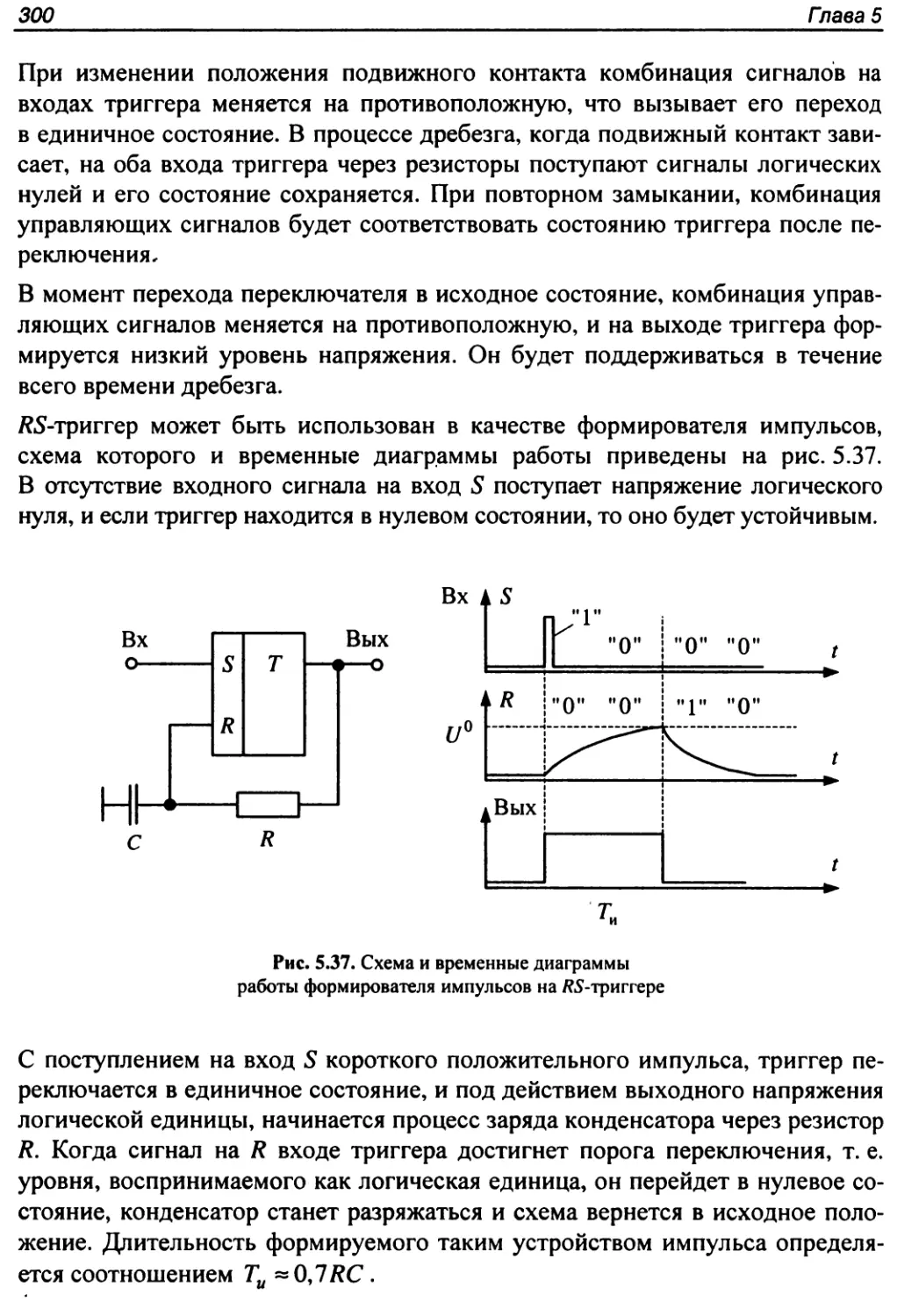

требуется дополнить недостающими. Чтобы результат в целом остался неиз-

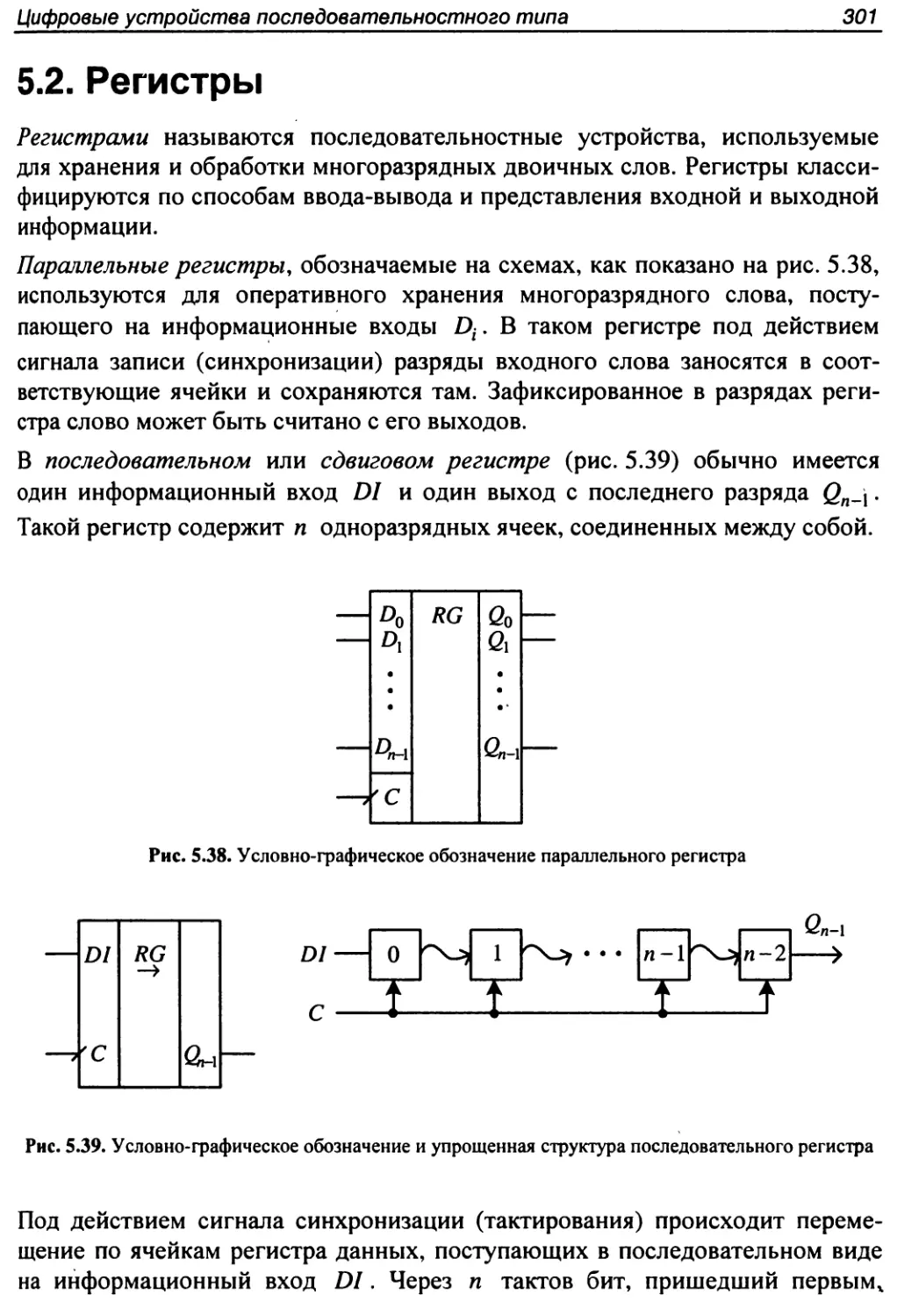

менным, эти разряды необходимо умножить на ноль, а остальные на едини-

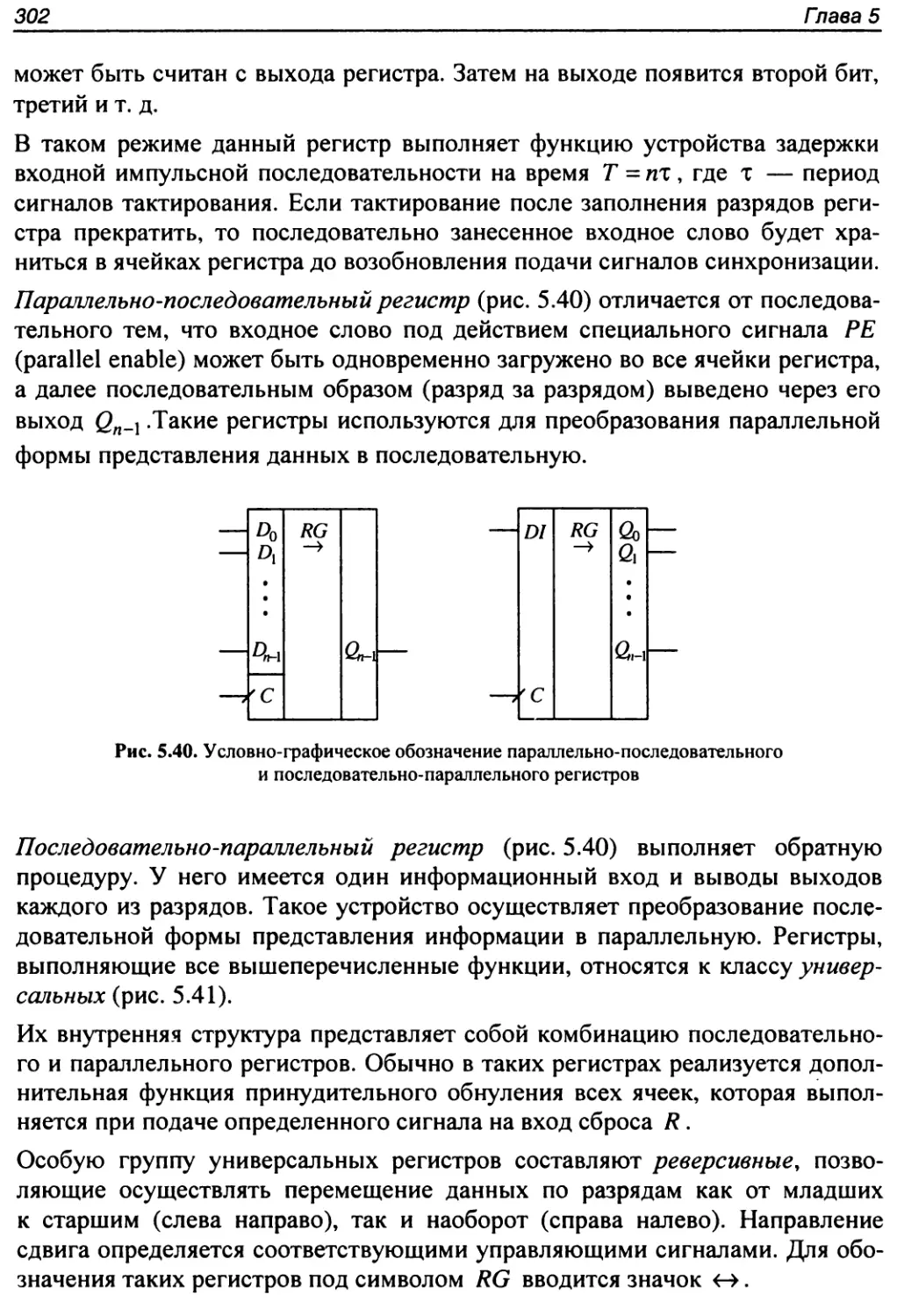

цу. В итоге запись числа 21 будет иметь вид 1-24 + 0-23 + 1-22 + 0-2* + 1-2°,

а само число в двоичной системе счисления запишется следующим образом,

10101.

Существуют и иные подходы для перевода десятичных чисел в двоичную

систему. Один из них основан на вычислении остатков от последовательного

деления исходного числа на два. Если 21 поделить на два, то получится целое

число 10 и остаток, равный 1. Он будет младшей значащей цифрой двоично-

го кода этого числа. Далее, полученное целое число опять делится на два, что

дает 5 и 0 в остатке. Это вторая значащая цифра. Деление продолжают, пока

получившееся целое число не станет равным единице, она же будет и цифрой

старшего двоичного разряда. Данную процедуру удобно записывать в виде

следующей цепочки действий:

21/2=10 ост. 1

10/2=5 ост. 0

5/2=2 ост. 1

2/2=1 ост. 0

1/2 ост. 1

Осуществить преобразование двоичного кода в десятичный можно, восполь-

зовавшись формулой (1.3). Например,

100112 = 1-24 + 0-23 + 0-22 + 1-21 + 1-2° = 16 + 2 + 1 = 19,0.

Кроме двоичной и десятичной систем счисления достаточно часто исполь-

зуют восьмеричную и шестнадцатеричную. В первой для представления

разрядов чисел применяют десятичные цифры от 0 до 7, а во второй для ото-

6

Глава 1

бражения цифр требуется 16 символов. В качестве первых десяти используют

цифры 0, 1, 2, ... 9, а остальные шесть обозначаются буквами А, В, С, D, Е, F,

которые соответствуют числам 10, 11, 12, 13, 14 и 15.

Правила перевода из одной системы счисления в другую аналогичны рас-

смотренным ранее. Например:

1238 = 1-8? + 2-81 + 3-8° = 64 + 16 + 3 = 831О,

AF5i6 = 10162 + 15161 + 516° = 10-256 + 15 16 + 5 = 280510.

Так как основания восьмеричной и шестнадцатеричной систем счисления

являются степенями двойки, то это существенно облегчает перевод чисел из

этих систем в двоичную и обратно. Для перевода из восьмеричной системы

в двоичную достаточно каждую цифру числа представить трехразрядным

двоичным кодом (триадой) и полученные комбинации нулей и единиц выпи-

сать в ряд.

Например: 1238 = (0012) (0102) (0112)= 1 010 0112. При необходимости пере-

вода из шестнадцатеричной системы в двоичную требуется проделать анало-

гичную процедуру, но преобразуя каждую цифру шестнадцатеричного кода

в четырехразрядную комбинацию (тетраду) двоичного:

AF516= (10102) (11112) (01012)= 1010 1111 01012.

Так же просто осуществляется и обратное преобразование, т. е. трансформа-

ция из двоичного кода в восьмеричный и шестнадцатеричный. В первом слу-

чае требуется двоичное число, начиная справа, разбить на триады, а во

втором — на тетрады, и каждую из них заменить цифрой или буквой в соот-

ветствующем коде. Например:

101111001012=010 111 100 101= 27458

101111000102 =0101 1110 0010 = 5Е216.

Такой подход нельзя использовать для преобразования двоичного кода в де-

сятичный и наоборот, т. к. отношение между основаниями этих систем счис-

ления не кратно степени двойки.

Формализовать процедуру трансформации десятичного кода в код, аналогии-*

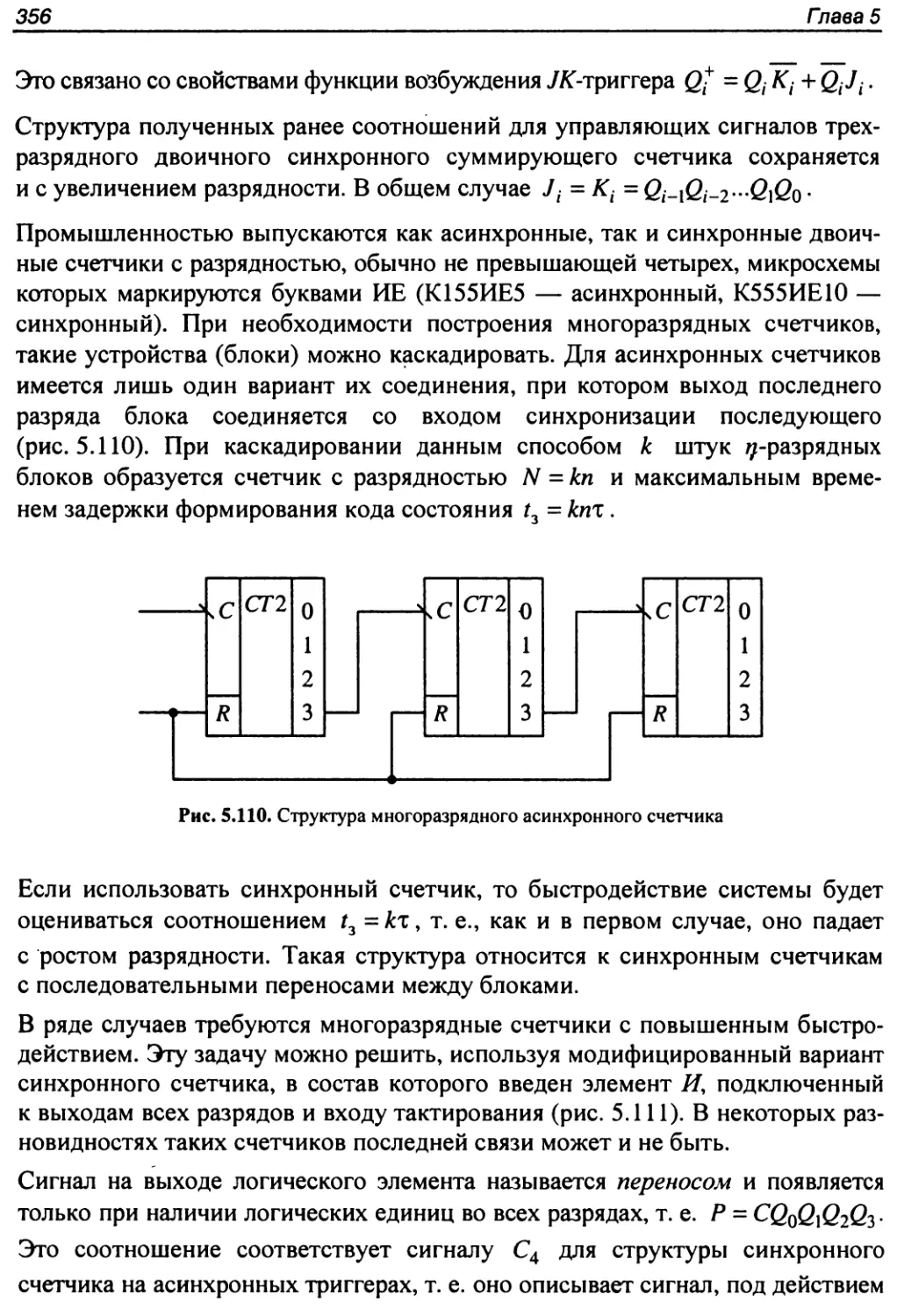

ный двоичному, можно, преобразовывая каждую цифру десятичного числа

в тетраду двоичного кода. Тогда трансформация, к примеру, числа 175 ю бу-

дет выглядеть следующим образом: 1—>0001; 7—>0111; 5—>0101, а его запись

примет вид 175ю = 0001 0111 0101.

Однако это выражение будет существенно отличаться от представления этого

же числа в двоичном коде, 175ю = 101011112. Отличие возникает из-за того,

что в предыдущем примере разряды в пределах каждой тетрады имеют дво-

ичные веса, меняющиеся от единицы до восьми, и, кроме того, каждая

Арифметические и логические основы цифровой техники

7

из тетрад имеет и свой десятичный вес — 1, 10, 100. При таком подходе об-

разуется новая система счисления, которая в данном случае называется дво-

ично-десятичной и относится к позиционным системам счисления с двойным

взвешиванием.

В ряде случаев использование такой системы оказывается достаточно удоб-

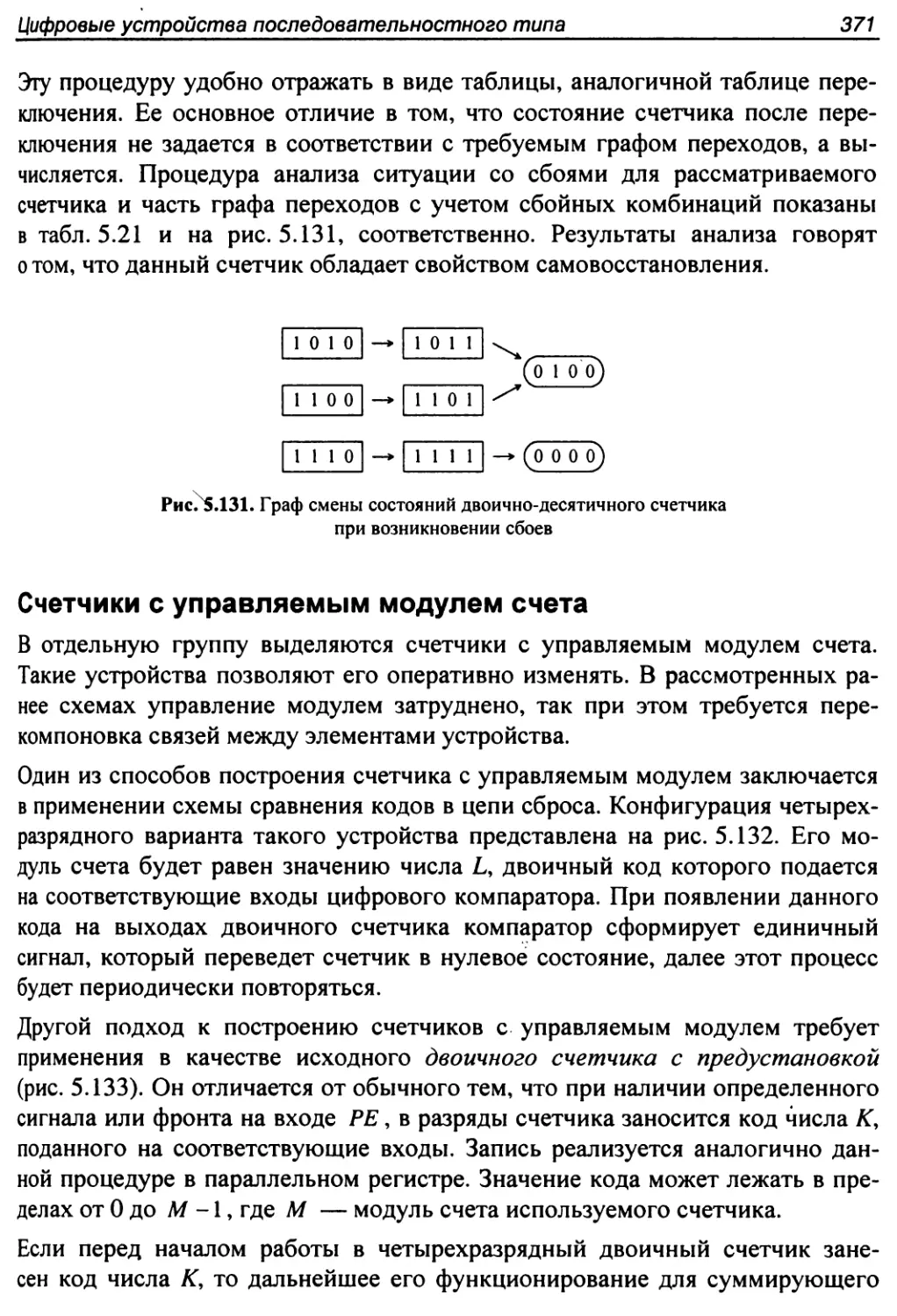

ным из-за упрощения процедуры преобразования. Однако выполнение ариф-

метических операций в двоично-десятичной и аналогичных системах счисле-

ния является более сложной процедурой, чем в обычных позиционных.

В табл. 1.1 приведены представления чисел от нуля до двадцати в различных

системах счисления, в том числе и позиционных.

Как уже отмечалось, в позиционных системах счисления веса разрядов могут

быть произвольными. При этом одна и та же последовательность чисел

в системах с одинаковым основанием будет представляться по-разному в за-

висимости от соотношения весов разрядов. В табл. 1.2 приведены различные,

используемые на практике, способы кодирования чисел от нуля до девяти.

В первом столбце представлены комбинации, соответствующие коду 8-4-2-1.

Название кода состоит из значений весовых коэффициентов соответствую-

щих разрядов. Если веса имеют значения 2-4-2-1, то для ряда десятичных

цифр кодовые комбинации будут выглядеть по-иному. Код 7-4-2-1 интересен

тем, что любая кодовая комбинация содержит не более двух единиц. Такое

свойство кода полезно для выявления ошибок при передаче сигналов, т. к.

если в принятой тетраде окажется три единицы, то это будет сигналом о воз-

никновении ошибки вследствие того, что таких комбинаций в данном коде не

существует. В позиционных системах счисления с одинаковым основанием,

но с различными соотношениями весов разрядов, одна и та же последова-

тельность чисел будет представляться по-разному.

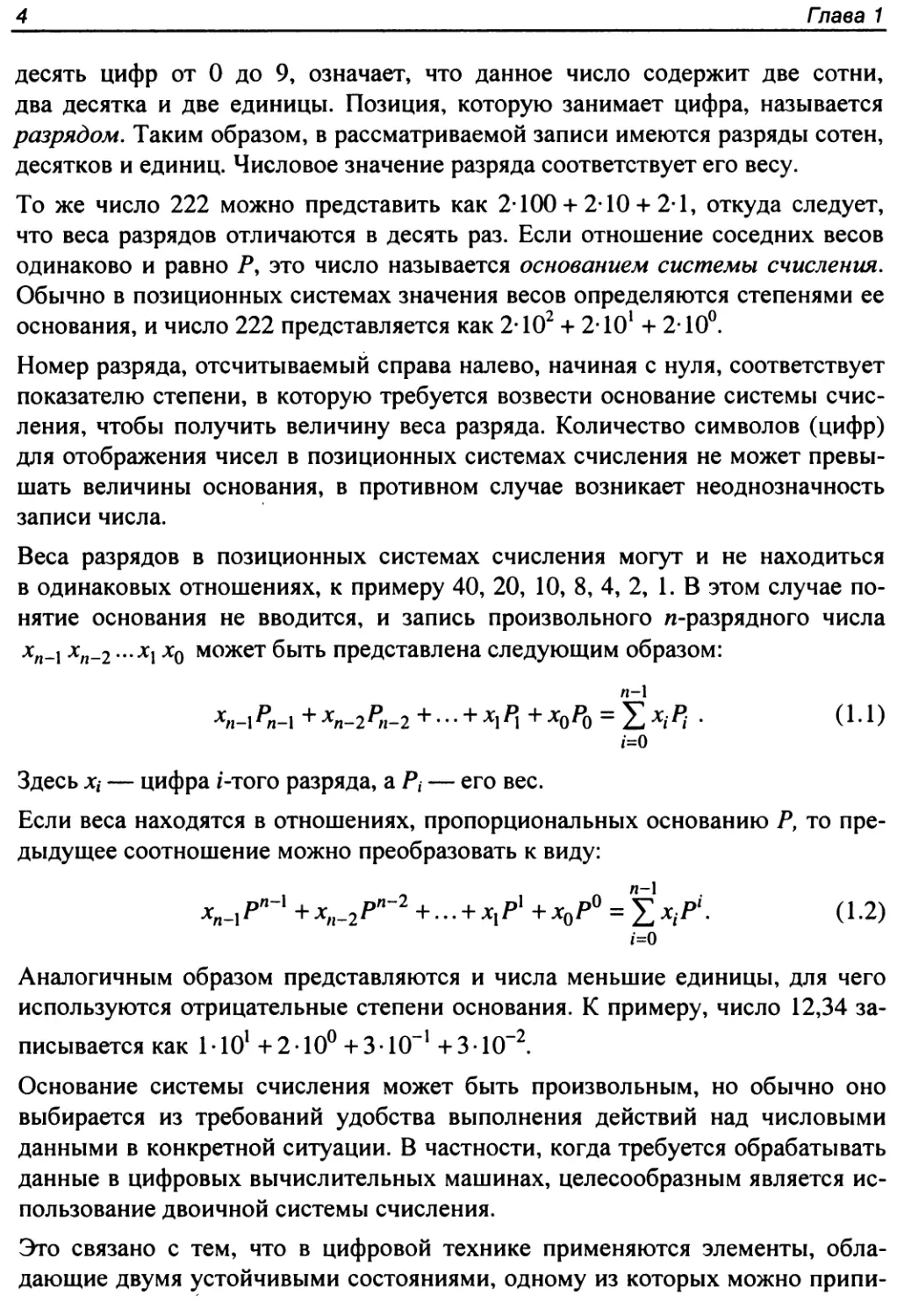

Таблица 1.1. Представление чисел в различных системах счисления

Дес. ЧИСЛО Непозици- онная (римская) Восьме- ричная Шестнадца- теричная Двоичная Двоично- десятичная

0 0 0 0000 0000

1 I 1 1 0001 0001

2 II 2 2 0010 0010

3 III 3 3 ООП ООП

4 IV 4 4 0100 0100

5 V 5 5 0101 0101

8

Глава 1

Таблица 1.1 (окончание)

Дес- ЧИСЛО Непозици- онная (римская) Восьме- ричная Шестнадца- теричная Двоичная Двоично- десятичная

6 VI 6 6 ОНО ОНО

7 VII 7 7 0111 0111

8 VIII 10 8 1000 1000

9 IX 11 9 1001 0001

10 X 12 А 1010 1 0000

11 XI 13 В 1011 1 0001

12 XII 14 С 1100 1 0010

13 XIII 15 D 1101 1 ООН

14 XIV 16 Е 1110 1 0100

15 XV 17 F 1111 1 0101

16 XVI 20 11 1 0000 1 оно

17 XVII 21 12 1 0001 1 0111

18 XVIII 22 13 1 0010 1 1000

19 XIX 23 14 1 ООП 1 1001

Особенность кодов, представленных в трех последних столбцах таблицы,

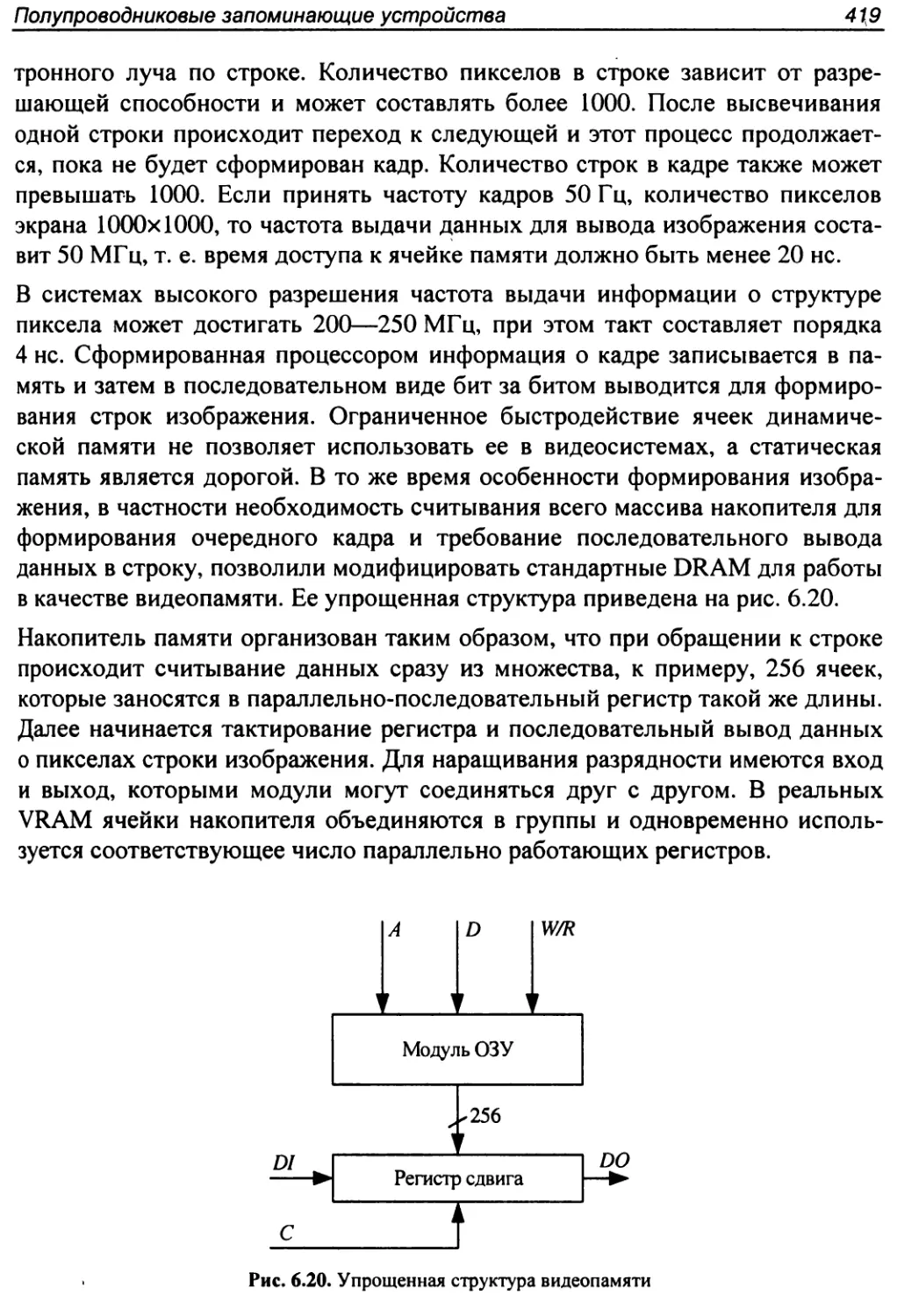

в том, что они относятся к классу непозиционных или невзвешенных. В коде

с избытком 3 сумма двоичных чисел в первой и последней строках, второй и

предпоследней и т. д. всегда дает кодовую комбинацию 1111. Сформировать

этот код можно путем прибавления к соответствующей десятичной цифре

тройки и преобразования полученного результата в двоичный код.

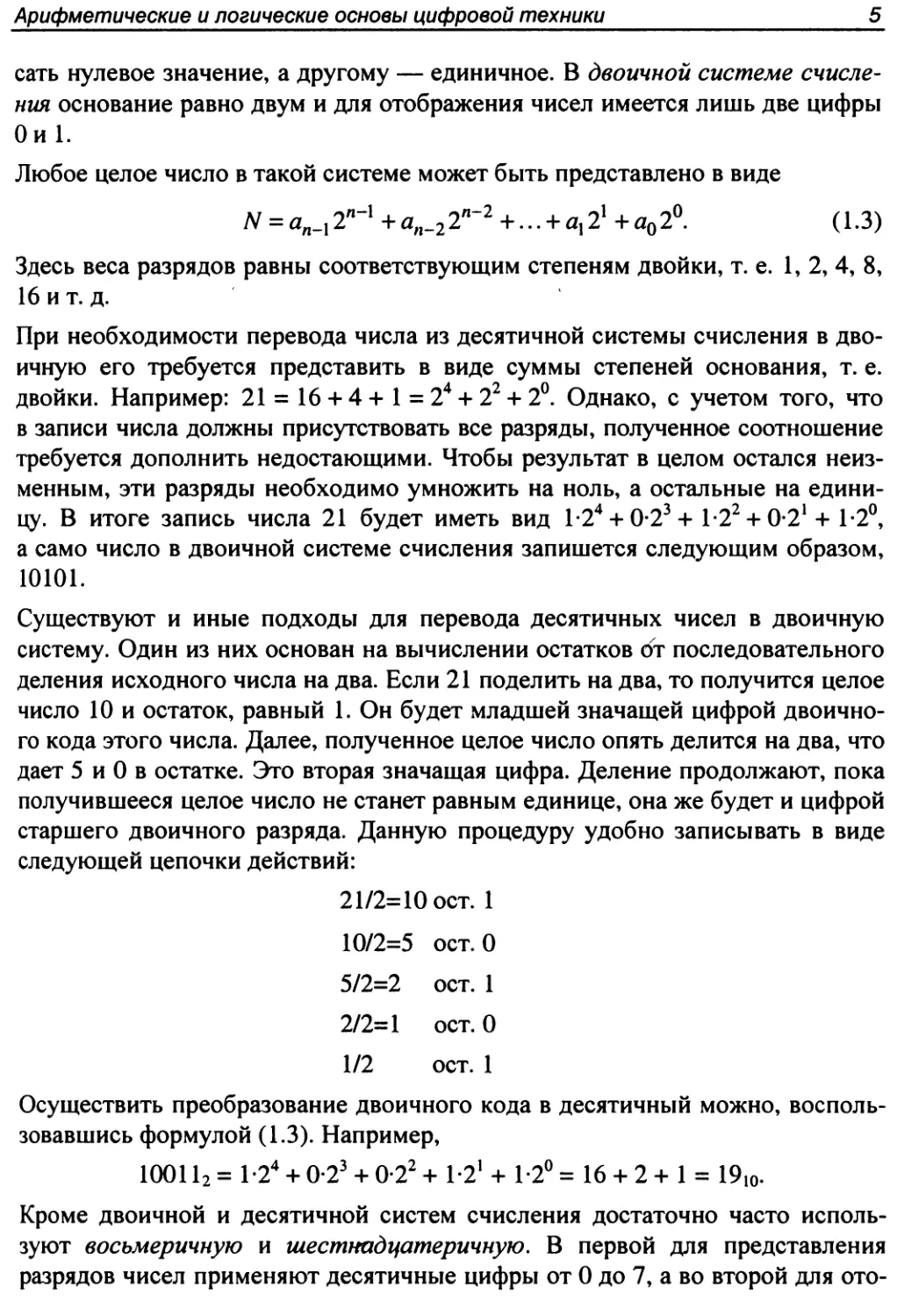

Таблица 1.2. Кодированное представление чисел в системах счисления с основанием два

Дес. цифра Код 8-4-2-1 Код 2-4-2-1 Код 7-4-2-1 Код с избытком 3 Код 2 из 5 Код Грея

0 0000 0000 0000 ООН 11000 0000

1 0001 0001 0001 0100 01100 0001

2 0010 0010 0010 0101 00110 ООН

3 ООН ООН ООН оно 00011 0010

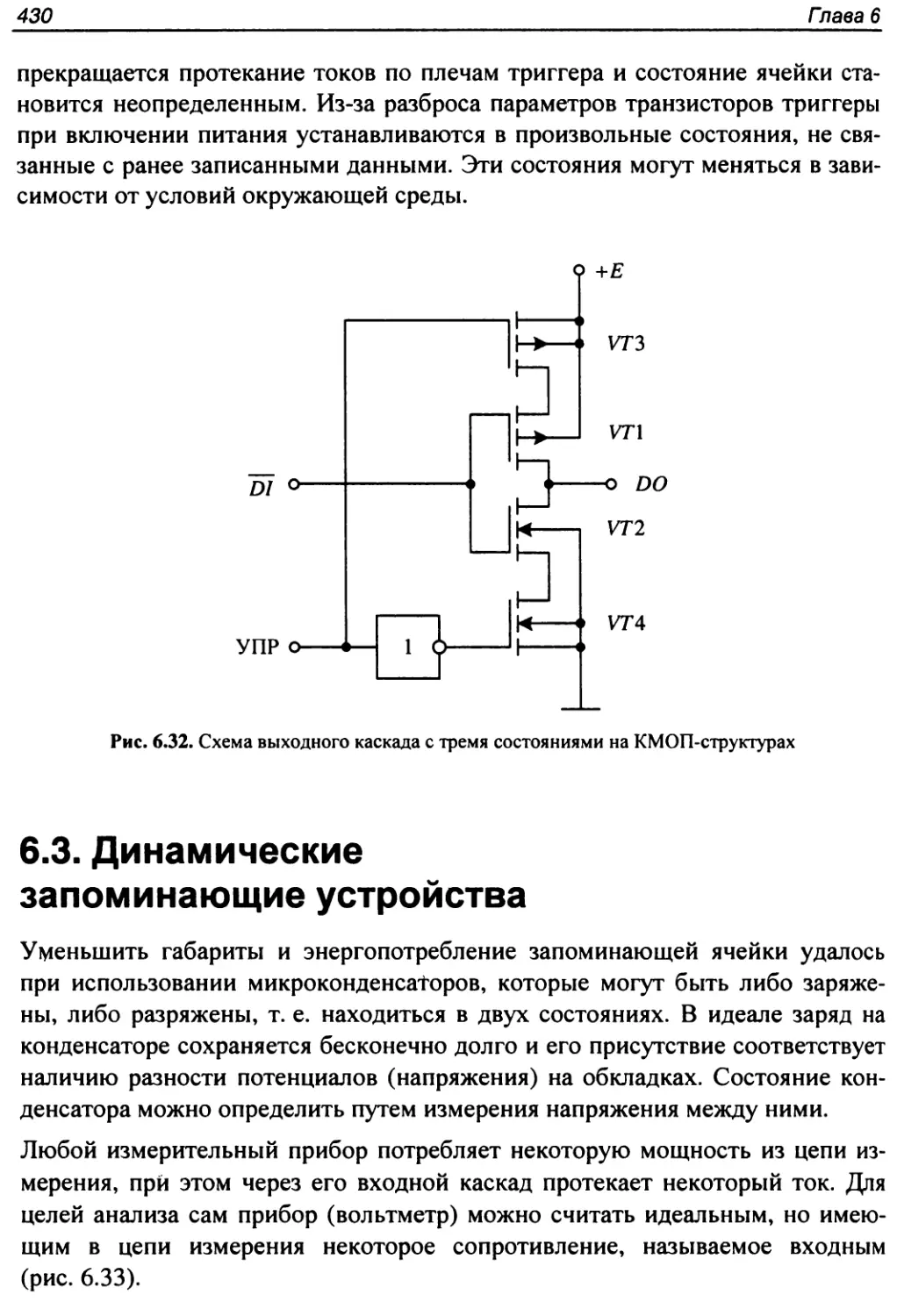

Арифметические и логические основы цифровой техники

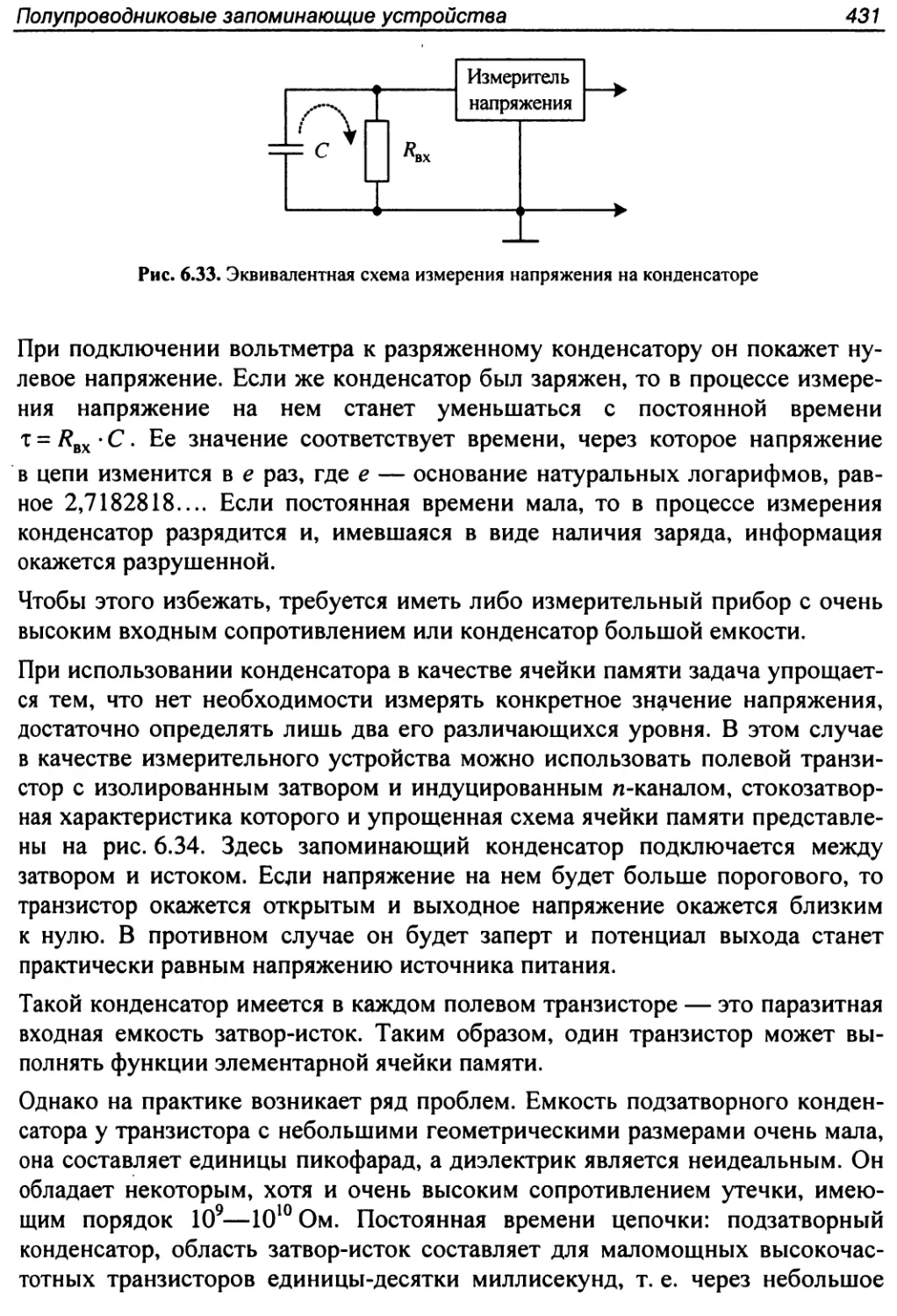

9

Таблица 1.2 (окончание)

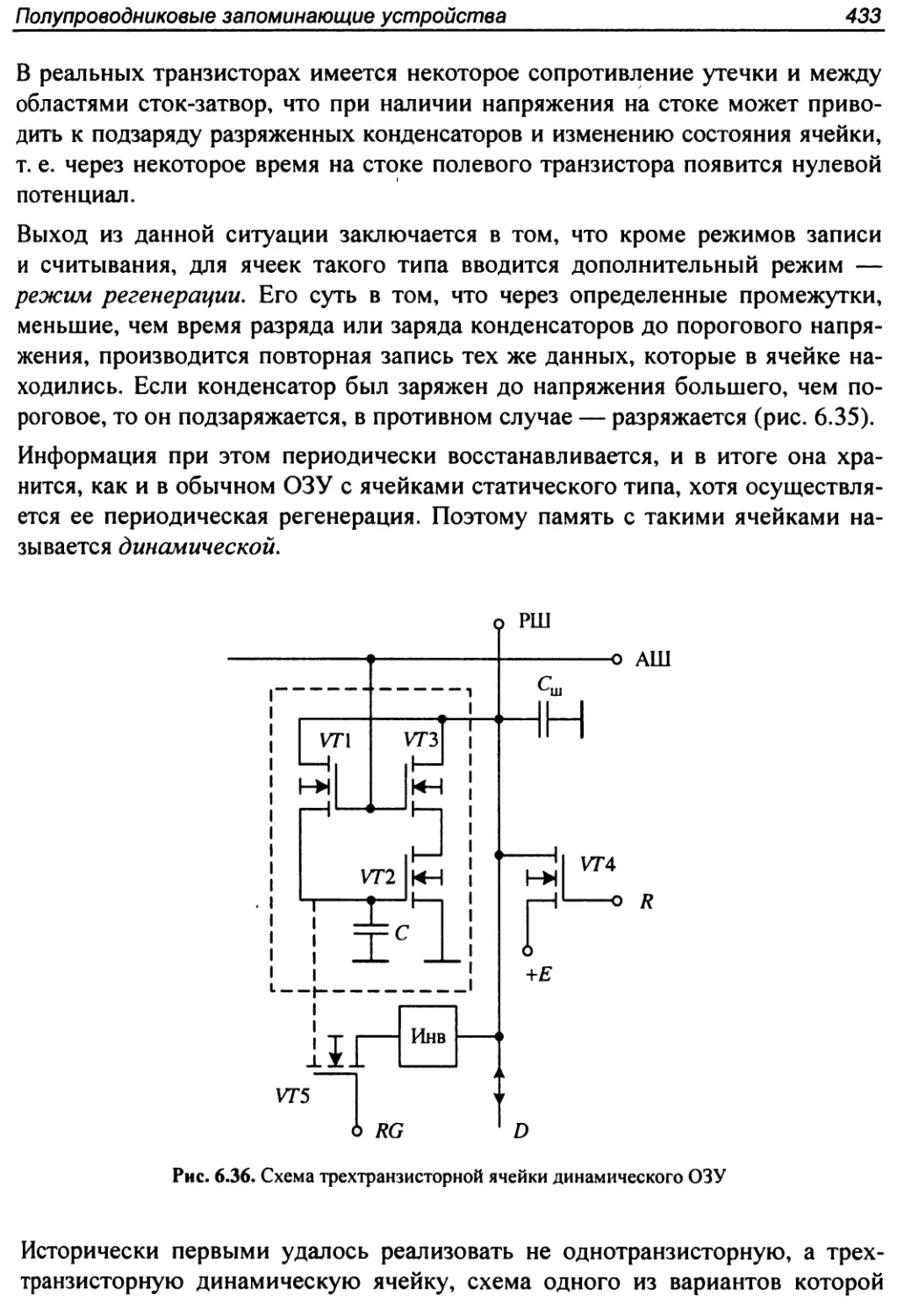

Дес. цифра Код 8-4-2-1 Код 2-4-2-1 Код 7-4-2-1 Код с избытком 3 Код 2 из 5 Код Грея

4 0100 0100 0100 0111 10001 ОНО

5 0101 1011 0101 1000 10100 0111

6 оно оно оно 1001 01010 0101

7 0111 0111 1000 1010 00101 0100

8 1000 1110 1001 1011 10010 1100

9 1001 1111 1010 1100 01001 1101

В коде 2 из 5 используются пятиразрядные комбинации нулей и единиц. Его

особенность в том, что в любой кодовой комбинации содержится по две еди-

ницы. Еще одна разновидность довольно часто применяемого кода — код

Грея, который обладает тем свойством, что представления соседних чисел

отличаются состоянием только одного из разрядов.

Все ранее рассмотренные способы кодирования основывались на предполо-

жении, что исходное число положительно. Однако для удобства выполнения

ряда арифметических операций в любой системе счисления можно ввести

понятие отрицательных чисел, значения которых будут меньше нуля. В деся-

тичной системе счисления для их записи используется знак , а такое же

по величине (по модулю) положительное число дополняется знаком "+”.

Так как в цифровых вычислительных машинах используются двухуровневые

сигналы, одному из которых приписывается значение логического нуля,

а другому единицы, то ввести аналогичные знаки не представляется возмож-

ным, т. к. любое число и символ должны быть выражены через комбинации

нулей и единиц. То есть и знак числа требуется отображать этими же симво-

лами.

При одном из подходов положительному знаку ставится в соответствие О,

а отрицательному 1 и знаковый разряд записывается левее самого старшего

значащего. Таким образом, число +9 будет выглядеть как 0 1001, а -9 сле-

дующим образом 1 1001. Однако в этом случае потребуется обязательное

указание на то, что старший разряд является знаковым, иначе первое число

будет воспринято как 9, а второе как 25. В так называемом модифицирован-

ном коде под знак отводят два дополнительных разряда, положительный ко-

дируется 00, а отрицательный 11.

Некоторые виды арифметических операций в цифровых вычислитель-

ных машинах удобнее производить, используя обратные и дополнительные

10

Глава 1

двоичные коды чисел. Формально обратный код получается из двоичного

(прямого) путем замены во всех разрядах нулей на единицы, а единиц на

нули. Таким образом, если прямой двоичный код числа 9 выглядит как 1001,

то обратный будет представлен комбинацией ОНО.

Дополнительный код образуется путем арифметического прибавления еди-

ницы в младший разряд обратного кода числа. Отсюда следует, что дополни-

тельный код 9 отобразится кодовой комбинацией 0111. Понятие допол-

нительного кода можно ввести для любой позиционной системы счисления.

Он представляет собой число, дополняющее исходное до значения веса сле-

дующего по старшинству разряда системы счисления.

В рассмотренном примере для представления числа 9 используется четырех-

разрядная двоичная кодовая комбинация. Вес следующего, более старшего

разряда в двоичной системе будет 24= 16. То есть дополнительным кодом

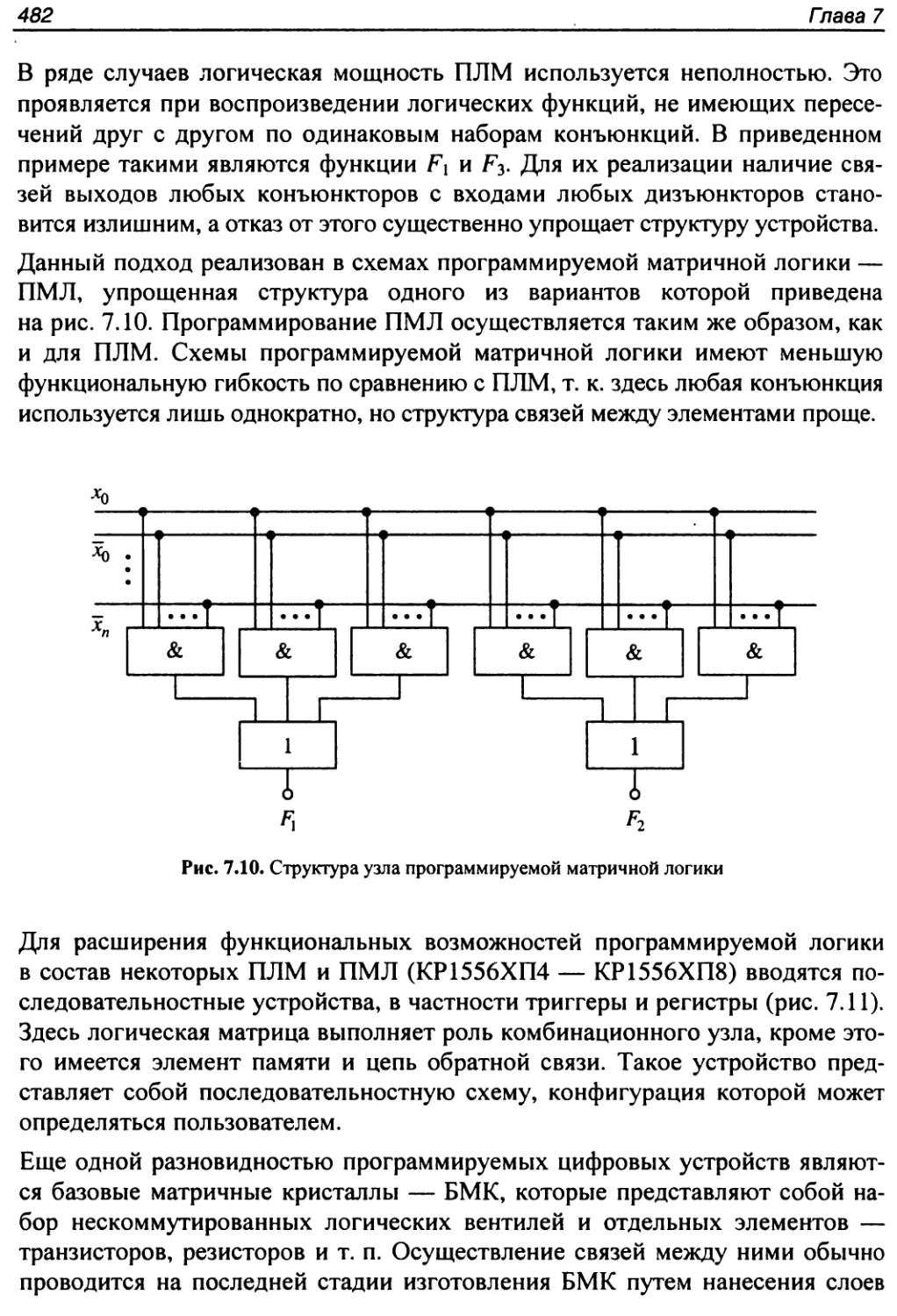

девятки будет число 16 - 9 = 7, двоичный код которого имеет вид 0111. Если

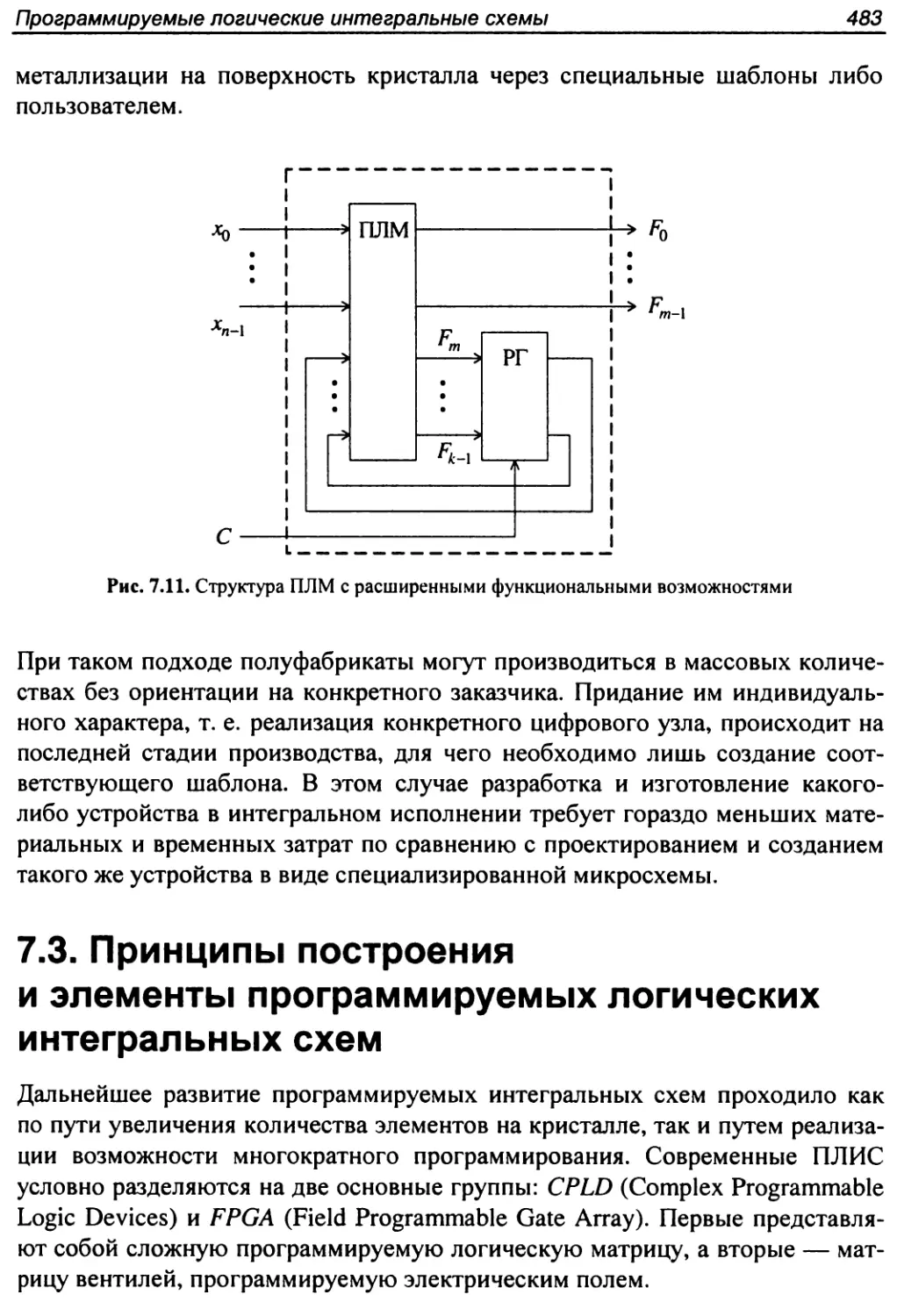

речь вести о десятичной системе счисления, то дополнительный код 9 дол-

жен определяться как 102 - 9 = 91.

1.2. Логические переменные и функции

При математическом описании различных процессов вводится понятие пере-

менной. Это некоторая независимая величина, которая принимает ряд значе-

ний в определенном диапазоне. Множество значений переменной может

быть как непрерывным, так и дискретным. В первом случае переменная при-

нимает любое значение из области, в которой она определена, а во втором

лишь ряд конкретных. Примером переменной первого вида является темпе-

ратура. Она меняется непрерывно и принимает любое значение из соответст-

вующего диапазона, причем соседние могут отличаться на бесконечно малую

величину. Примером дискретной переменной может служить цена товара.

Ее минимальные изменения кратны одной копейке, т. к. меньших денежных

единиц нет.

Над переменными можно проводить определенные математические действия.

Совокупность этих действий и правил их выполнения называется алгеброй

соответствующих переменных. Значениям одной переменной могут быть по-

ставлены в соответствие значения другой. Закон, определяющий это соответ-

ствие, называется функцией.

В особую группу выделяются переменные, принимающие лишь два фиксиро-

ванных значения. Например, если переменная описывает состояния переклю-

чателя, который может находиться либо во включенном, либо в выключен-

ном состояниях. Значению переменной для одного из них можно присвоить

Арифметические и логические основы цифровой техники

11

название ”Вкл”, а для другого "Выкл”, либо обозначить их по иному "А"

и "В”, или 0 и 1, учитывая в последнем случае, что это не цифры, а просто

символы для описания состояния переменной.

Переменные, имеющие лишь два значения, часто называются логическими

или Булевыми. Первое связано с тем, что они могут выступать как результат

анализа логического рассуждения, который бывает истиной или ложью. Со-

вокупность законов преобразования этих переменных и правил действий над

ними называется Булевой алгеброй или алгеброй логики.

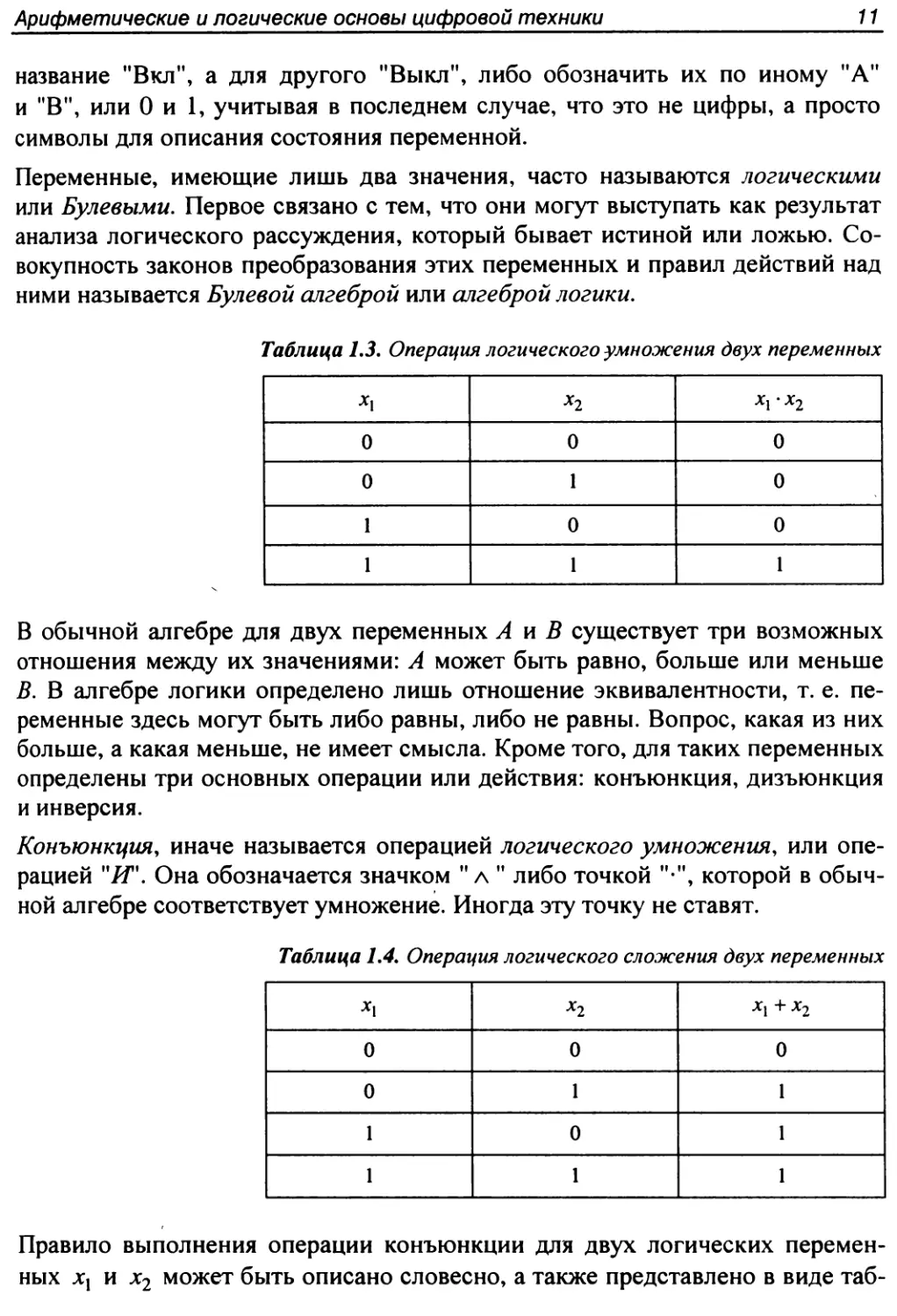

Таблица 1.3. Операция логического умножения двух переменных

*1 *2 *Г*2

0 0 0

0 1 0

1 0 0

1 1 1

В обычной алгебре для двух переменных А и В существует три возможных

отношения между их значениями: А может быть равно, больше или меньше

В. В алгебре логики определено лишь отношение эквивалентности, т. е. пе-

ременные здесь могут быть либо равны, либо не равны. Вопрос, какая из них

больше, а какая меньше, не имеет смысла. Кроме того, для таких переменных

определены три основных операции или действия: конъюнкция, дизъюнкция

и инверсия.

Конъюнкция, иначе называется операцией логического умножения, или опе-

рацией ”/Г'. Она обозначается значком ” л ” либо точкой которой в обыч-

ной алгебре соответствует умножение. Иногда эту точку не ставят.

Таблица 1.4. Операция логического сложения двух переменных

х\ х2

0 0 0

0 1 1

1 0 1

1 1 1

Правило выполнения операции конъюнкции для двух логических перемен-

ных jq и х2 может быть описано словесно, а также представлено в виде таб-

12

Глава 1

лицы (табл. 1.3). Результат логического умножения равен единице, только

если обе переменные одновременно принимают единичные значения. Данная

таблица полностью совпадает с таблицей умножения чисел 0 и 1.

Операция дизъюнкции, называемая иначе операцией логического сложения

либо операцией "ИЛИ", обозначается как значком "v", так и ”+". Данная

операция над двумя переменными определяется табл. 1.4.

Инверсия, называемая также операцией логического отрицания либо опера-

цией "НЕ", реализуется над одной переменной, преобразуя ее значение в про-

тивоположное. Эта операция обозначается в виде черточки сверху над соот-

ветствующей переменной, т. е. 1=0, 0=1.

В отличие от алгебры обычных переменных в алгебре логики не существует

операций умножения, деления, возведения в степень. Это связано с тем, что

логические переменные не принимают числовых значений, не могут быть

отрицательными, дробными и т. п.

Таблица 1.5. Основные соотношения алгебры логики для одной переменной

х + 0= х х-0=0

х + 1=1 х-1=х

х + х= X хх=х

х + х=1 хх=0

0 = 1, Т = 0 х =х

В Булевой алгебре справедливы соотношения, приведенные в табл. 1.5, кото-

рые можно проверить простым перебором значений переменной х, восполь-

зовавшись правилами выполнения соответствующих операций.

Для алгебры логики, как и для обычной алгебры, определен ряд законов вы-

полнения действий над переменными, в частности, коммутативный, ассоциа-

тивный и дистрибутивный.

Первый, иначе называемый переместительным законом, записывается

следующим образом: Xj + х2 = х2 + и Xj • х2 = х2 • Xj, из которого вытекает,

что при сложении и умножении логических переменных их можно менять

местами.

Арифметические и логические основы цифровой техники 13

Второй, ассоциативный закон, иначе называется сочетательным. Для трех

переменных его можно представить как:

х1+х2+х3=(х|+х2) + х3=х1+(х2+х3),

*Г Х2 • Х3 = (ХГ Х2 ) • Х3 = X, • (х2 • *3 ) ’

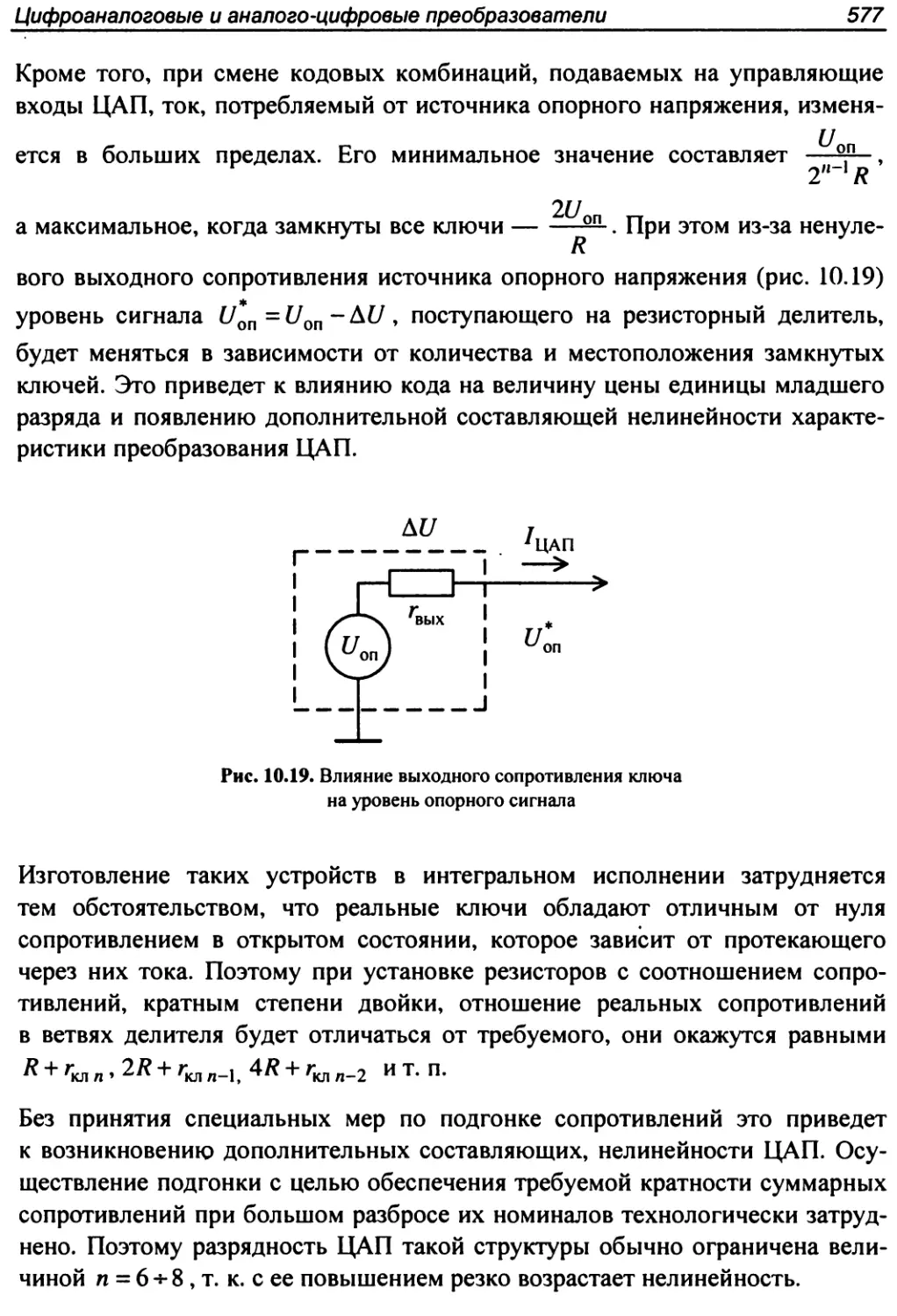

т. е. при выполнении логических операций, переменные можно объединять

в группы и выполнять соответствующие действия по очереди.

Дистрибутивный, или распределительный закон устанавливает правила

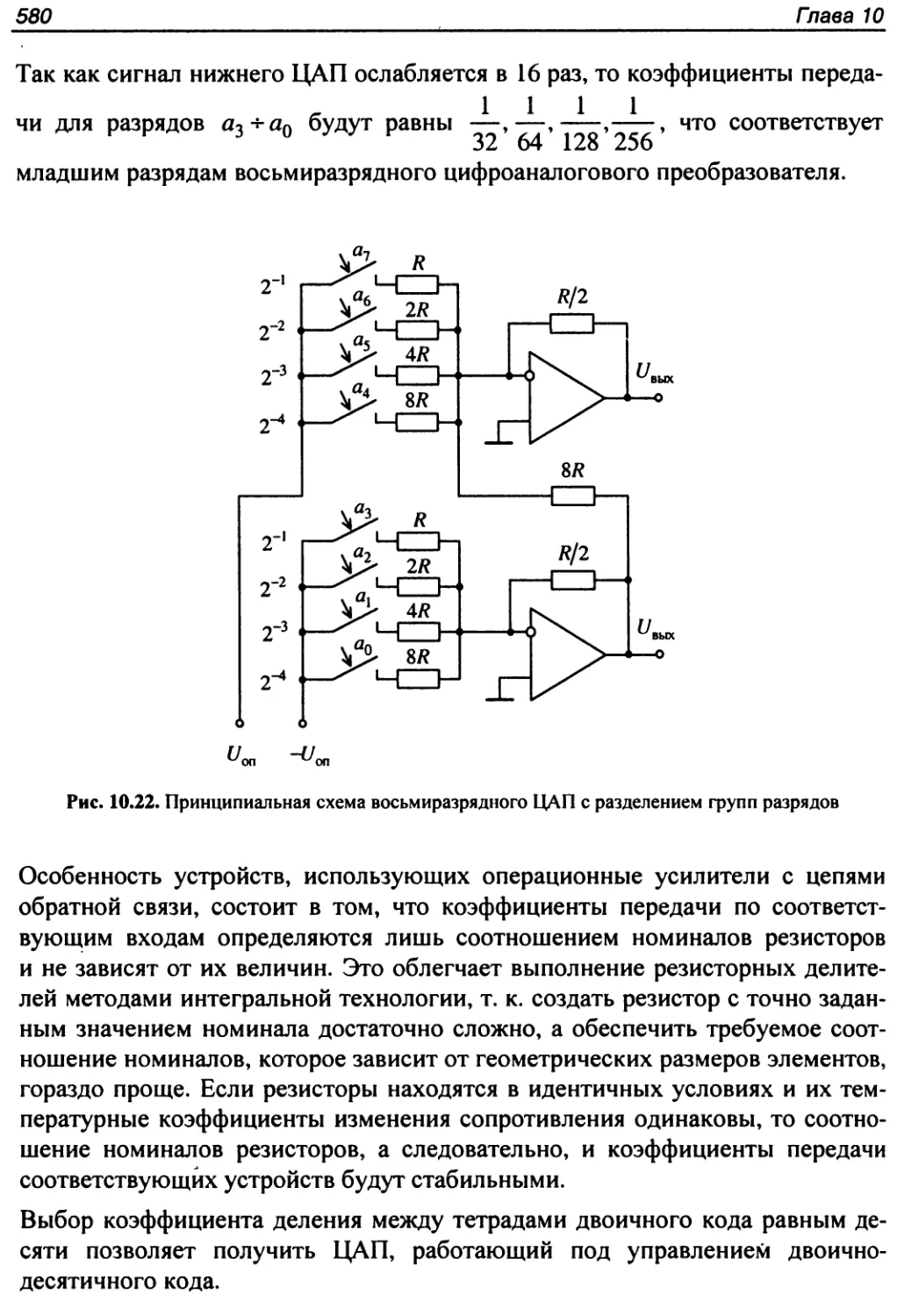

выполнения скобочных действий Xj • (х2 • х3) = jq • х2 + *г *з» или

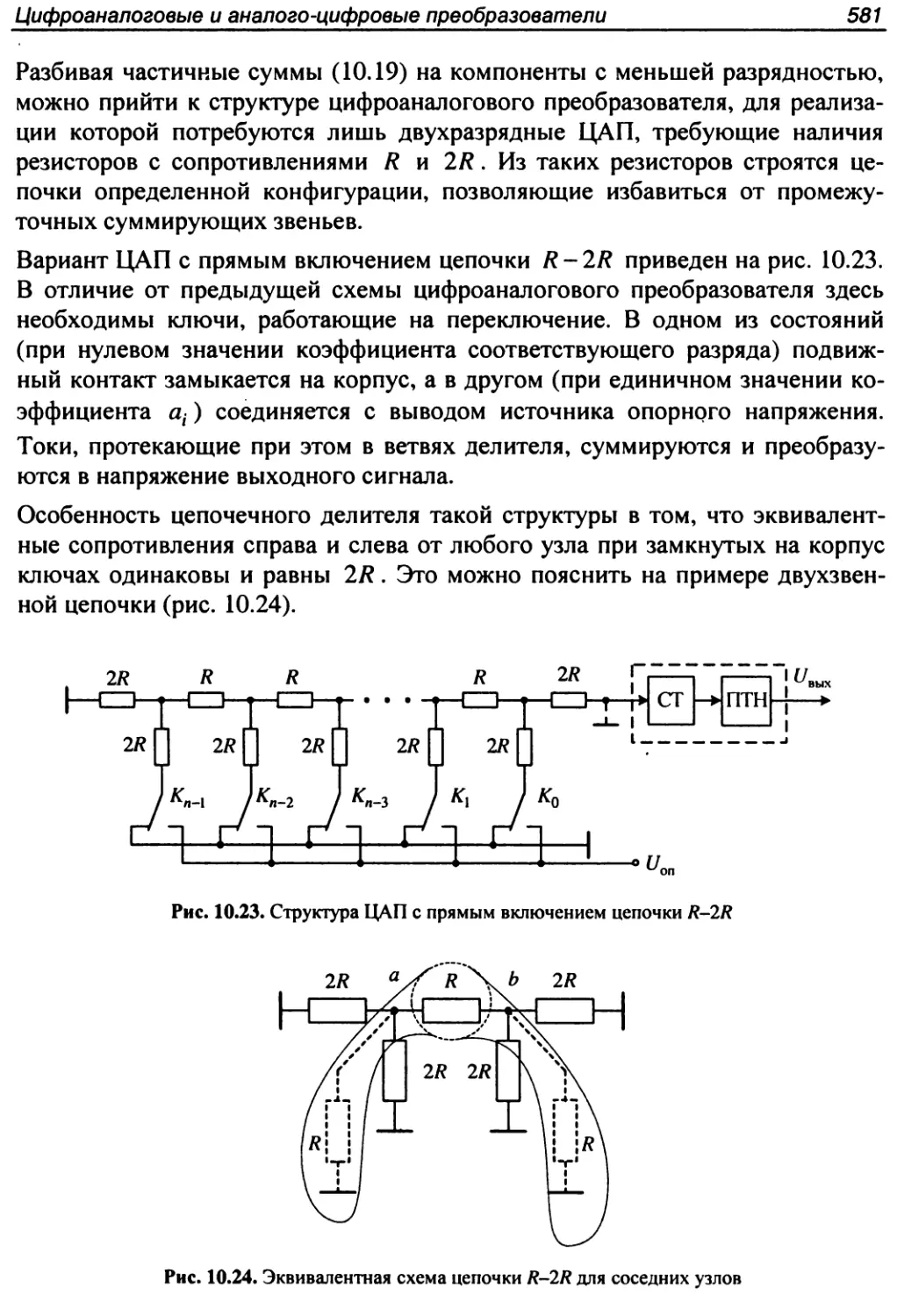

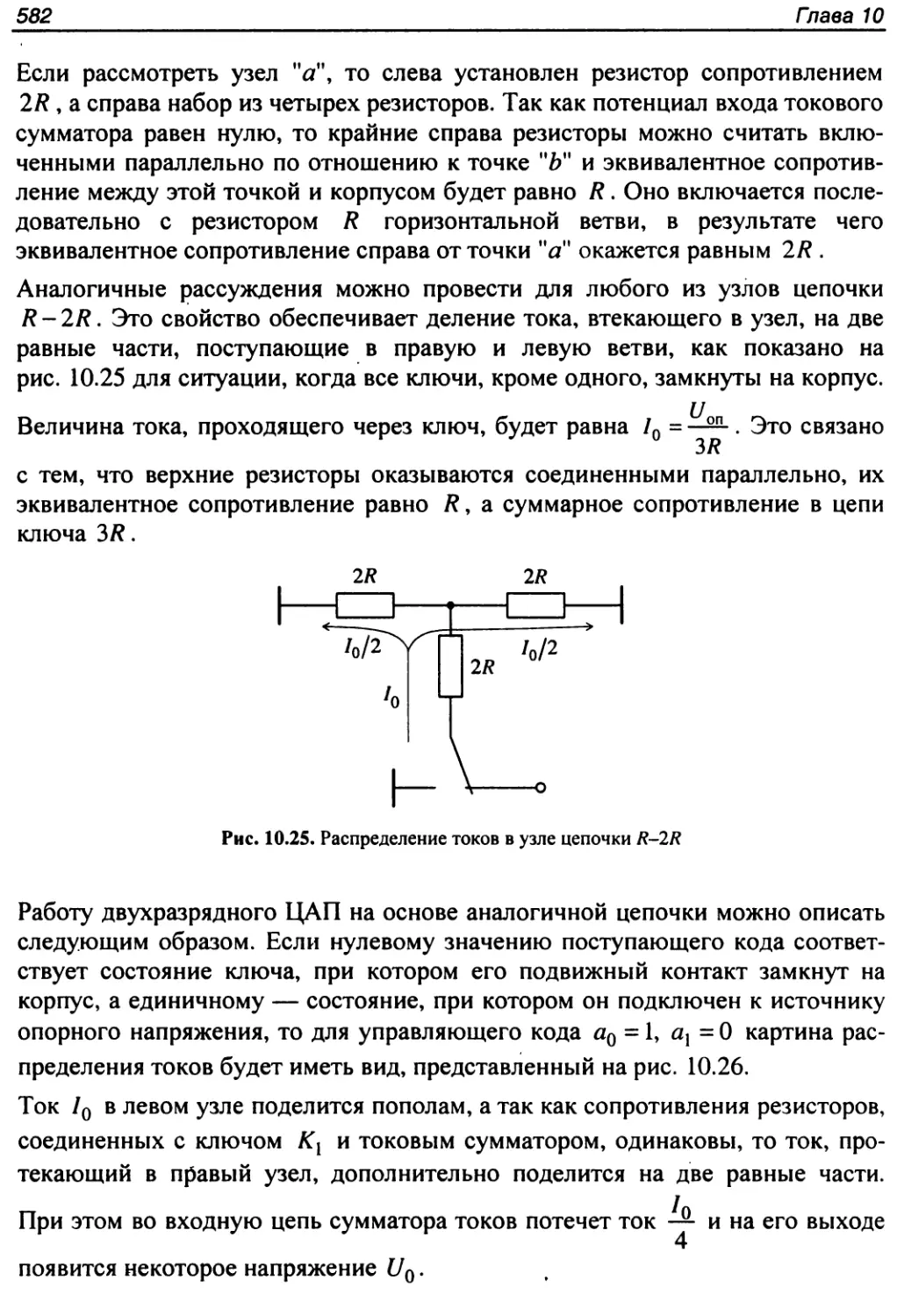

Xj х2 + xj -х3 = х1 (х2 +х3). Данные выражения представляют собой тожде-

ства, т. е. они справедливы при любых Значениях переменных.

К основным законам алгебры логики относятся и законы или правила

де Моргана, которые связывают операции логического сложения и умноже-

ния. Если в обычной алгебре умножение можно представить как многократ-

ное сложение, то логическое сложение может быть выражено через логиче-

ское умножение следующим образом:

X]+х2 + --- + х„ =х1-х2-...-хп , (1.4)

а умножение через сложение, как:

Х]-х2-...-х„ =Х] + х2 + ... + х„ , (1.5)

т. е. инверсия суммы логических переменных равна логическому произведе-

нию их инверсий, а инверсия произведения — сумме инверсий.

Если к обеим частям равенства применить одну и ту же процедуру, то оно не

изменится. Отсюда следует, что, проинвертировав обе части приведенных

соотношений, правила де Моргана можно представить в такой форме:

Х| +х2+... + х„ =Xj -х2-...-хп

(1.6)

Xj • х2 •... • хп = X] + х2 +... + хп .

Как и в алгебре непрерывных переменных, в алгебре логики под функцией

понимается некий закон, или правило, по которому переменным из одного набо-

ра (множества) ставятся в соответствие переменные из другого набора (множест-

ва). В обычной алгебре аргумент и функция могут принимать целые и дробные,

положительные, отрицательные значения, и количество функций от одного аргу-

мента не ограничено. Например, у = х, у = х2, у = х3, у = sin х, у = log х и т. п.

14

Глава 1

В алгебре логики из-за того, что как у переменной, так и у функции может

быть только два значения, число последних конечно.

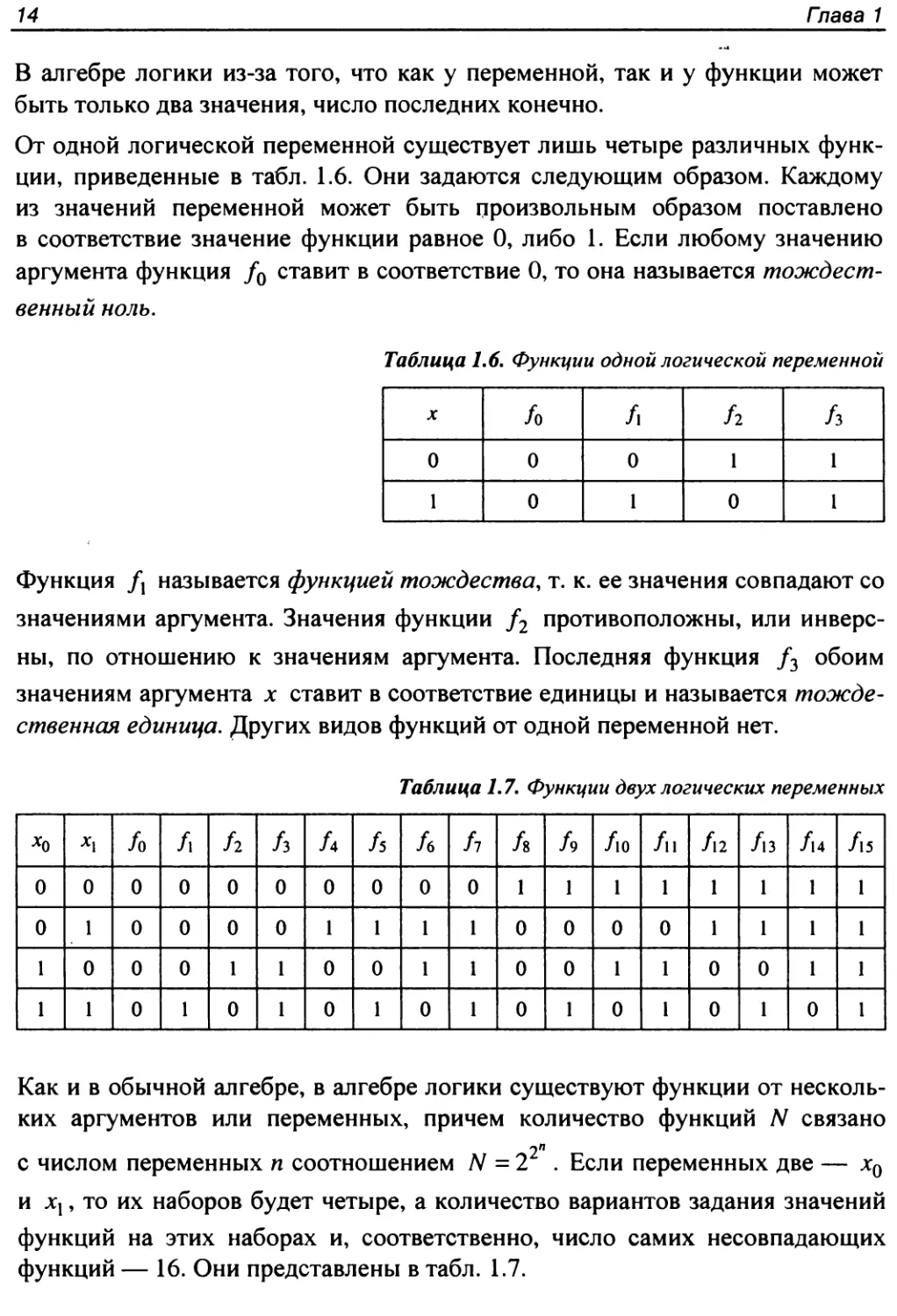

От одной логической переменной существует лишь четыре различных функ-

ции, приведенные в табл. 1.6. Они задаются следующим образом. Каждому

из значений переменной может быть произвольным образом поставлено

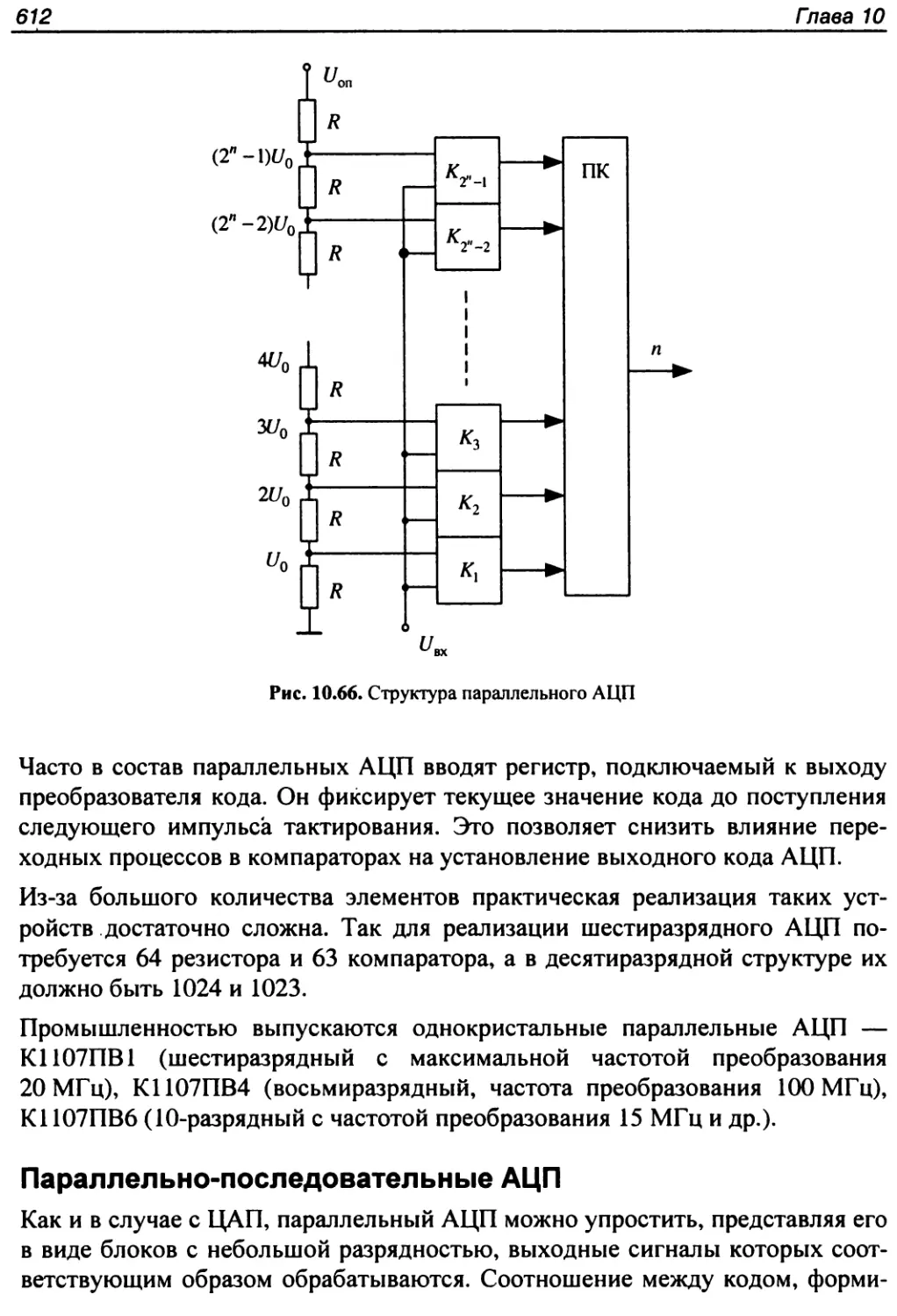

в соответствие значение функции равное 0, либо 1. Если любому значению

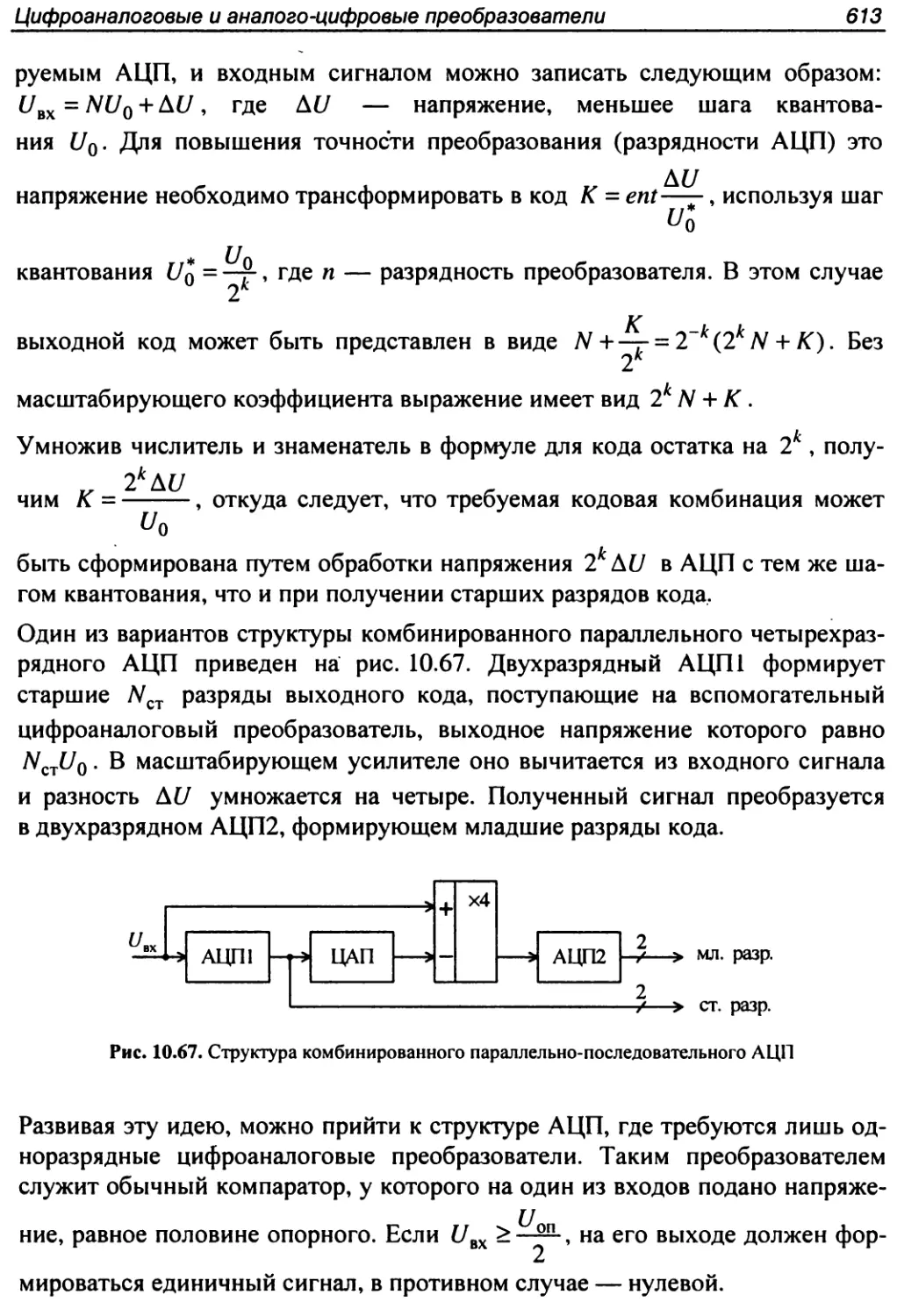

аргумента функция /0 ставит в соответствие 0, то она называется тождест-

венный ноль.

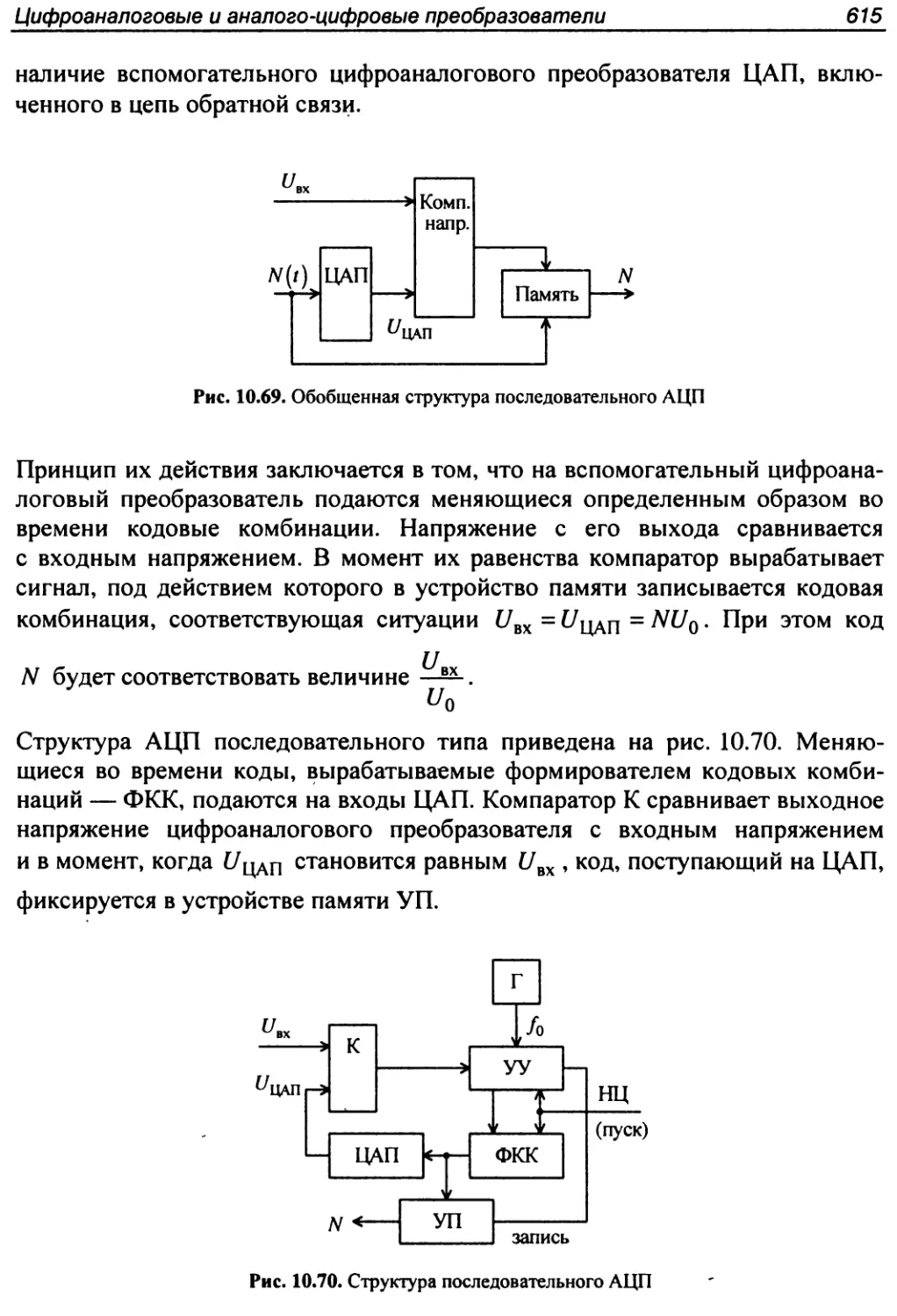

Таблица 1.6. Функции одной логической переменной

X /о А /2 /з

0 0 0 1 1

1 0 1 0 1

Функция fx называется функцией тождества, т. к. ее значения совпадают со

значениями аргумента. Значения функции /2 противоположны, или инверс-

ны, по отношению к значениям аргумента. Последняя функция /3 обоим

значениям аргумента х ставит в соответствие единицы и называется тожде-

ственная единица. Других видов функций от одной переменной нет.

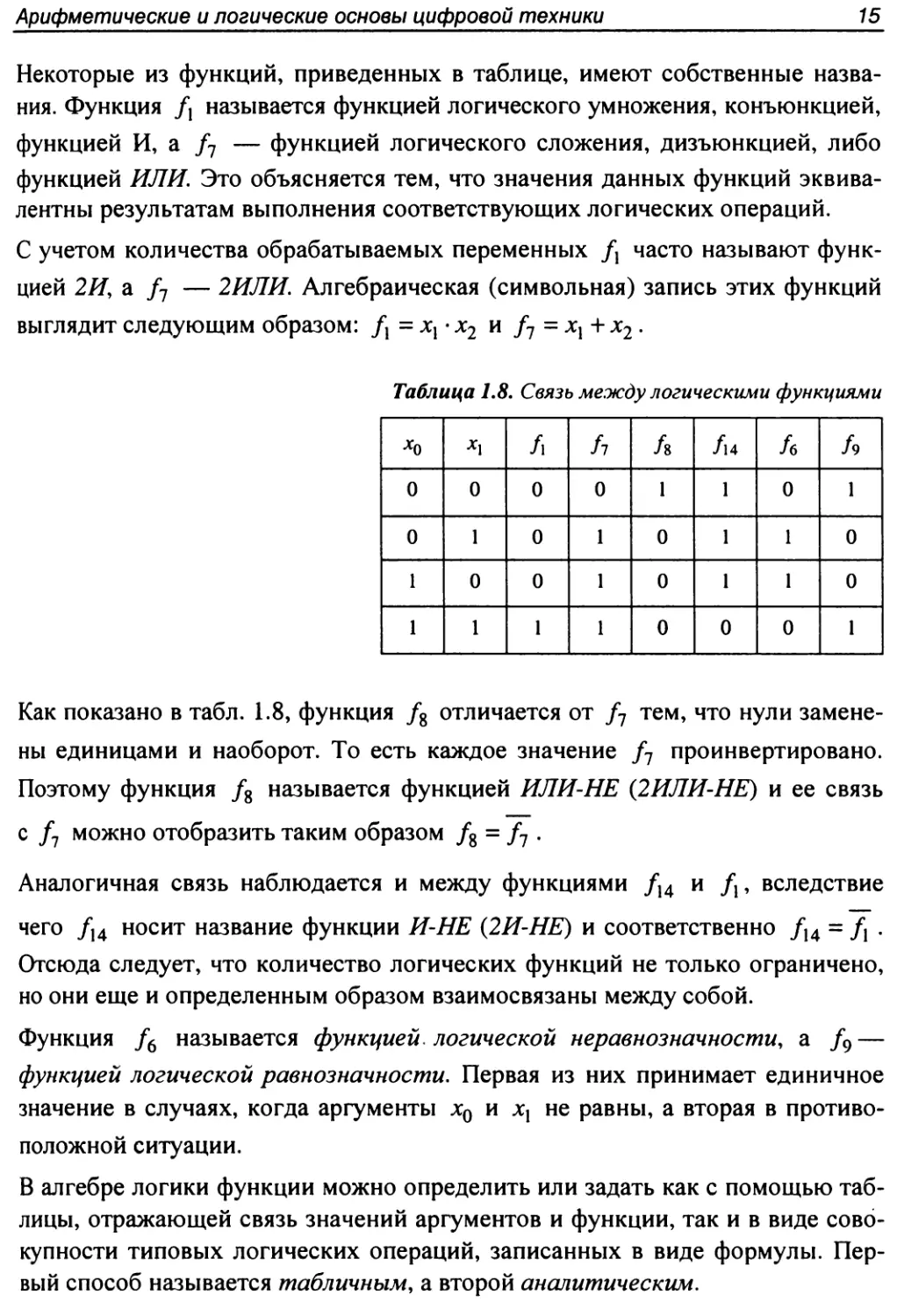

Таблица 1.7. Функции двух логических переменных

х0 х\ /о А А /з /4 /5 /б fl ft А /10 /11 /12 /13 /14 /15

0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Как и в обычной алгебре, в алгебре логики существуют функции от несколь-

ких аргументов или переменных, причем количество функций N связано

с числом переменных п соотношением /V = 2 . Если переменных две — х0

и хх, то их наборов будет четыре, а количество вариантов задания значений

функций на этих наборах и, соответственно, число самих несовпадающих

функций — 16. Они представлены в табл. 1.7.

Арифметические и логические основы цифровой техники 15

Некоторые из функций, приведенных в таблице, имеют собственные назва-

ния. Функция fx называется функцией логического умножения, конъюнкцией,

функцией И, а /7 — функцией логического сложения, дизъюнкцией, либо

функцией ИЛИ. Это объясняется тем, что значения данных функций эквива-

лентны результатам выполнения соответствующих логических операций.

С учетом количества обрабатываемых переменных fx часто называют функ-

цией 2И. а /7 — 2ИЛИ. Алгебраическая (символьная) запись этих функций

выглядит следующим образом: fx = хх • х2 и /7 = х\ + х2 •

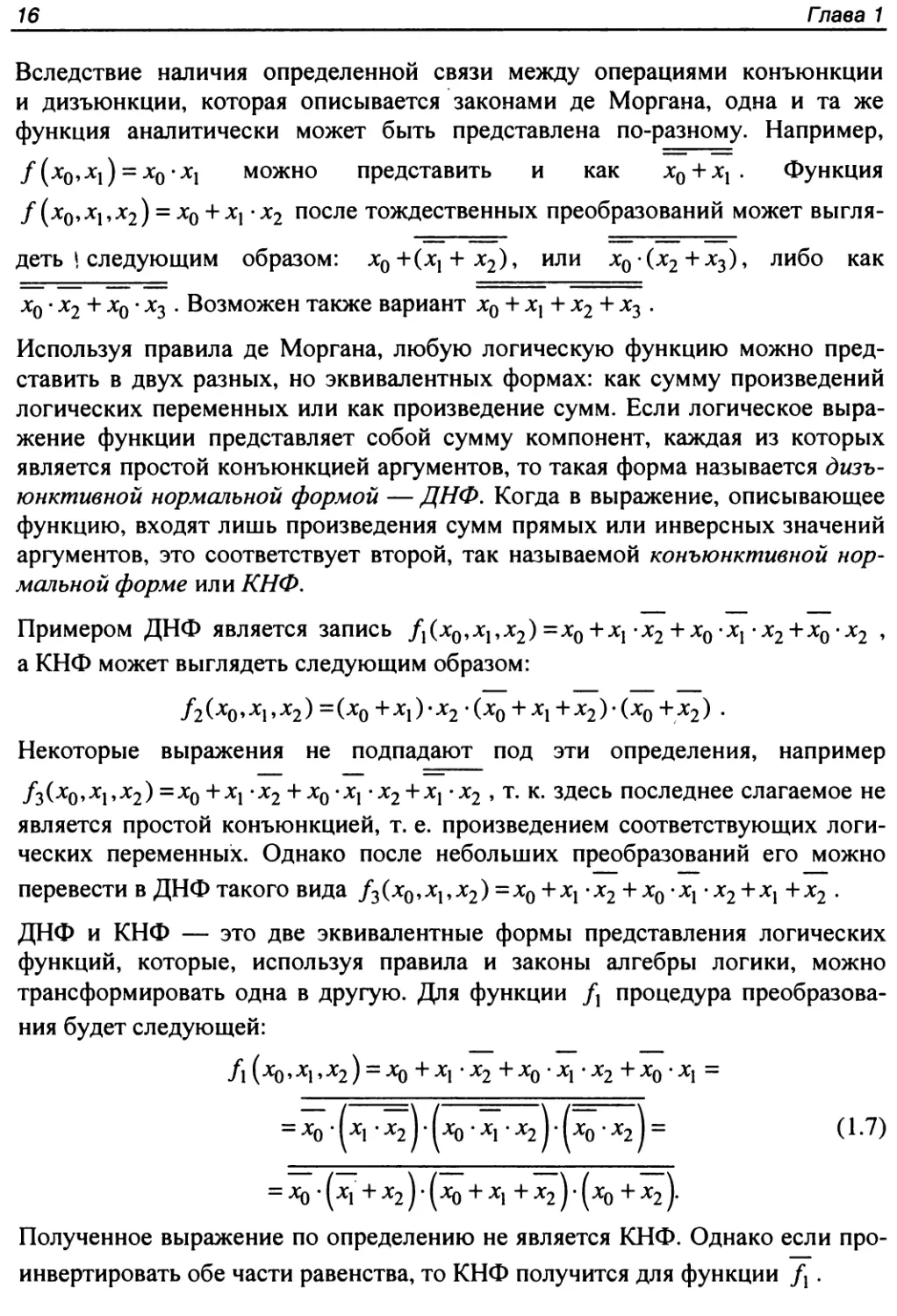

Таблица 1.8. Связь между логическими функциями

х0 х\ Л /7 Л /14 Л /9

0 0 0 0 1 1 0 1

0 1 0 1 0 1 1 0

1 0 0 1 0 1 1 0

1 1 1 1 0 0 0 1

Как показано в табл. 1.8, функция /8 отличается от /7 тем, что нули замене-

ны единицами и наоборот. То есть каждое значение /7 проинвертировано.

Поэтому функция /8 называется функцией ИЛИ-HE (2ИЛИ-НЕ) и ее связь

с /7 можно отобразить таким образом f% = /7 .

Аналогичная связь наблюдается и между функциями /14 и fx, вследствие

чего /14 носит название функции И-НЕ (2И-НЕ) и соответственно /14 = fx .

Отсюда следует, что количество логических функций не только ограничено,

но они еще и определенным образом взаимосвязаны между собой.

Функция /6 называется функцией, логической неравнозначности, а /9—

функцией логической равнозначности. Первая из них принимает единичное

значение в случаях, когда аргументы х0 и Xj не равны, а вторая в противо-

положной ситуации.

В алгебре логики функции можно определить или задать как с помощью таб-

лицы, отражающей связь значений аргументов и функции, так и в виде сово-

купности типовых логических операций, записанных в виде формулы. Пер-

вый способ называется табличным, а второй аналитическим.

16

Глава 1

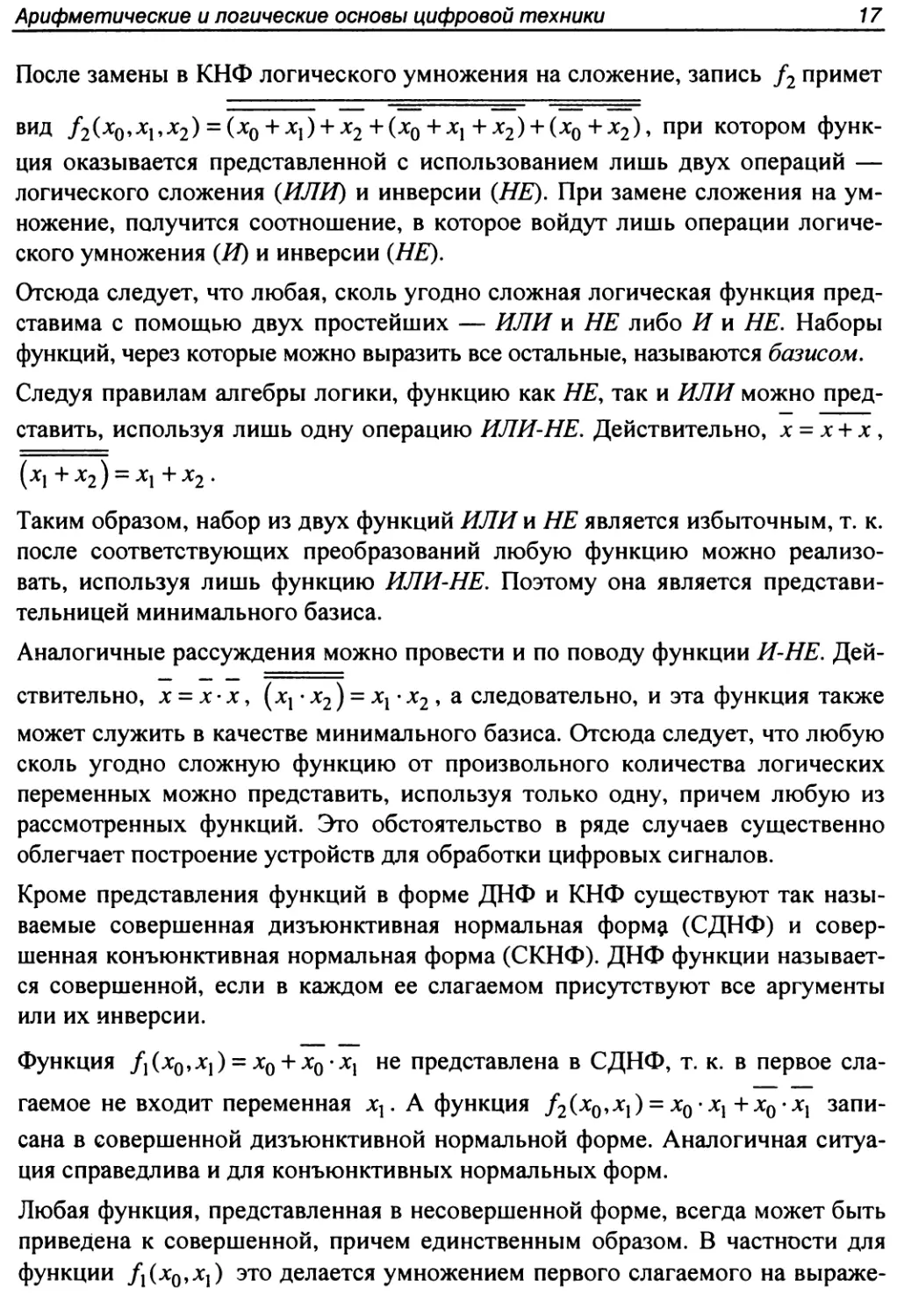

Вследствие наличия определенной связи между операциями конъюнкции

и дизъюнкции, которая описывается законами де Моргана, одна и та же

функция аналитически может быть представлена по-разному. Например,

f (х0’ Х1)= хо ’ х\ можно представить и как х0 + хх . Функция

У (хо,х1,х2)= хо + хгх2 после тождественных преобразований может выгля-

деть | следующим образом: х0 +(xj + х2), или х0 • (х2 + х3), либо как

х0 • х2 + х0 • х3 . Возможен также вариант х0 + Xj + х2 + х3 .

Используя правила де Моргана, любую логическую функцию можно пред-

ставить в двух разных, но эквивалентных формах: как сумму произведений

логических переменных или как произведение сумм. Если логическое выра-

жение функции представляет собой сумму компонент, каждая из которых

является простой конъюнкцией аргументов, то такая форма называется дизъ-

юнктивной нормальной формой — ДНФ. Когда в выражение, описывающее

функцию, входят лишь произведения сумм прямых или инверсных значений

аргументов, это соответствует второй, так называемой конъюнктивной нор-

мальной форме или КНФ.

Примером ДНФ является запись /1(х0,х1,х2)=х0-Ьх1 •х2-Ьхо х1 х2-Ьхо х2 ,

а КНФ может выглядеть следующим образом:

/2(х0,х1,х2)=(х0+х1)-х2-(х0 + х1+х2)-(х0+х2) .

Некоторые выражения не подпадают под эти определения, например

/3(хо,х!,х2) =х0 +xj •х2 + х0*х1 •х2+х1 -х2 , т. к. здесь последнее слагаемое не

является простой конъюнкцией, т. е. произведением соответствующих логи-

ческих переменных. Однако после небольших преобразований его можно

перевести в ДНФ такого вида /з(*0’х1’х2) =хо +хгх2 + хо ,хГх2+х1 +х2 •

ДНФ и КНФ — это две эквивалентные формы представления логических

функций, которые, используя правила и законы алгебры логики, можно

трансформировать одна в другую. Для функции J\ процедура преобразова-

ния будет следующей:

f\ (XfpX, ,х2) = Xq + хх • х2 + х0 • х( х2 + х0 • %! =

= х0 - (xj • х2 j-^Xo -х} -х2)-(х0 х2 j = (1.7)

= Хо-(х, +х2)-(хо+Х! + х2) • (х0 + х2).

Полученное выражение по определению не является КНФ. Однако если про-

инвертировать обе части равенства, то КНФ получится для функции fx.

Арифметические и логические основы цифровой техники

17

После замены в КНФ логического умножения на сложение, запись /2 примет

ВИД /2(ХО’Х1’Х2) =(хо+ х1) + х2+(Х0+х1 +%2) + (Х0+х2)’ ПРИ КОТОрОМ фуНК-

ция оказывается представленной с использованием лишь двух операций —

логического сложения (ИЛИ) и инверсии (НЕ). При замене сложения на ум-

ножение, получится соотношение, в которое войдут лишь операции логиче-

ского умножения (И) и инверсии (НЕ).

Отсюда следует, что любая, сколь угодно сложная логическая функция пред-

ставима с помощью двух простейших — ИЛИ и НЕ либо И и НЕ. Наборы

функций, через которые можно выразить все остальные, называются базисом.

Следуя правилам алгебры логики, функцию как НЕ. так и ИЛИ можно пред-

ставить, используя лишь одну операцию ИЛИ-HE. Действительно, х = х + х ,

(x1+x2) = *i+x2-

Таким образом, набор из двух функций ИЛИ и НЕ является избыточным, т. к.

после соответствующих преобразований любую функцию можно реализо-

вать, используя лишь функцию ИЛИ-HE. Поэтому она является представи-

тельницей минимального базиса.

Аналогичные рассуждения можно провести и по поводу функции И-НЕ. Дей-

ствительно, х = х • х, (xj • х2) = %! • х2 , а следовательно, и эта функция также

может служить в качестве минимального базиса. Отсюда следует, что любую

сколь угодно сложную функцию от произвольного количества логических

переменных можно представить, используя только одну, причем любую из

рассмотренных функций. Это обстоятельство в ряде случаев существенно

облегчает построение устройств для обработки цифровых сигналов.

Кроме представления функций в форме ДНФ и КНФ существуют так назы-

ваемые совершенная дизъюнктивная нормальная форма (СДНФ) и совер-

шенная конъюнктивная нормальная форма (СКНФ). ДНФ функции называет-

ся совершенной, если в каждом ее слагаемом присутствуют все аргументы

или их инверсии.

Функция /](хо,х1) = х0+ хо xi не представлена в СДНФ, т. к. в первое сла-

гаемое не входит переменная х}. А функция /2(х0,х1) = х0-х1 +xo*xi запи-

сана в совершенной дизъюнктивной нормальной форме. Аналогичная ситуа-

ция справедлива и для конъюнктивных нормальных форм.

Любая функция, представленная в несовершенной форме, всегда может быть

приведена к совершенной, причем единственным образом. В частности для

функции /Kx^Xj) это делается умножением первого слагаемого на вираже-

18

Глава 1

ние вида х + х = 1. Так как оно равно единице, то умножение на нее ничего

не изменит, но в итоге х, окажется представленной в виде СДНФ:

/|(ХО,Х1) = ХО + ХО-Х1 =ХО-(Х] +Х| j + X0'X| = Хо • Х| + Х0 • X, + Х0 X] .

Несмотря на то, что первый вариант функции выглядит проще, в ряде случа-

ев представление в форме СДНФ является необходимым, и, кроме того, при

алгебраическом описании функций, заданных в табличной форме, они авто-

матически приводятся к виду СДНФ.

Таблица 1.9. Табличное задание логической функции

Ло х, *2 У

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 1

Пусть некоторая функция у от трех переменных представлена в виде

табл. 1.9. Полное количество ее значений определяется числом переменных п

и будет равно 2" (в данном случае п = 3, 23 = 8). Для преобразования таб-

личной формы представления функции в алгебраическую выбирается строка,

где функция принимает единичное значение и записывается логическое про-

изведение всех переменных.

Те из них, которые принимают единичные значения, вводятся в соответст-

вующее произведение без инверсии, а равные нулю — с инверсией. Полу-

чившаяся при этом компонента называется конституентой единицы.

Далее эти компоненты логически суммируют. В итоге выражение для функции

будет иметь вид, соответствующий СДНФ: у = х0 • X] • х2 + х0 ’ xi ’ х2 + хо ’ Х1 ’ х2 •

Проверка правильности полученного результата может быть произве-

дена простым перебором значений переменных и вычислением функции.

Первое слагаемое, а значит, и вся функция, обращается в единицу, когда

Арифметические и логические основы цифровой техники 19

xQ = 1,jCj = 0,х2 = 0. Поэтому Xj ,х2 и входят в него с инверсиями, т. к. толь-

ко в таком случае хох1-х2=1ОО = 111 = 1. Аналогичным образом выгля-

дит ситуация для последних двух строк таблицы. На остальных наборах ни

одно из слагаемых в единицу не обращается, следовательно, функция будет

равна нулю.

Рассмотренную функцию можно представить и в конъюнктивной нормальной

форме — КНФ. В этом случае для каждого набора переменных, на котором

она обращается в ноль, записывают логическую сумму всех переменных. Ес-

ли значения переменных равны единице, то они должны входить туда с ин-

версией, а если нулю — то в прямом виде. Полученные суммы называются

конституентами нуля. Далее их логически перемножают. Для приведенной

ранее функции у запись в виде КНФ имеет вид, который одновременно

представляет собой и СКНФ:

У = (x0+Xj + х2)-(хо+х1 +х2)’(х0+х1 + Х2)Л,(х0+Х1 +х2)’(х0 + Х1 + х2^‘ (1-8)

Такое представление абсолютно эквивалентно предыдущему, но сложнее по

структуре из-за того, что на восьми наборах переменных функция лишь три

раза обращается в единицу и пять раз принимает нулевое значение. При ее

записи в виде СДНФ в выражение войдут три компоненты, а в форме СКНФ —

пять. Поэтому на практике часто используют ту форму представления, кото-

рая позволяет получить выражение минимальной сложности.

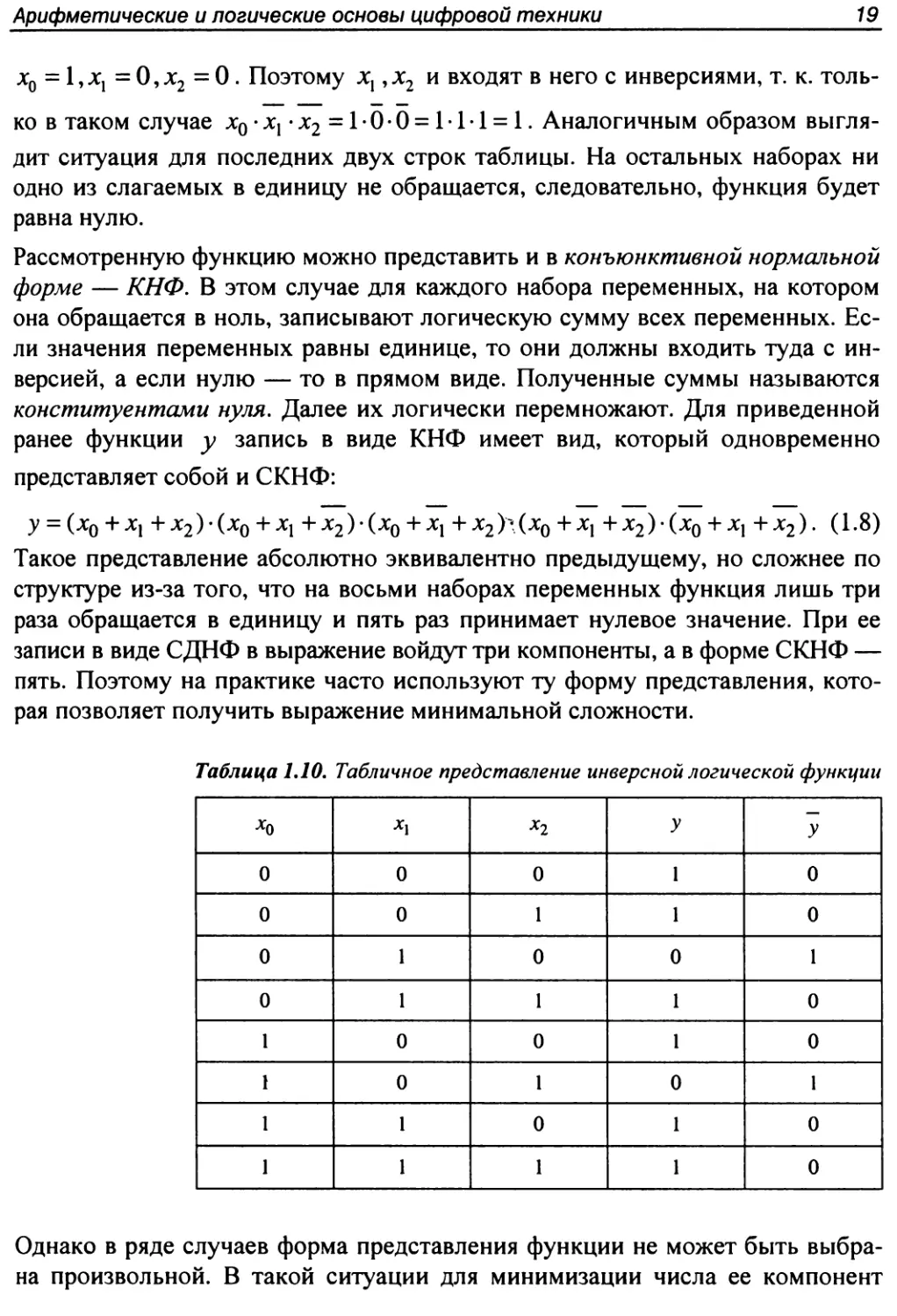

Таблица 1.10. Табличное представление инверсной логической функции

*0 *1 х2 У У

0 0 0 1 0

0 0 1 1 0

0 1 0 0 1

0 1 1 1 0

1 0 0 1 0

1 0 1 0 1

1 1 0 1 0

1 1 1 1 0

Однако в ряде случаев форма представления функции не может быть выбра-

на произвольной. В такой ситуации для минимизации числа ее компонент

20

Глава 1

используют следующий подход. Если требуется представление в форме

СДНФ, а количество единичных значений функции больше, чем нулевых, то

вводят новую функцию, инверсную по отношению к исходной (табл. 1.10).

Единичных значений у нее будет меньше, чем нулевых, и СДНФ окажется

проще. Для функции, представленной в данной таблице, при использовании

обычного подхода получим:

У = Хо • Xj • х2 + х0 • *1 • х2 + х0 ’ х\' х2 + х0 ’ х\' х2 + х0 * ХГ Л2 + х0 * ХГ х2 ’

а для инверсной функции выражение примет вид у = х0 • Xj • х2 + х0 • Xj • х2 .

Чтобы вернуться к исходной функции, достаточно проинвертировать обе

части последнего равенства у = х0 • хх • х2 + х0 • Xj • х2 . Хотя это и не СДНФ,

но данное выражение гораздо проще предыдущего, что в ряде случаев важ-

нее канонической формы представления.

Последнее связано с тем, что при разработке устройств, работающих с циф-

ровыми сигналами, их функционирование описывают в виде совокупности

логических функций, а затем реализуют с помощью электронных узлов. Чем

компактнее удается получить выражение для функции, тем проще аппаратно

реализовать соответствующую ей процедуру обработки.

В алгебре логики применяются специальные процедуры минимизации логи-

ческих функций, позволяющие в ряде случаев представить их с использова-

нием минимального количества логических операций. Некоторые функции

минимизировать, т. е. сократить количество входящих в их состав компонент,

нельзя, а для других это возможно и разными способами.

Пусть исходная функция представлена в ДНФ и имеет вид

у = х0 • Xj • х2 + х0 • Xj • х2 + х0 • Xj . Для ее преобразования можно воспользо-

ваться правилами и основными законами алгебры логики. Если из первых

двух слагаемых за скобки вынести произведение x0-Xj, то функция примет

вид у = х0-х1 -(х2+х2) + х0 *Xj . Так как сумма прямого и инверсного значе-

ний одной и той же переменной х2 равна единице, а умножение на единицу

оставляет результат неизменным, то

У = Х0 • Xj • (х2 + Х2) + Х0 • Xj = Х0 • Xj • 1 + Х0 • Xj = Xq ’ Xj + Xq * Xj .

В оставшемся выражении за скобки можно вынести х0, выражение в скобках

опять будет равно единице и в итоге у = х0 • хх = х0 • Xj = х0 • (xj + Xj) = х0.

То есть данная конкретная функция от трех переменных, ранее содержащая

три компоненты, будет равна х0.

Арифметические и логические основы цифровой техники

21

В ходе выполнения процедуры минимизации часть переменных исчезает.

Это, в частности, происходит при обработке пар слагаемых, представляющих

собой произведения переменных и отличающихся тем, что какая-либо пере-

менная входит в одно из слагаемых в прямом, а в другое — в инверсном ви-

де, причем все остальные компоненты слагаемых совпадают. В этом случае

из двух слагаемых получается одно с уменьшенным на единицу количеством

переменных.

Отсюда следует, что выражение х0 -х} х2 +хо ХГХ2 минимизировать мож-

но, а х0 • Xj • х2 + хо ’ ХГ х2 — нет. Если за скобки вынести х0, то в выражении

Xj • х2 + Xj • х2 число переменных не уменьшится.

Таким образом, для минимизации требуется просмотреть все компоненты,

входящие в состав функции, и попарно сгруппировать слагаемые, отличаю-

щиеся значениями лишь одной переменной. Затем вместо каждой из пар за-

писать выражение с уменьшенным на единицу числом переменных. Эта про-

цедура может повторяться несколько раз. В итоге форма представления

исходной функции будет содержать минимальное количество слагаемых и

переменных. Аналогичным образом проводится минимизация функций,

представленных в конъюнктивной форме.

Формализовать этот процесс можно, используя так называемые карты Кар-

но. Данный прием особенно удобен, если число аргументов логической

функции не превышает четырех-пяти. Для применения карт Карно исходная

функция должна быть представлена в совершенной дизъюнктивной нормаль-

ной форме — СДНФ, т. е. в виде сумм логических произведений, куда входят

все комбинации переменных.

Пусть некоторая функция fx от трех переменных представлена табл. 1.11.

В виде СДНФ она содержит пять слагаемых и выглядит следующим образом:

/] = х0 • Xj • х2 + х0 • Xj • х2 + х0 • Xj • х2 + х0 • Xj • х2 + х0 • Xj • х2 . Ее можно миними-

зировать аналитически, т. к. в данном выражении существуют пары слагае-

мых, в которых меняется значение лишь одной переменной. Это первое и

третье, четвертое и пятое. Проделав необходимые действия, получим

/1 = х! ‘ Х2 + Хо • Xj • Х2 + Хо • Х2 .

Однако для рассматриваемой функции процесс минимизации можно про-

должить дальше. Если в исходном выражении рассмотреть первое и второе

слагаемые, то можно сделать вывод, что обрабатывая их, удалось бы сокра-

тить переменную Xj, но в преобразованном выражении первое слагаемое уже

изменено и данная процедура формально не выполнима.

22

Глава 1

Таблица 1.11. Представление логической функции для минимизации

с помощью карт Карно

х0 *1 х2 V1

0 0 0 1

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 1

1 1 0 0

1 1 1 1

В то же время в соответствии с законами алгебры логики, в частности,

х+х=х, в любое выражение можно без изменения результата логически

прибавлять любые имеющиеся там слагаемые. Следовательно, если в перво-

начальную форму представления функции прибавить х0 • XJ • х2 , то после об-

работки этой компоненты со вторым слагаемым, получится х0-х2 . Выраже-

ние для fx примет вид Xj • х2 + х0 • х2 + х0 • х2 , соответствующий минимальной

дизъюнктивной форме представления рассматриваемой функции. Объедине-

ние слагаемых с одновременным уменьшением числа входящих в их состав

переменных часто называется склеиванием. В целом аналитическая процеду-

ра минимизации оказывается достаточно длительной даже для простых

функций.

Карта Карно представляет собой таблицу, количество клеток или ячеек в ко-

торой К равно числу значений, принимаемых функцией, которое связано

с количеством переменных п соотношением К = 2п. Для функции от трех

переменных карта Карно содержит восемь ячеек. Им приписываются все

возможные значения комбинаций аргументов. Совокупность аргументов

в каждой комбинации разбивается на две группы. У функции fx в качестве

одного из возможных вариантов разбиения в одну группу можно объединить

х0, Xj и отдельно рассматривать х2 либо сгруппировать х0, х2, a Xj пред-

ставлять отдельно. Возможны и иные варианты.

Столбцы обозначаются комбинациями логических произведений прямых

и инверсных значений соответствующих переменных группы. Для первого

случая разбиения они будут такими: х0 • хх, х0 • Xj, х0 • Xj, х0 • Xj.

Арифметические и логические основы цифровой техники

23

Комбинации аргументов, используемые в обозначении соседних столбцов,

должны отличаться лишь в одном разряде. То есть х0 %1 и х0-Х] , но не

х0 • и х0 • Xj , т. к. здесь меняют значения сразу обе переменные. Верхнюю

строку можно обозначить х2, а нижнюю х2 , однако возможен и вариант х2 , х2.

В итоге таблица будет иметь вид, представленный на рис. 1.1.

fl Л^-Х! Х0-Х! Xq-X! Xq-X!

Х2

1

Рис. 1.1. Форма представления карты Карно для логической функции от трех переменных

Далее карту Карно заполняют значениями функции, которые она принимает

на соответствующих наборах переменных. Если аргумент в наборе равен

единице, то в обозначение строки или столбца он входит без инверсии, а если

нулю — то с инверсией. Таким образом, для рассматриваемой функции

/1(О,О,О) = /1(хо,х1,х2) = 1> /1(О,О,1) = /1(хо,х],х2) = О и т. д. (рис. 1.2). Про-

цедура минимизации заключается в том, что расположенные рядом единицы

охватываются так называемыми контурами склейки, причем, как показано на

рис. 1.2, некоторые из единиц могут входить сразу в несколько контуров,

а некоторые ни в один. Количество ячеек в контуре должно быть равно од-

ному из чисел ряда 1, 2, 4, 8, 16 ... 2* .

Рис. 1.2. Карта Карно для логической функции /j

24

Глава 1

Из табл. 1.11 следует, что функция J\ принимает единичное значение, когда

х0 =хх =х2 =1, т. е. на наборе хоххх2, а также при х0 = х2 =1, X] =0. Таким

образом, в выражение для функции будут входить компоненты

х0Х]Х2 + х0х(х2 и при их склеивании исчезнет переменная х,.

Процедура минимизации с использованием карт Карно проводится следую-

щим образом. Проверяются переменные, обозначающие строки и столбцы

в контурах склейки, и если они меняют свое значение, то их не вносят в за-

пись соответствующей компоненты функции. Рассмотрение верхнего конту-

ра дает произведение хох2, т. к. X] меняет свое значение. Из следующего

контура получится выражение х1-х2.

Оставшаяся единица соответствует комбинации переменных х0Х]Х2 . Таким

образом, минимизированное выражение для функции будет иметь вид

/j = х0 х2+Х| х2+ х0 X] х2 , совпадающий с полученным в ходе первого

этапа ее минимизации аналитическим способом. Однако там добавление

вспомогательной компоненты, которая не изменила значения функции, по-

зволило устранить еще одну переменную и окончательное выражение полу-

чилось проще.

Аналогичный подход возможен и при использовании карт Карно. Для этого, как

показано на рис. 1.3, вводятся дополнительные контуры, охватывающие уже

склеенные единицы. Если ввести такой контур для нижней строки, то вместо

х0Х| х2 получится х0 • х2 и функция примет вид /] = х0 • х2 + х0 • х2 + х0 • х(,

полностью совпадающий с результатом аналитической минимизации.

Контуры склейки можно выбрать и как показано на рис. 1.4. В этом случае

выражение для функции станет таким fx = х0 • х2 + х0 • х( + х0 • х2 . Оно не сов-

Арифметические и логические основы цифровой техники

25

падает с предыдущим, но также является минимальной дизъюнктивной фор-

мой представления той же функции. Отсюда следует, что минимальных форм

может быть несколько.

Если штриховой линией охватить дополнительным контуром уже склеенные

единицы, то структура выражения fx = х0 • х2 + х0 * + хо * х2 + ХГ х2 » описы-

вающего функцию, усложнится, хотя сама функция не изменится. Поэтому

число контуров обычно стремятся выбрать минимальным.

Для некоторой функции /2 картина распределения ее значений в карте

Карно может выглядеть следующим образом (рис. 1.5). В этом случае

формируются два горизонтальных контура склейки, а нижняя правая

единица остается одна. Выражение для функции примет вид:

/2 = *ох2 +хох2 + хох1 х2 • В нем первые два слагаемых отличаются значени-

ем переменной х2 и полученное соотношение можно аналитически мини-

мизировать до /2 = х0 + хох1 х2 •

26

Глава 1

Эта же процедура реализуется и с использованием карты Карно, для чего по-

требуется образовать контур склейки, включающий в себя четыре рядом рас-

положенных единицы (рис. 1.6), и, проанализировав, какие из аргументов не

меняются, оставить только их в выражении для функции. В данном случае

неизменной остается лишь переменная х0, которая и войдет в окончательное

выражение.

Как уже отмечалось, склеивать расположенные соответствующим образом

единицы допускается, если их количество кратно степени двойки, т. е. 2, 4, 8,

16 и т. д.

Если сравнить комбинации аргументов для крайних клеток одной строки

карты Карно (рис. 1.6), то можно убедиться, что они также отличаются лишь

значением одной из переменных. Для левой нижней клетки комбинация име-

ет вид х0х1х2 ’ а Для правой — x0XjX2 • Так как эти компоненты входят в вы-

ражение, описывающее ДНФ функции, то в ходе дальнейшей минимизации

должно остаться произведение х}х2 . Таким образом, форма представления

рассматриваемой функции может быть дополнительно упрощена до вида

f2=x0 + xlx2-

Карта Карно является как бы разверткой объемной фигуры, поэтому можно

считать, что ее крайние клетки располагаются рядом и комбинации соответ-

ствующих переменных отличаются значением лишь одной из них. Это по-

зволяет вводить контуры склейки, охватывающие и крайние группы ячеек.

На карте такой контур условно представляется как разорванный. Его введе-

ние для приведенного примера трансформирует компоненту х0х}х2 в ххх2 .

Арифметические и логические основы цифровой техники

27

Как уже отмечалось, рассмотренная картина чередования переменных для

обозначения строк и столбцов не является единственно возможной. Альтер-

нативный вариант карты Карно для рассматриваемой функции выглядит, как

показано на рис. 1.7. Единицы и нули здёсь будут располагаться по-другому,

иными станут контуры склейки, но результат минимизации окажется тем же —

/2 =ХО + Х,Х2.

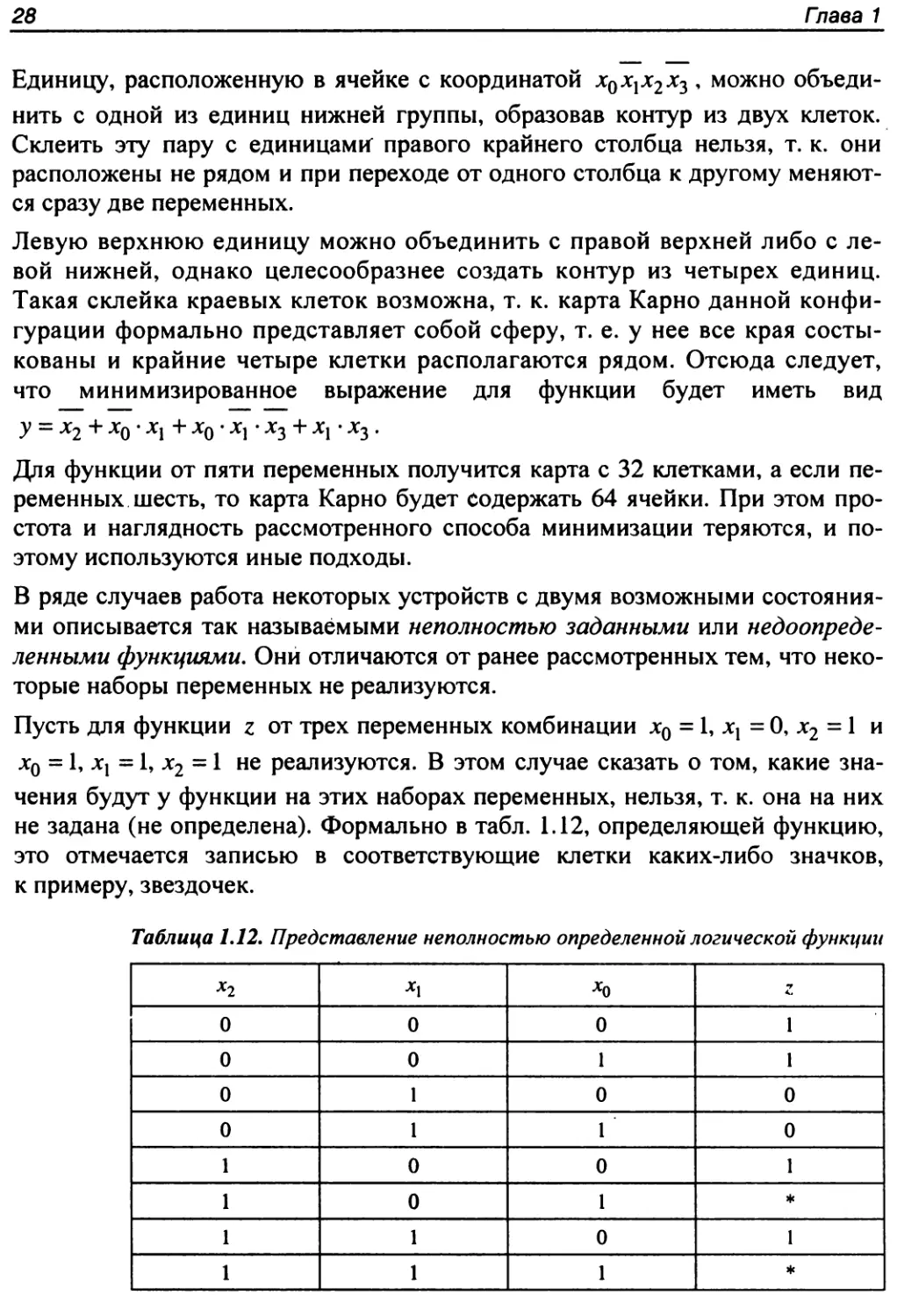

Пусть имеется некоторая функция у от четырех переменных и карта Карно

для нее выглядит следующим образом (рис. 1.8). Здесь одним контуром мож-

но охватить восемь единиц, находящихся в нижней части карты, а вторым —

четыре единицы в правом столбце.

Рис. 1.8. Карта Карно для функции у от четырех переменных

28

Глава 1

Единицу, расположенную в ячейке с координатой xojqx2x3 ’ можно объеди-

нить с одной из единиц нижней группы, образовав контур из двух клеток.

Склеить эту пару с единицами правого крайнего столбца нельзя, т. к. они

расположены не рядом и при переходе от одного столбца к другому меняют-

ся сразу две переменных.

Левую верхнюю единицу можно объединить с правой верхней либо с ле-

вой нижней, однако целесообразнее создать контур из четырех единиц.

Такая склейка краевых клеток возможна, т. к. карта Карно данной конфи-

гурации формально представляет собой сферу, т. е. у нее все края состы-

кованы и крайние четыре клетки располагаются рядом. Отсюда следует,

что минимизированное выражение для функции будет иметь вид

У = х2+хо*х1 + хо’хГхз + хГхз-

Для функции от пяти переменных получится карта с 32 клетками, а если пе-

ременных шесть, то карта Карно будет содержать 64 ячейки. При этом про-

стота и наглядность рассмотренного способа минимизации теряются, и по-

этому используются иные подходы.

В ряде случаев работа некоторых устройств с двумя возможными состояния-

ми описывается так называемыми неполностью заданными или недоопреде-

ленными функциями. Они отличаются от ранее рассмотренных тем, что неко-

торые наборы переменных не реализуются.

Пусть для функции z от трех переменных комбинации х0 = 1, Xj = 0, х2 = 1 и

х0 = 1, jq = 1, х2 = 1 не реализуются. В этом случае сказать о том, какие зна-

чения будут у функции на этих наборах переменных, нельзя, т. к. она на них

не задана (не определена). Формально в табл. 1.12, определяющей функцию,

это отмечается записью в соответствующие клетки каких-либо значков,

к примеру, звездочек.

Таблица 1.12. Представление неполностью определенной логической функции

*1 *1 *0 Z

0 0 0 1

0 0 1 1

0 1 0 0

0 1 1 0

1 0 0 1

1 0 1 *

1 1 0 1

1 1 1 *

Арифметические и логические основы цифровой техники

29

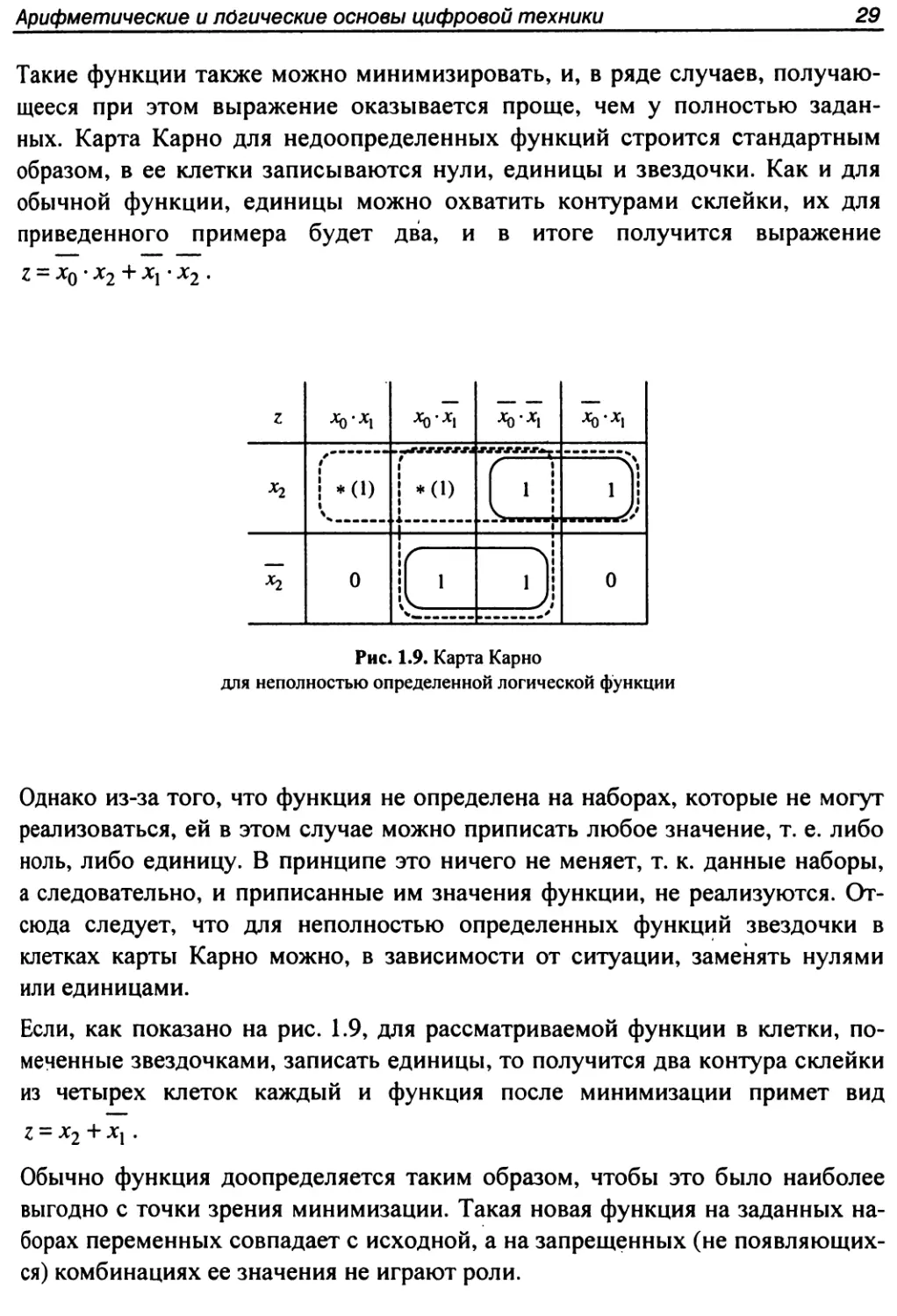

Такие функции также можно минимизировать, и, в ряде случаев, получаю-

щееся при этом выражение оказывается проще, чем у полностью задан-

ных. Карта Карно для недоопределенных функций строится стандартным

образом, в ее клетки записываются нули, единицы и звездочки. Как и для

обычной функции, единицы можно охватить контурами склейки, их для

приведенного примера будет два, и в итоге получится выражение

Z = X0-X2+Xl-X2.

для неполностью определенной логической функции

Однако из-за того, что функция не определена на наборах, которые не могут

реализоваться, ей в этом случае можно приписать любое значение, т. е. либо

ноль, либо единицу. В принципе это ничего не меняет, т. к. данные наборы,

а следовательно, и приписанные им значения функции, не реализуются. От-

сюда следует, что для неполностью определенных функций звездочки в

клетках карты Карно можно, в зависимости от ситуации, заменять нулями

или единицами.

Если, как показано на рис. 1.9, для рассматриваемой функции в клетки, по-

меченные звездочками, записать единицы, то получится два контура склейки

из четырех клеток каждый и функция после минимизации примет вид

Z = х2 + X] .

Обычно функция доопределяется таким образом, чтобы это было наиболее

выгодно с точки зрения минимизации. Такая новая функция на заданных на-

борах переменных совпадает с исходной, а на запрещенных (не появляющих-

ся) комбинациях ее значения не играют роли.

30

Глава 1

Контрольные вопросы

1. В чем различия позиционных и непозиционных систем счисления?

2. Сколько разрядов содержит двоичный код числа 100?

3. Какое из чисел больше — 1010, записанное в двоичной системе счисле-

ния, или же число А — в шестнадцатеричной?

4. Как выглядит представление числа 11 в пятеричной системе счисления?

5. Сколько ячеек содержит карта Карно для функции от двух переменных?

6. Может ли число ячеек в контуре склейки быть равным 6?

7. Какое значение, 0 или 1 можно приписать функции на отсутствующем на-

боре переменных?

8. Какое минимальное количество слагаемых может после минимизации

входить в выражение для логической функции?

Глава 2

Схемотехника цифровых

логических элементов

2.1. Принципы построения

логических элементов

Основная особенность логических элементов состоит в том, что они предна-

значены для работы с цифровыми сигналами, которые могут принимать лишь

два отличающихся друг от друга значения уровня напряжения или тока.

Обычно один из них близок к нулю и считается низким, а другой определяет-

ся напряжением питания и является высоким.

Низкий логический уровень обычно называют уровнем логического нуля,

а высокому логическому уровню приписывают значение логической единицы.

Так принято, хотя их можно называть ”Н" и "В", либо по-английски "L" (low) и ”Н"

(high), либо по-иному. С этой точки зрения такие электрические сигналы можно

рассматривать как некоторые переменные, принимающие лишь два значения.

Любой сигнал служит для передачи информации или сам является ее источ-

ником. В аналоговом сигнале S(f) (рис. 2.1) информация содержится в теку-

щем значении его уровня, т. е. любое изменение величины S(t) от любых

причин будет восприниматься как изменение сигнала и представляемой им

информации.

При наличии помехи в момент времени t2 зафиксируется значение сигнала

SA(r2), а не его истинная величина S(Z2). Это обстоятельство приводит

к невысокой помехоустойчивости и помехозащищенности аналоговых сис-

тем, так как воздействие помех искажает сигнал и содержащуюся в нем ин-

формацию.

Особенность систем, использующих цифровые сигналы, в том, что конкрет-

ные значения их уровней в первом приближении не играют роли, глав-

ное, чтобы эти уровни отличались друг от друга (рис. 2.2). Таким образом,

32

Гпава 2

при аналоговом подходе представленные здесь сигналы будут разными, а при

цифровом они неразличимы, что и обусловливает высокую помехоустойчи-

вость цифровых устройств.

Рис. 2.1. Пример представления непрерывного аналогового сигнала

V

В

U к

н

t

Рис. 2.2. Пример представления цифрового сигнала

То обстоятельство, что у цифровых сигналов только два значения уровней —

низкий и высокий (логический ноль и логическая единица), позволяет

использовать для описания работы цифровых устройств аппарат Булевой ал-

гебры или алгебры логики.

Первичная обработка цифровых сигналов производится в устройствах, кото-

рые называются логическими элементами. Они реализуют простейшие логи-

Схемотехника цифровых логических элементов

33

ческие операции над цифровыми сигналами, к которым относятся конъюнк-

ция (И), дизъюнкция {ИЛИ), отрицание {НЕ) и другие. Такие же названия

носят и соответствующие логические элементы.

В аналоговых электронных устройствах, например, усилителях, при измене-

нии входного сигнала выходной меняется пропорционально ему. Цифровые

устройства конструируются на тех же элементах, что и аналоговые, но они не

должны реагировать на изменения управляющих сигналов в определенных

пределах, т. е. напряжения, меняющиеся в пределах заштрихованных облас-

тей (рис. 2.3), должны восприниматься как уровни логического нуля и единицы.

Рис. 2.3. Возможные области изменений уровня цифрового сигнала

Для создания логических элементов, имеющих два различимых состояния,

можно использовать механические переключатели, электромагнитные реле,

электровакуумные и полупроводниковые приборы и, в частности, диоды.

Диод представляет собой прибор, обладающий разной проводимостью в за-

висимости от полярности приложенного к его электродам напряжения.

На принципиальных схемах он обозначается, как показано на рис. 2.4. Один

из электродов диода называется катодом, а другой анодом. Зависимость то-

ка, протекающего через диод, от приложенного напряжения — волыпампер-

ная характеристика имеет вид, представленный на рис. 2.5.

34

Гпава 2

Рис. 2.4. Условное обозначение диода на принципиальных схемах

Рис. 2.5. Вольтамперная характеристика полупроводникового диода

Когда к аноду подключается положительный, а к катоду отрицательный по-

люс внешнего источника напряжения, то при небольшой его величине через

диод протекает значительный ток, который, как и напряжение такой поляр-

ности, называется прямым. В широком диапазоне изменения прямых токов

напряжение на диоде остается практически неизменным и для кремниевых

структур составляет порядка 0,74-0,8 В. Условно можно считать, что при та-

ком напряжении диод начинает проводить прямой ток.

При смене полярности происходит запирание диода, и ток через него практи-

чески прекращается. Реально величина обратного тока для диодов, исполь-

зуемых в цифровых устройствах, составляет единицы-десятки микроампер.

С ростом обратного напряжения обратный ток диода остается практически

неизменным вплоть до электрического пробоя, при котором происходит его

резкое возрастание. Электрический пробой является обратимым, т. е. при

снижении обратного напряжения до величины меньшей пробивного, свойст-

ва диода восстанавливаются. Однако при пробое значительно увеличивается

мощность, рассеиваемая на диодной структуре, и если не принять специаль-

Схемотехника цифровых логических элементов

35

ных мер, то электрический пробой может перейти в необратимый тепловой

пробой и диод выйдет из строя.

Пусть на основе двух диодов и резистора, подключенного к источнику пита-

ния с напряжением +Е, собрана схема, представленная на рис. 2.6.

Вх1 Вх2 Вых

О О

О Е

Е О

Е Е

0,7

0,7

0,7

Е

0 0

0 1

1 0

1 1

0

0

О

1

Рис. 2.6. Схема логического элемента И на диодах

Проанализируем ситуацию на ее выходе, предполагая, что входными являют-

ся сигналы с уровнями нуля и напряжения питания.

Формально можно считать, что на входы Вх1 и Вх2 такой схемы поступают

логические переменные х0 и хх, а на выходе формируется некоторая функ-

ция у(х0>*1)-

Предположим, что напряжению, близкому к нулю, соответствует значение

логического нуля входных переменных и функции, а напряжению, близкому

кЕ — логической единицы. Если на оба входа подать нулевой сигнал, то че-

рез открытые при такой полярности напряжения диоды по резистору от ис-

точника питания потечет ток, и уровень напряжения на выходе составит по-

рядка 0,7 В, что много меньше напряжения источника питания и позволяет

приписать такому сигналу значение логического нуля. То есть в данной си-

туации значение функции у при х0 = х1 = 0 также будет равно логическому

нулю.

Если на первый вход (Вх1) подать нулевое напряжение, а второй (Вх2) со-

единить с положительным полюсом источника питания, то связанный с ним

диод закроется, но первый останется в проводящем состоянии и выходное

36

Гпава 2

напряжение, как и в предыдущем случае, будет близко к нулю. Следователь-

но, и значение функции у останется нулевым. Если входные сигналы поме-

нять местами, то ситуация на выходе не изменится, так как один из диодов

сохранит открытое состояние.

И лишь когда на оба входа поступит напряжение +£, соответствующее логи-

ческой единице, то диоды закроются и на выходе схемы появится сигнал вы-

сокого уровня, который можно трактовать, как логическую единицу. Рас-

смотренная ситуация приведена в таблице на рис. 2.6 рядом со схемой

устройства. Она описывает процедуру реализации конъюнкции или логиче-

ской функции И над двумя переменными, поэтому данная схема является

простейшим логическим элементом И, который часто называется 2И по чис-

лу обрабатываемых переменных.

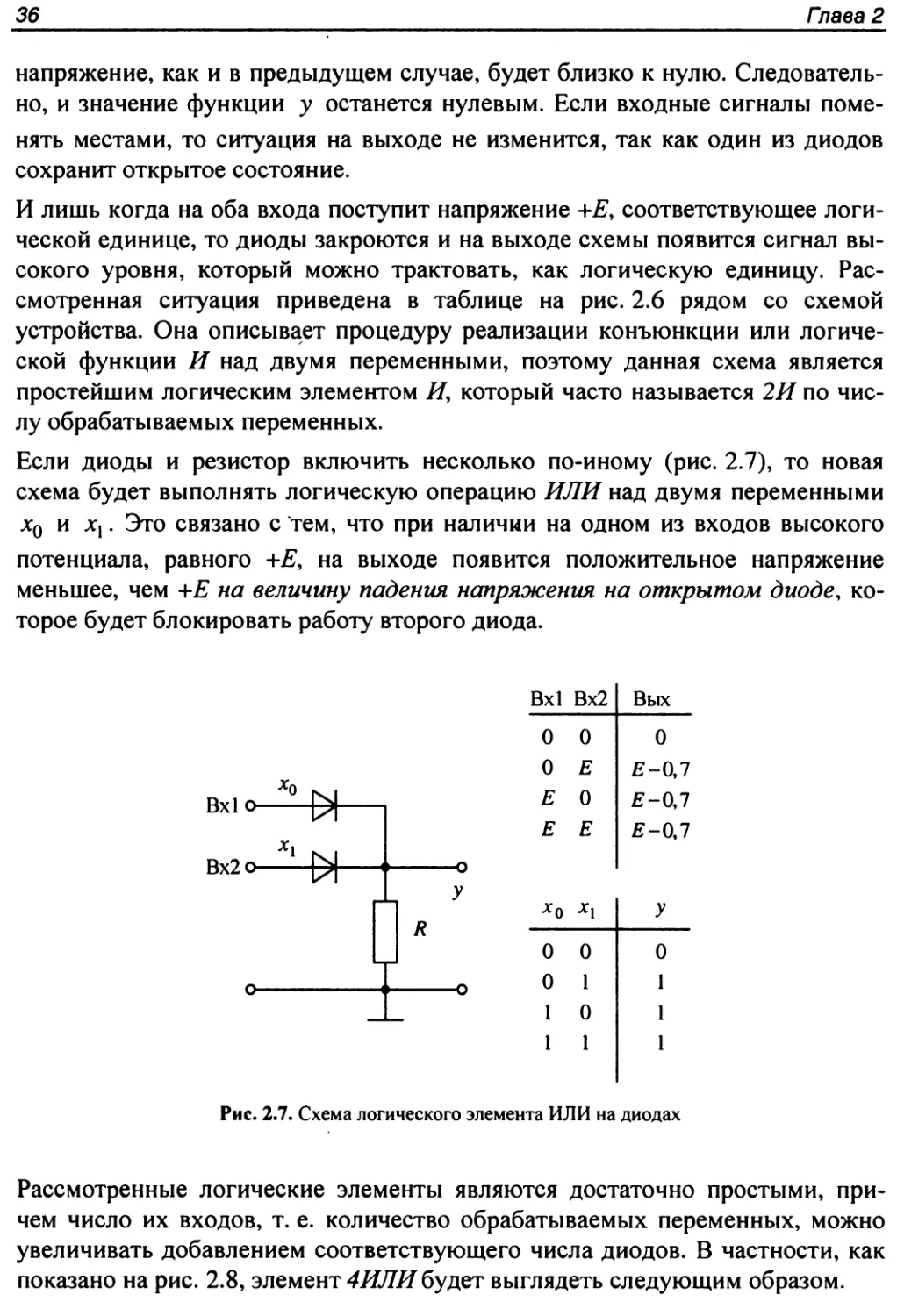

Если диоды и резистор включить несколько по-иному (рис. 2.7), то новая

схема будет выполнять логическую операцию ИЛИ над двумя переменными

х0 и . Это связано с тем, что при наличии на одном из входов высокого

потенциала, равного +Е, на выходе появится положительное напряжение

меньшее, чем +Е на величину падения напряжения на открытом диоде, ко-

торое будет блокировать работу второго диода.

Вх1 Вх2 Вых

0 0 0

0 Е

Е 0

Е Е

£-0,7

£-0,7

£-0,7

*о *1 У

0 0 0

0 1 1

1 0 1

1 1 1

Рис. 2.7. Схема логического элемента ИЛИ на диодах

Рассмотренные логические элементы являются достаточно простыми, при-

чем число их входов, т. е. количество обрабатываемых переменных, можно

увеличивать добавлением соответствующего числа диодов. В частности, как

показано на рис. 2.8, элемент 4ИЛИ будет выглядеть следующим образом.

Схемотехника цифровых логических элементов

37.

Рис. 2.8. Схема логического элемента 4ИЛИ

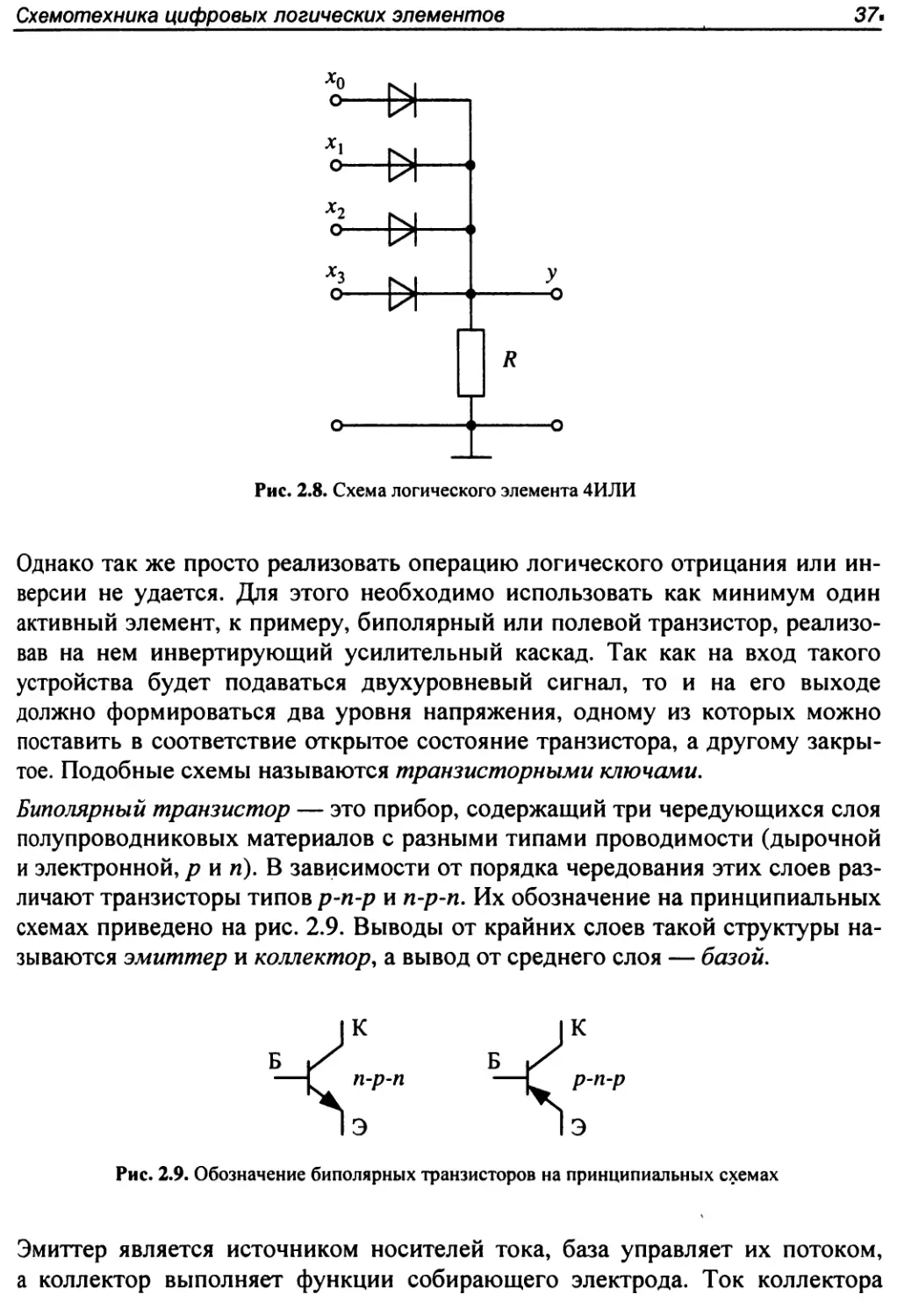

Однако так же просто реализовать операцию логического отрицания или ин-

версии не удается. Для этого необходимо использовать как минимум один

активный элемент, к примеру, биполярный или полевой транзистор, реализо-

вав на нем инвертирующий усилительный каскад. Так как на вход такого

устройства будет подаваться двухуровневый сигнал, то и на его выходе

должно формироваться два уровня напряжения, одному из которых можно

поставить в соответствие открытое состояние транзистора, а другому закры-

тое. Подобные схемы называются транзисторными ключами.

Биполярный транзистор — это прибор, содержащий три чередующихся слоя

полупроводниковых материалов с разными типами проводимости (дырочной

и электронной, р и и). В зависимости от порядка чередования этих слоев раз-

личают транзисторы типов р-п-р и п-р-п. Их обозначение на принципиальных

схемах приведено на рис. 2.9. Выводы от крайних слоев такой структуры на-

зываются эмиттер и коллектор, а вывод от среднего слоя — базой.

Рис. 2.9. Обозначение биполярных транзисторов на принципиальных схемах

Эмиттер является источником носителей тока, база управляет их потоком,

а коллектор выполняет функции собирающего электрода. Ток коллектора

38

Гпава 2

оказывается больше тока управления, который протекает по базовой цепи.

С этой точки зрения можно считать, что транзистор усиливает управляющий

сигнал по току, и этот коэффициент усиления обозначается 0 = —.

В схемах различных устройств транзистор включается таким образом, что

один из его электродов является общим для входной и выходной цепей, дру-

гой соединен со входом устройства, а третий — с его выходом. Наиболее

часто используется схема включения с общим эмиттером, которая выглядит,

как показано на рис. 2.10.

Рис. 2.10. Включение транзистора по схеме с общим эмиттером

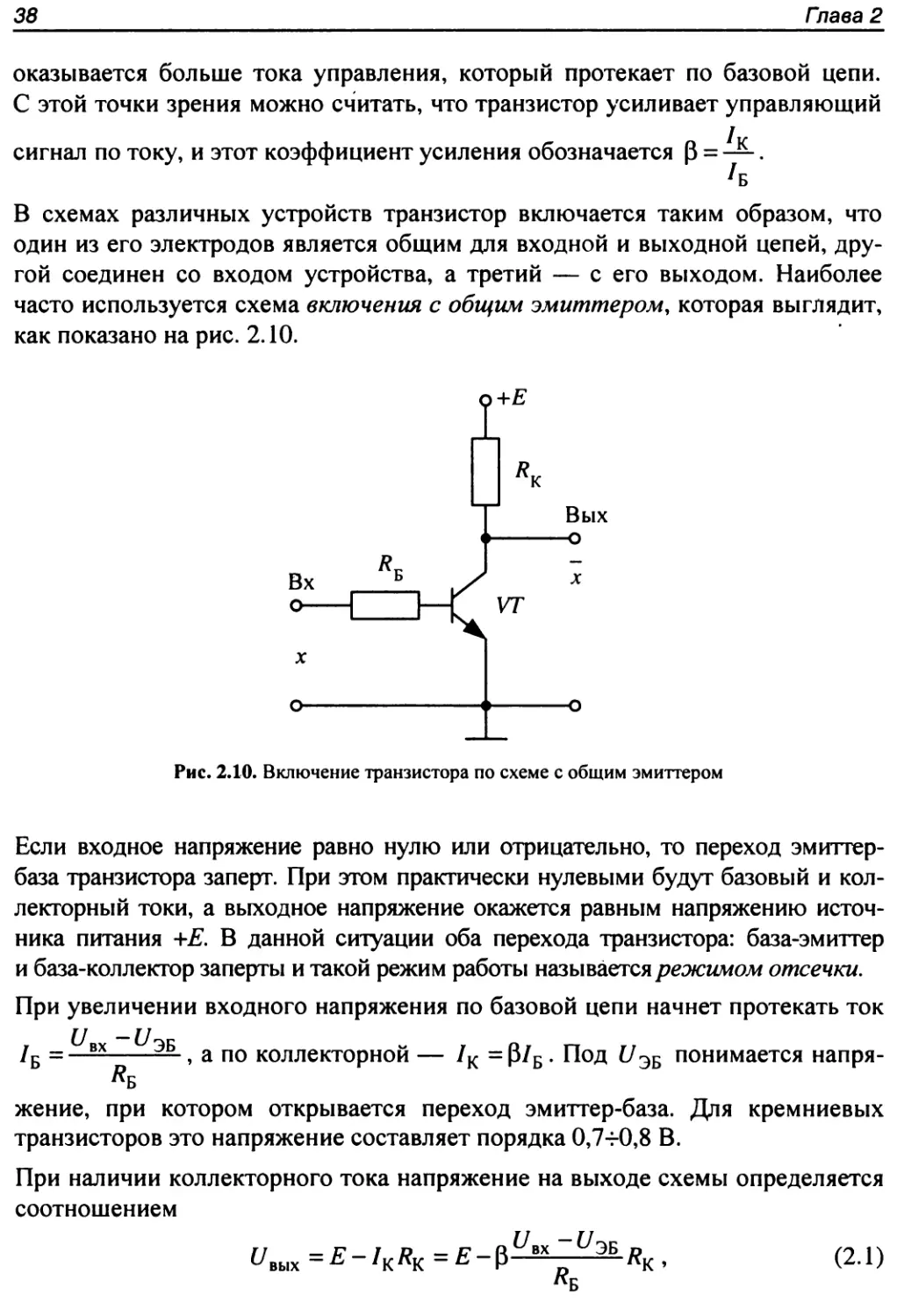

Если входное напряжение равно нулю или отрицательно, то переход эмиттер-

база транзистора заперт. При этом практически нулевыми будут базовый и кол-

лекторный токи, а выходное напряжение окажется равным напряжению источ-

ника питания +£. В данной ситуации оба перехода транзистора: база-эмиттер

и база-коллектор заперты и такой режим работы называется режимом отсечки.

При увеличении входного напряжения по базовой цепи начнет протекать ток

/Б =£^вх—Уэб , а п0 коллектОрНОи — =0/Б . Под иЭБ понимается напря-

ЛБ

жение, при котором открывается переход эмиттер-база. Для кремниевых

транзисторов это напряжение составляет порядка 0,74-0,8 В.

При наличии коллекторного тока напряжение на выходе схемы определяется

соотношением

t/вых =E-IKRK =Е-Р^£эб Лк, (2.1)

Схемотехника цифровых логических элементов

39

используя которое можно рассчитать и построить график зависимости вы-

ходного напряжения такого ключа от входного. Из формулы следует, что вы-

ходное напряжение станет равным нулю при 0^*—-^-RK=E. Отсюда

можно определить уровень входного сигнала + , при котором

Р

транзистор окажется полностью открытым и по его коллекторной цепи поте-

, Е

чет ток /к =--. В реальных схемах между коллектором и эмиттером от-

RK

крытого транзистора всегда имеется некоторое остаточное напряжение и ток

г ^ОСТ

будет равен /к =--—.

При дальнейшем увеличении входного сигнала ток базы возрастает, но кол-

лекторный останется практически неизменным, т. к. он ограничен величиной

напряжения питания и сопротивлением резистора в коллекторной цепи.

В данной ситуации ток, протекающий по базовой цепи, может быть выбран

больше, чем требуется для полного открывания транзистора. При этом оба

перехода — база-эмиттер и база-коллектор окажутся смещенными в прямом

направлении, что соответствует состоянию насыщения транзистора, при ко-

тором падение напряжения между коллектором и эмиттером составит

0,14-0,3 В.

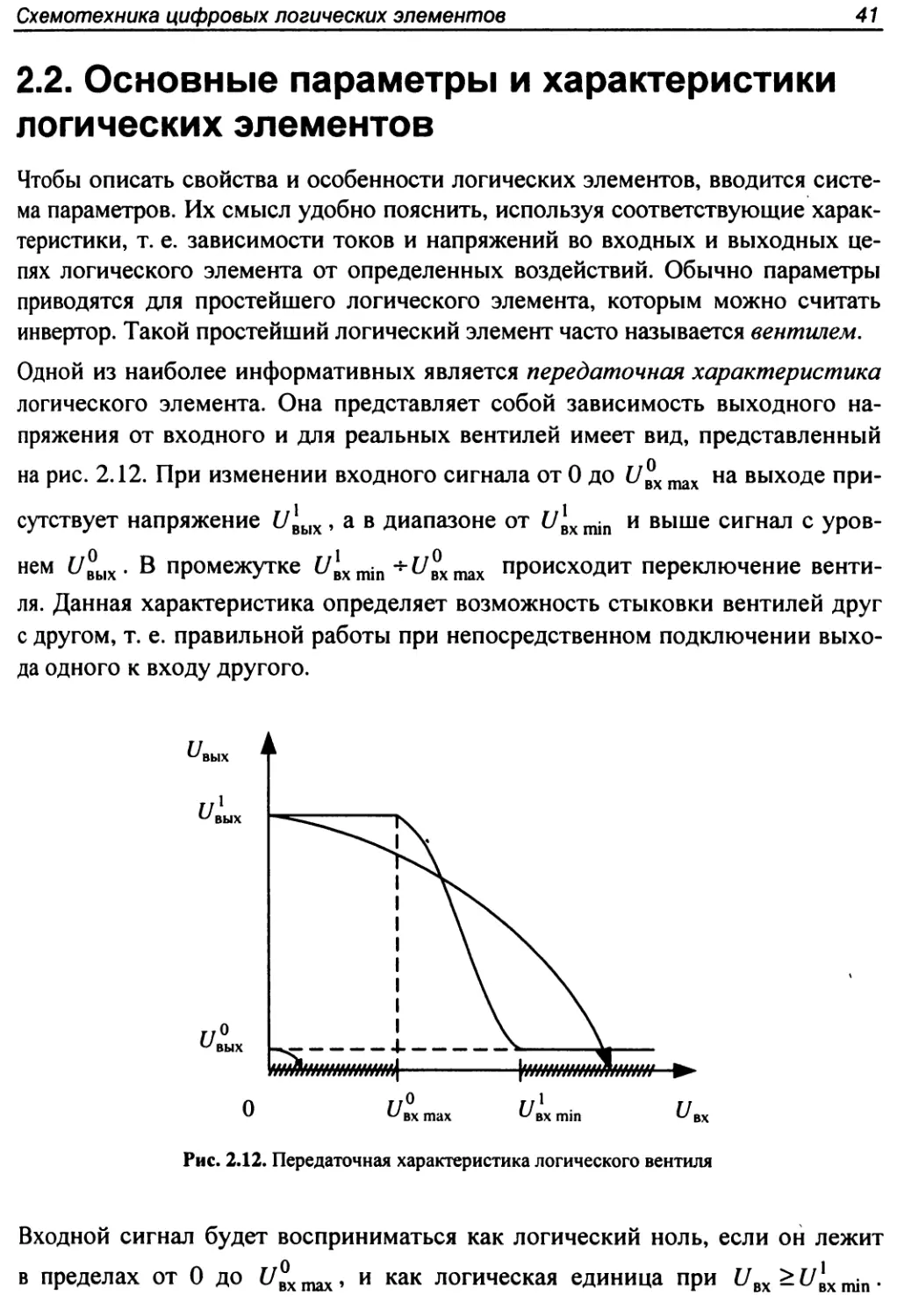

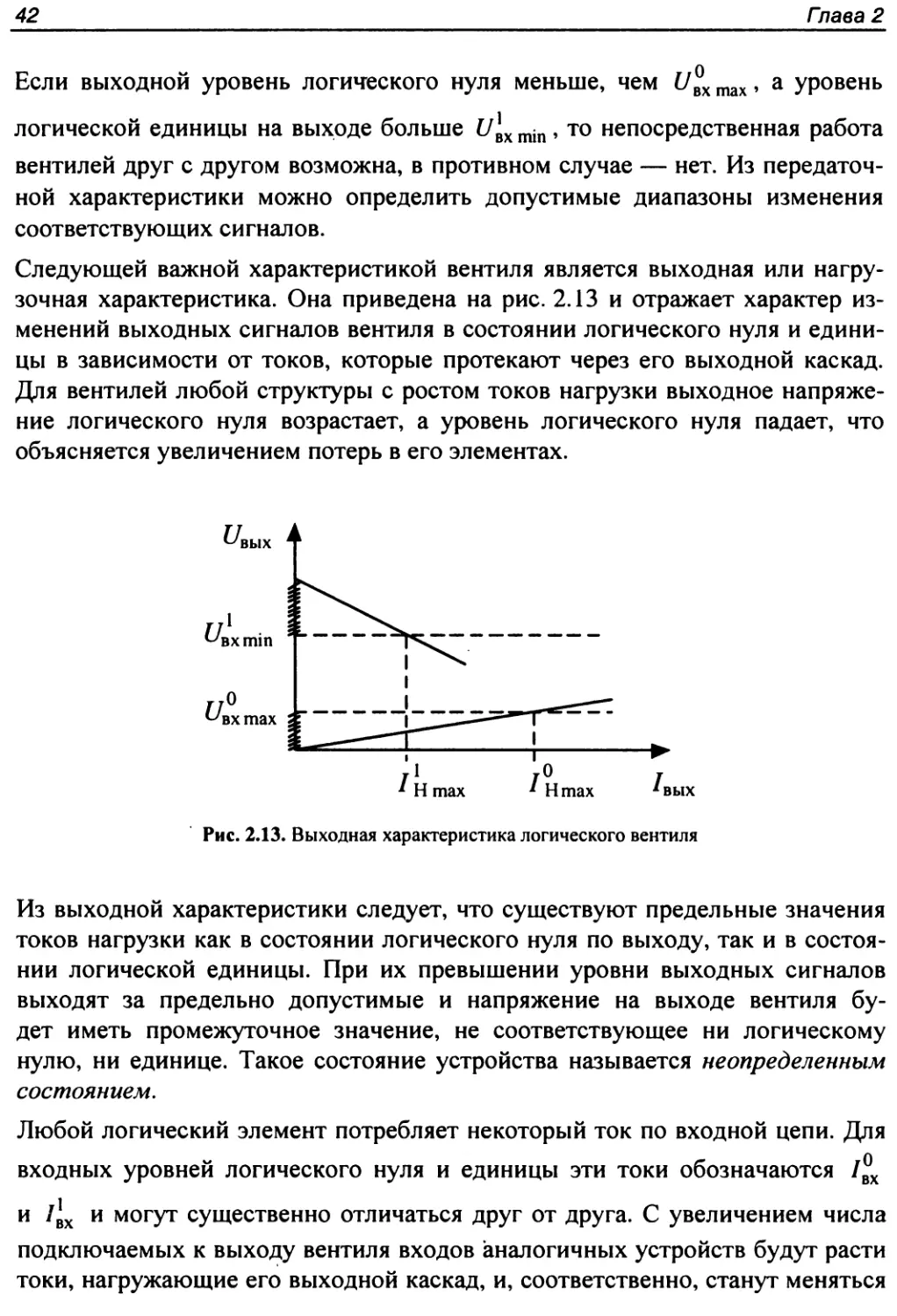

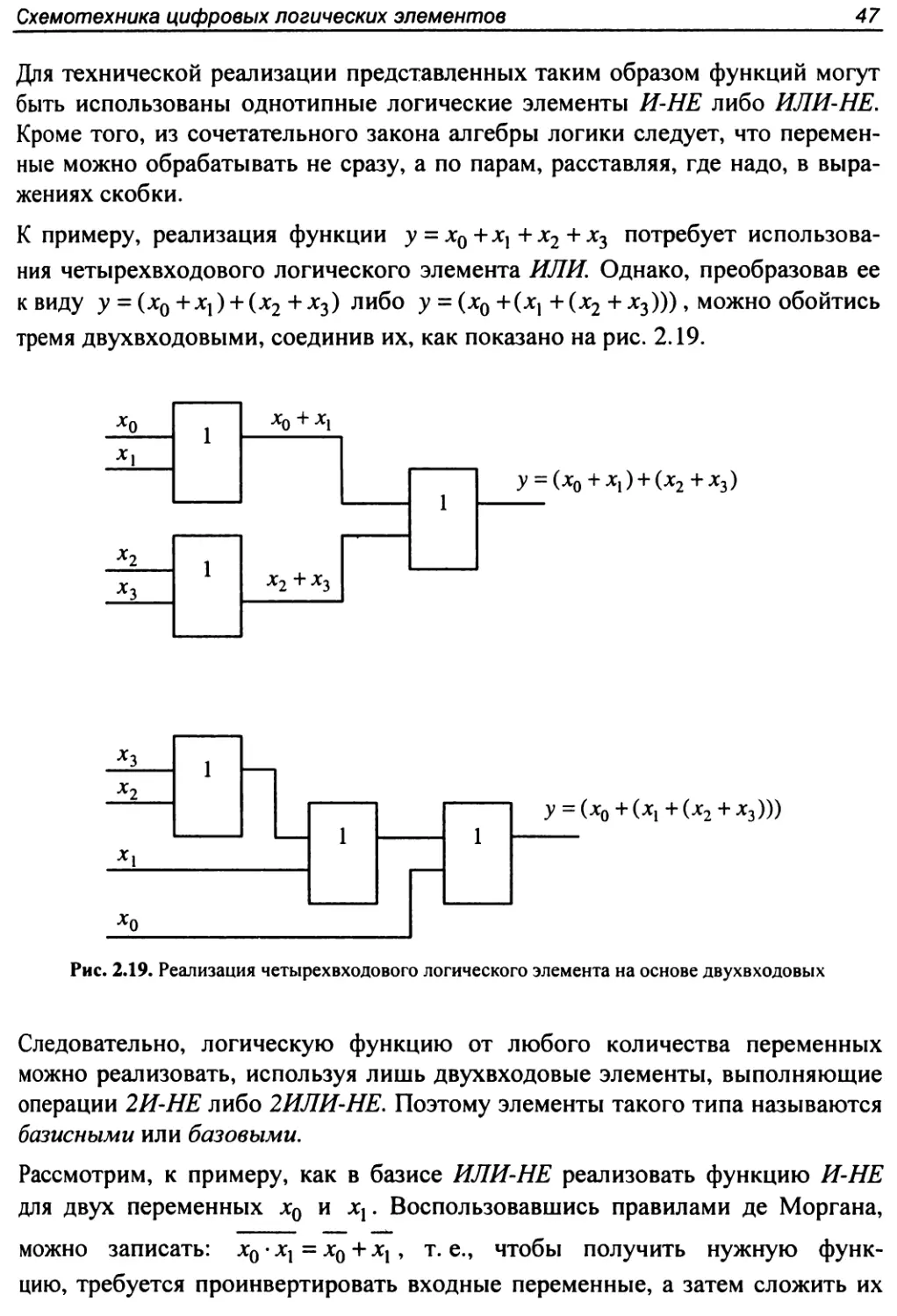

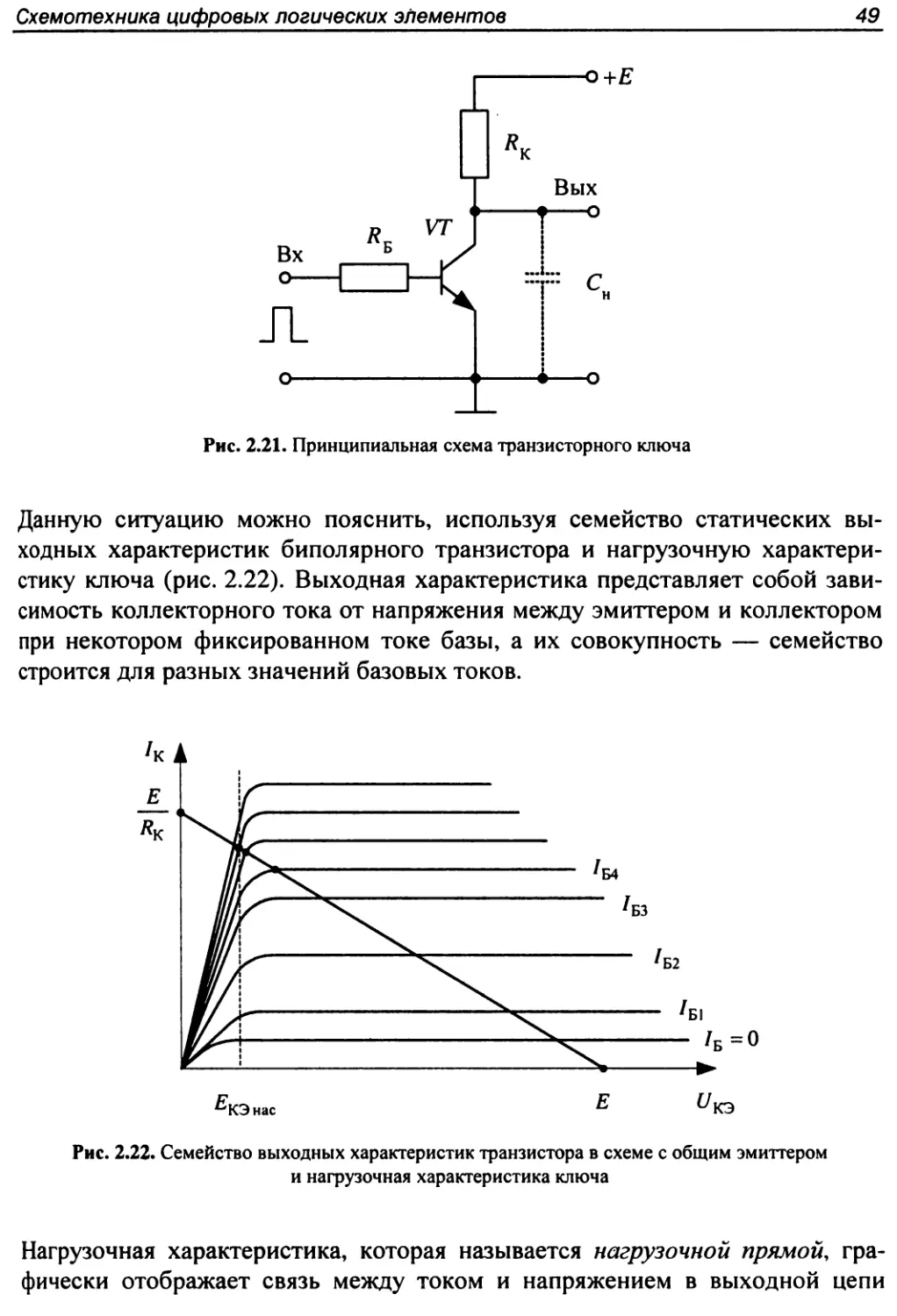

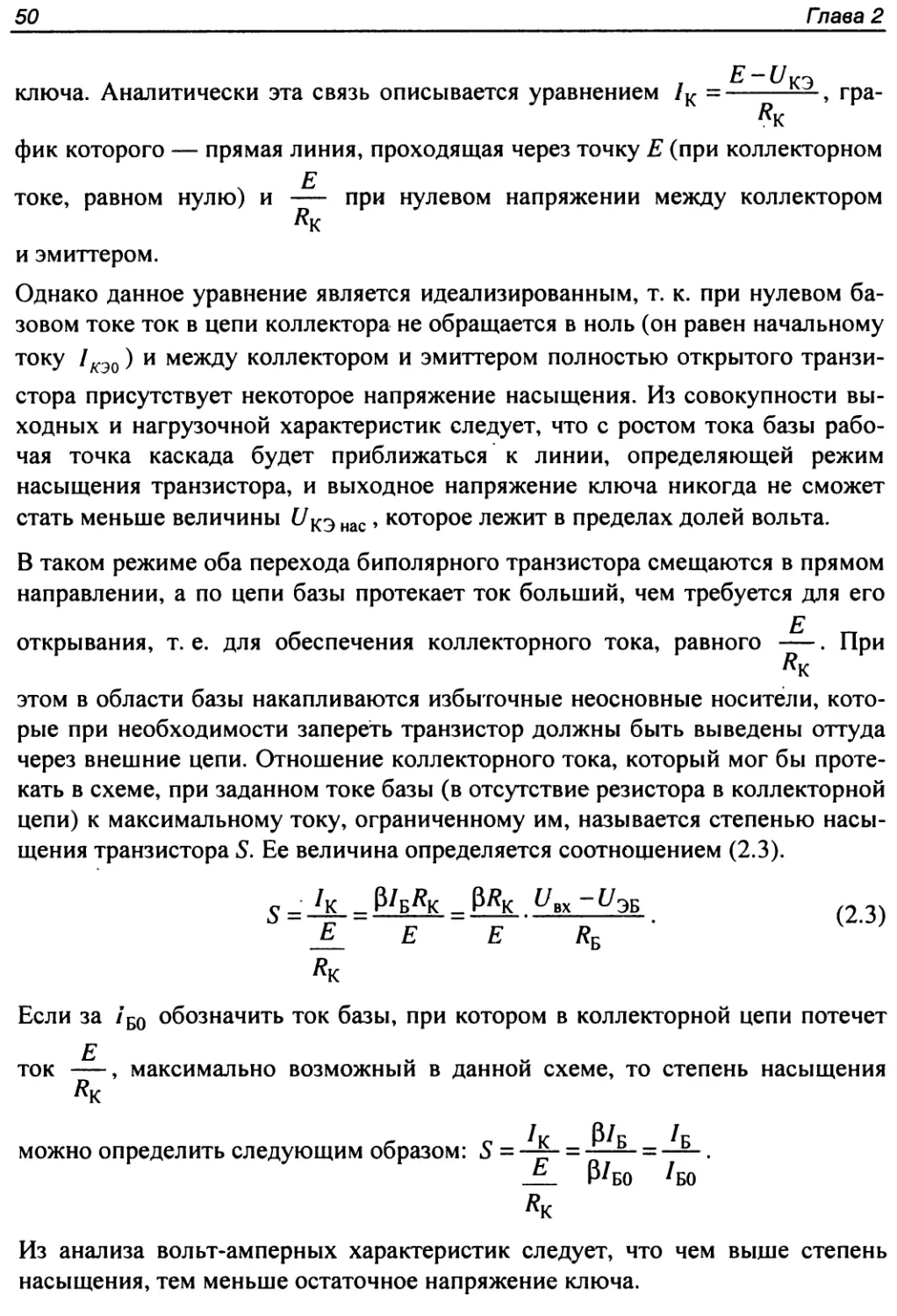

Рис. 2.11. Передаточная характеристика транзисторного ключа

40

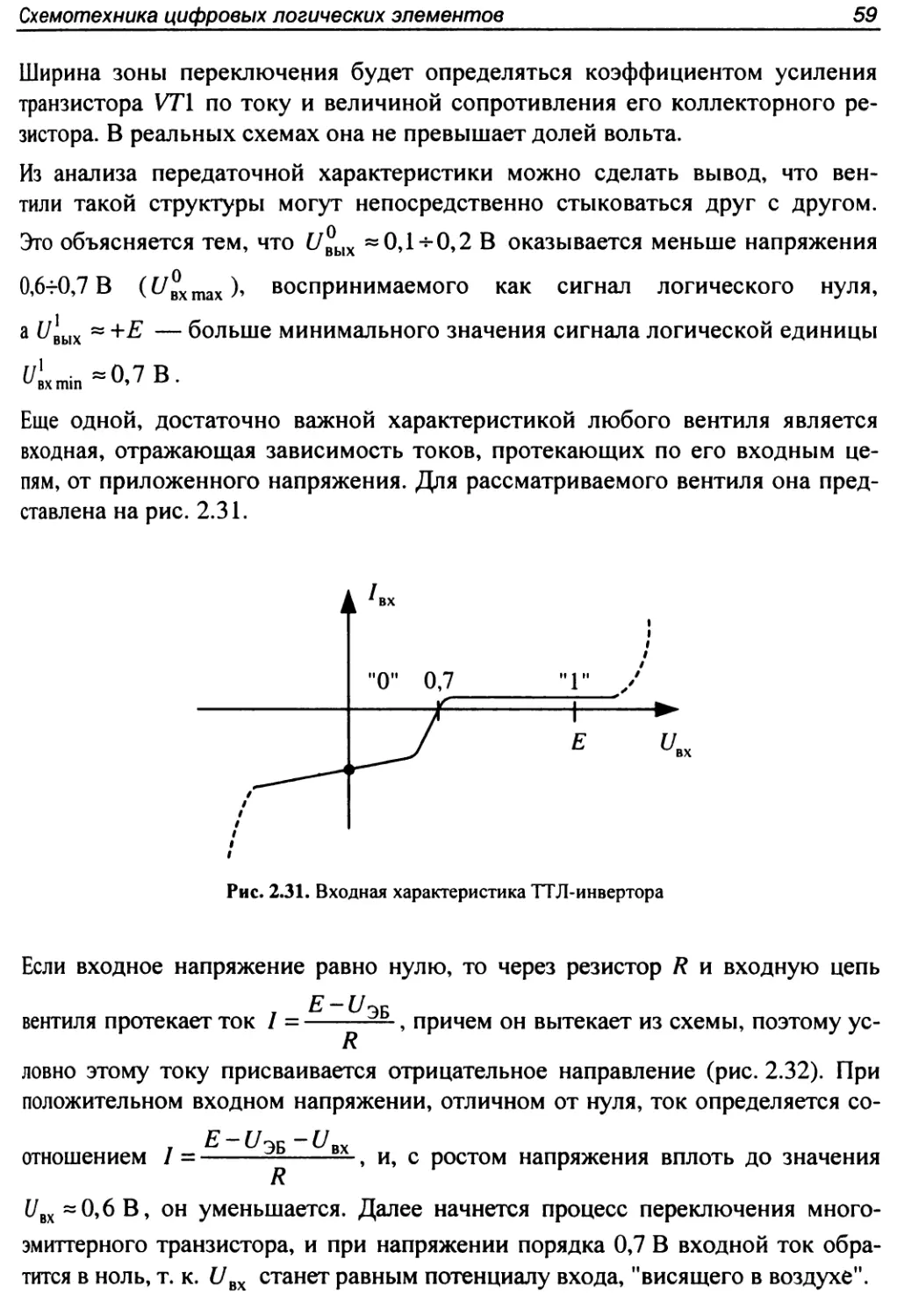

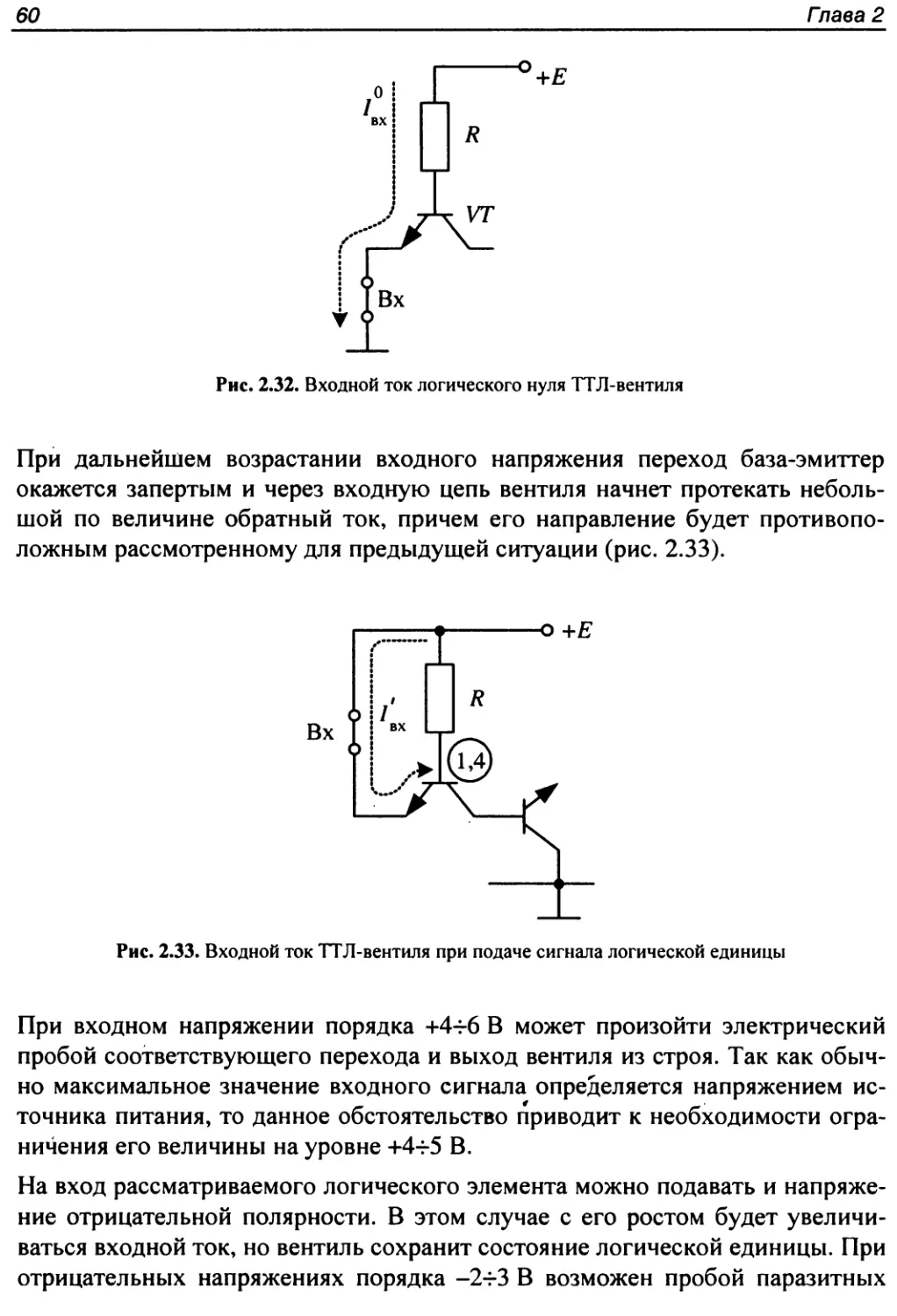

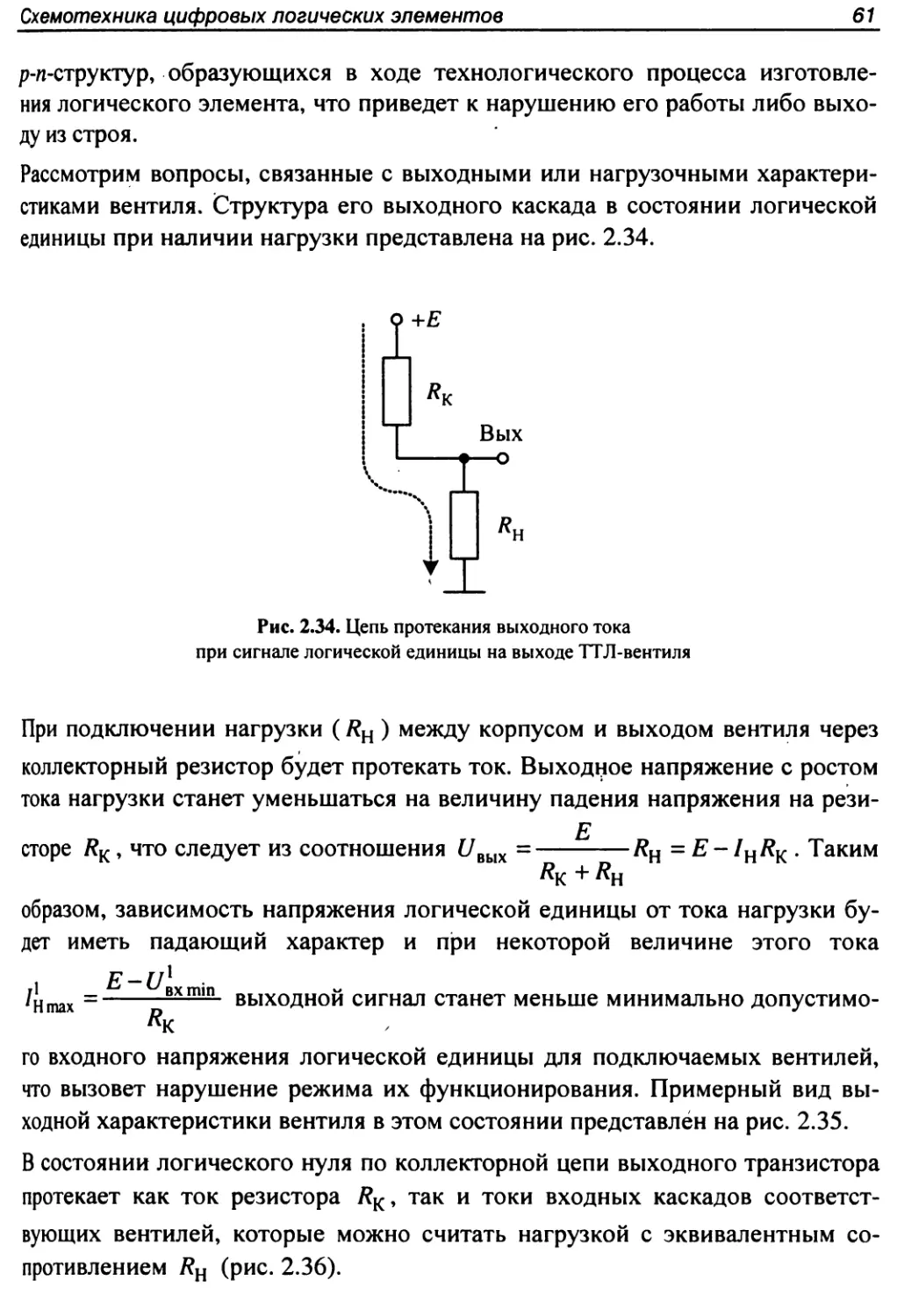

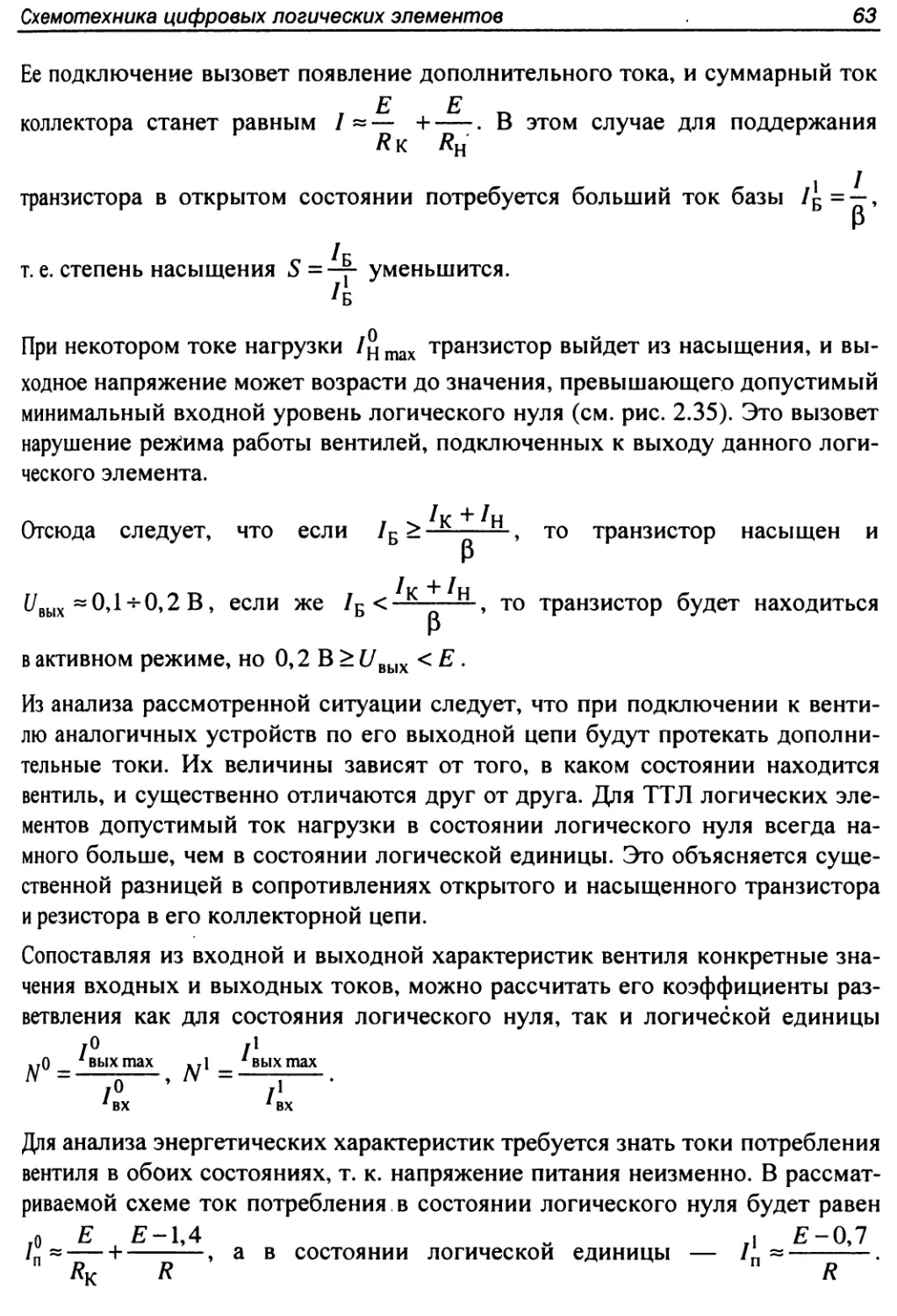

Гпава 2