Автор: Алексенко А.Г. Шагурин И.М.

Теги: электротехника микроэлектроника электроника электропитание издательство радио и связь микро-схемотехника

ISBN: 5-256-00693-2

Год: 1990

Текст

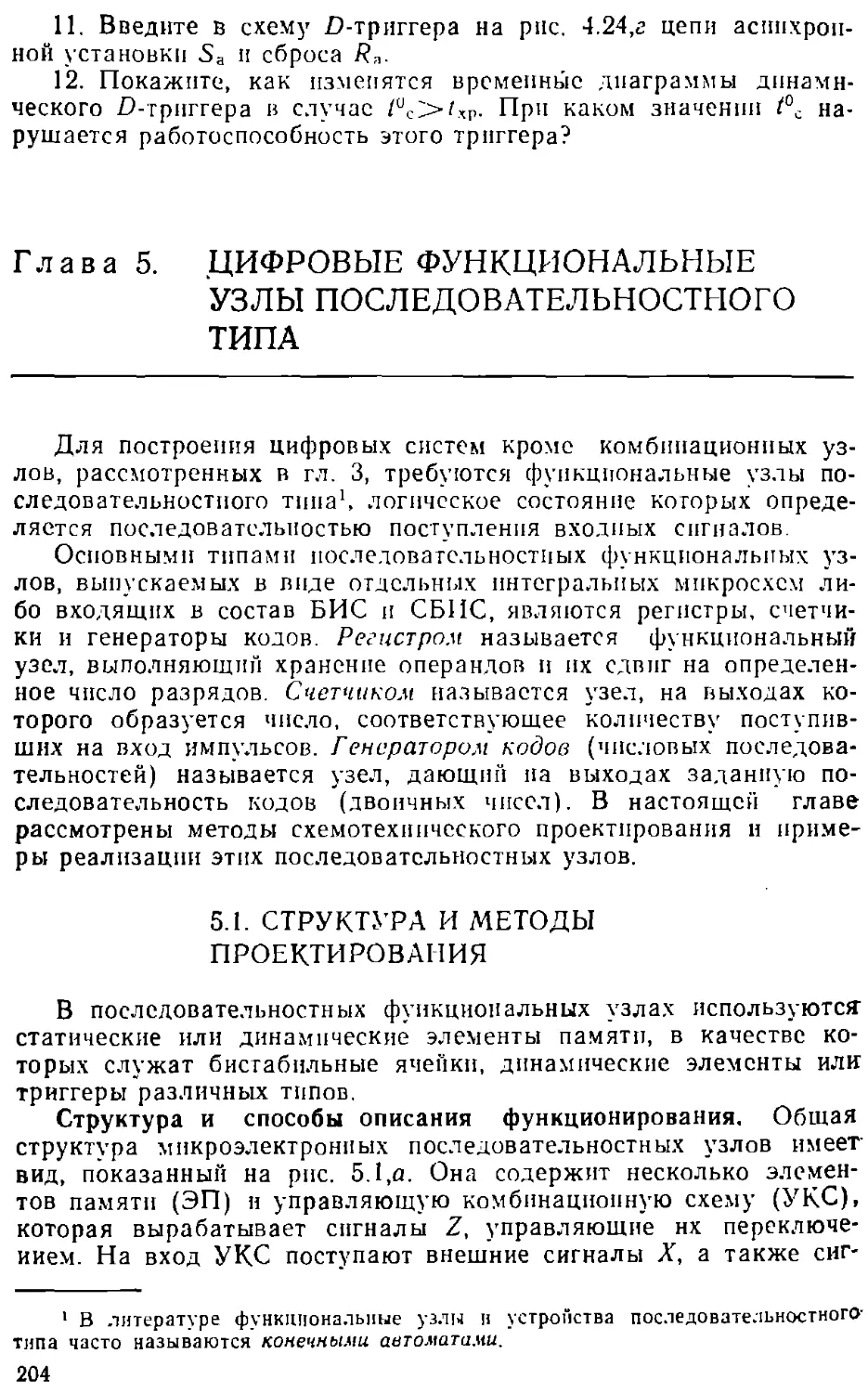

АГ Алексенко

ИМШагурин

МИКРО

СХЕМОТЕХНИКА

2-е издание,

переработанное

и дополненное

Допущено Госидарственным комитетом

СССР по народному образованию в ка-

честве учебною пособия для студентов

вузов, обучающихся по специальностям:

^Физика и технология материалов и

компонентов влектронмой техника»,

еМикроялвктрпника и полупроводнико-

вые приборы»

Москва

«Радио и связь»

«ро

ББК .32.852

А 46

УДК 621.3.049.77

Рецензенты: Доктор физ.-мат. наук. В. Д. Вернер н канд. техн, наук

В. В. Баринов

Редакция литературы по электронике

Алексенко А. Г., Шагурин И. И.

А 46 Микросхемотехника: Учеб, пособие для вузов. — 2-е изд.,

перераб. и доп. — М.: Радио и связь, 1990. — 496 с.: ил.

ISBN 5-256-00693-2.

Изложены основы схемотехнического проектирования цифровых и

аналоговых микросхем и микроэлектронных устройств на их основе. Рас-

смотрены вопросы разработки структурных и схемных решений для ана-

логовых и цифровых устройств, реализуемых в виде БИС и СБИС, и ти-

повые варианты их использования в аппаратуре. По сравнению с первым

изданием (1982 г.) значительно расширены разделы, посвященные вопро-

сам схемотехнического проектирования. Особое внимание уделено описа-

нию микропроцессоров и микропроцессорных систем.

Для студентов, обучающихся по специальностям радиоэлектронного

профиля; будет также полезна широкому кругу специалистов, связанных

с разработкой интегральных микросхем.

Учебное издание

АЛЕКСЕНКО АНДРЕЙ ГЕННАДЬЕВИЧ

ШАГУРИН ИГОРЬ ИВАНОВИЧ

микросхемотехника

Учебное пособие

Заведующий редакцией Ю. Н. Рысев

Редактор Г. Н. Астафуров

Переплет художника В. Я. В и г а и т

Художественный редактр Н. С. Шеин

Технический редактор И. Л. Ткаченко

Корректор 3. Г. Галушкина

ИБ № 1774

Сдано в набор 2.03.90. Подписано в печать 29.10.90

Формат 60X90‘/is Бумага писчая № 1 Гарнитура литературная

Печать высокая Усл. печ. л. 31,0 Усл. кр.-отт. 31

Уч.-изд. л. 31,93 Тираж 20 000 экз. Изд. № 22419

Зак. № 66 Цена 1 р. 40 к.

Издательство «Радио и связь». 101000 Москва, Почтамт, а/я 693

Типография издательства «Радио и связь». 101000 Москва, ул. Кирова, д. 40

ISBN 5-256-00693-2

© Алексенко А. Г., Шагурин И. И., 1990.

ПРЕДИСЛОВИЕ

Создание новых типов интегральных микросхем, являющихся

основной элементной базой современной РЭА различного назна-

чения, требует от разработчиков хорошего знания физических,

конструктивно-технологических и схемотехнических аспектов мик-

роэлектроники. В настоящем учебном пособии рассмотрены схе-

мотехнические вопросы микроэлектроники: схемотехнические ре-

шения, используемые в современных цифровых и аналоговых мик-

росхемах, и методы их проектирования. При этом предполагается,

что читатель знаком с основами физики, технологии и схемотех-

ники микросхем. Такое знакомство можно выполнить с помощью

ряда учебных пособий по основам микроэлектроники (например:

Степаненко И. П. Основы микроэлектроники. — М.: Сов. радио,

1980). Вопросы конструктивно-технологической реализации раз-

работанных схем в интегральном виде рассматриваются в ряде

других монографий и учебных пособий (например: Березин А. С.,

Мочалкина О. Р. Технология и конструирование интегральных

микросхем. — М.: Радио и связь, 1983). Список рекомендуемой ли-

тературы, приведенный в конце книги, поможет читателю позна-

комиться с основами микроэлектроники, а также более глубока

изучить отдельные вопросы микросхемотехники.

Следует отметить, что в процессе развития микроэлектроники

все более сложные электронные устройства реализуются в виде

БИС. Крупные узлы и блоки вычислительных машин, систем уп-

равления и другой РЭА, которые ранее создавались на микросхе-

мах малой и средней степени интеграции, теперь выпускаются в

виде БИС и сверхБИС. Методы проектирования таких сложно-

функциональных микросхем можно использовать для разработки

устройств аналогичного назначения на микросхемах малой степе-

ни интеграции. Таким образом, многие методы проектирования

и структурные решения, описанные в данном учебном пособии,

применимы для разработки как микросхем, так и РЭА.

Основой настоящего пособия послужили лекции по курсу

«Микросхемотехника», читаемые авторами в течение многих лет

студентам Московского инженерно-физического института и спе-

циалистам промышленности. Авторы надеются, что данное учеб-

ное пособие будет полезно для освоения ряда схемотехнических

курсов, читаемых для специальностей радиоэлектронного про-

филя.

Предлагаемое учебное пособие в первую очередь рассчитана

на студентов, специализирующихся по микроэлектронике в рам-

ках специальностей 20.02, 20.03 и ряда других, а также инжене-

ров, повышающих свою квалификацию в этой области. Оно будет

полезно специалистам по вычислительной технике, автоматике,

радиотехнике, измерительной технике и другим, связанным с раз-

работкой электронной аппаратуры на интегральных микросхемах.

Главы 1—8 написаны доктором техн, наук И. И. Шагуриным,

гл. 9—12 — доктором техн, наук А. Г. Алексенко, предисловие и:

введение — совместно обоими авторами.

3

ВВЕДЕНИЕ

Микроэлектроника является одной из наиболее быстро разви-

вающихся областей науки и техники. Непрерывно улучшаются тех-

нические характеристики и расширяются функциональные воз-

можности микроэлектронных изделий — интегральных микросхем.

Совершенствование микросхем достигается благодаря прогрессу

.во всех трех основных разделах микроэлектроники: физике, тех-

.нологии и схемотехнике. Настоящее учебное пособие посвящено

схемотехническому разделу микроэлектроники — микросхемотех-

1нике.

Микросхемотехника (интегральная схемотехника) — раздел

микроэлектроники, охватывающий исследования и разработку схе-

мотехнических решений (электрических и структурных схем), ис-

пользуемых в интегральных микросхемах и радиоэлектронной ап-

паратуре на их основе.

Интегральная микросхема (интегральная схема — ИС) —

микроэлектронное изделие, выполняющее определенную функцию

преобразования электрических сигналов, которое представляет со-

бой совокупность электрических соединенных компонентов1

(транзисторов, диодов, резисторов и др.), изготовляемых в еди-

ном технологическом цикле на общей диэлектрической или полу-

проводниковой основе (подложке).

Основными активными компонентами микросхем являются би-

полярные или МДП-транзисторы. В некоторых типах микросхем

совместно используются биполярные и МДП-транзисторы. В мик-

росхемах на основе арсенида галлия активным компонентом чаще

всего служит полевой транзистор с барьером Шотки.

Основной функцией интегральных микросхем является обработ-

ка (преобразование) информации, заданной в виде электрическо-

го сигнала: напряжения или тока. Электрические сигналы могут

представлять информацию в непрерывной (аналоговой) или диск-

ретной (цифровой) форме. Микросхемы, выполняющие обработку

1 Компоненты, входящие в состав ИС, принято называть элементами мик-

росхемы. Однако применение этого термина при описании цифровых ИС вызы-

вает появление стилистических погрешностей («элемент логического элемента»)

и может привести к ошибкам в восприятии материала из-за путаницы в поня-

тиях «логический элемент» (обычно называют просто «элемент») и «элемент'

микросхемы» (обычно также просто «элемент»). Поэтому для ясности изложе-

ния в настоящем учебном пособии определение «компонент микросхемы» Ис-

пользуется как синоним понятия «интегральный элемент».

4

этой информации, называются аналоговыми или цифровыми соот-

ветственно.

Параметром, определяющим уровень сложности микросхем, яв-

ляется степень компонентной интеграции, которая количественно

характеризуется величиной Кк = 1?Лгк, где NK — общее число ком-

понентов, расположенных на кристалле микросхемы. По уровню

сложности микросхемы1 условно подразделяются на малые (МИС,

Хк^1...2), средние (СИС, 2<Кк^З... 4), большие (БИС,

З..Г4^Лк<5) и сверхбольшие (СБИС, Кк^5). Если микросхема

содержит сложнофункциональные (интегрированные) компонен-

ты, занимающие большую площадь на кристалле, то при оценке

сложности они заменяются эквивалентным количеством простых

компонентов.

Современные интегральные микросхемы являются сложными

электронными устройствами, поэтому используются различные

уровни их схемотехнического представления. Наиболее детальный

уровень представления — электрическая схема в виде соединения

отдельных компонентов. Следующий, более общий уровень —

структурная схема, представляющая собой соединение отдельных

логических элементов и триггеров (для цифровых микросхем) или

аналоговых каскадов (для аналоговых микросхем). Эти элементы

и каскады выполняют элементарные логические (И—НЕ, ИЛИ—

НЕ и др.) или аналоговые (усиление, фильтрация и др.) опера-

ции, с помощью которых можно реализовать любую цифровую,

аналого-цифровую или аналоговую функцию. Они имеют относи-

тельно простую электрическую схему, которая обычно содержит

не более десяти — двадцати компонентов. Еще более высокий уро-

вень используется для представления сложнофункциональных

БИС и СБИС: микропроцессоров, микро-ЭВМ, аналого-цифровых

и цифро-аналоговых преобразователей и др. Их структура пред-

ставляется в виде соединения функциональных узлов и блоков.

Такое представление называется функциональной схемой. Струк-

тура входящих в ее состав функциональных узлов и блоков может

состоять из десятков и сотен простейших логических элементов

или аналоговых каскадов.

Важнейшей задачей, решаемой с помощью методов и средств

микросхемотехники, является схемотехническая разработка новых

типов интегральных микросхем. Исходное техническое задание на

проектирование микросхемы содержит описание функций, которые

она должна выполнять в электронной аппаратуре, и требования к

ее основным параметрам (мощность, быстродействие и др.). Про-

цесс разработки можно представить как последовательное преоб-

разование исходного описания микросхемы во все более деталь-

ные формы ее представления: функциональную, структурную,

электрическую схемы и т. д. Конечным результатом проектирова-

ния является такое представление микросхемы, используя которое

1 Классификация цифровых микросхем по степени функциональной интег-

рации (§ 1,5) соответствует данному делению.

5

можно изготовить ее образцы. Такой формой представления слу-

жат чертежи фотошаблонов и комплект конструкторской докумен-

тации, необходимые для изготовления микросхемы.

Таким образом, разработка микросхемы представляет собой

процесс нисходящего проектирования-, от общего описания к де-

тальному представлению. Основные этапы этого процесса, которые

выполняются при разработке СИС и не очень сложных БИС, по-

казаны на рис. В.1. Аналогично проектируются узлы и блоки,

входящие в состав сложпофупкциональных БИС и СБИС.

В современной мнкросхемотехникс используются различные

варианты схем логических элементов и аналоговых каскадов, ос-

новные типы которых анализируются в настоящем пособии. По-

этому на первом этапе схемотехнического проектирования микро-

схемы обычно производится выбор элементной базы из числа уже

Рнс. B.I. Основные этапы проектирования БИС

6

разработанных вариантов схем логических элементов или анало-

говых каскадов. В случае необходимости выполняется разработка

новых вариантов этих элементов и каскадов, которые имеют преи-

мущества по отдельным параметрам по сравнению с ранее пред-

ложенными схемами.

Стадия структурного проектирования микросхем состоит из

структурного синтеза, в ходе которого на той или иной элементной

базе создается структурная схема, которая обеспечивает выполне-

ние функций, определенных техническим заданием, и структурного

анализа, в процессе которого проверяется правильность функцио-

нирования синтезированной структуры при различных рабочих ус-

ловиях и производится приближенная сравнительная оценка ее

основных параметров. Обычно при проектировании микросхем соз-

дается несколько структурных вариантов. На основании резуль-

татов сравнения их параметров производится выбор одного или

нескольких наилучших вариантов. Если же полученные варианты

не удовлетворяют требованиям технического задания, то выполня-

ется синтез новых структурных вариантов.

Для выбранных структурных вариантов производится схемное

проектирование, в результате которого получается электрическая

схема разрабатываемой микросхемы. Эта стадия проектирования

состоит из этапов схемного синтеза, в ходе которого получается

электрическая схема, соответствующая выбранному варианту

структуры, и электрического анализа полученной схемы, в резуль-

тате которого определяются ее основные электрические парамет-

ры. При анализе обычно выполняется также параметрическая оп-

тимизация схемы, т. е. определение значений параметров компо-

нентов, при которых обеспечиваются наилучшие электрические па-

раметры проектируемой микросхемы. В процессе схемного проек-

тирования как правило разрабатывается несколько вариантов

электрических схем, которые отличаются структурой, элементной

базой и значениями основных параметров. По результатам анали-

за и сравнения разработанных вариантов электрических схем вы-

бирается один из ннх, наилучшнм образом удовлетворяющий тре-

бованиям технического задания.

Структурное и схемное проектирование являются двумя основ-

ными стадиями процесса схемотехнического проектирования мик-

росхем. При разработке микросхем малой интеграции выполняют-

ся только этапы схемного проектирования (см. рис. В.1). Методы

разработки структурных и электрических схем, их типовые вари-

анты, наиболее широко используемые в современных микросхемах,

и являются предметом изучения в настоящем учебном пособии.

На стадии конструкторско-технологического проектирования

важнейшим этапом является разработка технологии, на базе ко-

торой будут изготовляться микросхемы. На основе базовой техно-

логии разрабатывается физическая структура компонентов схемы,

определяются их параметры, которые используются прн расчете

электрических характеристик. В процессе проектирования в соот-

ветствии с электрической схемой разрабатывается топология мик-

росхемы, т. е. производится размещение компонентов на кристалле

и выполняется трассировка электрических соединений (металли-

ческих проводников) между ними. В процессе топологического

проектирования может выполняться физическое совмещение (ин-

теграция) отдельных компонентов, в результате чего могут обра-

зовываться интегрированные компоненты: мпогоэмиттерные и мно-

гоколлекторные транзисторы, совмещенные р-п-р-п структуры и

др. Далее производятся анализ полученной топологии с целью

проверки ее правильности; получение рисунков фотошаблонов, не-

обходимых для ее изготовления; конструктивная разработка (вы-

бор типа корпуса, тепловой расчет н обеспечение необходимого

теплоотвода и др.).

После топологического проектирования требуется уточнить па-

раметры компонентов с учетом их реальных размеров и размеще-

ния на кристалле. С использованием полученных уточненных па-

раметров выполняется повторный электрический анализ схемы.

Если окажется, что электрические характеристики и параметры

микросхемы, рассчитанные с учетом се реальной физической

структуры и топологии, не удовлетворяют требованиям техничес-

кого задания, то необходимо либо изменение структурной или

электрической схемы, либо изменение топологии илн физической

структуры микросхемы.

Характерной особенностью микросхемотехники является широ-

кое использование ЭВМ практически на всех этапах проектиро-

вания микросхем. Необходимость применения ЭВМ обусловлена

ограниченными возможностями экспериментального моделирова-

ния интегральных микросхем с изменением различных параметров

их компонентов. Ведь для получения экспериментальных образ-

цов микросхем необходимо выполнить весь трудоемкий и дорого-

стоящий процесс проектирования и изготовления, который зани-

мает несколько месяцев. Поэтому экспериментальное моделирова-

ние обычно заменяют «машинным» моделированием, анализируя

влияние различных факторов на параметры микросхем с помощью

их математических моделей, расчет которых производится на

ЭВМ. Наиболее эффективно выполняются с помощью ЭВМ этапы

структурного анализа, электрического анализа н параметрической

оптимизации (см. рис. В.1). Ведется также разработка формаль-

ных методов и алгоритмов для реализации с помощью ЭВМ этапов

функционального и структурного синтеза и разработки электри-

ческой схемы. Однако пока эти этапы выполняются в основном

разработчиками-схемотехниками.

Таким образом, в настоящее время специалисты-схемотехники

выполняют этапы проектирования, связанные с творческой дея-

тельностью и требующие определенного опыта и интуиции. Это

этапы выбора или разработки элементной базы, синтеза структур-

ной и электрической схемы, сравнительной оценки и отбора син-

тезированных вариантов. При этом разработчик производит как

качественные, так и приближенные количественные оцейки па-

раметров полученных схем. Методы получения таких оценок при-

водятся в настоящем пособии. Подробный анализ и параметриче-

ская оптимизация схем, отобранных по результатам приближен-

ных расчетов, производятся с помощью ЭВМ, для чего разрабо-

таны достаточно эффективные программы. В настоящее время с

помощью ЭВМ выполняются анализ функциональных н структур-

ных схем, содержащих до ]04... 105 логических элементов, анализ

электрических схем, содержащих до 102... 10э компонентов, пара-

метрическая оптимизация схем, содержащих до 102 компонентов.

При разработке сложнофункциональных БИС и СБИС исполь-

зуется другая процедура проектирования, так как электрический

расчет и непосредственное получение топологии схем, содержащих

десятки тысяч и более компонентов, оказываются чрезмерно тру-

доемкими даже с помощью современных ЭВМ. Такие БИС и

СБИС проектируются методом функциональных библиотек (ФБ),

при котором их функциональная схема синтезируется из стандарт-

ного набора цифровых или аналоговых блоков, узлов и элементов

(каскадов). Для каждого из них с помощью описанной выше про-

цедуры (см. рис. В.1) разрабатываются электрическая схема и то-

пология, определяются все основные параметры. Так формируется

библиотека схемотехнических и топологических решений, которые

компонуются в процессе проектирования БИС (СБИС), образуя

ее функциональную (структурную), электрическую схемы и топо-

логию. Для определения параметров БИС (СБИС) выполняется

ее моделирование с учетом параметров используемых функцио-

нальных блоков, узлов, элементов, приведенных в библиотеке. То-

пология реализуется путем размещения на кристалле и соедине-

ния готовых топологических фрагментов, имеющихся в ФБ. В ре-

зультате трудоемкость проектирования значительно сокращается.

На практике используются различные варианты метода ФБ. В

матричных БИС, реализованных на базовых матричных кристал-

лах (БЛТК.), элементы и узлы ФБ проектируются на основе одной

пли нескольких ячеек, расположенных на БМК в виде прямо-

угольной матрицы. Каждая ячейка содержит набор компонентов

(от 4... 5 до 30... 40), различные варианты соединения которых

позволяют получать те или иные элементы и узлы ФБ. Таким об-

разом, номенклатура, параметры и топология элементов н узлов

ФБ. используемых для реализации матричных БИС, определяются

топологией и компонентным составом ячеек БМК.

При проектировании БИС на стандартных ячейках использу-

ются ФБ, в которых топология всех элементов и узлов имеет вид

прямоугольников с одинаковой величиной одной из сторон. Такая

топологическая реализация и называется стандартной ячейкой. В

этом случае БМК не используется и стандартная ячейка может

быть изготовлена в любом месте кристалла. При разработке БИС

(СБИС) обеспечиваются достаточная плотность компоновки стан-

дартных ячеек и относительная простота трассировки соединений

между ними, что позволяет получать меньшую площадь кристалла

п более высокое быстродействие, чем для матричных БИС.

Оба описанных метода предусматривают автоматизированное

проектирование БИС с интерактивным участием специалиста-раз-

работчика на этапах оценки результатов, выбора варианта реше-

ния плн его коррекции. Наиболее высокую степень автоматизации

обеспечивает метод кремниевой компиляции, при котором исходное

описание проектируемой БИС (СБИС) автоматически транслиру-

ется во все более детальное представление ее фрагментов (блоков,

узлов, элементов). После ряда этапов трансляции получаются

электрические схемы и топология всех фрагментов, соединение

которых представляет БИС (СБИС), реализующую заданные

функции. Необходимые схемные и топологические решения для

фрагментов синтезируются в процессе проектирования либо по-

лучаются путем модификации готовых решений, имеющихся в ис-

пользуемой ФБ.

Таким образом, при проектировании новых типов интеграль-

ных микросхем микросхемотехника решает задачу разработки

схемных и структурных решений, учитывающих и использующих

специфические особенности интегральной технологии для нанлуч-

шего выполнения требований технического задания. Развитие мик-

росхемотехники и технологии изготовления микросхем обеспечи-

вает улучшение характеристик радиоэлектронной аппаратуры н

расширение ее функциональных возможностей, стимулируя даль-

нейшее внедрение микроэлектроники во все сферы человеческой

деятельности: производственную, управленческую, научную, куль-

турно-бытовую.

Глава 1. ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ

В современной науке и технике важнейшую роль играют циф-

ровые методы обработки информации. В связи с этим непрерывно

расширяется область применения цифровых систем — технических

средств, выполняющих законченный процесс обработки цифровой

информации, включающей ее прием, хранение, необходимые пре-

образования и выдачу.

Быстрое развитие цифровых систем началось в 40-х годах, ког-

да были построены первые цифровые вычислительные машины на

электромеханических реле, а затем на электронных лампах. Прог-

ресс электроники открыл перед цифровыми системами новые воз-

можности, сделав их незаменимыми помощниками человека прак-

тически во всех сферах его деятельности. Вслед за электронными

вычислительными машинами (ЭВМ) 1-го поколения, построенны-

ми на электронных лампах, в 50-х годах появились ЭВМ 2-го по-

коления на транзисторах. Эти ЭВМ обладали существенно расши-

ренными функциональными возможностями, повышенными быстро-

действием и надежностью. Возникла новая отрасль науки и тех-

ники — цифровая техника, изучающая принципы построения, ме-

тоды проектирования и способы технической реализации цифро-

вых систем. При этом цифровая техника использует достижения

смежных фундаментальных и прикладных наук, таких как мате-

матическая логика, кибернетика, электроника и др.

.Микроэлектроника способствовала дальнейшему развитию

цифровой техники. Микросхемы малой и средней степени интег-

рации (ИС и СПС) стали технической базой электронных цифро-

вых систем, в том числе ЭВМ 3-го поколения, разработанных в

60—70 годах. Развитие технологии, обеспечивая непрерывное по-

вышение степени интеграции микросхем, позволило создать на од-

ном кристалле полупроводника цифровые устройства, по своей

сложности и выполняемым функциям превосходящие ЭВМ, изго-

тавливающиеся ранее на дискретных компонентах. Такие микро-

схемы, называемые большими интегральными схемами (БИС),

являются базой ЭВМ 4-го поколения, выпуск которых начался в

конце 70-х годов. К этому поколению относятся современные мик-

ро-ЭВМ, в том числе персональные компьютеры, реализованные

11

на базе микропроцессоров, а также высокопроизводительные боль-

шие ЭВМ, построенные нз специализированных («заказных»)

БИС. В настоящее время ведутся интенсивные разработки ЭВМ

5-го поколения, которые отличаются сверхвысокой производитель-

ностью, расширенными возможностями ввода и вывода информа-

ции в звуковой (человеческая речь) и графической (рисунки,

письменный текст) форме, рядом признаков искусственного интел-

лекта; способностью самостоятельно составлять программу своих

действий для решения определенных классов задач, находить оп-

тимальные решения в сложных ситуациях и др. Эти ЭВМ будут

реализованы иа базе сверхбольших интегральных схем (СБИС) с

применением новых материалов (например, арсенид галлия, сверх-

проводящая керамика), с широким использованием новых прин-

ципов и способов представления и обработки информации (опти-

ческие, акустоэлектрические и др.).

На стыке микроэлектроники и цифровой техники развивается

самостоятельная область науки и техники — цифровая микросхе-

мотехника, предметом которой являются принципы и методы схе-

мотехнического проектирования цифровых интегральных микро-

схем, которое включает разработку их структуры (функционально-

логическое проектирование) и электрической схемы (схемное про-

ектирование). Непрерывное повышение степени интеграции проек-

тируемых микросхем, обеспечивающее реализацию на одном крис-

талле целых цифровых систем, требует от специалиста-микросхе-

мотехника не только знания основ цифровой техники, ио и освое-

ния таких ее разделов, как архитектура цифровых систем, микро-

программирование и др.

Цифровые интегральные микросхемы выполняют в цифровых

системах функции приема, хранения, преобразования (обработки)

и выдачи информации. Преобразование информации, представлен-

ной в цифровой форме, осуществляется путем выполнения опре-

деленной последовательности арифметических и логических опе-

раций. В этой главе приводятся способы цифрового представления

информации, рассматриваются основные арифметические и логи-

ческие операции, выполняемые при ее обработке, описывается

типовая структура современных цифровых систем.

1.1. СПОСОБЫ ПРЕДСТАВЛЕНИЯ

ИНФОРМАЦИИ

При выполнении различных операций в современных цифровых

системах числа обычно представляются в двоичной системе счис-

ления, основанием которой является число 2. При этом целое k-

разрядное десятичное число Лю записывается в виде л-разрядного

двоичного числа Аг:

Аю = а,(109=А2= “s аД2’), (1.1>

г=о /=о

где а, = 0, 1,..., 9 —цифра в Ам разряде десятичного числа: а> =

12

= 0 или 1 — цифра в j-м разряде двоичного числа. Введением

отрицательных степеней числа 2 представляются дробные числа.

Таким образом, в двоичном счислении любое число можно

представить двумя цифрами: 0 и 1. Для представления этих чисел

в цифровых системах достаточно иметь электронные схемы, кото-

рые могут принимать два состояния, четко различающиеся зна-

чением какой-либо электрической величины — потенциала или

тока. Одному из значений этой величины соответствует цифра 0,

другому 1. Относительная простота создания электронных схем с

двумя электрическими состояниями и привела к тому, что двоич-

ное представление чисел доминирует в современной цифровой

технике. При этом 0 обычно представляется низким уровнем по-

тенциала U°, а 1 — высоким уровнем U'. Такой способ представ-

ления называется «положительной логикой» *.

Перевод десятичного числа в двоичный код можно осуществ-

лять путем последовательного деления числа на 2. Остатки (0 или

1), получающиеся на каждом шаге деления, формируют двоичный

код преобразуемого числа, начиная с его младшего разряда. В

качестве старшего разряда двоичного кода записывается 1, полу-

ченная в результате последнего шага деления. Например, преоб-

разование числа Д1о=109 в двоичный код выполняется следую-

щим образом;

А>0 = 1О9=А2 = аеа5а4аза2а1ао = 1101101.

Цифровые системы оперируют действительными, целыми и дроб-

ными числами, которые могут иметь две формы представления: с

плавающей запятой, с фиксированной запятой.

При использовании плавающей запятой число состоит из двух

частей: мантиссы т, содержащей значащие цифры числа, и по-

рядка р, показывающего степень, в которую надо возвести осно-

вание счисления q, чтобы полученное при этом число, умноженное

на мантиссу, давало истинное значение представляемого числа:

Aq=mq?. (1.2)

В некоторых случаях разработчики цифровых систем применяют представ-

пение чисел в «огрицще.тьной логике», при которой 0 соответствует высокий

уровень электрического потенциала, а 1 — низкий уровень.

13

Мантисса и порядок представляются в двоичном коде. Обычно

число дается в нормализованном виде, когда его мантисса явля-

ется правильной дробью, причем первая значащая цифра (едини-

ца) следует непосредственно после запятой: например, =

= 0,1010-2'°= 10,10, где /и = 0,1010; р=10; q=2

При использовании фиксированной запятой число представля-

ется в виде единого целого, причем положение запятой в ис-

пользуемой разрядной сетке жестко фиксировано. Обычно числа

с фиксированной запятой даются в виде правильной дроби. Для

этого все числа умножают на масштабный коэффициент, чтобы

перевести их в правильную дробь. Цифровые системы, использую-

щие числа с плавающей запятой, сложнее систем, использующих

числа с фиксированной запятой, так как при этом требуется вы-

полнение операций как над мантиссами, так и над порядками.

Однако диапазон представляемых чисел при одинаковом числе

разрядов в системах с плавающей запятой значительно больше.

Для представления знака числа используется знаковый разряд

z, который обычно располагается перед числовыми разрядами.

Для положительных чисел значение знакового разряда 2 = 0, для

отрицательных чисел 2=1. Для чисел с плавающей запятой вво-

дятся отдельные знаковые разряды для мантиссы и для порядка

чисел.

Последовательность из восьми двоичных разрядов называется

байтом. Большинство современных цифровых систем обрабатывает

числа, содержащие целое число байтов. Наиболее широкое приме-

та б л и ц а 1.1

Наиболее распространенные двоичные коды чисел от 0 до 15

14

некие имеют системы, оперирующие одно-, двух- или четырехбай-

товыми числами (8, 16 или 32 разряда соответственно). Высоко-

производительные ЭВМ работают с числами, содержащими до

8... 10 байтов. В то же время для выполнения относительно прос-

тых задач, не требующих высокой скорости решения, часто ис-

пользуются системы с четырехразрядным представлением чисел.

Разрядность определяет диапазон представляемых чисел. Так,

диапазон однобайтовых чисел составляет от 0 до (28—1)=255,

двухбайтовых — от 0 до (2|6—1) =65535. Если один разряд (бит)

выделяется для указания знака, то с помощью одного байта пред-

ставляются числа в диапазоне ±(27—1)=±127, с помощью двух

байтов — в диапазоне ±(215—1) = ±32 767. Для представления

чисел с плавающей запятой чаще всего используется четыре бай-

та. При этом один двоичный разряд определяет знак числа, 23

разряда — мантиссу, восемь разрядов — знак и значение поряд-

ка. В результате диапазон представляемых чисел составляет от

±2127 до ±2-127, что вполне достаточно для большинства решае-

мых задач.

Для представления чисел со знаком в цифровых системах ис-

пользуется обратный1 или дополнительный 2 код (табл. 1.1). При

этом положительные числа представляются в обычном двоичном

коде. Обратный код отрицательного числа Аг образуется путем за-

мены 0 во всех- разрядах исходного двоичного числа Л2 на 1, и

наоборот. Дополнительный код отрицательного числа Аг получа-

ется из обратного прибавлением 1 к младшему разряду.

Помимо рассмотренных в цифровых системах используются и другие спо-

собы двоичного представления чисел. В качестве примера в табл. 1.1 прпведев

циклический код Грея. Особенность этого кода в том, что при переходе к

каждому последующему числу в коде изменяется значение только одного

двоичного разряда. При этом двухразрядиые числа образуют циклическую

последовательность 00—01 —11 —10—00 (0—1—2—3—0), трехразрядпые — по-

следовательность 000—001—011—010—110—111—101—100—000 (0—1—2—3—

4—5—6—7—0) и т. д. Такая цикличность кода является весьма удобной, на-

пример, для кодирования угловых перемещений в преобразователях угла по-

ворота в цифровой код.

В ряде случаев для записи чисел применяется восьмеричное или шестнад-

цатеричное счисление:

Лю=Лв= 2°а', (81) =а’г-8'+а’,-1-8'-,+ ... +а’1-81+а«0-8°;

41о=Л1о = Д|а,",(161) = а1’.. 164-а1’,-!-16*-‘+ ... Ч-а'%. 16°.

(1.3)

(1.4)

В шестнадцатеричном счислении для обозначения десятичных чисел 10, 11, 12,

Обратный код Аг двоичного числа Аг называется также дополнением до

' Т2КпКаК для каждого разряда числа П; + а, = 1.

Дополнительный код Аг числа Аг называется также дополнением числа

АО 2, так как для каждого разряда числа и, + й;=10 (число 2 в двоичной

15

13, 14, 15 используются латинские буквы А, В, С, D, Е, F соответственно. Вось-

меричные и шестнадцатеричные числа легко переводятся в двоичные. При этом

.каждый раздел восьмеричного числа представляется тремя двоичными разряда-

ми (триадой), а каждый разряд шестнадцатеричного числа — четырьмя двоич-

ными разрядами (тетрадой) в соответствии с табл. 1.1. Например, А2 =

= 10011011 =Д8 = 2338 = Ли=9В1в=Дю= 155 Восьмеричная и шестнадцатеричная

формы сокращают длину представленных, чисел и уменьшают количество оши-

бок, часто возникающих при записи или чтении оператором двоичных чисел.

Перевод десятичных чисел в двоичный код требует использования доста-

точно сложных схем преобразователей н занимает относительно долгое время.

Более просто и быстро осуществляется перевод десятичных чисел в двоично-

десятичный код. При этом цифра в каждом разряде десятичного числа заме-

няется соответствующим чстырехразрядным двоичным числом (тетрадой) сог-

ласно табл. 1.2. Например, число 4ю = 729 в двоичпо-десятпчном коде записы-

вается в виде Аи ю = 0111 0010 1001. Для выполнения сложения и вычитания

двончно-десятнчны.х чисел наиболее удобно использовать так называемые само-

дополняющие коды, к числу которых относятся Код Айкена, код «с избытком 3>

(см. табл. 1.2) и некоторые другие. Код Айкена отличается от обычного двонч-

но-десятлчного, имеющего весовые коэффициенты разрядов в тетрадах

8—4—2—1, другими значениями весовых коэффициентов разрядов: 2—4—2—1.

Код • с избытком 3» получается из обычного двоично-десятичного арифмети-

ческим прибавлением числа 3 (двоичное число ООН).

Как видно из табл. 1.2, обратный код А'-, ю числа, представленного в ка-

ком-либо самодополняюшем двоично-десятичном коде А'-.-ю, является его двоич-

ным дополнением до 9. Например, число 5 в коде <с избытком 3» А';'ю= Ю00

имеет обратный код A'z/io = 0111, соответствующий числу 4 в коде «с избыт-

ком 3*. которое «дополняет» число 5 до 9, так как 5-|-4 = 9.

Двоичное кодирование используется в цифровых системах не

только для обозначения числа, но и для представления букв и дру-

гих знаков. Наиболее часто в современной аппаратуре использу-

Таблица 1.2

Наиболее распространенные двончо-десятнчные коды чисел от 0 до 9

Десятичное число Двоично-десятичный код (3—1—2—1) Код Айкена (2—1 — 2—1) Код «с избытком 3»

Д ,0 ai ot а» ь» Ь, ь. ' с* Со

0 0 0 0 0 0 0 0 0 0 0 1 1

1 0 0 0 1 0 0 0 1 0 1 0 0

2 0 0 1 1 0 0 1 0 0 1 0 1

3 0 0 1 1 0 0 1 1 0 1 1 0

4 0 1 0 0 0 1 0 0 0 1 1 1

5 0 1 0 1 1 0 1 1 1 0 0 0

6 0 1 1 0 1 1 0 0 1 0 0 1

7 0 1 1 1 1 1 0 1 1 0 1 0

8 1 0 0 0 1 1 1 0 1 0 1 1

9 1 0 0 1 1 1 1 1 1 1 0 0

16

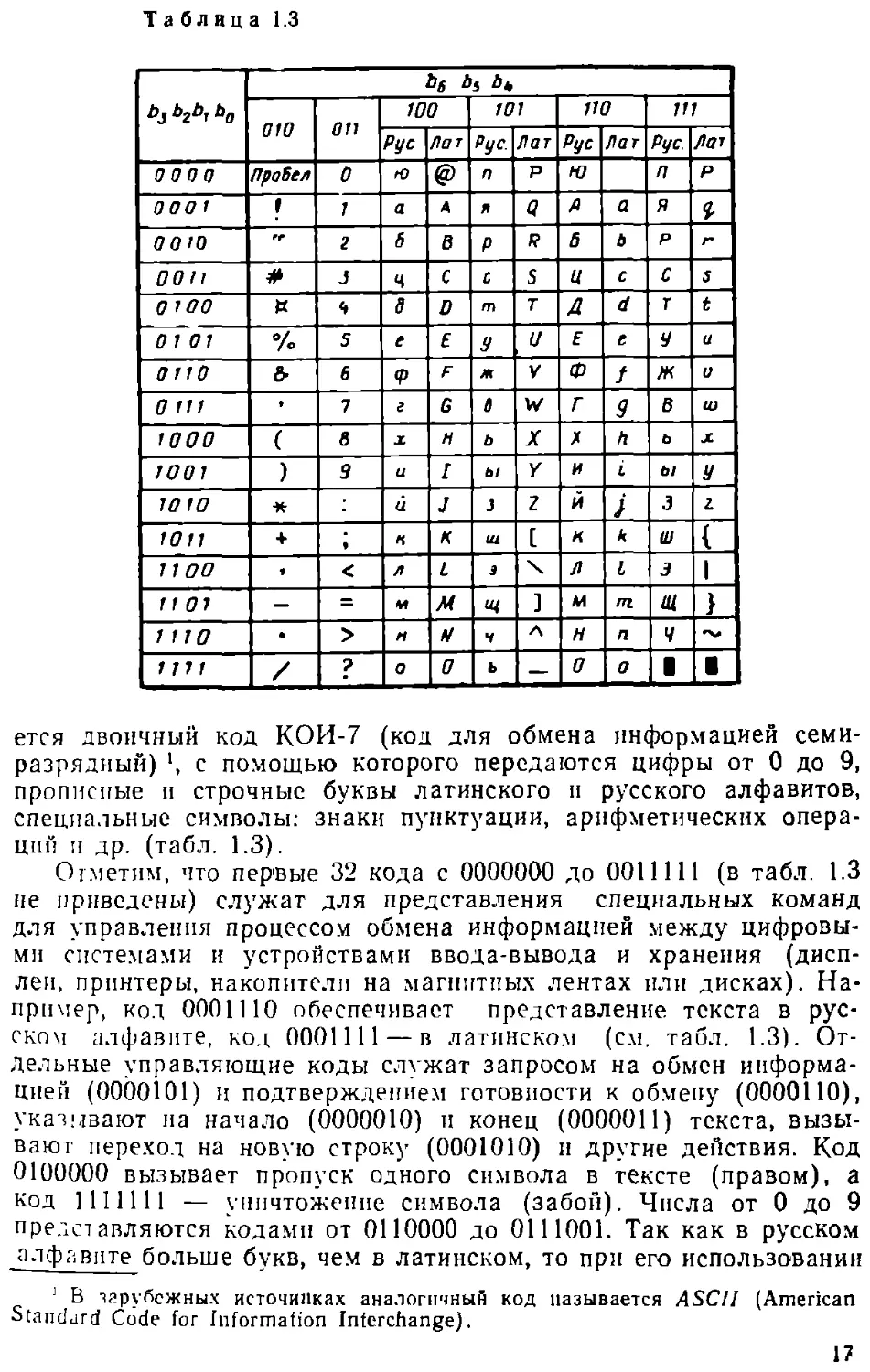

Таблица 1.3

*J *2*1 *0 bs bt b„

Oto Oil too tot Ito 111

Pyc Лат Pyc. Лат Pyc Лат Рус. Рат

0 000 Пробел 0 Ю © n P w п р

ООО 1 t 1 a A я a ft а я 3

00Ю * 2 6 В p R 6 ь р г*

ООП * J 4 c c s и с с 5

0 100 <t 9 D m T Д d т t

0 101 % 5 e E 3 и E е У и

otto & 6 <p F ж V Ф f ж и

0 111 » 7 г G 6 vv Г 3 в из

1000 ( 8 JL H b X Л ь X

>001 ) 3 a I bl Y И i ы У

1O1O * (1 J J 2 Й } 3 2.

ton + • к к tu I к к ш

ttoo V < л L 3 \ л L 3 1

1101 — = w M 4 ] м гп 01

1 110 > rt V V A н п ч

1111 / ? 0 0 b — 0 О 1

ется двоичный код КОИ-7 (код для обмена информацией семи-

разрядный) *, с помощью которого передаются цифры от 0 до 9,

прописные и строчные буквы латинского и русского алфавитов,

специальные символы: знаки пунктуации, арифметических опера-

ций и др. (табл. 1.3).

Отметим, что первые 32 кода с 0000000 до 0011111 (в табл. 1.3

не приведены) служат для представления специальных команд

для управления процессом обмена информацией между цифровы-

ми системами и устройствами ввода-вывода и хранения (дисп-

леи, принтеры, накопители на магнитных лентах или дисках). На-

пример, код 0001110 обеспечивает представление текста в рус-

ском алфавите, код 0001111 — в латинском (см, табл. 1.3). От-

дельные управляющие коды служат запросом на обмен информа-

цией (0000101) и подтверждением готовности к обмену (0000110),

указывают на начало (0000010) и конец (0000011) текста, вызы-

вают переход на новую строку (0001010) и другие действия. Код

0100000 вызывает пропуск одного символа в тексте (правом), а

код 1111111 — уничтожение символа (забой). Числа от 0 до 9

представляются кодами от 0110000 до 0111001. Так как в русском

алфавите больше букв, чем в латинском, то при его использовании

1 В зарубежных источниках аналогичный код называется ASCII (American

Standard Code for Information Interchange).

17

некоторые специальные символы, например [, {, Д и др., исклю-

чаются (см. табл. 1.3).

Для проверки правильности передачи и приема информации в

цифровых системах широко используется контроль четности. При

этом для каждого байта числа определяется количество единиц

в его разрядах и формируется дополнительный контрольный раз-

ряд (бит четности), который принимает значение р~\, если число

единиц четное, или р = 0, если число единиц нечетное. Например:

р=1 для числа 10110010, р = 0 для числа 01001010.

Контрольный разряд передается вместе с соответствующим

байтом информации. Принимающее устройство проверяет четность

каждого принятого байта и сравнивает ее со значением принятого

контрольного разряда. Если обнаруживается различие в значениях

четности, то это указывает на ошибку при передаче информации.

Контроль четности позволяет выявить единичные сбои, т. е. из-

менение значения одного разряда числа, а также те многократные

сбои, которые вызывают изменение четности. Как показывает

практика, контроль четности позволяет выявить до 80... 90% оши-

бок, возникающих при передаче информации из-за действия по-

мех, нарушения контактов в соединениях и других причин.

1.2. ВЫПОЛНЕНИЕ АРИФМЕТИЧЕСКИХ

ОПЕРАЦИИ

С целью упрощения цифровых систем для выполнения арифме-

тических операций над двоичными числами применяются специ-

альные алгоритмы. Так, операцию вычитания в цифровых систе-

мах реализуют с помощью операции сложения, представляя вычи-

таемое в обратном или дополнительном коде (см. табл. 1.1). Если

представить вычитаемое в обратном коде, то можно получить раз-

ность путем арифметического сложения уменьшаемого (в обычном

двоичном коде) п вычитаемого (в обратном коде). Если в зна-

ковом разряде образуется перенос, то эта 1 прибавляется к млад-

шему разряду суммы. Такое прибавление 1 называют цикличес-

ким переносом. Примеры сложения и вычитания чисел приведены

ниже. Исходные числа и результат операций представлены в об-

ратном коде: положительные числа (2 = 0) в прямом, отрицатель-

ные (2=1) — в инверсном виде:

2,->0 ;01 1ОО-<-Л2=Ло= 12, zA —> 1 1010104-Л г = А1 о — —21

+ — 1

11011-<-fi2 = Blo = —4, гв-> 1 ; 10001-<—В2 = В,о = — 14

-10 :00111 циклический , 1 ОЮКй-Тг

— 2 перенос 1 0 ;0111O^-S2

г,->1 01000-*-2=S1 о = 8 Zs “* 1 ill ООО*—5 2=51 о= —7.

18

Недостатком использования обратного кода является образо-

вание циклического переноса, который приводит к повторению опе-

рации сложения, что существенно увеличивает время выполнения

действий. Поэтому чаще используются перевод вычитаемого в до-

полнительный код (см. табл. 1.1) и его сложение с уменьшаемым.

При этом перенос, который может возникать в старшем разряде

числа, не учитывается, т. е. отпадает необходимость в цикличес-

ком переносе. Вычитание с применением дополнительного кода

выполняется быстрее, хотя преобразование чисел в дополнитель-

ный код несколько сложнее, чем в обратный. Ниже даны примеры

сложения и вычитания чисел со знаком, представленных в допол-

нительном коде. Полученный результат также представлен в до-

полнительном коде, т. е. в обычном коде, если zs = 0 (положитель-

ное число), или в преобразованном виде, если zs= 1 (отрица-

тельное число):

о ~ t +11 ч: йэ N Гм 00110^-Л 2 =А 10= 12 11 Ю0-—В2 = В)о = — 4 1 Zb-* * О1О11-<-Л2=4]о=—21 1ОО1О-<-В2 = В1о=—14

10 01000 1 01011-<-а2

+

2s->-0 U1 2 = *5' 1 о = 8 0 01110«-В2

zs_>" 1 11OO1^52 = S,o=—7.

Умножение пли деление двоичного числа на 2'1=2, 4, 8 и т. д.

производится путем сдвига цифр числа соответственно, вправо или

влево па k= 1, 2, 3 и т. д. разрядов.

Для умножения произвольных двоичных чисел А и В использу-

ются различные варианты метода частичных произведений. Один

из вариантов данного метода иллюстрируется ниже на примере.

При этом последовательно анализируются значения разрядов мно-

жителя В п формируются частичные произведения. Первое частич-

ное произведение 7?,=0 при значении младшего разряда Ьо = О или

Л?.—.4 при &о=1. Далее рассматриваются разряды Ь2 и т. д.

Если b,= 1, то очередное частичное произведение 7?.+! образуется

путем прибавления к предыдущему множимого А, сдвинутого вле-

во на I разрядов. Если &, = 0, то частичное произведение не меня-

ется: (прибавляется 0). Последнее частичное произведе-

ние Rn является результатом умножения P=AXB=Rn.

19

X 1101 :А2 1011 :В2 1101-*—А2 = Аю= 13, Пд = пв = 4 Х 1011*-В2 = Вю=11

1101 :Ri 00001101-*-а0= 1 (суммирование и.

+ 1101 + сдвиг)

2А : 100111 :Ri 101 10000-*-В;-2 А 101 1 1 101-Э-СДВИГ суммы

+ 100111 :/?з >-01011110->-(го) i = 0 (сдвиг)

8Л : 1101 /?2—>-00101111—>-(го) 2 = 1 (суммирование

10001111 :R< = Pi I и сдвиг) 101100004-52-2^ 11011111—>-сдвиг суммы R3->-01101111—>-(го) з= 1 (суммирова- । ние и сдвиг) Ю1Ю0004-В2-2Пл 100011111-»-сдвиг суммы Т?4->-10001111-*Р2 = Р,о = 143.

Второй пример иллюстрирует вариант реализации метода час-

тичных произведений, при котором умножение выполняется со

старших разрядов. При этом множитель В2 предварительно сдви-

гается влево на пА разрядов, где пл — число разрядов множимого

А2. Затем проверяется значение младшего разряда множимого До.

Если До=1, то первое частичное произведение 7?! образуется путем

арифметического сложения А и В-2"А (множитель, сдвинутый на

пА разрядов) и последующего сдвига суммы вправо на один раз-

ряд. При этом крайний правый разряд суммы выходит за пределы

разрядной сетки и не учитывается. Если а0= 1, то частичное про-

изведение образуется только сдвигом вправо на один разряд с по-

терей крайнего правого разряда. Далее проверяется значение

младшего разряда (r0)i полученного частичного произведения и

образуется второе частичное произведение R2 суммированием

и B-2"A со сдвигом суммы вправо на один разряд (при (г0),=

= 0). Аналогичная процедура получения частичных произведений

повторяется пв раз, где пв — число значащих разрядов множите-

ля. Последнее частичное произведение является результатом умно-

жения: P = Ay.B = Rn.

Таким образом, умножение двоичных чисел производится пу-

тем последовательного выполнения операций сложения и сдвига.

Поэтому умножение требует существенно большего времени рабо-

ты цифрового устройства, чем сложение и вычитание.

Дли деления двоичных чисел в цифровых системах чаще всего используется

метод деления с восстановлением. Если делимое Аг больше делителя В<, то

предварительно производится масштабирование делимого А* путем его сдвига

20

вправо на I разрядов, чтобы получить Л'2<В2. Затем сдвигом А'2 влево на

один разряд образуют число 2Л'2 и выполняют вычитание 2Л'2—В2. Если по-

лучаемый в результате промежуточный остаток Rt = 2A'2—B2 имеет отрица-

тельный знак (zRj = l), то старший разряд частного s_i=0, если положитель-

ный знак (гЯ1=0), то s_i=l. При s_i=l остаток удваивается сдвигом

влево, при s-i = 0 вместо остатка используется число 2А'г, которое также

удваивается. Из полученного значения 2Rt или 4Л'2 снова вычитается В2.

Если результат /?2 отрицательный, то следующий разряд частного S-2=0, если

положительный, то s_2=l. Вычитание выполняется с помощью одного из опи-

санных выше методов. Для получения частного S'2 с точностью до А-го знака

данная процедура повторяется k раз. При этом анализируется знак каждого

промежуточного остатка гЯ1 и следующий остаток определяется как разность

Я1 + 1 = 2Л,—В2, где Xi = Rt при Zju = 0, X< = 2R<_t при дя> = 1, где 1 = 0, 1, ..., k;

Хо = 2А2. В результате получаются частное от деления А2 на В2 в виде пра-

вильной дроби S'2=0, S—1, s-2, — ,s_k и остаток деления P’2—Rk-2~k. Значе-

ния частного S2 и остатка Р2 образуются в результате восстановления мас-

штаба с помощью сдвига S'2 н Р'2 влево на I разрядов.

Пример. Деление Л2 = 0,0111 на В2=0,1100: так как А2<В2, то масштаби-

рование не требуется

Ао=2Л2-*О,111О

В2-*0,1100

/6 = (2А2—В2)->- +0,0010>0, s-i= 1,

Л,=2/?.-Н),0100

Вг~*-0,1100

Л=(2/?1—B2)-f—0,1000<0, s-2=0,

Л2=4В.-*0,1000

Вг-ьОДЮО

Л2= (4J?i—В2)->—0,0100<0, s-s=o,

Л,=8/?,-* 1,0000

Вг-ьОДЮО

/?4=(8Л1—В2)-*0,0100>0, 3—4=1,

Получаем частное S2=0,1001 и остаток В2=0,01-2-3=0,000001.

Таким образом, деление чисел осуществляется путем последовательного вы-

полнения операций вычитания1 и сдвига. Знак результата при умножении в

делении получается суммированием знаковых разрядов без учета переноса,

получающегося при гЛ=ля=1.

Описанные выше методы выполнения арифметических опера-

ций, рассмотренные для чисел с фиксированной запятой, применя-

ются и для операций над мантиссами чисел с плавающей запятой.

Однако при этом требуется еще выполнение определенных опера-

ций с порядками чисел. При сложении и вычитании чисел с пла-

вающей запятой предварительно производится выравнивание

1 Можно заменить вычитание сравнением двух чисел 2А( и В2, последова-

тельно получая значения разрядов частного: s_(l+i) = l при 2Xi>B2; s_(,T1, = 0

прн 2Af<B2.

21

порядков рл и рв обоих чисел путем сдвига мантиссы од-

ного из них, например B2i на рл—рв разрядов вправо, ес-

ли рл>рв, либо влево, если рл<рв> Порядок результатов при

этом будет Ps=Pa- При умножении или делении чисел с плаваю-

щей запятой порядок результата равен соответственно сумме или

разности порядков: рз = рд±рв.

При использовании самодополняющнх двоично-десятичиых ко-

дов вычитание заменяется сложением аналогично тому, как это

производится для двоичных чисел в случае применения обратного

кода. При этом все отрицательные числа представляются в обрат-

ном самодополняющем коде. При вычитании вычитаемое преобра-

зуется в обратный код и производится его суммирование с умень-

шаемым. В случае образования переноса в старшем (знаковом)

разряде выполняется его прибавление к младшему разряду млад-

шей тетрады (циклический перенос). Затем производится допол-

нительная операция — коррекция кода в каждой нз тетрад.

Рассмотрим выполнение операции сложения-вычитанпя с применением ко-

да <с избытком 3». Исходные данные п результат операции при этом пред-

ставляются в коде <с избытком 3»: положительные числа (г=0) в прямом, а

отрицательные (z=l) — в обратном (инверсном) виде. При сложении сумми-

руются соответствующие тетрады двоичных разрядов. При вычитании вычи-

таемое сначала переводится в обратный код, а затем производится суммиро-

вание. Если при суммировании в тетраде не образуется перенос из старшего

разряда, то сумма, полученная в данной тетраде, превышает па 3 действи-

тельное значение результата в коде «с избытком 3». Поэтому для коррекции

значения суммы, полученной в этой тетраде, необходимо вычесть 3, что экви-

валентно прибавлению 1101 (3 в дополнительном коде). Если в тетраде обра-

зуется перенос, т. е десятичное число 16, то 10 поступает в виде двоичной 1

в младший разряд следующей тетрады, а 6 необходимо добавить к сумме,

полученной в данной тетраде. Но так как для коррекции кода необходима

вычесть 3, то достаточно добавить (6—3)=3, т. е. ООН. Переносы, возинкаю-

ь не прн коррекции, не учитываются. Знаковые разряды чисел также сумми-

руются. Перенос, образуемый в знаковом разряде, циклически переносится в

младший разряд младшей тетрады. Выполнение этих операций иллюстрируется

следующими примерами:

гл'. 0 : ОНО гг: । 1 j 1011 0111 А 2/1о А ю = 34 0011 Вю = —19

1 0-_0001 1010 циклический перенос

0 ; 0001 + -ООН 1011 jjQj коррекция

0 :0100J1000

4

1 —перенос не

учитывается

0 0100 I 100 : Лл2/1в=Л 10 = = 19

Zb' 0 оно 0111*. В/2/Ю = В10 = 34

0 + 0 0100 1001 1100: 4i0 1000 : В2/10

1 1110 0100

1101 ООП коррекция

1 1011 0111: 5S/io = <$ю= -15

I

1 — перенос не учитывается

22

Выполнение арифметических операций прн двоично-десятичном

представлении сложнее, чем при двоичном, из-за необходимости

коррекции. Однако при обработке большого количества данных

этот недостаток компенсируется простотой перевода чисел в дво-

ично-десятичную форму.

1.3. ОСНОВЫ БУЛЕВОЙ АЛГЕБРЫ

Теоретической основой проектирования цифровых систем явля-

ется булева алгебра, названная по имени ее основоположника

Д. Буля. В булевой алгебре различные логические выражения

(высказывания) могут иметь только два значения: «истинно» или

«ложно». Это условие называется законом «исключенного

третьего». Для обозначения истинности или ложности высказыва-

ний пользуются символами 1 или 0.

В общем случае логические выражения являются функциями

логических переменных А, В, С и др., каждая из которых может

иметь значения 0 или 1. Если имеется k логических переменных,

то они образуют 2А возможных логических наборов из 0 и 1. При

&=1 А=0 и А=1; прн k = 2 АВ = 00, 01, 10, 11 и т. д. Для каж-

дого набора переменных логическая функция F может принимать

значение 0 нли 1. Поэтому для k переменных можно образовать

//. = 22*различных логических функций. Таким образом, при k = 2

можно получить Z= = 16 функций н далее при увеличении k число

Ik растет чрезвычайно быстро: /3 = 256, /4 = 65 536 и т. д.

Все возможные логические функции k переменных можно обра-

зовать с помощью трех основных операций: логическое отрицание

(инверсия, операция НЕ), обозначаемое символом «—» над соот-

ветствующей переменной; логическое сложение (дизъюнкция, опе-

рация ИЛИ), обозначаемое символом «V», логическое умножение

(конъюнкция, операция И), обозначаемое символом «Д», который

для простоты записи обычно опускается. Для обозначения эквива-

лентности логических выражений используется знак « = ». В табл.

1.4 и 1.5 дано табличное представление логических операции от-

рицания, сложения, умножения для переменных А, В.

Для рассмотренных логических операций справедлив ряд ак-

сиом (тождеств) и законов, основные из которых даны в табл.

Таблица 1.4 Таблица 1.5 Табличное представление Табличное представление операций операции инверсии и конъюнкции дизъюнкции

А Г=А А в &=А+В F=A-B

0 1 0 1 0 о ! 0 1 0 1 0 1 1 1 0 0 0 1

23

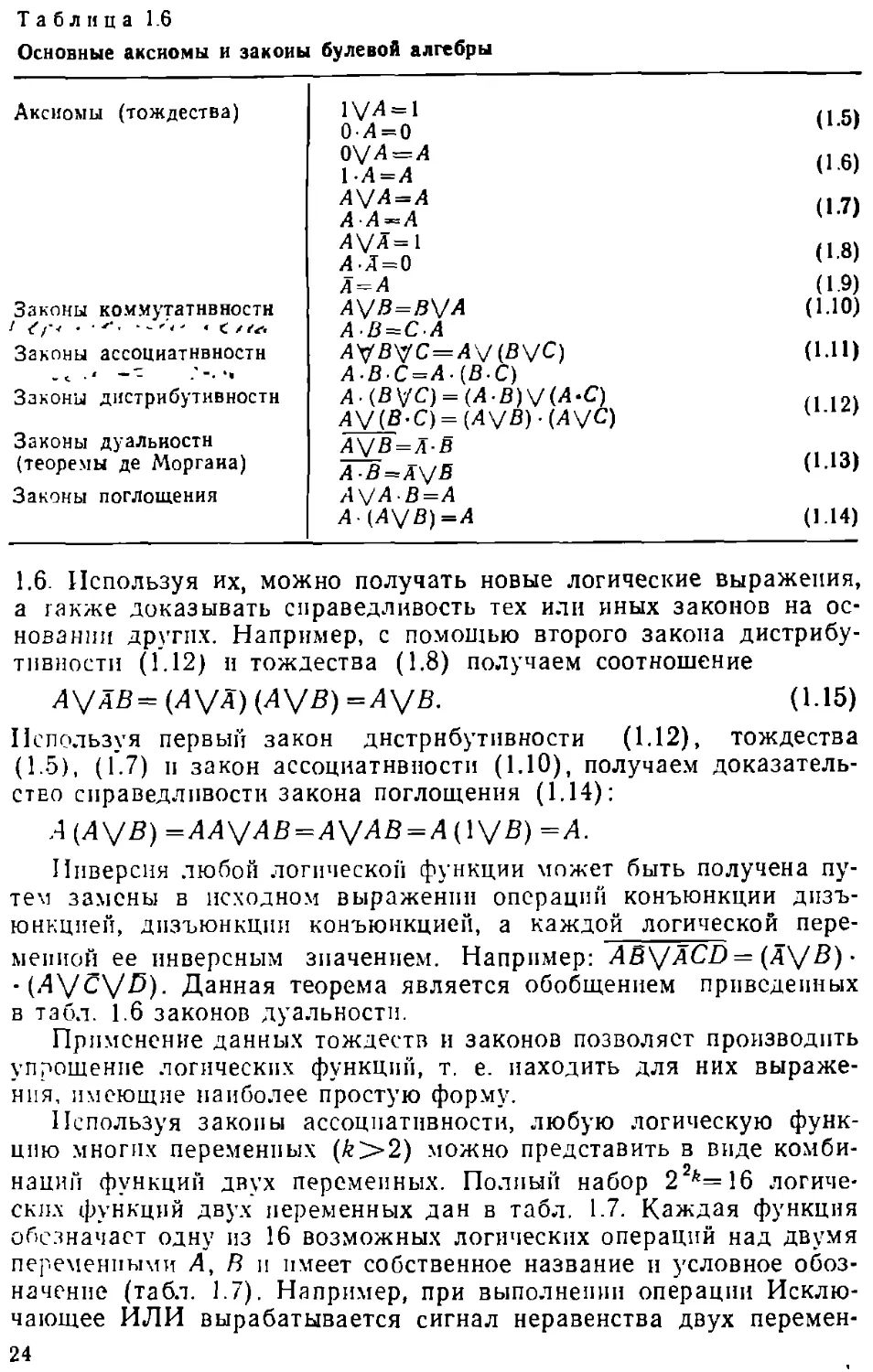

Таблица 1.6

Основные аксиомы и законы булевой алгебры

Аксиомы (тождества) 1= 1 / 1 сь 0Д = 0 (1'5' °УаАЛА (16) (17) AV/==o‘ <18) Л = А (1.9)

Законы коммутативности / Законы ассоциативности Законы дистрибутивности АУВ=В\/А (1.10) АВ = СА AVBVC=AV(BVC) (МП АВС=А(ВС) Д. (В(/С) = (A-В) V(A-C) ,112) AV(S-C) = (AVB)'(4VC) 1 1

Законы дуальности (теоремы де Моргана) Законы поглощения АуВ = ЛВ АВ=АуБ (113) А\/АВ=А А(А\/В)=А (1.14)

1.6. Используя их, можно получать новые логические выражения,

а также доказывать справедливость тех или иных законов на ос-

новании других. Например, с помощью второго закона дистрибу-

тивности (1.12) н тождества (1.8) получаем соотношение

Д\МВ=(4\М)(Л\/5)=Л\/Я- <115)

Используя первый закон дистрибутивности (1.12), тождества

(1.5), (1.7) п закон ассоциативности (1.10), получаем доказатель-

ство справедливости закона поглощения (1.14):

.4 (А\/В) =АА^АВ = А\/АВ = А(}\уВ) =А.

Инверсия любой логической функции может быть получена пу-

тем замены в исходном выражении операций конъюнкции дизъ-

юнкцией, дизъюнкции конъюнкцией, а каждой логической пере-

менной ее инверсным значением. Например: AB\/aCD = (А\/В)

(АусуИ). Данная теорема является обобщением приведенных

в табл. 1.6 законов дуальности.

Применение данных тождеств и законов позволяет производить

упрощение логических функций, т. е. находить для них выраже-

ния, имеющие наиболее простую форму.

Используя законы ассоциативности, любую логическую функ-

цию многих переменных (#>2) можно представить в виде комби-

наций функций двух переменных. Полный набор 22*=16 логиче-

ских функций двух переменных дан в табл. 1.7. Каждая функция

обозначает одну из 16 возможных логических операций над двумя

переменными 4, В и имеет собственное название и условное обоз-

начение (табл. 1.7). Например, при выполнении операции Исклю-

чающее ИЛИ вырабатывается сигнал неравенства двух перемен-

24

Таблица 1.7

Полный набор логических функций двух переменных

А о о 1 I

В 0 10 1

Условное обозначение и

алгебраическое выражение

Название функция

о

о

о

о

о

о

о

о

1

1

1

1

1

1

1

1

о о

о о

О I

О 1

I о

1 о

1 1

О Fo=O

1 Ft=AB

О Ft=A~B=AB

1 Л,=Л

О Ft=B^A=AB

1 Л = В

О F6=A®B=AB+AB

О 1 О

О 1 1

1 О О

1 0 1

1 1 О

1 1 1

F10=S

Fu = B-<-H=^+5

F12 = A

f,3=A-»B=J+B

F,<=A/B=AB

Fis=1

Постоянный 0

Конъюнкция

Запрет

Тождественность А

Запрет

Тождественность В

Исключающее ИЛИ

(неравнозначность)

Дизъюнкция

Операция Вебба (ИЛИ—НЕ)

Равнозначность (эквивалент-

ность)

Инверсия В

Импликация от В к Л

Инверсия А

Импликация от Л к В

Операция Шеффера (И—НЕ)

Постоянная 1

ных; F&—1 при Л =/=/?; /?6 = 0 при А = В. При выполнении операции

Равнозначность вырабатывается сигнал равенства переменных:

/4=1 при Л=В; 77б = 0 при А=£В. Для более сложных функций:

Запрет, Импликация, Равнозначность, Исключающее ИЛИ, опе-

рации Вебба и Шеффера — даны их выражения с помощью эле-

ментарных операций инверсии, дизъюнкции, конъюнкции.

Укажем некоторые соотношения между функциями двух пере-

менных, используемые при преобразованиях логических выраже-

ний:

F2=A = Л В = Л 3 = Л-*В =Л V В; (1.16)

Ft=B =7Л=лВ = Г11 = В-*Л =Л VB; (1.17)

Fs=A®B = AB\JaB = F')=A~B=AB\/AB. (1.18)

Справедливость этих соотношений следует из табл. 1.6, а также

легко доказывается с помощью законов дуальности.

Логические функции могут иметь различные формы представ-

ления: словесное, табличное, алгебраическое, графическое. Напри-

мер, функцию Fg = f(A, В), заданную в виде словесного описания:

Л> = 1, когда значения переменных А=В, и /4 = 0, когда Л=/=В,

можно представить в виде таблицы истинности (табл. 1.8) или в

алгебраической форме F<j = AB\/AB (см. табл. 1.7). Таблица ис-

тинности содержит все 2А возможных наборов значений логичес-

ких переменных и значения функции, соответствующие каждому

из наборов.

25

Таблица 1.8 Табличные истин- ности функции равнозначности Fg Таблица 1.9 Минтермы, макстермы и значения функция Fo

А в Минтермы Макстермы Значения функции

А в F'

0 0 1 0 0 та = АВ Л10=А\/Й Л>=1

0 1 0 0 1 Ш[ = АВ .Щ=А\/В /, = 0

I 0 0 1 0 т2=АВ !г= 0

1 1 1 1 1 т$=АВ ,M3 = AVB fs=l

Чтобы осуществить переход от табличного представления к ал-

гебраическому, каждому набору переменных ставится в соответст-

вие минтерм (конституента единицы) — конъюнкция всех пере-

менных, которые входят в прямом виде, если значение данной пе-

ременной в наборе равно 1, либо в инверсном виде, если значение

переменной равно 0. Для k переменных составляется q = 2h мннтер-

мов1: mo, mt,..., т7_,. Все минтермы двух переменных даны в

табл. 1.9. Значения функции F, соответствующие согласно таблице

истинности данному t-му набору переменных, будем обозначать

(см. табл. 1.9). Как видно из табл. 1.8 и 1.9, алгебраическое пред-

ставление функции является дизъюнкцией минитермов, соответ-

ствующих наборам переменных, для которых Д = 1: Рэ = [2т0\/

= 1-(АВ)У0-(ЛВ)\/0-(Д5)У’-(^) =ABV

УАВ.

В общем случае алгебраическое выражение любой логической

функции можно представить в следующей форме:

fim,, (1.19)

i-о

где f;, m, — значение функции (0 пли 1) и минтерм, соответствую-

щие (-му набору переменных. Такое представление функции назы-

вается ее совершенной дизъюнктивной нормальной формой

(СДНФ).

Другая алгебраическая форма представления функции получа-

ется при использовании макстермов. Макстермом (конституентой

0) называется дизъюнкция всех переменных, которые входят в

прямом виде, если значение данной переменной равно 1, либо в

инверсном виде, если значение переменной равно 0 (см. табл. 1.9).

Число макстермов, как и минтермов, для функции k переменных

равно q = 2‘‘. Алгебраическое выражение функции получается в ви-

де произведения

F= ’п (f.V^i). (1-20)

!=0

1 Номер (индекс) минтерма равен значению двоичного числа, которое обра-

зуется соответствующим набором переменных (см. табл. 1.9).

26

где ft, Mi — значение функции и макстерм, соответствующие i-му

набору переменных. Такое представление функции называется ее

совершенной конъюнктивной нормальной формой (СКНФ). Напри-

мер, для функции F9, используя табл. 1.9, получаем СКНФ в виде

F9 = (foVAfo) (Л(bVAt2) ЦЛ/Мъ) = (IV^VB) X

х (0VAV5) (0\MV£) UW^) = WVB) HV5).

На практике часто используется сокращенная форма записи

СДНФ и СКНФ, при которой указываются только номера минтер-

мов (макстермов), входящих в выражение функции

F=2(x,, .... хк)=П(у„ .... yt), (121)

где (xi, ..., Xk) — номера (индексы) минтермов, соответствующих

значениям Л=1; (t/i, ..., yt) — номера (индексы) макстермов, со-

ответствующих значениям f; = 0; 1, П — обозначения логического

сложения и умножения. При этом функция F9 (см. табл. 1.7 и

1.8), которую можно представить как дизъюнкцию минтермов та,

шз или конъюнкцию макстермов АЛ, М2, задается в виде: F9 =

= 1(0,3) или Л’9 = П(1,2). Используя законы булевой алгебры (см.

табл. 1.6), нетрудно доказать эквивалентность полученных СДНФ

и СКНФ функции F9.

Если в выражениях (1-19) и (1-20) вместо /( использовать

Ji — инверсии значений функции, то получается СДНФ и СКНФ

для функции, являющейся инверсией заданной. Например, из

табл. 1.9 получаем Вэ~А~ В=АВ\/АВ = (А\/В) (А\/В) =FS=

= АФВ.

Таким образом осуществляется переход от таблицы истинности

к алгебраическому представлению логической функции, и любая

логическая функция может быть представлена в виде СДНФ илн

СКНФ.

Обратный переход от алгебраического к табличному представ-

лению функции выполняется путем последовательной подстановки

в данное алгебраическое выражение всех q возможных наборов

переменных, определения соответствующих значений F=fi для

каждого 1-го набора (Os^is^p—1) и заполнения таблицы истин-

ности.

При относительно небольшом числе переменных (fe^6) весьма

удобным и наглядным является графическое представление логи-

ческих функции в виде так называемых карт минтермов. Наибо-

лее распространенной их формой являются карты Карно. На рис.

!-1 показаны карты Карно для функций £ = 2, 3, 4, 5 переменных.

Карта Карно содержит р = 2'1 клеток, причем каждой клетке соот-

ветствует один из q минтермов. Для иллюстрации этого па рис.

11,а.—в в клетках карт Карно записаны соответствующие им мин-

термы. Если требуется представить на карте Карно логическую

Функцию, заданную в виде СДНФ, то в клетках карты соответст-

вующих миитерм, входящих в СДНФ, ставятся 1. Остальные клет-

ки остаются незаполненными или заполняются 0. Примеры графи-

27

4ВХ 00 01 Н Ю

«ст леев ABCD

«СТ «ст мп мп

«СТ мсп мсв A8CD

«ст МП мп АВСВ

в

')

Рис. 1.1. Карты Карно и расположение в

них минтермов для функций двух (а),

трех (fi), четырех (я), и пяти (<?) перемен-

ных

Рис. 1.2. Примеры пред-

ставления функций на

карты Карно:

a = F = ABVAB‘, б-Р =

= А~ВС VABCVABCV

V ABC; e — F=ABC~DV

VABCDVABCDV ABCD

ческого представления функций, заданных в виде СДНФ, показа-

ны на рис. 1.2,а—в.

Каждой клетке карты поставлен также в соответствие один из

наборов логических переменных, который определяется номером

столбца и строки, на пересечении которых расположена клетка.

Например, на рис. 1.1,в на пересечении столбца с номером АВ =

= 01 и строки с номером С£)=10 расположена клетка, соответст-

вующая набору переменных ДВС£> = 0110 (минтерм ABCD). Бла-

годаря этому удобно представлять на карте Карио функции, за-

данные таблицами истинности. Если при i-м наборе переменных

значение функции в таблице истинности то в соответст-

58

вуюшей клетке карты Карно ставится 1 (т. е. соответствующий

миитерм mt входит в СДНФ функции). Если же F—fi = O, то клет-

ка оставляется пустой либо ставится 0 (т. е. соответствующий

минтерм не входит в СДНФ функции). Таким образом, между

представлением функции в табличной (таблица истинности), ал-

гебраической (в виде СДНФ) и графической (на карте Карно)

формах имеется однозначное соответствие.

Логическая функция F на карте Карио представляется сово-

купностью клеток, заполненных 1, инверсия функции F представ-

ляется совокупностью пустых клеток (или заполненных 0). На

рис. 1.2,а дано представление в виде карты Карно функции Иск-

лючающее ИЛИ F6 в соответствии с ее таблицей истинности (см.

табл. 1.7). Инверсия Fe, — F9—AB\/aB (см. табл. 1.8) представля-

ется на этой карте совокупностью пустых клеток.

Для логических функций с числом переменных й>6 карты

Карно становятся громоздкими (число клеток <?>64) и неудобны-

ми для практического применения. Поэтому использование карт

Карно можно рекомендовать при числе переменных'

Рассмотренные выше (см. табл. 1.7) логические функции были

определены, т. е. имели определенное значение ft = Q или /ч=1

при всех возможных наборах логических переменных. Такие логи-

ческие функции называются полностью определенными. Кроме них

имеется большой класс функций, значение которых определено

только для части логических наборов переменных. Такие функции

называются частично определенными. Наборы переменных, для

которых функция определена, называются рабочими, а для кото-

рых не определена — безразличными. Значения функции, соответ-

ствующие безразличным наборам, будем обозначать в таблицах

истинности и на картах Карно знаком «X». Если частично опре-

деленная функция представляется в виде СДНФ или СКНФ, то

указываются также минтермы (макстермы), соответствующие без-

различным наборам. При этом форма записи (1.19), (1.20) допол-

няется указанием мпнтермов (макстермов) с неопределенным

значением функции:

F = 2(xi, .... Xfc)+2H(x'. х'п); (1.22)

^=П(у...... 4ff)II„(fif'i. у'т), (1.23)

где л', у' — номера минтермов, для которых значение функции

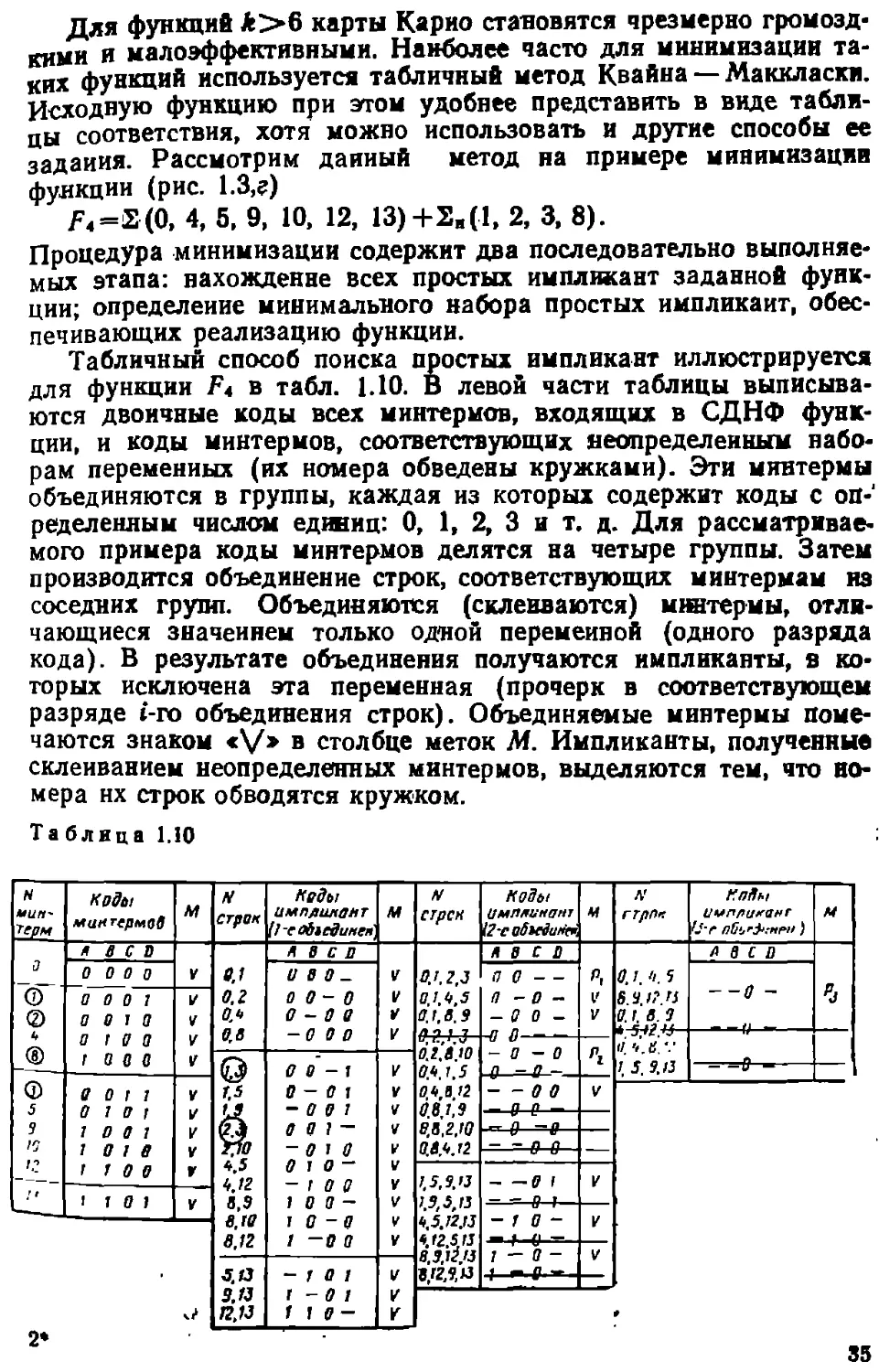

не определено. В качестве примера на рис. 1.3,а представлена час-

тично определенная функция F=S(0, 4, 5, 9, 10, 12, 13), SH(1, 2,

3, 8).

На практике безразличными являются такие наборы значений

логических переменных, которые при работе данного цифрового

устройства никогда не реализуются. Частично определенную функ-

1 Имеются специальные приемы, позволяющие выполнять с по-

мощью карт Карно представление и преобразование функций с числом перемен-

ных до А = 8...9. Однако изучение этих приемов выходит за рамки настоящего

Пособия,

29

цию можно сделать полностью определенной (доопределить),

приписав безразличным наборам какие-либо значения функции:

ft —0 или 1. Доопределение функции проводится таким образом,

чтобы упростить ее алгебраическое выражение и практическую

реализацию.

Как указано выше, любую логическую функцию можно пред-

ставить в виде СДНФ пли СКНФ, т. е. с помощью соответствую-

щей комбинации простейших логических функций И, ИЛИ. НЕ.

Набор простейших функций, с помощью которого можно выразить

любые другие, сколь угодно сложные логические функции назы-

вается функционально полным или логическим базисом. Таким об-

разом, набор функций И, ИЛИ, НЕ является одним из логичес-

ких базисов.

Логический базис называется минимальным, если удаление хо-

тя бы одной из входящих в него функций превращает этот набор

в функционально неполный. Логический базис И, ИЛИ, НЕ не яв-

ляется минимальным, так как с помощью законов дуальности

можно исключить из логических выражений функцию И либо

ИЛИ. В результате получаем минимальные базисы: И, НЕ и

ИЛИ, НЕ. Имеются минимальные логические базисы, содержа-

щие только одну функцию: Шеффера (И—НЕ) или Вебба

(ИЛИ—НЕ) (см. табл. 1.7). Функциональная полнота этих на-

боров функций следует из того, что с их помощью можно реали-

зовать все функции логических базисов {И, НЕ}, {ИЛИ, НЕ} в

соответствии с выражениями

Л\А=а, А-В=ДТВ=(А|В)|(А|В),

А±А=а, А+В = Дфб=(А|Д)|(А|В).

Электронные схемы, выполняющие простейшие логические опе-

рации, называются логическими элементами. Для реализации в

цифровых системах разнообразных логических функций достаточ-

но иметь логические элементы, реализующие операции того или

иного минимального базиса. Этот набор логических элементоз на-

зывается минимальным элементным базисом (или базой). В сов-

ременной микроэлектронике таким базисом чаще всего служат

элементы И—НЕ либо ИЛИ—НЕ.

Реализация цифровых систем с использованием только элемен-

тов минимального базиса часто приводит к излишней сложности

устройств и ухудшает их основные эксплуатационные параметры.

Поэтому для улучшения характеристик систем при их построении

обычно используют расширенные (избыточные) элементные бази-

сы. в которых кроме элементов И—НЕ, ИЛИ—НЕ входят схемы,

выполняющие функции И—ИЛИ—НЕ, Исключающее ИЛИ и др.

(см. гл. 2).

30

1.4. ПРЕОБРАЗОВАНИЯ ЛОГИЧЕСКИХ

ФУНКЦИИ

Используя законы и тождества булевой алгебры, можно полу-

чать для каждой логической функции множество эквивалентных

представлений. Чем проще логическое выражение функции, тем

меньше элементов требуется для ее реализации. В результате

микросхема, выполняющая эту функцию, будет иметь лучшие по-

казатели по быстродействию, потребляемой мощности, площади

кристалла. Сложность логической функции {Е} определяется ко-

личеством переменных, входящих в ее алгебраическое выражение

в прямом пли инверсном виде. Минимальным называется такое

эквивалентное представление функции, которое имеет минималь-

ную сложность. Процедура получения минимального представле-

ния функции называется минимизацией. В данном параграфе рас-

смотрены методы минимизации функций, заданных в дизъюнктив-

ной нормальной форме (ДНФ). Используя законы дуальности, эти

методы можно применить и для упрощения функций в конъюнк-

тивной нормальной форме (КНФ).

Представление функции в виде СДНФ (1.19) в большинстве

случаев не является минимальным. Используя для понижения

сложности операции склеивания АВ\/ АВ = А и поглощения А\/

\АВ=А, его часто можно существенно упростить. В результате

получается сокращенная ДНФ, которая является дизъюнкцией

конъюнктивных членов, которые могут не содержать всех пере-

менных, т. е. не быть мпптермами. Эти конъюнктивные члены на-

зываются импликантами. Для примера рассмотрим процедуру уп-

рощения функции

Л = АВС\/АВС\/аВС\/аВС\/аВС =

= ABC\J(aB\JaB) (C\Jc)=ABC\/AB\/aB =

= ABC\JX(B + B) =ABC\Ja = BC\Ja.

Исходная СДНФ, имеющая сложность {А7,} = 15, преобразуется в

ряд сокращенных ДНФ различной сложности: {Ei} = 15->7->4->3.

В результате получена ДНФ, содержащая всего две импликанты:

1 п ВС. Полученная ДНФ имеет минимальную сложность, т. е.

является минимальной ДПФ (МДНФ).

При проектировании цифровых устройств исходные логические

'пункции, заданные в виде СДНФ или сокращенной ДНФ, преоб-

разуются для получения МДНФ с помощью одного из разрабо-

танных методов минимизации.

Для минимизации функций относительно небольшого числа пе-

ременных (й^б) наиболее простым и наглядным является гра-

фический метод, использующий карты Карно. При использовании

этого метода исходная функция представляется иа картине Карно

(рис. 1.3). Минтермы, соответствующие двум соседним (в стрлб-

Це или ряду) клеткам карты Карно, отличаются значениями толь-

ко одной переменной. Поэтому дизъюнкция этих минтермов дает

31

Рис. 1.3. Примеры минимизации логических функций fi(a), Fa(6), Fj(e) в

F, (г) с помощью карт Карно

одну импликанту, в которой исключена переменная, имеющая

взаимониверсные значения. Например, для минтермов, соответ-

ствующих двум соседним клеткам, занятым 1, в третьем столбце

карты Карно на рис. 1.3,а получаем аВС\/АВС= (А\/А)-ВС**

— ВС. Таким образом, импликанта ВС включает в себя два мин-

терма: АВС и АВС.

Чтобы выделить на карте Карно клетки, представляющие одну

импликанту, их графически объединяют (обводят тонкой линией).

Импликанта ВС представляется на картах Карно двумя объеди-

ненными клетками. Такое объединение клеток на картах Карно

эквивалентно выполнению операции склеивания минтермов и поз-

воляет получать более простое выражение логической функции.

Поэтому для минимизации логических выражений вместо нх алге-

браических преобразований можно выполнять соответствующее

объединение клеток на картах Карно. Объединенные клетки будут

соответствовать импликантам, дизъюнкция которых даст сокра-

щенную ДНФ или МДНФ заданной функции.

В качестве примера на рис. 1.3,а представлена карта Карио

функции /д, получение МДНФ которой алгебраическим методом ।

показано выше. Первый член МДНФ соответствует объединению1

1 на рис. 1.3,а. Все клетки объединения 2 соответствуют минтер-

мам, которые имеют одну общую переменную А. Дизъюнкция этих

минтермов, как показано выше, равна А, т. е. второй член МДНФ

соответствует объединению 2 на рис. 1.3,а. Чем больше клеток

входит в объединение, тем меньше переменных входит в соответ-|

ствующую импликанту, т. е. проще получаемая ДНФ. I

32 1

Таким образом, минимизацию логических выражений можно

выполнять графическим объединением на карте Карно клеток, за-

нятых 1, и последующим получением алгебраического выражения

функции в виде сокращенной ДНФ, каждая импликанта которой

соответствует объединению нескольких клеток (мннтермов) или

одной необъедииеииой клетке. Процесс получения алгебраического

выражения функции, представленной па карте Карно, т. е. пере-

ход от графического представления к алгебраическому, называется

считыванием. При этом каждое объединение клеток считывается в

виде импликанты, в которую входят переменные или их инверсии,

общие для всех мннтермов, соответствующих этим клеткам. Необь-

единеииые клетки считываются в виде соответствующих минтер-

мов.

Полученные на основании законов булевой алгебры правила

минимизации путем объединения на картах Карно клеток, заня-

тых 1, формулируются для функций k^.4 переменных следующим

образом.

1. Объединяются две соседние клетки в столбце или ряду

(объединение 1 на рис. 1.3,а), четыре соседние клетки, составляю-

щие квадраты (объединение 4 на рис. 1.3,в).

2. Объединяются клетки (объединение 3 на рис. 1.3,6) или па-

ры клеток (объединение 2 на рис. 1.3,6), крайние в столбцах или

рядах.

3. Объединяются полные столбцы или ряды (объединение 2 на

рис. 1.3,а), пары рядом расположенных столбцов или рядов (объе-

динение 1 на рис. 1.3,г), а также крайние столбцы или ряды на

карте.

Карты Карно функций пяти (рис. 1.3,в) или шести перемен-

ных можно представить как две или четыре рядом размещенные

карты для четырех переменных. В пределах каждой половины

карты Карно пяти переменных (рис. 1.3,в) и каждой четверти кар-

ты шести переменных клетки объединяются по тем же правилам

1, 2, 3, как и для функции четырех переменных. Объединение кле-

ток, расположенных в разных половинах и четвертях, выполняется

в соответствии со следующим правилом (оно справедливо и для

функций четырех н менее переменных).

4. Объединяются клетки, пары соседних клеток (объединения

2. 3 на рис. 1.3,а), квадраты, столбцы, ряды, пары соседних

столбцов и рядов, расположенные симметрично относительно вер-

тикальной или горизонтальной оси карты Карно.

Количество импликант в получаемой сокращенной ДНФ равно

сумме числа объединений и необъединенных клеток. Для получе-

ния МДНФ следует включать в каждое объединение максималь-

но возможное число клеток и выбирать такой вариант объедине-

ния клеток, чтобы общее число объединений и оставшихся необъе-

диненных клеток было минимально. Прн этом одна и та же клет-

ка может входить в несколько объединений (см. рис. 1.3).

- 66 зз

На рис. 1.3,6,в приведены примеры минимизации функций:

F2=ACB\/ADD\/ASC\/ABcDVABCDyABCD =

= AS\/AD\/BCD\/ABCD,

F3 = CDEyACDy ABDEyACDEy АСБЕУ

\/ABCE\/ABCD\/ACDE\/ABCDE=

= CD\/ABE\/ADE\/A cdx/aece,

где помер объединения на карте совпадает с порядковым номе-

ром соответствующей импликанты в полученных МДНФ.

Используя различные варианты объединений для некоторых

функций, можно получать несколько различных МДНФ, одно из

которых выбирается для реализации в цифровом устройстве. На-

пример, на рис. 1.3,в вместо объединения 5 можно сделать объе-

динение 5' (показано штриховой линией). При этом пятая импли-

канта в МДНФ функции будет иметь вид АВСЕ вместо АБСЁ.

Если для заданной функции имеются безразличные наборы

входных переменных, которые обозначаются знаком X в соответ-

ствующих клетках карты Карно, то, как указано в § 1.3, можно

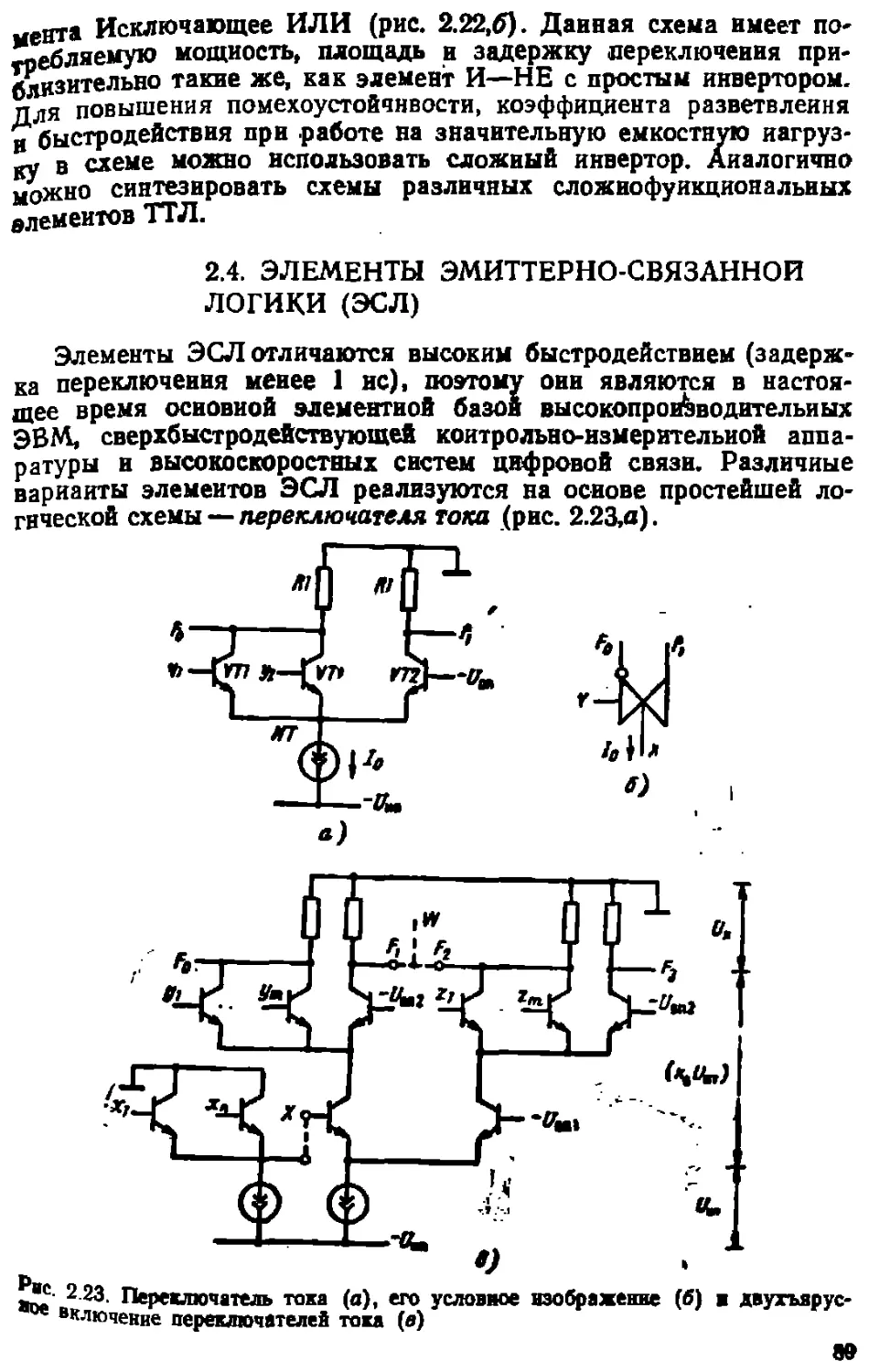

доопределить функцию, чтобы получить более простую МДНФ. В