Автор: Сигорский В.П. Зубчук В.И. Шкуро А.Н.

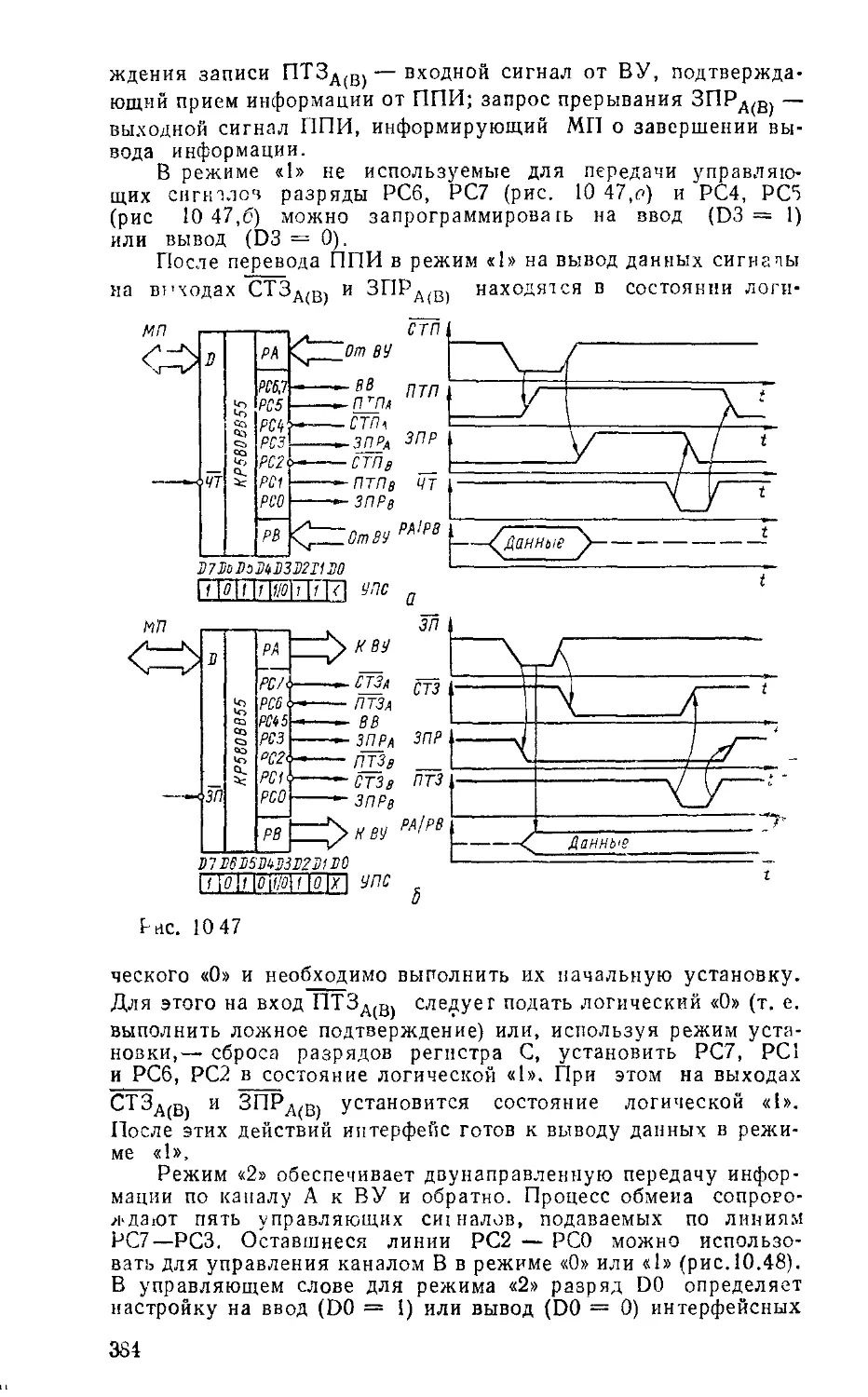

Теги: автоматика системы автоматического управления и регулирования интеллектуальная техника технология управления оборудование систем управления техническая кибернетика микрорадиоэлектронная аппаратура микроэлектроника электроника электротехника инженерия справочник схемотехника инженерное дело цифровая техника

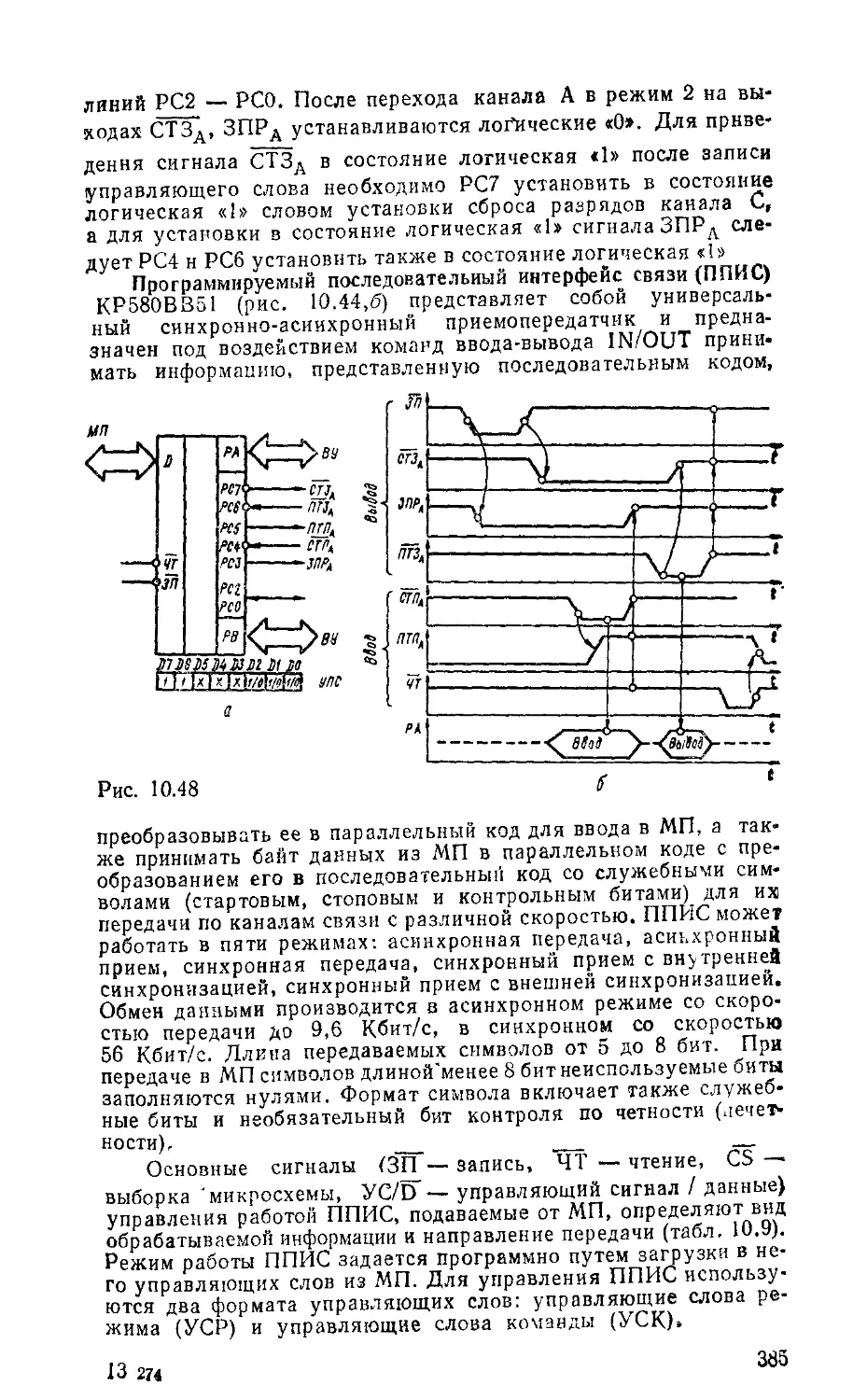

ISBN: 5-335-00584-Х

Год: 1990

В.И.ЗУБЧУК

В.П.СИГОРСКИЙ

А.Н.ШКУРО

СПРАВОЧНИК

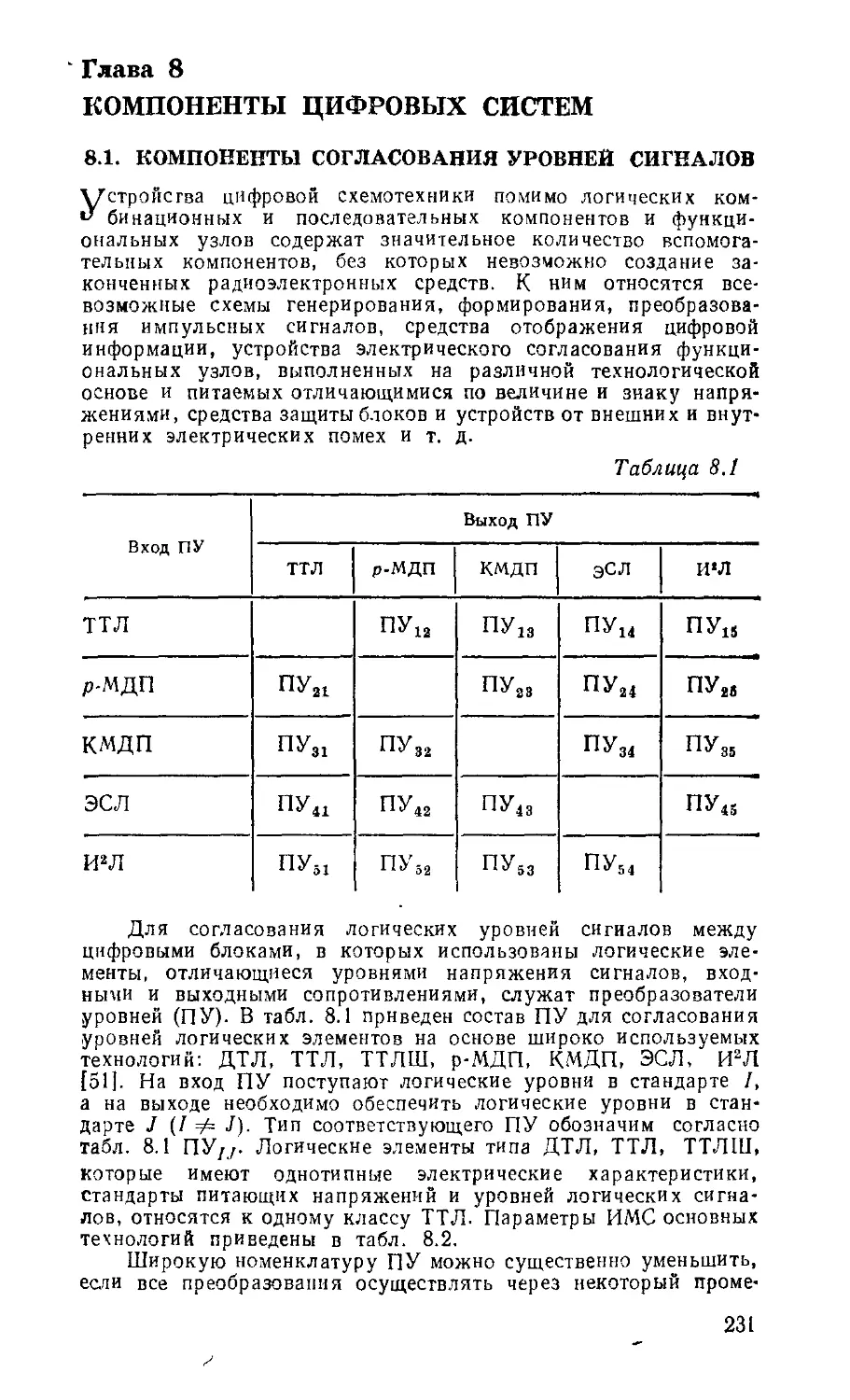

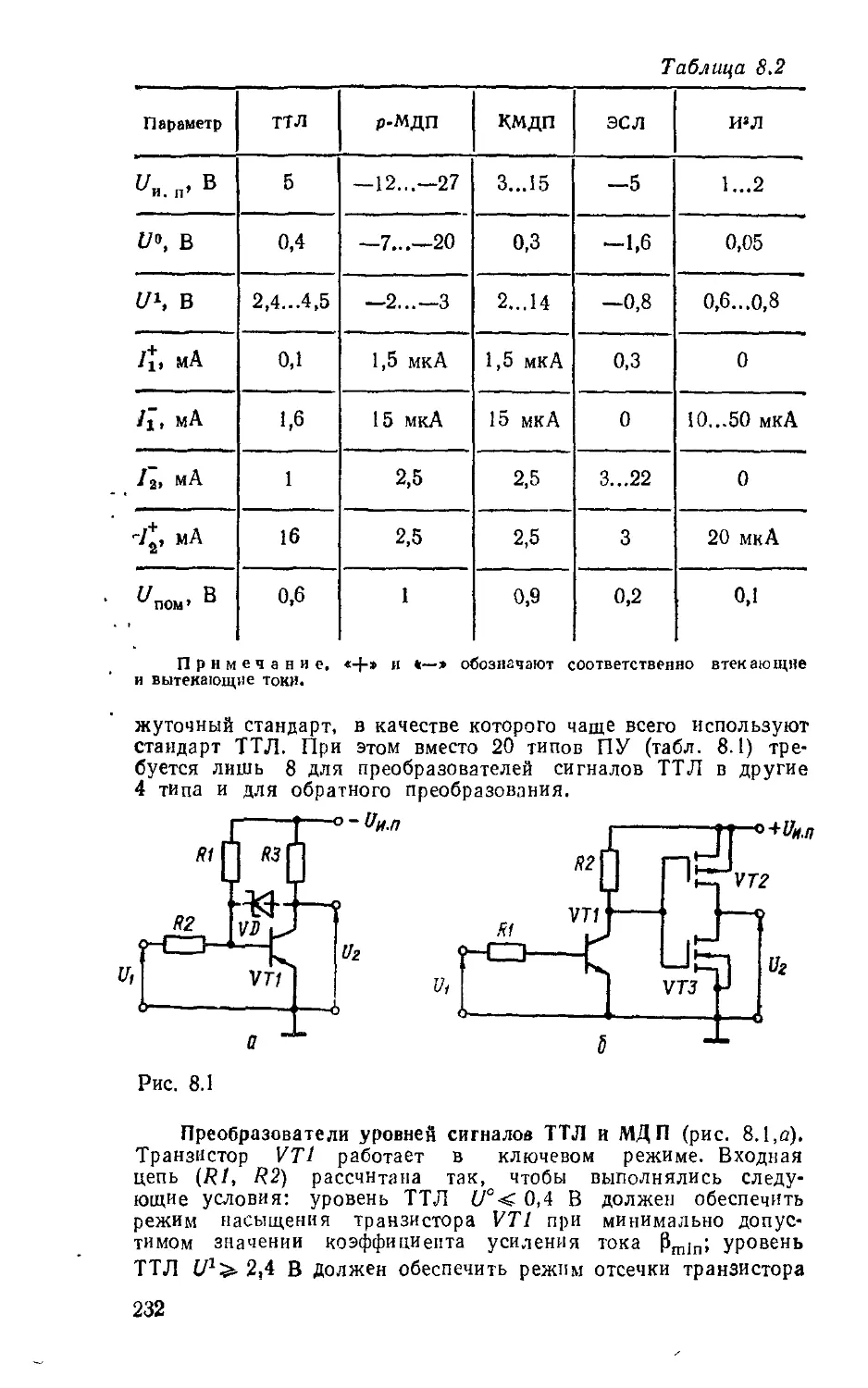

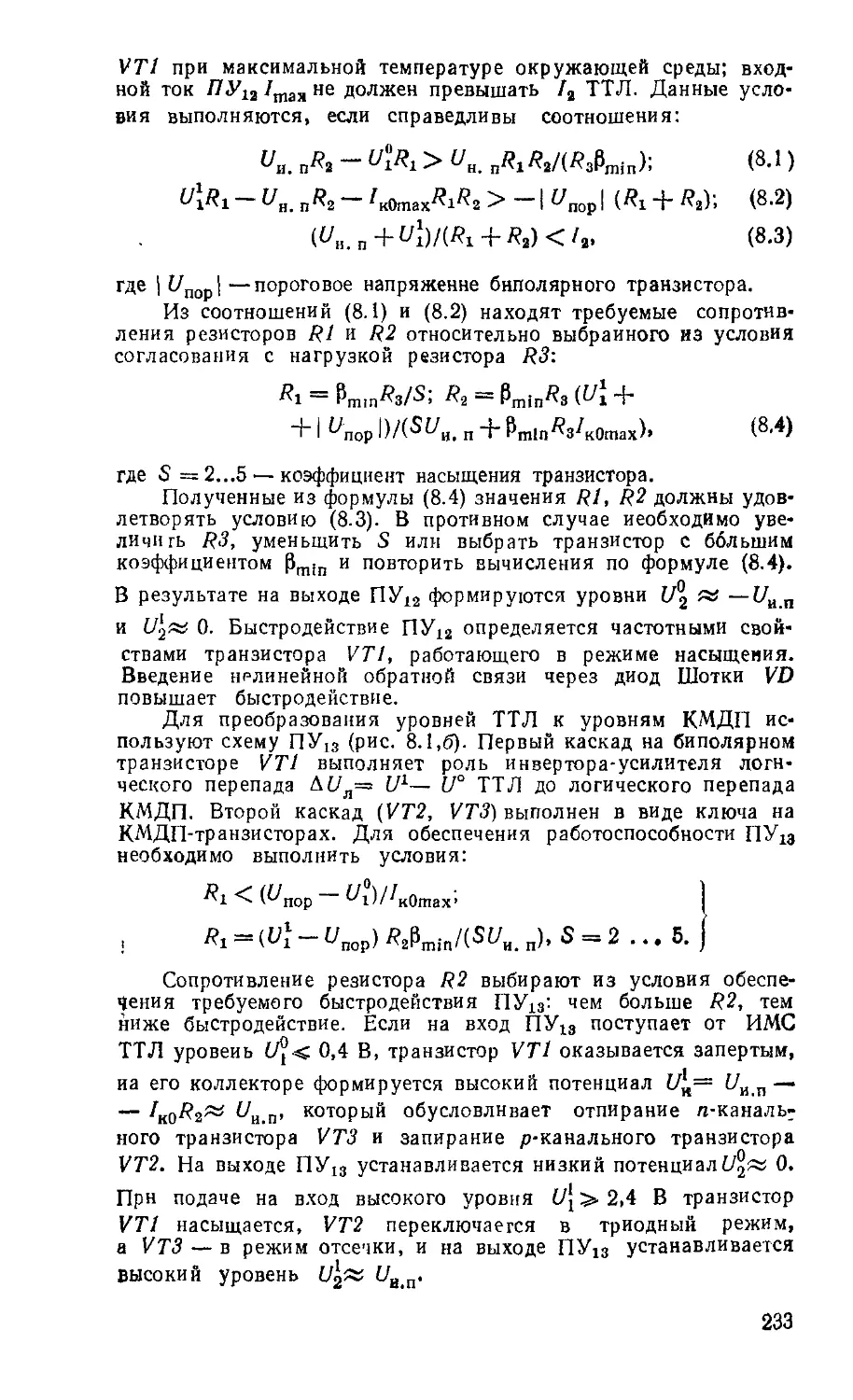

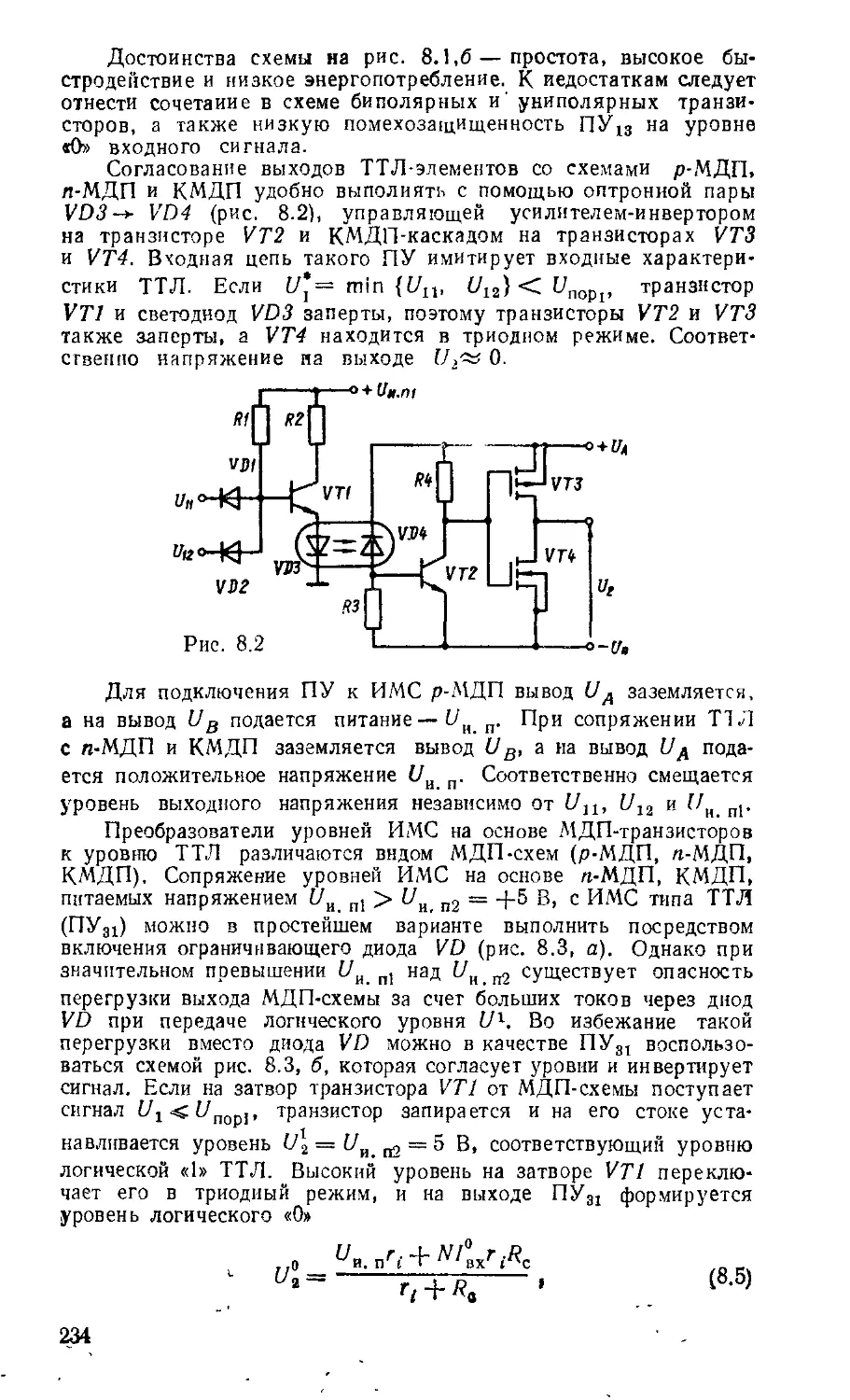

ПО

ЦИФРОВОМ

СХЕМОТЕХНИКЕ

Киев

«Техниках

1990

ББК 32.844.1Я2

3-91

УДК 681.51 (031)

Рецензент канд. техн, наук В. П. Денисенко

Редакция литературы по электронике, кибернетике и связи

Зав. редакцией 3. В. Божко

Зубчук В. И. и др.

3-91 Справочник по цифровой схемотехнике

/В. И. Зубчук, В. П. Сигорский, А. Н. Шкуро. —К.!

Тэхника, 1990.—448 с.

ISBN 5-335-00584-Х

Приведены схемные реализации цифровых интегральных

микросхем (ИМС) комбинационного (шифраторы, деши-

фраторы, преобразователи кодов, мультиплексоры, демуль-

типлексоры, сумматоры, компараторы) н последователь-

ностного (триггеры, счетчики, регистры, ОЗУ, ПЗУ,

ППЗУ) типов. Даны структуры и особенности функциони-

рования микропроцессорных комплектов с фиксирован-

ной и наращиваемой разрядностью и структуры одно-

кристальных микро-ЭВМ, а также рекомендации по их

применению при проектировании цифровых устройств.

Рассчитан на инженерно-технических работников,

занимающихся разработкой и эксплуатацией цифровой

техники, может быть полезен студентам вузов.

3—0993-70-19? 132.90 ББК 32.844.1я2

М202 (04)-90

ISBN 5-335-00584-Х ©Зубчук В.И., Сигорский В.П.,

Шкуро А, Н., 1990

ПРЕДИСЛОВИЕ

Г'ыстрое развитие современной микроэлектроники и, в частно-

Dctnu, цифровой схемотехники сопровождается вовлечением в

эту область все более широкого круга разработчиков новых функ-

циональных узлов, устройств и систем, а также пользователей

компонентной базы и традиционных схемотехнических решений

в новых прикладных областях. При этом специалист в области

цифровой схемотехники должен обладать обширными знаниями

в способах математического описания функционирования цифро-

вых схем на логическом и электрическом уровнях, знать совре-

менную компонентную базу цифровой схемотехники и предпо-

чтительные области ее применения, свободно ориентироваться

в промышленных сериях интегральных микросхем и перспекти-

вах их дальнейшего совершенствования, овладеть методами по-

строения структур цифровых устройств и систем, включая

средства микропроцессорной техники.

Уровень выполняемых разработок по цифровой схемотехни-

ке в значительной мере зависит от полноты и своевременности

обновления соответствующей теоретической и справочной лите-

ратуры. К настоящему времени сформировался и надежно за-

крепился существенный разрыв между литературой по теоре-

тическим вопросам схемотехники, освещающей методологию

построения цифровых элементов, устройств и систем, и справоч-

ной литературой, в которой обычно приводятся описания вы-

пускаемых промышленностью изделий электронной техники.

В данном справочнике изложены с единых позиций как методоло-

гические, так и информационные аспекты цифровой схемотехни-

ки. По замыслу авторов, справочник должен помочь в решении

задач схемотехнического проектирования, а также предоста-

вить разработчику первичную информацию. Изложение мате-

риала вполне доступно как для специалистов по электронной

технике, так и для студентов средних и высших учебных заве-

дений и подготовленных радиолюбителей.

Отзывы и пожелания просим направлять по адресу: 252601

Киев, 1, ул. Крещатик, 5. Издательство «Техника».

Глава 1

ЧИСЛА И КОДЫ

11. СИСТЕМЫ СЧИСЛЕНИЯ

О дискретной технике вся информация независимо от ее ха-

D рактера представляется в числовой форме, причем исполь-

зуются только позиционные системы счисления. В этих

системах любое целое неотрицательное n-разрядное число запи-

сывается в виде последовательности п цифр xn_ixn_.i...x1 х0.

Число а различных символов (0, 1, 2, а — 1), принятых

для представления цифр, определяет основание системы счисле-

ния. Вклад цифры в изображаемое число зависит как от этого

основания, так и от занимаемой ею позиции (разряда) в после-

довательности цифр. Цифра входит с весом ak и означает

xkak, а вся последовательность цифр хп^хп_2 ... выражаете

системе счисления с основанием а число

Xn-ia'1'1 + 4------Х1(214. хоа». (1.1)

Привычная десятичная система (а — 10) использует цифры

0, 1, 2, .... 9, так, что, например: 3175 = 3 • 10;,-f- 1 • 10*+

+ 7 • 10*+ 5 • 10°. В вычислительной технике преимупксгвьн-

ное значение получила двоичная система счисления [88|, для

которой достаточно двух цифр 0 и 1. Двоичный разряд пред-

ставляет собой наименьшее количество информации, называемое

битом. Последовательность двоичных цифр xrt_1xn_2...x1x0 слу-

жит записью двоичного числа

хп,^ + + .. • + + х„2».

Среди других систем счисления чаще всего используются

восьмеричная и шестнадцатеричная. В восьмеричной системе

цифры изображаются теми же символами, что и в десятичной,

а в шестнадцатеричной системе к ним добавляется еще шесть

символов А, В, С, D, Е, F, которые соответствуют десятичным

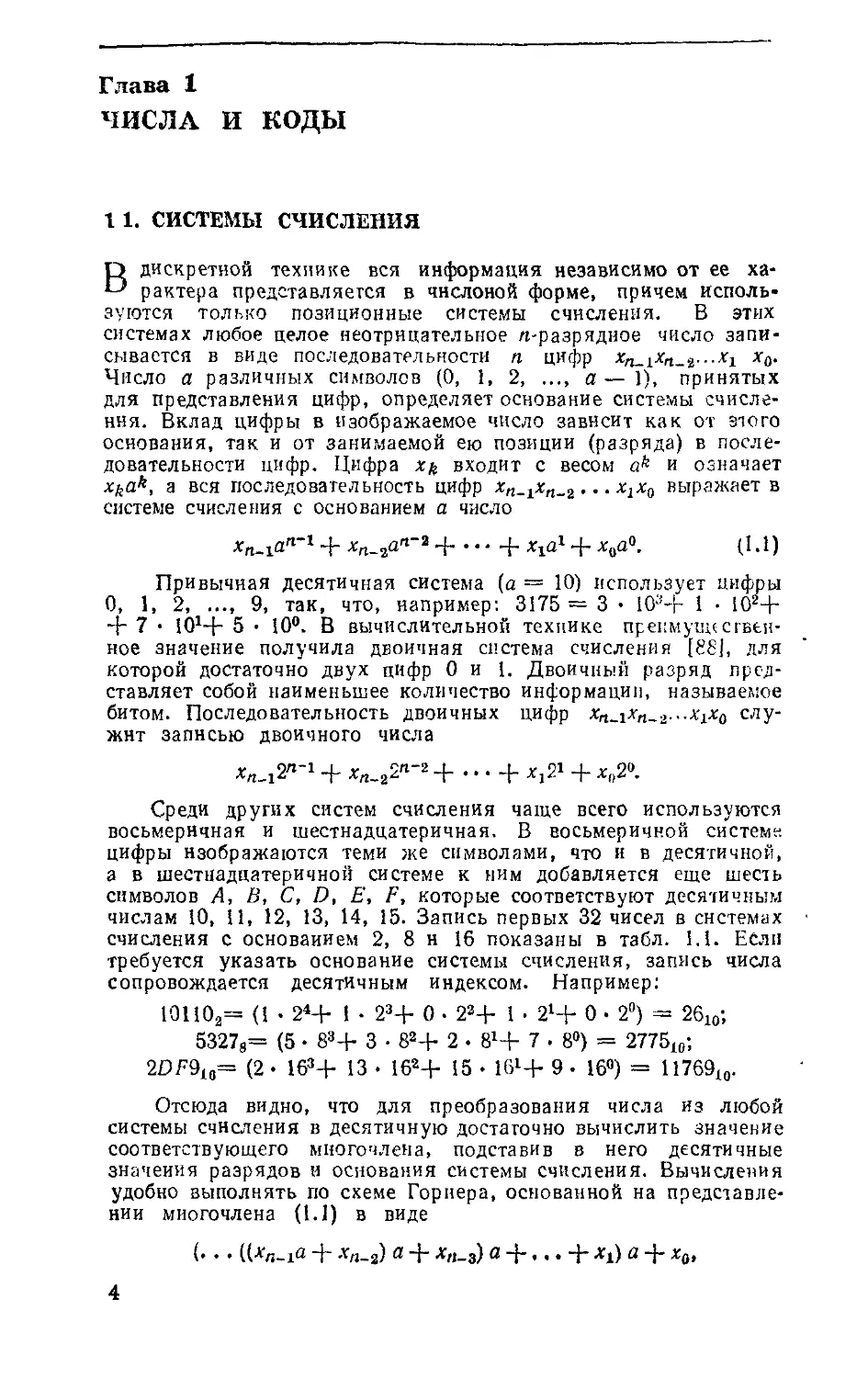

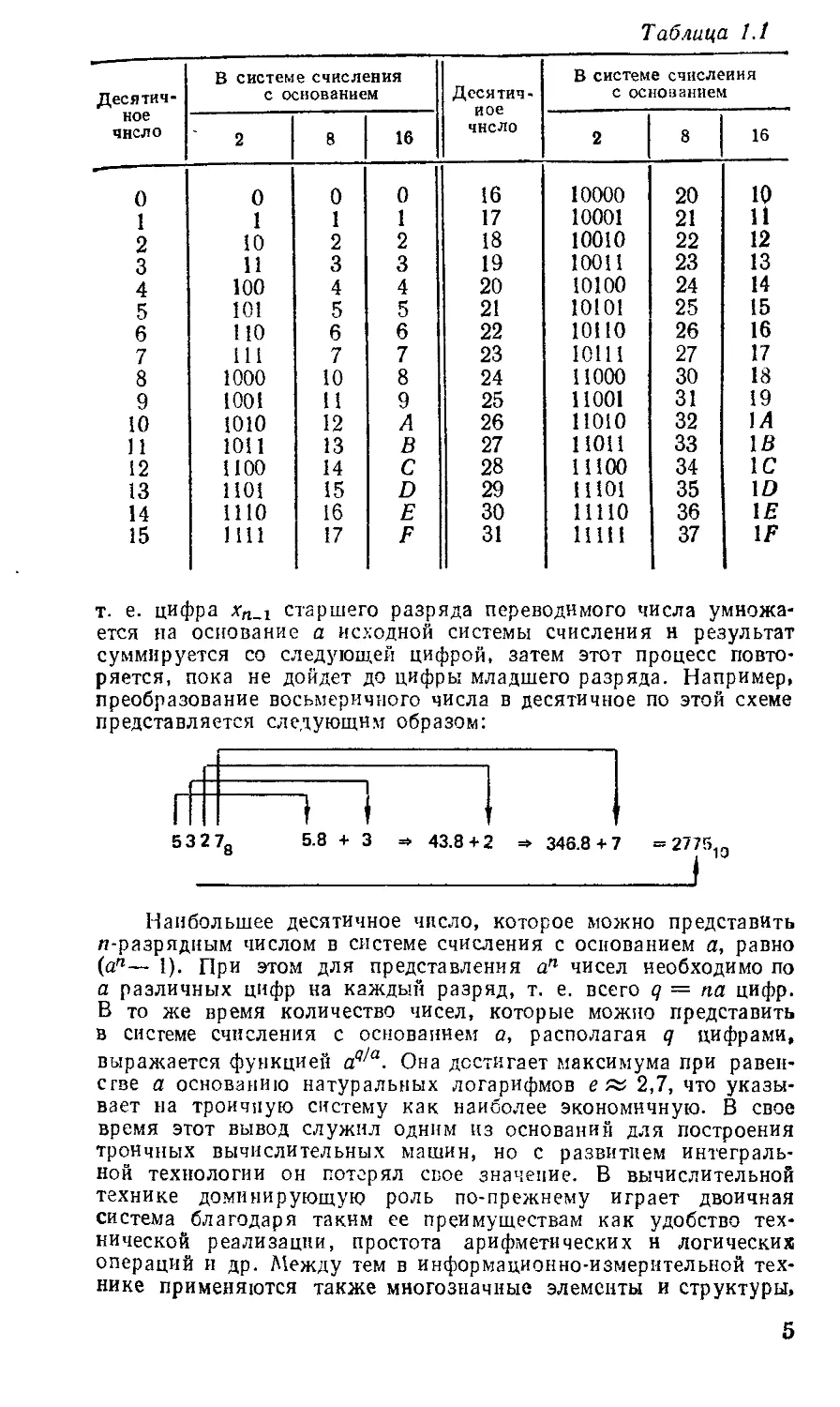

числам 10, 11, 12, 13, 14, 15. Запись первых 32 чисел в системах

счисления с основанием 2, 8 и 16 показаны в табл. 1.1. Если

требуется указать основание системы счисления, запись числа

сопровождается десятичным индексом. Например:

101103= (1 • 24+ 1 • 23+ 0 • 24- 1 • 2‘+ 0 • 2°) = 261О;

53278= (5 • 83+ 3 • 82+ 2 - 81+ 7 . 8°) = 277510;

2DF9I0= (2 • 163+ 13 • 164- 15 • 164- 9 - 16») = 1176910.

Отсюда видно, что для преобразования числа из любой

системы счисления в десятичную достаточно вычислить значение

соответствующего многочлена, подставив в него десятичные

значения разрядов и основания системы счисления. Вычисления

удобно выполнять по схеме Горнера, основанной на представле-

нии многочлена (1.1) в виде

(• • • ((Хп^а + х„.8) а + х„_3) а +... -f- хЦ а + х0,

4

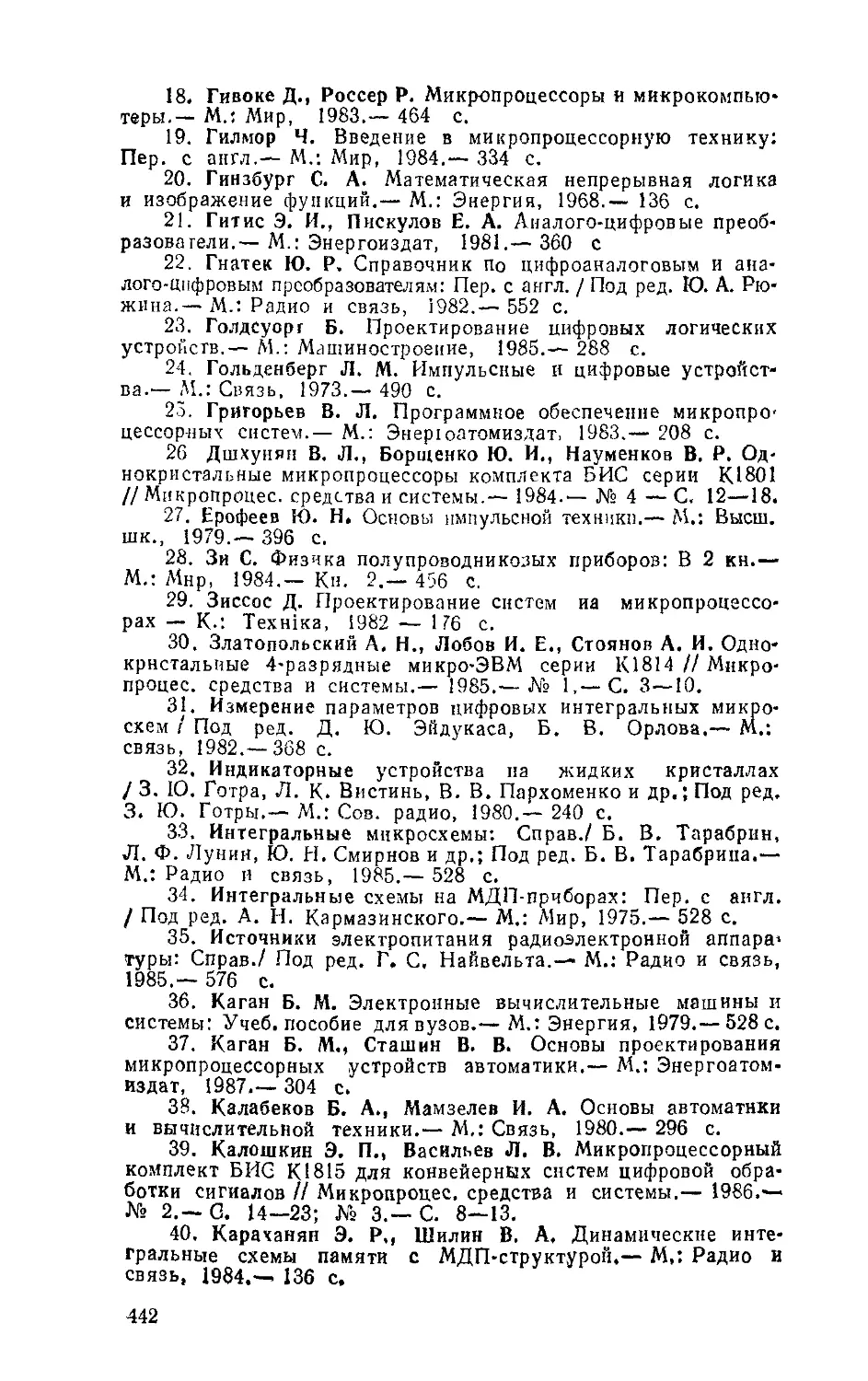

Таблица 1.1

Десятич- ное число В системе счисления с основанием Десятич- ное число В системе счисления с основанием

2 8 16 2 8 16

0 0 0 0 16 10000 20 10

1 1 1 1 17 10001 21 и

2 10 2 2 18 10010 22 12

3 11 3 3 19 10011 23 13

4 100 4 4 20 10100 24 14

5 101 5 5 21 10101 25 15

6 110 6 6 22 10110 26 16

7 111 7 7 23 10111 27 17

8 1000 10 8 24 11000 30 18

9 1001 11 9 25 11001 31 19

10 1010 12 А 26 пою 32 1А

11 1011 13 В 27 11011 33 1В

12 1100 14 С 28 11100 34 1С

13 1101 15 D 29 11101 35 1D

14 1110 16 Е 30 11110 36 1Е

15 1111 17 F 31 11111 37 1F

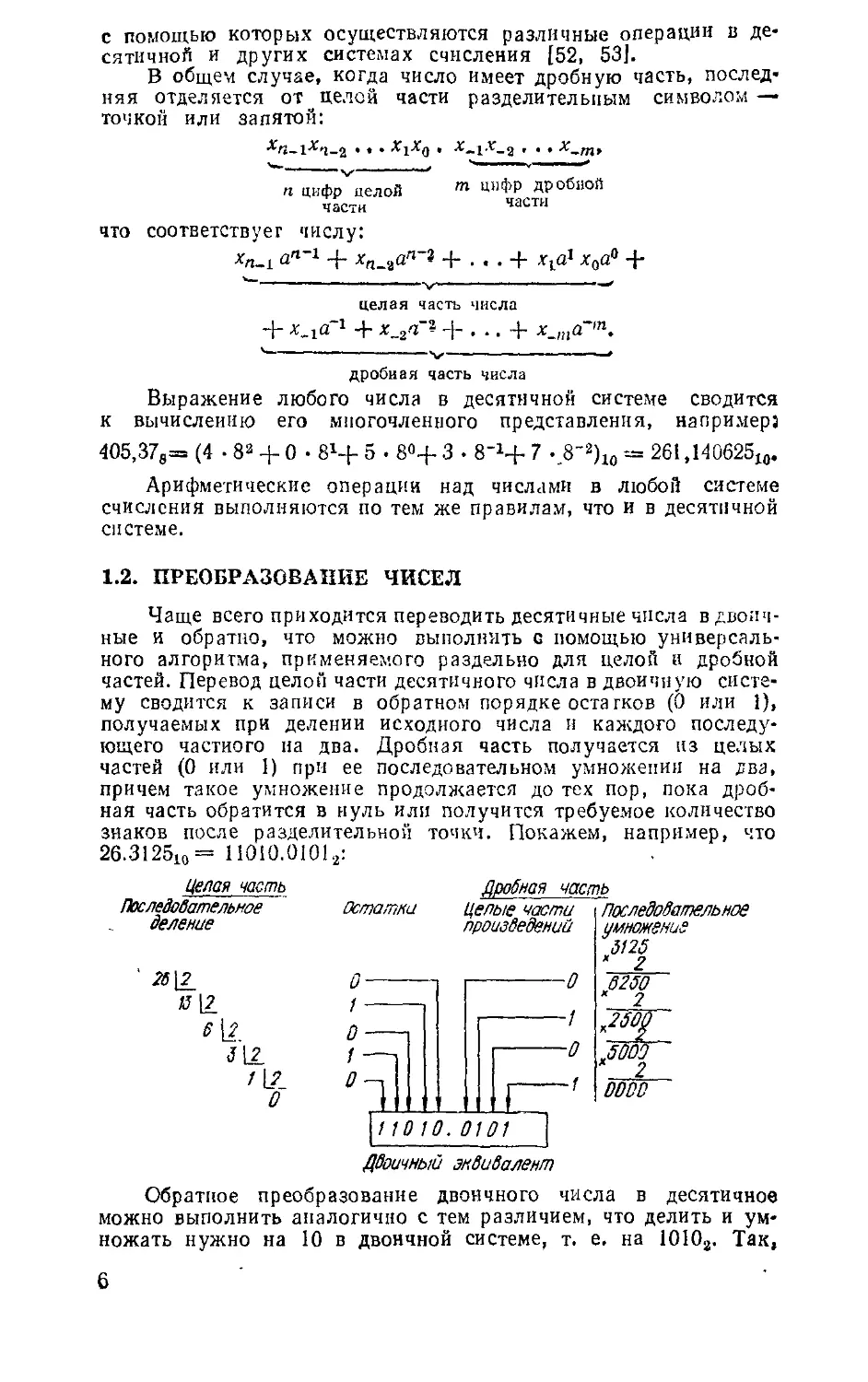

т. е. цифра хл_! старшего разряда переводимого числа умножа-

ется на основание а исходной системы счисления н результат

суммируется со следующей цифрой, затем этот процесс повто-

ряется, пока не дойдет до цифры младшего разряда. Например,

преобразование восьмеричного числа в десятичное по этой схеме

представляется следующим образом:

5327g 5.8 + 3 =» 43.8 + 2 => 346.8 + 7 = 2775,э

Наибольшее десятичное число, которое можно представить

«-разрядным числом в системе счисления с основанием а, равно

(ап— 1). При этом для представления ап чисел необходимо по

а различных цифр на каждый разряд, т. е. всего q = па цифр.

В то же время количество чисел, которые можно представить

в системе счисления с основанием о, располагая q цифрами,

выражается функцией cfl,a. Она достигает максимума при равен-

стве а основанию натуральных логарифмов е ж 2,7, что указы-

вает на троичную систему как наиболее экономичную. В свое

время этот вывод служил одним из оснований для построения

троичных вычислительных машин, но с развитием интеграль-

ной технологии он потерял свое значение. В вычислительной

технике доминирующую роль по-прежнему играет двоичная

система благодаря таким ее преимуществам как удобство тех-

нической реализации, простота арифметических н логических

операций и др. Между тем в информационно-измерительной тех-

нике применяются также многозначные элементы и структуры,

5

с помощью которых осуществляются различные операции в де-

сятичной и других системах счисления [52, 53].

В общем случае, когда число имеет дробную часть, послед-

няя отделяется от целой части разделительным символом —

точкой или запятой:

1Х'1-2 • • •

п цвфр\елой т «»*Р дробной

части час™

что соответствует числу:

*zi_i ап~1 + хп_,гап~^ 4- . . . + х^1 хоа° +

целая часть числа

+ х^а'1 4- х_2<? 4- ... 4- х_та~'п.

дробная часть числа

Выражение любого числа в десятичной системе сводится

к вычислению его многочленного представления, напримерз

405,378= (4 • 82 4-0 • 8Г4-5 • 8°4-3 • 8'Ч- 7 - 8'2)и --= 261,1406251о.

Арифметические операции над числами в любой системе

счисления выполняются по тем же правилам, что и в десятичной

системе.

1.2. ПРЕОБРАЗОВАНИЕ ЧИСЕЛ

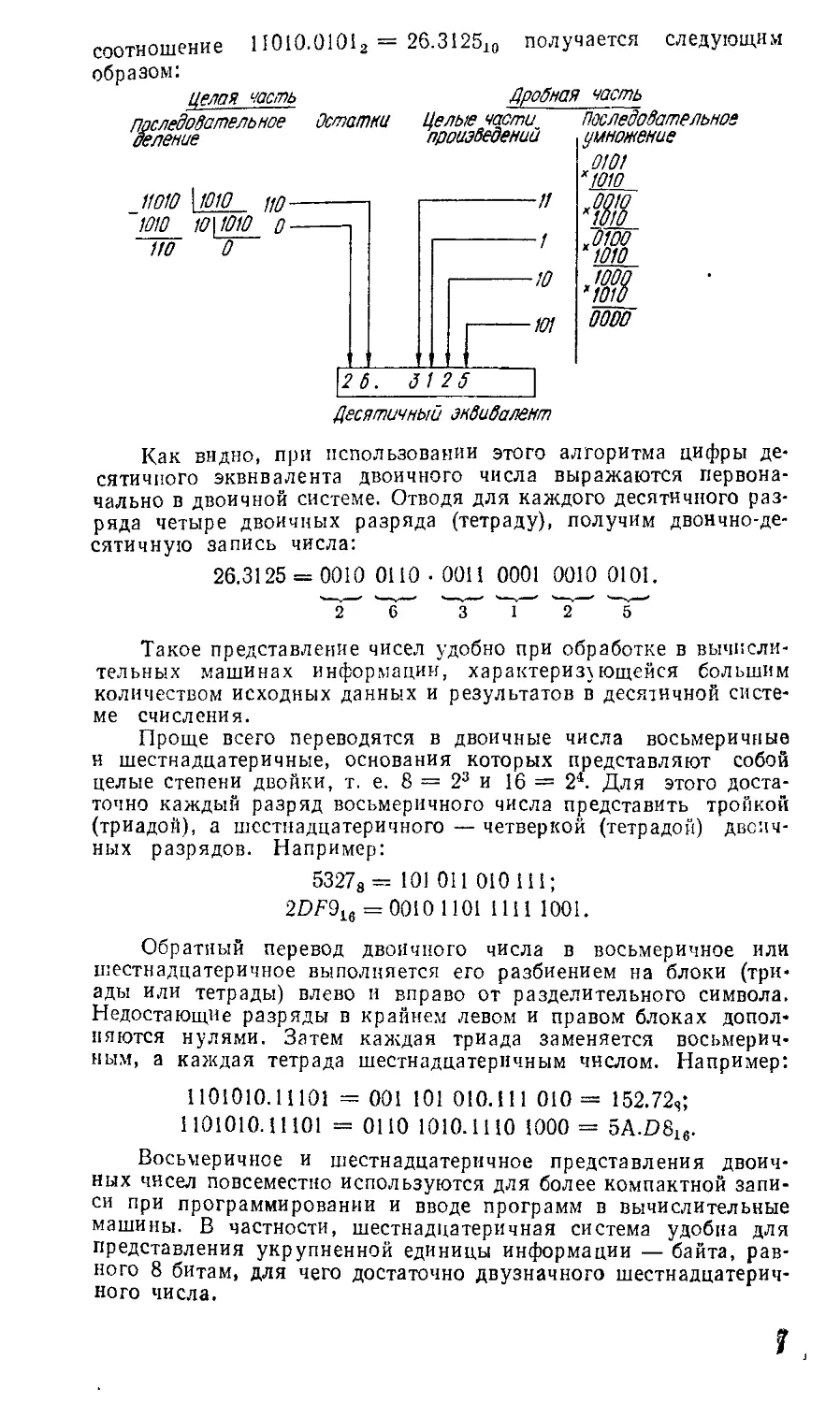

Чаще всего приходится переводить десятичные числа в двоич-

ные и обратно, что можно выполнять с помощью универсаль-

ного алгоритма, применяемого раздельно для целой и дробной

частей. Перевод целон части десятичного числа в двоичную систе-

му сводится к записи в обратном порядке остатков (0 или 1),

получаемых при делении исходного числа и каждого последу-

ющего частного на два. Дробная часть получается из целых

частей (0 или 1) при ее последовательном умножении на два,

причем такое умножение продолжается до тех пор, пока дроб-

ная часть обратится в нуль или получится требуемое количество

знаков после разделительной точки. Покажем, например, что

26.312510= 11010.01012:

Целая часть

Последовательное

деление

' 2в\2_

б\2.

д\2_

1\2_

О

Двоичный эквивалент

Обратное преобразование двоичного числа в десятичное

можно выполнить аналогично с тем различием, что делить и ум-

ножать нужно на 10 в двоичной системе, т. е. на 1010а. Так,

6

Дробная часть

соотношение 1 Ю10.01012 = 26.312510 получается следующим

образом:

целая часть

Последовательное Остатки

деление

Целые части

произведений

_пою \t010 уо

ио о

Последовательное

умножение

0101

ЧОЮ

,ООЮ

ЧОЮ

,0100

1010

0000

11

10

101

/

312 5

Десятичный эквивалент

Как видно, при использовании этого алгоритма цифры де-

сятичного эквивалента двоичного числа выражаются первона-

чально в двоичной системе. Отводя для каждого десятичного раз-

ряда четыре двоичных разряда (тетраду), получим двончно-де-

сятичную запись числа:

26.3125 = 0010 0110 . 0011 0001 0010 0101.

'~2~' '~С ’ "V

Такое представление чисел удобно при обработке в вычисли-

тельных машинах информации, характеризующейся большим

количеством исходных данных и результатов в десятичной систе-

ме счисления.

Проще всего переводятся в двоичные числа восьмеричные

и шестнадцатеричные, основания которых представляют собой

целые степени двойки, т. е. 8 = 23 и 16 = 24. Для этого доста-

точно каждый разряд восьмеричного числа представить тройкой

(триадой), а шестнадцатеричного — четверкой (тетрадой) двоич-

ных разрядов. Например:

53278 = 101 ОН 010 111;

2DF9U = 0010 1101 1111 1001.

Обратный перевод двоичного числа в восьмеричное или

шестнадцатеричное выполняется его разбиением на блоки (три-

ады или тетрады) влево и вправо от разделительного символа.

Недостающие разряды в крайнем левом и правом блоках допол-

няются нулями. Затем каждая триада заменяется восьмерич-

ным, а каждая тетрада шестнадцатеричным числом. Например:

1101010.11101 = 001 101 010.111 010 = 152.72,;

1101010.11101 = ОНО 1010.1110 1000 = 5A.D8le.

Восьмеричное и шестнадцатеричное представления двоич-

ных чисел повсеместно используются для более компактной запи-

си при программировании и вводе программ в вычислительные

машины. В частности, шестнадцатеричная система удобна для

представления укрупненной единицы информации — байта, рав-

ного 8 битам, для чего достаточно двузначного шестнадцатерич-

ного числа.

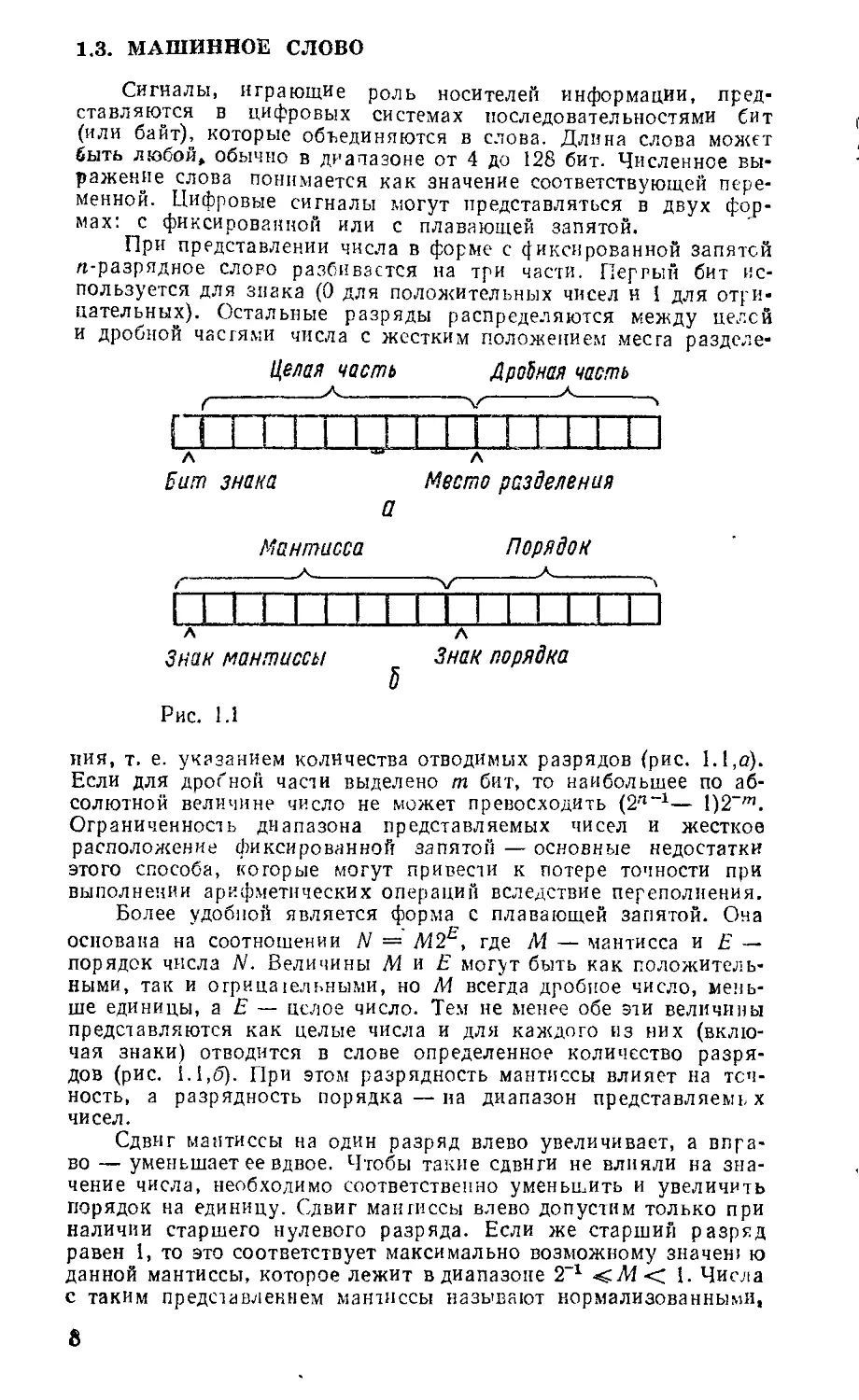

1.3. МАШИННОЕ СЛОВО

Сигналы, играющие роль носителей информации, пред-

ставляются в цифровых системах последовательностями бит

(или байт), которые объединяются в слова. Длина слова может

быть любой, обычно в диапазоне от 4 до 128 бит. Численное вы-

ражение слова понимается как значение соответствующей пере-

менной. Цифровые сигналы могут представляться в двух фор-

мах: с фиксированной или с плавающей запятой.

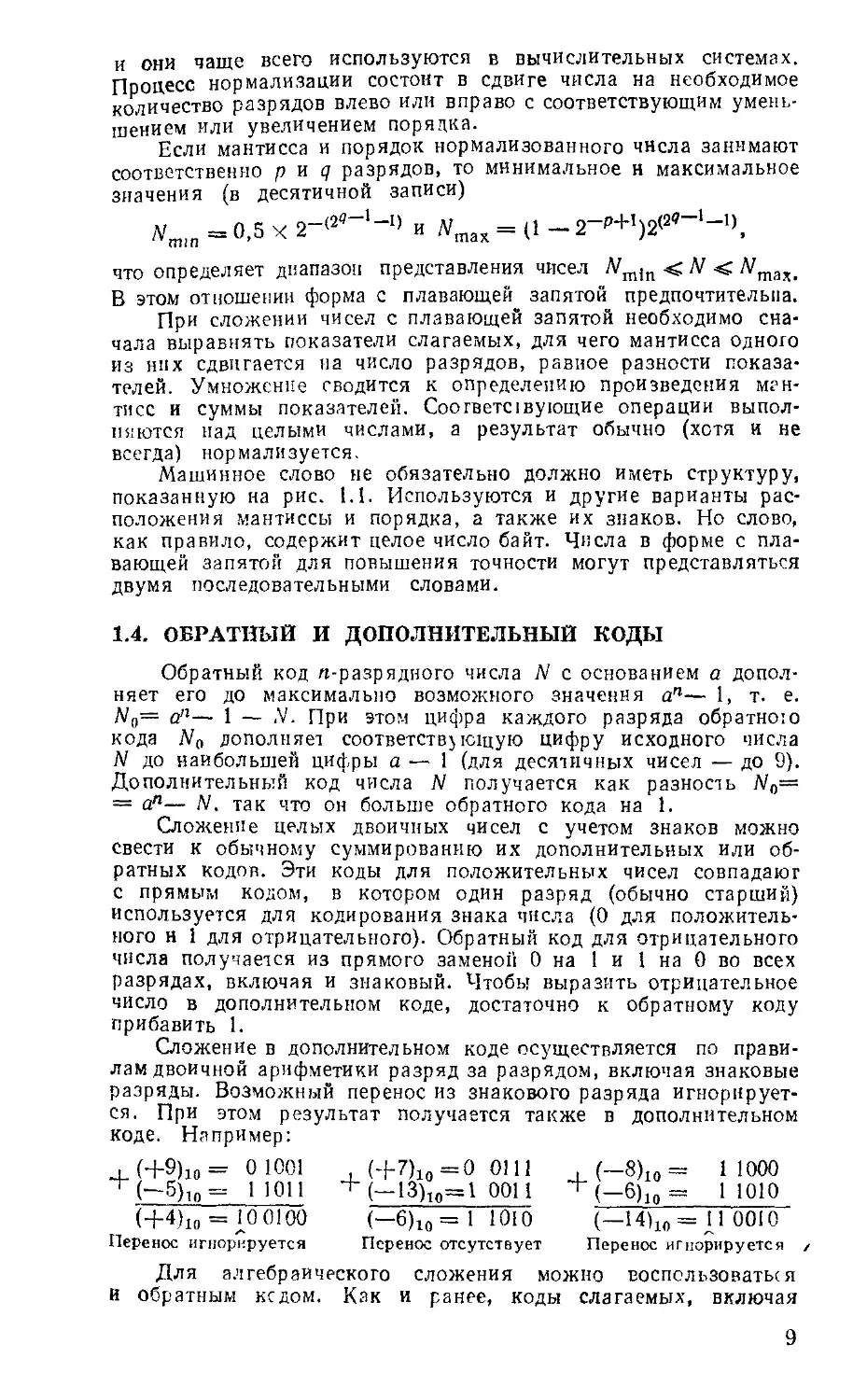

При представлении числа в форме с фиксированной запятой

n-разрядное слово разбивается на три части. Первый бит ис-

пользуется для знака (0 для положительных чисел н 1 для отри-

цательных). Остальные разряды распределяются между целей

и дробной частями числа с жестким положением места разделе-

Целая часть Дродная часть

(a v л ч

А " А

Бит знака Место разделения

а

Мантисса Порядок

Знак мантиссы Знак порядка

5

Рис. 1.1

лия, т. е. указанием количества отводимых разрядов (рис. 1.1,о).

Если для дробной части выделено т бит, то наибольшее по аб-

солютной величине число не может превосходить (2'г“1— 1)2“"'.

Ограниченность диапазона представляемых чисел и жесткое

расположение фиксированной запятой — основные недостатки

этого способа, которые могут привести к потере точности при

выполнении арифметических операций вследствие переполнения.

Более удобной является форма с плавающей запятой. Она

основана на соотношении N — М2Е, где М — мантисса и Е —

порядок числа N. Величины М и Е могут быть как положитель-

ными, так и отрица 1ельными, но 44 всегда дробное число, мень-

ше единицы, а £ — целое число. Тем не менее обе эти величины

представляются как целые числа и для каждого из них (вклю-

чая знаки) отводится в слове определенное количество разря-

дов (рис. 1.1,6). При этом разрядность мантиссы влияет на точ-

ность, а разрядность порядка—па диапазон представляем!, х

чисел.

Сдвиг мантиссы на один разряд влево увеличивает, а впра-

во — уменьшает ее вдвое. Чтобы такие сдвиги не влияли на зна-

чение числа, необходимо соответственно уменьшить и увеличить

порядок на единицу. Сдвиг мантиссы влево допустим только при

наличии старшего нулевого разряда. Если же старший разряд

равен 1, то это соответствует максимально возможному значен) ю

данной мантиссы, которое лежит в диапазоне 2-1 <44 < 1. Числа

с таким представлением мантиссы называют нормализованными,

в

и они чаще всего используются в вычислительных системах.

Процесс нормализации состоит в сдвиге числа на необходимое

количество разрядов влево или вправо с соответствующим умень-

шением или увеличением порядка.

Если мантисса и порядок нормализованного числа занимают

соответственно р и q разрядов, то минимальное и максимальное

значения (в десятичной записи)

Nmin = 0,5 X И ,Vmax = (1 - 2-₽+’)2^-‘,

что определяет диапазон представления чисел <Vmin с <V < Л/тах.

В этом отношении форма с плавающей запятой предпочтительна.

При сложении чисел с плавающей запятой необходимо сна-

чала выравнять показатели слагаемых, для чего мантисса одного

из них сдвигается на число разрядов, равное разности показа-

телей. Умножение сводится к определению произведения ман-

тисс и суммы показателей. Соогветовующие операции выпол-

няются над целыми числами, а результат обычно (хотя и не

всегда) нормализуется.

Машинное слово не обязательно должно иметь структуру,

показанную на рис. 1.1. Используются и другие варианты рас-

положения мантиссы и порядка, а также их знаков. Но слово,

как правило, содержит целое число байт. Числа в форме с пла-

вающей запятой для повышения точности могут представляться

двумя последовательными словами.

1.4. ОБРАТНЫЙ И ДОПОЛНИТЕЛЬНЫЙ КОДЫ

Обратный код п-разрядного числа N с основанием а допол-

няет его до максимально возможного значения ап— 1, т. е.

No— ап— 1 — .V. При этом цифра каждого разряда обратною

кода Na дополняет соответствующую цифру исходного числа

N до наибольшей цифры а — 1 (для десятичных чисел — до 9).

Дополнительный код числа N получается как разность Wo=

= ап— N. так что он больше обратного кода на 1.

Сложение целых двоичных чисел с учетом знаков можно

свести к обычному суммированию их дополнительных или об-

ратных кодов. Эти коды для положительных чисел совпадают

с прямым кодом, в котором один разряд (обычно старший)

используется для кодирования знака числа (0 для положитель-

ного и 1 для отрицательного). Обратный код для отрицательного

числа получается из прямого заменой 0 на 1 и 1 на 0 во всех

разрядах, включая и знаковый. Чтобы выразить отрицательное

число в дополнительном коде, достаточно к обратному коду

прибавить 1.

Сложение в дополнительном коде осуществляется по прави-

лам двоичной арифметики разряд за разрядом, включая знаковые

разряды. Возможный перенос из знакового разряда игнорирует-

ся. При этом результат получается также в дополнительном

коде. Например:

ц. (+9)ю- 0 1001

М-5)10- ИОН

(+4)10= 10 0100

Перенос игнорируется

(+7)1о=О 0111

+ (—13)10=1 0011

(-6)10=1 1010

Перенос отсутствует

(—8)10 = 1 1000

'(-6)ю- НОЮ

(—14)10= Н 0010

Перенос игнорируется

Для алгебраического сложения можно воспользоваться

и обратным кедом. Как и ранее, коды слагаемых, включая

9

и знаковые разряды, суммируются как двоичные числа. Но пере-

нос из старшего (знакового) разряда, если он возникает, не игно-

рируется, а прибавляется к младшему разряду суммы, которая

также получается в обратном коде. Такой перенос называется

круговым, а сложение — циклическим. Например:

(+15)1о = О1111

(—5)10 = 1 1010

Круговой 10 1001

перенос ~ri___> |

(+1О)1о = 01010

(+7)1о = ОО111

(—11)10= 1 0100

(—4)10= 11011

Круговой перенос

отсутствует

Если оба слагаемых имеют одинаковые знаки, то может

случиться переполнение, признаком которого служит различие

знаков слагаемых и суммы. Другой признак основан на том,

что переполнение происходит тогда и только тогда, когда при

сложении имеет место один из переносов — в знаковый разряд

или из знакового разряда, но не оба. В обратном коде этот при-

знак следует применять до кругового переноса.

Вычитание в дополнительном и обратном кодах сводится

к сложению путем замены знака (а значит, и кода) вычитаемого.

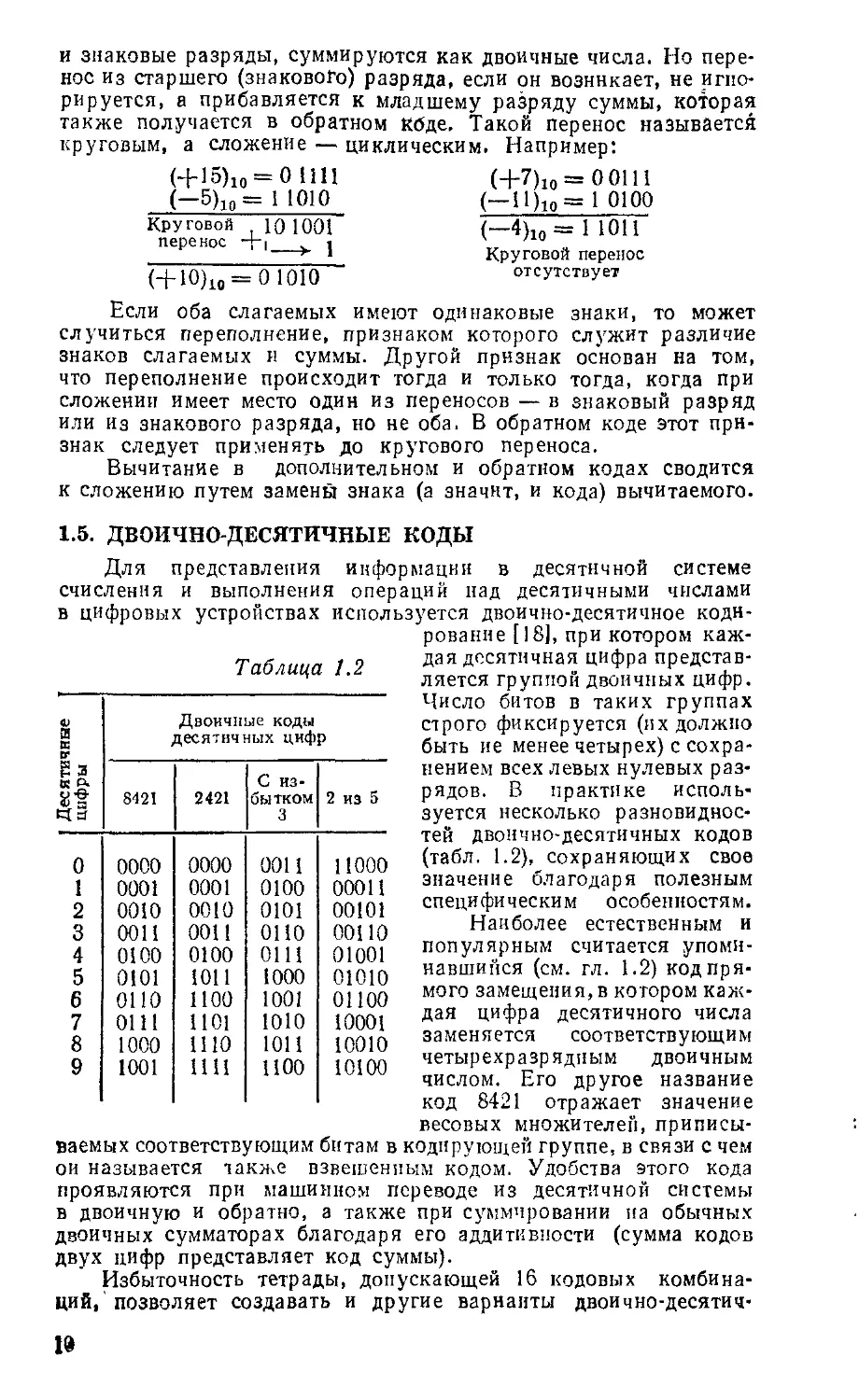

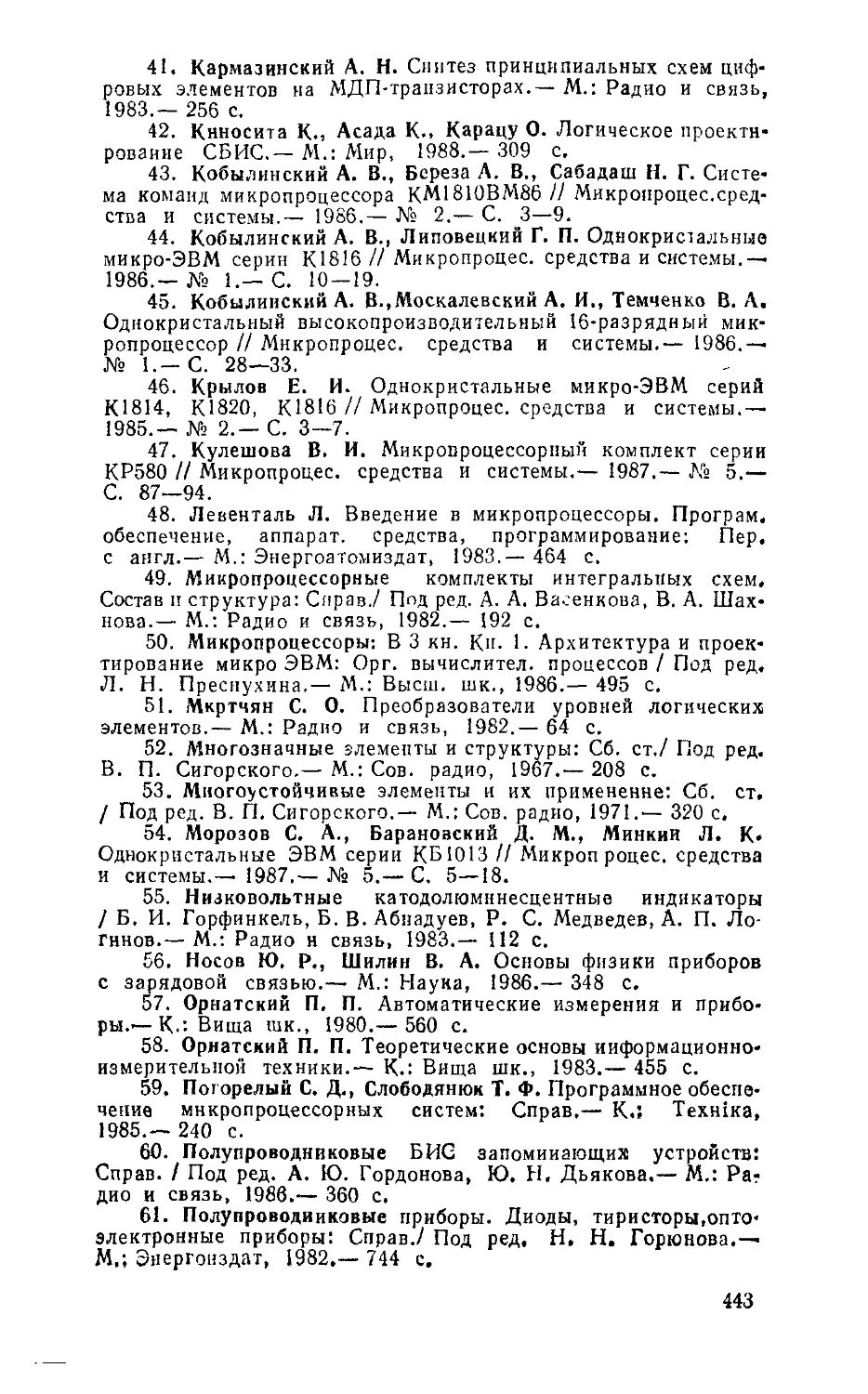

Таблица 1.2

Десятичные цифры Двоичные коды десятичных цифр

8421 2421 С из- бытком 3 2 из 5

0 0000 0000 ООН 11000

1 0001 0001 0100 00011

2 0010 0010 0101 00101

3 ООН ООП оно 00110

4 0100 0100 0111 01001

5 0101 1011 1000 01010

6 оно 1100 1001 01100

7 0111 1101 1010 10001

8 1000 1110 1011 10010

9 1001 ни 1100 10100

1.5. ДВОИЧНО-ДЕСЯТИЧНЫЕ КОДЫ

Для представления информации в десятичной системе

счисления и выполнения операций над десятичными числами

в цифровых устройствах используется двоично-десятичное коди-

рование [18], при котором каж-

дая десятичная цифра представ-

ляется группой двоичных цифр.

Число битов в таких группах

строго фиксируется (их должно

быть не менее четырех) с сохра-

нением всех левых нулевых раз-

рядов. В практике исполь-

зуется несколько разновиднос-

тей двончно-десятичных кодов

(табл. 1.2), сохраняющих свое

значение благодаря полезным

специфическим особенностям.

Наиболее естественным и

популярным считается упоми-

навшийся (см. гл. 1.2) код пря-

мого замещения, в котором каж-

дая цифра десятичного числа

заменяется соответствующим

четырехразрядным двоичным

числом. Его другое название

код 8421 отражает значение

весовых множителей, приписы-

ваемых соответствующим битам в кодирующей группе, в связи с чем

ои называется также взвешенным кодом. Удобства этого кода

проявляются при машинном переводе из десятичной системы

в двоичную и обратно, а также при суммировании на обычных

двоичных сумматорах благодаря его аддитивности (сумма кодов

двух цифр представляет код суммы).

Избыточность тетрады, допускающей 16 кодовых комбина-

ций, позволяет создавать и другие варианты двои ч но-десяти ч-

вых кодов с использованием четверки битов яа десятичный раз-

ряд. Одни из них код 2421 также взвешенный, но старший раз-

ряд имеет вес не 8, а 2. Его положительная особенность состоит

в том, что замена в кодирующей тетраде нулей на единицы,

а единиц, на нули превращает каждую десятичную цифру х

в 9__х, т. е. получается обратный код. Для превращения его

в дополнительный код достаточно прибавить единицу. Коды

с таким свойством называют самодополнительными. Они при-

меняются при выполнении арифметических операций над де-

сятичными числами в обратном или дополнительном коде.

Самодополнительным является и код с избытком 3, который

получается прибавлением 31о=ОО11а к каждой цифре кода

прямого замещения. Как и код 2421, он удобен для выполнения

операций над десятичными числами. При этом легко определяет-

ся перенос, так как сумма двух слагаемых, каждое из которых

берется с избытком 3, получится с избытком 6, что исключает

лишние кодовые комбинации (для получения правильного кода

суммы из полученного результата вычитается 3). Но этот код

в отличие от кодов 8421 и 2421 не является взвешенным, вслед-

ствие чего мало удобен для преобразования чисел из одной си-

стемы в другую.

Используются также двоично-десятичные коды, в которых

кодирующие тетрады дополняются избыточными битами с тем,

чтобы использовать эту избыточность для придания кодам спе-

цифических свойств, служащих для обнаружения ошибок и тем

самым для повышения надежности вычислительных систем.

Так, в коде 2 из 5 каждая десятичная цифра представляется

пятью разрядами, из которых два и только два содержат едини-

цы. Если появится ошибка в одном из двоичных разрядов, т. с.

если нуль превратится в единицу или единица превратится

в нуль, то общее число единиц окажется больше или меньше

двух, что можно обнаружить простым их подсчетом. Другой

способ обнаружения одиночной ошибки основан на использова-

нии бита, которым дополняется какой-либо код, для контроля

четности. Значение дополнительного бита выбирается таким,

чтобы общее число единиц в кодирующей группе всегда было

четным или нечетным (в зависимости от принятого правила кон-

троля). Рассмотренные способы обнаруживают одиночные ошиб-

ки, точнее, нечетное количество ошибок, по не реагируют на

двойные и вообще четное количество ошибок. Существуют более

сложные способы построения корректирующих кодов, исполь-

зуемых в технике связи, но в обычных вычислительных систе-

мах из-за громоздкости они не применяются.

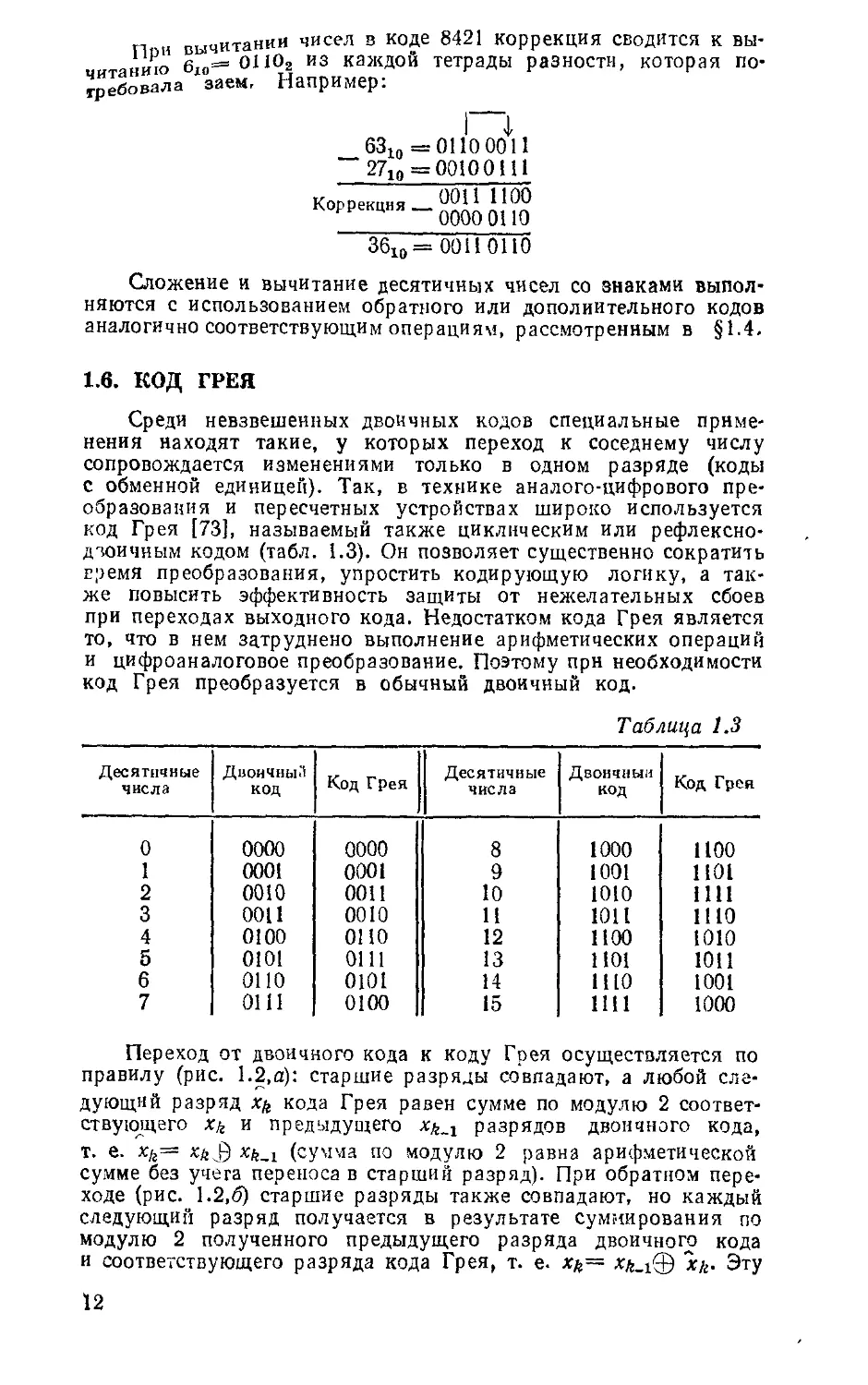

Операции над десятичными числами выполняются с помощью

несколько дополненной двоичной арифметики. Так, при сложе-

нии двух чисел в коде прямого замещения 8421 необходимо доба-

вить корректирующее слагаемое 6J0= 01102 к каждой тетраде,

в которой в процессе суммирования получена недопустимая

цифра (1010, 1011, 1100, 1101, 1110 п 1111) нли возник перенос

в следующую тетраду. Например:

, 3810 = ООН 1000 ~| , 2910 = 0010 1001 +5810 = 0101 1000

1610 = 0С01 оно

Коррекция , 0100 1110 0000 0110 Коррекция 10000001 0000 оно

5410 = 0101 0100 1000 0111

11

„ вычитании чисел в коде 8421 коррекция сводится к вы-

нию 6io:== 01102 из каждой тетрады разности, которая по-

требовала заем. Например:

1~

6310 =01100011

2710 =00100111

Коррекция _ «ОН }}00

3610= ООП ОНО

Сложение и вычитание десятичных чисел со знаками выпол-

няются с использованием обратного или дополнительного кодов

аналогично соответствующим операциям, рассмотренным в §1.4.

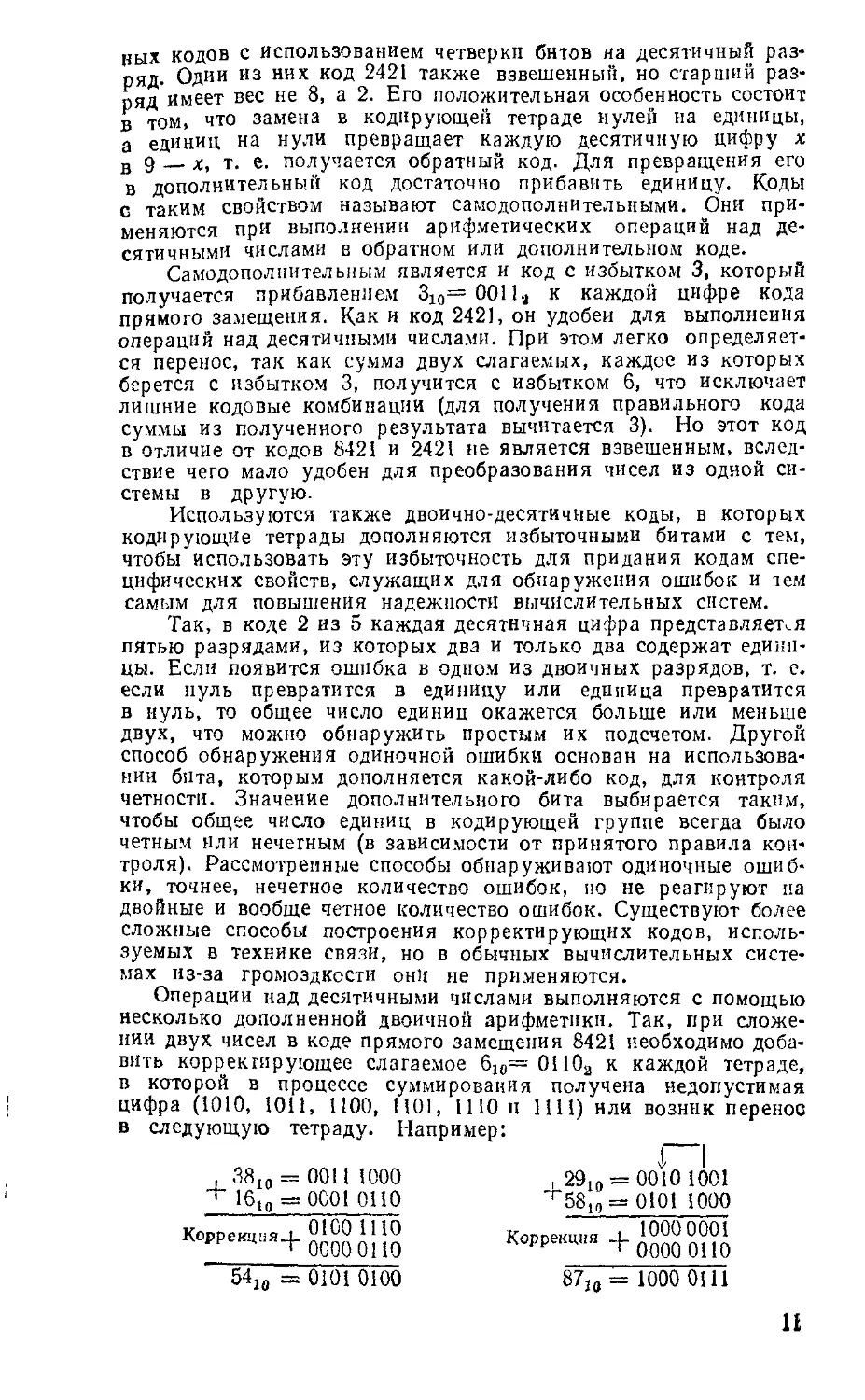

1.6. КОД ГРЕЯ

Среди невзвешенных двоичных кодов специальные приме-

нения находят такие, у которых переход к соседнему числу

сопровождается изменениями только в одном разряде (коды

с обменной единицей). Так, в технике аналого-цифрового пре-

образования и пересчетных устройствах широко используется

код Грея [73], называемый также циклическим или рефлексно-

двоичным кодом (табл. 1.3). Он позволяет существенно сократить

гремя преобразования, упростить кодирующую логику, а так-

же повысить эффективность защиты от нежелательных сбоев

при переходах выходного кода. Недостатком кода Грея является

то, что в нем затруднено выполнение арифметических операций

и цифроаналоговое преобразование. Поэтому при необходимости

код Грея преобразуется в обычный двоичный код.

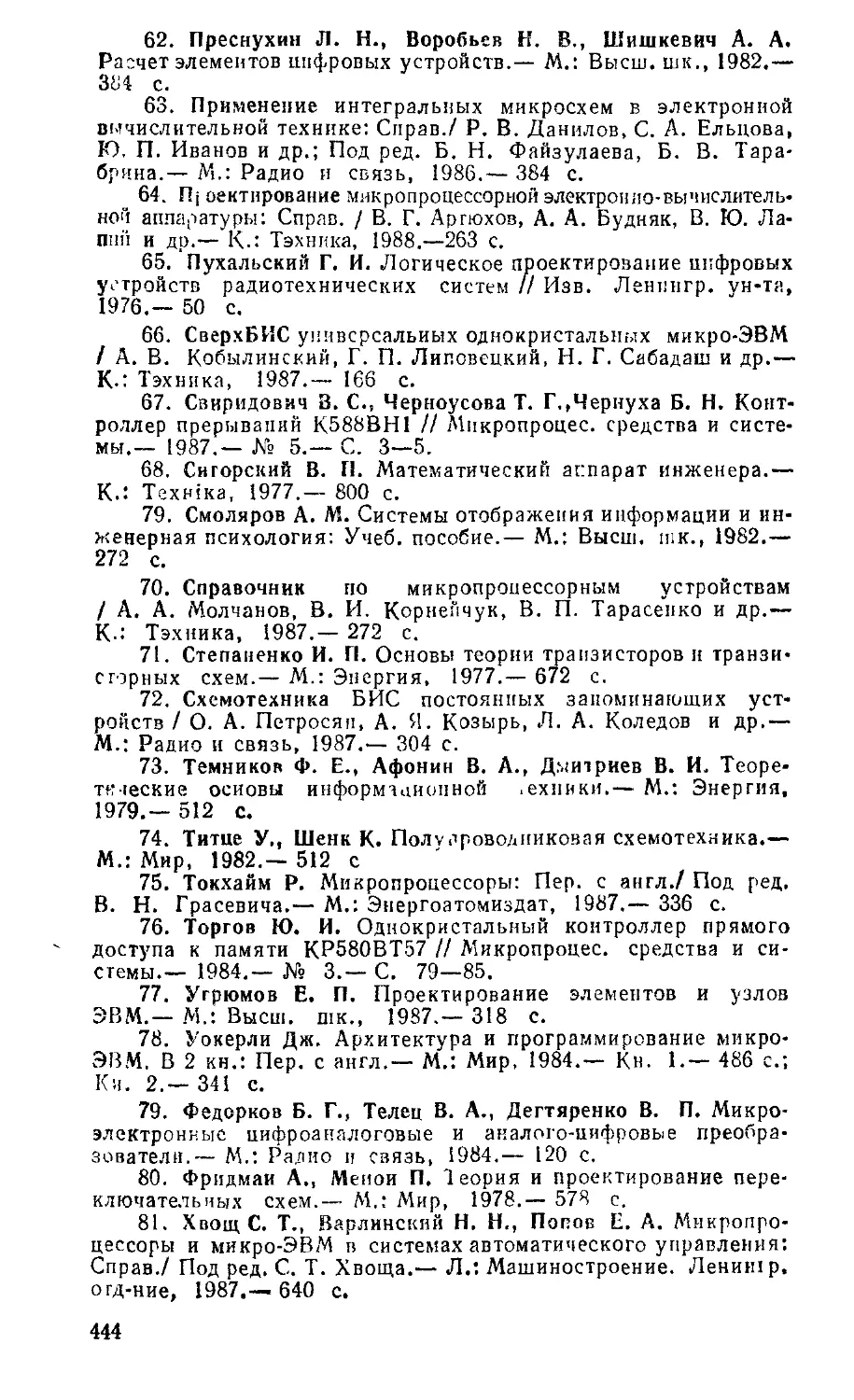

Таблица 1.3

Десятичные числа Двоичный код Код Грея Десятичные числа Двончныи КОД Код Грея

0 0000 0000 8 1000 1100

1 0001 0001 9 1001 1101

2 0010 ООП 10 1010 1111

3 ooh 0010 11 1011 1110

4 0100 оно 12 1100 1010

5 0101 0111 13 1101 1011

6 оно 0101 14 1110 1001

7 0111 0100 15 1111 1000

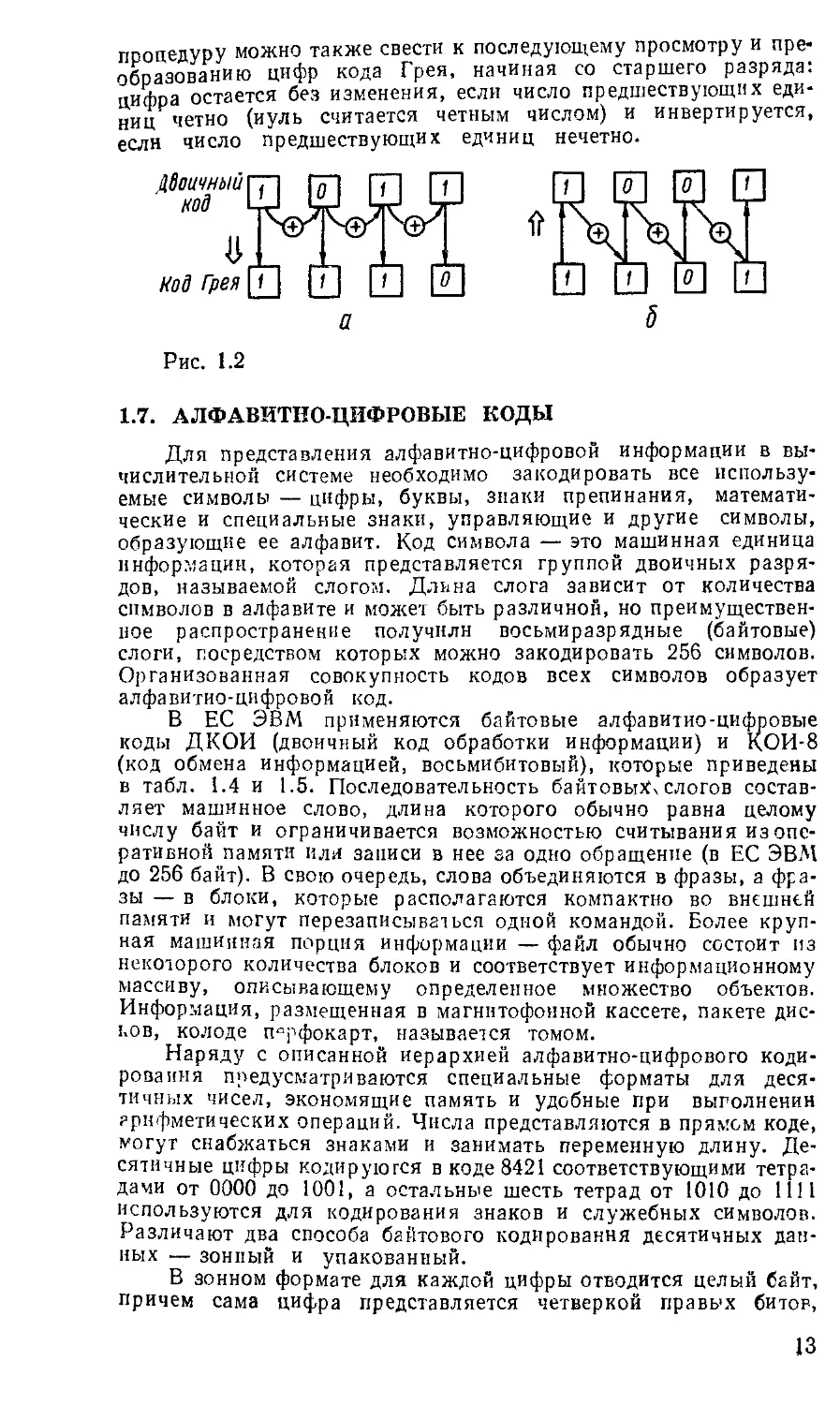

Переход от двоичного кода к коду Грея осуществляется по

правилу (рис. 1.2,а): старшие разряды совпадают, а любой сле-

дующий разряд Xk кода Грея равен сумме по модулю 2 соответ-

ствующего Xh и предыдущего х^ разрядов двоичного кода,

т. е. X/j= «йЭ xk-i (сумма по модулю 2 равна арифметической

сумме без учета переноса в старший разряд). При обратном пере-

ходе (рис. 1.2,6) старшие разряды также совпадают, но каждый

следующий разряд получается в результате суммирования по

модулю 2 полученного предыдущего разряда двоичного кода

и соответствующего разряда кода Грея, т. е. Эту

12

процедуру можно также свести к последующему просмотру и пре-

образованию цифр кода Грея, начиная со старшего разряда:

цифра остается без изменения, если число предшествующих еди-

ниц четно (нуль считается четным числом) и инвертируется,

если число предшествующих единиц нечетно.

Двоичный

нов

а

Рис. 1.2

1.7. АЛФАВИТНО-ЦИФРОВЫЕ КОДЫ

Для представления алфавитно-цифровой информации в вы-

числительной системе необходимо закодировать все использу-

емые символы — цифры, буквы, знаки препинания, математи-

ческие и специальные знаки, управляющие и другие символы,

образующие ее алфавит. Код символа — это машинная единица

информации, которая представляется группой двоичных разря-

дов, называемой слогом. Длина слога зависит от количества

символов в алфавите и может быть различной, но преимуществен-

ное распространение получили восьмиразрядные (байтовые)

слоги, посредством которых можно закодировать 256 символов.

Организованная совокупность кодов всех символов образует

алфавитно-цифровой код.

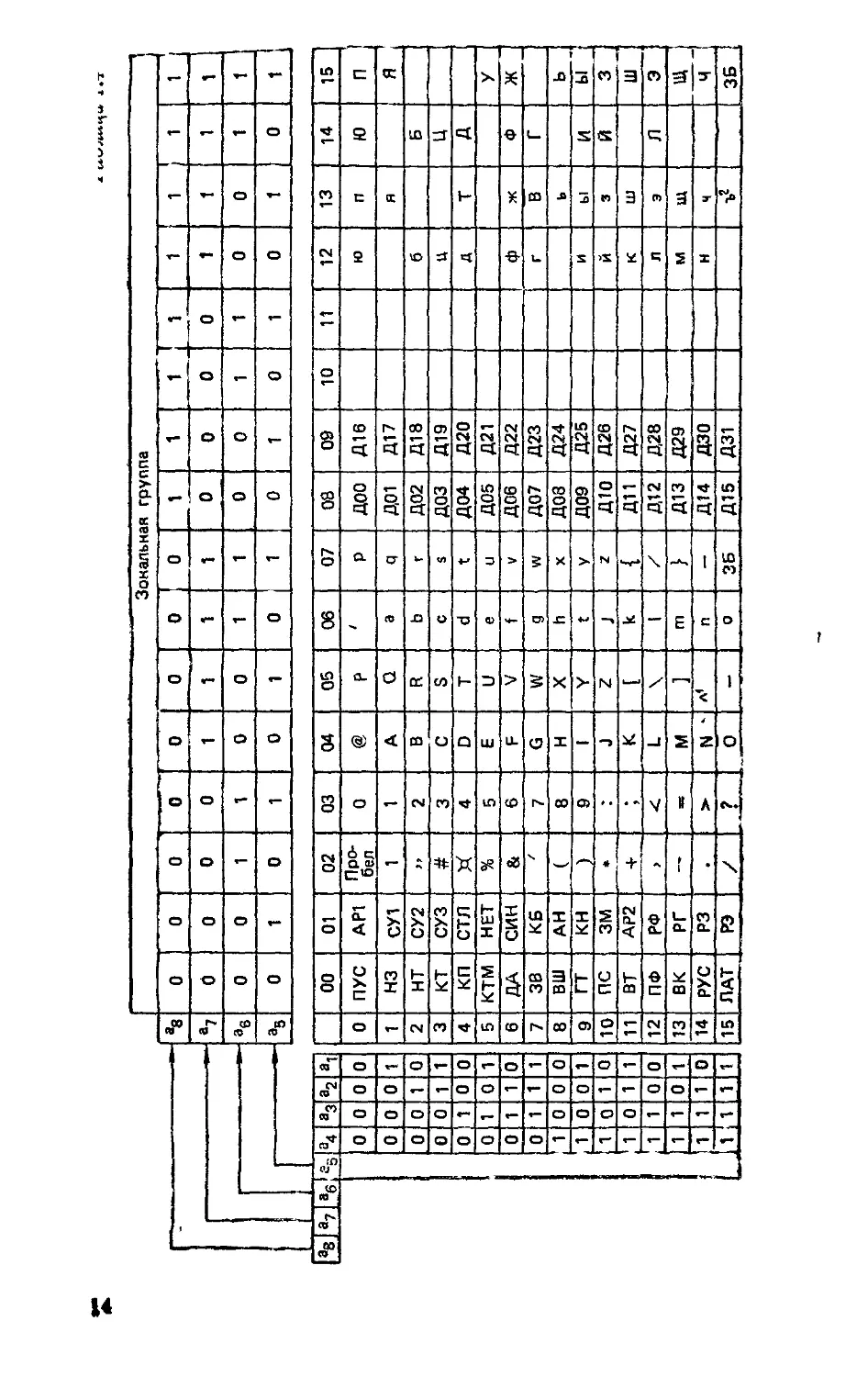

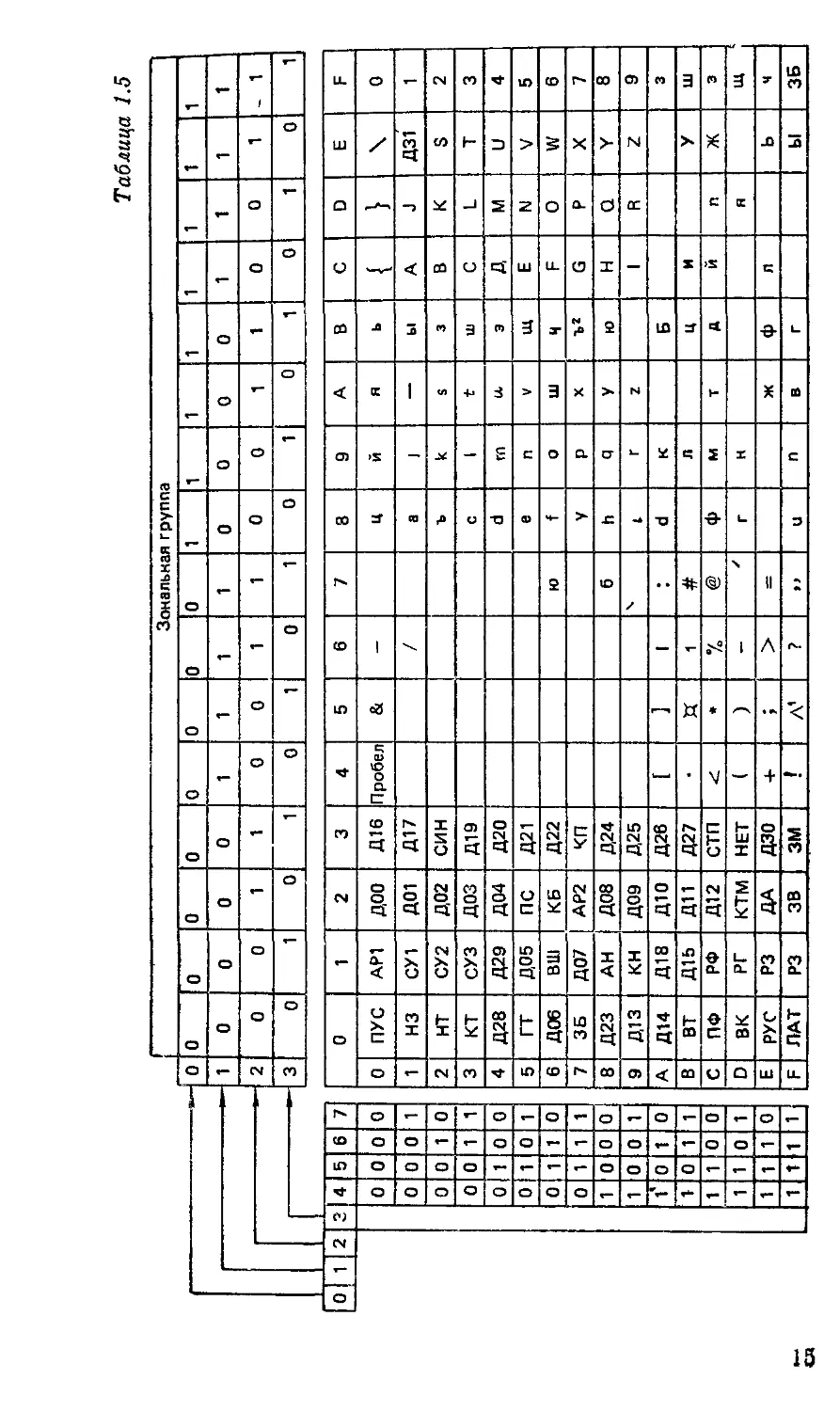

В ЕС ЭВМ применяются байтовые алфавитно-цифровые

коды ДКОИ (двоичный код обработки информации) и КОИ-8

(код обмена информацией, восьмибитовый), которые приведены

в табл. 1.4 и 1.5. Последовательность байтовых, слогов состав-

ляет' машинное слово, длина которого обычно равна целому

числу байт и ограничивается возможностью считывания из опе-

ративной памяти или записи в нее за одно обращение (в ЕС ЭВМ

до 256 байт). В свою очередь, слова объединяются в фразы, а фра-

зы — в блоки, которые располагаются компактно во внешней

памяти и могут перезаписываться одной командой. Более круп-

ная машинная порция информации — файл обычно состоит из

некоторого количества блоков и соответствует информационному

массиву, описывающему определенное множество объектов.

Информация, размещенная в магнитофонной кассете, пакете дис-

ков, колоде п°рфокарт, называется томом.

Наряду с описанной иерархией алфавитно-цифрового коди-

рования предусматриваются специальные форматы для деся-

тичных чисел, экономящие память и удобные при выполнении

арифметических операций. Числа представляются в прямом коде,

могут снабжаться знаками и занимать переменную длину. Де-

сятичные цифры кодируются в коде 8421 соответствующими тетра-

дами от 0000 до 1001, а остальные шесть тетрад от 1010 до 1111

используются для кодирования знаков и служебных символов.

Различают два способа байтового кодирования десятичных дан-

ных — зонный и упакованный.

В зонном формате для каждой цифры отводится целый байт,

причем сама цифра представляется четверкой правых битов,

13

“8 0 0 0 0 0 0

-

а7 0 0 0 0 1 1

Г-— а6 0 0 1 1 0 0

а5 0 1 0 1 0 1

|ав|а7|»6 гз а4 аз Э2 а1 00 01 02 03 04 0Е

0 0 0 0 0 ПУС API Про- бел 0 @ Р

0 0 0 1 1 НЗ СУ1 1 1 А Q

0 0 1 0 2 НТ СУ2 >> 2 В R

0 0 1 1 3 КТ СУЗ * 3 С S

0 1 0 0 4 КП стл 4 D Т

0 1 0 1 5 КТМ НЕТ % 5 Е и

0 1 1 0 6 ДА СИН & 6 F V

0 1 1 1 7 ЗВ КБ / 7 G W

1 0 0 0 8 вш АН ( 8 Н X

У 0 0 1 9 ГТ КН ) 9 I Y

1 0 1 0 10 ПС ЗМ * J Z

|± 0 1 1 11 ВТ АР2 > К 1

1 1 0 0 12 ПФ РФ > < L \

1 1 0 1 13 вк РГ М 1

1 1 1 0 14 РУС РЗ > N ‘ л<

-L LL 1 1 15 ЛАТ РЭ / 7 -..и... О —

Л t-4-V/444l^W' 4 »Т

Зональная группа

0 0 1 1 1 1 1 1 1 1

1 1 0 0 0 0 1 1 1 1

1 1 0 0 1 1 0 0 1 1

0 Lb 0 1 0 1 0 1 0 J

06 07 08 09 10 11 12 13 14 15

/ P Д00 Д16 ю п Ю П

а q Д01 Д17 я Я

ь r Д02 Д18 б 6

с s ДОЗ Д19 ц U

d t Д04 Д20 д т д

е u Д05 Д21 У

f V доб Д22 ф ж ф ж

g w Д07 Д23 г в г

h X ДОЗ Д24 ь ь

t У Д09 Д25 и ы и ы

J z ДЮ Д26 й 3 й 3_

к { Д11 Д27 К ш ш

1 / Д12 Д28 л э л э

m } Д13 Д29 м щ щ

n — Д14 ДЗО н ч ч

0 36 ДЮ Д31 ъг 36

0 0 0 0 О О 0

1 0 0 0 О 1 1

_ 2 0 0 1 1 О О

3 0 1 0 1 О

L^LiE 3 4 5 6 7 0 1 2 3 4 5

сд 0 0 0 0 0 ПУС API доо Д16 Пробел &

0 0 0 1 1 H3 СУ1 ДО1 Д17

0 0 0 0 1 1 0 1 2 HT СУ2 Д02 СИН

3 KT СУЗ ДОЗ ДЮ

0 1 0 0 4 Д28 Д29 Д04 Д20

0 1 0 1 5 ГТ Д05 ПС Д21

0 1 1 0 6 доб ВШ КБ Д22

0 1 1 1 7 ЗБ Д07 АР2 КП

1 0 0 0 8 Д23 АН Д08 Д24

1 0 0 1 9 Д13 КН Д09 Д25

f 0 1 0 A Д14 Д18 ДЮ Д26 [ ]

У 0 1 1 в ВТ ДЮ Д11 Д27 й

1 1 0 0 c ПФ РФ Д12 СТП

1 1 0 1 D BK РГ КТМ НЕТ ( )

1 1 1 0 E РУС РЗ ДА дао ц.

1 1 1 1 F ЛАТ РЗ ЗВ ЗМ 1 А’

Таблица 1.5

Зональная группа

0 0 1 1 1 1 1 1 1 1

1 1 0 0 0 0 1 1 1 1

1 1 0 0 1 1 0 0 1 - 1

1 0 1 0 1 0 1 0 1 0 1

6 7 8 9 А В С D Е F

- Ц й я ь } \ 0

/ а J — ы А J дз1 1

ъ к S 3 В К S 2

с I t ш с L т 3

d rn (Л э д М и 4

е n V Щ Е N V 5

ю f 0 ш ч F О W 6

V p X V G р X 7

б h q У ю н Q Y 8

ч I г Z I R Z 9

I • d К Б 3

1 # л ц и У ш

% Ф м т д й п ж э

- ✓ Г н я щ

> = ж ф л ь ч

? »> u п в г ы ЗБ

а четверку левых занимает специальный код, называемый зоной.

Код знака числа (если он нужен) помещается на место зоны

в младший разряд. В системе ДКОИ плюс кодируется четвер-

кой 1100, минус— 1101 и вона — 1111, а в системе КОИ-8

соответственно 1010, 1011 и 0101. Например, число —7.362

в зонном формате при работе с кодом ДКОИ имеет вид

1111 0111 1111 ООН 1111 ОНО 1101 0010

7 3 6 ' ^2

Упакованный формат использует каждый байт для представ-

ления двух чисел, кроме младшего байта, в котором правая

четверка битов отводится для кода знака. Если левая четверка

битов самого старшего байта окажется свободной, она заполняет-

ся нулями, т. е. десятичное число всегда занимает целое число

байтов. Например:

00000111 0011 0110 00101101

~~6~ ~Г' 2

При выполнении арифметических операции используется

только упакованный формат, в котором десятичное число может

занимать до 16 байт, что соответствует 31 десятичному разряду

и знаку. Зонный формат используется при операциях ввода-вы-

вода десятичных данных. В вычислительных системах преду-

сматривается возможность взаимного преобразования форматов,

причем информация о месте расположения разделительного

знака дробного числа фиксируется в самой программе.

Глава 2

АЛГЕБРА ЛОГИКИ

2.1. ЛОГИЧЕСКИЕ ФУНКЦИИ

Вследствие того что сигналы в цифровых системах представ-

ляются двоичными кодами, математическое моделирование

таких систем основано на использовании двузначной логики

(29; 68; 80], в которой переменные могут принимать только

одно из двух значений. Эти значения соответствуют двум воз-

можным состояниям реальных объектов (истинное или ложное

высказывание, высокое или низкое напряжение, наличие или

отсутствие данного признака и т. п.). Они обозначаются циф-

рами 0 и 1, буквами Л (ложно) и И (истинно) или вообще лю-

быми двумя различающимися символами. В технических при-

ложениях обычно используются цифровые обозначения, кото-

рые естественным образом связаны с двоичными кодами.

В общем случае логические переменные могут принимать

одно из k значений (fe-зиачная логика). Перечень всех k симво-

лов, соответствующих области значений, называют алфавитом,

а сами символы — буквами этого алфавита. Логические функции

могут зависеть от одной, двух и вообще любого числа перемен-

ных (аргументов). Областью определения /е-значной функции

от п переменных у = f (хъ х2. хп) служит множество набо-

ров (х1( х2, ..., хп), являющихся словами длины п, где каждый

из аргументов замещается буквами fe-ичнэго алфавита. Так как

количество всевозможных слов длины п в fe-ичном алфавите

16

павно количеству различных «-разрядных чисел с основанием k,

т е kn, а каждому такому слову можно сопоставить одно из

fe'значений, то общее количество fe-значных функций от п пере-

менных выражается числом Многозначная логика распо-

лагает собственным аппаратом и используется для математиче-

ского моделирования таких объектов, компоненты которых

характеризуются многими состояниями. Между тем двузначная

логика наряду о предельной простотой характеризуется и до-

статочной общностью, так как к ней можно свести и задачи мо-

делирования многозначных структур.

Количество всевозможных двоичных функций выражается

числом 2^п, а область определения таких функций представляет

собой всевозможные наборы из п двоичных цифр и их общее

количество равно 2™. При увеличении п количество двоичных

функций быстро возрастает (при п — 3 оно равно 256, а при

п = 5 уже превышает 4 млрд.). Но функции одной и двух пере-

менных еще можно перечислить и подробно исследовать, так

как их количество сравнительно невелико (4 при п = 1 и 16 при

п = 2).

2.2. ТАБЛИЦЫ СООТВЕТСГВИЯ

Множество функций п переменных можно представить с по-

мощью таблицы соответствия, столбцы которой отводятся для

2П слов длины п, а строки — для 22fl функций. При этом номера

столбцов определяются расположенными над ними «-разрядны-

ми двоичными числами, которые читаются по вертикали сверху

вниз. Номера функций отождествляются с г^-разрядными дво-

ичными числами, записанными в соответствующих строках таб-

лицы. Таблицу соответствия часто называют также таблицей

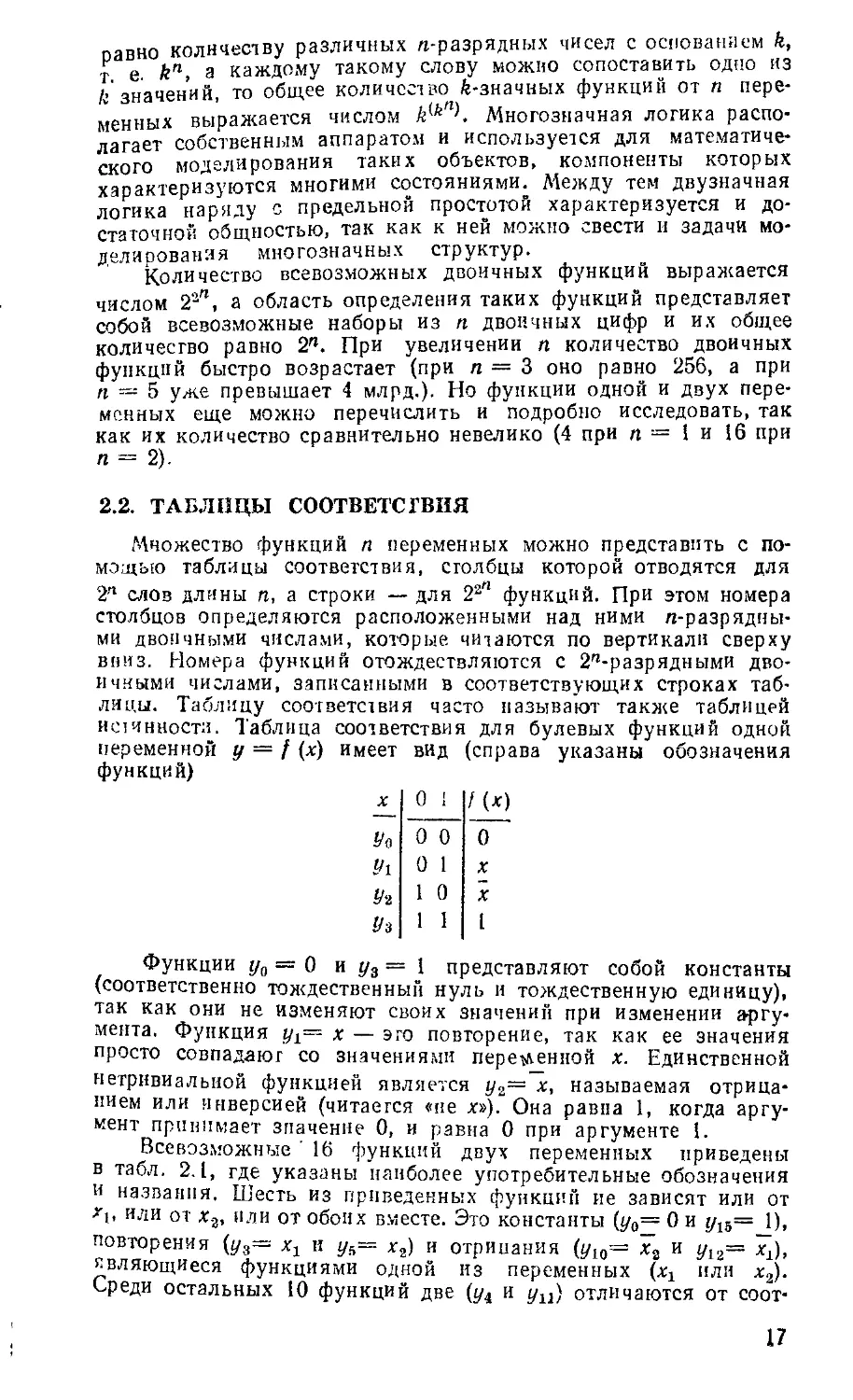

истинности. Таблица соответствия для булевых функций одной

переменной у — f (х) имеет вид (справа указаны обозначения

функций)

х

Уо

У1

Уз

Уз

0 1 / (х)

о о У

0 1 X

1 0 X

1 1 I

Функции у, = 0 и у3 — 1 представляют собой константы

(соответственно тождественный нуль и тождественную единицу),

так как они не изменяют своих значений при изменении аргу-

мента. Функция у}= х — эго повторение, так как ее значения

просто совпадают со значениями переменной х. Единственной

нетривиальной функцией является у2— х, называемая отрица-

нием или инверсией (читается «не х»). Она равна 1, когда аргу-

мент принимает значение 0, и равна 0 при аргументе 1.

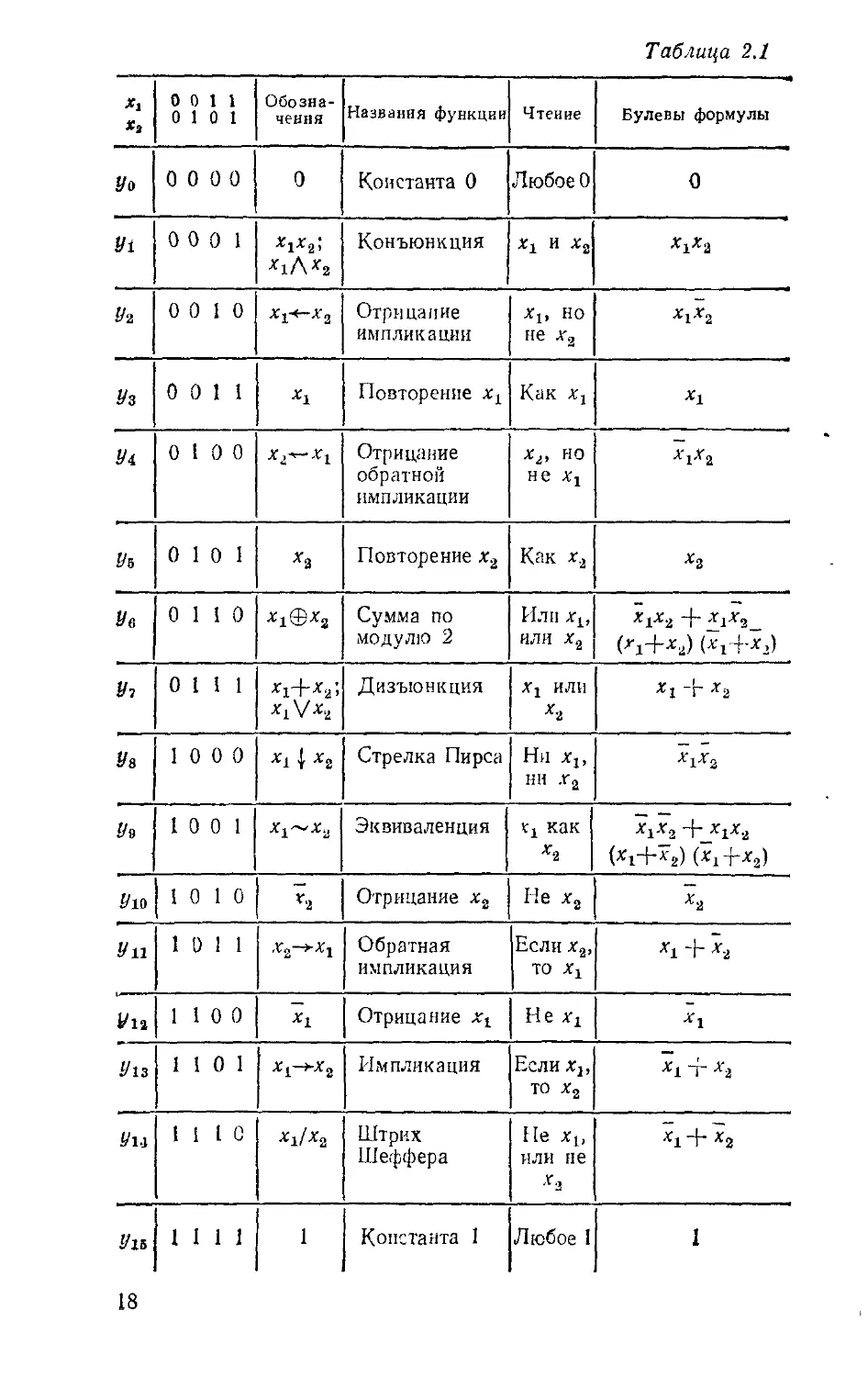

Всевозможные 16 функций двух переменных приведены

в табл. 2.1, где указаны наиболее употребительные обозначения

и названия. Шесть из приведенных функций ие зависят или от

'I, или от х.2, или от обоих вместе. Эта константы (у0= 0 и у13= 1),

повторения (у3= хг и у5= х2) и отрицания (у10= х2 и у12= xj,

являющиеся функциями одной из переменных (х2 или х2).

Среди остальных 10 функций две (у4 и у12) отличаются от соот-

17

Таблица 2.1

Xi Хг 0 0 11 0 10 1 Обозна- чения Названия функции Чтение Булевы формулы

Уй 0 0 0 0 0 Константа 0 Любое 0 0

Vi 0 0 0 1 ^1Г2» *1Л*2 Конъюнкция Xi И х2 XiX2

Уз 0 0 10 ХГ*~Х2 Отрицание импликации xlt но не х2 *1*2

Уз 0 0 11 *1 Повторение xL Как ха *1

У1 0 10 0 х^-х1 Отрицание обратной импликации х2( но не х1х2

Уз 0 10 1 хз Повторение х2 Как х2 х2

Ув 0 110 хх®х2 Сумма по модулю 2 Или или х2 Х1Х2 + ХЛ_ (х1+х2) (хг4-х,1

У, 0 111 *1+ха’> Дизъюнкция хг или Х2 Х1 -Г х2

Уз 10 0 0 Х1 1 Х2 Стрелка Пирса Ни х1( ни х2 х,х2

'Л 10 0 1 Эквиваленция как х2 XiX2 +_XiX2

Ую 10 10 Х2 Отрицание х2 Не х2 х2

Ун 10 11 Х2—>-Х1 Обратная импликация Если х2, ТО Xj *1 + *2

Ун 110 0 Х1 Отрицание xt Не л-! Х1

У1з 110 1 Х,->Х„ Импликация Если х2, то х2 Xi-i-x2

Уи 1110 Х1/Х2 Штрих Шеффера Не xL, или не -Ч Х1 + Х2

Ун 1111 1 Константа 1 Любое 1 1

18

в-тствующих им функций (у2 И у,3) лишь порядком расположе-

ния аргументов. Поэтому из 16 булевых функций двух пере-

менных оригинальными являются только восемь: У1, у2, уе, Ут,

и и», У13’ Ун- Можно также заметить, что среди булевых функ-

ций некоторого числа переменных содержатся всевозможные

функции меньшего числа переменных, которые называются вы-

рожденными функциями. Так, среди функций одной переменной

имеются две вырожденные — константы 0 и 1, которые можно

рассматривать как функции от нуля переменных. Функции

двух переменных содержат те же константы и четыре функции

одной переменной и т. д.

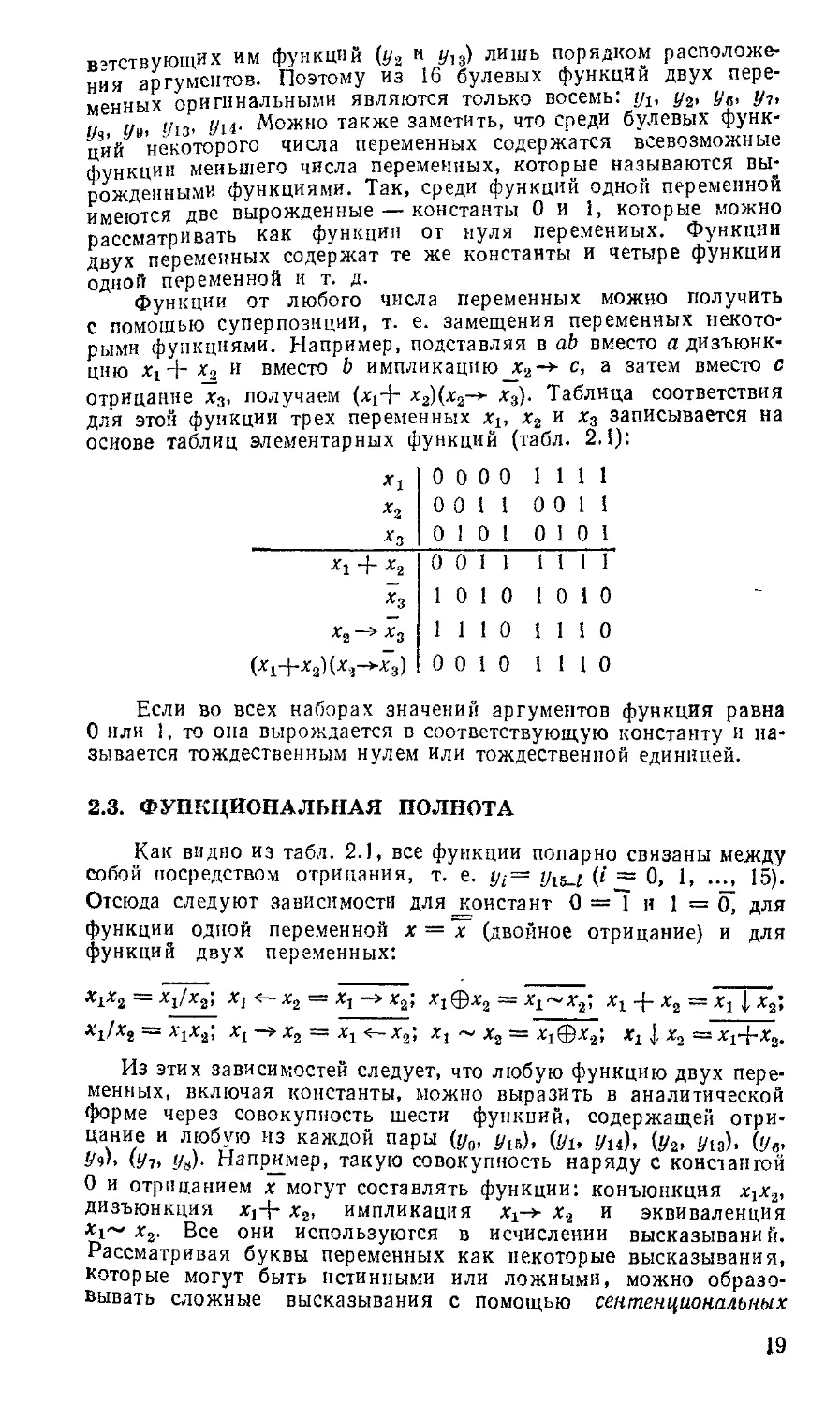

Функции от любого числа переменных можно получить

с помощью суперпозиции, т. е. замещения переменных некого-

рыми функциями. Например, подставляя в ab вместо а дизъюнк-

цию хг + х2 и вместо b импликацию х2-+ с, а затем вместо с

отрицание х3, получаем (хгН х2)(х3-> х3). Таблица соответствия

для этой функции трех переменных xlt х2 и х3 записывается на

основе таблиц элементарных функций (табл. 2.1):

*1

*2

______________£з_

+ х2

*3

х2 -> х3

(Xi4-x2)(x3->x3)

0000 1111

0011 0011

0 10 1 0 10 1

0 0 11 1111

10 10 10 10

1110 1110

0 0 10 1110

Если во всех наборах значений аргументов функция равна

0 или 1, то она вырождается в соответствующую константу и на-

зывается тождественным нулем или тождественной единицей.

2.3. ФУНКЦИОНАЛЬНАЯ ПОЛНОТА

Как видно из табл. 2.1, все функции попарно связаны между

собой посредством отрицания, т. е. у,— </l8j (г = 0, 1. 15).

Отсюда следуют зависимости для_констант 0 =~Т и 1 = (\ для

функции одной переменной х —~х (двойное отрицание) и для

функций двух переменных:

Xix2 — Xj/x2; Xj <— х2—• Xj —> х2; xlQx2— Xi~x2‘ xt -f- x2 — Xj | x2>

Xi/Xg = X*iX2; X1 —> X2 ~ Xj X/, Xj ~ X2 == Х|фх2; *1 I x2 = Xj4"X2.

Из этих зависимостей следует, что любую функцию двух пере-

менных, включая константы, можно выразить в аналитической

форме через совокупность шести функций, содержащей отри-

цание и любую из каждой пары (у0, ylt), ри), (у2, у18), (Уе,

Уч', (Уъ !/«) Например, такую совокупность наряду с константой

0 и отрицанием х могут составлять функции: конъюнкция хгх2,

дизъюнкция Xj-|- х2, импликация х2 и эквиваленция

х2. Все они используются в исчислении высказываний.

Рассматривая буквы переменных как некоторые высказывания,

которые могут быть истинными или ложными, можно образо-

вывать сложные высказывания с помощью сентенциональных

19

связок, соответствующих функциям этих переменных. При этом

отрицанию соответствует связка не, конъюнкции — и, дизъюнк-

ции — или, импликации — если, то и эквиваленции — если

и только если.

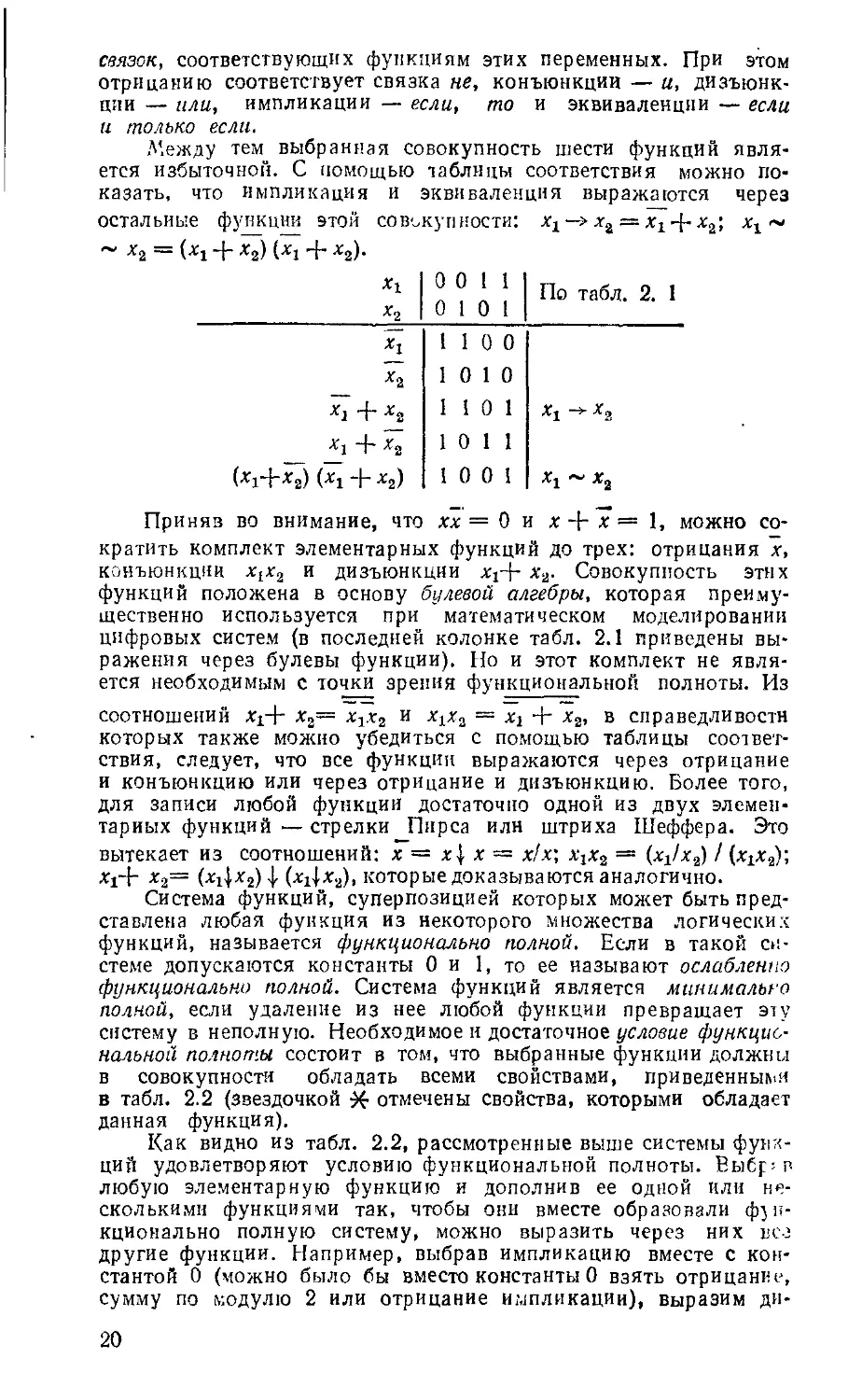

Между тем выбранная совокупность шести функций явля-

ется избыточной. С помощью таблицы соответствия можно по-

казать, что импликация и эквиваленция выражаются через

остальные функции этой совокупности: Xj-> х2 = хг + х2; хх ~

~ х2 = (%! + х2) (%i + х2).

Xi I 0 0 1 1 I п Л п .

л . По табл. 2. 1

х2 I 0 1 0 1 I

*1

Х1 + х2

*1 +

(*1+*г) (%! + х2)

110 0

10 10

1101 Xj -> х,

10 11

10 0 1 Xj ~ х2

Приняв во внимание, что хх = 0 и х + х = 1, можно со-

кратить комплект элементарных функций до трех: отрицания х,

КОНЪЮНКЦИИ Х,Х2 и ДИЗЪЮНКЦИИ Х1+ х2. Совокупность этих

функций положена в основу булевой алгебры, которая преиму-

щественно используется при математическом моделировании

цифровых систем (в последней колонке табл. 2.1 приведены вы-

ражения через булевы функции). Но и этот комплект не явля-

ется необходимым с точки зрения функциональной полноты. Из

соотношений Xi+ х$= Xjx2 и ххх2 = х2 + х2, в справедливости

которых также можно убедиться с помощью таблицы соответ-

ствия, следует, что все функции выражаются через отрицание

и конъюнкцию или через отрицание и дизъюнкцию. Более того,

для записи любой функции достаточно одной из двух элемен-

тарных функций — стрелки Пирса илн штриха Шеффера. Это

вытекает из соотношений: х = х| х = х/х; xjx2 = (xj/x2) / (хр:2);

*1+ х2~ (xit-Ч) Ф (*il*a)> которые доказываются аналогично.

Система функций, суперпозицией которых может быть пред-

ставлена любая функция из некоторого множества логических

функций, называется функционально полной. Если в такой си-

стеме допускаются константы 0 и 1, то ее называют ослабленио

функционально полной. Система функций является минимально

полной, если удаление из нее любой функции превращает эту

систему в неполную. Необходимое и достаточное условие функцио-

нальной полноты состоит в том, что выбранные функции должны

в совокупности обладать всеми свойствами, приведенными

в табл. 2.2 (звездочкой •X- отмечены свойства, которыми обладает

данная функция).

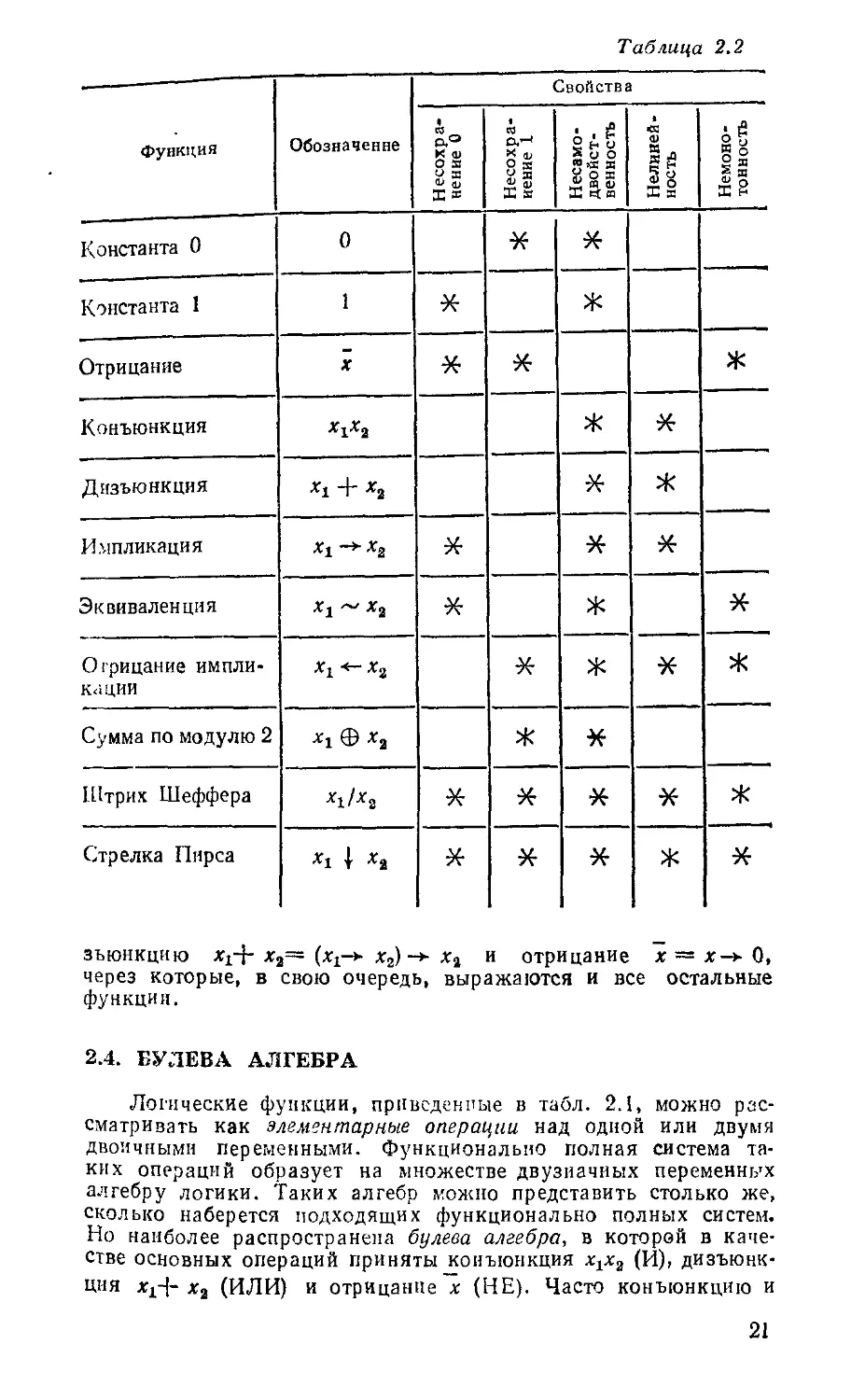

Как видно из табл. 2.2, рассмотренные выше системы функ-

ций удовлетворяют условию функциональной полноты. Выбр:в

любую элементарную функцию и дополнив ее одной или не-

сколькими функциями так, чтобы они вместе образовали фун-

кционально полную систему, можно выразить через них вег

другие функции. Например, выбрав импликацию вместе с кон-

стантой 0 (можно было бы вместо константы 0 взять отрицание,

сумму по модулю 2 или отрицание импликации), выразим ди-

20

Таблица 2.2

Функция Обозначение Свойства

Н есохр а- нение 0 I Несохра- иение 1 s и о Я*® = Л ВС и Нелиней- ность Немоно- J томность

Константа 0 0 X X

Константа 1 1 * *

Отрицание X * * *

Конъюнкция * X

Дизъюнкция + х2 X *

Импликация Xi ->х2 * X *

Эквиваленция *1 ~Х2 * * X

Отрицание импли- кации *1 *-х2 * * X *

Сумма по модулю 2 *1 Ф х2 * X

Штрих Шеффера Х1/х2 * X X X *

Стрелка Пирса Xj | Xg * X X * X

зъюнкцию xpf- х2~ (*i~> х2) -> х2 и отрицание х = х-> О,

через которые, в свою очередь, выражаются и все остальные

функции.

2.4. БУЛЕВА АЛГЕБРА

Логические функции, приведенные в табл. 2.1, можно рас-

сматривать как элементарные операции над одной или двумя

двоичными переменными. Функционально полная система та-

ких операций образует на множестве двузначных переменных

алгебру логики. Таких алгебр можно представить столько же,

сколько наберется подходящих функционально полных систем.

Но наиболее распространена булева алгебра, в которой в каче-

стве основных операций приняты конъюнкция XjX2 (И), дизъюнк-

ция хх-|- х2 (ИЛИ) и отрицание х (НЕ). Часто конъюнкцию и

21

дизъюнкцию называют соответственно логическим, произведением

и суммой, а отрицание — инверсией. Используются также и дру-

гие варианты обозначений: для конъюнкции х, Д х2, для дизъюн-

кции XjV х2 и для отрицания х'. Чтобы избежать в сложных фор-

мулах лишних скобок, которые появляются при суперпозиции

функций, установлен жесткий порядок выполнения операций—

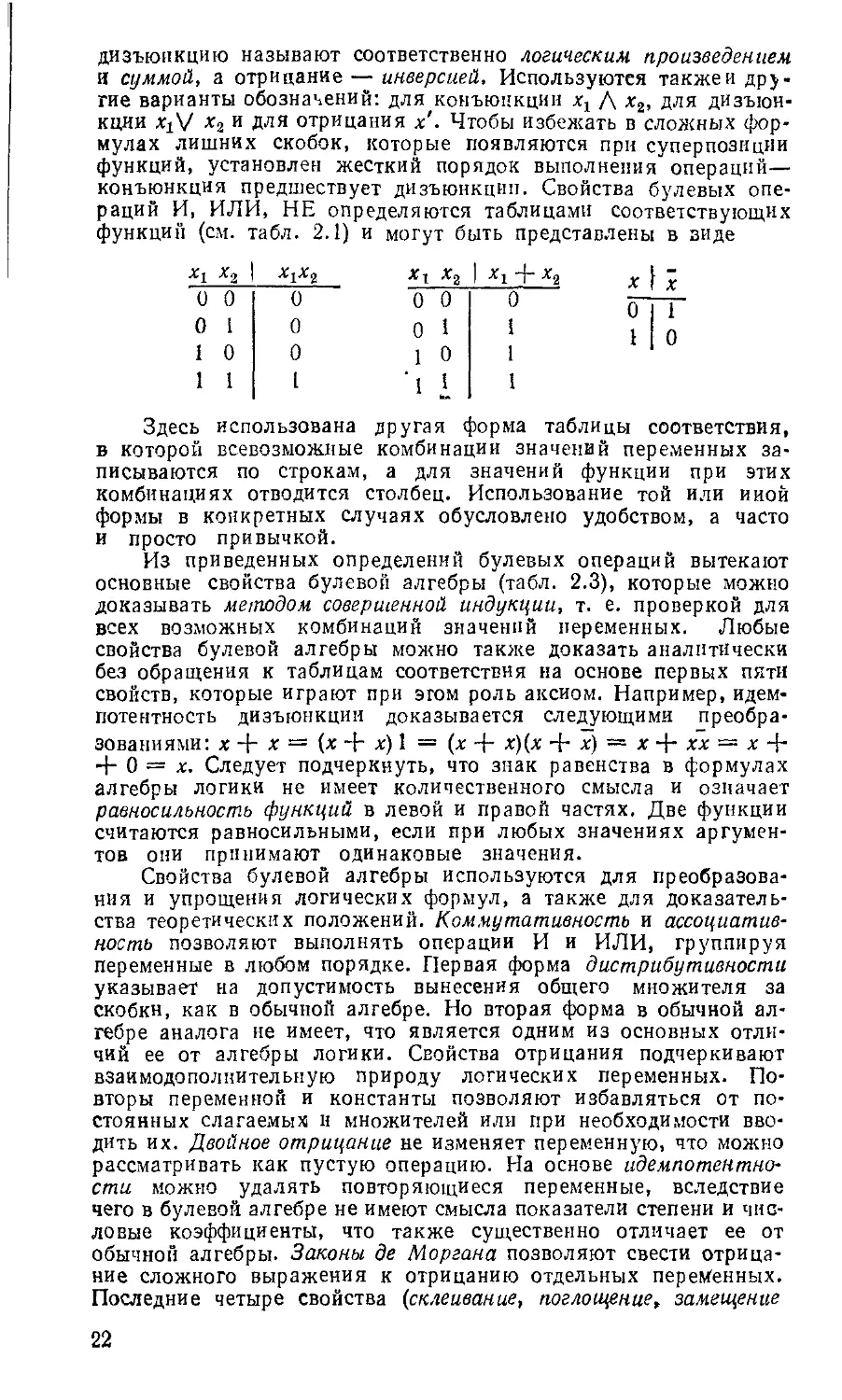

конъюнкция предшествует дизъюнкции. Свойства булевых опе-

раций И, ИЛИ, НЕ определяются таблицами соответствующих

функций (см. табл. 2.1) и могут быть представлены в виде

%1 х2 %1Х8 xt х2 1 *1 + *2 X 1 7

0 0 0 0 0 0 0 1 1

0 1 0 0 1 1 1 1 о

1 0 0 1 о 1

1 1 1 ’1 1 1

Здесь использована другая форма таблицы соответствия,

в которой всевозможные комбинации значений переменных за-

писываются по строкам, а для значений функции при этих

комбинациях отводится столбец. Использование той или иной

формы в конкретных случаях обусловлено удобством, а часто

и просто привычкой.

Из приведенных определений булевых операций вытекают

основные свойства булевой алгебры (табл. 2.3), которые можно

доказывать методом совершенной индукции, т. е. проверкой для

всех возможных комбинаций значений переменных. Любые

свойства булевой алгебры можно также доказать аналитически

без обращения к таблицам соответствия на основе первых пяти

свойств, которые играют при этом роль аксиом. Например, идем-

потентность дизъюнкции доказывается следующими преобра-

зованиями: X + X = (х + %) 1 = (х + Х)(х + х) = х+хх = х +

+ 0 = х. Следует подчеркнуть, что знак равенства в формулах

алгебры логики не имеет количественного смысла и означает

равносильность функций в левой и правой частях. Две функции

считаются равносильными, если при любых значениях аргумен-

тов они принимают одинаковые значения.

Свойства булевой алгебры используются для преобразова-

ния и упрощения логических формул, а также для доказатель-

ства теоретических положений. Коммутативность и ассоциатив-

ность позволяют выполнять операции И и ИЛИ, группируя

переменные в любом порядке. Первая форма дистрибутивности

указывает на допустимость вынесения общего множителя за

скобки, как в обычной алгебре. Но вторая форма в обычной ал-

гебре аналога не имеет, что является одним из основных отли-

чий ее от алгебры логики. Свойства отрицания подчеркивают

взаимодополнительную природу логических переменных. По-

вторы переменной и константы позволяют избавляться от по-

стоянных слагав,мых и множителей или при необходимости вво-

дить их. Двойное отрицание не изменяет переменную, что можно

рассматривать как пустую операцию. На основе идемпотентно-

сти можно удалять повторяющиеся переменные, вследствие

чего в булевой алгебре не имеют смысла показатели степени и чис-

ловые коэффициенты, что также существенно отличает ее от

обычной алгебры. Законы де Моргана позволяют свести отрица-

ние сложного выражения к отрицанию отдельных переменных.

Последние четыре свойства (склеивание, поглощение, замещение

22

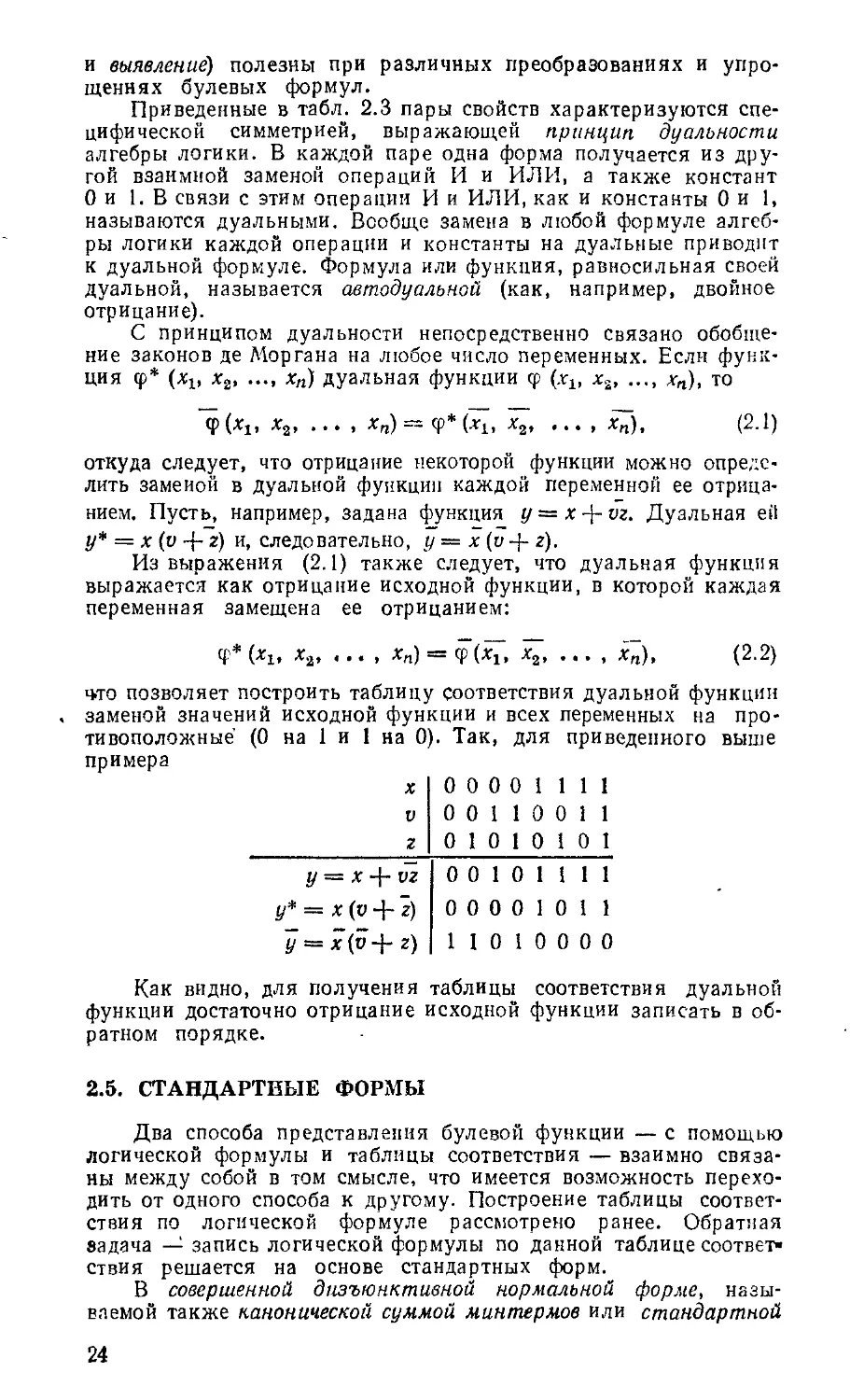

Таблица 2.3

Свойства Первая форма (') Вторая форма (")

1. Коммута- тивность *+У = У+Х ху^ух

2. Ассоциа- тивность X + [у +?) = = (х+ «/)+? X (уг) = (ху) z

3. Дистрибу- тивность X (у + г) = ху + хг х + уг = = (х + У) (х + z)

4. Дополнение X + X = 1 хх = 0

5. Повтор пе- ременной х + 0 = х х1 = х

6. Повтор константы x-f-1 =1 х0==0

7. Двойное отрицание X = X X = X

8. Идемпо- тентность X -]-х ~ X XX ~х

9. Законы де Моргана X + у = ху ху = х + у

10. Склеива- ние ХУ + ху = X (х+ у) (х + у)

И. Поглоще- ние ху — X X (X + у) = X

12. Замещение х-\-~xy = ху X (X + у) = ху

13. Выявление ху + ~хг - = ху + xz + уг (x + z/)£x + ?) = = (х + ^)(х + г) (у + г)

23

и выявление} полезны при различных преобразованиях и упро-

щениях булевых формул.

Приведенные в табл. 2.3 пары свойств характеризуются спе-

цифической симметрией, выражающей принцип дуальности

алгебры логики. В каждой паре одна форма получается из дру-

гой взаимной заменой операций И и ИЛИ, а также констант

О и 1. В связи с этим операции И и ИЛИ, как и константы 0 и 1,

называются дуальными. Вообще замена в любой формуле алгеб-

ры логики каждой операции и константы на дуальные приводит

к дуальной формуле. Формула или функция, равносильная своей

дуальной, называется автодуальной (как, например, двойное

отрицание).

С принципом дуальности непосредственно связано обобще-

ние законов де Моргана на любое число переменных. Если функ-

ция ф* (хх, х2...хп) дуальная функции ф (х1( х2, .... хп), то

ф(х1( х2, ... , хп) = Ф*(х[, ... , х7), (2.1)

откуда следует, что отрицание некоторой функции можно опреде-

лить заменой в дуальной функции каждой переменной ее отрица-

нием. Пусть, например, задана функция y—x-\-vz. Дуальная ей

у* = х (и + г) и, следовательно, у — х (v + г).

Из выражения (2.1) также следует, что дуальная функция

выражается как отрицание исходной функции, в которой каждая

переменная замещена ее отрицанием:

Ф* (х1( х2, , хп) = ф (xf, х2, ... , х„), (2.2)

ч.то позволяет построить таблицу соответствия дуальной функции

заменой значений исходной функции и всех переменных на про-

тивоположные (0 на 1 и 1 на 0). Так, для приведенного выше

примера

х 00001111

v 0 0 1 1 0 0 1 1

z 0 10 10 10 1

у = х + vz

у* = х (v + г)

у = x(v-f- г)

00101111

0 0 0 0 1 0 1 1

11010000

Как видно, для получения таблицы соответствия дуальной

функции достаточно отрицание исходной функции записать в об-

ратном порядке.

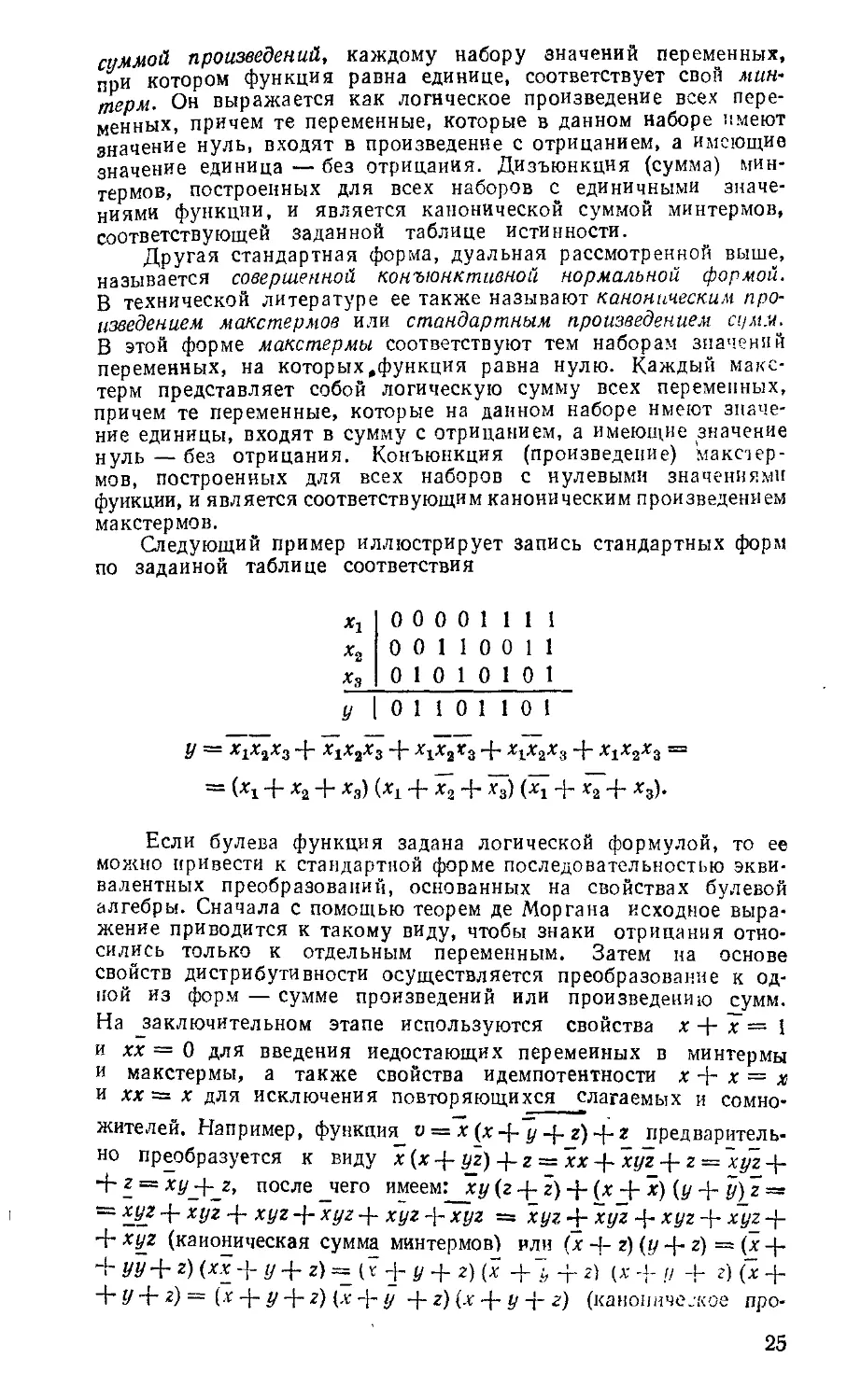

2.5. СТАНДАРТНЫЕ ФОРМЫ

Два способа представления булевой функции — с помощью

логической формулы и таблицы соответствия — взаимно связа-

ны между собой в том смысле, что имеется возможность перехо-

дить от одного способа к другому. Построение таблицы соответ-

ствия по логической формуле рассмотрено ранее. Обратная

задача — запись логической формулы по данной таблице соответ»

ствия решается на основе стандартных форм.

В совершенной дизъюнктивной нормальной форме, назы-

ваемой также канонической суммой минтермов или стандартной

24

суммой произведений, каждому набору значений переменных,

при котором функция равна единице, соответствует свой мин-

терм. Он выражается как логическое произведение всех пере-

менных, причем те переменные, которые в данном наборе имеют

значение нуль, входят в произведение с отрицанием, а имеющие

значение единица — без отрицания. Дизъюнкция (сумма) мин-

термов, построенных для всех наборов с единичными значе-

ниями функции, и является канонической суммой минтермов,

соответствующей заданной таблице истинности.

Другая стандартная форма, дуальная рассмотренной выше,

называется совершенной конъюнктивной нормальной формой.

В технической литературе ее также называют каноническим про-

изведением макстермов или стандартным произведением сумм.

В этой форме макстермы соответствуют тем наборам значений

переменных, на которых,функция равна нулю. Каждый макс-

терм представляет собой логическую сумму всех переменных,

причем те переменные, которые на данном наборе имеют значе-

ние единицы, входят в сумму с отрицанием, а имеющие значение

нуль—без отрицания. Конъюнкция (произведение) 'макстер-

мов, построенных для всех наборов с нулевыми значениями

функции, и является соответствующим каноническим произведением

макстермов.

Следующий пример иллюстрирует запись стандартных форм

по заданной таблице соответствия

хг 0 0 0 0 1 1 1 1

х2 0 0 1 1 0 0 11

х3 01010101

у 10 110 110 1

У = W3 + ^Х,^ + xj^ + Х,ХзХз + XjX^ =

= (Х1 + + Х3) (Xj + + v3) (Xj + + *з)-

Если булева функция задана логической формулой, то ее

можно привести к стандартной форме последовательностью экви-

валентных преобразовании, основанных на свойствах булевой

алгебры. Сначала с помощью теорем де Моргана исходное выра-

жение приводится к такому виду, чтобы знаки отрицания отно-

сились только к отдельным переменным. Затем на основе

свойств дистрибутивности осуществляется преобразование к од-

ной из форм — сумме произведений или произведению сумм.

На заключительном этапе используются свойства x + ~х — 1

и хх = 0 для введения недостающих переменных в минтермы

и макстермы, а также свойства идемпотентности х + х = х

и хх = х для исключения повторяющихся слагаемых и сомно-

жителей. Например, функция_ п = х(х-|-^+_г) + г предваритель-

но преобразуется к виду х (x-ф- уг) 4- г = хх 4- хуг_ 4- г = ~хуг +

4~ £ = хУ+_г, после _чего имеем:_ху (г -f- г) + (х + х) (у + у) г =

= xyz 4- xyz + xyz-j- хуг 4- хуг 4- xyz = xyz + xyz 4- xyz 4- xyz -j-

+ хуг (каноническая сумма минтермов) или (х z) (р 4- z) = (х 4-

4- УУ+г}(хх-\- (/+ г) == (г + у + г)(х + 4-z) (х у + г) (х 4-

4" У г) = (х + у + z) (х + у + г) (х у г) (каноническое про-

25

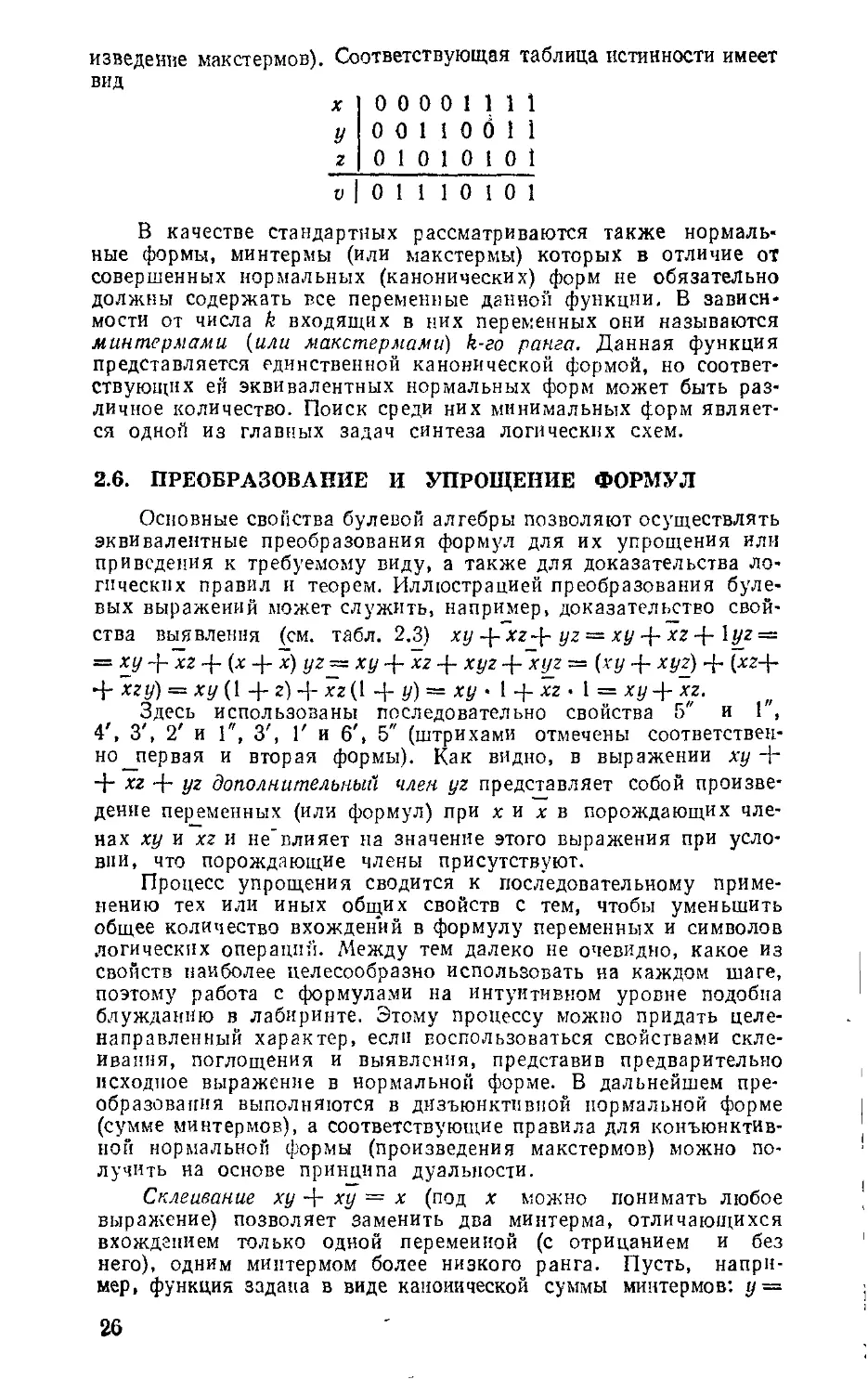

изведение макстермов). Соответствующая таблица истинности имеет

вид

х 00001111

у 0 0 110 6 11

z 0 10 10 10 1

v 0 1110 10 1

В качестве стандартных рассматриваются также нормаль-

ные формы, минтермы (или макстермы) которых в отличие от

совершенных нормальных (канонических) форм не обязательно

должны содержать все переменные данной функции. В зависи-

мости от числа k входящих в них переменных они называются

минтермами (или макстермами) k-го ранга. Данная функция

представляется единственной канонической формой, но соответ-

ствующих ей эквивалентных нормальных форм может быть раз-

личное количество. Поиск среди них минимальных форм являет-

ся одной из главных задач синтеза логических схем.

2.6. ПРЕОБРАЗОВАНИЕ И УПРОЩЕНИЕ ФОРМУЛ

Основные свойства булевой алгебры позволяют осуществлять

эквивалентные преобразования формул для их упрощения или

приведения к требуемому виду, а также для доказательства ло-

гических правил и теорем. Иллюстрацией преобразования буле-

вых выражений может служить, например, доказательство свой-

ства выявления (см. табл. 2.3) ху xz-\- yz = ху 4- xz -f- lyz =

= ху -ф- xz + (х 4- х) yz — ху 4- xz 4- xyz4- xyz = (ху 4- xyz} 4- (xz-\-

4- xzy) = xy (1 4-г) 4- xz(l 4- y) = xy • 1 4-xz • 1 = xy+xz.

Здесь использованы последовательно свойства 5" и 1 ,

4', 3', 2' и 1", 3', Г и 6', 5" (штрихами отмечены соответствен-

но_первая и вторая формы). Как видно, в выражении ху +

4- хг 4- У? дополнительный член уг представляет собой произве-

дение переменных (или формул) при х и х в порождающих чле-

нах ху и хг и не’влияет на значение этого выражения при усло-

вии, что порождающие члены присутствуют.

Процесс упрощения сводится к последовательному приме-

нению тех или иных общих свойств с тем, чтобы уменьшить

общее количество вхождений в формулу переменных и символов

логических операций. Между тем далеко не очевидно, какое из

свойств наиболее целесообразно использовать на каждом шаге,

поэтому работа с формулами на интуитивном уровне подобна

блужданию в лабиринте. Этому процессу можно придать целе-

направленный характер, если воспользоваться свойствами скле-

ивания, поглощения и выявления, представив предварительно

исходное выражение в нормальной форме. В дальнейшем пре-

образования выполняются в дизъюнктивной нормальной форме

(сумме минтермов), а соответствующие правила для конъюнктив-

ной нормальной формы (произведения макстермов) можно по-

лучить на основе принципа дуальности.

Склеивание ху 4- ху = х (под х можно понимать любое

выражение) позволяет заменить два минтерма, отличающихся

вхождением только одной переменной (с отрицанием и без

него), одним миптермом более низкого ранга. Пусть, напри-

мер, функция задана в виде канонической суммы минтермов: у —

26

as 444 4* 444 Ч" *1*2*3 Ч- *1*2*3 Ч- *1*2*3* Группируя_члены и

применяя операцию склеивания, имеем_ у — (*г*2*з Ч- *1*2*3) +

Ч- (*1*2*3 4- *1*2*з) Ч- *1*2*3 = *1*2 4- 4*2 + *1*3*3- ПРИ ДРУГ°М

варианте группирования получим у = 444 Ч~ (444Ч~*1*з*з) +

Ч- (*14*3 4- *1*2*з) = *1*2*3 + *2*3 4- *1*2-

Последующие упрощения основаны на свойствах погло-

щения и выявления. Поглощение %+*{/ — *> если под * и У

понимать не только переменные, но и любые булевы выражения,

позволяет исключить все минтермы, в которые в качестве со-

множителя входит некоторый другой минтерм более низкого

ранга. Наряду с этим дополнительный член, который вводится

на основе свойства выявления, можно использовать для погло-

щения и/или замещения других членов (минтермов). Эта опера-

ция, называемая обобщенным склеиванием, всегда возможна,

если исходная формула наряду с порождающими членами со-

держит минтермы, в которые в качестве сомножителя входит

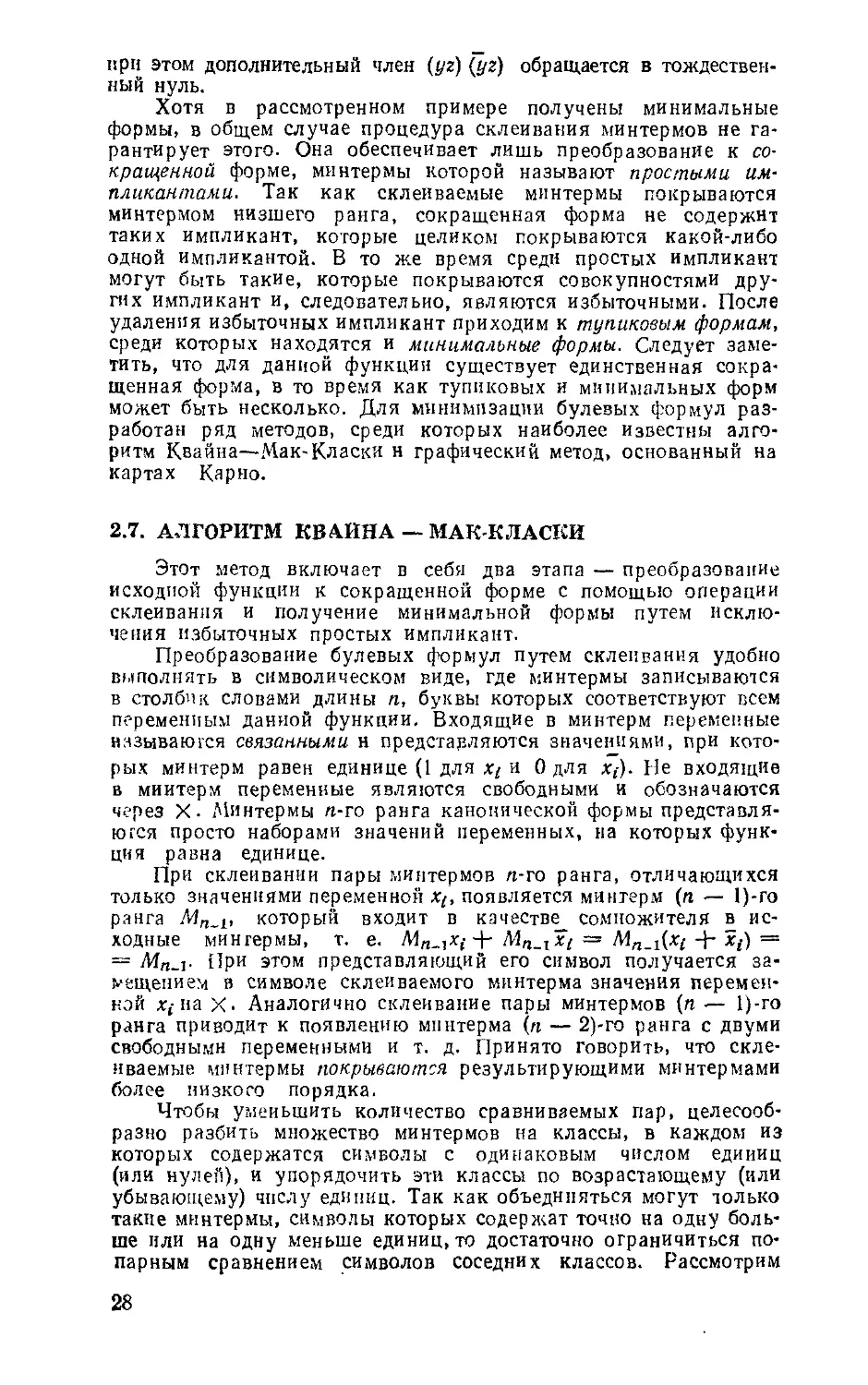

дополнительный член, например:

+уди=лу+zz+yz/+yz - лу+Jz+yz=zy + xz

yz —дополнительный член поглощение выявление

Здесь дополнительный член поглотил yzv, после чего уда-

ляется как не влияющий на значение полученного выражения.

В случаях, когда дополнительный член поглощает один из

порождающих членов, его удалять нельзя и, следовательно,

происходит замещение этого порождающего члена. Например)

x<xy+yz = x+xy+yzty = х+ху+у=х+у

у— дополнительный член поглощение замещение

Здесь дополнительный член поглощает минтерм уг и заме-

щает породивший его минтерм ху. Заметим, что это выражение

можно было бы упростить и без введения дополнительного члена

с помощью поглощения и замещения: х Ч" ху уг = х -р у 4"

4- уг = * Ч- У-

Применяя изложенную процедуру к рассматриваемому приме-

ру для первого варианта группирования 44 Ч~ 44 + *14*з> по’

лучаем 44 + 44 -|- 44 или хщ2 4- хгх2 4- 4%3. Аналогично вто-

рой вариант 444 44 4- 44 упрощается к виду ххх.2 4- *2*3+

4-44, что повторяет уже полученный результат для первого ва-

рианта. Таким образом, исходная формула преобразуется к двум

формам, которые в данном случае являются и минимальными. К

такому же результату можно было бы прийти, применяя только

простое склеивание, если в исходном выражении повторить мин-

терм 444 или 444, о чем, конечно, не так просто догадаться

в самом начале преобразования. Следует заметить, что с примене-

нием обобщенного склеивания можно упрощать формулы, задан-

ные в любой форме, а не обязательно в канонической. В то же

время эта операция не проходит, если порождающие члены содер-

жат различное вхождение (с отрицанием и без него) не одной, а

Двух или больше переменных. Например, х (уг) + * (уг), так как

27

при этом дополнительный член (yz) (yz) обращается в тождествен-

ный нуль.

Хотя в рассмотренном примере получены минимальные

формы, в общем случае процедура склеивания минтермов не га-

рантирует этого. Она обеспечивает лишь преобразование к со-

кращенной форме, минтермы которой называют простыми им-

пликантами. Так как склеиваемые минтермы покрываются

минтермом низшего ранга, сокращенная форма не содержит

таких импликант, которые целиком покрываются какой-либо

одной импликантой. В то же время среди простых импликант

могут быть такие, которые покрываются совокупностями дру-

гих импликант и, следовательно, являются избыточными. После

удаления избыточных импликант приходим к тупиковым формам,

среди которых находятся и минимальные формы. Следует заме-

тить, что для данной функции существует единственная сокра-

щенная форма, в то время как тупиковых и минимальных форм

может быть несколько. Для минимизации булевых формул раз-

работан ряд методов, среди которых наиболее известны алго-

ритм Квайна—Мак-Класки и графический метод, основанный на

картах Карно.

2.7. АЛГОРИТМ КВАИНА — МАК-КЛАСКИ

Этот метод включает в себя два этапа — преобразование

исходной функции к сокращенной форме с помощью операции

склеивания и получение минимальной формы путем исклю-

чения избыточных простых импликант.

Преобразование булевых формул путем склеивания удобно

выполнять в символическом виде, где минтермы записываются

в столбик словами длины п, буквы которых соответствуют всем

переменным данной функции. Входящие в минтерм переменные

называются связанными н представляются значениями, при кото-

рых минтерм равен единице (1 для Х( и 0 для х(). Не входящие

в миитерм переменные являются свободными и обозначаются

через X- АШнтермы n-го ранга канонической формы представля-

ются просто наборами значений переменных, на которых функ-

ция равна единице.

При склеивании пары минтермов n-го ранга, отличающихся

только значениями переменной X/, появляется минтерм (п — 1)-го

ранга Mn_L, который входит в качестве^ сомножителя в ис-

ходные минтермы, т. е. Л1л_,х(- -f- Mn_xxi — Mn_i(xt -ф- xt) —

— Mn_i- При этом представляющий его символ получается за-

мещением в символе склеиваемого минтерма значения перемен-

ной Х( на X- Аналогично склеивание пары минтермов (п— 1)-го

ранга приводит к появлению минтерма (п — 2)-го ранга с двумя

свободными переменными и т. д. Принято говорить, что скле-

иваемые минтермы покрываются результирующими минтермами

более низкого порядка.

Чтобы уменьшить количество сравниваемых пар, целесооб-

разно разбить множество минтермов на классы, в каждом из

которых содержатся символы с одинаковым числом единиц

(или нулей), и упорядочить эти классы по возрастающему (или

убывающему) числу единиц. Так как объединяться могут только

такие минтермы, символы которых содержат точно на одну боль-

ше или на одну меньше единиц, то достаточно ограничиться по-

парным сравнением символов соседних классов. Рассмотрим

28

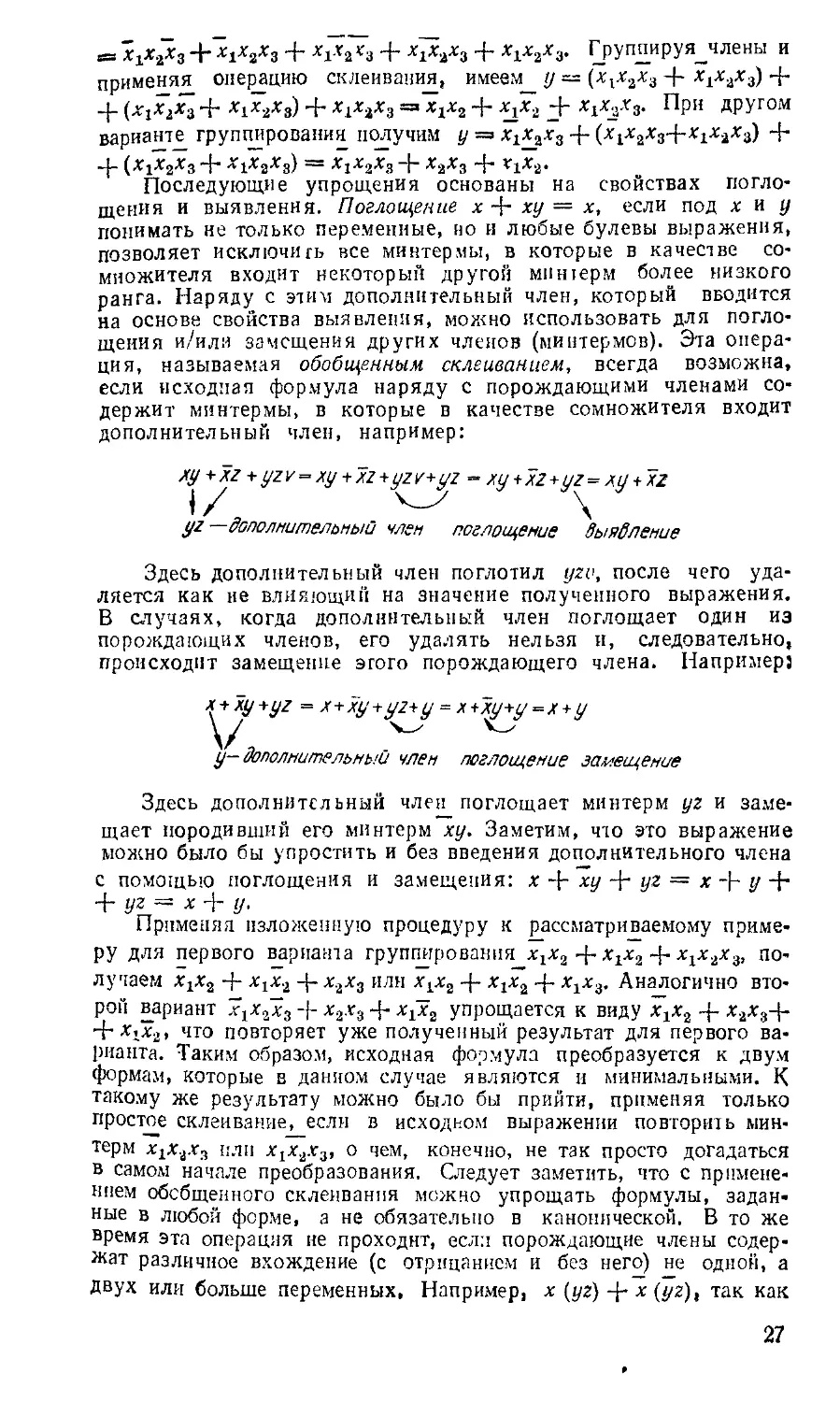

в качестве примера функцию четырех переменных,

таблицей соответствия:

заданную

«2

*з

0000000011111111

0000111100001111

0011001100110011

0101010101010 101

у |0001110101011100

Множество символов минтермов этой функции после упоря-

дочения и разбиения на классы представляют минтермы канони-

ческой формы:

ojooiljoil'

м = 1 । 0 1 0 1 1 1 0 1

4 |011000‘110|*

. О | 1 1 1 0 I 1 1 1 .

Объединяя минтермы и отмечая (значком V) те из них,

которые покрываются мпнтермами низшего ранга, имеем

б X 0 0 X 1 X 1 1' х

Л13 = 11 0 0 X 1 1 X 0 1 0 1 X X 0 0 1 ; м, = • о 2 1 0

X 0 1 1 1 1 1 1 X . X .

Неотмеченные символы соответствуют простым импликан-

там сокращенной формы у == x^Xj-h х1х2х^-{- х2х3х4+ х4х2х4+

+ x^gXjH- х2х3. Для минимизации этой формы строится таблица

покрытий, столбцы которой соответствуют минтермам канони-

ческой формы, а строки — простым импликантам (табл. 2.4).

Таблица 2.4

Простые иипликанты Минтеруы канонической формы i Обозначения , ПРОСТЫХ | импликант

0 1 0 0 0 0 1 I 0 I 0 1 1 0 0 1 1 1 и 0 0 i 1 1 1 0 1 i 1 1 0 1

0X11 V V А

0 1X1 V V В

X 0 1 1 V V С

10X1 V V D

1X01 V V Е

X 1 0 х V V V V F

29

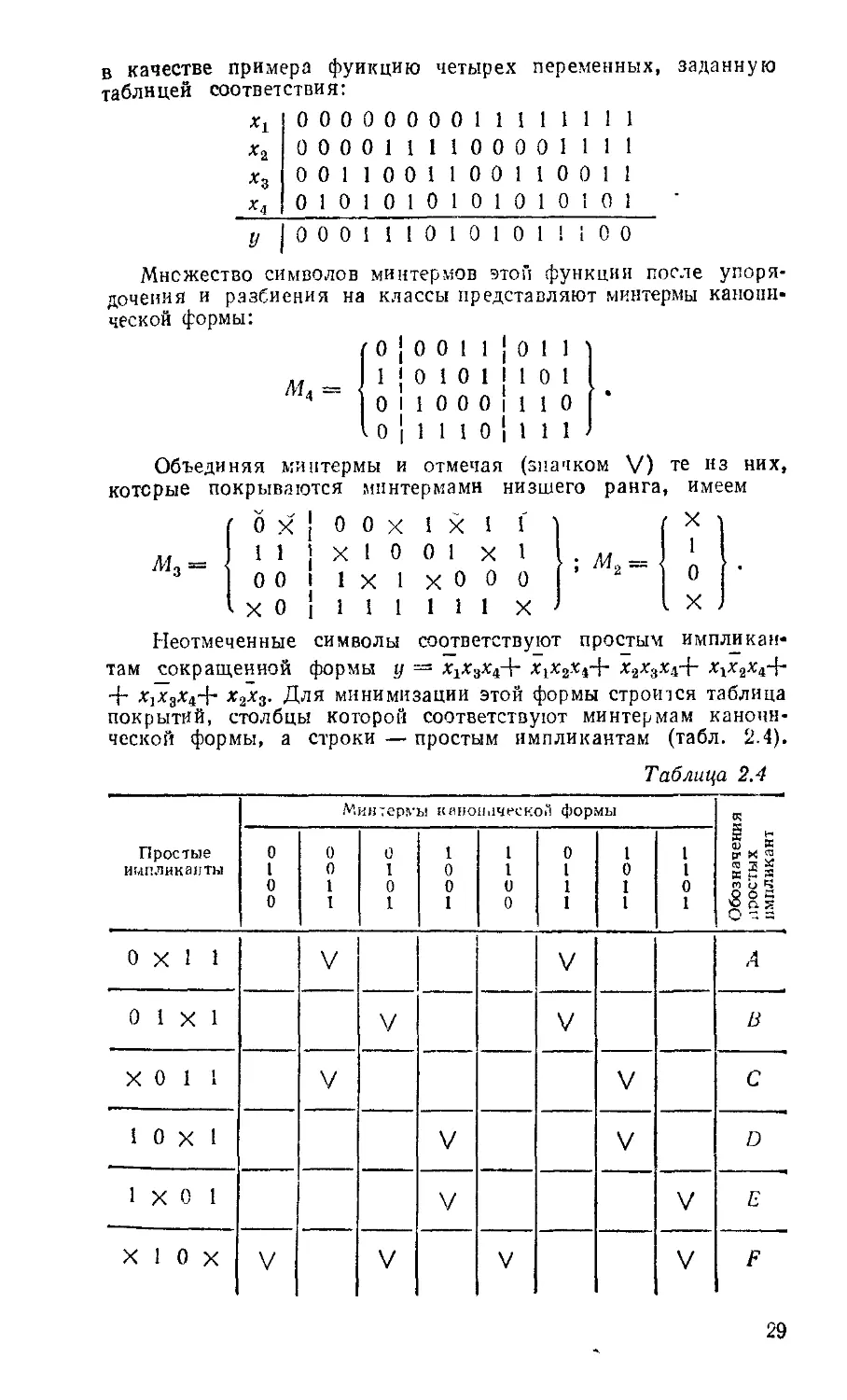

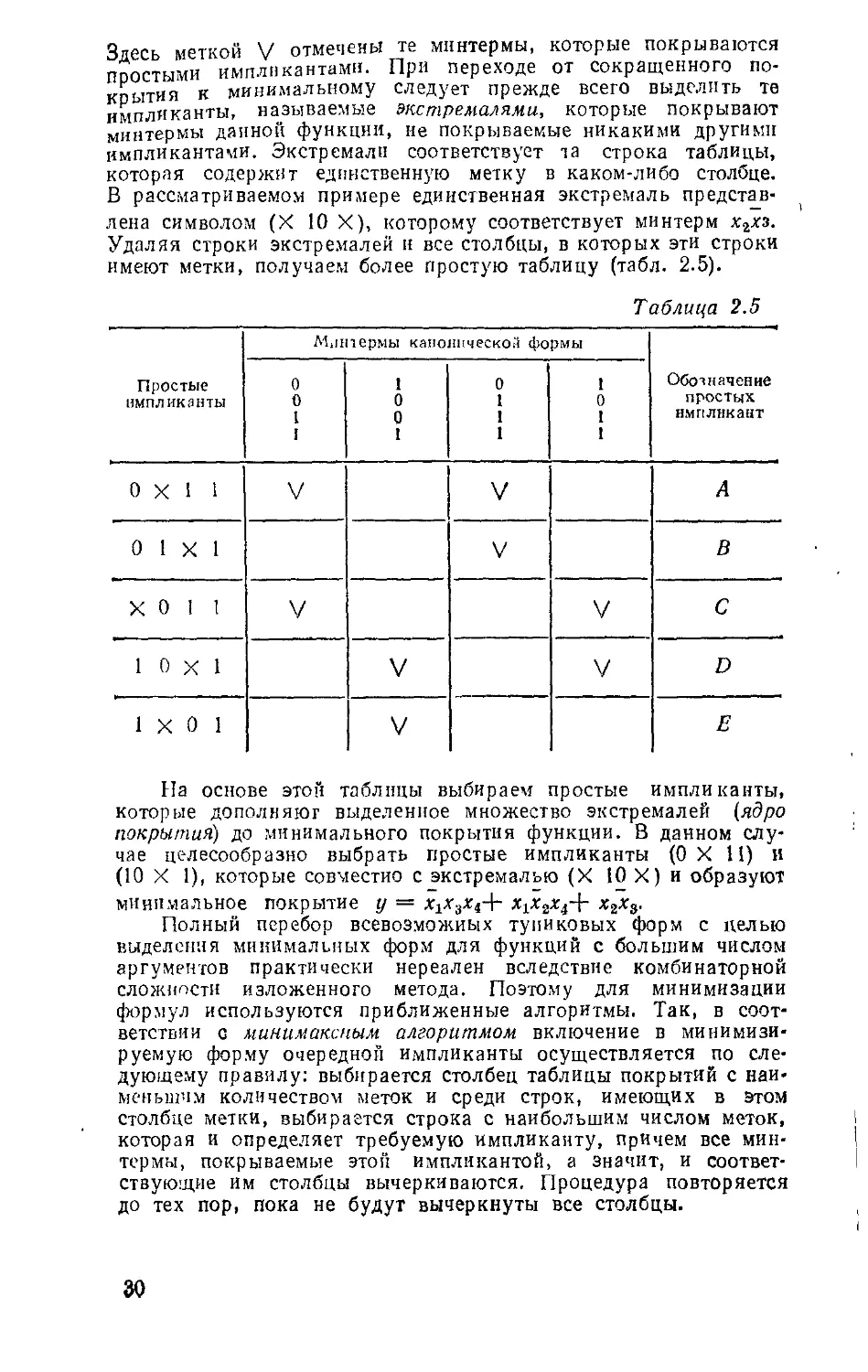

Здесь меткой V отмечены те минтермы, которые покрываются

простыми имплнкантами. При переходе от сокращенного по-

крытия к минимальному следует прежде всего выделить те

импликанты, называемые экстремалями, которые покрывают

минтермы данной функции, не покрываемые никакими другими

имплнкантами. Экстремали соответствует та строка таблицы,

которая содержит единственную метку в каком-либо столбце.

В рассматриваемом примере единственная экстремаль представ-

лена символом (X 10 X), которому соответствует минтерм х2хз.

Удаляя строки экстремалей и все столбцы, в которых эти строки

имеют метки, получаем более простую таблицу (табл. 2.5).

Таблица 2.5

Простые импликанты Минтермы канонической формы Обозначение простых ямплнкант

0 0 1 I 1 0 0 1 0 1 1 1 1 0 1 1

0X11 V V А

0 1X1 V В

X 0 I 1 V V С

10x1 V V D

1X01 V Е

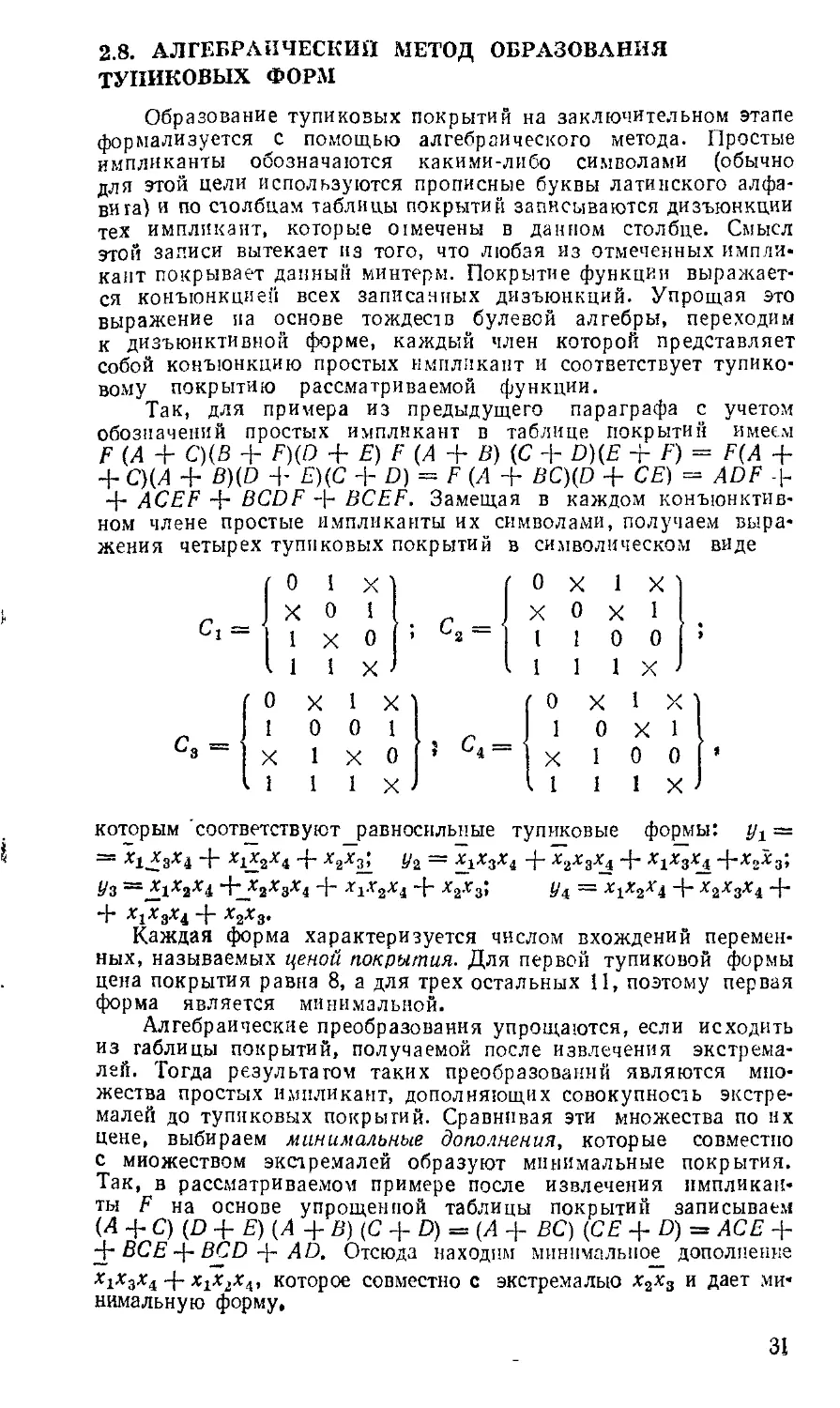

На основе этой таблицы выбираем простые импликанты,

которые дополняют выделенное множество экстремалей (ядро

покрытия) до минимального покрытия функции. В данном слу-

чае целесообразно выбрать простые импликанты (ОХ 11) и

(10 X 1), которые совместно с экстремалью (X 10 X) и образуют

минимальное покрытие у = х1х3Х4+ xxx2x4+ х2х3.

Полный перебор всевозможных тупиковых форм с целью

выделения минимальных форм для функций с большим числом

аргументов практически нереален вследствие комбинаторной

сложности изложенного метода. Поэтому для минимизации

формул используются приближенные алгоритмы. Так, в соот-

ветствии с минимаксным алгоритмом включение в минимизи-

руемую форму очередной импликанты осуществляется по сле-

дующему правилу: выбирается столбец таблицы покрытий с наи-

меньшим количеством меток и среди строк, имеющих в этом

столбце метки, выбирается строка с наибольшим числом меток,

которая и определяет требуемую импликанту, причем все мин-

термы, покрываемые этой импликантой, а значит, и соответ-

ствующие им столбцы вычеркиваются. Процедура повторяется

до тех пор, пока не будут вычеркнуты все столбцы.

30

2.8. АЛГЕБРАИЧЕСКИЙ МЕТОД ОБРАЗОВАНИЯ

ТУПИКОВЫХ ФОРМ

Образование тупиковых покрытий на заключительном этапе

формализуется с помощью алгебраического метода. Простые

импликанты обозначаются какими-либо символами (обычно

для этой цели используются прописные буквы латинского алфа-

вита) и по столбцам таблицы покрытий записываются дизъюнкции

тех импликант, которые отмечены в данном столбце. Смысл

этой записи вытекает из того, что любая из отмеченных импли-

кант покрывает данный минтерм. Покрытие функции выражает-

ся конъюнкцией всех записанных дизъюнкций. Упрощая это

выражение на основе тождеств булевой алгебры, переходим

к дизъюнктивной форме, каждый член которой представляет

собой конъюнкцию простых импликант и соответствует тупико-

вому покрытию рассматриваемой функции.

Так, для примера из предыдущего параграфа с учетом

обозначений простых импликант в таблице покрытий имеем

F (А + С)(В + F)(D + E)F(A + В)(С+ D)(E + F) = F(A +

+ C)(A + B)(D 4- £)(С 4- D) = F (А + BC)(D 4- СЕ) = ADF -|-

4- ACEF + BCDF 4- BCEF. Замещая в каждом конъюнктив-

ном члене простые импликанты их символами, получаем выра-

жения четырех тупиковых покрытий в символическом виде

с1 = 0 1 X X о 1 1 X о 11 1 X ; с2 = Ох 1 X X о х 1 110 0 1 1 1 X >

о X 1 X

10 0 1

X 1 X о

1 1 1 X

0 X 1 X

10X1

X 1 0 0’

1 1 1 X

С3 =

которым 'соответствуют равносильные тупиковые формы: ух

= хг *3х4 4- *1% 4- х2%з; у2 = х^х3х4 ф- х^х^ 4- х^х^ 4-х2х3;

Уз = *i*s*4 +j2x3xt 4- х4х2х4 4- x2.v3; yt = х^х^ 4- х2х3х4 ф-

4- *i*3*4 + Vs-

Каждая форма характеризуется числом вхождений перемен-

ных, называемых ценой покрытия. Для первой тупиковой формы

цена покрытия равна 8, а для трех остальных 11, поэтому первая

форма является минимальной.

Алгебраические преобразования упрощаются, если исходить

из таблицы покрытий, получаемой после извлечения экстрема-

лей. Тогда результатом таких преобразований являются мно-

жества простых импликант, дополняющих совокупность экстре-

малей до тупиковых покрытий. Сравнивая эти множества по их

цене, выбираем минимальные дополнения, которые совместно

с множеством экстремалей образуют минимальные покрытия.

Так, в рассматриваемом примере после извлечения пмпликан-

ты F на основе упрощенной таблицы покрытий записываем

(А 4- С) (D 4- Е) (А 4- В) (С 4- О) = (А 4- ВС) (СЕ 4- D) = АСЕ 4-

+ ВСЕ 4- BCD 4- AD. Отсюда находим минимальное дополнение

*1*з*4 4- которое совместно с экстремалью *2*з и Дает ми<

нимальную форму.

31

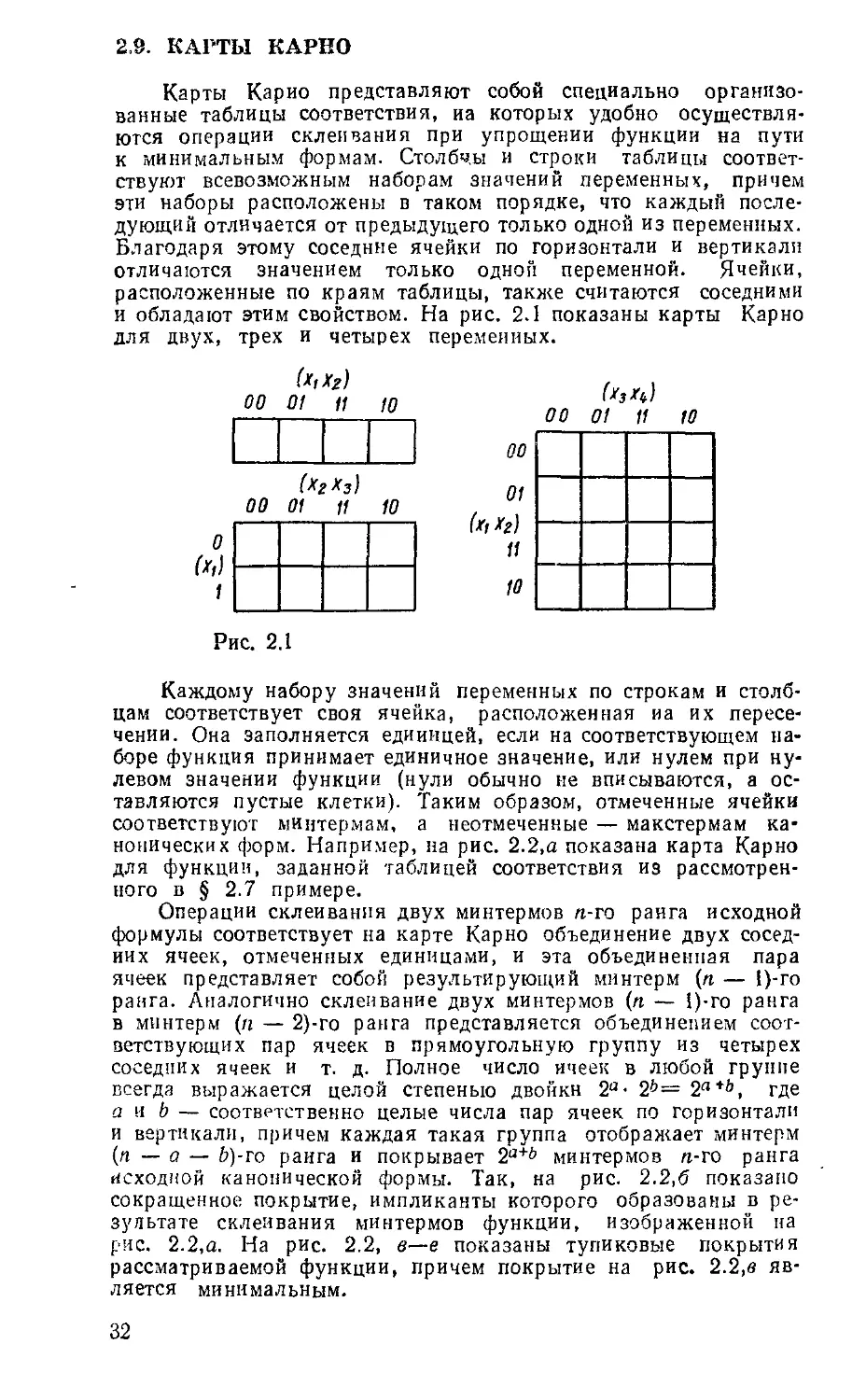

2.9. КАРТЫ КАРНО

Карты Карио представляют собой специально организо-

ванные таблицы соответствия, иа которых удобно осуществля-

ются операции склеивания при упрощении функции на пути

к минимальным формам. Столбцы и строки таблицы соответ-

ствуют всевозможным наборам значений переменных, причем

эти наборы расположены в таком порядке, что каждый после-

дующий отличается от предыдущего только одной из переменных.

Благодаря этому соседние ячейки по горизонтали и вертикали

отличаются значением только одной переменной. Ячейки,

расположенные по краям таблицы, также считаются соседними

и обладают этим свойством. На рис. 2.1 показаны карты Карно

для двух, трех и четырех переменных.

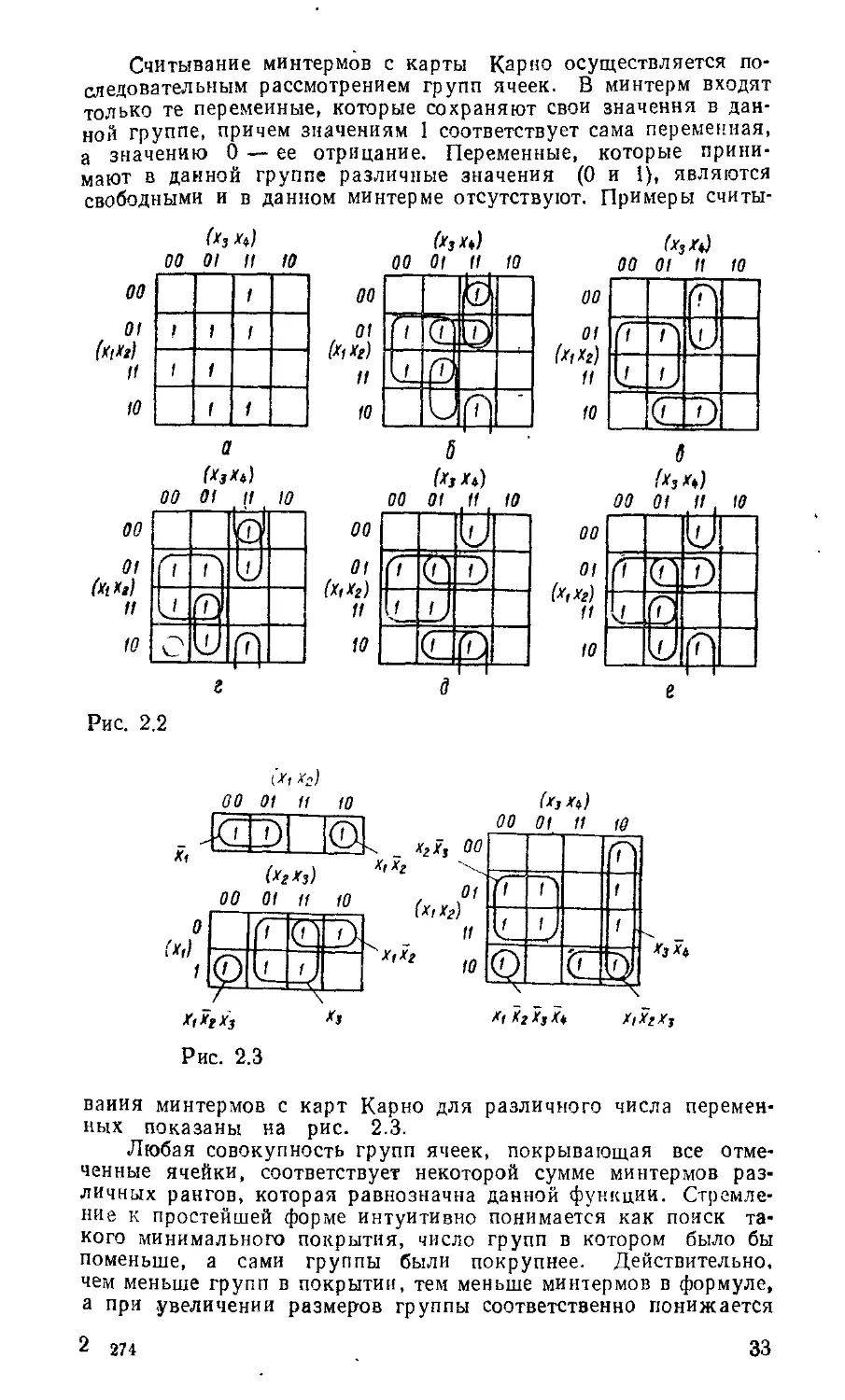

Каждому набору значений переменных по строкам и столб-

цам соответствует своя ячейка, расположенная иа их пересе-

чении. Она заполняется единицей, если на соответствующем на-

боре функция принимает единичное значение, или нулем при ну-

левом значении функции (нули обычно не вписываются, а ос-

тавляются пустые клетки). Таким образом, отмеченные ячейки

соответствуют ыицтермам, а неотмеченные — макстермам ка-

нонических форм. Например, на рис. 2.2,а показана карта Карно

для функции, заданной таблицей соответствия из рассмотрен-

ного в § 2.7 примере.

Операции склеивания двух минтермов n-го ранга исходной

формулы соответствует на карте Карно объединение двух сосед-

них ячеек, отмеченных единицами, и эта объединенная пара

ячеек представляет собой результирующий минтерм (п — 1)-го

ранга. Аналогично склеивание двух минтермов (п — 1)-го ранга

в минтерм (п — 2)-го ранга представляется объединением соот-

ветствующих пар ячеек в прямоугольную группу из четырех

соседних ячеек и т. д. Полное число ячеек в любой группе

всегда выражается целой степенью двойки 2°- 26=2a+b, где

а и b — соответственно целые числа пар ячеек по горизонтали

и вертикали, причем каждая такая группа отображает минтерм

(п — а — Ь)-го ранга и покрывает 2а+ь минтермов n-го ранга

исходной канонической формы. Так, на рис. 2.2,6 показано

сокращенное покрытие, импликанты которого образованы в ре-

зультате склеивания минтермов функции, изображенной на

рис. 2.2,а. На рис. 2.2, в—е показаны тупиковые покрытия

рассматриваемой функции, причем покрытие на рис. 2.2,в яв-

ляется минимальным.

32

Считывание минтермов с карты Карно осуществляется по-

следовательным рассмотрением групп ячеек. В минтерм входят

только те переменные, которые сохраняют свои значения в дан-

ной группе, причем значениям 1 соответствует сама переменная,

а значению 0 — ее отрицание. Переменные, которые прини-

мают в данной группе различные значения (0 и 1), являются

свободными и в данном минтерме отсутствуют. Примеры считы-

вания минтермов с карт Карно для различного числа перемен-

ных показаны на рис. 2.3.

Любая совокупность групп ячеек, покрывающая все отме-

ченные ячейки, соответствует некоторой сумме минтермов раз-

личных рангов, которая равнозначна данной функции. Стремле-

ние к простейшей форме интуитивно понимается как поиск та-

кого минимального покрытия, число групп в котором было бы

поменьше, а сами группы были покрупнее. Действительно,

чем меньше групп в покрытии, тем меньше минтермов в формуле,

а при увеличении размеров группы соответственно понижается

2 274

33

ранг минтерма, а значит, уменьшается "количество содержащихся

в нем переменных. Практически для отыскания минимальною

покрытия на карте Карно прежде всего выбирается отмеченная

ячейка, входящая в такую наибольшую группу, которая по-

крывает любые другие возможные группы с этой ячейкой. После

формирования этой наибольшей группы по тому же признаку

выбирается другая еще не покрытая ячейка и формируется ее

наибольшая группа. Этот процесс продолжается до тех пор, пока

все отмеченные- ячейки окажутся в тех или иных группах либо

останутся только такие непокрытые ячейки, которые можно

сгруппировать различными способами. Из возможных вариантов

выбираются те, которые приводят к минимальным покрытиям.

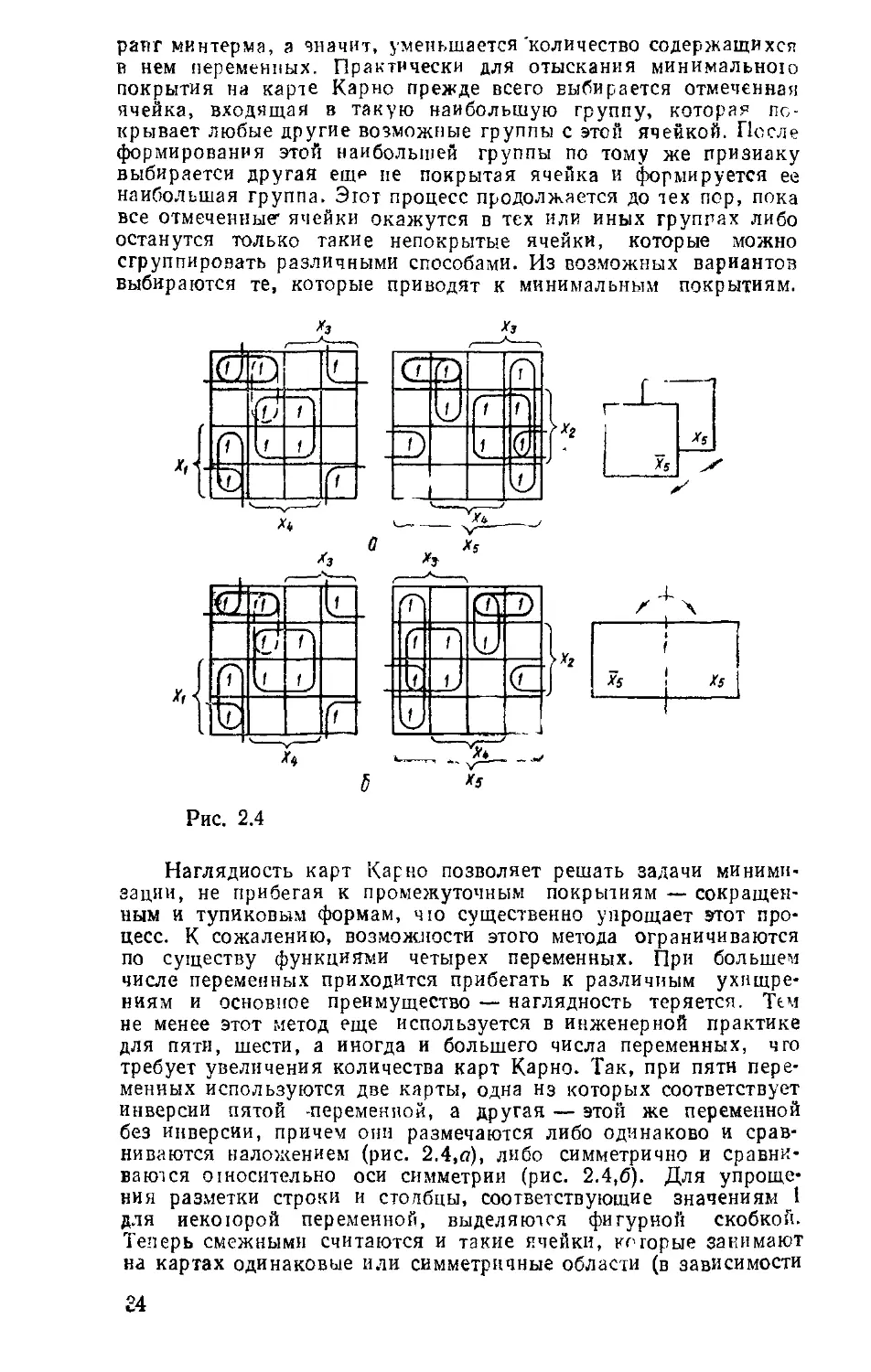

Рис. 2.4

Наглядность карт Карно позволяет решать задачи миними-

зации, не прибегая к промежуточным покрытиям — сокращен-

ным и тупиковым формам, что существенно упрощает этот про-

цесс. К сожалению, возможности этого метода ограничиваются

по существу функциями четырех переменных. При большем

числе переменных приходится прибегать к различным ухищре-

ниям и основное преимущество — наглядность теряется. Тем

не менее этот метод еще используется в инженерной практике

для пяти, шести, а иногда и большего числа переменных, чго

требует увеличения количества карт Карно. Так, при пяти пере-

менных используются две карты, одна нз которых соответствует

инверсии пятой -переменной, а другая — этой же переменной

без инверсии, причем они размечаются либо одинаково и срав-

ниваются наложением (рис. 2.4,<т), либо симметрично и сравни-

ваются относительно оси симметрии (рис. 2.4,6). Для упроще-

ния разметки строки и столбцы, соответствующие значениям 1

для некоторой переменной, выделяются фигурной скобкой.

Теперь смежными считаются и такие ячейки, которые занимают

на картах одинаковые или симметричные области (в зависимости

24

от способа разметки). В качестве примера на рис.

функция, заданная таблицей соответствия:

2.4 показана

Х1

*2

«3

Х4

Х5

00000000000000001111111111111111

00000000111111110000000011111111

00001111000011110000111100001111

00110011001100110011001100110011

01010101010101010101010101010101

f 11111100001101111000110011100111

Сначала строятся простейшие покрытия на каждой карте раз-

дельно, с которых списываются две функции: для левой карты

f = х^х4х8 + х2х4х6 + x1xsxixs + хгхгхахъ и для правой карты

fa = + VA + +'xix1V; + ВДЛ Затем ищу-

Рис. 2.5

тся такие импликанты в этих функциях, которые различаются

только вхождением ха и их можно объединить. В данном случае

это XjXjXgXj л XjXjXgXj (соответствующие им группы ячеек, обве-

денные жирной линией на рис. 2.4, а, совпадают при наложении,

а на рис. 2.4, б они расположены симметрично), в результате объ-

единения которых получается импликанта %jX2x3. Наконец, можно

также дополнять одну из карт несущественными нмпликантами, ко-

торые можно считать соседними импликантам другой карты н, объе-

диняя их между собой, упрощать результирующее выражение. Так,

в левую карту можно добавить импликанту х1х3х4х5 (на рис. 2.4

она показана пунктиром), которая, объединяясь с имплнкантой

правой карты х1х3х4х6, дает XjX3x4. Окончательное выражение по-

лучаем как сумму /л + /п с учетом выполненных преобразований:

f =_r2x4x- J- х2х4Т5 + + х3х4х8 + х2.г3х3 + х4х2 +

~Г^1Х2Х3 -f- XjXgX4.

Для функций шести переменных потребовалось бы четыре

карты Карно, а с каждой новой переменной количество тре-

буемых карт увеличивается вдвое и, например, для восьми пе-

ременных уже равно 16. В практике используются и другие

графические структуры, например, карты Вейча, которые отли-

чаются только способом разметки переменных. Ясно, что гра-

фические методы пригодны для минимизации вручную сравни-

тельно простых функций. В то же время машинные методы

2* 35

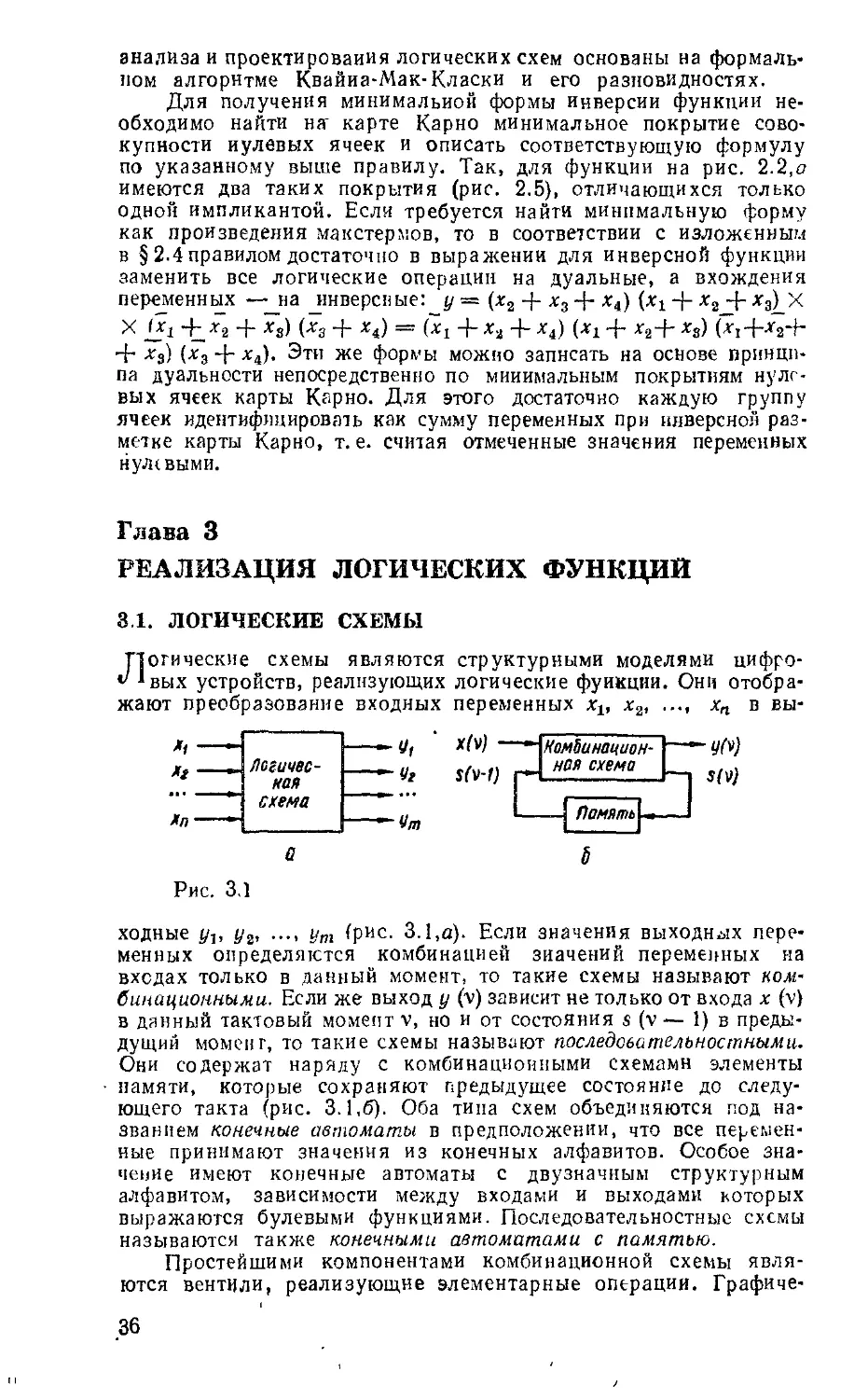

анализа и проектирования логических схем основаны на формаль-

ном алгоритме Квайиа-Мак-Класки и его разновидностях.

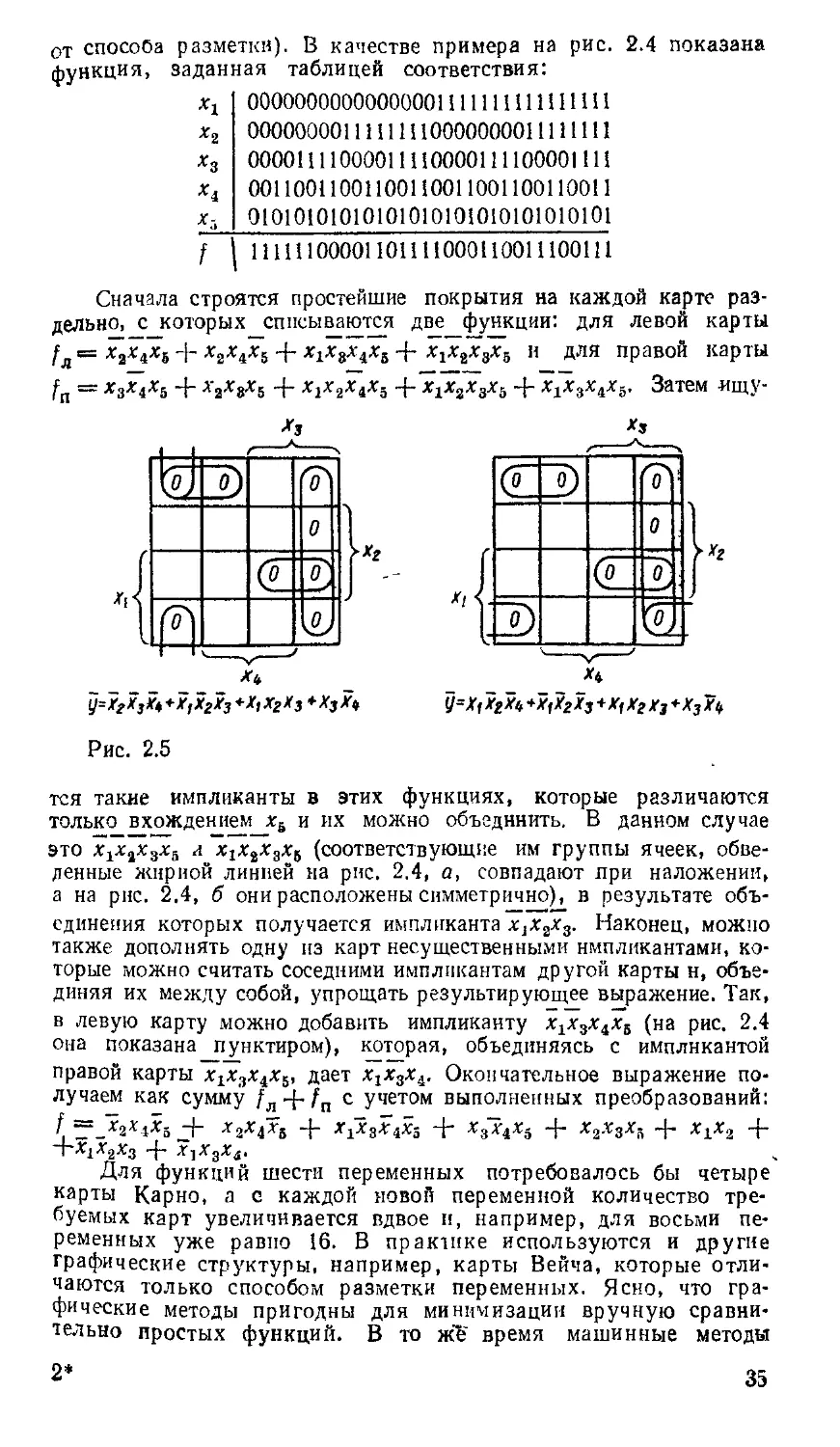

Для получения минимальной формы инверсии функции не-

обходимо найти ня карте Карно минимальное покрытие сово-

купности нулевых ячеек и описать соответствующую формулу

по указанному выше правилу. Так, для функции на рис. 2.2,о

имеются два таких покрытия (рис. 2.5), отличающихся только

одной импликантой. Если требуется найти минимальную форму

как произведения макстермов, то в соответствии с изложенным

в § 2.4 правилом достаточно в выражении для инверсной функции

заменить все логические операции на дуальные, а вхождения

переменных — на инверсные: у = (х2 + хй х4) (хг -j- х« -f- х3) X

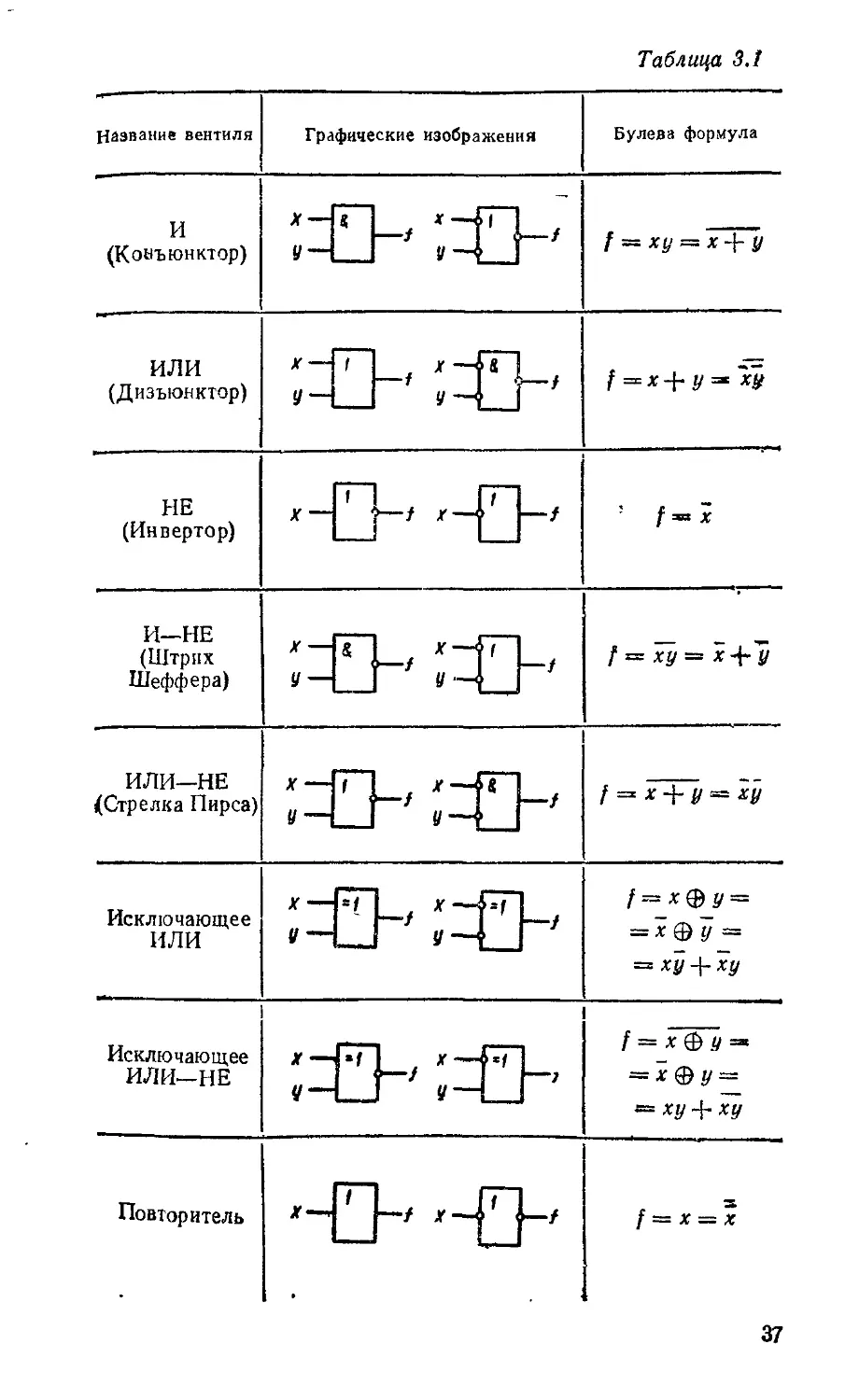

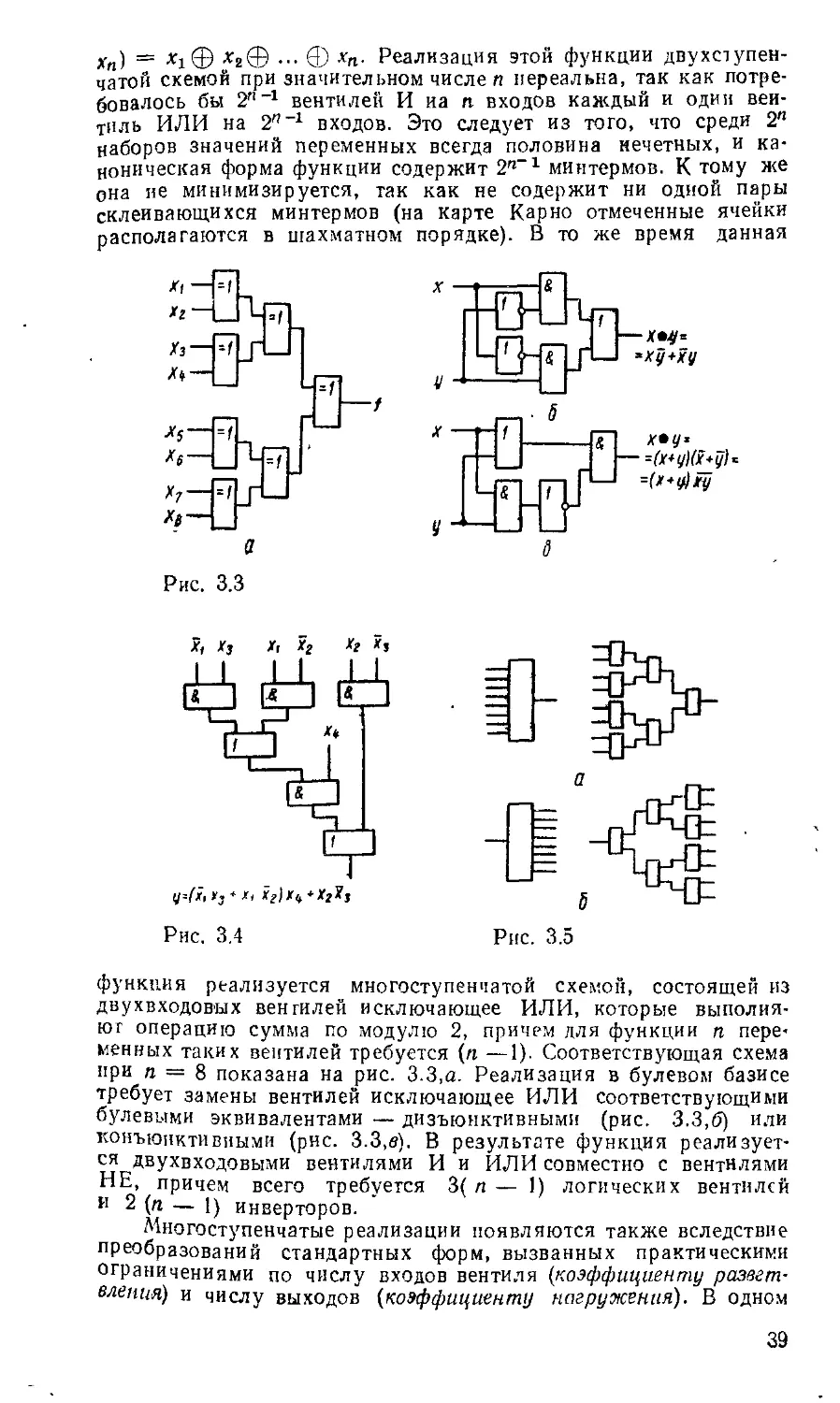

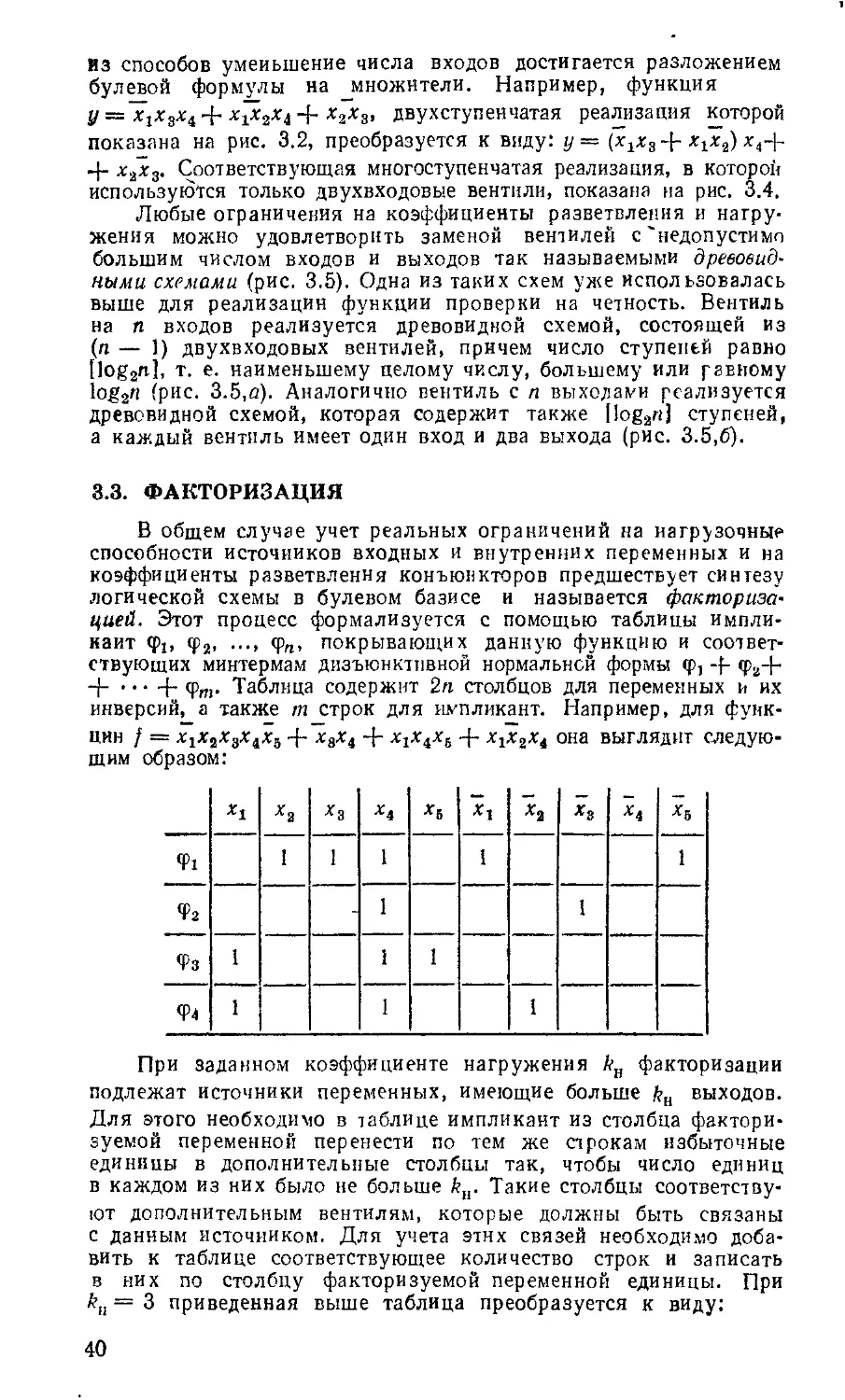

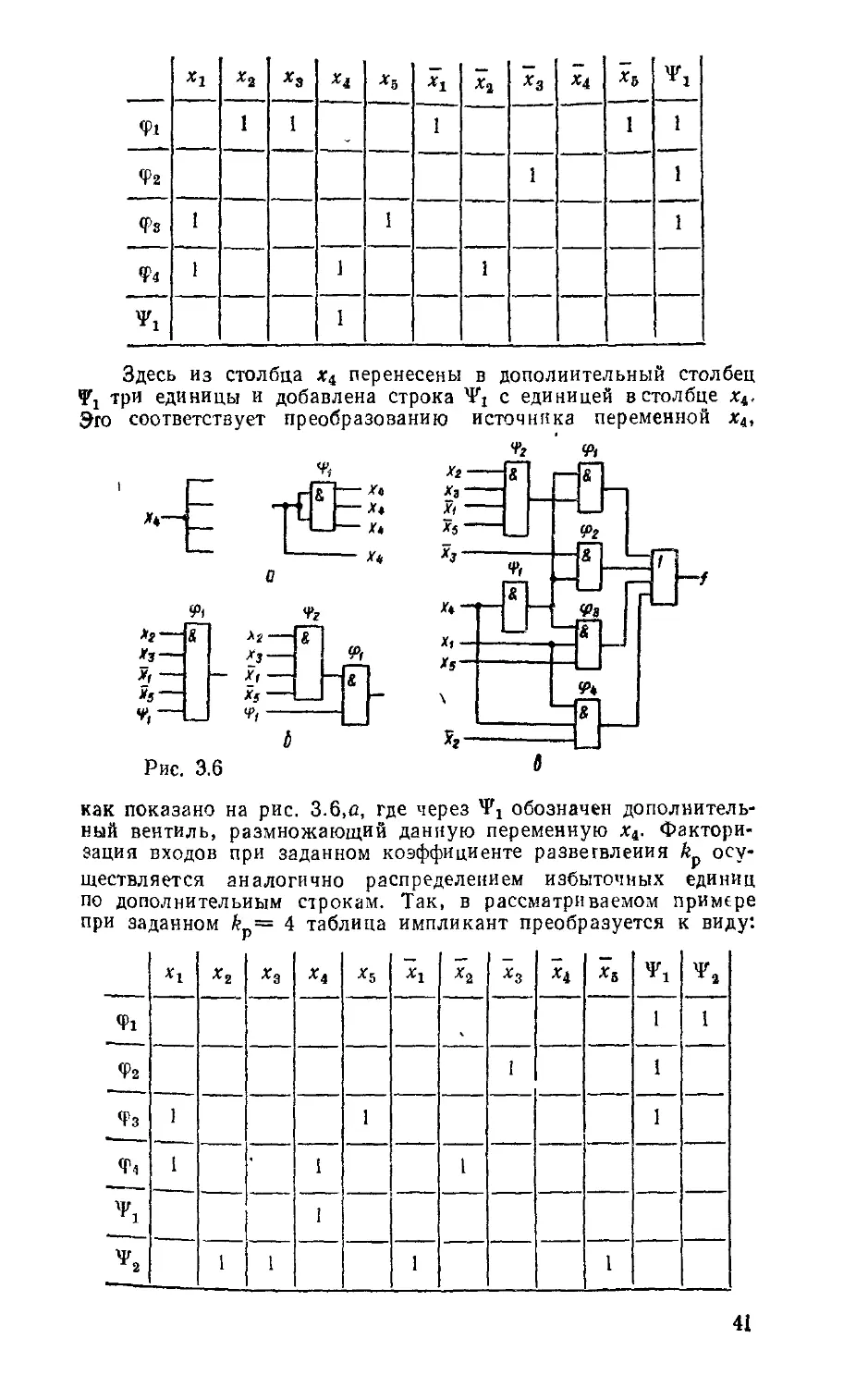

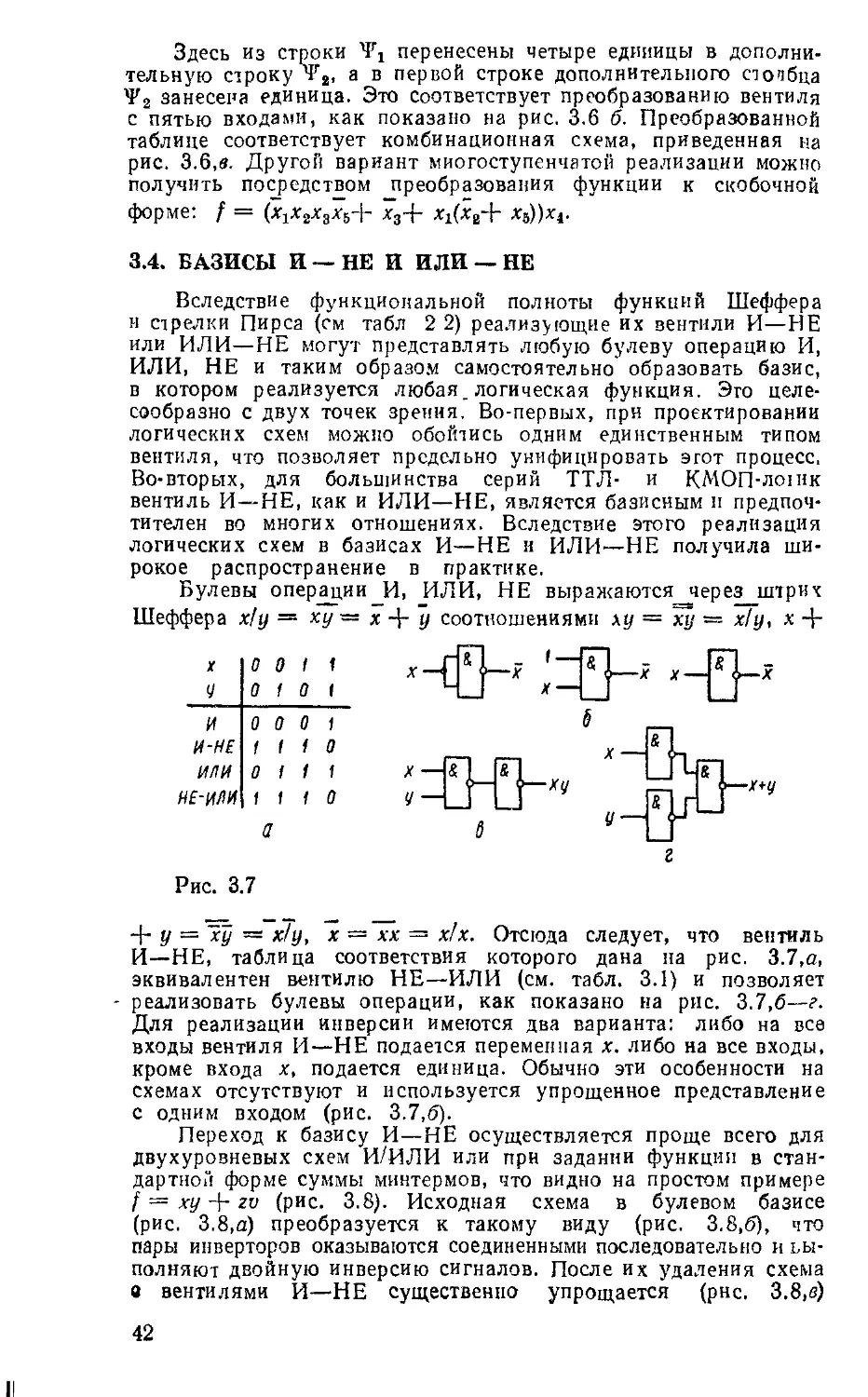

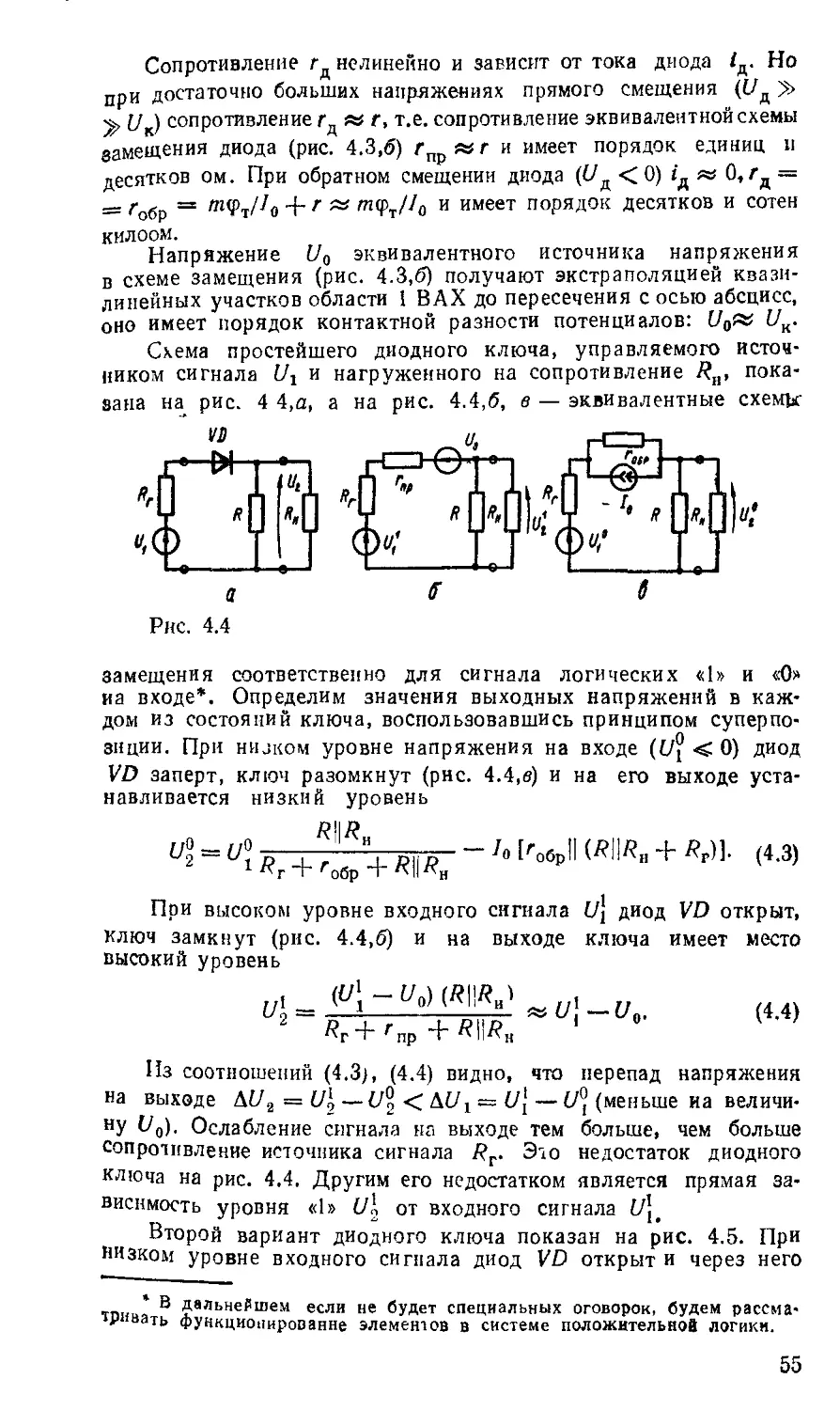

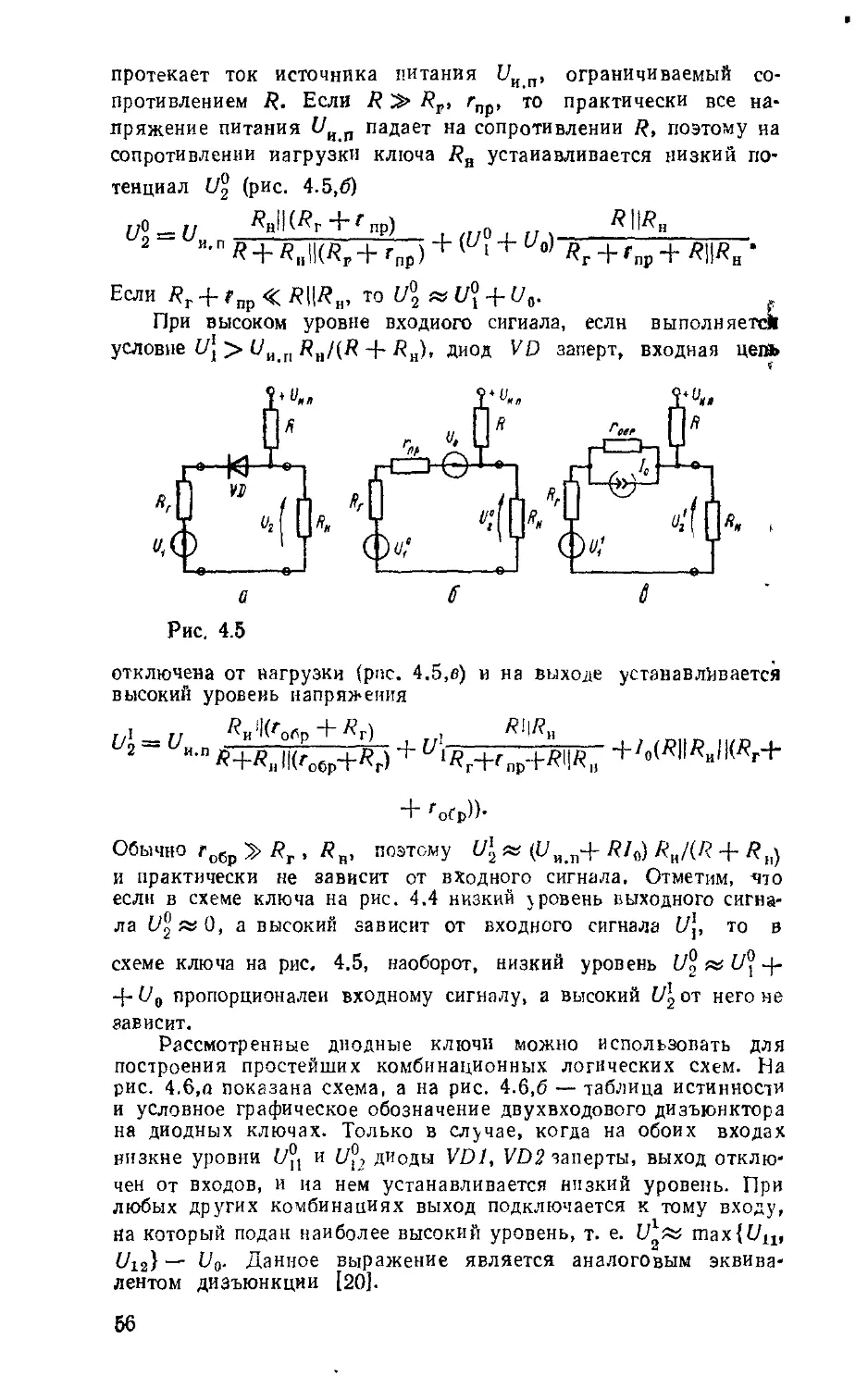

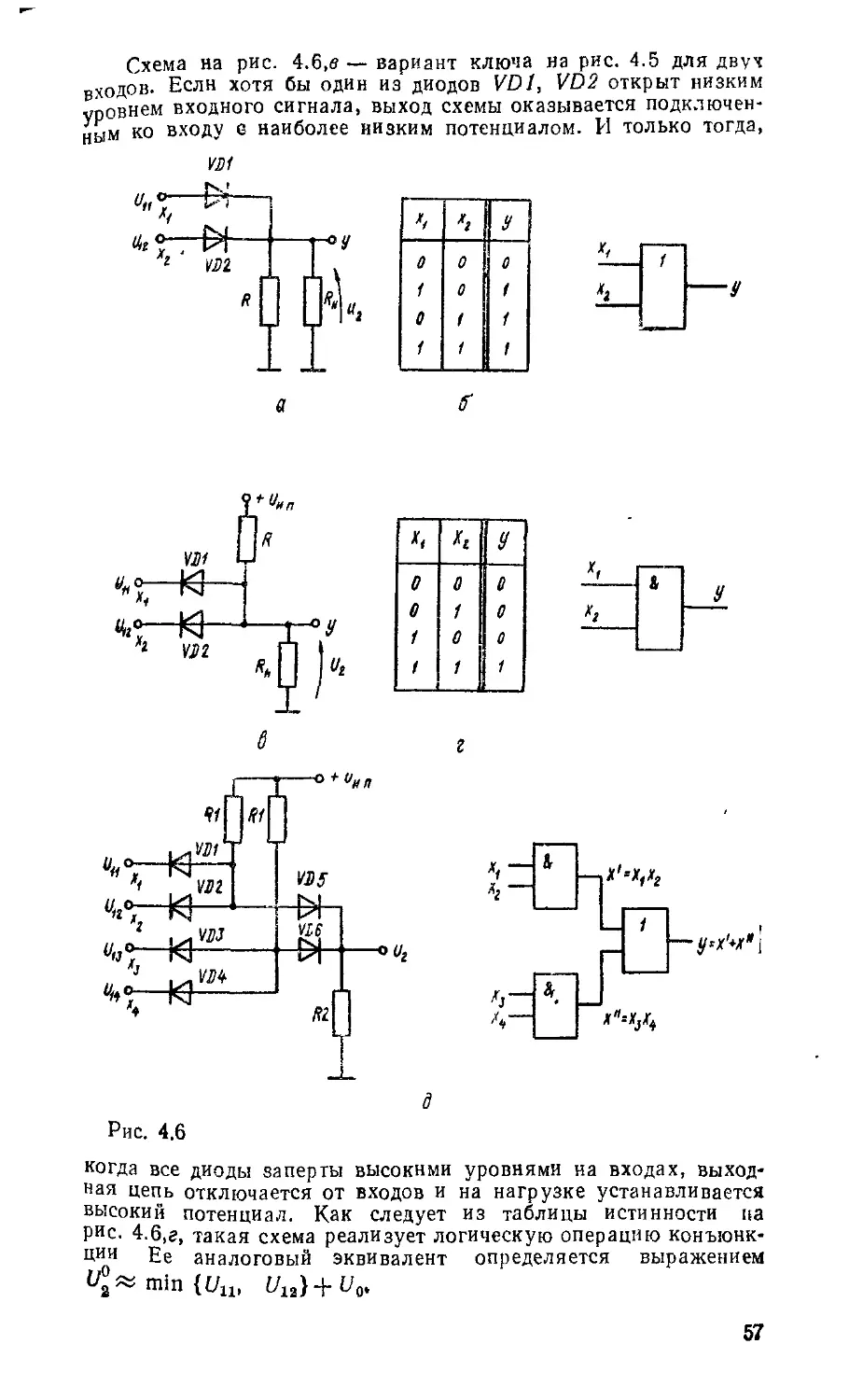

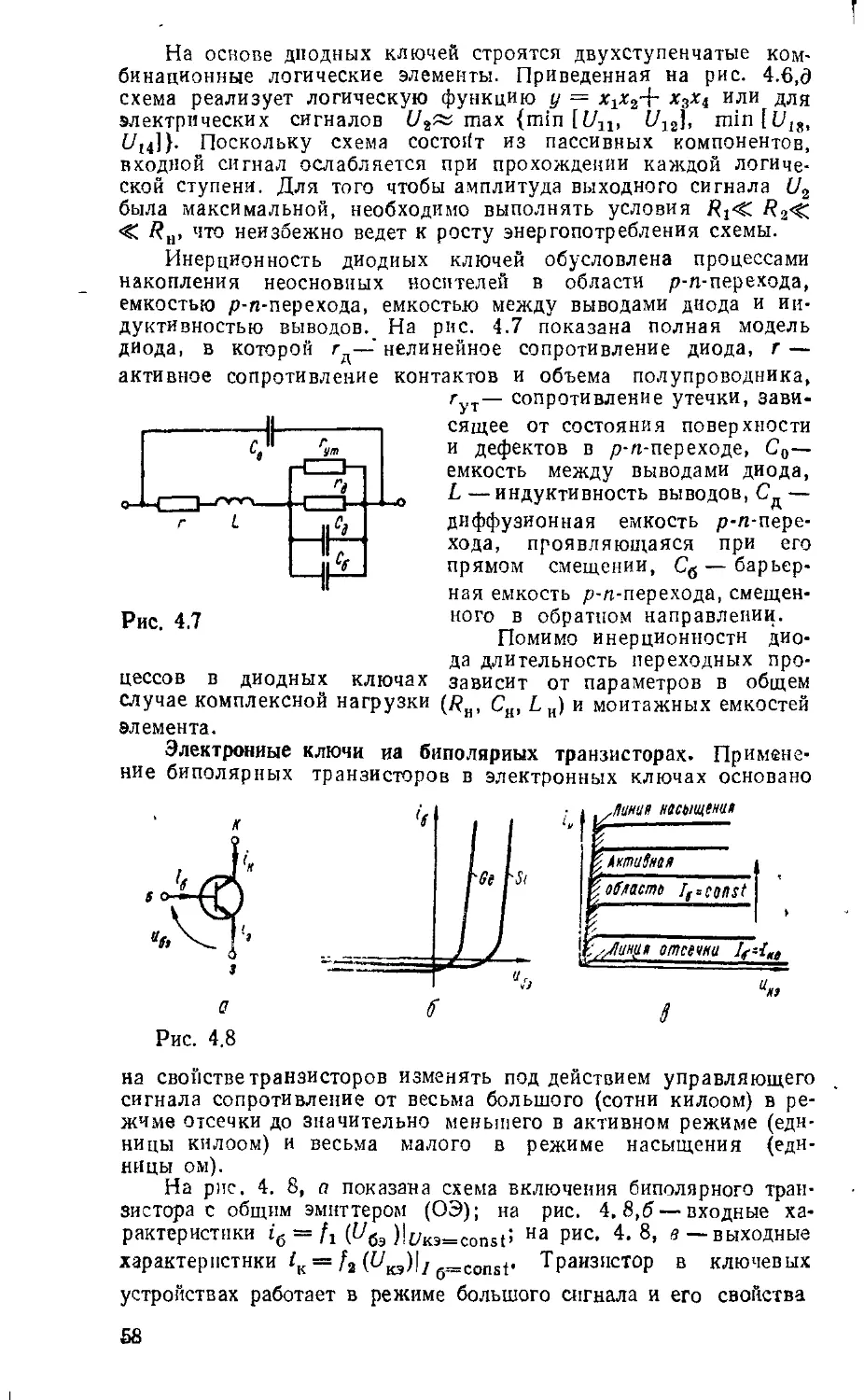

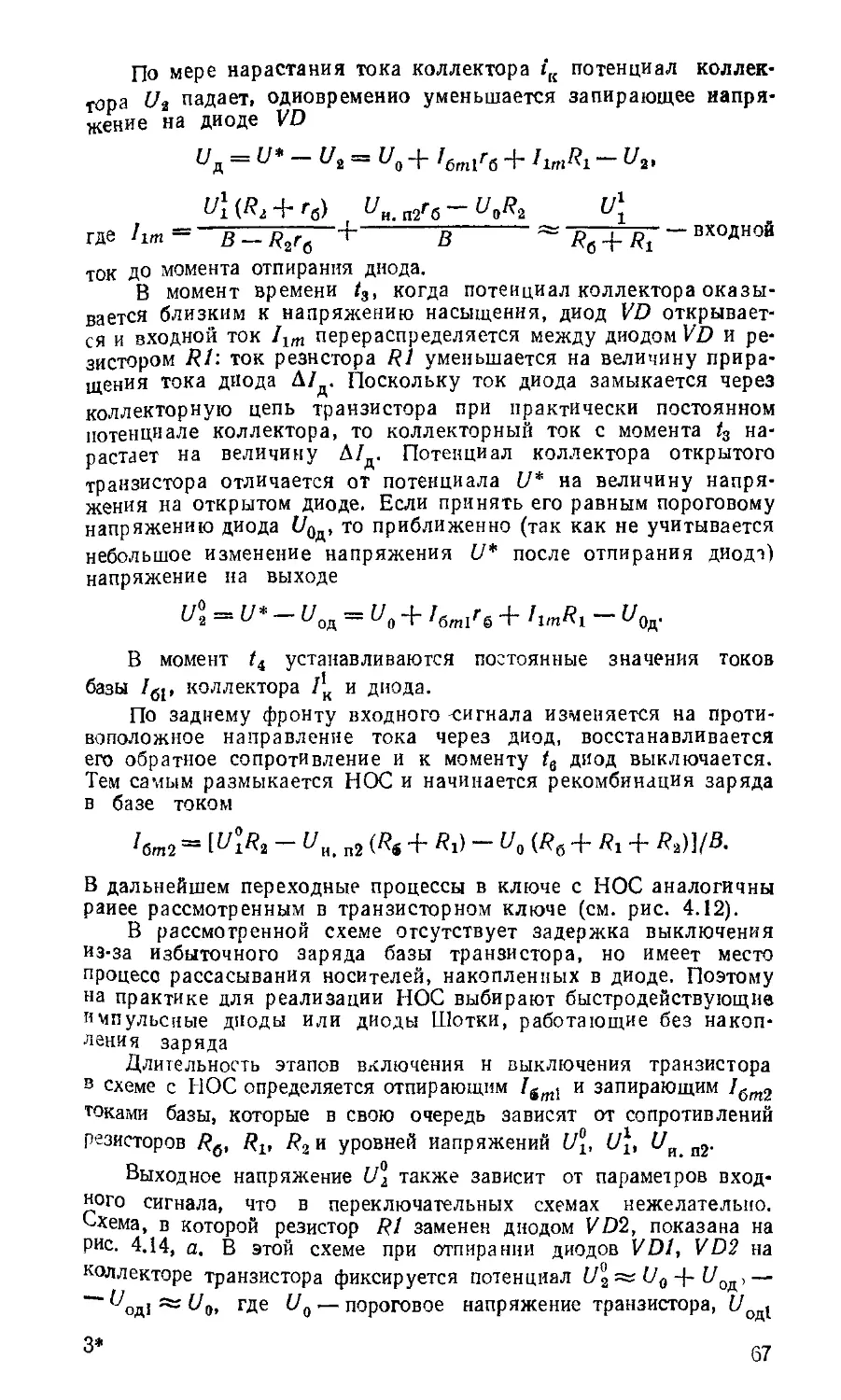

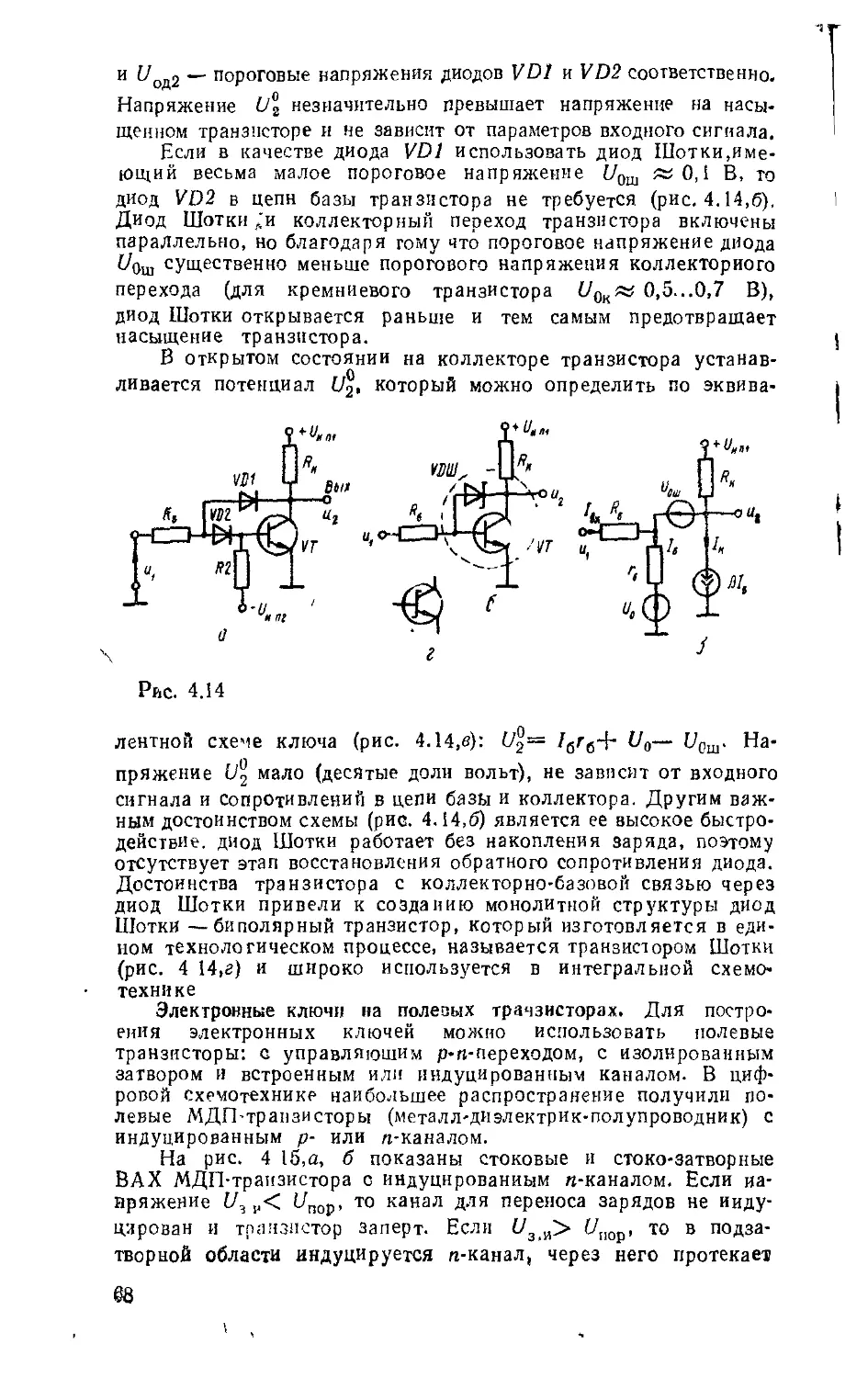

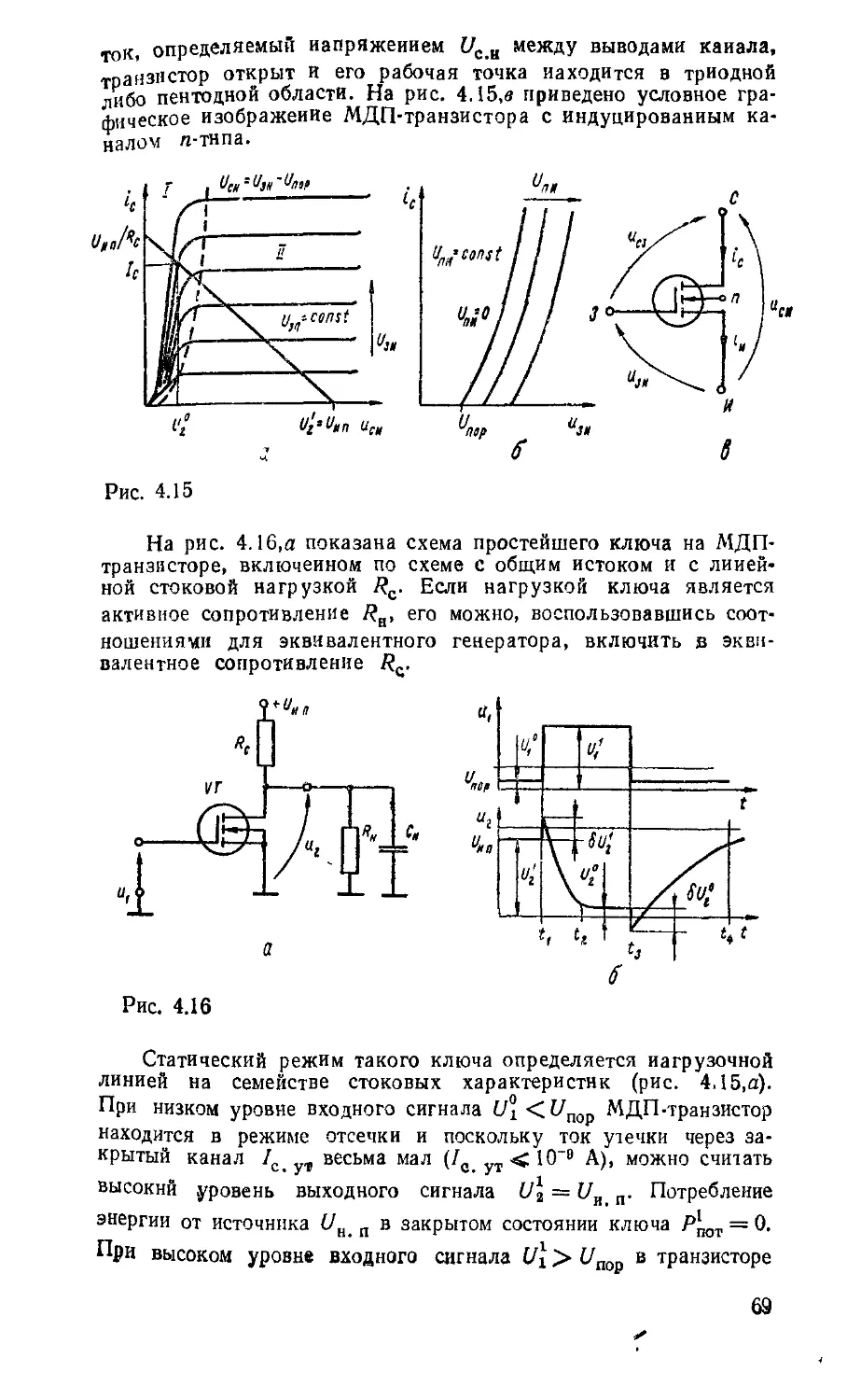

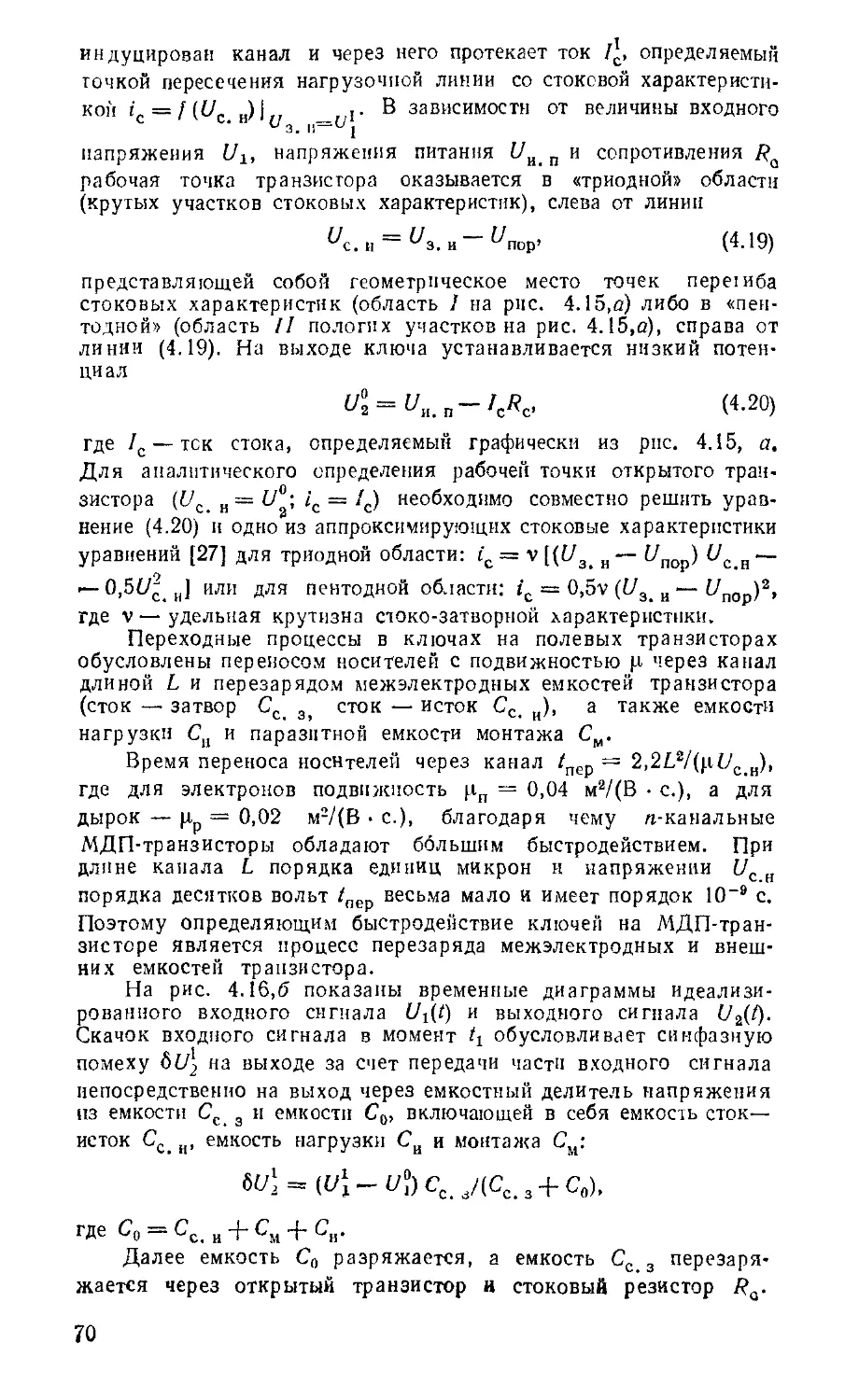

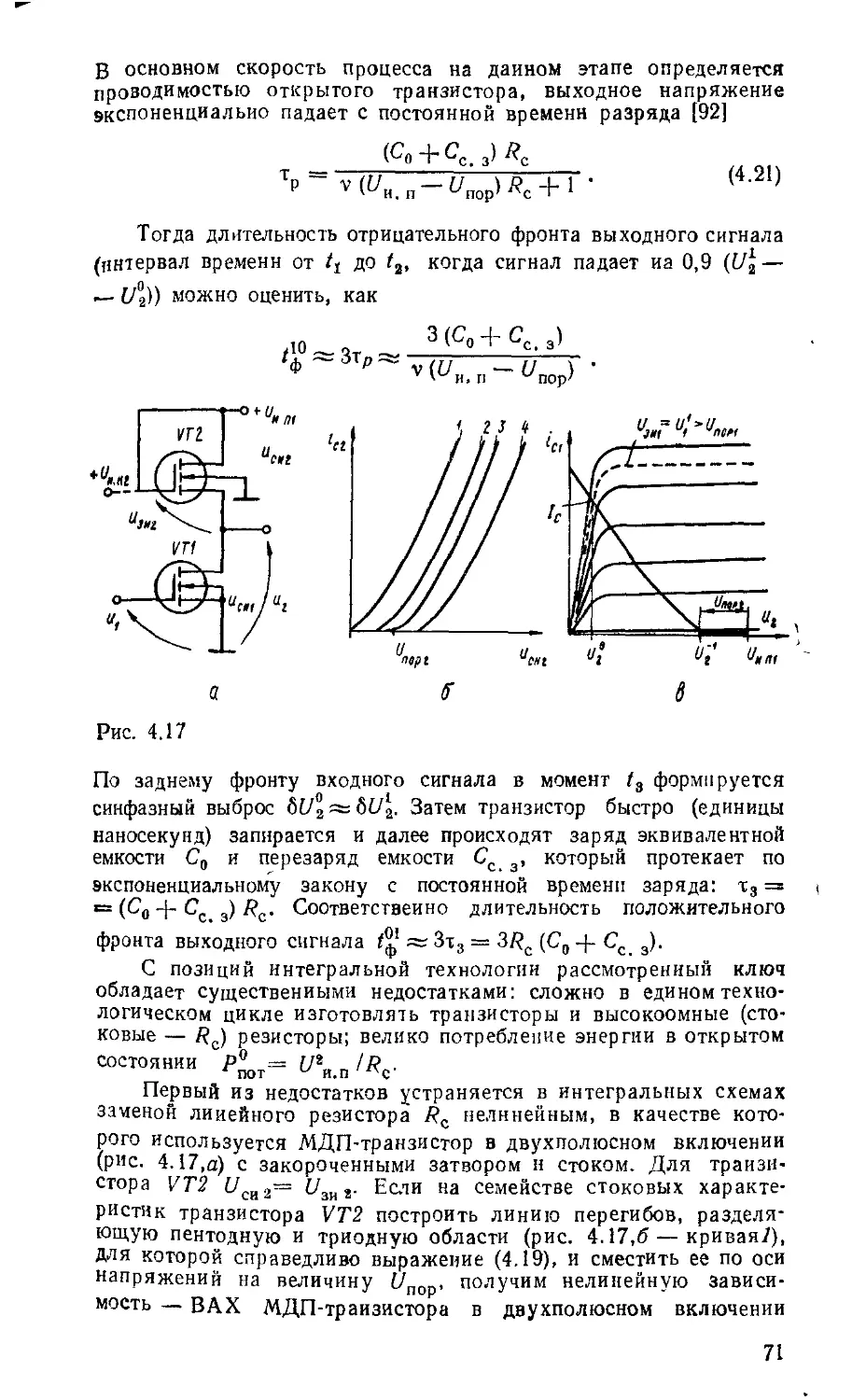

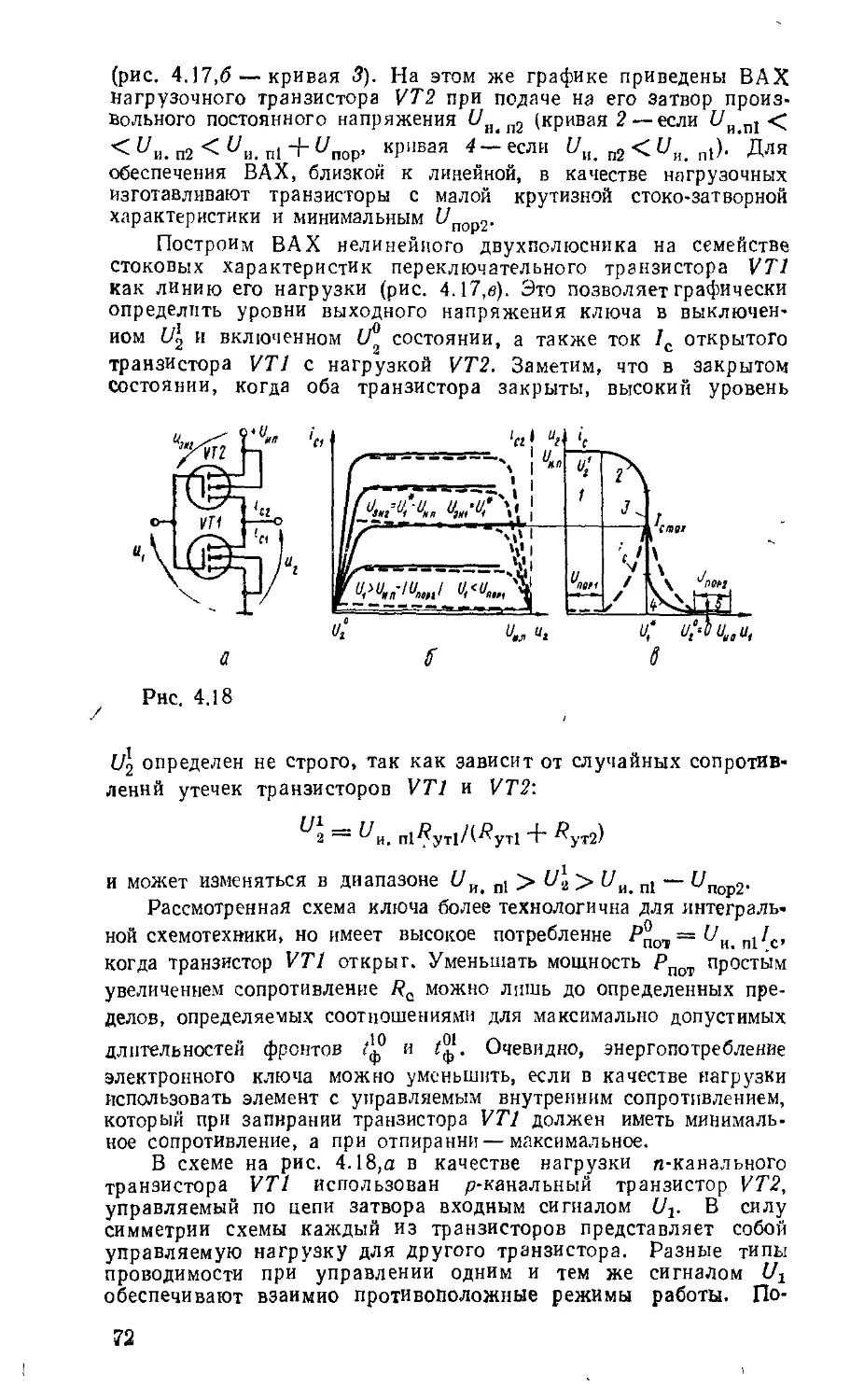

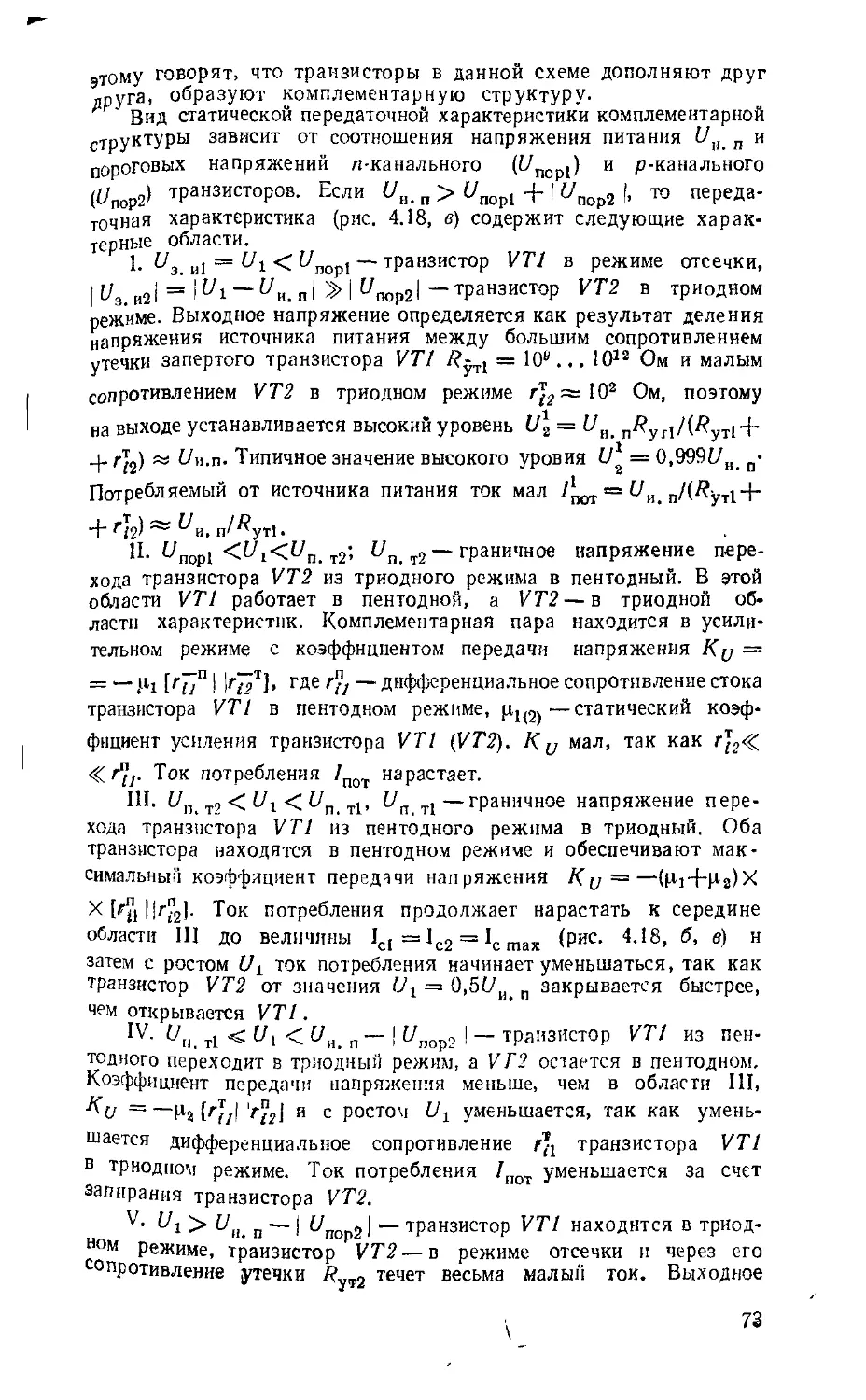

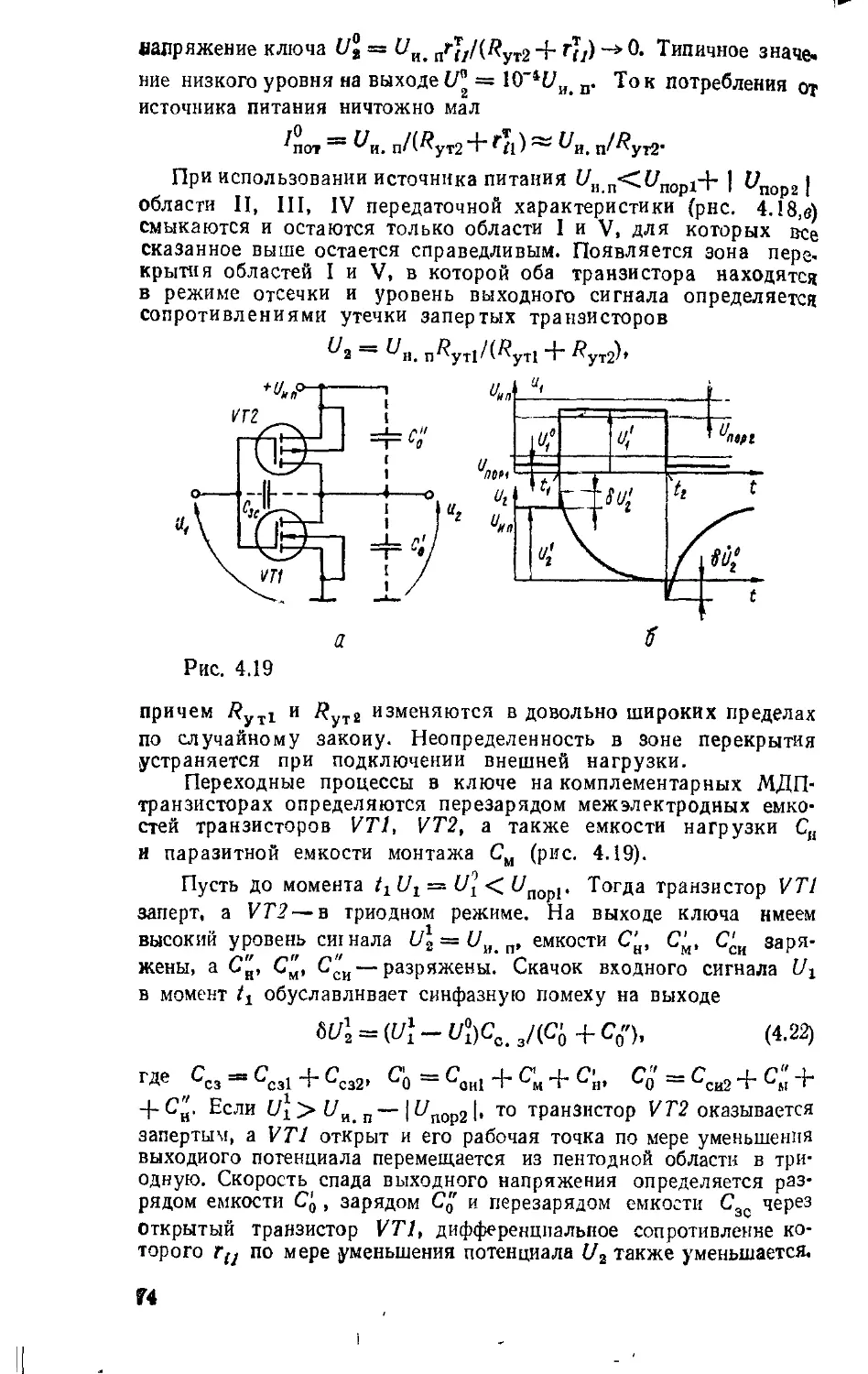

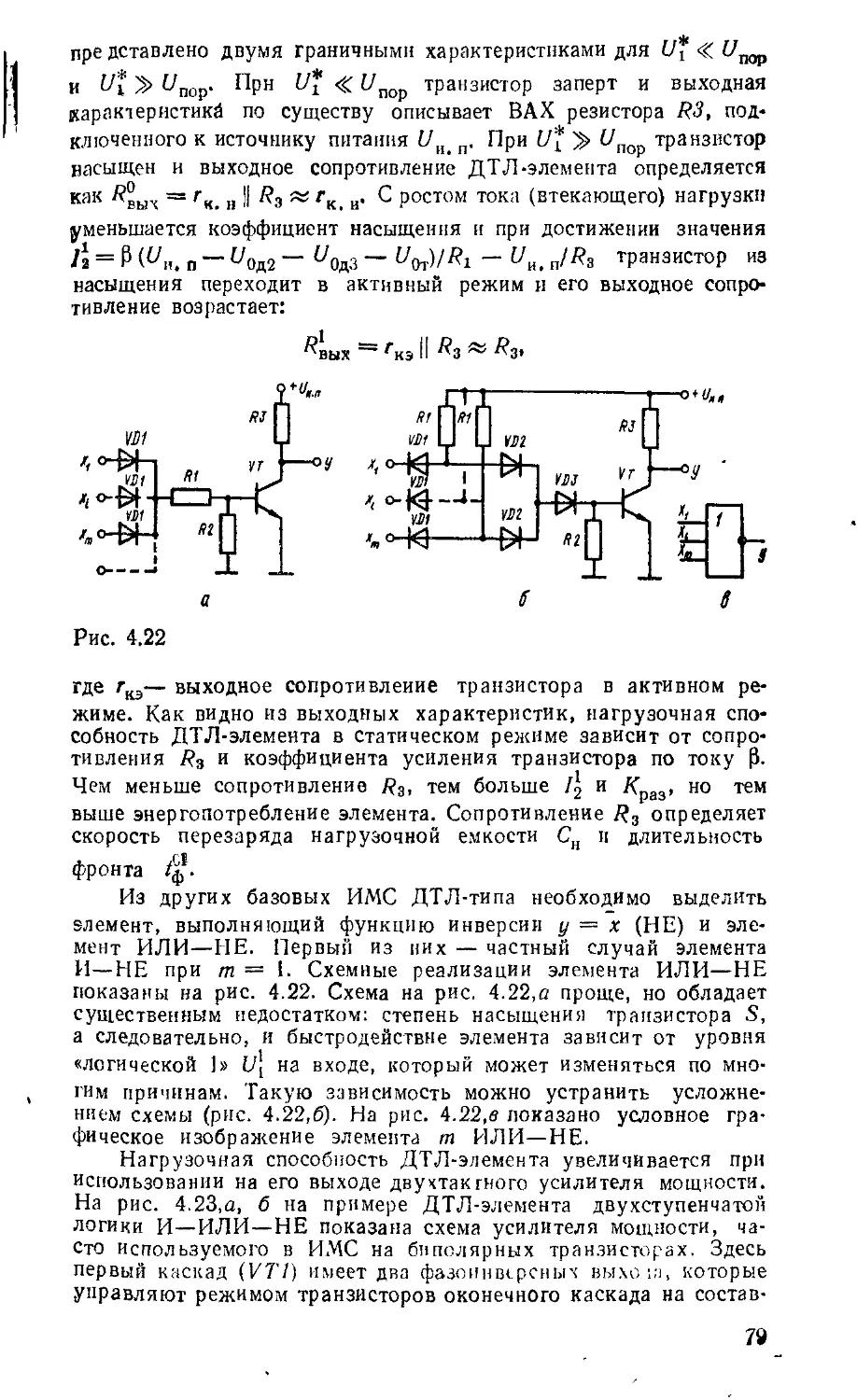

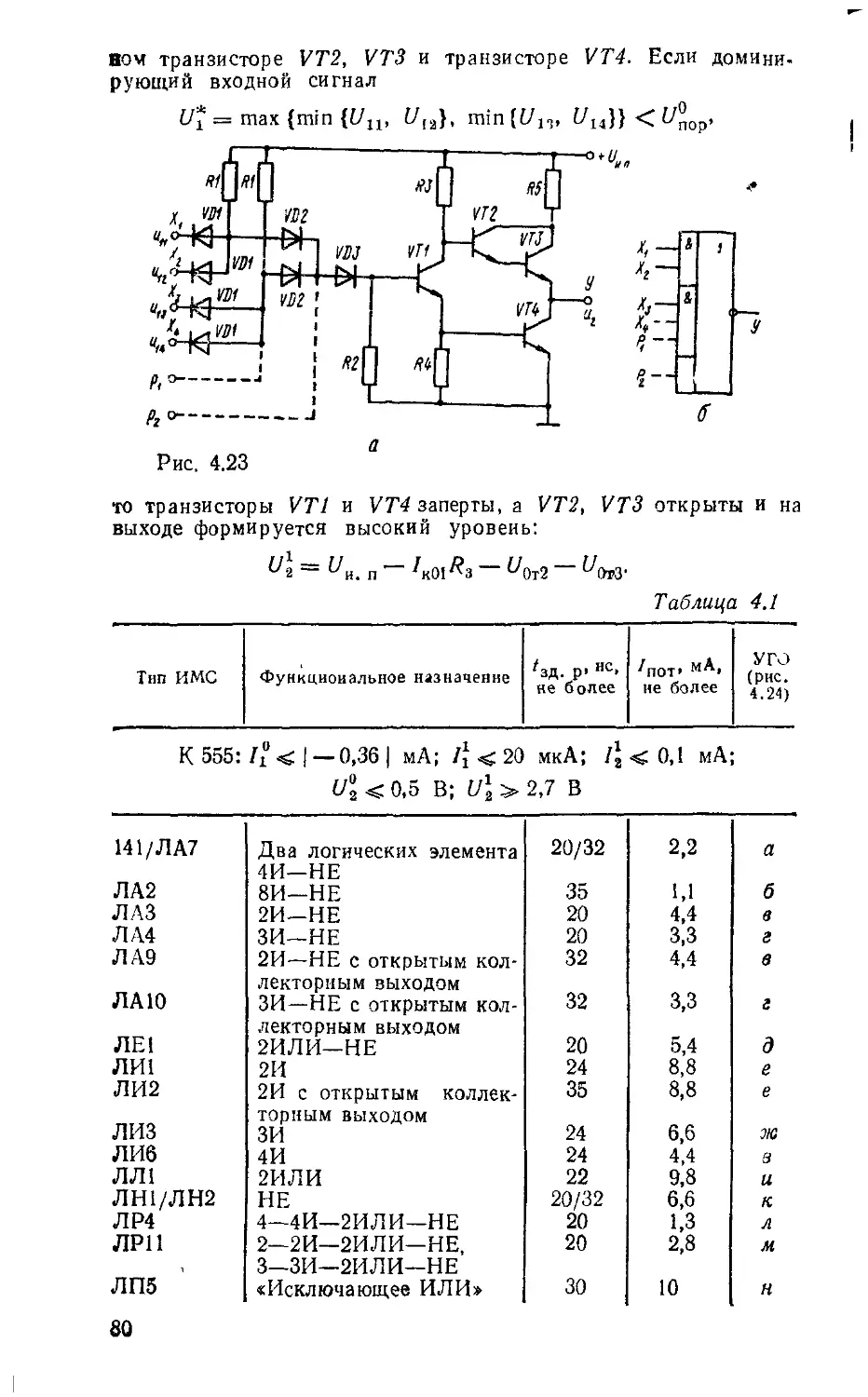

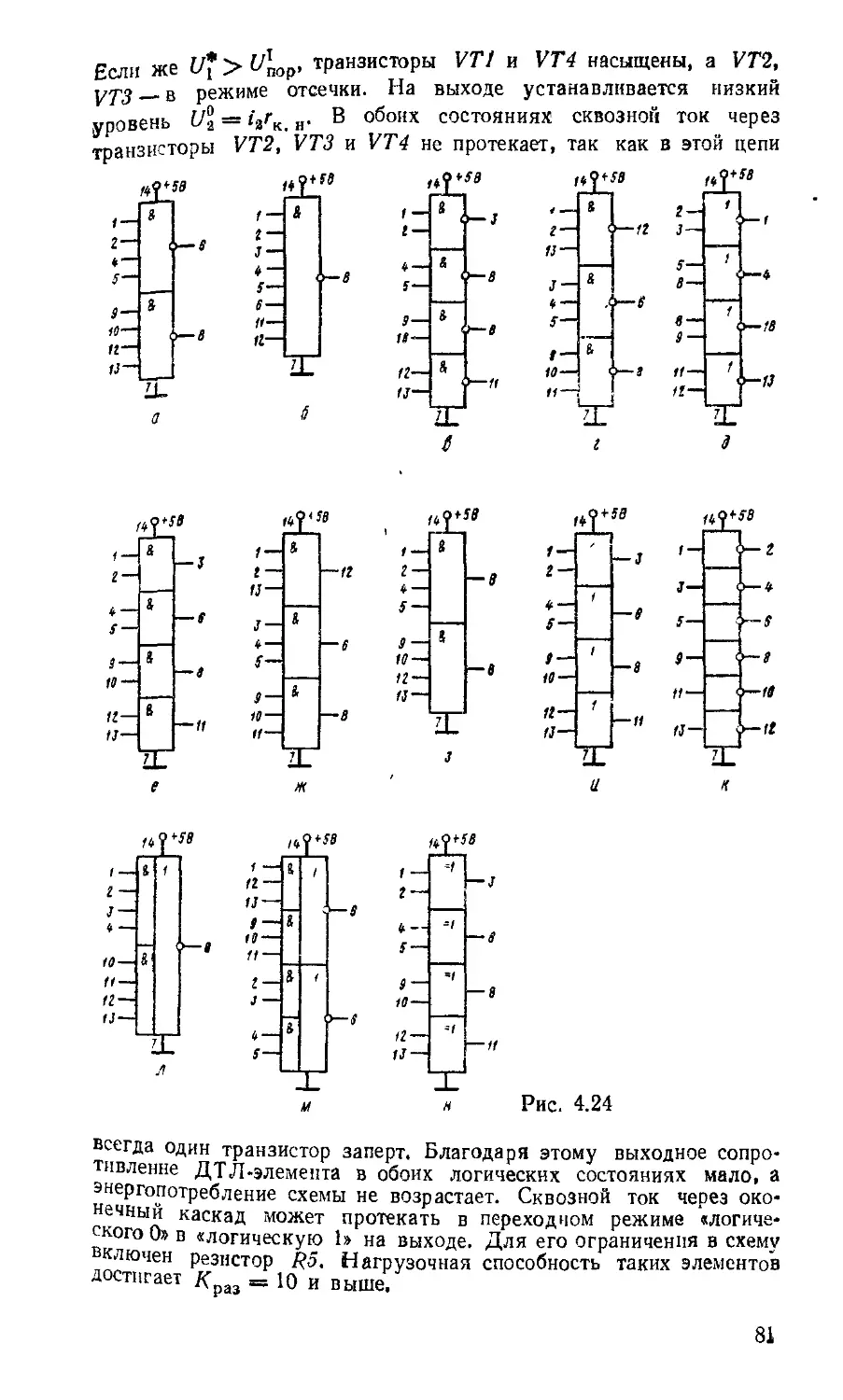

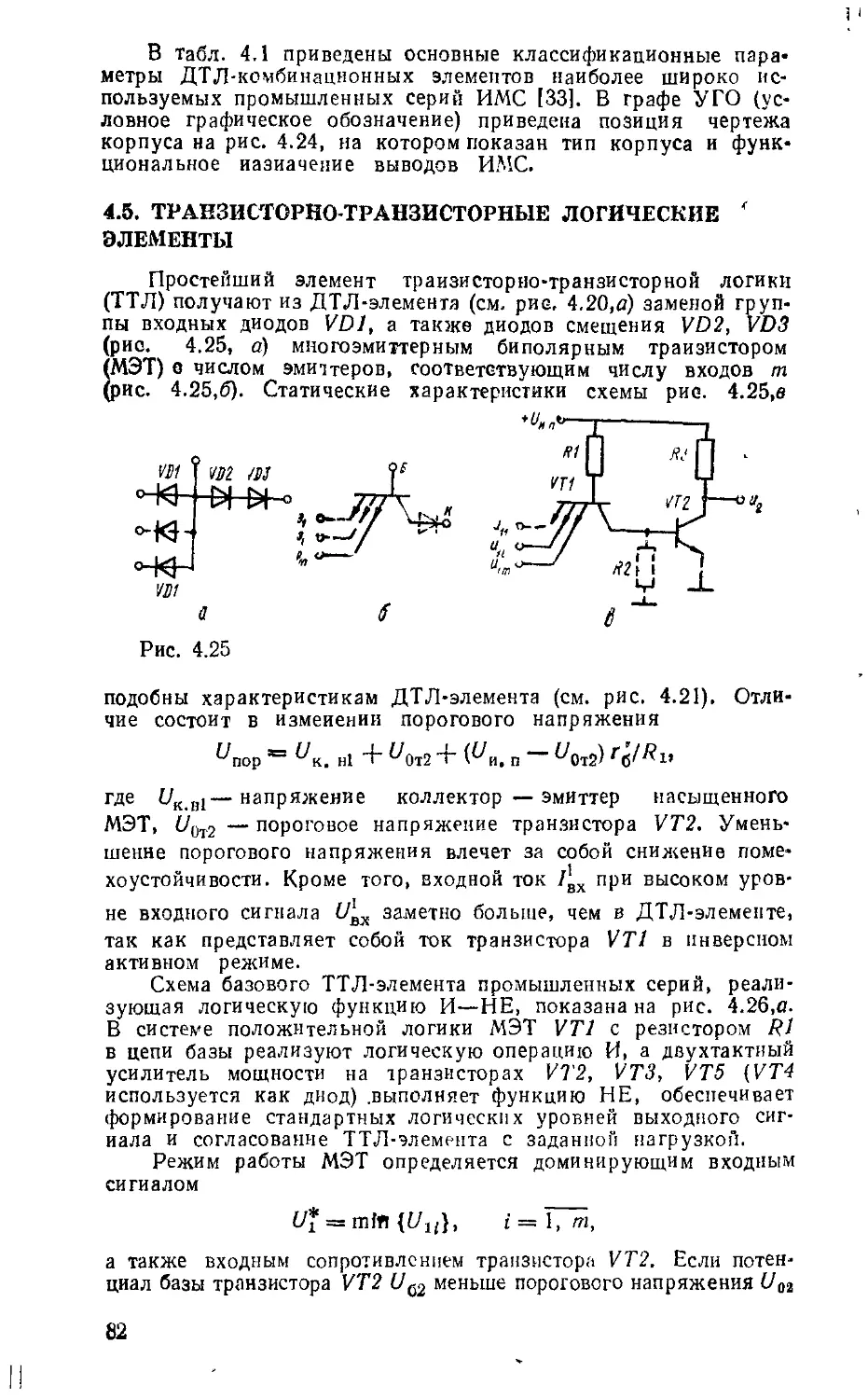

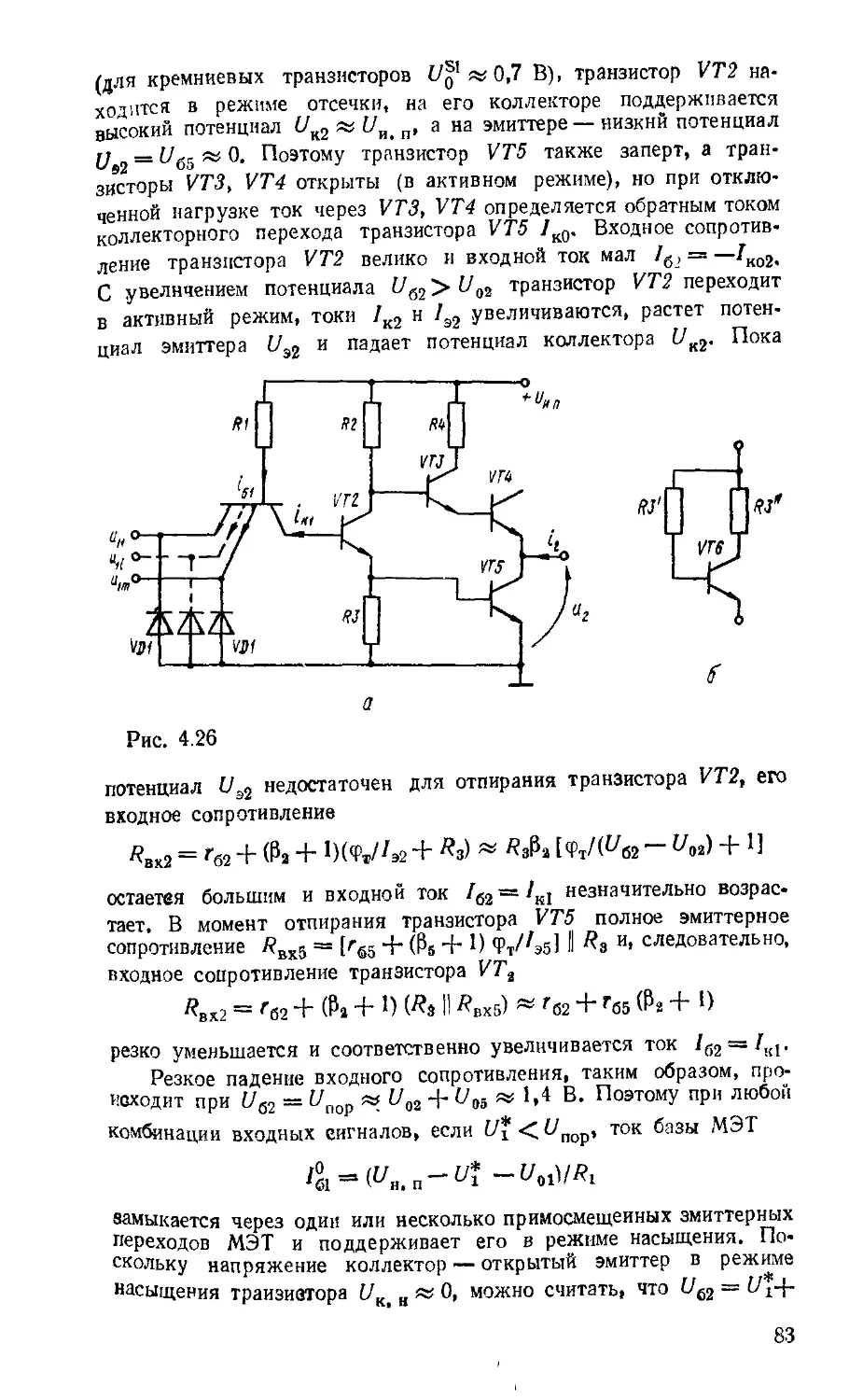

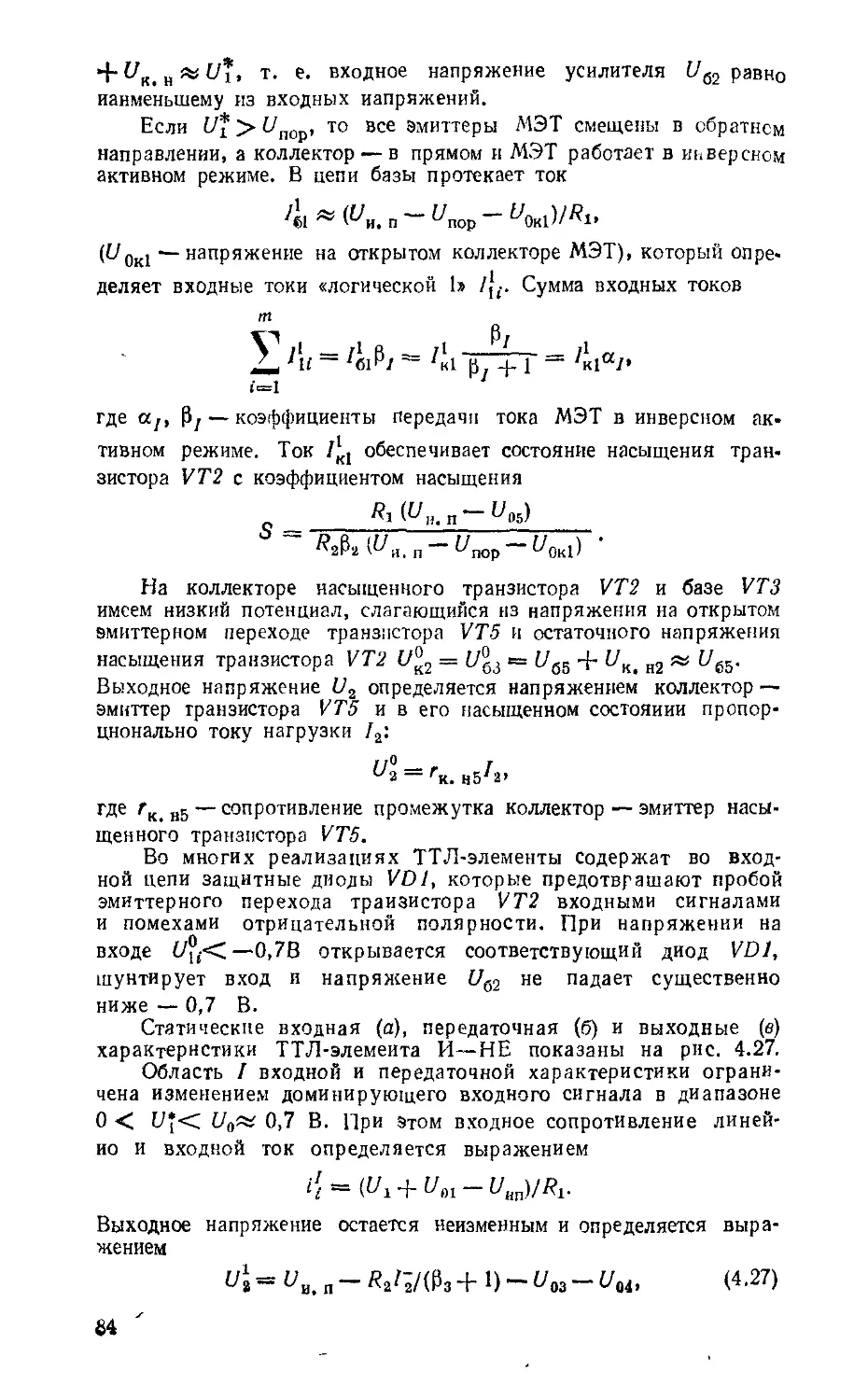

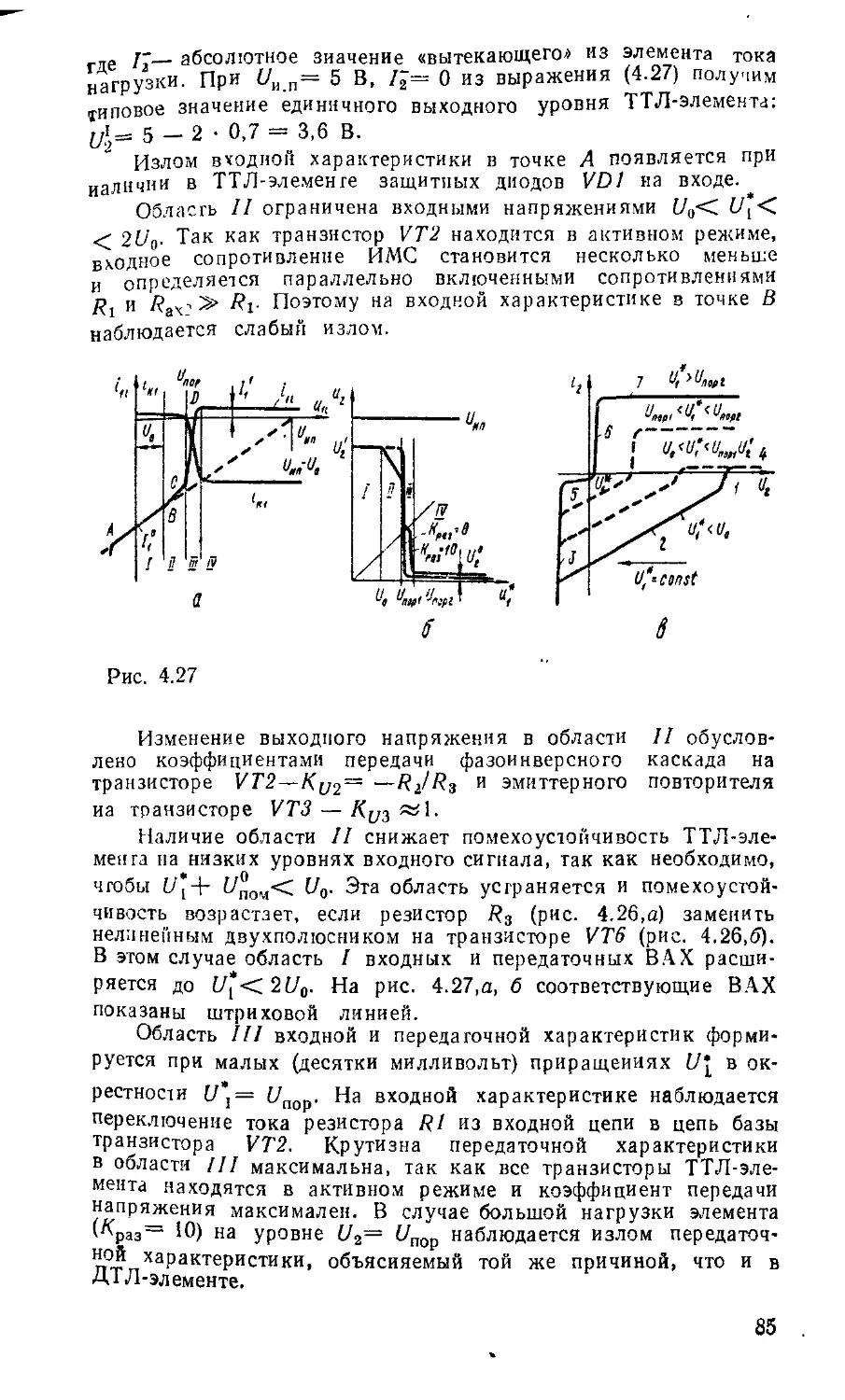

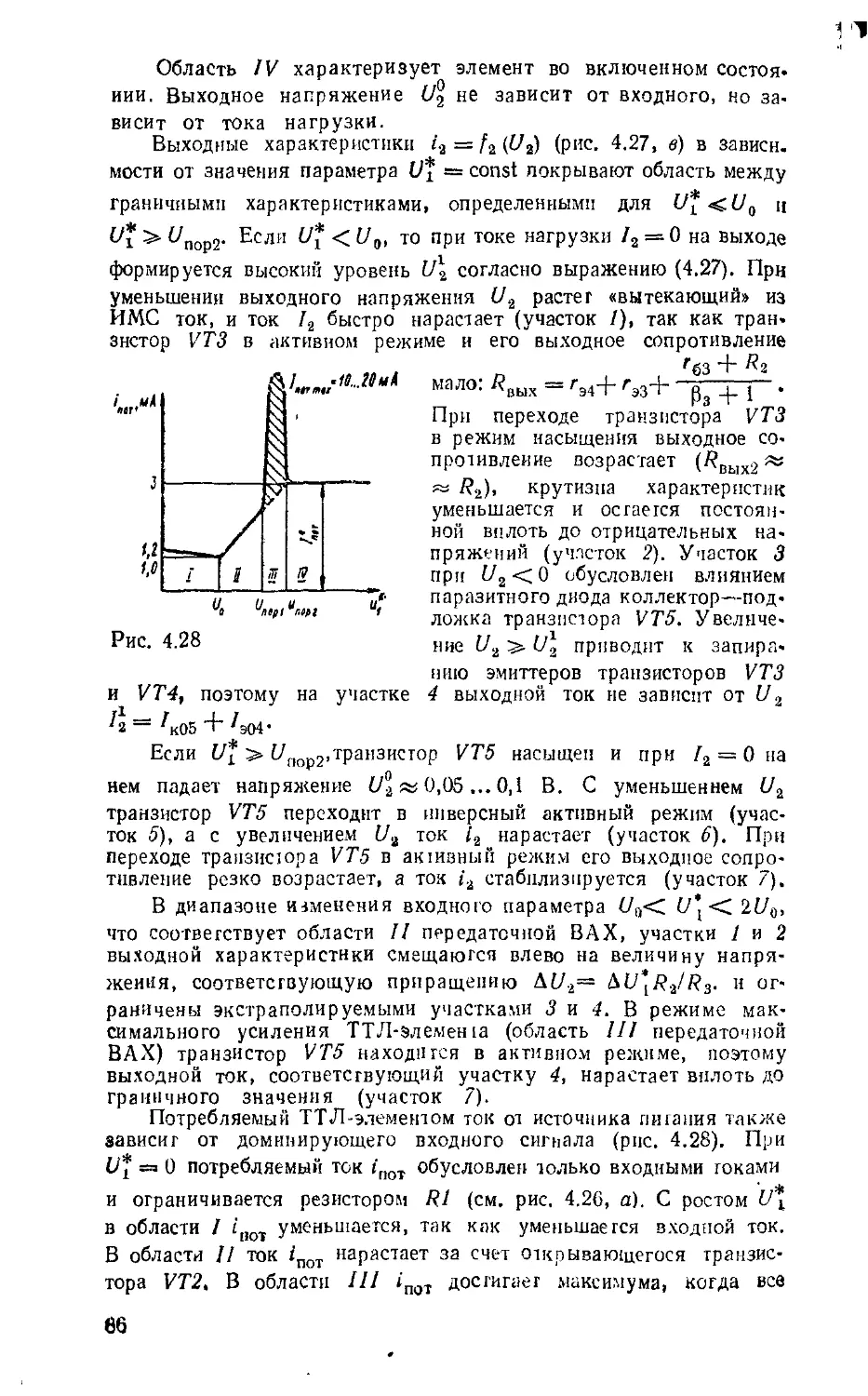

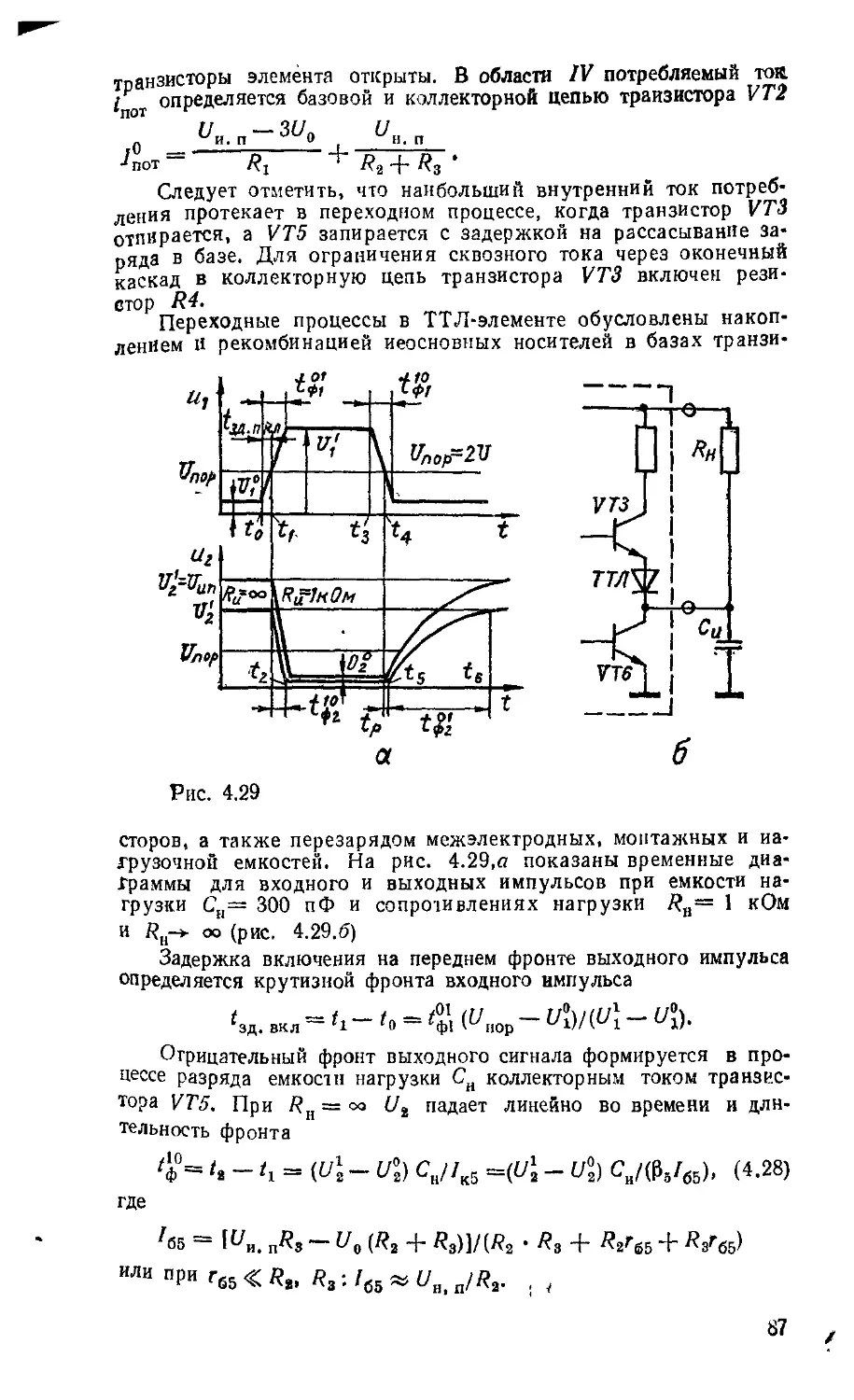

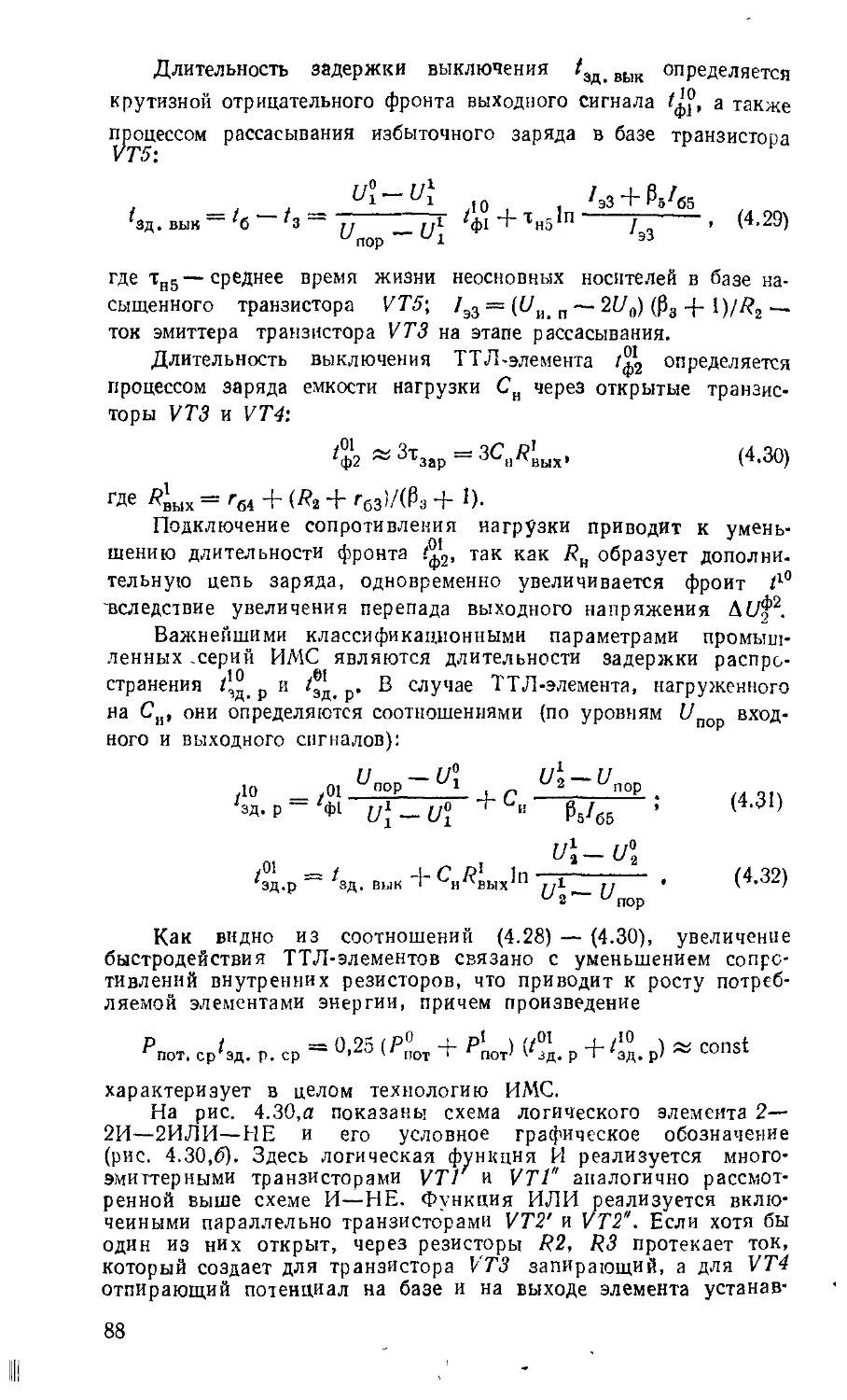

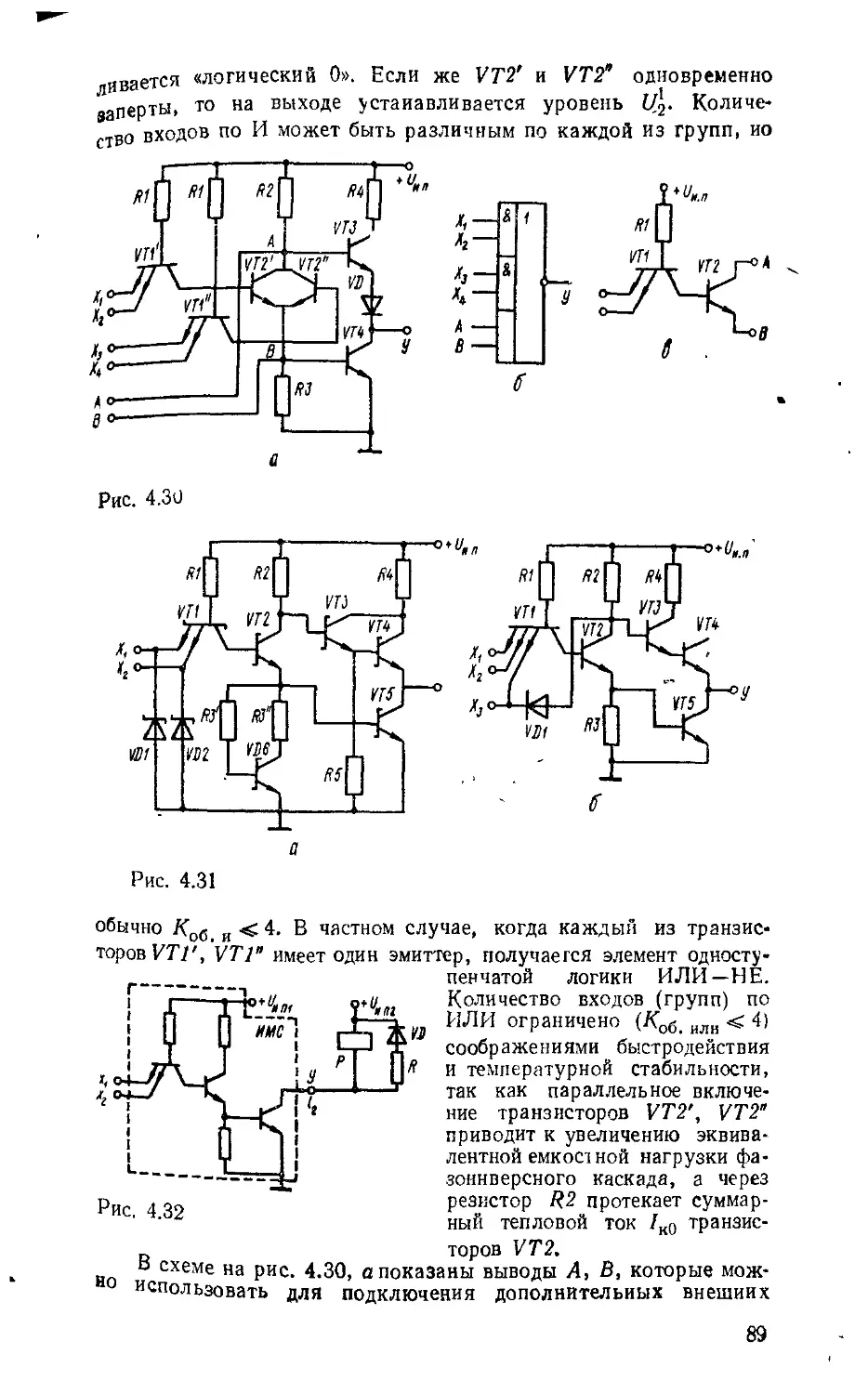

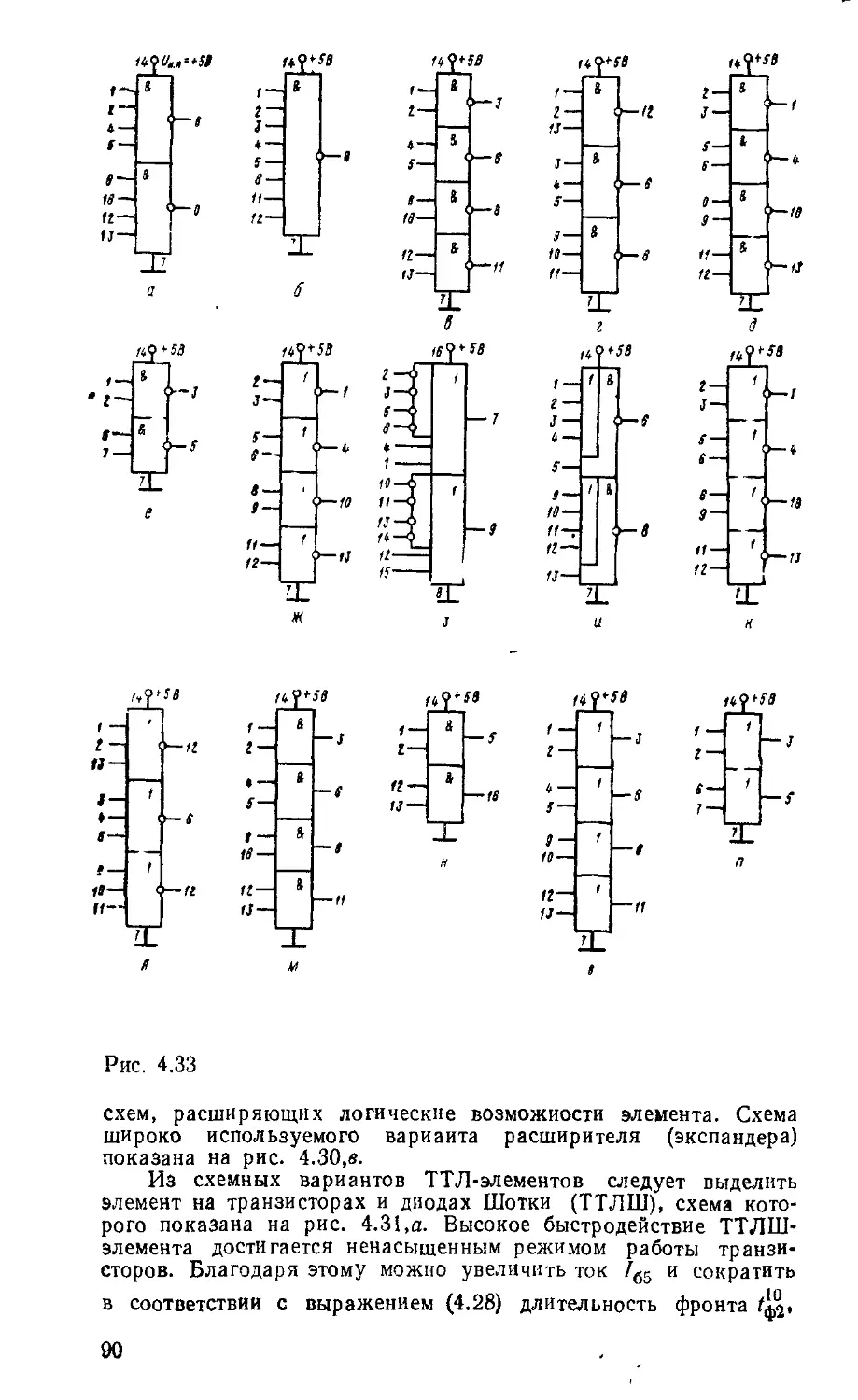

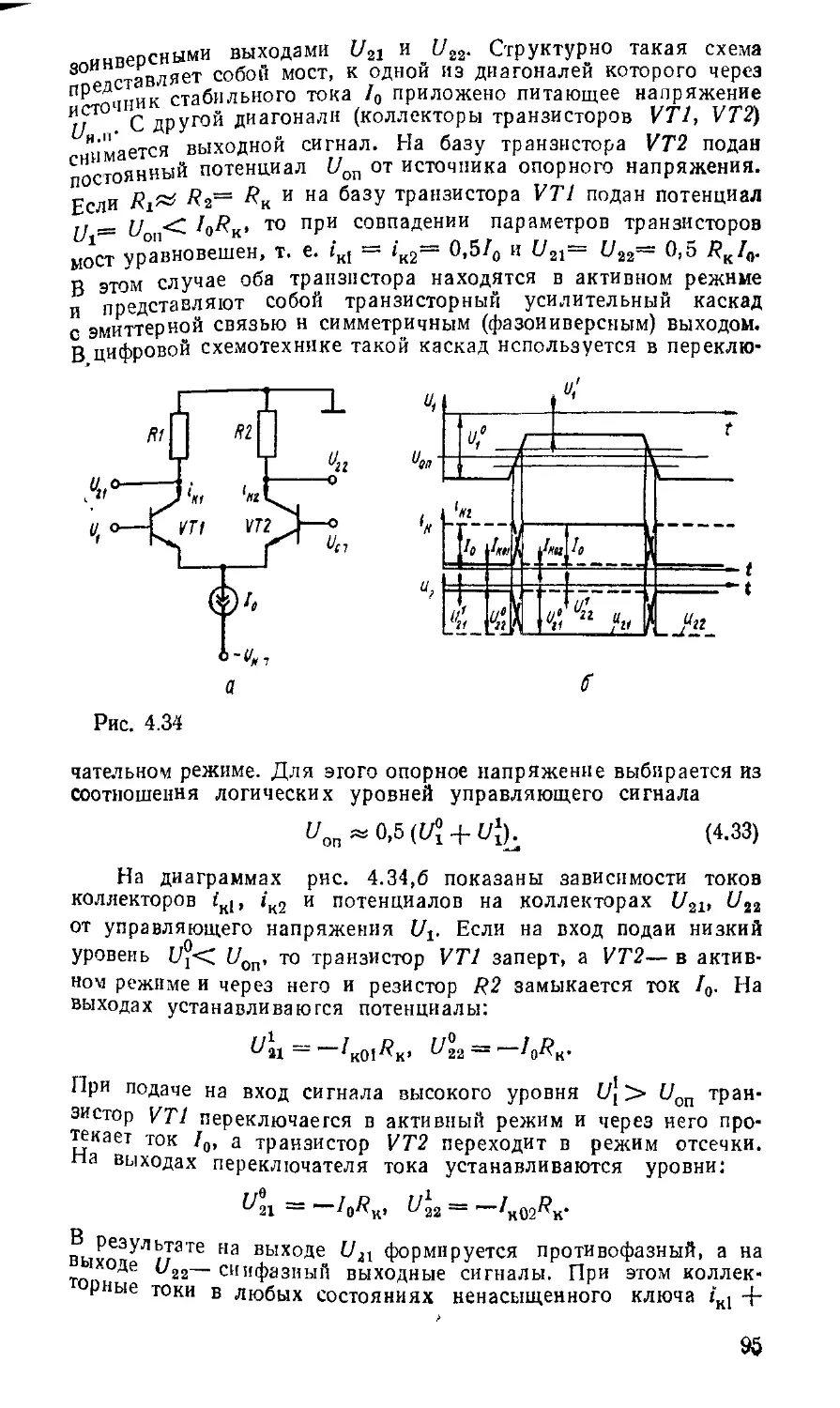

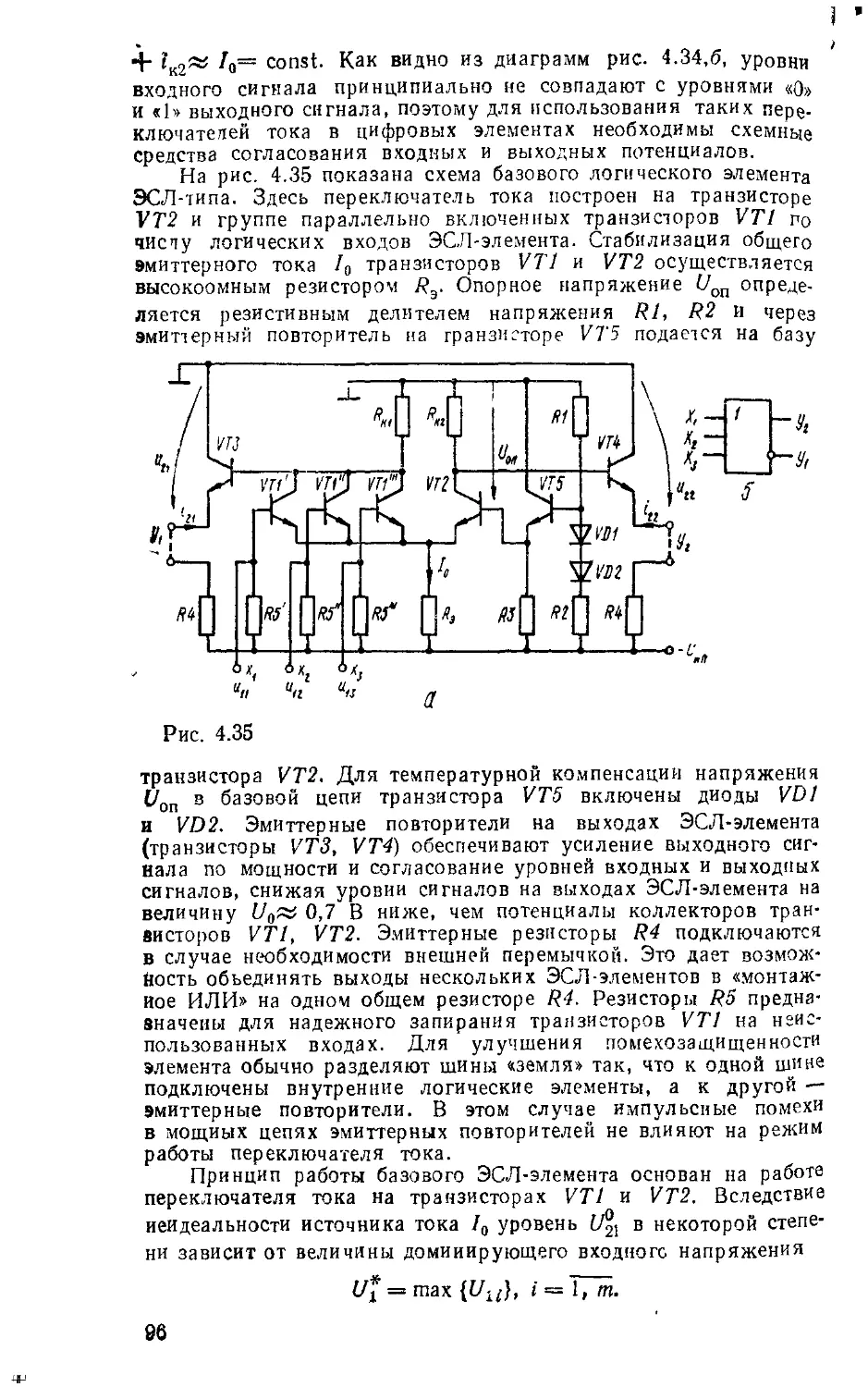

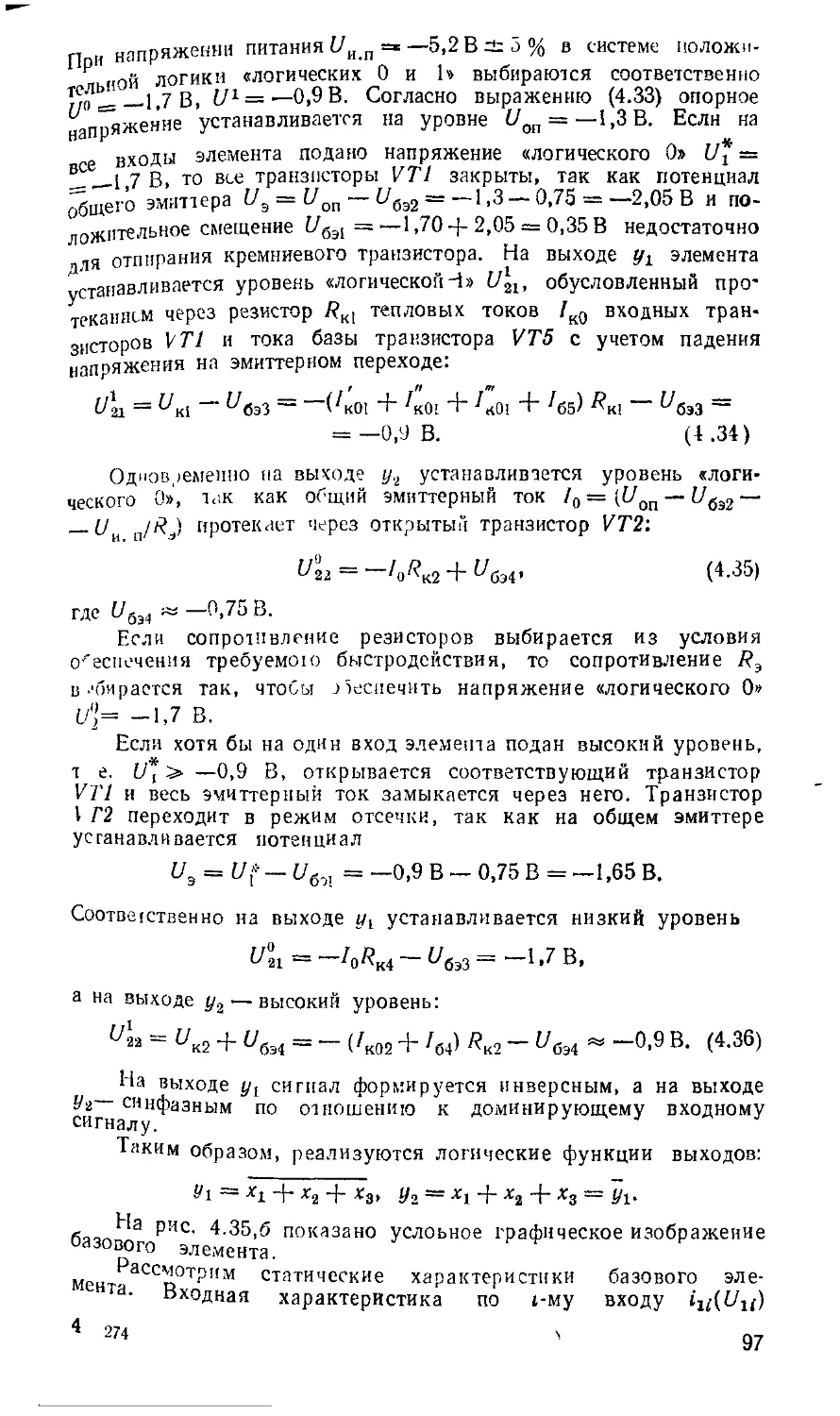

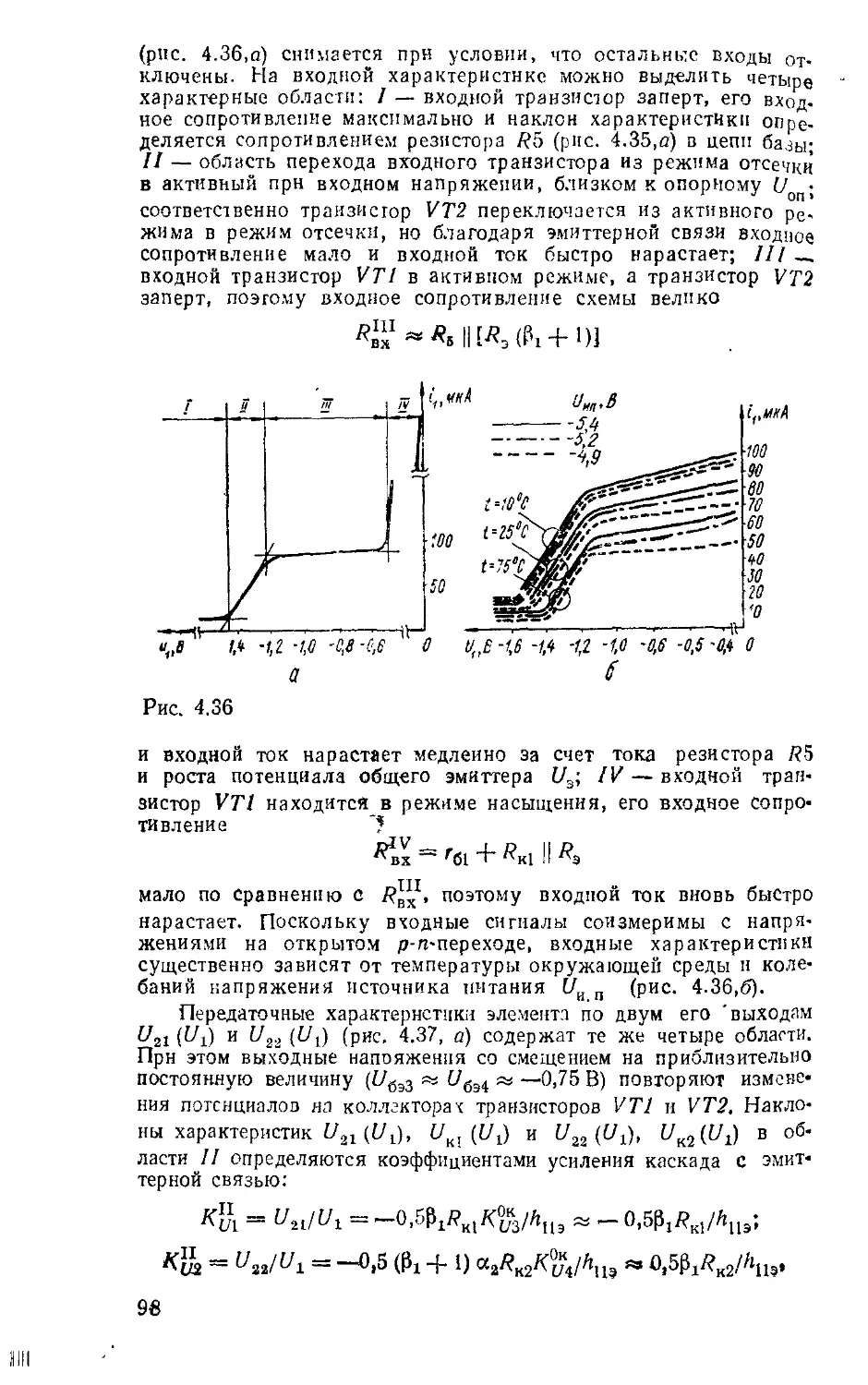

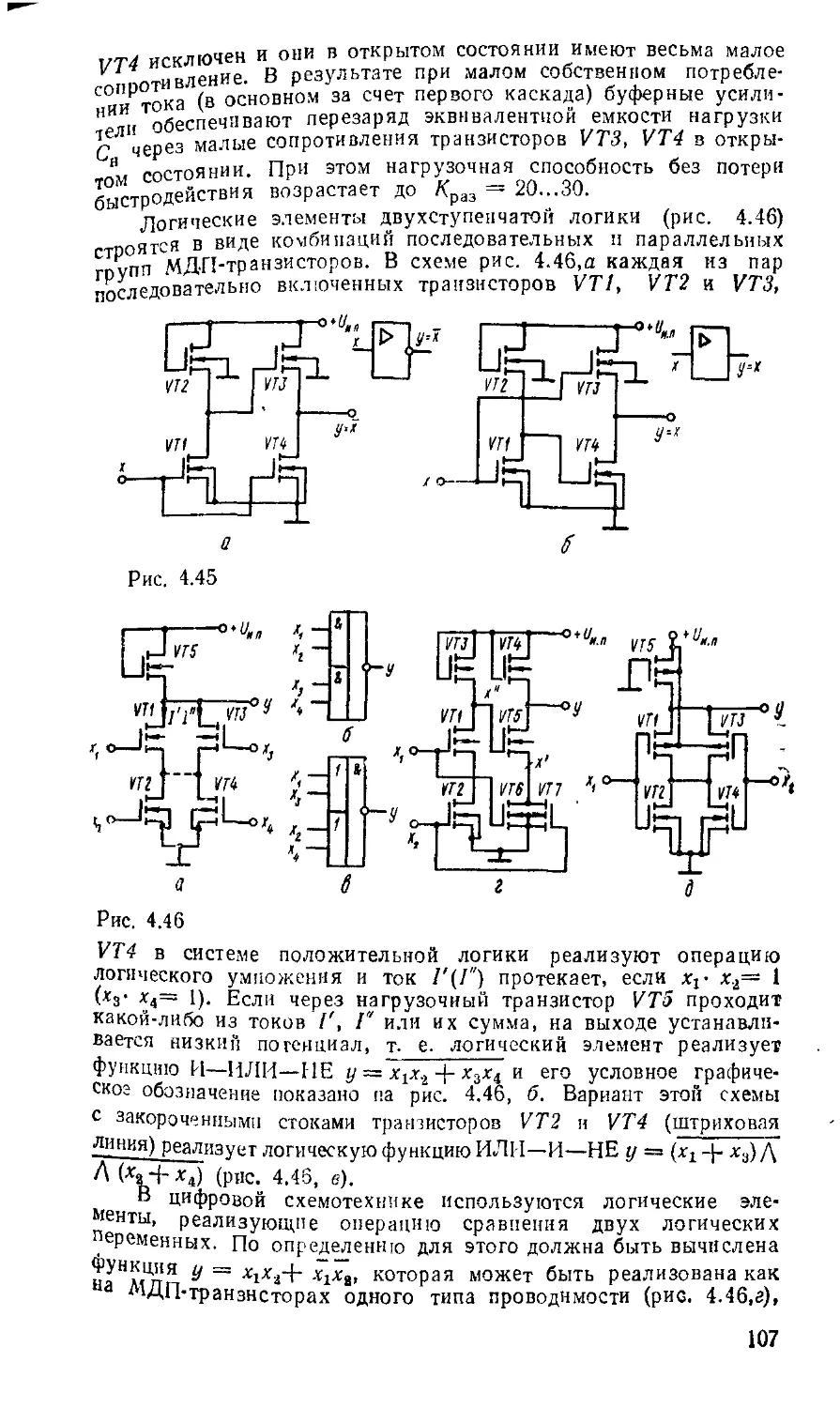

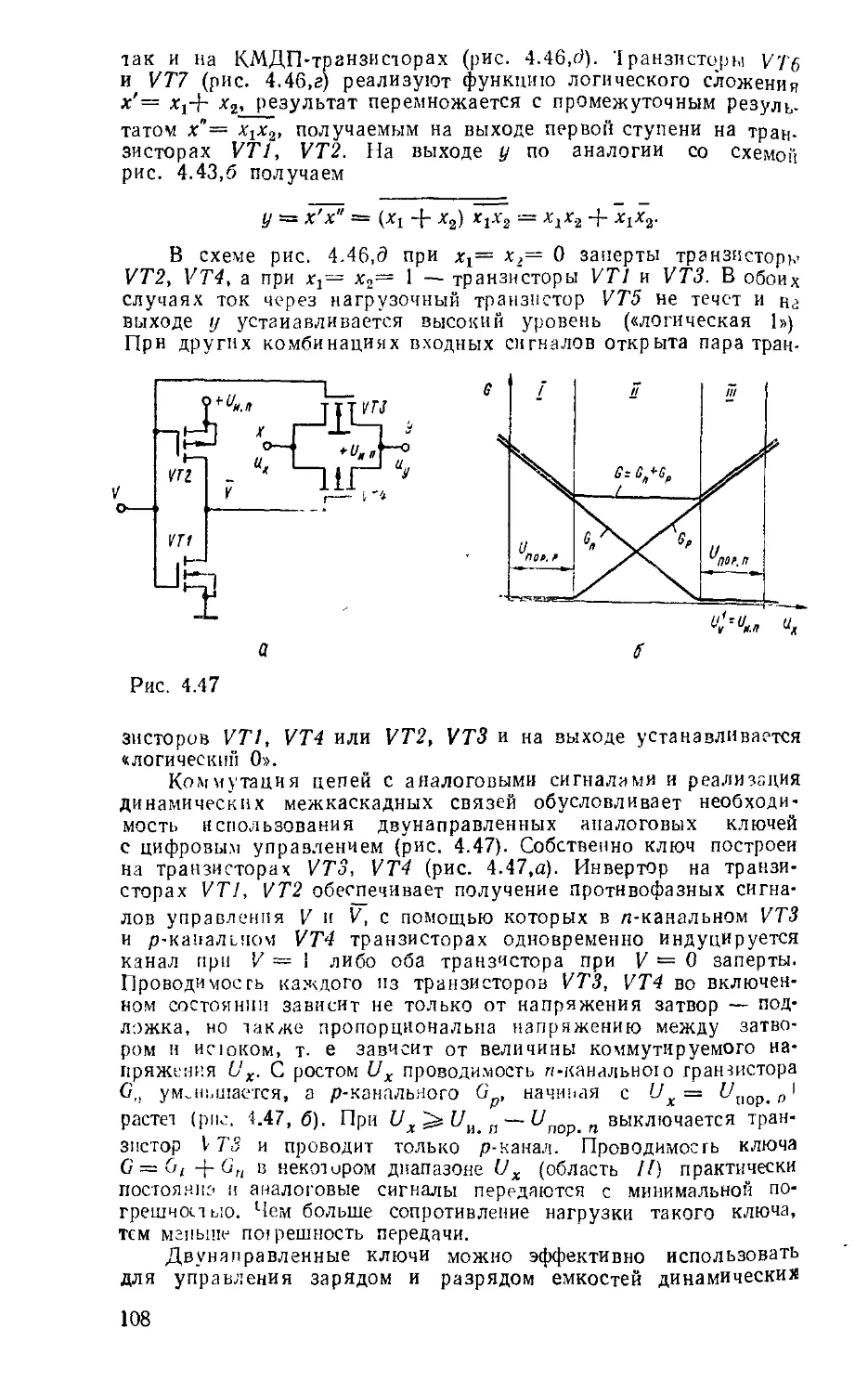

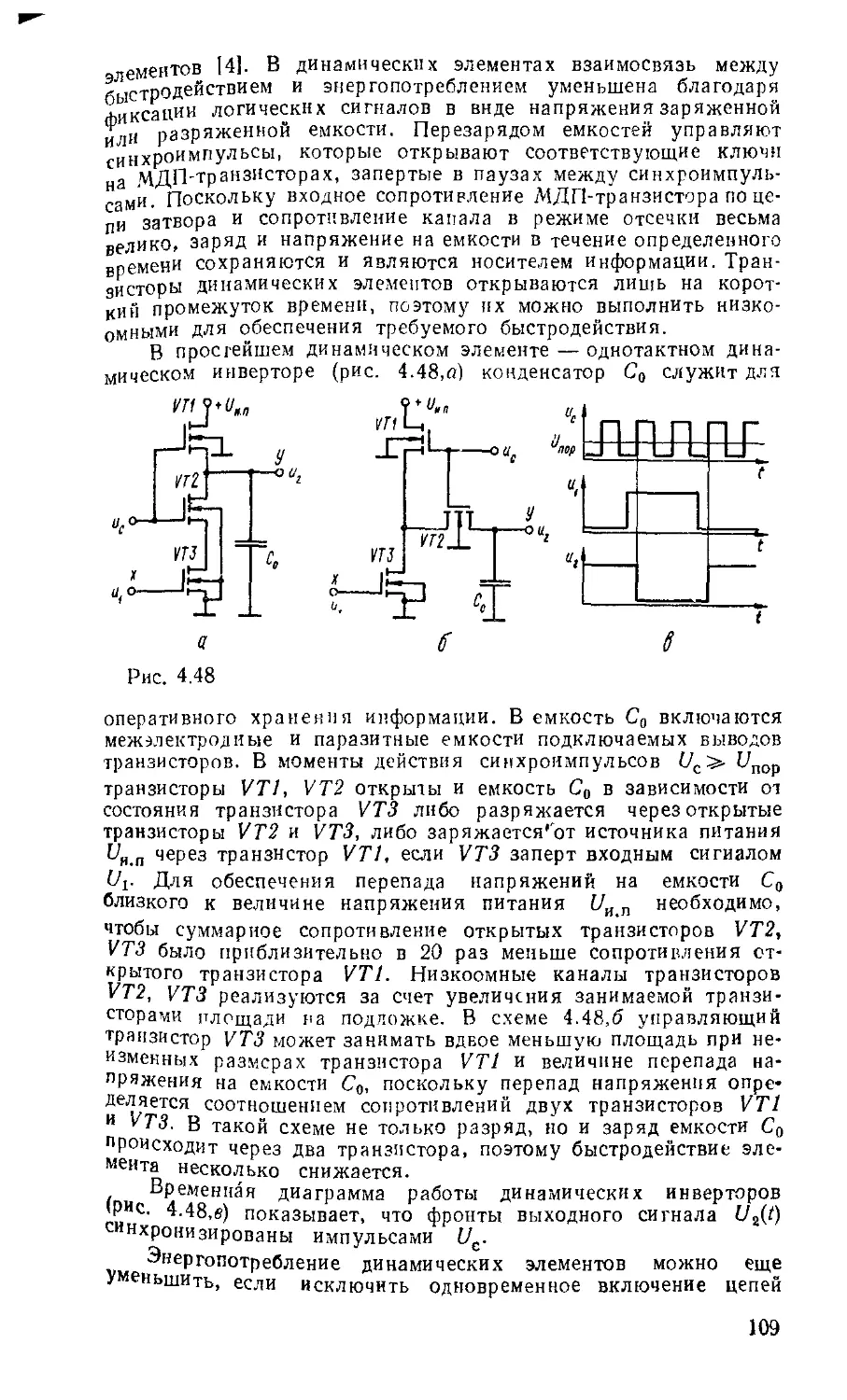

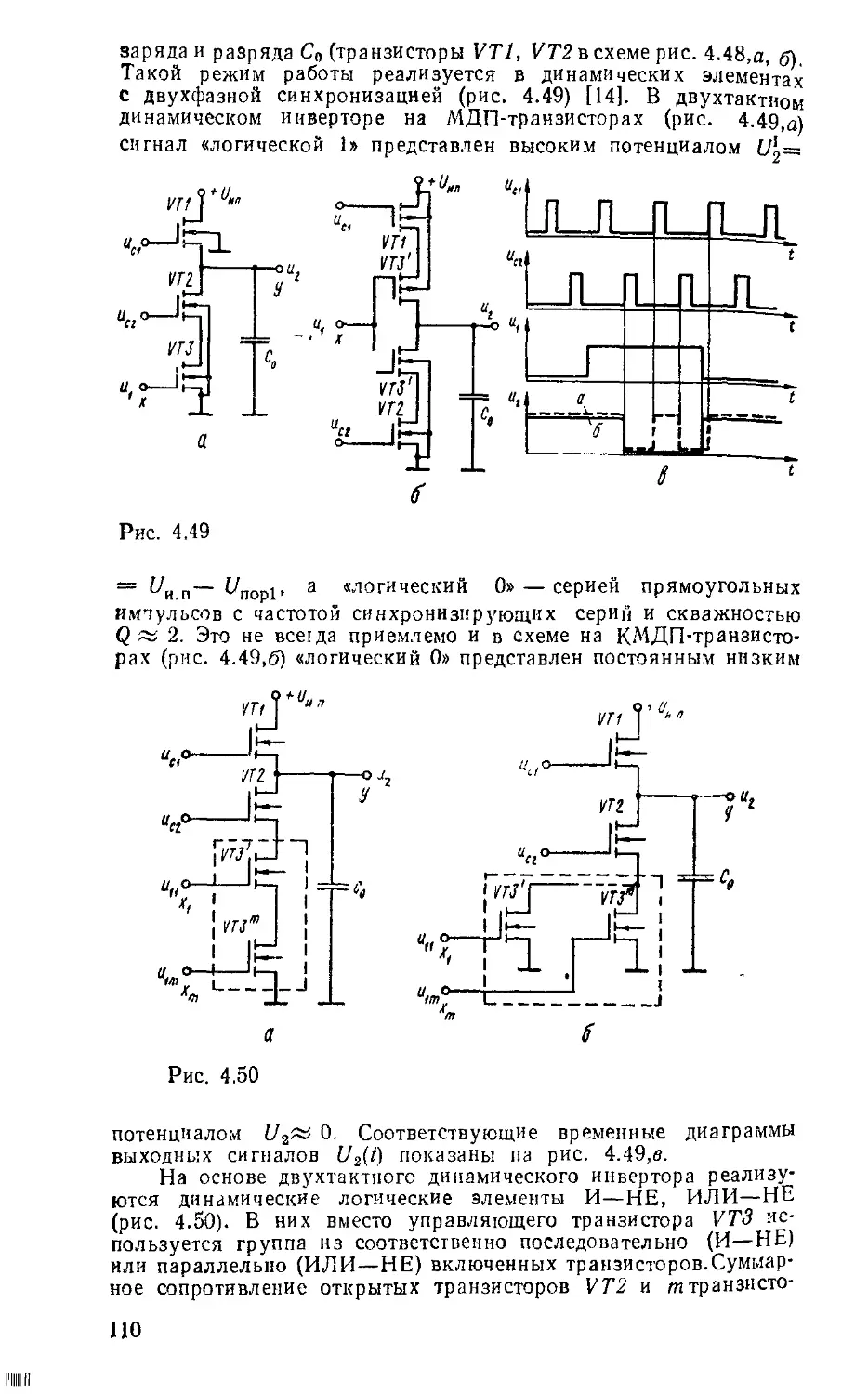

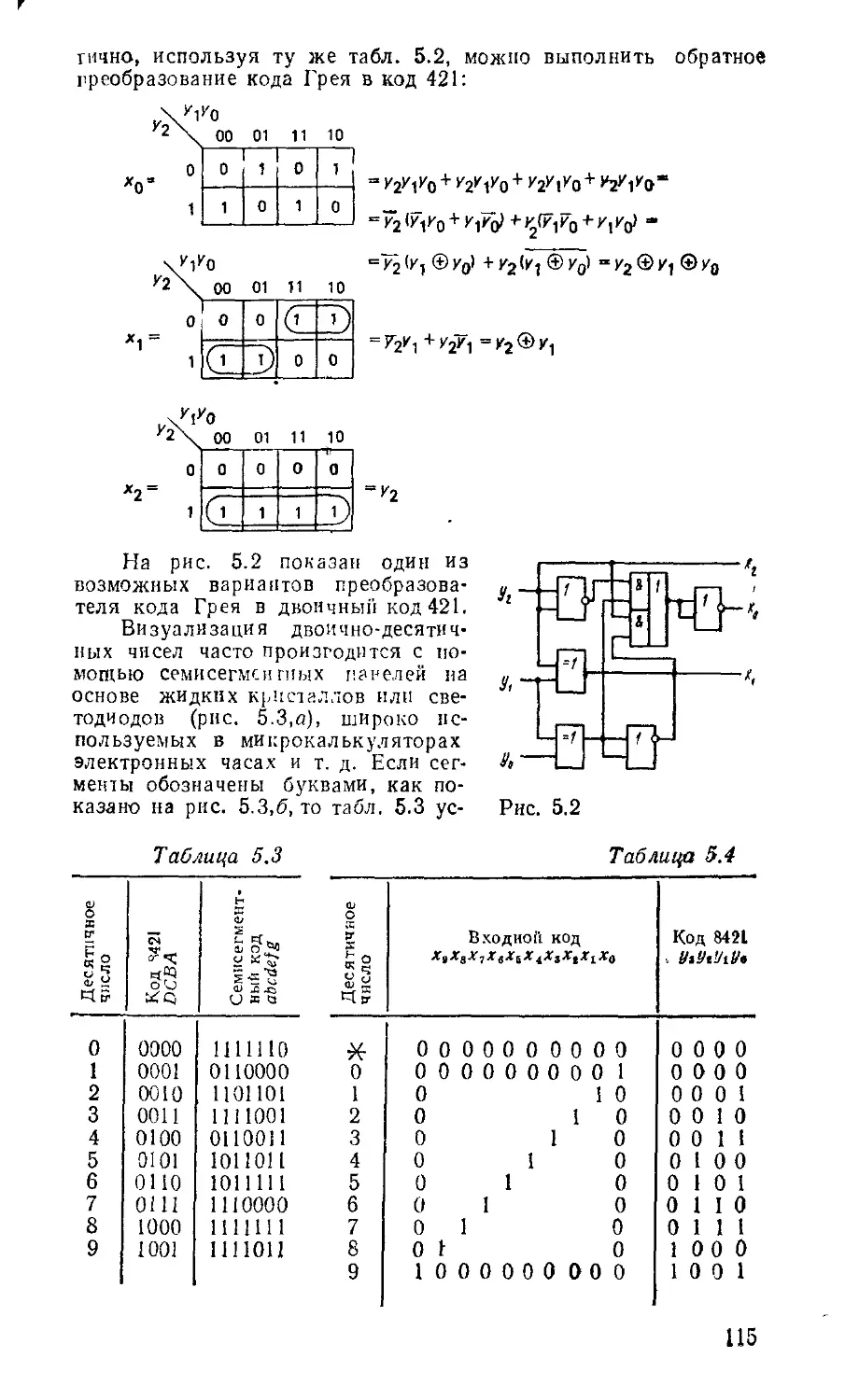

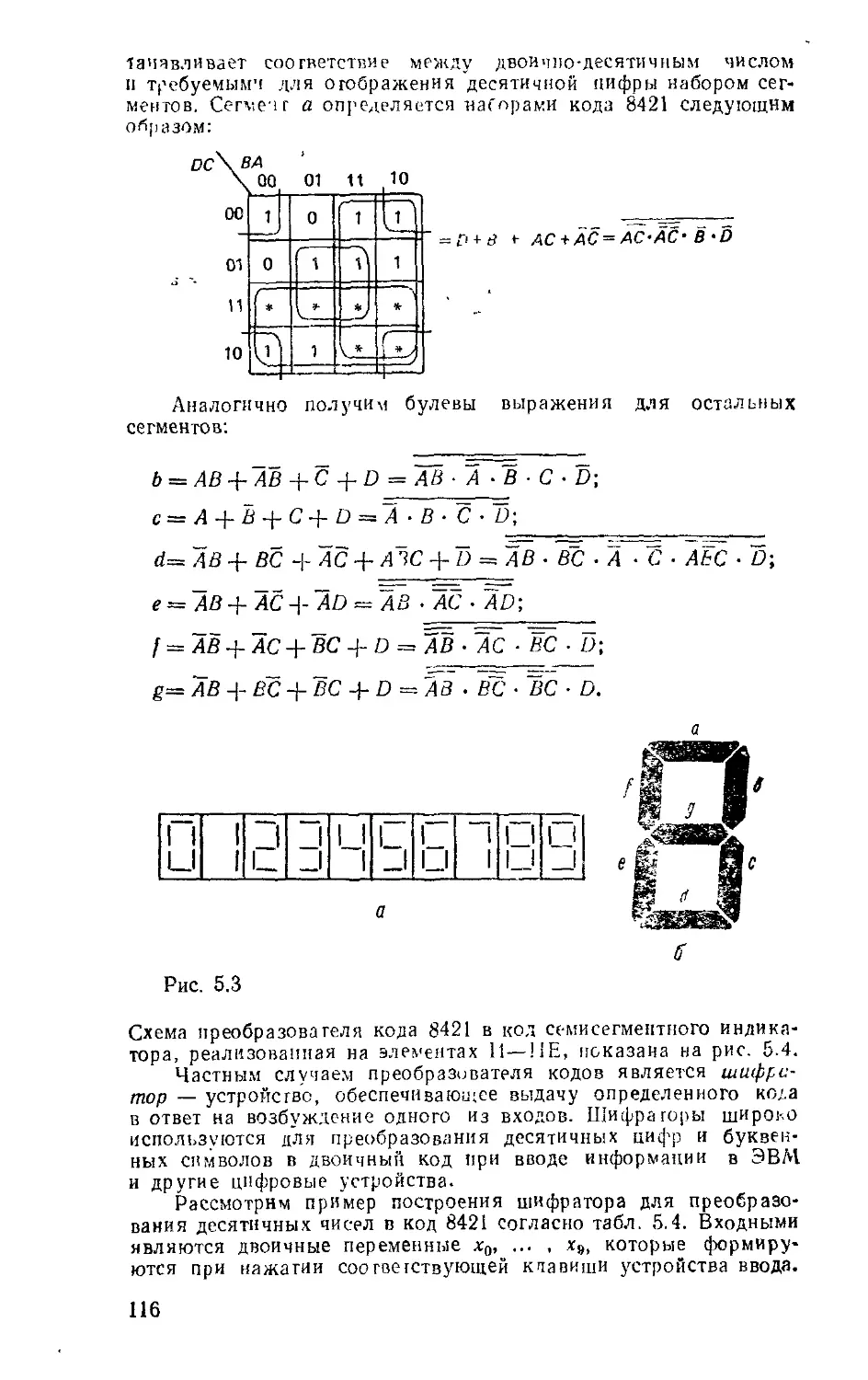

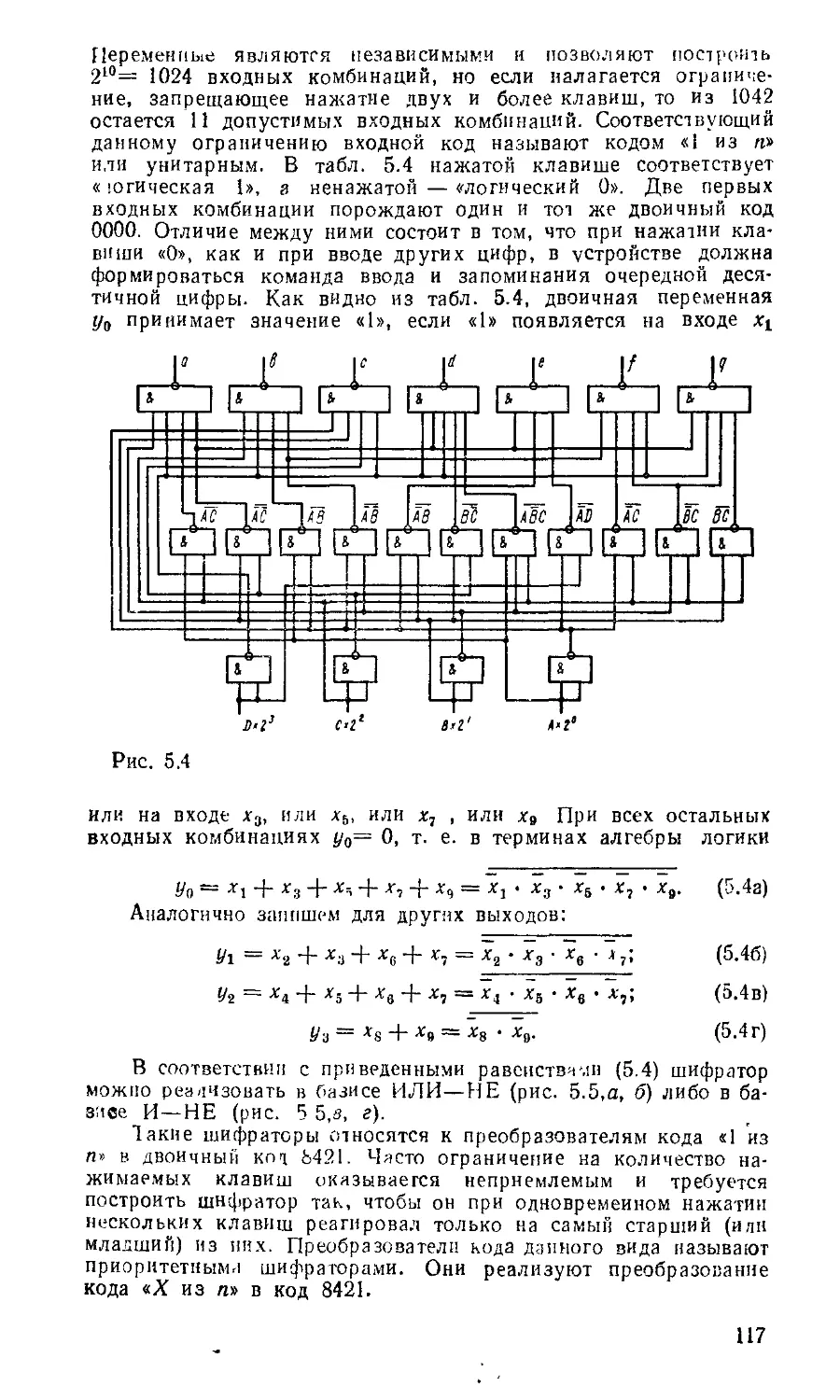

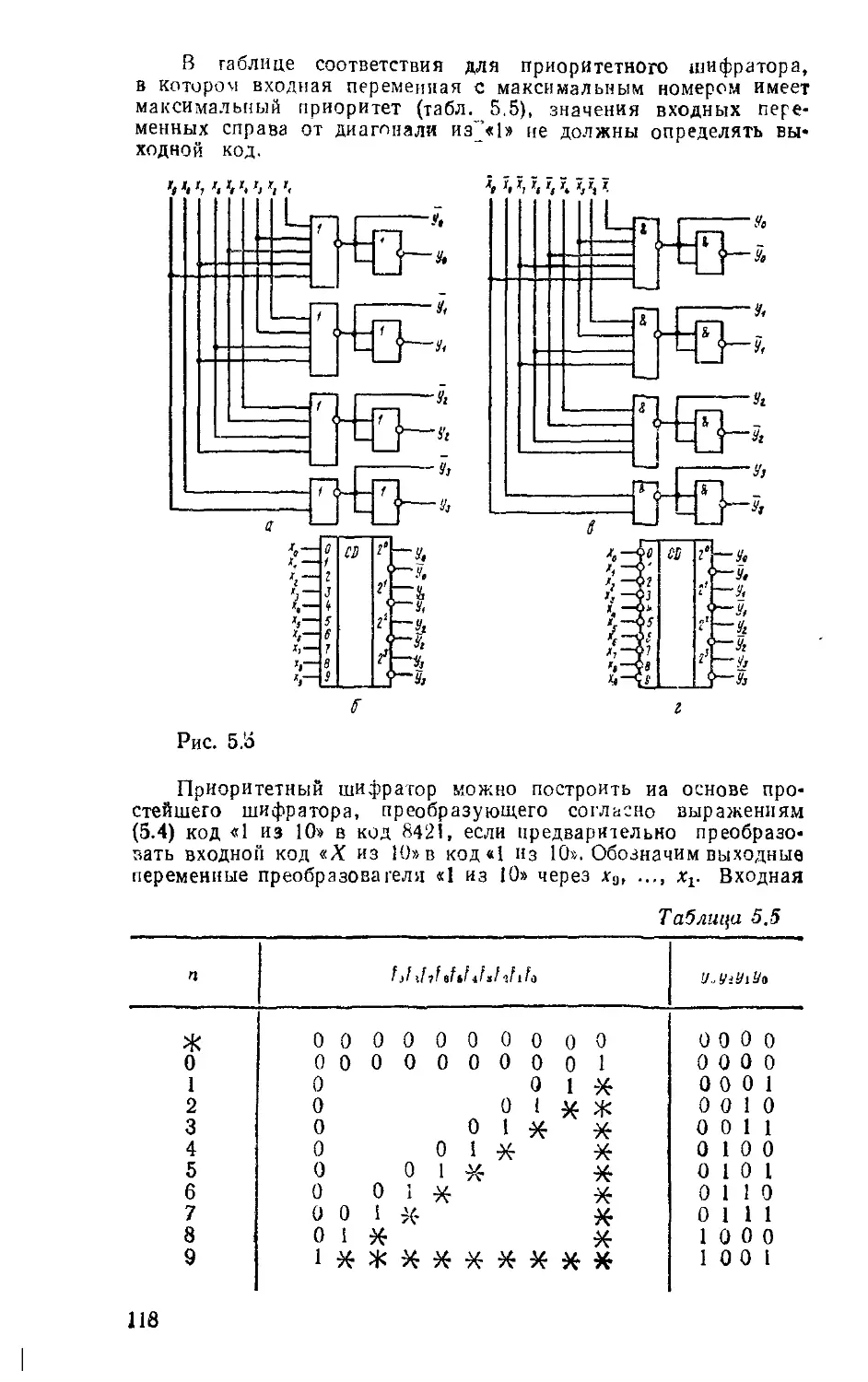

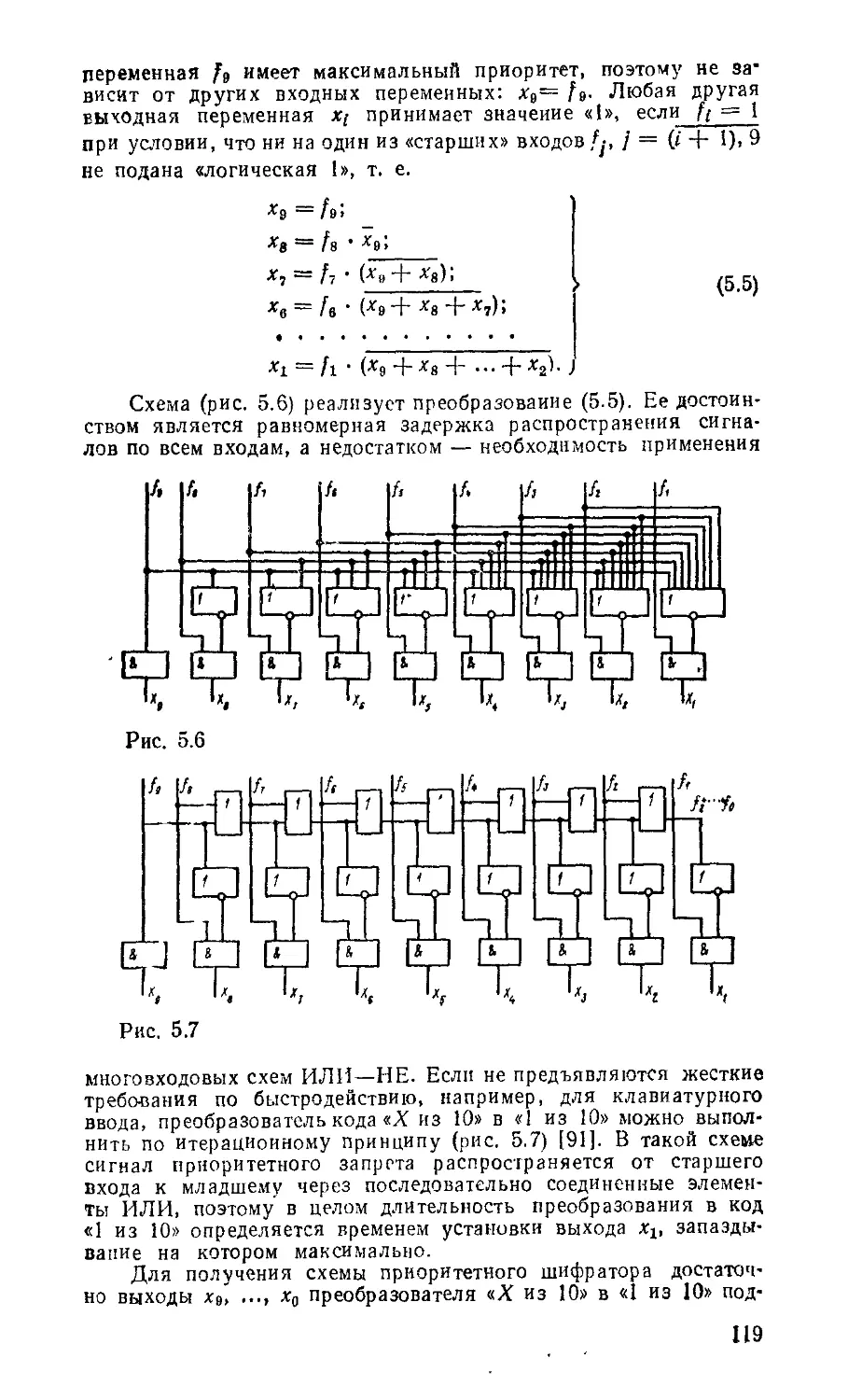

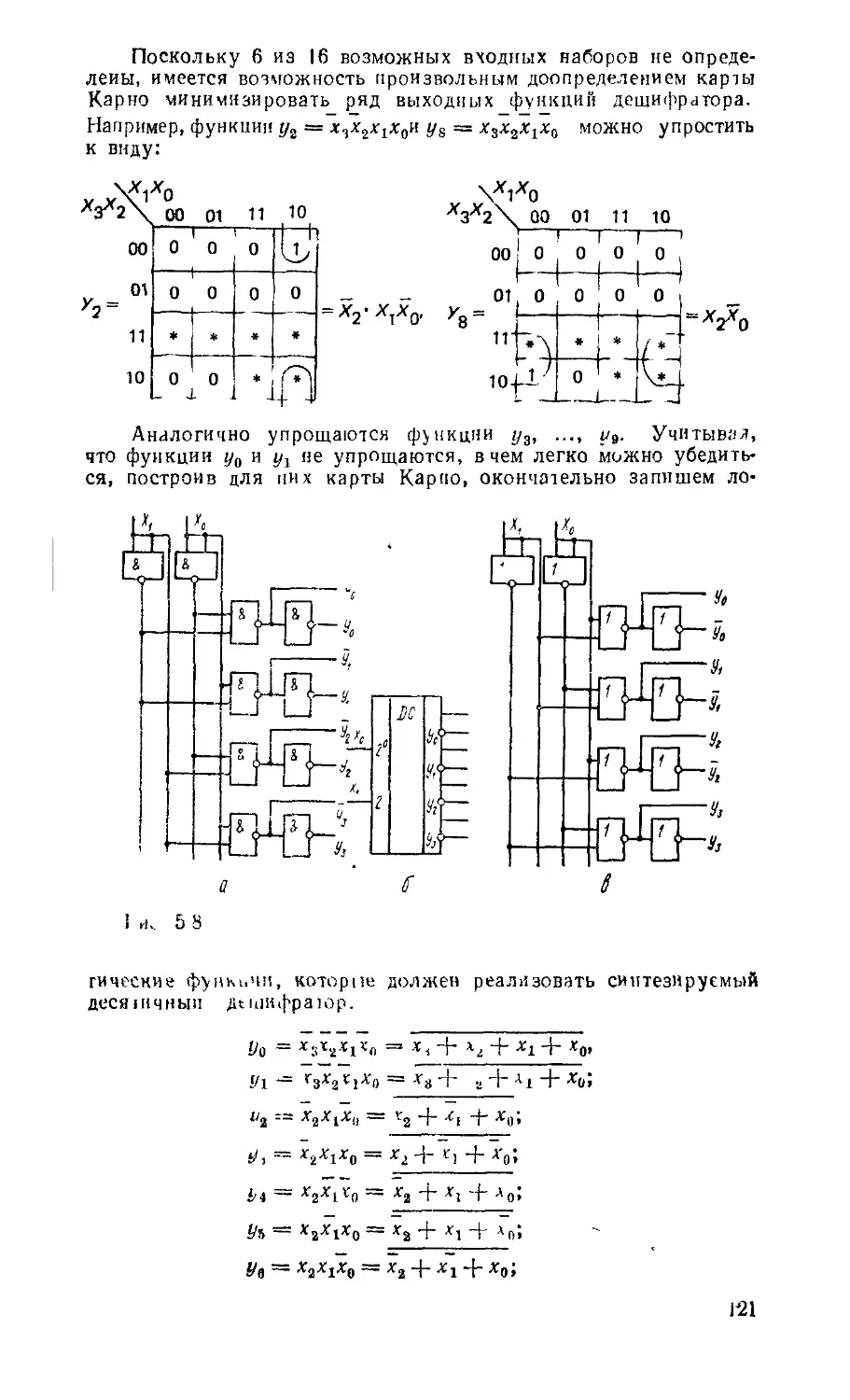

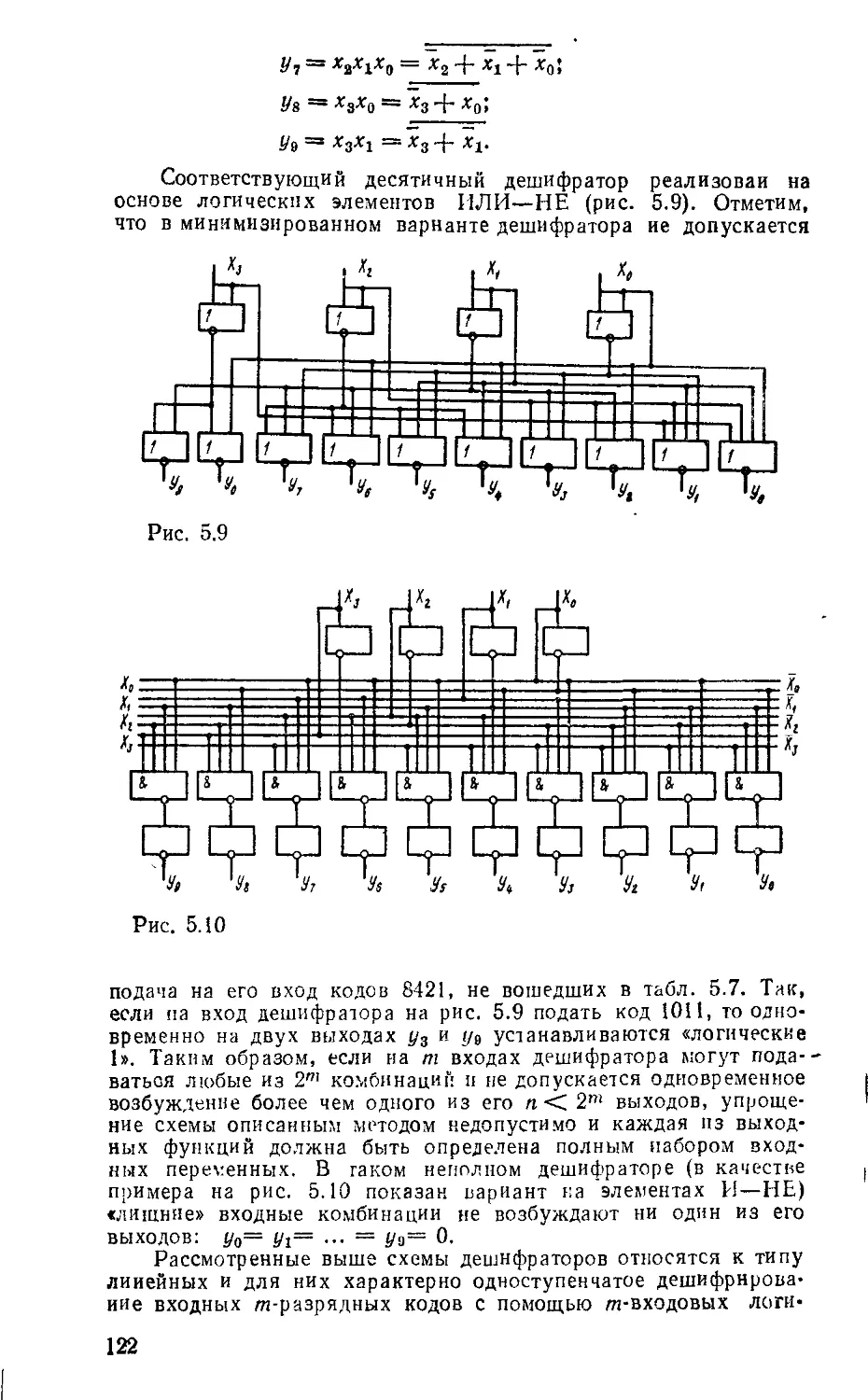

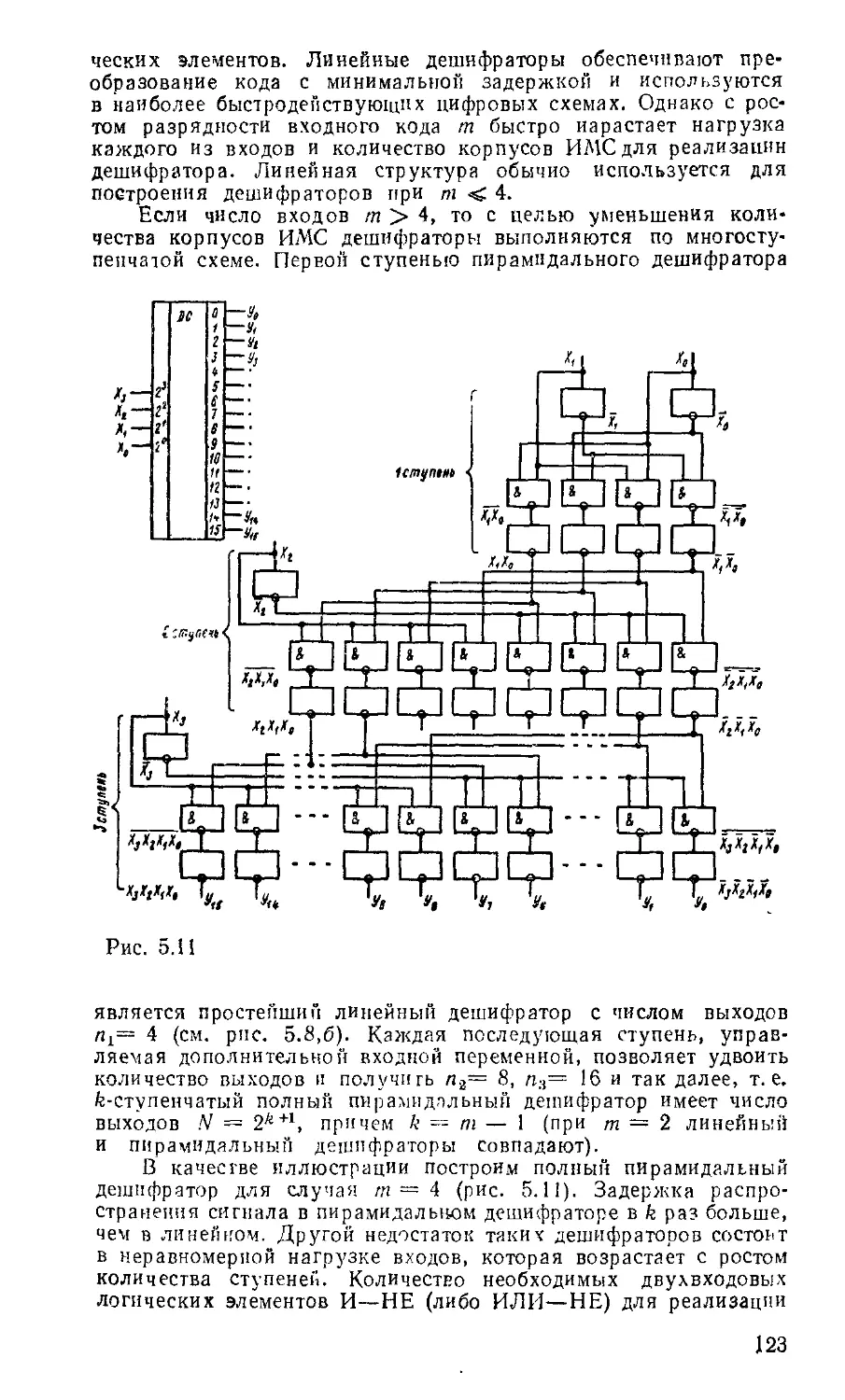

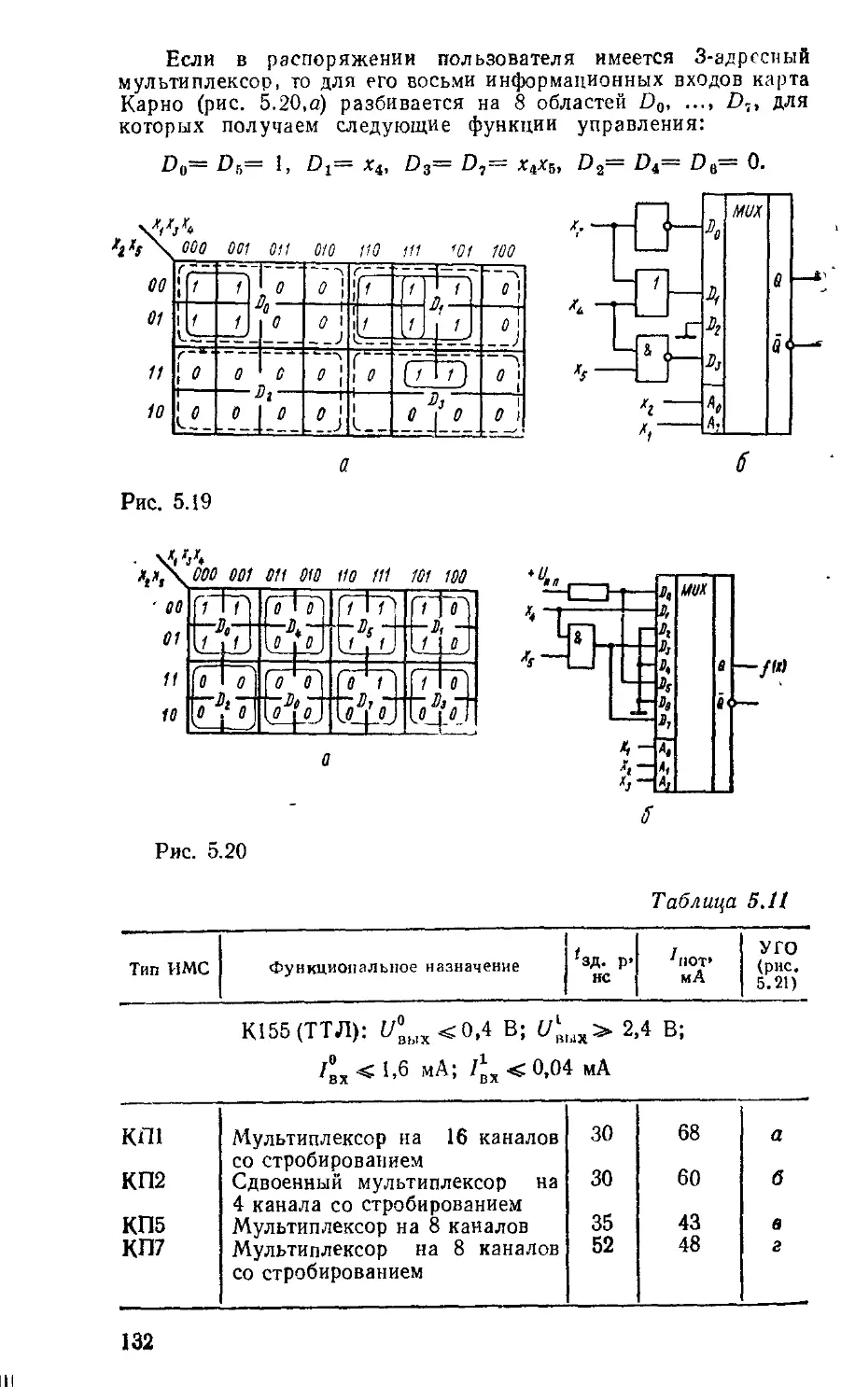

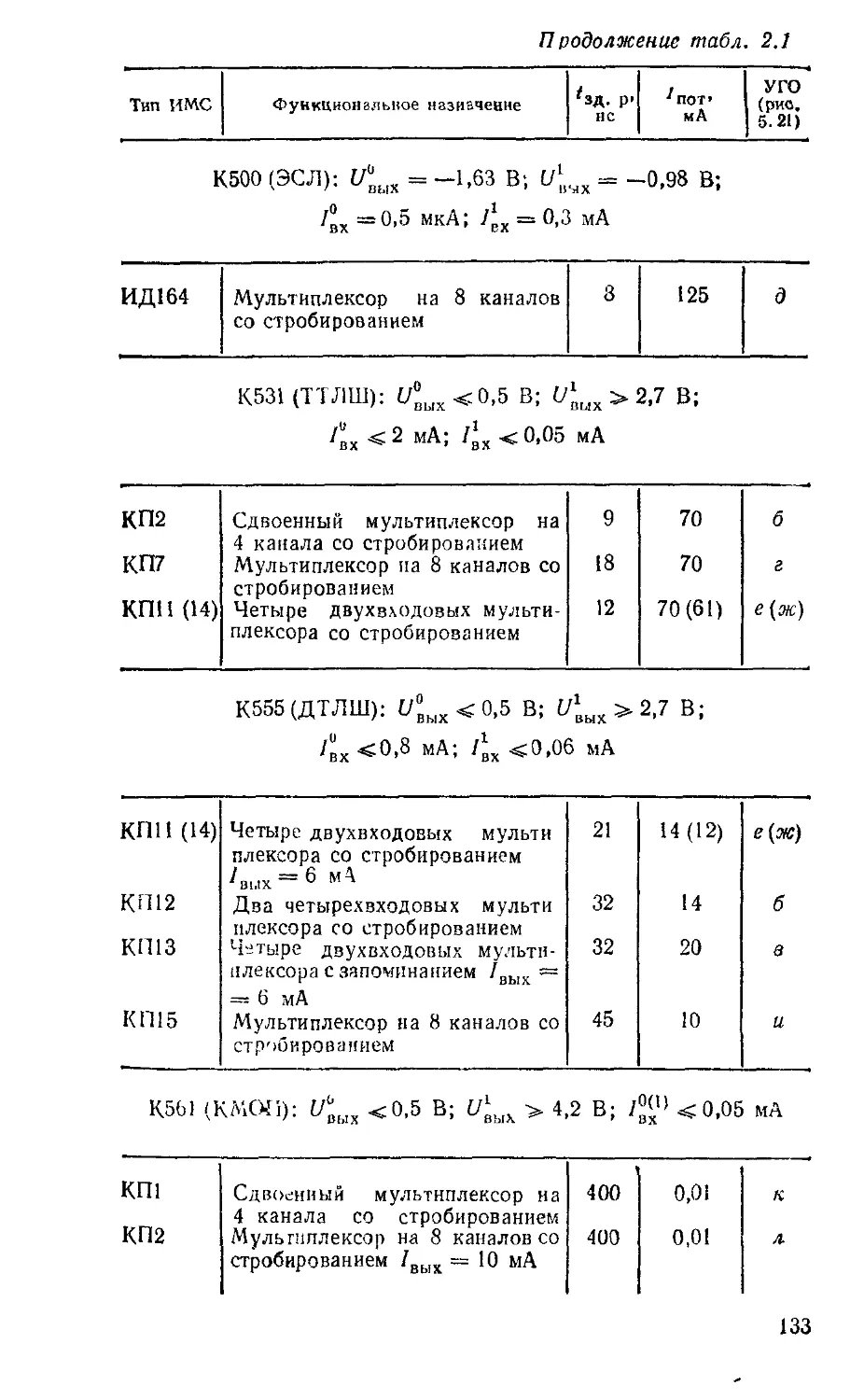

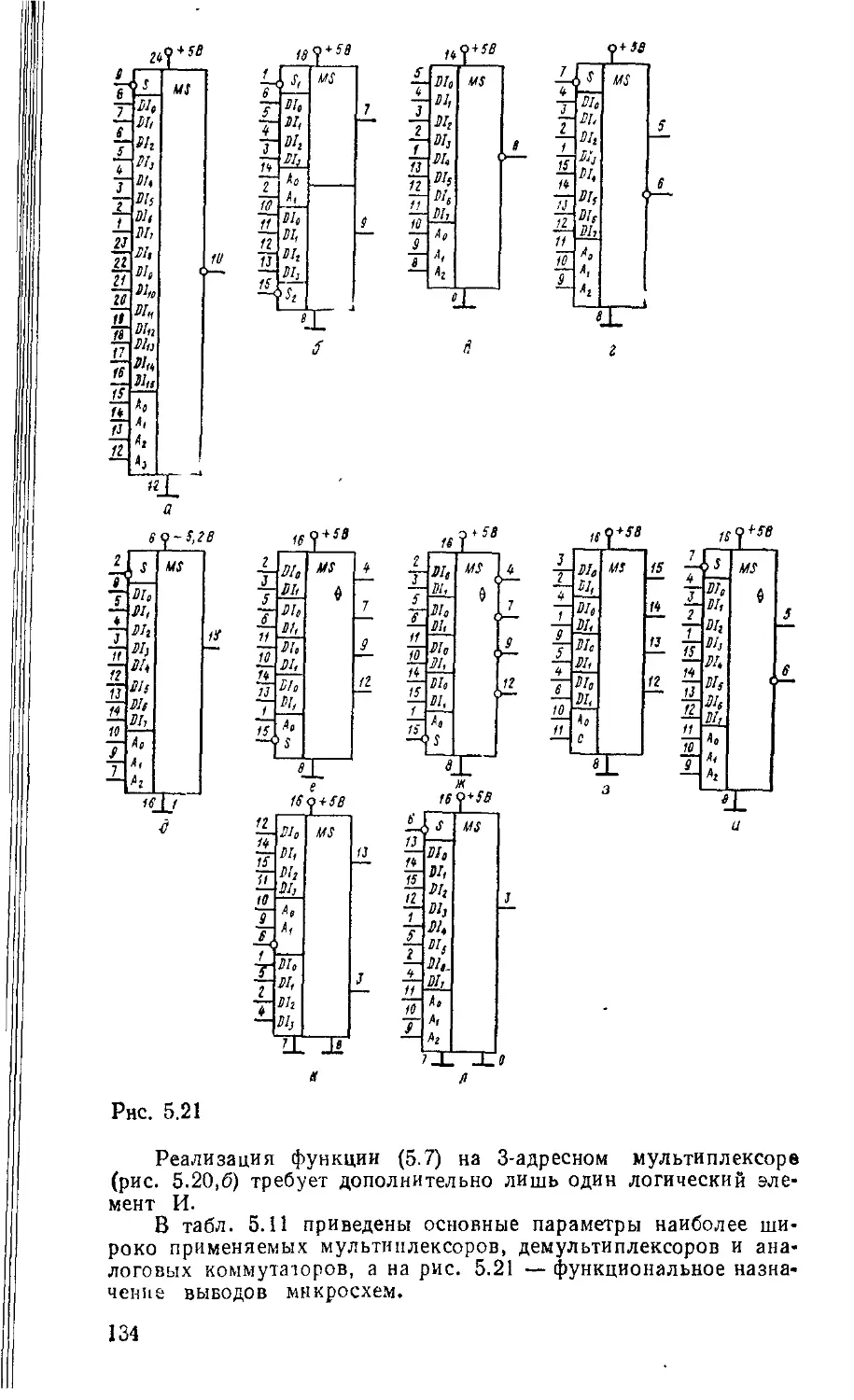

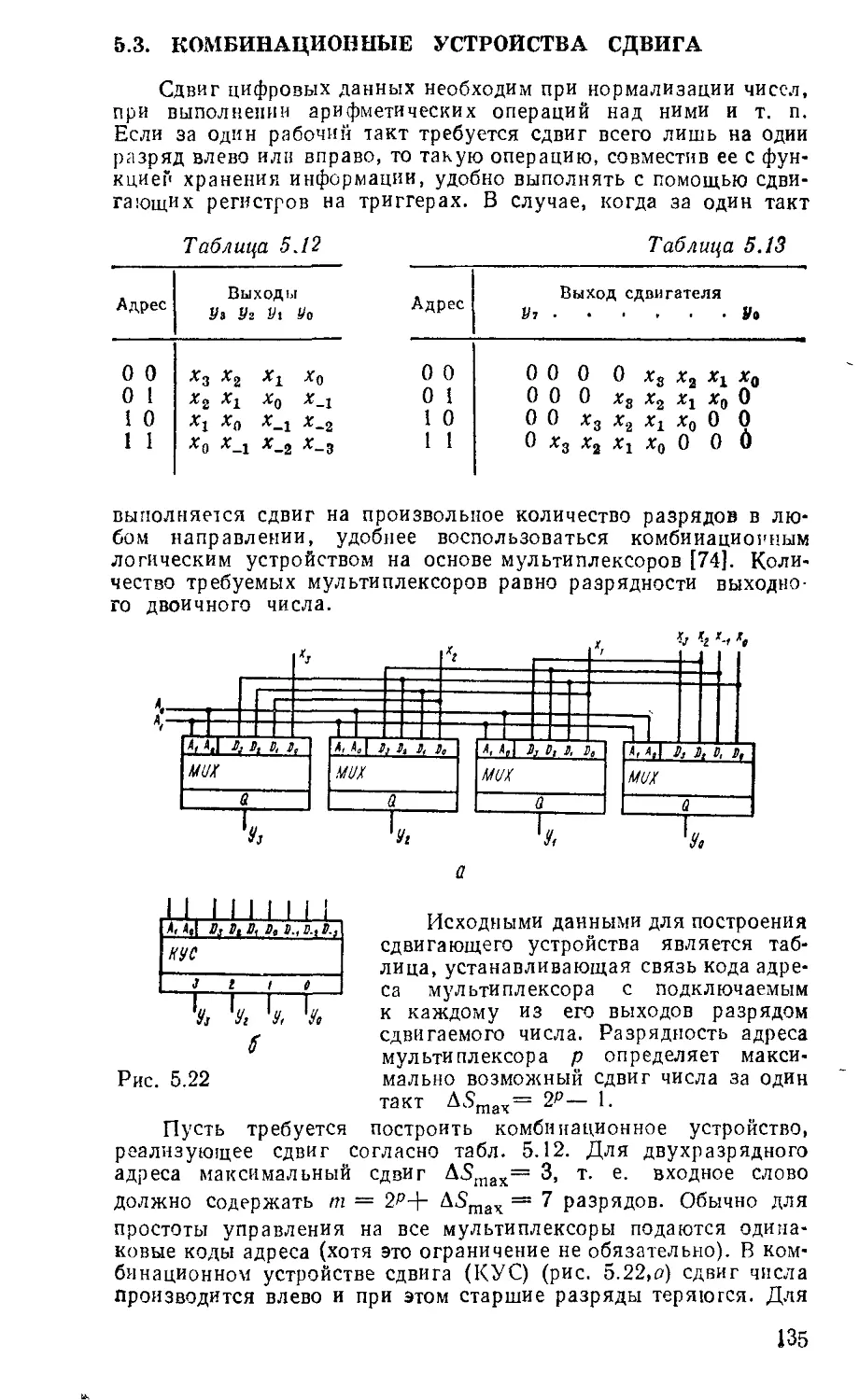

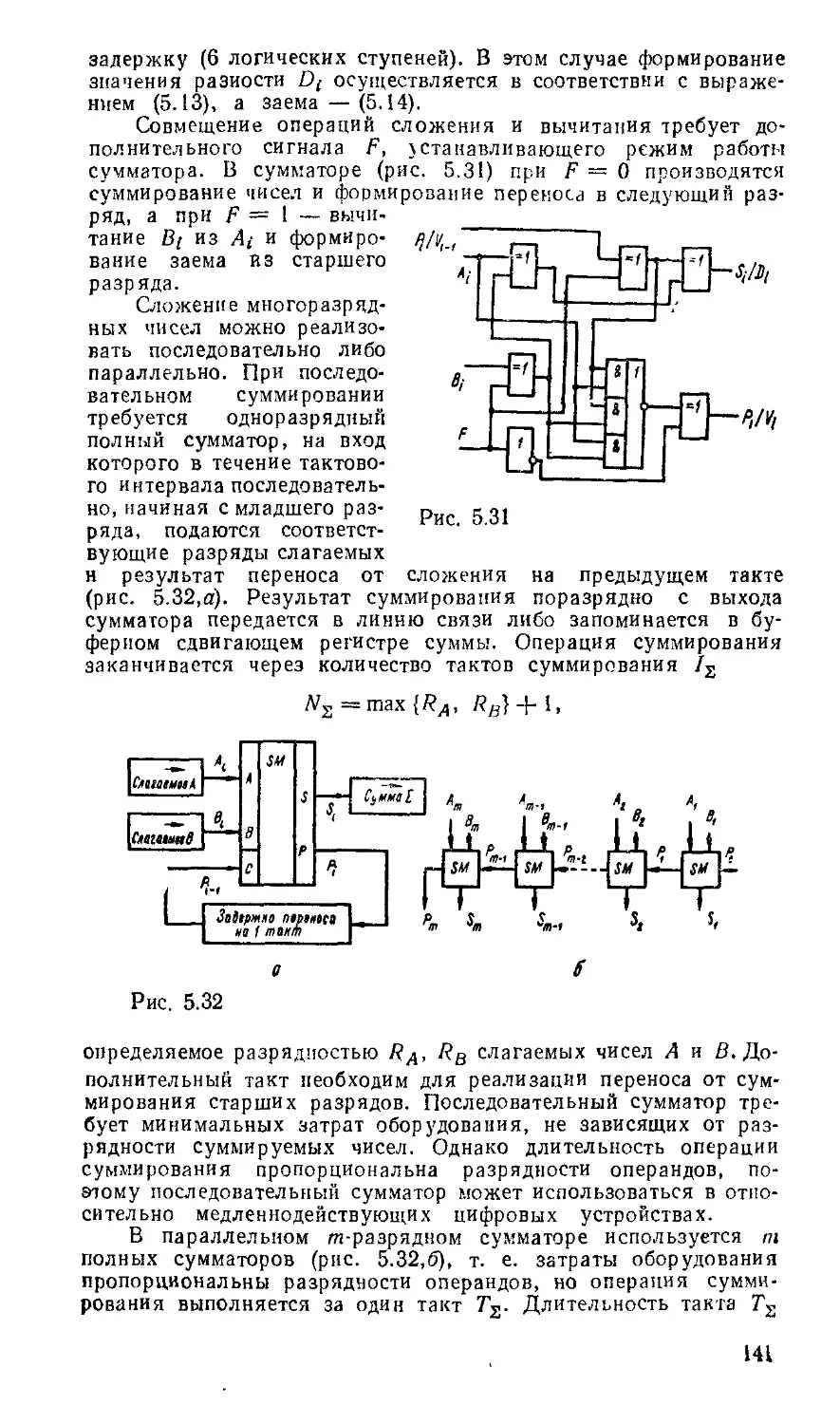

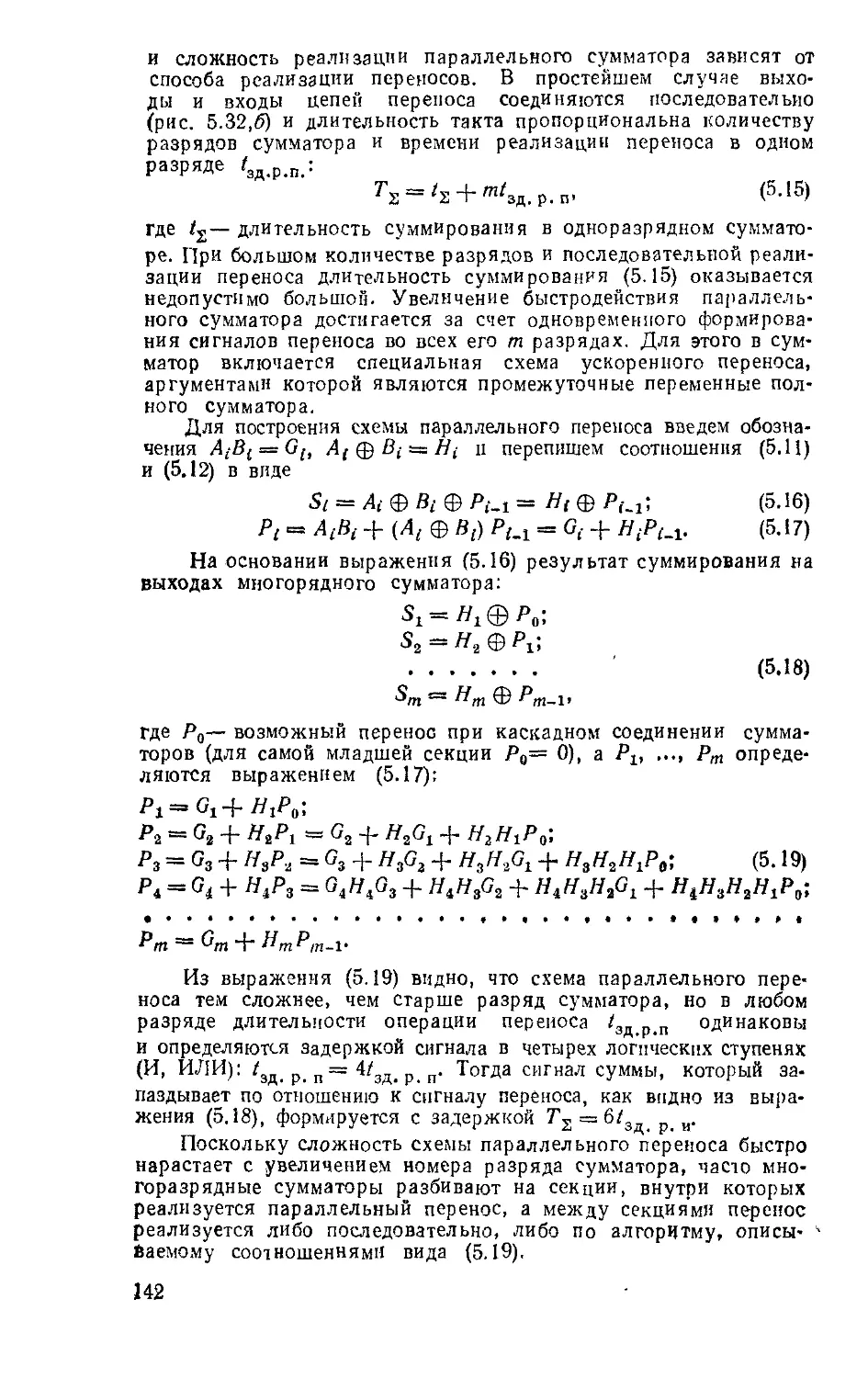

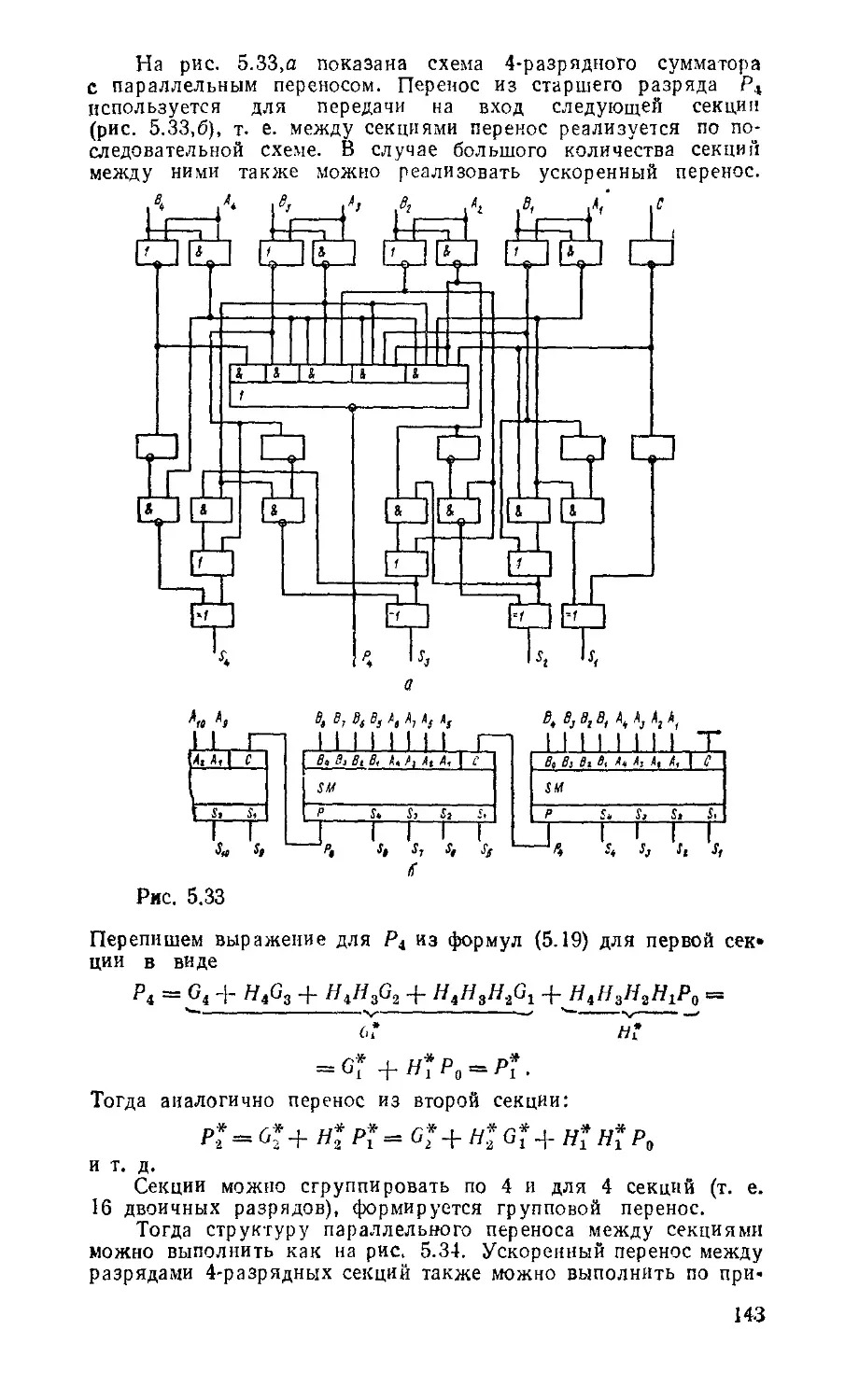

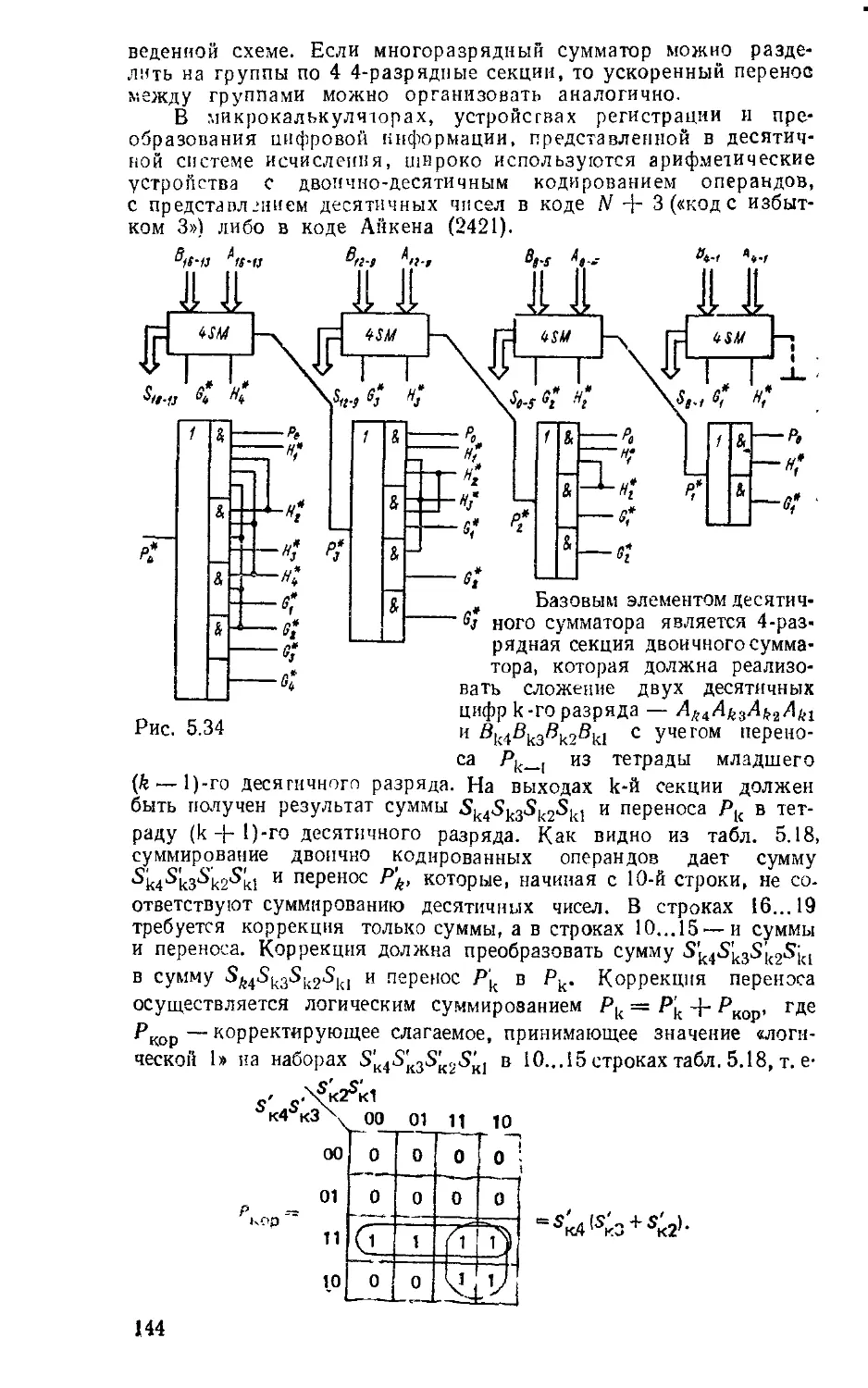

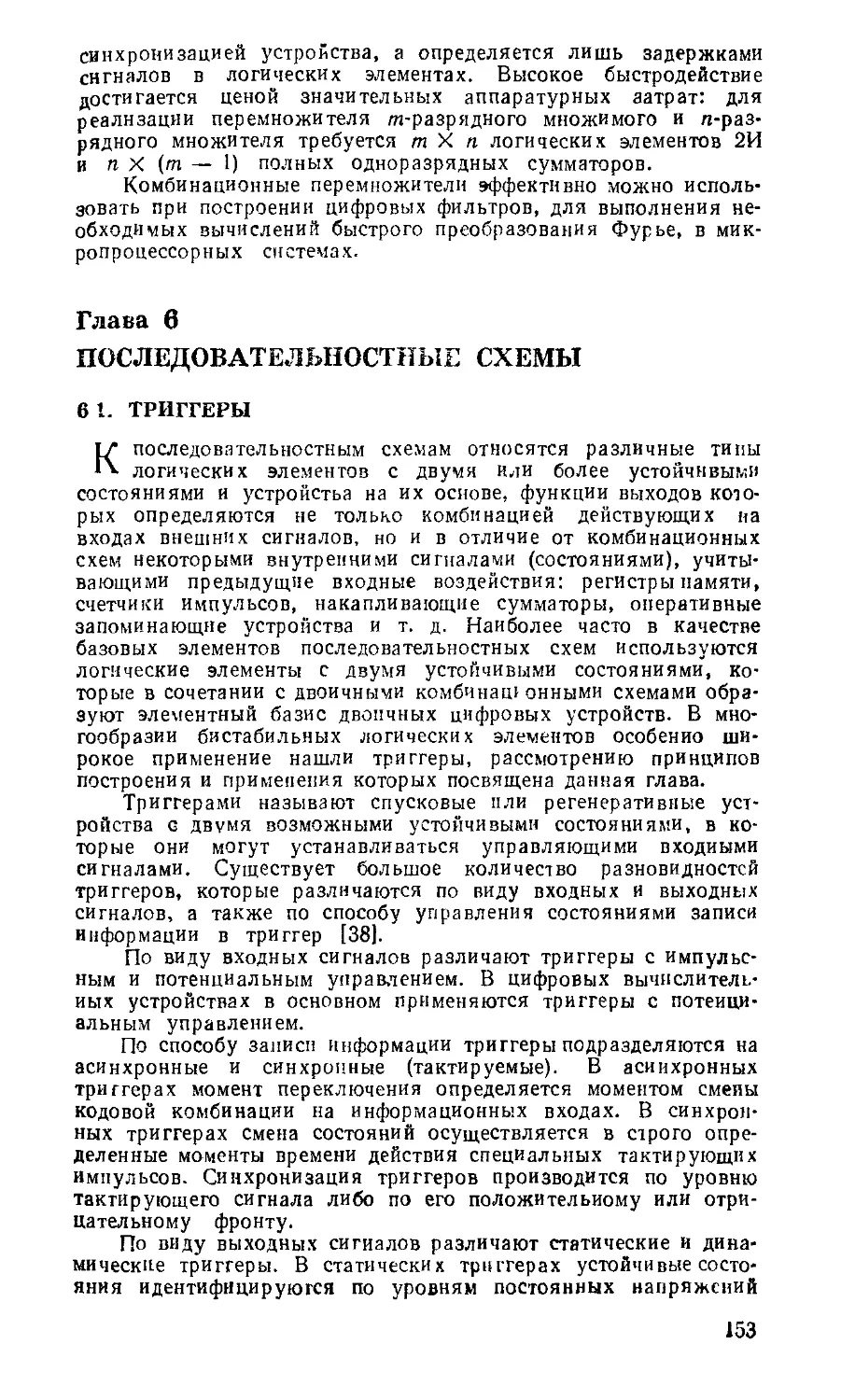

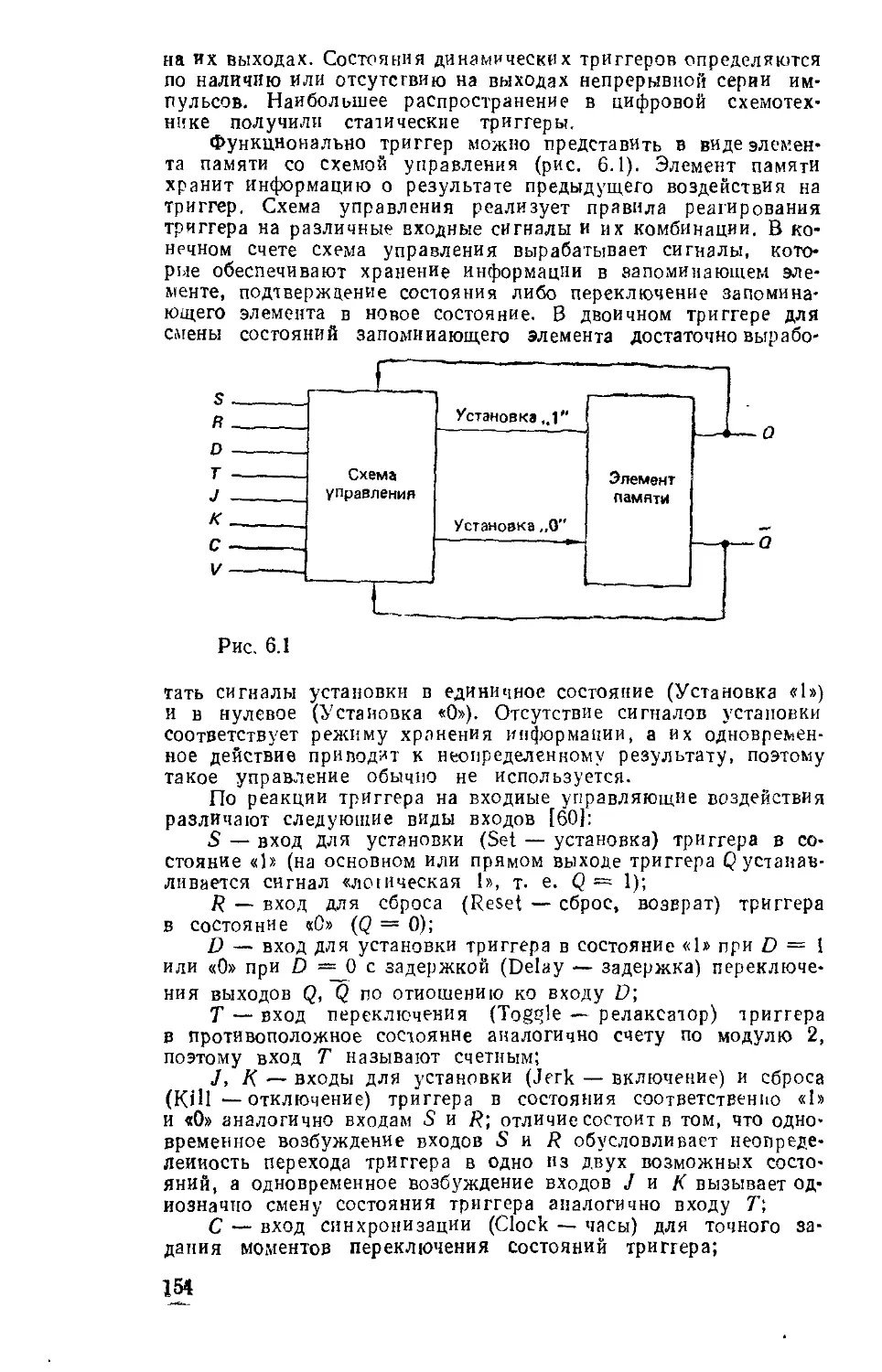

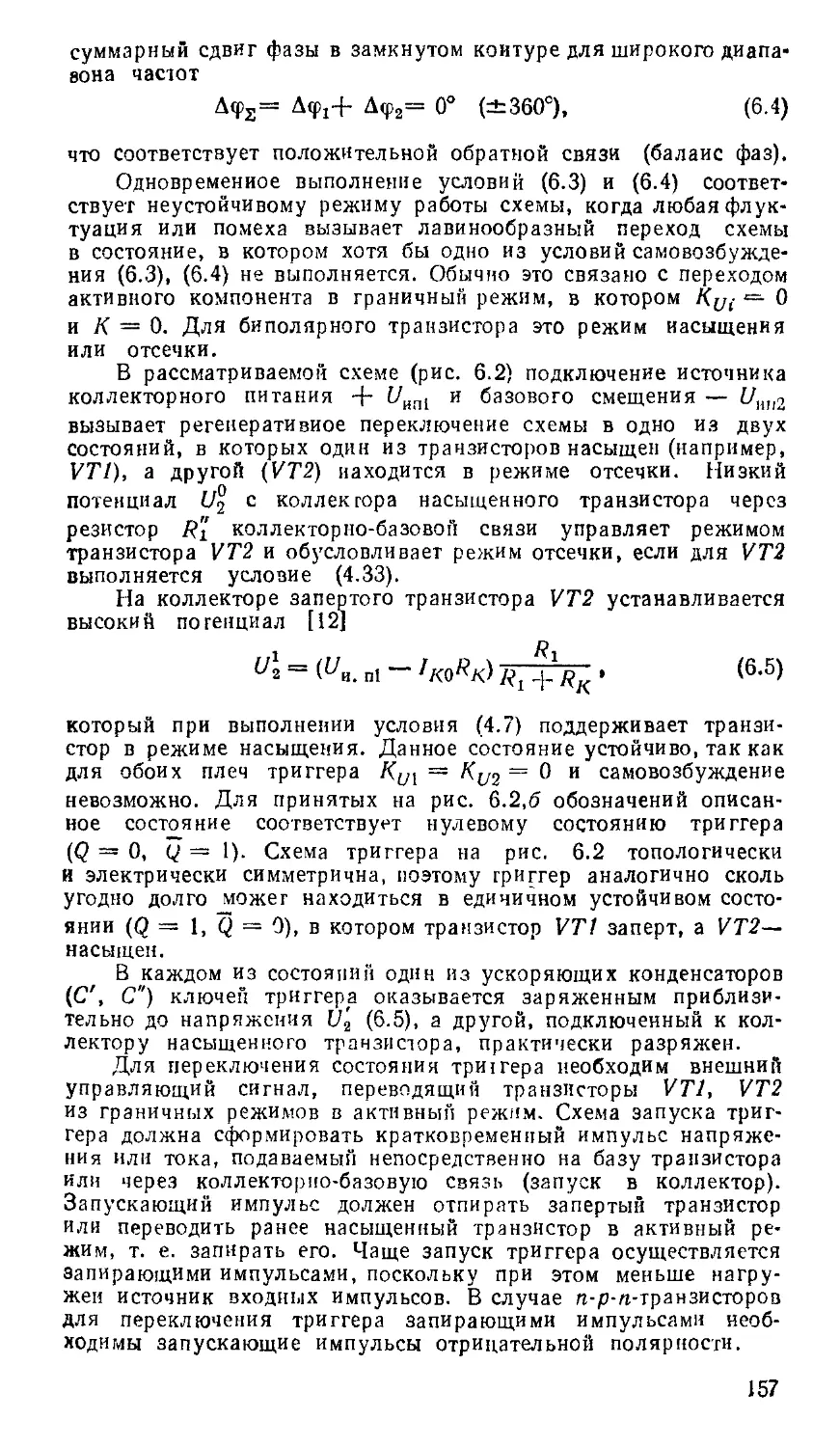

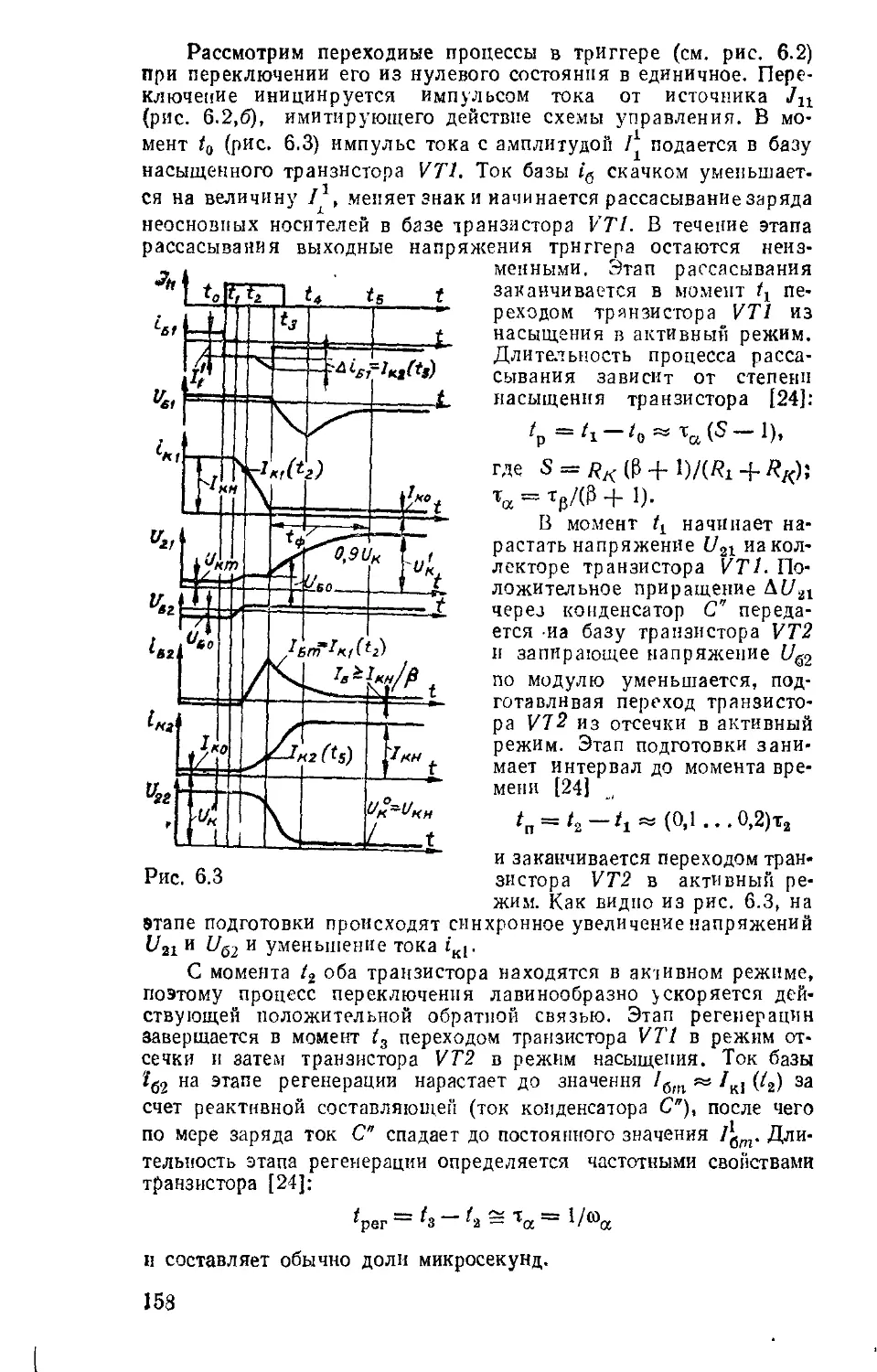

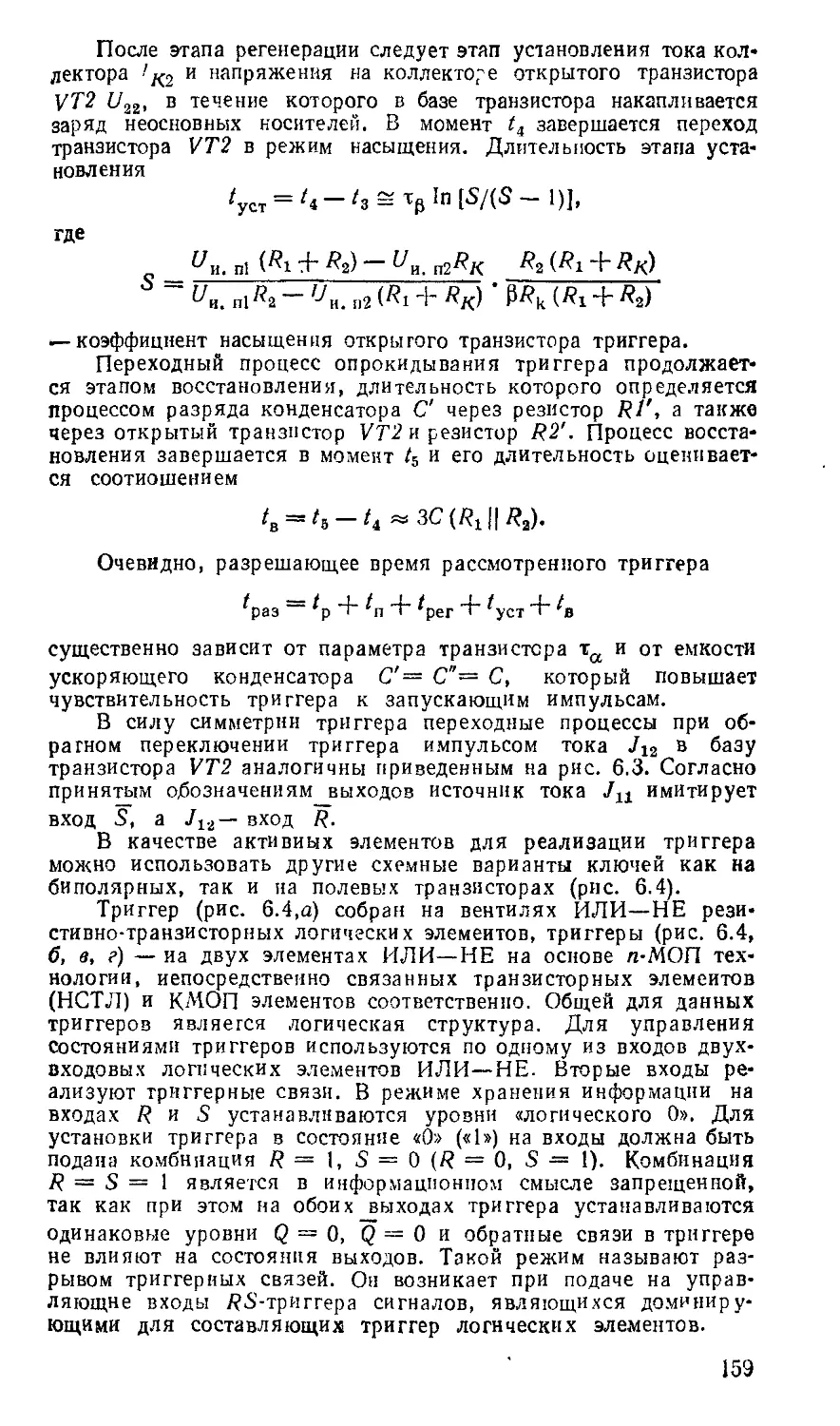

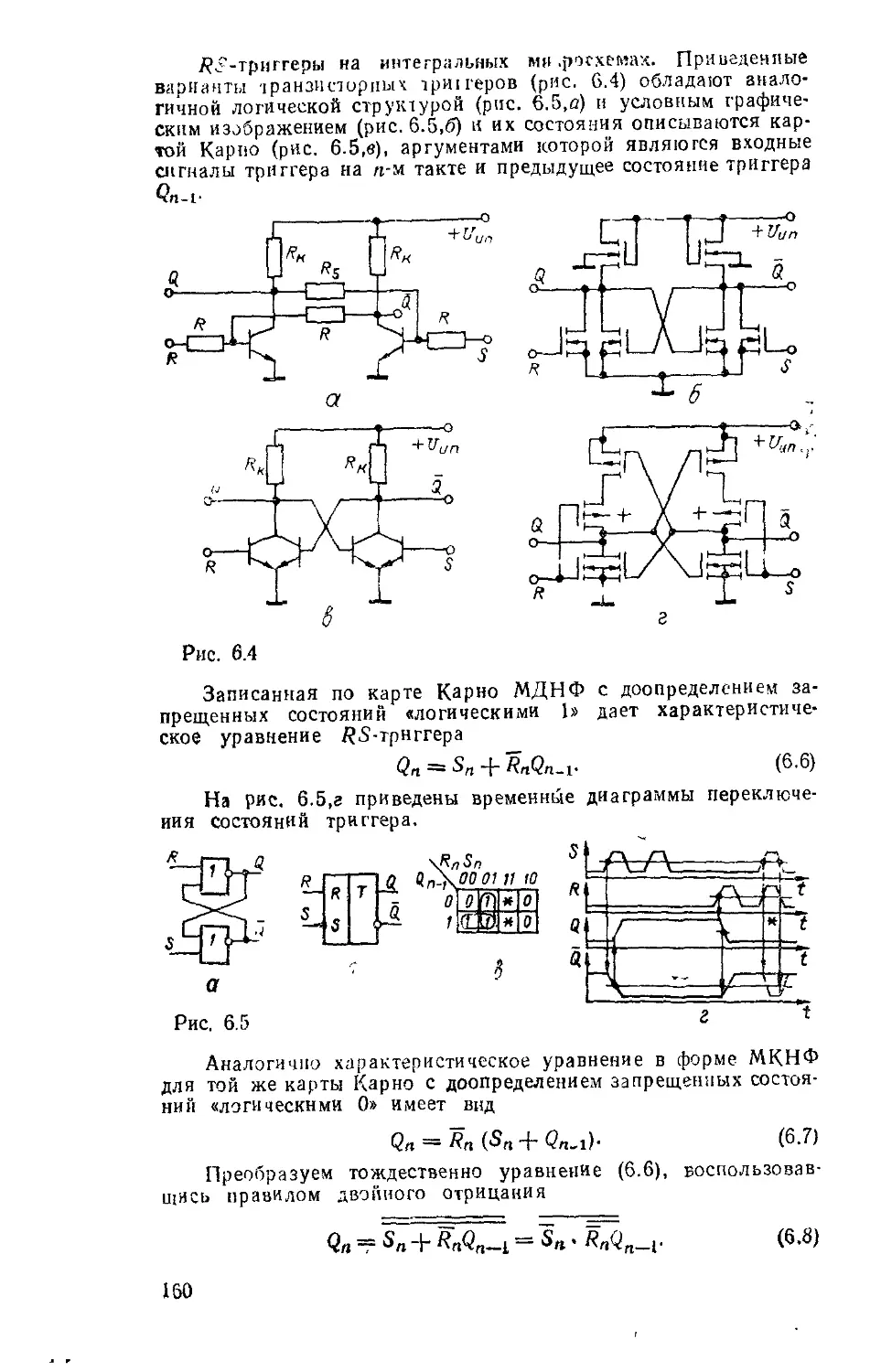

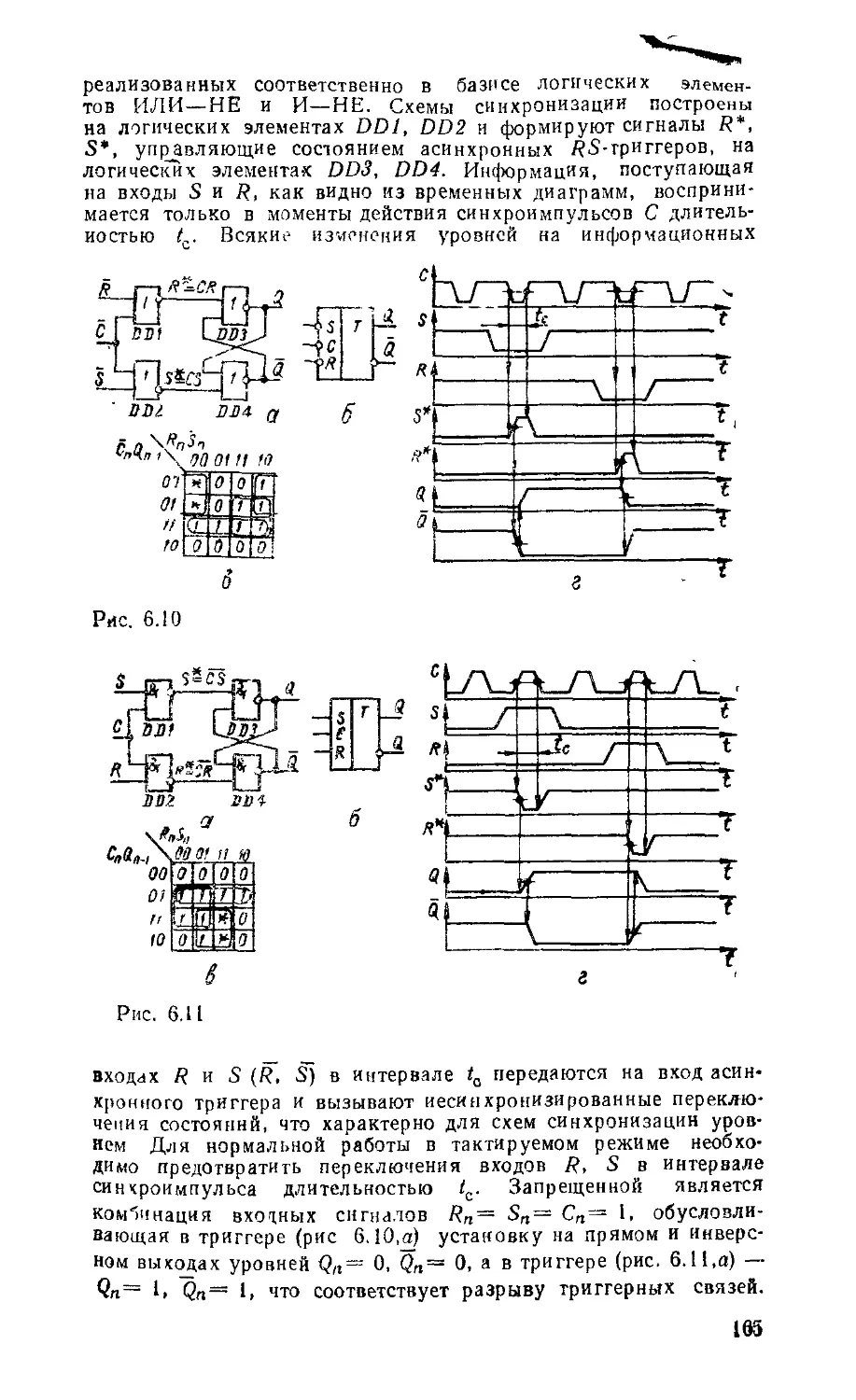

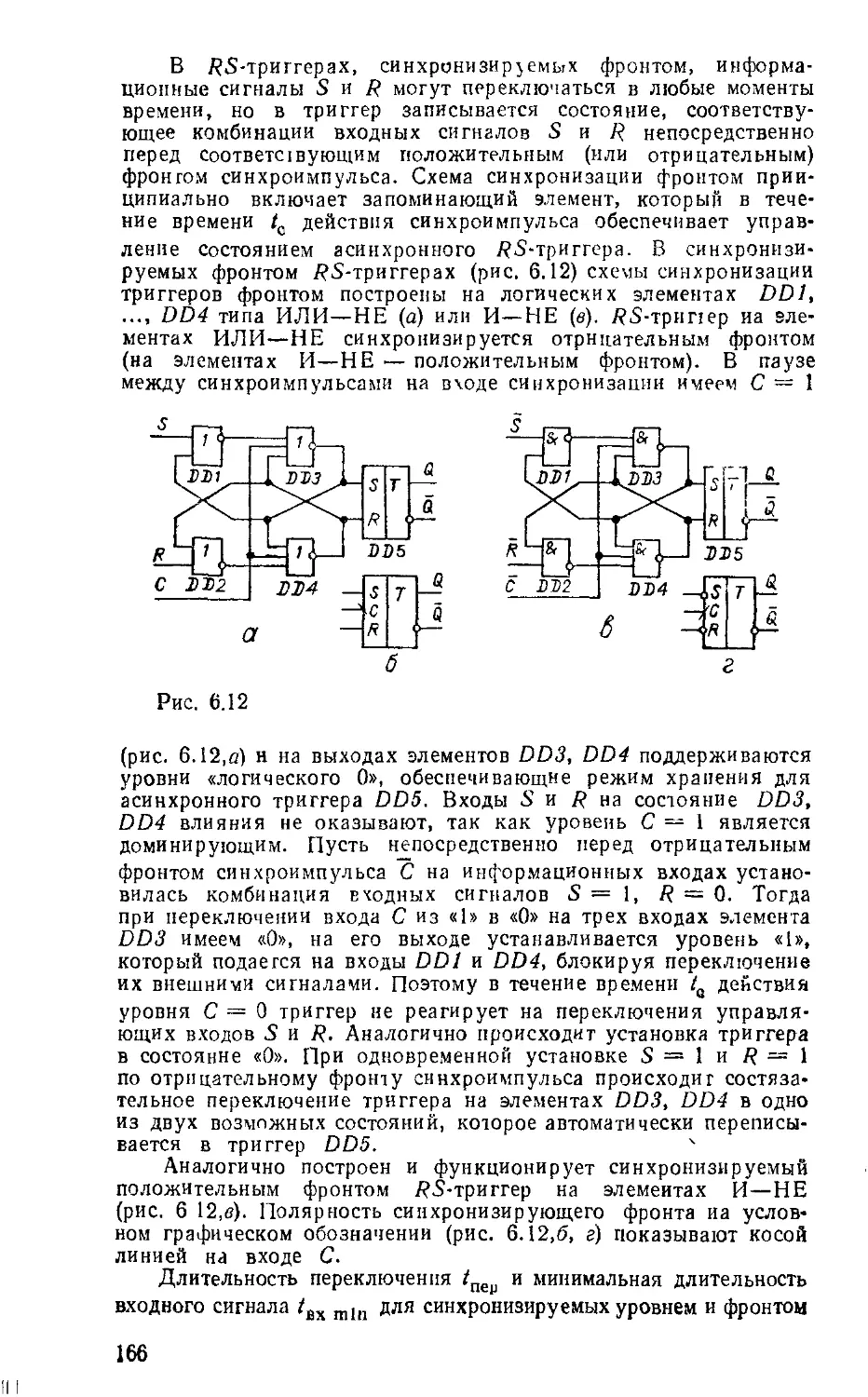

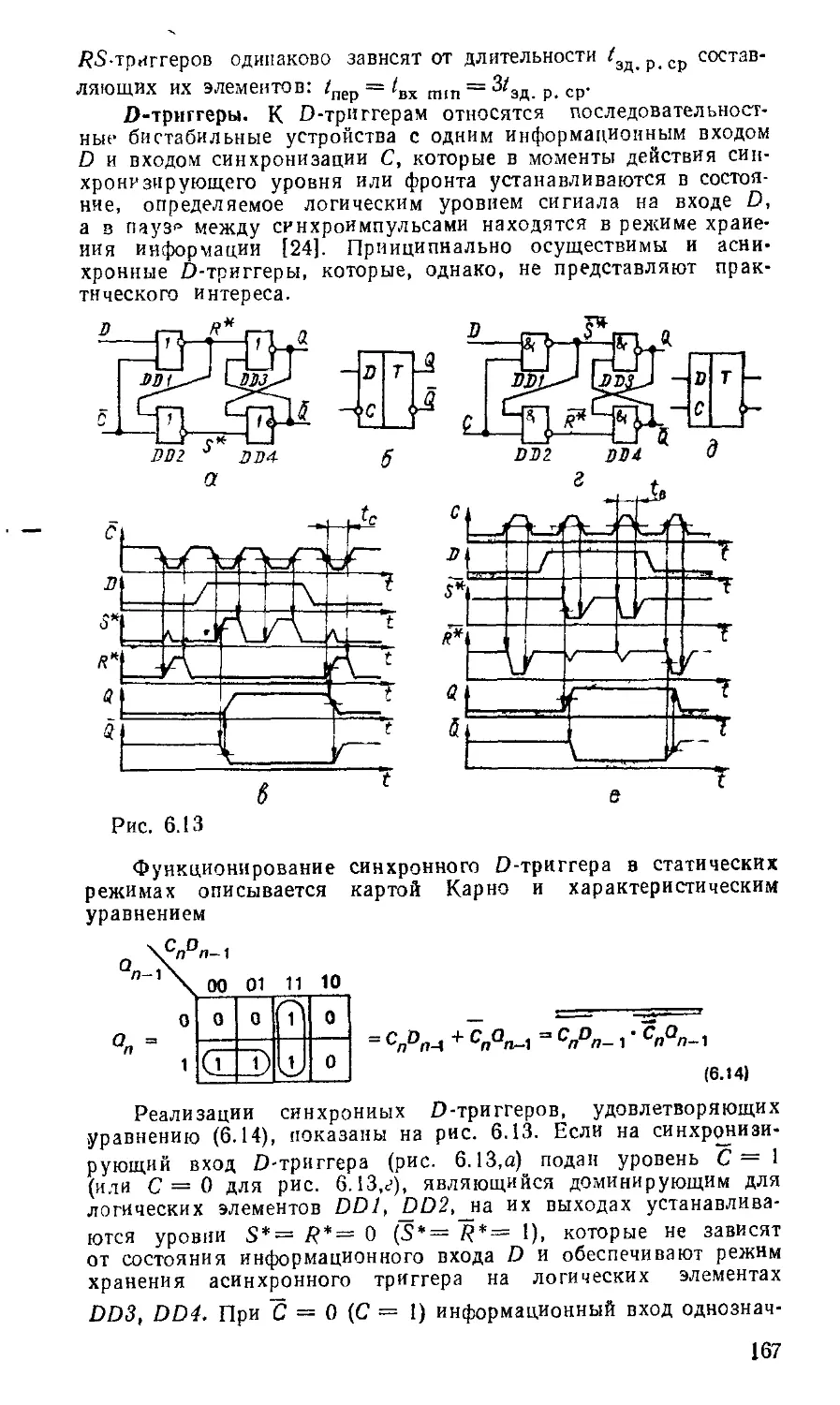

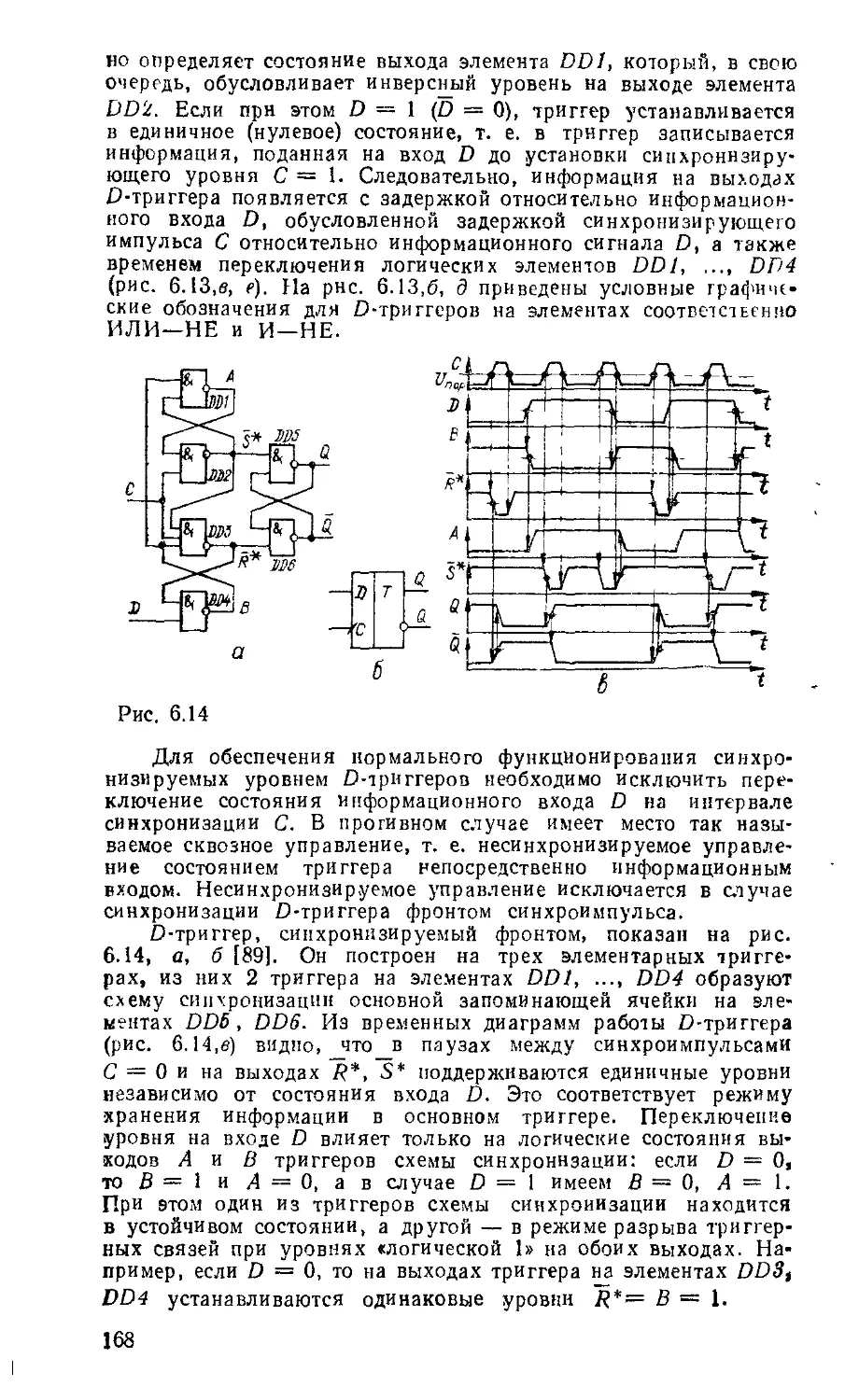

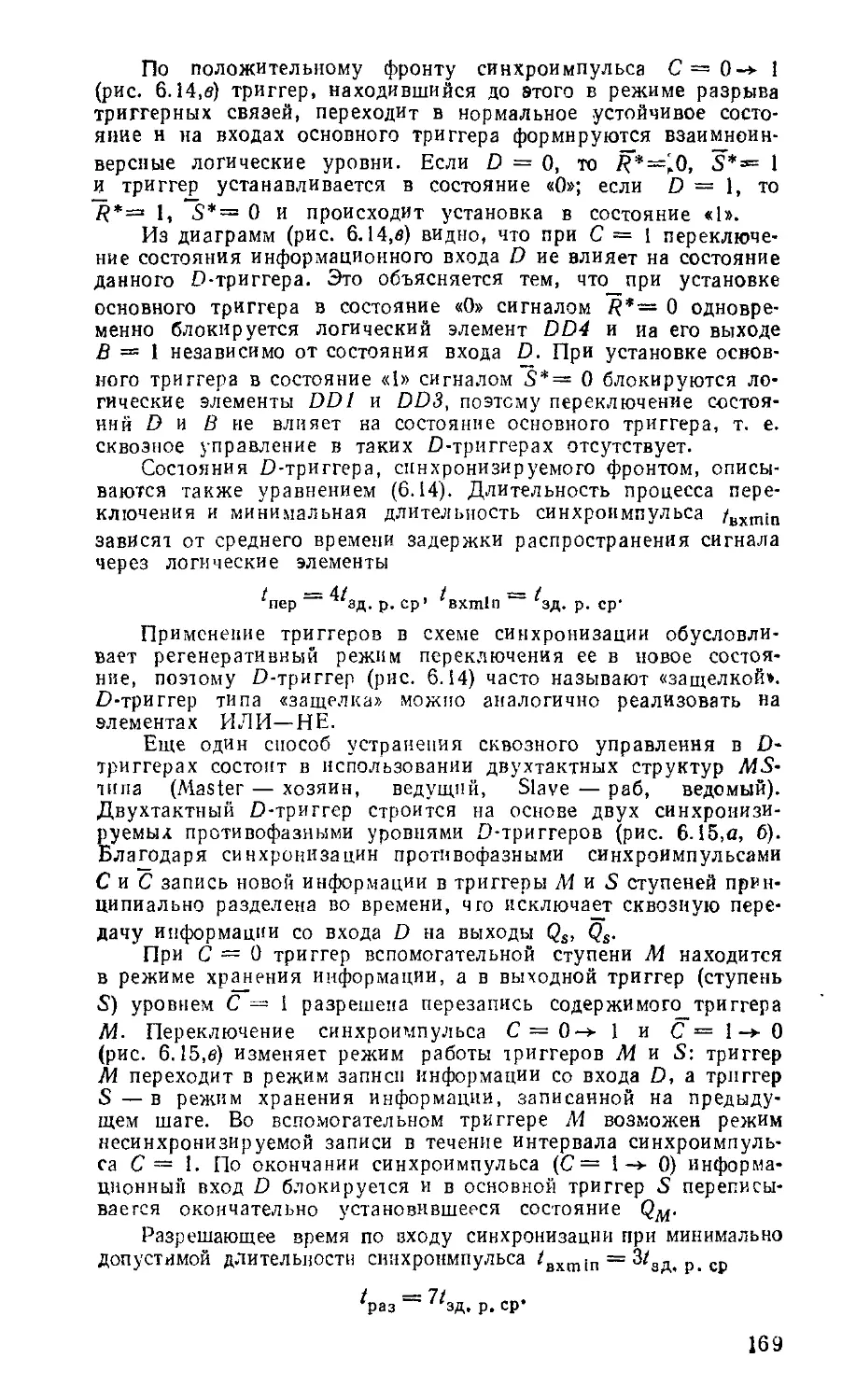

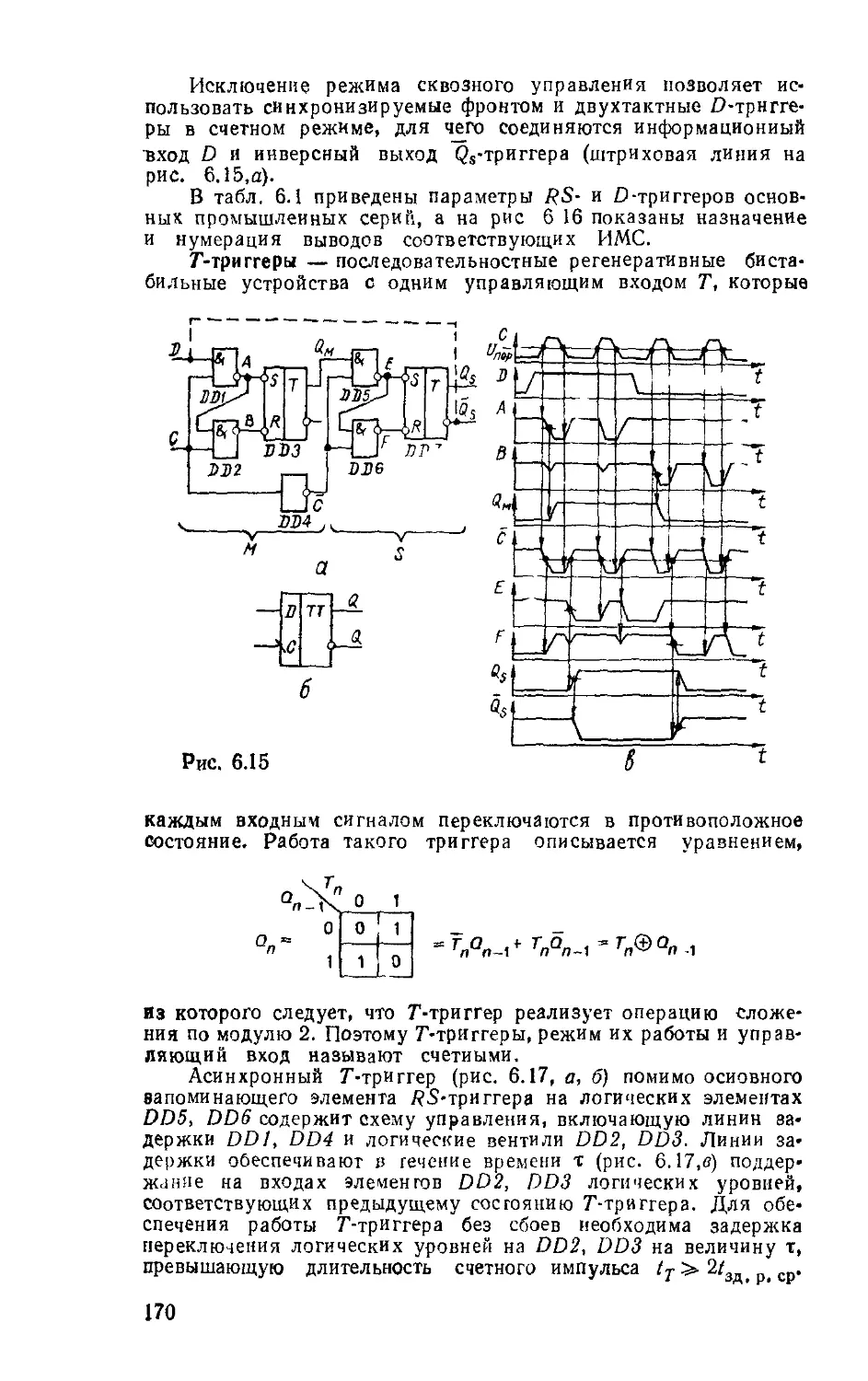

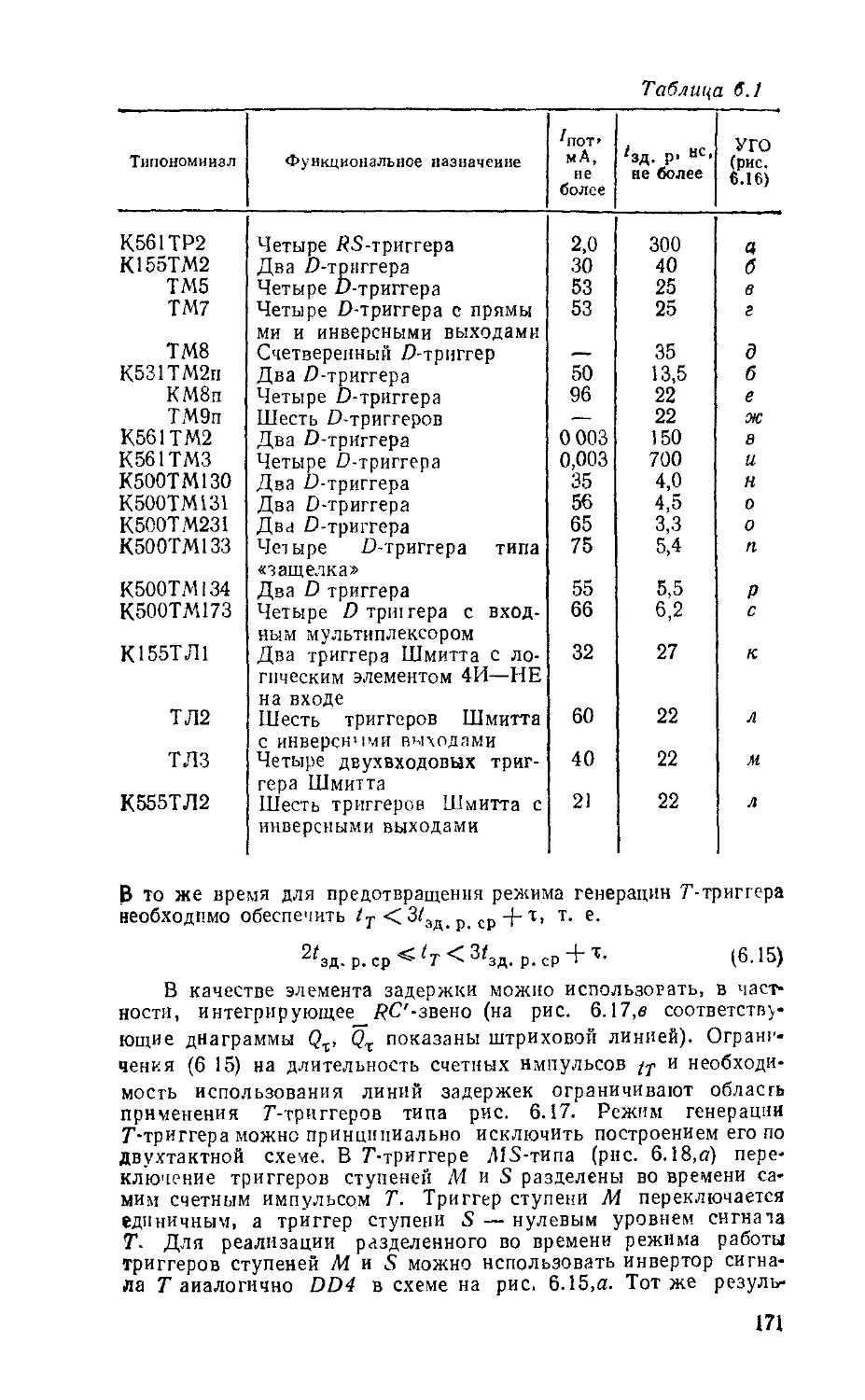

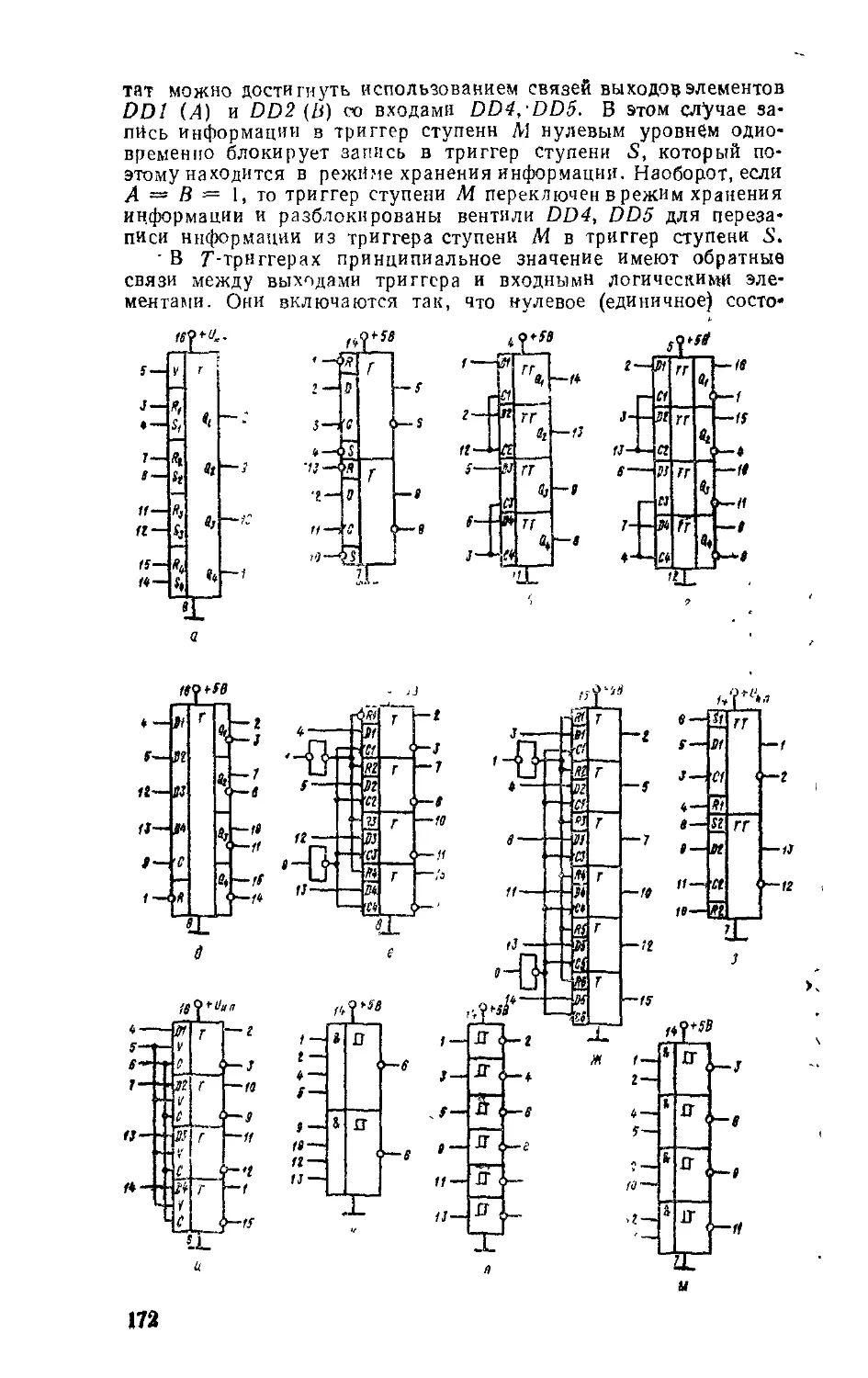

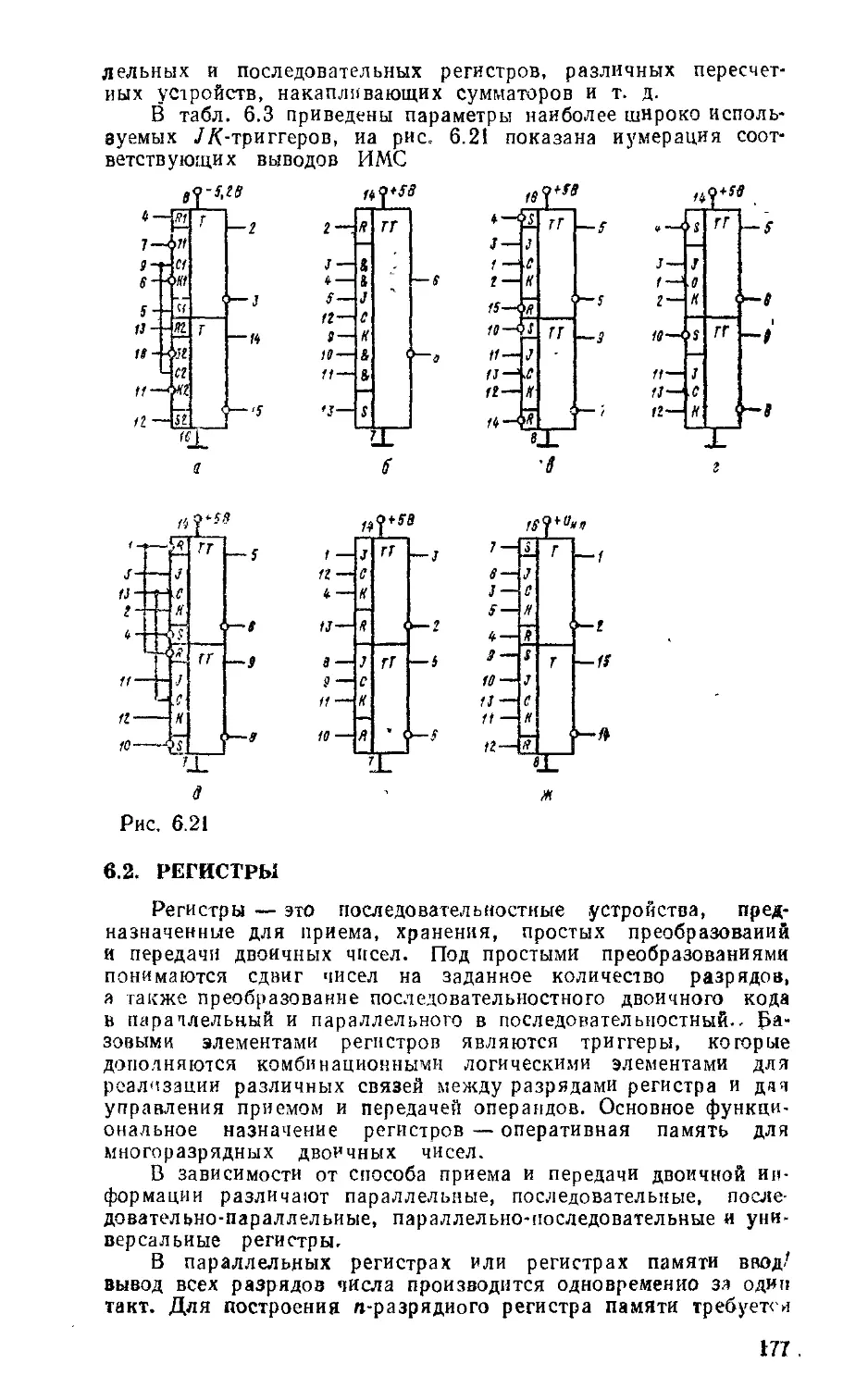

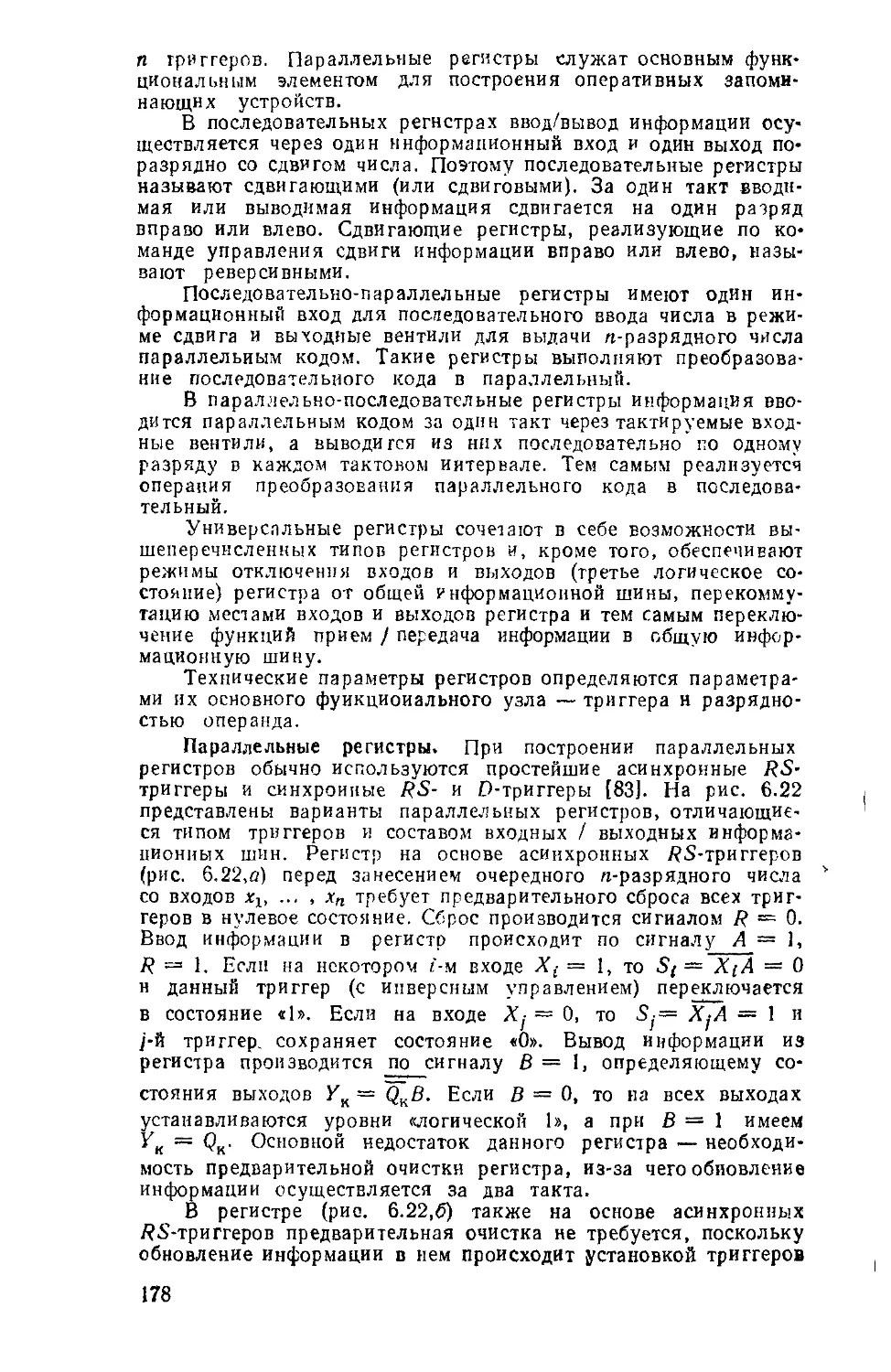

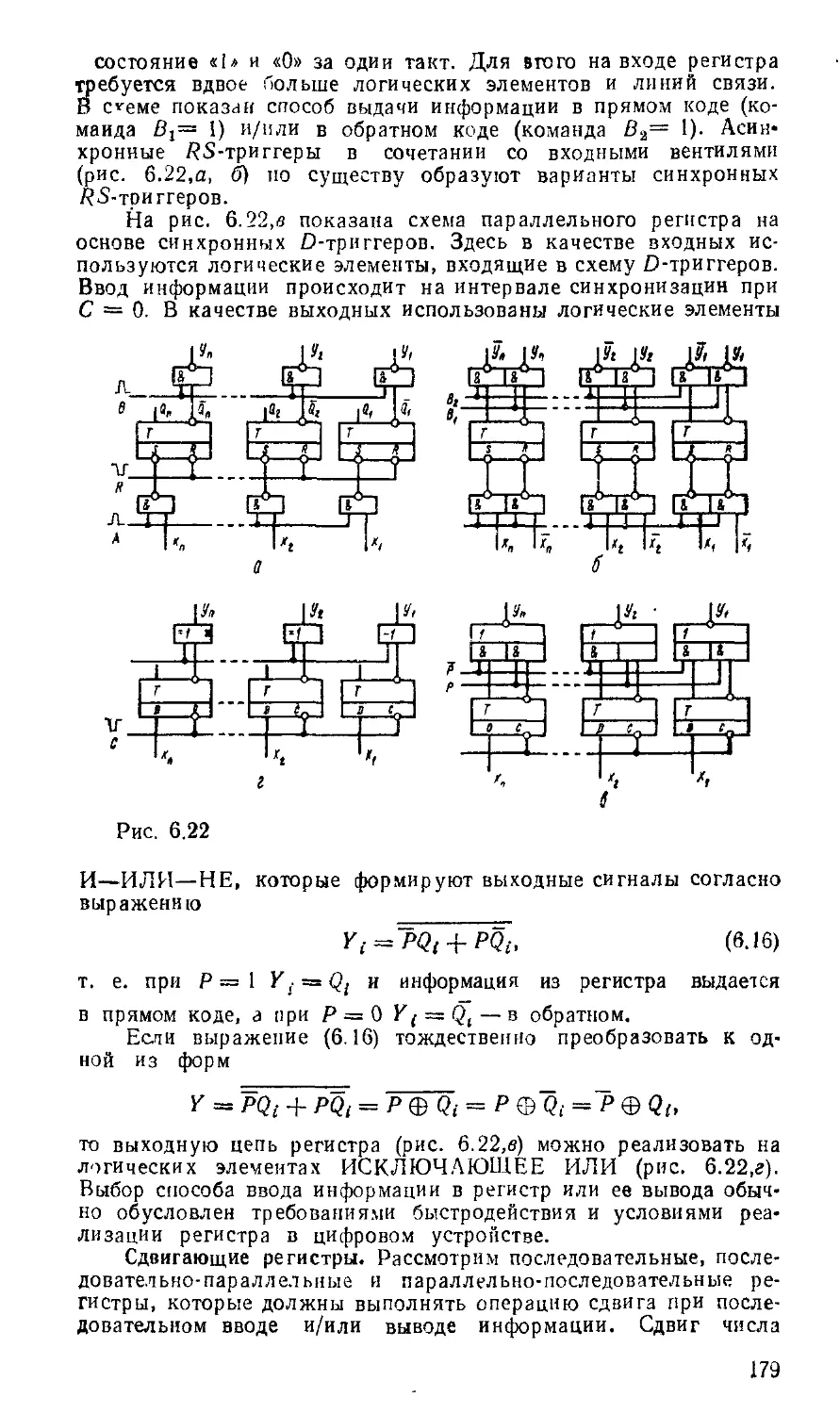

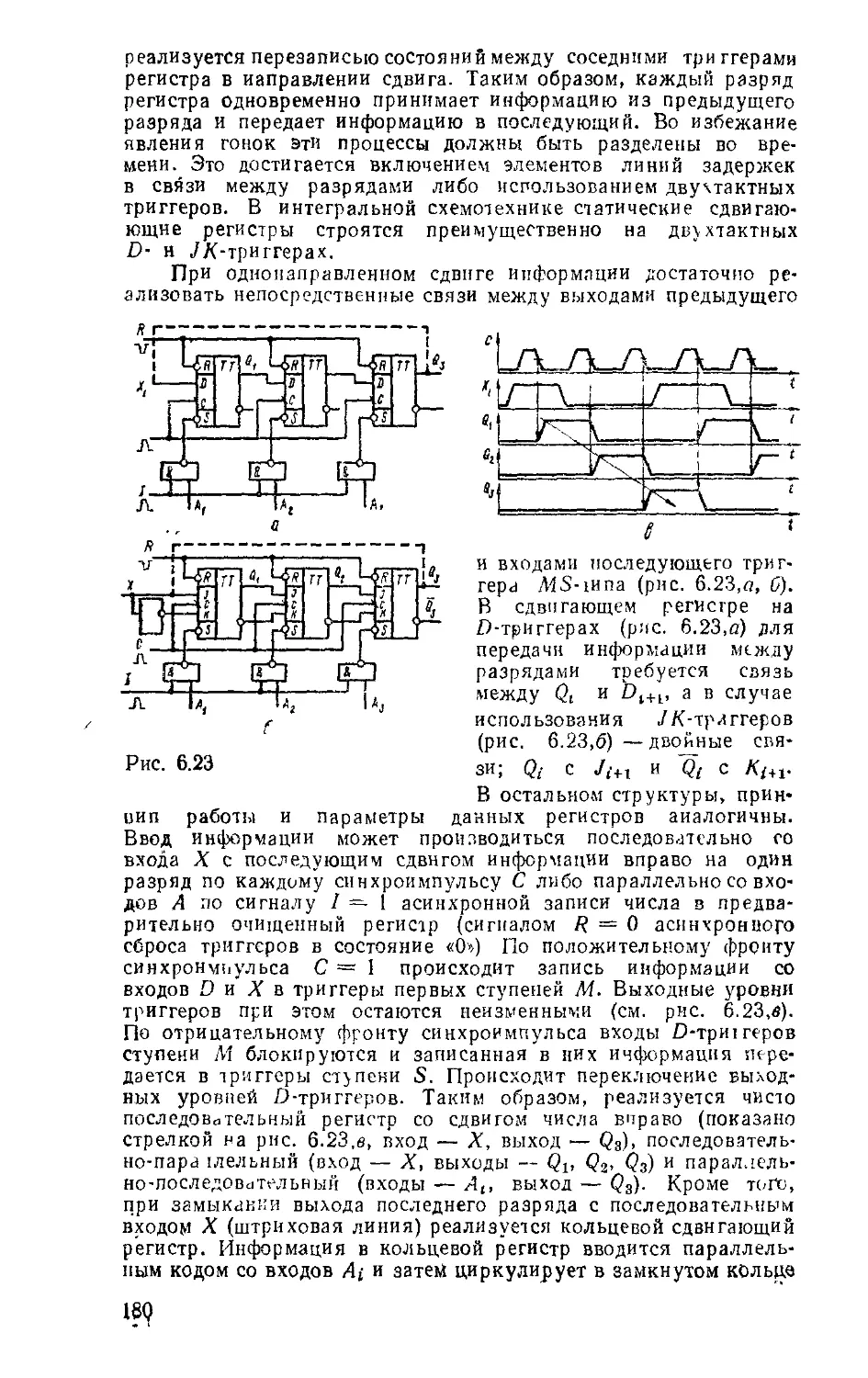

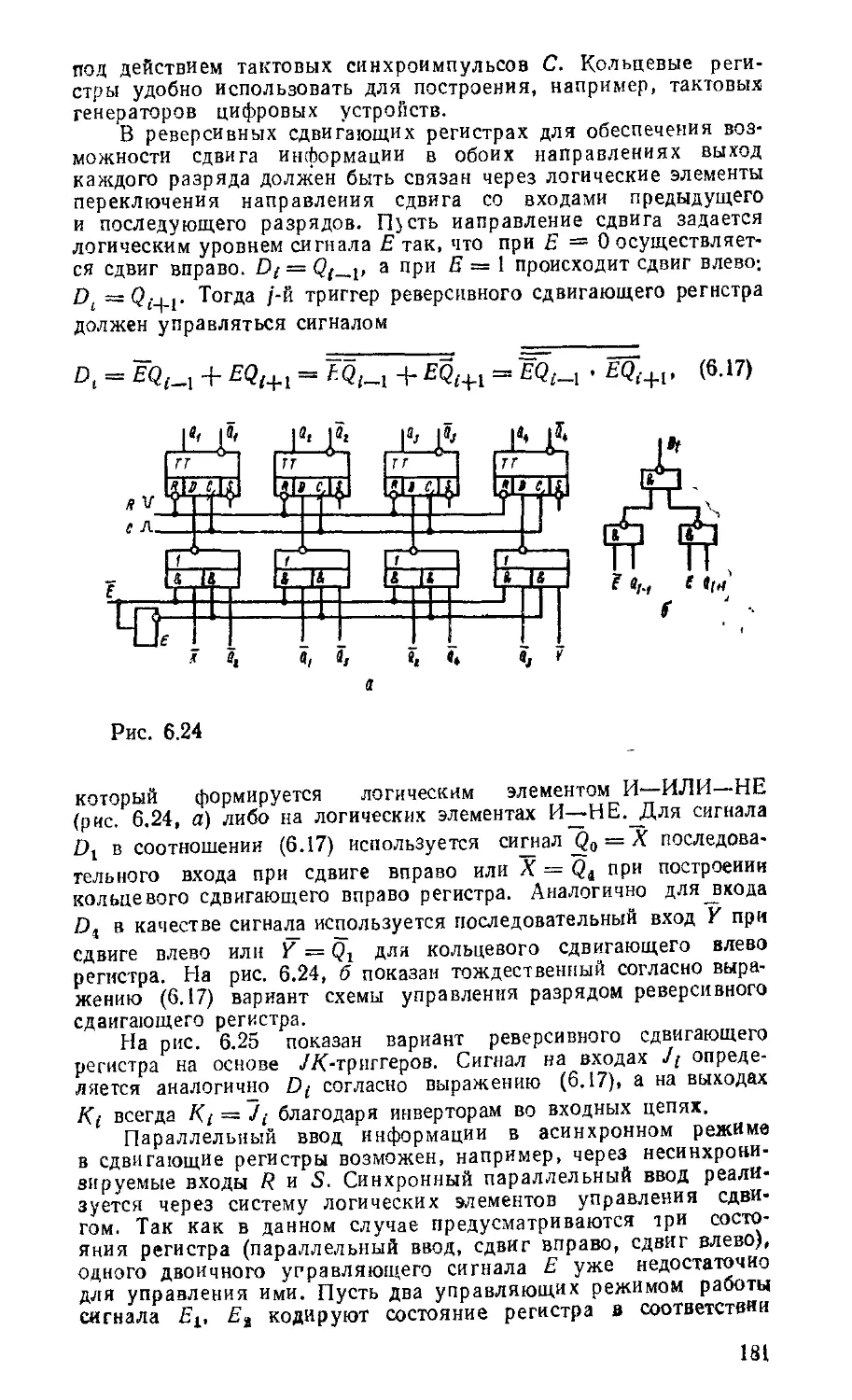

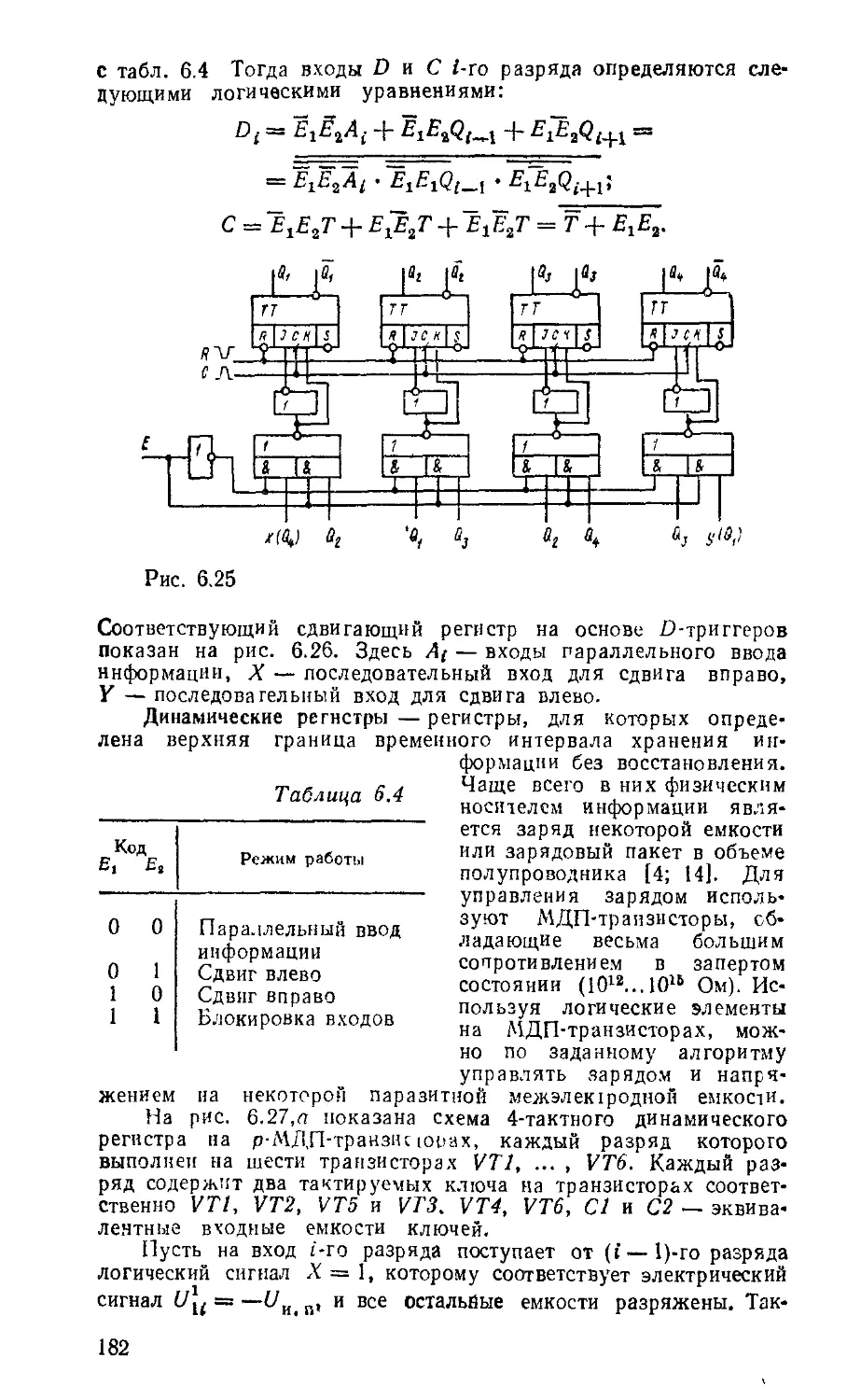

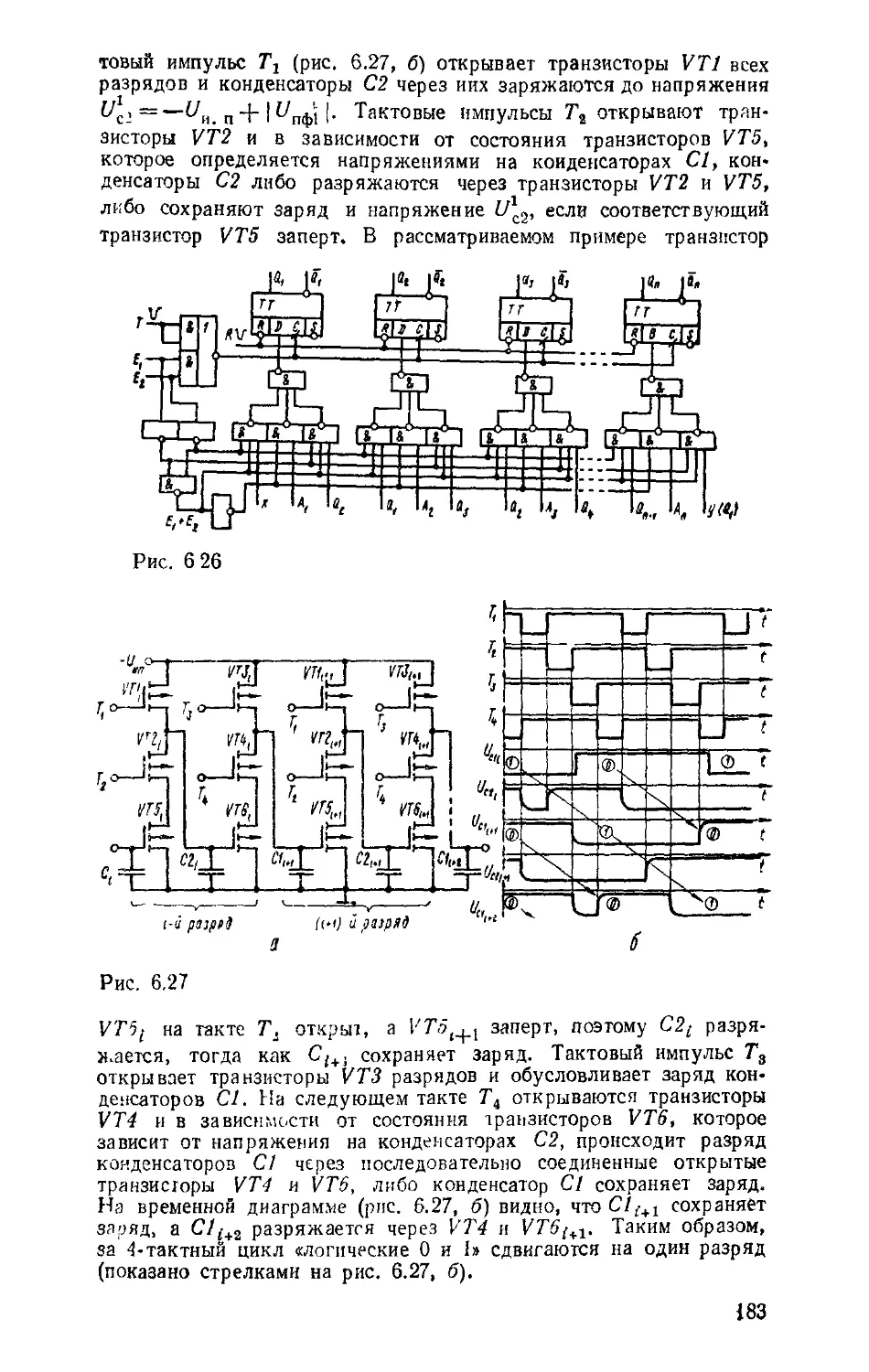

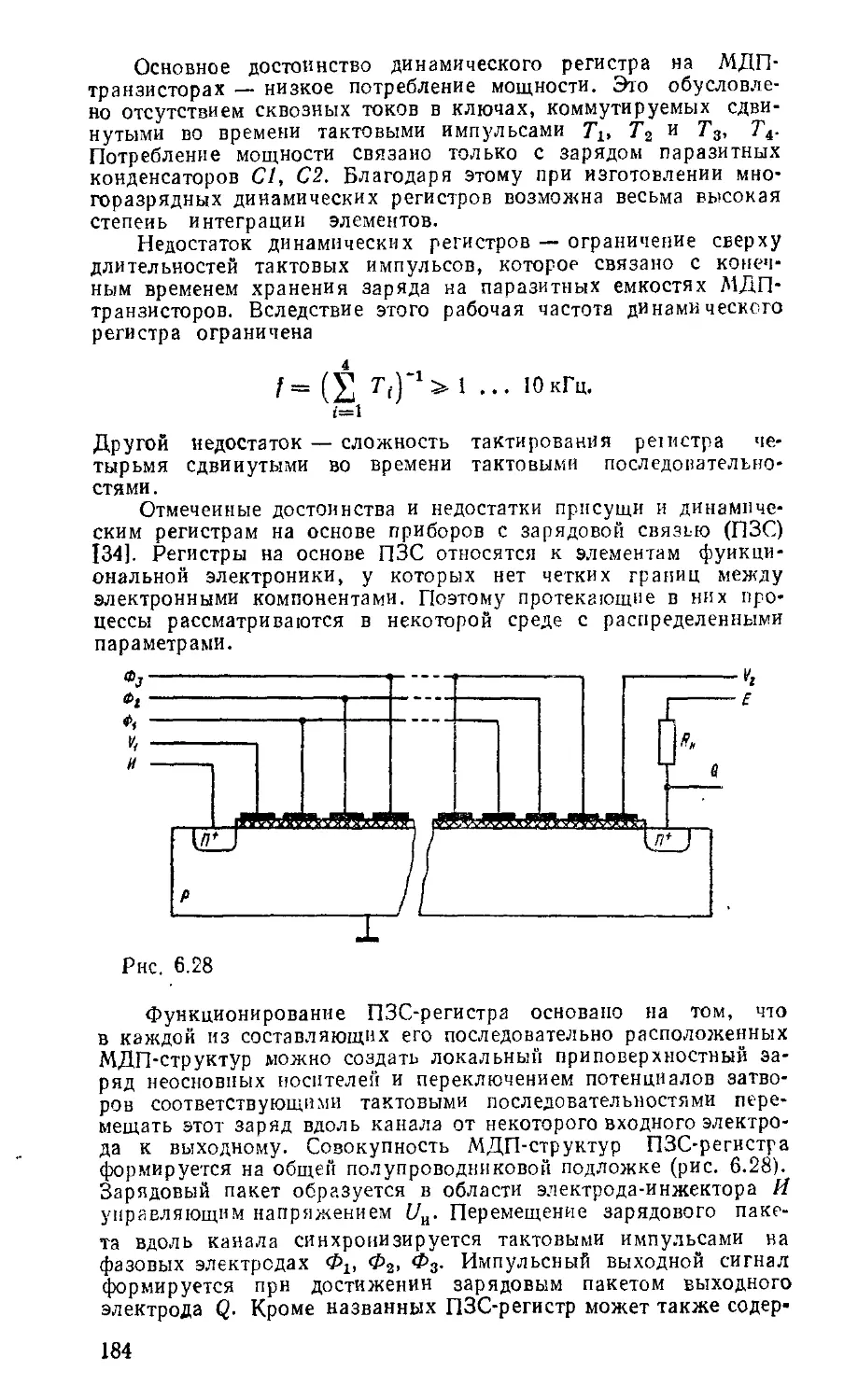

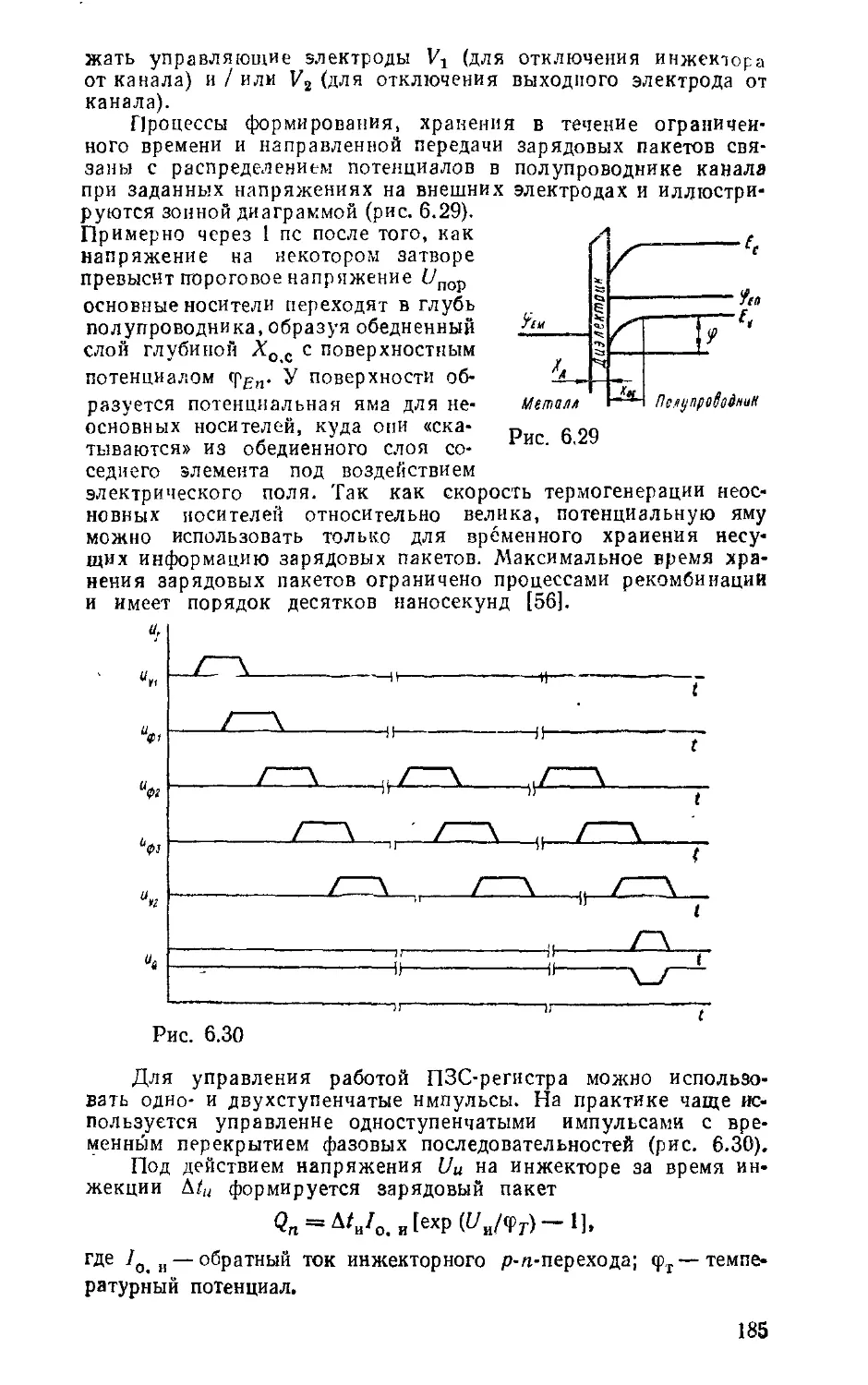

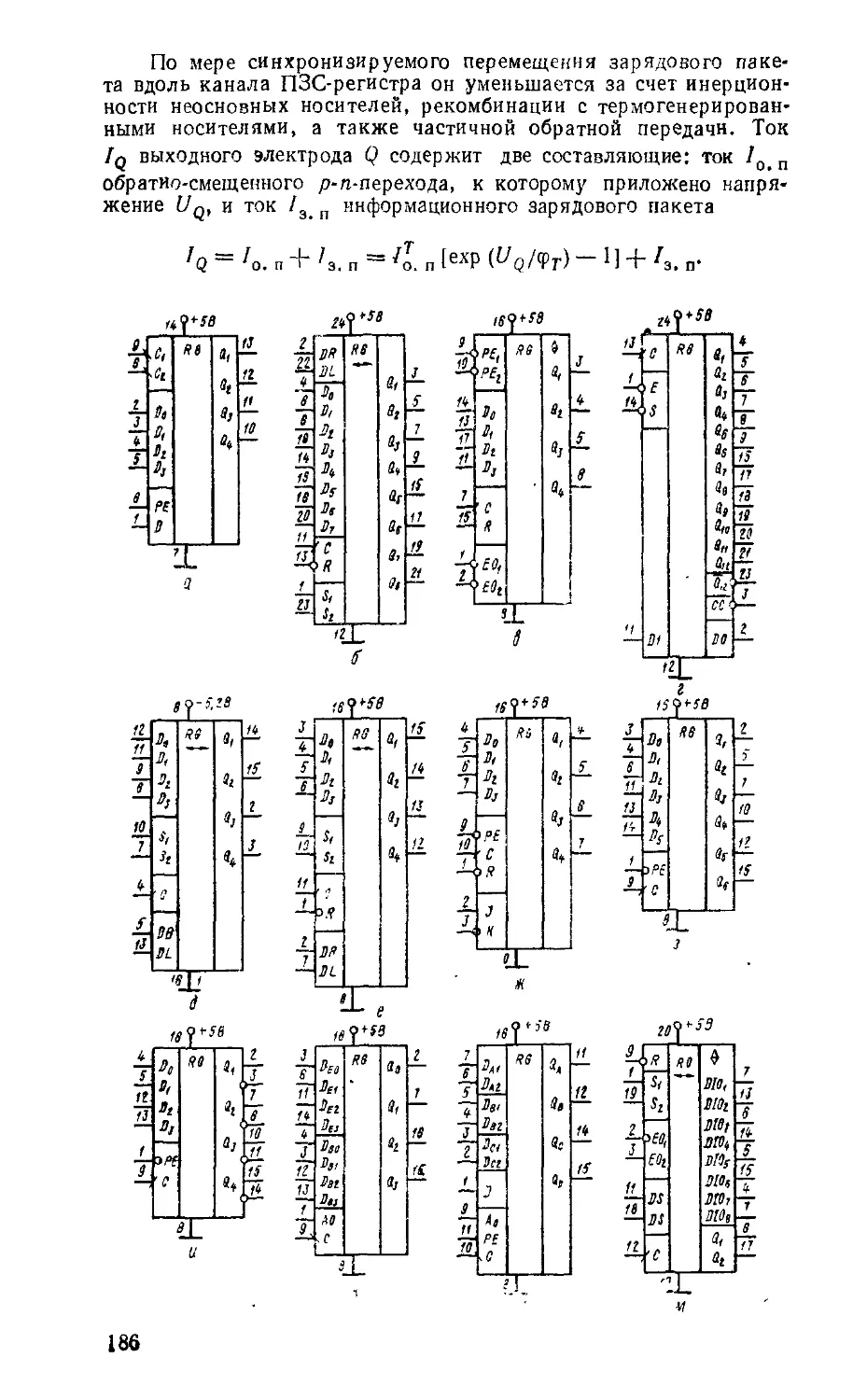

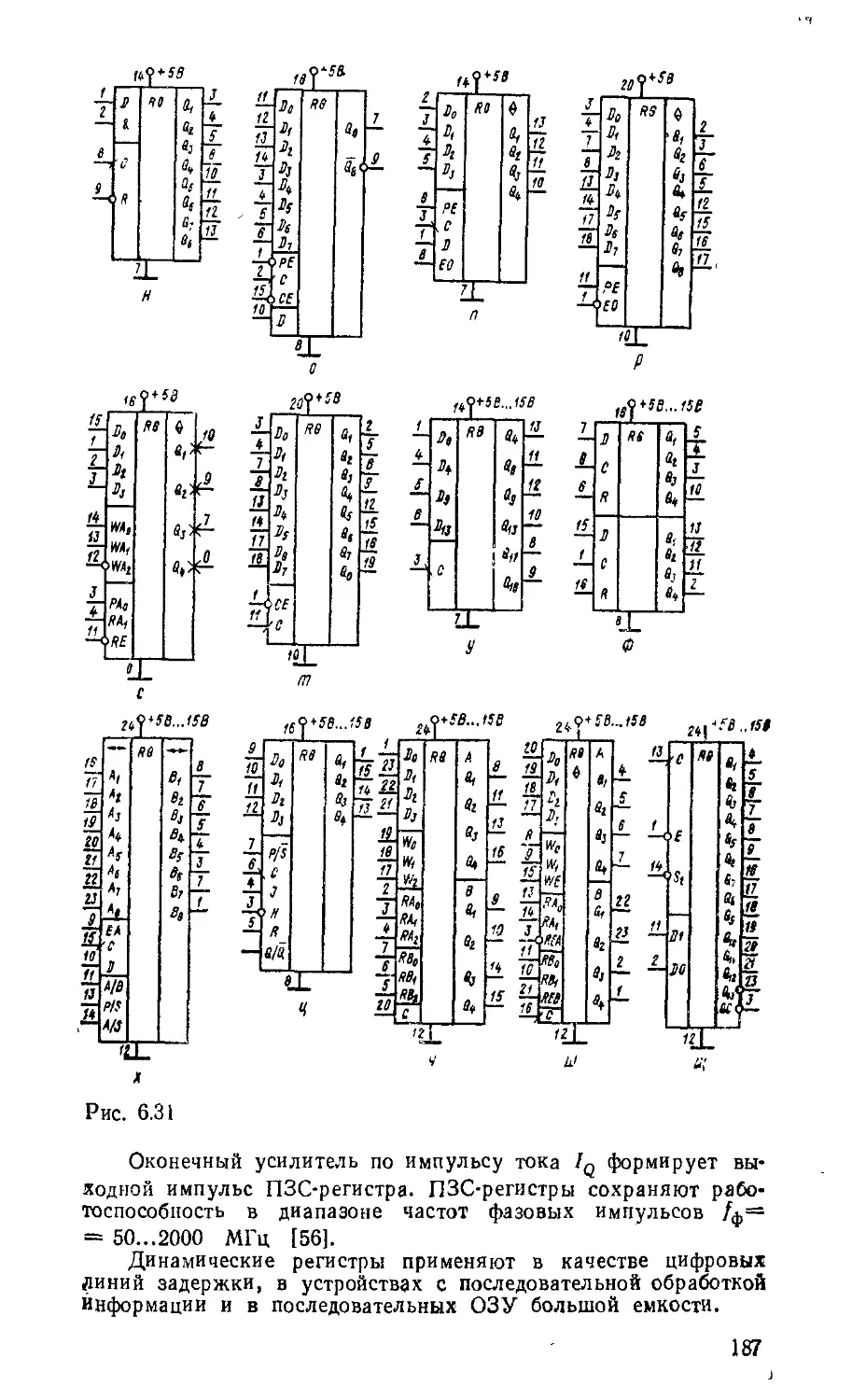

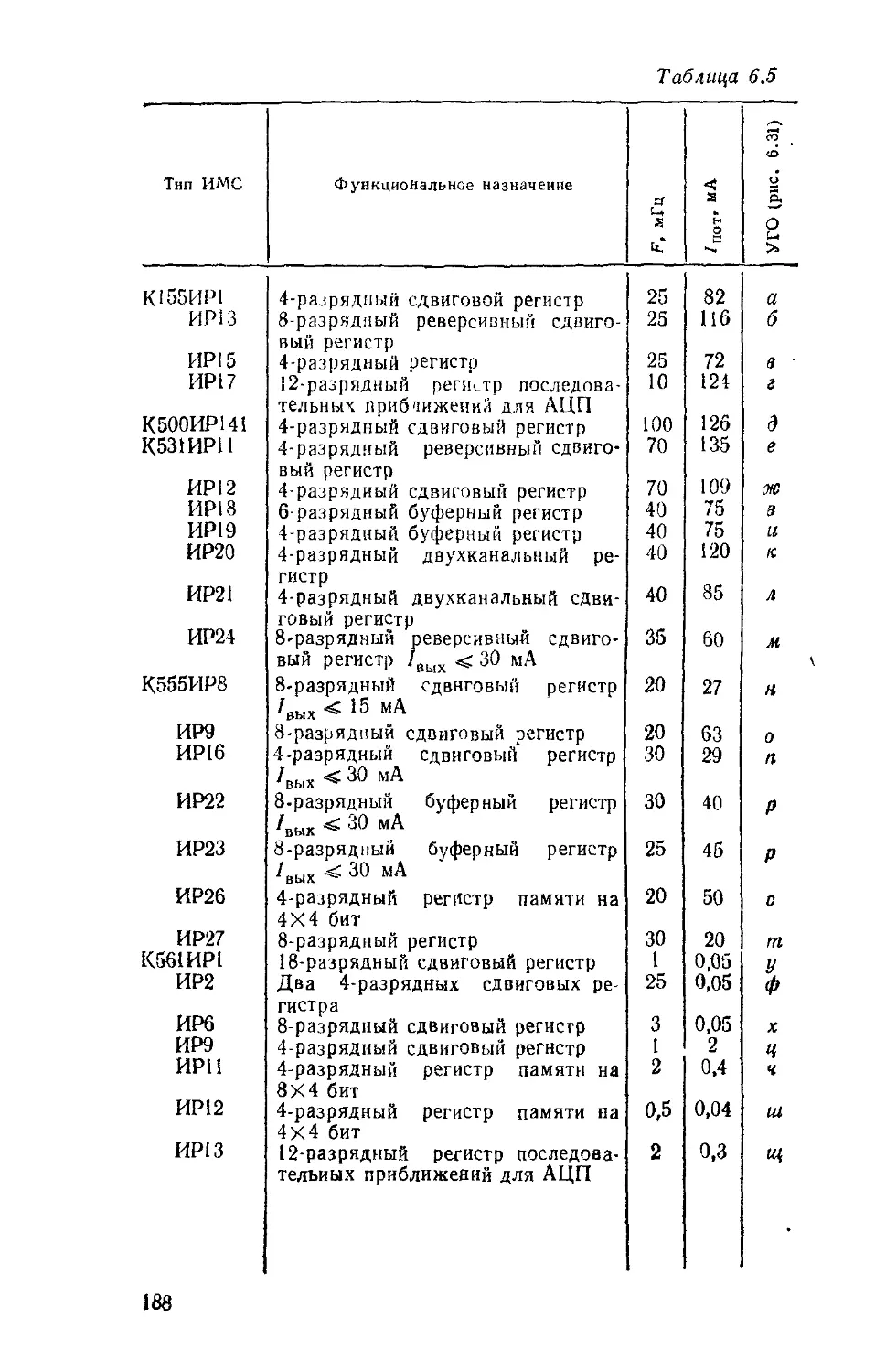

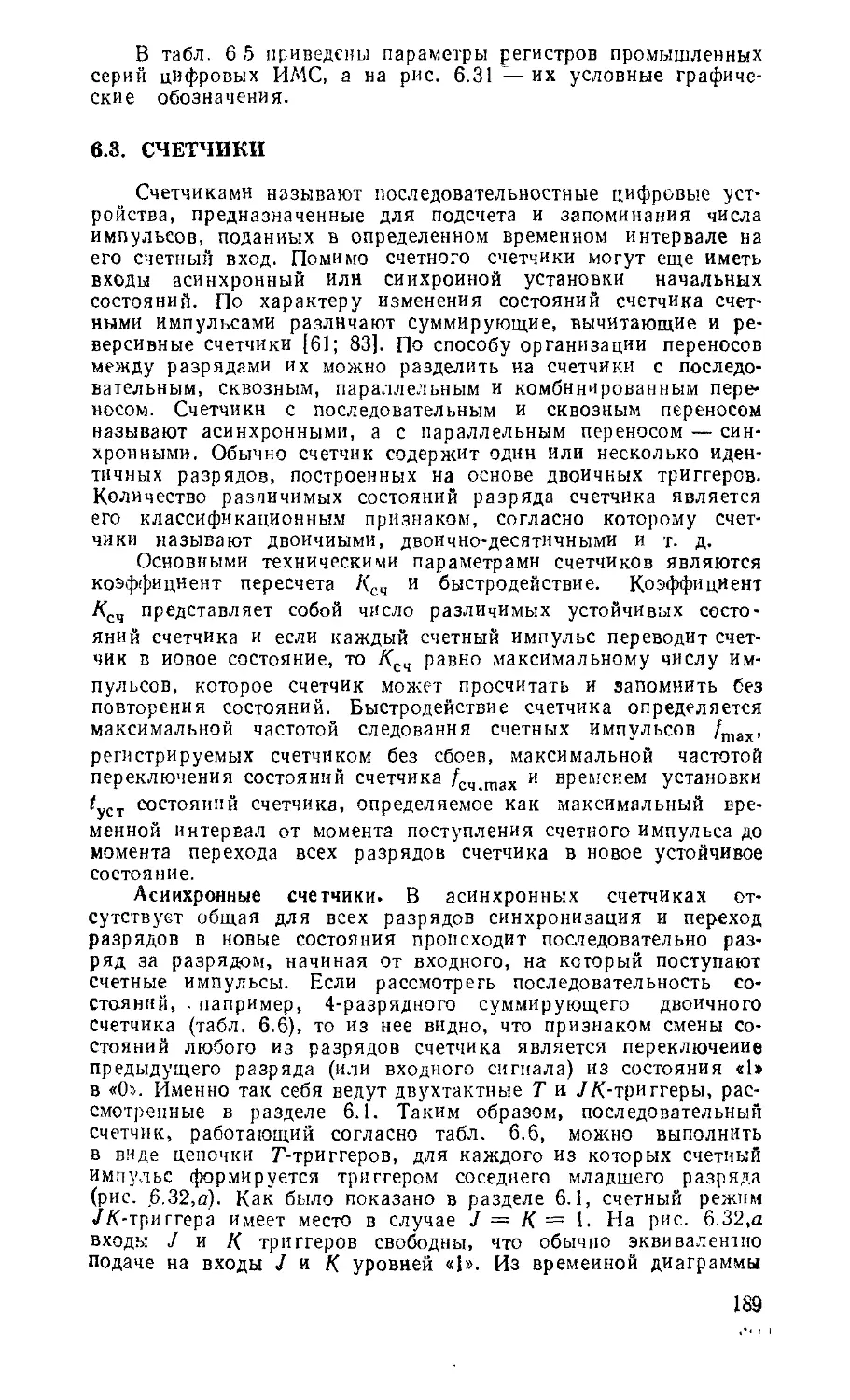

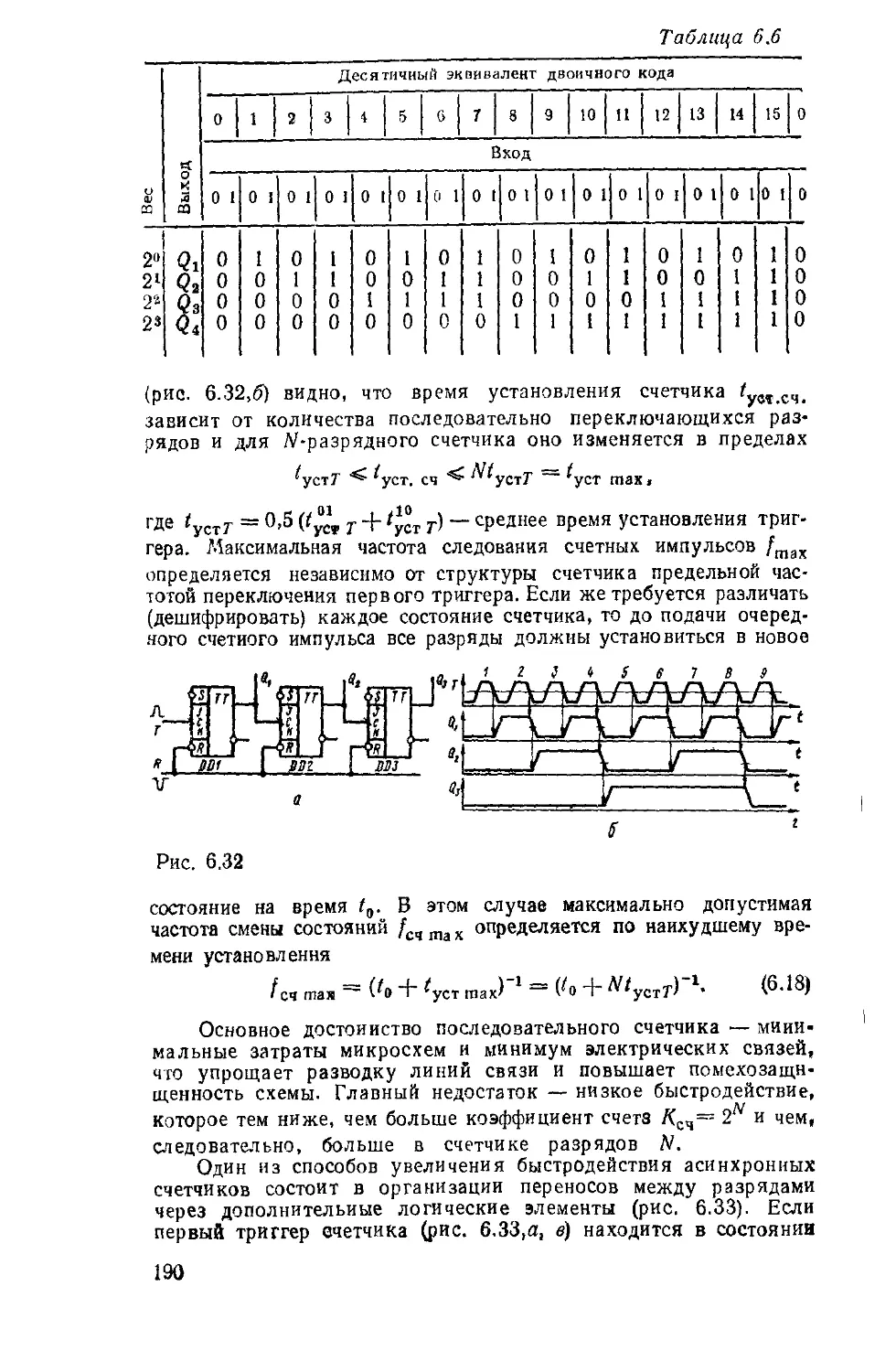

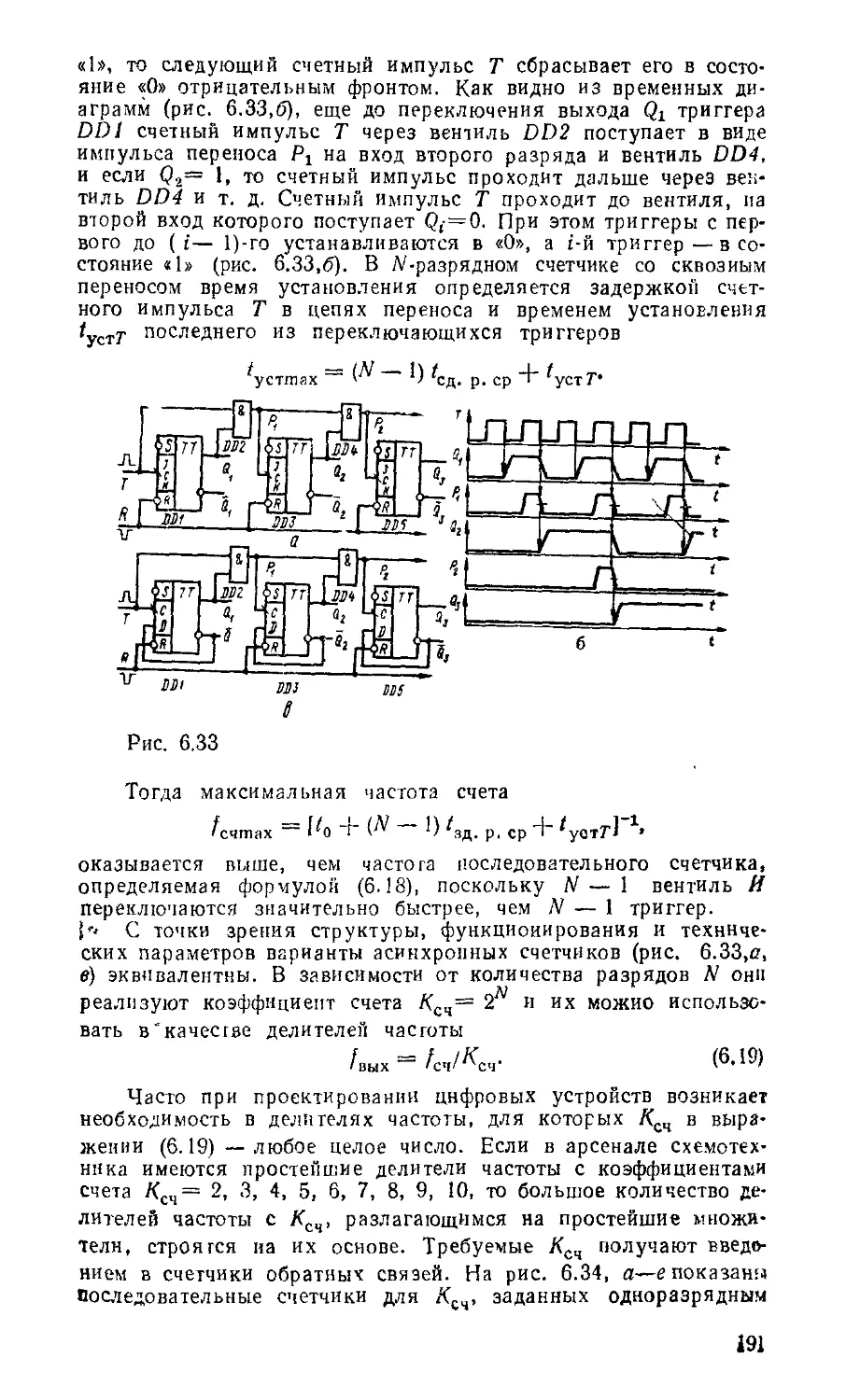

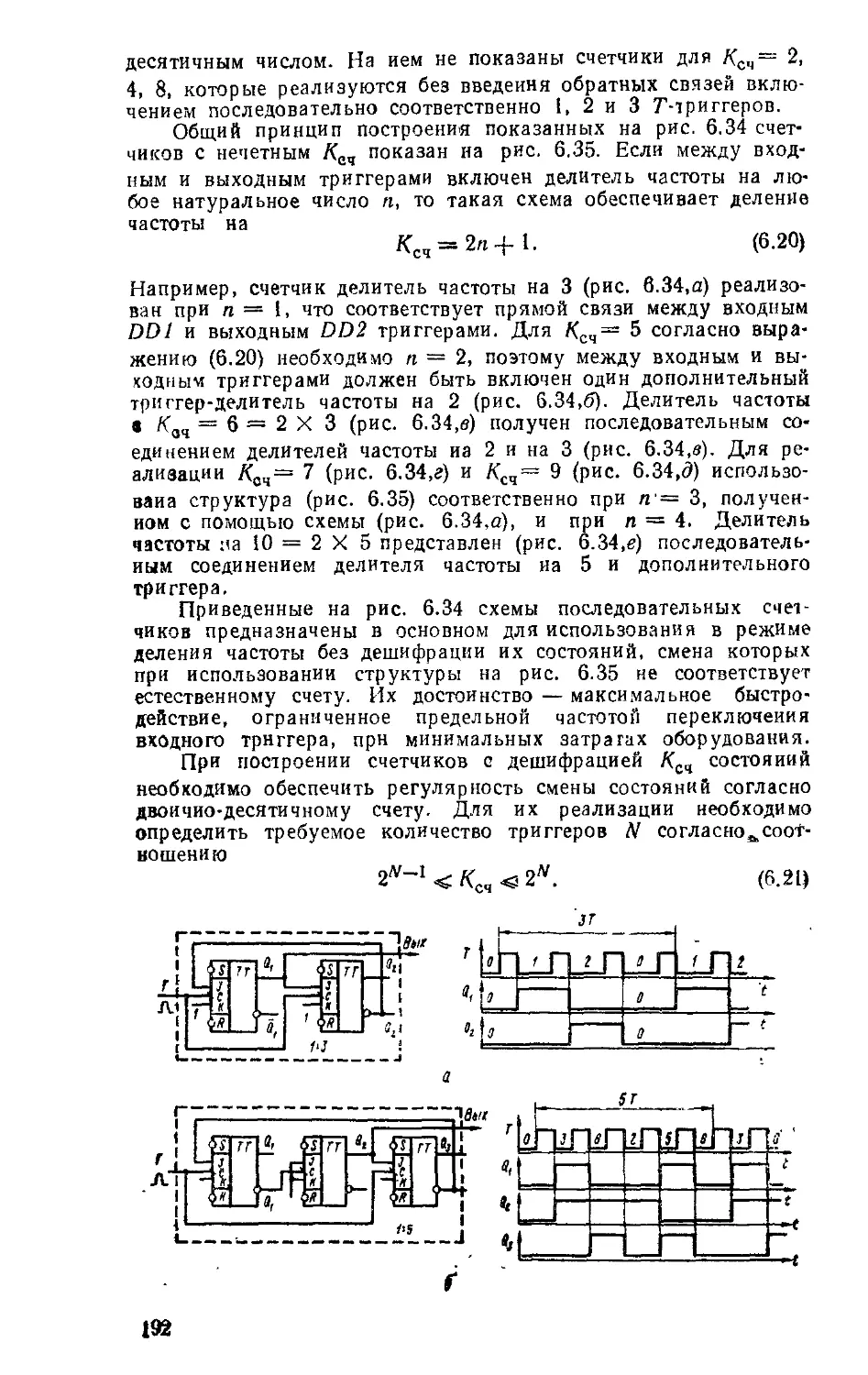

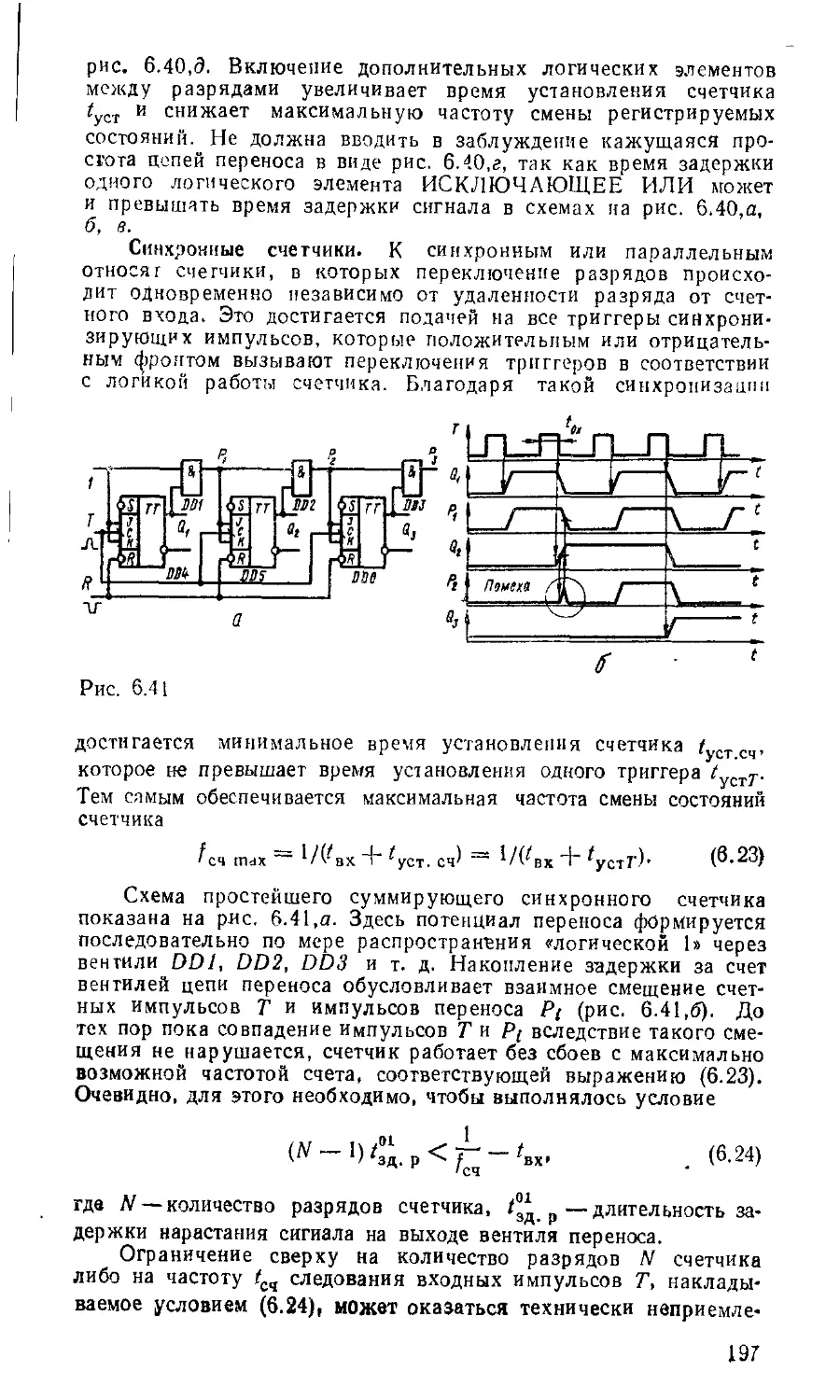

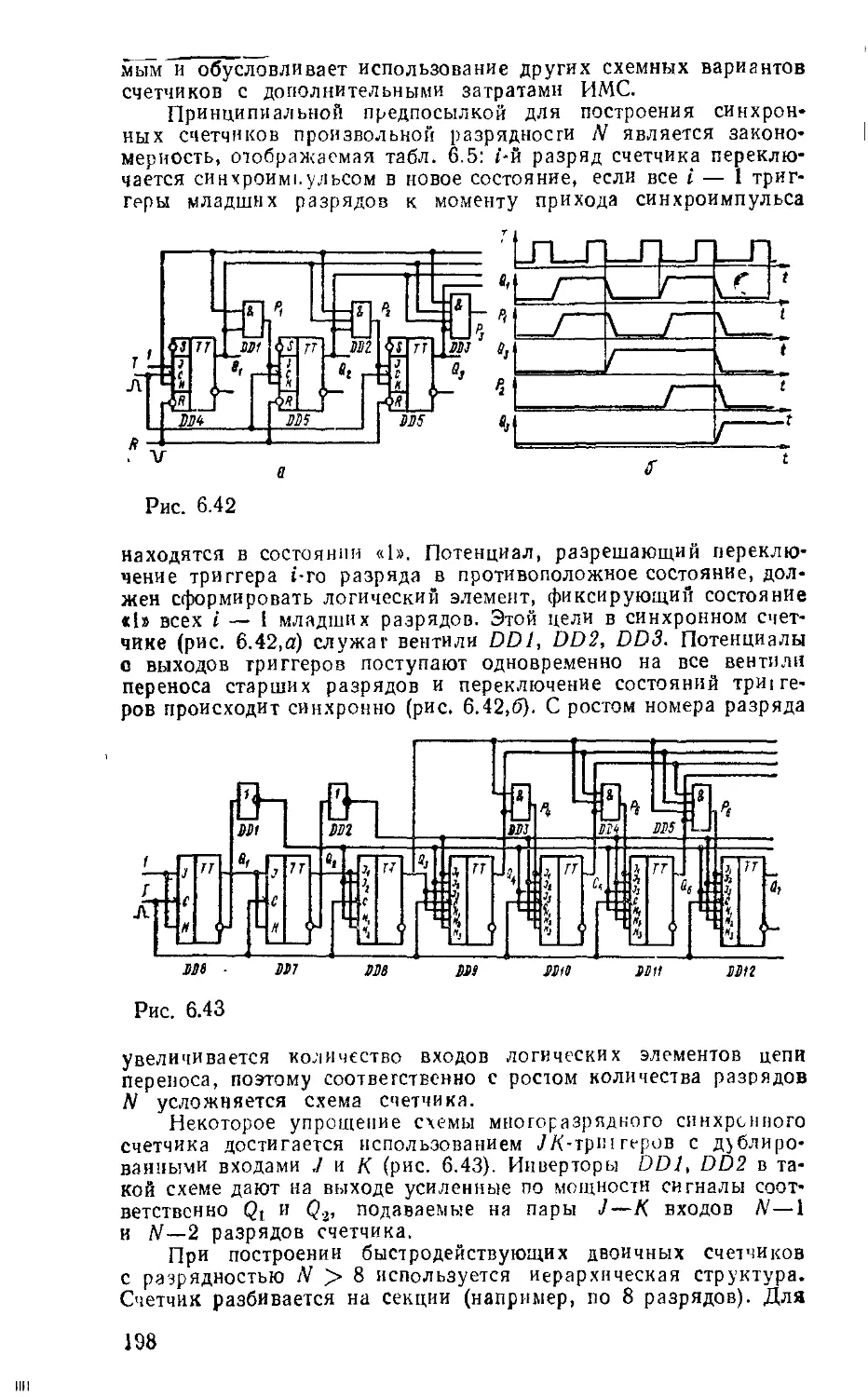

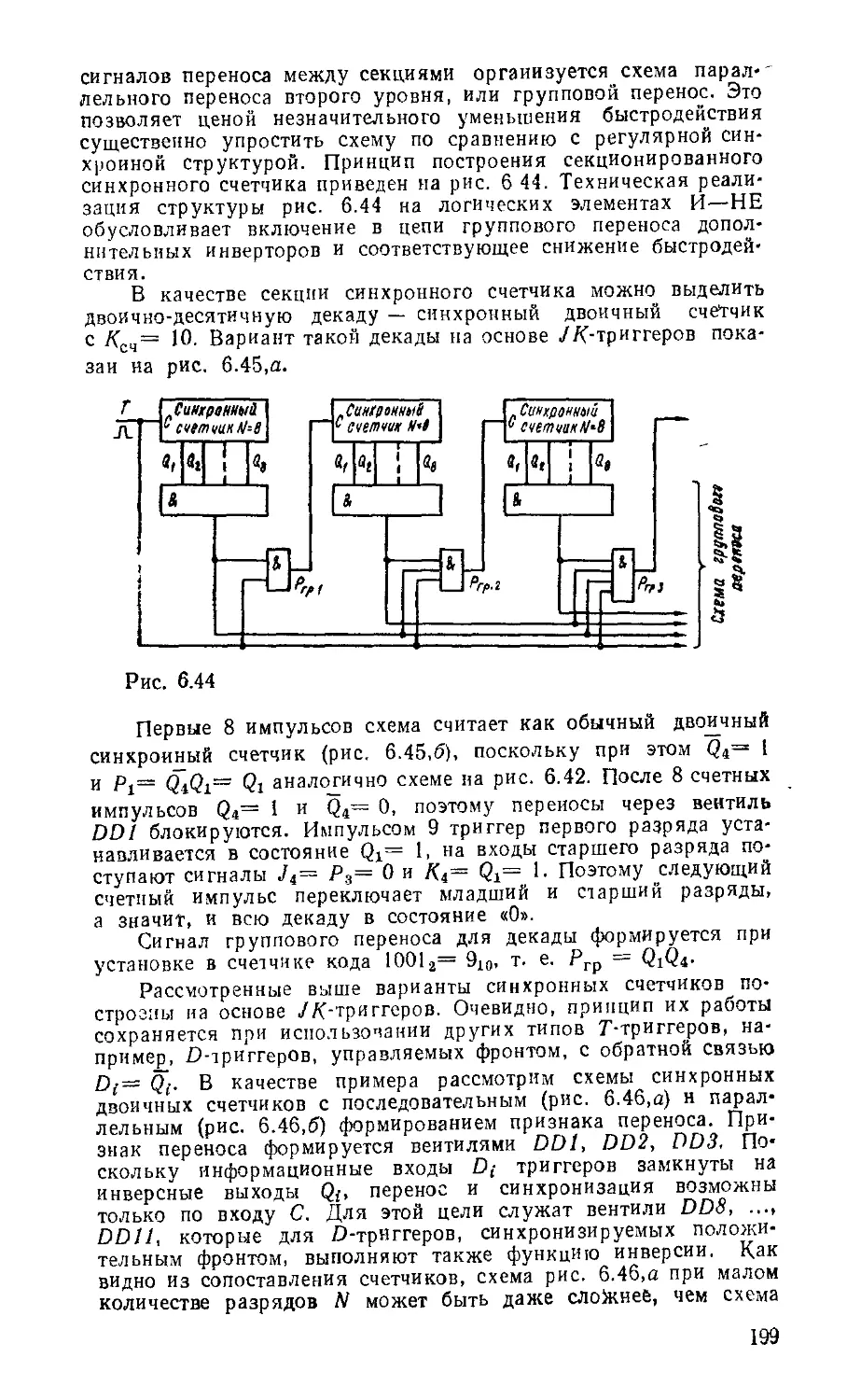

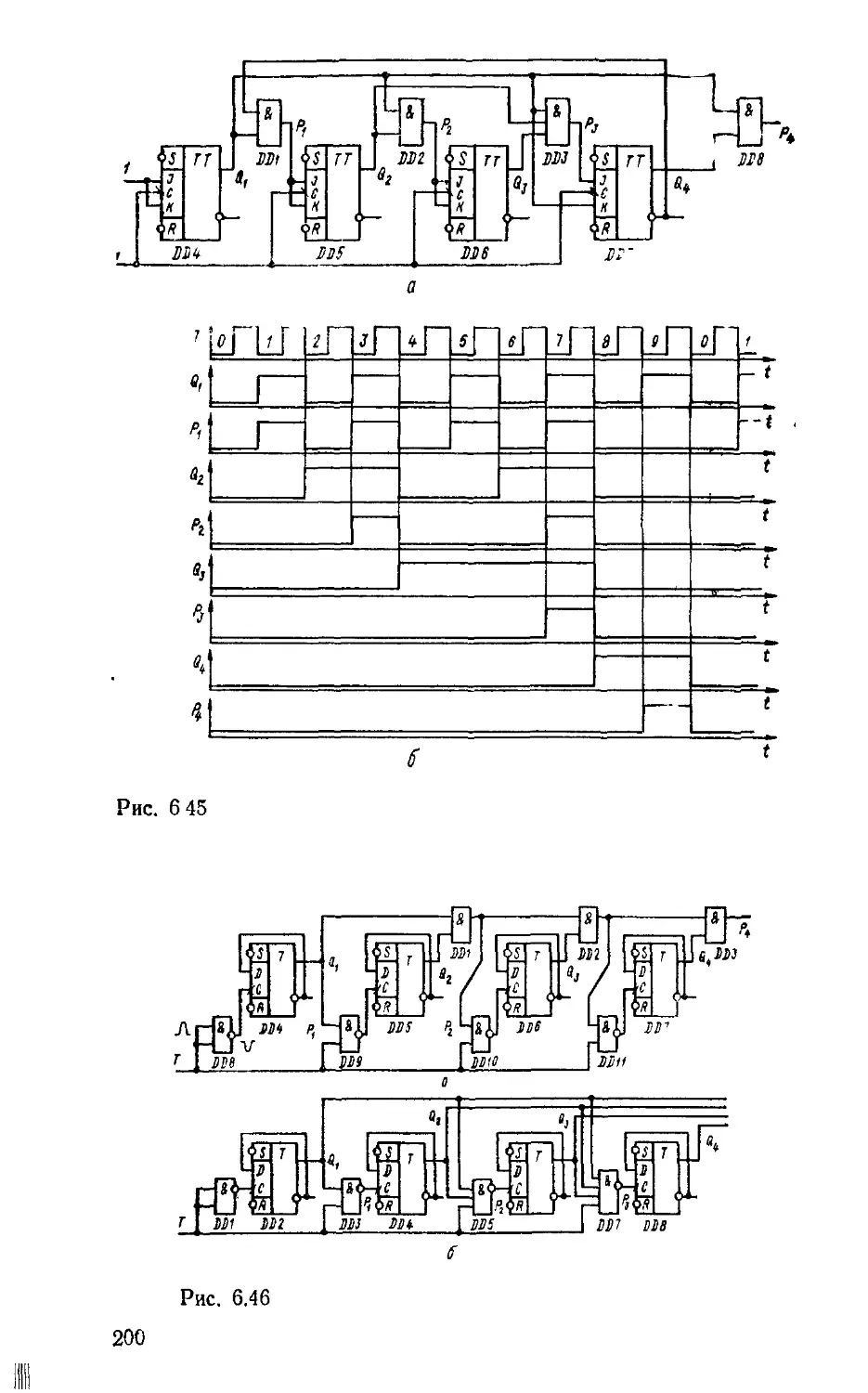

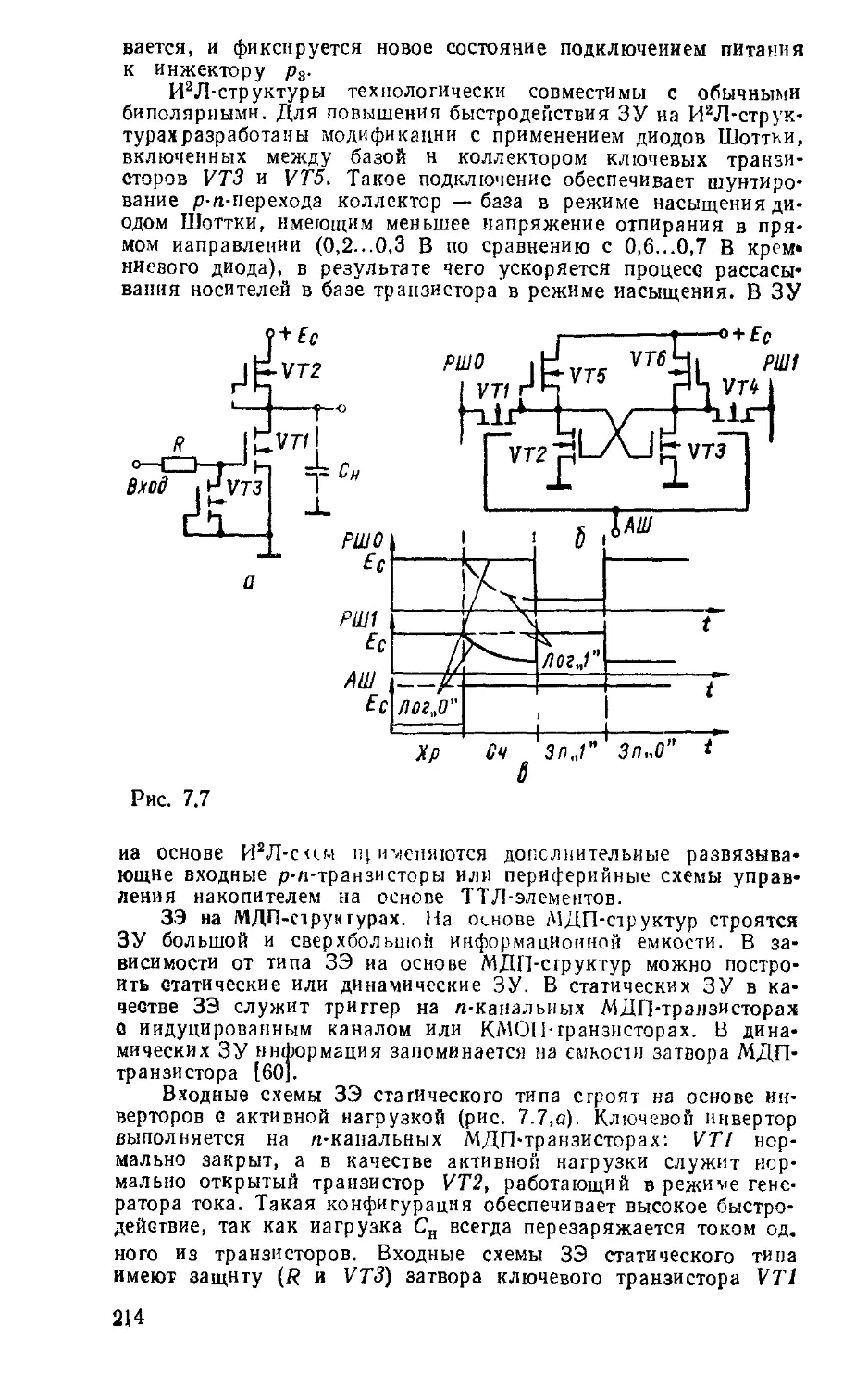

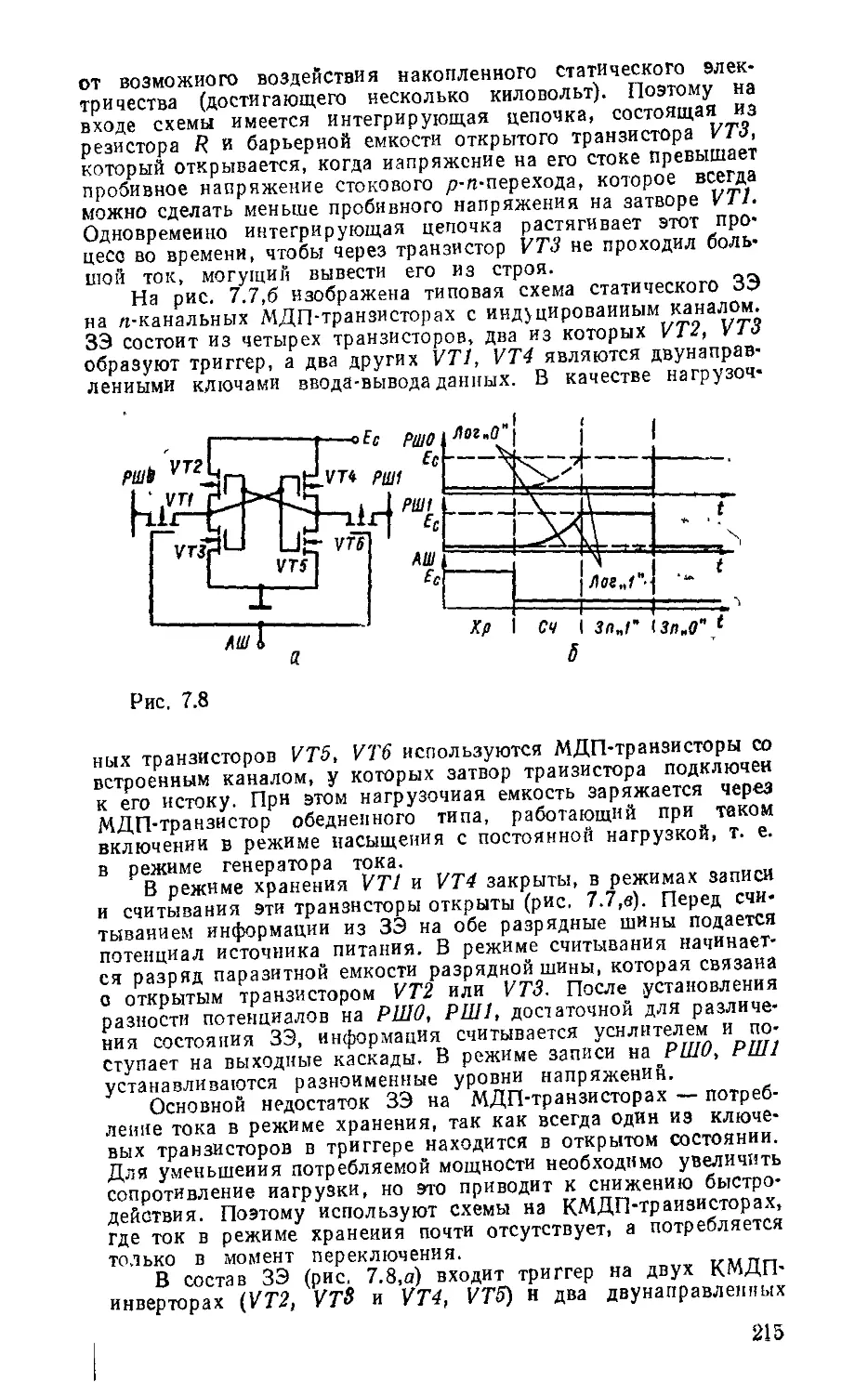

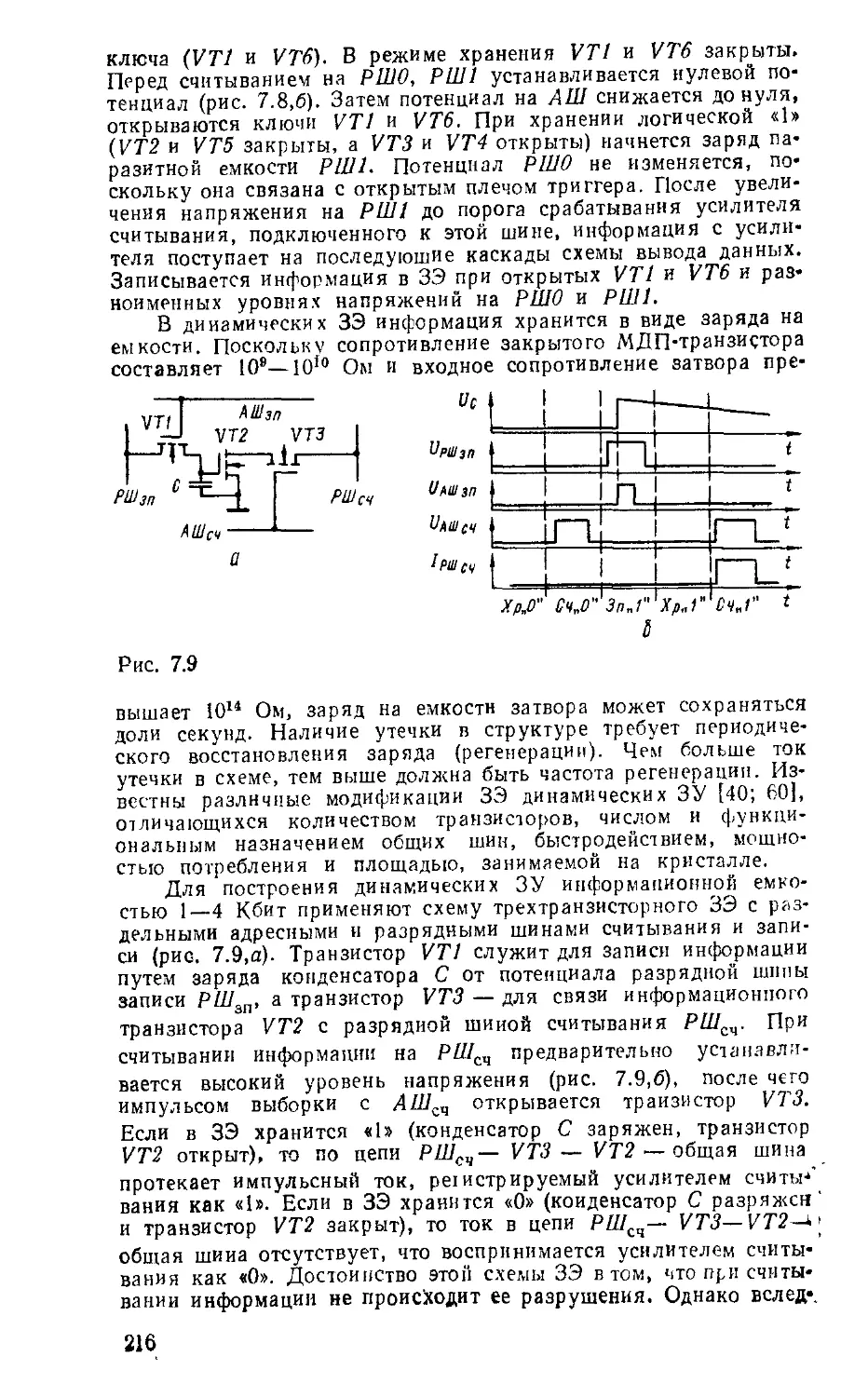

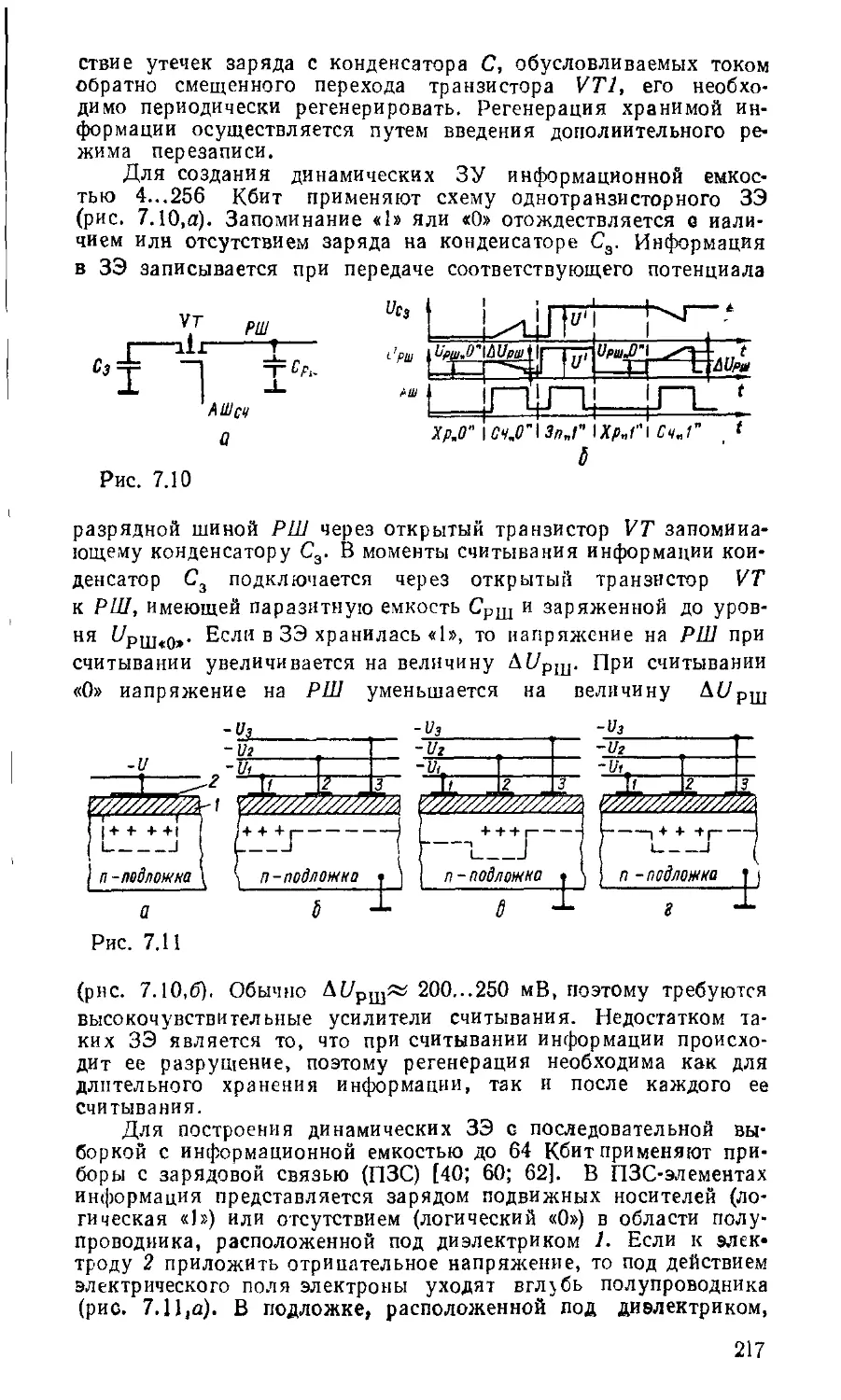

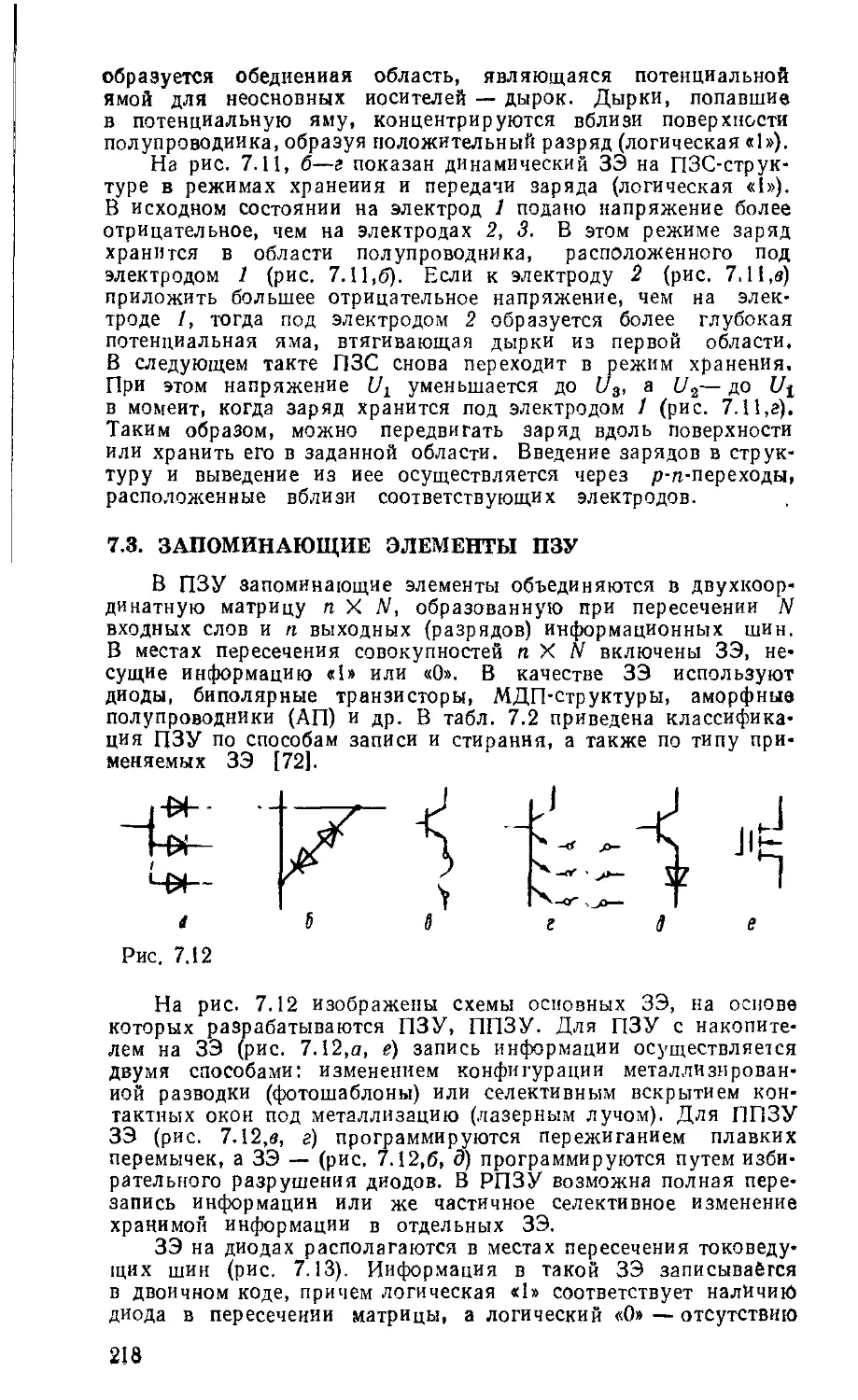

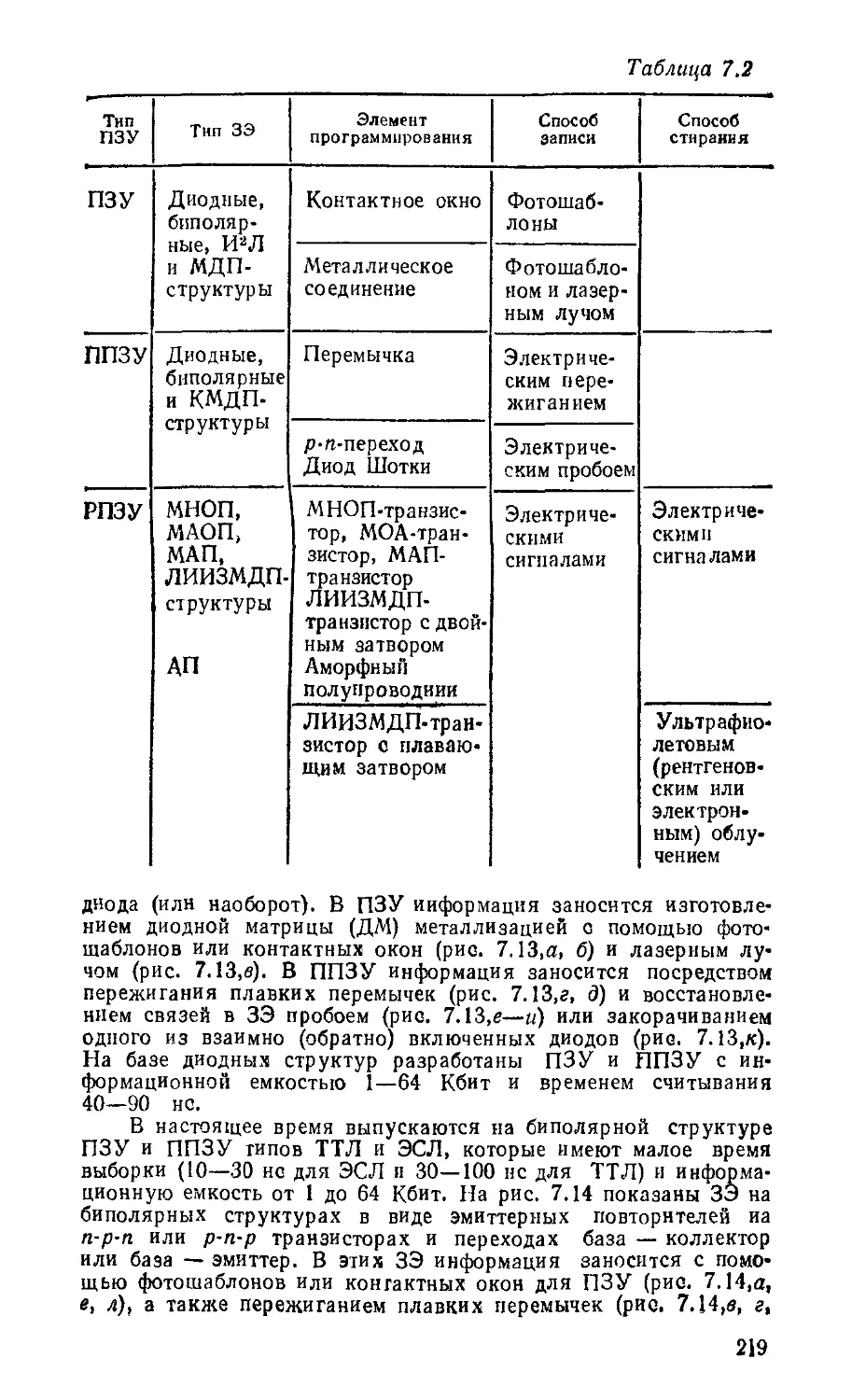

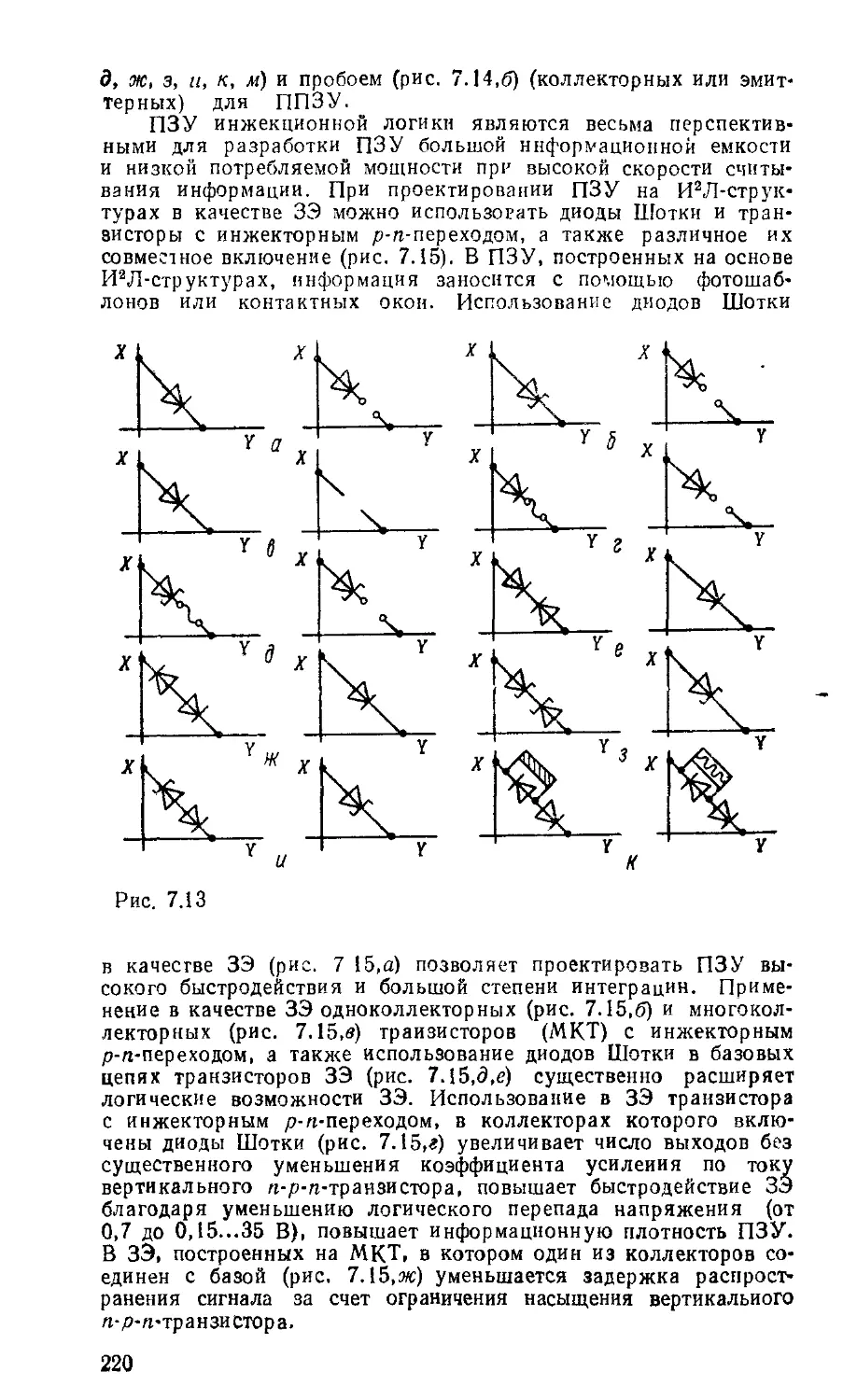

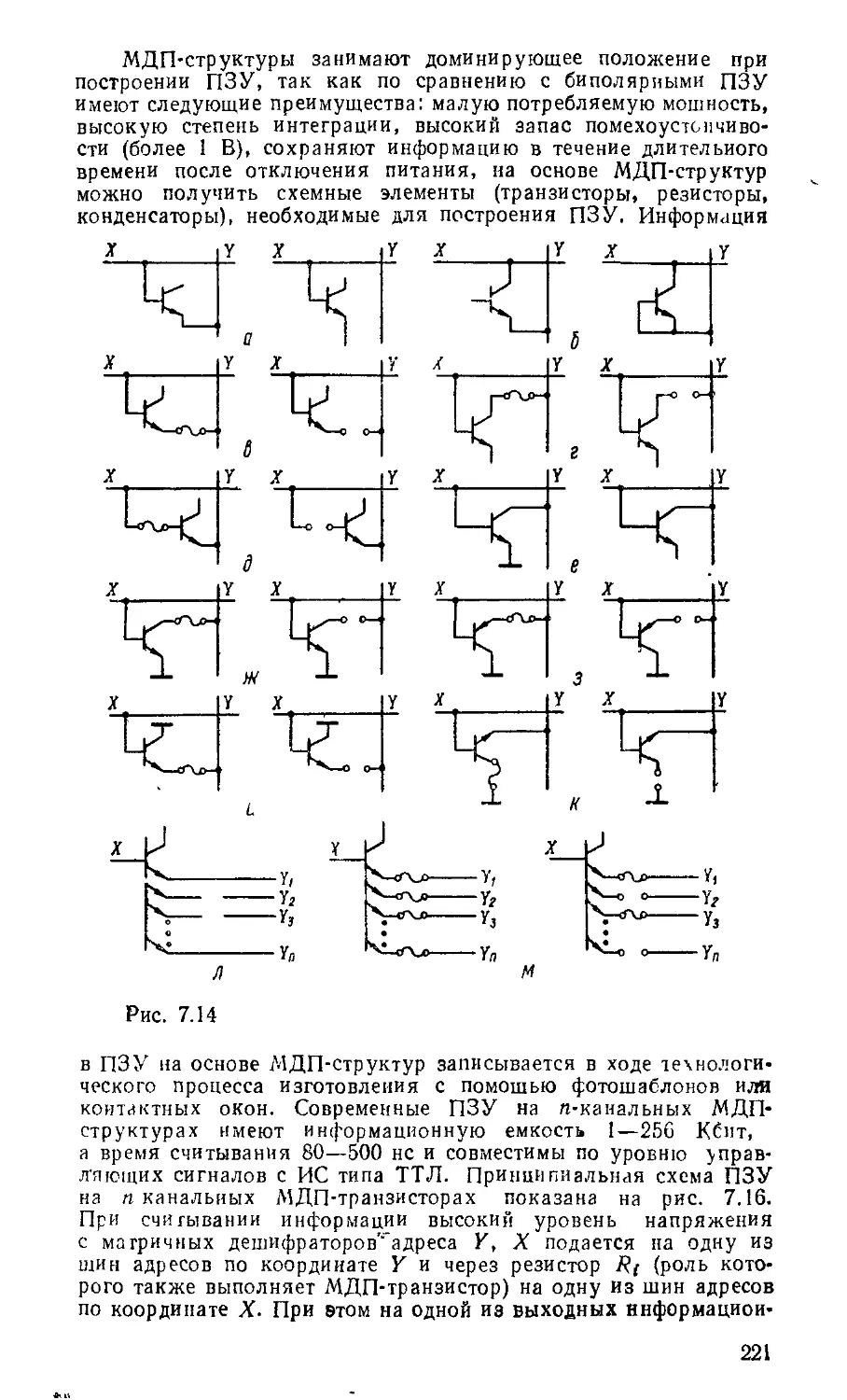

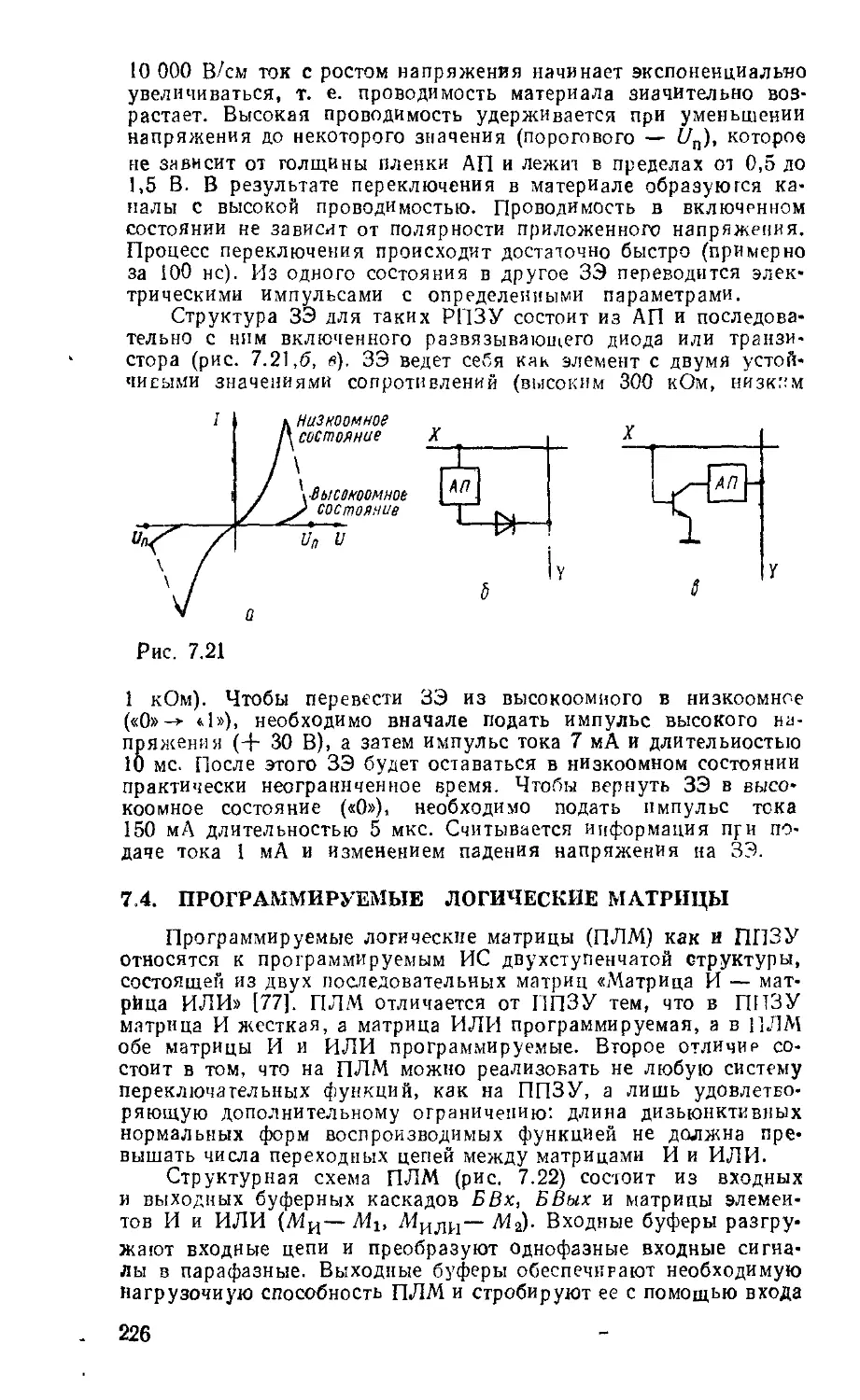

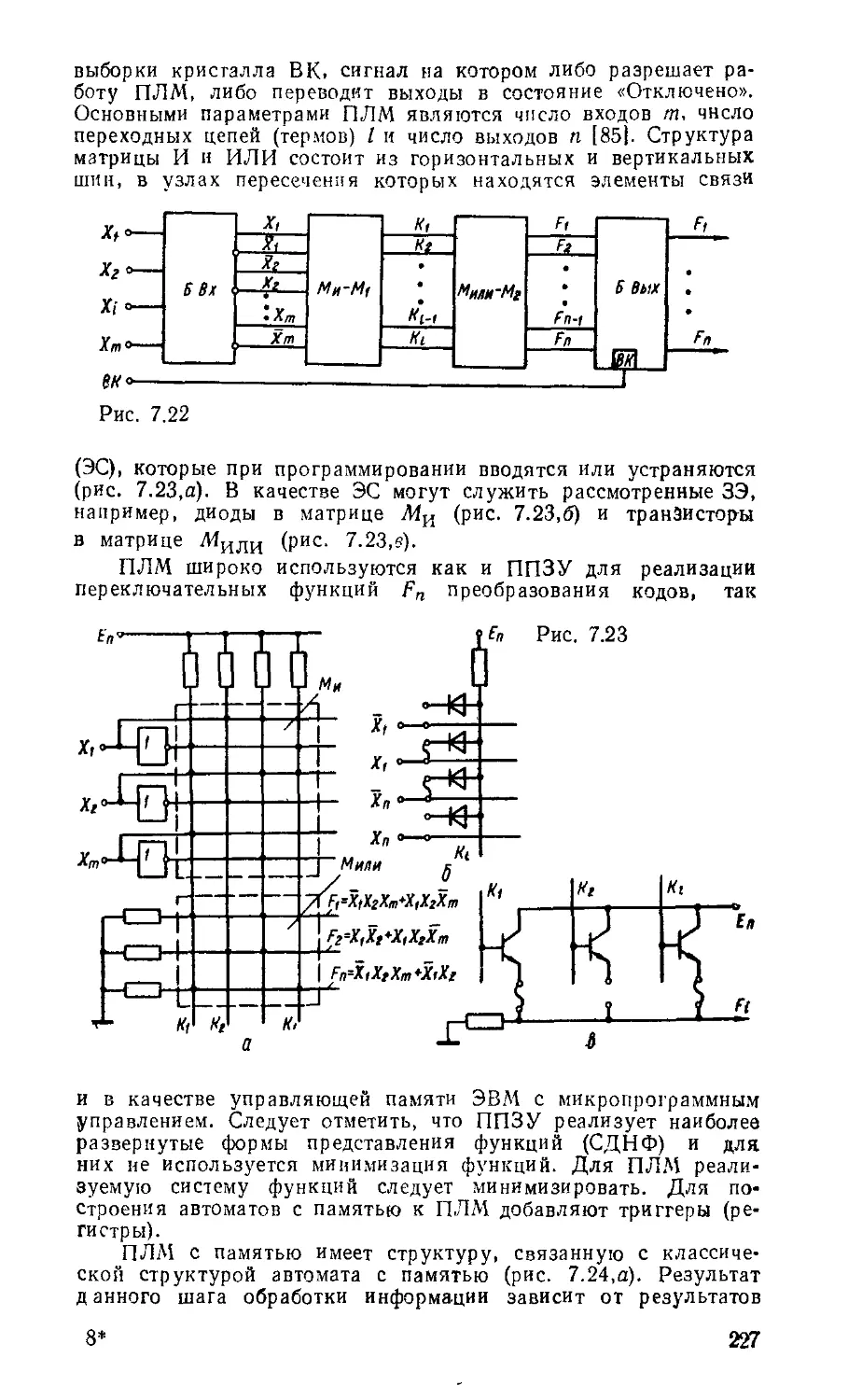

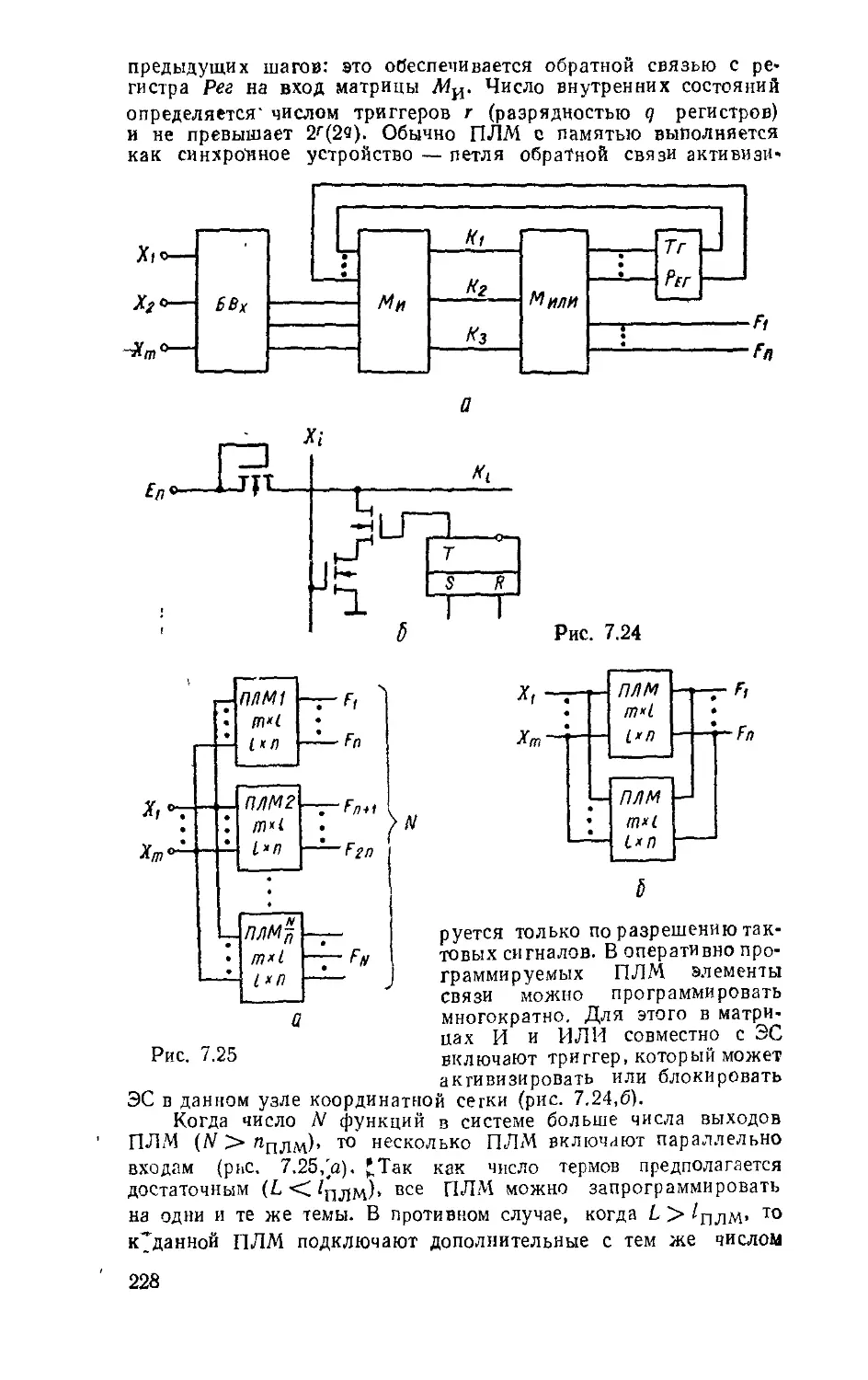

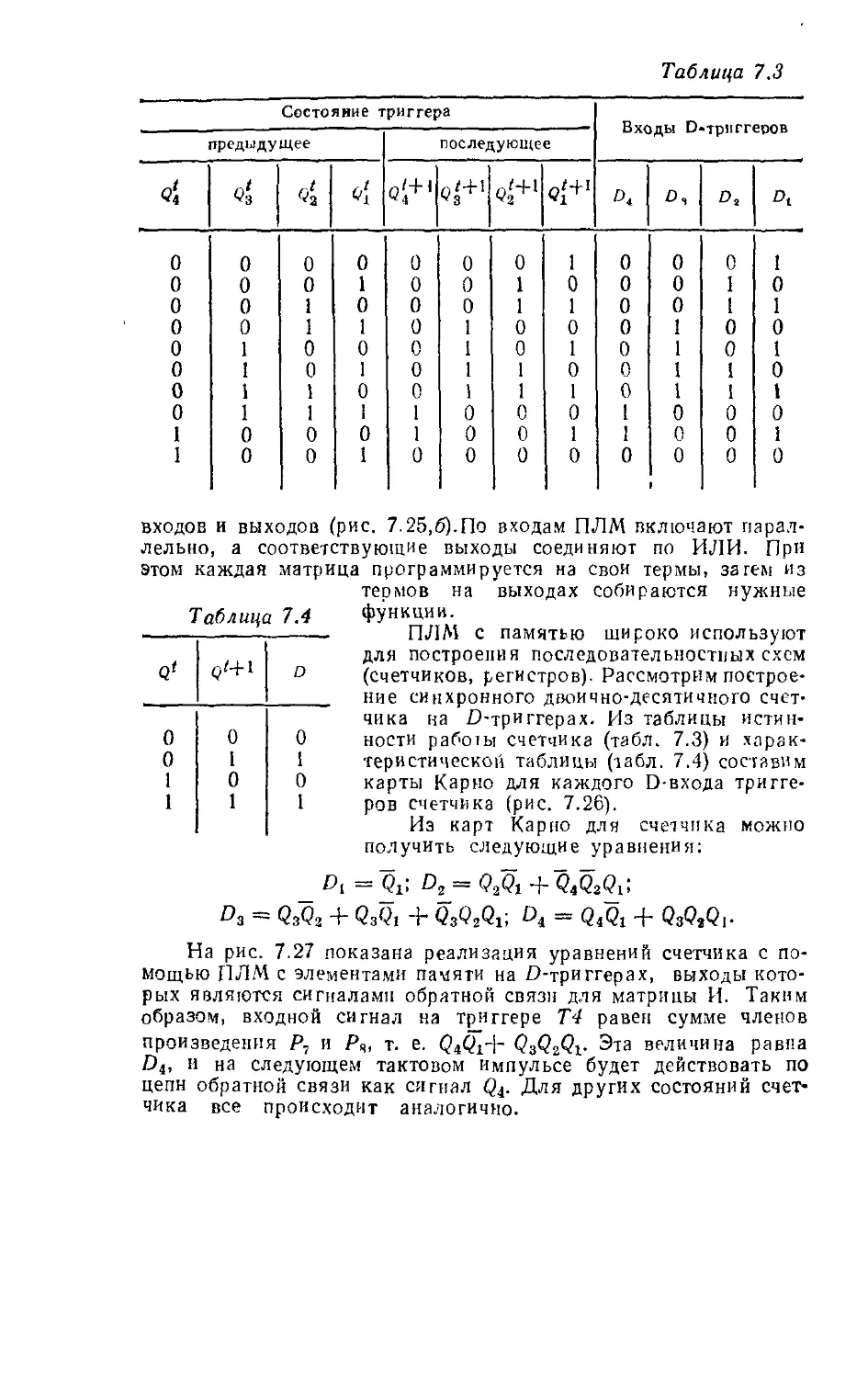

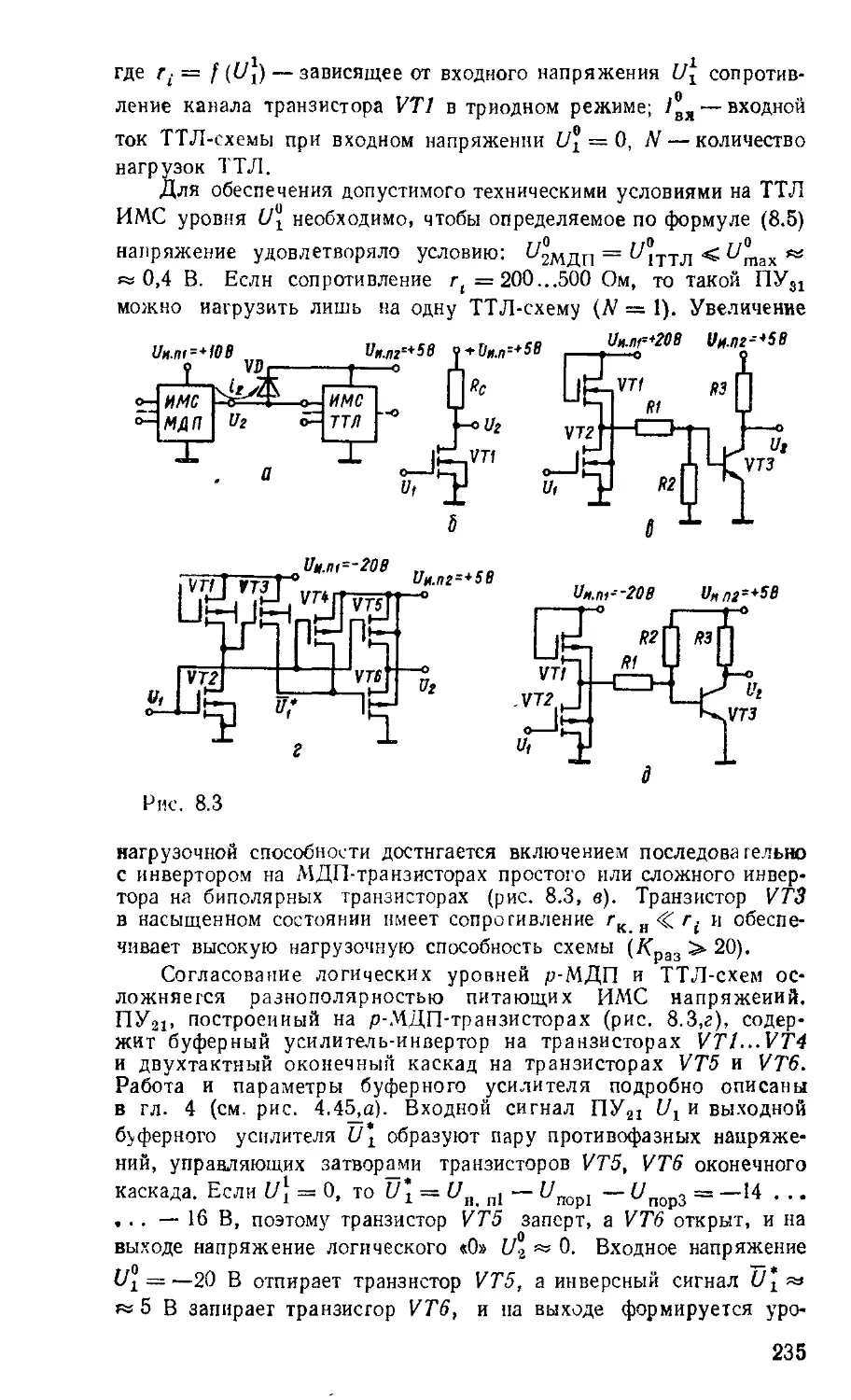

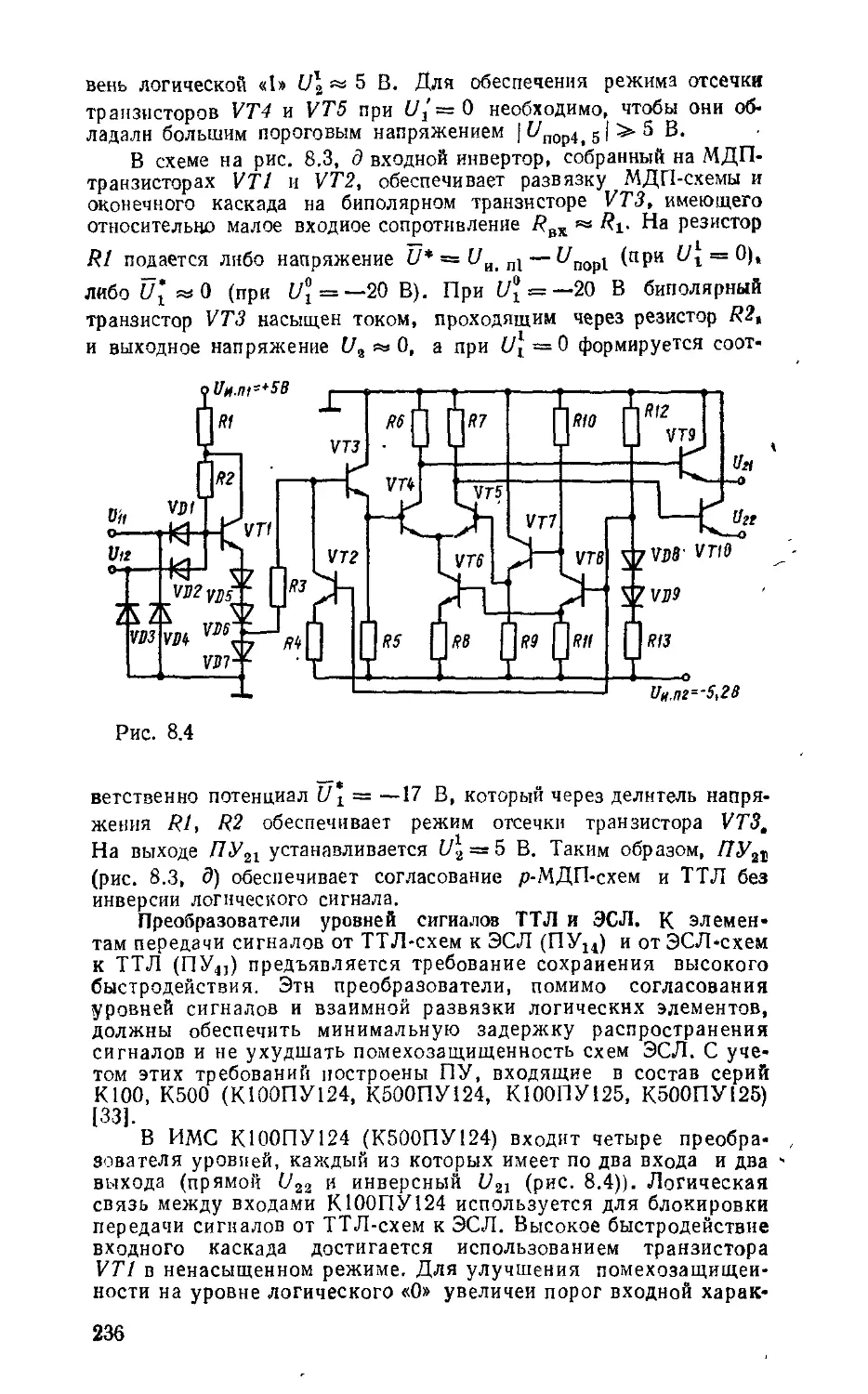

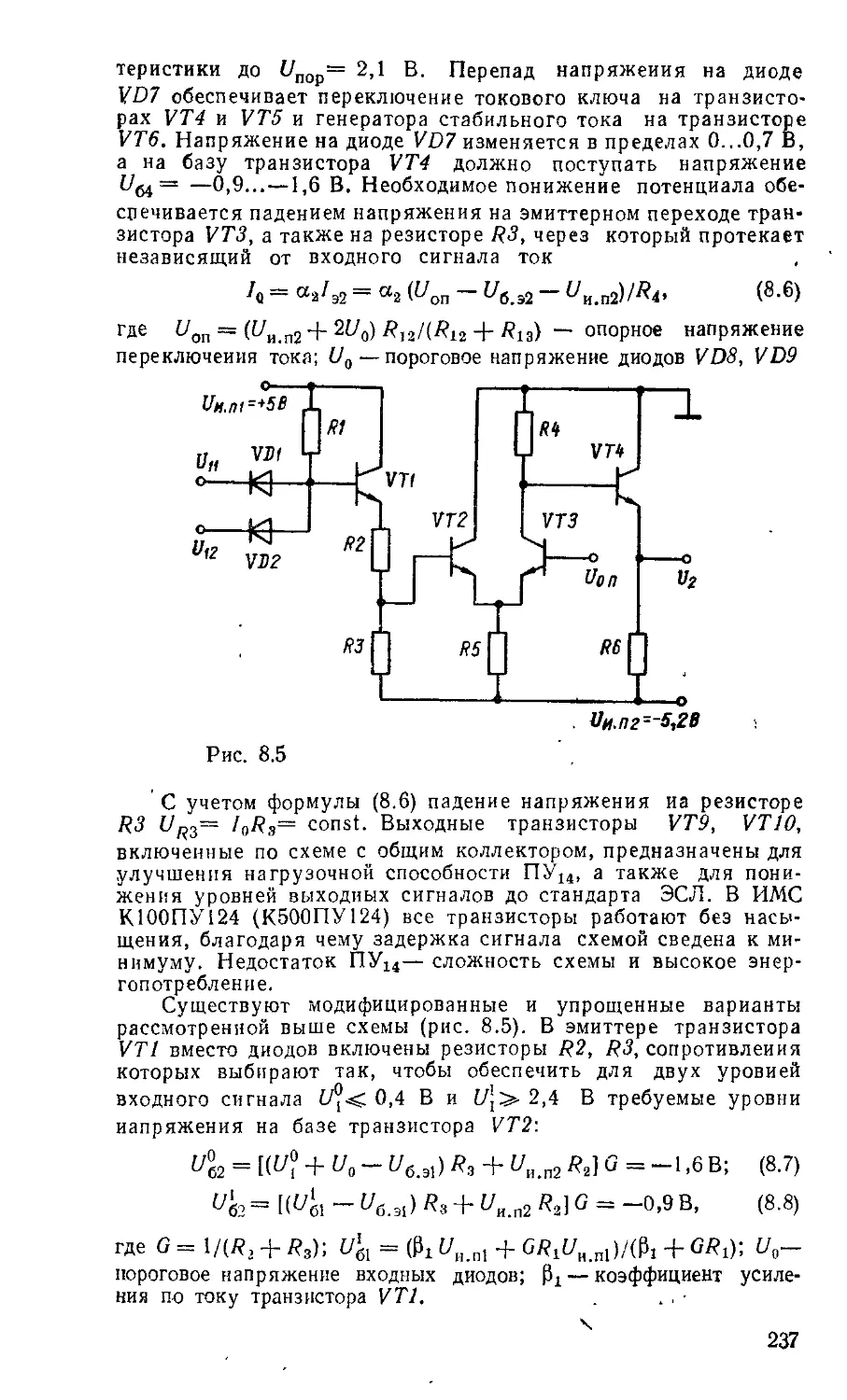

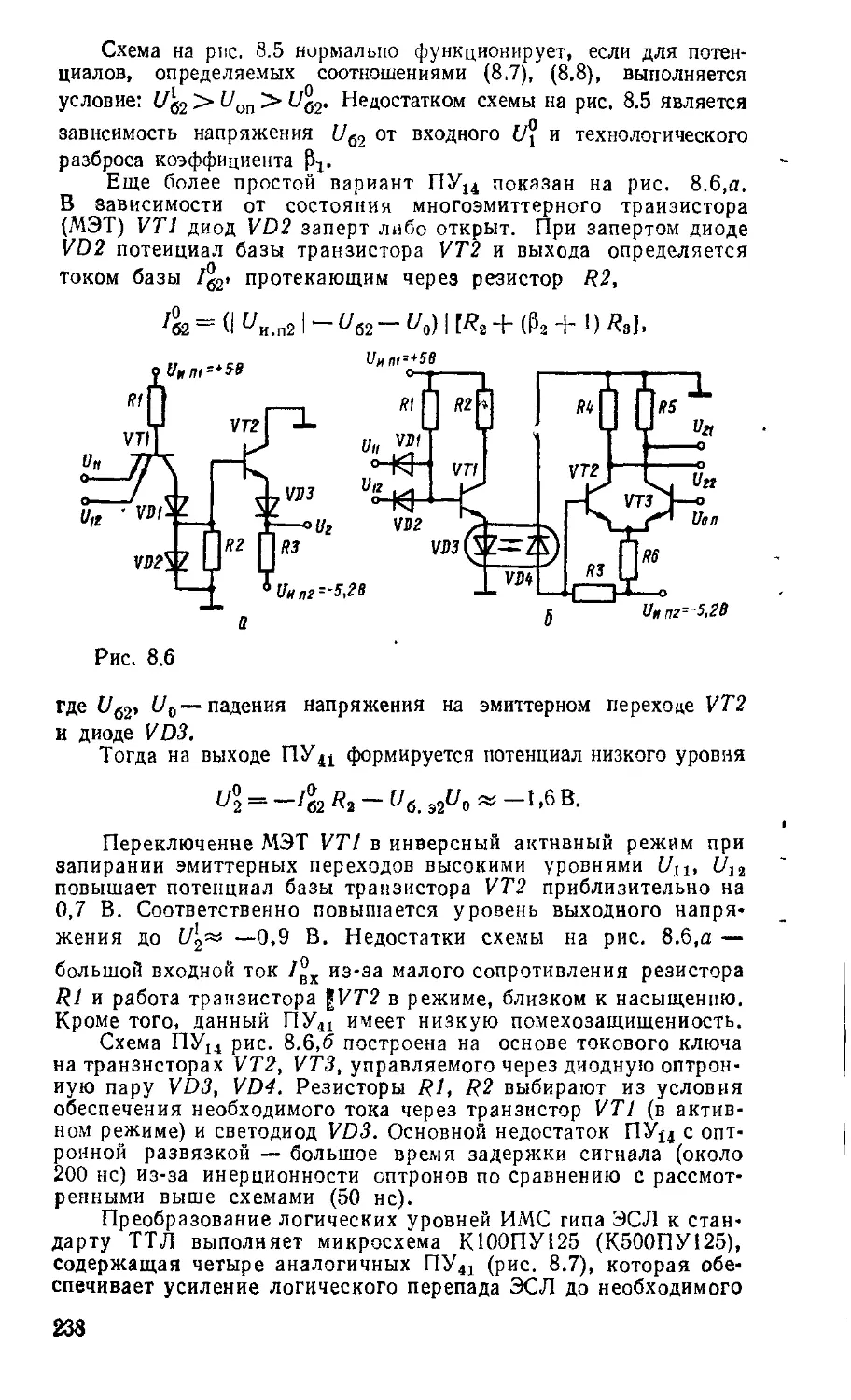

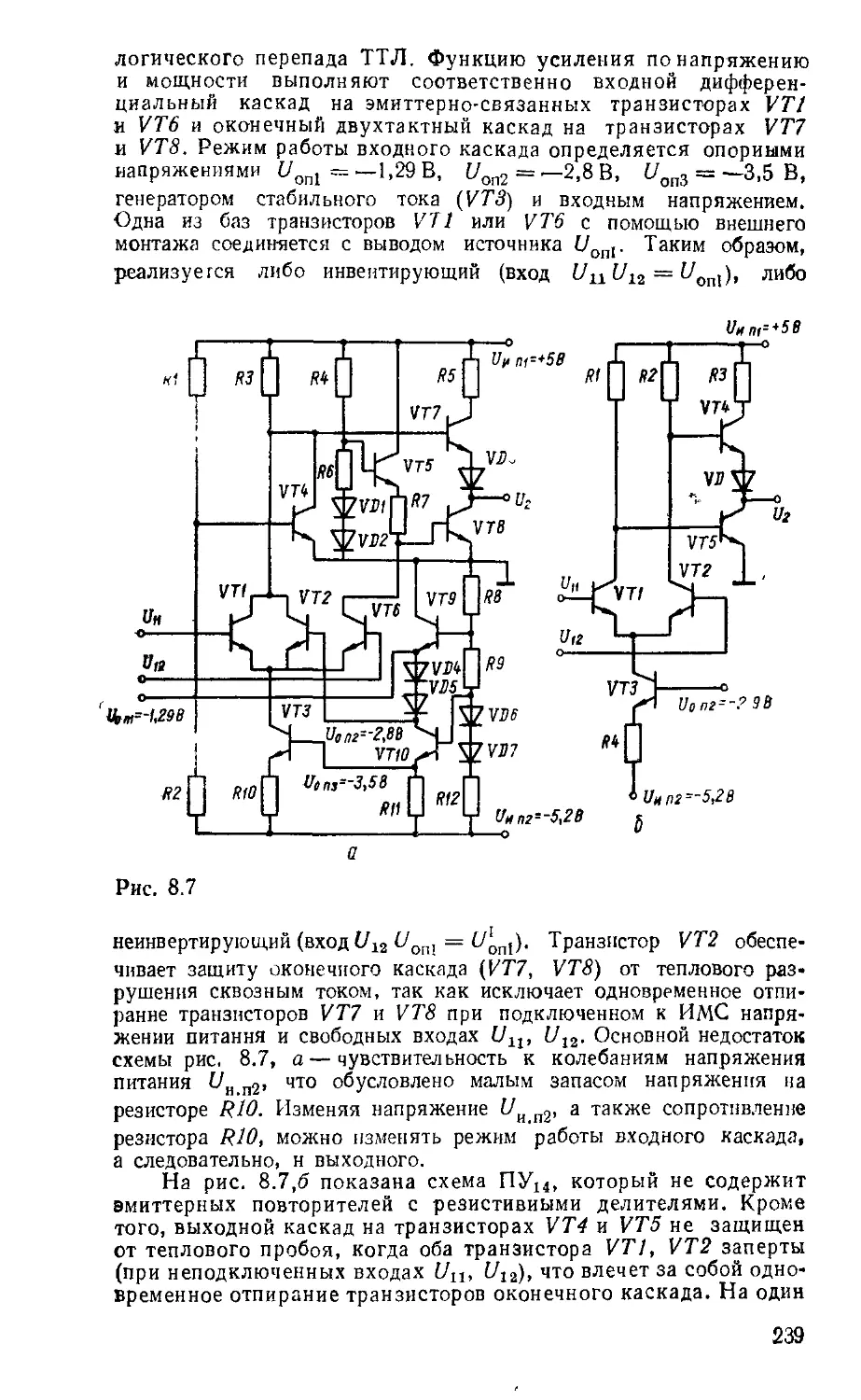

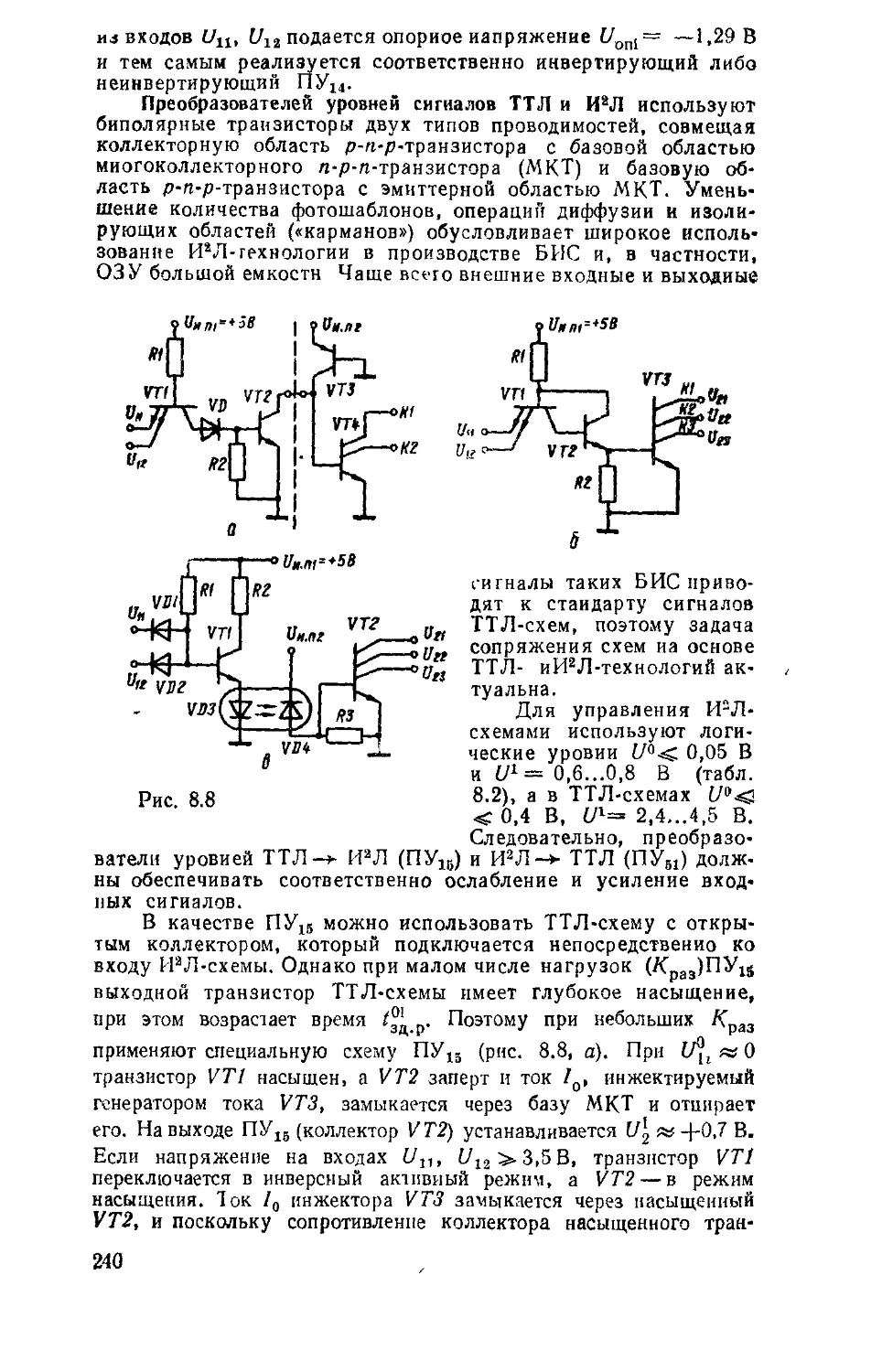

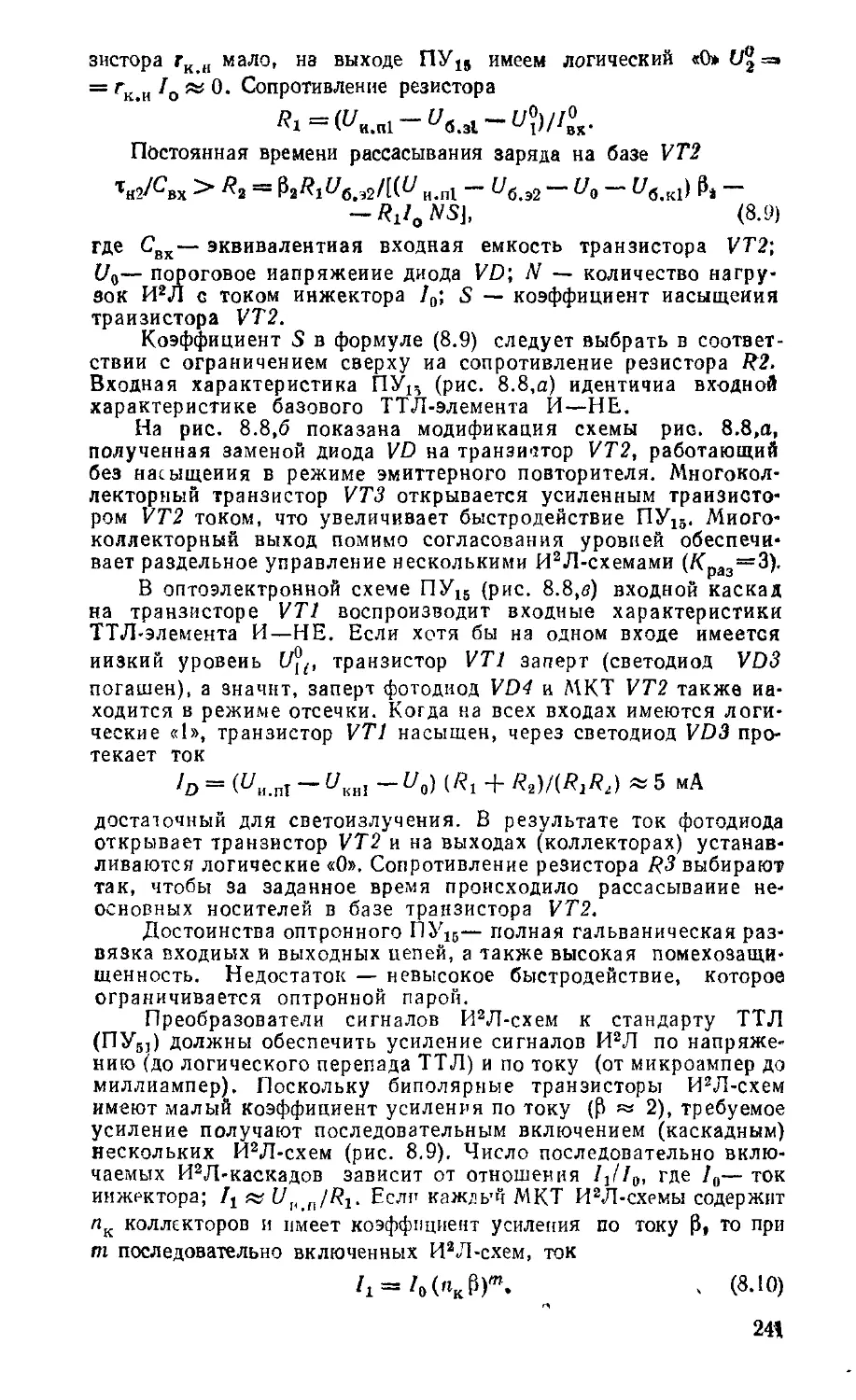

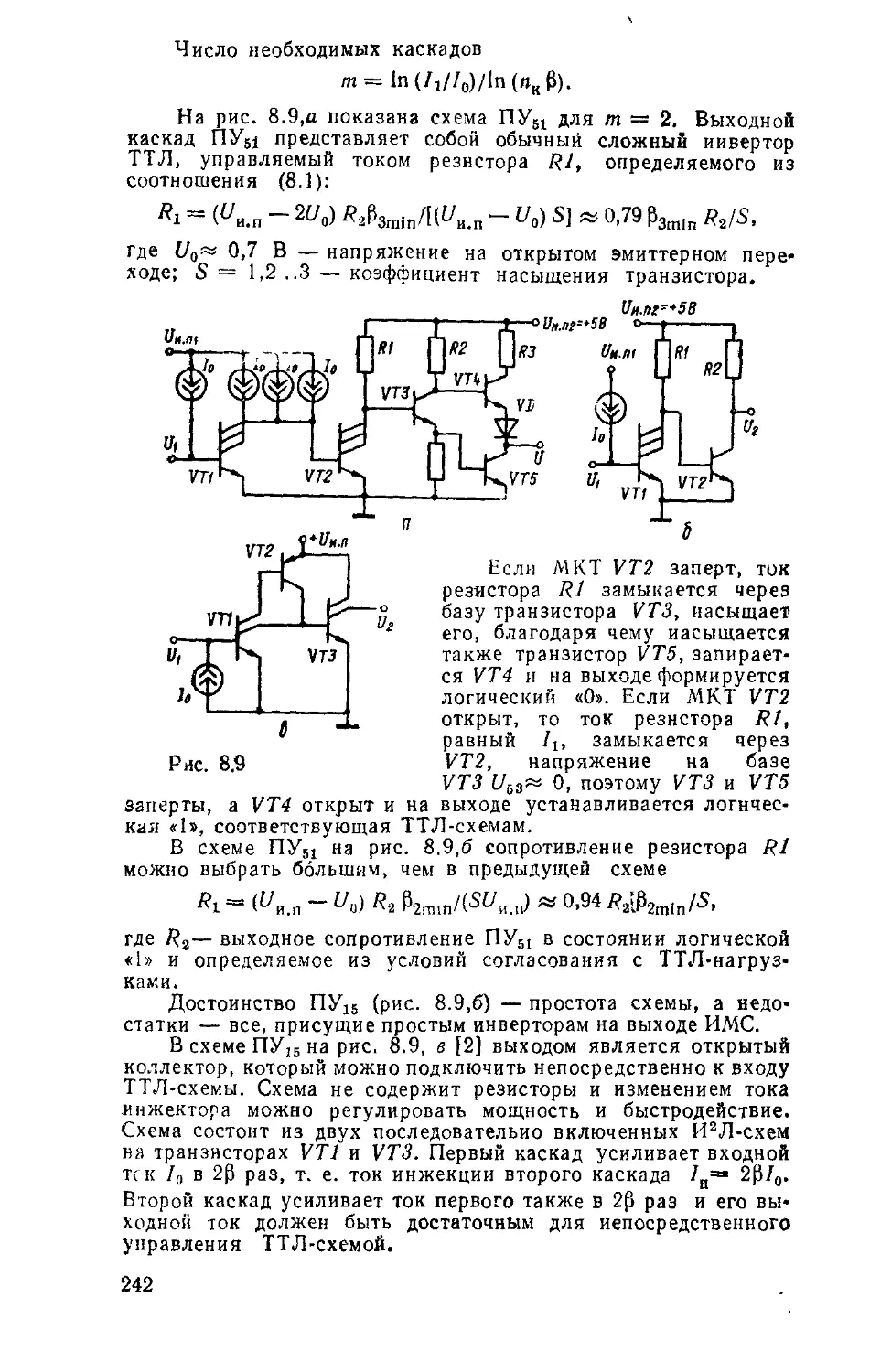

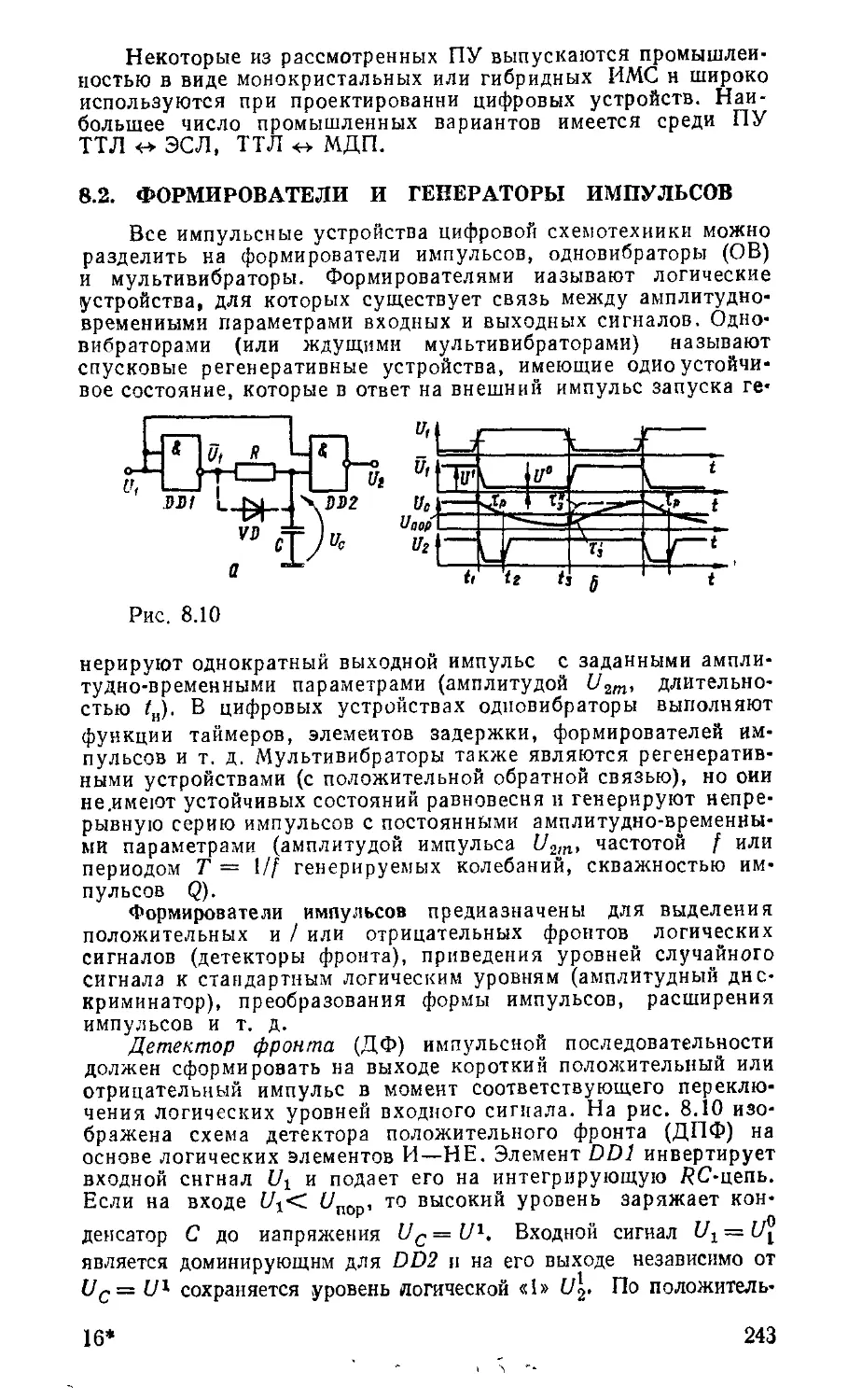

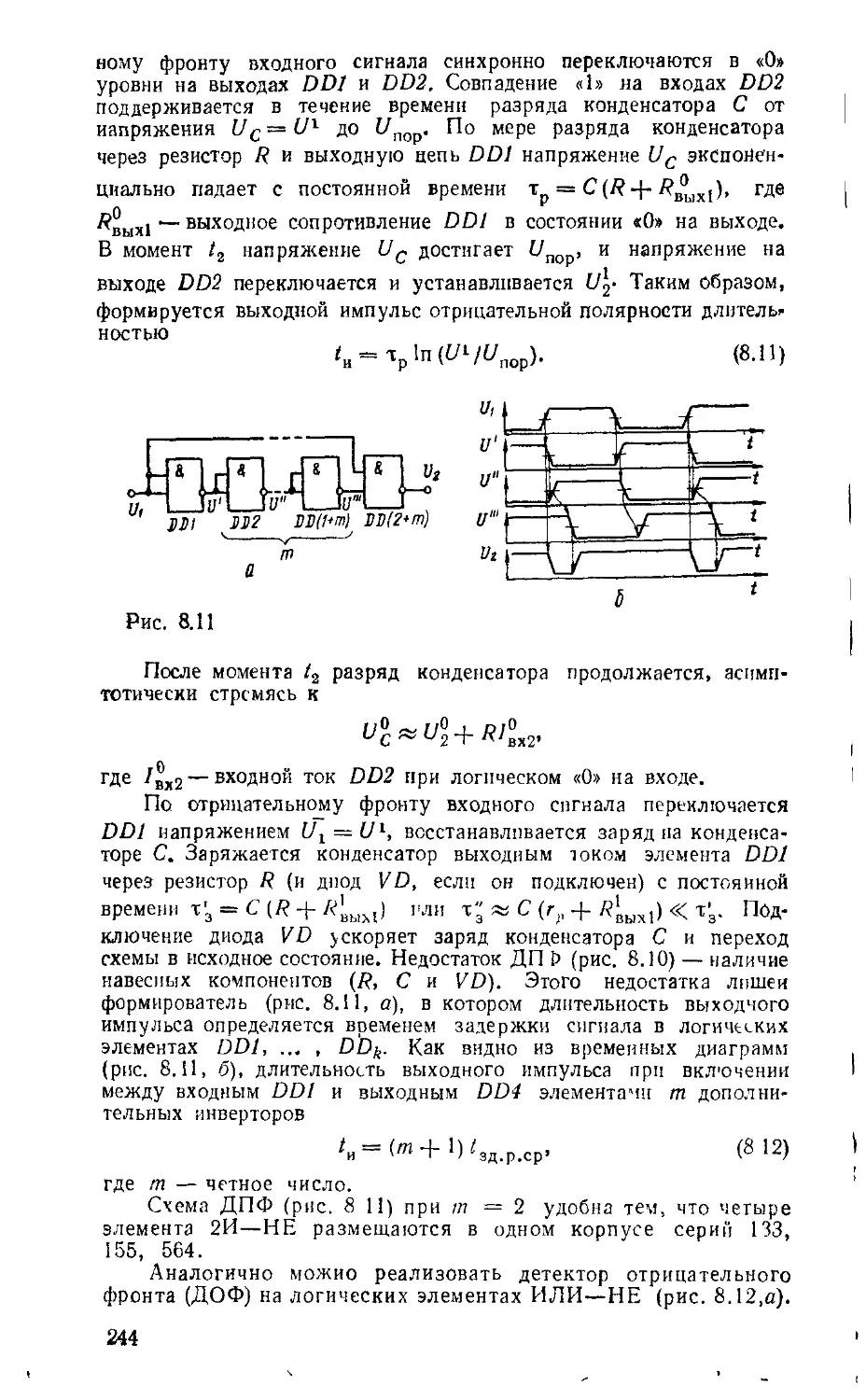

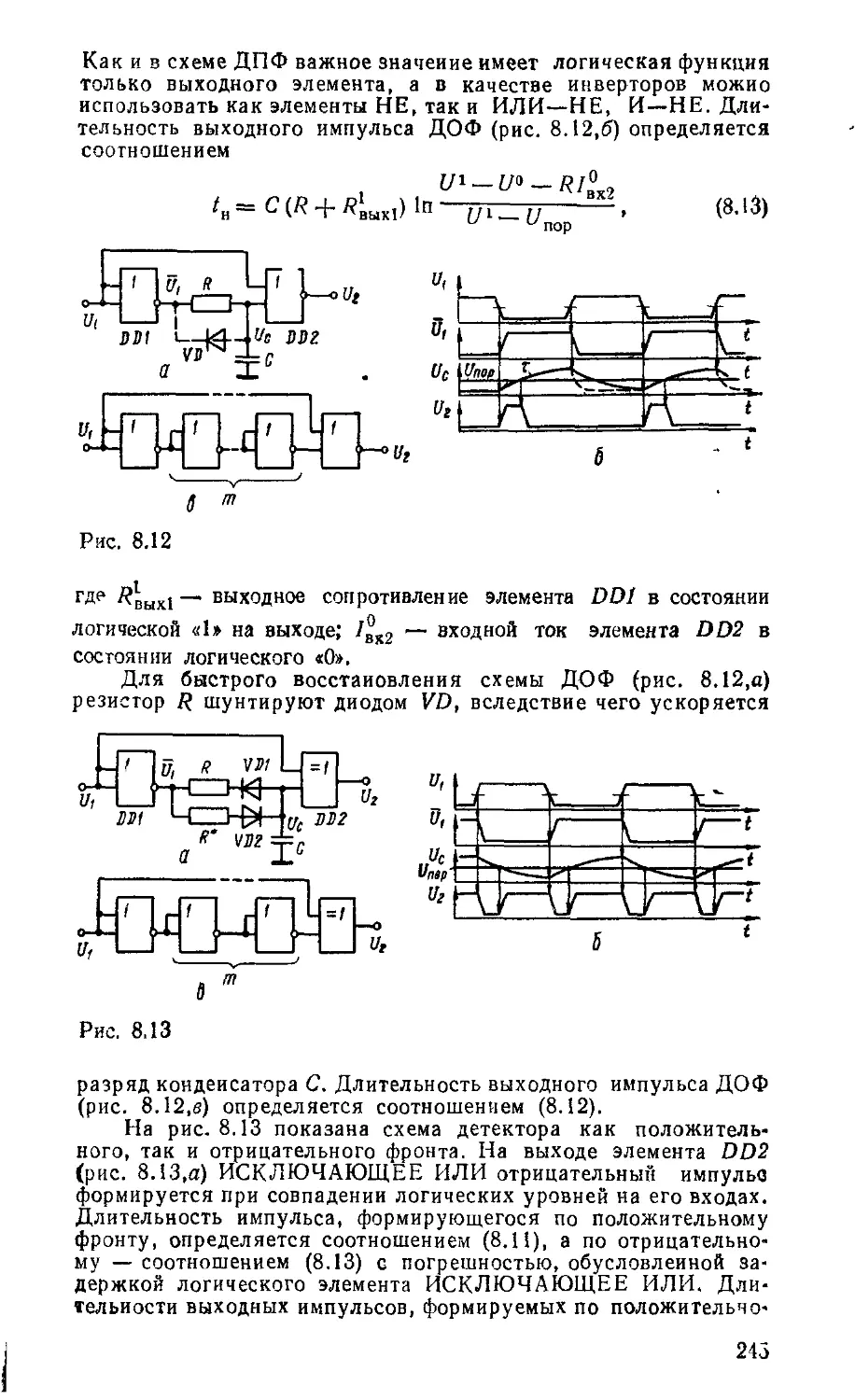

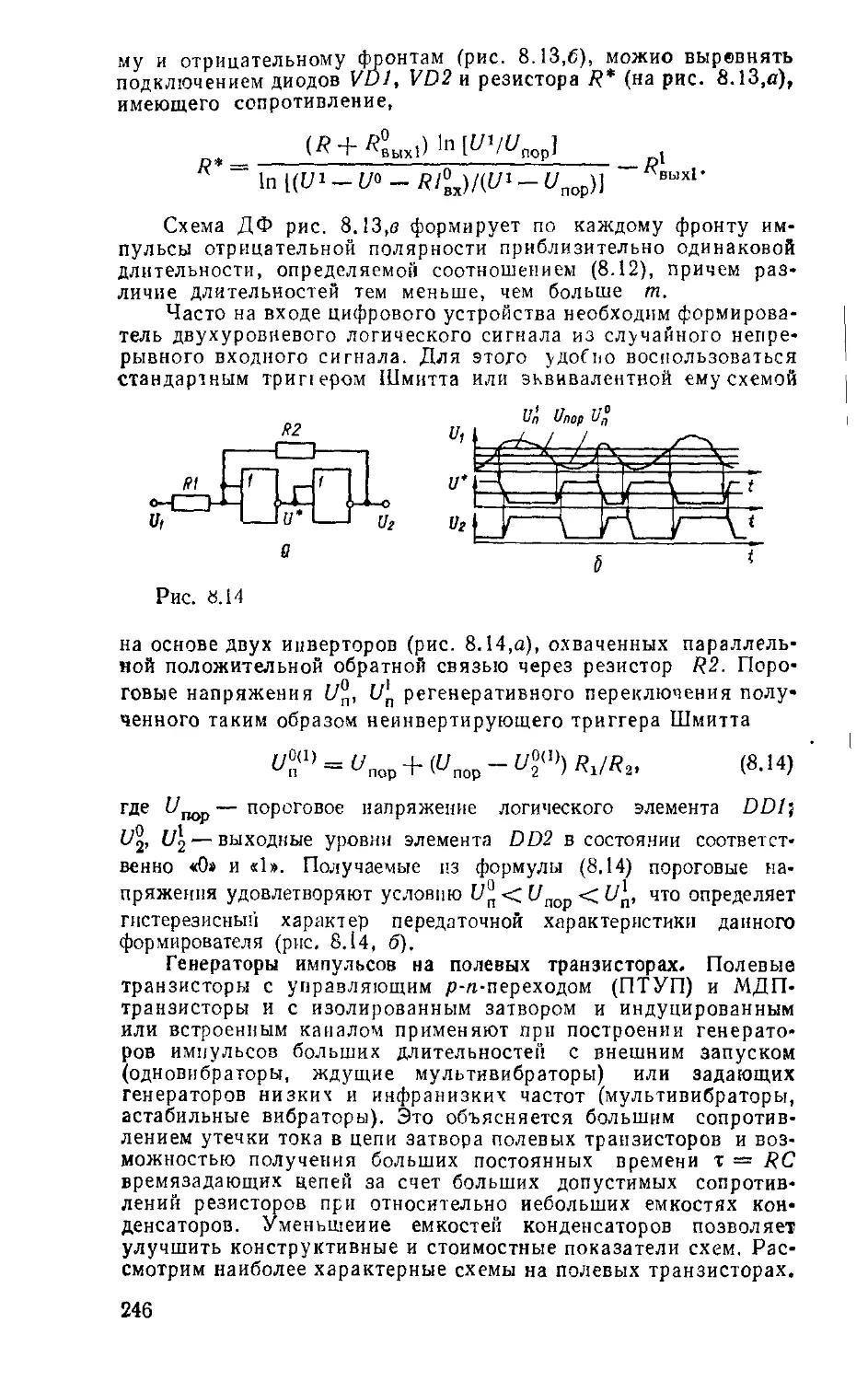

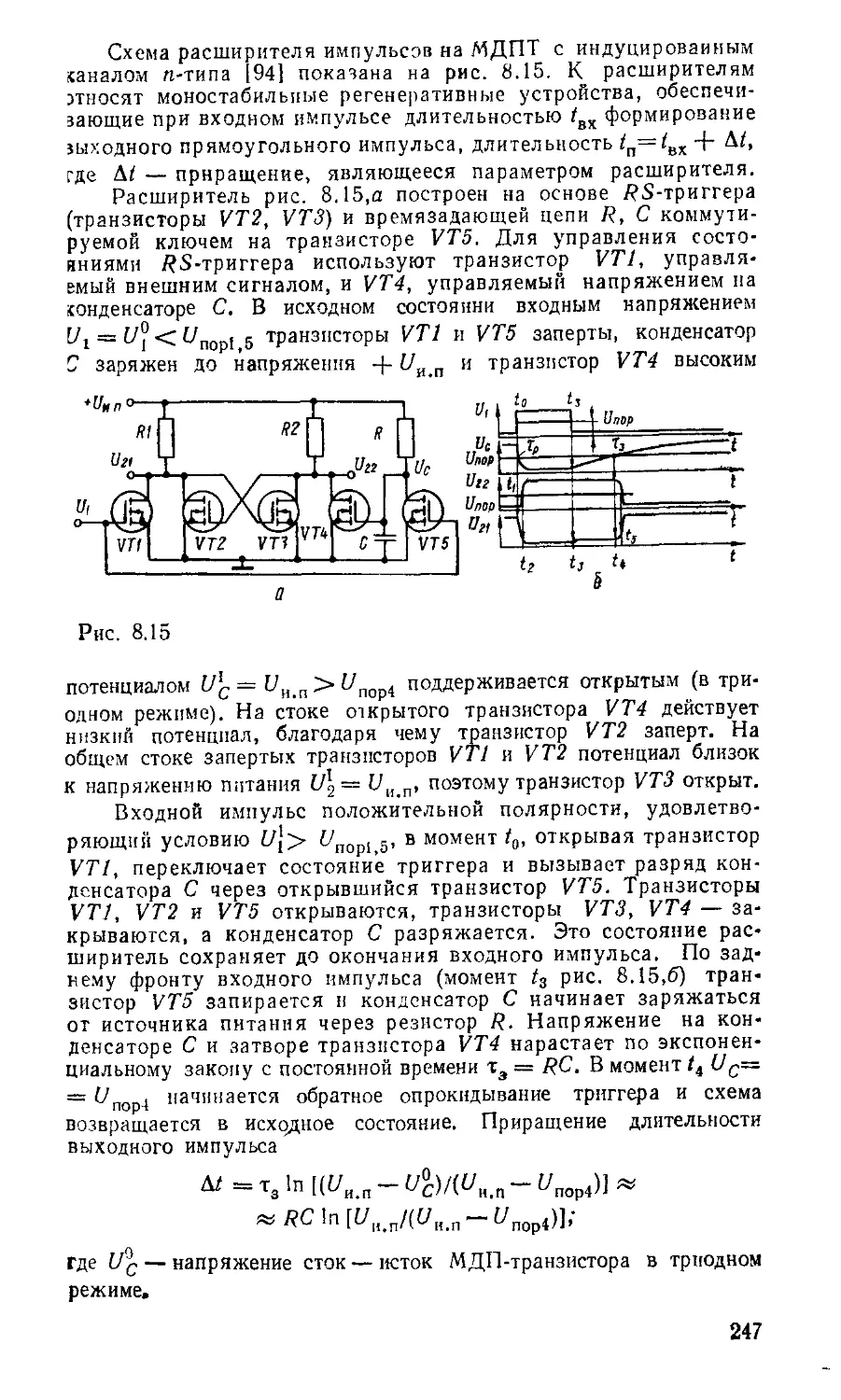

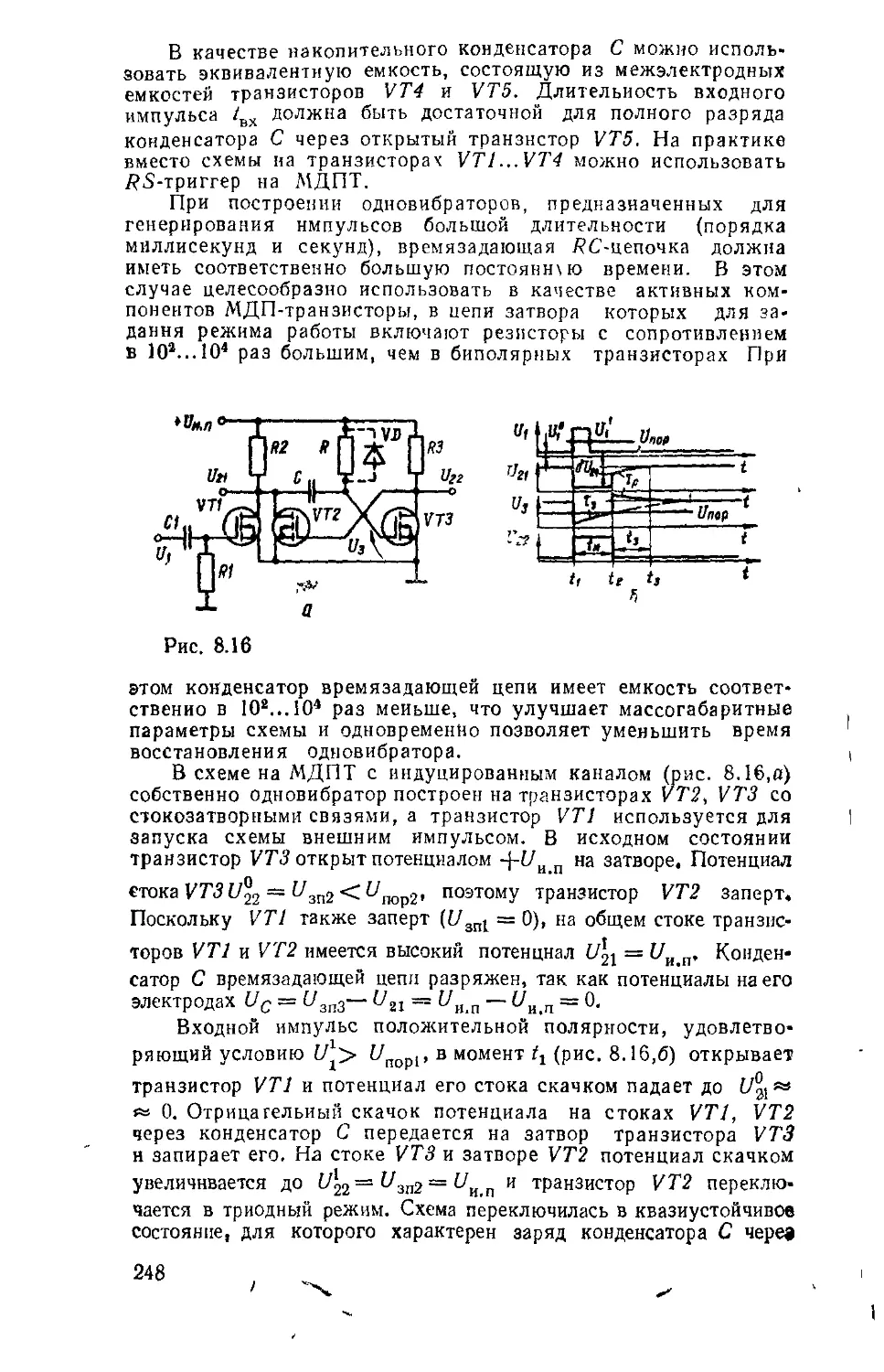

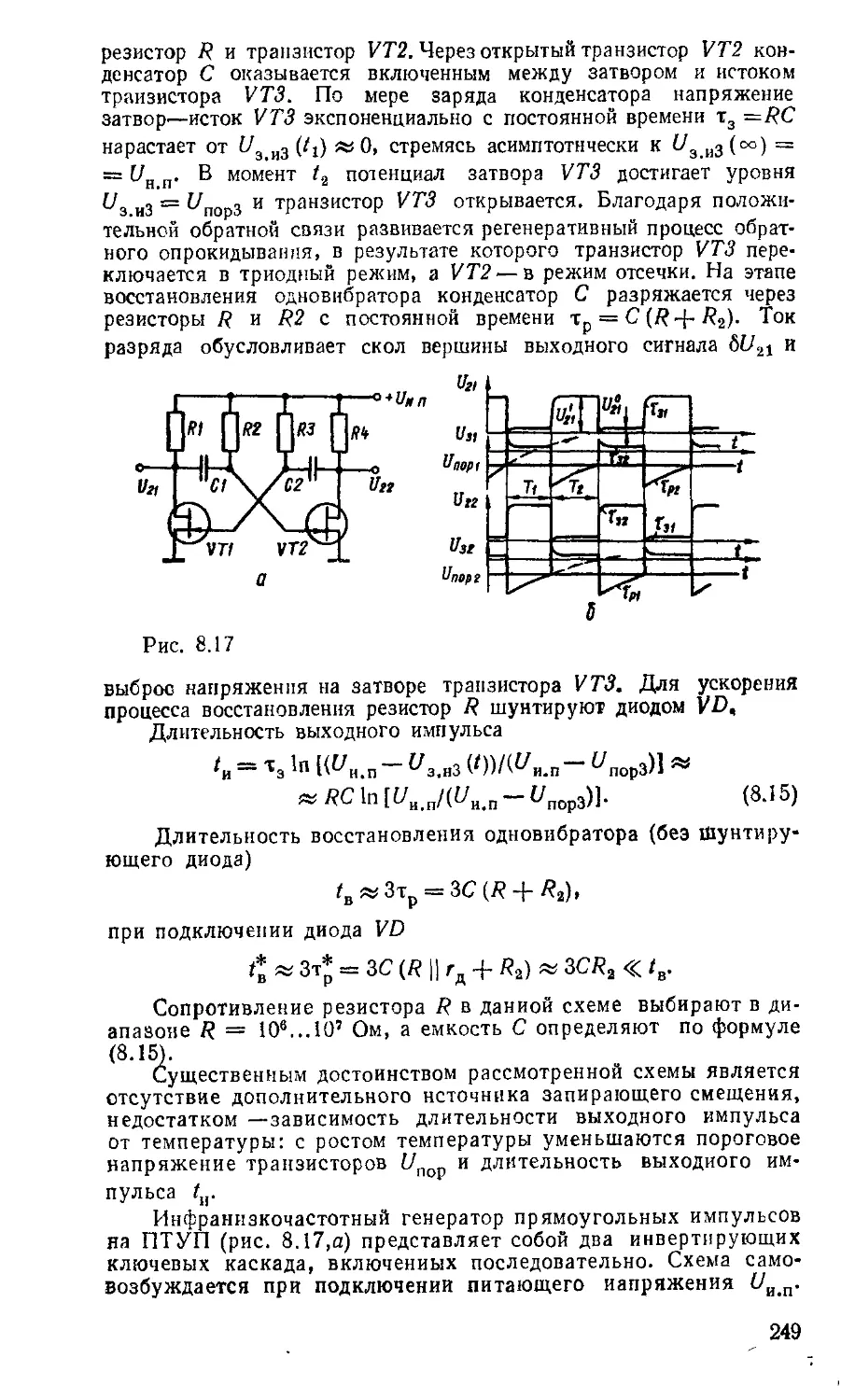

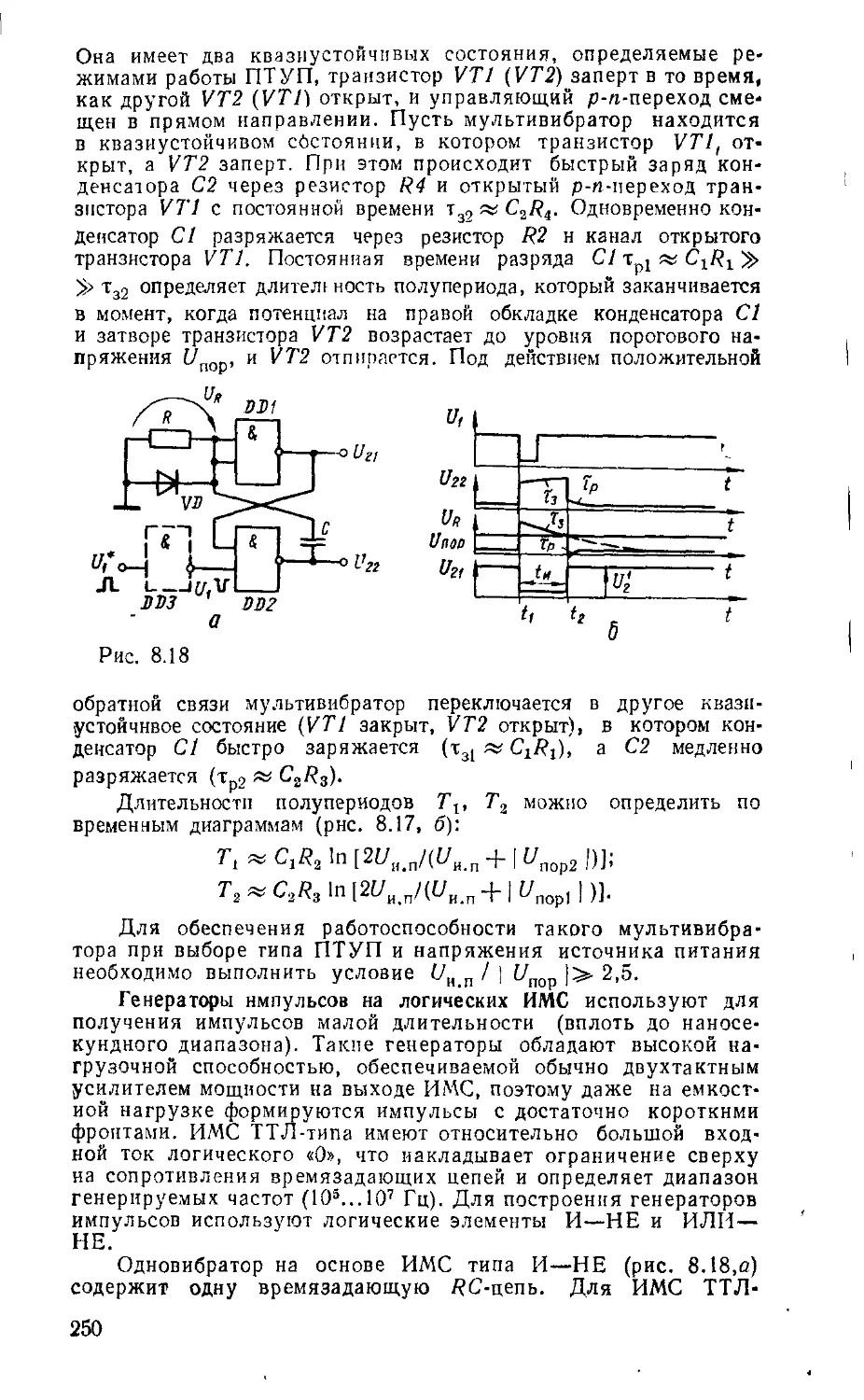

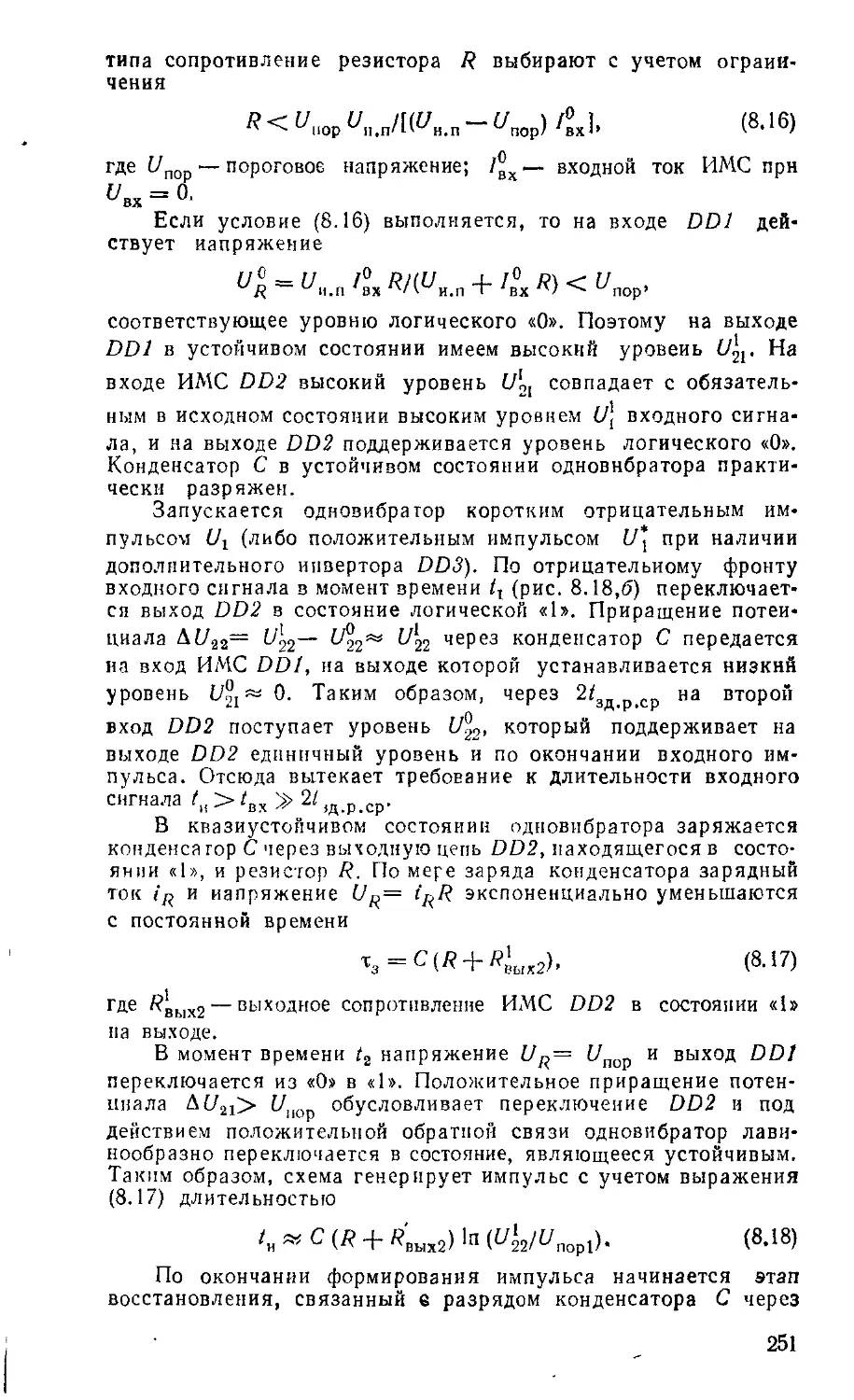

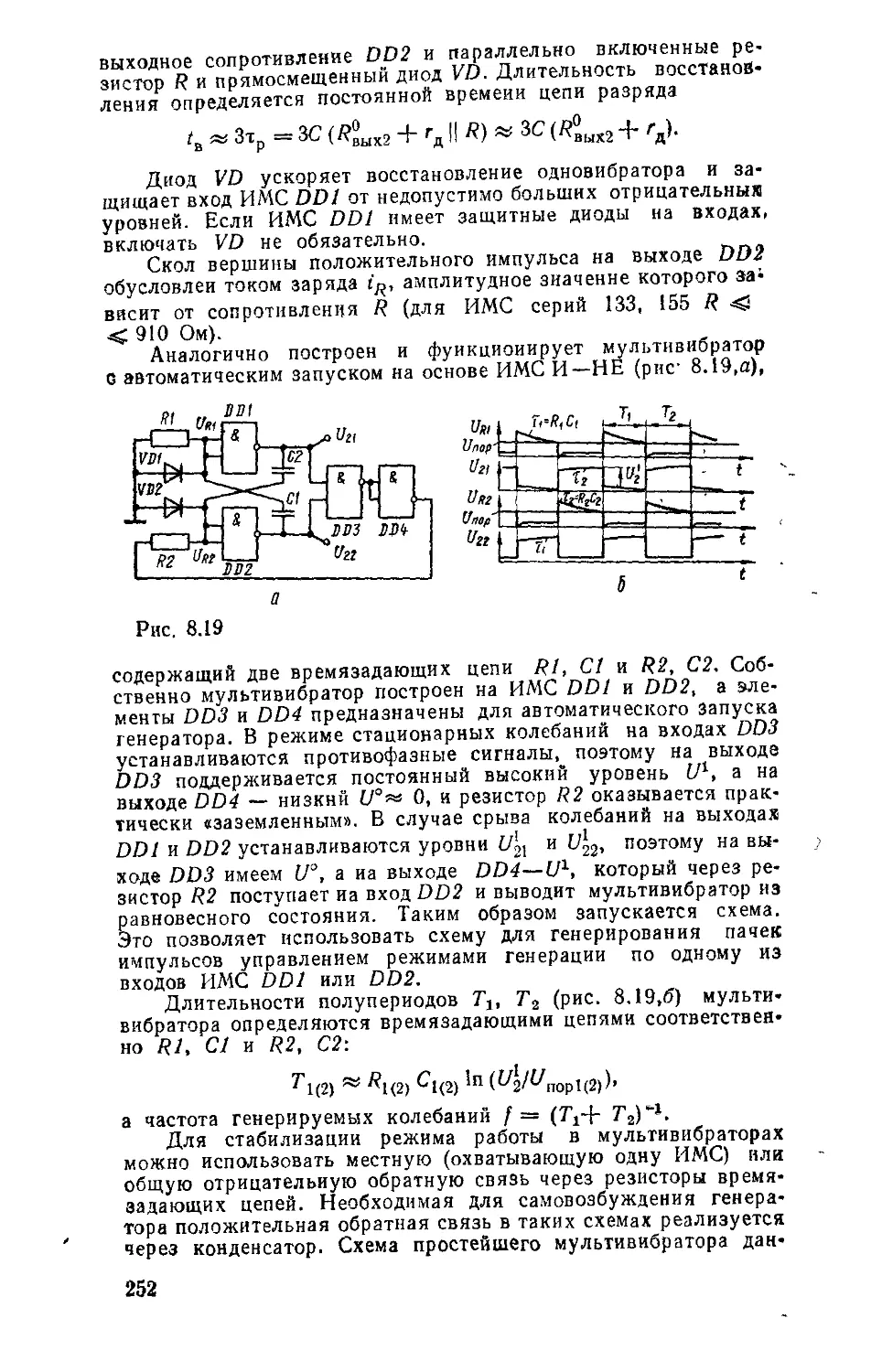

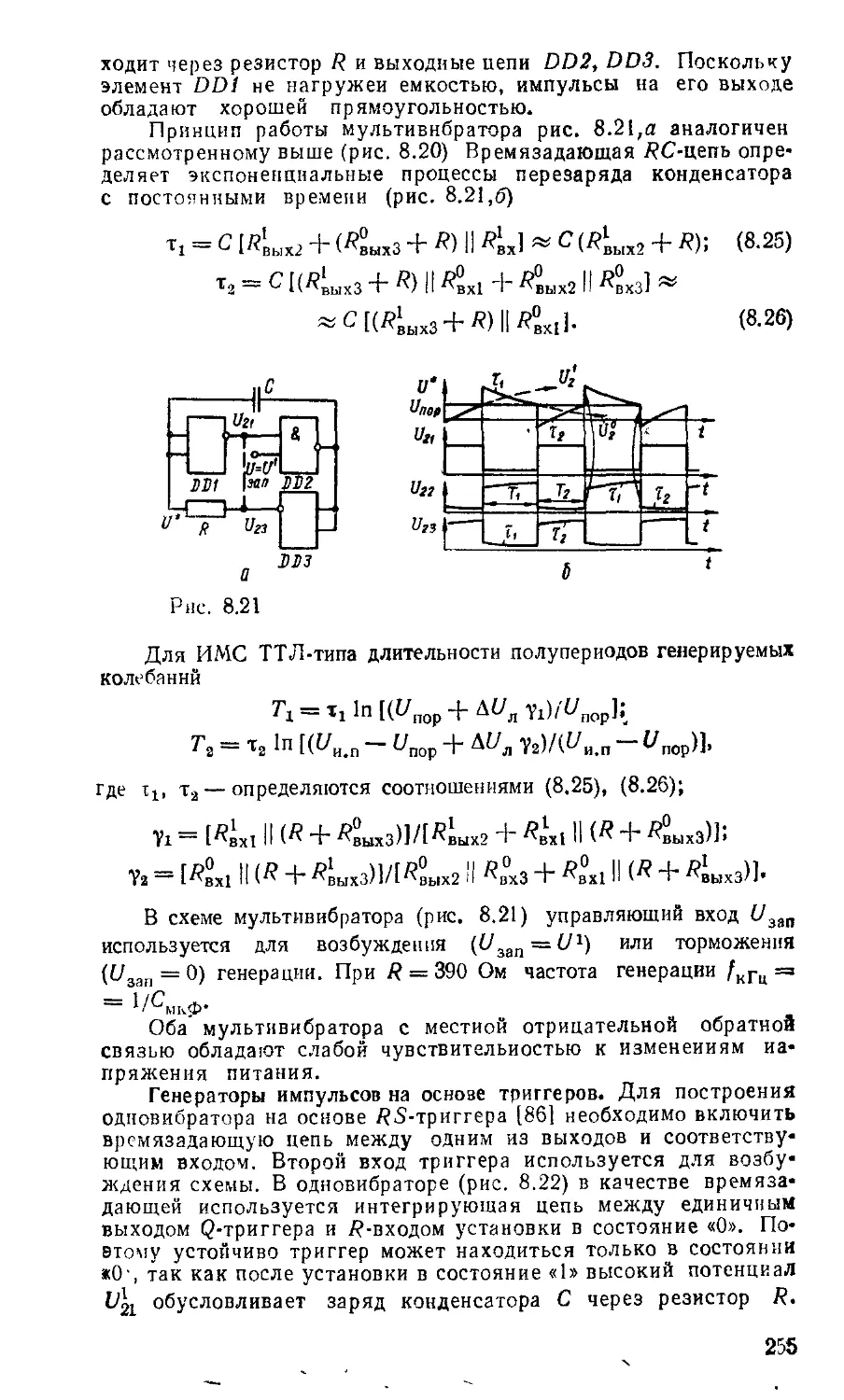

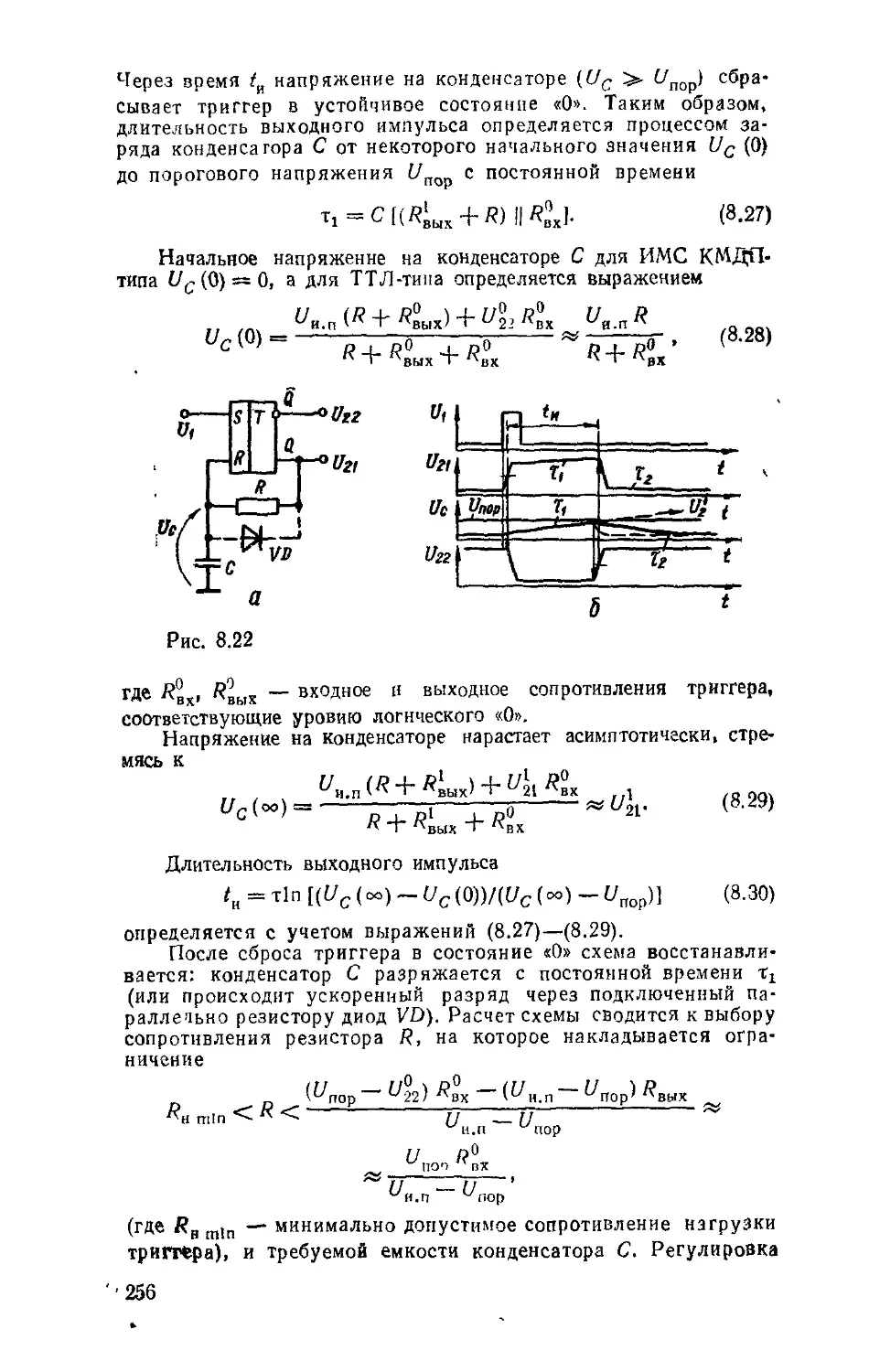

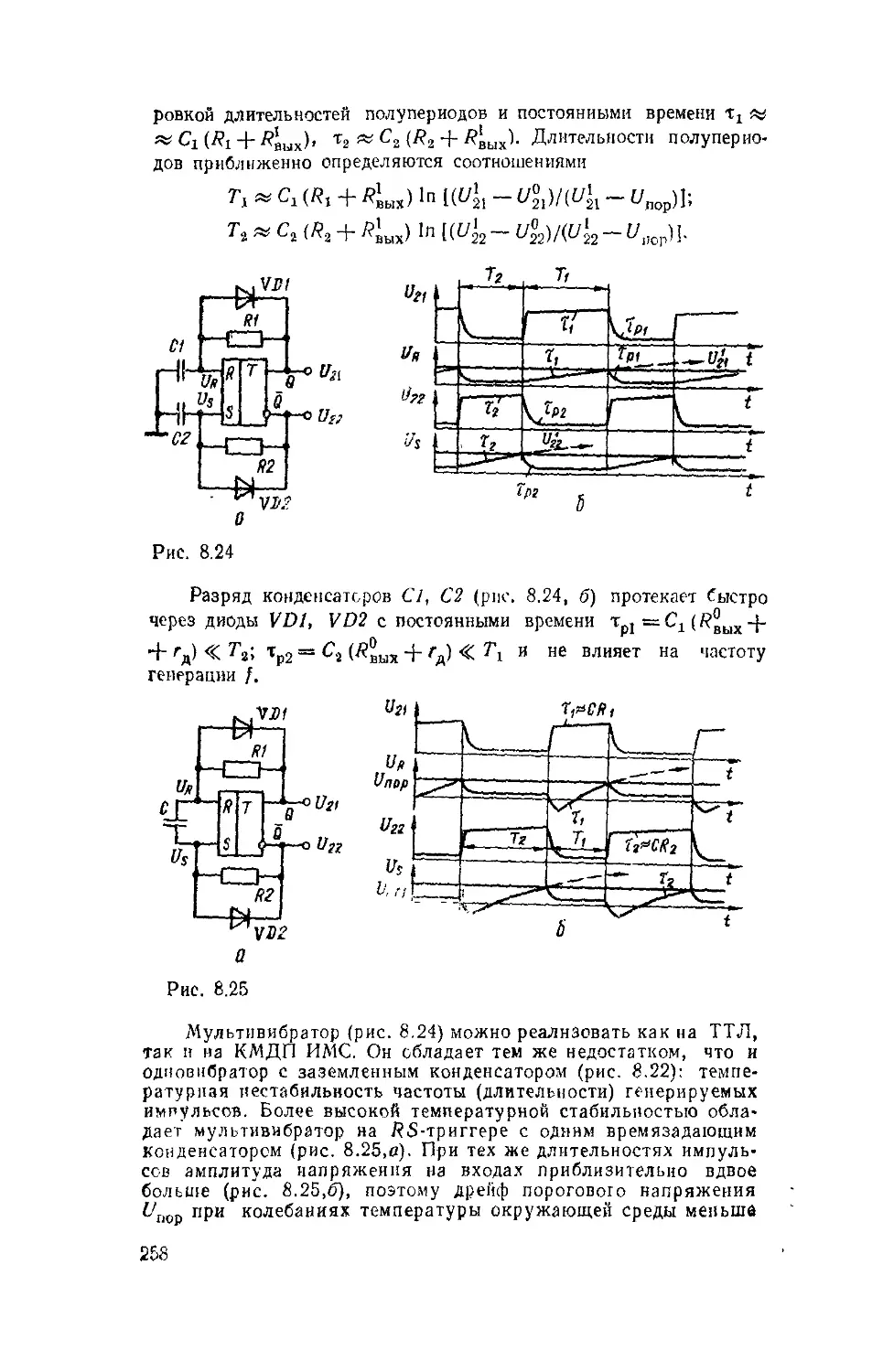

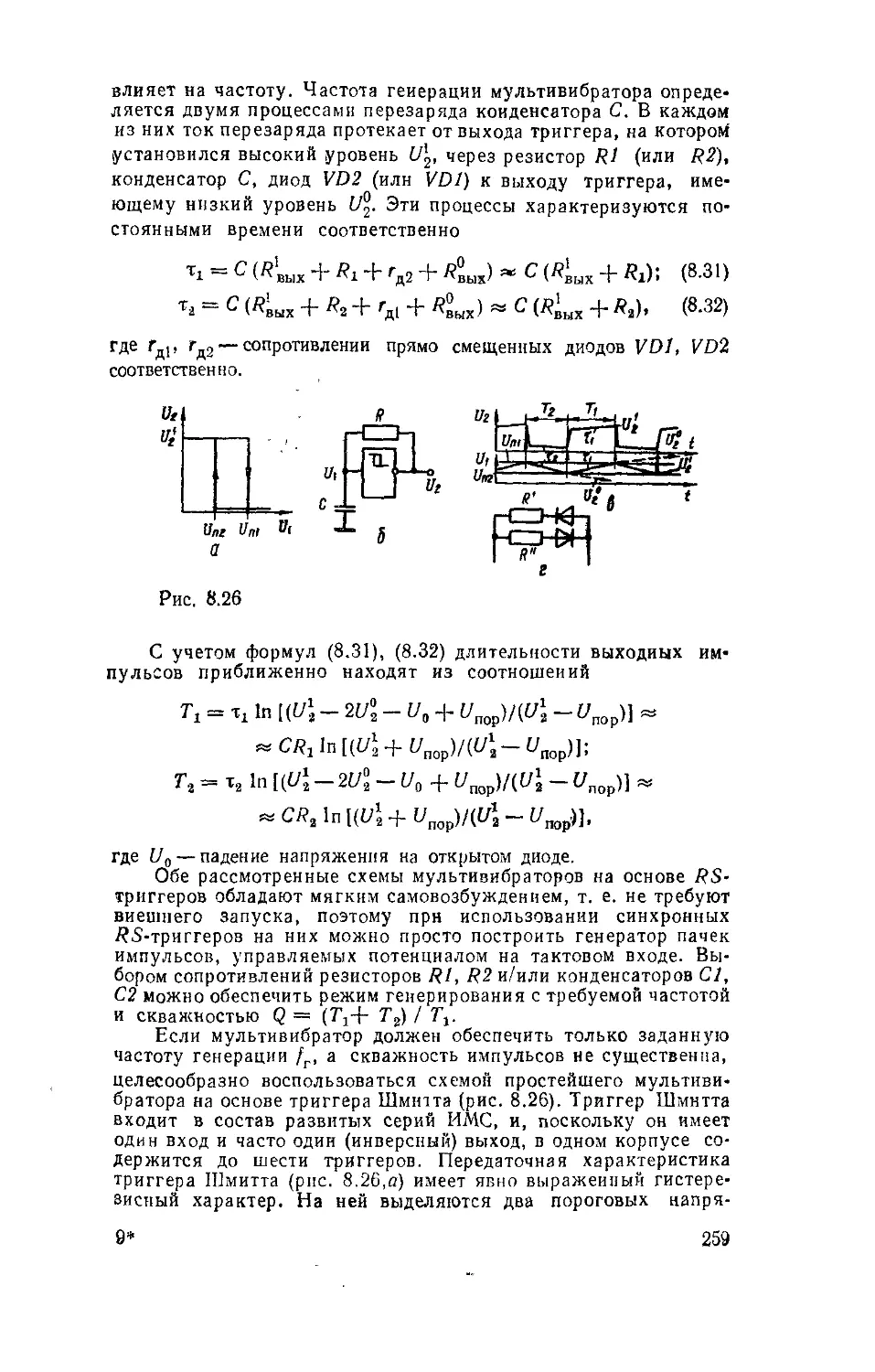

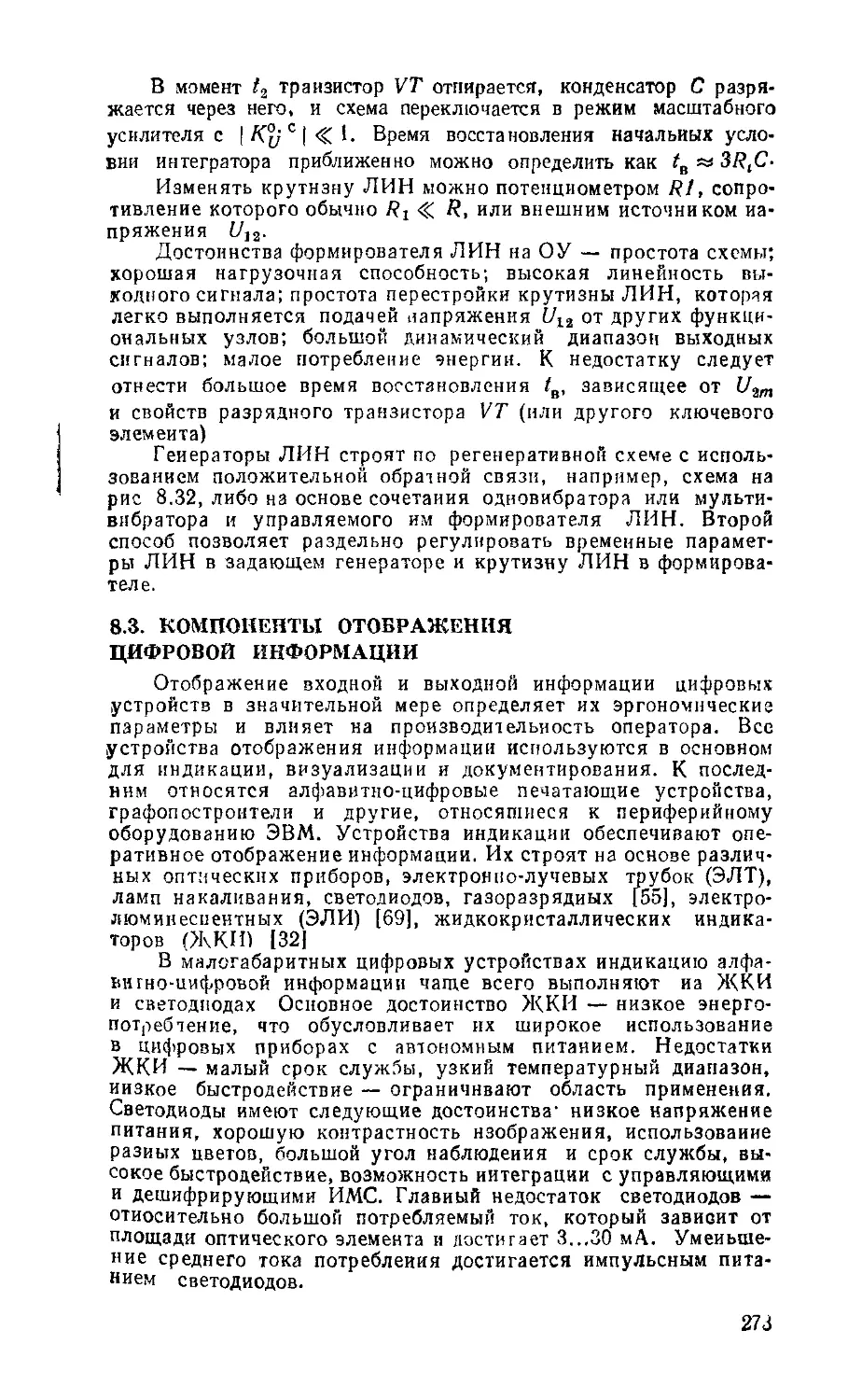

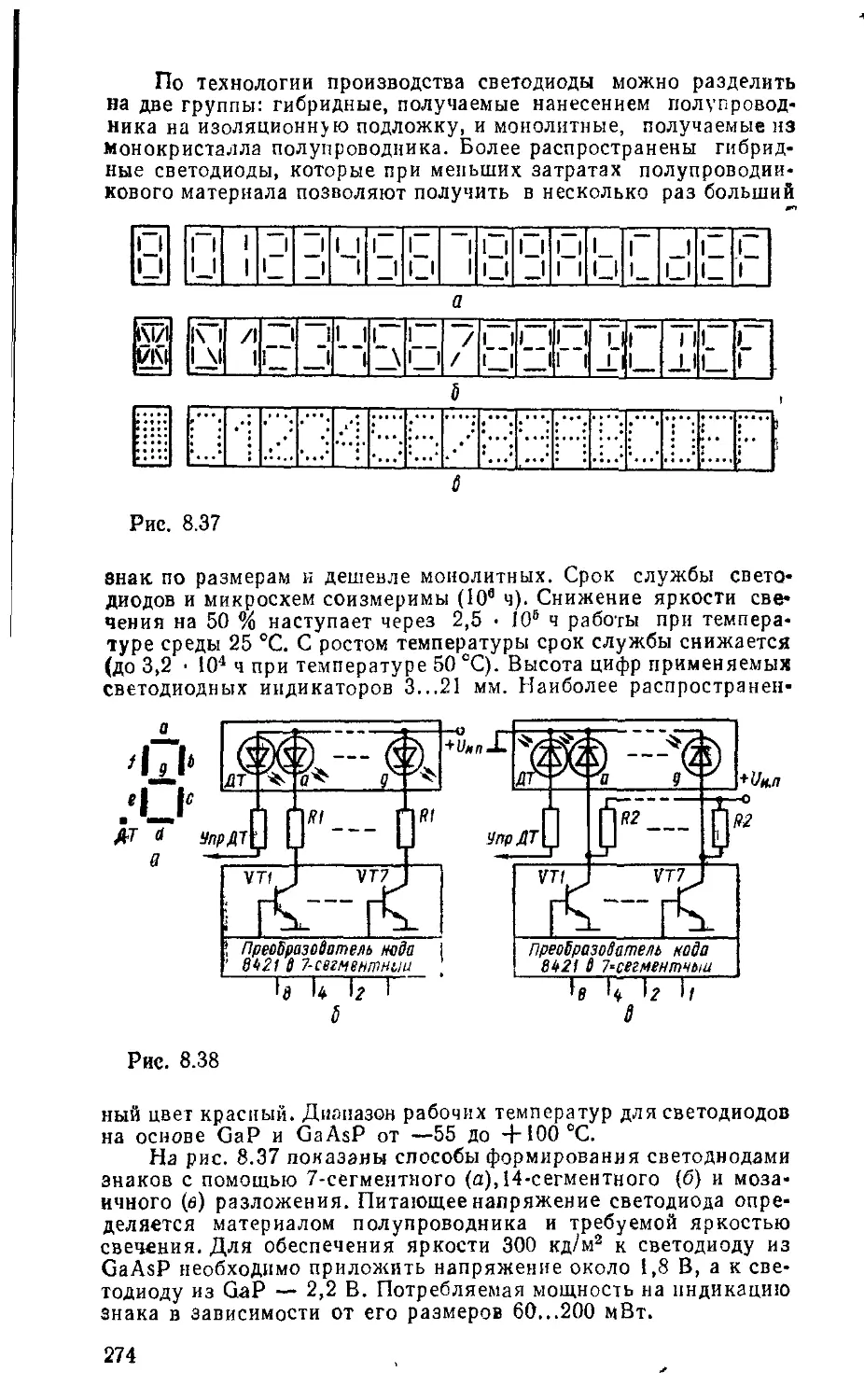

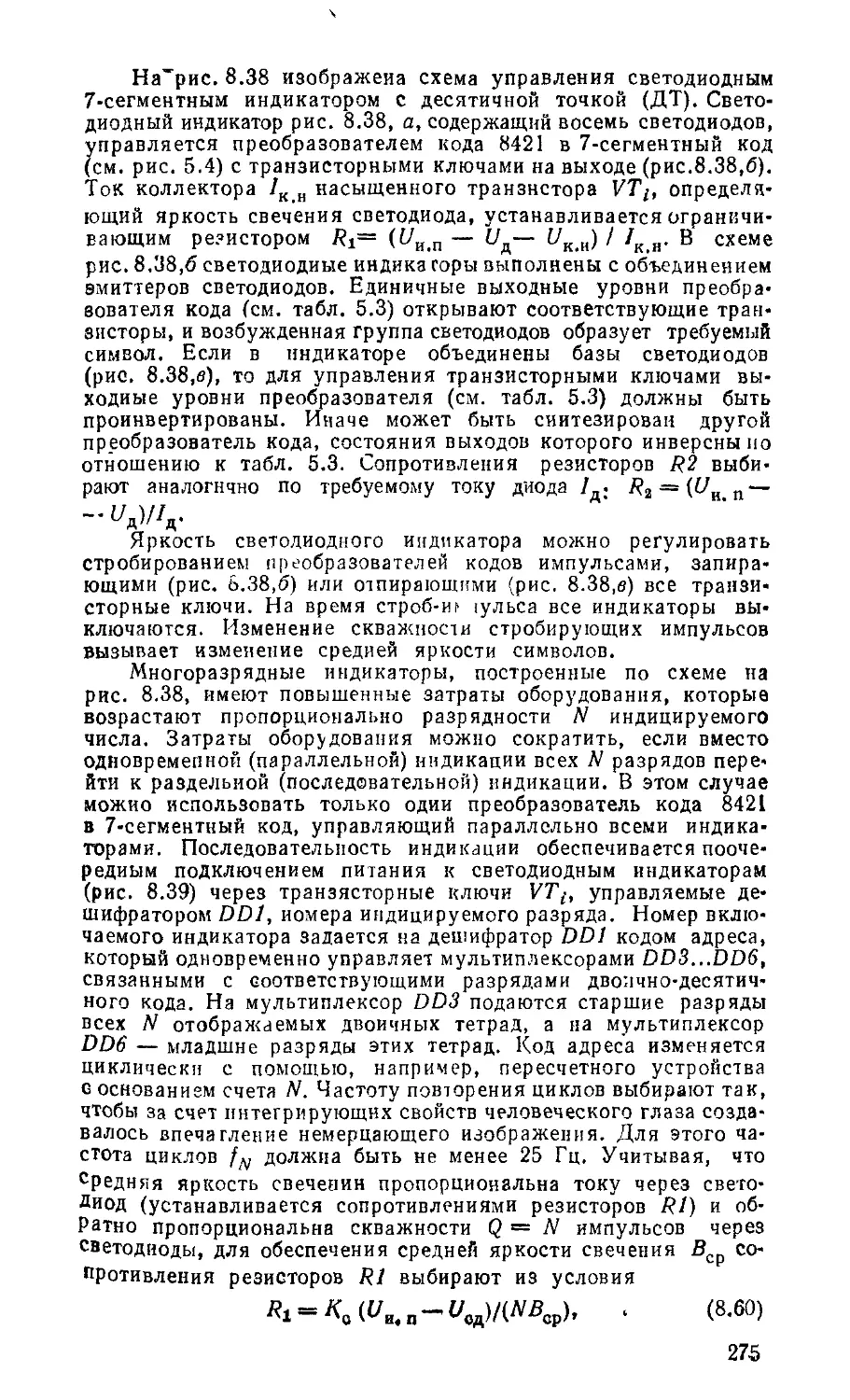

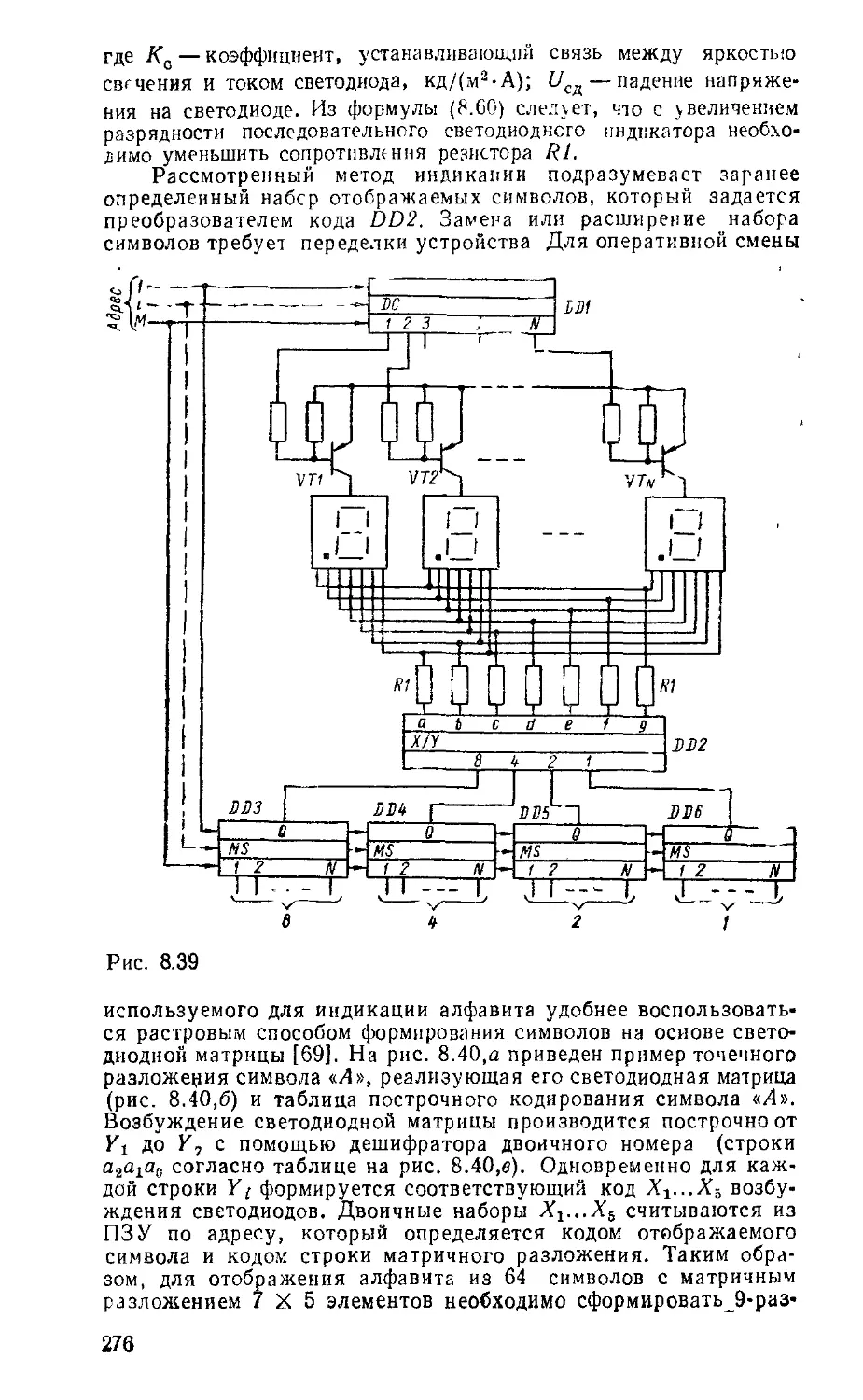

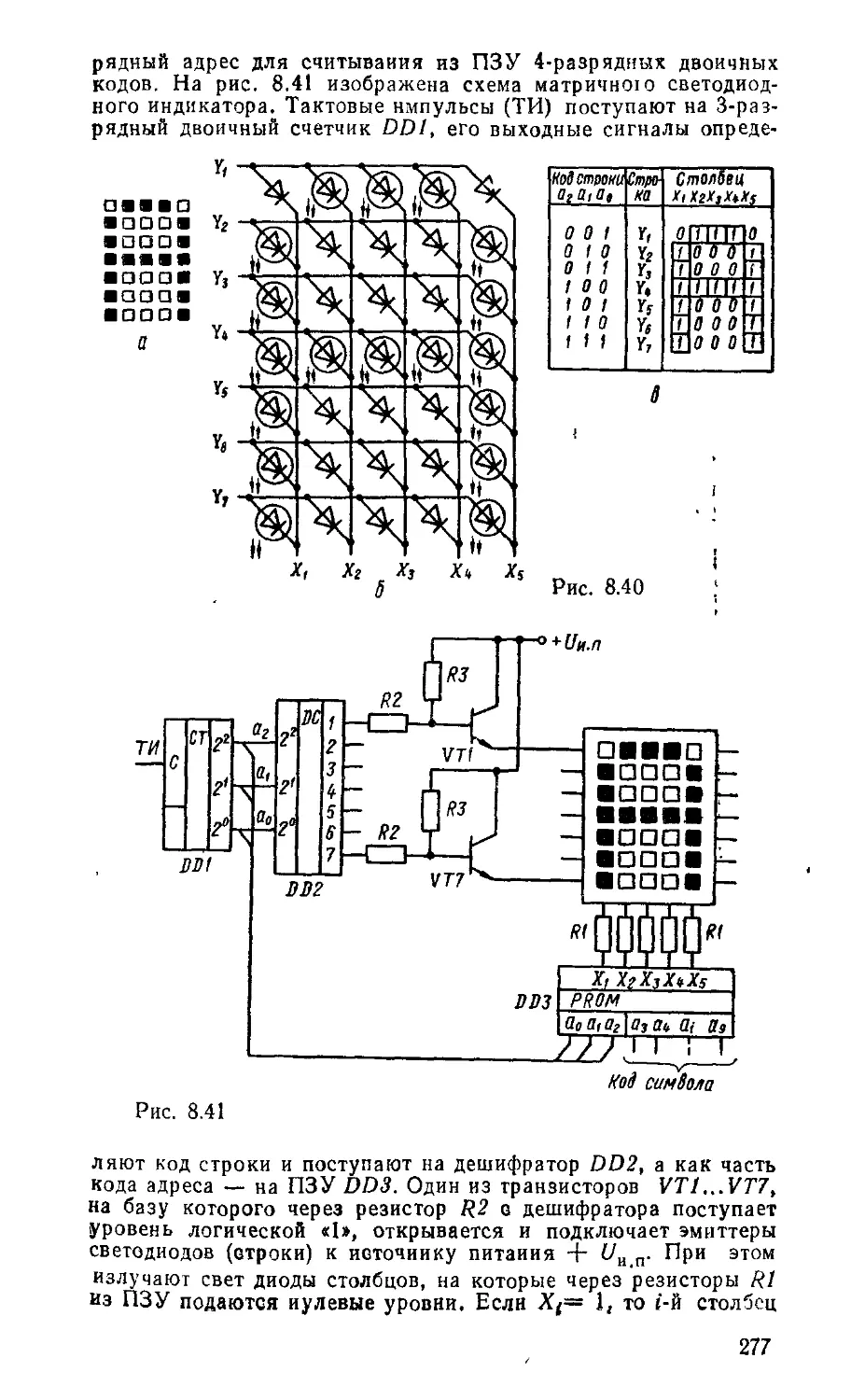

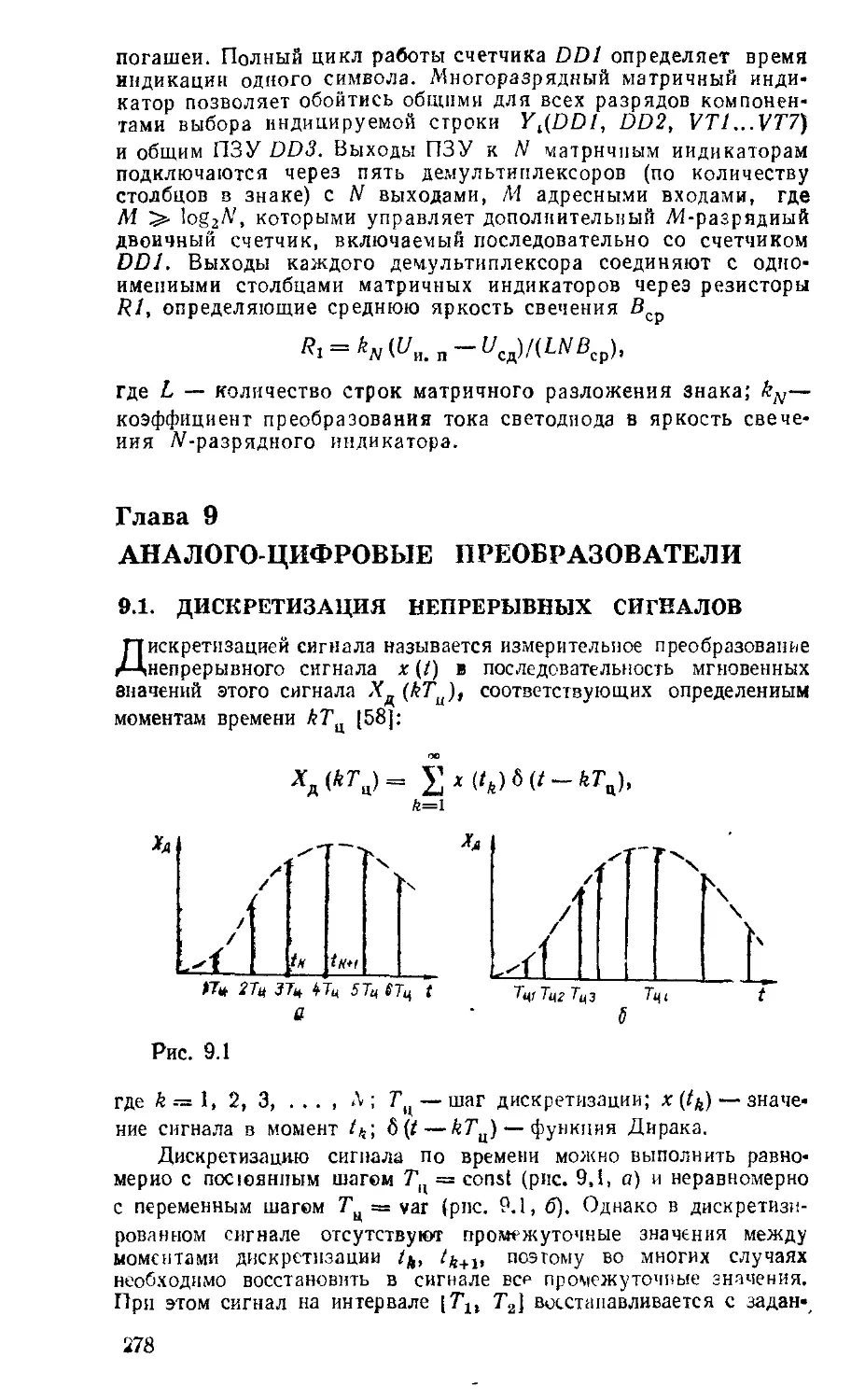

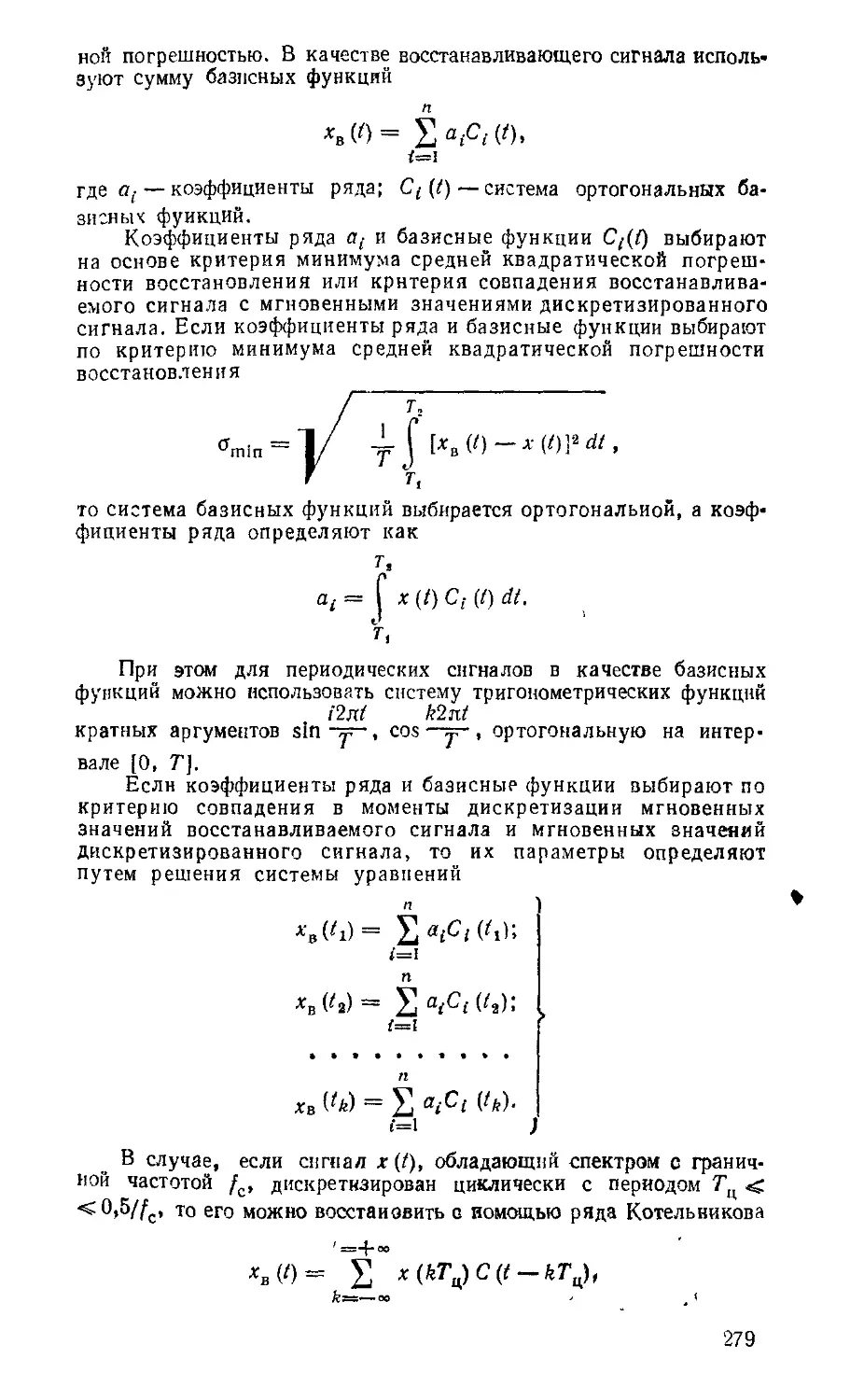

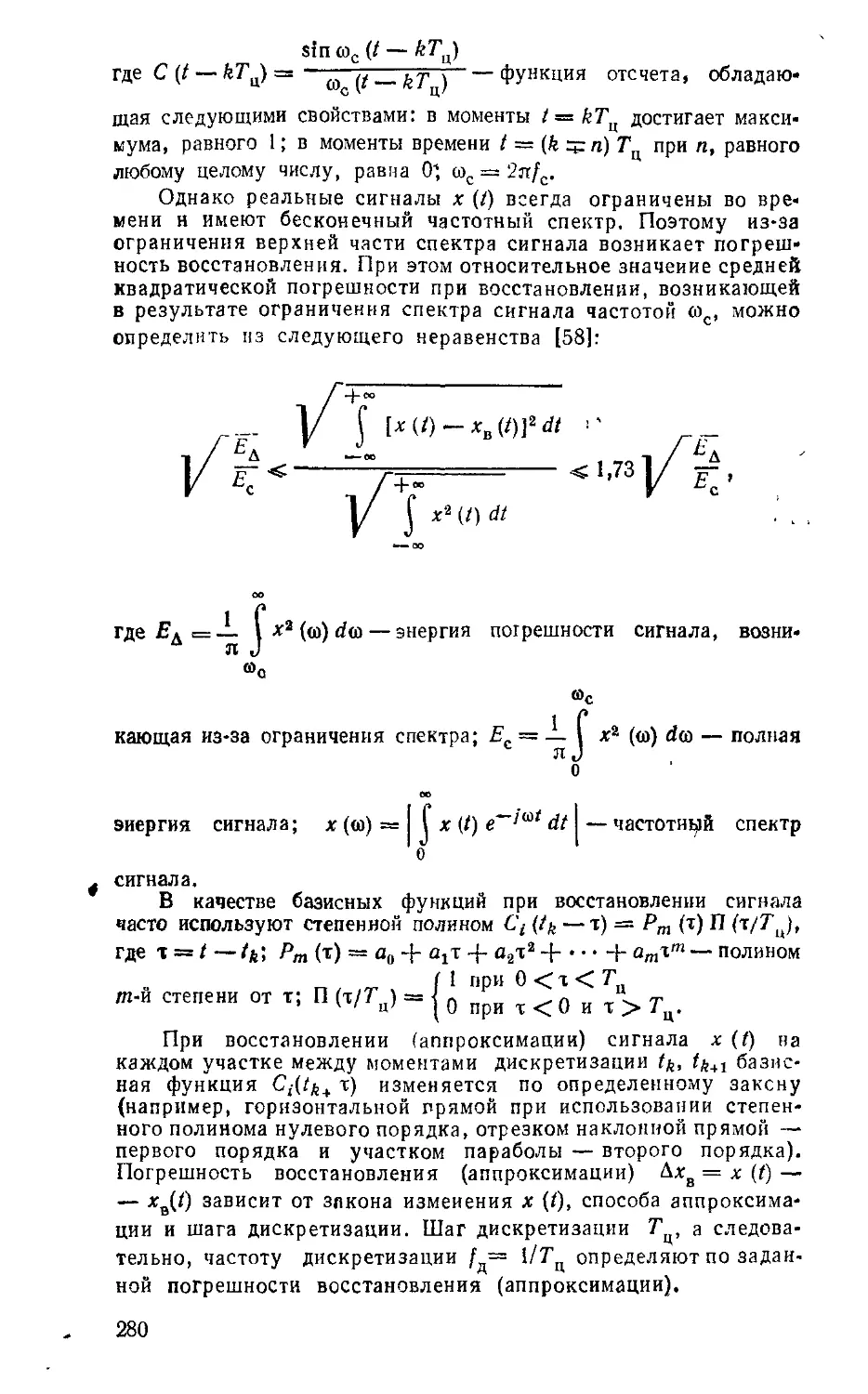

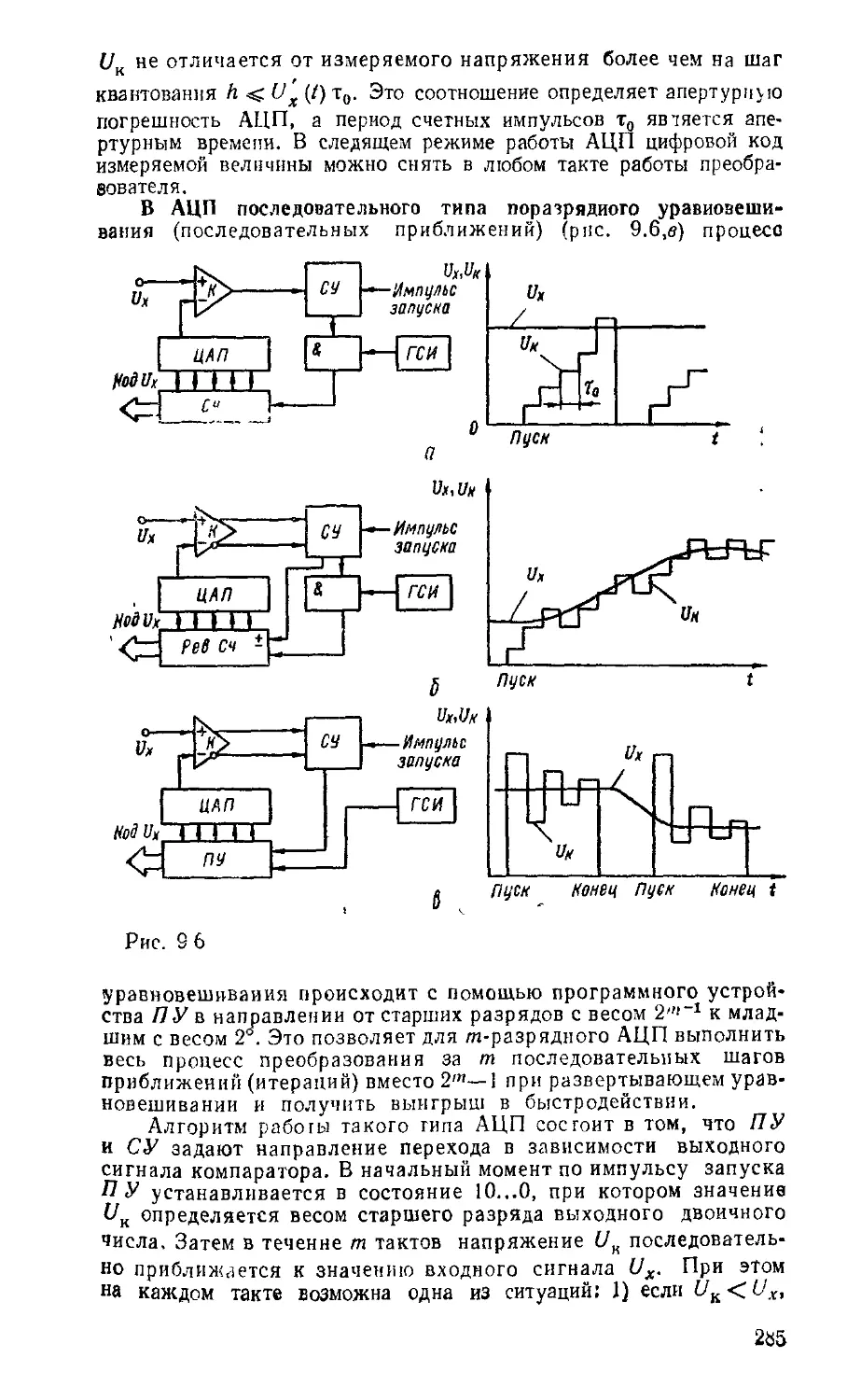

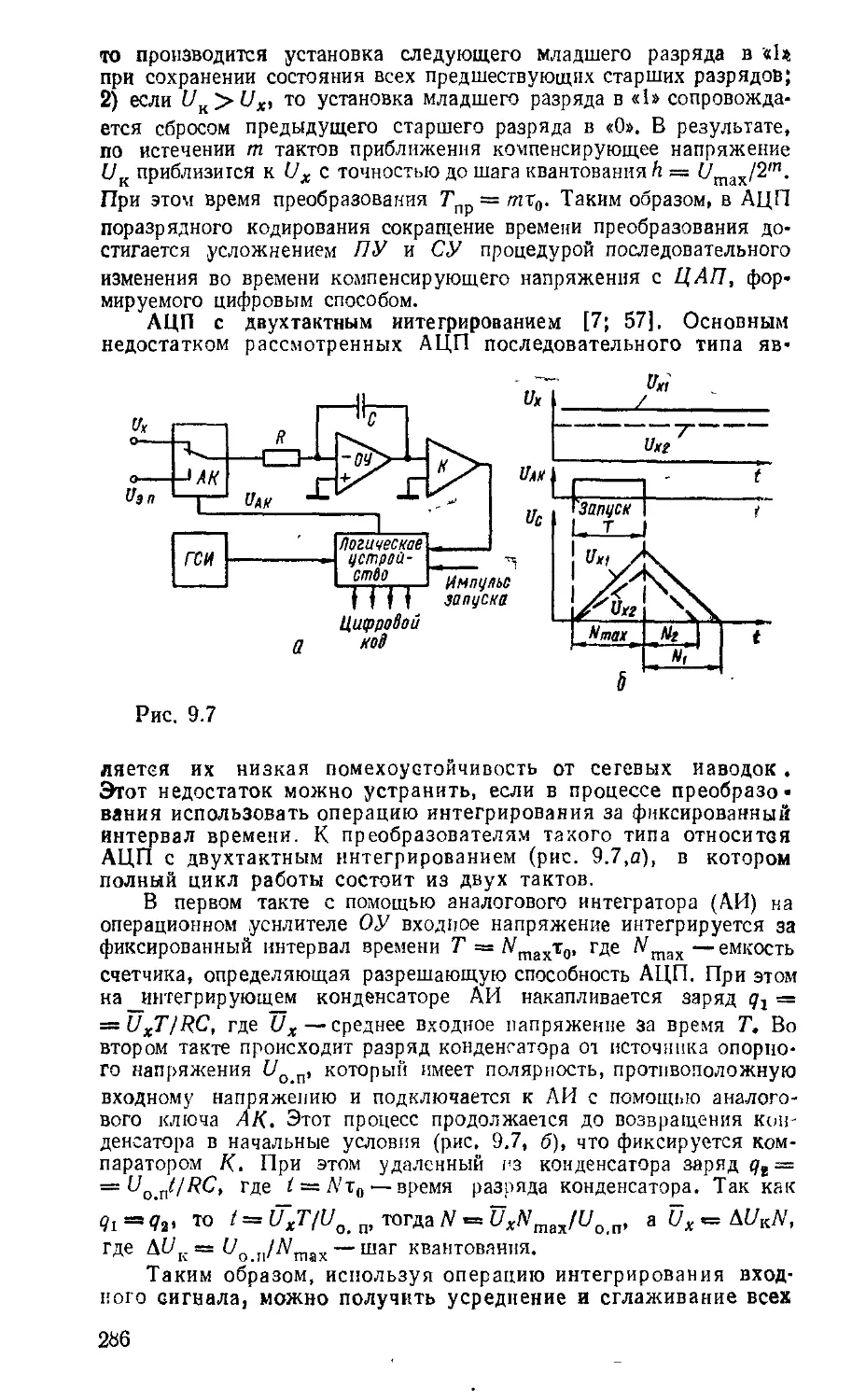

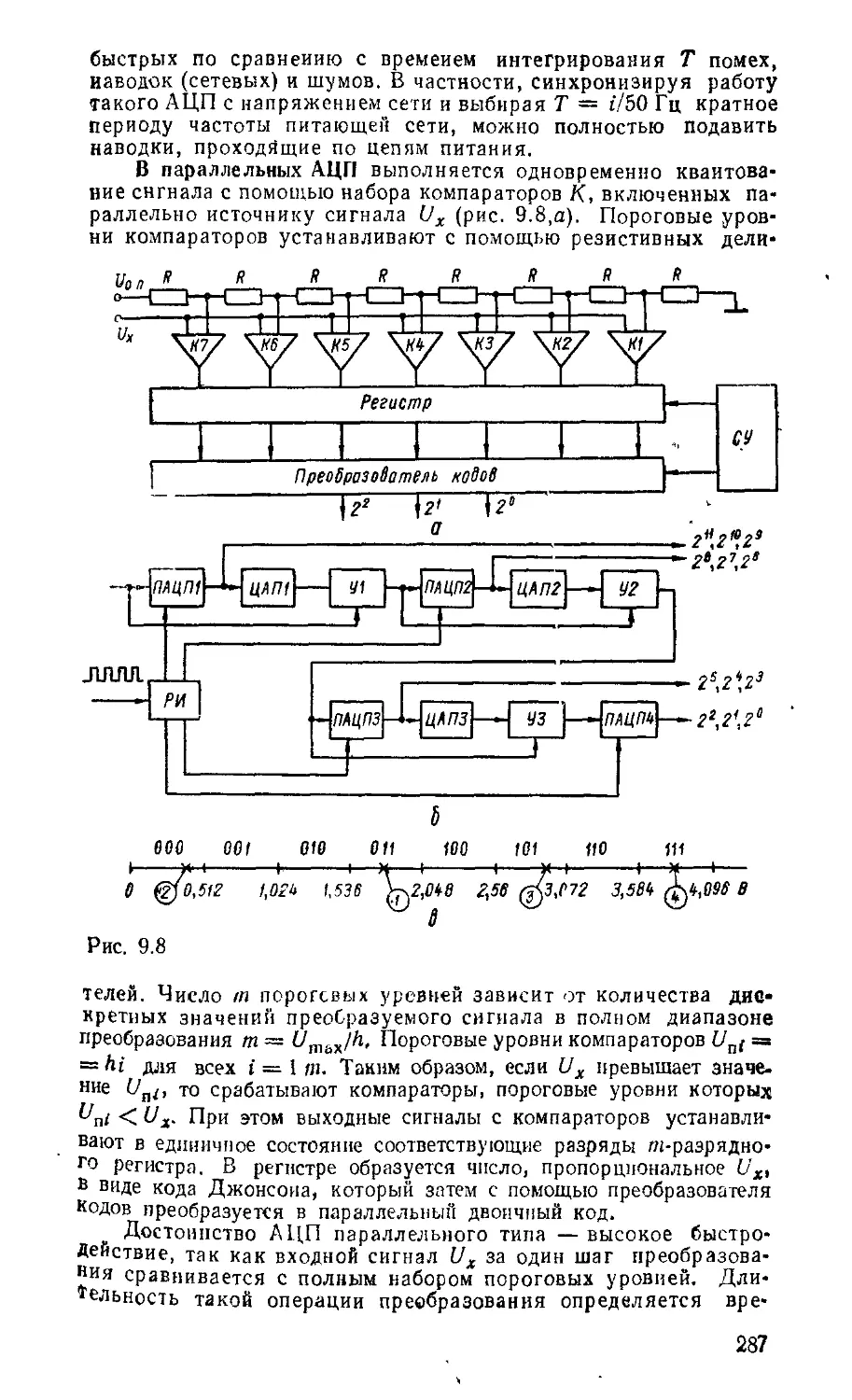

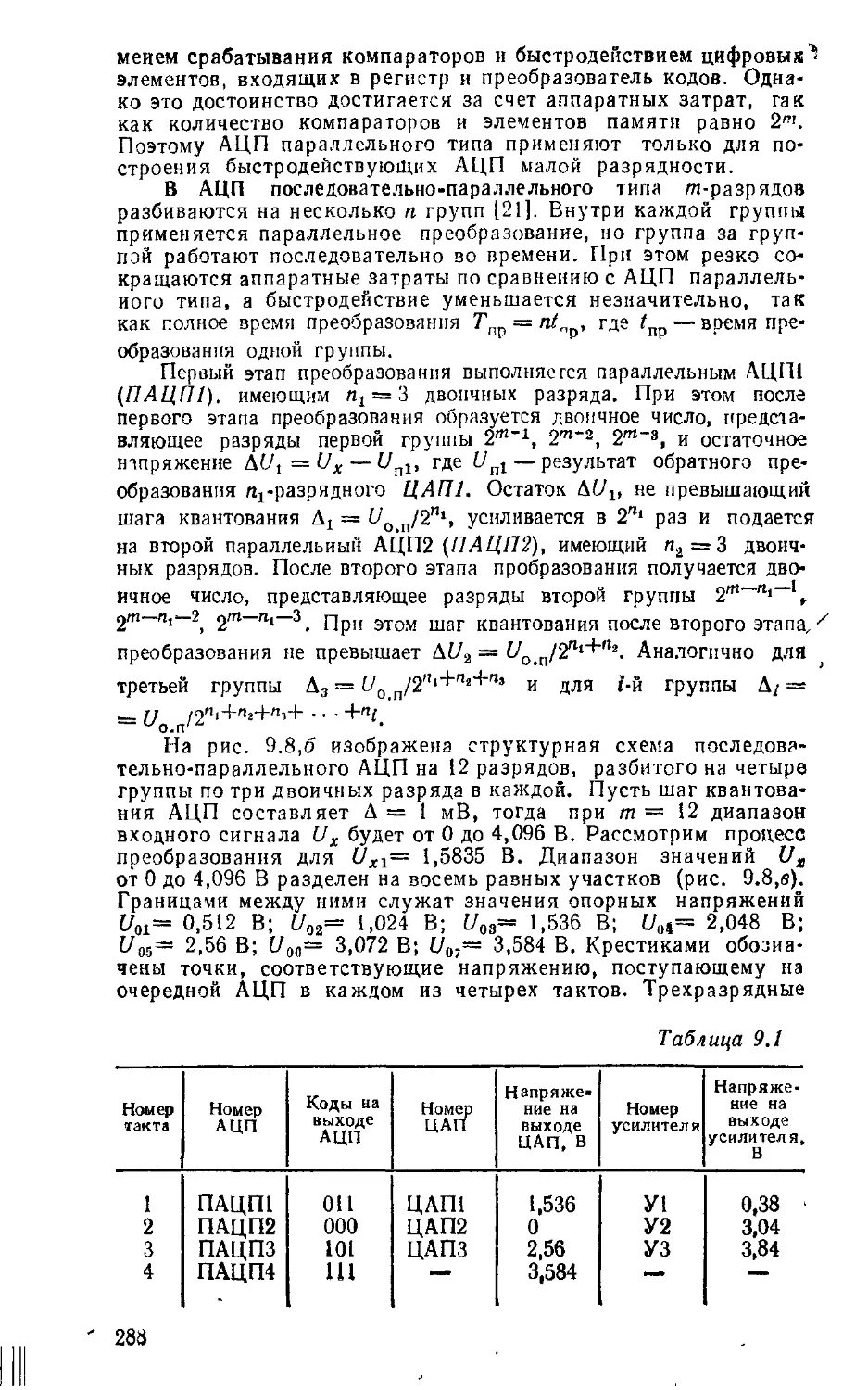

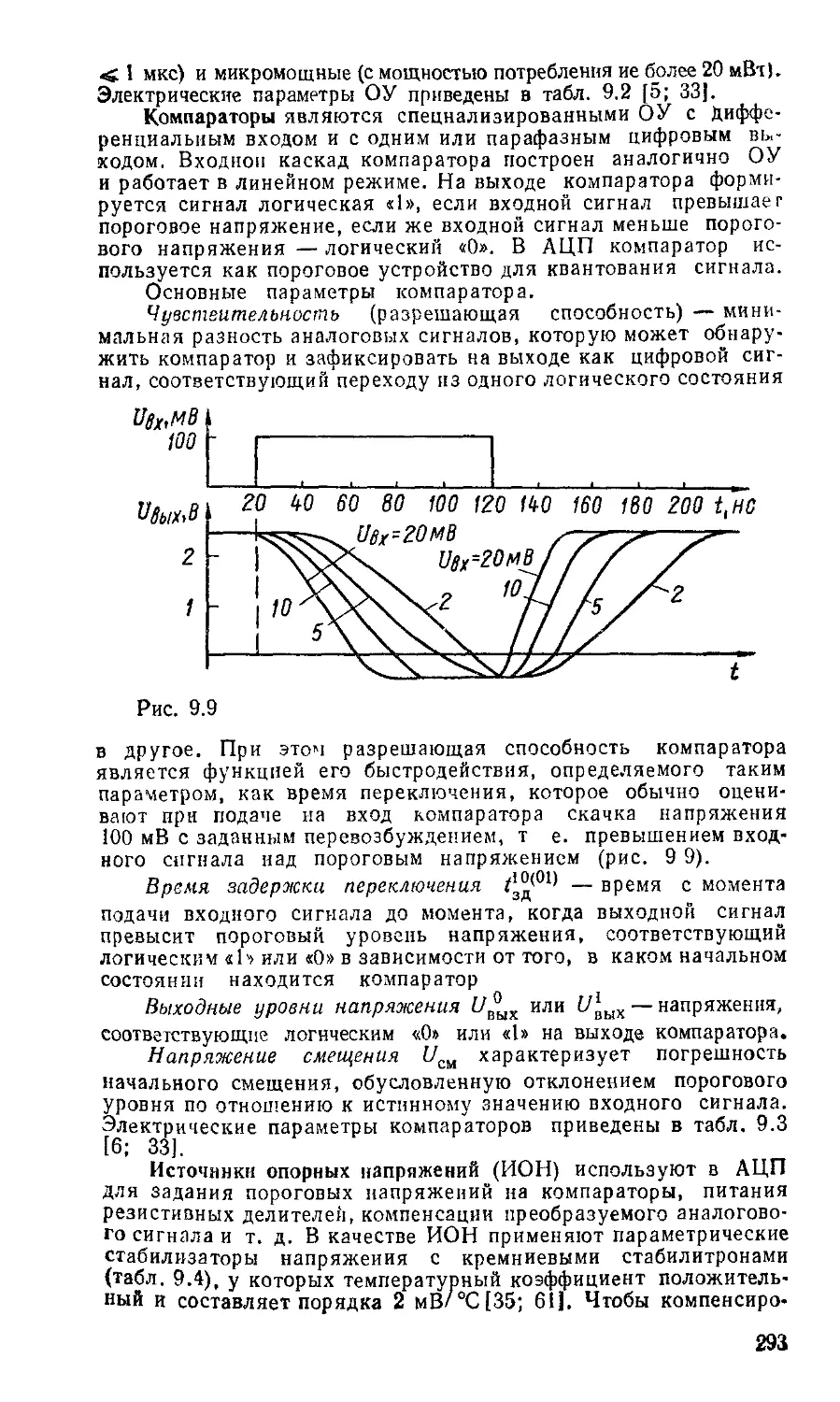

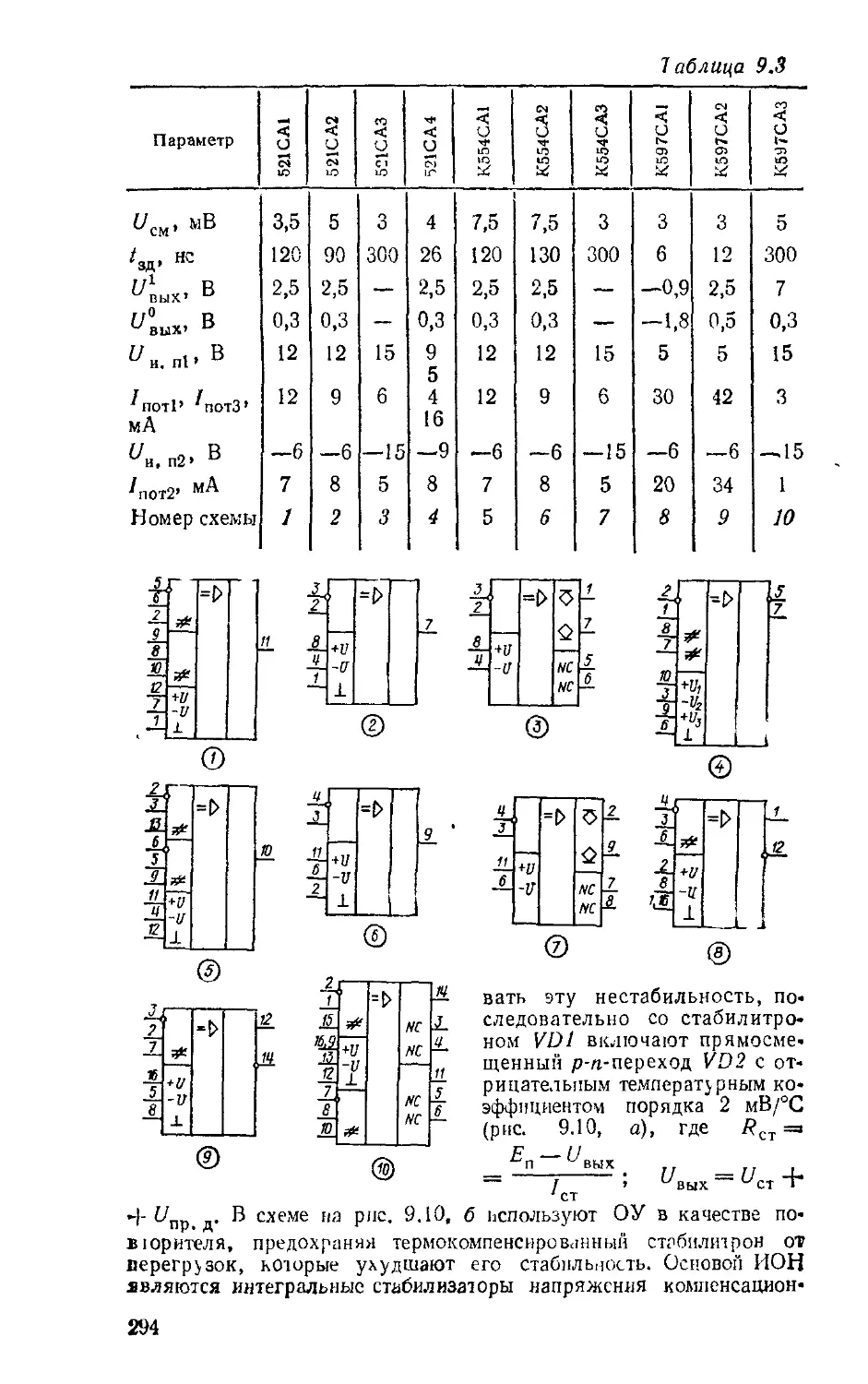

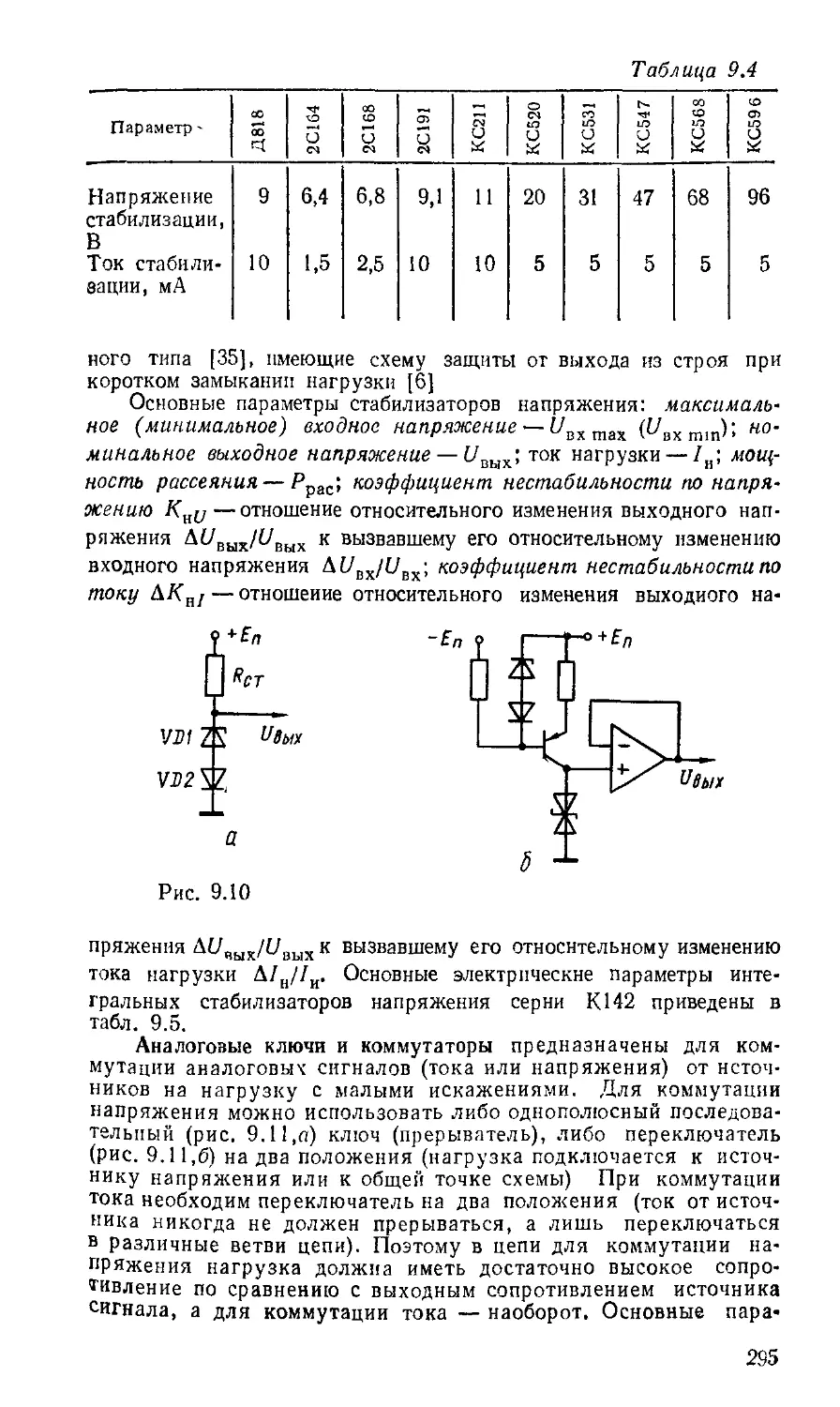

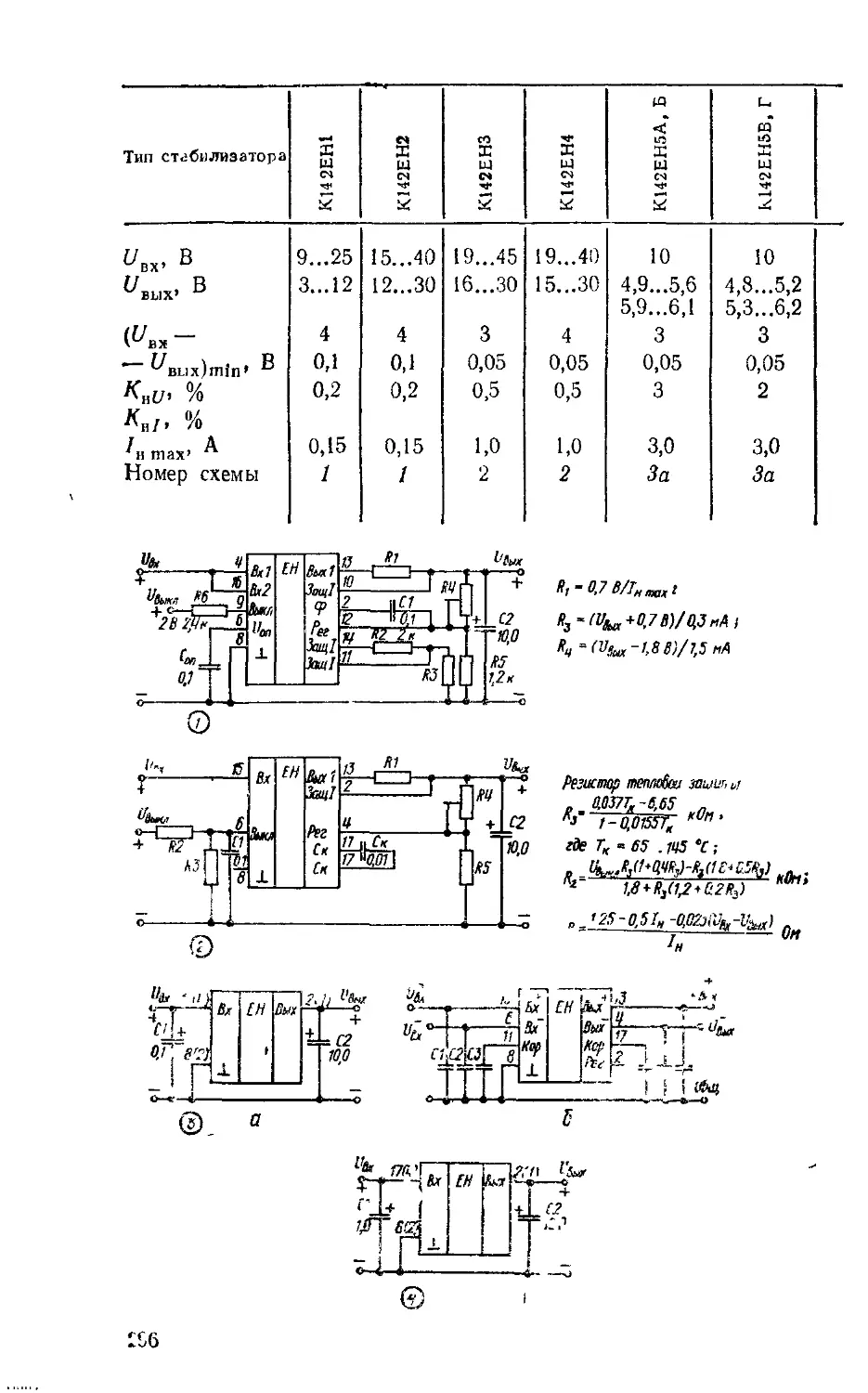

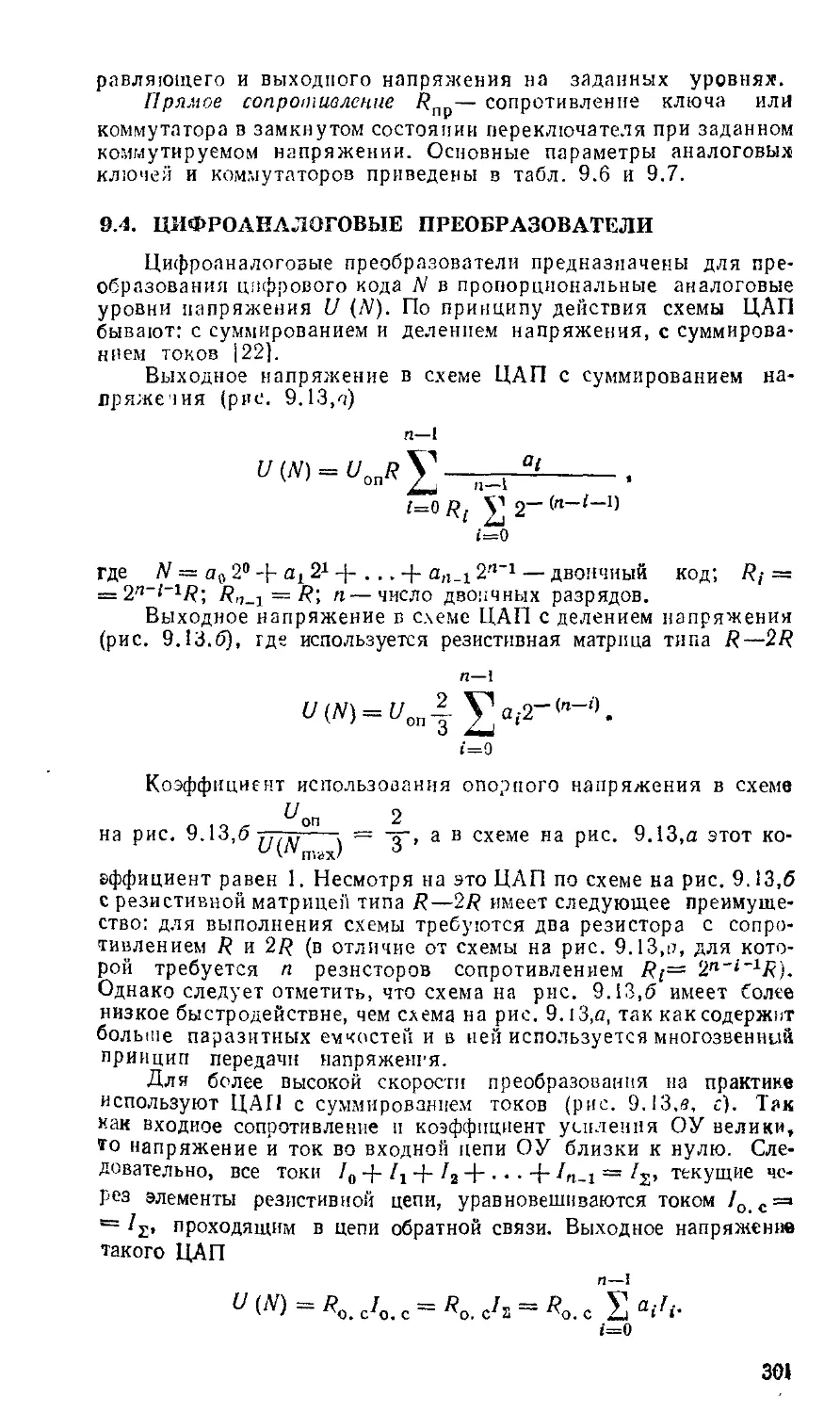

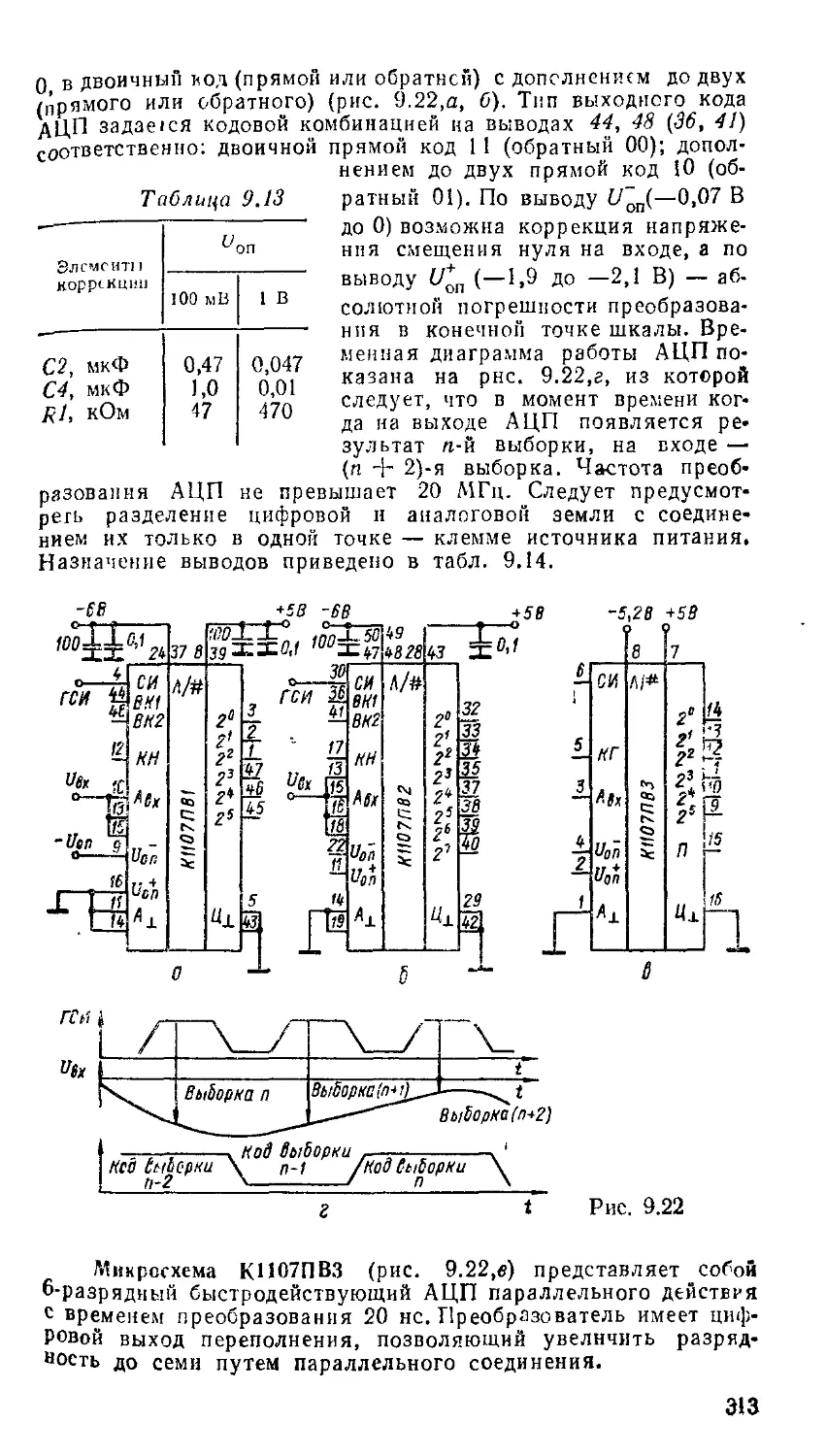

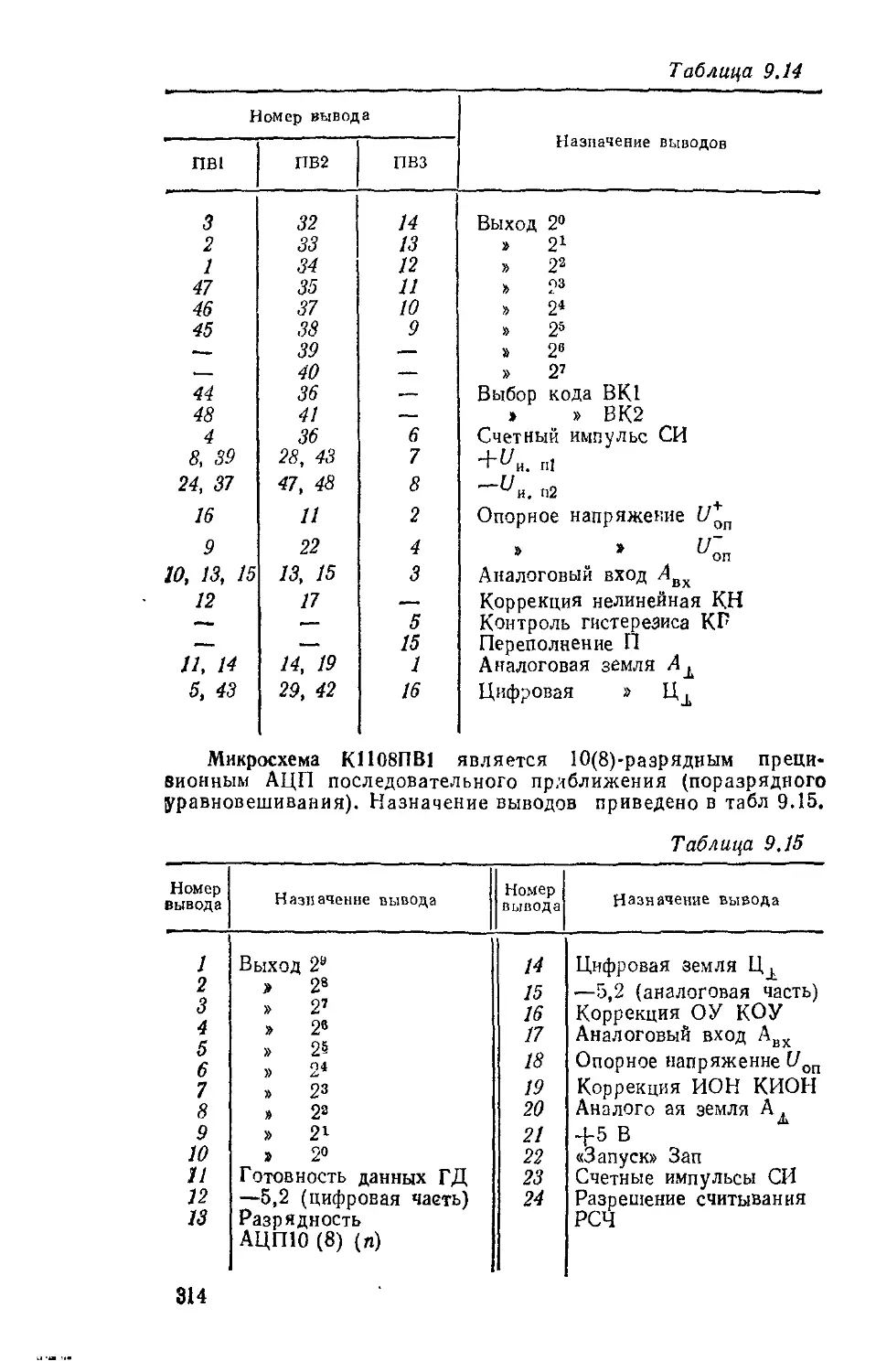

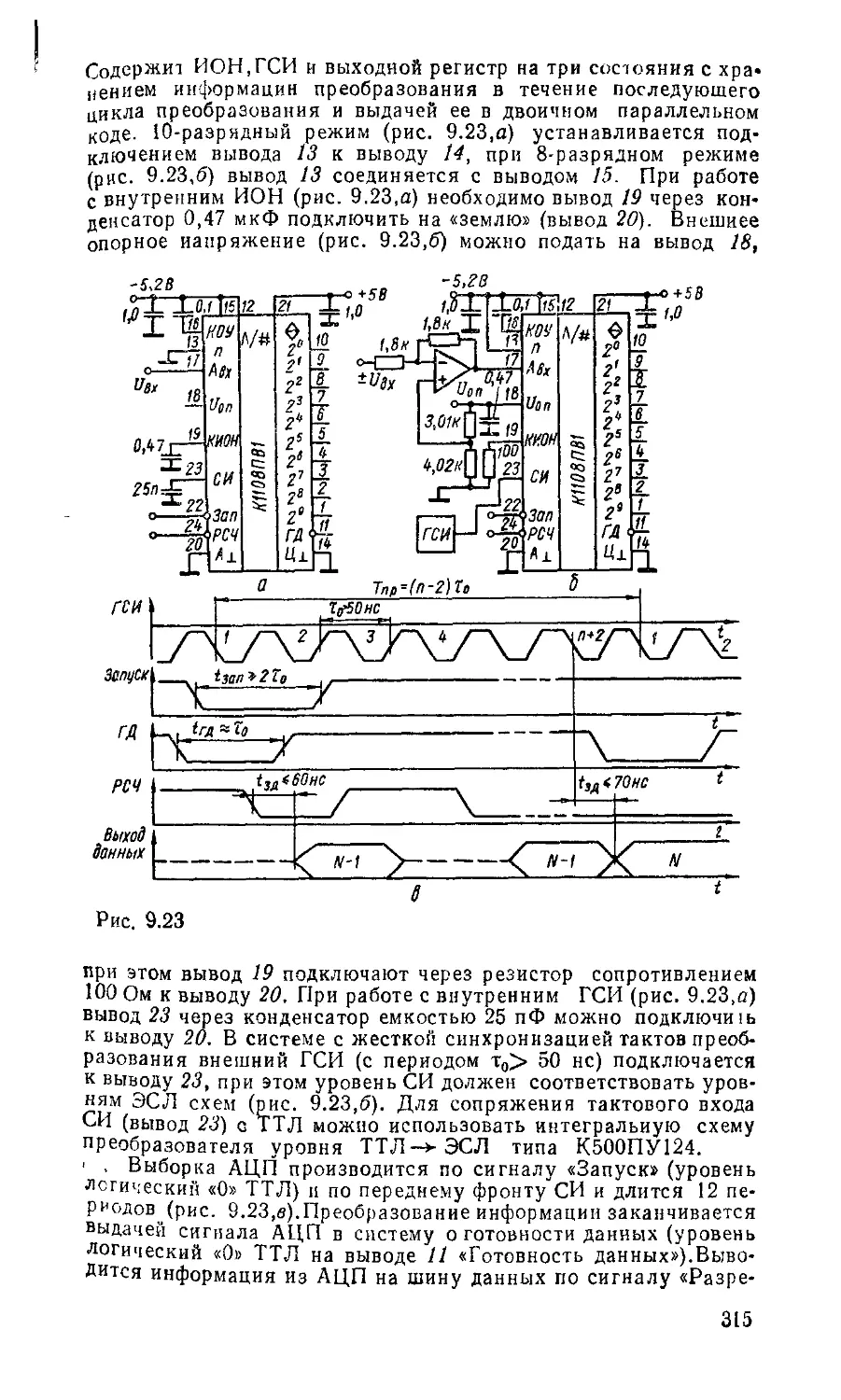

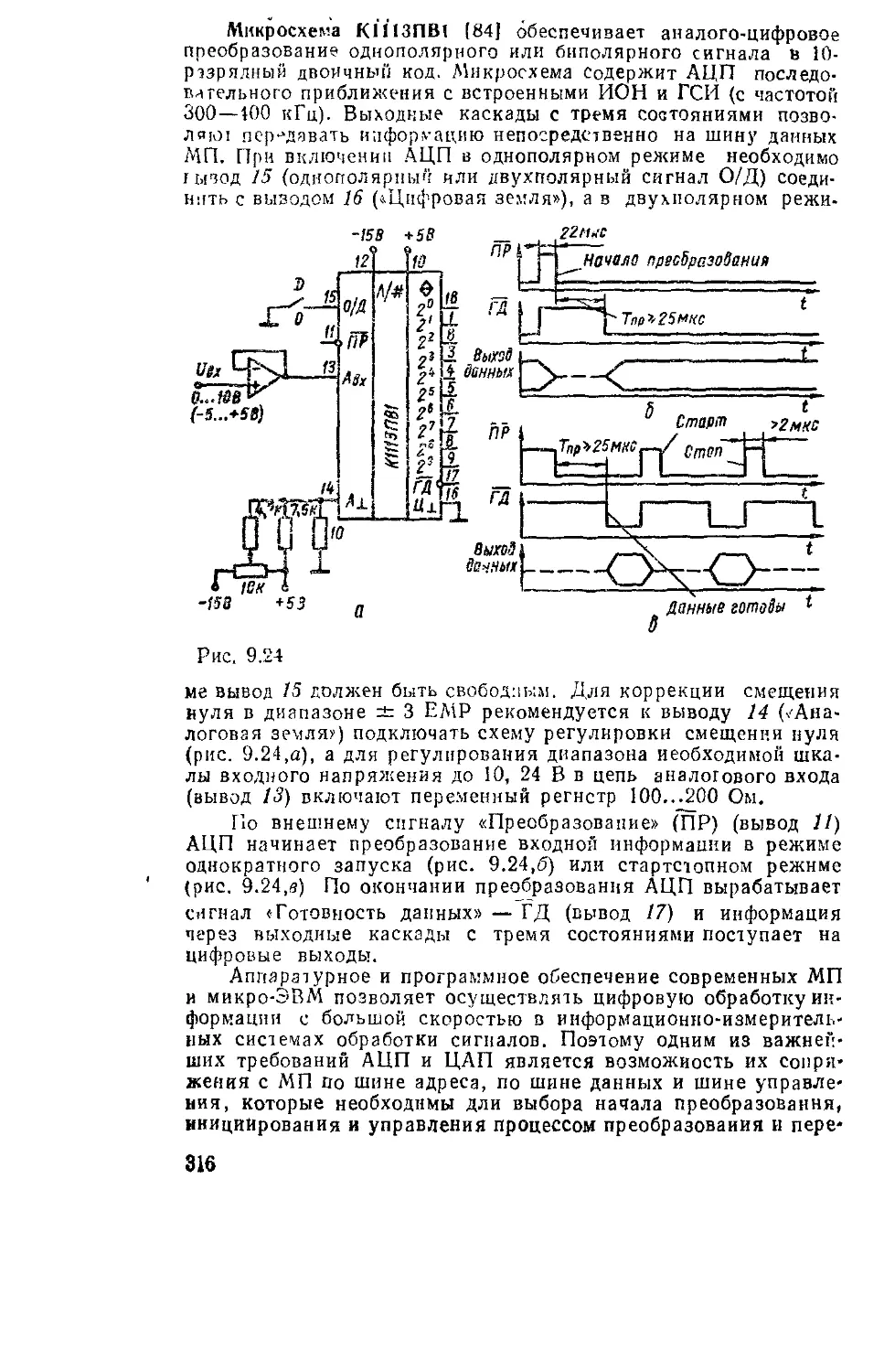

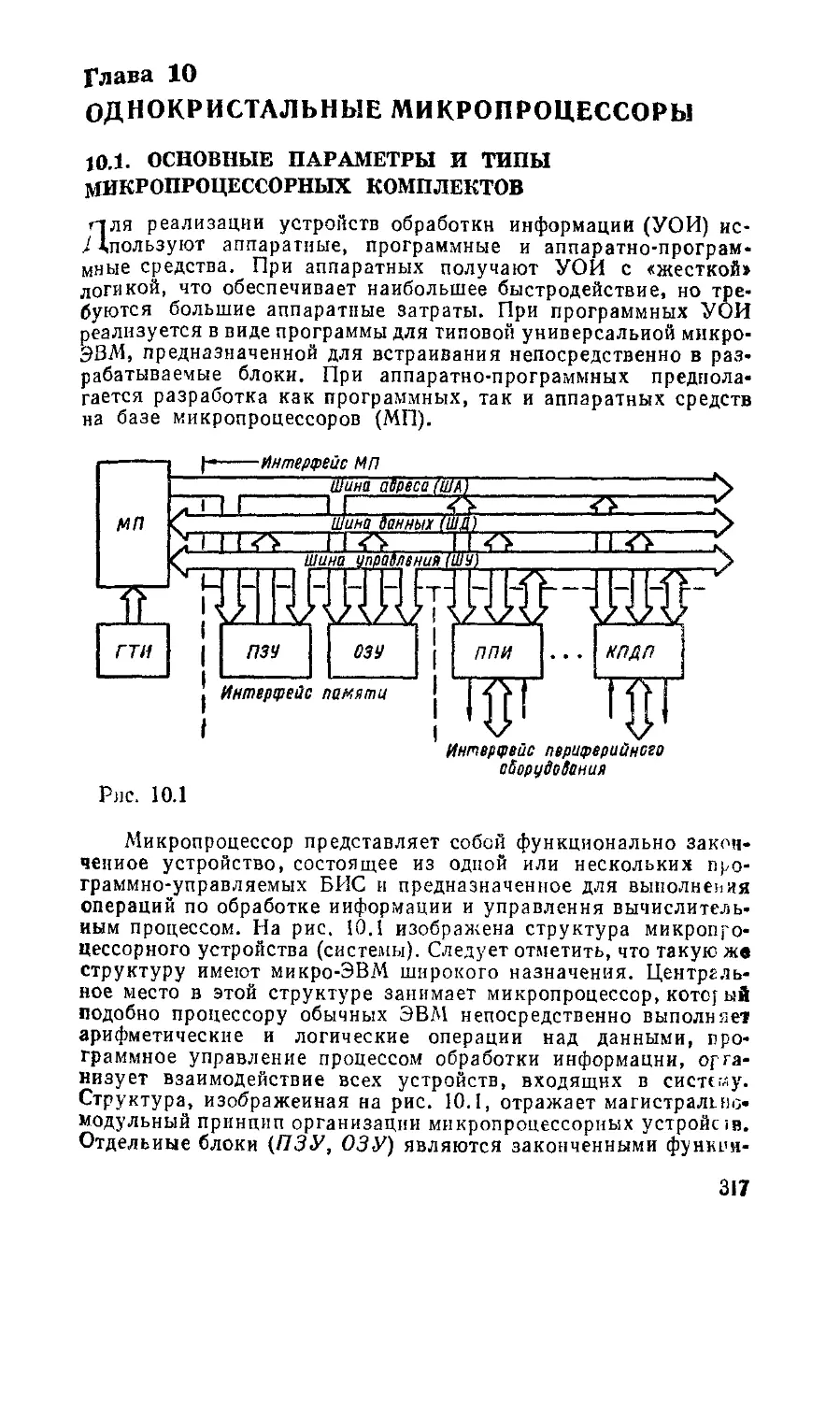

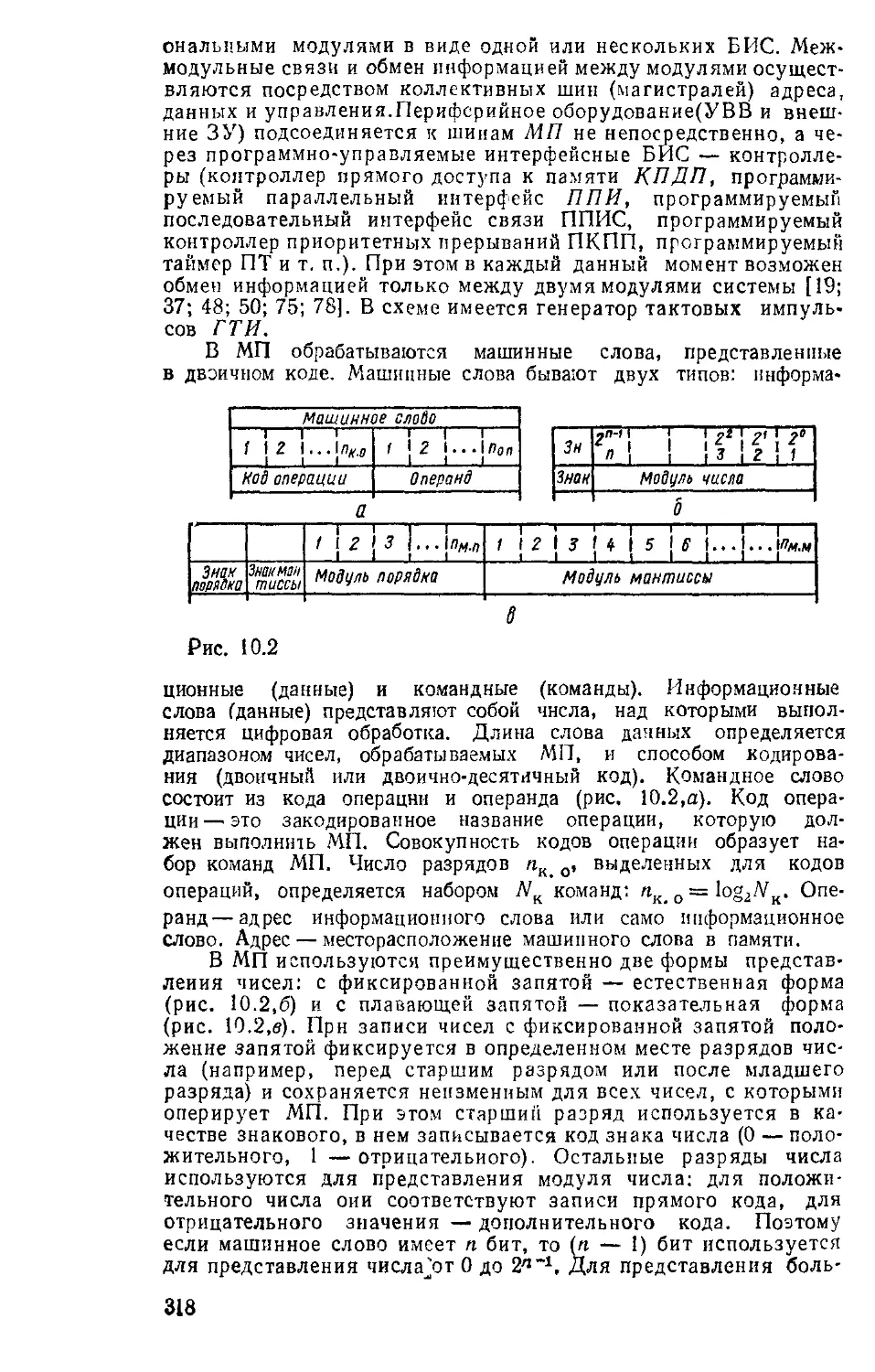

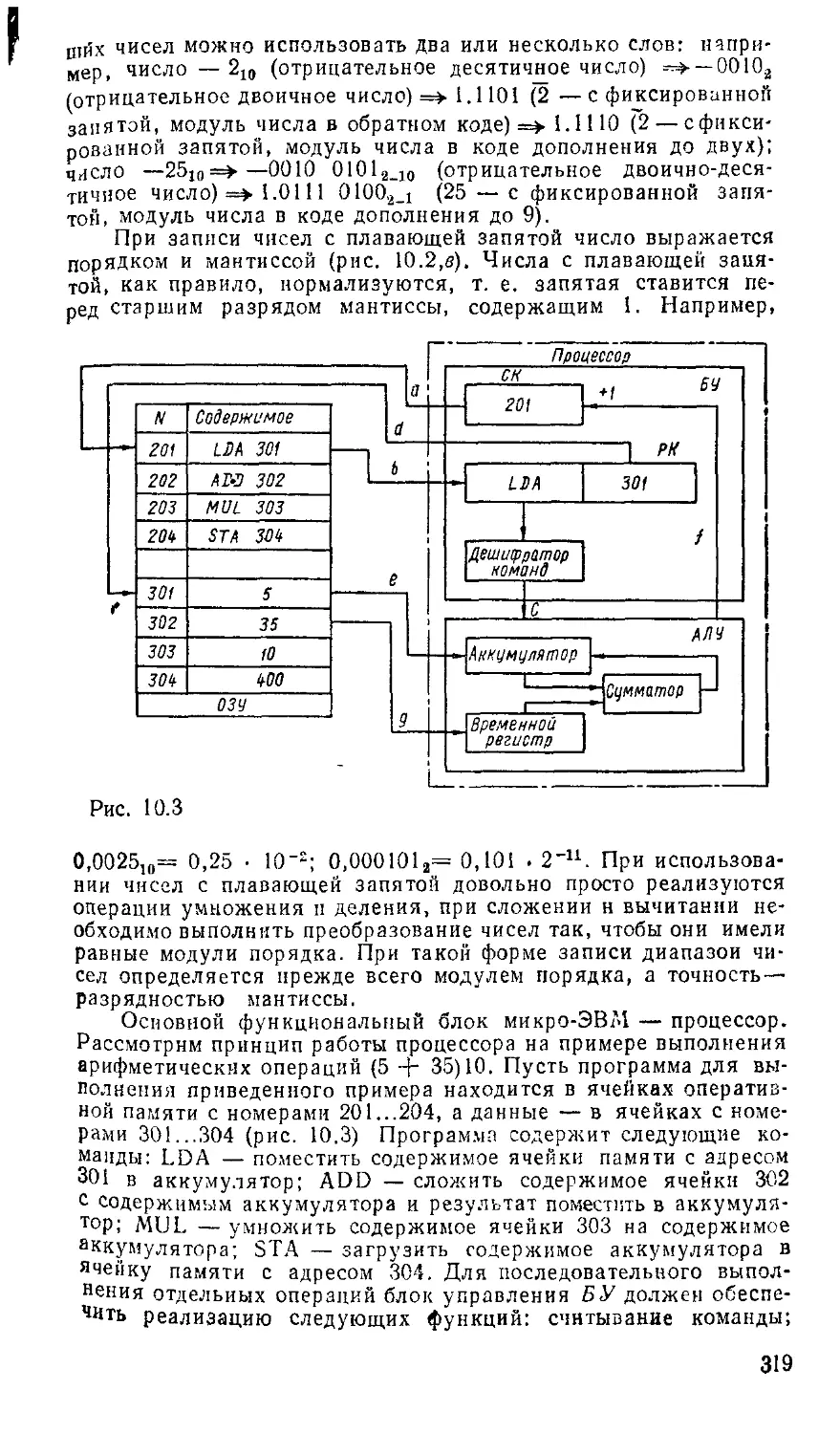

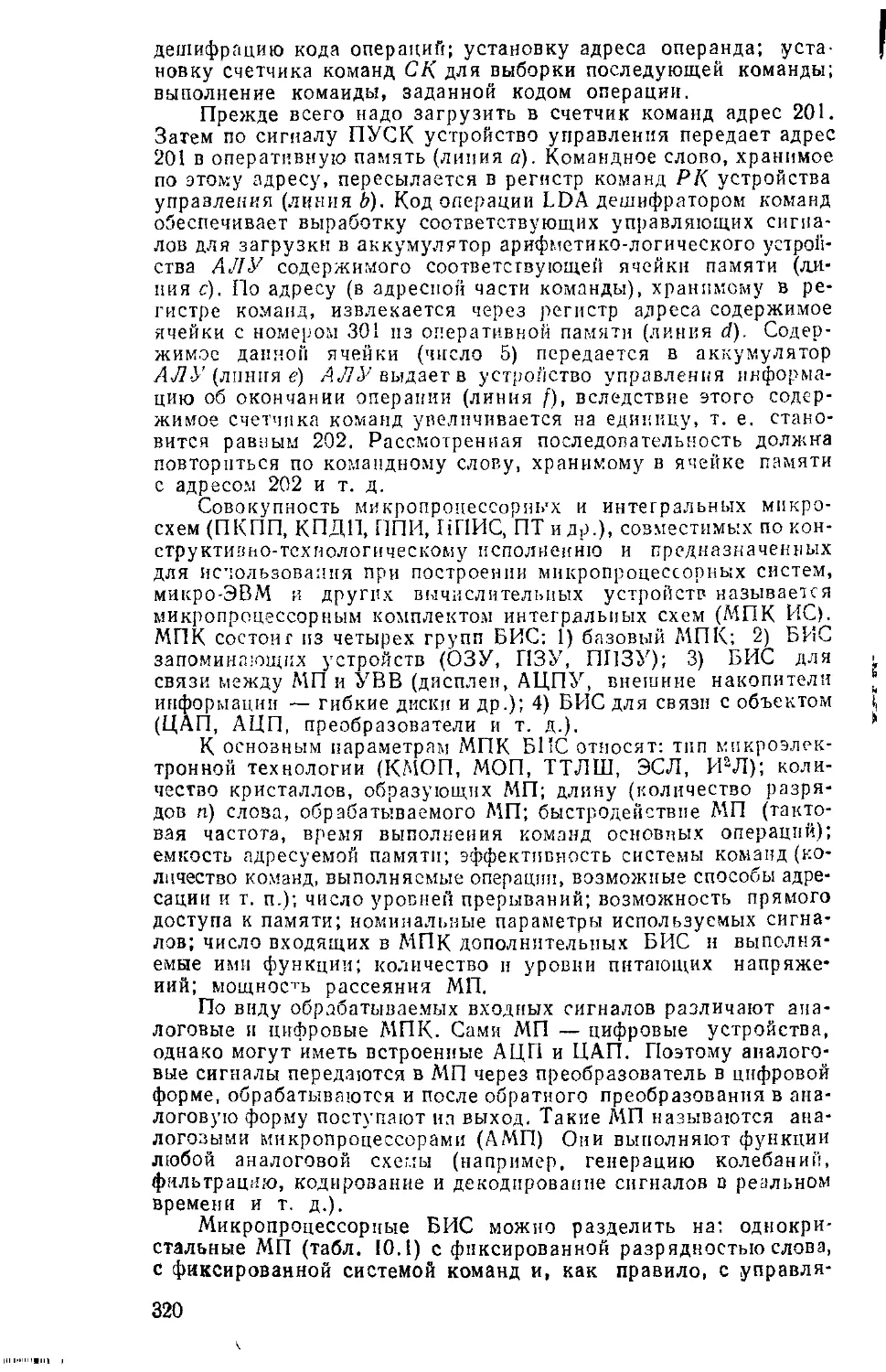

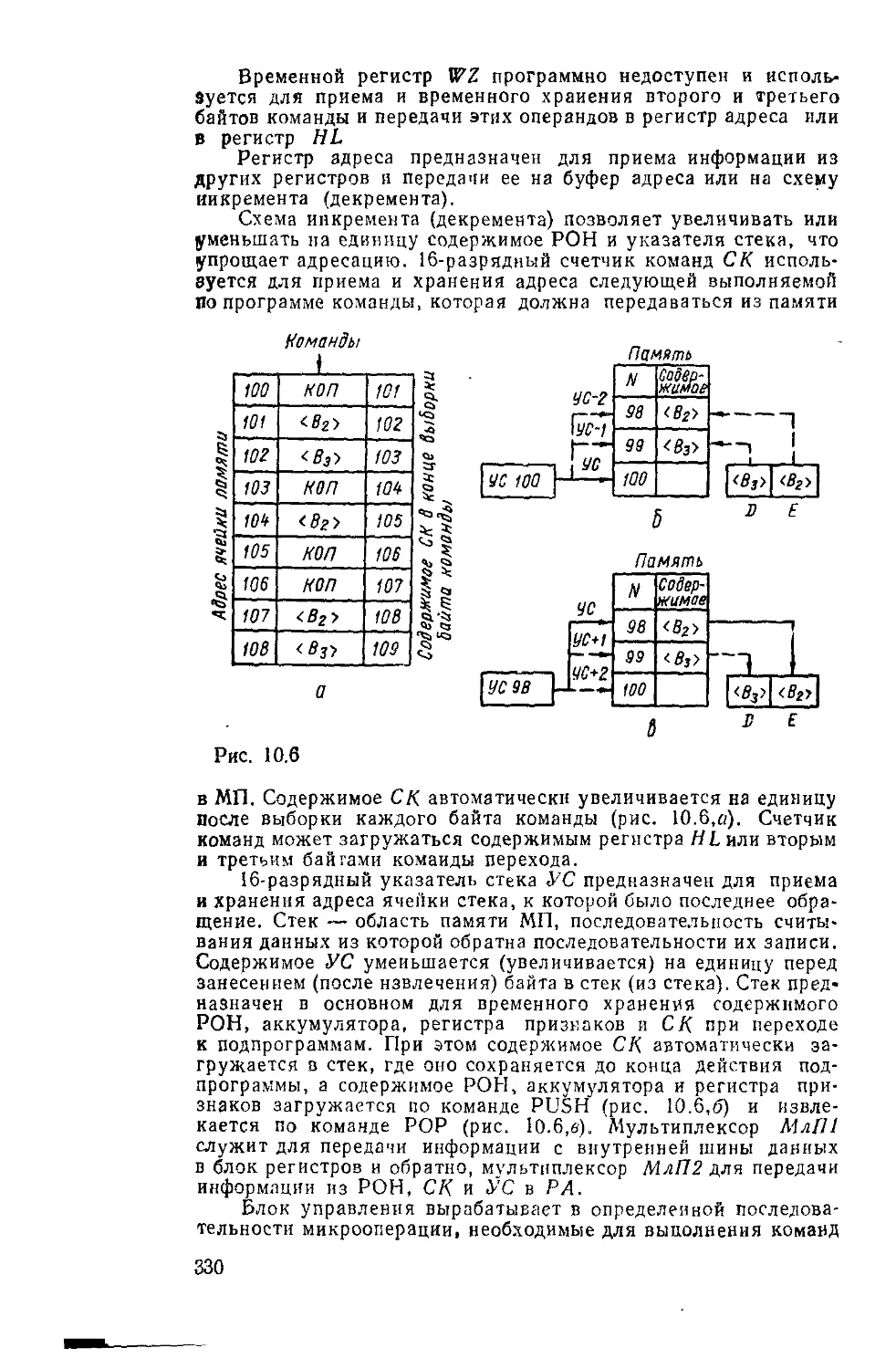

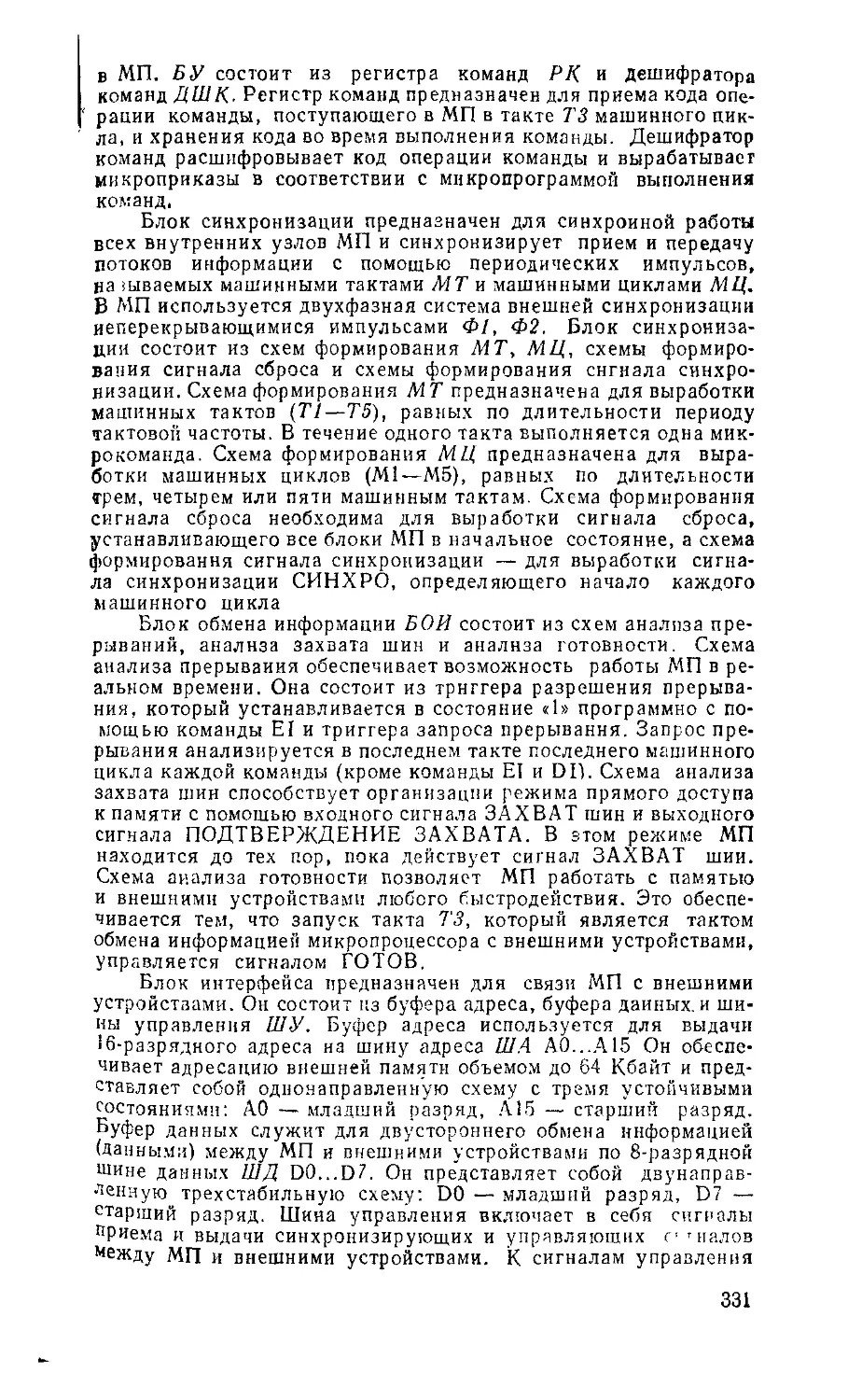

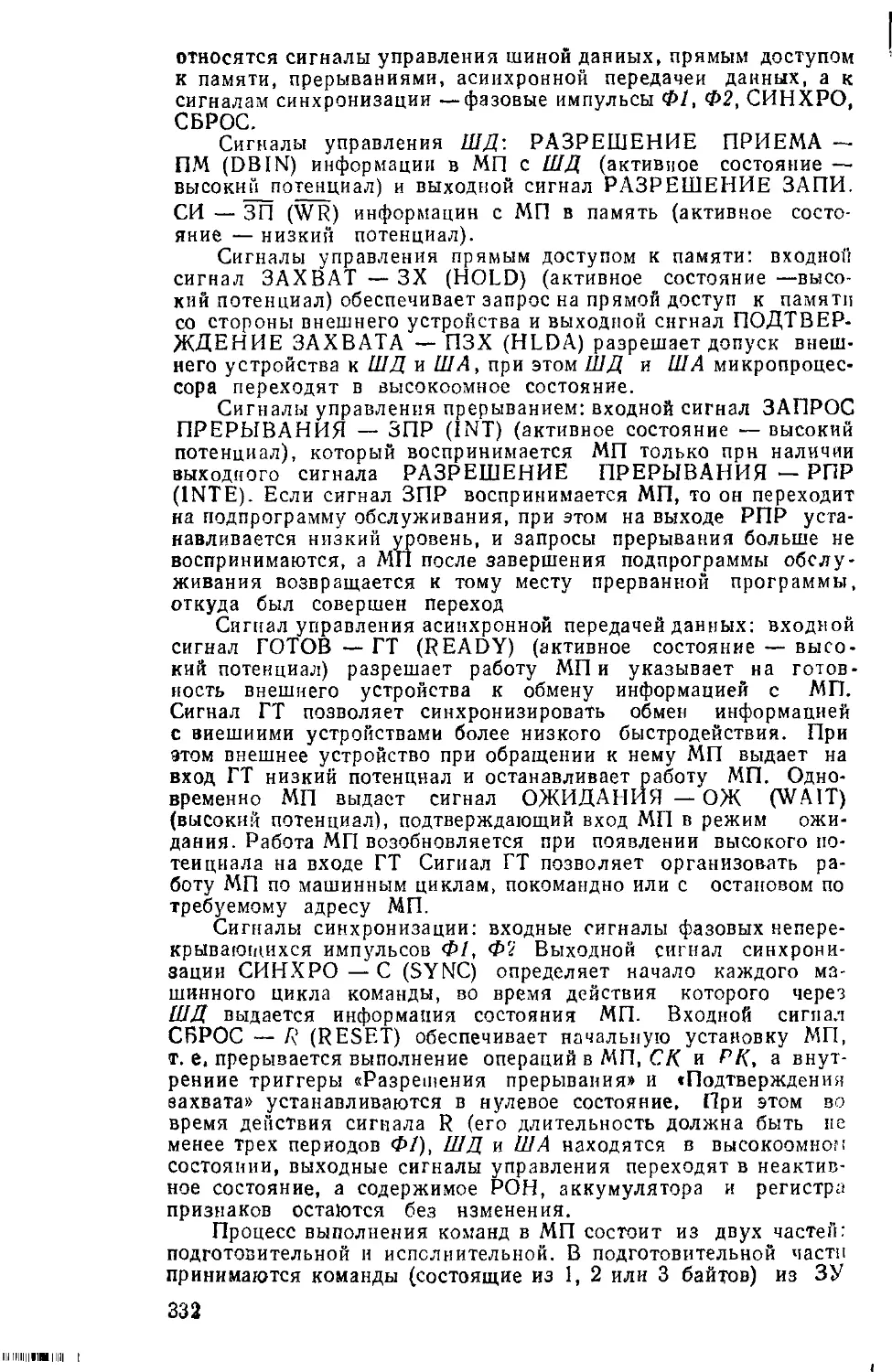

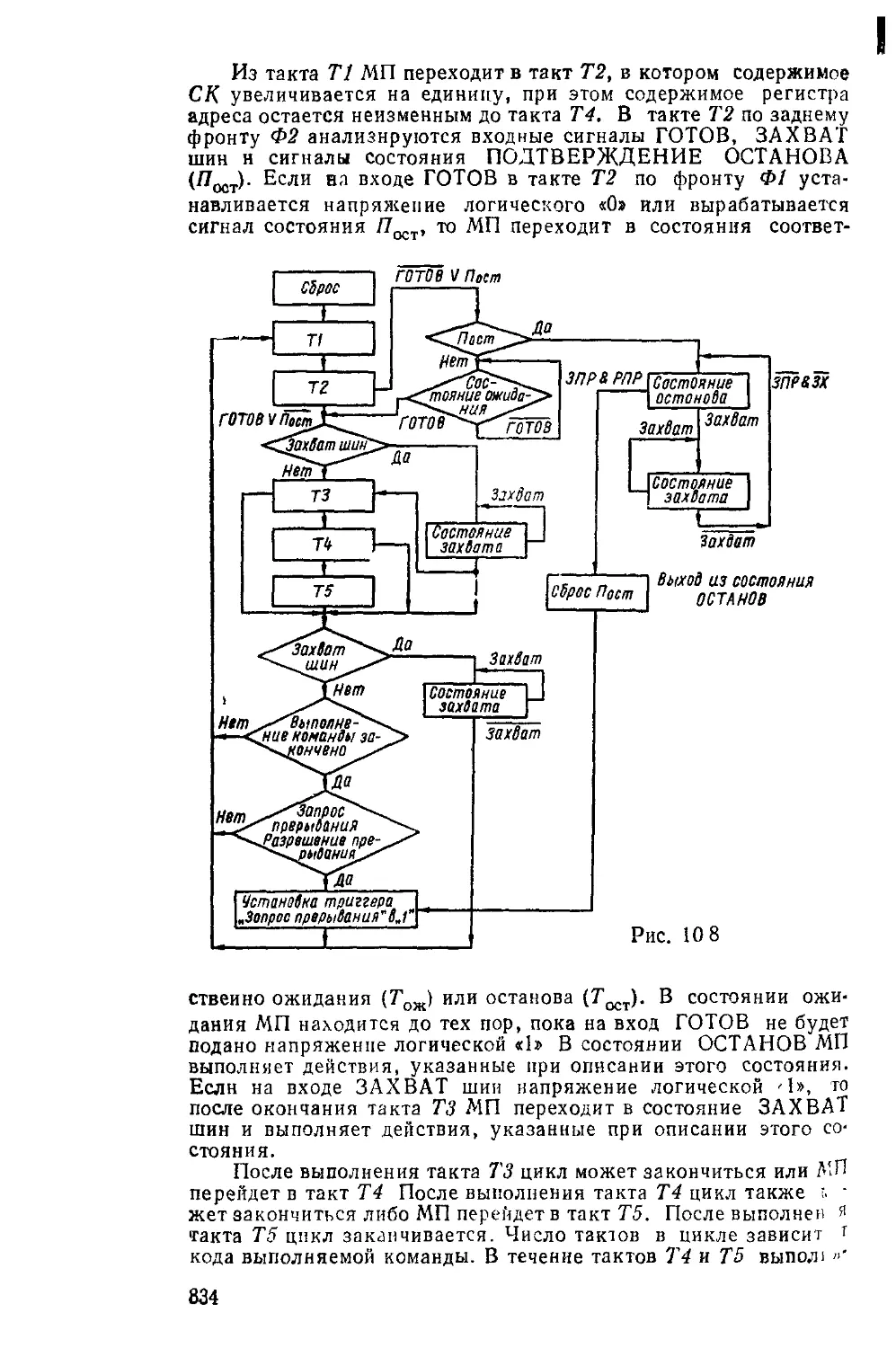

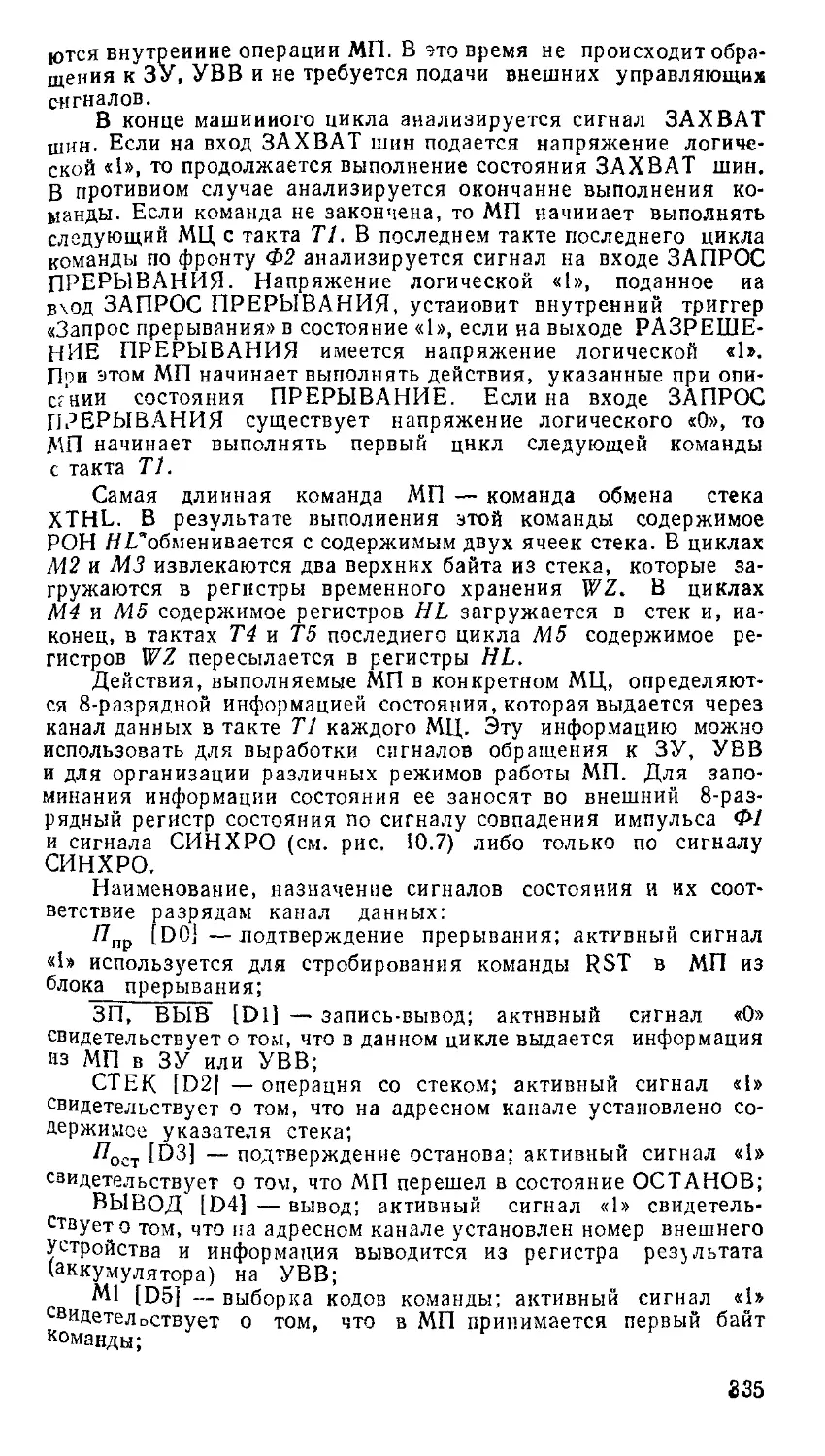

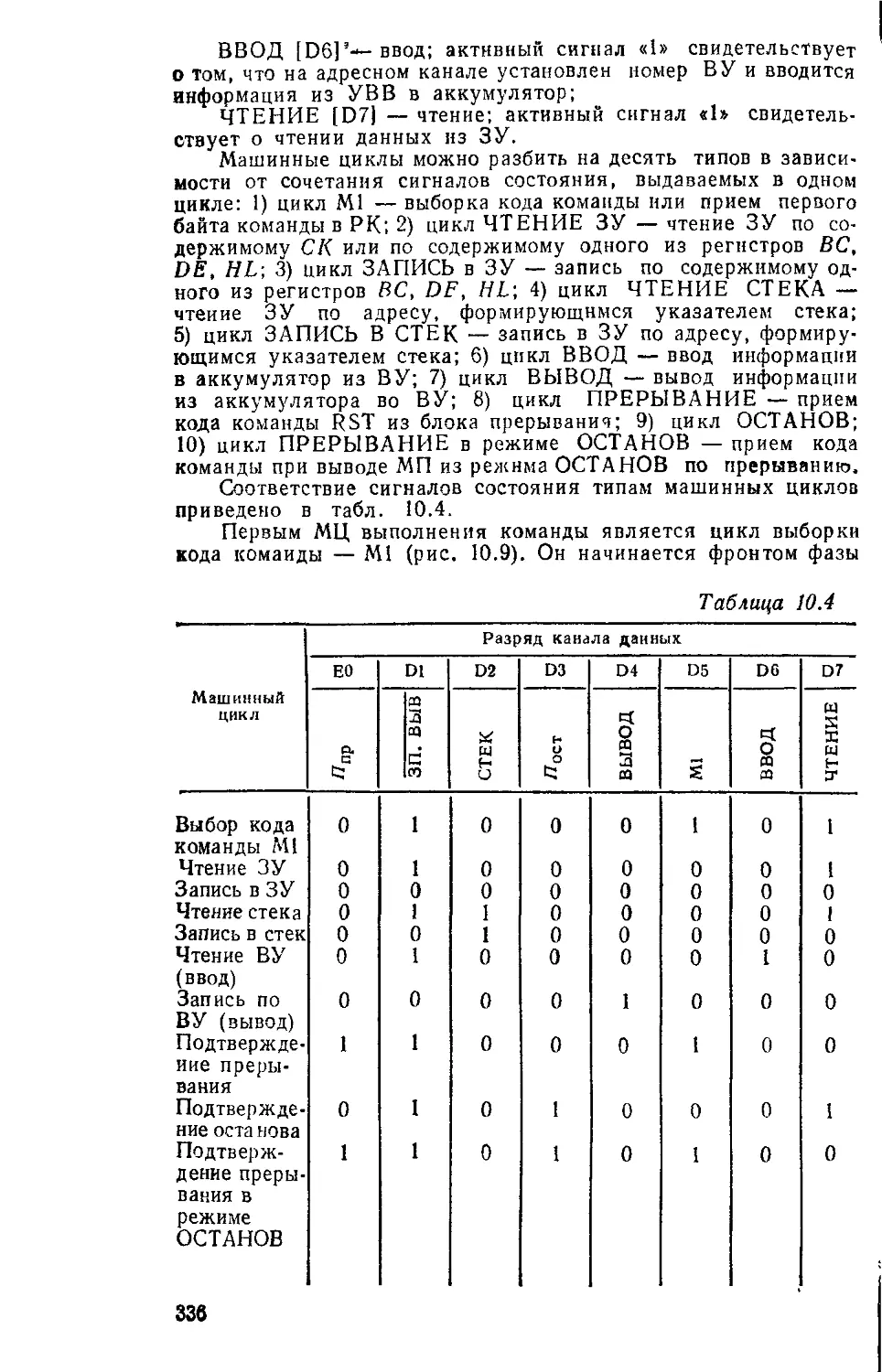

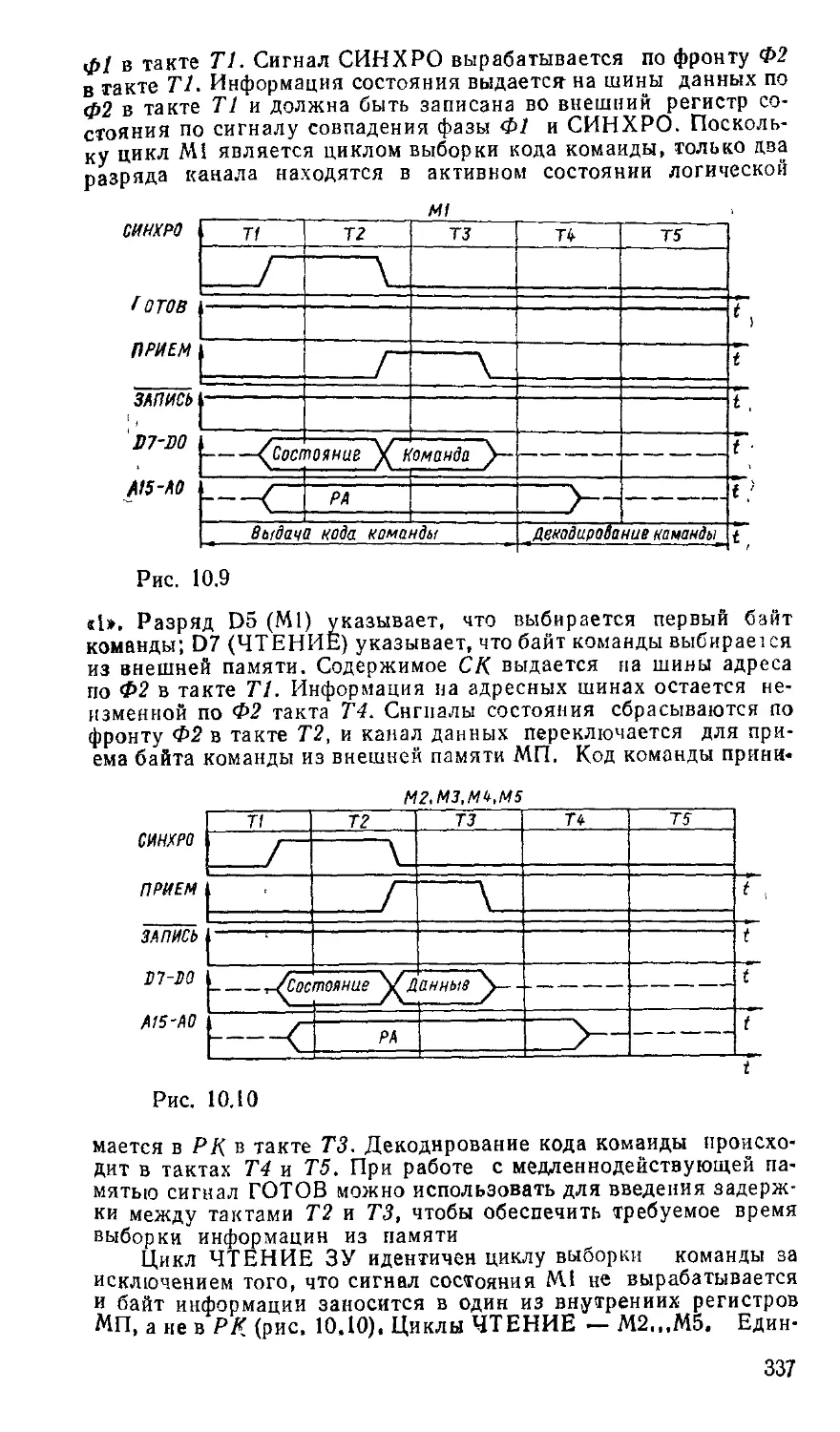

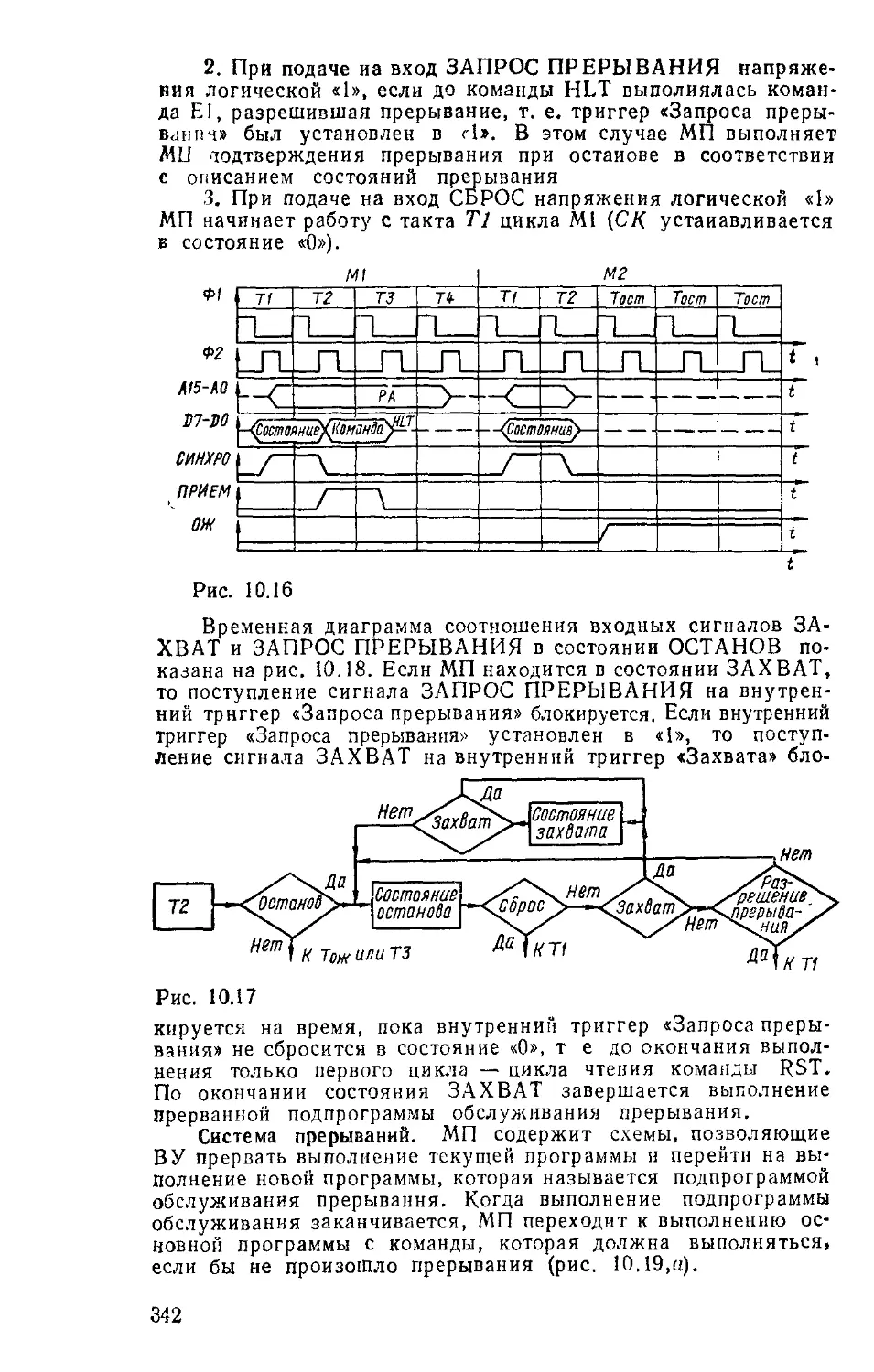

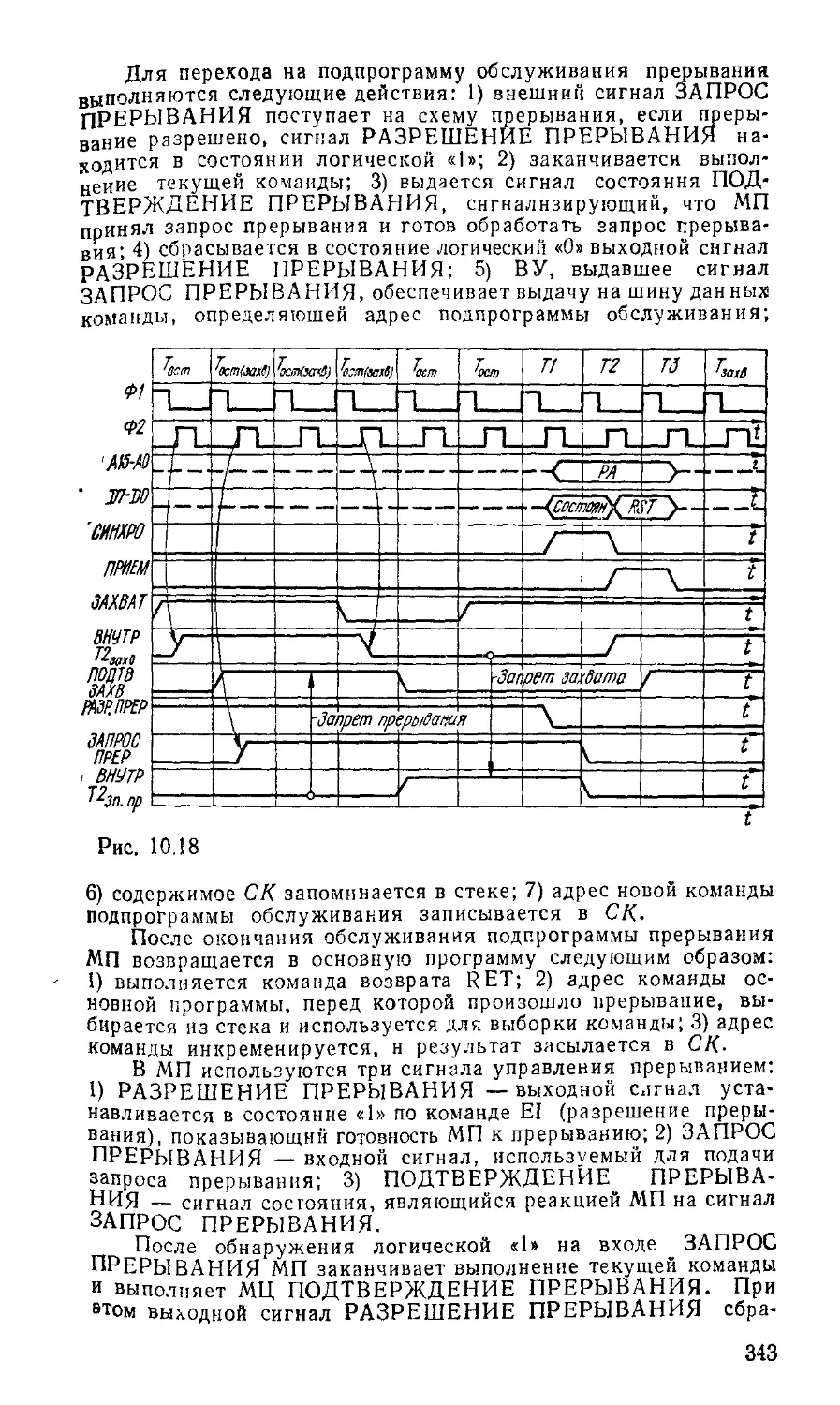

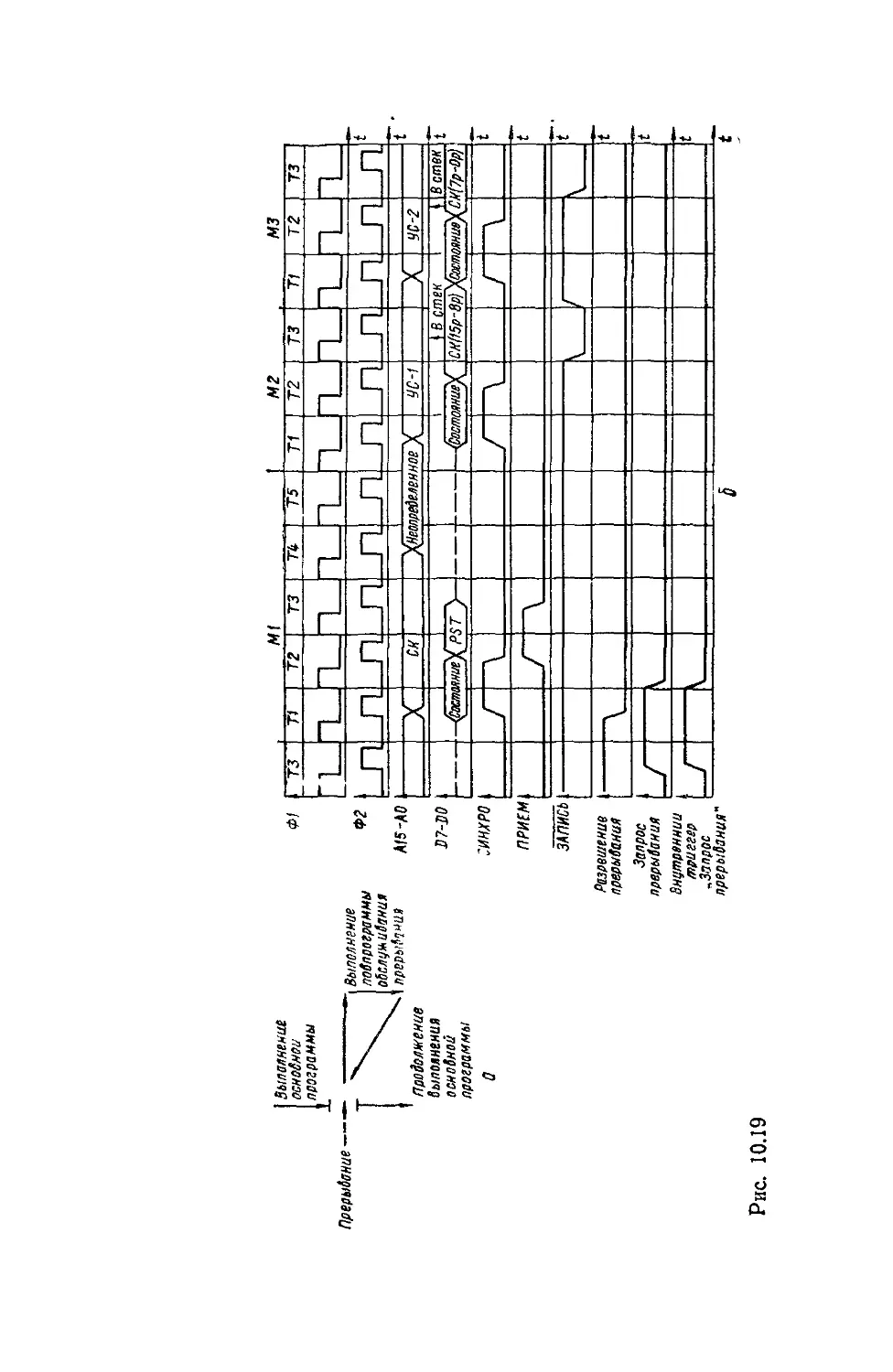

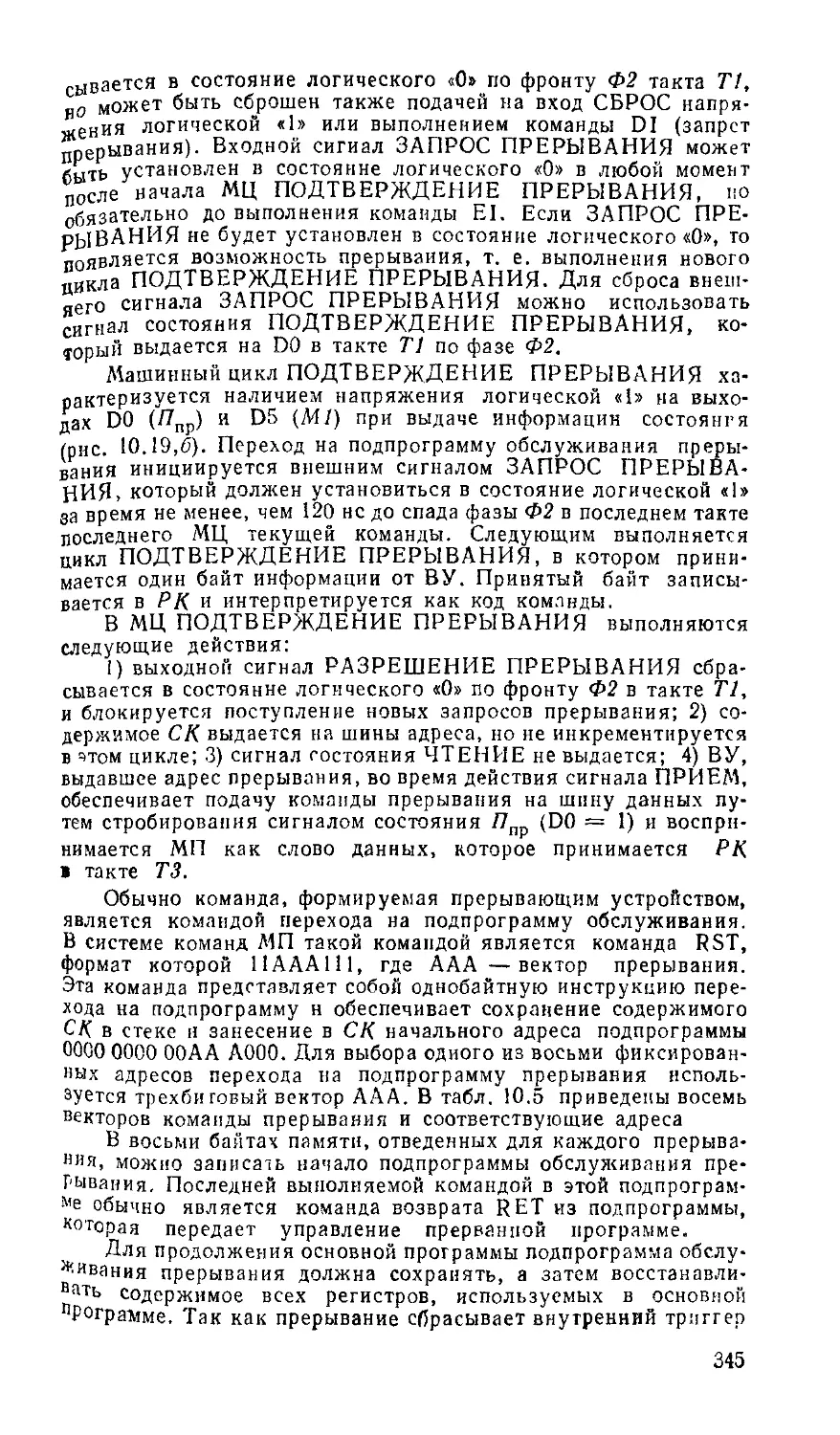

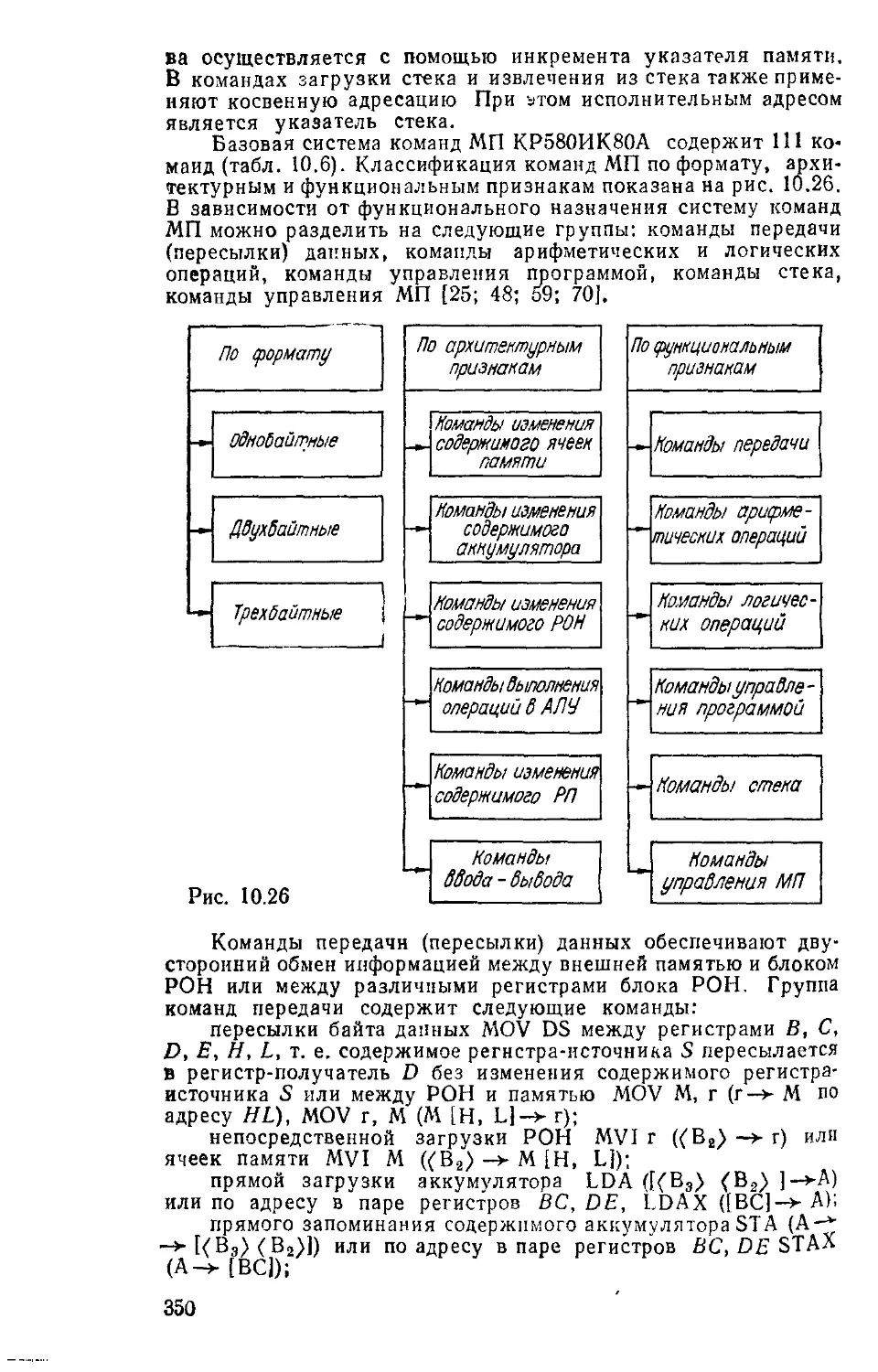

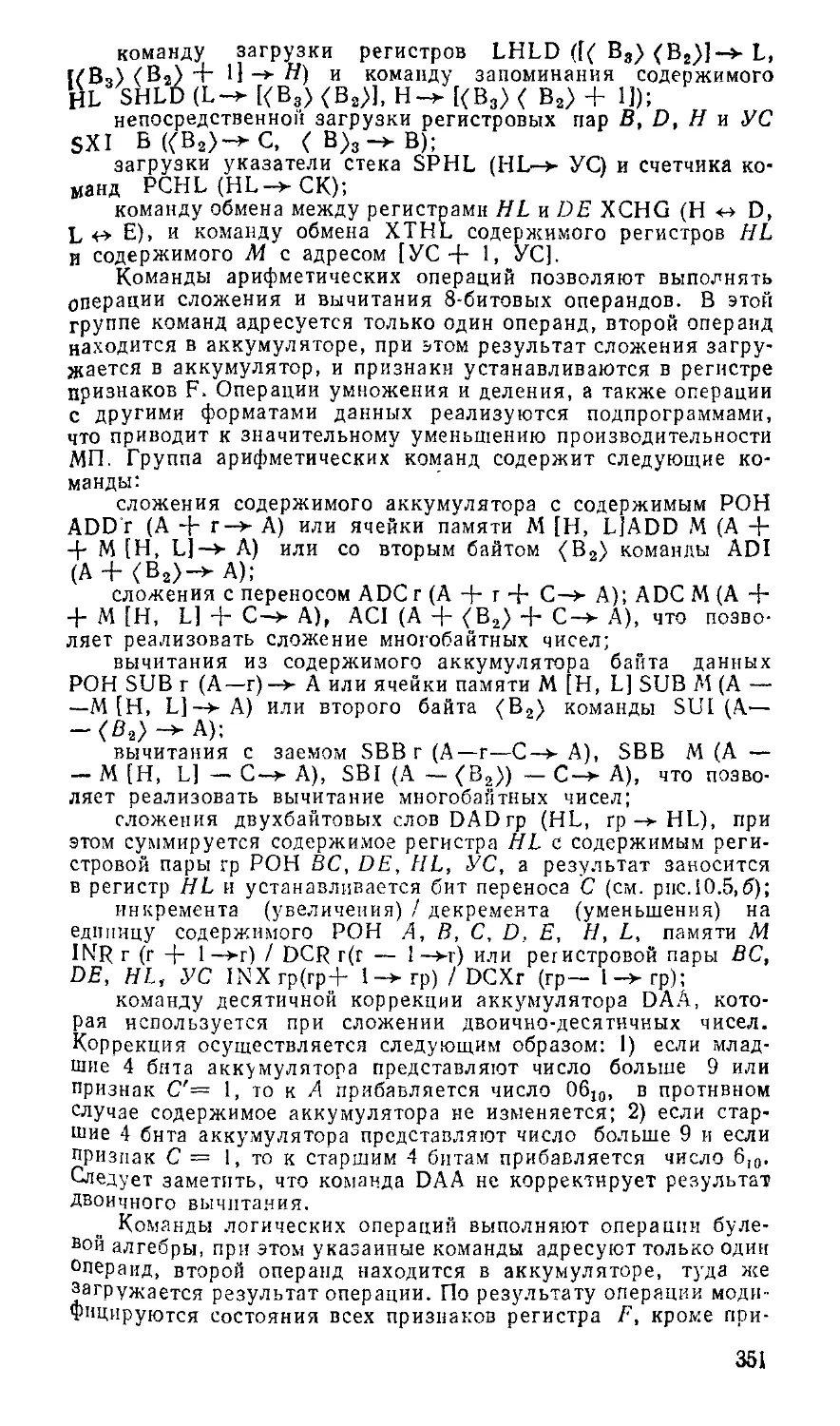

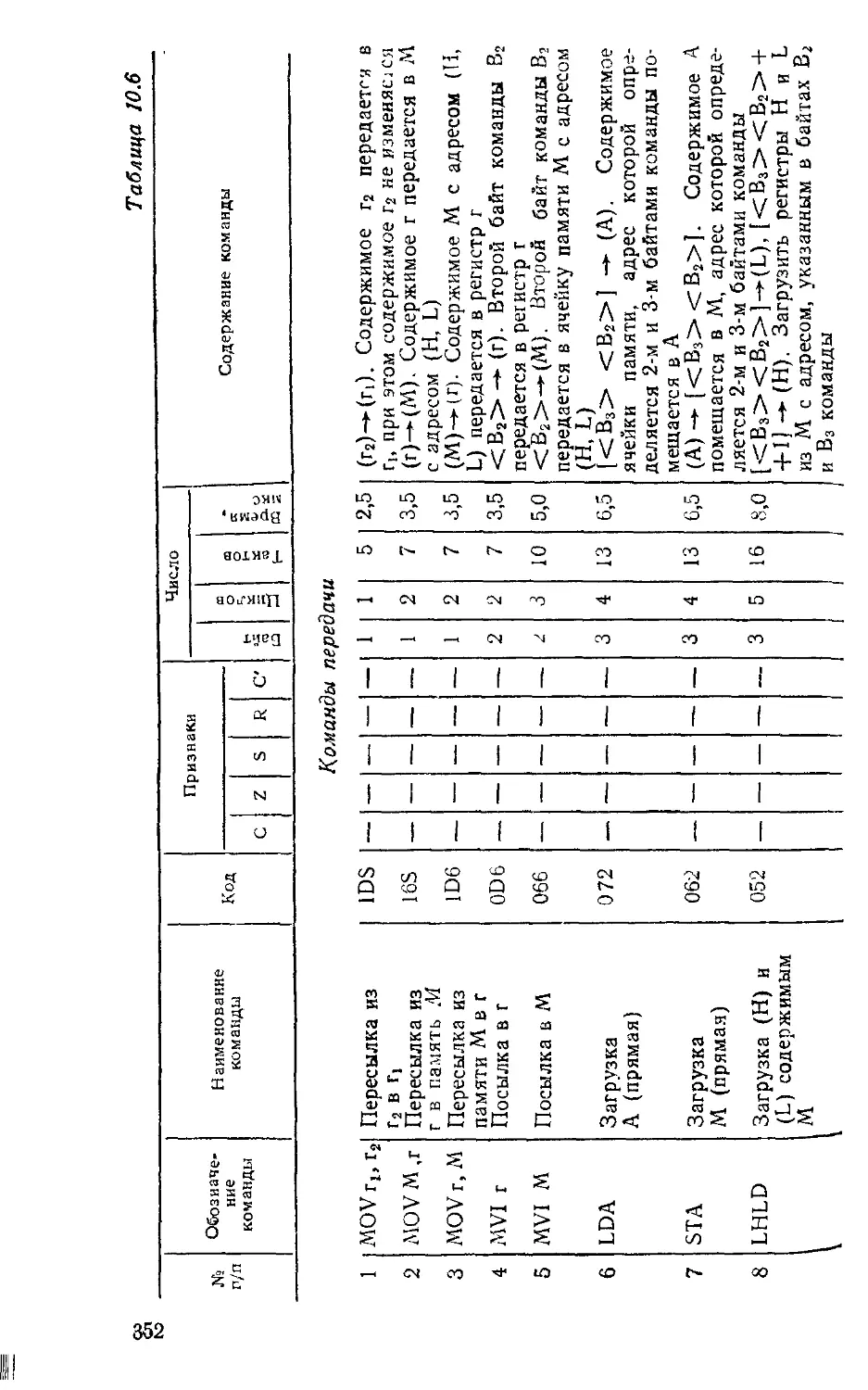

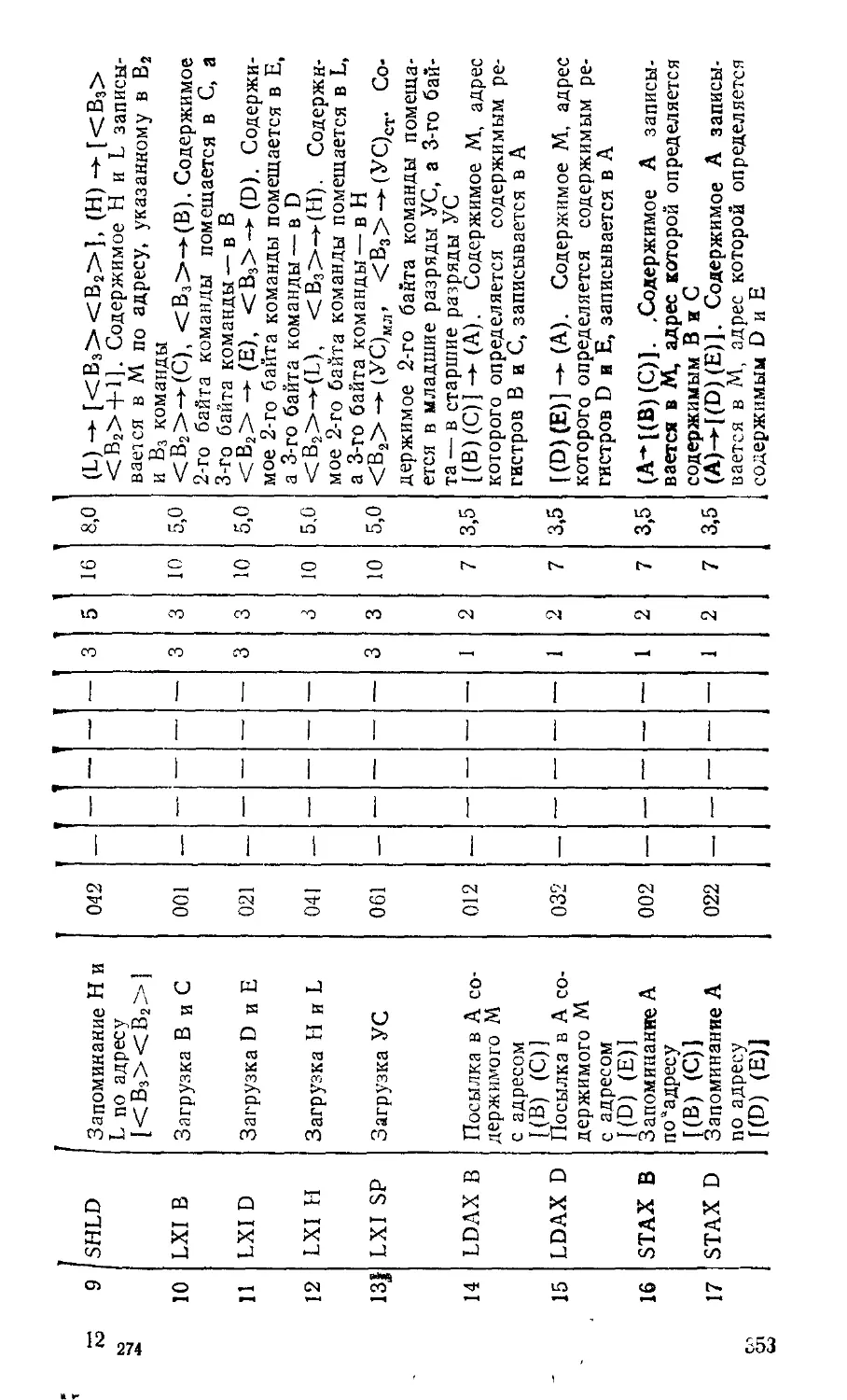

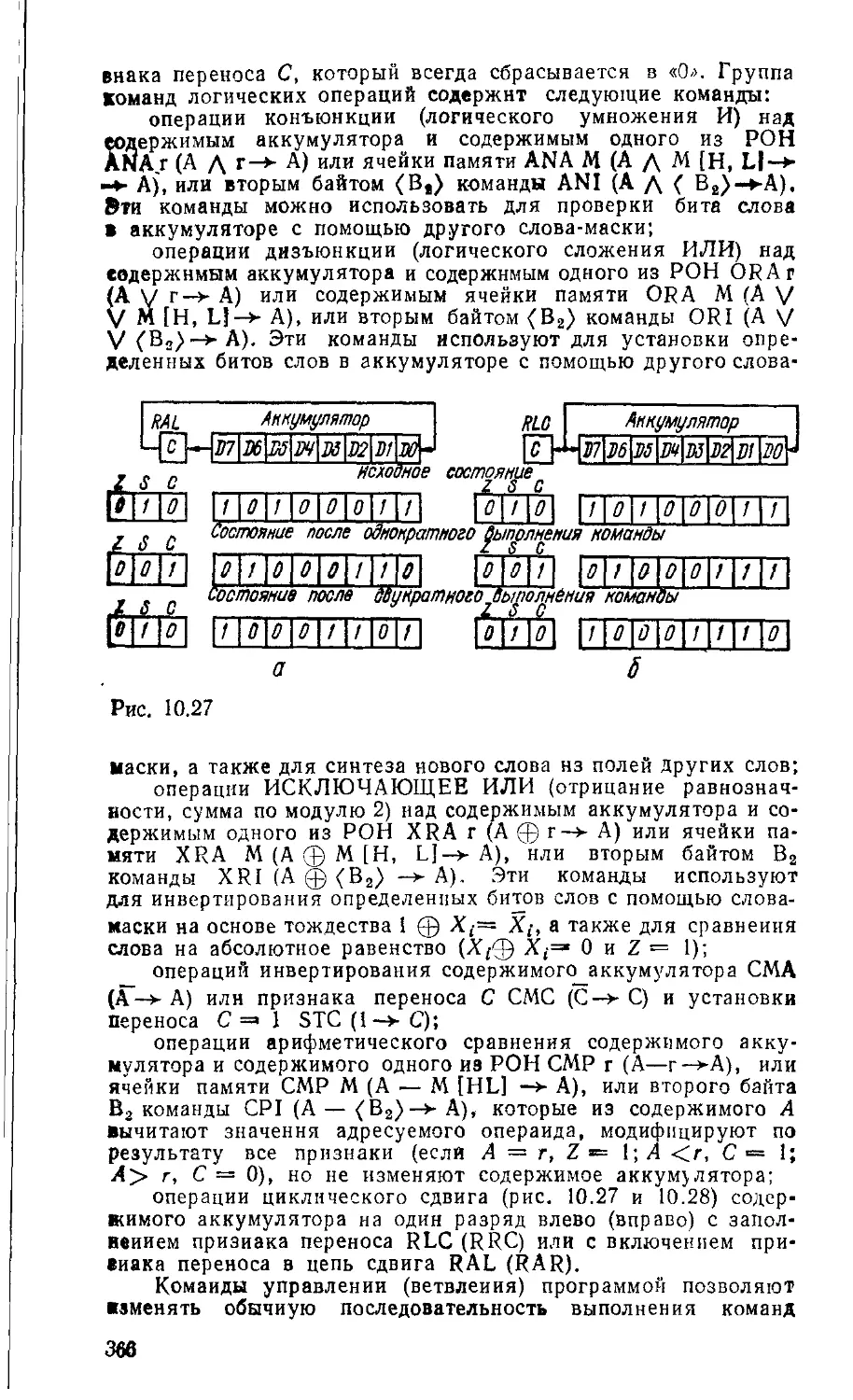

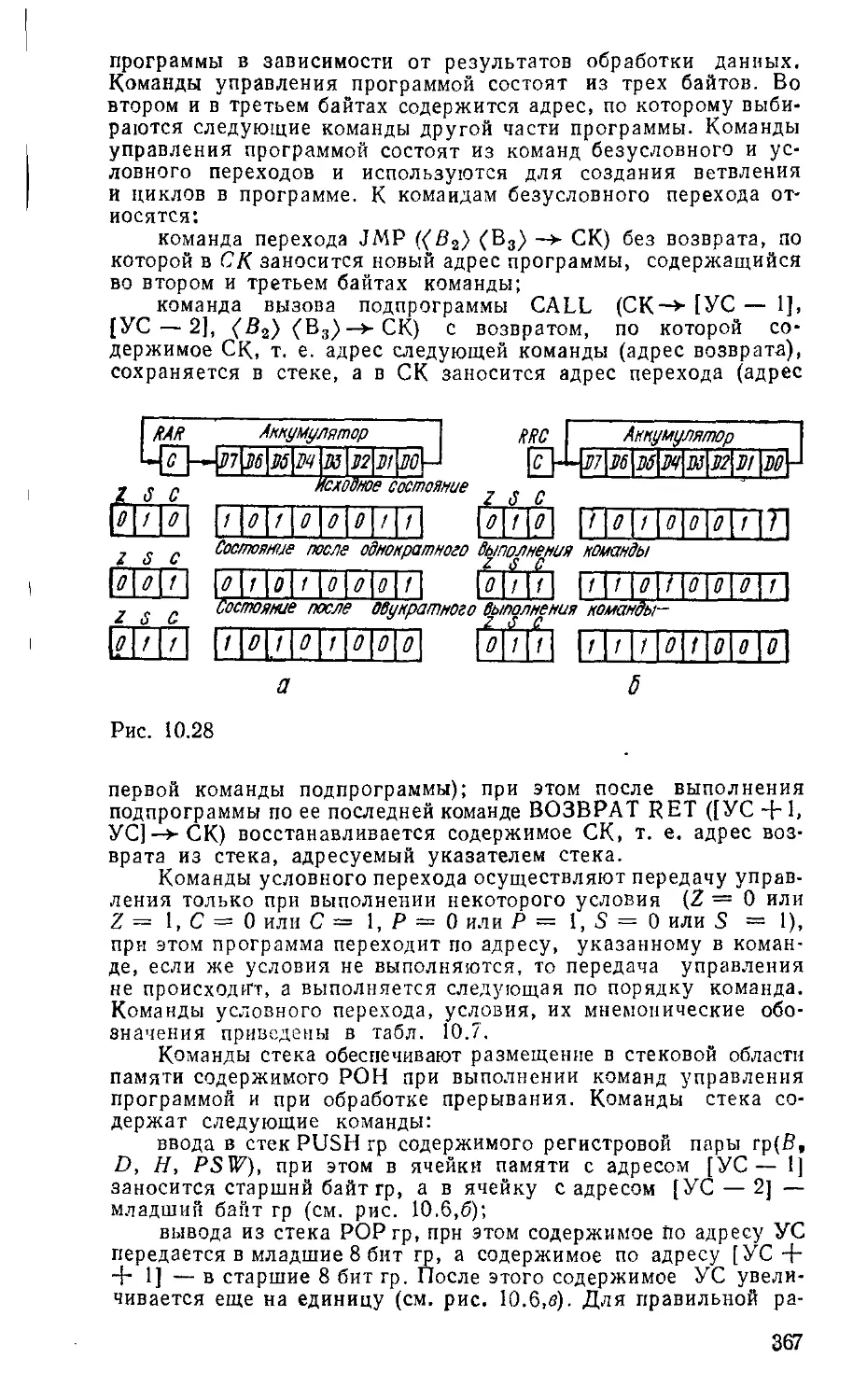

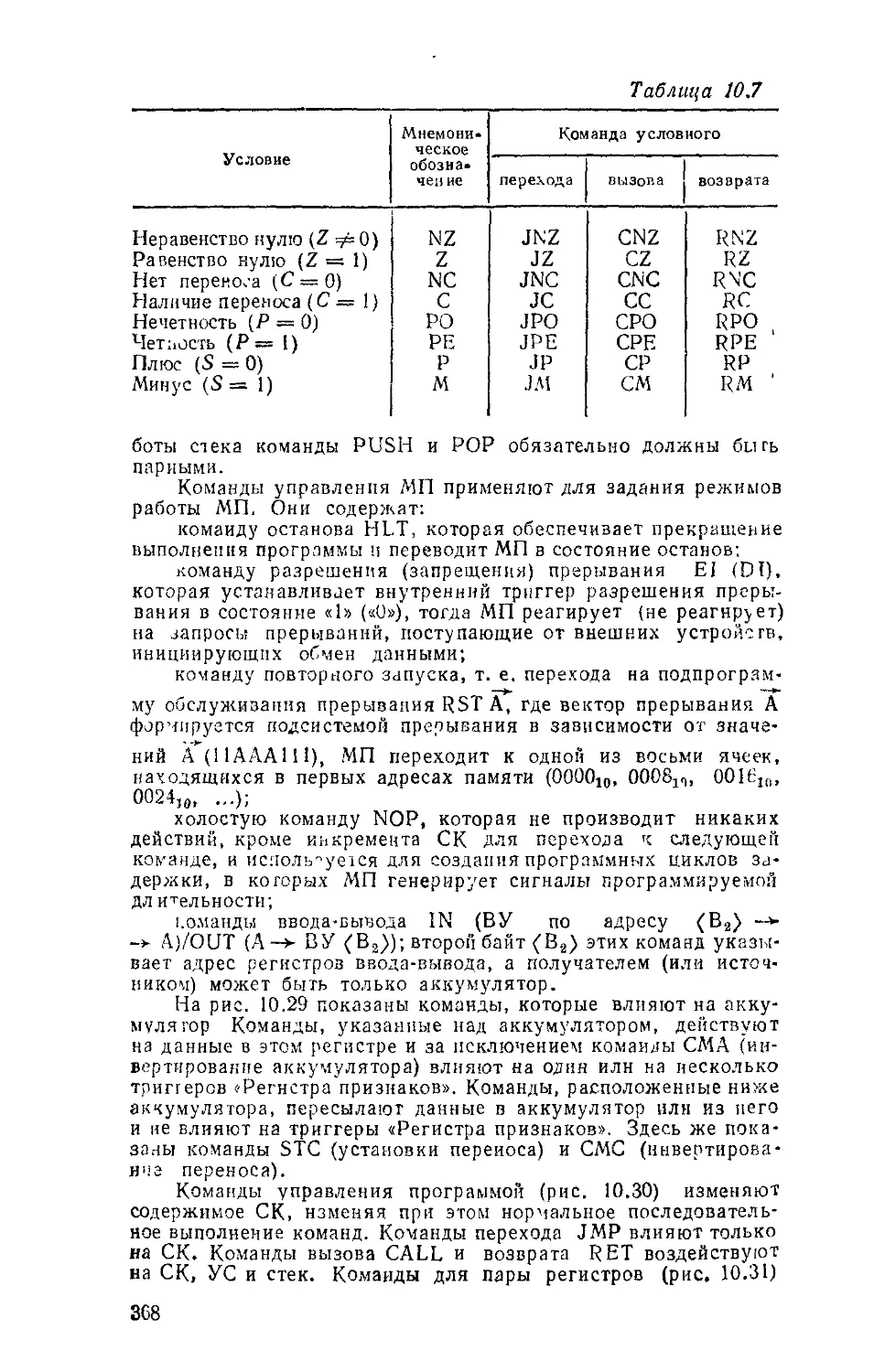

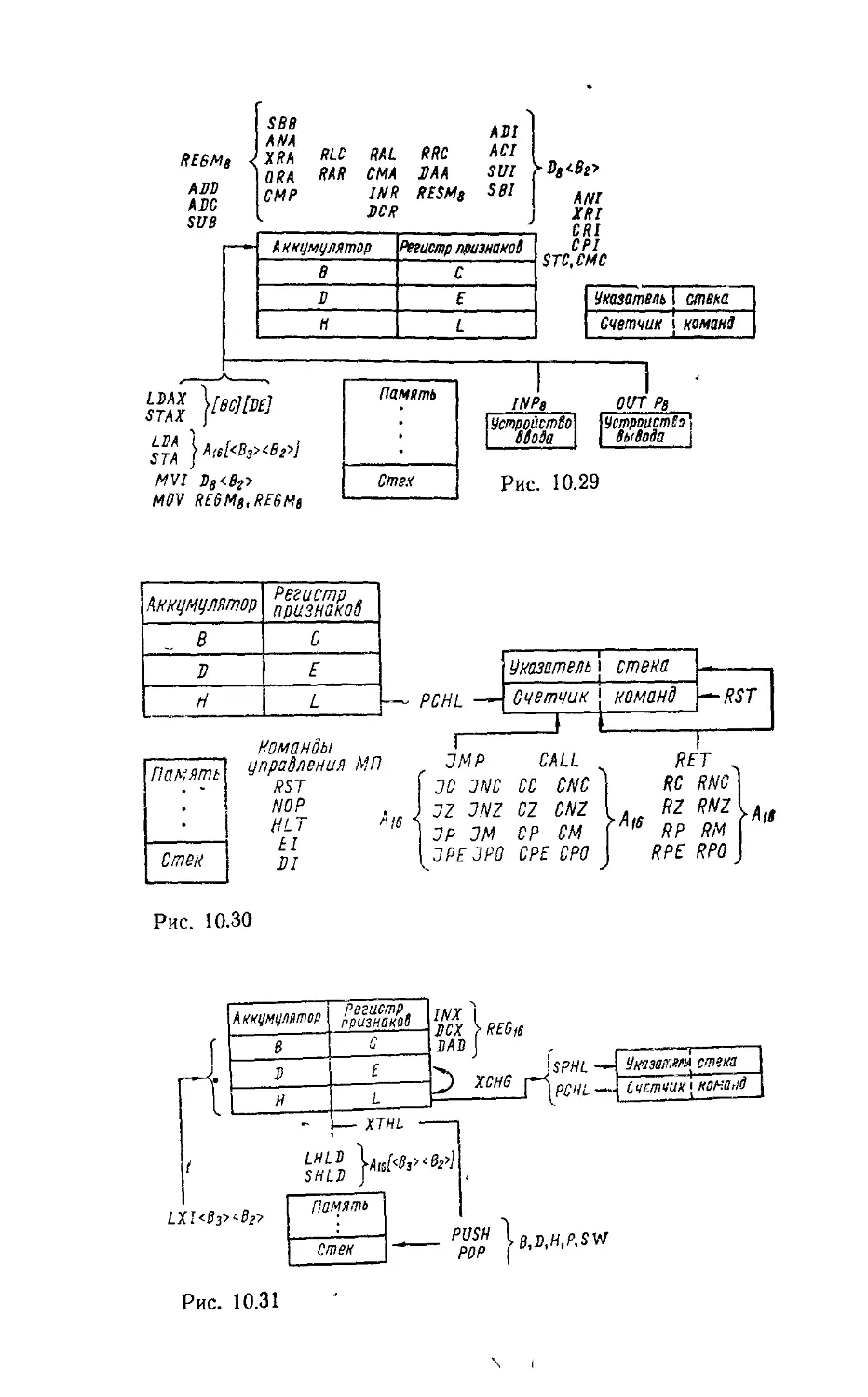

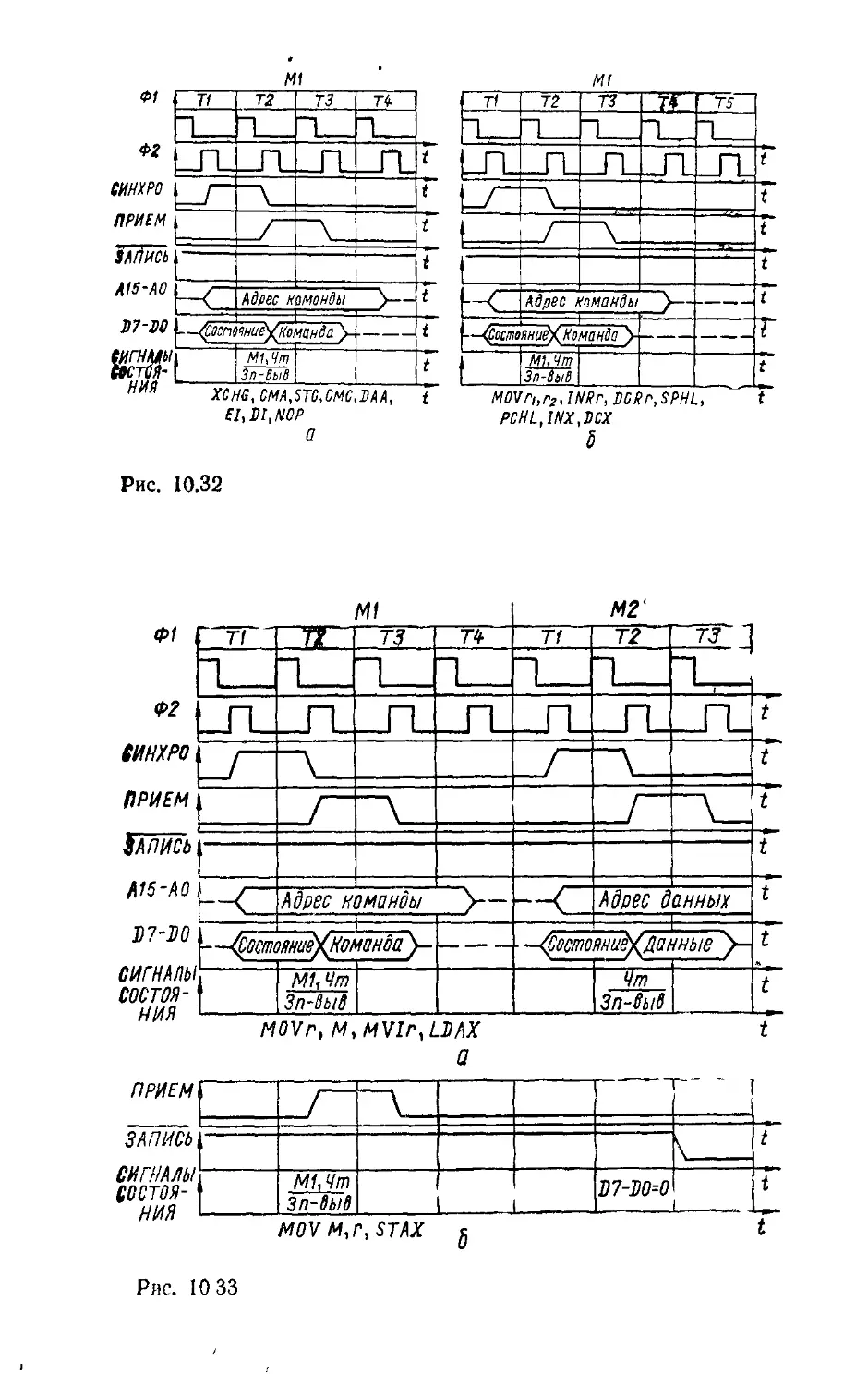

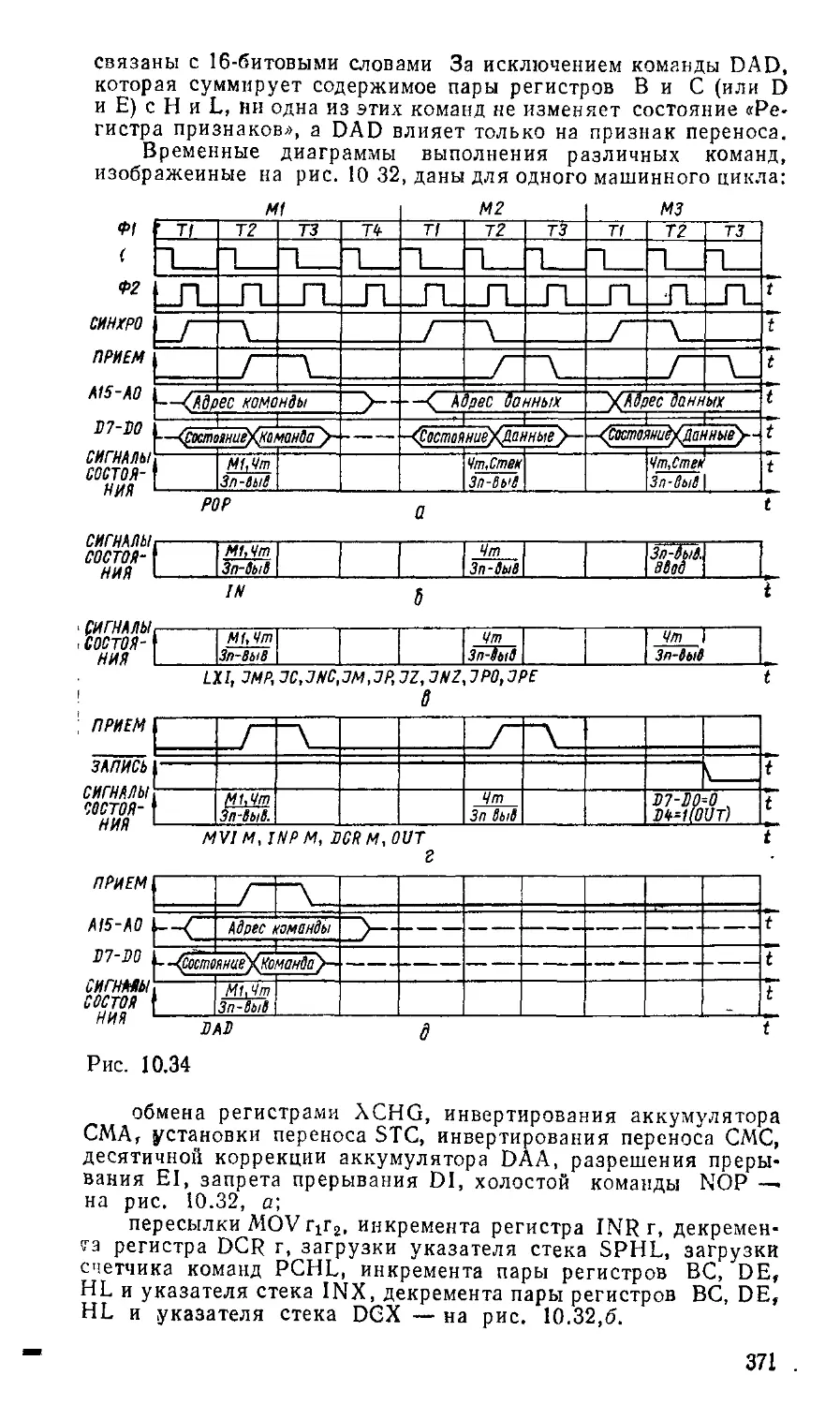

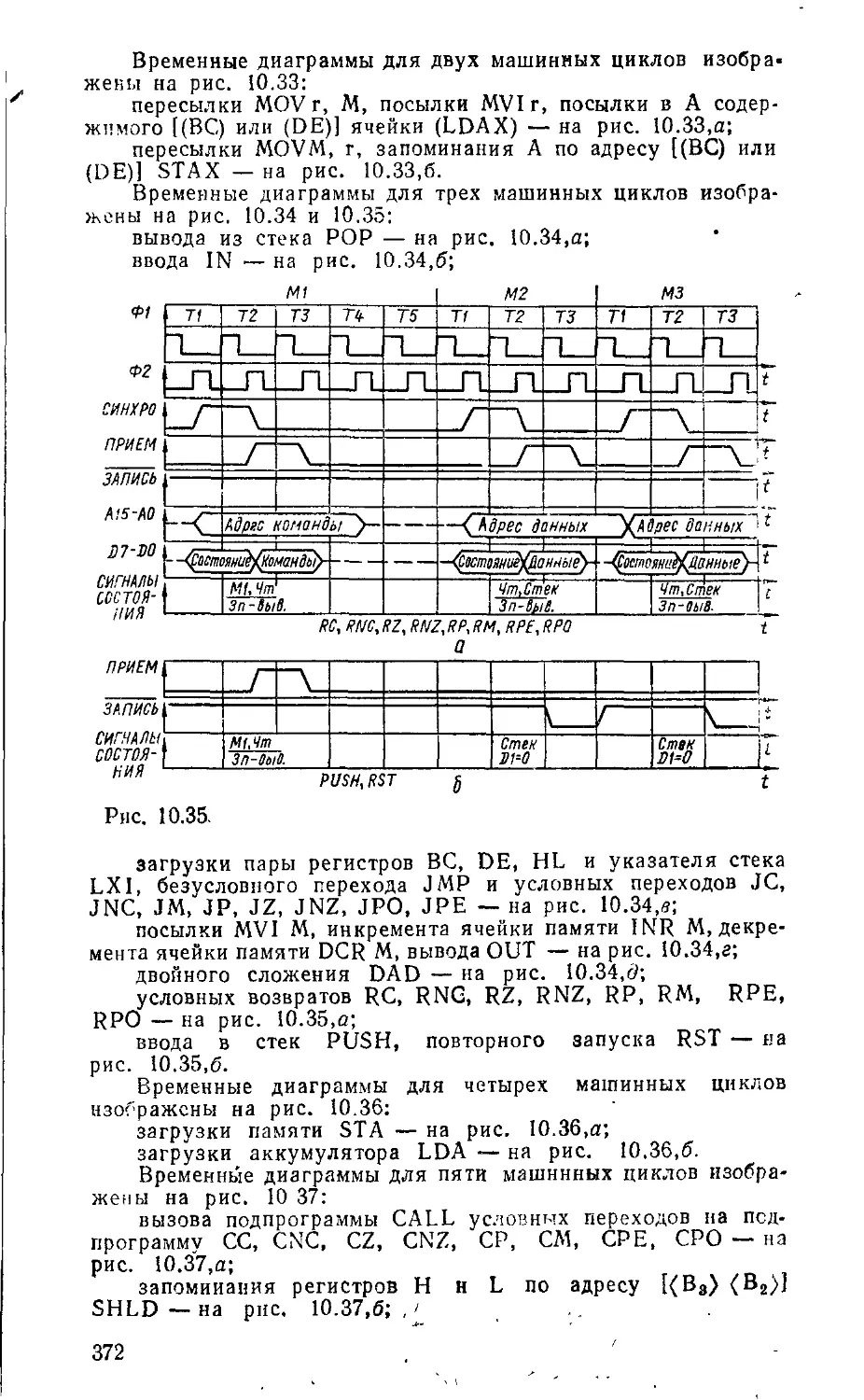

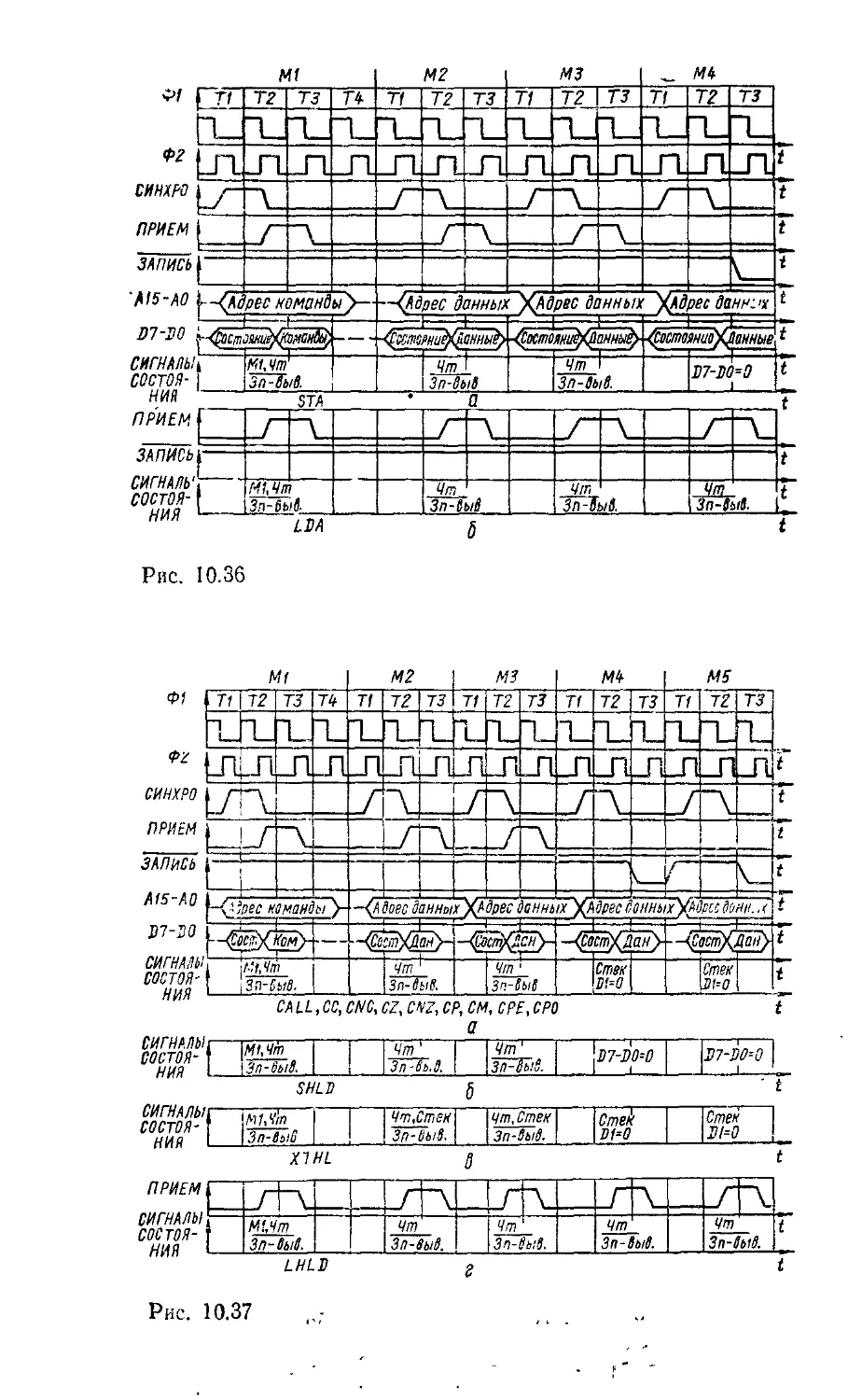

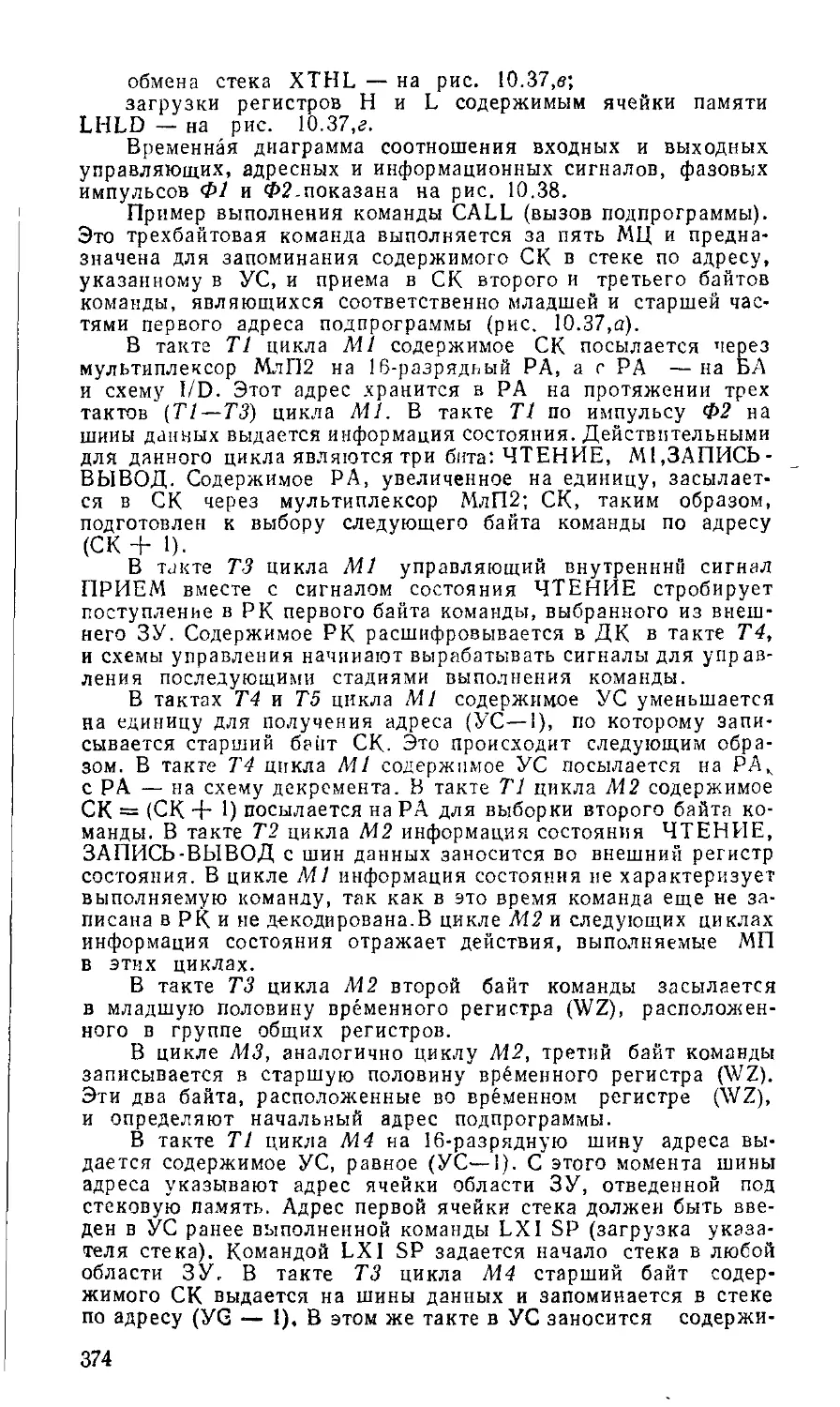

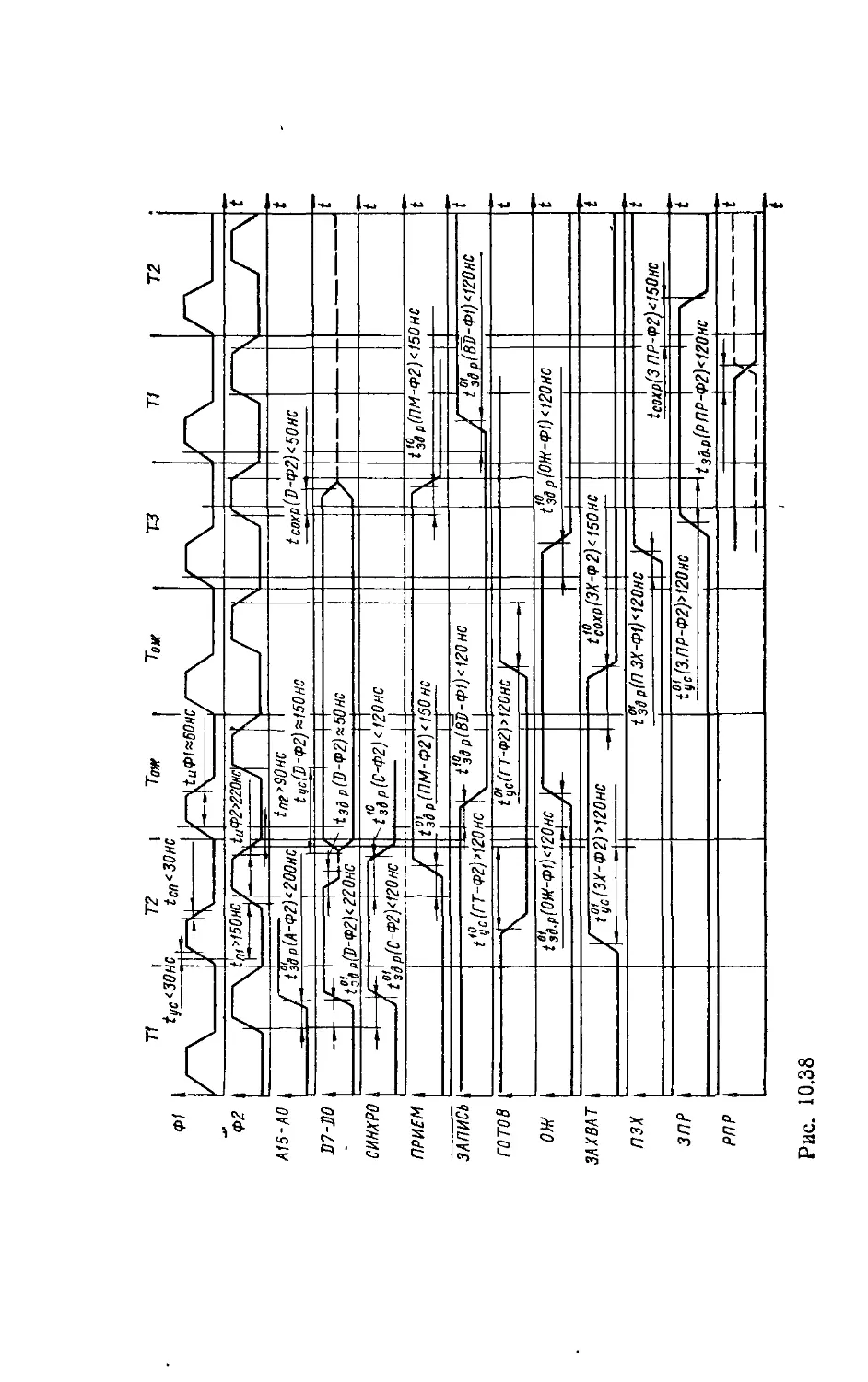

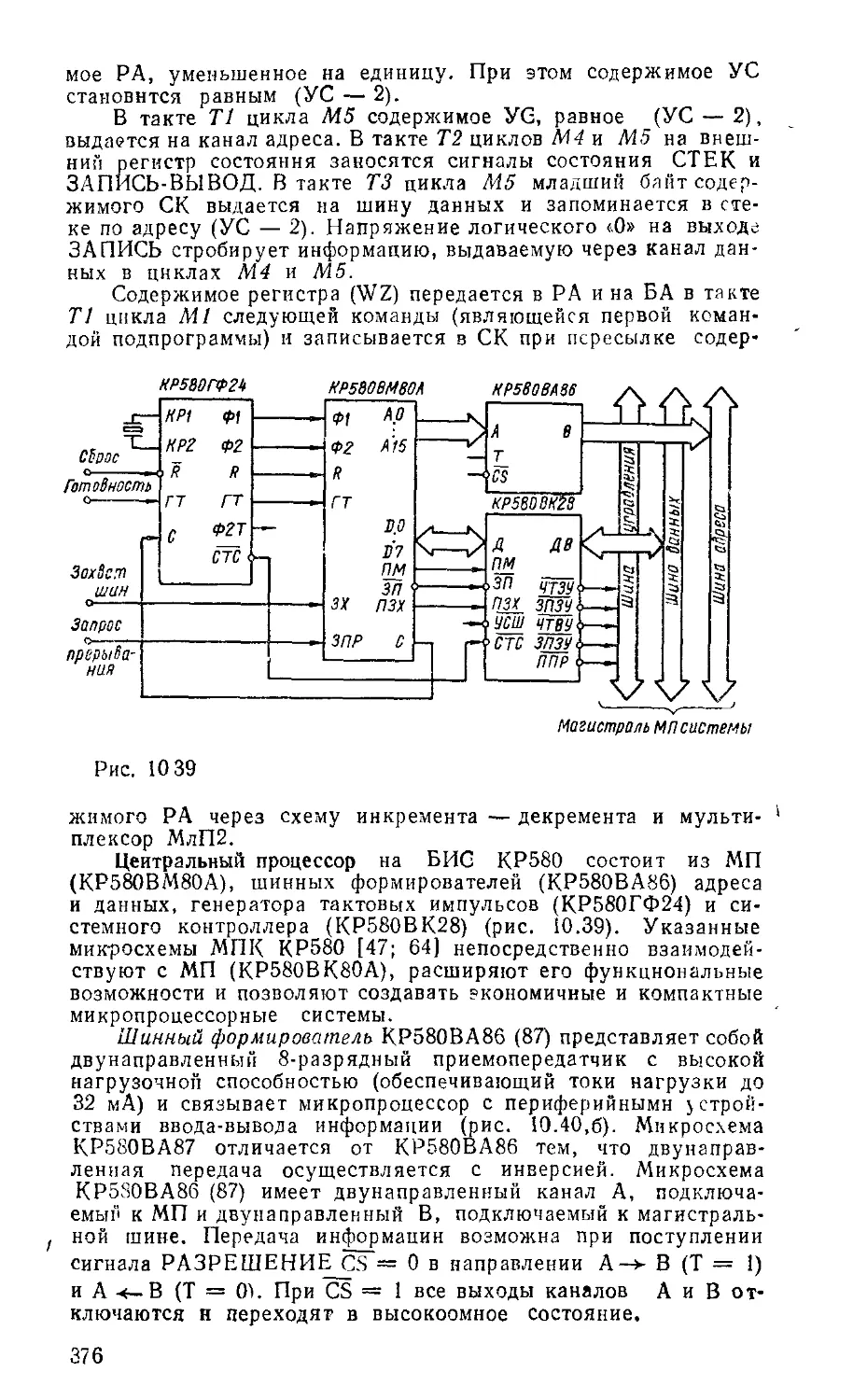

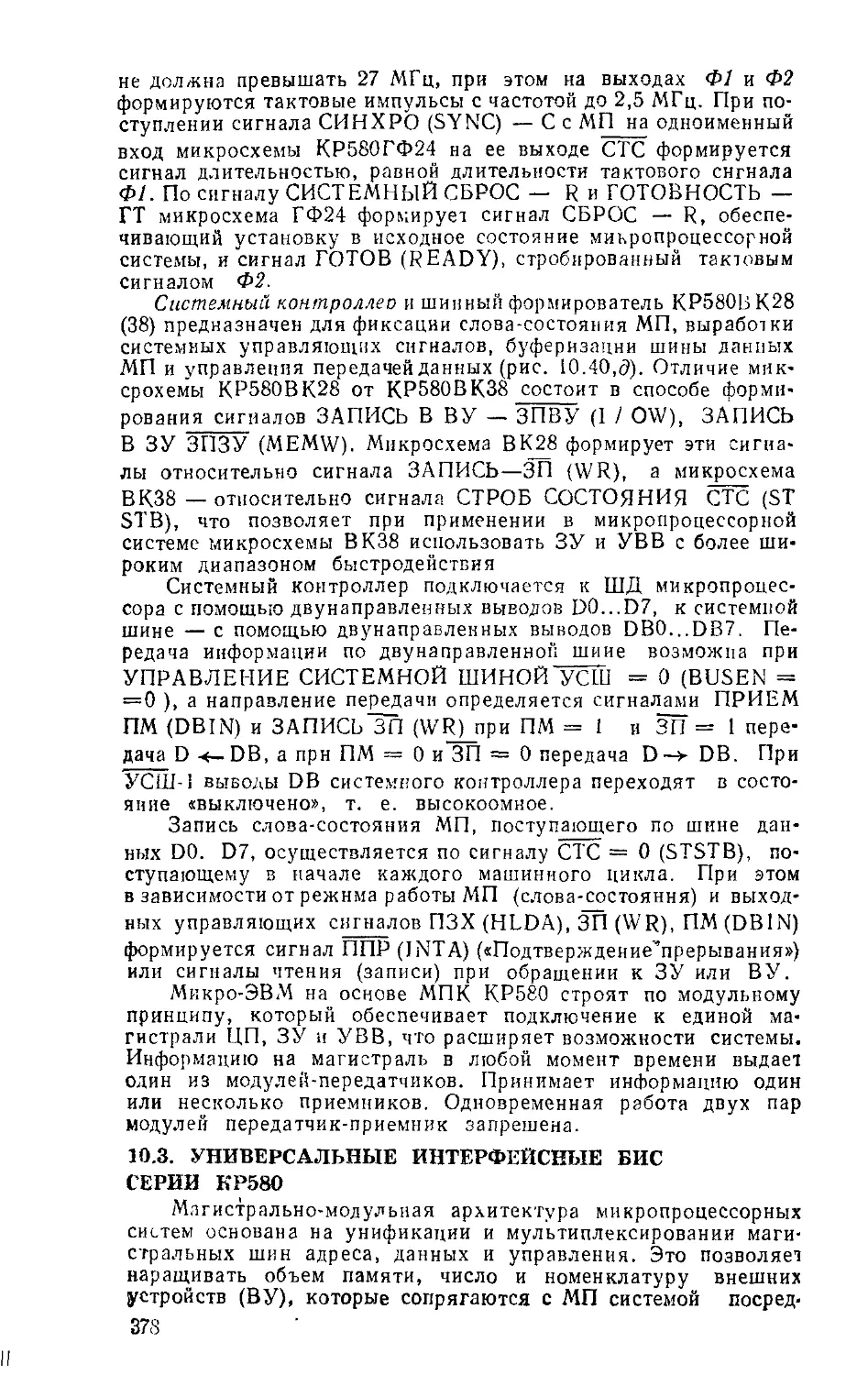

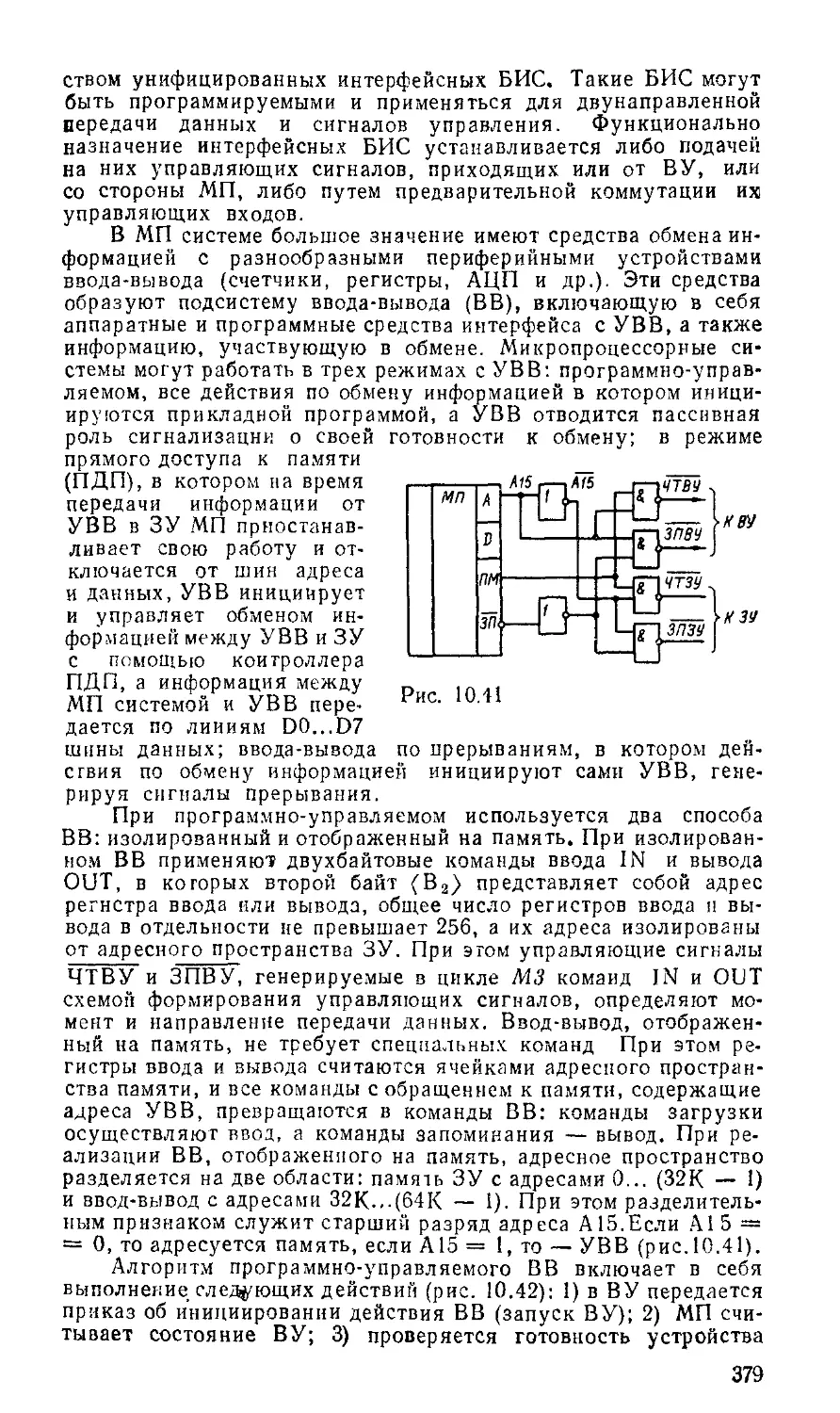

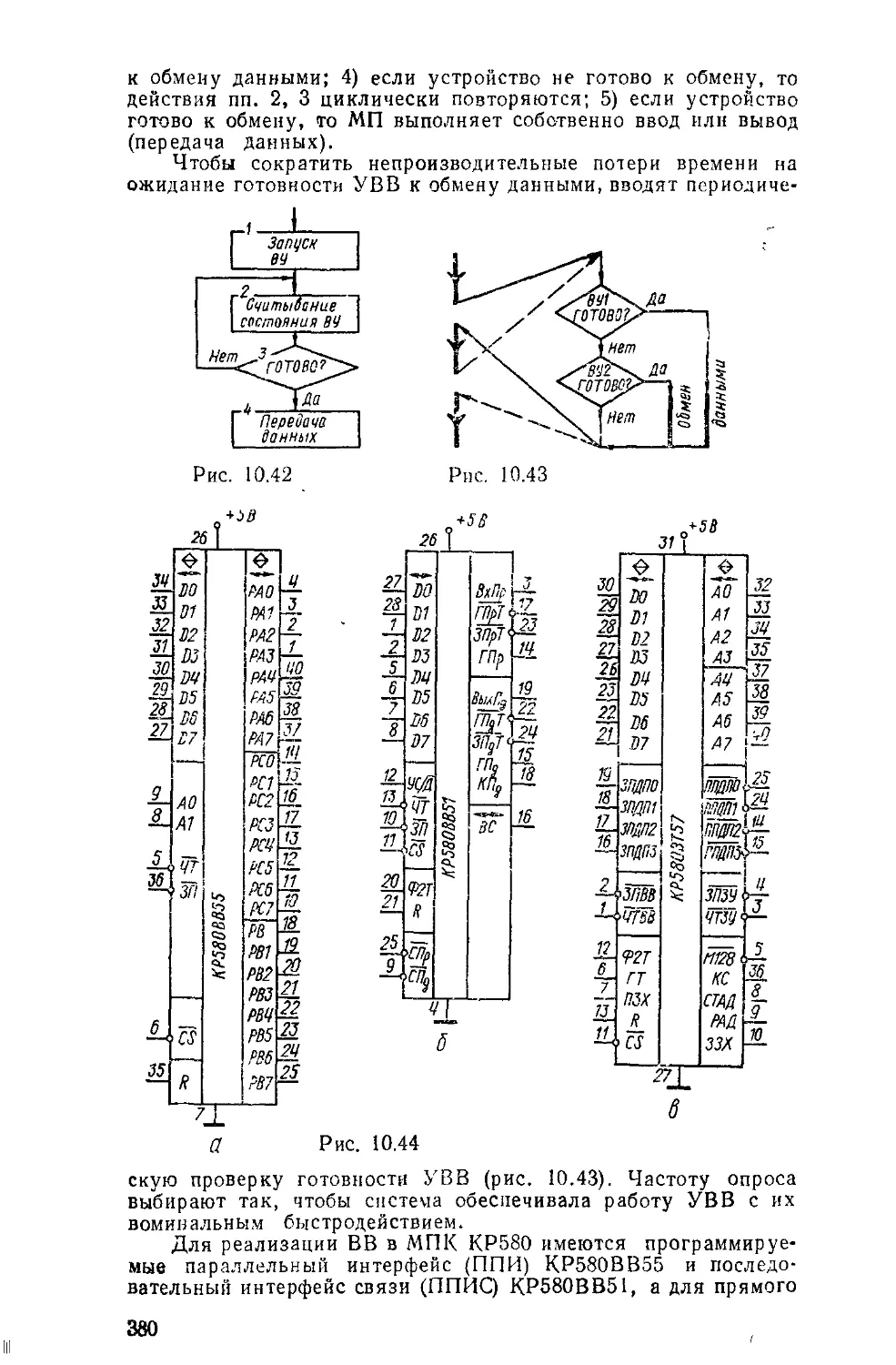

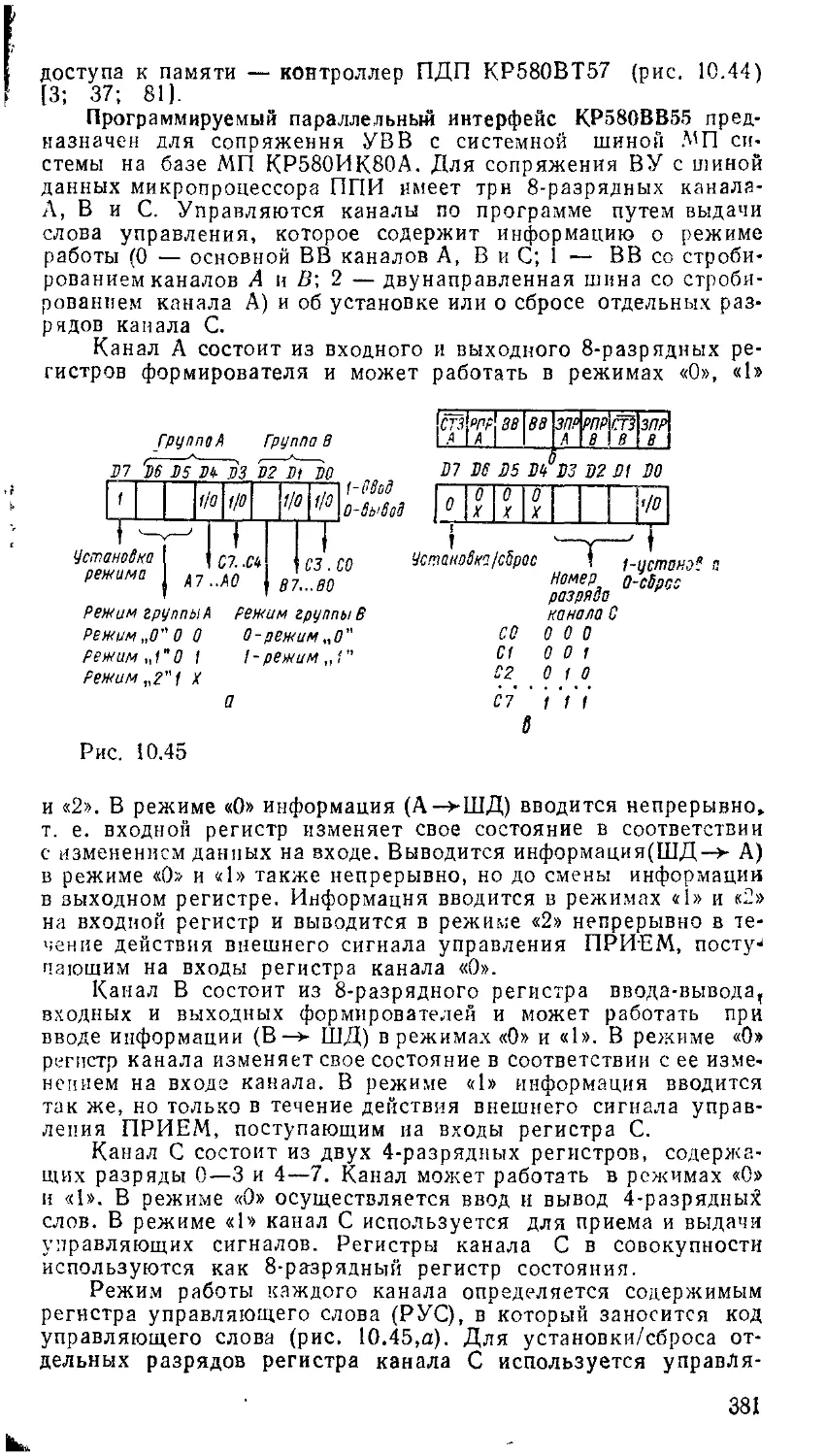

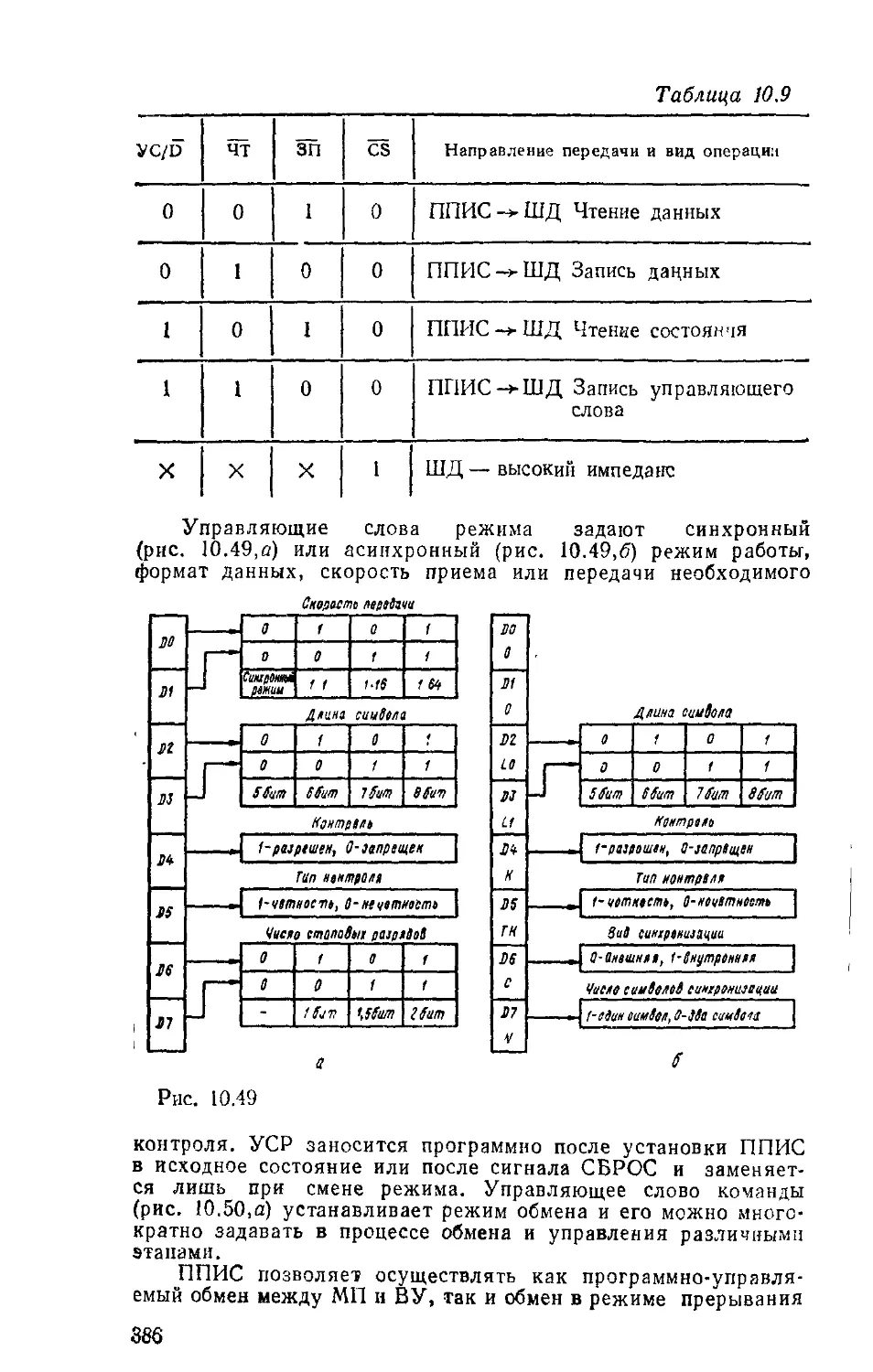

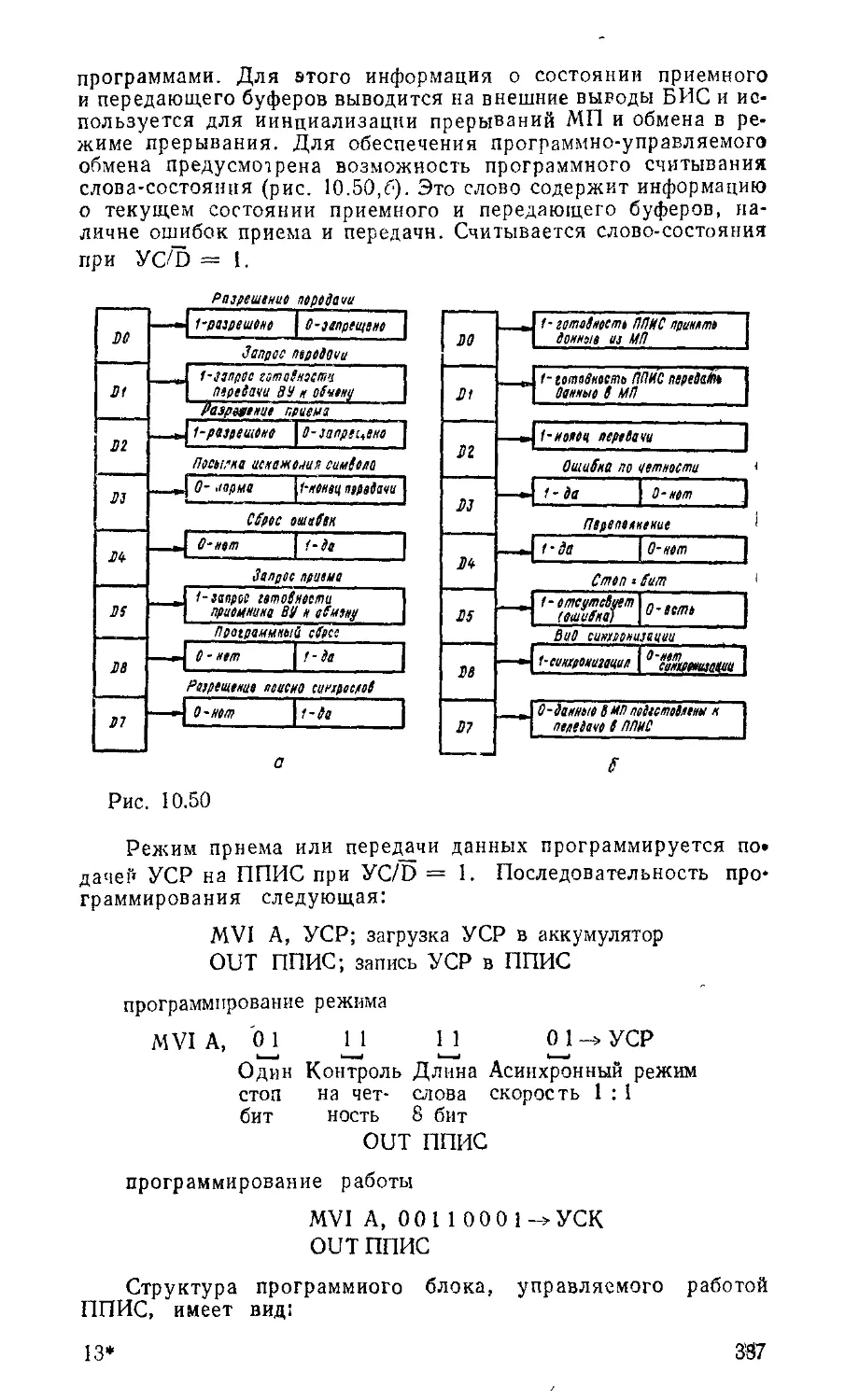

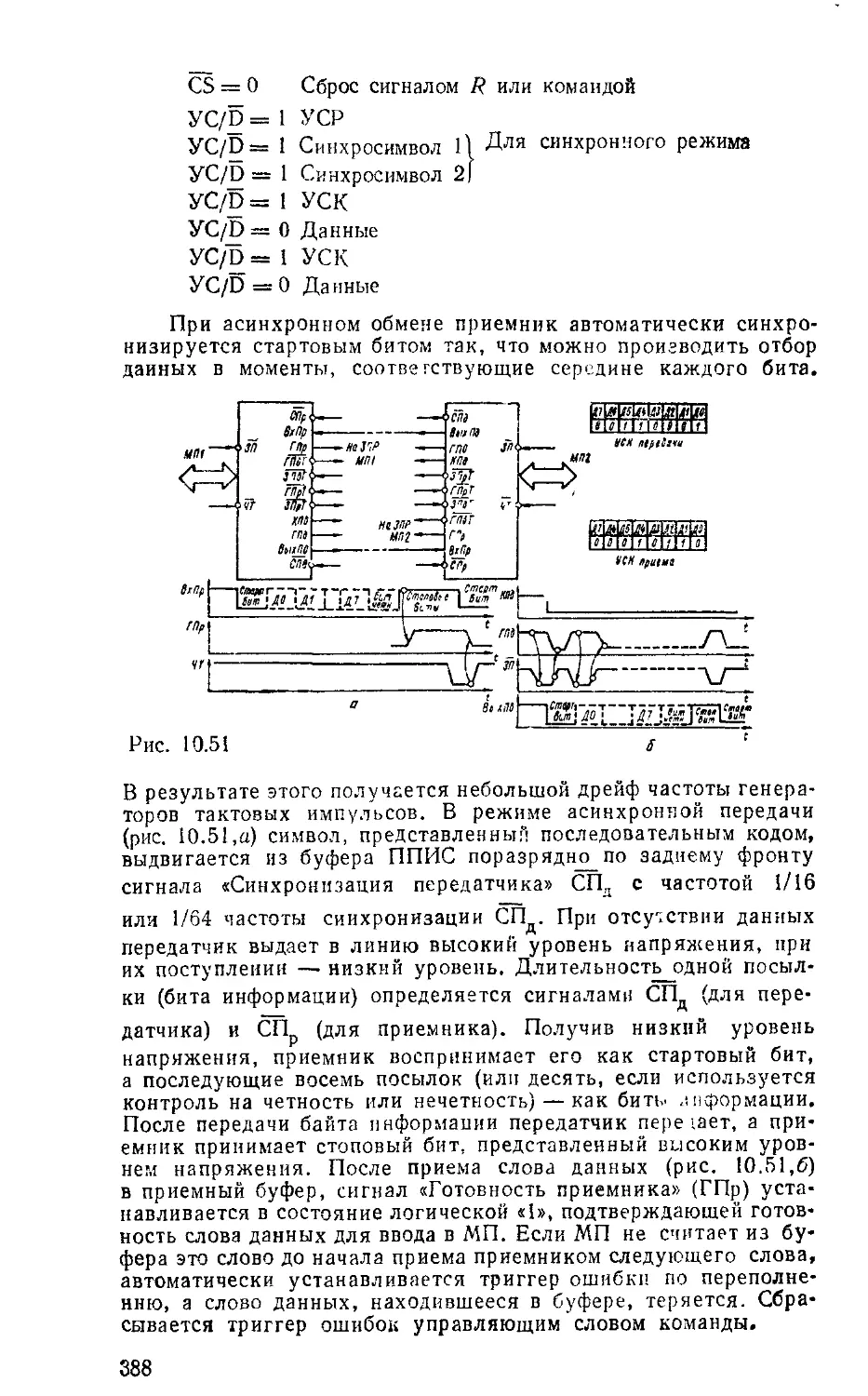

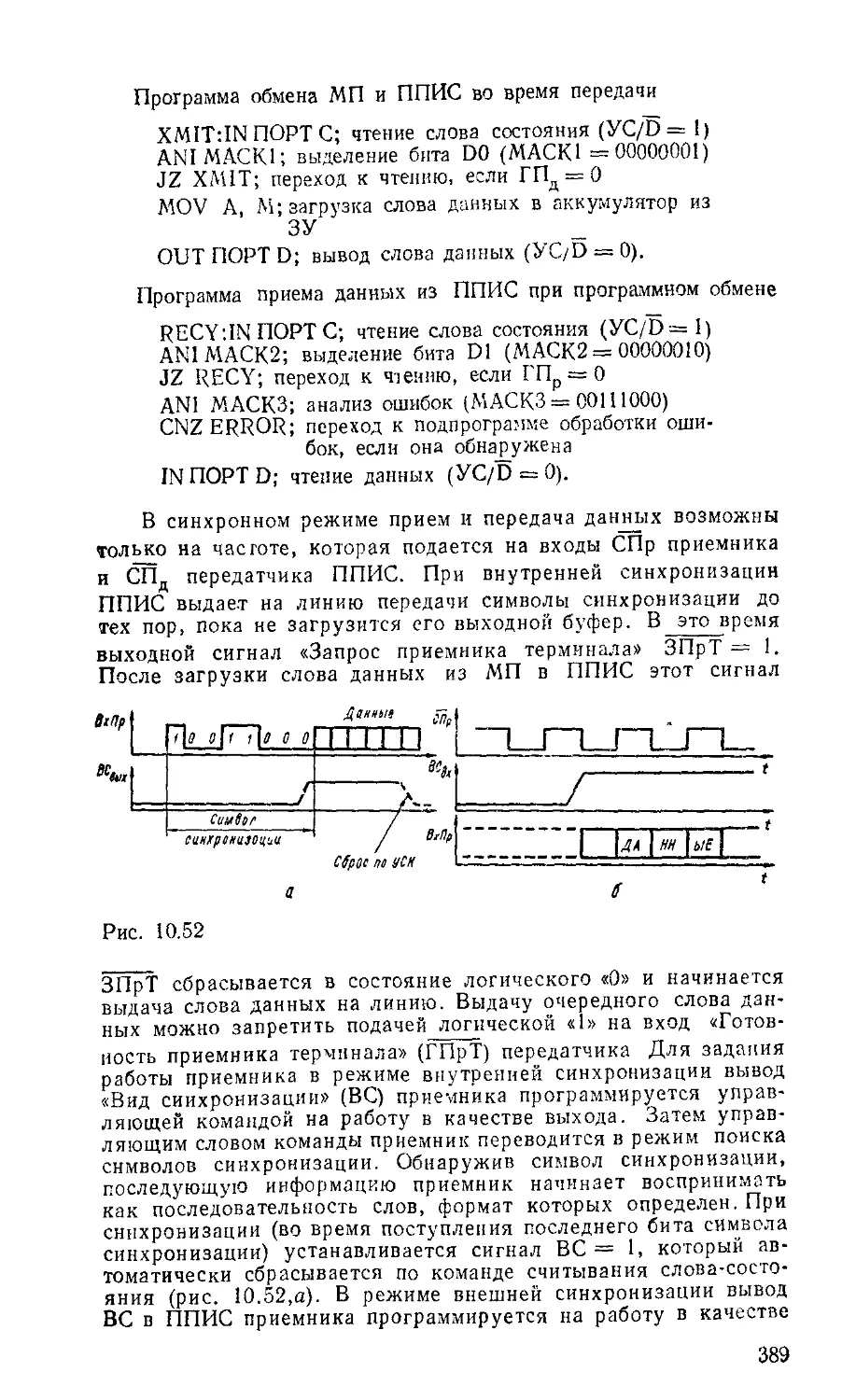

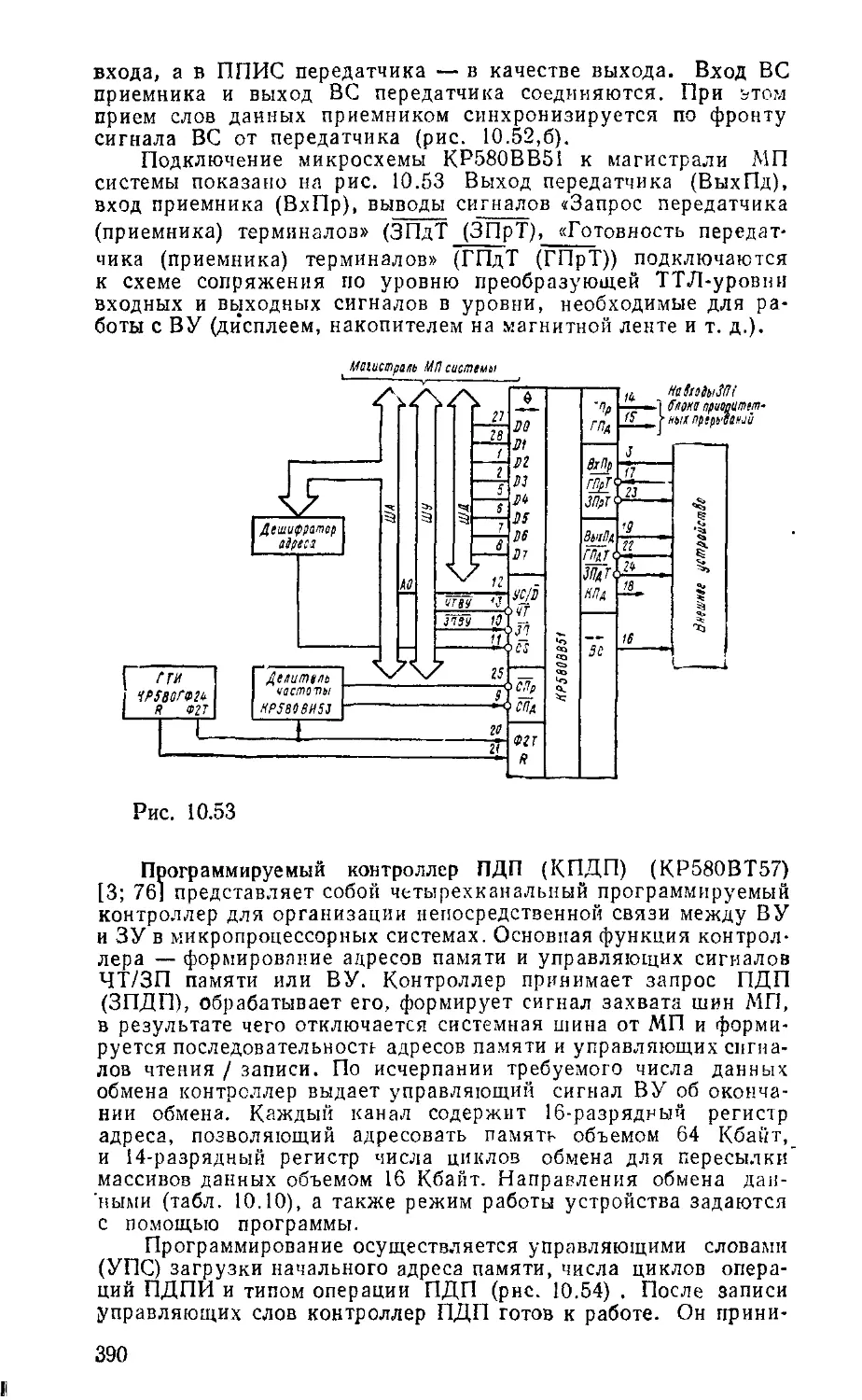

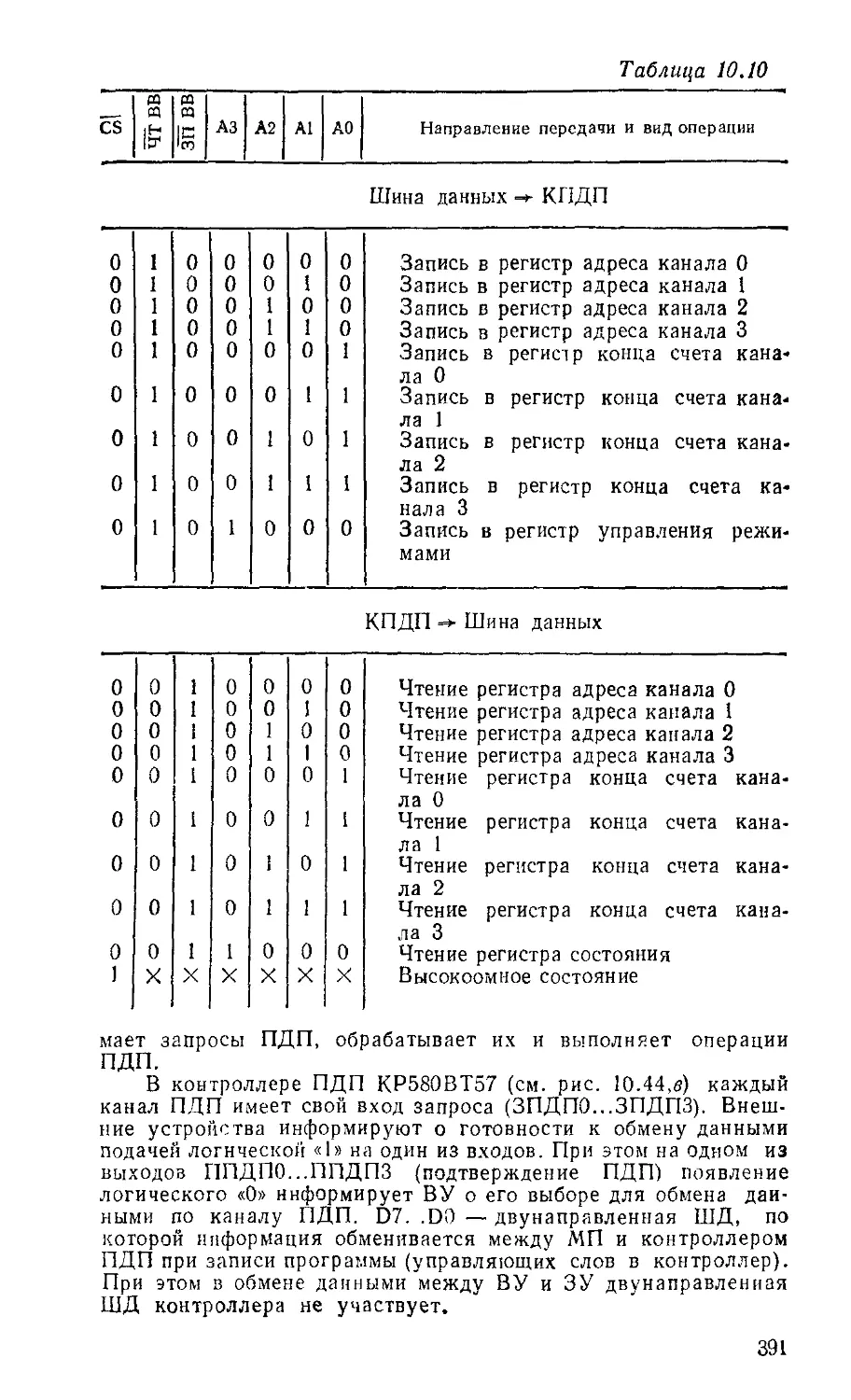

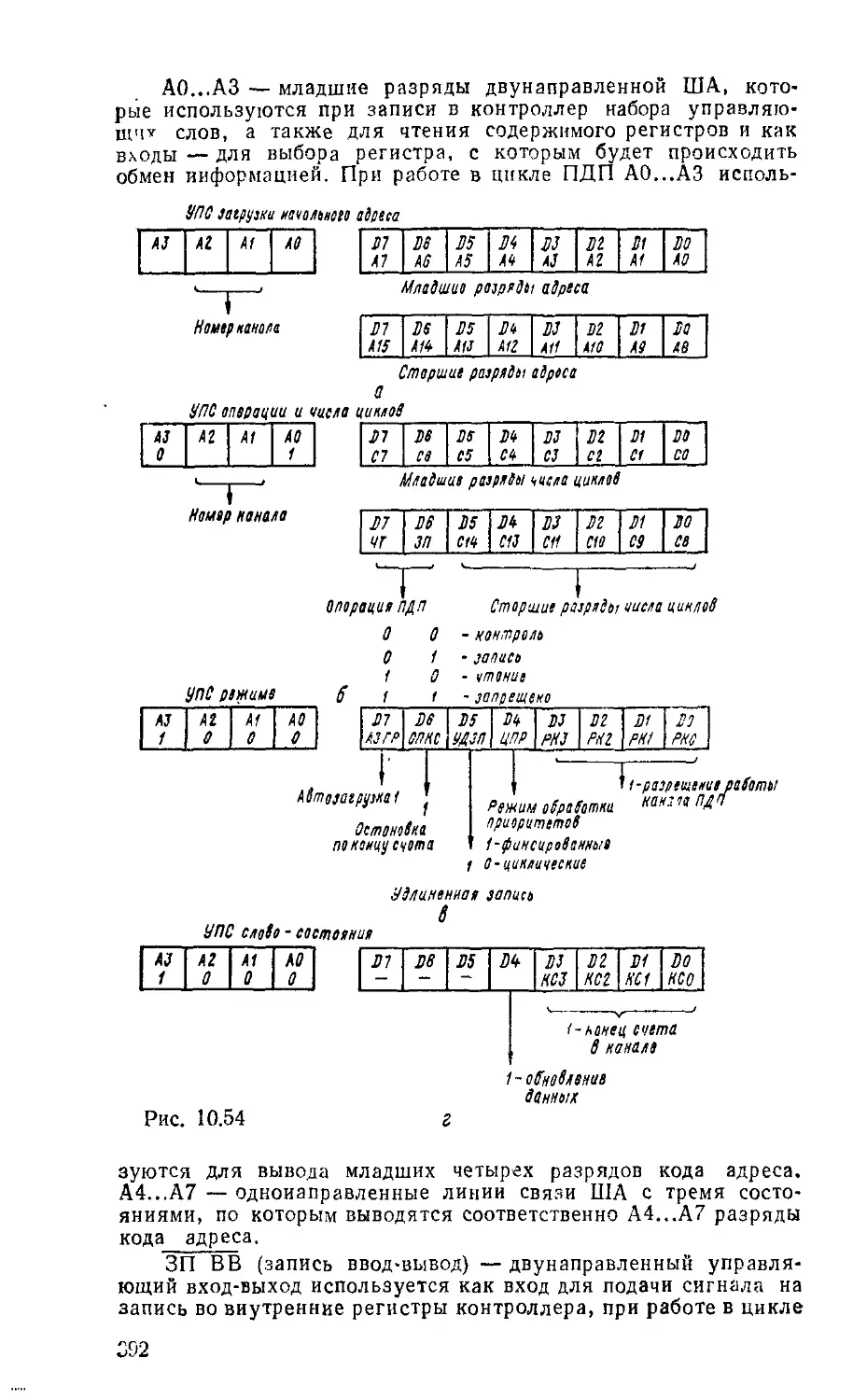

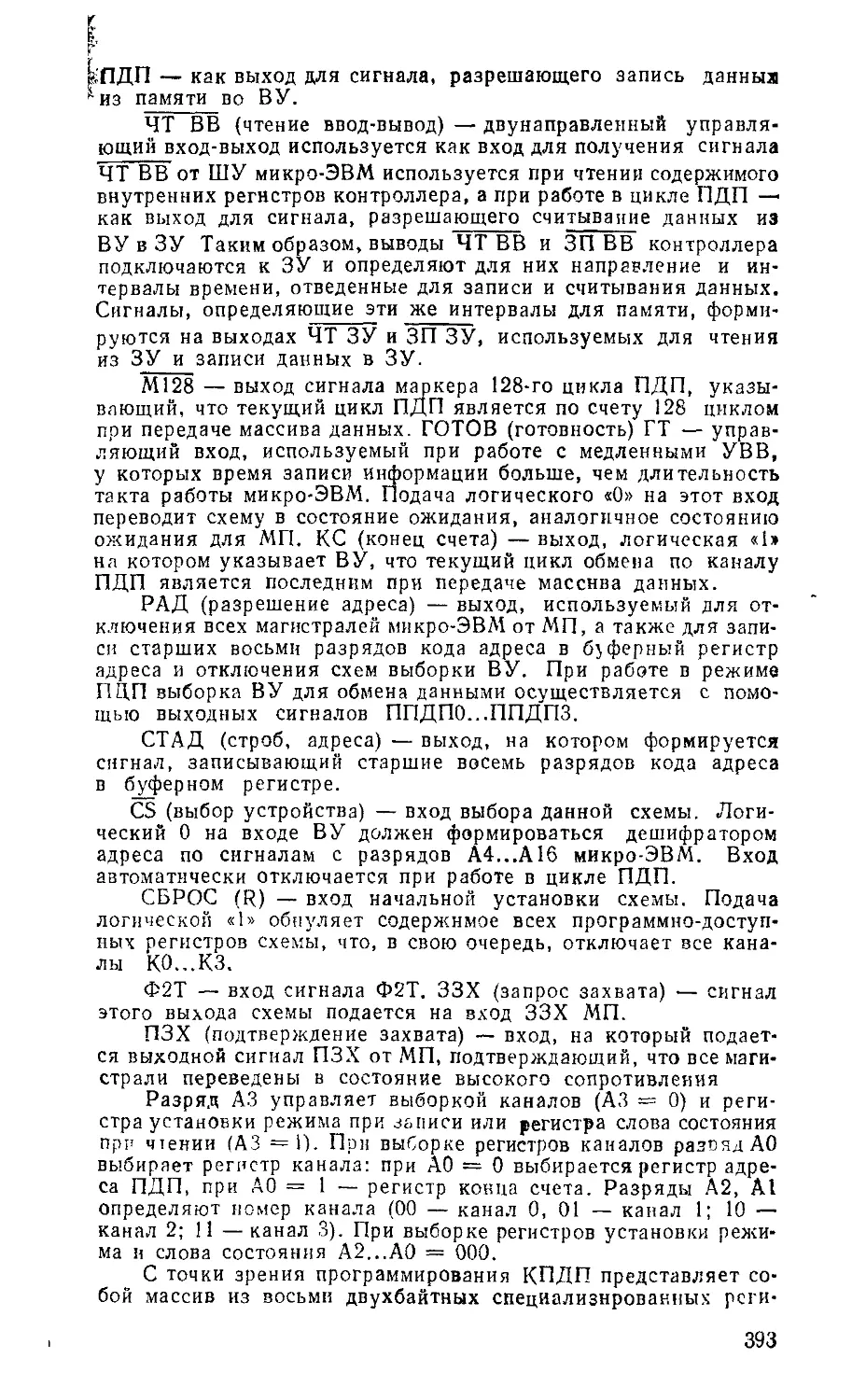

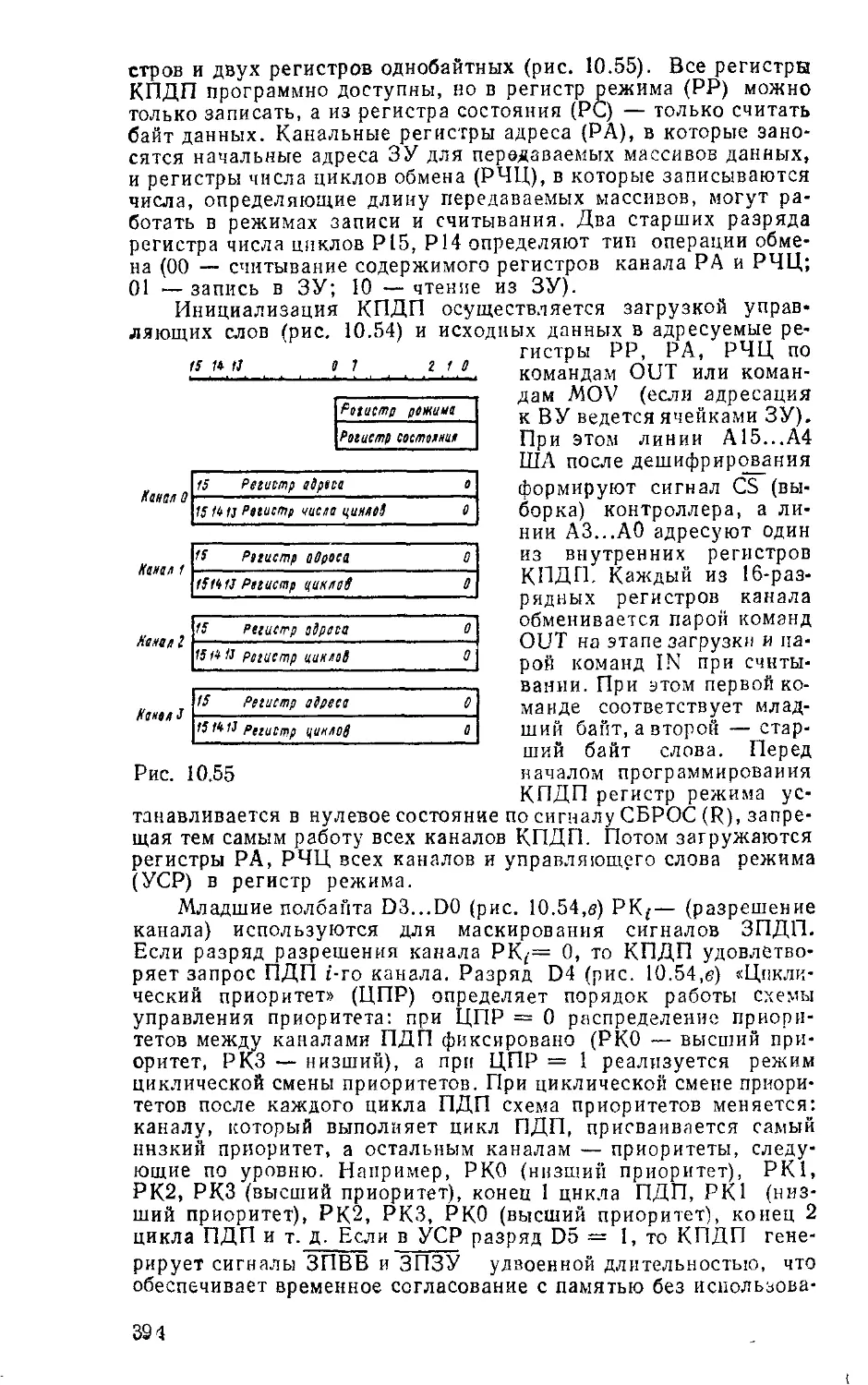

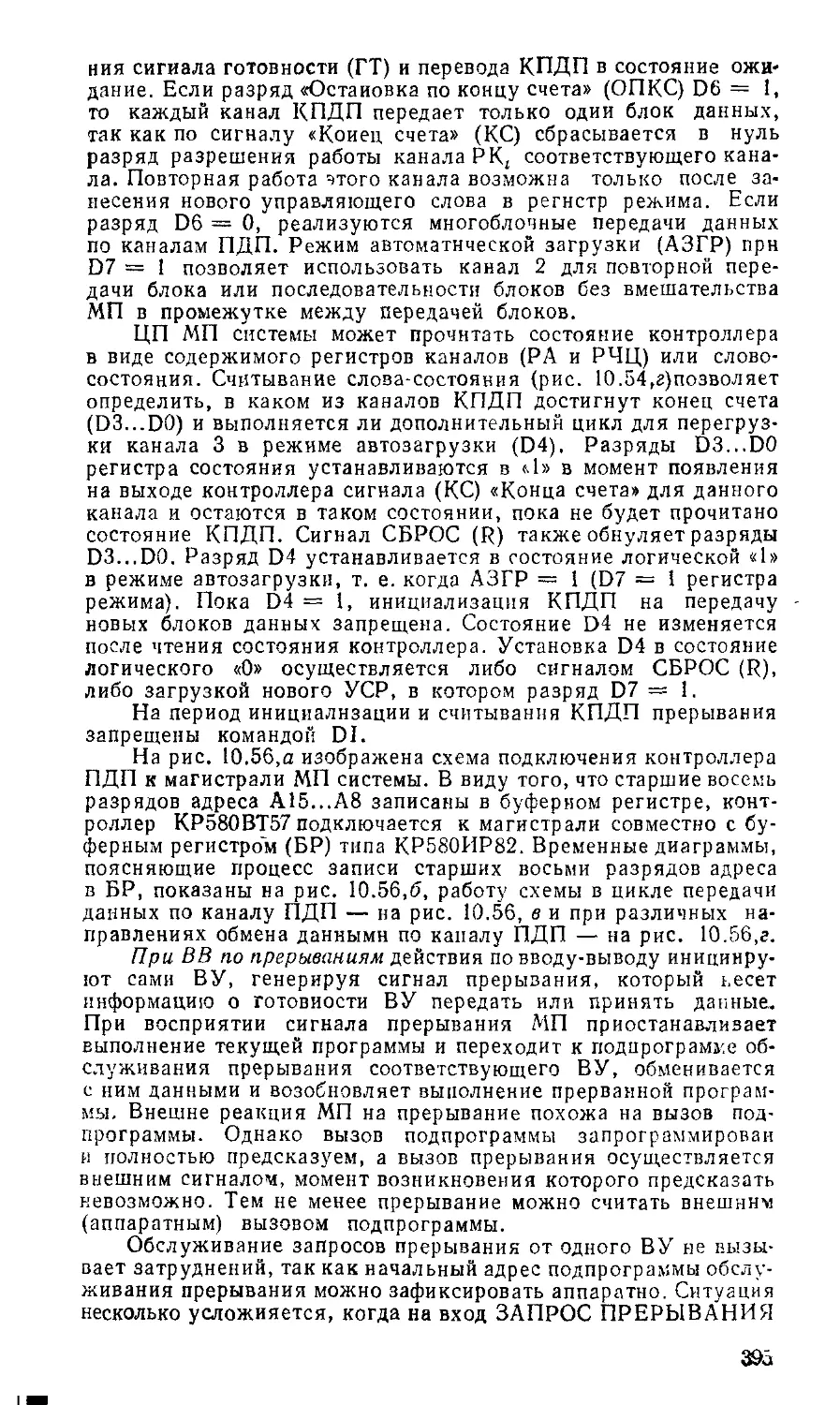

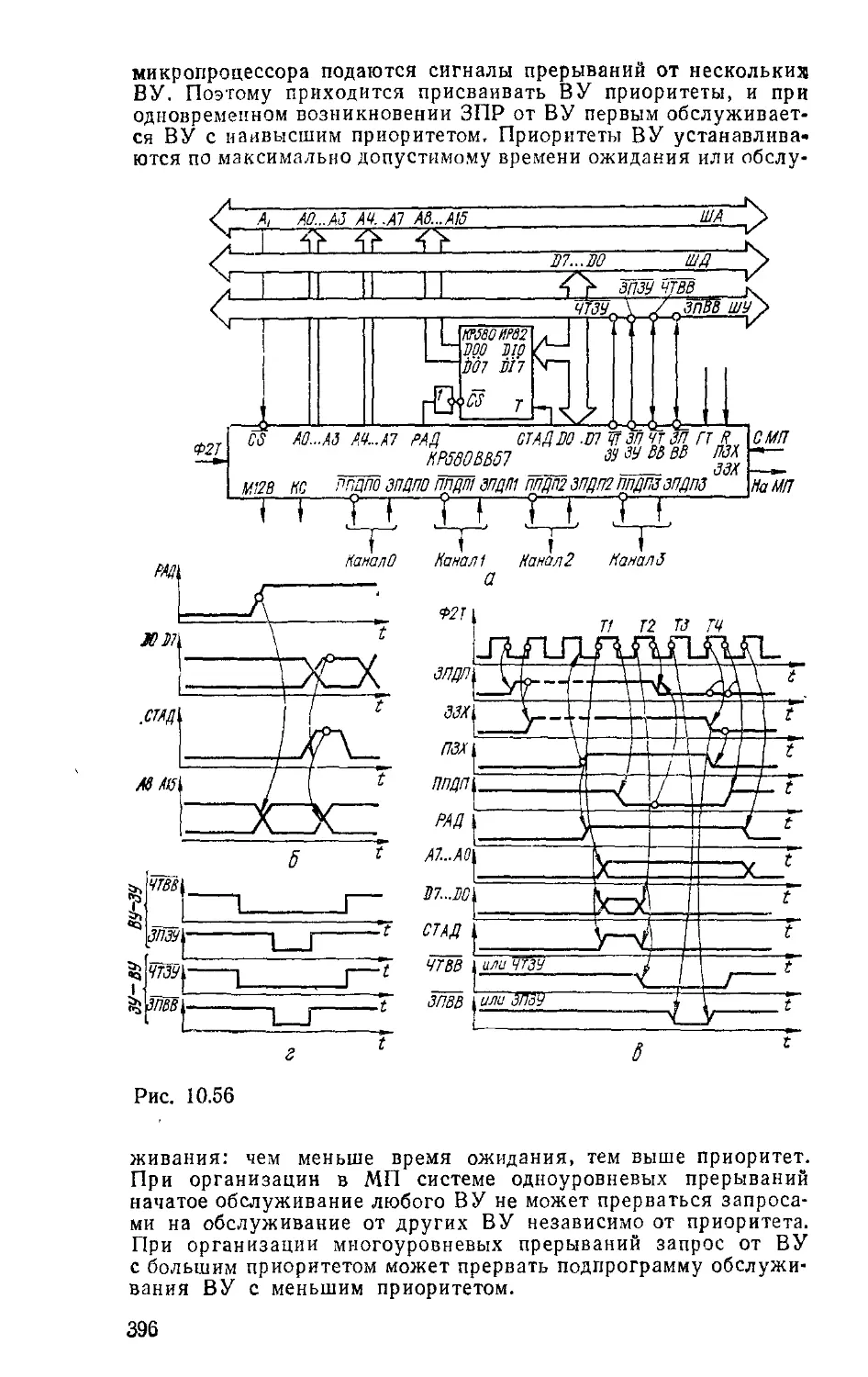

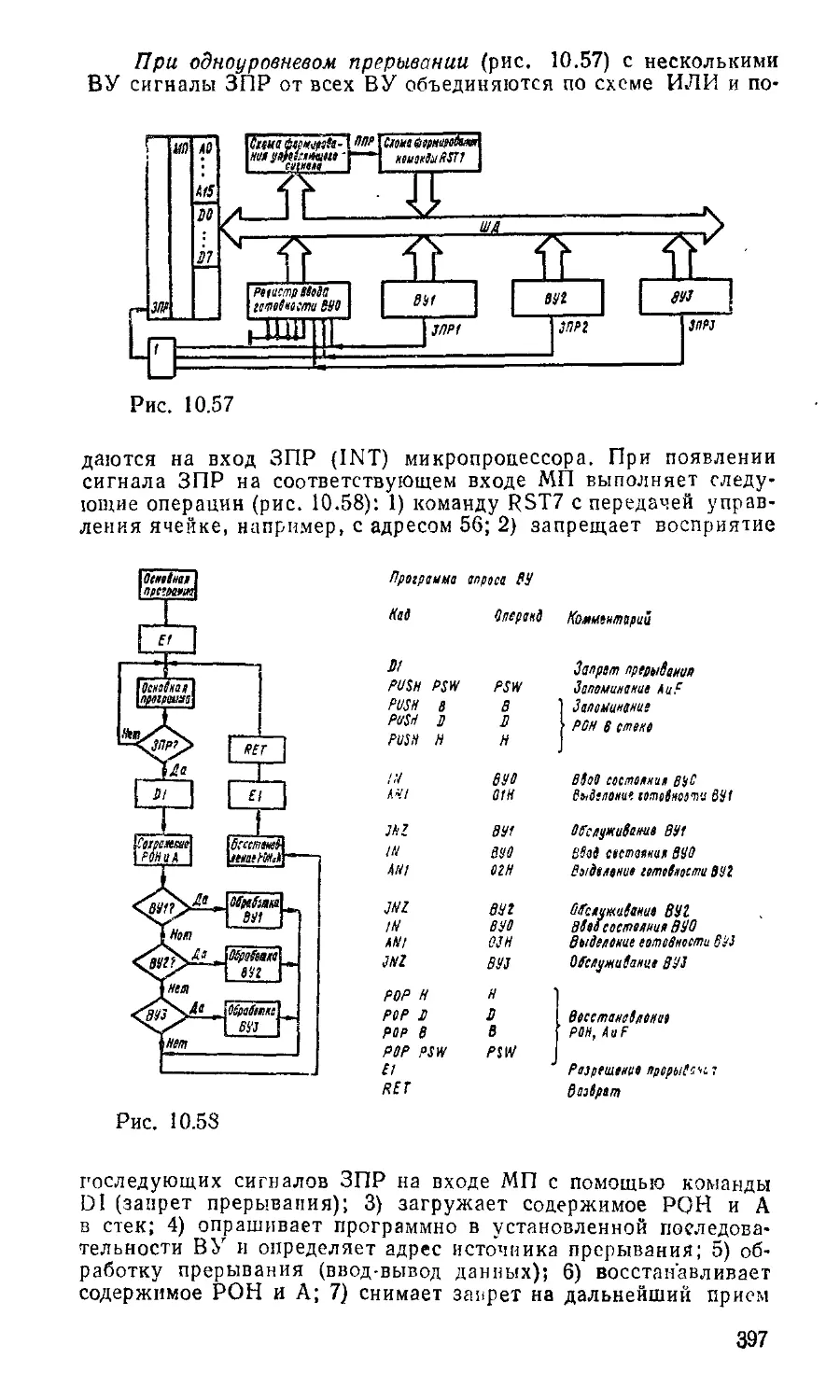

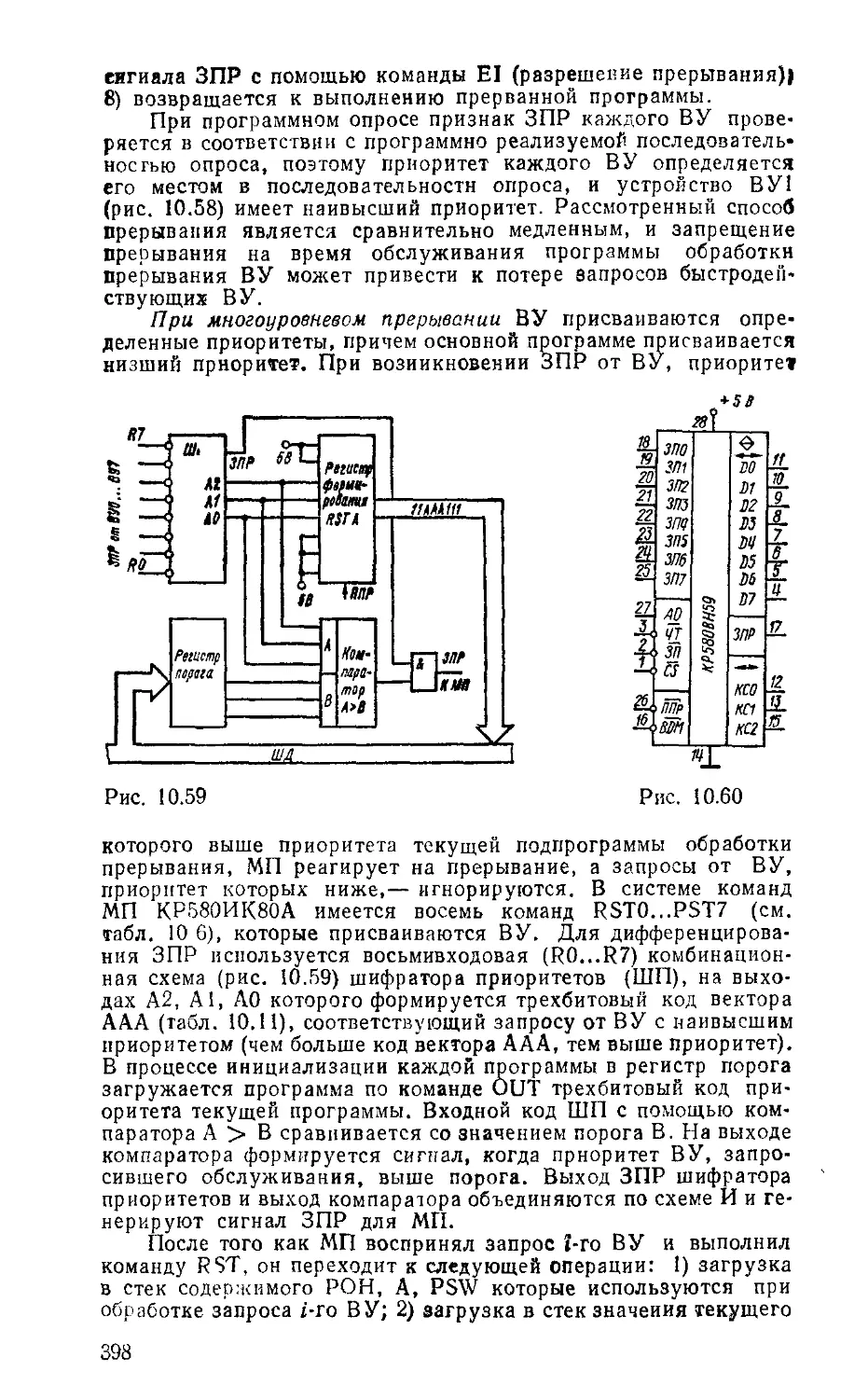

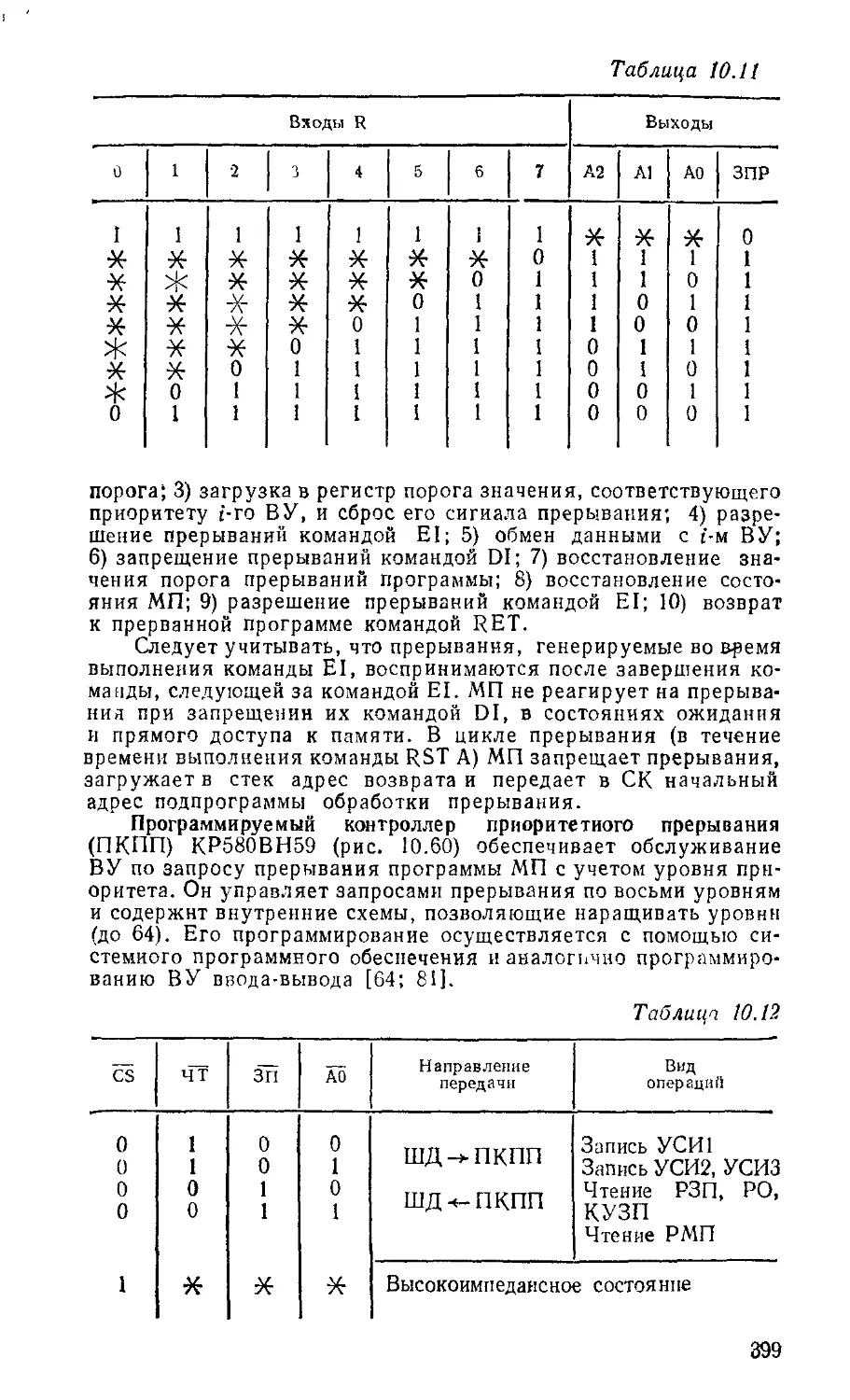

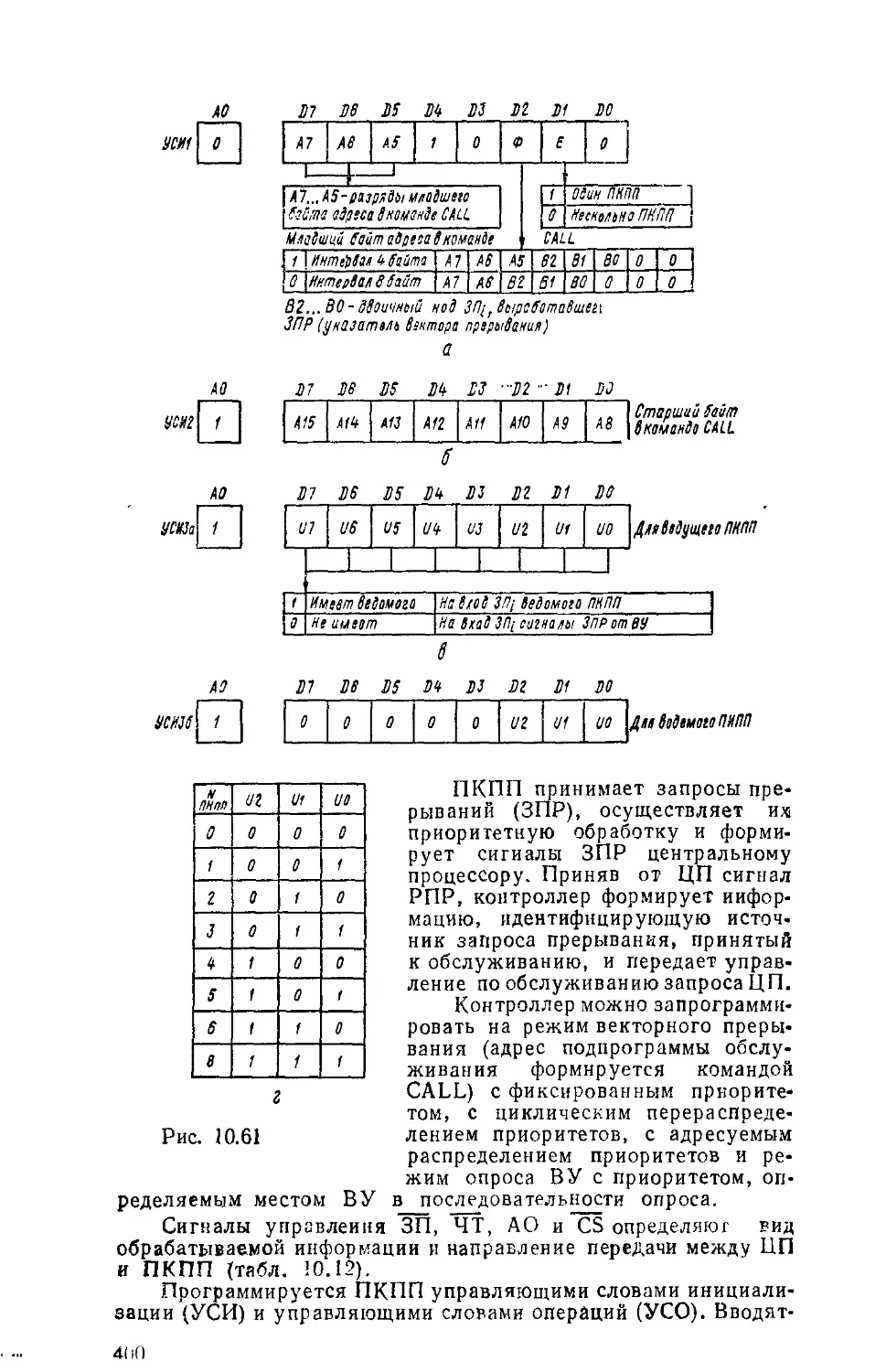

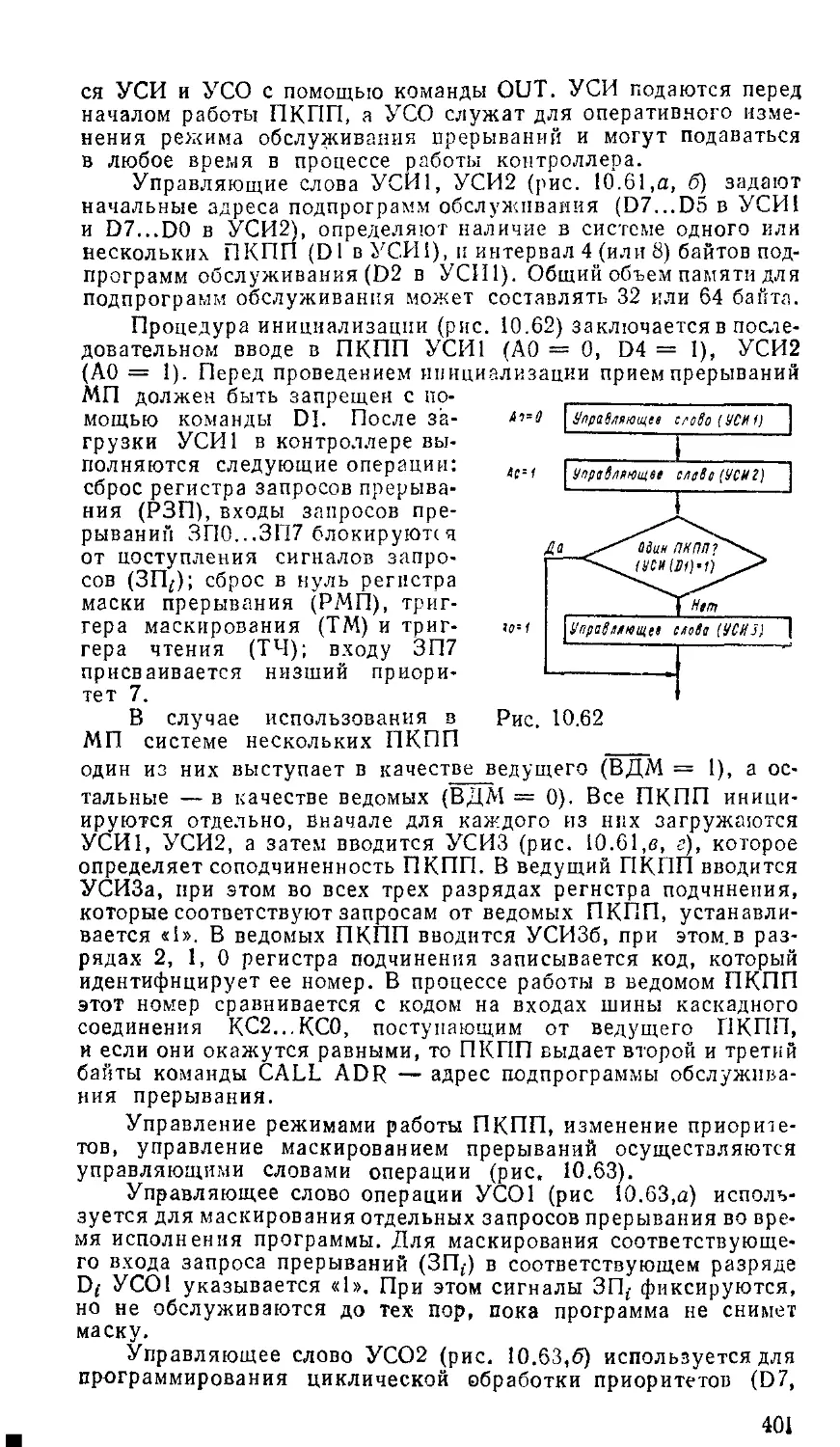

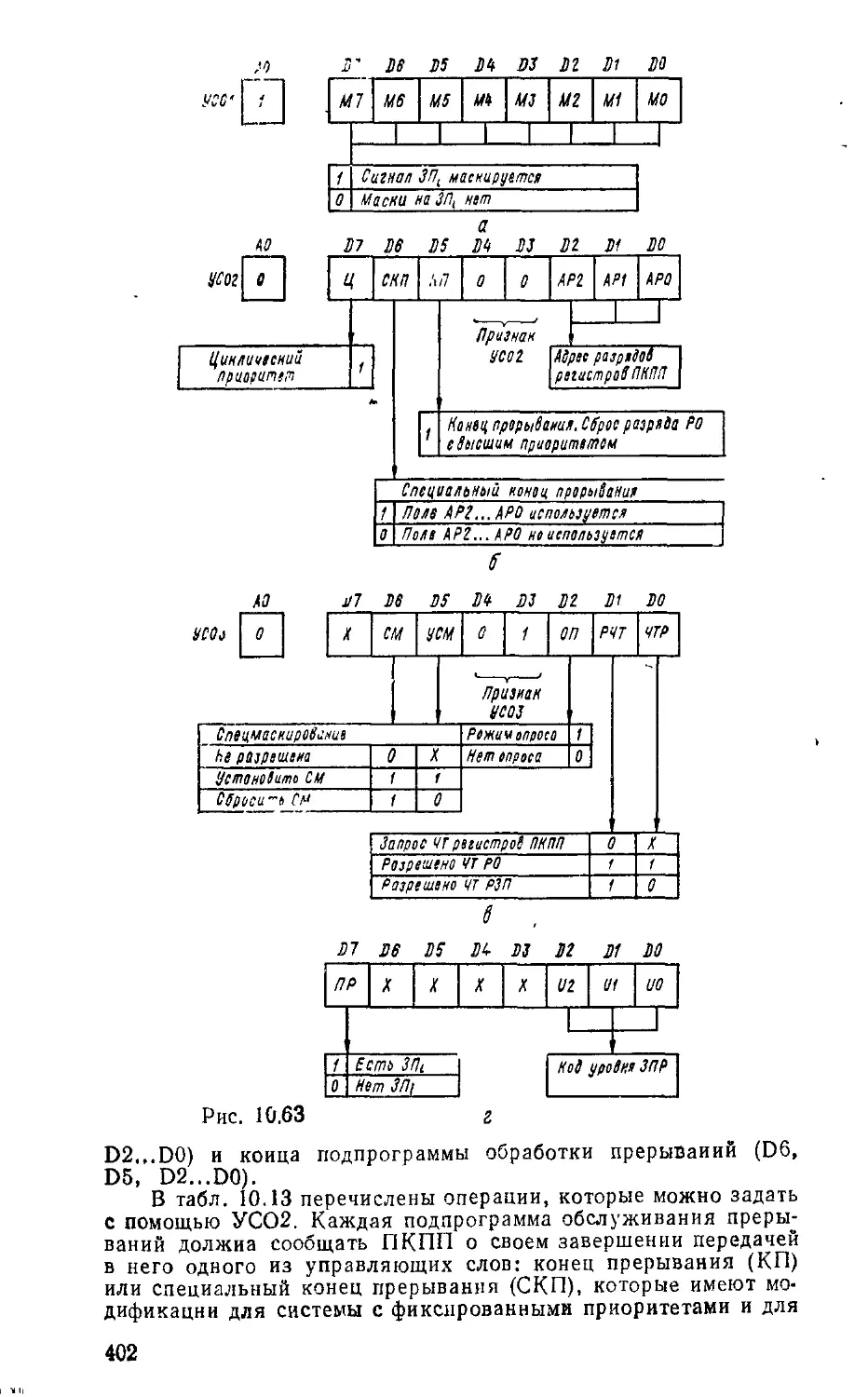

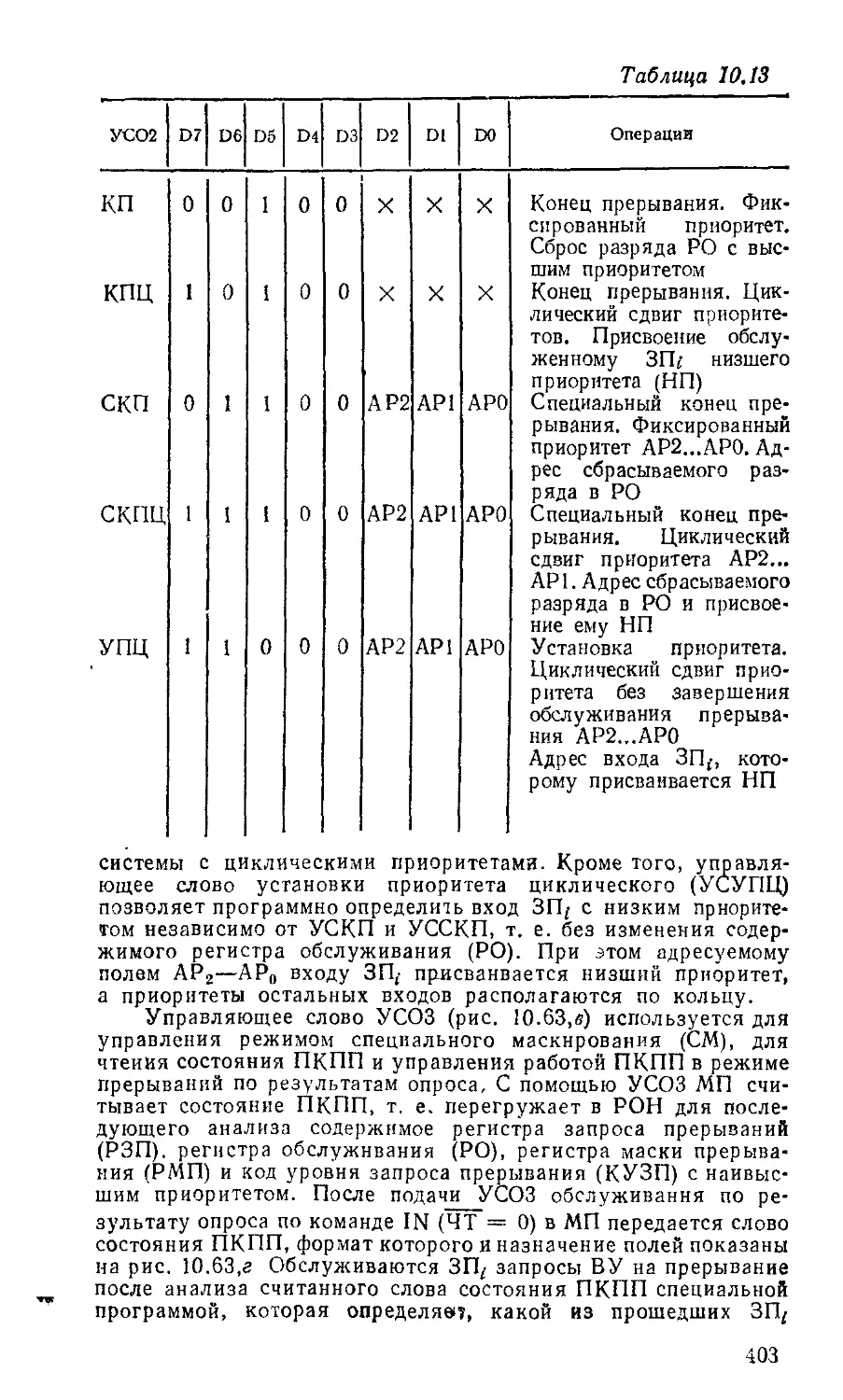

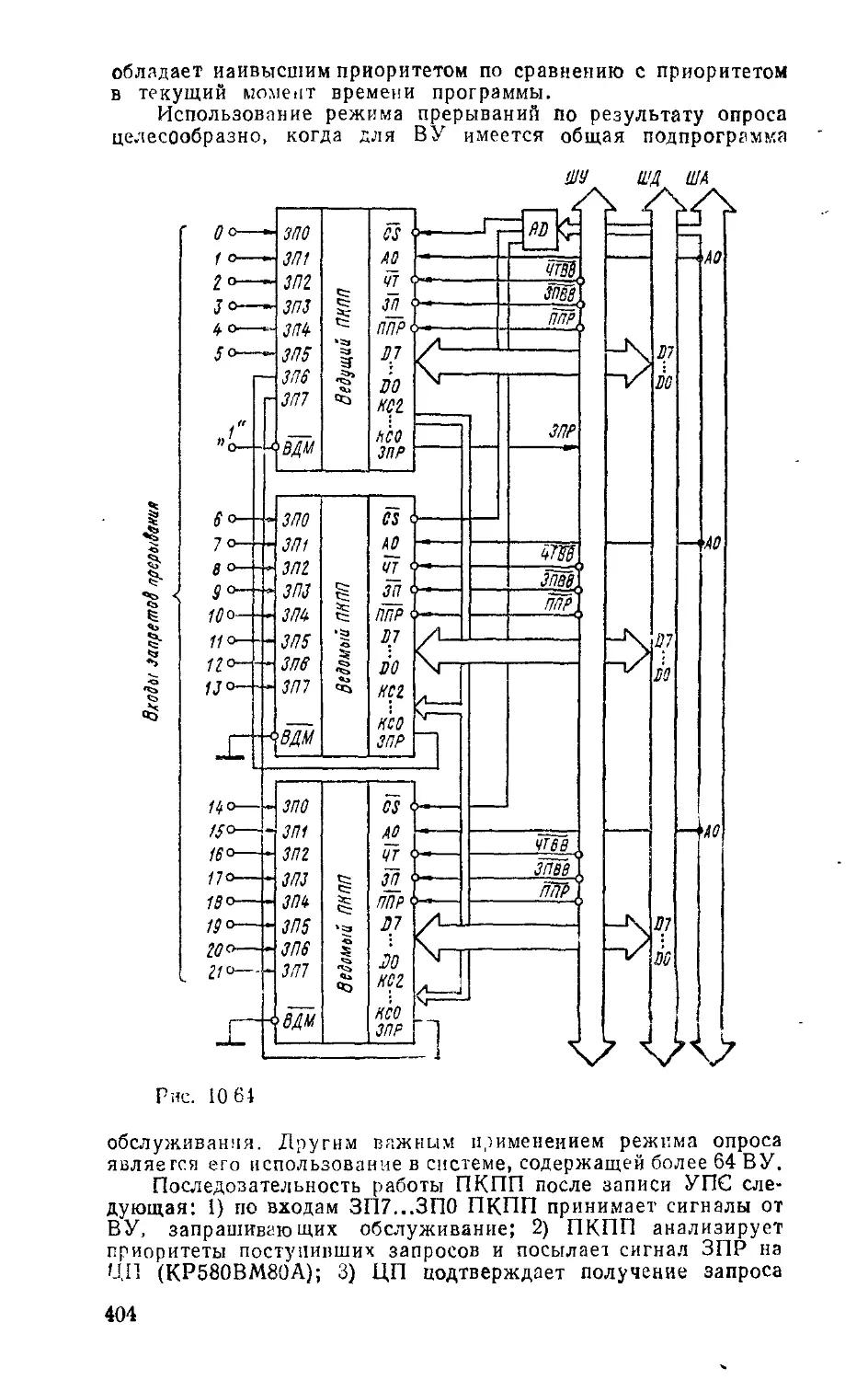

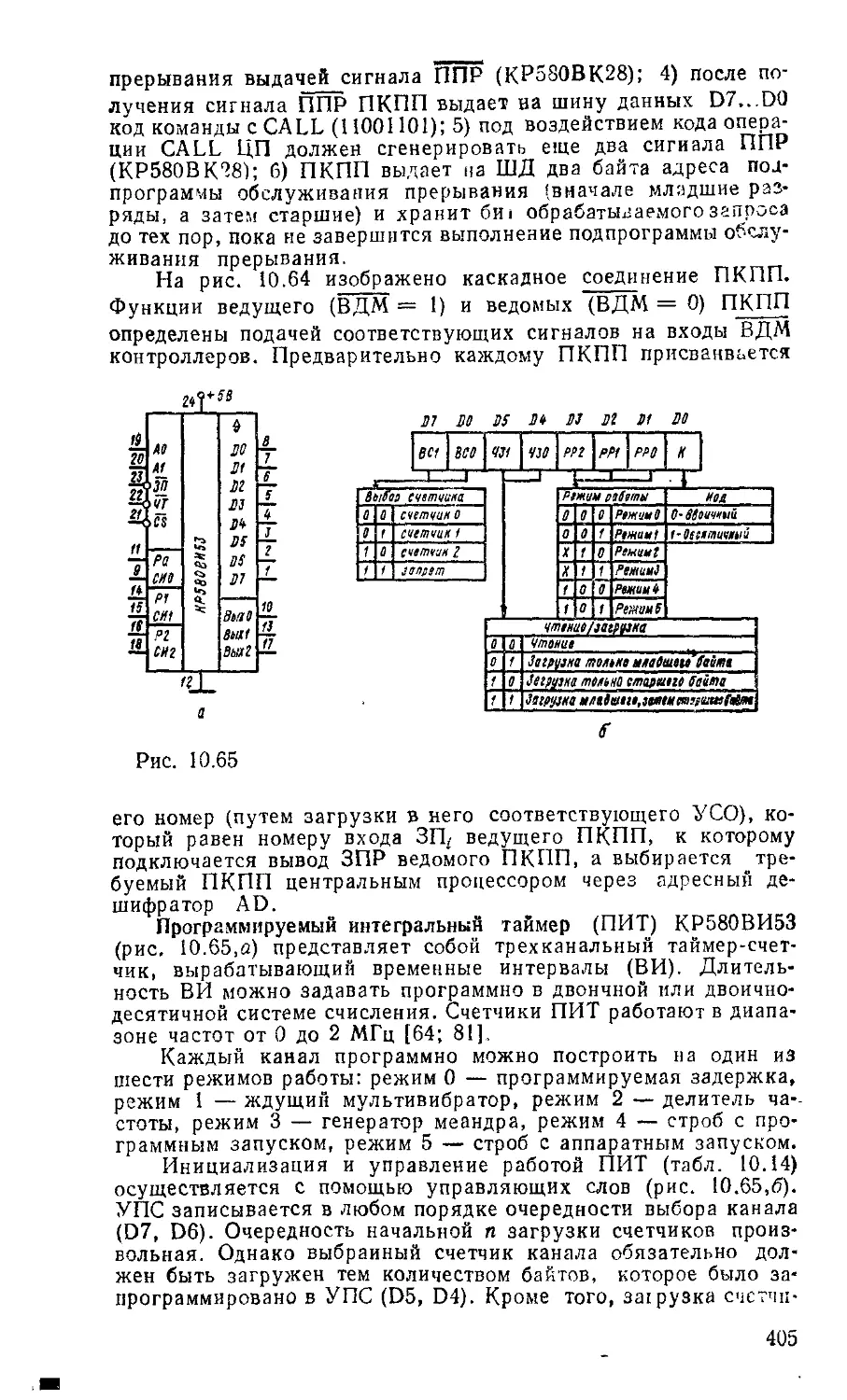

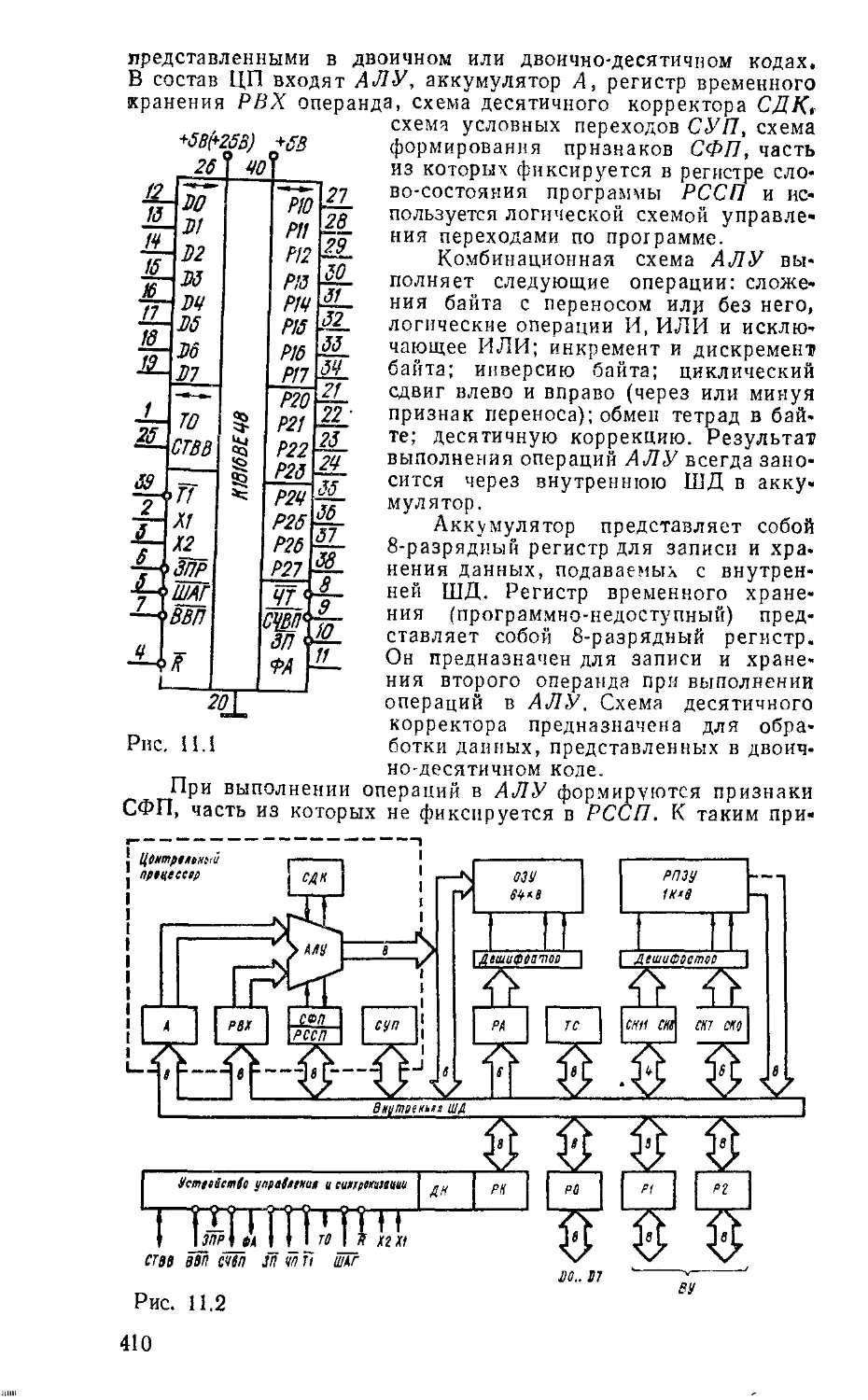

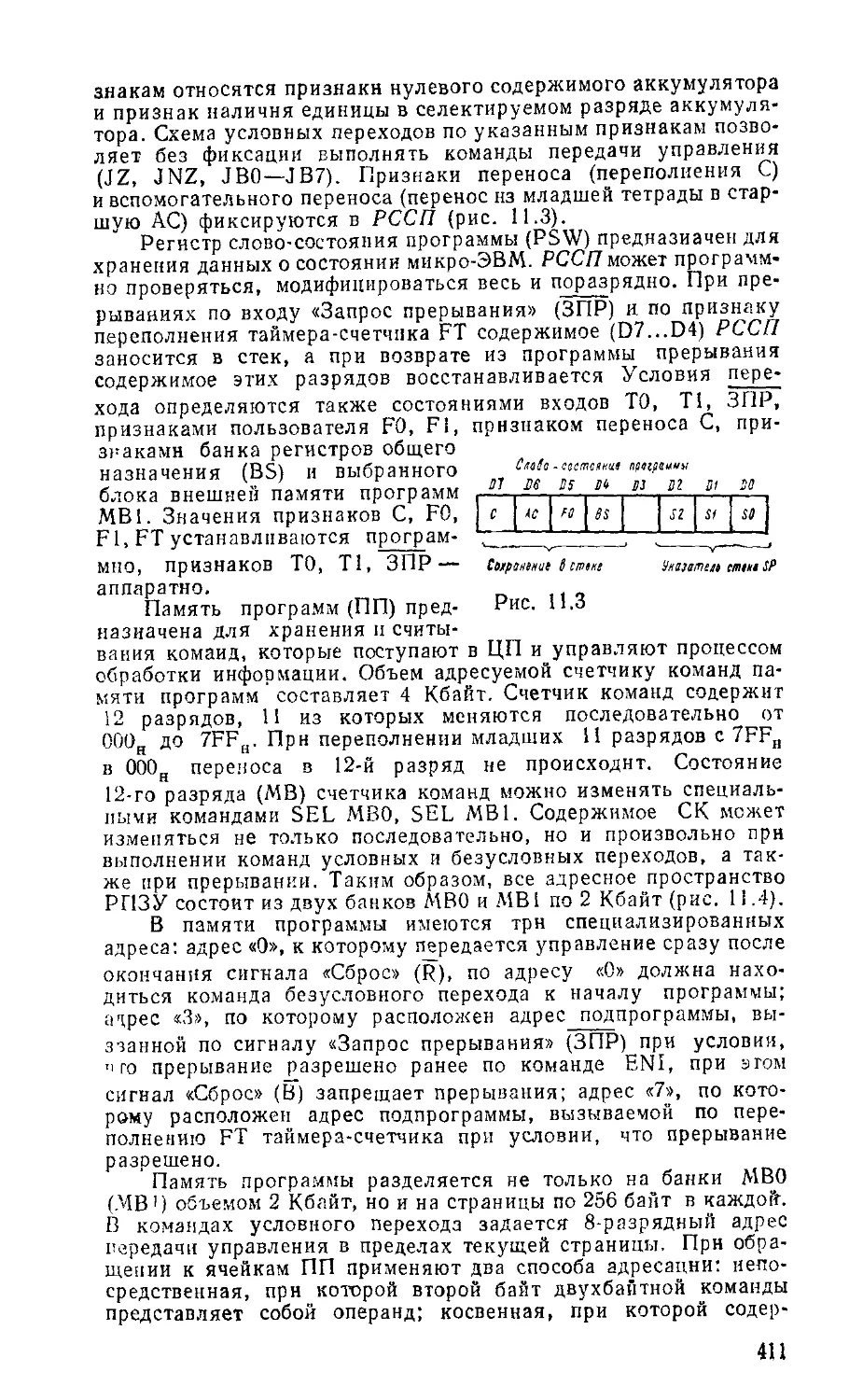

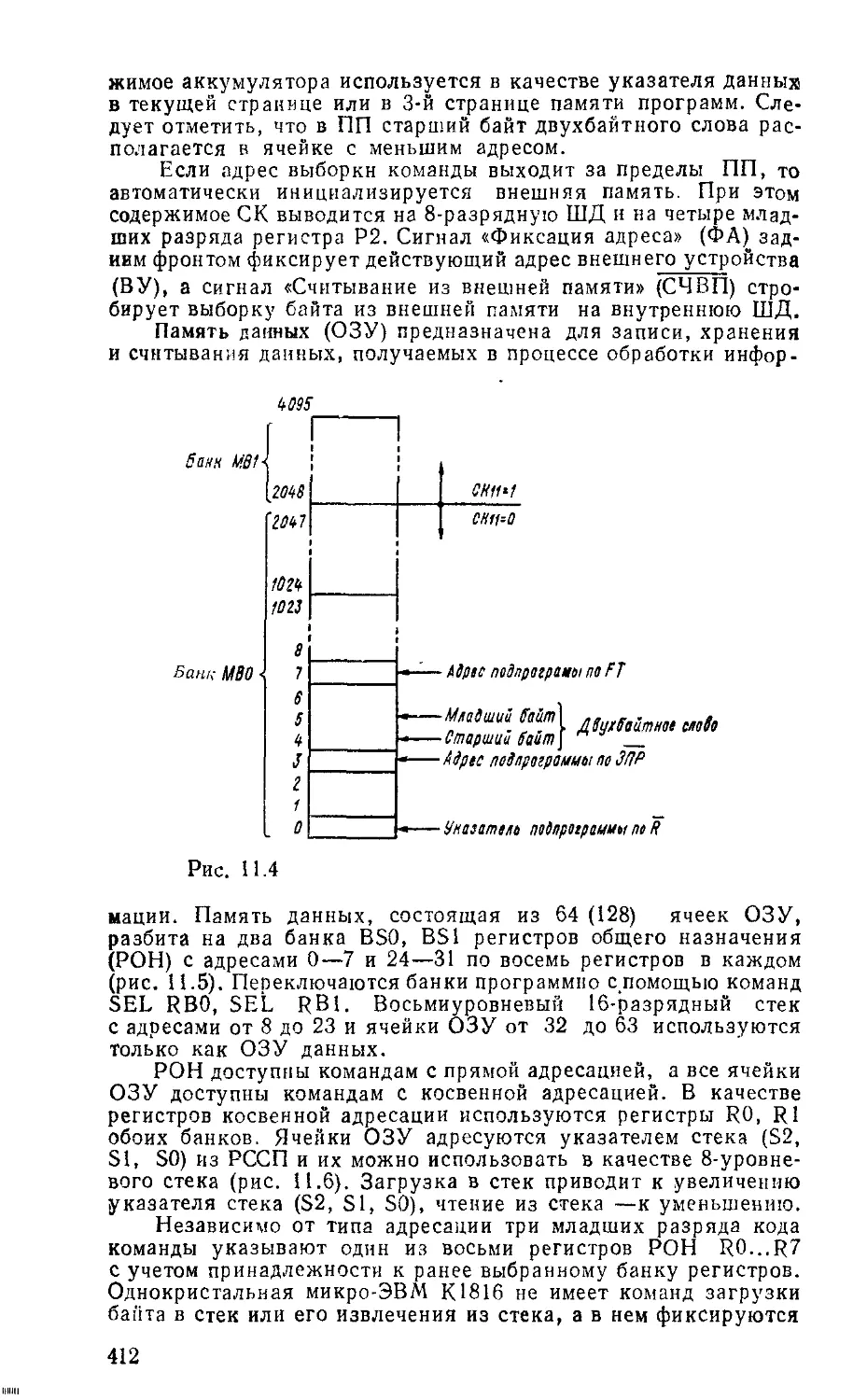

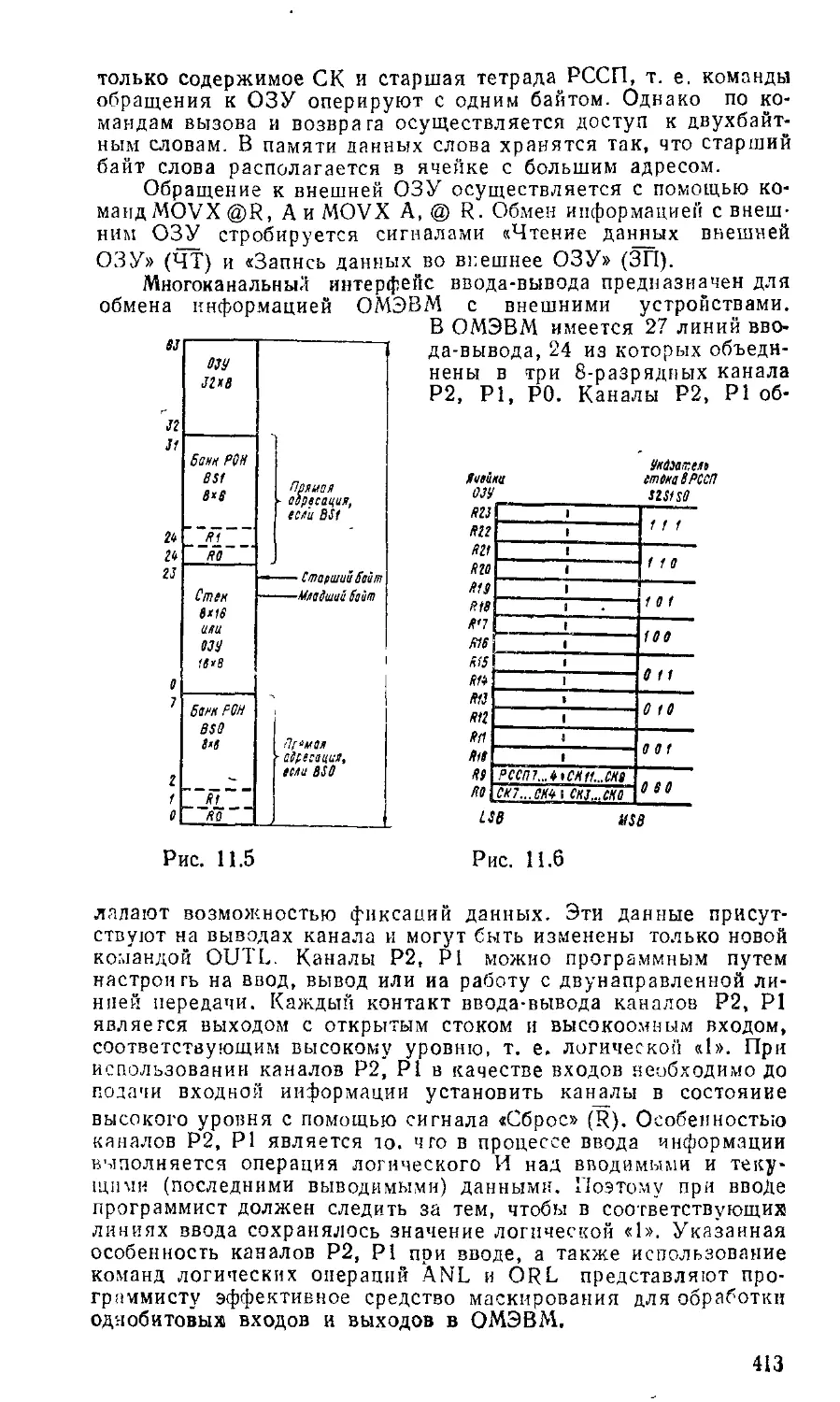

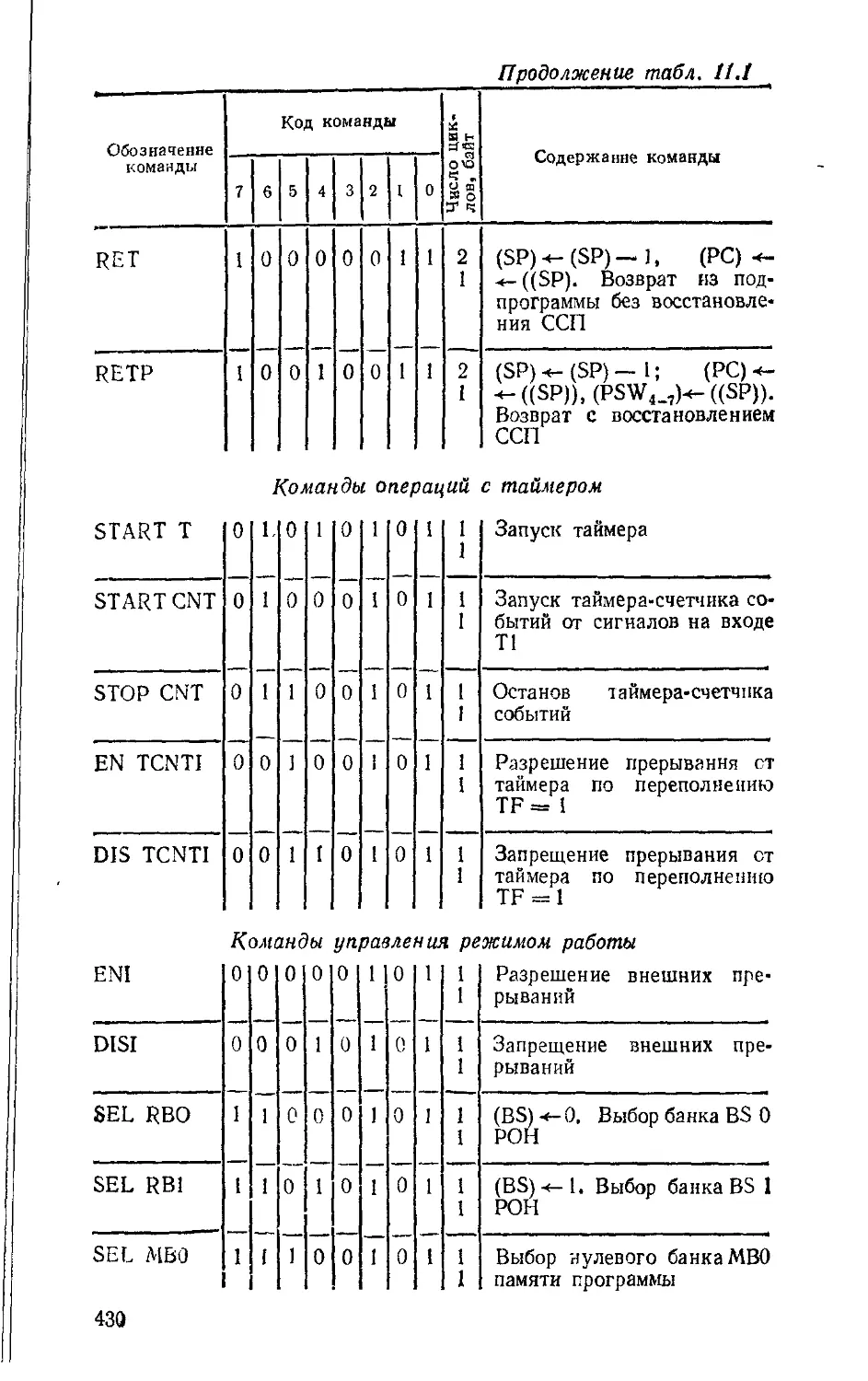

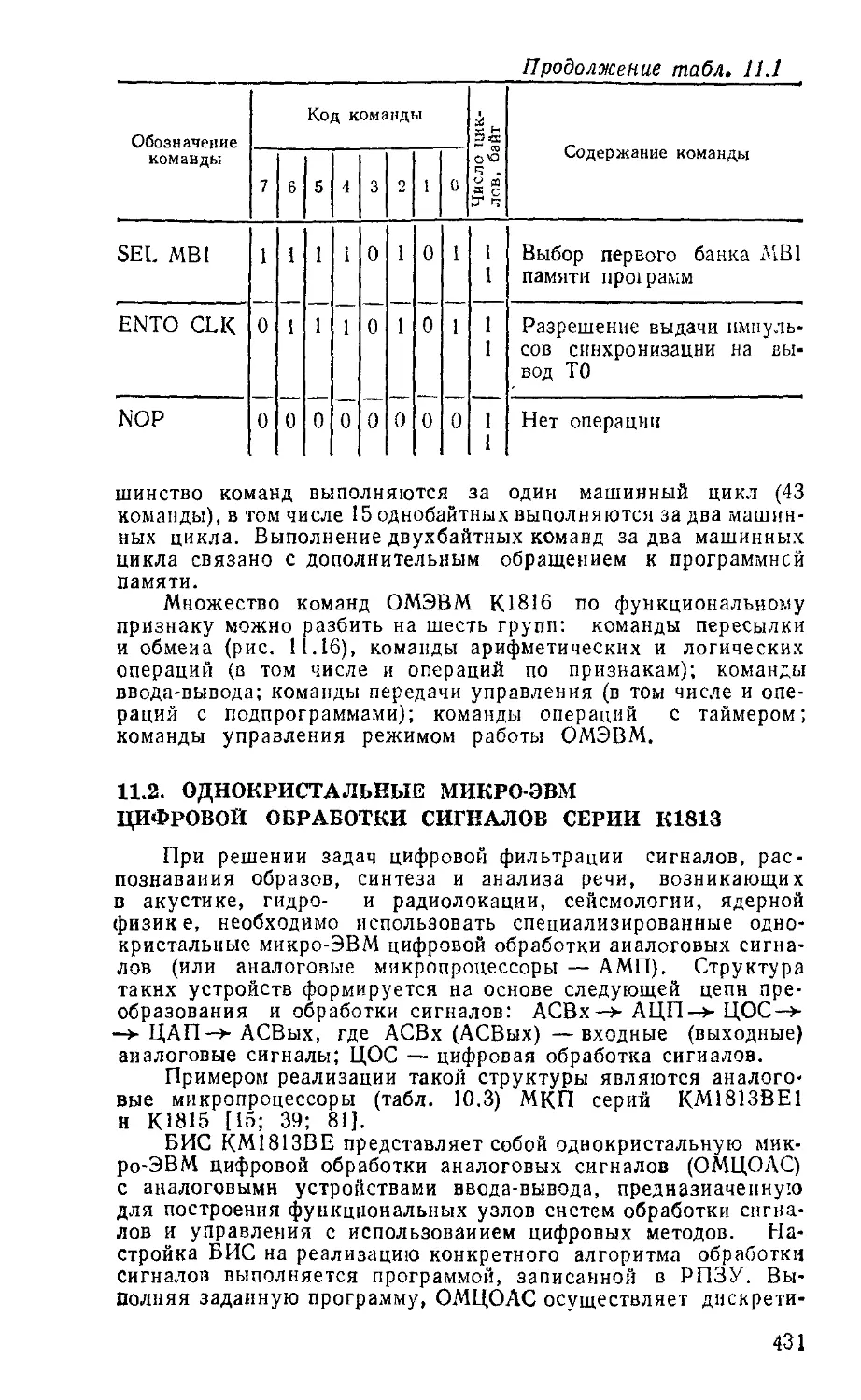

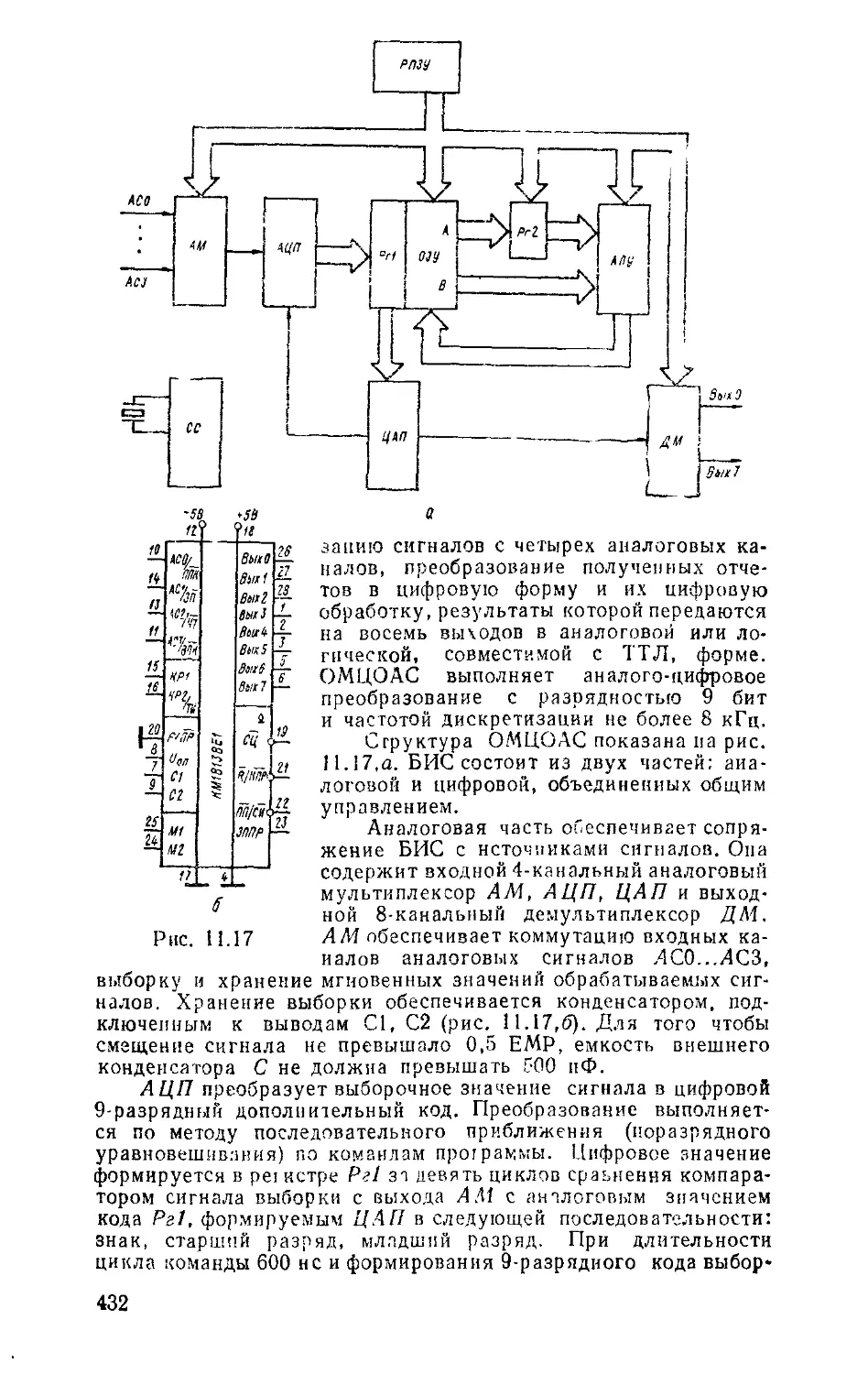

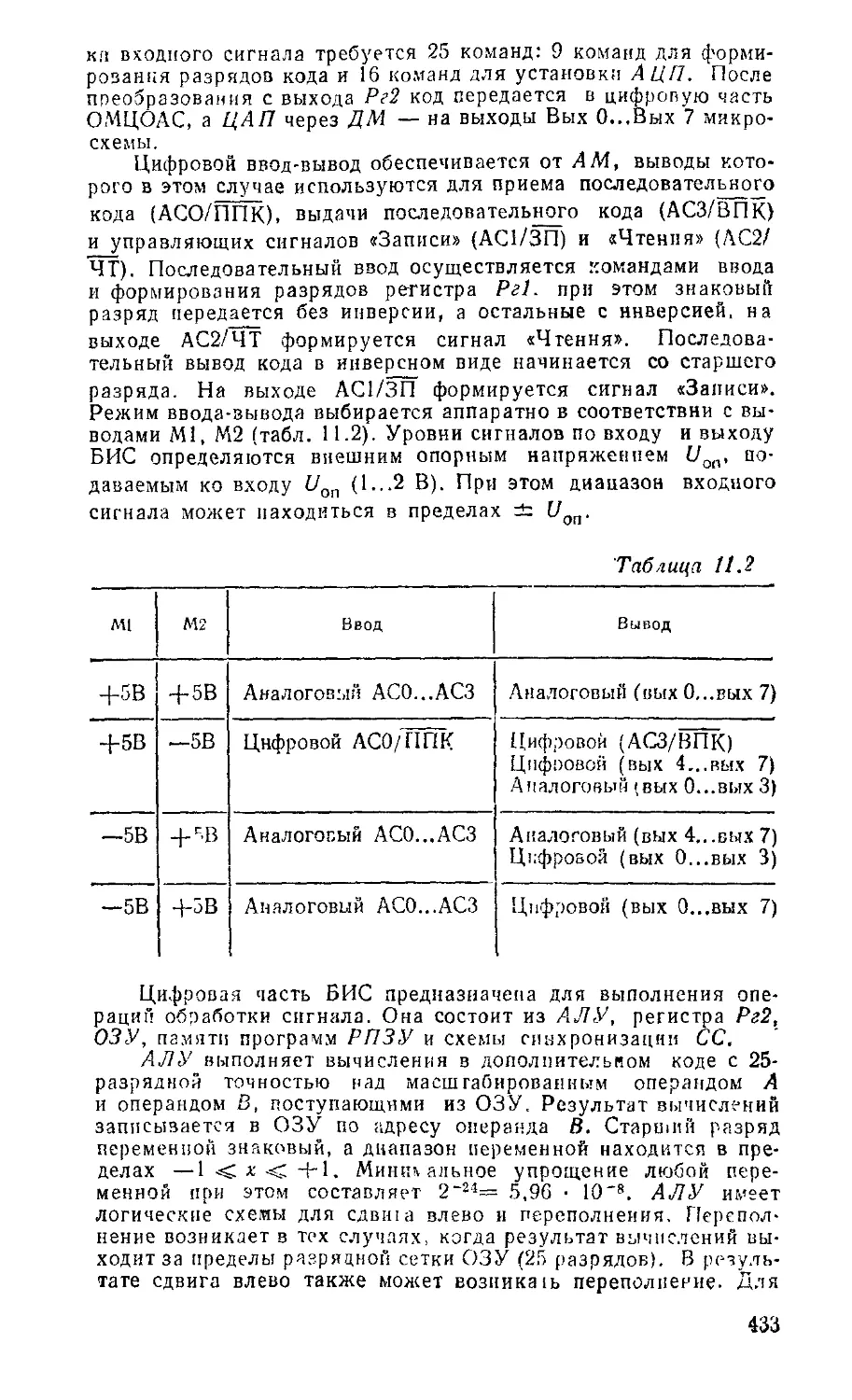

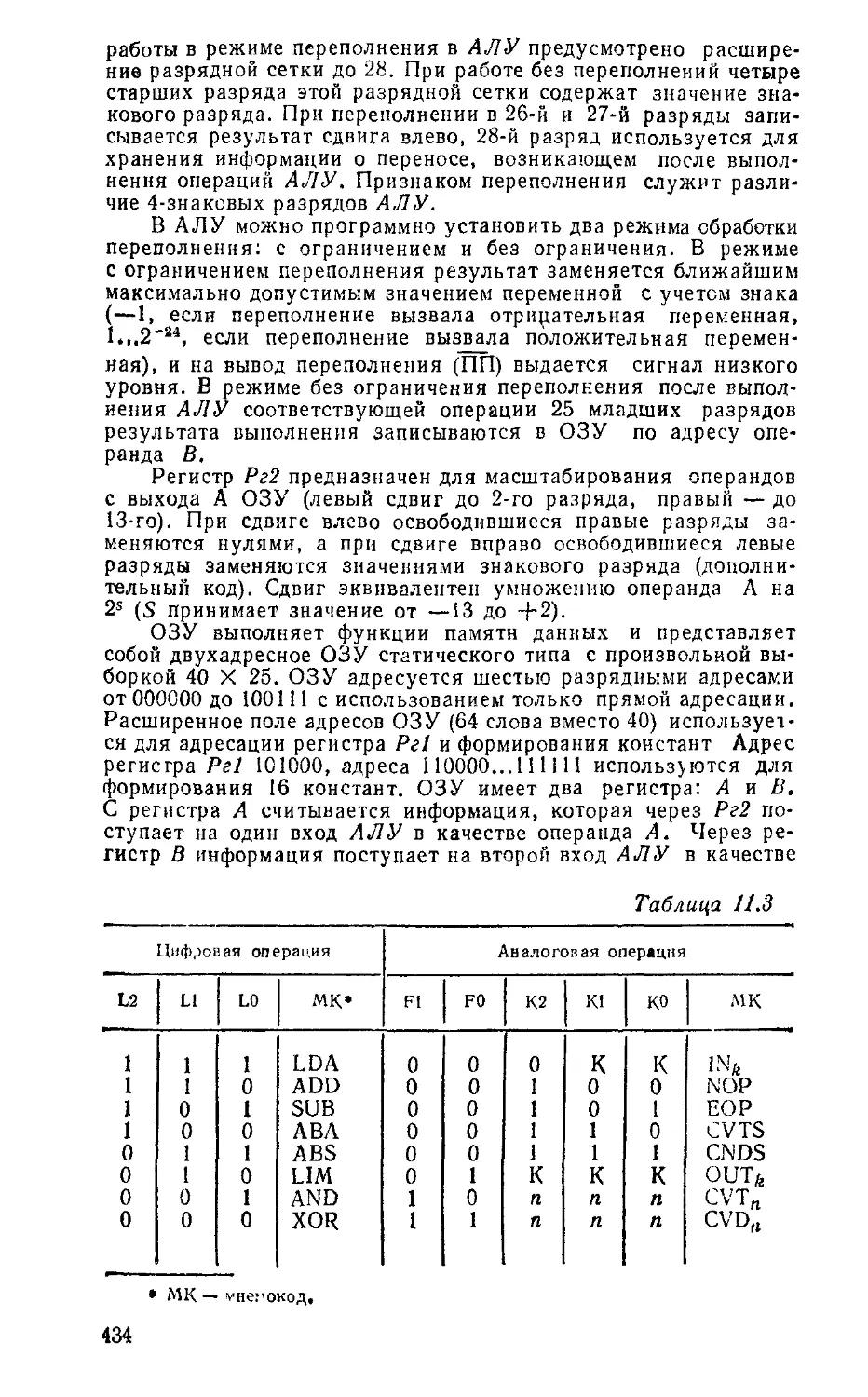

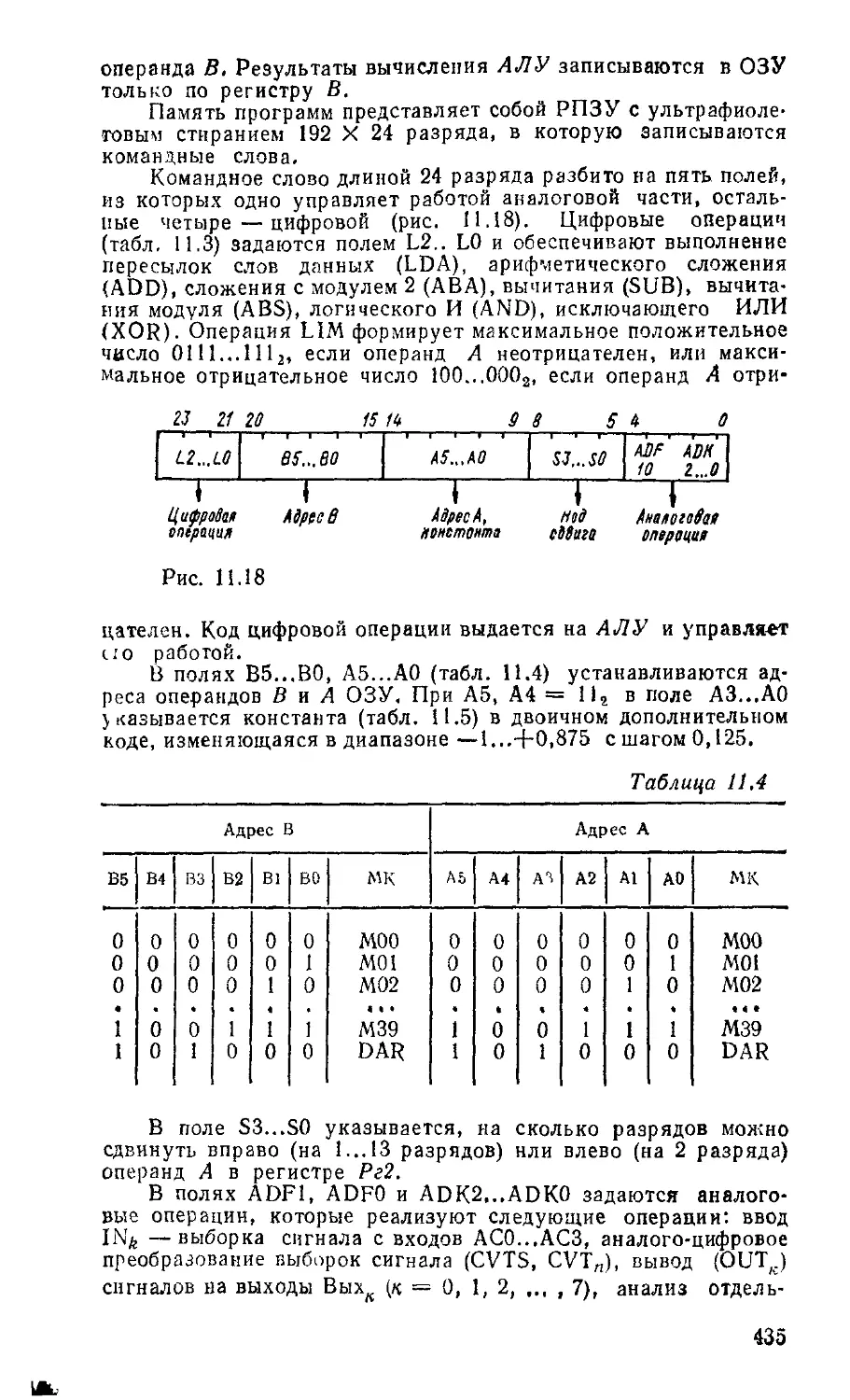

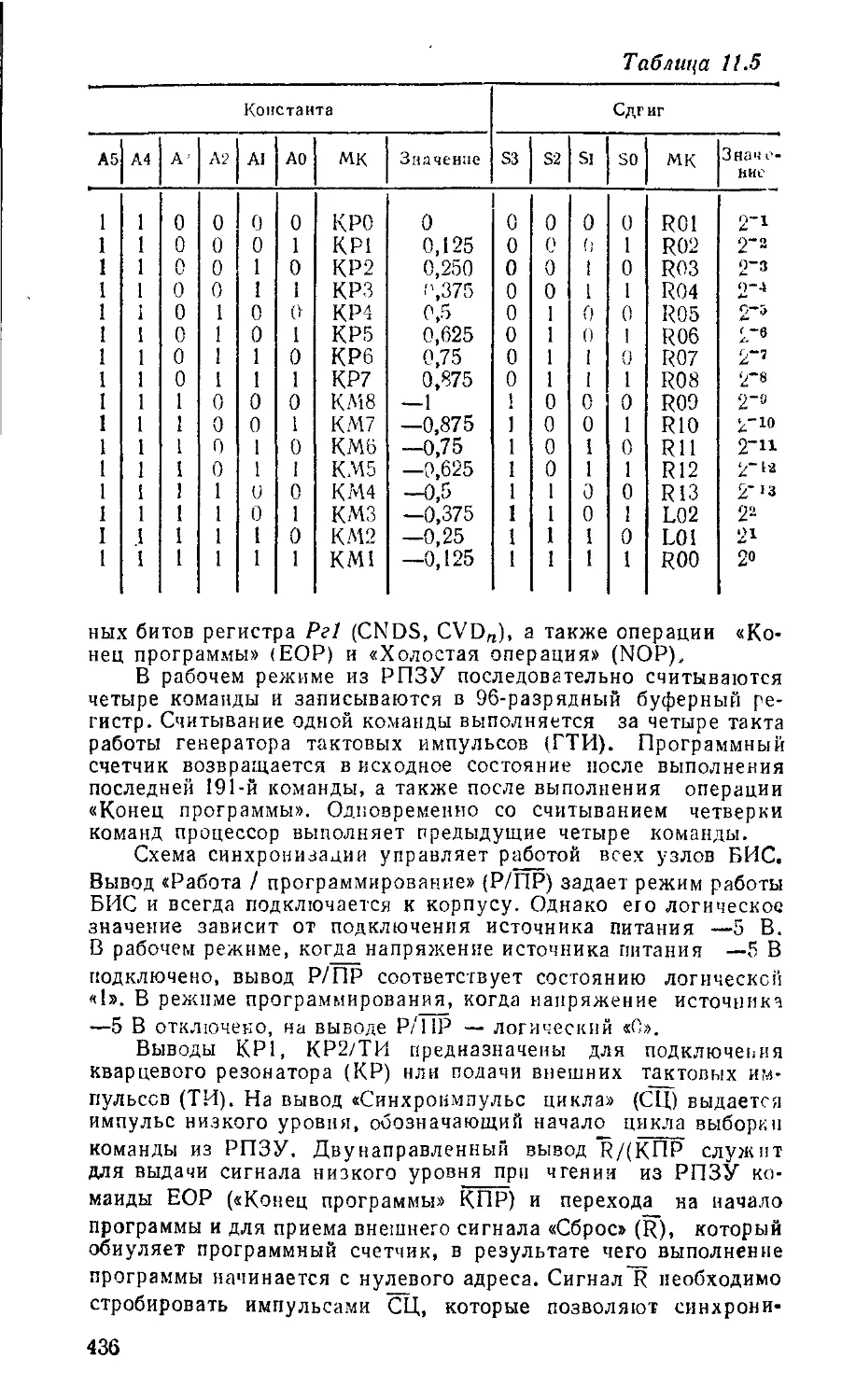

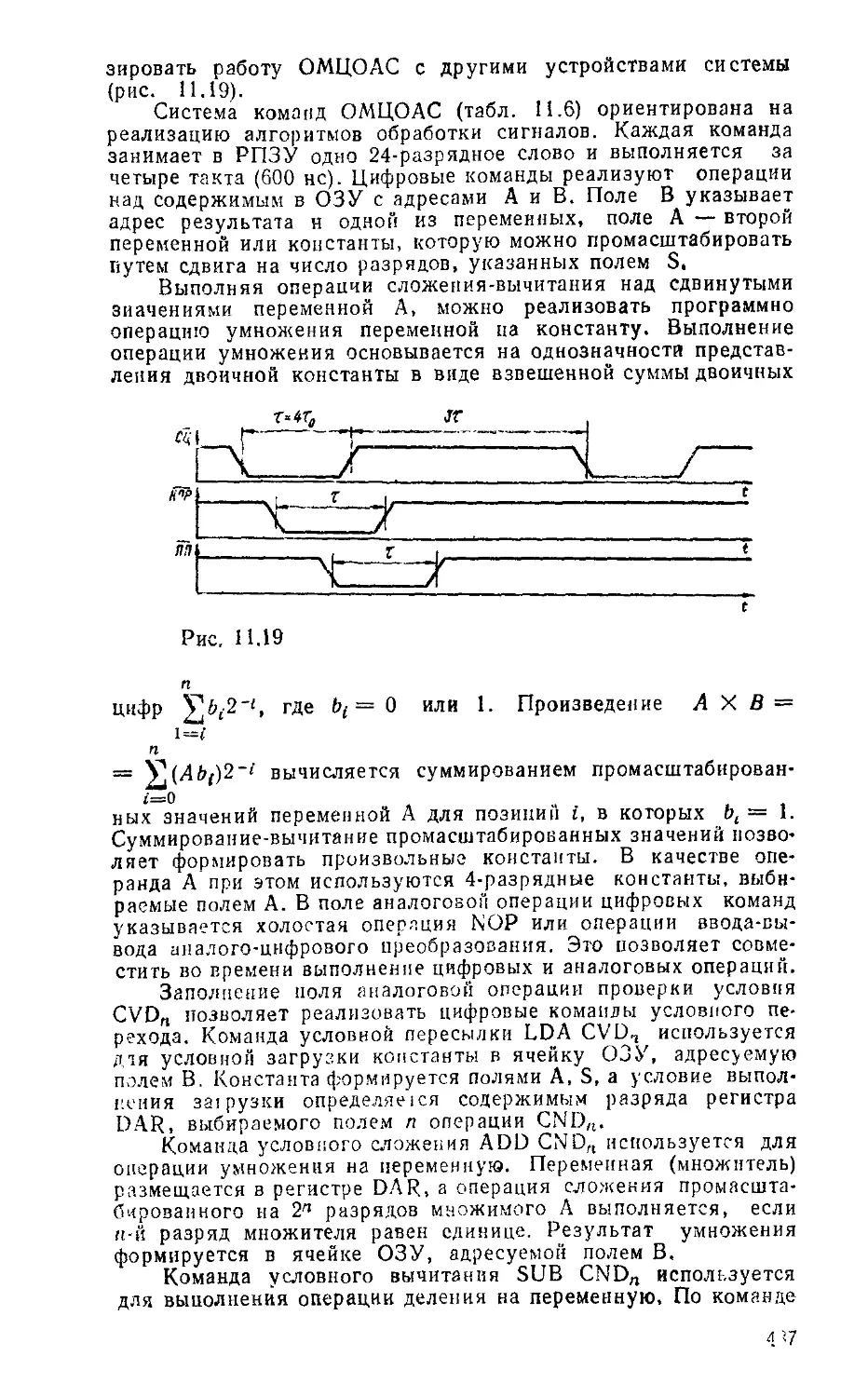

X + хч + *s) (хз + *<) — (-4 + x-t + хз) (Х1 + Х2~Ь xs) (xi +•*'2+