Автор: Размахин М.К. Русаков В.В.

Теги: электротехника электроника радиотехника статьи издательство радио и связь научно технический журнал журнал зарубежная радиоэлектроника

ISBN: 0373-2428

Год: 1988

7/1988

ISSN 0373-2428

ЗЙР9БЕ

«РАДИО И СВЯЗЬ»

ЗАРУБЕЖНАЯ

РАДИО

ЭЛЕКТРОНИКА

7/1988

ЕЖЕМЕСЯЧНЫЙ

НАУЧНО-

ТЕХНИЧЕСКИЙ

ЖУРНАЛ

ОРГАН

ВСЕСОЮЗНОГО

НАУЧНО-ТЕХНИЧЕСКОГО ОБЩЕСТВА

РАДИОТЕХНИКИ, ЭЛЕКТРОНИКИ И СВЯЗИ

ИМ. А. С. ПОПОВА

СПЕЦИАЛЬНЫЙ ВЫПУСК

ЭЛЕМЕНТНАЯ БАЗА ЭВМ СВЕРХВЫСОКОЙ

ПРОИЗВОДИТЕЛЬНОСТИ

НАУЧНЫЕ РЕДАКТОРЫ ВЫПУСКА:

АКАДЕМИК ВАЛИЕВ К. А., Д. Ф. М Н. ОРЛИКОВСКИИ А. А.

МОСКВА «РАДИО И СВЯЗЬ

ОСНОВАН В 1947 г.

РЕДАКЦИОННАЯ КОЛЛЕГИЯ:

Агаджанов П А, Андреев А. С, Бакут П А., Глинкин Л. И,

Давыдовский А И., Дулевич В. Е. Зудков П И Земсков Г. Г.,

Кобзарев Ю. Б., Квиринг Г Ю., Лихарев К. К-. Лощилов И Н,

Митяшев Б. И., Овчинников В. В , Палицкий В М„ Панфилов И П.,

Петрович Н. Т., Пузырев В. А., Пустовойт В И , Руссак В К.,

Симаков В. В , Солнцев В. А., Сретенский В. Н., Тихонов В И ,

Утямышев Р. И Яковлев В. П.

Главный редактор Размахнин М К

СОДЕРЖАНИЕ

Предисловие научного редактора

СТАТЬИ

Ш а г у р и н И И Биполярные базовые кристаллы для быстродей

ствующих цифровых матричных БИС . ... 5

Дятченко В. Н Родионов Ю П , Сквира А. В. Состояние

и перспективы развития сверхбыстродействующих биполярных ОЗУ 18

Гиваргизов Е. И. Получение полупроводниковых пленок иа изо

лирующих подложках и перспективы их применений 28

Старосельский В. И., Суетинов В И. Сверхскоростные

арсеиид-галлиевые ИС на полевых транзисторах с затвором Шотки 42

Бутакова Н. Г Зубов А. В. Гетеропереходные биполярные

транзисторы на их основе . ................ 56

Прокопьев А. И. Конструкции приборов с зарядовой связью

на арсениде галлия ......................................... 68

Казеинов Г Г, Михов В. М., Соколов А. Г Крем

ниевые компиляторы ... ... ... 81

Словарь англоязычных сокращений в области электроники, вычисли

тельной техники, информатики и связи ... 94

Зарубежная радиоэлектроника № 7

Редактор М. С. Гордон Техн, редактор 3 Н. Ратникова

Корректор А К Акименкова

Сдано в набор 26.04.88 Подписано в печать 01.06.88. Формат 70X100/16 Печать офсетная

Усл печ. л. 7,0 Усл. кр.-отт. 18,69. Уч.-изд. л. 12,08. № 22641 Заказ № 1085 Цена 1 р 40 к

Адрес редакции' 101000, Москва, Почтамт, а/я 693

Телефон 924-45 13

Ордена Трудового Красного Знамени Чеховский полиграфический комбинат ВО

«Союзполиграфпром» Государственного комитета СССР по делам издательств, полиграфии и книжной торговли

142300. г Чехов Московской области

£) Издательство «Радио и связь». «Зарубежная радиоэлектроника». 1988

2

ПРЕДИСЛОВИЕ

В комплексе проблем создания ЭВМ

сверхвысокой производительности (до

1 млрд. онер./с и выше) ведущее положе-

ние занимает проблема создания соот-

ветствующей элементной базы — сверх-

скоростных интегральных схем (ССИС)

[ 1 ]. Основную долю номенклатуры сверх-

скоростных процессорных ИС в настоя-

щее время составляют заказные и полу-

заказные кремниевые СБИС на основе ба-

зовых матричных кристаллов (БМК) на

биполярных транзисторах. В журнале «За-

рубежная радиоэлектроника» различным

аспектам разработки биполярных сверхско

ростных БИС были посвящены обзоры [2,

3].

В настоящем выпуске современный уро-

вень разработок биполярных БМК описан в

обзоре И И Шагурина.

Не менее важной задачей является раз-

работка элементной базы БИС сверх-

оперативной и оперативной памяти. Необ-

ходимо, в частности, создание БИС сверх-

оперативной памяти с временем выборки,

равным единицам наносекунд. В этой об-

ласти лидирующее положение занимают би-

полярные статические БИС памяти с произ-

вольной выборкой [4]. Состоянию и разви-

тию БИС этого класса посвящен в настоя-

щем выпуске обзор В. Н Дятченко и др

Наряду с биполярными сверхскоростными

БМК интенсивно развиваются КМОП БМК

в которых достигается более высокая

степень интеграции, чем в биполярных схе-

мах, однако при меньшем быстродействии.

Этой теме посвяшена работа Б. Н Фай

зулаева и А. Н. Кармазинского [5]

Наряду с БМК в мировой практике ин

тенсивно развивается новое направление

создания элементной базы многопроцессор-

ных ЭВМ сверхвысокой производитель

ности — транспьютерные СБИС Этому

направлению был посвящен сравнитель-

но недавно опубликованный прекрасный

обзор |6)

Повышение быстродействия кремниевых

МДП-схем возможно за счет применения

КНИ (кремний на изоляторе)-техноло! ии

В связи с развивающейся в настоящее

время технологией лазерной кристаллиза-

ции кремниевых пленок на диэлектриче-

ских подложках это направление которо

му в настоящем выпуске посвящен деталь-

ный обзор Е И Гиваргизова, обретает

новую жизнь.

Основную номенклатуру ССИС будут со-

ставлять кремниевые схемы. Однако в арсе-

нал материалов для ССИС уверенно внедря-

ются арсенид галлия и многослойные

структуры на основе гетеропереходов. Раз

витию этого направления в настоящем

выпуске посвящен обзор В И. Старосель-

ского и В. Н Суэтинова. В этом обзо-

ре основное внимание уделяется арсенид-

галлиевым ИС на полевых транзисторах с

затвором Шотки и объемным каналом. Эта

технология в мировой практике вышла на

уровень производства Наряду с этим пред-

ставляют большой интерес гетеропереход

ные ССИС на транзисторах с высокой

подвижностью электронов в двухмерном

электронном газе, которые создаются на

основе соединений AU1B , [7J Представляет

большой интерес обзор Н. Г. Бутаковой

и А В. Зубова по исследованиям и раз

работкам гетеропереходных биполярных

транзисторов (главным образом, на соеди

нениях AU1BV) и схем на их основе Приме-

нение GaAs эффективно для создания сверх

скоростных СБИС на ПЗС для регистровых

схем памяти. Конструкции и параметры ПЗС

на GaAs, включая гетеропереходные ПЗС,

рассматриваются в обзоре А. И. Прокопь

ева.

Большие возможности в повышении

быстродействия ССИС сулит применение

транзисторов на горячих электронах. Заин-

тересованному читателю следует обратиться

к книге [8]

Для создания высокоэффективных ССИС

необходимы не только разработка быстро-

действующих элементов, но и оптимальное

проектирование соединений на кристалле

Более того, задержки в соединениях могут

ограничивать быстродействие ССИС и, тем

самым, нивелировать преимущества приме-

нения сверхскоростных транзисторов [9]

В настоящий выпуск включен также об-

зор Г Г Казенного и др по кремние-

вым компиляторам — новой методологии

автоматизации проектирования БИС. На

звание этого подхода условно, так как оно

может быть успешно развито, например

как «арсенид-галлиевый компилятор» Этот

обзор удачно дополняет уже публиковав-

шиеся ранее в «Зарубежной радноэлектро

нике» обзоры по САПР БИС.

Нвдеемся, что настоящий выпуск будет

полезен разработчикам ССИС и ЭВМ

сверхвысокой производительности, а также

студентам и аспирантам, посвятившим себя

этой перспективной области техники.

Д. т н. Орликовский А А

3

СПИСОК ЛИТЕРАТУРЫ

1. Мельников В. А., Митропольский Ю К

Пути построения ЭВМ сверхвысокой про-

изводительности.— «Электронная вы-

числительная техника». Сб. статей под.

ред. В В. Пржиялковского, вып. I.

М «Радио и связь». 1987 г.

2. Гуляев Ю В. и др. Современные тех-

нологии изготовления структур СБИС:

состояние и перспективы развития.—

«Зарубежная радиоэлектроника», 1987 г.,

№ 5.

3. Бубенииков А Н. и др Новые техно-

логии изготовления и концентрации раз-

работки сверхскоростных больших ин

тегральных схем.— «Зарубежная радио-

электроника», 1985 г., № 9.

4 Орликовский А. А., Орлов Б. В

Старосельский В. И. Большие интеграль-

ные схемы сверхоперативной памяти.—

«Электронная вычислительная техника».

Сб статей под ред. В В. Пржиялков-

ского, вып. I.— М «Радио и связь»,

1987 г.

5. Файзулаев Б Н., Кармазинский А. Н.

Сверхскоростная элементная база на ос

нове КМОП-схемотехники. В сб. ст. под

ред. В. В. Пржиялковского, вып. I.—М.:

«Радио и связь», 1987 г.

6 Каляев А. В., Гузик В. Ф., Турута Е. Н

Системы на основе транспьютеров и язык

Оссам для них «Зарубежная радио

электроника», 1987, вып. 7.

7 Валиев К А., Орликовский А А.

Основные направления развития микро

электроники «Электронная вычисли-

тельная техника» Сб. ст под ред.

В. В. Пржиялковского, вып 1. М.:

«Радио и связь», 1987

8. Пожела Ю., Ю ене В. Физика сверх-

быстродействующих транзисторов.—

Вильнюс Мокслас, 1985 г.

9. Файзулаев Б. Н. Теория матричных БИС

и СБИС ЭВМ — В кн.: «Электронная

вычислительная техника». Сб ст под.

ред В В. Пржиялковского, вып. 1.—

М.: «Радио и связь», 1987 г.

4

СТАТЬИ

УДК 621.3.049

БИПОЛЯРНЫЕ БАЗОВЫЕ КРИСТАЛЛЫ

ДЛЯ БЫСТРОДЕЙСТВУЮЩИХ ЦИФРОВЫХ МАТРИЧНЫХ БИС

Д. т. н. Шагурин И. И

ВВЕДЕНИЕ

Идея использования базового кристалла

для реализации широкой номенклатуры ин-

тегральных микросхем возникла одновре-

менно с рождением микроэлектроники. Вы-

пушенная в 1961 г. первая промышленная

серия микросхем SN51 фирмы Texas Intru-

ments (США) была реализована на осно-

ве базового кристалла, содержащего фик-

сированный набор транзисторов, резисторов

и конденсаторов. Меняя рисунок соедине-

ния этих компонентов, удается создать

определенные типы схем- различные вариан-

ты логических элементов или триггеры.

Однако затем развитие микроэлектроники

пошло по пути выпуска микросхем, для

которых состав и размещение компонентов

на кристалле определяются в соответствии

с заданными функциями схемы. При

этом достигается более высокое быстро-

действие и уменьшается площадь кристал-

ла по сравнению с микросхемами на ба-

зовых кристаллах.

Широкое применение базовых кристаллов

началось в 70-х годах, когда, возникла

задача реализации большой номенклатуры

специализированных БИС при относительно

небольшом объеме выпуска каждого типа

этих микросхем Современные базовые

кристаллы содержат от нескольких десят-

ков до нескольких тысяч ячеек, распо-

ложенных в виде прямоугольной мвтри

цы, поэтому они называются базовыми

матричными криствллами (БМК). Каждая

базовая ячейка (БЯ) представляет собой

логический элемент либо нвбор отдельных

компонентов, достаточный для реализации

одного или нескольких элементов На основе

БЯ создаются различные функциональные

элементы цифровых БИС: логические венти-

ли, триггеры, мультиплексоры, регистры

и др. Для определенного набора этих

элементов создается функциональная биб-

лиотека—комплект схемотехнических и то-

пологических вариантов их реализации на

базе одной или нескольких БЯ В состав

библиотеки обычно входят 50.. 100 наибо-

лее часто используемых функциональных

элементов. Используя функциональную

библиотеку, современные САПР формиру-

ют принципиальную схему и разрабаты-

вают топологию соединений компонентов

БЯ на базовом кристалле в соответствии

с заданной структурно-логической схемой

проектируемой БИС. Использование БМК

в качестве звготовки, на которой требуе-

мая структурно-логическая схема создает-

ся с помощью ввтоматизироваиного проек-

тирования и изготовления соответствую-

щей системы соединений БЯ, позволяет от-

носительно быстро (за 6—10 недель) и с

минимальными затратами получить специа-

лизированные БИС различной степени

сложности. Такие БИС называются матрич-

ными*.

Впервые БМК для реализации широкой

номенклатуры быстродействующих матрич-

ных БИС (МБИС) были использованы

фирмой Amdahl (США), которая в 1975 г

выпустила ив иих высокопроизводитель-

ные ЭВМ модели 470 V/6. [1] Быстрый

рост производства и применения БМК на-

чался в конце 70-х годов, когда были

разработаны достаточно эффективные

САПР, обеспечивающие выполнение основ-

ных этапов разработки матричных БИС

[2-4] В настоящее время зарубежными

фирмами выпускается несколько сотен ти-

пов БМК [6], отличающихся элементной

базой, конструкцией и технологией изго-

товления. Из них свыше 100 типов БМК

реализуется на биполярных транзисторах и

используется для создания быстродейст-

вующих цифровых МБИС. В табл. 1 и 2

приведены основные характеристики ряда

современных биполярных БМК [6, 14, 38,

46, 48 49, 55|. Достаточно полный об-

зор перспективных технологических вариан-

* В зарубежной литературе БИС данного

класса получили название «полузаказных» (semi-

custom)

5

СП

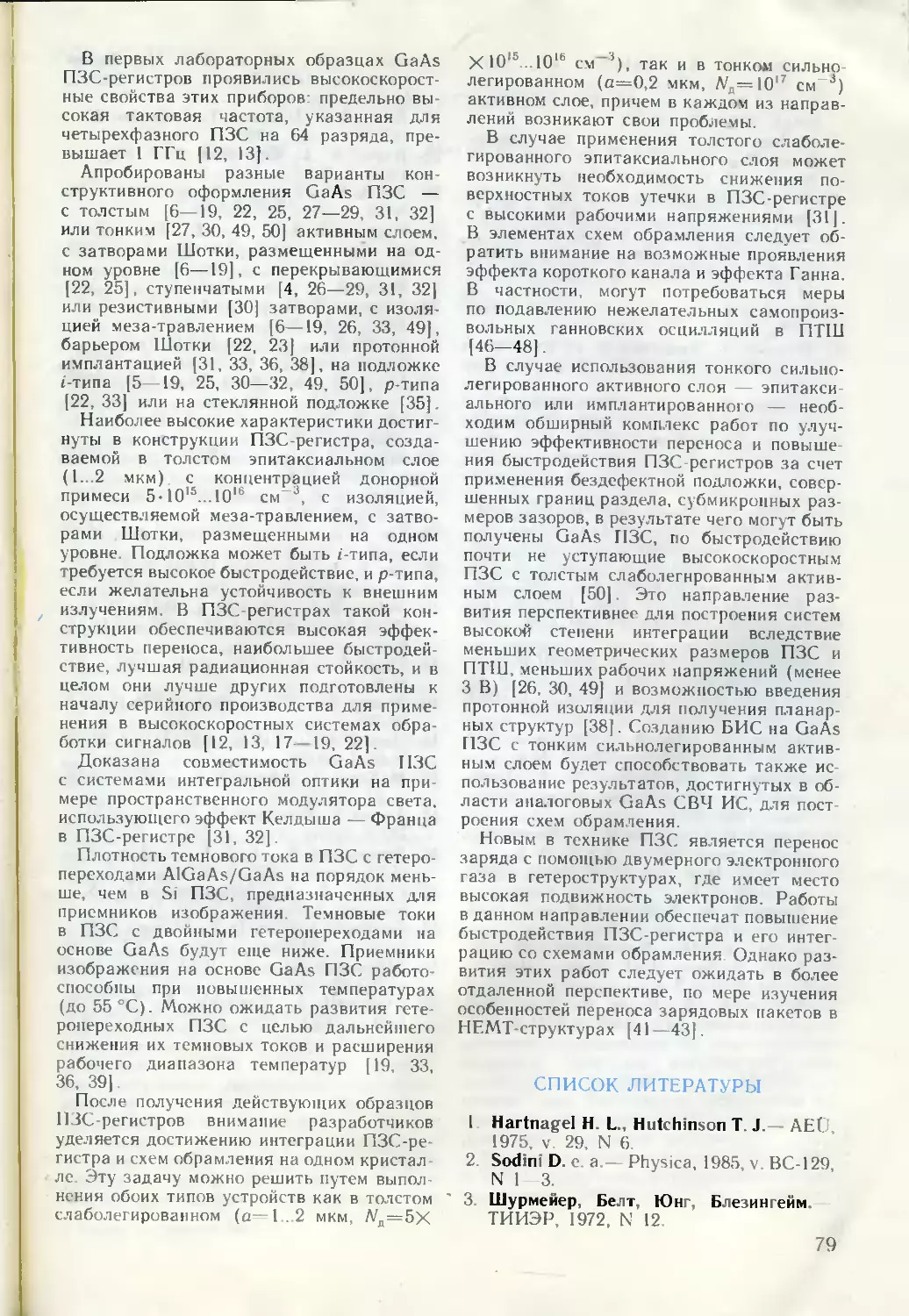

Основные параметры БМК класса ЭСЛ/ТПЛ

Таблица I

Фирма Год разра бот к и Тип Вазоный элемент Степень интег- рации пент./ крист. Площадь кристалла. мм2 Задержка переклю чеиия. нс/вент. Потребляемая мощность мВт/вент. Мощность рассей паомаи БМК, Вт Мини мильный размер элементов, мкм Число внешних выводов

Motorola 1982 MCA 2500 эсл 2472 6,58X6.85 0,25 3,2 12 2,0 149

1986 MCA 2800 эсл* 2800 1,0 0,36 2.5 1; 24

MCA 10000 эсл 10000 95 0,15 1,0 10 30 1,5 256

Fairchild 1983 FGE 2000 эсл 2448 0,36 3,8 3.0...8,0 1,5 132

1986 FGX 12000 12269 0,12. 0,20 1,5 18 300

Siemens 1985 SH 100C тпл 2500 0,45 20 144

SH 100E тпл 9000 10,92X11,73 0,2 6,0 20 0.5 320

Honeywell 1984 HT 5000 тпл* 5000 7,35+7,55 0.6 1.0 2,3 2,0 148

1986 HE 12000 тпл 12000 10X10 0,15 1,2 15 1,25 319

1985 HE 8000 тпл 8000 0,15/0,6 6,0/1,3 6.7 1,5

Advanced Microdevices 1983 MCA 1200 эсл 1200 0,9 4,4 4 1,5 68

1985 MPA 2500 эсл* 3700- 0,4 0.6 I...4 144

5200 120

MPA 1850 эсл 1800 1,2

Applied Microcircuits 1983 1500 эсл 1700 0,9 1.7 2,5 148

1985 3500 эсл 3500 0,5 0,7 3,5 148

National Semiconductor 1983 эсл 2472 0,3 1,9 4.8 180

Signetics 1983 эсл 2200 60 0,45 2,3 5,9 144

Ferranti 1986 ULA тпл* 10000 1,4 0,008 0,5 0,1...2 108

MEC 1983 MPB 6320 эсл 2000 7,5X7,2 0.6 9 6,0 1,5 132

1986 МРВ 63XX эсл 5000 0,25 3.3

NTT 1986 эсл/нпл 7000 8X8 0,1 2 3 8,3 1,0 142

эсл 15000 9,5X9.3 0,3 1.1 1.5 180

Mitsubishi 1981 эсл 2000 10,02X7.76 0.8 0,54 2,5 224

эсл 5000 8,7X8,4 0,2 3,3

IBM 1979 эсл* 1500 5,7 X 5,7 1,5/0,8 0,85/1,7 1,8 2,0 116

Vatic. Systems 1985 BA 2 эсл* 1712 1,0 1.0 88

Fujitsu 1985 E.T 3000 эсл* 3162 0,22 2,4 144

1986 Г.Т 50(X) эсл 5000 0,16 1,5

Texas Instruments 1986 TGE 8000 эсл 8584 0 2 04 4 11 1,5

• БМК с выходными ТТЛ трансляторами

** Значения вдержки и потребляемой мощности регулируются заданием токи питания

Таблица 2

Основные параметры БМК класса ТТЛ/И I

Фирма Год раз- работ ки Тип Базовый элемент Степень интег- рации, вент / крист. Площадь кристалла, мм1 2 За- держ- ка пере- клю- чения нс/ вент По- треб ляе мая мощ и ость, мВт/ аеит. Мощ ность, рас сеи- вае мая БМК, Вт Мини- маль- ный раз мер эле- мен- тов, м:<м Чис- ло внеш- них выво лов

IBM 1981 ТТЛ 7740 7,0Х 7,0 1.8 0,35 3,0 2,5 200

1982 ТТЛ 10000 7,39X7,39 1,4 0,34 5,0 2,5 374

1981 штл 3500 4,7X4,7 3,0 0,5 0,5 1,5

Fairchild 1983 FGT штл 3100 48 1,0 0,36 1,2 2.0 132

ТТЛ 1000 2,0 1,8 1,5 2.0 /6

Signetics 1982 ишл 2016 4 0,2 0,3 84

Raytheon 1982 ишл 2376 2.3 0,35 0,75 84

Fujitsu 1981 В 2000 ТТЛ 2100 0,95 0,65 1.2 120

NEC 1981 ТТЛ 846 2,3 1,4 1,2 72

Hitachi, NTT 1979 И2Л 5100 4,8X5,3 10 0,5 0,5 81

Exar Integ- rated Sys- tem* 1980 ХР 500 И2Л 5200 50 42

Custom In 1983 GAC-8000 и2 л 7600 20 64

tegrated Cercuits*

Texas Inst- 1981 TAT 008 штл 1008 2,5 0.6 0,9 3,0 108

ruments 1984 TAT 020 штл 2500 1,25 0,22 1.5 128

Harris Se- miconductor 1981 штл 1560 1.5 0.6 2,0

National Se- miconductor 1983 ТТЛ 2920 1.0 0.4 1.4 180

* Мощность регулируется заданием тока питания

тов изготовления биполярных БМК дан в

[2, 5]. Ниже рассмотрены основные схе-

мотехнические и конструктивные особен-

ности биполярных БМК, обсуждаются тен

денции их развития.

1. ЭЛЕМЕНТНАЯ БАЗА

Элементной базой МБИС служат логи-

ческие элементы, которые реализуются на

основе набора компонентов, входящих в

состав БЯ Эти элементы называются ба-

зовыми. По типу используемых базовых эле-

ментов биполярные МБИС делятся на два

основных схемотехнических класса:

МБИС на основе модификаций эмиттерно-

связанных и токопереключательных логи-

ческих элементов (ЭСЛ/ТПЛ);

МБИС на основе модификаций тран-

зисторно транзисторных и интегрально-

инжекционных логических элементов

(ТТЛ/И2Л).

Компонентный состав и топология БЯ раз-

рабатывается таким образом, чтобы обеспе-

чить наиболее эффективную реализацию

базового элемента. Поэтому схемотехниче-

ский класс МБИС обычно определяется

типом БЯ в исходном БМК.

Наиболее распространенные варианты ба-

зовых элементов для МБИС класса

ЭСЛ/ТПЛ представлены на рис. 1. Одно-

ярусные элементы ЭСЛ (рис. 1, а),

выполняющие логическую функцию ИЛИ

HE/ИЛИ, используются в БМК, разрабо-

танных фирмами Amdahl, Fairhild (США),

Toshiba, NTT (Япония), Ferranti (Велико

бритаиия) и рядом других [1,6—8]. В этих

схемах обычно используются транзисторные

источники тока (ИТ, рис. 2, а) и отри

цательное напряжение питания, величина

которого в различных разработках состав-

ляет от —1,6 до —3,3 В В одном из БМК

фирмы IBM используется положительное

напряжение питания £„=1,7 В, которое

вырабатывается расположенным на кри

сталле специальным источником напряже-

ния [1[ При этом источники тока (ИТ)

в схеме (рис. 1, а) подключаются к об

щей шине.

7

Рис. 1. Основные варианты базовых элементов

ЭСЛ/ТПЛ: одноярусные элементы ЭСЛ ТПЛ (а),

двухъярусный элемент ЭСЛ (б), трехъярусный

элемент ТПЛ (о)

Встроенный источник положительного

напряжения питания используется также в

БМК фирм Ferranti, Interdesign. В БМК,

выпускающихся этими фирмами в 70-х —

начале 80-х годов в качестве базового ис-

пользовался одноярусный элемент ТПЛ

(элемент ЭСЛ без выходных эмиттериых

повторителей) [9]. Однако а последних раз-

работках БМК фирмы Ferranti в качестве

базового служит одноярусный элемент ЭСЛ

[10] Эи фирмы применяют для изготов-

ления БМК технологию с коллекторной

изолирующей диффузией (КИД). Получае

мые при этом транзисторы имеют высокий

инверсный коэффициент уситения (б,« 10)

Путем их инверсного включения в опи-

санных БМК реализуются транзисторные

Рис 2. Схемы источников тока для элементов

ЭСЛ/ТПЛ резисторный (а), транзисторный (б),

инверсно-транзисторный (а)

ИТ (рис. 2, в). В последних разработках

БМК фирмы Ferranti со степенью интегра

ции от 400 до 8—10 тыс. элементов реали-

зованы значения /э=1,5 нс при потребляе-

мой мощности 0,1 мВт [11]* Таким обра-

зом, в этих БМК достигнута работа пере-

ключения Л„«0,1 пДж, что в несколько

раз ниже чем для других типов БМК

класса ЭСЛ/ТПЛ.

Двухъярусные элементы ЭСЛ (рис. 1,6)

содержат существенно больше компонентов

и занимают большую площадь. Однако

они могут одновременно реализовать до

четырех более сложных логических функций

типа И—ИЛИ—НЕ. При электрическом

соединении коллекторов транзисторов раз-

ных переключателей тока в этом элемен-

те дополнительно реализуются операции

Монтажное И. Таким образом, логические

возможности двухъярусных элементов зна-

чительно шире, чем одноярусных** Их при-

менение позволяет реализовать сложные ло-

гические функции с помощью меньшего

числа элементов обеспечивает более высо-

кое быстродействие цифровых устройств и

пониженное потребление мощности. Поэто-

му двухъярусные элементы ЭСЛ являются

наиболее распространенной элементной ба-

зой для сверхбыстродействующих МБИС

Базовые кристаллы для них выпускают

фирмы Motorola, Fairchild, Signetics

(США), NEC (Япония). RTC (Франция)

[12 14 55, 69]. Типовое напряжение пита-

ния для этих элементов составляет Еп=

=- 4,5В Для обеспечения необходимой

стабильности рабочих токов в двухъярус-

ных элементах ЭСЛ обычно используются

транзисторные ИТ (рис. 2 6). Отметим, что

в некоторых БМК между коллекторами

транзисторов в нижнем ярусе переключа-

* Здесь и далее значения задержки переклю-

чения даны для элементов, имеющих одну-две

нагрузки

** Еще более широкими логическими возмож-

ностями обладают трехъярусные элементы ЭСЛ.

Однако они требуют повышенного напряжения

питания поэтому в современных матричных БИС

практически не используются

8

телей тока включается резистор, обеспе-

чивающий выравнивание потенциалов их

коллекторов (штриховая на рис. 1, б).

Благодаря этому достигается уменьшение

задержки переключения элемента при по-

ступлении сигнала иа вход нижнего яру-

са [12].

Элементы ТПЛ отличаются от элементов

ЭСЛ отсутствием выходных эмиттерных

повторителей, что позволяет уменьшить

потребляемую мощность, однако приводит

к снижению коэффициента разветвления на

выходе и увеличению задержки переключе-

ния при работе иа емкостную нагрузку

Трехъярусиый элемент ТПЛ (рис. 1, в)

служит в качестве базового в БМК фирмы

Siemens (ФРГ) [15, 16] двухъярусные

используются в ряде других БМК [17—

19, 46, 55]

С целью повышения быстродействия и

снижения потребляемой мощности МБИС

обычно применяют базовые элементы с по-

ниженным логическим перепадом. Для

элементов ЭСЛ этот перепад составляет

1/л=0,5...0,6 В для ТПЛ — 1Л=0,4.. 0,5 В.

Так как в линиях связи между микро-

схемами в сверхбыстродействующих циф-

ровых устройствах принят стандартный

для серийных микросхем ЭСЛ перепад

{/л=0,8 В то для согласования внешних

и внутренних сигналов в МБИС включа-

ются буферные схемы-трансляторы, преоб

разующие уровни входных и выходных на-

пряжений (входные и выходные трансля

торы).

В качестве выходного буферного эле-

мента-транслятора в МБИС ЭСЛ/ТПЛ обыч-

но используется одноярусный элемент ЭСЛ

со стандартными выходными уровнями 0 и 1

</°вых=-1,6...-1,8 В, 1/вых=—0,7...—0,9 В

В большинстве современных сверхбыстро-

действующих БМК выходной транслятор

реализуется в виде температурно-компенси-

рованной схемы (рис. 3), аналогичной эле-

Рис. 3. Схема температурно-компенсированного

выходного транслятора ЭСЛ-уровней

ментам ЭСЛ серии F100K фирмы Fairhild

[' •

Штриховой линией на рис. 3 показано

подключение внешних резисторов R, при ра-

боте иа согласованные линии связи. Сопро-

тивление Rc=Zo где 2о — волновое

сопротивление линий связи, которое в сов

ременных цифровых системах обычно со-

ставляет 50 или 75 Ом (реже 25 Ом)

В качестве входных трансляторов исполь-

зуются одноярусные элементы ЭСЛ или

ТПЛ, имеющие опорное напряжение £о=

= (1^ых+Ьи/2«-1.2 В. В ряде типов

БМК в базовые элементы ЭСЛ и ТПЛ

вводится резистор /?д (рис. 1, а), сни-

жающий уровни {/°вых. t/Bblx таким образом,

чтобы обеспечить выполнение условия

(£7О+£7') = (Б^ЫХ+(7ВЫХ). При этом базовые

элементы могут непосредственно восприни-

мать внешние сигналы с уровнями t/BMX,

t/ без включения входных трансляторов

[!2f.

Особенностью элементов ЭСЛ и ТПЛ

является необходимость введения в БМК

специальных схем источников опорных на-

пряжений, которые частично компенсиру-

ют изменения логических уровней в диа-

пазоне рабочих температур и напряжений

питания, обеспечивая работоспособность

МБИС. Используемые варианты этих схем

весьма разнообразны, начиная с простей-

ших резисторно-диодных делителей напря-

жения и кончая достаточно сложными схе-

мами, содержащими до 15—20 компонен-

тов Каждая схема обеспечивает необ-

ходимые напряжения для нескольких рядом

расположенных элементов (обычно от

4 до 10—20). В зависимости от степени

интеграции БМК число таких источников

на кристалле может достигать нескольких

десятков. На рис. 4 приведены схемы

источников, используемых в БМК на двухъ-

ярусных элементах ЭСЛ фирмы NTT [13]

и трехъярусных элементах ТПЛ фирмы Sie

mens [15]. Эти источники достаточно слож-

ны, для них приходится использовать до

10 % общей площади БМК и мощности,

потребляемой МБИС. Однако благодаря их

применению j ается обеспечить работоспо-

собность МБИС класса ЭСЛ/ТПЛ в диапа-

зоне температур —30 СС +85 °C (иногда

—10...+70 °C) при 5 ..10 % отклонениях на-

пряжения питания от номинального зна-

чения

В ряде разработок используются ва

рианты схем ЭСЛ/ТПЛ, не требующие

источников опорных напряжений К ним от-

носятся элементы непороговой логики

(НПЛ) и дифференциальной эмиттерно-

связанной логики (ДЭСЛ).

9

Рис. 4. Схемы температурно компенсируй ^их исючников опорных ннпряжений для двухъярусного

элемента (СЛ (в) и трехъярусиого элемента ТПЛ (в)

Элемент НПЛ (рис 5, а) представляет

собой одноярусный элемент ТПЛ. из кото-

рого исключен опорный транзистор. В ре-

зультате данный элемент не имеет четко

выраженного порога переключения на пере-

даточной характеристике и его помехо-

устойчивость составляет всего несколько

милливольт. Изменение потенциала на выхо-

де элемента ТПЛ начинается уже при

небольших изменениях входного сигнала,

поэтому задержка переключения в ло-

гических цепях из таких элементов ока

зывается в несколько раз меньше, чем

при использовании элементов ЭСЛ, ТПЛ.

Емкость, шунтирующая резистор в эмиттер-

ной цепи, служит для ускорения включе-

ния транзисторов Чтобы реализовать не-

обходимую помехозащищенность цифро-

вых устройств, элементы НПЛ используют-

ся в них совместно с элементами ТПЛ,

обеспечивающими требуемую помехоустой

чивость Элементы НПЛ применяются сов-

местно с элементами ЭСЛ в качестве ба-

зовых в БМК, разработанных фирмой

NTT (Япония) [7,66]. В одной из разра-

боток БМК этой фирмы используется

комбинированная базовая ячейка (рис. 5, б),

которая может выполнять функции либо

элемента НПЛ с выходными эмиттерны

ми повторителями, либо одноярусного эле-

мента ЭСЛ [7]. В последнем случае к

элементу подключается опорный тран-

зистор, как показано на рис. 5. б В качестве

ускоряющей емкости (0 3 пФ) служит эмит-

тсрный переход дополнительного тран-

зистора, база которого подключена к

напряжению питания £„. Для пи

тания базовых элементов используется

термокомпенсируемый встроенный источник,

обеспечивающий на кристалле напряжение

£„= — 1,97 В

На рис. 5, в показан трехъярусный

вариант элемента ДЭСЛ, использование та-

кого элемента требует передачи парафаз

ных (дифференциальных) логических сиг-

налов Таким образом, число необходимых

соединений с МБИС удваивается, что тре-

бует увеличения площади БМК Этот не-

Рис. 5. Варианты сверхбыстродействующих элементов ЭСЛ ТПЛ: элемент НПЛ (а), коммутируемый

элемент ЭСЛ НПЛ (б), элемент ТПЛ с дифференциальными входами (в)

10

достаток частично компенсируется отсутст-

вием источников опорных напряжений и

линий для подводки этих напряжений

к элементам. Использование парафазиых

сигналов позволяет обеспечить достаточно

высокую помехоустойчивость схем при

пониженных значениях логического перепа-

да ((Л, «О,10...0,15 В). В результате су-

щественно (в 3—4 раза) сокращается

задержка переключения [20, 31]

Этементы ТТЛ, И2Л и различные их

модификации используются в качестве ба-

зовых для реализации МБИС, имекТщих

меньшее быстродействие, чем МБИС на базе

ЭСЛ/ТПЛ. Наиболее широкое применение

в МБИС находят элементы ТТЛ с дио-

дами Шотки (рис. 6, а) Так, фирма

IBM использует МБИС на элементах ТТЛ

для реализации ряда серий быстродействую-

щих ЭВМ [21, 22]. Для питания этих

элементов используется пониженное напря-

жение питания £п=1,5...1,7 В, при этом ло-

гический перепад имеет величину £/„=1,2...

1,4 В В ряде БМК используются диодные

(рис. 5, а) или транзисторные цепочки

подключенные к выходу элемента ТТЛ для

уменьшения логического перепада [21 —23].

В этом случае при любых значениях

Еп величина перепада составляет £/л=

=0,7 .0,8 В и быстродействие повышается

приблизительно в 1,5 раза Для ускоре-

ния переключения элементов ТТЛ, работаю

щих на длинные соединения, их выходной

резистор в некоторых БМК шунтируется

дополнительным резистором (см. штрихо-

вую линию на рис. 6, а), благодаря

чему возрастает величина тока заряда

паразитной емкости нагрузки При этом

удается существенно повысить быстродейст-

вие МБИС ценой относительно небольшо-

го возрастания мощности [22]. В БИС фир

мы NTT (Япония) используются элементы

ТТЛ, в которых токозадающий резистор не

подключен к базе выходного транзистора,

а выходной резистор подключается только

при работе на линии связи большой

длины [24]. В современных БМК, изго

тавливаемых по технологии с минималь-

ными размерами 1,5.. 2,0 мкм, работа пере-

ключения элементов ТТЛ составляет А„—

= 1 пДж. При этом типовые значения за-

держек переключения х,= 1 2 нс

Элементы И2 Л (рис. 6, б), которые исполь-

зовались в матричных БИС, выпускавшихся

в 70-е годы, в настоящее время нахо

дят ограниченное применение Это обуслов

лено в первую очередь их значительной

задержкой переключения, которая состав-

ляет обычно <з~Ю нс. Тем не менее от-

дельные типы БМК И2Л и МБИС на их осно

ве выпускаются фирмами Hitachi (Япония),

Texas Instruments, Cherry Semiconductor,

Exar, Custom. Integrated Circuits, Fairchild

(США) [6] *

Элементы Шотки-транзисторной логики

(ШТЛ, рис. 6, в) и инжекционной

Шотки логики (ИШЛ^ рис. 6, г) можно

считать разновидностями элементов ТТЛ,

И2Л Для элементов ШТЛ, ИШЛ харак

терны малые значения логического пере-

пада U =0,2.. 0,3 В, благодаря чему дости-

гается такое же быстродействие (t3=l .

2 нс) при меньшем, чем для элементов

ТТЛ, потреблении мощности (приблизитель-

но в два раза) Различные варианты

БМК на элементах ШТЛ, разработанные

фирмами Signeties, IBM, Harris Semicon-

ductor, Texas Insruments, Fairchild описа

ны в [25—27].

Элементы ИШЛ были предложены спе-

циалистами фирмы Philips На базе этих

элементов выпускают БМК фирмы Signeties,

Raytheon [6, 28]. Элементы ШТЛ. ИШЛ

имеют похожую схему и отличаются толь-

ко способом ограничения насыщения вы

ходиого транзистора. В элементах ШТЛ

коллекторный переход выходного транзисто-

ра шунтируется диодом Шотки, а в эле-

ментах ИШЛ — продольным р—п -р-

транзистором, интегрированным вместе с

п—р n-транзистором в единую функцио-

нальную структуру. Так как в элементах

ШТЛ необходимо создавать два вида кон-

тактов Шотки (например из Pt и сплава

TiW), отличающихся высотой потенциаль

ного барьера, то технология изготовления

этих БМК сложнее, чем для ИШЛ. Од

нако, как показывает проведенное срав

Рис 6. Основные варианты базовых элементов ТТЛ И Л элемент ТТЛ простым инвертором

(а), элемент И Л (б), элемент ШТЛ (в) элемент ИШЛ (г), элемент ШТЛ с двухэмиттерным

транзистором (д)

11

некие 24 29], элементы ШТЛ имеют не-

сколько лучшее быстродействие

В БМК фирмы Fairchild используется

элемент ШТЛ с двухэмиттерным тран-

зистором (рис. 6, д), один из элемен-

тов которого подключается к базе и таким

образом ограничивает степень насыщения.

В этом элементе требуется только один

тип диодов Шотки, что упрощает тех-

нологию изготовления БМК

В базовых элементах ТТЛ, И2Л, ШТЛ,

ИШЛ используется пониженное напряже-

ние питания обычно 1,5...3,0 В Такое

напряжение подается на БМК от внеш-

него источника питания или формируется

с помощью встроенного источника, под-

ключенного к стандартному внешнему

напряжению Еп=5 В.

В качестве выходных трансляторов в

БМК класса ТТЛ/И2Л (включая ШТЛ,

ИШЛ) обычно используется элемент ТТЛ

со сложным инвертором, один вариант ко-

торого показан иа рис. 7. Питание трансля-

тора осуществляется от внешнего источни-

ка с напряжением Еп=+5 В Данный

транслятор обеспечивает высокое быстро-

действие при работе на большую ем-

костную нагрузку (до нескольких сотеи

пикофарад) и реализует на выходе стан-

дартные для серийных микросхем ТТЛ

уровни: Г/°ых 0,2...0,3 В; Ь^ых=3...4 В.

Эти уровни могут непосредственно вос-

приниматься элементами ТТЛ, И2Л, ШТЛ,

ИШЛ, поэтому входные трансляторы в БМК

класса ТТЛ/И2Л обычно не включаются.

Исключение составляют некоторые из БМК

фирмы IBM, где для питания МБИС ТТЛ

используются отрицательные напряжения

Еп=—1 5 и —4,25 В а в качестве вы-

ходного транслятора служит эмиттерный

повторитель [21 ].

Необходимо отметить, что выходные транс-

ляторы ТТЛ-типа часто используются также

в БМК класса ЭСЛ/ТПЛ. Например, фир-

ма Motorola выпустила БМК, где базовым

служит двухъярусный элемент ЭСЛ, а вы-

ходным транслятором ТТЛ-элемент со

Рис. 7. Схема выходного транслятора ТТЛ-уров-

ней

сложным инвертором. Для питания этих

БМК используется напряжение i'=-f-5 В.

Той же фирмой разработаны БМК, в ко-

торых совместно применяются выходные

ЭСЛ и ТТЛ-трансляторы Питание таких

БМК осуществляется от двух источников

питания Е =4-5 В, Е„г=—5,2 В Выход-

ные ТТЛ-траисляторы с базовыми эле-

ментами ЭСЛ или ТТЛ используются также

в БМК фирм Ferranti [9, 10], IBM [6],

Honeywell [30], Applied Semiconductor

[6], Advanced Microdevices [32].

2. КОНСТРУКТИВНЫЕ ВАРИАНТЫ

СОВРЕМЕННЫХ БИПОЛЯРНЫХ БМК

На основе рассмотренных разновид-

ностей базовых элементов реализованы

различные типы биполярных БМК, от-

личающиеся своей конструктивной реализа-

цией.

Типовая конструкция БМК состоит из

прямоугольной матрицы вентилей, распо-

ложенных в центре кристалла, и разме-

щенных на его периферии вспомогатель-

ных и буферных схем (входных и выход-

ных трансляторов, источников напряже-

ния), контактных площадок для подклю-

чения внешних выводов (рис 8).

Различаются два основных варианта БЯ

вентильного и компонентного типа. Вен-

тильная БЯ представляет собой базовый

элемент, компоненты которого заранее сое-

динены на кристалле с помощью фикси-

рованной системы соединений. При проек-

тировании МБИС на таких БЯ разраба-

тывается система соединения вентилей в

необходимую логическую схему. Компонент-

Рис 8 Типовая конструкция современного бипо-

лярного БМК

/ — трансляторы уровней и контактные пло падки,

2 — базовые ячейки, 3 каналы для вертикаль-

ных трасс (1-й слон металлизации), 4 — каналы

для горизонтальных трасс (2-й слой металли

зации)

12

ная БЯ (макроячейка) представляет собой

набор из нескоммутированных или частич-

но ском.мутированных компонентов. В про

цессе разработки МБИС из этих компо-

нентов формируются требуемые базовые

элементы и макроэлементы либо выбира-

ется набор необходимых элементов и макро-

элементов из готовой функциональной биб-

лиотеки. Затем разрабатывается система их

соединения в заданную цифровую схему.

Применение макроячеек позволяет реализо-

вать более разнообразные и эффективные

схемотехнические варианты элементов, уз-

лов н блоков МБИС, обеспечить повышен-

ное быстродействие и пониженное потреб

ление мощности. Поэтому БЯ типа макро-

ячеек используются в большинстве типов

биполярных БМК.

Обычно компонентный состав макроячей-

ки БМК типа ЭСЛ или ТПЛ содержит

10—15 транзисторов и столько же резисто-

ров различных номиналов, необходимых

для реализации нескольких вариантов

двух- или трехъярусных базовых элемен-

тов На рис 9 а приведен компонент-

ный состав макроячейки БМК ТПЛ

фирмы Siemens, имеющего степень интегра

ции 9300 эквивалентных вент./кристалл

[16]. Компонентный состав макроячейки

для БМК ТТЛ содержит обычно 2—4 тран

зистора, 3 4 резистора. На рис 9, б пока-

зан состав макроячейки БМК ТТЛ фирмы

IBM, со степенью интеграции около 10 тыс

вент./кристалл (21 ]. В кристаллах, где ба-

зовыми являются одноярусные элементы

ЭСЛ, НПЛ, И2Л, ШТЛ, ИШЛ, используют-

ся БЯ вентильного типа.

В ряде БМК высокой степени инте-

грации помимо матрицы БЯ содержатся

некоторые специализированные функцио-

нальные блоки. Чаще всего в БМК

вводятся блоки памяти, обычно с изме

няемой организацией [14, 32—37, 55].

Например, БМК типа QM 1600 фирмы

Applied Microcircuits содержит 1600 элемен

тов ЭСЛ и два модуля ОЗУ емкостью по

640 бит, на базе которых изменением ри-

сунка соединений можно реализовать раз-

личные варианты организации от 1280Х

Х1 бит до 32X40 бит [36]. В БМК типа

Am МРА 3525 фирмы Advanced Microdevi-

ces наряду с матрицей макроячеек ЭСЛ

эквивалентной 3800 вентилям, входят четы

ре модуля ОЗУ с организацией 16х

X 18 бит, соединением которых можно полу

чить блоки памяти емкостью 64x18,

32x36, 16x72 бит (32]. В некоторые БМК

включаются программируемые логические

матрицы (ПЛМ), либо целый набор функ-

циональных блоков: сумматор умножитель

модуль памяти.

В современных БМК реализуется не-

сколько топологических вариантов размете

ния БЯ. До последнего времени наибо-

лее распространенным был вариант, при

котором несколько рядом расположенных

БЯ (чаще всего четыре) объединяются

в топологические фрагменты, между ко

торыми оставались свободные места (ка-

налы) межсоединений нижпего уровня ме-

таллизации (рис. 8) Такой вариант топо

логии реализован в большинстве современ-

ных БМК, выпускаемых фирмами Motorola,

Fairchild, IBM, Fujitsu, NTT и др.

При высокой степени интеграции (свы-

ше 4—5 тыс. вентилей) более удобным

для проектирования МБИС является струк

тура из нескольких макроблоков, каждый

из которых представляет собой матрицу

БЯ со степенью интеграции 1—2 тыс. вен

тилей или какой-либо функционально закон-

ченный блок, например ОЗУ или ПЛМ

По периферии макроблоков располагаются

буферные каскады, обеспечивающие пере-

дачу логических сигналов по межблочным

линиям связи. Для их проведения между

блоками оставляются достаточно широкие

межблочные каналы. На базе каждого

макроблока может быть реализован до-

статочно сложный функциональный узел

Их соединение позволяет реализовать

матричные сверх БИС выполняющие функ-

ции сложных цифровых систем микро-

процессоров, микроконтроллеров, микро-

ЭВМ В качестве примера можно при

вести один из последних БМК фирмы

Siemens [16], который содержит четыре

макроблока по 484 макроячейки и 256

Рис. Я. Компонентный состав «вкроячеек ТПЛ («) и ТТЛ (б)

13

входных-выходных трансляторов в каждом,

расположенных на кристалле площадью

10 9X11 7 мм2. По своим логическим воз

можностям данный БМК эквивалентен 9000

вентилям

Другим топологическим вариантом яв

ляется бесканальная структура БМК, часто

называемая в литературе «морем венти-

лей» — sea of gate [38]. Данная струк-

тура характеризуется сплошным размеще-

нием БЯ (без промежуточных каналов)

При этом соединения нижнего слоя про-

водятся не между компонентами БЯ а

над ними В результате в два-три раза

увеличивается степень интеграции, так как

вся площадь БМК оказывается занятой БЯ

Часть БЯ, попавших под соединения пер-

вого слоя, остается неиспользуемой. Одиа-

ко в целом площадь БМК используется

более эффективно, так как в зависимости

от реализуемой функциональной схемы мож-

но менять относительную долю БЯ, вы-

деляемых для выполнения логических функ

ций или остающихся под межсоединения-

ми При этом требуется применять более

совершенные САПР обеспечивающие эф

фективное использование возможностей,

предоставляемых такой гибкой структурой

БМК, для улучшения характеристик проек-

тируемых МБИС

Как следует из вышесказанного, структур-

но-топологические варианты БМК тесно свя-

заны с особенностями реализации меж

соединений Число трасс для проведения

соединений, передающих логические сигна-

лы между элементами и узлами МБИС, за

висит от степени интеграции. Для выбо-

ра оптимального числа трасс /VT можно

использовать эмпирическое соотношение

[7]:

Ar=m,,(A\)<’,

где /V, — общее число базовых эле-

ментов реализуемых иа основе БМК (сте-

пень интеграции), т,, — среднее число

логических входов и выходов в этих эле-

ментах, р«0 7 0 75. Кроме сигнальных

трасс на кристалле размещаются шины

питания, а в БМК типа ЭСЛ и ТПЛ

также линии для подключения опорных

напряжений В результате требуемое число

трасс для БМК со степенью интеграции

Аэ=1000 элементов составляет Ат=600...

800, а при Аэ=10000 достигает Мт=

=3.. 4 тыс. Размещение на кристалле та-

кого числа трасс является сложной пробле-

мой, одним из путей решения которой

является увеличение числа слоев межсоеди-

нений. Если до 80 х годов в биполярных

БМК применялась двухслойная система

соединений с шагом размещения провод-

ников в каналах h—15 20 мкм, то в совре-

менных разработках обычно используется

трехслойная металлизация [4 7, 13, 21, 22,

38, 39, 66, 69], есть сообщения о при-

менении четырехслойной металлизации [13,

33, 35, 39]. При этом в верхнем слое,

имеющем наименьшее удельное сопротив-

ление, реализуются шины питания. Шаг

соединений в нижних слоях уменьшен до

6...10 мкм при толщине d=0,5...1,0 мкм.

В верхнем слое для снижения сопротив-

ления шин питания проводники изготав-

ливают достаточно широкими (20.. 50 мкм)

и толстыми (до 3...4 мкм) Благодаря

этому уменьшается падение напряжения на

шинах питания, что позволяет расширить

рабочий диапазон температур и напряжений

питания, повысить помехоустойчивость

МБИС.

Достаточно жесткие требования к кон-

струкции шнн питания обусловлены тем,

что быстродействующие биполярные МБИС

потребляют достаточно большую мощ-

ность Р=2.5 В При типовом напряже-

нии питания £„=5 В ток в шинах питания

достигает значения /„= 1А Конструкция

шин питания должна обеспечить падение

напряжения на них, ие превышающее

50 .100 мВ так как иначе нарушается

работоспособность МБИС из за рассогласо

вания порогов переключения и уровней ло

гических сигналов

Важной конструктивной проблемой при

проектировании БМК является реализация

требуемого числа внешних выводов, доста

точного для эффективного использования

функциональных возможностей кристалла

Для оценки требуемого числа выводов

обычно используется эмпирическое правило

Рента

где <7=0,5.. 0,75. Базовые кристаллы со сте-

пенью интеграции до Л; =1000 элементов

размещались в корпусах, имеющих несколь

ко десятков выводов (обычно 67. 90) Для

современных МБИС, содержащих 2.5 тыс

элементов используются корпуса или бес

корпусные носители кристаллов, имеющие

100 200 выводов [7, 40, 41].

Для последних конструкций кристаллов

характерно матричное размещение контакт-

ных площадок по поверхности кристалла и

многорядное расположение выводов по че-

тырем сторонам корпуса [42 44] Наиболее

сложные биполярные БМК. разработанные

фирмами NEC (7000 вентилей) и Siemens

(9300 вентилей), имеют соответственно 208

и 320 выводов [7 16].

14

3 ПЕРСПЕКТИВЫ И ТЕНДЕНЦИИ

РАЗВИТИЯ МБИС

Обзор современного состояния и перспек-

тив развития МБИС, данный в [2, 44 47,

52, 57], показывает, что объем их про-

изводства ежегодно возрастает в среднем

на 30 %, а стоимость продаж к 1988-

1989 гг превысит 1 млрд, дол Из 60 фирм,

выпускающих БМК, около 20 производят

биполярные БМК (см. табл. 1, табл. 2).

Большинство фирм выпускает семейства,

состоящие из нескольких БМК (от 3—4 до

6—8 типов), совместимых по основным

электрическим и конструктивным характе-

ристикам но отличающихся степенью инте-

грации, площадью кристалла, потребляемой

мощностью и стоимостью Обычно семей-

ство БМК перекрывает диапазон степеней

интеграции от нескольких сотеи до не-

скольких тысяч вентилей. Благодаря этому

заказчик может выбрать БМК параметры

которого в наибольшей степени соответ-

ствуют требованиям к МБИС, проектируе-

мой на его основе. В табл 1 и 2 при-

ведены параметры наиболее крупных БМК

из семейств, выпускаемых указанными за-

рубежными фирмами.

Как показывает обзор характеристик

биполярных БМК (см табл 1 и 2),

в настоящее время достигнута степень ин-

теграции 5 10 тыс. вентилей при площади

кристалла 50. .100 мм2. Таким образом, при

современной технологии изготовления БИС,

обеспечивающей минимальные размеры

Д=1,5.2,0 мкм, реализуется плотность раз-

мещения порядка 100 вент./мм2. В послед-

них разработках биполярных БМК достиг-

нуты задержки переключения

для базовых элементов ЭСЛ/ТПЛ: /,=

= 100...300 пс при потребляемой мощности

Р=2 .5 мВт [13, 38, 39, 46, 48, 49, 50,

61, 66, 69].

для базовых элементов ШТЛ: /3=500...

800 пс при мощности Р— 0,1 .0,5 мВт

[39, 51].

Таким образом, по быстродействию би-

полярные БМК по-прежнему опережают

КМОП-кристаллы, где реализованы мини-

мальные значения /3=0,7...1,5 нс [6,52

55]

Обеспечение дальнейшего роста степе-

ни интеграции МБИС при одновременном

повышении быстродействия потребует не

только совершенствования технологии и

развития схемотехники, но и увеличения

мощности, рассеиваемой на кристалле В на-

стоящее время разработаны БМК, в кото-

рых обеспечено рассеивание мощности до

12...20 Вт при воздушном охлаждении

[2, 12, 16, 46, 48, 69] Перспективным

способом дальнейшего повышения рассеи-

ваемой БИС мощности является создание

на кристалле микроканалов, по которым

циркулирует охлаждающая жидкость Та-

кой способ охлаждения позволяет в пер-

спективе повысить мощность, рассеиваемую

кристаллом до 100—1000 Вт [56].

Преимуществами КМОП-БМК являются

более высокая степень интеграции (при

близительно в два раза) и пониженное

потребление мощности (в два-три раза на

максимальной рабочей частоте) [38, 45].

Благодаря этим достоинствам выпуск и

применение БМК этого типа росли в 80-е

годы более быстрыми темпами, чем произ-

водство биполярных БМК- Однако разра

ботанные в последние годы новые вариан-

ты технологии (изоляции глубокими канав

ками, многослойная металлизация и др )

позволили существенно повысить быстро-

действие и плотность упаковки биполяр

ных микросхем [38, 48, 57, 58] Пре-

имущества биполярных БИС перед КМОП-

БИС особенно сильно проявляются при ра

боте на линии связи значительной длины

(— 1 мм и более). Поэтому биполярные

БМК перспективны для создания цифро

вых устройств с нерегулярной (нерекурсив-

ной) структурой, например, микропроцес-

соров, интерфейсных схем, тогда как пре

имущества КМОП БМК проявляются при

реализации достаточно регулярных (рекур-

сивных) структур типа блоков оперативной

и постоянной памяти, ПЛМ, матричных

умножителей и т. п. [39].

Приведенные в [59] оценки показывают,

что биполярные схемы имеют преимущества

по быстродействию и работе переключе-

ния при изготовлении по технологии,

обеспечивающей минимальные размеры

А=0,5.. 1,0 мкм. В [60] отмечаются труд-

ности реализации хороших характеристик

МОП-транзисторов при длине канала менее

0,5 мкм, обсуждаются пути их преодо-

ления. В [39J указывается, что биполяр-

ные транзисторы будут иметь преимущества

при минимальных размерах Д«0,1 мкм.

Таким образом можно прогнозировать сов

местное развитие биполярных и КМОП-

матричных БИС с учетом определенной

специфики использования БМК того или

иного класса в зависимости от структуры

реализуемых устройств и требуемых тех-

нических характеристик

В последние годы выполнен ряд успеш-

ных разработок БИС, изготовленных по

совмещенной МОП-биполярной технологии

(Bi—MOS) [52, 55, 62] С использова

нием этой технологии фирмами Hitachi

(Япония), Motorola (США) изготовлены

БМК, содержащие соответственно 2500 и

15

6144 вентилей, имеющих задержку пере-

ключения 7’а=(),8 ..0.9 нс. Разработанные

БМК данного класса сочетают высокое

быстродействие, характерное для биполяр-

ных БИС, с пониженным потреблением

мощности, свойственным КМОП БИС.

Основным конкурентом кремниевых бипо-

лярных МБИС в области сверхбыстро-

действующих устройств являются БИС,

реализуемые на арсенид-галлиевых БМК.

В настоящее время рядом фирм США

(Harris Semiconductor. Honeywell. Texas

Instrument и др.) реализованы БМК иа

арсениде галлия, имеющие степень интегра-

ции до 1000 -3000 вентилей, максималь-

ную рабочую частоту /П1МХ=1--3 ГГц [49,

63 65] Базовые элементы этих БМК

имеют задержки переключения /,—50...

100 пс при минимальной нагрузке (коль-

цевой генератор) и /З=200...300 пс при типо-

вой нагрузке Эти показатели несколько

лучше, чем параметры, характеризующие

быстродействие базовых элементов ЭСЛ/

ТПЛ в биполярных БМК на базе кремния.

Однако арсенид таллиевые БМК имеют бо-

лее сложную технологию изготовления,

высокую стоимость, меньшую степень ннтс

грации Поэтому по имеющимся прогнозам

и оценкам основной областью применения

арсенид галлиевых БМК будут цифровые

устройства и системы, работающие с часто-

той /mdx^5 ГГц. тогда как на кремниевых

биполярных БМК будут реализовываться

цифровые МБИС, имеющие рабочую часто-

ту в диапазоне 0,5...5 ГГц.

Создание в начале 80 х годов новых эф

фективных средств автоматизированного

проектирования кремниевых компиля-

торов обеспечило реализацию разра

ботки специализированных БИС методом

стандартных элементов При этом топо-

логия проектируемого цифрового устройства

автоматически создается из набора топо-

логических фрагментов, реализующих функ-

ции стандартных элементов (вентилей,

триггеров, функциональных узлов и бло

ков) из имеющейся библиотеки. В данном

методе не используется предварительно

разработанная стандартная заготовка в ви

де БМК, поэтому получаемая топология

в наибольшей степени соответствует кон-

кретной структуре проектируемого устройст-

ва и не содержит лишних (неиспользуе-

мых) элементов и компонентов В резуль

тате площадь, занимаемая БИС на кристал-

ле, оказывается в 1,2 2 0 раза меньше,

чем при использовании БМК [67] Однако

типовые сроки разработки и изготовления

БИС методом стандартных элементов со

ставляют 12—16 недель, тогда как для

МБИС эти сроки не превышают 8 9 не-

16

дель [45| В настоящее время за рубе-

жом выпуск МБИС в 3- 4 раза превы-

шает выпуск БИС па стандартных эле

ментах. Однако темпы роста производства

последних составляют 70 ..80 % в год, что

существенно выше, чем для МБИС (30...

40 %). Поэтому по прогнозам к 1989—

1990 гг. БИС на стандартных элементах

превзойдут МБИС по объему выпуска

[45, 671

В условиях такой острой конкуренции

разработчики БМК и МБИС видят выход

в дальнейшем сокращении сроков их проек

тирования и выпуска Например, фирма

Fairchild сократила срок разработки МБИС

до двух недель путем использовании САПР

на базе супер-ЭВМ типа Cray IS и при-

менения автоматизированной установки для

электронно-лучевой литографии [68] Отме-

чается также экономическая эффективность

использования БМК при относительно ма

лых объемах выпуска БИС По имеющим-

ся оценкам применение МБИС экономи-

чески целесообразно при объеме их вы-

пуска менее 25 50 тыс., а БИС на

стандартных элементах — при объеме

выпуска более 50... 100 тыс. шт [38, 64|.

Оценивая перспективы дальнейшего раз-

вития биполярных БМК, можно сделать вы-

вод, что в течение ряда лет они оста

нутся основной элементной базой для реа-

лизации быстродействующих специализиро-

ванных БИС и СБИС. Уже в ближай-

шие годы предполагается появление би-

полярных БМК со степенью интеграции

50 - 80 тыс. вентилей, имеющих задержки

переключения /3= 100...200 пс при потреб-

ляемой мощности Р=10 мкВт [39|. Даль-

нейшее улучшение характеристик биполяр-

ных БМК будет достигнуто путем сни

жения минимальных размеров компонентов

до значений Д=0,1 .0,5 мкм, использова-

ния базовых элементов НПЛ, ДЭСЛ

ШТЛ с пониженными логическими перепа

дами 1/л=0,1...0,2 В и уменьшенным на-

пряжением питания /:п=1,0...2,0 В, приме-

нения конструкций кристалла, допускающих

увеличение потребляемой МБИС мощности

до 50... 100 Вт Совершенствование тех-

нологи, схемотехники и конструкции поз-

волит реализовать биполярные БМК со

степенью интеграции свыше 100 тыс вен

тилей, обеспечивающих задержки переклю

чения С=5О...1ОО пс.

СПИСОК ЛИТЕРАТУРЫ

I Жуковский В. А., Кушнер Ю К-, Бу-

бенников А. И.— Зарубежная радио-

электроника, 1979, N 11.

2. Окуда Н„ Сугаи М., Гото И,— ТИИЭР,

1986 т. 74 N 12

3. Van Cleemput W M.— Computer Design,

1983, v 22, N 2

4 Петренко А. И и др Зарубежная

радиоэлектроника, 1985, N 8

5. Бубенииков А Н и др Зарубежная

радиоэлектроника, 1985, N 9.

6. Smith D EDN 1986 v. 31, N 5.

7. Suzuki M., Horiguchi S , Sudo T D

IEEE J., 1983, v. SC 18, N 5.

8. Tatsuki M Kato S., Okabe M.— Proc.

IEEE Custom Integrated Circuits Conf.,

Portland, 1985.

9. Cox A., Davis A. 1980 WESCON

Proffessional Program Anahaim, 1980,

pap. 30/4.

10. Elektromkschau 1983, v. 17 N 4, p 16

18

11 EDN 1985, v. 30. N 8, p 20.

12. Lee S. S., Bass A. S.-— IEEE J., 1982,

v SC-17, N 5.

13. Suzuki M., Horiguchi S. IEEE J , 1984,

v SC-19, N 4

14 Gautier J L., Pasoquet D., Pouvil P.—

L’Onde Electronique, 1983, v. 63, N 12.

15. Brackelman W. c. a.— IEEE J., 1979,

v. SC-14, N 5

16. Brackelman W. e. a.- IEEE J., 1985,

v. SC 20, N 5.

17 Sato F e. a.— IEEE J., 1980, v. SC-15,

N 5.

18. Кокс P.— Электроника, 1984, т. 57, N 13.

19 Suzuki M e. a. — IEEE J., 1985, v. SC 20,

N 5.

20 Электроника 1986, т. 59, N 20, c. 29—34

21 Гани В Л., Клара Н. С., Викари К-—

Электроника, 1982, т 55, N 14.

22. Dansky А. Н,— IBM J., 1981, v. 25. N 3.

23 Армстронг Р.— Электроника, 1981, т. 54,

N 1

24. Hingarh Н. К. 1980 WESCON Prof-

fessional Program, Anahaim, 1980,

pap. 30/5.

25. Chen J Z e. a. IBM J., 1981, v. 25,

N 3

26. Sander T. e. a.— Custom Integrated

Circuits Conference, Rochester, 1981

27. Спрэтт Д., Торренто M. Электроника,

1984, т. 57, N 5

28. Пите Р.— Электроника, 1982, т. 55, N 24.

29 Lohstroh J.— IEEE J., 1982, v. SC 17,

N 8.

30. EDN, 1984, v. 29, N 20, p. 259, 260.

31 EDN, 1986, v. 31, N 15, p. 46.

32. Smith D. EDN, 1985, v. 30, N 22.

33 Берисфорд P— Электроника, 1983,

т. 56, N 4

34. Electronic News, 1985 v. 31, N 1576,

p 86.

35. Brenner Sea International of

Solid-State Circuits Conference, Digest

of papers, 1983

36. Уэбер Г. Электроника, 1985, т. 58,

N 11

37. Klein К- e. a — IEEE J., 1982, v SC 17,

N 3.

38. Коул Б.— Электроника, 1985, т. 58, N 20.

39. Коул Б.— Электроника, 1986, т. 59, N 7

40. Sato Т. е. a. IEEE Trans., 1984,

v. ED-31, N 2

41. EDN, 1984, v. 29, N 25, p. 70, 1?4

42. Чернышев А А., Стадник А А Тю-

хии А. А. Зарубежная радиоэлект-

роника, 19«4. N 9.

43. Хеймен Д. Электроника, 1984, т. 57,

N 19

44. Махалинген M ТИИЭР, 1985, т. 75,

N 9.

45. Бурбон Б. Р.— Электроника 1984, т. 57,

N 18.

46. Лайнбек Д. Р.— Электроника, 1987,

т. 60, N 3

47 Электроника, 1986, т 59, N 1, с. 21—42.

48. Коул Б. Электроника, 1987, т. 60,

N 12

49 Мануэль Г.— Электроника, 1985, т. 58,

N 19.

50 Gonausser Е. е а.— IEEE J., 1984,

V. SC-19, N 3.

51. Sigiyama Y. с. a.— Proceedings of

Custom Integrated Circuits Conf., 1981.

52. Холтон У. С., Кевин Р. К ТИИЭР,

1986, т 74 N 12

53. Moknoff N.— Computer Design, 1985,

v. 24, N 5.

54. Электроника, 1987, т. 60, N 2, с. 88 89.

55. Electronic Engineering, 1987, v. 59, N 22,

p 78 105.

56 Tuekerman D В Pease R F W

IEEE Electron Dev Lett., 1981, v. EDL 2,

N 1.

57. Нии T X. Тан Д Д ТИИЭР, 1986,

т. 74, N 12

58 Коул Б.— Электроника, 1986, т 59,

N 18.

59. Лохстрох Р. ТИИЭР, 1981, т. 69, N 7

60. Коул Б.— Электроника, 1985, т. 58,

N 25.

61. Drobac S.— Electronic Design, 1987,

v. 35, N 10

62. Коул Б. Электроника, 1986, т. 59, N 5.

63. Bond J - Comp. Design, 1987, v. 26, N 2.

64. EDN, 1986, v 31, N 15, p 112—120

65. Коул Б.— Электроника, 1986, т. 59,

N 19.

66. H Ichino a. о. IEEE J., 1987,

v SC-22, N 2.

67. Лайнбек Д. P.— Электроника, 1984,

т 57, N 16

68. Беннет И. Электроника, 1985, т. 58,

N 17.

69. М. Suzuku а. о,— IEEE J., 1987, v. SC 22,

N 1

17

УДК 621 327 67

СОСТОЯНИЕ И ПЕРСПЕКТИВЫ РАЗВИТИЯ

СВЕРХБЫСТРОДЕЙСТВУЮЩИХ БИПОЛЯРНЫХ ОЗУ

Дятченко В Н, к т. н. Родионов Ю

П,, к т, н Скаира А В.

ВВЕДЕНИЕ

В последнее десятилетие усилия разра-

ботчиков микросхем в основном сосредо-

точены на создании сверхбыстродействую-

щей элементной базы для ЭВМ IV и

V поколений. Это связано с тем, что для

решения современных задач физики, аэроди

иамики,баллистики, метеорологии, обработ

ки изображений и речевых данных, эконо

мики, искусственного интеллекта и других

необходимо увеличить в текущем десяти-

летии быстродействие ЭВМ на три поряд-

ка (1].

В настоящее время в мире функциони-

руют около 200 супер-ЭВМ, производимых

фирмами США (Cray, ETA, CDC) [2] и Япо-

нии(NTT, Hitachi, NEC) [3] и др. Быстро-

действие современных супер ЭВМ достигает

100...150 Мфлоп (1 Мфлоп—106 опер /с над

числами с плавающей запятой) при емко-

сти центрального ОЗУ около 10е 64-раз-

рядных слов. К 1990 г. предполагается

довести быстродействие супер-ЭВМ до

1000 Мфлоп (например, предполагаемое

быстродействие ЭВМ Isis, Франция, фирмы

Bull составит 1 Гфлоп), емкость централь

ной памяти до 2048 Мбайт (например,

у машины Сгау-3). Тактовая частота су-

пер-ЭВМ при этом вплотную приблизится

к субнаносскундному диапазону. Предпола-

гаемая длительность цикла основной памя

ти в ЭВМ Isis составит 35 пс [3].

Для решения поставленных задач в Япо-

нии [4| и США [5] приняты и осуще-

ствляются долговременные национальные

программы по созданию сверхскоростных

ИС (ССИС) —элементной базы супер-ЭВМ.

1 ТЕНДЕНЦИЯ РАЗВИТИЯ

БИПОЛЯРНОЙ ТЕХНОЛОГИИ БИС

ПАМЯТИ

Улучшение параметров, характеризую-

щих быстродействие и плотность разме-

щения компонентов ИС на биполярных

транзисторах, достигается разработкой сле-

дующих принципиально новых конструктив-

но-технологических решений

формирование самосовмешающихся

сверхинтегрированных субмикронных тран

зисторных структур с плоскими эмиттер

18

ными переходами и пассивными р+-об-

ластями базы [6];

создание транзисторных структур с вер-

тикальными t/образными изолирующими

канавками [6];

формирование структур с многоуровневой

металлизацией.

Самосовмешенная транзисторная струк-

тура с поликремниевым эмиттером, мно-

гоуровневой разводкой и вертикальными

Д-образными изолирующими канавками по-

казана на рис. 1 [7]. Разработка и приме-

Рис, 1 Структура современного биполярного

транзистора с самосовмещеннем областей

Эволюция параметров

Параметры транзистора и элементной базы БИС

ЮР DOPOS DXIS

С3бо X 10~15, Ф 30 34

^кбо X К)-15, Ф 100 41

г '-'КИО X 10 |А, Ф 200 130

<6 Ом 1470 360

fr ХЮ9, Гц 2 3

‘зл р.ср ОЗУ X 10 _|2с/вент. — —

а X 10~9, с 7,э 2d

^гпш , мкм 3,0 3,0

р** 'потр X Ю~3 Вт 784 350

Год разработки 1978 1979

Источник 18] I9J

* минимальная технологическая проектная норма,

время задержки распространения сигнала в вентиле .

Рис, 2. Влияние граничной частоты усиления

биполярных транзисторных структур на быстро-

действие статических ОЗУ

нение технологических методов с t/ образ-

ной изоляцией и поликремниевой развод

кой позволили повысить частоту отсечки

fT транзисторных структур в 5—7 раз

(табл 1), что дало существенное уве-

личение быстродействия схем ОЗУ (рис. 2).

В табл. 1 использованы следующие об-

щепринятые сокращенные названия тех-

нологий биполярных интегральных схем:

ЮР — V (Isolation Oxide Polysilicon

V — groove) — технология с боковой окис-

ной изоляцией компонентов и заполнением

изолирующих ^-образных канавок поли-

кремнием;

IOP-L — разновидность технологии ЮР

с вертикальными (1/-образными) канав-

ками-

OXISS (Oxide Isolated process-S) — тех-

нология с боковой окисной изоляцией ком-

понентов;

PSA (Polysilicon Self-Aligned) техно-

логия с использованием принципа са-_

мосовмещения при формировании полу-

проводниковых слоев транзисторных струк-

тур;

APSA (Advanced PSA) — усовершен-

ствованная технология PSA,

ISO-S (Isolation Oxide-S) — традицион-

ная технология с боковой окисной изо-

ляцией («изоплаиар») с масштабированием

размеров;

SST (Super-Self-ahgned process Technolo-

gy) — технология, использующая принцип

самосовмещения при формировании транзи-

сторных структур (усовершенствованная

технология PSA);

OST (Oxide Surrounded Transistor) —

технология с боковой диэлектрической изо-

ляцией компонентов;

BIT 1 (Bipolar Integrated Technology) —

интегральная технология биполярных ИС

Применение новейших биполярных тех

нологий позволило ведущим фирмам Япо

нии и США успешно справиться с выпол-

нением первых этапов национальных про

грамм по разработке ССИС Отметим

наиболее важные достижения, полученные

в ходе их реализации.

Японская фирма NTT Corp на основе

суперсамосовмещенного процесса (SST 1А)

и литографии с минимальным размером

1 мкм изготовила ряд биполярных логиче

ских ИС и статических ЗУ с задержкой

биполярных транзисторных структур и элементной базы БИС Таблица 1

Технология БИС

PSA APSA APSA APSA SST 1 ISO S SST-2 SSMA SST-4 OS1 ЮР 1 BIT-1

30 31 13 30 25 21 6,8 15 30 20 4 5

40 43 22 80 21 20 14 18 30 4 ) И 5

НО 84 69 НО 50 34 60 42 100 100 7 5

1000 290 360 360 310 840 2200 388 430 650 — —

2 4 4 3 6...8 9 7 12.4 3...4 5 15 5

600 320 290 — 63*** 150...600 — 80 — 350 160 150...600

— — 23 2.7 4.5 1,5 0.85 5,4 — — —

2,0 2,0 2,0 2,0 2,9 1,0 2.0 1,0 2,0 1,5 1,0 2,0

0.8 1 85 1,48 527 500 1500 700 950 900 5 1,5 0,3

вент вент вент вент. вент. вент.

1979 1980 1981 1983 1984 1983 1984 1984 1983 1985 1986 1986 •

[10] 111] |12] [13] |14] |13] |15] |16] (17] |18] |19] 119]

указана четность ЗУПВ или .тонического вентиля. *** непороговая логика (кольцевой генератор) *Gapcp

/ва время выборки адреса в ОЗУ.

среднее

19

сигнала на вентиль в кольцевом генера-

торе 30-10 12 с при граничной частоте

транзисторов (15...20) • 109 Гц (20]. По тех-

нологии с четырьмя уровнями разводки и

проектными нормами 2 мкм создан бипо-

лярный матричный кристалл на 8300 вен

тилей, а также ЭСЛ ОЗУ емкостью 16 К

со временем выборки 15 нс и емкостью

4 К с быстродействием 3,5 нс (21].

Специалисты фирмы Fujitsu на основе

технологии SST-1.A разработали биполяр-

ную элементную базу СБИС с задержкой

325-10-12 с/вент. с типовой нагрузкой при

токе питания 0.2-10—3 А Особенность этой

транзисторной структуры — глубокая U об

разная изолирующая канавка с толстым

слоем защитного окисла под участками, где

располагаются соединительные шины. В чи

ело схем, разработанных по этой техноло-

гии, входит ОЗУ емкостью 1 К с временем

выборки 850-10—12 с рассеиваемой мощ

ностью950-10 3 Вт [ 15] (см. табл. 1). Даль-

нейшее совершенствование суперсамосовме-

щенных транзисторных структур с изоля

цией щелевого типа позволило разработать

серию сверхбыстродействующих ОЗУ емко-

стью 4 К с временем выборки при работе

в кольцевом генераторе 2,3-10-9 с (22],

1,1-10 -9 с (23], емкостью 5К с организа-

цией 512 словХ 10 разрядов и временем вы-

борки 1,0-10 9 с [24] и 16 К с быстродей-

ствием 3,5-10—9 с (25] и 2,8-10—9 с [26]

Быстрыми темпами разворачиваются ра-

боты по созданию комплементарных верти-

кальных биполярных структур [6], конку-

рирующих с КМОП-схемами по таким пока-

зателям, как малая мощность потребления

и высокая помехоустойчивость, обусловлен-

ные их комплементарностью.

Специалисты фирмы Hitachi разработали

технологию быстродействующих биполяр

ных цифровых схем, обеспечивающую вы

сокое качество вертикальных р—п—р и

п—р—п-транзисторов [27] в одном кристал-

ле.

Фирма IBM разрабатывает комплемен-

тарную биполярную технологию с верти-

кальными р п—р-транзисторами, в кото-

рой для формирования эмиттерных обла-

стей используется слой поликремния, леги

рованный большой дозой бора [28]

Фирма Fairchild на базе новой технологии

FAST-Z предполагает выпустить серию ИС

ЭСЛ типа с задержкой (0,08...0,1) • Ю-9

с/вент Технология FAST-Z близка к техно-

логии SST-1A. Для проектных норм 1,5 мкм

транзисторная структура с самосовмещени-

ем областей имеет размеры 1,5-3,5 мкм2

граничная частота таких транзисторов со-

ставляет 10‘° Гц. При переходе на проект-

ные нормы 1 мкм граничная частота во-

20

зрастает до (15 . 18) • 109Гц. По техноло-

гии FAST-Z изготовлено ЭСЛ ОЗУ емкостью

64 К со временем выборки 15-10 9 с

(29], размером запоминающего элемента

200 мкм2 и площадью кристалла 26 мм2.

При использовании аналогичной технологии

с проектными нормами 1 мкм фирма Fair

child рассчитывает получить статическое

ОЗУ емкостью 256 К с такими же размера-

ми кристалла и быстродействием, как для

предыдущей схемы

Фирма Bipolar Integrated Technology

Inc. (BITI) разработала биполярную тех-

нологию, в которой используются проектные

нормы 2 мкм и поликремниевые само-

совмещенные электроды эмиттера и базы

Эта технология позволила получить тран-

зисторы площадью 14 мкм2 и вентили с за-

держкой 300-10 12 с/вент. в нагруженном

состоянии при рассеиваемой мощности

300-10 ь Вт/вент При использовании тех-

нологии BIT-1 применяются те же мето-

ды и оборудование, что и при изго-

товлении КМОП БИС (19]. Главный ре-

зультат применения нового технологическо-

го процесса создание сверхминиатюрно-

го транзистора с граничной частотой 5 ГГц

при рабочем токе 50-10 6 А. Емкости пе

реходов составляют рекордно малую вели-

чину порядка 5-10 15 Ф Двухвходовый

вентиль ИЛИ—НЕ выполненный по техж>

логии BIT-1 занимает площадь 770 мкм2

и позволяет получить уровень интеграции,

эквивалентный возможностям КМОП-тех

нологии с проектными нормами 1,5 мкм

Другие фирмы США также добились су-

щественных успехов в реализации бипо

лярной технологии с (7-образными канав-

ками Так, фирма Т1 по технологии Impact-X

выпустила серию логических микросхем на

основе ТТЛ, ШТЛ и ЭСЛ-базисов 32-раз-

рядный микропроцессорный набор, ЭСЛ

ОЗУ, ППЗУ емкостью 64 К с диодами Шот

ки и др. Эта технология обеспечивает бы-

стродействие нагруженных ТТЛ вентилей

5-10 9 с при потребляемой мощности

0,5-10-3 Вт ШТЛ вентилей — 0,8-10—9 с

при мощности 0,1-Ю—з Вт и ЭСЛ венти

лей 0,2-10 9 с при мощности 5-10 1 Вт [30]

Фирма AMD (США) в 1985 г. объявила

о разработке биполярного ППЗУ емкостью

128 К с временем выборки 35-10 9 с по тех-

нологии IMOX-III Slot [30].

Эта технология реализует ионно-имплан-

тированные транзисторные структуры с са-

мосовмещением и щелевой изоляцией. По

данной технологии получены образцы ЭСЛ

ОЗУ емкостью 1КХ4 с временем выборки

10 нс; ЭСЛ ОЗУ емкостью 16 КХ 1 с быст

родействием 15 нс В первой половине 1986 г.

подготовлено к выпуску ЭСЛ ОЗУ 4КХ4

и ОЗУ со встроенными логическими схема-

ми емкостью 512X9 бит для реализации

кэш-памяти.

2 ДИНАМИКА ИЗМЕНЕНИЯ

ОСНОВНЫХ ПАРАМЕТРОВ

БЫСТРОДЕЙСТВУЮЩИХ ОЗУ

Повышение производительности и емко-

сти памяти ЭВМ новых поколений тре-

бует улучшения параметров всей элемент-

ной базы, в том числе и ОЗУ.

Динамика изменения быстродействия и

плотности упаковки логических элементов

биполярных СБИС с размером кристалла

не больше 25 мм2 в зависимости от техно-

логических проектных норм показана на

рис. 3. Наиболее полно технологические

успехи реализуются в конструкции и разме-

рах ячеек памяти (ЯП) биполярных ОЗУ,

изменения которых во времени показаны

на рис 4

Основной схемотехнической элементной

базой биполярных ОЗУ, используемых в

большинстве современных супер-ЭВМ, яв

ляется ЭСЛ-логика, сохраняющая 2—4-

кратное преимущество по быстродействию

по сравнению с МОП-схемами. На ЭСЛ-

схемах реализуются процессоры, быстро-

действующая регистровая и кэш-память

для супер-ЭВМ (фирмы Byll СА, Hitachi

NEC, Cray и др.). Для основной памяти

планируется постепенный переход от ЭСЛ

ОЗУ к КМОП кристаллам, работающим

п| и температуре жидкого азота (77 К)

(ЭВМ серии Cyber фирмы ЕТА) [31]. Фир-

ма Cray Corp для ЭВМ Сгау-3 пред

полагает использовать логику на GaAs-

полевых транзисторах с барьером Шотки

Рис. 4 Изменение минимальных размеров ячеек

памяти биполярных статических ОЗУ

[32]. Статические и динамические ОЗУ,

изготовленные по КМОП-технологии, будут

использованы для построения дополнитель-

ной буферной памяти для обмена дан

ными между оперативной памятью и па-

мятью на магнитных дисках.

Основная концепция развития мульти-

процессорной архитектуры параллельной

обработки данных в ЭВМ новых поколе-

ний находит свое отражение в развитии

схемотехники ОЗУ с многоразрядной и логи-

чески перестраиваемой структурой, со встро-

енной логикой и многопортовой организа-

цией для параллельной обработки инфор-

мации. Усилия разработчиков, направ-

ленные на достижение максимальной

информационной емкости на кристалле ОЗУ,

приводят к тому, что каждые два года до-

стигнутая информационная емкость увели-

чивается в четыре раза (рис. 5). К настоя-

щему времени максимальная реализованная

1К(ТТЛ)\

Число вентилей на кристалл

(Skp^25mmz Р*р=2.0 Вт)

50К 20 К ЮК 5К 2К JK

Потребляемый ток/вентиль, мА

Рис. 3. Зависимость быстродействия, потребляе-

мой мощности и степени интеграции биполярных

БИС от технологической проектной нормы

(за

ГбК(И^\

(А К (ЗОЛ)

г 6ЧК

(БИ-КМОП)

1К(ЭСЛГ< \(ЗСЛ)

,К(зсл^^К^(эсл)

, , (ЯШ ж(3^-^^'^з2к(з7л)

1976 1976 1980 1982 1984 Годы

Рис. 5. Динамика изменения информационной

емкости и быстродействия биполярных статиче-

ских ОЗУ

21

Таблица 2

Конструктивные н электрические характеристики биполярных статических ОЗУ (1978...1986 гг)

Параметры ОЗУ Значения параметров для ОЗУ фирм

Fujitsu Hitachi NTT NTT NTT Hitachi МТ NEC IBM

Организация, бит Потребляемая мощ- 256X4 1К 256Х 4 256X4 256X Х4 4К 4К 1КХ4 5К

ность, Вт Время выборки инфор 0.784 0,8 0,5 0,7 0,95 0,35 0,3 1,5 2,4

мацни, нс Размер ячейки памя- 7.5 5,5 2,7 1,5 0,85 25 20 4,5 1,0

ти, мкм2 2756 2896 2050 1980 1048 2475 1122 1600 760

Размер кристалла, мм2 8,7 7,6 9,0 9,0 6,25 21,4 9,9 14,7

Элементная база ЭСЛ ЭСЛ ЭСЛ ЭСЛ ЭСЛ И’Л/ТТЛ И'Л/ТТЛ ЭСЛ ЭСЛ

Год разработки 1978 1979 1981 1983 1984 1978 1978 1983 1986

Источник |8] [38] |13| [15] 116] [9] [9] 113] [24]

Окончание табл. 2

Параметры ЗУПВ Значения параметров для ОЗУ фирм

NTT Fujitsu Hitachi IBM IBM Hitachi IBM Hitachi

Организация I6KX1 16КХ1 16КХ 1 32К 8КХ8 64К 64 К 16КХ4

Потребляемая мощ- ность, Вт 0,53 0,7 2,0 — 0,27 1.3 0.9 0,5

Время выборки ин- формации нс 23 15 3,5 3,0 25 10 15 13

Ширина импульса записи, нс 20 15 4,0 — — —

Размер ячейки памя ти, мкм2 980 750 495 618 — 524 190

Размер кристал та мм2 Элементная база 33 21 4 — 37,4 55,4 24 30

И2Л И2 Л ЭСЛ ЭСЛ МТЛ И2 Л И'Л КМОП

ЭСЛ ЭСЛ ЭСЛ ЭСЛ ЭСЛ ЭСЛ

Г од разработки 1982 1983 1986 1985 1983 1985 1985 1986

Источник [39] [13] [25] [40] [41] [37] [42] [36] к

емкость составляет 4 Мбит для динамиче-

ских КМОП ОЗУ, 64 К для статических

биполярных ОЗУ [33] и 128 К для биполяр-

ных ПЗУ [34]

Освоено производство ЭСЛ ОЗУ емкостью

16 и 32 К [34] с быстродействием (3...

5)-10 9 с, которые предполагается исполь-

зовать в основной оперативной памяти (на

пример, в разрабатываемой супер-ЭВМ

Cray 2) [2] Для сравнения в первой су-

пер-ЭВМ ILLIAC IV (1971 г) использова-

лись ОЗУ емкостью 256 бит, а в современ-

ной машине Cray 1 основная оперативная

память, построенная на ЭСЛ ОЗУ емкостью

4 К, включает 3- 10s кристаллов с рассеивае-

мой мощностью 5 Вт/кристалл [35]. Для

реализации сверхбыстродействующих ОЗУ с

информационной емкостью более 64 К в [36]

предлагается использовать совмещенную

биполярную и КМОП (БИ—КМОП)-техно-

логию, в которой удачно разрешены про-

тиворечивые требования к информационной

емкости, потребляемой мощности, быстро-

действию и площади кристалла. Сравни

тельные данные, представленные на Ме-

ждународной конференции по интегральным

схемам КМОП и БИ—КМОП ЗУИВ ем-

костью 64 К, подтверждают прогноз

перспективности БИ КМОП-технологин

(табл. 2).

3 СХЕМОТЕХНИКА

БЫСТРОДЕЙСТВУЮЩИХ

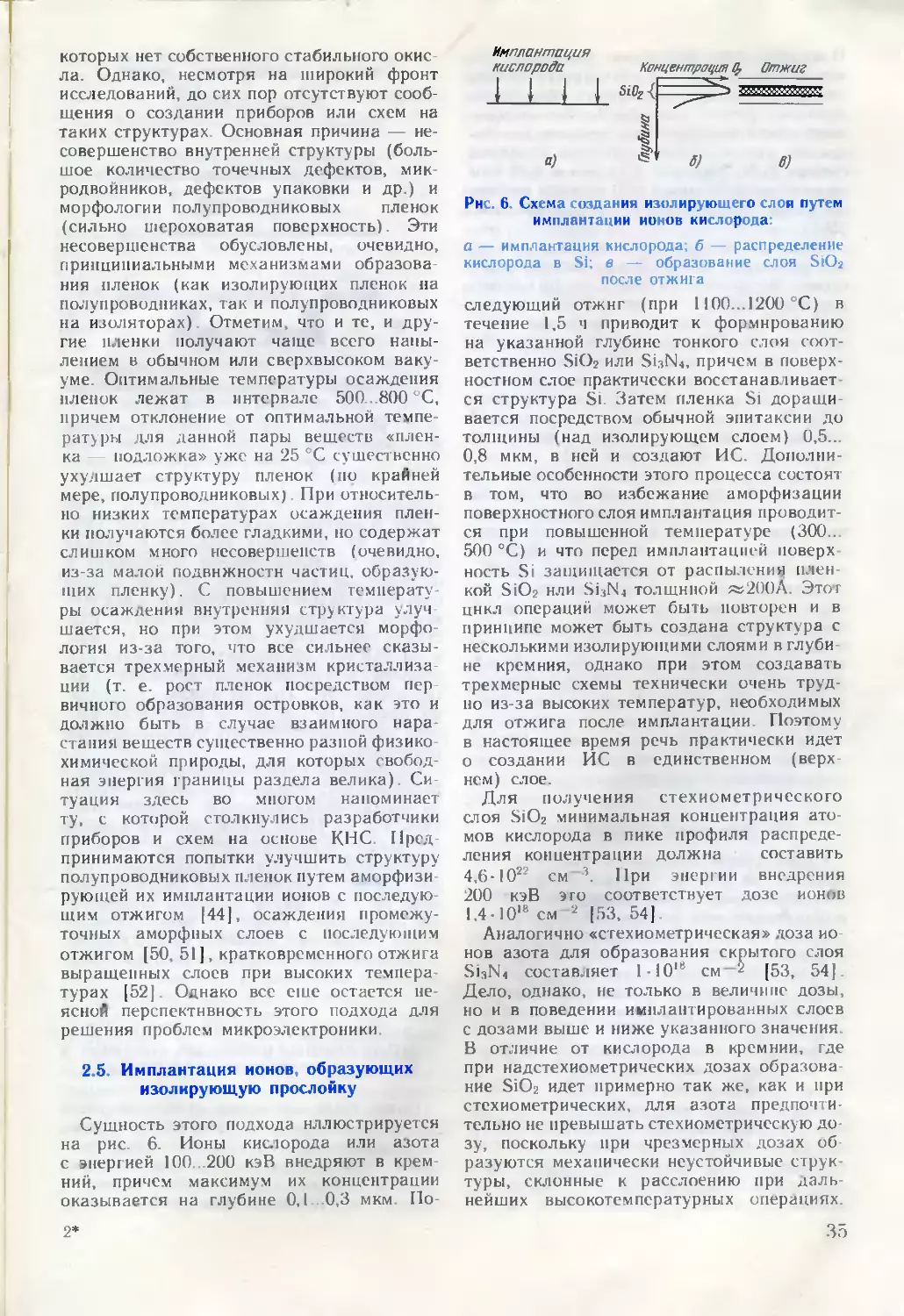

БИПОЛЯРНЫХ ОЗУ