Автор: Шило В.Л.

Теги: электроника микросхемы справочник радиоэлектроника

ISBN: 5-88604-031-3

Год: 1993

Текст

В.Л. Шило

ПОПУЛЯРНЫЕ МИКРОСХЕМЫ КМОП

Справочник

СЕРИИ:

К176, К561, 564, КР1561, 1564

Москва «Ягуар» 1993

ББК 32.85

ШилоВ.Л.

Популярные микросхемы КМОП. Справочник.— М.: Издательство «Ягуар»> 1993.— 64 с., илл. - (Серия

«Отечественные микросхемы и их зарубежные аналоги»).

ISBN 5-88604-031-3

В справочнике приводятся 95 типов отечественных и зарубежных микросхем КМОП. Рассматриваются логические элемент ы. триггеры,

счетчики .регистры и более сложные микросхемы средней степени интеграции. Даются структурные схемы, параметры, цоколевки, а

также рекомендации по применению. Рекомендуется для радиолюбителей, студентов и специалистов, занимающихся разработкой,

эксплуатацией и ремонтом радиоэлектронной аппаратуры.

Ш 2404020000—400 Без объявлений ББК 32. 85

Я46 (03) - 93

ISBN 5-88604-031 -3

© Издательство «Ягуар» 1993

©ШилоВ.Л. 1993

ОГЛАВЛЕНИЕ

Микросхемы : зарубежные - отечественные 4

Как найти микросхему ? 5

Мнемонические обозначения 6

1. Логический элемент 8

2. Микросхемы И, И, ИЛИ, Z, «Искл. ИЛИ» 12

3. Микросхемы с инверторами и преобразователями уровня is

4. Коммутаторы цифровых и аналоговых сигналов 2’2

5. Триггерные микросхемы 24

6. СчеТЧИКИ . 27

7. Регистры за

8. Дешифраторы 47

9. Арифметические схемы 53

10. Микросхемы ФАП и мультивибратор 59

МИКРОСХЕМЫ : ЗАРУБЕЖНЫЕ - ОТЕЧЕСТВЕННЫЕ

Таблица 1

Фирма RCA; се- рми; CD4OO0A и CD4000B Обозначение Серна Стр.

К176 564 K56I KP156I

CD4000 ЛП4 + 15

01 JIE5 + + + 15

02 ЛЕ6 + + + 15

03 ТМ1 + 21

07 ЛП1 + 19

08 ИМ1 + + 53

09 ПУ2 + 20

10 ПУЗ + 21

11 ЛА7 + + 13

12 ЛА8 + + 13

13 ТМ2 + + 25

15 ИР2 + + • 36

16 КТ1 + 22

17 ИЕ8 + 29

18 ИЕ19 + 35

20 ИЕ16 + 34

23 ЛА9 + + + 13

24 ИЕ1 + 27

25 ЛЕЮ + + + 15

27 ТВ1 + + + 27

28 ИД1 + + 47

29 ИЕ14 + 34

30 ЛП2 + + 18

31 ИР4 + 37

34 ИР6 + + 38

35 ИР9 + + 21

41 - 19

42 тмз + + 26

43 ТР2 + + 24

46 гп + 59

49 ЛН2 + + 19

50 ПУ4 + + + 21

51 КП2 + + + 23

52 КП1 + + +

54 УМ1 + 51

55 ИД4 + 50

56 ИД5 + 50

60 35

61 РУ2 + + + 58

66 ктз + + + 22

70 ЛП14 + 17

81 ЛИ2 + 19

93 ТЛ1 + + + 14

98 АГ1 + + 62

101 ИП6 + 54

107 ЛАЮ + 13

108 ИР12 + + 43

109 ПУ6 + 21

181 ИПЗ + 56

182 ИП4 + 58

Таблица 2

Фирма Motorola; серия MCI4000 Фирма RCA серии: CD4000A CD4000B Обозначе- мис Серия Стр.

564 К 561 KPI561

MCI 4040 40 ИЕ20 + 36

50 50 КПЗ + 24

76 76 ИР14 — + 46

94 94 ПР1 + 47

161 •

194 194 ИР15 + 45

502 502 ЛН1 + + 18

516 516 ИЕН + + 32

519 519 КП4 + 16

520 520 ИЕ10 + + + 32

531 101 СА1 + + 54

554 554

555 555 ИД6 + 52

556 556 ИД7 + 52

580 108

581 181 ИПЗ + 56

582 182 ИП4 + 58

585 63 ИП2 + + 54

Таблица 3

Серна 54НС Серия 1564 Стр.

02 ЛЕ1 15

11 ЛИЗ 13

14 ТЛ2 14

20 ЛА1 13

30 ЛА2 13

66 ЛЕ4 15

77 ТМ5 26

192 ИЕ6 28

193 ИЕ7 28

4

I

КАК НАЙТИ МИКРОСХЕМУ ?

Эквивалент Стр,

Мультивибратор

АП CD4098 62

ФАП

JT1 CD4046 59

Шифратор

Дешифраторы

ИД1 CD4028 47

2 - 49

3 — 49

4 CD4055 50

5 CD4056 50

6 МС14555 52

7 МС14556 52

Счетчики

ИЕ1 CD4024 27

2 ТА5971 27

3 * 28

4 —

5

6 54НС192

7 54НС193 28

8 CD4017 29

9 CD4022 30

10 МС14520 32

11 МС14516 32

12 * 33

13 — 33

14 CD4029 34

16 CD4020 34

19 CD4018 35

20 МС14040 36

21

Сумматор

ИМ1 CD4008 53

рочие микросхемы

ИП2 МС1585 54

3 CD40181 56

4 CD40182 58

6_ CD40101 54

Регистры

ИР1

2 CD4015 36

4 CD4031 37

6 CD4034 38

9 CD4035 41

10 CD4006 42

11

12 CD4O1O8 43

13 54С905 43

14 МС14076 46

15 МС14194 45

Мультиплексоры

КП1 CD4052 23

2 CD4051 23

3 МС14050 24

4 МС14519 16

Коммутаторы

КТ1 CD4016 22

ктз CD4066- 22

Микросхемы И

ЛА1 54НС20 13

2 54НС30 — # "в

7 CD4011 —ff -

8 CD4012 —

9 CD4023

_ 10 CD40107 ——

Ь Микросхемы ИЛИ

ЛЕ1 ’ 54НС02 15

4 54НС66

5 CD4001

6 CD4002 -X —

10 CD4025

Микросхемы И

ЛИ1,2 CD4081 13

3 54НС11

Инверторы

ЛН1 МС14502 18

2.3 _ CD4049 19

Микросхемы И/Ш

Микросхема И/ИТ И

ЛС2 _ 4019 16

оочие микросхемы

ЛШ CD4007 19

2 CD4030 18

4 CD4000 15

11 - —X-

12 — 13

14 _ CD4070 18

П| теобоазователь кода

ПР1 MCI 4094 47 I

Преобразователь уровня

ПУ1 — 20

2 CD4009 —w —

3 CD4010 21

4 CD4050 — №

5 -

6 CD40109 -—ж —

7 22

8 — —х —

„ Запоминающие устройства

РУ2 CD4061 58

Компаратор

СА1 МС14531 54

Триггер JK

ТВ1 CD4027 1 _ 21

Гоиггеоы Шмитта

ТЛ1 CD4093 14

2 54НС14 —/г —

Триггеры D

ТМ1 CD4003 25

2 CD4013 — X —

3 CD4042 26

54НС77 —X—‘

Триггеры RS

ТР2 CD4043 24

Усилитель индикации

УМ1 CD4054 1 51

5

Мнемонические обозначения

Л0...Л5 — operand А

А^В — parity

А, АВ

ALU, arithmetic logic unit

A/S — asyncro! syncro

B0...B3 — operand В

B/D, 2/10 — binary!decimal

C — clock input

Cjj — count down

CE — clock enable

CEP — count enable parallel

CET — count enable trickle

CLR — clear

Cm — carry input

Coati Cn+1

CPU — central processor unit

CS — chip select

Си — count up

CRU — carry lock ahead unit

D — data

Do...Dn — parallel data inputs

DEMUX — demultiplexer

DS1 — data serial input

DIL, DIR—D-inputs left, right

DSL, DSR — data shift left, right

E — enable

EC — enable clock, count

EE — enable even

El — enable input

EO — enable output

F0...F3 —function output

G, GS — group signal

H — histeresys control input

I/O — input! output

J К — «jump and keep»

M — mode control

MSB — most significant bit

MUX — multiplexer

OE — odd enable

— байт А для арифметико-логического устройсва, АЛУ;

— вход равенства операндов и в АЛУ;

— выходы неравенства операндов Л и В;

— АЛУ;

— выход для переключения синхронного и асинхронного режимов;

— операнд В, байт В\

— вход переключения счета: двоичного В и десятичного £>;

— тактовый вход;

— счет на уменьшение;

— вход разрешения счета;

— вход разрешения параллельного счета;

— «трюковый» вход разрешения счета, необходимый для,каскадирова-

ния микросхем;

— вход очистки счетчика, сброс;

— вход для единицы переноса, Сюс;

— carry output — выход переноса старшего разряда;

— центральное процессорное устройство, ЦПУ;

— выбор кристалла, доступ к определенной микросхеме устройства;

— счет на увеличение;

I

— схема ускоренного переноса, СУП;

— вход данных D для триггера, регистра, счетчика;

— входы параллельной загрузки данных в счетчики, регистры;

— демультиплексор;

— последовательный вход данных;

— последовательные входы загрузки данных в регистр слева и справа;

— входы для последовательного сдвига данных влево и вправо;

— разрешение;

— разрешение счета;

— четный вход разрешения;

— разрешение приема входных данных;

— разрешение по выходу;

— выходы функций АЛУ;

— групповой сигнал генерации переноса;

— вход установки пределов гистерезиса логического элемента;

— один провод порта, он же вход или выход по команде;

— входы J и К для установки УК-триггера;

— вход переключения режимов;

— старший значащий разряд;

— мультиплексор;

— нечетный вход разрешения;

PI,P — polarity input

P — carry propagation

PE — parallel enable load

P/S — parallel/ serial

Q,Q— outputs

QCC — Q output conversion complete

Preset — previous set

R — reset

RA,RB — read A, В

RE — read enable

RS — reset/set flip-flop, latch

Rt, Ct — timing components

S — set

SE — set enable

St — start, strobe

SAR — successive approximation register

SI — serial input

SIL,SIR — serial inputs left, right

SR — syncro reset

SUB — subractor

SUM — summator

So.>>Sfi — select inputs

SO, ТЕ — sum odd, sum even

TO... Tn — sum outputs

TC — terminal count

T/C — thrue/complement

ТС о, ТС и — terminal count down, up

U/D — up/down

W, WA, WB — write inputs

WE — write enable

Z — state Z, 3-state

Y — logic output

B, H

x

-I > t

l_,4

q, q

Q,Q

Qn, Qn+i

— вход переключения полярности;

— сигнал распространения переноса;

— разрешение параллельной нагрузки;

— вход переключения параллельного и последовательного режима

приема данных;

— выходы: прямой Q и инверсный Q;

— выход завершения преобразования;

— предварительная установка;

— вход сброса данных в ноль;

— чтение из памяти по адресам Л и В;

— разрешение чтения;

— А 5-триггер, А5-за щелка;

— времязадающее АС-звено;

— начальная установка состояния, запись!;

— разрешение параллельной записи слова Po...Dn;

— вход запуска или вход строба;

— регистр последовательного приближения РПП;

— вход последовательный;

— входы последовательные слева и справа;

— сброс данных в ноль синхронно с тактовым импульсом;

— вычитатель;

— сумматор;

— входы выбора;

— выходы сумм четности jthсчетности

— выходы разрядов сумм;

— выход окончания счета;

— переключение кодов прямого и дополнительного кодов;

— выход окончания счета на уменьшение и на увеличение;

— управление реверсивным счетчиком: болыпе/меньше;

— входы записи;

— разрешение записи;

— разрыв выходного провода;

— выход логического элемента;

— высокий и низкий статические уровни;

— вход безразличен к логическим сигналам;

— положительный фронт запуска;

— отрицательный срез запуска;

— полный импульс запуска для двухступенчатых триггеров;

— состояния выходов перед тактовым перепадом запуска;

— результирующие выходные уровни;

— состояние выхода в данный момент tn и в последующий tn+b

7

1. Логический элемент КМОП

Сокращение КМОП—начальные буквы четырех

слов из полного определения: комплементарные по-

левые транзисторы со структурой металл—окисел—

полупроводник. Слово комплементарный переводит-

ся как взаимно дополняющий. Так называют пару

транзисторов, сходных по абсолютным значениям

параметров, но с полупроводниковыми структурами,

взаимно отображенными как бы в виде негатива и

позитива.

Логический элемент состоит из р-канального

{positive) и «-канального {negative) транзисторов, ко-

торые образуют инвертор.

Исток и подложка р-канального МОП транзистора

подключены к положительному полюсу источника

питания Uu.n., стоковая нагрузка Rc — к отрицатель-

ному. Затвор, изолированный от канала высококаче-

ственным диэлектриком SiOi — это одна обкладка

конденсатора, а поверхность полупроводниковой

подложки— вторая. Если затвор заземляем (даем с

помощью 5 J низкий логический уровень И), поверх-

ность кристалла заполняется + зарядами. Две техно-

логические области р+ перемыкаются. Это области

истока и стока, где содержание дырок—повышенное.

Создается поверхностный канал проводимости, течет

ток стока /с и появляется высокий уровень выходного

напряжения (/вых. Переключив S/, присоединим за-

твор к +{/и.п. Конденсатор «затвор-подложка» не бу-

дет заряжен, канал проводимости не замкнут, на вы-

ходе потенциал нулевой. Этот каскад — р-канальный

МОП-инвертор.

Меняя напряжение затвор-исток плавно, снимем

передаточную характеристику этого инвертора. Вы-

ходной уровень «единицы» меньше t/и.п. ввиду значи-

тельного сопротивления канала (Як=1к0м...10к0м).

Исток и подложку «-канального МОП-транзистора

надо заземлить. Если затвор заземлить (даем от Si

низкий логический уровень//), конденсатор «затвор-

подложка» не будет заряжен, канал не наводится, ток

стока не течет и на выходном проводе потенциал (/вых

~ (/и.П.

Даем на затвор высокий уровень В, конденсатор «за-

твор-подложка» заряжен, поверхность подложки

обогащена электронами, течет ток стока. Выходное

напряжение низкое, но (/вых несколько больше ну-

левого потенциала. Присоединив затвор к движку ре-

зистора, снимаем передаточную характеристику, где

отмечаем пороговое напряжение образования «-ка-

нала.

Включим л- и р-канальный транзисторы ’’столби-

ком'', затворы их объединим. Получаем логический

элемент (ЛЭ) КМОП. Нагрузочный резистор Rc не

нужен. Подключив затворы к движку потенциомет-

ра, снимаем передаточную характеристику схемы

при очень большом сопротивлении нагрузки. Харак-

теристика имеет два излома в точках пороговых по-

тенциалов р- и л-транзнсторов и наклонную часть

усилительного режима, когда оба транзистора откры-

ты.

8

Заменив потенциометр переключателем 5/, можем

испытать DD1 как инвертор. Даем на затворы уро-

вень В, канал р-транзистора VT1 разомкнут, а п-ка-

нал VT2 обогащен. На выходе инвертора—логиче-

ский уровень низкий.

Даем на затворы уровень Н, замыкается р-канал

VT1 и через этот контакт в выходной провод проходит

высокий логический уровень. Хотя оба электронных

контакта на землю и на плюс неидеальные, внутрен-

нюю эквивалентную схему ЛЭ можно заменить двух-

полюсным тумблером S2. Учтем, что входное сопро-

тивление нагрузочных полевых ЛЭ имеет порядок

1О10 Ом и более.

Простейшую структуру, позволяющую совместить

р- и n-канальные транзисторы, размещают на п-под-

ложке, на поверхности которой исток и сток р-ка-

нального транзистора выполняются непосредствен-

но.

Для л-канального транзистора устраивается р-кар-

Ман. Знаки + означают повышенную степень легиро-

вания, вблизи поверхности кармана выполняются ис-

ток и сток п-канального транзистора. Подложку

данной структуры следует присоединить к +(/и.п., а

«карман» — к т.е. к «земле».

п ~ подложка р - карман

Схема инвертора создается металлизацией поверх-

ности (в более новых разработках алюминиевая

пленка заменяется поликремниевой—это хороший

проводник, однако не имеющий полупроводниковых

свойств монокристаллического кремния).

К затворам присоединен защитный стабилитрон

VD1. Во-первых, он защищает затворы от пробоя их

диэлектрика избыточными входными потенциалами,

во-вторых, создает ток утечки зарядов, накапливаю-

щихся в статическом состоянии в конденсаторах «за-

твор-канал» Сз.к. Если заряды q генерируются вблизи

поверхности подложки постоянно (термо-, электро-

генерация), то потенциал t/з.и. а^/С3.и. быстро уве-

личится до напряжения пробоя тонкого одномикрон-

ного слоя S1O2. Обратное сопротивление диода VD1

создает достаточный шунтовой путь утечки этого то-

ка.

Полную защиту инвертора обеспечивают шесть ди-

одов и резистор Л-200...2000 Ом, ограничивающий

пиковый уровень тока заряда конденсатора

Сз.и "5...15пФ. Этот резистор защищает выход пред-

ыдущего инвертора от перегрузки, ток которой может

быть опасным, если число нагружающих входов-ин-

верторов очень велико (десятки).

Диоды VD1...3 защищают затворы от пробоя как по

изоляции, так и на «карман». Пробивное напряжение

VD1—25В, a VD2 и VD3—50В.

Диоды VD4 и VD5 защищают выходной провод от

пробоя на «подложку» и «карман» (Г/прб“50В). Диод

VD6 защищает канал прн ошибочной перемене по-

лярности напряжения питания микросхемы. В об-

щем, инвертор КМОП в микросхемах общего приме-

нения защищен от статических пробоев не хуже ин-

вертора ТТЛ.

DD1

Вход

п - подложка

Выход

Для инверторов КМОП напряженне низкого логи-

ческого уровня Н практически равно 0, а высокого В

— напряжению питания t/и.п. Это может быть в том

случае, если номинал нагрузки Ян во много раз боль-

ше, чем сопротивление замкнутого канала.

Если последовательно включены логический эле-

мент—источник DD1 н ЛЭ-нагрузка DD2, условие

выполняется автоматически, т.к. входное сопротив-

ление ЛЭН не менее, чем на семь порядков превыша-

ет внутреннее сопротивление канала ЛЭИ (на уровне

5кОм и более). Однако, через внутреннее сопротив-

ление каналов заряжается и разряжается входная ем-

кость ЛЭН (5... 15пф).

Длительность фронта и среза импульса на входе

традиционных КМОП ЛЭН серий К176 и К561 нахо-

дятся на уровне 50... 150 нс. Быстродействие логиче-

ских устройств не превышает поэтому 3 МГц при

внешних нагрузках.

Быстродействие новых серий 54НС, 74НС, FAST,

К1564 увеличено в 5... 10 раз. Толщина слоя подзат-

ворного окисла, а также площадь транзисторов суще-

ственно уменьшены. Как результат, импульсное бы-

стродействие сопоставимо с микросхемами ТТЛ

Шоттки.

Инвертор КМОП (если Rh очень велико) в статиче-

ских состояниях ток пнтання не потребляет, посколь-

ку разомкнут либо транзистор УТ/, либо УТ2, поэто-

му сквозного тока нет. В этом—замечательное

свойство микросхем КМОП: они не потребляют ток

питания, если входные сигналы не изменяются. Чем

больше частота сигнала, тем больше ток, потребляе-

мый инвертором КМОП. Динамический импульс то-

ка потребления складывается нз двух частей: во-пер-

вых, сквозной ток через VT1 и VT2, когда одни нз них

«полузакрыт», а другой—«полуоткрыт»; во-вторых,

ток заряда паразитных емкостей. Сравнив осцилло-

граммы входного' напряжения Г7ВХ и импульсов по-

требляемого тока 1лот.дин., обнаруживаем, что ЛЭ

КМОП потребляет ток только во время фронта и среза

t/вх. Для инвертора К176ЛП1 амплитуда тока ока-

жется 1... 1,3 мА. Максимальный ток потребления /пог

” /пот.дин. будет наблюдаться на такой частоте, когда

импульсы тока как бы «слипнутся» (1...3МГц; им-

пульсы тока следуют в два раза чаще). Зависимость

/потСЯ линейная, поэтому на таком принципе можно

сделать даже простейший частотомер. На предельной

частоте энергия, потребляемая на 1 бит, у КМОП

инверторов хуже, чем у ТТЛ Шоттки.

10

Помехоустойчивость ЛЭ КМОП определяется раз-

бросом их передаточных характеристик (кривые для

инвертора 1 и 2). На кривой 1 отмечен наименьший

потенциал входного нуля (т.е. на входе еще сохраня-

ется напряжение «единицы»), на кривой 2 зафикси-

рован наибольший потенциал, дающий на входе ин-

вертора «нуль». Здесь отмечена помехоустойчивость

от «нуля» и от «единицы».

Можно отметить аналогичные потенциалы и для не-

ннвертнрующего ЛЭ. В общем, помехоустойчивость

от «земли» не хуже 0.3Г/и.п., а от шины питания {/и.п.-

0,7ии.п.

Прибыльно

(В)

Ошибка

(Hl

Для переключения синхронных микросхем КМОП

совершенно необходимо, чтобы фронт н срез тактово-

го импульса были бы достаточно крутыми (быстрее

5... 15 мкс). Пологий фронт импульса долго держит

инвертор в линейном режиме, поэтому течет чрез-

мерный ток потребления. Кроме того, при медленно

нарастающем тактовом перепаде С полученный от

предыдущего триггера DDJ низкий уровень Q/ на

входе триггера DD2 не зафиксируется и будет сбро-

шен. Вывод: тактовые последовательности с медлен-

но нарастающими фронтами следует формировать с

помощью триггера Шмитта.

Необходимо принимать особые меры защиты эле-

ментов КМОП. Во-первых, все входные сигналы не

должны выходить за пределы напряжения питания

1/и.п. Если проектируются мультивибраторы (автоге-

нераторы и ждущие), в них следует ограничить токи

перезарядки конденсаторов микроампернымн уров-

нями, включив последовательные резисторы. Во-вто-

рых, входы КМОП не должны оставаться неприсоедн-

ненными. Реально опасны случаи разъединения

печатных плат, находящихся под питанием, когда

через разъем сигналы от одной платы поступают на

другую. Здесь следует предусматривать шунтирую-

щие резисторы: к проводам Un.n. или нулевому. В-

третьнх, многие микросхемы КМОП могут работать

от сигналов ТТЛ. Здесь следует подключать резисто-

ры утечки от входа КМОП на питание ТТЛ 5 В.

Следует принимать меры защиты выходов микро-

схемы КМОП. Надо избегать случайных замыканий

выходов буферных элементов с повышенным выход-

ным током на провод питания. Нельзя соединять вы-

ходы обычных элементов непосредственно, посколь-

ку произойдет замыкание одного из каналов на

источник питания.

Если требуется параллельное соедииенне входов и

выходов элементов, они должны быть из одного кор-

пуса микросхемы. Нельзя применять емкости нагруз-

ки Сн>5000 пФ для буферных и высоковольтных око-

нечных элементов, поскольку такой незаряженный

конденсатор равноценен перемычке короткого замы-

кания.

Первые микросхемы КМОП были низковольтными.

Это отечественная серия К176 и аналогичная зару-

бежная CD4000A. Напряжение питания для микро-

схем этих серий было равно 9 В. Оно лимитировалось

напряжением пробоя и-кармана. Схемотехника этих

серий была оригинальной.

Последующая эволюция технологии позволила по-

высить предел напряжения питания Яи.п. до 15 В.

Вместе с тем нижний предел Яи.п. составляет 3 В.

Быстродействие микросхем КМОП растет пропорци-

онально увеличению напряжения питания. Поэтому

для усовершенствованных серий К561 (аналог—се-

рия CD4000B) при Г/и.п.в15 В типовое значение вре-

мени (зд,р,ср"50 нс на логический элемент, при стати-

ческой рассеиваемой мощности—0.4 мкВт на эле-

мент.

Перспективная, так называемая HCMOS-логика

(здесь Я—начальное сокращение перевода слова high

— высококачественная) выполняется с помощью

процессов ионной имплантации и с заменой металли-

ческих пленок областей затворов на поликремние-

вые. Микросхемы такого исполнения конкурируют

по быстродействию (10... 15 нс) с микросхемами на

структурах с барьером Шоттки, конкретно с ТТЛ се-

рией 74LS (К555).

В последние годы оригинальная номенклатура се-

рин CZM000 практически не расширяется, поскольку

гораздо удобнее оказалось изготавливать по техноло-

гии КМОП все большее число аналогов микросхем

ТТЛ с сохранением их структуры, цоколевки и циф-

ровой маркировки. Наиболее известна 74ЯС (более

ранний вариант —серия 74С). В плоском корпусе эти

кристаллы маркируются как серия 54 НС (отечест-

венный вариант—серия К1564). Микросхемы серии

74ЯС можно просто устанавливать на место анало-

гичной микросхемы серии 74, 74LS, 74ALS, К155,

К555, К1533. Напряжение питания для* микросхем,

аналогичных 74НС, находится в пределах 3...7 В.

2. Микросхемы И, И, ИЛИ, Z, «искл. ИЛИ»

В основе всех цифровых микросхем КМОП находят-

ся элементы И, И, ИЛИ и коммутативный ключ

(КК). С помощью КК реализуются выходы с третьим

состоянием очень большого выходного импеданса Z

(практически разомкнуто). Полевые транзисторы

можно соединять последовательно «столбиком», поэ-

тому элементы И, ИЛИ строятся по разным схемам.

Для КМОП принято, чтобы 1 отображалась высоким

уровнем, а 0—низким.

Один двухвходовой канал И нз микросхемы

К561ЛА7 содержит четыре разноканальных ПТ: VTJ

и VT2 — a VT3, VT4 — ^-канальные. На эквива-

лентной ключевой схеме выходы АиВ получают че-

тыре возможных логических сигнала от переключа-

телей S1 н S2.

Если последовательно перебрать все комбинации

напряжений высоких и низких уровней, поступаю-

щих на входы АнБот57н52,н рассмотреть уровни

на выходе Q, получим таблицу состояний инвертора

И. Когда от S1 и S2 на входы А и Б поданы напряжения

высокого уровня Б, п-каналы транзисторов VT1 и VT2

будут замкнуты, а каналы VT3 и VT4 разомкнуты. На

выходе Q окажется напряжение низкого уровня Я.

Если на вход А илн В поступает хотя бы один низкий

уровень, один нз каналов VT3 или VT4 оказывается

замкнутым и на выходе Q появляется напряжение

высокого уровня. В результате вертикальная колонка

данных на выходе соответствует функции И.

Если на входы А н В подать два положительных

импульса, сигнал на выходе Q будет соответствовать

площади нх совпадения (но с инверсией!). •

12

Добавив к элементу И инвертор, реализуем логику

И (см. четырехканальную микросхему КР1561ЛИ2,

зарубежный эквивалент СР4О81Б). Не имеют анало-

гов микросхемы ЛИ1, ЛИЗ и К176ЛШ2. К564ЛА10

снабжена оконечными n-канальными МОП-транзи-

сторамн с открытыми стоками; ее аналог СР40107Б

изготавливается в 8-контактном корпусе. Микросхе-

мы ЛА серии 1564 имеют плоский корпус, серин

К561—пластмассовый, с выводами в две линии.

С0^01078

156 МА1

КР1561ЛИ2

М76ЛП12

13

Микросхема К561ТЛ1 — четверка двухвходовых

элементов И с передаточной характеристикой тригге-

ра Шмитта. Эта микросхема есть в вариантах

К1561ТЛ1 и 564ТЛ1, зарубежный аналог—CD4093B.

Передаточная характеристика каждого ЛЭ имеет два

порога: срабатывания и отпускания. Разность (£7срб-

^0ТП)_есть напряжение гистерезиса Ur, которое для

данной микросхемы пропорционально напряжению

питания. При ^/и.п"'5В гистерезис £7г-О.6В, если

17и.п“10В( [/г"2В. Передаточная характеристика это-

го элемента иаыхШвх) имеет вид петли, ширина ко-

торой Ui—есть запас помехоустойчивости ЛЭ. Триг-

геры Шмитта совершенно необходимы для

формирования тактовых последовательностей, пере-

ключающих состояния триггеров, счетчиков, регист-

ров.

Если фронт импульса медленнее, чем 15 мкс,

КМОП-схемы переключаются ненадежно. Фронт и

срез импульса на выходе триггера Шмнтта не зависят

от формы входного сигнала. Перепады получаются

калиброванными с длительностью около 100 нс при

t/и.п.-9В. Среднее время задержки распространения в

элементе И меиее 600 нс при ии.п -5 В и 300 нс при

ии.п.“Ю В

K56IM1

156Ш2

Для формирования импульсов, построения помехо-

устойчивых генераторов удобна микросхема

1564ТЛ2. Ее зарубежный аналог: 54ЯС14. Обе эти

микросхемы— «потомки»микросхем ТТЛ: 533ТЛ2,

К555ТЛ2,54Z-S14 и 74Z-S14. Все они взаимозаменяе-

мы непосредственно.

К561ЛЕ5

Устройство базового элемента ИЛИ (это один канал

микросхемы К561ЛЕ5), как бы обратное по сравне-

нию с элементом И: здесь параллельно соединены

п-канальные и последовательно р-канальные транзи-

сторы. На эквивалентной схеме транзисторы замене-

ны ключами. Только совпадение низких входных

уровней на входах Л и 5 даст высокий уровень на

выходе Q, так как в этот момент замыкаются оба

верхних р-канальных транзистора VTI и РТ2. При-

сутствие хотя бы одного высокого уровня В на входах

Л, В означает замыкание одного из параллельных

п-канальных транзисторов VT3, VT4.

14

1/WS6ME5

Состояние выхода Q в зависимости от уровней, по-

следовательно поступающих от переключателей SJ и

52, дают столбик данных, соответствующий функции

ИЛИ. Осциллограмма отклика на выходе ИЛИ пока-

зывает, что длительность действия инвертированного

сигнала на выходе Q соответствует времени действия

обоих входных сигналов.

К176/1ЯЬ

F Е D F+E+D £ S

К561/1Е10

К561ЛЕ5

15

Как в виде отдельных микросхем—цифровых муль-

типлексоров, так и в качестве частей схем регистров

и счетчиков применяется комбинированная структу-

ра И/ИЛИ. По четыре таких канала содержат одно-

типные микросхемы К564ЛС2 и 1564КП4. На выходы

D1...D4 можно с помощью входов разрешения Е1а и

Е/в пропускать либо слово AJ...A4, либо BL..B4 со-

гласно логическому уравнению

Dn=( АпЕ1а+ВпЕ/в).

Входы управления Е/а и Е1ц можно использовать

для реализации функции Л+Л. Микросхемы удобно

применять в регистрах со сдвигом вправо и влево, для

переключения прямого и комплементарного выход-

ных кодов, для переключения преобразований И,

ИЛИ, «искл. ИЛИ». Скорость переключения каналов

50..ЛОО нс.

15S4KM-

К5ВМС2

16

Микросхема CD4037 содержит три бифазных пары,

каждая из которых коммутирует входной сигнал С по

двум выходам D и Е. Три канала этой микросхемы,

содержащие структуры И/ИЛИ с выходными инвер-

торами, управляются общими сигналами Е1а и Е1в.

На выходах D и Е_можно получить прямые С или

инвертированные С выходные данные. Микросхема

имеет два вывода питания: коллекторного Г/и.п.к. и

стокового t/и.п.с. Это необходимо, если данные прихо-

дят от устройства, где £/и.п.с.шЗВ. Микросхема удобна

для кодирования и декодирования сигналов с расщеп-

ленной фазой в бифазных системах связи, цифровой

магнитной записи на ленту, диски, барабан, а также

в устройствах магнитной памяти иа сердечниках.

Время задержки распространения от входа С до выхо-

да D не превышает 250 нс.

Состояния бифазиой пары И/ИЛИ нз микросхемы CD4037A

Вход Выход

Кл кв D Е

0 0 1 1

1 0 £ С

0 1 С С

1 1 0 0

Чтобы построить ЛЭ с третьим Z-состояиием, после-

довательно с выходом инвертора надо добавить двух-

полярный полевой ключ коммутации КК. За инвер-

тором DDI следует пара разнополярных полевых

транзисторов VT1 и VT2. Показаны управляющие

затворами потенциалы с противоположными фазами

Ф! и Ф2 : p-канал VT2 замкнут при низком уровне

импульса Ф2, п-канал—при высоком уровне ФЕ За

период ti ключ КК разомкнут, поскольку на затворы

VTI и VT2 поданы закрывающие уровни. На время /2

КК замыкается, так как сразу оба транзистора VT1 и

V72 получают открывающие сигналы Ф1^В и Ф2=/Е

В дополнение к предыдущей схеме включаем инвер-

тор DDE формирующий две фазы сигнала управле-

ния Ф! и Ф2=Ф1. Канал данных разомкнется, когда

от переключателя SI подается напряжение низкого

уровня. Выходная часть схемы станет высокоомной, с

очень большим сопротивлением Z. Сигналы в выход-

ной провод пройти не могут. Много таких выходов

можно присоединить к одному проводу шины данных.

Если от переключателя S/ подается уровень Л, КК

замкнут и выход данным разрешен. Используя ин-

верторы с третьим состоянием Z, когда их выходы

требуется соединить, важно, как и для микросхем

ТТЛ, соблюдать правило: сигналы разрешения долж-

ны быть сформированы так, чтобы для соседних кана-

лов они не перекрывались (по-другому, должен быть

защитный интервал—пауза).

Ключ коммутации позволяет существенно упро-

стить схемы одно- и двухступенчатых триггеров.

3 Зак. 37300

Микросхемы К176ЛП2 и К561ЛП2 содержат по че-

тыре базовых элемента исключающее ИЛИ. В прин-

ципальной схеме одного канала кроме трех инверто-

ров применен ключ коммутации КК. Показано

расположение четырех элементов исключающее

ИЛИ в корпусе Л П2. Логическое состояние для одно-

го канала дайной микросхемы (сумматора по модулю

2) в столбике выходных состояний имеют два нуля:

один тривиальный 0 ф 0=0, второй—нуль в млад-

шем разряде суммы 1+1“10, или 1 ф 1 = 0. Микро-

схему «искл.ИЛИ» {exclusive OR — сокращенно ЕХ-

OR) из-за этого свойства разработчики используют в

импульсных и аналоговых схемах. Особенно известен

—фазовый компаратор. Выпускается также анало-

гичная по цоколевке микросхема КР1561ЛП14

(CZ74O7O), которая содержит четыре элемента «нскл.

Состояния исключающее ИЛИ К561ЛП2 и исключающее

ИЛИ КР1561ЛП14

Вход Выход

Л в Для ЛП2 Для ЛП14

0 0 0 1

1 0 1 0

0 1 1 0

1 1 0 1

КР!56МЛ!Ь

К561ЛЛ2

ИЛИ», инверсные выходные данные которых показа-

ны в последнем столбце таблицы.

Время 1зд,р,ср для элемента из ЛП2 составляет

40...150 нс при (7н.п.“10В, время фронта и среза вы-

ходного импульса 25... 150 нс. •<

3. Микросхемы с инверторами и преобразователями

уровня -;'-

Для полного использования свойств сложных мик-

росхем, а также для построения множества «нетипо-

вых» схемотехнических узлов, разработчики активно

используют микросхемы, в которых содержится не-

сколько инверторов, которые обычно имеют повы-

шенную нагрузочную способность.

Микросхема К561ЛН1 содержит шесть стробируе-

мых инверторов. Каждый инвертор (точнее, двухвхо-

довый элемент ИЛИ) имеет вход Dn и выход Q«. Кро-

ме того, на вторые входы всех шести инверторов от

общего вывода 12 (разрешение по входу ED подается

разрешающий сигнал с активным низким уровнем.

Если здесь входной уровень высокий, входы Dn запре-

щаются, а все выходы Qn имеют низкий выходной

сигнал.

Второй общий вход управления Е0-разрешение по

выходу при высоком входном уровне переводит все

выводы в состояние Z (т.е. разомкнуто; выходное со-

противление более 10 МОм). Третье состояние упро-

щает работу выходов инверторов на шину данных.

Нагрузочная способность каждого инвертора—два

ТТЛ-входа /°вых=3.2 мА. Данная микросхема пригод-

на для перехода к устройствам ТТЛ. Микросхема

К561ЛН1 работает как от напряжения стокового пи-

тания ии.п.с.=15В, так и от коллекторного С7и.п.к.“5 В.

При (/и.п.с.^15 В наибольшее время задержки рас-

пространения составляет 65 нс, время перехода от

18

Z — состояния к высокому выходному уровню 40 НС.

При С/и.п.с =5 В все переходные процессы затягивают-

ся в 3 раза.

Состояние входов и выходов инверторов в микросхеме

К561ЛН1 __________________________

Разрешение Вход Dn Выход Qn

по выходу Е0 по входу EI

И н И В

и н в н

и в X н

в X X Z

Микросхема К561ЛНЗ сходна с ЛН1 по логике рабо-

ты входов управленияEI (вывод!) иЕО (Z; вывод 15),

но имеет шесть каналов без инверсии.

Микросхема К561ЛН2 содержит шесть буферных

инверторов. Для микросхемы необходимо лишь одно

напряжение питания (на вывод 14), поэтому она

удобна как транслятор логических уровней. Если на

вывод 14 подано коллекторное напряжение 17и.п.“5В,

то можно передавать уровни от КМОП к ТТЛ, причем

нагрузочная способность инвертора— два ТТЛ входа

(т.е. 1вых 3.2 мА при выходном напряжении низко-

го уровня не менее 0.4В). Микросхема Л Н2 непосред-

ственно заменяет К176ПУ2 и К176ПУЗ. При

ии.п.=5В время задержки распространения— не бо-

лее 80нс, при (7и.п." 10В — не более 55 нс.

Микросхема CD4041A содержит четыре буферных

устройства. У каждого из них один вход и два выхода:

прямой и инверсный. Выходные инверторы спроекти- .

рованы с малым внутренним сопротивлением кана-

лов и имеют, поэтому, повышенную нагрузочную

способность по току: вытекающему и стекающему.

Микросхему используют как преобразователь уров-

ней КМОП-ТТЛ, а также как набор ключей для об-

служивания резистивных матриц в цифро-аналого-

вых преобразователях.

Микросхема К176ЛП1—многоцелевая. Она содер-

жит набор КМОП-транзисторов по три р- и л-каналь-

ных. С помощью нескольких корпусов К176ЛП1

можно реализовать как цифровые, так и аналоговые

узлы: формирователи-обосгрители, инверторы, по-

роговые детекторы, усилители. Время переключения

инвертора в К176ЛП1 не превышает 50 ис. Здесь по-

казано несколько применений этой микросхемы и

указано, какие выводы корпуса следует соединять

между собой.

з

Схема 1. Три инвертора. Соединить выводы: 14, 2 и

11; 8 и 13; 1 и 5; 7, 4 и 9.

Схема 6. Инвертор с большим током в обоих направ-

лениях. Соединить: 6, 3 и 10; 14, 12 и 11; 7, 4 и 9; 13,

8, 1,5 и 12.

выход /

Выход 2

(вход 21

Схема 2. Трехвходовая схема ИЛИ. Соединить: 13 и

2;1и11;12,5и8;7,4и9.

Схема 7. Пара двунаправленных ключей коммута-

ции. Соединить: 1,5 и 12; 2 и 9; 11 и 4; 8, 3 и 10; 6 и 3.

s

3

10

Схема 3. Трехвходовая схема И. Соединить: 1, 12 и

13; 2, 4 и 11; 4 и 8; 5 и 9.

J

Схема 4. Буферный инвертор с большим стекающим

током. Соединить: 6, 3 и 10; 8, 5 и 12; 11 и 14; 7, 4 и 9.

Существует несколько типов микросхем КМОП, со-

держащих от четырех до шести каналов (с инверсией

или без инверсии), предназначенных для согласова-

ния логических уровней КМОП (напряжение высо-

кого уровня 3...15 В, низкого — нуль) и ТТЛ (напря-

жение высокого уровня не менее 2,3 В, низкого — не

более 0,3 В). Заметим, что большинство этих схем

преобразует уровни от КМОП к ТТЛ. Как указыва-

лось, инверторы К561ЛН1 и К561ЛН2 так же можно

использовать для преобразования уровней КМОП—

ТТЛ.

Схема 5. Буферный инвертор с большим вытекаю-

щим током. Соединить: 6,3 и 10; 13, 1 и 12; 14, 2и 11;

7 и 9.

Преобразователь уровней от КМОП к ТТЛ

К176ПУ1 содержит пять инверторов. Для него требу-

ются два источника питания: 5 В (вывод 1) и 9 В

(вывод 14). Шесть преобразователей логических

уровней от КМОП к ТТЛ содержит микросхема

К176ПУ2. Эти инверторы можно использовать также

в тех устройствах логики КМОП, где требуются боль-

шие выходные токи 7'вых и 7°Вых /например, при

перезаряде нагрузочной емкости.

20

Шесть преобразователей без инверсии расположено

в корпусе К176ПУЗ. В качестве замены К176ПУ2

можно применить К561ЛН2, а вместо ПУЗ — преоб-

разователь К56ШУ4 во всех схемах. Нагрузочная

способность схем ПУ2 и ПУЗ — два ТТЛ-входа

(7°вых = 3,2 мА). Микросхемам К176ПУ1 — ПУЗ тре-

буется два напряжения питания. На вывод 1 подается

питание для ТТЛ-части Пи.п.к." 5 В,

на вывод 16 (или 14) — питание для КМОП-транзи-

сторов, т.е. ии.п.с • 9 В. Время переходного процесса

преобразования уровней от низкого к высокому не

превышает 50... 100 ис, от высокого к низкому —

16...40 нс. Каждый из четырех преобразователей

уровней от КМОП к ТТЛ, входящих в микросхему

К176ПУ5, отличается комплементарными выхода-

ми. Для ПУ5 требуется два источника питания.

М76ПУ5

К1761Ш

Микросхема К561ПУ4 содержит шесть преобразо-

вателей уровня — буферных усилителей. По пара-

метрам она сходна с К561ЛН2. Вывод 16 свободный.

Канал К561ПУ4 обеспечивает импульсы тока для

двух ТТЛ-нагрузок.

Микросхема К564ПУ6 содержит четыре канала

сдвига логических уровней СУ от низкого напряже-

ния к высокому. Необходимы два напряжения пита-

ния: на вывод 1 коллекторное Г/И.п.к. “ 5 В, на вывод

16—стоковое 1/и.п.с.до 15В. В этом случае получается

преобразование логических уровней ТТЛ в уровни

КМОП. Входные данные ТТЛ подаются на входы

A...D, выходные КМОП выделяются на выходах

Qa...Qd. Каждый каскад СУ имеет также входы раз-

решения ЕЛ... ED.

1

2

К5Ш1У6

А

вл-

в±

1в -

в

н.п. с

-ED

“О

12

10 я

^ЕС

Преобразование ТТЛ—КМОП без инверсии данных

разрешается при высоких уровнях на входах EA...ED.

При низком уровне на входе резрешения соответст-

вующий выход данных переходит в разомкнутое со-

стояние. Разрешающие импульсы должны быть низ-

ковольтными. Выходной сигнал канала ПУ

переключается либо к высокому уровню (если на вхо-

де—высокий, сплошная линия), либо к низкому (ес-

ли на входе—низкий, штриховая линия). При этом

значения времени задержки распространения уров-

ней «разомкнуто Z» до высокого В или низкого Н

составят: /зд.р. - 375 нс, Л7‘3д.р=60 ис,

f,1зд.р.w 325 нс. Времена формирования сигнала при

этом г‘°зд.р.в 300 ис, и А зд.р.= 115 нс. Для 564ПУ6

нет ограничений последовательности включения пи-

Состояния преобразователя высокого логического уровня в

низкий (микросхема К564ПУ6)

Вход Выход QB, QC, QD)

А, В. С, D £А, ЕВ, ЕС, ED

Н В Н

В в В

X н Z

тающих напряжений t/и.п.к. и £/и.п.с. и подачи вход-

ных сигналов. Микросхему можно эксплуатировать

при условии t/и.п.к. > t/и.п.с., что соответствует преоб-

разованию от высокого уровня к низкому.

21

Преобразователи уровней ТТЛ—КМОП К564ПУ7с

инверсией и К564ПУ8 без инверсии располагаются в

плоских корпусах с шагом выводов 1.27 мм.

4. Коммутаторы цифровых и аналоговых сигналов

Поскольку канал полевого транзистора размыкает-

ся и замыкается при изменениях управляющего по-

тенциала и затвор тока управления не потребляет,

полевой ключ может разрывать последовательные

электрические цепи. Такой электронный контакт и

цепь его нагрузки с источником управляющего по-

тенциала гальванически не связаны. На этом основан

принцип как одиночного ключа коммутации, так и

многопозиционных полупроводниковых переключа-

телей, так называемых коммутаторов.

Коммутаторы могут иметь много входов и один вы-

ход, либо быть дифференциальными. Дифференци-

альный коммутатор посылает сигнал из выбранной

пары проводов в выходную двухпроводную линию.

Электронные контакты КМОП двунаправленные,

поэтому сигнал можно подать на выход коммутатора

(это теперь одиночный вход), и, выбрав адрес, напра-

вить ток на один из многих выходов (номинально—

входы) . Коммутаторы КМОП пропускают как анало-

говые, так и цифровые сигналы. В последнем

варианте одна и та же микросхема может работать

как цифровой мультиплексор и как демультиплек-

сор.

Микросхемы К176КТ1 и К561КТЗ—это четырехка-

нальные коммутаторы, которые имеют одинаковую

принципиальную схему и цоколевку. Эквивалентная

схема ключа—однополюсная, т.е. только на замыка-

ние электронного контакта. Управляющей кнопкой

служит вход EI, активный уровень замыкания сигна-

ла на котором высокий £7 = В.Для микросхем

К176КТ1 сопротивление канала примерно 500 Ом

при напряжении открывания на входе EI 9В. Неиден-.

тичность сопротивления каналов t 10 Ом. канал

пропустит цифровые уровни с амплитудой до £/ц.п.,

либо аналоговые с амплитудой от пика до пика до

if/n,n./2. При нагрузке 10 кОм на частоте 10 кГц

отношение сигналов на выходе канала в замкнутом и

разомкнутом состояниях не хуже 65 дБ. Степень изо-

ляции управляющей цепи от канала соответствует

сопротивлению 10 2 Ом. Прохождение сигнала с час-

тотой 900 кГц на нагрузку 1 кОм из канала в канал

оценивается на -50дБ. Время задержки распростране-

ния сигнала в канале 10...25 нс. Коммутаторы можно

применить в следующих аналоговых узлах: переклю-

чатели-мультиплексоры, ключи выборки сигнала,

прерыватели-модуляторы для операционных усили-

22

телей, коммутационные ключи, модуляторы-демо-

дуляторы. Можно делать коммутаторы для нестан-

дартных ЦАП и АЦП, а также схемы цифрового

управления частотой, фазой, коэффициентом усиле-

ния сигнала. Удобно делать «врезки» одних сигналов

в другие.

Коммутатор К651КТЗ имеет малое сопротивление

включенного канала 80 Ом, согласование каналов с

точностью -5 Ом.

К176КТ1

КВ61КГЗ

вход1—

2

Выход 1—

выход 2 —

4

Вход 2—

г

EI2--

EI3—

7

п

— Е11

&EI4

—Вход Ч

—Выход Ч

— выход 3

—Вход J

Микросхемы К562КП2 и К561КП1—демультиплек-

соры, содержащие восемь каналов коммутации циф-

ровых и аналоговых сигналов. Микросхема КП2 име-

ет восемь входов и один выход. В микросхеме КП1 те

же восемь каналов образуют четырехканальный диф-

ференциальный коммутатор. Положительное пита-

ние подается на вывод 16, а на вывод 7—отрицатель-

ное. Для восьмиканального варианта нужен

трехразрядный код управления (Л,В,С). Для четырех

каналов достаточно два разряда управления А и В.

Если иа входе разрешения EI уровень высокий, все

каналы разомкнуты.

Управление каналами в микросхемах КПЗ и КП1

Вход КП2 Включен канал КП2 Вход КП1 Выключен канал КП!

EI с в л Е! в А

Н н н . н 1 Н И н (1С, 1D)

н н н в 2 Н н в (2С, 2D)

н Н в н 3 н в н (ЗС, 3D)

н н в в 4 н в в (4С, 4D)

н в н н 5 в X X

н в н в 6

н в в н 7

н в в в 8

в X X X —

№

Вход 5 —

Вход 1 I-

Выход —

Вход 8 —

Входд —

EI £

--

-BxodJ

— Вход 2

— Bxodi

— Вход 4

—А

Входь)

S

Входы С

Входы В

Сопротивление включенного канала при t/и.п.с "5 В

составляет 0.5...2.5 кОм; при £/н.п.с-15 В оно умень-

шается до 0.13...0.28 кОм. Время задержки распрост-

ранения не превышает 30 нс.

КП1 и КП2 можно вклчючить с одним источником

питания 15 В. Если это напряжение поделить на два:

7.5 В+7.5 В « 15 В, то отрицательное напряжение -

7.5 В (вывод 7) позволит передавать двухполярное

аналоговое напряжение с амплитудой до ±7-5 В, т.е.

ОТ -t/и.п.э. ДО t/и.п с-

Двухпроводную линию связи с уплотнением кана-

лов можно построить на двух микросхемах КП1. От

четырех источников U1...U4, не имеющих общей точ-

ки, сигналы через коммутатор попадают на диффе-

ренциальный приемник-усилитель. После приемного

демультиплексора на четырех независимых выходах

получаем выборки сигналов U1...U4. Переключение

адресов А, В и команды £7 на приемной станции сле-

дует синхронизировать с передающей.

DD1 К5В1КП1

DD? К5Б1КШ

X В и

А В EI

23

микросхема КР1561 КПЗ—восьмиканальная, с де-

шифратором, вывода для отрицательного питания

нет. Четырехканальный мультиплексор КП4 рас-

смотрен ранее как элемент И/ИЛ И. Для него время

задержки включеиия/выключения менее 50 нс при

1/и.п“ЮВ и Сн"15 пФ.

КР1561Ш

5. Триггерные микросхемы КМОП

Среди микросхем КМОП присутствуют все типы

триггеров: RS, D и JK, Наиболее популярны D-триг-

геры, причем в микросхемах ТМ1 и ТМ2 их содер-

жится по два, а в ТМЗ—четыре. Микросхема ТВ1

содержит два универсальных УК-триггера.

Микросхема К561ТР2 содержит четыре /?5-тригге-

ра, что удобно для накапливания 4-разрядных двоич-

ных слов. Каждая защелка имеет третье выходное

Z-состояние. Выходы переходят в Z-состояние, если

на вход EI дается низкий уровень. Каждый триггер

состоит из Л5-защелки (два инвертора ИЛИ), инвер-

тора и ключа _ком мутации КК, который управляется

от шии £ и £, объединяющих все четыре канала.

Входов данных два: £ и 5. Низкие уровни на них

состояние выходов не меняют. Если /?“1 и S=»l, триг-

гер эту информацию не защелкивает, но на выходе Q

транслируется 5=1 (пока она присутствует).

Время задержки распространения сигнала для триг-

гера К561ТР1 не превышает 200 нс, время перехода к

состоянию Z не более 100 нс.

Состояния RS-защелки в микросхеме К561ТР2

Вход Выход Qn

EI Sn Rn

н X X Z

в В Н в

в Н В н

в В В в ♦

в Н Н Не меняется

Применив Я5-защелку, можем устранить генера-

цию ложных единиц, возникающих от дребезга пере-

ключаемого контакта 5/. На выходе DDI получим

единственный гарантированный импульс записи.

24

Устройство на /?5-триггерах позволяет последова-

тельно загружать данные от четырех шин данных

A...D в общую, выходную. Например, по команде За-

грузка В (активный уровень—низкий) данные от вы-

бранной шины В проходят через четыре усилителя

микросхемы DD2, фиксируются четырьмя триггера-

ми микросхемы DD6, если на входе разрешения этой

шины Е1В присутствует высокий уровень. На входах

разрешения EIA, EIC, E1Dдолжны быть низкие уров-

ни, размыкающие выходы (следовательно, сигналы

Загрузка В и Разрешение EIB должны быть инверс-

ными). Выходные сигналы передаются в четырехпро-

водную шину через инверторы, содержащиеся в мик-

росхеме DD9 К561ЛН2. Зафиксированные в DD6

данные можно на определенное время сохранить. Для

полного сброса даем на вход R высокий уровень.

Микросхемы К176ТМ1 и К561ТМ2 содержат по два

D-триггера, причем триггер в ТМ1 имеет только вход

сброса В, а в ТМ2 есть оба входа асинхронного управ-

ления 5 и R. Триггер переключается по положитель-

ному перепаду на тактовом входе С, при этом логиче-

ский уровень, присутствующий на входе D

передается на выход Q. Входы сброса R и установки 5

триггера независимы от тактового входа С и имеют

высокие активные уровни. Максимальная тактовая

частота до 5 МГц, но время фронта тактового сигнала

не должно превышать 5 мкс. С другой стороны, дли-

тельность тактового импульса не должна быть менее

100 нс. Время установления выходных данных—бо-

лее 25 нс.

Q2 02 02 R2 D2

М /3| /21 7/1 /р[ 31 Л

К176ТМ!

4 2| J| 4 5| *| 7[

QI Д7 Cl R1 D1 -*

02 $2 С2 R2 D2 S2

/4| 7j| 721 "1 Ml Л Л

KJ75TM2

d Я Я *1 *1 41

Q1 01 Cl R1 DI SI

25

Микросхема К561ТМЗ содержит четыре D-тригге-

ра, каждый из которых имеет индивидуальный вход

D и два выхода Q и Q. Тактовый вход С—общий, как

и вход переключения полярности Р. Если на входе Р

уровень низкий, информация от входа D появится на

выходе Q во время низкого уровня тактового импуль-

са С. Если на входе Р—высокий уровень, данные пе-

редаются при высоком уровне на входе С.

Если на вход С пришел перепад (положительный

при /М) и отрицательный при Р-1), информация,

присутствующая во время этого перепада на вход D,

задерживается до прихода тактового импульса проти-

воположной полярности. Длительность тактового

импульса должна превышать 120 нс, время хранения

состояния триггера также более 120 нс.

Управление триггером в микросхеме К561ТМЗ

Вход

С р

Я н

1 я

в в

1 в

Выход Q

Трансляция D

Фиксация 1)

Трансляция D

Фиксация D

Микросхема 1564ТМ5—это КМОП-эквивалент

микросхемы ТТЛ К555ТМ5. Содержит две пары D-

триггеров, составляющих две защелки по два бита.

Загрузка разрешается, если Е1=В, при этом текущий

сигнал на входе D (это 1 или 0) отображается на

выходе Q. Если на входе £7 состоялся перепад от В к

Я, то сигнал защелкивается; по входу D приема нет.

Состояния триггеров из микросхемы 1564ТМ5

Режим Вход Выход

EI D Q

Разрешен прием данных на входе В я Я

Данные защелкиваются в в в

я X Q

Микросхемы К561ТВ1 состоят из двух независимых

JX-триггеров. Каждый триггер имеет асинхронные

входы R и S, два выхода Q и Q. Данные можно подать

на синхронные входы J и К согласно первым четырем

строкам таблицы. Сигнал, поданный на вход J или К,

26

появится на выходах Q и Q после прихода на тактовый

вход С положительного перепада. Отрицательный

перепад на входе С на информацию в триггере не

влияет.

Cot лом нии триггера в микросхемах К176 и К561ТВ1

U,n Q2 02 С2 W K2J2 82

75| К) Ц| !2{ У1 Ю1 Я

К561Г81

Последние три строки таблицы отображают дейст-

вие асинхронных входов 5 и /?. Пока на этих входах

присутствует напряжение высокого уровня, на выхо-

дах Q и Q также будут напряжения высокого уровня.

Максимальная тактовая частота для триггера из

TBI составляет 3 МГц (для делителя частоты :2).

Длительность тактового импульса должно превы-

/[ 21 j| 41 5l fl 71 8

Of QI Cl R1 K1 JI SI

шать 170 нс; однако время фронта и среза не должно

быть короче 5 нс. Длительность импульсов 5 и /?—не

менее 120 нс.

6. Счетчики

Счетчики-делители составляют несколько групп:

И ЕЗ-И Е5, И Е12 и И Е13 предназначены для постро-

ения схем электронных секундомеров, часов, тайме-

ров; счетчики ИЕ8 и ИЕ9 имеют дешифрированные

выходы (10 и 8 коммутаторных выводов соответст-

венно); ИЕН и ИЕ14—однотипные, реверсивные.

Разные способы деления частот реализуются на счет-

чиках ИЕ2, ИЕ10, ИЕ16, ИЕ19.

Микросхема К176ИЕ1 — шести разрядный счетчик-

делитель, который удобно использовать совместно с

таймером. Каждый отсчет кода на выходах соответст-

вует отрицательному перепаду на тактовом входе С,

Сброс выходных данных в ноль—асинхронный, когда

на вход R придет высокий уровень.

Микросхема К176ИЕ2—счетчик, который может

работать как двоичный и как десятичный. Счетчик

имеет пять двоичных выходов (выводы 10...14) иодин

десятичный (15). По входам S1...S4 (выводы 4...7)

можно записать в счетчик предварительные данные.

По входу R счетчику дается асинхронный сброс. На

вывод 3 подается сигнал тактовой частоты/. По входу

2/10 переключается формат счета. Если на входе

2/10 уровень высокий, счетчик работает как двоич-

ный; при низком, нулевом потенциале—как десяти-

чный, и на выходе 15 появляются импульсы с часто-

той f/10.

Простейшее включение счетчика НЕ2: выводы 2 и

16 соединить, выводы 4,5,6,7 и 8—заземлить. На вы-

вод 3 подать частоту f. На выводах 14, 13, 12, И, 10

появятся частоты //2, //4, //8, //16, //32 соответст-

венно. Вывод ЕС (т.е. 2) служит для разрешения сче-

та.

—38

2П0

EC

C(f)~

Sl~

К176ИЕ2

— f(2)

— f/в

—f/16

Выходы

27

I

Микросхема К176ИЕЗ—счетчик, который снабжен

дешифратором для «зажигания» элементов семисег-

ментных индикаторов. Тактовая частота / подается

иа вывод 4. На выводах 2 и 3 получим частоты //2 и

//6. Выводы 8... 13 и 1 — это выходы для присоедине-

ния к каждому из семи сегментов цифрового индика-

тора HG1.

Если индикатор светодиодный, с общим катодом,

вывод 6 следует заземлить. Если индикатор с общим

анодом, на вывод 6 надо дать высокий потенциал. Для

жидкокристаллических индикаторов на этот вывод G

подается модулирующая частота 30...200 Гц. Сброс

показаний индикатора в нуль дается по входу R: на

вывод 5 подаем единицу.

Микросхема К176ИЕ4—десятичный вариант пред-

ыдущего счетчика ИЕЗ. Отличается тем, что на выво-

де 2 выделяется последовательность с частотой //10,

а на выводе 3 —//4.

Назначение счетчиков ИЕЗ и ИЕ4—обслуживание

семисегментного индикатора в электронных часах

или в цифровом измерительном приборе.

Микросхема К176ИЕ5—счетчик для генерации се-

кундных импульсов в электронных часах и других

программаторах и таймерах. К выводам 9 и 10 под-

ключается кварцевый резонатор, либо сюда подается

эталонная частота от постороннего генератора. Час-

тота кварцевого резонатора / может быть 16384 Гц

(т.е. 214 Гц), либо 32768 Гц, что соответствует 215 Гц.

На буферных выходах 11 и 12 присутствует сформи-

рованная последовательность единиц и нулей с час-

тотой /, На выводе 1 имеется частота //28. Вывод 4

дает частоту//214 а вывод 5—//215, Таким образом,

на выводе 4 будет последовательность секундных ин-

тервалов при входной частоте /=214, а на выводе 5

секундная последовательность появится при/=215Гц.

Чтобы счетчик давал секундную последовательность,

выводы 1 и 2 следует перемкнуть, поскольку вывод

2—это вход частоты //28.

/

2

3

1Гц (0.5 Гц)____5

6

7

2Гц(1Гц)_____4

Сброс

8 „ноль"

J~1— я

13

ю

3

S

--------им./1

—---- контроль

----Я122М

<0

RZ2M

СЗ

3...20

Ю1

Гк8*32768Гц

(1638<гГц)

£4

62

?точна ^грубо

Микросхемы 1564ИЕ6 и 1564ИЕ7—счетчики синх-

ронные, четырехразрядные, реверсивные. По цоко-

левке и применению взаимозаменяемые со счетчика-

ми 533ИЕ6, 533ИЕ7, К555ИЕ6 и К555ИЕ7. Счетчик

ИЕ7 двоичный, считает от 0 до 15 и до 0. Счетчик

ИЕ6—двоично-десятичный, пределы реверсивного

счета: 0...9...0. Положительный перепад на тактовом

входе увеличения Си (или уменьшения Ср) прибав-

ляет к содержимому (или вычитает из него) единицу.

Если R=PE-Wy можно асинхронно загрузить в счет-

чик байт D0...D3., который появится на выходах

Q0...Q3 с задержкой 40 нс. Соединив оба выхода окон-

чания счета ТС и и TCd непосредственно с Ср и Ср

следующей микросхемы, получим 8-разрядный счет-

чик, который не будет полностью синхронным. На-

28

правление счета следует менять во время плоской

вершины тактового импульса Ср (или Ср). При низ-

ких потенциалах Си-Сц=Н счетчики на переключа-

ются.

1564ИЕ7

I56CHE6

156ЫЕ6.ИЕ7

Режимы счетчиков 1564И Е6 и ИЕ7

- Входы Выходы

я РЁ CD DO D1 D2 D3 Qi Q2 Qi тсо TCD

Сброс В X X' Я X X X X я Я Я Я В я

В X X В X X X X я Я Я Я в в

н н X Я Я я и я я я Я я в я

ИЕ6 и н X в Я н я я я н Н я в в

Параллельная загрузка для н н я X в я я в я в

н н В X в я я в Qn в в

ИЕ7 и н Я X в в в в в в В в я в

н н В X в в в в в в В в в в

Счет н в 1 В X X X X На увеличение в в

н в в -I X X X X На уменьшение в в

Микросхемы К176ИЕ8 и К561ИЕ8—десятичные

счетчики-делители. Они имеют 10 дешифрирован-

ных выводов QO...Q9. Внутренняя схема содержит пя-

тикаскадный счетчик Джонсона и дешифратор, кото-

рый преобразует двоичный код в сигнал,

появляющийся последовательно на каждом выходе

счетчика. Если на входе разрешения счета ЕС при-

сутствует низкий уровень, счетчик выполняет свои

операции синхронно с положительным перепадом на

тактовом входе С. При высоком уровне на входе ЕС

Состояния счетчиков К176ИЕ8 и К561ИЕ8

Вход Режим

Л с ЕС

в X X <20- Свых-В, QI...Q9 -Н

и в I- Счетчик работает

я 1 я

я я X Код без изменений

я X в » *

я В J

я я » »

действие тактового входа запрещается и счет оста-

навливается (см. третью линию на диаграмме). При

высоком уровне на входе сброса R счетчик очищается

до нулевого отсчета.

/? С ЕС cfax М Z74 Q8

29

На каждом выходе дешифратора высокий уровень

появляется только на период тактового импульса с

соответствующим номером. Счетчик имеет выход пе-

реноса Свых* Положительный фронт выходного

сигнала переноса появляется через десять периодов

тактовой последовательности и используется поэто-

му как тактовый сигнал для счетчика следующей де-

кады. Максимальная тактовая частота — 2МГц. Дли-

тельность импульса запрета счета должна превышать

300 нс, длительность тактового импульса не должна

быть меньшей, чем 250 нс, а сброса—275 нс.

В схеме применения счетчика К561ИЕ8 с укорочен-

ным циклом от выхода N, где 2 </У < 9, импульс

подается на сброс 7?5-тригтера (используются ключи

DD2.3 и DD2.4 дополнительной микросхемы

К561ЛЕ5). Если N-6, то счетчик ИЕ8 будет работать

как делитель на 6, что необходимо для устройства

отсчета секунд и минут для часов. Выходной сигнал с

частотой /вых"/вх/ЛГ появляется на выходе переноса и

используется для запуска следующего каскада. До-

полнительный /?5-триггер запускается при совпаде-

нии тактового импульса /вх и импульса нулевого от-

счета от К561ИЕ8.

Если выбраноЛГ< 6, тона выходе переноса не сможет

выделиться положительный фронт (см. диаграмму).

В этом случае в качестве сигнала переноса (такт сле-

дующему счетчику) используйте импульс от выхода

Q0. Счетчик ИЕ8—одна из наиболее популярных

КМОП-микросхем.

Микросхема К561ИЕ9—счетчнк-делитель на 8. Од-

нотипный с предыдущим, ои имеет в основе четырех-

разрядный счетчик Джонсона. Особенность счетчика

Джонсона—в выходном сигнале отсутствуют «клы-

ки» помех. Выходных состояний у данного счетчи-

ка—восемь, соответствующих счету от 0 до 7. Диаг-

рамма выходных сигналов ИЕ9 совпадает с

диаграммой ИЕ8 в части действия импульсов: запрет

счета и сброса. При восьмом тактовом импульсе цикл

счета завершает сигнал выходного переноса Свых, по-

/? С ЕС СВых Qb Q7

/»| zj| ;/| /fl I al

K5S1HE9

'I q Ji *i si si 7i 'I

fl/ flfl fl2 flfl flfl flJ -L

30

Многокаскадная схема асинхронная, хотя каждый

из счетчиков ИЕ8 и ИЕ9—синхронные.

Длительность тактового импульса должна превы-

шать 250 нс, поэтому максимальная тактовая часто-

та—2МГц. При напряжении питания 15 В требуется

обеспечить длительность импульса сброса более 300

нс, время его последействия составляет 275 нс. При

напряжении питания 1/и.п.“5В оно окажется равным

1мкс. Схема симметричного деления интервалов на

число 2<У<8 строится аналогично схеме для ИЕ8.

Состояния счетчика К561ИЕ9

Вход Режим

R с ЕС

В X X СО “ Свых " В, Q1...Q7-H

Н L Счетчик работает

Н 1 н » »

н н X Код без изменений

н X В » »

н В » »

н L н » »

Запрет

такта

Сброс

Микросхема К561ИЕ10 содержит два синхронных

двоичных счетчика-делителя без дешифраторов.

Каждый счетчик основан на четырех D-триггерах.

Линии С и ЕС (тактовая и разрешения тактов) взаи-

мозаменяемые, но отличаются противоположными

активными уровнями, поэтому можно организовать

счет по каждому фронту такта: по положительному и

по отрицательному.

В обычном режиме на вход ЕС следует подать напря-

жение высокого уровня, поэтому ход счета окажется

синхронным с каждым положительным тактовым им-

пульсом. Счетчик работает при напряжении высоко-

го уровня на входе сброса R. Нулевые уровни на вы-

ходах Q получатся, если на входе асинхронного

сброса R будет присутствовать Напряжение низкого

Состояния счетчика К561ИЕ10

Вход

С ЕС л

1 В н

н н

] X н

X 1 н

_г н н

В н

X X в

Режим

Счетчик работает

» »

Код не меняется

* »

> »

* »

Асинхонный сброс

Я - J" Сброс

QJ--------------------------- 1 _ I_____________

(Двоичный счет)

м_____________________________Н И I_________________________________ ГЩ77

(Десятичный счет)

31

уровня. По второй строке таблицы видно, что напря-

жение низкого уровня на тактовом входе может быть

разрешающим, тогда тактовым станет вход ЕС. Счет-

ным перепадом станет отрицательный на входе ЕС.

Последовательное соединение синхронных счетчи-

ков будет асинхронным. Выход Q3 первого счетчика

надо соединить со входом ЕС последующего, подав на

его тактовый вход напряжение низкого уровня.

При напряжении питания [/и.п."15В максимальная

тактовая частота достигает 4МГц, минимальная дли-

тельность импульсов: сброса 80 нс, разрешения 140

нс. При питании 5В значения этих параметров в три

раза хуже: 1.5 МГц, 250 нс, 400 нс. Восьмая линия

диаграммы сигналов показывает выходной сигнал Q3

(дес) десятичного варианта да иного счетчика (микро-

схема CD4518B).

л -л ч я ч ч ч

Cl ECJ Q01 QH Q21 Q3I Я1

Микросхема К561ИЕ11—двоичный четырехраз-

рядный реверсивный счетчик. Его удобно применять

для подсчета приращения данных, причем несколько

корпусов ИЕ11 можно соединять в многокаскадные

четыре выхода Q0... Q3, входы предварительной запи-

си-установки S0...S3, а так же вход разрешения этой

операции ЛЕ. Вход и выход переноса Свх и Свых имеют

активные напряжения низкого уровня.

синхронные, либо асинхронные счетчики. У счетчика с Q2 S2 st Qi и/д я

g| /»| /J] п\ ;/| io\ it

32

Состояние счетчика К561ИЕ11

Активный тактовый перепад С—положительный;

сброс в ноль Л—асинхронный при высоком уровне на

входе Л. Счет на увеличиние и на уменьшение пере-

ключается по входу U/D (Больше/Меньше). Микро-

схема считает, если на вход переноса Свх» а также на

входе SE и Я даны низкие уровни. Если на входе U/D

высокий уровень, код на выходах будет увеличивать-

ся. Если £// D присоединен к низкому уровню, содер-

жимое счетчика будет уменьшаться на единицу при

каждом положительном скачке на входе С.

Для_асинхронного каскадирования следует соеди-

нить Свых с тактовым входом С последующей микро-

схемы. При синхронном каскадировании следует так-

товые входы соединить параллельно и дать сигнал

Вход Режим

С Свх U/D SE я

1 1 х х —।—[ X В н н X X X oq Й; X X Я Я я в X Й: й: й; Й: «1 Не считает Код меньше Код меньше Предварительная установка Сброс

переноса СВых на вход переноса Свх последующего,

более старшего счетчика.

Сигнал C//D можно менять без помех для счета при

высоком уровне на тактовом входе С.

Микросхема К176ИЕ12 содержит два двоичных

счетчнка-делнтеля и генераторную часть. Микросхе-

ма специализирована для работы в электронных ча-

сах с динамической индикацией. Генератор стабили-

зируется кварцевым резонатором 32768 Гц, который

вместе с сопутствующими деталями замыкает цепь

обратной связи внутреннего генератора (выводы А и

А,т.е. 12и 13). Для контроля работы генератора есть

вывод К (14). Секундные метки дает делитель на 216

на своем выходе S1 (вывод 4). На выходе S2 (вывод

6)—частота сигнала 2Гц. Делитель вырабатывает

сигнал Е==1О24Гц. Это звук для будильника (вывод

11). Навыходах TL..T4 следуют импульсы с частотой

К176ИЕ/2

ШбОГц)

128 Гц, взаимно сдвинутые, как показано на диаграм-

ме. Эти импульсы поочередно зажигают четыре ин-

дикатора минут и часов; скважность их свечения 1:4

позволяет экономить мощность потребления.

Второй делитель микросхемы дает минутные отсче-

ты, длительность которых 20 с. Он получает тактовую

частоту 57в1Гц и делит ее на 60. Сброс первому и

второму счетчикам можно дать положительным им-

пульсом по входам R1 (вывод 5) и R2 ((вывод 9).

Микросхема К176ИЕ13 работает в комплекте с

ИЕ12. Она содержит иа кристалле: счетчики минут и

часов, регистр памяти для будильника, цепи сравне-

ния текущего и записанного времени, формирователь

звукового сигнала. Приняв цифры в двоичном коде,

микросхема последовательно переводит их в семисег-

ментные, но с помощью дополнительных дешифрато-

ров К176ИД2 или ИДЗ.

5 Зак. 37300

33

Когда от ИЕ12 приходит единица по проводу Т1, на

выходах Q0...Q3 появляется двоичный код текущей

минуты, в момент Т2 транслируется цифра десятка

минут, ТЗ — единицы часов, Т4 — первый или второй

десяток часов. На эти же моменты подается импульс

питания на соответствующий индикатор. На выходе

С (вывод 12)—импульс мигающей секундной точки.

Сигнал от вывода К (6) используется для гашения

индикаторов через ИД2 или ИДЗ. От вывода 7 (HS)

звуковой сигнал через драйвер возбуждает «пьёзопи-

щалку».

Микросхема К561ИЕ14—четырехразрядный ревер-

сивный счетчик. Может работать как двоичный и как

десятичный. Для повышения быстродействия внут-

ренняя структура снабжена схемой ускоренного пе-

реноса. У счетчика четыре разрядных выхода Q0...Q3

и выход переноса Свых. Вход тактовых импульсов С

единый на увеличение и на уменьшение. Если на

дополнительной микросхеме К561ЛА7 собрать за-

щелку, получим раздельные тактовые входы на уве-

личение и на уменьшение: Си и Со. Если на вход

поступит высокий уродень, на вход переключения

направления счета С/D микросхемы ИЕ14 попадет

низкий уровень и счет будет уменьшаться. На другом

выходе С схемы формируется единая тактовая сетка,

которую следует подать на вывод 15 ИЕ14.

Запрещается счет, т.е. действие тактового импуль-

са, если на вход переноса дается высокий уровень

Свх=В. С помощью входа разрешения предваритель-

ной записи SE, когда на нем присутствует напряже-

ние высокого уровня, можно записать в счетчик на-

чальный код по входам SO...S3. Если на эти провода

поданы напряжения низкого уровня, то соответству-

ющие разряды получат нулевой отсчет. Чтобы счет-

чик давал приращение (или уменьшение) содержи-

мого иа единицу при каждом положительном

тактовом перепаде С, на входы Свх и SE надо дать

низкие уровни.

Нормальный уровень на выходе переноса Свых вы-

сокий. Он переходит к низкому, если в режиме

«Больше» счет стал максимальным (или минималь-

ным в режиме «Меньше»). В это время на входе СВх

сигнал разрешающий, т.е. напряжение низкого уров-

ня. Если вывод Свх не используется, его следует под-

ключить к нулю._Счет будет в двоичном формате,

если на входе В/D (Бинарный/Децимальный) при-

сутствует напряжение высокого уровня. Счет десяти-

чный получится, если на вход В/D дано напряжение

низкого уровня. Счетчик увеличивает содержимое,

если на вход С/D (Больше/Меньше) дан высокий

уровень. При напряжении низкого уровня на входе

С/D счет уменьшается.

Соединив параллельно тактовые входы нескольких

ИЕ14, получим быстрый синхронный счет. Макси-

мальная тактовая частота для счетчика. К561И Е14—

2МГц при Си.п.=ЮВ, время установления режимов

после их переключения—более 460 нс, длительность

времени импульса предварительной записи по вхо-

дам S0...S3 не менее 320 нс (660 нс при питании 3 В).

вви вви ж/

BBL?

BB:.^

t

, I j£ bbls nets

KSSIMEtS__________

BBL11

К BBL12

KB

Микросхема К561ИЕ16 содержит 14-разрядный

асинхронный счетчик пульсаций. Счетчик имеет ка-

скад, обостряющий тактовые импульсы. Входная

часть имеет формирователь и первый триггер «мас-

тер-помощник». Выходной провод Q0 получает сиг-

нал от буферного инвертора.

34

BBL5 BB1.B

ияя йЮ 09 07 08 В C 00

/5| /41 Ц| 12\ П\ ?0\

К56Ш16

Tc

---KK -

BDIJJ

Каскад /

KB

00

Ha каскад 2

Bo

Выход 00

DB1./5

ООШ

Сигналы управления счетчиком К561ИЕ16

Вход управления Сигнал Режим

Бинарный/Децимальный (В/Р) Больше/Меньше (U/D) Разрешение установки (SE) Вход переноса (запрет тактовых импульсов) 1 (В) 0 (В) 1 0 1 0 1 0 Двоичный счет Десятичный счет Счет на увеличение Счет на уменьшение Прием от параллельных входов Нет приема После тактового перепада не считает Считает

Счетчик сбрасывает выходные сигналы в нуль при

напряжении высокого уровня на входе сброса Л. Со-

держимое счетчика увеличивается как отклик на

каждый отрицательный перепад на тактовом входе.

Максимальная тактовая частота достигает 3 МГц,

длительность импульса сброса должна превышать

550 нс.

Микросхема CD4060—весьма популярный 14-раз-

рядный двоичный счетчик-делитель пульсаций. От-

личается от предыдущего выводами от входных ин-

верторов, чтобы можно было использовать их в схеме

as ai ав я с с

/4 tf| ц| «| ff| ю\ j|

CDW6G

'I 2| fl ‘I *1 *| 1 «I

an an ai3 as at Q6 аз

аз аь as ав 07 аз as а» ап шз

автогенератора, а так же измененным, поэтому ком-

плектом выходов разрядов. Между выводами 10 и 11

(С и С) можно включить пьезорезонатор или конден-

сатор. Максимальная частота генерации—4 МГц. От

вывода 9 можно взять сформированную последова-

тельность Свых. Общий сброс выходов в ноль получит- i-

ся, если на вход R дать высокий уровень.

Микросхема К561ИЕ19—пятиразрядный синхрон-

ный счетчик по схеме Джонсона. От каждого триггера

счетчика сделан инверсный выход QO...Q4 через бу-

ферные инверторы. Счетчик имеет пять входов пред-

варительной записи S0...34, тактовый вход С, вход

последовательных данных D, вход сброса R. Входами

S0...S4 можно пользоваться, если подать высокий

уровень разершения установки на вход ЗЕ.

5*

35

Показанная на диаграмме сигналов фазировка вы-

ходных импульсов Q0...Q4 позволяет строить на

ИЕ19 каскады деления частоты на число N, где 2 Для

деления на четное число N=2,4,6,8,10 добавочные

элементы ненужны. Требуется присоединитько вхо-

ду D выход Q4 при делении на 10, Q3 — на 8, Q2 — на

6, Q1 —на4иОО — на 2. При необходимости деления

на нечетное число ко входу надо присоединить через

двухвходовой элемент И два выходных сигнала, вы-

брав их согласно рисунку. Максимальная тактовая

частота для счетчика 2 МГц, максимальное время

установления выходных сигналов—300нс.

q 10 20

С ПП П П ППП ПП ППППП П ПППППППП.Л-

а I__________________________________________сброс

О Разрешение

...- установки

Микросхема КР1561ИЕ20 содержит 12-раз рядный

счетчик пульсаций с полным набором выходов Qn от

каждого разряда. Сброс в ноль асинхронный, если на

вход Я дан высокий уровень. Каждый шаг выходного

кода появляется синхронно с отрицательным перепа-

дом тактового импульса С, поскольку внутренние

триггеры двухступенчатые «мастер-помощник». При

напряжении питания 5В импульс С должен быть дли-

тельнее 400 нс (при 10 В — 120 нс), но время спада и

нарастания его не должны быть более 15 мкс. Дли-

тельность импульса Reset не менее 1.25 мкс и 0.6 мкс

соответственно

02 М 06 Q8 О',О Q12

и*.п ап ею Q8 аз я с ai

/5| м 131 /21 п! Я?|

КР158МЕ20

/| 7| II

ак as os ал аь аз ao -L

7. Регистры

Среди микросхем среднего уровня интеграции, вы-

полненных на логических элементах КМОП, важное

место занимают четырех-, восьми- и двенадцатнраз-

рядные регистры.

Микросхемы К561ИР2 содержат два независимых,

четырех раз рядных регистра сдвига. Все триггеры ре-

гистров двухступенчатые, D-типа. От каждого триг-

гера есть выход Q. Данные вводятся через последова-

36

Состояния регистра из микросхемы К561ИР2

Вход Выход

С D R Со Qn

_г н н И Qn /

1 в н В Qn!

-I X н Qi Без изменения Qn

X X в н _ fl

I

тельный вход D. Данные принимаются от этого входа

и сдвигаются поразрядно после каждого положитель-

ного перепада на входе С. Сброс в ноль выходных

данных Q происходит, когда на вход асинхронного

сброса R дано напряжение высокого уровня.

Четыре выхода каждого регистра позволяют преоб-

разовать последовательный код, принятый по входу

£>, в параллельный, отображаемый через четыре так-

та на выходах Q0...Q5. Из одного корпуса ИР2 можно

сделать восьмиразрядный регистр-преобразователь,

соединив последовательно оба регистра.

Тактовая частота регистра 2.5 МГц, но для устойчи-

вости переключения триггеров длительность такто-

вого перепада не должна превышать 15 мкс. В качест-

ве формирователя используйте триггер Шмитта ТЛ1

или ТЛ2.

Микросхема К176ИР4— 64-каскадный статический

регистр сдвига. Данные подаем на первый каскад,

(вход D, вывод 15). Они будут сдвигаться к выходам

Q и Q синхронно с положительным перепадом на вхо-

де С. Накопленное «длинное» слово надо хранить в

регистре при низком уровне на входе С. Имеется вход

режима М—mode control. Если Л/=0, регистр данные

принимает от входа D; прн Л/=1 включается режим

рециркуляции, здесь вход данных Rd, вывод 7.

Несколько корпусов ИР4 можно соединить последо-

вательно. Входы С либо просто соединяем вместе,

либо используем выход задержанной тактовой после-

довательности Cdl- В первом случае выше скорость

работы, но требуется мощный драйвер импульсов С;

во втором — упрощается схема формирования сигна-

лов С. выход Q — мощный, работает на ТТЛ-нагруз-

ку. Главное применение: последовательные регистры

для задержки потока данных.

D М CQL

/«I /j| n\ 7/1 7g|

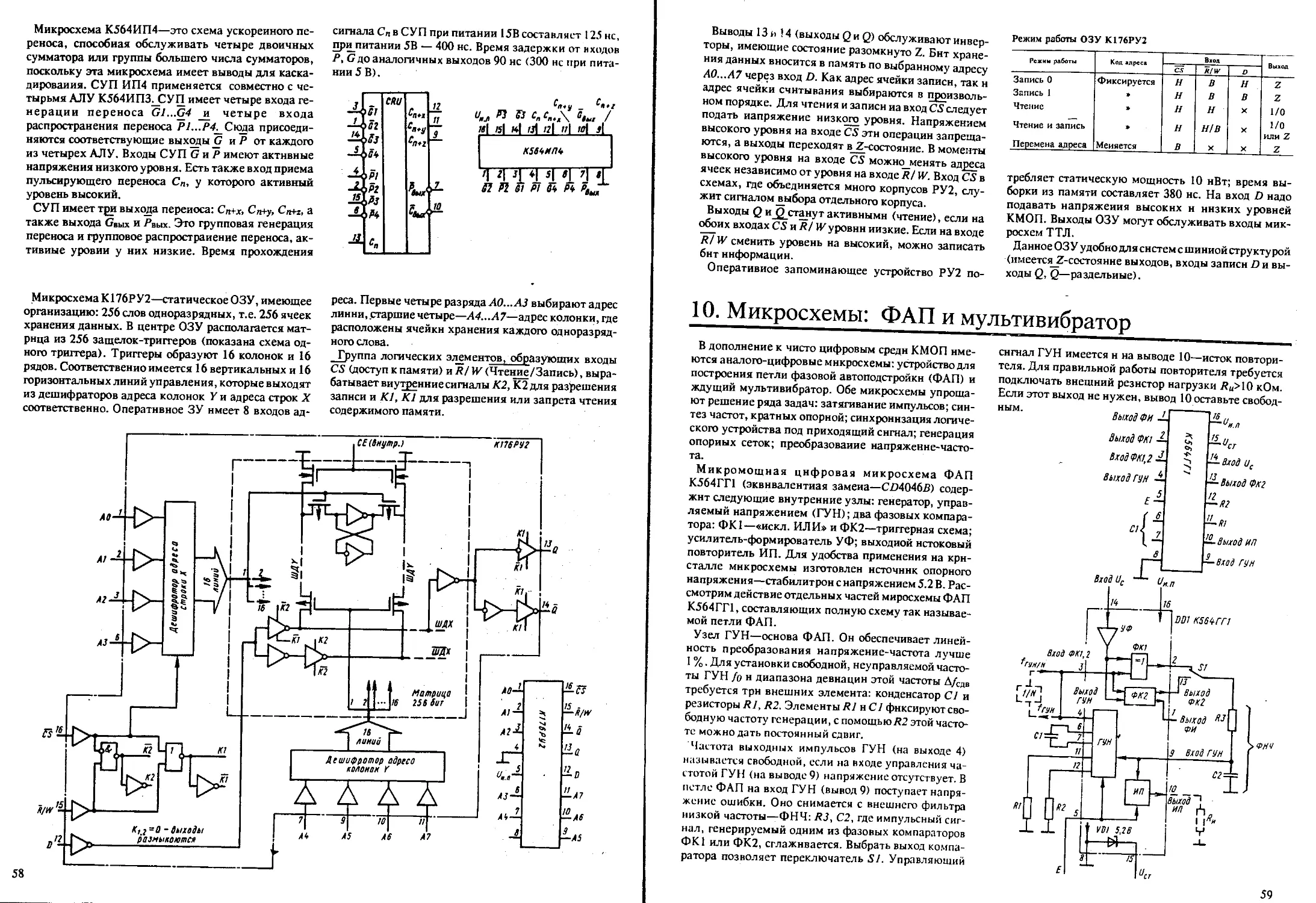

К176ИР4-