Автор: Бойко В.И.

Теги: компьютерные технологии программирование электроника электротехника

ISBN: 5-94157-466-5

Год: 2004

Текст

УДК 681.3(075.8)

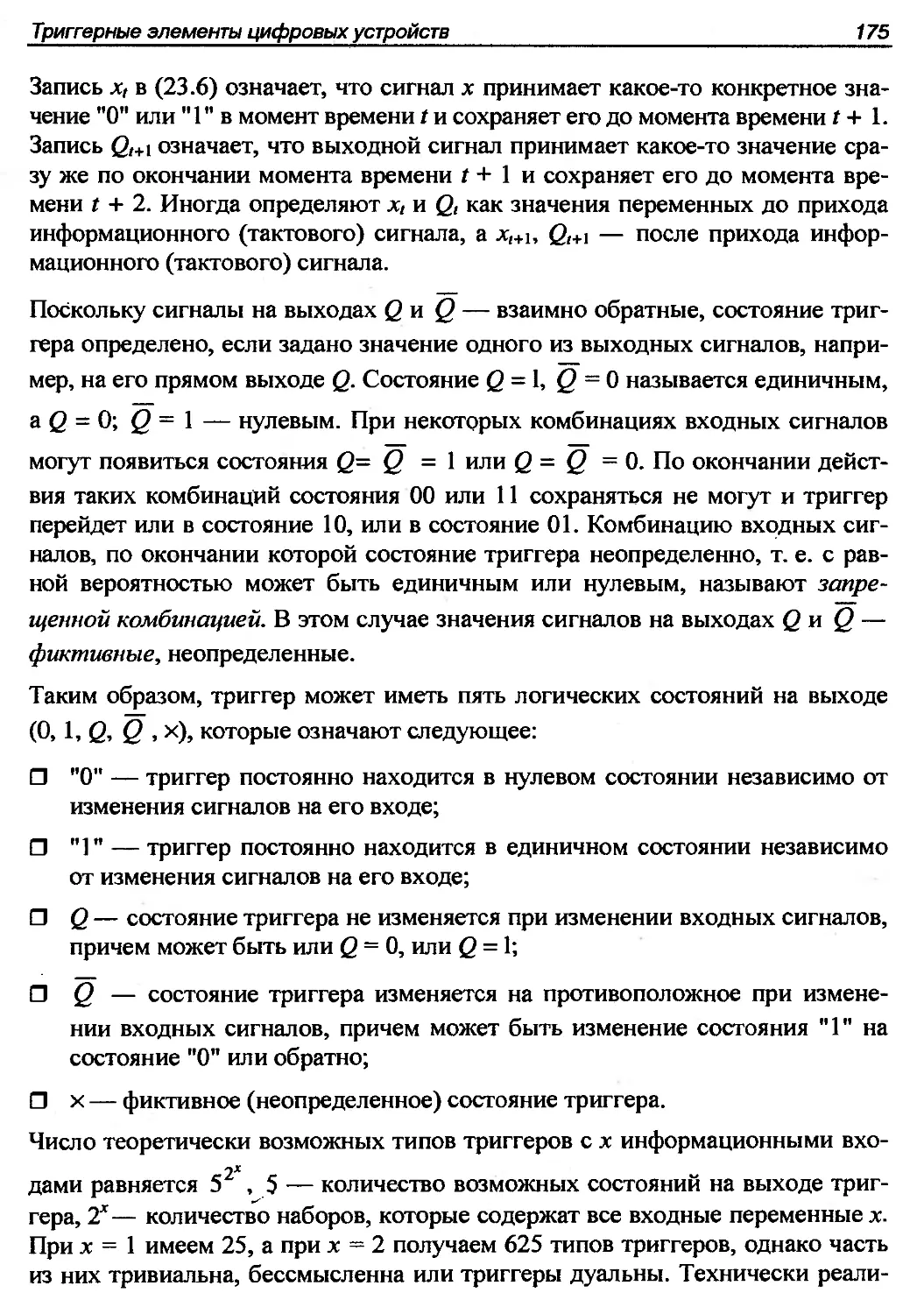

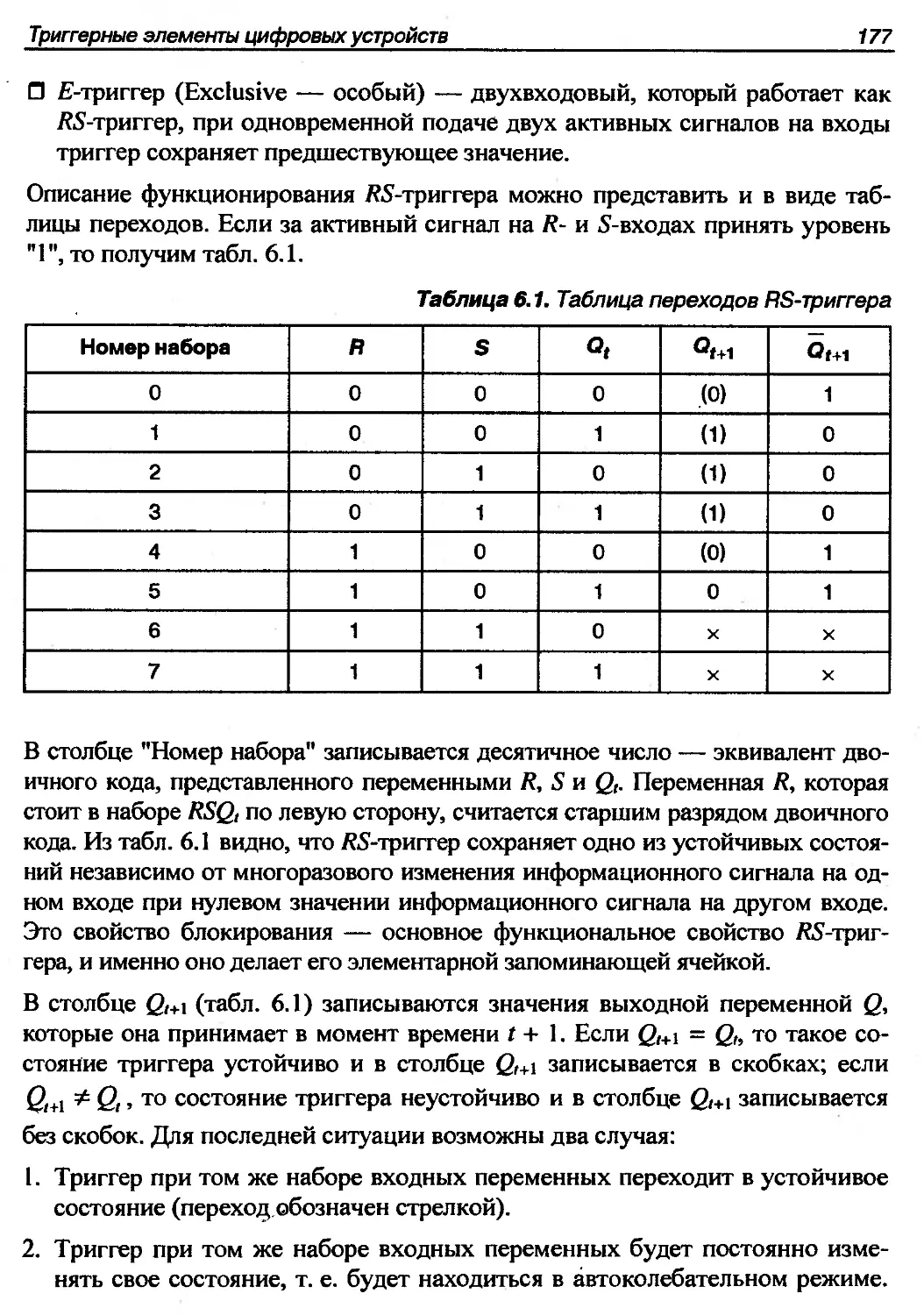

ББК 32.973-02я73

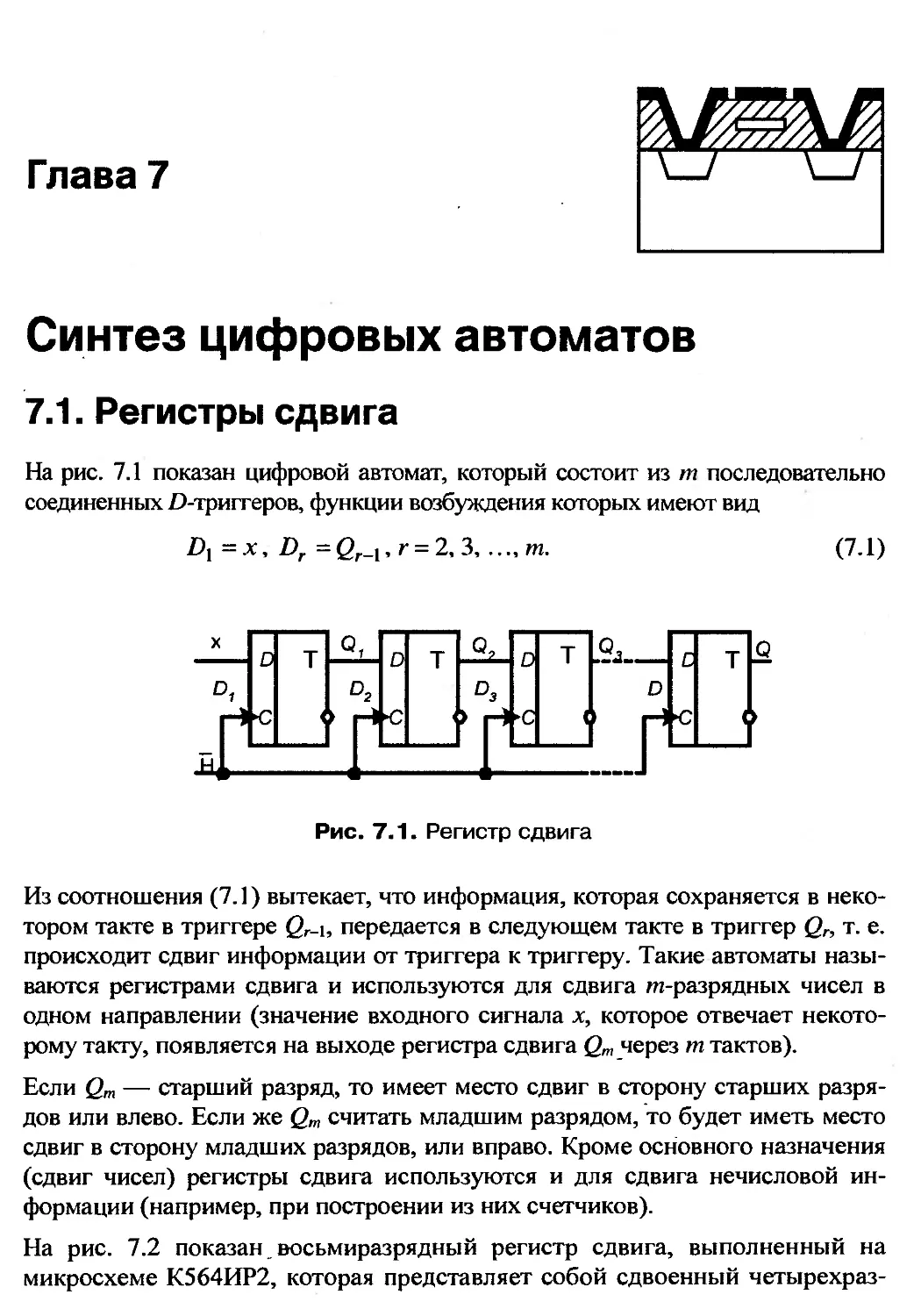

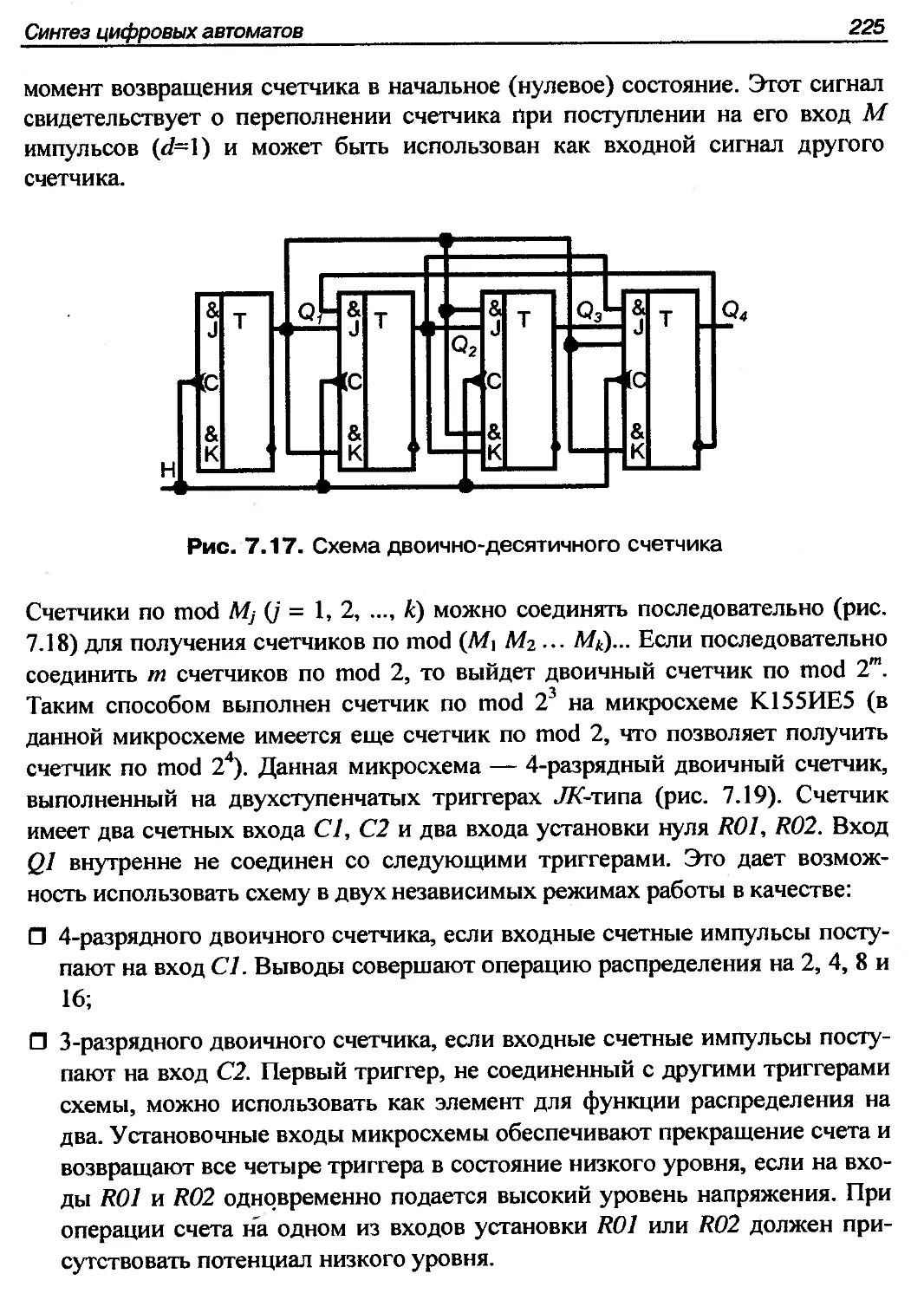

Б72

Бойко В. И. и др.

Б72 Схемотехника электронных систем. Цифровые устройства/

Авторы: В. И. Бойко, А. Н. Гуржий, В. Я. Жуйков, А. А. Зори,

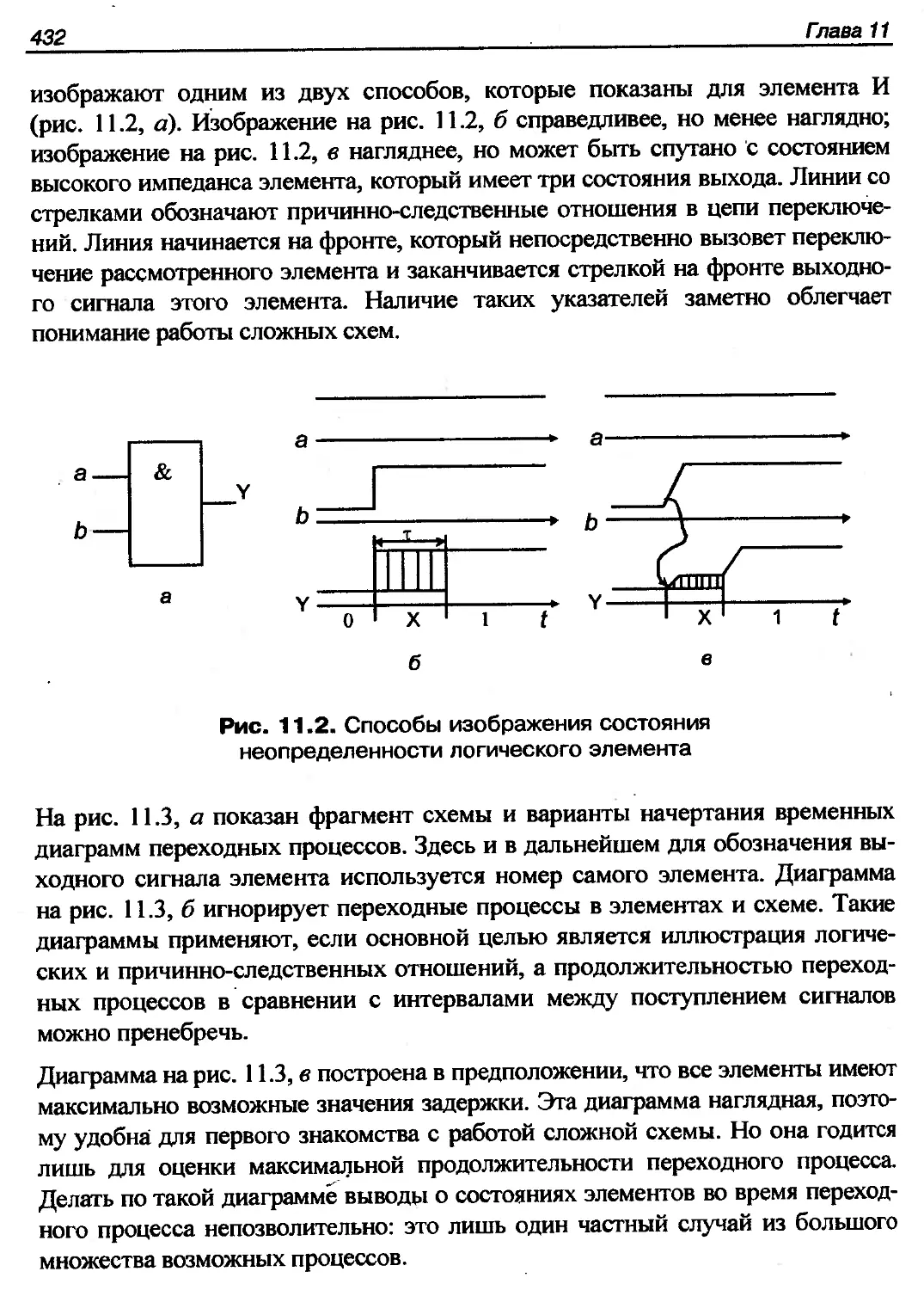

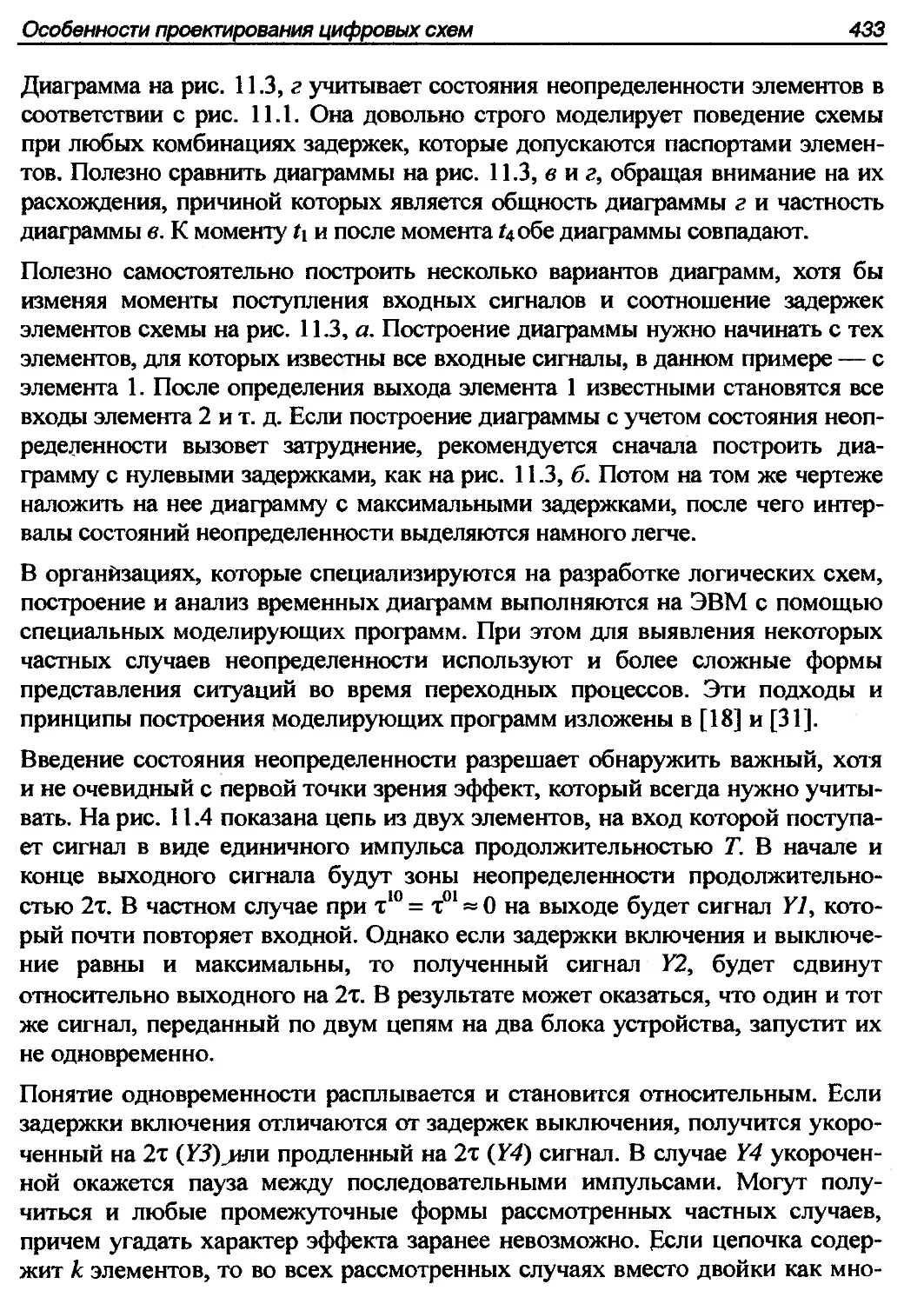

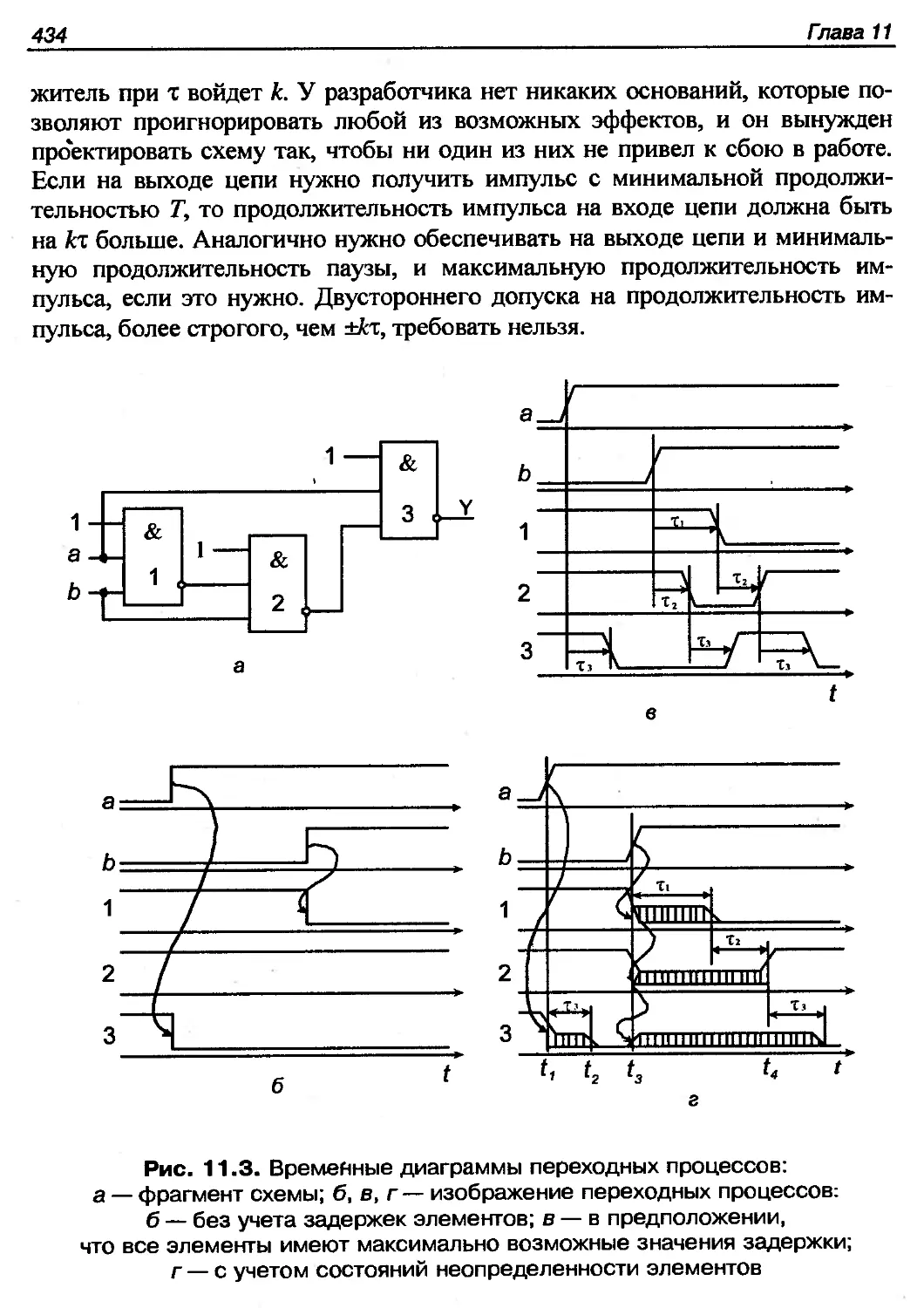

В. М. Спивак, В. В. Багрий. — СПб.: БХВ-Петербург, 2004. — 512 с.: ил.

ISBN 5-94157-466-5

В книге рассматриваются следующие темы: теоретические основы син-

теза цифровых устройств, классификация и характеристика логических

элементов, синтез комбинационных схем и цифровых автоматов. Содержа-

ние теоретического материала соответствует программам подготовки бака-

лавров, инженеров и магистров направления "Электроника” специальностей

"Электронные системы" и "Физическая и биомедицинская электроника"

согласно требованиям государственных стандартов Украины и России. От-

ражены схемотехнические особенности современных цифровых элементов,

описаны алгоритмы проектирования комплексных цифровых систем.

Для студентов, преподавателей и специалистов

в области электронной и микропроцессорной техники

УДК 681.3(075.8)

ББК 32.973-02я73

Группа подготовки издания:

Главный редактор

Зам. главного редактора

Зав. редакцией

Редактор

Компьютерная верстка

Корректор

Дизайн обложки

Зав. производством

Екатерина Дондукова

Игорь Шишигин

Григорий Добин

Анатолий Хрипов

Натальи Смирновой

Наталия Першакова

Игоря Цырульникова

Николай Тверских

Затверждено М(нютерством осени i науки УкраТни як пщручнйк

для студенпа вищих навчальних заклала

Лицензия ИД Ng 02429 от 24.07.00. Подписано в печать 02.07.04.

Формат 70х100’/1в. Печать офсетная Усл. печ. л. 41,28.

Тираж4000 экэ. Заказ Ng 3400.

"БХВ-Петербург", 190005, Санкт-Петербург, Измайловский пр., 29.

Гигиеническое заключение на продукцию, товар Ng 77.99.02.953.Д.001537.03.02

от 13.032002 г. выдано Департаментом ГСЭН Минздрава России.

Отпечатано с готовых диапозитивов

в ГУП “Типография "Наука"

199034, Санкт-Петербург, 9 линия, 12

ISBN 5-94157-466-5

С ОМД Групп, 2004

С Оформление, издательство "БХВ-ПетербурГ, 2004

Содержание

Вступление................................................................................................................... 1

Глава 1. Математические основы цифровой схемотехники •••••«•••••••••••••••••••в 3

1.1. Системы исчисления. Правила перевода из одной системы исчисления

в другую................................................................................3

1.2. Коды с выявлением ошибок..........................................................9

1.3. Коды с исправлением ошибок.......................................................11

1.4. Двоичная арифметика..............................................................15

1.5. Формы представления чисел........................................................16

Контрольные вопросы и задания..........................................................20

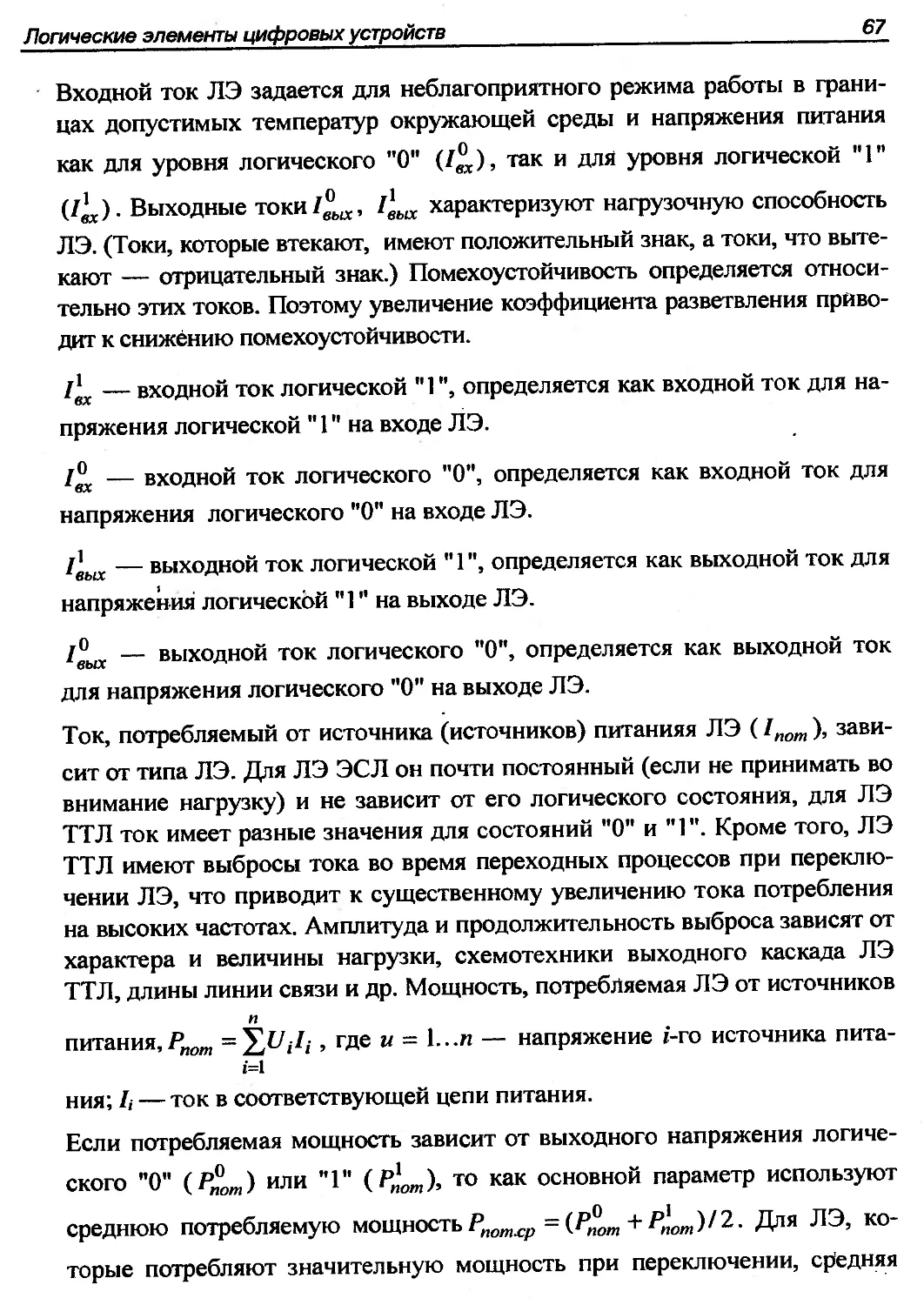

Глава 2. Алгебра логики и теоретические основы синтеза

цифровых устройств................................................................................................23

2.1. Элементы математической логики..................................................23

2.2. Основные законы алгебры логики..................................................24

2.3. Формы логических функций и их использование для синтеза

логических схем........................................................................28

2.4. Логические элементы и схемы. Принцип двойственности.............................36

2.5. Классификация логических устройств..............................................39

Контрольные вопросы и задания..........................................................42

Глава 3. Методы минимизации булевых функций............................................ 45

3.1. Целые минимизации логических устройств..........................................45

3.2. Метод непосредственных преобразований...........................................45

3.3. Метод Карно—Вейча...............................................................47

3.4. Минимизация методом Квайна и Мак-Класки.........................................52

Контрольные вопросы и задания..........................................................56

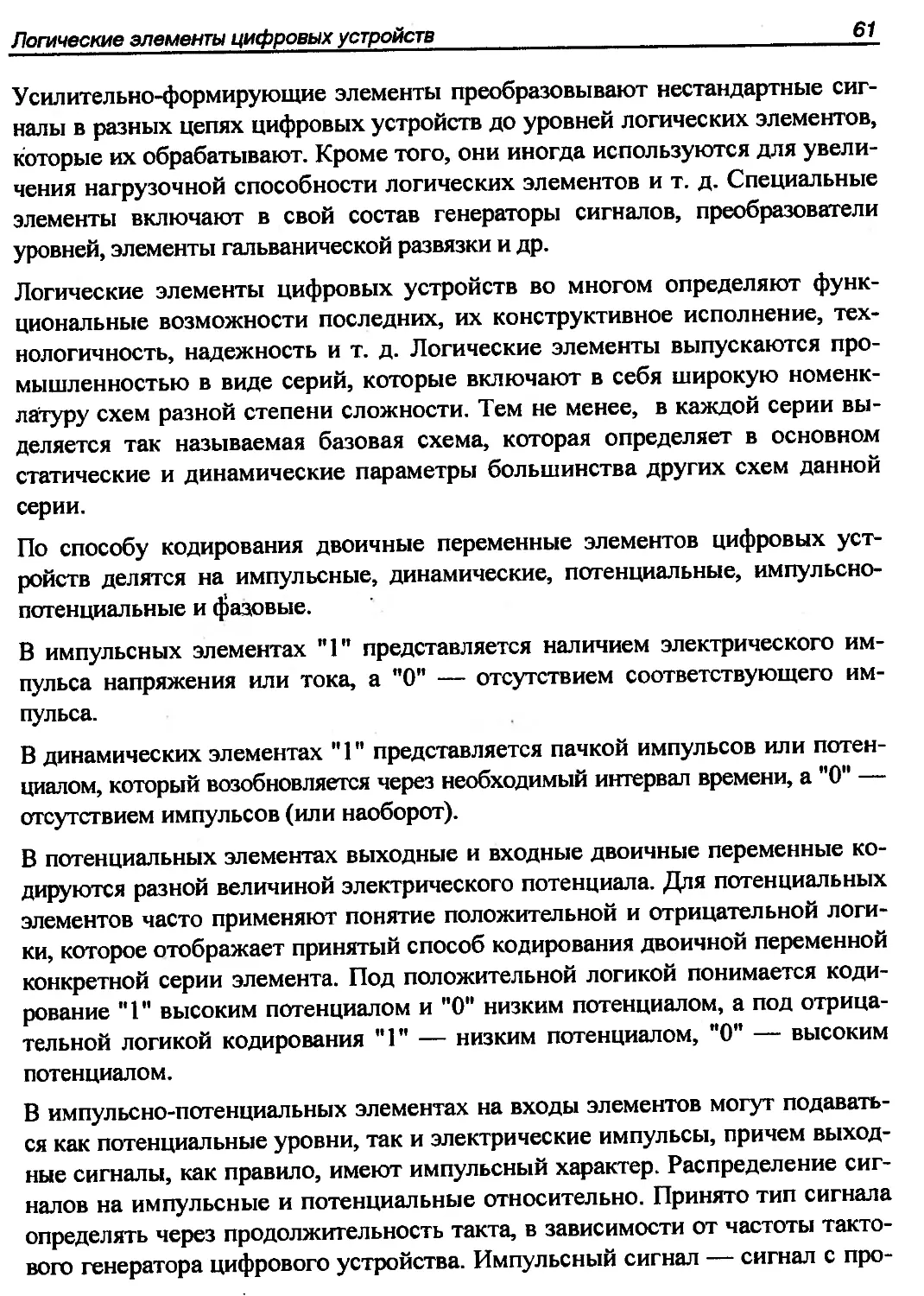

Глава 4. Логические элементы цифровых устройств .......................................59

4.1. Классификация элементов и их сравнительная характеристика.......................59

4.2. Общие характеристики элементов цифровых устройств...............................63

4.3. БЛЭ транзисторно-транзисторной логики...........................................72

4.3.1. Состав, схемотехника и принцип действия БЛЭ.................................72

4.3.2. Разновидности схемотехники элементов ТТЛ....................................77

4.3.3. Способы повышения быстродействия............................................80

IV

Содержание

4.4. БЛЭ эмиттерно-связанной логики (ЭСЛ).............................84

4.4.1. Особенности схемотехники.....................................84

4.4.2. Принцип действия и функциональные возможности БЛЭ ЭСЛ........86

4.4.3. Способы повышения быстродействия.........................89

4.5. БЛЭ на МДП-транзисторах......................................90

4.5.1. Особенности использования МДП-транзистора................90

4.5.2. Схемотехника БЛЭ КМОП-типа...............................92

4.6. БЛЭ интегрально-инжекционной логики..........................95

Контрольные вопросы и задания.....................................98

Глава 5. Синтез комбинационных схем-------......._........._......_.......101

5.1. Этапы построения логической схемы...........................101

5.2. Синтез логических устройств в заданном базисе ЛЭ............102

5.3. Особенности построения логических устройств

на реальной элементной базе......................................104

5.4. Логические элементы для реализации сложных функций..........108

5.5. Мультиплексоры и демультиплексоры............................ПО

5.6. Синтез комбинационных схем на мультиплексорах...............116

5.7. Дешифраторы, дешифраторы-демультиплексоры и шифраторы.......120

5.8. Сумматоры...................................................133

5.9. Десятичные сумматоры........................................138

5.10. Компараторы................................................142

5.11. Преобразователи двоично-десятичного кода в двоичный код.........150

5.12. Преобразователи двоичного кода в двоично-десятичный код....157

5.13. Взаимное преобразование двоичного кода и кода Грэя.........164

Контрольные вопросы и задания....................................166

Глава 6. Триггерные элементы цифровых устройств............________........169

6.1. Основные понятия. Классификация и их общие характеристики........169

6.2. Асинхронный RS-триггер и его разновидности..................176

6.3. Асинхронные триггеры с одним входом.........................186

6.4. Синхронные триггеры.........................................190

6.5. Синтез произвольных триггерных структур на универсальных

D- и УК-триггерах................................................197

6.6. Примеры использования триггеров.............................200

Контрольные вопросы и задания....................................209

Глава 7. Синтез цифровых автоматов----.......-----...............-.....-.211

7.1. Регистры сдвига............................................ 211

7.2. Счетчики по mod М...........................................216

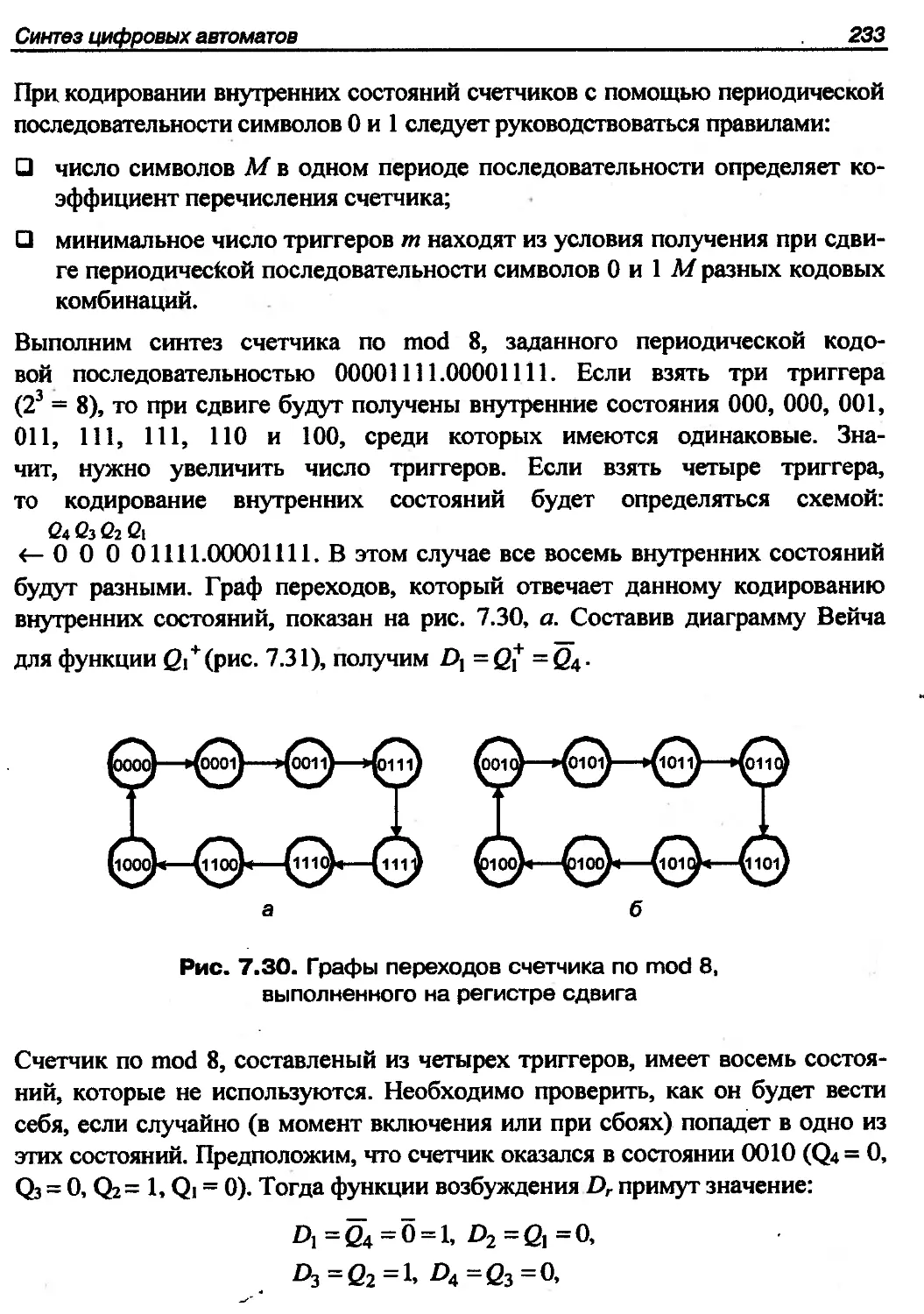

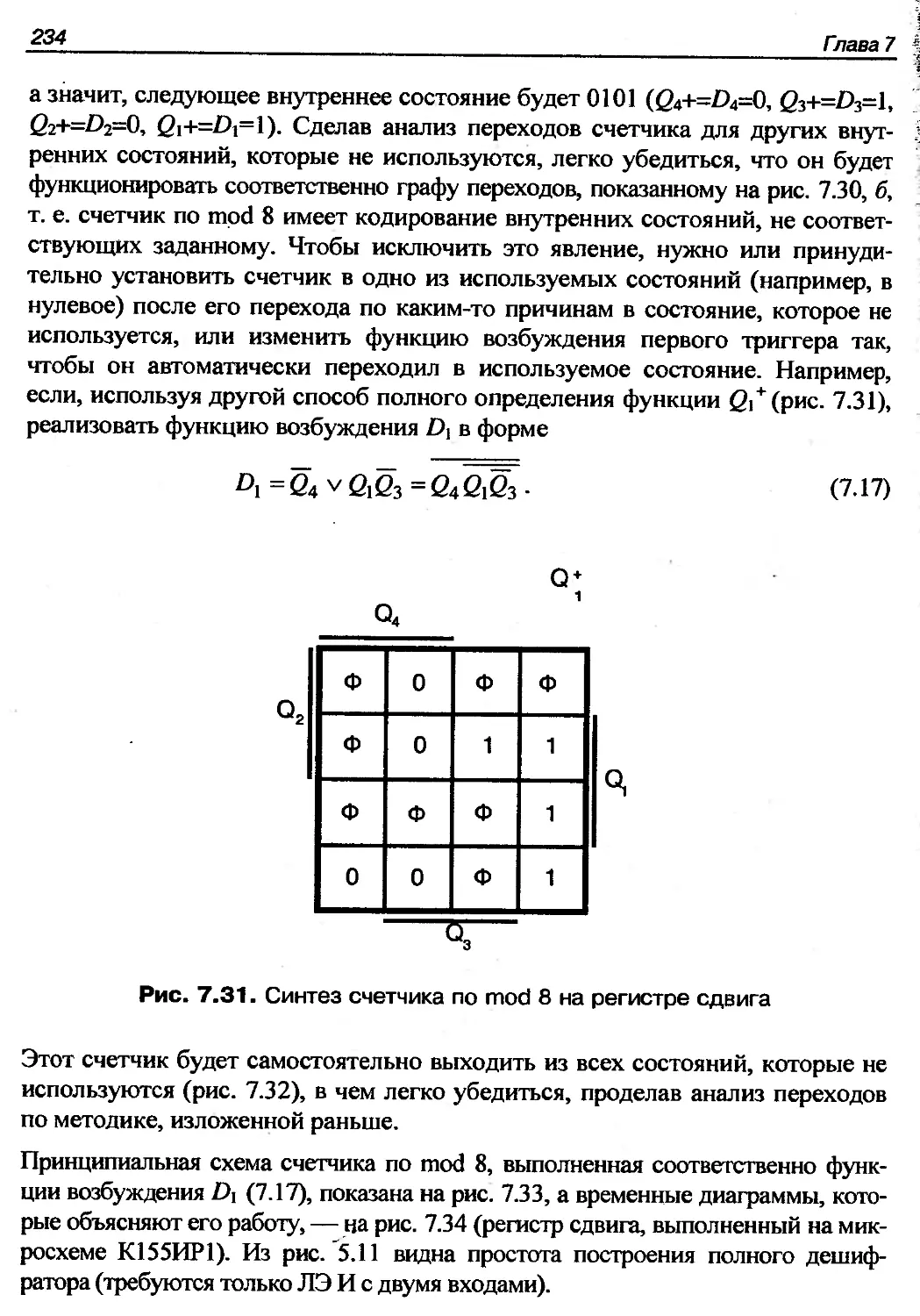

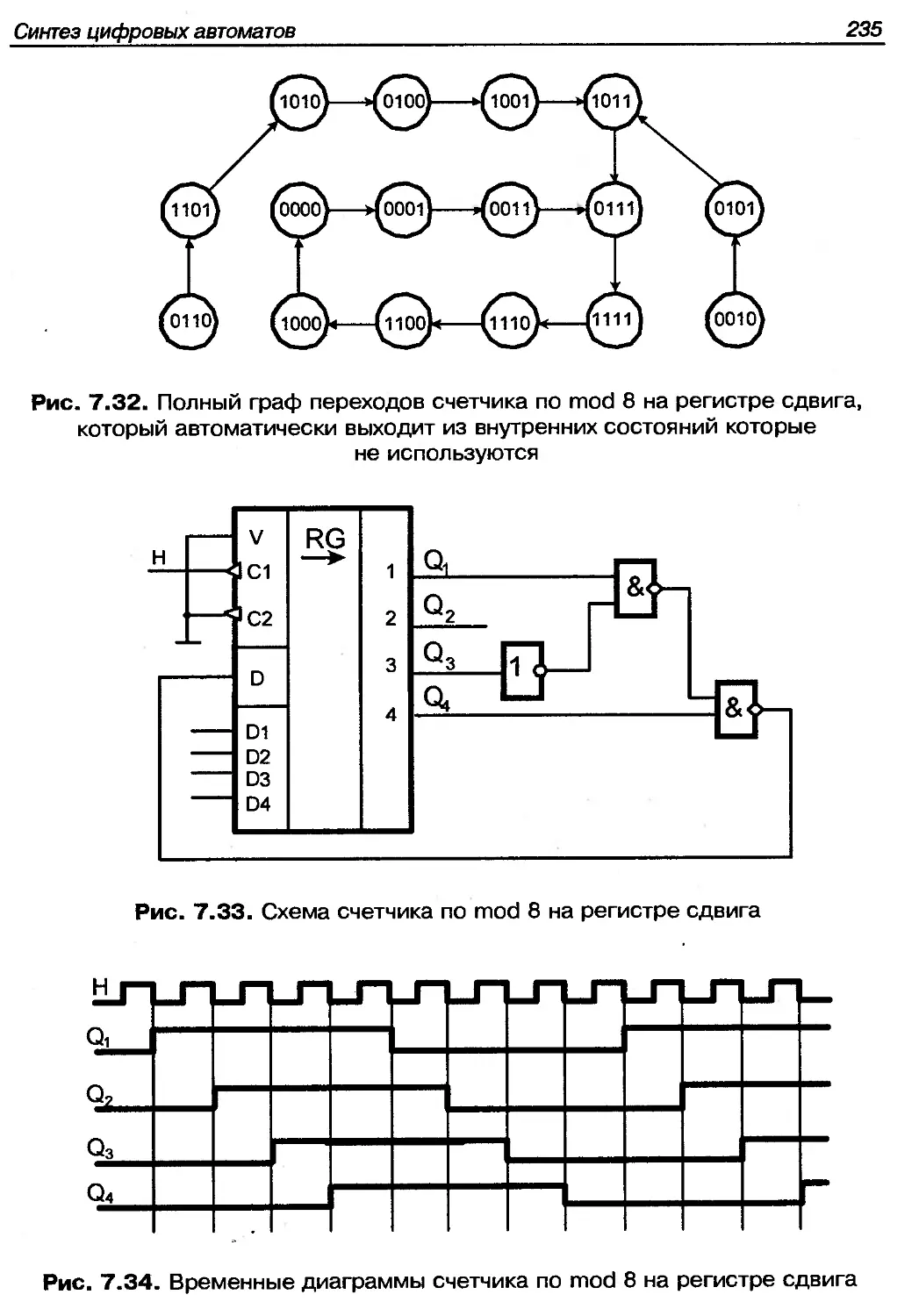

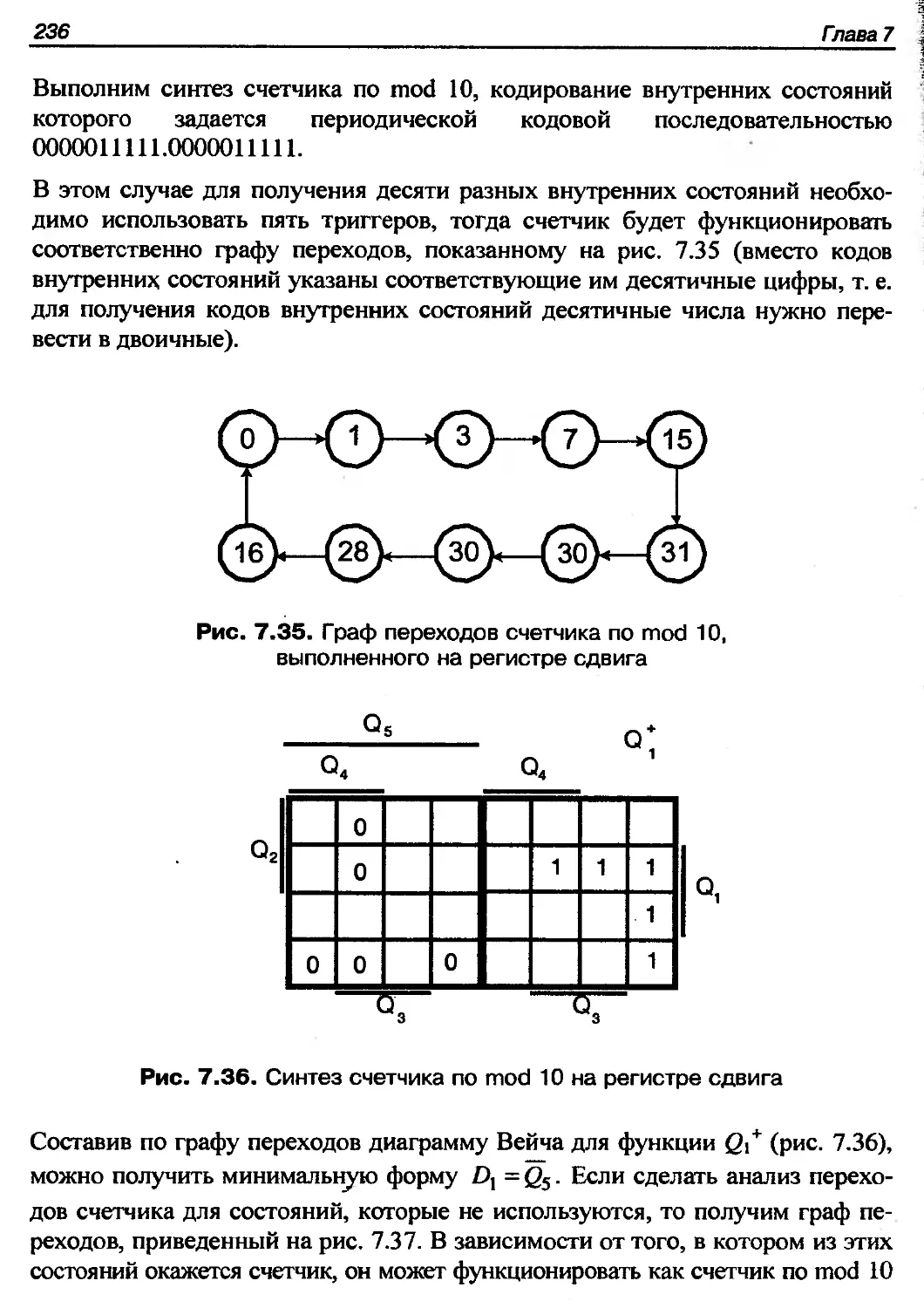

7.3. Счетчики на регистрах сдвига................................231

7.4. Реверсивные счетчики........................................239

7.5. Счетчики с переменным коэффициентом пересчета и цифровые

фазоинверторы....................................................245

Содержание

V

1.6. Последовательные двоичные сумматоры и цифровые интеграторы..................250

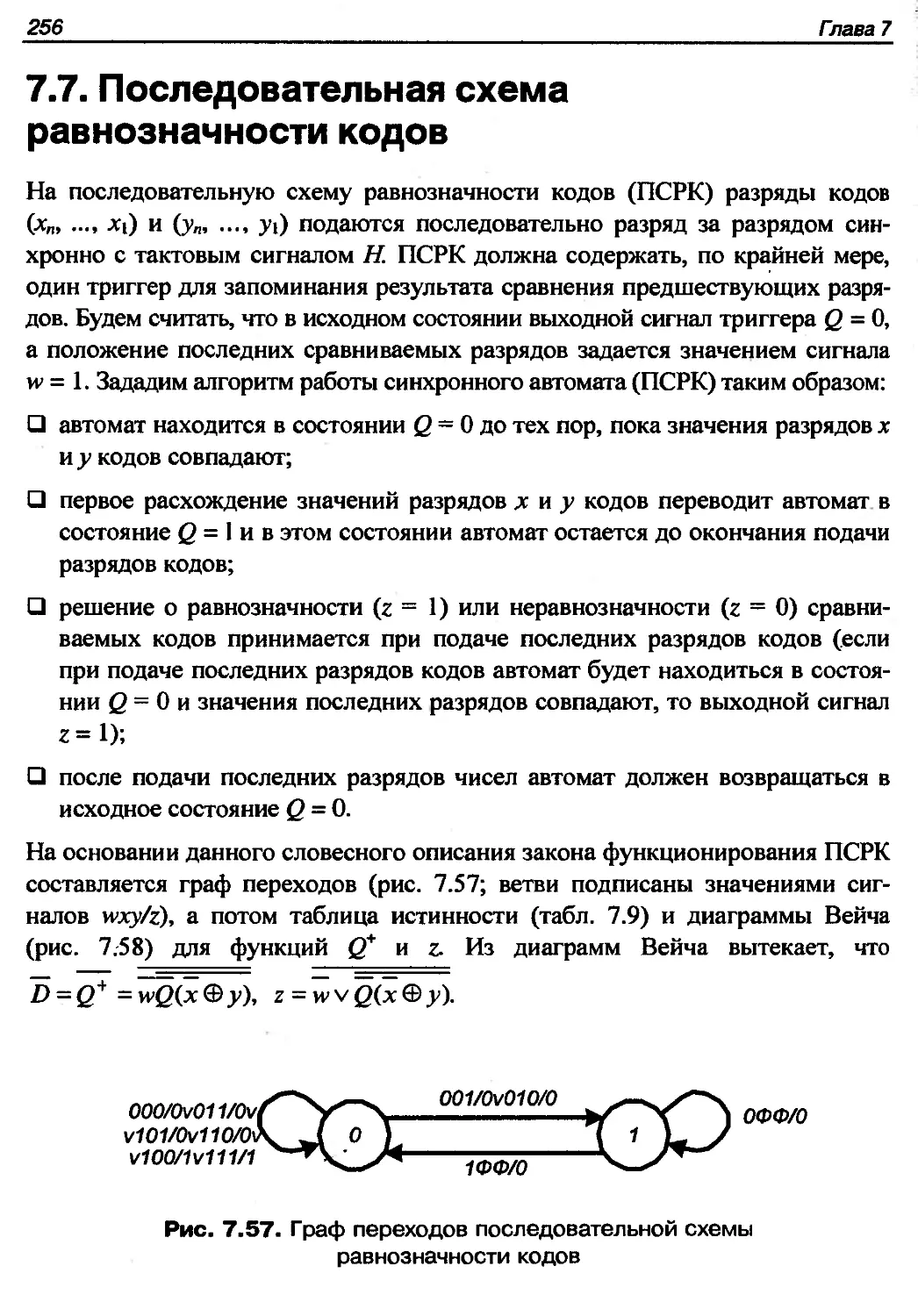

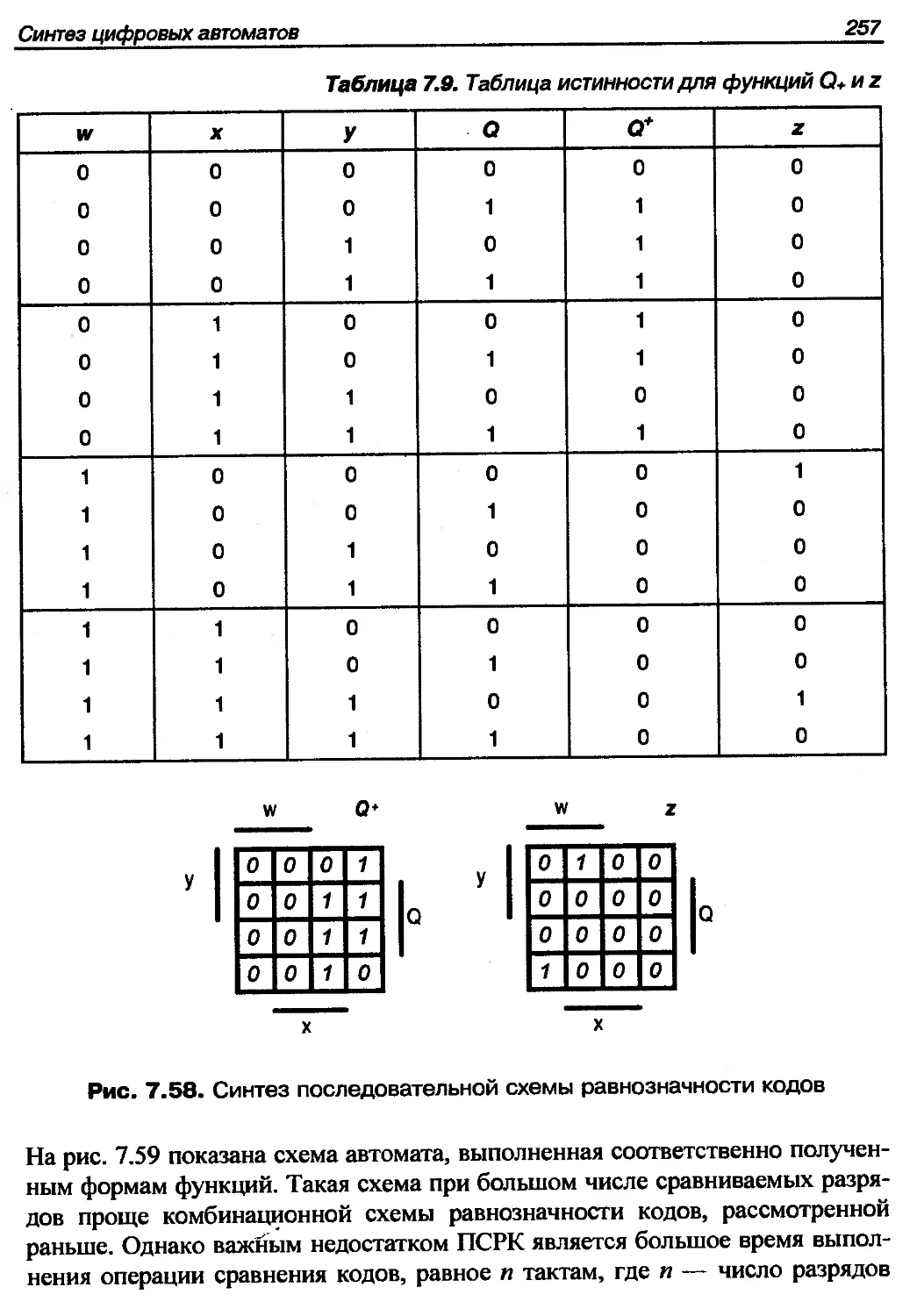

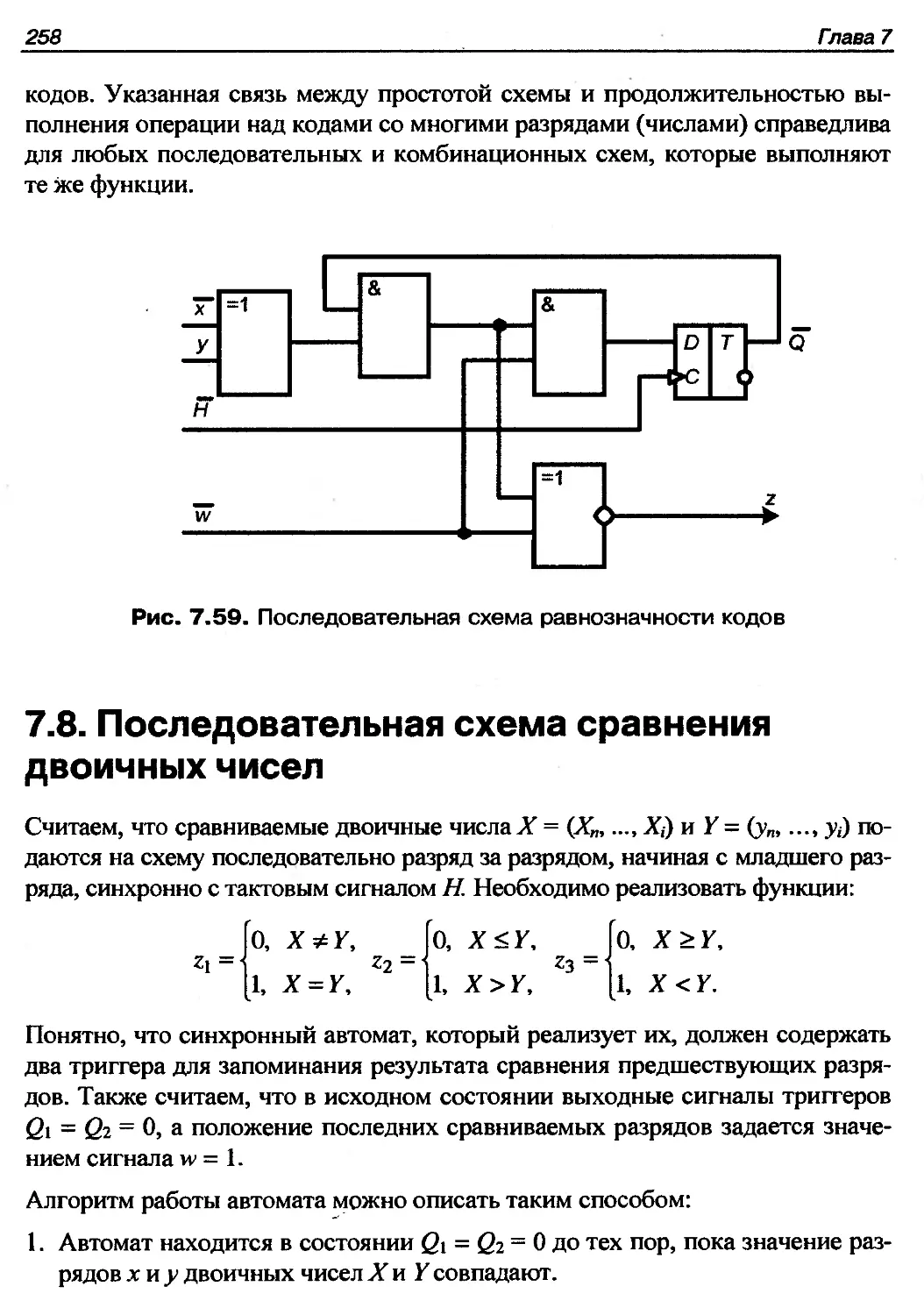

7.7. Последовательная схема равнозначности кодов.................................256

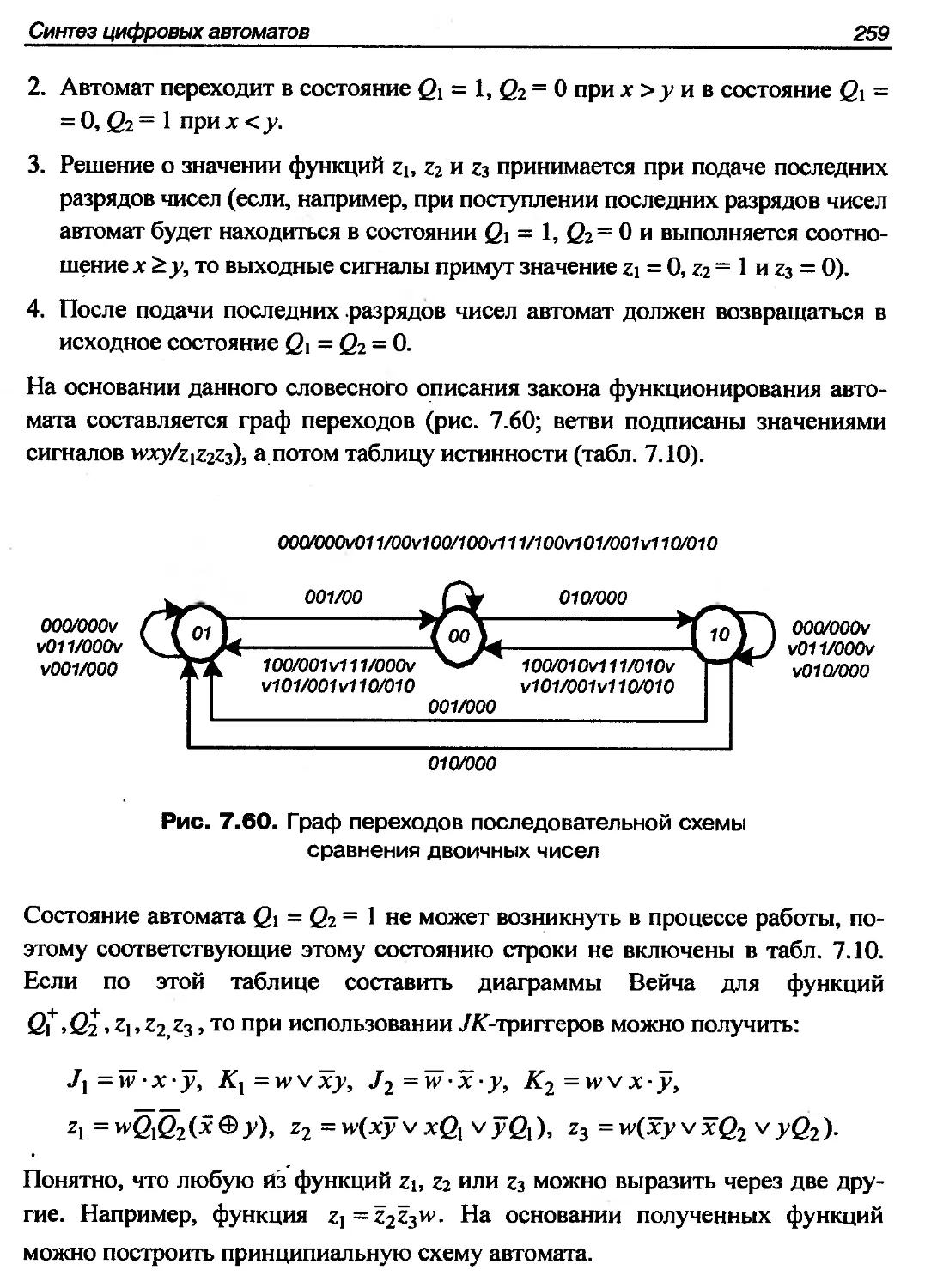

7.8. Последовательная схема сравнения двоичных чисел.............................258

Контрольные вопросы и задания....................................................261

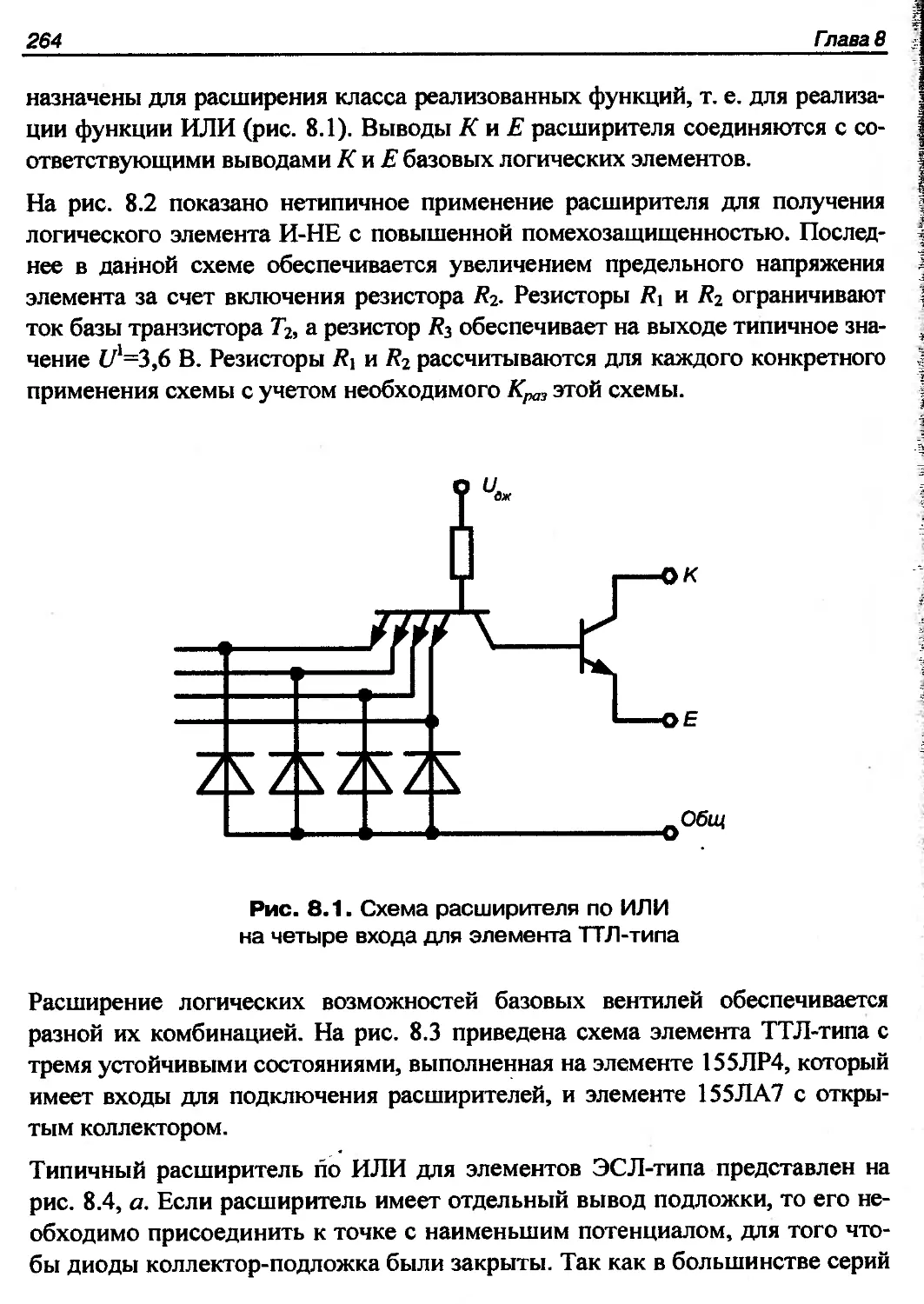

Глава 8. Специальные элементы цифровых устройств .........._____________..................263

8.1. Логические расширители.....................................................263

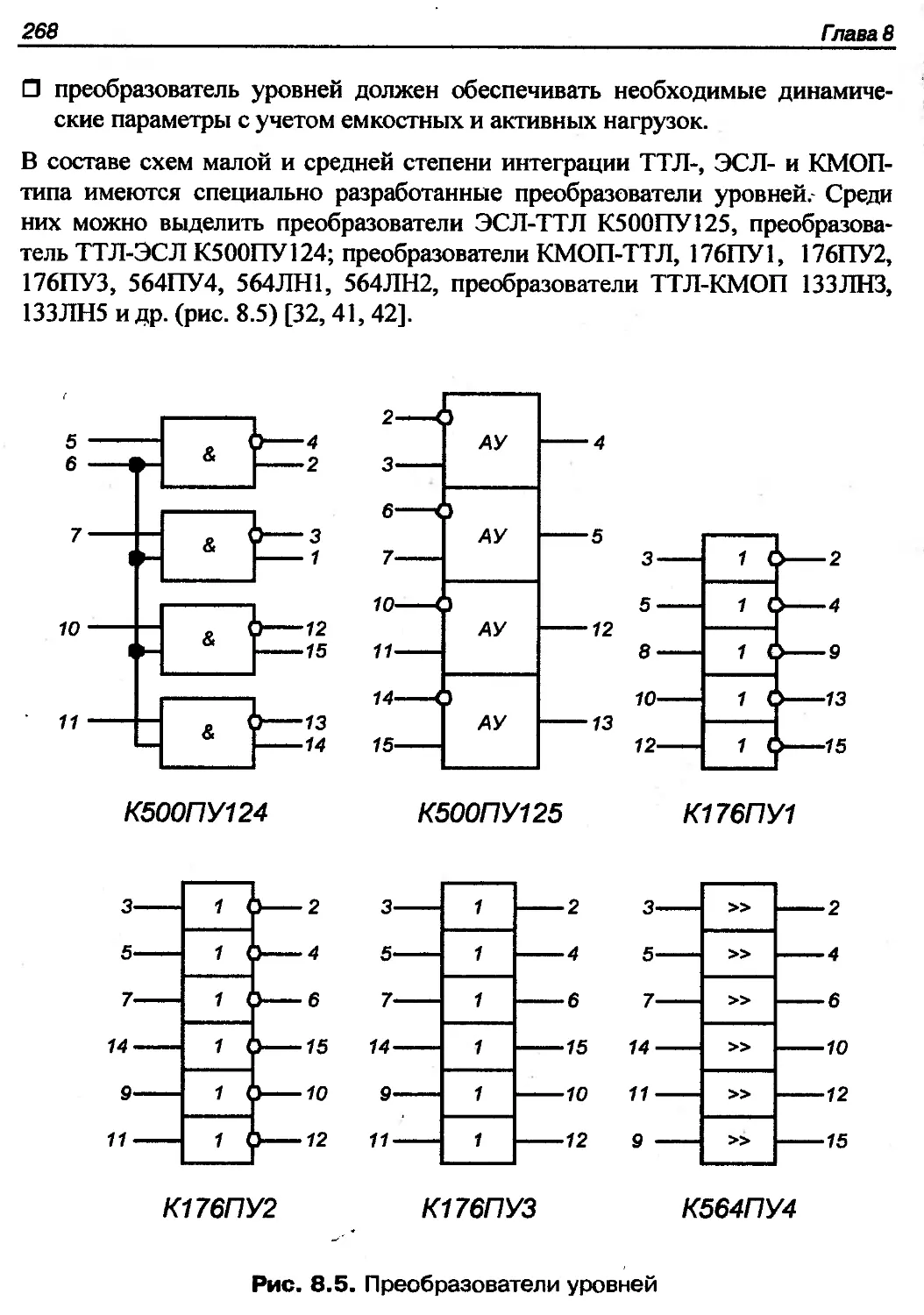

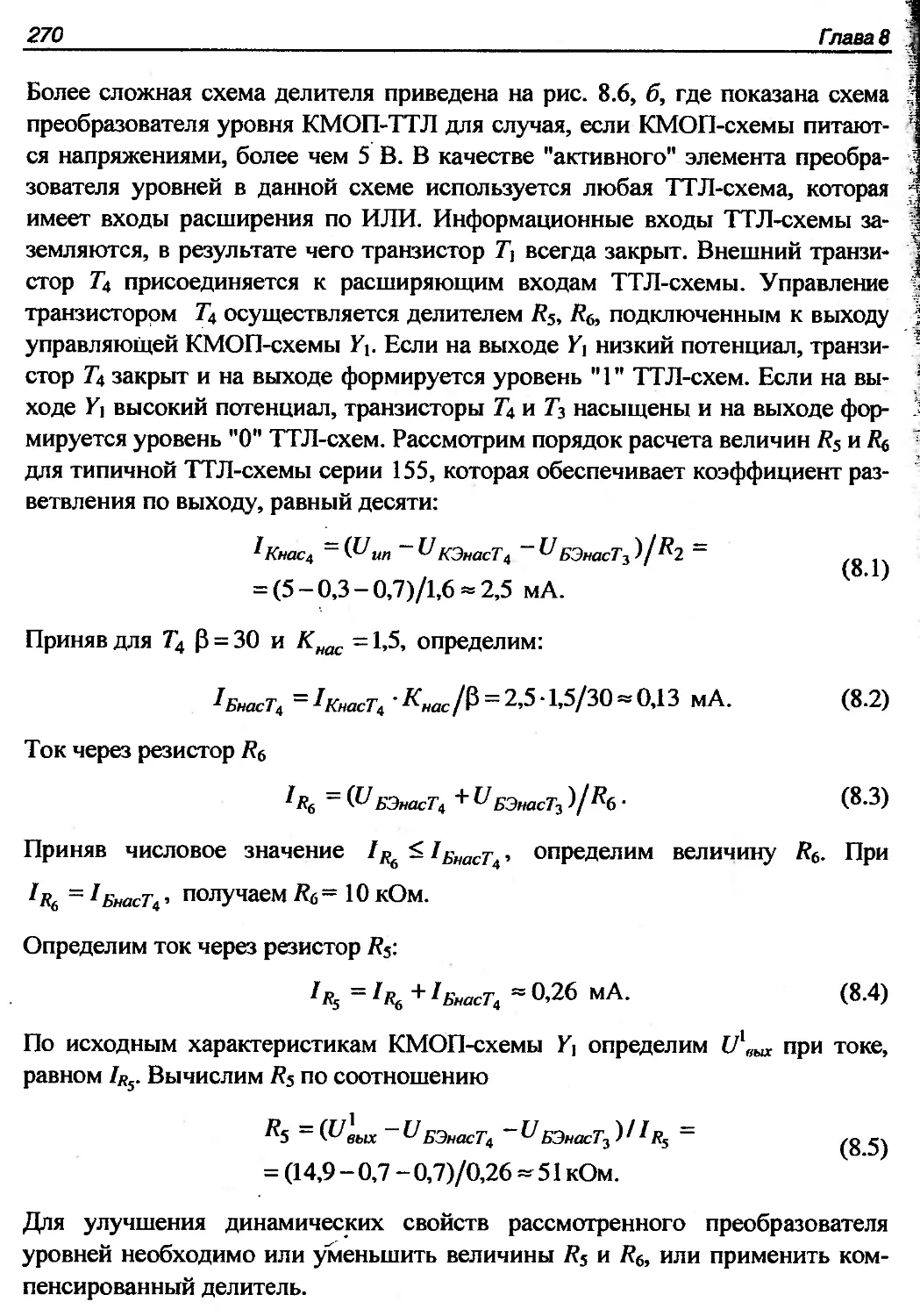

8.2. Преобразователи уровней....................................................267

8.3. Генераторы и одновибраторы.................................................278

8.4. Разностные преобразователи и детекторы событий (фронтов)...................315

8.5. Интегральные таймеры.......................................................320

Контрольные вопросы и задания....................................................330

Глава 9. Полупроводниковые оперативные запоминающие устройства ...331

9.1. Микросхемы статических ОЗУ.................................................332

9.2. Микросхемы динамических ОЗУ................................................354

9.3. Применение микросхем оперативных запоминающих устройств....................366

Контрольные вопросы и задания....................................................376

Глава 10. Микросхемы постоянных запоминающих устройств ...................379

10.1. Микросхемы ПЗУМ...........................................................379

10.2. Микросхемы ППЗУ...........................................................387

10.3. Микросхемы РПЗУ...........................................................392

Контрольные вопросы и задания....................................................426

Глава 11. Особенности проектирования цифровых схем............................... 429

11.1. Переходные процессы в логических схемах...................................429

11.2. Гонки.....................................................................435

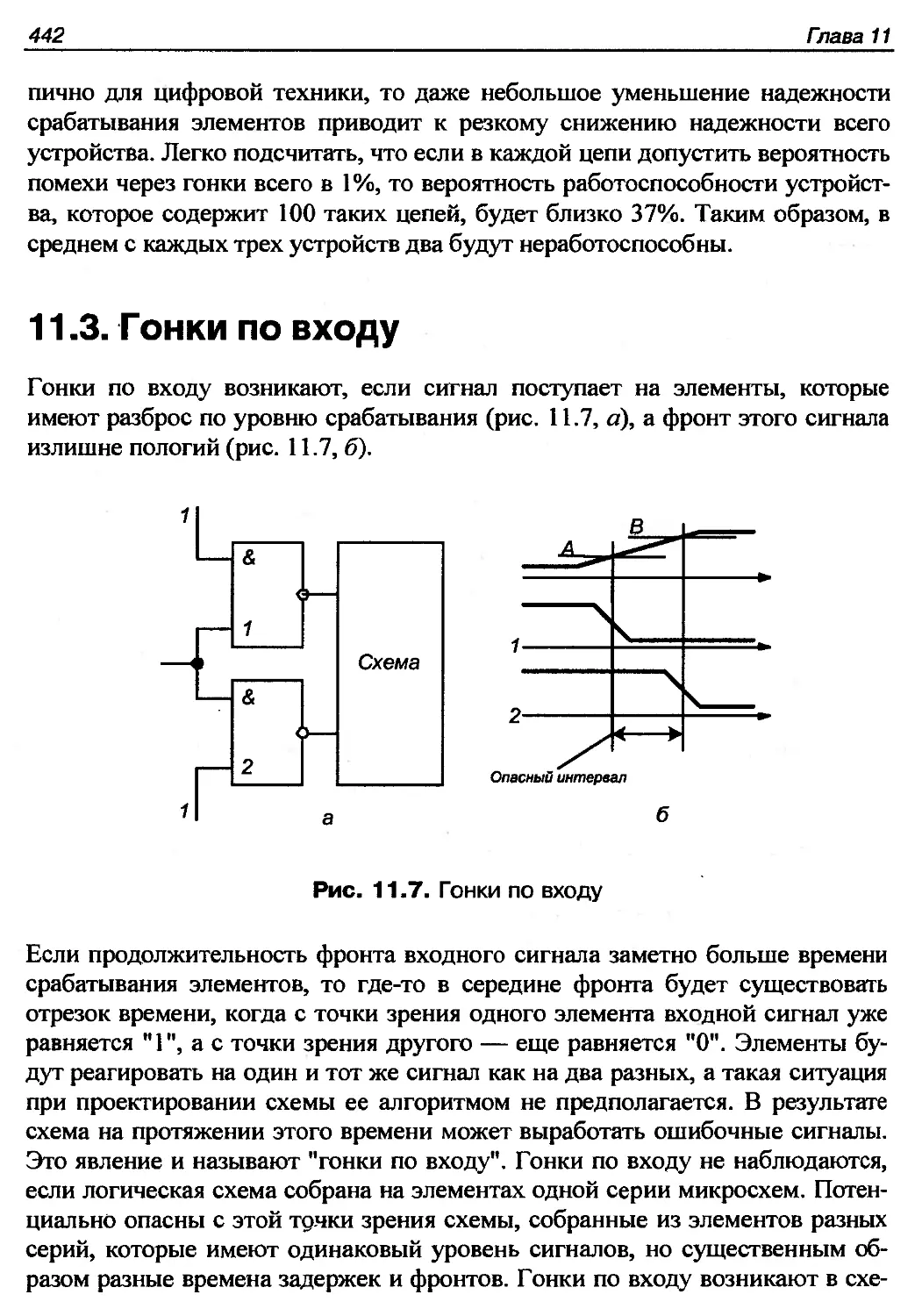

11.3. Гонки по входу............................................................442

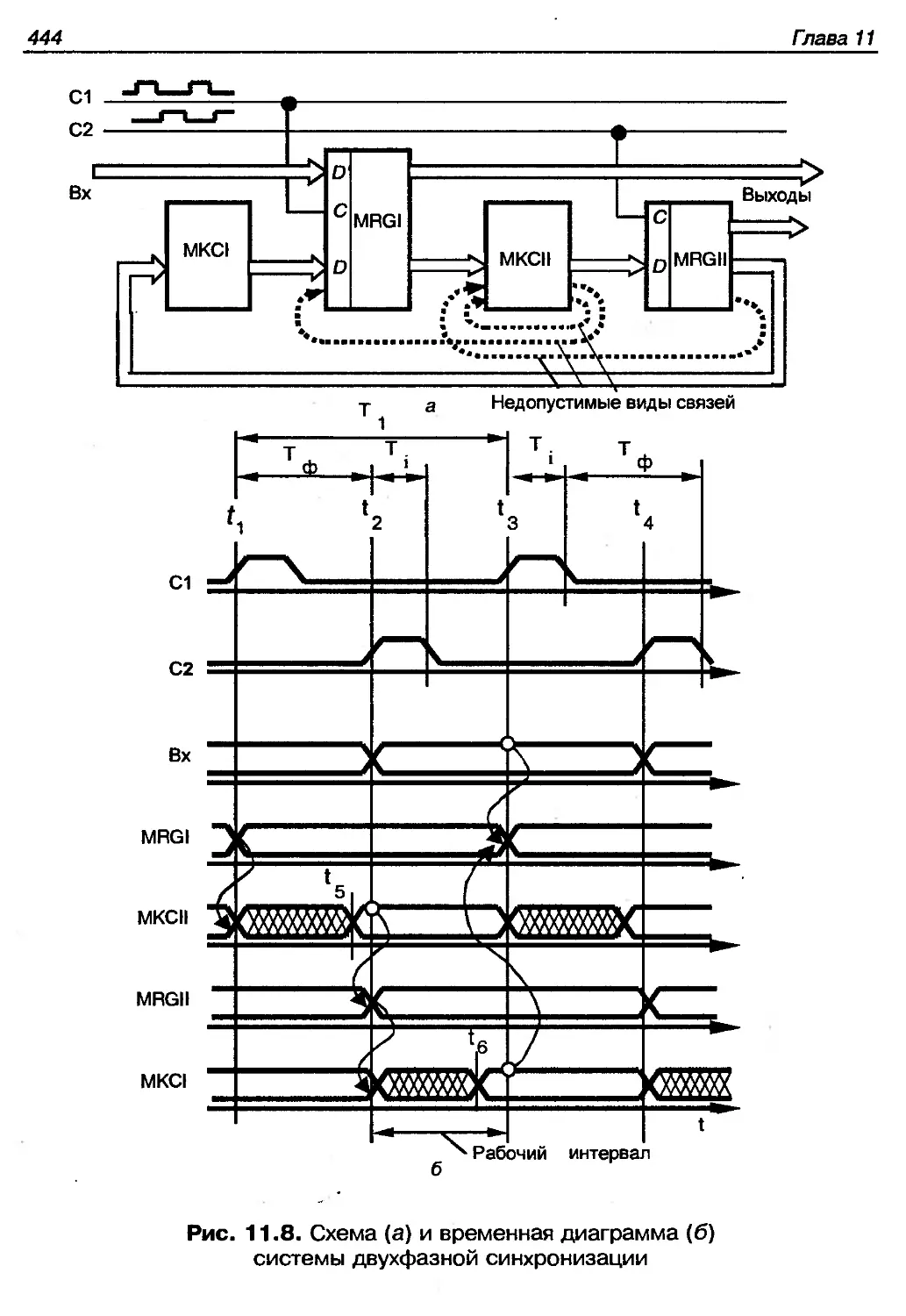

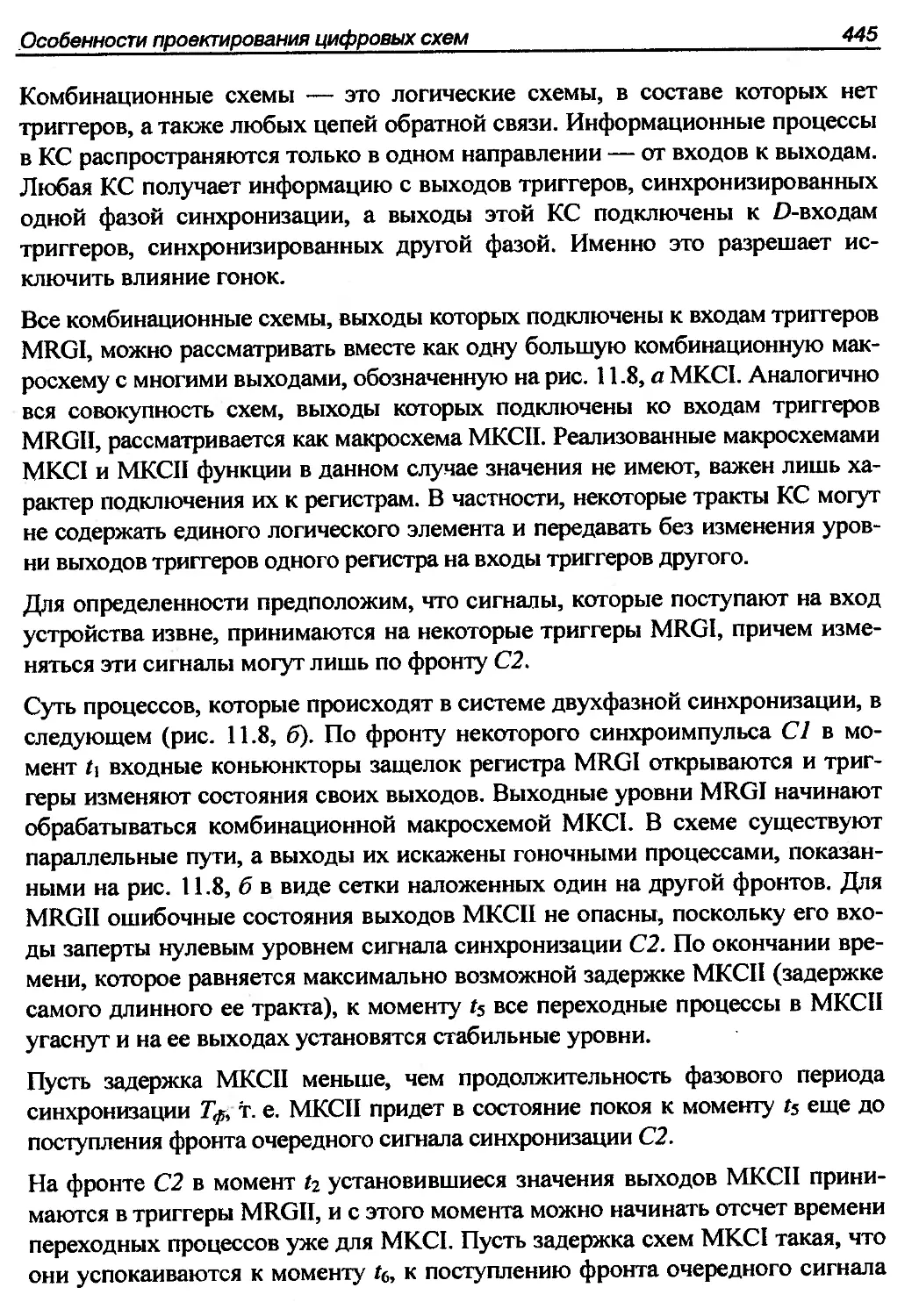

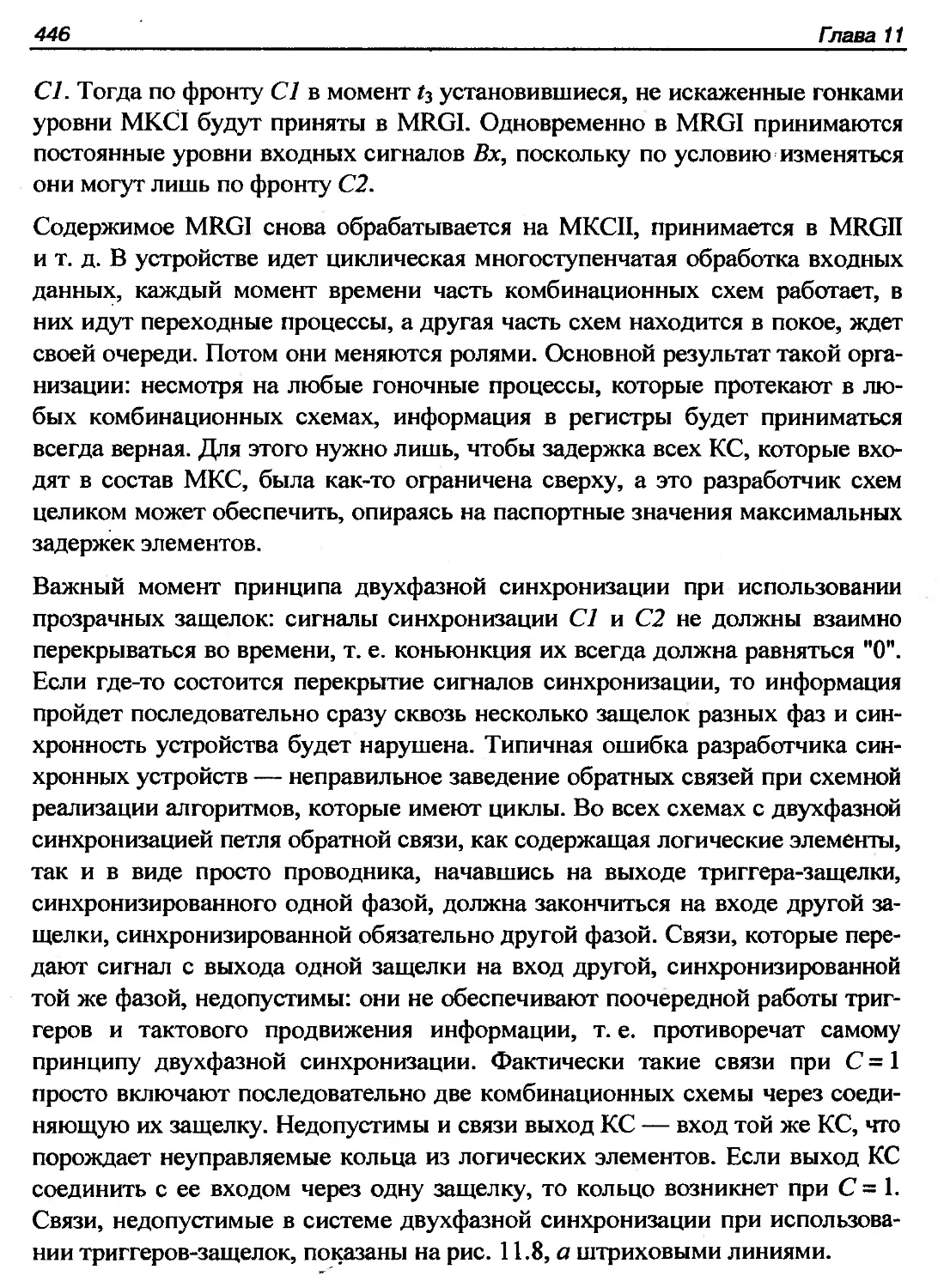

11.4. Система двухфазной синхронизации..........................................443

11.5. Временные соотношения двухфазной синхронизации............................447

11.6. Однофазная синхронизация..................................................455

11.7. О проектировании схем с обратными связями.................................464

Контрольные вопросы и задания....................................................465

Глава 12. Применение цифровых интегральных микросхем........................ 467

12.1. Помехи и помехоустойчивость цифровых устройств.............................467

12.2. Рекомендации по монтажу интегральных микросхем.............................476

Контрольные вопросы и задания....................................................492

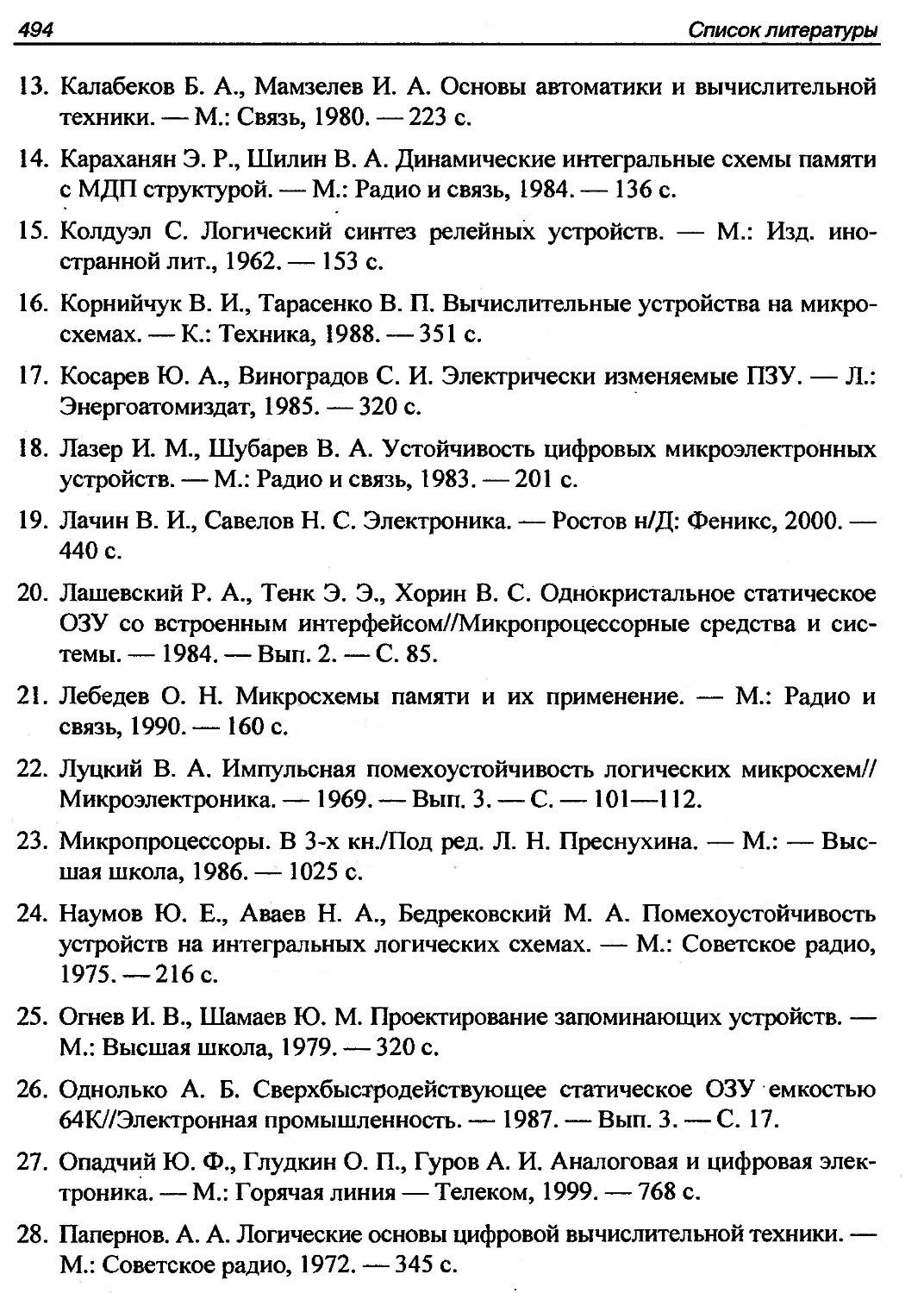

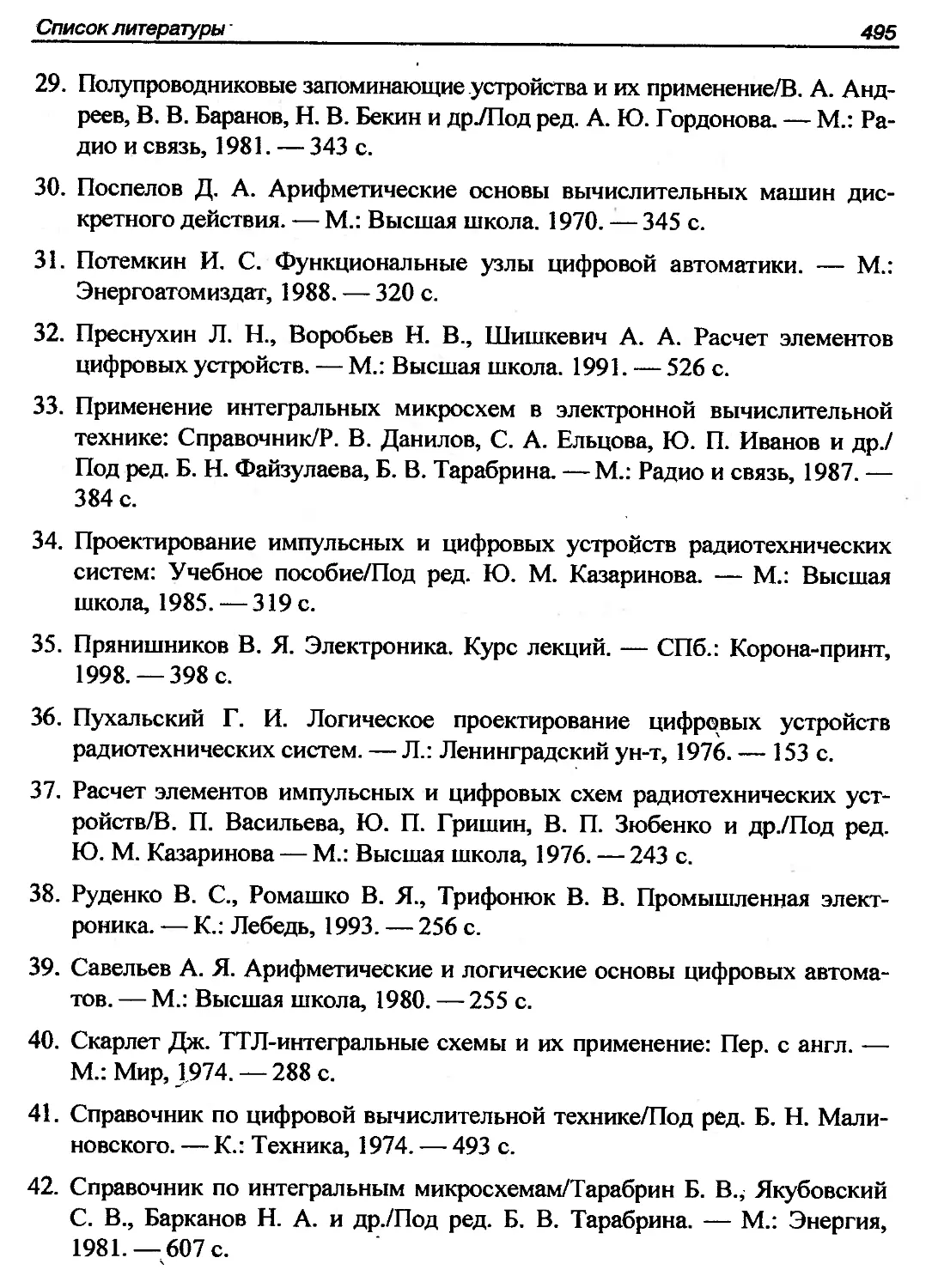

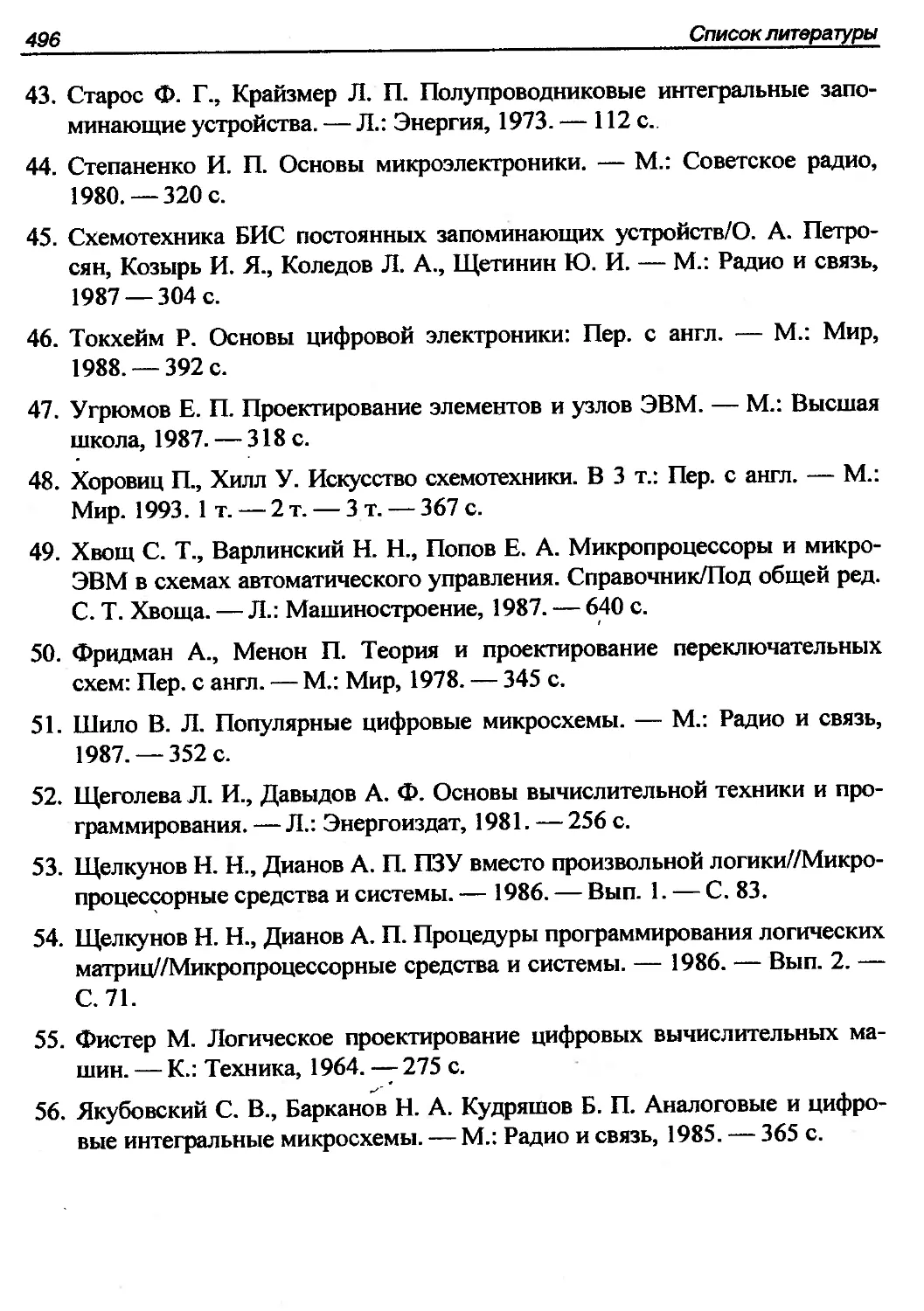

Список литературы ................................................................................................493

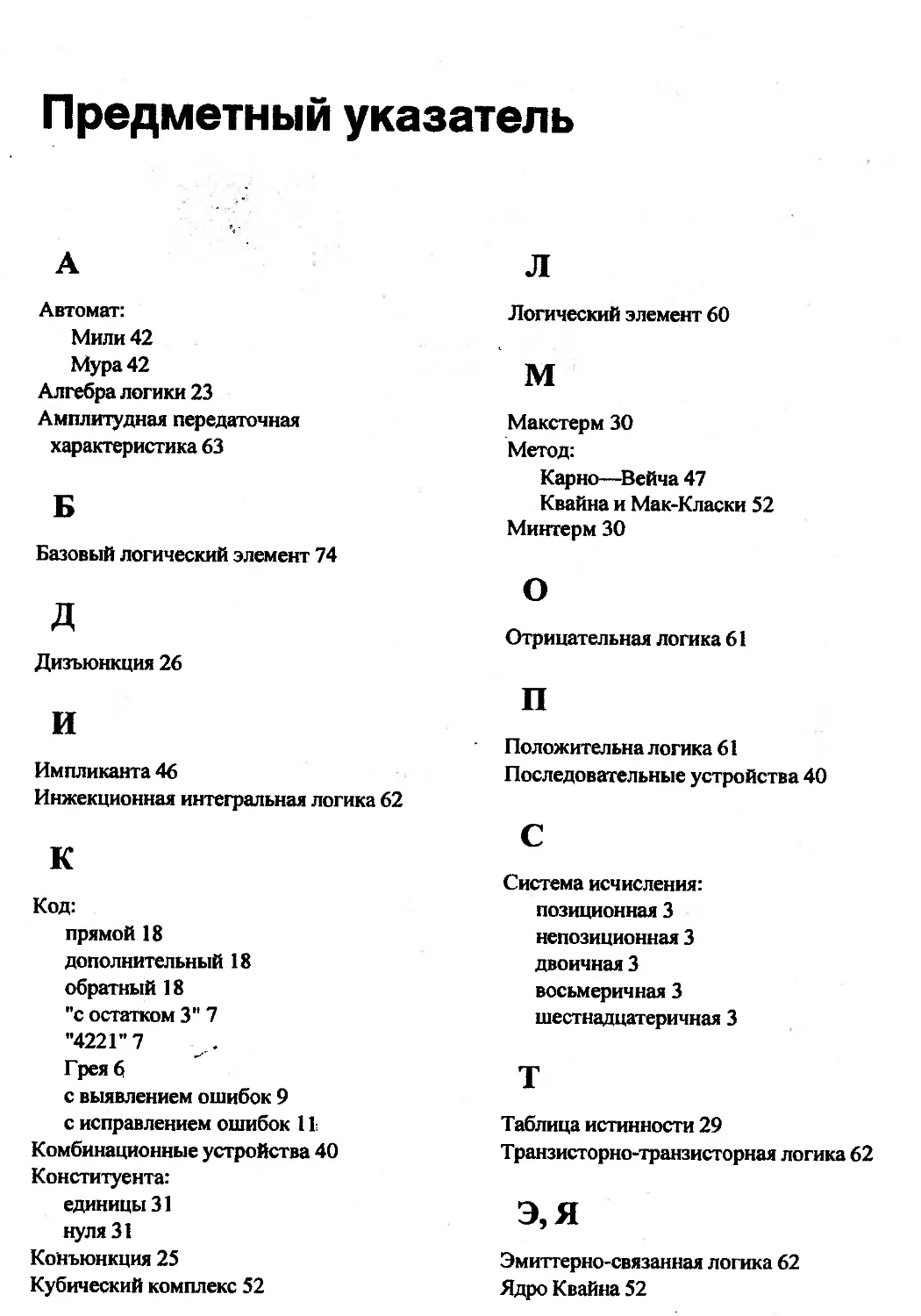

Предметный указатель ..........................................................................................497

Вступление

Обмен информацией в электронных системах происходит при помощи сиг-

налов. Носителями сигналов могут быть разнообразные физические величи-

ны — токи, напряжения, магнитные состояния, световые волны. Отличают

аналоговые (непрерывные) сигналы и дискретные.

Дискретные сигналы проще сохранять и обрабатывать, они меньше поддают-

ся искажению под воздействием помехи, такие искажения легче обнаружить

и исправить. Поэтому дискретные сигналы находят более широкое практиче-

ское применение, чем непрерывные. Существуют два типа дискретных сиг-

налов: первый получен за время дискретизации по уровню или по времени

непрерывных сигналов; второй — в виде набора кодовых комбинаций зна-

ков, чисел или слов. Преобразование непрерывного информационного мно-

жества аналоговых сигналов в дискретное множество называется дискрети-

зацией или квантованием по уровню. Второе представление в виде слов

является более универсальным и распространненым. Оно применяется для

кодирования человеческого языка на бумаге (письма), в математике, в циф-

ровой электронике.

Наиболее вероятно, что в недалеком будущем цифровая электроника займет

монопольное положение на рынке электронных систем и устройств. Сегодня

цифровые персональные компьютеры и контроллеры (ЭВМ) практически вы-

теснили аналоговые электронные вычислительные машины, которые были

созданы раньше. То же самое происходит с аппаратурой радиосвязи, радиове-

щания и телевидения (телевизорами, радиоприемниками, видеомагнитофона-

ми, звукозаписью, фотоаппаратурой).

Полностью вытеснить аналоговую технику цифровая в принципе не сможет,

т. к. физические процессы, от которых электронная система получает инфор-

мацию, имеют аналоговую природу. В этом случае необходимы на входе и вы-

ходе цифроаналоговые и аналого-цифровые устройства.

Цифровая схемотехника — область науки, техники и производства, которая

связана с разработкой, исследованием, проектированием и изготовлением

электронных систем, где преобразование и обработка информации происхо-

дят по закону дискретной функции. Промышленное развитие цифровой схе-

2

Вступление

мотехники имеет два направления: энергетическое (силовое), связанное с

преобразованием постоянного и переменного токов для нужд металлургии,

электротяги, электроэнергетики и информационное, к которому относятся

средства измерения, контроля и регулирования технологических процессов

производства, научных исследований в технических и гуманитарных сферах.

Из учебников Наиболее распространена монография американских специали-

стов П. Хоровица и У. Хилла "Искусство схемотехники" в трех томах [48],

которая в странах СНГ с 1980 года выдержала четыре переиздания. В них

объем материала значительно превышает требования программ, мало инфор-

мации о современном развитии схемотехники, в особенности цифровой.

Для анализа современных микропроцессорных систем знание технической

реализации алгоритмов исключительно важно. Например, в полупроводнико-

вых цифровых микросхемах, на которых построены контроллеры и персо-

нальные компьютеры, широко используют логические вентили на транзи-

сторно-транзисторной логике (TTL) и логике на комплектарных полевых

транзисторах КМОП (CMOS). Стандартные микросхемы серий К155 и К133

характеризуются средним энергопотреблением и быстродействием 10 нс.

Микросхемы с меньшими затратами энергии — К134 — имеют улучшенное

быстродействие. Серии К131 имеют повышенную выходную мощность.

Микросхемы с диодами Шоттки (ТТЛШ) (К531) при более высоких, чем в

стандартных, затратах имеют быстродействие в три раза выше (3 нс). Серия

маломощных микросхем ТТЛШ (К555) при том же быстродействии, что и

стандартные, потребляет мощность в несколько раз меньше. Перспективными

являются серии КР1531 (с быстродействием 3 нс) и КР1533 (с быстродействи-

ем 4 нс). Причем последняя имеет в два раза меньшее энергопотребление.

В результате изучения курса "Цифровая схемотехника" студент должен

знать: принципы построения и функционирования устройств цифровой схе-

мотехники; принципы выбора методов анализа и синтеза электронных уст-

ройств с заданными характеристиками, а также уметь: рассчитать электрон-

ные цепи; обобщить динамические показатели электронных устройств;

выполнить расчеты разнообразных электронных устройств с организацией

банка данных.

Глава 1

Математические основы

цифровой схемотехники

1.1. Системы исчисления.

Правила перевода из одной системы

исчисления в другую

Системой исчисления называют систему приемов и правил, которые позво-

ляют устанавливать взаимно однозначное соответствие между любым числом

и его представлением в виде совокупности конечного числа символов. В за-

висимости от способа изображения чисел с помощью цифр системы исчис-

ления делятся на позиционные и непозиционные [1, 13, 52].

В непозиционных системах любое число определяется как некоторая функ-

ция от численных значений совокупности цифр, которые представляют это

число. Цифры в непозиционных системах исчисления отвечают некоторым

фиксированным числам. Пример непозиционной системы — римская систе-

ма исчисления. В электронных цифровых устройствах применяются позици-

онные системы исчисления. Позиционной система исчисления называется

потому, что значение каждой входящей в число цифры зависит от ее поло-

жения в записи числа.

Любая позиционная система исчисления с основой q может быть представ-

лена в виде полинома

\q) = rnQn + rn-\qn~X + - + П91 + ro9° + »

где A — число в позиционной системе исчисления с основой q\ г, — коэф-

фициент; п — степень и индекс.

Позиционные системы исчисления бывают разными в зависимости от осно-

вы: десятичные с основой десять, восьмеричные с основой восемь, двоичные

4

Глава 1

с основой два и т. д. В дальнейшем, чтобы явно указать систему исчисле-

ния, которая используется, будем записывать число в скобках и в индексе

указывать основу системы исчисления.

В двоичной системе исчисления коэффициентами г,- являются цифры 0 и 1, а

основой — число 2. В общем виде число в двоичной системе исчисления бу-

дет записано как:

А2 = rn 2п + rn_| 2"-1 +... + q 2’ + r02° + 2’1.

Цифровые устройства используют элементы, которые имеют только два

устойчивых состояния, поэтому двоичная система исчисления приобрела

широчайшее распространение для представления и обработки информации.

Восьмеричная система применяется для выполнения вспомогательных функ-

ций, сокращает запись числовой информации и обеспечивает простоту пере-

вода в двоичную систему, поскольку любая восьмеричная цифра легко заме-

няется двоичным трехразрядным числом — триадой. Наиболее удобной и

короткой по записи является шестнадцатеричная позиционная система. Ос-

новой системы служит число 16, а как коэффициенты приняты цифровые и

буквенные символы: 0, 1,2,3,4, 5, 6, 7, 8, 9, А, В, С, D, Е, F.

Перевод из десятичной системы в любую позиционную систему исчисления

проводится методом последовательного деления на основу новой системы до

тех пор, пока остаток от деления не будет меньше основы системы. Число в

новой системе записывается в виде остатков от деления, начиная с послед-

него остатка, справа налево. Дробное число записывается в виде целых час-

тей чисел, которые получают при умножении только дробной части на осно-

ву, начиная сверху после запятой, и при этом задается точность вычислений.

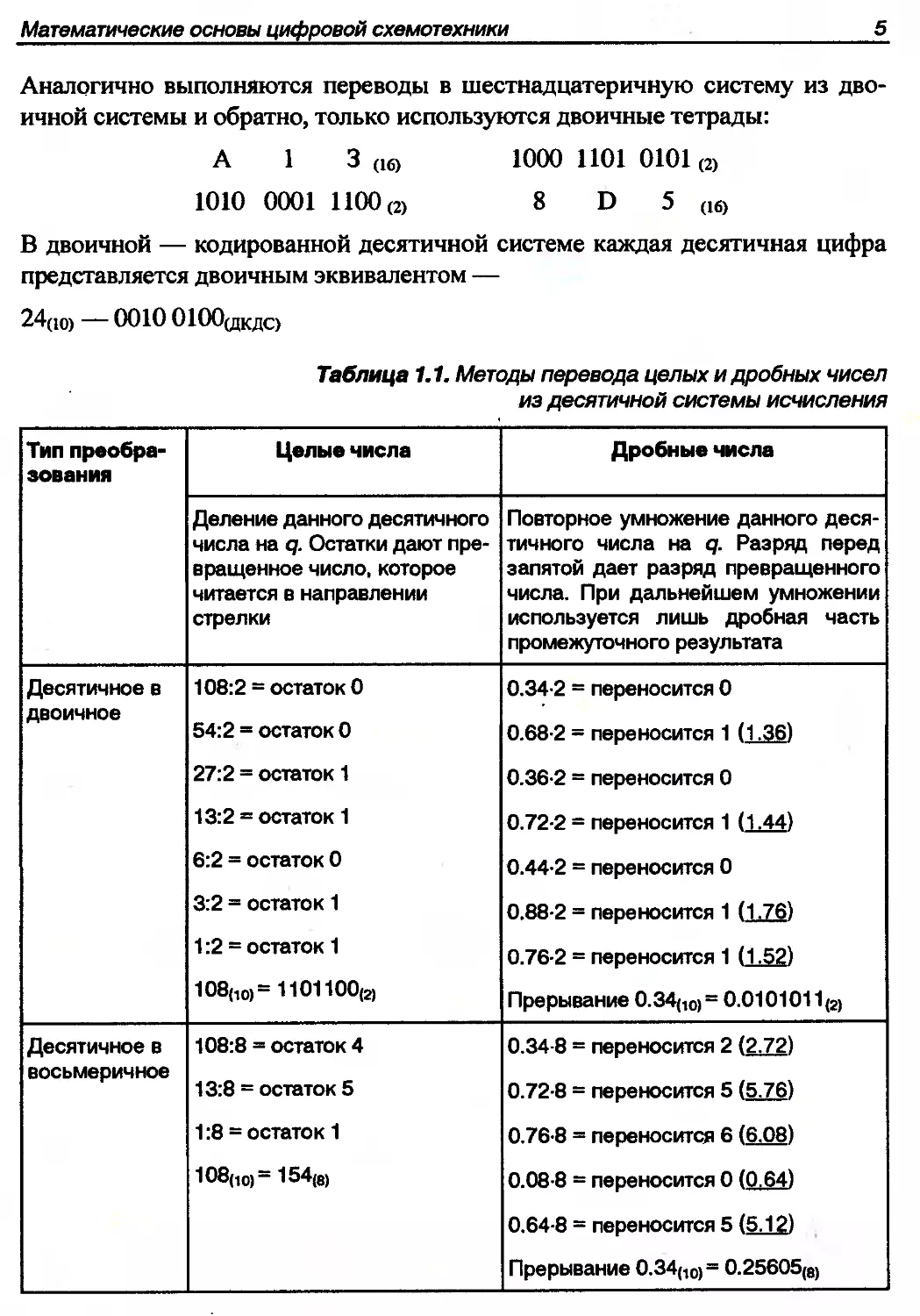

Практический интерес представляют пересчеты с десятичной и в десятичную

системы. Алгоритм пересчета и некоторые примеры приведены в табл. 1.1—

1.2.

Для перевода числа из восьмеричной системы в двоичную следует любое

восьмеричное число заменить эквивалентным трехразрядным числом:

2 4 5 1 да

010 100 101 001 (2)

Двоичное число при переводе в восьмеричную систему делится на триады

справа налево, и каждая триада заменяется восьмеричным числом:

101 001 111®

5 1 7 да

Математические основы цифровой схемотехники 5

Аналогично выполняются переводы в шестнадцатеричную систему из дво-

ичной системы и обратно, только используются двоичные тетрады:

А 1 3 (16) 1000 1101 0101 (2)

1010 0001 1100 (2) 8 D 5 (16)

В двоичной — кодированной десятичной системе каждая десятичная цифра

представляется двоичным эквивалентом —

24(ю) — 0010 0100(дкдо

Таблица 1.1. Методы перевода целых и дробных чисел

из десятичной системы исчисления

Тип преобра- зования Целые числа Дробные числа

Деление данного десятичного числа на q. Остатки дают пре- вращенное число, которое читается в направлении стрелки Повторное умножение данного деся- тичного числа на q. Разряд перед запятой дает разряд превращенного числа. При дальнейшем умножении используется лишь дробная часть промежуточного результата

Десятичное в двоичное 108:2 = остаток 0 54:2 = остаток 0 27:2 = остаток 1 13:2 = остаток 1 6:2 = остаток 0 3:2 = остаток 1 1:2 = остаток 1 108(ю)= 1101100(2) 0.34-2 = переносится 0 0.68-2 = переносится 1 (1.36) 0.36-2 = переносится 0 0.72-2 = переносится 1 (1.44) 0.44-2 = переносится 0 0.88-2 = переносится 1 (1.76) 0.76-2 = переносится 1 (1.52) Прерывание 0.34(10) = 0.0101011(2)

Десятичное в восьмеричное 108:8 = остаток 4 13:8 = остаток 5 1:8 = остаток 1 Ю8(10)= 154(e) 0.34-8 = переносится 2 (2.72) 0.72-8 = переносится 5 (5.76) 0.76-8 = переносится 6 (6.08) 0.08-8 = переносится 0 (0,64) 0.64-8 = переносится 5 (5.12) Прерывание 0.34(10)= 0.25605(8)

6

Глава 1

Таблица 1.1 (окончание)

Тип преобра- зования Целые числа Дробные числа

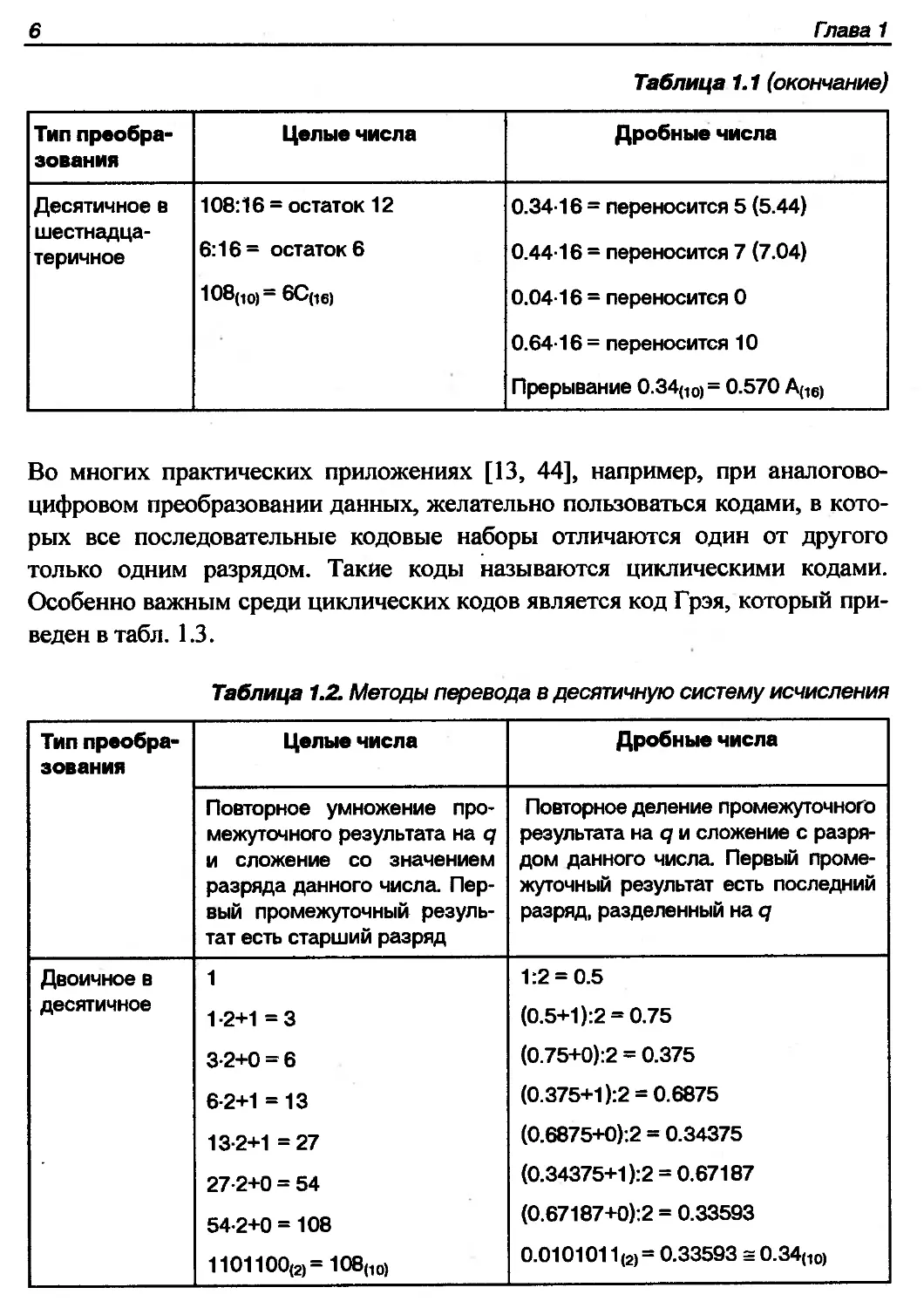

Десятичное в шестнадца- теричное 108:16 = остаток 12 6:16= остаток 6 108(ю)= 6С(1в) 0.34-16 = переносится 5 (5.44) 0.44-16 = переносится 7 (7.04) 0.04-16 = переносится 0 0.64-16 = переносится 10 Прерывание 0.34(10) = 0.570 А(16)

Во многих практических приложениях [13, 44], например, при аналогово-

цифровом преобразовании данных, желательно пользоваться кодами, в кото-

рых все последовательные кодовые наборы отличаются один от другого

только одним разрядом. Такие коды называются циклическими кодами.

Особенно важным среди циклических кодов является код Грэя, который при-

веден в табл. 1.3.

Таблица 1.2. Методы перевода в десятичную систему исчисления

Тип преобра- зования Целые числа Дробные числа

Повторное умножение про- межуточного результата на q и сложение со значением разряда данного числа. Пер- вый промежуточный резуль- тат есть старший разряд Повторное деление промежуточного результата на q и сложение с разря- дом данного числа. Первый проме- жуточный результат есть последний разряд, разделенный на q

Двоичное в десятичное 1 1-2+1 =3 3-2+0 = 6 6-2+1 = 13 13-2+1 =27 27-2+0 = 54 54-2+0 = 108 1101100(2)= 108(10) 1:2 = 0.5 (0.5+1 ):2 = 0.75 (0.75+0):2 = 0.375 (0.375+1 ):2 = 0.6875 (0.6875+0):2 = 0.34375 (0.34375+1 ):2 = 0.67187 (0.67187+0):2 = 0.33593 0.0101011(2)= 0.33593 = 0.34(10)

Математические основы цифровой схемотехники

7

Таблица 1.2 (окончание)

Тип преобра- зования Целые числа Дробные числа

Восьмерич- ное в деся- тичное 1 1-8+5= 13 13-8+4 = 108 154(8)= Ю8(10) 5:8 = 0.625 (0.625+01:8 = 0.078125 (0.078125+61:8 = 0.75976 (0.75976+5):8 = 0.71997 (0.71997+21:8 = 0.33999 0,25605(8)= 0.33999 = 0.34(10)

Шестнадца- теричное в десятичное 6 6-16+12= 108 6С(16)= 108(1о) А:16 = 0.625 (0.625+01:16 = 0.039062 (0.039062+61:16 = 0.75976. (0.75976+7):16 = 0.71997 (0.71997+51:16 = 0.33999 О.57ОА(}6)= 0.33999 = 0.34(ю)

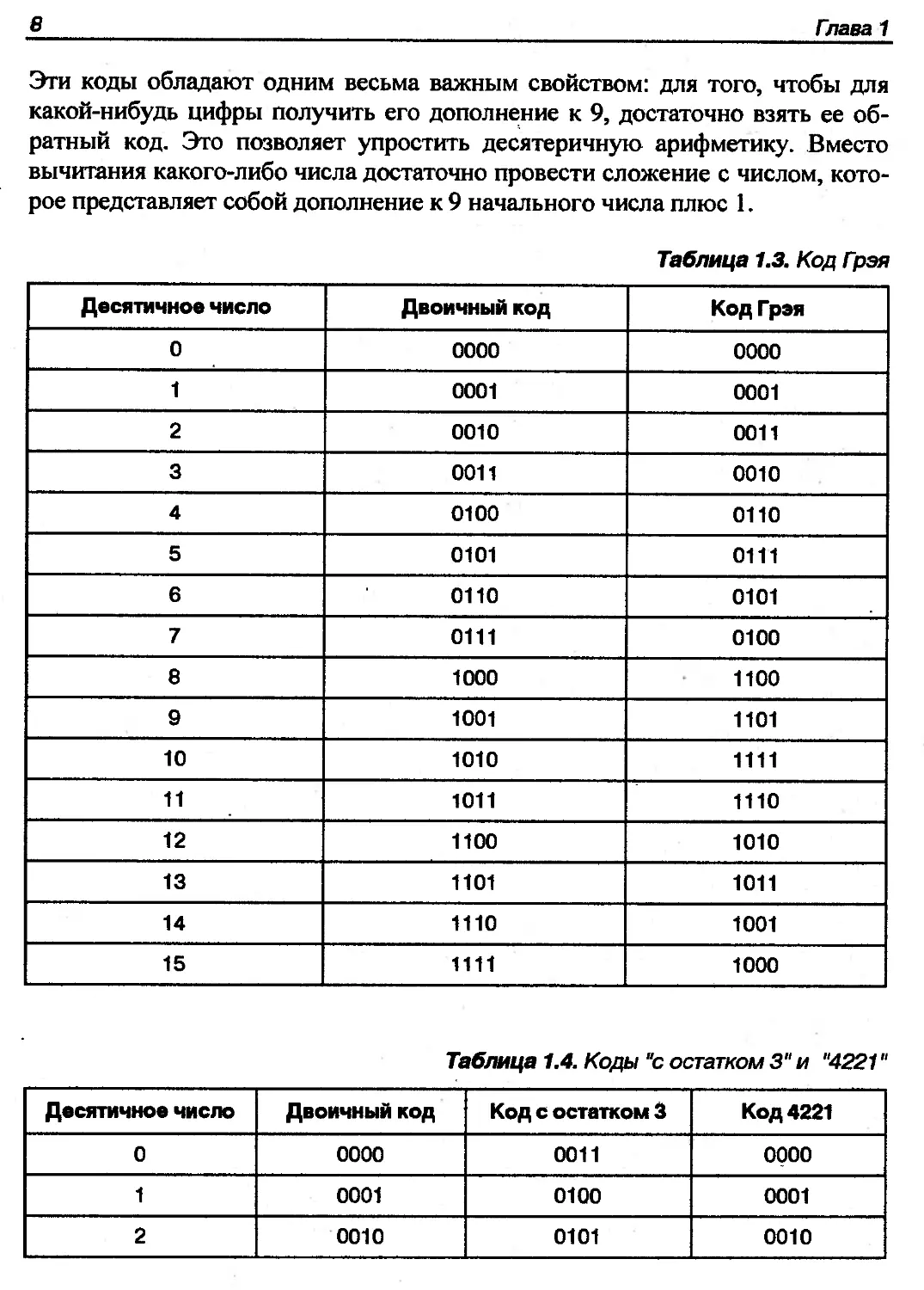

Код Грэя используется в механических шифраторах угла поворота вала, при

"параллельном кодировании" — методе быстродействующего аналогово-циф-

рового преобразования. Это позволяет предотвратить ошибки, поскольку в

этом случае при переходе между двумя закодированными значениями все

разряды никак не могут измениться одновременно. Если бы использовался

чисто двоичный код, то при переходе, например, от 7 до 8, на выходе можно

было бы получить число 15.

Коды Грэя могут содержать любое число разрядов. Существует простое пра-

вило для формирования состояний кода Грэя: начинать надо из нулевого со-

стояния, а потом для получения каждого следующего выбрать самый млад-

ший разряд, изменение которого приводит к образованию нового состояния,

и взять его инверсное значение.

Существует ряд других кодов, которые обладают интересными и полезными

свойствами, например, код "с остатком 3" или код "4221" (см. табл. 1.4). Для

того чтобы любую цифру от 0 до 9 записать в коде с остатком 3, надо приба-

вить к ней число 3, а потом выразить результат в 4-разрядном двоичном коде.

При использовании кода "4221" каждая цифра также записывается в виде 4-

разрядной группы. Однако ее разряды, начиная с левого, представляют ве-

личины 4, 2, 2 и 1.

в

Глава 1

Эти коды обладают одним весьма важным свойством: для того, чтобы для

какой-нибудь цифры получить его дополнение к 9, достаточно взять ее об-

ратный код. Это позволяет упростить десятеричную арифметику. Вместо

вычитания какого-либо числа достаточно провести сложение с числом, кото-

рое представляет собой дополнение к 9 начального числа плюс 1.

Таблица 1.3. Код Гсэя

Десятичное число Двоичный код Код Грэя

0 0000 0000

1 0001 0001

2 0010 0011

3 0011 0010

4 0100 0110

5 0101 0111

6 0110 0101

7 0111 0100

8 1000 1100

9 1001 1101

10 1010 1111

11 1011 1110

12 1100 1010

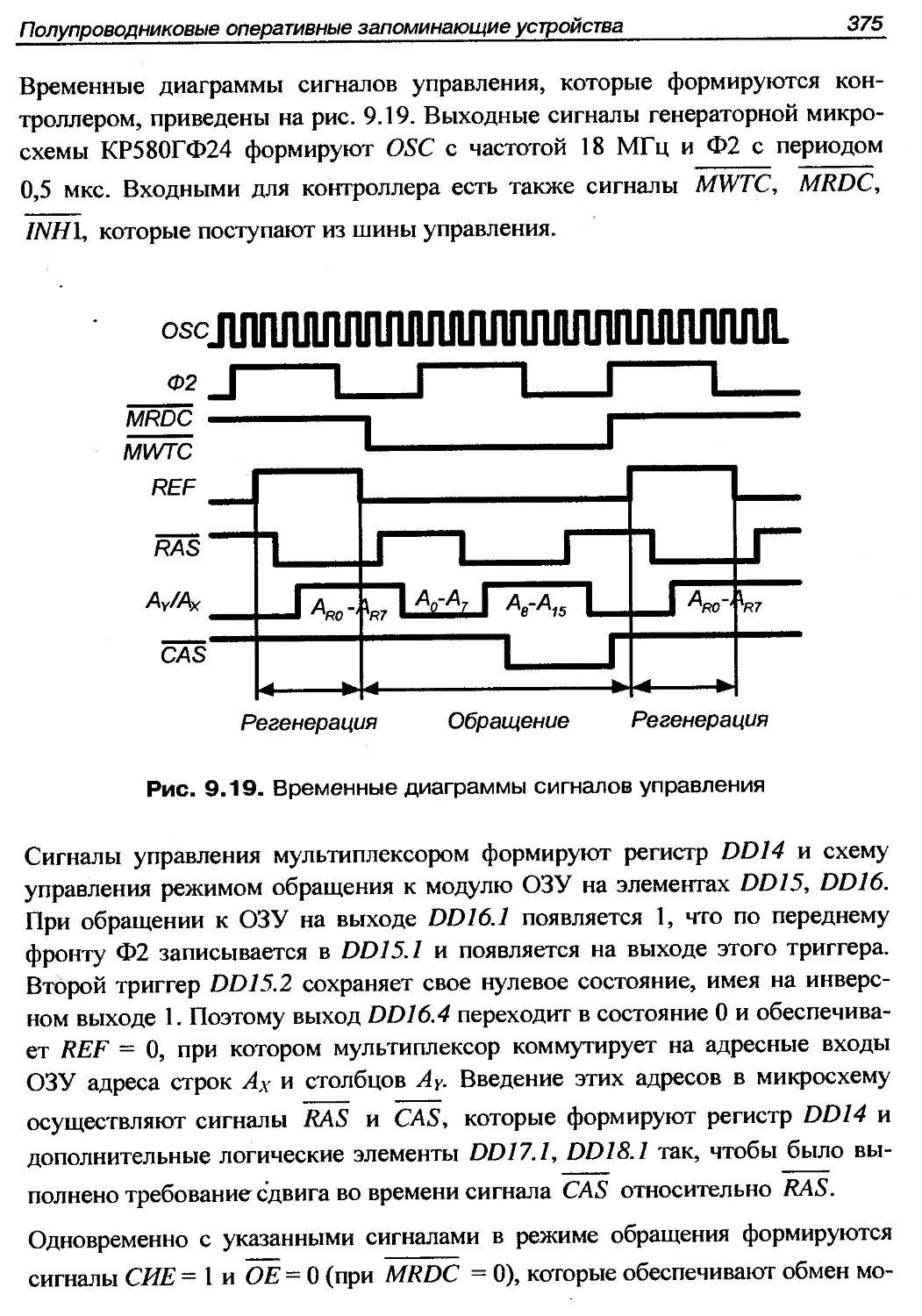

13 1101 1011

14 1110 1001

15 1111 1000

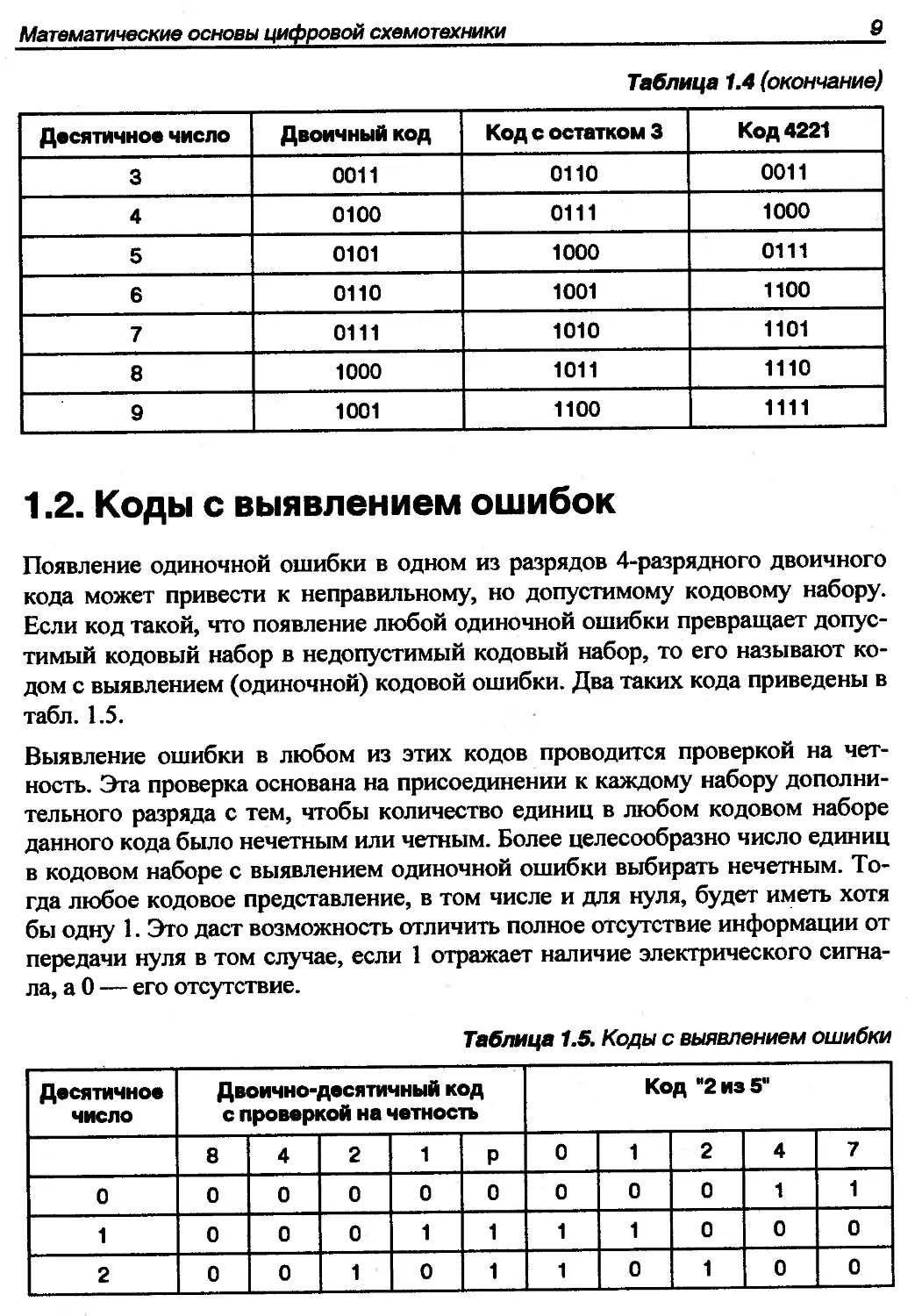

Таблица 1.4. Коды "с остатком 3" и "4221"

Десятичное число Двоичный код Код с остатком 3 Код 4221

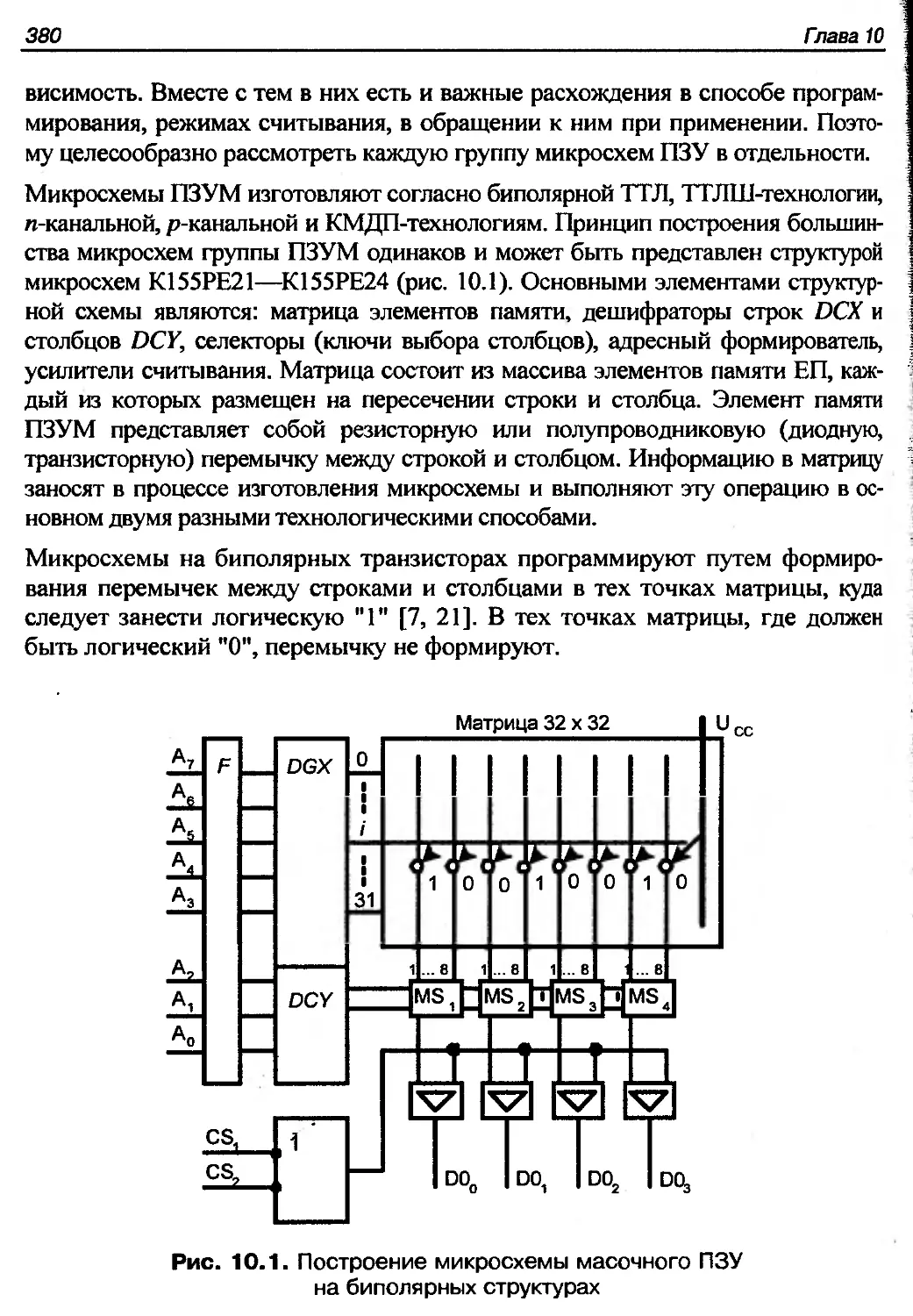

0 0000 0011 0000

1 0001 0100 0001

2 0010 0101 0010

Математические основы цифровой схемотехники

9

Таблица 1.4 (окончание)

Десятичное число Двоичный код Код с остатком 3 Код 4221

3 0011 0110 0011

4 0100 0111 1000

5 0101 1000 0111

6 0110 1001 1100

7 0111 1010 1101

8 1000 1011 1110

9 1001 1100 1111

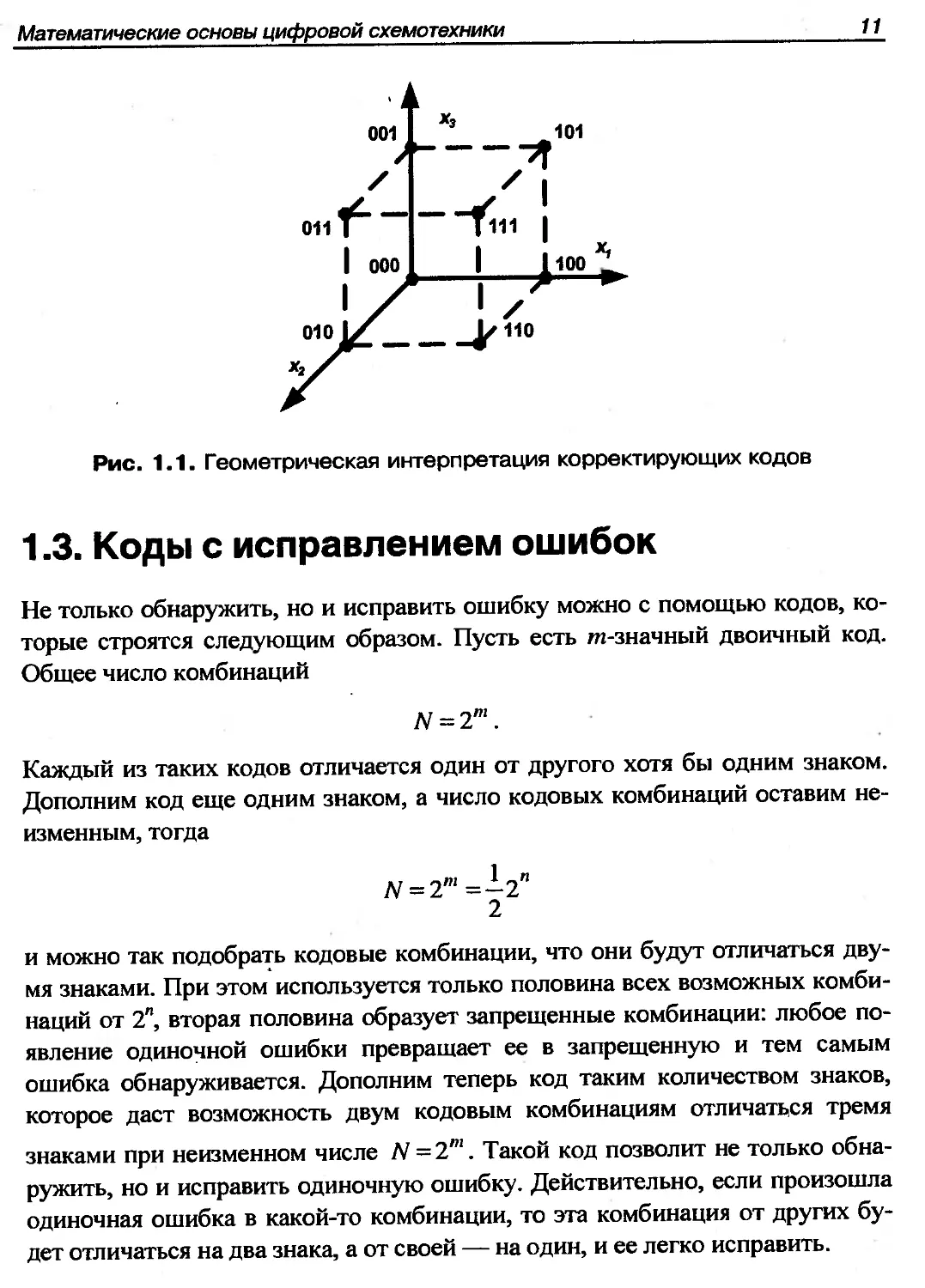

1.2. Коды с выявлением ошибок

Появление одиночной ошибки в одном из разрядов 4-разрядного двоичного

кода может привести к неправильному, но допустимому кодовому набору.

Если код такой, что появление любой одиночной ошибки превращает допус-

тимый кодовый набор в недопустимый кодовый набор, то его называют ко-

дом с выявлением (одиночной) кодовой ошибки. Два таких кода приведены в

табл. 1.5.

Выявление ошибки в любом из этих кодов проводится проверкой на чет-

ность. Эта проверка основана на присоединении к каждому набору дополни-

тельного разряда с тем, чтобы количество единиц в любом кодовом наборе

данного кода было нечетным или четным. Более целесообразно число единиц

в кодовом наборе с выявлением одиночной ошибки выбирать нечетным. То-

гда любое кодовое представление, в том числе и для нуля, будет иметь хотя

бы одну 1. Это даст возможность отличить полное отсутствие информации от

передачи нуля в том случае, если 1 отражает наличие электрического сигна-

ла, а О — его отсутствие.

Таблица 1.5. Коды с выявлением ошибки

Десятичное число Двоично-десятичный код с проверкой на четность Код "2 из 5"

8 4 2 1 Р 0 1 2 4 7

0 0 0 0 0 0 0 0 0 1 1

1 0 0 0 1 1 1 1 0 0 0

2 0 0 1 0 1 1 0 1 0 0

10

Глава 1

Таблица 1.5 (окончание)

Десятичное число Двоично-десятичный код с проверкой на четность Код "2 из 5"

3 0 0 1 1 0 0 1 1 0 0

4 0 1 0 0 1 1 0 0 1 0

5 0 1 0 1 0 0 1 0 1 0

6 0 1 1, 0 0 0 0 1 1 0

7 0. 1 1 1 1 1 0 0 0 1

8 1 0 0 0 1 0 1 0 0 1

9 1 0 0 1 0 0 0 1 0 1

Дополнительный разряд р называется контрольным разрядом четности. Код,

который состоит из всех 10 возможных комбинаций 5-разрядных кодовых

наборов с двумя единицами, называется кодом "2 из 5".

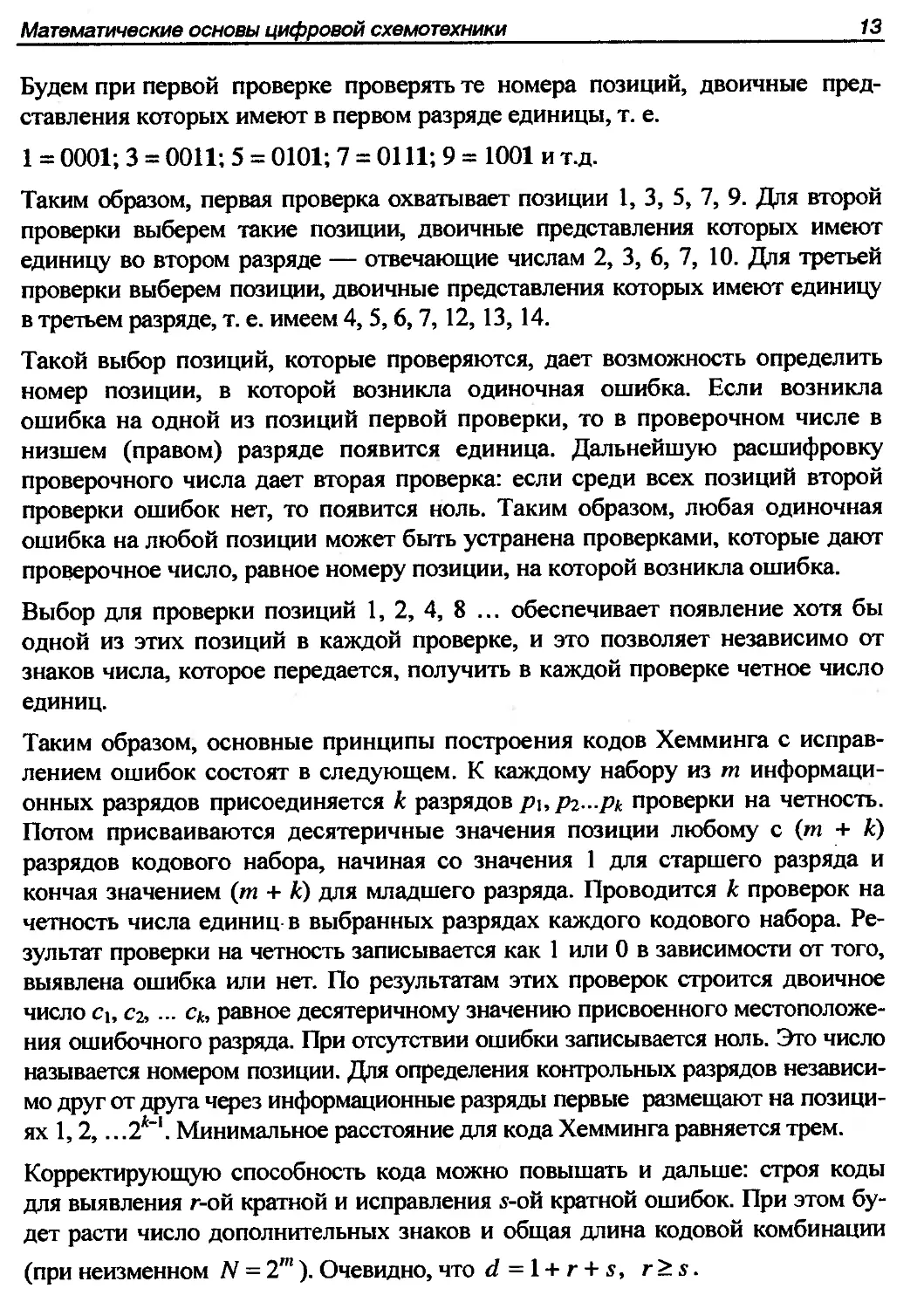

При построении корректирующих кодов часто прибегают к геометрической моде-

ли. Допустим, есть алфавит, который состоит из трех символов. Из них можно со-

ставить следующие комбинации: ООО, 001, 010, 011, 100, 101, 110, 111. В трехмер-

ном пространстве на осях найдем точки с координатами кода (рис. 1.1). Помеха

может исказить сигнал, т. е. вместо 0 появится 1 или наоборот. Очевидно, что если

кодовые комбинации отличаются одна от одной длиной ребра d = 1, то помеха

переведет один сигнал в другой и обнаружить ошибку в этом случае нельзя. Ее

можно обнаружить, если кодовые комбинации отстоят одна от одной на два ребра,

т. е. 000, 011,101, ПО. Для исправления необходимо, чтобы комбинации отлича-

лись на три единицы: 000, 111. Пространство, представленное на рис. 1.1, назы-

вается пространством Хемминга, а величина d — расстоянием по Хеммингу или

минимальным кодовым расстоянием. Например, минимальное кодовое расстояние

для кодов из табл. 1.5 равняется двум. Очевидно, что это расстояние всегда целое

число, равное числу разрядов, в которых отличаются двоичные числа, соответст-

вующие точкам в пространстве Хемминга. В общем случае пространство Хеммин-

га имеет п координат и изображается «-мерным кубом.

Для построения «-разрядного кода с выявлением ошибок нужно не больше

половины от 2” возможных комбинаций разрядов. Выбор кодовых наборов

проводится таким образом, чтобы при преобразовании одного допустимого

кодового набора в другой допустимый кодовый набор по крайней мере два

разряда имели противоположные значения.

Математические основы цифровой схемотехники

11

Рис. 1.1. Геометрическая интерпретация корректирующих кодов

1.3. Коды с исправлением ошибок

Не только обнаружить, но и исправить ошибку можно с помощью кодов, ко-

торые строятся следующим образом. Пусть есть ш-значный двоичный код.

Общее число комбинаций

N = 2m.

Каждый из таких кодов отличается один от другого хотя бы одним знаком.

Дополним код еще одним знаком, а число кодовых комбинаций оставим не-

изменным, тогда

N = 2n,=-2n

2

и можно так подобрать кодовые комбинации, что они будут отличаться дву-

мя знаками. При этом используется только половина всех возможных комби-

наций от 2", вторая половина образует запрещенные комбинации: любое по-

явление одиночной ошибки превращает ее в запрещенную и тем самым

ошибка обнаруживается. Дополним теперь код таким количеством знаков,

которое даст возможность двум кодовым комбинациям отличаться тремя

знаками при неизменном числе 7V=2'". Такой код позволит не только обна-

ружить, но и исправить одиночную ошибку. Действительно, если произошла

одиночная ошибка в какой-то комбинации, то эта комбинация от других бу-

дет отличаться на два знака, а от своей — на один, и ее легко исправить.

12

Глава 1

Определим общее число дополнительных знаков, необходимых для выявления

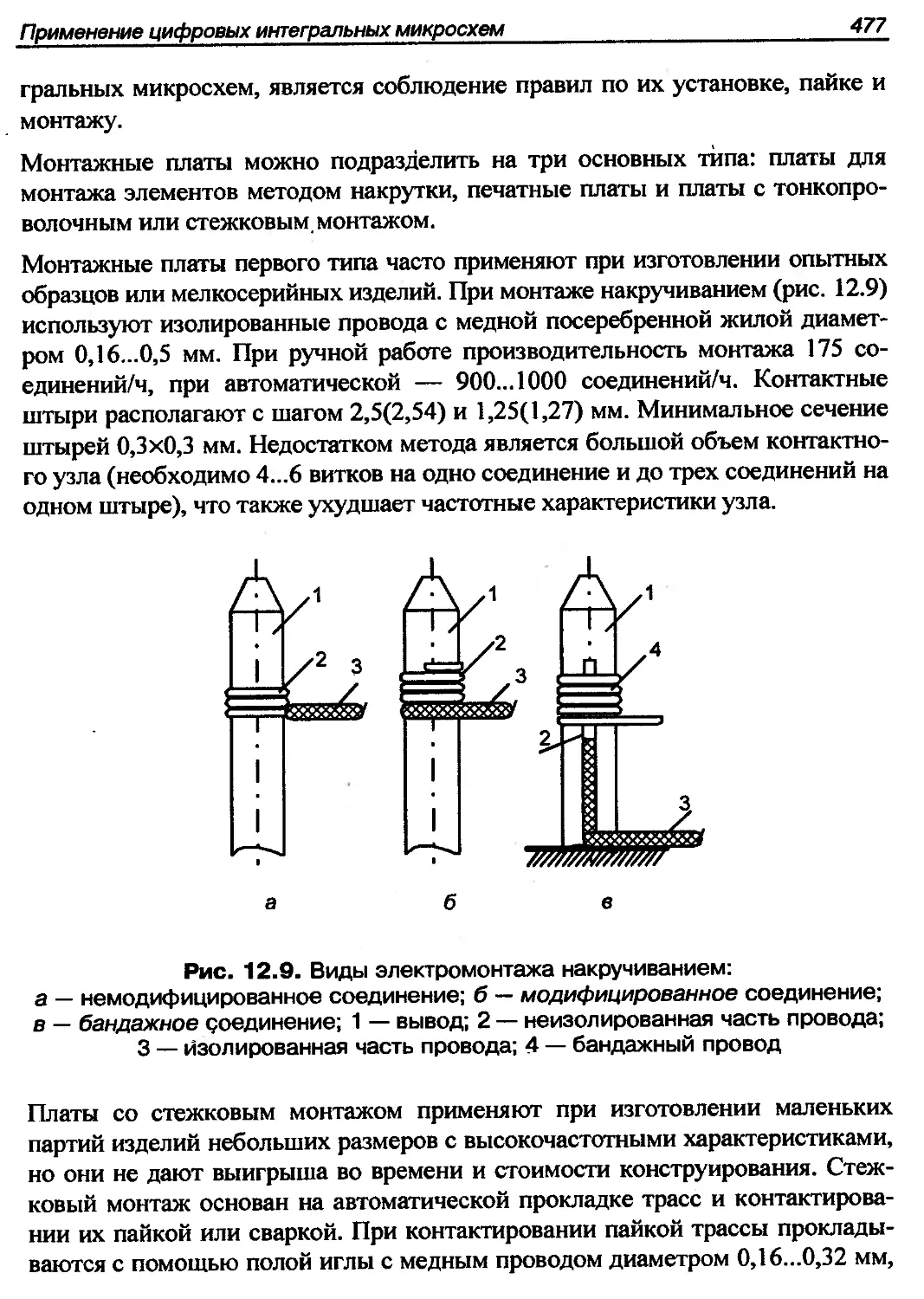

и исправления одиночных ошибок. Пусть из общего числа позиций п для пере-

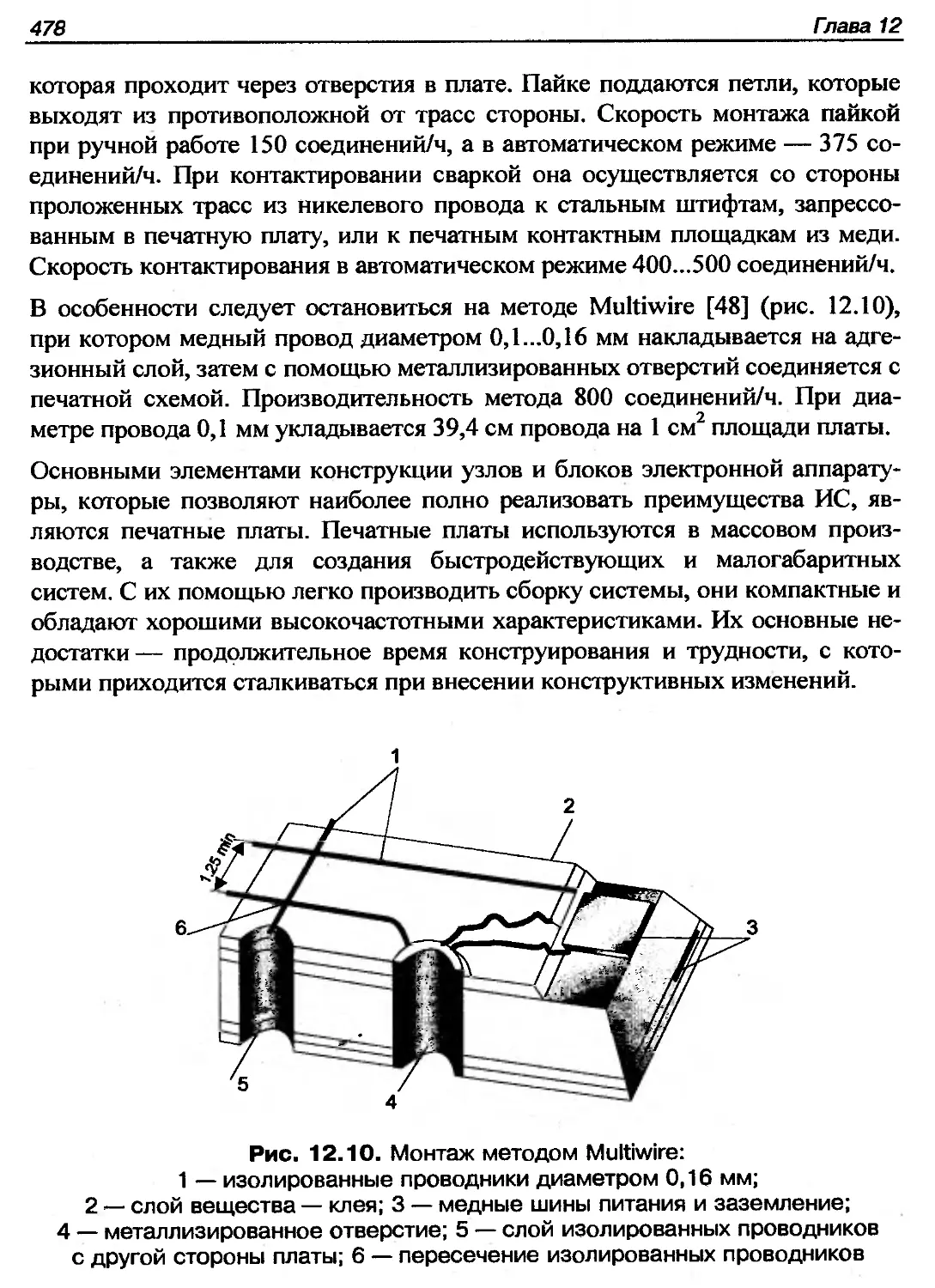

дачи информации используется фиксированное число позиций т. Другие пози-

ции к = п - т используются как проверочные. Символы, которые ставятся на к

проверочных позициях, определяются при кодировании проверкой на четность

каждой А-ой группы информационных символов. Сигнал кодируется так, чтобы

в результате любой из проверок выходило четное число. На приемном конце

на некоторых позициях появляются единицы вместо нулей и нули вместо еди-

ниц. При приеме также проводится проверка на четность.

Построим код, который разрешал бы обнаружить и исправить одиночную

ошибку. Пусть принята кодовая комбинация с ошибкой или без нее. Сделаем

в ней последовательно к проверок. После каждой проверки запишем 0, если

результат свидетельствует об отсутствии ошибки на позициях, т. е. сумма

единиц четная. Результат свидетельствует о наличии ошибки, если сумма

единиц нечетная и тогда записывается 1. Запись справа налево полученной

последовательности единиц и нулей дает двоичное число. Отсутствию ошиб-

ки в принятой кодовой комбинации будет отвечать число, составленное из

нулей. Проверочное число должно описывать (т + к + 1) событий. Следова-

тельно, число А: определяется на основе неравенства 2к >т + к + 1, и посколь-

2"

ку п = т + к, то 2т <--.

п + 1

Это соотношение позволяет определить максимальное т при данном п

или минимальное п для данного т. Соответствующие значения приведены в

табл. 1.6.

Определим позиции, которые надлежит проверить в любой из к проверок.

Если ошибок нет, то на всех позициях, которые проверяются, будет 0, если в

низшем разряде числа стоит 1, то это означает, что вследствие первой про-

верки выявлена ошибка.

Таблица 1.6. Соотношения для корректирующих кодов

п m к п m к

1 0 1 6 3 3

2 0 2 7 4 3

3 1 - 2 8 4 4

4 1 3 9 5 4

5 2 3 10 6 4

Математические основы цифровой схемотехники 13

Будем при первой проверке проверять те номера позиций, двоичные пред-

ставления которых имеют в первом разряде единицы, т. е.

1 = 0001; 3 = ООН; 5 = 0101; 7 = 01 И; 9 = 1001 и т.д.

Таким образом, первая проверка охватывает позиции 1, 3, 5, 7, 9. Для второй

проверки выберем такие позиции, двоичные представления которых имеют

единицу во втором разряде — отвечающие числам 2, 3, 6, 7, 10. Для третьей

проверки выберем позиции, двоичные представления которых имеют единицу

в третьем разряде, т. е. имеем 4, 5, 6, 7,12,13,14.

Такой выбор позиций, которые проверяются, дает возможность определить

номер позиции, в которой возникла одиночная ошибка. Если возникла

ошибка на одной из позиций первой проверки, то в проверочном числе в

низшем (правом) разряде появится единица. Дальнейшую расшифровку

проверочного числа дает вторая проверка: если среди всех позиций второй

проверки ошибок нет, то появится ноль. Таким образом, любая одиночная

ошибка на любой позиции может быть устранена проверками, которые дают

проверочное число, равное номеру позиции, на которой возникла ошибка.

Выбор для проверки позиций 1, 2, 4, 8 ... обеспечивает появление хотя бы

одной из этих позиций в каждой проверке, и это позволяет независимо от

знаков числа, которое передается, получить в каждой проверке четное число

единиц.

Таким образом, основные принципы построения кодов Хемминга с исправ-

лением ошибок состоят в следующем. К каждому набору из ш информаци-

онных разрядов присоединяется к разрядов р\, рг-.рк проверки на четность.

Потом присваиваются десятеричные значения позиции любому с (т + к)

разрядов кодового набора, начиная со значения 1 для старшего разряда и

кончая значением (т + к) для младшего разряда. Проводится к проверок на

четность числа единиц в выбранных разрядах каждого кодового набора. Ре-

зультат проверки на четность записывается как 1 или 0 в зависимости от того,

выявлена ошибка или нет. По результатам этих проверок строится двоичное

число с'ь с'2, ... с к, равное десятеричному значению присвоенного местоположе-

ния ошибочного разряда. При отсутствии ошибки записывается ноль. Это число

называется номером позиции. Для определения контрольных разрядов независи-

мо друг от друга через информационные разряды первые размещают на позици-

ях 1,2,. . .2*"’. Минимальное расстояние для кода Хемминга равняется трем.

Корректирующую способность кода можно повышать и дальше: строя коды

для выявления r-ой кратной и исправления s-ой кратной ошибок. При этом бу-

дет расти число дополнительных знаков и общая длина кодовой комбинации

(при неизменном N = 2'" ). Очевидно, что d = 1 + г + s, r>s.

14

Глава 1

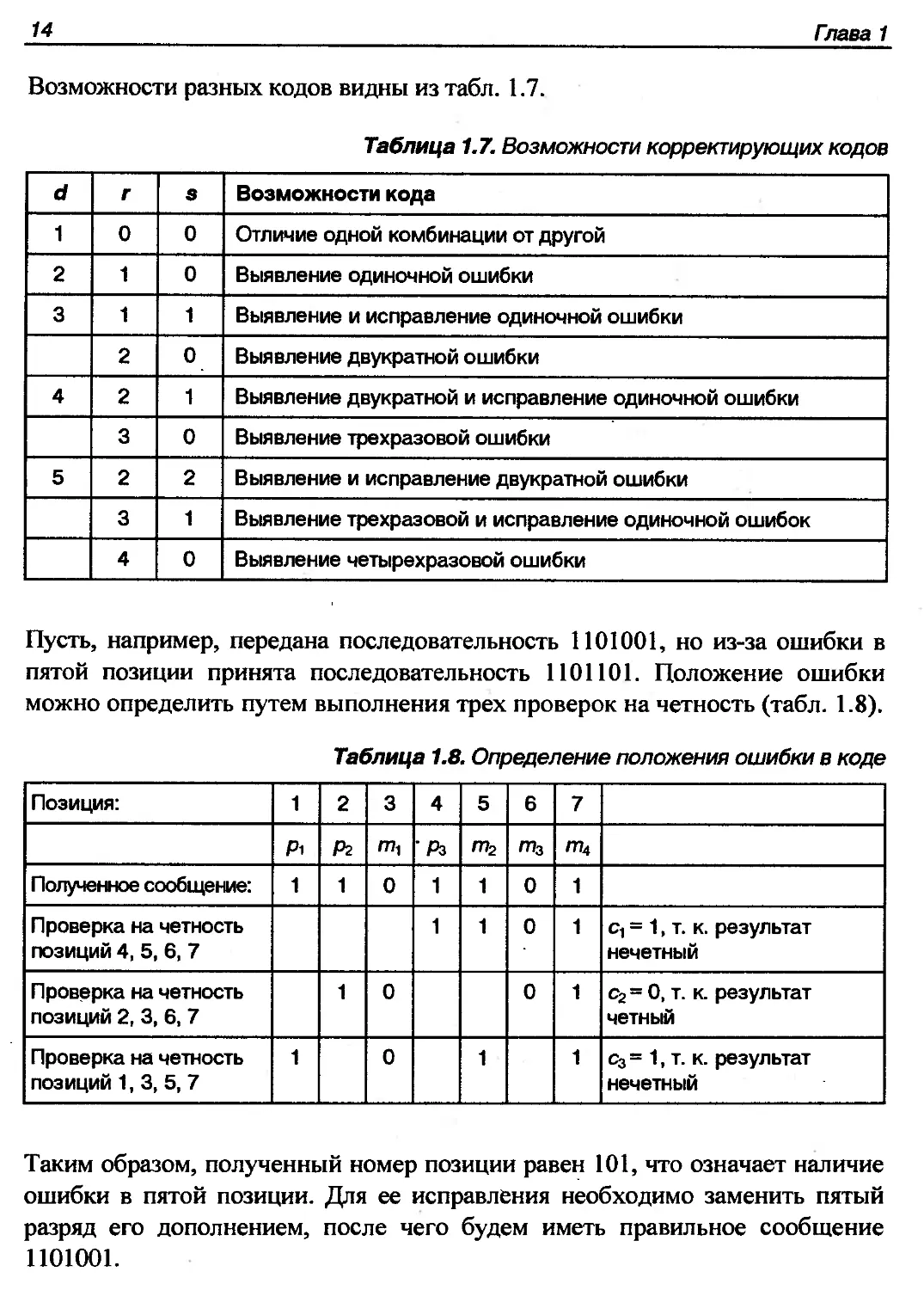

Возможности разных кодов видны из табл. 1.7.

Таблица 1.7. Возможности корректирующих кодов

d г 3 Возможности кода

1 0 0 Отличие одной комбинации от другой

2 1 0 Выявление одиночной ошибки

3 1 1 Выявление и исправление одиночной ошибки

2 0 Выявление двукратной ошибки

4 2 1 Выявление двукратной и исправление одиночной ошибки

3 0 Выявление трехразовой ошибки

5 2 2 Выявление и исправление двукратной ошибки

3 1 Выявление трехразовой и исправление одиночной ошибок

4 0 Выявление четырехразовой ошибки

Пусть, например, передана последовательность 1101001, но из-за ошибки в

пятой позиции принята последовательность 1101101. Положение ошибки

можно определить путем выполнения трех проверок на четность (табл. 1.8).

Таблица 1.8. Определение положения ошибки в коде

Позиция: 1 2 3 4 5 6 7

Pi Pi Рз Л?2 лтз т4

Полученное сообщение: 1 1 0 1 1 0 1

Проверка на четность позиций 4, 5, 6, 7 1 1 0 1 с, = 1, т. к. результат нечетный

Проверка на четность позиций 2, 3, 6, 7 1 0 0 1 с2 = 0, т. к. результат четный

Проверка на четность позиций 1, 3, 5, 7 1 0 1 1 с3 = 1, т. к. результат нечетный

Таким образом, полученный номер позиции равен 101, что означает наличие

ошибки в пятой позиции. Для ее исправления необходимо заменить пятый

разряд его дополнением, после чего будем иметь правильное сообщение

1101001.

Математические основы цифровой схемотехники

15

1.4. Двоичная арифметика

Арифметические действия над двоичными числами выполняются соответст-

венно приведенным ниже выражениям [30, 39].

Сложение Вычитание Умножение

0+0=0 0-0=0 0-0=0

1+0=1 1-0=1 1-0=0

0+1=1 1-1=0 0-1=0

1+1= 10 10-1=1 1(1=1)

Сложение двух многоразрядных двоичных чисел проводится поразрядно с

учетом единиц переполнения от предшествующих разрядов.

1011

+ 1011

10110

Вычитание многоразрядных двоичных чисел, аналогично сложению, начина-

ется из младших разрядов. Если занять единицу в старшем разряде, образу-

ются две единицы в младшем разряде.

1010

-ОНО

0100

Умножение представляет собой многоразовое сложение промежуточных

сумм и сдвиги.

10011

х 101

10011

00000

10011

1011111

Процесс деления состоит из операций вычитания, которые повторяются.

101010 111

- 111 ПО

0111

- Ш

0000

16

Гпава 1

1.5. Формы представления чисел

В ЭВМ применяются две основные формы представления чисел: полулога-

рифмическая с плавающей запятой и натуральная с фиксированным положе-

нием запятой.

При представлении чисел с фиксированной запятой положение запятой за-

крепляется в определенном месте относительно разрядов числа и сохраня-

ется неизменным для всех чисел, которые изображаются в данной разряд-

ной'сетке. Обычно запятая фиксируется перед первым (старшим) разрядом и

в разрядной сетке могут быть представлены только числа, которые по моду-

лю меньше 1. Для кодирования знака двоичного числа используется стар-

ший ("знаковый") разряд (ноль отвечает плюсу, единица — минусу).

При выполнении арифметических действий над правильными дробями мо-

гут получаться двоичные числа, по абсолютной величине больше или рав-

ные единице, что называется переполнением разрядной сетки, и старшие

разряды числа теряются. Для исключения возможности переполнения при-

ходится вводить масштаб величин, которые принимают участие в вычисле-

ниях. Числа, которые по абсолютной величине меньше единицы младшего

разряда разрядной сетки, также теряются и называются машинным нулем.

Недостатками представления чисел с фиксированной запятой являются:

П необходимость предшествующего расчета и введения в машину масштаб-

ных коэффициентов, что является довольно сложной работой (масштаб-

ные коэффициенты служат для уменьшения чисел, которые превышают

единицу или равны ей);

П зависимость относительной точности от значения поступающих чисел.

Максимальная относительная точность достигается при выполнении дей-

ствий с максимально возможными числами.

Использование представления чисел с фиксированной запятой позволяет уп-

ростить схемы машины, повысить ее быстродействие, но представляет опре-

деленные трудности для программирования. Поэтому представление чисел с

фиксированной запятой используется как основное только в микроконтрол-

лерах.

В универсальных ЭВМ основным является представление чисел с плавающей

запятой. Представление числа с плавающей запятой в общем случае имеет

вид:

А = m-qn,

где q — основа системы исчисления; п — целое число, называемое порядком

числа Л; т — мантисса числа A (|m| < 1).

Математические основы цифровой схемотехники 17

Поскольку в ЭВМ применяется двоичная система исчисления, то А = m -2п,

причем порядок и мантисса представлены в двоичной форме.

Если в записи числа старшая цифра отлична от нуля, число считается норма-

лизованным; если старшая цифра ноль — число не нормализовано. Нормали-

зация чисел в процессе вычисления выполняется в ЭВМ автоматически. При

этом мантисса числа сдвигается влево до момента появления в старшем раз-

ряде сетки ближайшей единицы. Здесь же проводится соответствующее

уменьшение порядка числа. В случае переполнения разрядной сетки, напри-

мер, при сложении нормализованных чисел одного порядка, проводится нор-

мализация вправо на один разряд. Нормализованное представление чисел

позволяет сохранять в разрядной сетке большее количество цифр и, значит,

повышает точность вычислений.

Преимуществом ЭВМ с плавающей запятой есть больший диапазон пред-

ставления чисел (причем без введения масштаба) по сравнению с ЭВМ с

фиксированной запятой. Так, если взять одинаковую разрядность и опреде-

лить количество разрядов в мантиссе через тц, то диапазон представленных

чисел в ЭВМ с фиксированной запятой будет равен:

2-Л| <|д|<1 —2-Л|,

в то время как для ЭВМ с плавающей запятой (для нормализованных чисел)

2-И1.2-(2"2-1) < |д| < (1 _ 2~"1) • 22"2"’,

где П2 — количество разрядов в порядке; (2”2 -1) — максимальное значение по-

рядка^-”1 — минимальное значение мантиссы (0,00...1...1);(1-2-Л1) — макси-

мальное значение мантиссы (0,11...1).

Сравнивая между собой приведенные соотношения, можно заключить, что

для ЭВМ с плавающей запятой диапазон представленных чисел больше. Ши-

рокий диапазон представления чисел с плавающей запятой удобен для науч-

ных и инженерных расчетов, но для выполнения действий нужны операции

отдельно с мантиссами чисел и отдельно с порядками, что усложняет цифро-

вые устройства и замедляет выполнение операций.

Цифровую информацию принято вводить в определенном формате, заданном

числом разрядов [30, 46]. Каждая двоичная цифра, т. е. один двоичный раз-

ряд числа, называется битом информации. Восемь бит образуют байт. Четыре

байта образуют 32-разрядное слово. Двойное слово содержит 64 двоичных

разряда. Используется также формат полуслова — два байта.

18

Глава 1

С целью упрощения схем вычитание в ЭВМ заменяется сложением специ-

ально построенных кодов чисел. Применяются следующие коды чисел: пря-

мой, обратный и дополнительный. Прямой код числа позволяет дать изобра-

жение числа с учетом знака. Поэтому прямой код положительного числа

совпадает с его записью, а прямой код отрицательного числа отличается от

обычной записи числа знаковым разрядом, в который заносится единица.

В ЭВМ прямой код применяется только для представления положительных

двоичных чисел. Для представления отрицательных чисел применяется или

дополнительный, или обратный код, поскольку над отрицательными числа-

ми в прямом коде неудобно выполнять арифметические операции.

Дополнительный и обратный коды положительного числа совпадают с его

прямым кодом. Правила для образования дополнительного и обратного кода

заключаются в следующем:

□ для образования дополнительного кода отрицательного числа необходимо

в знаковом разряде поставить единицу, а все цифровые разряды инверти-

ровать (заменить 1 на 0, а 0 — на 1), после чего прибавить 1 к младшему

разряду;

□ для образования обратного кода отрицательного числа необходимо в знако-

вом разряде поставить единицу, а все цифровые разряды инвертировать.

Пример:

Число Прямой код Обратный код Дополнительный код

Х= + 0,10101 [Х]ПР= 0,10101 [Х]ОБ=0,10101 [Х]ДОп = 0,10101

У=-0,01011 [У]ПР= 1,01011 [У]ОБ= 1,10100 [У]Доп= 1.Ю101

Прямой код можно получить из дополнительного и обратного кода по тем

же правилам, которые служат для нахождения дополнительного и обратного

кодов.

При сложении чисел в обратном коде разряды значащих чисел складываются

поразрядно справа налево, а знаковые разряды складываются как разряды

целых чисел; единица переполнения, которая получается в знаковом разряде,

прибавляется к младшему разряду суммы. Последнее действие носит назва-

ние циклического переноса.

При сложении чисел в дополнительном коде значащие разряды складывают-

ся поразрядно, знаковые разряды — как разряды целых чисел, а единица пе-

реполнения, которая получается в знаковом разряде, не учитывается.

Математические основы цифровой схемотехники

19

Если знаковый разряд результата равен нулю, то получено положительное

число, которое представлено в прямом коде. Если в знаковом разряде едини-

ца, то результат отрицательный и представлен в обратном или дополнитель-

ном коде.

Пример:

а) Прямой код Обратный код Сложение

[х]пр=0,10101 0,10101 0,10101

. Гу1пР=1,01001 v 1,10110 1,10110

[х+у]пр=0,01100 10,01011

1

х+у = 0,01100

Проверим в десятеричном коде эквивалентными целыми числами:

х = +21; у = -9; х + у = +12 = 01100(2)

б) Прямой код [х]пр=1,10101 [y]npEEOQ1001_ [х+у]пр= 1,01100 Обратный код Сложение 1,01010 1,01010 0,01001 0,01001 1,10011 [х+у ]об = 1,10011

Проверка: х = -21; у = +9; х + у = -12=1,01100(2)

в) Прямой код Сдвиг [х]пр=1,11010 1,011010 Гу1пп=1,01100 1,001100 Дополнительный код 1,100110 1,110100 Сложение 1,100110 1,110100

[х+у]доп =11,011010

Проверка: х = -26; в = -12; х + в = -38 = 1,100110(2)

Для того чтобы избежать ошибок при выполнении бинарных операций, перед

переводом чисел в обратные и дополнительные коды необходимо выравни-

вать количество разрядов прямого кода операндов.

20

Глава 1

При сложении чисел, меньших единицы, могут быть получены числа, по абсо-

лютной величине больше единицы. Для выявления переполнения разрядной

сетки в ЭВМ применяются модифицированные прямой, обратный и дополни-

тельный коды. В этих кодах знак кодируется двумя разрядами, причем знаку

"плюс" отвечает комбинация 00, а знаку "минус" — комбинация 11.

Правила сложения для модифицированных кодов те же, что и для обычных.

Единица переноса из старшего знакового разряда в модифицированном до-

полнительном коде отбрасывается, а в модифицированном обратном коде

передается в младший цифровой разряд.

Признаком переполнения служит появление в знаковом разряде суммы ком-

бинации 01 при сложении положительных чисел (положительное переполне-

ние) или 10 при сложении отрицательных чисел (отрицательное переполне-

ние). Старший знаковый разряд в этих случаях содержит истинное значение

знака суммы, а младший является старшей цифрой значащего числа. Для

коррекции переполнения число надо сдвинуть в разрядной сетке на один раз-

ряд вправо, а в старший знаковый разряд, который освободился, поместить

цифру, равную новому значению младшего знакового разряда. После кор-

ректирования переполнения мантиссы результата необходимо увеличить на

единицу порядок результата.

Пример:

Сложение

Х= 0,101011

+ Y= 0,110100

X+Y = 1,011111

Сложение в модифицированном коде:

Х=00,101011

+ Y= 00,110100

X+Y= 01,011111 —> 00,1011111

Контрольные вопросы и задания

1. В чем различия позиционной системы исчисления и непозиционной?

2. Каковы преимущества и недостатки десятичной, восьмеричной и двоич-

ной систем исчисления?

Математические основы цифровой схемотехники 21

3. Приведите правила перевода из десятичной системы исчисления в двоич-

ную систему и наоборот.

4. Приведите правила перевода из десятичной системы исчисления в вось-

меричную систему и наоборот.

5. Приведите правила перевода из десятичной системы исчисления в шест-

надцатеричную систему и наоборот.

6. Запишите двоично-десятичный код числа 21.

7. Превратите число 247(ю) по схеме (10) —> (2) —> (8) -» (10).

8. Как. представляются отрицательные числа в двоичном коде?

9. Используя двоичные коды, определите разность десятичных чисел 24 и 56.

10. В чем состоит особенность кода Грэя?

11. Объясните, как происходит выявление одиночной ошибки в одном разря-

де двоичного кода?

12. Какие основные формы представления чисел в ЭВМ?

13. Что такое нормализация чисел и переполнения разрядной сетки ЭВМ?

14. Приведите правила образования обратного и дополнительного кода.

Глава 2

Алгебра логики

и теоретические основы синтеза

цифровых устройств

2.1. Элементы математической логики

Математическая логика является частью формальной логики и служит теоре-

тической основой построения электронных вычислительных машин и цифро-

вых устройств. Наиболее широкое применение из области математической

логики получила алгебра логики [15, 28, 50, 55].

Базой алгебры логики являются понятия о высказывании, истинности и лож-

ности высказывания, связях между высказываниями. Высказывание или

логический аргумент в зависимости от значения бывают истинными или

ложными. Значение высказывания может изменяться с изменением обстоя-

тельств, и таким образом высказывание меняет оценку своей истинности.

С точки зрения логики, высказывания можно разделить на:

П высказывание истинно постоянно (математически их принимают равны-

ми 1);

П высказывание ложно постоянно (математически их принимают равными 0);

□ высказывание, которое может быть истинным или ложным в зависимости

от определенных условий, т. е. принимать значение 1 или 0 попеременно.

По смыслу высказывания бывают простые и сложные. Простое высказывание —

логический аргумент (переменная) — входит в состав сложного высказыва-

ния логической функции, которая зависит от истинности или ложности аргу-

мента. Обычно простое высказывание обозначается малыми буквами латин-

ского или русского алфавита: х, е, z, tn, р, а, Ь. Сложные высказывания или

логические функции, обозначают большими буквами латинского или русско-

го алфавита: A, F, Р, X, Y, S, Q. Связи между высказываниями-аргументами

24

Глава 2

по своей логике разные, и из-за этого значение сложного высказывания непо-

стоянное.

Разные комбинации значений входных переменных в логических функциях

называются наборами. Функция является полностью заданной, если указаны

ее значения для всех наборов значений входных переменных. Сопоставляя

каждому набору значение функции, равное 0 или 1, можно получить таблич-

ное задание данной функции, которое называется таблицей истинности или

таблицей соответствия.

Рассмотрим логические функции п аргументов, задаваясь набором аргумен-

тов и таблицей истинности, в которой определяется значение функции для

каждого сочетания аргументов. Для определения конечного числа функций

используется формула 2 , значит, для двузначной системы набор функции

двух переменных равняется 16, а одной переменной — 4. Логические двоич-

ные функции получили название булевых по имени английского математика

XIX века Дж. Буля. Наименование, обозначение и значение всех шестнадца-

ти функций Буля для двузначной системы двух переменных дано в табл. 2.1

вместе с названиями схем логических элементов.

2.2. Основные законы алгебры логики

В алгебре логики введена следующая система аксиом [9, 10], которая опре-

деляет свойства и отношения основных операций:

a+b=b+a

a(b + c) = ab + ac

a + bc-(a + b)(a + c)

a + a-1

a+a= b + b

da =bb

На основе этих аксиом выводятся все теоремы, которые выражают основные

законы алгебры логики. Их еще называют системой равносильных преобра-

зований функции или равнозначностями:

1. Законы нулевого множества

О-а-О

0 + a-a

0-adc...z = 0,

Алгебра логики и теоретические основы синтеза цифровых устройств

25

т. е. конъюнкция любого числа переменных обращается в ноль, если ка-

кая-нибудь одна переменная имеет значение 0, независимо от значений

других переменных.

2. Законы универсального множества

la = a

1 + а = 1

l + a + b + ... + z = 1,

т. е. дизъюнкция любого числа переменных обращается в единицу, если

хотя бы одна из ее переменных имеет значение 1, независимо от значений

других переменных.

3. Законы идемпотентности (повторения, тавтологии)

аа...а = а

а + а + .... + а = а.

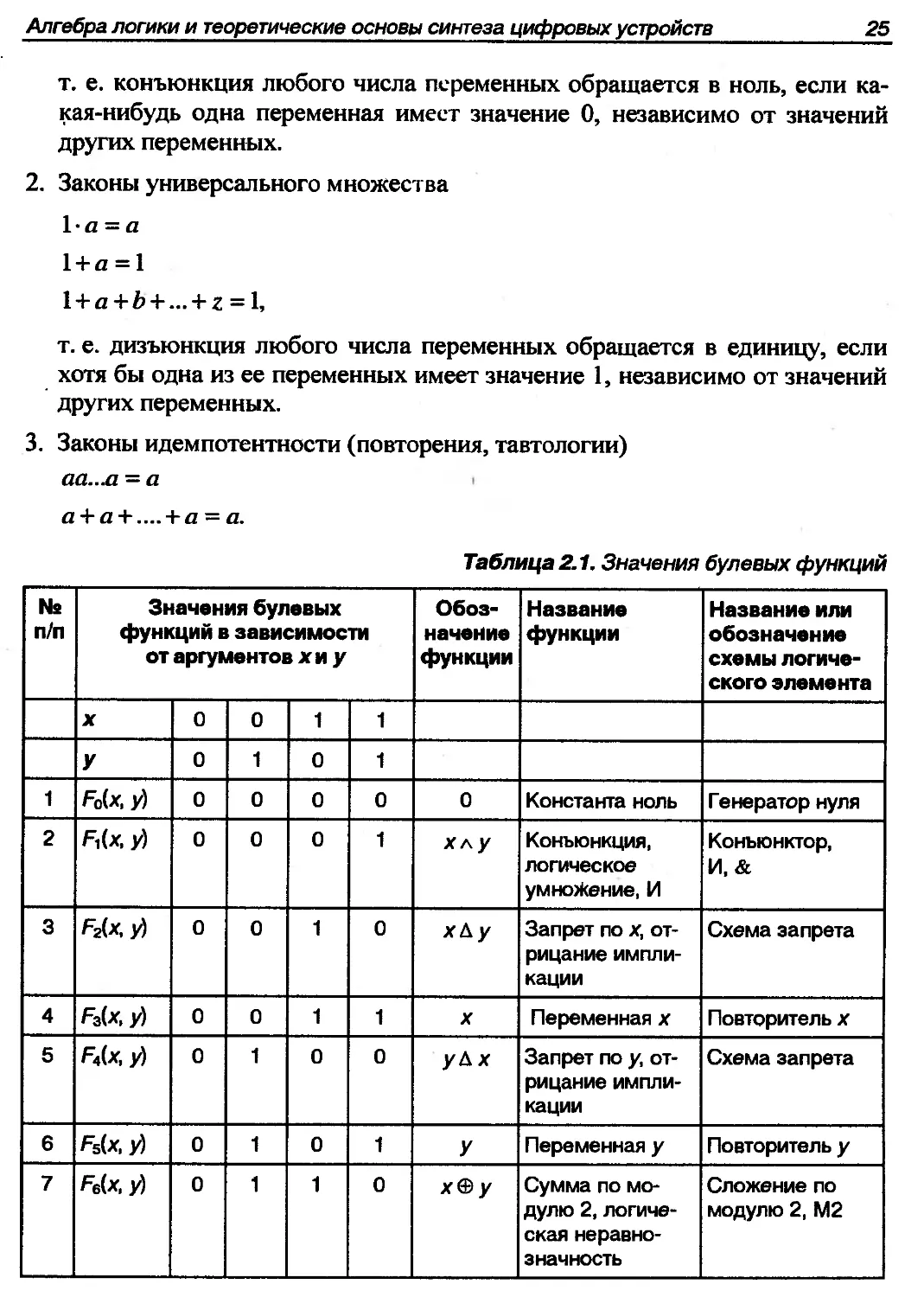

Таблица 2.1. Значения булевых функций

Ns п/п Значения булевых функций в зависимости от аргументов х и у Обоз- начение функции Название функции Название или обозначение схемы логиче- ского элемента

X 0 0 1 1

У 0 1 0 1

1 F0(x, у) 0 0 0 0 0 Константа ноль Генератор нуля

2 Fi(x, у) 0 0 0 1 хлу Конъюнкция, логическое умножение, И Конъюнктор, И, &

3 F2(x, у) 0 0 1 0 хД у Запрет по х, от- рицание импли- кации Схема запрета

4 F3(x, у) 0 0 1 1 X Переменная х Повторитель х

5 Ых, у) 0 1 0 0 уД х Запрет по у, от- рицание импли- кации Схема запрета

6 Fs(x, у) 0 1 0 1 У Переменная у Повторитель у

7 F6(x, у) 0 1 1 0 X® у Сумма по мо- дулю 2, логиче- ская неравно- значность Сложение по модулю 2, М2

26

Глава 2

Таблица 2.1 (окончание)

№ п/п Значения Булевых функций в зависимости от аргументов хи у Обоз* начение функции Название функции Название или обозначение схемы логиче- ского элемента

X 0 0 1 1

У 0 1 0 1

8 FAx, у) 0 1 1 1 XV у Дизъюнкция, логическое сло- жение, ИЛИ Дизъюнктор, ИЛИ

9 FB(x, у) 1 0 0 0 хХу X vy Стрелка Пирса, отрицание дизъюнкции Элемент Пирса, ИЛИ-НЕ

10 F9(x, у) 1 0 0 1 хву Эквивалентность Равнозначность

11 Fo(x, у) 1 0 1 0 У Отрицание, инверсия у Инвертор НЕ

12 Fn(x, у) 1 0 1 1 у->х Импликация от ук X Элемент импликации

13 Fi2(x, У) 1 1 0 0 X Отрицание, инверсия х Инвертор НЕ

14 6з(* У) 1 1 0 1 х—> у Импликация отхк у Элемент импли- кации

15 Fi4(x, у) 1 1 1 0 х/у Штрих Шеффе- ра, отрицание конъюнкции Элемент Шеф- фера, И-НЕ

16 F15(x, у) 1 1 1 1 1 Константа еди- ница Генератор еди- ницы

4. Законы двойной инверсии

a = a,

т. е. двойную инверсию можно снять.

5. Законы дополнительности:

а) логическое противоречие

aa =0,

т. е. конъюнкция любой переменной и ее инверсии есть 0.

Алгебра логики и теоретические основы синтеза цифровых устройств 27

б) закон исключенного третьего

a + a =1,

т. е. дизъюнкция любой переменной и ее инверсии есть 1.

6. Коммутативный (закон перемещения) закон

ab — ba

a + b = b + a,

т. е. результаты выполнения операций конъюнкции и дизъюнкции не за-

висят от того, в каком порядке следуют переменные.

7. Ассоциативные (сочетательные) законы

a(bc) = (ab)c = abc

a + (b + c) = (a + b) + c = a + c + b,

t. e. для записи конъюнкции или дизъюнкции скобки можно опустить.

8. Дистрибутивные (распределительные) законы:

а) конъюнкции относительно дизъюнкции

a(6 + c) = ah + ac;

б) дизъюнкции относительно конъюнкции

a + be = (a + b)(a + с).

9. Законы поглощения

a(a + b) = a

a(a + b)(a + c)...(a + w) = a

a + ab = a

a + ab + ac + ... + aw = a

a(a + b) = ab

a + ab = a + b.

10. Законы склеивания (распространения)

ab + ab = a

(a + b)(a + b) = a.

2 Зак. 3400

28

Глава 2

11. Законы обобщенного склеивания

ab + ac + bc = ab + ac

(a + b)(a + c)(b + c) = (a + b)(a + c)

(a + b)(a +c') = ac + ab.

12. Законы де Моргана (законы инверсии):

а) для двух переменных

ab = a + b,

т. е. инверсия конъюнкции есть дизъюнкция инверсий;

a + b = ab ,

т. е. инверсия дизъюнкции есть конъюнкция инверсий;

б) для п переменных

abc...w = a + b + c+... + w

a + b + c + ... + w = abc...w.

13. Теорема разложения

F(a,b,...,w) = aF(l,b,...,w) + aF(O,b,...,w)

F(a,b,...,w') = [a + F(0,b,...,w)]x[a + F(l,b,...,w)]

aF(a,a,b,c,...,w) = aF(l,O,b,c,...,w)

aF(a,a,b,c,...,w) = aF(O,l,b,c,...,w)

a + F(a,a,b,c,...,w') = a + F(O,l,b,c,...,w)

a + F(a,a,b,c,...,w) = a + F(l,O,fe,c,...,w).

2.3. Формы логических функций

и их использование

для синтеза логических схем

Зависимость выходных переменных yh выраженная через совокупность

входных переменных x(x0 с помощью операций алгебры логики, но-

сит название функции алгебры логики. Для «-разрядного двоичного кода х„_ь...,

A jAo существует 2" разных значения у,.

Алгебра логики и теоретические основы синтеза цифровых устройств 29

Функция называется полностью определенной, если заданы 2" ее значений.

Если часть значений функции не задана, то она называется частично опре-

деленной или неполностью определенной.

Иногда известно, что по условиям работы устройства появление некоторых

входных кодов невозможно, и поэтому значения функции алгебры логики на

этих кодах не задаются. При этом возникают так называемые факультатив-

ные или необязательные значения функции, которые могут задаваться про-

извольными. Входные коды, для которых функция алгебры логики имеет

факультативные значения, называются запрещенными.

Для описания функций алгебры логики могут быть использованы разные

способы. Основными из них являются описание функций в словесной форме,

в виде таблиц истинности, алгебраических выражений, последовательностей

десятичных чисел, а также кубических комплексов:

1. Словесное описание функций алгебры логики. Словесный вид описа-

ния наиболее часто применяется для первичного, начального описания

поведения логического устройства.

Пример: Логическая функция трех переменных равняется единице, если

хотя бы две входные переменные равняются единице.

2. Описание функций алгебры логики в виде таблицы истинности. Таб-

лица, которая содержит все возможные комбинации входных переменных

xn-i,..., х\хо и соответствующие им значения выходных переменных у», на-

зывается таблицей истинности или комбинационной таблицей. В общем

случае таблица истинности содержит 2" строк.

Пример: Составим таблицу истинности для функций алгебры логики (см.

табл. 2.2) из предыдущего примера.

Таблица 2.2. Таблица истинности логической функции трех переменных

*2 *1 Хо У

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

30

Глава 2

3. Описание функций алгебры логики в виде алгебраического выраже-

ния. Алгебра логики позволяет создавать сложные функции, аргументы

которых есть функции других двоичных аргументов. Операция замены ар-

гумента одной функции другими, более простыми функциями носит на-

звание суперпозиции функции. Многоразовое использование принципа

суперпозиции дает возможность получить функции желательного числа

аргументов.

Элементарная конъюнкция получается конъюнкцией конечного множества

логических переменных и их инверсий.

Пример: P(x,y,z) = xyz.

Элементарная дизъюнкция получается дизъюнкцией конечного множест-

ва логических переменных и их инверсий.

Пример: Р(х,y,z) = х+ y + z

Количество переменных в элементарной конъюнкции (дизъюнкции) на-

зывается ее длиной и определяет ее ранг.

Пример: Р(х, y,z,w) = х+ у + z + w есть дизъюнкция четвертого ранга.

Минтермом называют функцию, которая принимает единичное значение

при одном из всех возможных наборов аргументов, а макстермом назы-

вают функцию, которая принимает нулевое значение при одном из воз-

можных наборов и единичное значение при всех других. Минтерм алгеб-

раически представляет собой конъюнкцию аргументов, а макстерм —

дизъюнкцию аргументов. Если используется двоичная система и число

наборов аргументов и, то число минтермов или макстермов А=2".

Дизъюнкция любого числа элементарных конъюнкций называется дизъ-

юнктивной нормальной формой (ДНФ).

Пример: a + bc + abc + abc.

Конъюнкция любого числа элементарных дизъюнкций называется конъ-

юнктивной нормальной формой (КНФ).

Пример: a(a + b)(b + с)(?7 + b + с ).

Нормальные формы логических функций принято называть канонически-

ми. Логическую функцию, заданную любым аналитическим выражением,

можно непосредственно превратить в нормальную дизъюнктивную (или

конъюнктивную) формы.

Алгебра логики и теоретические основы синтеза цифровых устройств 31

Для этого необходимо:

• выразить все операции через операции конъюнкции, дизъюнкции и ин-

версий;

• избавиться от инверсии над целыми выражениями, перейдя к форме, в

которой есть инверсии только отдельных переменных;

• раскрыть скобки, применяя закон дистрибутивности;

• привести конъюнкции (дизъюнкции) к элементарным.

Если в состав логической формулы входят наборы элементарных конъ-

юнкций одинакового ранга, связанные дизъюнкцией, то такая форма

представления логической функции носит название совершенной дизъ-

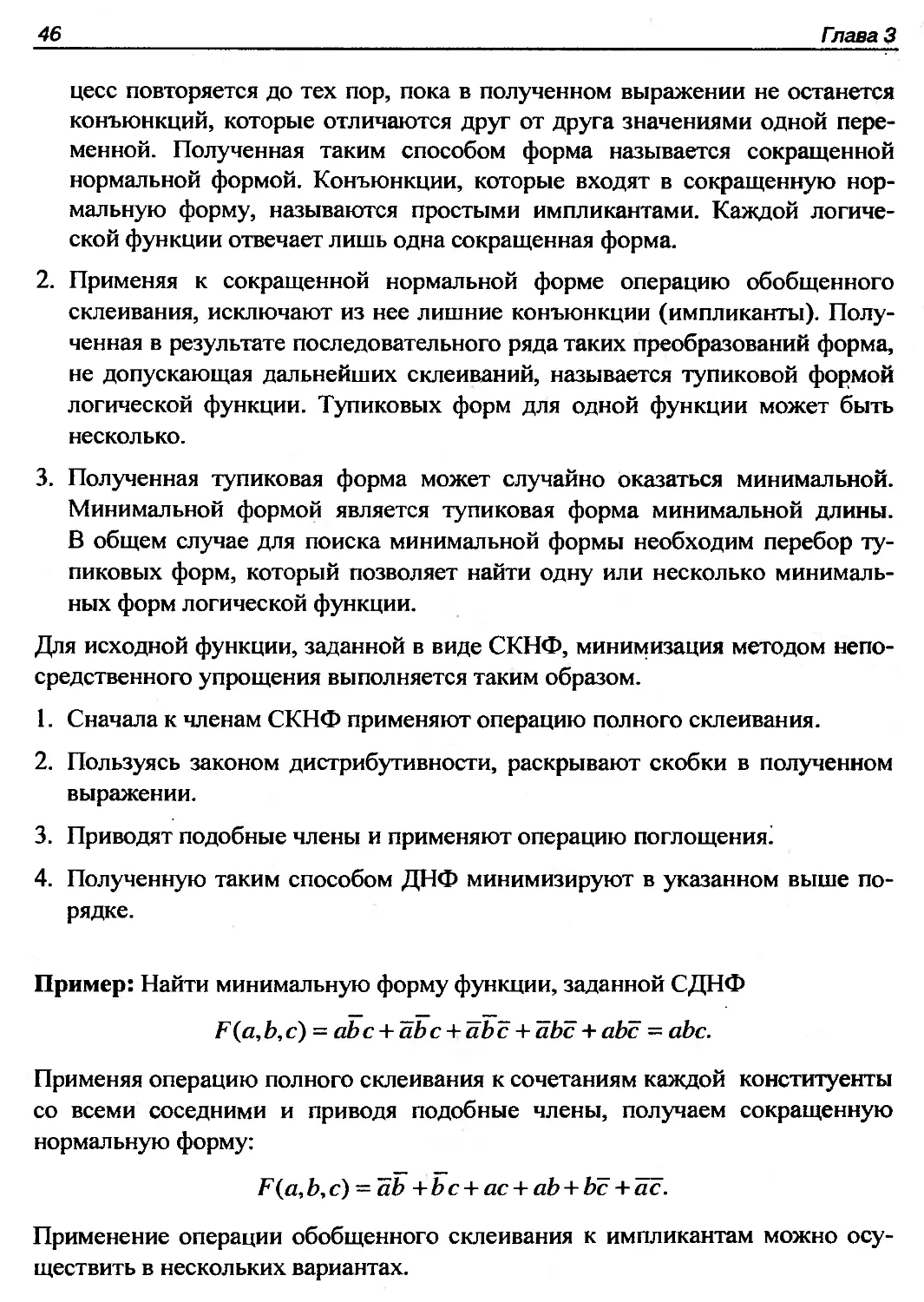

юнктивной нормальной формы (СДНФ). Правило образования СДНФ

функции п аргументов заключается в следующем.

• По каждому набору двоичных переменных, при котором функция при-

нимает значение единицы, составить элементарные конъюнкции (мин-

термы).

• В элементарную конъюнкцию записать неинвертированными переменные,

заданью единицей в таблице истинности, а инвертированными те перемен-

ные, которые в таблице истинности заданы нулем. Полученные соединения

называют конституентами единицы.

• Элементарные конъюнкции соединить знаком дизъюнкции.

Совершенной нормальной конъюнктивной формой (СКИФ) логической

функции принято называть такое ее выражение, которое содержит элемен-

тарные дизъюнкции одного ранга, связанные конъюнкцией. Правило обра-

зования СКНФ п аргументов заключается в следующем.

• По каждому набору двоичных переменных, при котором функция при-

нимает значение нуля, составить элементарные дизъюнкции (мак-

стермы).

• В элементарные дизъюнкции записать неинвертированными перемен-

ные, заданные нулем в таблице истинности, а инвертированными те

переменные, которые в таблице истинности заданы единицей. Полу-

ченные суммы называют конституентами нуля.

• Элементарные дизъюнкции соединить знаком конъюнкции.

Пример: Пусть таблицей истинности задана функция F(x2, %i, х0) (табл. 2.3),

и нужно образовать ее СДНФ и СКНФ.

32

Глава 2

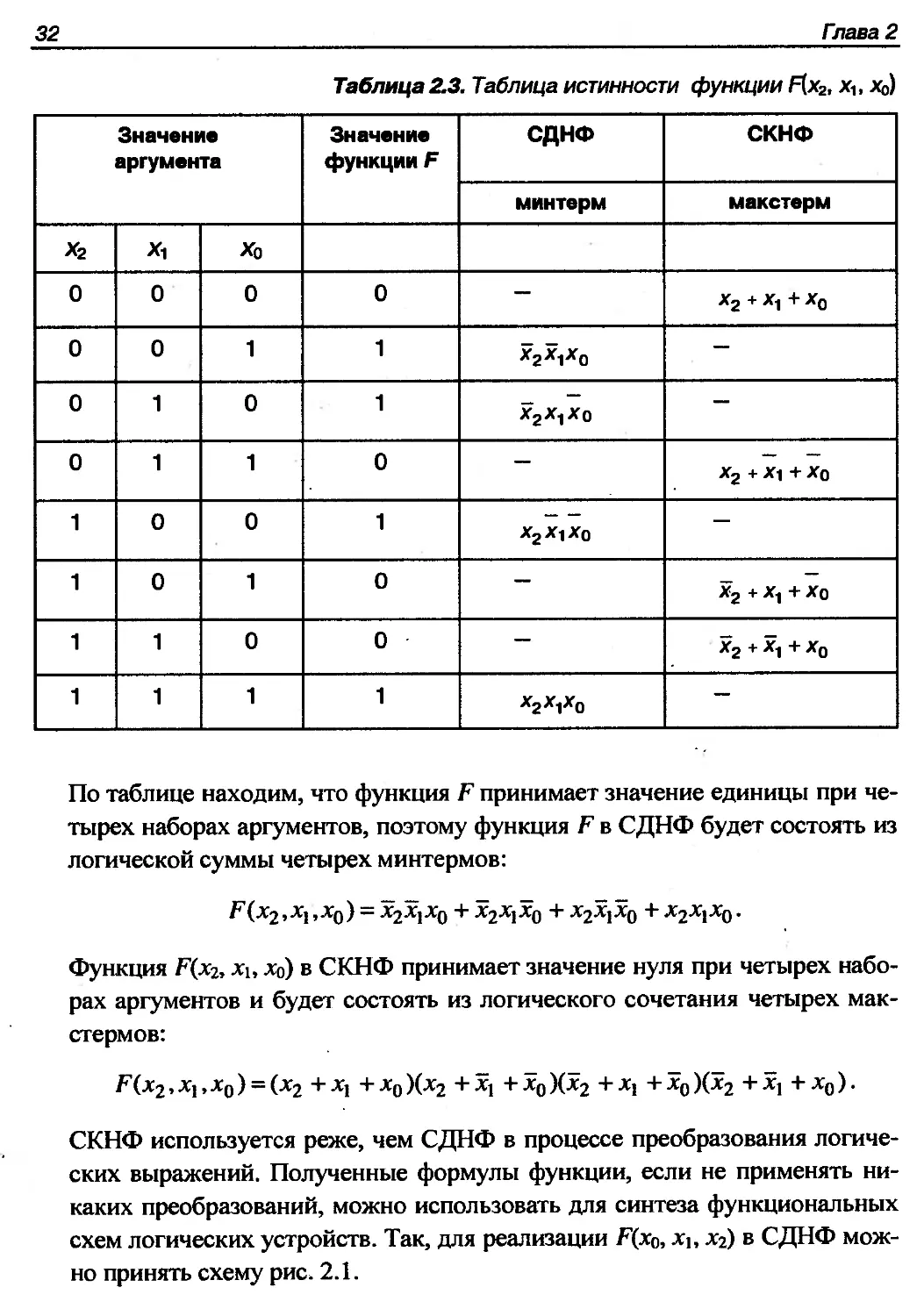

Таблица 2.3. Таблица истинности функции F[x2, xu х0)

Значение аргумента Значение функции F СДНФ СКНФ

минтерм макстерм

*2 *1 Хо

0 0 0 0 — X2 + X, + x0

0 0 1 1 о к Ik” Ik —

0 1 0 1 X2XfXo —

0 1 1 0 — x2 + XI + Xo

1 0 0 1 X2XiX0 —

1 0 1 0 — x2 + Xi + XO

1 1 0 0 — x2 + Xf + x0

1 1 1 1 X2XiX0 —

По таблице находим, что функция F принимает значение единицы при че-

тырех наборах аргументов, поэтому функция F в СДНФ будет состоять из

логической суммы четырех минтермов:

F(x2,X] >хо) = *2*1х0 + *2х1*0 + х2*1-*0 + Л2х1х0 •

Функция F(x2, хь х0) в СКНФ принимает значение нуля при четырех набо-

рах аргументов и будет состоять из логического сочетания четырех мак-

стермов:

F(x2,Xj,x0) = (x2 +*1 +*о)(х2 +*1 +*оХ*2 +х1 +*о)(*2 +*1 +*о)-

СКНФ используется реже, чем СДНФ в процессе преобразования логиче-

ских выражений. Полученные формулы функции, если не применять ни-

каких преобразований, можно использовать для синтеза функциональных

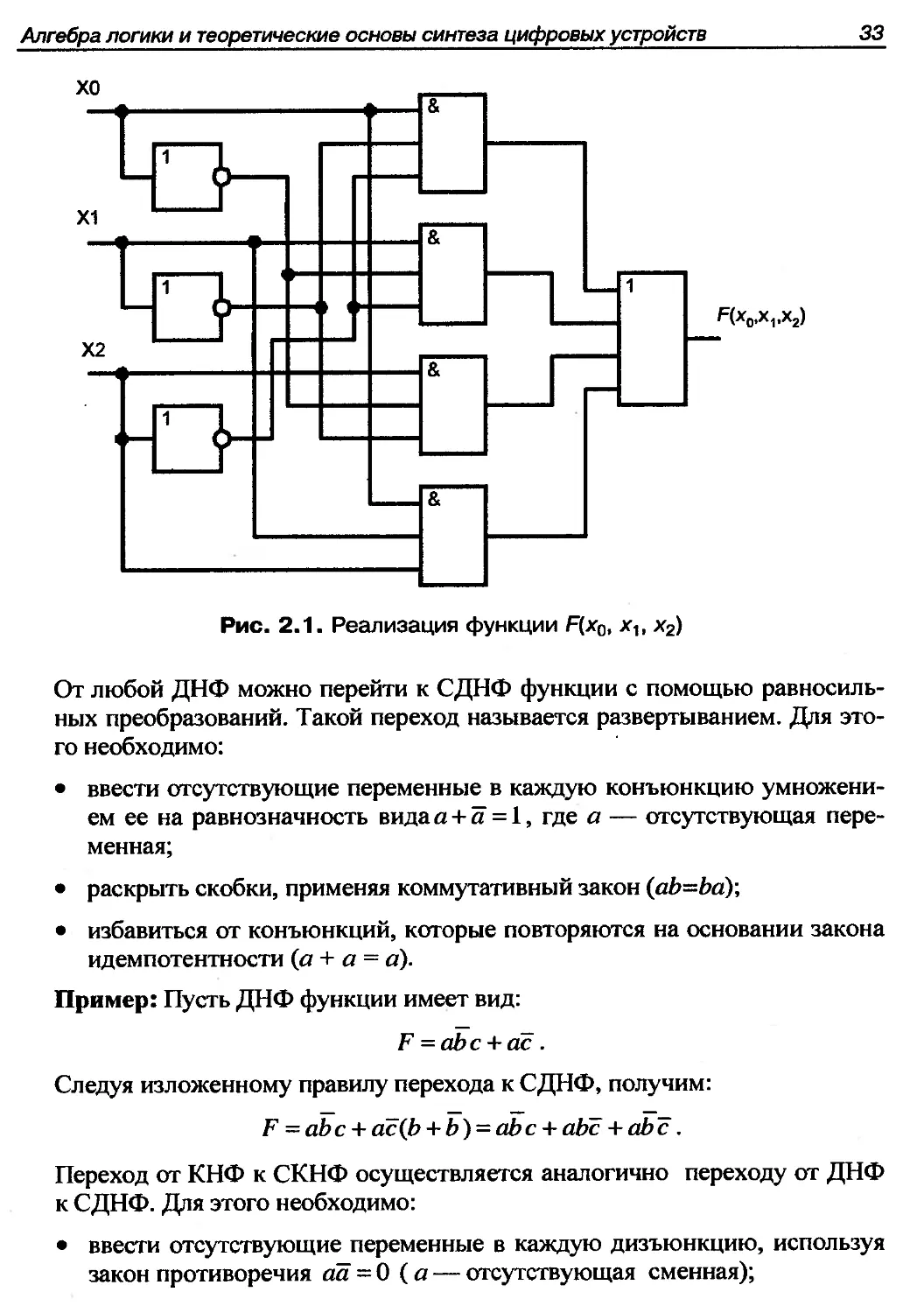

схем логических устройств. Так, для реализации F(x0, хь х2) в СДНФ мож-

но принять схему рис. 2.1.

Алгебра логики и теоретические основы синтеза цифровых устройств

33

От любой ДНФ можно перейти к СДНФ функции с помощью равносиль-

ных преобразований. Такой переход называется развертыванием. Для это-

го необходимо:

• ввести отсутствующие переменные в каждую конъюнкцию умножени-

ем ее на равнозначность видая + а =1, где a — отсутствующая пере-

менная;

• раскрыть скобки, применяя коммутативный закон (ab—ba)',

• избавиться от конъюнкций, которые повторяются на основании закона

идемпотентности (я + a = я).

Пример: Пусть ДНФ функции имеет вид:

F = abc + ас .

Следуя изложенному правилу перехода к СДНФ, получим:

F = abc + ac(b + b) = abc + abc +abc .

Переход от КНФ к СКНФ осуществляется аналогично переходу от ДНФ

к СДНФ. Для этого необходимо:

• ввести отсутствующие переменные в каждую дизъюнкцию, используя

закон противоречия яя = 0 (я — отсутствующая сменная);

34

Гпава 2

• выполнить преобразования, применяя второй закон дистрибутивности

a + be = (a + b) (a + с) и коммутативный закон a + b- b + a\

• избавиться от дизъюнкций, которые повторяются, на основании закона

идемпотентности aa = a.

Пример: Развертывание КНФ вида:

F = (a + b)(b + с)(а + с)

в СКНФ осуществляется таким образом:

F = (а+ Ь + 0)(Ь + с + 0)(а + с + 0) =

= (a + b + cc)(b + с + da)(a +с +bb) =

= (а +b + c)(b +с + а)(а + с + b)(a + b + с ){Ь +с + а)(а +с + Ь).

4. Описание функций алгебры логики в виде последовательности деся-

тичных чисел. Иногда для сокращения записи функцию алгебры логики

представляют в виде последовательности десятичных чисел [27]. При

этом последовательно записывают десятичные эквиваленты двоичных

кодов соответствующих конституент единицы или нуля.

Пример: Записать в виде последовательности чисел функцию Г(х2, хь хп)

из предшествующего примера.

Решение. В СДНФ первая конституента "единица" отвечает двоичному

коду 001. Десятичный эквивалент этого кода равен 1. Аналогично запи-

сываются другие конституенты

F(x2, хь х0) = Е (1,2, 4, 7) = v(l, 2, 4, 7).

F(x2, ху, хо) = П(0, 3, 5,6) = л(0, 3, 5, 6).

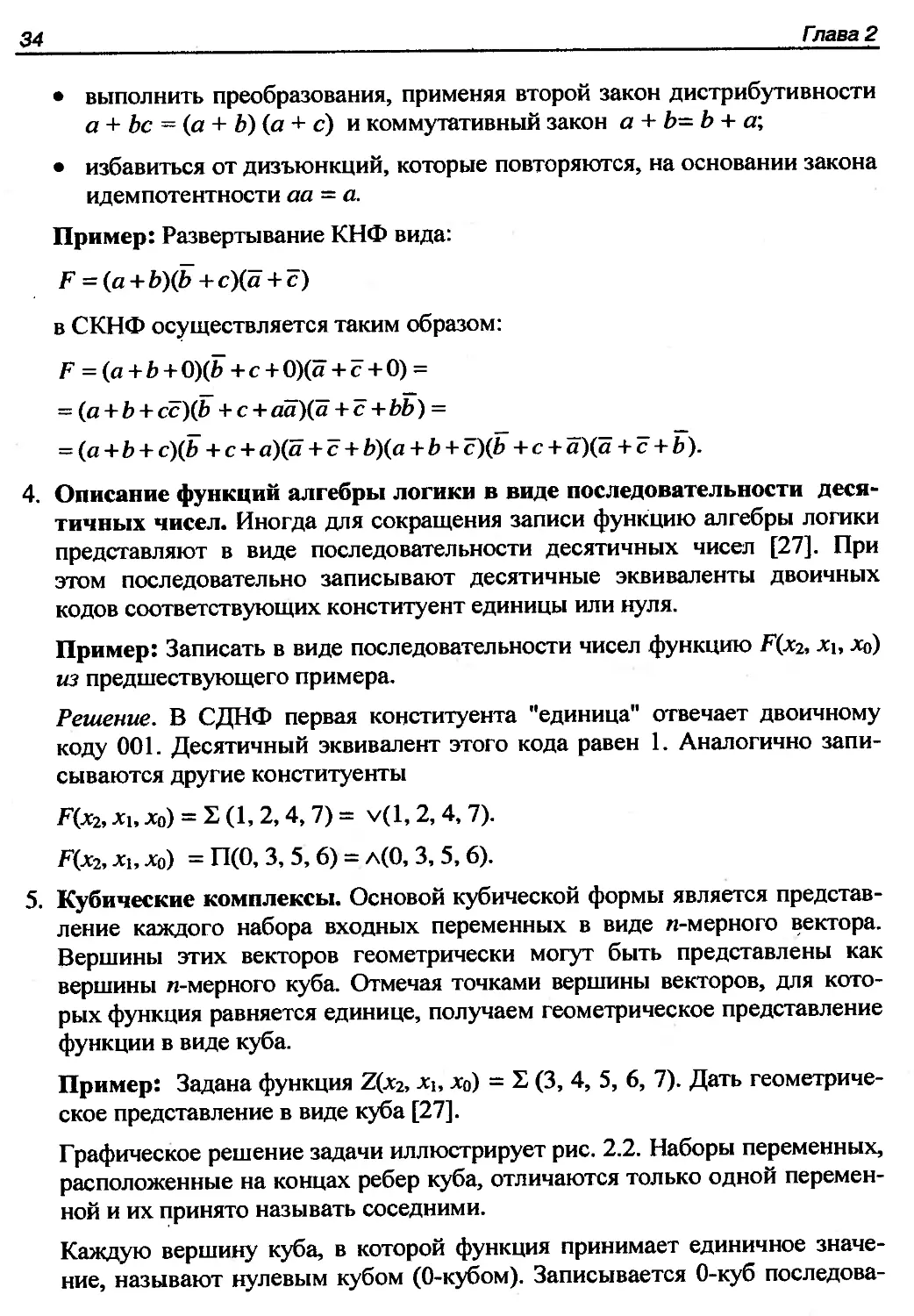

5. Кубические комплексы. Основой кубической формы является представ-

ление каждого набора входных переменных в виде «-мерного вектора.

Вершины этих векторов геометрически могут быть представлены как

вершины «-мерного куба. Отмечая точками вершины векторов, для кото-

рых функция равняется единице, получаем геометрическое представление

функции в виде куба.

Пример: Задана функция Z(x2, Xi, хо) = 2 (3, 4, 5, 6, 7). Дать геометриче-

ское представление в виде куба [27].

Графическое решение задачи иллюстрирует рис. 2.2. Наборы переменных,

расположенные на концах ребер куба, отличаются только одной перемен-

ной и их принято называть соседними.

Каждую вершину куба, в которой функция принимает единичное значе-

ние, называют нулевым кубом (0-кубом). Записывается 0-куб последова-

Алгебра логики и теоретические основы синтеза цифровых устройств 35

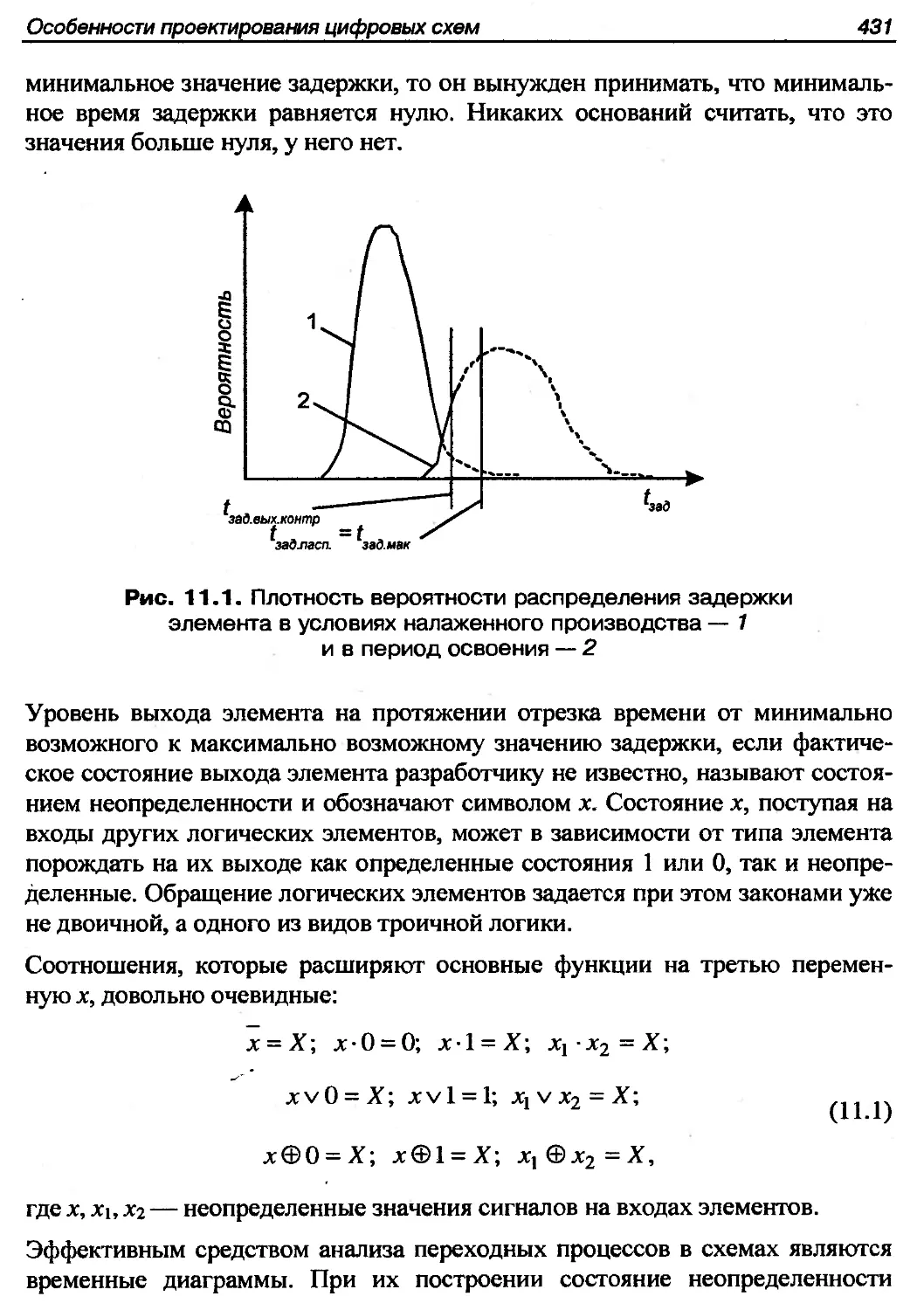

тельностью входных переменных, которые образовали его, т. е. кодом, со-

ответствующим конституенте единицы. Множество нулевых кубов обра-

зовывает нулевой кубический комплекс Ко.

Рис. 2.2. Геометрическое представление функции

Если два нулевых куба комплекса Ко отличаются только по одной коор-

динате (переменной), т. е. два набора переменных, для которых функция

равна единице, являются соседними, то они образуют единичный куб (1-

куб). Геометрически это отвечает ребру начального «-мерного куба. Запи-

сывается 1-куб последовательностью общих элементов его 0-кубов с про-

черком в месте несовпадающих элементов. Множество единичных кубов

образует единичный кубический комплекс К[.

Аналогично, если два единичных куба комплекса К отличаются только по

одной координате (переменной), то они образуют двоичный куб (2-куб).

Геометрически это отвечает грани начального «-мерного куба. Записыва-

ется 2-куб последовательностью общих элементов его 1-кубов, а множест-

во двоичных кубов образует двоичный кубический комплекс К2. И т. д.

Размерность куба (его ранг) определяется числом несовпадающих коор-

динат, т. е. числом прочерков в его записи. Объединение кубических ком-

плексов Ко, Ki, ...,Km для функции логической алгебры «-переменных об-

разует ее кубический комплекс

K(z) = v(Ko,K},...,Km)...

Пример: Для логической функции Z(x2, х\, х0) = Z(3, 4, 5, 6, 7) записать

кубические комплексы.

Решение. Нулевой кубический комплекс содержит пять членов по числу

конституент единицы функции

ЛЬ = (011,100, 101,110, 111).

36

Гпава 2

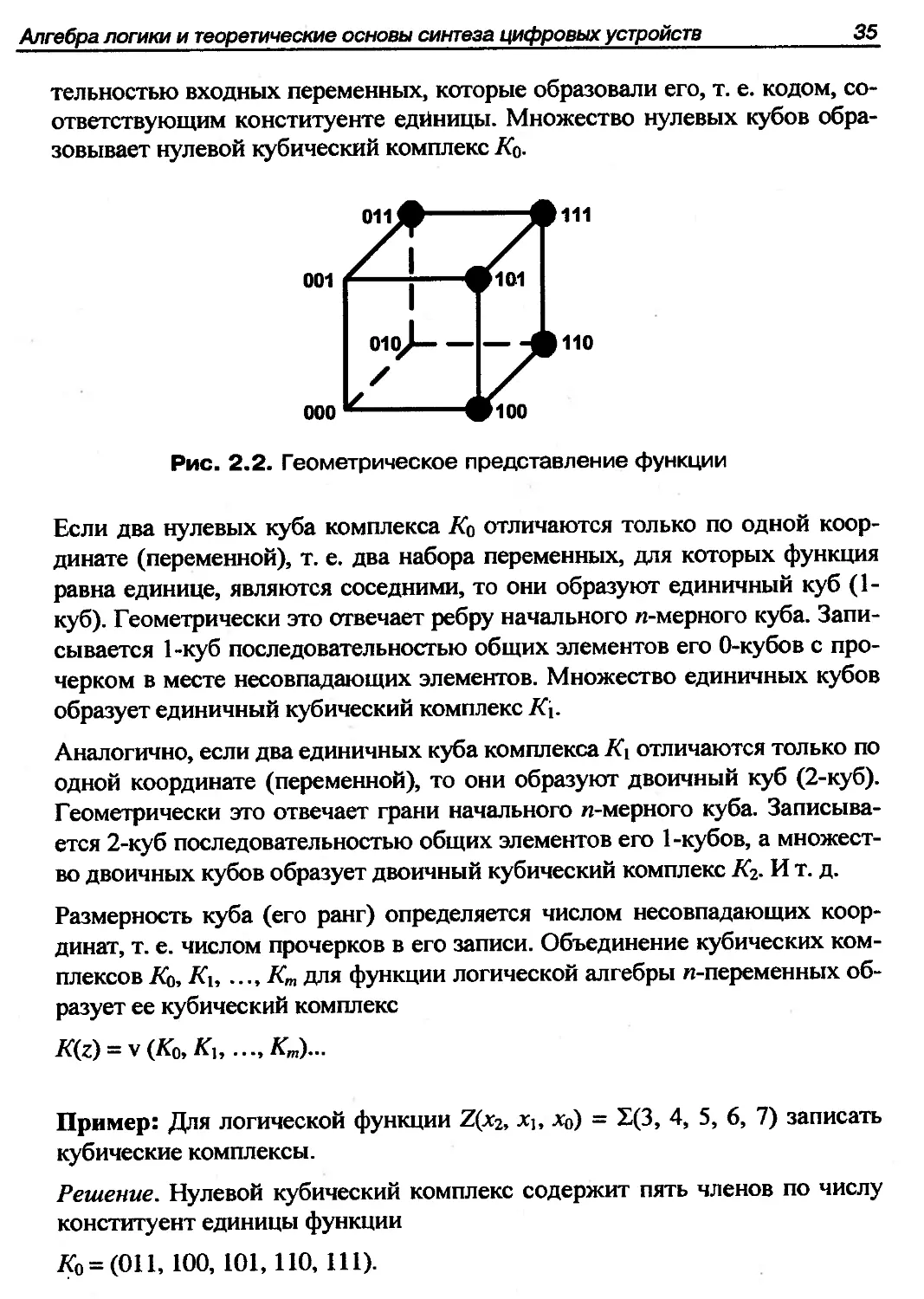

Сравнивая записанные 0-кубы, можно увидеть, что 1-й и 5-й кубы отли-

чаются только первым членом. Поэтому они образуют 1-куб вида

-11 (рис. 2.3, а). Аналогично 2-й и 3-й, 0-кубы образуют 1-куб 10-

и т. д. Единичный кубический комплекс заданной функции будет иметь

вид:

Kt =(-11, 10-, 1-0. 11-, 1-1).

Аналогично может быть получен и двоичный кубический комплекс (рис.

2.3, б), что состоит из одного 2-куба:

/<2 = (1-)

а

Рис. 2.3. Кубические комплексы:

а — единичные; б — двоичные

2.4. Логические элементы и схемы.

Принцип двойственности

Соответственно перечню логических операций различают три основных ло-

гических элемента (ЛЭ): И, ИЛИ, НЕ. Условные графические обозначения

этих ЛЭ показаны на рис. 2.4.

Число входов элементов И, ИЛИ может быть произвольным, а элемент НЕ

имеет всегда только один вход.

При сравнении операций И, ИЛИ можно заметить, что, если в условиях, ко-

торые определяют операцию И, значения всех переменных и самой функции

Алгебра логики и теоретические основы синтеза цифровых устройств

37

заменить их инверсией, а знак логического умножения — знаком логическо-

го сложения, получим постулаты, которые определяют операцию ИЛИ:

если х, • х0 = у, то X] + х0 = у;

если X] + х0 = у, то X] • х0 = у.

Рис. 2.4. Условные графические обозначения логических элементов

Это свойство взаимного преобразования постулатов операций логического

сложения и умножения носит название принципа двойственности.

Две функции алгебры логики называются двойственными, если одна вытекает

из другой заменой каждой операции конъюнкции на операцию дизъюнкции, и

наоборот. Принцип двойственности формулируется так: если функции и F2

равносильные, то равносильны им функции F\ и F2.

Например, для функции F(a,b) = ab + ab двойственной является функция

F* (а, Ь) = (а + Ь)(а + Ь).

Нужно отличать двойственные формы функции от инверсных функций, ко-

торые вытекают из исходных их инвертированием. При этом не только все

операции заменяются на двойственные, но и все переменные заменяются их

инверсиями.

Например, для функции F(a,b) = ab + ab инверсной будет функция

F(a, b) = ab + ab = (а + b)(a + b).

Важным практическим следствием принципа двойственности есть тот факт,

что при записи логических выражений и, значит, построении логических

схем, можно обойтись только двумя типами операций. Например, операция-

ми И и НЕ или ИЛИ и НЕ.

Совокупность ЛЭ, которая позволяет реализовать логическую схему произ-

вольной сложности, называется функционально полной системой. Таким об-

38

Глава 2

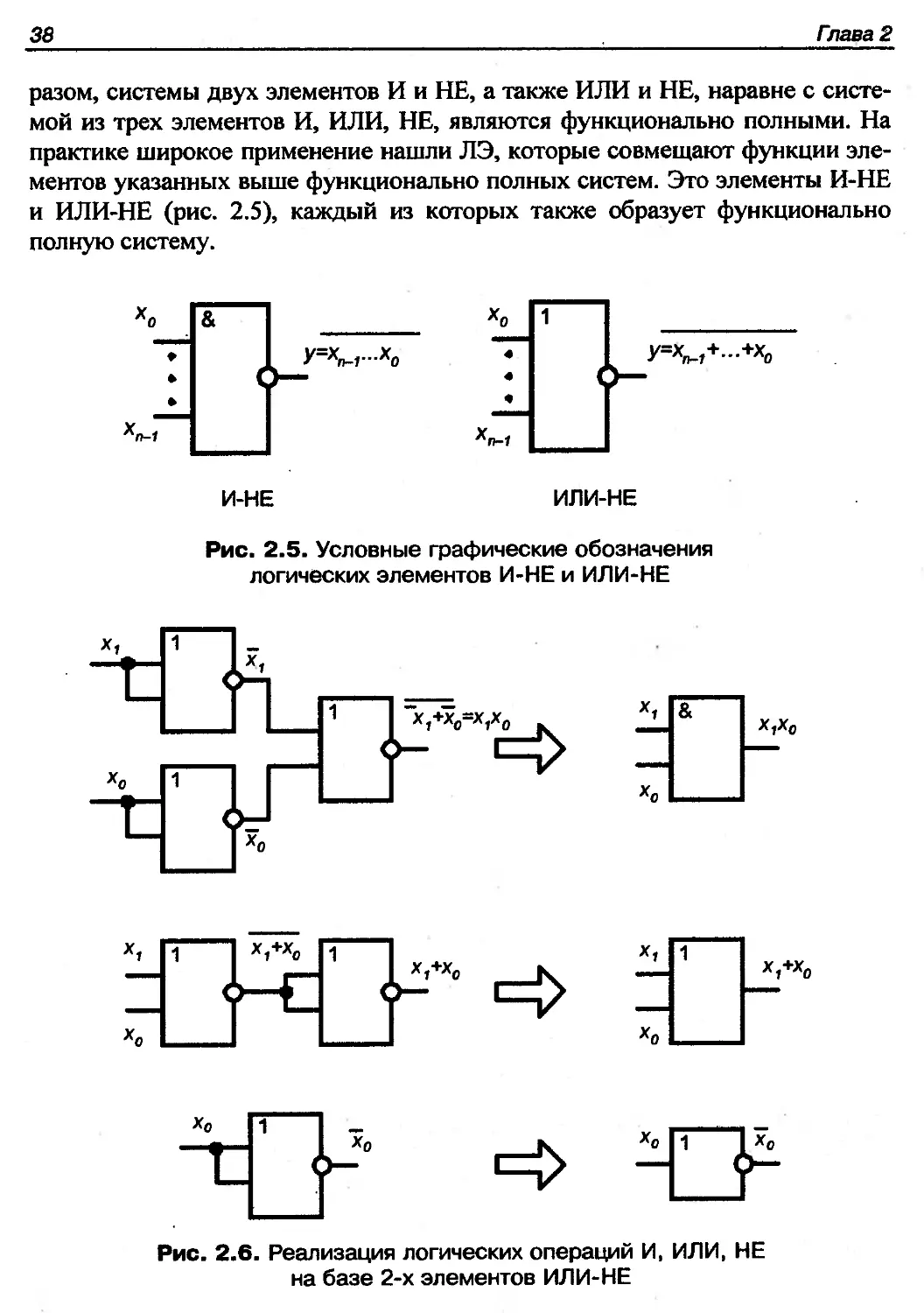

разом, системы двух элементов И и НЕ, а также ИЛИ и НЕ, наравне с систе-

мой из трех элементов И, ИЛИ, НЕ, являются функционально полными. На

практике широкое применение нашли ЛЭ, которые совмещают функции эле-

ментов указанных выше функционально полных систем. Это элементы И-НЕ

и ИЛИ-HE (рис. 2.5), каждый из которых также образует функционально

полную систему.

ИЛИ-НЕ

И-НЕ

х0 1

Рис. 2.5. Условные графические обозначения

логических элементов И-НЕ и ИЛИ-НЕ

х,х0

х,+х0

х0 1

Рис. 2.6. Реализация логических операций И, ИЛИ, НЕ

на базе 2-х элементов ИЛИ-НЕ

Алгебра логики и теоретические основы синтеза цифровых устройств 39

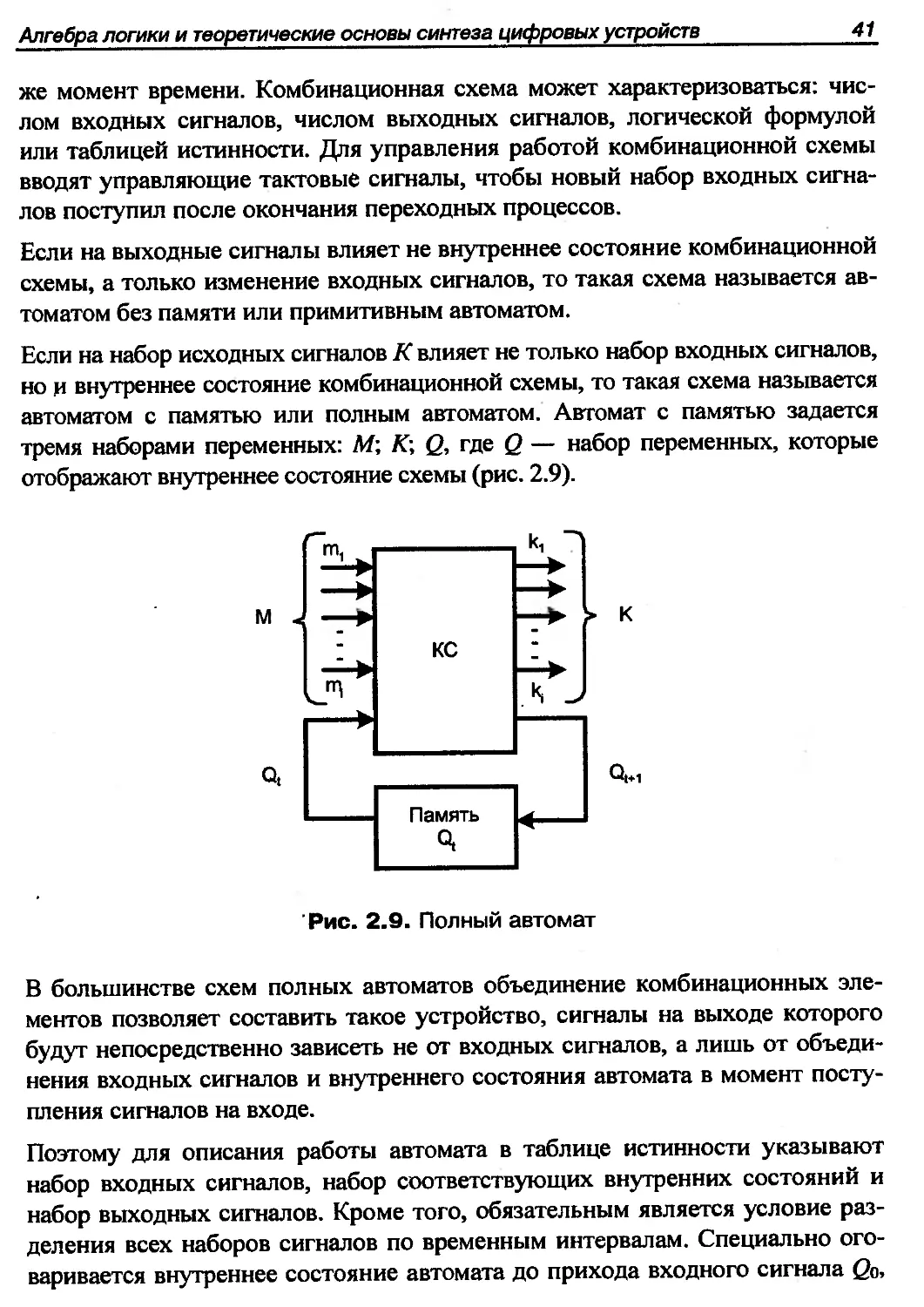

Рассмотрим выполнение операций И, ИЛИ, и НЕ на элементах ИЛИ-НЕ.

В соответствии с принципом двойственности, если jq • х0 = z, то jq + х0 = z -

Инвертируя правую и левую части первого выражения, получа-

ем jq + х0 = z =Х]Х0, т. е. логическая операция И может быть заменена опе-

рациями ИЛИ и НЕ. На рис. 2.6 приведены примеры реализации основных

логических операций с использованием только элементов ИЛИ-НЕ.

На основании аналогичных соображений можно показать выполнение основ-

ных логических операций с использованием только элемента И-НЕ (рис. 2.7).

Рис. 2.7. Реализация логических операций

на базе 2-х элементов И-НЕ

2.5. Классификация логических устройств

Логические устройства могут быть классифицированы по разным признакам. По

способу ввода/вывода (информации) логические устройства делятся на последо-

вательные, параллельные и последовательно-параллельные.

40

Глава 2

Последовательным называется устройство, в котором входные переменные

подаются на вход, а выходные переменные снимаются с выхода не одновре-

менно, а последовательно, разряд за разрядом.

Параллельным называется устройство, в котором все разряды входных пере-

менных подаются на вход, и все разряды выходных переменных снимаются с

выхода одновременно.

В последовательно-параллельных устройствах входные и выходные пере-

менные представлены в разных формах. Или переменные подаются последо-

вательно символ за символом на вход, а с выхода они снимаются одновре-

менно, или наоборот.

По принципу действия все логические устройства делятся на два класса:

комбинационные и последовательные.

Комбинационными устройствами или автоматами без памяти называют ло-

гические устройства, выходные сигналы которых однозначно определяются

только действующей в данный момент на входе комбинацией переменных и

не зависят от значений переменных, которые действовали на входе ранее.

Последовательными устройствами, или автоматами с памятью, называют

логические устройства, выходные сигналы которых определяются не только

действующей в данный момент на входе комбинацией переменных, но и всей

последовательностью входных переменных, которые действовали в предше-

ствующие моменты времени.

Комбинационную схему можно представить в виде m-Л-полюсного элемента

(рис. 2.8). Входное слово (входной алфавит) комбинационной схемы задается

набором символов М = (т\ m2 ...т^, а выходное слово (выходной алфавит)

принимает значения из выходных символов К = (к\ k2...kj)...

Входное

слово

Рис. 2.8. Комбинационная схема

В дискретный момент времени совокупность выходных сигналов однозначно

определяется набором входных сигналов, которые поступили на вход в тот

Алгебра логики и теоретические основы синтеза цифровых устройств 41

же момент времени. Комбинационная схема может характеризоваться: чис-

лом входных сигналов, числом выходных сигналов, логической формулой

или таблицей истинности. Для управления работой комбинационной схемы

вводят управляющие тактовые сигналы, чтобы новый набор входных сигна-

лов поступил после окончания переходных процессов.

Если на выходные сигналы влияет не внутреннее состояние комбинационной

схемы, а только изменение входных сигналов, то такая схема называется ав-

томатом без памяти или примитивным автоматом.

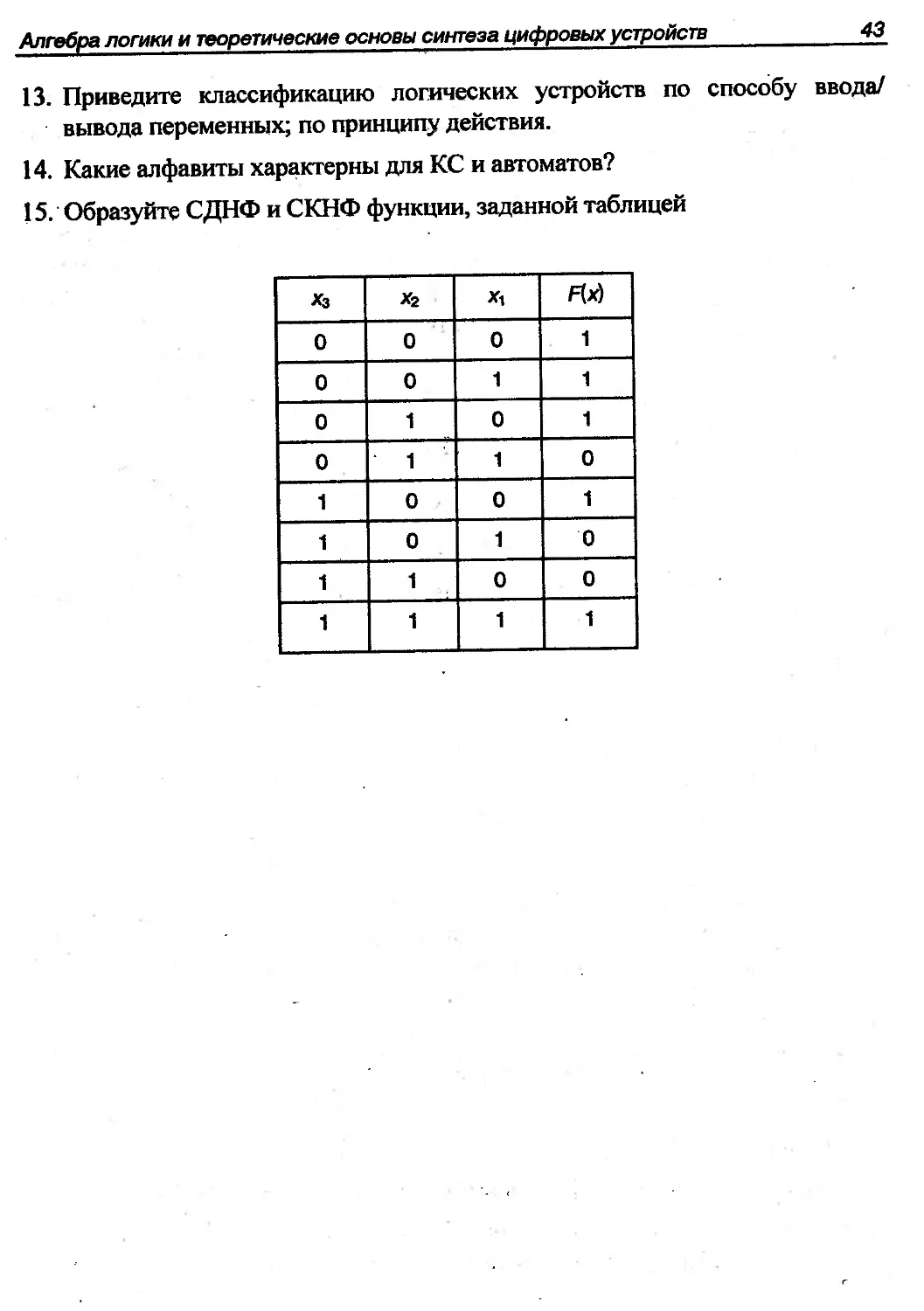

Если на набор исходных сигналов К влияет не только набор входных сигналов,

но и внутреннее состояние комбинационной схемы, то такая схема называется

автоматом с памятью или полным автоматом. Автомат с памятью задается

тремя наборами переменных: М\ К\ Q, где Q — набор переменных, которые

отображают внутреннее состояние схемы (рис. 2.9).

Рис. 2.9. Полный автомат

В большинстве схем полных автоматов объединение комбинационных эле-

ментов позволяет составить такое устройство, сигналы на выходе которого

будут непосредственно зависеть не от входных сигналов, а лишь от объеди-

нения входных сигналов и внутреннего состояния автомата в момент посту-

пления сигналов на входе.

Поэтому для описания работы автомата в таблице истинности указывают

набор входных сигналов, набор соответствующих внутренних состояний и

набор выходных сигналов. Кроме того, обязательным является условие раз-

деления всех наборов сигналов по временным интервалам. Специально ого-

варивается внутреннее состояние автомата до прихода входного сигнала Qo,

42

Глава 2

внутреннее состояние автомата, которое изменяется с приходом входного

сигнала Qt, и внутреннее состояние автомата после нового изменения вход-

ного сигнала Qt+i.

Различают два типа автоматов. Автомат, у которого выходная переменная в

любом такте f, зависит от внутреннего состояния и от входной переменной,

называется автоматом Мили и задается уравнением Kj = f (Qi, М,). Автомат, у

которого выходная переменная в момент Г, зависит только от внутреннего

состояния в ti-м такте, называется автоматом Мура и задается уравнением Kj =

=f(Qi).

Контрольные вопросы и задания

1. Что называется булевыми константами и переменными в алгебре логики?

2. Почему логическое высказывание называется сложным?

3. По какой формуле определяется конечное число функций для двух аргу-

ментов двузначной системы?

4. Что отображают теоремы булевой алгебры? Сформулируйте теоремы де

Моргана, поглощения и склеивания.

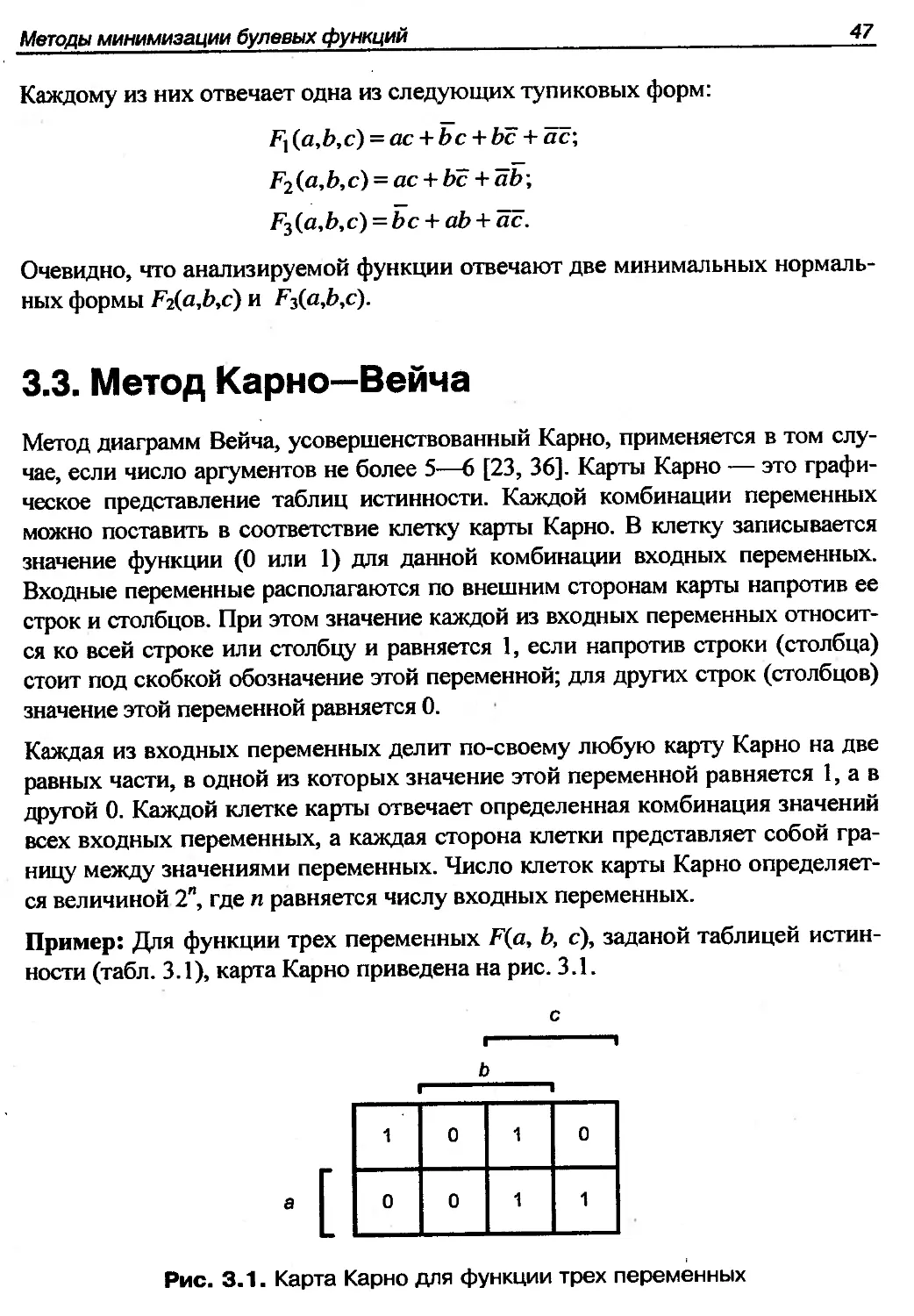

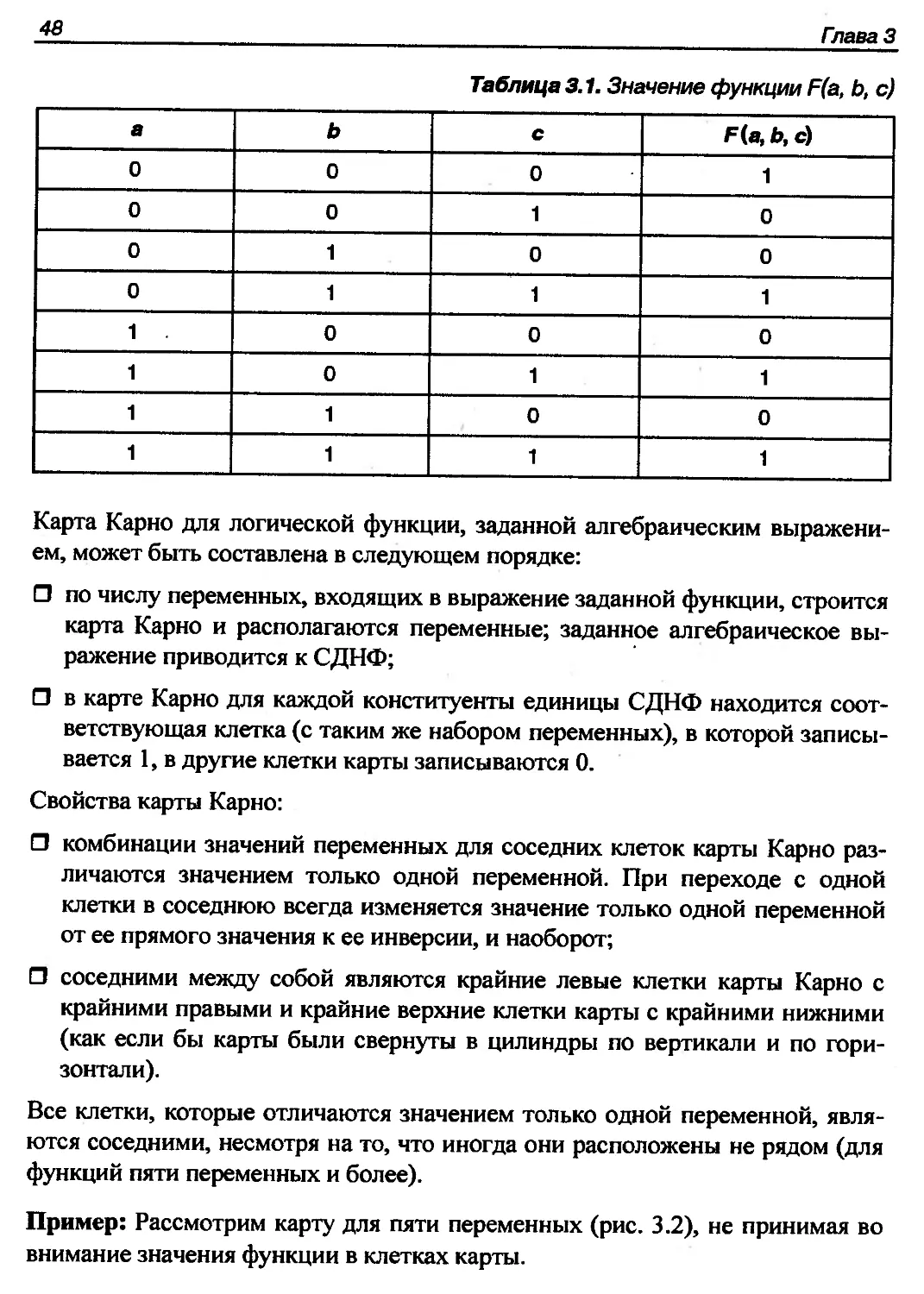

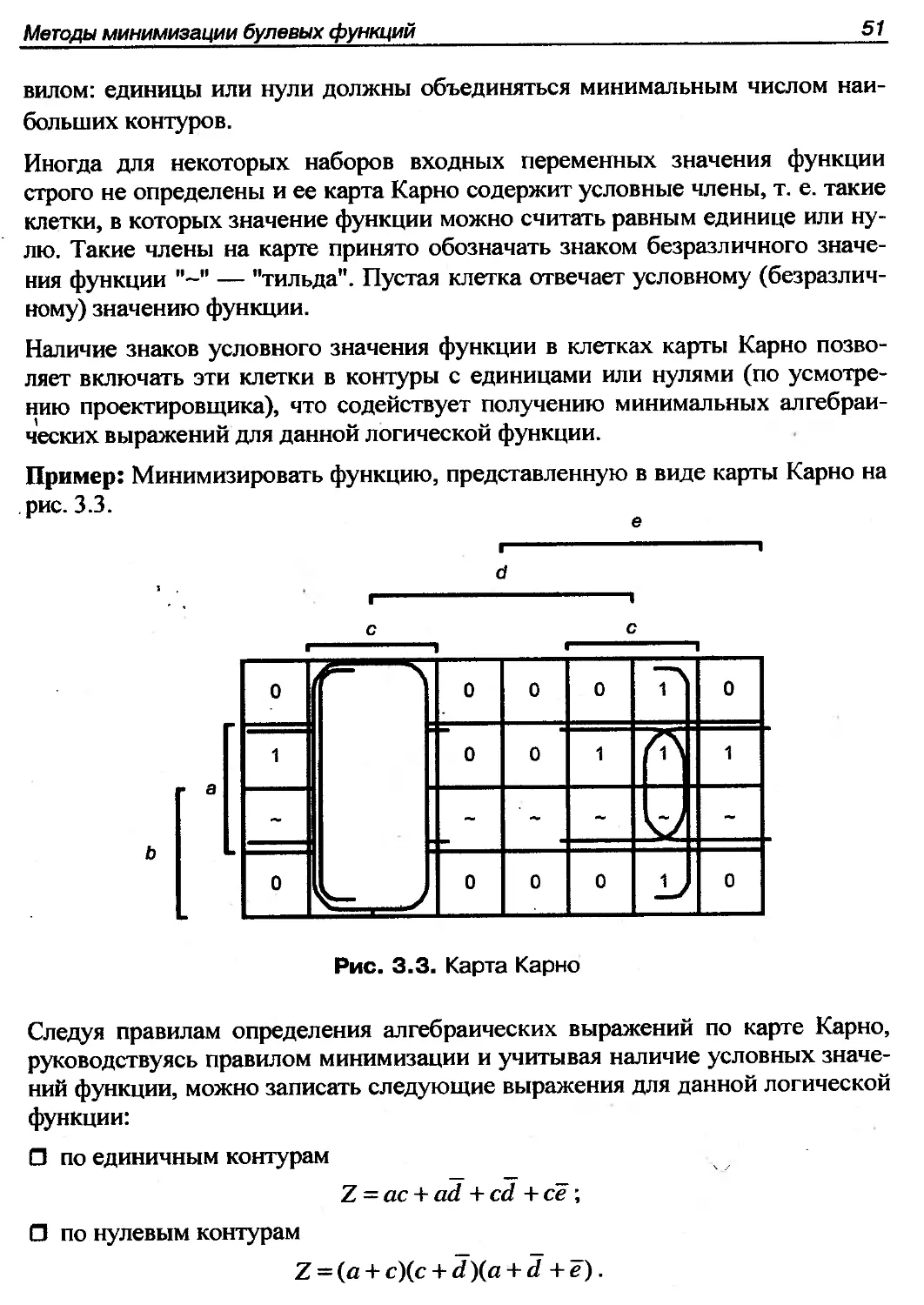

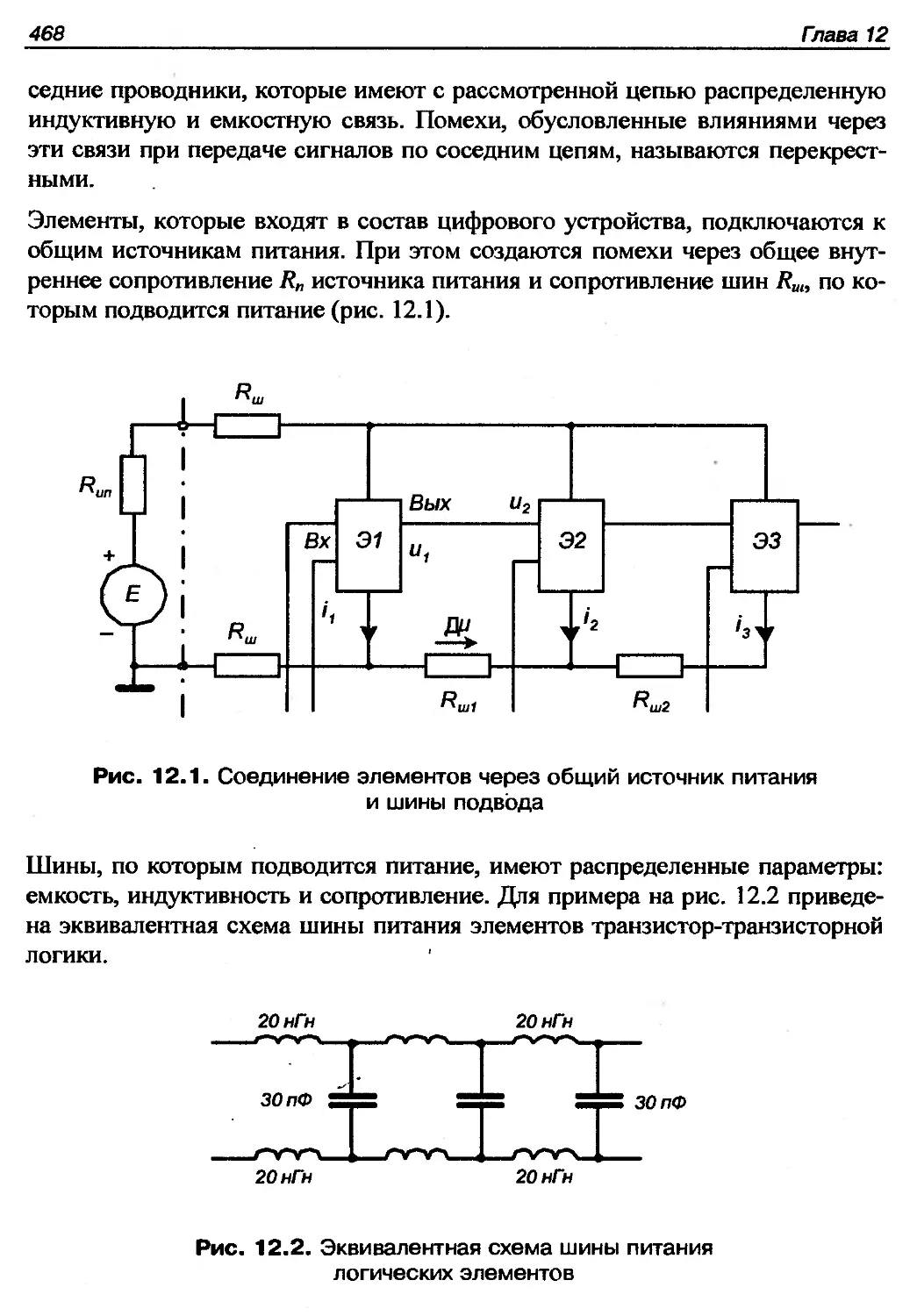

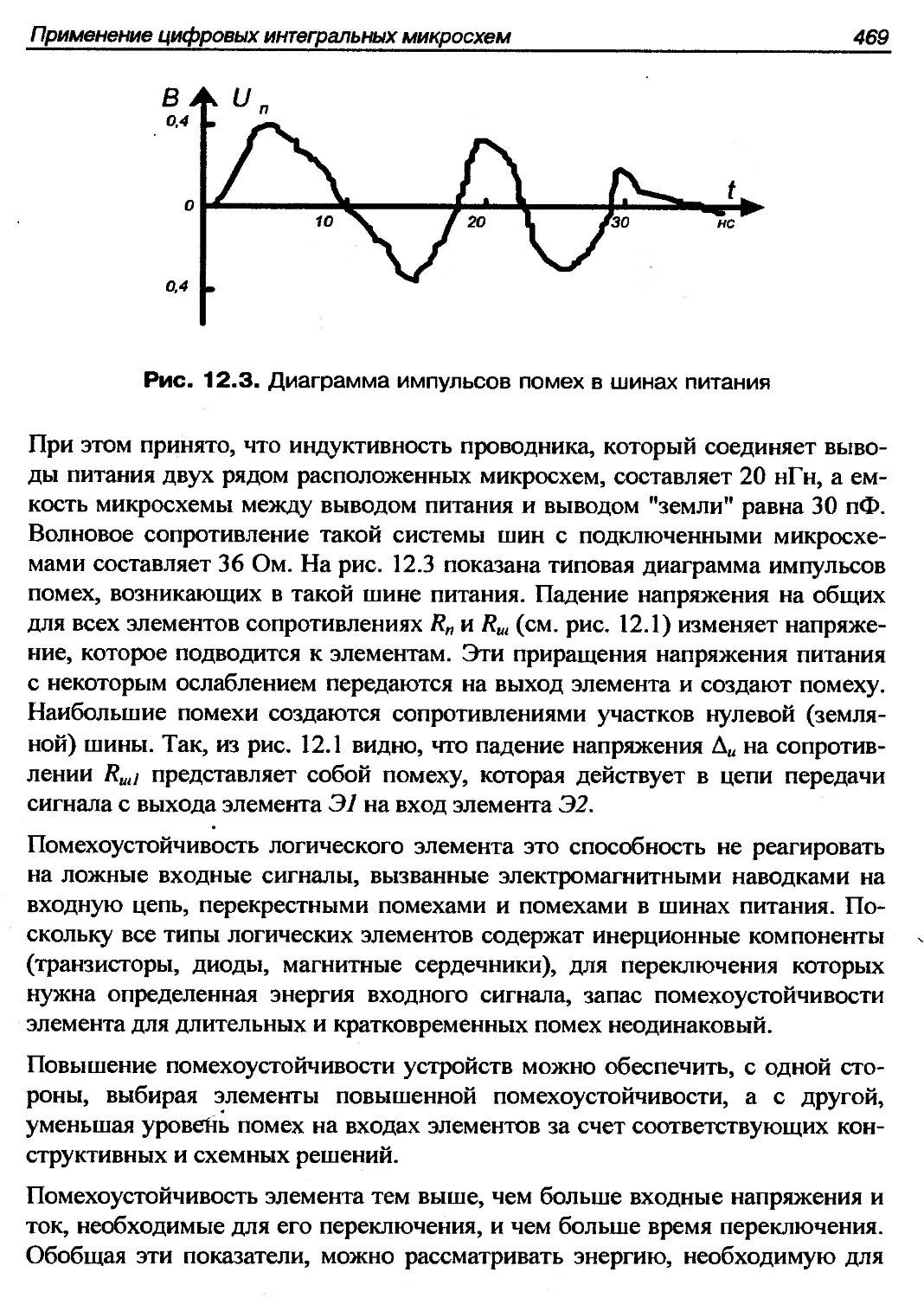

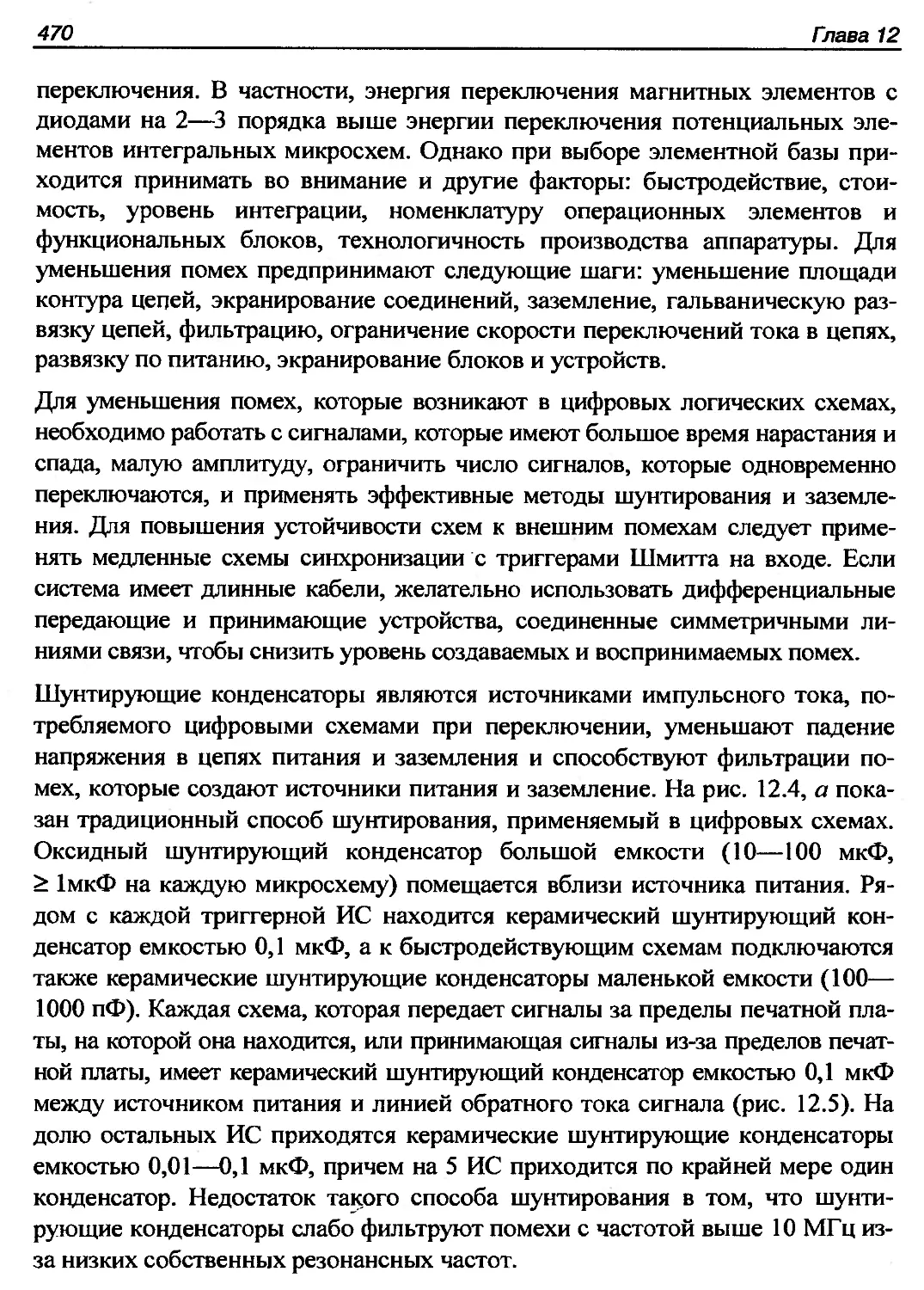

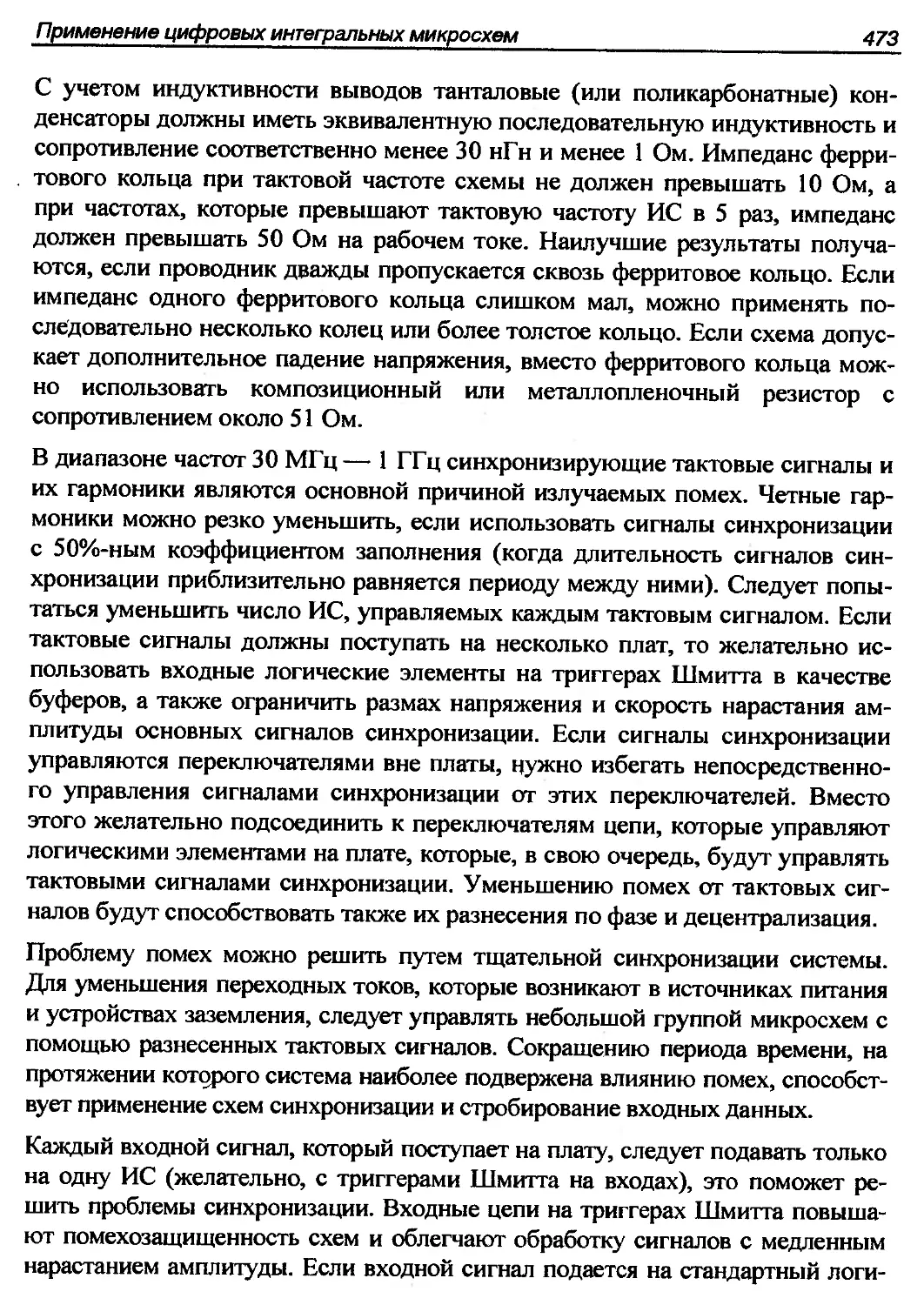

5. Назовите основные операции булевой алгебры. Как они описываются с