Текст

БИБЛИОТЕКА ПО АВТОМАТИКЕ

Выпуск 60

П. НАСЛЭН

ОСНОВЫ ЦИФРОВОЙ

ВЫЧИСЛИТЕЛЬНОЙ

ТЕХНИКИ

Перевод с французского

канд. техн. наук О. И. АВЕНА

ГОСУДАРСТВЕННОЕ ЭНЕРГЕТИЧЕСКОЕ ИЗДАТЕЛЬСТВО

МОСКВА

1962

ЛЕНИНГРАД

Редакционная коллегияз

И. В. Антик, А. И. Бертинов, С. Н. Вешеневский,

в, С. Кулебакин, В. С. Малов, В. Э. Низе, А. Д. Смирнов,

Б. С. Сотсков

ЭЭ-5(4)-3

Книга представляет собой популярное изложение

основ цифррвой техники: кодирования, элементов,

принципов построения цифровых вычислительных

машин.

В книге описывается ряд новейших элементов и

устройств .автоматики и вычислительной техники —

криогенные элементы, параметроны, трансфлюксоры,

прогрессивные системы памяти и т. д.

Книга предназначается для широкого круга

инженеров и техников, интересующихся вопросами

вычислительной техники, а также может быть полезной

студентам старших курсов вузов.

ПРЕДИСЛОВИЕ АВТОРА К ПЕРВОМУ ИЗДАНИЮ

Применение цифровых вычислительных машин для научных

целей, в промышленности, экономике, для управления

производственными процессами стремительно растет.

Чтобы быть в состоянии использовать все возможности цифровых

вычислительных машин, как студенты технических вузов, так и

инженеры и техники должны иметь представление об их устройстве,

о методах программирования и работе основных блоков машин.

Устройство цифровых вычислительных машин вряд ли изменилось

со времени описания его Чарльзом Бэбедж. Значение вычислительных

машин выходит за рамки собственно вычислительной техники и их

применение, пожалуй, в неменьшей степени важно для целей

автоматического управления, в частности в дискретных системах

управления, широко распространенных в промышленности.

Данная книга имеет целью дать основы того, о чем говорилось

выше, вхвозможно более доступной форме, в духе заметок, о

которых сказано в конце введения. Книга соответствует программе

курса, который мы читаем в Высшей национальной школе армии

и в Электротехническом институте.

Мы особенно благодарны руководству учебными занятиями

Армии за разрешение выпустить нашу книгу массовым тиражом.

Большая часть книги была опубликована в 1957 г. в журнале

*Mesures et Contr61e iadustrieb в номерах с марта по июнь.

Редакции этого журнала мы также приносим благодарность.

ПРЕДИСЛОВИЕ КО ВТОРОМУ ФРАНЦУЗСКОМУ

ИЗДАНИЮ

Быстрое распространение первого издания данной книги

показало нам, что характер изложения и содержание ее удовлеторяют

большое число читателей. Именно поэтому при подготовке ко

второму изданию книга не была подвергнута сколько-нибудь серьезной

переработке.

В первой части мы удовлетворились заменой различных

программ умножения двух чисел любого знака универсальной

программой умножения и деления чисел, представленных в закодированной

форме.

Вторая часть приведена в порядок включением описания

логических схем на транзисторах и новых магнитных элементах,

которые даны шосле схем на лампах, а также переработкой

изложения устройства систем электростатической памяти.

Кроме того, современные достижения заставили нас добавить

несколько параграфов, посвященных запоминающим устройствам

на магнитной пленке, феррорезонансным схемам и параметрическим

колебаниям (параметронам), устройствам емкостной памяти и

схемам со сверхпроводящими элементами (криотронам). Ошибки,

обнаруженные в первом издании, были исправлены, и мы счастливы

поблагодарить здесь тех из наших читателей, которые дали нам

свои заключения.

Автфр

ПРЕДИСЛОВИЕ РЕДАКТОРА К РУССКОМУ ИЗДАНИЮ

Современные электронные цифровые вычислительные машины

представляют собой область техники, внутри которой можно

выделить целый ряд самостоятельных направлений. Первым таким

направлением является технология элементов. Обязанная своим

возникновением электронным лампам и электромагнитным реле,

современная вычислительная техника строится почти исключительно на

основе так называемой «техники твердого тела», т. е. на элементах,

использующих в своей работе электрические и магнитные явления в

твердых телах. Большинство машин, построенных в последние годы

и разрабатываемых в настоящее время, использует в качестве

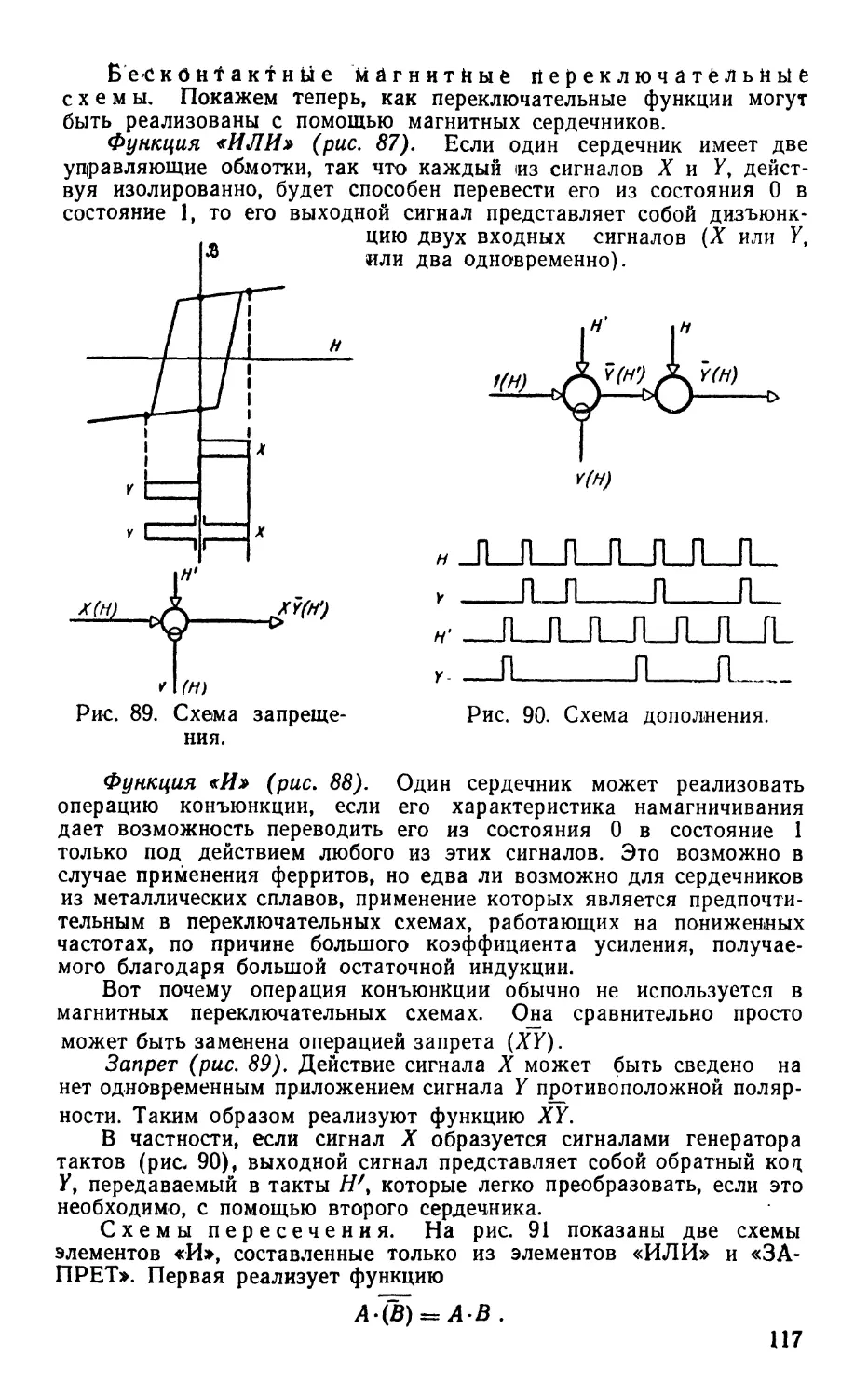

основных'элементов полупроводниковые приборы и, в частности,

транзисторы. Переход к транзисторам позволил уменьшить габариты

машины от десятков кубических метров до нескольких кубических

дециметров, а количество потребляемой электроэнергии — от

десятков киловатт до сотен ватт. Наиболее перспективным в этом

направлении представляется сейчас использование тонких магнитных

пленок, комбинированных полупроводниковых элементов, а также

элементов, основанных на явлении сверхпроводимости. Разработка

элементов, размеры которых только на один-два порядка отличаются

от размеров молекул, привела к тому, что эта новая область

технологии получила название «молектроники». Элементы такого типа

обладают временем переключения порядка единиц наносекунд, что

уже приближается к предельному быстродействию, обусловливаемо

му скоростью передачи информации по соединительным линиям.

Рассматриваемое направление вызвало к жизни теорию

надежности электронных устройств, которая в настоящее время

представляет собой достаточно развитую самостоятельную научную

дисциплину. Одним из наиболее существенных результатов здесь явилось

доказательство принципиальной возможности построения сколь

угодно надежных схем из ненадежных элементов.

Второе направление, тесно примыкающее к первому, — это

разработка теории переключательных функций. В рамках этой теории

решаются задача формального описания работы вычислительных

схем, а также задача построения алгоритмов минимизации,

позволяющих чисто формальным способом строить схемы, выполняющие

данные вычислительные функции при минимальном числе

используемых элементов. Теория переключательных функций открывает путь

для создания машин, разрабатывающих схемы вычислительных

устройств, т. е. машин, создающих машины. Своим возникновением

теория переключательных функций обязана работам английского

ft

математика Дж. Буля, впервые сформулировавшего в своей книге

«Законы мышления> (1854 г.) основные законы алгебры логики.

Большой вклад в развитие теории переключательных функций был

сделан советским ученым проф. М. А. Гавриловым. Теория

временных переключательных функций разрабатывалась Ю. Я. Базилевским.

Третье теоретическое направление связано с созданием теории

структур цифровых вычислительных машин. Это направление

возникло в последние годы в связи с тем, что возможности увеличения

быстродействия машин чисто технологическими средствами уже в

значительной степени исчерпаны. Другая рассматриваемая здесь

задача состоит в построении наиболее экономичных структур,

отвечающих заданным техническим условиям. До последнего времени

всякая цифровая вычислительная машина, как универсальная, так

и специализированная, состояла из трех основных устройств, а

именно: арифметического устройства, запоминающего устройства и

устройства управления. Отдельные машины отличались одна от другой

только значениями ряда параметров этих устройств. Многие

машины, разрабатываемые в настоящее время, представляют собой

сложные комплексы, состоящие из большого количества устройств,

работающих автономно и связанных между собой общей системой

управления и общими каналами передачи информации. В таких системах

достигается возможность наиболее эффективного использования

каждого отдельного устройства.

Работы в рассмотренных трех направлениях призваны дать

ответ на вопрос: как строить цифровую вычислительную машину?

Другая группа направлений ставит целью изучение объекта работы

вычислительной машины, т. е. информации. Прежде всего, очень важно

решить проблему создания входных и выходных устройств машины,

т. е. проблему связи машины с человеком. Наибольшее значение

имеют здесь исследования, связанные с разработкой теории и

созданием устройств, преобразующих информацию, представленную

человеческим голосом или написанным текстом, в форму кодов, с

которыми оперирует машина, а также устройств, преобразующих

выходные сигналы машины в форму, наиболее удобную для восприятия

человеком.

Следующая проблема связана с представлением информации

внутри машины. Особо здесь следует отметить разработку так

называемых самокорректирующих кодов, позволяющих обнаруживать и

исправлять ошибки, обусловленные отдельными сбоями в работе

вычислительных элементов. К этой же группе вопросов следует

отнести проблему наиболее экономичного представления информации

внутри машины. Задача сводится здесь к удовлетворению

противоречивых требований — достижения максимальных возможностей

контроля и самоконтроля при максимальной структурной надежности и

минимальном числе используемых элементов.

Наконец, исследования в последней группе направлений

призваны дать ответ на вопрос: как должна работать цифровая

вычислительная машина? Одной из проблем здесь является разработка

численных методов решения математических задач. Развитие

вычислительной техники оказывает, в свою очередь, существенное влияние

на развитие математики, так как, с одной стороны, вычислительные

четоды в математике разрабатывались до последнего времени с

учетом того, что вычисления будут производиться вручную, а с дру

6

rofi стороны, целый ряд задач, на поиски аналитических решений

которых затрачивались огромные усилия, потерял актуальность в

связи с появлением вычислительных машин.

Следующим направлением является разработка теории и

практических способов программирования, т. е. перевода условий задачи

и описания способа ее решения с языка человека на язык машины.

Наиболее актуальной в настоящее время является разработка

методов автоматического программирования, позволяющих предельно

автоматизировать.этот процесс. Здесь следует отметить как работы

по созданию «компилирующих», «интерпретирующих» и тому

подобных программ, позволяющих автоматически составлять программу

вычислений по исходным данным, записанным в форме, близко

совпадающей с формой, обычно используемой в математической

литературе, так и работы в области автоматического в полном смысле

этого слова программирования, т. е. составления машиной

неизвестного заранее алгоритма для решения задачи или класса задач на

основе минимума исходных данных.

В заключение следует отметить работы по созданию единых

алгоритмических языков, в одинаковой степени пригодных для использо

вания как машиной, так и человеком. Одним <из достигнутых

результатов здесь является возможность организации совместной работы

нескольких машин над решением одной задачи. При этом мосут

быть реализованы преимущества, даваемые разделением труда и

специализацией.

Такова в общих чертах основная проблематика современной

цифровой вычислительной техники. Из сказанного должно быть ясно, чт©

задача написания единой монографии, освещающей хотя бы в

небольшой степени большинство перечисленных здесь вопросов,

связана с существенными трудностями, обусловленными как чрезвычайно

большим объемом материала, так и его разносторонностью.

Предлагаемая читателю книга известного французского инженера Пьера

Наслэна интересна прежде всего тем методом, который автор избрал

для изложения материала. Автор как бы предлагает читателю

участвовать вместе с ним в построении цифровой вычислительной

машины, очень простой как по объему, так и технологически, но

обладающей, тем не менее, всеми характерными свойствами

современных машин. Для того чтобы приступить к такому построению,

прежде всего нужно знать, как представляются в машине числа и

как выполняются над ними основные операции сложения и

вычитания. В качестве элемента для изготовления устройств, выполняющих

операции сложения и вычитания, автор избрал простейшее, с его

точки зрения, а именно, электромагнитное реле. Такой выбор кажет-

ся-несколько странным, и по всей вероятности, может быть объяснен

тем, что основу книги составляют работы автора, опубликованные

в 1957 г. Параллельно с построением устройств читатель знакомится

со способами описания работы этих устройств средствами

переключательных функций.

Итак, выполнение операций сложения и вычитания

автоматизировано. Теперь необходимы средства для автоматического хранения

получаемых результатов и получения новых исходных данных, над

которыми (можно было бы выполнять операции. Для этого на тех же

реле строится небольшое запоминающее устройство с местным

блоком управления. После этого можно приступать к завершающему

этапу работы, а именно, к построению устройства управления. Одно-

7

временно рассматриваются структура команд и основные методы

программирования.

Во второй части книги описывается принцип действия большого

количества элементов цифровых вычислительных схем, начиная с

реле и кончая такими современными разработками, как трансфлюк-

соры и криотроны. ,

Книга рассчитана, в основном, на мало подготовленного

читателя, что и обусловливает стиль изложения. Однако, несмотря па

это, автору удалось избежать чрезмерных упрощений и достаточно

четко сформулировать большую часть наиболее актуальных в

настоящее время проблем. Все это делает книгу интересной, главным

образом для читателя, впервые знакомящегося с основами цифровой

вычислительной техники.

В ряде случаев автором были допущены неточности, главным

образом терминологического характера, которые по возможности

исправлялись при переводе и редактировании. Удивляет также полное

отсутствие в тексте книги ссылок на работы советских ученых, вклад

которых в развитие цифровой вычислительной техники является в

настоящее время общепризнанным.

А. В. Шилейко

ВВЕДЕНИЕ

Не будет лишним напомнить в начале этой книги, что

существуют два совершенно различных типа вычислительных машин:

аналоговые и цифровые.

Аналоговые машины, являясь по существу моделями

реальных физических систем, дают возможность изучать эти системы.

В подобных машинах исходные переменные математической

задачи представляются пропорциональными им значениями -физических

величин, таких как электрическое напряжение или угловое

перемещение вала. Математические операции — сложение,

умножение, деление, интегрирование, дифференцирование и т. д. —

осуществляются в аналоговых машинах с помощью в большей или

меньшей степени специализированных электрических,

электронных или электромеханических устройств. Для решения

какой-либо системы уравнений соответствующие устройства соединяются

так, чтобы составить систему, работа которой в точности

описывалась заданными уравнениями. Если, как это и бывает в

большинстве случаев, решаемые уравнения являются математическим

описанием некоторой реальной системы, то аналоговая машина

образует модель этой системы. На одинаковые внешние

воздействия реальная система и ее модель реагируют одинаково. Более

•того, если выбор некоторой части параметров системы

относительно свободен, то инженер, меняя на модели эти параметры

произвольным образом, имеет возможность выбрать оптимальный

режим работы системы. Очевидны те преимущества, которые

дает подобное моделирование, позволяющее имитировать в

лаборатории экспериментальные исследования, которые в реальных

условиях будут более длительными и дорогими. Точность

аналоговой машины обусловлена точностью ее вычислительных и

измерительных устройств.

По крайней мере на первый взгляд принцип действия

цифровых вычислительных машин резко отличается от принципа

действия аналоговых машин. Цифровые вычислительные машины

можно рассматривать скорее как средства машинизации работы групп

вычислителей. Они автоматически выполняют всю совокупность

операций, предусматриваемых численными методами решения

математических задач. Таким образом, изучение работы

вычислителей позволит нам выявить те функции, которые способна

осуществить автоматическая цифровая вычислительная машина.

2—895

9

Во-первых, математик, специалист по численным методам,

должен привести исходную задачу к форме, удобной для расчетов

на клавишных счетных машинах, имеющихся в вычислительном

бюро, т. е. представить задачу в виде последовательности

простейших арифметических операций: сложения, вычитания,

умножения, деления, в некоторых случаях извлечения корня. Таким

образом, дифференциальные уравнения4 будут заменены

уравнениями в конечных разностях, интегралы — конечной суммой

и т. д.

Точность в этом случае ограничивается только количеством

знаков в обрабатываемых числах. Подобная подготовительная

работа необходима также, когда вычисления предполагается пре-4

I

I

' 1

I

I

I

_J

т

Рис. 1. Блок-схема автоматической цифровой

вычислительной машины.

доставить автоматической вычислительной машине. В случае

вычислений, осуществляемых вручную, план расчетов,

подготовленный подобным образом, служит для составления расчетных

листов для вычислений, которые могут быть выполнены

добросовестными расчетчиками не очень высокой квалификации. Работа этих

последних заключается главным образом в чтении чисел в

определенных графах их расчетных листов, вводе этих чисел с

помощью клавиатуры в счетные машины, выполнении операций,

указанных в расчетных листах, и в переписывании результата в

предназначенную для этой цели графу. В общем случае эти

результаты будут использованы на дальнейших стадиях расчета,

предусмотренных инструкциями, в отдельных случаях заиисан-

ными на том же листе.

Этот вид расчетов складывается из трех весьма различных

видов операций:

1) операция вычисления, осуществляемая на клавишной

машине;

2) операция накопления цифровых данных и промежуточных

результатов или, иначе говоря, операция запоминания, осуществ-

10

ляемая с помощью записи чисел в соответствующих клетках

расчетного листа;

3) операция организации или программирования, результатом

которой является последовательность команд, характеризующих

операции, выполняемые над записанными числами; заметим, что

эти программы сами могут быть записаны на расчетном листе.

Те же самые операции мы обнаруживаем при работе

автоматической цифровой вычислительной машины, укрупненная блок-схема

которой представлена на рис. 1. Все в этой схеме напоминает

расчетный лист. Запоминающее устройство (память) 2 хранит

исходные данные задачи, результаты промежуточных вычислений и

программу Выполнения операций. Запоминающее устройство

связано двусторонней связью с вычислительным устройством 5,

называемым также арифметическим устройством. В одном

направлении передаются исходные данные для выполняемых операций,

а в другом — частичные результаты для записи в запоминающем

устройстве.

Устройство управления 5 передает другим устройствам

машины Сигналы управления в соответствии с командами,

извлекаемыми Шаг за шагом из запоминающего устройства таким образом,

чтобы осуществить программу вычисления. Следовательно, мы

предполагаем, что выполнение отдельной команды осуществляется

в два приема: во-первых, она должна быть извлечена из памяти

и помещена временно в специальный регистр1 устройства

управления 4, называемый регистром команд; во-вторых, она должна

быть интерпретирована или расшифрована, чтобы на ее основании

могли быть сформированы управляющие сигналы,

воздействующие на арифметическое и запоминающее устройства с целью вы-

выполнения определенных элементарных операций. Эти операции

должны быть синхронизированы специальным устройством

синхронизации, иначе называемым генератором тактовых сигналов.

Наконец, оператор должен располагать устройствами,

позволяющими, с одной стороны, ввести в машину исходные данные и

команды, например с помощью клавиатуры, и, с другой стороны,

обеспечивающими возможность ознакомиться с полученными

результатами. Эти устройства представляют собой входные / и вы-

хддные 6 органы машины, обеспечивающие в известном смысле

связь машины с внешним миром.

Эти замечания весьма общего характера были сделаны для

определения круга вопросов, возникающих при изучении

вычислительных процессов на автоматических цифровых машинах. При

последующем изложении они будут служить также для

формирования некоторых понятий о природе и происхождении различных

задач, которые мы будем изучать в дальнейшем.

Начиная с этой отправной точки, мы попытаемся шаг за

шагом ознакомить читателя с теми теоретическими изысканиями,

которые привели к выработке основных принципов работы

автоматических вычислительных машин. В этой связи особенно

важным представляется убедить читателя, что работа машины проста,

логична и естественна, исключая, может быть, трудности произ-

* Регистром здесь и В дальнейшем будет называться

совокупность запоминающих ячеек, предназначенных для хранения одного

числа или одной команды. (Прим. ред.)

2*

11

водственниго характера. Итак, мы последуем совету Декарта и

пойдем от простого к сложному, мало-помалу строя" упрощенную1

автоматическую цифровую машину, используя узлы, технология

изготовления которых сама по себе проста настолько, насколько

это возможно. Ознакомившись, таким образом, с основными

задачами автоматических вычислений и принципами устройства

цифровой вычислительной машины, мы перейдем к обзору

различных элементов и устройств, эффективно используемых в

современных машинах.

Дав представление о двоичной системе счисления, основной

в автоматических вычислениях, мы покажем, как с помощью схем

на электромагнитных реле можно легко осуществить такие

элементарные операции, как сложение и вычитание. В этой связи мы

объясним законы и символику алгебры логики.

В дальнейшем нам понадобятся устройства памяти,

обеспечивающие возможность извлечения из них в случае надобности

данных и необходимую связь с оператором.

Рассмотрение основных способов кодирования и

программирования дает нам возможность легко перейти к рассмотрению

способов передачи информации между различными устройствами

машины и объяснить необходимость в запоминающем устройстве

для команд, счетчике и дешифраторе команд. Показав

необходимость нарушения последовательности программы и предложив

средства для ее осуществления, мы сможем установить подробную схему

нашей машины и уточнить последовательность операций.

Доведя элементарную машину до пускового состояния, мы

приступим к детальному составлению программ и рассмотрим

несколько характерных примеров. Затем мы скажем несколько слов

о входных и выходных устройствах, позволяющих соответственно

вводить в машину исходные данные и команды и извлекать из

нее конечные результаты.

Далее мы перейдем к рассмотрению работы различных узлов

машины в порядке, соответствующем их важности, и покажем,

как они практически изготовляются на основе современных

элементов: германиевых диодов, ферритовых сердечников,

ультразвуковых линий задержки, магнитных барабанов и т. д.

1 Мы действительно построили подобную машину,

предназначенную для учебных целей, в соответствии с планом Центральной

лаборатории я военного училища (CODA или Демонстрационного

вычислительного центра армии). Логические функции выполняются

в ней с помощью телефонных реле, запоминающее устройство

выполнено на двойных триодах Машина содержит 128 регистров

памяти, из которых 24 электронных, а 104 используют перфокарты.

Глава первая

СТРУКТУРА УНИВЕРСАЛЬНОЙ ЦИФРОВОЙ

ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ

ДВОИЧНАЯ СИСТЕМА СЧИСЛЕНИЯ

Обычно мы осуществляем вычисления в десятичной системе

счисления. Физическое представление какого-либо числа,

могущего принимать любые значения от 0 до 9, требует в случае

использования этой системы применения устройства, обладающего

десятью различными состояниями, каждое из которых будет

соответствовать одной из цифр. Это имеет место в клавишных

механических счетных машинах, где, например, на цифровых колесах

счетчиков или соответствующих устройствах кассовых аппаратов

имеется десять цифр.

Но современные цифровые вычислительные машины строятся

главным образом на электрических, магнитных или электронных,

а не на механических устройствах и элементах. Элементы

современных цифровых вычислительных машин характеризуются, как

правило, наличием двух рабочих состояний; например, это может

быть замкнутое или разомкнутое состояние контакта, проводящее

или запертое состояние электронной лампы, наличие или отсутствие

тока или напряжения в части схемы, намагничивание магнитного

материала в том либо в другом направлении и т. д. Именно это

обстоятельство и обусловило рождение идеи — использовать в

вычислительных машинах систему счисления, построенную на основе

числа 2, или двоичную систему счисления.

Тем не менее различают два типа машин. Одни работают в

чисто двоичной системе, т. е. оперируют с числами, выраженными

в двоичной системе.^ причем оператор может игнорировать это

обстоятельство — необходим просто автоматический перевод

данных, представленных в десятичной системе, в их эквивалент в

двоичной системе в момент ввода их в машину и обратное

преобразование во время извлечения результата. Другие машины,

напротив, работают в десятичной системе, и тогда

последовательность цифр в числах, с которыми они оперируют, представляется

в двоичной системе или по крайней мере эти машины

используют устройства, двоичные по своей основе.

■13

Для простоты будем считать, что изучаемая нами машину

работает в чисто двоичной системе.

В десятичной системе счисления последовательные цифры лк*

бого числа имеют весовые коэффициенты, представляющие co6oJ

степени 10, возрастающие справа налево. Таким образом, числ«

1 957 представляется следующим образом:

1 957 = 7 X (Ю)о + 5 X (10)i + 9 X (Ю)2 + 1 X (Ю)8.

Двоичная система располагает только двумя цифрами: 0 и 1

Число, выраженное в двоичной системе, представляется в виД{

последовательности степеней 2: 1, 2, 4, 8, 16, 32, 64 и т. д. Сталс

быть, двоичное число 1101 имеет смысл

1 X (2)о + 0 X (2)*'+ 1 X (2)2+1Х(2)8

и соответствует, следовательно, числу в десятичной системе:

1 + 4 + 8=13.

Табл. 1 содержит перечень 16 первых двоичных чисел и их десятич

ные эквиваленты.

Таблица 1

Число в

десятичной

Код в двоичной системе

Условное обозначение

системе

8

2

1

8

4

2

I

0

0

0

0

0

1

0

0

0

1

1

2

0

0

1

0

1

3

0

0

1

1

1

|

4

0

1

0

0

5

0

1

0

1

(

6

0

1

1

0

1

7

0

1

1

1

1

|

8

1

0

0

0

9

1

0 ,

0

1

1

10

1

0

1

0

1

11

1

0

I

1

1

1

12

1

1

0

0

-

13

1

1

0

1

■

14

1

1

1

0

1

15

1

1

1

1

I

Отметим чередование 0 и 1 в последовательных столбцах.

Правый столбец соответствует младшему разряду. Нули и

единицы в нем чередуются через каждый шаг. Следующий столбец

содержит попеременно пару 0 и пару 1. Третий столбец справа

образован из групп по четыре 0 и по четыре 1. Наконец, левый

столбец содержит последовательно группу из восьми 0 и группу

из восьми 1. Число цифр каждой группы соответствует весу

данного разряда. Эта периодичность условно представлена в таблице

линиями и пропусками (крайние правые, колонки). Линия

соответствует 1, а пропуск — 0.

N

В общем виде числа, заключенные между 0 и (2 —1)

включительно, можно выразить посредством N двоичных цифр. Точно

так же и л десятичных цифр позволяют записать все числа от 0

до (10"—1) включительно.

14

Если наибольшее число из N двоичных чисел равно

наибольшему числу из л десятичных чисел, то мы сможем записать:

2N — 1 = 10" —1 ,

откуда-

N logio 2 = п.

Следовательно, требуется приблизительно в 3,3 раза больше

двоичных цифр, чем десятичных, чтобы выразить одно и то же число.

В частности, 10 двоичных цифр обладают емкостью, несколько

большей чем емкость 3 десятичных цифр, поскольку

2io= 1 024.

ПЕРЕВОД ИЗ ДЕСЯТИЧНОЙ СИСТЕМЫ В ДВОИЧНУЮ

Изучим теперь, как можно перевести число, выраженное в

десятичной системе, в двоичную систему. Сначала посмотрим, что

мы сделали для выделения различных цифр десятичного числа

1 957, начиная с разряда единиц. Разделим это число на 10:

1 957 = 10 X 195 + 7.

Остаток 7 представляет разряд единиц. Разделим снова частное

на 10:

195=10x19 + 5.

Остаток 5 относится к разряду десятков. Наконец, остаток и

частное последнего деления на 10 выражают соответственно разряды

сотен и тысяч:

19= 10 X 1 +9.

Таким же образом, посредством деления на 2 легко образуем в

приведенном ниже примере двоичный эквивалент десятичного

числа 59:

59 = 2 X 29 + / ; 7 = 2x3 + /;

29 = 2 X 14 + /; 3 = 2x1 + /.

14 = 2x7 + 0;

Следовательно, двоичный эквивалент числа 59 запишется как

11011

Проверим, правильно ли это:

1 +2 + 8+ 16 + 32 = 59.

Ручной перевод числа из десятичной системы в двоичную

значительно ускоряется введением промежуточной восьмеричной

системы, т. е. системы с основанием 8. В самом деле, основание

этой системы равно как раз третьей степени числа 2 и двоичный

эквивалент числа, выраженного в восьмеричной системе, легко

получается последовательной записью двоичных эквивалентов

каждой из цифр числа, записанных тремя двоичными разрядами.

Очевидно что такой перевод легко осуществляется в уме.

Следовательно, двоичный эквивалент восьмеричного числа 354

запишется как

011 101 100

С другой стороны, восьмеричный эквивалент какого-либо числа,

записанного в двоичной системе, получается разделением цифр

числа в группы по три, начиная справа, и записью эквивалентов

каждой из этих групп в восьмеричной системе (к тому же

одинаковых с их эквивалентами в десятичной системе). Что касается

перевода из десятичной системы в восьмеричную, то он легко

осуществляется последовательным делением на 8. Применим эти

15

соображения для перевода числа 1 957, записанного в десятичной

системе, в двоичную систему. Сначала найдем его восьмеричное

представление:

1 957 = ЙХ 244 + 5;

244 = 8X 30 + 4;

30 = 8X5+6.

Следовательно, восьмеричное представление числа 1 957 запишется

как число

3645

Оно легко переводится в двоичное число

011 110 100 101.

Теперь проверим, что 3 645 действительно является восьмеричным

представлением десятичного числа 1 957:

5 + 4Х8 + 6Х (8)2 + 3 X (8)8 = 1 957.

Точно так же двоичное представление дробного числа,

записанного в Десятичной системе, вычисляется последовательным

умножением на 2. Целые части последовательных произведений

соответствуют последовательности цифр двоичного представления

дробного числа. Определим, например, двоичное представление

числа 0,58:

0,58X2 ==/,16;

0,16 X 2 = 0,32;

0,32 X 2 = 0,64;

0,64X 2 = /,28;

0,28 X 2 = 0,56;

0,56X2 =/,12.

Отсюда результат: 0,100101.

В результате умножения на 8 получается таким же образом

восьмеричное представление дробного числа, записанного в

десятичной системе. Например, для десятичного числа 0,583:

0,583 X8 = 4,644;

0,664 X 8 = 5,312;

0,312X8 = 2,496.

Отсюда получается восьмеричное представление 0,452, двоичный

эквивалент которого можно записать сразу:

0,100101010.

Таким образом, видно, что если мы вправе менять основание

нашей системы счисления, то лучше выбрать в качестве этого

основания 8, а никоим образом не 12. Основание 12 не дает

абсолютно никакого преимущества, разве только облегчает расчеты в.

уме. И наоборот, выбор в качестве основания 8 значительно

упрощает расчеты, а иногда и отдельные устройства

автоматических вычислительных машин, поскольку в этом случае легко

обеспечивается последовательное вычисление двоичного представления

каждой цифры,

16

СЛОЖЕНИЕ ЦИФР В ДВОИЧНОЙ СИСТЕМЕ,

ОСНОВНЫЕ ЛОГИЧЕСКИЕ ОПЕРАЦИИ

Таблица сложения имеет в двоичной системе весьма простую

форму, а именно:

0 + 0 = 0;

0 + 1-1;

1 + 1 = 10.

При сложении двух двоичных чисел система запоминания «в

уме» идентична той, к которой мы привыкли, применяя

десятичную систему счисления, таким образом

110 1

+ 10 11

110 0 0

Займемся сначала сложением двух цифр в двоичной системе,

обозначив их а и Ь. Обозначим через 5 цифру наименьшего

разряда суммы, а через R — цифру переноса в старший разряд.

Таблица сложения, приведенная выше, дает нам возможность

составить следующую таблицу для четырех возможных

комбинаций значений 0 и 1 цифр а и Ь\

а

ь

s

R

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

Мы сразу замечаем, что Я = 1, если а и Ь одновременно равны

1. Мы замечаем также, что значение R равно обычному

произведению а и 6, и, следовательно, мы можем записать:

R = a-b (1)

а

Ь

аЪ

0

0

0

0

1

0

1

0

0

1

1

1

17

Заметим, не останавливаясь на подробностях, что эта операция

«совпадения» соответствует логической операции «пересечения»1.

Значение наименьшего разряда суммы S равно 1, если а или

Ь% но не обе сразу, равны 1. Это операция «или исключающее»,

называемая еще «дилемма»: одно или другое, но не оба. Она

соответствует тому, что в арифметике называют «сумма по модулю

2», т. е. остаток от деления суммы на 2. Эта операция

записывается как

S = a©*. (2)

Операцию сложения по модулю 2 удобно выразить с помощью

операции конъюнкции («И»), определенной выше, и двух других

элементарных логических операций: отрицания или дополнения и

дизъюнкции («ИЛИ» включающее).

«Отрицание» или «дополнение», которое обозначается чертой

сверху, определяется очень просто с помощью следующей таблицы

(читают «НЕ а»):

а

а

0

1

1

0

Операция «дизъюнкция» обозначается символом «V» и задается

таблицей:

а

Ь

a v Ь

0

0

0

0

1

1

1

0

1

1

1

1

(а\/Ь) равно нулю, только когда а и Ь одновременно равны нулю.

Отрицание (av&) эквивалентно конъюнкции («И») отрицаний а и

Ь: _ _

a \jb = а ♦ Ь.

Точно так же, если мы обратимся к конъюнкции, мы увидим, что

аЬ равно нулю, если или а, или 6, или оба равны нулю. Другими

словами, отрицание аЪ эквивалентно дизъюнкции («ИЛИ»)

отрицаний а и Ь

ab —~a\z~b.

Возвратимся теперь к выражению для 5. Мы можем записать его

двумя различными способами с помощью определенных выше

1 В отечественной литературе чаще применяют название

конъюнкция или функция «И» (Прим. ред.).

18

операций. Прежде всего мы видим, что S«l, если а«1 и 6 = 0, если

а «О и Ь = 1 (только а или только 6), что записывается как

5 = а-Ъу а-b. (3)

Очевидно, что оба члена этого выражения не могут одновременно

принять значения 1. Но мы снова можем сказать- 5=1, если а или

Ь равны 1, но не а и bt и это запишется как

5 = (а V Ь) (о1>) . (4)

Легко обнаружить равнозначность этих двух выражений. Заменим

во втором отрицание а - Ь его выражением, полученным выше:

5 = (a v Ь) {а V Ъ). (5)

Так как для функций «И» и «ИЛИ» справедливы переместитель-

ный и сочетательный законы, можно раскрыть скобки и написать:

S = аа у ЬЪ У a b У ~аЬ .

Очевидно, что

а-а = 0 и b'b = 0,

поскольку двоичная переменная не может быть равна

одновременно нулю и единице. Не менее очевидно, что в общем виде

О v х = х*.

Можно, следовательно, исключить два члена а • а и b • b в

приведенном выше выражении и сразу получить окончательный

результат. В качестве упражнения подвергнем обратному

преобразованию выражение (3), представив его теперь в форме конъюнкции

дизъюнкций:

ab V ab = (a у a) {b V б) (а V Ь) (а У1) .

Очевидно, что

a у а = 1 и b у ~b= 1 ,

поскольку двоичная переменная обязательно равна или 0, или 1.

С другой стороны, не менее очевидно, что в общем виде

1 •* = JC.

Следовательно, в вышеприведенном выражении мы можем

исключить две скобки (а У а) и (by Ь) и мы, таким образом, снова

получаем выражение (5), эквивалентное (4).

ПЕРЕКЛЮЧАТЕЛЬНЫЕ СХЕМЫ

НА ЭЛЕКТРОМАГНИТНЫХ РЕЛЕ

Покажем теперь, как соответствующее включение контактов

электромагнитных реле позволяет очень легко осуществлять

рассмотренные выше логические операции. Обмотку возбуждения реле

* Видно, что операция V сравнима с операцией за

исключением того, что 1 V 1 = 1.

19

а)

б)

мы будем обозначать строчной буквой, а соответствующей

прописной буквой будем обозначать контакты1 этого же реле. Рассмотрим

сначала^ показанный на рис, 2, а нормально открытый (т. е.

разомкнутый, когда обмотка реле обесточена, и замкнутый* когда она

возбуждена) контакт. Если такой контакт управляет возбуждением

обмотки Ь второго реле, то эта обмотка будет возбуждена одно-

временно с первой: это —

операция «тождества»:

Ь = а.

Рассмотрим теперь нормально

закрытый (т. е. замкнутый, когда

обмотка реле обесточена, и

наоборот) контакт (рис. 2, б). Если

этот контакт управляет

возбуждением обмотки с реле с, то эта

обмотка будет возбуждена, когда

обмотка реле а обесточена, и

наоборот. Это соответствует

операции «дополнения» или «отрицания»

с —а.

Вот почему в схемах нормально

закрытые контакты обозначаются

большой буквой с чертой сверху.

Одно и то же реле может

иметь большое число нормально

открытых и нормально закрытых

контактов, и именно в этом

преимущество релейных схем по

отношению к эквивалентным им

электронным. В частности, если

имеется необходимость получить в

одной схеме некоторую

переменную и ее отрицание, используют

инвертор, показанный на рис. 2,в.

Операция конъюнкции легко

осуществляется включением

последовательно двух нормально открытых контактов А и В (рис. 3):

реле г возбуждено, только когда оба контакта одновременно

замкнуты, другими словами, если обмотки реле а и Ь одновременчо

возбуждены:

r = ab = АВ.

Следовательно, такая схема обеспечивает перенос при сложении

Рис. 2. Схемы эквивалентности

и дополнения на

электромагнитных реле.

1 В наших схемах контакты всегда представлены в их рабочих

состояниях, нормально открытые — разомкнутыми и нормально

закрытые—замкнутыми. Кроме того, когда гоказаны обмотки, их

положение не связано с соответствующими контактами; понятно, что

когда обмотка реле возбуждена, его нормально открытые контакты

замыкаются, в то время как нормально закрытые контакты

размыкаются.

20

Рис. 3. Схема конъюнкции («И»)

c-avb - A v8

Рис 4 Схема дизъюнкции («ИЛИ»)

9

А

В

s

-CZb

-л-

А В

s-abvab

Рис. 5. Схема суммирования по модулю 2

двух Двоичных цифр. Точно так Же Дизъюнкция («ИЛИ») получает*

сп в результате параллельного включения двух нормально

открытых контактов А и В (рис. 4). Достаточно, чтобы один из двух кон-

Рис. 6. Другая схема суммирования по

модулю 2.

+

Рис. 7. Другая схема суммирования

по модулю 2.

тактов был замкнут (обмотка одного из двух реле возбуждена),

чтобы обмотка реле с была также возбуждена.

Рассмотрим теперь операцию сложения по модулю 2, которая

соответствует формированию цифр суммы двух двоичных чисел.

Сначала используем выражение (3) (рис. 5, а). Член а*Ь

получается последовательным включением нормально открытого А и

22

нормально закрытого В контактов; точно так же член а*Ъ

получается в результате включения последовательно нормально за»

крытого контакта А и нормально открытого контакта В.

Наконец, полное выражение 5 получится при параллельном включении

этих двух схем. Схема упрощается применением двух инверторов

(рис. 5,6). Очевидно, что цепь замкнута и обмотка реле 5

возбуждена, если только одно из двух реле возбуждено.

Воспользуемся теперь выражением (5), которому соответствует

рис. 6, а. В этом случае можно снова выгодно использовать два

инвертора (рис. 6,6). Но эта схема не обладает никакими

достоинствами по сравнению со схемой на рис. 5,6.

Наконец, попытаемся реализовать формулу (4). Чтобы это

сделать, нам необходимо одно дополнительное реле с, снабженное

одним нормально закрытым контактом и возбуждаемое при а • Ь

(рис. 7). Однако эта схема хуже двух предыдущих.

ДВОИЧНЫЙ СУММАТОР

Мы видели, как строится релейная схема, способная выполнить

сложение двух двоичных цифр. Однако такая схема не является

двоичным сумматором. Действительно, перенос, получающийся при

сложении цифр от предыдущего разряда, может добавляться к

сумме двоичных цифр каждого данного разряда. Таким образом,

получаются уже 3 двоичные цифры, которые должны быть сложены.

Сумматор на двух полусумматорах. Первое

решение состоит в осуществлении операции в два этапа (рис. 8,а).

Для двоичного разряда п начинают со сложения двух цифр ап и

Ьп этого разряда: здесь получается перенос ап • Ьп и сумма по

модулю 2 будет:

cn = an®bn = anbn V "апЬп .

Затем на втором этапе добавляют к сумме перенос гп_^{ » полу-'

чающийся от предшествующего более низкого разряда1. Так

получаются окончательный результат Sn и второй перенос {an@bn) r„_j_i

Видно, что два переноса взаимно исключаются, потому что

нельзя одновременно иметь ап • Ьп (ап и Ьп) и ап ®Ьп(ап или

Ьп, но не обе одновременно). Стало быть, их можно объединять без

предосторожностей.

Природа этой операции оправдывает название полусумматор,

данное схеме сложения двух двоичных цифр, поскольку необходи-

1 Видно, что мы нумеруем последовательность цифр тем же

номером слева направо, т. е. в направлении, в котором мы обычно

пишем числа. Таким образом, лри этом условии порядок индикации

обратен порядку нумерации разрядов. Следовательно, перенос rn_j_i

является результатом предыдущего разряда п, нами

рассматриваемого. Это может быть и не очень логично, но нужно выбирать

между этой нелогичностью, соответствующей нашим привычкам,

или логикой, соответствующей нумерации цифр в порядке, обратном

их обычной записи, что немногим более удобно.

23

мо использовать две подобные схемы для построения полного

сумматора.

На рис. 8,6 представлена принципиальная релейная схема,

осуществляющая эту операцию. Эта очень простая схема обладает тем

не менее серьезным неудобством. В релейных схемах стараются

всеми возможными способами добиться такого положения, когда

Ьп

dnbn

все контакты принимают необходимые состояния до подключения

к ним тока. Это возможно для реле ап и Ьп , но не для реле

переноса гп+у Перенос от разряда п может быть правильным только

после того, как предыдущий разряд принял определенное значение.

Он в свою очередь может изменять перенос в последующий разряд

и т. д. В наиболее неблагоприятном случае перенос, образованный

от сложения двух цифр наименьших разрядов, может

распространиться до старших разрядов:

111111

+000001

10 0 0 0 0 0

24

Переключение контактов реле происходит не мгновенно. Исключая,

таким образом, особые положения, нужно предусмотреть при

сложении двух двоичных чисел из п цифр промежуток времени,

соответствующий срабатыванию п последовательных реле.

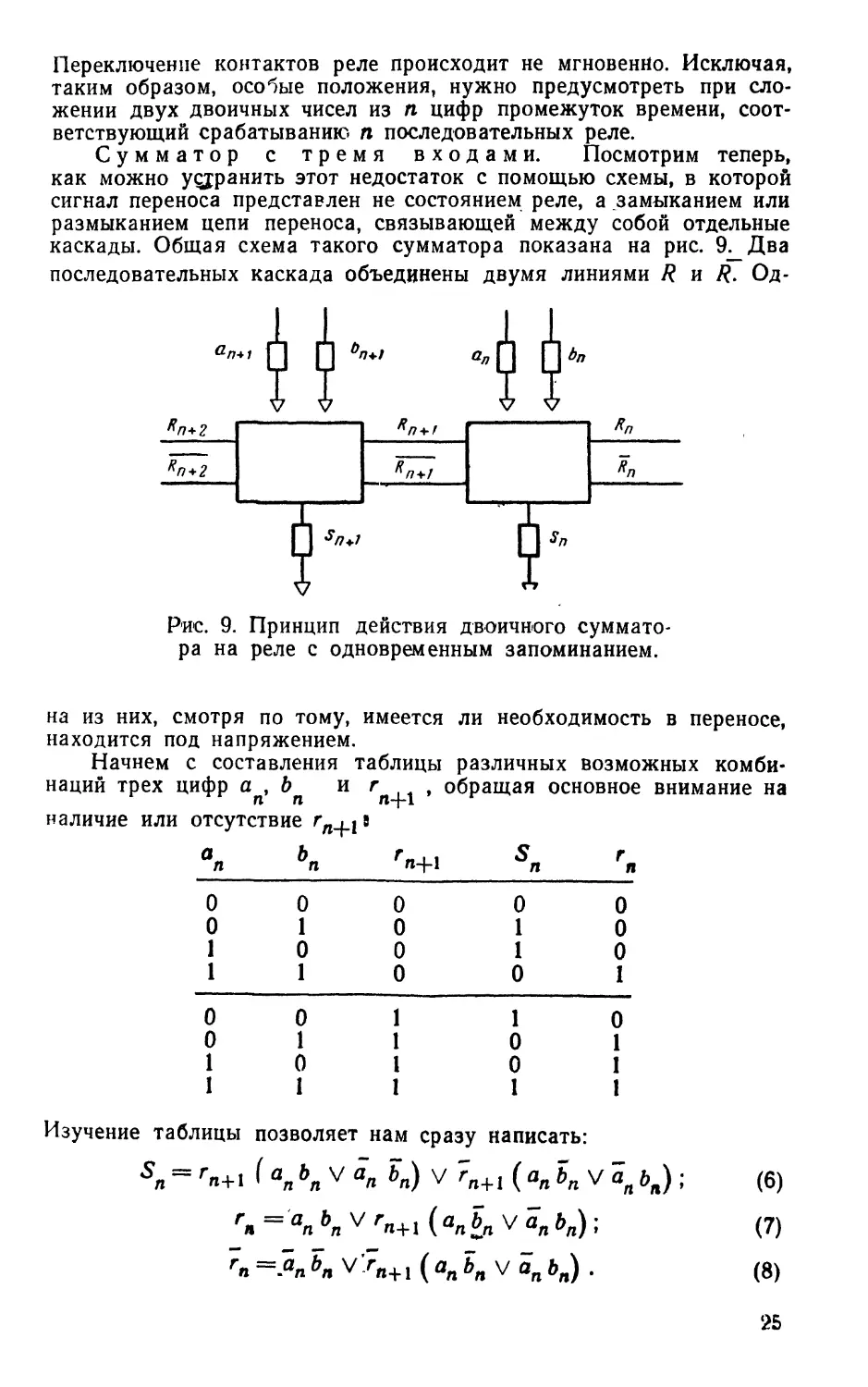

Сумматор с тремя входами. Посмотрим теперь,

как можно устранить этот недостаток с помощью схемы, в которой

сигнал переноса представлен не состоянием реле, а замыканием или

размыканием цепи переноса, связывающей между собой отдельные

каскады. Общая схема такого сумматора показана на рис. 9. Два

последовательных каскада объединены двумя линиями R и /?. Од-

Rn+2

Rn+1

Рис. 9. Принцип действия двоичного

сумматора на реле с одновременным запоминанием.

на из них, смотря по тому, имеется ли необходимость в переносе,

находится под напряжением.

Начнем с составления таблицы различных возможных

комбинаций трех цифр а , Ь и г , обращая основное внимание на

п п П-\-\

наличие или отсутствие гп_^г t

а

п

К

гп+1

п

г

я

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

0

0

1

0

0

1

1

0

0

1

1

0

1

1

0

1

0

1

1

1

1

1

1

Изучение таблицы позволяет нам сразу написать:

S„ = rn+i( а„Ьп V ап Ьп) v 7a+l (anbnv \Ьл) ; (6)

г» =ЧЛ v rn+i («„£. V аяЬя); (7)

\ =Л> Ьп V >п+, ( ап Ъп v а„ Ьп) . (8)

25

В выражении (7) можно заметить, что значения гп в

четвертой и восьмой строках таблицы определяются членом ап Ьп . Точно

так лее член ап Ьп выражения (8) определяет значения гп в

первой и пятой строках.

Чтобы убедиться в этом, запишем, например, выражение,

составленное для гп у читая таблицу строка за строкой:

rn = апЬп T^i V~~ bn гя+, V ап bn rn+l V[anbnrn+I .

/I»

V

V

A

[sn * Rn., (anbn V an b„) V Лл+/ (апЪпУ йпbn)

Rn = anbn V fi„+f (anbn Man bn)

[KnmanbnV fi^l, (anb„ Vanb„)

Рис. 10. Каскад двоичного сложения на реле.

Перегруппируем члены:

rn ~anbn( rn+l V ^) V гл+1 ( ап Ьп V ап Ьп)

Подставляя сюда очевидное соотношение

1,

получаем выражение (7).

26

Отметим, наконец, что перенос в самый младший разряд

всегда равен нулю. Итак, если мы оперируем над числом из N

двоичных цифр, мы запишем:

На рис. 10 показан каскад двоичного сумматора на реле. Эта

схема, являясь реализацией уравнений (6)—(8), тем не менее дает

экономию в числе операций, поскольку сигнал Sn может быть

получен с помощью одного единственного инвертора Ьп ,

Хорошо

• а)

Хорошо

б)

Плохо

Рис. 11. Условные обозначения: два провода,

пересекающиеся и не имеющие электрического

контакта (а); четырехполюсное соединение (б).

Обозначение (в) не используется в этой книге.

Повторим, что в этой схеме значение 1 или 0 переменных

г^+1 и г j соответствует не состоянию контактов реле, а

наличию или отсутствию тока в соответствующих линиях Я j 11

^я+Г пеРеДаюи*их сигнал переноса, полученный в предыдущем

каскаде. Именно состояние контактов этого каскада, так же как

и характер переноса, который он получает с предшествующего ему

каскада, определяют, какая из этих двух линий находится под

напряжением: Rn+\, если имеется новый перенос, и Rn+\ —в

противоположном случае. В такой схеме значения всех сигналов

переноса и, следовательно, сигналов суммы устанавливаются сразу

после того, как реле а и Ь всех каскадов принимают

соответствующие состояния. :

Схемы, реализующие члены в скобках при г п_ц или гп+{ ,

питаются, следовательно, от линий Rn+\ или Rn+\ , в то время

как схемы, соответствующие членам апЬп и ап Ьп, подключены

прямо к зажиму источника питания, предполагаемому здесь

положительным. Сделаем еще одно замечание относительно схемы

рис. 10. Мы не отметили на ней черными кружками точки соединения

проводов. Мы не будем делать это также и в дальнейшем, ибо очень

легко забыть одну или две точки на репродукции чертежа, который

станет тогда непонятным. Такой способ начертания схемы приводит

к двусмысленности только в случаях пересечения проводов. На

27

рис. 11 показаны два провода, пересекающиеся без контакта

(рис. И, а), и соединение, представленное согласно принятому

и, к сожалению, нормализованному обозначению (рис. И, в).

С нашей стороны мы запретим себе пользование обозначением по

рис. 11, в и будем представлять соединение четырех проводов

всегда так, как показано на рис. 11, б. Использование точек

становится тогда совершенно ненужным. Хочется высказать пожелание,

чтобы правила, описанные выше, в скором времени были

изменены.

ВЫЧИТАНИЕ

В действительности проблема вычитания сводится к проблеме

представления отрицательных чисел. Здесь можно предложить два

разных способа. Первый из них, называемый «чисто алгебраическим

представлением», заключается в выражении абсолютного значения

и знака обычным способом. Знак, как и цифры, является двоичной

переменной. Этот способ очень удобен для операций умножения и

деления, поскольку достаточно оперировать с произведением или

с частным абсолютных значений и добавлять знаки обычным

образом. Напротив, он неудобен для алгебраического сложения или

вычитания, так как нужно начинать со сравнения двух абсолютных

величин, чтобы знать, какое из двух чисел должно вычитаться из

другого.

Второй способ, называемый «смешанным алгебраическим

представлением», использует дополнительный код, и это вынуждает нас

прежде всего уточнить положение запятой.

Положение запятой может быть выбрано произвольно.. Тем не

менее по различным причинам, которые будут ясны из

последующего, удобно представлять себе ее справа от старшего двоичного

разряда, другими словами, оперировать с абсолютными значениями

чисел, меньших единицы. Это, очевидно, приводит к выбору

подходящего масштаба для переменных исследуемой задачи. Однако

мы увидим в дальнейшем, что это неудобство может быть

преодолено применением так называемой «плавающей запятой».

Для уяснения сути ограничимся 5-разрядными двоичными

числами. Пусть, например, имеется число

0,1101.

Веса цифр, расположенных справа от запятой, представляют собой

последовательность отрицательных степеней 2:

JL j__ j_ j__

2 ; 4 ' S 1 16

или иначе

JL _1_.J_._L

16 ' 16 ' 16 ' 16

Таким образом, записанное выше является двоичным эквивалентом

13/16.

2Я

Дополнительный код: вычитание. Рассмотрим

снова число 0,1101 и прибавим к нему двоичный эквивалент 2:

0,1101

+ 10,0000

10,1101

Машина не учитывает второй двоичный разряд слева от запятой

(разряд 2) и, следовательно, исходное число не претерпевает

каких-либо изменений после этой операции.

Выполним теперь операцию (а^Ь), где а и Ь — числа, меньшие

единицы. Результат этой операции в двоичной системе счисления

будет представляться так же, как и результат операции:

2 + (а — Ь) или а + (2 — Ь).

Отсюда мы видим, что для вычитания числа Ь из числа д

достаточно прибавить к числу а дополнение до 2 числа Ь. Возникает

вопрос: как удобнее получить это дополнение. Исследуем дополнение

числа 0,1101 до 2 или его двоичного эквивалента 13/16:

10,0000

-0,1Ю1

1,0011

Последнее число является двоичным эквивалентом числа 19/16,

которое дополняет число 13/16 до 2. Цифра слева от запятой

характеризует знак: 0 для положительного числа, 1 —« для дополнения

положительного числа до 2, которое служит нам для

представления того же числа с измененным знаком.

Вместо дополнения до 2 найдем дополнение до наибольшего

числа, которое мы смогли бы выразить теми же пятью двоичными

цифрами, т. е. до 1,1111. Это последнее число является двоичным

эквивалентом числа 2 — ——или в двоичной записи:

16

10,0000

-0,0001

1,1111

Итак, найдем дополнение числа 0,1101 до 1,1111

1,1111

-0,1101

1,0010

Этот дополнительный код назван «дополнительным ограниченным»1

в противоположность «дополнительному истинному» или дополни-

1 В отечественной литературе такой код получил (название

«обратный». Этим словом мы будем пользоваться в дальнейшем.

(Прим. ред:)

29

тельному до 2. Образовать его обычно легче, поскольку для этого

нужно просто заменить 0 на 1 и наоборот.

После сказанного ясно, что дополнительный код образуется

прибавлением к обратному коду одного младшего разряда:

К. О. 0,1101 1,0010

+ 0,0001

К. Д. 0,1101 1,0011

Проще можно сказать, что дополнительный код получается

последовательным инвертированием цифр, начиная с высшего разряда

(т. е. слева в нормальном написании) и вплоть до самого

младшего значащего разряда, который остается неизменным. Применим

эти соображения для образования двоичного кода разности

13 7 \

— — — . Двоичный код 7/16 запишется, как 0,0111. Образуем

1о 16 /

его дополнительный код с помощью обратного кода:

К. О. 0,0111: 1,1000

+0,0001

К. Д. 0,0111: 1,1001

Прибавим полученное число к двоичному коду числа 13/16:

0,1101

+ 1,1001

10,0110

Так как мы не учитываем второй двоичный разряд слева от

запятой, результат будет равен 0,0110. Это и есть двоичный код

разности 6/16.

/7 13 \

Осуществим теперь «обратное» вычитание! — — ^ля это"

го прибавим к двоичному коду числа 7/16 дополнение к 13/16,

которое мы образовали выше:

0,0111

+ 0,0011

1,1010

Единица слева от запятой характеризует отрицательное число,

абсолютное значение которого мы найдем, определяя его

дополнительный код:

К. О. 1,1010: 0,0101

+ 0,0001

К. Д. 1,1010: 0,0110

Легко находим искомое абсолютное значение 6/16.

40

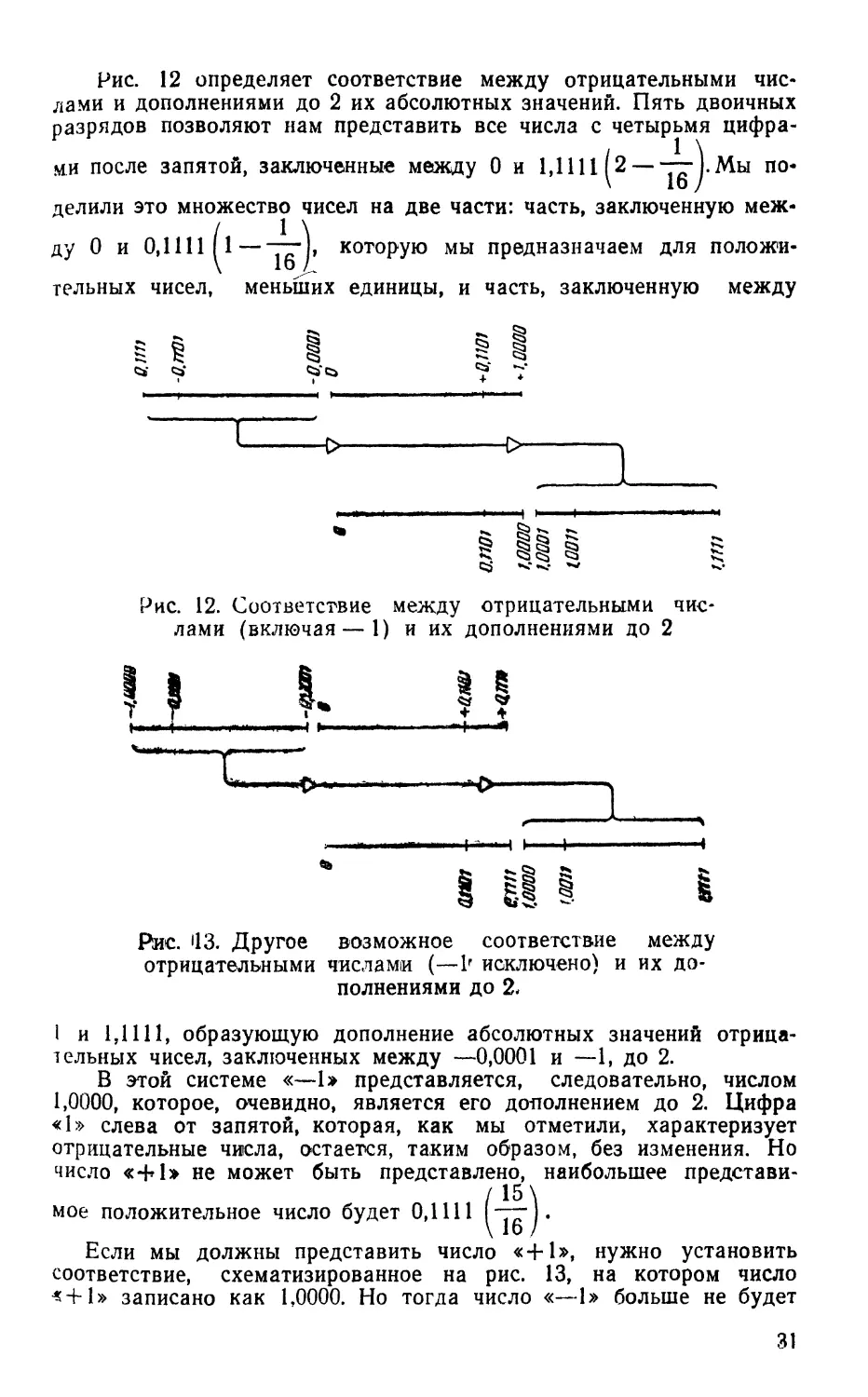

Рис. 12 определяет соответствие между отрицательными

числами и дополнениями до 2 их абсолютных значений. Пять двоичных

разрядов позволяют нам представить все числа с четырьмя цифра-

/ 1 \

ми после запятой, заключенные между 0 и 1,111112— —I.Мы

поделили это множество чисел на две части: часть, заключенную

между 0 и 0,1111^1—которую мы предназначаем для

положительных чисел, меньших единицы, и часть, заключенную между

1

I 11 1 i

Рис. 12. Соответствие между отрицательными

числами (включая — 1) и их дополнениями до 2

1

i §

-1 ш» Щ

Рис. »13. Другое возможное соответствие между

отрицательными числами (—1Г исключено) и их

дополнениями до %

I и 1,1111, образующую дополнение абсолютных значений

отрицательных чисел, заключенных между —0,0001 и —1, до 2.

В этой системе «—1» представляется, следовательно, числом

1,0000, которое, очевидно, является его дополнением до 2. Цифра

«1» слева от запятой, которая, как мы отметили, характеризует

отрицательные числа, остается, таким образом, без изменения. Но

число «-М» не может быть представлено, наибольшее представи-

15>

мое положительное число будет 0,1111 ^—

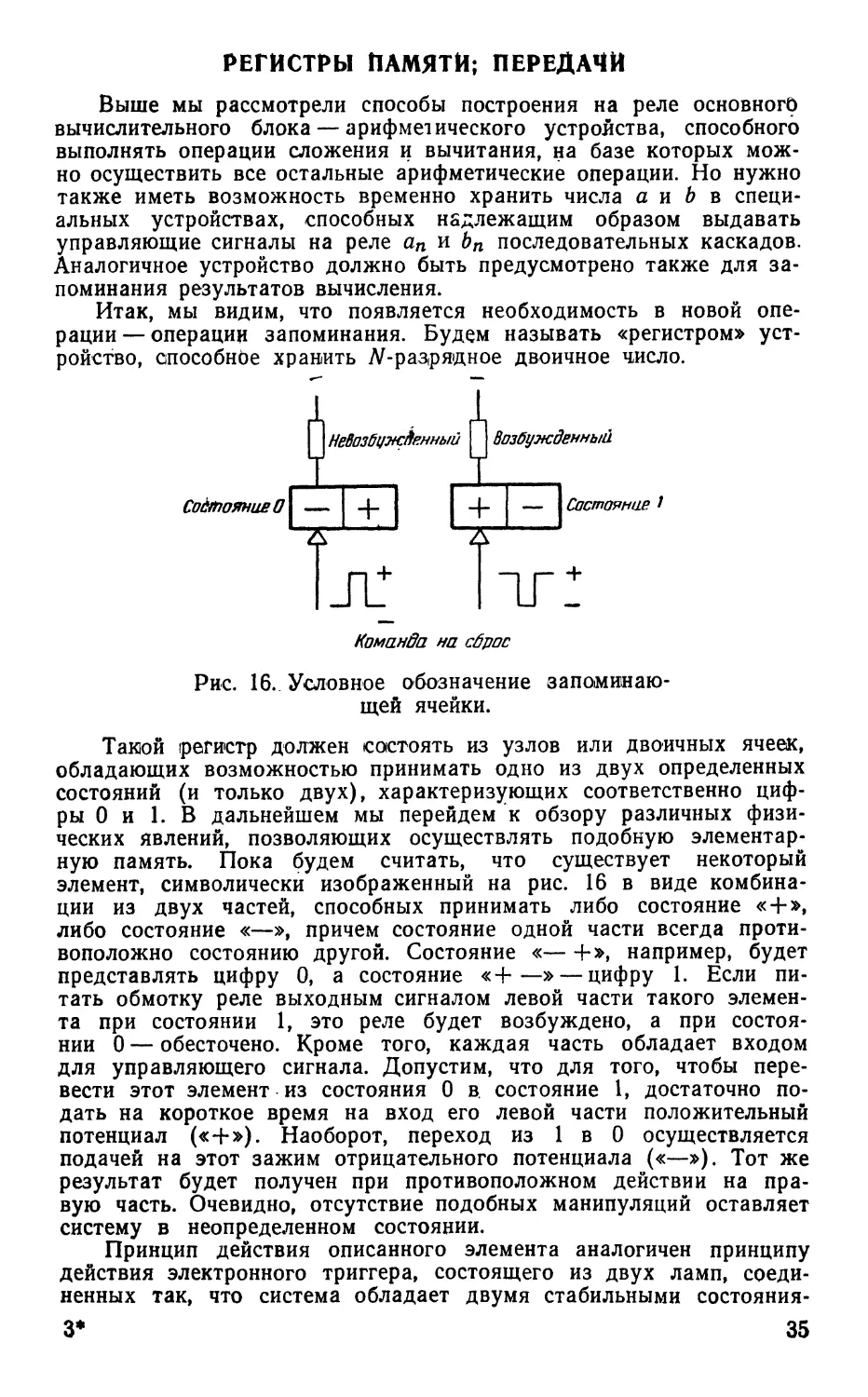

Если мы должны представить число «+1», нужно установить

соответствие, схематизированное на рис. 13, на котором число

*-Н» записано как 1,0000. Но тогда число «—1» больше не будет

31

пред ставимым, наименьшее отрицательное число —0,1111

представляется как 1,0001. Последняя система неудобна, так как вводит

исключения в интерпретацию цифр слева от запятой.

ДВОИЧНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА РЕЛЕ

(|рис. 14)

Сказанное выше позволяет нам легко получить разность а—Ь

двух чисел с цифрами ап и Ьп. Эта разность получается, как мы

это только что видели, прибавлением к а дополнения Ь. Но можно

также (это более просто с технической точки зрения) прибавить

к а обратный код Ъ и к полученному результату прибавить единицу

младшего разряда. Эта последняя операция получается

автоматически, если при сложении сообщить сигналу переноса в младший

разряд значение 1 вместо 0 [см. уравнение (9)]. Итак, если мы

оперируем с числами из N двоичных цифр, мы будем иметь для

вычитания1:

Что касается образования обратного кода, то он__легко

получается для каждого двоичного разряда подстановкой Ьп вместо Ьп,

и наоборот, в соответствии с уравнениями (6), (7) и (8), откуда

для разряда

sn « r^Ti ( % bn v ап bn) v rn+1 ( an bn V an bn); (11)

Образование обратного кода достигается с помощью

подключения трех дополнительных инверторов. Нормально открытые

контакты инвертора вычитания связываются с нормально закрытыми

контактами инвертора сумматора, и наоборот. Соответствующие

схемы представлены на рис. 14. Коммутация между выходами

сумматора и вычитателя обеспечивается реле аСу обмотка которого

должна быть возбуждена при вычитании и обесточена при

сложении. Обмотка этого реле будет возбуждаться в надлежащий

момент от дешифратора команд. Инвертор Ас коммутирует операции

для младшего разряда или разряда ранга N в соответствии с

уравнением (6) для сложения и уравнением (10) для вычитания.

В каскаде старшего разряда (разряда ранга 0) цепи

образования переноса могут быть упразднены. Тем не менее может быть

выгодным использовать линию R$ для приведения в действие

схемы сигнализации (аварийной схемы), которая показывает, что

емкость устройства превышена и автоматически останавливает

машину. Другой вид сумматора-вычитателя. При

использовании реле и диодов получается значительно более простая

схема, показанная на рис. 15. Восемь возможных комбинаций зна-

1 Точнее, коррекция младшего разряда суммы необходима в тех

случаях, когда второе слагаемое имеет отрицательный знак. (Прим.

ред.)

32

3—895

33

чений трех переменных а , Ь ' и г ,, приведены в таблице на

П П /1+1

этом рисунке. Для каждой из комбинаций возбуждается одна из

восьми вертикальных шин, пронумерованных на рис. 15 от 0 до 7,

как и строки в таблице. Рассмотрим, например, комбинацию 4.

Qn

л

Л^Л

АЛ.

А

АА

А

А

А

Л

А

А

АЛЛ

А

£-£-5.

АЛ

Ал.

-Л

Ьп

п

4\sn

к

ап

Ьп

Vfi

К

4

s7

R7

0

0

0

о 1

0

0

1

0

4

0

0

1

1

0

0

i

1

0

1

о

1

0

0

0

5

0

1

1

0

1

1

0

2

1

0

0

1

0

0

1

6

1

0

1

0

1

1

i

3

1

1

о 1

0

1

1

0

7

1

1

1

1

1

0

0

Рис. 15. Сумматор-вычитатель на реле и диодах.

Из таблицы видно, что при этой комбинации должны быть под

напряжением R% и R~ Ясно, что связь между шинами не

может осуществляться простым соединением точек, так как тогда ток

может распространиться по одной из горизонтальных шин до

другой вертикальной шины и по ней к другой горизонтальной, которая

ошибочно окажется под напряжением. Однако можно осуществить

соединения, указываемые таблицей с помощью диодов,

пропускающих ток только в направлении от вертикальных шин к

горизонтальным. Результаты сложения или вычитания в соответствии с

сигналами дешифратора команд коммутируются контактами реле ас.

Отсюда видно, что «матричная» схема «коммутации» или

«кодирования» имеет большие преимущества.

34

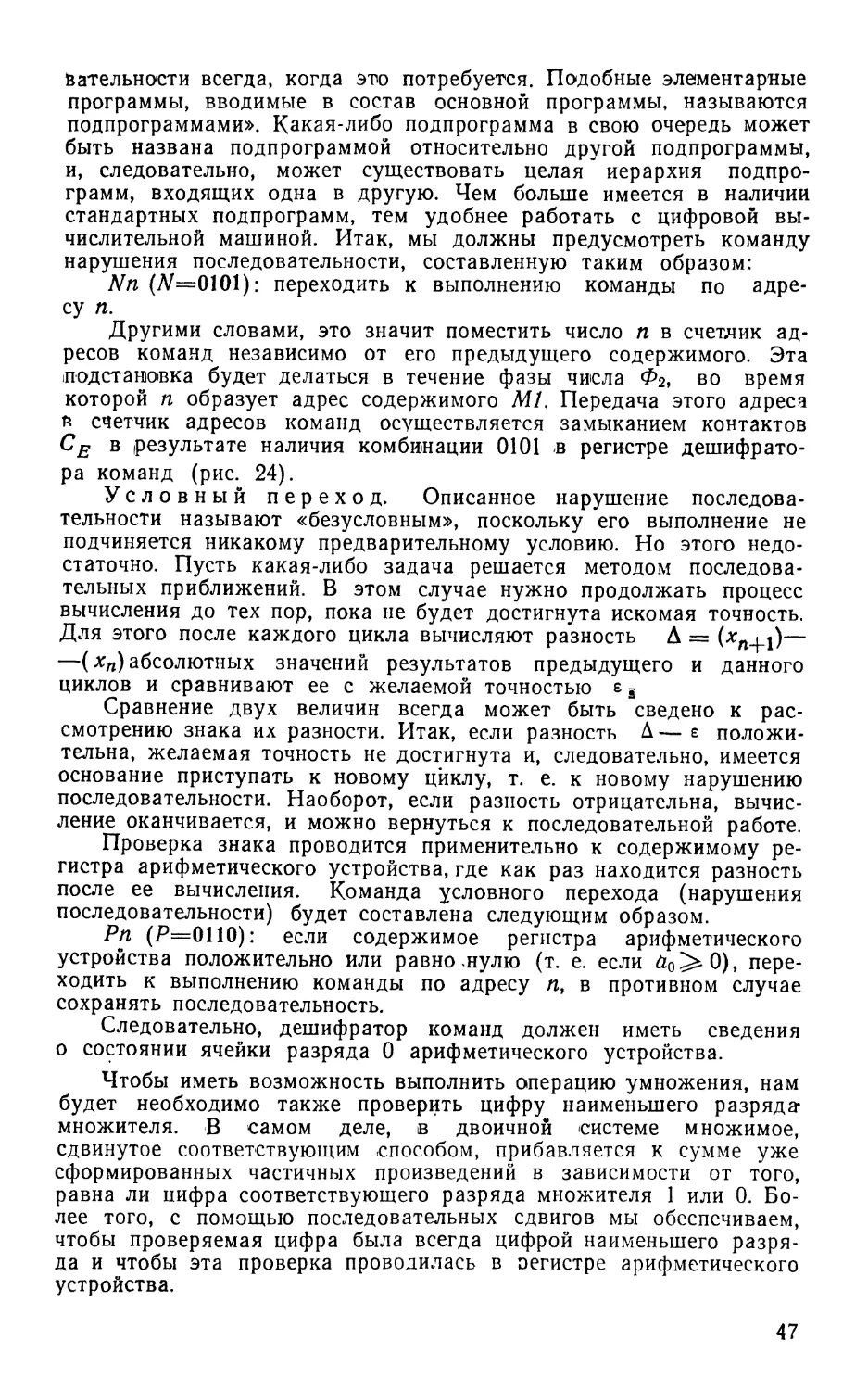

РЕГИСТРЫ ПАМЯТИ; ПЕРЕДАЧИ

Выше мы рассмотрели способы построения на реле основного

вычислительного блока — арифметического устройства, способного

выполнять операции сложения и вычитания, на базе которых

можно осуществить все остальные арифметические операции. Но нужно

также иметь возможность временно хранить числа а и Ь в

специальных устройствах, способных надлежащим образом выдавать

управляющие сигналы на реле ап и Ъп последовательных каскадов.

Аналогичное устройство должно быть предусмотрено также для

запоминания результатов вычисления.

Итак, мы видим, что появляется необходимость в новой

операции—операции запоминания. Будем называть «регистром»

устройство, способное хранить УУ-разрядное двоичное число.

СодтояниеО — -\- -f-

ii—j —

— I Состояние t

s\i it:

Команда на сброс

Рис. 16.. Условное обозначение зап0)минаю-

щей ячейки.

Таной регистр должен состоять из узлов или двоичных ячеек,

обладающих возможностью принимать одно из двух определенных

состояний (и только двух), характеризующих соответственно

цифры 0 и 1. В дальнейшем мы перейдем к обзору различных

физических явлений, позволяющих осуществлять подобную

элементарную память. Пока будем считать, что существует некоторый

элемент, символически изображенный на рис. 16 в виде

комбинации из двух частей, способных принимать либо состояние «+»,

либо состояние «—», причем состояние одной части всегда

противоположно состоянию другой. Состояние « Ь», например, будет

представлять цифру 0, а состояние «Н »— цифру 1. Если

питать обмотку реле выходным сигналом левой части такого

элемента при состоянии 1, это реле будет возбуждено, а при

состоянии 0 — обесточено. Кроме того, каждая часть обладает входом

для управляющего сигнала. Допустим, что для того, чтобы

перевести этот элемент из состояния 0 в. состояние 1, достаточно

подать на короткое время на вход его левой части положительный

потенциал («+»). Наоборот, переход из 1 в 0 осуществляется

подачей на этот зажим отрицательного потенциала («—»). Тот же

результат будет получен при противоположном действии на

правую часть. Очевидно, отсутствие подобных манипуляций оставляет

систему в неопределенном состоянии.

Принцип действия описанного элемента аналогичен принципу

действия электронного триггера, состоящего из двух ламп,

соединенных так, что система обладает двумя стабильными состояния-

3*

35

ми, в каждом из которых одйа лампа проводит в то время, когда

другая заперта. Система меняет свое состояние, если

положительный импульс подается на сетку запертой лампы или

отрицательный — на сетку проводящей лампы.

Но не будем углубляться в электронику и вернемся к нашей

схематической модели. Для передачи числа с какого-либо регистра

Ri на регистр R2 (рис. 17) достаточно замкнуть на мгновение

контакты С, управляемые реле с. Очевидно, что передача

осуществляется только в направлении стрелок и что, следовательно, состояние

регистра R2 изменяется под воздействием регистра Ri. Примени-

р р р р

Ft I Г

Ус Ус Ус Ус

ШШ ШВ ШВ ЕШ

2 ЕШШШЗШ

Рис. 17. Передача между двумя

регистрами замыканием контактов С.

тельно к этой операции говорят, что содержимое регистра R\

«считывается» и «записывается» в регистре R2. Итак, видно, что

основные свойства регистра состоят, с одной стороны, в

способности заменять свое содержимое на новое при записи и с другой,

при считывании сохранять его неизменным.

В автоматической цифровой вычислительной машине исходные

данные задачи, так же как и промежуточные результаты,

хранятся в запоминающем устройстве, часто содержащем весьма большое

число регистров — несколько десятков тысяч, например. Регистры

не соединены между собой непосредственно. Они связываются с

регистрами арифметического устройства с помощью набора шин р

(рис. 18), количество которых равно количеству цифр в

рассматриваемом числе. Таким образом, для передачи числа из регистра/?

на регистр А нужно замкнуть контакты RL и АЕ> вызывая тем

самым соответственно считывание из R и запись в А. Обратное

соединение получается в результате замыкания контактов

считывания AL и записи RE. На рисунке символов (А) обозначено

содержимое регистра А.

Запоминающая ячейка на реле. На рис. 19 в качестве

примера показано, как можно построить запоминающую ячейку

с помощью двух реле р и q, одно из которых р имеет две обмотки р\

и р2. Шина, которая ему соответствует, состоит в этом случае из

двух проводов, один из которых находится под положительным

36

напряжением, а другой — под отрицательным. Положение,

представленное на рис. 19, соответствует нулевому состоянию шины. Таким

образом, если замкнуть контакт считывания L, шина будет в том же

состоянии, что и реле р, не изменяя состояния самого реле. Если

замкнуть контакт записи £, в то время, когда шина находится в

состоянии 0, обмотка реле q оказывается возбужденной, контакт Q

Аг° V 1 (R) -~а

Рис. 18. Передача между двумя регистрами

посредством набора шин.

размыкается и реле р оказывается обесточенным, если оно было

предварительно возбуждено. Наоборот, если шина находится в

состоянии 1, реле р оказывается возбужденным по обмотке ри и

блокирующий контакт р2 замыкается. Контакт Q замкнут, поскольку

реле д не возбуждено. Обмотка р2 находится при этом под

напряжением, и контакты р сохраняют свое состояние, противоположное

показанному на рис. 19, после размыкания контакта записи Е.

Устройство счетчика. Довольно часто оказывается

необходимым заменять операцию сложения двух чисел операцией

сложения многих чисел или сальдирования. Предположим, что

подобный случай имеет место в нашей гипотетической машине. Накапли-

37

Рис.

19 Запоминающая ячейка на

реле.

вающим счетчиком называется устройство, обладающее

собственным регистром А, к содержимому которого прибавляются все

поступающие по входным шинам числа. Таким образом, можно

подсчитывать сумму последовательности чисел, посылая их одно

за другим да вход накапливающего счетчика.

Начиная с этого момента,

будем предполагать, что наша

машина работает с

10-разрядными двоичными числами1,

включая разряд слева от

запятой. Операция счета

производится в два приема -(рис. 20).

В момент tu когда зажим «+»

сумматора-вычитателя

находится под напряжением,

содержимое регистра А и число,

передаваемое в этот момент

шинами, формируются и

записываются в дополнительный

регистр Л', так как контакты X'

тогда замкнуты. Затем в

момент t2, когда реле х?

находится под напряжением,чконтакты

X' размыкаются, отсоединяя регистр А' от схем счета, а контакты

X' замыкаются, вызывая перенос содержимого А' в А. Питание реле

х' осуществляется через контакт X, замыкаемый только для

некоторого числа определенных операций.

Очевидно, контакты AL и АЕ позволяют в соответствующий

момент считать содержимое регистра А или записать в него число,

взятое из запоминающего устройства.

Впервые на примере этой схемы мы сталкиваемся с

последовательностью действий при выполнении одной операции. В

дальнейшем мы еще более убедимся в том, какую важную роль играет

разделение циклов работы цифровых вычислительных машин на

отдельные последовательные фазы.

Организация запоминающего устройства

(рис. 21). Предположим, например, что запоминающее

устройство состоит из 64 регистров по 10 ячеек каждый (рис. 21),

пронумерованных от 0 до 63. Между прочим, такая емкость

совершенно недостаточна для реальной вычислительной машины. Входы

«считывание» и «запись» регистра с номером i могут быть связаны

с шинами через контакты Ljh £*.Эти контакты управляются

обмотками // и в{. Для работы с таким запоминающим устройством

необходимо обеспечить выбор данного регистра и осуществление

операций считывания и записи. Для этого каждая пара обмоток

// и et связана, с одной стороны, с одной из линий S/, выходящих

из коммутатора запоминающего устройства, а с другой стороны —

с .парой контактов МL и МЕ, общих для всех обмоток. Работа

коммутатора, которую мы сейчас будем изучать, такова, что линия

5/, соответствующая выбранным данным, должна находиться под

1 В реальных машинах числа, с которыми оперирует машина,

содержат много десятков двоичных цифр.

за

напряжением. В этот момент данные считываются либо

записываются, смотря по тому, замкнут ли контакт считывания ML, который

замыкает цепь обмотки lt , или контакт записи МЕ, который

замыкает цепь обмотки е/. Состояние всех других элементов

запоминающего устройства остается неизменным.

Коммутатор. Порядковый номер регистра в запоминающем

устройстве называется его «адресом», другими словами, он

определяет его расположение в устройстве. Адрес, заключенный между

Рис. 20. Общая схема арифметического устройства.

0 и (2^ —1) выражается с помощью р двоичных цифр, которые

можно записать в регистре из р ячеек, каждая из которых

воздействует на обмотку реле.

В нашей гипотетической машине р = 6 (действительно,

2е = 64). Следовательно, наш регистр коммутатора содержит

шесть ячеек, питающих шесть обмоток реле, обозначенных на рис. 23

от /я4 до В дальнейшем мы покажем основание для подобной

нумерации.

для упрощения изучим работу коммутатора на восемь

положений от So до S7, управляемого тремя реле (т0, тх и т2),

связанными^ с регистром, имеющим емкость три двоичные цифры

(рис. 22). Работа коммутатора должна описываться восемью

переключательными функциями:

«So — niQ m-i ni2',

Si = ttiQ тп\ ш% \

39

S% = fflQ ПХ\ ffl2 \

S3 = mQ mi m<i;

«S4 = mo n%\ Ш2

55 ~ /По Шх n%2 *,

56 = mo mi /7Z2;

Sq = /По /Hj /П2 .

Левые части представляют собой состояния реле для каждого

из состояний регистра, соответствующих числам от 0 до 7. Эта

система уравнений реализуется, как это легко (Проверить, пирамидой

контактов, показанной на рис. 22.

А

А

Рис. 21. Запоминающее устройство. Замыкание одного из

(контактов или МЕ, управляемых дешифраторами,

обеспечивает соединение зажимов считывания или записи

ячейки соответствующего регистра с выходом

переключателя, находящимся под напряжением.

40

Действительно, контакты М0 могут быть общими для линий

So — S3, а контакты MQ— для _линий 5'4 — S7.

Также первый контакт Mt может быть общим для линий

S0 и Si, а первый контакт М — для линий S2 и S3, между тем как

второй контакт Mi может быть общим для линий 64 и S5, а

второй контакт Mi — общим для линий Se и 57. И наконец, оче-

Д7;

MS

Рис. 22. Восьмиканальный дешифратор.

$ О S1 S2

S62 $63

Рис. 23. 64-канальный дешифратор и его

запоминающее устройство.

видно, нужно столько же контактов, сколько имеется пар

выходных шин. Тут мы видим первый пример уменьшения числа

контактов, которое может быть достигнуто после систематического

изучения системы переключательных функций, подобной системе,

приведенной выше, и определяющей работу коммутатора. Из

сказанного ясно, как перейти к схеме из 6 реле с 64 выходами (рис. 23).

Шесть реле, пронумерованных от 4 до 9, по причине, которая станет

ясной из дальнейшего, питаются от специального регистра,

называемого «регистром адресов», MS, в который предварительно

записываются адреса, поступающие в коммутатор.

4—895

41

ПОНЯТИЯ КОДИРОВАНИЯ И ПРОГРАММИРОВАНИЯ

Теперь мы располагаем простыми арифметическим и запоми-

нающим устройствами. Мы умеем осуществить передачу в регистр

А арифметического устройства числа, адрес которого записан в

регистре MS замыканием контактов лЕ, арифметического

устройства и контактов М запоминающего устройства. Можно также

передать содержимое регистра арифметического устройства в

регистр запоминающего устройства с адресом, обозначенным в MS,

замыкая контакты AL<1 и МЕ. Операция сложения числа,

извлекаемого из запоминающего устройства, с содержимым регистра

арифметического устройства требует замыкания контактов ML t

которые соединяют выходы «считывание» избранного регистра с

набором шин, и замыкания контакта А', который в свою очередь

включает арифметическое устройство. Осуществление операции

вычитания требует, кроме того, переключения контактов Ас

арифметического устройства.

Нам остается посмотреть, как и в какие моменты эти

различные операции производятся; другими словами, мы должны теперь

изучить конструкцию устройств управления.

Изучение кодирования и программирования позволит нам

выделить те действия, которые должны осуществляться этими

устройствами.

Вычислительная машина способна осуществить ограниченное

количество элементарных операций, заданных заранее, каждая из

которых соответствует выполнению данной команды. Перечень

команд, который машина способна интерпретировать и выполнить,

составляет ее словарь. Каждая команда обозначается порядковым

номером, позволяющим ее опознать. Например, в двоичной

системе счисления число из четырех цифр позволяет определить одну

из шестнадцати команд. Набор команд, соответствующий решению

данной ^ задачи, образует программу. Для удобства программиста,

который составляет эту программу на листе бумаги, перед тем как

передать ее в машину, каждой команде полезно сопоставить

букву, называемую часто «рабочей буквой». Можно рассматривать

соответствующий порядковый номер1, как двоичный эквивалент

этой буквы.

Но указание кода операции недостаточно для выполнения

элементарной операции. Необходимо задать также адрес регистра

запоминающего устройства, хранящего число, над которым будет

выполняться операция. Полная команда состоит, следовательно,

из кода операции и адреса, выраженных посредством их двоичных

эквивалентов. Программист на листе бумаги обозначает каждое

действие посредством буквы, таким же образом он пишет адрес

в десятичной системе. Входные устройства машины будут

выполнять перевод этих указаний в двоичную систему. Мы, таким

образом, видим, что в нашей релейной машине команда выражается

1 Двоичное число, обозначающее данную команду, получило

название «кода операции». В дальнейшем мы будем пользоваться

этим термином. (Прим. ред.)

42

с помощью 10 двоичных цифр: 4 для кода операции (разряды of

О до 3) и 6 — для адреса (разряды от 4 до 9). Теперь мы видим,

почему мы обозначили цифрами 4—9 реле управления нашего

коммутатора.

В начале этого параграфа мы рассмотрели четыре

элементарные операции, которые теперь полезно уточнить, придавая каждому

коду операции его двоичный эквивалент:

Ля(Л=сложение 0001): добавить содержимое регистра с

адресом п к содержимому регистра арифметического устройства и

сохранить в этом регистре полученную таким образом сумму.

5/г(5=вычитание 0010): вычесть содержимое регистра с

адресом п из содержимого регистра арифметического устройства и

сохранить разность в этом регистре.

#/г(/?=замена ООП): заменить содержимое регистра

арифметического устройства содержимым регистра запоминающего

устройства с адресом п.

7л(Г=передача 0100): заменить содержимое регистра с

адресом п содержимым регистра арифметического устройства.

Это очень йростой перечень, который мы будем дополнять в

дальнейшем новыми командами. Отметим при этом, что требуемые

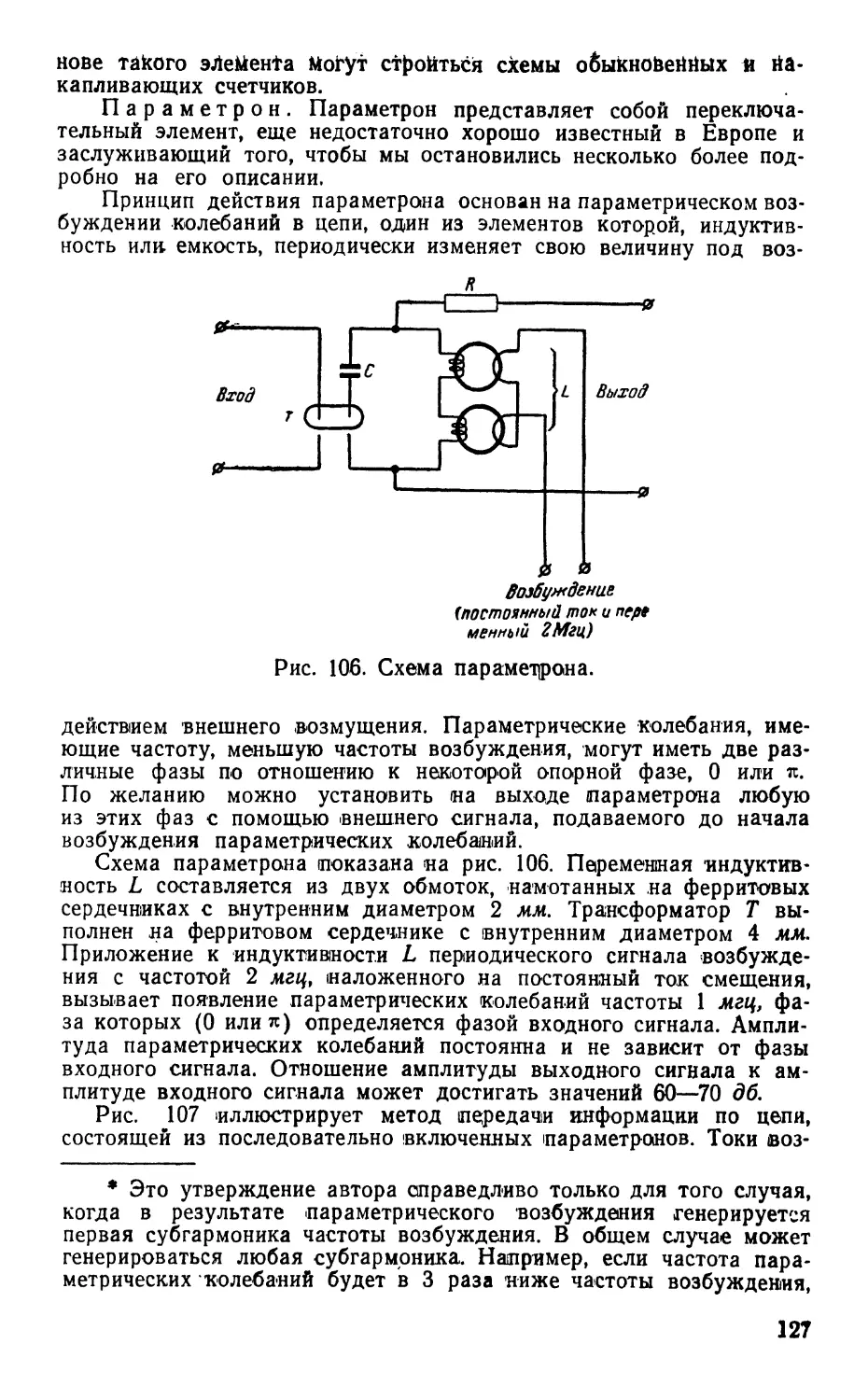

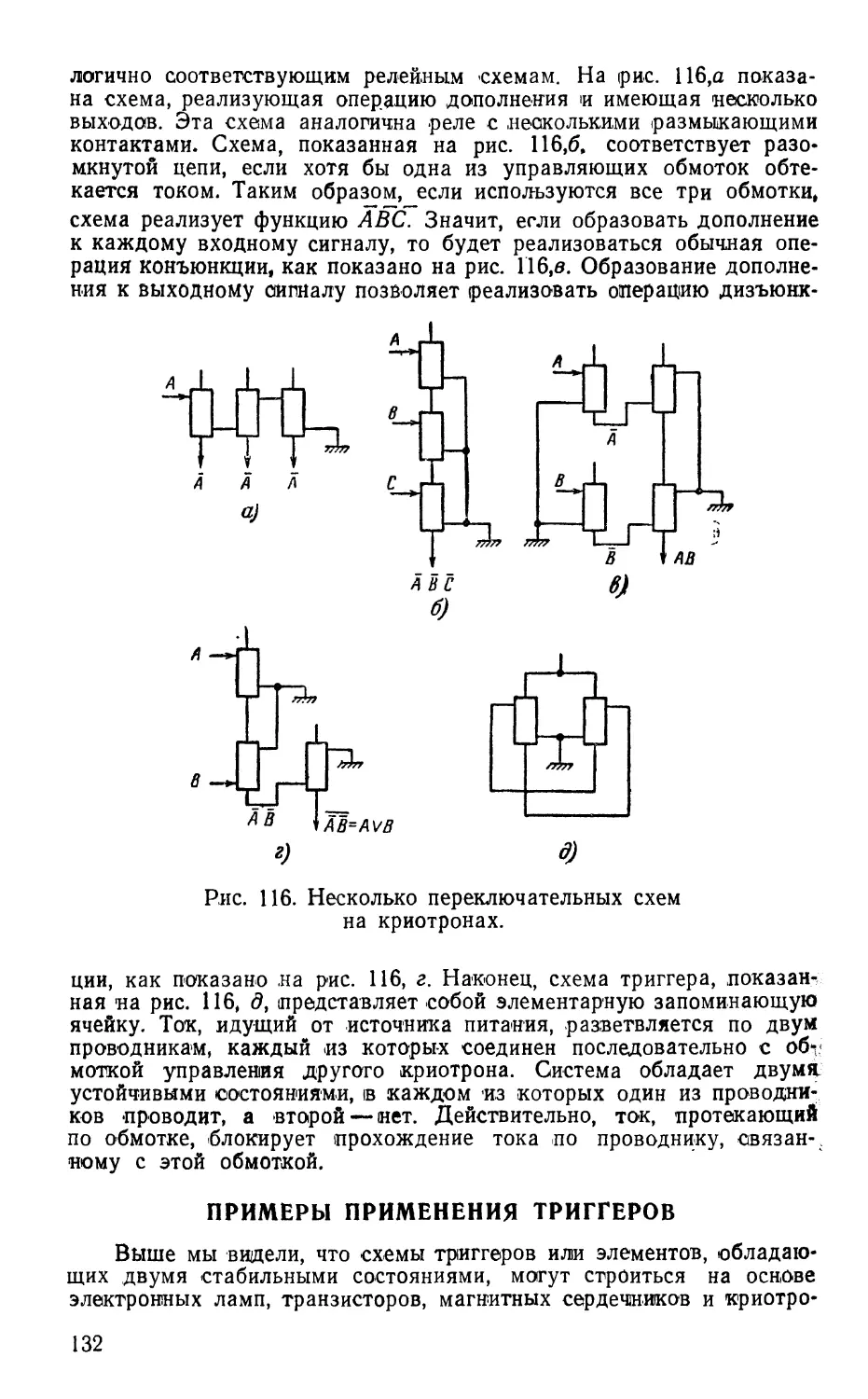

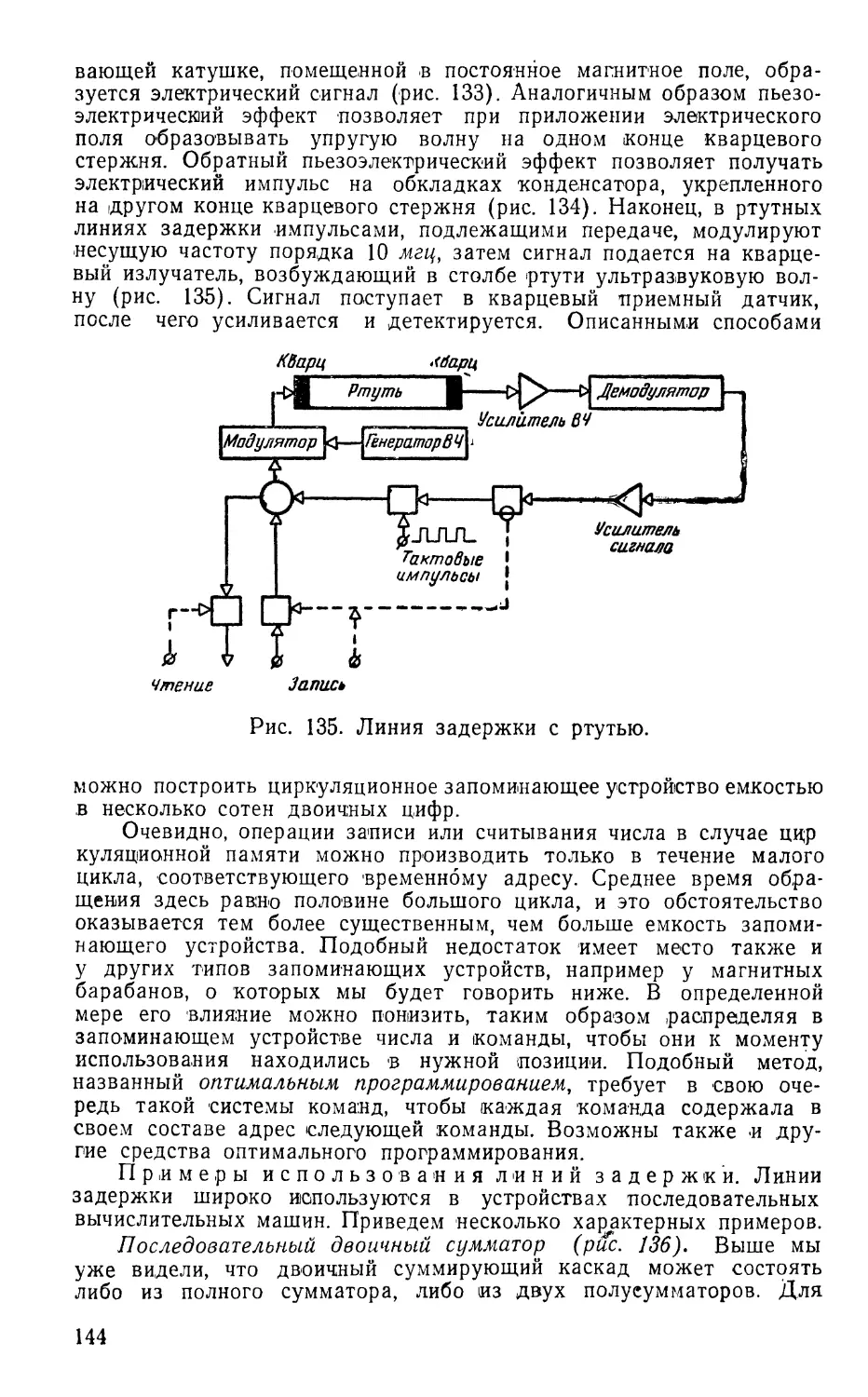

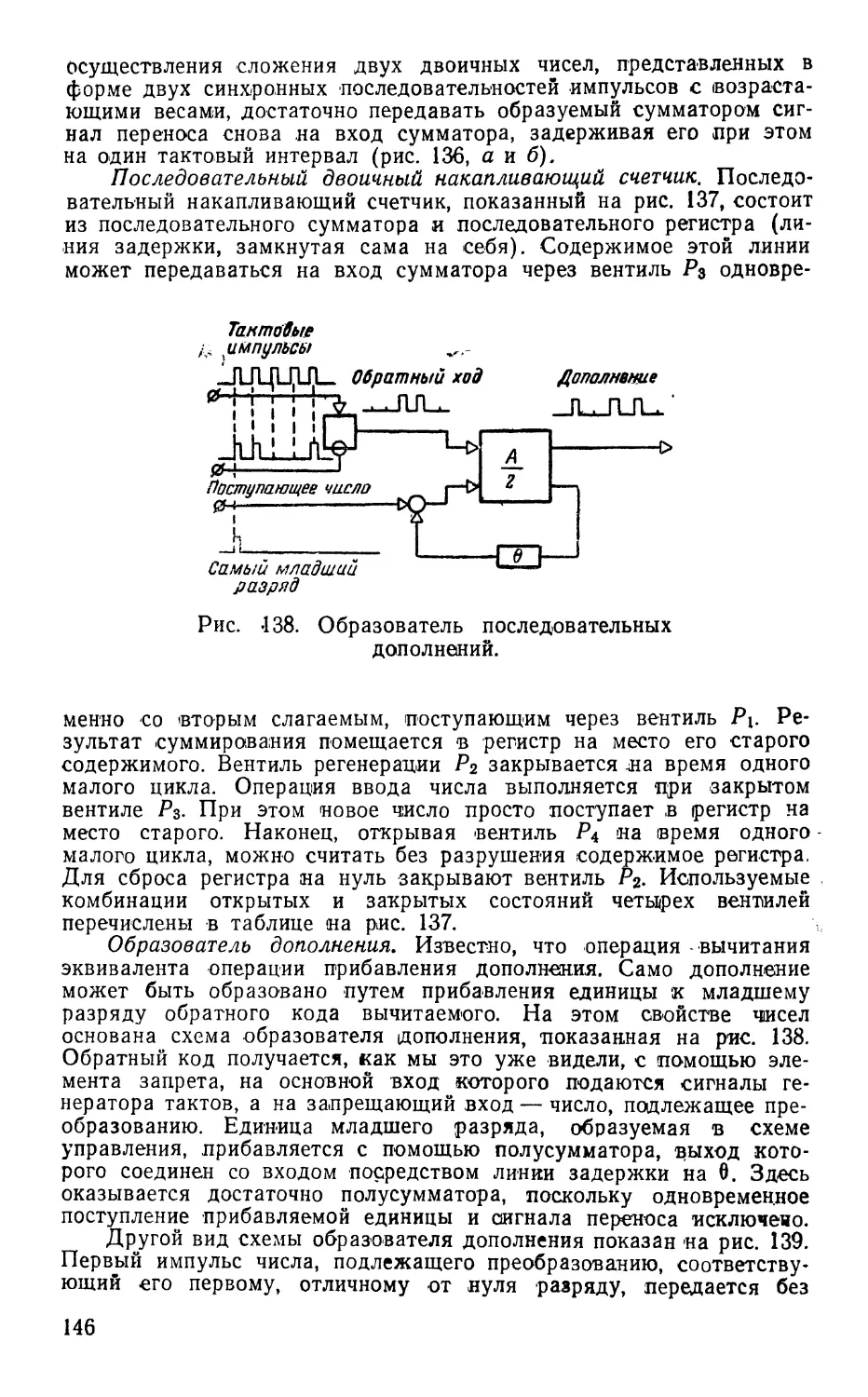

для выполнения операций числа должны определяться не