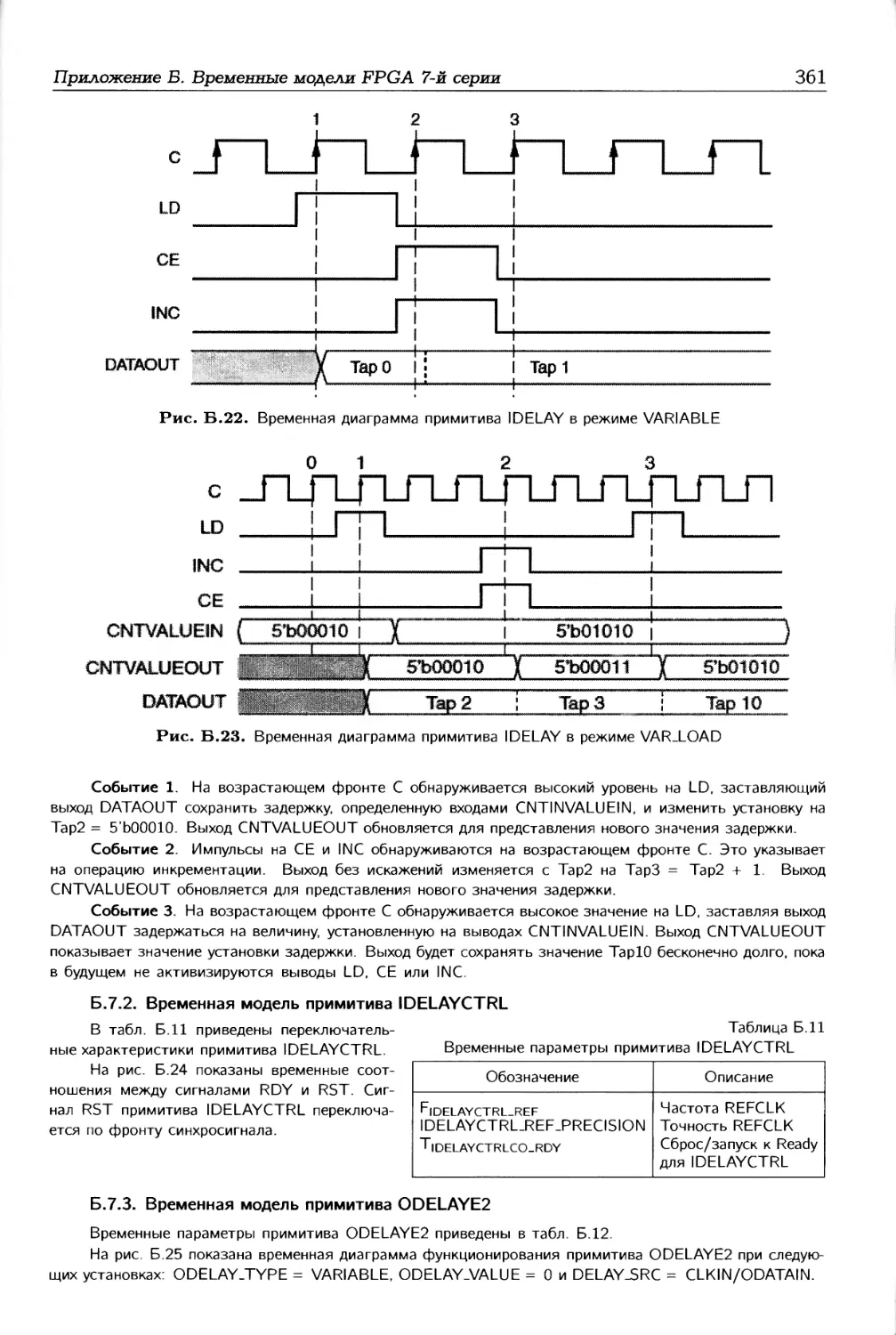

Автор: Соловьев В.В.

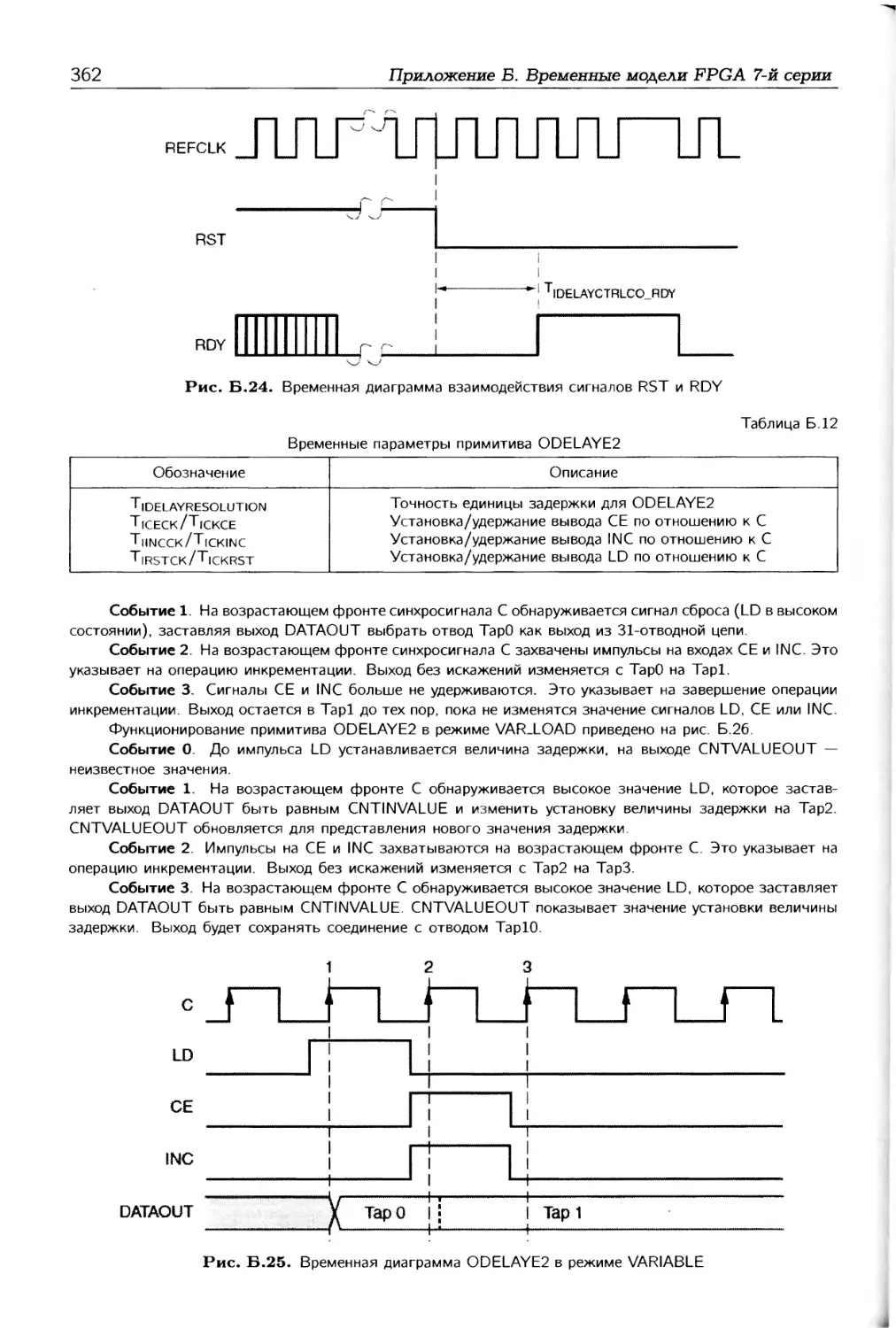

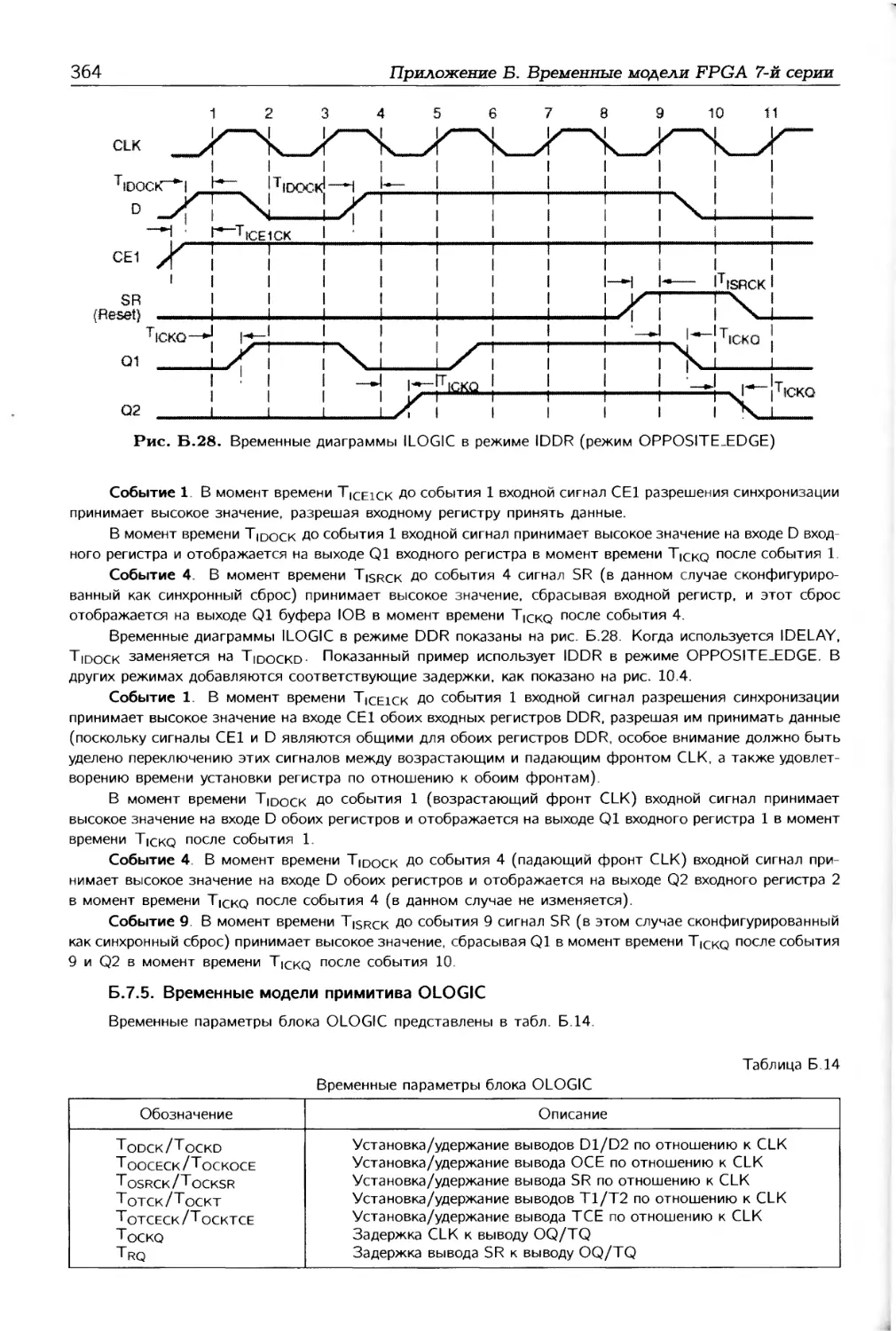

Теги: компьютерные технологии полупроводниковые устройства программирование

ISBN: 978-5-9912-0500-9

Год: 2016

Текст

CPLD и FPGA 7-й серии

Соловьев В. В.

Архитектуры ПЛИС

Соловьев В. В.

Архитектуры ПЛИС

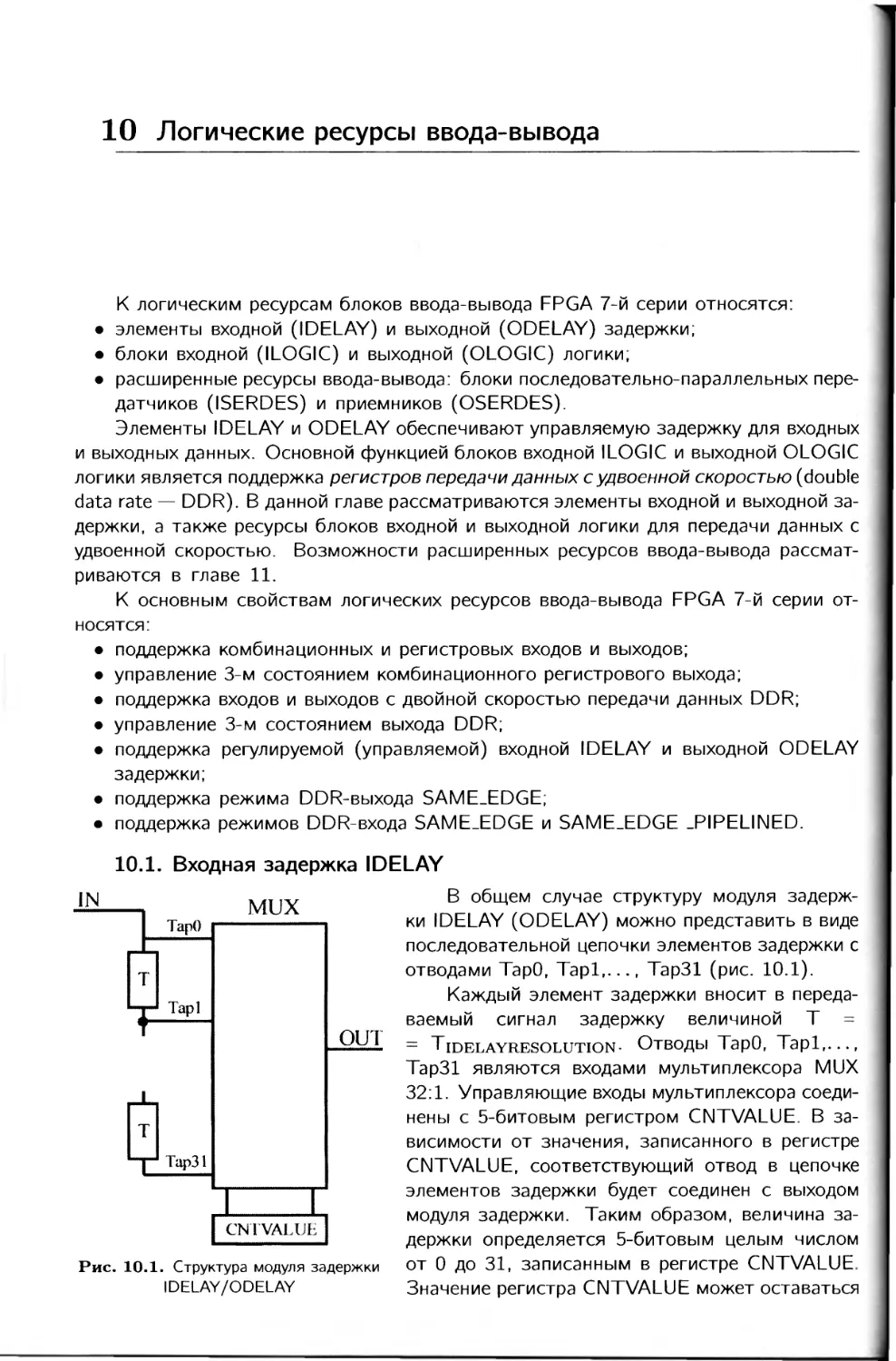

фирмы XILINX:

CPLD и FPGA 7-й серии

Москва

Горячая линия - Телеком

2016

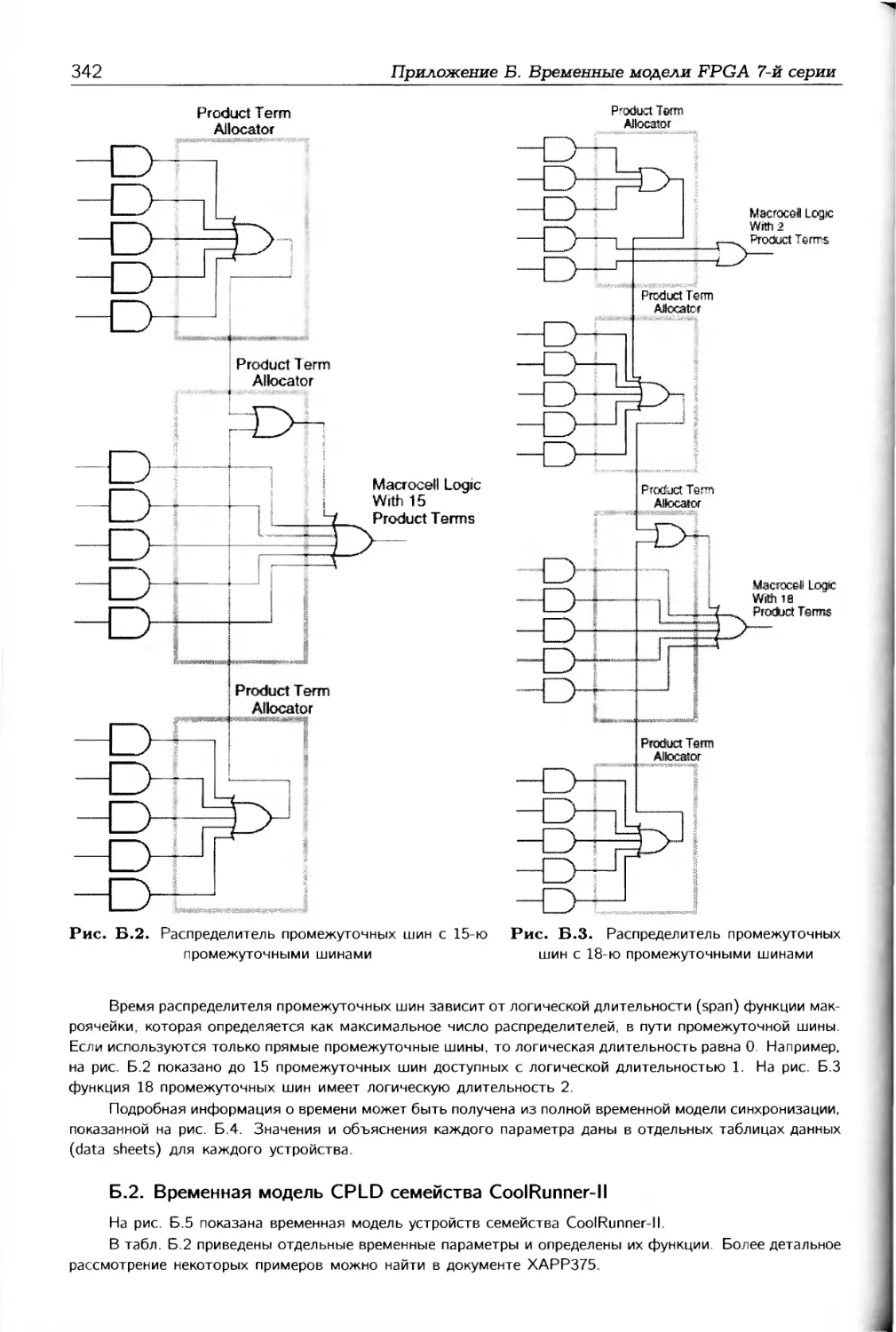

УДК 681.3

ББК 32.852.3

С60

Рецензенты: ведущий инженер-конструктор ООО «Регула» (г. Минск) А. А. Козин,

канд. техн, наук, гл. инженер проекта ООО «Сенсор-М» (г. Минск) В. А. Радишевский

Соловьев В. В.

С60 Архитектуры ПЛИС фирмы Xilinx: CPLD и FPGA 7-й серии. - М.: Горячая линия -

Телеком, 2016. - 392 с.: ил.

ISBN 978-5-9912-0500-9.

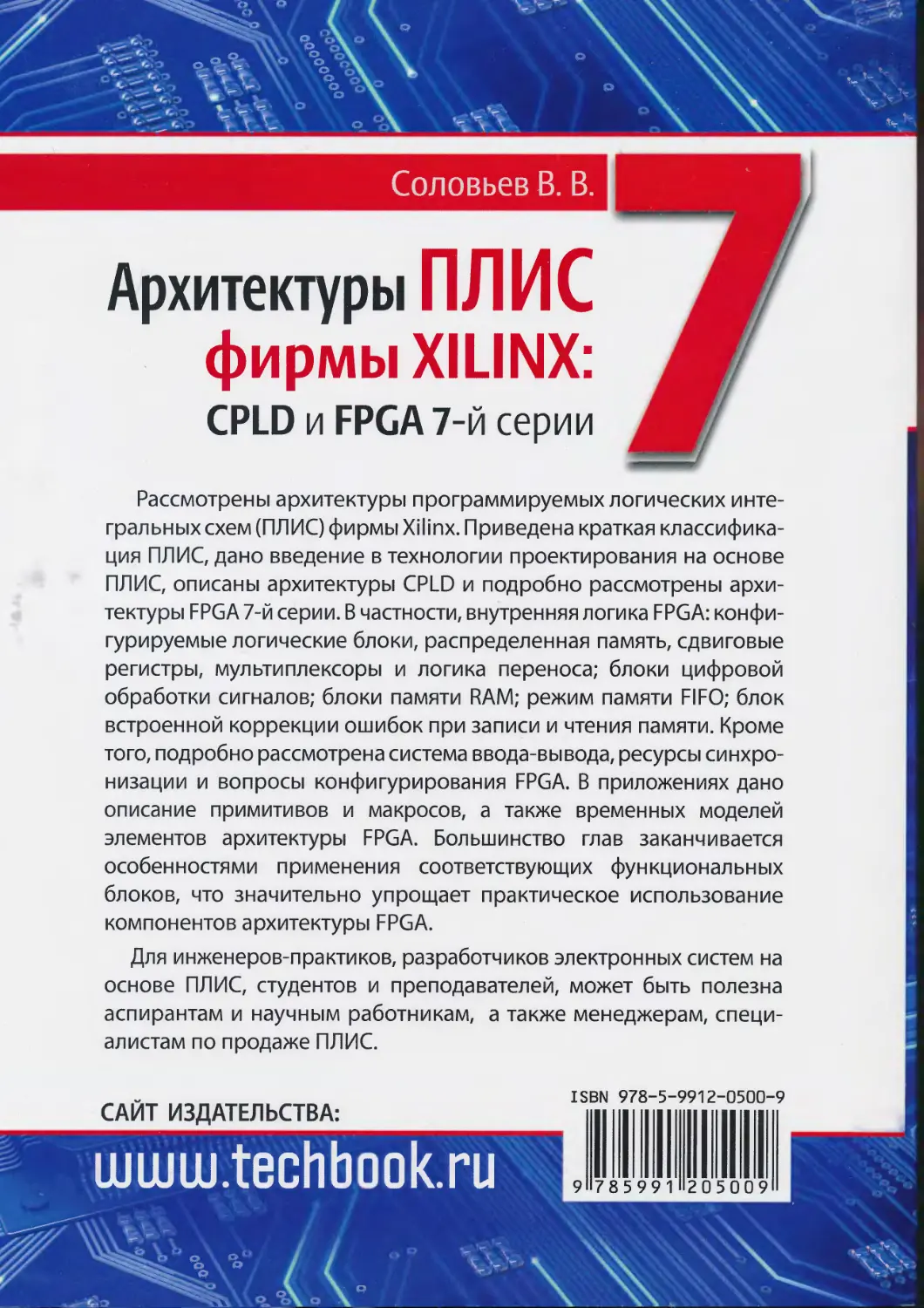

Рассмотрены архитектуры программируемых логических интегральных схем

(ПЛИС) фирмы Xilinx. Приведена краткая классификация ПЛИС, дано введение в техно-

логии проектирования на основе ПЛИС, описаны архитектуры CPLD и подробно рассмот-

рены архитектуры FPGA 7-й серии. В частности, внутренняя логика FPGA: конфигури-

руемые логические блоки, распределенная память, сдвиговые регистры, мультиплексоры

и логика переноса; блоки цифровой обработки сигналов; блоки памяти RAM; режим па-

мяти FIFO; блок встроенной коррекции ошибок при записи и чтения памяти. Кроме того,

подробно рассмотрена система ввода-вывода, ресурсы синхронизации и вопросы конфи-

гурирования FPGA. В приложениях дано описание примитивов и макросов, а также вре-

менных моделей элементов архитектуры FPGA. Большинство глав заканчивается особен-

ностями применения соответствующих функциональных блоков, что значительно упро-

щает практическое использование компонентов архитектуры FPGA.

Для инженеров-практиков, разработчиков электронных систем на основе ПЛИС,

студентов и преподавателей, может быть полезна аспирантам и научным работникам,

а также менеджерам, специалистам по продаже ПЛИС.

ББК 32.852.3

Адрес издательства в Интернет WWW.TECHBOOK.ru

Справочное издание

Соловьев Валерий Васильевич

Архитектуры ПЛИС фирмы Xilinx: CPLD и FPGA 7-й серии

Редактор Ю. Н. Чернышов

Компьютерная верстка Ю. Н. Чернышова

Обложка художника О. Г. Карповой

Подписано в печать 01.11.2015. Формат 70х100/16. Усл. печ. л. 31,85.

Тираж 300 экз. (1-й завод 100 экз.) Изд. № 150500

ООО «Научно-техническое издательство «Горячая линия-Телеком»

ISBN 978-5-9912-0500-9

© В. В. Соловьев, 2016

© Издательство «Горячая линия-Телеком», 2016

Предисловие

Моей жене, детям и внукам.

В настоящее время программируемые логические интегральные схемы (ПЛИС)

широко используются в качестве элементной базы при разработке различных элек-

тронных проектов. Однако с расширением области использования и возрастанием

ответственности решаемых с помощью электроники задач также увеличивается слож-

ность проектов, реализуемых на ПЛИС. Для решения указанных проблем производи-

тели ПЛИС и средств проектирования на их основе предлагают ряд новых технологий

проектирования на ПЛИС. К таким технологиям, в частности, относится использова-

ние языков высокого уровня для описания проектов электронной аппаратуры (вместо

традиционных графических редакторов), применение всех архитектурных возможнос-

тей, которые предоставляют современные ПЛИС, и др. Таким образом, данная книга

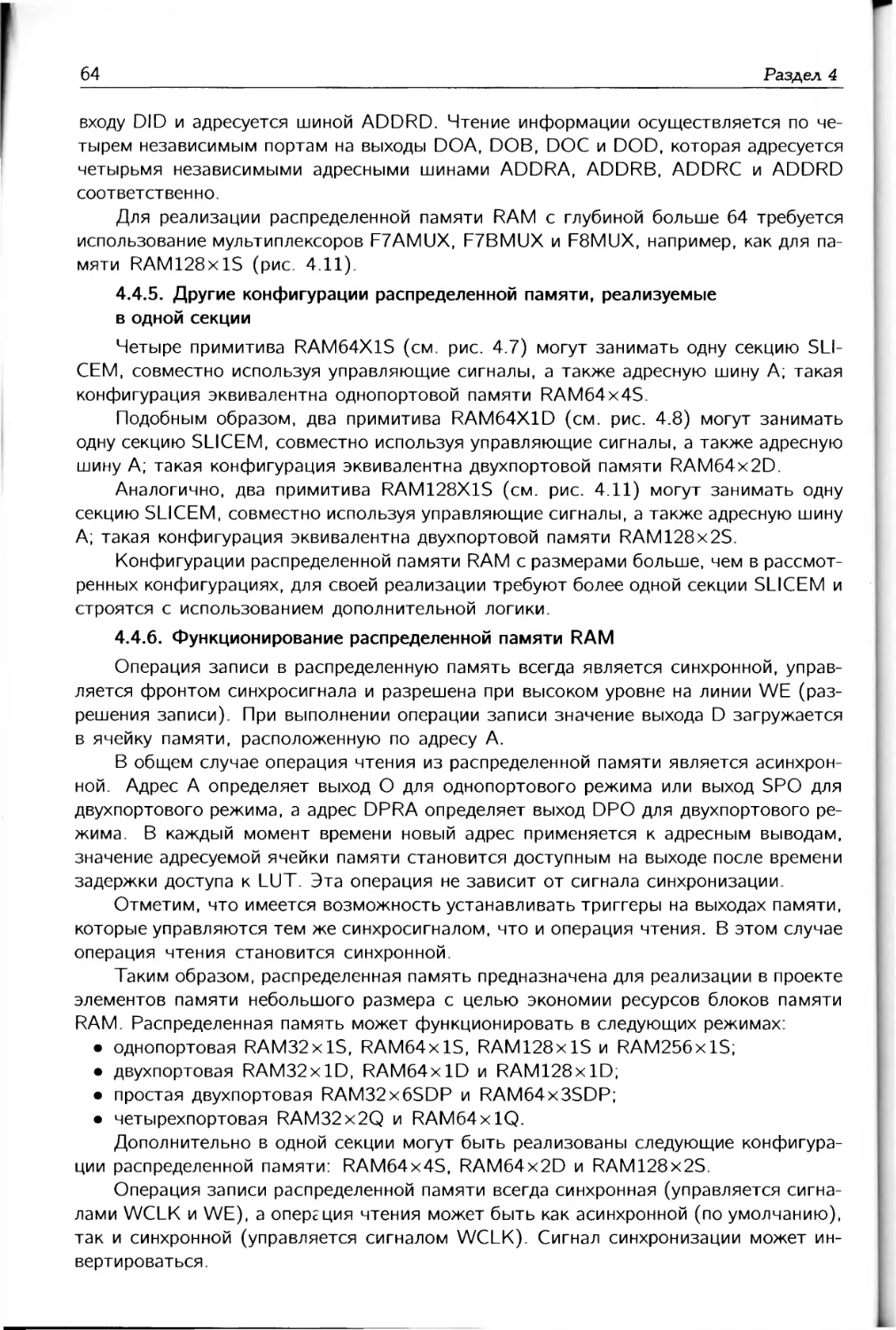

посвящена одной из технологий проектирования на основе ПЛИС: рассмотрению ар-

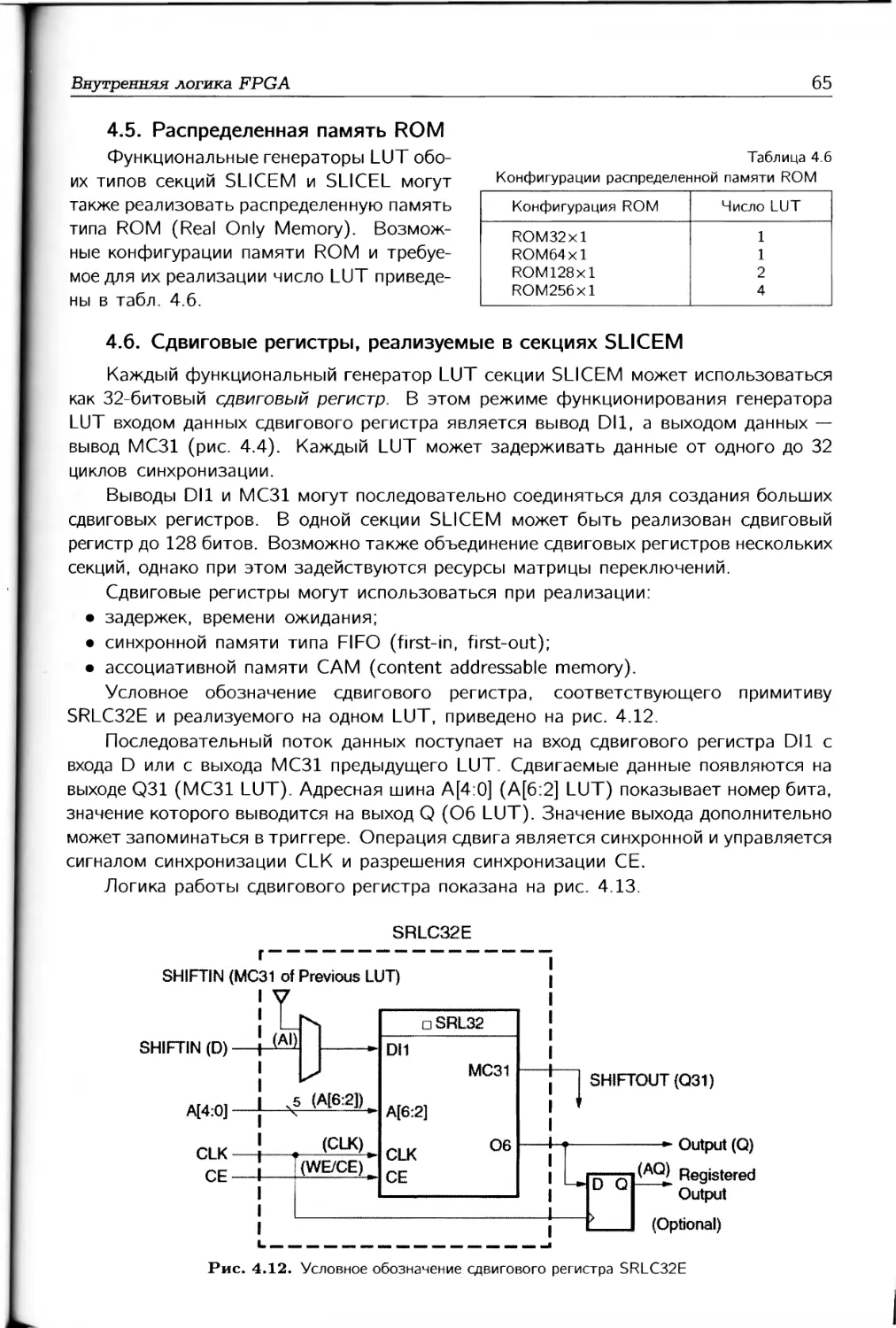

хитектур CPLD и FPGA 7-й серии фирмы Xilinx.

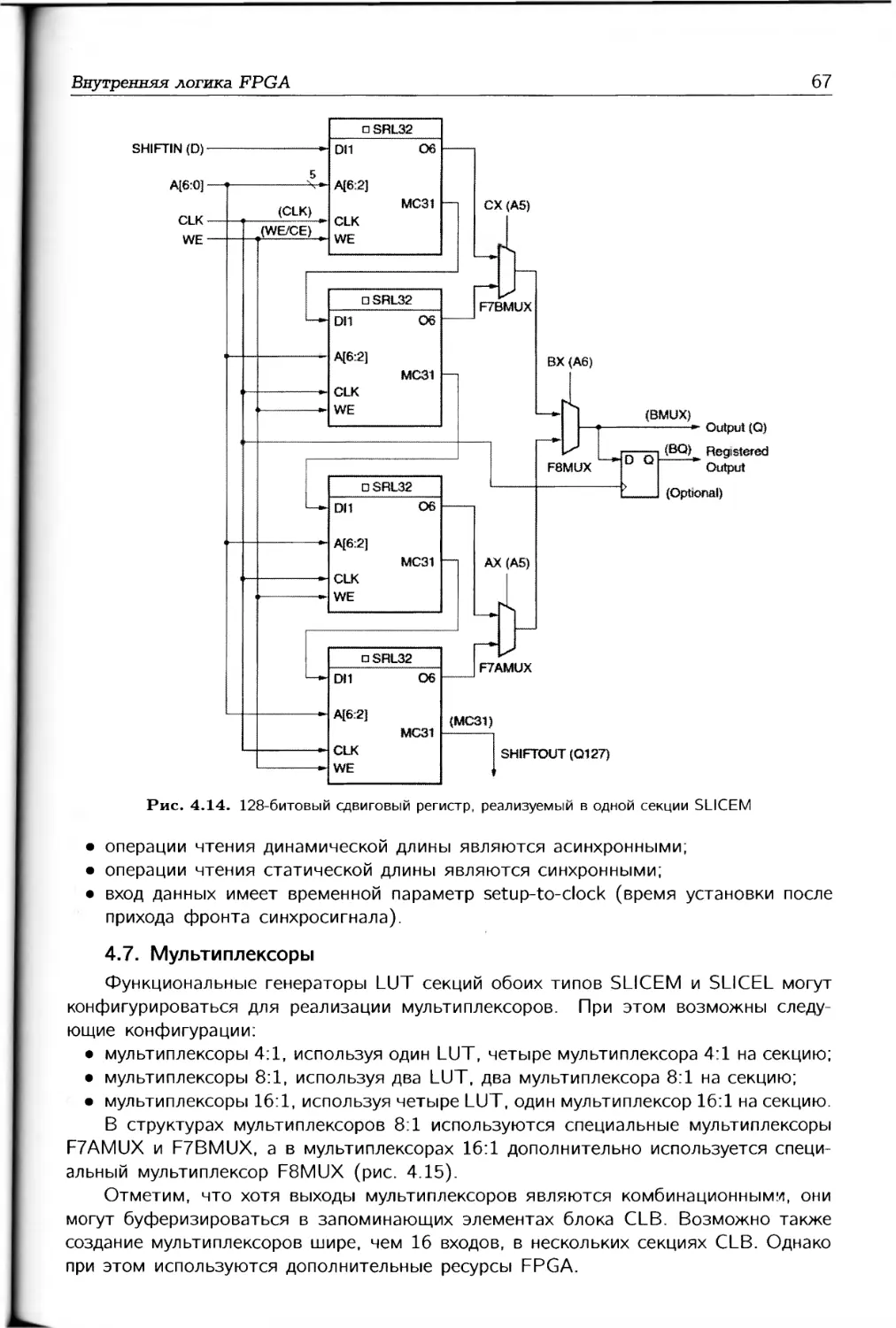

Несколько десятилетий назад ПЛИС выпускали практически все известные про-

изводители микросхем. К настоящему времени число производителей ПЛИС несколь-

ко сократилось. Наиболее известными фирмами-производителями ПЛИС являют-

ся Altera и Xilinx, которые вместе занимают около 70 % мирового рынка. Кроме

того, ПЛИС производят такие фирмы, как Achronix, Atmel, Lattice Semiconductor,

MicroSemi (Actel), Tabula и др. ПЛИС фирмы Xilinx отличает большая функциональ-

ная мощность (несколько миллионов логических элементов), возможность использо-

вания логических элементов в качестве памяти (в дополнение к встроенным блокам

памяти), большое количество блоков цифровой обработки сигналов, большое число

триггеров (способствующих конвейерной обработке данных). Благодаря этим качест-

вам ПЛИС фирмы Xilinx получили широкое распространение среди разработчиков

электронной аппаратуры.

Архитектура FPGA 7-й серии фирмы Xilinx (по утверждению фирмы Xilinx) во-

брала в себя все лучшее, что до этого времени было разработано в области совер-

шенствования архитектур ПЛИС, причем не только фирмой Xilinx, но и другими про-

изводителями Поэтому архитектура FPGA 7-й серии стала базовой архитектурой для

следующих поколений FPGA: UltraScale. Микросхемы систем на одном кристалле SoC

фирмы Xilinx также строятся на основе архитектур FPGA 7-й серии.

В настоящей книге информация из технической документации систематизирована

таким образом, чтобы можно было изучать архитектуру современных ПЛИС фирмы

Xilinx: от общих свойств до конкретных деталей. Отметим, что степень детализации

информации является достаточной для возможности практического использования

каждого компонента архитектуры. Книга содержит большой объем справочной ин-

формации. Чтобы не отвлекать внимание читателя, большинство справочной инфор-

мации вынесено в приложения.

Первая глава является введением в проблематику современных ПЛИС. Приво-

дится краткая классификация ПЛИС согласно их историческому развитию, дается

4

Предисловие

введение в технологии проектирования на основе ПЛИС, приводится характеристика

программируемых микросхем фирмы Xilinx, а также описываются основные свойства

FPGA 7-й серии.

Вторая и третья главы посвящены FPGA фирмы Xilinx, а именно семействам

XC9500XL и CoolRunnerlL В электронных проектах CPLD часто устанавливаются на

плату вместе с FPGA, их основной функцией является управление порядком пода-

чи напряжений питания для всей системы, а также конфигурированием и инициа-

лизацией FPGA.

В четвертой главе описывается архитектура внутренней логики FPGA 7-й серии:

конфигурируемые логическое блоки CLB, секции, функциональные генераторы LUT,

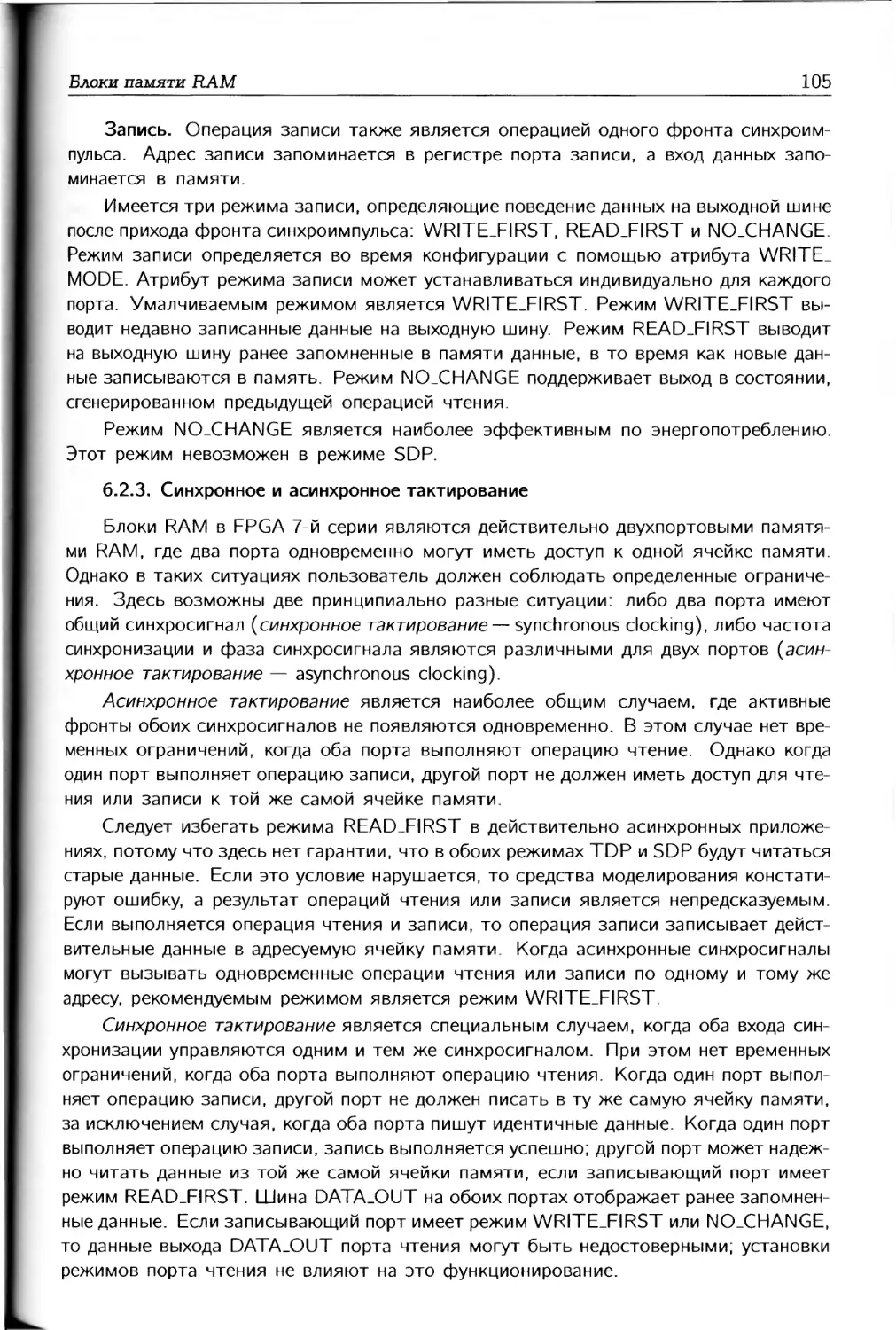

распределенная память RAM и ROM, сдвиговые регистры, мультиплексоры, а также

логика переноса. Отметим, что четвертая и все последующие главы заканчиваются

особенностями применения соответствующих функциональных блоков.

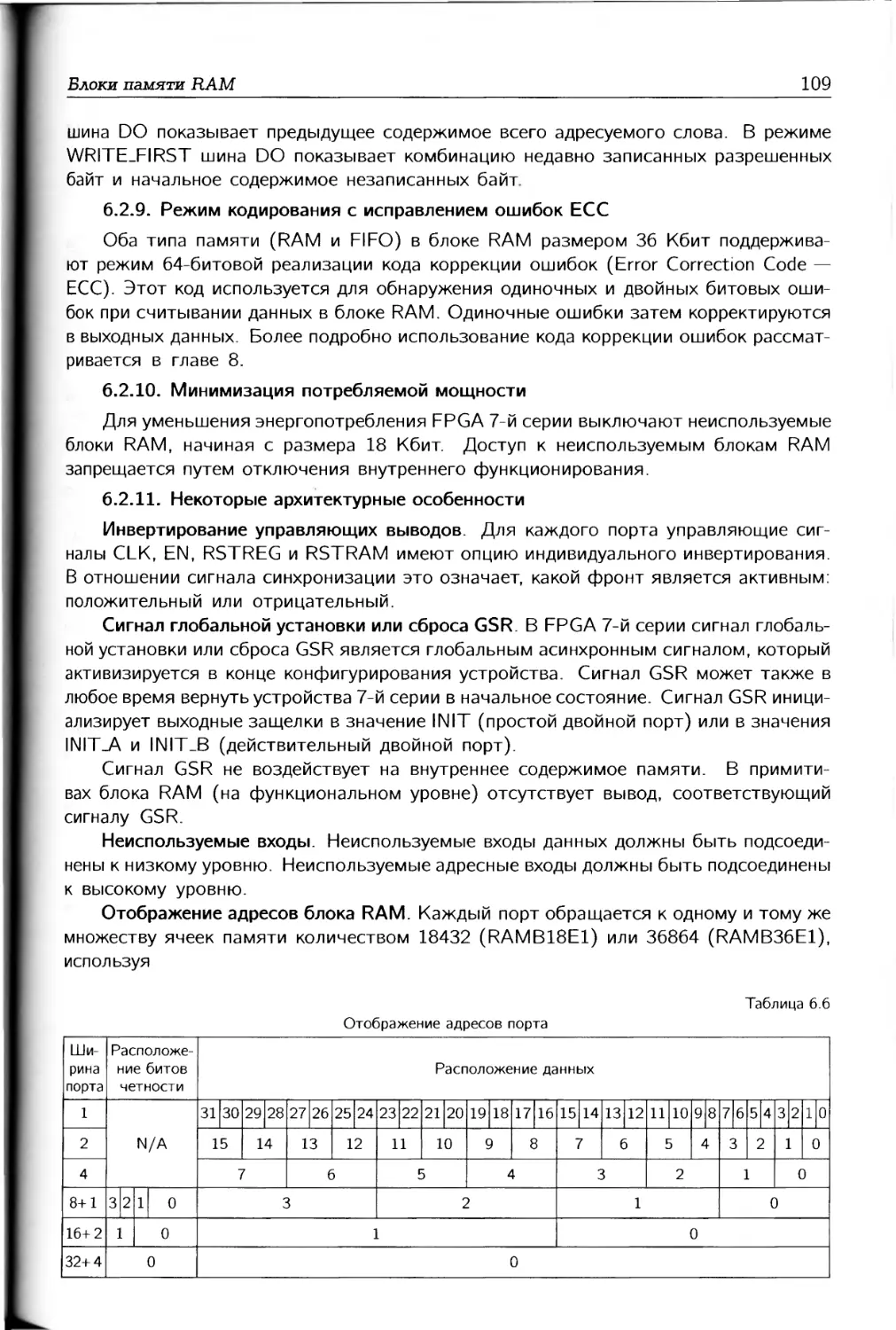

Практически ни один современный проект на ПЛИС не обходится без решения

задач цифровой обработки сигналов (ЦОС). Поэтому пятая глава посвящена секции

цифровой обработки сигналов DSP48E1. Здесь рассматривается общая архитектура

секции DSP48E1, а также такие элементы, как арифметическо-логическое устройст-

во, детектор шаблона, логика обнаружения переполнения и потери значимости, другие

функциональные возможности секции DSP48E1. Особое внимание уделено особен-

ностям применения секции DSP48E1.

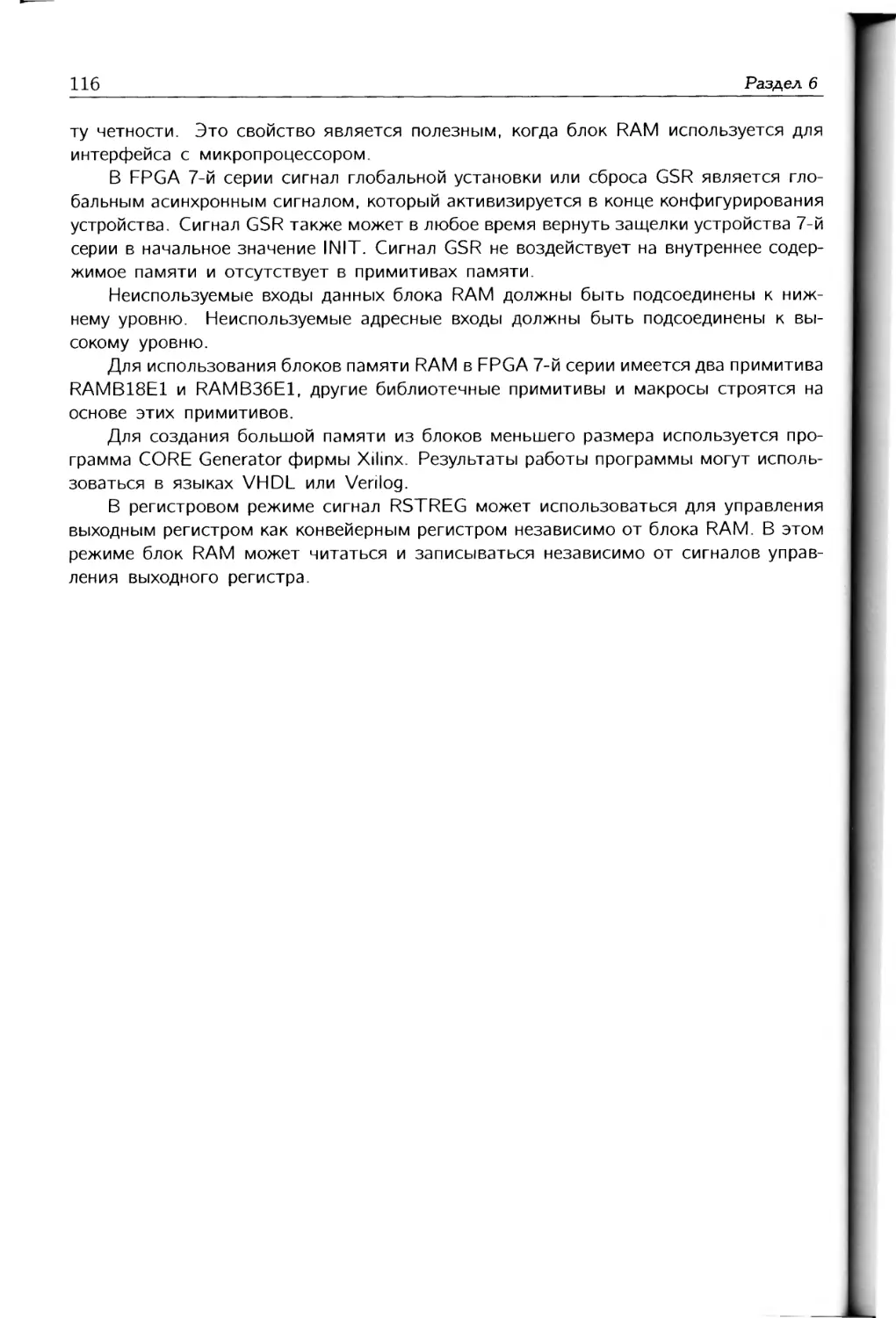

Редко какой из современных проектов обходится без использования памяти.

Шестая глава посвящена встроенным блокам памяти RAM. Рассматривается архи-

тектура блоков RAM, режимы функционирования, а также особенности применения,

в частности, каскадирование блоков RAM, побайтная запись в память, использова-

ние конвейерных регистров.

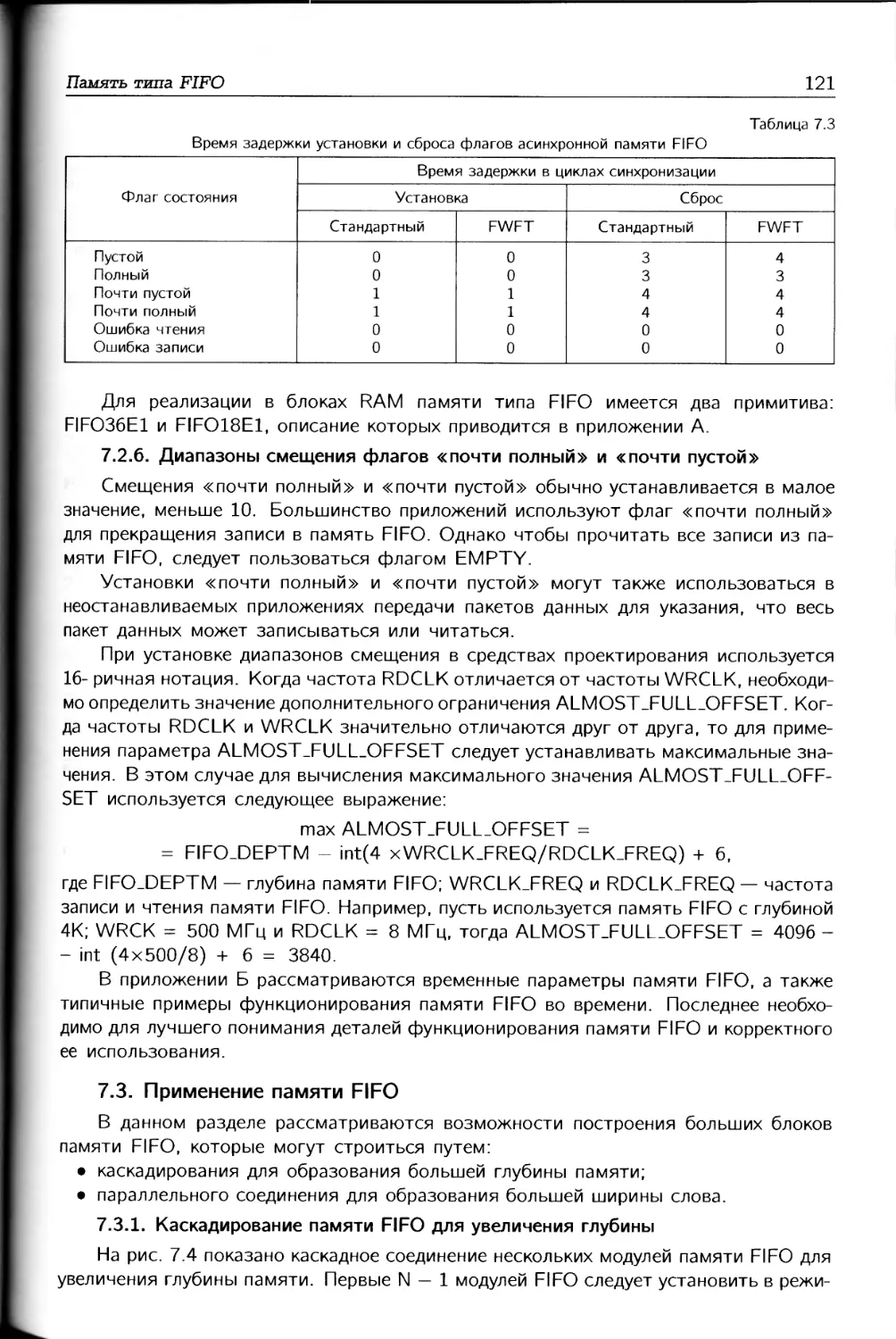

Блоки памяти RAM FPGA 7-й серии могут также функционировать в режиме

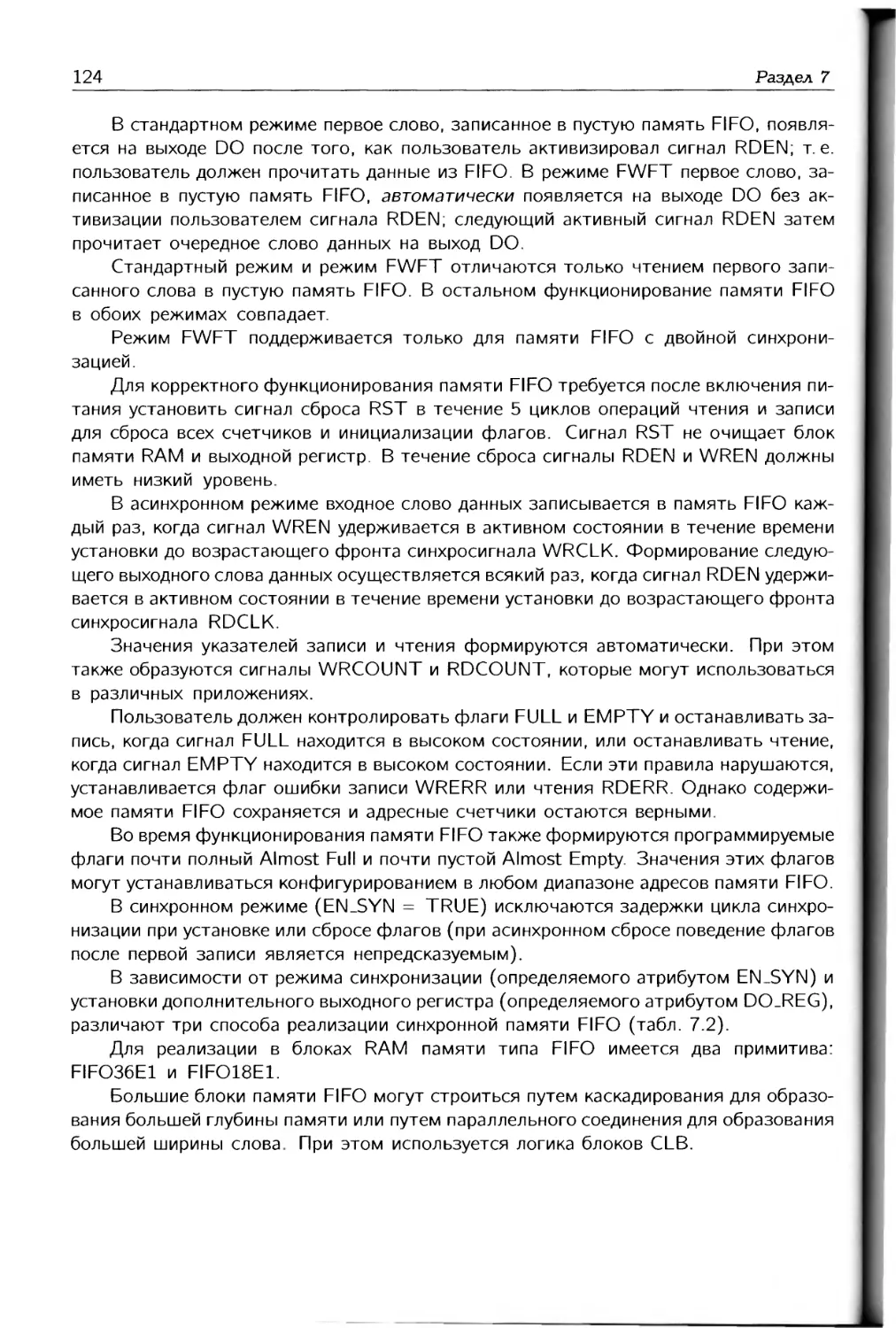

памяти типа FIFO. Седьмая глава посвящена рассмотрению свойств памяти FIFO:

описывается общая архитектура памяти FIFO, рассматриваются режимы функциони-

рования, а также особенности применения памяти FIFO.

Блоки памяти FPGA 7-й серии как в режиме RAM, так и в режиме FIFO позво-

ляют использовать механизм коррекции ошибок при записи и чтении данных. Для

этого служит блок встроенной коррекции ошибок ЕСС. В восьмой главе описывается

архитектура, функционирование и особенности применения блока ЕСС.

В FPGA 7-й серии кардинальному усовершенствованию подверглись архитекту-

ры элементов ввода-вывода. Это связано с необходимостью поддержки современных

стандартов передачи данных, в частности дифференциальных стандартов, а также

с необходимостью упрощения использования микросхем ПЛИС на системной плате.

Поэтому в FPGA 7-й серии совокупность всех элементов ввода-вывода названа сис-

темой ввода-вывода SelectlO. В книге системе SelectIO посвящены девятая, десятая

и одиннадцатая главы.

В девятой главе описывается общая концепция системы ввода-вывода FPGA 7-

й серии, приводится архитектура блоков ввода-вывода, рассматривается механизм

цифрового управления импедансом DCI, а также отмечаются особенности применения

ресурсов системы ввода-вы вода.

Десятая глава посвящена логическим ресурсам ввода-вывода, к которым отно-

сятся входная IDELAY и выходная ODELAY задержки, а также блоки входной ILOGIC

и выходной OLOGIC логики. Элементы IDELAY и ODELAY обеспечивают управляе-

мую программируемую величину задержки для входных и выходных данных. Основной

Предисловие

5

функцией блоков входной и выходной логики является поддержка регистров передачи

данных с удвоенной скоростью.

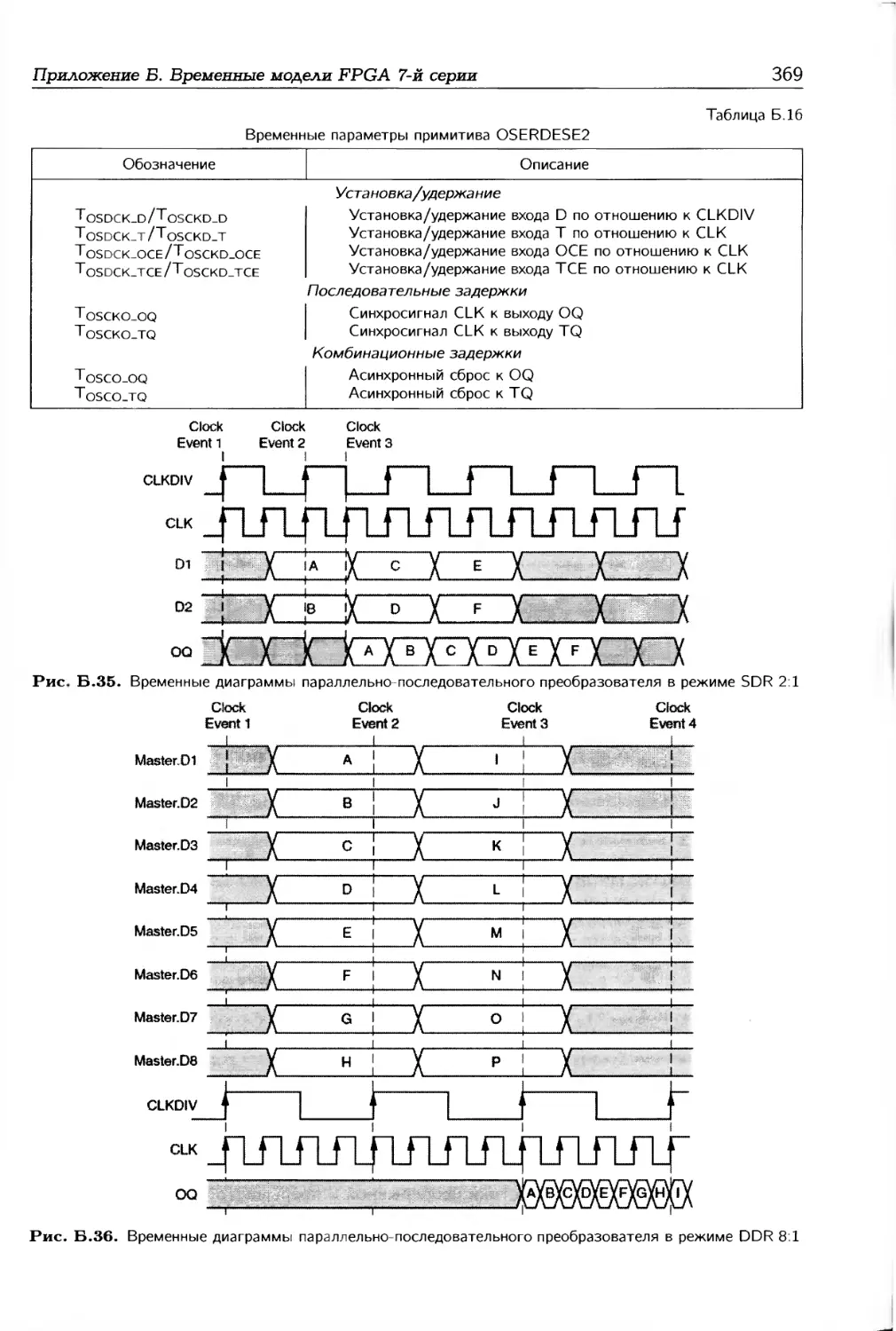

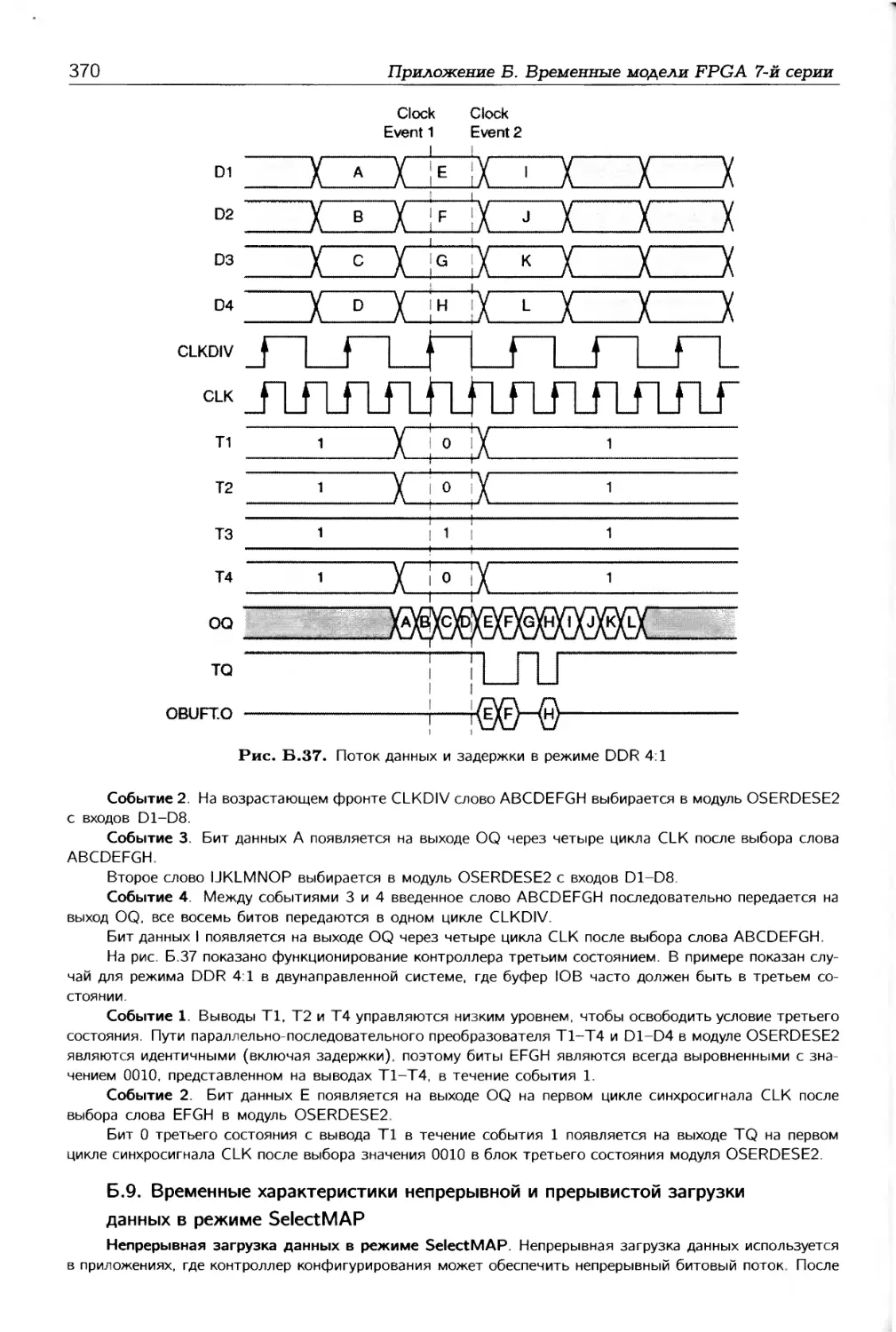

В одиннадцатой главе рассматриваются расширенные логические ресурсы ввода-

вывода. К последним относятся последовательно-параллельный ISERDESE2 и парал-

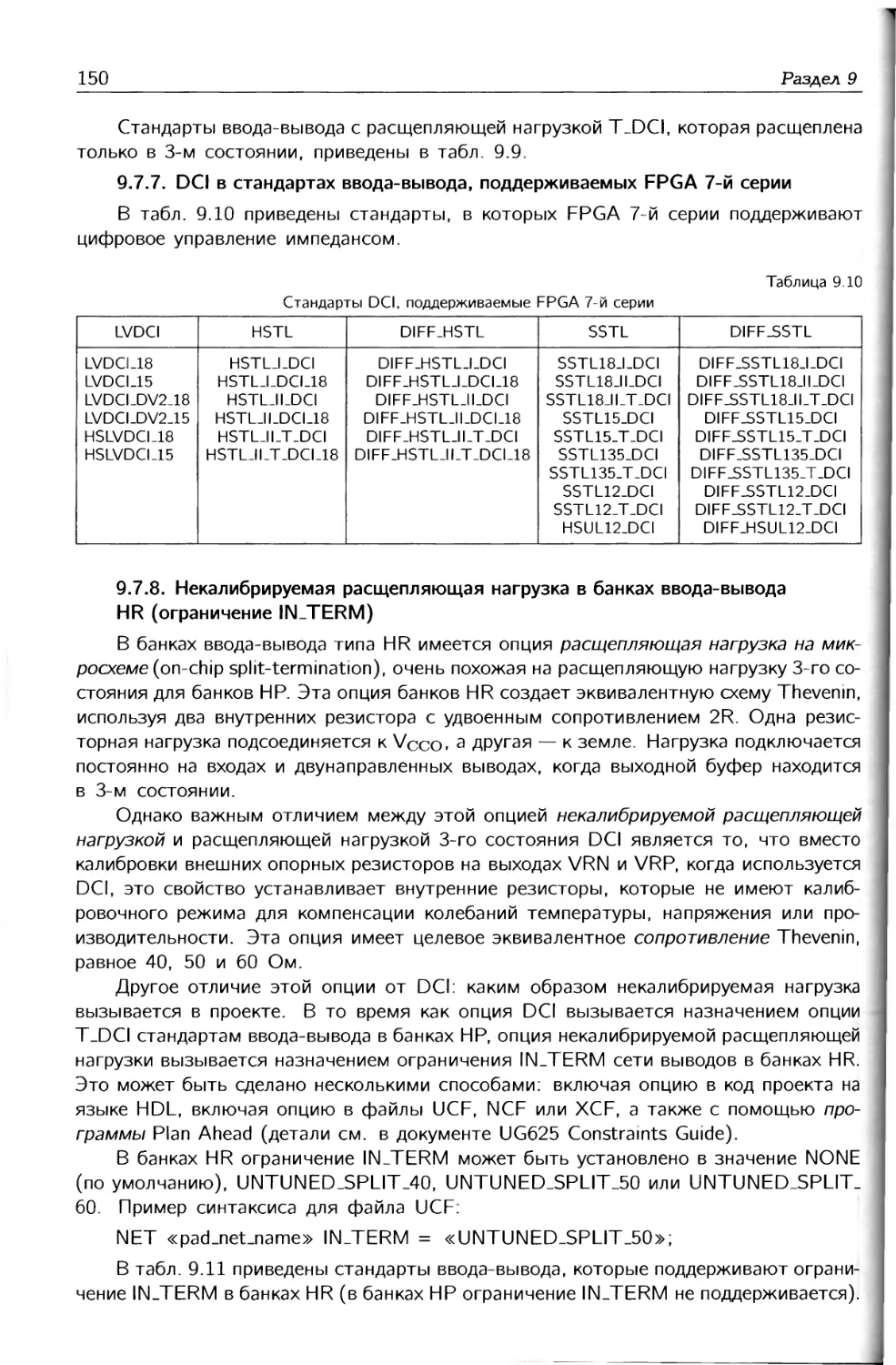

лельно-последовательный OSERDESE2 преобразователи, подмодуль BITSLIP и па-

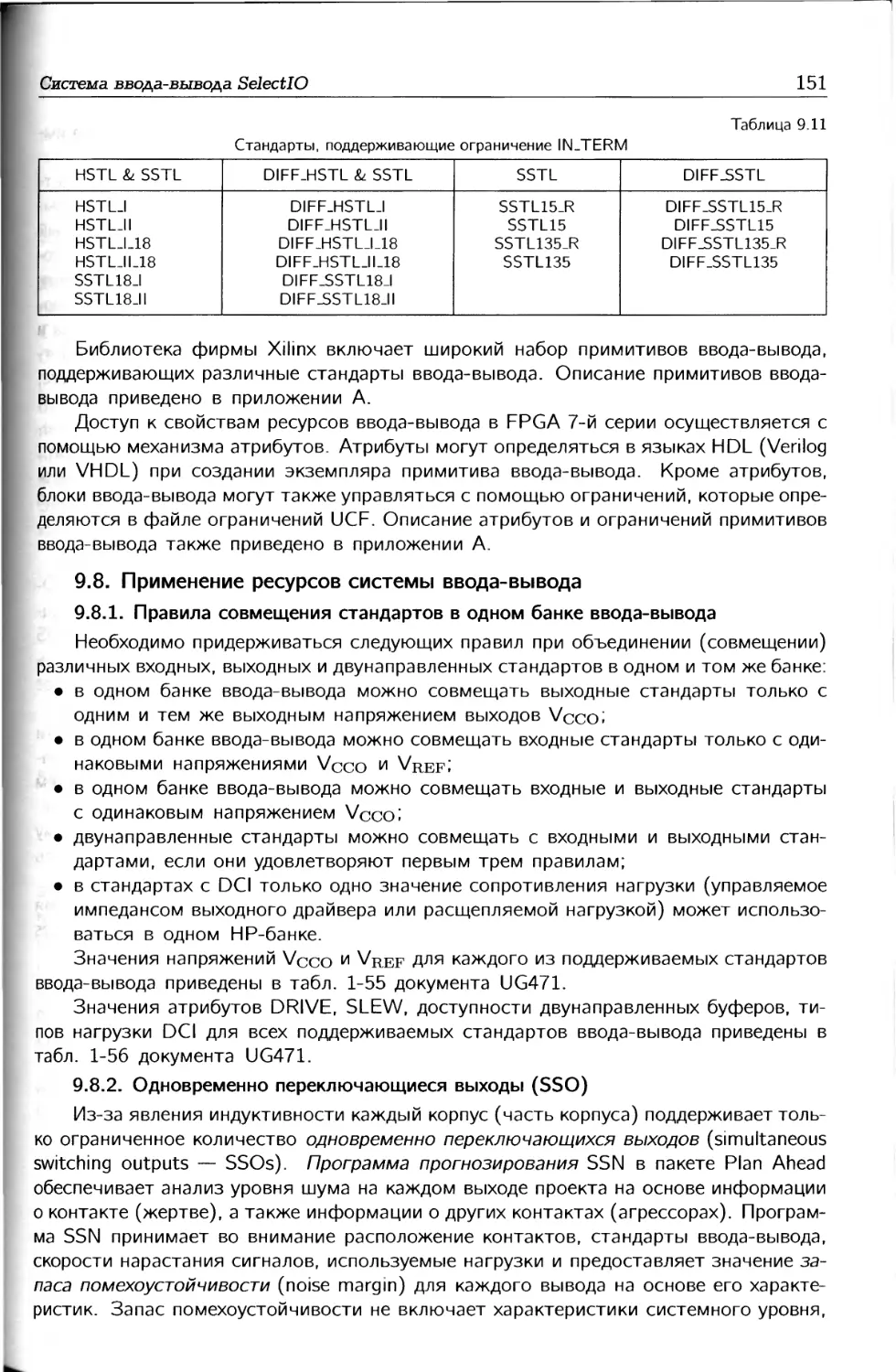

мять FIFO ввода-вывода. Расширенные логические ресурсы могут использоваться для

высокоскоростной последовательной передачи данных между микросхемами FPGA,

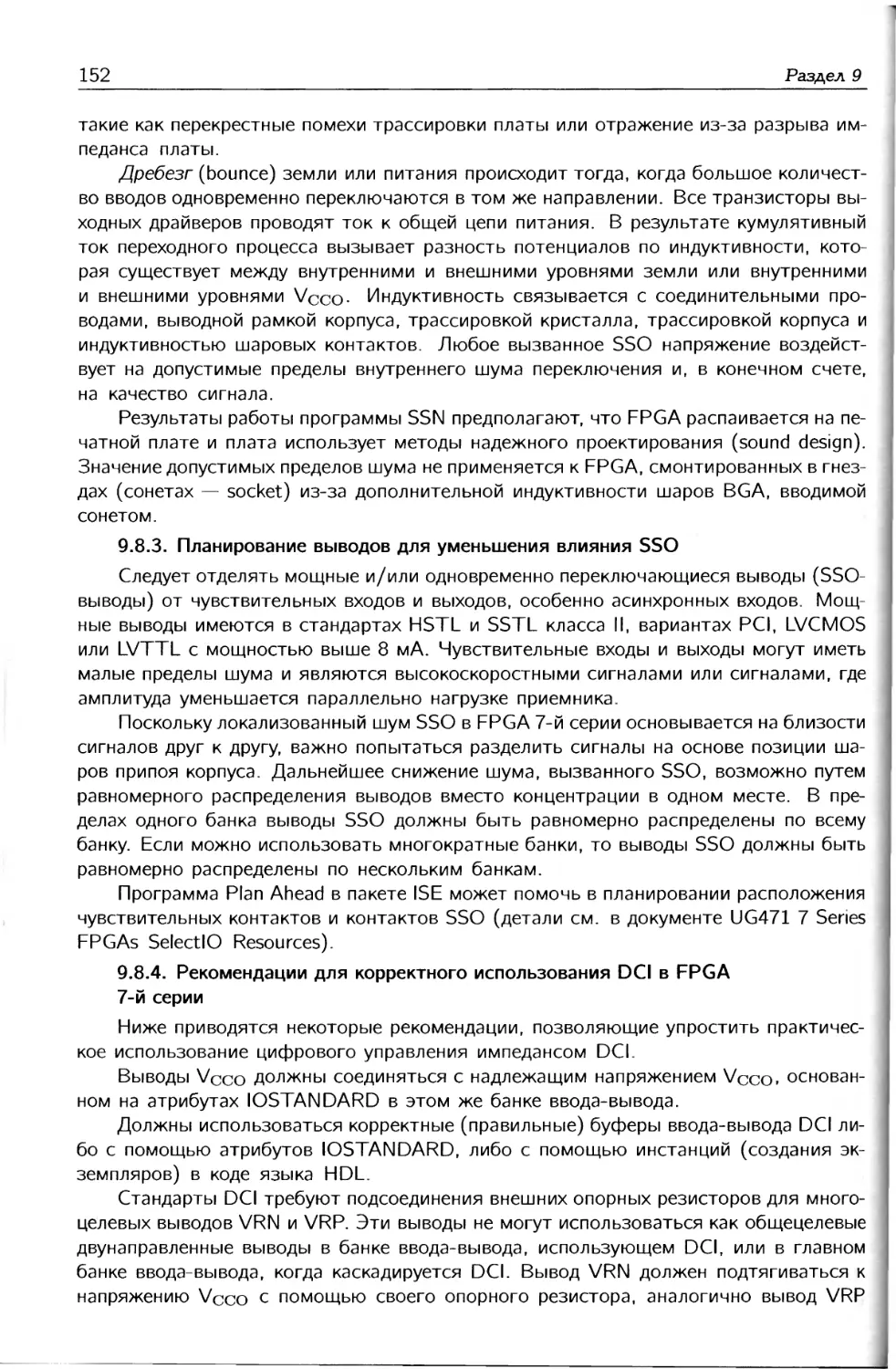

расположенными на одной печатной плате.

Ресурсы синхронизации FPGA 7-й серии описываются в двенадцатой главе. Здесь

рассматривается общая архитектура ресурсов синхронизации, специализированные

входы синхронизации, ресурсы глобальной и региональной синхронизации. Ресурсы

синхронизации в FPGA 7-й серии управляются буферами синхронизации и блоками

формирования синхросигналов СМТ. Особенности использования буферов синхро-

низации также рассматриваются в двенадцатой главе.

Тринадцатая глава посвящена блока формирования синхросигналов СМТ. Каж-

дый блок СМТ содержит два блока: ММСМ и PLL. Блок PEL реализует некоторое

подмножество функций блока ММСМ, поэтому в данной главе в основном рассмат-

риваются свойства блока ММСМ. Блок ММСМ в FPGA 7-й серии предоставляет

широкие возможности по формированию внутренних синхросигналов на основе внеш-

него опорного синхросигнала. При этом возможны целочисленное и дробное деление

частоты, фильтрация флуктуаций, статический и динамический фазовый сдвиг, пе-

реключение опорных синхросигналов и др.

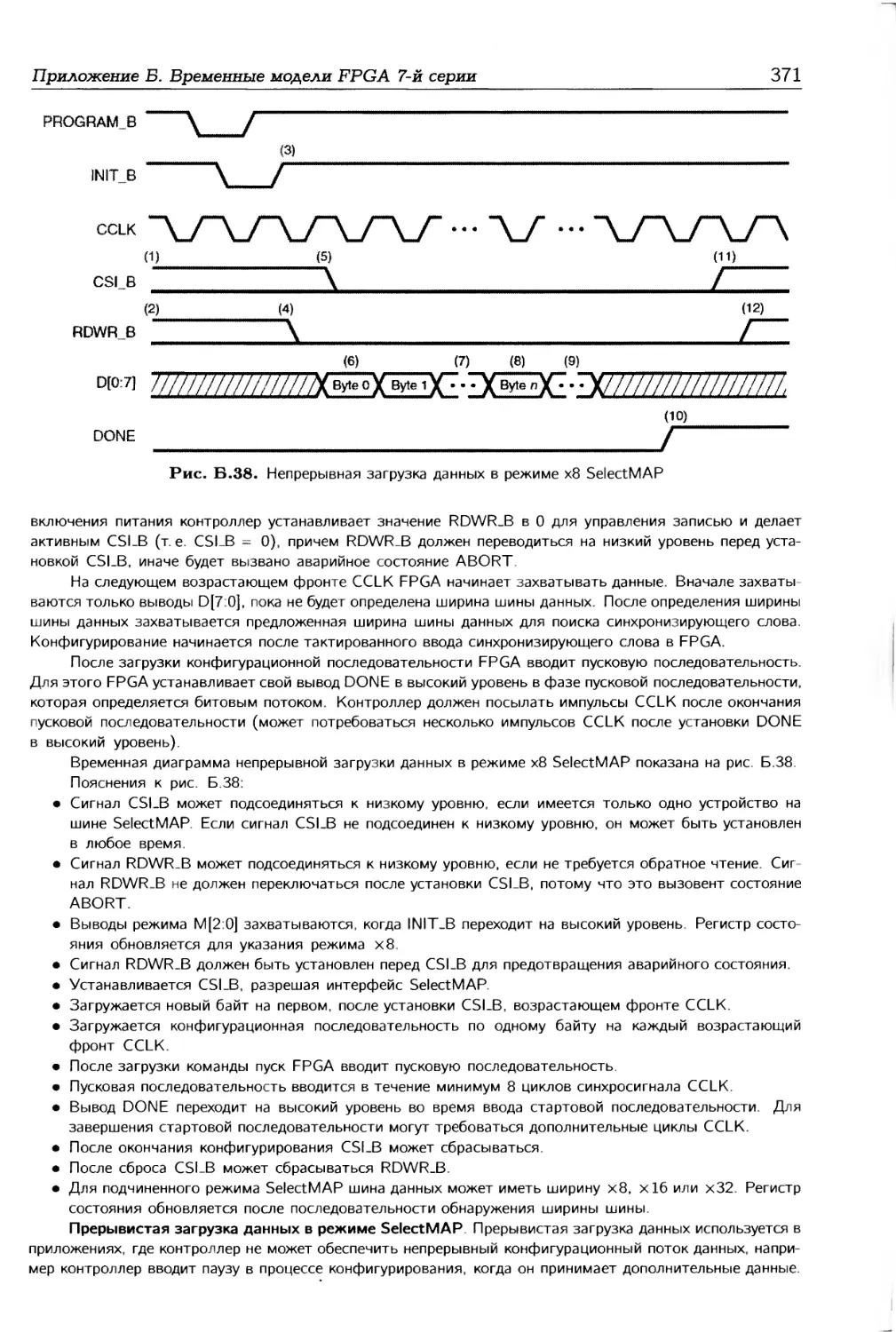

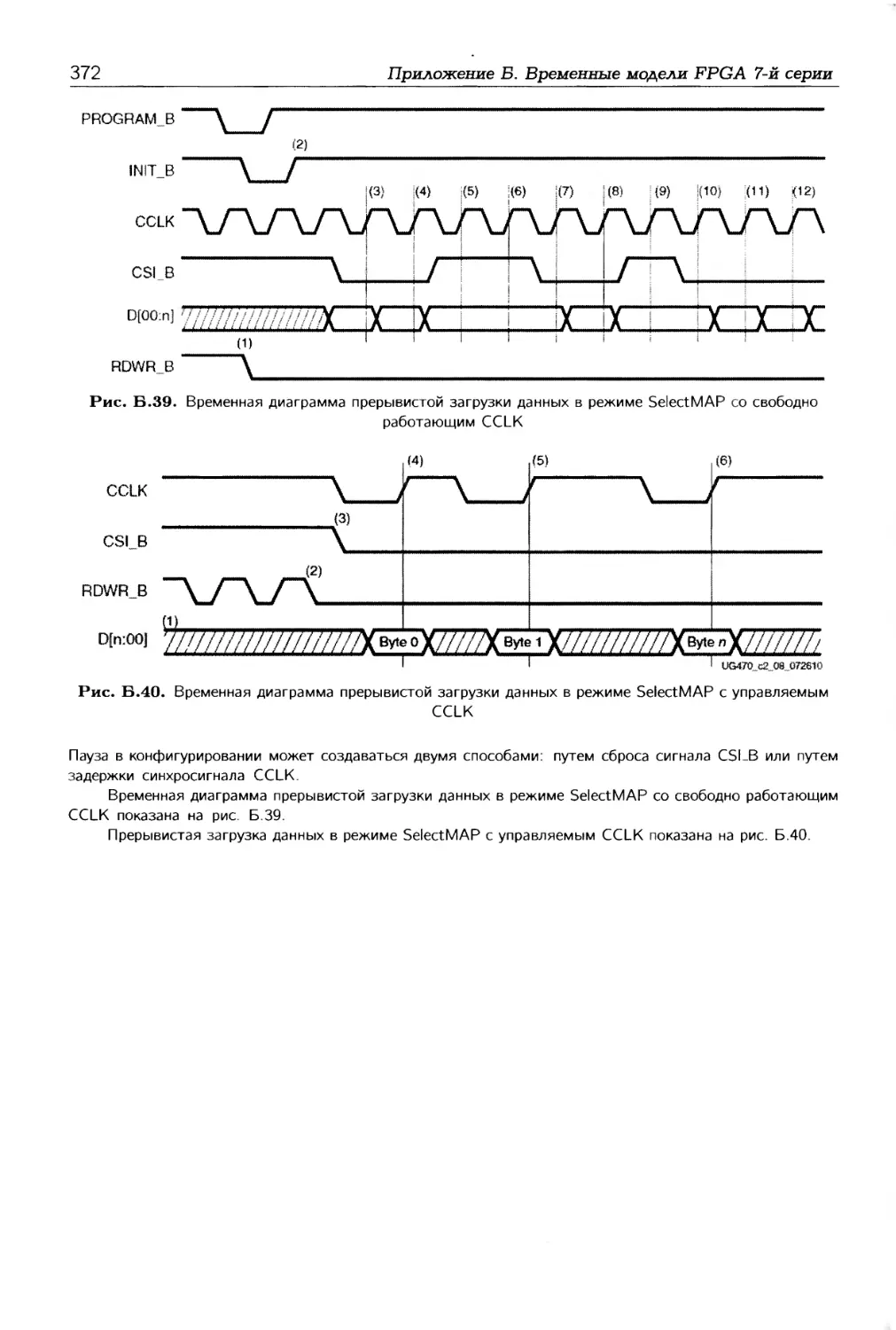

В четырнадцатой главе рассматриваются вопросы конфигурирования FPGA 7-й

серии, без которого не обходится ни один проект на ПЛИС. FPGA 7-й серии пре-

доставляют большое разнообразие способов конфигурирования. При этом возмож-

ны главные и подчиненные режимы, простые базовые решения, конфигурирование с

низкой стоимостью и высоким быстродействием, конфигурирование от специальных

ППЗУ фирмы Xilinx или от промышленных ППЗУ по стандартным интерфейсам, а

также конфигурирование по JTAG-стандарту.

Отметим, что каждая глава заканчивается выводами, где в сжатой форме пред-

ставлена основная информация, излагаемая в данной главе. В некоторых случаях

для быстрого изучения вопроса читатель может сразу обратиться к выводам в конце

главы, а затем уточнить детали из содержания главы и приложений.

В приложении А в основном описываются примитивы и макросы, которые могут

использоваться при разработке проектов на FPGA 7-й серии. Приложение Б содержит

описание временных моделей элементов архитектуры FPGA 7-й серии.

В списке основной литературы приводятся ссылки на техническую документацию,

которая непосредственно использовалась при написании данной книги. Дополнитель-

ная литература включает отдельные документы, которые упоминались в тексте книги

для уточнения конкретных деталей. Список литературы, относящейся к данной теме,

включает ранее изданные книги по архитектурам ПЛИС, а также некоторые книги и

статьи, которые не потеряли актуальность и могут быть полезны в вопросах проек-

тирования на основе ПЛИС.

Книга предназначена прежде всего для разработчиков электронных систем на

основе ПЛИС. Инженеры-практики, которые впервые приступают к проектированию

на ПЛИС фирмы Xilinx, найдут в книге много технической информации: от описания

общей архитектуры до конкретных рекомендаций по практическому использованию.

Инженеры, которые имеют опыт разработки проектов на ПЛИС других производи-

телей, найдут в книге много интересной информации, которая может вызвать у них

6

Предисловие

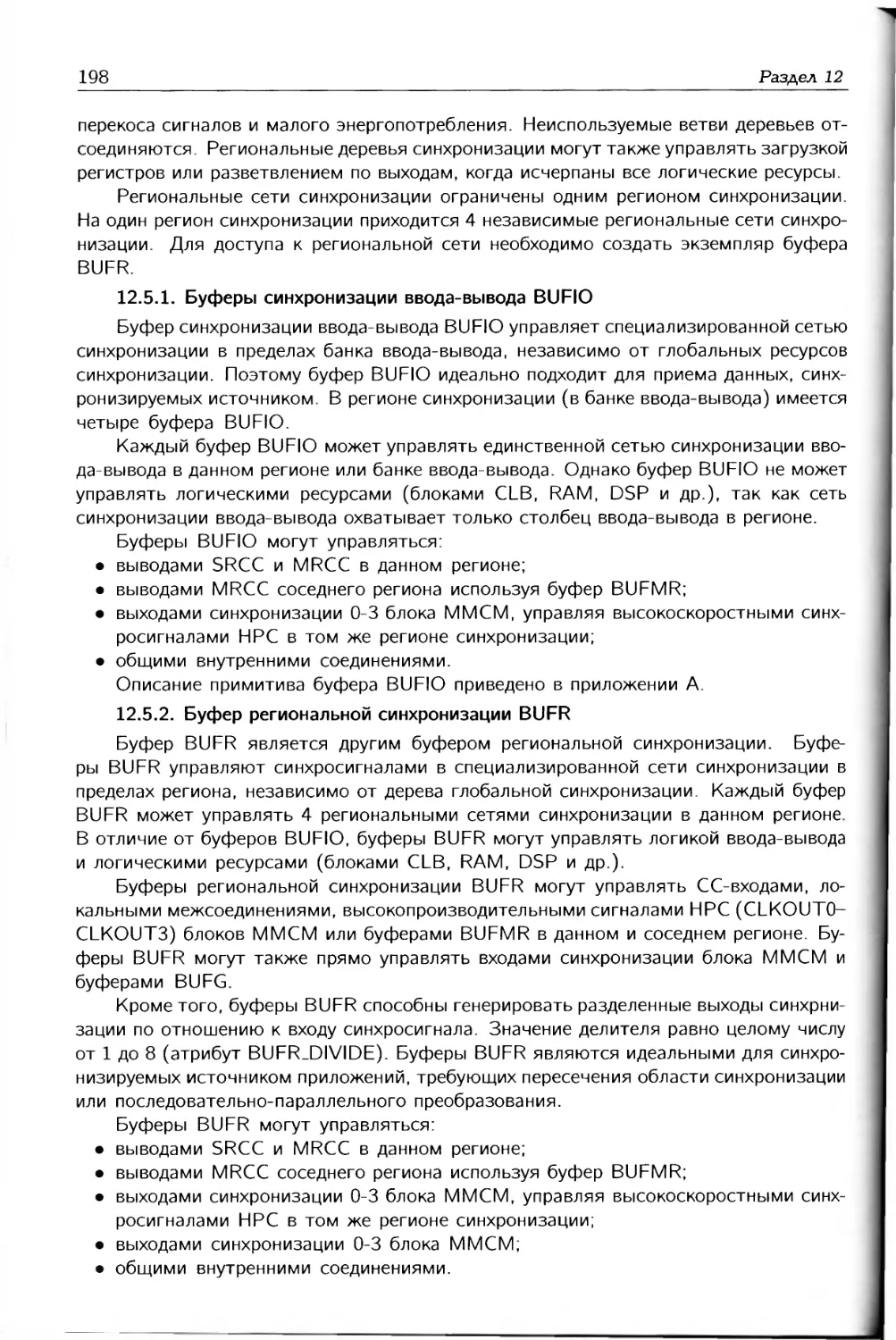

желание проектировать на ПЛИС фирмы Xilinx. Инженеры, уже проектирующие на

ПЛИС фирмы Xilinx, также могут узнать из книги много новой информации, которая

по каким-либо причинам была упущена из их поля зрения.

Книга также предназначена для студентов и преподавателей технических универ-

ситетов соответствующих специальностей. К сожалению, в настоящее время отсутст-

вуют отечественные учебные пособия по архитектурам современных ПЛИС. Поэтому

преподаватели найдут в книге много полезной информации для подготовки лекций,

практических и лабораторных занятий, а студенты — ответы на поставленные во-

просы.

Книга может быть также полезна аспирантам и научным работникам как источник

информации об архитектурных возможностях современных ПЛИС. Последние могут

быть использованы при разработке новых методик, методов и алгоритмов проекти-

рования на основе ПЛИС.

Книга, безусловна, будет весьма полезна менеджерам, специалистам по продаже

ПЛИС фирмы Xilinx и средств проектирования на их основе, поскольку менеджеры

в первую очередь должны хорошо знать все архитектурные свойства и возможности

каждого семейства ПЛИС, чтобы грамотно их предложить потенциальным клиентам.

Работа выполнена при частичной финансовой поддержке Белостокского техно-

логического университета (Республика Польша), грант S/WI/1/2013.

1 Программируемые логические интегральные схемы

1.1. Введение в программируемые логические интегральные схемы

Понятие программируемые логические интегральные схемы (ПЛИС) с течением

времени менялось, и в настоящее время этот термин не совсем точно отражает опре-

деляемый предмет. Попытаемся разобраться, что такое ПЛИС.

1.1.1. Что такое ПЛИС?

Прежде всего, под ПЛИС понимаются микросхемы большой и сверхбольшой сте-

пени интеграции, которые пользователь может сам программировать.

Способы программирования могут быть самые разные: с помощью специального

оборудования (программаторов), с помощью кабеля от персонального компьютера, от

микропроцессора или от постоянного запоминающего устройства (ПЗУ), находящихся

на одной плате с ПЛИС и др. Главное, что пользователь (разработчик) может купить

готовую ПЛИС и сам ее запрограммировать в домашних (лабораторных) условиях.

При этом ему не надо обращаться к услугам производителей ПЛИС, как в случае за-

казных специализированных микросхем (Application Specific Integrated Circuit — ASIC).

Программирование ПЛИС заключается в изменении своей внутренней архитекту-

ры для выполнение определенных функций. Например, стандартные логические мик-

росхемы выполняют заранее определенные при их изготовлении функции, а ПЛИС

может выполнять те функции, которые для нее определит пользователь. Производи-

тели выпускают ПЛИС незапрограммированными, т. е. исходная ПЛИС не выполняет

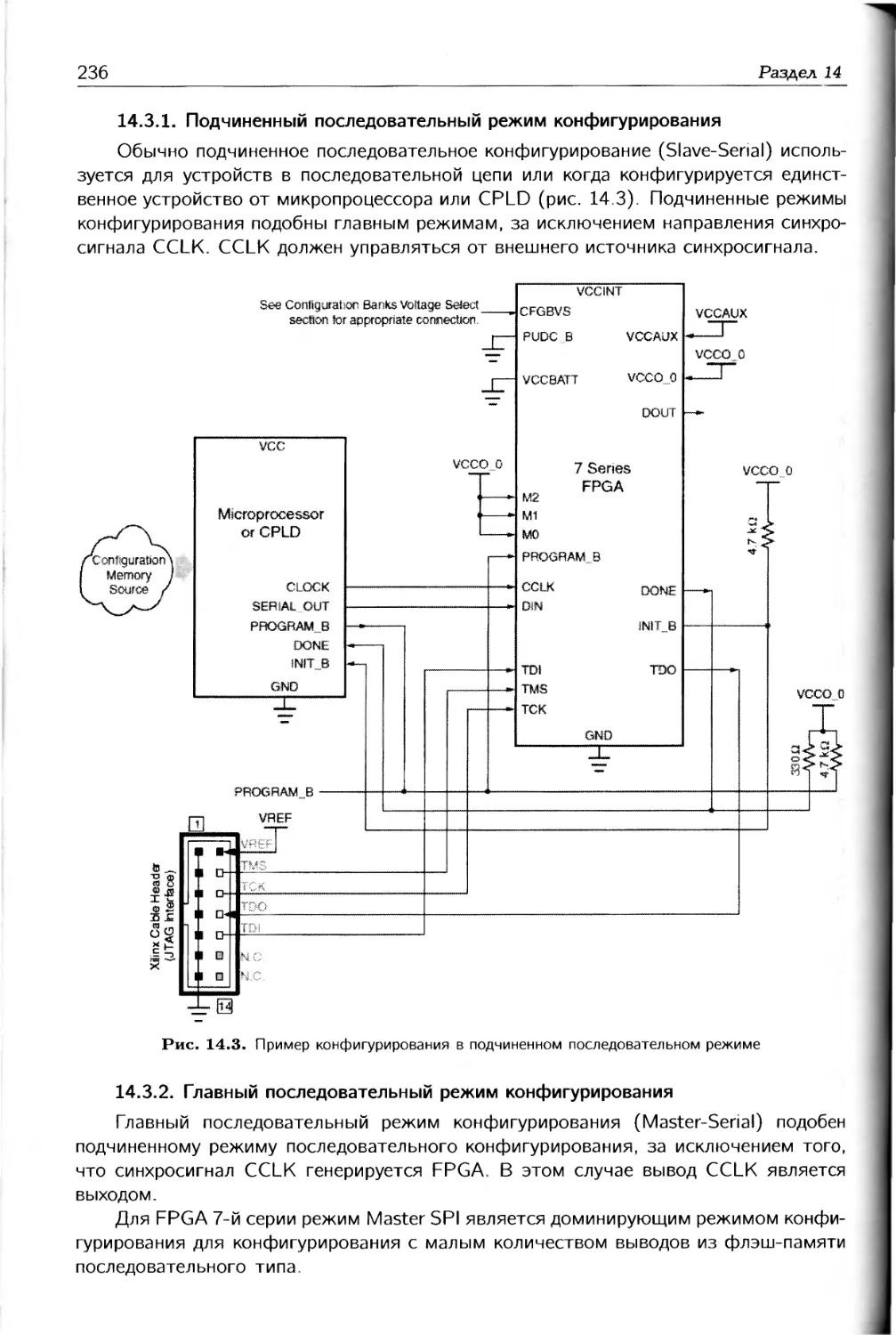

никаких функций.

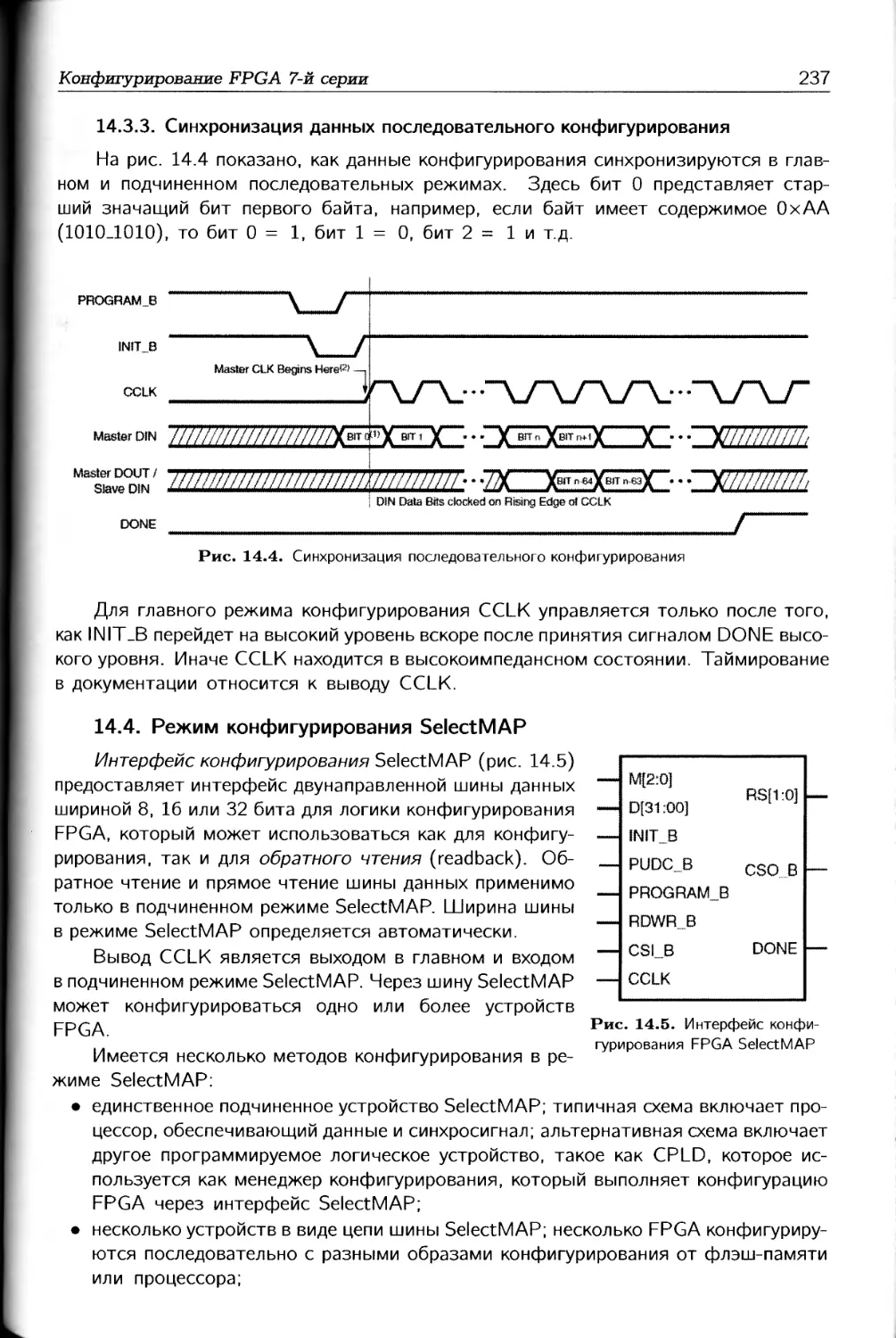

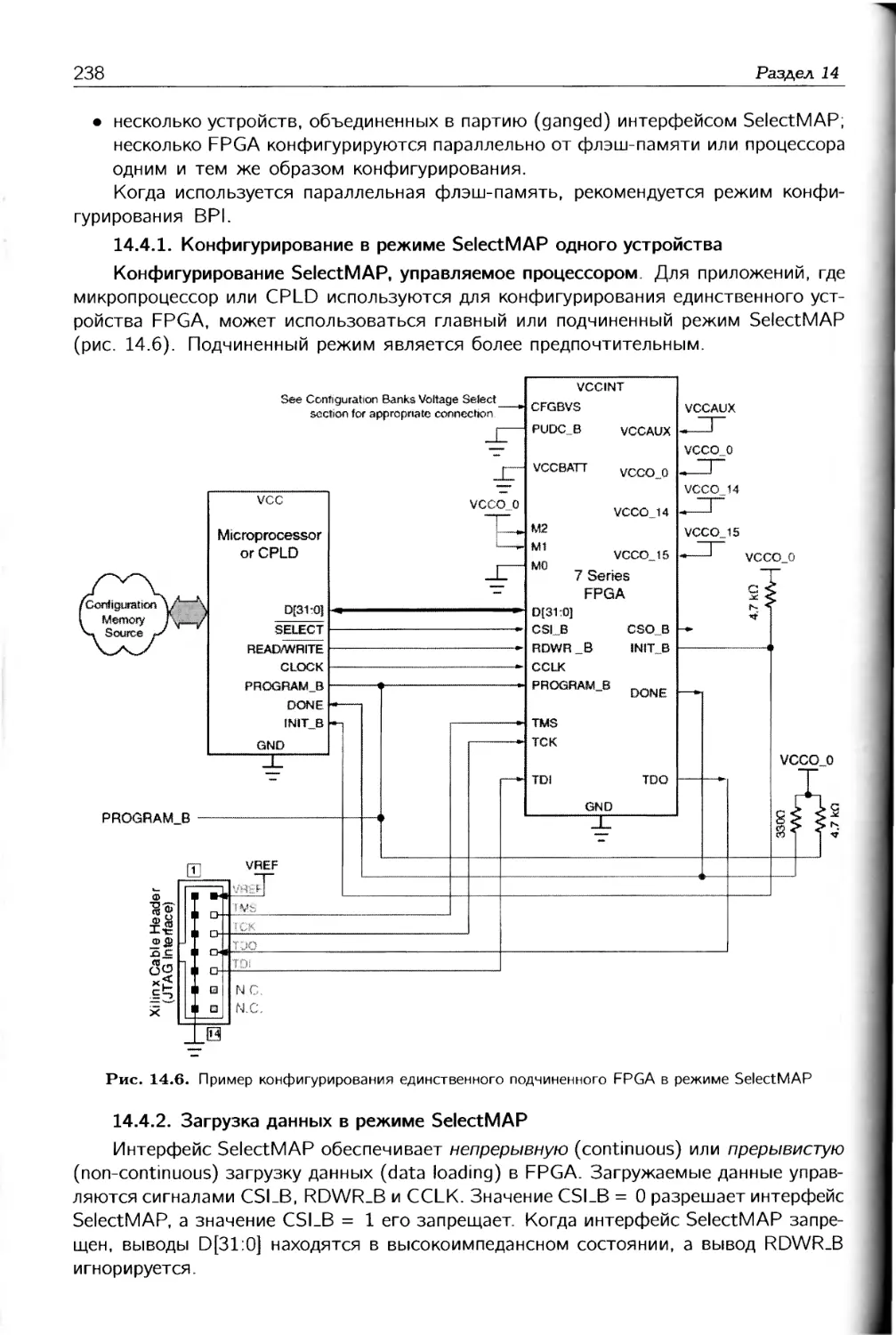

Если после программирования и выключения питания ПЛИС сохраняет свою

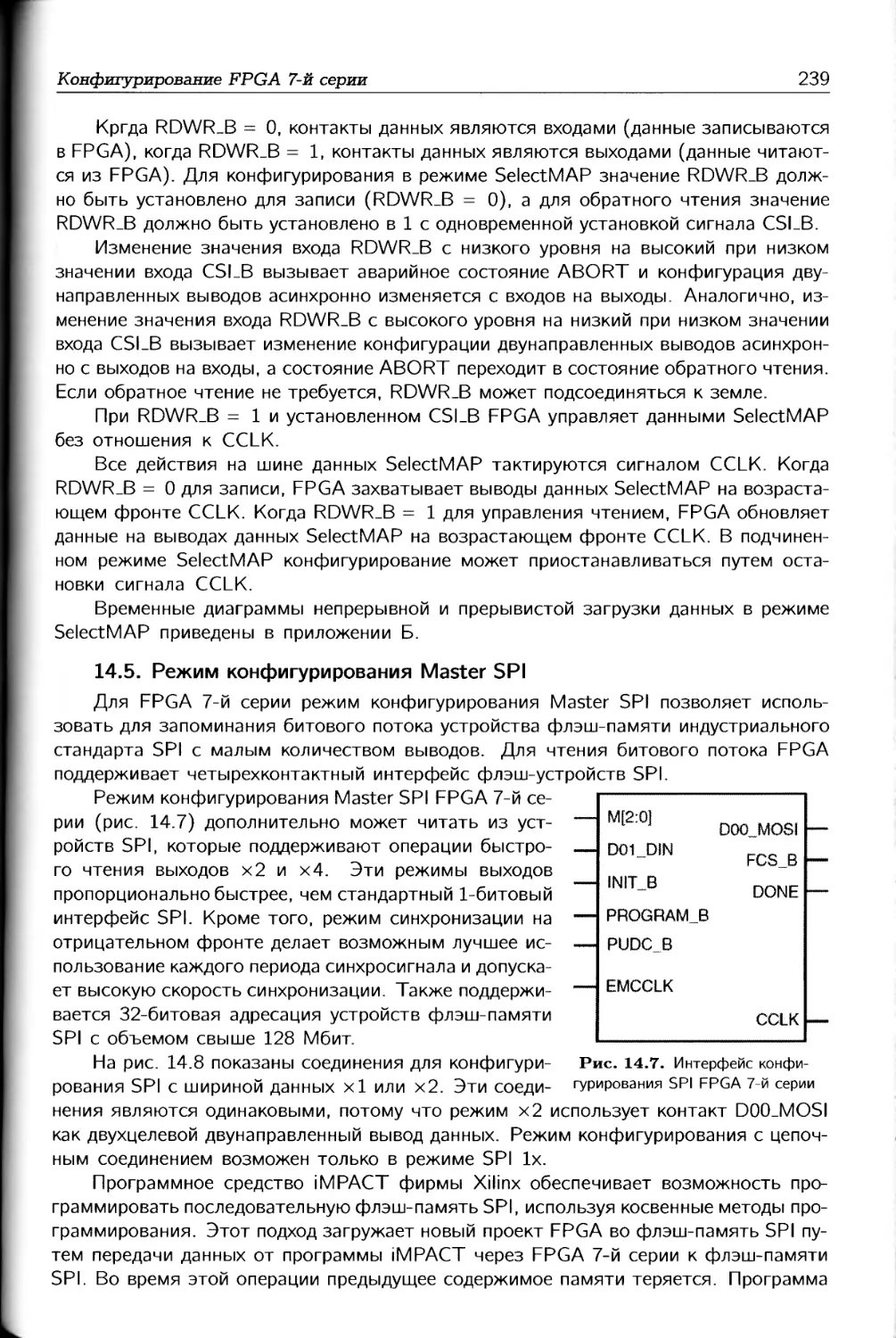

внутреннюю структуру и может выполнять заданные функции при каждом следую-

щем включении питания, говорят о программировании ПЛИС. Такие ПЛИС также

называют энергонезависимыми. Энергонезависимая ПЛИС может вначале програм-

мироваться с помощью программатора, а затем устанавливаться на плату, и может

программироваться уже после установки на плату. В последнем случае говорят о

программировании в системе (In-System Programmable — ISP).

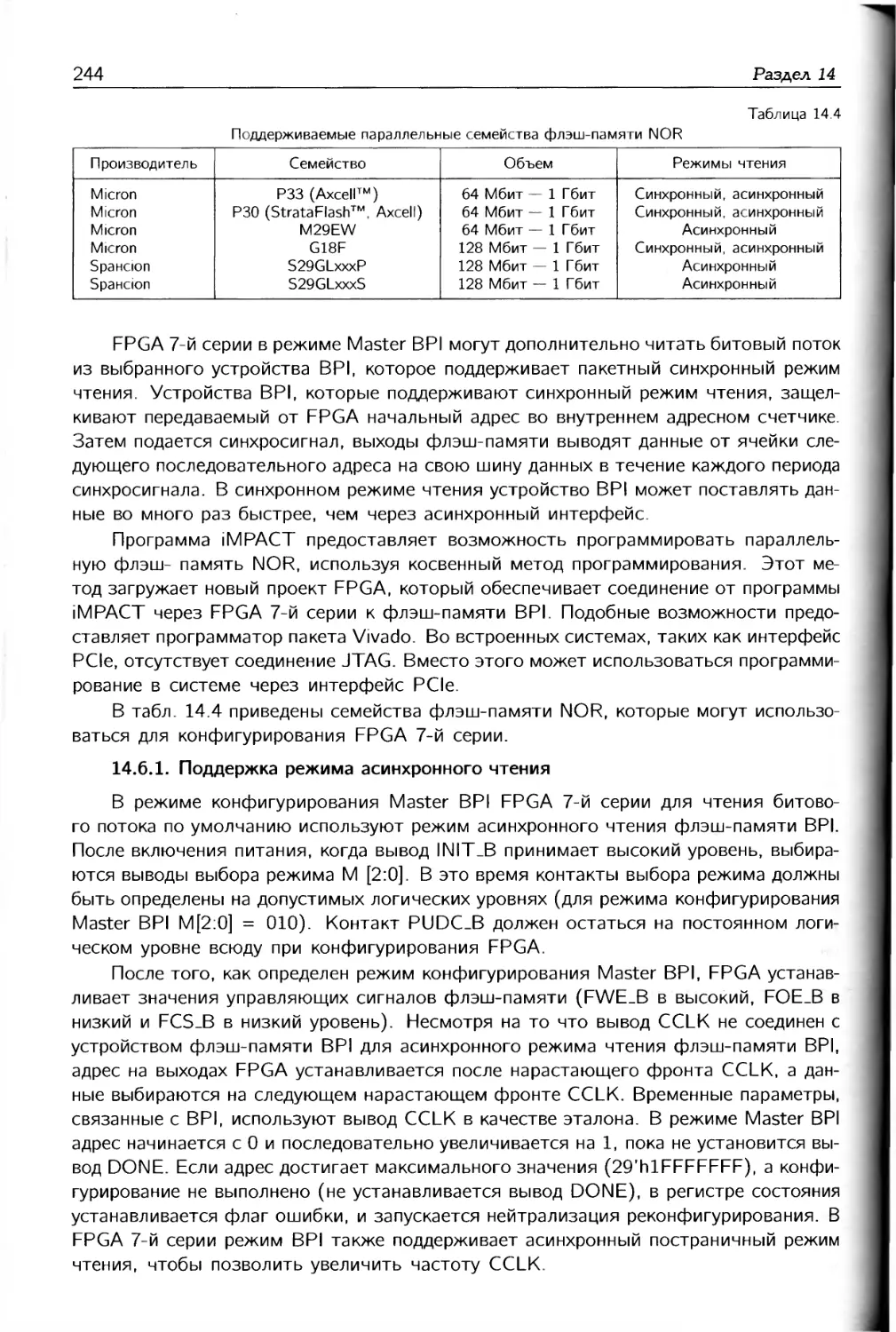

Если после программирования и выключения питания ПЛИС не сохраняет свою

внутреннюю структуру (т. е. является энергозависимой) и при следующем включе-

нии питания ее необходимо настраивать заново, говорят о конфигурировании ПЛИС.

Конфигурирование ПЛИС всегда выполняется после установки ПЛИС на плате. Со-

временные ПЛИС допускают десятки тысяч перепрограммирований и неограниченное

число раз конфигурирований.

1.1.2. Чем ПЛИС отличаются от микроконтроллеров?

Это один из ключевых вопросов, который разделил армию разработчиков элек-

троники на поклонников ПЛИС и приверженцев микроконтроллеров.

По способу использования микроконтроллеры и ПЛИС мало чем отличаются друг

от друга: и те и другие перед применением необходимо программировать (конфигу-

рировать). Главное отличие микроконтроллеров от ПЛИС: при программировании

8

Раздел 1

микроконтроллер не изменяет свою архитектуру. При программировании микрокон-

троллера в его память записывается программа (и, возможно, данные), которая за-

тем выполняется процессором микроконтроллера. Сама архитектура микроконтрол-

лера (процессор, порты ввода-вывода, периферийные устройства и соединения между

ними) остаются низменными. В отличие от микроконтроллеров ПЛИС при програм-

мировании изменяет свою внутреннюю архитектуру. Благодаря этому архитектуру

ПЛИС можно настроить на выполнение конкретных функций и задач.

При обработке данных микроконтроллер последовательно выполняет команды за-

писанной в память программы, причем выполнение одной команды может занимать

несколько циклов процессора. ПЛИС в одном временном цикле параллельно обра-

батывает некоторую порцию данных, поступающих на все входы ПЛИС. Поскольку

ПЛИС имеют существенно больше внешних выводов, чем микроконтроллер, то при

использовании ПЛИС значительно (на порядки, т. е. в 10...100 раз) возрастает ско-

рость обработки данных.

Кроме того, каждый внешний вывод ПЛИС, за исключением небольшого коли-

чества специализированных (dedicated) выводов, является двунаправленным выводом

общего назначения. Поэтому пользователю ПЛИС, в отличие от микроконтроллеров,

предоставляются практически неограниченные возможности по определению ширины

и расположению внешних шин и сигналов, подсоединяемых к ПЛИС.

Что использовать в конкретном проекте, ПЛИС или микроконтроллер, во многом

зависит от предыдущего опыта разработчика, имеющихся средств проектирования и

особенностей проекта. Обычно функционально сложные и быстродействующие про-

екты реализуются на ПЛИС, а простые и не требующие высокого быстродействия —

на микроконтроллерах.

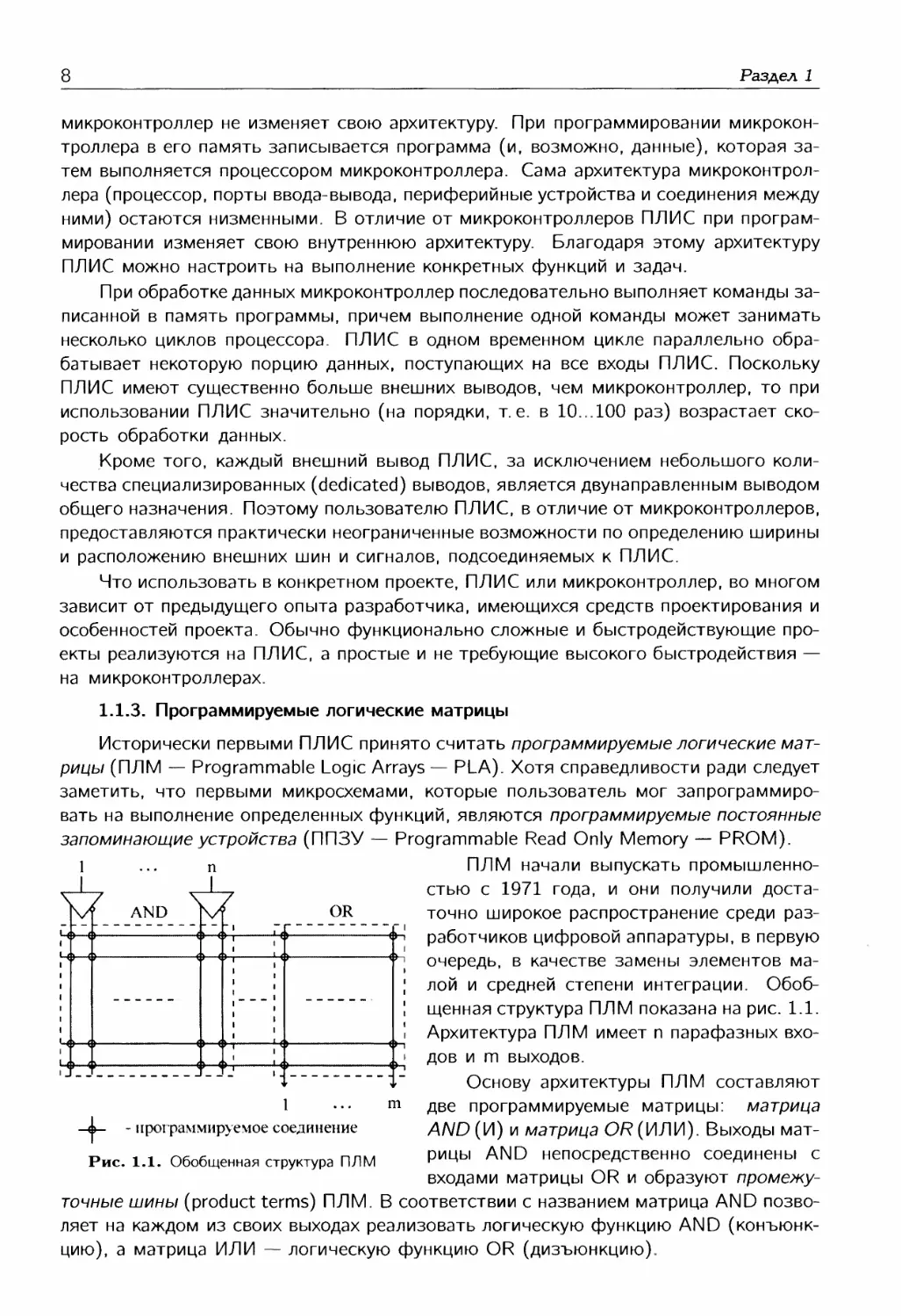

1.1.3. Программируемые логические матрицы

Исторически первыми ПЛИС принято считать программируемые логические мат-

рицы (ПЛМ — Programmable Logic Arrays — PLA). Хотя справедливости ради следует

заметить, что первыми микросхемами, которые пользователь мог запрограммиро-

вать на выполнение определенных функций, являются программируемые постоянные

запоминающие устройства (ППЗУ — Programmable Read Only Memory — PROM).

- программируемое соединение

Рис. 1.1. Обобщенная структура ПЛМ

ПЛМ начали выпускать промышленно-

стью с 1971 года, и они получили доста-

точно широкое распространение среди раз-

работчиков цифровой аппаратуры, в первую

очередь, в качестве замены элементов ма-

лой и средней степени интеграции. Обоб-

щенная структура ПЛМ показана на рис. 1.1.

Архитектура ПЛМ имеет п парафазных вхо-

дов и m выходов.

Основу архитектуры ПЛМ составляют

две программируемые матрицы: матрица

AND (И) и матрица OR (ИЛИ). Выходы мат-

рицы AND непосредственно соединены с

входами матрицы OR и образуют промежу-

точные шины (product terms) ПЛМ. В соответствии с названием матрица AND позво-

ляет на каждом из своих выходах реализовать логическую функцию AND (конъюнк-

цию), а матрица ИЛИ — логическую функцию OR (дизъюнкцию).

Программируемые логические интегральные схемы

9

Поэтому на ПЛМ очень легко реализуются системы булевых функций (СБФ),

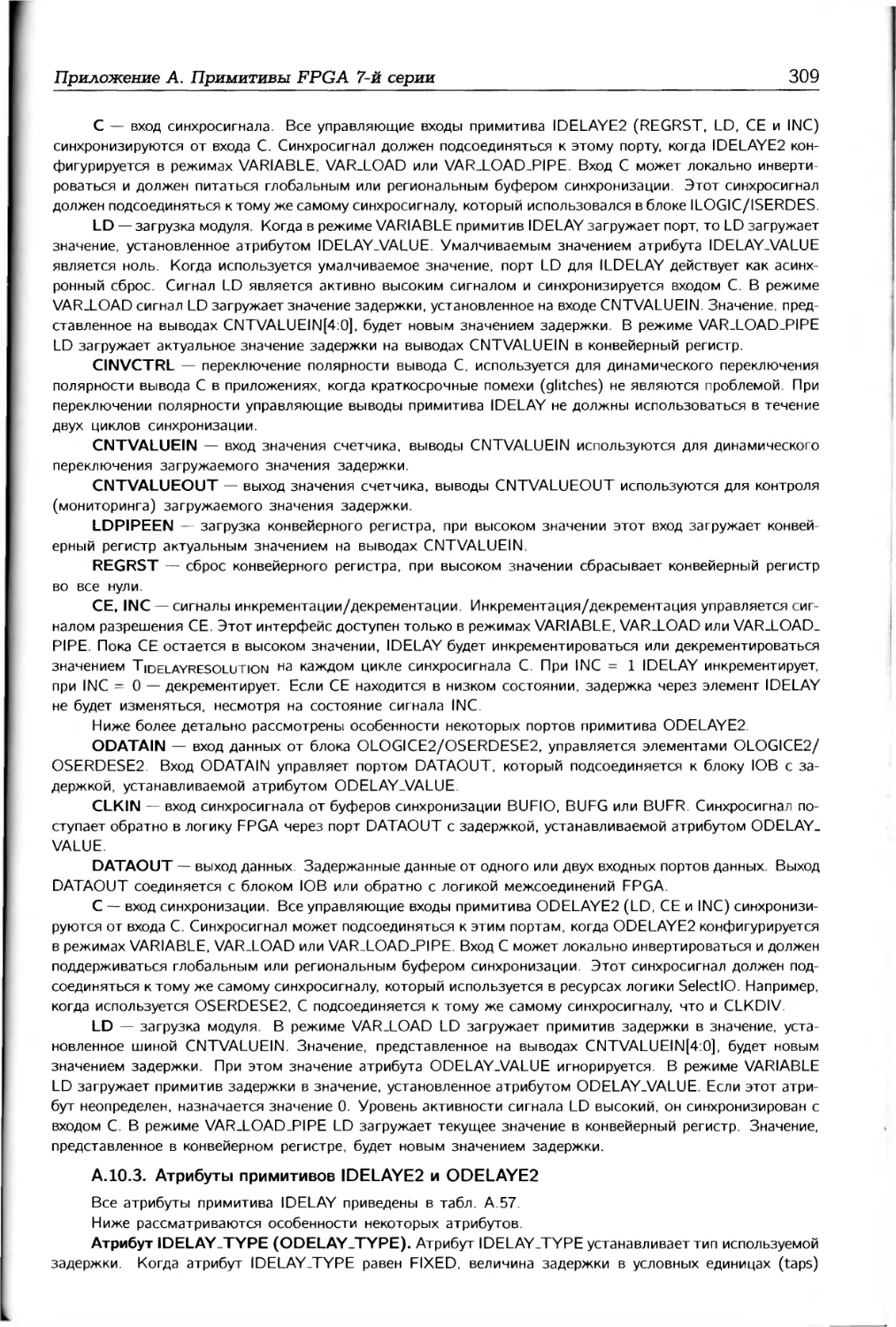

представленные в дизъюнктивной нормальной форме (ДНФ). Фактически, архитек-

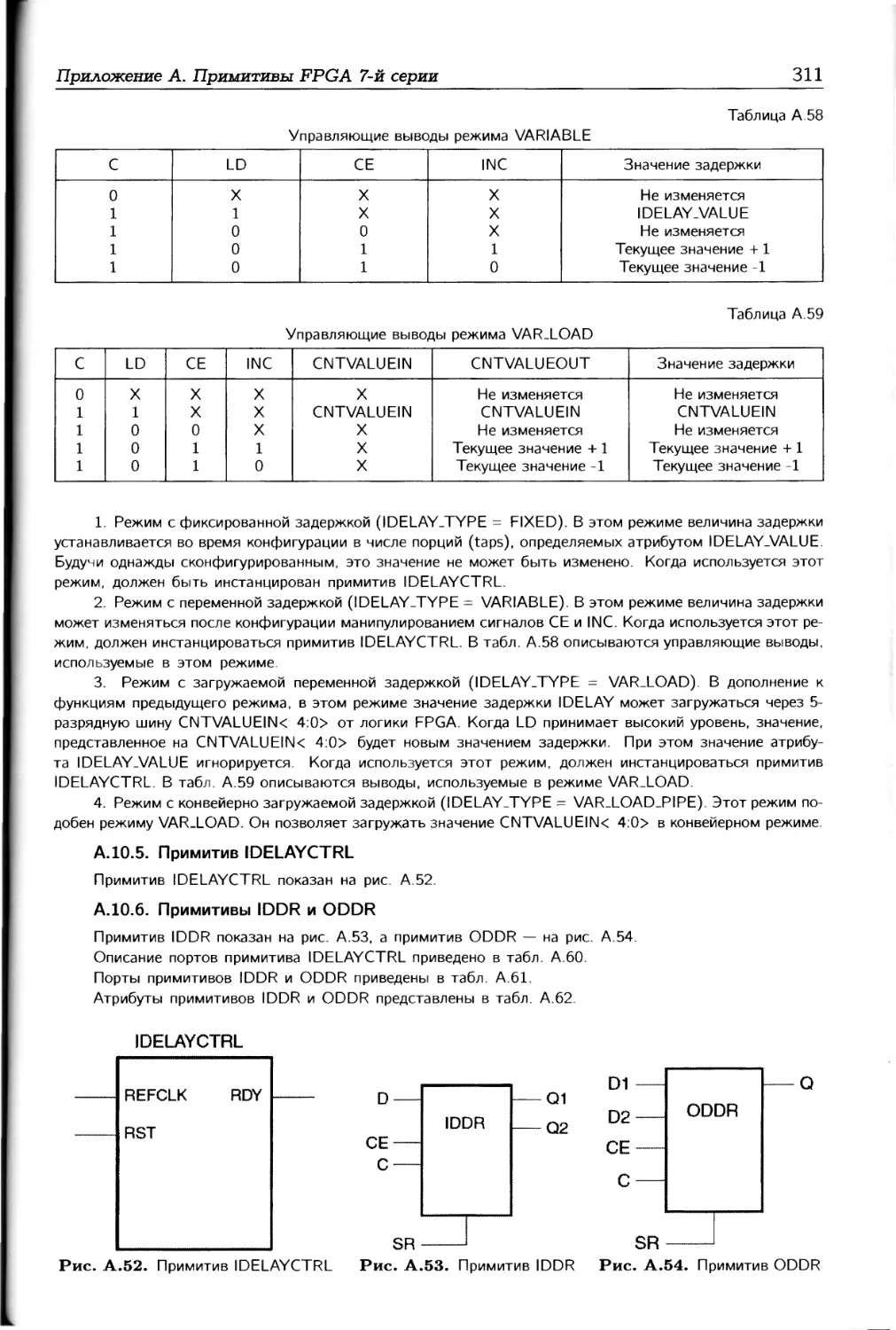

тура ПЛМ повторяет табличное представление СБФ, при этом на матрице AND реали-

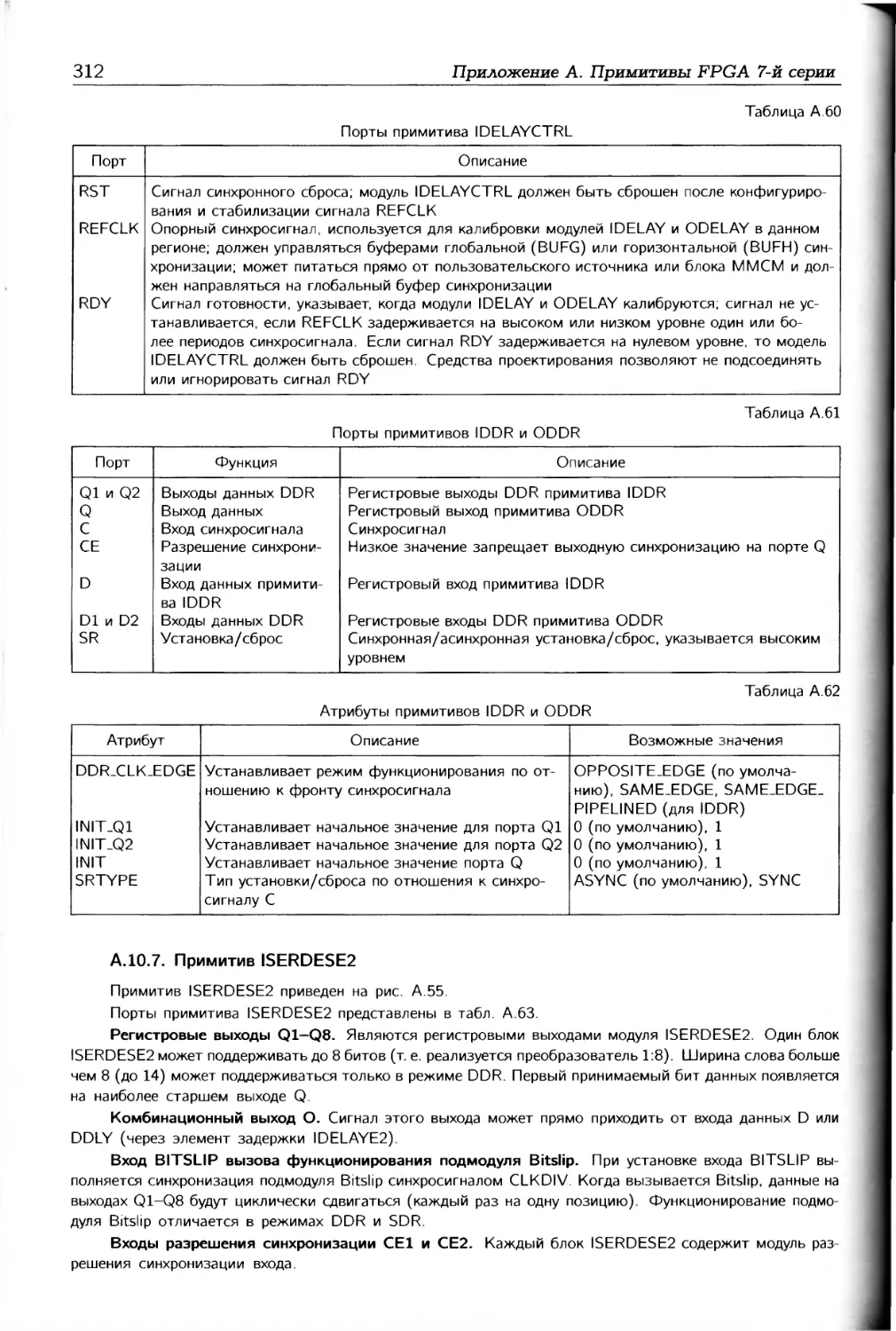

зуются отдельные элементарные конъюнкции, а на матрице OR — логическая сумма

этих конъюнкций.

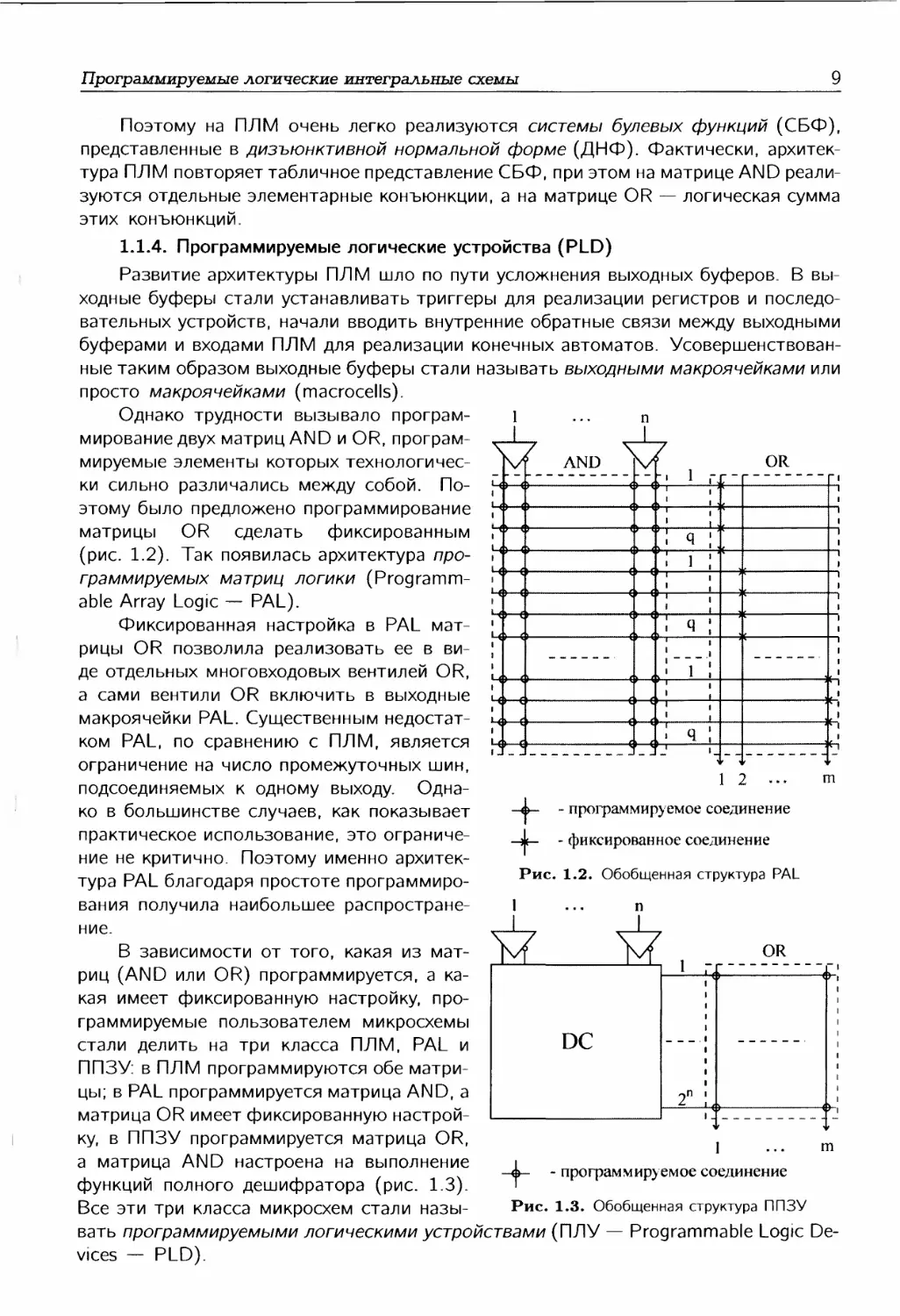

1.1.4. Программируемые логические устройства (PLD)

Развитие архитектуры ПЛМ шло по пути усложнения выходных буферов. В вы-

ходные буферы стали устанавливать триггеры для реализации регистров и последо-

вательных устройств, начали вводить внутренние обратные связи между выходными

буферами и входами ПЛМ для реализации конечных автоматов. Усовершенствован-

ные таким образом выходные буферы стали называть выходными макроячейками или

просто макроячейками (macrocells).

Однако трудности вызывало програм-

мирование двух матриц AND и OR, програм-

мируемые элементы которых технологичес-

ки сильно различались между собой. По-

этому было предложено программирование

матрицы OR сделать фиксированным

(рис. 1.2). Так появилась архитектура про-

граммируемых матриц логики (Programm-

able Array Logic — PAL).

Фиксированная настройка в PAL мат-

рицы OR позволила реализовать ее в ви-

де отдельных многовходовых вентилей OR,

а сами вентили OR включить в выходные

макроячейки PAL. Существенным недостат-

ком PAL, по сравнению с ПЛМ, является

ограничение на число промежуточных шин,

подсоединяемых к одному выходу. Одна-

ко в большинстве случаев, как показывает

практическое использование, это ограниче-

ние не критично. Поэтому именно архитек-

тура PAL благодаря простоте программиро-

вания получила наибольшее распростране-

ние.

В зависимости от того, какая из мат-

риц (AND или OR) программируется, а ка-

кая имеет фиксированную настройку, про-

граммируемые пользователем микросхемы

стали делить на три класса ПЛМ, PAL и

ППЗУ в ПЛМ программируются обе матри-

цы; в PAL программируется матрица AND, а

матрица OR имеет фиксированную настрой-

ку, в ППЗУ программируется матрица OR,

а матрица AND настроена на выполнение

функций полного дешифратора (рис. 1.3).

Все эти три класса микросхем стали назы-

OR

1 Ф ф

Ч>—

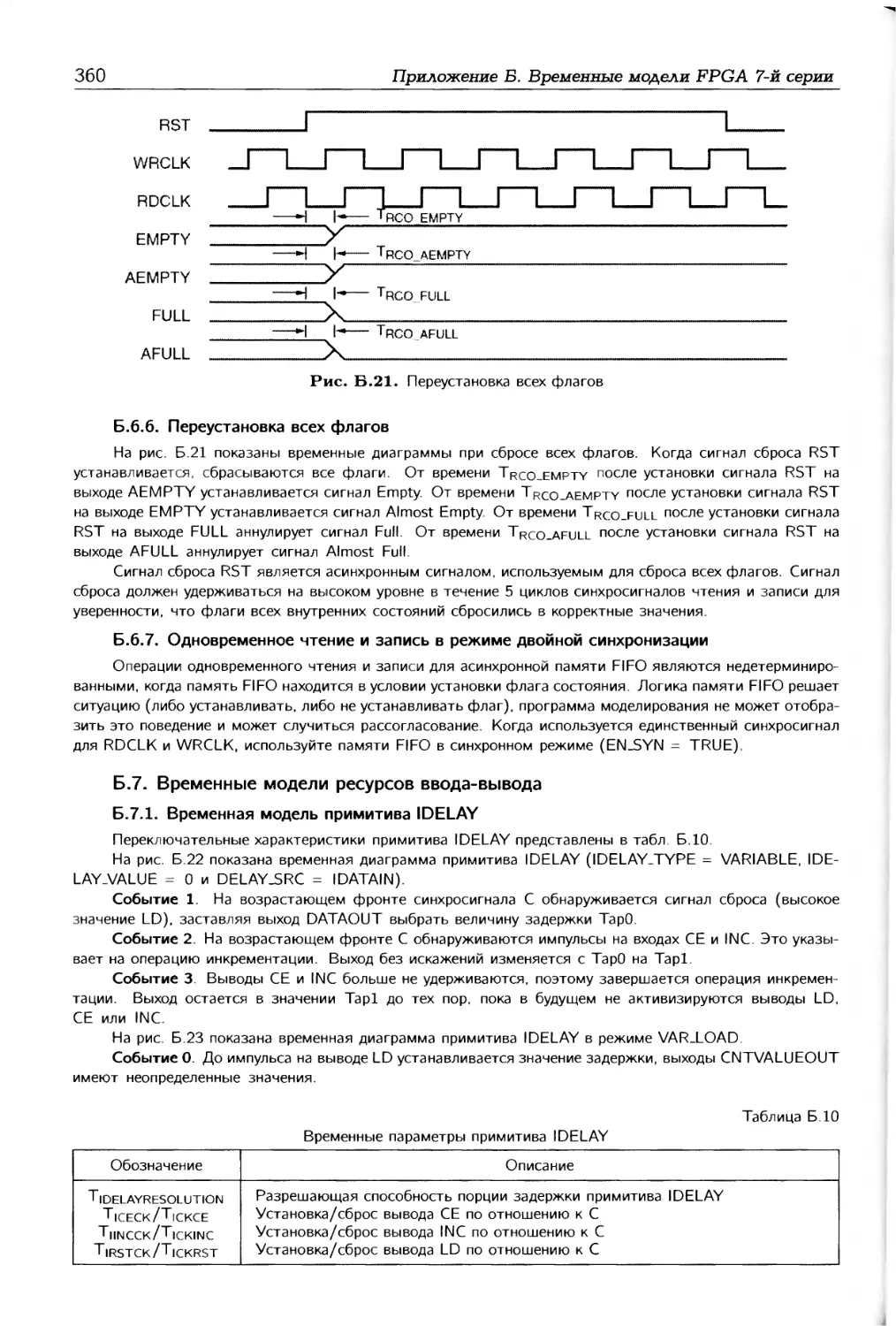

Ч>—О

-0—0

О—О

«»—о

0—0

зе-

1 2 ... m

—- программируемое соединение

—з|е— - фиксированное соединение

Ч)—О

•О—о

-0—0-

чз—о

О-Чн

о—о-

О-

Ч>—О-

о—о

о—о

о—о

о—о

о—о

о—о

•о—о

Ч >—{>

Рис. 1.2. Обобщенная структура PAL

ч >- - програм м ируемое соединение

OR

1 ... m

Рис. 1.3. Обобщенная структура ППЗУ

вать программируемыми логическими устройствами (ПЛУ — Programmable Logic De-

vices — PLD).

10

Раздел 1

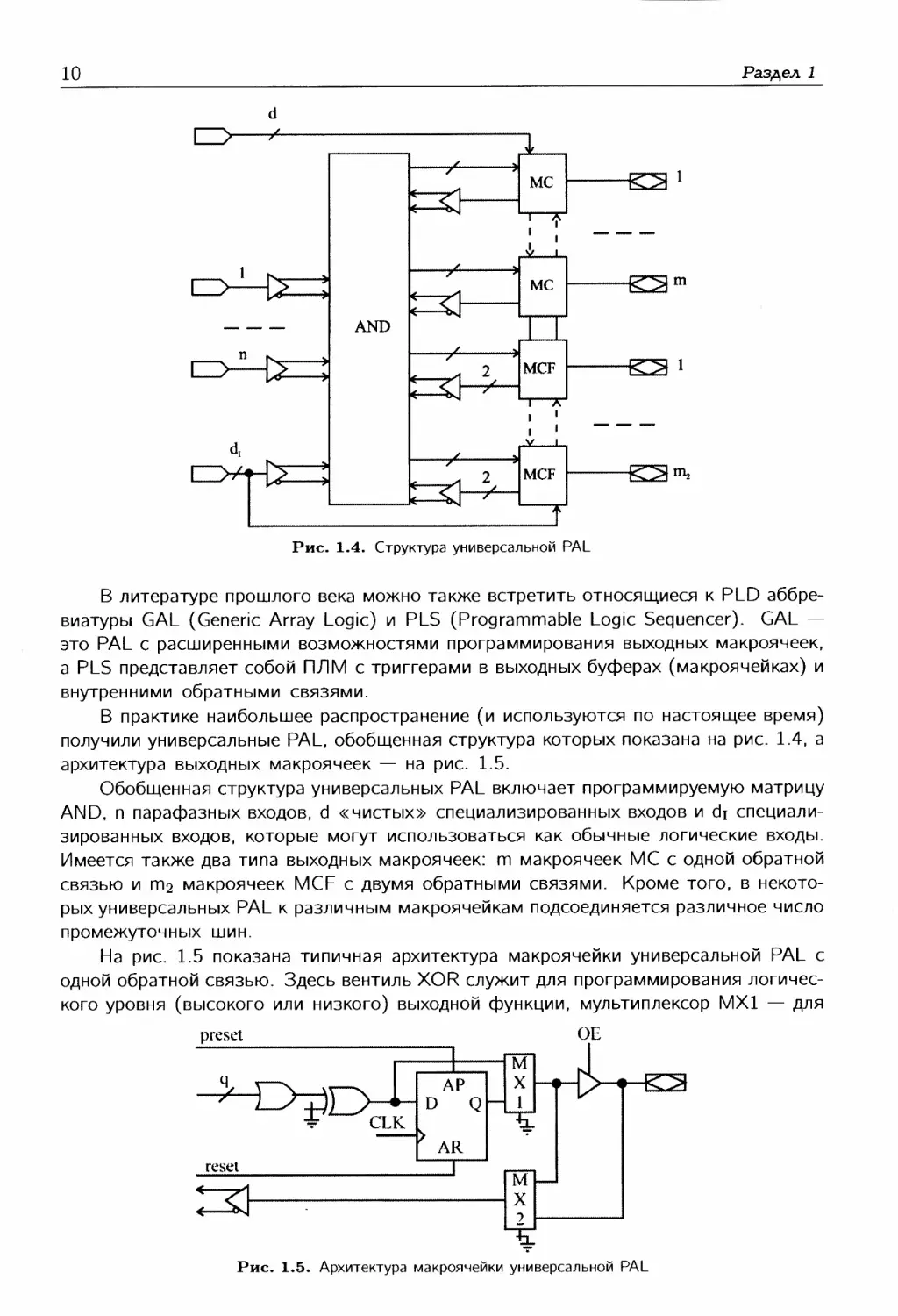

Рис. 1.4. Структура универсальной PAL

В литературе прошлого века можно также встретить относящиеся к PLD аббре-

виатуры GAL (Generic Array Logic) и PLS (Programmable Logic Sequencer). GAL —

это PAL с расширенными возможностями программирования выходных макроячеек,

a PLS представляет собой ПЛМ с триггерами в выходных буферах (макроячейках) и

внутренними обратными связями.

В практике наибольшее распространение (и используются по настоящее время)

получили универсальные PAL, обобщенная структура которых показана на рис. 1.4, а

архитектура выходных макроячеек — на рис. 1.5.

Обобщенная структура универсальных PAL включает программируемую матрицу

AND, п парафазных входов, d «чистых» специализированных входов и di специали-

зированных входов, которые могут использоваться как обычные логические входы.

Имеется также два типа выходных макроячеек: m макроячеек МС с одной обратной

связью и m2 макроячеек MCF с двумя обратными связями. Кроме того, в некото-

рых универсальных PAL к различным макроячейкам подсоединяется различное число

промежуточных шин.

На рис. 1.5 показана типичная архитектура макроячейки универсальной PAL с

одной обратной связью. Здесь вентиль XOR служит для программирования логичес-

кого уровня (высокого или низкого) выходной функции, мультиплексор МХ1 — для

Рис. 1.5. Архитектура макроячейки универсальной PAL

Программируемые логические интегральные схемы 11

программирования типа выхода (регистрового или комбинационного), МХ2 — для

определения точки подключения обратной связи. В макроячейках с двумя обратными

связями мультиплексор МХ2 отсутствует.

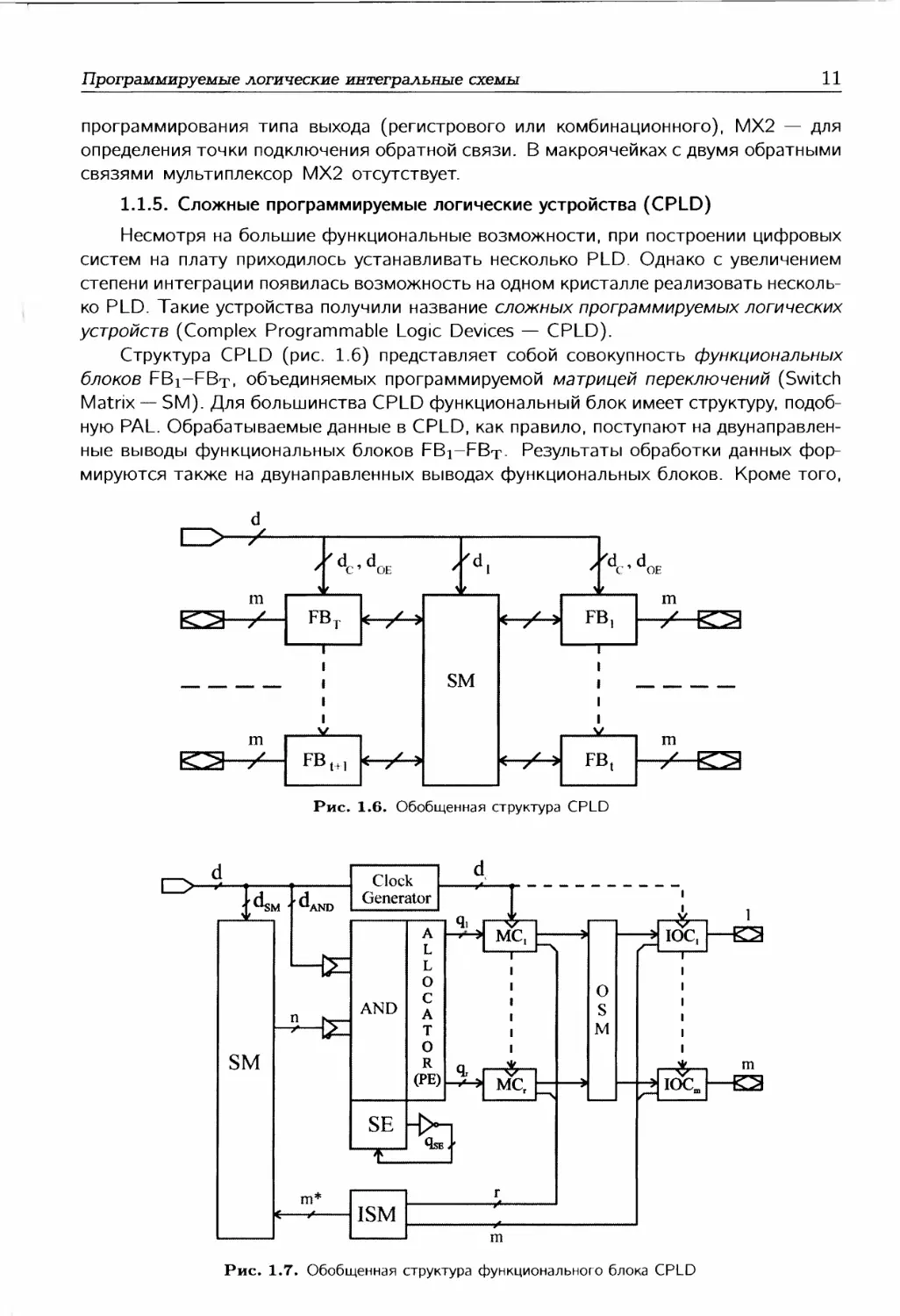

1.1.5. Сложные программируемые логические устройства (CPLD)

Несмотря на большие функциональные возможности, при построении цифровых

систем на плату приходилось устанавливать несколько PLD. Однако с увеличением

степени интеграции появилась возможность на одном кристалле реализовать несколь-

ко PLD. Такие устройства получили название сложных программируемых логических

устройств (Complex Programmable Logic Devices — CPLD).

Структура CPLD (рис. 1.6) представляет собой совокупность функциональных

блоков FBx-FBt, объединяемых программируемой матрицей переключений (Switch

Matrix — SM). Для большинства CPLD функциональный блок имеет структуру, подоб-

ную PAL. Обрабатываемые данные в CPLD, как правило, поступают на двунаправлен-

ные выводы функциональных блоков FBj-FBt- Результаты обработки данных фор-

мируются также на двунаправленных выводах функциональных блоков. Кроме того,

Рис. 1.7. Обобщенная структура функционального блока CPLD

12

Раздел 1

CPLD имеет d специализированных (dedicated) входов, de из которых могут исполь-

зоваться для синхронизации триггеров, doE — для управления третьим состоянием

выходных буферов, a dj могут использоваться как обычные логические выводы.

Обобщенная структура функционального блока CPLD показана на рис. 1.7. Она

включает программируемую матрицу AND, г макроячеек MCi,...,MCr и m внешних вы-

водов, управляемых ячейками ввода-вывода IOC1,...,IOCm. Промежуточные шины от

матрицы AND к макроячейкам подключаются с помощью распределителя (allocator)

промежуточных шин. Некоторые CPLD имеют общий расширитель (Shared Expander —

SE) промежуточных шин, в этом случае распределитель промежуточных шин назы-

вают параллельным расширителем (Parallel Expander — РЕ) промежуточных шин.

1.1.6. Программируемые пользователем вентильные матрицы (FPGA)

Заметим, что основными преобразователями информации в архитектурах PLD и

CPLD являются программируемые матрицы AND и OR. Параллельно с развитием ар-

хитектур PLD/CPLD также развивался другой класс программируемых пользователем

микросхем, которые получили название программируемые пользователем вентильные

матрицы (Field Programmable Gate Arrays — FPGAs).

Основными преобразователями информации в FPGA являются функциональные

генераторы типа LUT (Look Up Table)*. Функциональный генератор LUT представ-

ляет собой небольшое ОЗУ с одним выходом. В зависимости от записанной в ОЗУ

информации она может реализовать любую булеву функцию, аргументы которой по-

ступают на адресные входы ОЗУ. Таким образом, LUT представляет собой функци-

ональный генератор, который может реализовать любую булеву функцию от неболь-

шого числа аргументов (обычно 4-6).

Отметим, что ранее встречались FPGA, в которых в качестве функциональных ге-

нераторов использовались мультиплексоры. При этом аргументы реализуемой функ-

ции подавались на управляющие входы мультиплексоров.

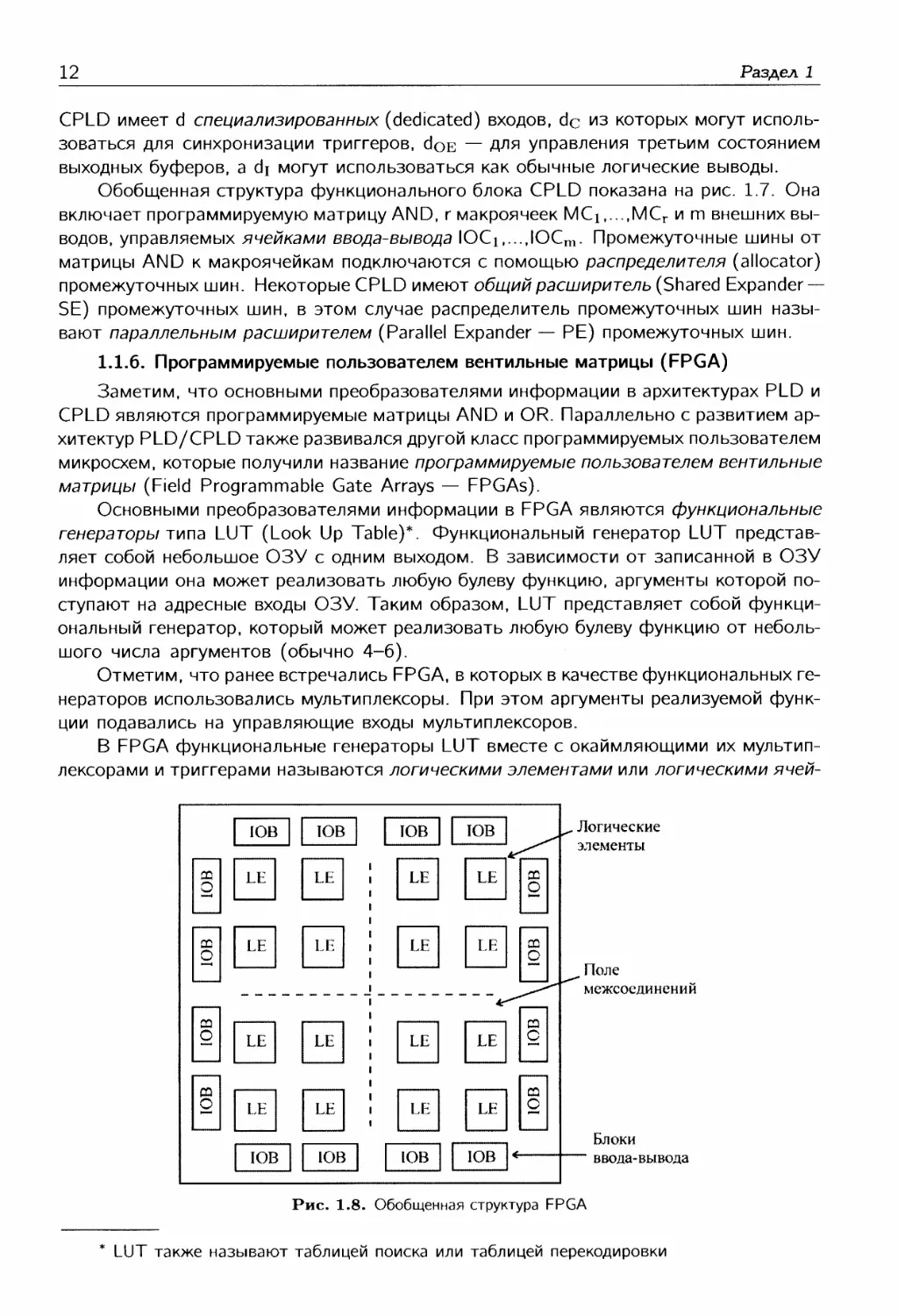

В FPGA функциональные генераторы LUT вместе с окаймляющими их мультип-

лексорами и триггерами называются логическими элементами или логическими ячей-

LUT также называют таблицей поиска или таблицей перекодировки

Программируемые логические интегральные схемы

13

ками (Logic Cells). Традиционно FPGA реализуется в виде матрицы логических эле-

ментов, между которыми находится программируемое поле межсоединений (рис. 1.8),

а по краям располагаются блоки ввода-вывода (Input-Output Block — IOB).

Кроме основных компонентов для логического преобразования сигналов, архи-

тектуры CPLD и FPGA также содержат целый ряд вспомогательных компонентов,

таких как:

• периферийная шина для передачи сигналов управления элементами ввода/вы-

вода;

• специализированные (dedicated) входы и связанные с ними деревья трассировки

глобальных сигналов (синхронизации, разрешения выходных буферов, установки

или сброса триггеров);

• генераторы синхросигналов;

• специализированные выводы для программирования (конфигурирования);

• схемы граничного сканирования JTAG и др.

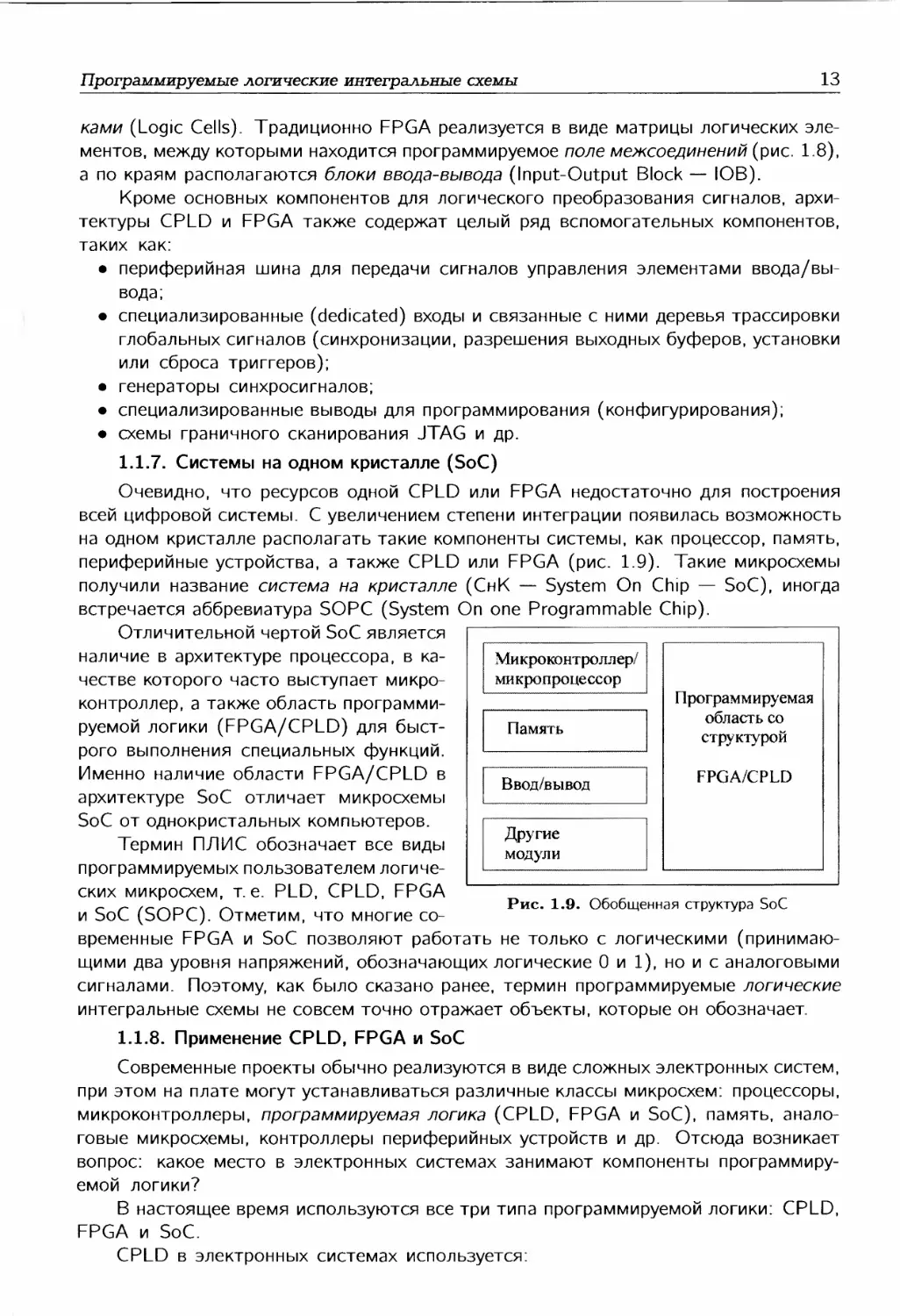

1.1.7. Системы на одном кристалле (SoC)

Очевидно, что ресурсов одной CPLD или FPGA недостаточно для построения

всей цифровой системы. С увеличением степени интеграции появилась возможность

на одном кристалле располагать такие компоненты системы, как процессор, память,

периферийные устройства, а также CPLD или FPGA (рис. 1.9). Такие микросхемы

получили название система на кристалле (СнК — System On Chip — SoC), иногда

встречается аббревиатура SOPC (System On one Programmable Chip).

Отличительной чертой SoC является

наличие в архитектуре процессора, в ка-

честве которого часто выступает микро-

контроллер, а также область программи-

руемой логики (FPGA/CPLD) для быст-

рого выполнения специальных функций.

Именно наличие области FPGA/CPLD в

архитектуре SoC отличает микросхемы

SoC от однокристальных компьютеров.

Термин ПЛИС обозначает все виды

программируемых пользователем логиче-

ских микросхем, т. е. PLD, CPLD, FPGA

и SoC (SOPC). Отметим, что многие со-

временные FPGA и SoC позволяют работать не только с логическими (принимаю-

щими два уровня напряжений, обозначающих логические 0 и 1), но и с аналоговыми

сигналами. Поэтому, как было сказано ранее, термин программируемые логические

интегральные схемы не совсем точно отражает объекты, которые он обозначает.

1.1.8. Применение CPLD, FPGA и SoC

Современные проекты обычно реализуются в виде сложных электронных систем,

при этом на плате могут устанавливаться различные классы микросхем: процессоры,

микроконтроллеры, программируемая логика (CPLD, FPGA и SoC), память, анало-

говые микросхемы, контроллеры периферийных устройств и др. Отсюда возникает

вопрос: какое место в электронных системах занимают компоненты программиру-

емой логики?

В настоящее время используются все три типа программируемой логики: CPLD,

FPGA и SoC.

CPLD в электронных системах используется:

Микроконтроллер/

микропроцессор

Память

Ввод/вывод

Другие

модули

Программируемая

область со

структурой

FPGA/CPLD

Рис. 1.9. Обобщенная структура SoC

14

Раздел 1

• для управления порядком подачи напряжений на микросхемы системы;

• управления конфигурированием FPGA и других конфигурируемых компонентов

системы;

• преобразования уровней напряжений сигналов для частей системы, работающих

с сигналами с различными уровнями напряжения;

• реализации сложных и быстрых конечных автоматов (контроллеров).

FPGA в электронных системах используется:

• для реализации электронных систем малой и средней сложности;

• в качестве сопроцессоров для высокопроизводительной обработки информации и

реализации специальных функций, например, при цифровой обработке сигналов.

SoC в электронных системах используется:

• для реализации всей электронной системы или некоторых ее частей на одной

микросхеме.

Кроме того, FPGA часто применяются в качестве прототипа (макета) специали-

зированных микросхем ASIC. При этом проект вначале реализуется на FPGA, прове-

ряются основные концепции и идеи, заложенные в проект, а затем проект переносится

на ASIC. Использование FPGA в качестве прототипа ASIC позволяет значительно со-

кратить время и стоимость разработки проекта.

1.1.9. Технологии проектирования на основе ПЛИС

Появление ПЛИС изменило традиционное проектирования цифровых систем.

Вместо долгой и утомительной процедуры разработки принципиальной схемы про-

екта, а также выполнения всех последующих действий (отладки, проектирования пе-

чатной платы и др.), стало возможным описать функции проекта на языке проекти-

рования и выполнить программирование ПЛИС.

В общем случае проектирование на основе ПЛИС представляет собой новую идео-

логию проектирования электронных систем, когда один разработчик может в домаш-

них условиях создать сложную электронную систему. Но не все так просто. Для

создания электронной системы проектировщик должен обладать целым рядом опре-

деленных знаний и навыков, которые называются технологиями проектирования на

основе ПЛИС. К таким технологиям относятся:

• архитектуры ПЛИС;

• языки проектирования;

• программные и аппаратные средства автоматизированного проектирования;

• блоки интеллектуальной собственности (IP-ядра) и проектирование на основе IP-

ядер;

• методологии проектирования на основе ПЛИС;

• цифровая обработка сигналов;

• проектирование со встроенными микропроцессорами;

• проектирование интерфейсов;

• отладка проектов;

• проектирование печатных плат для проектов на ПЛИС;

• обеспечение целостности сигналов;

• энергосбережение;

• конфигурирование ПЛИС;

• динамическое и частичное реконфигурирование ПЛИС;

• защита проекта и др.

Программируемые логические интегральные схемы

15

Архитектуры ПЛИС. Разработчик электронных систем на основе ПЛИС обязан

очень хорошо знать архитектуру используемой микросхемы. Это очевидно. Разра-

ботчик также должен знать все архитектуры ПЛИС, выпускаемые данным произ-

водителем, чтобы выбрать наиболее подходящую микросхему. Желательно также

знать архитектуры ПЛИС других производителей, чтобы сравнивать их возможности

с требованиями проекта и, может быть, перейти к проектированию на ПЛИС дру-

гого производителя.

Хорошее знание архитектуры ПЛИС позволяет:

• разрабатывать эффективные проекты, которые в наибольшей степени использу-

ют имеющиеся архитектурные возможности ПЛИС;

• не тратить время на разработку функциональных блоков, которые включаются

в проект установкой одной опции (автор неоднократно наблюдал такие ситуации

у начинающих разработчиков);

• разрабатывать проекты с минимальной потребляемой мощностью, максималь-

ным быстродействием, минимальной стоимостью и за короткий промежуток вре-

мени.

Языки проектирования. Фактически, использование языков описания аппара-

туры — это новая технология проектирования цифровых систем, кардинально от-

личающаяся от различных схемотехнических подходов, связанных с использованием

графических редакторов. Современные языки проектирования позволяют не только

описывать структуру и поведение устройства, но также подготавливать последова-

тельность тестовых векторов для анализа, выполнять проверку результатов модели-

рования, эмулировать внешнюю среду проекта, различными способами отображать

результаты моделирования и др.

Другими словами, язык проектирования — это мощный инструмент, использу-

емый на многих этапах представления проекта: от системного уровня до уровня

отдельных транзисторов, и на многих этапах разработки проекта: от логического

синтеза до функционального и временного моделирования.

Наиболее широко используемыми языками проектирования в настоящее время

являются Verilog [1] и VHDL, на системном уровне используются языки SystemVerilog,

SystemC, C/C++ и др.

Средства автоматизированного проектирования. Разработка современной элек-

тронной системы невозможна без использования средств автоматизированного про-

ектирования, которые делятся на программные и аппаратные. Программные средства

проектирования, как правило, обеспечивают:

• ввод проекта (текстовый, графический, смешанный);

• библиотеку примитивов и стандартных функциональных блоков;

• компиляцию проекта (нахождение ошибок, формирование базы данных и машин-

ного представления проекта);

• функциональное и временное моделирование;

• отображение проекта на структуру конкретной ПЛИС;

• программирование (конфигурирование) ПЛИС.

Кроме того, современные средства проектирования предоставляют целый ряд

дополнительных программ для:

• цифровой обработки сигналов;

• проектирования на основе 1Р-ядер;

• оценки и оптимизации потребляемой мощности;

• высокоуровневого проектирования;

• проектирования на основе встроенных процессоров;

16

Раздел 1

• интеграции отдельных частей цифровой системы в одно целое;

• разработки проектов на основе SoC и др.

Аппаратные средства проектирования. Все аппаратные средства проектирования

на ПЛИС можно разделить на следующие категории:

• программаторы;

• кабели для программирования ПЛИС в системе (на плате) или для конфигури-

рования ПЛИС;

• учебные платы;

• макетные платы;

• комплекты разработчиков (development kits).

Как было сказано ранее, программаторы — это специальные устройства для про-

граммирования ПЛИС и конфигурационных ППЗУ. Конфигурационные ППЗУ служат

источником данных в режимах конфигурирования, когда ПЛИС выступает в качестве

главного (управляющего) устройства. В этом случае ПЛИС автоматически сама себя

конфигурирует, загружая данные из ППЗУ, при каждом включении питания.

Кабели для программирования используются при конфигурировании или про-

граммировании ПЛИС в системе от персонального компьютера.

Учебные платы используются при обучении студентов различным вопросам про-

ектирования электронных систем на основе ПЛИС. Обычно учебные платы содержат

кнопочные переключатели для подачи входных сигналов, светодиоды для отобра-

жения состояний выходных сигналов, семисегментные дисплеи, дисплеи типа LCD,

контроллеры стандартных интерфейсов (VGA, PS/2, RS-232, USB, 12С), гнезда для

подключения внешней памяти, дополнительные разъемы для внешних выводов и др.

ПЛИС на учебных платах обычно конфигурируются от персонального компьютера с

помощью кабеля для программирования.

Макетные платы — это более сложные устройства по сравнению с учебными пла-

тами. Они предназначены для физической отладки проектов на ПЛИС конкретного

семейства. Часто макетные платы ориентированы на определенную область приме-

нения: цифровая обработка сигналов, проектирование со встроенными микропроцес-

сорами, проектирование систем телекоммуникации и др.

Комплекты разработчиков представляют собой полный набор программных и ап-

паратных средств, достаточных для разработки электронной системы на ПЛИС опре-

деленного семейства. Комплекты разработчиков также ориентированы на определен-

ную область применения. Комплект разработчика обычно включает: программное

средство проектирования, макетную плату, библиотеку IP-ядер, кабели для конфи-

гурирования и др.

Блоки интеллектуальной собственности (IP-ядра). Чтобы два раза «не изобре-

тать велосипед», были придуманы блоки интеллектуальной собственности (Intellectual

Property — IP), или просто IP-ядра. IP-ядро представляет собой некоторый ранее

разработанный отлаженный и сертифицированный проект, который предлагается для

использования как составная часть в других проектах. Из IP-ядер формируются биб-

лиотеки, которые постоянно пополняются. В базовую комплектацию промышленных

программных средств проектирования может входить часть этих библиотек.

За дополнительную плату можно приобрести библиотеки IP-ядер таких компо-

нентов, как основные арифметические блоки, приемопередатчики, контроллеры ин-

терфейсов протоколов, контроллеры памяти, микропроцессоры, блоки DSP, а также

библиотеки IP-ядер для решения задач проектирования из очень широкой области

использования: обработка звука, обработка видеоинформации и изображений, авто-

мобильная электроника, основная логика, интерфейсные шины и ввод-вывод, сети и

Программируемые логические интегральные схемы

17

телекоммуникация, цифровая обработка сигналов, математика, интерфейсы памяти,

сетевые базы данных и др.

Библиотеки IP-ядер предлагают уже готовые проекты в таких областях, как мо-

дуляция и демодуляция сигналов; коррекция ошибок; видео и обработка изображений;

беспроводная связь; широковещательная передача; промышленность; робототехника;

медицина; космос и оборона; автомобильная техника и др.

Кроме того, промышленные программные проекты автоматизированного проек-

тирования предоставляют специальные средства проектирования на основе 1Р-ядер,

а также генераторы 1Р-ядер.

Методологии проектирования на основе ПЛИС. Среди всего разнообразия мето-

дологий проектирования кратко рассмотрим только модульное, пошаговое и вирту-

альное проектирование, которые используются при разработке электронных систем

на ПЛИС.

Технологические и архитектурные особенности ПЛИС позволили предложить но-

вые методологии проектирования: модульное и пошаговое проектирование. Архитек-

тура современных FPGA часто строится в виде столбцов различного типа. Каждый

тип столбцов состоит из функциональных блоков определенного вида: логических,

цифровой обработки сигналов, ввода-вывода, памяти и др.

При модульном проектировании каждая часть модуля проекта может разрабаты-

ваться независимыми группами инженеров. В последующем разработанный модуль

размещается в одном или нескольких соседних столбцах ПЛИС, причем никакая дру-

гая логика в эти столбцы размещена быть не может. Несмотря на некоторую избыточ-

ность по стоимости модульного проектирования, гарантируется сохранение основных

параметров каждого модуля независимо от их расположения в ПЛИС.

Пошаговое проектирование разрешает модифицировать любой столбец ПЛИС на

уровне регистровых передач. При этом в столбец может быть добавлена некоторая

логика, что запрещено при модульном проектировании. Сочетание модульного и по-

шагового проектирования обеспечивает достаточно хорошие результаты.

Виртуальное проектирование позволяет значительно сократить время разработки

проекта. На уровне регистровых передач схема проекта, как правило, имеет иерар-

хическое представление. Однако средства размещения и трассировки ПЛИС преоб-

разуют его в плоское или одноуровневое представление. В результате, если произ-

вести незначительные изменения в одном из блоков на уровне регистровых передач и

пересинтезировать только этот блок, все равно будет выполнен повторный синтез

всего устройства.

Концепция виртуального макетирования ПЛИС позволяет выполнять планиро-

вание компоновки кристалла и осуществлять предварительный временной анализ до

выполнения этапов размещения и разводки. Данный подход позволяет также выпол-

нять синтез, размещение и разводку индивидуально для каждого блока устройства. В

результате значительно сокращается время разработки устройства.

Цифровая обработка сигналов (digital signal processing — DSP). Цифровая об-

работка сигналов является неотъемлемой частью современных электронных систем

на ПЛИС. Технология проектирования на ПЛИС DSP-приложений поддерживается

на разных уровнях:

• архитектуры FPGA включают специальные DSP-блоки для высокой скорости вы-

полнения операций цифровой обработки сигналов;

• промышленные программные пакеты включают специальные программные сред-

ства (редактор DSP, генератор DSP);

18

Раздел 1

• библиотека IP-ядер содержит широкий набор элементов для реализации как от-

дельных DSP-приложений (фильтры, аналогоцифровые и цифро-аналоговые пре-

образователи, вычислители тригонометрических функций, модули быстрого пре-

образования Фурье и др.), так и уже готовые проекты, требующие минимальной

адаптации.

Все программные средства проектирования DSP-приложений, как правило, рабо-

тают совместно с пакетом MATLAB/Simulink. В электронных системах FPGA часто

выступают в качестве DSP-процессоров и по своей производительности часто пре-

восходят стандартные DSP-процессоры.

Проектирование со встроенными микропроцессорами. Современные ПЛИС мо-

гут содержать микропроцессоры (или микроконтроллеры). Имеется два способа ре-

ализации микропроцессоров в ПЛИС: аппаратный и программный. При аппаратной

реализации микропроцессора часть кристалла изначально отводится под микропро-

цессор, а оставшаяся часть — под ПЛИС. В таком случае микросхема ПЛИС называ-

ется системой на кристалле (System on Chip — SoC). При программной реализации

микропроцессора часть кристалла ПЛИС конфигурируется для реализации функций

м и кроп роцессора.

Имеется два способа аппаратной реализации микропроцессора в ПЛИС. В первом

из них микропроцессор реализуется в виде отдельной полосы (решение фирмы Altera),

содержащей процессорное ядро, ОЗУ, элементы ввода-вывода и другие процессорные

устройства. Эта процессорная полоса может реализовываться на одном кристалле

ПЛИС или на отдельном кристалле, который объединяется с ПЛИС в одном корпусе.

Во втором способе микропроцессор реализуется непосредственно в структуре ПЛИС

(решение фирмы Xilinx).

Имеется также два способа программной реализации микропроцессора. В первом

(soft) микропроцессор описывается на уровне RTL и реализуется на ПЛИС вместе с

остальной логикой проекта. Во втором случае (firm) микропроцессорное ядро реали-

зуется в виде уже размещенных и разведенных конфигурируемых блоков, такая реа-

лизация называется микропрограммной. Программная реализация микропроцессора

медленнее аппаратной. Преимуществом программной реализации микропроцессора

является то, что микропроцессор может быть реализован на любой FPGA, которая

располагает достаточным количеством ресурсов. Кроме того, на одной ПЛИС может

быть реализовано несколько микропроцессорных ядер и таким образом может быть

построена мультипроцессорная система.

Кроме рассмотренных подходов реализации микропроцессоров, предлагаемых

производителями ПЛИС, любые микропроцессоры и микроконтроллеры могут быть

реализованы на ПЛИС программно с помощью соответствующих 1Р-ядер.

Проектирование интерфейсов. Данную технологию можно разделить на три час-

ти: приемопередатчики, интерфейсы внешней памяти и интерфейсы стандартных

протоколов.

Приемопередатчики представляют собой высокоскоростные последовательные

соединения типа точка-точка, используемые для соединения различных микросхем

на одной плате. Для реализации таких соединений используются дифференциаль-

ные пары (differential pairs). Имеется много различных стандартов, поддерживаемых

приемопередатчиками: Fibre Channel (оптический кабель), InifiniBond, PCI Express,

RapidlO, SkyRoil, 10G Ethernet и др.

Важными параметрами, которыми характеризуются приемопередатчики, являют-

ся: восстановление синхронизации (clock data recovery— CDR); глазковая диаграмма

или глазковая маска; окно достоверности данных. Приемопередатчики, реализуемые

Программируемые логические интегральные схемы

19

в ПЛИС, часто позволяют конфигурировать некоторые свои параметры. Наиболее

часто конфигурируются следующие параметры приемопередатчиков:

• определение разделителей;

• амплитуда выходного сигнала;

• согласующие резисторы выходных буферов;

• внесение предискажений;

• реализация компенсации.

При проектировании микропроцессорных и встроенных систем на ПЛИС часто

объема памяти внутренних (встроенных) блоков ПЛИС бывает недостаточно. В этом

случае используются внешние микросхемы памяти, для которых на ПЛИС необходимо

предусмотреть соответствующие интерфейсы. Современные ПЛИС поддерживают

интерфейсы со следующими типами памяти: DDR4, DDR3 SDRAM, DDR2 SDRAM,

LPDDR3, LPDDR2, RLDRAMII, RLDRAMIII, QRDII SRAM, QRDII+SRAM.

Реализация интерфейсов внешней памяти поддерживается усовершенствованной

архитектурой ПЛИС, специальным программным обеспечением (настраиваемыми

функциями, генератором интерфейса памяти), эталонными проектами, демонстра-

ционными платами и моделями для компьютерного моделирования.

ПЛИС также поддерживают ряд интерфейсов стандартных протоколов, среди ко-

торых особое место занимает стандарт шины PCI Express. Протокол PCI Express,

называемый также PCIe, является последовательным интерфейсом общего назначе-

ния, который может использоваться в устройствах связи, во встроенных системах,

в серверах, мобильных и настольных приложениях, системах хранения данных и др.

Протокол PCI Express может также использоваться в качестве интерфейса перифе-

рийных устройств, интерфейса от микросхемы к микросхеме и моста к другим стан-

дартам, таким как 1394b, USB2.0, InfiniBand™ и Ethernet.

Интерфейсы стандартных протоколов в ПЛИС поддерживаются настраиваемыми

IP-ядрами, макетными платами и эталонными примерами.

Отладка проектов. Главной проблемой при отладке систем на ПЛИС является

то, что отсутствует возможность установить пробник внутри ПЛИС. Имеется мно-

го различных подходов к решению данной проблемы. Одним из них является метод

граничного сканирования (boundary scan), суть которого заключается в том, что все

триггеры устройства последовательно соединяются в одну цепочку, в результате обра-

зуется один большой сдвиговый регистр. Значение этого сдвигового регистра может

последовательно выводиться на внешние контакты, например, по JTAG-формату. Од-

нако с увеличением размера ПЛИС данный подход становится весьма трудоемким и

мало пригодным для практического использования.

Для отладки проектов на современных ПЛИС используют специальные програм-

мные средства, называемые логическими анализаторами. Логический анализатор

позволяет исследовать поведение внутренних сигналов во время работы проекта на

ПЛИС без использования внешних выводов. Другими словами, логический анализа-

тор помогает отлаживать проект на ПЛИС, зондируя состояние внутренних сигналов

в проекте без использования внешнего оборудования.

Данные, полученные с помощью логического анализатора, могут храниться в

памяти ПЛИС, а также в определенные моменты времени выводиться на внешние

интерфейсы.

Проектирование печатных плат для проектов на ПЛИС. Значительное увеличение

быстродействия и числа выводов ПЛИС привело к возникновению ряда проблем у

разработчиков печатных плат.

20

Раздел 1

Увеличение быстродействия микросхем непосредственно связано с увеличением

крутизны фронтов сигналов, которая, в свою очередь, приводит к увеличению уров-

ня шума и перекрестных помех. В связи с этим при разработке плат необходимо

применять дополнительные меры по анализу искажений сигналов и их устранению.

Современные стандарты высокоскоростных интерфейсов ввода-вывода требуют

строго определенных значений волнового сопротивления подключаемых проводников.

ПЛИС позволяют конфигурировать внутренние согласующие резисторы для удовлет-

ворения требованиям различным стандартам. Более того, многие ПЛИС поддержива-

ют опцию цифрового управления импедансом (digitally controlled impedance — DCI),

которая позволяет автоматически выполнять согласование значения волнового со-

противления в зависимости от изменений температуры и напряжения питания.

В ряде случаев многие проблемы передачи сигналов на печатной плате могут

быть решены путем отказа от передачи параллельных данных и перехода на высо-

коскоростную последовательную передачу данных, например, с помощью реализован-

ных в ПЛИС универсальных асинхронных приемопередатчиков (universal asynchronous

receiver/traHcmitter — UART).

Еще одна проблема печатных плат при использовании ПЛИС — это пиковые зна-

чения тока напряжения питания при включении системы. Для решения этой проблемы

часто на плату системы устанавливается CPLD, которая управляет порядком подачи

напряжений питания на все FPGA и SoC, расположенные на плате.

Обеспечение целостности сигналов. Понятие целостности сигналов включает в

себя ряд различных аспектов, таких как изменение формы сигнала при его прохож-

дении через проводник, отражение сигнала от конца несогласованного проводника,

а также перекрестные помехи. Все эти явления присущи как сигналам внутри крис-

талла, так и сигналам на плате. Проблемы целостности сигналов внутри кристалла

уже решены производителями ПЛИС, в то время как на плате эти проблемы должен

решать пользователь.

Когда сигнал в одном из соседних проводников переходит с одного логического

уровня на другой, то он провоцирует кратковременную импульсную помеху в дру-

гом проводнике. При этом первый проводник называется «агрессором», а второй —

«жертвой». Такого рода помехи также называются перекрестными, поскольку «жерт-

ва» также может оказывать воздействие на «агрессора». Перекрестные помехи

провоцируют возникновение шумов и задержку сигналов. Кроме того, проводников-

агрессоров может быть несколько. Точный анализ современных схем требует, чтобы

влияние каждого проводника-агрессора было проанализировано и учтено индивиду-

ально.

Перекрестные помехи на платах также называются коммутационными шумами.

В качестве обратной цепи для коммутационных шумов служит «земля». Когда не-

сколько сигнальных цепей используют одну и ту же цепь обратной связи (т. е. цепь

земли), то коммутационные шумы проходят по общей цепи и называются шумами

общего провода. Для уменьшения влияния шумов общего провода сигнальные цепи

должны, по возможности, иметь различные общие провода. Поэтому микросхемы

ПЛИС имеют множество выводов цепей земли и питания, которые стараются рав-

номерно распределить на корпусе микросхемы. При монтаже микросхемы ПЛИС на

плате все выводы земли и питания должны быть подсоединены — это способствует

уменьшению шумов общего провода.

С возрастанием скорости передачи сигналов обостряются проблемы целостности

сигналов. Одним из путей решения этих проблем является использование дифферен-

циальных пар вместо отдельных проводников. Отметим, что буферы ввода-вывода

Программируемые логические интегральные схемы

21

ПЛИС поддерживают большое число стандартов с дифференциальными выводами.

Второй способ — использование внутренних согласующих резисторов вместо внеш-

них резисторов. Большинство ПЛИС также позволяют конфигурировать внутренние

согласующие резисторы.

Энергосбережение. Энергосбережение представляет собой серьезную проблему,

которая должна решаться на всех уровнях проектирования системы на ПЛИС. Про-

изводители ПЛИС предоставляют ряд технологий (методов) для снижения энергос-

бережения, а также программные средства для оценки энергопотребления проекта.

Энергосбережение ПЛИС поддерживается:

• многочисленными опциями для снижения потребляемой мощности в различных

элементах архитектуры ПЛИС;

• анализатором потребляемой мощности;

• опцией снижения потребляемой мощности в программных средствах автомати-

зированного проектирования.

Конфигурирование ПЛИС. Чтобы разработать эффективную электронную систе-

му на ПЛИС, важно рассмотреть, какой режим конфигурирования ПЛИС лучше всего

соответствует требованиям системы.

В общем случае современные ПЛИС допускают 5 режимов конфигурирования:

• последовательная загрузка, ПЛИС в режиме ведущий (master);

• последовательная загрузка, ПЛИС в режиме ведомый (slave);

• параллельная загрузка, ПЛИС в режиме ведущий (master);

• параллельная загрузка, ПЛИС в режиме ведомый (slave);

• последовательная загрузка через JTAG-порт.

При выборе режима конфигурирования необходимо рассмотреть следующие во-

просы:

• где будут храниться конфигурационные данные;

• время конфигурирования (время готовности системы к работе после включе-

ния питания);

• стоимость схемы конфигурирования;

• предусматривается ли в будущем изменение конфигурационных данных;

• предусматривается ли удаленное обновление системы и др.

Каждый режим конфигурирования использует определенные контакты ПЛИС и

может временно использовать другие многофункциональные контакты только во вре-

мя конфигурирования. Когда конфигурирование заканчивается, эти многофункцио-

нальные контакты становятся доступными для общего использования. Режим конфи-

гурирования может также установить ограничения напряжения для некоторых банков

ввода-вывода ПЛИС.

Динамическая и частичная реконфигурация ПЛИС. Под динамической реконфи-

гурацией понимается конфигурация ПЛИС «на лету», т. е. во время работы системы.

В принципе, любую ПЛИС можно переконфигурировать во время работы системы,

вот только будет ли после этого система работать. При динамической реконфигура-

ции ПЛИС возникает ряд вопросов:

• как отключить выводы ПЛИС во время конфигурации;

• как сократить время конфигурации;

• как сохранить содержимое регистров, установленных до конфигурации;

• как сохранить работоспособность системы во время конфигурации ПЛИС и др.

Первый вопрос самый простой — для большинства ПЛИС сигнальные выводы

во время конфигурации автоматически переводятся в высокоимпедансное состояние.

Время конфигурации ПЛИС можно сократить путем увеличения ширины шины, по

22

Раздел 1

которой передаются конфигурационные данные. Традиционные ПЛИС не позволяют

положительно ответить на два последних вопроса. Однако ПЛИС от фирмы Atmel

позволяют решить эти проблемы.

До недавнего времени необходимость внесения даже небольших изменений в кон-

фигурацию ПЛИС требовало переконфигурирования всего устройства. Последние по-

коления ПЛИС допускают частичную реконфигурацию устройства. При этом значи-

тельно уменьшается время реконфигурации.

Защита проекта. Поскольку большинство ПЛИС конфигурируются всякий раз

при включении питания, в этот момент возможен несанкционированный доступ к

данным конфигурирования. Большинство средств защиты проектов на ПЛИС под-

держивают следующие возможности:

• встроенное дешифрование по стандарту (AES) с поддержкой 256-разрядного клю-

ча, алгоритм безопасности проекта промышленного стандарта (FIPS 197 Certi-

fied);

• энергозависимая и энергонезависимая программная поддержка ключа;

• ограничение доступных инструкций стандарта JTAG во время включения питания

в безопасном режиме;

• поддержка аутентификация POF и защита от атаки по сторонним каналам;

• отключение всех инструкций JTAG от момента включения питания, до момента,

пока устройство не инициализировано.

В мире известно около двух десятков фирм — разработчиков и производителей

ПЛИС. Одним из таких производителей является фирма Xilinx, занимающая 30...40 %

всего мирового объема производства ПЛИС.

Данная книга посвящена рассмотрению архитектур ПЛИС фирмы Xilinx, т. е. пер-

вой из технологий проектирования на основе ПЛИС.

1.2. ПЛИС фирмы Xilinx

1.2.1. Историческая справка

Первые ПЛИС фирмы Xilinx по архитектуре FPGA начали производиться в сере-

дине 80-х годов прошлого столетия. Изобретателями FPGA фирмы Xilinx считаются

Росс Фримен (Ross Freemen) и Бернард Вондершмитт (Bernard Vonderschmitt). До

появления FPGA фирмы Xilinx уже были известны и широко использовались PLD со

структурой PAL. Однако сложные системы строились на основе заказных микросхем

ASIC и полузаказных микросхем вентильных матриц. Отсюда возник естественный

вопрос: а нельзя ли соединить возможность программирования микросхем пользо-

вателем с мощностью заказных ASIC. Эту проблему решила фирма Xilinx, предло-

жив программируемые пользователем вентильные матрицы (Field Programmable Gate

Arrays — FPGA).

Первые FPGA изготавливались по CMOS-технологии, а для хранения информа-

ции использовалось энергозависимое статическое ОЗУ (SRAM). FPGA фирмы Xilinx

организованы в виде массива логических элементов (Logic Element) или логических

ячеек (Logic Cell), состоящих из функциональных генераторов LUT, представляющих

собой таблицу перекодировки (Look-Up Table — LUT), мультиплексоров и триггеров.

Логические элементы в FPGA фирмы Xilinx группируются в виде конфигурируемых

логических блоков (Configurable Logic Blocks — CLB).

В настоящее время фирма Xilinx производит такие классы микросхем програм-

мируемой логики, как CPLD, FPGA и SoC.

Программируемые логические интегральные схемы

23

1.2.2. CPLD фирмы Xilinx

Фирмой Xilinx выпускается две серии ПЛИС с архитектурой CPLD: XC9500XL и

CoolRunner-IL CPLD фирмы Xilinx строятся на основе популярной архитектуры PAL:

программируемая матрица AND и фиксированная матрица OR. Оособенностями

CPLD фирмы Xilinx являются:

• высокая производительность (задержка сигналов от входа до выхода — до 5 нс);

• возможность перепрограммирования в системе (не менее 10 000 циклов запись/

стирание);

• программируемый режим пониженной потребляемой мощности для каждой мак-

роячейки;

• расширенная возможность защиты запрограммированной информации от копи-

рования;

• мощный выход (24 мА);

• малая статическая потребляемая мощность;

• широкий выбор корпусов упаковки;

• простота использования.

Семейство XC9500XL разрабатывалось для тесного взаимодействия с FPGA се-

мейств Virtex, Spartan и XC4000XL, позволяя системным проектировщикам оптималь-

но разделять логику между быстрыми интерфейсными схемами, какими являются

CPLD, и устройствами с высокой логической плотностью, т. е. FPGA. Параметры

CPLD семейства XC9500XL представлены в табл. 1.1.

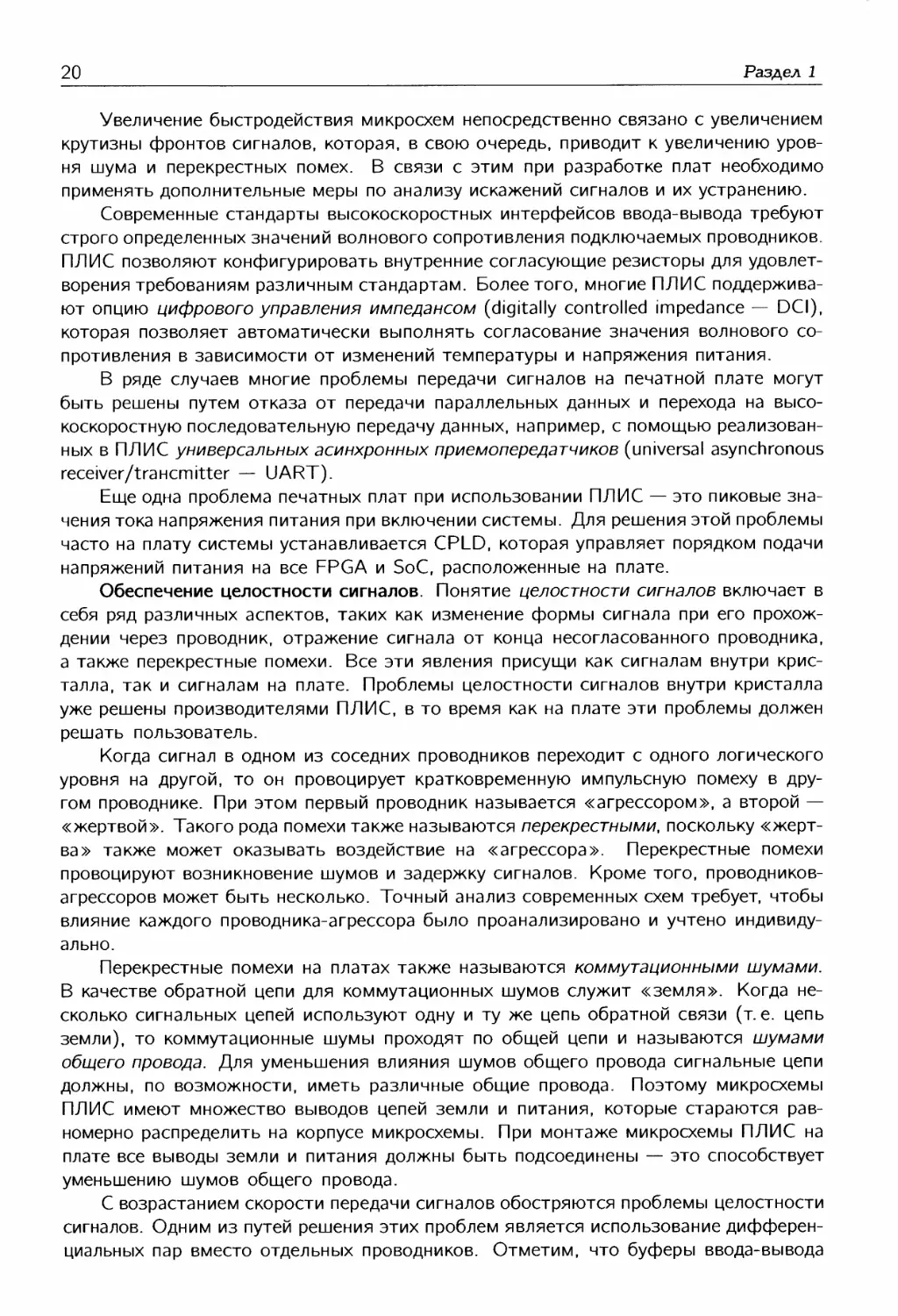

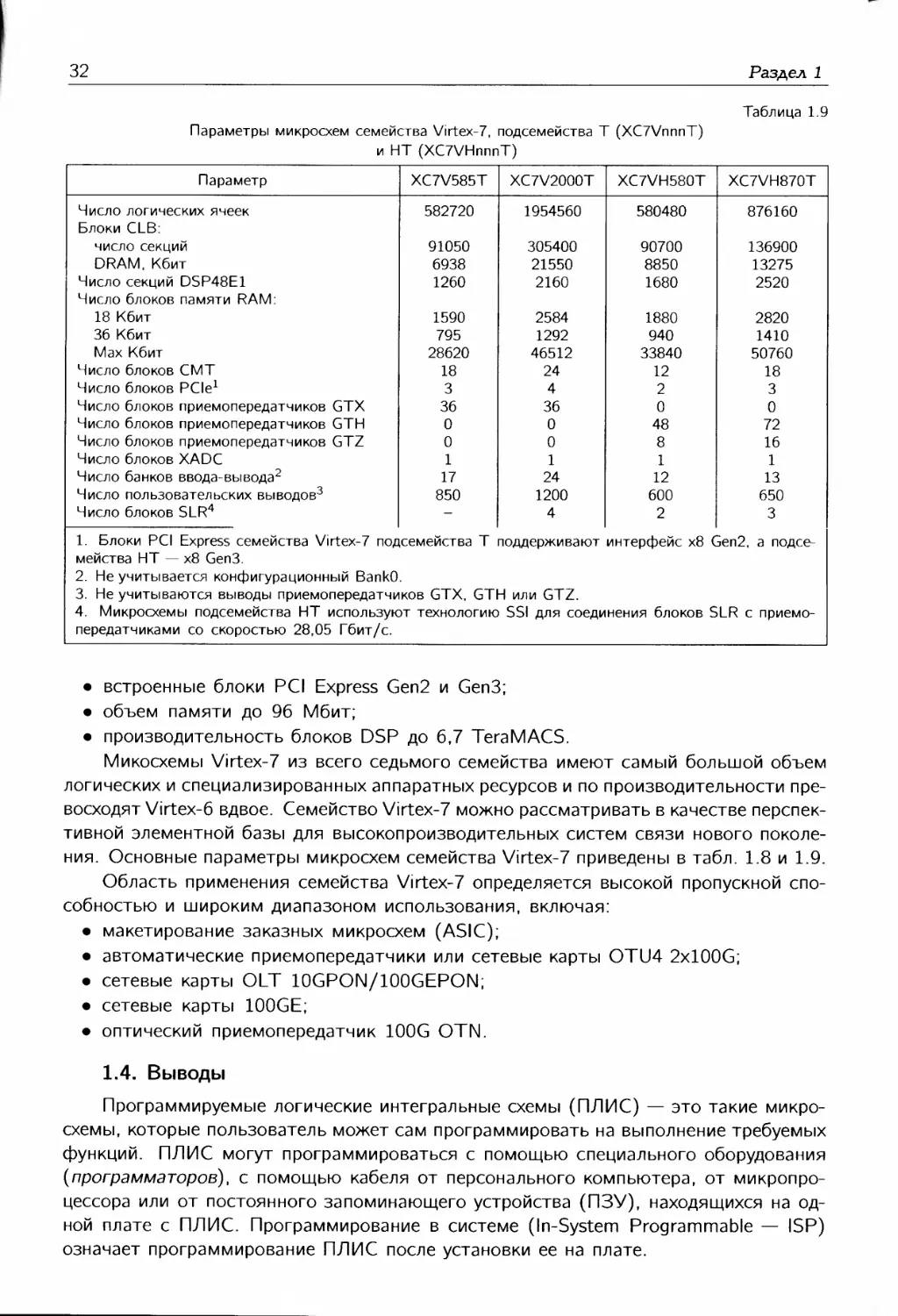

Таблица 1.1

Параметры CPLD семейства XC9500XL

Параметр XC9536XL XC9572XL XC95144XL XC95288XL

Число системных вентилей Число макроячеек Максимальное число термов, подсоединяемых к одной макроячейке Число глобальных синхросигналов Чисор локальных синхросигналов функционального блока Число пользовательских выводов Уровни входных сигналов, В Уровни выходных сигналов, В Задержка на комбинационной части, нс Максимальная частота функционирования, МГц 800 36 90 3 18 36 2,5/3,3/5 2,5/33 5 178 1600 72 90 3 18 72 2,5/3,3/5 2,5/3,3 5 178 3200 144 90 3 18 117 2,5/3,3/5 2,5/3,3 5 178 6400 288 90 3 18 192 2.5/3.3/5 2,5/3,3 6 208

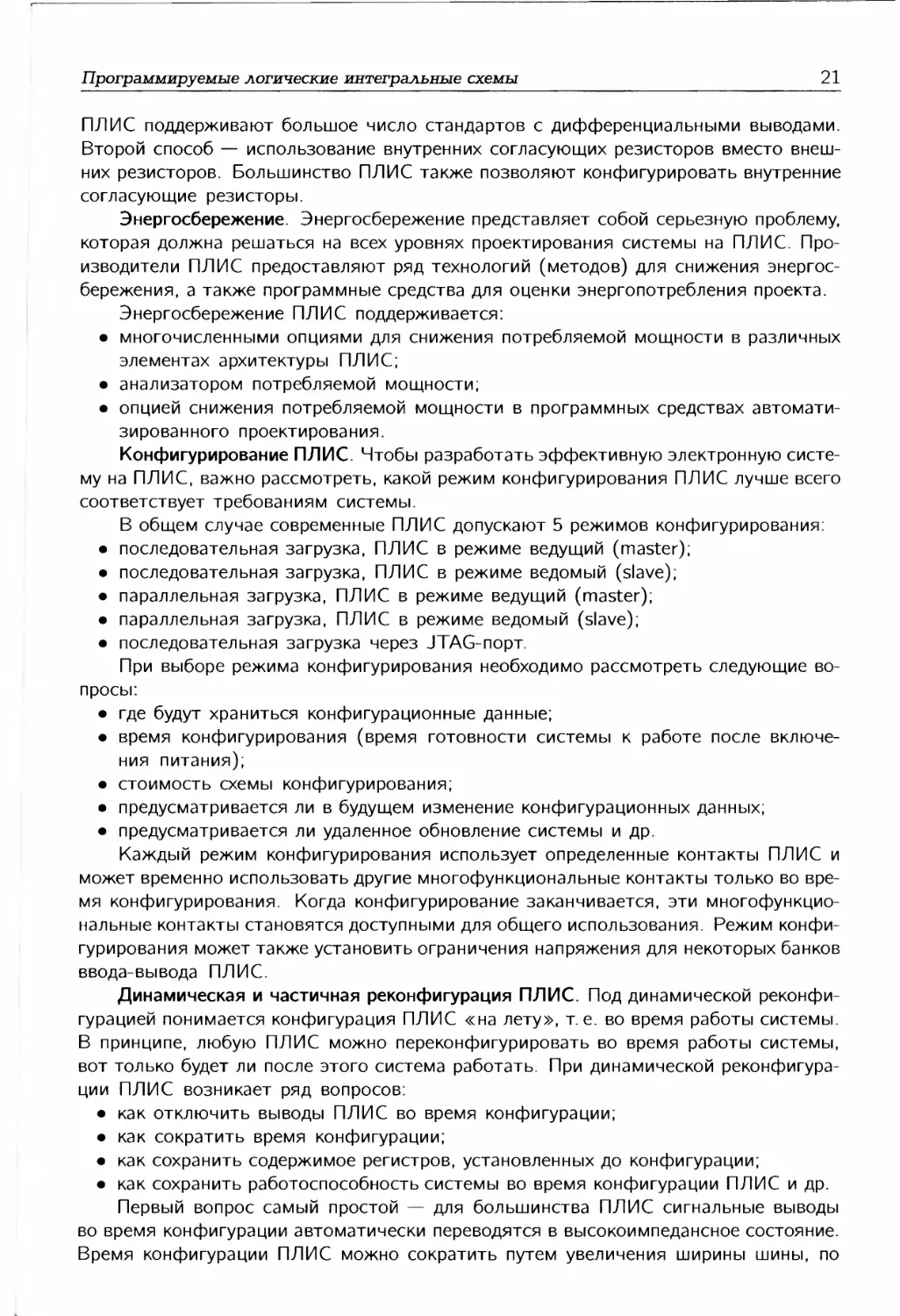

Таблица 1.2

Параметры CPLD семейства CoolRunnerll

Параметр ХС2С32А ХС2С64А ХС2С128 ХС2С256 ХС2С384 ХС2С512

Число системных вентилей 750 1500 3000 6000 9000 12000

Число макроячеек 32 64 128 256 384 512

Число пользовательских выводов 33 64 100 184 240 270

Задержка на комбинационной 3,8 4,6 5,7 5,7 7,1 7,1

части, нс Максимальная частота функцио- нирования, МГ ц 323 263 244 256 217 179

Число блоков ввода-вывода 2 2 2 2 4 4

Делитель синхросигнала (Clock — — X X X X

Devider) Управление энергопотреблением (DataGATE) — — X X X X

24

Раздел 1

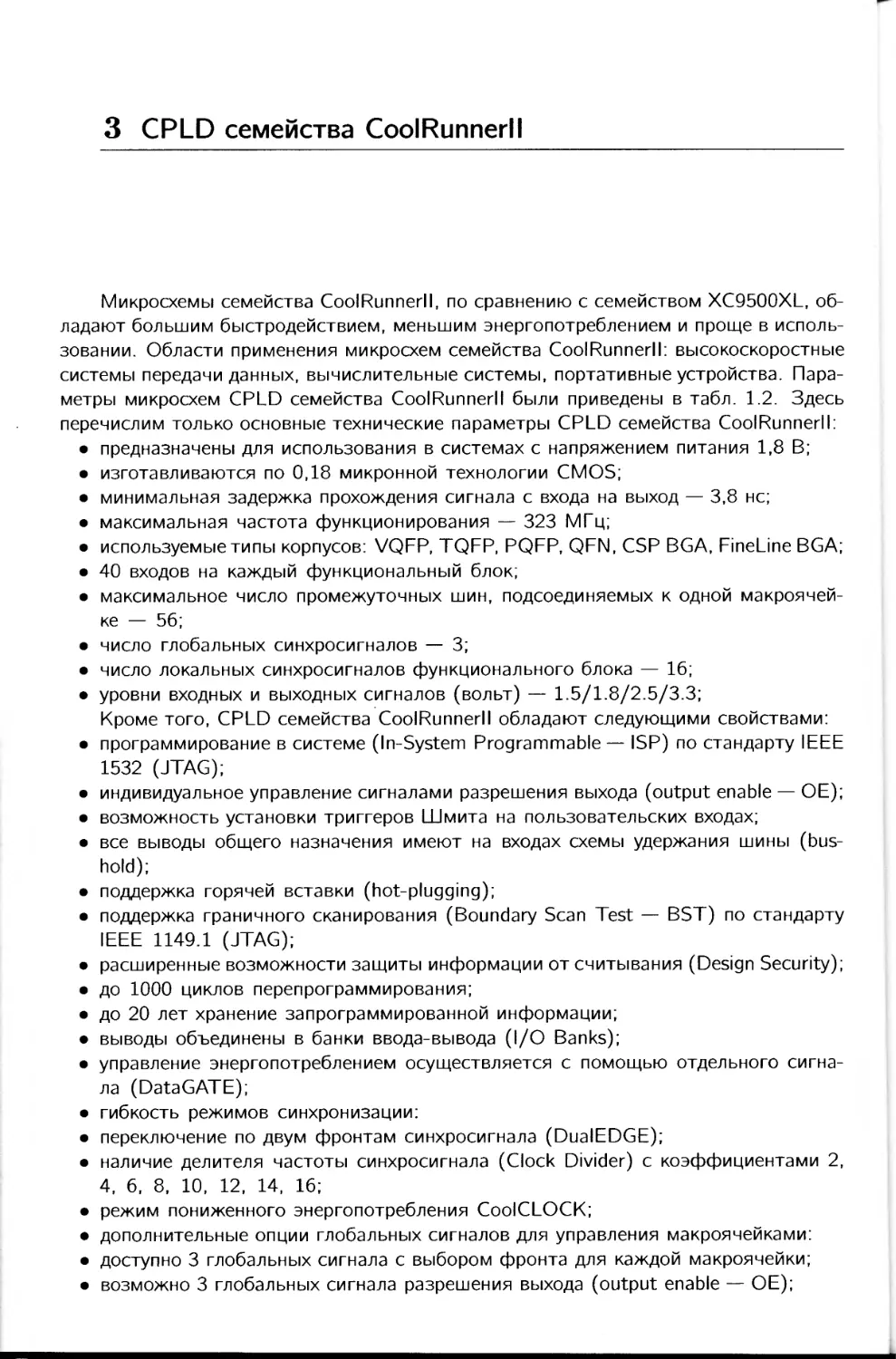

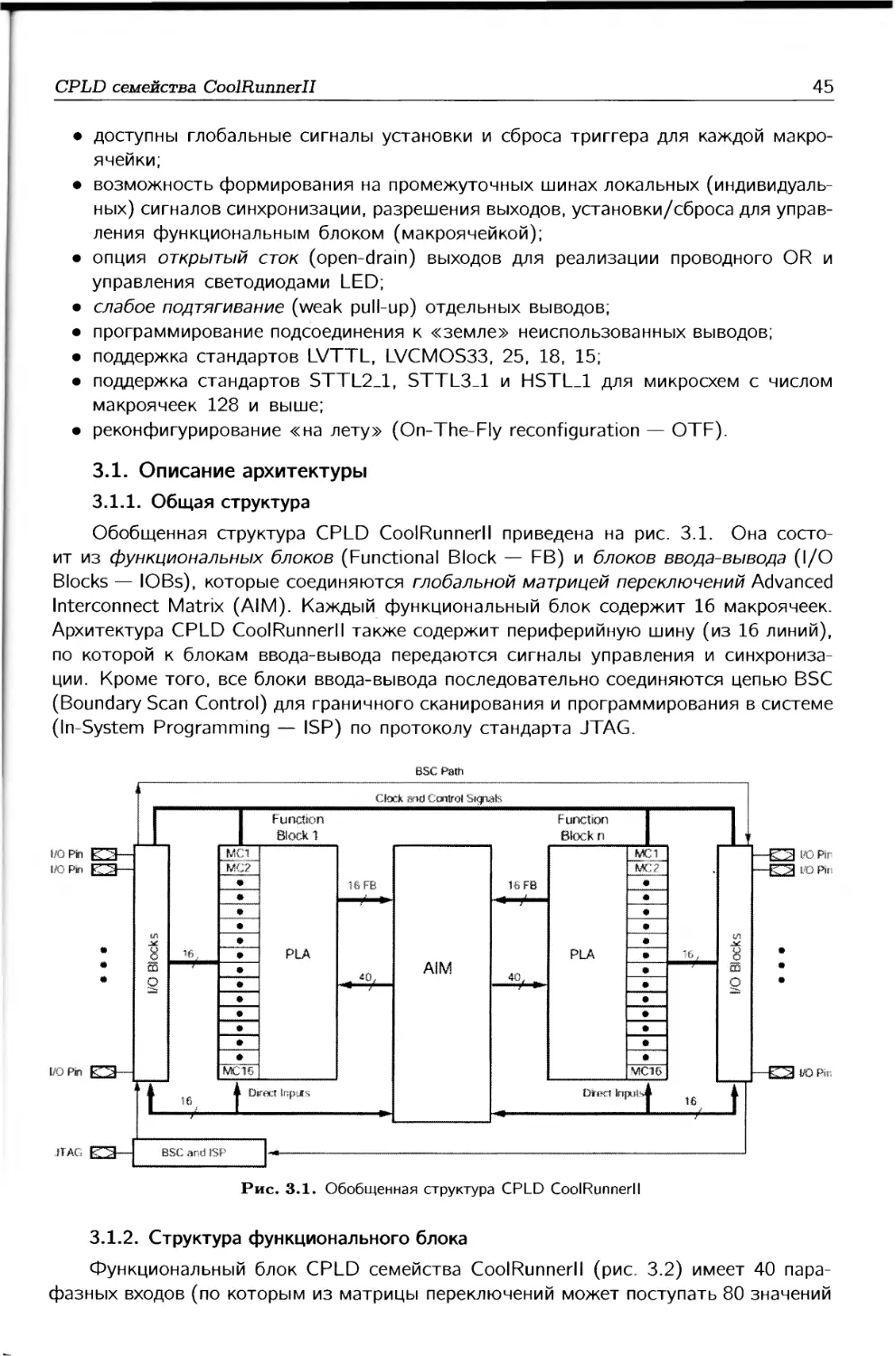

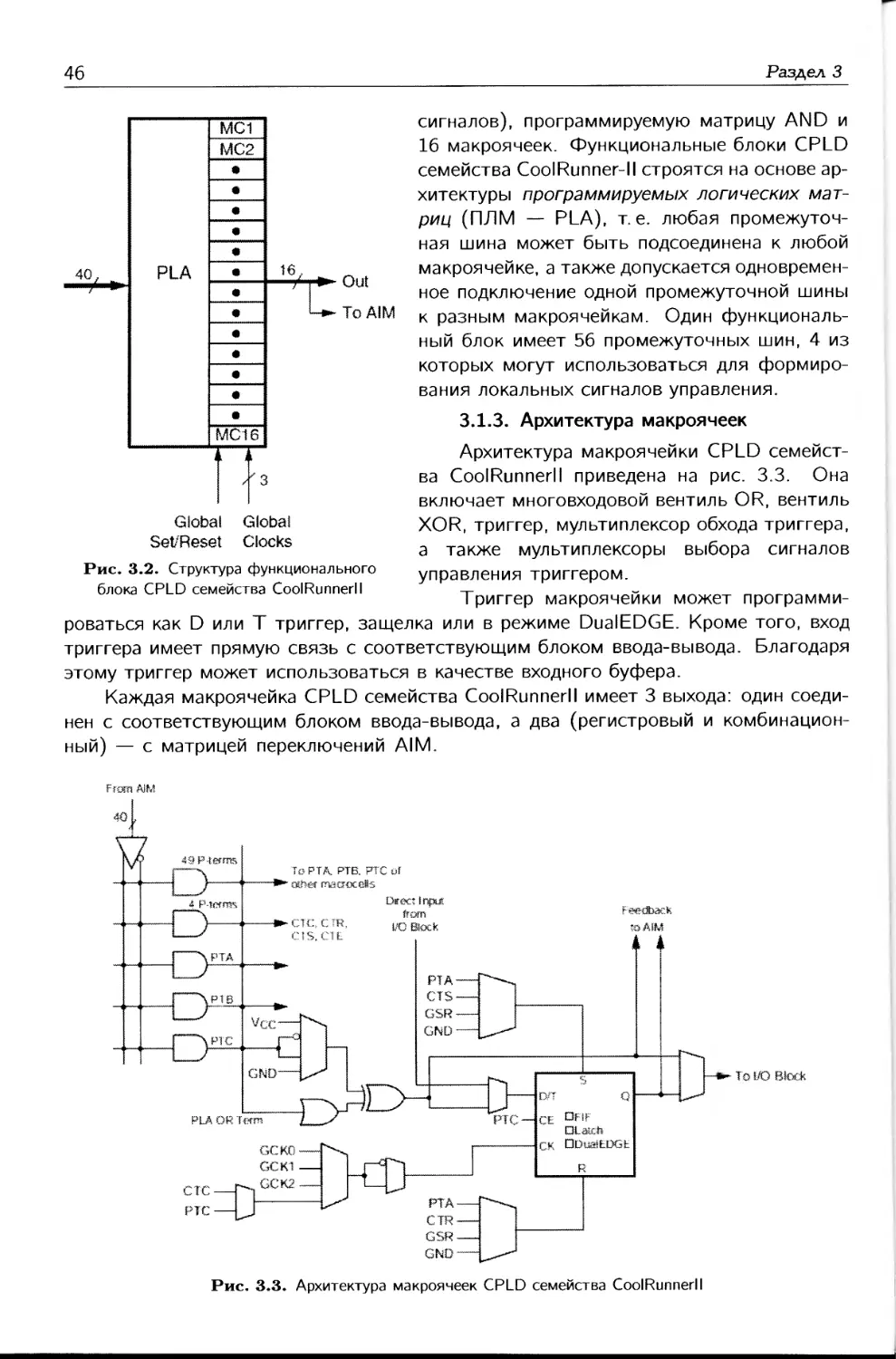

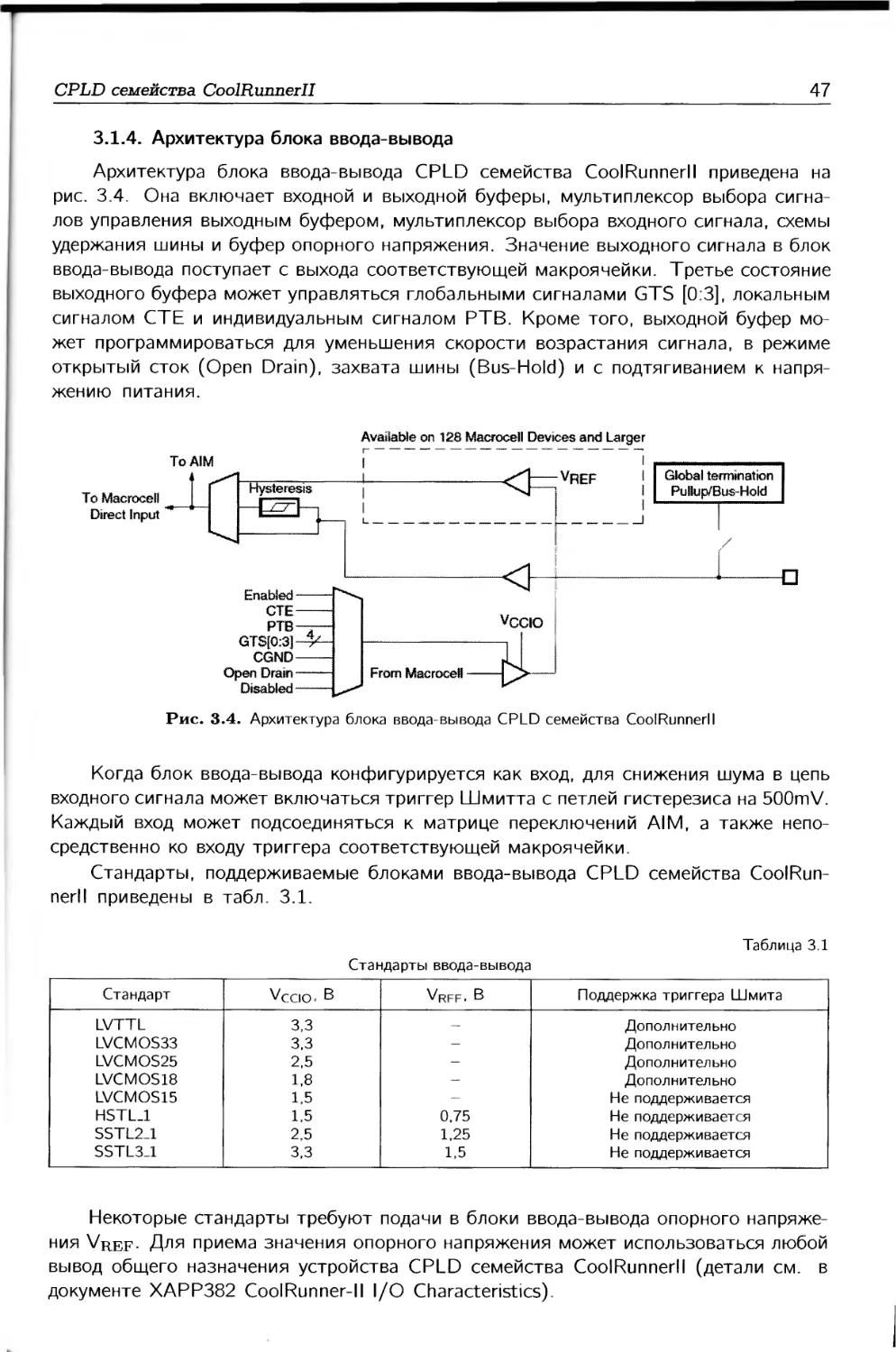

Микросхемы семейства CoolRunnerll, по сравнению с семейством XC9500XL, об-

ладают большим быстродействием, меньшим энергопотреблением и проще в исполь-

зовании. Области применения микросхем семейства CoolRunnerll: высокоскоростные

системы передачи данных, вычислительные системы, портативные устройства.

Параметры CPLD семейства CoolRunnerll представлены в табл. 1.2.

1.2.3. FPGA фирмы Xilinx

Несмотря на ряд положительных качеств CPLD, производимых фирмой Xilinx,

все-таки наибольшую популярность, мировое признание и 30...40 % мирового объема

программируемой логики фирме Xilinx приносят ее FPGA. В свое время фирма Xilinx в

больших объемах производила такие семейства FPGA, как ХС2000, ХС3000, ХС4000,

Spartan-Il, Spartan-3, Virtex-4, -5, -6. До недавнего времени верхом совершенства

считалась и до сих пор широко используется архитектура FPGA семейства Spartan-6.

Однако в 2012 году фирма Xilinx предложила новую линейку семейств FPGA 7-й

серии: Artix-7, Kintex-7 и Virtex-7. По утверждению фирмы Xilinx, в FPGA 7-й се-

рии воплотились все мировые достижения в области разработки архитектур FPGA,

причем не только фирмы Xilinx. Для сравнения возможностей микросхем из различ-

ных семейств в табл. 1.3 приведены максимальные значения основных параметров

микросхем FPGA 7-й серии и Spartan-б из предыдущего поколения ПЛИС.

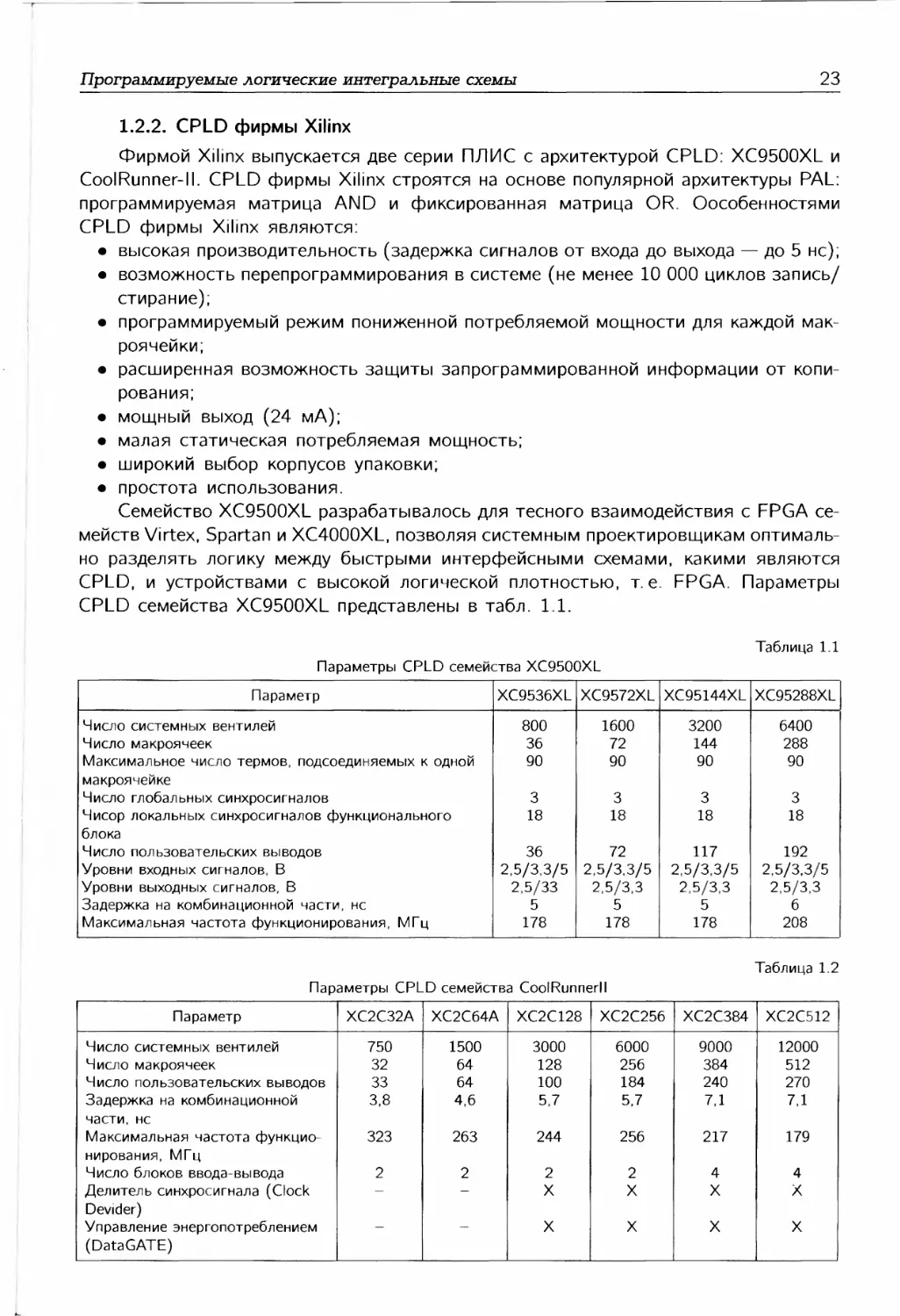

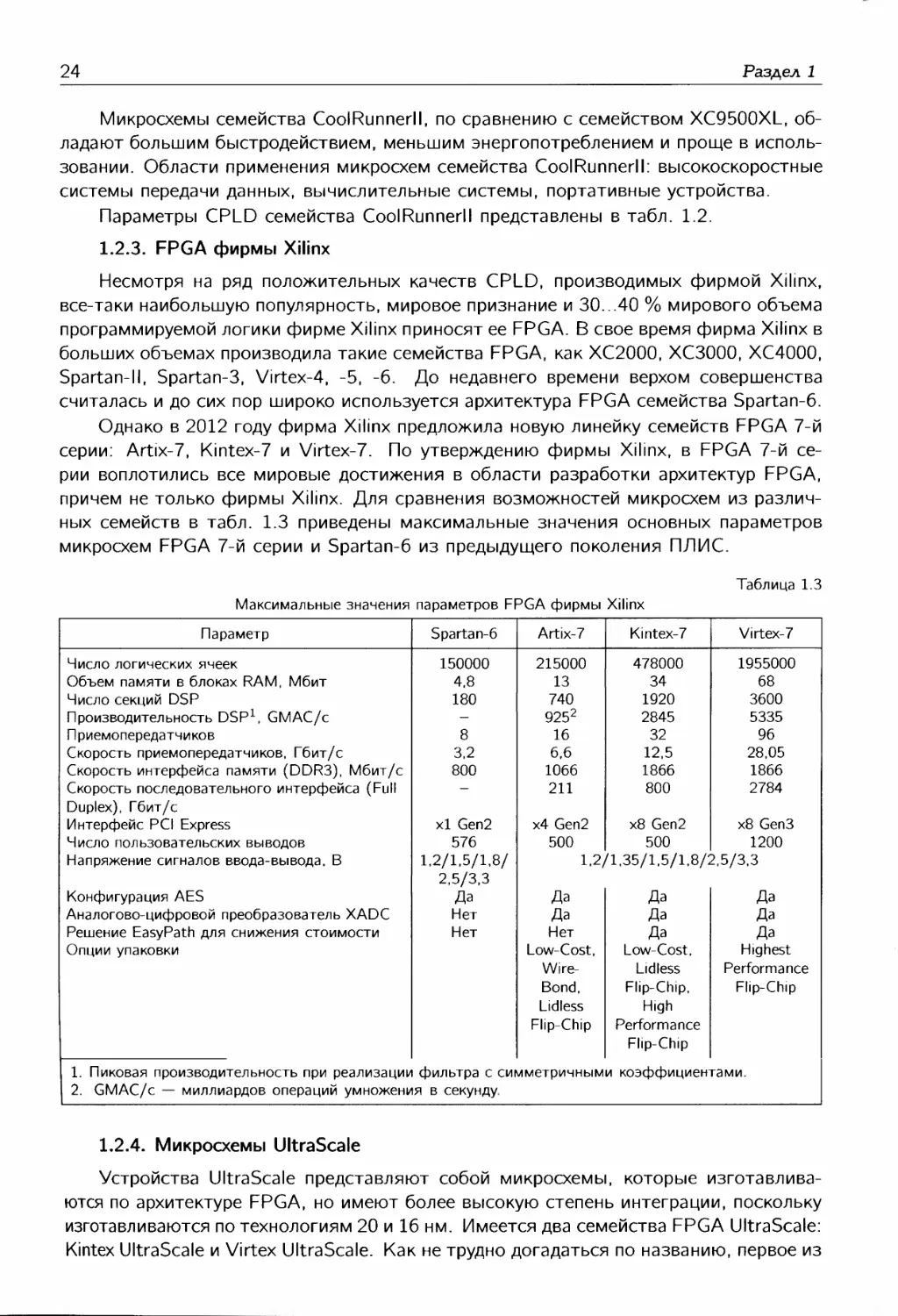

Таблица 1.3

Максимальные значения параметров FPGA фирмы Xilinx

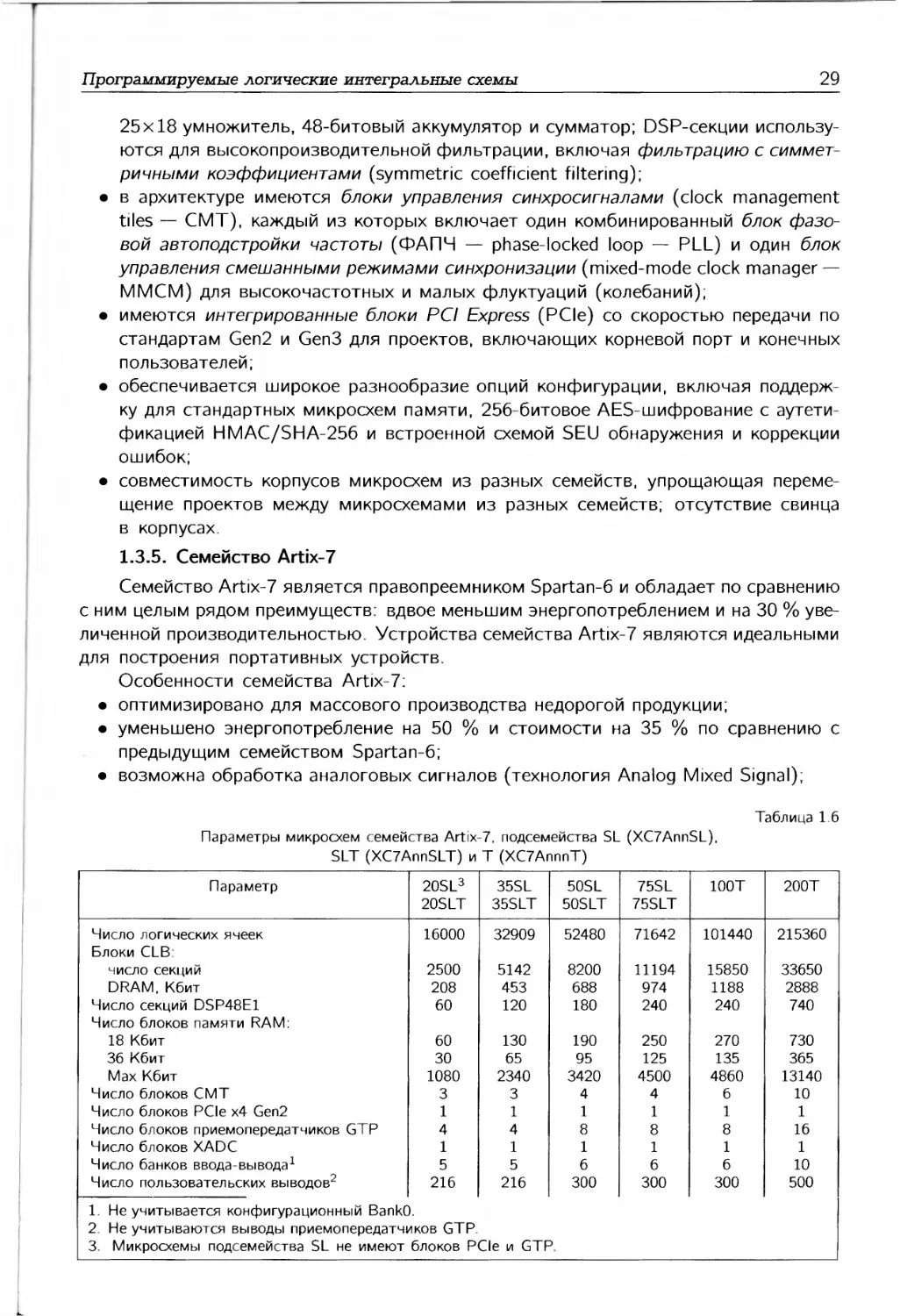

Параметр Spartan-6 Artix-7 Kintex-7 Virtex-7

Число логических ячеек Объем памяти в блоках RAM, Мбит Число секций DSP Производительность DSP1, GMAC/c Приемопередатчиков Скорость приемопередатчиков, Гбит/с Скорость интерфейса памяти (DDR3), Мбит/с Скорость последовательного интерфейса (Full Duplex), Гбит/с Интерфейс PCI Express Число пользовательских выводов Напряжение сигналов ввода-вывода, В Конфигурация AES Аналогово-цифровой преобразователь XADC Решение EasyPath для снижения стоимости Опции упаковки 1. Пиковая производительность при реализации 2. GMAC/c — миллиардов операций умножени 150000 4,8 180 8 3,2 800 xl Gen2 576 1,2/1,5/1,8/ 2,5/3,3 Да Нет Нет фильтра с сиг я в секунду. 215000 13 740 9252 16 6,6 1066 211 х4 Gen 2 500 1.2/ Да Да Нет Low-Cost, Wire- Bond, Lidless Flip-Chip иметричным 478000 34 1920 2845 32 12,5 1866 800 x8 Gen 2 500 '1,35/1,5/1,8/; Да Да Да Low-Cost, Lidless Flip-Chip, High Performance Flip-Chip и коэффициен 1955000 68 3600 5335 96 28,05 1866 2784 x8 Gen3 1200 >.5/3,3 Да Да Да Highest Performance Flip-Chip гами.

1.2.4. Микросхемы UltraScale

Устройства UltraScale представляют собой микросхемы, которые изготавлива-

ются по архитектуре FPGA, но имеют более высокую степень интеграции, поскольку

изготавливаются по технологиям 20 и 16 нм. Имеется два семейства FPGA UltraScale:

Kintex UltraScale и Virtex UltraScale. Как не трудно догадаться по названию, первое из

Программируемые логические интегральные схемы

25

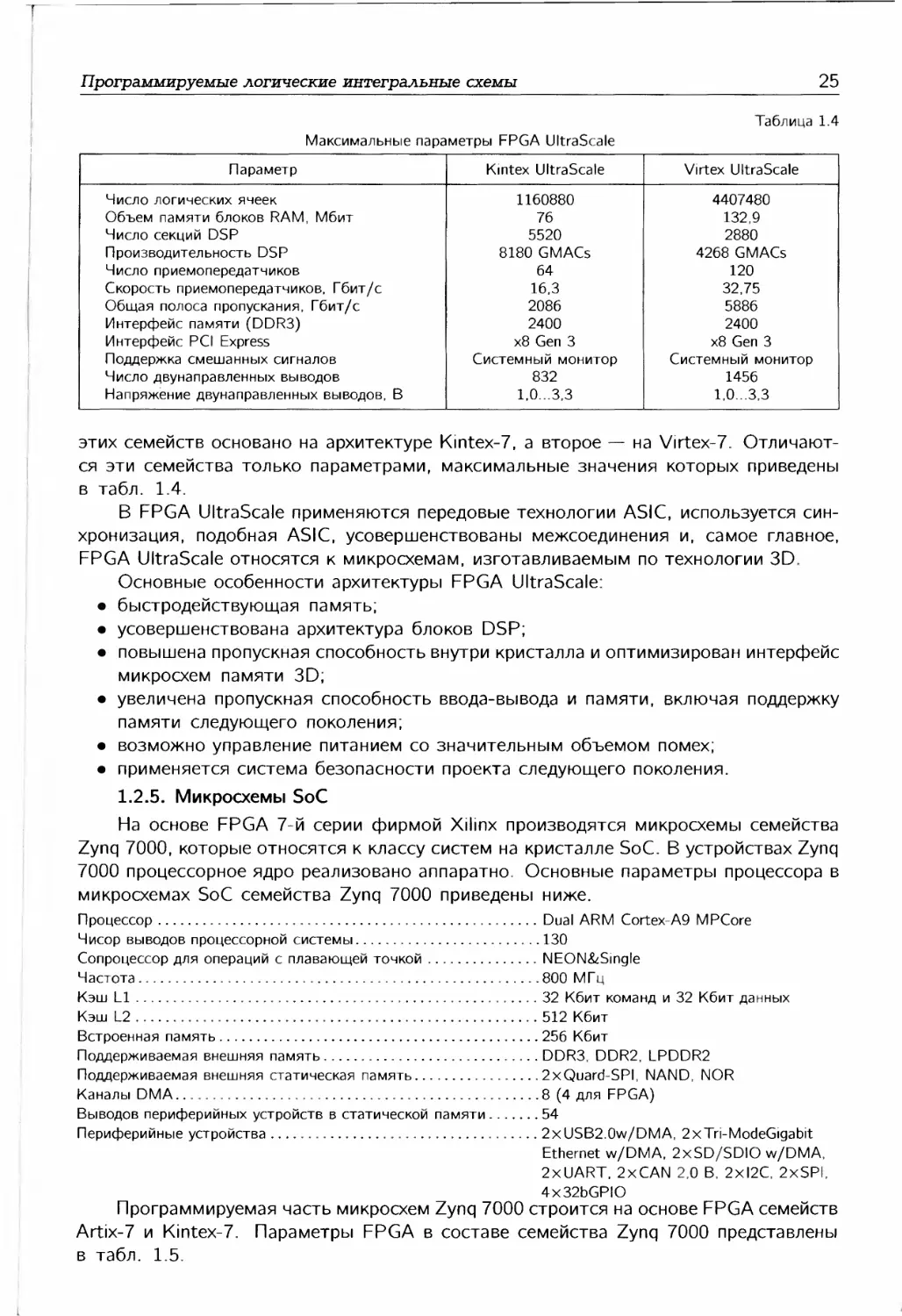

Таблица 1.4

Максимальные параметры FPGA UltraScale

Параметр Kintex UltraScale Virtex UltraScale

Число логических ячеек Объем памяти блоков RAM, Мбит Число секций DSP Производительность DSP Число приемопередатчиков Скорость приемопередатчиков, Гбит/с Общая полоса пропускания, Гбит/с Интерфейс памяти (DDR3) Интерфейс PCI Express Поддержка смешанных сигналов Число двунаправленных выводов Напряжение двунаправленных выводов, В 1160880 76 5520 8180 GMACs 64 16,3 2086 2400 х8 Gen 3 Системный монитор 832 1,0...3,3 4407480 132,9 2880 4268 GMACs 120 32,75 5886 2400 x8 Gen 3 Системный монитор 1456 1,0...3,3

этих семейств основано на архитектуре Kintex-7, а второе — на Virtex-7. Отличают-

ся эти семейства только параметрами, максимальные значения которых приведены

в табл. 1.4.

В FPGA UltraScale применяются передовые технологии ASIC, используется син-

хронизация, подобная ASIC, усовершенствованы межсоединения и, самое главное,

FPGA UltraScale относятся к микросхемам, изготавливаемым по технологии 3D.

Основные особенности архитектуры FPGA UltraScale:

• быстродействующая память;

• усовершенствована архитектура блоков DSP;

• повышена пропускная способность внутри кристалла и оптимизирован интерфейс

микросхем памяти 3D;

• увеличена пропускная способность ввода-вывода и памяти, включая поддержку

памяти следующего поколения;

• возможно управление питанием со значительным объемом помех;

• применяется система безопасности проекта следующего поколения.

1.2.5. Микросхемы SoC

На основе FPGA 7-й серии фирмой Xilinx производятся микросхемы семейства

Zynq 7000, которые относятся к классу систем на кристалле SoC. В устройствах Zynq

7000 процессорное ядро реализовано аппаратно. Основные параметры процессора в

микросхемах SoC семейства Zynq 7000 приведены ниже.

Процессор...............................................

Чисор выводов процессорной системы......................

Сопроцессор для операций с плавающей точкой.............

Частота.................................................

Кэш L1..................................................

Кэш L2..................................................

Dual ARM Cortex-A9 MPCore

130

NEON&Single

800 МГц

32 Кбит команд и 32 Кбит данных

512 Кбит

Встроенная память.....................................

Поддерживаемая внешняя память.........................

Поддерживаемая внешняя статическая память.............

Каналы DMA............................................

Выводов периферийных устройств в статической памяти..

Периферийные устройства..............................

256 Кбит

DDR3, DDR2, LPDDR2

2xQuard-SPI, NAND, NOR

8 (4 для FPGA)

54

2xUSB2.0w/DMA, 2xTri-ModeGigabit

Ethernet w/DMA, 2xSD/SDIO w/DMA,

2xUART, 2xCAN 2,0 B, 2xl2C, 2xSPI,

4x32bGPIO

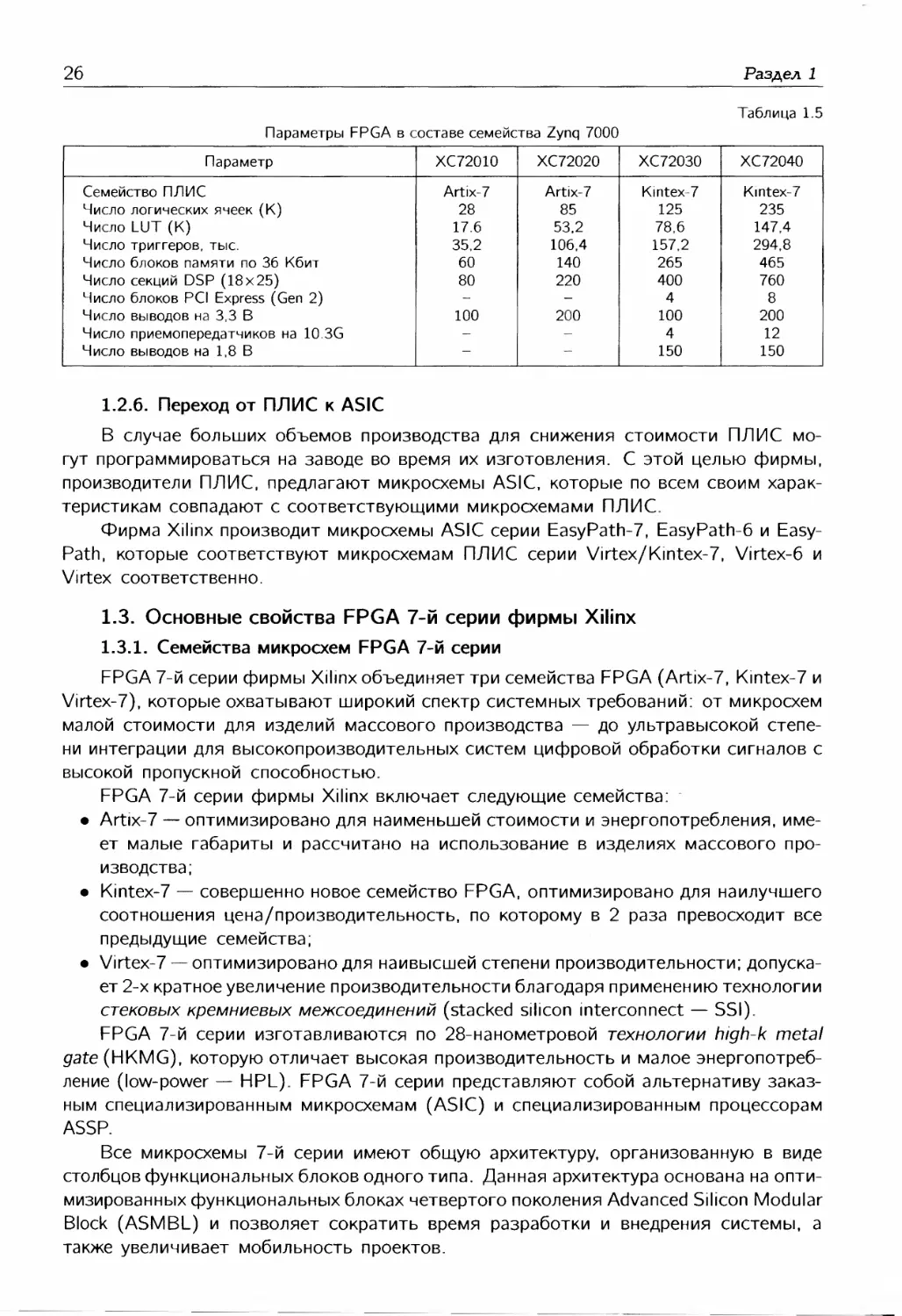

Программируемая часть микросхем Zynq 7000 строится на основе FPGA семейств

Artix-7 и Kintex-7. Параметры FPGA в составе семейства Zynq 7000 представлены

в табл. 1.5.

1

26

Раздел 1

Таблица 1.5

Параметры FPGA в составе семейства Zynq 7000

Параметр XC72010 ХС72020 ХС72030 ХС72040

Семейство ПЛИС Artix-7 Artix-7 Kintex-7 Kintex-7

Число логических ячеек (К) 28 85 125 235

Число LUT (К) 17.6 53,2 78,6 147,4

Число триггеров, тыс. 35,2 106,4 157,2 294,8

Число блоков памяти по 36 Кбит 60 140 265 465

Число секций DSP (18x25) 80 220 400 760

Число блоков PCI Express (Gen 2) — — 4 8

Число выводов на 3,3 В 100 200 100 200

Число приемопередатчиков на 10.3G — — 4 12

Число выводов на 1,8 В — — 150 150

1.2.6. Переход от ПЛИС к ASIC

В случае больших объемов производства для снижения стоимости ПЛИС мо-

гут программироваться на заводе во время их изготовления. С этой целью фирмы,

производители ПЛИС, предлагают микросхемы ASIC, которые по всем своим харак-

теристикам совпадают с соответствующими микросхемами ПЛИС.

Фирма Xilinx производит микросхемы ASIC серии EasyPath-7, EasyPath-6 и Easy-

Path, которые соответствуют микросхемам ПЛИС серии Virtex/Kintex-7, Virtex-6 и

Virtex соответственно.

1.3. Основные свойства FPGA 7-й серии фирмы Xilinx

1.3.1. Семейства микросхем FPGA 7-й серии

FPGA 7-й серии фирмы Xilinx объединяет три семейства FPGA (Artix-7, Kintex-7 и

Virtex-7), которые охватывают широкий спектр системных требований: от микросхем

малой стоимости для изделий массового производства — до ультравысокой степе-

ни интеграции для высокопроизводительных систем цифровой обработки сигналов с

высокой пропускной способностью.

FPGA 7-й серии фирмы Xilinx включает следующие семейства:

• Artix-7 — оптимизировано для наименьшей стоимости и энергопотребления, име-

ет малые габариты и рассчитано на использование в изделиях массового про-

изводства;

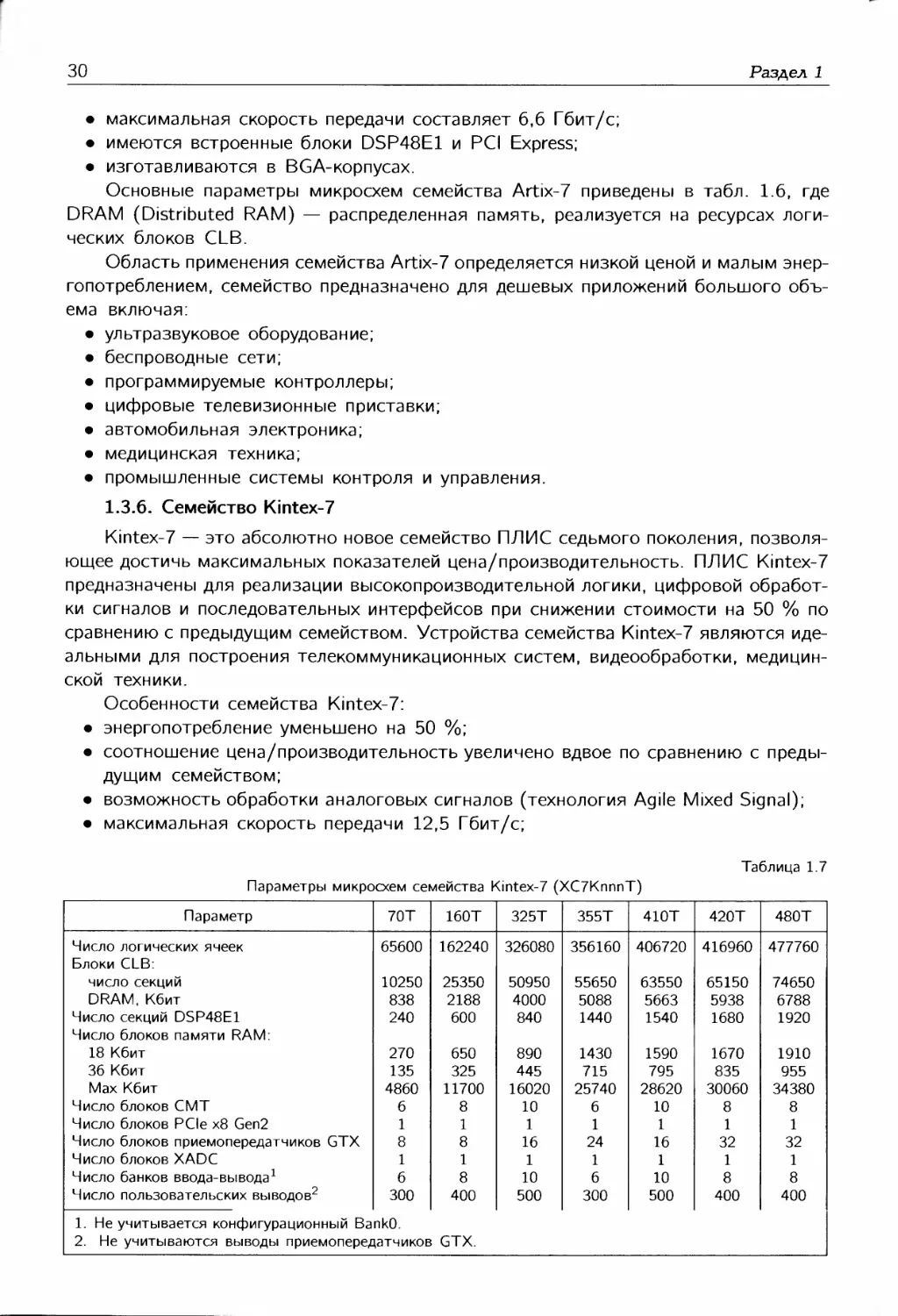

• Kintex-7 — совершенно новое семейство FPGA, оптимизировано для наилучшего

соотношения цена/производительность, по которому в 2 раза превосходит все

предыдущие семейства;

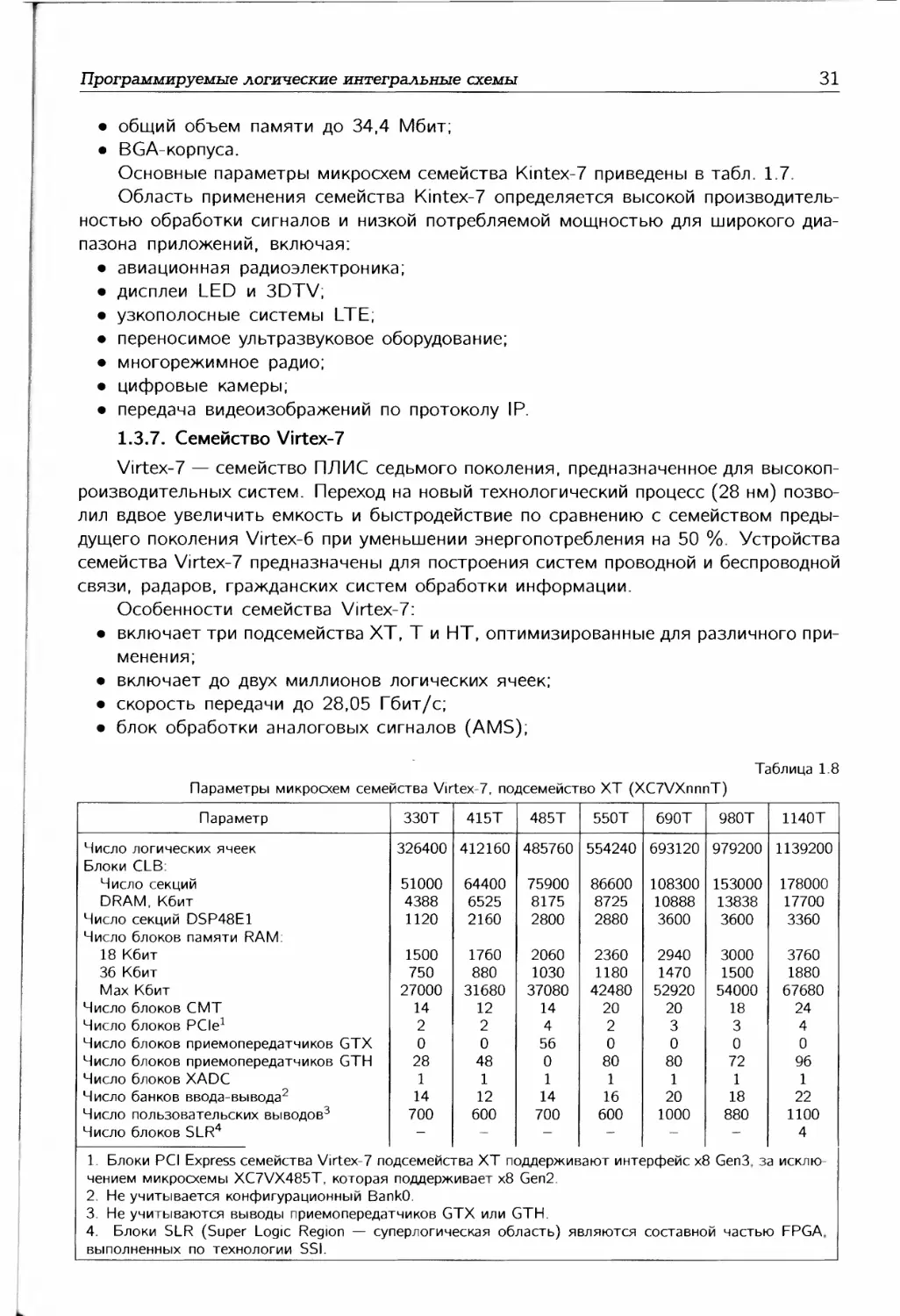

• Virtex-7 — оптимизировано для наивысшей степени производительности; допуска-

ет 2-х кратное увеличение производительности благодаря применению технологии

стековых кремниевых межсоединений (stacked silicon interconnect — SSI).

FPGA 7-й серии изготавливаются по 28-нанометровой технологии high-k metal

gate (HKMG), которую отличает высокая производительность и малое энергопотреб-

ление (low-power — HPL). FPGA 7-й серии представляют собой альтернативу заказ-

ным специализированным микросхемам (ASIC) и специализированным процессорам

ASSP.

Все микросхемы 7-й серии имеют общую архитектуру, организованную в виде

столбцов функциональных блоков одного типа. Данная архитектура основана на опти-

мизированных функциональных блоках четвертого поколения Advanced Silicon Modular

Block (ASMBL) и позволяет сократить время разработки и внедрения системы, а

также увеличивает мобильность проектов.

Программируемые логические интегральные схемы

27

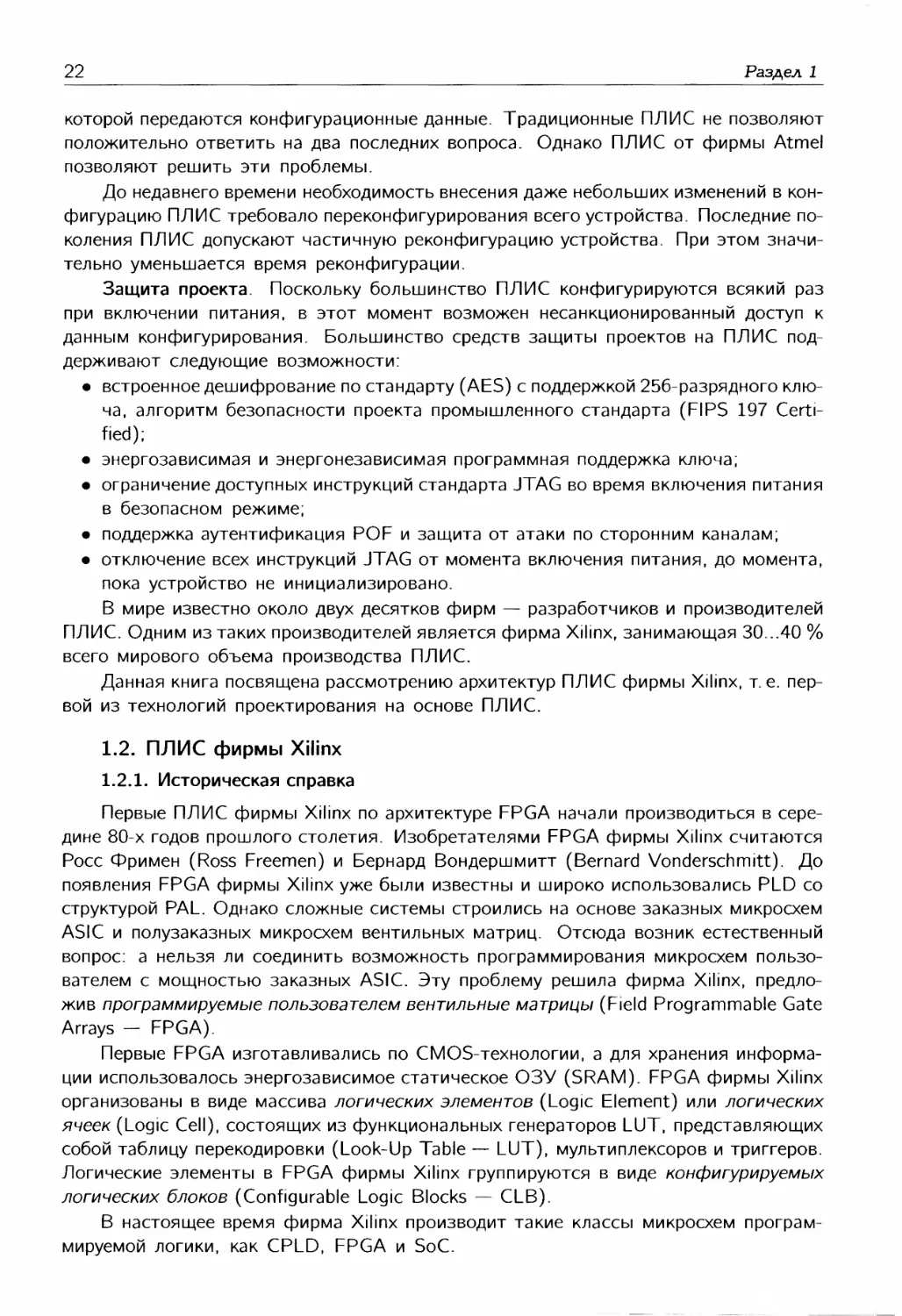

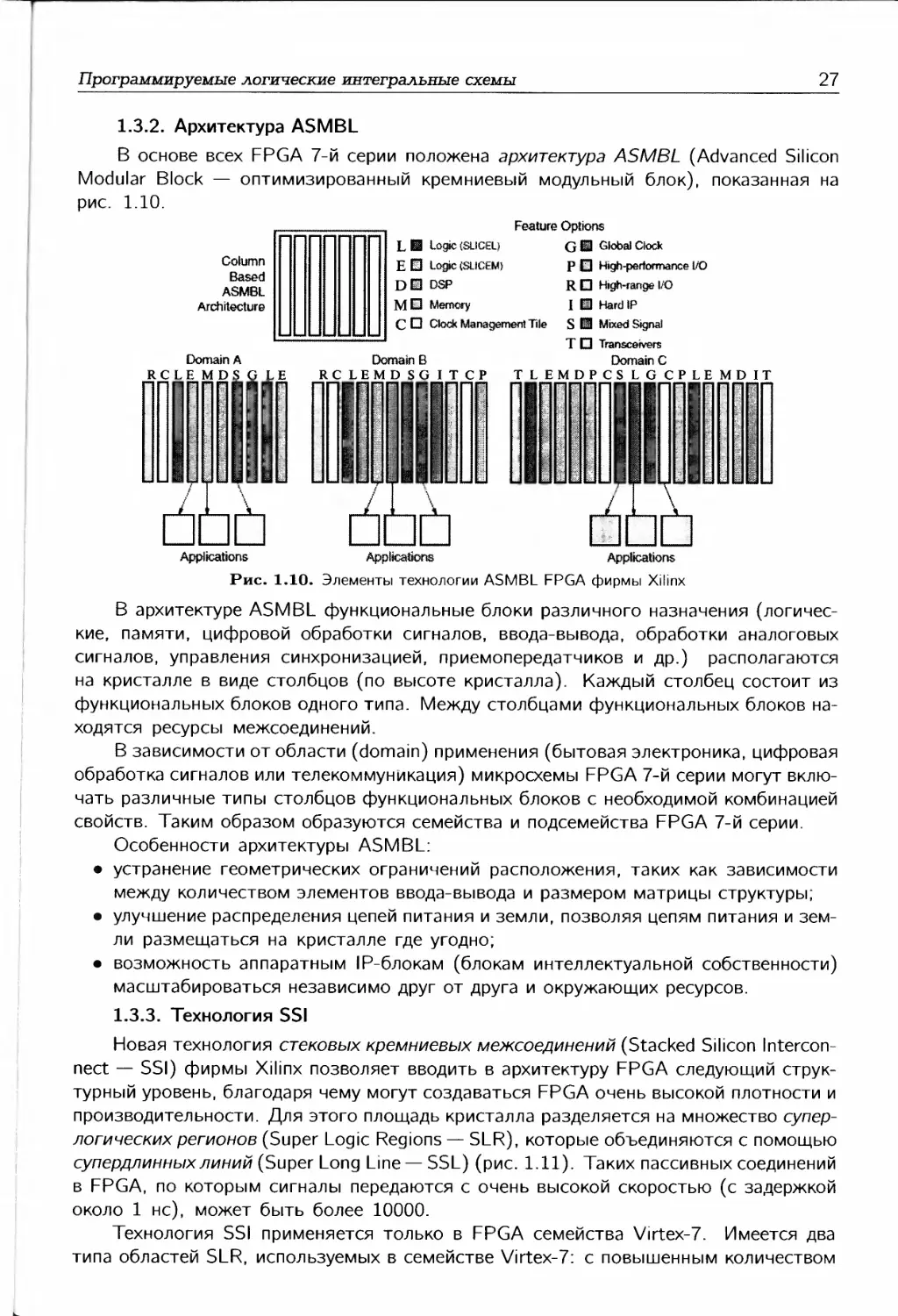

1.3.2. Архитектура ASMBL

В основе всех FPGA 7-й серии положена архитектура ASMBL (Advanced Silicon

Modular Block — оптимизированный кремниевый модульный блок), показанная на

рис. 1.10.

Feature Options

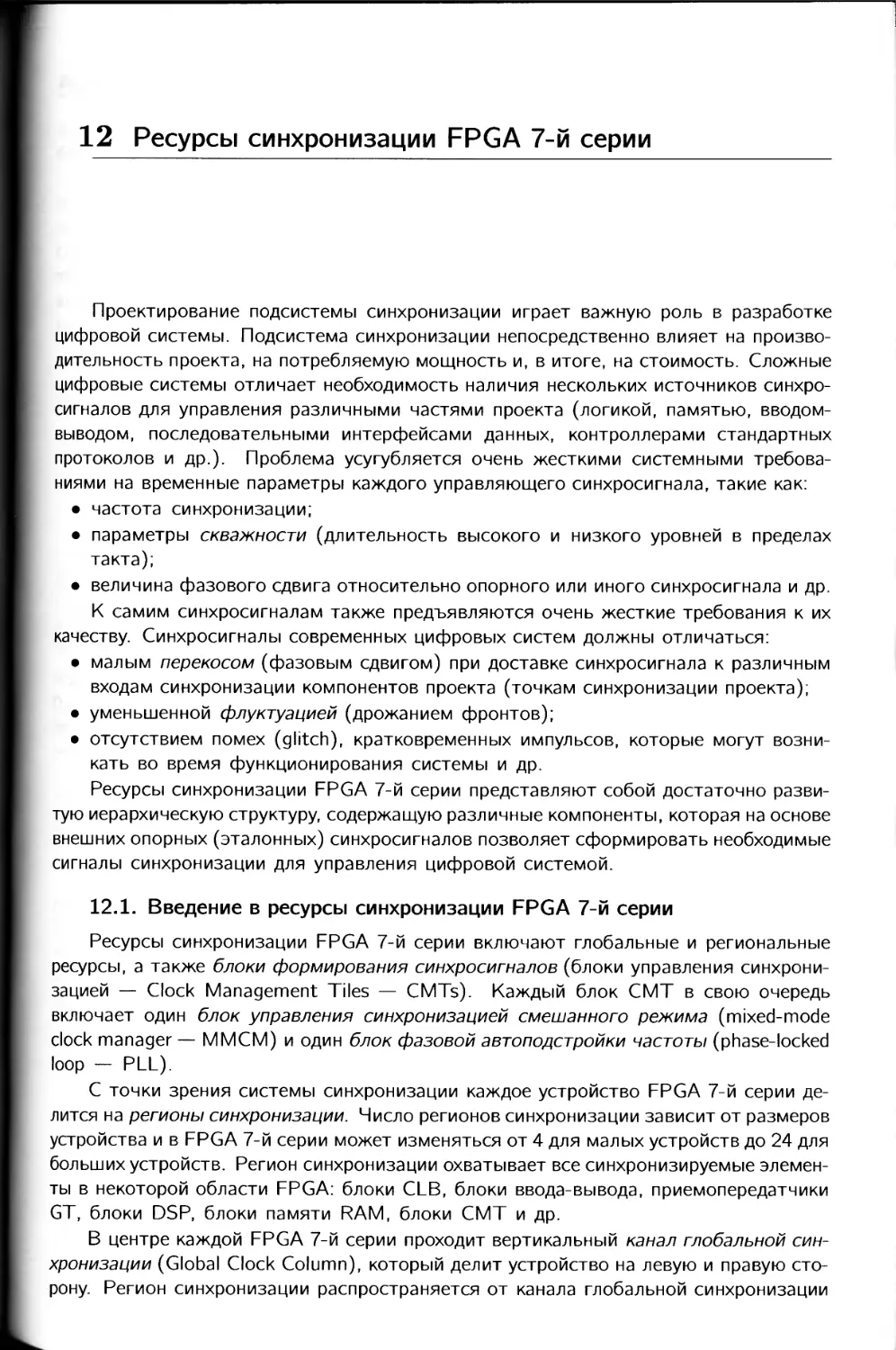

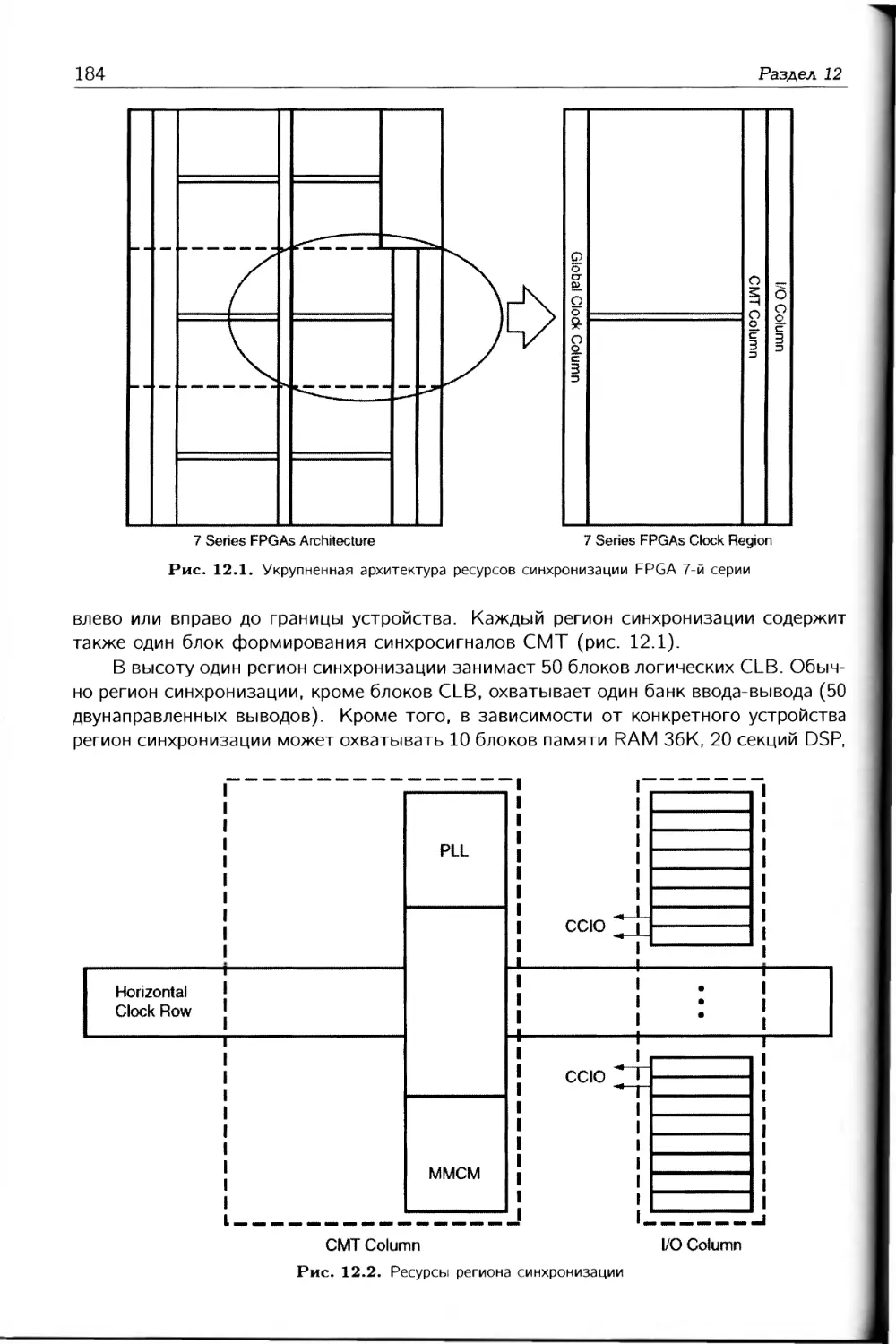

Column

Based

ASMBL

Architecture

GlU Global Clock

P О High-performance I/O

R О High-range I/O

I EO Hard IP

S HI Mixed Signal

TO Transceivers

L Ш Logic (sliced

E □ Logic (SLICEM)

D@ DSP

MO Memory

CO Clock Management Tile

Рис. 1.10. Элементы технологии ASMBL FPGA фирмы Xilinx

Applications

Domain C

Applications

В архитектуре ASMBL функциональные блоки различного назначения (логичес-

кие, памяти, цифровой обработки сигналов, ввода-вывода, обработки аналоговых

сигналов, управления синхронизацией, приемопередатчиков и др.) располагаются

на кристалле в виде столбцов (по высоте кристалла). Каждый столбец состоит из

функциональных блоков одного типа. Между столбцами функциональных блоков на-

ходятся ресурсы межсоединений.

В зависимости от области (domain) применения (бытовая электроника, цифровая

обработка сигналов или телекоммуникация) микросхемы FPGA 7-й серии могут вклю-

чать различные типы столбцов функциональных блоков с необходимой комбинацией

свойств. Таким образом образуются семейства и подсемейства FPGA 7-й серии.

Особенности архитектуры ASMBL:

• устранение геометрических ограничений расположения, таких как зависимости

между количеством элементов ввода-вывода и размером матрицы структуры;

• улучшение распределения цепей питания и земли, позволяя цепям питания и зем-

ли размещаться на кристалле где угодно;

• возможность аппаратным IP-блокам (блокам интеллектуальной собственности)

масштабироваться независимо друг от друга и окружающих ресурсов.

1.3.3. Технология SSI

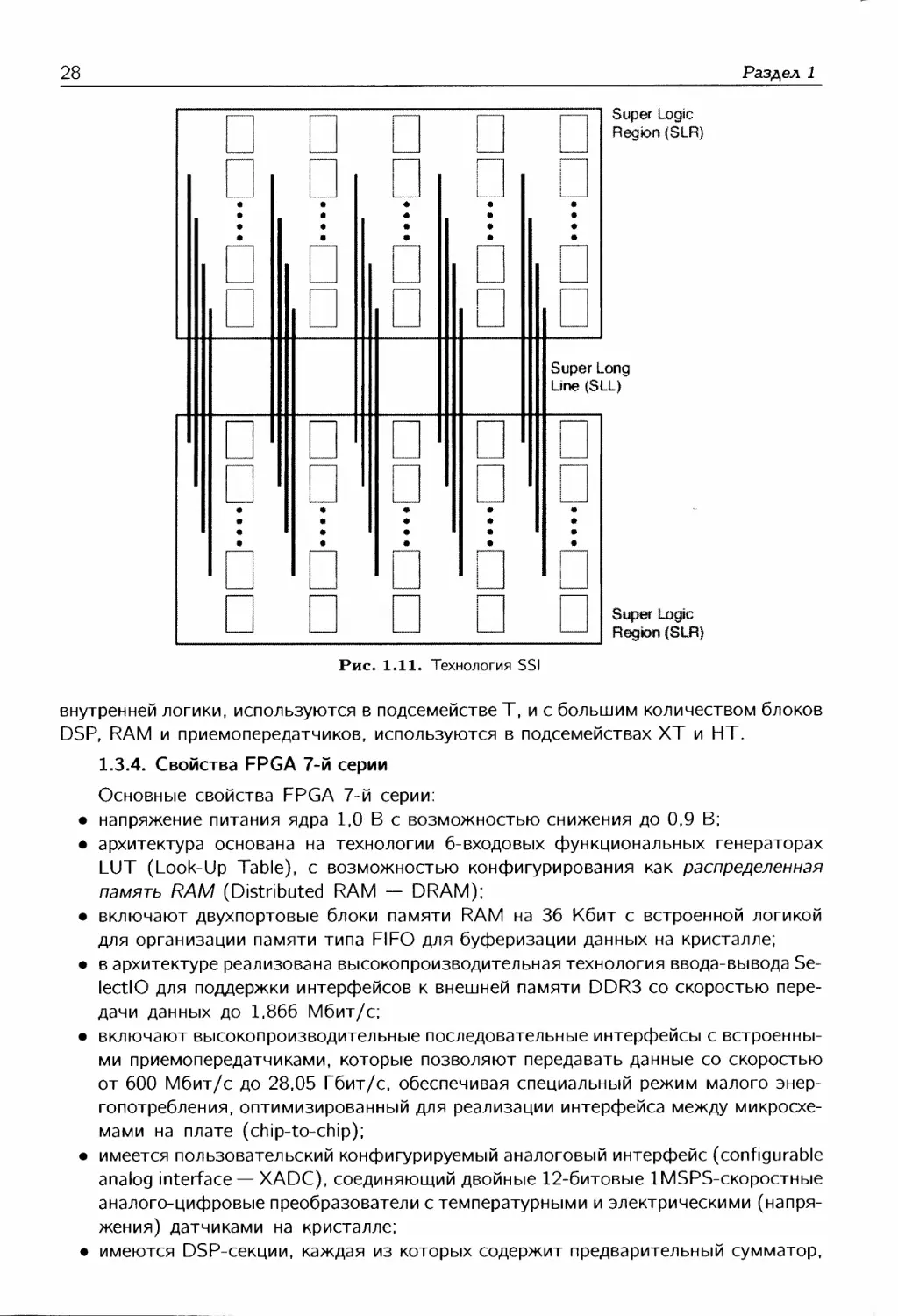

Новая технология стековых кремниевых межсоединений (Stacked Silicon Intercon-

nect — SSI) фирмы Xilinx позволяет вводить в архитектуру FPGA следующий струк-

турный уровень, благодаря чему могут создаваться FPGA очень высокой плотности и

производительности. Для этого площадь кристалла разделяется на множество супер-

логических регионов (Super Logic Regions — SLR), которые объединяются с помощью

супердлинных линий (Super Long Line — SSL) (рис. 1.11). Таких пассивных соединений

в FPGA, по которым сигналы передаются с очень высокой скоростью (с задержкой

около 1 нс), может быть более 10000.

Технология SSI применяется только в FPGA семейства Virtex-7. Имеется два

типа областей SLR, используемых в семействе Virtex-7: с повышенным количеством

28

Раздел 1

внутренней логики, используются в подсемействе Т, и с большим количеством блоков

DSP, RAM и приемопередатчиков, используются в подсемействах XT и НТ.

1.3.4. Свойства FPGA 7-й серии

Основные свойства FPGA 7-й серии:

• напряжение питания ядра 1,0 В с возможностью снижения до 0,9 В;

• архитектура основана на технологии 6-входовых функциональных генераторах

LUT (Look-Up Table), с возможностью конфигурирования как распределенная

память RAM (Distributed RAM — DRAM);

• включают двухпортовые блоки памяти RAM на 36 Кбит с встроенной логикой

для организации памяти типа FIFO для буферизации данных на кристалле;

• в архитектуре реализована высокопроизводительная технология ввода-вывода Se-

lectlO для поддержки интерфейсов к внешней памяти DDR3 со скоростью пере-

дачи данных до 1,866 Мбит/с;

• включают высокопроизводительные последовательные интерфейсы с встроенны-

ми приемопередатчиками, которые позволяют передавать данные со скоростью

от 600 Мбит/с до 28,05 Гбит/с, обеспечивая специальный режим малого энер-

гопотребления, оптимизированный для реализации интерфейса между микросхе-

мами на плате (chip-to-chip);

• имеется пользовательский конфигурируемый аналоговый интерфейс (configurable

analog interface — XADC), соединяющий двойные 12-битовые lMSPS-скоростные

аналого-цифровые преобразователи с температурными и электрическими (напря-

жения) датчиками на кристалле;

• имеются DSP-секции, каждая из которых содержит предварительный сумматор,

Программируемые логические интегральные схемы

29

25x18 умножитель, 48-битовый аккумулятор и сумматор; DSP-секции использу-

ются для высокопроизводительной фильтрации, включая фильтрацию с симмет-

ричными коэффициентами (symmetric coefficient filtering);

• в архитектуре имеются блоки управления синхросигналами (clock management

tiles — СМТ), каждый из которых включает один комбинированный блок фазо-

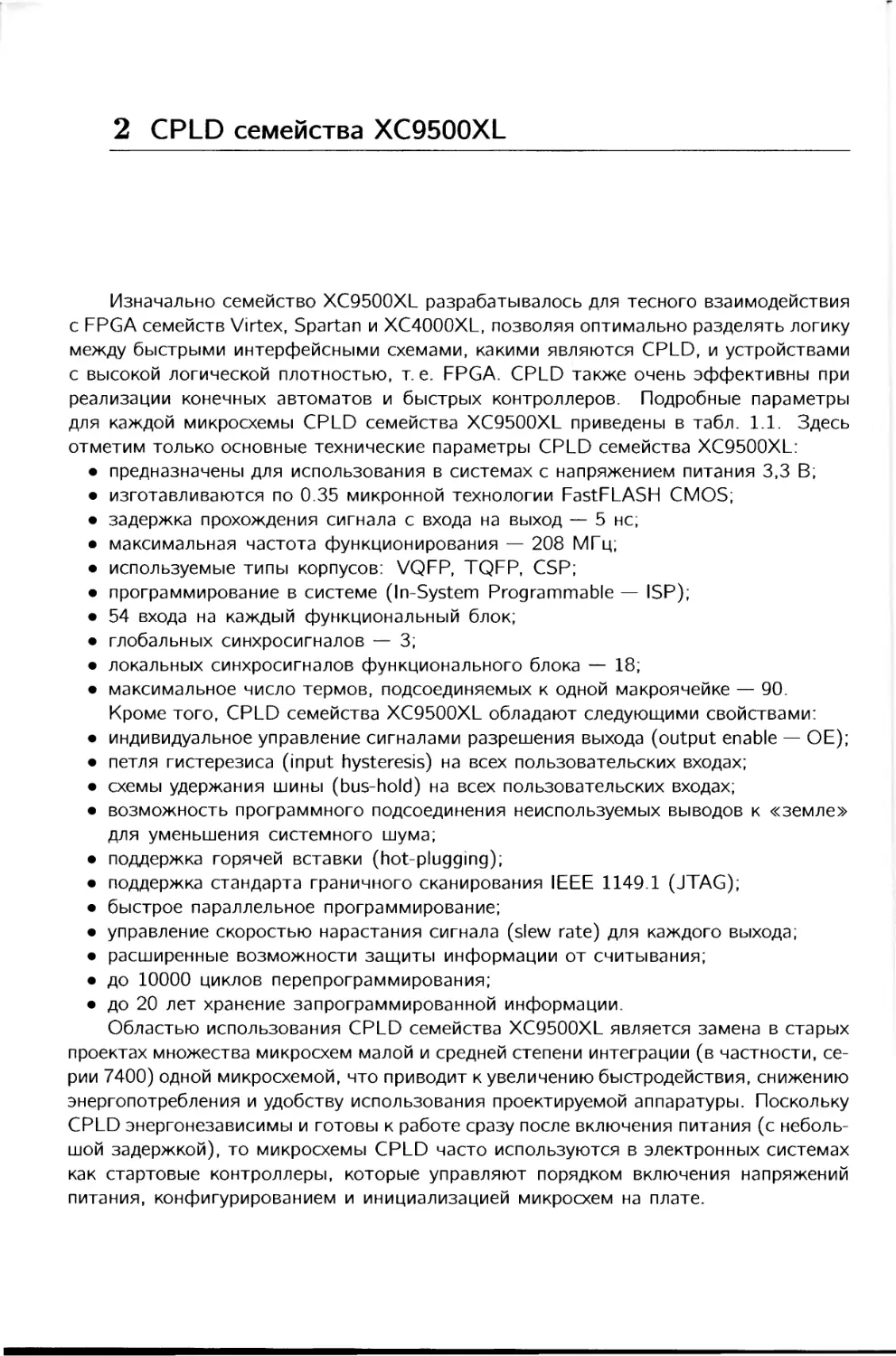

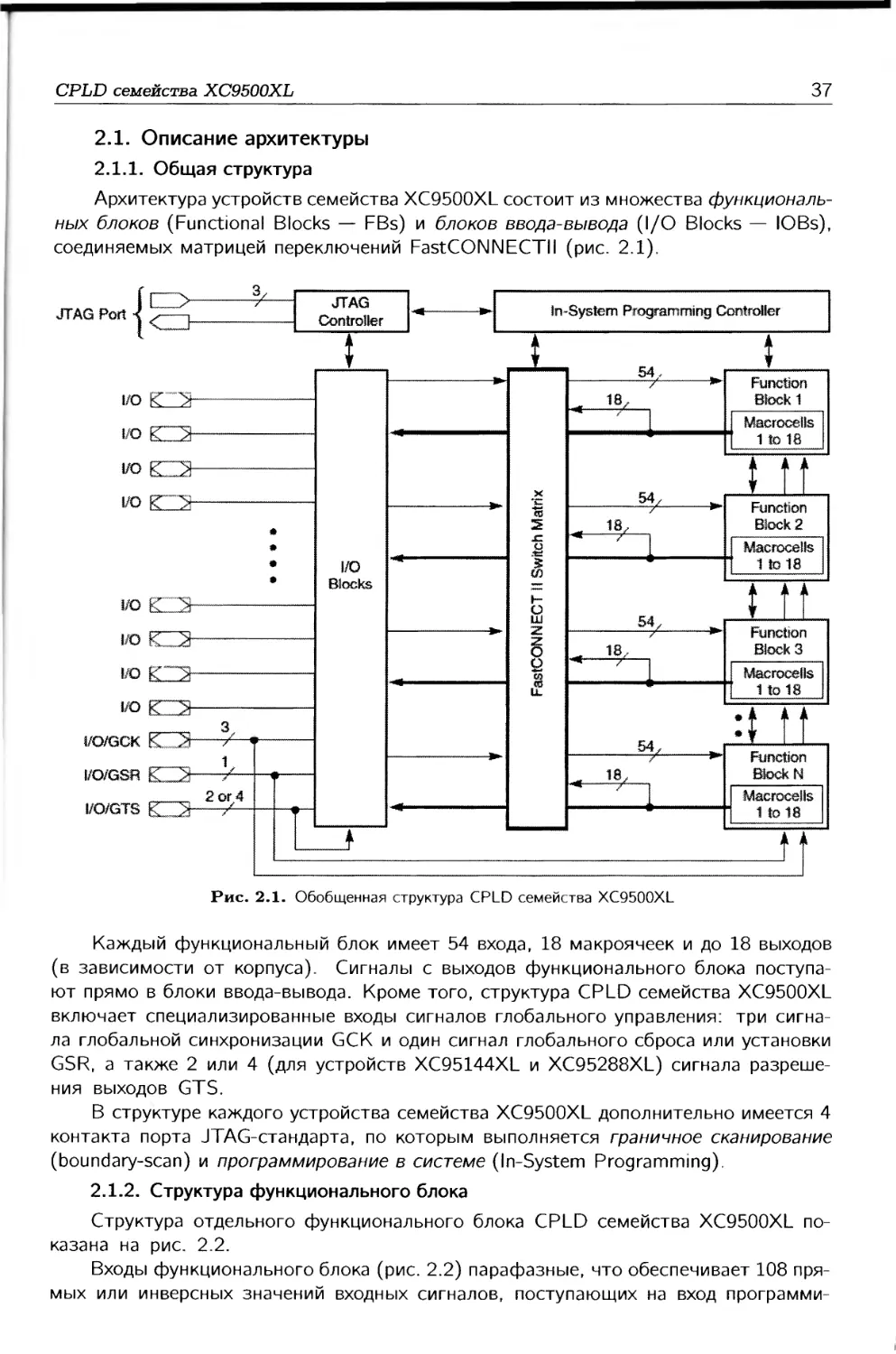

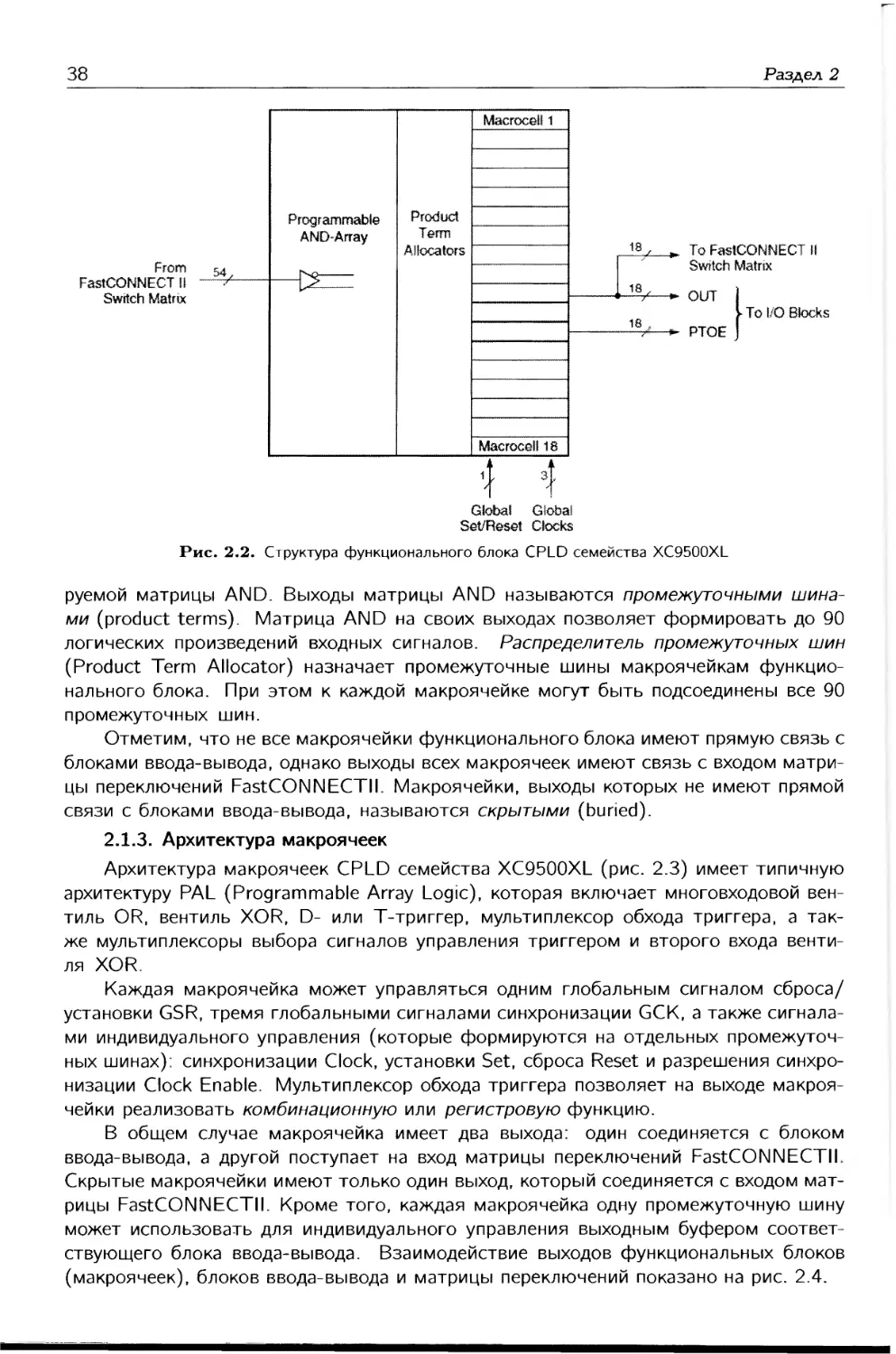

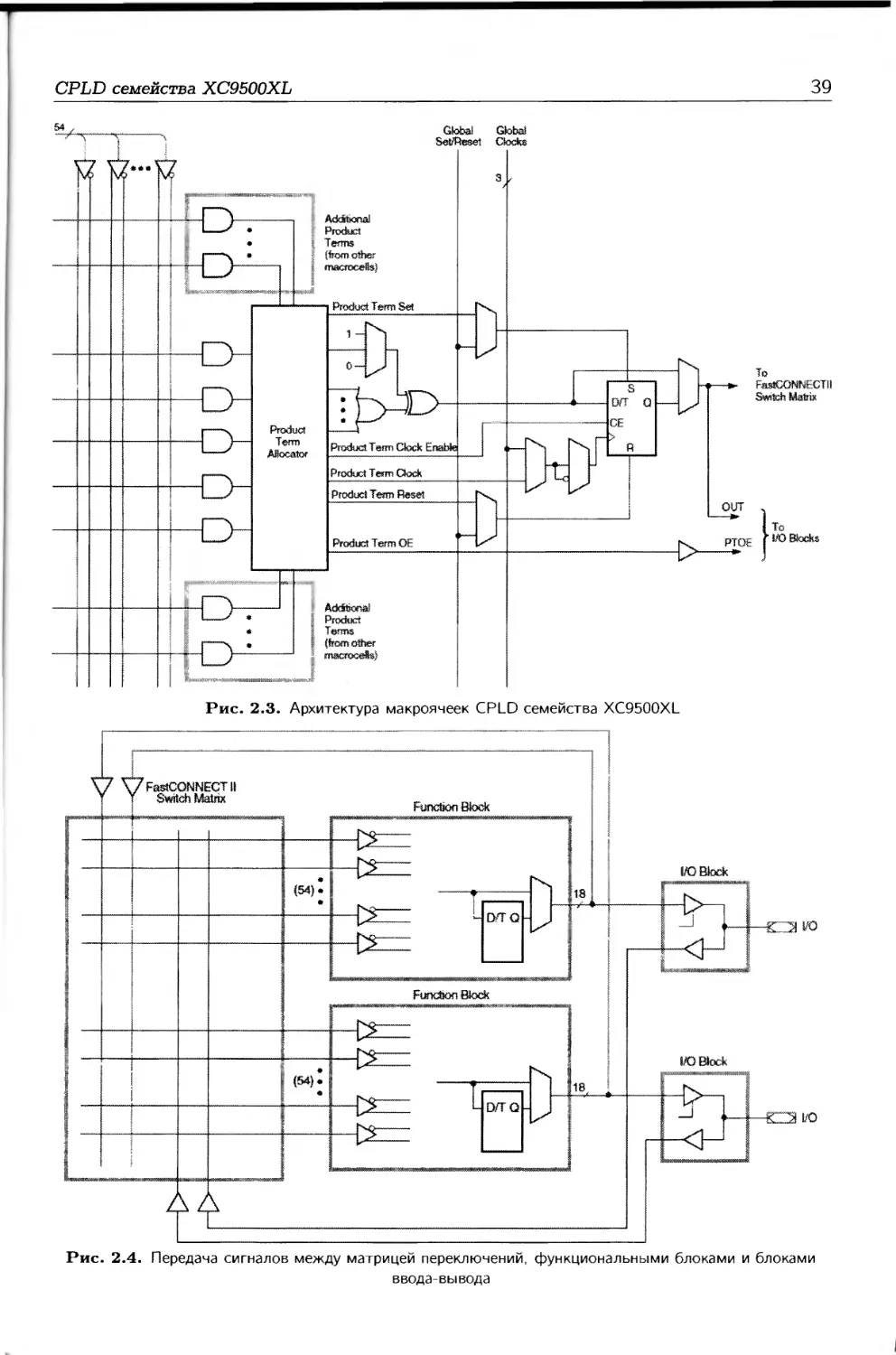

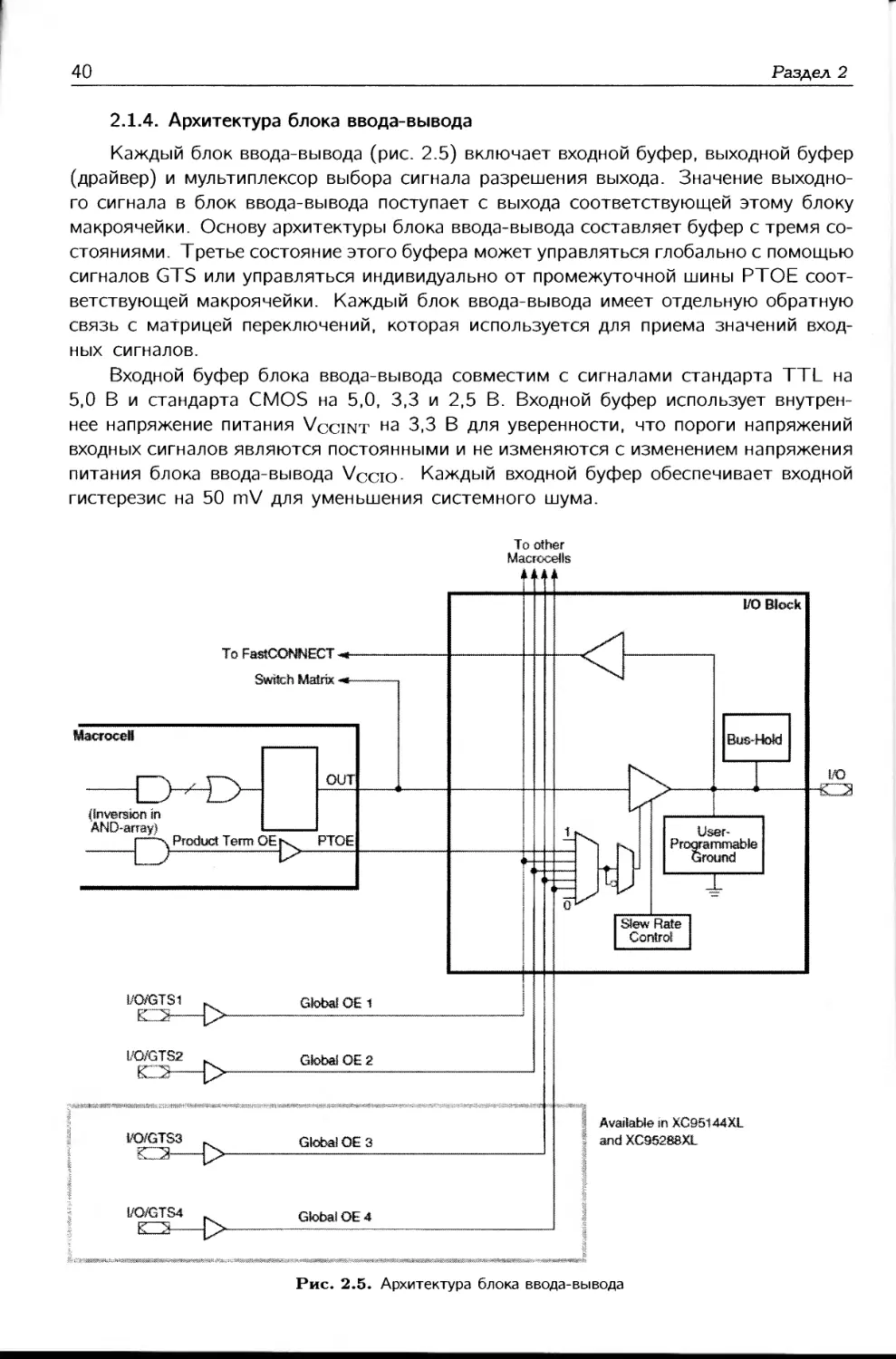

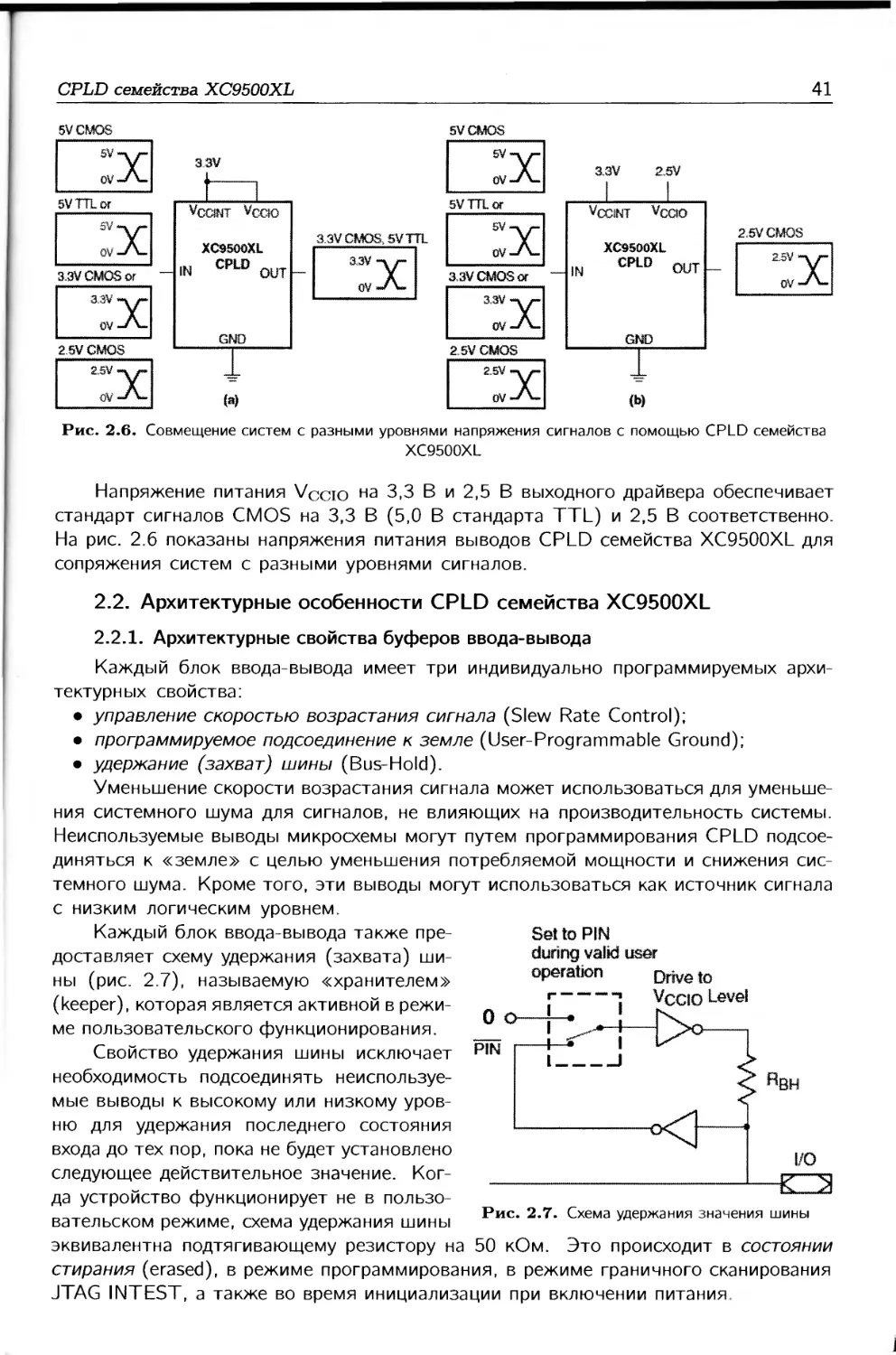

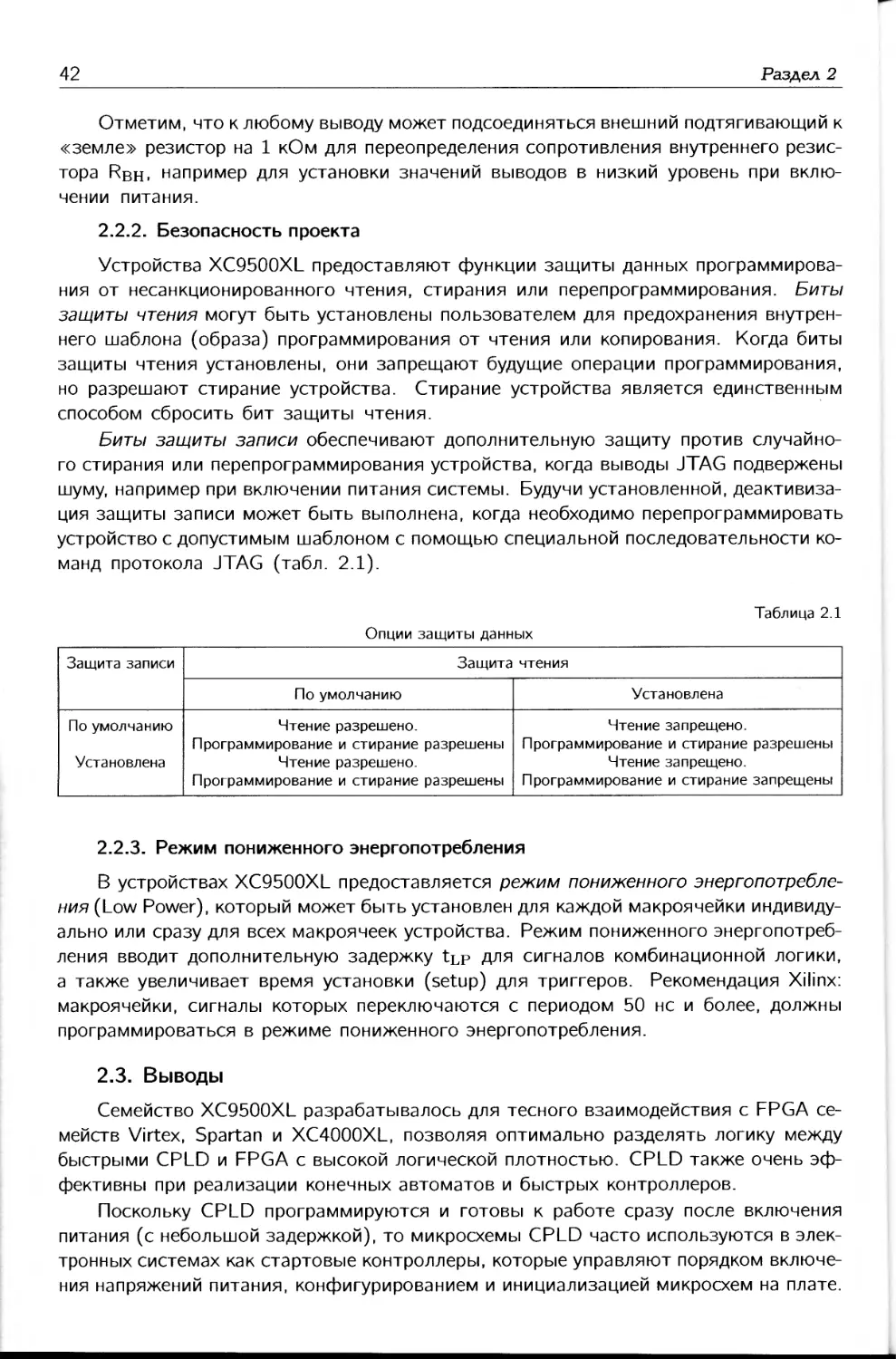

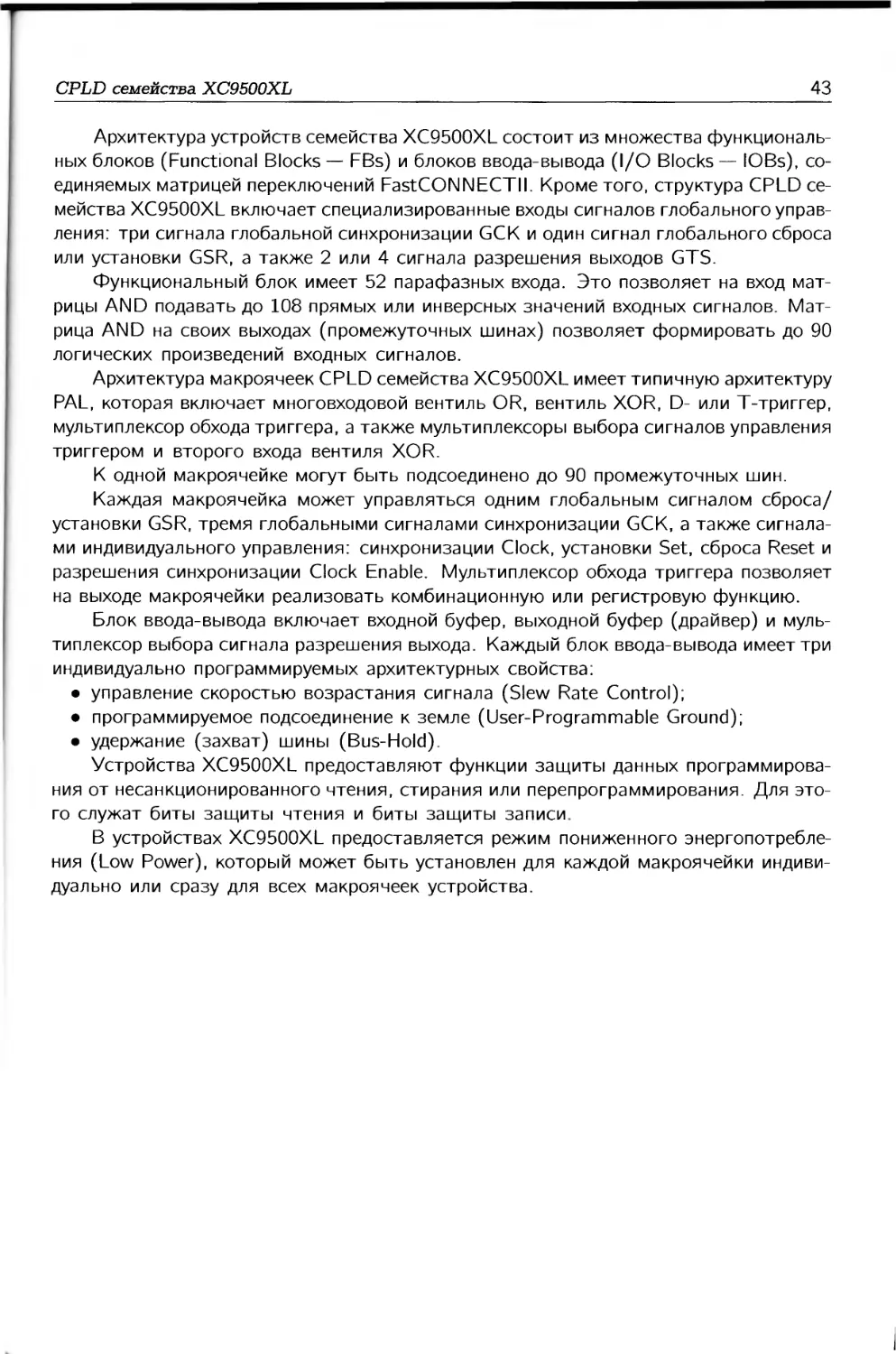

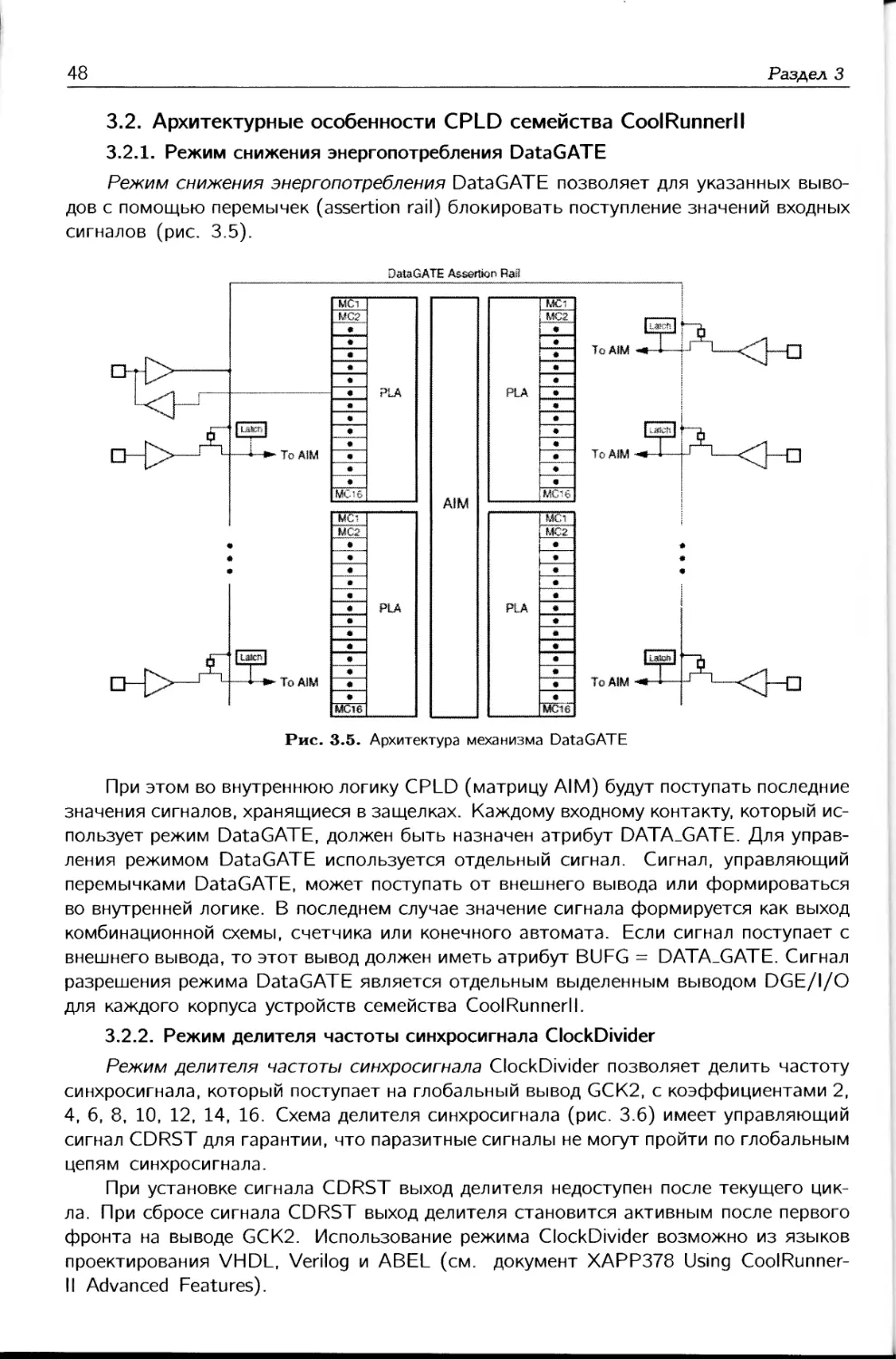

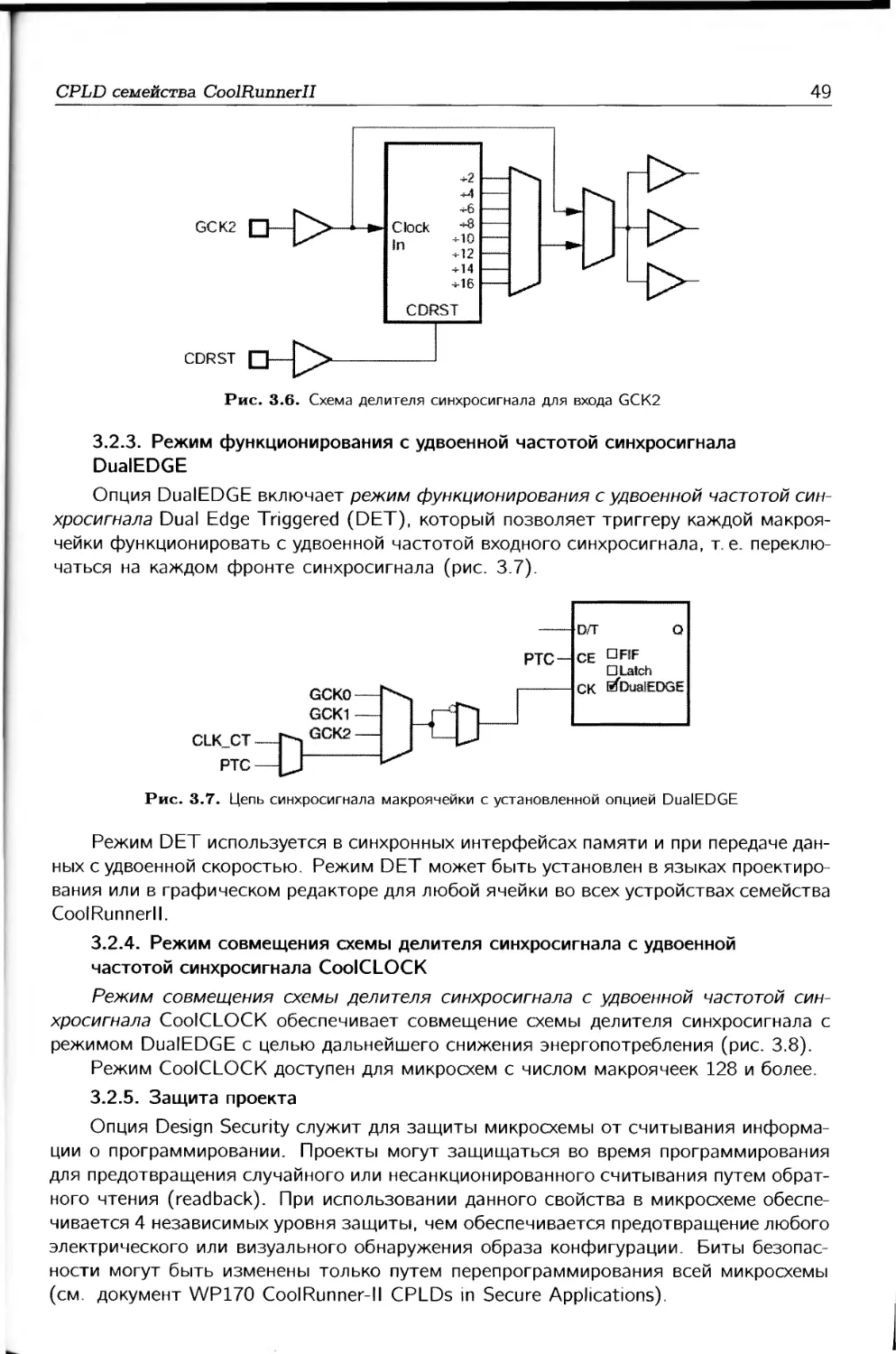

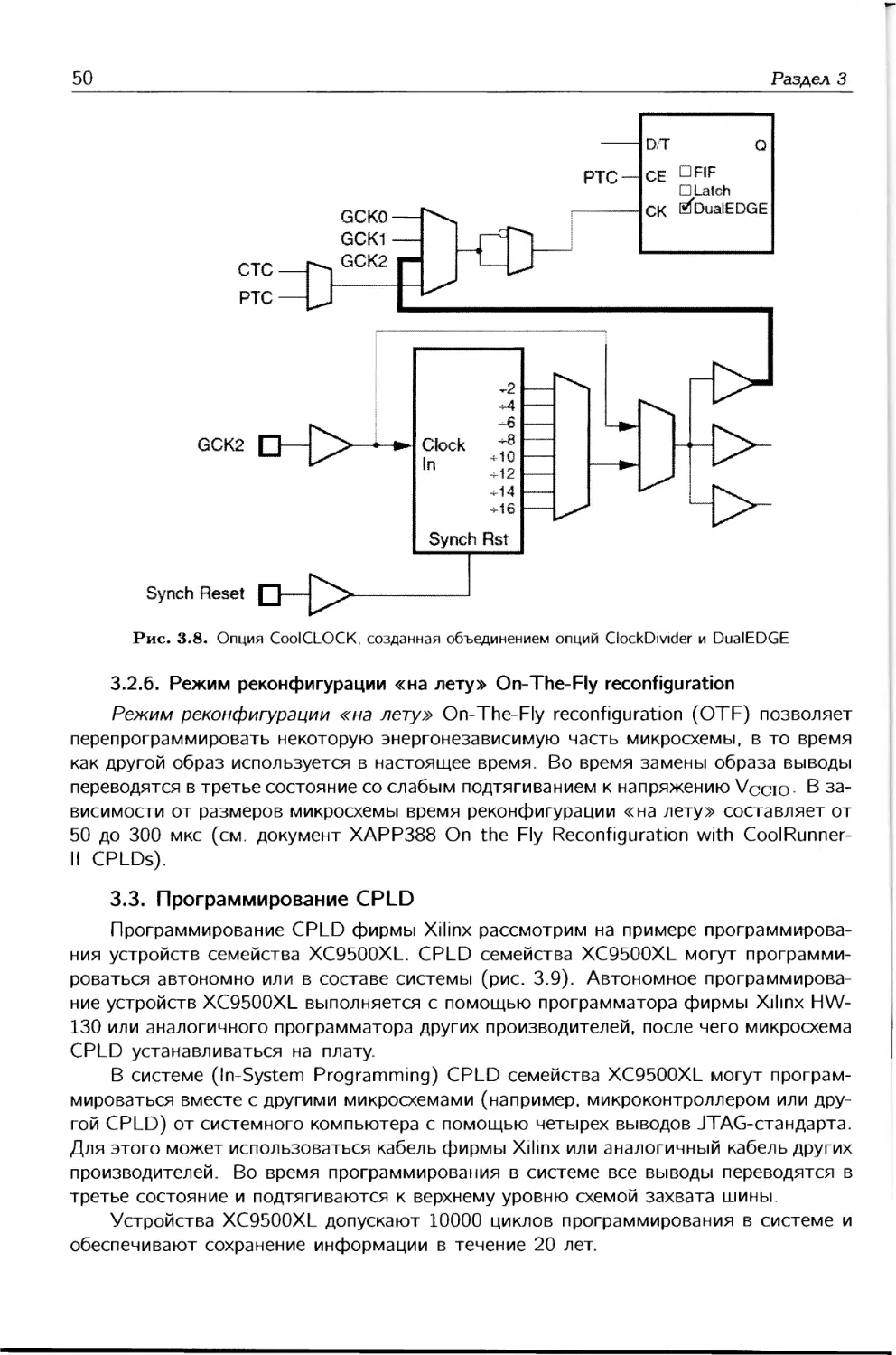

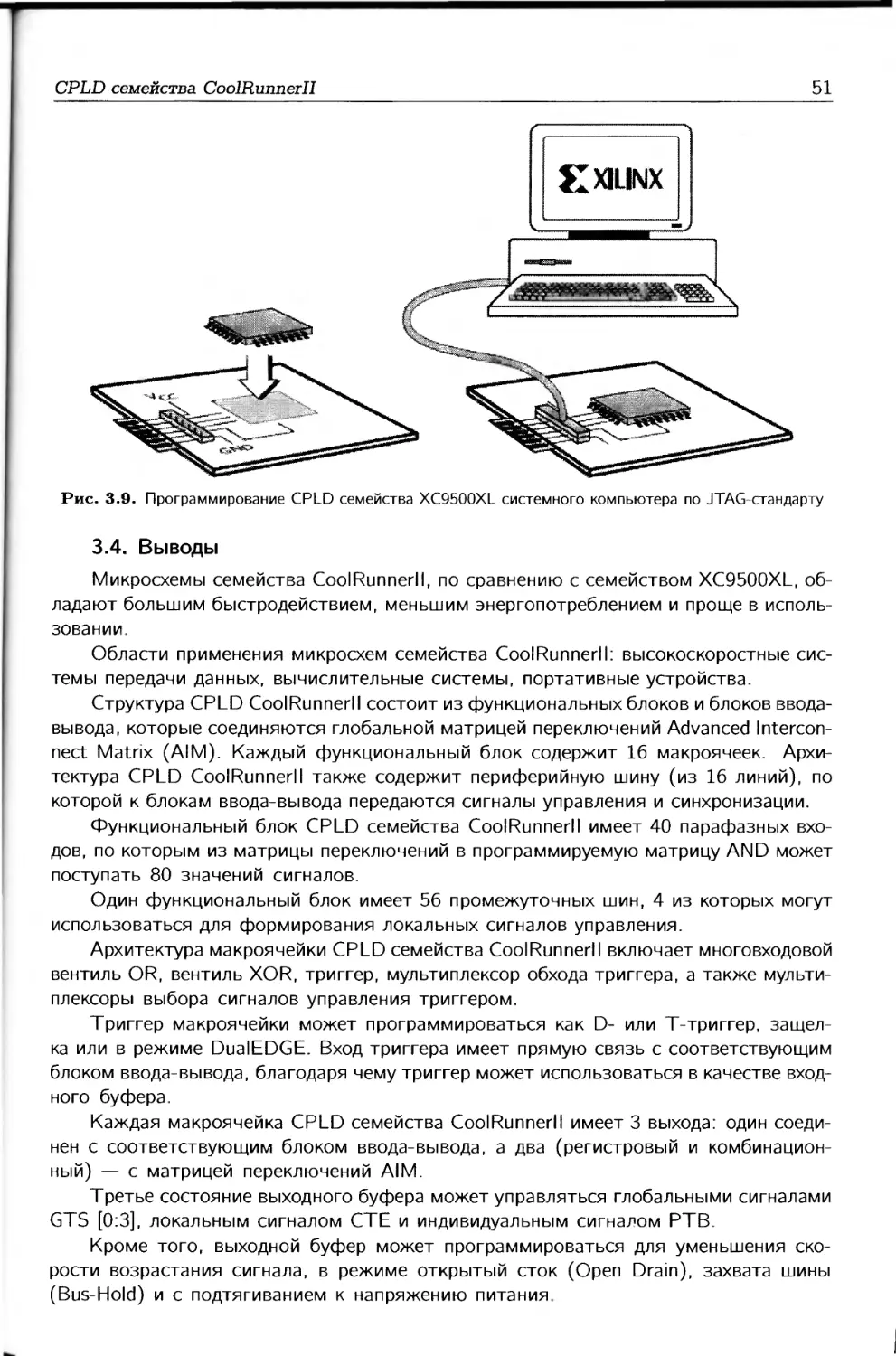

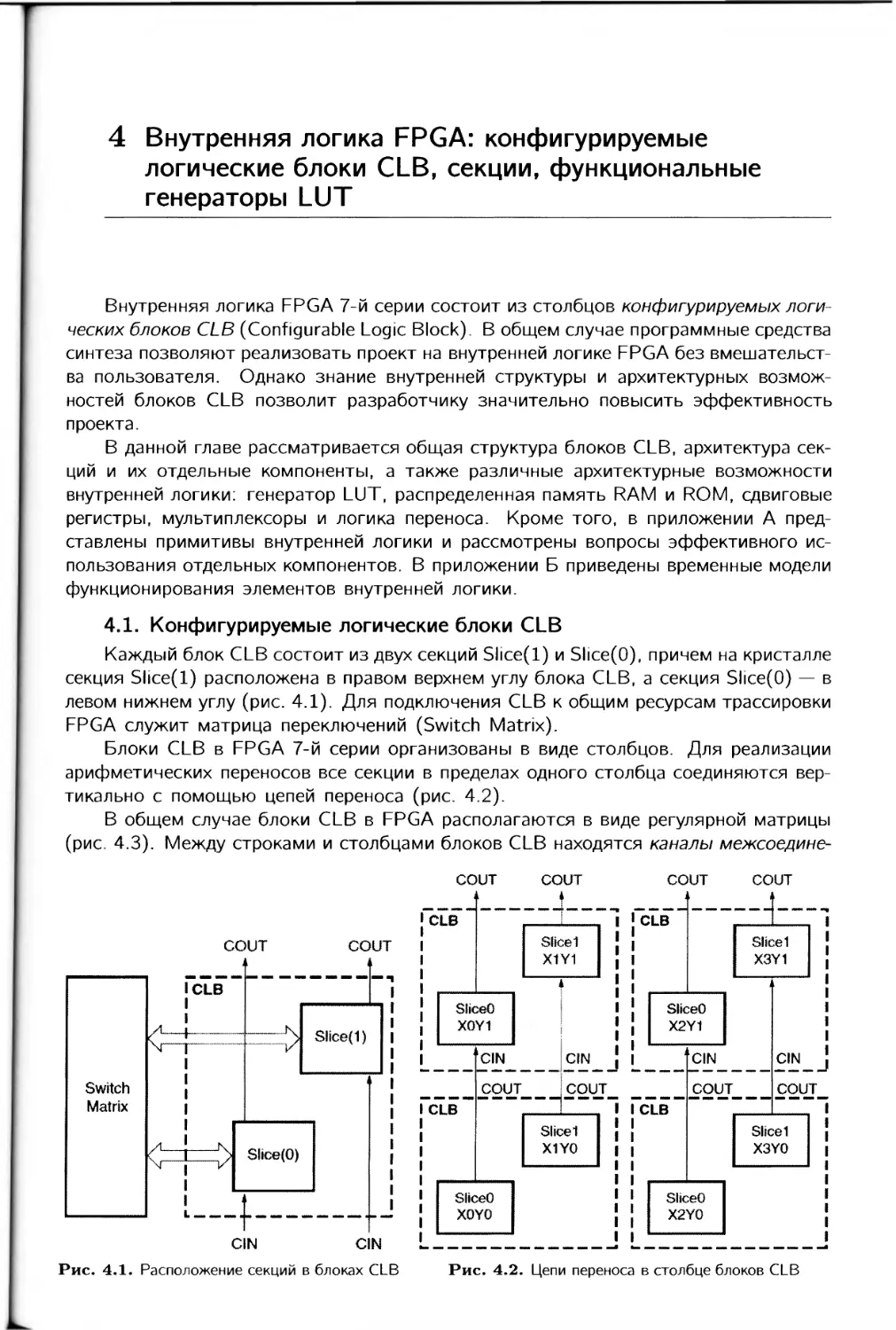

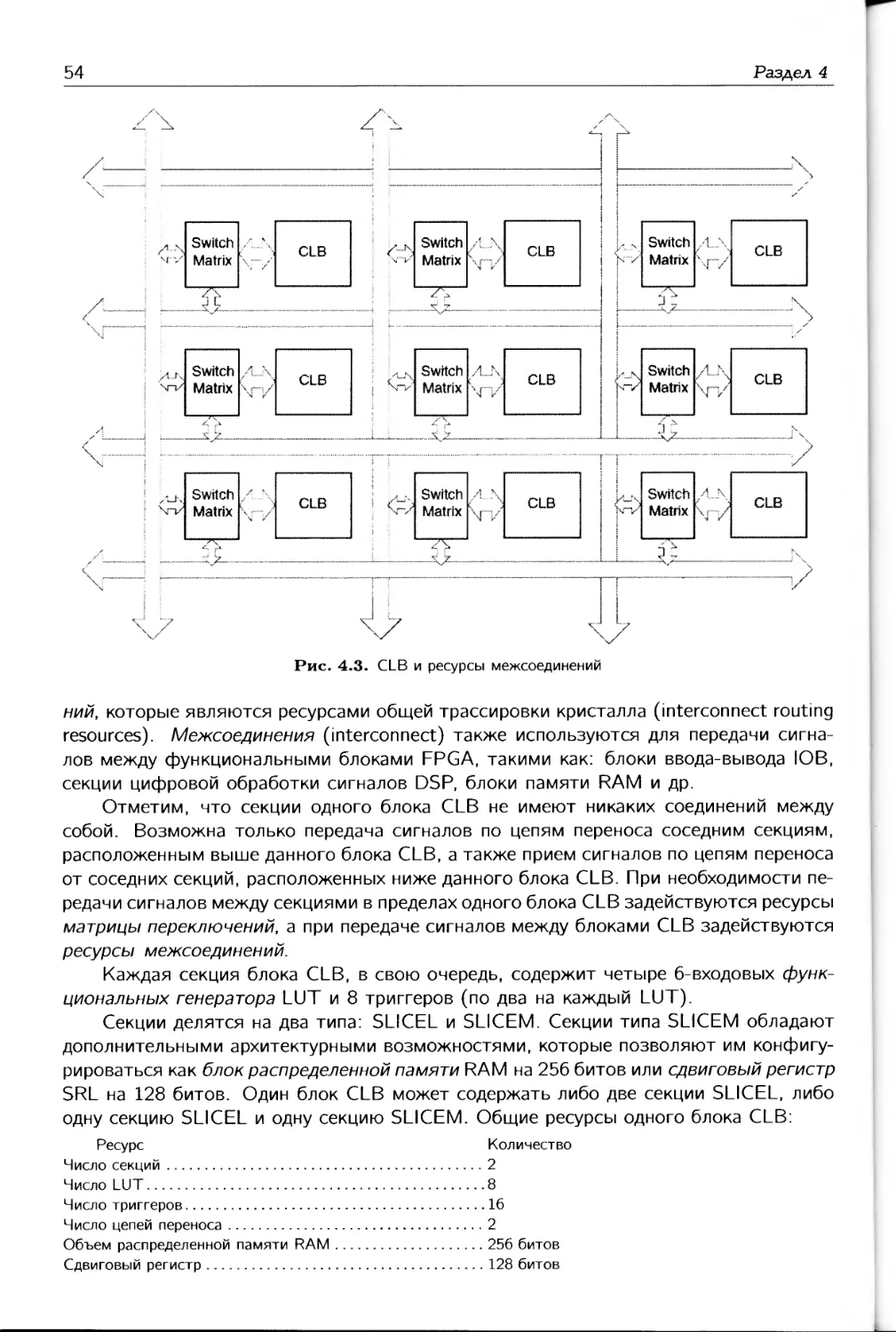

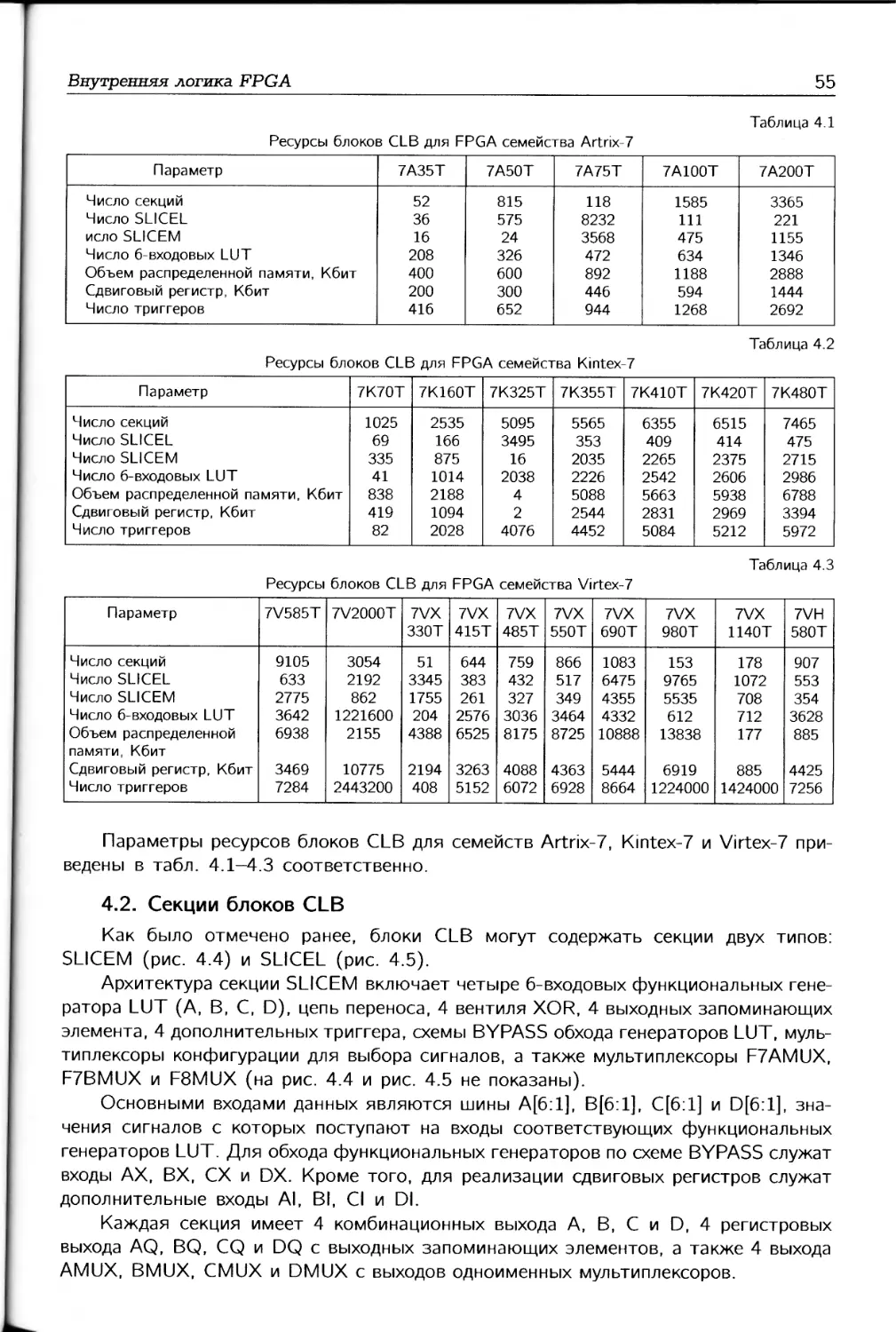

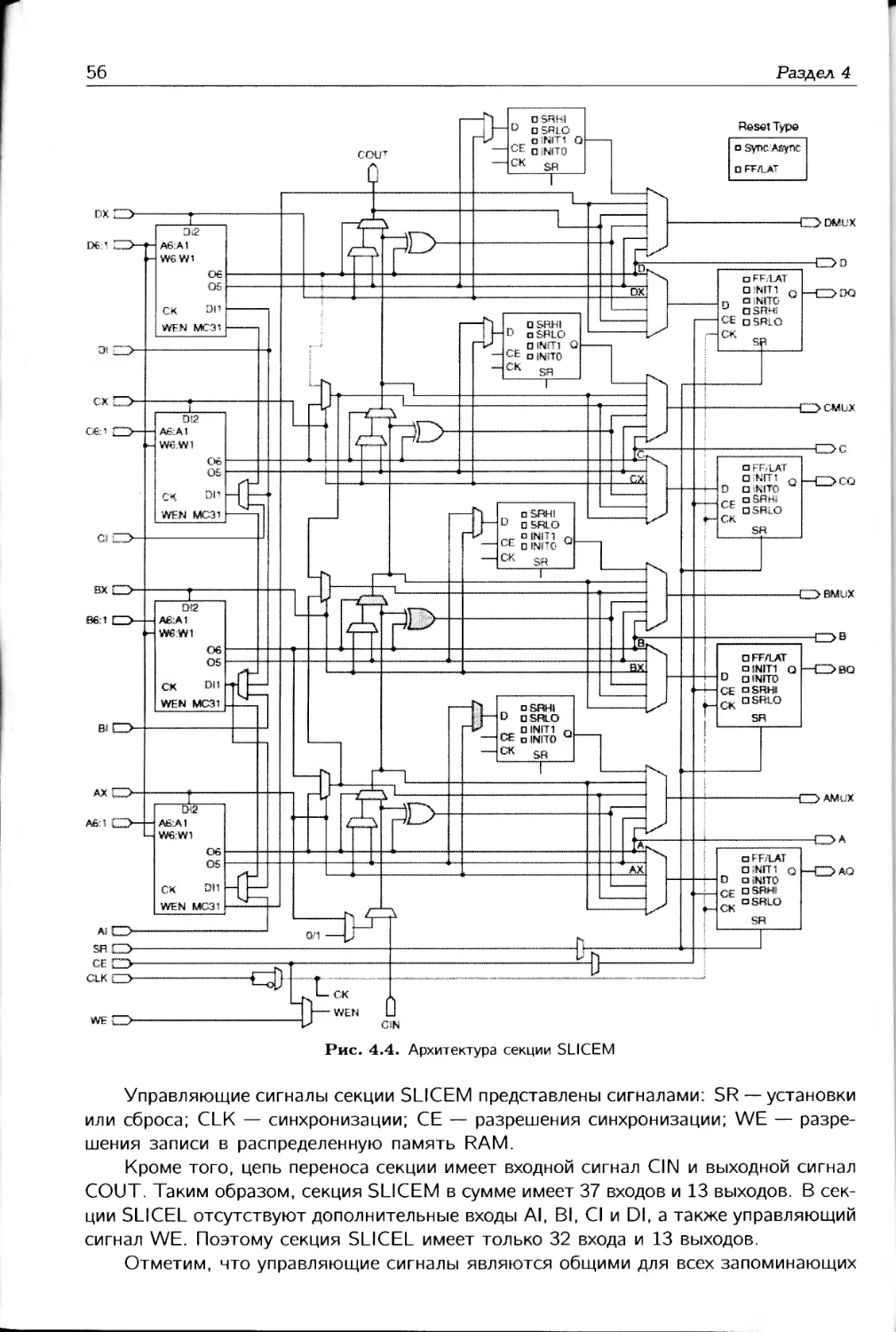

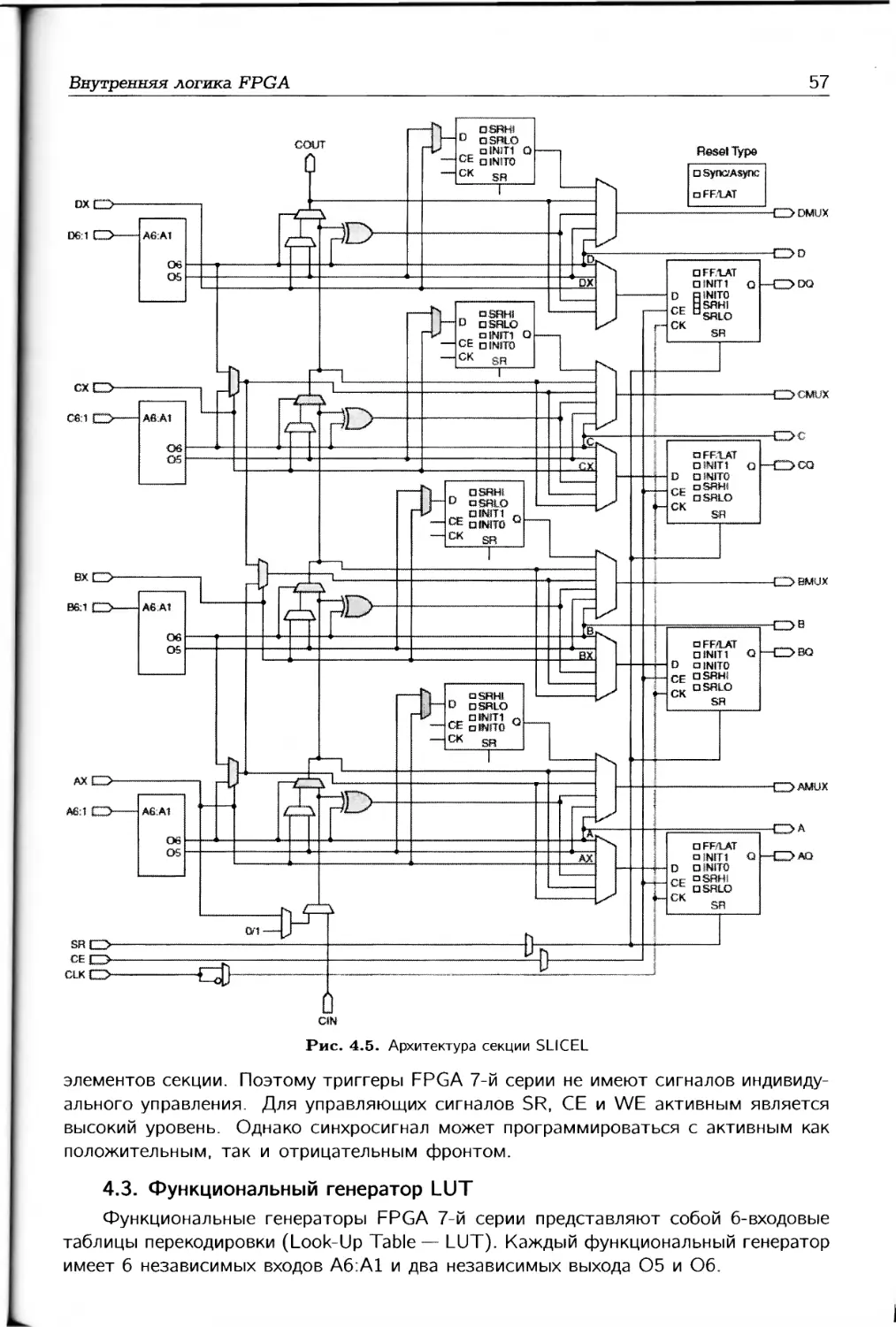

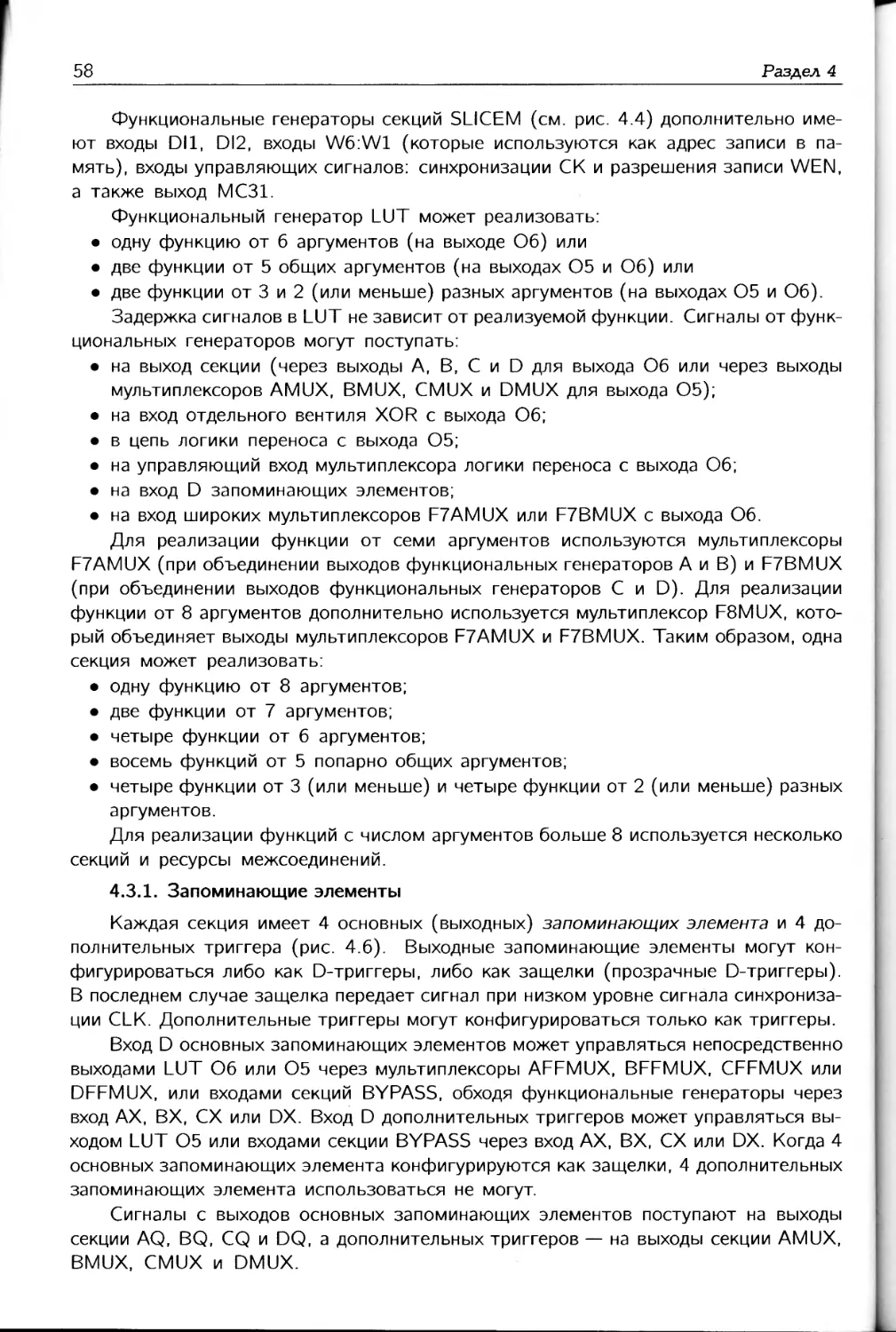

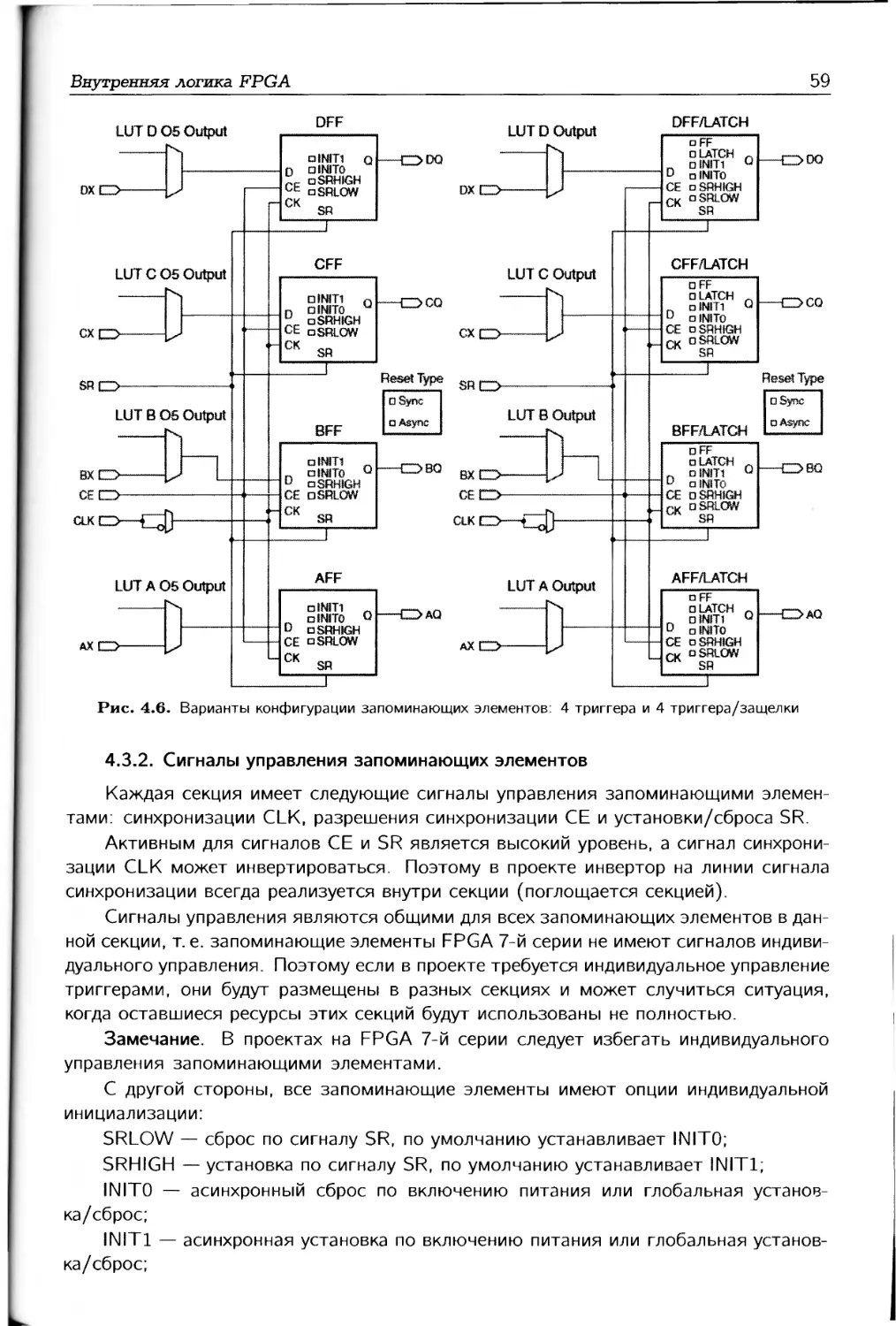

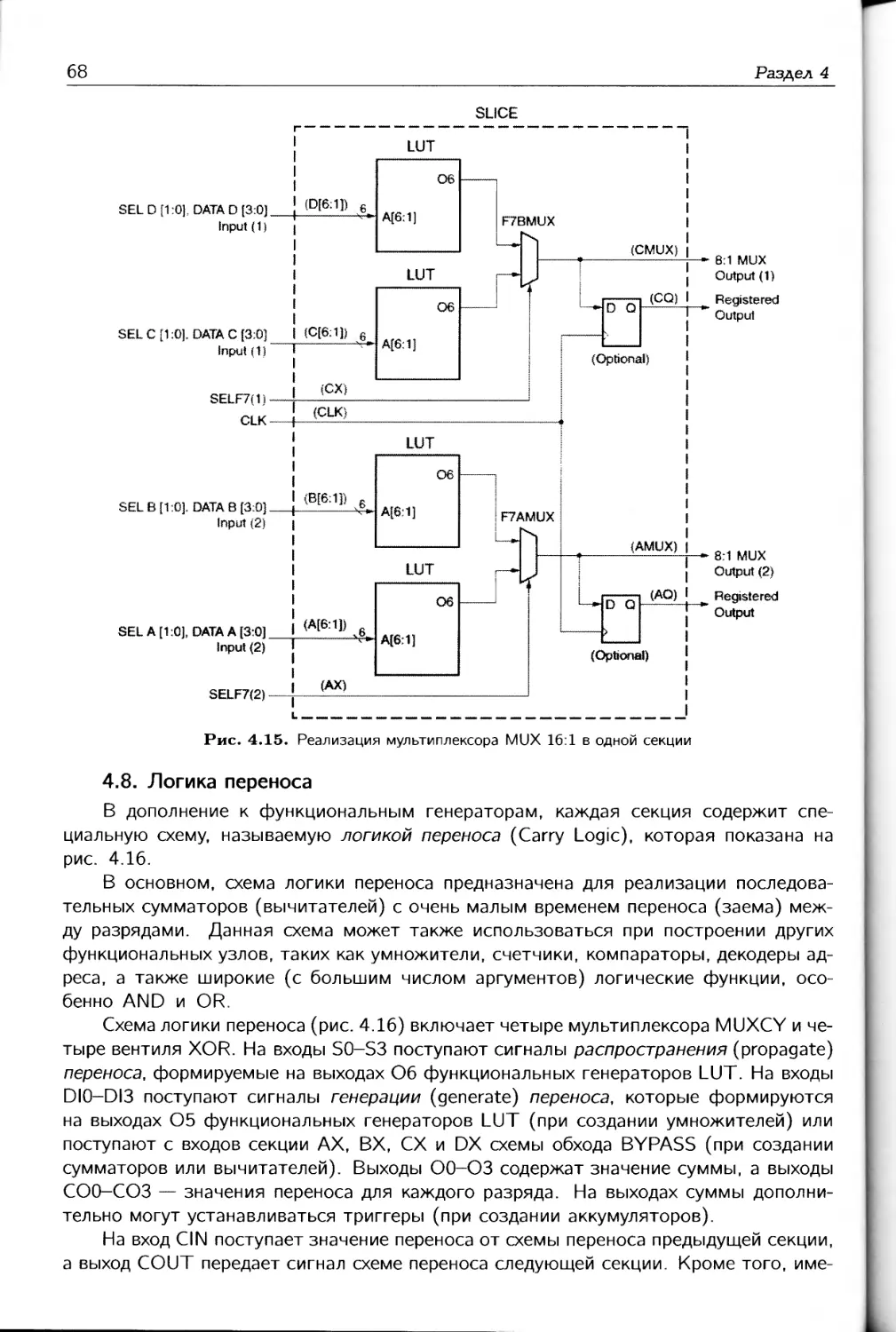

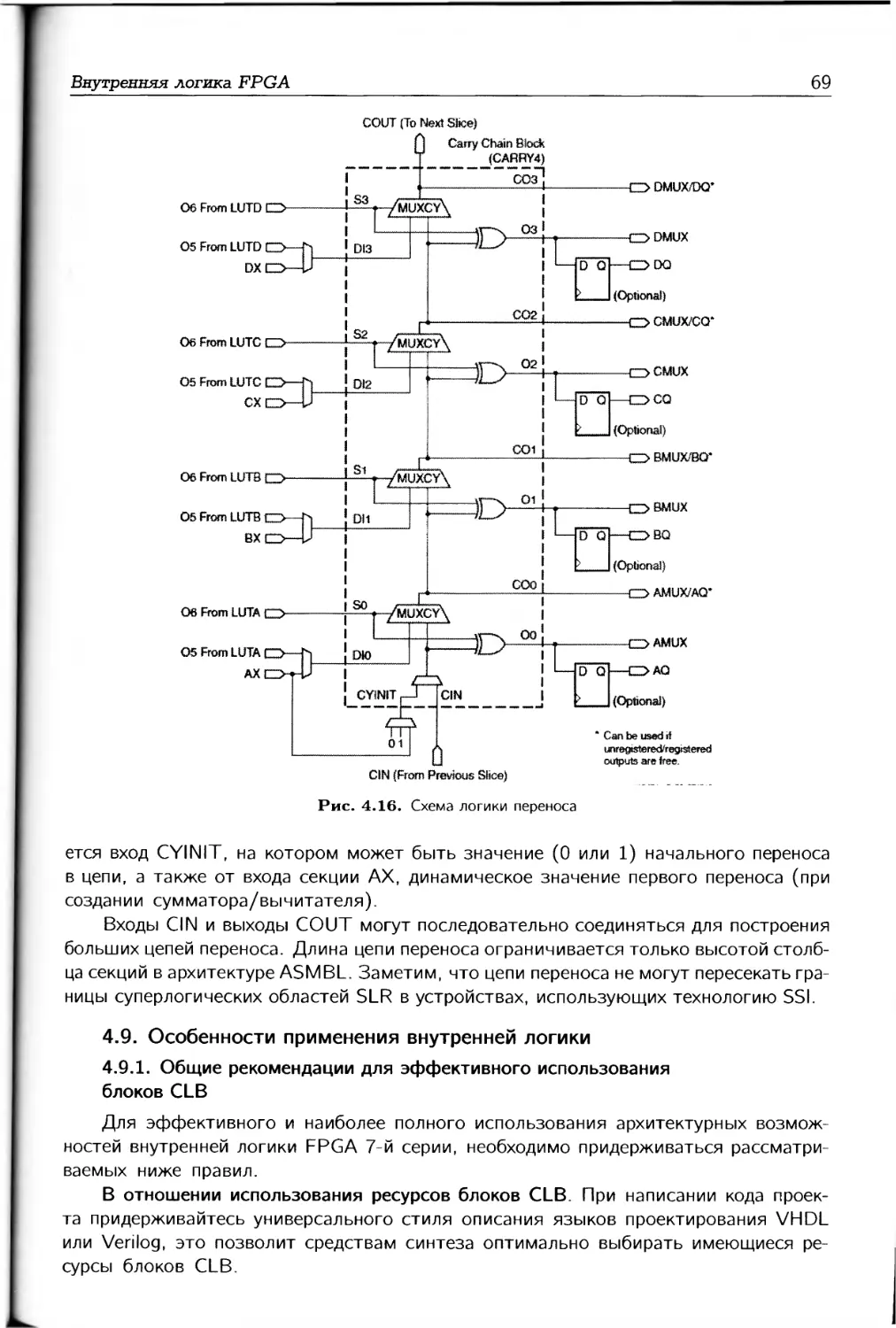

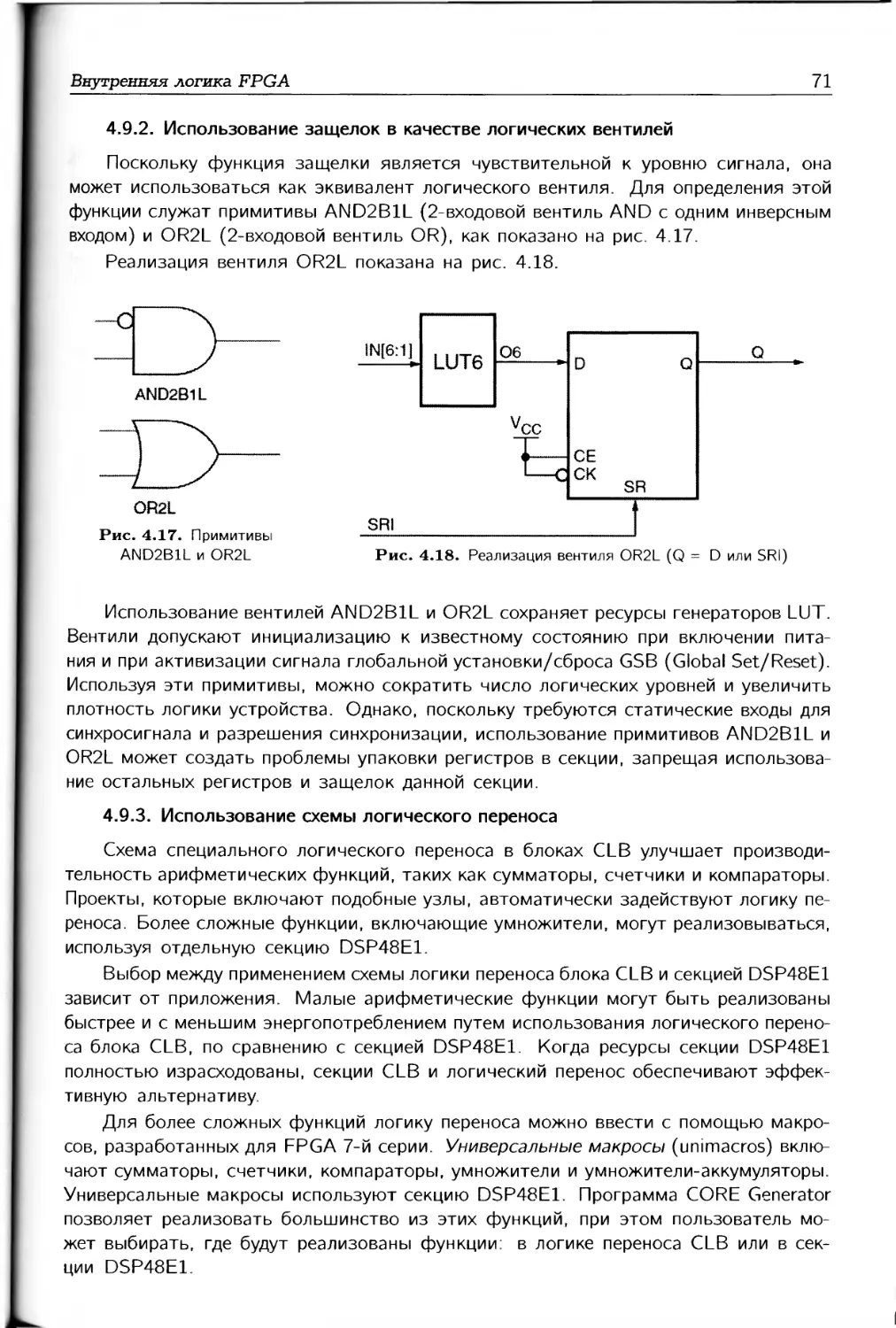

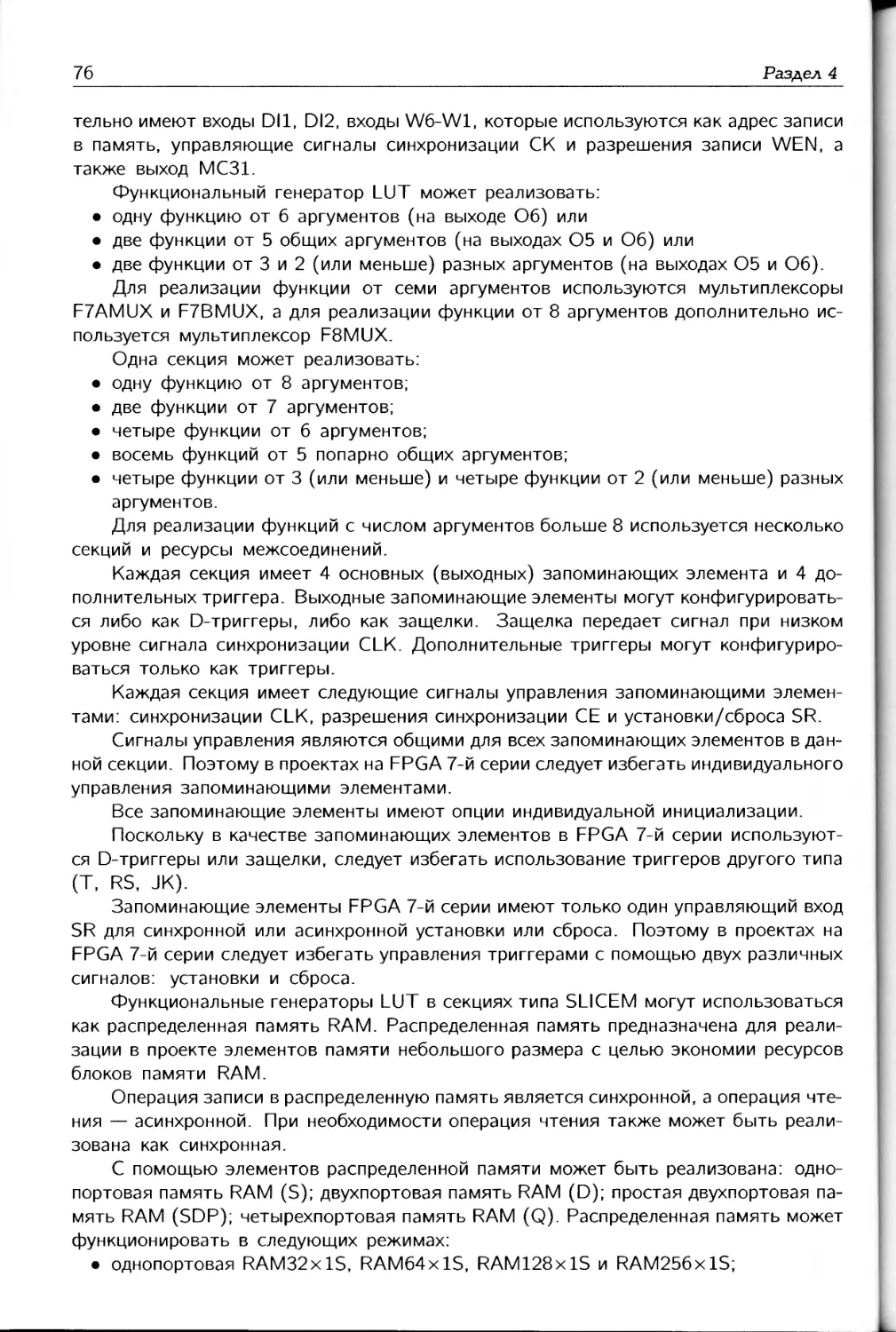

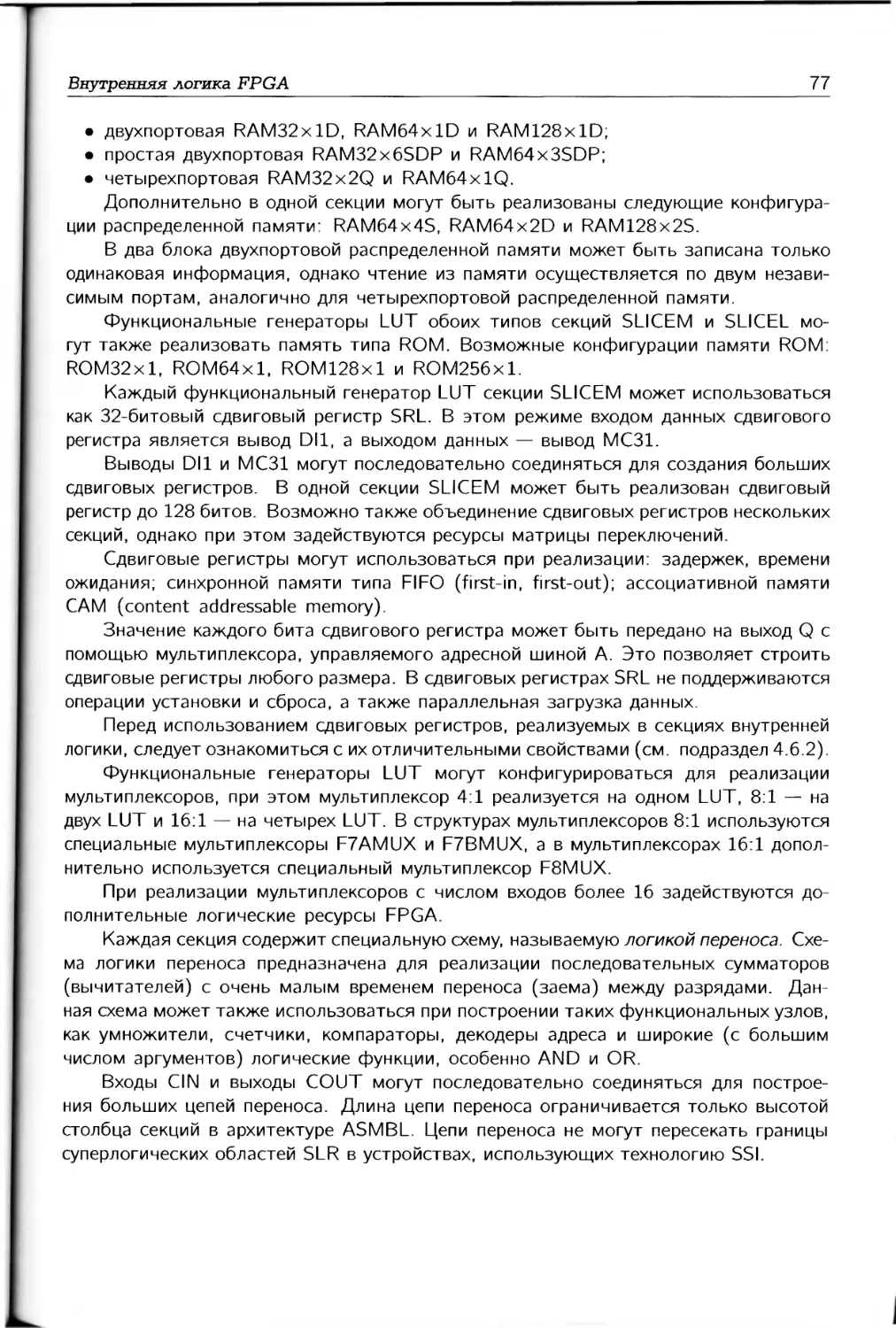

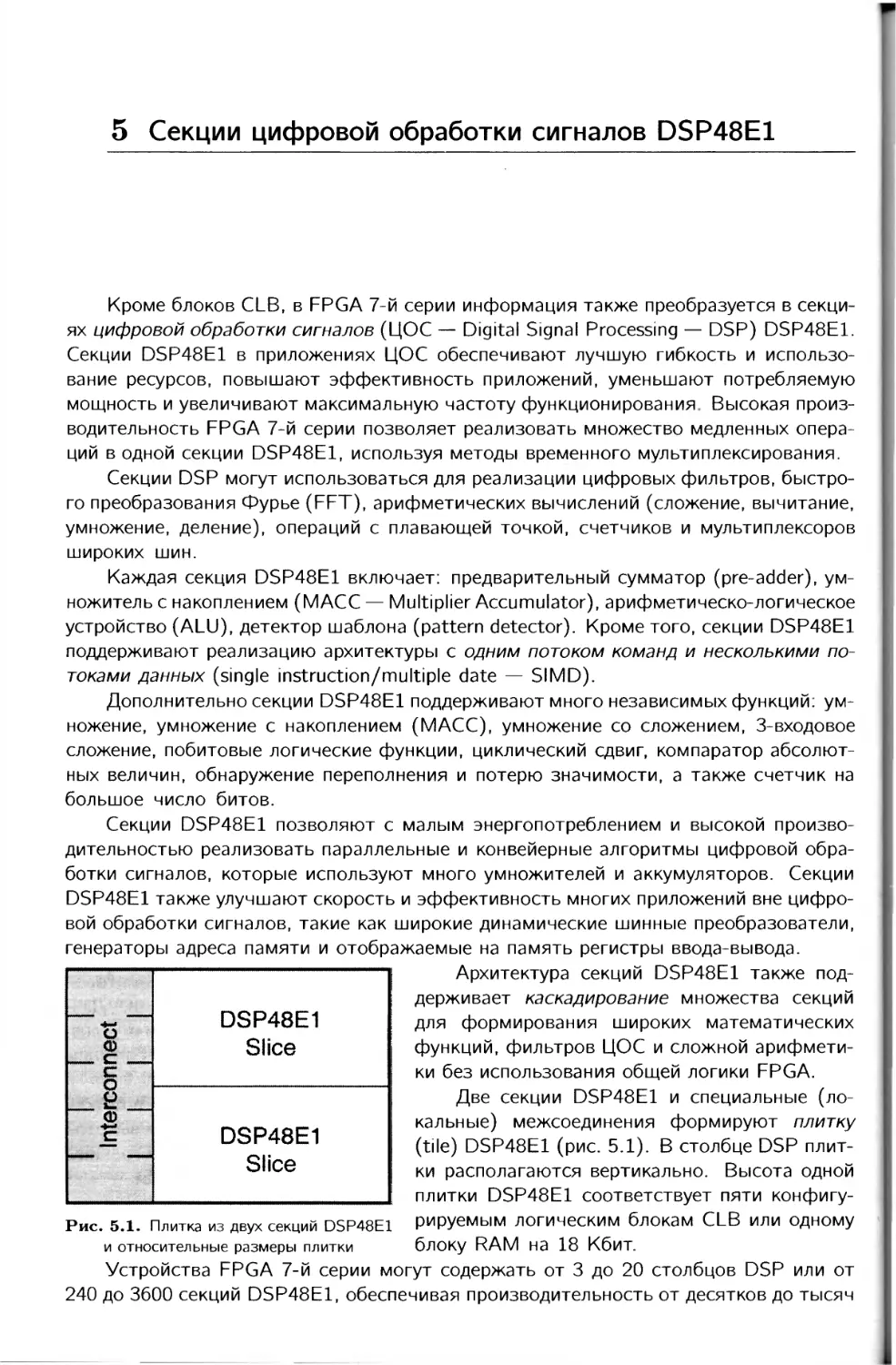

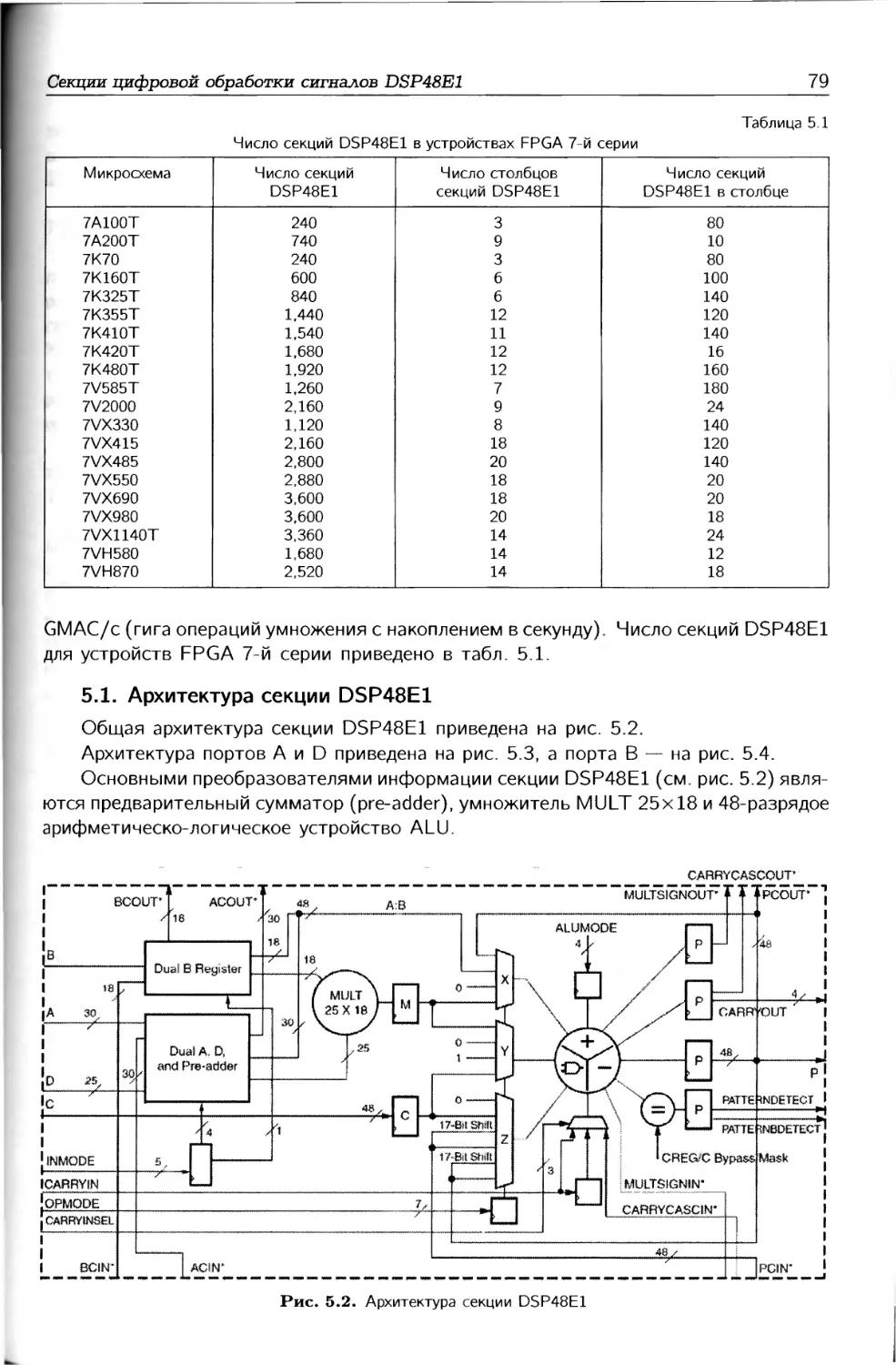

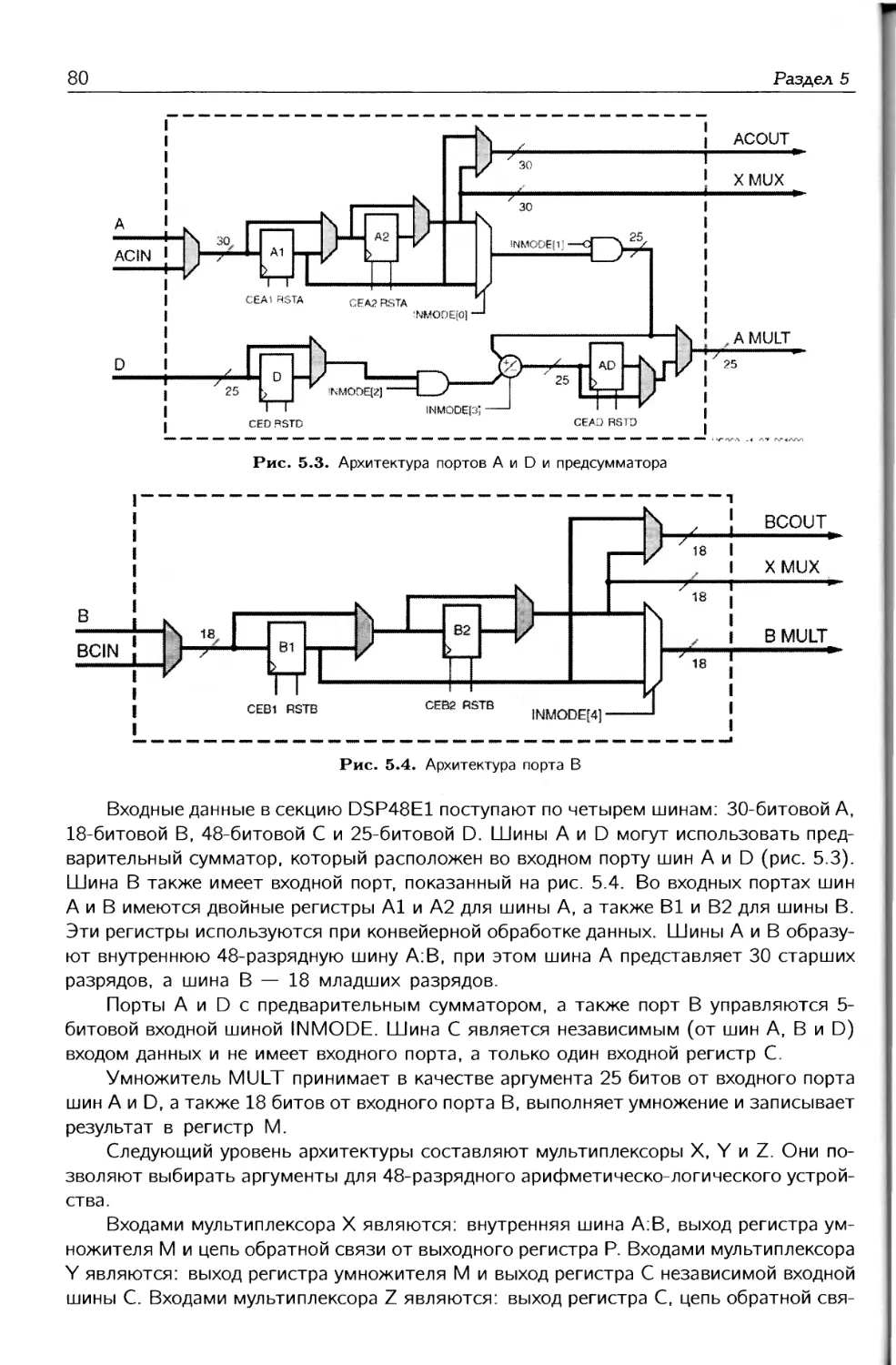

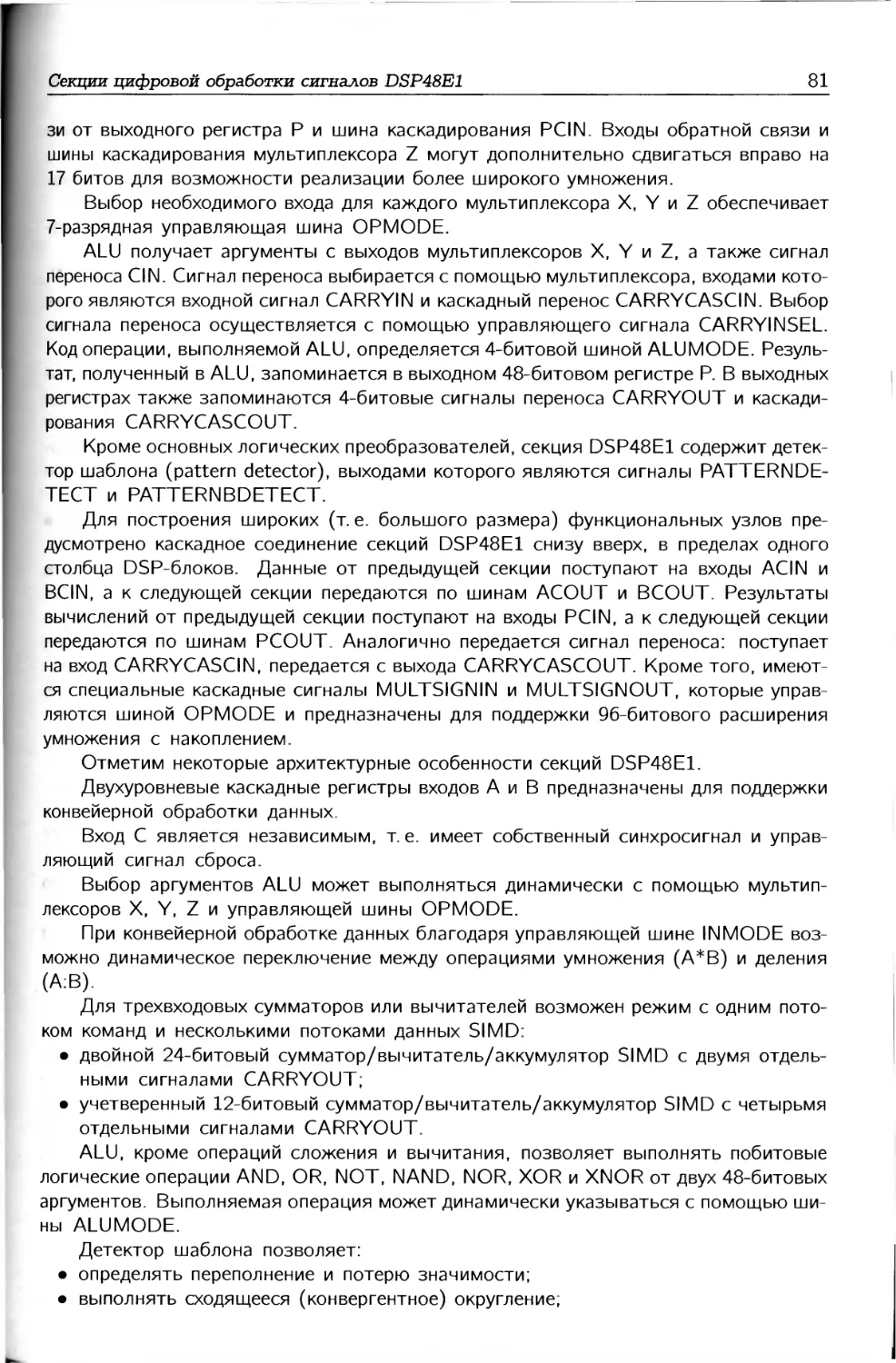

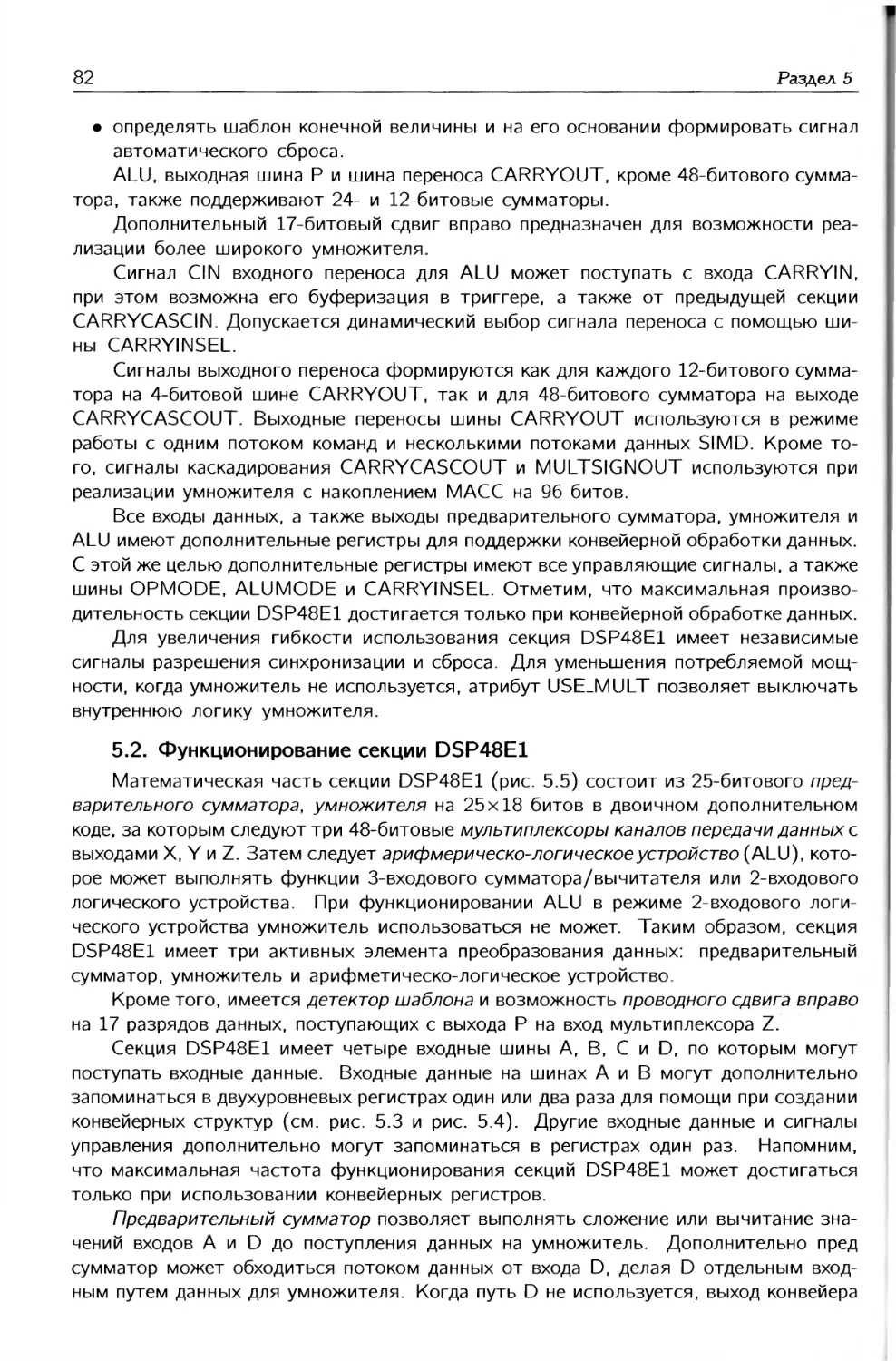

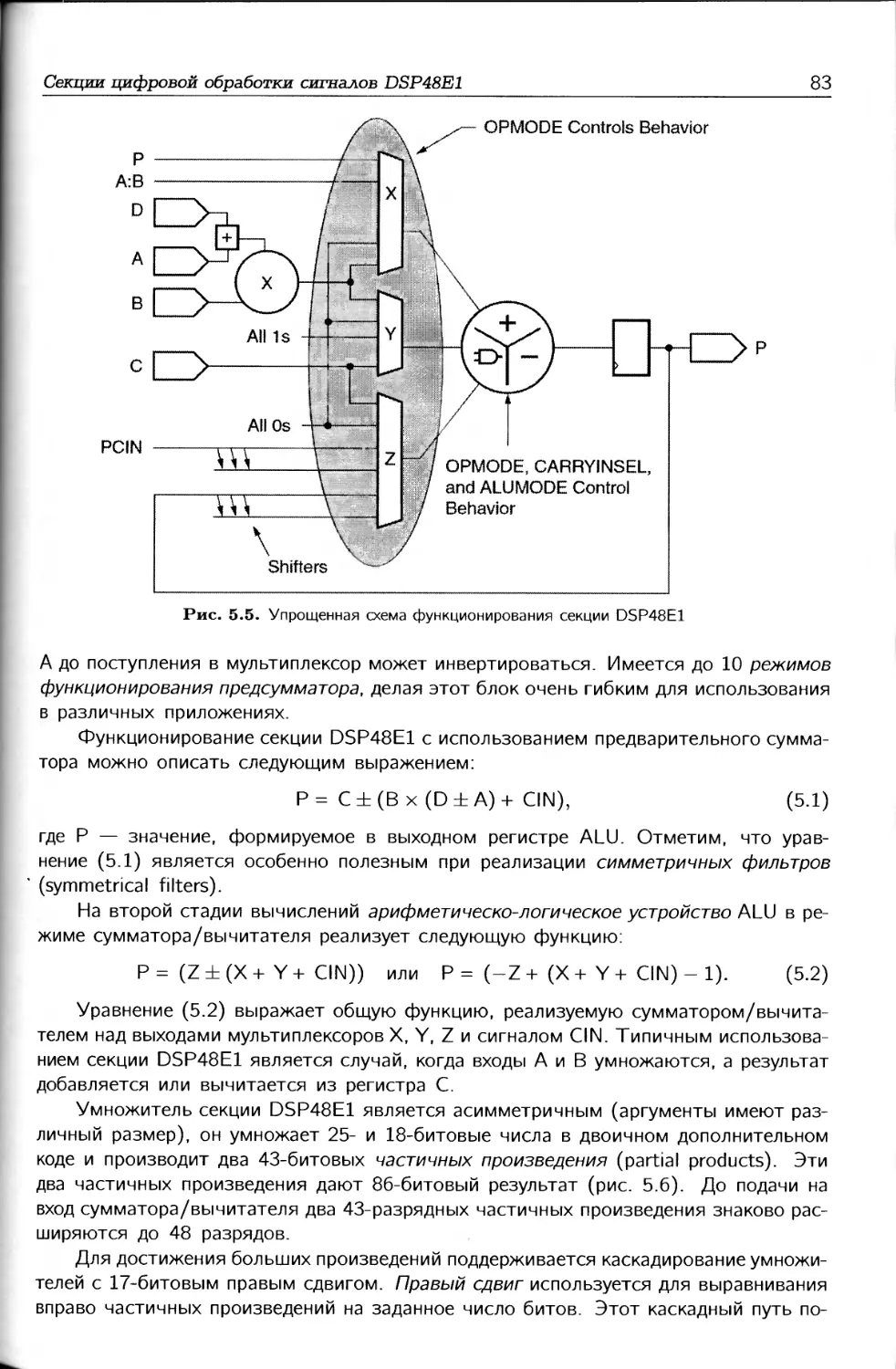

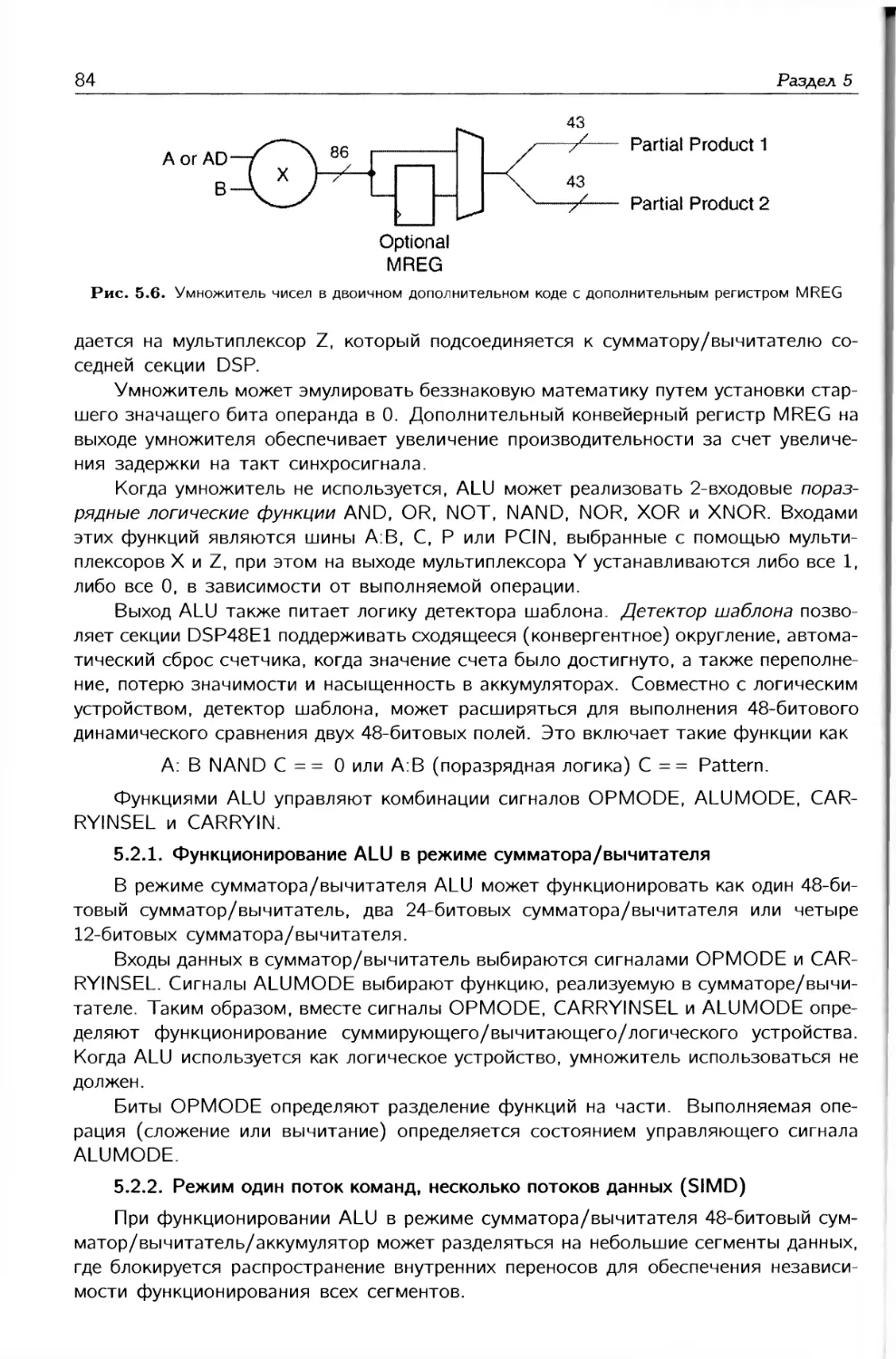

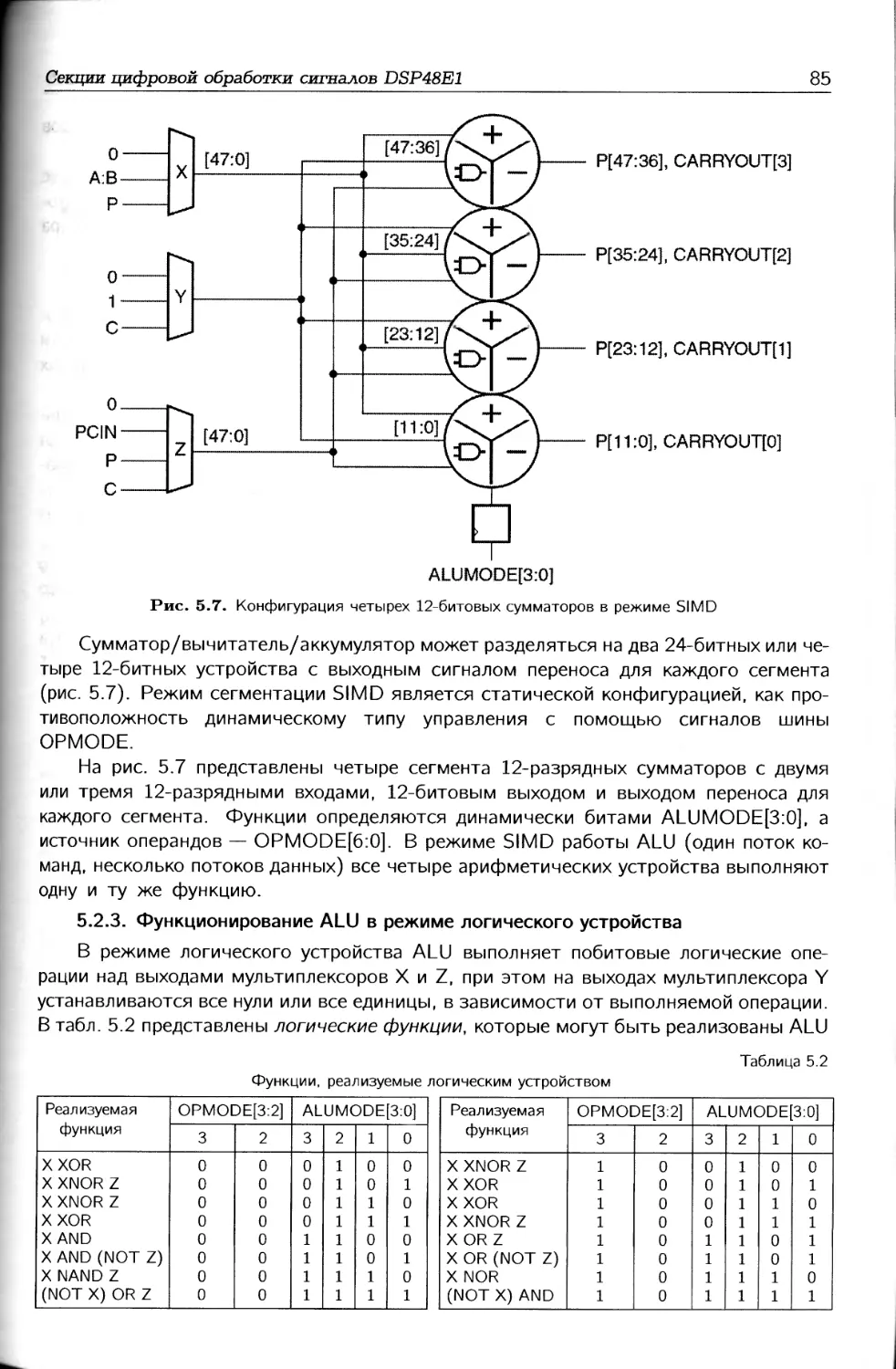

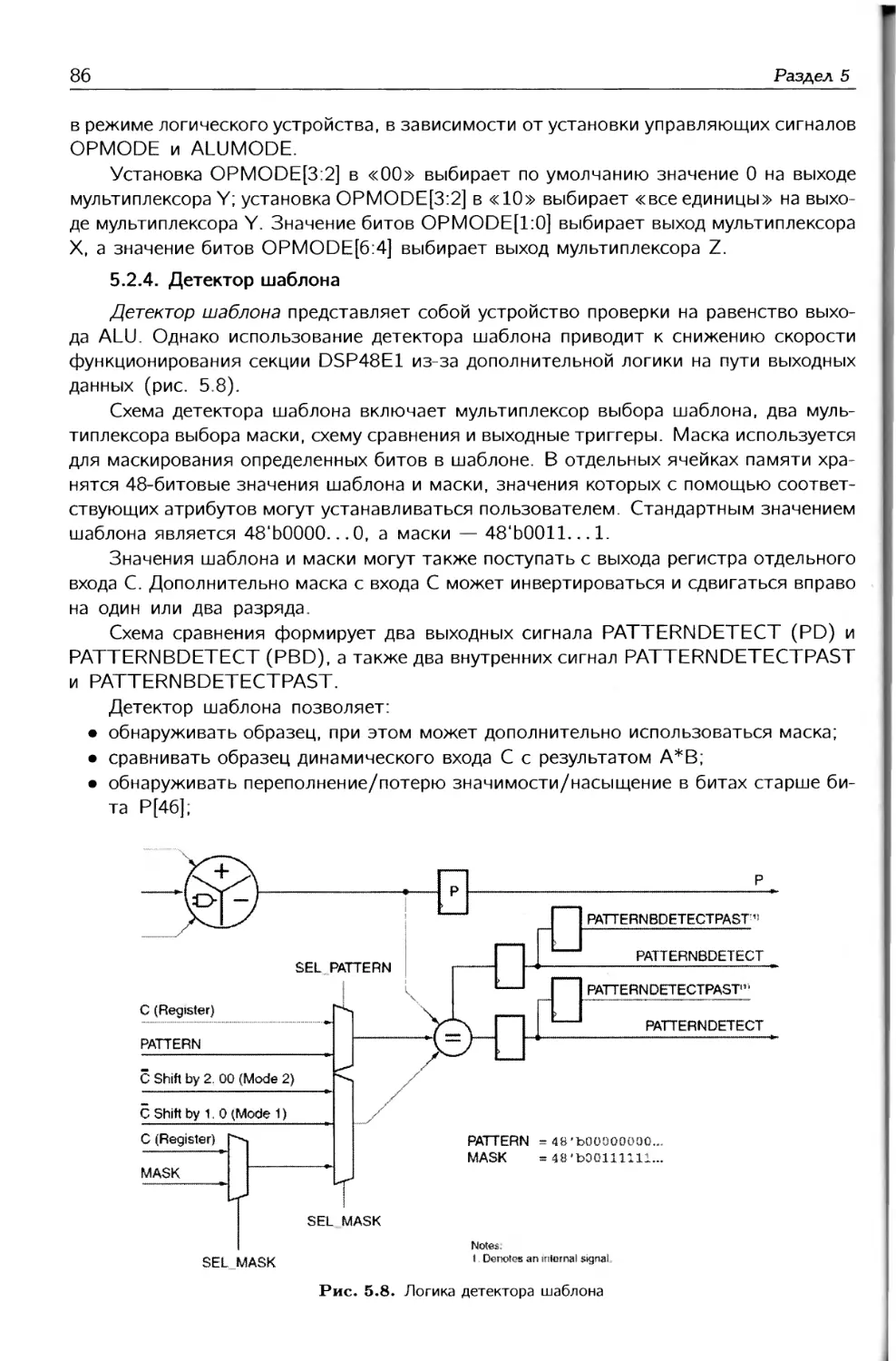

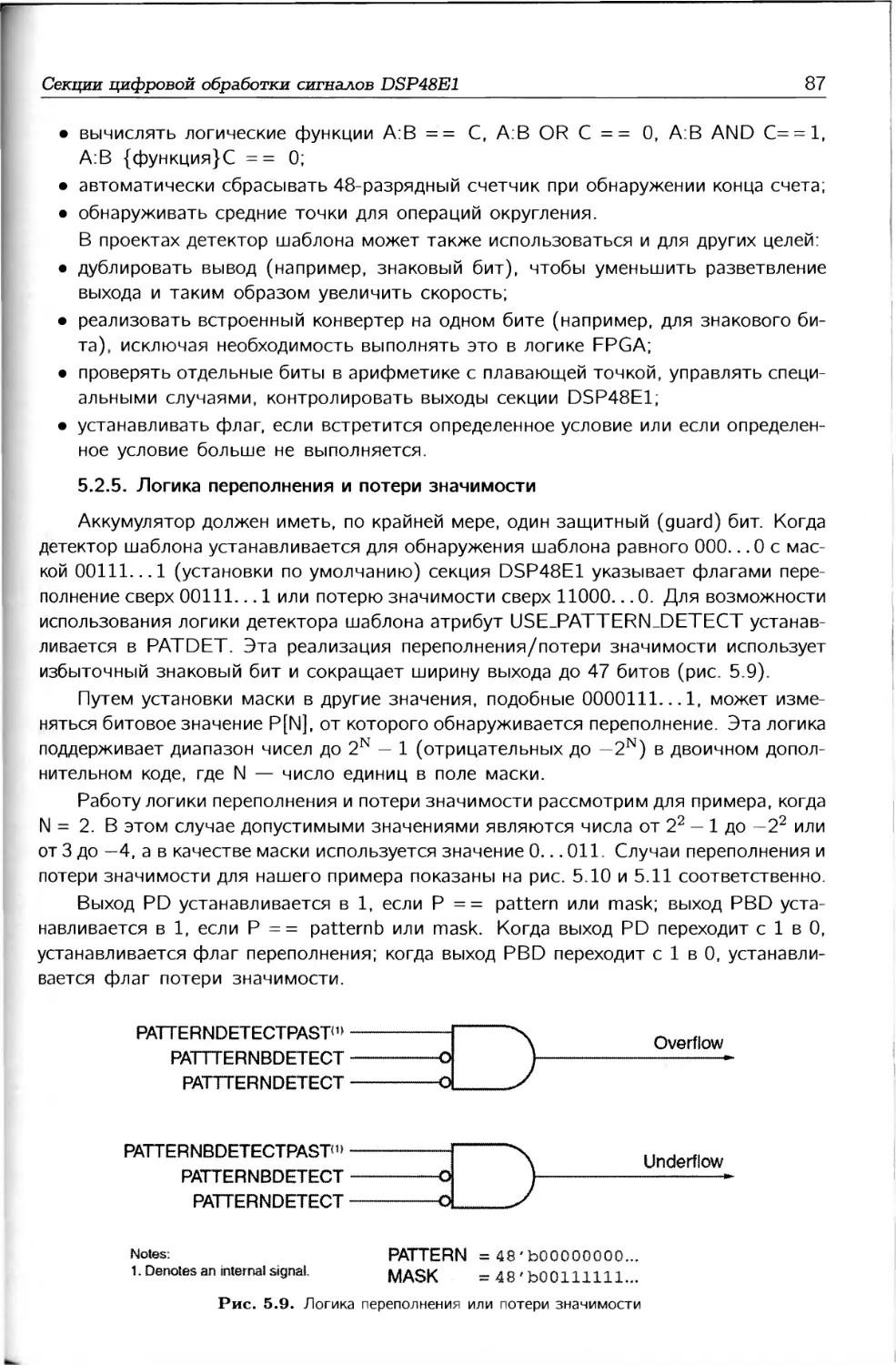

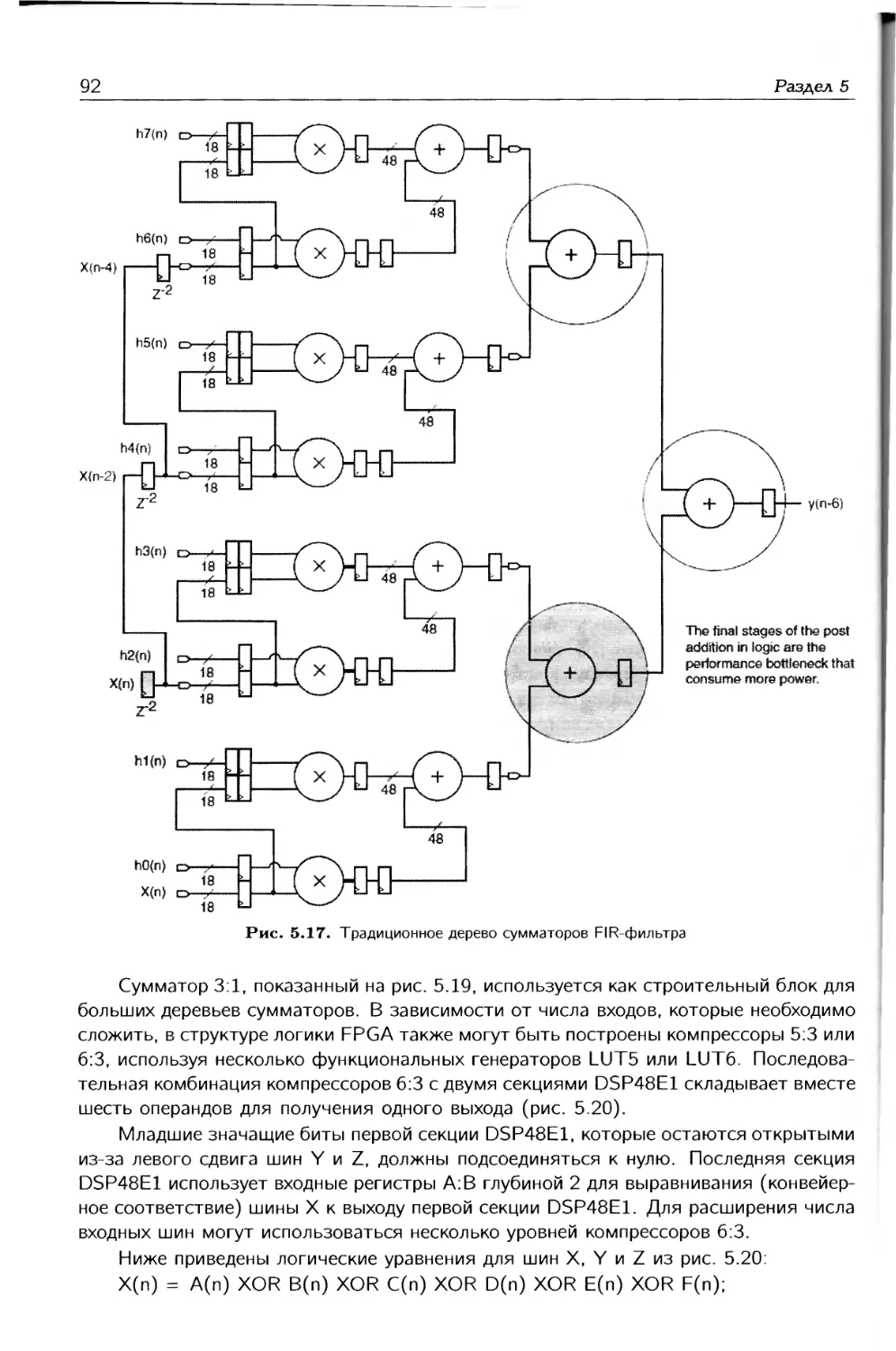

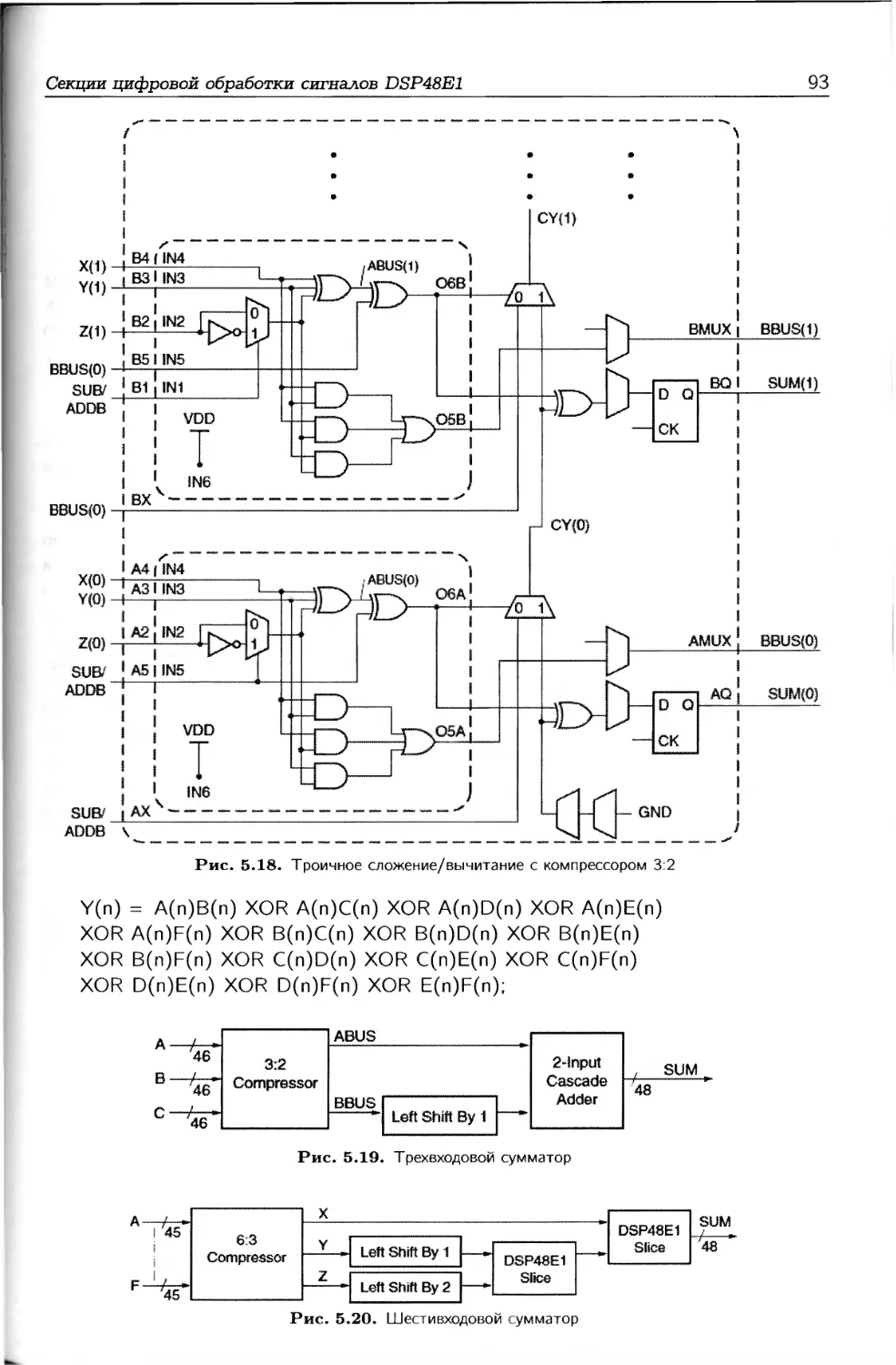

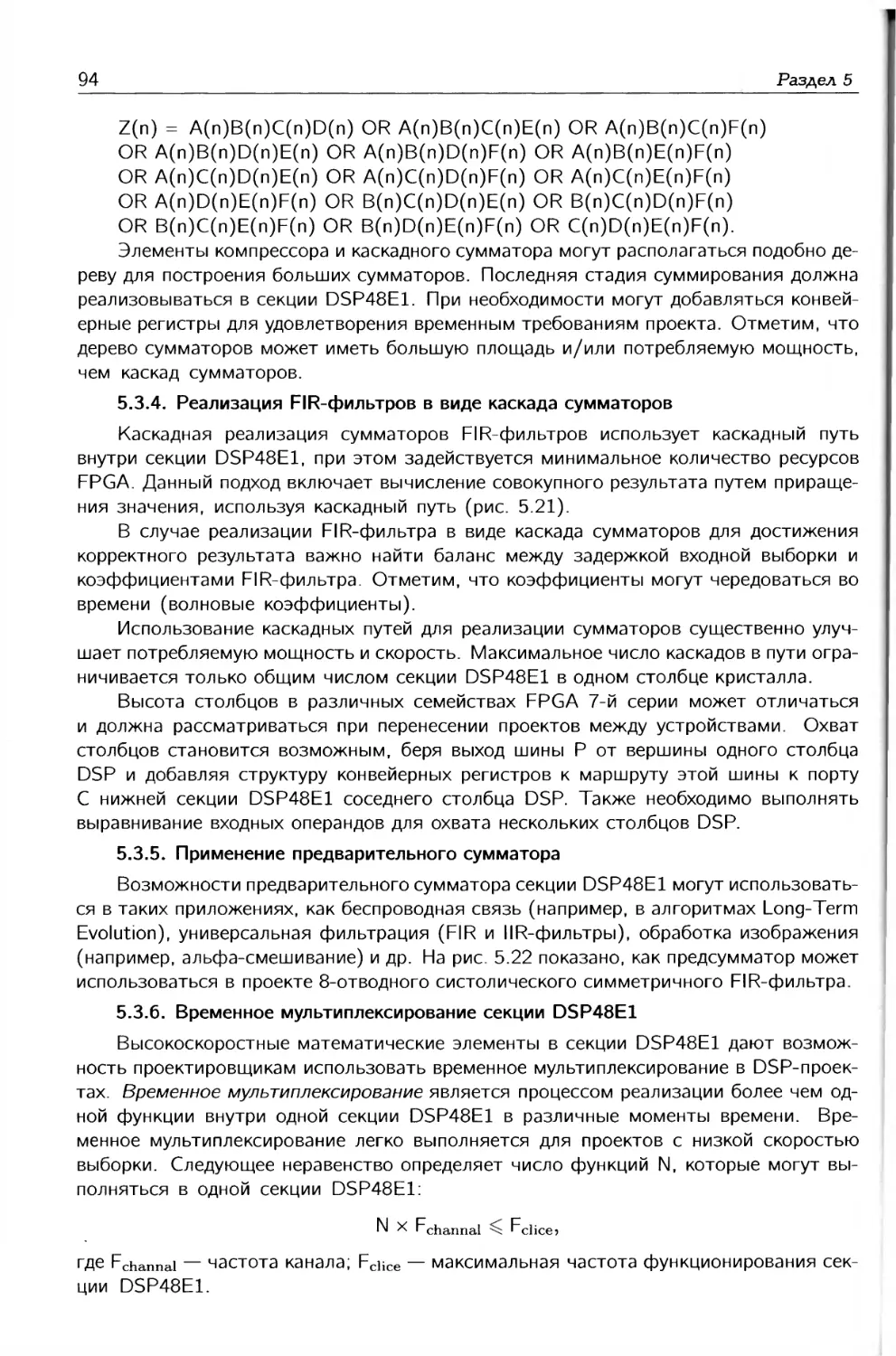

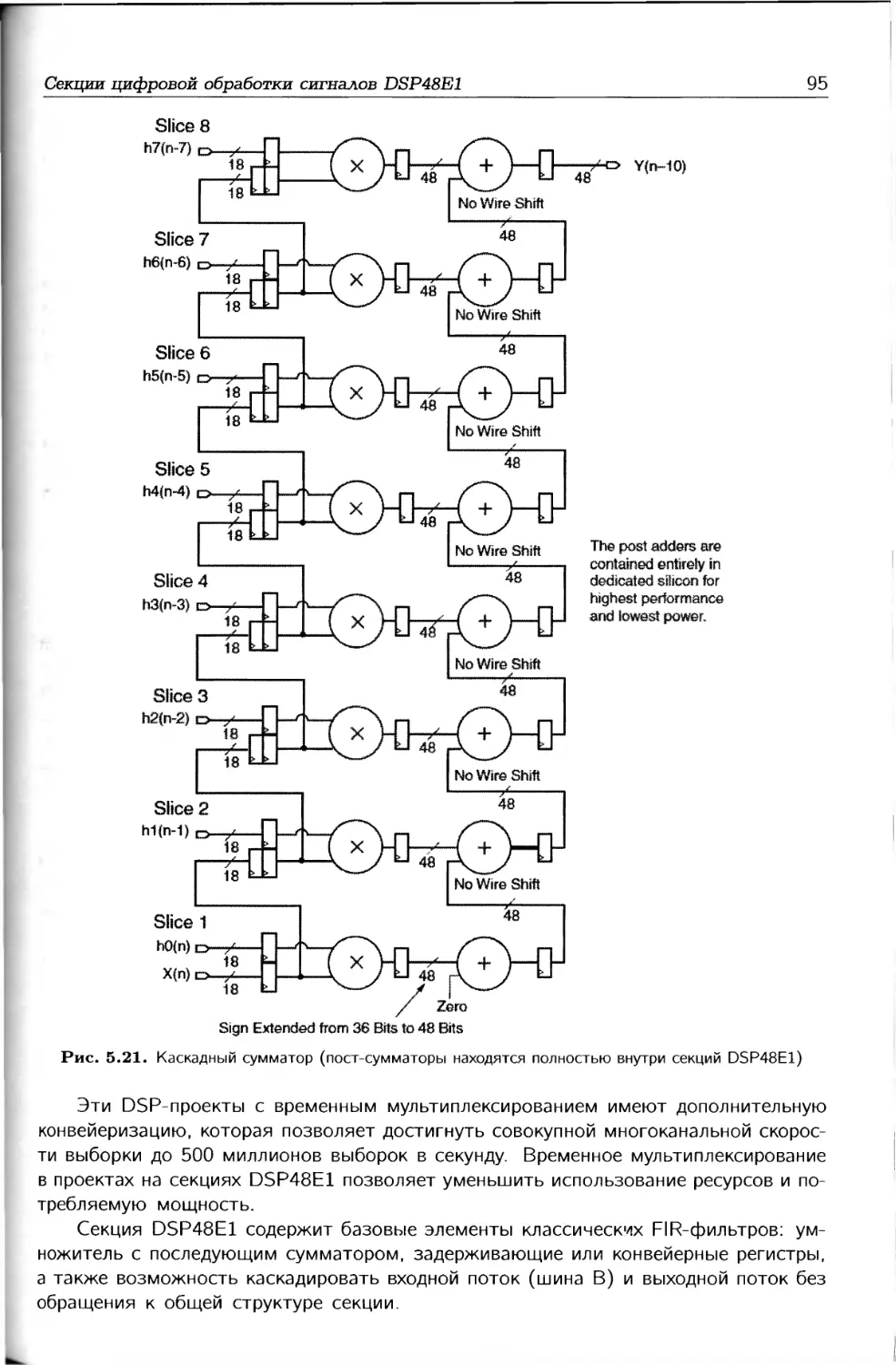

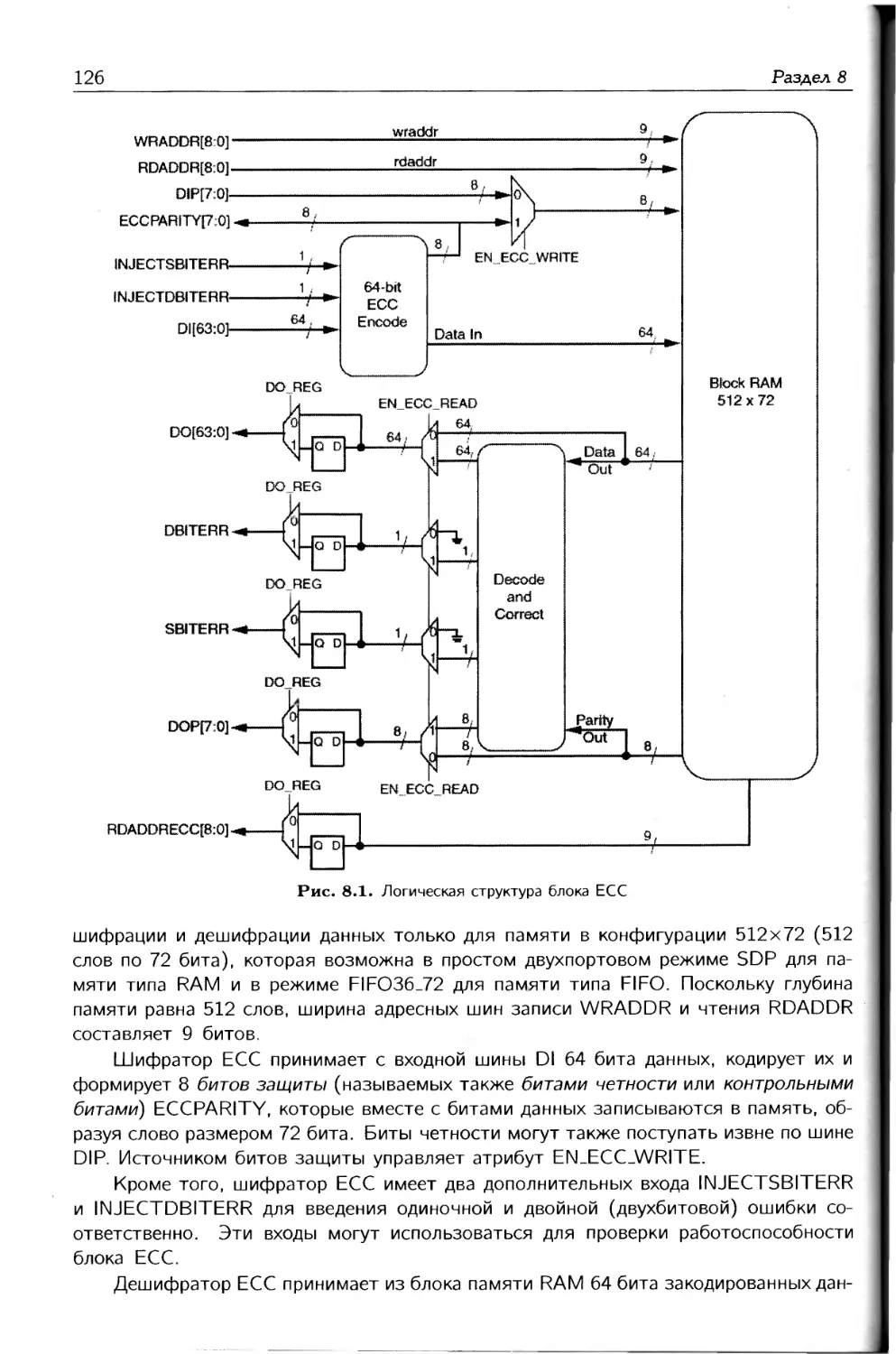

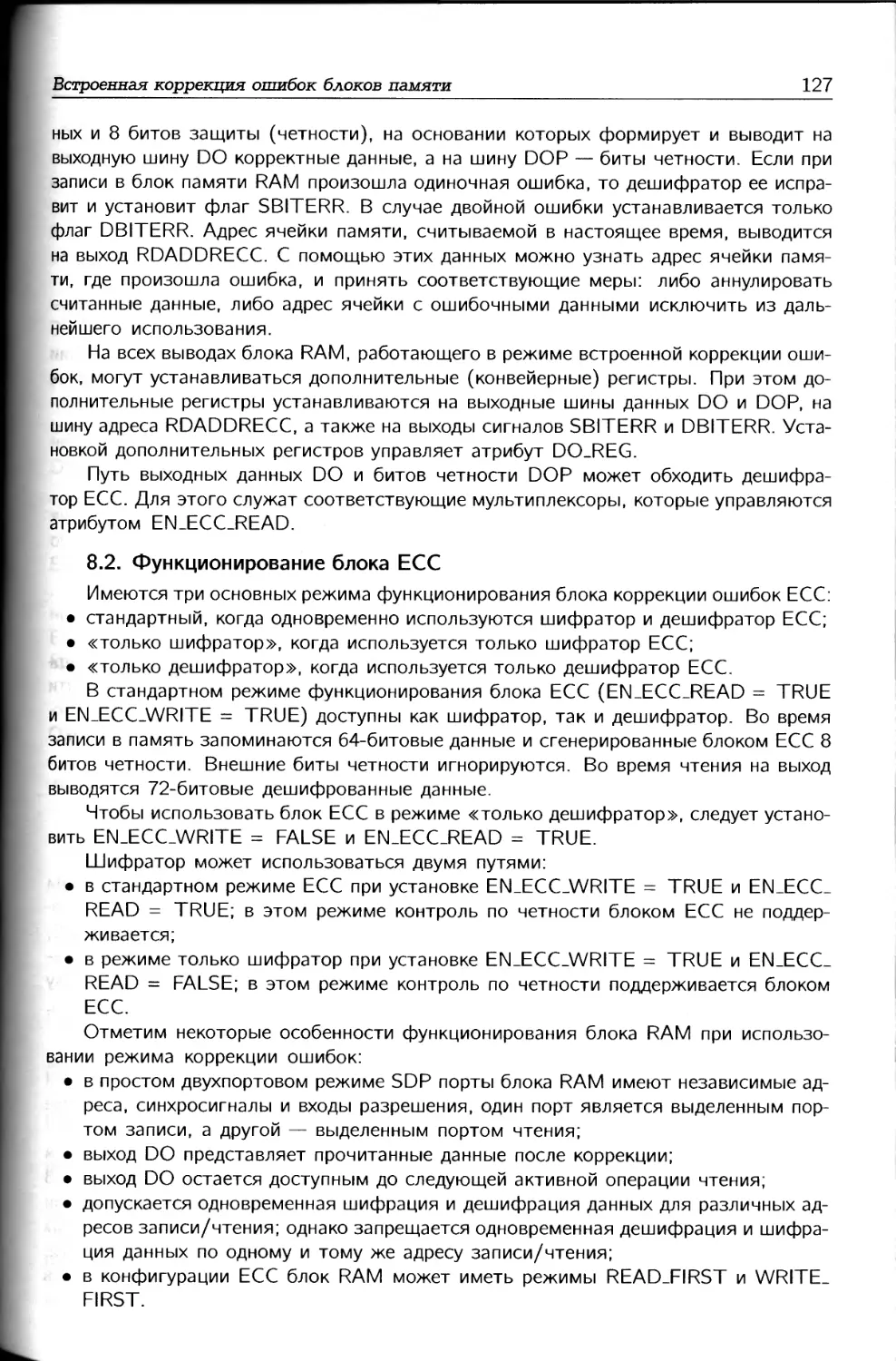

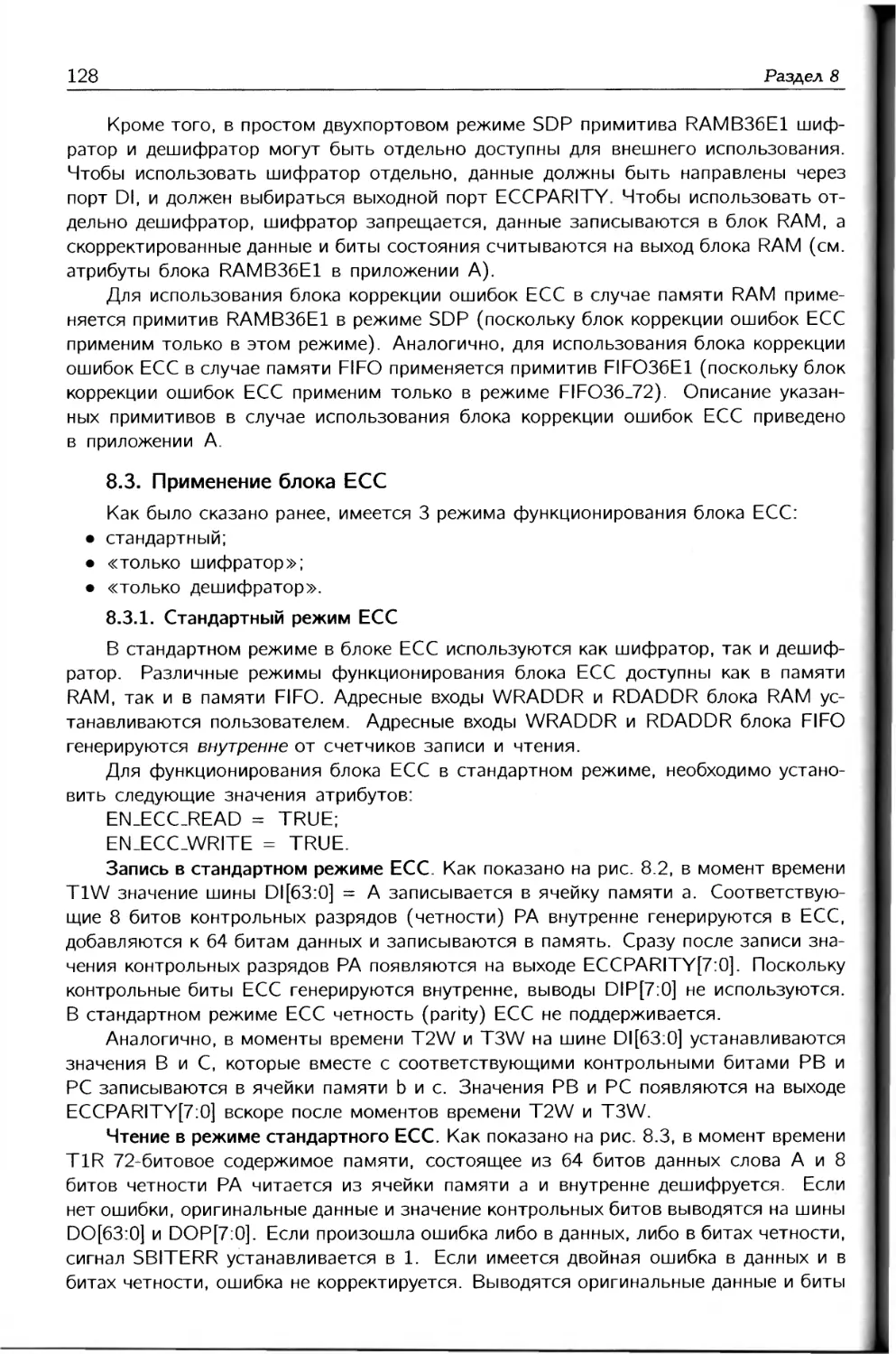

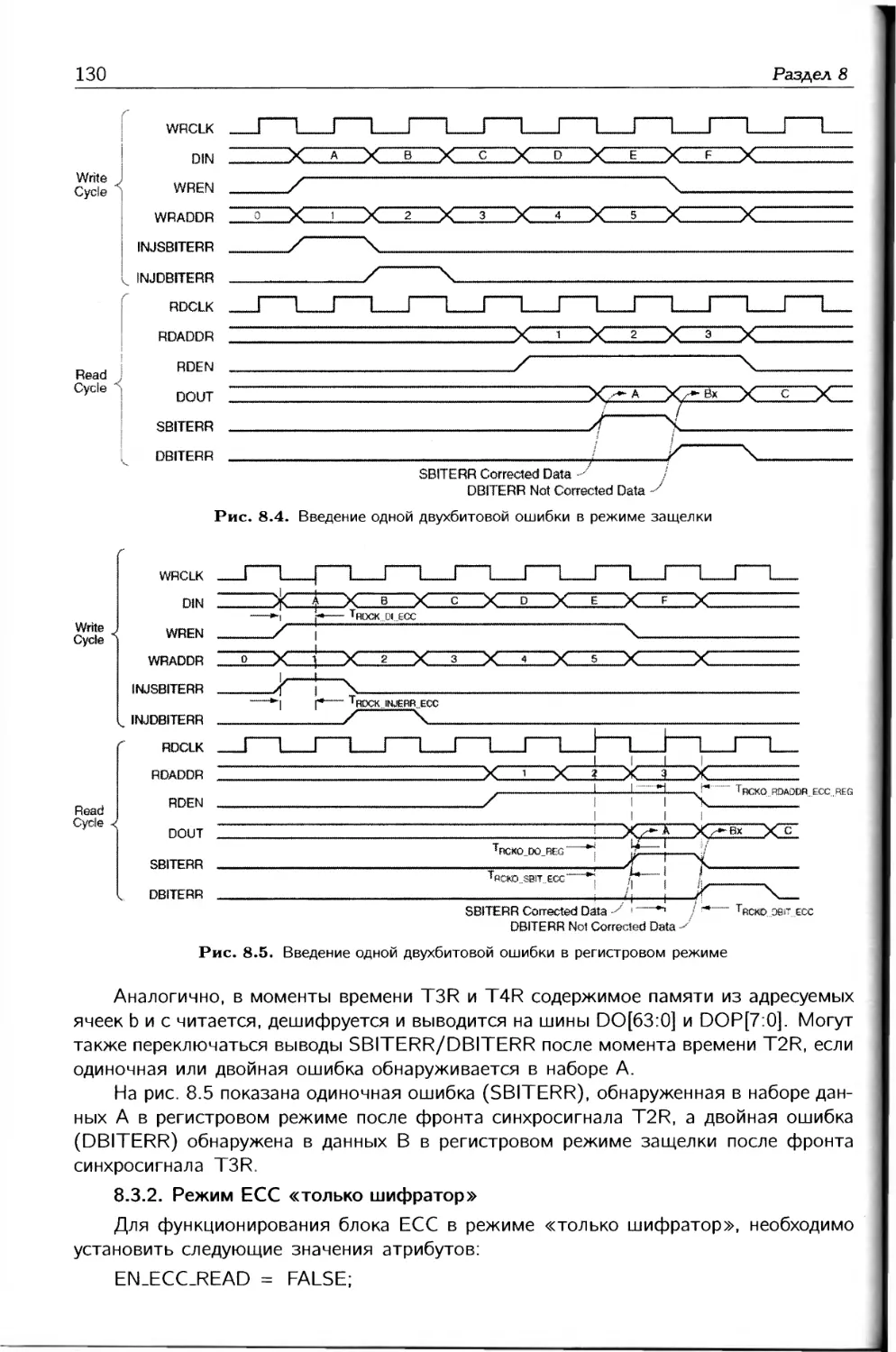

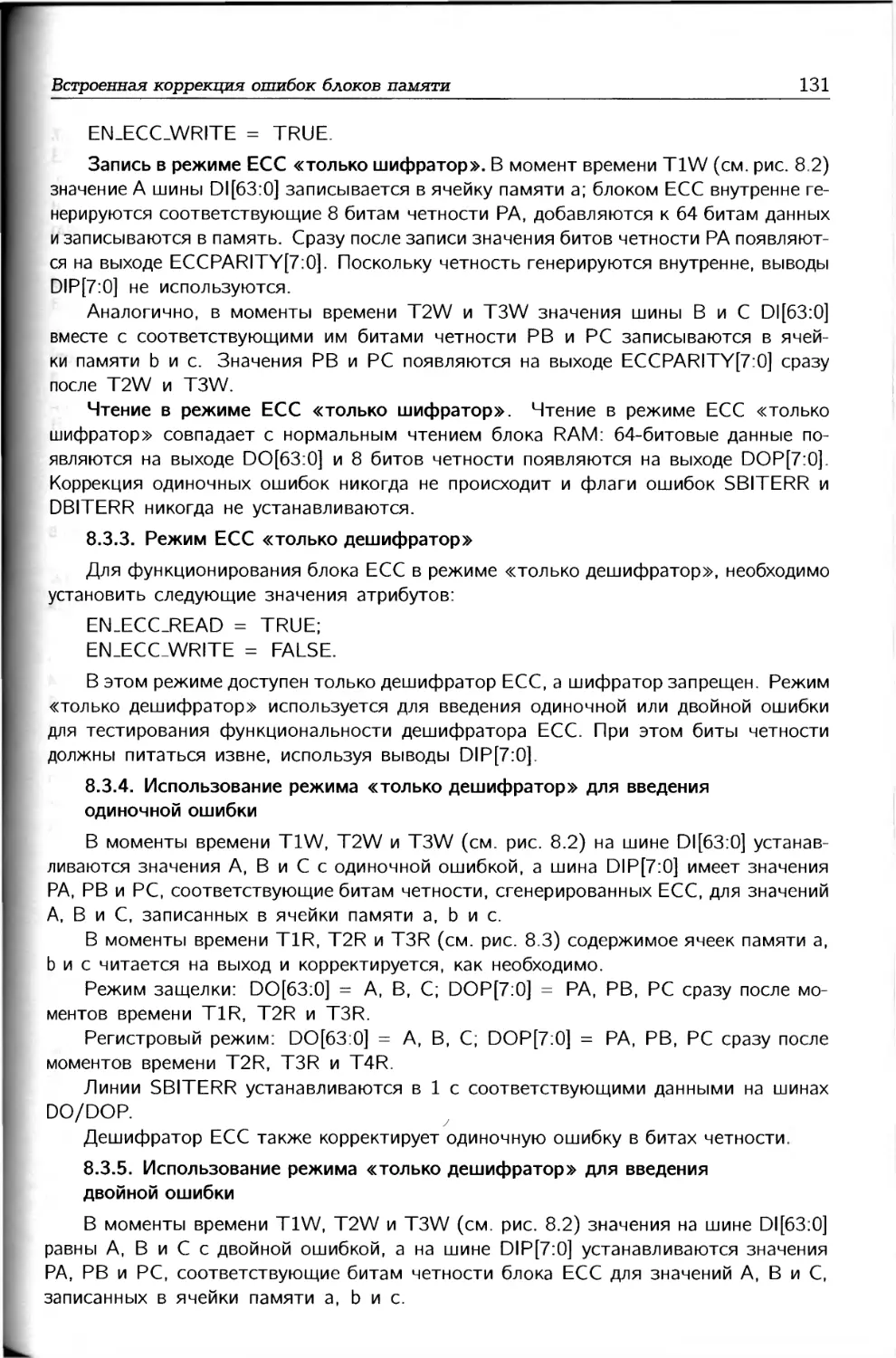

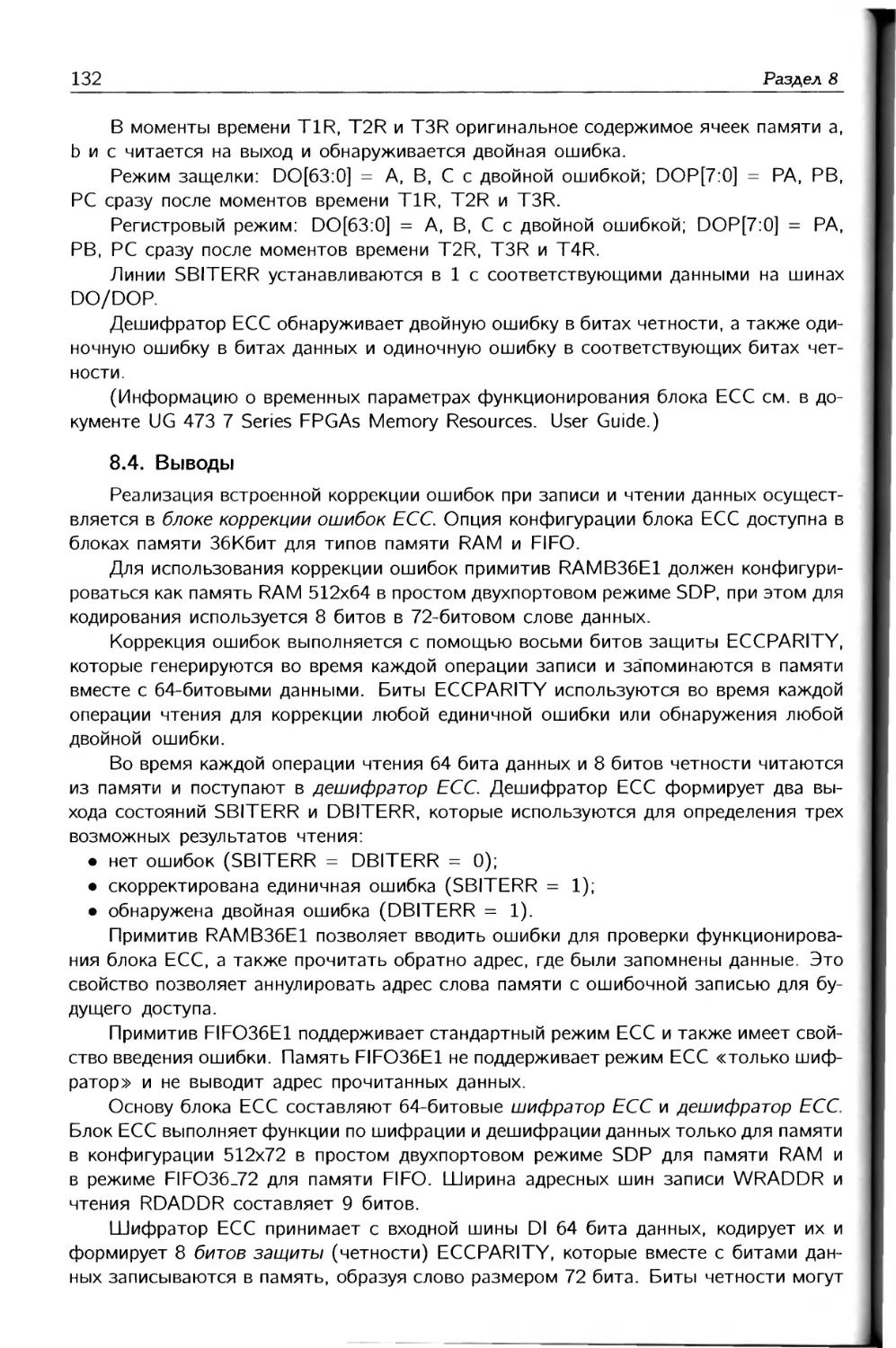

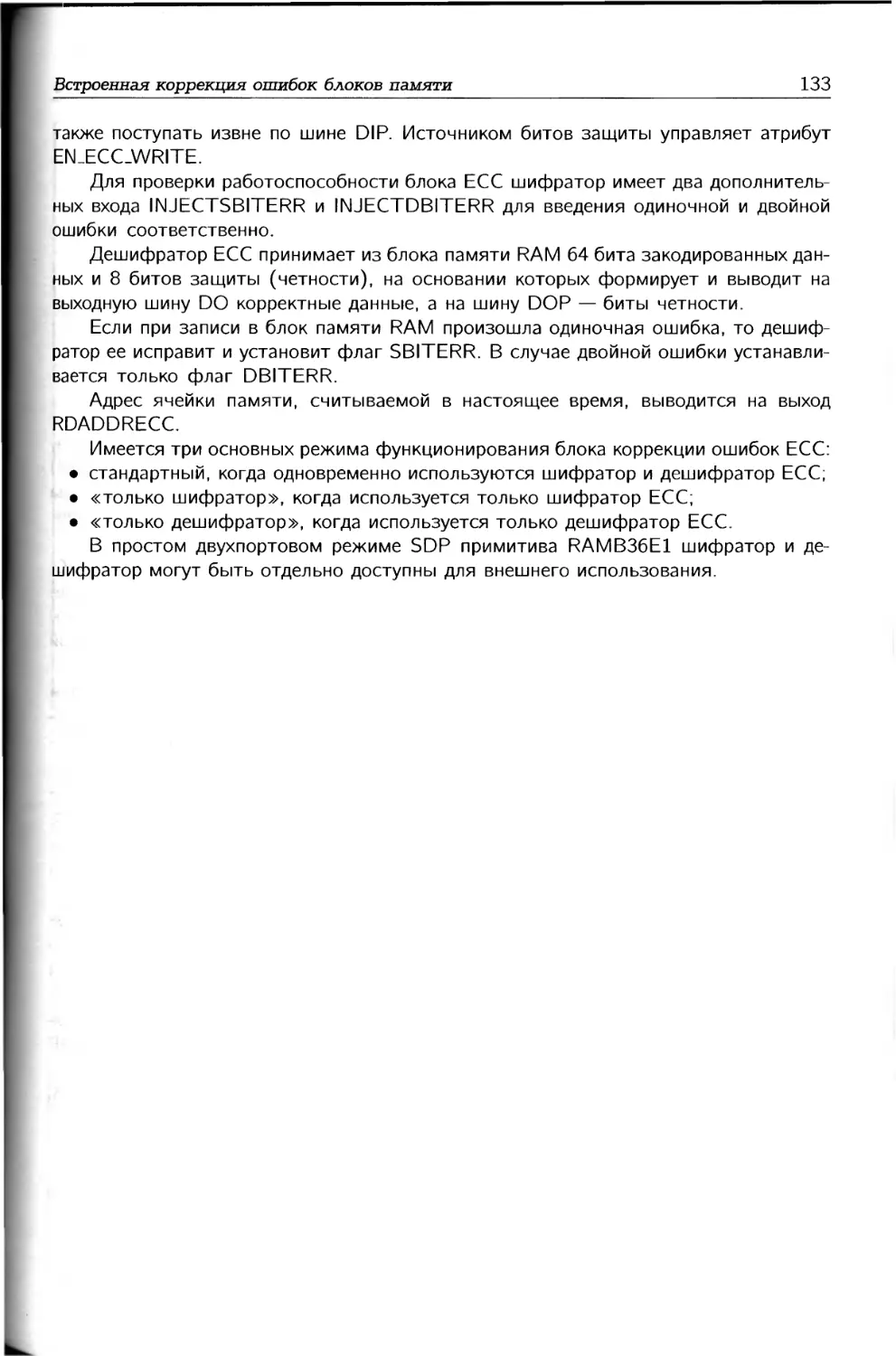

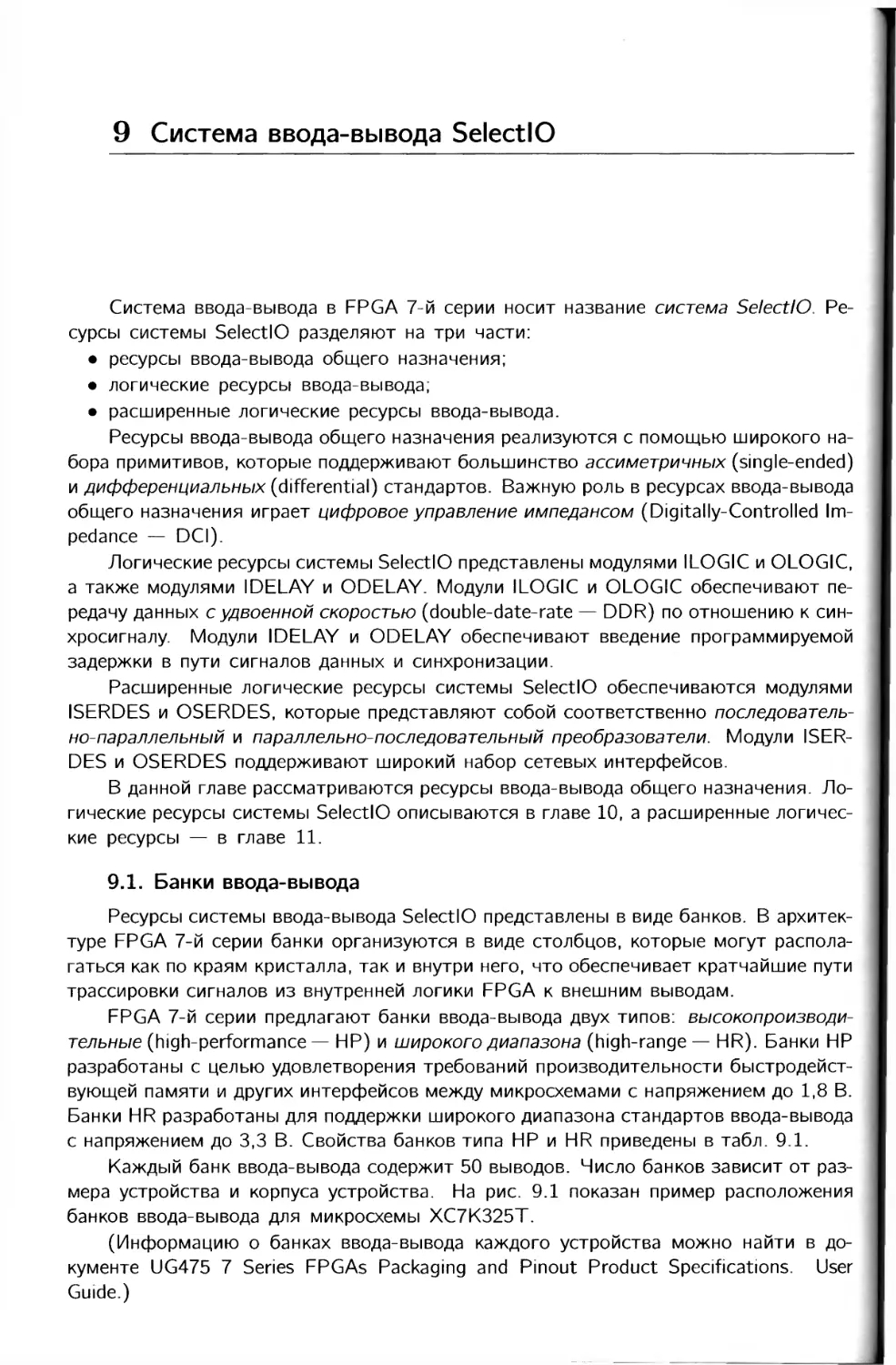

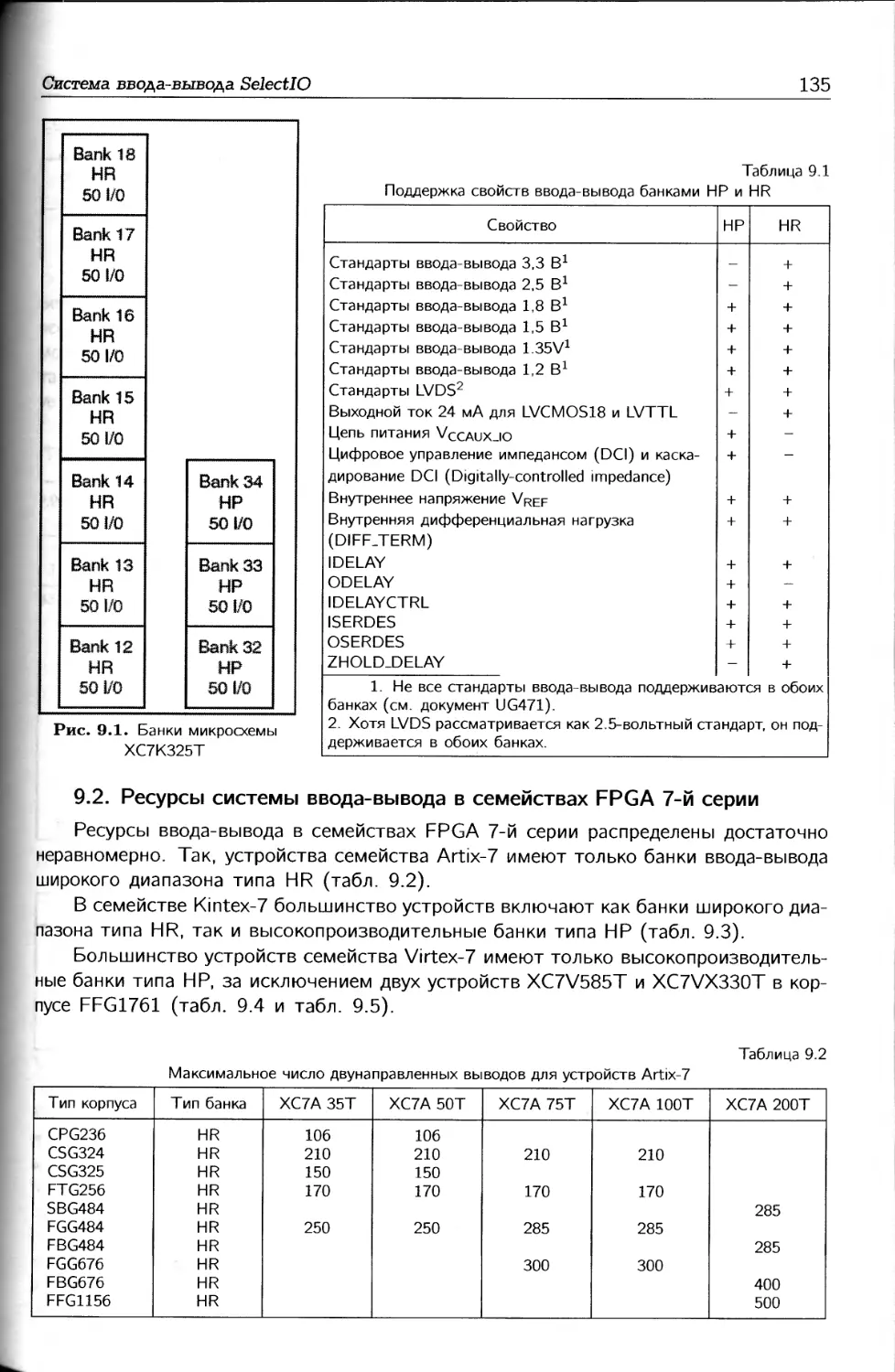

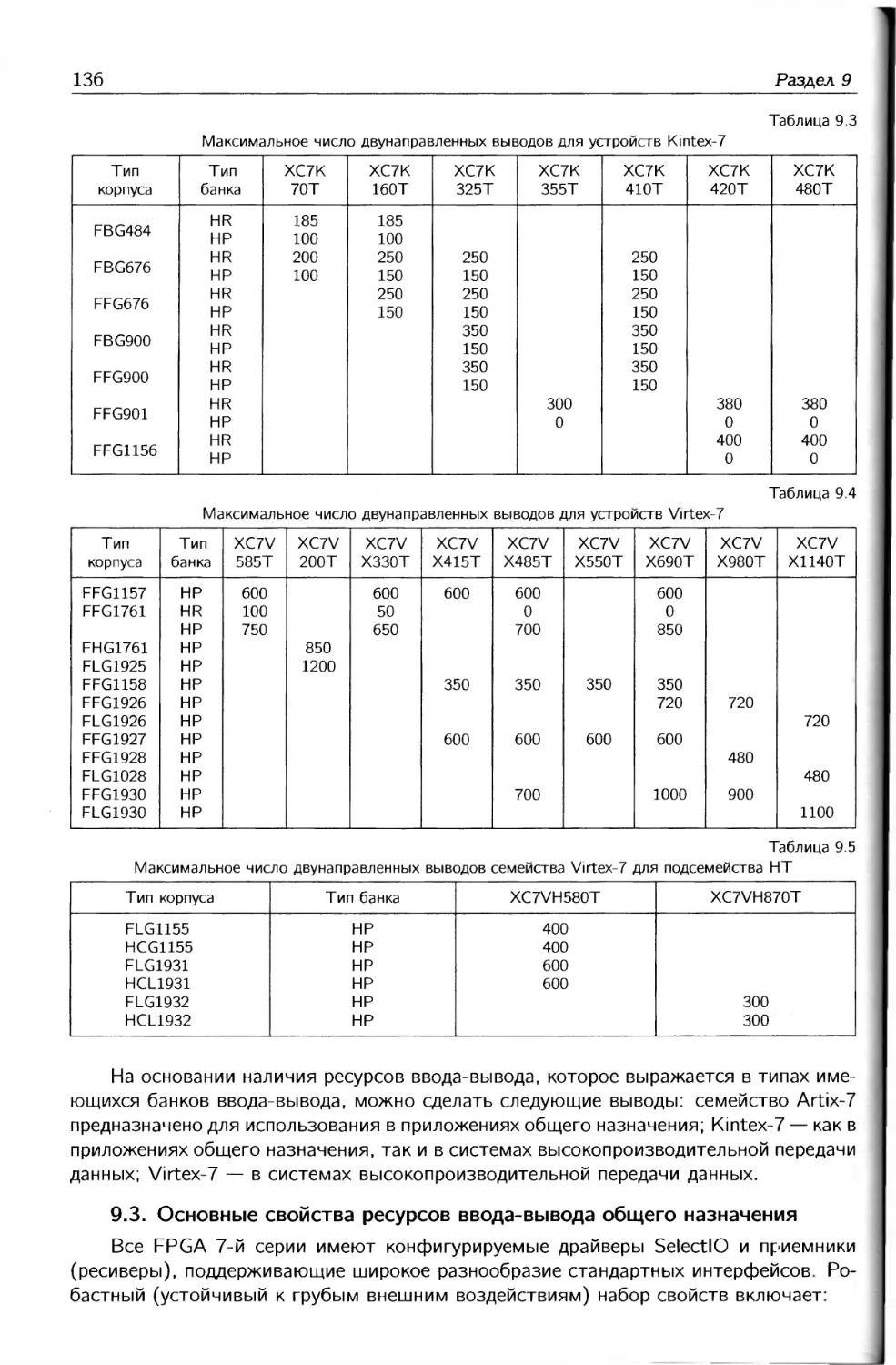

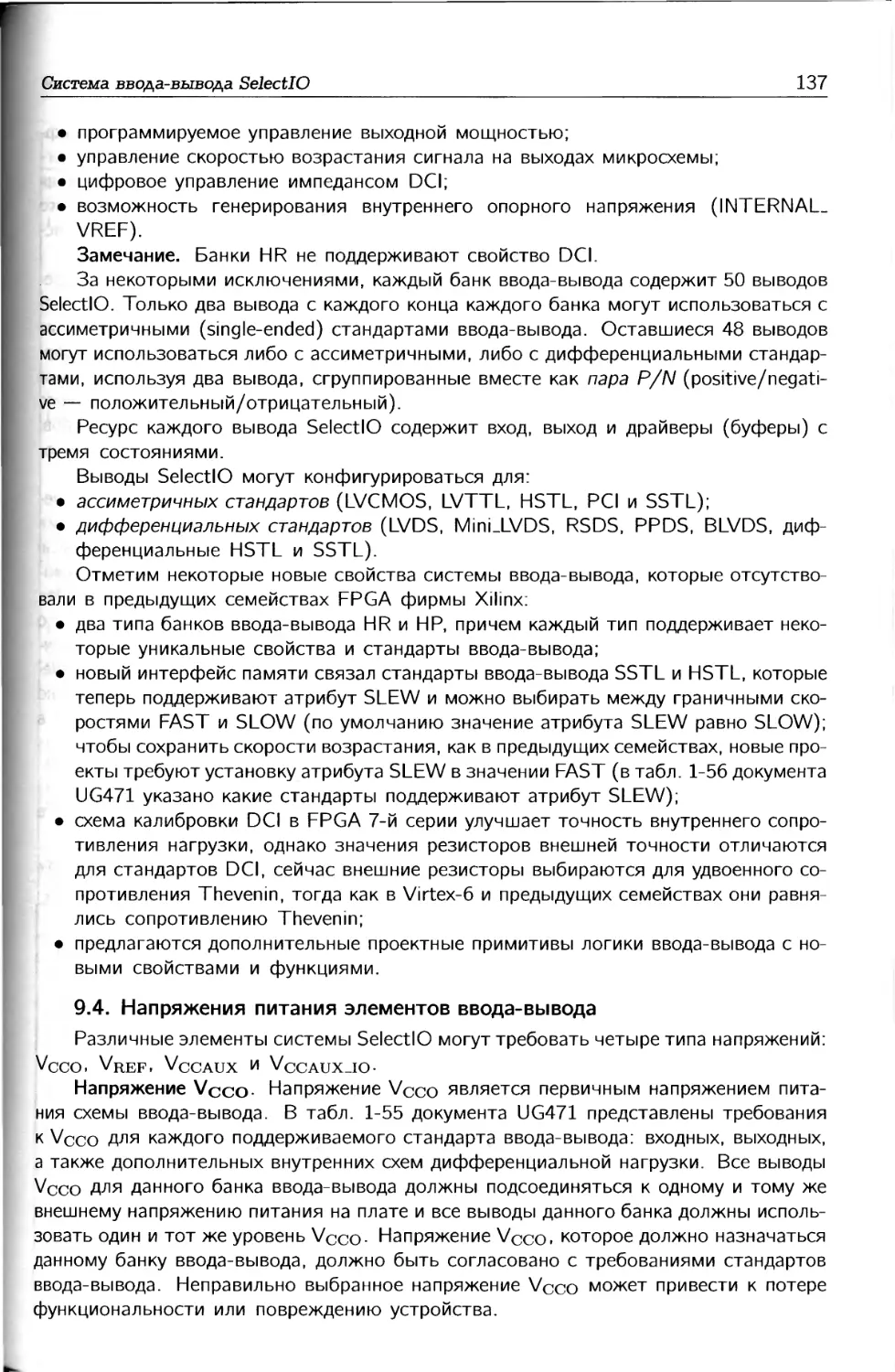

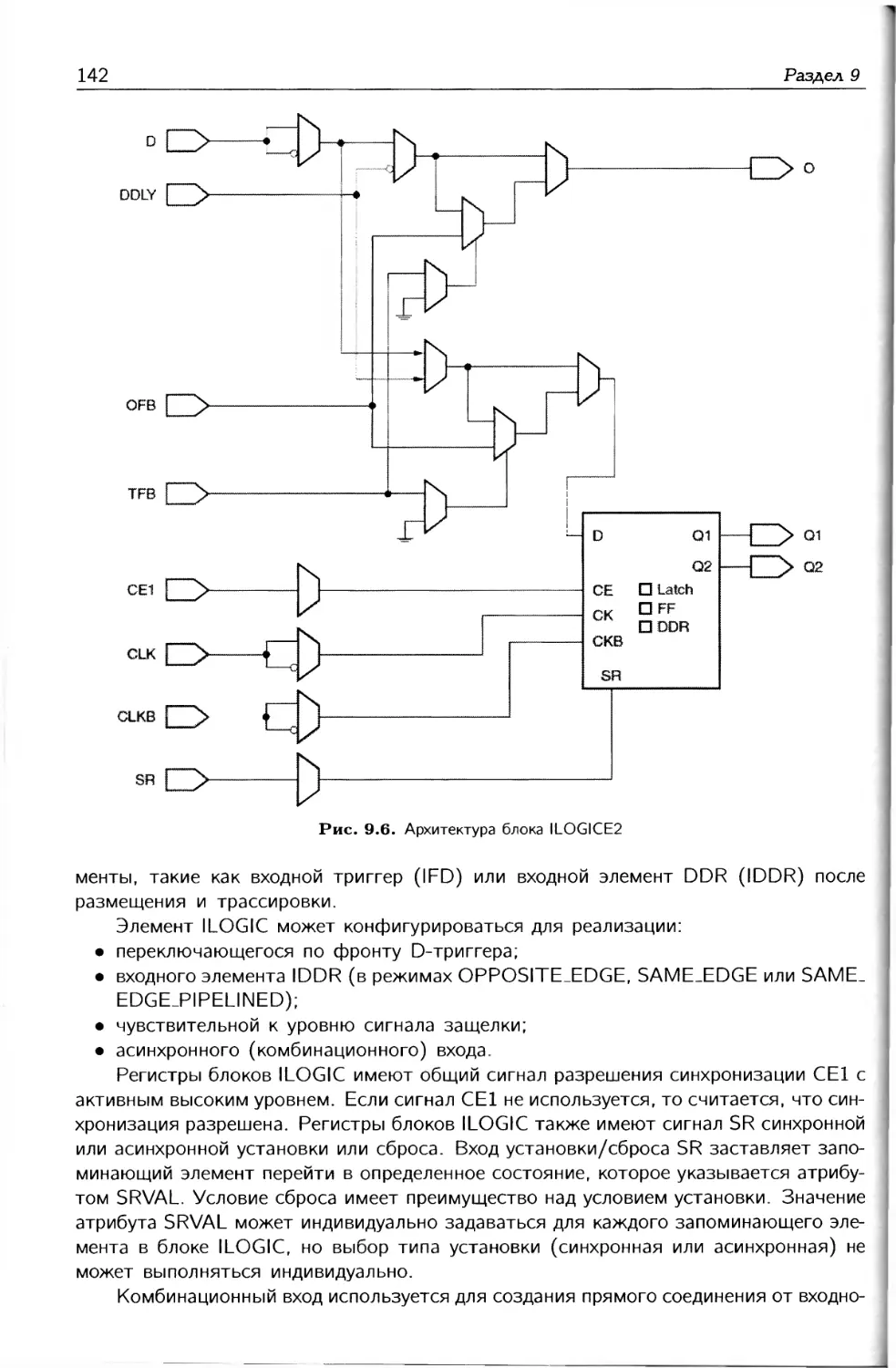

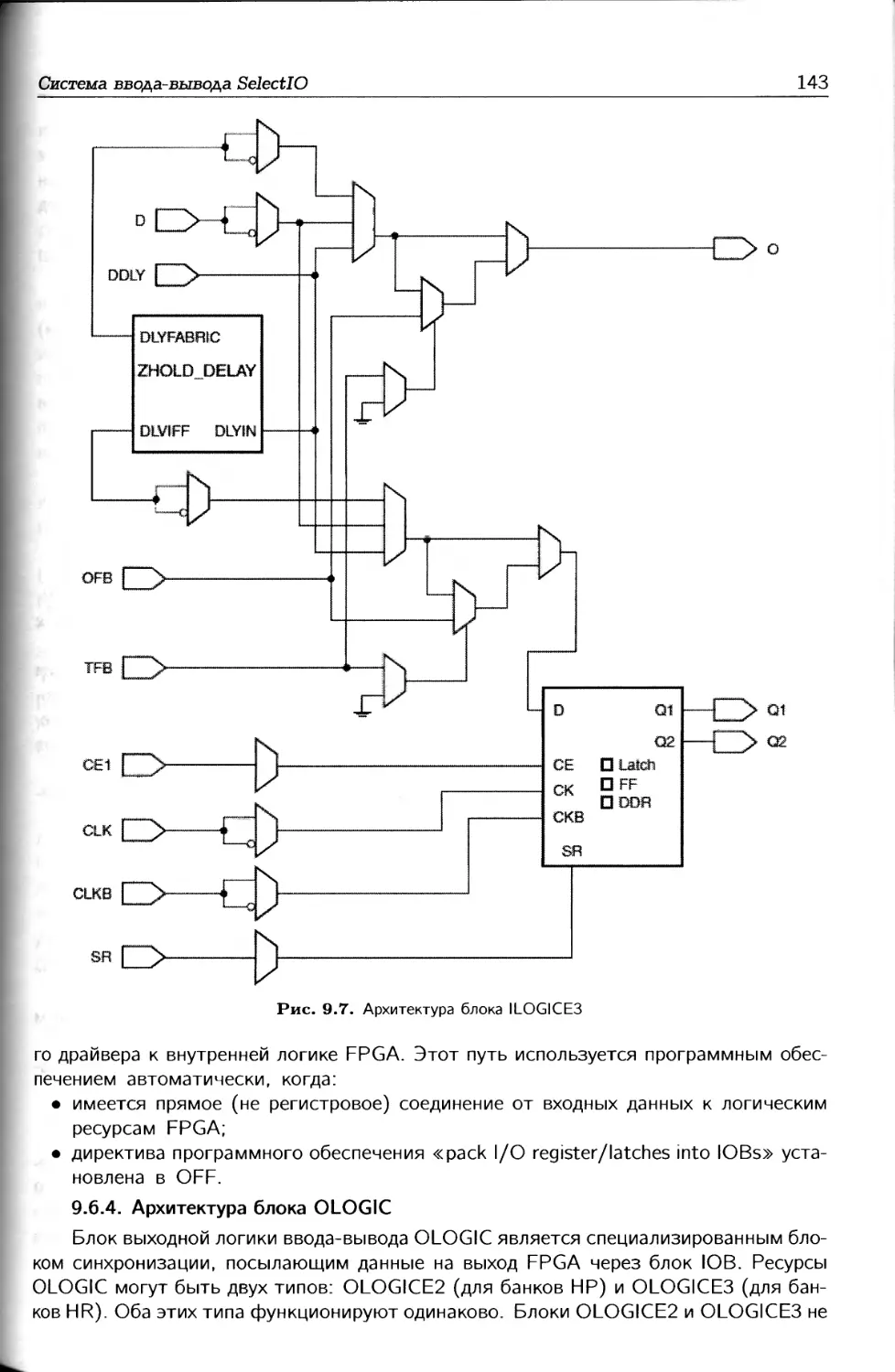

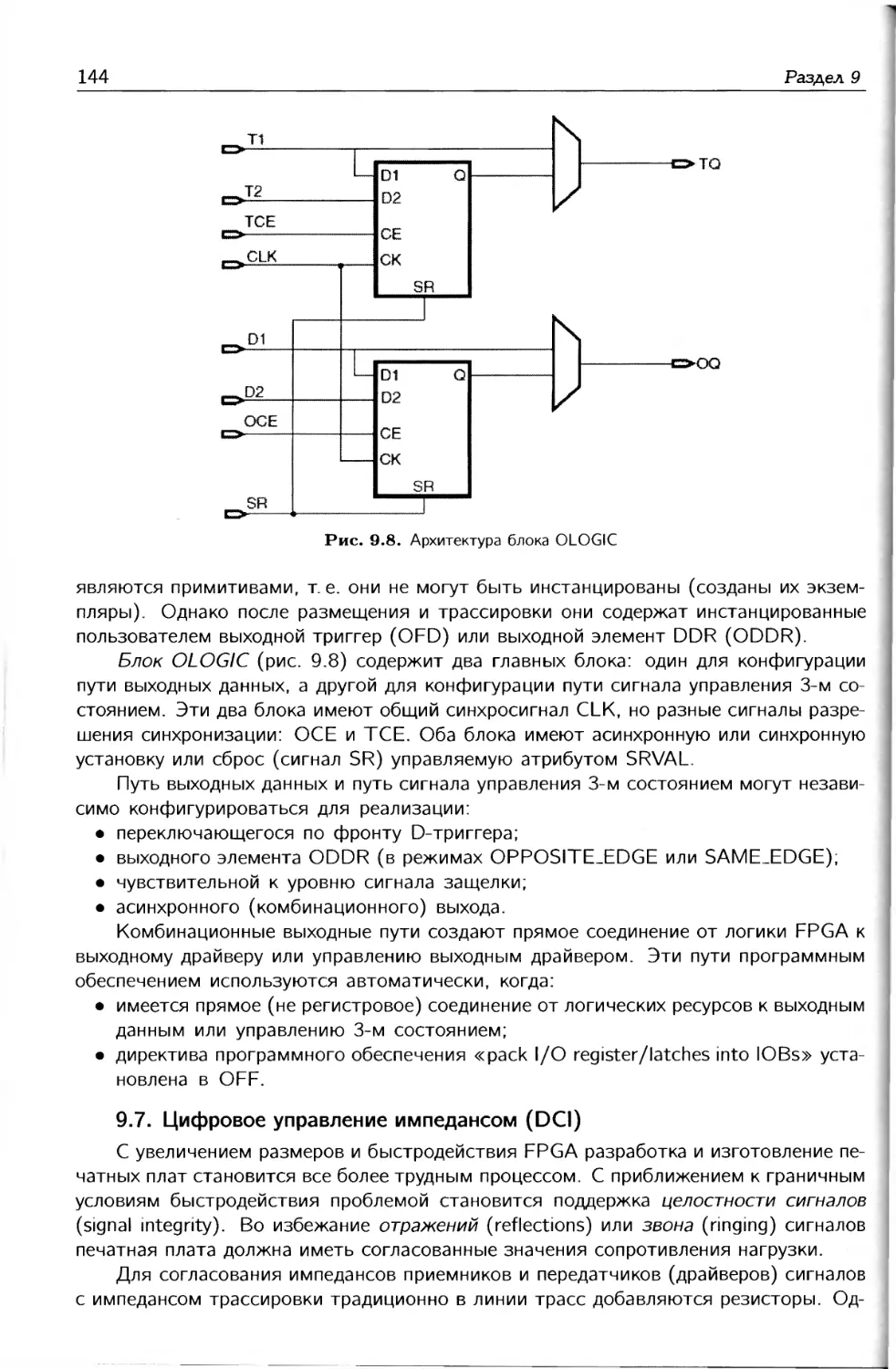

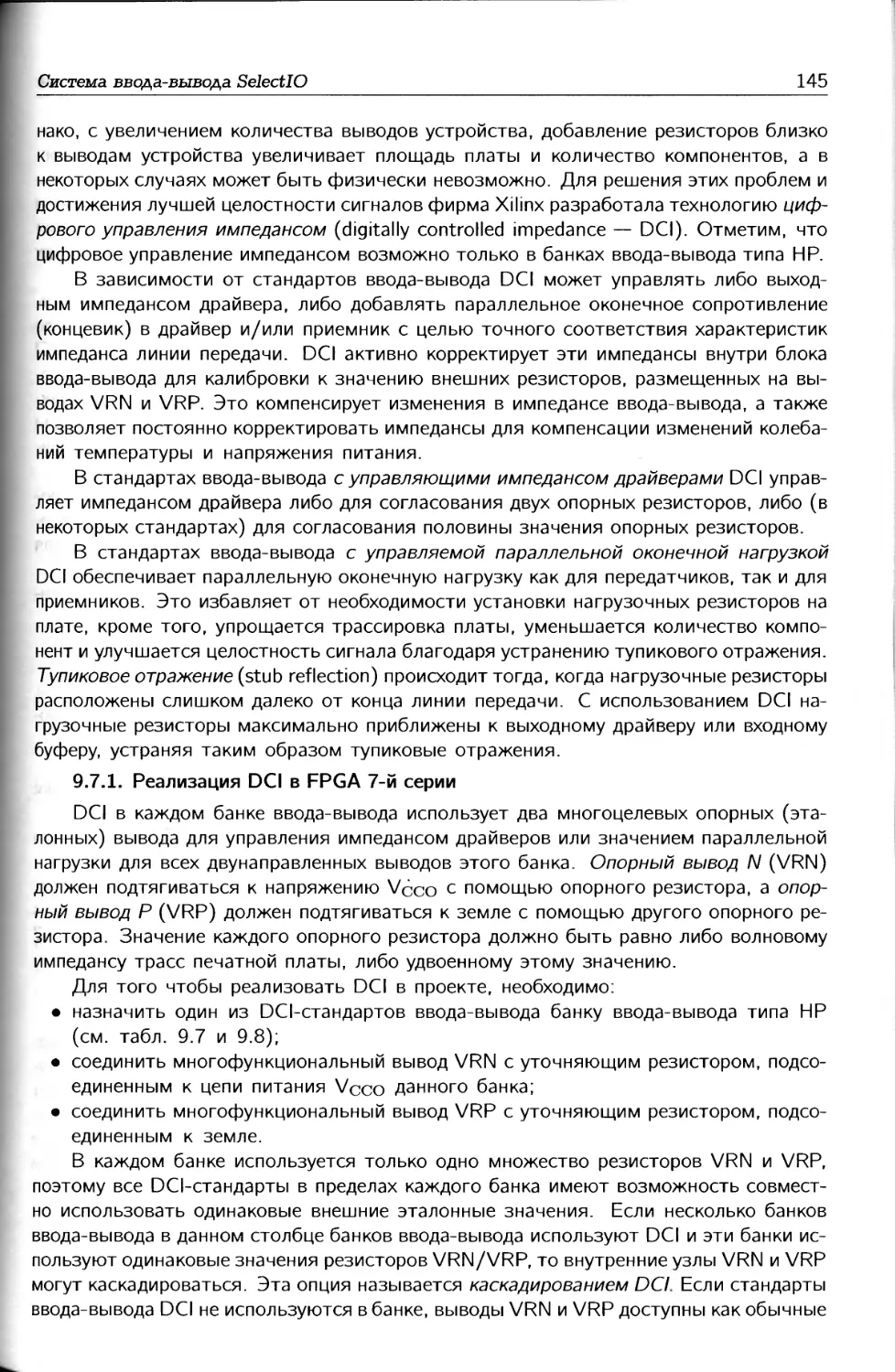

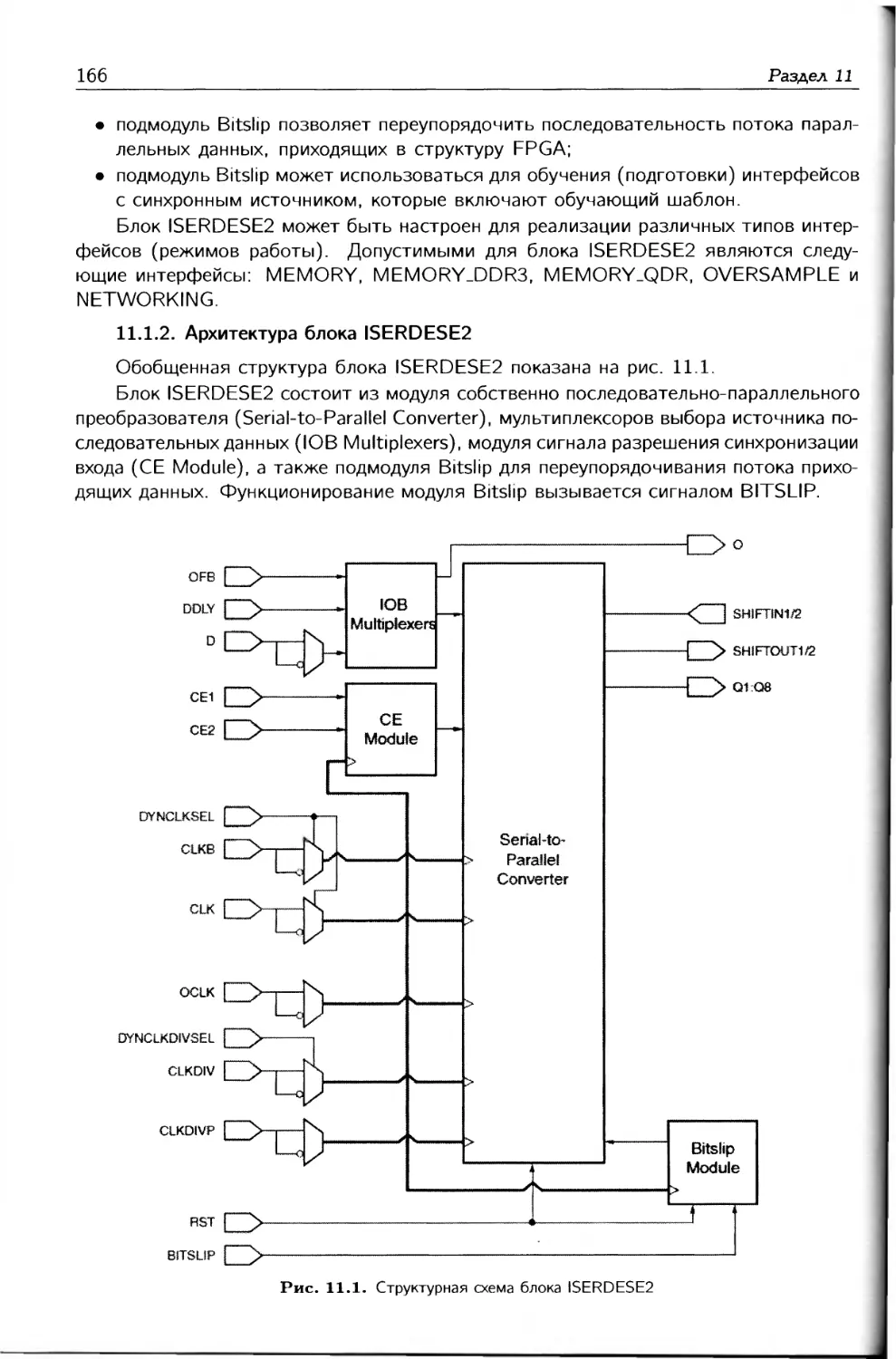

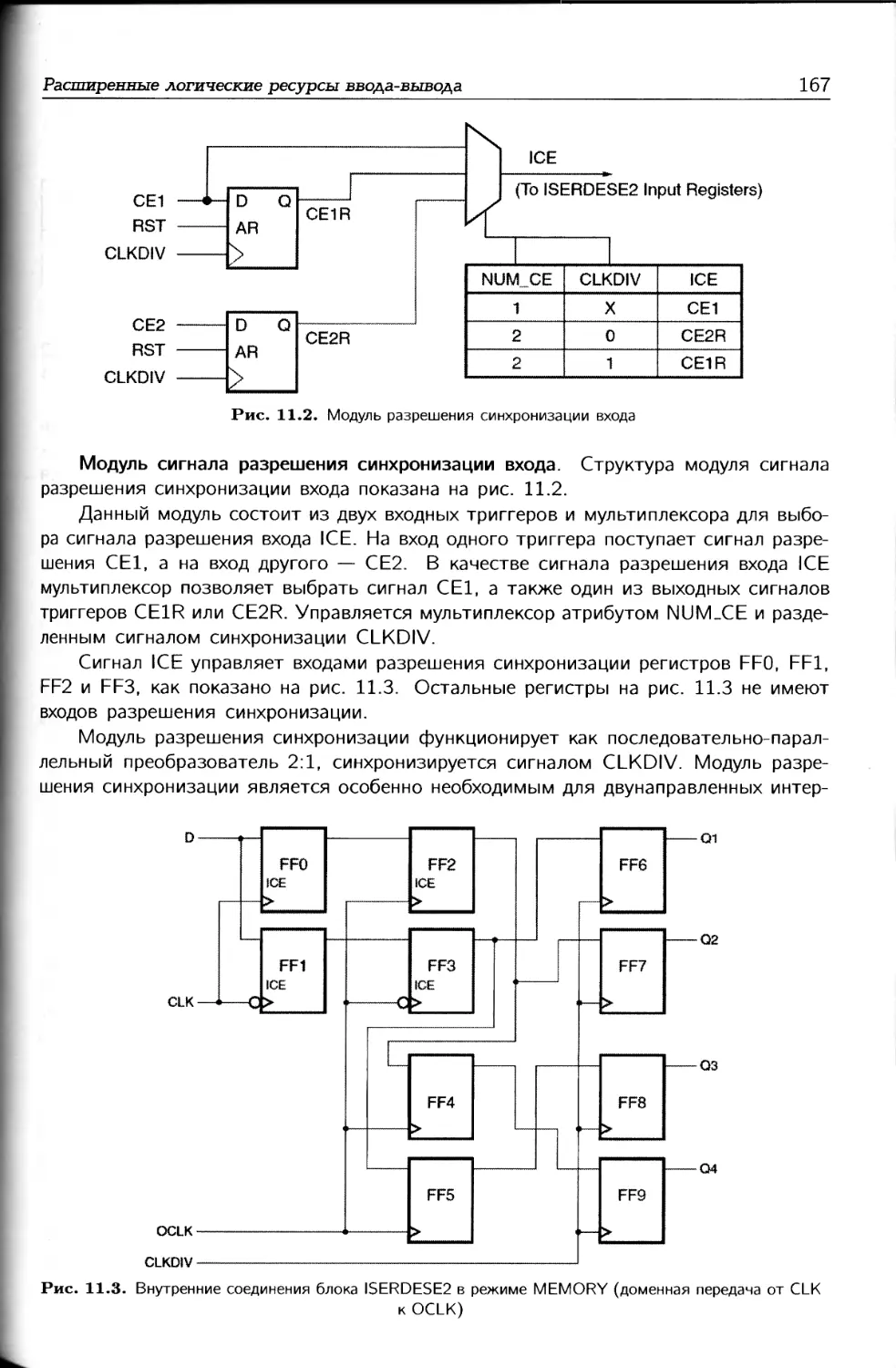

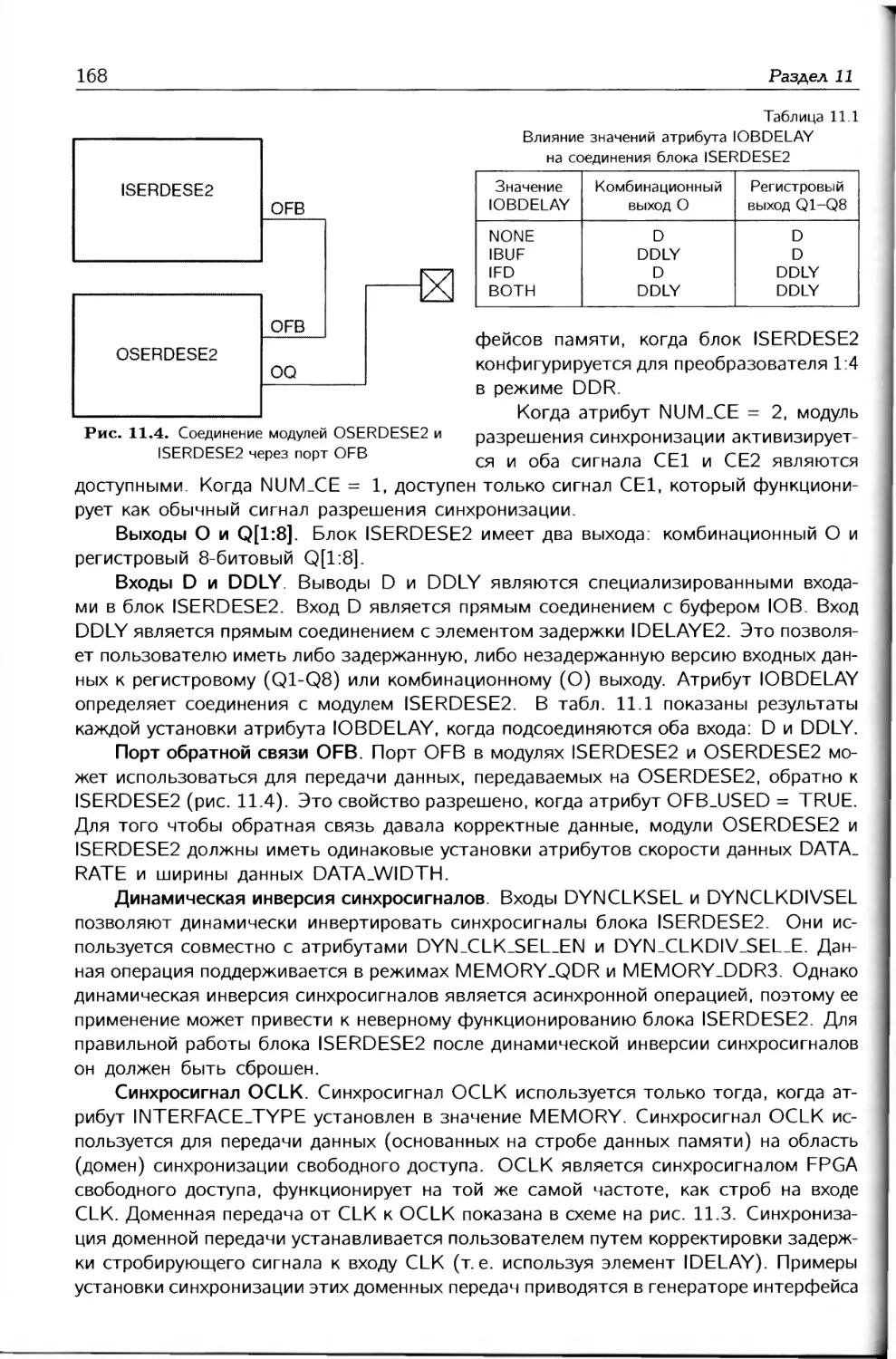

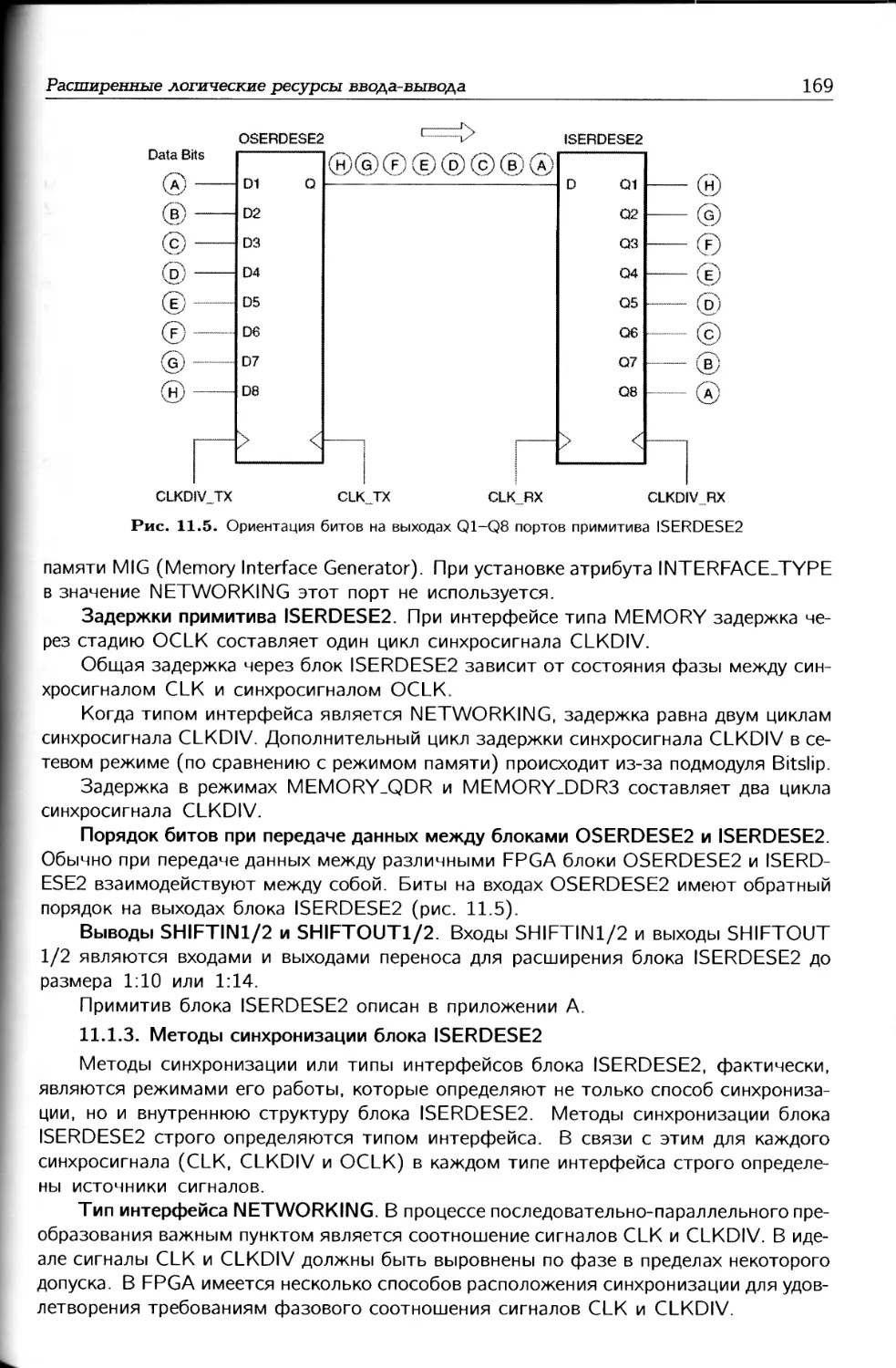

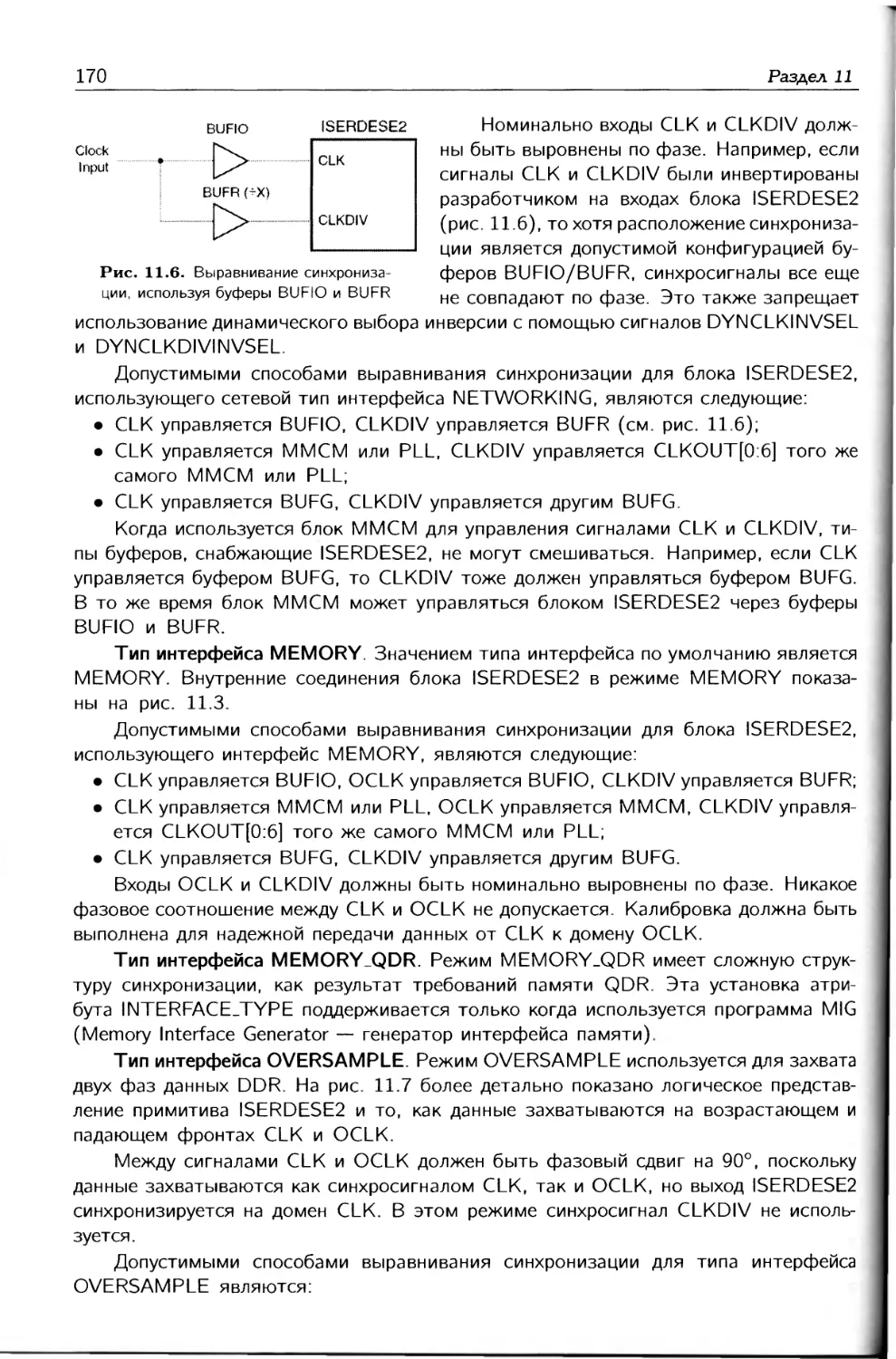

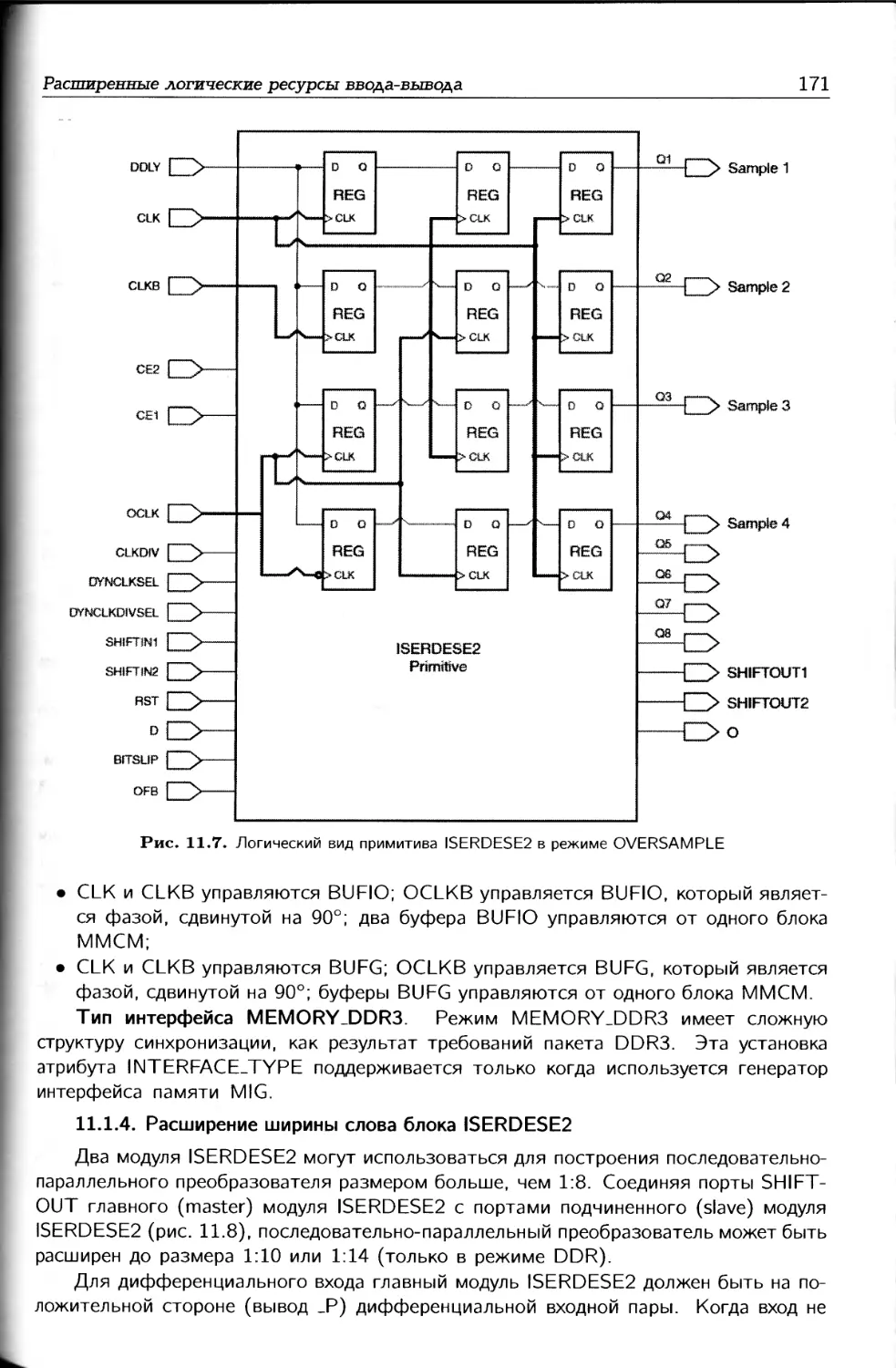

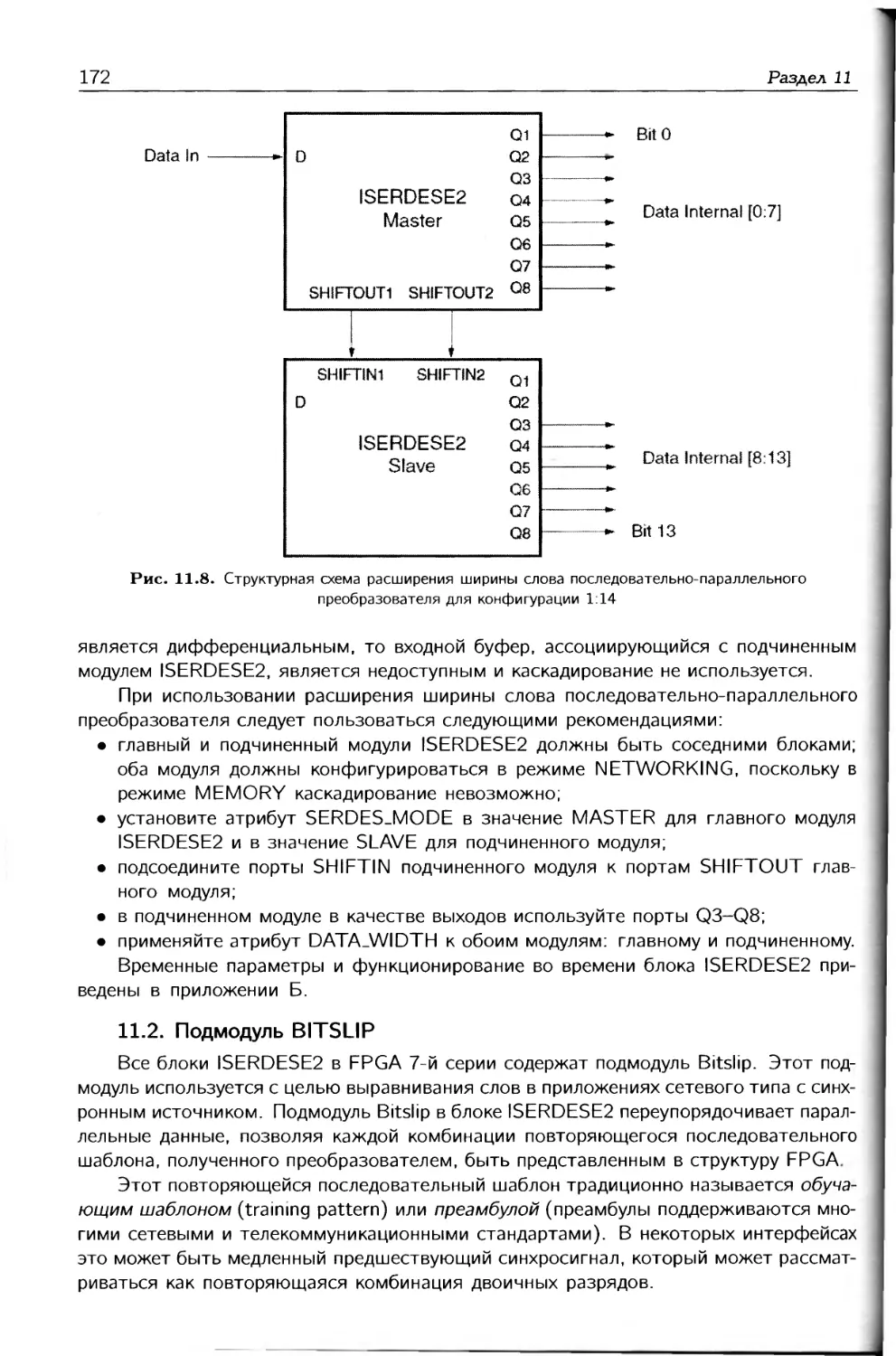

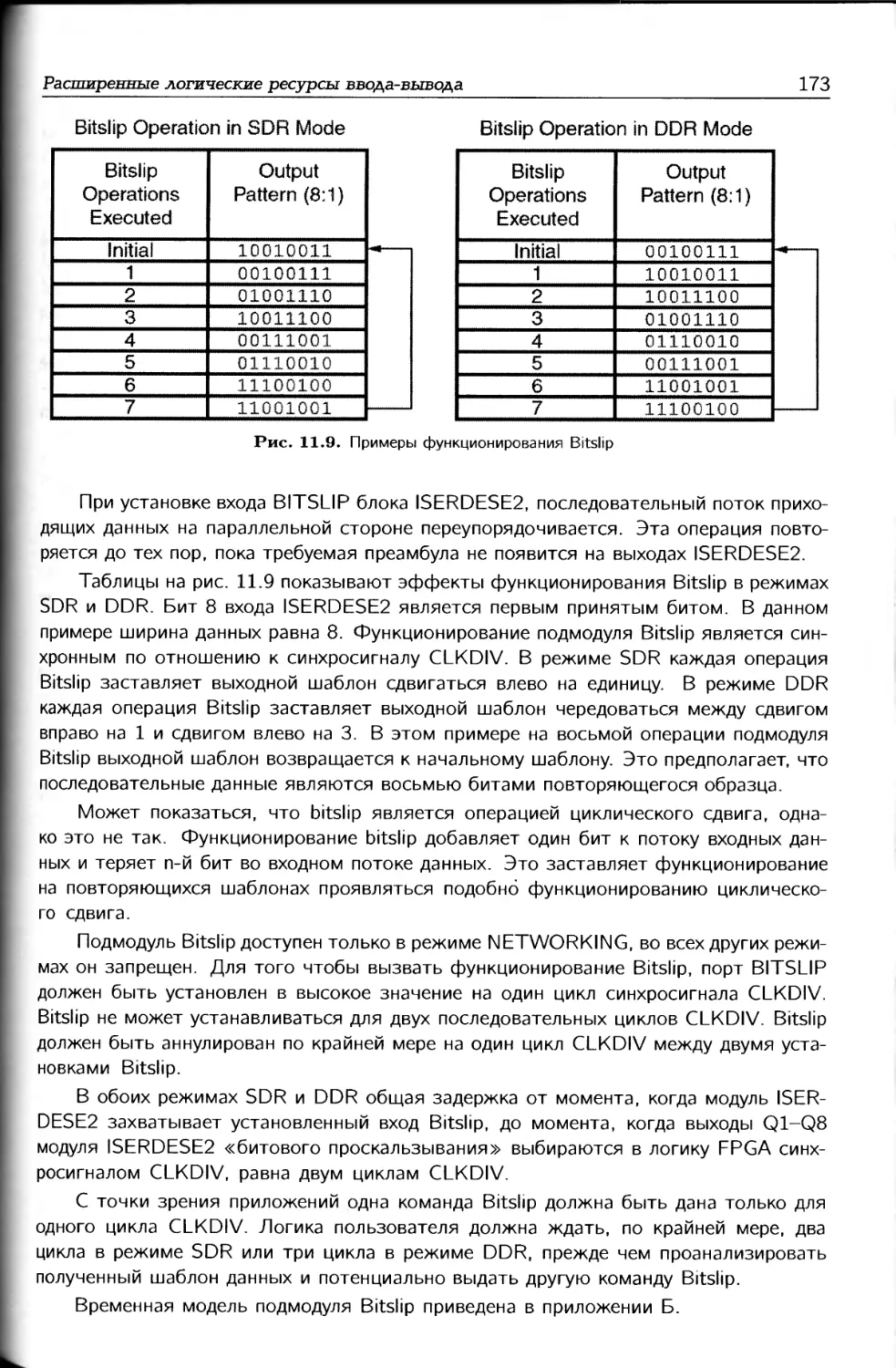

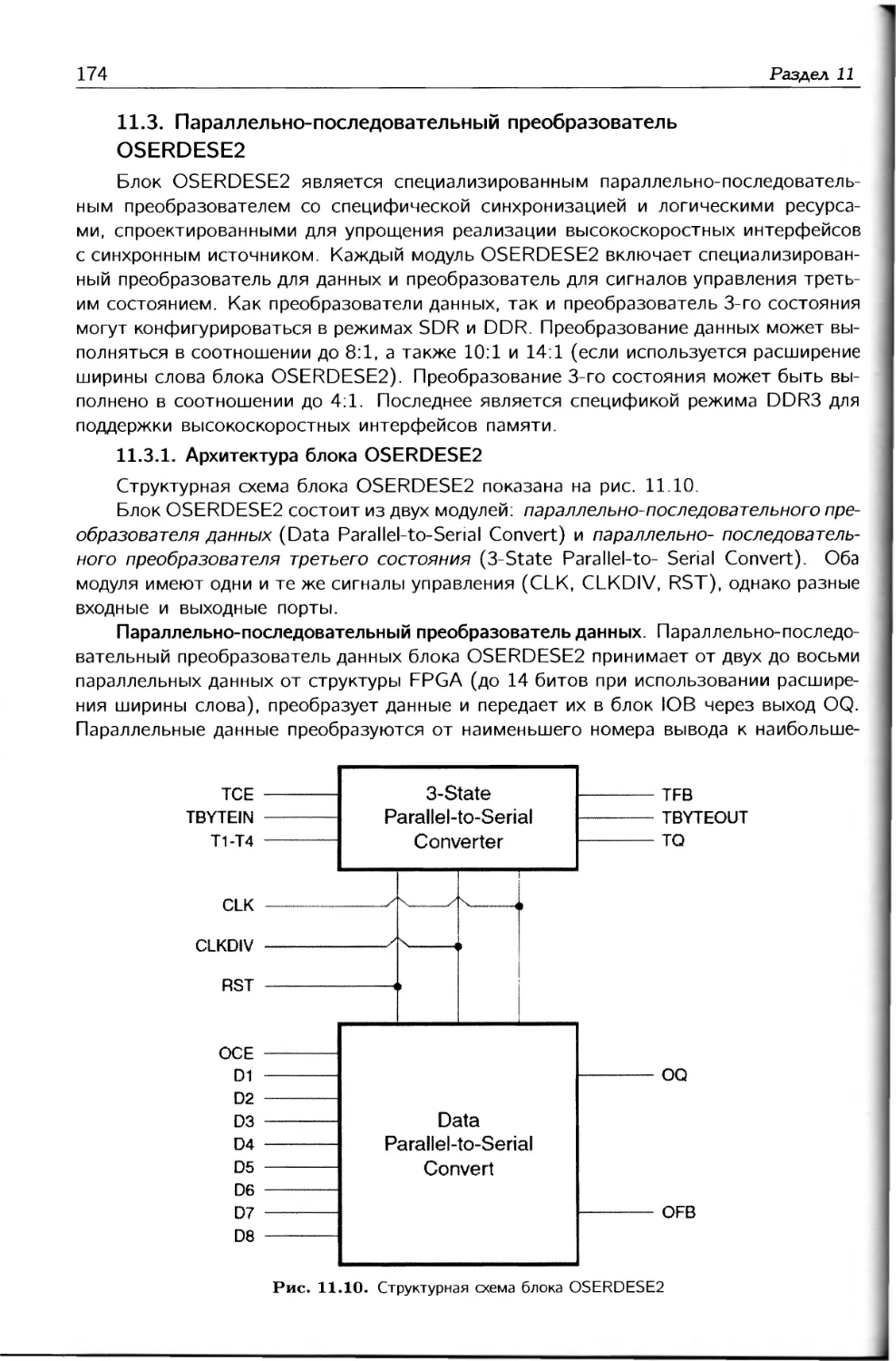

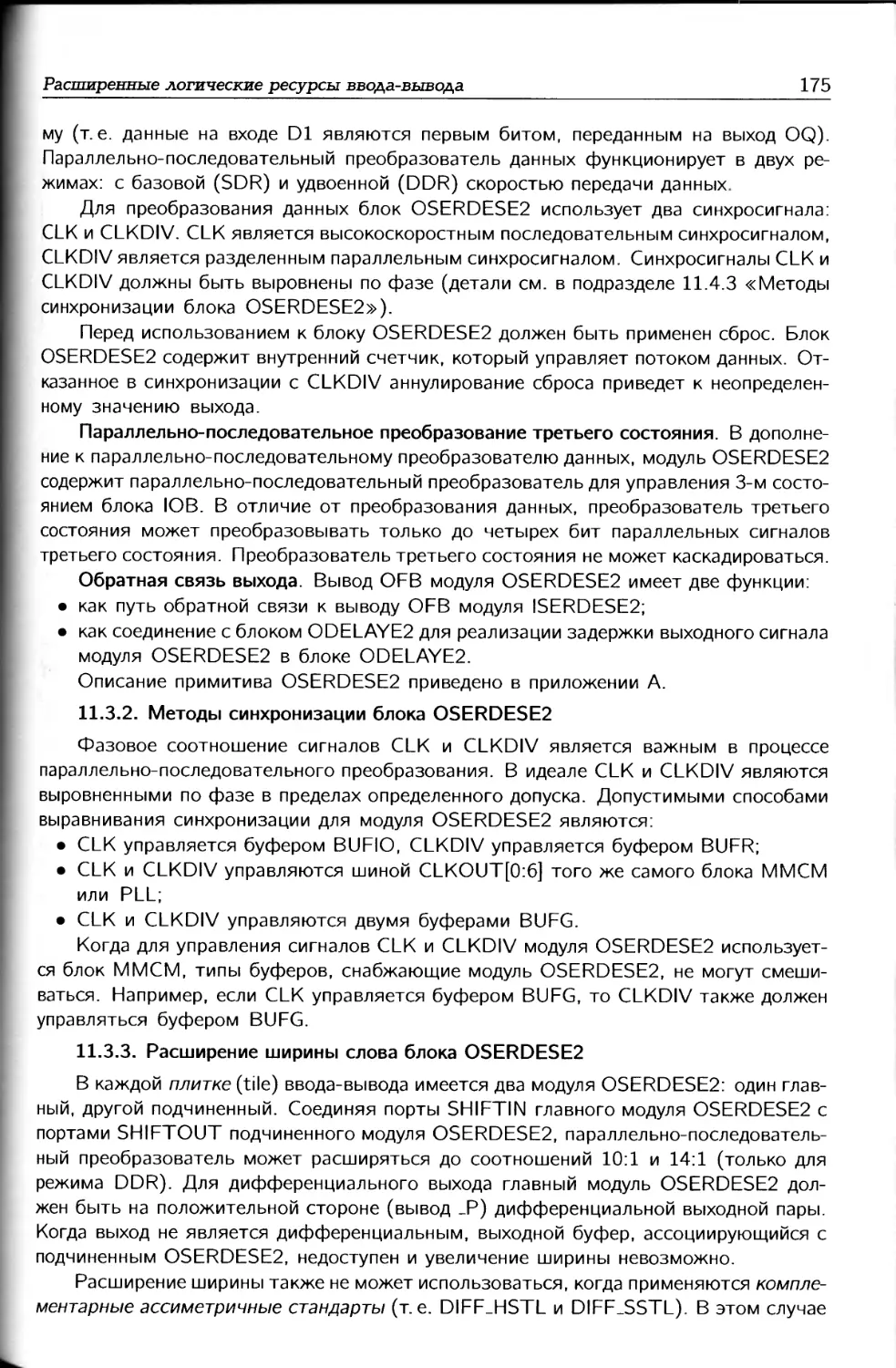

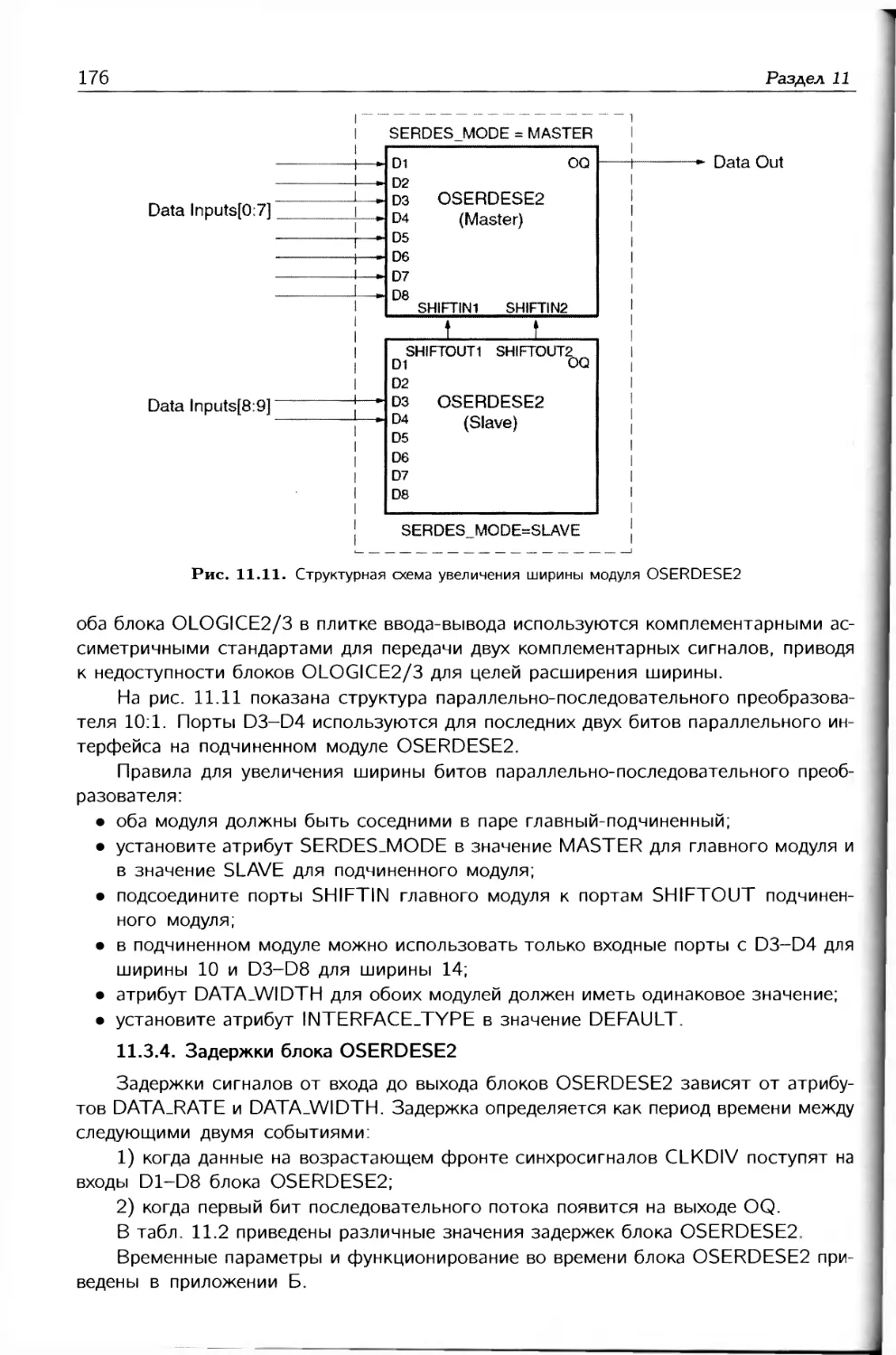

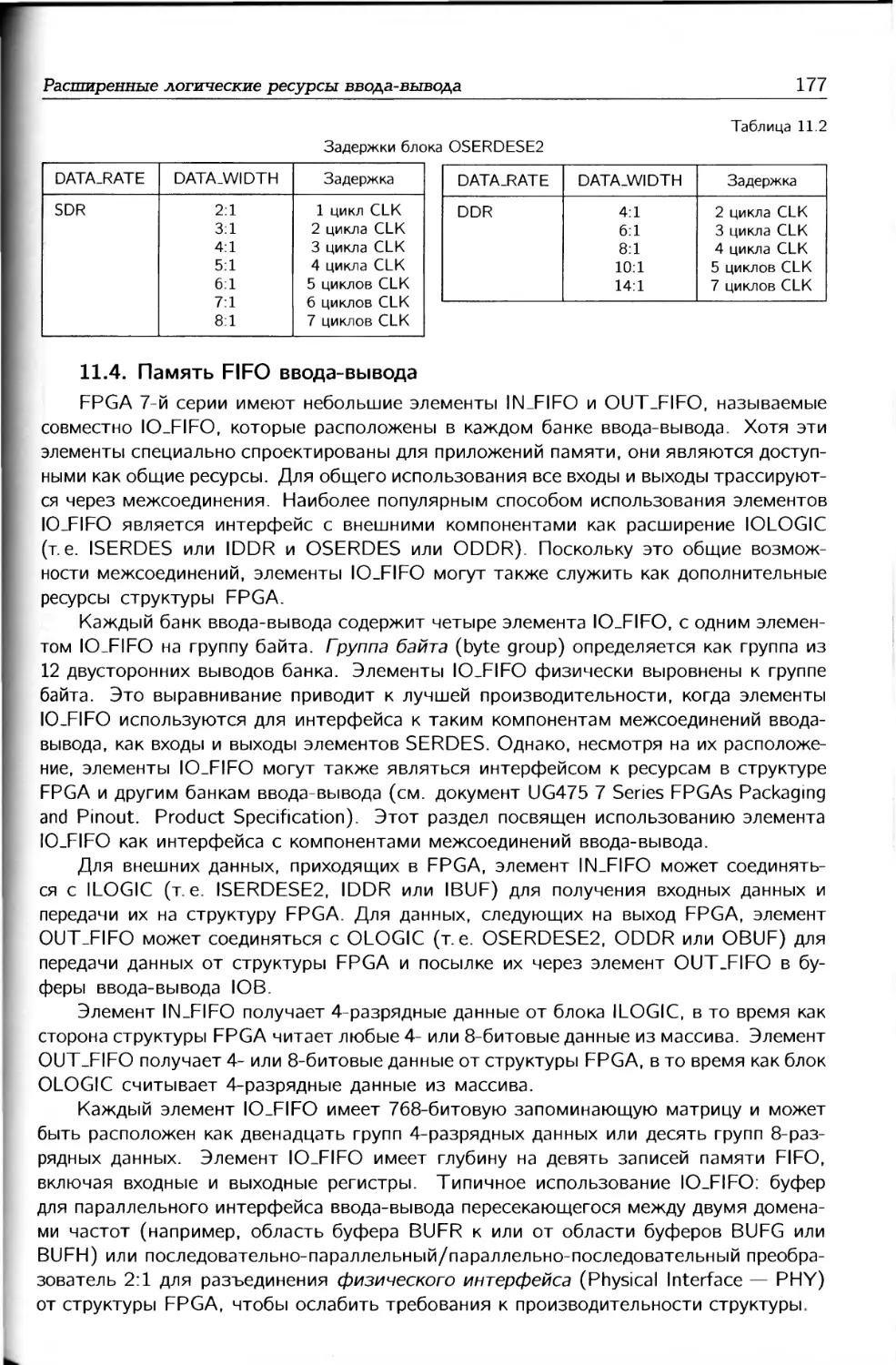

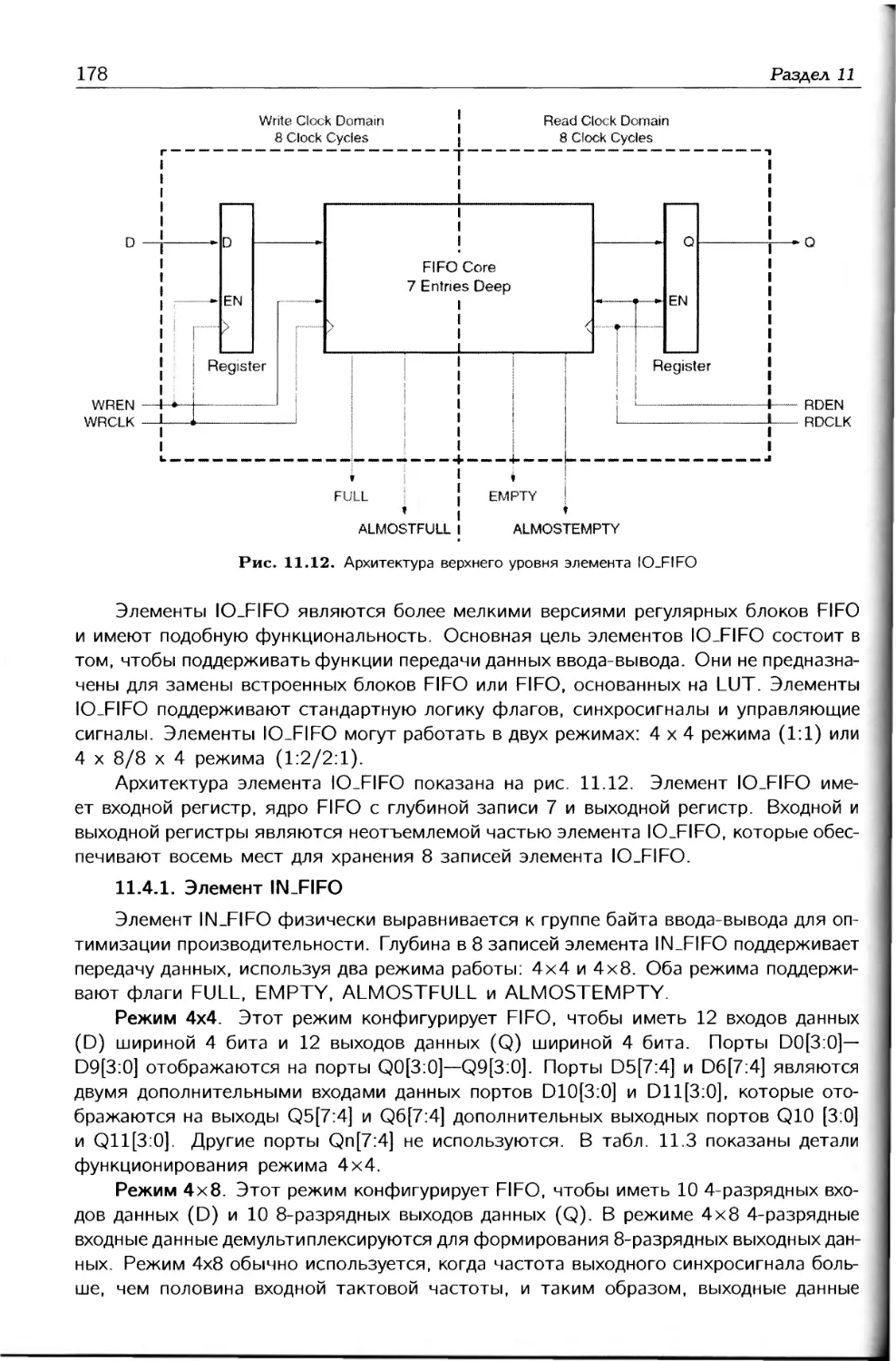

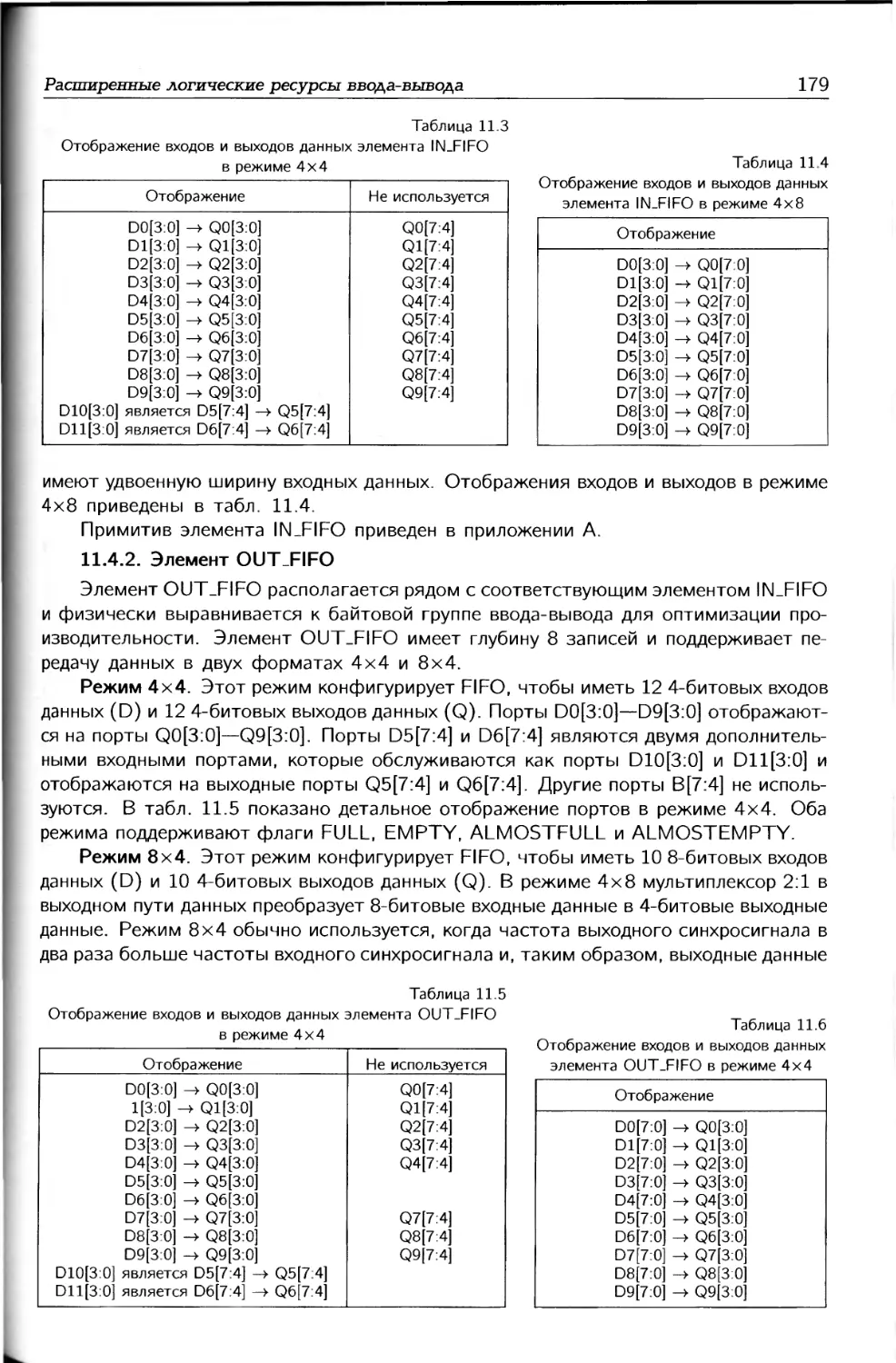

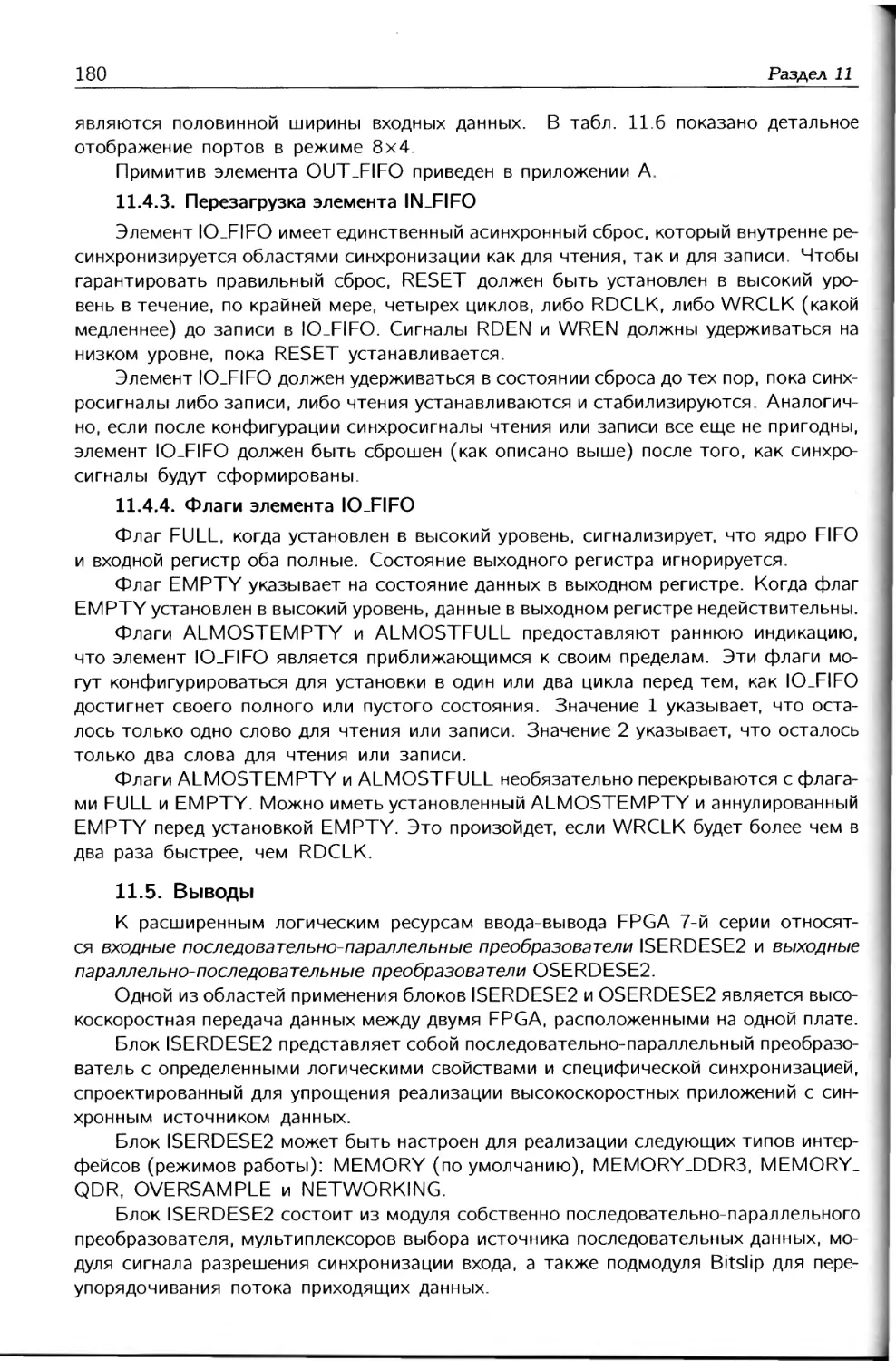

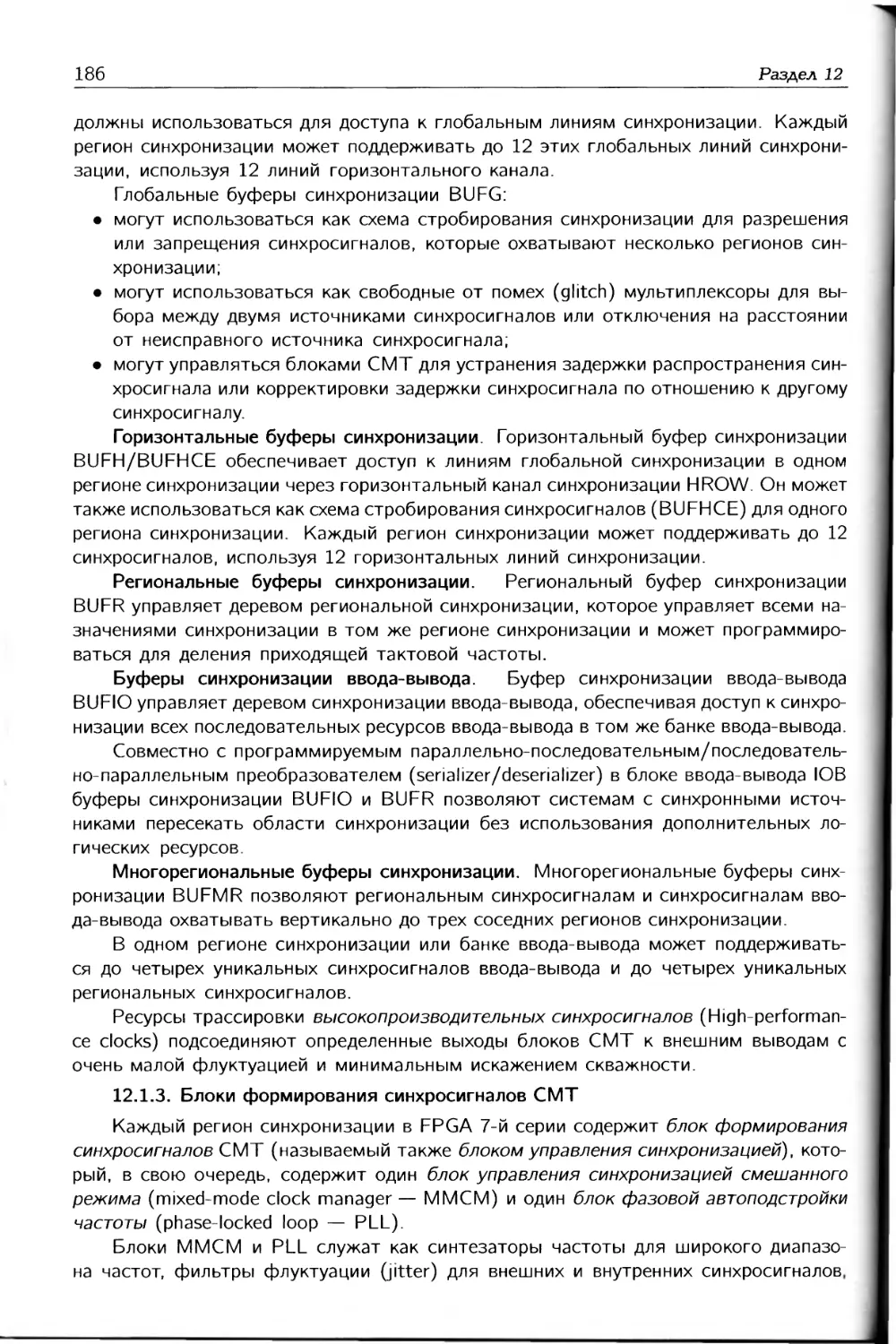

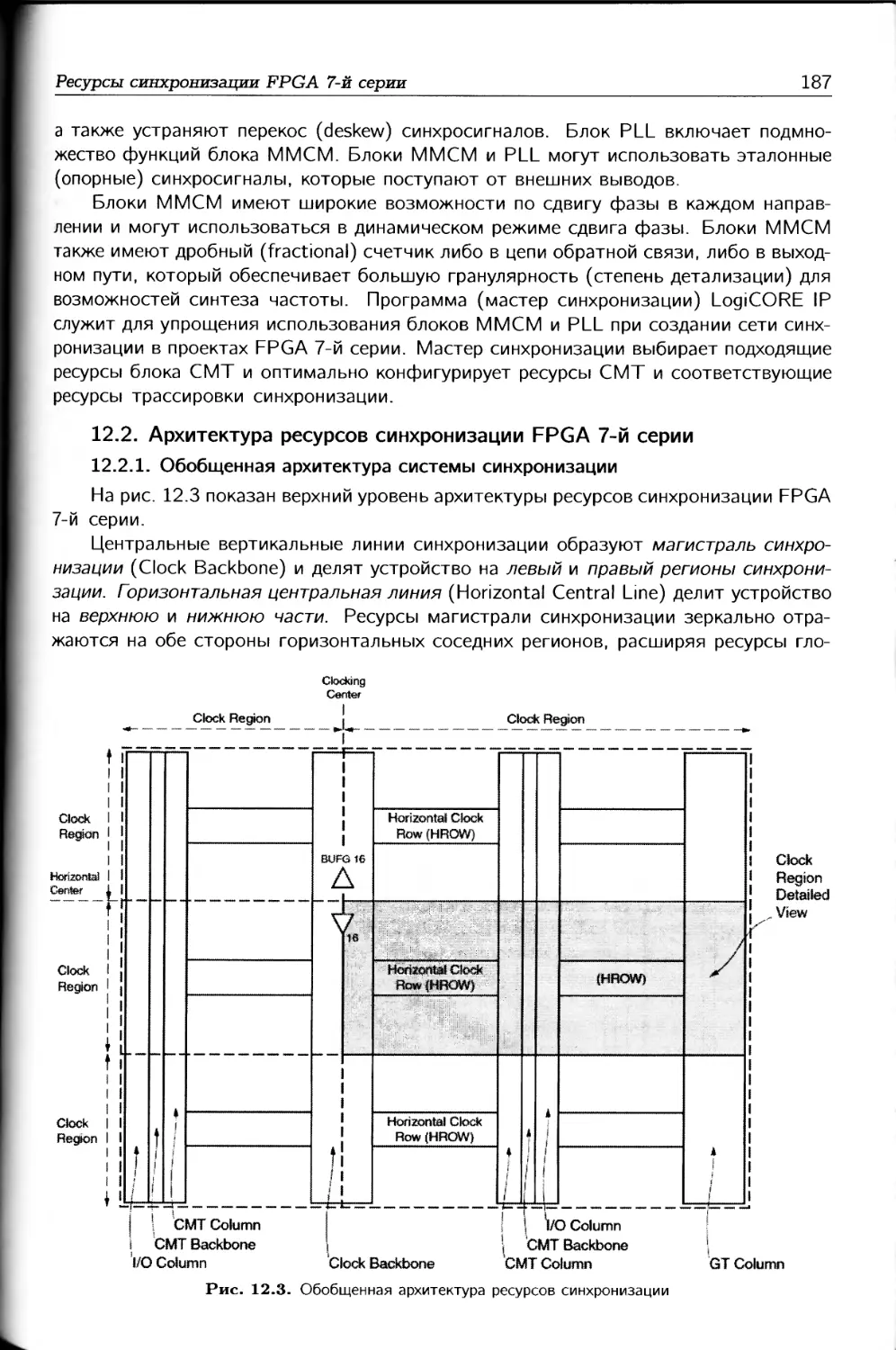

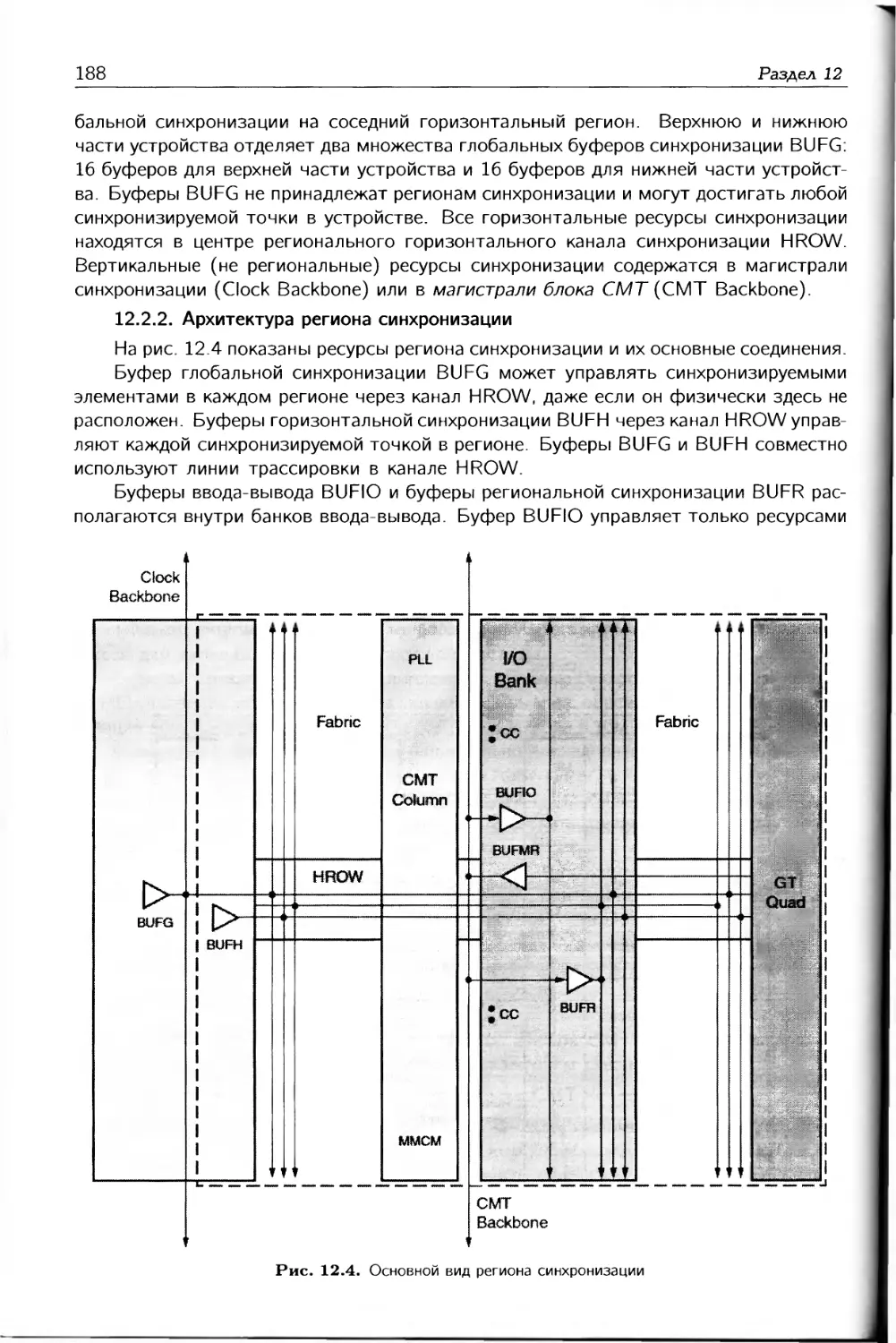

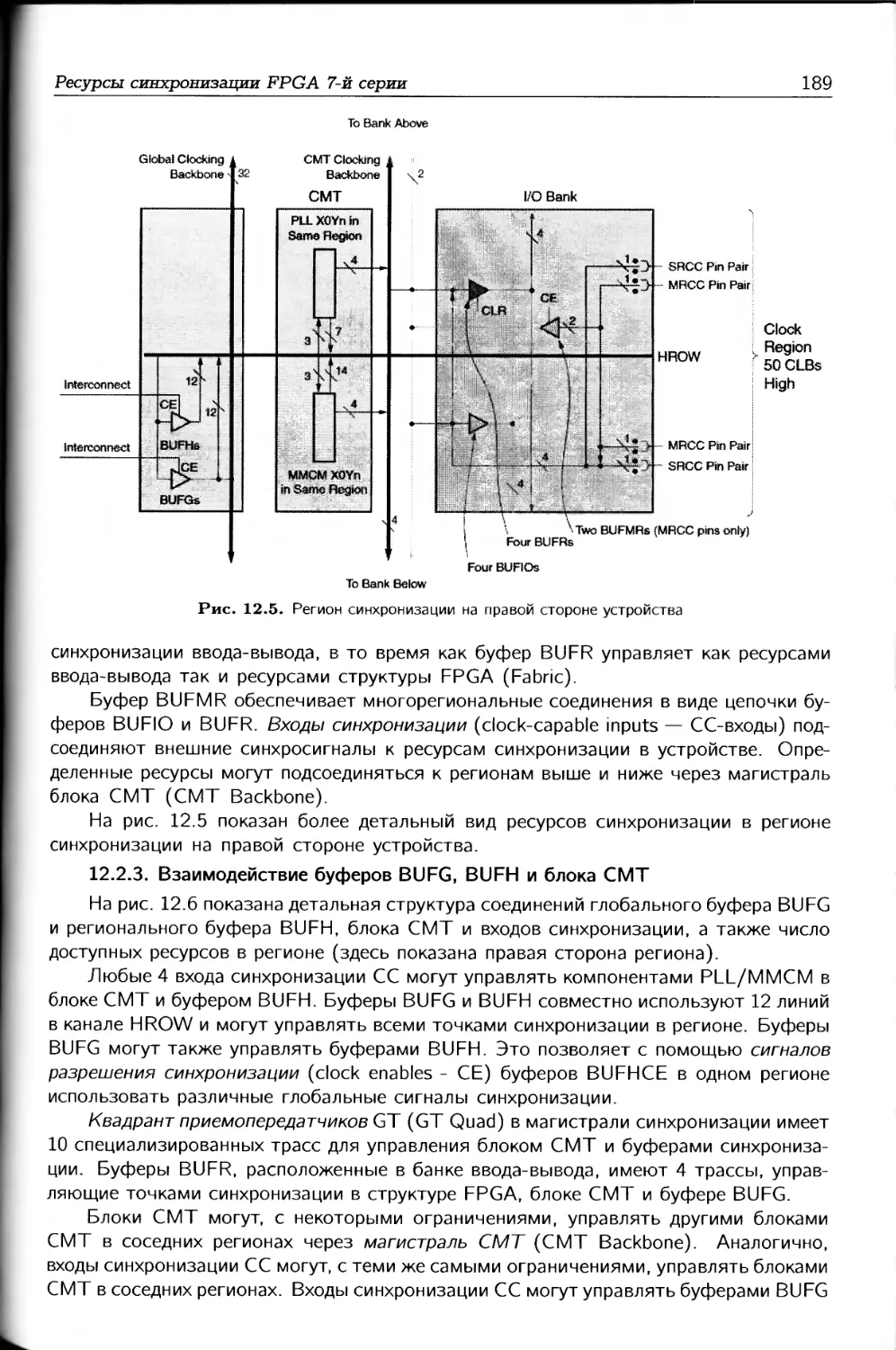

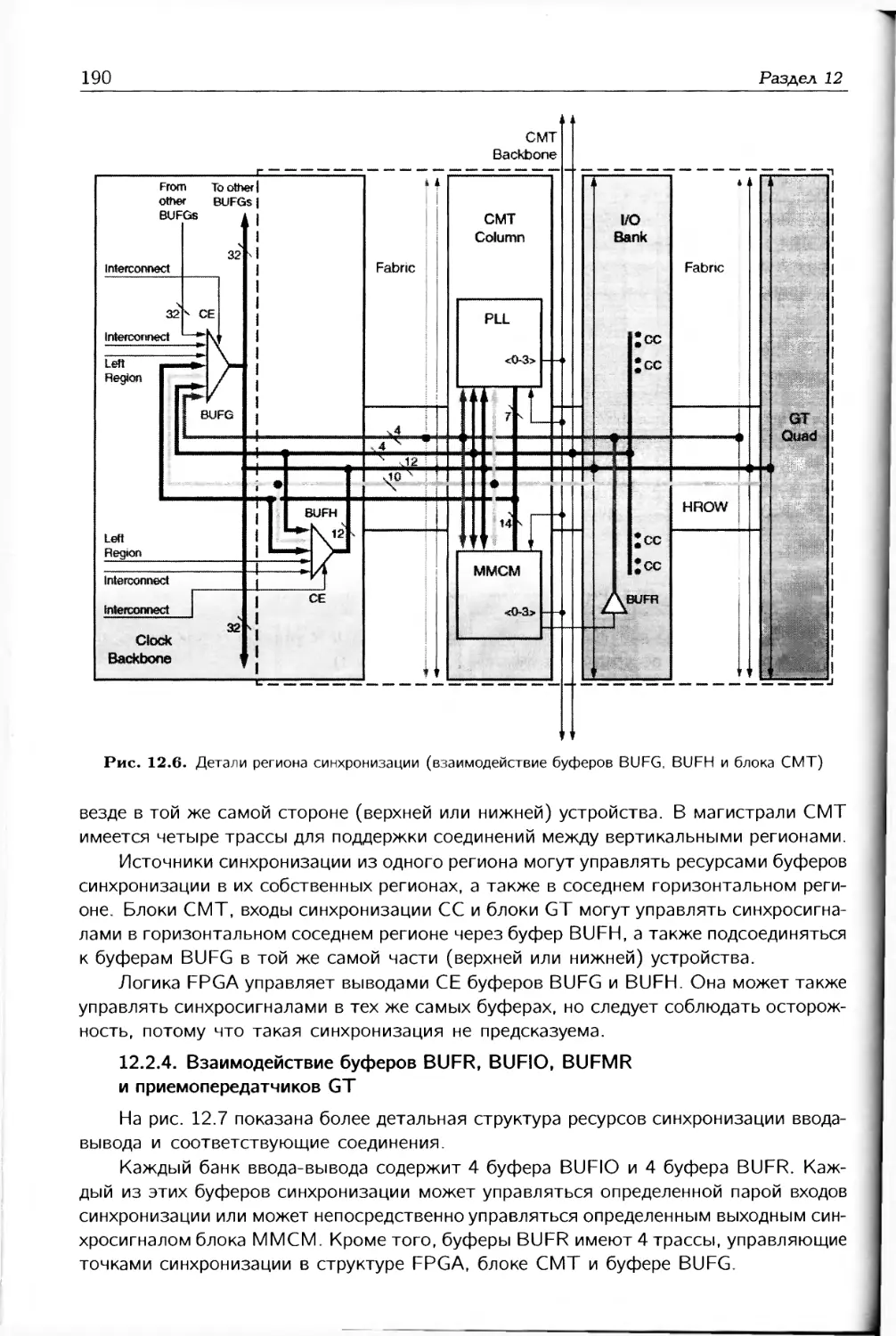

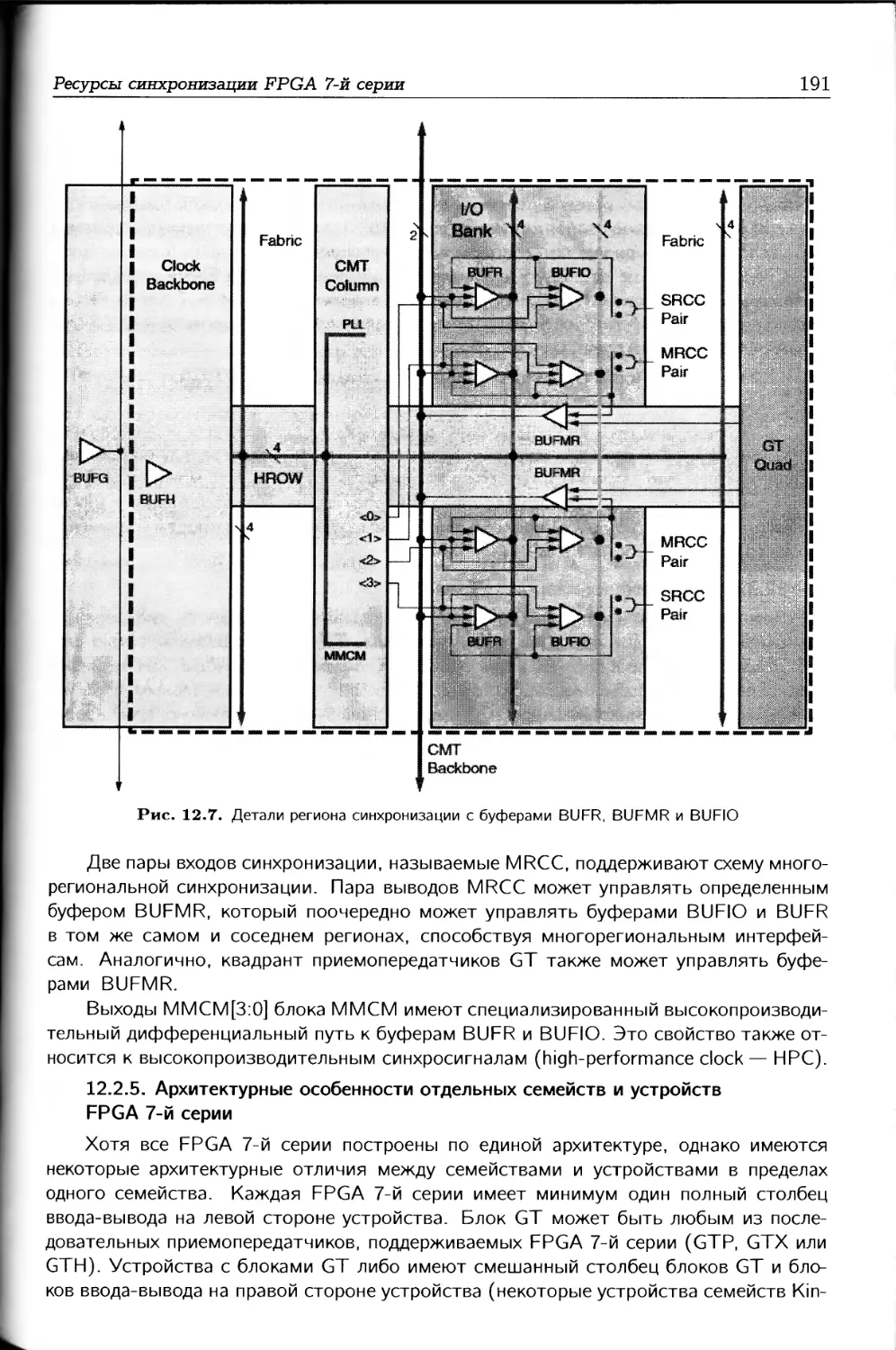

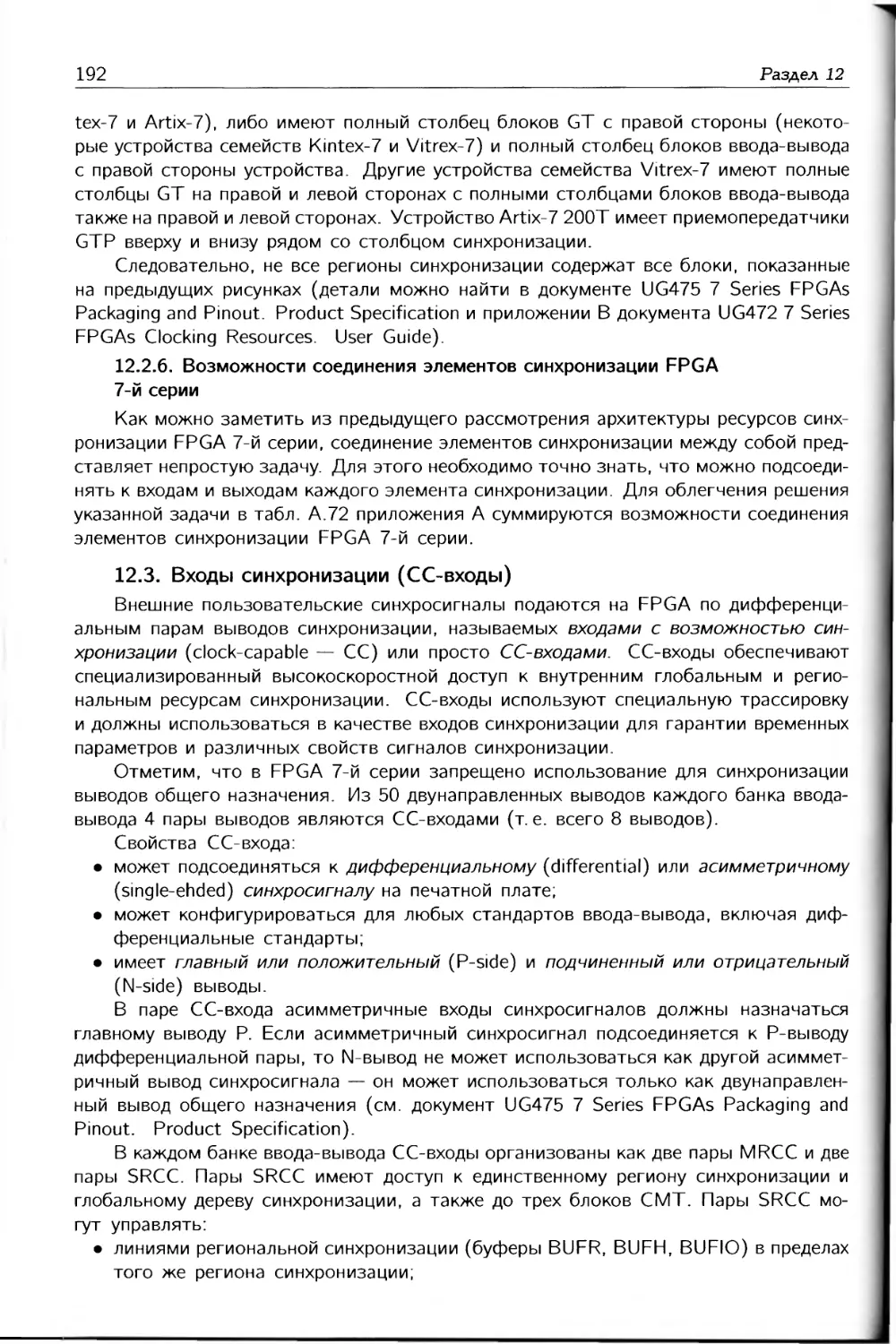

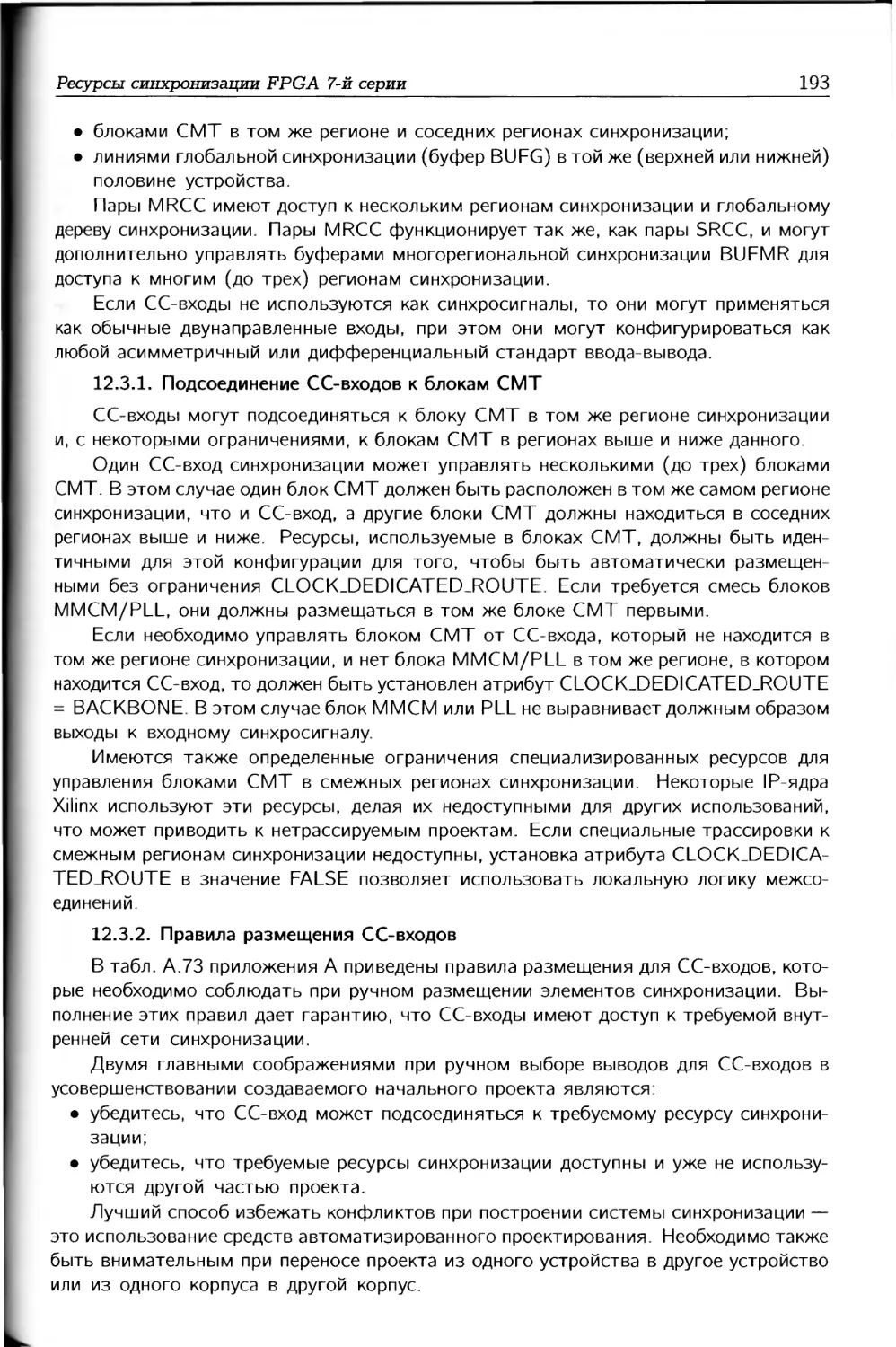

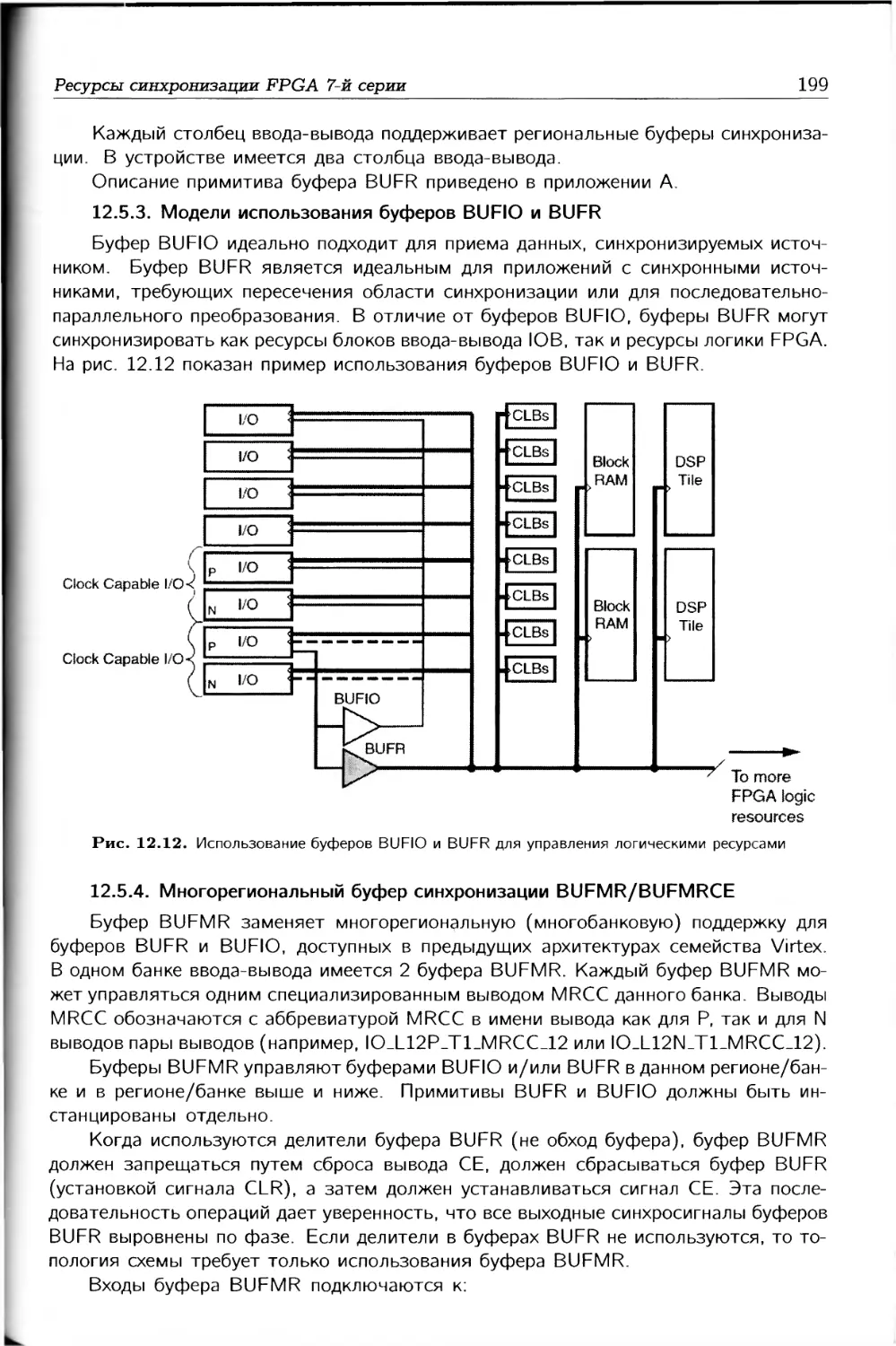

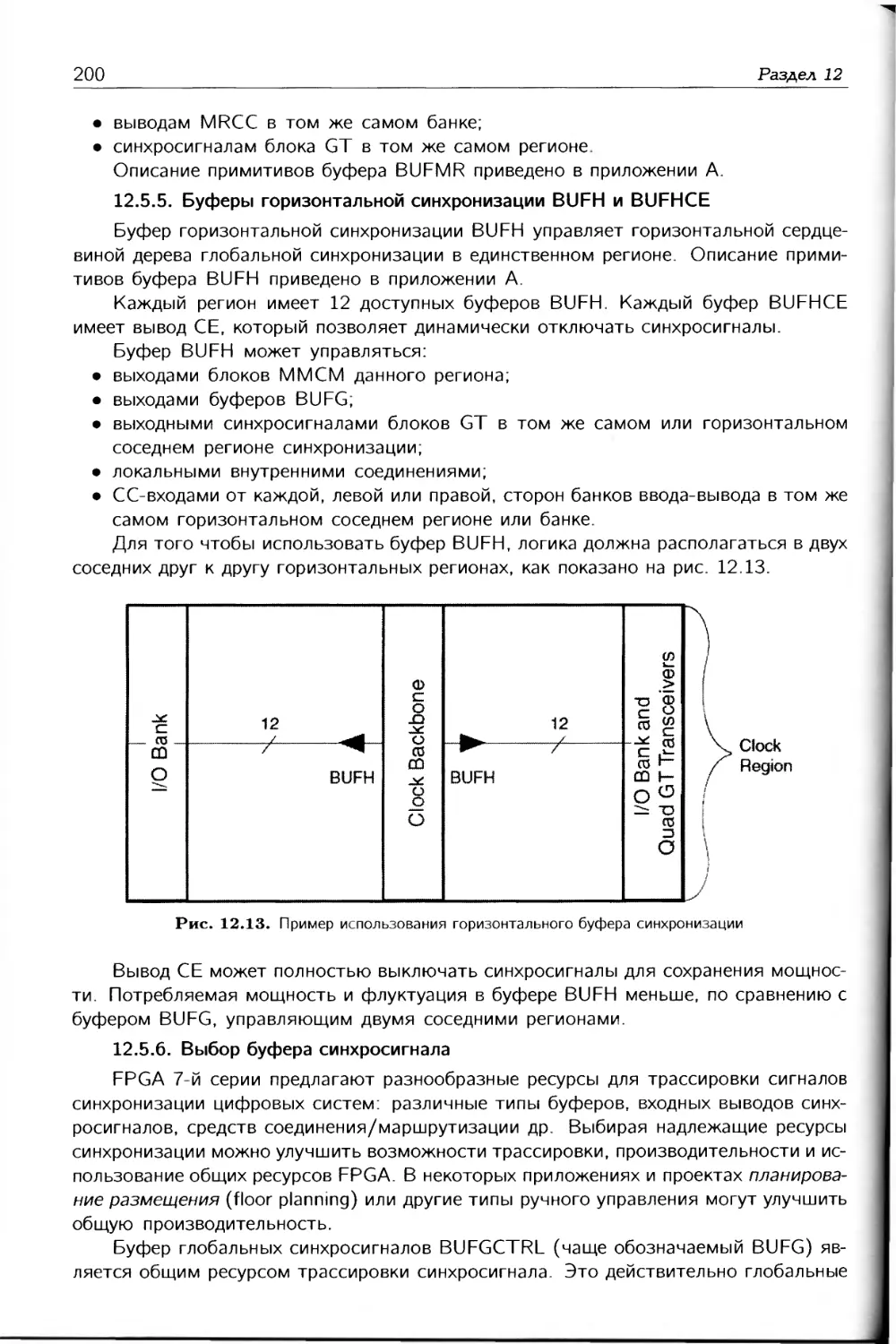

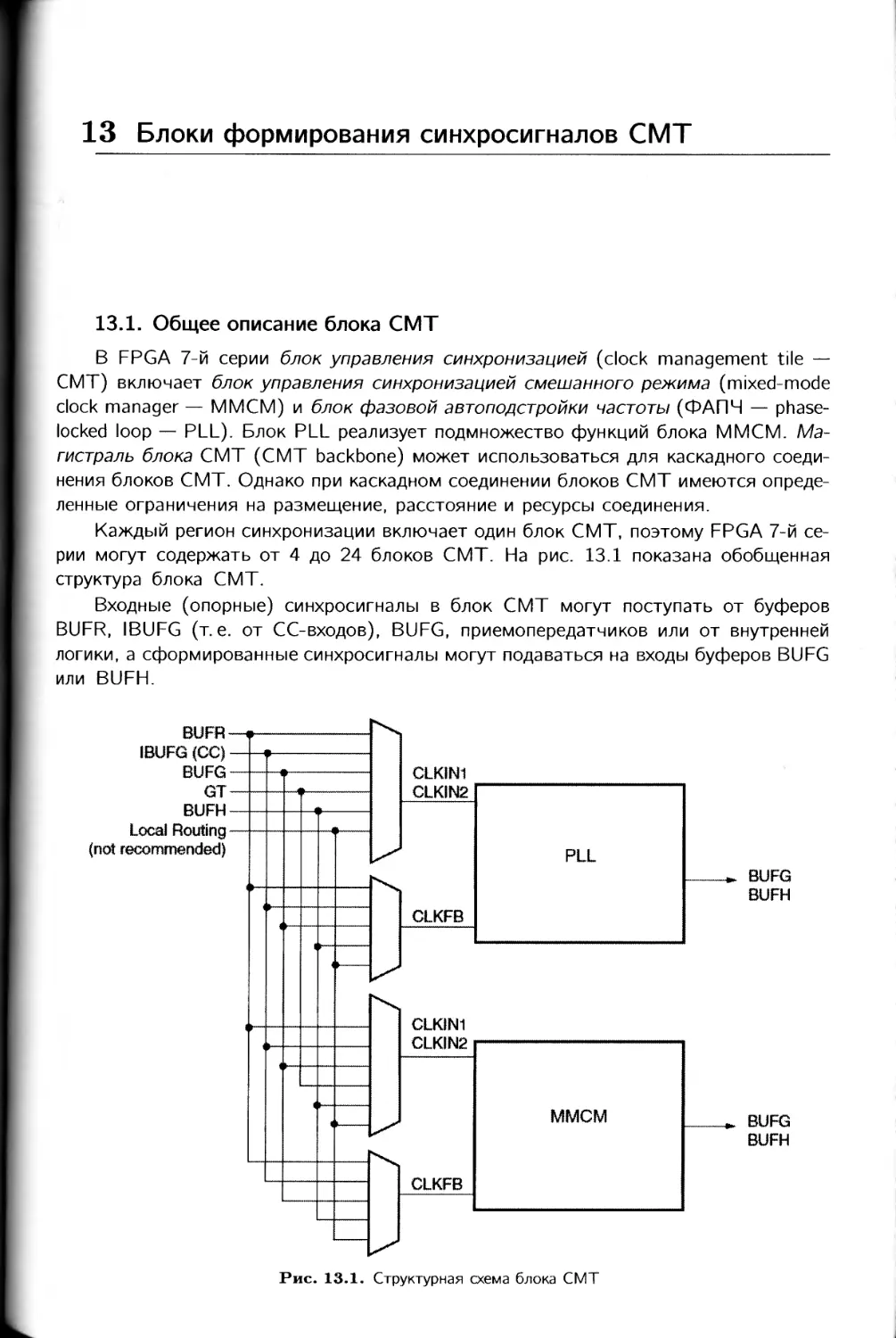

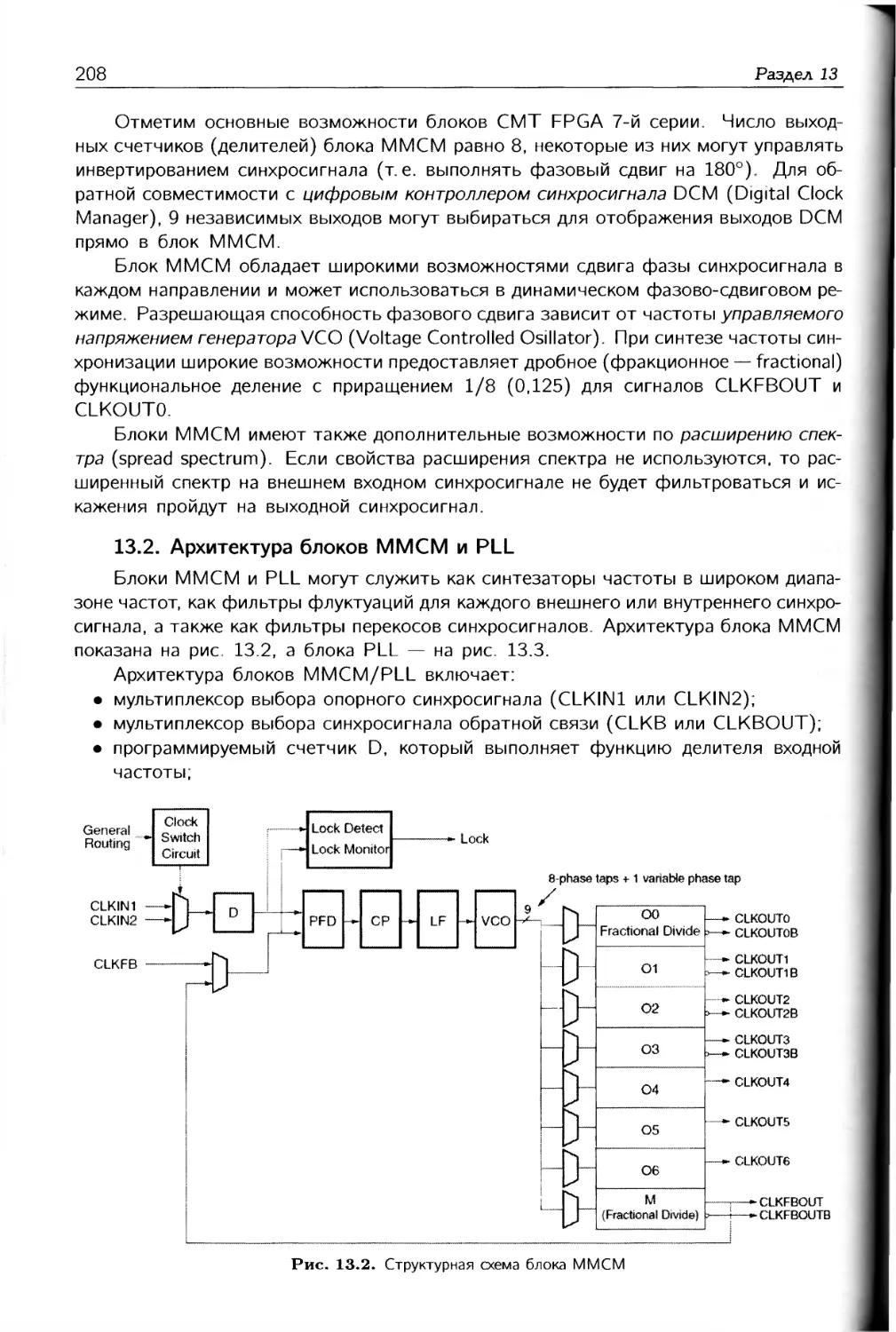

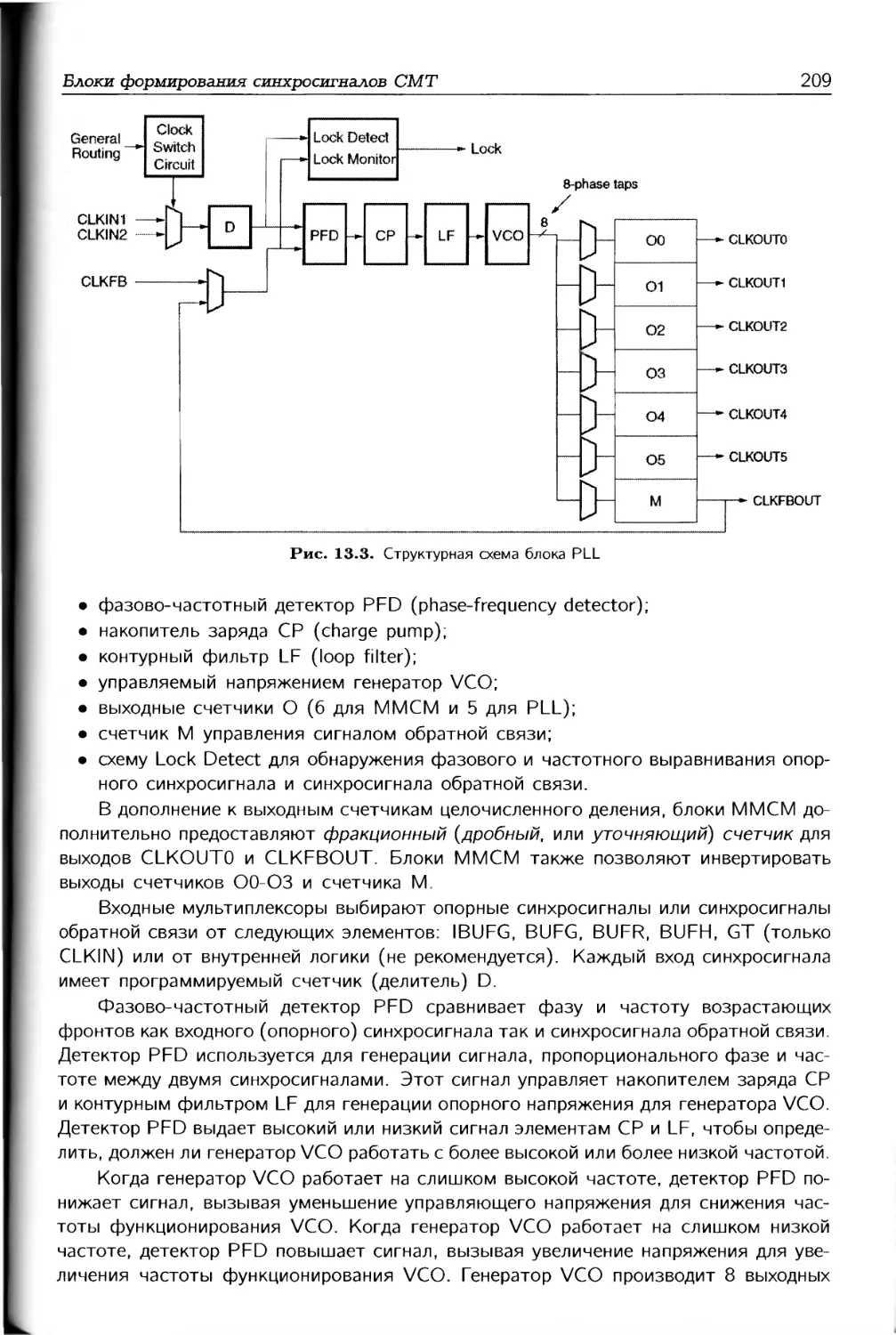

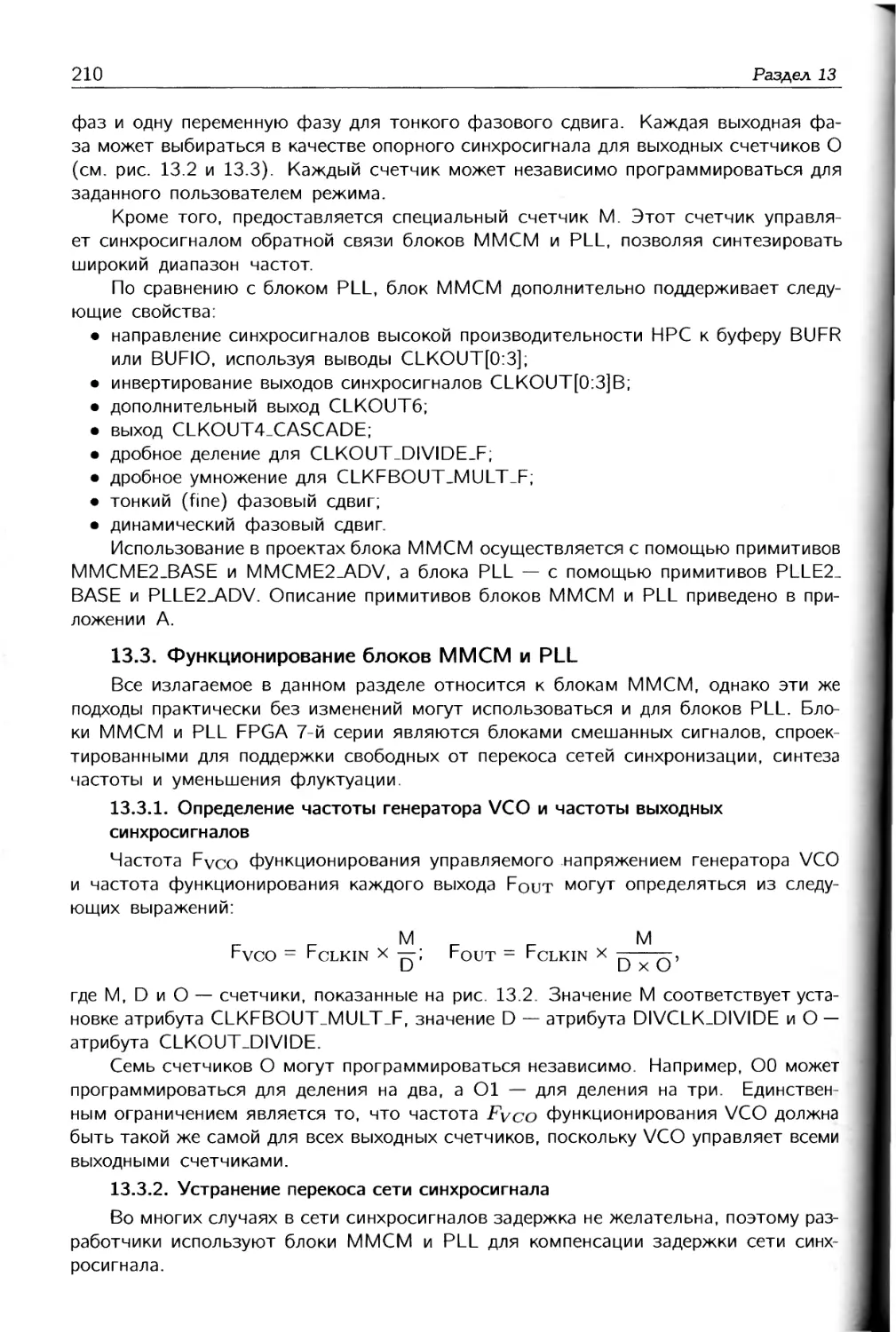

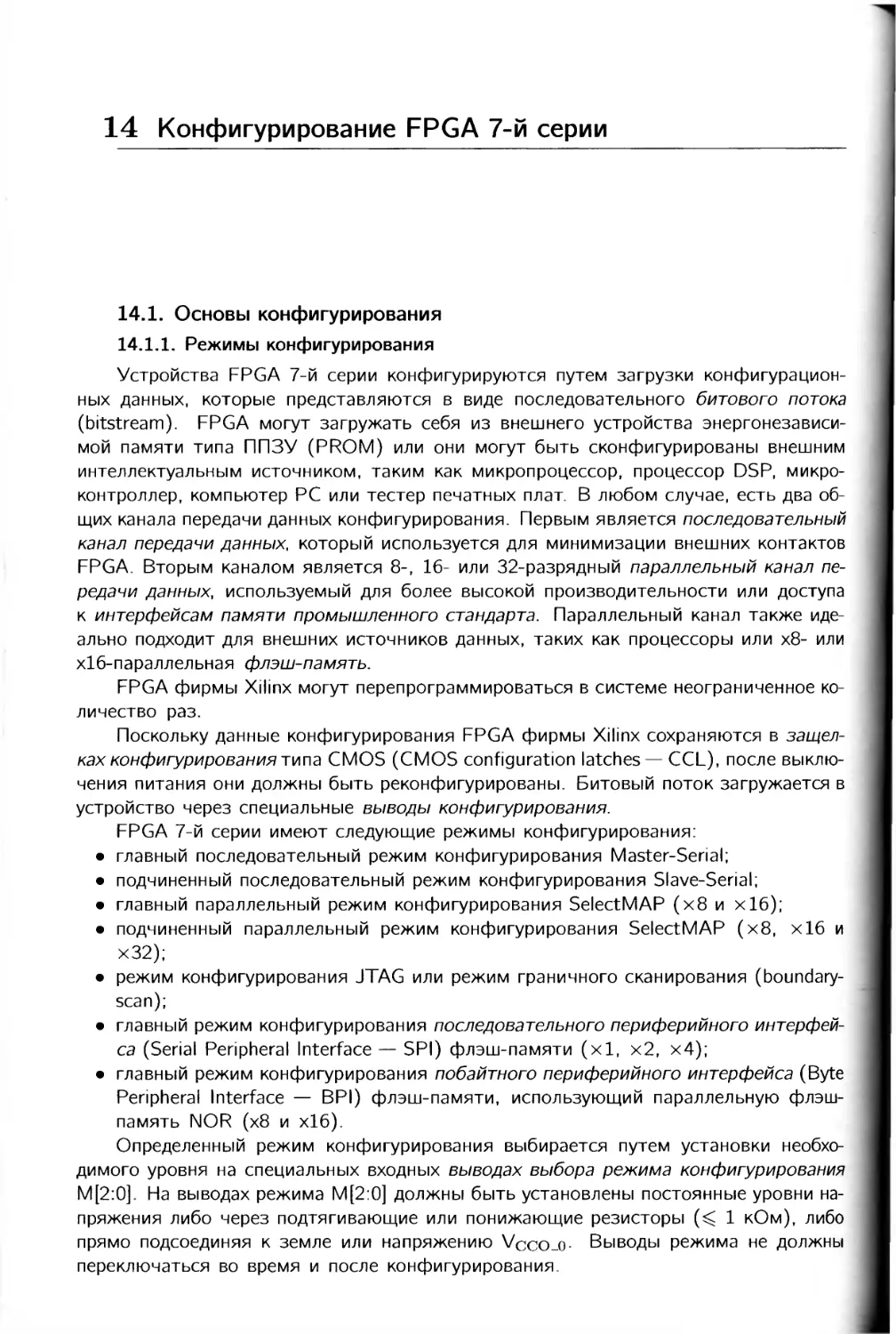

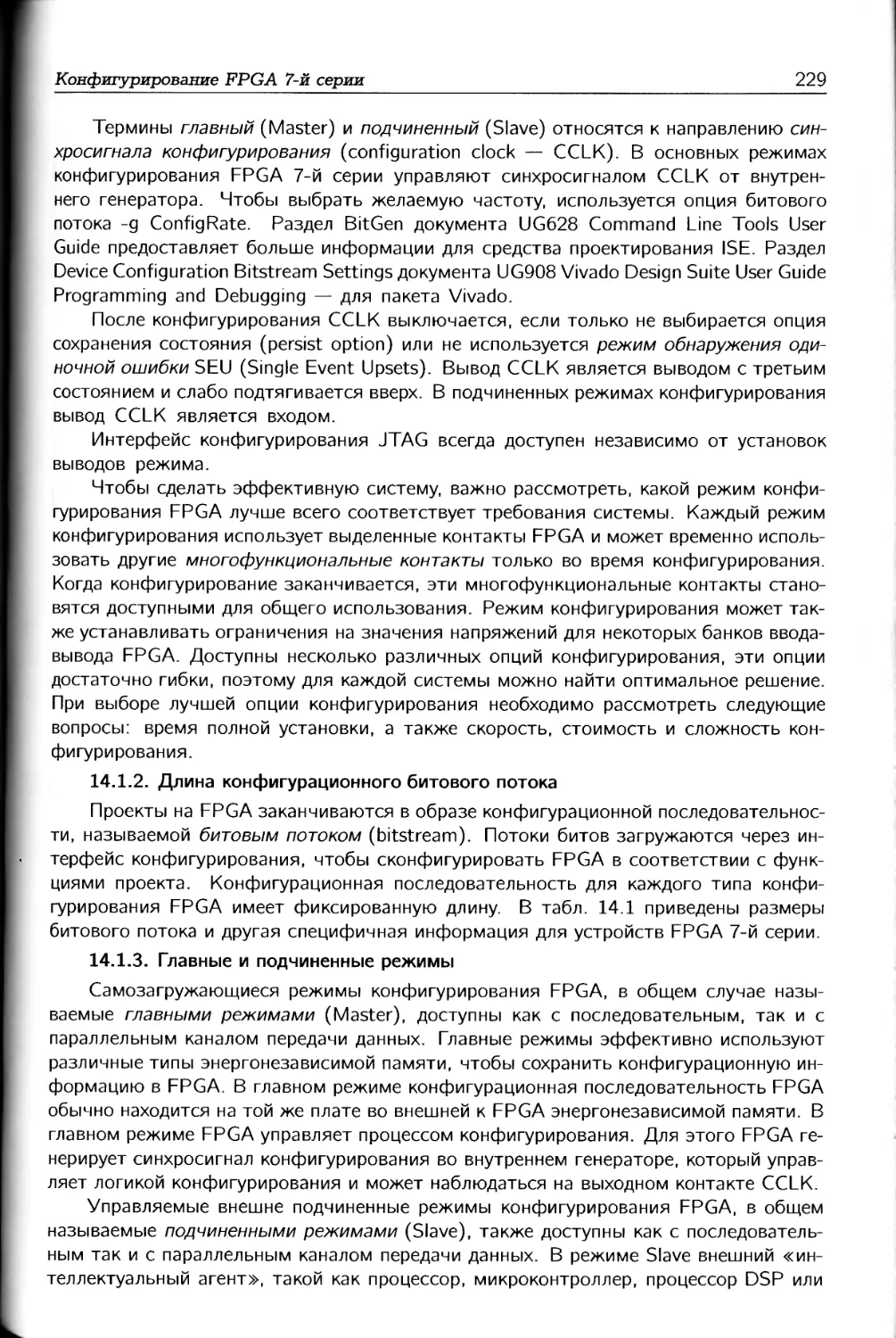

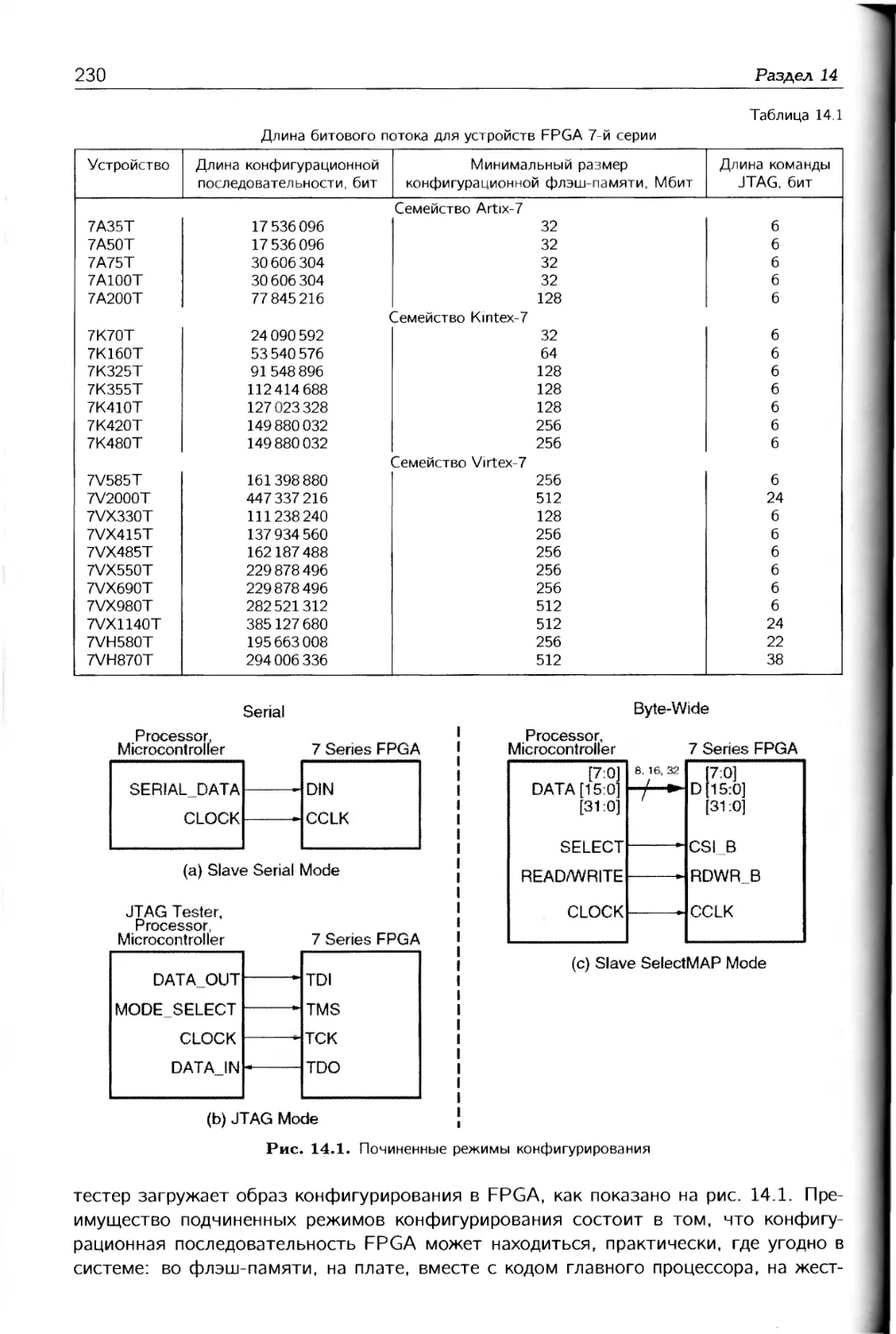

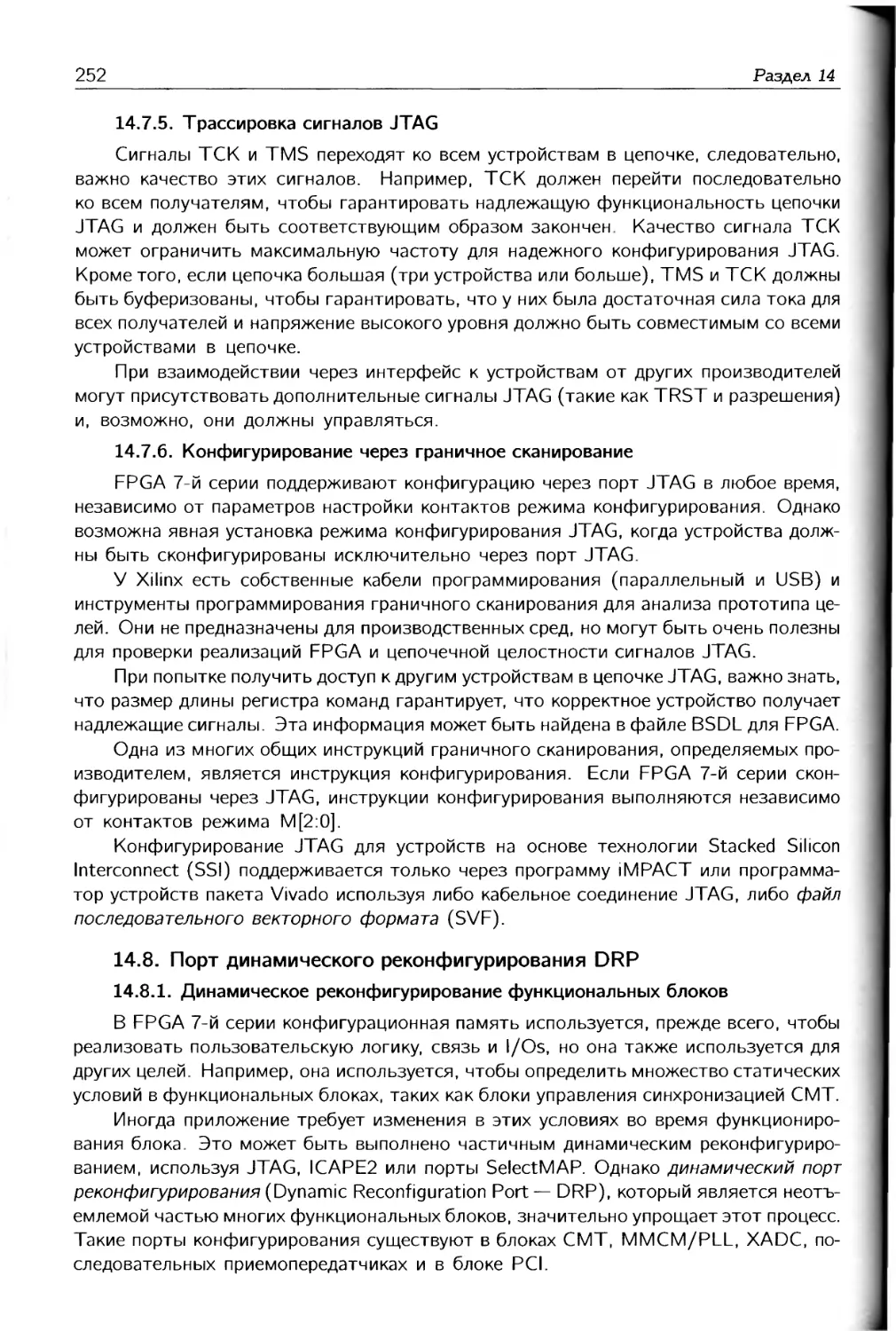

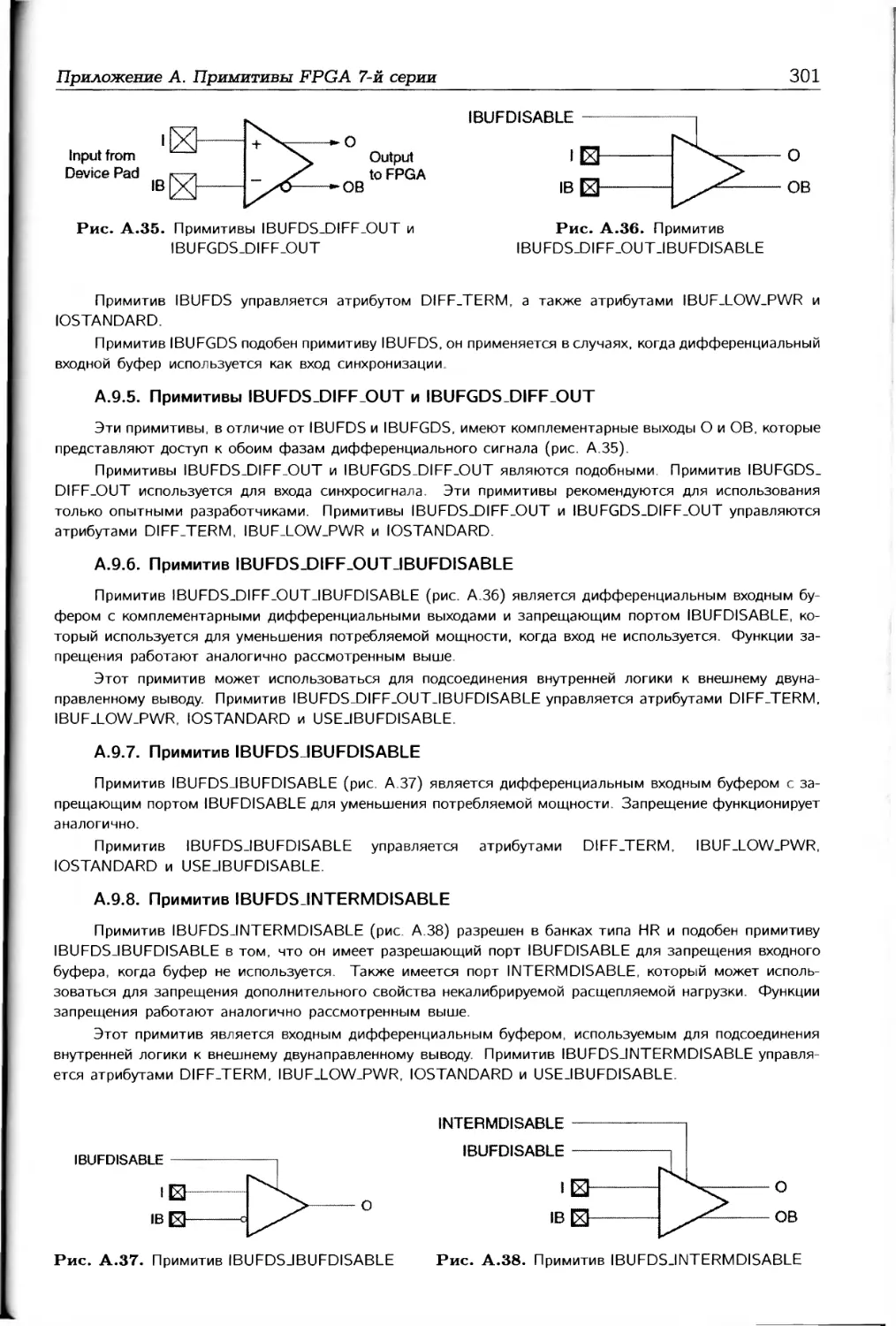

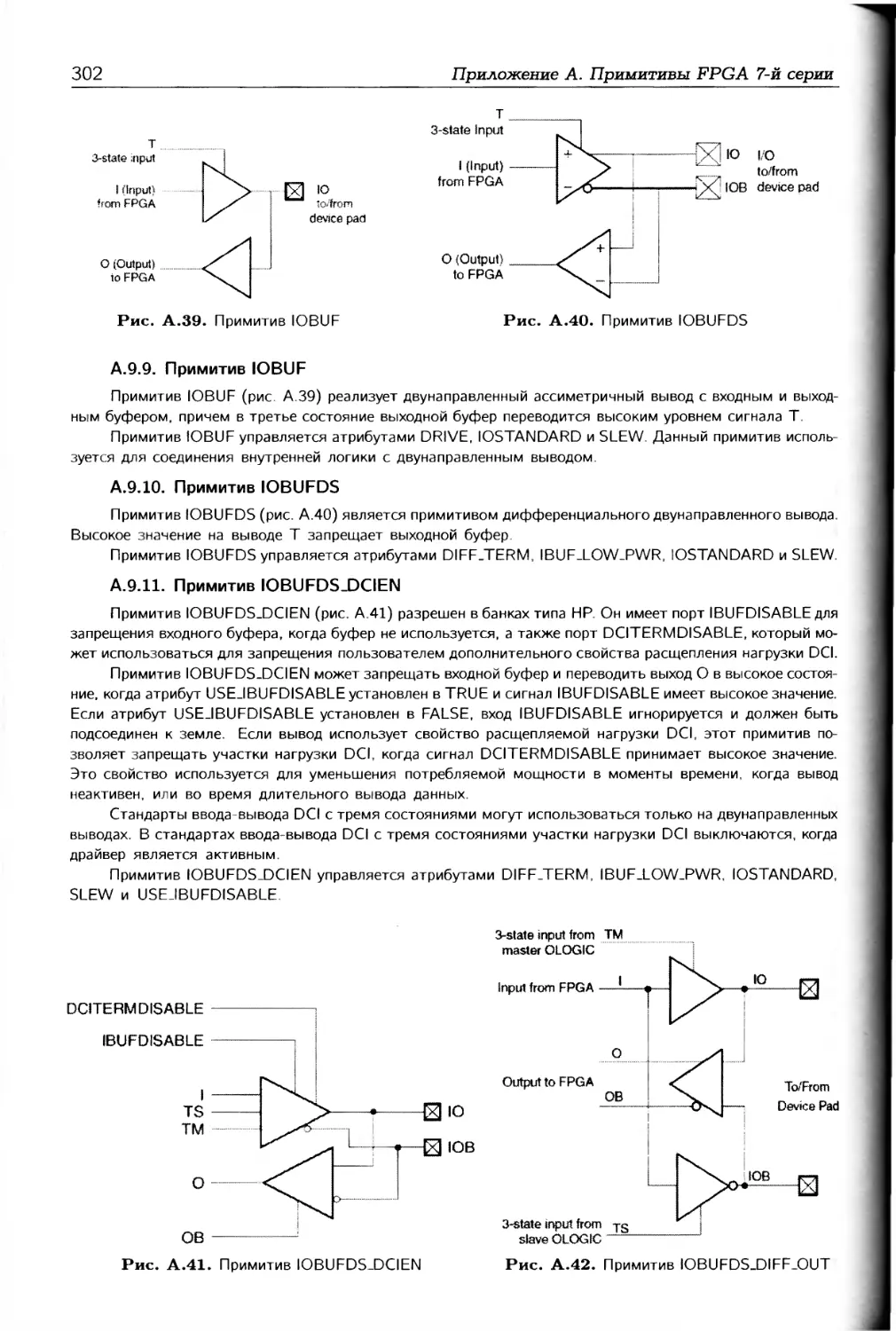

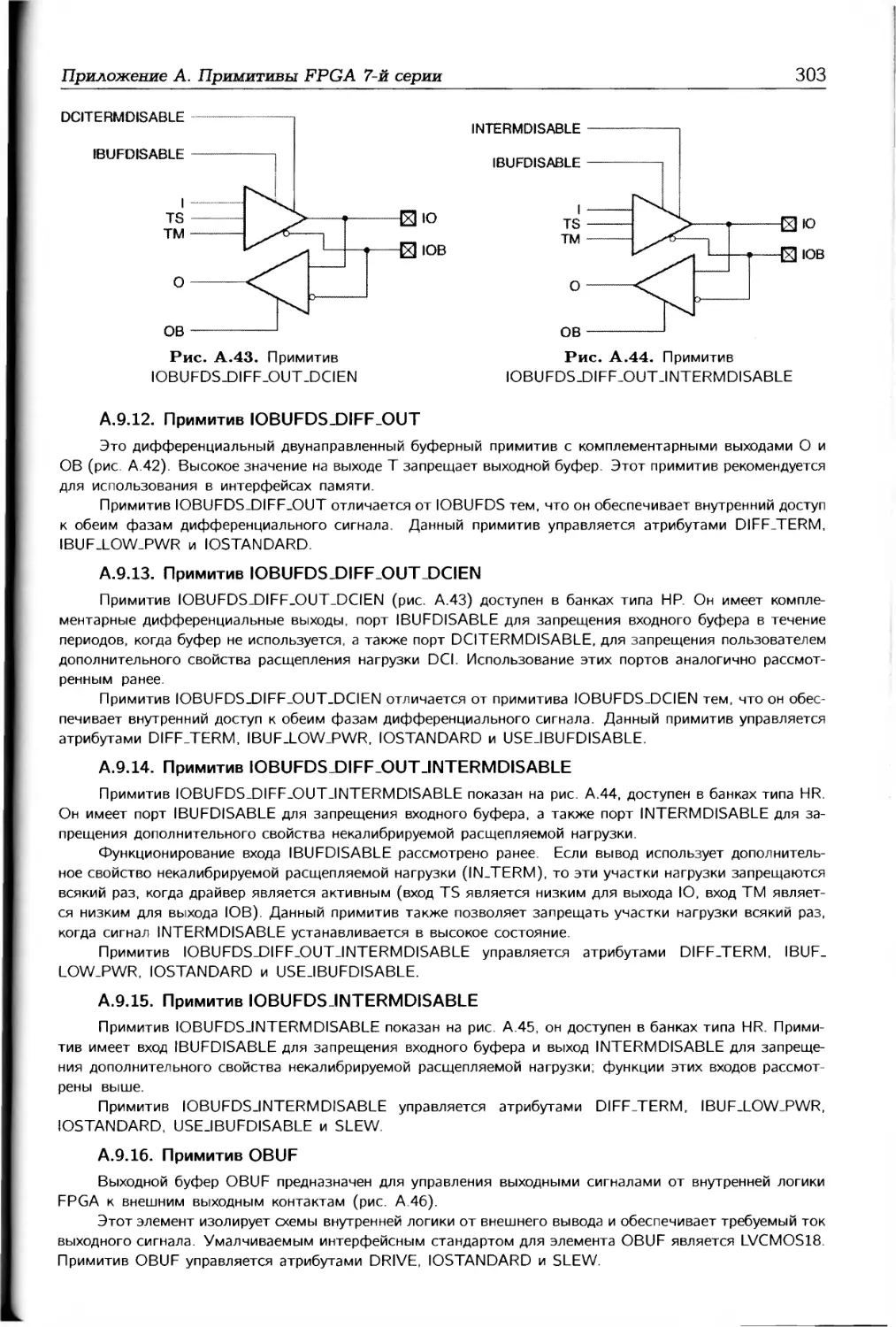

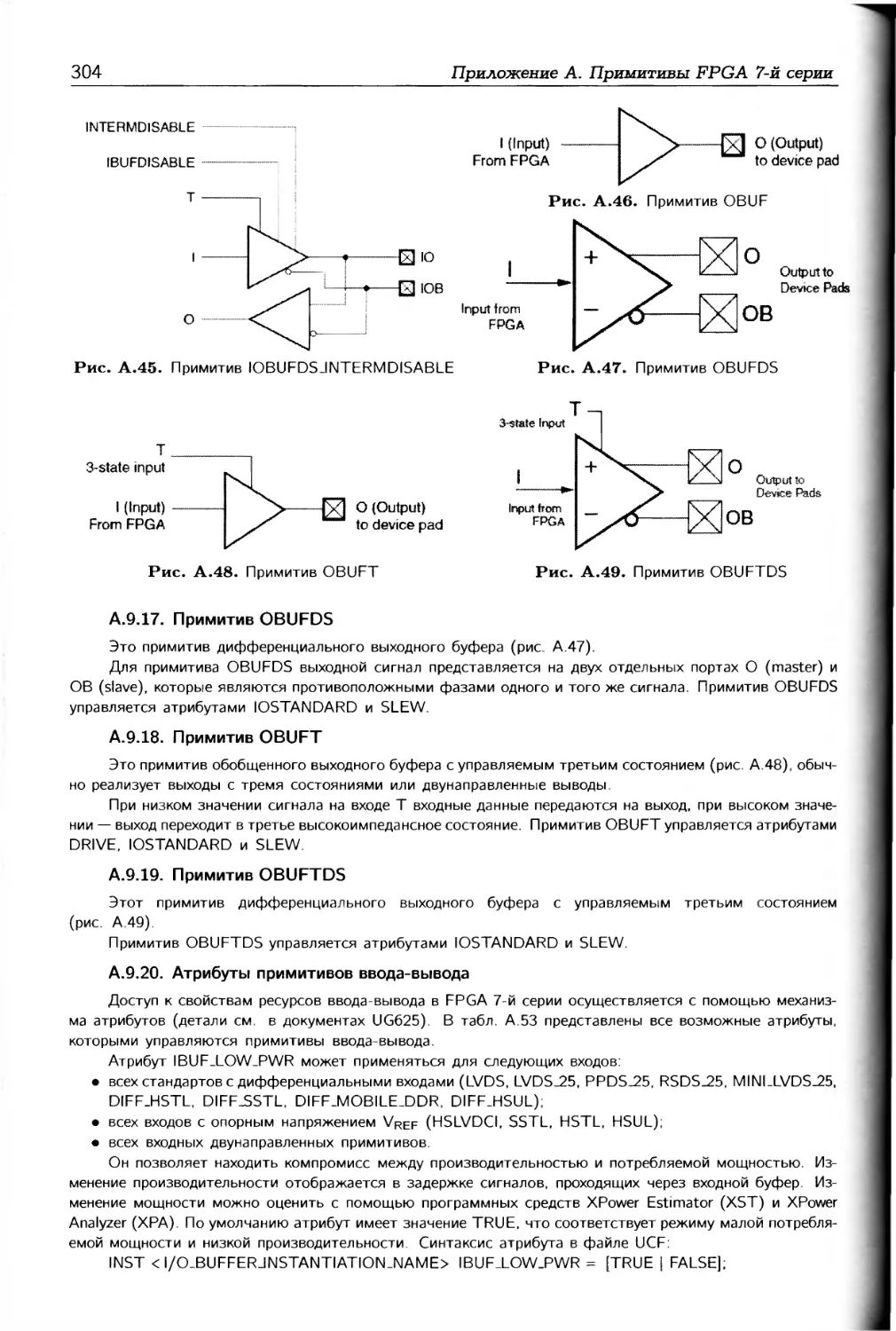

вой автоподстройки частоты (ФАПЧ — phase-locked loop — PLL) и один блок