Текст

К. ДЖ. ТЕРБЕР

АРХИТЕКТУРА

ВЫСОКОПРОИЗВОДИТЕЛЬНЫХ

ВЫЧИСЛИТЕЛЬНЫХ

СИСТЕМ

Перевод с английского

В. М. АМОЧКИНА, А. С. МИРКОТАН

МОСКВА «НАУКА»

ГЛАВНАЯ РЕДАКЦИЯ

ФИЗИКО-МАТЕМАТИЧЕСКОЙ ЛИТЕРАТУРЫ

ББК 22:18

Т35

УДК 519.6

LARGE SCALE

COMPUTER

ARCHITECTURE

_ PARALLEL

AND ASSOCIATIVE

PROCESSORS

KENNETH J. THURBER

1976

T e p б e p К. Дж. Архитектура высокопроизводительных вы¬

числительных систем/Пер. с англ.— М.: Наука. Главная редакция

физико-математической литературы, 1985.— 272 с.

К. Дж. Тербер

Архитектура высокопроизводительных вычислительных систем

Редактор И. А. Рудпев

Художественный'редактор Г. М. Коровина

Технический редактор И. Ш. Апсельрод

Корректоры: О. А. Бутусова, О. М. Березипа

ИБ Ло 11795

Сдано в набор 25.02.85. Подписано к печати 05.10.85. Формат бОхЭО'Ле. Бумага тип. № 3.

Гарнитура обыкновенная. Печать высокая. Уел. печ. л. 17. Уел. кр.-отт. 17. Уч.-изд.

л. 21,24. Тираж 8400 экз. Заказ № 618. Цена 2 р. 30 к.

Ордена Трудового Красного Знамени издательство «Наука»

Главная редакция физико-математической литературы

4-я типография издательства «Наука»

. 630077 Новосибирск-77, Станиславского, 25

© 1976, by Hayden

Book Company, Inc.

Перевод на русский язык.

Издательство «Наука»,

Главная редакция

физико-математической

литературы, 1985

1702070000—155 ,

Т 053 (02) -85 34-85

ОГЛАВЛЕНИЕ

Предисловие к русскому переводу . .........

Предисловие

Глава 1. ВВЕДЕНИЕ

Для чего нужны специализированные вычислительные машины? .

Классификация архитектур машин .

Типовые задачи для ОКМД-машин . . . . ' . . . .. .

ОКМ Д-процессоры . .

Вычислительные системы' с массивом процессоров (параллельные

процессоры)

Ассоциативные процессоры

Заключение

Упражнения ...

Г л а в а 2. АССОЦИАТИВНАЯ ОБРАБОТКА ■ .

Введение

'Применения . . . . . • .

Наиболее общий тип архитектуры ассоциативного процессора

Принцип перехода состояния _ .

-МЕМЕХ — первая ассоциативная архитектура4

Криогенная каталоговая память — первая аппаратная реализация

ассоциативной памяти *

Разрешение множественных откликов и алгоритм Левина

Ассоциативные процессоры в роли универсальных вычислительных

машин . . . . . . . . - . ,

SIMDA — машина с обработкой битовых срезов

Запоминающие устройства с распределенной логикой ....

Процессоры с ассоциативпой базой данных, вычислительные машипы

для информационных систем . . .

Ассоциативные процессоры с высокой степенью параллелизма

Л1 погомерпые миогорежимные запоминающие устройства .

Заключение

Упражнения ....

Глава 3. ОСНОВНЫЕ ТИПЫ АРХИТЕКТУР ПАРАЛЛЕЛЬНЫХ ПРО¬

ЦЕССОРОВ

Введение ....

Ячеечные автоматы фон Неймана

Яростраиствепная машина Унгера

Уашипа Холланда .

фтогоиальная машина .

V \ л п~>11а СквайРа п Пеле

v лли^ — вычислительная

устройством

Система SOLOMON ‘ I

Система SOLOMON II

машина с векторным арифметическим

G

7

9

9

10

12

13

14

15

10

17

18

18

19

20

37

45

46

48

52

56

59

71

79

92

95

96

98

98

99

102

105

108

110

111

114

121

Применение системы SOLOMON

Система ILLTAC III ’ * ’

IAC — итерационная вычислительная система с массивом процессоров

PC — планарная вычислительная машина

ALPS параллельная вычислительная система с ассоциативными про¬

цессорами

Система ILLIAC IV

Maiггины I и II Рорбахера . . . . .

РЕРЕ — параллельная вычислительная система с ансамблем процес¬

сорных элементов

Вычислительная мантина с ячеечной структурой на базе языка APL

Совершенная тасовка

Машина Кэннона !!!*'*

Машина Jloyca для расшифровки кодов Хэмминга

Еще один параллельный процессор на базе языка APL .

Другие типы итерационных вычислительных машин

Заключение

Упражнения !!!!!!!**

Глава 4. ILLIAC IV. ....

Введение

Архитектура ILLIAC IV ... *

Аппаратная часть ILLIAC “IV . ’

Программное обеспечение ILLIAC IV

Заключение

Упражнения

Глава 5. СИСТЕМА РЕРЕ .

Введение

Архитектура РЕРЕ

Программное обеспечение РЕРЕ .

Заключение

Упражнения

Глава 6. ПРОЦЕССОР STARAN . .

Введение

Архитектура STARAN .

Процессор STARAN . ' .

Программное обеспечение STARAN .

Система ввода/вывода STARAN . . .

Варианты процессора STARAN . .

Заключение .

Упражнения .

Глава 7. СЕМЕЙСТВО OMEN . .

Введение

Описание архитектуры OMEN ...

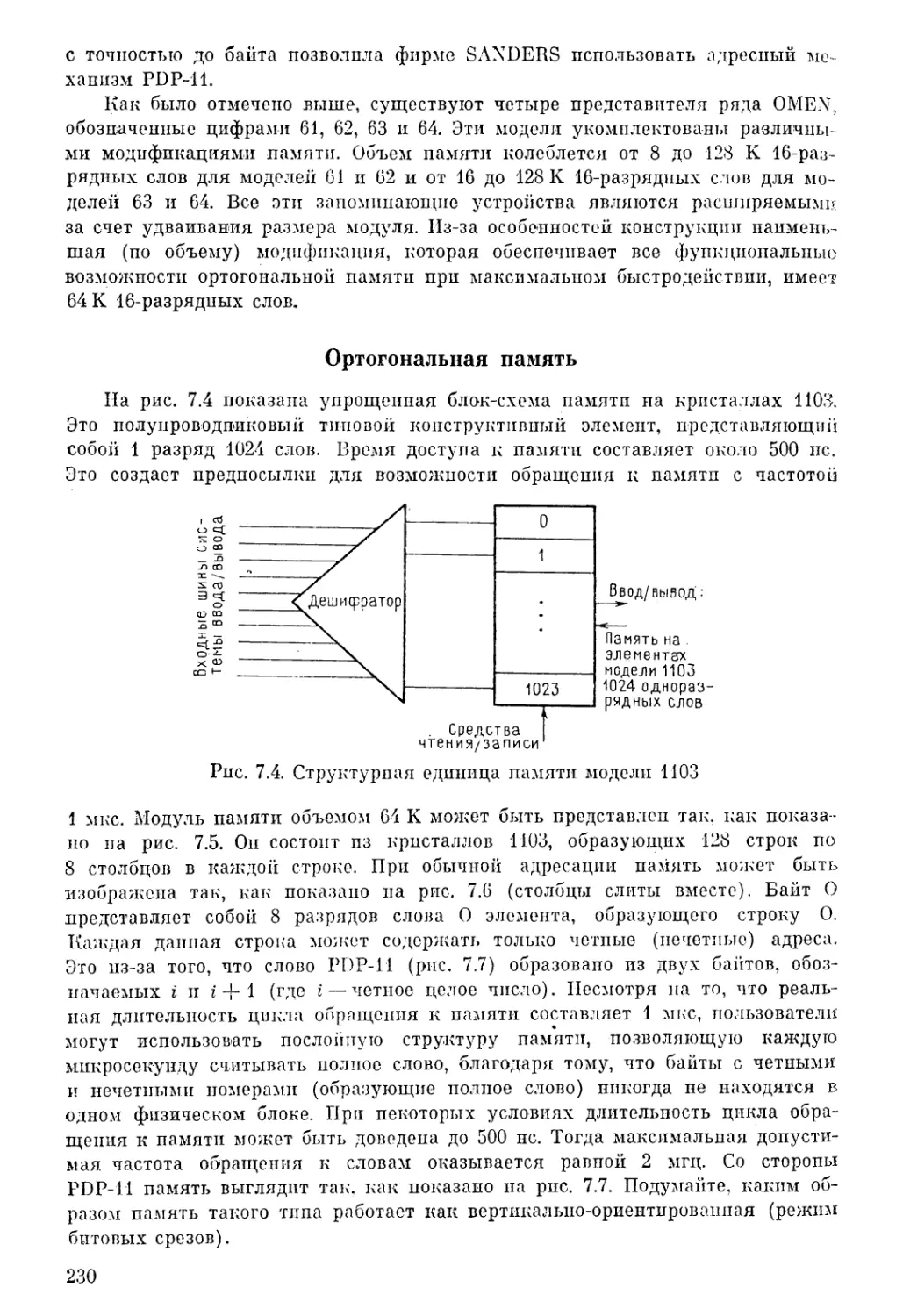

Ортогональная память ...

Взаимосвязи ПЭ в OMEN .

ВАУ системы OMEN ....... . . .

Программное обеспечение OMEN .... ...

Конфигурация машин семейства OMEN . . ...

Заключение

Упражнения .... ... ....

Глава 8. ОЦЕНКА ПРОИЗВОДИТЕЛЬНОСТИ .

Введение

Оценка производительности ,

122

122

125

128

129

130

131

130

137

142

142

141)

149

152

150

157

159

159

159

К)!

180

185

185

180

18(5

195

195

204:

205

207

207

207

213

217

221

222

224

224

220

220

220

230

234

235

238

23 S

289

240

241

24 I

24.2

4

Оценка ОКМД-машин

Заключение .

Упражнения . *

Глава 9. БУДУЩЕЕ ОКМД-МАШИН

Введение . • • • •

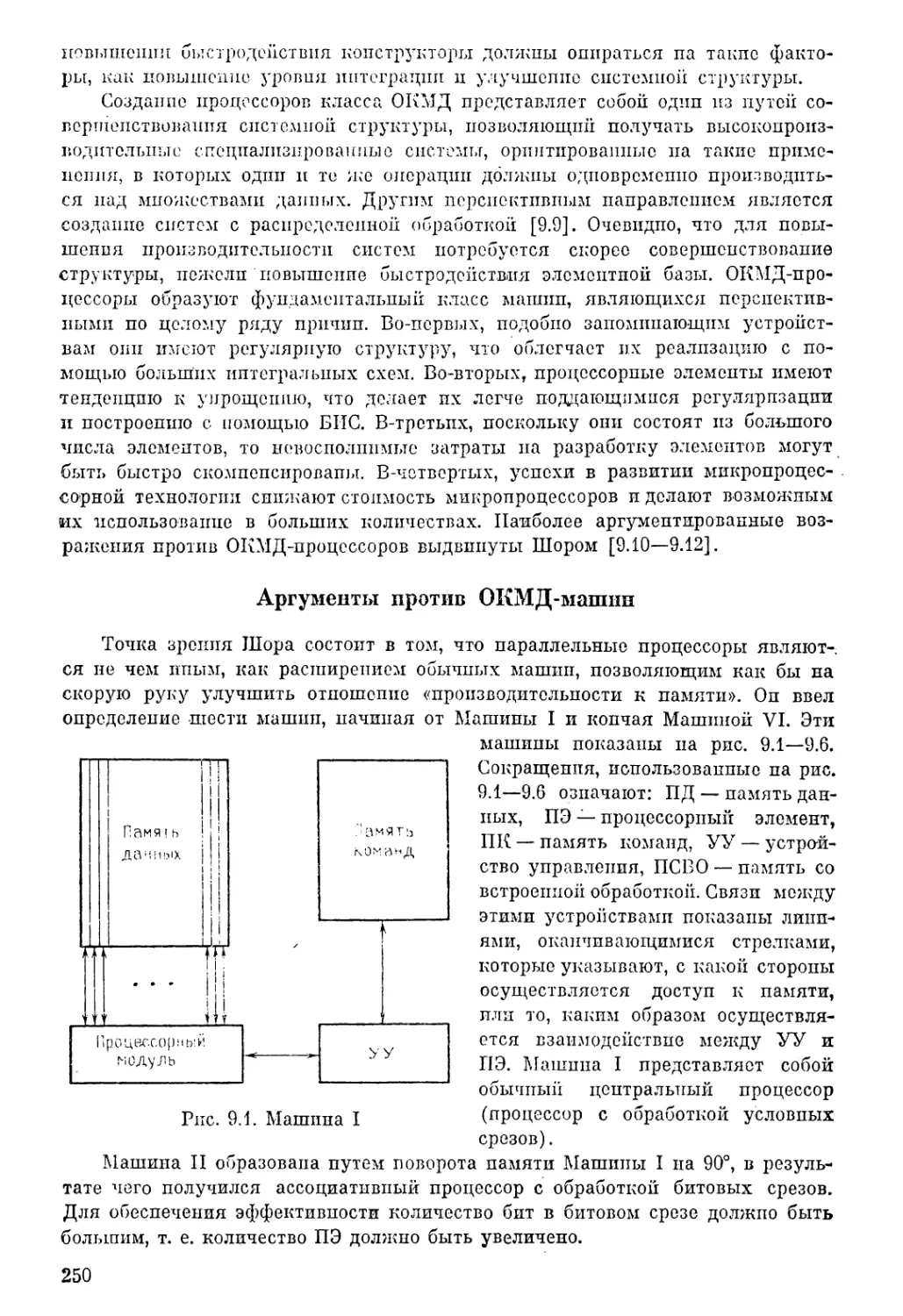

Аргументы против ОКЛГД машин

Параллельные или миогоматпитшые системы? .

ТТотепнстальнъте возможности ОКМД-процессоров

Показатели стоимости

Эффективность параллельных процессоров .

Заключение

Список литературы

24 7

24 S

248

240

240

2Г)()

2 о 8

2 5 (>

2 о 0

2(H)

2(32

204

ПРЕДИСЛОВИЕ К РУССКОМУ ПЕРЕВОДУ

Распараллеливание и конвейеризация составляют основной структурный

принцип повышения производительности вычислительных систем. Непосредст¬

венный подход к реализации в явном виде распараллеливания ветвей вычисле¬

ний приводит к построению ОКМД-систсм, имеющих один поток ко.манд и мно¬

го потоков данных (т. е. одно устройство управления и много параллельных

обрабатывающих устройств). Характерными представителями последних явля¬

ютсяПараллельные системы с общим'управлением н ассоциативные системы,

которым посвящена предлагаемая в переводе па русский язык книга известно¬

го американского специалиста К. Дж. Тербера.

В отечественной и зарубежной литературе большое внимание уделено

разного типа параллельным и ассоциативным системам, их примеры даны в це¬

лом ряде книг. Данная книга отличается тем. что она целиком ориентирована

только на ОКМД-снстемы и содержит систематически и достаточно полно из¬

ложенный материал но основам построения и оценки ОК.МД-снсяем с подроб¬

ными описаниями таких их характерных представителей, как ILLIAC IV, РЕРЕ,

OMEN, ST ARAN и другие.

Книга выдержала проверку временем. Приведенные в иен исходные кон¬

цепции положены в основу многих новых проблемно ориентированных и спе¬

циализированных параллельных систем и процессоров. Концепции построения

функциональных аналогов физических систем находят применение в полу¬

пивших, в последние годы быстрое развитие специализированных параллельных

процессорах на базе сверхбольших интегральных схем с прямой аппаратурной

реализацией многих таких функций, которые традиционно возлагались на про¬

граммное обеспечение.

Концентрированный и систематически изложенный материал книги

К. ,Дж* Тербера может служить как развернутым справочником по основам

построения высокопроизводительных параллельных систем с общим управле¬

нием и ассоциативных систем, так и учебным пособием но этим вопросам.

ПРЕДИСЛОВИЕ

Полью кппгп является систематизированное описание ассоциативных п па¬

ра ТЛСЛЫ1ЫХ процессоров, а также технических идей п решений, заложенных в

их архитектуре?

В книге рассматривается только один класс архитектур, а именно, архитек¬

туры характеризующиеся Одиночным потоком Команд и Множественным пото¬

ком Данных (ОКМД). .Материал охватывает следующие темы:

Г) Соотношение между ОКМД-архитектурой п другими типами архитектур

(глава I).

‘ 2) Важнейшие принципы, заложенные в архитектурах ассоциативных (гла¬

ва 2) и параллельных (глава 3) процессоров.

3) Описание четырех существующих вычислительных систем, являющихся

главными представителями семейства ОКМ Д-машин: ILLIAC IV (глава 4),

РЕРЕ (глава 5), STARAN (глава G) и OMEN (глава 7).

4) Основные методы оценки характеристик ОКМД-машпн, включая уже ап¬

робированные методы п методы, которые можно было бы или, вернее сказать,

следовало бы применять (глава 8).

- 5) Аргументы за и против ОКМД-архптектуры (глава 9).

Книга призвана служить справочным и учебным пособием по основным ти¬

пам ОКМД-машпн, созданных до 1974 г. В виде конспекта отта ужо была ис¬

пользована кате пособие на факультете вычислительной техники, информатики

и управления университета штата Миннесота в 1974—1975 учебном году. На ос¬

новании опыта, полученного в процессе преподавания настоящего курса, пред¬

ставляется целесообразным следующий порядок изучения книги.

1) Аспирантам специализированных групп рекомендуется двухсеместровыгг

курс, при этом в первом семестре следует изучить главы 1, 2, 3, 8 и 9, а во вто¬

ром — главы 4, 5, 6 и 7. Изучение курса может быть продолжено и в третьем

семестре в форме самостоятельной работы над специальными вопросами, инте¬

рес к которым возник в процессе изучения материала в двух предыдущих се¬

местрах.

2) Для аспираптов л студентов, прослушавших курсы по логической орга¬

низации вычислительных машин, программированию на языке ассемблера и тео¬

рии принятия решений, изучение книги может проходить в рамках дв\гх курсов,

а пмоппо:

пт-лпт кРаткп,\ обзорный одпос-емсстровый курс по теоретическим основам

ОКМД-машттщ базирующийся па материале глав 2 и 3, с привлечением тех раз¬

делов глав 4, 5, В и 7, в которых оштсаиы конкретные машины;

о) трехсеместровый курс с изучением в первом семестре глав 1 л 2, во вто-

ром семестре — глав 3. 8 и 9 и в третьим семестре — глав 4. 5. В и 7.

Книга может служить дополнительным учебным пособием поп изучении

~V™T0T'/VP вьгшслителытых машин, при этом в основном используется матери¬

ал глав 4, о, В и 7.

точполПеС0ПИе ВЫМИСЛЯТ0ЛЫ1°п машины к той пли пион категории по поддается-

ОКМЛ-\ отгсашпо и может рассматриваться как особое искусство. В области

пнейню1™!11 ТТМС0ТСЯ много проблем, связанных с терминологией, классифпка-

пнкщолгу311аЧ°11ИеМ П Т‘ ^1ТИга посвящена перспективному паправлеппто, воз-

касается ■ В^П^01*0(»Се РазвТ1Т11Я вычислительной техники. Перспективность эта

ставляет с ,(-°^.ыио“ ст°по1тн создателей машин, чем пользователей. Книга пред-

восколько го0*1 П°™У представить в рациональной и упорядоченной форме

пструкцпп вычислительных машин, взаимосвязь которых обуслов-

7

леиа наличием некоторого общего с нонет на, называемого ОКМД-иараллслизмом.

Очевидно, рассматриваемые машины не идентичны друг другу, но они сходны

в том, что их создали для решения задач, в которых используются свойства

ОКМД архлт е кт у ры.

Используя книгу в качестве руководства, студент может проникнуться тех¬

ническими идеями; эти идеи, возможно, встретятся при рассмотрении конструк¬

ций, созданных на базе основных принципов рассматриваемой архитектуры я

воплощающих эти принципы с учетом различных ограничений. И вычислитель¬

ных системах общего назначения, таких как, например, семейство IBM .‘UiU, кон¬

структорские решении обычно бывает трудно вы делит г» на фоне множества фак¬

торов (обусловленных участием в разработке большого количества людей, не¬

совершенством фирменной документации и т. д.). Однако в области ОКМД-ма-

шин имеются документы и официальные доклады, которые детально отражают

замыслы разработчиков и то. как эти замыслы воплощены в созданных конст¬

рукциях. Цель книги состоит в том, чтобы с единых позиций рассмотреть все

конструкции данного типа.

Основная черта рассматриваемых конструкций состоит в том, что при ре¬

шении широкого круга задач используется одно общее свойство (ОКМД) или

общая совокупность свойств (ассоциативность и ОКМД).

Автор надеется, что. увидев, как другие пытаются использовать указанные

свойства, читатель захочет ближе познакомиться с процессом конструирования.

Помимо того, что книга полностью охватывает всю область ОКМД-архитектур,

в ней еще есть стремление объяснить читателю причины того, что один и тот

же базовый принцип под влиянием тех или иных требований может порождать

различные, по взаимосвязанные архитектуры. Конструкторские задачи должны

быть поставлены так, чтобы дать студенту необходимый практический опыт,

благодаря которому он сможет участвовать в развитии и совершенствовании

конструкций конкретных вычислительных машин. ОКМД-архитектуры пред¬

ставляют собой хорошее ноле деятельности дли студентов, поскольку задачи

конструирования оказываются точно очерченными благодаря присущим данной

архитектуре ограничениям. Автор надеется, что книга позволит читателю с раз¬

личных сторон рассмотреть одну нз основных концепций современной вычисли¬

тельной техники (концепцию параллелизма) и послужит стимулом дальнейшего

сове рнт с и с т в о в а ни я э т о й кон ц е и ции.

Книга состоит из описаний машин, каждое из которых по объему соответст¬

вует одной лекции. Общим для всех рассматриваемых машин является заложен¬

ный .в них основной принцип построения. Отдельное описание какой-либо ма¬

шины по возможности представляет собой замкнутый раздел книги. При напи-

ч анпп каждого раздела автор стремился в краткой н содержательной форме по¬

казать области применения и основные конструкторские идеи.

Архитектуры машин объединены в несколько групп по признаку свойств,

которые определяют их сущность. Разные архитектуры, описанные в книге, от¬

личаются друг от друга скорее по способу технической реализации, нежели по

принципу построения. Совокупность разработанных архитектур настолько мно¬

гообразна, что бесспорное отнесение какой-либо из тшх к той или пион катего¬

рии практически невозможно из-за большого числа переменных величин, опи¬

сывающих архитектуру. Например, ассоцпацивпые процессоры охватывают диа¬

пазон от процессоров с обработкой простых битовых срезов (глава 2) до про¬

цессоров с обработкой сложных битовых срезов (глава 0), от процессоров с про¬

стой распределенной логикой (глава 0) до вычислительных систем со сложной

распределсчшои логикой и высокой степенью параллелизма (глава 2).

По мере того как читатель будет знакомиться с описываемыми конструк¬

циями, у пего могут возникнуть другие предложения по классификации ма¬

шин. что, отчасти, является целью данной книги, а именно, сопоставление ма¬

шин. отличающихся по конструкции, с целью выявить заложенные в них прин¬

ципы. Кроме того, читатель всегда будет иметь возможность без предубеждения

относиться к новым видам архитектур, пути создания которых ыамечепы в этой

книге.

Глава 1

ВВЕДЕНИЕ

Для чего нужны специализированные вычислительные машины?

Большинство задач пользователей может быть решено с помощью широко

распространенных универсальных вычислительных машин. Однако существует

немало сфер примепения, в которых к характеристикам вычислительных

средств предъявляются специальные требования. Многие задачи просто не мо¬

гут быть решены на серийных универсальных машинах. В частности, во мно¬

гих случаях применение специализированных машин продиктовано соображе¬

ниями надежности.

Имеется класс задач, требующих очень высокой скорости вычислений,

обеспечение которой с помощью универсальной вычислительной системы со¬

вершенно нецелесообразно с точки зрения стоимости. Такие задачи требуют

высокой пропускной способности при обработке структурированных данных.

Одним из подобных применений является противоракетная оборона. Большое

число задач такого типа пе может быть решено на вычислительных машинах

общего назначения при сколько-нибудь приемлемой стоимости решения. Этот

класс задач образует область применения, в которой с успехом могут быть

использованы ассоциативные и параллельные вычислительные системы.

Ассоциативные п параллельные процессоры всех типов являются специа¬

лизированными вычислительными машинами. Хотя на них могут решаться

различные задачи, но все они должны быть основаны па похожих вычисли¬

тельных методах. ТТн в коем случае подобные машины пе следует считать

универсальными. Благодаря наличию повторяющихся структурных элементов

они открывают простор для эффективного (с точки зрения стоимости) приме¬

нения оольших пптегралытьтх схем. Развитие в последние годы, микропроцес¬

соров может в значительной степени способствовать тому, что специализиро¬

ванные системы станут эффективными во многих применениях.

Ассоциатнвпые и параллельные процессоры оказываются полезными при

решении задач, требующих очепь высокой пропускной способности и рабо¬

тающих со структурированными данными. Характерными примерами обла¬

стей, в которых могут потребоваться такпо процессоры, являются обработка

метеорологических данных, обработка в реальпом масштабе времепи радио-

вациоциьтх сигналов, противоракетная оборона, управление воздушным

механизмы внртуальпой памяти, механизмы защиты в операци¬

ях системах, а также решение систем дифференциальных уравнений. Рас-

риваемый тип машин следует применять в тех случаях, когда:

быть имототся БТ)ТС°ъне требования по быстродействию, которые пе могут

выполиепы при использовании обычных вычислительных систем;

9

2) необходимо обеспечить системе возможность приспосабливаться к из¬

меняющимся требованиям путем более прогрессивной технологии наращива¬

ния оборудования;

3) одним из непременных требований пользователя является возмож¬

ность поэтапной модернизации системы.

Если имеются две различные вычислительные машины, удовлетворяющие

предъявляемому требованию, то решающим фактором при выборе следует

считать показатель стоимостной эффективности. Однако нельзя отдать

предпочтение машине, имеющей самый лучший показатель удельной стоимо¬

сти, если эта машина пе удовлетворяет требованиям, обусловленным специ¬

фикой применения, рти требования включают все критерии, по которым

должна оцениваться система; К ним следует отнести наличие математичес¬

кого обеспечения, возможности наращивания, требования к размеру помеще¬

ния, коэффициент готовности и надежность.

^Соображения стоимости не ограничиваются только цепой машины, но

также включают расходы в течение жизненного цикла, стоимость установки,

стоимость электроэнергии и расходы по перепрограммированию. Если предъ¬

являемым требованиям удовлетворяет несколько машин, то главным крите¬

рием, определяющим окончательный выбор, является критерий стоимостной

эффективности.

Классификация архитектур машин

Описапие машин с точки зрения потоков команд (инструкций) и даппых

было предложено Флинном [1.2], который ввел понятия одиночного и мно¬

жественного потоков как для команд, так и для данных. Это привело к рас¬

пределению всех машин по четырем классам архитектур. Из рассмотрения

характера потока может быть выведен ряд свойств машин различных типов.

На рис. 1.1 показаны четыре класса машин в соответствии с типами потоков.

ОД: Одиночный по¬

ток данных

МД: Множественный

поток данных

ОК: Одиночный

поток команд

Однопроцессорная

система

Параллельный!

процессор и ассоциа¬

тивный процессор

МК: Множествен¬

ный поток

команд

Процессор поточной

обработки

(конвейерная систе¬

ма)

Многопроцессорная или

многомашинная вычис¬

лительная система

Рис. 1.1. Классификация основных типов архитектур процессоров

Эти классы следующие: одиночный поток команд и одиночный поток дапных

(ОКОД, однопроцессорная система); множественный поток команд и множе¬

ственный поток данных (МКМД, миогрпроцессорпая и мпогомашинная вы¬

числительные системы); одиночный поток команд и множественный поток

10

ых (ОКМД, ассоциативный пли параллельный процессор); множествен¬

ный поток команд и одиночный поток данных (МКОД, нроцессо'р поточной

обработки*)). Примерами перечисленных архитектур являются IBM 300,

Univac 1108, ILLIAC IV и CDC STAR 100 соответственно.

В последующих главах ОКМД-архитектура будет подвергнута детально¬

му исследованию. В этой главе будут суммированы характерные черты рас¬

сматриваемой архитектуры. В ОКМД-системах заложен принцип,, согласно

которому одип набор базовых управляющих команд ’ применяется к несколь¬

ким процессорным элементам, с каждым из которых, в свою очередь, связа¬

на последовательность данных. Все процессорные элементы должны рабо¬

тать синхронно и согласованно, каждый со своим набором данных. Эта осо¬

бенность определяет свойства задач, которые целесообразно решать на

ОКМД-процессорах, а именно: 1) множественность наборов данных; 2) оди¬

наковость вычислительных операций, выполняемых па всех наборах; 3) от¬

сутствие непредсказуемых изменений в характере потоков данных; 4) не¬

различимость процессорных элементов с точки зрения обработки любых

наборов.

Бывают случаи, когда у разработчика может возникнуть потребность

создать внутри системы некоторую структуру с целыо извлечь выгоду из

особенностей решаемой задачи. С этой точки зрения конструкция ОКМД-про-

цессора имеет ограничения, обусловленные самим принципом его работы а

временной зависимостью потоков данных. Необходимо учитывать особенно¬

сти источника потоков информации и имеющиеся в этих потоках разрывы,

смысловое содержимое потоков и его взаимосвязь с предыдущим содержимым.

Система должна быть настроена на частоту поступления информации в

потоке. Если процессор может быть адекватно согласован с частотой поступ¬

ления дапных и имеются алгоритмы, построенные такцм образом, что вычис¬

ления производятся параллельно над большинством потоков, то ОКМД-про-

цессор позволяет достичь производительности, на несколько порядков пре¬

вышающей производительность последовательных процессоров. Вдобавок

может быть использовано менее сложное оборудование и математическое обес¬

печение, чем те, которые понадобились бы при последовательном решении за¬

дачи, если, конечно, такое решение вообще возможно.

Дальнейшее обсуждение, касающееся анализа машин с позиции потоков

команд и дапных, можно найти в работах Хоббса и др. [1.3], Холлаидера

[1.4] и Белла [1.5]. В работе Холлаидера ^дается сравнительный анализ при¬

менимости различных основных типов архитектур. ОКМД-архитектура рас¬

сматривается как имеющая применение, ограниченное несколькими высоко-

быстродействующими типами систем или такими задачами, в которых стро¬

ятся функциональные модели физических систем.

ОКМД-процессоры оказываются полезными в ограниченной области спе-

ппальпых применений, которую очень легко охарактеризовать. ОКМД-архи¬

тектура представляет собой новое соотношение между объемом оборудова¬

ли, приходящегося па логику, и объемом оборудования, приходящегося на

память, с целыо получения более высокой скорости обработки. Полезность

Данной архитектуры обусловлена существованием задач, требующих очень

высокого быстродействия, и тем, что она позволяет разработчику так строить

(Jlpin ^аКПе пР°ДессоРы иногда называют конвейерными или магистральными.

11

систему, что эти высокие требования по быстродействию могут быть удовлет-

В'Ф с и ы э ф ф е кт и в и ы м с i т о с о б о м.

Из четырех категорий машин, выделенных па основе концепции пото¬

ков команд и данных, только ОКМД-архлтектура является существенно спе¬

циализированной. Другие категории, а именно, однопроцессорная система,

процессор поточной обработки и многопроцессорный или многомашинный

комплекс, находят широкое применение в универсальных вычислительных

системах. Па базе машин названных классов можно построить и специализи¬

рованные вычислительные системы, но в этих случаях сиециализнрованиость

выражается, в основном, в изменении таких характеристик, как- коэффици¬

ент готовности, надежность, возможность приспособить конфигурацию систе¬

мы к конкретной задаче, наличие специализированных вычислительных

операций.

Типовые задачи для ОКМД-машин

Область применения ОКМД-машин включает: аппарат сохраняющих бу¬

феров в механизме виртуальной памяти [1.0], распределение ресурсов [1.7],

аппаратные диспетчеры [1.8], обработку прерываний [1.9], механизм за¬

щиты [1.0], составление расписаний [1.7], сложные алгоритмы фильтрации

в радиолокационных станциях [1.1], расчет траекторий в реальном масштабе

времени [1.10], управление воздушным движением [1.11], сжатие информа¬

ции [1.12], мультиплексирование каналов связи [1.13], информационно-поис¬

ковые системы [1.14], сортировку [1.15], обработку символьной информации

[1.10]. распознавание образов [1.17], обработку изображений [1.18], обработ¬

ку данных от гидролокатора [1.19], обработку данных наблюдения за поверх¬

ностью морей и океанов [1.20], обработку графической информации [1.21],

динамическое программирование [1.22], дифференциальные уравнения [1.23],

нахождение собственных значений и собственных векторов [1.24], операции

с матрицами [1.25], анализ потоков в сетях [1.20], воспроизведение докумен¬

тов [1.27], машинную обработку документов [1.28], поиск информационных

файлов [1.29], компиляцию [1.30], автоматическое реферирование [1.31], уп¬

равление данными [1.32], доказательство теорем [1.33], машинную графику

[1.34], обработку метеорологической информации [1.35] и противоракетную

оборону [1.1].

Реальная потребность в ОКМД-машлшах основывается на стоимостных

соображениях. Например, для того чтобы ускорить процесс получения резуль¬

тате» при расчете прогноза погоды, министерство военно-морского флота ис¬

пользовало программу, работающую на четырехмашпипом комплексе, который

создан па базе универсальных машин, связанных между собой по принципу

ОК.МД-архитектуры с целью сократить время расчета прогноза. Такое реше¬

ние позволило при четырехкратном увеличении количества оборудования

увеличить быстродействие приблизительно в три раза. До сих пор ОКМД-

процесеоры были слишком дорогостоящими, и поэтому считалось, что они

имеют ограниченное применение. Чем более специализированным является

процессор, тем меньше возможность его использования в универсальных си¬

стемах. В то же время чем более специализированным является процессор,

тем лучше он может подойти для решения отдельпых задач.

В пастолщое время главной причиной, по которой пользователи не уста¬

навливают у себя ОКМД-процессоры, является объем неокупаемых затрат,

12

за чего пользователи предпочитают обходиться менее быстро действу ющн-

ми* машинами. Решение «опроса о том, являются ли потребности действи¬

тельными или надуманными, останется за рынком.

J3 последующих главах будут подробно рассмотрены (ЖМД-архитсктура

и ряд требований, которым она должна удовлетворять, с точки зрения при¬

менения. Будут обсуждены вопросы, касающиеся архитектуры, характерис¬

тик конструктивных особенностей и структуры ОКМД-процессоров в сопо¬

ставлении с ожидаемыми или запроектированными показателями. Проблема

неокупасмых затрат при разработке остается открытой.

С разработкой недорогих микропроцессоров на БИСах появляется воз¬

можность создавать ОКМД-машины, имеющие очень небольшую стоимость.

По мере развития вычислительной техники ОКМД-машины будут играть все

более значительную роль. Будущее ОКМД-машпн никогда ранее не представ¬

лялось столь благоприятным.

ОКМД-процессоры

ОКМД-архитектура — это архитектура специализированных вычисли¬

тельных машин. Существуют две основные формы ОКМД-архитектуры, а

именно, ассоциативный процессор и вычислительная система с массивом

процессоров или параллельный процессор*). Ассоциативный процессор —

это ОКМД-лроцессор, базовым процессорным элементом которого является

слово ассоциативной памяти. Параллельные процессоры имеют более слож¬

ные элементы, и эти элементы определенным образом связаны между собой.

Каждая из этих концепций будет подробно обсуждаться в последующих

главах.

Для того чтобы различать типы процессоров, будем пользоваться следуй^

щей термине логи ой:

1) ОКМ Д-процессор — вычислительная система, архитектура которой ха¬

рактеризуется одиночным потоком команд и множественным гготоком данных.

2) Вычислительная система с массивом процессоров (параллельный про¬

цессор) — ОКМД-процедсор, в котором каждый процессорный элемент опре¬

деленным образом связап с другими элементами. В общем случае элементы

могут выполнять довольно сложные функции. В ряде ранних систем (пыне

ушедших в историю) представление о таких процессорах ограничивалось

двумерным массивом процессорных элементов. Данная формулировка опре¬

деляет вычислительную систему с массивом процессоров или параллельпый

процессор как ОКМ Д-процсссор, предназначенный для обработки массивов

данных.

3) Ансам.пль — вычислительная система с массивом процессоров (па¬

раллельный процессор), в котором связи между отдельными элементами ие

обладают регулярной структурой. Это определение относится к особому виду

параллельного процессора, элементы которого не имеют определенного вида

связи друг с другом.

4) Ассоциативный процессор — ОКМД-процессор, в котором главным

средством активации элемента является ассоциативный процесс. В общем

случае элементы ассоциативного процессора имеют произвольные взаимо-

*) Такие процессоры часто называют матричными. {Примеч. пер.)

13

связи и функционально являются очень простыми. Подобный процессор обыч¬

но строится на базе ассоциативной памяти.

Как легко видеть, данные определения являются интуитивными и, сле¬

довательно, неточными. Этого следовало ожидать, поскольку имеется большое

число мелких особенностей, делающих каждую систему уникальной. Все по¬

следующие главы посвящены всестороннему анализу как ассоциативных,

так и параллельных процессоров. Ансамбли будут рассмотрены в гл. 3, в ко¬

торой описываются параллельные процессоры.

| Ввод/вывод

Вычислительные системы с массивом процессоров

(параллельные процессоры)

Структурная схема типичной вычислительной системы с массивом про¬

цессоров (параллельный процессор — Г1П) приведена на рис. 1.2. Основыва¬

ясь на предыдущих определениях, следует отметить следующие характерные

черты параллельных процессоров.

Управление множеством процессорных элементов осуществляется одним

управляющим устройством. Имеются два типа накопителей: одни — для хра¬

нения программ,, другой — для хранения дапных. В устройстве управления

отсутствует локальная память как для программ (за исключением микро¬

программ), так и для данных. Все процессорные элементы идентичны и име¬

ют идентичные устройства для хранения данных. Между процессорными эле¬

ментами существует связь некоторого определенного типа. Наконец, данные

могут поступать в систему как

путем непосредственного ввода в

процессорные элементы, так б

через устройство управления.

Все активные процессорные-

элементы должны работать стро¬

го согласованно друг с другом*

Они работают параллельно, т. е.

синхронно. Процессорный эле¬

мент называется активным

тогда и только тогда, когда

обрабатывается выделенная ему

порция данных из потока. Если

процессорный элемспт не обра¬

батывает поток дапных, он счи¬

тается неактгСвным. Всякий раз.

когда процессорный элемецт- по¬

лучает очередную управляющую

команду, он может либо выпол¬

нить ее, либо проигнорировать

(в зависимости от предыдущих

состояний и/или числовых значе¬

ний обрабатываемых величии),

при этом - он не может сделать ничего другого. Если нужно, процессор может

работать как единое целое. Обычно параллельный процессор взаимодействует с

универсальной- машипой через устройство управления. Универсальный процес-

Рпс. 1.2. Блок-схема параллельного про¬

цессора

14

лор называемый обычно ведущим, осуществляет управление всем мас¬

сивом процессорных элементов. Устройство управления непосредственно ру¬

ководит исполнением программ. Если структура внутренних перекрестных

связей очень проста или вообще отсутствует, то параллельный процессор с та¬

ким произвольным способом взаимодействия между элементами называется

ансамблем.

Ассоциативные процессоры

Ассоциативный процессор определяется как устройство обработки дан¬

ных, в котором данпые хранятся, считываются и обрабатываются без точной

адресации их расположения в памяти. Структурная схема типичного ассоциа¬

тивного процессора показана па рис. 1.3. Этот ОКМДгпроцессор иостроен на

| Ввод / вывод

! Регистр Регистр Обрабатывающее

i резудьта- выборки устройство

I уоз по- слов (логика и/или

| иска арифметика.)

Рис. 1.3. Блок-схема ассоциативного процессора

оазе ассоциативного запоминающего устройства, состоящего из ассоциа¬

тивных ячеек памяти. Данные могут быть сопоставлены по некоторому кри¬

терию (равно, меньше чем и т. д.) с информацией, хранящейся в памяти,

для чего выполняются следующие действия: 1) запись данных в регистр

Данных; 2) выделение' разрядов, подлежащих сравнению, с использованием

регистра маски и 3) запись битового набора, описывающего искомое подмно¬

жество данных в файле, в регистр выборки слов. Результатом сравнения бу^

Дет битовый набор в регистре результатов поиска, снабженного указателем

15

па «первое откликнувшееся слово». Этот указатель называется устройством

разрешения множественных откликов, он указывает на «самое верхнее сло¬

во», удовлетворяющее критерию поиска, т. е. на «самый верхний бит» реги¬

стра результатов поиска.

Ячейка ассоциативной памяти является основным элементом, из которых

строится система. При желании ассоциативный процессор может быть создан

и без использования специальных устройств, но за выполнение функ¬

ций ассоциативной памяти придется поплатиться потерей быстродействия.

Процессорное оборудование, обеспечивающее соответствующую аппаратную

поддержку, включает, по крайней мере, одно полное последовательное ариф¬

метическое устройство на каждое слово ассоциативной памяти.

Два главных отличия ассоциативных процессоров от параллельных за¬

ключается в типе запоминающего устройства и в отсутствии взаимных свя¬

зей ме'/кду процессорными элементами. Если рассматривать ассоциативное

запоминающее устройство как память для хранения данных, то ассоциатив¬

ный процессор может быть назван параллельным процессором или ансамб¬

лем. Однако, поскольку свойство ассоциативности является очень лажным,

ассоциативные процессоры будут рассматриваться как самостоятельный

класс машин с ОКМД-архитектурой.

Заключение

Имеется много оснований для разработки, создания и применения спе¬

циализированных вычислительных систем. Главная причина состоит в том,

что такие системы способны обеспечить высокую производительность, могут

функционировать в жестких внешних условиях или иметь высокие показате¬

ли надежности, недостижимые для вычислительных систем общего назначе¬

ния. Комбинация универсальной и специализированной вычислительных ма¬

шин представляет собой наиболее эффективное гГо стоимости решение в тех

областях, где требуются высокие вычислительные возможности и где нет же¬

стких внешних условий.

В последующих главах подробно обсуждаются несколько типов вычисли¬

тельных систем, относящихся к категории ОКМД. Процессоры данного типа

могут быть отнесены либо к классу ассоциативных, либо к классу параллель¬

ных систем. Будут исследованы основпые типы архитектур в каждом из этих

классов и обсуждены их особенности. Параллельные системы показывают на¬

илучшие характеристики при решении таких задач, как расчет прогноза по¬

годы или противоракетная оборона. Ассоциативные процессоры оказываются

наиболее полезпыми в таких применениях, как управление виртуальной па¬

мятью или механизм защиты памяти. Главные из создаппых к настоящему

времени ОКМД-процсссоров подробно обсуждаются в последующих главах.

Цель книги состоит в том, чтобы помочь читателю увидеть, как различ¬

ные фирмы, производящие вычислительную технику, воплощают в своих кон¬

струкциях идею ОКМД-архитсктуры. В книге не будет никаких попыток су¬

дить о правомерности топ или иной конструкции. Первыми будут рассмат¬

риваться ассоциативные процессоры как более простые.

Об ОКМД-машипах написано несколько хороших обзоров. Наиболее суще¬

ственные из них цитируются [ 1.36—1.44].

16

У it р а ж нения

1. расскажите о наиболее существенных различиях между архитектурами

О КОД, МКОД, ОКМД и мкмд.

2. Приведите пример вычислительной системы для каждой из архитектур

/0КОД, МКОД, ОКМД и МКМД).

3. Покажите, почему конвейерный процессор не является адекватной реа¬

лизацией МКОД-архитсктурьт. Расскажите о тех особенностях МКОД-архптек-

турьт, которые -затрудняют ее реализацию. Расскажите о скрытых трудностях,,

возникающих при попытке дать классификацию архитектур на простой одно¬

родной основе.

' 4. Покажите основные различия между ассоциативными и параллельными

процессорами. %

5. Покажите основные различия между ансамолями и ассоциативными

процессорами.

6. Расположите ОКОД. МКОД, ОКМД и МКМД-архитектуры в ряд по та¬

ким показателям, как гибкость, функциональная расширяемость, отказоустой¬

чивость и модульность.

Глава 2

АССОЦИАТИВНАЯ ОБРАБОТКА

Введение

Глава посвящена обсуждению базовой архитектуры/ реализующей ассо¬

циативную обработку информации. Будут рассмотрены исторические предпо¬

сылки ассоциативности и возможные применения ассоциативных процессоров.

Будет дано описание и анализ работы ассоциативного процессора наиболее

■общего типа, а также приведены примеры* использования ассоциативного про¬

цессора общего типа.

Концепция ассоциативности или ассоциаций не пова. Она уходит в глубь

вёковг во времена Аристотеля. Ассоциация может рассматриваться как уста¬

новление соответствия мождУ объектами. В труде «О памяти и воспомина¬

ниях» Аристотель определил три вида ассоциаций. Это ассоциации по сходст¬

ву, контрасту ,и близости. Лок и Хыо дополнили этот перечень ассоциацией

идей, а также ассоциациями, соответственно, по причине и следствию. Позже

возникло философское учение об ассоциациях. Это учение утверждало, что

знание извлекается из отдельного простого практического опыта.. Поэтому

оно может быть представлено в терминах таких основных опытов. Более позд¬

ние исследования механизма, ассоциаций проводились на основе биологиче¬

ских наук, изучения нервной системы и деятельности мозга. Обширный обзор

истории учения об ассоциациях и связанных с ними философских концепций

■содержится в работе Замепека [2.1].

Принципы построения ассоциативных процессоров обсуждались почти

двадцать лет [2.2, 2.3]. Однако реальные применения ассоциативных систем

рассматривались лишь последние пять лет*). В течение этого периода прин¬

цип ассоциативной обработки был воплощен в различных формах, известных

под различными названиями. К числу таких форм относятся: каталоговые за¬

поминающие устройства [2.3], ассоциативные запоминающие устройства [2.4],

накопители с параллельным поиском [2.5], запоминающие устройства с ад¬

ресацией по данным [2.6], запоминающие устройства с адресацией по содер¬

жимому [2.7], ассоциативные процессоры [2.8], ассоциативные вычислитель¬

ные системы [2.9], машины с распределенной логикой [2.10], накопители с рас¬

пределенной логикой [2.11], ассоциативные параллельные процессоры [2.12],

тегированные запоминающие устройства [2.13], магазинные ассоциативные

запоминающие устройства [2.14], процессоры с ассоциативной памятью [2.15].

Поскольку эти устройства работают по одному и тому .же основному принци¬

пу (ассоциативности), то все они в книге будут именоваться ассоциативными

процессорами.

*) Речь идет о периоде до 1975 г. (Примеч. пер.)

18

Применения

Для ассоциативных процессоров предлагались многочисленные области?

применения. До середипы 70-х годов с практической точки зрения были рас¬

смотрены лишь немногие из них. Дело в том, что технические проблемы, стоя¬

щие на пути реального воплощения ассоциативных процессоров, очень слож¬

ны. Было предложено большое число различных применении, по практиче¬

ски ни одно из них не было детально исследовано. Работы велись с целью-

доказать применимость ассоциативного процессора вообще, а не с целыо полу¬

чить экономически эффективную конструкцию такого процессора. Сейчас

наблюдается отход от этой позиции. В настоящее время в очень немногих слу¬

чаях доказана эффективность применения ассоциативного процессора. Зато

там, где их эффективность доказана, ассоциативные процессоры показывают

очень высокие характеристики и действительно оказываются очень полезны¬

ми. Примечательным примером эффективного решения задачи является ме¬

ханизм виртуальной памяти [2.16].

ВеДутся детальные исследования ряда перспективных применений. Этш

перспективные применения включают проблемы, имеющие высокую степень*

общности. Имеется в виду устранение узких мест в машинах общего назначе¬

ния, аппаратная поддержка критических участков вычислительного процесса

в системах реального времени, а также улучшение характеристик существую¬

щих систем путем увеличения их пропускной- способности без переработки^

всей конструкции. В большинстве таких применений используются небольшие

ассоциативные устройства, ограниченные несколькими сотнями слов памяти*,

в отличие от ассоциативпых процессоров, предлагавшихся на раннем этапе-

развития этих устройств, когда считалось, что они могут иметь тысячи или

миллионы слов.

Типичными применениями в машинах общего назначения, где ассоциатив¬

ные устройства используются для ликвидации узких мест, являются меха¬

низмы защиты, механизмы виртуальной памяти, а также ассоциативные про-'

цессоры, работающие с дисковой памятью для хранения файлов. Ассоциатив*

ные процессоры используются как управляющие устройства при выполнении,

таких "функций, как обработка прерываний, управление памятью, распреде¬

ление ресурсов, а также в аппаратных диспетчерах.

Ассоциативные процессоры используются для улучшения характеристик-

машин общего назначения в таких применениях, как сжатие данных, ком¬

мутация и мультиплексирование данных,. управление воздушным движением

и обработка радиолокационной информации. Другими сферами применения,,

в которых ассоциативные процессоры представлялись эффективными, по сте¬

пень их истинной полезности не выяснена до конца, являются поиск и печать-

Документов, компиляция программ, матричные вычисления, работа с больши¬

ми файлами данных и решение дифференциальных уравнепий.

Очевидно, области применения для ассоциативных процессоров #существу¬

ют- Практика же показывает, что использование ассоциативпых процессоров

пока ограничено из-за технических трудностей их разработки. В настоящее

премя технические возможности построения ассоциативных процессоров до¬

статочно развиты для того, чтобы можно было вплотную рассматривать во¬

просы их практического осуществления. Будущее ассоциативных процессоров

представляется блестящим.

Наиболее общий тип архитектуры ассоциативного процессора

Ведущая концепция архитектуры ассоциативного процессора уже сформи¬

ровалась. Она может использоваться в разнообразных применениях от меха¬

низма виртуальной памяти до решения ряда задач управления воздушным

движением, таких как обнаружение конфликтных ситуаций, выявление кор¬

реляций между трассами, уточнение параметров трасс и подготовка данных

для отображения. В последующих параграфах описываются эта наиболее об¬

щая архитектура и способы ее воплощения, поясняемые примерами конкрет¬

ных конструкций.

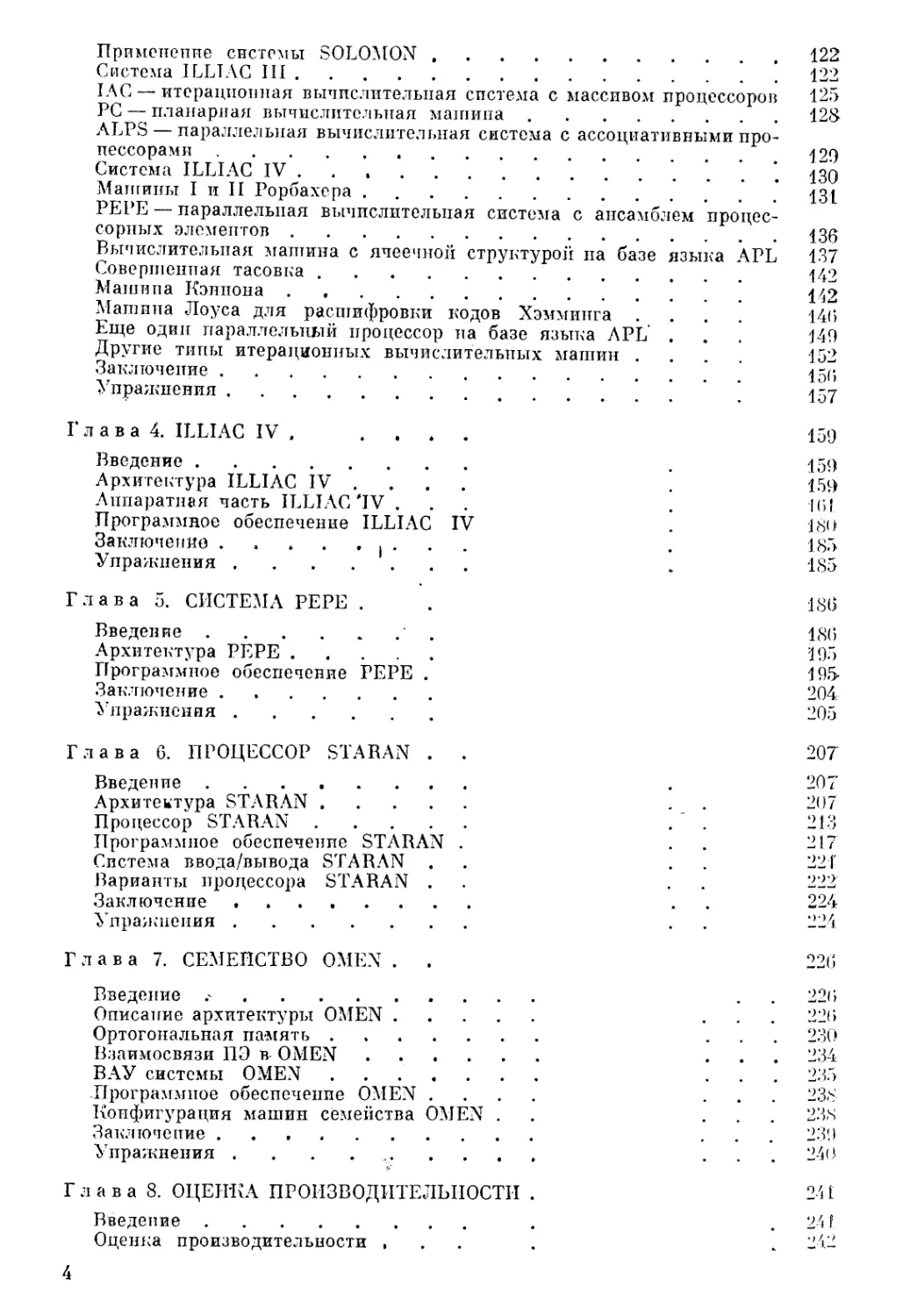

Принцип работы. Па рис. 2.1 изображена блок-схема, отражающая наибо¬

лее общую архитектуру ассоциативного процессора [2.17]. Эта архитектура

содержит четыре регистра (данных, маски, результатов поиска и выборки

ОЮ

111

110

000

ООО

000

[oooj

000

Per и от р

Регистр

данных

маски

Слыо

1 110

111

101

0

и

□

□

С/030

2 011

111

101

0

[~о~|рпорГ|

□

Слово

3 010

110

101

0

□

□

□

С л озо

4 101

110

101

1101 |

И

□

□

С по во

5 110

000

001

0

Ш

□

□

С о о а о

6 010

110

000

[oioj

□

□

□

Олово

7 010

110

010

0

И

и

□

Слово

8 111

111

011

0

□

□

□

Доле

’

-

4 Рсгислр

[10';V (1 b -

Чатов

no'/с ка

Регистр

выборки

слов

Аппарат¬

ные сред¬

ства об -

работки

Рис. 2.1. Принцип работы ассоциативного процессора

слов), устройство разрешения множественных откликов (РМО), массива ассо¬

циативной памяти и аппаратных средств обработки слов. Процессор, изобра¬

женный на рис. 2.1, имеет 8 слов памяти. Важно отметить отсутствие каких-

либо устройств преобразования адресов. По существу, адресов вообще нет. Ад¬

ресация данных в процессоре осуществляется по их содержимому или по ка¬

ким-либо параметрам, связанным с содержимым.

Каждое слово памяти разбито на разрядные группы переменной длины,

называемые полями. Поля не обязательно должпы состоять из последователь¬

но расположенных разрядов. Регистры данных и маски содержат такое же ко-

20

личество разрядов, что п слово памяти. Регистры результатов поиска и вы-

tfopnu слов содержат но одному разряду па каждое слово памяти.

Битовый срез (например, г-й битовый срез) представляет собой битовый

гектор’ составленный из i-x разрядов всех выбранных слов и не зависящий

от содержимого остальных слов.

Пример]»! операций, осуществляемых ассоциативными процессором: маски¬

рованный поиск иа равенство, различные виды последовательно-поразрядных

операций поиска па неравенство, последовательно-поразрядные арифметиче¬

ские операции над полями, последовательно-поразрядный поиск максимума

(минимума), позволяющий находить максимальное (минимальное) записан¬

ное в памяти слово.

В ассоциативных процессорах, ориентированных на пекоторые примене¬

ния, отдельные элемент],г базовой архитектуры могут выступать пеявно. В ме¬

ханизме виртуальной памяти может оказаться ненужным регистр выборки

слов. Каждое слово памяти может понадобиться в любой момент времени. Ре¬

гистр маски может использоваться но умолчанию. Поля поиска могут быть

■известны и предусмотрены заранее. В некоторых системах обработки данных,

таких как управление воздушным движением, может быть введено' большее

количество регистров. В вычислительной системе STARAN (см. гл. 6) имеется

три регистра, указывающих направление поиска слов (X, У и W), чьи функ¬

ции аналогичны функциям регистров выборки слов и результатов поиска, по¬

казанных на рис. 2.1 [2.18].

Организация работы системы осуществляется устройством управления,

выполняющим разнообразные функции. В некоторых применениях устройство

управления может быть очень простым. В системе STARAN устройство уп¬

равления включает вычислительную машину PDP-11 и дополнительный мик¬

росеквенсор *).

Ассоциативный процессор, работающий с восемью словами и четырьмя

■3-битовыми нолями, изображенный на рис. 2.1, дан в качестве небольшого при¬

мера, иллюстрирующего работу ассоциативных систем. В регистре данных за¬

писано слово, которое нужно сравнить с содержимым памяти. Регистр маски

указывает те разряды искомых слов, которые должны быть включены в опе¬

рацию поиска. В регистре результата записан результат поиска. Регистр вы¬

борки слов выбирает слова, участвующие в поиске.

В данном примере слово 7, как показывает содержимое регистра выборки

слов, не вошло в число выбранных. Содержимое регистра маски показывает,

что в поиске участвует содержимое только первого поля регистра данных.

В процессе выполнения операций ассоциативного процессора, а именно, по¬

иска па равенство, будет произведено сравнение содержимого первого поля

регистра поиска с содержимым соответствующих полей всех выбранных слов.

И* таких слов только слова 3 и 6 удовлетворяют условию поиска; эти слова

после завершения поиска отмечены единицей в регистре результата. Слово 7

также должно было бы удовлетворить условию поиска. Однако содержимое ре¬

гистра выборки слов показывает, что оно не вошло в набор слов, выбранных

Для участия в операции сравнения.

Устройство, определяющее порядок выполнения операций иа уровне

рззрядов. {Примеч. пер.)

21

Во многих системах за операцией поиска должпа следовать операция счи¬

тывания (идентифицируемые слова последовательно считываются) или дру¬

гая операция поиска (регистр результатов может быть переписан в регистр

выборки, чтобы сто можно было использовать в качестве нового содержимого-

регистра выборки).

Может быть произведена серия операций поиска, результаты которых ло¬

гически объединятся, т. е. данные, находящиеся в регистре результатов поис¬

ка, логически перемножаются с содержимым регистра выборки слов, форми¬

руя тем самыхг новое содержимое последнего.

Число встроенных логических функций может быть весьма велико. Эти

логические функции нужны для повышения эффективности вычислений. К не¬

отъемлемым атрибутам системы относится устройство разрешения множест¬

венных откликов*) (РМО). На рис. 2.1 устройство РМО показапо стрелкой. Ес¬

ли в результате поиска получены отклики от пескольких слов, то РМО указы¬

вает па «первый отклик» или, ипаче, па «самое верхнее» слово, для которога

выполнилось условие поиска.

Архитектура ассоциативного процессора и проблемы реализации. Раньше

считалось, что ассоциативные процессоры должны заменить вычислительные

машины общего назначения. В конце концов они стали рассматриваться как

специализированные системы. В качестве технологической базы вместо крио¬

тронов стали использоваться запоминающие устройства на магнитной прово¬

локе или на полупроводниковых элементах. В настоящее время основной упор

в технологии сделан на специализированные полупроводниковые процессоры.

Ниже описывается ряд конструкторских проблем, которые обычно приходится,

решать при разработке рассматриваемых устройств. .

Первая проблема, которую необходимо решить при разработке, состоит

в том, хранить ли программу в некоторой области ассоциативной памяти ас¬

социативного процессора или в отдельной памяти с произвольным доступом,

связанной с устройством управления. Учитывая факторы стоимости, програм¬

мы обычно хранятся в отдельной памяти с произвольным доступом (ОЗУ),

В тех случаях, когда программа всегда- остается неизменной, может исполь¬

зоваться память с доступом только по чтению (ПЗУ). Хранение программ в

ОЗУ обеспечивает защиту содержимого-ассоциативной памяти от программных

сшибок, снижает требования к пропускной способности шип, по которым пе¬

ремещаются данные, хранящиеся в ассоциативной памяти, экономит ячейки

ассоциативной памяти (которые стоят дороже ячеек ОЗУ), а также дает воз¬

можность иметь разные временные циклы для ОЗУ и ассоциативной памяти.

Это обеспечивает гибкость при подборе быстродействия системы применитель¬

но к решаемой задаче.

Другой проблемой, возникающей при разработке, является выбор типа

связи между ячейками. Эвиитом и Дэвисом [2.19] были описаны четыре ва¬

рианта связи: 1) передача общего операнда во все выбранные ячейки памяти;

2) управление выбором полей для обеспечения работы с парой операндов,

находящихся в одном слове, 3) использование сдвиговых регистров для орга¬

низации связи между соседними словами, и 4) построение многозвенных се¬

тей с попарными связями по входу/выходу для организации взаимодействия

*) В качества сипоппма слова «отклик» употребляется слово «совпадение».

{Примеч. пер.)

22

Л16/КДУ несмежными словами. При реализации упор обычно делаются на типы

связи 1, 2 и 3 и ограниченное применение связи типа 4, которая осуществля¬

йся путем многократных сдвигов в сдвиговом регистре. Обычно в сдвиго¬

вом регистре сдвиг производится только по направлению вверх. Счетчик, под¬

считывающий число откликов, может быть реализован на базе автономного

сдвигового регистра, эквивалентного регистру результатов поиска,, в обход

счетчика в устройстве управления/

Необходимо также рассмотреть схему извлечения данных. В одном из

■возможных вариантов используется схема разрешения множественных совпа¬

дений, реализованная в виде отдельного устройства или на базе внешнего уп¬

равляющего устройства и набора регистров памяти. Другим методом извле¬

чения является алгоритм Левина [2.20] (подробно описанный ниже в этой же

главе). Ввиду того, что для реализации алгоритма Левина требуется аппарату¬

ра с уникальными свойствами, в устройстве обработки слов обычно реализу¬

ется модифицированный вариант этого алгоритма (двойной опрос каждого

-столбца разрядов, один раз на единицу и один раз на пуль, чтобы определить

•столбец, который бы отвечал состоянию X в системе Левина).

Конструкторские решения в части внешних *) элементов касаются опре¬

деления количества и размера регистров и объема аппаратных средств, необ¬

ходимых для ассоциативного процессора с пословной обработкой. Аппаратные

средства, закрепляемые за каждым словом, могут включать от одного до не¬

скольких регистров и последовательный сумматор. В некоторых системах ис¬

пользуется байтовая арифметика [2.21]. Многие ассоциативные процессоры со¬

держат только два регистра и РМО [2.22]. В системе STARAN имеется три

регистра, для которых может быть задана последовательность микроопераций,,

делающая их аналогичными последовательному арифметическому устройству,

а в системе SIMDA [2.21] обеспечивается обработка 4-битовых полей. Могут

использоваться группы, состоящие из нескольких регистров, обеспечивающие

аппаратную поддержку текущих операций по загрузке и выгрузке регистров.

В архитектуре системы SIMDA реализованы параллельные операции над

•словами. Конструкторские решения, касающиеся обеспечения поразрядной об¬

работки, связаны, с выбором между принципами обработки битовых срезов,

байтовых срезов или параллельной обработки слов. Количество логических уст¬

ройств, которыми окружается массив ассоциативной памяти, играет важную

роль в определении пропускной способности системы.

Из числа упомянутых архитектур для арифметических операций обычно

используется схема с поразрядно-последовательной обработкой, показанная

па рис. 2.2. Этот подход мож-ет быть реализован путем использования -запоми¬

нающего устройства с произвольным доступом и неразрушающим чтением,

п котором направление расположения информации повернуто на-90° по срав¬

нению с обычными устройствами памяти. Слово обычной памяти образует

битовый срез ассоциативного процессора. Размеры запоминающего устройства

Должны быть выбраны такими, чтобы ассоциативный процессор имел значи¬

тельно больше слов, чем битовых срезов. Стоимость реализации такого под-

хода, без учета стоимости внешнего оборудования, столь же невелика, как и

стоимость памяти с произвольным доступом.

*) По отношению к ассоциативной памяти. (Примеч. пер.)

23

Все операции выполняются с битовыми срезами с помощью внешнего уст¬

ройства обработки слов. Вели каждую ячейку памяти можно было бы снаб¬

дить аппаратными средствами для выработки сигналов наличия/отсутствия от¬

клика, то это увеличило бы быстродействие системы с ассоциативной обра¬

боткой. Обычно сначала происходит считывание битового среза и затем во

внешних по отношению к памяти цепях генерируются сигналы наличия/отсут¬

ствия отклика. Таким образом, слова ОЗУ становятся битовыми срезами ассо¬

циативного процессора.

Если но каким-либо причинам невозможно использовать память с пераз-

рушаюгцим считыванием, то во избежание потерь информации вводится цикл?

Регистр операнда —

Регистр маски

Адрес

Ввод

словных

срезов

IL

Входной регистр

I

слово 1

Внешнее

обрабаты¬

вающее уст-

ройст во, па ¬

мять резуль¬

татов. вывод

битовых

срезав

5 б од

битового

среза _

С л с в о N

♦

Вывод срезов

~СЛОЙ

Рис. 2.2. Ассоциативный процессор с обработкой битовых срезов

«чтение/восстановление». В этом случае ввод или вывод слов обычно произво¬

дится в поразрядно-последовательной форме. Внешние логические элементы и

устройство запоминания откликов могут состоять из одного сигнального раз¬

ряда на каждое слово и схемы поэтапного выбора слов или нескольких ре¬

гистров, последовательного сумматора и схемы поэтапного выбора слов. В со¬

став внешнего оборудования могут быть включены каналы и средства ввода/

/вывода. Одним из возможных вариантов организации ввода/вывода является

параллельный канал, с помощью которого выводятся или вводятся бито¬

вые срезы.

Основной поиск па равенство осуществляется поразрядпо-иоследователь-

по. Поиск на равенство с полем, содержащим п разрядов, выполняется за п

циклов обработки битовых срезов. Читатель должен был уже догадаться, что

описанный процессор с фуикдпопалыюй точки зрения является стандартным

24

.1СС(>цпатппым процессором. о кото])ом шла речь в начало главы. Принцип об-

-работв1 и битовых срезов был использован фирмой Goodyear при создании си¬

стемы STARAN [2.20].

Процессор с побайтово-последовательной обработкой очень похож па про¬

цессор с обработкой битовых срезов за исключенном того, что информация из¬

влекается в виде байтов. Произвольный доступ осуществляется с точностью

-(О байта. 13 случаях, когда не используются большие поля или требуется до¬

ступ к битовым разрезам, скорость обработки уменьшается. С другой стороны,

поиск па равенство будет производиться быстрее, чем в машинах, работающих

с битовыми срезами, во столько раз, сколько разрядов содержится в байте,

при условии, конечно, что байт используется целиком. В системах такого ти¬

па логические элементы обычно не встраиваются в память процессора и, сле¬

довательно, их функции могут быть реализованы отдельными устройствами.

Входное слово т

Слово 1

Слово п

Рис. 2.3. Ассоциативный процессор с распределенной логикой

Вычислительная система SIMDA фирмы Texas Instruments [2.21] представля¬

ет собой пример подобного процессора. В машинах с обработкой как бито¬

вых. так и байтош,их срезов, когда имеется необходимость считывания инфор¬

мации. возникают очевидные проблемы ввода/вывода.

Большую активность в области технологии создания ассоциативных про¬

цессоров проявила фирма Honeywell. Ею выбран вариант, основанный на ирип-

Цппе распределенной логики, показанной на рис. 2.3. Втот подход характери¬

зуется тем, что логические элементы распределены по памяти и встроены в

каждую запоминающую ячейку. Вместо того чтобы считывать содержимое

ячейки памяти во внешнее обрабатывающее устройство, операнд предоставля¬

ется ей самой.

Ячейка памяти в запоминающем устройстве такого типа состоит из за¬

поминающего триггера и, по крайней мере, элемента типа ИСКЛЮЧАЮЩЕЕ

IU»- Сигнал наличия или отсутствия отклика, поступающий от каждой ячей¬

25

Регистр операнда

Регистр маски

Ячейка 1

Ячейка 2

Ячейка m

—

Массив г

? * m ячеек

!

1

—*

Выход

Выходной

регистр

ки, комбинируется с другими сигналами с привязкой к словам, что обеспе¬

чивает выработку сигнала о наличии или отсутствии отклика в слове. За

один временной никл памяти может быть осуществлен параллельный поиск на

равенство по всем ячейкам памяти. Для облегчения решения проблемы вво¬

да/вывода, которая является главной в системах с обработкой битовых срезов,

может быть реализована возможность записи как битовых, "так и словпых

срезов. Время, затрачиваемое на выработку сигнала о наличии или отсутствии

отклика при обработке словпых срезов, может быть больше, чем время счи¬

тывания одиночного битового среза. Однако это время будет меньше, чем то,

которое необходимо для осуществления всех поисков на равенство с помощью

битовых срезов. Длительность цикла в памяти с распределенной логикой может

быть больше, чем длительность цикла в памяти с битовыми срезами.

Считывание битового среза может быть осуществлено с помощью одной

одноразрядной операции поиска на равенство. Операции поиска на неравенст¬

во должны производиться поразрядно-последовательно, как в машине с би¬

товыми срезами. Эти операции могут быть ускорены путем одновременного

манипулирования с целыми наборами разрядов, образующими в слове поиска

непрерывные поля из нулей или единиц. Ускорение обработки происходит

всегда за исключением случая, когда искомое слово состоит из чередующихся:

пулей и единиц.

Могут быть сконструированы специализированные процессоры с распре¬

деленной логикой, в которых некоторые операции поиска на неравенство или

на максимум производятся одновременно для всей памяти. Процессоры тако¬

го типа являются сугубо специализированными. Для осуществления опера¬

ции сложения в системе, построенной по принципу распределенной логики и:

снабженной тогулчО устройством хранения откликов, внешнему устройству уп¬

равления необходимо выполнить четыре операции поиска и шесть операций:

записи на каждый бит. Для осуществления сложения в системе, работающей

с битовыми срезами, при использовании последовательного сумматора и одного-

запоминающего регистра требуется две операции чтения и одна операция

записи па каждый бит.

Потребовалось немало времспи для разработки конструкции аппаратных

средств, применяемых в ассоциативных процессорах. В следующем параграфе

более подробно дается сравнительная оценка процессоров с обработкой бито¬

вых срезов и с распределенной логикой. Машипы с обработкой битовых срезов-

имеют более высокие показатели при выполнении арифметических операций

и применяются сравнительно недавно.

Основное различие между машинами, работающими с битовыми срезами,

и машппами с распределенной логикой обусловлено различием решаемых ими

задач. Стороиппкн машин, работающих с битовыми срезами, сделали оснезной

упор па задачи с вычислительным уклопом, для которых применяются боль¬

шие ассоциативные процессоры. Приверженцы процессоров с распределенной

логикой сконцентрировали внимание на применении этих устройств для уп¬

равления многопроцессорными вычислительными системами. Машины с обра-

работкой байтовых срезов предназначены для решения задач вычислительного-

характера. Во всех подходах наблюдается тенденция К небольшим процессо¬

рам, содержащим -порядка одпой-двух сотен слов. Сторонники систем с рас¬

пределенной логикой отстаивают, похоже, более полезную концепцию, по-

крайней мере она выглядит более предпочтительной для тех применений, ко-

26

ч>рм° MOJiK.no назвать пли боглом анализе. Примеров же применении, в кото-

•iix процессоры с обработкой битовых пли байтовых срезов могут быть эф¬

фективно использованы, пока недостаточно.

Схема типичного устройства управления показана па рис. 2.4. Оно состоит

из логических схем, предназначенных для активации цепей разрядов и слов

ассоциативного процессора; счетчиков и ограничивающих регистров, служа¬

щих чдля начальной, конечной и текущей локализации поля, находящегося в

Рис. 2.4. Устройство управления ассоцпативпым процессором

обработке; регистров ввода/вывода; регистра преобразования параллельного

кода в последовательный; памяти с произвольным доступом, в которой могут

храниться данные, и регистра команд, служащего для хранения команды, вы¬

полняемой устройством управления. С помощью счетчиков Л и В и связанных

с ними ограничивающих регистров могут быть заданы два совершенно неза¬

висимых поля. Счетчик С служит для обработки разрядов тега*). При ариф¬

метических операциях разряды тега могут использоваться как значащие.

В следующем параграфе приведен практический пример, который .должеп

-Поя;нить многое из изложенных положений. Этот пример также явится даль¬

ни Тегом называется группа служсбпых разрядов, предназначенных для

ДСхгп1фикац1Ш типа данного. {Прицеп, пер.)

*

27

пошлей детализацией принципов построения управляющего устройства, не¬

обходимого для управления типичным ассоциативным процессором.

Достижение баланса между обрабатывающим устройством и памятью.

В рассматриваемом примере будет показано применение ассоциативной об¬

работки в системе управления воздушным движением [2.23]. Задачи, реша¬

емые системой, включают определение корреляции между трассами, уточне¬

ние и прогнозирование трасс, обнаружение конфликтов п отображение данных

на экранах дисплеев.

Процесс расчета взаимного расположения трасс занимает большую часть

времени универсальной вычислительной машины типа ARTS III [2.21]. На

ассоциативном процессоре эта задача может быть решена значительно быст¬

рее и проще. Рассмотрим использование ассоциативной памяти для хранения

трасс. Поместим каждую трассу в слово памяти. Параллельно для всех коор¬

динатных позиций каждой отдельной трассы введем дескриптор отклонений в

сторону увеличения или уменьшения. Эта операция создала вокруг каждой

трассы блоки или кубы. Выполним серию операций поиска на неравенство но

отношению к заданной принадлежащей к трассе, находящейся на входе ко¬

ординате. Это дает возможность определить блок или куб, с которыми пере¬

сечется данная трасса. Затем программа записывает входное слово в ну ясный

формуляр в файле трасс. Позже все трассы могут быть одновременно

уточнены.

Не создает больших трудностей ситуация, когда новая трасса отождеств¬

лялась более чем с одной трассой из числа хранящихся в файле. Питатель,

интересующийся решением этой задачи, может обратиться к исследованию

системы управления воздушным движением, выполненному фирмой 1'iiiva'c

[2.2-4].

При записи трассы в процессор модифицируется ее системный номер, ис¬

пользуемый в процедуре уточнения параметров. Таким образом обрабатыва¬

ется каждая трасса, полученная от локатора. В ассоциативном процессоре

эта обработка реализуется очень просто. Степейь трудности задачи опреде¬

ления корреляции между трассами с помощью ассоциативного процессора оп¬

ределяется количеством операций ввода/вывода, требуемых для реализации,

корреляционной процедуры, и количеством битовых срезов, участвующих в

операции поиска на неравенство.

Задача уточнения и прогнозирования включает решение системы урав¬

нений движения. Эти вычисления могут .выполняться параллельно, благодаря

способности системы' работать с множественным потоком данных. Чтобы на

вычислительных операциях система была эффективной, ассоциативный про¬

цессор должен иметь достаточно малую длительность цикла. Федеральное

авиациопное агентство (ФАЛ) использует систему уравнений движения в уг¬

ловых координатах, которые легко решаются на ассоциативном процессоре.

Решение уравнений в угловых координатах требует большого количества опе¬

раций ввода/вывода, необходимых для табличного просмотра угловых коэффи¬

циентов и значений sin и соя, участвующих в уравнениях. Для того чтобы

решение уравнений в угловых коордипатах осуществлялось достаточно быст¬

ро,- требуются хорошие средства обработки битовых срезов.

В настоящее время в рассматриваемой системе управления воздушным

движением не реализован алгоритм обнаружения конфликтных ситуаций. В ис¬

следовании системы [2.23] был предложен двухэтаиный алгоритм обнаружо-

28

рия конфликтов. На первом этапе путем обследования трех- или двумерной

области воздушного пространства, окружающей каждую трассу, па предмет

обнаружения других самолетов, находящихся поблизости, производилось пред¬

варительное выявление трасс, которые могут вступить в конфликт между со¬

бой. Если в окрестности трассы, находился другой самолет, то производился

детальный расчет с использованием аэродинамических параметров на предмет

возможности возникновения конфликтной ситуации. Расчет выполнялся ме¬

тодом построения полуокружностей с центром в точке нахождения самолета

и ориентированных в направлении его полета.

Ассоциативный процессор с успехом справляется с обеими операциями.

Однако для достижения требуемого показателя пропускной способности про¬

цессор должен обладать хорошими средствами для выполнения поиска па не¬

равенство и арифметических операций. Если вначале производить грубую

отбраковку, то реальный объем вычислений, который необходимо выполнить*

можно значительно сократить.

Отображение информации почти целиком состоит из операций ввода/вы¬

вода. Функция системы отображения заключается в периодическом считыва¬

нии правильных трасс, с которыми была произведена операция уточнения*

и помещении их в обновляемый буферный массив. Таким образом, пультам

управления предоставляется доступ к самой последней информации. Одновре¬

менно, на случай машинного сбоя, фиксируются контрольные точки возврата.

Операторьт-уиравлснцы имеют возможность наблюдать за разными зонами

воздушного пространства, центры которых определяются (с помощью соответ¬

ствующих программ) районом, находящимся в секторе контроля, за которым

ведется наблюдение. При отображении информации необходимо выполнять,

большое количество преобразований координат. Реализация отображения тре¬

бует хорошей системы ввода/вывода и эффективных средств выполнения

арифметических операций над битовыми срезами.

При исследовании системы управления воздушным движением ставилась

задача определить, могут ли применяться в этой системе ассоциативные про¬

цессоры, и после этого разработать и настроить ассоциативный процессор*

предназначенный для использования в системе управления воздушным дви¬

жением; процессор должен иметь достаточные возможности для выполнения

арифметических операций над битовыми срезами и достаточную пропускную

способность ввода/вы вода.

В принципе было показано, что ассоциативный процессор применим для

решения данной задачи. Испытания, проведенные в Кпоксвнлле, шт. Теннесси,

подтвердили полезность ассоциативного процессора [2.24]. Основываясь на

Данных эксперимента в Кпоксвилло, ФАА заказало три опытных разработки,

Цель которых состоит в определении того, какой тин ассоциативного процес¬

сора следует воплотить в жизнь, имея в виду применение в системе управ¬

ления воздушным движением.

Как было установлено выше при обсуждении вопроса о том, являются

ли требования реалистическими или пет, требования к ассоциативному про¬

цессору основаны на возрастающей интенсивности воздушного движения. Энер¬

гетический кризис может явиться причиной того, что реальная интенсивность

воздушного движения, приводящая к критической нагрузке, наступит не так

скоро, как ожидалось, во всяком случае позже, чем ФАА заменит свое обо¬

рудование.

29

Таблица 2.1

Сравнительные данные для двух типов ассоциативных процессоров

Операции

Процессор с распределенной

логикой

Процессор с обработкой бито¬

вых срезов

Поиск на равенство

Поразрядно-параллельный

Поразрядно-последова¬

тельный

Прочие операции по¬

Поразрядно-последова¬

Поразрядно-последова¬

иска

тельные

тельные

Арифметические

Поразрядно-последова¬

Поразрядно-последова¬

операции

тельные

тельные

Запись слов

Поразрядно-параллельная

11 о р а з р я д но-п ос л е д ов а-

тсльная

Чтение слов

Поразрядно-параллельное

Поразрядно-последова¬

тельное

Хотя в настоящее время представляется вероятным выдвижение требова¬

ния об увеличении возможностей вычислительной машины ARTS III, работа¬

ющей в системе управления воздушным движением, за счет ввода ассоциатив¬

ного процессора, все же имеется ряд дополнительных обстоятельств, которые

могут привести к тому, что это требование не будет воплощено в жизнь. Не¬

смотря па это, пример ассоциативного процессора, способного работать в си¬

стеме управления воздушным движением, все же будет рассмотрен.

Конструкция ассоциативного процессора для системы управления воздуш¬

ным движением была предложена Тербсром [2.23]. Она объединяет черты,

присущие схемам ассоциативных процессоров с распределенной логикой и с

обработкой битовых срезов. Основная особенность предлагаемого процессора

заключается в том, что он предназначается для решения задачи, требующей,

чтобы коне груктор при создании ассоциативного процессора стремился к до¬

стижению как высоких показателей системы ввода/вывода, так и к балансу

между обрабатывающими устройствами и памятью; II-з этого, очевидно, выте¬

кает необходимость учета временных соотношений и Создания специализиро¬

ванных аппаратных средств ассоциативной обработки.

Предложенный ассоциативный процессор состоит из ассоциативной памя¬

ти, позволяющей производить арифметические операции над словами. Ариф¬

метический блок представляет собой последовательный сумматор. Ассоциа¬

тивный процессор может производить арифметические операции над храня¬

щимися в ном данными поразрядно-последовательным способом параллельно

над всеми словами. Рассматриваемый процессор' создай на оспове объедине¬

ния «концепции распределенной логики и обработки битовых срезов. Требова¬

ния, вытекающие из необходимости применения процессора в системе управ¬

ления воздушным движением, были сформулированы исходя из постановки

задачи федеральным авиационным агентством. Основное условие, поставленное

ФАА, заключалось в том, чтобы увеличить вычислительные возможности си¬

стемы ARTS III до уровня, отвечающего состоянию воздушного движения в

1980 г., и при этом не производить замены всей системы в целом.

Рассматривались два основных типа ассоциативных процессоров: процес¬

соры с распределенной логикой и процессоры с обработкой битовых срезов.

50

Наиболее существенное различие между этими двумя типами процессорами?

состоит в том, что в процессоре с распределенной логикой для каждого раз¬

ряда имеется свое обрабатывающее устройство, а в процессоре с обработкой

битовых срезов обрабатывающее устройство связано с целым словом. Разли¬

чия' между этими двумя тинами процессоров просуммированы в табл. 2.1.

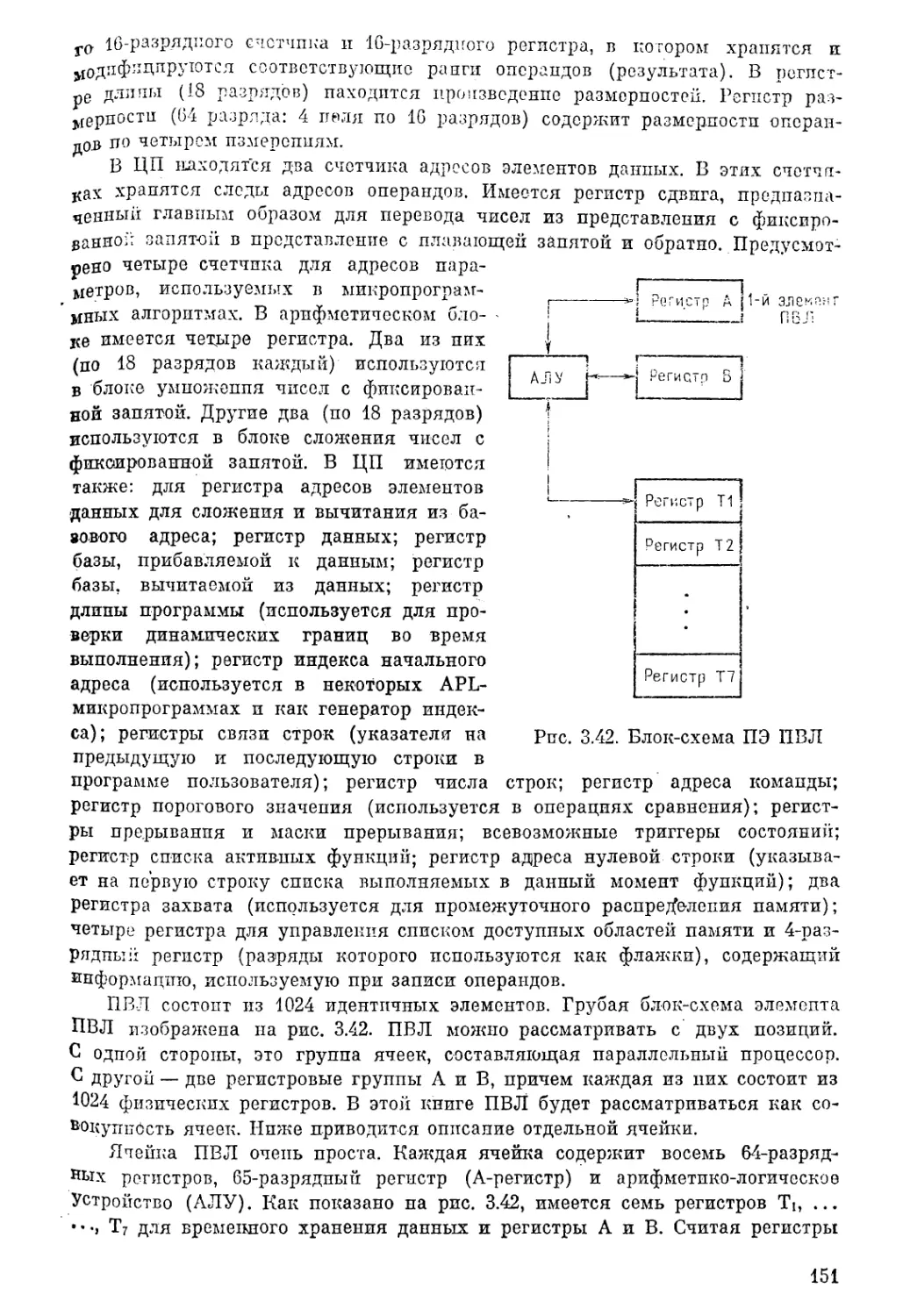

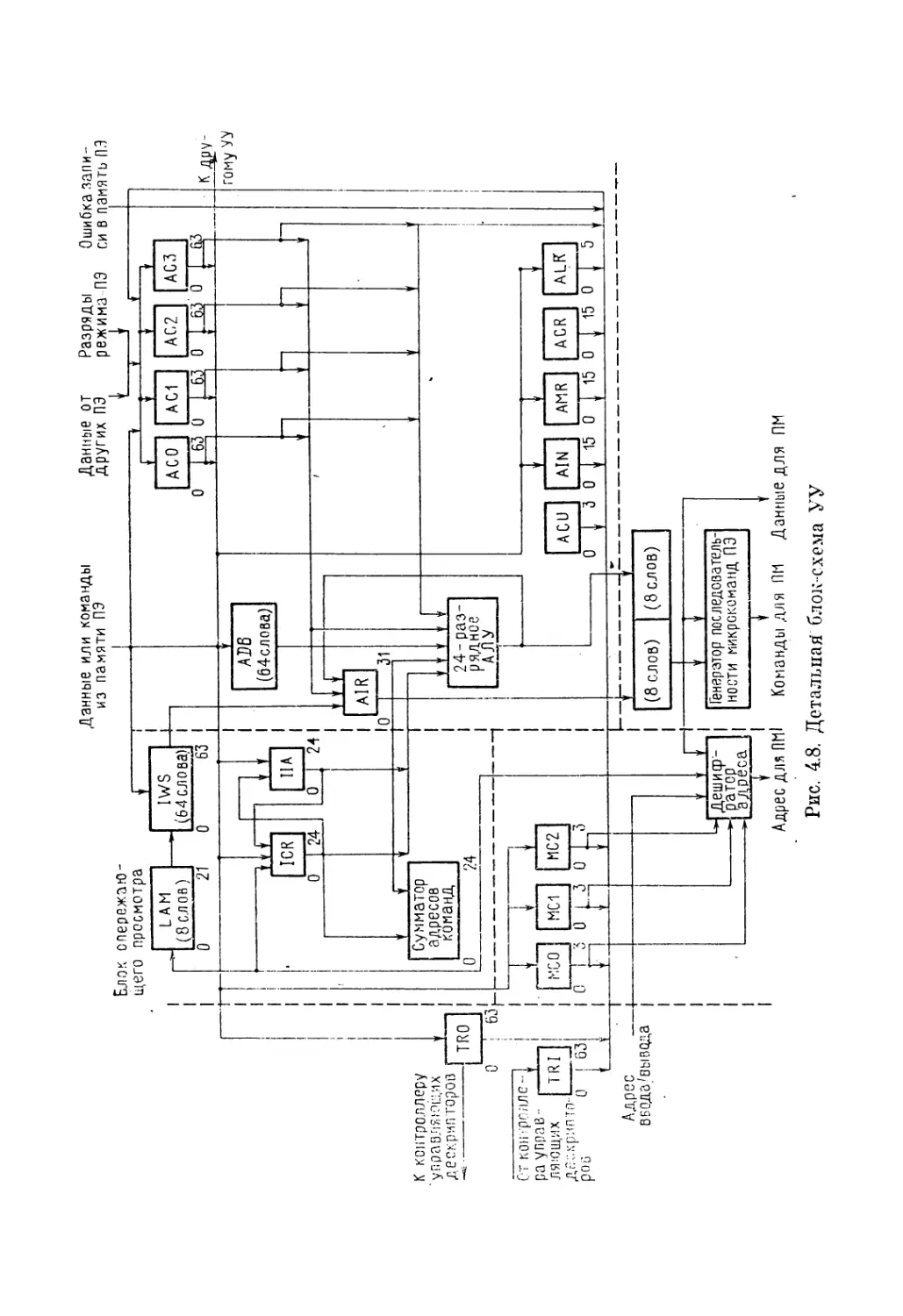

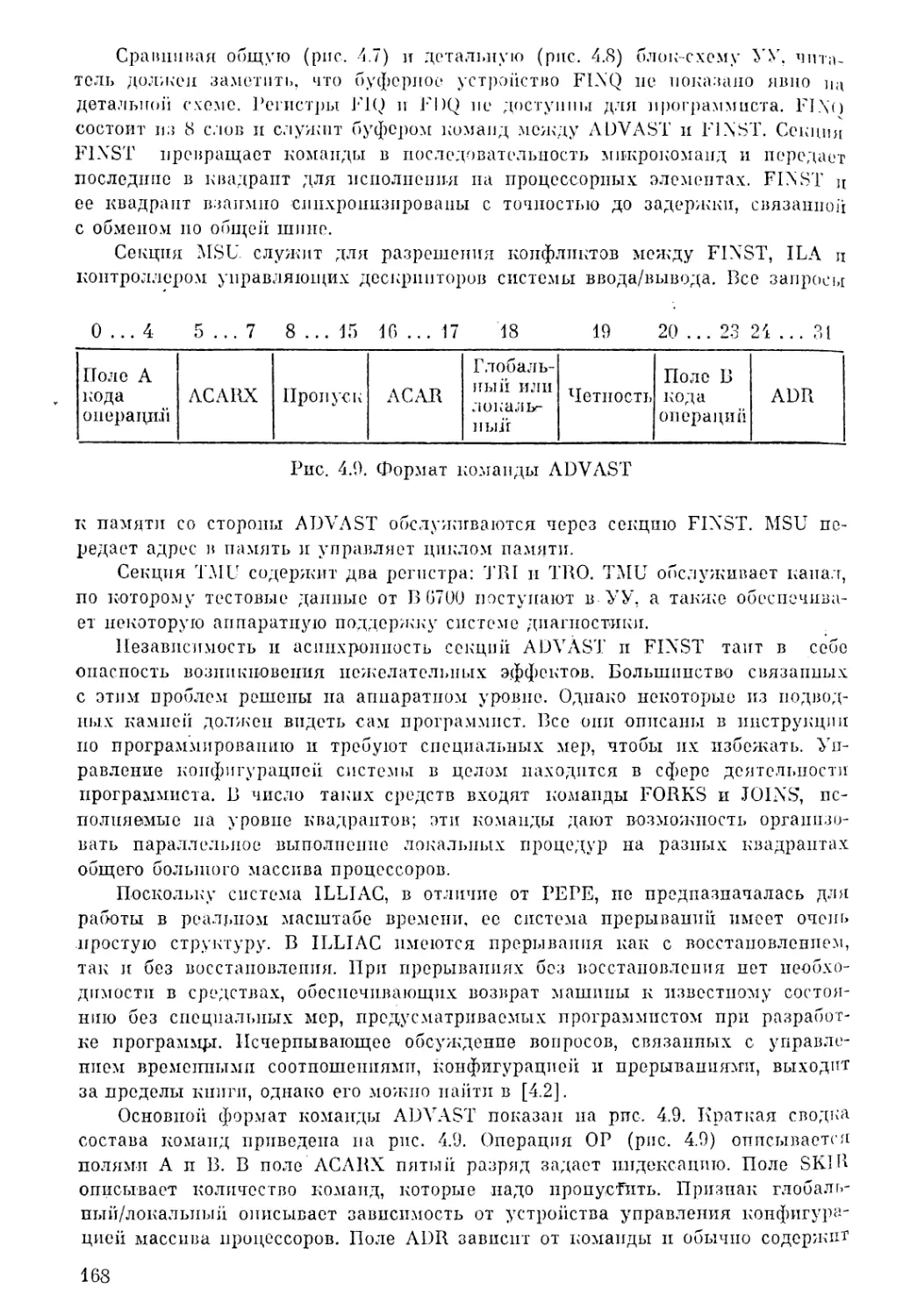

Рис. 2.5. Блок-схема гибридного ассоциативного процессора. (Типичное слово