Автор: Яценков В.С.

Теги: компьютерные технологии вычислительная техника микропроцессоры радиотехника микроконтроллеры

ISBN: 978-5-9912-0030-1

Год: 2008

Текст

В. С. Яцонков

Мккрокошроллеры

с аппаратной повдтиой USB

УДК 681.325.5

ББК 32.97

Я 92

Серия «Современная электроника» основана в 2001 г.

Яценков В. С.

Я 92 Микроконтроллеры Microchip с аппаратной поддержкой USB. -

М.: Горячая линия-Телеком, 2008. - 400 с.: ил.

ISBN 978-5-9912-0030-1.

В настоящее время использование шины USB является наиболее попу-

лярным методом для подключения периферийных устройств к компьютеру.

Микроконтроллеры Microchip серии PIC18F2455/2550/4455/4550 включают

в себя не только аппаратную поддержку шины USB, но и других популярных

протоколов обмена данными, а также функциональные модули таймеров,

АЦП, ЦАП и ШИМ, что позволяет создавать на основе этих микроконтрол-

леров самые разнообразные оконечные устройства, взаимодействующие

с персональным компьютером. В книге приведено полное техническое опи-

сание микроконтроллеров Microchip PIC18F2455/2550/4455/4550, рассмотре-

ны примеры практического применения.

Для специалистов, занимающихся разработкой устройств на основе

микроконтроллеров, радиолюбителей и студентов радиотехнических специ-

альностей

ББК 32.97

Адрес издательства в Интернет www.techbook.ru

Справочное издание

Яценков Валерий Станиславович

Микроконтроллеры Microchip с аппаратной поддержкой USB.

Редактор А. Ю. Петкин

Компьютерная верстка Ю. Н. Рысева

Обложка художника В. Г. Сетина

Подписано в печать 25.04.07. Формат 70*100/16. Усл. печ. л. 33,25. Изд. № 730

ООО «Научно-техническое издательство «Горячая линия-Телеком»

Заказ № 01

ISBN 978-5-9912-0030-1

© В. С. Яценков, 2008

© Оформление издательства

«Горячая линия-Телеком», 2008

Отпечатано в типографии ООО "ТИЛЬ-2004", 1007023, Москва,

ул. Электрозаводская д. 21

Введение

При разработке микроконтроллерных устройств, которые должны взаимодей-

ствовать с персональным компьютером, большое значение имеет правильность

выбора протокола обмена данными. В настоящее время наиболее популярным

протоколом обмена данными между компьютером и периферийными устройст-

вами является протокол шины USB (Universal Serial Bus, универсальная после-

довательная шина). По этой шине могут передаваться как большие массивы

данных (иногда в режиме реального времени), так и управляющие команды. Бла-

годаря такой универсальности, спектр периферийных устройств, подключаемых к

компьютеру почти не ограничен с технической точки зрения.

Большинство периферийных устройств разрабатывается на основе различ-

ных микроконтроллеров. Достаточно давно разработаны специализированные

микросхемы-трансиверы, обслуживающие обмен по шине USB и являющиеся

промежуточным звеном между собственно микроконтроллером и шиной. Оче-

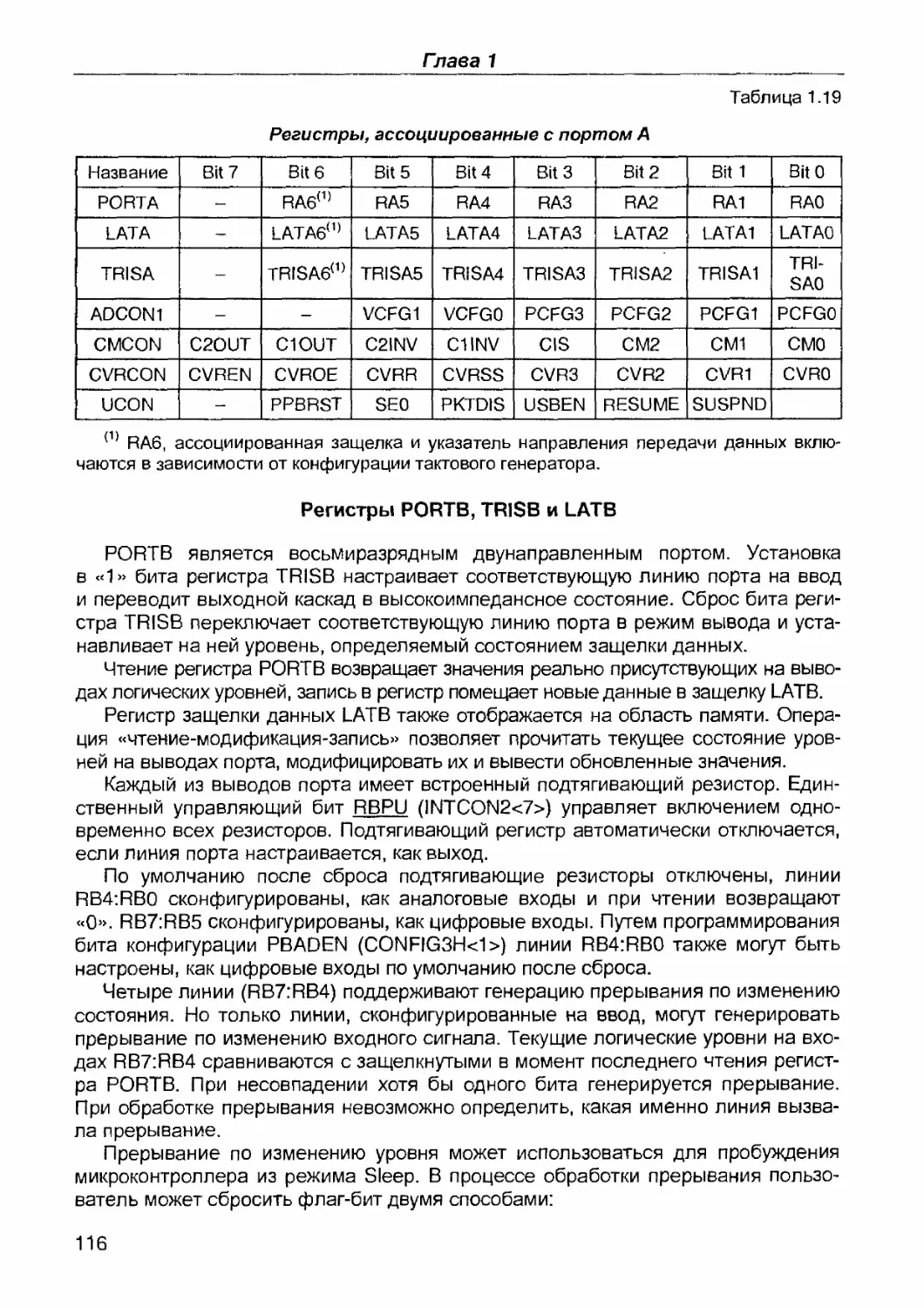

видно, что следующим логическим шагом стала интеграция трансивера USB в

состав микроконтроллеров, аналогично тому, как в них ранее были интегрирова-

ны модули АЦП, ШИМ, USART и прочие.

В ассортиментной линии Microchip первой модификацией микроконтроллера

со встроенной поддержкой USB были однократно программируемые

PIC16C745/765. В данной книге мы не рассматриваем эту модификацию, по-

скольку сейчас доступна более мощная по всем параметрам модификация

PIC18F2455/2550/4455/4550 с FLASH-памятью программ.

Основными достоинствами микроконтроллеров PIC18F2455/2550/4455/4550

являются функциональная наполненность и низкое энергопотребление на основе

различных программируемых опций энергосбережения и фирменной технологии

nanoWatt™.

Параметры модуля USB:

. Совместимость с USB V2.0.

• Поддержка низкоскоростного (1.5 Мбит/с) и высокоскоростного (12 Мбит/с)

режимов.

. Поддержка управляющей, по прерыванию, изохронной и пакетной передачи.

. Поддержка до 32 конечных точек (16 двунаправленных).

. 1 кБ ОЗУ двойного доступа для нужд USB.

• Встроенный трансивер USB.

. Встроенный источник питания USB.

. Возможность подключения внешнего трансивера USB.

• Потоковый порт SPP для ввода-вывода потока параллельных данных через

USB.

Режимы управления энергопотреблением:

. Run: процессор включен, периферия включена.

. Idle: процессор остановлен, периферия включена.

• Sleep: процессор и периферия выключены.

• Типовой потребляемый ток в режиме Idle до 5,8 мкА.

• Типовой потребляемый ток в режиме Sleep до 0,1 мкА.

3

Введение

• Генератор модуля Timerl: потребление до 1,1 мкА при 32 кГц, 2 В.

. Сторожевой таймер: до 2,1 мкА.

Гибкая структура генератора тактовых импульсов:

• Четыре режима кварцевого генератора, включая особо точный для USB

• Четыре режима внешнего тактирования, до 48 МГц

. Блок встроенного генератора:

- 8 выбираемых пользователем частот, от 31 кГц до 8 МГц;

- возможность подстройки частоты для компенсации дрейфа.

• Вторичный генератор, на основе генератора модуля Timerl, 32 кГц.

• Возможность независимого тактирования процессора и модуля USB.

• Мониторинг тактовых импульсов:

- возможность безопасного останова при пропадании импульсов основного

тактового генератора.

Опции периферии:

• Втекающий и вытекающий ток до 25 мА.

• Три внешних прерывания.

• Четыре модуля таймеров.

• До двух модулей захвата/сравнения/ШИМ:

- захват 16 бит, с разрешением до 6,25 нс (TCY/16);

- сравнение 16 бит, с разрешением до 100 нс (TCY).

. ШИМ с разрешением от 1 до 10 бит

. Расширенный модуль захвата/сравнения/ШИМ (ЕССР):

- различные выходные режимы;

- полярность по выбору;

- программируемая «мертвая зона»;

- автоотключение и авторестарт;

. Расширенный модуль USART (EUSART):

- поддержка шины LIN.

. Модуль ведущего синхронного последовательного порта (MSSP) с поддерж-

кой SPI (все четыре режима) и 12С (ведущий и ведомый).

• До 13 модулей 10-разрядного АЦП с программируемым временем выборки.

• Сдвоенный аналоговый компаратор с мультиплексированием входов.

Специальные опции микроконтроллера:

• Структура, оптимизированная под компилятор С, с расширенным набором

команд.

• 100000 циклов перезаписи памяти программ.

• 1000000 циклов перезаписи памяти данных EEPROM.

• Срок хранения памяти программ и данных более 40 лет.

• Возможность самопрограммирования (смены прошивок).

• Наличие приоритетов прерываний.

• Аппаратный умножитель 8x8.

• Расширенный сторожевой таймер:

- программируемый период от 41 мс до 131 с.

• Программируемая защита кода.

• Внутрисхемное программирование по двум проводам.

• Одно напряжение программирования 5 В (ICSP).

• Внутрисхемная отладка по двум проводам (ICD).

• Опционально назначаемый порт ICD/ICSP (только в 44-выводном корпусе).

• Широкий диапазон напряжений питания, от 2,0 до 5,5 В.

4

Введение

Параметры микроконтроллеров

Прибор Память программ Память данных I/O АЦП, кан.

байт слов RAM EEPROM

PIC18F2455 24К 12288 2048 256 24 10

PIC18F2550 32К 16384 2048 256 24 10

PIC18F4455 24К 12288 2048 256 35 13

PIC18F4550 32К 16384 2048 256 35 13

Прибор ССР/ ЕССР (ШИМ) SPP MSSP EUSART Компара- торы Таймеры

SPI l2C

PIC18F2455 2/0 - 4- 4- 1 2 1/3

P1C18F2550 2/0 - 4- 4- 1 2 1/3

PIC18F4455 1/1 4- 4- 4- 1 2 1/3

PIC18F4550 1/1 4- 4- 4- 1 2 1/3

5

Глава 1. Структура и базовые функции микроконтроллеров

семейства PIC18F2455/2550/4455/4550

Расположение и назначение выводов

Количество и назначение выводов корпуса зависит от типа корпуса и конкрет-

ного варианта микроконтроллера. На рис. 1.1 показано размещение выводов для

корпусов типа DIP, а на рис. 1.2 для корпусов типа TQFP и QFN. На рис. 1.3. при-

ведена внутренняя структура PIC18F2455/2550 (28 выводов), а на рис. 1.4. внут-

ренняя структура PIC18F4455/4550 (44 вывода)

28-Pin PDIP, SOIC

MCLFWPP/RE3------►

RA0/AN0"—

RA1/AN1 *—"

RA2/AN2/Vkef-/CVhef —*

RA3/AN3/VHEF+ *—*

RA4 Л0СК1/С10UT/RCV

RA5/AN4'SS/HLVDIN/C2OUT —*

Vss----

OSCVCLKI-----

OSC2/CLKO/RA6-----

RC0/T1OSO/T13CKI-*-►

rci;tiosi/ccp2(1>;u6e -*-*

RC2/CCP-I ——

VlJSE *—-

RB7/KBI3/PGD

RB6/KBI2/PGC

RBS/KB11/PGM

RB4/AN11/KBI0

RB3/AN9/CCP 2(1 b'VPO

RB2/AN8/INT2/VMO

RB1 /AN 10/INT1/SCK/SCL

RBO/AN12/INTO/FLTO/SDl/SDA

Voo

Vss

RC7/RX/DT/SDO

RCfi/TX'CK

RC5/D+/VP

RC4/D-/VM

40-Pin PDIP

MCLRA/PP/RE3

RAO/ANO

RA1/AN1

RA2/AN2/VE!EF-/CVREF

RA3/AN3/Vref+

RA4.Q0CKI/C1OUT/RCV

RA5/AN4/SS/HLVDIN/C2OLFT

RE0/AN5/CK1SPP

RE1/AN6/CK2SPP

RE2/AN7/OESPP

VOD

VSS

OSCl/CLKI

OSC2/CLKO/RA6

RCO/TlOSOCri3CKI

RCI/TIOSI/CCP^’VUOE

RC2/CCP1/P1A

Vusb

RDO/SPPO

RD1/SPP1

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/PGM

RB4/AN11/KBI0/CSSPP

RB3/AN9/CCP2'1>/VPO

RB2/AN8/iNT2/VMO

RB1/AN10/INT1/SCK/SCL

RBO/AN 12/INT0/FLT0/SDI/SDA

VDD

Vss

RD7/SPP7/P1D

RD6/SPP6/P1C

RD5/SPP5/P1B

RD4/SPP4

RC7/RX/DT/SDO

RC6/TX/CK

RC5/D+/VP

RC4/D-/VM

RD3/SPP3

RD2/SPP2

Рис. 1.1. Расположение выводов корпусов типа DIP:

(1) Вывод RB3 является альтернативным для мультиплексирования ССР2

6

Структура и базовые функции микроконтроллеров

RC7;RX'DT'SDO

RD4/SPP4

RO5/SPP5/PW

RD6;SPP6,-P1C

RO7.'SPP7;P1C

Vdd

RBO/AFJ г 2, INTOFlTO/SDI/SDA

RB1 'AM O'INT1,-SCK/SCL

RB2/AN8/INT2rVMO

RB3'AN9.'CCP2<1,/VPO

44-Pin QFN

PIC18F4455

PIC18F4550

27

24

23

шиж

llllllllltl

NC/ICRST<2>,'ICVh-1?)

RCO/11OSO/T13CKI

OSC2;CLKO/RA6

OSC1/CLKI

vss

Vc-Q

P.E2/AN7/OESPP

RE1/ANG/CK2SPP

RE0/AN5/CK1SPP

RA5-AN4/SS/HLVDIN/C2OUT

RA4/T0CKI/C1OUT.-RCV

Рис. 1.2. Расположение выводов корпусов типа TQFP, QFN.

<1) Вывод RB3 является альтернативным для мультиплексирования ССР2. Специ-

альные опции ICPORTS доступны в определенных случаях

7

Гпава 1

Шина данных <В>

4

Табл указателе‘2ъ

Носика

OSC1<2>^-

OSC2'2) Й~*

T1OSO

нию напряжения

тактирования

Vusb [Х]«

Сброс по вклю-

чению питания

внутреннего

генератора

Сторожевой

таймер

Генератор

ЙМГц

Защелка данных

УпревпеН|Яе

гфогршлмироа

Внутрисхемный

отладчик

Память

Стек Л уроеень

Защелка ком

ер запуска

MCLRA/pp/RE3(11

Рис. 1.3. Внутренняя структура PIC18F2455/2550 (28 выводов):

(1) RE3 мультиплексируется с MCLR и доступен только тогда MCLR отключен.

(2) OSC1/CLKI и OSC2/CLKO доступны только в определенных режимах генератора и ко-

гда выводы не используются как порты I/O.(3) Вывод RB3 является альтернативным для

мультиплексирования ССР2

|fclatu|pclatii]

: PCU I РСН ; PCL]

3;fl?tenKa адреса

Память

программ

i24;32Kg)

Заишт® дачных

Декодер

команд и

модуль

У

Управляющее сигмапы

конечного автомата

▼ ▼

|prodh| prodl]

I Мультиплексор 8ХВ

_______Л Регулятор И

напряжения USB

RAO/ANO

RA1/AN1

RA2/AN2A/REF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT/RCV

RA5/AN4/SS/HLVDIN/C2OUT

OSC2/CLKO/RA6

RB0/AN12/INT0/FLT0/SDI/SDA

RB1 /AN 1O/l NT1 /SCK/SCL

RB2/AN8/INT2/VMO

RB3/AN9/CCP2[3)/VPO

RB4/AN11/KBI0

RB5/KBI1,'PGM

RB6/KBI2/PGC

RB7/KBI3/PGD

RC0/T1OSO/T13CKI___

RC1/T1 OSVCCP2p,/UOE

RC2/CCP1

RC4/D-/VM

RC5/D+/VP

RC6/TX/CK

RC7/RX/DT/SDO

8

Структура и базовые функции микроконтроллеров

Шиня данных <В>

PORTA

Защелка адреса

osc-i'21

oscz(2>

IMESC

T1OSI

T1OSO

tCpGC*3’

ICPGOP*

ICRST™

внутреннего

генератора

Таймерзапуска

такт генератора

Сброс го вклю-

чению литания

Генератор

8 МГц

данных

(2Кб’,

Внутрисхемный

отладчик

I..i

Защелке данных

Защелка адреса

[pCLATu|pQ-Ath|

[PCU I РСН ] PCL]

Счетчик команд

г

Сгех31 кроееик

Геол защелка

Шина команд <16>

Защелка ROM

Декодер команд

м модуль

Таймер включе-

нии питаная

Сторожевой

Сорос го CHUM

ICPORTSP®—*

Мониторинг

гактироБзмия

mclr!”

[pRODH| PROCL

р^ыиплексорВХб

I RAO/ANO

RA1/AN1

RA2fAN2/VRbF-/CVREF

RA3/AN3/VP.EF+

RA4/TCCKVC1OUT/RCV

' RA5/AN4/SS/HLVD1N/C2OUT

OSC2/CLKO/RA6

R30'AN12/INTO/FLTO/SDI/SD/

RB1/AN10/INTVSCK/SC.L

RB2/AN8/INT2A/MO

RB3/AN9/CCP2'4>/VPO

RB4/AN11/KBI0'CSSPP

RB5/KBI1/PGM

RB6/KBI2/PGC

RB7/KBI3/PGD

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2W>AJOE

RC2/CCP1/P1A

RC4/D-/VM

RC5/D+A/P

RC6/TX/CK

RC7/RX/DT/SDO

RD0/SPP0:RD4/SPP4

RO5/SPP5/P1B

RD6/SPPC/P1C

RD7/SPP7/P1D

RE0/AN5/CK1SPP

RE1/AN6/CK2SPP

RE2/AN7/OESPP

MCLRA/PP/RE3(1t

Рис. 1.4. Внутренняя структура PIC18F4455/4550 (44 вывода):

(1) RE3 мультиплексируется с MCLR и доступен только тогда MCLR отключен.

(2) OSC1/CLKI и OSC2/CLKO доступны только в определенных режимах генератора и ко-

гда выводы не используются как порты I/O.<3) Этот вывод доступен только в 44-выводном

корпусе TQFP при определенных условиях. (4)Вывод RB3 является альтернативным для

мультиплексирования ССР2

9

Глава 1

Таблица 1.1

Назначение выводов PIC18F2455/2550

Обозначение вывода Но- мер Тип Бу- фер Описание

MCLR/Vpp/RE3 MCLR Vpp RE3 1 I P 1 ST ST Вход общего сброса или напряжения программирования Общий сброс низким уровнем Вход напряжения программирования Цифровой вход

OSC1/CLKI OSC1 CLKI 9 J 1 A A Подключение резонатора или вход внешних тактов Кристалл резонатора или вход внешних тактов Только вход внешних тактов; всегда ас- социирован с функцией вывода OSC1 (см. также вывод OSC2)

OSC2/CLKO/RA6 OSC2 CLKO RA6 10 О 0 I/O TTL Подключение резонатора или выход тактовых импульсов Подключен к кварцу в режиме кварцево- го генератора Выход импульсов частотой % от входной на OSC1 Порт ввода-вывода общего назначения

RAO/ANO RAO ANO 2 I/O 1 TTL A Цифровой вход/выход Аналоговый вход 0

RA1/AN1 RA1 AN1 3 I/O 1 TTL A Цифровой вход/выход Аналоговый вход 1

RA2ZAN2/VrEFJCVref RA2 AN2 Vref- CVref 4 I/O 1 1 0 TTL A A A Цифровой вход/выход Аналоговый вход 2 Вход опорного напряжения АЦП (низкое) Выход опорного уровня компаратора

RA3/AN3/VrEF+ RA3 AN3 Vref+ 5 I/O 1 1 TTL A A Цифровой вход/выход Аналоговый вход 3 Вход опорного напряжения АЦП (высокое)

RA4/T0CKI/C1OUT /RCV RA4 TOCKI сюит RCV 6 I/O 1 о I ST ST TTL Цифровой вход/выход Вход внешних счетных импульсов моду- ля TimerO Выход компаратора 1 Вход RCV USB-трансивера

10

Структура и базовые функции микроконтроллеров

Обозначение вывода Но- мер Тип Бу- фер Описание

RA5/AN4/SS/ HLVDIN/C2OUT 7

RA5 I/O TTL Цифровой вход/выход

AN4 I A Аналоговый вход 4

SS I TTL Вход выбора SPI

HLVDIN I A Вход модуля обнаружения перепада «High/Low»

C2OUT 0 - Выход компаратора 2

RBO/AN12/1NTO/FLTO/ 21

SDI/SDA

RB0 I/O TTL Цифровой вход/выход

AN12 I A ' Аналоговый вход 12

INTO I ST Внешнее прерывание 0

FLTO I ST Вход ошибки ШИМ (модуль ССР1)

SDI I ST Вход данных SPI

SDA I/O ST Вход/выход данных 12С

RB1/AN10/INT1/SCK/ 22

SCL

RB1 I/O TTL Цифровой вход/выход

AN10 I A Аналоговый вход 10

INT1 I ST Внешнее прерывание 1

SCK I/O ST Вход/выход синхроимпульсов для режи- ма SPI

SCL I/O ST Вход/выход синхроимпульсов для режи- ма 12С

RB2/AN8/INT2/VMO 23

RB2 I/O TTL Цифровой вход/выход

AN8 I A Аналоговый вход 8

INT2 I ST Внешнее прерывание 2

VMO 0 - Выход VMO USB-трансивера

RB3/AN9/CCP2/VPO 24

RB3 I/O TTL Цифровой вход/выход

AN9 I A Аналоговый вход 9

ССР2П) I/O ST Вход Capture2/ выход Сотраге2/ выход PWM2

VPO 0 -

RB4/AN11/KBI0 25

RB4 I/O TTL Цифровой вход/выход

AN11 I A Аналоговый вход 11

KBIO I TTL Вывод прерывания по изменению со- стояния

11

Глава 1

Обозначение вывода Но- мер Тип Бу- фер Описание

RB5/KBI1/PGM RB5 кви PGM 26 I/O t I/O TTL TTL ST Цифровой вход/выход Вывод прерывания по изменению со- стояния Включение низковольтного программи- рования ICSP

RB6/KBI2/PGC RB6 KBI2 PGC 27 I/O I I/O TTL TTL ST Цифровой вход/выход Вывод прерывания по изменению со- стояния Внутрисхемная отладка и тактирование ICSP

RB7/KBI3/PGD RB7 KBI3 PGD 28 I/O I I/O TTL TTL ST Цифровой вход/выход Вывод прерывания по изменению со- стояния Внутрисхемная отладка и данные ICSP

RCO/T10SO/T13CK1 RCO T1OSO T13CKI 11 VO 0 I ST ST Цифровой вход/выход Вход генератора Timerl Вход внешних импульсов Т1тег1Я1тегЗ

RC1/T1OSI/CCP2/ UOE RC1 T1OSI CCP2l2> UOE 12 I/O I I/O ST CMOS ST Цифровой вход/выход Вход генератора Timerl Вход Capture2/ выход Сотраге2/выход PWM2 Выход QE внешнего USB-трансивера

RC2/CCP1 RC2 CCP1 13 I/O I/O ST ST Цифровой вход/выход Вход Capturel/выход Comparel/выход PWM1

RC4/D-/VM RC4 D- VM 15 I I/O I TTL TTL Цифровой вход/выход Отрицательная диф.линия USB (вход/выход) Вход VM внешнего USB-трансивера

RC5/D+/VP RC5 D+ VP 16 I I/O 0 TTL TTL Цифровой вход/выход Положительная диф.линия USB (вход/выход) Вход VP внешнего USB-трансивера

12

Структура и базовые функции микроконтроллеров

Обозначение вывода Но- мер Тип Бу- фер Описание

RC6/TX/CK 17

RC6 I/O ST Цифровой вход/выход

ТХ О — Асинхронная передача EUSART

СК I/O ST Синхронные такты EUSART (см. RX/DT)

RC7/RX/DT/SDO 18

RC7 I/O ST Цифровой вход/выход

RX 1 ST Асинхронный прием EUSART

DT I/O ST Синхронные данные EUSART (см. RX/DT)

SDO о - Выход данных SPI

Vusb 14 О - Встроенный регулятор USB 3.3V

Vss 8,9 р - «Земля» для логики и портов вво- да/вывода

Vdd 20 р - Напряжение питания для логики и портов

Обозначения: TTL - совместимый по уровням с TTL логикой; CMOS - совместимый

с CMOS; ST - триггер Шоттки на входе, с уровнями CMOS; О - выход, I - вход,

Р - питание.

Примечания:

1. Подключено к ССР2, когда бит конфигурации ССР2МХ сброшен.

2. По умолчанию подключен к ССР2, когда бит конфигурации установлен.

Таблица 1.2

Назначение выводов PIC1BF4455/4550

Обозначение вывода Номер вывода Тип БУ' Фер Описание

PDIP QFN TQFP

. MCLR/Vpp/RE3 MCLR Vpp RE3 1 18 18 I P I ST ST Вход общего сброса или напряжения программиро- вания Общий сброс низким уров- нем Вход напряжения про- граммирования Цифровой вход

OSC1/CLKI OSC1 CLKI 13 32 30 I I A A Подключение резонатора или вход внешних тактов Кристалл резонатора или вход внешних тактовых импульсов Только вход внешних так- тов; всегда ассоциирован с функцией вывода OSC1 (см. также вывод OSC2)

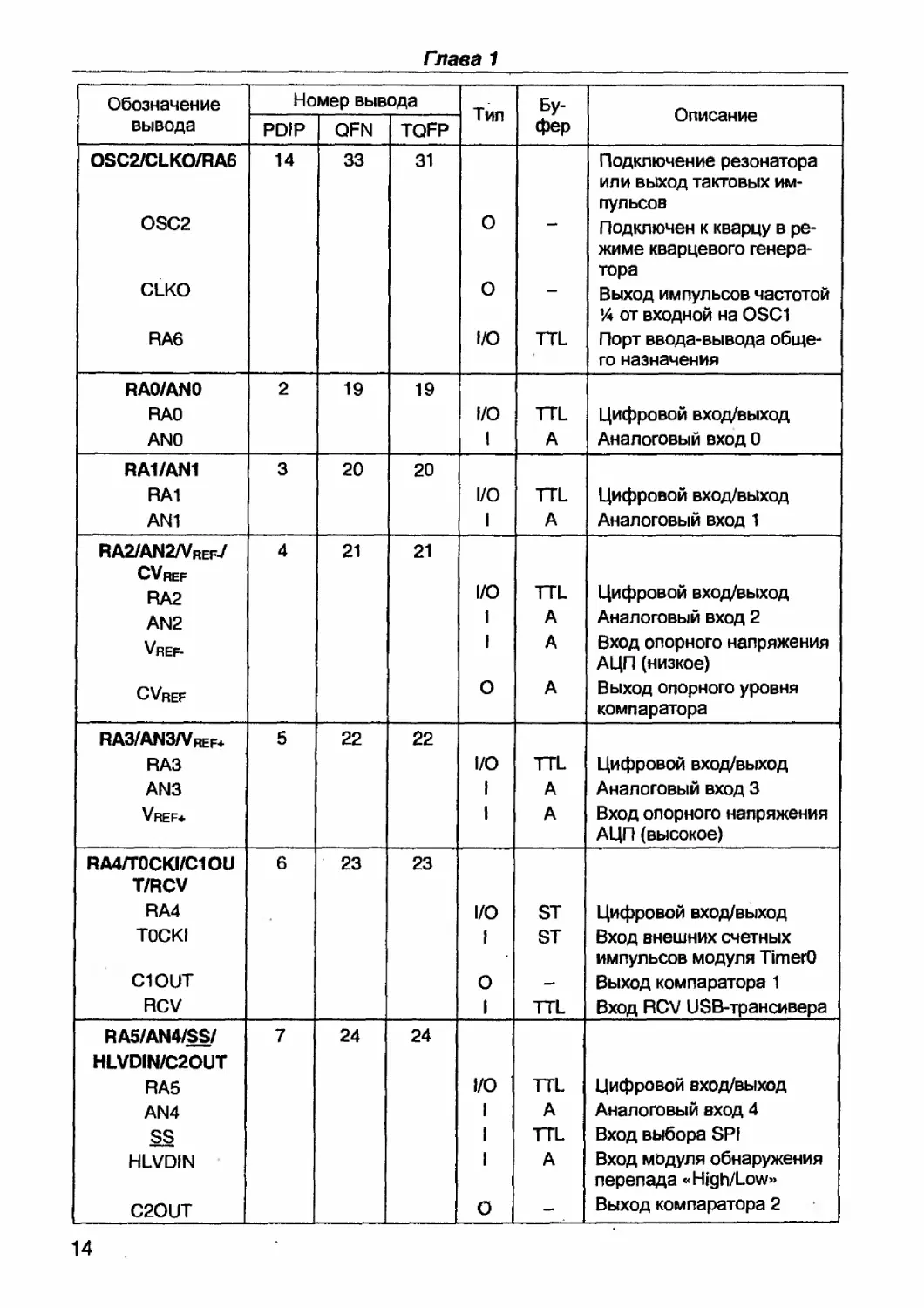

13

Гпава 1

Обозначение вывода Номер вывода Тип Бу- фер Описание

PDIP QFN TQFP

OSC2/CLKO/RA6 14 33 31 Подключение резонатора или выход тактовых им- пульсов

OSC2 0 Подключен к кварцу в ре- жиме кварцевого генера- тора

CLKO 0 — Выход импульсов частотой % от входной на OSC1

RA6 I/O TTL Порт ввода-вывода обще-

го назначения

RAO/ANO 2 19 19

RAO I/O TTL Цифровой вход/выход

ANO I A Аналоговый вход 0

RA1/AN1 3 20 20

RA1 I/O TTL Цифровой вход/выход

AN1 I A Аналоговый вход 1

RA2/AN2/Vref7 4 21 21

CVref

RA2 I/O TTL Цифровой вход/выход

AN2 I A Аналоговый вход 2

Vref- I A Вход опорного напряжения АЦП (низкое)

CVref 0 A Выход опорного уровня компаратора

RA3/AN3/VrEF+ 5 22 22

RA3 I/O TTL Цифровой вход/выход

AN3 I A Аналоговый вход 3

Vref+ I A Вход опорного напряжения АЦП (высокое)

RA4/T0CKI/C1 OU 6 23 23

T/RCV

RA4 I/O ST Цифровой вход/выход

TOCKI I ST Вход внешних счетных импульсов модуля TimerO

сюит 0 — Выход компаратора 1

RCV I TTL Вход RCV USB-трансивера

RA5/AN4/SS/ HLVDIN/C2OUT 7 24 24

RA5 I/O TTL Цифровой вход/выход

AN4 I A Аналоговый вход 4

SS I TTL Вход выбора SPI

HLVDIN I A Вход модуля обнаружения перепада «High/Low»

C2OUT о - Выход компаратора 2

14

Структура и базовые функции микроконтроллеров

Обозначение вывода Номер вывода Тип Бу- фер Описание

PDIP QFN TQFP

RB0/AN12/INT0/ FLTO/SDI/SDA 33 9 8

RB0 I/O TTL Цифровой вход/выход

AN12 I A Аналоговый вход 12

INTO I ST Внешнее прерывание 0

FLTO I ST Вход ошибки ШИМ (мо- дуль ССР1)

SDI I ST Вход данных SPI

SDA I/O ST Вход/выход данных lzC

RB1/AN10/INT1/ 34 10 9

SCK/SCL

RB1 I/O TTL Цифровой вход/выход

AN10 I A Аналоговый вход 10

INT1 I ST Внешнее прерывание 1

SC К I/O ST Вход/выход синхроим- пульсов для режима SPI

SCL I/O ST Вход/выход синхроим- пульсов для режима 12С

RB2/AN8/INT2/ 35 11 10

VMO

RB2 I/O TTL Цифровой вход/выход

AN8 I A Аналоговый вход 8

INT2 I ST Внешнее прерывание 2

VMO 0 . - Выход VMO USB- трансивера

RB3/AN9/CCP2/ 36 12 11

VPO

RB3 I/O TTL Цифровой вход/выход

AN9 I A Аналоговый вход 9

CCP2(1) I/O ST Вход Capture2/ выход

VPO о - Сотраге2/ выход PWM2

RB4/AN11/КВГО/ 37 14 14

CSSPP

RB4 I/O TTL Цифровой вход/выход

AN11 I A Аналоговый вход 11

КВЮ I TTL Вывод прерывания по из-

менению состояния

CSSPP о - Выход сигнала выбора кристалла SPP

RB5/KBI1/PGM 38 15 15

RB5 I/O TTL Цифровой вход/выход

KBI1 I TTL Вывод прерывания по из- менению состояния

PGM I/O ST Включение низковольтного программирования ICSP

15

Гпава 1

Обозначение Номер вывода Бу- Описание

вывода PDIP QFN TQFP фер

RB6/KBI2/PGC RB6 KBI2 PGC 39 16 16 I/O I I/O TTL TTL ST Цифровой вход/выход Вывод прерывания по из- менению состояния Внутрисхемная отладка и тактирование ICSP

RB7/KBI3/PGD RB7 KBI3 PGD 40 17 17 I/O I I/O TTL TTL ST Цифровой вход/выход Вывод прерывания по из- менению состояния Внутрисхемная отладка и данные ICSP

Rconroso/ Т13СК1 RC0 T1OSO Т13СК1 15 34 32 I/O О I ST ST Цифровой вход/выход Вход генератора Timerl Вход внешних импульсов Timed/ТггпегЗ

RC1/T1OSI/CCP2 /UOE RC1 T1OSI ССР2(г) UOE 16 35 35 I/O I I/O ST CMO ST Цифровой вход/выход Вход генератора Timerl Вход Capture2/ выход Compare2 / выход PWM2 Выход ОЕ внешнего USB- трансивера

RC2/CCP1/P1A RC2 ССР1 Р1А 17 36 36 I/O I/O О ST ST TTL Цифровой вход/выход Вход Caplure 1 /выход Com- pare 1 / выход PWM1 Расширенный выход ШИМ ССР1, канал А

RC4/D-/VM RC4 D- VM 23 42 42 I I/O I TTL TTL Цифровой вход/выход Отрицательная дифлиния USB (вход/выход) Вход VM внешнего USB- трансивера

RC5/D+/VP RC5 D+ VP 24 43 43 I I/O О TTL TTL Цифровой вход/выход Положительная дифлиния USB (вход/выход) Вход VP внешнего USB- трансивера

16

Структура и базовые функции микроконтроллеров

Обозначение Номер вывода Бу- Описание

' вывода PDIP QFN TQFP фер

RC6/TX/CK RC6 ТХ СК 25 44 44 I/O О I/O ST ST Цифровой вход/выход Асинхронная передача EUSART Синхронные такты EUSART (см. RX/DT)

RC7/RX/DT/SDO RC7 RX DT SDO 26 1 1 I/O 1 I/O О ST ST ST Цифровой вход/выход Асинхронный прием EUSART Синхронные данные EUSART (см. RX/DT) Выход данных SPI

RD0/SPP0 RDO SPPO 19 38 38 I/O I/O ST TTL Цифровой вход/выход Данные параллельного потокового порта

RD1/SPP1 RD1 SPP1 20 39 39 I/O I/O ST TTL Цифровой вход/выход Данные параллельного потокового порта

RD2/SPP2 RD2 SPP2 21 40 40 I/O I/O ST TTL Цифровой вход/выход Данные параллельного потокового порта

RD3/SPP3 RD3 SPP3 22 41 41 I/O I/O ST TTL Цифровой вход/выход Данные параллельного потокового порта

RD4/SPP4 RD4 SPP4 27 2 2 I/O I/O ST TTL Цифровой вход/выход Данные параллельного потокового порта

RD5/SPP5/P1B RD5 SPP5 Р1В 28 3 3 I/O I/O О ST TTL Цифровой вход/выход Данные параллельного потокового порта Выход расширенного ШИМ ССР1,каналВ

RD6/SPP6/P1C RD6 SPP6 Р1С 29 4 4 I/O I/O О ST TTL Цифровой вход/выход Данные параллельного потокового порта Выход расширенного ШИМ ССР1, канал С

17

Глава 1

Обозначение Номер вывода Тип Бу- Описание

вывода PDIP QFN TQFP фер

RD7/SPP7/P1D RD7 SPP7 P1D 30 5 5 I/O I/O 0 ST TTL Цифровой вход/выход Данные параллельного потокового порта Выход расширенного ШИМ ССР1, канал D

RE0/AN5/CK1SPP RE0 AN5 CK1SPP 8 25 25 I/O I О ST A Цифровой вход/выход Аналоговый вход 5 Выход 1 тактов SPP

RE1/AN6/CK2SPP RE1 AN6 CK2SPP 9 26 26 I/O I 0 ST A Цифровой вход/выход Аналоговый вход 6 Выход 2 тактов SPP

RE2/AN7/OESPP RE2 AN7 OESPP 10 27 27 I/O I о ST A Цифровой вход/выход Аналоговый вход 7 Выход включения SPP

Vss 12, 31 6, 30, 31 6, 29 p - Общий провод для логики и портов ввода/вывода

Vdd 11, 32 7, 8, 28, 29 7, 28 p - Питание для логики и пор- тов ввода/вывода

Vusb 18 37 37 о - Выход встроенного регу- лятора 3.3V USB

NC/ICCK/ICPGC ICCK ICPGC 12 I/O I/O ST ST Не подключен или такты порта ICD/ICSP(3) Тактирование внутрисхем- ного отладчика Такты программирования ICSP

NC/ICD17ICPGD ICDT ICPGD 13 I/O I/O ST ST Не подключен или такты порта ICD/ICSP(3) Данные внутрисхемного отладчика Данные программирова- ния ICSP

NC/ICRST/ICVPP ICRST ICVpp 33 I p - Не подключен или такты порта ICD/ICSP(3) Вход общего сброса Вход напряжения про- граммирования

18

Структура и базовые функции микроконтроллеров

Обозначение вывода Номер вывода Тип Бу- фер Описание

PDIP QFN TQFP

NC/ICPORTS ICPORTS 34 Р - Не подключен или эмуля- ция 28-выводнбго кри- сталла Разрешает эмуляцию 28- выводного кристалла, если подключен к Vss

NC - 13 - - - Свободный вывод

Обозначения: TTL - совместимый по уровням с TTL логикой; CMOS - совместимый с

CMOS; ST - триггер Шоттки на входе, с уровнями CMOS; О - выход, I - вход, Р - питание.

Примечания:

1. Подключено к ССР2, когда бит конфигурации ССР2МХ сброшен.

2. По умолчанию подключен к ССР2, когда бит конфигурации установлен.

3. Эти выводы находятся в состоянии «свободный», пока не установлен бит ICPRT.

Вывод NC/ICPORTS в состоянии «свободен», пока бит ICPRT не установлен и DEBUG не

сброшен.

Типы корпусов

На рис. 1.5 - 1.8 показаны внешний вид и типовые размеры различных типов

корпусов, применяемых при производстве семейства PIC18F2455/2550/4455/4550.

Рис. 1.5. Корпус PDIP 28 выводов

19

Гпава 1

Рис. 1.6. Корпус SOIC 28 выводов

Рис. 1.7. Корпус PDIP 40 выводов

20

Структура и базовые функции микроконтроллеров

Рис. 1.8. Корпус TQFP 44 вывода

Рис. 1.9. Безвывсдный корпус QFN, 44 контакта

21

Глава 1

Источники тактовых импульсов

Микроконтроллеры семейства PIC18F2455/2550/4455/4550 содержат иные,

чем у предыдущих кристаллов серии PIC18, тактовые генераторы и систему так-

тирования контроллера. Добавление модуля USB с его высокими требованиями к

стабильности источника тактирования сделало необходимым использование от-

дельного источника, который удовлетворяет требованиям как низкоскоростного,

так и высокоскоростного USB порта.

По этой причине приборы PIC18F2455/2550/4455/4550 имеют новую секцию

тактового генератора, вырабатывающего импульсы с частотой 48МГц для полно-

скоростного USB модуля. Поскольку он тактируется от первичного источника так-

тов, предусмотрено использование предделителей и постделителей, что позво-

ляет выбирать частоту тактирования в широком диапазоне. Структура тактового

генератора показана на рис. 1.10.

Рис. 1.10. Структура тактового генератора

22

Структура и базовые функции микроконтроллеров

Остальные опции системы тактирования аналогичны применяемым в других

микроконтроллерах серии PIC18, и мы рассмотрим их далее.

Работой генератора в микроконтроллерах PIC18F2455/2550/4455/4550 управ-

ляют два регистра конфигурации и два управляющих регистра. Регистры конфи-

гурации CONFIG1L и CONFIG1H задают режим генератора и опции предделите-

ля/постделителя USB. Биты регистров конфигурации могут быть настроены толь-

ко при программировании кристалла, и их изменение возможно только при по-

вторном программировании.

Регистр OSCCON определяет режим Active Clock, в первую очередь он использу-

ется в управлении переключением тактов в режимах ШИМ. Регистр OSCTUNE при-

меняется для подстройки внутреннего источника частоты INTSRC, а также указывает

источник низкой частоты, который используется в некоторых специальных случаях.

Типы тактовых генераторов

Семейство PIC18F2455/2550/4455/4550 может тактироваться от одного из

двенадцати различных источников тактовых импульсов. В отличие от остального

семейства PIC18, четыре из этих источников могут работать с двумя типами ре-

зонаторов одновременно. Путем программирования битов FOSC3:FOSCO поль-

зователь может выбирать один из следующих режимов:

1. XT Кварц/керамический резонатор

2. XTPLL Кварц/керамический резонатор с включенной ФАПЧ

3. HS Высокочастотный кварц/резонатор

4. HSPLL Высокочастотный кварц/резонатор с включенной ФАПЧ

5. ЕС Внешние такты с выходом F0Sc/4 на вывод RA6

6. ЕСЮ Внешние такты, и вывод R6 как порт ввода/вывода

7. ECPLL Внешние такты с ФАПЧ, выход Fosc/4 на вывод RA6

8. ECPIO Внешние такты с ФАПЧ, и вывод R6 как порт ввода/вывода

9. INTHS - Внутренний генератор, как источник тактов микроконтроллера,

и генератор HS, как источник тактов USB

10. INTXT Внутренний генератор, как источник тактов микроконтроллера,

и генератор XT, как источник тактов USB

11. INTIO Внутренний генератор, как источник тактов микроконтроллера,

генератор ЕС, как источник тактов USB, порт ввода/вывода на RA6

12. INTCKO Внутренний генератор, как источник тактов микроконтроллера,

генератор ЕС, как источник тактов USB, выход Fosc/4 на вывод RA6.

Типы генераторов и функционирование USB

Поскольку реализация полноскоростного интерфейса USB предъявляет осо-

бые требования к источнику тактовой частоты, то и подходы к его реализации

отличаются от применявшихся ранее. В предыдущих кристаллах PICmicro® ядро

и все периферийные модули тактировались от общего источника. В семействе

PIC18F2455/2550/4455/4550 первичный тактовый генератор является частью мо-

дуля USB. Модуль USB не может быть тактирован от другого источника. Вычис-

лительное ядро микроконтроллера и периферийные модули по-прежнему могут

тактироваться от внешнего или внутреннего источника по выбору пользователя.

В соответствии с требованиями стандарта USB, для тактирования модуля

нужны импульсы с частотой или 6 МГц или 48 МГц, в зависимости от скорости

23

Глава 1

Рис.1.11. Схема включения резонатора:

(1) Значения С1 и С2 см. в таблице значений.(2) Резистор Rs может потребоваться при

использовании кристалла со срезом типа АТ.(• Значение Rf зависит

от выбранного режима

передачи данных. Но нет никакой необходимости тактировать микроконтроллер

именно с этой частотой. Настройки тактового генератора позволяют гибко выби-

рать источник и частоту тактирования для остальной части устройства.

Прежде чем перейти к описанию настроек генератора для тактирования моду-

ля USB, рассмотрим способы подключения кварцевого или керамического резо-

натора и внешнего источника тактовых импульсов. Пользователям, уже знако-

мым с аналогичной информацией для предыдущих версий микроконтроллеров,

рекомендуется обратить внимание на реализацию умножителя частоты на осно-

ве петли ФАПЧ.

В режимах HS, HSPLL, XT и XTPLL кварцевый или керамический резонатор

подключают к выводам OSC1 и OSC2. Схема включения обычная, она показана

на рис. 1.11.

Таблица 1.3

Примеры значений номиналов конденсаторов для различных

керамических резонаторов

Режим Частота, МГц OSC1, пФ OSC2, пФ

XT 4,0 33 33

HS 8,0 16,0 27 22 27 22

Таблица 1.4

Примеры значений номиналов конденсаторов для различных

кварцевых резонаторов

Режим Частота, МГц OSC1, пФ OSC2, пФ

XT 4,0 27 27

4,0 27 27

HS 8,0 22 22

20,0 15 15

Приведенные в табл. 1.3 и 1.4 данные являются ориентировочными и предна-

значены для начального определения значений. При разработке устройства не-

обходимо провести его тестирование на устойчивость генерации и стабильность

частоты во всем диапазоне рабочих температур и питающих напряжений.

24

Структура и базовые функции микроконтроллеров

При разработке и эксплуатации устройств необходимо учитывать следующие

нюансы:

Чем больше емкость конденсаторов С1 и С2, тем больше стабильность, но

больше время запуска генератора.

При напряжении питания ниже 3 В, а также при использовании некоторых

специфических типов керамических резонаторов независимо от напряжения,

может понадобиться использовать режим HS или переключиться в режим квар-

цевого генератора.

Поскольку кварцевые и керамические резонаторы от разных производителей

могут иметь разные характеристики, пользователю может понадобиться прокон-

сультироваться с производителем относительно параметров внешних элементов.

Если применяется кристалл с низковольтной спецификацией, во избежание

его перегрузки может потребоваться резистор Rs.

Всегда проверяйте работу генератора за пределами штатных значений пи-

тающего напряжения и температуры. Это повышает надежность работы устрой-

ства в целом.

Встроенный постделитель позволяет получать тактовую частоту иную, чем ре-

зонансная частота кварца или керамического резонатора. Коэффициент деления

частоты определяется битами конфигурации CPUDIV. Пользователь может вы-

брать коэффициенты 1/1,1/2,1/3 или 1/4 относительно резонансной частоты.

В режиме HS может быть использован внешний источник тактовой частоты.

В этом случае вывод OSC2/CLKO оставляют свободным, а источник импульсов

подключают, как показано на рис. 1.12.

Такты от

внешнего

источника

PIC18FXXXX

Свободный -<----- OSC2 (В РЕЖИМЕ HS)

Рис. 1.12. Тактирование от внешнего источника в режиме HS

При работе в режимах ЕС, ECIO, ECPLL и ЕСРЮ подразумевается подклю-

чение внешнего источника тактовых импульсов к выводу OSC1. В этом случае

не требуется выдерживать интервал времени для запуска генератора после

сброса по питанию или при выходе из режима SLEEP (разумеется, при усло-

вии, что внешний генератор уже вошел в рабочий режим к моменту сброса

микроконтроллера).

В режимах ЕС и ECPLL частота тактовых импульсов делится на 4 и получен-

ные импульсы подаются на вывод OSC2. Этот сигнал может быть использован

для тестирования или синхронизации внешней логики. Подключение в этом ре-

жиме показано на рис. 1.13.

Такты от

внешнего

источника

FOSC/4-

OSC1/CLKI

PIC18FXXXX

OSC2/CLKO

Рис. 1.13. Тактирование от внешнего источника (конфигурация ЕС и ECPLL)

25

Глава 1

Такты от

внешнего

источника

OSC1/CLKI

PIC18FXXXX

RA6 -----► I/O (OSC2)

Рис. 1.14. Тактирование от внешнего источника (конфигурация ECIO и ЕСРЮ)

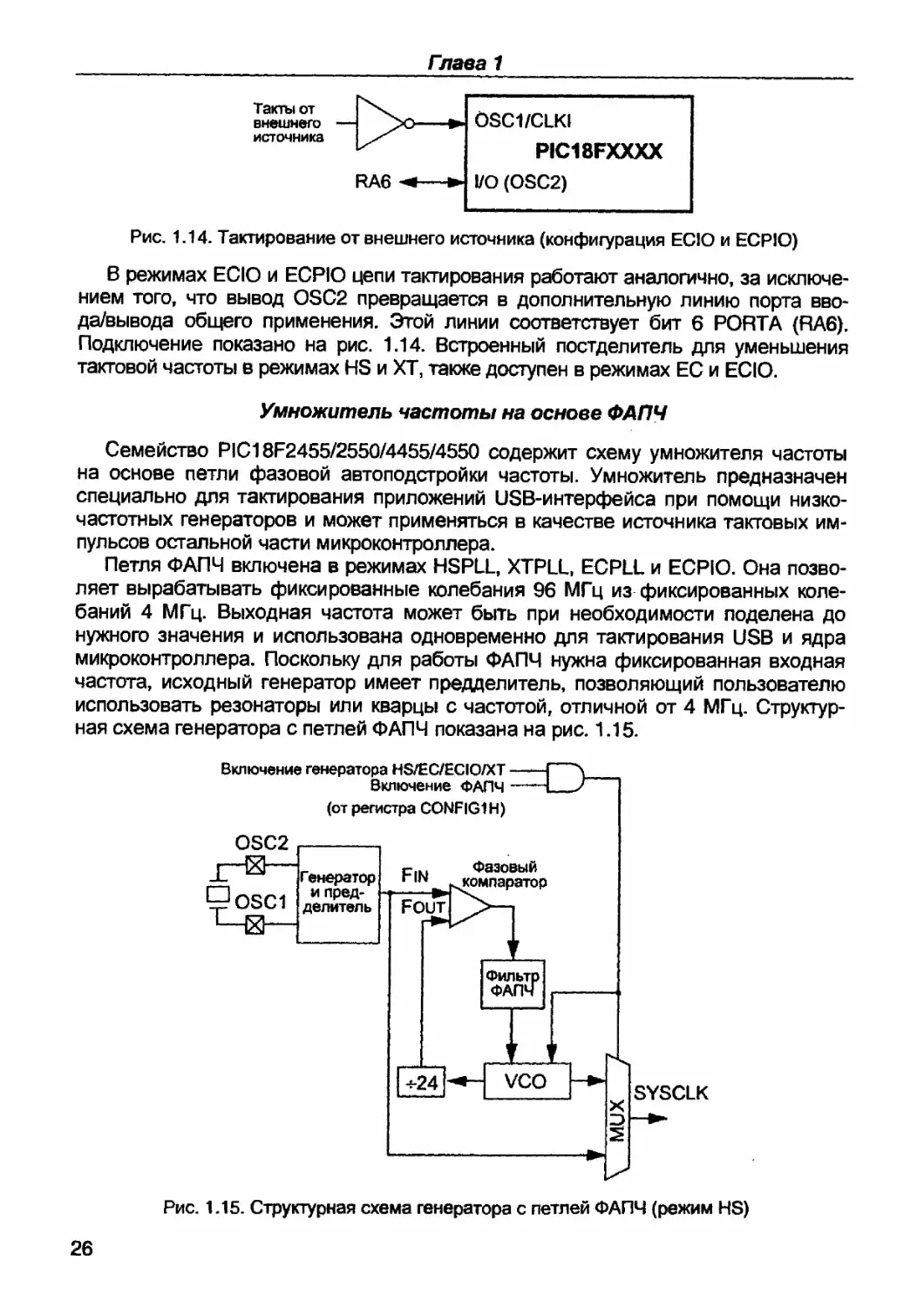

В режимах ЕСЮ и ЕСРЮ цепи тактирования работают аналогично, за исключе-

нием того, что вывод OSC2 превращается в дополнительную линию порта вво-

да/вывода общего применения. Этой линии соответствует бит 6 PORTA (RA6).

Подключение показано на рис. 1.14. Встроенный постделитель для уменьшения

тактовой частоты в режимах HS и XT, также доступен в режимах ЕС и ЕСЮ.

Умножитель частоты на основе ФАПЧ

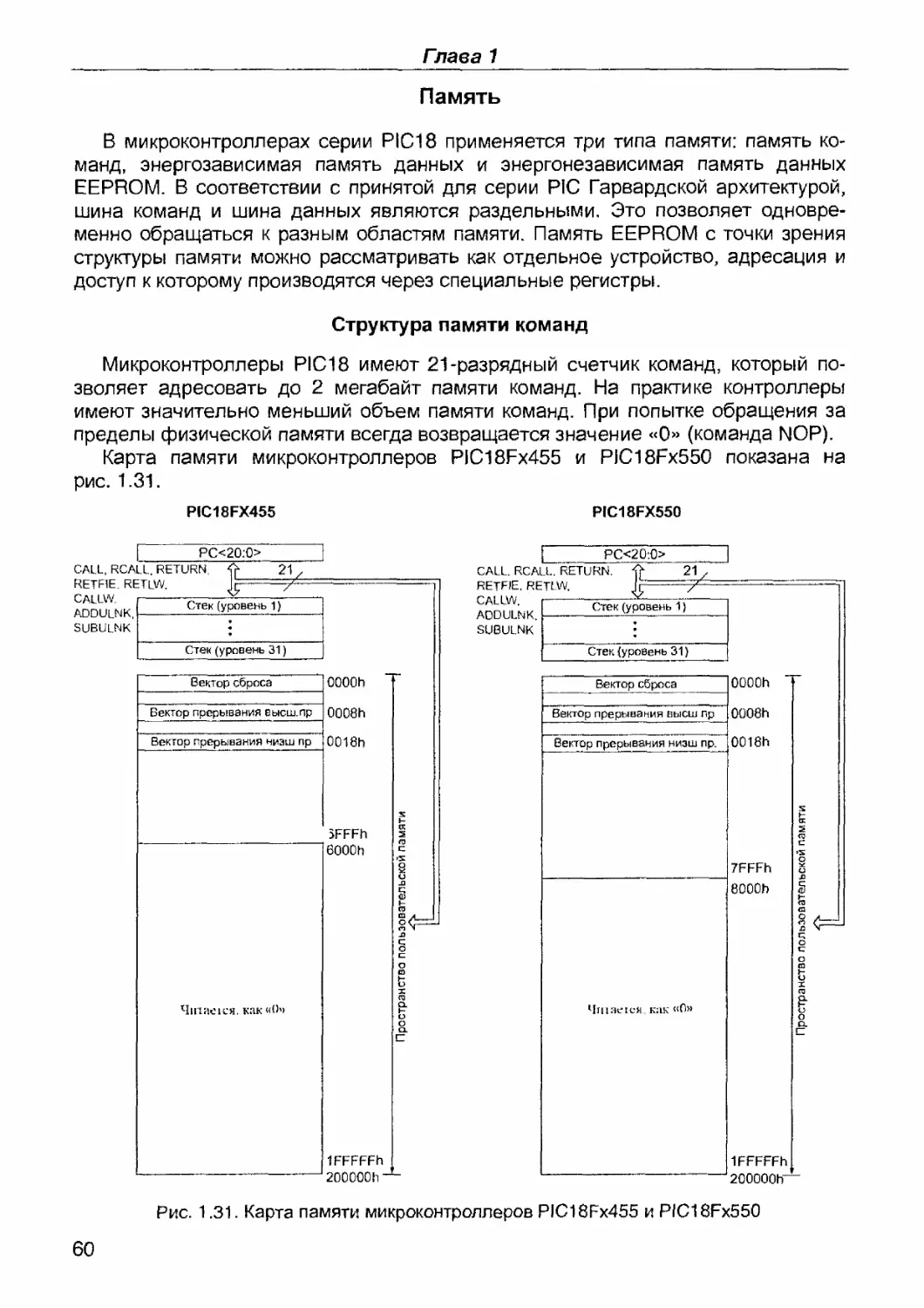

Семейство PIC18F2455/2550/4455/4550 содержит схему умножителя частоты

на основе петли фазовой автоподстройки частоты. Умножитель предназначен

специально для тактирования приложений USB-интерфейса при помощи низко-

частотных генераторов и может применяться в качестве источника тактовых им-

пульсов остальной части микроконтроллера.

Петля ФАПЧ включена в режимах HSPLL, XTPLL, ECPLL и ЕСРЮ. Она позво-

ляет вырабатывать фиксированные колебания 96 МГц из фиксированных коле-

баний 4 МГц. Выходная частота может быть при необходимости поделена до

нужного значения и использована одновременно для тактирования USB и ядра

микроконтроллера. Поскольку для работы ФАПЧ нужна фиксированная входная

частота, исходный генератор имеет предделитель, позволяющий пользователю

использовать резонаторы или кварцы с частотой, отличной от 4 МГц. Структур-

ная схема генератора с петлей ФАПЧ показана на рис. 1.15.

Рис. 1.15. Структурная схема генератора с петлей ФАПЧ (режим HS)

26

Структура и базовые функции микроконтроллеров

Кроме того, существует постделитель, позволяющий менять частоту импуль-

сов, поступающих с ФАПЧ на ядро микроконтроллера. Благодаря этому, микро-

контроллер может работать на частоте, отличающейся от частоты тактирования

модуля USB. В отличие от постделителя для режимов XT, HS и ЕС, в данном

случае доступны коэффициенты 1/1, 1/2, 1/3, 1/4 и 1/6 от значения на выходе

ФАПЧ.

В режимах HSPLL, ECPLL и ECPIO можно использовать высокочастотные

кварцы, с рабочей частотой до 48МГц. При помощи предделителя эту частоту

можно поделить до 12 раз, получив 4 МГц, необходимые ФАПЧ. В режиме XTPLL

можно использовать только входные колебания 4 МГц, поступающие на ФАПЧ

напрямую.

Блок встроенного генератора

Семейство PIC18F2455/2550/4455/4550 содержит встроенный генератор, вы-

рабатывающий два различных тактовых сигнала, любой из них может быть ис-

пользован для тактирования микроконтроллера. Если периферия USB не ис-

пользуется, то встроенный генератор позволяет обойтись без внешних элемен-

тов на выводах OSC1 и OSC2. Основной генератор представляет собой источник

импульсов 8 МГц, которые можно использовать непосредственно для тактирова-

ния микроконтроллера. Эти импульсы поступают также на постделитель INTOSC,

который позволяет получить импульсы с частотой от 31 кГц до 4 МГц. Выход

INTOSC включен, когда выбрана частота тактирования от 125 кГц до 8 МГц.

Вторым источником импульсов является RC-генератор INTRC, имеющий но-

минальную частоту 31 кГц. INTRC включается, когда выбран в качестве источни-

ка тактовой частоты. Кроме того, он включается автоматически, если включены

следующие опции:

- таймер запуска по включению питания

- отказоустойчивый монитор частоты

- сторожевой таймер

- ускоренный запуск.

Эти опции подробно рассмотрены далее, в описании специальных модулей и

опций микроконтроллера.

Источник тактовой частоты (INTOSC напрямую, INTRC напрямую или INTOSC

через делитель) определяется настройкой битов конфигурации IRCF регистра

OSCCON.

Режимы встроенного генератора и тактирование USB

Когда встроенный генератор используется в качестве источника тактовых им-

пульсов микроконтроллера, то модуль USB следует тактировать от другого ис-

точника (независимый внешний источник или кварц/резонатор на выводах OSC1,

OSC2). Выбор источника для тактирования USB определяется особенностями

конкретного выбранного режима внутреннего генератора. Существует четыре

режима работы встроенного генератора:

INTHS. Тактирование USB происходит от генератора в режиме HS.

INTXT. Тактирование USB происходит от генератора в режиме XT.

INTCKO. Тактирование USB происходит от внешнего источника, через вывод

OSC1/CLKI. На выходе OSC2/CLKO присутствует FOsc/4.

INTIO. Тактирование USB происходит от внешнего источника, через вывод

27

Гпава 1

OSC1/CLKI. (RA6). Вывод OSC2/CLKO работает как линия двунаправленного порта Регистр OSCTUNE

bit7 INTSRC бит выбора источника низкочастотного сигнала 1 = 31.25 кГц поступает от источника 8 МГц INTOSC через делитель на 256 0 = 31 кГц поступает от встроенного генератора INTRC

bit 6-5 Не используются. Читаются, как 0.

bit 4-0 TUN4:TUN0 Биты подстройки частоты 01111 = Максимальная частота

00001

00000 = Центральная частота, соответствует заводской калибровке

11111

10000 = Минимальная частота

Встроенные генераторы калибруются на фабрике, но могут быть настроены и

в приложении пользователя путем записи новой калибровочной константы в ре-

гистр OSCTUNE. Настроечная характеристика (функция частоты от значения

константы) линейная во всем диапазоне настройки.

Как только в OSCTUNE записано новое значение, частоты INTOSC и INTRC

начинают смещаться к новому значению. Это происходит не мгновенно. Частота

INTRC устанавливается через 8 тактов (примерно 256 мкс). Частота INTOSC ста-

билизируется через 1 мс. Выполнение программного кода продолжается и во

время сдвига частоты, индикация окончания сдвига не предусмотрена.

Регистр OSCTUNE также содержит бит INTSRC. Этот бит позволяет пользо-

вателю выбрать, какой внутренний генератор является источником тактов, когда

установлена опция частоты 31 кГц. Более подробно этот вопрос рассмотрен в

разделе «Управляющий регистр генератора».

Дрейф частоты и его компенсация

Несмотря на то, что встроенные генераторы откалиброваны на фабрике, зна-

чение частоты может незначительно дрейфовать в ту или иную сторону в зави-

симости от напряжения питания и температуры корпуса. Генераторы INTOSC и

INTRC не связаны между собой, и дрейф частоты в них происходит абсолютно

независимо. Корректировка частоты INTOSC также не влияет на частоту INTRC.

Для корректировки частоты INTOSC необходимо знать, в какую сторону, и на

какую величину производить компенсацию. Например, при использовании модуля

EUSART, подстройка необходима, если начинает появляться ошибка кадрирова-

ния или принимаемые данные содержат ошибки в асинхронном режиме. Ошибка

кадрирования означает, что частота тактирования слишком велика. Необходимо

уменьшить частоту путем уменьшения константы. С другой стороны, ошибки дан-

ных означают, что частота слишком низка.

28

Структура и базовые функции микроконтроллеров

Для вычисления величины корректировки можно использовать сравнение час-

тоты тактирования устройства с опорной частотой. Используется два таймера:

один тактируется периферийными тактами, тогда как другой тактируется от фик-

сированного опорного источника, такого как генератор таймера Timerl. Оба тай-

мера сбрасываются, но таймер, тактируемый опорной частотой, генерирует пре-

рывание. Когда происходит прерывание, считывают значение из таймера, такти-

руемого от внутреннего генератора, и сбрасывают оба таймера. Если значение

таймера, тактируемого от внутреннего генератора, больше, чем ожидалось из

расчетов, значит, частота внутреннего генератора слишком высока, и наоборот.

И, наконец, модуль ССР может использовать свободно работающий таймер

Timerl или Timer3, тактируемый от блока внутреннего генератора, и некое внешнее

событие с заведомо известным периодом (например, импульсы внешнего образцово-

го генератора). Момент первого события захватывается в регистры CCPRxH:CCPRxL

и сохраняется для дальнейшего использования. Затем, когда захвачен момент вто-

рого события, время первого события вычитается из времени второго события (под

временем понимают значение таймера). Поскольку период следования внешнего

события известен, можно рассчитать разницу времени между событиями.

Если измеренное время намного больше, чем расчетное, внутренний генера-

тор работает слишком быстро, и наоборот.

Настройки генератора для USB

Когда микроконтроллер PIC18F4550 применяется для обмена данными по

USB, то для его работы требуется тактовая частота 6 МГц или 48 МГц в зависи-

мости от заданного режима скорости USB. Поэтому при разработке и программи-

ровании приложений нужно заранее обдумать выбор частоты генератора и его

тип. В табл. 1.5 перечислены все варианты конфигурирования тактового генера-

тора, совместимые с работой USB.

Таблица 1.5

Варианты конфигурирования тактового генератора, совместимые с USB

Входная частота генерато- ра, МГц Делитель ФАПЧ (PLLDIV2:PLLDIV0) Режим генератора (FOSC3:FOSCO) Делитель ядра (CPUDIV1 :CPUDIV0) Тактовая частота микрокон- троллера

48 Нет(1) ЕС, ECIO Нет (00) 48

2(01) 24

3(Ю) 16

4(11) 12

48 12 (111) ЕС, ECIO Нет (00) 48

2(01) 24

3(Ю) 16

4(11) 12

ECPLL, ECPIO 2 (00) 48

3(01) 32

4(Ю) 24

6(11) 16

29

Глава 1

Входная частота генерато- ра, МГ ц Делитель ФАПЧ (PLLDIV2:PLLD1V0) Режим генератора (FOSC3-.FOSCO) Делитель ядра (CPUDIV1:CPUDIV0) Тактовая частота микрокон- троллера

40 10(110) ЕС, ЕСЮ Нет (00) 40

2(01) 20

3(Ю) 13.33

4(11) 10

ECPLL, ЕСРЮ 2(00) 48

3(01) 32

4(10) 24

6(11) 16

24 6(101) HS, ЕС, ЕСЮ Нет (00) 24

2(01) 12

3(Ю) 8

4(11) 6

HSPLL, ECPLL, ЕСРЮ 2(00) 48

3(01) 32

4(10) 24

6(11) 16

20 5(100) HS, ЕС, ЕСЮ Нет (00) 20

2(01) 10

3(Ю) 6,67

4(11) 5

HSPLL, ECPLL, ЕСРЮ 2(00) 48

3(01) 32

4(10) 24

6(11) 16

16 4(011) HS, ЕС, ЕСЮ Нет (00) 16

2(01) 8

3(10) 5,33

4(11) 4

HSPLL, ECPLL, ЕСРЮ 2(00) 48

3(01) 32

4(10) 24

6(11) 16

12 3 (010) HS, ЕС, ЕСЮ Нет (00) 12

2(01) 6

3(10) 4

4(11) 3

HSPLL, ECPLL, ЕСРЮ 2(00) 48

3(01) 32

4(Ю) 24

6(11) 16

30

Структура и базовые функции микроконтроллеров

Входная частота генерато- ра, МГ ц Делитель ФАПЧ (PLLDIV2:PLLDIV0) Режим генератора (FOSC3;FOSCO) Делитель ядра (CPUDIV1:CPUDIV0) Тактовая частота микрокон- троллера

8 2(001) HS, ЕС, ECIO Нет (00) 8

2(01) 4

3(10) 2,67

4(11) 2

HSPLL, ECPLL, ЕСРЮ 2 (00) 48

3(01) 32

4(10) 24

6(11) 16

4 1 (000) XT, HS, ЕС, ECIO Нет (00) 4

2(01) 2

3(Ю) 1,33

4(11) 1

HSPLL, ECPLL, XTPLL, ECPIO 2 (00) 48

3(01) 32

4(10) 24

6(11) 16

Примечание:(1) Действителен, если бит конфигурации USBDIV сброшен

Обозначения: Все тактовые частоты, кроме 24 МГц, эксклюзивно ассоциированы с ра-

ботой USB в режиме полной скорости (частота тактов USB 48 МГц). Жирный шрифт ука-

зывает на настройки, при которых поддерживается совместимость с низкоскоростным

USB (системная частота 24 МГц, частота тактов USB 6 МГц).

Управление источниками тактирования

По аналогии с другими микроконтроллерами PIC18, семейство

P1C18F2455/2550/4455/4550 имеет опцию, позволяющую источнику тактирования

переключаться с основного генератора на альтернативный низкочастотный ис-

точник. В данном семействе предусмотрено два альтернативных источника. Ко-

гда выбран альтернативный источник, различные функции управления энергопо-

треблением по-прежнему доступны.

В общем случае, доступны три разновидности источников тактирования:

- первичные генераторы;

- вторичные генераторы;

- блок встроенных генераторов.

Первичные генераторы включают в себя режимы «внешний кристалл» и

«внешний резонатор», «внешнее тактирование» и блок встроенных генераторов.

Индивидуальный режим определяется содержимым битов конфигурации

FOSC3:FOSCO. Детали настройки рассматриваются далее.

31

Глава 1

Вторичные генераторы представляют собой внешние источники, не подклю-

ченные к выводам OSC1 и OSC2. Эти источники могут продолжать работать и

после того, как контроллер переведен в режим управления энергопотреблением.

Микроконтроллеры PIC18F2455/2550/4455/4550 используют генератор тайме-

ра Timerl, как вторичный генератор. Этот генератор (во всех режимах управле-

ния энергопотреблением) часто является источником опорного времени для раз-

личных функций, таких, как часы реального времени. Наиболее часто стандарт-

ный часовой кристалл 32768 Гц подключается к выводам RC0/T1OSO/T13CKI

и RC1/T1OSI/UOE. Как и в случае рассмотренных выше генераторов режима XT

и HS, между каждым выводом и землей следует подключить нагрузочный кон-

денсатор (рис. 1.11). Более детально этот вопрос рассмотрен в описании модуля

Timerl.

Кроме своей работы в качестве первичного генератора, блок встроенных ге-

нераторов доступен и в режимах управления энергопотреблением. Источник

INTRC также применяется для тактирования нескольких специальных модулей,

таких, как сторожевой таймер и монитор тактовой частоты.

Регистр OSCCON

bit7 IDLEN бит включения режима Idle (свободен).

1 = Устройство входит в режим «простоя» по инструкции SLEEP.

О = Устройство входит в режим Sleep по инструкции SLEEP.

bit6-4 ICRF2:ICRF0 биты выбора частоты встроенного генератора.

111 = 8 МГц (INTOSC работает напрямую).

110 = 4 МГц.

101 =2 МГц.

100 = 1 МГц’3*

011 = 500 кГц.

010 = 250 кГц.

001 = 125 кГц.

000 = 31 кГц (от 1NTOSC/256 или INTRC напрямую/2*.

bit3 OSTS бит статуса тайм-аута при запуске генератора’1*.

1 = тайм-аут для запуска генератора исчерпан, генератор работает.

0 = запуск еще идет, первичный генератор не готов.

bit2 IOFS бит стабильности частоты INTOSC.

1 = Частота INTOSC стабильна.

0 = Частота INTOSC нестабильна.

bitl-0 SCSI :SCS0 биты выбора системы тактирования.

1 х = блок внутреннего генератора.

01 = генератор модуля Timerl.

00 = первичный генератор.

(1) Зависит от состояния бита конфигурации IESO

’2) Источник выбирается битом INTSRC (OSCTUNE<7>), см. текст

(3* Выходная частота по умолчанию после сброса.

32

Структура и базовые функции микроконтроллеров

Регистр OSCCON управляет несколькими параметрами системы тактирова-

ния, как в обычном режиме, так и в режиме энергосбережения. Биты SCS1.SCS0

определяют источник тактовых импульсов. Доступными источниками являются

первичные импульсы (определяемые битами конфигурации FOSC3:FOSCO), вто-

ричные импульсы (генератор модуля Timerl) и блок внутреннего генератора. Ис-

точник тактирования меняется немедленно после изменения соответствующих

битов, в течение периода следования импульсов. Биты SCS обнуляются при

любых вариантах сброса!

Биты IRCF2:IRCF0 определяют выходную частоту импульсов блока внутрен-

него генератора, тактирующих микроконтроллер. Если контроллер тактируется от

блока внутреннего генератора, то изменение этих битов приводит к немедленно-

му изменению частоты на выходе генераторов. По умолчанию после сброса вы-

ходная частота блока встроенного генератора устанавливается равной 1 МГц.

Если установлена выходная частота 31 кГц (IRCF2JRCF0 = ООО), пользователь

может выбирать, какой из внутренних генераторов будет источником. Выбор осуще-

ствляется при помощи бита INTSRC (регистр OSCTUNE<7>). Установка этого бита

указывает на генератор INTOSC, как источник импульсов 31,25 кГц. Импульсы полу-

чаются путем деления на 256 постделителем INTOSC. Сброс бита INTSRC устанав-

ливает в качестве источника генератор INTRC с номинальной частотой 31 кГц.

Эта опция позволяет пользователю выбрать настраиваемый и более точный

INTOSC в качестве источника тактирования, пока установлен режим энергосбе-

режения с очень низкой тактовой частотой. Независимо от установки INTSRC,

генератор INTRC всегда остается источником тактов для таких периферийных

модулей, как сторожевой таймер и монитор тактовой частоты.

Биты OSTS, IOFS и T1RUN показывают, какой источник тактовой частоты сей-

час тактирует контроллер. Бит OSTS индицирует, что таймер запуска генератора

переполнен и первичный источник тактирует контроллер в режиме тактирования

от первичного источника. Бит 1OFS индицирует, когда внутренний генератор ста-

билизировался и выдает тактирующие импульсы в режиме RC-генератора. Бит

T1RUN (T1CON<6>) индицирует, что генератор таймера Timerl используется в

качестве источника в режиме вторичного тактирования. В энергосберегающих

режимах из этих трех битов в один момент времени может быть установлен

только один бит. Если ни один из этих битов не установлен, это означает, что

тактирование происходит от INTRC, или блок внутреннего генератора только что

стартовал, и его частота пока еще не стабильна.

Бит IDLEN определяет, как будет выполнена команда SLEEP: с переходом в

обычный режим SLEEP, или в один из режимов ожидания/бездействия (Idle

modes).

Применение флагов и управляющих битов регистра OSCCON рассмотрено

также в разделе «Энергосберегающие режимы».

Примечания:

1. Следует включить таймер Timerl, прежде чем его генератор будет ис-

пользован в качестве вторичного источника тактов. Для этого необходимо

установить бит T1OSCEN в регистре управления таймером (T1CON<3>). Ес-

ли модуль Timerl не включен, то попытки подключить вторичный источник

будут проигнорированы.

2. Прежде, чем подключать генератор модуля Timerl, следует быть уве-

ренным, что он запущен и работает. В противном случае возможна очень

большая задержка, пока генератор стартует.

33

Глава 1

Влияние режимов энергосбережения

на различные источники тактовых импульсов

Если установлен режим PRIJDLE, назначенный ранее первичный генератор

продолжает работать без перерыва. Во всех остальных энергосберегающих ре-

жимах генератор, использующий вывод OSC1, отключается. Если модуль USB не

включен, на выводах OSC1 и OSC2 прекращаются колебания.

В режимах вторичного тактирования (SECLRUN и SECJDLE) генератор Timerl

работает и выдает тактовую частоту. Генератор также может работать во всех энер-

госберегающих режимах, если требуется тактировать модули Timerl или Timer3.

В режимах тактирования от встроенного генератора (RC_RUN и RCJDLE) им-

пульсы поступают от блока внутреннего генератора. Выход INTRC 31 кГц может

быть использован непосредственно как источник тактовых импульсов или для

дополнительных модулей (см. разделы «Сторожевой таймер», «Монитор такто-

вой частоты» и «Двухскоростной запуск»). Выход INTOSC 8 МГц может поступать

напрямую или через постделитель. Выход INTOSC отключается, если импульсы

поступают напрямую с выхода INTRC.

Независимо от того, находится ли контроллер в режиме ожидания (Idle), ис-

точник тактирования USB продолжает работать. Если контролер тактировался от

генератора на основе кварца или резонатора, этот генератор продолжает такти-

ровать модуль USB. Ядро и остальные модули переключаются на другой источ-

ник тактовых импульсов.

Если выбран переход в полноценный режим SLEEP по команде SLEEP, то все

источники тактовой частоты останавливаются. Следовательно, переключения

всех транзисторов прекращаются, и потребляемый ток состоит только из суммы

токов утечек.

Режим SLEEP не может быть реализован, если модуль USB работает

и осуществляет обмен данными. Существует лишь одно исключение, когда

прибор получает команду «Останов» через USB. Как только модуль USB полу-

чает эту команду, он переключается в режим энергосбережения, и весь микро-

контроллер переходит в режим SLEEP.

Включение какого-либо модуля, способного работать в режиме SLEEP, увели-

чивает потребляемый ток. Для работы модуля сторожевого таймера необходим

генератор INTRC. Для использования таймера Timerl в качестве часов реально-

го времени также понадобится соответствующий генератор. Некоторые опцио-

нальные возможности могут быть реализованы без потребления энергии от ис-

точника питания прибора. Это, например, внешние прерывания, последователь-

ный порт в режиме «ведомого» и т.д.

Задержки по включению питания

Задержки по включению питания управляются двумя таймерами. Поэтому

в большинстве приложений не требуются дополнительные внешние элементы

цепи сброса. Таймеры задержек позволяют удерживать контроллер в состоянии

сброса, пока питание не стабилизируется на должном уровне, а первичный гене-

ратор не выйдет в стабильный режим.

Первый таймер - это PWRT, таймер включения питания, который обеспечи-

вает фиксированную задержку при включении. Таймер включается сбросом бита

конфигурации PWRTEN.

34

Структура и базовые функции микроконтроллеров

Второй таймер - это таймер запуска тактового генератора OST, призванный

удерживать кристалл в состоянии сброса, пока генератор не стабилизируется

(режимы XT и HS). Таймер OST отсчитывает 1024 импульса тактового генерато-

ра, прежде чем позволит генератору тактировать микроконтроллер.

Если в слове конфигурации указан режим генератора HSPLL, то прибор удер-

живается в состоянии сброса дополнительные 2 мс, чтобы петля ФАПЧ успела

захватить входную тактовую частоту.

Энергосберегающие режимы

В семействе PIC18F2455/2550/4455/4550 предусмотрено семь режимов опти-

мального потребления энергии питания. В свою очередь, режимы потребления

делятся на три категории:

. Работа (Run)

• Ожидание (Idle)

• Засыпание (Sleep)

Эти категории определяют, какая часть микроконтроллера тактируется и с ка-

кой частотой. Режимы Run и Idle могут использовать три доступных типа источни-

ка тактирования (первичный, вторичный и блок встроенного генератора). В ре-

жиме Sleep источники тактирования не используются.

Энергосберегающие режимы, примененные в рассматриваемом семействе

приборов, включают в себя некоторые опции, примененные в более ранних микро-

контроллерах серии PICmicro®. Это опция переключения источника тактирования,

позволяющая приборам серии PIC18 использовать генератор таймера Timerl вме-

сто первичного генератора. Также используется традиционный для всех приборов

PICmicro® режим Sleep, когда не работает ни один тактовый генератор.

Выбор энергосберегающих режимов

Выбирая энергосберегающий режим, необходимо определиться с двумя во-

просами: будет ли микроконтроллер тактироваться или нет, и выбрать источник

тактирования. Бит IDLEN регистра OSCCON<7> управляет тактированием кон-

троллера, тогда как биты SCS1:SCS0 регистра OSCCON<1:0> выбирают источ-

ник тактирования (см. выше описание регистра OSCCON). Индивидуальные ре-

жимы, источники тактирования и задействованные модули сведены в табл. 1.6.

Таблица 1.6

Энергосберегающие режимы

Режим Биты OSCCON Тактирование модулей Доступные частоты и источники

IDLEN(1) SCSI: SCSO Ядро Перифе- рия

Sleep 0 - Нет Нет Все генераторы отключены

PRI_RUN - 00 Да Да Первичный источник, все его режимы Нормальный режим полного потребления

35

Гпава 1

Режим Биты OSCCON Тактирование модулей Доступные частоты и источники

IDLEN(1) SCSI: SCSO Ядро Перифе- рия

SEC_RUN - 01 Да Да Вторичный - генератор тай- мера Timerl

RC_RUN - 1x Да Да Блок внутреннего генератора(2)

PRI JDLE 1 00 Нет Да' Первичный - все режимы.

SECJDLE 1 01 Нет Да Вторичный - генератор Timerl

RCJDLE 1 1x Нет Да Блок внутреннего генератора(2>

(1) Значение IDLEN используется, когда выполнена команда SLEEP.

(2) Включая INTOSC и его постделитель, равно как и INTRC.

Переход от одного энергосберегающего режима к другому начинается с за-

грузки нового значения в регистр OSCCON. Биты SCS1:SCSO выбирают источник

тактирования и определяют, какой режим - Run или Idle будет использован. Из-

менение этих битов переключает прибор на новый источник (допуская, что он

работает). Переключение в режим Idle или Sleep происходит в момент выполне-

ния команды SLEEP и зависит от состояния бита IDLEN в этот момент.

В зависимости от текущего режима и того, какой режим ожидается, не всегда

может потребоваться оперировать всеми этими битами. Переход в другой режим

может быть осуществлен переключением битов выбора источника или измене-

нием состояния бита IDLEN перед выдачей команды SLEEP. Если бит IDLEN ус-

тановлен корректно, может оказаться достаточным только команды SLEEP.

Переход между источниками тактовых импульсов занимает два цикла старого

источника и три цикла нового. Эта формула предполагает, что новый источник

уже запущен и стабилен.

Три бита указывают текущий источник и его статус:

.OSTS (OSCCON<3>).

. IOFS (OSCCON<2>).

. T1RUN (T1CON<6>).

Как правило, только один из этих битов будет установлен в определенном

энергосберегающем режиме. Если установлен бит OSTS, устройство тактируется

от первичного источника. Если установлен бит IOFS, то генератор INTOSC выда-

ет стабильные 8 МГц на делитель, откуда они поступают на прибор. Если уста-

новлен бит T1RUN, то источником является генератор таймера Timerl. Если же

ни один из этих битов не установлен, то либо прибор тактируется от источника

INTRC, либо генератор INTOSC еще не стабилен.

Если блок внутреннего генератора сконфигурирован, как первичный источник,

при помощи битов FOSC3.FOSCO, то в режимах PRI_RUN и PRI JDLE могут быть

установлены два бита - OSTS и IOFS. Это означает, что первичный источник (в

данном случае INTOSC) генерирует стабильные 8 МГц. Ввод другого режима

энергопотребления на этой же частоте очистит бит OSTS.

Внимание! Если напряжение питания меньше, чем 3 В, может случиться

так, что будет установлена тактовая частота больше, чем допустимая для

микроконтроллера при пониженном напряжении питания. При несоблюдении

допустимого соотношения VDD/FOSC микроконтроллер может работать не-

корректно.

36

Структура и базовые функции микроконтроллеров

Напомним также, что выполнение команды SLEEP не обязательно означа-

ет, что микроконтроллер перейдет в режим Sleep. Это зависит от состоя-

ния бита IDLEN.

В режимах вида «Run» тактируются как ядро, так и периферийные модули.

Различие состоит только в источнике тактов.

Режим PRI_RUN - это обычный режим работы с полным энергопотреблени-

ем. Этот режим установлен по умолчанию после сброса, исключая случай, когда

установлен двухскоростной запуск. В этом режиме бит OSTS установлен. Бит

IOFS может быть установлен, если первичным источником является блок внут-

реннего генератора.

Режим SEC_RUN - это режим совместимости с опцией «переключение ис-

точника», доступной в других приборах серии PIC18. В этом режиме ядро и пе-

риферия тактируются от генератора Timerl. Это дает возможность иметь по-

ниженное энергопотребление при достаточно стабильном источнике тактовых

импульсов. Переход в этот режим осуществляется установкой битов

SCSI :SCS0 в состояние «01».

При этом начинается тактирование от генератора Timerl, первичный генера-

тор отключается, флаг-бит T1RUN (T1CON<6>) установлен, флаг-бит OSTS

сброшен (рис. 1.16).

Внимание! Генератор Timerl должен быть запущен перед установкой ре-

жима SECRUN. Если флаг-бит T1RUN не сигнализирует о готовности гене-

ратора, то вхождение в режим SEC_RUN не произойдет. Если генератор

включен, но не «разогнался», то случится задержка тактирования до полного

запуска генератора. В обоих этих случаях возможен непредсказуемый резуль-

тат попытки переключения режима!

При переходе из режима SEC_RUN в PRI_RUN периферия и ядро продолжа-

ют тактироваться от генератора Timerl, пока не стартует первичный генератор.

Когда переключение закончено, флаг-бит T1RUN сбрасывается, OSTS устанав-

ливается. Биты IDLEN и SCS не затрагиваются, генератор Timerl продолжает

работать (рис. 1.17).

В режиме RC_RUN ядро и периферия тактируются от блока внутреннего генера-

тора с использованием мультиплексора INTOSC. Первичный генератор отключается.

Если используется источник INTRC, то рассматриваемый режим обеспечивает наи-

лучшее сбережение энергии питания из всех режимов серии «Run». Этот режим удо-

бен для приложений, не требующих быстрого тактирования на всем протяжении ра-

боты или некритичных к тактовой частоте и ее стабильности.

* Смена тактирования обычно происходит за 2-4 tosc

Рис. 1.16. Смена тактирования при переходе в режим SEC_RUN

37

Гпава 1

T0ST = 1024 Tosc, TpLl - 2 мс Эти интервалы показаны не в масштабе.

Рис. 1.17. Переход из режима SEC_RUN в PRI_RUN (HSPLL)

Если в качестве первичного источника объявить блок внутреннего генератора

(INTRC или INTOSC), то в момент исполнения кода не будет заметных различий

между режимами PRI_RUN и RC_RUN. Тем не менее, при входе в режим

RC_RUN и выходе из него все равно будет существовать задержка переключе-

ния. Поэтому, если первичным источником является блок внутреннего генерато-

ра, использовать режим RC_RUN не рекомендуется.

Вход в этот режим осуществляется установкой бита SCS1 = 1. Кроме того,

рекомендуется сбросить бит SCS0, несмотря на то, что он игнорируется.

Это обеспечит совместимость с будущими устройствами. Когда источник

тактирования переключен на мультиплексор INTOSC (рис. 1.18), первичный

генератор отключается, а флаг-бит OSTS сбрасывается. Биты IRCF могут быть

модифицированы в любой момент с целью немедленного изменения тактовой

частоты.

Если биты IRCF и бит INTSRC сброшены, то выход INTOSC выключен и флаг-

бит IOFS остается сброшенным. Таким образом, индикация об источнике такти-

рования будет отсутствовать. Тактирование предоставляет источник INTRC.

'Смена тактирования обычно происходит за 2-4 Tgs(-

Рис. 1.18. Переход в режим RC„RUN

38

Структура и базовые функции микроконтроллеров

Рис. 1.19. Переход из режима RC_RUN в PRLRUN

Если биты IRCF выводятся из состояния «все сброшены» (включая, таким об-

разом, выход INTOSC), или бит INTSRC установлен, то флаг-бит IOFS переходит

в «1» после того, как выходные колебания INTOSC стабилизируются. Тактирова-

ние микроконтроллера продолжится по истечении интервала стабилизации

Т !Obst-

Если биты IRCF имели изначально ненулевые значения или INTSRC был ус-

тановлен перед установкой SCS1 и генератор INTOSC уже стабилен, то бит IOFS

останется установленным в «1».

При переходе из режима RC_RUN в режим PRLRUN контроллер продолжает

тактироваться от мультиплексора INTOSC, пока стартует первичный источник.

Когда он готов, происходит переключение (рис. 1.19). По окончании переключе-

ния флаг-бит IOFS сбрасывается, флаг-бит OSTS устанавливается, и контроллер

далее тактируется от первичного генератора. Биты IDLEN и SCS при переключе-

нии не меняются. Источник INTRC продолжает работать, если включен модуль

сторожевого таймера или монитор тактовой частоты.

Внимание! Если напряжение питания меньше, чем 3 В, может случиться

так, что будет установлена тактовая частота больше, чем допустимая для

микроконтроллера при пониженном напряжении питания. При несоблюдении

допустимого соотношения VDD/FOSC микроконтроллер может работать не-

корректно.

Режим Sleep

Режим Sleep у микроконтроллеров семейства PIC18F2455/2550/4455/4550

полностью идентичен этому режиму у остальных микроконтроллеров PICmicro.

Он включается после сброса бита IDLEN (состояние по умолчанию после сброса)

и исполнения инструкции SLEEP. При этом отключается тактовый генератор. Все

флаг-биты источников тактирования сбрасываются.

Вхождение в режим Sleep из любого другого режима не требует переключения

источника тактирования, потому что в этом режиме ядро и большая часть перифе-

39

Глава 1

Q11 Q2i Q3 IQ4 |Q1

Рис. 1.20. Диаграмма тактирования при входе в режим Sleep

рии не требует тактирования. Если включен сторожевой таймер, он продолжает

тактироваться от источника INSRC. Если включен генератор Timerl, он тоже

продолжает работать (рис. 1.20).

Выход из режима Sleep происходит по прерыванию, по сбросу и по перепол-

нению сторожевого таймера. Но тактирование прибора не начинается до тех пор,

пока источник, заданный битами SCS1:SCS0, не будет готов, или будет тактиро-

ваться от блока внутреннего генератора, если включен двухскоростной запуск

или монитор тактовой частоты. В таком случае бит OSTS установится, когда так-

тирование будет происходить от первичного источника (рис.1.21). Состояние би-

тов IDLEN и SCS при выходе из Sleep не меняется.

OSC1

Выход ФАПЧ

Такты CPU

Такты

периферии

Счетчик

команд

; qi---------------------Q2; оз; 04; qi ;Q2; оз ;Q4 ;qi ;q2 ;оз^ Q4; qi оз; Q4‘

: Л П Л Л П Л П Л П ПЛ ДЛ П П Г

РсТ г У рс + 4 ~ X рс + 6 Г~

+ I

Пробуждение Установлен бит OSTS

TOSt = Tosc' Tpll ~ мс Эти интервалы показаны не в масштабе.

Рис. 1.21. Тактирование при выходе из Sleep (HSPLL)

Режим Idle

Режим Idle позволяет избирательно отключить тактирование ядра, сохраняя

тактирование периферийных модулей. Применение этого режима позволяет раз-

работчику более гибко использовать режимы энергосбережения.

Если бит IDLEN = 1 когда выполняется команда SLEEP, то периферия такти-

руется от источника, заданного битами SCS1:SCS0, но тактирование ядра пре-

кращается. Флаг-биты источников тактирования не меняются. Таким образом,

режим Idle является компромиссным решением, позволяющим экономить энер-

гию источника, обходясь без задержки на запуск тактового генератора (как это

происходит при выходе из Sleep).

Если включен сторожевой таймер, он продолжает тактироваться от источника

INSRC. Если включен генератор Timerl, он тоже продолжает работать.

Поскольку ядро не выполняет никакие команды, выйти из режима Idle можно

только по сбросу, по прерыванию или по переполнению сторожевого таймера.

Структура и базовые функции микроконтроллеров

Рис. 1.22. Диаграмма тактирования при входе в режим Idle

Когда происходит пробуждающее событие, ядро начинает тактироваться не

мгновенно, а по истечении некоторого интервала TCsd- Когда вычислитель начи-

нает исполнение кода программы, он продолжает тактироваться от того источни-

ка, от которого тактировался в момент входа в Idle. Например, при пробуждении

из режима RCJDLE микроконтроллер переходит в режим RC„RUN и, соответст-

венно, тактируется от встроенного RC-генератора.

При пробуждении по причине переполнения сторожевого таймера контроллер

переходит в ту разновидность режима Run, которая определена битами

SCS1:SCS0.

Режим PRIJDLE уникален тем, что не отключается первичный источник так-

тирования. Это позволяет работать с чувствительными к тактовой частоте при-

ложениями, поскольку генератор не нужно «разгонять» каждый раз при смене

режима или переключаться на другой источник.

Для вхождения в режим PRIJDLE из режима PRLRUN (рис. 1.22) достаточно

установить бит IDLEN = 1 и выполнить команду SLEEP. При переходе из других

режимов серии «Run» необходимо сначала установить бит IDLEN, затем обнулить

биты SCS, и лишь после этого выполнить команду SLEEP. Несмотря на то, что яд-

ро не тактируется, периферия продолжает получать тактовые импульсы от источ-

ника, определенного битами FOSC3:FOSCO. Бит OSTS остается установленным.

При выходе из режима PRIJDLE состояние битов IDLEN и SCS не изменяется

(рис 1.23).

Режим SEC IDLE прекращает тактирование ядра, но периферия продолжает

тактироваться от генератора Timerl. Для перехода в этот режим из режима

SECJ4UN достаточно установить бит IDLEN = 1 и выполнить команду SLEEP.

Если контроллер ранее находился в режиме ином, чем SEC_RUN, то следует

сначала установить бит IDLEN, затем установить биты SCSI :SCS0 в состояние

Рис. 1.23. Диаграмма тактирования при выходе из режима Idle

41

Гпава 1

«01» и после этого выполнить команду SLEEP. Когда тактирование переключает-

ся на генератор модуля Timerl, первичный генератор отключается, флаг-бит

OSTS сбрасывается и флаг-бит Т1 RUN устанавливается.

После выхода из режима периферия продолжает тактироваться от генератора

Timerl. По истечении интервала TCSD ядро начинает исполнение команд, такти-

руясь от генератора Timerl. Состояние битов IDLEN и SCS не изменяется; гене-

ратор Timerl продолжает работать.

Внимание! Генератор Timer! должен стабильно работать перед перехо-

дом в режим SECJDLE. Если бит включения генератора T1OSCEN не уста-

новлен. то команда SLEEP будет проигнорирована и переход в режим

SECJDLE не произойдет.

Если генератор Timer! включен, но еще не вошел в рабочий режим, то

тактирование будет задержано на время «разгона» генератора. В этой си-

туации возможен непредсказуемый результат выполнения команды SLEEP.

Режим RCJDLE прекращает тактирование ядра, но периферия продолжает

тактироваться от блока встроенного генератора через мультиплексор INTOSC.

Из режима RC„RUN переход осуществляется путем установки бита IDLEN = 1 и

выполнения команды SLEEP. Для перехода из других режимов необходимо сна-

чала установить бит IDLEN, затем биты SCS1:SCS0 в состояние «10» и выпол-

нить команду SLEEP. Несмотря на то, что в данном случае бит SCS0 игнорирует-

ся, настоятельно рекомендуется обнулять его для совместимости с будущими

версиями микроконтроллера. Мультиплексор INTOSC может быть использован для

получения более высокой тактовой частоты путем модификации битов IRCF до ис-

полнения команды SLEEP. Когда тактирование переключено на мультиплексор

INTOSC, первичный генератор отключается, и флаг-бит OSTS сбрасывается.

Если биты IRCF установлены в любое ненулевое значение, или установлен

бит INSRC, то включается выход INTOSC. Когда, по истечении интервала Тювбт.

выходные колебания становятся стабильными, устанавливается флаг-бит IOFS.

Когда происходит пробуждающее событие, периферия продолжает тактиро-

ваться от мультиплексора INTOSC. После задержки TCSD ядро начинает испол-

нение команд, тактируясь также от мультиплексора. Значение битов IDLEN и SCS

не изменяется. Если включены сторожевой таймер или монитор тактовой часто-

ты, они продолжают тактироваться от источника INTRC.

Выход из режимов Idle и Sleep

Выход из энергосберегающих режимов Sleep и Idle происходит по прерыва-

нию, по переполнению сторожевого таймера или по сбросу.

Любое из доступных прерываний может перевести контроллер в режим Run.

Но для этого к моменту выполнения команды Sleep прерывания должны быть

разрешены установкой управляющего бита в одном из регистров, INTCON или

PIE. Как только случается событие прерывания, устанавливается соответствую-

щий флаг-бит и начинается возврат из энергосберегающего режима. Если бит

GIE/GIEH (]NTCON<7>) установлен, начинается исполнение кода, расположенно-

го по вектору прерывания. В ином случае возобновляется исполнение кода с те-

кущей позиции.

Реакция на переполнение сторожевого таймера зависит от того, в каком ре-

жиме находился контроллер на момент события. Если код программы не испол-

нялся (все режимы группы Idle и режим Sleep), то происходит возврат из режима

42

Структура и базовые функции микроконтроллеров

энергосбережения и возобновляется исполнение кода. Если контроллер нахо-

дился в режиме Run, то происходит его сброс (подробнее см. раздел «Стороже-

вой таймер»).

Сторожевой таймер и постделитель очищаются при исполнении команд

SLEEP и CLRWDT, при отключении источника тактирования таймера и при мо-

дификации битов IRCF регистра OSCCON (если источником тактирования явля-

ется первичный генератор).

Рассмотрим выход по сбросу. Обычно, контроллер удерживается в состоянии

сброса при помощи таймера запуска до момента готовности первичного источни-

ка. После этого устанавливается бит готовности OSTS. Если новым источником

тактирования является блок внутреннего генератора, то устанавливается, наобо-

рот, флаг-бит IOFS.

Задержка выхода по сбросу до момента начала исполнения кода зависит от

обоих генераторов, их состояния до и после «пробуждения», а также типа гене-

ратора, если новым источником тактирования является первичный генератор.

Различные значения задержек сведены в табл. 1.7.

Таблица 1.7

Задержка выхода по сбросу из режимов Sleep и Idle

Источник тактирования Задержка выхода Бит готовности генератора (OSCCON)

До выхода После выхода

Первичный генератор (режим PRIJDLE) XT, HS Нет OSTS

XTPLL, HSPLL

EC

INTOSC(3) IOFS

T1OSC или INTRC(1) XT, HS Tost41 OSTS

XTPLL, HSPLL TosT + trc(4)

EC Tcsd(2)

intosc(2) T iobst(5) IOFS

INTOSC(3) XT, HS Tqst(5) OSTS

XTPLL, HSPLL Tost + trc(4)

EC Tcsd(2)

intosc(2) Нет IOFS

Нет (режим Sleep) XT, HS Tost(4) OSTS

XTPLL, HSPLL T ost + Lc(4>

EC Tcsd12)