Автор: Королев А.Г.

Теги: виды компьютеров радиоаппаратура (радиоэлектронная аппаратура) электроника игровые приставки

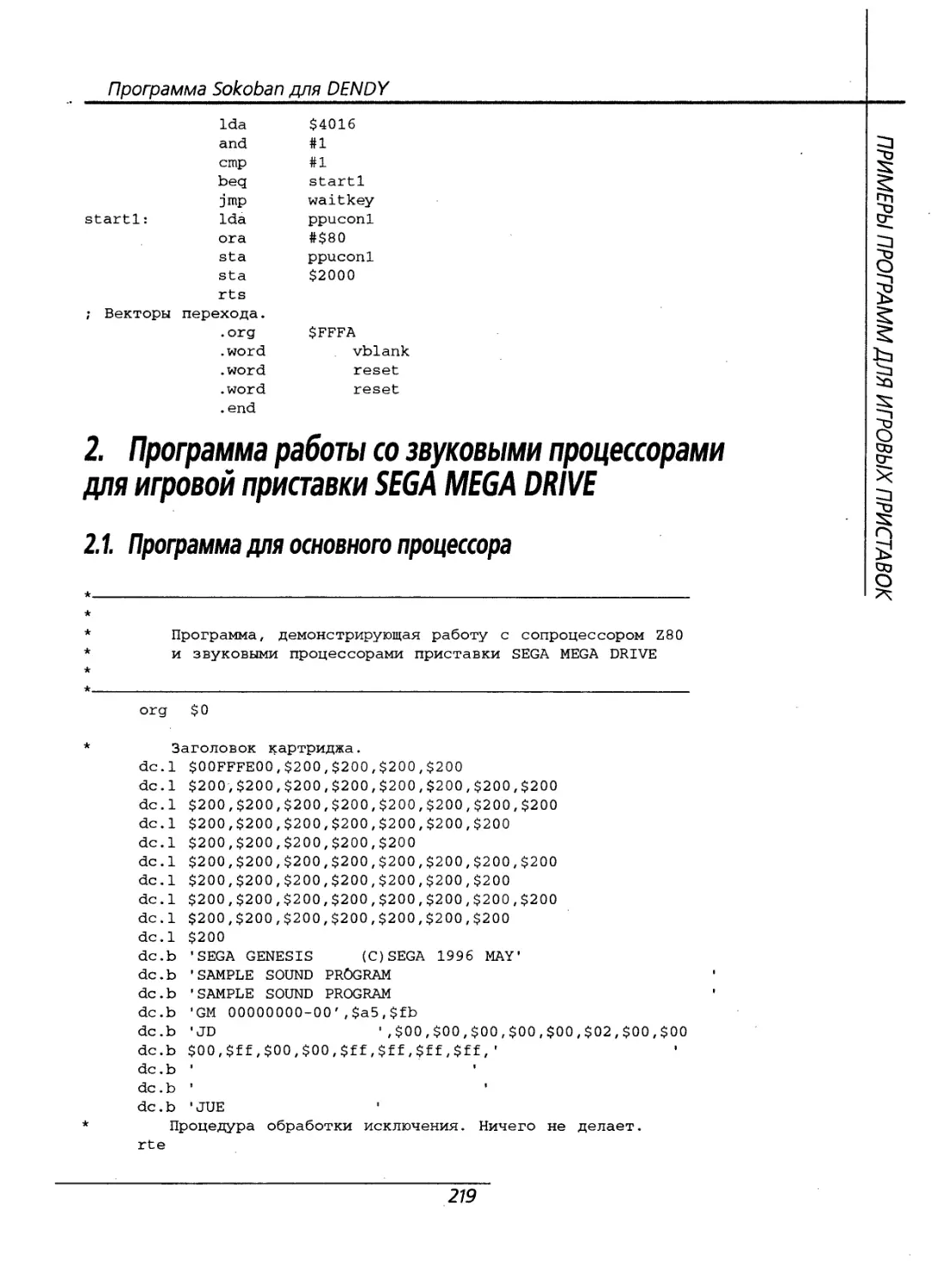

ISBN: 5-94074-065-0

Год: 2002

Текст

=

Самые популярные модели известных зарубежных фирм

Полный комплект структурных и принципиальных схем

Качественное графическое исполнение схем и рисунков

Подробное описание работы узлов и блоков

Методика проведения основных регулировок

Характерные неисправности и способы их устранения

BEHBY[NES]

БВМЕ BBY

БАМЕ BOY

SEGA MEGA DRIVE

SONY PLAYSTATID

Х13ОХ

РЕМОНТ И ОБСЛУЖИВАНИЕ

Серия «Ремонт и обслуживание»

КОРОЛЕВ А. Г.

Выпуск 21

Игровые приставки

DENDY [NES]

GAME BOY

SEGA MEGA DRIVE

SONY PLAYSTATION

Москва, 2002

УДК 004.388.4

ББК 32.844

К68

Королев А. Г.

К68 Игровые приставки. DENDY [NES], GAME BOY, SEGA MEGA DRIVE, SONY PLAYSTA-

TION. - M.: ДМК Пресс, 2002. - 240 с.: ил. (Ремонт и обслуживание; Вып. 21).

ISBN 5-94074-065-0

В предлагаемой книге рассмотрены различные модели современных игровых видеоприста-

вок (консолей) известных фирм - NINTENDO, SEGA и SONY.

Приведены подробные описания основных микросхем приставок, а также структурные

и принципиальные схемы; представлены рекомендации по обнаружению и устранению ха-

рактерных неисправностей. Для каждой модели рассмотрены система команд процессора

и программная архитектура.

Издание предназначено для подготовленных радиолюбителей и специалистов, занимаю-

щихся ремонтом аппаратуры; может использоваться как справочник при разработке перифе-

рийных устройств и написании программного обеспечения для игровых консолей.

Все права защищены. Любая часть этой книги не может быть воспроизведена в какой бы то ни было форме и какими

бы то ни было средствами без письменного разрешения владельца авторских прав.

Материал, изложенный в данной книге, многократно проверен. Но, поскольку вероятность наличия технических

ошибок все равно существует, издательство не может гарантировать абсолютную точность и правильность приводи-

мых сведений. В связи с этим издательство не несет ответственности за возможный ущерб любого вида, связанный

с применением или неприменимостью любых материалов данной книги.

ISBN 5-94074-065-0

© ДМК Пресс, 2002

/

Содержание

Предисловие.................................................................. 6

Краткая история игровых приставок................................................7

Этап 1.8-разрядные приставки ..................................................8

Этап 2. 16-разрядные приставки ................................................8

Этап 3. 32- и 64-разрядные системы ............................................9

Этап 4. Современные модели ...................................................10

Игровая приставка DREAMCAST ................................................ 11

Игровая приставка PLAYSTATION 2 ..............................................1 1

Игровая приставка Х-ВОХ ....................................................11

ГЛАВА 1

Игровая приставка DENDY ........................................................12

I. I. Технические характеристики..............................................13

1.2. Архитектура и принцип работы ............................................13

1.2.1. Структурная схема ...................................................13

1.2.2. Центральный процессор................................................14

1.2.3. Адресное пространство ...............................................18

1.2.4. Видеопроцессор ......................................................19

1.2.5. Звуковой процессор ..................................................24

1.2.6. Структура картриджа ............................................... 25

1.2.7. Организация ввода/вывода ............................................26

1.3. Принципиальная схема ....................................................27

•1.3.1 . Модуль процессора .................................................TJ

1.3.2. Картридж .......................................................... 32

1.3.3. Модулятор............................................................33

1.3.4. Игровые пульты ......................................................33

1.3.5. Блок питания ....................................................... 35

1.4. Характерные неисправности ...............................................36

ГЛАВА 2

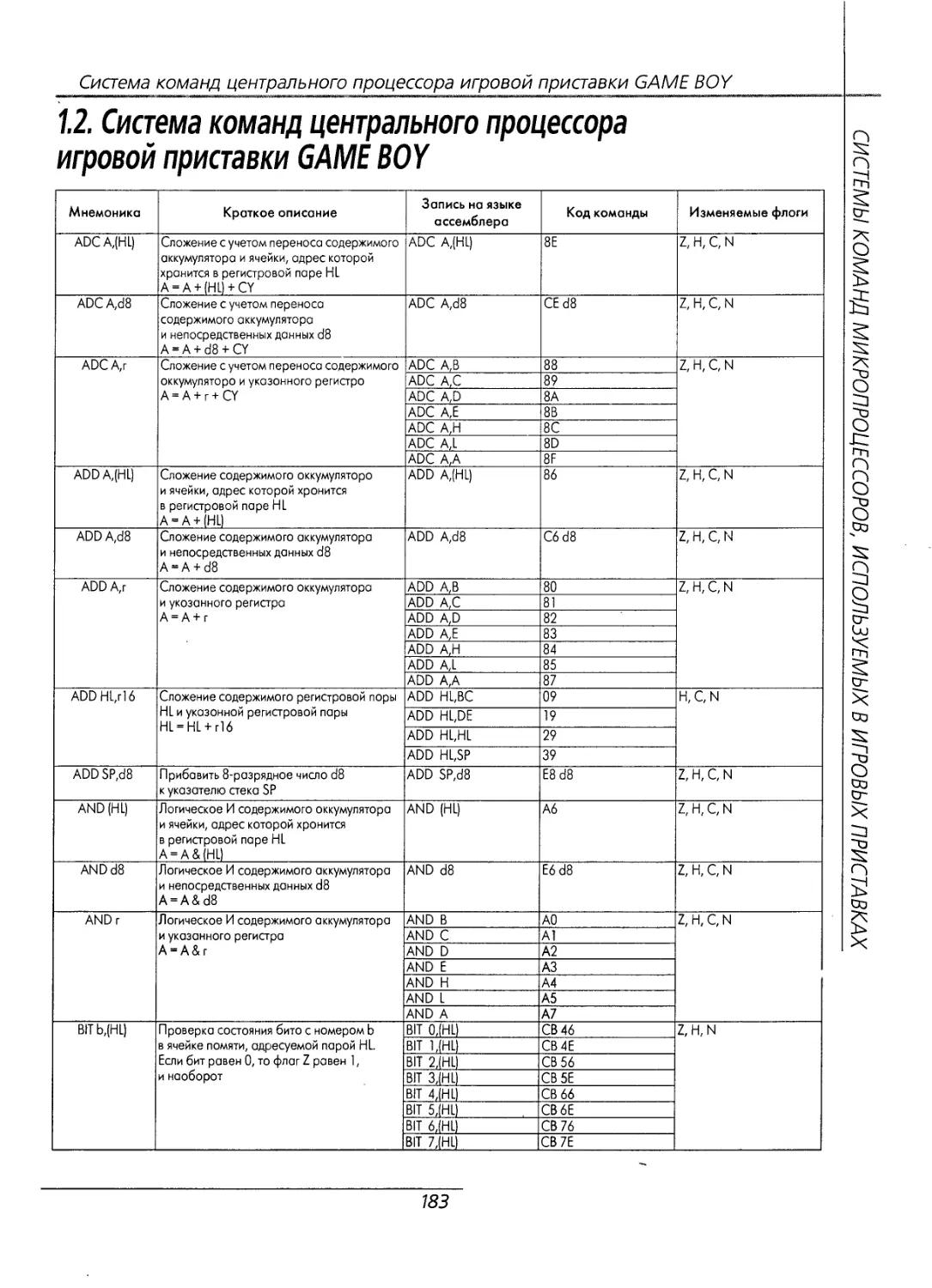

Игровая система GAME BOY........................................................38

2.1. Технические характеристики ..............................................39

2.2. Архитектура и принцип работы ............................................39

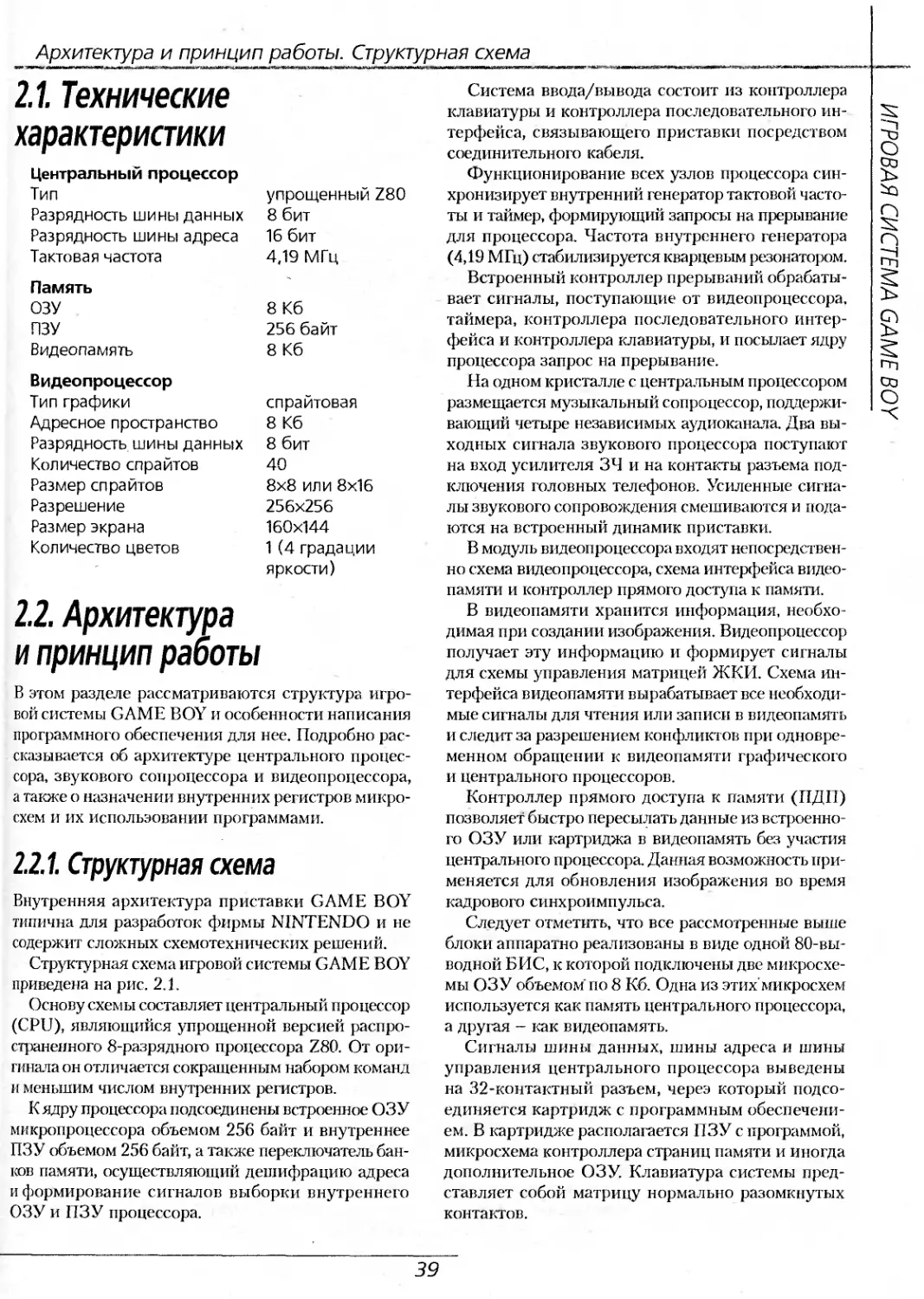

2.2.1. Структурная схема ...................................................39

2.2.2. Центральный процессор................................................40

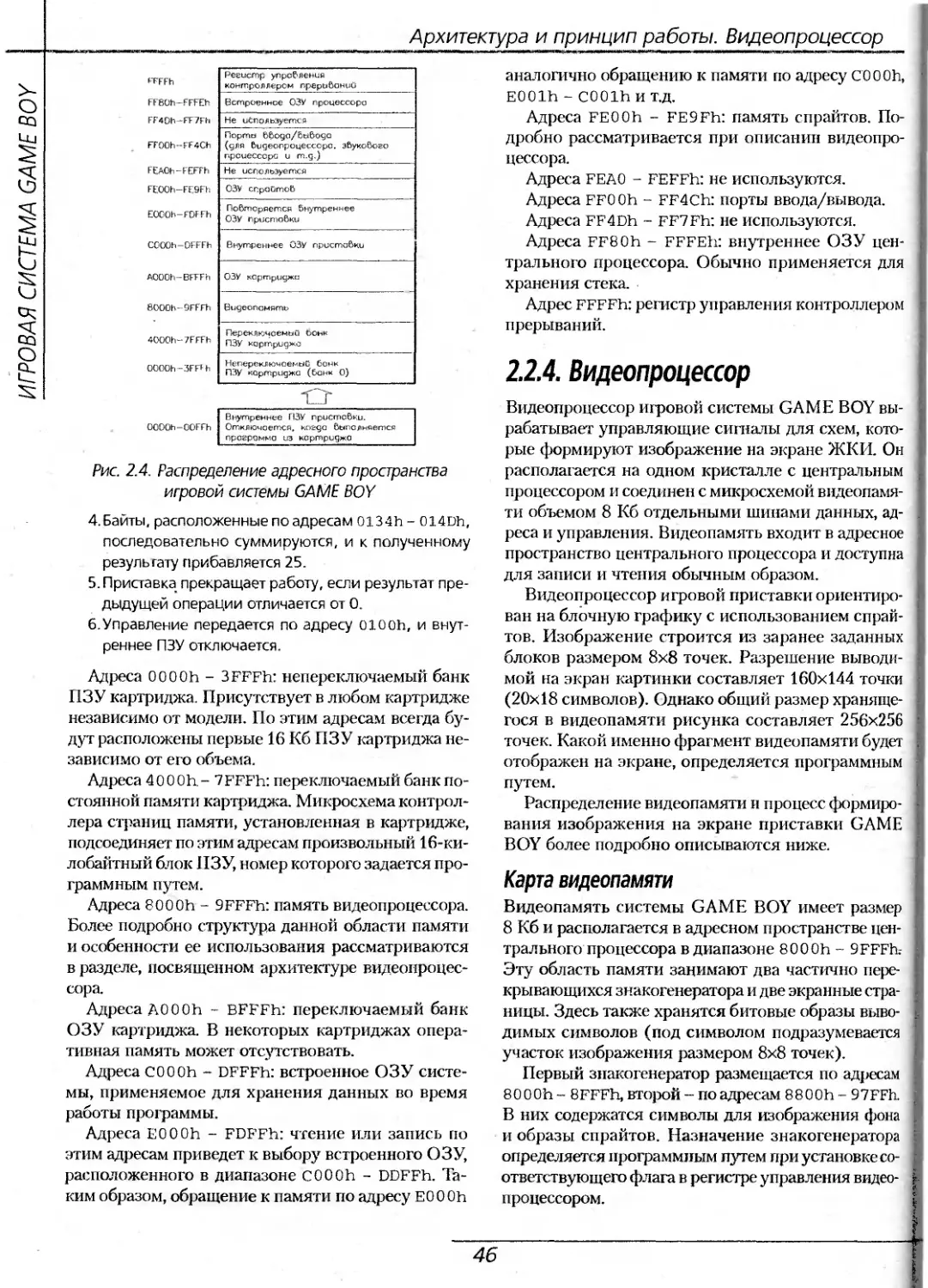

2.2.3. Адресное пространство ...............................................45

2.2.4. Видеопроцессор ......................................................46

2.2.5. Звуковой процессор ................................................. 52

2.2.6. Структура картриджа ............................................... 57

2.2.7. Организация ввода/вывода ............................................60

Игровые приставки

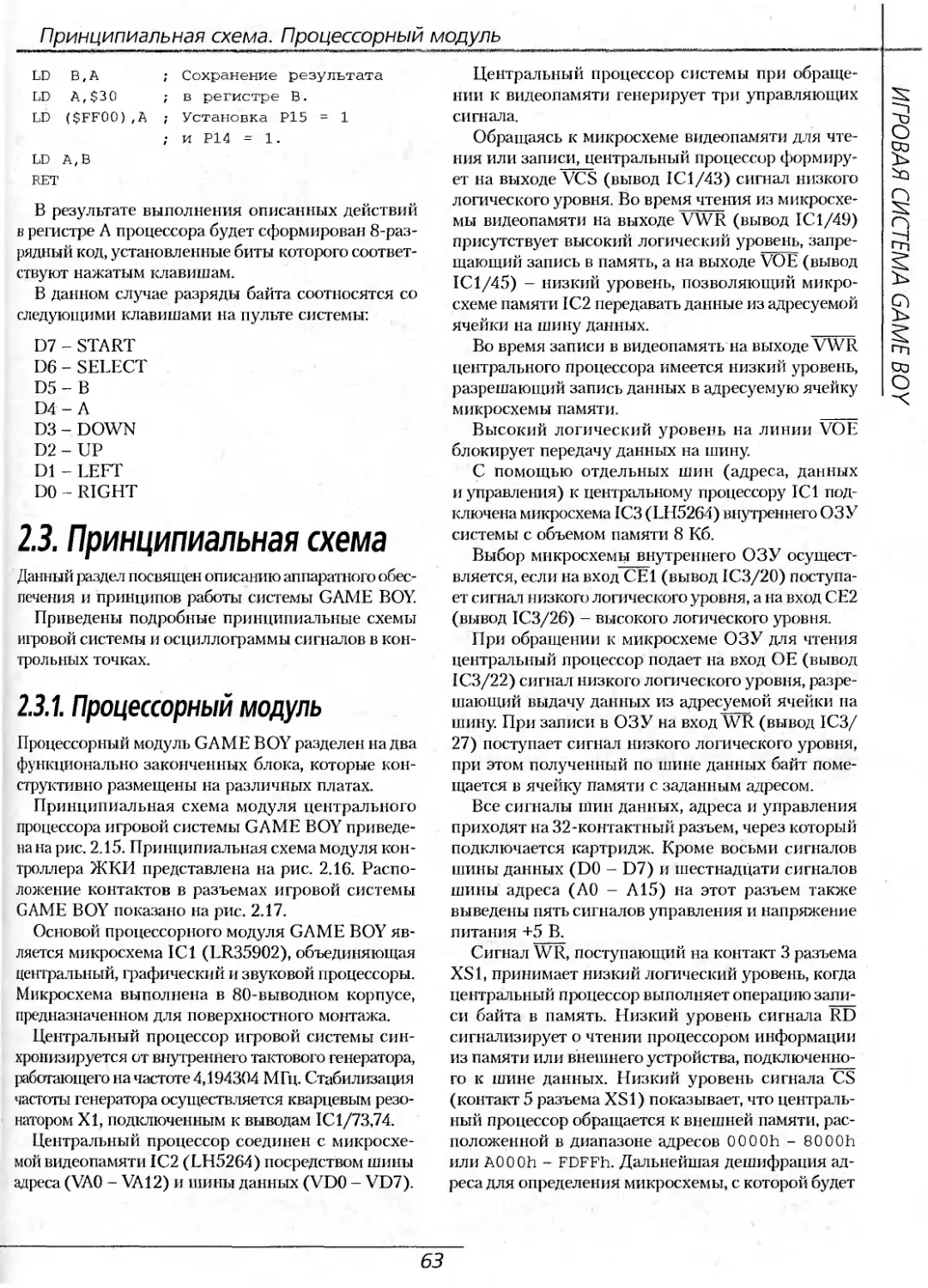

2.3. Принципиальная схема .....................................................63

2.3.1. Процессорный модуль...................................................63

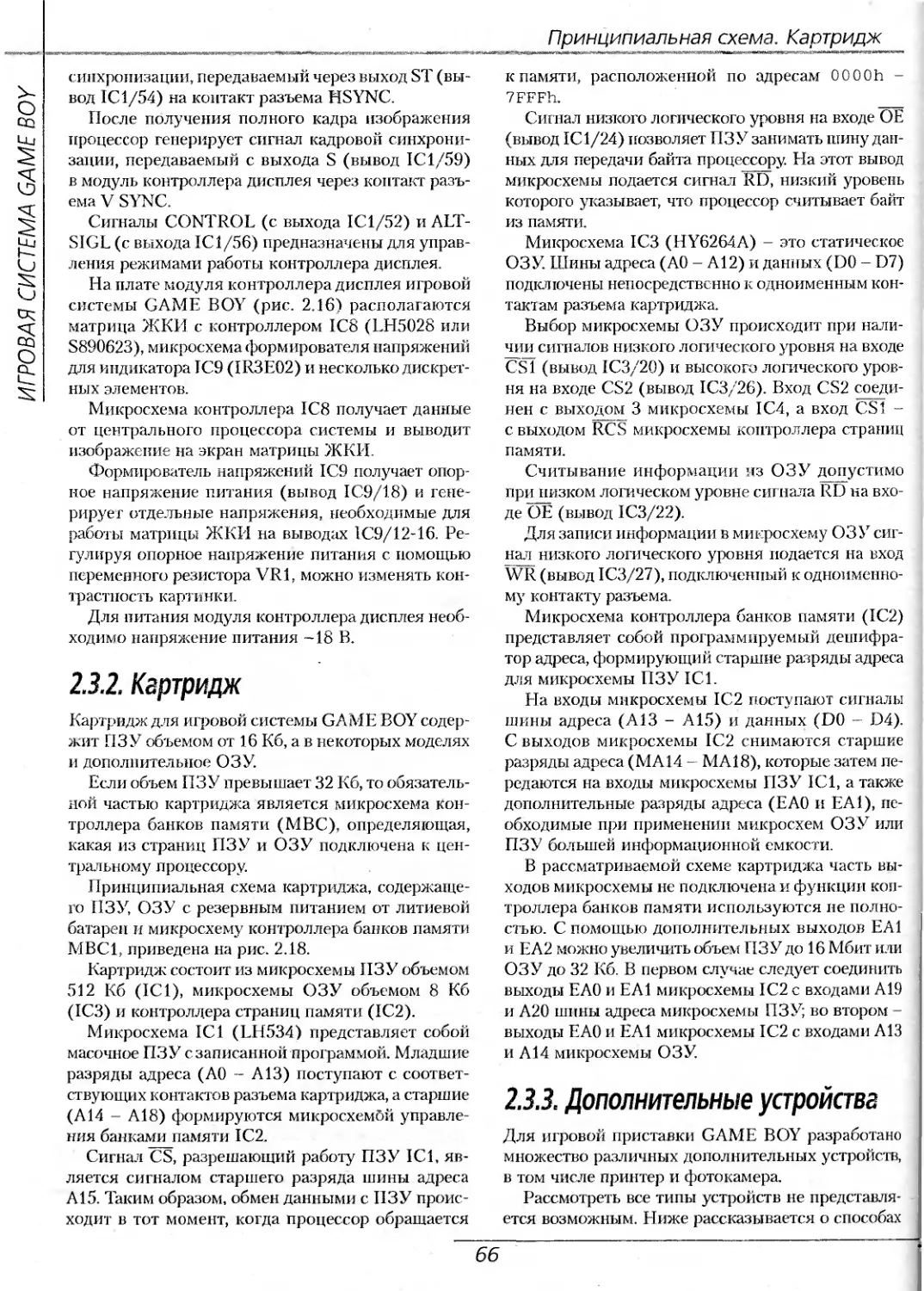

2.3.2. Картридж .............................................................66

2.3.3. Дополнительные устройства ............................................66

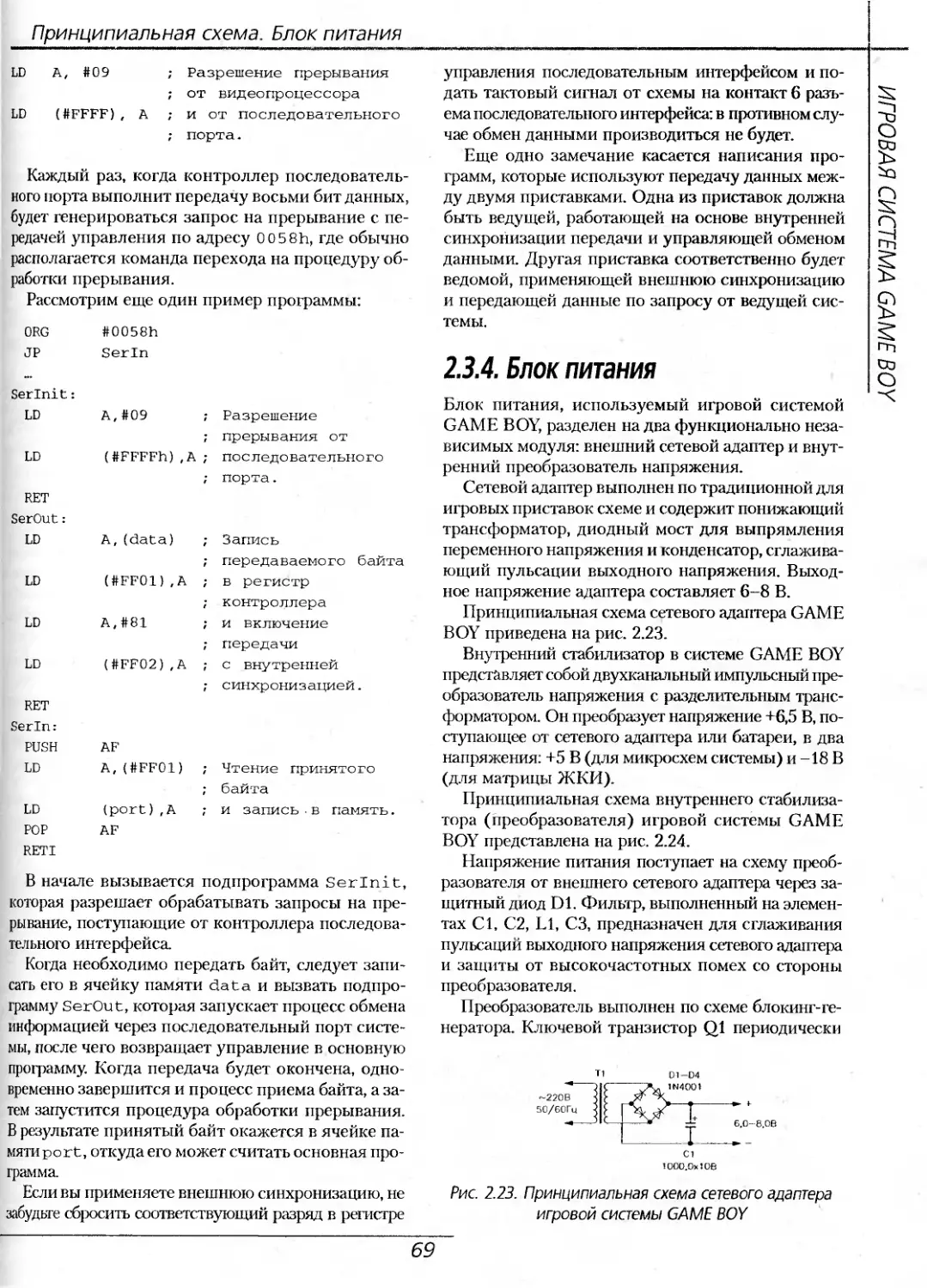

2.3.4. Блок питания ........................................................ 69

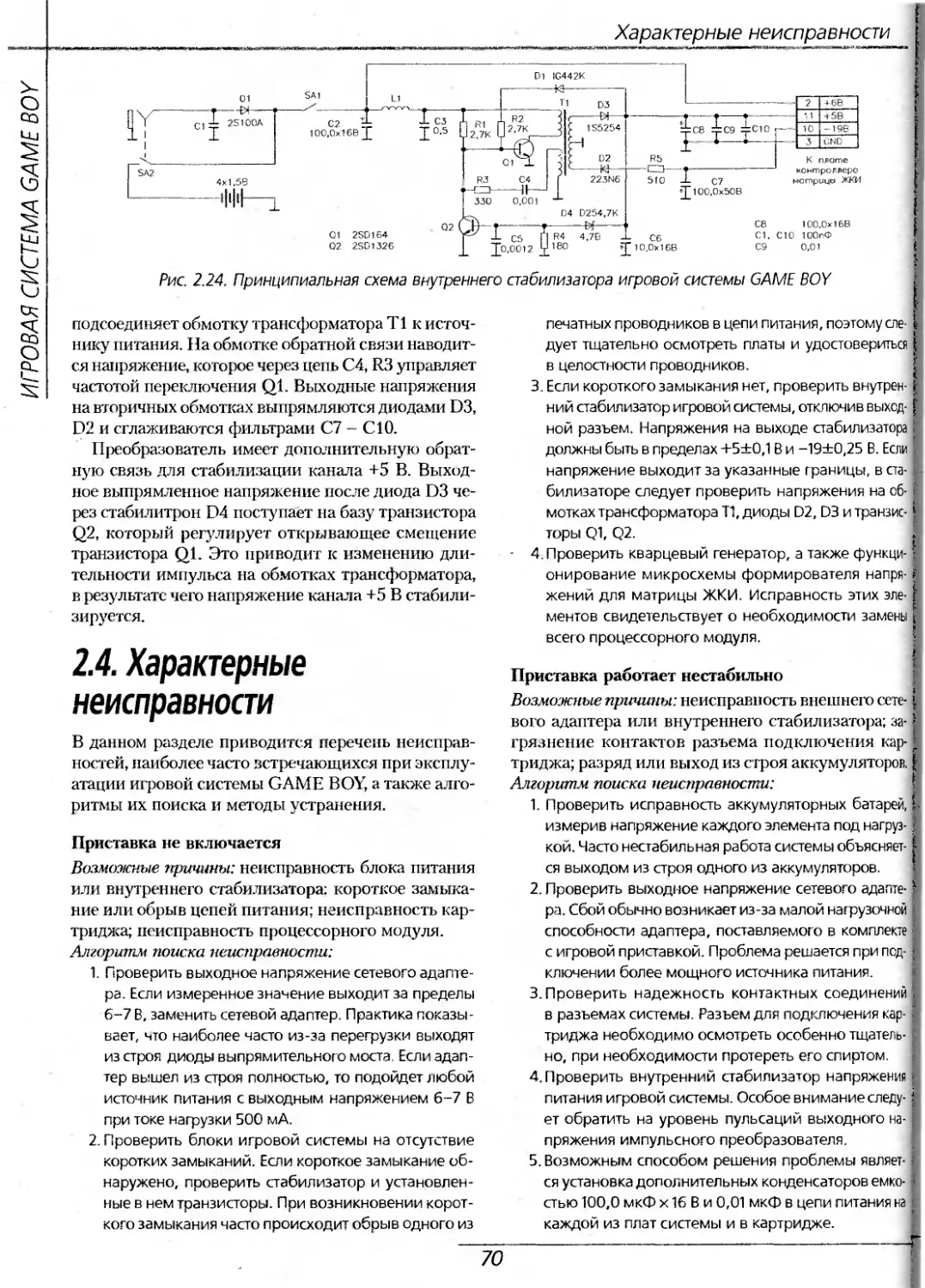

2.4. Характерные неисправности ........................................... 70

ГЛАВА 3

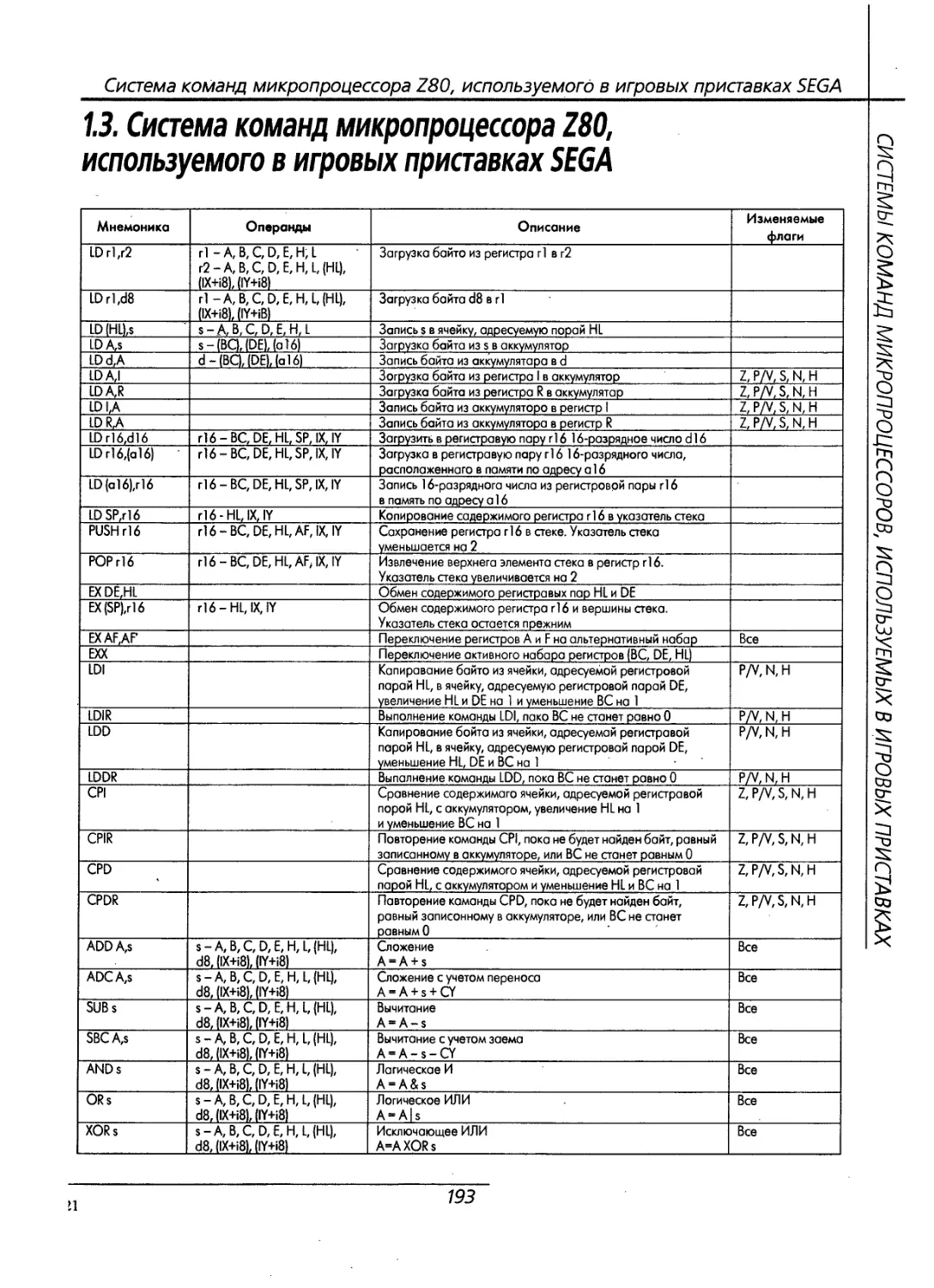

Игровая приставка SEGA MEGA DRIVE............................................... 72

3.1. Технические характеристики ...............................................73

3.2. Архитектура и принцип работы .............................................73

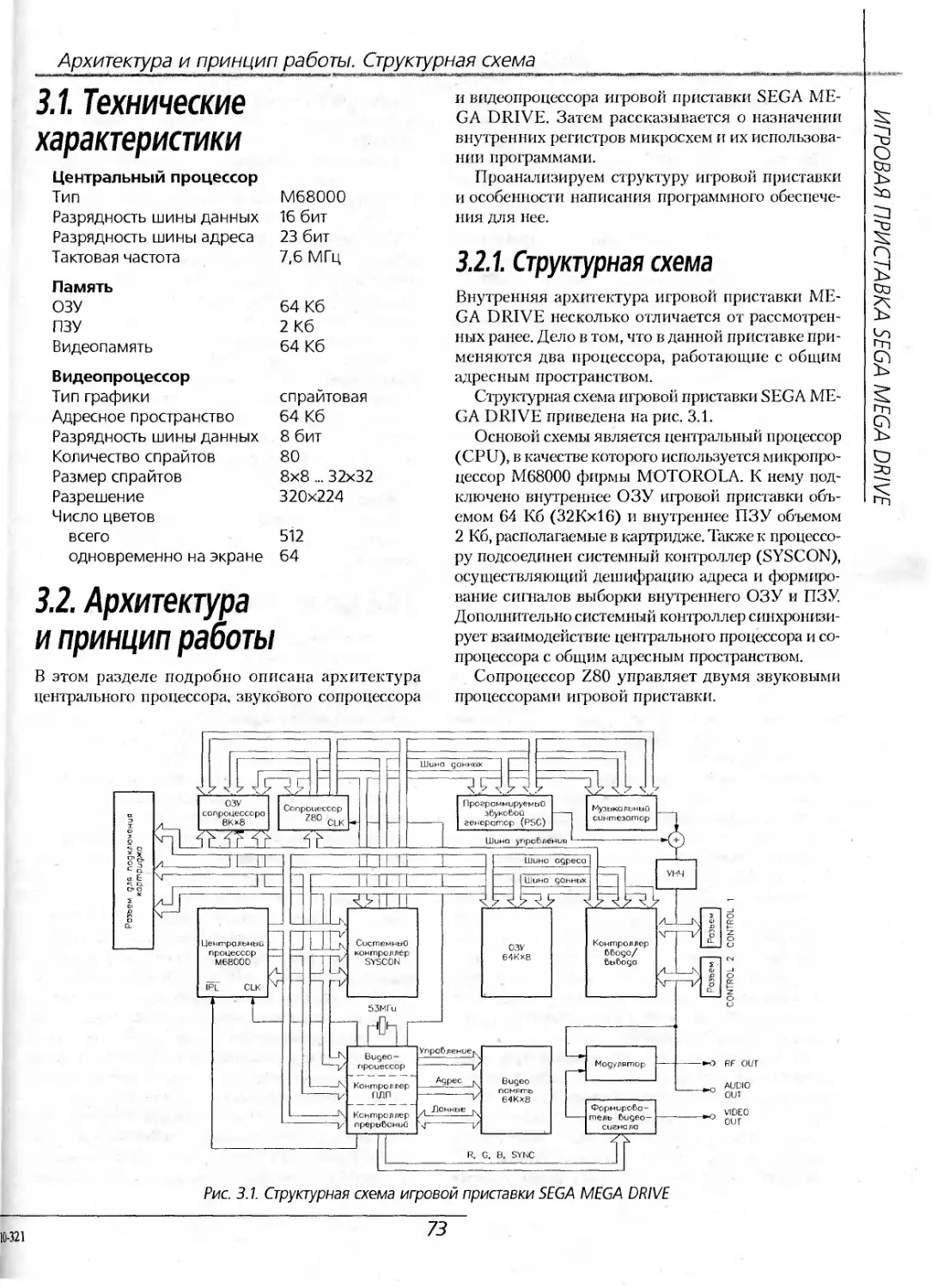

3.2.1. Структурная схема ....................................................73

3.2.2. Центральный процессор.................................................74

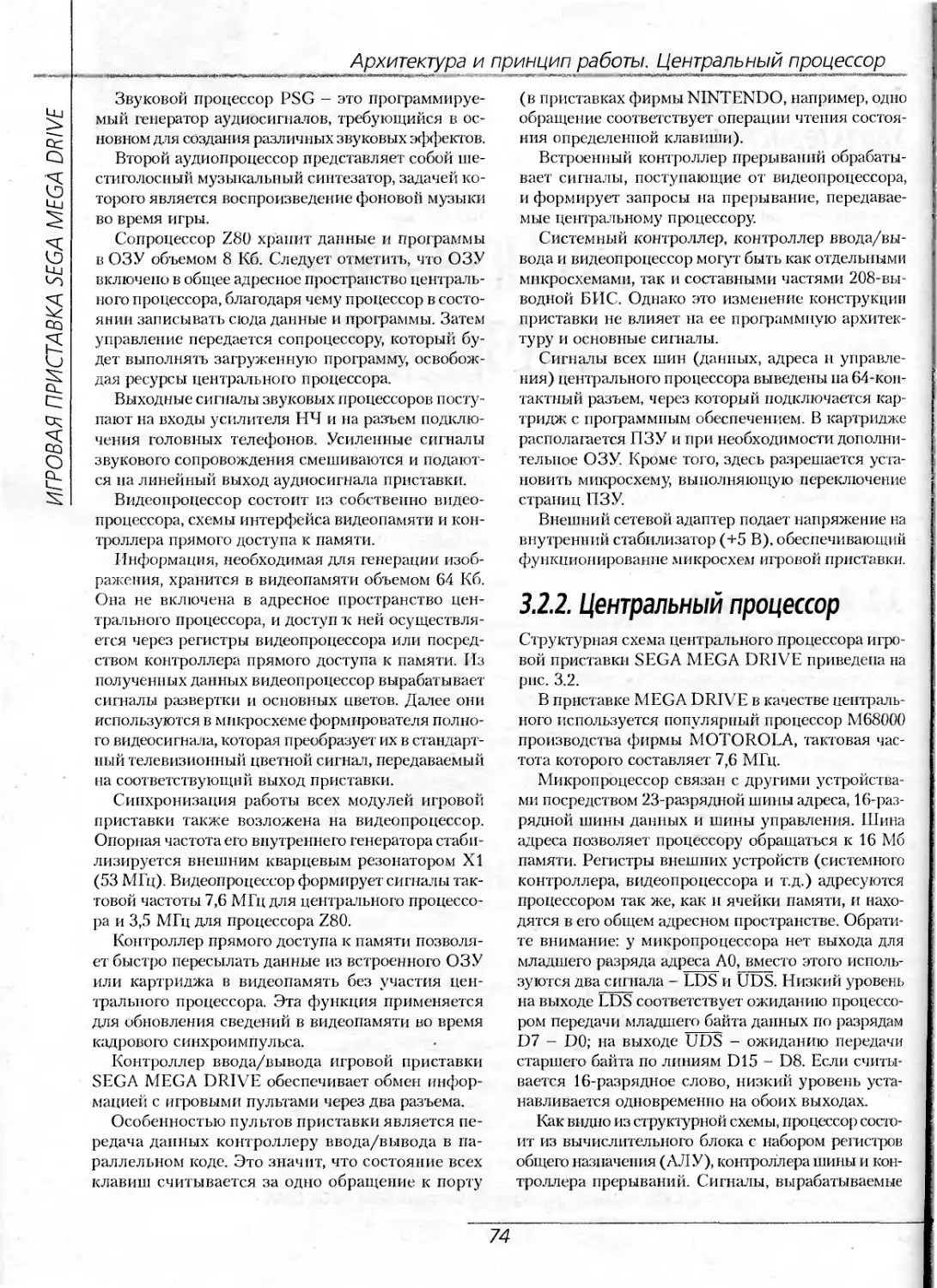

3.2.3. Адресное пространство ................................................80

3.2.4. Видеопроцессор ..................................................... 80

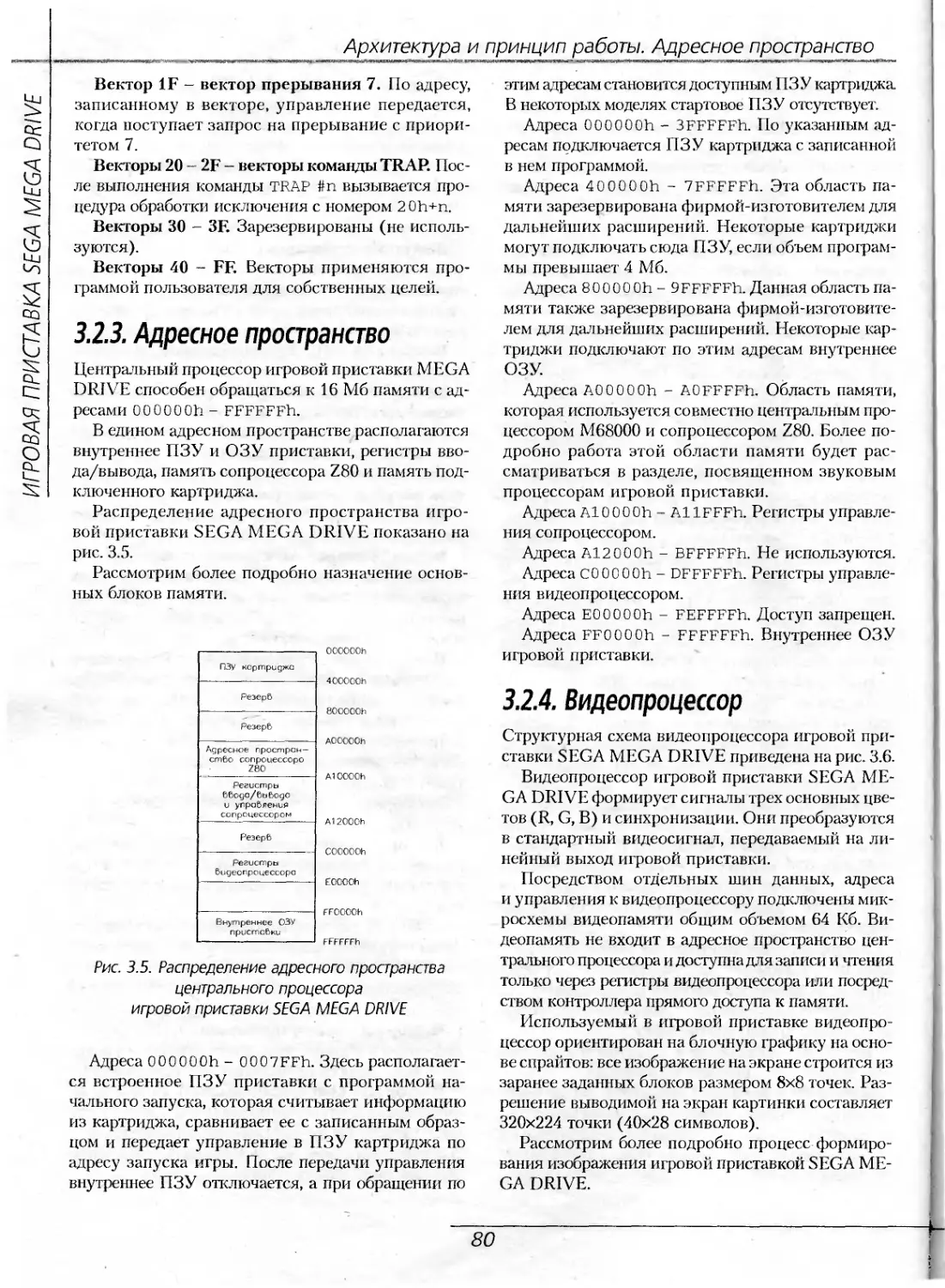

3.2.5. Звуковой процессор ...................................................90

3.2.6. Структура картриджа ..................................................95

3.2.7. Организация ввода/вывода .............................................97

3.3. Принципиальная схема ....................................................101

3.3.1. Процессорный модуль..................................................101

3.3.2. Картридж ...............................................;............109

3.3.3. Модулятор ...........................................................109

3.3.4. Игровые пульты ......................................................109

3.3.5. Блок питания ...................................................... 109

3.4. Характерные неисправности ...............................................112

ГЛАВА4

Игровая приставка SONY PLAYSTATION 114

4.1. Технические характеристики..............................................115

4.2. Архитектура и принцип работы ...........................................115

4.2.1. Структурная схема ...................................................115

4.2.2. Центральный процессор ...............................................117

4.2.3. Адресное пространство ...............................................128

4.2.4. Внутренние контроллеры ............................................ 131

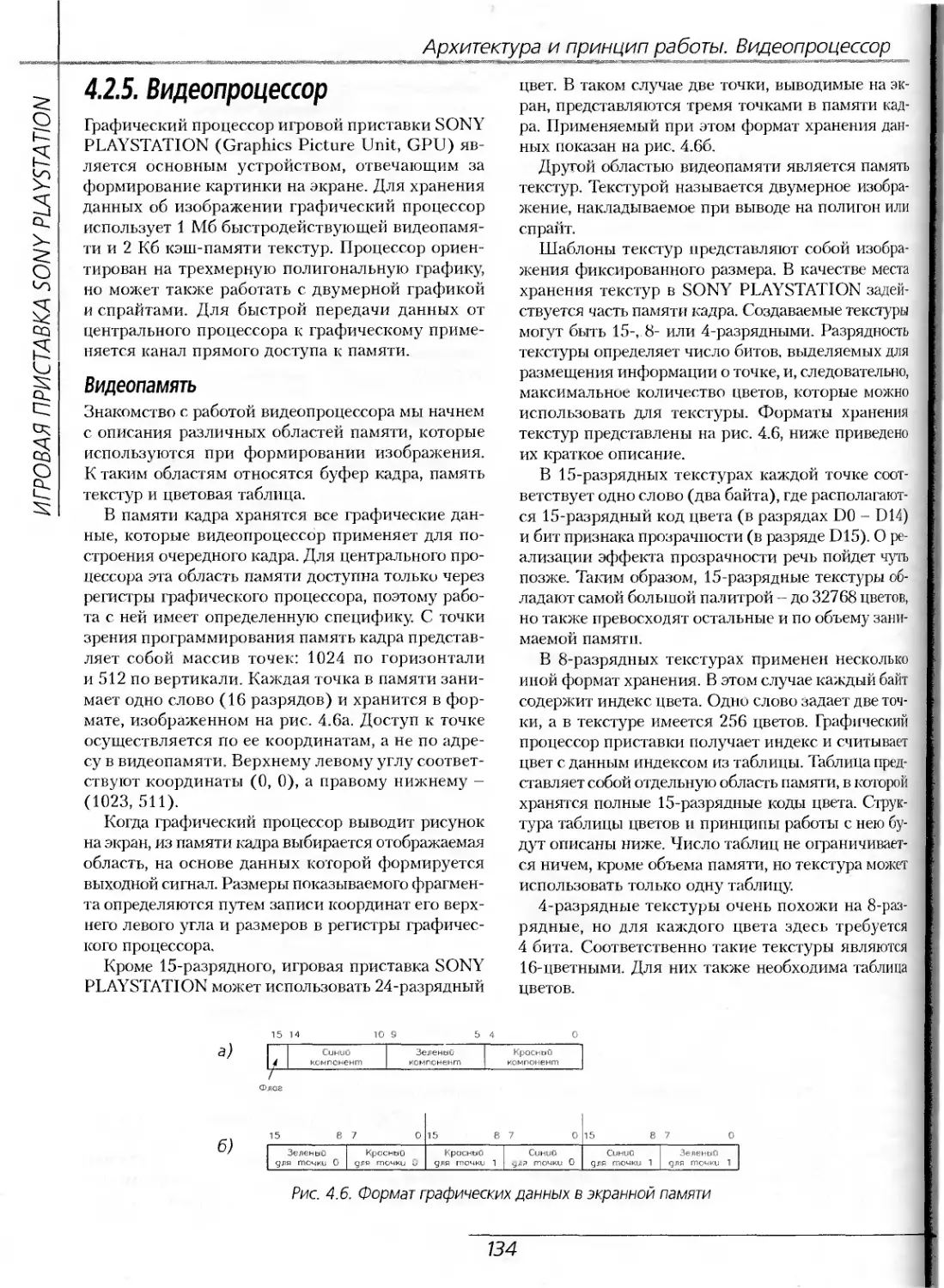

4.2.5. Видеопроцессор .....................................................134

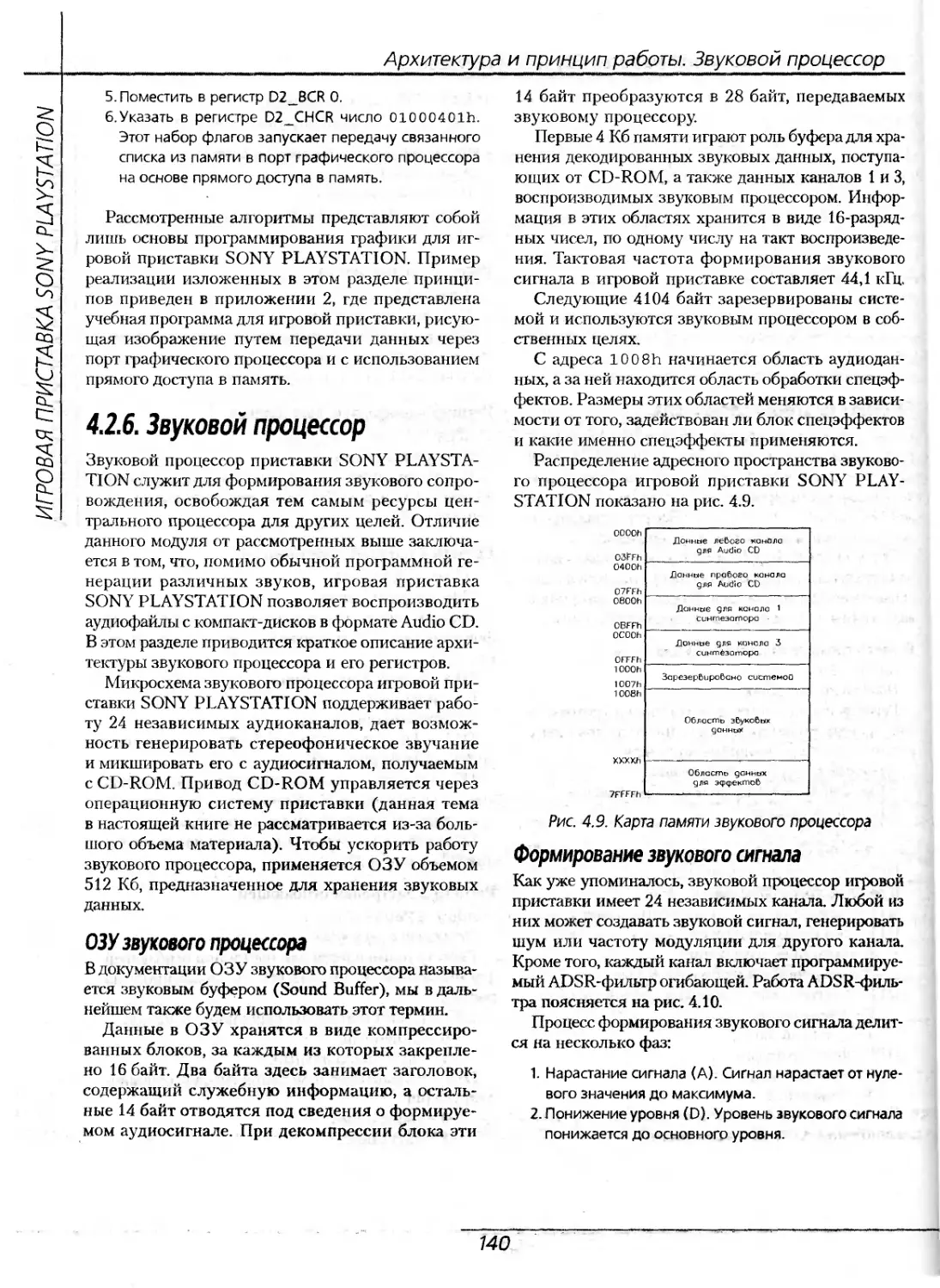

4.2.6. Звуковой процессор .................................................140

4.3. Принципиальная схема ...................................................143

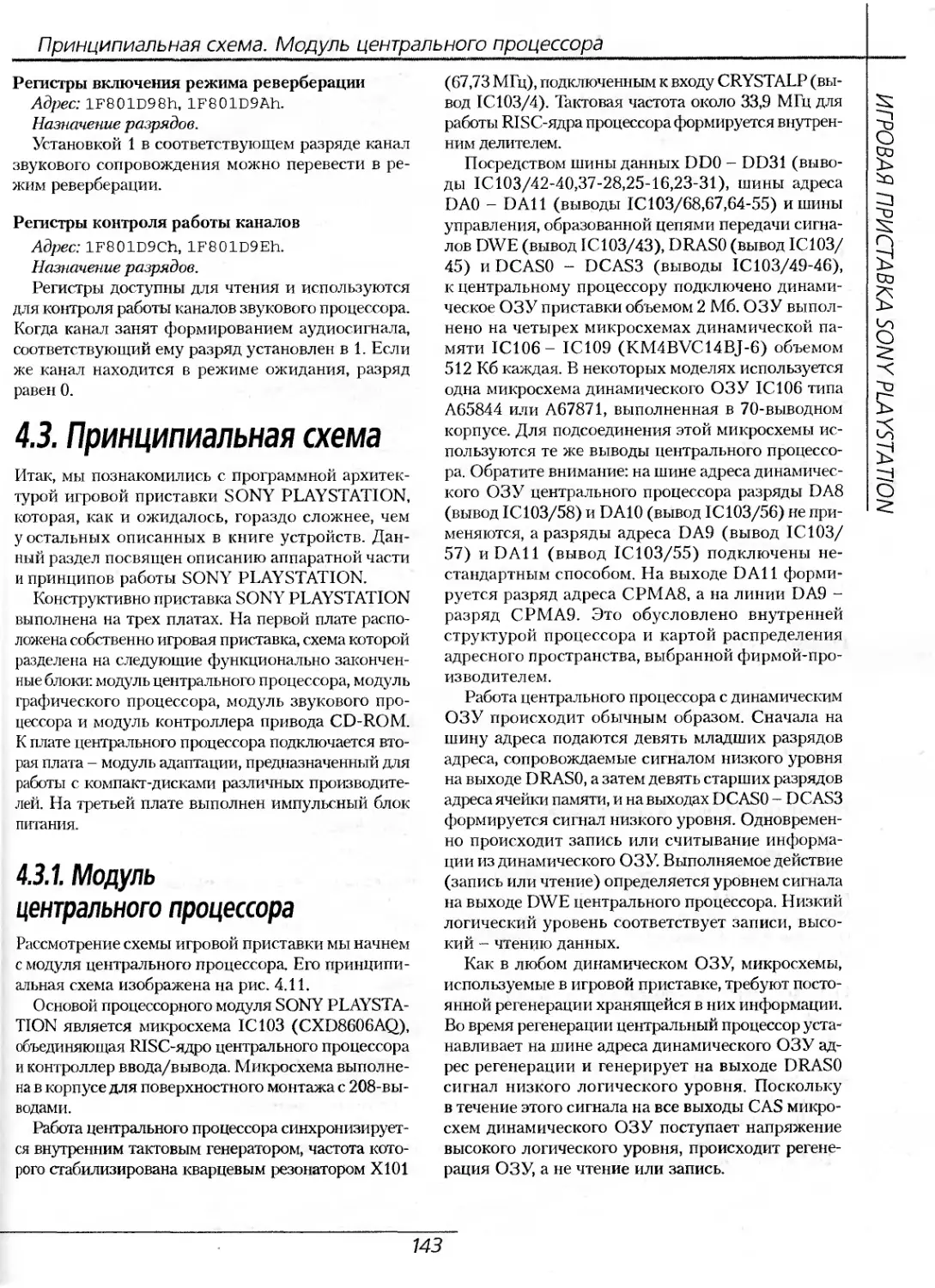

4.3.1. Модуль центрального процессора......................................143

4.3.2. Модуль графического процессора ......................................148

4.3.3. Модуль декодера и звукового процессора ..............................154

4.3.4. Модуль контроллера привода CD-ROM ..................................154

4.3.5. Модуль адаптации ...................................................155

4.3.6. Игровой пульт........................................................155

4.3.7. Блок питания .......................................................155

4.4. Характерные неисправности ..............................................161

4

Содержание

ГЛАВА 5

Программирование для приставок..........................................164

5.1. Создание программ для игровых приставок...........................165

5.1.1. Использование инструментальных средств .......................165

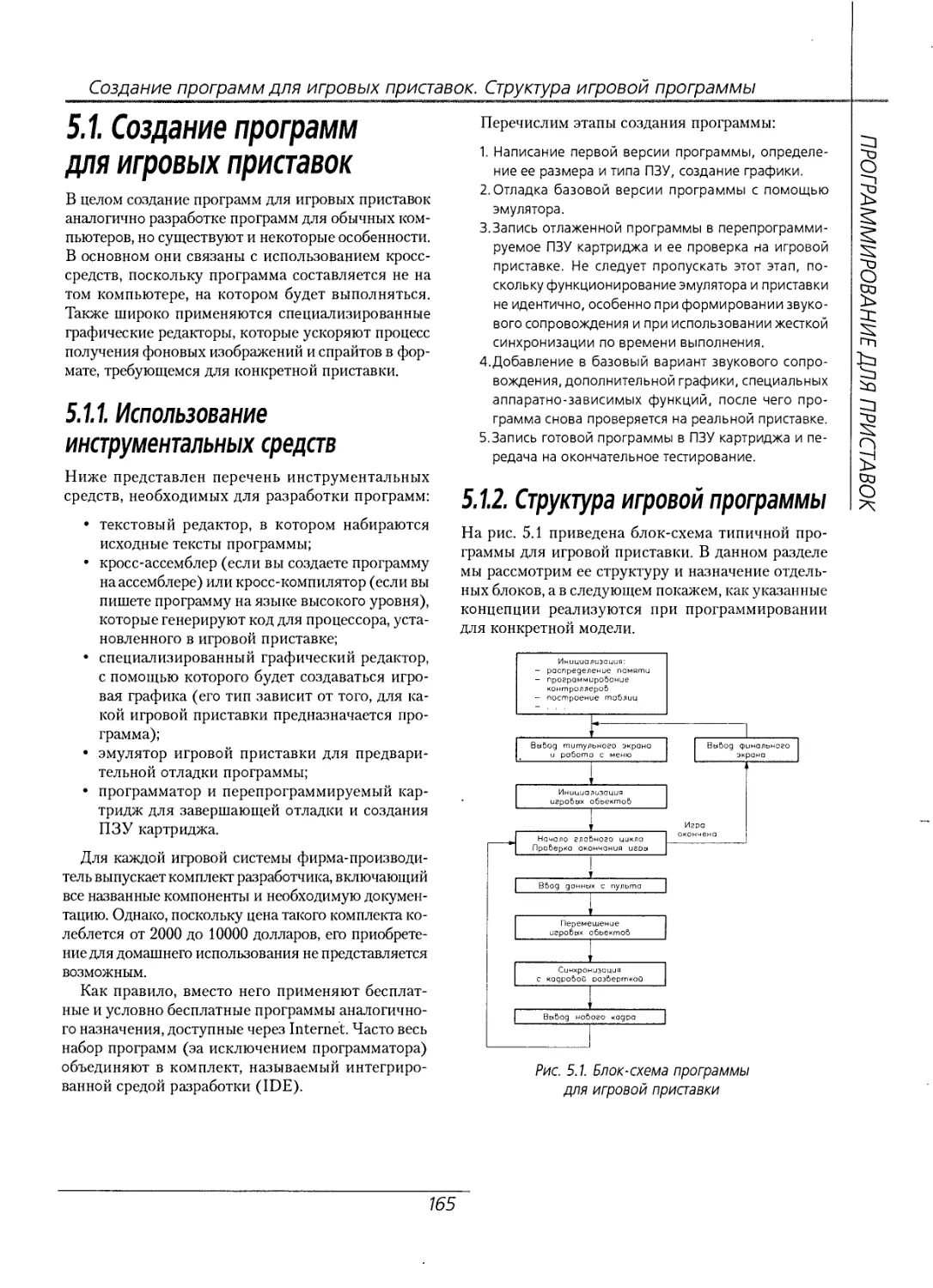

5.1.2. Структура игровой программы ..................................165

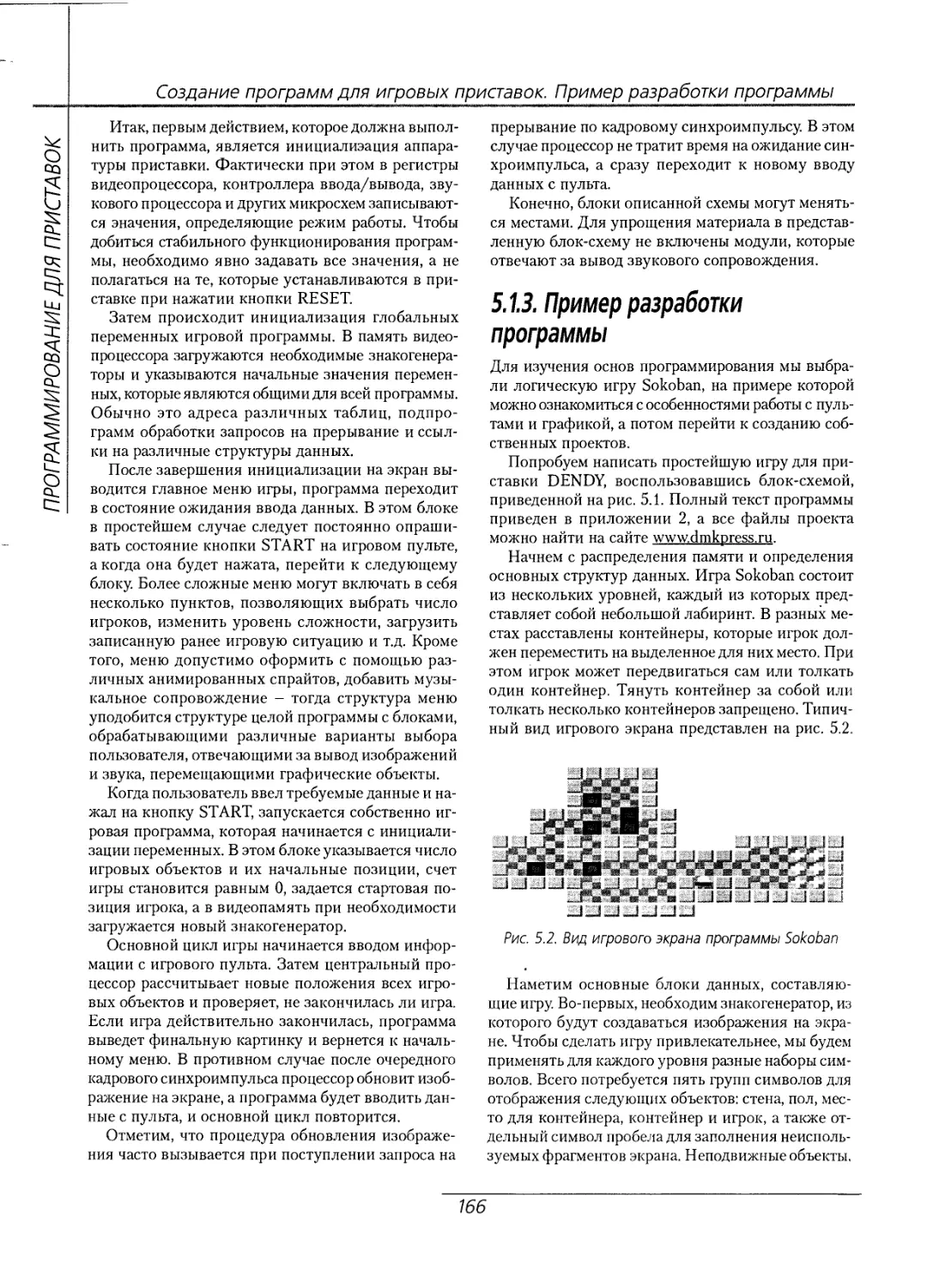

5.1.3. Пример разработки программы ..................................166

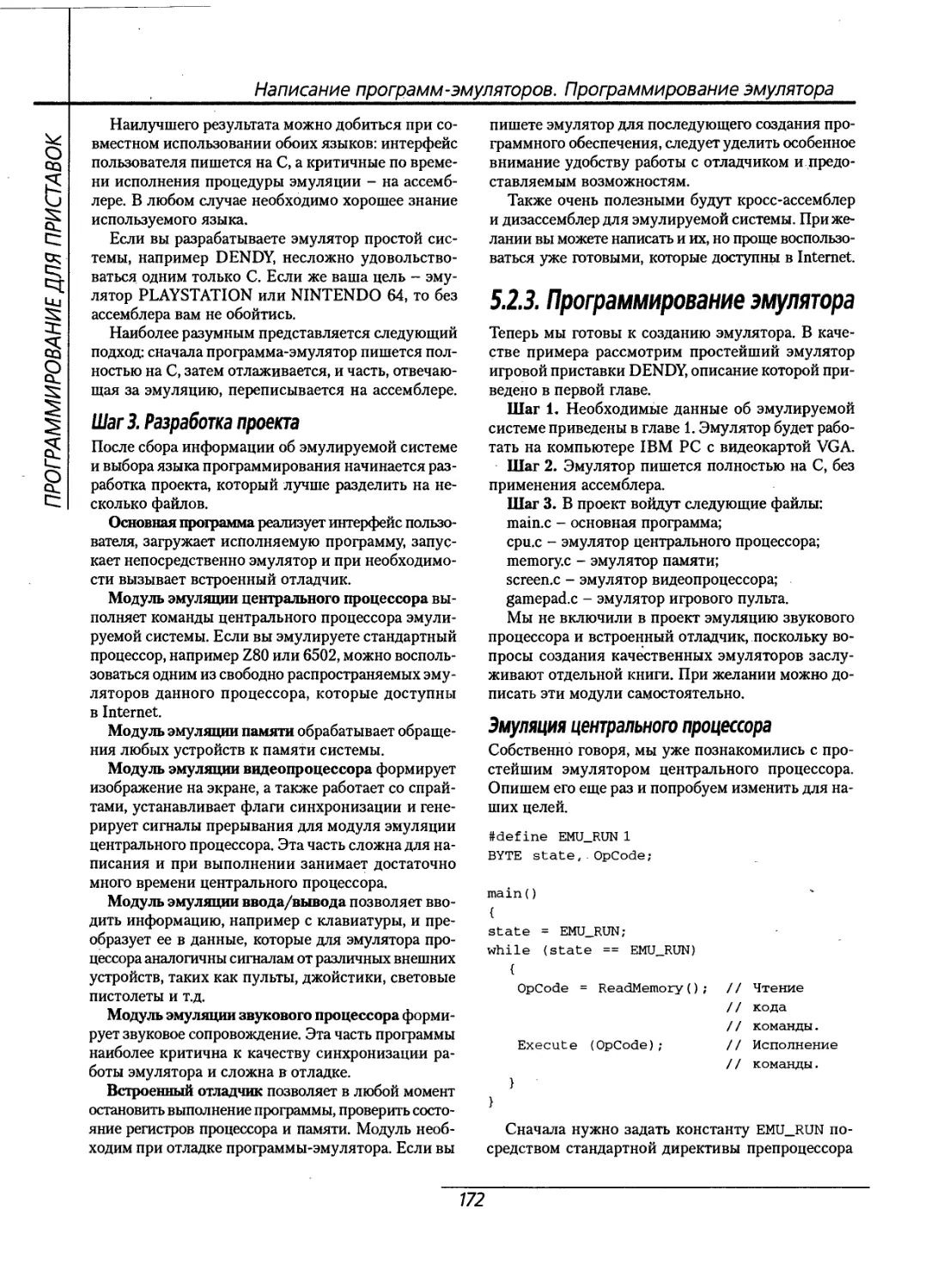

5.2. Написание программ-эмуляторов....................................170

5.2.1. Что и как эмулировать ........................................170

5.2.2. Подготовка к написанию эмулятора ............................171

5.2.3. Программирование эмулятора ...................................172

ПРИЛОЖЕНИЕ 1

Системы команд микропроцессоров,

используемых в игровых приставках.......................................178

ПРИЛОЖЕНИЕ 2

Примеры программ для игровых приставок..................................204

Литература .............................................................234

Сайты Internet..........................................................234

5

Предисловие

Повсеместное распространение компьютеров, сопровождавшееся падени-

ем цен на интегральные микросхемы, открыло широкому кругу людей доступ

к компьютерным играм.

Однако не каждый может позволить себе приобрести современный ком-

пьютер только для проведения досуга; кроме того, требовались хотя бы на-

чальные знания по работе с ним. Сначала это серьезно ограничивало сферу

распространения компьютерных игр, что, возможно, и устраивало их созда-

телей, но совершенно не устраивало продавцов.

Тогда мир электронных развлечений пополнился игровыми автоматами,

установленными в барах, кафе и торговых центрах. Следующим шагом стал

выпуск игровых приставок, позволяющих наслаждаться игрой, сидя дома

в любимом кресле.

Что такое типичная игровая приставка? Это специализированный микро-

компьютер, спроектированный специально для запуска игровых программ

и применяющий обычный телевизор для вывода изображения и звукового

сопровождения. Для работы в приставку нужно поместить картридж, кото-

рый представляет собой сменное запоминающее устройство с программой

для определенной игры. Все управление осуществляется при помощи пуль-

та, назначение кнопок которого становится ясным практически сразу.

Современные игровые приставки, например PANASONIC 3.DO и SONY

PLAYSTATION, уже не используют картриджи для хранения программного

обеспечения. Теперь программы записываются на лазерные компакт-диски,

что привело к усложнению игр и повышению их качества. Наличие CD-ROM

превратило приставку из простого игрового устройства в целый досуговый

центр, позволяющий прослушивать музыку или воспроизводить фильмы

с Video CD.

Первой на российский рынок попала игровая приставка DENDY, которая

проложила широкую дорогу к сердцам детей и кошелькам их родителей. За-

тем появились и более сложные приставки, благодаря чему любители элек-

тронных игр за пять лет перешли от простейших 8-разрядных систем типа

DENDY и GAME BOY к сложным 32-разрядным консолям SONY PLAYSTATION.

На сегодняшний день в России распространены самые разнообразные иг-

ровые системы, что вызывает огромный интерес к вопросам их схемотехни-

ки и программного обеспечения. Однако предлагаются обычно только опи-

сания игр, а имеющийся минимум технических сведений разбросан по

разным источникам и часто недоступен из-за малого тиража.

Целью настоящей книги является объединение и систематизация инфор-

мации об устройстве наиболее популярных игровых приставок, для чего

была проведена значительная работа по поиску последних данных в сети

Internet и в зарубежных изданиях. Результаты этой работы перед вами.

Для каждой приставки приводятся структурная и принципиальная схемы,

рассматривается программная архитектура. Большое внимание уделено

описанию специализированных процессоров и возможным заменам эле-

ментной базы приставок на более доступные компоненты, один из разделов

посвящен методам ремонта.

Книга может быть использована как справочник при разработке про-

граммного обеспечения или нестандартных внешних устройств. Однако она

не является учебником по программированию на языке ассемблера, для

этой цели предназначены издания, указанные в списке литературы.

В конце книги приведен также список сайтов, содержащих сведения об иг-

ровых приставках и программах-эмуляторах, ответы на некоторые вопросы

программирования, а также другую полезную информацию. Этим смогут

воспользоваться читатели, имеющие доступ к сети Internet.

КРАТКАЯ ИСТОРИЯ

ИГРОВЫХ ПРИСТАВОК

Наверное, моментом, с которого началась история

игровых видеоприставок, следует считать появле-

ние персональных компьютеров и зарождение

электронной игровой индустрии.

Первые игры были не так увлекательны, посколь-

ку создавались для алфавитно-цифровых дисплеев

и могли заинтересовать только компьютерных фана-

тов. Настоящий успех пришел с разработкой удоб-

ных, дешевых и простых компьютеров, способных

выводить картинку на Э1фан обычного телевизора.

В это время распространились Apple, ZX Spectrum,

Atari и другие системы, теперь ставшие классикой.

Тогда же появились и первые электронные игро-

вые автоматы, которые представляли собой компью-

тер с игровой программой, записанной в ПЗУ. Вы-

сокая стоимость обусловила использование этих

устройств в барах, торговых центрах и других об-

щественных местах, но не дома. Тем не менее и они

сослужили хорошую службу: познакомили с ком-

пьютерными играми миллионы людей и Подгото-

вили рынок.

Следующим, шагом, приблизившим выход ком-

пактных видеоприставок, стало удешевление их

производства. Резкое снижение цен сделало про-

стейший компьютер доступным для обычной семьи.

Что же такое игровая видеоприставка? Это спе-

циализированный бытовой компьютер, разработан-

ный для выполнения игровых программ. Приставка

содержит все компоненты обычного компьютера:

процессор, память, устройства ввода/вывода инфор-

мации. Однако имеется несколько особенностей.

Во-первых, изображение выводится на экран

обычного телевизора с разрешением ниже, чем

у монитора. Во-вТОрых, игровые приставки не осна-

щаются полноразмерной клавиатурой: для управ-

ления игрой достаточно простейшего пульта или

джойстика. В-третьих, в видеоприставках может

быть меньший объем памяти.

Для первых приставок программы распростра-

нялись в виде картриджей, представляющих собой

плату с установленными на ней микросхемами

ПЗУ и ОЗУ. В ПЗУ находилась программа, кото-

рая запускалась после установки картриджа в спе-

циальный разъем приставки.

Главным преимуществом видеоприставок явля-

ется простота их использования. Подключите теле-

визор и пульт, вставьте картридж - и можно начи-

нать игру, правила которой быстро становятся

понятными. Не требуется изучать операционную

систему или принципы распределения памяти.

За несколько лет приставки прошли практичес-

ки такой же путь, как и компьютеры. От приставок

типа DENDY с медленным 8-разрядным процессо-

ром производители перешли сначала к 16-, а затем

к 32- и 64-разрядным. Одновременно увеличивал-

ся объем памяти - от 2 Кб в DENDY до нескольких

мегабайтов в современных приставках.

Значительным шагом вперед стало использование

компакт-дисков вместо картриджа с ПЗУ, что позво-

лило повысить сложность игр, улучшило их графит

ческое оформление и музыкальное сопровождение,

превратив видеоприставку в развлекательный центр.

Видеоприставки даже опередили персональные

компьютеры в применении специализированных

графических ускорителей. ПК достигли того же со-

отношения «качество графики/производитель-

ность» только с появлением разработок компании

3DFX, а ведь именно эта величина в значительной

мере определяет успех работы компьютера в каче-

стве игрового устройства. i

Итак, обратимся к игровым приставкам, полу-

чившим наибольшее распространение.

КРАТКАЯ ИСТОРИЯ ИГРОВЫХ ПРИСТАВОК

Этап 1.8-разрядные

приставки

Первой игровой приставкой, получившей широкое

распространение, была MASTER SYSTEM фирмы

SEGA, построенная на основе популярного процессо-

ра Z80. Она выпускалась в 1984-1986 годах, после

чего производство было прекращено, и в Советский

Союз попало ограниченное количество экземпляров.

Настоящий бум на территории СССР начался

с появлением игровых приставок под торговой

маркой DENDY.

И сотворила NINTENDO DENDY,

И была DENDY медленна и неуклюжа,

И только Super Mario носился над водою...

NINTENDO, DENDY, день первый.

Игровая приставка NINTENDO ENTERTAIN-

MENT SYSTEM (NES), более известная в России

под именем одного из ее аналогов - DENDY, стала

ответом компании NINTENDO на выход пристав-

ки SEGA MASTER SYSTEM.

Основой приставки послужил аналог распро-

страненного процессора 6502 с тактовой частотой

около 1,8 МГц. Простота в обращении и удачный ди-

зайн сделали свое дело, и приставка буквально в те-

чение года завоевала всемирную популярность, чему

в значительной мере способствовала поддержка про-

изводителей программного обеспечения, большой ас-

сортимент игр и регулярно выходящие новинки.

Графический процессор приставки NES форми-

ровал изображение размером 256x224 точки, что

было стандартом для 8-битных приставок, и палитрой

из 52 цветов, из которых одновременно выводились на

экран 26. Звуковой процессор поддерживал пять неза-

висимых каналов звукового сопровождения.

По техническим характеристикам NES (DENDY)

была значительно слабее SEGA MASTER SYSTEM,

но, благодаря грамотной рекламе и активной помо-

щи разработчиков игр, смогла не только обойти кон-

курента, но и практически полностью вытеснить

компанию SEGA с рынка 8-разрядных приставок.

Официальная поддержка игровой платформы

DENDY продолжалась до 1994 года, однако в на-

шей стране эти приставки и игры к ним не утрати-

ли своей популярности - благодаря достаточно

низкой цене и простоте в эксплуатации.

И увидела NINTENDO, что-DENDY хороша весьма,

И сотворила NINTENDO GAME BOY,

И был GAME BOY маленький и черно-белый...

NINTENDO, GAME BOY, день второй.

Огромный успех приставки DENDY побудил

компанию NINTENDO создать переносную кар-

манную игровую систему.

Этап 2. 16-разрядные приставки

Основными требованиями для такого устрой-

ства стали относительно невысокая цена и малое

энергопотребление. Выпуск первой партии GAME

BOY сопровождался мощной рекламной кампани-

ей. Результат превзошел все ожидания: GAME

BOY покупали даже несмотря на то, что к моменту

появления приставки для нее существовало только

две. игры - Super Mario Land и Tetris. Главными

преимуществами новой системы были ее неболь-

шие-габарихы и возможность переноски.

Основой приставки стал 8-разрядный процес-

сор, работающий на тактовой частоте около 4 МГц

и являющийся упрощенной версией самого попу-

лярного из 8-разрядных микропроцессоров - Z80.

Видеопроцессор формировал на жидкокристалли-

ческом дисплее изображение размером 160x144

точки с четырьмя градациями яркости, звуковой

процессор позволял получать четырехканальное

звуковое сопровождение. Кроме того, разрешалось

соединять две (а с помощью специального блока -

и четыре) приставки для совместной игры.

На протяжении первых пяти лет GAME BOY,

даже несмотря на черно-белый экран, находился

в зените славы. Позднее уровень продаж снизился,

и компания NINTENDO выпустила на рынок но-

вые модификации: POCKET GAME BOY - игро-

вая система меньших размеров в разноцветных

корпусах и с более контрастным экраном; COLOR

GAME BOY - долгожданная версия с цветным

дисплеем; а также SUPER GAME BOY - доба-

вочный модуль к приставке SUPER NINTENDO,

позволяющий использовать картриджи для GA-

ME BOY.

В настоящее время названные приставки все еще

активно продаются. Выпущено немало аксессуаров,

позволяющих сохранить интерес к системе, которая,

к слову сказать, на рынке уже более 10 лет и по уров-

ню продаж до сих пор превосходит другие.

Этап 2.16-разрядные

приставки

Вслед за 8-разрядными процессорами появились

16-разрядные. И вскоре на смену простейшим иг-

ровым приставкам пришли более сложные модели.

На этом этапе наблюдаются лишь количествен-

ные изменения: повысились разрядность и быстро-

действие процессора, увеличился объем памяти,

улучшилась графика. Но никаких качественных

изменений не произошло. Графика осталась спрай-

товой, изображение на экране по-прежнему строи-

лось из заранее созданных блоков, а игровые про-

граммы так же записывались в ПЗУ картриджа.

Время революционных изменений впереди, а по-

ка просматривается лишь поиск путей улучшения

8

Этап 3. 32- и 64-разрядные системы

приставок: два процессора в SEGA MEGA DRIVE,

сложный видеопроцессор в SUPER NINTENDO и т.д.

Первой 16-разрядной игровой приставкой стала

SEGA GENESIS. Усовершенствованные модели

этой приставки называются SEGA MEGA DRIVE

и SEGA MEGA DRIVE 2.

И увидела SEGA, что NINTENDO

богатеет весьма,

И сотворила SEGA GENESIS,

И была GENESIS первой 16-разрядной...

SEGA, GENESIS, день третий.

SEGA GENESIS была выпущена в 1989 году.

В то время графическое оформление игр и звук,

предоставляемые этой приставкой, явились про-

сто образцом для подражания. Основную массу

игр позаимствовали с игровых автоматов (именно

поэтому игры для SEGA, как правило, аркадные).

Приставку оснастили процессором М68000 фир-

мы MOTOROLA с тактовой частотой, увеличенной

до 7,6 МГц, что стало большим шагом вперед. Кро-

ме центрального процессора, имелся дополнитель-

ный 8-разрядный процессор Z80, который мог вы-

полнять свои программы, освобождая центральный

процессор.

Несмотря на некоторые ограничения в одновре-

менном выводе цветов на экран (всего 64 цвета),

игры с участием специального персонажа - Ёжика

Соника, фирменного знака SEGA - прекрасно про-

давались.

Приставки SEGA и сегодня продолжают пользо-

ваться спросом, но к настоящему времени они делят

рынок 16-разрядных игровых систем с приставкой

SUPER NINTENDO, о которой речь пойдет ниже.

И побежала NINTENDO за SEGA,

И сотворила NINTENDO SNES,

И была SNES сложна весьма...

NINTENDO, SUPER NINTENDO, день четвертый.

Итак, SNES, или SUPER NINTENDO, появилась

в октябре1991 года - в тот момент, когда рынком

16-разрядных игровых систем практически безраз-

дельно владела фирма SEGA.

Процессор 65С816, используемый в SUPER .

NINTENDO, был гораздо слабее по производитель-

ности, чем процессор в SEGA MEGA DRIVE. Поэто-

му в приставку установил и мощный видеопроцессор,

позволяющий обрабатывать спрайты значительно

быстрее и качественнее и выводить на экран одно-

временно 256 цветов (всего поддерживалось 32768

цветов). Кроме того, для повышения качества зву-

ка был встроен отдельный аудиопроцессор SONY.

В целом же SUPER NINTENDO - это усовер-

шенствованный вариант DENDY, без каких-либо

коренных изменений. И снова более слабая по

техническим характеристикам видеоприставка

завоевала популярность благодаря качеству и раз-

нообразию программного обеспечения.

Этап 3.32- и 64-разрядные

системы

С появлением 32-разрядных микропроцессоров

в мире игровых приставок произошли кардиналь-

ные изменения.

Во-первых, в конкурентную борьбу на рынке

игровых систем включились такие фирмы, как

MATSUSHITA ELECTRIC (PANASONIC) и SONY.

Во-вторых, существенно изменились принципы

формирования изображения. На смену плоской

спрайтовой графике пришла трехмерная полиго-

нальная, с улучшенным разрешением экрана и уве-

личенным количеством цветов.

В этом классе устройств наибольшее распро-

странение получили три системы: 3DO от PANA-

SONIC, PLAYSTATION от SONY и NINTENDO 64,

выпущенная, естественно, фирмой NINTENDO.

И решил PANASONIC сделать игру,

И выпустил PANASONIC 3DO,

И была 3DO с CD-ROM,, и могла

музыку играть...

PANASONIC, 3DO, день пятый.

Сразу же оговоримся, что игровая система 3DO

не является собственной разработкой компании

PANASONIC, а изготавливается по лицензии фир-

мы 3DO (эта фирма не занимается производством,

а только продает свои проекты). Так что, кроме

PANASONIC 3DO, вы можете встретить и SAM-

SUNG 3DO, и GOLDSTAR 3DO, отличающиеся

лишь дизайном.

Игровая система 3DO стала одной из первых 32-

разрядных игровых видеоприставок, появившихся

на российском рынке. Использование CD-ROM, ко-

торые тогда имелись не на каждом компьютере, ка-

чественная графика и большой выбор программно-

го обеспечения сделали эту приставку на некоторое

время самой популярной 32-разрядной моделью.

Заглянем внутрь творения PANASONIC. В ка-

честве центрального применяется 32-разрядный

RISC-процессор ARM60, работающий с тактовой

частотой 12,5 МГц. К нему подключено ОЗУ емкос-

тью 2 Мб, а также энергонезависимое ОЗУ емкос-

тью 32 Кб, где можно сохранить игровую ситуацию

на время выключения приставки. Кроме того, в ПЗУ

объемом 1 Мб записана операционная, система.

В качестве дополнительного процессора (видео-

процессора) задействована специальная заказная

микросхема, формирующая изображение с разре-

шением 320x240 точек и выводящая одновременно

32768 цветов (из 16,7 млн). Аудиопроцессор дает

КРАТКАЯ ИСТОРИЯ ИГРОВЫХ ПРИСТАВОК

121

9

КРАТКАЯ ИСТОРИЯ ИГРОВЫХ ПРИСТАВОК

возможность получать стереофоническое звуковое

сопровождение.

Для чтения программ приставка оборудована

двухскоростным приводом CD-ROM. Встроенное

программное обеспечение позволяет работать

с дисками формата Audio CD и Photo CD.

Имеются стандартные 9-контактные разъемы,

к которым можно подключить до 8 игровых пуль-

тов, а также 30-контактный разъем расширения для

дополнительных устройств.

Но вскоре лидерство захватила видеоприставка

SONY PLAYSTATION, поскольку система 3DO пере-

стала поддерживаться производителями программ-

ного обеспечения и техническое обслуживание ухуд-

шилось, что привело к ее исчезновению из продажи.

О былой популярности 3DO свидетельствует

разработанная фирмой CREATIVE плата 3DO

Blaster, которая позволяет запускать игры для ви-

деоприставки на персональном компьютере.

И решила SONY обогнать 3DO,

И создала SONY PLAYSTATION,

И распространилась PLAYSTATION весьма...

SONY, PLAYSTATION, день шестой.

Итак, SONY PLAYSTATION - самая распро-

страненная на сегодняшний день 32-битная при-

ставка. Она способна воспроизводить игровые диски

с логотипом PLAYSTATION, аудиодиски, а с помо-

щью поставляемого отдельно видеомодуля - ви-

деодиски формата MPEG.

Эта видеоприставка увидела свет в 1994 году

в Японии, причем ее производитель, фирма SONY,

не была известна в игровом мире. Просто компания

NINTENDO предложила SONY сделать CD-ROM

для приставки SUPER NINTENDO, но к финансо-

вому согласию партнеры так и не пришли, и в ре-

зультате SONY выпустила собственное изделие.

Успех был ошеломляющий: к лету 1995 года

объем продаж достиг миллиона приставок, и это

только в Японии! Осенью 1995 года SONY начала

поставки на американский рынок, причем столь же

удачно: только за первую неделю было продано бо-

лее 100 тыс. штук.

Модель PLAYSTATION представляла собой вер-

шину технической мысли, включая практически

все новейшие разработки: 32-битный RISC-процес-

сор R3000A с тактовой частотой 33,87 МГц; ЗО-уско-

ритель, выполняющий 80 млн инструкций в секун-

ду; звуковое сопровождение Dolby Surround на 24

канала. Кроме того, на экран могло выводиться

более 16 млн цветов, а разрешение составляло

640x480 точек. Но и это еще не все. Приставка име-

ла память 2 Мб и дополнительно 512 Кб звуковой

памяти, а также двухскоростной привод CD-ROM.

Этап 4. Современные модели

Следует также упомянуть и о 64-разрядной игро-

вой видеоприставке NINTENDO 64. В ней исполь-

зуется уникальный 64-разрядный RISC-процессор,

на порядок увеличивший реализм восприятия

графики. Это произошло за счет повышения до

500 МГц скорости обмена с памятью, достигнутого

с помощью современных технологий. Новый трех-

мерный джойстик с дополнительным аналоговым

блоком дает возможность задать любое направле-

ние в диапазоне от 0° до 360°.

Модель NINTENDO 64 - результат сотрудниче-

ства компаний NINTENDO и SILICON GRAPHICS.

Приставка уверенно поддерживает трехмерную гра-

фику благодаря спаренным процессорам MIPS Tech-

nologies и Silicon Graphics с тактовой частотой ос-

новного 64-разрядного процессора 93,75 МГц

и частотой графического процессора 62,5 МГц. В ре-

зультате их слаженной работы практически исчеза-

ет текстурное разложение задних планов изображе-

ния и движущихся объектов при их приближении.

Приставка имеет 4,5 Мб оперативной памяти и эк-

ранное разрешение до 640x480 точек. Воспроизве-

дение более 16 млн цветов и 100-канальный звук

удовлетворят самый взыскательный вкус.

Фирма NINTENDO учла основной недостаток

своей предыдущей системы, SNES, - слабый процес-

сор. По вычислительной мощности NINTENDO 64 -

несомненный лидер. Но, к сожалению, в приставке

используются не компакт-диски, а картриджи. Ем-

кость картриджа не превышает 32 Мб, что несоиз-

меримо с 650 Мб обычного CD. Уже несколько лет

компания NINTENDO обещает выпустить для своей

приставки CD-ROM, однако «воз и ныне там».

Так были совершены игровые приставки

И все воинство их.

И плодились они, и размножались,

И владычествовали над сердцами детскими

И карманами родительскими.

Этап 4. Современные модели

Пока идет эволюция процессоров, развиваются

и игровые видеоприставки. А на рынке приставок

продолжается конкурентная борьба.

Можно выделить несколько особенностей совре-

менной игровой системы: 64- или 128-разрядный

центральный процессор, 128- или 256-разрядный

графический процессор, не менее 8 Мб памяти, дис-

ковод для DVD, порты для подключения различных

устройств, в том числе модема для выхода в Internet.

Итак, игровая приставка превращается в мульти-

медийный развлекательный центр с множеством

функций.

10

Этап 4. Современные модели

В настоящее время на рынке присутствуют: SEGA

с новой разработкой DREAMCAST; SONY, пред-

ложившая модель с легко предсказуемым назва-

нием PLAYSTATION 2; на подходе MICROSOFT

с Х-ВОХ.

Игровая приставка DREAMCAST

С точки зрения аппаратуры лидером среди игро-

вых видеоприставок до последнего времени была

NINTENDO 64. Однако ее 64-разрядный продессор

с тактовой частотой 90 МГц не идет ни в какое

сравнение с RlSC-процессороМ Hitachi SH4

(200 МГц), используемым в DREAMCAST. Кро-

ме того, у DREAMCAST имеется 128-разрядный

видеопроцессор на базе кристалла NEC Power VR2.

Такая вычислительная мощь позволяет получить

чрезвычайно динамичные игры с реалистичными

объектами и великолепными имитациями воды,

тумана и света.

Самым большим преимуществом аппаратуры

PLAYSTATION являлось использование дисков

CD-ROM: компакт-диски вмещают до 650 Мб ин-

формации, что в 20 раз превышает емкость самого

большого картриджа NINTENDO. Однако DREAM-

CAST превзошел соперника и здесь: в нем приме;

няется специальная технология компакт-дисков

двойной плотности, называемая GD-ROM. На GD

помещается 1,2 Гб информации, a DREAMCAST

снабжен 12-скоростным дисководом.

Сейчас можно сказать, что успех или провал дан-

ной системы зависит только от поддержки произ-

водителей программного обеспечения.

Игровая приставка PLAYSTATION 2

Эта видеоприставка не только сопоставима с самы-

ми современными ПК, но по целому ряду парамет-

ров превосходит их.

в sony playStation 2 применен 128-раз-

рядный процессор Emotion Engine (^ISC-архи-

тектура MIPS IV) с тактовой частотой 300 МГц.

Процессор имеет два целочисленных блока, два ариф-

метических сопроцессора и специальный SIMD-блок

для обработки мультимедиа-комавд (аналог блоков

MMX, SSE и 3DNow! в архитектуре х86).

Упомянем также сопроцессор для обработки изоб-

ражений, помимо всего прочего включающий в себя

декодер MPEG-2 H обладающий быстродействием

150 млн пикселов в секунду. Оперативная память

объемом 32 Мб по быстродействию более чем втрое

превосходит память компьютеров IBM PC.

Видеопроцессор PLAYSTATION 2 базируется

на параллельном рендеринг-процессоре Graphic

Synthesizer с встроенным динамическим ОЗУ объ-

емом 4 Мб. Скорость обмена по шине «видеопроцес-

сор-память» составляет 48 Гб/с. Тактовая частота

видеоускорителя и памяти - 150 МГц. Производи-

тельность видеопроцессора игровой приставки

PLAYSTATION 2 выше, чем у nVidia GeForce256.

SONY PLAYSTATION 2 обеспечивает звуковое со-

провождение по технологиям Dolby Digital (АС-3)

и DTS.

Для связи с внешними устройствами в этой мо-

дели имеется слот PC Card, порты USB и i.Link

(IEEE 1394), а также привод DVD-ROM. Разуме-

ется, к портам можно подключать разнообразные

периферийные устройства - сетевые карты, моде-

мы, винчестеры, ZIP-дисководы и пр., в том числе

и от сторонних производителей. х

Игровая приставка Х-ВОХ

Итак, компания MICROSOFT обратила внимание

на рынок игровых видеоприставок и собирается

выпустить свою систему, называемую Х-ВОХ.

Пока устройство находится в стадии разработки,

можно привести только предварительные сведения

об ожидающем нас монстре.

В качестве центрального используется стандарт-

ный процессор Intel Pentium III с тактовой частотой

600 МГц. К нему подключены 64 Мб памяти, специа-

лизированный звуковой процессор и графический

процессор с аппаратным ускорением 2D- и 3D-rpa-

фики. Микросхема графического процессора разра-

батывается компанией nVidia, а значит, его произво-

дительность будет, вероятно, на несколько порядков

выше, нежели у любого другого ускорителя на рынке.

Конечно, в наличии все необходимые аксессуа-

ры: DVD-ROM, возможность расширения, выход

в Internet; уже предусмотрено объединение несколь-

ких консолей в сеть. В Х-ВОХ, помимо ставших уже

стандартными карт с энергонезависимым ОЗУ, ко-

торые предназначены для хранения данных на вре-

мя отключения питания, появится жесткий диск.

А теперь угадайте, какая система будет записана

в ПЗУ приставки? Правильно, Windows. Точнее,

специально разработанный для Х-ВОХ вариант, ос-

нованный на ядре Windows 2000.

В целом видеоприставка Х-ВОХ выглядит много-

обещающе, а зная снособность MICROSOFT к из-

влечению прибыли, можно с уверенностью говорить

о том, что ее модель составит серьезную конкурен-

цию как DREAMCAST, так и PLAYSTATION 2.

Итак, мы полагаем, в будущем нам будет во что

и на чем играть.

Шоу должно продолжаться.

Продолжение следует...

КРАТКАЯ ИСТОРИЯ ИГРОВЫХ ПРИСТАВОК

11

ИГРОВАЯ ПРИСТАВКА DENDY

Игровая приставка NES (NINTENDO ENTERTAINMENT SYSTEM), более из-

вестная в нашей стране под именем DENDY (а также КЕНГА, FAMICOM

и еще под несколькими псевдонимами), одной из первых появилась на

российском рынке и познакомила тысячи людей с увлекательным миром

компьютерных игр.

Она подключается к обычному телевизору через антенный или НЧ вход.

К приставке можно подсоединить два игровых пульта GAMEPAD или один

пульт GAMEPAD и световой пистолет ZAPPER. На корпусе устройства рас-

полагаются клавиши включения питания и перезапуска системы. Назначе-

ние кнопок на игровом пульте будет понятно даже тем, кто не знает анг-

лийского языка и потому не в состоянии перевести надписи.

Внутри устройства располагаются центральный процессор, являющий-

ся аналогом известного микропроцессора 6502, аудио- и видеопроцессо-

ры. Имеется также оперативное запоминающее устройство объемом 2 Кб.

В игровом картридже находится ПЗУ с записанным в нем программным

обеспечением и дополнительной видеопамятью. В некоторых модифика-

циях содержится дополнительная память, позволяющая сохранять теку-

щую игровую ситуацию.

Модели отличаются друг от друга размером встроенного ОЗУ и звуко-

вым процессором. По этой причине картриджи, нормально функциониру-

ющие на одних приставках, не работают с другими.

Кроме того, приставки в зависимости от модификации формируют ви-

деосигнал либо в системе PAL, либо в системе NTSC. Параметры этих

устройств неодинаковы, и картридж, помеченный как «NTSC only», не смо-

жет корректно работать с игровой приставкой системы PAL.

Архитектура и принцип работы. Структурная схема

1.1. Технические 1.2. Архитектура

характеристики и принцип работы

Центральный процессор В этом разделе архитектура игровой приставки

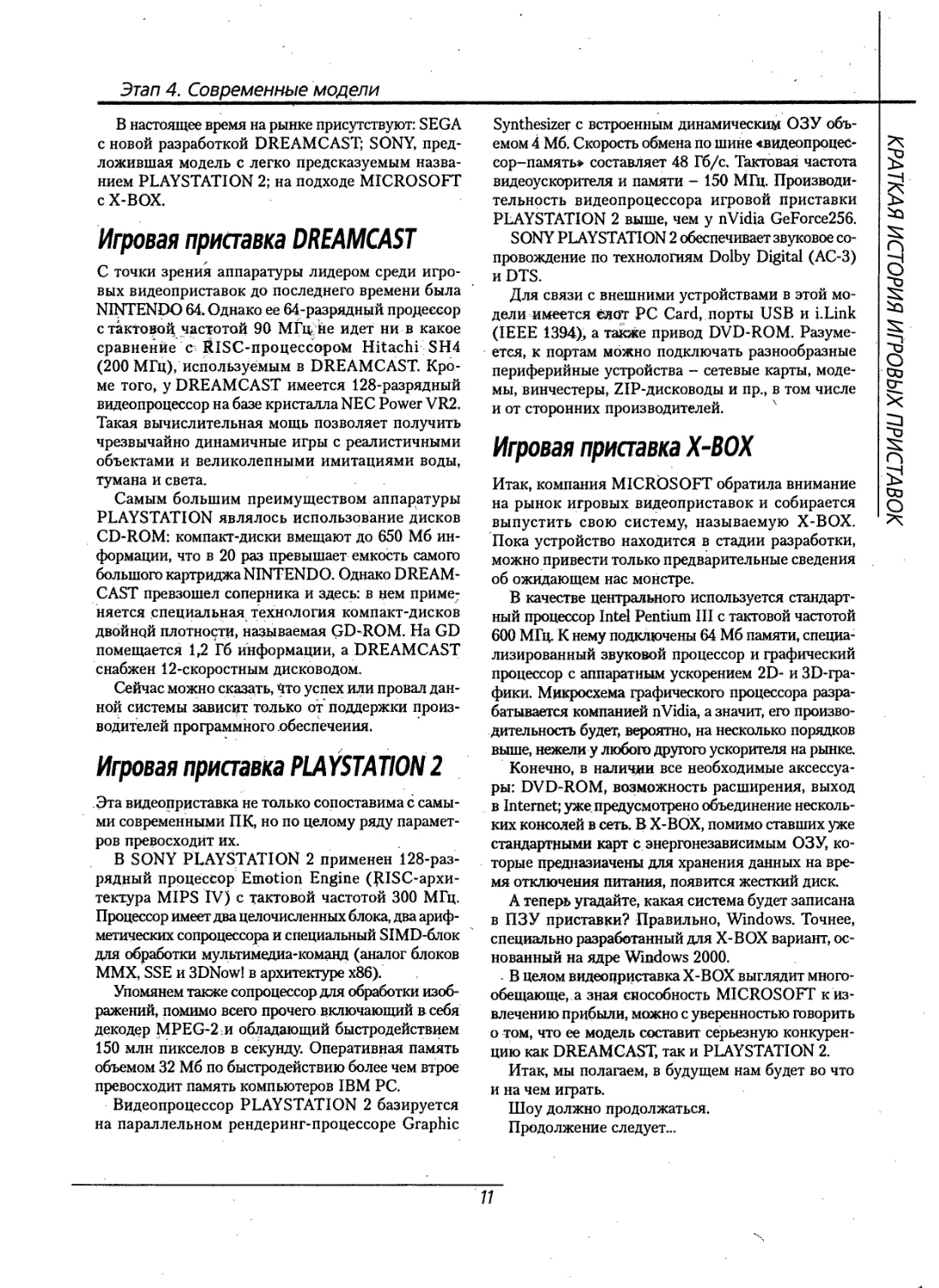

Тип Разрядность шины данных Разрядность шины адреса Тактовая частота Память ОЗУ аналог 6502 8 бит 16 бит 1,773447 МГц 2 Кб DENDY рассматривается с точки зрения програм- мирования, подробно описываются центральный процессор, способы формирования изображения, работа аудиопроцессора. Особое внимание уделено внутренним регис- трам игровой приставки и особенностям программ- ного обеспечения.

ПЗУ отсутствует

Видеопамять Видеопроцессор 2 Кб 1.2.1. Структурная схема

Тип графики спрайтовая Структурная схема игровой приставки DENDY

Разрядность шины адреса 14 бит приведена на рис. 1.1.

Разрядность шины данных 8 бит Основой приставки является центральный про-

Количество спрайтов 64 цессор (CPU). Во всех приставках, совместимых со

Размер спрайтов 8x8 или 8x16 стандартом NES, используется процессор, анало-

Разрешение 256x240 точек гичный известному микропроцессору 6502.

Количество цветов На одном кристалле с центральным размещен

всего 52 и музыкальный сопроцессор. В оригинальной при-

одновременно на экране 16 ставке, производимой фирмой NINTENDO, при- меняется аудиопроцессор, реализующий четыре

Рис. 1.1. Структурная схема игровой приставки DENDY

13

Архитектура и принцип работы. Центральный процессор

ИГРОВАЯ ПРИСТАВКА DENDY

аналоговых и один цифровой канал звука. Однако

большинство приставок, поставляемых в Россию,

являются корейскими аналогами, в них встроен зву-

ковой сопроцессор без цифрового канала.

Контроллер прямого доступа к памяти (Direct

Memory Access, DMA) также располагается на кри-

сталле центрального процессора.

Игровые пульты и другие устройства подключа-

ются к шине данных через модуль ввода/вывода,

представляющий собой два буферных регистра.

В самостоятельный блок выделено также ОЗУ

объемом 2 Кб, которое предназначено для хранения

переменных, игровых данных, стека процессора и т.д.

Формирование картинки на экране телевизора

обеспечивает видеопроцессор приставки (PPU).

Информация об изображении хранится в видеопа-

мяти (VRAM) объемом 2 Кб. Эта память ие связана

с основной памятью приставки, доступ к пей осущест-

вляется только через регистры PPU. Видеопроцес-

сор формирует стандартный видеосигнал, который

подается па выходной разъем приставки.

Находящийся в корпусе модулятор преобразует

сигналы изображения и звука в ВЧ сигнал, пред-

назначенный для подачи на антенный вход телеви-

зора.

В пультах установлены кнопки управления

и микросхема интерфейса, осуществляющая пере-

дачу байта данных центральному процессору при-

ставки.

В картридже, который подключается к пристав-

ке через 60-контактный (или 72-контактный в мо-

дели NES) разъем, располагаются постоянное запо-

минающее устройство объемом от 16 до 256 Кб,

в котором записана игровая программа, и память

видеопроцессора.

Оперативная память с питанием от батарейки

(SRAM), куда записывается игровая ситуация на

время выключения приставки, также может нахо-

диться в картридже. Чтобы задействовать все ре-

сурсы графического процессора, некоторые кар-

триджи содержат дополнительное ПЗУ или ОЗУ

для видеопроцессора (VRAM/VROM).

Если объем ПЗУ картриджа превышает 32 Кб, то

его обязательной частью является контроллер стра-

ниц памяти (МВС), который осуществляет пере-

ключение страниц, используемых центральным

процессором.

Питающее напряжение (+5 В) для приставки

поступает от сетевого адаптера через встроенный

стабилизатор.

1.2.2. Центральный процессор

В данном разделе рассматриваются архитектура

процессора, его внутренние регистры, способы ад-

ресации, система команд и прерывания. Здесь

приводится лишь справочная информация; более

полные сведения о программировании на языке ас-

семблера для процессора 6502 можно найти в изда-

ниях, указанных в конце книги, и в сети Internet.

Как отмечалось выше, в игровых приставках,

совместимых со стандартом NES, используется

центральный процессор, который аналогичен из-

вестному микропроцессору 6502 фирмы MOS

TECHNOLOGY. От оригинала он отличается от-

сутствием десятичного режима выполнения ариф-

метических команд. В PAL-версии приставки так-

товая частота процессора составляет 1,773447 МГц,

а в NTSC-версии - 1,7897725 МГц.

Микропроцессор обменивается информацией

с другими устройствами посредством 16-разрядиой

шипы адреса, 8-разрядиой шины данных и шины

управления. 16 разрядов шины адреса позволяют

процессору обращаться к 64 Кб памяти (65535 байт).

Регистры внешних устройств адресуются про-

цессором так же, как и ячейки памяти, и находятся

в общем адресном пространстве микропроцессора.

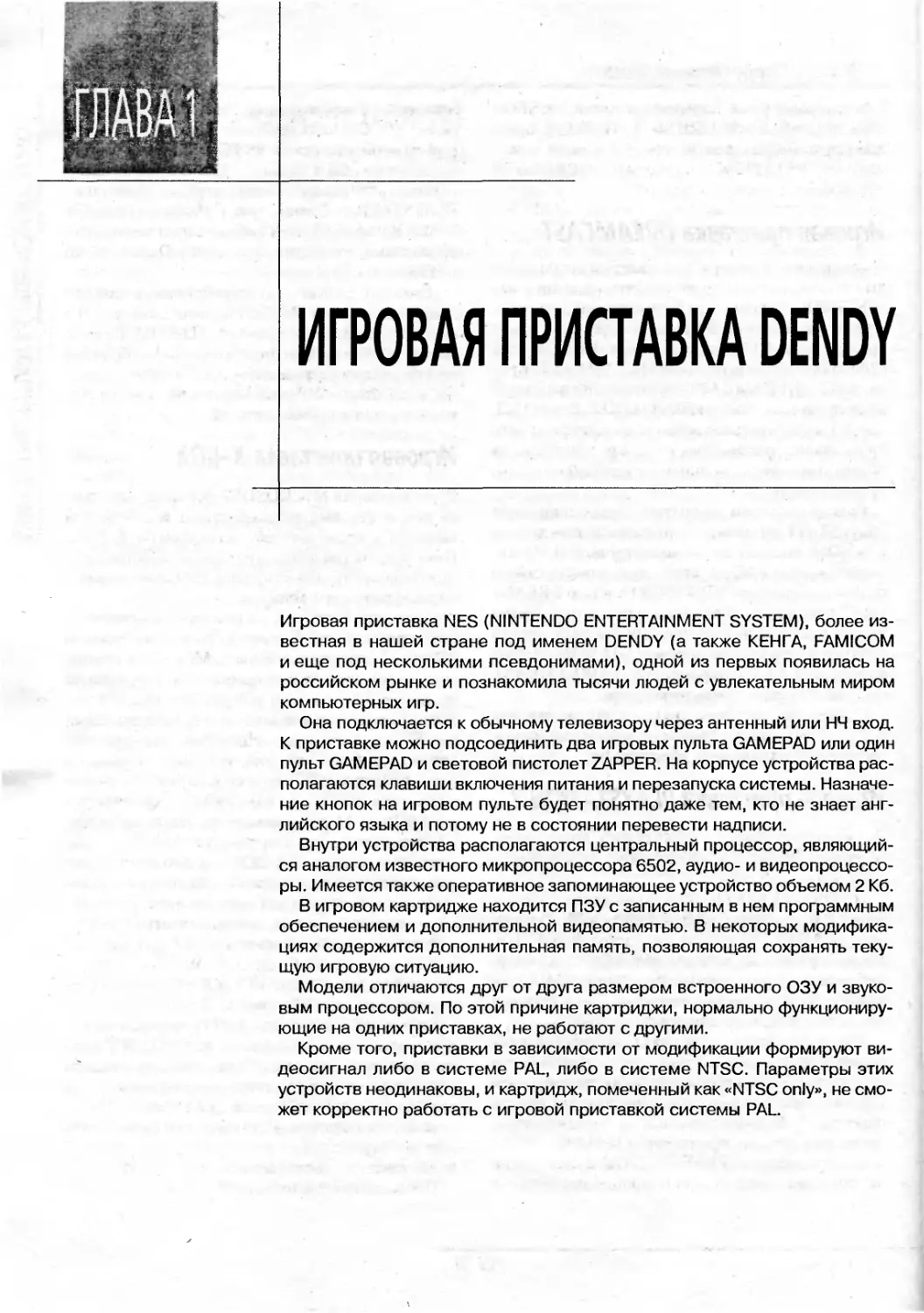

Структурная схема центрального процессора иг-

ровой приставки DENDY приведена на рис. 1.2.

Рис. 1.2. Структурная схема центрального процессора

игровой приставки DENDY

Регистры процессора

Центральный процессор игровой приставки DEN-

DY содержит пять 8-разрядных регистров и один

16-разрядиый. Каждый регистр имеет свое имя

и отличается по способам использования.

Аккумулятор является наиболее часто применя-

емым регистром микропроцессора. Он служит для

загрузки данных в другие регистры, проведения

любых математических, и логических операций,

а также для иных целей. Фактически это 8-разряд-

ный регистр, который в программах на языке ас-

семблера обозначается буквой «А».

Индексный регистр X задействуется микропро-

цессором для доступа к ячейкам памяти посред-

ством индексного метода адресации, о котором

14

Архитектура и принцип работы. Центральный процессор

рассказывается ниже. Этот 8-разрядный регистр не-

обходим при обработке таблиц, хранящихся в памяти.

Индексный регистр Y по своему назначению и ис-

пользованию аналогичен индексному регистру X.

Однако в их функционировании есть некоторые

различия, которые будут рассмотрены при описа-

нии методов адресации микропроцессора.

Регистр состояния процессора Р хранит инфор-

мацию о режиме работы процессора и о результа-

тах проведенных вычислений. Каждый бит этого

8-разряднбго регистра является флагом, то есть

изменяет свое состояние при определенных усло-

виях. На работу процессора можно влиять путем

модификации содержимого этого регистра.

Структура регистра состояния центрального про-

цессора игровой приставки DENDY приведена на

рис. 1.3.

|n|v|i|b[o|i[z. |с|

7 6 5 4 3 2 10

Рис. 1.3. Структура регистра состояния

центрального процессора игровой приставки DENDY

Рассмотрим назначение отдельных разрядов ре-

гистра.

Флаг С играет роль флага переноса, который

используется при выполнении сложения или вычи-

тания. Разряд С регистра состояния процессора

становится равным 1, если результат выполнения

команды сложения больше 255 (OFFh) или если

результат выполнения команды вычитания мень-

ше 0. Таким образом, этот флаг представляет собой

как бы дополнительный разряд аккумулятора, по-

зволяющий проводить арифметические операции

с числами, разрядность которых превышает 8 бит.

Флаг Z - флаг нулевого результата, который ра-

вен 1, если результатом выполнения команды явля-

ется 0.

Флаг I - флаг прерываний, устанавливаемый

и сбрасываемый командами процессора SEI и CLI.

1 в этом разряде запрещает процессору обрабатывать

запросы прерывания, поступающие по линии IRQ.

Более подробно эта тема рассматривается при опи-

сании системы прерываний процессора.

Флаг D - флаг десятичного режима. Микропро-

цессор игровой приставки не поддерживает работу

арифметических команд в двоично-десятичном коде,

поэтому состояние данного флага не влияет на функ-

ционирование процессора. Программист может ис-

пользовать этот бит регистра состояния по своему

усмотрешпо. Состояние флага изменяется программ-

но командами SED и CLD. Оригинальный микро-

процессор 6502 позволяет складывать и вычитать

числа как в двоичном, так и в двоично-десятич-

ном коде. Если флаг D равен 0, то операнды ко-

манд сложения и вычитания рассматриваются

как двоичные числа, а если установлен в 1 - как

двоично-десятичные.

Флаг В - флаг программного прерывания, уста-

навливается при выполнении команды BRK.

Флаг V - флаг переполнения. Равен 1, если ре-

зультат арифметической операции над числами со

знаком выходит за допустимые пределы или если

при выполнении арифметической операции осущест-

влялся перенос из шестого разряда в седьмой.

Флаг N - флаг знака, который равен седьмому

разряду результата арифметической операции.

Указатель стека S содержит младший байт адре-

са первой свободной ячейки в специальной струк-

туре данных, называемой стеком. В стек можно за-

писывать данные, а при обработке прерываний или

при вызове подпрограммы здесь сохраняется адрес

возврата. В рассматриваемом микропроцессоре стек

всегда располагается в первой странице памяти, ко-

торая нахоДится в диапазоне 010 Oh - OlFFh, таким

образом, для указания адреса вершины стека доста-

точно 8-разрядного регистра. Стек растет вниз, то

есть от адреса OlFFh к адресу 010Ch.

Счетчик команд PC представляет собой един-

ственный 16-разрядный регистр центрального про-

цессора игровой приставки DENDY. Его назначе-

ние - указывать адрес команды, которая выполняется

микропроцессором. Центральный процессор при-

ставки регулярно извлекает команду, размещенную

в памяти по адресу, на который указывает счетчик

команд, увеличивает значение счетчика, обрабаты-

вает команду и повторяет этот цикл снова. Коман-

ды перехода позволяют изменить содержимое про-

граммного счетчика и задать необходимый порядок

выполнения команд, размещенных в памяти.

Способы адресации

Большинство команд процессора обеспечивают

выполнение действий с какими-либо данными.

Например, для сложения нужны два числа. Один

из операндов микропроцессора приставки всегда

размещается в аккумуляторе, куда после выполне-

ния команды помещается результат. Второй операнд

содержится в памяти по исполнительному адресу.

Исполнительный адрес - это фактический номер

ячейки памяти, начиная с которой располагаются

необходимые для процессора команды или данные.

Возможные приемы формирования процессором

исполнительного адреса называются способами ад-

ресации. Описываемый процессор насчитывает три-

надцать различных способов адресации (см. ниже).

Некоторые методы формирования исполнитель-

ного адреса в процессоре игровой приставки DEN-

DY представлены на рис. 1.4.

Аккумуляторная адресация. При использова-

нии этого способа операция производится над со-

держимым аккумулятора.

ИГРОВАЯ ПРИСТАВКА DENDY

15

Архитектура и принцип работы. Центральный процессор

ИГРОВАЯ ПРИСТАВКА DENDY

а)

д)

PC

РС+1

б)

в)

0020

+Х

I

002А

е)

0020

Регистр А

Старший

байт

адреса

операнда

Код

команды

Базовый

адрес

б нулевой

странице

0026

0027

PC

РС+1

ЗЕ61

Операнд

Младший

байт

адреса

операнда

Регистр X

г)

PC

Регистр А

РС+1

РС+2

3000

ж)

0016

0017

Код

команды

Младший

байт

базового

адреса

Старший

байт

базового

адреса

3012

Старший

байт

базового

адреса

Млодший

байт

базового

адреса

Регистр X

Оперонд

Регистр А

Регистр Y

Код

команды

PC

РС+1

Адрес

в нулевой 16

странице

3620

3629

Операнд

Рис. 1.4. Методы формирования исполнительного адреса в процессоре игровой приставки DENDY

Например:

LSR А ; Логический сдвиг байта

; из аккумулятора вправо.

Неявная адресация. Для команд, применяющих

такой метод, расположение данных строго фикси-

ровано и дополнительных указаний не требуется.

Например:

ТАХ ; Переслать данные из А в X.

Непосредственная адресация. В этом случае

8-разрядный операнд хранится в памяти сразу за

кодом команды, то есть по адресу РС+1 (рис. 1.4а).

В программах на языке ассемблера непосредственная

адресация обозначается знаком # перед операндом.

Прямая адресация. При работе с данным алгорит-

мом адресации в команде указывается адрес располо-

жения операнда в памяти компьютера (рис. 1.46).

Прямая адресация нулевой страницы. Если опе-

ранд расположен в нулевой странице памяти (адре-

са 00 0Oh - OOFFh), можно задействовать команды

с прямой адресацией нулевой страницы, которые

занимают меньше места в памяти и быстрее вы-

полняются. Первый байт адреса всегда равен О

и подставляется процессором автоматически. Эта-

пы формирования исполнительного адреса пред-

ставлены на рис. 1.4в.

Индексированная по X адресация. Все коман-

ды, применяющие этот метод, занимают в памя-

ти компьютера три байта. Первый байт содержит

код команды, второй и третий - базовый адрес. -

Исполнительный адрес операнда получается сум-

мированием базового адреса с содержимым регис-

тра X, как показано на рис. 1.4г.

Индексированная по Y адресация. Аналогична

рассмотренной выше, только вместо регистра X ис-

пользуется регистр Y.

Индексированная по X адресация нулевой стра-

ницы. В данном случае команды занимают два байта:

первый содержит код команды, а второй - базовый

адрес в нулевой странице памяти. Исполнительный

адрес операнда образуется путем сложения базово-

го адреса с содержимым регистра X микропроцес-

сора, как показано на рис. 1.4д. При попытке адре-

соваться за пределы нулевой страницы (если сумма

базового адреса и содержимого индексного регис-

тра больше OFFh) формируется исполнительный

адрес ООО Oh.

Индексированная по Y адресация нулевой стра-

ницы. Аналогична рассмотренному выше способу,

16

Архитектура и принцип работы. Центральный процессор

только вместо регистра X применяется регистр Y

микропроцессора.

Индексно-косвенная адресация. Команды с та-

ким методом адресации всегда двухбайтные. Пер-

вый байт включает в себя код команды, а второй -

базовый адрес в нулевой странице памяти. Испол-

нительный адрес вычисляется по следующему ал-

горитму (рис. 1.4е):

1. Базовый адрес суммируется с содержимым регис-

тра X. При этом старший байт полученного адреса

всегда равен 00b (то есть FFh + 02h = Olh), а не

OlOih.

2. Из ячейки с вычисленным адресом считывается

младший байт адреса операнда.

3. Адрес ячейки памяти увеличивается на 1. Если ад-

рес был OFFh, то следующий адрес будет OOh, то

есть адресации за пределы нулевой страницы не

происходит.

4. Из ячейки памяти с полученным адресом считыва-

ется старший байт адреса операнда.

5. Из ячейки памяти с вычисленным адресом извле-

кается операнд.

Косвенно-индексная адресация. Команды, ис-

пользующие данный метод, также занимают в па-

мяти компьютера два байта. Первый байт содержит

код операции, а второй - адрес в нулевой странице.

Исполнительный адрес операнда вычисляется по

следующему алгоритму (рис. 1.4ж):

1. Из ячейки памяти, расположенной в нулевой стра-

нице по указанному в команде адресу, извлекается

младший байт базового адреса.

2. Адрес ячейки памяти увеличивается на 1. Если ад-

рес был OFFh, то следующий адрес будет ooh, то

есть адресации за пределы нулевой страницы не

происходит.

3. Из ячейки памяти с полученным адресом считыва-

ется старший байт базового адреса.

4. К базовому адресу прибавляется содержимое ре-

гистра Y.

5. Из ячейки памяти с вычисленным адресом извле-

кается операнд.

Относительная адресация. Этот метод адресации

применяется в командах перехода. Первый байт ко-

манды содержит код операции, а второй - смещение

в диапазоне от -128 до 127. Отрицательное смеще-

ние указывается в дополнительном коде. При вы-

полнении команды перехода смещение прибавля-

ется к содержимому программного счетчика для

получения адреса следующей выполняемой коман-

ды. Не забывайте, что смещение складывается с со-

держимым программного счетчика, когда тот указы-

вает на команду, идущую за командой перехода.

Косвенная адресация. С данным методом способ-

на работать только команда безусловного перехода

JMP. При этом в команде задается адрес ячейки

памяти, содержащей адрес перехода. Обратите

внимание: выхода за пределы страницы при из-

влечении адреса перехода из памяти не будет, то

есть старший байт адреса не изменится. Напри-

мер, при выполнении команды JMP ($C0FF)

младший байт адреса извлекается из ячейки па-

мяти с адресом с 0 FFh, а старший байт - из ячей-

ки с адресом СО0Oh, а не Cl 0 Oh, как можно было

бы ожидать.

Система команд

Центральный процессор игровой приставки DEN-

DY способен выполнять 56 различных команд. Все

команды процессора делятся на следующие основ-

ные группы:

• команды пересылки данных: LDA, STA, LDX,

STX, LDY, STY, TAX, TAY, ТХА, TYA, TSX, TXS;

• команды арифметических операций: INC, DEC,

INX, INY, DEX, DEY, ADC, SBC;

• команды логических операций: AND, ORA, EOR;

• команды сравнения: CMP, CPX, CPY, BIT;

• команды сдвига: ASL, ASR, ROL, ROR;

• команды перехода: BCC, BCS, BEQ, BNE, BMI,

BPL, BVC, BVS, JMP;

• команды работы с подпрограммами: J SR, RTS;

• команды управления процессором: CLC, SEC,

CLD, SED, CLV, CLI, SEI, RTI, BRK, NOP;

• команды работы co стеком: PHA, PHP, PLA, PLP.

Полная информация о системе команд централь-

ного процессора игровой приставки DENDY приве-

дена в приложении 1.

Система прерываний

Центральный процессор игровой приставки DENDY

может обрабатывать три независимых запроса на

прерывание. В таком случае выполнение програм-

мы приостанавливается, в стеке сохраняется ре-

гистр состояния процессора и текущее значение

программного счетчика, а затем из памяти считы-

вается вектор прерывания.

Вектор прерывания - это адрес программы, ко-

торая должна выполняться каждый раз, когда цен-

тральный процессор получает запрос на прерыва-

ния от внешних устройств.

Прочитав из памяти вектор прерывания, процес-

сор записывает его в программный счетчик и запус-

кает процедуру обработки прерывания.

Рассмотрим возможные типы прерываний и про-

цедуры их обработки.

Маскируемое прерывание IRQ. Процедуру обра-

ботки данного прерывания центральный процессор

выполняет каждый раз, когда получает сигнал низ-

кого уровня по шине IRQ, если флаг I в регистре

состояния сброшен. Эту процедуру также можно

ИГРОВАЯ ПРИСТАВКА DENDY

77

Архитектура и принцип работы. Адресное пространство

ИГРОВАЯ ПРИСТАВКА DENDY

вызвать, выполнив команду процессора BRK. В слу-

чае программного прерывания перед началом его

обработки в регистре состояния процессора уста-

навливается флаг В.

При обслуживании запроса на прерывание в сте-

ке сохраняются состояния программного счетчика

и регистра состояния процессора, после чего вы-

полняется программа, адрес начала которой запи-

сан в ячейках памяти FFFEh и FFFFh. Для возвра-

та из прерывания применяют команду RTI. При

этом из стека считываются сохраненные значения

регистра состояния микропроцессора и программ-

ного счетчика, а затем продолжается исполнение

прерванной программы.

В стандартной конфигурации игровой пристав-

ки сигнал запроса маскируемого прерывания IRQ

выведен на разъемы расширения и подключения

картриджа, однако игровые программы используют

только возможность программного прерывания

при выполнении команды BRK.

Немаскируемое прерывание NMI. Это самый

важный запрос на прерывание в игровой пристав-

ке. Любая программа обязательно содержит проце-

дуру его обработки.

Каждый раз, когда заканчивается формирование

очередного кадра (50 раз в секунду для стандарта

PAL и 60 раз в секунду для стандарта NTSC), по

переднему фронту кадрового гасящего импульса

видеопроцессор приставки формирует сигнал за-

проса немаскируемого прерывания и посылает его

центральному процессору.

Процессор прерывает исполнение программы,

сохраняет в стеке значения программного счетчика

и регистра состояния, после чего запускает проце-

дуру обслуживания немаскируемого прерывания,

адрес которой записан в ячейках памяти FFFAh

и FFFBh. Возврат из процедуры обработки осущест-

вляется также командой RTI.

Особая важность этого прерывания для игровой

приставки объясняется тем, что центральный про-

цессор может обмениваться данными с видеопамя-

тью только в те моменты, когда формируется кадро-

вый гасящий импульс, начало которого и вызывает

запрос на прерывание. Таким образом, программа

обработки немаскируемого прерывания в любой

видеоигре осуществляет запись в регистры видео-

процессора и пересылку заранее подготовленных

данных в видеопамять.

Сброс микропроцессора. Данное прерывание

происходит при включении питания приставки

и при поступлении сигнала низкого уровня на вход

RESET. При этом центральный процессор копиру-

ет в программный счетчик содержимое ячеек памя-

ти с адресами FFFCh, FFFDh и начинает выполне-

ние программы. Состояние регистров процессора

не изменяется.

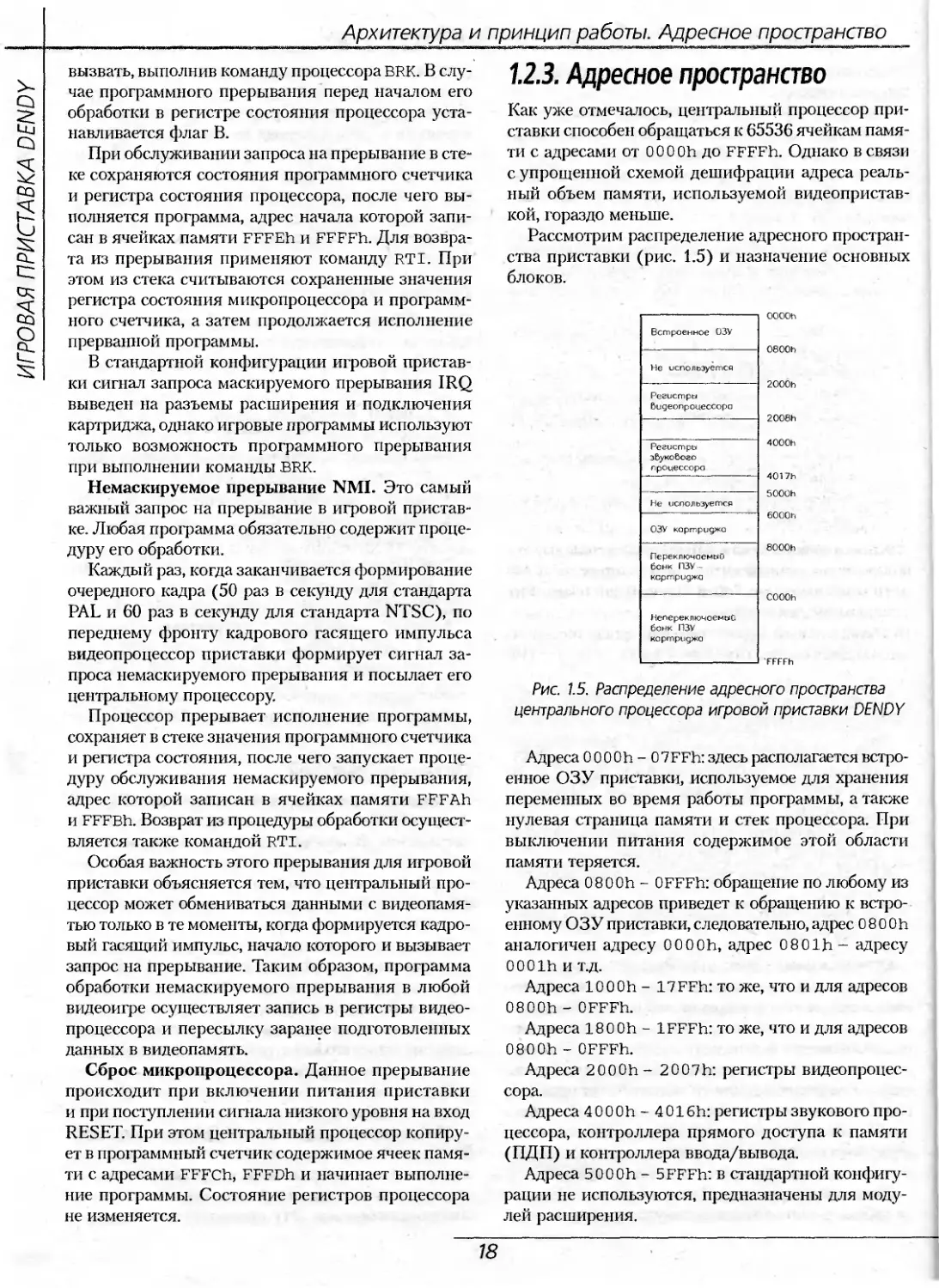

1.2.3. Адресное пространство

Как уже отмечалось, центральный процессор при-

ставки способен обращаться к 65536 ячейкам памя-

ти с адресами от 0 0 0 Oh до FFFFh. Однако в связи

с упрощенной схемой дешифрации адреса реаль-

ный объем памяти, используемой видеопристав-

кой, гораздо меньше.

Рассмотрим распределение адресного простран-

ства приставки (рис. 1.5) и назначение основных

блоков.

Рис. 1.5. Распределение адресного пространства

центрального процессора игровой приставки DENDY

Адреса 0 0 0 Oh - 0 7FFh: здесь располагается встро-

енное ОЗУ приставки, используемое для хранения

переменных во время работы программы, а также

нулевая страница памяти и стек процессора. При

выключении питания содержимое этой области

памяти теряется.

Адреса 0800h - OFFFh: обращение по любому из

указанных адресов приведет к обращению к встро-

енному ОЗУ приставки, следовательно, адрес 0 8 0 Oh

аналогичен адресу OOOOh, адрес 0 801h- адресу

0 0 0 lh и т.д.

Адреса 1000h - 17FFh: то же, что и для адресов

0800h - OFFFh.

Адреса 180Oh - IFFFh: то же, что и для адресов

0800h - OFFFh.

Адреса 200Oh - 2007h: регистры видеопроцес-

сора.

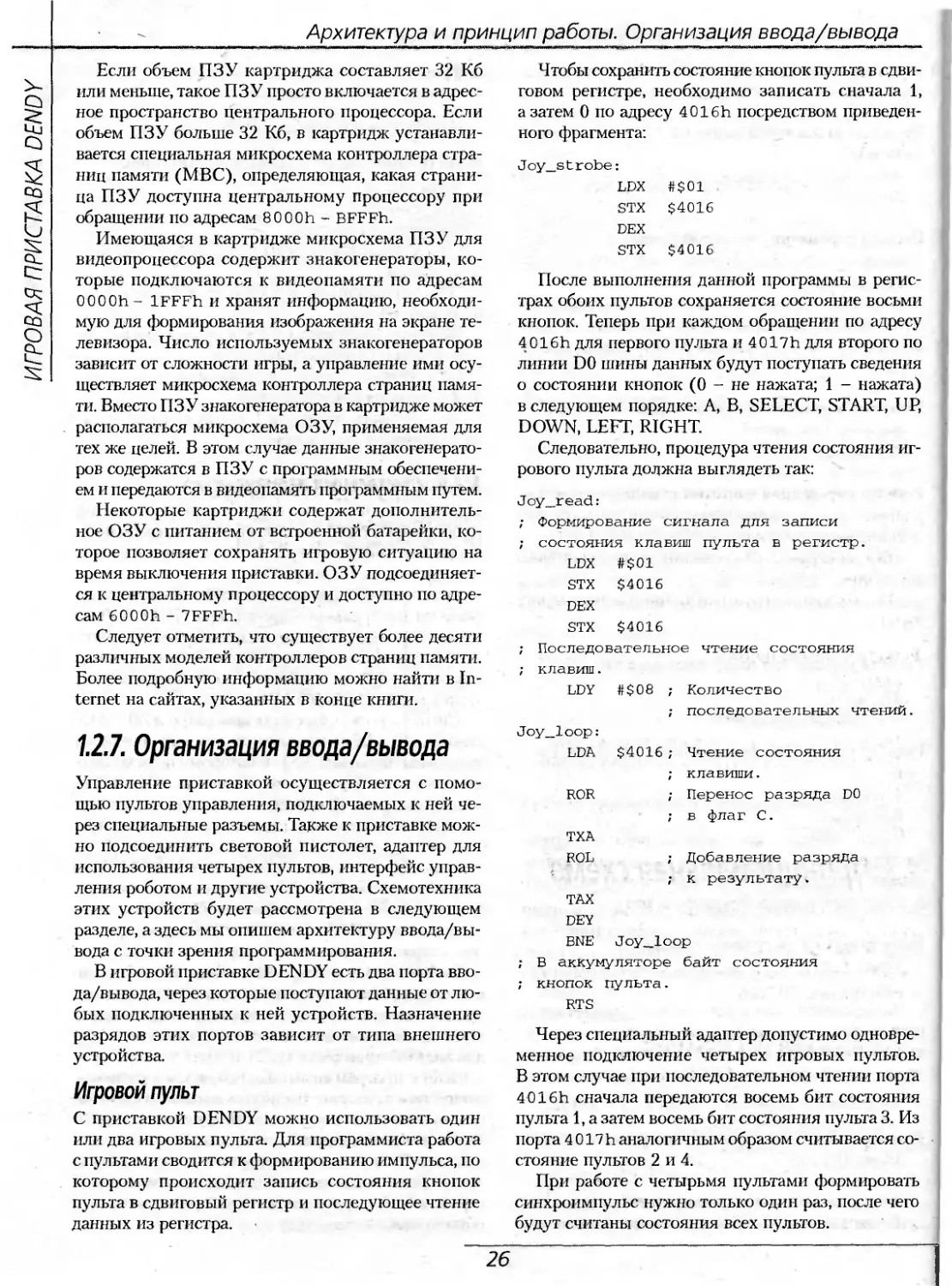

Адреса 4000h-4016h: регистры звукового про-

цессора, контроллера прямого доступа к памяти

(ПДП) и контроллера ввода/вывода.

Адреса 5000h - 5FFFh: в стандартной конфигу-

рации не используются, предназначены для моду-

лей расширения.

18

Архитектура и принцип работы. Видеопроцессор

Адреса 6О 0 Oh - 7FFFh: оперативная память кар-

триджа. Может отсутствовать.

Адреса 8 0 0 Oh - BFFFh: переключаемый байк по-

стоянной памяти программ картриджа. В простей-

ших картриджах не применяется.

Адреса СО0Oh - FFFFh: непереключаемый банк

постоянной памяти программ картриджа. Присут-

ствует в любом картридже независимо от размера

памяти. По этим адресам всегда подключаются по-

следние 16 Кб ПЗУ картриджа. В шесть ячеек ПЗУ

с адресами FFFAh - FFFFh записаны адреса проце-

дур обслуживания прерываний.

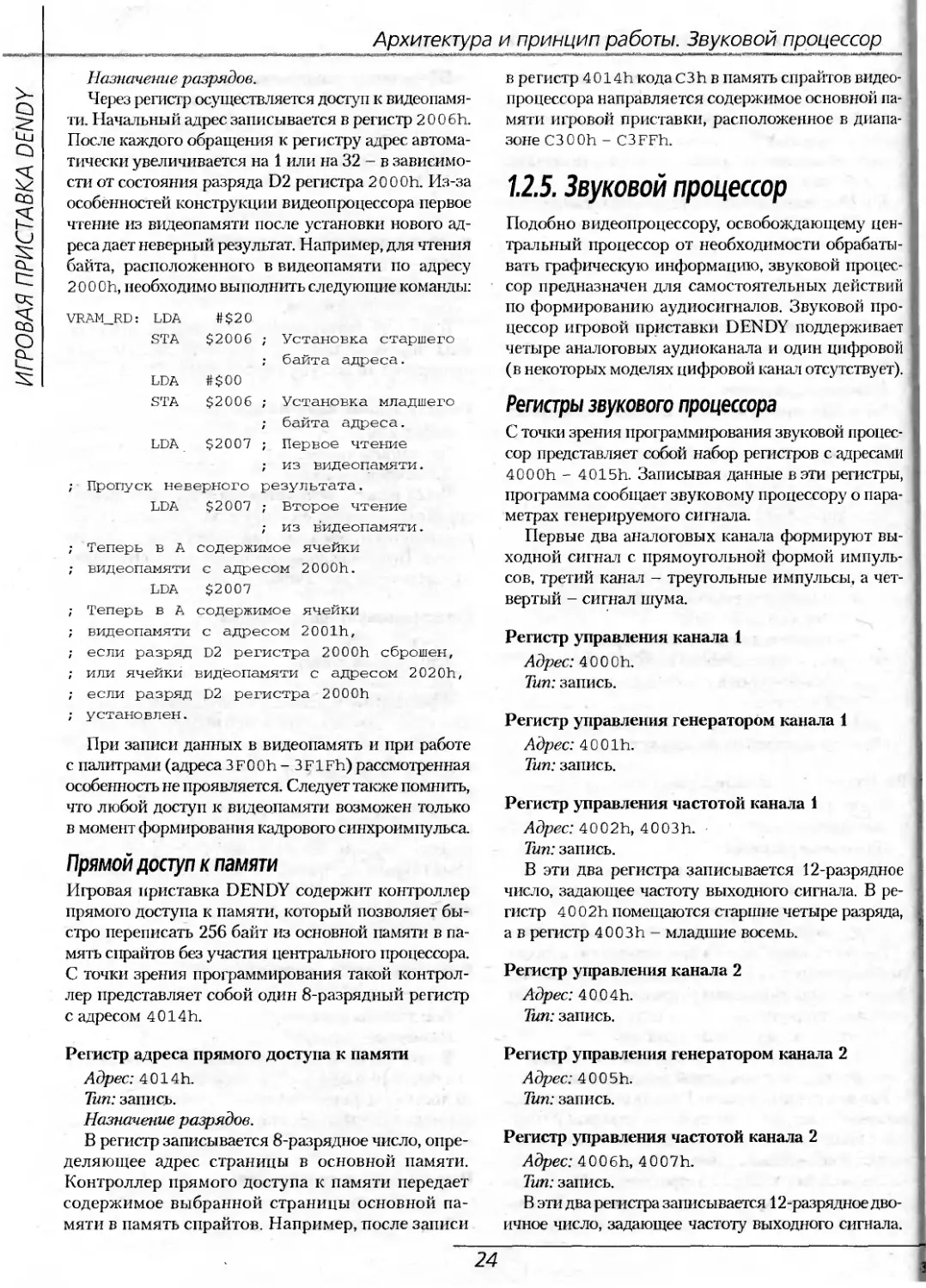

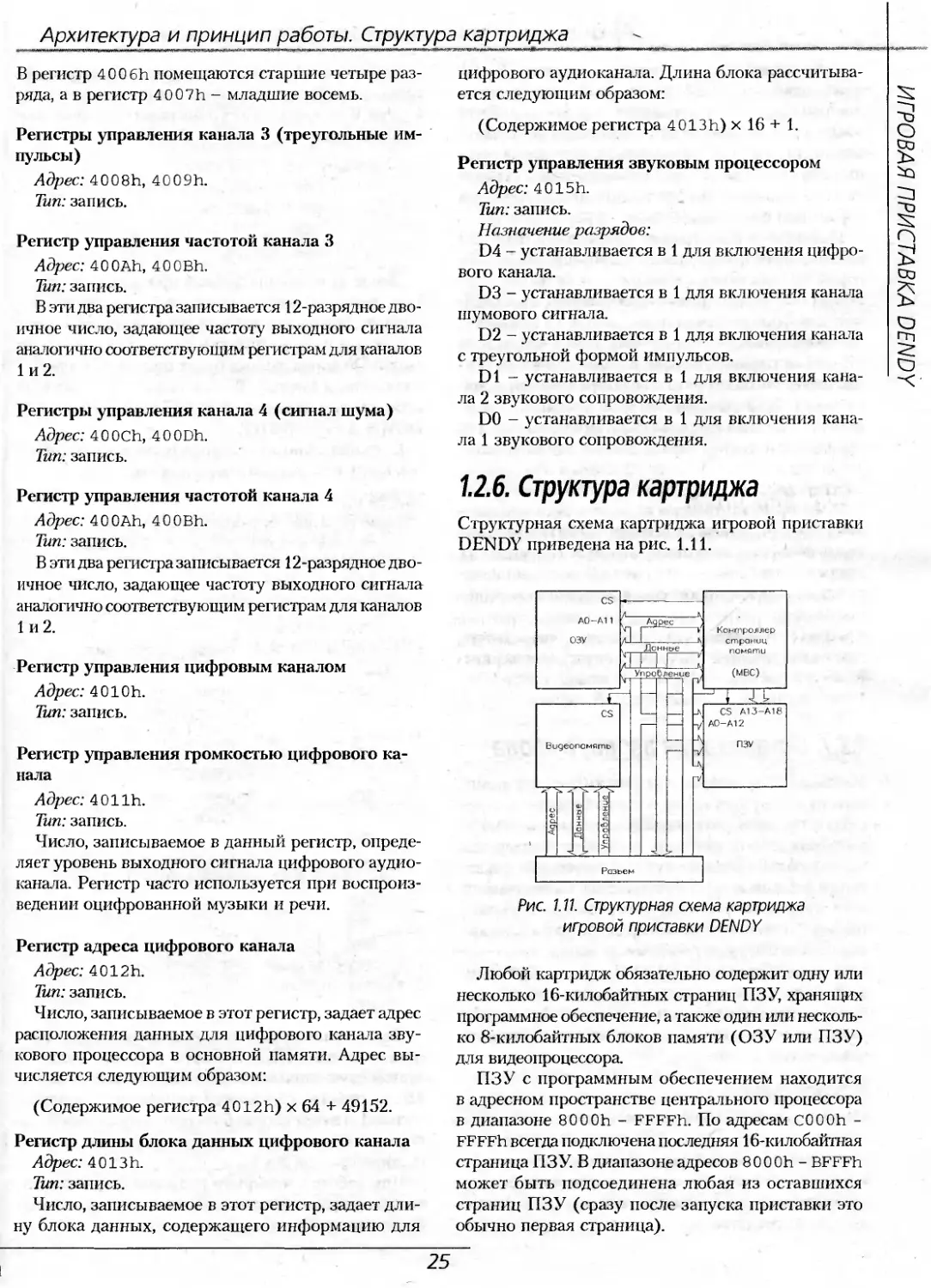

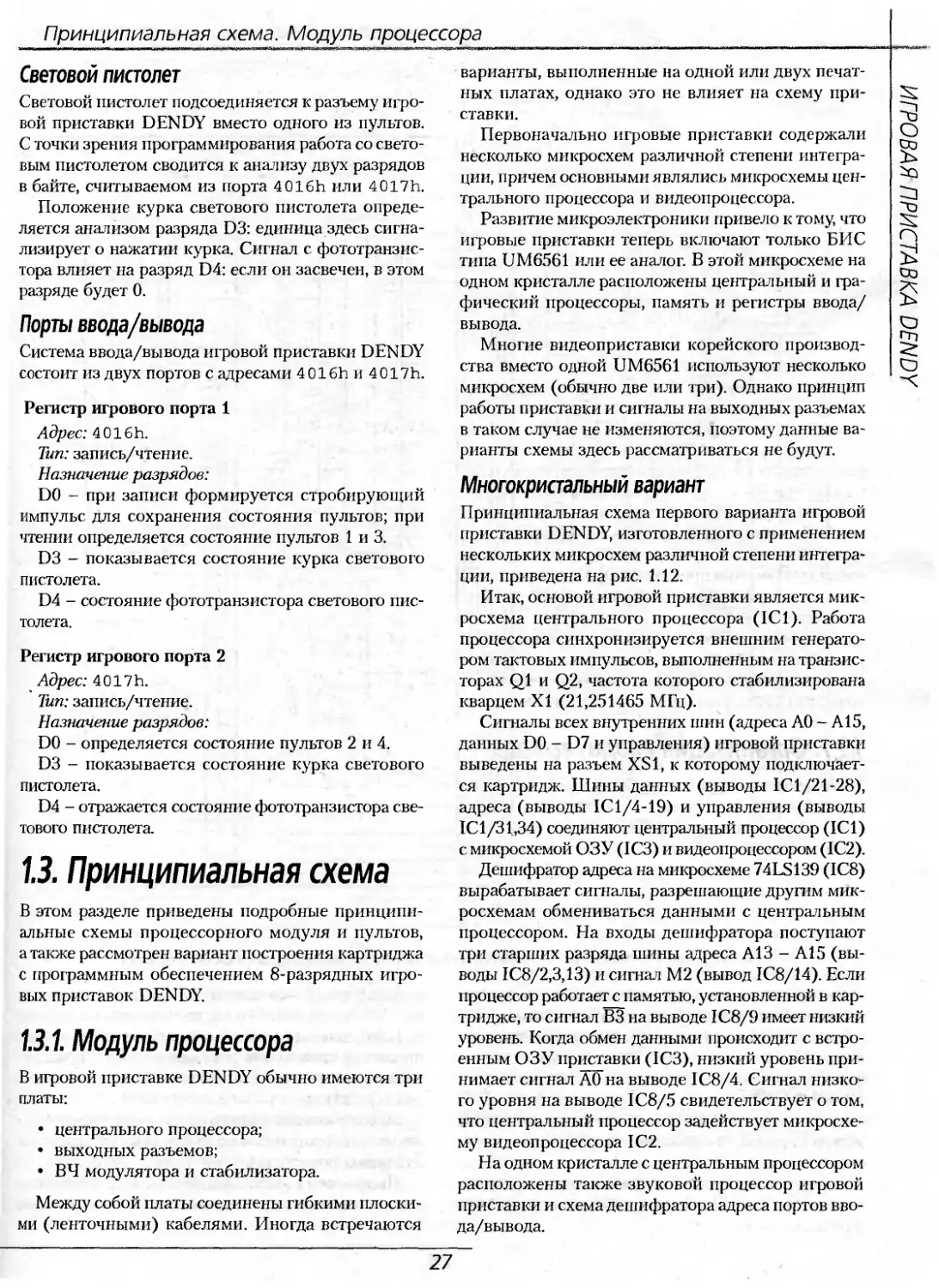

12.4. Видеопроцессор

Видеопроцессор игровой приставки DENDY пред-

назначен для формирования изображения на экране

телевизора. Характеристики видеопроцессора в зна-

чительной мере определяют возможности пристав-

ки и качество выводимой картинки.

В ранних моделях DENDY применялась отдель-

ная микросхема видеопроцессора НА6538, в более

поздних - микросхема UM6561, объединяющая все

микросхемы приставки в одном корпусе. С точки

зрения параметров видеопроцессора названные

микросхемы аналогичны.

Описываемый видеопроцессор ориентирован на

блочную графику с использованием спрайтов. Ин-

формация об изображении хранится в видеопа-

мяти, которая не входит в адресное пространство

центрального процессора. Доступ к видеопамяти

осуществляется через регистры видеопроцессора.

Часто в картридже располагается отдельный блок

видеопамяти, подключаемый вместо встроенной.

Это делается для ускорения работы видеопроцессо-

ра и улучшения графики.

Различия между PAL- и NTSC-версиями при-

ставки проявляются при выводе данных на экран.

В системе PAL размер картинки составляет 256x240

точек. В NTSC разрешение меньше - 256x224 точ-

ки. Информация об изображении, выходящем за

эти границы, остается в видеопамяти, но не появ-

ляется на экране.

В результате длительность кадрового гасящего

импульса изменяется (см. ниже), что может при-

вести к несовместимости между названными вер-

сиями устройства.

Рассмотрим более подробно структуру видеопа-

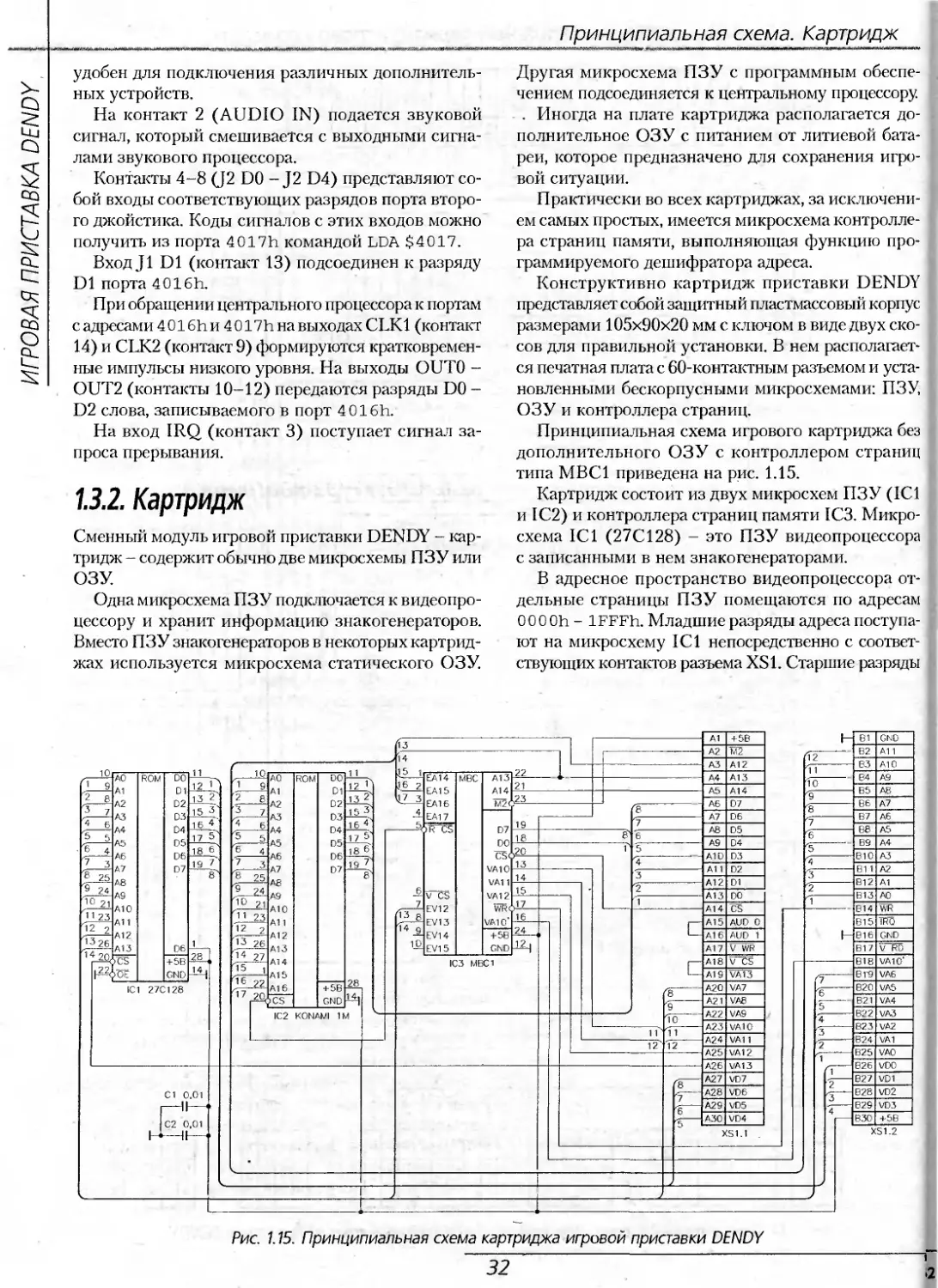

мяти игровой приставки и процесс формирования

изображения на экране телевизора.

Карта видеопамяти

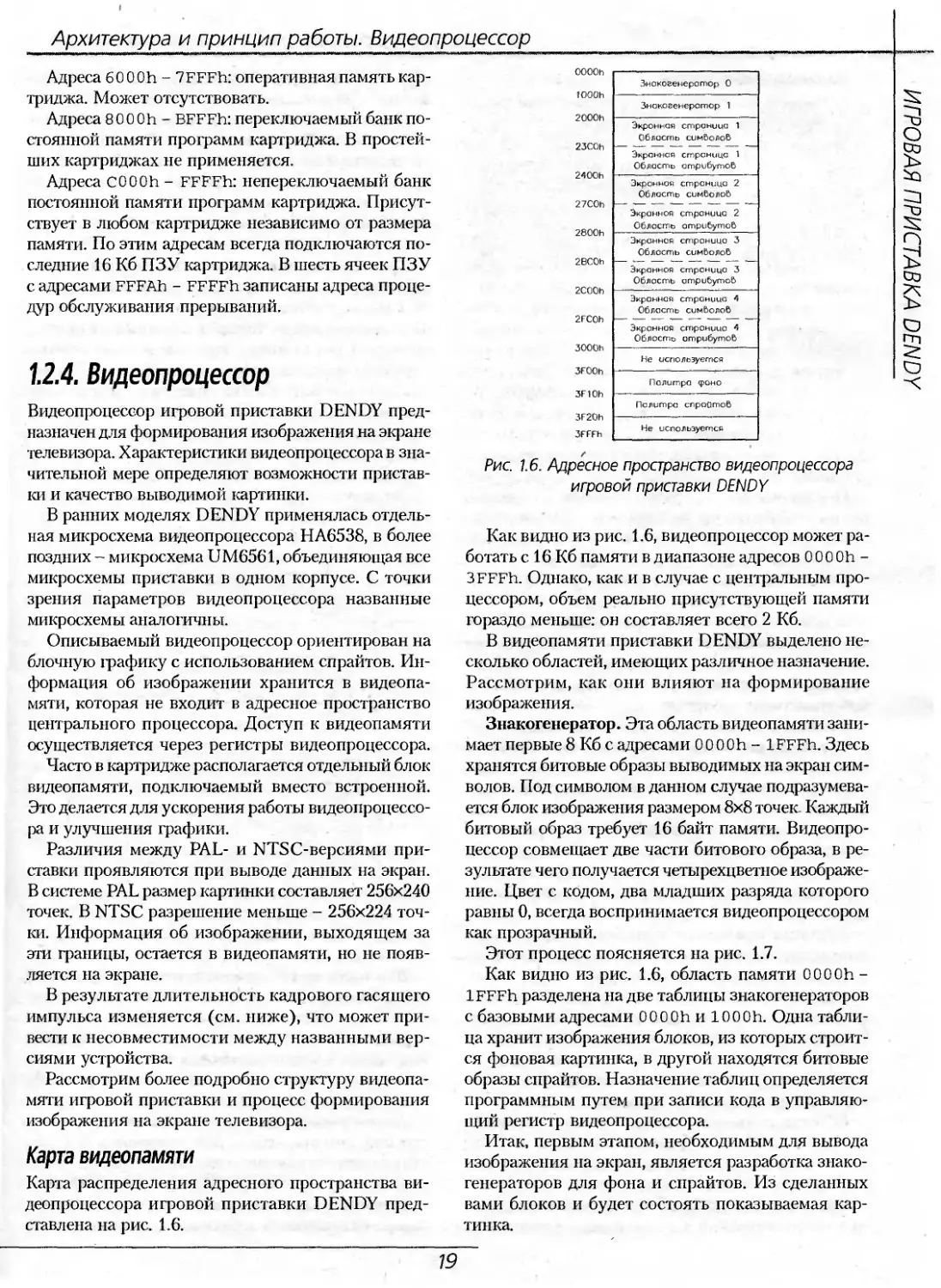

Карта распределения адресного пространства ви-

деопроцессора игровой приставки DENDY пред-

ставлена на рис. 1.6.

Знокоеене ротор 0

Знакогенеротор 1

Экронноя строницо 1

Область символов

Экранной страница 1

Область атрибутов

Экронноя страница 2

Область символов

Экранной страница 2

Область атрибутов

Экронноя страница 3

Область символов

Экранной строницо 3

Область атрибутов

Экранная страница 4

Область символов

Экронноя строницо 4

Область атрибутов

Не используется

Палитра «рано

Палитра спрайтов

ИГРОВАЯ ПРИСТАВКА DENDY

Не используется

OOOOh

lOOOh

2000h

23C0h

2400h

27COh

2800h

2BCOh

2COOh

2FCOh

3000b

3F00h

3F10h

3F20h

3FFFh

Рис. 1.6. Адресное пространство видеопроцессора

игровой приставки DENDY

Как видно из рис. 1.6, видеопроцессор может ра-

ботать с 16 Кб памяти в диапазоне адресов OOOOh-

3FFFh. Однако, как и в случае с центральным про-

цессором, объем реально присутствующей памяти

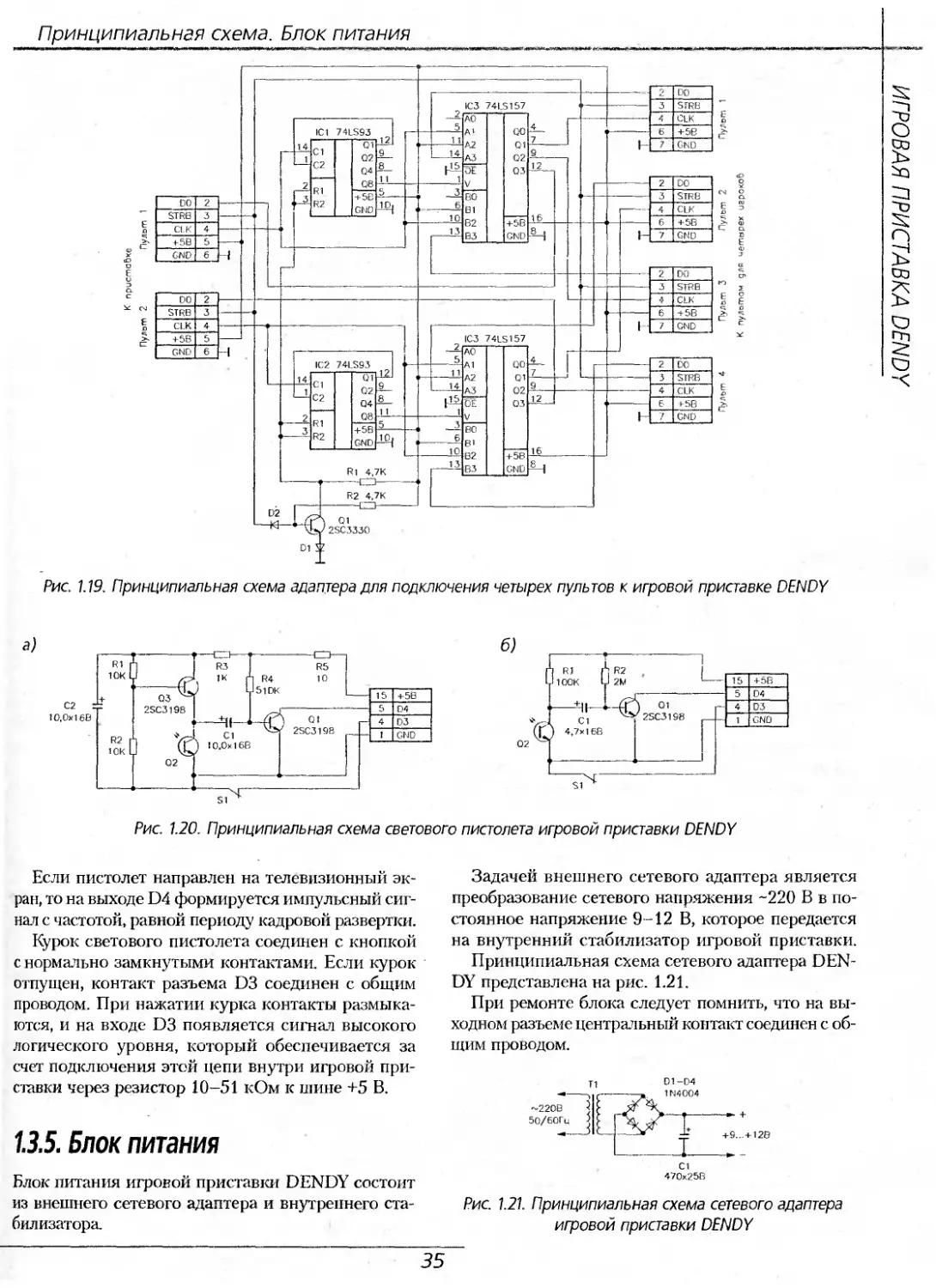

гораздо меньше: он составляет всего 2 Кб.

В видеопамяти приставки DENDY выделено не-

сколько областей, имеющих различное назначение.

Рассмотрим, как они влияют на формирование

изображения.

Знакогенератор. Эта область видеопамяти зани-

мает первые 8 Кб с адресами 0 0 0 Oh - IFFFh. Здесь

хранятся битовые образы выводимых на экран сим-

волов. Под символом в данном случае подразумева-

ется блок изображения размером 8x8 точек. Каждый

битовый образ требует 16 байт памяти. Видеопро-

цессор совмещает две части битового образа, в ре-

зультате чего получается четырехцветное изображе-

ние. Цвет с кодом, два младших разряда которого

равны 0, всегда воспринимается видеопроцессором

как прозрачный.

Этот процесс поясняется на рис. 1.7.

Как видно из рис. 1.6, область памяти OOOOh -

IFFFh разделена на две таблицы знакогенераторов

с базовыми адресами OOOOh и 100Oh. Одна табли-

ца хранит изображения блоков, из которых строит-

ся фоновая картинка, в другой находятся битовые

образы спрайтов. Назначение таблиц определяется

программным путем при записи кода в управляю-

щий регистр видеопроцессора.

Итак, первым этапом, необходимым для вывода

изображения на экран, является разработка знако-

генераторов для фона и спрайтов. Из сделанных

вами блоков и будет состоять показываемая кар-

тинка.

19

Архитектура и принцип работы. Видеопроцессор

ИГРОВАЯ ПРИСТАВКА DENDY

СОДЕРЖИМОЕ ВИДЕОПАМЯТИ

0010: 00010000 (10h) 0018: 00000000 (OOh)

ООП: 00000000 (00h) 0019 : 00101000 (28h)

0012 : 01000100 (44h) 001A: 01000100 (44h)

0013 : 00000000 (00h) 001B: 10000010 (82h)

0014: 11111110 (FEh) 001C: 00000000 (OOh)

0015: 00000000 (OOh) 001D: 10000010 (82h)

0016: 10000010 (82h) 001E: 10000010 (82h)

0017: 00000000 (00h) Разряд 0 РЕЗУЛЬТАТ СОВМЕЩЕНИЯ 001F: 00000000 Разряд 1 (OOh)

00 00 00 01 00 00 00 00 ... 1..

00 00 10 00 10 00 00 00 . .2.2.

00 11 00 00 00 11 00 00 .3. . .3

10 00 00 00 00 00 10 00 2 2.

01 01 01 01 01 01 01 00 1111111.

10 00 00 00 00 00 10 00 2 2.

11 00 00 00 00 00 11 00 3 3 .

Об 00 00 00 00 00 00 00

экране не показываются и размер видимого изобра-

жения по вертикали уменьшается до 224 точек.

Предположим, что на экран нужно вывести бук-

ву «А», битовый образ которой уже размещен в зна-

когенераторе по адресу OOlOh (рис. 1.7). Если ак-

тивна первая экранная страница, то запись числа

0lh в видеопамять по адресу 2 0 0 Oh приведет к по-

явлению буквы в верхнем левом углу экрана (толь-

ко в PAL-версии).

Сразу за областью символов начинается область

атрибутов экранной страницы, занимающая 64 бай-

та. Каждая ячейка области атрибутов хранит ин-

формацию о цвете четырех смежных квадратов

размером 2x2 символа, которые в свою очередь

образуют квадрат 4x4 символа. Таким образом,

два младших бита ячейки области атрибутов пер-

вой экранной страницы с адресом 23C0h содер-

жат данные о цвете для символов, располагающих-

ся в ячейках области символов первой экранной

страницы с адресами 2 0 0 Oh, 2 0 0 lh, 2 02 Oh и 2 02 lh.

Структура экранной страницы игровой пристав-

ки DENDY представлена на рис. 1.8.

Рис. 1.7. Формирование символов

в игровой приставке DENDY

Обычно в ПЗУ игрового картриджа содержится

один или несколько заранее записанных знакогене-

раторов. Микросхема контроллера управления стра-

ницами памяти подключает один из них в адресное

пространство видеопроцессора, и все его символы

становятся доступными для вывода на экран.

Экранная страница. В адресном пространстве

видеопроцессора DENDY располагаются четыре

экранные страницы. Однако установленной в игро-

вой приставке памяти хватает только для размеще-

ния двух экранных страниц, одна из которых назы-

вается активной. Как программы используют эти

страницы, будет объяснено ниже. Каждая экранная

страница делится на область символов и область

атрибутов. '

Активная экранная страница - это страница ви-

деопамяти, содержимое которой служит для фор-

мирования изображения на экране.

Область символов - часть экранной страницы,

включающая информацию о номерах элементов зна-

когенератора, из которых строится изображение.

Область атрибутов - часть экранной страницы,

где хранятся сведения о цвете элементов знакоге-

нератора, из которых строится изображение.

Область символов каждой экранной страницы

содержит 960 байт и представляет собой сетку из

30 строк по 32 символа в каждой. Таким образом,

размер экрана равен 256x240 точек.

Важное отличие NTSC-версии приставки состо-

ит в том, что верхний и нижний ряды символов на

а)

6)

32 знакоместо (256 точек)

2000Н 2001h

2020h 202lh

2040h

2360h

2380h 2381h

23A0h 23A1h

23C0h

23C8h

23D0h

23D8h

23E0h

23E8h

23F0h

23F8h

2002h|

| 201 Ph

201Eh 201Fh

203Eh 203Fh

205Fh

237Fh

23A2h|

|23BDh

239Eh

23BEh

239Fh

23BFh

8 знакомест

23C1h 23C2h 23C3h|23C4h 23C5h 23C6h

23C9h

23C7h

23CAh

23CDh

23Dlh

23D6h

23CEh

23CFh

23D7h

23DFh

23E7h

23E9h

23F1h

23F2h

23F5h

23EEh

23F6h

23F9K 23FAH 23FBh|23FCh 23FDh 23FEH

23EFh

23F7h

23FFh

Рис. 1.8. Структура экранной страницы

видеопроцессора игровой приставки DENDY:

а - область символов; б - область атрибутов

Для получения номера цвета точки, изображенной

где-либо на экране, требуются два бита из соответ-

ствующего банта атрибутов и два бита из битового

образа, записанного в знакогенераторе. В результате

получается 4-разрядное число в диапазоне 0-15, од-

нозначно задающее номер цвета в палитре (рис. 1.9).

Внутренней видеопамяти игровой приставки до-

статочно только для размещения двух экранных

страниц. Это приводит к возникновению эффекта,

называемого отражением экранных страниц. Четы-

ре основных случая отражения рассмотрены ниже.

1оризонталъное отражение. В этом режиме по-

парно объединяются экранные страницы 0,1 и 2,3,

20

Архитектура и принцип работы. Видеопроцессор

—ji_

2000h 200th

2020h 2021h

2040h 2041h

2060h 2061h

“XZ

2022h 2023h

2042h 2043h I

2062h 2063h

2002h 2003h

| 7 | 6 j 5 | 4 j 3 | 2 | 1 | 0 |

Байт атрибутов

23C0h

Область символов

Рис. 1.9. Формирование цветовой информации

в видеопроцессоре игровой приставки DENDY

то есть запись в экранную страницу 0 идентична

записи в экранную страницу 1.

Вертикальное отражение. В данном режиме объ-

единяются экранные страницы 0, 2 и 1, 3. Запись

в экранную страницу 0 идентична записи в экран-

ную страницу 2.

Режим одного экрана. В таком случае используется

одна экранная страница с установленным номером.

Режим четырех экранов. Если в картридже уста-

новлено дополнительное ОЗУ для видеопроцессора,

то можно работать со всеми четырьмя экранными

страницами.

Режим отражения экранных страниц видеопамя-

ти полностью зависит от контроллера страниц па-

мяти, находящегося в картридже. Внутренние схе-

мы видеопроцессора не позволяют менять этот

режим. Некоторые контроллеры страниц памяти

модифицируют его путем записи кода в управляю-

щий регистр во время выполнения программы.

Палитра. В памяти видеопроцессора игровой

приставки по адресам 3F00h-3FlFh располагают-

ся палитра фона и палитра спрайтов. Каждая па-

литра содержит по 16 цветов, которые могут быть

одновременно использованы для раскрашивания

изображения. 4-разрядный код, образованный как

объяснялось выше, однозначно определяет номер

цвета в палитре.

В каждую ячейку палитры помещается 8-разряд-

ное значение, устанавливающее цвет точки на экра-

не. Шестой и седьмой разряды записанного в ячей-

ке числа игнорируются.

Необходимо учитывать также эффект, называе-

мый отражением палитр. Каждая четвертая ячей-

ка палитры отражается на аналогичную ячейку

другой палитры, то есть в адресном пространстве

видеопроцессора совмещены ячейки с адресами

3FOOh и 3F10h, 3F04h и 3F14h, 3F08h и 3F18h,

3F0Ch и 3 FICh, поскольку цвет с двумя младшими

битами 00 всегда определяется как прозрачный

и не влияет на окраску изображения. Содержимое

ячейки памяти с адресом 3F00h задает цвет фона

для всего экрана.

Возможности видеопроцессора

Разнообразие и качество программного обеспече-

ния игровой приставки в значительной степени

определяются возможностями видеопроцессора

и теми манипуляциями с графической информаци-

ей, которые он в состоянии производить сам, в то

время как центральный процессор приставки занят

другими задачами.

Игровая приставка DENDY, как уже было сказано,

создавалась для использования спрайтовой графи-

ки. Спрайты - графические блоки фиксированно-

го размера, которые обрабатываются видеопроцес-

сором независимо от основного изображения.

Видеопроцессор DENDY позволяет выводить иа

экран до 64 спрайтов размером 8x8 или 8x16 точек

каждый, передвигать спрайты и фон независимо

друг от друга и плавно прокручивать фоновую кар-

тинку в любом направлении. Рассмотрим эти функ-

ции устройства более подробно.

Спрайты. Если в игре используются спрайты раз-

мером 8x8 точек, то их изображения хранятся в одном

из знакогенераторов, расположенных в видеопамяти.

Если применяются спрайты размером 8x16 точек, то

изображения спрайтов с четными номерами помеща-

ются в знакогенератор 0 (с базовым адресом 000Oh),

а с нечетными - в знакогенератор 1 (с базовым адре-

сом 10 0 Oh). Иногда контроллер страниц памяти, уста-

новленной в картридже, дополнительно подключает

ПЗУ, где изображения спрайтов записаны заранее.

Память спрайтов. Это отдельная страница памя-

ти видеопроцессора, которая содержит информацию

о специальных графических блоках - спрайтах.

Память спрайтов занимает 256 байт, которые не

входят в адресное пространство видеопроцессора.

Для каждого из 64 спрайтов, с которыми может ра-

ботать видеопроцессор игровой приставки, отведе-

но по четыре байта.

В этих байтах располагается следующая инфор-

мация:

1. Координата верхнего левого угла спрайта по вер-

тикали.

2. Номер блока с изображением спрайта в знакогене-

раторе.

3. Атрибуты спрайта:

D7 - отражение спрайта относительно вертикаль-

ной оси:

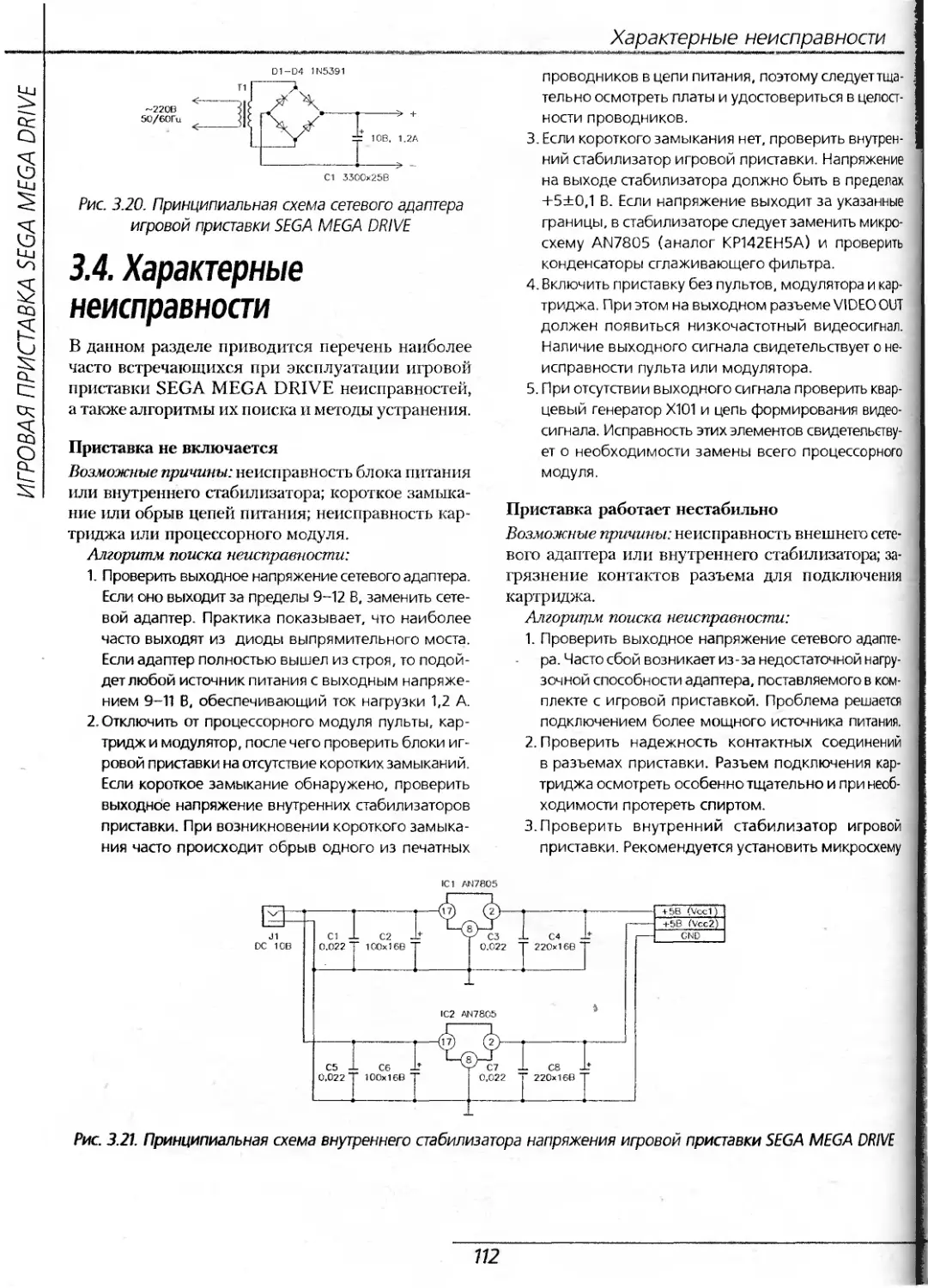

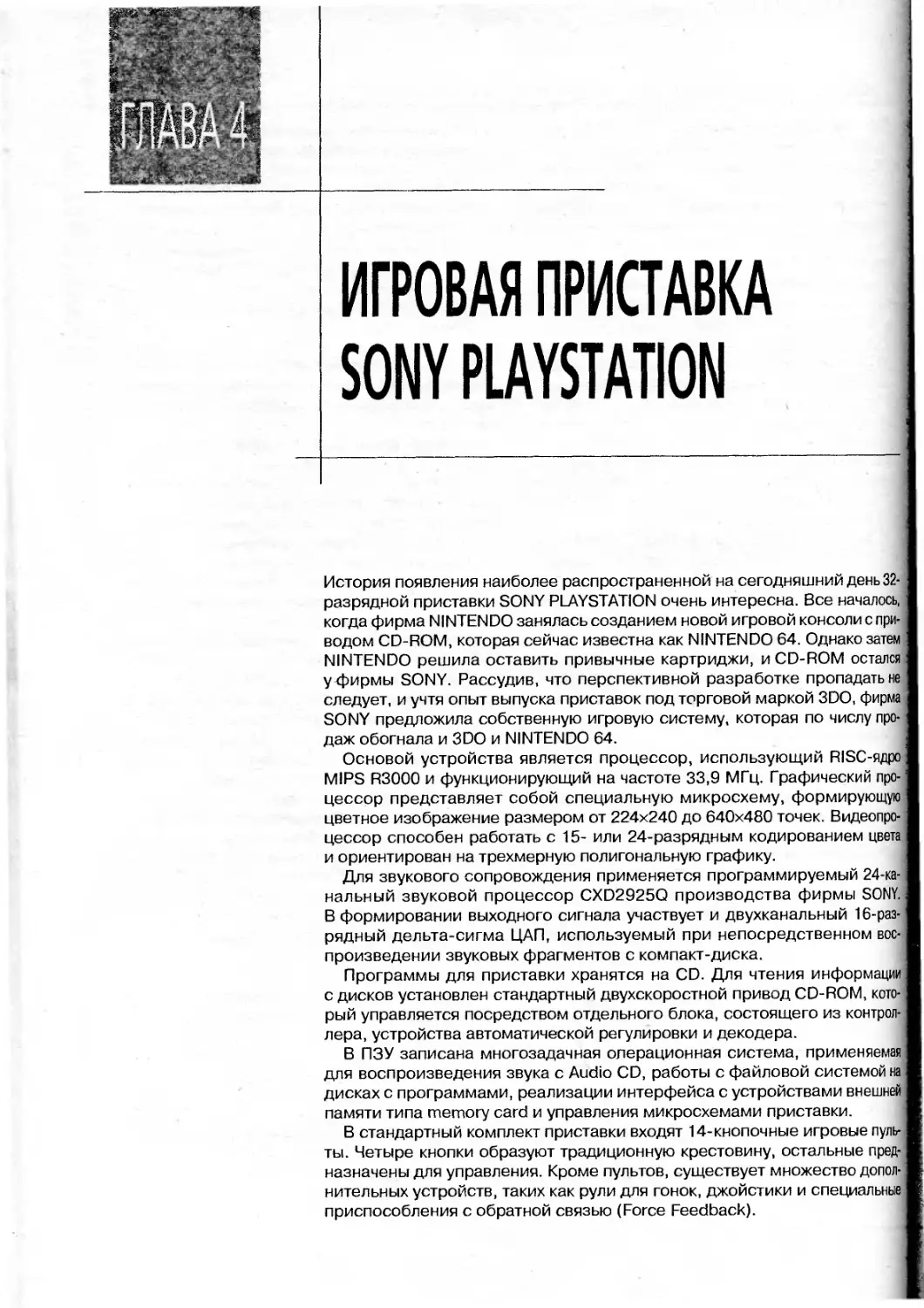

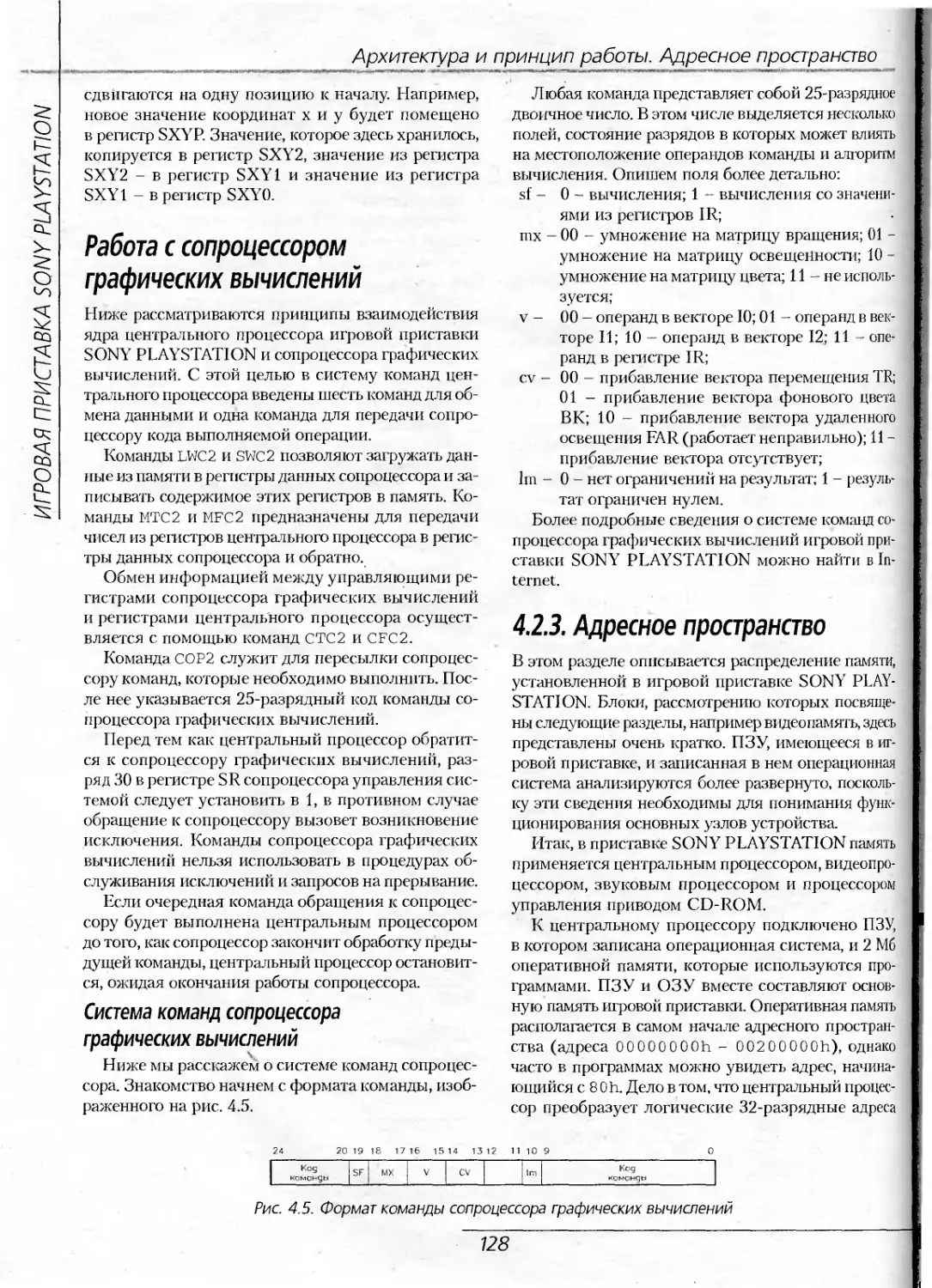

1 - выводится зеркальное отражение спрайта;