Текст

Б. А. ГОЛОВКИН

ПАРАЛЛЕЛЬНЫЕ

ВЫЧИСЛИТЕЛЬНЫЕ

СИСТЕМЫ

МОСКВА «НАУКА»

ГЛАВНАЯ РЕДАКЦИЯ

ФИЗИКО-МАТЕМАТИЧЕСКОЙ ЛИТЕРАТУРЫ

1980

22.18

Г 61

УДК 519.6

Параллельные вычислительные системы. Г о-

л о в к и в Б. А.— М.: Наука. Главная редакция*

физико-математической литературы, 1980.

В книге рассматриваются параллельные вычис-

лительные системы (вычислительные системы па-

раллельной обработки информации): многомашин-

ные, многопроцессорные, магистральные (конвейер-

ные), матричные, ассоциативные, с комбинирован-

ной и перестраиваемой структурой и некоторые*

другие. Системы таких типов отличаются повышен-

ной гибкостью и обладают высокими характерис-

тиками пройзводительности и надежности.

Дается систематическое описание организации»

структуры и функционирования параллельных вы-

числительных систем. В описании приводятся

структурные схемы и основные характеристики не-

скольких десятков отечественных и зарубежных,

параллельных вычислительных систем.

Книга рассчитана па инженеров и научных ра-

ботников в области вычислительной техники, прог-

раммирования и обработки информации, а также-

на студентов старших курсов и аспирантов соот-

ветствующих специальностей.

34-80. 1702070000

053(02)-80

(©Издательство «Наука»

Главная редакция

физико-математической*

литературы, 1980

ОГЛАВЛЕНИЕ

Предисловие . . ♦ ....... i . . 6

1. Эволюция вычислительных систем: от последовательных систем к

параллельным..................................................... 9

1.1. Эволюция однопроцессорных систем........................... 9

1.1.1. Параллельная обработка разрядов слов. Совмещение процес-

сов ввода-вывода и вычислений (9). 1.1.2. Совмещение операций и

опережающий просмотр команд и данных (11).

4.2. Эволюция многомашинных и многопроцессорных систем (на при-

мере систем IBM)................................................14

1.2.1. Ранние многомашинные системы с косвенной связью (14).

1.2.2. Ранние многомашинные системы с прямой связью. Система

DCS (15). 1.2.3. Слабо и сильно связанные системы (16). 1.2.4. Мно-

гомашинная система с вспомогательным процессором ASP (17).

1.2.5. Структуры многомашинных и многопроцессорных систем.

Тенденции развития (19).

4.3. Краткий обзор......................................... • 21

2. , Организация структуры и функционирования параллельных вычи-

слительных систем ..........................................

2.1. Классификация вычислительных систем......................

2.1.1. Признаки в схема классификации. Нотация классов (24).

2.1.2. Описание классов вычислительных систем (26).

2.2. Потоки команд и данных. Пословная и поразрядная обработка. '

Основные структуры и определения................................28

2.2.1. Одиночные и множественные потоки команд и данных (28).

2.2 2. Посло4ная и поразрядная обработка (31) 2.2.3. Основные

структуры и определения (32). 2.2.4. Коммутация потоков команд

и данных (38).

2.3. Некоторые основные соотношения между структурами вычисли-

тельных систем................................................ 42

2.4. Структура связей в параллельных вычислительных системах . 47

2.4.1. Межпроцессорные связи в вычислительных системах в се-

тях и их классификация (47). 2.4.2. Внутренние связи в многопро-

цессорных системах (53).

2.5. Структура связей между центральной частью вычислительных

систем и каналами ввода-вывода..................................55

2.5.1. Основные типы структуры связей (55). 2.5.2. ^Сопряжение с

периферийными устройствами (61).

*2.6. Структура многопроцессорных систем с языками высокого уровня 68

2.7. Краткий обзор............................................ 79

2.7.1. Обзор монографий, сборников и обзоров (80). 2.7.2. Обзор

схем классификации и структур параллельных вычислительных

систем (89).

*3. Многомашинные и многопроцессорные системы на базе однопро-

цессорных ЭВМ......................................................

.3.1. Концепция и ранние системы......................... * * 99

3.1.1. Концепция комплексирования однопроцессорных ЭВМ (99)*

3.1.2. Система Минск-222 (101). 3.1.3. Система КЛАСС (103)*

3.1.4. Система Днепр-2 (104).

4* 3

3.2. Системы на базе ЭВМ БЭСМ-6 . ......................... . . 106» '

3.2.1. Структура ЭВМ БЭСМ-6 (106). 3.2.2. Многомашинные систе-

мы на базе ЭВМ БЭСМ-6 (109). 3.2.3. Библиографическая справка

(117).

3.3. Системы на' базе ЭВМ семейства ЕС...........................11$

3.3.1. Структура семейства ЕС ЭВМ (118). 3.3.2. Многомашинные

и многопроцессорные системы на базе ЕС ЭВМ (123). 3.3.3. Биб-

лиографическая справка (136).

3.4. Системы на базе ЭВМ семейств АСВТ-М и СМ ЭВМ .... 137

3.4.1. Структура семейств АСВТ-М и СМ ЭВМ (137). 3.4.2. Много-

машинные и многопроцессорные системы на базе АСВТ-М и СМ

ЭВМ (146). 3.4.3. Библиографическая справка (149).

3.5. Системы на базе ЭВМ семейств IBM 360 и IBM 370. Семейство

IBM ЗОЗХ....................................................... 150

~ 3.5.1. Структура семейств IBM 360 и IBM 370 (150). 3.5.2. Многома-

шинные и многопроцессорные системы на базе ЭВМ семейств I

IBM 360 и IBM 370 (153). 3.5.3. Система IBM 360/67 (156). 3.5.4. Си-

стемы IBM 360/65 МР, 370/158 МР, 370/168 МР (158). 3.5.5. Семей-

ство IBM ЗОЗХ и новые разработки фирмы IBM (160). 3.5.6. Биб-

лиографическая справка (162).

3.6. Системы на базе ЭВМ семейства4 DEC PDP-11 . . . . . 164

3.6.1. Структура семейства PDP-11 (164). 3.6.2. Многомашинные и

многопроцессорные системы на базе ЭВМ семейства PDP-11 (167).

3.6.3. Библиографическая справка (169).

4. Многопроцессорные системы t • 171

4Л. Концепция и ранние системы .................................17®

4.1,1. ' Разработки концепций многопроцессорных систем (171).

4.1.2. Система RW 400 (176). 4.1.3. Система D825 (177). 4.1.4. Сис-

тема СЕЮ 3600 (180). 4.1.5. Система PHILCO 213 (183). 4.1.6. Систе-

ма LARC (184). 4.1.7. Система PILOT (187). 4.1.8. Система GAM-

MA 60 (189). 4.1.9. Система STRETCH (190). 4.1.10. Основные поло-

жения концепции организации многопроцессорных систем (192).

4.1.11; Библиографическая справка (200).

4.2. Системы семейства Эльбрус...........................* . 201

4.2.1. Концепция построения систем семейства Эльбрус (201).

4.2.2. Структура систем семейства Эльбрус (205). 4;2.3. Библиогра-

фическая справка (213).

4.3. Системы фирмы Burroughs.....................................214

4.3.1. Концепция построения систем фирмы Burroughs (214).

4.3.2. Структура систем фирмы Burroughs (217). 4.3.3 Библио-

графическая справка (228).

4.4 Системы семейства UNIVAC 1100 .......................... 229*

4.4.1. Структура семейства UNIVAC 1100 (229). 4.4.2. Системы

UNIVAC 1108 и 1406 (232). 4.4.3. Система UNIVAC 1110 (237). 4.4.4.

Системы UNIVAC 1100/10, 1100/20, 1100/40, 1100/80 (239). 4.4.5. Би-

блиографическая справка (244).

4.5. Системы семейства DEC System 10.............................245

4.6. Системы фирмы Honeywell....................................- 250<

4.7. Система SYMBOL .............................................255

5. Магистральные системы........................................261

5.1. Концепция и ранние системы..................................261

5.2. Системы фирмы Control Data ............................... 265

5.2.1. Системы CDC 6600 и 7600 и другие'системы семейств CDC

6000 и 7000 (265). 5.2.2. Системы семейств CYBER 70 и 170 (273).

5.2.3. Система STAR 100 (277). 5.2.4. Библиографическая справка

(280).

5.3. Системы IBM 360/91 и IBM 360/195 ........................ 282г

5.4. Система MU5 ................................................. 285»

4

5.5. Система ASC . ♦ . ..................... . < . • . 288

5.6. Система AMDAHL 470 V/6.....................................292

5.7. Система CRAY 1............................,................296

6. Матричные, ассоциативные и подобные им системы..............303

6.1. Концепция и ранние системы..................-. . . . 303

6.2. Вычислительная система М-10........................... . 307

6.3. Система РЕРЕ..............................................31£

6.4. Система ILLIAC IV '.......................................318

6.5. Системы BSP, DAP, IBM 3838 и другие матричные системы . . 327

6.6. Система STARAN и другие ассоциативные системы .... 339

7. Системы с комбинированной и перестраиваемой структурой. Отка-

зоустойчивые системы ..........................................354

7.1. Концепция и ранние системы................................354

7.1.1. Концепция систем с комбинированной структурой (354).

7.1.2. Применение микропроцессоров (357). 7.1.3? Концепция систем

с перестраиваемой структурой (358). 7.1.4. Концепция устойчи-

вости вычислительных систем к отказам (362).

7.2. Системы с комбинированной и перестраиваемой структурой . 368.

7.2.1. Системы семейства OMEN 60 (368). 7.2.2. Система МИНИ-

МАКС (371). 7.2.3. Система СУММА (374). 7.2.4. Библиографиче-

ская справка (376).

7.3. Отказоустойчивые системы..................................377

7.3.1. Системы JPLSTAR и *UDS (377). 7.3.2. Система PLURIBUS

(382). 7.3.3. Система TANDEM 16 (386). 7.3.4. Системы С. шшр/

Cm* и С. vmp. (387). 7.3.5. Система COMTRAC (396). 7.3.6. Систе-

мы FTMP и SIFT (399). 7.3.7. Вычислительная система космиче5-

ского корабля «Шаттл» (404). 7.3.8. Библиографическая справка

(406).

7.4. Новые концепции и разработки..............................411

7.4.1. Модульная асинхронная развиваемая система (411). 7.4.2. Ре-

курсивные вычислительные машины (415). 7.4.3. Управляющие

системы с перестраиваемой структурой (418). 7.4.4. Библиографи-

ческая справка (421).

8. Количественные характеристики структур систем. Производитель-

ность и стоимость систем.......................................422

8.1. Количественные характеристики структур вычислительных си-

стем ...........................................................422

8.1.1. Формализация описания^структур систем (422). 8.1.2. Опе-

рации над формальными описаниями структур систем (432).

8.2. Производительность и стоимость параллельных вычислительных

систем......................................................... 436

8.2.1. Оценка и прогноз увеличения производительности парал-

лельных вычислительных систем (436). 8.2.2. Отношение произво-

дительности к стоимости вычислительных систем (447).

8.3. Краткий обзор..........................................., 451

Литература ................................................... 460

Предметный указатель . 4 518

ПРЕДИСЛОВИЕ

В книге рассматриваются . многомашинные, многопроцессор-

ные, магистральные (конвейерные), ассоциативные и матричные

системы, системы с векторным потоком данных и ансамбли про-

цессоров, а также системы с комбинированной и перестраивае-

мой структурой. Большой интерес к этим системам и их значение

определяются тем, что они отличаются большой гибкостью и

обеспечивают высокие и рекордные показатели производитель-

ности, надежности, готовности и живучести. В последние годы

значительно повысилось отношение производительности таких

систем к их стоимости, что особенно важно для расширения

области применения систем.

В ближайшее время ожидается существенное расширение раз-

работок рассматриваемых типов вычислительных систем, увели-

чение их производства, улучшение характеристик и расширение

области применения, особенно в связи с развитием микропро-

цессорной техники и техники больших интегральных схем.

Быстрое развитие разнообразных и сложных вычислительных

систем приводит к изменению <и уточнению терминологии и к

появлению новых понятий, что особенно характерно для рассмат-

риваемой области вычислительной техники. В этих условиях

большие трудности вызывает терминология. При написании кни-

• ги была использована терминология, получившая наибольшее

распространение, хотя она во многих случаях и не является

общепринятой и устоявшейся.

Для описываемых в книге вычислительных систем было вы-

брано название «параллельные вычислительные системы» (вы-

числительные системы параллельной обработки информации).

Характерной особенностью рассматриваемых в книге систем

является то, что они имеют, по меньшей мере, более одного уст-

ройства управления или более одного центрального обрабатываю-

щего устройства, которые работают одновременно. Вследствие

этого в центральной части таких систем имеется, по мёньшей

мере, два параллельных потока команд или данных. Кроме этого,

методы программирования и методы вычислительной математики

для таких систем в большинстве случаев также называются

параллельными. Поэтому, выбрав слово «параллельный» в каче-

стве корневого, можно с достаточной степенью однозначности

6

говорить о средствах и методах параллельной обработки инфор-

мации — параллельных вычислительных системах, параллельном

программировании и параллельных вычислительных методах. При

этом, однако, не достигается полная однозначность, так как, на-

пример, элементы параллельной обработки информации имеются

Рис. 0.1. Схема логических связей между главами.

и в однопроцессорных ЭВМ: параллельность обработки разрядов

слова в арифметико-логическом устройстве, совмещение во вре-

мени работы устройств ЭВМ, опережающий просмотр команд и

данных и другие.

В первой главе настоящей книги описывается эволюция вы-

числительных машин и систем в направлении от последователь-

ной обработки информации к параллельной обработке. Во второй

главе дается систематическое изложение организации структуры

и функционирования разного типа параллельных вычислитель-

ных систем. В последней главе рассматриваются числовые ха-

рактеристики структур вычислительных систем, а также оценка

и прогноз увеличения производительности параллельных вычис-

лительных систем и отношение их производительности к стои-

мости. В остальных главах приводится сжатое описание несколь-

ких десятков характерных параллельных вычислительных систем

разнообразных типов. При этом основное внимание уделяется

действующим и новейшим ристемам, описываются также ряд ха-

7

рактерных ранних систем и ряд концепций параллельных вы-

числительных систем. Описание ориентирована на организацию

структуры и функционирования вычислительных систем и иллю-

стрировано структурными схемами систем. Схема логических

связей между главами книги приведена на рис. 0.1.

По тематике параллельных вычислительных систем опубли-

ковано несколько тысяч работ. Рассмотреть такое количество

работ или даже просто перечислить их наименования в книге

ограниченного объема не представляется возможным. В целях

облегчения знакомства читателей с литературой по параллельным

вычислительным системам и более глубокого их изучения в книгу

включены краткий обзор и библиографическая справка по

параллельным системам, разнесенные по соответствующим раз-

делам.

Книга рассчитана на читателей, знакомых с основами пост-

роения структур ЭВМ, и предназначена для инженеров и науч-

ных работников в области вычислительной техники, программи-

рования и обработки информации, а также для студентов и аспи-

рантов соответствующих специальностей.

В. А. Головкин

t ЭВОЛЮЦИЯ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ!

ОТ ПОСЛЕДОВАТЕЛЬНЫХ СИСТЕМ К ПАРАЛЛЕЛЬНЫМ

1.1. Эволюция однопроцессорных систем

1.1.1. Параллельная обработка разрядов слов. Совмещение

процессов ввода-вывода и вычислений. В основу большинства

однопроцессорных систем положена концепция вычислительной

машины Дж. фон Неймана, изложенная в отчете, подготовлен-

ном в середине Сороковых годов и в‘ последующем несколько раз

переиздававшемся [35]. В качестве основных устройств универ-

сальной автоматической ЭВМ были выделены арифметико-логи-

ческое устройство, память для хранения как данных, так и ко-

манд, устройство управления и устройства ввода и вывода

(рис. 1.1). Уже в первых машинах осуществлялась параллельная

обработка разрядов каждого слова в параллельном арифметико-

логическом устройстве. При обмене информацией в трактах

ввода-вывода и между устройствами машины разряды каждого f

слова данных и каждой команды (или _их частей) передавались

параллельно. Другие процессы в ЭВМ были последовательными,

а потоки команд и данных — одиночными.

Следует отметить, что известны ЭВМ с последовательными

арифметико-логическими устройствами, обрабатывающие инфор-

мацию бит за битом. Такие машины имеют сравнительно низкую

производительность и используются, в основном, как вспомога-

тельные вычислительные устройства..

В вычислительных машинах со структурой, изображенной "на

рис. 1.1, ввод и вывод информации осуществлялся через ариф-

метико-логическое устройство, поэтому на время ввода и вывода

вычисления прекращались. В целях повышения производитель-

ности вычислительных машин в середине пятидесятых годов

было осуществлено совмещение во времени процессов, вво^а-вы-

вода и вычислений путем организации непосредственного обмена

с памятью при вводе и выводе, минуя арифметико-логическое

устройство (рис. 1.2).'

Такая структура вычислительных машин обладала существен-

ным недостатком — снижением производительности во время

ввода ч и вывода информации из-за необходимости подробного

контроля и управления операциями ввода-вывода со -стороны

устройства управления. Поэтому на пути совмещения процессов

ввода-вывода и вычислений был сделан следующий и основной

шаг —в состав машины был включен независимый канал ввода-

вывода, представляющий собой фактически небольшую специали-

зированную ЭВМ (рис. 1.3).

Канал может выполнять функции ввода-вывода одновремен-

йо (параллельно) с работой арифметико-логического устройства

Рис. 1.1. Структурная схема машицы Дж. фон Неймана. Одинарными ли-

ниями показаны связи для сигналов управления, а двойными линиями —

связи для данных и команд.

и обеспечивает независимый доступ к памяти и автономное уп-

равление операциями ввода-вывода. Устройство управления сох-

раняет только общие функции координации ввода-вывода, связан-

' ные, например, с началом и окончанием ввода-вывода или с

реакцией на нестандартные ситуации. Программа самого канала

размещается обычно в основной памяти машины, поэтому при

Рис. 1.2. Структурная схема вычислительной машины с организацией не-

посредственного обмена с памятью при вводе и выводе. Одинарными лини-

ями показаны связи для сигналов управления, а двойными линиями — свя-

зи для данных и команд.

его работе осуществляется занятие Циклов памяти для выборки

команд канала, что приводит на время обмена к некоторому

снижению производительности машины по сравнению с потенци-

ально достижимой производительностью при полном распарал-

10

леливании процессов ввода-вывода и вычислений. Вычислитель-

ная машина может быть оборудована несколькими каналами,

способными осуществлять свои функции одновременно (парал-

лельно).

Таким образом, при работе вычислительной машины, имею-

щей каналы ввода-вывода, процесс • вычислений и один или

Рис. 1.3. Структурная схема вычислительной машины с каналом ввода-вы-

вода. Одинарными линиями показаны связи для сигналов управления,

а двойными линиями — связи для данных и команд.

несколько процессов ввода-вывода могут выполняться одновре-

менно (параллельно).

1.1.2. Совмещение операций и опережающий просмотр комаид

и данных. Другим направлением распараллеливания процессов в

ЭВМ явилось совмещение во времени этапов выполнения сосед-

них операций в центральной части машины.

Идеи об использовании принципа совмещения операций в

целях повышения скорости вычислительных машин, а также об

объединении машин и о создании многопроцессорных систем с

общей основной памятью высказал академик С. А. Лебедев

1251] на сессии АН СССР (1957 г.). Приведем некоторые выдерж-

ки из его доклада.

«Некоторые возможности повышения скорости электронных

вычислительных машин имеются... в случае использования прин-

ципа совмещения операций. Выполнение арифметических дейст-

вий в значительной мере может быть совмещено по времени с

обращением к памяти. При этом можно отказаться от стандарт-

ного цикла выполнения операций, когда вызов следующей

команды производится после отсылки результата в запоминаю-

щее устройство, и производить выборку команд перед отсылкой

результатов в запоминающее устройство... Благодаря такому из-

менению цикла работы машины на выполнение арифметического

действия.... дополнительно добавляется время, идущее на вызов

следующей команды.

А

Возможное ускорение работы машины за счет совмещения

вызова команд и чисел по двум независимым каналам также

может дать сокращение времени...

Помимо быстродействия арифметического устройства, сущест-

венным фактором, определяющим скорость работы машин, явля-

ется время обращения к ’запоминающему устройству... Одним из

решений уменьшения времени обращения к запоминающему

устройству является создание дополнительной «сверхбыстродей-

ствующей памяти» сравнительно небольшой емкости. Создание

такой «памяти» позволит сократить время для выполнения стан-

дартных вычислений...

Некоторые весьма важные задачи, в особенности многомерные

вадачи математической физики, не могут успешно решаться при

скоростях работы современных электронных вычислительных

машин, и требуется существенное повышение их быстродействия.

Одним из возможных путей для решения таких задач может

явиться параллельная работа нескольких машйй, объединенных

одним общим дополнительным устройством управления и с обес-

печением возможности передачи кодов чисел с одной машины 'на

другую. Однако может оказаться более целесообразным создание

ряда параллельно работающих отдельных устройств машины.

В такой машине должна иметься общая основная «память» для

хранения чисел и команд, необходимых для решения задачи. Из

этой «памяти» числа и команды, требующиеся для решения того

или иного этапа задачи, поступают на ряд сверхбыстродействую-

щих запоминающих устройств сравнительно небольшой емкости.

Каждое такое сверхбыстродействующее запоминающее устройст-

во связано со своим арифметическим устройством. Эти устройст-

ва имеют свое индивидуальное управление. Помимо этого,

должно быть предусмотрено общее управление всей машиной в

целом.

Для более полного использования арифметических устройств

требуется, чтобы заполнение «сверхбыстродействующей памяти»

из общей «памяти» машины осуществлялось одновременно с вы-

полнением вычислений» [251].

Несмотря на то,-что эти идеи были высказаны более 20 лет

назад — очень большой срок для вычислительной техники — и что

за это время прошли смены поколений вычислительных машин,

они актуальны и сейчас.

Продолжим рассмотрение вопросов совмещения операций.

Методы совмещения операций были усовершенствованы,

а область их действия расширена. Стал применяться опережаю-

щий просмотр нескольких команд и данных с соответствующей

Выборкой из памяти и предварительной подготовкой к выполне-

ркю операций. Была организована асинхронная работа устройств

машины,, что потребовало ввести в их состав местные устрой-

ства управления и позволило иметь в фазе выполнения сразу

несколько соседних команд. При такой организации функциони-

42

рования машины в данный момент времени первая из группы

совместно выполняемых команд проходит последний этап выпол-

нения и занимает одно из устройств машины, следующая за ней

команда проходит предпоследний этап выполнения и занимает

другое устройство и т. д. К очередному интервалу времени пер-

вая из рассматриваемых команд оказывается выполненной,

л остальные команды переходят к очередным этапам выполнения

и занимают соответствующие этим этапам устройства. В фазу

выполнения вводится новая команда, которая занимает устройст-

во для выполнения первого этапа операции, освободившееся пос-

ле выполнения первого этапа последней из команд, совместно

выполнявшихся на предыдущем интервале времени, и так далее.

Такая организация функционирования направлена на обеспе-

чение полной загрузки каждого устройства машины. Однацо,

вследствие- разного количества и неидентичности этапов выпол-

нения ‘различных операций, а также вследствие прерываний ли-

нейных участков программы ветвлениями, устройства машины

работают все же с перерывами.

Дальнейшим развитием организации функционирования вы-

числительных машин с совмещением во времени выполнения со-

седних операций явилась магистральная (конвейерная) органи-

зация функционирования, которая рассматривается в последую-

щих разделах данной книги.

В целях согласования скоростей работы арифметико-логиче-

ского устройства и памяти были совмещены во времени обраще-

ния -к памяти. Наиболее простой способ реализации такого сов-

мещения состоит в разделении памяти на несколько секций с

раздельным обращением к ним. Количество секций обычно равно

небольшой степени* числа два. Каждая секция снабжается собст-

венным адресным и числовым регистрами. Кроме этого, вво-

дится чередование адресов, суть которого состоит в следующем.

Пусть память разбита на п = 2т секций. Тогда ячейки памяти

с адресами 0, 1, ..., n — 1 реализуются как первые ячейки в каж-

дой из п последовательно расположенных секций памяти, ячейка

с адресами n, п + 1, ..., 2п — 1 — как вторые ячейки в этих сек-

циях и т. д. В адресном поле команды номер секции кодируется

в т младших разрядах адреса, а номер ячейки внутри секции —

в старших разрядах адреса.

При такой организации обращения к ячейкам памяти с после-

довательно увеличивающимися (уменьшающимися) адресами

(что является типичным) осуществляются последовательно к

жаждой секции, с циклическим возвратом к начальной секции.

В наиболее благоприятном случае цикл работы памяти сокра-

щается в п раз по сравнению с циклом работы ее отдельной

секции.

Более сложные способы реализации совмещения обращений

ж памяти состоят в построении многовходовой памяти, которая

допускает одновременное обращение к ней со стороны нескольких

13

устройств и разрешает возникающие при этом конфликты однов-

ременного обращения.

Перечисленные способы организации параллельных процессов

функционирования однопроцессорных систем являются вполне

устоявшимися и находят применение также и в параллельных

системах. В дальнейшем, за исключением характерных случаев,,

они в целях краткости изложения упоминаться не будут.

1.2. Эволюция многомашинных и многопроцессорных

систем (на примере систем IBM) [744]

*

Многомашинные и многопроцессорные системы получил»

наибольшее распространение среди параллельных систем. Рас-

смотрим их эволюцию на фоне развития однопроцессорных ЭВМ.

Это удобно сделать на примере фирмы IBM (International Busi-

ness Machines).

Фирма IBM, подобно большинству изготовителей универсаль-

ных ЭВМ, до 1960 г. прилагала незначительные усилйя для

комплексирования двух или более ЭВМ. В 1955 г. ею были соз-

даны специализированные многомашинные (дуплексные) систе-

мы, расположенные в нескольких местах по периметру Северной

Америки. Они предназначались для обработки информации в;

целях противовоздушной обороны. Эта разработка известна под

названием SAGE (Semi-Automatic Ground Equipment)— Полуав-

томатическое наземное оборудование. В системе резервирования

билетов для американских авиалиний SABRE (1958 г.) была ис-

пользована специализированная дуплексная система. Первона-

чально она представляла собой связку двух машин IBM 7090,.

каждая из которых способна обрабатывать сообщения от мно-

жества терминалов. Одна из машин осуществляла обработку со-

общений в оперативном режиме, а другая находилась в горячем

резерве.

1.2.1. Ранние многомашинные системы с косвенной связью..

До 1961—1962 гг. большинство крупных пользователей устанав-

ливали несколько машин в одном месте, причем в большинстве

таких случаев общей для этих процессоров*) была память на

магнитных лентах, на которых хранились библиотеки программ.

Память на магнитных дисках для программ и данных редко

использовалась до 1961—1962 гг., и почти всегда она была ин-

дивидуальной для каждой конкретной машины.

Ранние многомашинные системы с общей внешней памятью

на магнитных дисках включали в себя машины IBM 1410, косвен-

♦) В литературе под процессором понимается как вычислительная ма-

шина без периферийного оборудования (центральная часть), так и сово-

купность устройства управления и арифметико-логического устройства^

а также арифметико-логическое устройство. В настоящей книге использу-

ются 'все три понятия, при этом выбор того или иного из них в каждом

конкретном случае определяется контекстом.

14

2io связанные одна с другой или с большой машиной, такой как

IBM 7010 или IBM 7090, при помощи этой внешней памяти

<рис. 1.4). Память на магнитных дисках использовалась в режи-

ме разделения оборудования, при этом основной целью было

обеспечение высокой готовности системы. Если одна из машин

Тис. 1.4. Структурная схема многомашинной (слабо связанной) вычисли-

тельной системы с косвенной связью. Двухмашинная конфигурация. Одна

из машин может быть ориентирована на функции ввода-вывода.

выходила из строя или требовала профилактики, то другая мог-

ла быть использована для пакетной или оперативной обработки.

Такая связь между машинами через внешнюю Память Классифи-

цируется как слабая. Динамическое распределение программ и

данных между двумя машинами было относительно редким и

'требовало больших усилий по программированию.

1.2.2. Ранние многомашинные системы с прямой связью»

«Система DCS. В начале 1960-х годов группы крупных пользова-

телей ЭВМ в интересах научных, исследований, применяли другую

методику комплексирования машин семейства IBM 7040/7090.

.Две машины, одной из которых являлась IBM 7040 или IBM 7044

<704Х), а другой — большая машина IBM 7090 или IBM 7094

(709Х), непосредственно связывались между собой в систему,

которая получила наименование DCS (Direct Coupled System)—

система с прямой связью (рйс. 1.5). Первая из машин была

Рис. 1.5. Упрощенная структурная схема двухмашинной (слабо связанной)

вычислительной системы с прямой связью. Внешний вычислитель выполня-

ет функции ввода-вывода. t

внешним вычислителем, обслуживающим низкоскоростные пери-

-ферийные устройства и линии связи, а вторая выполняла функ-

ции центрального вычислителя. В системе использовался адаптер

жаналов для связи между машинами, а не общая память на

15

магнитных дисках. Связь между машинами через адаптер ка-

налов также классифицируется как слабая.

Входные потоки информации поступали от устройств счи-

тывания информации с перфокарт во внешний вычислитель иг

передавались от него при помощи адаптера каналов в централь-

ной вычислитель. После обработки информация поступала в об-

ратном направлении из центрального вычислителя во внешний

для последующей печати и перфорации.

Таким образом, основной функцией внешнего вычислителя в

системе DCS было управление устройствами считывания и печа-

ти информации. В то время политика цен фирмы IBM привела

к такой ситуации, что присоединять устройства ввода-вывода, к

машине IBM 704Х было значительно дешевле, чем к машине

IBM709X.

1.2.3. Слабо и сильно связанные системы. За время от начала *

1960-х годов фирма IBM активно разрабатывала многомашинные '

системы обоих типов — с косвенной связью при помощи общей

внешней памяти на магнитных дисках и с прямой связью машин

при помощи адаптера каналов. По степени связанности обе такие

системы, как отмечалось выше, относятся к слабо связанным.

При создании крупных вычислительных систем для обработ-

ки информации в научных целях и в целях экономических рас-

четов часто требуются:

— вычислительные мощности, превышающие возможности

одной машины; _

— более высокак готовность по сравнению с той, которую

может об еспечить^одн сопроцессор пая система с учетом ее отказов

и профилактики;

— уменьшение числа прерываний в системах, ориентирован-

ных на работу с линиями связи, путем выделения специального

процессора для работы-с- линиями связи и отделения прерываний

от пакетйой обработки;

— функциональное разграничение помещений для вычисли-

тельных машин, при котором все перфокарты обрабатываются

в одном месте, печать осуществляется в другом месте, работа с

машинными лентами — в третьем и т. д.; ъ

— несколько поколений прикладных программ и связанных

с ними операционных систем или оборудования. Для выполнения

этих требований однопроцессорные системы оказываются недо-

статочными/

Фирмы Burroughs, CDC (Control Data), DEC (Digital Equip-

ment), Honeywell/GE, Univac/RCA и некоторые другие много вни-

мания уделяли многопроцессорным системам. В таких системах

два или более- центральных процессоров имеют общую оператив-

ную память и общие периферийные устройства и работают в

.режиме разделения этого оборудования под управлением единой

операционной системы (рис. 1.6). Связь между процессорами

через оперативную память классифицируется как сильная»

16 *

К 1971г. фирма Burroughs разработала и выпустила многопроцес-

сорную систему В 6700, фирма CDC выпустила многопроцессор-

ную систему CDC6500, в которой два процессора CDG6400 име-

ют общую оперативную память, и многопроцессорную систему

CDG6700, в которой процессор CDC6400 имеет общую оператив-

ную память с процессором CDC 6600, фирма DEG выпустила.

многопроцессорные системы DEC

1055 и 1077, фирма Honeywell/

/GE — многопроцессорные системы

Н 6060к Н 6080 и другие системы

семейства Н 600 и, наконец, фирма

Ufiivac — многопроцессорную систему

UNIV АС 1108. Конкуренты фирмы

IBM использовали решения по аппа-

ратуре и программному обеспече-

нию, подобные решениям, принятым

в многопроцессорной системе IBM

360/65 МР и полностью дуплексной

системе IBM 360/67.

Архитектура систем CDC 6500

и CDC 6700 была типичной архи-

Рис. 1.6. Упрощенная струк-

турная схема многопроцессор-

ной (сильно связанной) вычи-

слительной системы.

тектурой сильно связанных си-

стем. Единственная копия операционной системы управляла од-

новременной работой двух процессоров в системе. "

1.2.4. Многомашинная система с вспомогательным процессором

ASP. К середине 60-х годов фирма IBM продолжила и л интенси-

фицировала создание прямо связанных систем. В этих условиях

объявление в 1964 г. семейства машин IBM 360 обескуражило-

пользователей систем DCS, поскольку первоначально в семействе*

IBM 360 не предусматривались средства поддержки комплекси-

рования машин.

В семействе IBM 360 в полной мере закреплялись архитектур-

ные решения фирмы ДВМ для больших однопроцессорных си-

стем с учетом текущей стоимости устройств. На этом фоне про-

явилась экономическая неэффективность многомашинных систем-

Мультиплексный канал семейства IBM 360 обеспечивал присое-

динение множества низкоскоростных периферийных устройств

как к большим, так и к малым машинам. В частности, аномалия*

стоимости присоединения устройств ввода-вывода, которая сти-

мулировала интерес к системам DCS, не имела места в семействе-

IBM 360, стоймость периферийных устройств которого практи-

чески не зависела от того, к какой машине семейства они присое-

диняются.

Пользователи систем DCS использовали соединение двух ма-

шин для выполнения одной задачи не только в связи с анома-

лией стоимости. В течение 1961—1966 гг. они создали библиотеки*

ярепроцессорных, постпроцессорных, служебных, и сервисных

программ для внешних вычйслителёй IBM704X систем DCS^

2 В. А. Головкин

1Z

возможности которых в системах DCS вообще использовались

мало — первоначально загрузка машин IBM 704 X составляла

20—30% их номинальной производительности вне зависимости

ют загрузки центральных вычислителей IBM 709Х. Было создано

•большое число программ для машины IBM 704Х, применение ко-

торых существенно расширило функции внешнего вычислителя,

в системе DCS. Так, например, были созданы и соединены с си*-

•стемой ввода-вывода программы для редактирования и печати

данных без участия центрального вычислителя, которые запуска-

лись по самому высокому приоритету по запросу на ввод-вывод

ют дорогого центрального вычислителя. В оставшееся время на

внешнем вычислителе выполнялись другие служебные операции.

При этом учитывалось, что машина IBM 704Х имеет команды

юбработки символьной информации, удобные для реализации

•служебных программ, тогда как машина IBM 709Х ориентирова-

ла на пословную обработку при решении научных задан и не

имеет команд обработки символьной информации.

Машина IBM 704Х осуществляла мультипрограммную обра-

ботку, а машина IBM 709Х в то же время выполняла одну рабо-

ту из пакета, при этом обеспечивался доступ почти ко всей

юперативной памяти второй машины и ко всем ее лентам и

дискам. Таким образом, было осуществлено специализированное

мультипрограммирование для машины IBM704X, но не была

решена ни одна из задач распределения памяти и устройств,

так остро вставщих в мультипрограммной операционной системе

для семейства IBM 360.

Ориентация на однопроцессорные системы и бедность функ-

ций в версиях операционной системы семейства IBM 360

(OS/360), объявленных в 1964—1966 гг., задерживали переход

пользователей систем DCS к машинам семейства IBM 360 вплоть

до 1968—1969 гг. К этому времени фирма IBM объявила о

присоединенном вспомогательном процессоре ASP (Attached

Support Processor) для OS/360.

Вспомогательный процессор присоединяется к основной обыч-

но более мощной машине при помощи адаптера канал-канал

{рис. 1.7), в результате чего образуется слабо связанная система

из двух машин семейства IBM 360 (IBM 370). Устройства ввода-

вывода основной машины заменяются связью канал-канал с вспо-

могательным процессором. Вспомогательный процессор может

присоединяться более чем к одной основной машине, образуя

•слабо связанную систему из нескольких машин. Он*может также

составлять однопроцессорную конфигурацию без основных .ма-

шин. В последнем случае вспомогательный процессор называет-

ся локальным (LASP).

С функциональной точки зрения ASP был выполнен хорошо.

Однако, операционная система OS/360 в 1968 г., когда начина-

лось внедрение ASP, была все еще весьма плохой по показателю

эффективность-стоимость. *

18

Вначале вспомогательный процессор использовался для рабо-

ты с низкоскоростными устройствами ввода-вывода и для эпизо-

дических вспомогательных работ и выполнял функции простога

мультизадачного монитора под управлением OS/360 аналогична

Рис. 1.7. Структурная схема многомашинной (слабо связанной) вычисли-

тельной системы с вспомогательным процессором. Двухпроцессорная кон-

фигурация.

внешнему вычислителю системы DCS. Кроме этого, он использо-

вался для обработки единственного пакета подобно центральному

вычислителю системы DCS.

За время с 1969 г. функции вспомогательного процессора были

существенно расширены подобно тому, как это было сделано для

внешнего вычислителя системы DCS.

Была реализована предварительная работа с лентами и дис-

ками. Управление двумя или более основными машинами осу-

ществлялось одним вспомогательным процессором. При этом

функции одной из основных машин мог выполнять набор ресур-

сов вспомогательного процессора для пакетной обработки в вида

памяти, периферийных устройств и процессорного времени. Была

реализовано приоритетное планирование работы основной маши-

ны (основных машин), учитывающее такие важные факторы, как:

— оценка времени выполнения;

— оценка процессорного времени;

— оценка требующейся памяти;

— внешние приоритеты и другие факторы.

1.2.5. Структуры многомашинных и многопроцессорных си-

стем. Тенденции развития. Методика слабого и сильного связы-

вания процессоров является основной методикой’ комплексиро-

вания вычислительных машин фирмы IBM, включая семейства

IBM 360 и 370. Сильная связанность, при которой процессоры

2* ' 19*

^разделяют общую оперативную память, поддерживается фирмой

для систем двух идентичных процессоров (рис. 1.8). Слабая свя-

занность, при которой процессоры связаны посредством адаптера

каналов и (или) они разделяют общее периферийное оборудова- •

.нйе, поддерживается фирмой, когда процессоры не являются

Рис. 1.8. Сильная связанность двух процессоров.

идентичными. При этом слабо связанная система может содер-

жать пару сильно связанных процессоров (рис. 1.9). На практике

такое построение системы является типичным, если от системы

требуется обеспечить высокую готовность при оперативной ра-

боте с сетью терминалов или с сетью удаленных абонентов.

-Отметим, наконец, что фирмой IBM выпущено несколько двух-

процессорных сильно связанных систем семейств IBM 360 и 370,

^которые рассматриваются в последующих материалах настоящей

лсниги.

На базе опыта применения систем семейства IBM 370 можно

•ориентировочно определить основные тенденции развития много-

машинных и многопроцессорных систем фирмы IBM.

'Популярность сильно связанных систем, видимо, будет воз-

растать. Большие системы семейства IBM 370 и следующего

^поколения будут, как правило, содержать по меньшей мере два

-сильно связанных центральных процессора с легко разделяемыми

.наборами модулей памяти, каналов и периферийных устройств.

Как сильно связанные, так и слабо связанные системы получат

полную поддержку операционной системы.

В будущем перспективы применения слабо связанных систем

общей памятью на дисках представляются более предпочти-

тельными по сравнению со слабо связанными системами при

ломощи адаптеров каналов. Недостатком связывания процессоров

•через адаптер канал-канал является с л ишь м широкий спектр

-состава информации, передаваемой через канал. Обычно един-

ственный канал данного процессора используется для связи с

20

другим процессором в целях передачи всех входных и выходных

потоков системы, а также для обмена всеми видами сообщений

между процессорами. Другим недостатком такой связи является

необходимость синхронизации работы процессоров. Один из

процессоров не может передавать информацию другому процес-

сору, пока этот другой процессор выдает информацию первому.

Рис. 1.9. Слабая связанность однопроцессорной системы с двухпроцессорной

(сильно связанной) системой. Типичный пример устройства с прямым до-

ступом— дисковая память.

Третий недостаток состоит в том, что для хранения данных, по-

лученных из канала, часто требуется последующая отсылка их

на диск (при наличии общих дисков хранение данных на них

попутно обеспечивает возможность возврата к данным на дисках

и широкие возможности для организации очередей). К преиму-

ществам связывания при помощи адаптера канал-канал относятся

низкая стоимость аппаратуры, высокая надежность и хорошие

возможности передачи коротких сообщений между процессорами.

Фирма IBM будет, вероятно, отстаивать, единую операционную

систему для многомашинных и многопроцессорных систем, ко-

торые могут быть поставлены в рамках одного семейства или

поколения. Внешние спецификации и общая архитектура такой

операционной системы будут сохранены и расширены в следую-

щем поколении.

1.3. Краткий обзор

Организация структур и функционирования вычислительных

машин, включая каналы и совмещение во времени работы уст-

ройств машин, подробно рассмотрены в книгах [26, 140, 141, 187t

21

188, 198, 315, 412] и во многих других работах. Совмещение опе-

раций и процессоры с просмотром вперед описаны в [581, 884].

Во второй из этих работ, например, дан обзор уже реализованных

в ЭВМ и новых методов ускорения работы процессора при помо-

щи опережающего просмотра. Рассмотрены варианты структуры

такого процессора, ограничения распараллеливания вычислений,

налагаемые отношениями конфликта и предшествования прос-

матриваемых команд. Исследованы вопросы оптимизации. В обо-

их работах совмещение операций и просмотр вперед связываются

с магистральным (конвейерным) способом обработки информации.

Эволюция вычислительных систем от однопроцессорных к

многопроцессорным системам описана в [281]. Соответствующий

материал положен в основу п. 1.1.1. Изложение материалов

п. 1.2 основано на работе [744]. Кроме этого, в части материала

п. 1.2 также использованы некоторые материалы из [281], а в

п. 1.2.4 —из [203].

Упомянутые в начале п. 1.2 вычислительные системы фирмы

IBM, созданные для систем SAGE и SABRE, описаны в [114,

339, 696, 710, 1208] и в [114, 474, 707, 837, 1062, 1069] соответ-

ственно. Система DCS представлена в [281, 842, 947], а система

с вспомогательным процессором ASP — в [203, 281, 842, 947].

Сильно связанные системы описаны также в £1177*]. Материалы

о других многомашинных и многопроцессорных системах пред-

ставлены в дальнейших разделах настоящей книги. В заверше-

ние изложения эволюции однопроцессорных, многомашинных и

многопроцессорных систем перечислим ее главные цели и этапы,

следуя, в основном, [281].

Введение в однопроцессорные системы совмещения операций

и опережающего просмотра команд и данных было направлено

на повышение производительности. На первых этапах развития

многомашинных систем главная цель состояла в разгрузке ос-

новной, обычно достаточно мощной, вычислительной машины от

функций ввода-вывода и передаче этих функций меньшей и бо-

лее подходящей для этого машине. Кроме этого, при построении

дуплексных систем преследовалась цель повышения готовности,

надежности и живучести. В дальнейшем возможности многома-

шинных систем стали использоваться также и для повышения

производительности.

Первые многопроцессорные системы создавались с целью

достижения высокой готовности, которая обеспечивалась путем

объединения в группы одинаковых устройств, способных выпол-

нять одни и те же функции и в результате реконфигурации под-

держивать систему в работоспособном, состоянии даже в тех слу-

чаях, когда сохраняется в действии лишь часть системы исход-

ного состава. После того, как эта цель была достигнута, возмож-

ности многопроцессорных систем стали использоваться также

и для повышения производительности. При этом во всех

случаях важное значение имеет большая гибкость многопро-

«2

цессорных систем и высокая степень связанности ее устройств.

Высокая готовность, надежность и живучесть многопроцес-

сорных систем обеспечивается за счет применения резервирова-

ния различных устройств и осуществления в необходимых слу-

чаях реконфигурации системы. Повышение производительности

обеспечивается за счет:

— возможности параллельного решения независимых задач

и частей задач;

— повышения эффективности работы и улучшения распреде-

ления нагрузки в системе, в том числе при помощи динамиче-

ского перераспределения загрузки и распараллеливания вычис-

лений;

— реализации наиболее экономичного обслуживания экст-

ренных заданий и заданий при пиковых нагрузках;

— достижения наиболее эффективного использования ресур-

сов без создания новых типов архитектуры систем. ,

2. ОРГАНИЗАЦИЯ СТРУКТУРЫ И ФУНКЦИОНИРОВАНИЯ

ПАРАЛЛЕЛЬНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

2.1. Классификация вычислительных систем [109]

Описываемая ниже классификация основана на многочислен-

ных схемах классификации вычислительный систем, в первую

очередь, на схемах из работ [410, 493, 635, 796].

2.1.1. Признаки и схема классификации. Нотация классов»

В качестве основных признаков классификации, характерзую-

щих организацию структуры и функционирования вычислитель-

ных систем с точки зрения, главным образом, параллельности

работы, выберем следующие:

1) тип потока команд в центральной части вычислительной

системы;

2) тип потока данных в центральной части вычислительной

системы; 1

3) способ обработки-данных в центральных устройствах, об-

работки;

4) степень связанности компонент вычислительной системы;

5) степень однородности основных компонент вычислитель-

ной системы;

6) тип внутренних связей в вычислительной системе.

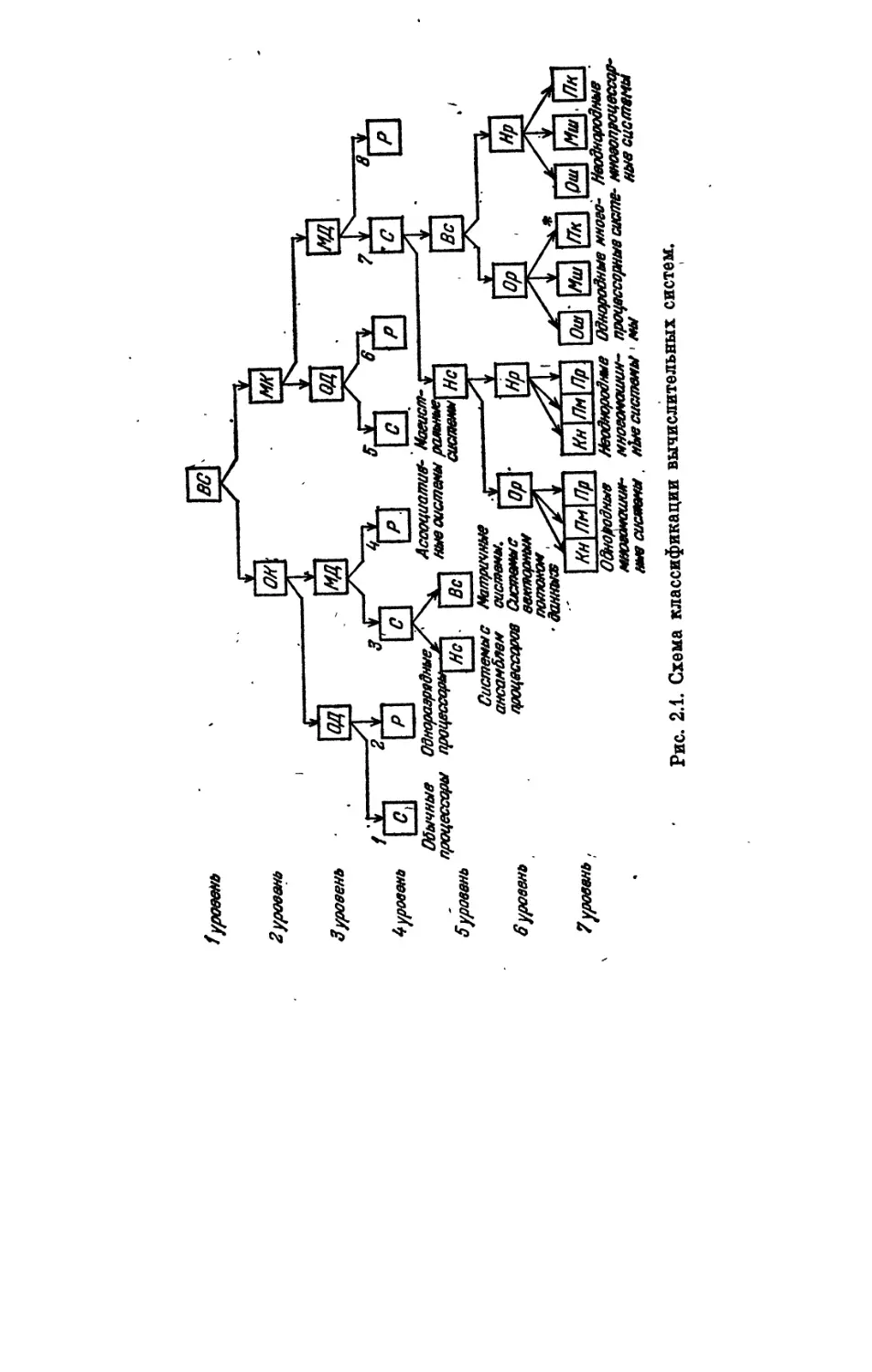

Эти шесть признаков определяют базовую схему классифи-

кации, содержащую семь уровней иерархии, в которой переход

от каждого ьго уровня к следующему более низкому i + 1-му

уровню определяется соответствующим i-м признаком (рис. 2.1).

В этой схеме и в вводимой далее нотации классов вычислитель-

пых систем используются следующие условные обозначения:

а) ВС — вычислительные системы;

б) ОК, МК — одиночный и множественный потоки команд

соответственно;

в) ОД, МД — одиночный и множественный потоки данных

соответственно;

г) С, Р — пословная и поразрядная обработка данных в цен-

тральных обрабатывающих устройствах соответственно;

д) Нс, Вс — низкая и высокая степень связанности вычисли-

тельной системы соответственно;

е) Ор, Нр — однородная и неоднородная вычислительная

система соответственно;

24

2уровень

j

3уровень

4 уровень

Обычные

процессоры

3уровень

вуровень

7 уровень,

Рис. 2.1. Схема классификации вычислительных систем.

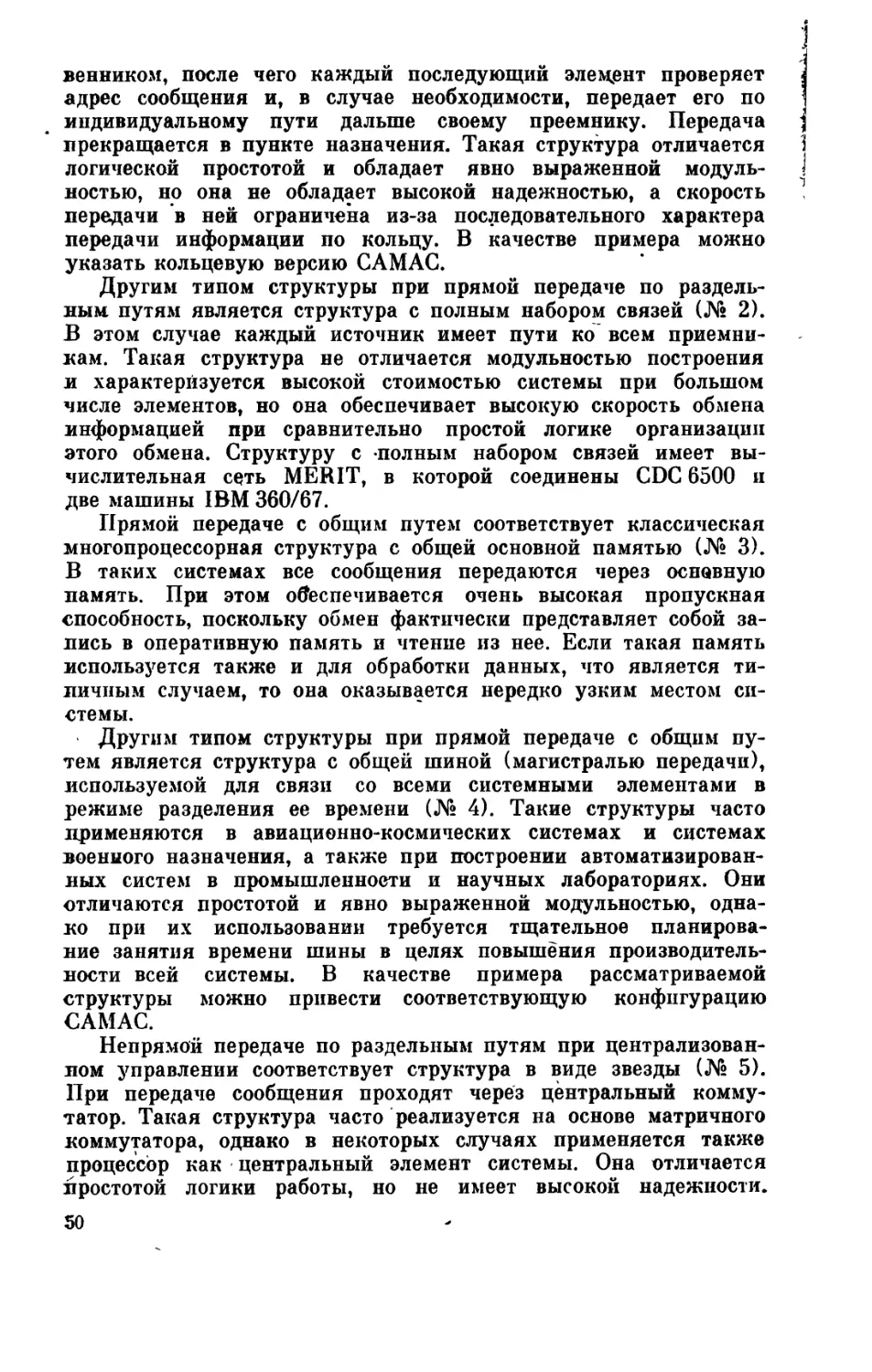

ж) Кн, Пм, Пр — системы со связями «канал-канал», через

общую внешнюю память и непосредственно между процессора-

ми соответственно; Ош, Мш, Пк — системы со связями через

одну общую шину с разделением ее времени, со связями через

множество шин при использовании многовходовых модулей опе-

ративной памяти и с перекрестными связями при помощи мат-

ричного коммутатора соответственно.

Обозначения (нотации) классов систем будем составлять из

условных обозначений каждого узла схемы, начиная с узлов,

второго уровня, через которые нужно пройти по стрелкам от узла

ВС до узла данного класса систем включительно, отделяя, для

удобства записи, условные' обозначения узлов первых трех уров-

ней от условных обозначений узлов последних трех уровней на-

клонной чертой. Так, например, класс вычислительных систем,,

помеченный на рис. 2.1 звездочкой (*), имеет обозначение

МКМДС/ВсОрПк. Оно расшифровывается следующим образом:

вычислительная система с множественным потоком команд и

множественным потоком данных в центральной части, с послов-

ной обработкой данных в центральных обрабатывающих устрой-

ствах, с высокой . степенью связанности и однородной структу-

рой, с перекрестными связями между процессорами и модулями

памяти. Обозначения классов для более высоких уровней иерар-

хии схемы, соответственно, сокращаются.

2.1.2. Описание классов вычислительных систем. Первые три

признака классификации характеризуют организацию функцио-

нирования вычислительных систем и определяют в общих чер-

тах их структуру. Эти признаки являются двузначнымй и поэ-

тому образуют, в совокупности, 8 классов систем — см. на рис. 2.1

классы №№ 1, 2, ..., 8 четвертого уровня. Переход от пер-

вого ко второму уровню соответствует разделению систем по

типу потока команд — одиночный или множественный — между

модулями оперативной памяти и устройствами управления или

процессорами. При переходе к третьему уровню системы

разделяются по типу потока данных— одиночный или множест-

венный — между центральными обрабатывающими устройствами

и модулями памяти. Далее при переходе к четвертому уровню

иерархии системы разделяются по способу обработки данных

в центральных устройствах обработки — пословная или пораз-

рядная обработка.

Системы с одиночными потоками команд и данных и с пос-

ловной обработкой данных ОКОДС представляют собой обычные

процессоры, а с поразрядной обработкой данных ОКОДР — одно-

разрядные процессоры. Системы с одиночным потоком команд

и множественным потоком данных имеют в качестве харак-

терных представителей для случая пословной обработки дан-

ных ОКМДС матричные системы и ансамбли процессоров,

а для случая поразрядной обработки ОКМДР — ассоциативные

системы.

26

Типичными представителями класса систем с множественным

потоком команд и одиночным потоком данных при пословной

обработке информации МКОДС являются магистральные (кон-

вейерные) системы. В качестве систем с поразрядной обработ-

кой МКОДР можно представить системы с конвейером однораз-

рядных обрабатывающих устройств.

Многомашинные и многопроцессорные системы образуют

класс систем с множественными потоками команд и данных и

с пословной обработкой МКМДС. В качестве систем с поразряд-

ной обработкой МКМДР можно представить* системы однобито-

вых процессоров, связанных между собой.

Последние три признака схемы классификации (рис. 2.1) оп-

ределяют классы систем со сложной структурой. На схеме по-

казаны классы пятого, шестого и седьмого уровней для реаль-

но существующих вычислительных систем. При переходе к пя-

тому уровню схемы происходит разделение на системы с низкой

и высокой степенью связанности, к шестому уровню — на одно-

родные и неоднородные системы и, наконец, при переходе к седь-

мому уровню системы разделяются по типу связей между уст-

ройствами их центральной части.

Низкая степень связанности для систем типа ОКМДС озна-.

чает, что обрабатывающие устройства имеют индивидуальные

блоки оперативной памяти и связаны с устройством управления,

но не имеют непосредственных связей между собой. Высокая

степень связанности для систем такото класса означает, что об-

рабатывающие устройства имеют индивидуальные блоки опера-

тивной памяти и, по меньшей мере, связаны линиями с сосед-

ними обрабатывающими устройствами. Типичные представители

первых систем — ансамбли процессоров, а вторых — матричные

системы (а также системы с векторным потоком данных, имею-

щие общую оперативную память).

Наиболее сложную структуру имеют многомашинные и мно-

гопроцессорные системы. Первые из них характеризуются низ-

кой степенью связанности, а вторые — высокой степенью связан-

ности, поскольку многопроцессорные системы, в отличие от

многомашинных, имеют общую оперативную память. Многома-

шинные системы содержат обычно конструктивно законченные

вычислительные машины и могут состоять как из машин одного

типа, так и из машин различных типов. В состав многопроцес-

сорных систем могут входить как однотипные, так и разно-

типные процессоры. Поэтому предусмотрены классы одно-

родных и неоднородных многомашинных *и многопроцессорных

систем (МКМДС/НсОр и Нр, МКМДС/ВсОр и Нр) соответ-

ственно.

Характерными типами срязи в однородных и неоднородных

многомашинных системах являются связи канал-канал (Кн) при

помощи адаптера, через внешнюю память на магнитных дисках

и лентах (Пм) и непосредственно между процессорами для об-

‘ 27

мена сигналами о состоянии друг друга, прерывания работы и

для прямого управления (Пр). Многомашинные системы могут

иметь различные комбинации этйх типов связей, что условна

показано на рис. 2.1 путем плотного расположения друг к другу

узлов схемы Кн, Пм и Пр. Если одновременно реализовано не-

сколько видов связей, то в нотации класса системы указываем

обозначения каждого из них и группу обозначений заключаем

в круглые скобки. .

Характерными типами связей в однородных и неоднордных

многопроцессорных -системах между их процессорными модуля-

ми и модулями оперативной памяти являются связи при помо-

щи одной шины с разделением времени обмена информацией

при помощи этой шины (Ош), многошинные связи с примене-

нием многовходовых модулей оперативной памяти (Мш) и пере-

крестные связи при помощи сосредоточенного или распределен-

ного перекрестного (матричного) коммутатора (Пк). В связи

с тем, что связь между процессорами через оперативную память

является определяющей в многопроцессорных системах, другие-

виды связей В таких системах* (например, через общую внешнюю

память) можно в нотациях не указывать. При необходимости бо-

лее подробного описания можно воспользоваться дополнительно»

тем же способом записи связей, что описан выше для многома-

шинных систем. Отметим, что шины и матричный коммутатор

используются и для присоединения внешних устройств.

Ряд параллельных вычислительных систем обладает призна-

ками более чем одного класса. Так, например, ортогональные-

системы являются комбинацией систем типа ОКОДС и ОКМДР.

Такого рода системы с признаками отличающихся друг от дру-

га классов естественно считать системами с комбинированной

структурой. Некоторые системы в процессе работы могут так

изменять режим функционирования, что «переходят» из одного

класса в другой. Такие системы естественно считать системами

с перестраиваемой структурой.

2.2. Потоки команд и данных. Пословная и поразрядная

обработка. Основные структуры и определения

2.2.1. Одиночные и множественные потоки команд и данных»

Понятия одиночных и множественных потоков команд и данных

и четыре соответствующих класса вычислительных систем ОКОДг

ОКМД, МКОД и МКМД введены М. Дж. Флинном [410]. •

Под потоком команд понимается последовательный ряд ко-

манд, выполняемых системой, а под потоком данных — последо-

вательный ряд данных, вызываемых потоком команд, включая

промежуточные результаты. Множественность и число потоков

определяются как максимально возможное число одновременных

операций (команд) или операндов (данных), находящихся в оди-

28

наковой стадии обработки (на наиболее узком участке организа-

ционной структуры).

Упрощенные структурные схемы систем типа О КОД, ОКМД^

МКОД, МКМД изображены, на рис. 2.2—2.5, которые приведены

в [821] и воспроизведены в [188].

В системах типа ОКМД одно устройство управления осущест-

вляет управление работой множества процессорных модулей такг

Потокдан-

ных для

обработки

Поток данных

после обработ-

ки (результаты)

Рис. 2.2. Упрощенная структурная схема'систем типа ОКОД.

что каждый из них выполняет одну данную команду, затем еле*

дующую и т. д., т. е. реализуется синхронный параллельный вы*

числительный процесс. Подмножества процессорных модулей1

могут пропускать выполнение команд, что определяется при по-»

мощи операций маскирования.

В системах такого типа реальная скорость обработки инфор-

мации сильно зависит от возможностей загрузки процессорных

модулей (от возможностей распараллеливания).

В системах типа МКОД процесс обработки разбивается' на*

несколько этапов, каждому из которых соответствует один из=

процессорных модулей. Эти модули составляют в совокупности

магистраль обработки (конвейер процессоров). Реальная ско-

рость обработки зависит от возможностей заполнения магистра-

ли. Наиболее высокая скорость обработки достигается при выпол-

нении длинных линейных участков программ с однородными

операциями. При частых прерываниях линейных участков

командами ветвления скорость обработки снижается.

В системах типа МКМД несколько устройств управления осу-

ществляют управление одновременным выполнением различных

участков одной и той же программы, т. е. реализуется асинхрон-

ный параллельный вычислительный процесс. Такие системы обла-

дают большой гибкостью. Реальная скорость обработки информа-

ции зависит от возможностей загрузки процессоров, однако, если

распараллеливание вычислений при выполнении данной програм-

мы затруднено, то можно,^воспользовавшись наличием нескольких

устройств управления, одновременнно выполнять несколько

программ, повышая тем самым загрузку процессоров. Системы

29

Потоки данных

после обработки

(результаты)

Рис. 2.3. Упрощенная структурная схема систем типа ОКМД.

Поток данных

после обработ-

ки (результаты)

Рис. 2.4. Упрощенная структурная схема систем типа МКОД.

Рис. 2.5. Упрощенная структурная схема систем типа МКМД.

типа МКМД отличаются высокой надежностью вследствие хо-

роших возможностей взаимного резервирования однотипных

устройств и машин.

Схема четырех классов включена в базовую схему классифи-

кации (п. 2.1) и составляет, с учетом переходов по уровням ие-

рархии, ее первый, второй и третий уровни (рис. 2.1).

Более подробно системы различных типов рассматриваются

в последующих разделах.

2.2.2. Пословная

вычислительные системы имеют

ры и функционирования. Опи-

сание систем на базе четырех

классов ОКОД, ОКМД, МКОД,

МКМД оказывается слишком

грубым. Для более детального

описания целесообразно учиты-

вать признаки пословной и по-

разрядной обработки следую-

щим образом [ 796].

Схему четырех классов вы-

числительных систем ОКОД,

ОКМД, МКОД, МКМД можно

и поразрядная обработка. Современные

сложную организацию структур

Рис. 2.6. Схема четырех классов

вычислительных систем.

представить в виде квадрата

(рис. 2.6). Верхняя вершина

соответствует классу ОКОД.

Переход из нее к левой вершине связывается с размножением

потока данных, в результате чего получается класс ОКМД,

а переход от верхней к правой вершине связывается с размно-

жением потока команд, в результате чего получается класс

МКОД. Переход из левой и правой вершин к нижней связыва-

ется с размножением потока команд и потока данных соответст-

венно, в результате чего получается один и тот же класс МКМД.

Схема четырех классов обладает рядом недостатков. Так, нап-

ример, структурно различные ассоциативные и матричные систе-

мы попадают в один и тот же класс ОКМД. Системы с комби-

нированной и перестраиваемой структурой могут занимать два

и даже три класса из четырех.

В целях улучшения схемы ее можно модифицировать так,

чтобы обеспечивалось различие между пословной обработкой (С)

и поразрядной обработкой (Р). Такая схема изображена на

рис. 2.7*). Она содержит восемь классов. Ассоциативные и мат-

ричные системы занимают в этой схеме разные классы — ОКМДР

♦) Четвертую букву (Д) в обозначениях восьми классов можно было

бы опустить, так как при этом сохраняется однозначность обозначений.

Она оставлена в нотации для того, чтобы переход от четырех (восьми)

классов к восьми (четырем) соответствовал просто добавлению (исключе-

нию) обозначений пословной и поразрядной обработки (С и Р) в нотации

классов систем.

31

и ОКМДС соответственно. Схема обладает лучшими возможно-

стями локализации классов систем с комбинированной и пере-

страиваемой структурой. Так, например, если в исходной схеме

системы занимают два или три класса из четырех, то в моди-

фицированной схеме они могут занимать два или три класса из

Рис. 2.7. Схема классов вычисли-

тельных систем с учетом послов-

ной и поразрядной обработки.

восьми соответственно, т. е. их

описание при помощи классифи-

кации становится более опреде-

ленным, хотя, конечно, не одно-

значным.

Модифицированная схема вось-

ми классов включена в базовую

схему классификации (п. 2.1) и

составляет ее четвертый уровень

(рис. 2.1).

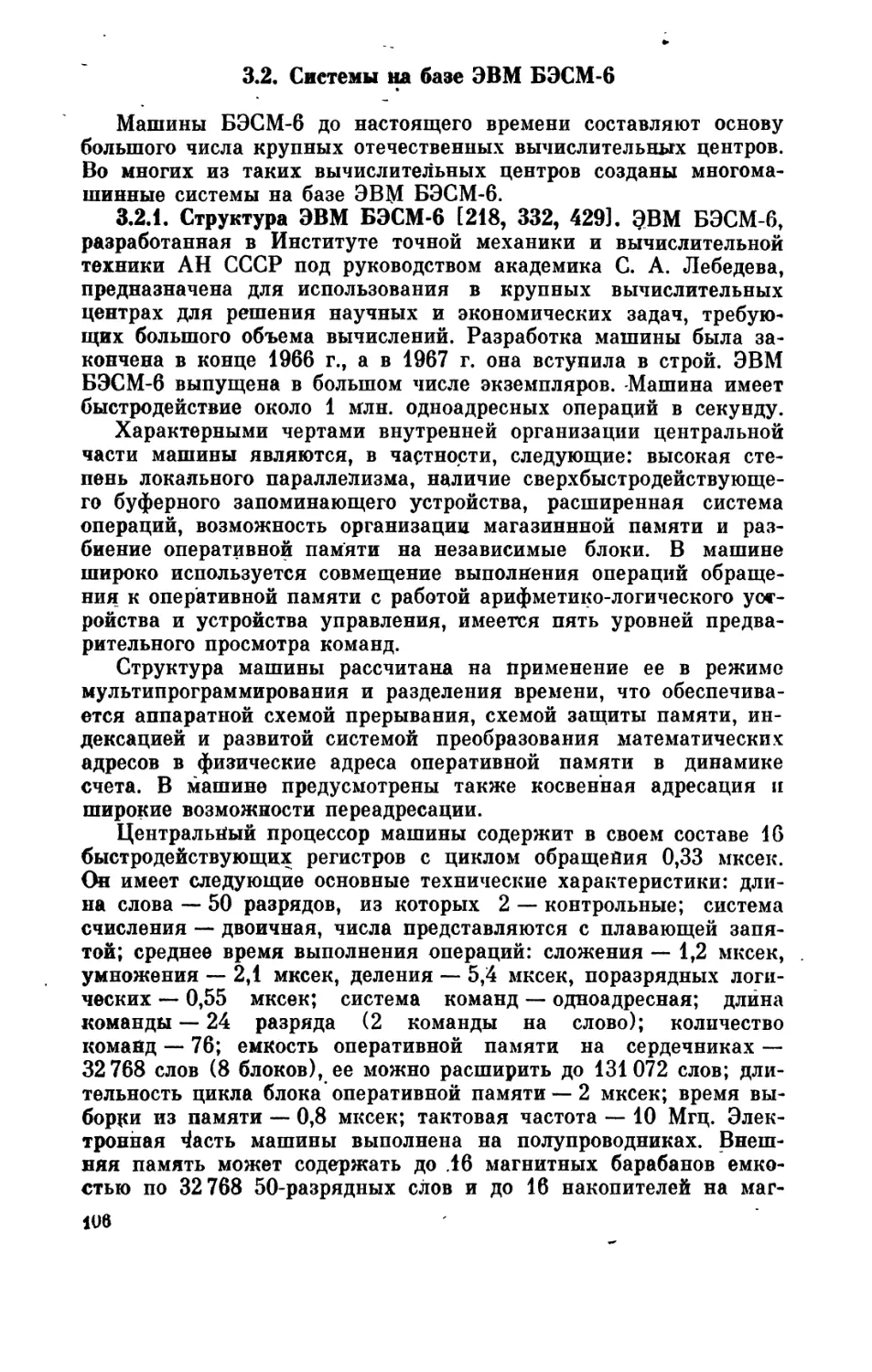

2.2.3. Основные структуры и

определения 1110, 111]. Упрощен-

ные структурные схемы типовых

представителей вычислительных

систем указанных выше восьми

классов изображены на рис. 2.8

(109J. Номера структурных схем

вычислительных систем на этом

рисунке соответствуют номерам классов вычислительных систем,

представленных в четвертом уровне схемы классификации

на рисунке 2.1. Отметим, что разделение памяти по типам на

рисунке 2.8 отражает, в первую очередь, ее функциональные

признаки, а не конкретную конструкцию.

Системы ОКОДС и ОКОДР представляют собой обычный и

одноразрядный процессоры соответственно и осуществляют пос-

ледовательную обработку информации. Остальные системы явля-

ются параллельными и осуществляют параллельную обработку

информации.

Параллельная обработка информации представляет собой од-

новременное выполнение двух или более частей одной и той же

программы двумя или более процессорными модулями вычисли-

тельной системы [4931. Ее следует отличать от мультипрограм-

мирования, основное содержание которого составляет разделение

времени и оборудования между двумя или более программами, *

функционирующими одновременно и размещенными полностью

или частично в оперативной памяти. Возможен мультипрограмм-

ный режим параллельной обработки.

Вычислительные системы параллельной обработки информа-

ции или, более коротко, параллельные вычислительные системы

содержат два или более процессорных модулей и подразделяют- .

ся на три основных класса: ОКМД, МКОД и МКМД. Они пред-

•ставляют собой такие системы, в центральной части которых

имеется два цли более потока команд и (или) данных.

32

Системой типа ОКМД называется некоторая параллельная

вычислительная система с единственным общим модулем управ-

ления работой множества процессорных модулей, причем все или

часть этих модулей одновременно выполняют поток команд [1221J.

Такие системы подразделяются на системы с пословной обра-

боткой ОКМДС и системы с поразрядной обработкой ОКМДР.

Условные обозначения:

□-память данных с

выборнойразрядов1

гп-память данных с выбор-

ш ной слов

г-у-память данных с выбор-

СЗ* ной разрядных срезов

-процессор (арифме-

О тино-лоеичеснов

устройства)

(^-устройствоуправления .

Рис. 2.8. Структурные схемы вычислительных систем.

Основными типами систем ОКМДС являются ансамбли про-

цессоров, системы с векторным потоком данных и матричные си-

стемы. Характерной особенностью таких систем является то, что

они обрабатывают данные параллельно и обращаются к ним при

помощи адресов, а не при помощи тэгов (признаков — флажков,

меток) или выборки по содержимому ячеек памяти [8211.

Ансамбли процессоров представляют собой такие параллель-

ные системы типа ОКМДС, в которых процессорные модули

упорядочиваются общим потоком управления и обработки, как

правило, это — сравнительно небольшие процессоры без взаимо-

связей либо с низкой степенью связанности 112211.

3 В. А. Головкин , 33

• Системы с векторным потоком данных и матричные системы

представляют собой такие параллельные системы типа ОКМДС,

в которых процессорные модули упорядочиваются общим пото-

ком управления и обработки, как правило, это — сравнительно

небольшие процессоры с высокой степенью связанности [1221].

В первых системах процессоры обычно имеют общую оператив-

ную память и являются фактически составными арифметико-

логическими устройствами обработки, которые выполняют по-

следовательно команду за командой над векторами операндов. Во

вторых системах процессоры имеют индивидуальную оператив-

ную память и составляют матричную конфигурацию со связями

между непосредственными соседями.

Тот факт, что системы типа ОКМДС могут быть как с низкой,

так и с высокой степенью связанности, отмечен условно на ри-

сунке 2.8 при помощи прерывистой линии, связывающей изобра-

жения процессоров.

Основным типом систем ОКМДР являются ассоциативные

системы. Характерной особенностью таких систем является то,

что их процессорные модули (или память с встроенной логиче-

ской обработкой) реализуют адресацию на основе свойств содер-

жимого дайных в большей степени, чем с помощью адресов

1821, 1221].

Ассоциативные системы подразделяются на системы с ассо-

циативной памятью и системы с ассоциативными процессорами

(ассоциативные матричные системы). Системы с ассоциативной

памятью представляют собой такие параллельные системы типа

ОКМДР, которые оперируют с данными при доступе к ним при

помощи тэгов или выборки по содержимому ячеек памяти в

ббльшей степени, чем при помощи адресов. Системы с ассоциа-

тивными процессорами представляют собой такие параллельные

системы типа ОКМДР, которые обычно оперируют со срезами

разрядов данных (срез разряда данных — это совокупность раз-

рядов одной и той же фиксированной позиции в множестве слов

данных) 1821J.

Перейдем к вычислительным системам типа МКОД. К па-

раллельным системам типа МКОДС относятся магистральные

(конвейерные) системы — такие системы, в которых осуществля-

ется одновременное выполнение нескольких команд при помощи

последовательного прохождения слов потока данных через ма-

гистраль (конвейер) нескольких специализированных блоков об-

работки. При этом обработка разбивается на соответствую-

щее число подзадач (этапов), каждая из которых выполняется

на одном из указанных специализированных блоков обработ-

ки [1229].

Принцип магистральной (конвейерной) обработки основан на

разделении вычислительного процесса на несколько подпроцессов,

каждый из которых выполняется на отдельном устройстве. При

этоц последовательные процессы могут выполняться одновремен-

М

но на своих устройствах подобно тому, как это имеет место в

промышленных технологических процессах. Принцип конвейер-

ной обработки может применяться на различных уровнях иерар-

хии вычислительного процесса, начиная с уровня построения

логических схем устройств [1112]. В зависимости от уровня при-

менения принципа конвейерной обработки можно выделить, рас-

сматривая уровни снизу вверх, арифметико-магистральные, ко-

мандно-магистральные и макромагистральные системы [796,800],

а в зависимости от типа применяемых команд обработки среди

магистральных систем можно выделить системы с обычными и

системы с векторными командами 11112, 1211J.

Как отмечалось выше, в качестве систем МКОДР можно рас-

сматривать системы с конвейером одноразрядных процессоров.

Системой типа МКМД называется некоторая параллельная вы-

числительная система с несколькими модулями управления рабо-

той нескольких процессорных модулей, причем эти модули выпол-

няют несколько потоков команд. Число процессоров составляет

обычно величину в пределах от 2 до 10, но может составлять и

несколько десятков и более, в особенности для микропроцессор-

ных систем. Основные типы систем МКМДС — многопроцессор*

ные и многомашинные системы.

Многопроцессорной системой называется такая параллельная

система типа МКМДС, которая содержит два или более сильно

связанных центральных процессора, общую для них оперативную

память и, целиком или частично, общие периферийные устрой-

ства, включая периферийные процессоры и канаМы ввода-вывода,

управление которыми, как единым комплексом, осуществляет

единственная операционная система [694, 744]. В вычислитель-

ной системе могут быть несколько копий одной операционной

системы. Таким образом, многопроцессорная вычислительная си-

стема содержит два или более процессорных модулей, функцио-

нирующих под единым управлением [281], и осуществляет одно-

временную обработку нескольких команд и данных при общей

иерархической памяти [1229].

Более подробно характерные черты многопроцессорных си-

стем можно представить следующим образом [281].

Многопроцессорная система включает два или несколько

центральных устройств обработки информации — центральных

процессорных модулей. Эти устройства могут иметь как одина-

ковые, так и различные характеристики. Основная память (опе-

ративная память)* должна находиться в общем пользовании и

должна быть доступной для всех процессоров системы. Процес-

соры могут иметь некоторую собственную память. В системе

должен быть общий доступ ко всем устройствам ввода-вывода,

включая каналы, устройства управления и периферийное обору-

дование. В системе должна быть единая интегрированная опе-

рационная система, осуществляющая общее управление аппа-

ратными и программными средствами. При этом должна быть

3* 35

предусмотрена возможность тесного взаимодействия аппаратных

средств и программного обеспечения:

— на уровне системного программного обеспечения при вы-

полнении системных задач;

т - на программном уровне при выполнении частей одной и

той же программы несколькими процессорами или при выпол

нении нескольких независимых программ (мультипрограммный

режим параллельной обработки);

— па уровне обмена данными;

— на уровне аппаратных прерываний. Следует отметить, что

взаимодействие аппаратных и программных средств зависит не

только от организации взаимных связей, но и от системного про-

граммного обеспечения и процедур обработки данных. Базовая

структурная. схема многопроцессорной системы изображена на *

рис. 2.9.

Многомашинной системой называется такая параллельная си-

стема типа МКМДС, которая содержит обычно две или более

бднопроцессорных или многопроцессорных слабо связанных меж-

ду собой вычислительных систем с общей внешней намятые

й/или со связями через каналы ввода-выврда, работающих сов-

местно под управлением своих операционных систем. В системе

Возможны непосредственные связи между процессорами в целях

управления. В ее состав могут входить однопроцессорные и мно-

гопроцессорные системы одного и того же или различных типов,

а также такие вычислительные системы, как магистральные,

матричные, ассоциативные и другие.

Как отмечалось выше, в качестве систем МКМДР можно рас-

сматривать системы связанных между собой одноразрядных про-

цессоров. *

В п. 2.1.2 упоминались системы с комбинированной структу-

рой и системы с перестраиваемой структурой. Системами с ком-

бинированной структурой будем называть такие параллельные

вычислительные системы, структуры которых характеризуются

комбинацией признаков существенно отличающихся друг от

друга классов.

Одним из наиболее известных типов систем с комбинирован-

ной структурой являются ортогональные системы. Они представ-

ляют собой такие параллельные системы, которые ведут обработ-

ку двумя процессорами — обычным процессором типа ОКОДС и

ассоциативным процессором типа ОКМДР — и используют об-

щую для них оперативную память в режиме разделения обору-

дования 1821]. Они являются системами с высокой степенью

связанности, поскольку пара процессоров имеет общую опера-

тивную память.

Системами с перестраиваемой структурой будем называть та-

кие параллельные вычислительные' системы, которые обладают

возможностью в процессе работы изменять тип структуры и, в

предельном случае, осуществлять «переходы» от одного класса

36

к другим существенно отличным классам. Такие системы в пос-

ледние годы получили быстрое-развитие в связи с разработкой

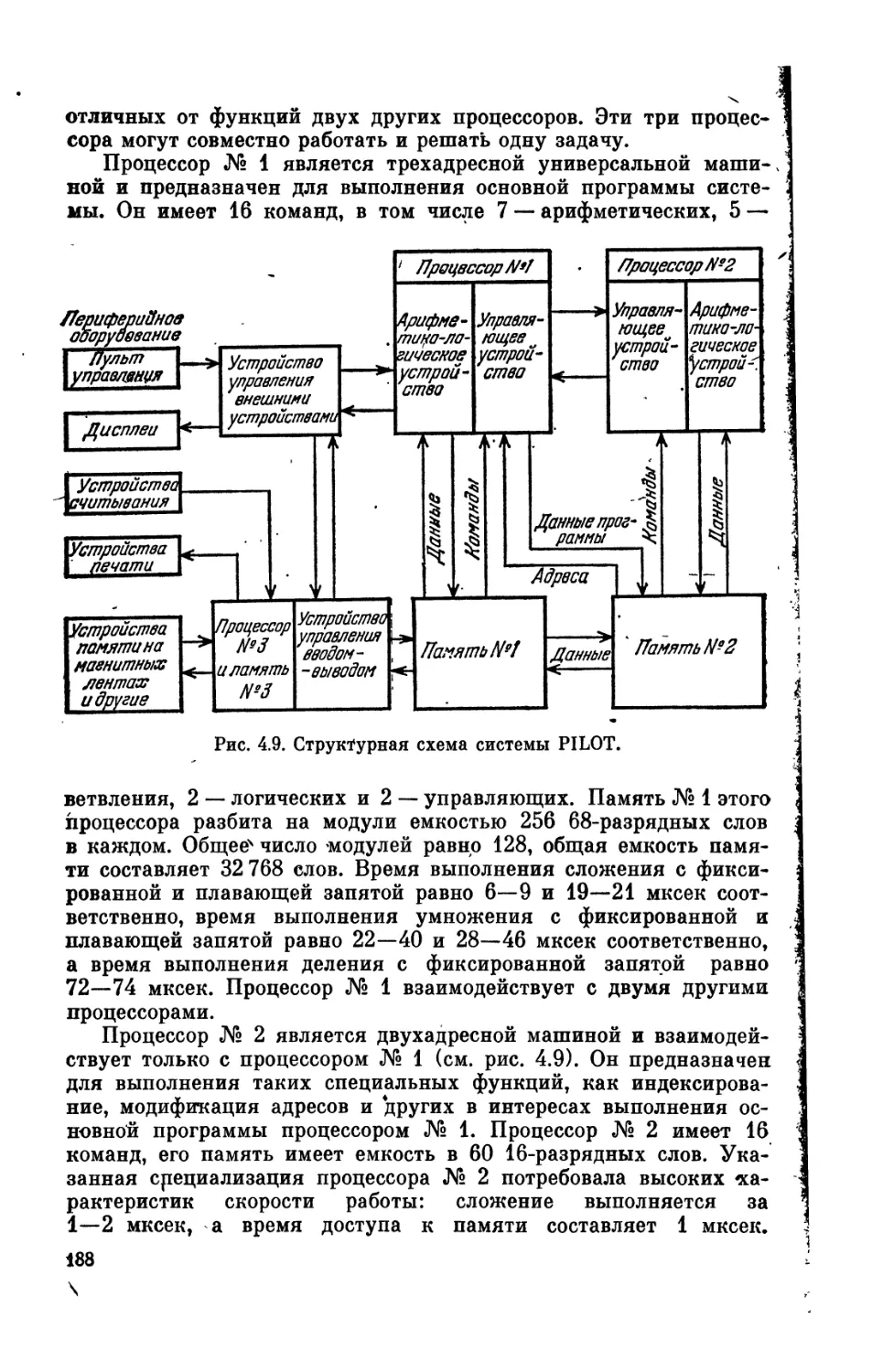

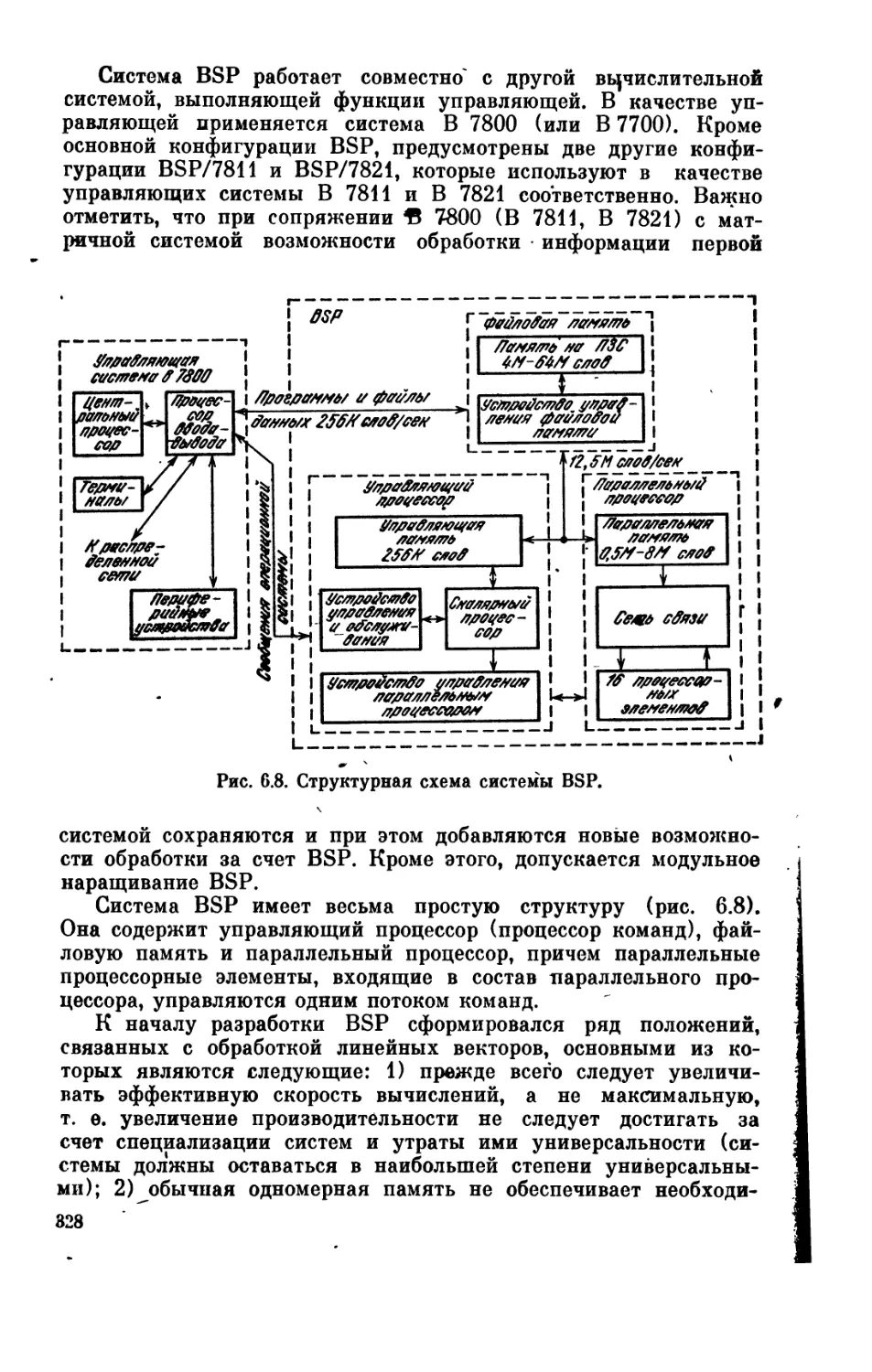

и созданием распределенных вычислительных систем на базе