Автор: Точчи Р.Дж. Уидмер Н.С

Теги: компьютерные технологии компьютерные науки переводная литература цифровые системы

ISBN: 5-8459-0586-9

Год: 2004

Текст

Цифровые системы

Теория и практика

8-е издание ---------------

I •»»! I 4 • •

Рональд Дж. Точчи,"Нил С. Уидмер

Ronald J. Tocci

Monroe Community College

Neal S. Widmer

Purdue University

Digital Systems

Principles and Applications

Eight edition

Upper Saddle River, New Jersey

Columbus, Ohio

Рональд Дж. Точчи

Колледж Монро

Нил С. Уидмер

Университет Пердью

Цифровые системы

Теория и практика

8-е издание

Сканирование

Игорь Пономарёв

Преобразование

http://librus.ru

Москва • Санкт-Петербург • Киев

2004

ББК 32.973.26-018.2.75

Т64

УДК 681.3.07

Издательский дом “Вильямс”

Зав. редакцией С.Н. Тригуб

Перевод с английского М.В. Бойко, А.В. Высоцкого, СЛ. Огородника

Под редакцией В.В. Марченко

По общим вопросам обращайтесь в Издательский дом “Вильямс” по адресу:

info@williamspublishing.com, http://www.williamspublishing.com

Точчи, Рональд, Дж., Уидмер, Нил, С.

Т64 Цифровые системы. Теория и практика, 8-е издание. : Пер. с англ. —

М. : Издательский дом “Вильямс”, 2004. — 1024 с. : ил. — Парал. тит.

англ.

ISBN 5-8459-0586-9 (рус.)

В восьмом издании книги более широко рассмотрены программируемые ло-

гические устройства (ПЛУ). Эта технология быстро вытесняет в современных

цифровых системах микросхемы малой (МИС) и средней степени интеграции

(СИС). Благодаря тому, что ПЛУ рассматриваются в самых разнообразных раз-

делах этой книги, читатель может получить представление об альтернативных

путях реализации цифровых логических схем — от простейших логических

элементов до сложных систем.

К этой книге прилагается компакт-диск с описанием микросхем ТТЛ- и

КМОП-серий, а также спецификации шинных интерфейсов. Компакт-диск так-

же содержит демонстрационную версию компилятора языка CUPL — програм-

мы PAL Expert, созданной компанией Logical Devices, Inc.

Книга будет полезна студентам, аспирантам и специалистам, изучающим

теорию и практику применения цифровых устройств.

ББК 32.973.26-018.2.75

Все названия программных продуктов являются зарегистрированными торговыми марками

соответствующих фирм.

Никакая часть настоящего издания ни в каких целях не может быть воспроизведена в ка-

кой бы то ни было форме и какими бы то ни было средствами, будь то электронные или меха-

нические, включая фотокопирование и запись на магнитный носитель, если на это нет пись-

менного разрешения издательства Prentice Hall, Inc.

Authorized translation from the English language edition published by Prentice Hall, Ptr.,

Copyright © 2001

All rights reserved. No part of this book may be reproduced or transmitted in any form or by

any means, electronic or mechanical, including photocopying, recording or by any information

storage retrieval system, without permission from the Publisher.

Russian language edition published by Williams Publishing House according to the Agreement

with R&I Enterprises Internationa], Copyright © 2004

ISBN 5-8459-0586-9 (pyc.)

ISBN 0-13-085634-7 (англ.)

© Издательский дом “Вильямс”, 2004

© Prentice Hall, Inc., 2001

Оглавление

Введение 20

Глава 1. Введение в предмет 31

Глава 2. Системы счисления и коды 53

Глава 3. Логические элементы и булева алгебра 83

Глава 4. Комбинационные логические схемы 139

Глава 5. Триггеры и родственные им устройства 217

Глава 6. Цифровая математика: схемы и операции 313

Глава 7. Счетчики и регистры 375

Глава 8. Семейства логических интегральных микросхем 475

Глава 9. Логические схемы средней степени интеграции 579

Глава 10. Сопряжение с аналоговым миром 679

Глава 11. Запоминающие устройства 761

Глава 12. Применение программируемых логических устройств 865

Приложение А. Введение в микропроцессоры и микрокомпьютеры 915

Приложение Б. Спецификации некоторых интегральных схем 943

Приложение В. Элементы логических схем 955

Глоссарий 960

Предметный указатель 1018

Содержание

Введение

Глава 1. Введение в предмет

1.1. Численные представления

Аналоговое представление

Цифровое представление

1.2. Цифровые и аналоговые системы

Преимущества цифровой техники

Ограничения цифровой техники

Цифровое будущее

1.3. Цифровые системы счисления

Десятичная система

Десятичный счет

Двоичная система

Двоичный счет

1.4. Представление двоичных величин

Цифровые сигналы и временные диаграммы

1.5. Цифровые и логические схемы

Логические схемы

Цифровые интегральные схемы

1.6. Параллельная и последовательная передача информации

1.7. Память

1.8. Цифровые компьютеры

Основные элементы компьютера

Центральное процессорное устройство

Типы компьютеров

Резюме

Глава 2. Системы счисления и коды

2.1. Преобразование из двоичной системы счисления в десятичную

2.2. Преобразование из десятичной системы счисления в двоичную

Последовательное деление

Диапазон счета

2.3. Восьмеричная система счисления

Преобразование из восьмеричной системы счисления в десятичную

Преобразование из десятичной системы счисления в восьмеричную

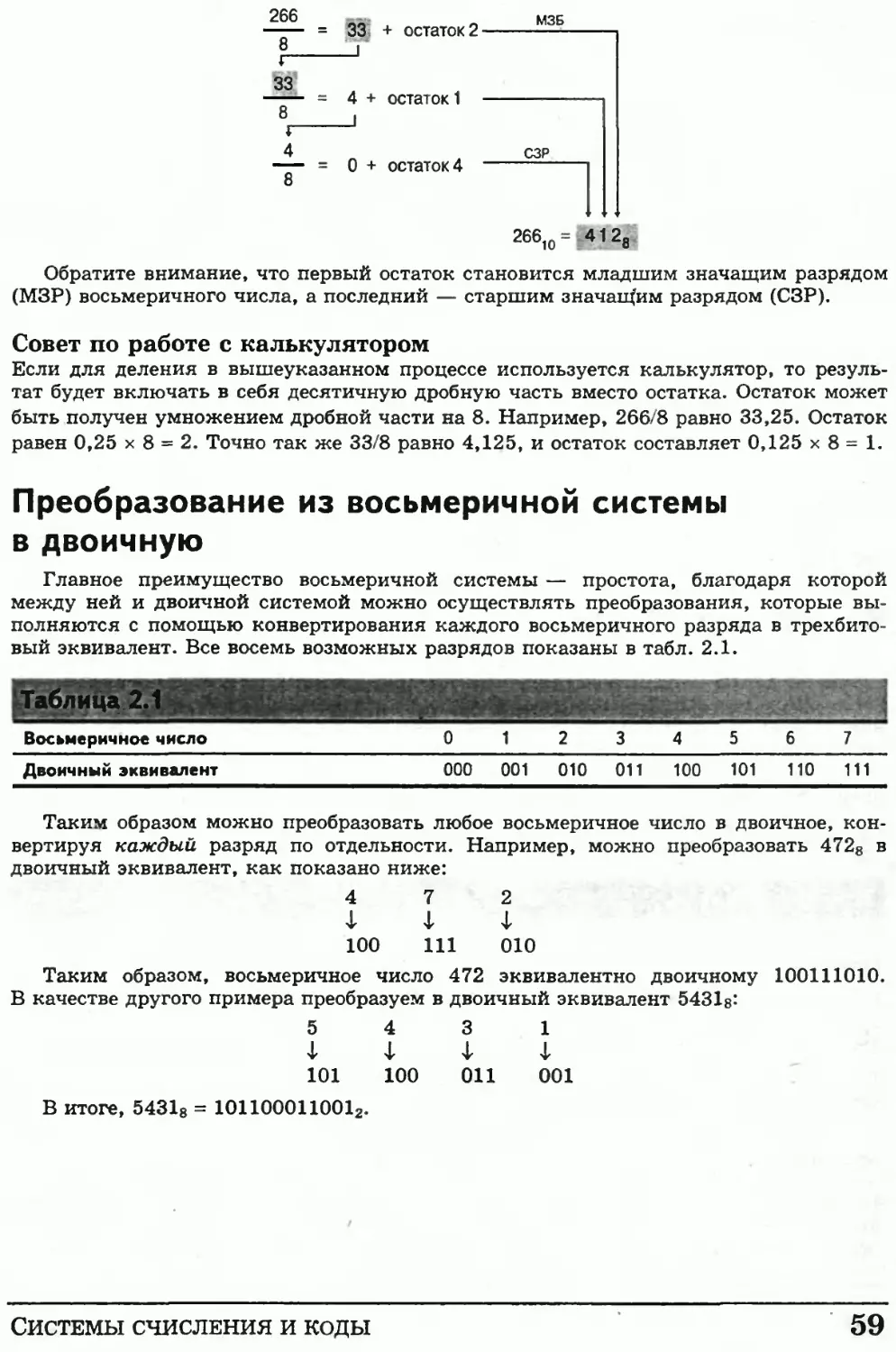

Преобразование из восьмеричной системы в двоичную

Преобразование из двоичной системы в восьмеричную

Восьмеричный счет

2.4. Шестнадцатеричная система счисления

Преобразование из шестнадцатеричной системы в десятичную

Преобразование из десятичной системы в шестнадцатеричную

Преобразование из шестнадцатеричной системы в двоичную

Преобразование из двоичной системы в шестнадцатеричную

Шестнадцатеричный счет

Преимущества шестнадцатеричной и восьмеричной систем

Выводы

2.5. Двоично-десятичный код

Двоично-десятичное кодирование

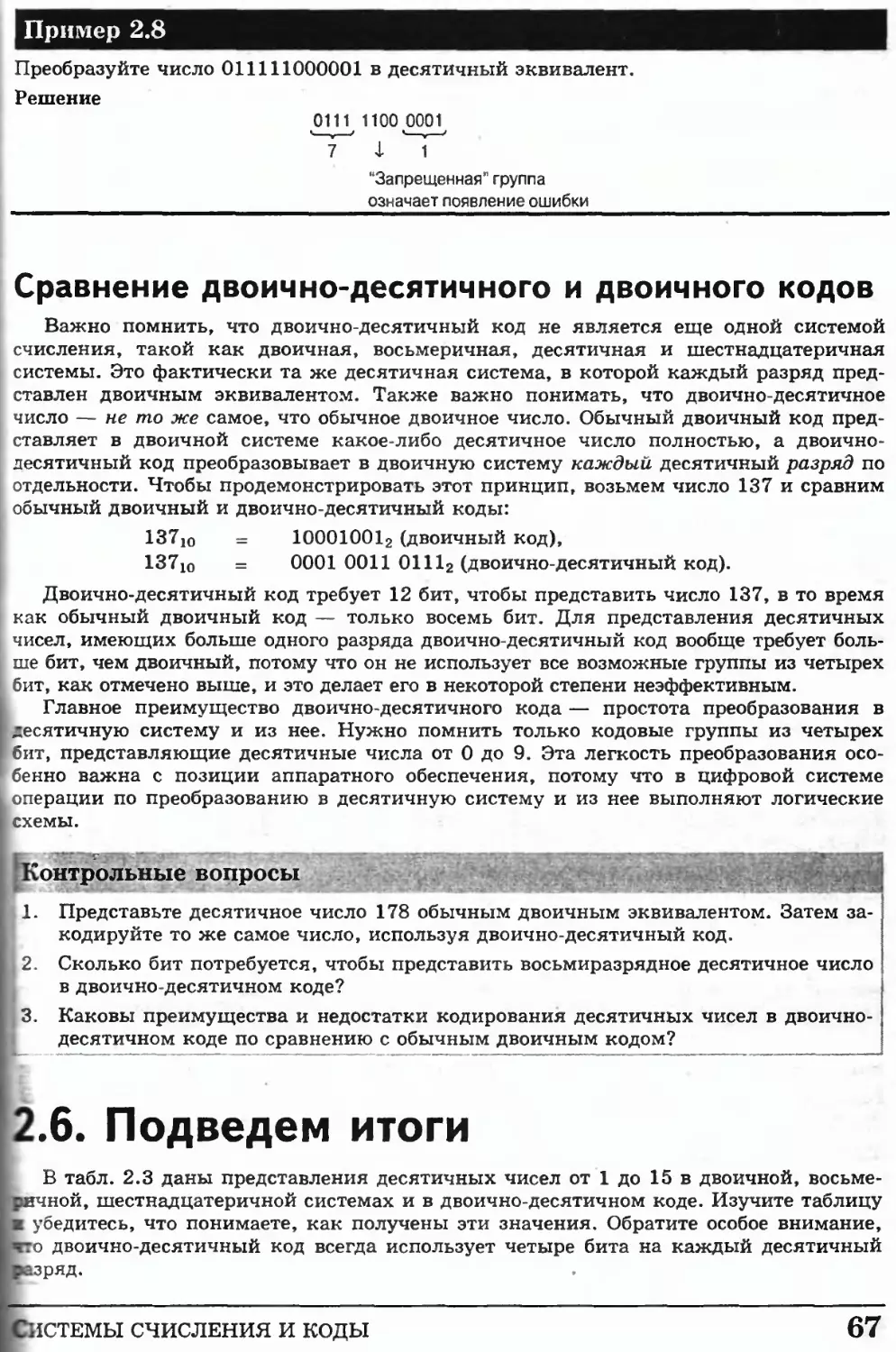

Сравнение двоично-десятичного и двоичного кодов

2.6. Подведем итоги

2.7. Байт 68

2.8. Алфавитно-цифровые коды 69

ASCII-код 69

2.9. Метод проверки четности для обнаружения ошибок 72

Бит четности 73

2.10. Применение 75

Резюме 76

Глава 3. Логические элементы и булева алгебра 83

3.1. Булевы константы и переменные 85

3.2. Таблицы истинности 86

3.3. Логический элемент ИЛИ и операция ИЛИ 87

Логический элемент ИЛИ 88

Выводы 88

3.4. Логический элемент И и операция И 91

Логический элемент И 92

Выводы , 93

3.5. Операция НЕ 95

Логический элемент НЕ (инвертор) 95

Выводы 96

3.6. Алгебраическое описание логических схем 96

Схемы с инверторами 97

3.7. Расчет выходных сигналов логических схем 98

Определение уровня выходного сигнала на схеме 99

3.8. Получение логических схем из булевых выражений 100

3 9. Логические элементы И-НЕ и ИЛИ-НЕ 102

Логический элемент ИЛИ-НЕ 102

Логический элемент И-НЕ 104

3.10. Булевы теоремы 106

Теоремы для нескольких переменных 108

3.11. Теоремы де Моргана 110

Следствия теорем де Моргана 112

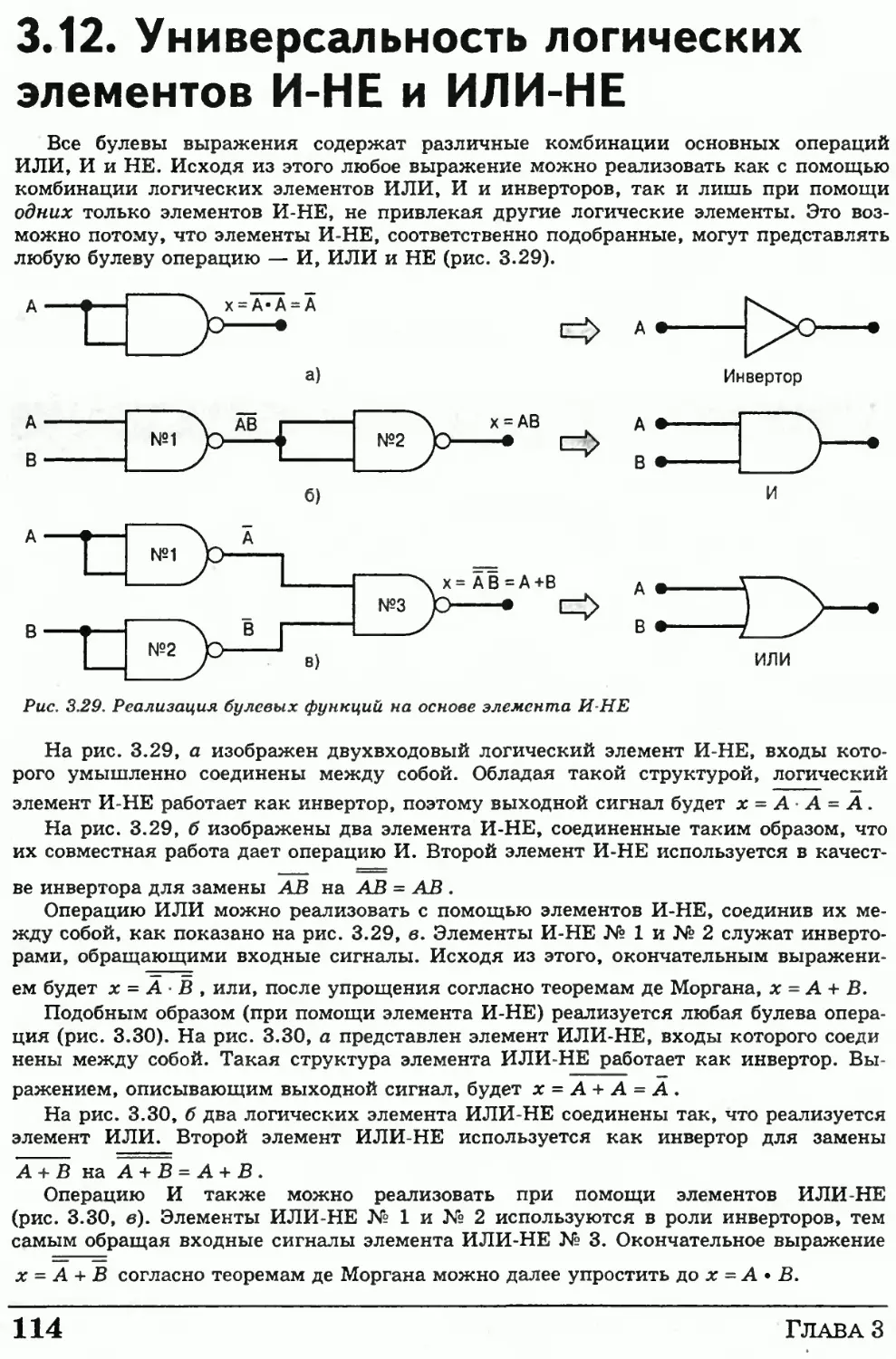

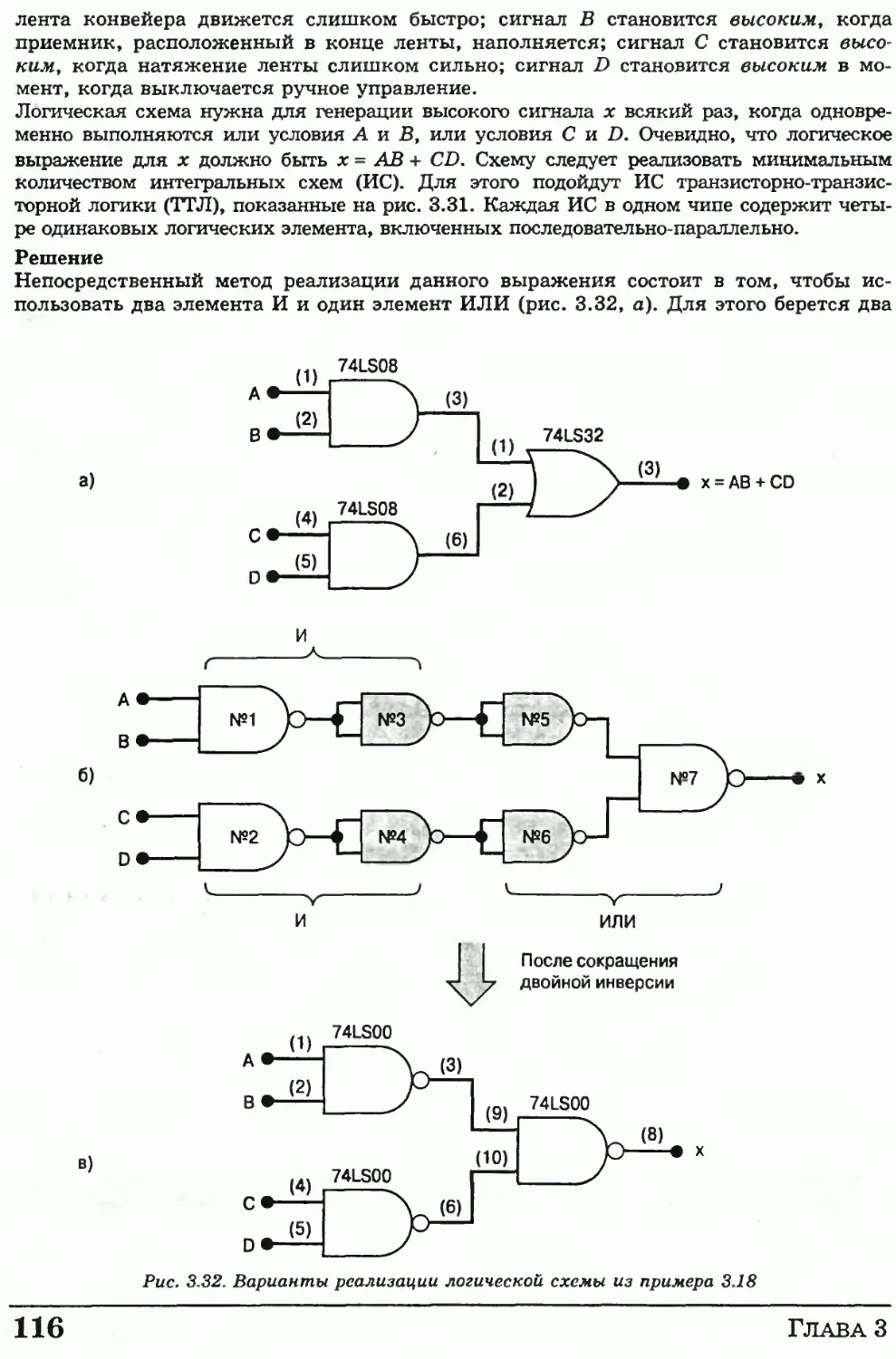

3.12. Универсальность логических элементов И-НЕ и ИЛИ-НЕ 114

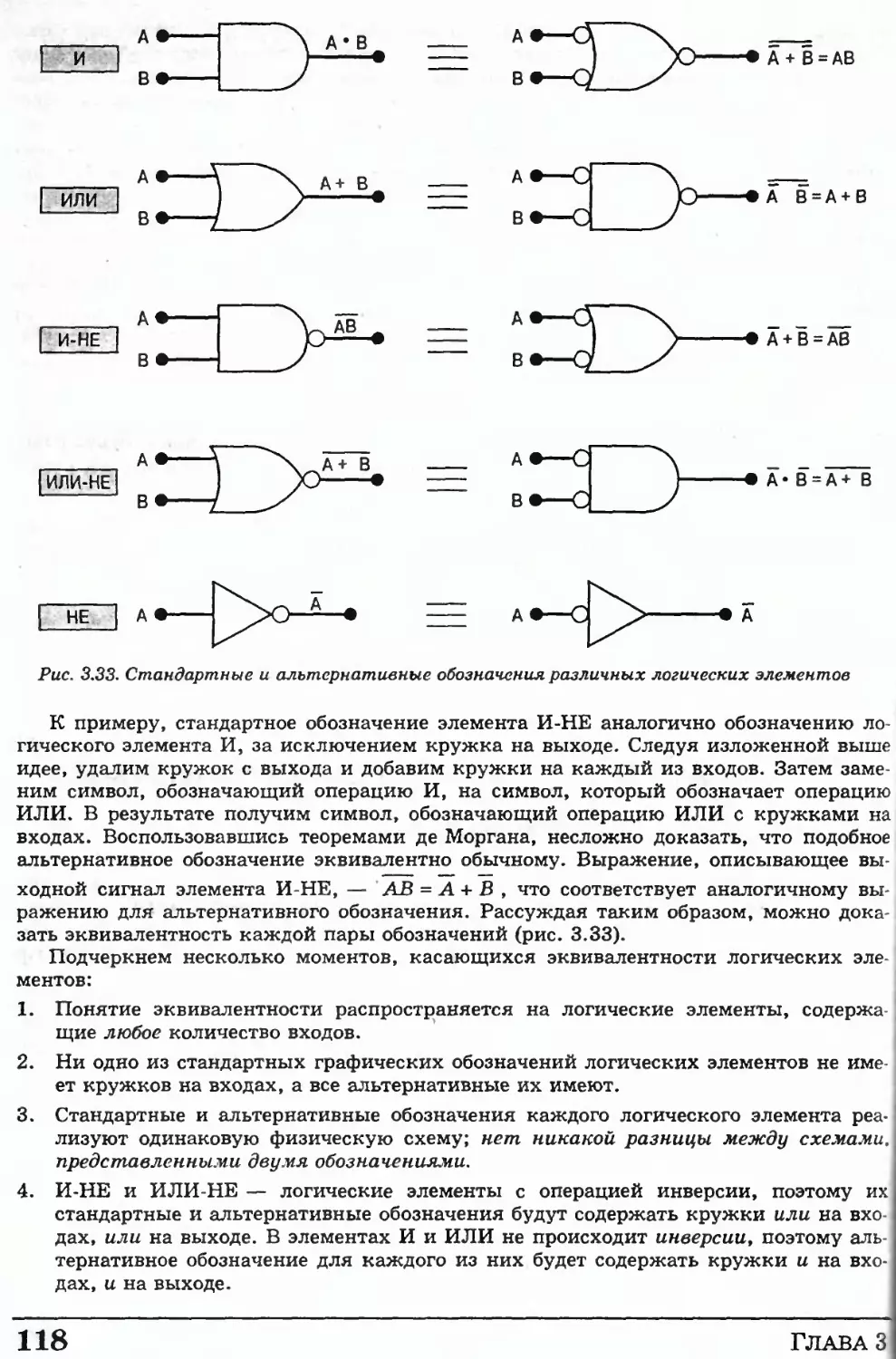

3.13. Альтернативное представление логических элементов 117

Интерпретация обозначений логических элементов 119

Резюме 120

3.14. Использование различных представлений логических элементов 121

Какой же вариант схемы более предпочтителен? 122

Размещение кружков, обозначающих инверсию 122

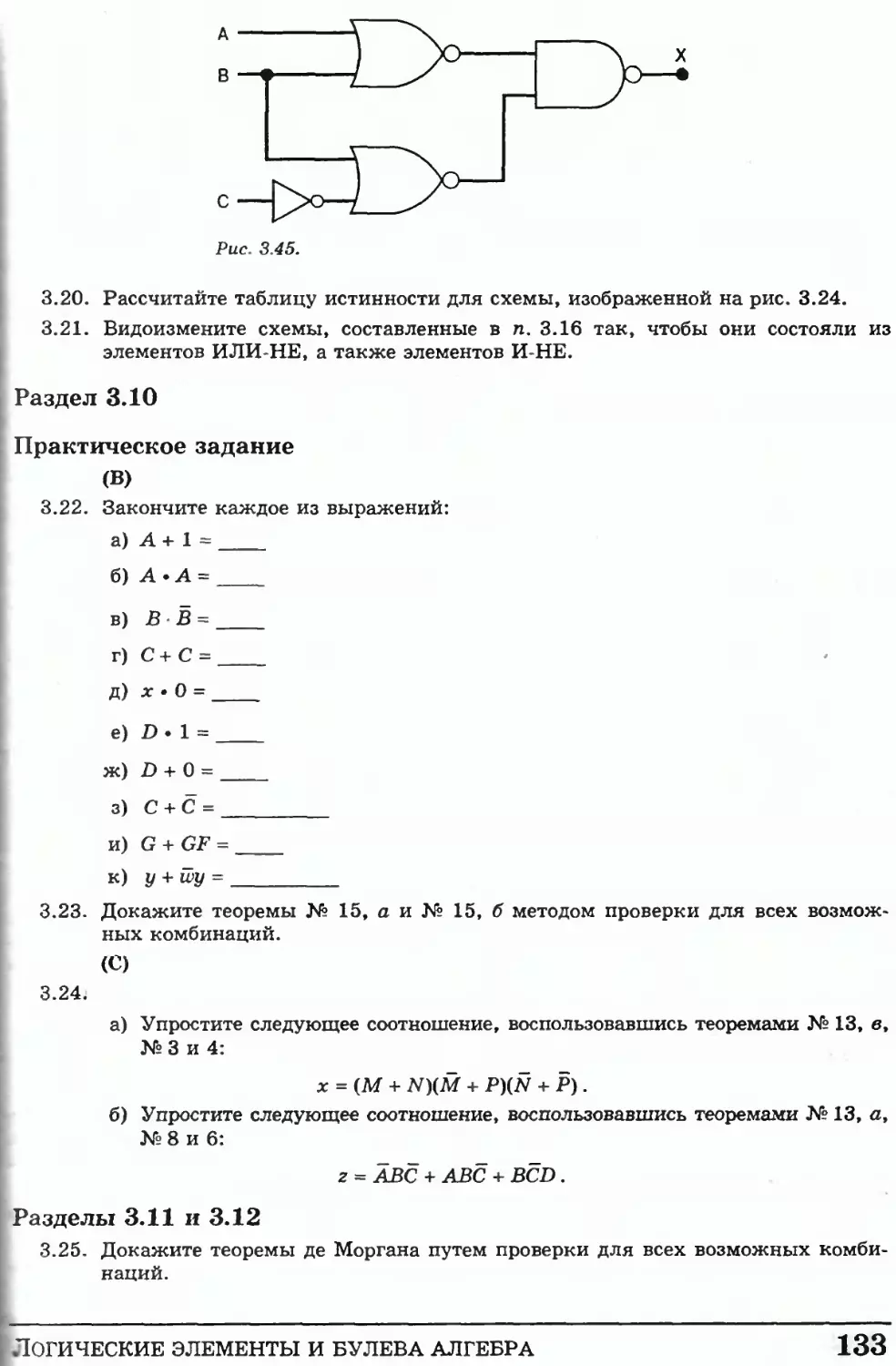

Анализ схем 124

Объявленные уровни 126

Маркировка низких логических сигналов 126

Маркировка сигналов, обладающих двумя активными состояниями 127

3.15. Стандарт представления логических элементов IEEE/ANSI 127

Традиционные обозначения или обозначения IEEE/ANSI? 128

Резюме 129

Глава 4. Комбинационные логические схемы 139

4.1. Дизъюнктивная форма выражения 141

Конъюнктивная форма 141

4.2. Упрощение логических схем 142

4.3. Алгебраическое упрощение 142

4.4. Проектирование комбинационных логических схем 147

Полная методика проектирования 149

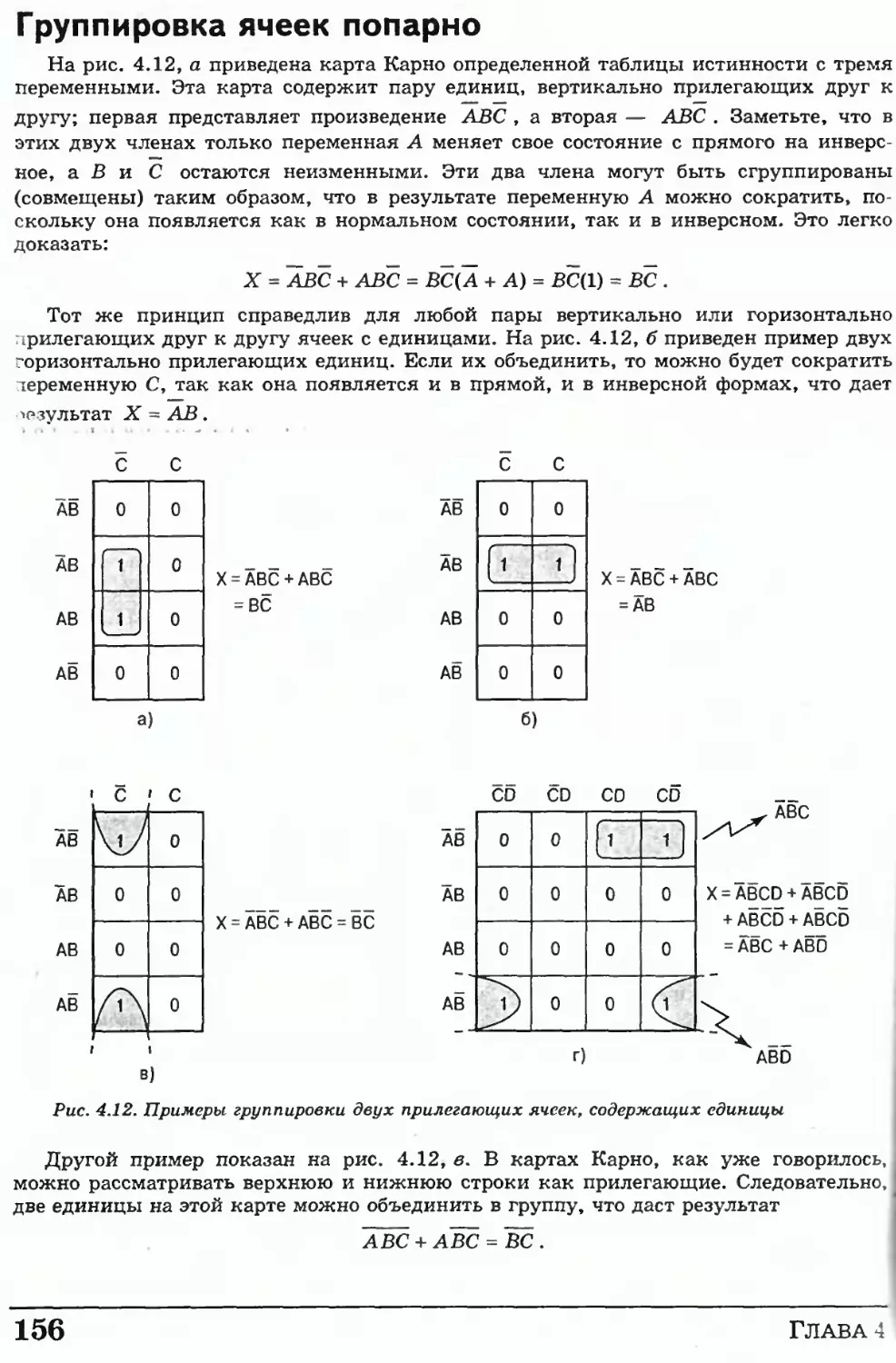

4.5. Метод карт Карно 154

Структура карт Карно 154

Содержание 7

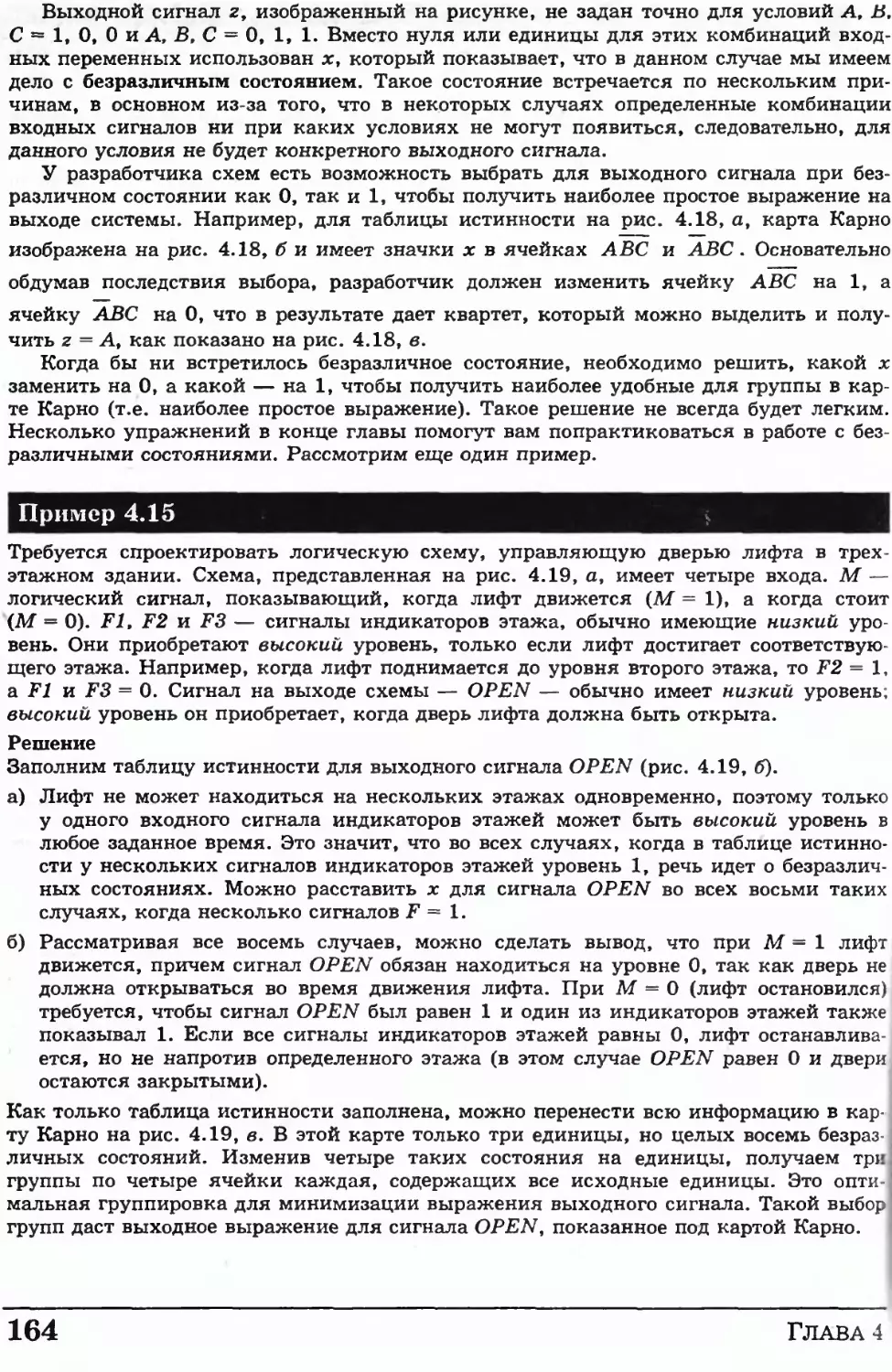

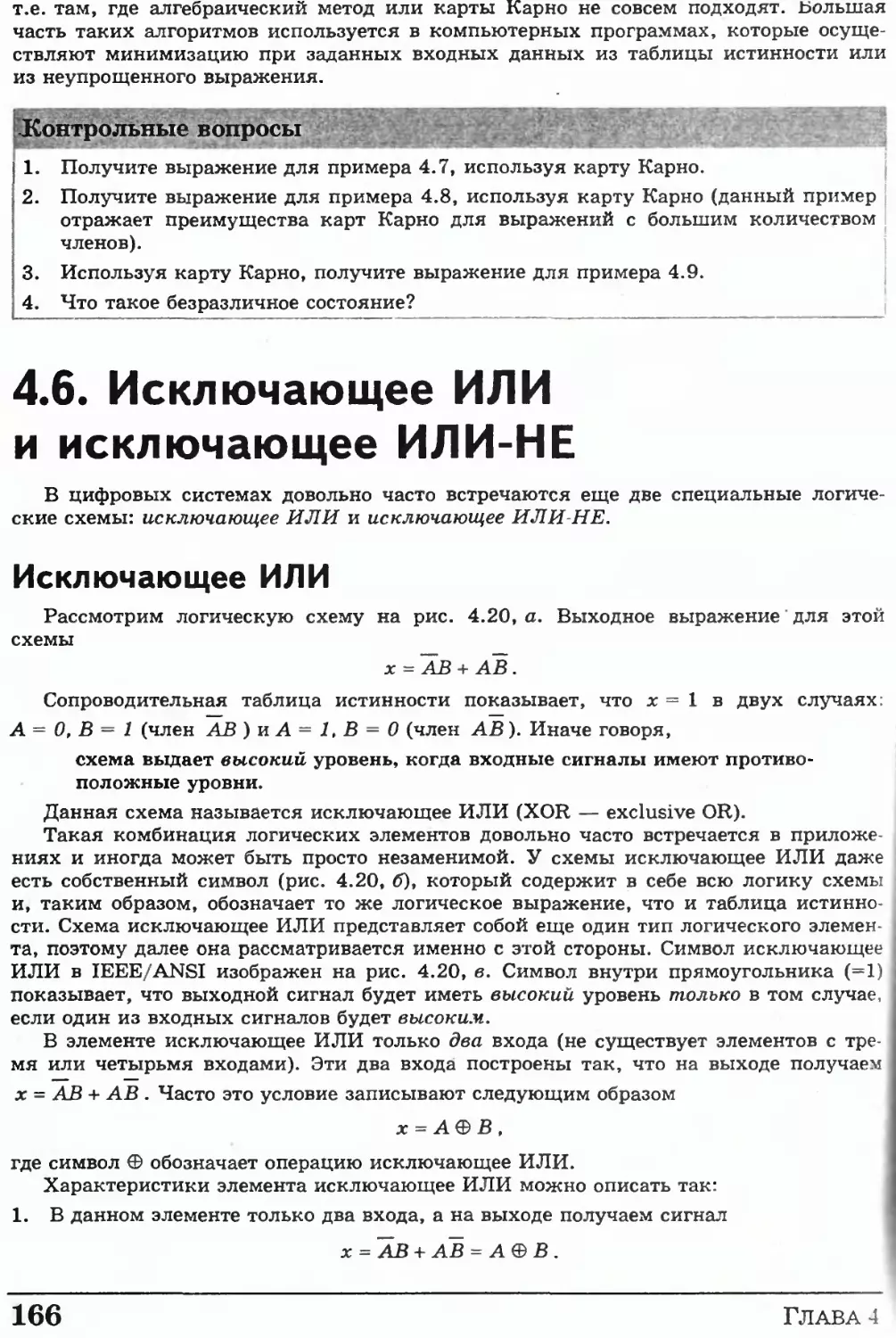

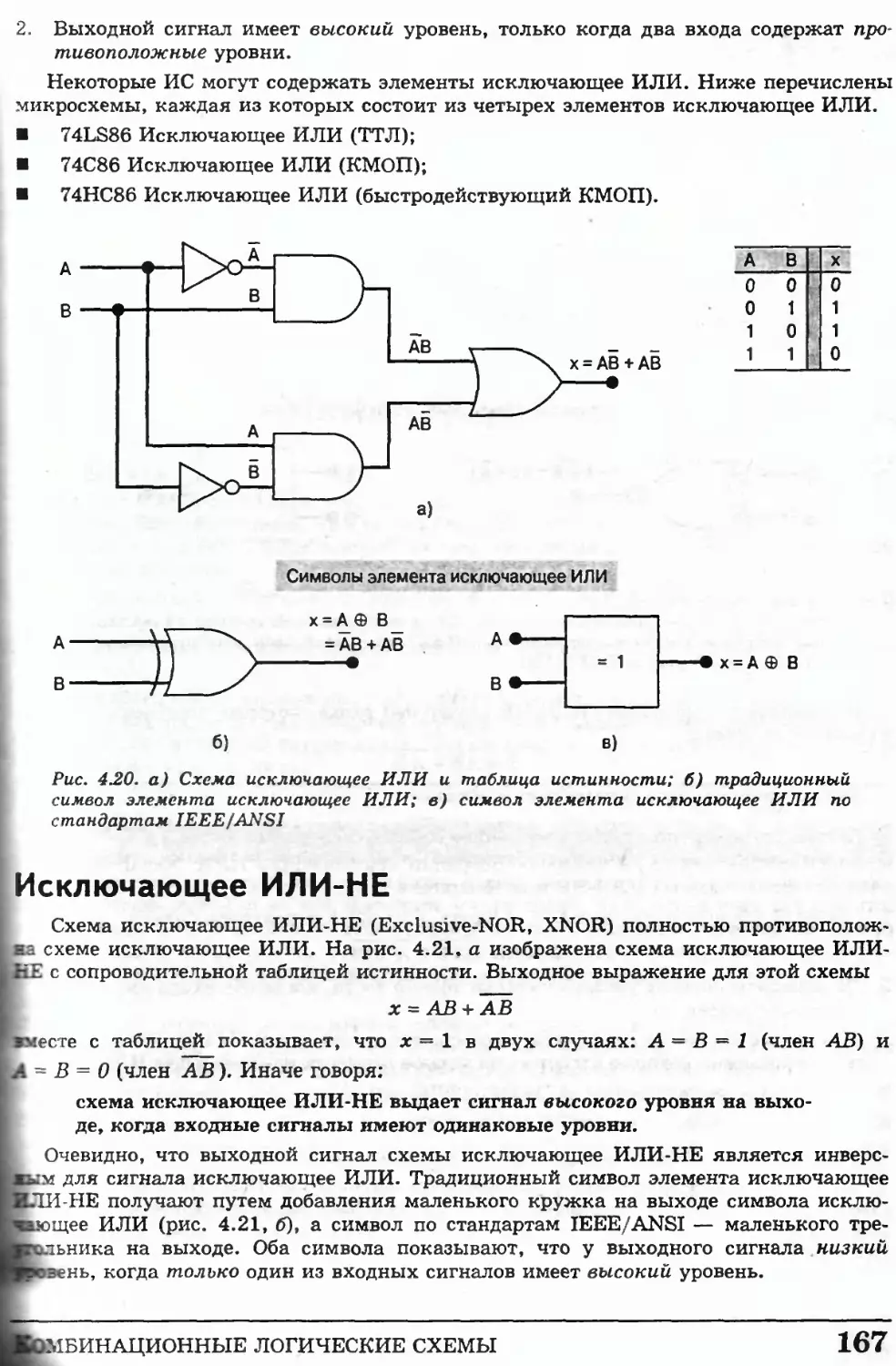

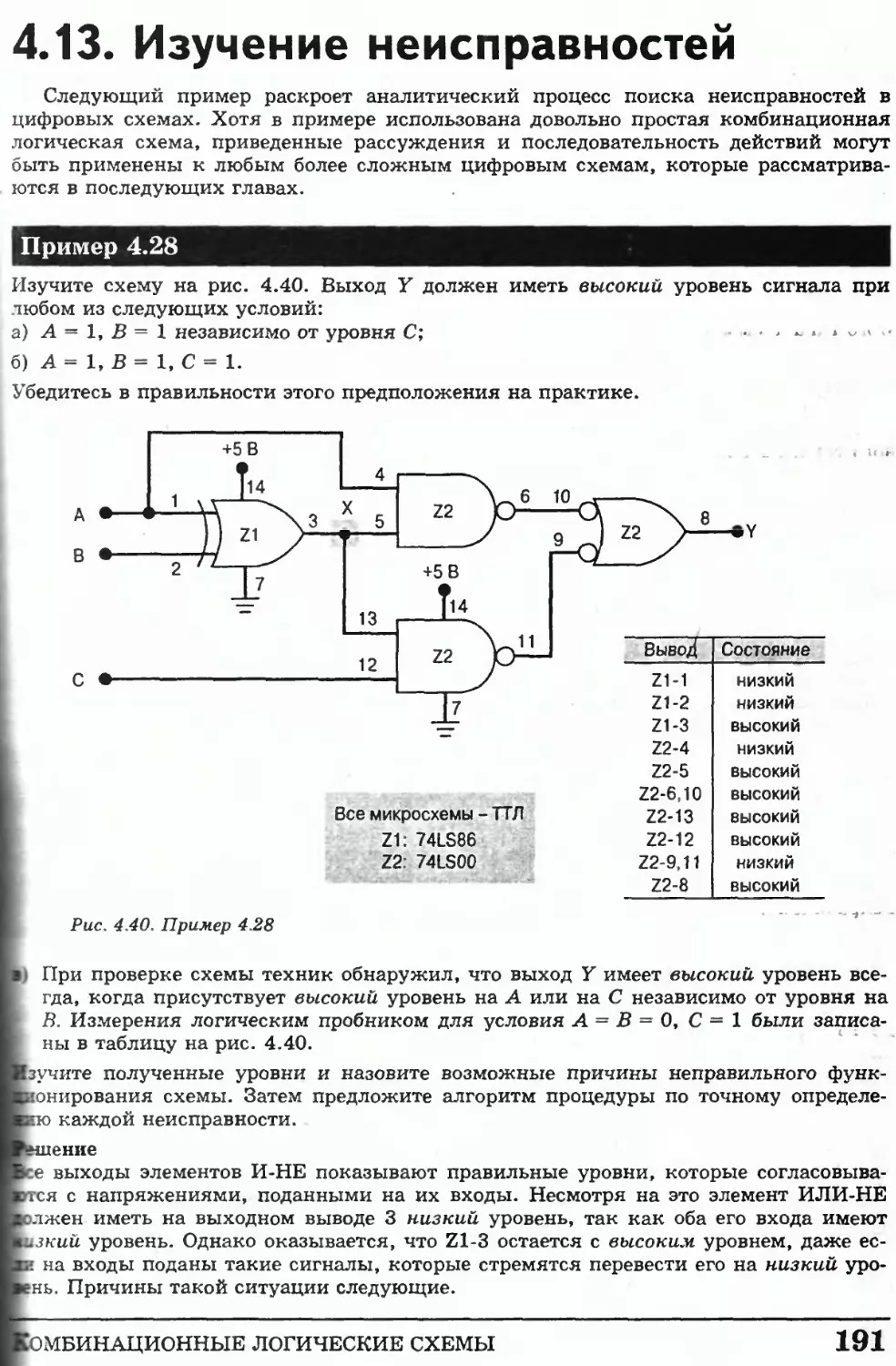

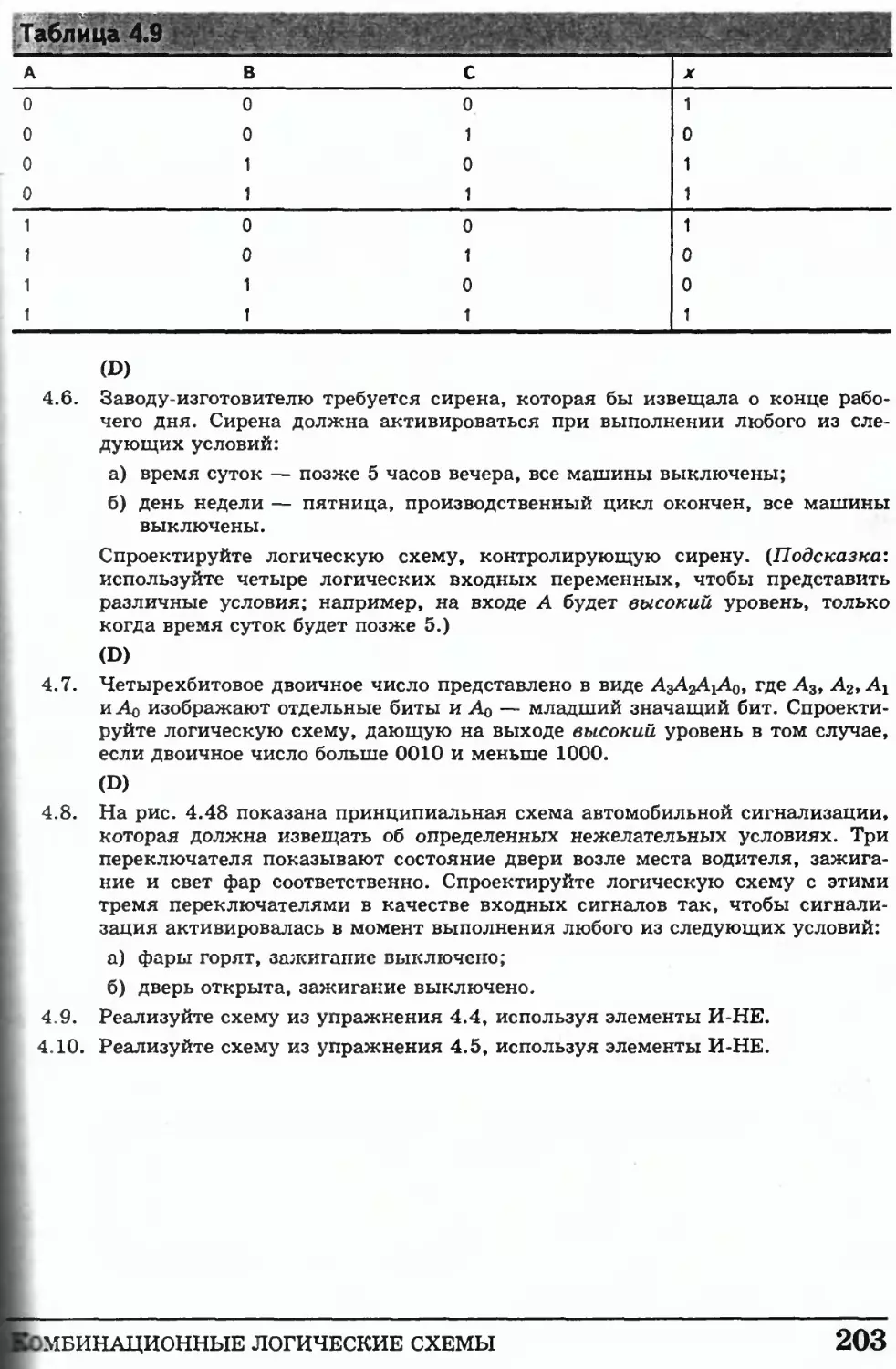

Группировка Группировка ячеек попарно Группировка ячеек по четыре (квартеты) Группировка ячеек по восемь (октеты) Полный процесс упрощения Как заполнять карту Карно, исходя из выходного выражения Безразличное состояние Резюме 4.6. Исключающее ИЛИ и исключающее ИЛИ-НЕ Исключающее ИЛИ Исключающее ИЛИ-НЕ 4.7. Генератор и проверочное устройство сигнала четности 4.8. Разрешающие/запрещающие схемы 4.9. Основные характеристики цифровых ИС Биполярные и униполярные цифровые ИС Семейство ТТЛ Семейство КМОП Питание и общий провод Диапазоны напряжения логических уровней Неподключенные (плавающие) входы Коммутационная диаграмма логических схем 4.10. Поиск неполадок в цифровых системах 4.11. Внутренние неполадки в цифровых ИС Неисправность внутренних схем Внутреннее замыкание входов на общий провод или источник питания Внутреннее замыкание выхода на общий провод или источник питания Разомкнутый вход или выход Замыкание между двумя выводами 4.12. Внешние неполадки Разомкнутый сигнальный провод Замкнутый сигнальный провод Неисправный источник питания Перегрузка на выходе 4.13. Изучение неисправностей 4.14. Программируемые логические устройства Программирование ПЛУ Инструментальные программные средства Введение в CUPL Цикл разработки Резюме 155 156 157 158 158 162 163 165 166 166 167 172 173 176 177 178 179 179 180 180 181 182 184 184 184 184 186 187 188 189 189 190 190 191 193 194 195 197 199 201

Глава 5. Триггеры и родственные им устройства 5.1. Защелка на элементах И-НЕ Установка защелки (триггера) Сброс триггера Одновременная установка и сброс Резюме Другие обозначения Терминология 5.2. Защелка на элементах ИЛИ-НЕ Состояние триггера при включении схемы 5.3. Поиск неполадок 5.4. Тактовые сигналы и синхронные триггеры Синхронные триггеры Время установки и время удержания триггера 5.5. Синхронные S-C-триггеры 217 220 221 222 222 223 223 224 226 229 229 231 232 233 234

8 Содержание

Внутреннее строение S-C-триггеров, управляемых фронтом 236

5.G. Синхронные J-K-триггеры 238

Внутреннее строение J-K-триггеров. управляемых фронтом 240

5.7. Синхронный D-триггер 241

Реализация D-трш гера 242

Параллельная передача данных 242

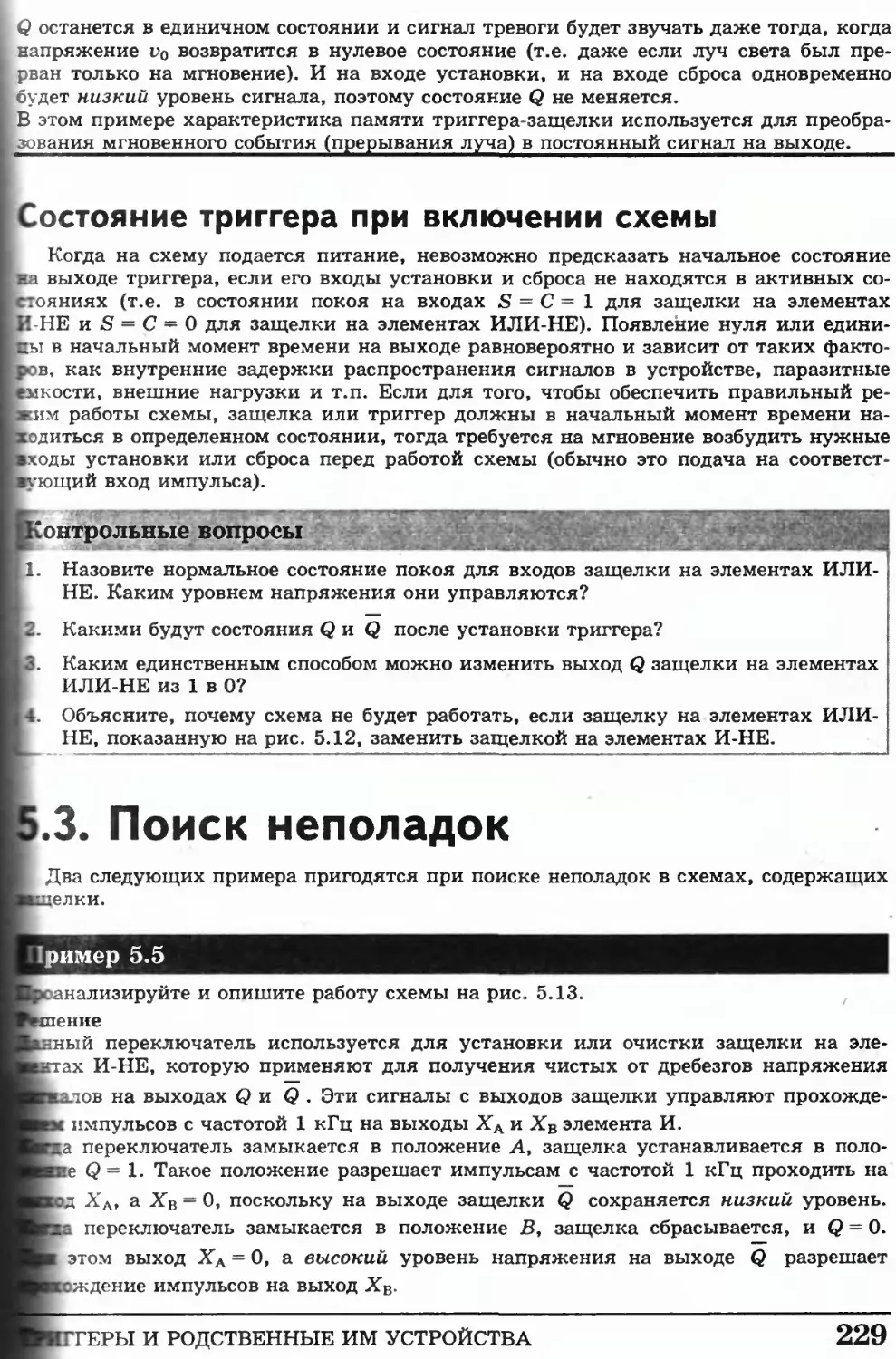

5.8. Защелка на D-триггере (прозрачная защелка) 243

5.9. Асинхронные входы 245

Маркировка асинхронных входов 247

5.10. Обозначение IEEE/ANSI 249

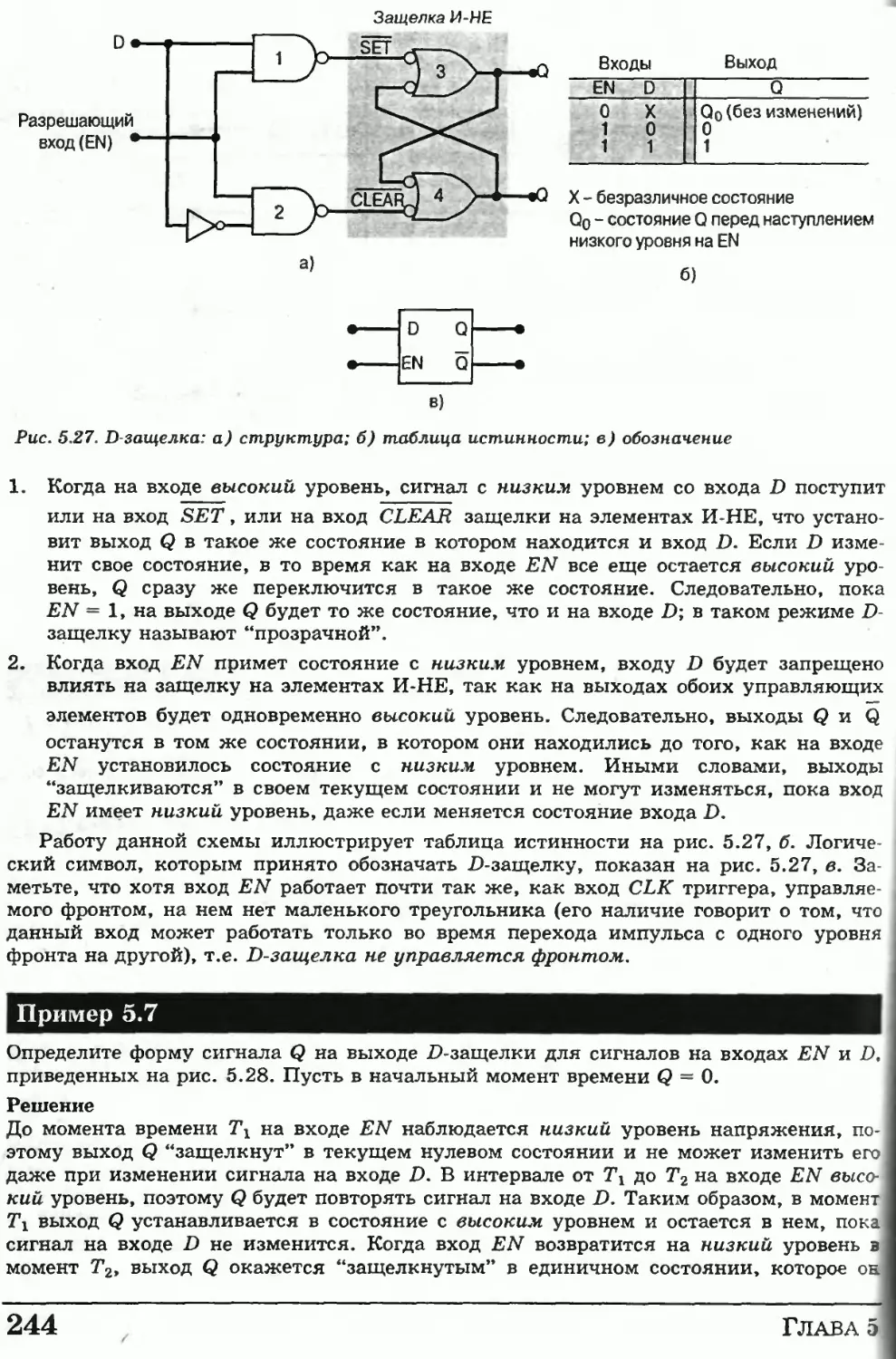

5.11. Временные процессы в триггерах 250

Моменты установки и удержания 251

Задержки распространения сигнала 251

Максимальная частота синхронизации Лдах 251

Время нахождения тактовых импульсов на высоком и низком уровнях 252

Ширина активного асинхронного импульса 252

Время нарастания тактового сигнала 252

Реальные ИС 252

5.12. Потенциальные проблемы согласования по времени

в схемах с триггерами 254

5.13. Триггеры Master/Slave 256

5.14. Применение триггеров 257

5.15. Синхронизация триггеров 257

5.16. Обнаружение последовательности входных импульсов 259

5.17. Хранение и передача данных 260

Параллельная передача данных 261

5.18. Последовательная передача данных: сдвиговые регистры 262

Требование к величине времени удержания 264

Последовательная передача между регистрами 264

Операция сдвига влево 265

Сравнение параллельного и последовательного типов передач 265

5.19. Деление частоты и счет 266

Счет 267

Диаграмма переходов 268

Коэффициент пересчета 269

5.20. Прикладная задача 270

5.21. Триггер Шмитта 272

5.22. Одновибратор (ждущий мультивибратор) 274

Одновибратор без повторного запуска 274

Одновибратор с повторным запуском 275

Реальные устройства 276

Ждущий мультивибратор 277

5.23. Анализ последовательных схем 277

5.24. Генератор тактовых (синхронизирующих) импульсов 280

Генератор на основе триггера Шмитта 280

Таймер 555 в качестве несинхронизированного мультивибратора 280

Кварцевые генераторы тактовых импульсов 282

5.25. Поиск неисправностей в схемах с триггерами 282

Разомкнутые входы 283

Короткозамкнутые выходы 284

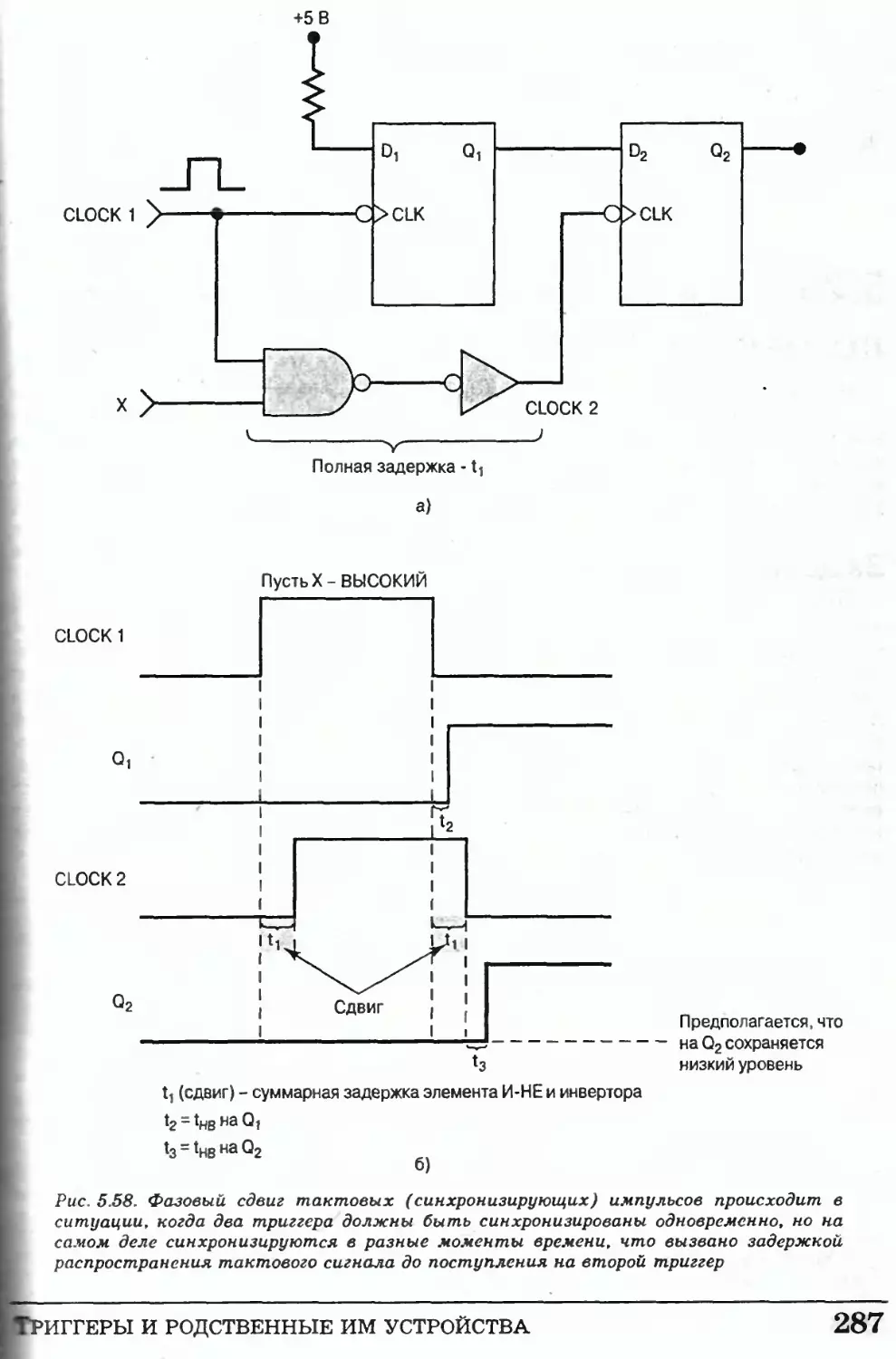

Фазовый сдвиг тактовых (синхронизирующих) импульсов 286

5.26. Применение программируемых логических устройств 288

Защелка на элементах И-НЕ 288

D-защелка 289

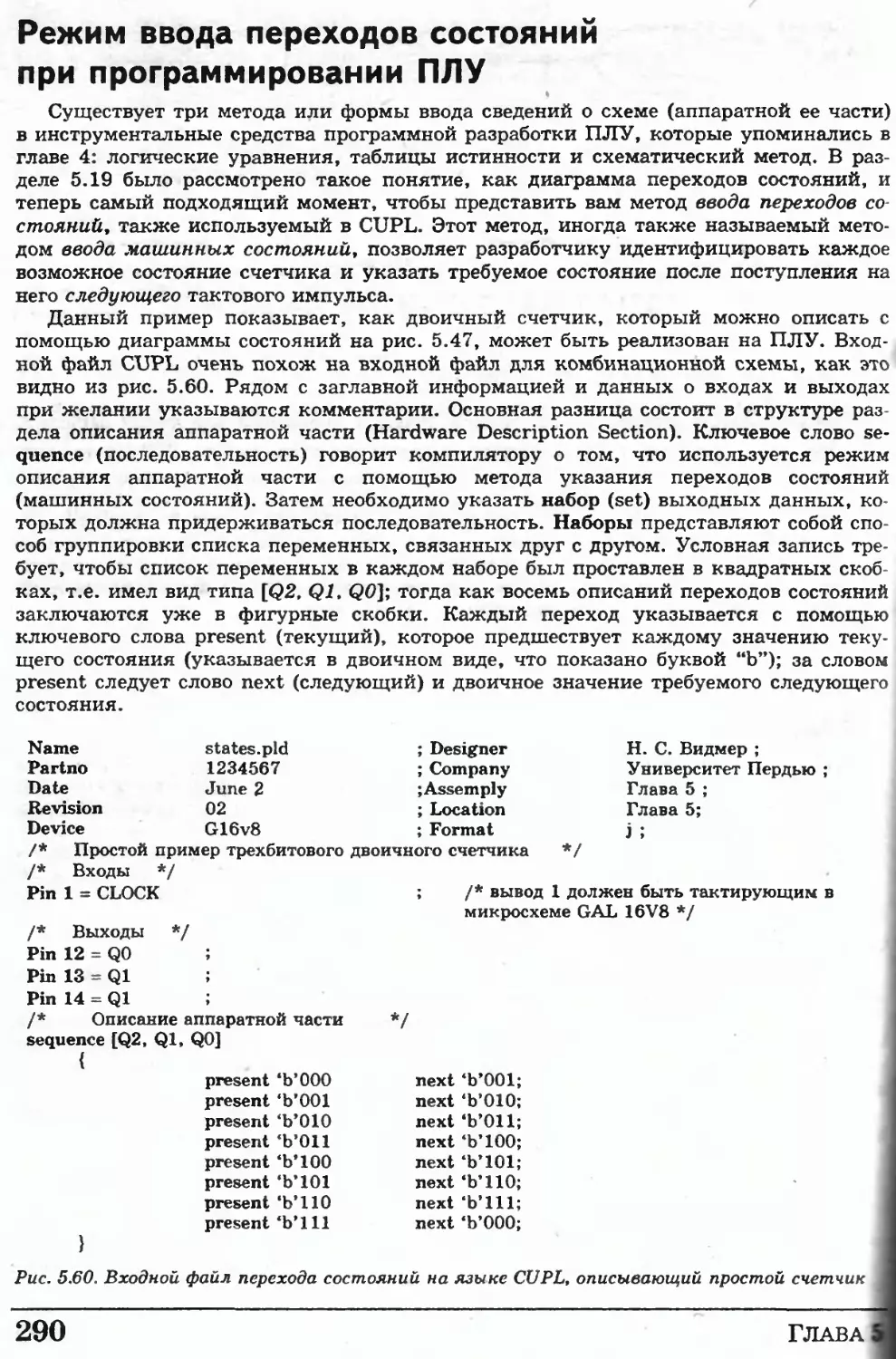

Режим ввода переходов состояний при программировании ПЛУ 290

Резюме 292

Содержание

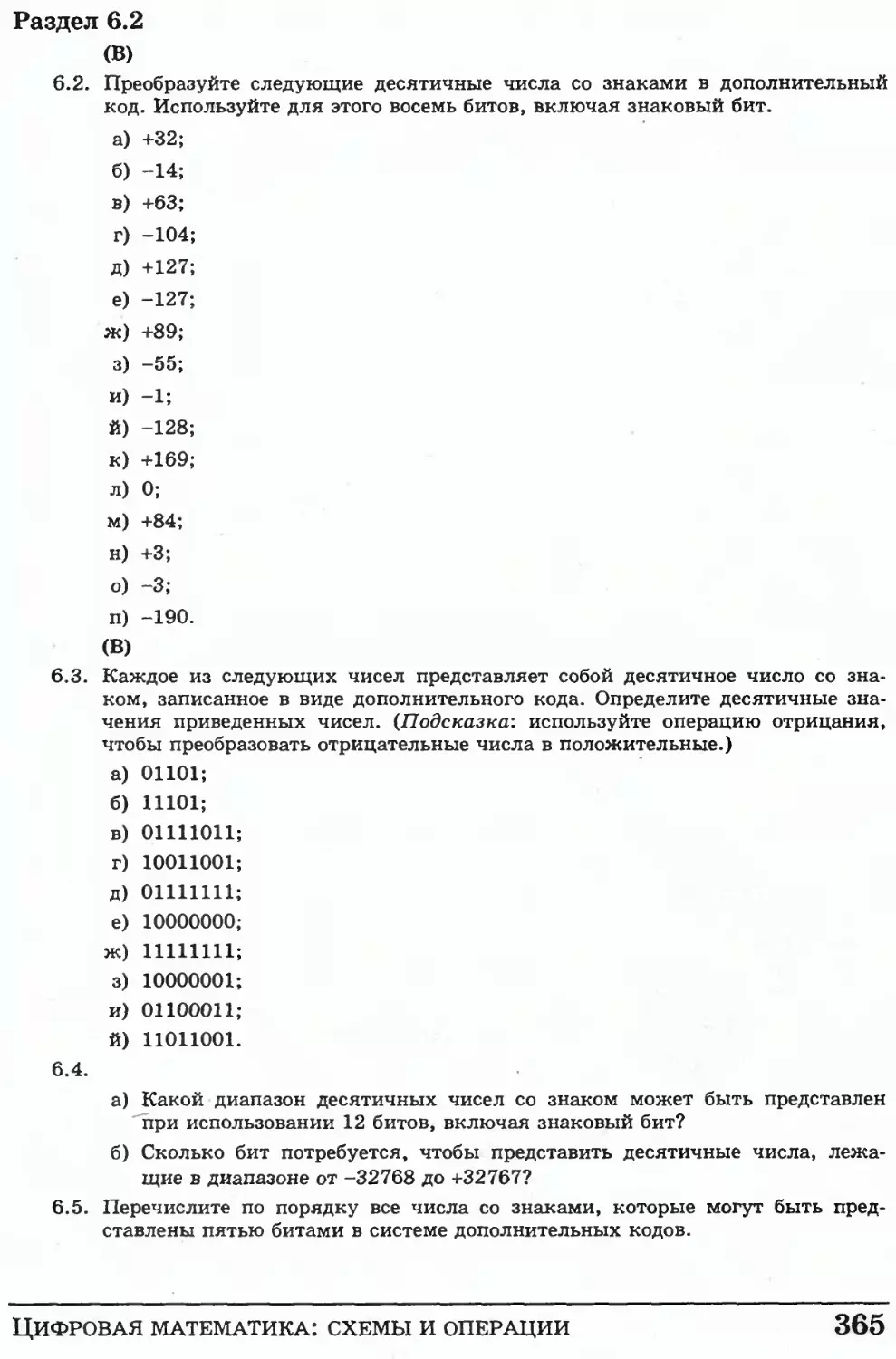

Глава 6. Цифровая математика: схемы и операции 313

6.1. Двоичное сложение 314

6.2. Представление чисел со знаком 315

Обратный код 316

Дополнительный код 317

Представление чисел со знаком в системе дополнительных кодов 317

Отрицание 319

Особый случай представления чисел через дополнительный код 320

6.3. Сложение в системе дополнительных кодов 322

6.4. Вычитание в системе дополнительных кодов 324

Переполнение 325

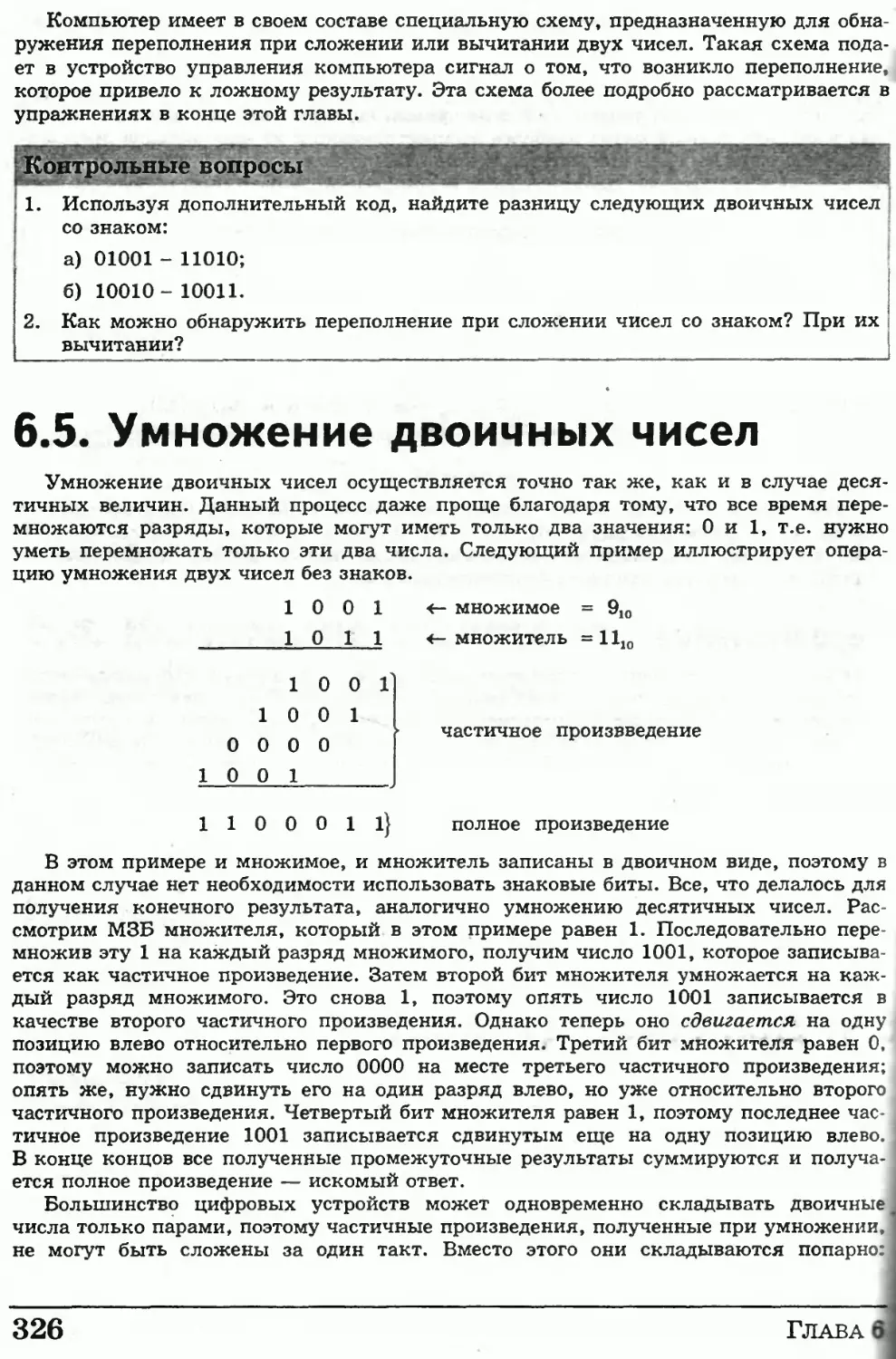

6.5. Умножение двоичных чисел 326

Умножение в системе дополнительных кодов 327

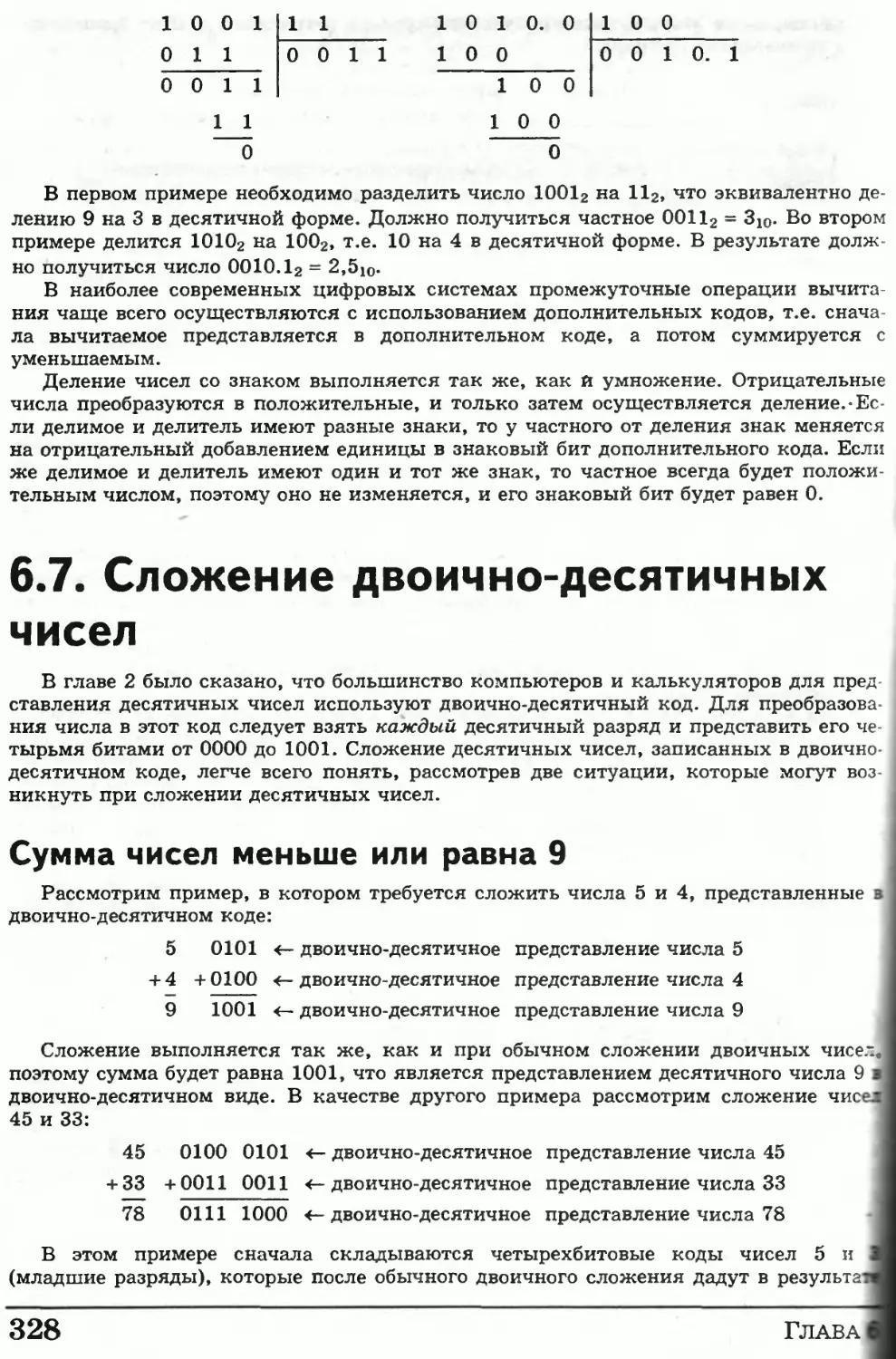

6.6. Двоичное деление 327

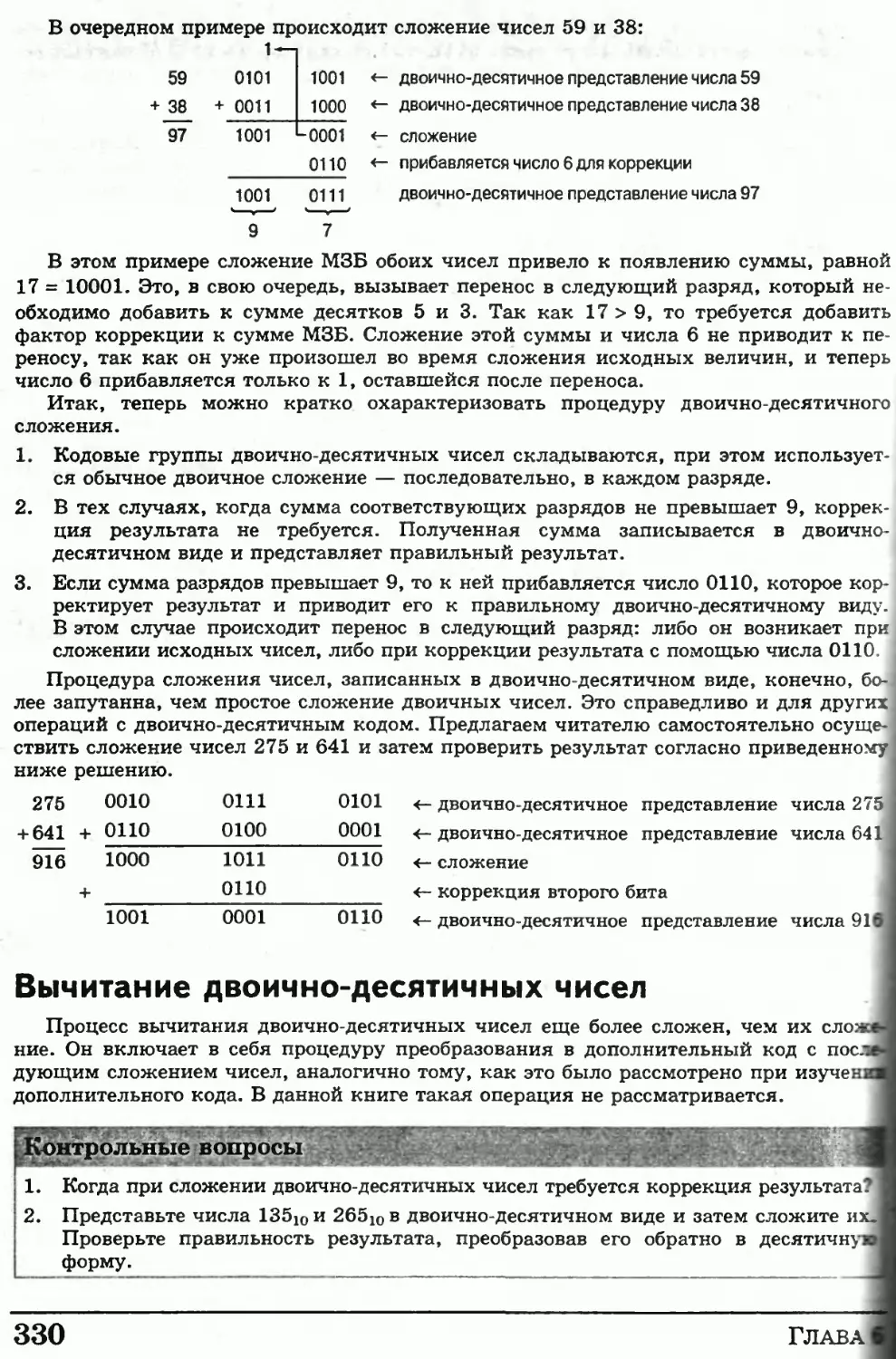

6.7. Сложение двоично-десятичных чисел 328

Сумма чисел меньше или равна 9 328

Сумма чисел больше 9 329

Вычитание двоично-десятичных чисел 330

6.8. Арифметика шестнадцатеричных чисел 331

Сложение шестнадцатеричных чисел 331

Вычитание шестнадцатеричных чисел 332

Представление чисел со знаком в шестнадцатеричном виде 333

6.9. Арифметические схемы 334

Арифметико-логическое устройство 334

6.10. Параллельный двоичный сумматор 335

6.11. Принцип работы полного сумматора 337

Минимизация методом карт Карно 338

Полусумматор 339

6.12. Параллельный полный сумматор с регистрами 340

Обозначения, описывающие работу регистров 340

Последовательность операций 342

6.13. Распространение сигнала переноса 342

6.14. Параллельный сумматор на базе ИС 343

Последовательное подключение параллельных сумматоров 345

6.15. Система дополнительных кодов 346

Сложение 346

Вычитание 346

Комбинация сложения и гычитания 348

6.16. Двоично-десятичный сумматор 350

Последовательное соединение двоигно-десятг'чных сумматоров 352

6.17. Интегральные схемы АЛУ 353

АЛУ на базе ИС 74LS382/HC382 354

Расширение АЛУ 356

Другие АЛУ 357

6.18. Обозначения стандарта IEEE/ANSI 358

6.19. Пример поиска неисправностей 358

6.20. Полный сумматор на основе ПЛУ 360

Резюме 363

Глава 7. Счетчики и регистры 375

Часть I 376

7.1. Асинхронные счетчики 376

Прохождение сигнала 378

Коэффициент пересчета 378

Деление частоты 379

7.2. Счетчики с коэффициентом пересчета менее 2N 380

10

Содержание

Диаграмма переходов состояний 382

Отображение состояний счетчика 382

Изменение коэффициента пересчета 384

Основной алгоритм 385

Десятичные счетчики/двоично-десятичные счетчики 385

7.3. Интегральные схемы асинхронных счетчиков 386

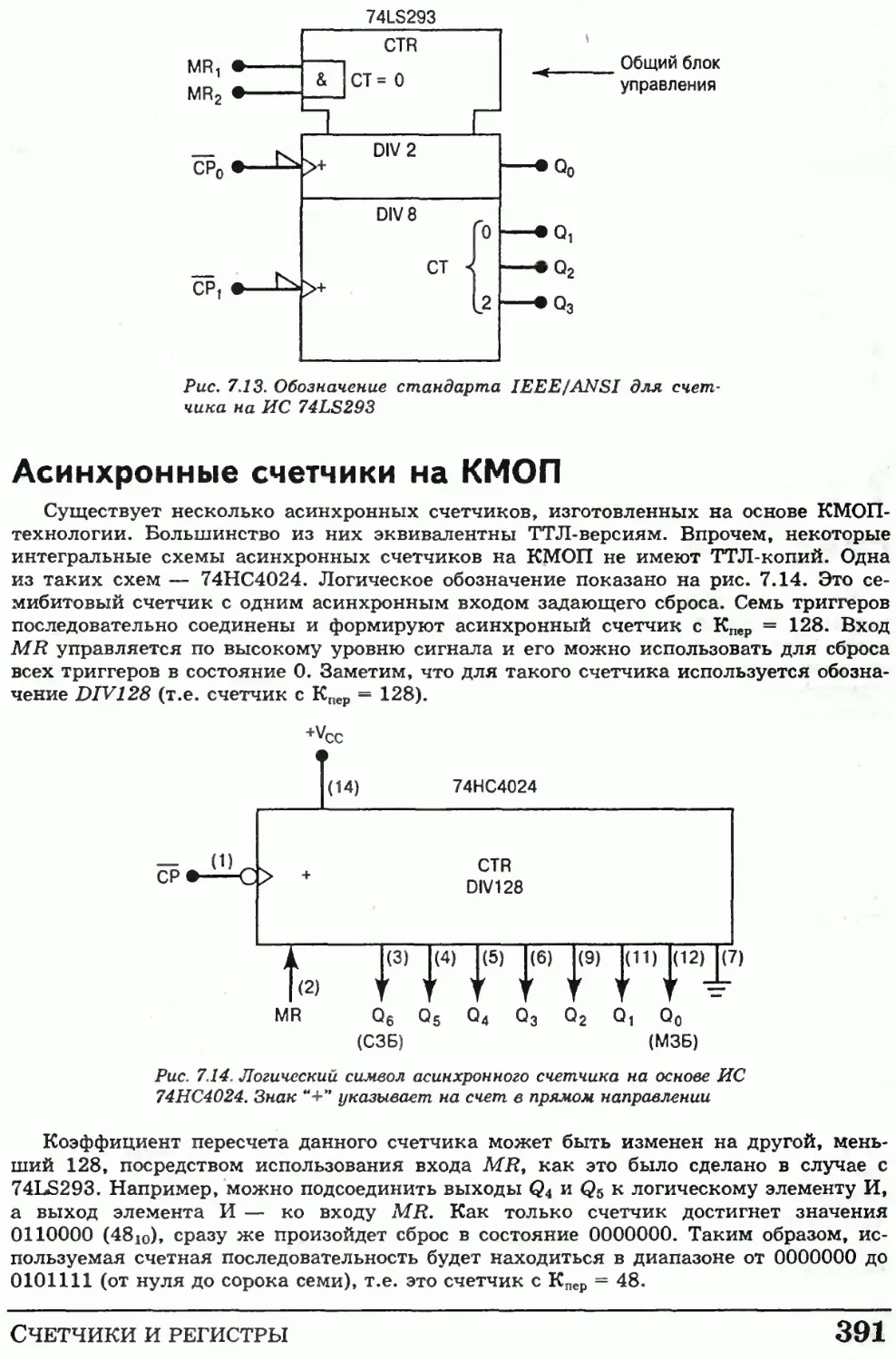

Обозначение стандарта IEEE/ANSI для счетчика на ИС 74LS293 390

Асинхронные счетчики на КМОП 391

7.4. Асинхронные вычитающие счетчики 392

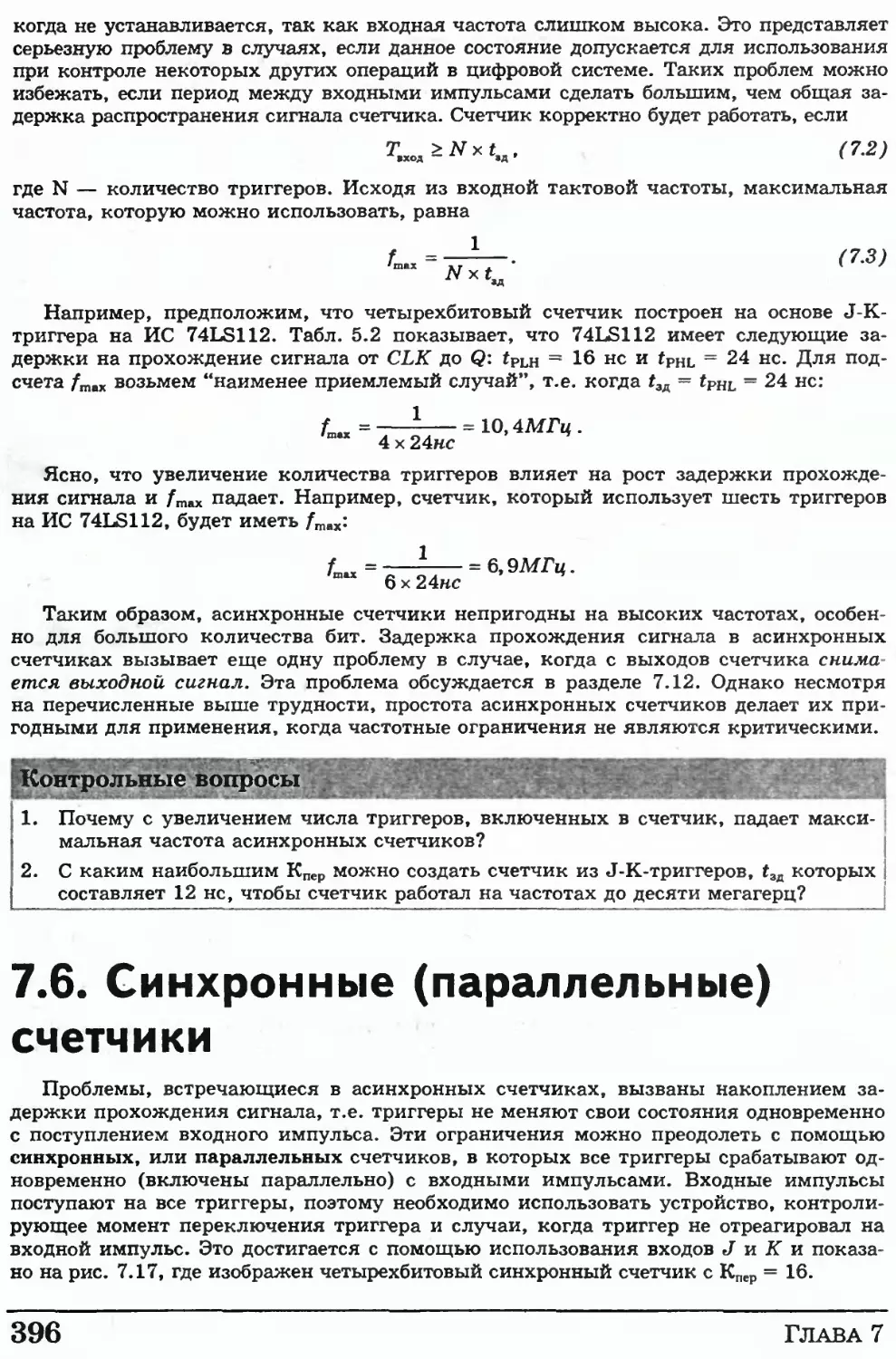

7.5. Задержка на распространение сигнала в асинхронных счетчиках 394

7.6. Синхронные (параллельные) счетчики 396

Работа схемы 398

Преимущество синхронных счетчиков по сравнению с асинхронными 398

Действующие ИС 399

7.7. Синхронные вычитающие и реверсивные счетчики 400

7.8. Предустанавливаемые счетчики 401

Синхронная предустановка 403

7.9. ИС 74ALS193/HC193 403

Входы синхронизации СРи и CPd 403

Вход задающего сброса 403

Предустановочные входы 403

Счетные выходы 404

Выходы конечного счета 404

Регулируемые значения коэффициента пересчета, используемые в ИС

74ALS193/HC193 408

Многокаскадная схема 409

7.10. Еще о системах обозначений стандарта IEEE/ANSI 410

Управляющая зависимость (С) 411

Направление счета (+ или -) 411

Зависимость И (G) 412

7.11. Декодирование значения счетчика 412

Декодирование, управляемое по высокому уровню сигнала 413

Декодирование, управляемое по низкому уровню сигнала 415

Декодирование двоично-десятичного счетчика 415

7.12. Сбои при декодировании 416

Стробирование 418

7.13. Последовательное включение двоично-десятичных счетчиков 419

7.14. Проектирование синхронного счетчика 420

Основная идея 421

Таблица возбуждений для J-K-триггера 421

Методика разработки 422

Управляющий элемент для шагового двигателя 426

7.15. Счетчик на сдвиговых регистрах 429

Кольцевой счетчик 429

Запуск кольцевого счетчика 430

Счетчик Джонсона 431

Декодирование счетчика Джонсона 433

ИС счетчиков на сдвиговых регистрах 433

Резюме части I 434

Часть II 435

7.16. Применение счетчиков: счетчик частоты 435

Полная схема счетчика частоты 437

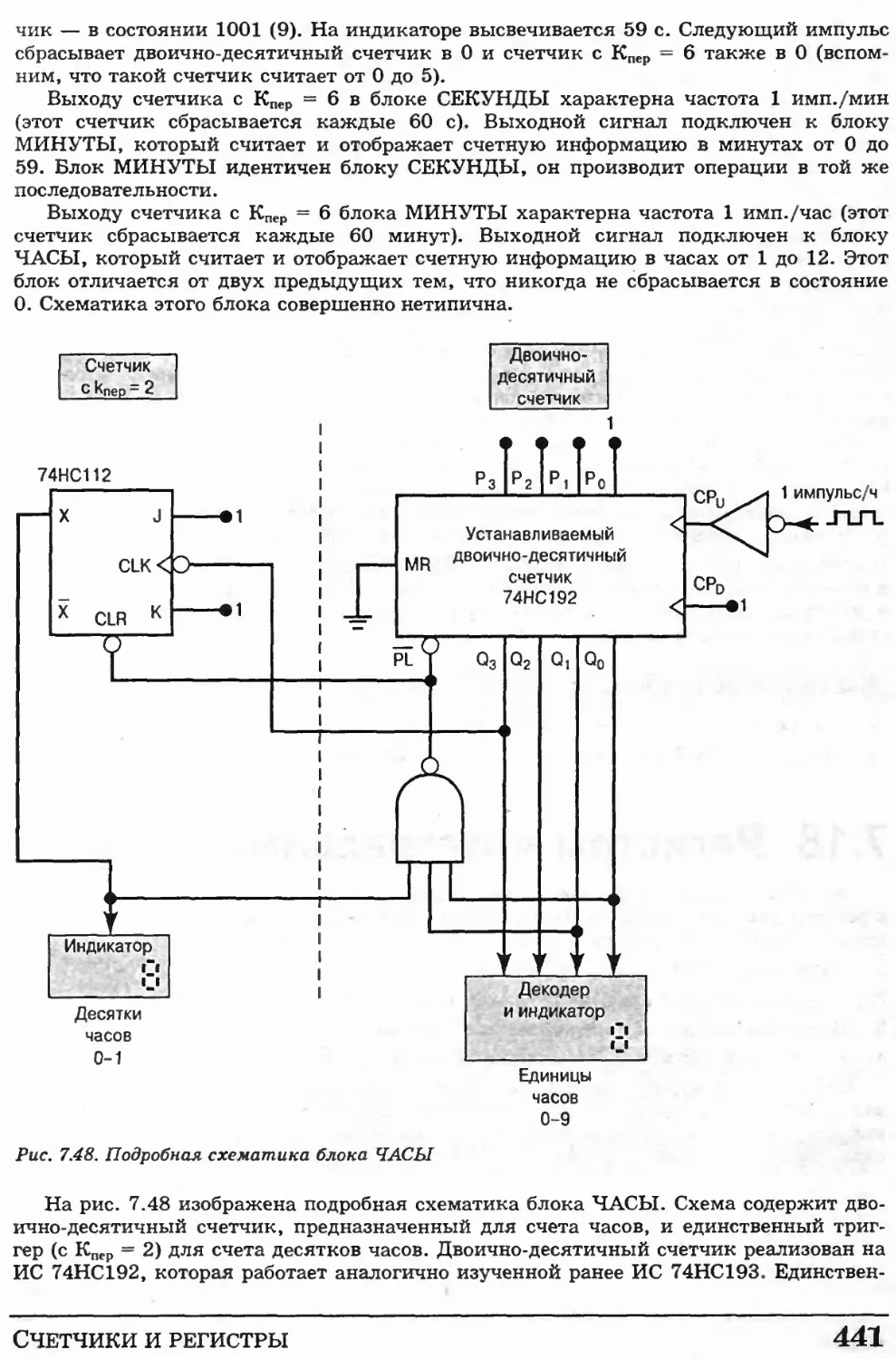

7.17. Применение счетчиков: цифровые часы 439

7.18. Регистры интегральных схем 442

7.19. Параллельный вход/параллельный выход — ИС 74ALS174/74HC174 443

7.20. Последовательный вход/последовательный выход — ИС 4731В 444

Содержание

11

7.21. Параллельный вход/последователья.ый выход — ИС

74ALS165/74HC165 446

7.22. Последовательный вход/параллельный выход —

ИС 74ALS164/74HC164 448

7.23. Условные обозначения регистров стандарта IEEE/ANS1 450

7.24. Решение основных проблем 452

7.25. Программирование ПЛУ при помощи булевых выражений для работы

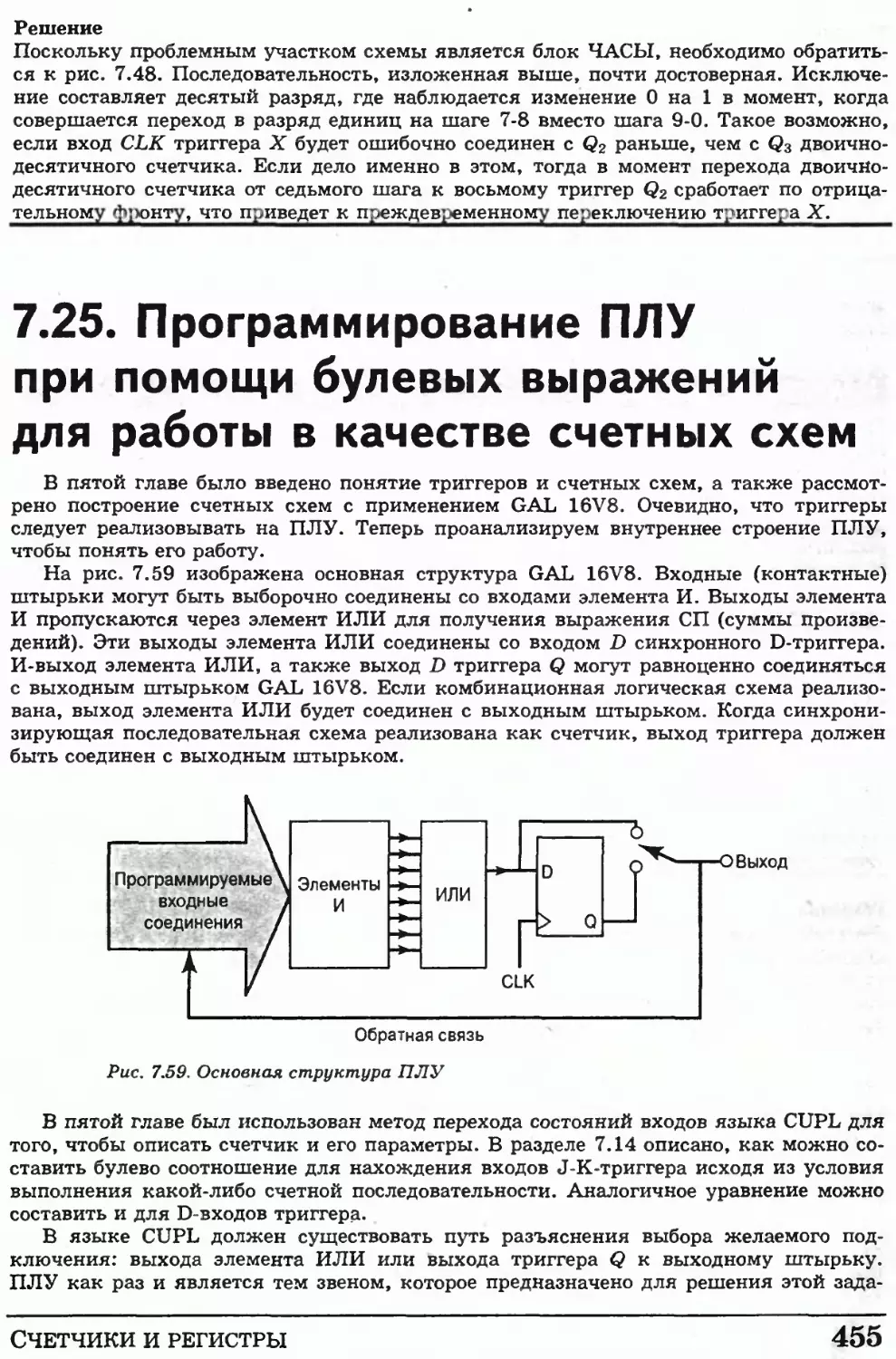

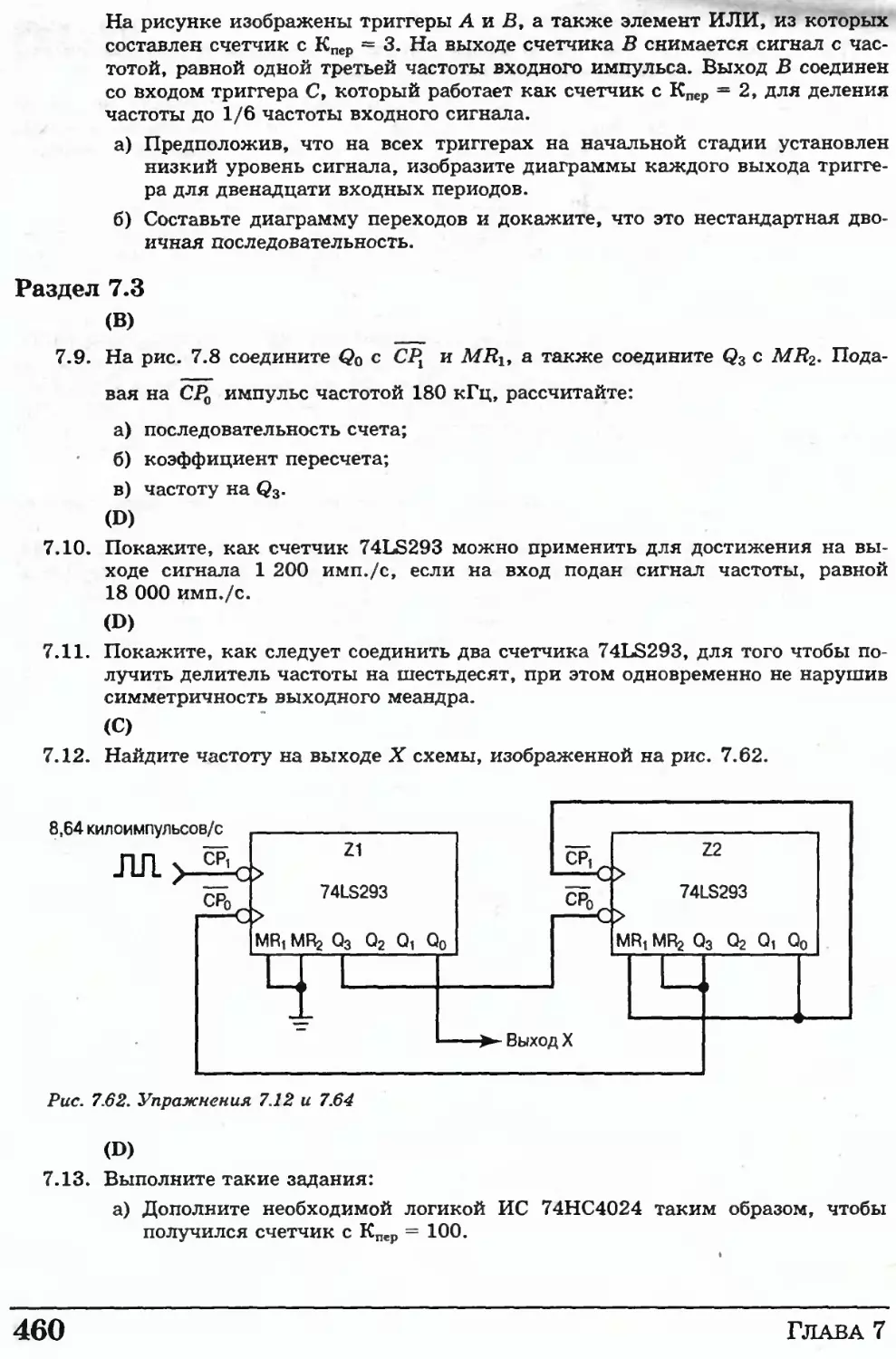

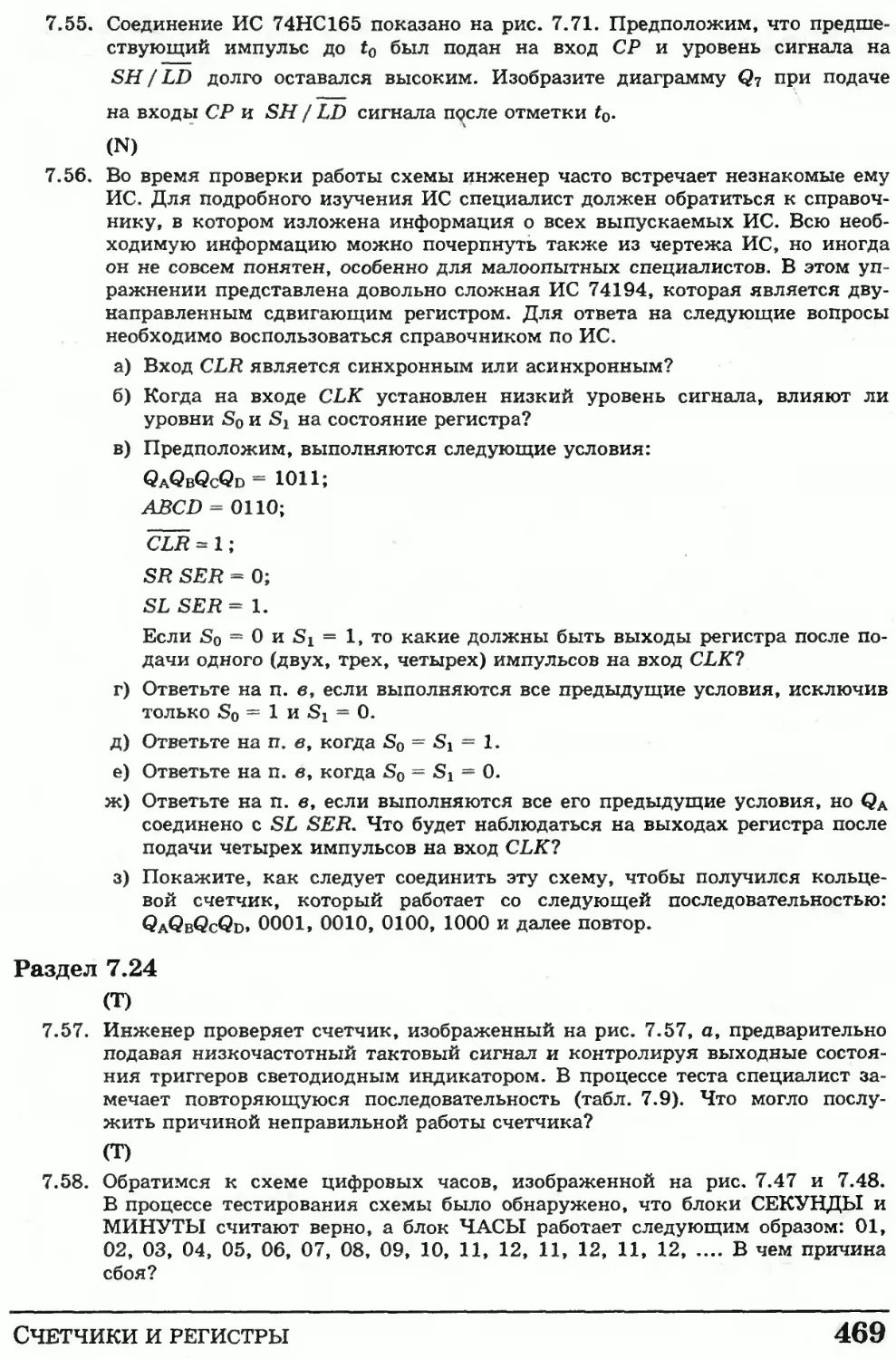

в качестве счетных схем 455

Другой метод 456

Резюме 458

Глава 8. Семейства логических интегральных микросхем 475

8.1. Терминология цифровых ИС 477

Параметры тока и напряжения 477

Коэффициент разветвления 478

Задержки распространения 478

Требования к мощности 479

Произведение задержки сигнала на мощность рассеяния 480

Помехоустойчивость 481

Запрещенные уровни напряжения 483

Функционирование логических схем в режимах источника тика

и нагрузки 483

Корпуса ИС 483

8.2. Логическое семейство ТТЛ 487

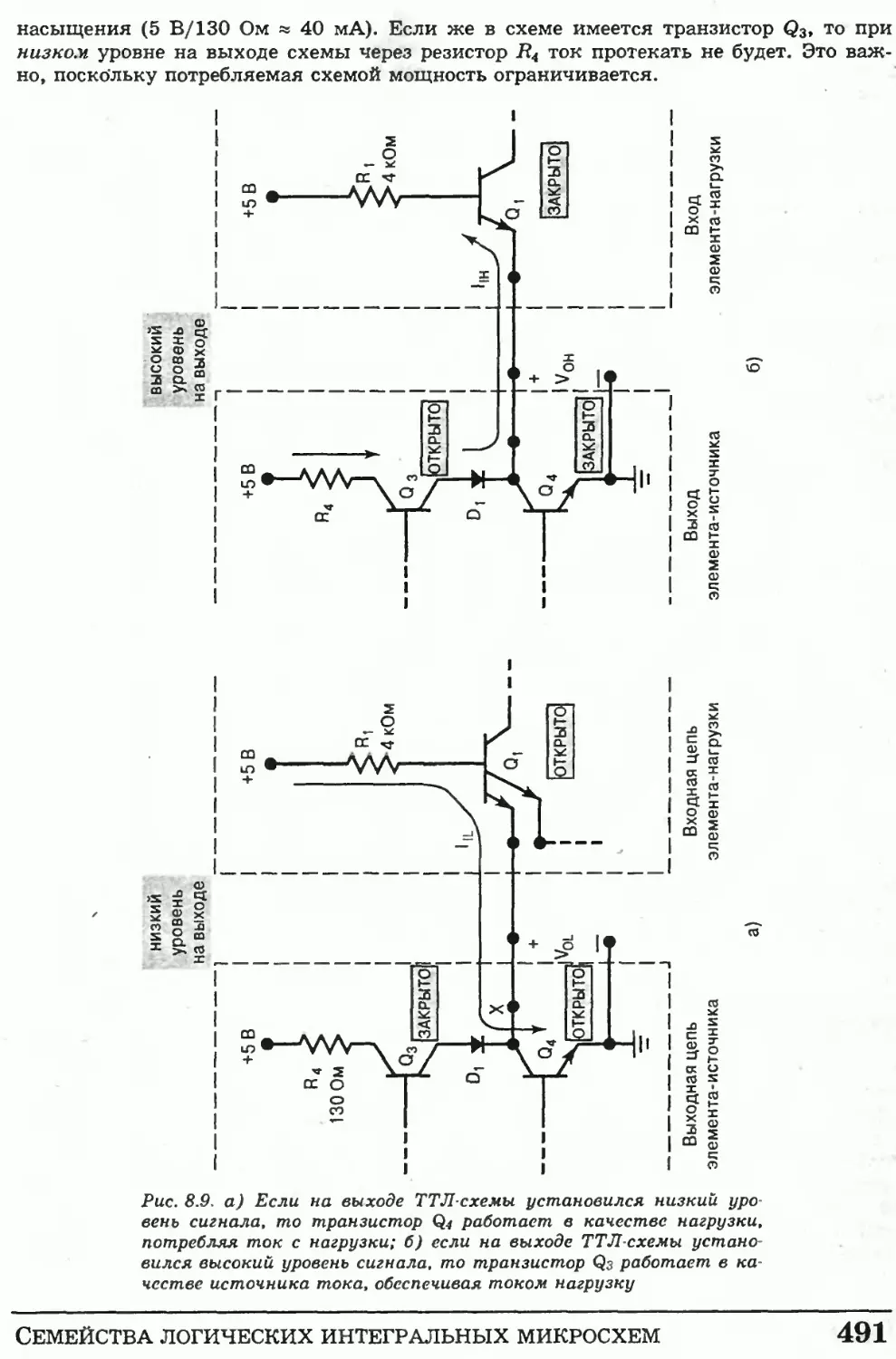

Функционирование схемы в состоянии с низким уровнем 488

Функционирование схемы в состоянии с высоким уровнем 489

Функционирование в режиме нагрузки - 490

Функционирование в режиме источника тока 490

Схема с двухтактным выходом 490

Элемент ТТЛ ИЛИ-НЕ 492

Резюме 492

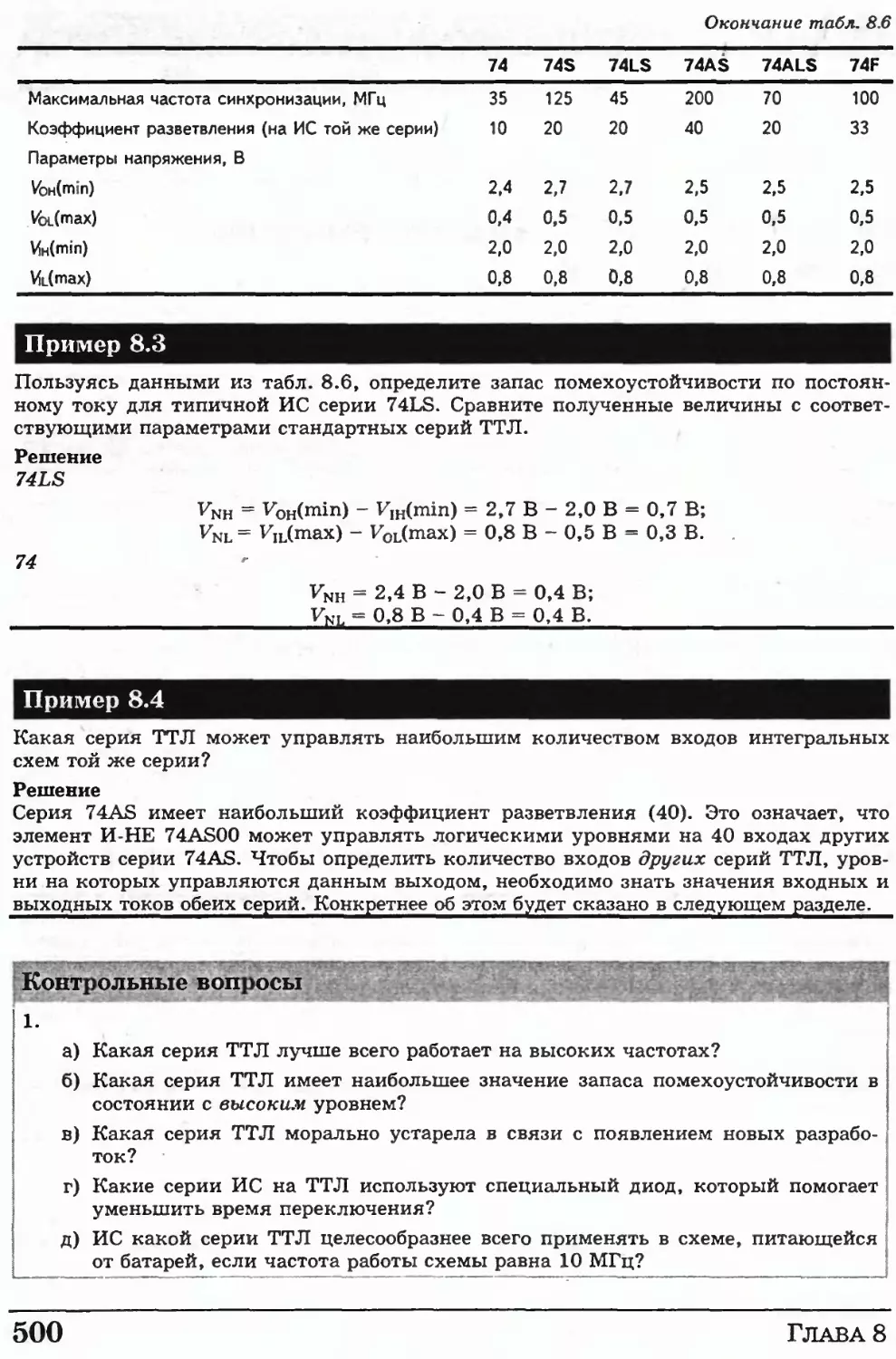

8.3. Технические характеристики ТТЛ 493

Диапазон значений температур и напряжений источника питания 494

Уровни напряжения 495

Максимальные .значения напряжений 495

Рассеяние мощности 496

Задержки распространения сигнала 496

8.4. Характеристики различных серий ТТЛ 497

Стандартная серия 74 ТТЛ 497

Серия 74S ТТЛ на базе транзисторов Шотки 497

Серия 74LS на маломощных транзисторах Шотки 498

Серия 74AS на улучшенных транзисторах Шотки 498

Серия 74ALS на маломощных улучшенных транзисторах Шотки 499

74F — быстродействующие схемы на ТТЛ 499

Сравнение характеристик ТТЛ различных серий 499

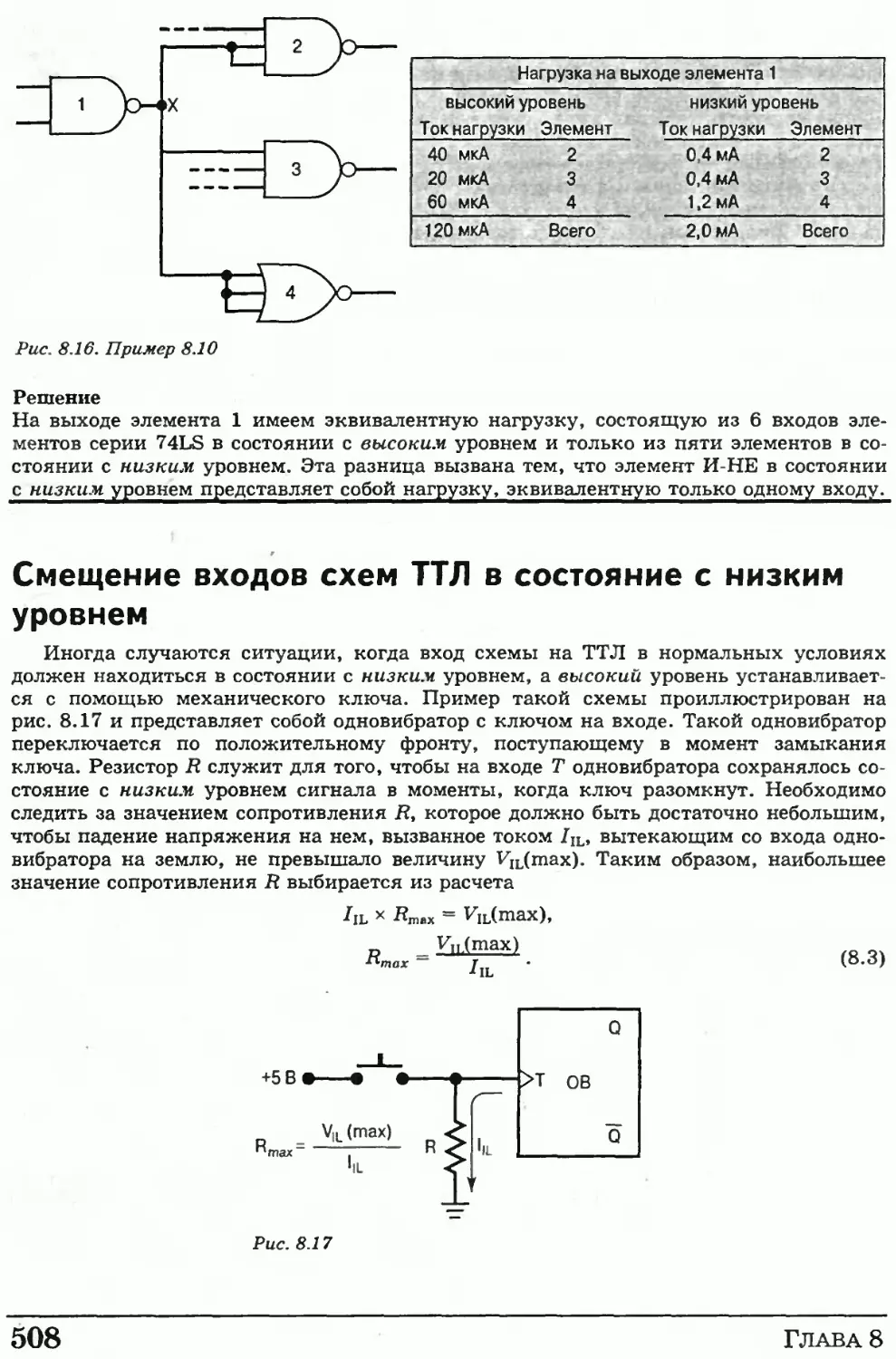

8.5. Коэффициент нагрузки и коэффициент разветвления в схемах на ТГЛ 501

Определение коэффициента разветвления 502

8.6. Другие характеристики ТТЛ 506

Неподключенные (плавающие) входы 506

Неиспользуемые входы 506

Замкнутые входы 507

Смещение входов схем ТТЛ в состояние с низким уровнем 508

Переходы тока 509

8.7. МОП-технология 510

Полевой канальный МОП-транзистор 511

Ключи на полевых транзисторах 512

12

Содержание

8.8. Цифровые схемы на полевых транзисторах 513

8.9. Комплементарная МОП-логика 514

Инвертор на КМОП 514

Элемент И-НЕ на КМОП 515

Элемент ИЛИ-НЕ на КМОП 516

RS-триггер на КМОП 517

8.10. Характеристики различных серий ИС на КМОП 517

Серии 4000/14000 518

Серия 74С 518

Серии 74НС/НСТ (быстродействующие КМОП-структуры) 518

Серии 74АС/АСТ (улучшенные КМОП-структуры) 518

Серии 74АНС/АНСТ (улучшенные быстродействующие КМОП-

структуры) 519

Биполярная КМОП-логика 519

Напряжение источника питания 519

Логические уровни напряжения 520

Запас помехоустойчивости 520

Мощность рассеяния 520

Увеличение PD с ростом частоты 521

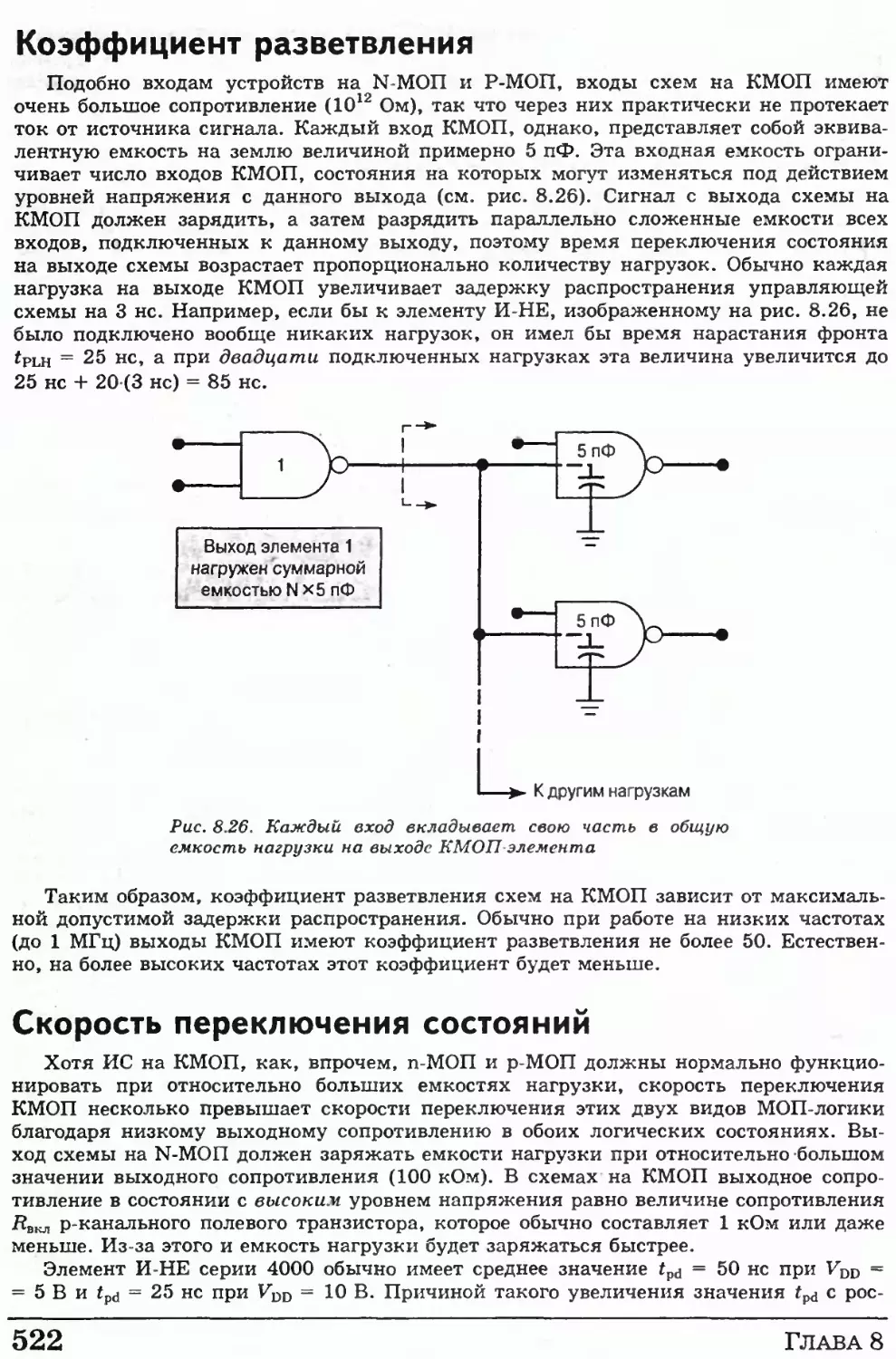

Коэффициент разветвления 522

Скорость переключения состояний 522

Неиспользуемые входы 523

Статическая чувствительность 523

Фиксация 524

8.11. Низковольтная технология 525

Семейство КМОП 525

Семейство биполярной КМОП-логики 526

8.12. Выходы с открытым коллектором/стоком 528

Выходы с открытым коллектором/стоком 529

Буфер/драйвер с открытым коллектором/стоком 531

Обозначения стандарта IEEE/ANSI для выходов с открытым

коллектором/стоком 533

8.13. Тристабильные логические выходы (выходы с тремя состояниями) 534

Преимущества тристабильных структур 535

Тристабильные буферы 535

Тристабильные ИС 537

Обозначение тристабильных выходов согласно стандарту IEEE/ANSI 537

8.14. Высокоскоростная логика шинного интерфейса 538

8.15. Цифровые ИС семейства ЭСЛ \ 540

Базовая схема ЭСЛ 540

Элемент ИЛИ/ИЛИ-НЕ на ЭСЛ 540

Характеристики ЭСЛ 542

8.16. Передаточный логический элемент (двунаправленный переключатель)

на КМОП 544

8.17. Сопряжение интегральных схем 547

8.18. Управление КМОП на базе ТТЛ 548

Управление высоковольтными устройствами на КМОП с помощью ТТЛ 548

8.19. Управление ТТЛ на базе КМОП 549

Управление ТТЛ в состоянии с высоким уровнем с помощью КМОП 550

Управление ТТЛ в состоянии с низким уровнем с помощью КМОП 550

Управление ТТЛ с помощью высоковольтных устройств на КМОП 552

8.20. Аналоговые компараторы напряжения 553

8.21. Поиск неисправностей 554

Использование логического импульсного генератора и пробника при

тестировании схемы 555

Поиск замкнутых узлов 555

Содержание 13

Токовый детектор 556

Резюме 557

Глава 9. Логические схемы средней степени интеграции 579

9.1. Дешифраторы 580

Разрешающие входы 581

Преобразование двоично-десятичного кода в двоичный 585

Преобразование двоично-десятичного кода в десятичный 587

Применение дешифраторов 587

9.2. Преобразование двоично-десятичного кода в семисегментный 589

Сравнение индикаторов на светоизлучающих диодах с общим анодом

и общим катодом 591

9.3. Жидкокристаллические индикаторы 592

Управление ЖКИ 593

Типы ЖКИ 593

9.4. Шифраторы 596

Приоритетные шифраторы 598

Приоритетный шифратор 74147, преобразующий десятичный код

в двоично-десятичный 598

Ключевой шифратор 600

9.5. Поиск неисправностей * 603

9.6. Мультиплексоры (селекторы данных) 606

Базовый мультиплексор с двумя входами 606

Мультиплексор с четырьмя входами 607

Мультиплексор с восемью входами 608

ИС 74ALS157/HC157 (четыре мультиплексора с двумя входами) 610

9.7. Применение мультиплексоров 612

Маршрутизация данных 612

Преобразование параллельного кода в последовательный 613

Установка последовательности передачи данных 614

Формирование логической функции 616

9.8. Демультиплексоры (распределители данных) 617

Демультиплексор с 1 входом и 8 выходами 618

Синхронизируемый демультиплексор 620

Охранные системы наблюдения 620

Синхронные системы передачи данных 623

Приемник 623

Полное описание работы схемы . 625

9.9. Дополнительные сведения о поиске неисправностей 627

9.10. Компараторы величин 631

Входы данных 631

Выходы 631

Последовательное соединение 631

Применение 633

9.11. Преобразователи кодов 635

Основной принцип преобразования кодов 635

Процесс преобразования 636

Реализация схемы 637

Другие варианты построения преобразователей кодов 639

9.12. Шины данных 639

9.13. Тристабильный регистр 74ALS173/HC173 641

9.14. Функционирование шины данных 643

Передача данных 645

Сигналы на шине данных 645

Упрощенная временная диаграмма сигналов на шине данных 647

Расширение шины 647

14

Содержание

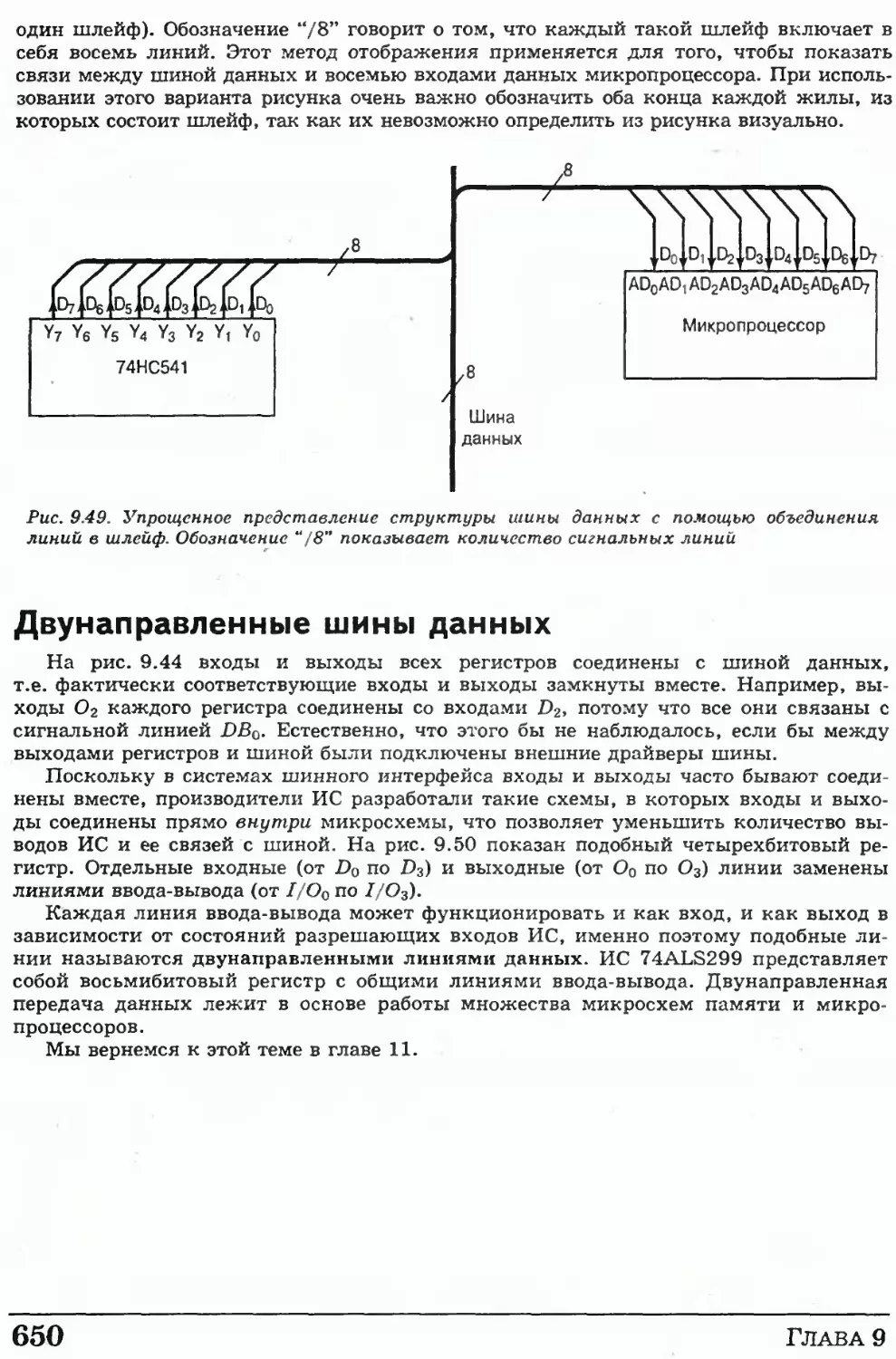

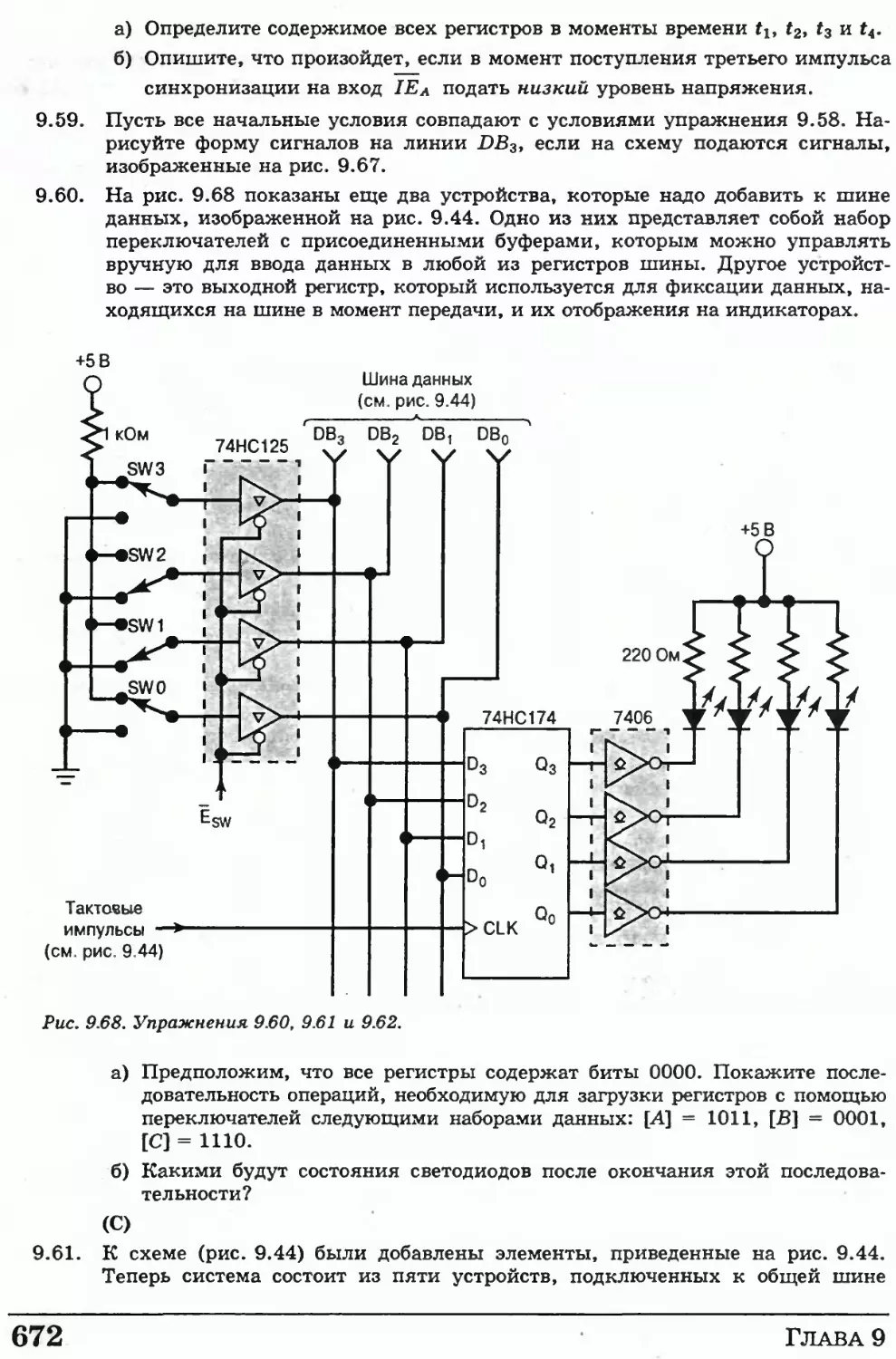

Упрощенное представление шины данных 649

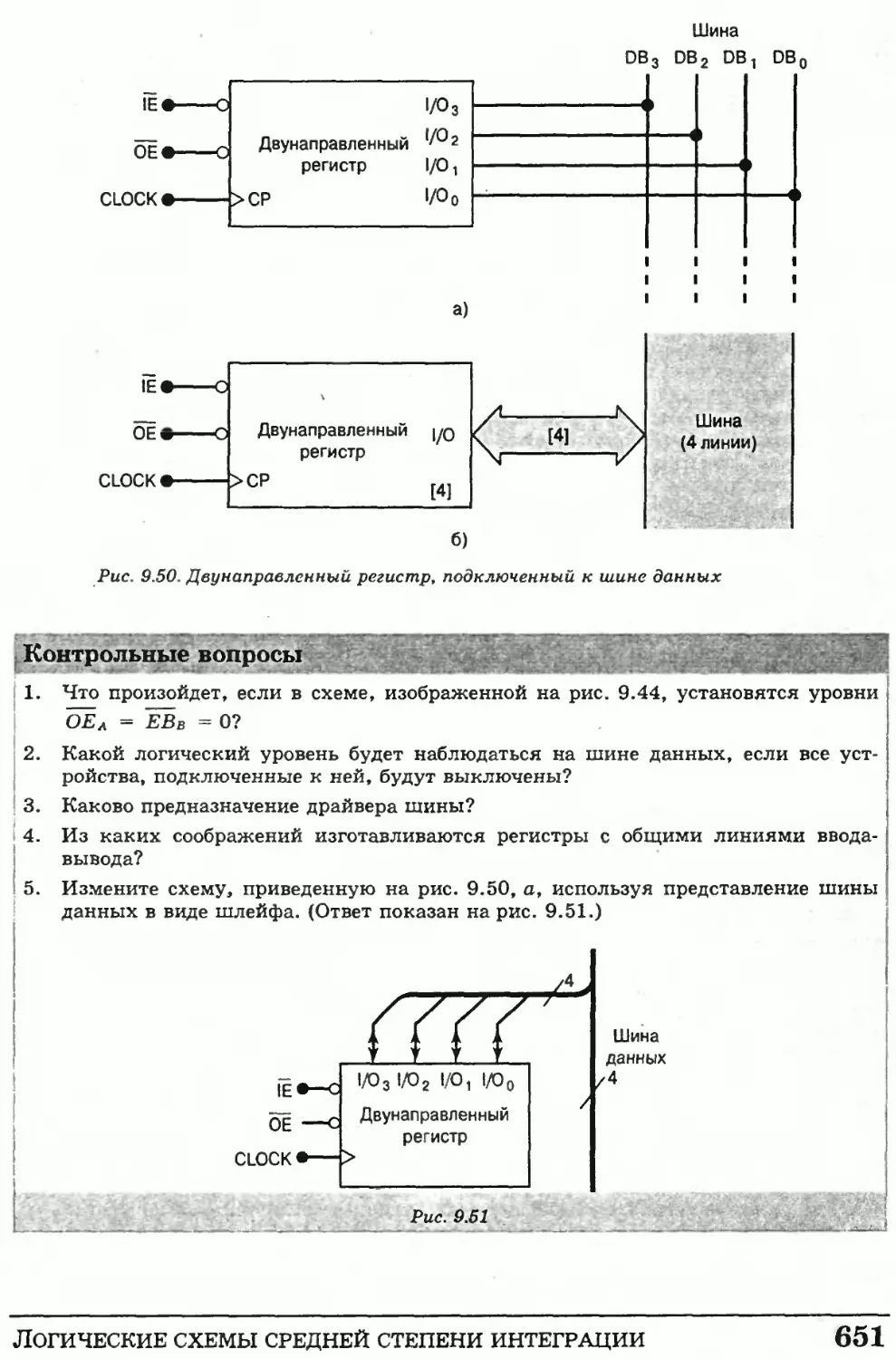

Двунаправленные шины данных 650

9.15. ПЛУ и таблицы истинности 652

Приоритетный шифратор 654

Резюме 655

Глава 10. Сопряжение с аналоговым миром 679

10.1. Сопряжение с аналоговым миром 680

Сравнительный обзор цифровых и аналоговых систем 680

10.2. Цифро-аналоговое преобразование 682

Аналоговый выходной сигнал 684

Весовые коэффициенты входных битов 684

Разрешающая способность(величина шага квантования) 685

Процентная разрешающая способность 687

Физический смысл разрешающей способности 688

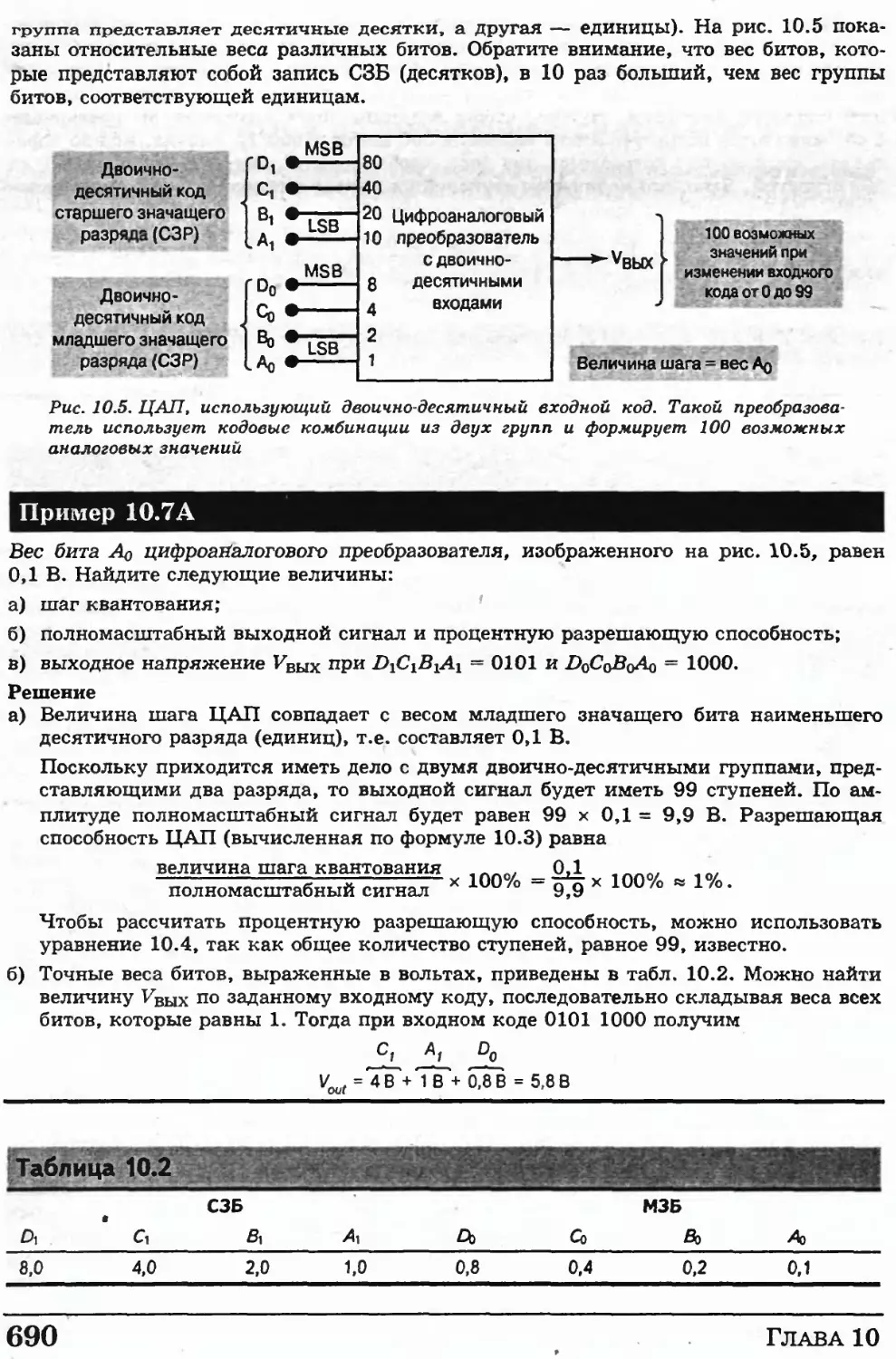

Двоично-десятичный входной код 689

Биполярные ЦАП 691

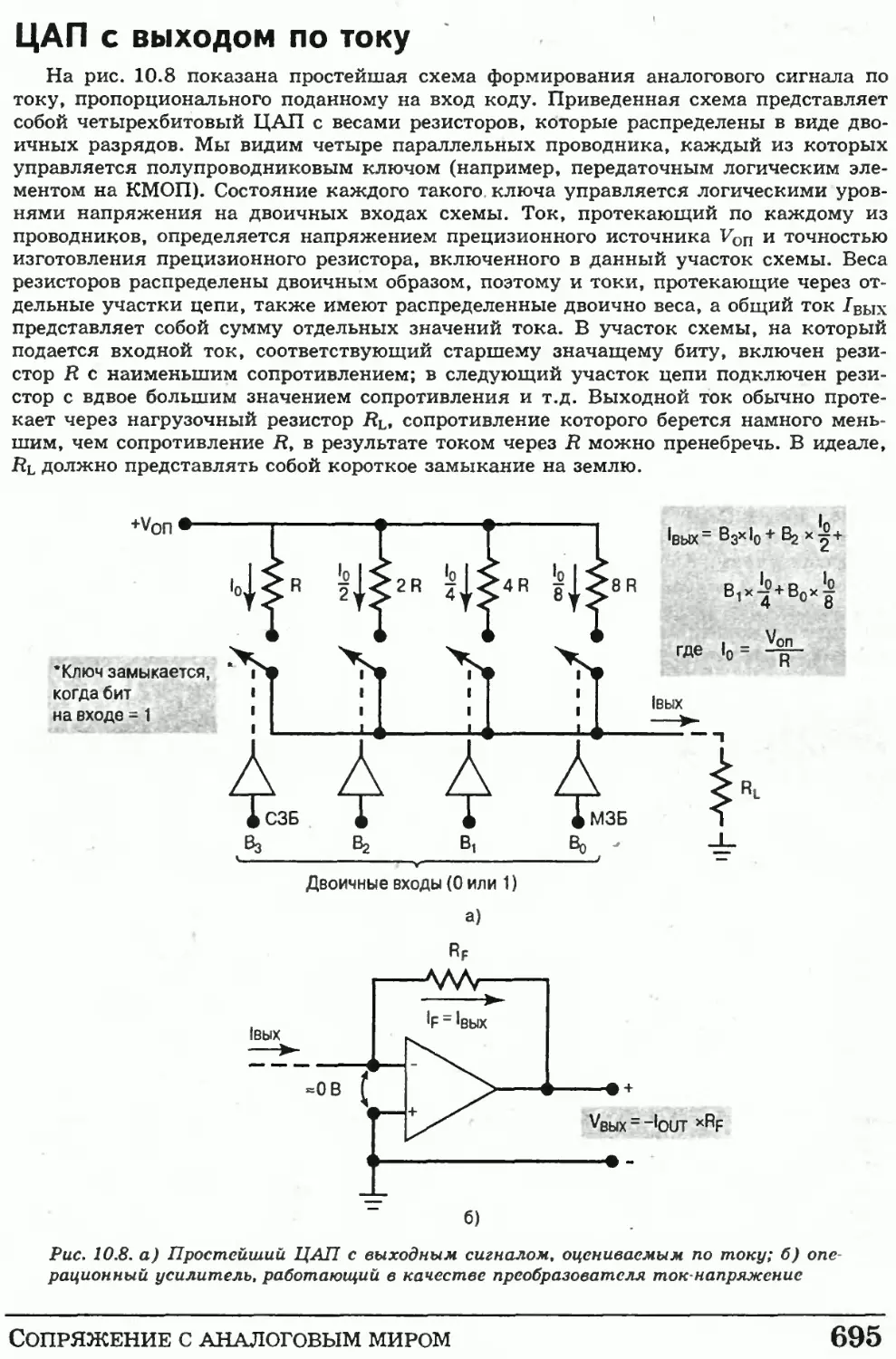

10.3. Строение цифро-аналогового преобразователя 692

Точность преобразования 694

ЦАП с выходом по току 695

Резистивная цепь типа R/2R 696

10.4. Характеристики цифро-аналоговых преобразователей 698

Разрешающая способность 698

Точность 698

Погрешность смещения нуля 699

Время установления сигнала 700

Монотонность 700

10.5. Цифро-аналоговые преобразователи на интегральных схемах 700

10.6. Применение цифро-аналоговых преобразователей 701

Управление 701

Автоматический контроль 702

Восстановление сигнала 702

Аналого-цифровое преобразование 702

ЦАП с последовательной передачей данных 702

10.7. Поиск неисправностей в цифро-аналоговых преобразователях 702

10.8. Аналого-цифровое преобразование 704

10.9. Интегрирующие аналого-цифровые преобразователи 706

Разрешающая способность и точность аналого-цифровых

преобразователей 709

Время преобразования tc 710

10.10. Сбор данных 711

Восстановление оцифрованного сигнала 713

Помеха дискретизации 714

10.11. Аналого-цифровые преобразователи поразрядного уравновешивания 716

Время преобразования 718

Реальная ИС: АЦП поразрядного уравновешивания ADC0804 719

10.12. Аналого-цифровые преобразователи параллельного типа 723

Время преобразования 725

10.13. Другие методы аналого-цифрового преобразования 726

Реверсивные интегрирующие аналого-цифровые преобразователи (АЦП

следящего типа) 726

Аналого-цифровые преобразователи с двойным интегрированием 726

Аналого-цифровые преобразователи “напряжение/частота” 727

Сигма/дельта модуляция 728

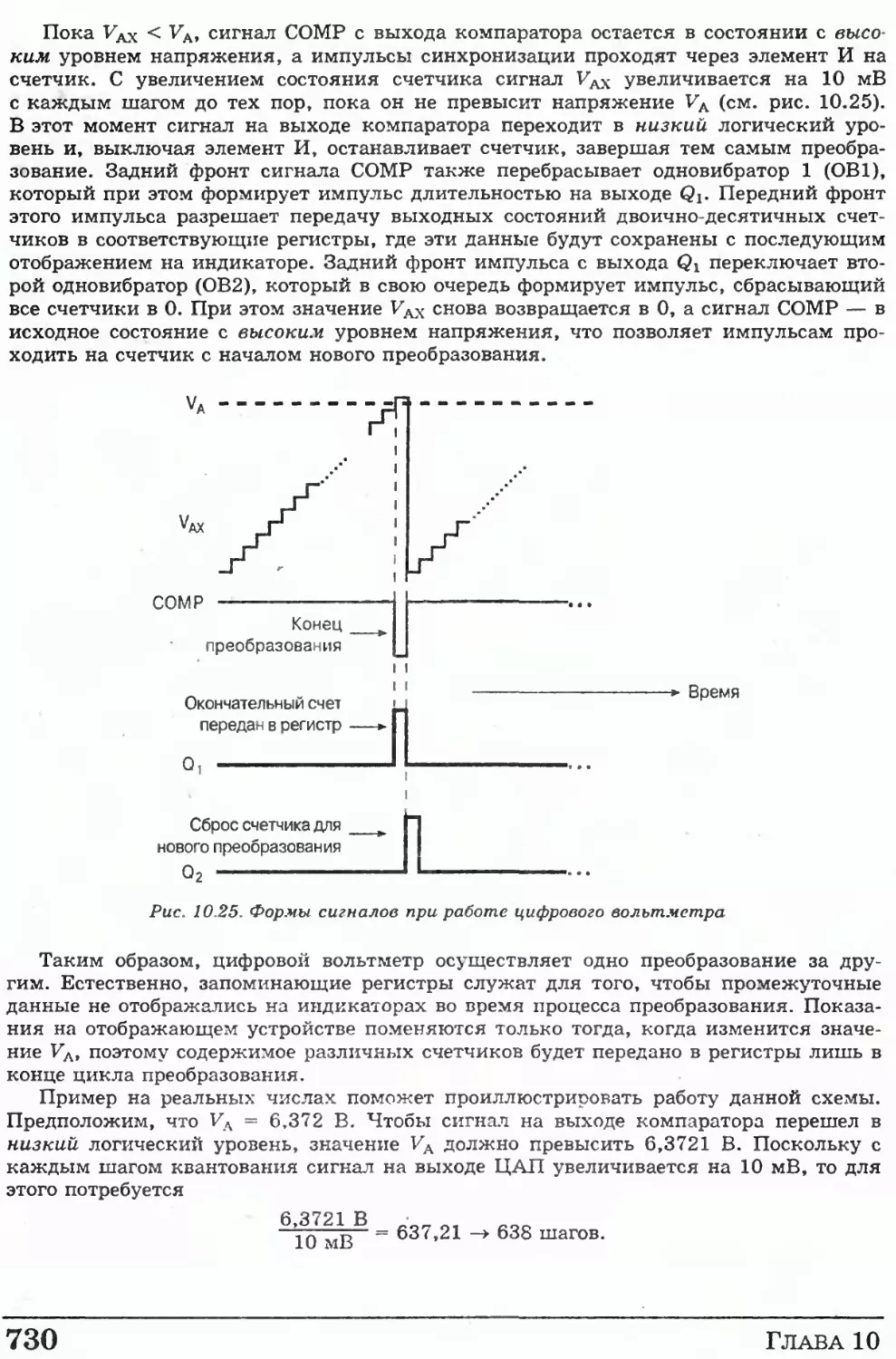

10.14. Цифровые вольтметры 729

10.15. Схемы выборки и хранения 732

Содержание

15

10.16. Мультиплексирование 733

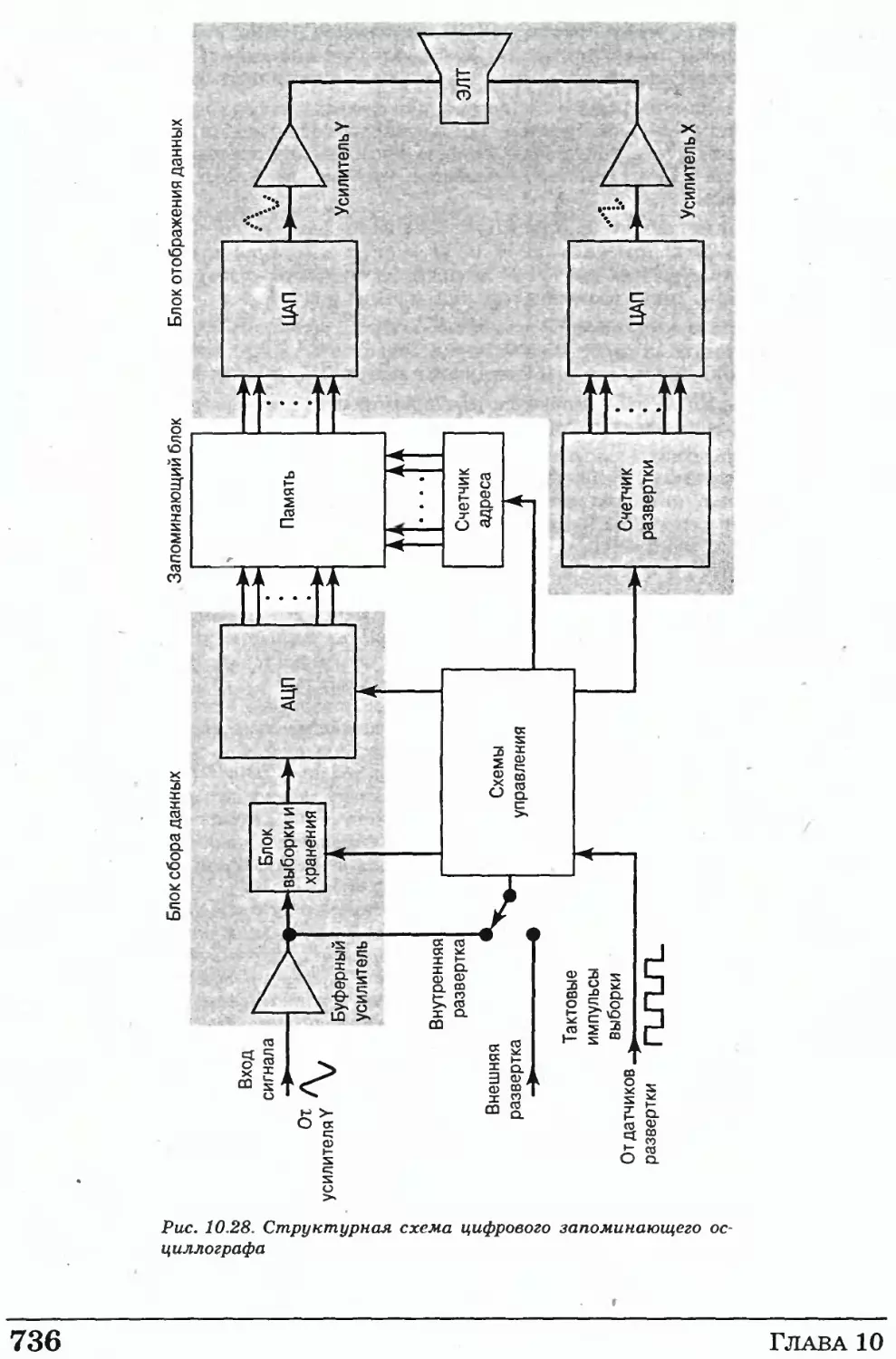

10.17. Цифровой запоминающий осциллограф 734

Другие области применения 737

10.18. Цифровая обработка сигналов 737

Цифровая фильтрация 738

Резюме 741

Глава 11. Запоминающие устройства _ 761

11.1. Терминология систем памяти 763

11.2. Общие принципы функционирования схем памяти 767

Входы адреса 768

Вход чтения/записи R/W 768

Включение памяти 769

11.3. Соединение схем памяти с центральным процессором 771

11.4. Постоянные запоминающие устройства 772

Структурная схема ПЗУ 773

Операция чтения 774

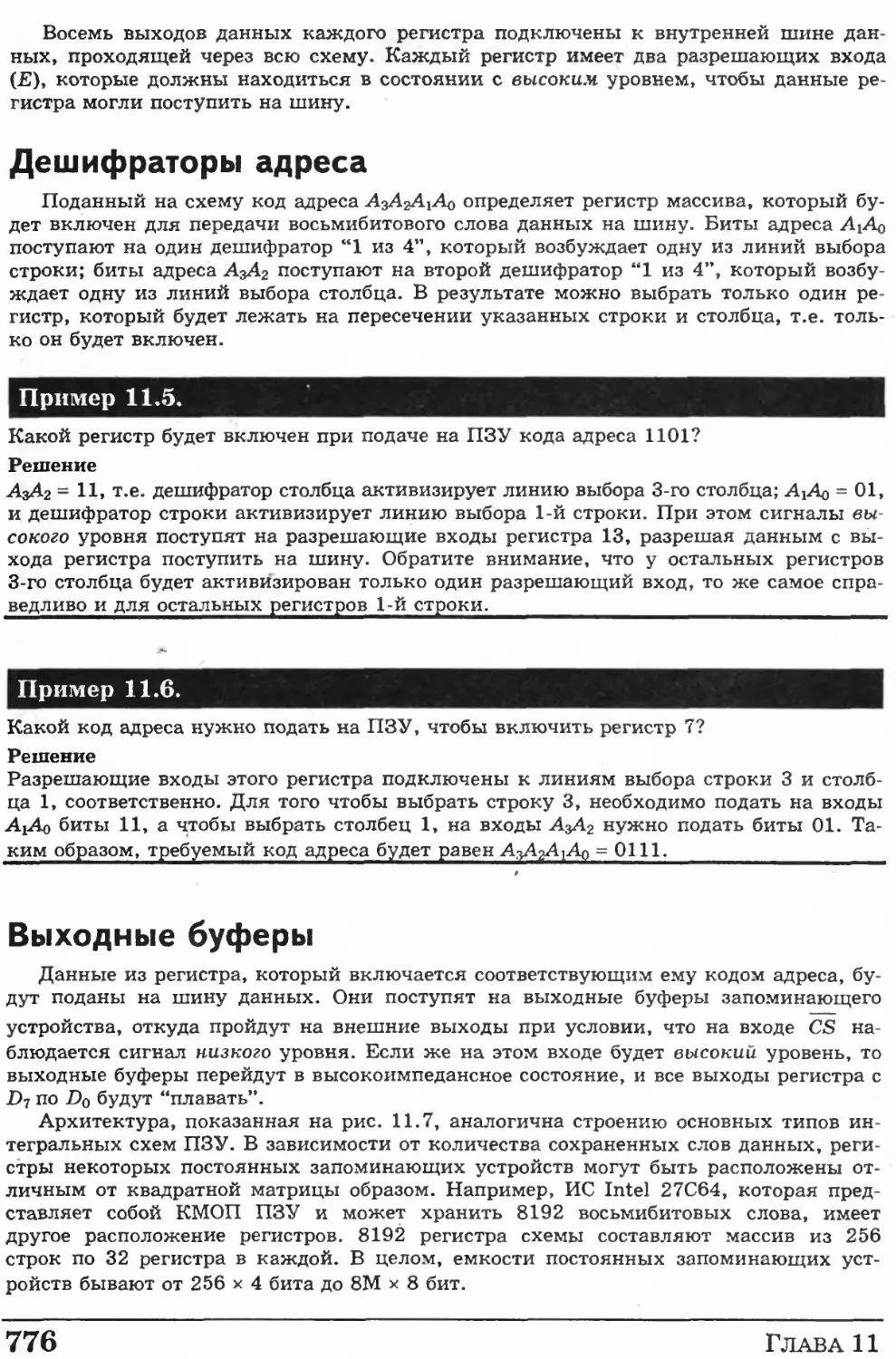

11.5. Архитектура ПЗУ 775

Массив регистров 775

Дешифраторы адреса 776

Выходные буферы 776

11.6. Временные параметры ПЗУ 777

11.7. Типы ПЗУ 778

Программируемое по фотошаблону ПЗУ 778

Программируемые ПЗУ (ППЗУ) 781

Стираемые программируемые постоянные запоминающие уса ройства

(СППЗУ) 783

Электрически стираемое программируемое ПЗУ(ЭСППЗУ) 785

Постоянные запоминающие устройства на компакт-дисках CD ROM 788

11.8. Флэш-память 789

КМОП ИС флэш-памяти 28F256A 791

Команда чтения 792

Команды стирания/подготовки к стиранию ' 793

Команда стирания с последующим контролем 793

Команды подготовки к программированию/программирования 794

Команда программирования с последующим контролем 794

11.9. Применение ПЗУ 794

Программно-аппаратное обеспечение 794

Запоминающие устройства для хранения программы самозагрузки 795

Таблицы данных 795

Преобразователь данных 796

Генераторы функций 796

Вспомогательные запоминающие устройства 797

11.10. Полупроводниковые ОЗУ 798

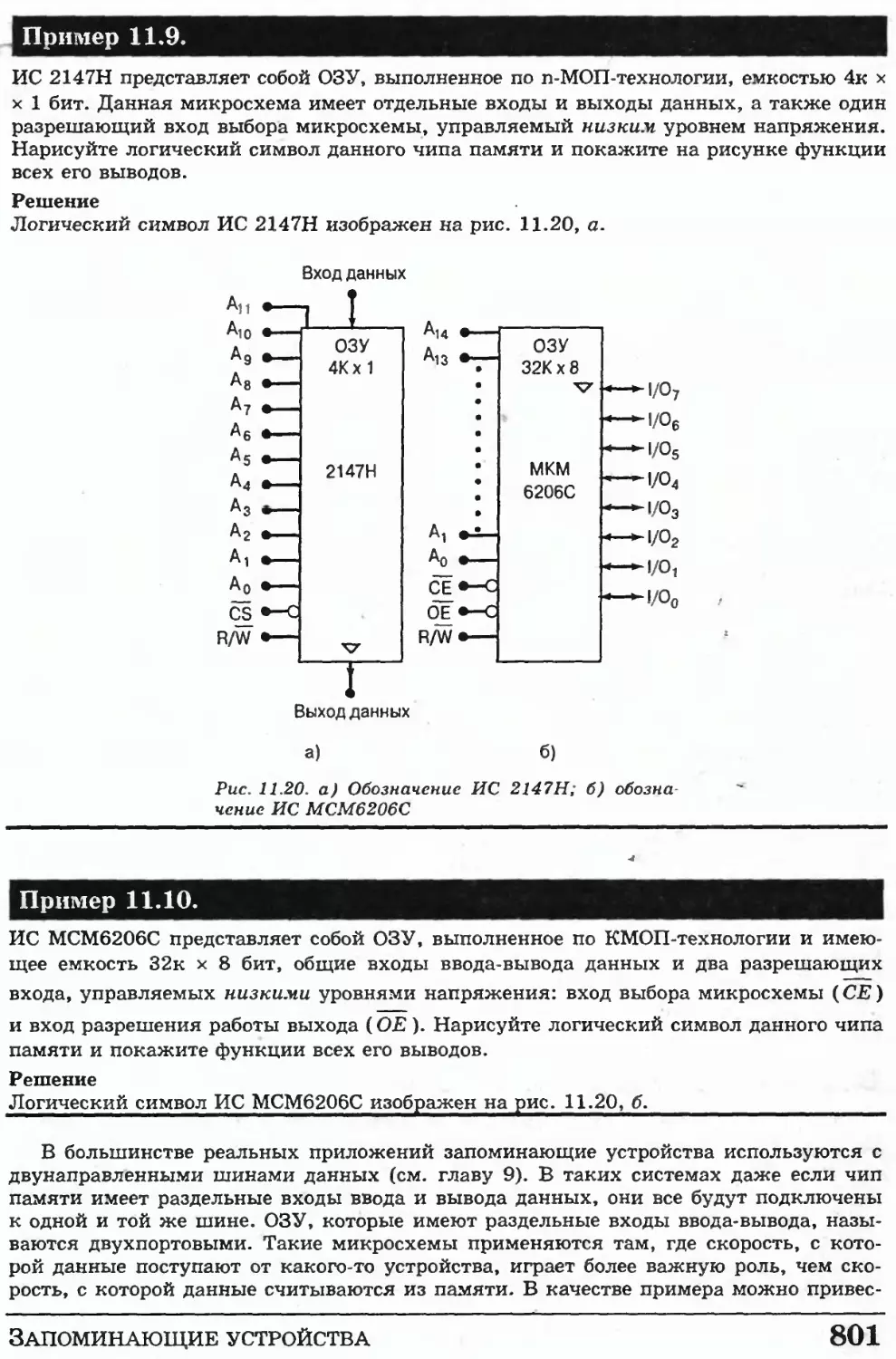

11.11. Архитектура ОЗУ 798

Операция чтения 799

Операция записи 800

Выбор микросхемы 800

Входы ввода-вывода 800

11.12. Статические ОЗУ (SRAM) 802

Временные процессы в статических ОЗУ 802

Цикл чтения 803

Цикл записи 805

Реальная микросхема статической памяти 806

11.13. Динамические ОЗУ (DRAM) 808

11.14. Структура и функционирование динамических ОЗУ 809

16 Содержание

Мультиплексирование адресов 811

11.15. Циклы чтения/записи динамического ОЗУ 815

Цикл чтения динамического ОЗУ 815

Цикл записи динамического ОЗУ 816

11.16. Обновление информации в динамическом ОЗУ 818

11.17. Технологии динамической памяти 821

Модули памяти 822

FPM DRAM 822

EDO DRAM 823

SDRAM 823

DDR SDRAM 823

SLDRAM 823

DR DRAM 824

11.18. Увеличение длины слов данных и емкости памяти 824

Расширение длины слова данных 824

Расширение емкости запоминающих устройств 827

Неполная дешифрация адреса 830

Объединение чипов динамической памяти 832

11.19. Специальные функции памяти 833

Хранение информации при отключении питания 833

Кэш-память 834

Память FIFO 835

Кольцевые буферы 836

11.20. Поиск неисправностей в системах оперативной памяти 836

Функционирование ОЗУ 837

Тестирование дешифрирующих логических элементов 840

Тестирование полной системы оперативной памяти 841

11.21. Тестирование ПЗУ 845

Резюме 846

Глава 12. Применение программируемых логических устройств 865

12.1. Фундаментальные понятия схемотехники ПЛУ 867

Обозначения ПЛУ 868

12.2. Архитектура ПЛУ 869

ППЗУ 869

Программируемая матричная логика 871

Программируемая пользователем матричная логика 873

12.3. ПЛУ GAL 16V8 (типовая матричная логика) 874

Простой режим 878

Сложный режим 881

Буферизованный режим 882

12.4. Привязка карты пережигания языка CUPL к архитектуре ПЛУ

GAL 16V8 886

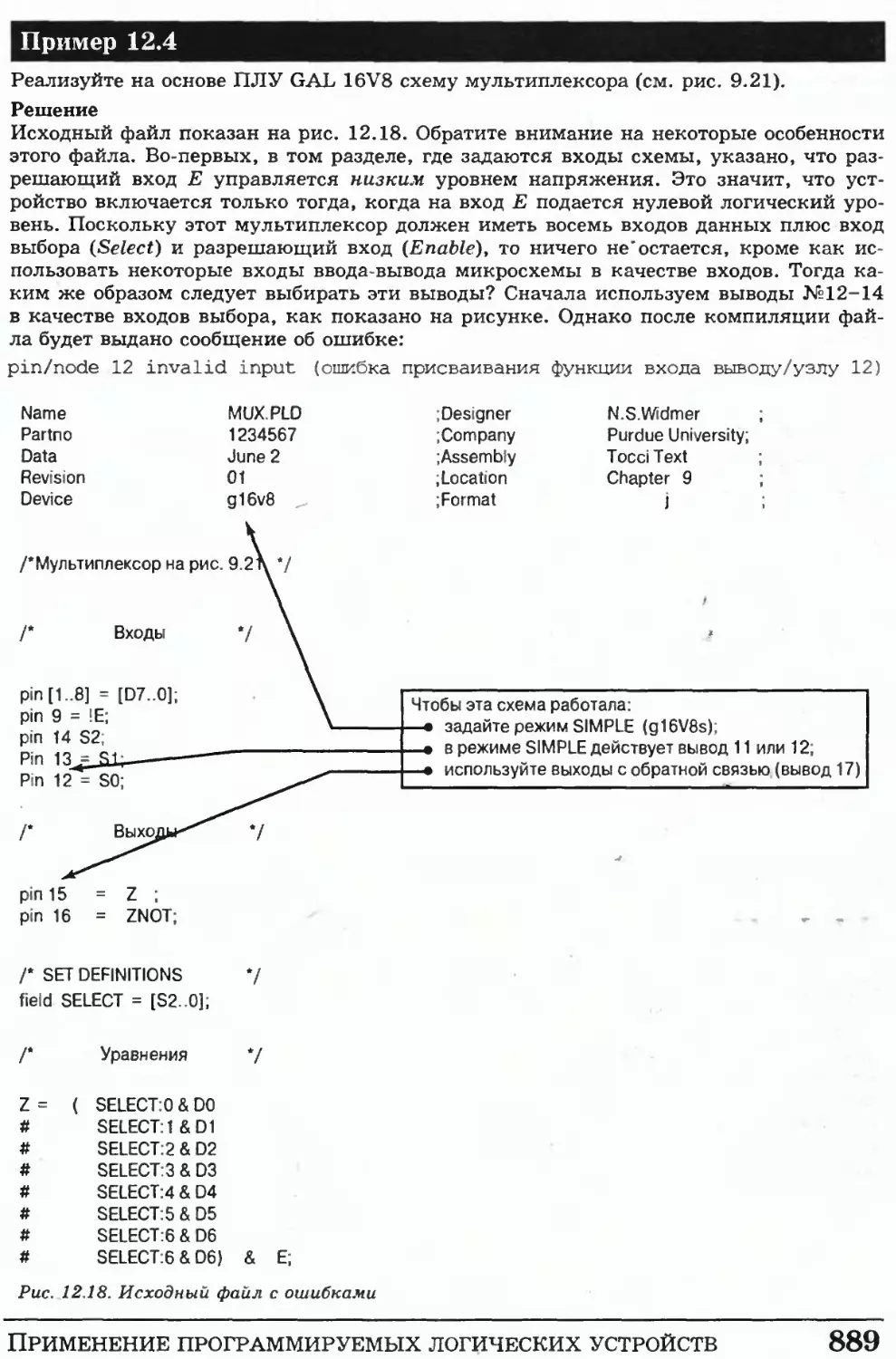

12.5. Проблемы проектирования 888

Схема разрешения конфликтов 890

Дешифрация состояний счетчика 892

12.6. ПЛУ GAL 22V10 897

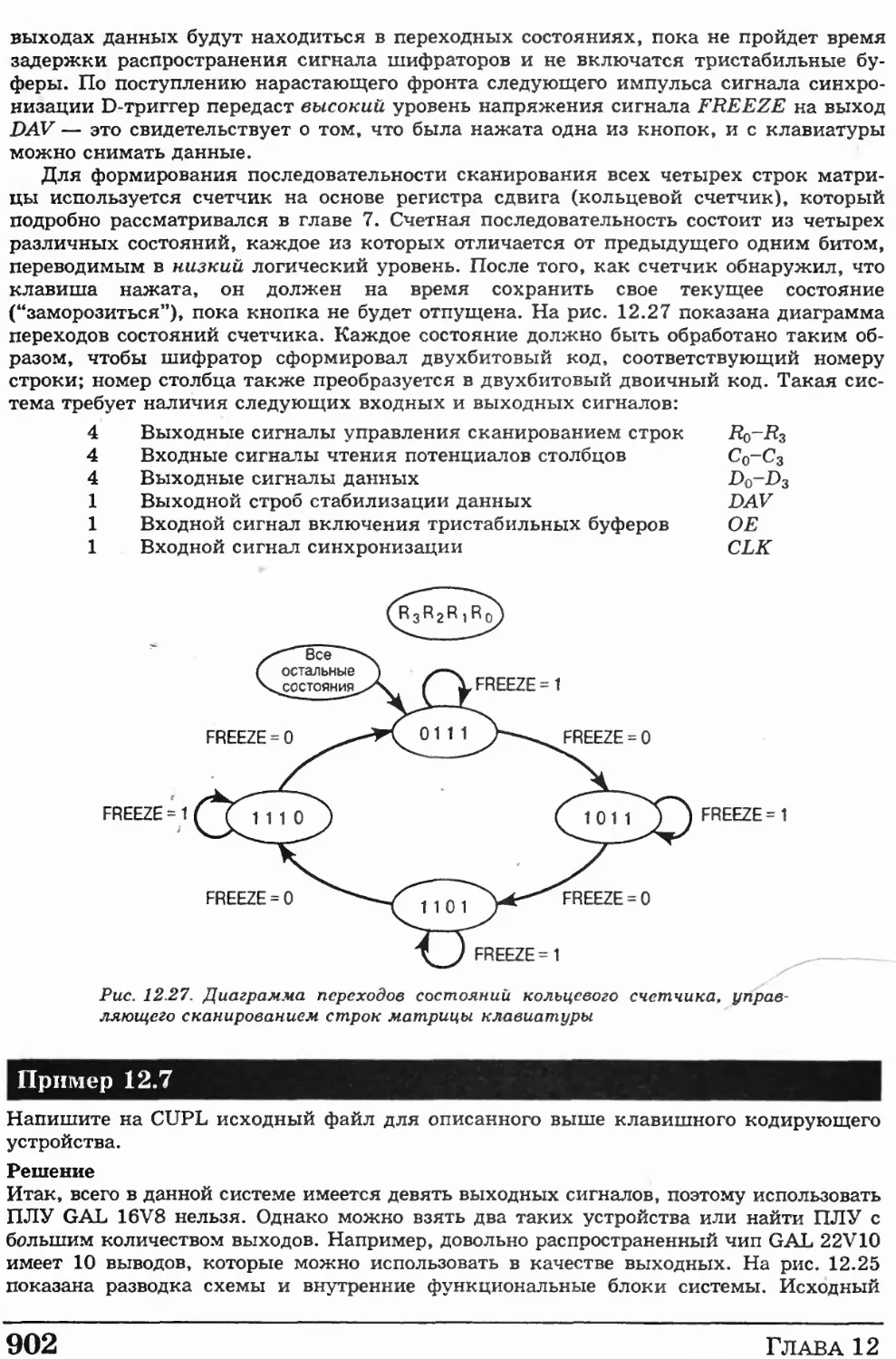

12.7. Клавишное кодирующее устройство 900

12.8. Разработка более совершенных ПЛУ 906

Тенденции развития программного обеспечения 908

Резюме 909

Приложение А. Введение в микропроцессоры и микрокомпьютеры 915

А.1. Что такое цифровой компьютер? 917

А.2. Как компьютер “думает”? 917

А.З. Секретный агент “89” 918

Содержание 17

A. 4. Организация простейшей компьютерной системы 919

Арифметико-логическое устройство (АЛУ) 920

Запоминающее устройство 920

Устройство ввода 921

Устройство вывода 921

Интерфейс 921

Устройство управления 922

Центральное процессорное устройство (ЦПУ) 922

А. 5. Основные элементы микрокомпьютеров 923

Микропроцессор (МПУ) 924

А. 6. Машинные слова 926

Типы машинных слов 926

А.7. Командные слова 927

Многобайтовые команды 928

А. 8. Выполнение программы машинного языка 930

Выполнение программы 933

А.9. Структура типичного микрокомпьютера 935

Системные шины 936

Порты ввода-вывода 937

Временные процессы 938

А. 10. Комментарии 940

Резюме 940

Приложение Б. Спецификации некоторых интегральных схем 943

Приложение В. Элементы логических схем 955

Триггеры 955

Булевы теоремы 957

Таблицы истинности логических элементов 958

Обозначения логических элементов 958

Глоссарий 960

Предметный указатель 1018

18

Содержание

Тебе Кэп, за твою долгую любовь и за миллионы спо-

собов, которыми ты освещаешь жизнь всех, к кому

прикасаешься.

—Рональд Дж. Точчи

Моей жене, Крис, и нашим детям Джону, Брэду,

Блейку, Мэтту и Кэйти: они имели все права на мое

время и внимание, потраченные на завершение этого

издания.

—Нил С. Уидмер

Введение

Данная книга представляет собой фундаментальное изложение основных принци-

пов и технологий построения современных цифровых схем и предназначена для ис-

пользования в качестве учебного пособия для студентов технических специальностей.

Материал книги доступен независимо от того, владеет ли читатель начальными зна-

ниями в области электроники, хотя подобные навыки только облегчили бы понима-

ние этого материала. Те разделы, где эти знания необходимы, можно попросту опус-

тить без ущерба для понимания логических принципов в целом.

Что нового?

Восьмое издание выгодно отличается от седьмого. Книга написана простым язы-

ком, и разобраться в ней сможет не только специалист. Материал седьмого издания

частично был изменен и расширен с целью более полного и подробного описания.

Появились новые примеры, контрольные вопросы в конце каждого раздела, введены

упражнения для самостоятельного выполнения после каждой главы. Все это сделано

для лучшего усвоения новых знаний и закрепления уже пройденного материала.

Описание ПЛУ

Наиболее значительное изменение по сравнению с седьмым изданием книги Циф-

ровые системы: принципы и возможные применения — новый подход в изучении

программируемых логических устройств (ПЛУ). В виде ПЛУ можно реализовать лю-

бую логическую схему, начиная от простейших логических элементов и заканчивая

сложными цифровыми системами. Революционные изменения в технологии неиз-

менно влекут за собой изменения в изложении соответствующих тем (например, пе-

реход от вакуумной лампы к транзистору, или скачок от транзисторных схем к схе-

мам на основе операционных усилителей). Пятнадцать последних лет технология

двигалась навстречу программируемой логике. В современных цифровых системах

малые и средние интегральные схемы в основном уже выполняют второстепенные

функции. Программируемые устройства, матрицы логических элементов, заказные

ИС разрабатываются на основе последних достижений в области цифровых систем.

Однако чтобы понять, как создаются эти микросхемы, нужно в первую очередь озна-

комиться с элементами, из которых они состоят. Это дешифраторы, мультиплексоры,

сумматоры, буферные устройства, триггеры, регистры, счетчики и т.д. Важнейшим

этапом вводных лабораторных занятий является разводка и тестирование этих эле-

ментов. Занятия способствуют установлению четкой терминологии — двоичные вхо-

ды и выходы, действие физического устройства, практические ограничения. Боль-

шим плюсом есть совместный (дискуссионный) поиск причин каких-либо неисправ-

ностей.

Отметим, что текстовое,, графическое описание схем или даже компьютерное мо-

делирование не могут дать равноценной замены работе с макетами. В качестве маке-

тов можно использовать программируемые устройства, которые ничем не будут усту-

пать средним интегральным схемам. Современная технология подразумевает созда-

ние схем отдельных базовых элементов в качестве ПЛУ, поэтому наряду со знаниями

об этих элементах необходимо расширять знания и о программируемых устройствах.

Скорее всего, читатель сможет разрабатывать логические схемы с использованием

ПЛУ прежде, чем разберется во всех деталях его работы. Сперва предлагается изу-

чить последовательность программирования на относительно простых схемах. По ме-

ре знакомства с более сложными схемами читатели будут узнавать и о преимущест-

вах различных языков программирования. В итоге, после изучения всех основных

элементов, станет понятной схематика ПЛУ, все его возможности и ограничения.

Очередность

Подойти к описанию ПЛУ можно по одному из трех путей: а) опустить весь ма-

териал, касающийся ПЛУ, не нарушая при этом последовательности изложения;

б) вынести его как отдельную тему, в виде последних разделов глав 4, 5, 6, 7 и 9

прежде, чем читать главу 12; в) изучение ПЛУ можно представить как независимый

курс, и включить в программу лекций и лабораторных занятий. Такой механизм

обеспечит максимальную гибкость графиков чтения различных курсов.

Преподаватели довольно редко читают главы в той последовательности, в которой

они приведены здесь. Книга написана таким образом, что каждая глава большей ча-

стью основана на предыдущем материале, однако их порядок можно немного изме-

нить. Первую часть главы 6 (арифметические операции) можно прочесть после

главы 2 (системы счисления), хотя в этом случае еще не скоро встретится упомина-

ние об арифметических схемах из шестой главы. Большую часть материала главы 8

(характеристики ИС) можно рассмотреть раньше (после главы 4 или 5), и это не вы-

зовет серьезных недоразумений.

Курс лекций, составленный по этой книге, может быть рассчитан как на один,

так и на два семестра. Если это семестровый курс и количество отведенного времени

невелико, то некоторые темы можно просто исключить. Ниже приведен список раз-

делов и глав, отсутствие которых практически не нарушает целостности изложения.

Очевидно, выбор будет зависеть от программы, намеченных целей и пожеланий сту-

дентов.

Глава 1: Все Глава 8: Разделы 11, 14-21

Глава 2: Раздел 6 Глава 9: Разделы 5, 9, 15

Глава 4: Разделы 7, 10-14 Глава 10: Разделы 7, 14-18

Глава 5: Разделы 3, 24-26 Глава 11: Разделы 17-21

Глава 6: Разделы 5-7, 11, 13, 16-20 Глава 12: Все

Глава 7: Разделы 10, 14, 23-25

Типы упражнений

Седьмое издание содержало четыре типа упражнений: сложные (С), на выявление

неисправностей в схемах (Т). на усвоение нового материала (N), на разработку схем

(D). В восьмом издании добавился еще один тип упражнений, который обозначается

как (В). Это задачи, касающиеся базовых моментов того, о чем говорится в отдель-

ных главах. Также появилось больше упражнений, направленных на понимание из-

ложенного материала. Если задание не относится к вышеперечисленным, значит, оно

имеет промежуточный уровень сложности, где-то между трудным и основным.

Перечни технических характеристик

Технические спецификации отдельных интегральных схем приведены в приложе-

нии Б, которое представлено в конце книги.

Технология ИС

В этом издании, как и в двух предыдущих, больше внимания уделено технологии

КМОП, которая занимает ведущее положение в области малых и средних интеграль-

ных схем, хотя на данный момеш в целом преобладает ТТЛ-технология.

Примеры промышленного применения

Примеры, приведенные в предыдущих изданиях, мы использовали и здесь для

ответа на возникающий у некоторых студентов вопрос: “А зачем все это нужно

знать?” Примерами могут служить схемы управления копировальных аппаратов,

устройства циклового программного управления технологическими жидкостями,

датчики контроля над напряжением бортового питания на космическом корабле,

цифровой термостат, функциональный преобразователь таблиц соответствия. Приме-

ВВЕДЕНИЕ

21

ры использования ПЛУ раскрывают дополнительные возможности реализации экви-

валентных СИС и МИ С. Приводятся новые решения, объединяющие несколько раз-

личных типов схем и методов исполнения в одну автономную систему ПЛУ. Напри-

мер, на рис. Р.1 показана схема управления шаговым двигателем, где элемент GAL

16V8, выступающий как схема сопряжения, включает в себя контроллер последова-

тельности, дешифратор и буферизованные выходы с тремя состояниями. Это очень

полезное практическое решение при работе с шаговыми двигателями в лаборатории.

На рис. Р.2 изображена схема для клавишного кодирующего устройства, которое

часто используется в качестве устройства ввода в микропроцессорах и друглх цифро-

вых системах. Схема состоит из последовательности кольцевых счетчиков, шифрато-

ров и контролируемого выхода с тремя состояниями. Схемы, приведенные в приме-

рах, достаточно просто создаются и их можно использовать как отдельные элементы

в последующих экспериментах.

Входы контроллера Интерфейс

последовательности GAL16V8

. Рис. Р.1. Схема управления шагового двигателя, показанная на рис. 12.20

Изменения в содержании глав

Произошли изменения и в тематике отдельных глав:

Глава 1. Взгляд на “цифровое будущее” основывается на последних достижениях

науки и техники.

Глава 2. Теперь в этой главе описаны новые и усовершенствованы старые мето-

ды использования калькуляторов для перехода от одной системы счисления к

другой.

Глава 3. Несколько сократилось рассмотрение стандартных обозначений логиче-

ских элементов (IEEE).

Глава 4. а) Появилась информация об использовании карт Карно, включая де-

тальный пример “безразличных состояний” элемента; б) ПЛУ представлено как

альтернативная основа для создания логических схем. По возможности просто

показаны общие принципы действия таких устройств на примере схем, про-

граммируемых с помощью технологии плавких перемычек. Указано, какая вы-

22

Введение

числительная техника и программное обеспечение понадобятся при разработке

схем в виде ПЛУ, а также их место во всем этом процессе. Рассмотрен специ-

альный язык высокого уровня, используемый для описания подобных элемен-

тов. И, как результат, приводится пример реализации простой комбинационной

логической схемы.

D3

D2

DAV

Рис. Р2. Схема клавишного кодирующего устройства, показанного на

рис. 12.25

Глава б. Логические схемы с обратной связью, включая сдвиговые регистры и

D-защелки, созданные на основе ПЛУ. Опираясь на существующее в вышеупо-

мянутом языке описания определение перехода между логическими состояния-

ми, простой счетчик реализован в виде программируемого устройства.

Глава 6. Появился новый раздел, посвященный описанию четырехбитового сум-

матора на основе ПЛУ. Наряду с отдельными (индексированными) переменны-

ми, для логического объединения четырехбитовых массивов информации в язык

описания введено представление о наборе данных.

Глава 7. а) Убран материал по устаревшей интегральной схеме 74178 больше

места уделено ИС 74165, 74174; б) наряду с буферизацией выходов ПЛУ, описа-

ны еще два метода задания последовательности состояний счетчика (конечный

автомат).

Введение

23

Глава 8. Развитие технологии вынудило существенно изменить тематику этой

главы. Добавлена информация о корпусах с матричным расположением шаро-

вых выводов. Все примеры и технические характеристики приводятся только

для серии усовершенствованных маломощных интегральных схем серии ТТЛ с

диодами Шотки, тогда как параметры основной схемы описаны при помощи бо-

лее понятного стандарта ТТЛ. Также объединены в один раздел технологии МОП

и КМОП, с акцентом на КМОП-структурах как наиболее популярных на сего-

дняшний день. При этом вся информация о МОП-структурах с р- и п-каналами

сводится к их текущему промышленному применению. Усовершенствован мате-

риал по ЭСЛ. Также обновлено содержание раздела о низковольтных технологи-

ях. Чтобы исключить избыточные сведения, описания схем со свободным кол-

лектором и свободным стоком были объединены; в лучшем виде представлена

трехуровневая логика. Линии передачи и необходимость их оконечной нагрузки

рассмотрены вкратце, наряду с ними описана серия устройств сопряжения для

высокоскоростных шин.

Глава 9. «Здесь рассматриваются цветные жидкокристаллические дисплеи и тех-

нология изготовления экранов ноутбуков. Раздел о газоразрядных дисплеях и

два раздела стандартных обозначений IEEE из книги убраны. Также показана

возможность описания ПЛУ с помощью метода таблиц истинности. Действие

стандартных функций средних интегральных схем получено на основе програм-

мируемых логических устройств.

Глава 10. Расширен раздел, посвященный дискретизации аналоговых сигналов,

теореме Найквиста и наложению спектров. Описание возможностей применения

АЦП и ЦАП в быстро развивающейся области цифровой электроники дополнено

поверхностным ознакомлением с цифровым сигнальным процессором.

Глава 11. Весь материал по программируемым устройствам был либо отредакти-

рован, либо перенесен в другие главы, большей частью в главу 12. Рассмотрено

еще больше понятий и терминов, которые часто встречаются в литературе ком-

пьютерного направления (например, момент переходного состояния в технологии

динамических ОЗУ или понятие времени ожидания (задержки) и как оно влияет

на скорость выполнения операций, описание кэшей первого и второго уровней,

которые имеются у всех современных компьютеров). Поскольку кольцевые бу-

феры широко используются в системах ЦОС, они будут представлены в виде мо-

дулей памяти.

Глава 12. Теперь эта глава начинается с обзора внутренней архитектуры элемен-

тарного ПЛУ. Материал главы 11 седьмого издания был модифицирован и объе-

динен с материалом главы 12. Приводится пример использования популярной

схемы GAL 22V10 в качестве сумматора. Также показано, как создаются имею-

щие большое практическое значение схемы универсального задающего устройст-

ва для шагового двигателя и клавишного кодирующего устройства с использова-

нием только одного ПЛУ. Появилась информация о других языках описания ап-

паратных средств, о концепции построения более совершенных вентильных

матриц, программируемых пользователем

Приложение А. Материал по микропроцессорной технике (глава 13 в предыду-

щих изданиях) носил характер поверхностного введения в этот достаточно

сложный и очень важный предмет, поскольку в большинстве учебных программ

на него выделяется отдельный курс. Поэтому мы вынесли эту тему в виде при-

ложения, чтобы впоследствии убрать ее вообще. Читатели могут высказать свое

мнение по этому поводу на Web-узле нашей книги http://www/prenhall.corn/

tocci.

24

Введение

Что осталось из прошлых изданий?

Все характерные особенности изложения материала в предыдущих изданиях, за-

воевавших огромную популярность у читателей, мы сохранили и здесь. Например,

подход к описанию основных логических операций и логических элементов при по-

мощи блок-схем этих элементов, не вдаваясь в детали их внутреннего строения, об-

легчает понимание материала на ранних этапах изучения книги. Или же рассмотре-

ние основных электротехнических характеристик интегральных схем только после

полного усвоения принципов бинарной логики. Глава 8 знакомит читателя с внут-

ренней архитектурой ИС. В итоге он может интерпретировать значения на входах и

выходе логического модуля и, исходя из этого, предложить возможную схему его

строения.

Описание каждой новой темы или устройства состоит из следующих этапов: рас-

смотрение принципа действия; изучение примеров и возможностей применения, час-

то с использованием реально существующих ИС; контрольные вопросы по материалу

каждого раздела; практические упражнения ко всей главе, находящиеся в ее конце.

Отметим, что в книге представлены упражнения различных степеней сложности,

причем они ориентированы не на обычное заучивание основных принципов, приве-

денных в главе, а требуют их понимания и умения использовать в разных ситуаци-

ях. В результате студент обретает уверенность в собственных силах и углубляет зна-

ния по данной теме.

Сведения о стандарте IEEE/ANSI для обозначений логических элементов обсуж-

даются отдельно и практически не влияют на ход изложения. Поэтому при желании

их можно убрать полностью или частично без потерь для содержания. Информация о

поиске неисправностей в логических схемах представлена с 4 по 11 главу. Здесь опи-

саны всевозможные принципы и технологии, детально рассмотрены отдельные слу-

чаи, представлены 25 примеров поиска возникших неисправностей и 60 упражнений

на эту тему. Однако для получения хороших практических навыков, необходимых

для устранения неполадок в электронных схемах, без лабораторного практикума на

макетах не обойтись.

В восьмом издании собрано более 200 примеров, около 400 вопросов и более

450 упражнений. В некоторых из упражнений (помещенных в конце каждой главы)

представлены типичные микрокомпьютерные системы с использованием логических

устройств, описанных ранее в соответствующей главе.

С помощью алфавитного указателя читатель сможет быстро найти информацию

по любой ИС, которая встречалась или на которую были ссылки в тексте. Также

вместе собраны таблицы с наиболее часто встречающимися теоремами булевой алгеб-

ры, краткое резюме основных логических элементов, таблицы истинности для триг-

геров, что очень полезно при решении задач или работе в лаборатории.

Толковый словарь содержит краткое описание всех терминов, выделенных в тек-

сте жирным шрифтом.

Дополнительные средства

Книге сопутствует основательное дополнение, содержащее много составных час-

тей. Каждая из них имеет определенное назначение и может использоваться незави-

симо или в совокупности с остальными.

К изданию бесплатно прилагается компакт-диск, который содержит:

полный перечень технических спецификаций интегральных схем компании

Texas Instruments, Inc., включая все серии ТТЛ, КМОП, а также спецификации

шинных интерфейсов;

принципиальные схемы (часть из которых вошла в книгу), представленные в

формате файлов двух программ Electronics Workbench™ и CircuitMaker®. Сту-

денты, имеющие доступ к первой из них, могут спокойно работать с этими фай-

лами, при подготовке к лабораторным занятиям. О том, как получить пользова-

ВВЕДЕНИЕ

25

тельскую версию программы, можно узнать на сайте компании Electronics

Workbench — www.electronicsworkbench.com;

демонстрационная версия компилятора языка CUPL — PAL EXPERT от компа-

нии Logical Devices, Inc. Лицензионный вариант этого мощного программного

продукта читатели книги могут приобрести со скидкой, указав при заказе реги-

страционный номер #РгеН5Р1-2000.

Для студентов

Пакет программ StudyWizard Tutorial Software. Студенты смогут лучше разо-

браться в материале, отвечая на вопросы, а также проверить знание терминоло-

гии при помощи этой программы. К сожалению, данный пакет не идет в ком-

плекте с книгой.

Руководство по лабораторному практикуму: моделирование и разработка Грего-

ри Мосса (Gregory Moss). В заданиях, связанных с программируемой логикой,

используется программное обеспечение CUPL. Эта версия содержит новые маке-

ты и модели, изменения, касающиеся ПЛУ согласно изменениям в тексте книги,

а также несколько новых рисунков. (ISBN 0-13-086588-5)

Руководство по лабораторному практикуму: поиск и устранение неисправно-

стей, предложенное Джимом деЛохом (Jim DeLoach) и Фрэнком Амбросио (Frank

Ambrosio), включает более 40 экспериментальных примеров нахождения, анали-

за и ликвидации неполадок в электронных схемах. (ISBN 0-13-089703-5)

Настольный справочник студента, составленный Фрэнком Амбросио, способст-

вует закреплению знаний по всем темам. Старое издание изменилось в соответ-

ствии с изменениями в тексте самой книги, и сейчас содержит полностью обнов-

ленные схемы. (ISBN 0-13-085639-8)

Web-узел, посвященный этой книге (www.prenhall.com/tocci). Здесь открыта для

студентов бесплатная дистанционная система обучения, воспользовавшись кото-

рой можно проверить понимание ключевых моментов по отдельным темам.

Web-узел, посвященный электронике (www.prenhall.com'electronics). Включает

дополнительные задачи поиска и устранения неисправностей, ссылки на Web-

ресурсы промышленных предприятий, интервью со специалистом в области

электроники и многое другое.

Для преподавателей

Web-узел, посвященный этой книге (www.prenhall.com/tocci). Преподаватель

может разместить здесь свой конспект лекций, воспользовавшись нашей про-

граммой-построителем Syllabus Builder. Это хороший способ для проведения за-

нятий в режиме реального времени или самостоятельного изучения.

Web-узел, посвященный электронике (www.prenhall.com/electronics). Здесь на-

ходится электронный вариант журнала Prentice Hall Electronics Technology

Journal, а также всевозможные дополнения к тексту книги, помещенные сюда

для упрощения доступа. Обратитесь в наше территориальное представительство с

просьбой предоставить Вам имя пользователя и код доступа.

Поддержка сетевых курсов. Если, согласно Вашему учебному плану, курс циф-

ровой электроники выносится на дистанционное обучение, обратитесь в наше

представительство за списком программных решений.

Руководство преподавателя содержит последовательно изложенные решения

всех упражнений, которые встречаются в тексте. (ISBN 0-13-085635-5)

Сборник ответов к лабораторным работам включает в себя все результаты двух

лабораторных практикумов. (ISBN 0-13-085637-1)

26

Введение

Компакт-диск, содержащий все рисунки из текста, оформленные в виде слайдов

программы PowerPoint. 150 слайдов дополнительно включают пояснения к этим

рисункам. (ISBN 0-13-089704-3)

Тестовые задания. Это сборник из сотен вопросов, которые можно использовать

в качестве тестов и экзаменов. (ISBN 0-13-085636-3)

PH Test Manager — это компьютеризованная версия предыдущего пункта (для

платформы Windows). Представлена в виде компакт-диска, позволяет редакти-

ровать вопросы и включать в них графические объекты. Имеет сложную про-

грамму графического вывода. (ISBN 0-13-085641-Х)

Благодарности

Мы искренне признательны всем, кто рецензировал седьмое издание и заполнял

обширную анкету: Майклу Г. Истмэну (Michael G. Eastman) из Рочестерского техно-

логического института; доктору Уолтеру Э. Тэйну (Walter Е. Thain) из Южного госу-

дарственного политехнического университета; Майклу Э. Клеммеру и Джону Данну

(Michael Е. Clemmer, John Dunn) из технического института в городе Ноксвилл; а так-

же Курту Нэлти из Остинского колледжа. Их критика, комментарии и рекомендации

сыграли неоценимую роль при окончательном формировании восьмого издания.

Также выражаем глубокую благодарность нашим коллегам: профессору Фрэнку

Амбросио из колледжа Монро за основательную работу над каталогами, книгами Ру-

ководство Преподавателя и Настольный Справочник Студентах профессору Грего-

ри Моссу из университета Пердью за многочисленные советы относительно содержа-

ния отдельных тем и в особенности раздела современной программируемой логики;

профессору Энтони Окстоби (Anthony Oxtoby) из того же университета за техниче-

ский обзор тем, связанных с обработкой цифровых сигналов. Мы высоко ценим по-

мощь, оказанную со стороны Дэвида Мота (David Mot) из компании Logical

Devices, Inc., любезно предложившего специальную оценочную версию программы

CUPL по нашей просьбе, а также Майка Гастингса (Mike Hastings) из компании Texas

Instruments, Inc., предоставившего технические характеристики логических схем.

Проект такой величины требует внимательного, профессионального редактирова-

ния, и здесь нам на выручку снова пришло издательство Prentice Hall. Мы благода-

рим за помощь главного редактора Скотта Самбуччи (Scott Sambucci), его первого

помощника Кэйти Брэдфорд (Katie Bradford), производственного редактора Стива

Робба (Steve Robb) и Алекса Вульфа (Alex Wolf) и редактора печати Брета Воркмэна

(Bret Workman).

И наконец, хотим сказать огромное спасибо нашим женам и детям за понимание

и поддержку.

Рональд Дж. Точчи (Ronald J. Tocci)

Нил С. У ид мер (Neal S. Widmer)

Введение

27

Web-узел, посвященный этой

книге

Создание Web-узла для этой книги

Страница издательства Prentice Hall: виртуальная

среда обучения

Технология сейчас развивается очень большими темпами, поэтому за изменения-

ми нужно постоянно следить. С этой целью издательство Prentice Hall и создало се-

тевую среду обучения для студентов и преподавателей — сопутствующий нашей кни-

ге Web-узел.

Его назначение состоит в том, чтобы более полно, с учетом последних достижений

науки и техники раскрыть тематику отдельных глав. Особое внимание уделено ин-

формации, имеющейся на Web-узлах такого же направления, что обеспечивает чита-

телей солидным запасом полезных ссылок. На страницах Web-узла собраны:

Для преподавателя

Программа Syllabus Manager™ позволяет разместить конспект лекций в сети.

Syllabus Manager™ поможет шаг за шагом создать сетевой вариант курса, мо-

дифицировать его, разместить ссылки на нашу страницу, а также на другие ре-

сурсы в Internet. Чтобы это сделать, не обязательно знать язык HTML.

Материал доступен студентам на протяжении всего периода обучения. Все, что

им будет нужно знать — Internet-адрес нашей страницы и пароль для доступа к

конспекту, который укажете Вы.

Если курс лекций уже размещен при помощи программы Syllabus Manager™,

студенты смогут войти в него из любой точки нашего Web-узла.

Щелкнув левой кнопкой мыши на текущей дате, студент увидит список пунктов

сегодняшнего задания. С целью экономии времени каждый из пунктов напря-

мую связан с конкретным разделом в конспекте лекций.

Чтобы добавить задание, укажите с помощью мыши желаемые сроки его выпол-

нения, название, инструкции, а также будет оно повторяться или нет.

Гиперссылки создаются очень просто. Чтобы создать гиперссылку, нужно впи-

сать необходимый URL в соответствующую строку. Это автоматически отобра-

зится в тексте конспекта.

Завершенный вариант курса лекций размещается на наших серверах. Обновлять

информацию можно с любого компьютера, подключенного к Internet. Все изме-

нения, внесенные в конспект, станут доступны студентам при следующем посе-

щении.

Для студента

В резюме глав выделены все ключевые понятия, встречающиеся в тексте книги.

28

Web-узел, посвященный этой книге

Система интерактивной проверки знаний дополнительно содержит небольшие

советы к заданиям и автоматически выставляет оценку. В нее входят вопросы в

виде тестов либо вопросы, требующие ответа “да” или “нет”, есть задания на

сравнение или такие, где необходимо представить развернутый ответ.

После того как Вы закончите выполнение заданий, специальная программа оповеще-

ния результатов Results Reporter проанализирует работу, графически отобразит ко-

личество правильных и неправильных ответов и даст полную раскладку всех вопро-

сов. Студенты могут отправить результаты проверки на любой из четырех адресов

электронной почты — преподавателю, его ассистенту, кому-то из сокурсников.

Доска объявлений позволяет размещать свои вопросы и давать ответы или ком-

ментарии на вопросы других.

Форум обеспечивает диалог в реальном времени с пользователем нашего Web-

узла, который может находиться где угодно в пределах страны. Это отличная

возможность для проведения всякого рода обсуждений и семинаров.

Чтобы воспользоваться всеми этими возможностями, нужно просто посетить Web-

узел книги Цифровые системы: принципы и возможные применения по адресу

www. prenhall. com/tocci

От издательства

Вы, читатель этой книги, и есть главный ее критик и комментатор. Мы ценим

ваше мнение и хотим знать, что было сделано нами правильно, что можно было сде-

лать лучше и что еще вы хотели бы увидеть изданным нами. Нам интересно услы-

шать и любые другие замечания, которые вам хотелось бы высказать в наш адрес.

Мы ждем ваших комментариев и надеемся на них. Вы можете прислать нам бу-

мажное или электронное письмо, либо просто посетить наш Web-сервер и оставить

свои замечания там. Одним словом, любым удобным для вас способом дайте нам

знать, нравится или нет вам эта книга, а также выскажите свое мнение о том, как

сделать наши книги более интересными для вас.

Посылая письмо или сообщение, не забудьте указать название книги и ее авторов,

а также ваш обратный адрес. Мы внимательно ознакомимся с вашим мнением и обя-

зательно учтем его при отборе и подготовке к изданию последующих книг. Наши ко-

ординаты:

E-mail: inf o@williamspublishing. com

WWW: http: //www.williamspublishing.com

Информация для писем из:

России: 115419, Москва, а/я 783

Украины: 03150, Киев, а/я 152

Web-узел, посвященный этой книге

29

Глава 1

Введение в предмет

Содержание:

1.1. Численные представления

1.2. Цифровые и аналоговые системы

1.3. Цифровые системы счисления

1.4. Представление двоичных величин

1.5. Цифровые и логические схемы

1.6. Параллельная и последовательная передача информации

1.7. Память

1.8. Цифровые компьютеры

В этой главе:

различия между аналоговым и цифровым представлениями;

преимущества и недостатки цифровой техники по сравнению с анало-

говой;

назначение аналого-цифровых преобразователей (АЦП) и цифроаналого-

вых преобразователей (ЦАП);

основные характеристики двоичной цифровой системы;

перевод двоичного числа в его десятичный эквивалент;

счет в двоичной числовой системе;

типичные цифровые сигналы и временные диаграммы сигналов;

различие между параллельной и последовательной передачей информации;

описание свойств памяти;

описание основных компонентов цифровых компьютеров и их назначение;

различие между аналоговыми микрокомпьютерами, микропроцессорами и

микроконтроллерами.

Введение

В сегодняшнем мире термин цифровой стал частью нашего ежедневного общения

благодаря повсеместному использованию цифровых систем и цифровой техники поч-

ти во всех областях жизни: в компьютерах, автоматике, робототехнике, в медицине

и на производстве, транспорте, развлечениях, космических исследованиях и т.д. Вы

находитесь в преддверии удивительного образовательного путешествия, на протяже-

нии которого откроете фундаментальные принципы, понятия и операции, общие для

всех цифровых систем, — от простейших ключей с двумя состояниями и до наиболее

сложных компьютеров. В книге описаны принципы работы цифровых систем, а так-

же даны практические рекомендации по анализу цифровых систем или их сбоев.

Начнем с представления базовых концепций, которые являются фундаментальной

частью цифровых технологий; эти концепции будут расширены далее по ходу книги.

Мы также представим некоторую терминологию, необходимую для ознакомления с

новой областью знаний.

1.1. Численные представления

В науке, технологии, бизнесе и во многих других областях деятельности мы по-

стоянно имеем дело с величинами. Величины измеряют, изучают, записывают, над

ними производят арифметические операции, за ними наблюдают, т.е. используют

тем или иным способом в большинстве физических систем. Важно, что при работе с

различными величинами мы можем представить их значения точно и эффективно.

Существуют два основных способа представления численных значений величин: ана-

логовый и цифровой.

Аналоговое представление

При аналоговом представлении величина отображается напряжением, током или

движением стрелки измерительного прибора пропорционально значению данной ве-

личины. В качестве примера может служить автомобильный спидометр, в котором

32

Глава 1

отклонение стрелки прибора пропорционально скорости машины. Угловое положение

стрелки отображает значение скорости автомобиля, при этом стрелка следит за лю-

быми изменениями этой величины при разгоне или торможении автомобиля.

Другой пример — ртутный термометр, в котором высота столбика ртути пропор-

циональна температуре в комнате. Как только температура повышается или понижа-

ется, ртуть также пропорционально поднимается или опускается так, что ее уровень

отображает значение температуры.

В качестве еще одного примера аналоговой величины можно привести обычный

микрофон. В этом приборе выходное напряжение генерируется пропорционально ам-

плитуде звуковых волн, попадающих в микрофон. Изменения выходного напряже-

ния в точности повторяют изменения входного звука.

Перечисленные выше аналоговые величины имеют общую важную характеристи-

ку: они могут варьироваться в непрерывном диапазоне значений. Скорость автомо-

биля может иметь любое значение между 0 и, скажем, 100 километрами в час. Точно

так же и выходной сигнал микрофона может иметь любое значение в диапазоне от 0

до 10 мВ (например, 1 мВ; 2,3724 мВ; 9,9999 мВ).

Цифровое представление

При цифровом представлении величины отображаются не пропорциональными

величинами, а символами, которые называются разрядами. В качестве примера

возьмем электронные часы, которые показывают время суток в форме десятичных

разрядов, соответствующих часам и минутам (иногда и секундам). Как известно,

время суток изменяется постоянно, что нельзя сказать о показаниях электронных

часов, — они меняются с шагом 1 за минуту (или за секунду). Другими словами, та-

кое цифровое представление времени суток изменяется дискретными шагами по

сравнению со временем на аналоговых часах, где показания циферблата меняются

непрерывно.

Главную разницу между аналоговыми и цифровыми величинами можно записать так:

Аналоговый = непрерывный

Цифровой = дискретный (шаг за шагом)

Благодаря дискретной природе цифрового представления нет никакой двусмысленно-

сти при чтении значения цифровой величины, тогда как значение аналоговой вели-

чины часто может иметь различные интерпретации.

Пример 1.1

Какие из приведенных ниже величин аналоговые, а какие цифровые?

а) переключатель с десятью различными позициями;

б) ток в электрической розетке;

в) температура комнаты;

г) песчинки на пляже;

д) спидометр автомобиля?

Решение

а) цифровая;

б) аналоговая;

в) аналоговая;

г) цифровые, так как песчинки могут иметь только дискретные (целочисленные)

значения, а не любое возможное значение в непрерывном диапазоне;

д) аналоговая, если спидометр со стрелкой; цифровая, если он индикаторный.

Введение в предмет

33

Контрольные^вопроеёг

1. Кратко опишите основную разницу между аналоговыми и цифровыми величи-

нами.

1.2. Цифровые и аналоговые системы

Цифровая система — это комбинация устройств, разработанных для обработки

логической информации или физических величин, которые представлены в цифровой

форме. Эти устройства чаще всего электронные, но могут быть механическими, маг-

нитными или пневматическими. Наиболее распространенные цифровые системы в

мире — это цифровые компьютеры и калькуляторы, цифровое оборудование по обра-

ботке аудио- и видеоданных, телефонные системы.

Аналоговая система содержит устройства, которые оперируют с физическими ве-

личинами, представленными в аналоговой форме. В аналоговой системе амплитуда

выходного сигнала в колонке радиоприемника может иметь любое значение между

нулем и максимальным пределом. Другие обычные аналоговые системы — это уси-

лители звука, устройства записи и воспроизведения на магнитной ленте, обычный

плавный (реостатный) выключатель света.

Преимущества цифровой техники

Все большее число приложений в электронике, как, впрочем, и большинство дру-

гих технологий используют цифровую технику, чтобы осуществлять операции, кото-

рые когда-то выполнялись при помощи аналоговой техники. Основные причины рос-

та популярности цифровых технологий заключаются в следующем.

1. Цифровые системы, как правило, легче разрабатывать. Так происходит потому,

что используемые схемы принадлежат к ключевым схемам, в которых важны не

точные значения напряжения или тока, а лишь диапазон (высокий или низкий

сигнал), в который они попадают.

2. Легко осуществить хранение информации. Хранение осуществляется с помощью

специальных устройств и схем, которые могут считывать цифровую информацию

и сохранять ее сколь угодно долго. Запоминающие устройства сверхбольшой ем-

кости могут хранить миллиарды бит информации на сравнительно малом физи-

ческом пространстве. Аналоговые устройства хранения информации, наобо-

рот, имеют крайне ограниченные возможности.

3. Большая точность. Цифровые системы могут оперировать любым необходимым

количеством десятичных знаков путем простого увеличения числа ключевых

схем. В аналоговых системах точность обычно ограничена тремя или четырьмя

знаками, потому что значения тока или напряжения непосредственно зависят от

номиналов компонент схемы и подвержены влиянию случайных флуктуаций на-

пряжения (шумов).

4. Возможность запрограммировать действие. Достаточно легко спроектировать

цифровые системы, в которых работа контролируется набором хранящихся ко-

манд, или программой. Аналоговые системы также можно программировать, но

разнообразие и сложность имеющихся в распоряжении операций строго ограни-

чены.

5. Цифровые схемы менее подвержены шумам. Паразитные флуктуации напряже-

ния (шумы) некритичны для цифровых систем, потому что точные значения на-

* Ответы к контрольным вопросам приведены в конце той главы, к которой они относятся.

34

Глава 1

пряжения для них не столь важны (шум не настолько большой, чтобы нельзя

было отличить высокий уровень сигнала от низкого).

6. Большее количество схемотехнических решений может быть изготовлено на

интегральных схемах (ИС). Конечно, и аналоговая схемотехника выиграла от

бурного развития ИС-технологий, но ее относительная сложность, а также ис-

пользование компонентов, которые не могут быть эффективно интегрированы

(высокоемкие конденсаторы, прецизионные резисторы, катушки индуктивности,

трансформаторы), помешали аналоговым системам добиться такой же высокой

степени интеграции.

Ограничения цифровой техники

У цифровой техники есть один важный недостаток:

Реальный мир в основном аналоговый.

Большинство физических величин аналоговые по своей природе — это именно те

величины входных и выходных наблюдаемых сигналов, с которыми оперирует и ко-

торые контролирует система. В качестве примеров можно привести температуру,

давление, координату, скорость, уровень жидкости, скорость потока и т.д. У нас во-

шло в привычку выражать эти величины в цифровом виде, например, когда мы гово-

рим, что температура равна 64' (63,8°, если требуется большая точность), то на самом

деле мы делаем цифровое приближение аналоговой по своей сути величины.

Чтобы воспользоваться преимуществами цифровой техники при работе с аналого-

выми входными и выходными сигналами, надо следовать трем следующим инструк

циям:

1. Перевести реальные аналоговые входные сигналы в цифровую форму.

2. Обработать цифровую информацию.

3. Перевести цифровые выходные сигналы обратно в реальную аналоговую форму.

На рис. 1.1 показана блок-схема такого алгоритма для типичной системы контро-

ля температуры. После измерения аналоговой температуры полученное значение

конвертируется в цифровую величину с помощью аналого-цифрового преобразовате-

ля (АЦП). Цифровая величина затем обрабатывается цифровыми устройствами, ко-

торые могут включать или не включать цифровой компьютер. Его цифровой выход-

ной сигнал конвертируется обратно в аналоговую величину с помощью цифроанало-

гового преобразователя (ЦАП). Этот аналоговый выходной сигнал подается на

контроллер, который выполняет некоторые действия по корректировке температуры.

Температура

(аналоговая

форма)

Рис. 1.1. Блок-схема системы контроля температуры, которая требует аналого-цифрового

преобразования, для использования устройства цифровой обработки

Введение в предмет

35

Еще олин наглядный пример преобразования между аналоговой и цифровой фор-

мами — аудиозапись. Компакт-диски (CD) завоевали индустрию звукозаписи благо-

даря гораздо более эффективным средствам для записи и воспроизведения музыки.

Процесс состоит главным образом в следующем: (1) звуки инструментов и человече-

ский голос продуцируют аналоговый сигнал в микрофоне; (2) этот аналоговый сигнал

конвертируется в цифровую форму с использованием аналого-цифрового преобразо-

вания; (3) цифровая информация хранится на поверхности компакт-диска; (4) во

время воспроизведения проигрыватель компакт-дисков считывает цифровую инфор-

мацию с поверхности диска и преобразовывает ее в аналоговый сигнал, который за-

тем усиливается и подается на громкоговорители, используемые для прослушивания.

Потребность в преобразовании между аналоговой и цифровой формами информа-

ции можно рассматривать как недостаток, потому что аппаратура становится более

сложной и дорогой. Другой фактор, который иногда также важен, — дополнительное

время, необходимое для описанных выше преобразований. Однако во многих прило-

жениях эти факторы компенсируются многочисленными преимуществами цифровой

техники, так что преобразование между аналоговыми и цифровыми величинами ста-

ло в современных технологиях практически всеобщим.

В некоторых ситуациях, напротив, использование аналоговой техники проще и

экономически оправдано. Например, процесс генерирования и поступления электри-

чества в дома и офисы в основном осуществляется с помощью аналоговой схемотех-

ники.

На практике очень часто можно видеть и цифровые, и аналоговые методы, ис-

пользуемые в одной и той же системе, для получения преимуществ каждой из них.

В таких гибридных системах одна из наиболее важных задач на этапе разработки за-

ключается в определении того, какие части системы будут аналоговыми, а какие

цифровыми.

Цифровое будущее

Достижения в сфере цифровой технологии в течение трех последних десятилетий

были феноменальными, но это только начало. Число областей применения цифровых

ситем продолжает расти, и, вероятно, что к тому момоенту, когда вы прочитаете эти

строки, некоторые из “технологий будущего” уже станут обычным явлением. Воз-

можно, ваш автомобиль уже оснащен встроенным компьютером, который превраща-

ет приборную панель в центр беспроводной коммуникации, информации и навига-

ции. Вы уже можете использовать голосовые команды для отсылки или получения

электронной почты, вызова информации о ситуации на дорогах, проверки техниче-

ского состояния машины, отправки факса, заказа еды в дорогу и просто переключе-

ния радиостанций или смены компакт-дисков — и все это без единого движения ру-

ками или отрыва внимания от дороги. Или, например, у хронически больного ребен-

ка может быть вшитый в руку микропроцессорный датчик, который позволяет

врачам следить за его пульсом, кровяным давлением, температурой, активностью

иммунной системы и другими биологическими данными независимо от того, где на-

ходится ребенок. Данные могут отслеживаться и просматриваться докторами или

медсестрами по радиосканеру, расположенному отдельно (как делал, например, док-

тор Мак-Кой из сериала StarTrek) — лечение назначается так быстро, как только в

нем возникает необходимость и с минимальной задержкой.

Если эти плоды цифровой эры еще не материализованы, не волнуйтесь — они

близко... вместе с еще большими достижениями такого же рода. Уже скоро ваши за-

понки или сережки смогут взаимодействовать при помощи низкоорбитальных спут-

ников и иметь большие вычислительные мощности, чем ваш сегодняшний домашний

или офисный компьютер. Телефоны смогут получать, сортировать и, возможно, отве-

чать на входящие звонки так же, как это делают высококлассные секретари. Дети в

школах смогут делиться мыслями со сверстниками и собирать информацию по всему

миру. Когда вы захотите посмотреть определенную телевизионную программу в

36

Глава 1

удобное для вас время, вся информация, которую вы увидите, будет передана в ваш

дом за одну секунду и сохранена в памяти вашего телевизора или компьютера. Чи-

тая о какой-либо местности, расположенной в 5000 километрах от дома, вы сможете

физически ощутить там свое присутствие. И это лишь верхушка айсберга!

Другими словами, цифровая технология не только продолжит свое сверхскорост-

ное вторжение во все области нашей жизни, но и прорубит окно туда, где мы еще не

были даже в мечтах. Поэтому сейчас наша первоочередная задача — узнать как

можно больше о цифровой технологии и, уверенно чувствуя себя в седле, наслаж-

даться поездкой.

. .

Контрольные вопросы

1. В чем преимущества цифровой техники по сравнению с аналоговой?

2. Каковы основные ограничения при использовании цифровой техники?

1.3. Цифровые системы счисления

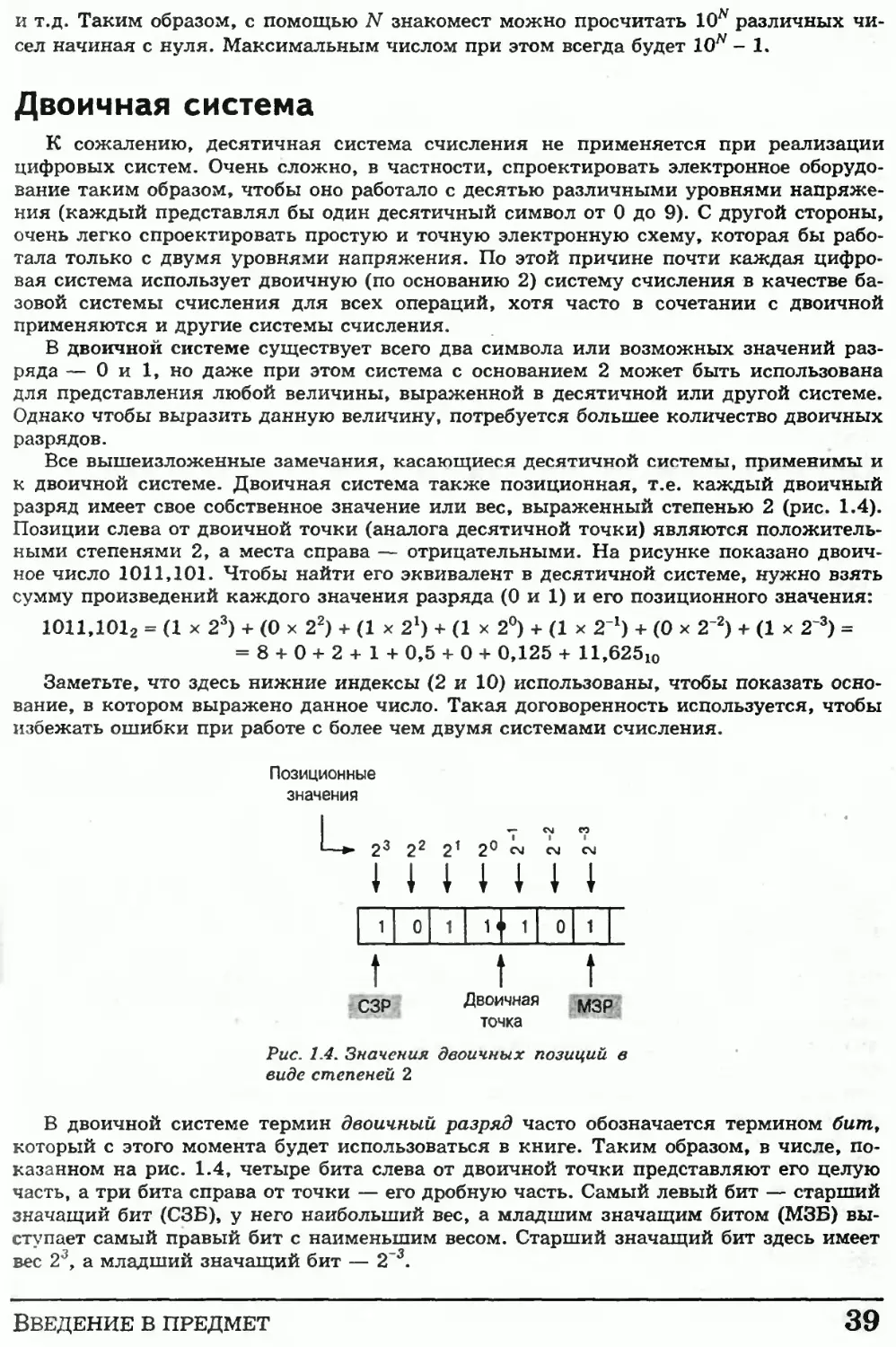

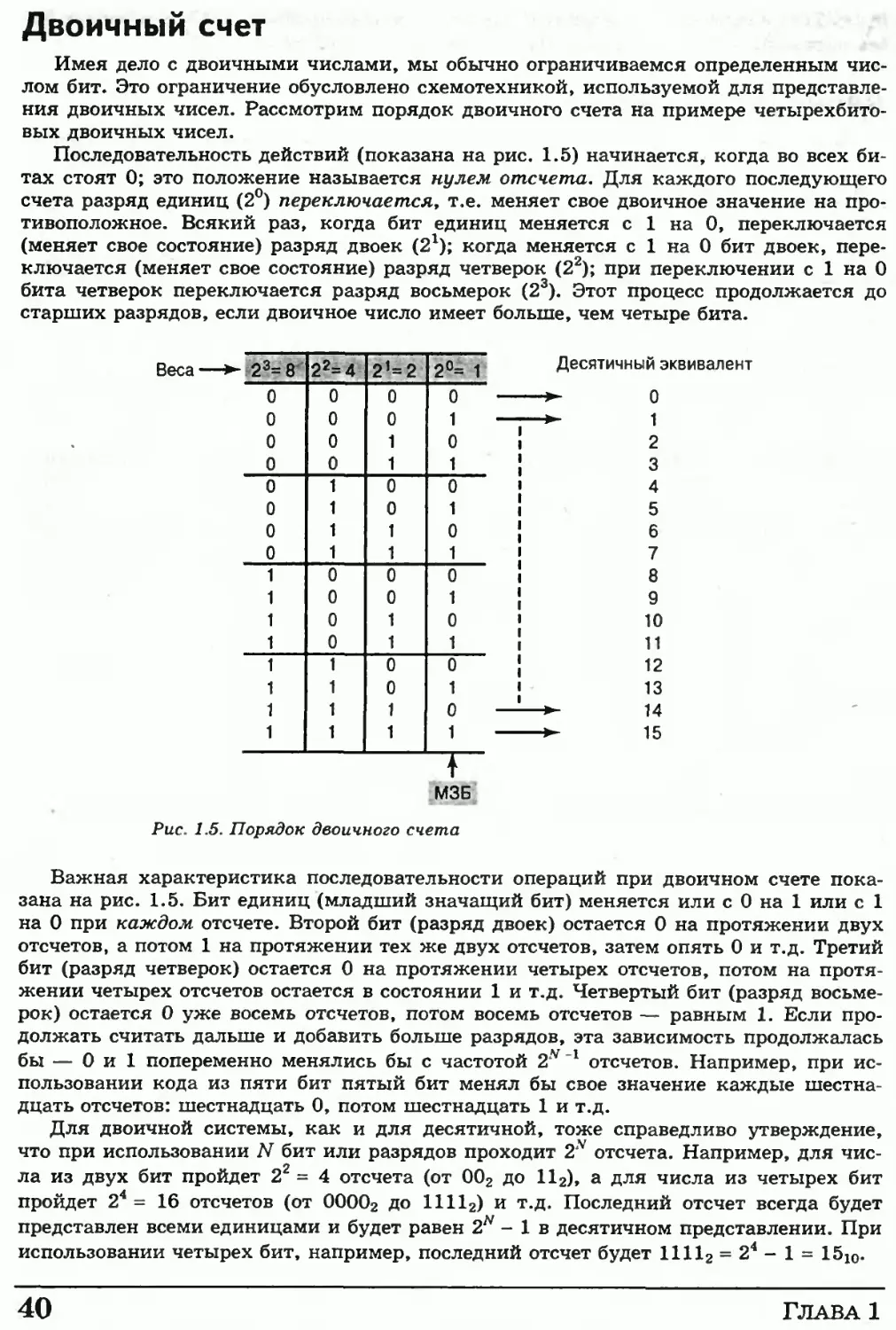

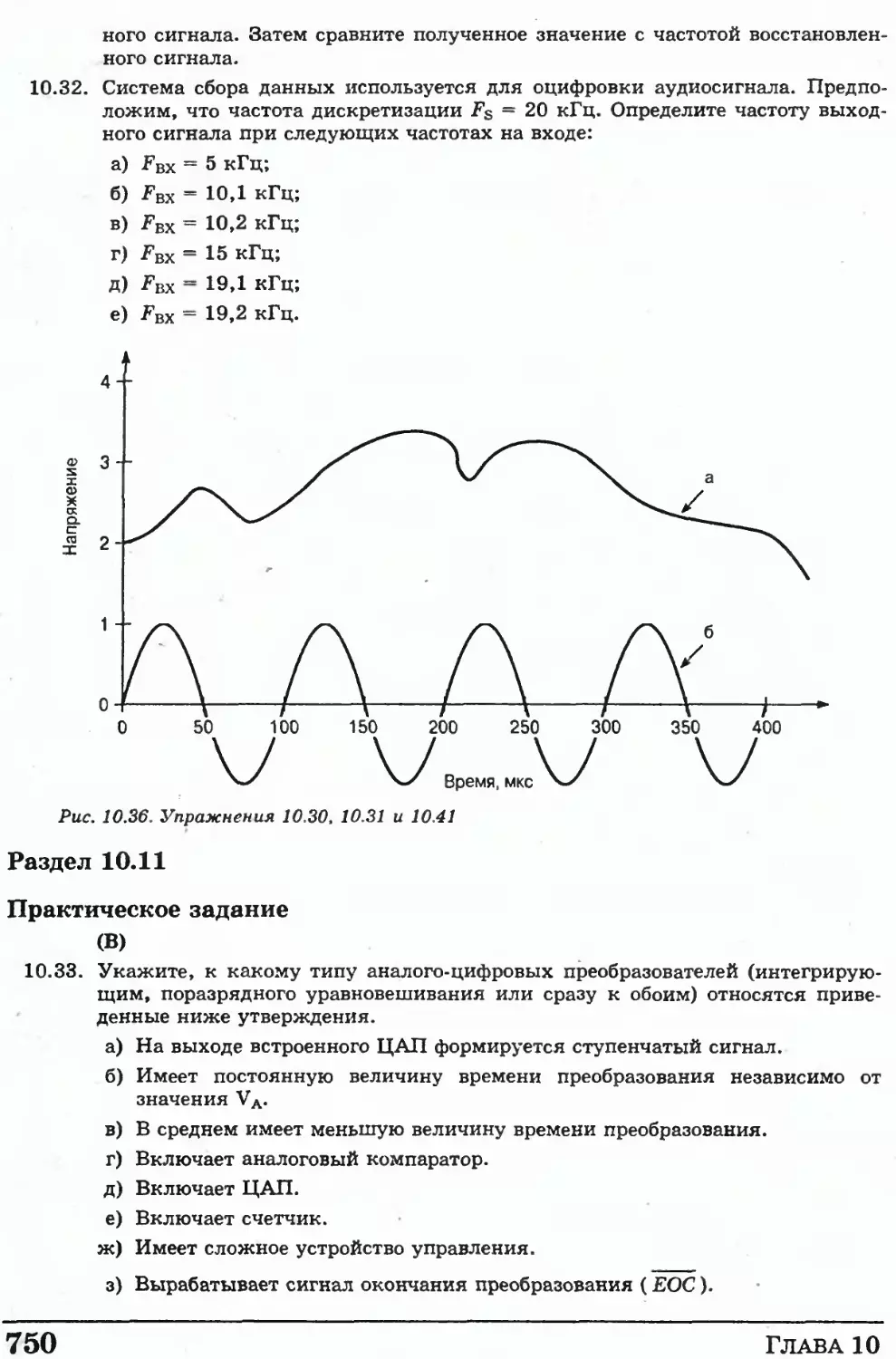

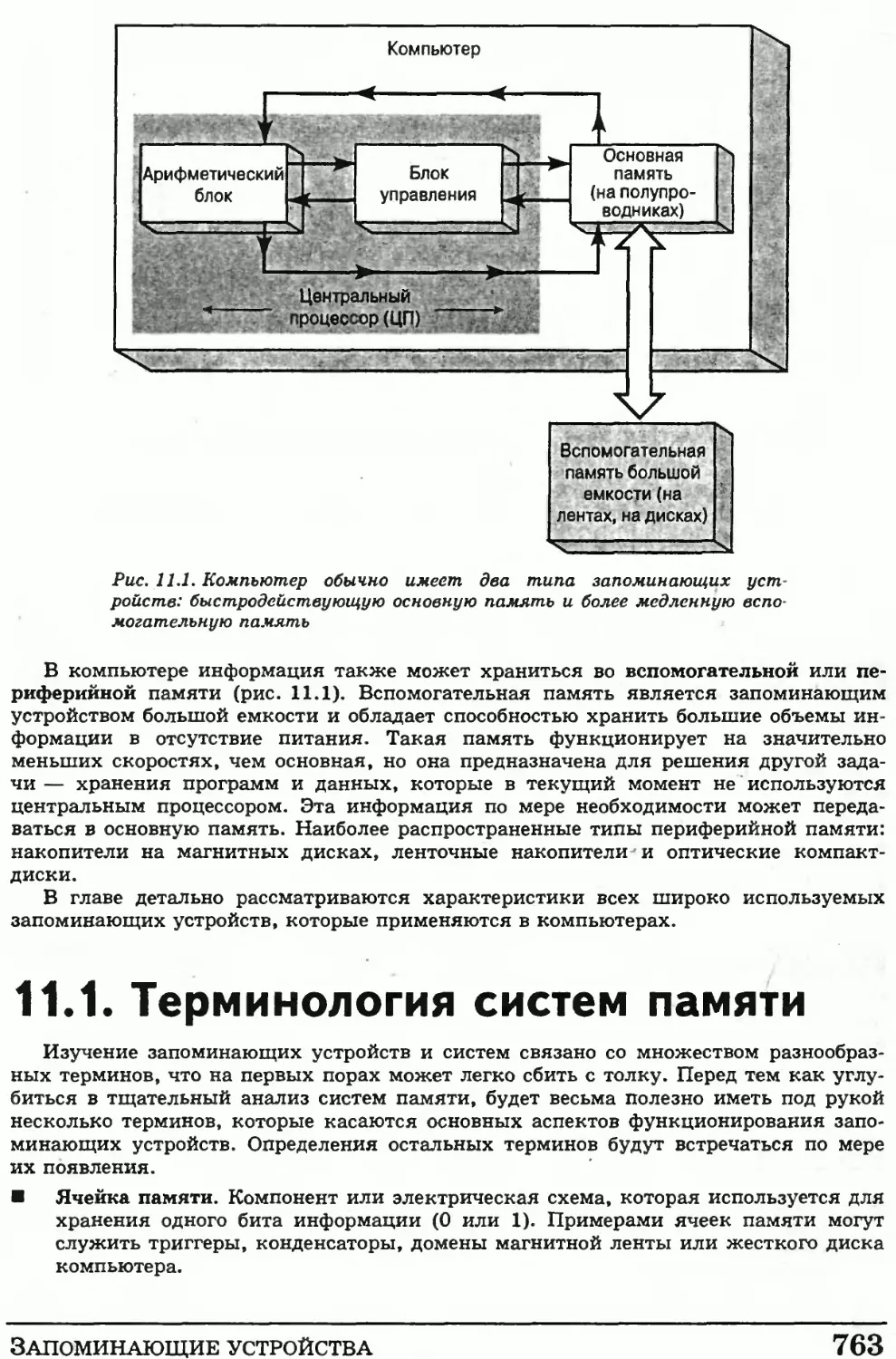

Цифровые технологии используют разнообразные системы счисления. Наиболее