Автор: Шахмнова В.А.

Теги: компьютерные технологии электротехника полупроводниковые устройства микропроцессы

ISBN: 5-256-00373-9

Год: 1988

Похожие

Текст

•РАДИОСВЯЗЬ*

СПРАВОЧНИК

МИКРОПРОЦЕССОРЫ и МИКРОПРОЦЕССОРНЫЕ КОМПЛЕКТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

Шина адреса и данных

Структурная схема микро-ЭВМ на МП К серии К1801

В Л

D12-D15

Организация 16-разрядного процессора на микросхемах серии КМ 1804

1 КМ1804ВР2

РОЗ PQ0

PF3 PFO

IC

СТ IN

IOV

IZ

т СО

D I

А

КМ1804ВС1

В

РОЗ PQ0

PR3 PRO

С4

F3

OVR

Z СО

т

+ 5 В

«4

^12-Y15

СПРАВОЧНИК

МИКРОПРОЦЕССОРЫ и МИКРОПРОЦЕССОРНЫЕ КОМПЛЕКТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

В ДВУХ ТОМАХ

ТОМ 2

Под редакцией В. А. ШАХНОВА

МОСКВА «РАДИО И СВЯЗЬ», 1988

Б БК 32.852

М59

УДК 681.325.5—181.4:621.3.049.771.14(03)

Рецензент: Чл.-корр. АН СССР Л. Н. Преснухин

Редакция литературы по электронной технике

Микропроцессоры и микропроцессорные комплекты М59 интегральных микросхем: Справочник: В 2 т. / Н. Н. Аверьянов, А. И. Березенко, Ю. И. Борщенко и др.; Под реД. В. А. Шахнова.—М.: Радио и связь, 1988. — Т. 2.— 368 с.: ил.

ISBN 5-256-00373-9

Приведены классификация микропроцессоров и микропроцессорных комплектов больших интегральных микросхем и сведения о микропроцессорных комплектах универсального назначения. Приводятся данные о структуре и системах команд микропроцессоров, временных соотношениях сигналов, примеры использования микропроцессоров в аппаратуре.

Для инженерно-технических работников, разрабатывающих электронную управляющую и вычислительную аппаратуру.

2403000000—048

М 046(01)—88 >06—87

ББК 32.852

ISBN 5-256-00373-9 (т. 2) ISBN 5-256-00371-2

© Издательство «Радио и связь», 1988

Содержание тома 1

Предисловие редактора

Глава I. Общие сведения о микропроцессорных микросхемах

1.1. Терминология

1.2. Система обозначений

1.3. Условия эксплуатации

1.4. Система параметров

1.5. Классификация микропроцессоров и микропроцессорных комплектов микросхем

Глава 2.' Микропроцессоры серий К145ИК18, К145ИК19

2.1. Микросхема К745ИК1801-2

2.2. Микросхема КД45ИК1807

2.3. Микросхемы К145ИК1809 и К145ИК1810

2.4. Микросхема К145ИК1812

2.5. Микросхема К145ИК1814

2.6. Микросхема К145ИК1901

2.7. Микросхема К145ИК1906

2.8. Микросхема К145ИК1907

2.9. Микросхема К145ИК1908

2.10. Микросхема К145ИК1914

2.11. Микросхема К145ИК1915

Глава 3. Микропроцессорный комплект серии КР580

3.1. Микросхема КР580ВМ80А

3.2. Микросхема КР580ВВ51А

3.3. Микросхема КР580ВИ53

3.4. Микросхема КР580ВВ55А

3.5. Микросхема КР580ВТ57

3.6. Микросхема КР580ВН59

3.7. Микросхема КР580ВВ79

3.8. Микросхема КР580ВА93

3.9. Микросхема КР580ВГ75

3.10. Микросхема КР580ВК91А

3.11. Микросхема КР580ГФ24

3.12. Микросхемы КР580ВК28 и КР580ВК38

3.13. Микросхемы КР580ИР82 и КР580ИР83

3.14. Микросхемы КР580ВА86 и КР580ВА87

3.15. Рекомендации по применению

Глава 4. Микропроцессорный комплект серии КР581

4.1. Микросхема КР581ИК1

4.2. Микросхема КР581ИК2

4.3. Микросхемы КР581РУ1, КР581РУ2 и

КР581РУЗ

4.4. Микросхема КР581ВЕ1

Глава 5. Микропроцессорный комплект серии К583

5.1. Микросхема К583ВС1

5.2. Микросхема К583ИК1

5.3. Микросхема К583КП1

5.4. Микросхема К583ВМ1

5.5. Микросхема К583ХЛ1

5.6. Микросхема К583ВГ1

5.7. Микросхема К583ВА1

5.8. Микросхема К583ВА2

5.9. Микросхема K583BA3

5.10. Микросхема К583ВА4

5.11. Рекомендации по применению

Глава 6. Микропроцессорный комплект серии К584

6.1. Микросхема К584ВМ1

6.2. Микросхема К584ВУ1

6.3. Микросхема К584ВГ1

6.4. Микросхема К584ВВ1

6.5. Рекомендации по применению

Глава 7. Микропроцессорный комплект серии КР587

7.1. Микросхема КР587ИК2

7.2. Микросхема КР587ИК1

7.3. Микросхема КР587ИКЗ

7.4. Рекомендации по применению

Глава 8. Микропроцессорный комплект серии К588

8.1. Микросхема К588ВС2

8.2. Микросхема К588ВУ2

8.3. Микросхема К588ВР2

8.4. Микросхема К588ВГ1

8.5. Микросхема К588ВА1

8.6. Микросхема К588ИР1

8.7. Микросхема К588ВГ2

8.8. Микросхема К588ВТ1

Глава 9. Микропроцессорный комплект серии К589

9.1. Микросхема К589ИК02

9.2. Микросхема К589ИК03

9.3. Микросхема К589ИК01

9.4. Микросхема К589ИК14

9.5. Микросхема К589ИР12

9.6. Микросхемы К589АП16 и К589АП26

9.7. Микросхема К589ХЛ4

3

Глава 10. Микропроцессорный комплект серии К1800

10.1. Микросхема К1800ВС1

10.2. Микросхема К1800ВУ1

10.3. Микросхема К1800ВБ2

10.4. Микросхема К1800ВГЗ

10.5. Микросхема К1800ВА4

10.6. Микросхема К1800РП6

10.7. Микросхема К1800ВА7

10.8. Микросхема К1800ВР8

10.9. Микросхема К1800РП16

10.10. Рекомендации по применению

Приложение 1. Корпуса микропроцессорных микросхем

Приложение 2. Краткие сведения о микропроцессорных микросхемах, не вошедших в том 1 справочника

Содержание тома 2

Предисловие......................... 6

Глава 11. Микропроцессорный комплект серии К1801

(Ю. И, Борщенко, В. Л. Дшхунян, Э. Е. Иванов, П. Р. Машевич, В. В. Теленков)

11.1. Микросхема К1801ВМ1 ... 7

11.2. Микросхема КМ1801ВМ2 ... 14

11.3. Микросхема КМ1801ВМЗ ... 15

11.4. Микросхема К1801ВП1-30 ... 21

11.5. Микросхема К1801ВП1-33 ... 23

11.6. Микросхема К1801ВП1-34 ... 31

11.7. Микросхема К1801ВП1-35 ... 34

11.8. Микросхема КР1801РЕ2 ... 38

11.9. Микросхема К573РФЗ .... 40

11.10. Рекомендации по применению 42

Глава 12. Микропроцессорный комплект серии КР1802

(А. И. Березенко, С. Е. Калинин, Л. И. Корягин)

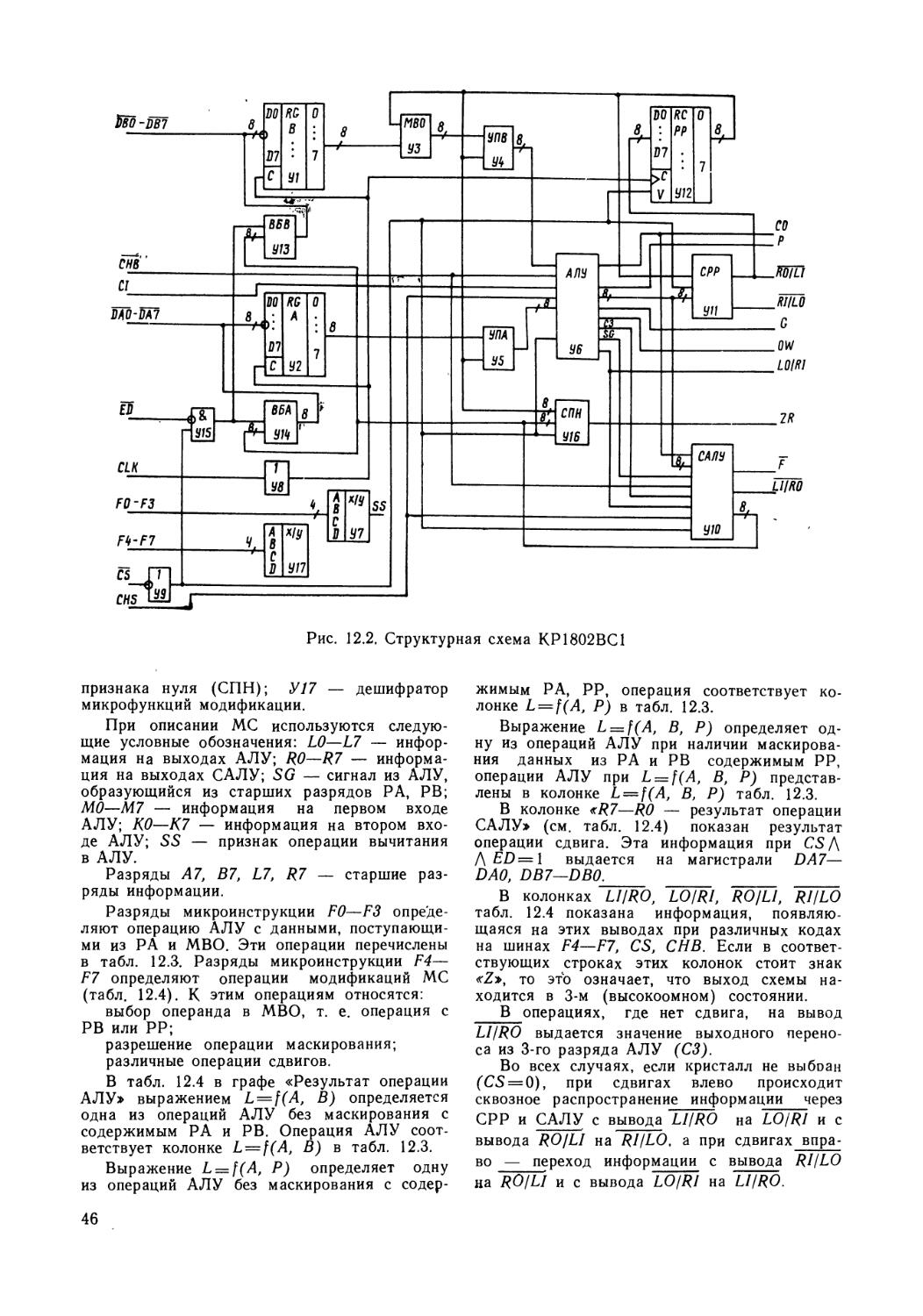

12.1. Микросхема КР1802ВС1 ... 44

12.2. Микросхема КР1802ИР1 ... 53

12.3. Микросхема КР1802ВР1 ... 57

12.4. Микросхема КР1802ВР2 ... 61

12.5. Микросхема КР1802ВРЗ ... 71

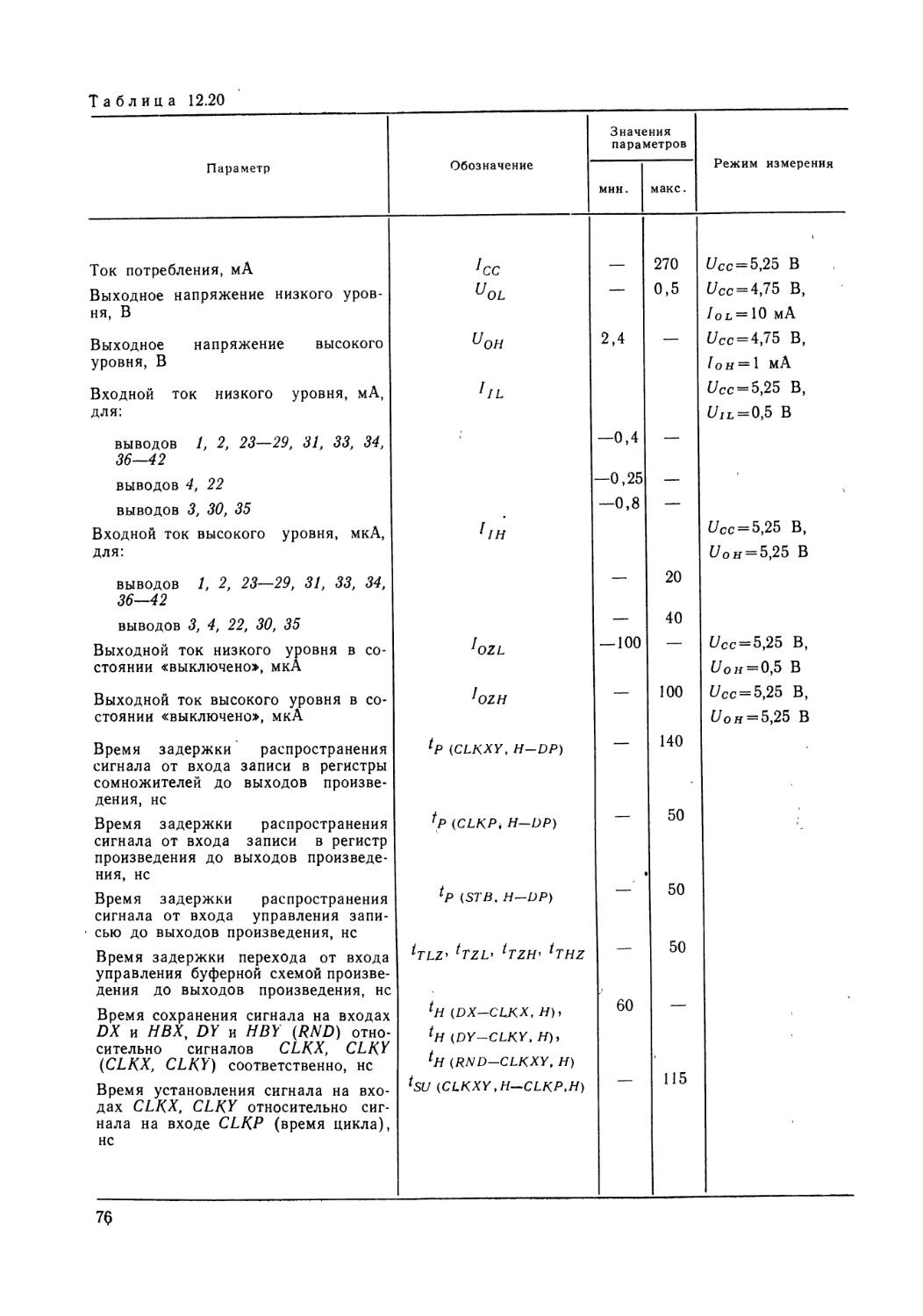

12.6. Микросхема КМ1802ВР4 , 79

12.7. Микросхема КМ1802ВР5 ... 84

12.8. Микросхема КР1802ИМ1 ... 89

12.9. Микросхема КР1802ИП1

12.10. Микросхема КР1802ВВ1 .

12.11. Микросхема КР1802ВВ2 .

12.12. Микросхема КР1802КП1 .

12.13. Микросхема КР1802ВВЗ .

97

107

111

118

125

Глава 13. Микропроцессорный комплект серии КМ 1804

(И. Е. Лобов, В. Т. Никифоровский, Б. Л. Толстых, И. И. Тонких, В. С. Хорошунов)

13.1. Микросхема КМ1804ВС1 . . . 132

13.2. Микросхема КМ1804ВС2 . . 136

13.3. Микросхема КМ1804ВР1 . 145

13.4. Микросхема КМ1804ВР2 . . 146

13.5. Микросхемы КМ1804ВУ1 и КМ1804ВУ2 .................154

13.6. Микросхема КМ1804ВУЗ . . . 158

13.7. Микросхема КМ1804ВУ4 . . . 159

13.8. Микросхема КМ1804ВН1 . 164

13.9. Микросхема КМ1804ВРЗ . . . 169

13.10. Микросхема КМ1804ВА1 . . . 171

13.11. Микросхема КМ1804ВА2 . 174

13.12. Микросхема КМ1804ВАЗ . 177

13.13. Микросхема КМ1804ИРЗ . 177

13.14. Микросхема КМ1804ГП . . 182

13.15. Микросхема КМ1804ВУ5 . . 186

13.16. Микросхема КМ1804ВЖ1 . . 191

13.17. Микросхема КМ1804ИР1 . 196

13.18. Микросхема КМ1804ИР2 . 198

13.19. Рекомендации по применению . 200

Глава 14. Микропроцессорный комплект серии КА 1808

(В. В. Горовой, В. А. Евдокимов)

14.1. Микросхема КА1808ВМ1 205

14.2. Микросхема КА1808ИР1 . 211

14.3. Микросхема КА1808ВВ1 213

14.4. Микросхема КА1808ВУ1 215

14.5. Рекомендации по применению . . 217

Глава 15. Микропроцессорный комплект серии К1809

(С. К. Иванова, Р, А. Лашевский, О. И. Хмельницкая)

15.1. Микросхема К1809ВВ1 .... 219

15.2. Микросхема К1809ВВ2 .... 225

15.3. Микросхема КМ 1509КП 1 . . . 230

4

Глава 16. Микропроцессорный комплект серии КМ 1810

(А. В. Кобылинский, А. И. Заика, Г. П. Липовецкий, И. П. Обуховский, В. М. Калатинец, Н. Н. Аверьянов,

В. А. Темченко, Л. В. Проценко,

Г. В. Литвинский, А. Н. Фионик,

И. Л. Трунина — § 16.1, 16.2, 16.6;

Г. Г. Нестеренко, А. В. Поветин,

А. М. Могилевский, А. С. Кусин,

В. И. Фирсов, Г. Ю. Немеровский —

§ 16.3—16.5)

16.1. Микросхема КМ1810ВМ86 . . 232

16.2. Микросхема КР1810ВН59А . 264

J6.3. Микросхема КР1810ВБ89 . . 275

16.4. Микросхема КР1810ВГ88 . . . 285

16.5. Микросхема КР1810ГФ84 . . . 289

16.6. Рекомендации по применению . 294

Глава 17. Микропроцессорный комплект серии К1811

(И. Е. Лобов, В. Т. Никифоровский, Б. Л. Толстых, Н. Н. Тонких, В. С. Хорошунов)

17.1. Микросхема КН1811ВМ1 . . 297

17.2. Микросхемы КН1811ВУ1, КН1811ВУ2, КН1811ВУЗ ... 300

17.3. Микросхема КМ1811ВТ1 . . 304

17.4. Соединение микросхем серии КН1811..............................307

Глава 18. Микропроцессор серии КМ1813ВЕ1 (А. А. Кузнецов, И. Ю. Луцкий, Г. Ф. Страутманис)

Глава 19. Микропроцессоры серии

К1814

(И. Е. Лобов, В. Т. Никифоровский, Б. Л. Толстых, Н. Н. Тонких, В. С. Хорошунов)

Глава 20. Однокристальные микро-ЭВМ серии KPI816 (А. В. Кобылинский, А. И. Заика, Г. П. Липовецкий, И. П. Обуховский, В. М. Калатинец, Н. Н. Аварьянов, В. А. Темченко, Л. В. Проценко, Г. В. Литвинский, А. Н. Фионик, Н. Л. Трунина)

Приложение 1. Корпуса микропроцессорных микросхем (Л. И. Якушкина) 353

Приложение 2. Краткие сведения о дополнительных микропроцессорных комплектах микросхем, не пошедших в справочник (В. А. Шахнов) .... 360

Приложение 3. Краткие сведения о микросхемах запоминающих устройств, применяемых в микропроцессорных системах (В. А. Шахнов)...............360

Приложение 4. Цифровые (логические) микросхемы, применяемые в микропроцессорных системах (В. А. Шахнов) , 362

Предисловие

Во второй том справочника включены описания микропроцессорных комплектов микросхем, широко применяемых в электронной и электронно-вычислительной аппаратуре, в порядке возрастания номеров серий, начиная с серйи К1801. Во втором томе сохранена структура представления данных, принятая для первого тома.

Вначале даются общие сведения о микропроцессорном комплекте, его составе, условиях эксплуатации, особенностях применения, конструктивном исполнении. Затем приводится описание каждой микросхемы, входящей в комплект, которое включает в себя условное графическое обозначение микросхемы, назначение выводов корпуса, временные диаграммы работы, статические и динамические параметры, систему микрокоманд. Описание каждого комплекта микропроцессорных микросхем заканчивается конкретными рекомендациями по его применению в аппаратуре.

В приложениях приведены сведения о конструктивном исполнении корпусов микросхем, краткие сведения о новых микропроцессорных комплектах, освоенных промышленностью за время подготовки к изданию справочника, а также общая характеристика и перечни микросхем запоминающих устройств и цифровых микросхем, применяемых при проектировании микропроцессорных систем.

Глава 11

Микропроцессорный комплект серии К1801

Микропроцессорный комплект серии К1801, микросхемы которого изготовляются по n-МДП-технологии, предназначен для построения широкого класса микроконтроллеров, мик

ро-ЭВМ, управляющих микропроцессорных систем. Высокая функциональная мощность, сравнительно высокое быстродействие при умеренной потребляемой мощности, совмести-

Таблица 11.1

Тип микросхемы Функциональное назначение Тип корпуса

К1801ВМ1 16-разрядный микропроцессор, 500 тыс. операций «Регистр — регистр» в секунду 429.42-5 х

КМ1801ВМ2 16-разрядный микропроцессор, 1 млн. операций «Регистр—регистр» в секунду 2123.40-6

КМ1801ВМЗ К1801ВП1-30 16-разрядный микропроцессор, 1,5 млн. операций «Регистр—регистр» в секунду Управление динамическим ОЗУ 2136.64-1 429.42-5

К1801ВП1-33 К1801ВП1-34 К1801ВП1-35 КР1801РЕ2 К573РФЗ Контроллер интерфейса параллельного ввода/вывода Устройство передачи информации Устройство последовательного ввода/вывода Постоянное запоминающее устройство Репрограммируемое ПЗУ 429.42-5 429.42-5 429.42-5 239.24-1 210Б.24-5

Таблица 11.2

Параметр Обозначение CO О К CU S H <u S S’ Я J X я s ® 2 w S oo e g

Выходное напряжение низ- ^OL 0,5

кого уровня, В Выходное напряжение высо- ион (2,4)

кого уровня, В Ток утечки на входе, мкА 1 LI 1

Ток утечки на выходе, мкА 1LO 10

Продолжение

Параметр Обозначение (Я о СК Си s ь х О) <и S • J 5* Я У ® я си* S s я я S 00 X S'-

Входное напряжение низко- UIL 0,7

го уровня, В Входное напряжение высо- UIH (2,2)

кого уровня, В Входная емкость, пФ С, 10

Выходная емкость, пФ со 15

6

Таблица 11.3

Параметр Обозначение Значения параметров; макс, (мин.)

Напряжение питания, В исс 5,25 (4,75)

Максимальное входное на- UI max 5,25

пряжение, В Минимальное входное на- UI min. (-0,5)

пряжение, В Выходной ток низкого уровня, мА OL 3,2

Выходной ток высокого ^ОЧ (-1,0)

уровня, мА Ёмкость нагрузки, пФ Cl 100 '

Температура окружающей среды, °C Т +70 (-Ю)

мость по системе команд с самыми массовыми в стране микроЭВМ семейства «Электроника» обеспечивают МПК серии К1801 практически неограниченные области применения.

В состав серии К1801 входят микросхемы однокристальных микропроцессоров, способных вести обработку 16-разрядных операндов, периферийных контроллеров, созданных на основе базового матричного кристалла серии К1801ВП1 и микросхемы ПЗУ (табл. 11.1).

Общие для всех микросхем комплекта электрические параметры приведены в табл. 11.2.

Общие для всех микросхем комплекта предельно допустимые значения электрических параметров приведены в табл. 11.3.

у ( Z5 t 31 ( 32 ч 33 ч 35 ( 29 ( 30 , 5 ( 3 ( 2 ( 6 ( 1 ( 39 ( 21 ; >8Р )SP 4RQ1 JRQZ JRQ3 WCLO >ACLO WMR >SP )SACK >SP )CLC >RPLY \GND CPU AD0< АЛ1 < ADZ< AD3< ADK AD 5< AD6< AD7< AD8< AD 9( ADKD AD1K AD12< AD13< AD1¥< AD№ IAK0<. DMGfr BSY< I ft IT < SELU SELZ< SYffC< DIN< DOUT( WTBTt . 9 ; и ; is , f7 : is 79 ; » >—2? 36 bi j 37 ; 4Z

Рис. 11.1. Условное графическое обозначение К1801ВМ1

кодирован полный набор микрокоманд для все£ типов команд;

блок прерываний, организующий приоритетную систему прерываний ОМП. Выполняет прием и предварительную обработку внешних и внутренних запросов на прерывание вычислительного процесса;

интерфейсный блок, выполняющий обмены информацией между ОМП и устройствами,

11.1. Микросхема К1801ВМ1

Микросхема К1801ВМ1 —однокристальный 16-разрядный микропроцессор (ОМП), предназначен для обработки цифровой информации в системах управления технологическими процессами, в контрольно-измерительной аппаратуре и системах связи, а также решения в составе ЭВМ инженерно-технических и экономических задач.

Условное графическое обозначение микросхемы приведено на рис. 11.1, назначение выводов— в табл. 11.4, структурная схема показана на рис. 11.2.

В состав микросхемы входят следующие основные функциональные блоки, объединенные информационно-управляющими связями:

16-разрядный операционный блок, выполняющий операции формирования адресов команд и операндов, логические и арифметические, хранения операндов и результатов;

блок микропрограммного управления, вырабатывающий последовательность микрокоманд на основе кода принятой команды. В нем за-

Ж^ЗЭ А» ^”.37 ^38

-^5

-&2

' ,SP \,

Жя

Рис. 1,1.2. Структурная схема KJ801BM1

7

Таблица 11.4

Вывод Обозначение Тип вывода Функциональное назначение выводов

1 CLC Вход Синхронизация

2 SACK Вход Подтверждение выборки

3, 6, 26, 27 SP — Резервные

4 DMGO Выход Предоставление прямого доступа

5 DMK Вход Требование прямого доступа

7 SEL1 Выход Выборка первого регистра вво-да/вывода

8 SEL2 Выход Выборка второго регистра ввода/ вывода

9—20, 22—25 ADO —AD15 Вход/вы-ход Разряды адреса/данных

21 GNU •— Общий

28 BSY Выход Сигнал занятости канала

29 DCLO Вход Авария источника питания

30 ACLO Вход Авария сетевого питания

31 IRQ1 Вход Первый запрос радиального прерывания

32 IRQ2 Вход Второй запрос радиального прерывания

33 IRQ3 Вход Третий запрос радиального прерывания

34 INIT Вход/выход Установка исходного состояния

35 VIRQ Вход Требование прерывания

36 IA KO Выход. Предоставление прерывания

37 DOUT Выход Вывод данных (запись данных)

38 DIN Выход Ввод данных (чтение данных)

39 RPLY Вход Синхронизация пассивного устройства (ответ)

40 WTBT Выход Вывод байта (запись/байт)

41 SYNC Выход Синхронизация активного устройства (обмен)

42 Ucc — Напряжение питания

расположенными на системной магистрали. Осуществляет арбитраж при операциях прямого доступа к памяти. В интерфейсном блоке формируется последовательность управляющих сигналов системной магистрали;

блок системной магистрали, связывающий внутреннюю магистраль ОМП с внешней. В нем производится управление усилителями приема и выдачи информации на совмещенные выводы адресов и данных;

схема тактирования, обеспечивающая синхронизацию внутренних блоков.

Основные параметры К1801ВМ1:

Разрядность............ 16 двоичных

разрядов

Представление чисел . . Дополнительный код с фиксированной запятой

Система команд . . . Безадресная, одноадресная, двухадресная

8

Виды адресации

Число регистров общего назначения (РОН) . . Число линий запросов на прерывания . . . . Системная магистраль .

Адресное пространство . Тактовая частота . . .

Максимальное быстродействие выполнения команд сложения в составе ЭВМ при регистровом методе адресации .

Потребляемая мощность

Регистровая, косвенно-регистровая автоинкрементная, косвенно-автоинкрементная, косвенноавтодекрементная, индексная, косвенноиндексная

8

4

Типа МПИ с совмещенными шинами для передачи адреса и данных 64К байт

От 100 кГц до 5 МГц

До 500 тыс. операций/с До 1,2 Вт

Сигналы ADO—AD15 определяют адреса и данные, которые передаются по совмещенной системной магистрали.

Группы сигналов SYNC, DIN, DOUT, WTBT, RPLY управляют передачей информации по системной магистрали. Сигнал SYNC, вырабатываемый процессором, означает, что адрес находится на выводах системной магистрали. Этот сигнал сохраняет активный уровень до окончания текущего обмена информацией.

Сигнал RPLY означает, что данные приняты или установлены на информационных выводах. Этот сигнал вырабатывается пассивным устройством в ответ на сигналы DIN и DOUT.

Сигнал DIN предназначен для организации двух процедур обмена информацией по магистрали:

ввода данных — ОМП вырабатывает D1N во время действия сигнала SYNC, когда он готов принять данные от пассивного устройства;

ввода адреса вектора прерывания — сигнал DIN вырабатывается совместно с сигналом 1АКО при пассивном уровне сигнала SYNC.

Сигнал DOUT означает, что данные, выдаваемые ОМП, установлены на выводах системной магистрали.

Сигнал WTBT предназначен для организации двух процедур обмена информацией: вырабатывается в адресной части цикла для указания о том, что далее следует вывод данных (слова или байта);

формируется при выводе данных из ОМП для указания о выводе байта.

Сигнал VIRQ вырабатывается внешним устройством для информирования ОМП о том, что оно готово передавать адрес вектора прерываний. В ответ на этот сигнал (если преры

вание разрешено) ОМП вырабатывает сигналы DIN и IAKO.

Сигнал IRQ1 определяет положение внешнего переключателя «Программа — пульт». Низкий уровень этого сигнала означает, что переключатель должен находиться в положении «Пульт». Этот сигнал переводит ОМП в состояние, аналогичное состоянию после выполнения команды HALT.

Сигналы IRQ2 и IRQ3 вызывают прерывание программы, выполняемой процессором, по фиксированным адресам 000100 * и 000270 соответственно. Прерывание происходит при переходе сигналов из высокого уровня в низкий.

Сигнал IAKO ОМП вырабатывается в ответ на внешний сигнал VIRQ. Этот сигнал является выходным для ОМП и входным для первого устройства, подключенного к системной магистрали (электрически ближе расположенного к ОМП и, следовательно, имеющего более высокий приоритет). Если это устройство не требовало прерываний (не устанавливало сигнал VIRQ), то оно транслирует сигнал IAKO к следующему устройству. Устройство, требующее прерывания ОМП, запрещает распространение этого сигнала. Сигнал IAKO, последовательно проходя через все устройства, обеспечивает их поочередный опрос и различный приоритет обслуживания.

Сигнал DMR вырабатывает внешнее активное устройство, требующее передачи ему системной магистрали.

Сигнал DMGO процессор устанавливает в ответ на внешний сигнал DMR. Этот сигнал последовательно проходит через внешние устройства и предоставляет системную магистраль устройству с наивысшим приоритетом, запросившему прямой доступ к памяти. Это устройство прекращает трансляцию сигнала DMGO и устанавливает сигнал SACK, который вырабатывается устройством прямого доступа к памяти (ПДП) в ответ на сигнал ОМП DMGO. Сигнал SACK означает, что устройство ПДП может производить обмен данными, используя стандартные циклы обращения к системной магистрали.

Сигнал BSY предназначен для управления устройствами умощнения магистрали. Низкий уровень этого сигнала означает, что ОМП начинает обмен по магистрали. Переход сигнала из низкого уровня в высокий означает окончание обмена.

Сигнал аварии источника питания DCLO вызывает установку ОМП в исходное состояние и появление сигнала IN1T. Сигнал аварии сетевого питания ACLO означает переход ОМП на обработку прерывания по сбою питания. Высокий уровень этого сигнала означает, что сетевое напряжение питания в норме.

При появлении одного из сигналов обращения к внешним регистрам расширения ввода/вывода SELI, SEL2 адрес на выводах системной магистрали соответствует адресу од

* Значения адресов, векторов прерываний, кодов команд приводятся в восьмеричной системе счисления.

9

ного из внешних регистров расширения вво-да/вывода. Сигнал SEL1 устанавливается при обращении по фиксированному адресу 177716, сигнал SEL2— по адресу 177714.

Совместно с сигналами DIN или DOUT происходит соответственно ввод данных в ОМП из регистров или вывод из ОМП на регистры. Установка сигнала RPLY от регистров расширения ввода/вывода не требуется. По длительности сигналы SEL1 и SEL2 совпадают с сигналом BSY.

Для режима пуска ОМП при включении питания необходимо обеспечить временную последовательность сигналов DCLO и ACLO, представленную на рис. 11.3.

После включения напряжения питания ОМП устанавливает сигнал IN IT и ожидает снятия сигнала DCLO. После снятия сигнала DCLO происходят ввод информации из регистра расширения ввода/вывода по адресу 177716 и формирование значений счетчика команд (СК). В разряды 0—7 СК загружается нулевая информация, в разряды 8—15 — информация из соответствующих разрядов регистра ввода/вывода, обращение к которому происходит по сигналу SEL1.

Регистр состояния процессора загружается константой 340. Микросхема анализирует состояние запросов на прерывания. Если незамаскированных запросов нет, то происходят ввод первой команды и ее выполнение.

Сигнал 1NIT является ответом ОМП на сигнал DCLO. Его используют для установки периферийной части системы в исходное состояние. При вводе этого сигнала в ОМП происходит сброс триггеров запроса радиальных прерываний и блокирования сигнала DMR.

Системная магистраль позволяет адресовать 64К байта. Верхние 8К байт адресного пространства резервируются для управления периферийными устройствами и регистрами

Рис. 11.3. Временная диаграмма режима начального пуска К1801ВМ1 при включении питания

данных. Системная магистраль ОМП позволяет организовать канал обмена информацией, аналогичный каналу ЭВМ «Электроника-60», в котором связь между двумя устройствами осуществляется по принципу «активный — пассивный».

Активное устройство управляет прохождением информации по системной магистрали, разрешает прерывания, обеспечивает предоставление прямого доступа к памяти. Пассивное устройство передает информацию только под управлением активного устройства.

При обращении ОМП к памяти или внешним устройствам возможны следующие виды обменов (циклов) информацией по системной магистрали: «Ввод» (чтение), «Вывод»

(запись), «Ввод — пауза — вывод» (Чтение — модификация — запись).

Цикл «Ввод — пауза — вывод» включает ввод данных, выполнение арифметико-логических операций и вывод результата без повторения передачи адреса, т. е. результат записывается по адресу последнего выбранного операнда.

Ниже иллюстрируются некоторые виды обмена информацией по системной магистрали.

При выполнении цикла «Ввод» данные передаются от пассивного устройства к активному. Временная диаграмма этого цикла приведена на рис. 11.4. Черта над обозначением сигнала указывает, что активным уровнем является низкий уровень сигнала.

Порядок выполнения операций следующий: процессор на выводах системной магистрали устанавливает адрес и выдает сигнал В5У;

синхронно с выдачей и снятием адреса ОМП устанавливает и снимает сигнал синхронизации SYNC, по которому происходит запоминание адреса пассивным устройством;

после установки сигнала SYNC ОМП снимает адрес, устанавливает сигнал DIN и ожидает поступление сигнала RPLY от пассивного устройства. Если в течение 64 тактов частоты синхронизации сигнал не появился, то ОМП переходит к обслуживанию внутреннего прерывания по ошибке обращения к системной магистрали;

после приема сигнала RPLY ОМП принимает данные от пассивного устройства и снимает сигнал DIN;

после снятия сигнала DIN пассивное устройство снимает сигнал RPLY, завершая операцию передачи данных;

после снятия сигнала RPLY пассивным устройством ОМП снимает сигналы SYNC и BSY. Если системная магистраль не предоставляется устройству ПДП, то ОМП сразу после снятия сигнала SYNC может начать новый цикл обращения к магистрали. В этом случае сигнал BSY не снимается.

Во время цикла «Ввод» сигнал WTBT не вырабатывается.

Кроме ОМП активным устройством на системной магистрали может быть устройство ПДП. В режиме ПДП обмен информацией происходит без вмешательства ОМП под управлением устройства ПДП. Последнее выпол-

10

Рис. 11.4. Временная диаграмма цикла «Ввод». Заштрихована область прихода сигнала RPLY, для которой соблюдается данная диаграмма: 6 = 404-70 нс; 6 = 504-80 нс

Рис. 11.5. Временная диаграмма

цикла прямого доступа к памяти

няет адресацию, синхронизацию, вырабатывает управляющие сигналы для организации стандартных циклов обращения к системной магистрали.

Временная диаграмма ПДП приведена на рис. 11.5. Устройство ПДП устанавливает сигнал DMR, в ответ на который ОМП формирует сигнал DMGO, затем, получив сигнал DMGO, вырабатывает сигнал SACK и снимает сигнал DMR. Микросхема снимает сигнал DMGO и ожидает завершение операции ПДП. Устройство ПДП начинает выполнять циклы передачи данных, аналогичные циклам «Ввод», «Вывод» или «Ввод — пауза — вывод». После окончания обмена данными устройство ПДП снимает сигнал SACK, возвращая управление магистралью процессору.

Регистры общего назначения (РОН) используются в качестве индексных и накопительных регистров автоинкрементной и автодекрементной адресаций. Среди восьми РОН два регистра (R6 и R7) имеют специальное назначение. Регистр R6 используется в качестве указателя стека (УС) и содержит адрес последней ячейки стека, R7 является счетчиком команд (СК) и содержит адрес очередной выполняемой команды.

Кроме РОН программно доступным регистром является регистр состояния процессора (РСП), содержащий информацию о текущем приоритете ОМП, значения кодов условий ветвлений программы, состояние Т-бита, используемого при отладке программы и вызывающего прерывание программы:

11

15 876543210

Таблица 11.5

I/O т N Z V с

Приоритет Прерывание по Т-разряду

Отрицательный результат

Нулевой результат

Арифметическое переполнение

Перенос

Если 7-й разряд РСП находится в состоянии 1, то внешние устройства не могут вызвать прерывание текущей программы, в противном случае внешние устройства вызывают прерывание.

Установка отдельных разрядов кодов ветвления выполняется в следующих случаях:

Z=l, если результат равен 0;

N=\, если результат отрицателен;

С=1, если в результате выполнения операции произошел перенос из самого старшего разряда или если при операциях сдвига вправо или влево из самого младшего или самого старшего разряда была выдвинута 1;

V=l, если в результате выполнения операции произошло арифметическое переполнение.

При загрузке информации в РСП может быть установлен или очищен Т-разряд. Если он установлен, то после завершения выполнения текущей команды будет вызвано прерывание программы с адресом вектора прерывания 14. Используют Т-разряд в отладочных программах для организации такого режима выполнения отлаживаемой программы, при котором исполнение интересующих пользователя команд вызывает прерывание программы и переход на программу связи с оператором. Для работы совместно с системным ПЗУ в РСП введены два дополнительных разряда (10 и 11), обеспечивающих изменение режима реакции на прерывания.

Система команд ОМП К1801ВМ1 (табл. 11.5) соответствует ЭВМ типа «Электроника-60».

Безадресные команды содержат только код операции.

Формат одноадресных команд имеет вид

коп Метод адресации РОН

15 6 5 3 2 0

Разряды 15—6 содержат код операции, определяющий исполняемую команду. Разряды 5—0 образуют 6-разрядное поле адресации операнда приемника, которое, в свою очередь, 12

Обозначение команды Код команды Команда

HALT 000000 Останов

WAIT 000001 Ожидание

RTI 000002 Возврат из прерывания

ВРТ 000003 Командное прерывание для отладки

ЮТ 000004 Командное прерывание для ввода/вывода

RESET 000005 Сброс внешних устройств

RTT 000006 Возврат из прерывания

JMP 0001DD Безусловный переход

RTS 00020Z? Возврат из подпрограммы

JSR NMRDD Обращение к подпрограмме

EMT 104000— 104377 Командное прерывание для системных программ

TRAP 104400 —104777 Командное прерывание

NOP 000240 Нет операции

Cl.C 000241 Очистка С

CLV 000242 Очистка V

CLZ 000244 Очистка Z

CLN 000250 Очистка У

SEC 000261 Установка С

SEV 000262 Установка V

SEZ 000264 Установка Z

SEN 000270 Установка У

see 000277 Установка всех разрядов (/V, Z, V, С)

CCC 000257 Очистка всех разрядов (N, Z, V, С)

SWAB 0003Z)Z) Перестановка байтов

CLR (B) *050iZ)Z) Очистка

COM (B) *051Z)D Инвертирование

INS (B) *052Z)Z) Прибавление 1

DEC (B) *053Z)D Вычитание 1

NEG (B) *0540 Z) Изменение знака

ADC (B) *055Z)D Прибавление переноса

SBC (B) *056DD Вычитание переноса

TST (B) *05700 Проверка

ROR (B) *06000 Циклический сдвиг вправо

ROL(B) *06100 Циклический сдвиг влево

A5Z? (B) *06200 Арифметический сдвиг вправо

ASL (B) *06300 Арифметический сдвиг влево

MARK 0064 AW Восстановление указателя стека (УС)

SXT 006700 Расширение знака

MTPS 106455 Запись слова состояния процессора (ССП)

MFPS 106700 Чтение ССП

MOV (B) *15500 Пересылка

CMP (B) *25500 Сравнение

BIT (B) *35500 Проверка разрядов

BIC (B) *45500 Очистка разрядов

BIS *55500 Логическое сложение

XOR 074ЯОО Исключающее ИЛИ

ADD 065500 Сложение

SUB 165500 Вычитание

BR 0004AWX Ветвление безусловное

BNE 0010XXX Ветвление, если не равно 0

BEQ 0014XXA Ветвление, если равно 0

Окончание табл. 11.5

Обозначение команды Код команды Команда

BGE 0020X XX Ветвление, и равно 0 если больше

BLT QQ24XXX Ветвление, ше 0 если мень-

BGT 0030ХХХ Ветвление, 0 если больше

BLE . 0034ХХХ Ветвление, если меньше или равно 0

SOB 077PRNN Вычитание 1 и ветвление

BPL \0G0XXX Ветвление, если плюс

ВМ1 imxxx Ветвление, если минус

'в HI ю\оххх Ветвление, если больше

В LOS юиххх Ветвление, или равно если меньше

BVC IQ20XXX Ветвление, если нет арифметического переполнения

BVS \024XXX Ветвление, тическое если арифме-переполнение

BHIS, вес 1030ХХХ Ветвление, или равно если больше

BLO, BCS \Q34XXX Ветвление, если меньше

Прим ечание. В — байтовые команды; SS —

ют метод адресации. Разряд 3 определяет прямую или косвенную адресацию.

Формат двухадресных команд имеет вид

КОП Метод адресации РОН Метод адресации РОН

15

3 2 0

12 11 9 8 6 5

поле адресации операнда источника; DD — поле адресации операнда приемника; /V/V — смещение (6 разрядов); XXX — смещение (8 разрядов)- R — регистр общего назначения.

* Разряд, принимающий значения: 0—для команд с операцией над словами; 1 — для команд с операцией над байтами

Поле адресации Поле адресации операнда источника операнда приемника

Поле адресации операнда источника используется для выборки операнда источника, поле адресации операнда приемника — для выборки операнда источника и занесения результата.

Источниками прерываний, расположенными в соответствии с приоритетностью обработки (при одновременном появлении нескольких запросов), являются:

ошибка обращения к магистрали;

резервный или запрещенный код в регистре команд;

Т-бит в РСП;

сигнал аварии сетевого питания ACLO\

сигналы радиальных прерываний IRQ1, IRQ2, IRQ3;

сигнал векторного прерывания VIRQ.

Установка 7-го разряда РСП в 1 позволяет игнорировать сигналы прерывания VIRQ, IRQ2, IRQ3.

Прерывание текущего процесса и последующая его обработка производятся после Ъы-

Рис. 11.6. Временная диаграмма приема адреса вектора прерывания. Заштрихована область прихода сигнала RPLY, для которой соблюдается данная диаграмма: =40—70 нс

13

Памяти иЛи регистра внешнего устройства) может прервать выполнение программы на любой фазе исполнения команды.

Временная диаграмма приема вектора прерывания показана на рис. 11.6. Последовательность операций при этом следующая. Устройство, которому необходимо обслуживание, выставляет сигнал требования прерывания VIRQ. Если прерывание разрешено, то ОМП помещает в стек содержимое СК и РСП и последовательно устанавливает сигналы DIN и IAKO. Устройство принимает сигнал IAKO и запрещает его распространение к другим устройствам, помещает адрес вектора прерывания на выводы системной магистрали, вырабатывает сигнал RPLY и снимает сигнал VIRQ.

Процессор принимает адрес вектора прерывания и последовательно снимает сигналы DIN и IAKO. Устройство завершает передачу вектора и снимает сигнал RPLY.

Микросхема ОМП загружает новое содержимое СК и РСП из двух последовательных ячеек, первая из которых определяется адресом вектора прерывания, после чего переходит к выполнению программы обслуживания данного устройства.

Основные параметры микросхемы К1801ВМ1 приведены в табл. 11.2 и 11.3.

11.2. Микросхема КМ 1801ВМ2

Микросхема КМ 1801ВМ2 — однокристаль-ный микропроцессор, является дальнейшим развитием ОП К1801ВМ1. Она обладает бо-

Рис. 11.7. Условное графическое обозначение КМ1801ВМ2

лее высоким быстродействием, расширенной системой команд и рядом новых функциональных возможностей.

Основные параметры КМ1801ВМ2

Быстродействие выполнения регистровых команд типа «Сложение».................До 1000 тыс.

операций/с

Быстродействие выполнения команд типа «Умножение» ........................ До 100 тыс.

операций/с

Максимальная тактовая частота .................... 10 МГц

Мощность потребления . . До 1,7 х Вт

Условное графическое обозначение микросхемы приведено на рис. 11.7, структурная схема показана на рис. 11.8. Назначение выводов соответствует микросхеме К1801ВМ1 и имеет следующие особенности.

Сигнал выходной тактовой синхронизации CLCO имеет частоту, равную половине частоты входной синхронизации CLCI. Он предназначен для организации систем, обладающих повышенной надежностью, в которых несколько процессоров должны работать синхронно.

Микросхема КМГ1801ВМ2 наряду с синх7 ронной адресной частью обмена по системной магистрали имеет возможность асинхронной работы при передаче адреса. Это обеспечивается с помощью входного сигнала AR «Адрес принят». После выдачи адреса на системную магистраль ОМП ожидает появления сигнала AR. Низкий уровень входного сигнала AR свидетельствует о том, что пассивное устройство приняло адрес и ОМП может продолжать цикл обмена по системной магистрали.

Микросхема ОМП обладает встроенной логической схемой обращения в область адресного пространства от 160000 до 163777 включительно. Для обращения в эту область используются сигналы WRQ и WAKI, которые могут применяться для организации обмена в многопроцессорных вычислительных системах.

Сигнал SEL, устанавливаемый процессором в фазе чтения одновременно с сигналом DIN, определяет процедуру чтения внешнего регистра ввода/вывода. Обычно таким регистром является регистр начальных условий пуска ОМП в составе ЭВМ. Если ОМП устанавливает сигнал SEL в фазе выдачи адреса, то это означает, что обмен идет с системной памятью, в качестве которой используется микросхема КР1801РЕ2. Системная память помимо специальных программ (начального пуска, резидентного тестового обеспечения, пультового терминала) позволяет расширять систему команд с помощью программной реализации в ней дополнительных команд.

Системная память при работе с ОМП является «скрытой», т. е. ее адреса в программном режиме не занимают адресного пространства ОЗУ. Тем самым она дополняет оперативную память. Системная память программно

14

9 AM

8_ API 2 AP2_ 1 AP3^ S_ AP^ £ APS* f APS

2_ API 30 apI 38 AP^ 37 AW ^АРП 15 APi2

(34 APII 33 APlt

32 APIS

Рис. 11.8. Структурная схема KM1801BM2

Ш Л7

WAHI 11

P/fK 12

SACK 13 PM60 74

RfLY 17 POUT & WTBT ?

SYNC 21 PIN Ъ AJ *23

IAKO 24

доступна с помощью специальных команд ОМП.

Сигнал HALT аналогичен сигналу IRQ1, сигнал EVNT «Прерывание от таймера» аналогичен сигналу IRQ2 в ОМП К1801ВМ1.

По сравнению с • К1801ВМ1 ОМП КМ1801ВМ2 может выполнять дополнительные команды расширенной арифметики (табл. 11.6). Команды плавающей запятой (MU.L, DIV, ASH, FDIV) выполняются на программном уровне с помощью системного ПЗУ КР1801РЕ2.

Таблица 11.6

Обозначение команды Код Команда

MUL 070/?SS Умножение

DIV 071/?SS Деление

ASH Q72RSS Сдвиг на N разрядов

ASHC ,073RSS одного слова Сдвиг на N разрядов

FADD 07500/? двойного слова Сложение с плавающей

FSUB 07501/? запятой Вычитание с плавающей

FMUL 07502/? запятой Умножение с плавающей

FDIV 07503/? запятой Деление с плавающей запятой X.

11.3. Микросхема КМ1801ВМЗ

Микросхема КМ1801ВМЗ— 16-разрядный однокристальный микропроцессор, включающий операционный блок, блок микропрограмм

ного управления, блок прерываний, диспетчер памяти и блок управления системной магистрали.

Отличительной особенностью КМ1801ВМЗ являются большой объем адресуемой памяти, высокое быстродействие и возможность подключения сопроцессора арифметики чисел с плавающей запятой (СППЗ).

Основные параметры КМ1801ВМЗ

Разрядность чисел и 16 разрядов с воз-команд ....... можностью представления и обработки 32-разрядных слов

Объем адресуемой памяти .......................... 4М байт

Принцип управления . . Микропрограммный Число команд . . . . 72 с фиксированной запятой, 46 с плавающей запятой (при подключении

СППЗ) Число регистров общего назначения ............ 8

Производительность операций «Регистр — регистр» ................Сложение в потоке

1,5 млн. операций/с; умножение 100 тыс. операций/с; деление 50 тыс. операций/с Число линий запросов на прерывание............. 4

Мощность потребления . 1,5 Вт

Условное графическое обозначение микросхемы приведено на рис. 11.9, назначение выводов— в табл. 11.7, структурная схема показана на рис. 11.10.

Микросхема содержит шесть регистров общего назначения (R0—R5), три регистра —

15

52

46

33

59

48

49

50

51

62

53

54 6/ 58 87

56

HLT

IPQO

PPPTRP 'FPPRB a/u

FL

4 | 5 t \SSYNC >К PLY

8 ) BMP

7 t 'SACK

50 < > CLC

32 < <6NB1

64 } * &cc

55

10

11

12

15 16

17

18 HUO Y A3J9

AU6

AB12 AD13 AD14 AD15 A16 A17

wtbt <M£

GNB2

9

42

59 33526-6535^515049484755

1011 2526 3031

Рис. 11.10. Структурная схема КМ1801ВМЗ

CPU

HLTM

Рис. 11.9. Условное графическое обозначение КМ1801ВМЗ

47

указателя стека R6 (SP), используемых в режимах операционной системы (KSP), пользователя (USP) и в пультовом режиме (HSP), и регистр R7, который служит также счетчиком команд (PC). Регистр SP содержит адрес последней заполненной ячейки стека, а PC — адрес команды, следующей за выполняемой.

Программно доступным регистром является также регистр состояния процессора PSW. Информация, содержащаяся в PSW, влияет на режимы выполнения команд и прерываний, определяет режим работы диспетчера памяти:

ветвления

Признак режима отладки

режим Предыдущий режим

6

Регистр PSW доступен также из процессора по физическому адресу 17777776.

Назначение разрядов регистра PSW:

разряды 0—3 (N, Z, V, С) — признаки знака, нуля, переполнения и переноса, описывающие результат последней выполненной команды;

разряд 4 (Т) — признак режима отладки;

разряды 5, 6, 7 — код приоритета внешних прерываний IRQ (3—*0);

разряды 13, 12 — предыдущий режим работы МП; *

разряды 15, 14 — текущий режим работы МП (11—режим пользователя, 00 — режим операционной системы).

В микросхеме используются три типа команд: безадресные, одноадресные и двухадресные. В безадресных командах код команды содержит только код операции. В кодах одноадресных и двухадресных команд содержится информация, определяющая: выполняемую функцию (код операции); регистры общего назначения, используемые при выборке операндов; метод адресации.

Система команд КМ1801ВМЗ включает команды МП КМ1801ВМ2 и дополнительные команды, которые приведены в табл. 11.8.

Диспетчер памяти обеспечивает:

расширение емкости адресуемой памяти с 64К до 256К или до 4М байт;

преобразование виртуальных адресов в физические и защиту памяти в системах с разделением времени;

использование различных областей адресов для режима пользователя и режима операционной системы (ОС).

Расширение емкости адресуемой памяти осуществляется преобразованием 16-разрядно-го виртуального адреса в 18- или 22-разрядный физический адрес. Преобразование выполняется с помощью набора 16 регистров — адресов страниц PAR и 16 регистров — описателей страниц PDR

16

Таблица 11.7

Вывод Обозначение Тип вывода Функциональное назначение выводов

10—25 ADO—AD15 Вход/выход Мультиплексирование во времени информации адресов и данных

26—30 А16—А20 Выход Адресная информация

31 A21/NS Выход Мультиплексирование во времени информации адреса А21 и информации о том, что считывается из памяти: команда или данные

3 SYNC Выход Фронт сигнала. Указывает на то, что выдан адрес. Обмен по магистрали продолжается до тех пор, пока присутствует сигнал

1 DIN Выход Сигнал управления вводом данных

2 DOUT Выход Сигнал управления выводом данных

5 RPLY Вход Сигнал ответа. Указывает на то, что, данные выставлены на магистрали во время чтения или приняты во время записи

63 WTBT Выход Во время фронта сигнала SYNC указывает на тип обмена: запись либо чтение. Во время записи информации указывает на формат данных: байт или слово

4 SSYNC Вход Сигнал ответа при опознании адреса, вызывает снятие адреса с магистрали

6 DMG Выход Сигнал разрешения на захват магистрали по прямому доступу к памяти

7 SACK Вход Сигнал подтверждения запроса прямого доступа к памяти

8 DMR Вход Сигнал запроса прямого доступа к памяти

9 GND — Общий

33 1NIT Входвыход Сигнал установки периферийной части системы в начальное состояние

46 ACLO Вход Сигнал включения источника питания переменного напряжения

47 FfLT Вход Сигнал останова

48—51 IRQ3—IRQ0 Вход Сигналы запроса на прерывание МП

43 Ucc — Напряжение питания

62 I AR Выход Сигнал разрешения прерывания

52 DCLO Вход Сигнал включения источника питания постоянного напряжения

53 FPPTRP Вход/выход Сигнал прерывания от СППЗ

54 FPPRD Вход Во время включения МП высокий уровень указывает, что СППЗ подключен, далее низкий уровень указывает, что СППЗ готов начать выполнение следующей команды

55 HLTM Выход Сигнал указывает, что МП в пультовом режиме

56 DREADY Вход Сигнал указывает, что СППЗ выставил на магистраль данные во время процедуры записи

57 FL Вход Сигналы длинного целого

58 FD Вход Сигналы двойной точности

59 WO Вход Сигнал режима включения МП

60 CLC Вход Тактовый сигнал

61 LIN Выход Сигнал стробирует в СППЗ загрузку команды

32 GND1 — Общий

64 Ucc Напряжение питания

Примечание. Выводы 38—41 не задействованы.

17

Таблица 11.8

Формат регистра PDR имеет вид

Обозначение команды Код Команда

MFPD 1065SS Засылка данных в стек текущей моды по адресу предварительной моды

MFPI 0065SS Засылка команды в стек текущей моды по адресу предварительной моды

MTPD 1066SS Засылка данных из стека текущей моды по адресу предварительной моды

MTPI 0066SS Засылка команды из стека текущей моды по адресу предварительной моды

Примечание. SS — поле адресации операн да источника.

Диспетчер памяти преобразует все адреса автоматически, поэтому пользователь работает в области виртуальных адресов. Область виртуального адреса делится на восемь отдельных страниц. Каждая виртуальная страница имеет свой код защиты. Есть три вида защиты памяти: разрешены запись и чтение, разрешено только чтение, запрещен любой доступ. Все попытки запрещенного доступа вызывают прерывание МП.

Диспетчер памяти обеспечивает три режима работы: ОС, пользователя и пультовый. Для каждого режима работы существует свой набор регистров PARjPDR.

Регистры PAR/PDR включают два набора по восемь 27-разрядных регистров PAR/PDR для режимов ОС и пользователя и четыре 16-разрядных регистра адреса страницы PARH для обеспечения пультового режима. Физические адреса регистров PAR/PDR приведены в табл. 11.9.

При 18-разрядном физическом адресе базовый адрес страницы в регистре PAR содержится в разрядах 0—11, а при 22-разрядмом— в разрядах 0—15.

7 6 5 4 3 2 1 0

Поле PLF определяет длину страницы в блоках (один блок — 32 слова) и позволяет установить ее от 0 до 1778.

Разряд 3 (ED) — направление расширения страницы: при ED = 0 — расширение вверх, при ED= 1 — расширение вниз. При расширении вверх PLF устанавливается на 1 больше необходимой длины. При расширении вниз в PLF заносится дополнительный код длины страницы.

Поле ACF определяет тип доступа к странице памяти: 00 — недоступна, прерывание при любом обращении; 01—доступна только по чтению, прерывание при попытке записи; 10 — не используется, прерывание при любом обращении; 11 — разрешены чтение и запись.

Разряд 6 (IT)—признак записи, указывает, что в страницу произведена запись. Разряд W очищается автоматически при записи в PAR и PDR данной страницы. Установлен этот признак может быть только аппаратно логической схемой управления диспетчера памяти (ДП).

Регистры состояния диспетчера памяти. Диспетчер памяти содержит три регистра состояний: SR0, SR2, SR3. Четвертый регистр состояния SR1 аппаратно не реализован, и при обращении по адресу этого регистра (17777574) всегда считываются нули. В случае нарушения условия защиты памяти процессор немедленно прерывается и переходит к программе обработки прерывания по вектору 2508 в области памяти ОС. Регистры состояния SR0 и SR2 служат для анализа возникшего прерывания.

Регистр SR0 (адрес 17777572) содержит флаги ошибок, бит разрешения преобразования адреса в ДП и другую информацию, необходимую ОС для обработки ошибки и возврата к прерванной программе.

Формат регистра SR0 имеет вид

Таблица 11.9

Номер регистра Режимы ОС Режимы пользователя

PAR PDR РАН | PDR

0 17772340 17772300 17777640 17777600

1 17772342 17772302 17777642 17777602

2 17772344 17772304 17777644 17777604

3 17772346 17772306 17777646 17777606

4 17772350 17772310 17777650 17777610

5 17772352 17772312 17777652 17777612

6 17772354 17772314 17777654 17777614

7 17772356 17772316 17777656 17777616

Номер страницы —-*

Назначение разрядов регистра SR0:

разряд 15 (NR)—ошибка по запрету доступа. Возникает при попытке обращения к недоступной или неиспользуемой странице;

разряд 14 (PL)—ошибка по нарушению длины страницы;

18

разряд 13 (RO) — ошибка по записи. Возникает при попытке записи в страницу, доступную только по чтению;

разряд 8 (Л4) — бит, устанавливающий ди-агнрстический режим работы ДП; при установленном М выполняется преобразование адреса только последнего обращения в память приемника;

разряды 5, 6 — режим МП (пользователя или ОС), при обращении к которому произошла ошибка ДП;

разряды 1, 2, 3 — номер страницы, при обращении к которой произошла ошибка ДП;

разряд О (EN) — бит включения ДП. При EN = 1 выполняются преобразование адресов и защита памяти в ДП.

Регистр SR2 (адрес 17777576) содержит виртуальный адрес первого слова выполняемой команды. Он не изменяется, если в данной команде произошло прерывание по ошибке ДП. Доступен только по чтению.

Регистр SR3 (адрес 1777757) содержит два разряда. Разряд 4 содержит бит AS. При Л5=1 адрес физический, 22-разрядный, при AS = 0—18-разрядный. Разряд 5 содержит бит UM. При UM = 1 устанавливается для внешней аппаратуры режим включения схем преобразования адресов.

Формирование физического адреса в ДП изображено на рис. 11.11.

В сумматоре выполняется сложение виртуального адреса VA (разряды 6—12) с выбранным PAR (разряды 0—11) при 18-раз-рядном адресе и PAR (разряды 0—15) при 22-разрядном адресе. В результате полный физический адрес содержит разряды 0—5 виртуального адреса и разряды 6—17 (21) — результат суммы.

Система прерываний процессора. Прерывания делятся на аппаратурные и командные. Часть аппаратных прерываний вызывает немедленный переход, к их обработке. Это так называемые фатальные ошибки. Они возникают при ошибках системной магистрали, ДП, СППЗ. Анализ таких аппаратных прерываний. Как авария источника питания, внешний сигнал HALT, прерываний IRQ (разряды 0—3), переполнения стека в моде операционной системы производится после завершения очередной команды в соответствии с приоритетом, указанным в табл. 11.10. К командам прерывания относятся EMT, TRAP, ВРТ, ЮТ, а также (если учитывать алгоритм выполнения) и резервные коды. Вектора прерываний приведены в табл. 11.11.

При прерывании МП помещает в стек PC и PSW и считывает новые значения PC и PSW из ячеек, определяемых вектором прерывания, причем загрузка PC и PSW ведется из области памяти операционной системы. Особый случай представляет собой возникновение фатальной ошибки в ходе выполнения микропрограммы обработки прерывания, так называемой «двойной ошибки». В этом случае процессор переходит в пультовый режим.

В пультовой режим процессор переходит при: выполнении команды HALT в моде ОС;

возникновении «двойной ошибки»; возникновении внешнего сигнала HALT — Q и отсутствии в этот момент других, более приоритетных прерываний.

При входе в пультовый режим процессор загружает в стек HSP константу 1000008; загружает в стек регистры PSW и РС\ заносит в

Таблица 11.10

Приоритет Прерывание

Высший Команда HALT Нечетный адрес Ошибка ДП Зависание Команды прерывания Прерывание по Т-биту Переполнение стека Сбой питания

Самый низкий Внешний сигнал HALT IRQ3 IRQ0

Таблица 11.11

Вектор Прерывание

004 Зависание, нечетный адрес, пе-

реполнение стека

010 Резервные и запрещенные ко-

манды

014 Прерывание по Т-биту

020 Прерывание по команде

024 Сбой питания

030 Прерывание по команде MTPI

034 Команды прерывания

250 Ошибка диспетчера памяти

244 Прерывание СППЗ

Из систем- IRQ3— IPQO

ной магист-

рали

19

Таблица 11.12

^£TLTlJXriJXriJnJTJTJTJTJXrTJXriJTJT_ -(Адрес fy^amut) (Данные) (Адрес2 дпк]| |_

I___I

МГ---1 I ..............

иШ |___|

® 1_Г^ I—|—

Рис. 11.12. Временные диаграммы циклов «Чтение» (а), «Запись» (б) и «Чтение/модифика-ция/запись» (в)

Рис. 11.13. Временная диаграмма цикла «За-прос/предоставление прямого доступа»

Виртуальный адрес

VA15 VA14

Назначение регистра PARH

О

1

О

1

170000

167600

177600

Формирование начального адреса программы пультового режима (ПЗУ) Формирование начального адреса ОЗУ программы пультового режима Адресация ко всей области памяти Формирование начального адреса страницы старшего банка

регистр PSW значение 3408, а в PC — 0; включает ДП на преобразование виртуальных адресов в 22-разрядные физические и переходит к выполнению программы, расположенной по виртуальному адресу 0.

В ДП с целью реализации пультового режима введены четыре регистра адреса страницы PARH (табл. 11.12), адресация к которым производится двумя старшими разрядами виртуального адреса. Регистр PARH2 позволяет осуществлять обращение ко всему адресному пространству путем записи в него соответствующего кода. Адрес регистра PARH2— 177512.

В пультовом режиме существуют некоторые отличия в выполнении команд и прерываний. Например, команды RT1 и RTT выполняются без учета значения Т-бита.

При включении питания извне устанавливается сигнал DCLO и МП переходит в режим ожидания сигнала ACLO. При поступлении сигнала ACLO МП начинает выполнение одной из процедур начального пуска в зависимости от сигнала WO:

WO — 0. МП загружает PSW содержимым 26-й ячейки памяти, PC — содержимым 24-й ячейки и начинает выполнение программы с этого адреса;

WO—\. МП загружает в PSW константу 340, а PC—173000 и начинает выполнение программы с этого адреса.

При выполнении любой команды МП осуществляет хотя бы одно обращение к каналу, называемое циклом обращения к каналу. Перед каждым циклом МП осуществляет процедуру захвата канала.

Цикл «Чтение». Цикл разделен на фазы передачи адреса и приема данных. Адрес из МП сопровождается сигналом SYNC, снимается после приема сигнала SSKAC, и затем выставляется сигнал DIN. Микросхема переключает элементы входа/выхода на выводах AD0—

20-

AD15 на прием и ожидает сигнал RPLY. Фаза приема данных. После приема сигнала RPLY МП принимает данные и снимает сигналы DIN и SYNC.

Цикл «Запись». Передача адреса сопровождается сигналом WTBT, который снимается одновременно со снятием адреса и указывает, что происходит цикл «Запись». После окончания фазы передачи адреса МП выставляет на выводы ADO—AD15 данные и сигнал DOUT и ожидает сигнал RPLY. После приема сигнала RPLY МП снимает сигнал DOUT, данные и сигнал SYNC. По снятию сигнала DOUT пассивное устройство снимает сигнал RPLY.

Цикл «Чтение — модификация — запись». Цикл разделен на фазы передачи адреса, при ема и записи данных. Фаза записи начинается после того, как пассивное устройство сняло сигнал RPLY в ответ на снятие сигнала DIN.

Временные диаграммы циклов «Чтение», «Запись» и «Чтение — модификация — запись» изображейы на рис. 11.12, циклов «Запрос — предоставление прямого доступа» — на рис. 11.13.

Основные параметры микросхемы КМ1801ВМЗ приведены в табл. 11.2 и 11.3.

11.4. Микросхема К1801ВП1-30

Микросхема К1801ВП1-30 построена на основе базового матричного кристалла микросхемы К1801ВП1. Она предназначена для управления ОЗУ (УОЗУ) динамического типа, выполненного на основе микросхем серии К565РУЗ и КР565РУ6, и выполняет:

прием, хранение и преобразование адреса для накопителя ОЗУ;

регенерацию памяти;

связь накопителя ОЗУ и буферного регистра данных с каналом передачи информации ЭВМ типа «Электроника-60»;

специальные функции управления системными областями памяти при работе с ОМП К1801ВМ1.

Условное графическое обозначение микросхемы приведено на рис. 11.14, назначение выводов — в табл. 11.13, структурная схема показана на рис. 11.15, временные диаграммы работы — на рис. 11.16.

В состав структурной схемы входят: счетчик адресов регенерации (СЧАР), буферный регистр адреса (БРА), мультиплексор адресов (МПА), регистр режима (РР), компаратор ад-

Таблица 11.13

Вывод Обозначение Тип вывода Функциональное назначение выводов

Л 2 AD5, AD4 Входы Разряды адреса/данных

5, 4 AD3, AD2 Входы/ выходы Разряды адреса/данных

5—7 ADI, AD14, ADO Входы Разряды адреса/данных

8 DIN Вход Чтение данных

9 DOUT Вход Запись данных

10 CLC Вход Синхронизация

И RASO Выход Сопровождение адреса строки накопителя (полублок I)

12 LOCK Выход Блокировка

13 RPLY Выход Ответ

14 C Выход Сигнал стробирования записи в буферный регистр данных

15 DME Выход Выборка данных памяти

16 RAS1 Выход Сигнал сопровождения адреса строки накопителя

17 RSEL Вход Выборка регистра режима

18 WE Выход Сигнал сопровождения записи в накопитель

19 CASO Выход Сигнал сопровождения адреса столбца накопителя (полублок I)

20 CAS1 Выход Сигнал сопровождения адреса столбца накопителя (полублок II)

21 GND — Общий

22—28 A0—A6 Выход Разряды адреса накопителя

29 WTBT Вход Запись/байт

30 DCLO Вход Авария источника питания

31 AD15 Вход Разряд адреса/данных

32 SYNC Вход Обмен

33 MSEL Вход Выборка памяти

34—41 AD13 —AD6 Вход Разряды адреса/данных

42 Ucc — Напряжение питания

Рис. 11.14. Условное графи ческое обозначение

К1801ВП1-ЗО

ё ? з s S 01 * fed MCC AO A1 Al A3 A<t-A5 AB 22 23 Z¥ ~~15 ZB 11 ^16 ^20 r 15 12 . Zf

NASO( NASH. CASO( CASK WE <

'SYNC 'UIN 'HOUT 'WTBT

J3ME ( C

MSEL 'KSEL 'JDCLO LOOK

ftPLYt

CLC

0ND1 Ucc '

Рис. 11.15. Структурная схема К1801ВП1-30

ресов (КМПА), блок синхронизации (БС), буферные усилители мощности (УМ).

Счетчик адресов регенерации включает делитель тактовой частоты (разряды 0—5) и счетчик адресов (разряды 6—13). В режиме регенерации содержимое разрядов 7—13 через МПА поступает на выводы АО—А6 и является адресом регенерации (АР).

Буферный регистр адреса содержит 16 разрядов и предназначен для хранения адреса, поступающего по системной магистрали. Содержимое разрядов 1—7 при выдаче адреса строки (АС) поступает через МПА на выводы АО—А6, при выдаче адреса колонки (АК) на выводы АО—А6 поступает содержимое разрядов 8—14. Кроме того, содержимое разрядов 8—14 поступает на КМПА для выработки сигналов LOCK. Содержимое разряда 0 исполь

зуется в БС для определения номера байта, при выполнении процедуры записи байта. Сигнал SYNC фиксирует запись инфор!мации в БРА.

Мультиплексор адресов предназначен для раздельной во времени выдачи адреса ОЗУ в виде 7-разрядных АС и АК при циклах обмена с накопителем ОЗУ, а также 7-разрядно-го АР.

Регистр режима предназначен для хранения служебных признаков режима работы. ОМП К1801ВМ1. Содержит два разряда (РР2 и РРЗ), доступных по чтению и записи из системной магистрали (разряды AD2 и AD3). Информация, хранимая в РР, влияет на установку сигнала LOCK.

Компаратор адресов вырабатывает сигнал блокировки LOCK, служащий для выборки областей системного ПЗУ и блокировки этих об-ластей^ в адресном пространстве внешних устройств. Установка сигнала на выводе LOCK происходит в следующих случаях:

адрес находится в диапазоне 16OOOO-5— 163777 при наличии 1 в РР2\

адрес находится в диапазоне 160000— 173777 при наличии 1 в РРЗ\ *

адрес обращения находится в диапазоне 173000—173777 независимо от состояния РР2 и РРЗ.

Компаратор адресов вырабатывает признак «Свой» для БС при обращении по адресу в диапазоне 177600—177677, который осуществляет запуск БС при отсутствии сигнала MSEL. Выделение данной области системного ОЗУ происходит при низком уровне сигнала DCLO.

Блок синхронизации вырабатывает сигнал управления внутренними узлами УОЗУ, накопителем ОЗУ, внешним буферным регистром данных, а также отрабатывает сигналы управления по каналу ЭВМ.

Регенерация информации в накопителе ОЗУ динамического типа производится по принципу: один цикл регенерации по одному адресу строки в течение периода, равного

Рис. 11.16. Временные диаграммы работы К1801ВП1-30

22

64 периодам тактового сигнала CLC. Полная регенерация информации в памяти по всем адресам происходит за 2 мс при тактовой частоте 4,2 МГц. В БС введена схема запуска текущего цикла регенерации к окончанию цикла обмена, информацией. При отсутствии циклов обмена с памятью в течение времени, равного 32 периодам тактовой частоты после получения БС запроса на регенерацию, очередной цикл регенерации производится принудительно. , Запрос на очередной цикл регенерации происходит через 16 периодов тактовой частоты после изменения адреса СЧАР.

Сигналы RAS0 и RAS1 вырабатываются одновременно.

Диапазон изменения частоты тактового сигнала CLC от 4,2 до 8 МГц.

Цикл чтения из памяти возможен при: сигнале SYNC, фиксирующем адрес обращения ADO—AD15 в БРА; сигнале MSEL\ отсутствии сигнала WTBT в адресной части; отсутствии очередного цикла регенерации памяти.

Выходные сигналы DME и RPLY УОЗУ вырабатывает при наличии входного сигнала ША.

' Сигнал RASO устанавливается в том случае, если при выдаче адреса AD15=\, а сигнал RAS1 — если AD15 — 0.

Сигналы CASO и CAS1 вырабатываются одновременно.

Цикл записи в память возможен при: сигнале SYNC, фиксирующем адрес обращения ADO—AD15 в БРА; сигнале MSEL; сигнале Щ7ГВГ, который в адресной части является признаком записи; сигнале DOUT-, отсутствии очередного цикла регенерации памяти.

При записи байта УОЗУ вырабатывает сигнал CASO, если AD0—\ в адресной части. При записи слова УОЗУ вырабатывают сигналы CASO и CAS1 одновременно.

Сигнал блокировки LOCK УОЗУ вырабатывает в фазе выдачи адреса. Задержка появления сигнала LOCK относительно установки адреса на выводе ADO—AD 15 не более 100 нс.

Микросхема УОЗУ приходит в состояние готовности за время, соответствующее прохождению семи синхронизирующих импульсов CLC.

Сигнал DCLO производит установку СЧАР в нулевое состояние и РР в режим «останов».

Основные параметры К1801ВП1 -30 приведены в табл. 11.2 и 11.3.

11.5. Микросхема К1801ВП1-33

Микросхема К1801ВП1-33 применяется для организации интерфейса накопителя на гибких магнитных дисках (НГМД) типа «Электроника ГМД-7012». Совместно с микросхемой К1801ВП1-34 выполняет функции контроллера интерфейса 16-разрядного программируемого параллельного ввода/вывода и контроллера байтового параллельного интерфейса.

Условные графические обозначения и структурные схемы интерфейса НГМД, контроллера интерфейса параллельного ввода/вывода и контроллера байтового параллельного интерфейса приведены на рис. 11.17 и 11.18, назначение выводов дано в табл. 11.14.

Интерфейс накопителя на гибких магнитных дисках. Установка микросхемы в режим интерфейса НГМД производится подачей на выводы RC0—RC3 напряжения высокого уровня.

Микросхема осуществляет передачу информации между процессором, и контроллером НГМД с помощью регистра команд и состояния (РКС), регистра данных (РД). Регистры считываются и загружаются программно.

Регистр команд и состояния имеет следующий формат:

|15|14|13|12|11|1О|9|8|7|6|5|4|3|2|1 |0| | INITTR IE I US F3F2F1GO

ERROR DONE

Назначение разрядов регистра:

GO (Пуск) — инициирует прием контроллером НГМД команды (только для записи);

F1—F3 — разряды команды (только для записи);

US (Выбор привода) — указывает на выбор одного из двух дисководов для выполнения требуемой команды (только для записи);

DONE (Завершено) — указывает на то, что выполнение команд завершено (только для чтения);

IE (Предоставление прерывания) — устанавливается программно для осуществления прерывания по завершении выполнения коман-ды, сбрасывается канальным сигналом INIT (для чтения и записи);

TR (Требование передачи)—требование записи (считывания) данных через регистр данных (только для чтения);

1NIT (Установка) — устанавливается программно для приведения НГМД в исходное состояние;

ERROR (Ошибка) — устанавливается, если в процессе выполнения команды произошла ошибка (только для чтения).

Разряды 8—13 не используются.

Список команд приведен в табл. 11.15.

Регистр данных имеет следующий формат:

|15114|13|12]11|1О|9|8|7|6|5|4|3|2|1 Гр

D7 D6D5D4D3D2 DI D0

Разряды 0—7 предназначены для хранения данных (D0—D7).

Разряды 8—15 не используются.

Интерфейсные сигналы контроллера НГМД включают:

23

SET (Начальная установка — вырабатывается микросхемой для приведения механизма и электронной части НГМД в исходное состояние;

DONE (Завершено) — устанавливается контроллером НГМД для индикации того, что текущая команда выполнена (либо в случае ошибки);

RUN (Пуск) — устанавливается микросхемой для инициирования передачи команды или байта данных;

OUT (Вывод) — вырабатывается контроллером НГМД для указания направления передачи байта информации (при низком уровне сигнала информации передается от НГМД к микросхеме);

TR (Запрос передачи)—устанавливается контроллером НГМД для индикации того, что он готов принять (передать) байт информации;

DI (Вход данных) — линия для приема последовательной информации;

DO (Выход данных)—линия для передачи последовательной информации;

SHFT (Сдвиг) — линия синхронизации при

Таблица 11.14

ема (передачи) последовательной информации; длительность отрицательного импульса не менее 200 нс, период 1 мкс;

ERR (Ошибка)—устанавливается контроллером НГМД при обнаружении ошибки; при этом прекращается выполнение текущей команды и устанавливается сигнал DONE.

С помощью выводов RC4 и RC5 можно переадресовать регистры микросхемы. Соответственно изменяются адреса векторов прерываний. Адреса регистров и векторов прерываний, соответствующие комбинациям уровней напряжений на выводах RC4, RC5, приведены в табл. 11.16.

При низком уровне сигнала DONE запись команды, содержащей лог. 1 в нулевом разряде, в регистр команд вызывает установку сигнала RUN, который инициирует прием команды контроллером НГМД. Контроллер НГМД снимает сигнал DONE и выставляет на линию SHFT серию из восьми импульсов. После снятия сигнала DONE происходит сброс сигнала RUN, а серия импульсов синхронизирует выдачу команды в последовательном коде

Вывод Обозначение Тип вывода Функциональное назначение выводов

2 RCO FBI ВО <

RC1 RUN < 28

~Т~~ RC2 set\ 29

RCJ

V1R0' 35

RCU

6 805 IAKO< . 36

Я > ВI ABO <

'SHFT AB1 < . 10

«7/7 AB2 < 11

'EM

J74 АВЗ <

'BONE AB4 < 7g

> ТВ AB5 < Л

'оит AB6 < t 15

33 ( 'IAKI ABT < ( 16

AB8 < „ 17

'INIT

AB9 <

4/ ABlOi 7g 7g

2^ 'SYNC 'BIN 'BOUT AB J J < AB12< ABlk (

'WTBT AB15 < Л

'BS RPLY < r jy

{ВВП ucc : p

Интерфейс накопителя на гибких магнитных дисках

Рис. 11.17, Условное графическое обозначение К1801ВП1-33 в режиме интерфейса НГМ (а)

1—6 RC3, RC0—RC5 . Входы Выбор режима

7 SHFT Вход Сдвиг данных

8 OUT Вход Вывод данных

, 9—16 AD0—AD7 Входы / Разряды адреса/данных

выходы

17—20 AD8—AD11, Входы Разряды адреса/данных

22, 24 AD12, AD14

25 AD15 Выход Разряд адреса/данных

21 GND — Общий

23 BS Вход Внешнее устройство

26 DI Вход Вход данных

27 DO Выход Выход данных

28 RUN Выход Пуск

29 SET Выход Начальная установка

30 ERR Вход Ошибка

31 DONE Вход Завершено

32 TR Вход Требование передачи

33 IAKI Вход Разрешение прерывания

34 INIT Вход Установка исходного состояния

35 VIRQ Выход Требование прерывания

36 IA KO Выход Предоставление прерывания

37 DOUT Вход Чтение данных

38 DIN Вход Запись данных

RPLY Выход Ответ

WTBT Вход Запись/байт

SYNC Вход Обмен

Ucc — Напряжение питания

Контроллер интерфейса параллельного ввода/вывода

1—4 RC3, RCO, Входы Выбор режима

RC1, RC2

5 RDO Выход Задержка ответа

6 RD1 Вход Задержка ответа

7 CSRO Выход Регистр состояния РСО

24

2 RCO PIC urn < .27 28

NBB (

3 RC1 BIB < ^26

4 BOB' &

RC2 OPP' t 31

1 рсз CSPO CSP1 7

с

RBO

m }35

О RBI IAM< 136

32 REQA ABO' AB1 < . 9 710 r it

30 PEQB AP2 < AB3 < AP4 < Hi 3

AP5 < AB6 ' AP7 (

33 ( 3

UNIT AP8 < APB < . 17 718

лг тг! 'SYNC 'BIN 'BOUT 'WTBT AP10' ABH' API2' API4' APIS' k 19 Ho П22

23 1

> BS RPLY' Л

21 , (GNU Ucc - {42

2 7 BOO BPIC IN < > 27

J Z PCI OUT' >-28

¥ PCZ SET'

40 ! >sos AOS' ( 7

'SOS SC-A' ( 8

5 ( 'AO-A VIRQ' t 35

6 \AC~A IAKO' , 36

30 EPP ABO ' ( 9

31 BONE AB! ' AB2 ( 10 . 11

32 TP АВЗ < . 12 ’ /7

AB4 < ' tr.

AB5 ( AB6 ' . /¥

1 REC 715 ’ 1£

AB7 < AB8 ' AB3 < AB 10' . Ю

33 t 'IAPI 777 718

J4 ( UNIT П9 . 20

ABU ( AB 12 (

'SYNC \~22

38 , 77; 'BIN 'BOUT AB14' AB 15' r 25

23 ( > BS RPLY' r 39

21 \GNB Ucc J . 42

Окончание табл. 11.14

Вывод Обозначение Тип вывода Функциональное назначение выводов

8 CSR1 Выход Регистр состояния РС1

9—16 AD0—AD7 Входы/ Разряды адреса/данных

выходы

7-20, AD8—AD11, Входы Разряды адреса/данных

22, 24 AD12, AD14

21 GND •— Общий

25 AD15 Выход Разряд адресауданных

23 BS Вход Внешнее устройство

26 BIB Выход Вывод старшего байта

27 DTR Выход Ввод данных

28 NDR Выход Вывод данных

29 BOR Выход Вывод младшего байта

30 REQB Вход Требование В

31 ORR Выход Чтение выходного регистра

32 REQA Вход Требование Л

33 1AK1 Вход Предоставление прерывания

34 1N1T Вход Установка

35 VIRQ Выход Требование прерывания

36 IAKO Выход Предоставление прерывания

37 DOUT Вход Запись данных (по каналу)

38 DIN Вход Чтение данных (по каналу)

39 RPLY Выход Ответ

40 WTBT Вход Запись/байт

41 SYNC Вход Обмен

42 Ucc — Напряжение питания

Рис. 11.17. Условное графическое обозначение К1801ВП1-33 в режимах контроллера интерфейса параллельного ввода/ вывода (б) и контроллера байтового параллельного интерфейса (в)

Контроллер байтового параллельного интерфейса

1 REQ Вход Требование

2—4 RC0—RC2 Входы Выбор режима

5 АО-А Вход Готовность приемника

6 АС-А Вход Запрос приемника

7 AC-S Выход Запрос источника

8 SC-A Выход Стробирующий сигнал прием-

9—16 AD0—AD7 Входы ника Разряды адреса/данных

17-20, AD8—AD11, выходы Входы Разряды адреса/данных

22, 24 25 AD12, AD14 AD15 Выход Разряд адреса/данных

21 GND Общий

23 BS Вход Внешнее устройство

26 SC-S Вход Стробирующий сигнал источ-

27 1N Выход ника Ввод данных

28 OUT Выход Вывод данных

29 SET Выход Начальная установка

30 ERR Вход Ошибка

31 DONE Вход Завершено

32 TR Вход Требование передачи

33 1AK1 Вход Предоставление прерывания

34 1N1T Вход Установка

35 VIRQ Вход Требование прерывания

36 IAKO Выход Предоставление прерывания

37 DOUT Вход Запись данных (по каналу)

38 DIN Вход Чтение данных (по каналу)

39 RPLY Выход Ответ

40 SO-S Вход Готовность источника

41 SYNC Вход Обмен

42 Ucc — Напряжение питания

25

Рис. 11.18. Структурная схема К1801ВП1-33 в; режимах интерфейса НГМД (а), контроллера интерфейса параллельного ввода/вывода (б)*и контроллера байтового параллельного интерфейса (в)

г)

который используется для работы по прерыва-с нию. Требование прерывания VIRQ, возникает с появлением сигнала DONE при наличии , в регистре команд разрешения прерывания IE.

Временные диаграммы процедур «Запись в буферный регистр» и «Чтение буферного регистра» приведены на рис. 11.19.

Контроллер интерфейса параллельного ввода/вывода. Установку микросхемы в режим контроллера интерфейса параллельного ввода/вывода производят подачей определенных уровней напряжения на выводы RC0—RC3. Помимо выбора режима работы микросхемы

Таблица 11.15

Код микроконструкции

F2 | F1

Функция

на вывод DO. В зависимости от принятого кода команды контроллер НГМД устанавливает сигналы OUT и TR. При установленном сигнале TR в зависимости от состояния сигнала OUT обращение к регистру данных вызывает установку сигнала RUN, который сбрасывается после снятия сигнала TR, и серию импульсов на выводе SHFT (восемь для синхронизации адреса вектора и дорожки, семь для синхронизации данных). По окончании выполнения команды устанавливается сигнал DONE,

о

о

о о

1

1

1

1

о

о

1 1 о о

1 1

о

1

о 1 о 1 о

1

Запись в буферный регистр

Чтение буферного регистра

Запись сектора

Чтение сектора Не используется Чтение регистра

Запись сектора с меткой

Чтение регистра ошибки

26.

Таблица 11.16

1 Вывод Обозначение Уровень сигнала Адрес РКС Адрес РД я Л о и 2 Q. « * «щах < и С я

5 6 RC4 RC5 Низкий Низкий 177170 177172 264

5 6 RC4 RC5 Высокий Низкий 177174 177176 270

5 6 RC4 RC5 Низкий Высокий 177200 177202 274

5 6 RC4 RC5 Высокий Высокий ХХХХХО ХХХХХ2 XXX

Примечание. X — состояние разрядов адреса безразлично.

комбинации напряжений на этих выводах осуществляют переадресацию регистров и векторов прерываний. Адреса регистров и вектора прерываний, соответствующие определенным комбинациям напряжений на выводах RC0— RC3 в режиме контроллера параллельного ввода/вывода, приведены в табл. 11.17.

Микросхема осуществляет прием и передачу информации с помощью регистра состояния (PC), регистра приемника (РП) и регистра источника (РИ). Регистры источника и приемника выполнены на двух микросхемах К1801ВП1-34. Структурная схема контроллера приведена на рис. 11.20.

Микросхема содержит регистр состояния, компаратор адресов, блок прерываний и блок управления регистрами РП и РИ. Регистр состояния имеет следующий формат:

Сигналы управления регистрами приемника и источника:

DTR (Ввод данных) — вырабатывается микросхемой при чтении регистра приемника;

NDR (Вывод данных) — вырабатывается микросхемой при записи в регистр-источник;

BIR (Вывод старшего байта) — вырабатывается микросхемой при записи старшего байта в регистр-источник;

BOR (Вывод младшего байта) —вырабатывается микросхемой при записи младшего байта в регистр-источник;

ORR (Чтение выходного регистра) — вырабатывается микросхемой при чтении регистра-источника;

RD0 (Задержка ответа, выход) — выход разрыва цепочки формирования сигнала RPLY-

RD1 (Задержка ответа, вход) — вход разрыва цепочки формирования сигнала RPLY.

С помощью /?С-цепочки, включенной между выводами RDI и RD0, можно увеличивать длительность импульсов DTP и NDR.

Требование прерывания VIRQ возникает при появлении хотя бы одного из сигналов

QUT

|l5|l4|l3|l2|ll|io| 9 | 8 | 7 | 6 | 5 | 4 | 3 | 21 1 | 0 [

I I IEA J CSR7|

REQB REQA IEB CSR0

Назначение разрядов регистра PC следующее:

CSR1, CSR0 (РСО1, РСОО) — разряды, которые могут использоваться для имитации запросов прерывания в режиме автономной проверки (для чтения и записи);

REQA (Требование А) — требование прерывания А (только для чтения) ;

REQB (Требование В) — требование прерывания В (только для чтения);

IEA (Разрешение А)—разрешение преры-вания А, сбрасывается сигналом INIT (для чтения и записи);

IEB (Разрешение В) — разрешение преры-вания В, сбрасывается сигналом INIT (для чтения и записи).

Рис. 11.19. Временные диаграммы процедур «Запись в буферный регистр» (а) и «Чтение буферного регистра» (б)

27

Таблица 11.17

Вывод Обозначение Уровень сигнала Адрес PC Адрес РИ Адрес РП Адрес вектора прерывания А (В)

1 RC3 Низкий <

2 3 RC0 RC1 Высокий Низкий 167770 167772 167774 300 (304)

4 RC2 Высокий

1 RC3 Высокий

2 3 RC0 RC1 Высокий Низкий 167760 1677762 167764 310 . (314)

4 RC2 Высокий

1 RC3 Низкий

2 3 RC0 RC1 Низкий Высокий 167750 167752 167754 320 (324)

4 RC2 Высокий

/ RC3 Высокий

2 3 RC0 RC1 Низкий Высокий 167740 167442 167744 330 (334)

4 RC2 Высокий

1 RC3 Низкий

2 3 RC0 RC1 Высокий Высокий XXXXX0 ХХХХХ2 ХХХХХ4 ххо . (ХХ4)

4 RC2 Высокий

REQA, REQB при наличии в регистре состояния соответствующего разрешения прерываний IEA, IEB. При одновременном появлении сигналов REQA и REQB более высокий приори

тет имеет требование В. Выполнение процедуры прерывания стандартное.

Контроллер байтового параллельного интерфейса. Установку микросхемы в режим кон-

Рис. 11.20. Структурная схема контроллера интерфейса параллельного ввода/вывода

28-

троллера байтового параллельного интерфейса производят подачей определенных уровней напряжения на выводы RC0—RC2. Помимо выбора режима работы микросхемы комбинации напряжений на этих выводах осуществляют переадресацию регистров и векторов прерываний. Адреса регистров и векторов прерываний, соответствующие определенным комбинациям напряжений на выводах RC0—RC2, приведены в табл. 11.18.

Микросхема осуществляет прием и передачу информации с помощью регистров состояния источника (РСИ) и приемника (РСП), регистров источника (РИ) и приемника (РП).

Регистры источника и приемника выполнены на одной микросхеме К1801ВП1-34. Структурная схема контроллера приведена на рис. 11.21. Микросхема содержит регистры состояния РСИ и РСП, компаратор адресов, блок прерываний и блок управления регистрами РИ, РП.

Регистр состояния источника имеет следующий формат:

|15|14|13|12111 |1O|9 |8|7|6|5|4|3|2|l|0|

ERR AR IEA

Назначение разрядов регистра:

IEA — разрешение прерывания по приему, сбрасывается начальным сигналом INIT (для чтения и записи);

AR — требование приема (только для чтения) ;

Рис. 11.21. Структурная схема контроллера интерфейса байтового параллельного ввода вывода

ERR — ошибка (только для чтения).

Регистр состояния приемника имеет следующий формат:

|l5|l4jl3|l2|l 1 |ю| 9 | 8 | 7 | 6 | 5|4|з|2|1]о|

ERR SET TR IET DONE

Назначение разрядов регистра:

DONE — завершено (только для чтения);